Mar. 4, 1986

MASTER IMAGE CHIP ORGANIZATION TECHNIQUE OR METHOD

Inventors: John Balyoz, Deerwood Dr., Box [76] 247, R.D. #3. Hopewell Junction, N.Y. 12533; Chi S. Chang, 14 Shale Dr., Wappingers Falls, N.Y. 12590; Barry C. Fox, 26 Miron Dr., Poughkeepsie, N.Y. 12603; John A. Palmieri, 10 Montfort Woods Rd., Wappingers Falls, N.Y. 12590; Majid Ghafghaichi, 352 Vassar Rd., Poughkeepsie, N.Y. 12603; Teh-Sen Jen, 66 Star Mill Rd., Fishkill, N.Y. 12524; Donald B. Mooney, 26 Hagan Dr., Poughkeepsie, N.Y. 12603

Appl. No.: 457,786

Jan. 13, 1983 Filed:

## Related U.S. Application Data

Continuation of Ser. No. 224,240, Jan. 12, 1981, aban-[60] doned, which is a division of Ser. No. 974,576, Dec. 29. 1978, Pat. No. 4,295,149.

Int. Cl.4 ...... H01L 21/88 U.S. Cl. ...... 29/577 C [52]

ABSTRACT [57]

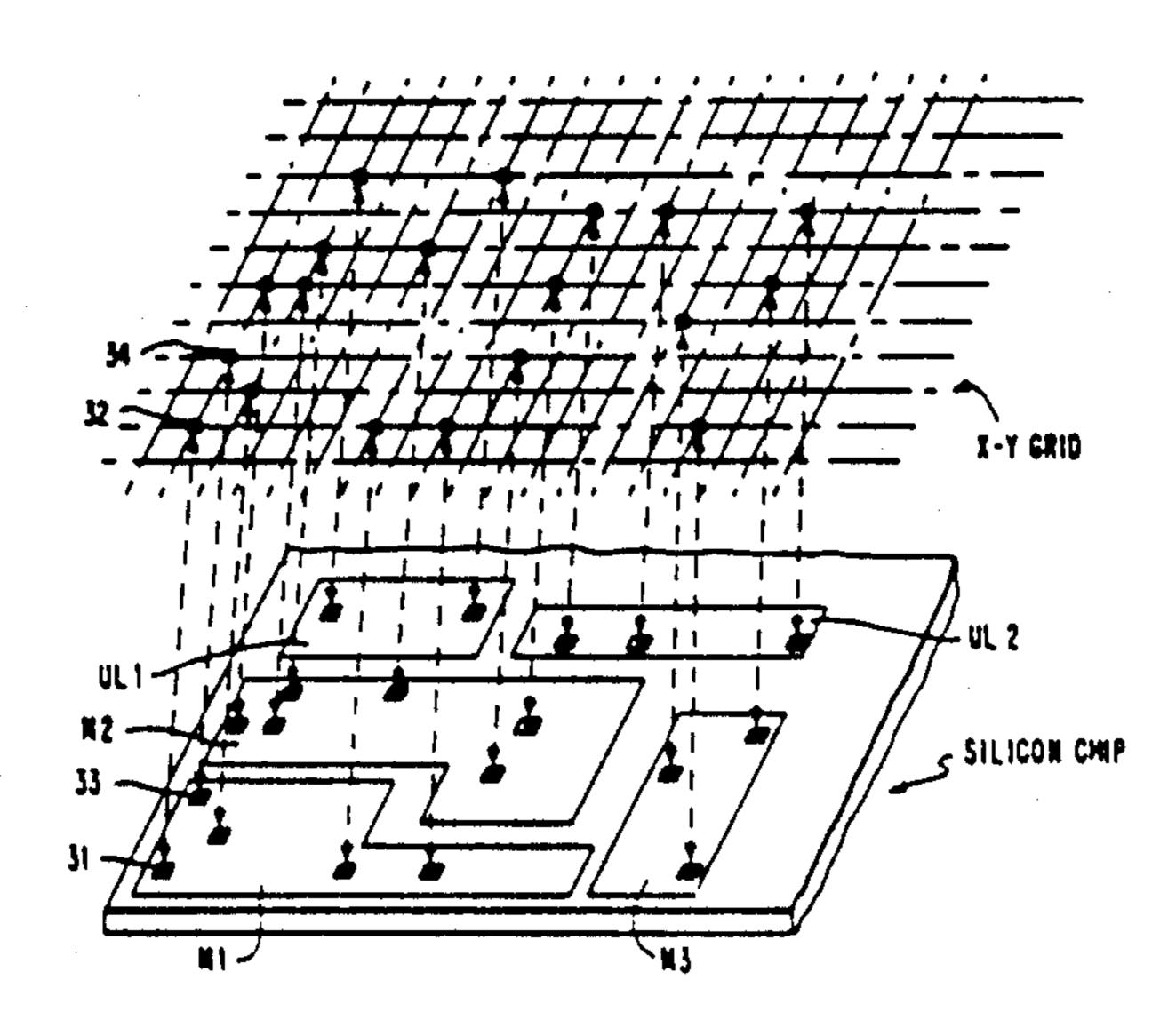

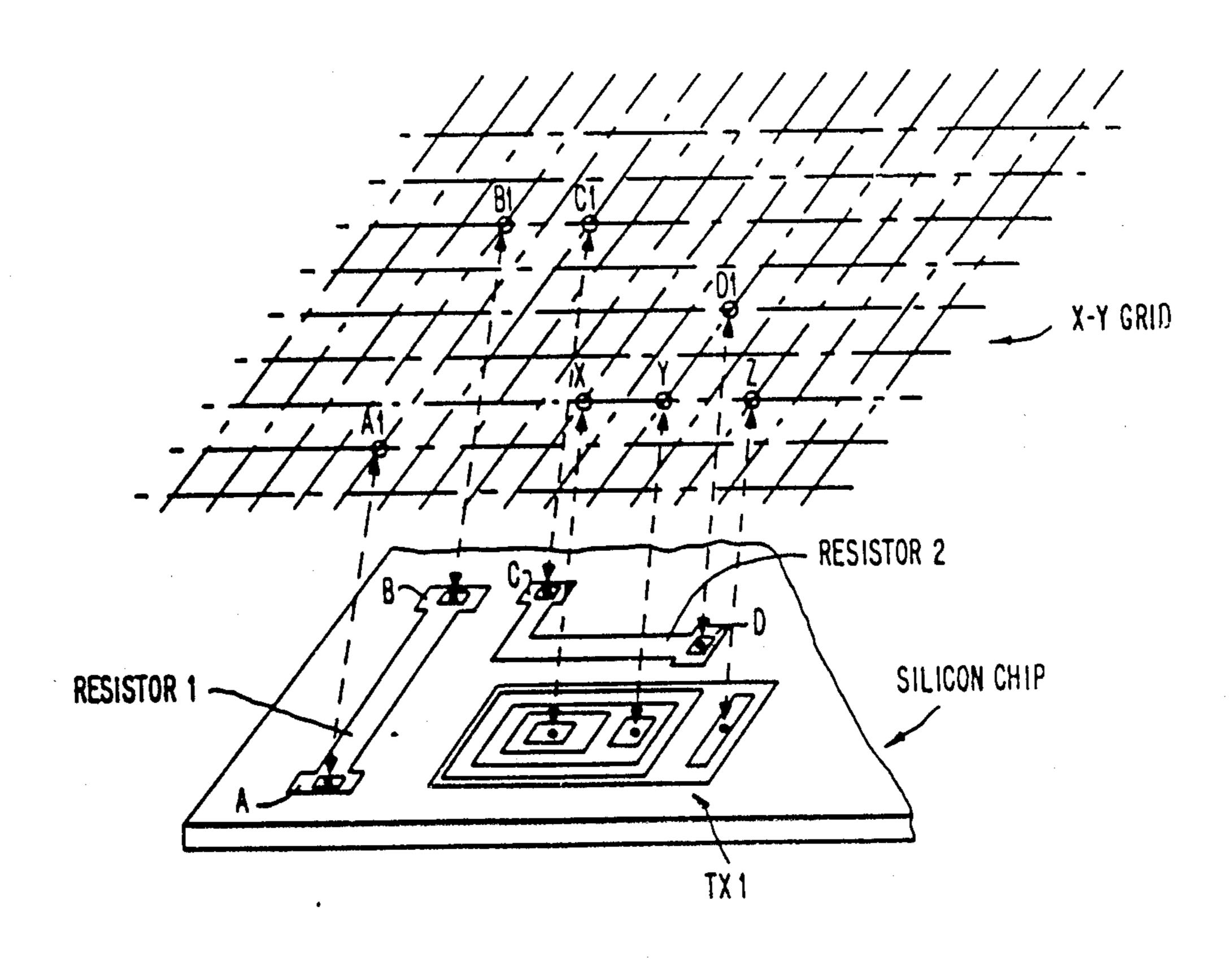

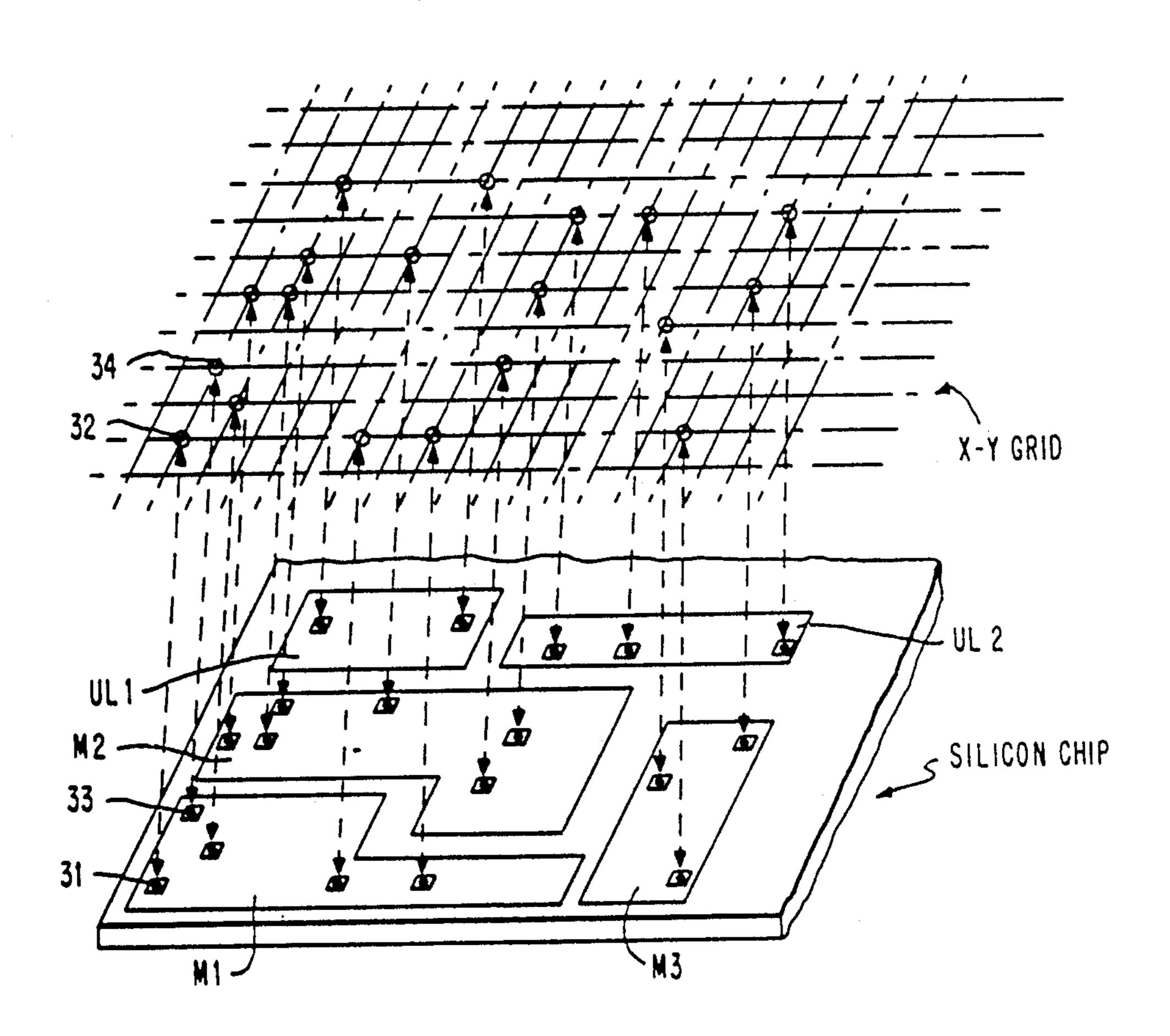

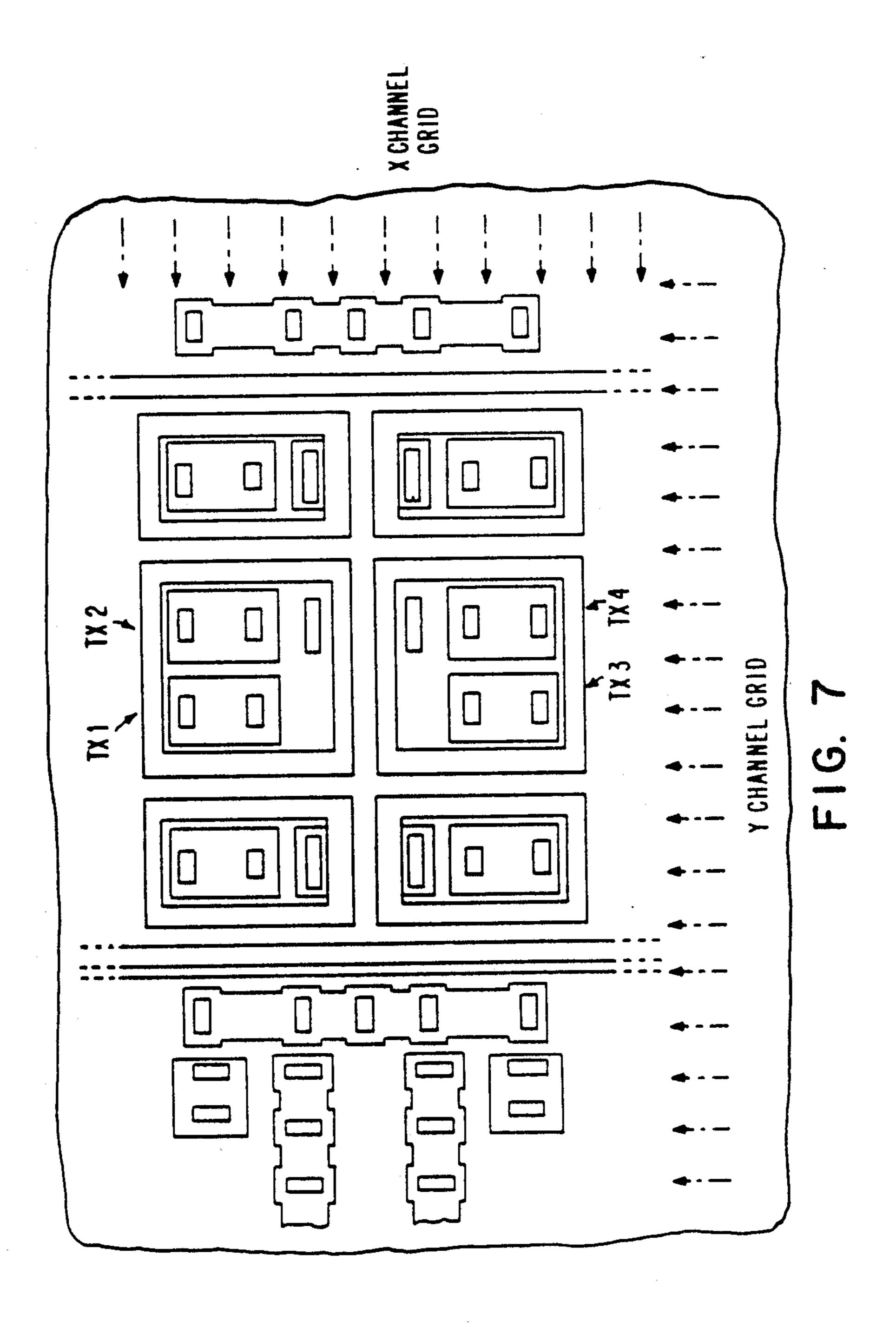

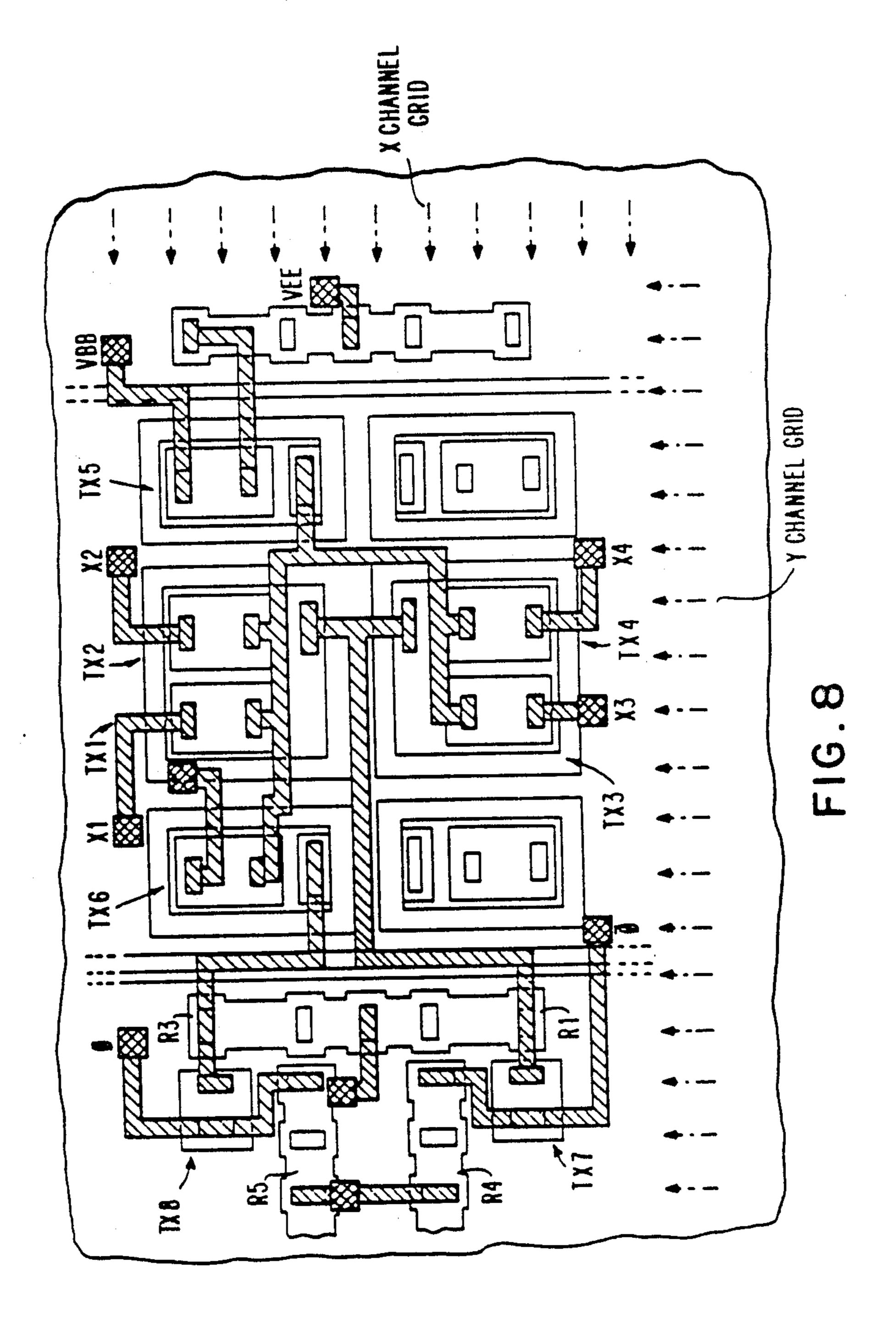

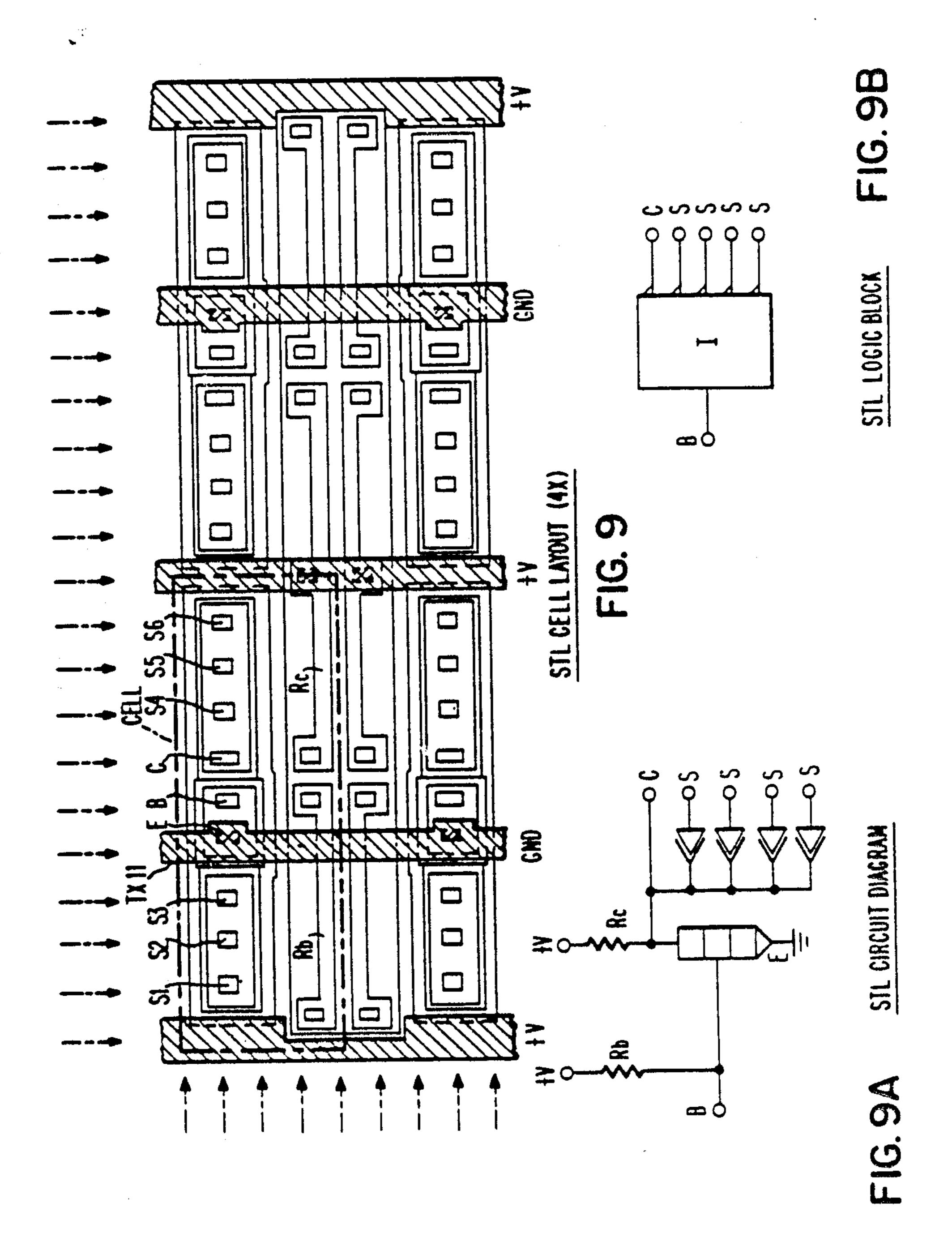

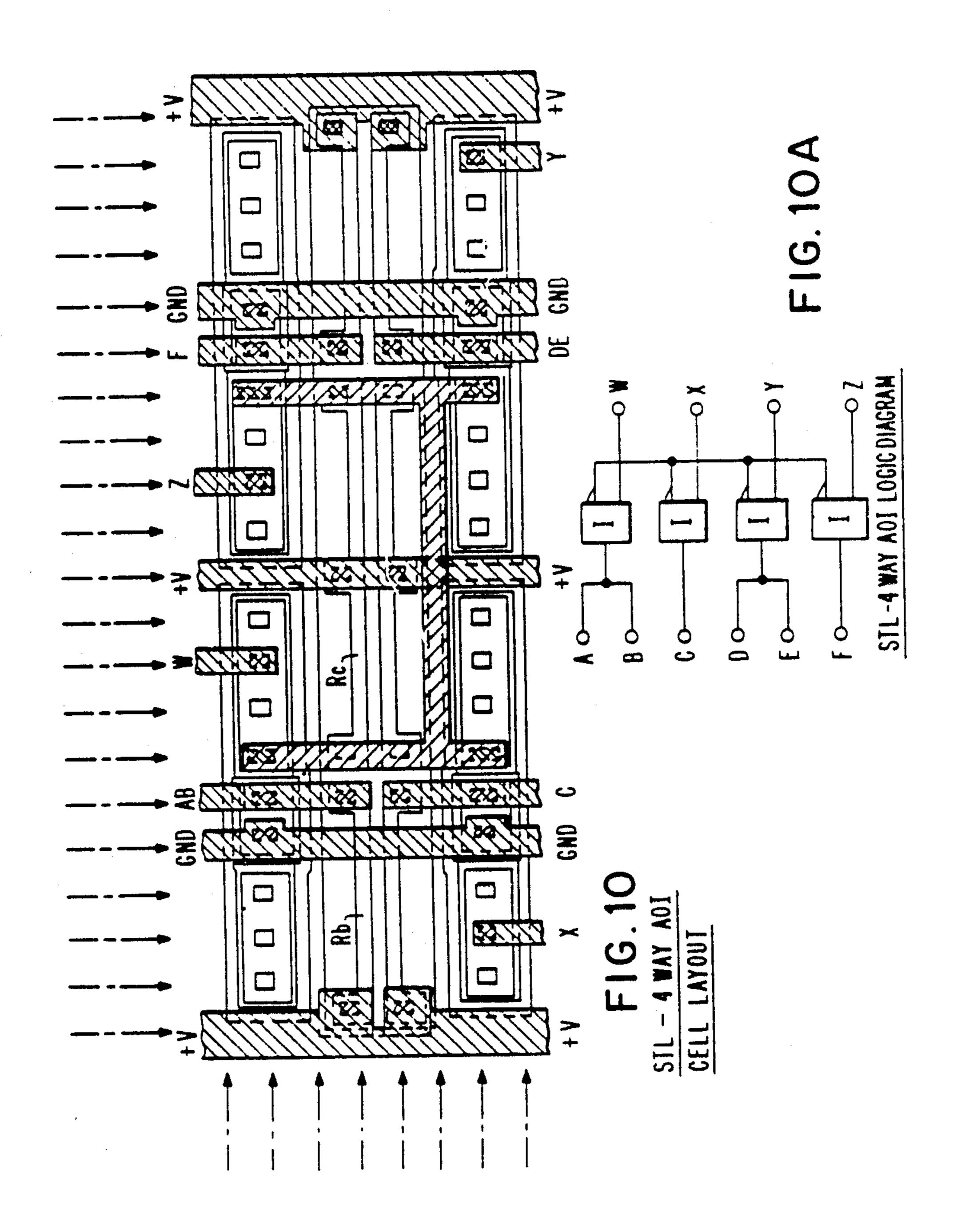

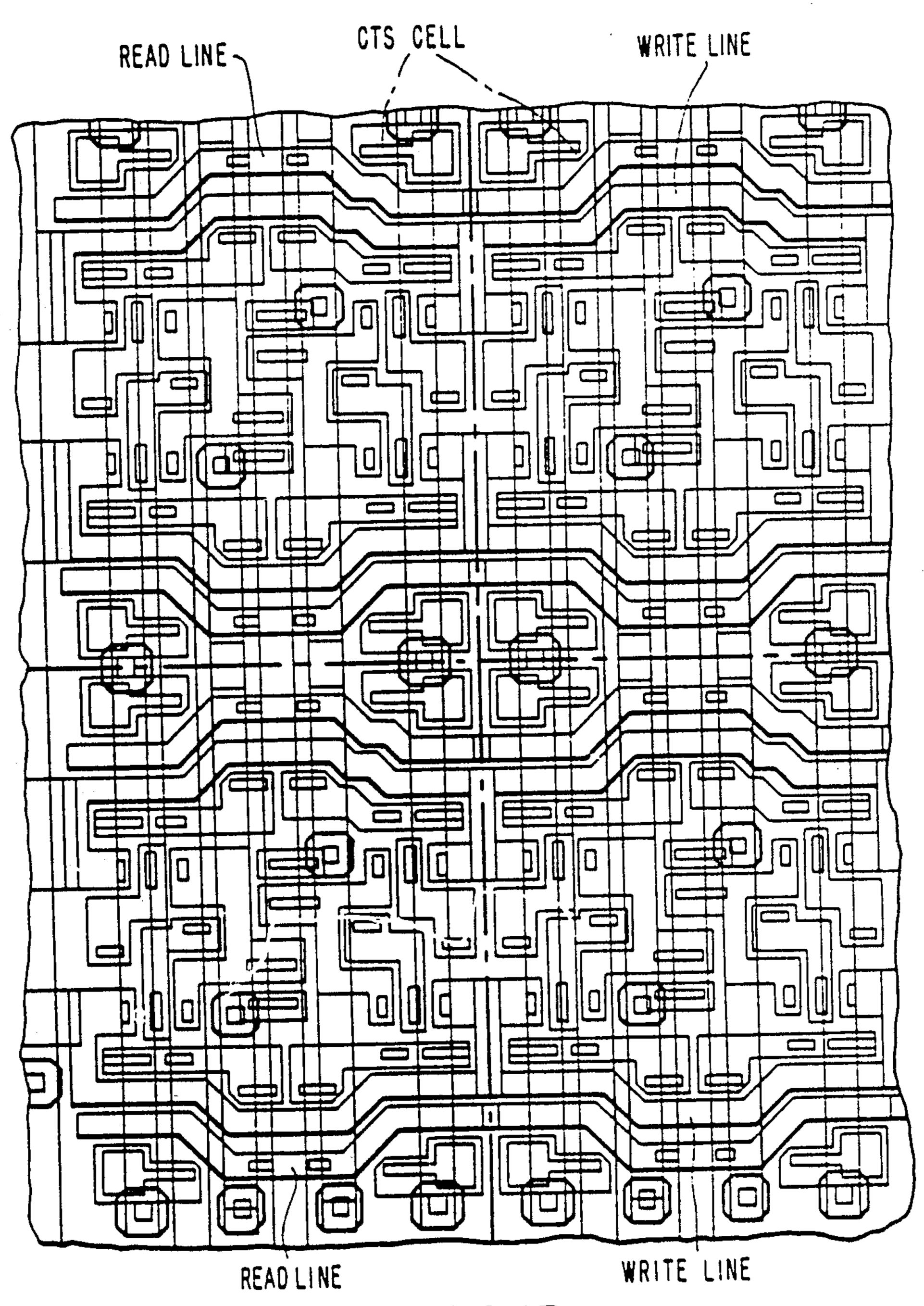

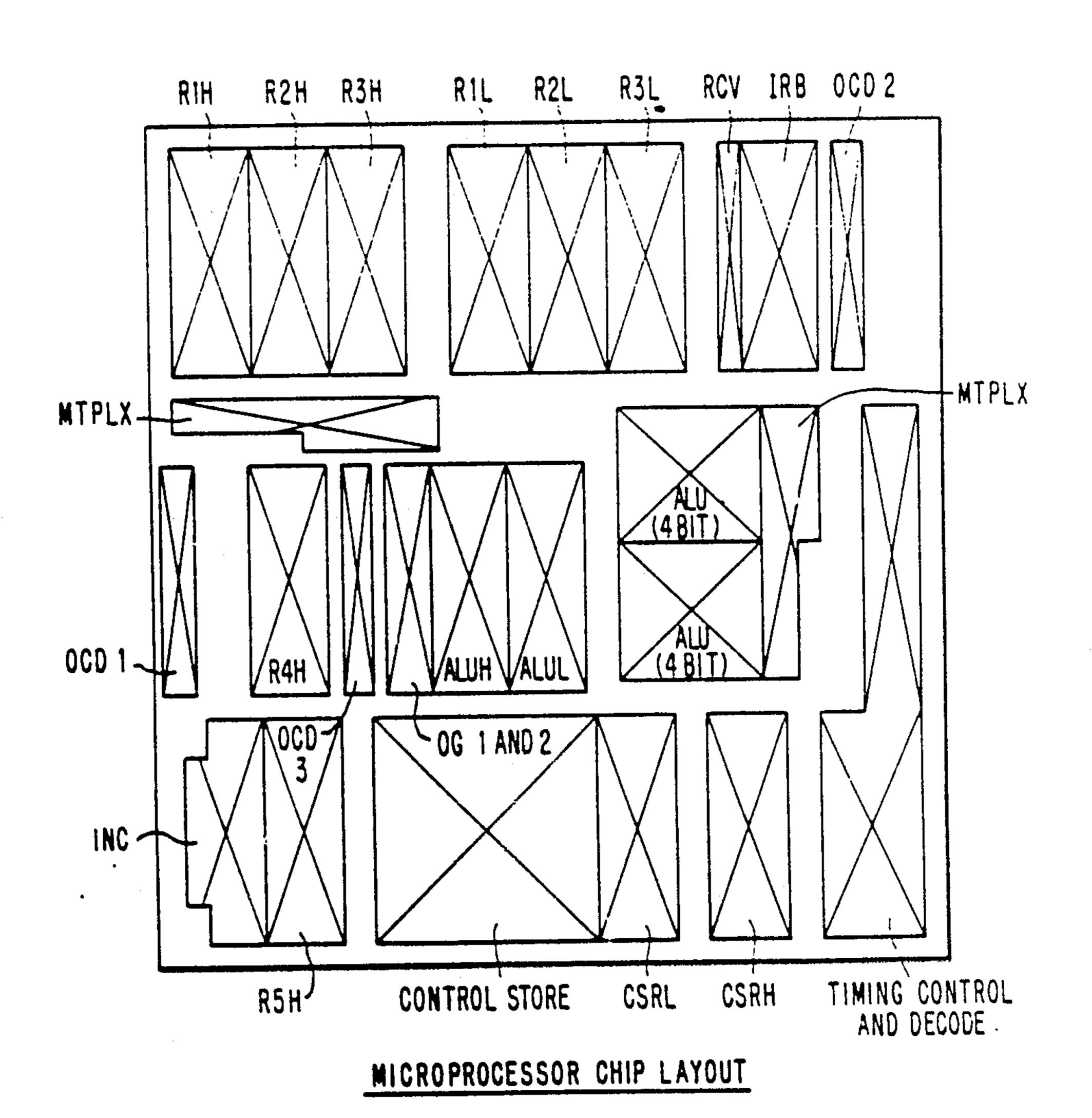

A method for forming an improved integrated circuit chip structure having a surface from which regions of different conductivity type are arranged in a plurality of electrically isolated macro circuits, each macro circuit including interconnected components, a first X pattern of equally spaced parallel conductors overlying and electrically insulated from said chip structure surface. said first X pattern of conductors being selectively connected to at least certain ones of said plurality of macro circuits, a second Y pattern of equally spaced parallel conductors overlying and electrically insulated from said first pattern of parallel conductors, said second Y pattern of conductors being selectively connected to at least selected certain ones of said first pattern of electrical conductors, said spacing one from another of said first X pattern of conductors being equal to said spacing one from another of said second Y pattern of conductors, said first pattern of conductors being orthogonal of said second pattern of conductors, and each of said connections occurring exclusively at points in space corresponding to X-Y intersections of an X-Y coordinate system, where said X-Y coordinate system geometrically corresponds identically to said X-Y pattern of conductors.

## 1 Claim, 15 Sheets Drawing, 82 Pages Specification

The file of this unexamined application may be inspected and copies thereof may be purchased (849 O.G. 1221, Apr. 9, 1968).

FIG. 1

FIG. 2

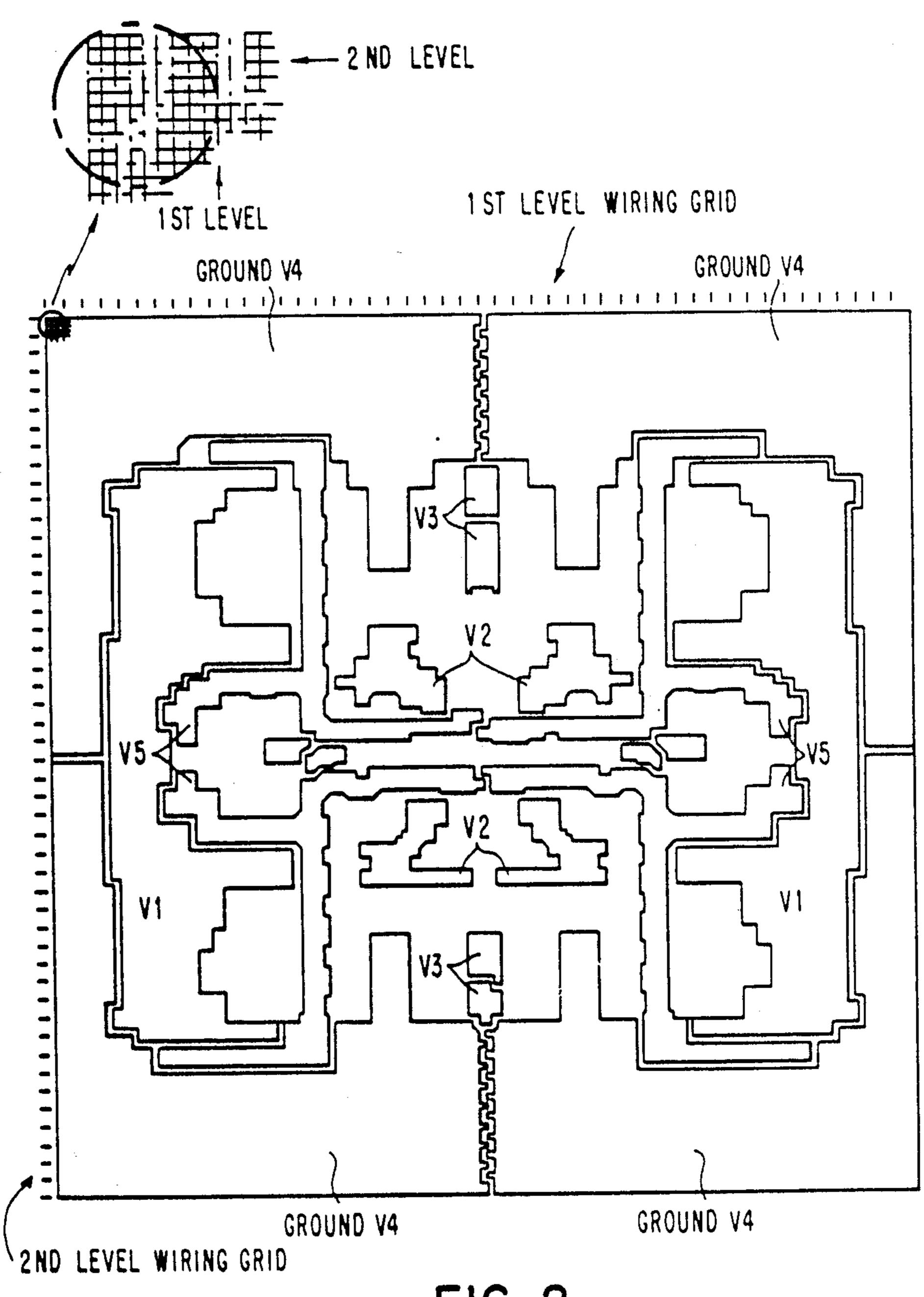

FIG. 3

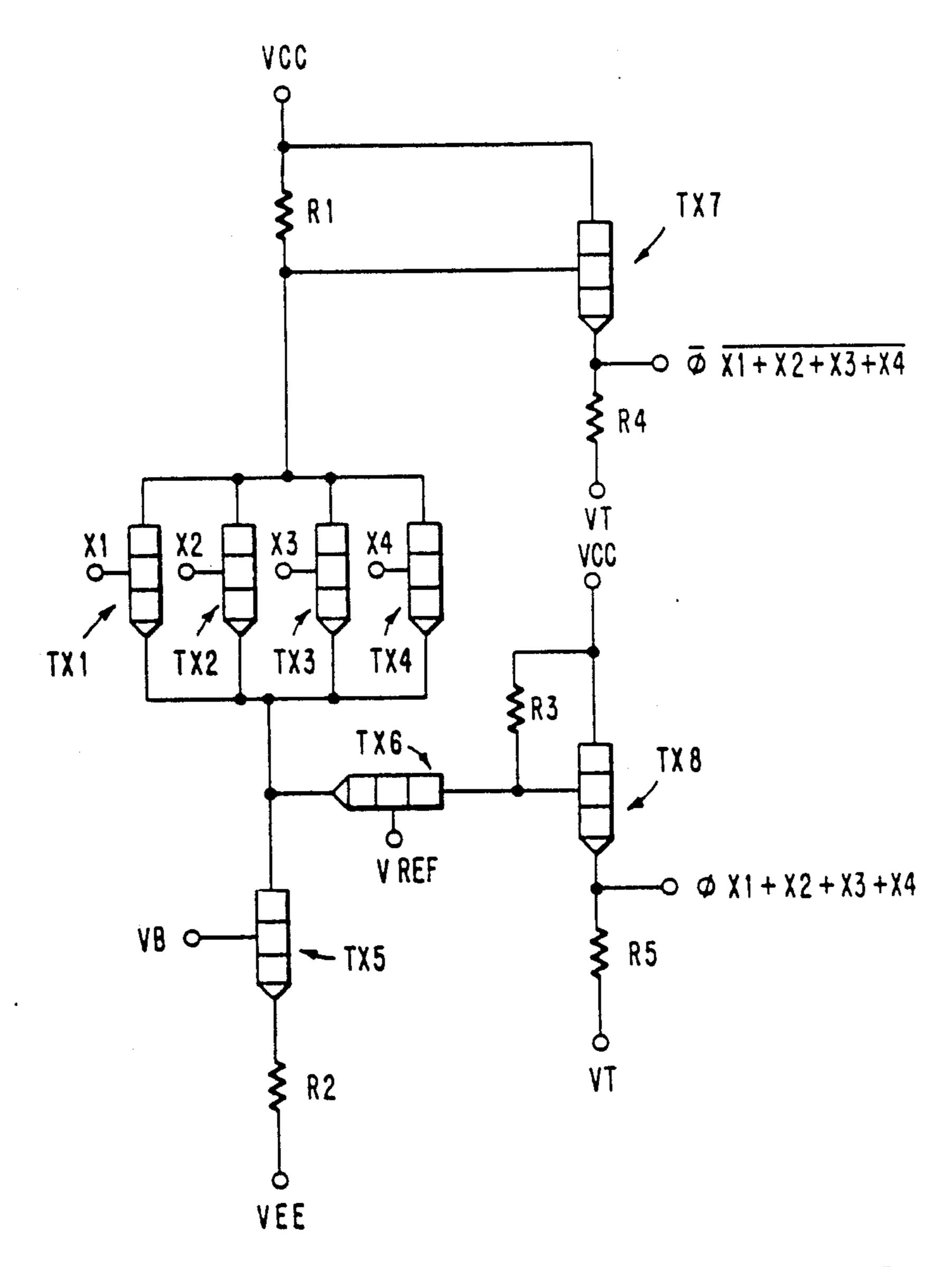

BASIC CURRENT SWITCH EMITTER FOLLOWING CIRCUIT WITH IN-PHASE

AND OUT OF-PHASE OUTPUTS

(4 INPUTS, 2 OUTPUTS)

FIG. 6

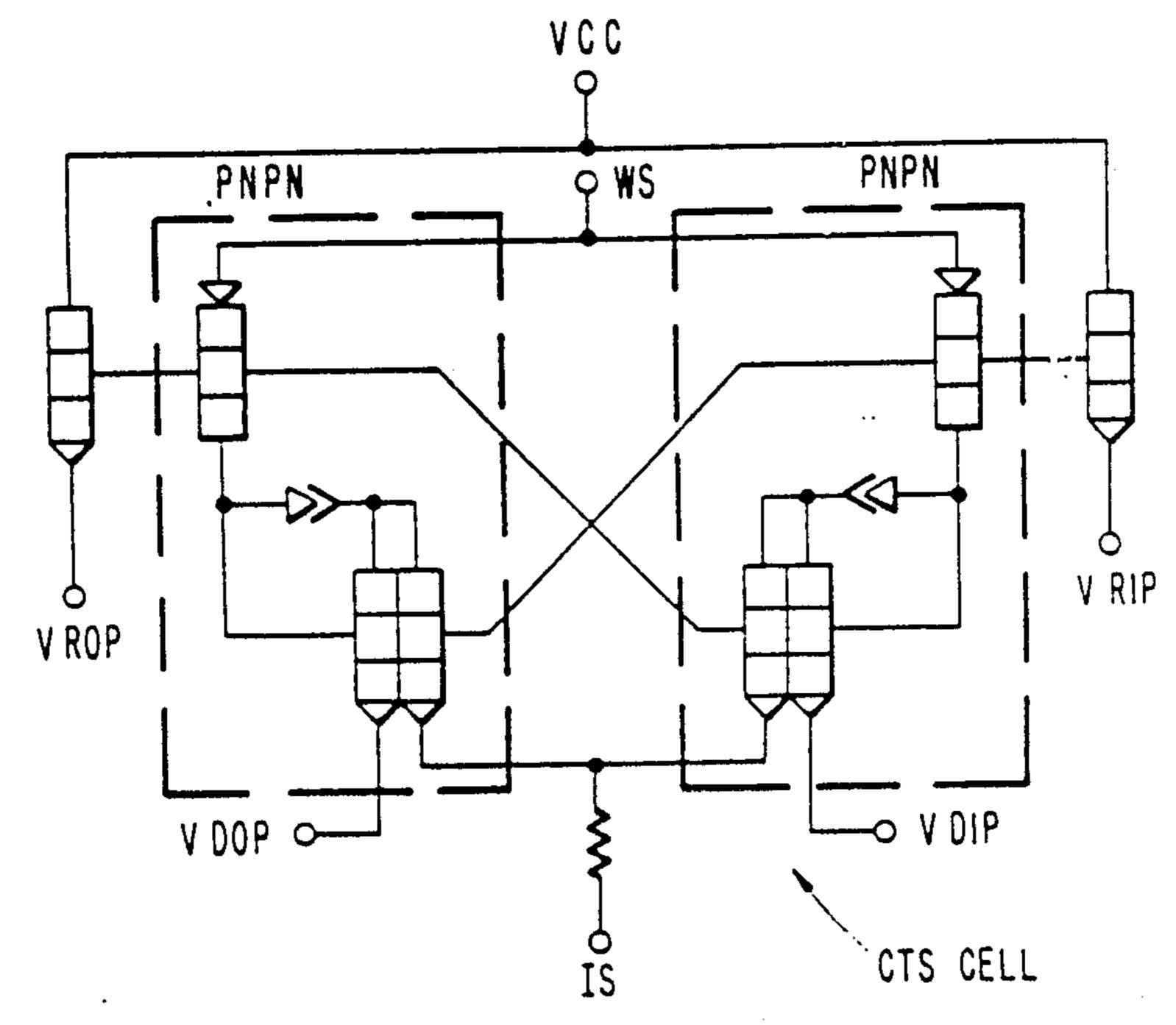

FIG. 11

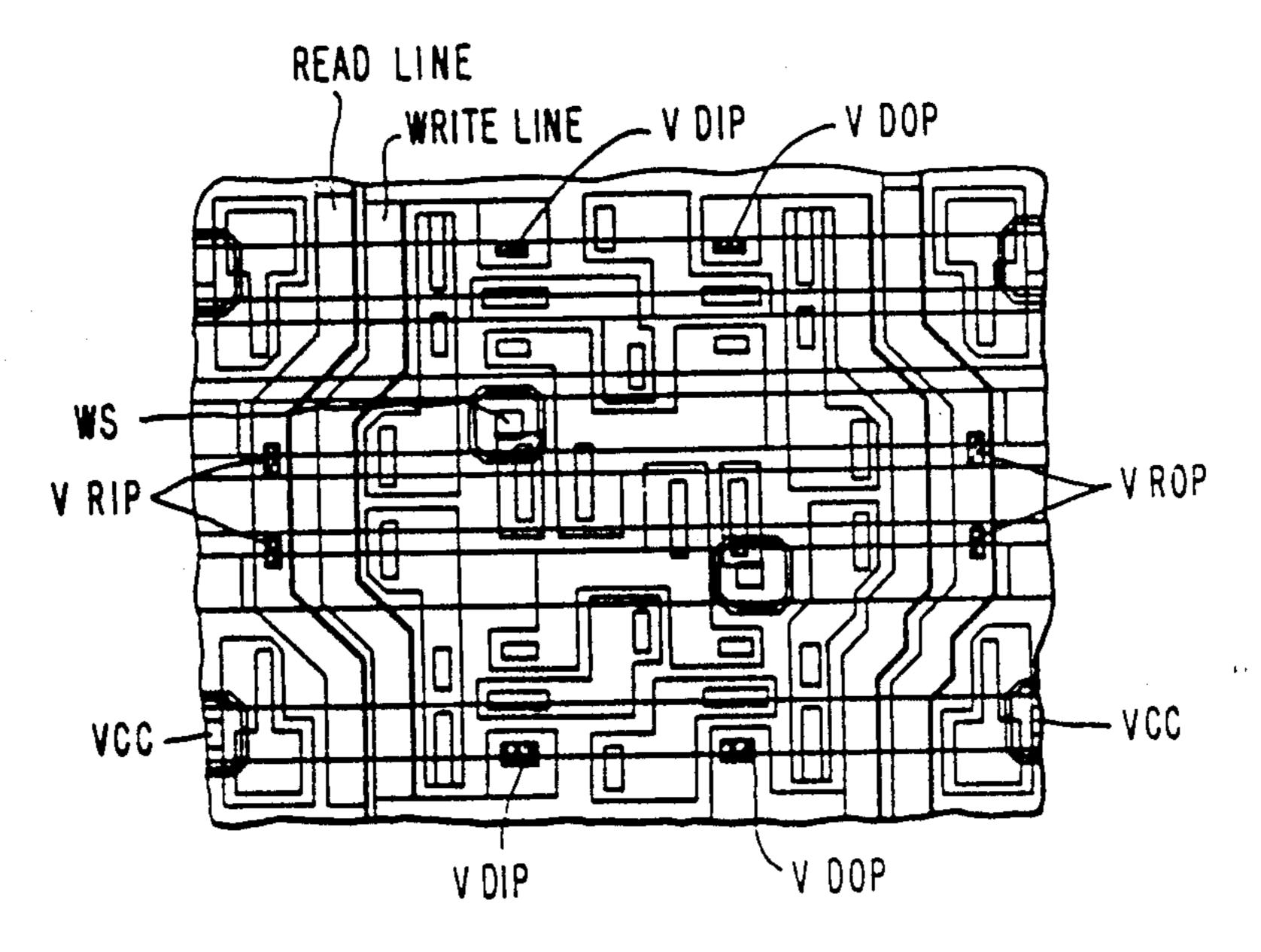

FIG. 12

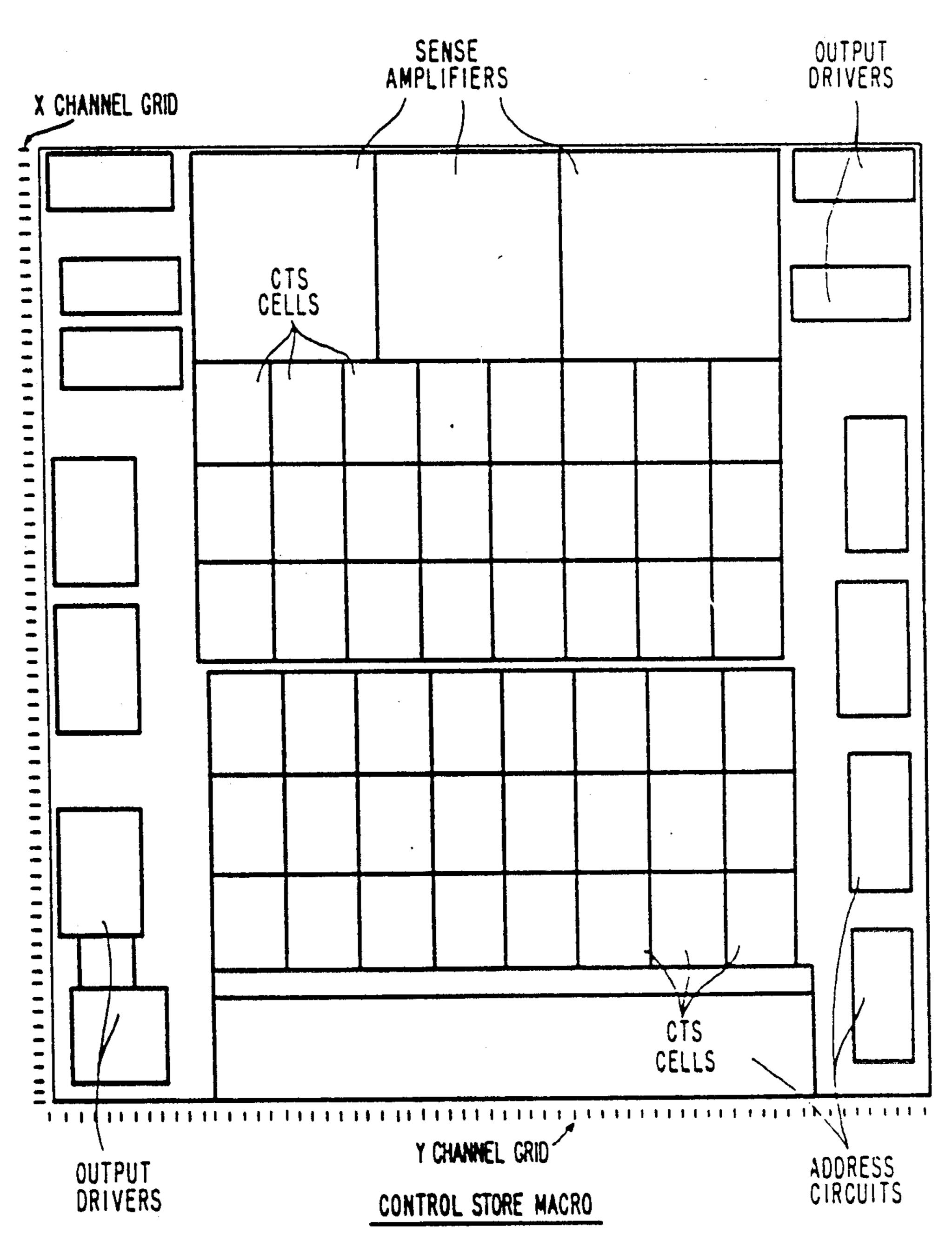

FIG. 13

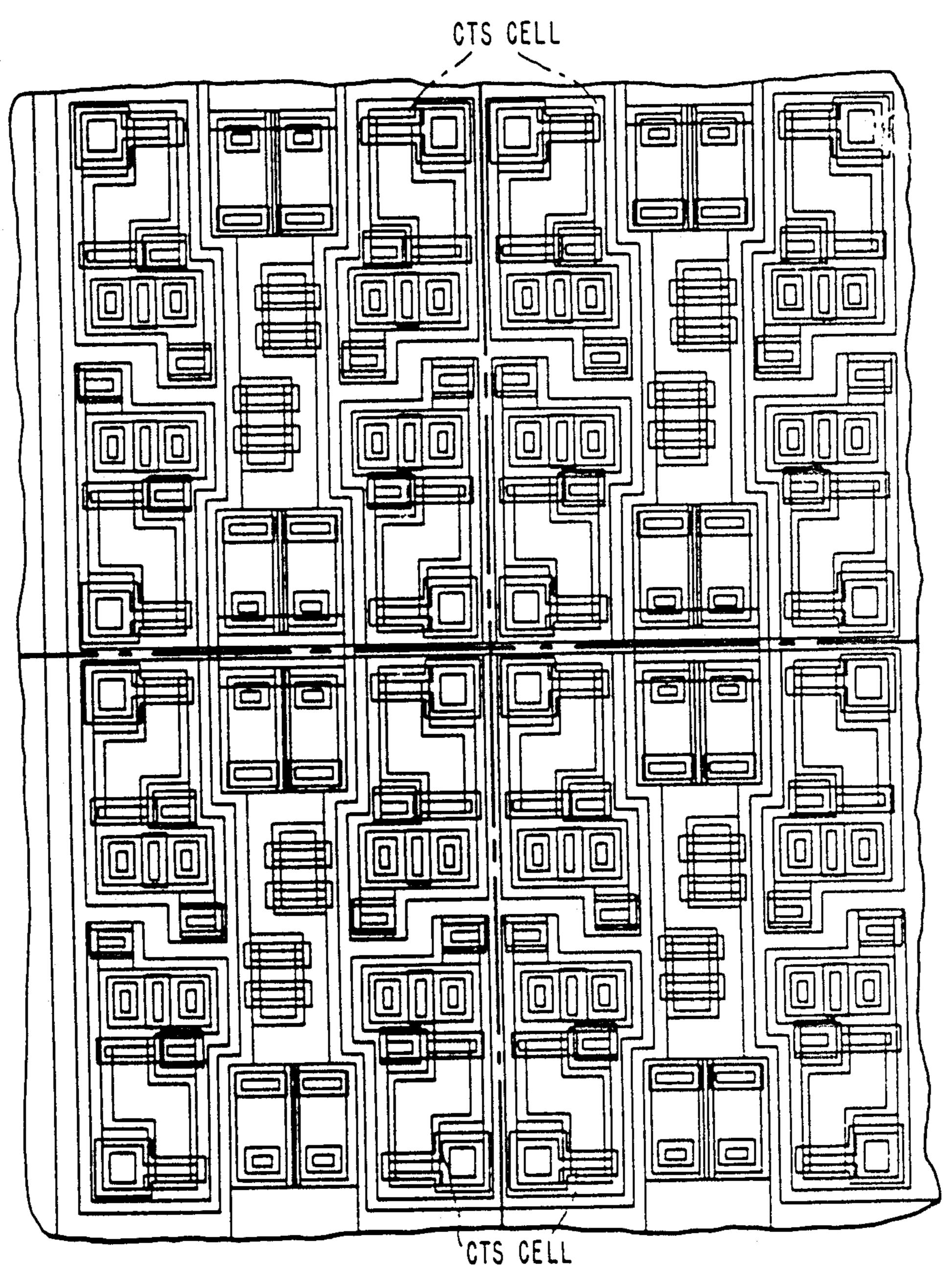

F1G.14

FIG.15

F1G.16