#### US00RE49912E

# (19) United States

## (12) Reissued Patent

## Kimura

## (10) Patent Number: US RE49,912 E

### (45) Date of Reissued Patent: \*Apr. 9, 2024

#### (54) **SEMICONDUCTOR DEVICE**

- (71) Applicant: ROHM CO., LTD., Kyoto (JP)

- (72) Inventor: Akihiro Kimura, Kyoto (JP)

- (73) Assignee: ROHM CO., LTD., Kyoto (JP)

- (\*) Notice: This patent is subject to a terminal dis-

claimer.

- (21) Appl. No.: 17/360,663

- (22) Filed: Jun. 28, 2021

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 10,679,927

Issued: Jun. 9, 2020

Appl. No.: 16/185,478

Filed: Nov. 9, 2018

U.S. Applications:

(63) Continuation of application No. 15/866,825, filed on Jan. 10, 2018, now Pat. No. 10,163,760, which is a (Continued)

#### (30) Foreign Application Priority Data

| Sep. 8, 2011 | (JP) 2011-195828 |

|--------------|------------------|

| Sep. 8, 2011 | (JP) 2011-195829 |

|              | (Continued)      |

(51) **Int. Cl.**

*H01L 23/495* (2006.01) *H01L 21/48* (2006.01)

(Continued)

(52) **U.S. Cl.**

CPC .... *H01L 23/49541* (2013.01); *H01L 21/4853* (2013.01); *H01L 21/4882* (2013.01); (Continued)

(58) Field of Classification Search

CPC ........... H01L 23/49541; H01L 21/4853; H01L 21/4882; H01L 23/293; H01L 23/3121; (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,041,902 A 8/1991 McShane 5,216,283 A 6/1993 Lin (Continued)

#### FOREIGN PATENT DOCUMENTS

JP 1997-153571 6/1997 JP 2002-083915 3/2002 (Continued)

#### OTHER PUBLICATIONS

Office Action, issued in the corresponding Japanese Patent application No. 2012-142779, dated Apr. 26, 2016, 4 pages.

(Continued)

Primary Examiner — Tuan H Nguyen (74) Attorney, Agent, or Firm — HAMRE, SCHUMANN, MUELLER & LARSON, P.C.

#### (57) ABSTRACT

A semiconductor device includes a plurality of die pad sections, a plurality of semiconductor chips, each of which is arranged in each of the die pad sections, a resin encapsulation portion having a recess portion for exposing at least a portion of the die pad sections, the resin encapsulation portion configured to cover the die pad sections and the semiconductor chips, and a heat radiation layer arranged in the recess portion. The heat radiation layer includes an elastic layer exposed toward a direction in which the recess portion is opened. The heat radiation layer directly faces at least a portion of the die pad sections. The elastic layer overlaps with at least a portion of the die pad sections when seen in a thickness direction of the heat radiation layer.

#### 65 Claims, 57 Drawing Sheets

#### Related U.S. Application Data

continuation of application No. 15/265,176, filed on Sep. 14, 2016, now Pat. No. 9,892,996, which is a continuation of application No. 14/549,920, filed on Nov. 21, 2014, now Pat. No. 9,484,336, which is a continuation of application No. 13/606,581, filed on Sep. 7, 2012, now Pat. No. 8,921,999.

#### (30) Foreign Application Priority Data

| Sep. 8, 2011  | (JP) | 2011-195830 |

|---------------|------|-------------|

| Jun. 26, 2012 | (JP) | 2012-142779 |

### (51) **Int. Cl.**

H01L 23/433

(2006.01)

H01L 21/56

(2006.01)

H01L 23/00

(2006.01)

H01L 23/29

(2006.01)

H01L 23/31

(2006.01)

H01L 23/373

(2006.01)

H01L 27/02

(2006.01)

#### (52) **U.S. Cl.**

#### (58) Field of Classification Search

CPC ...... H01L 23/3142; H01L 23/3157; H01L 23/373; H01L 21/561; H01L 21/565; H01L 23/3731; H01L 23/4334; H01L 23/49503; H01L 23/49555; H01L

23/49568; H01L 23/49575; H01L 23/49589; H01L 27/021; H01L 24/73; H01L 2224/32245; H01L 2224/48091; H01L 2224/48137; H01L 2224/48247 See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,440,169    | A             | 8/1995  | Tomita et al.      |

|--------------|---------------|---------|--------------------|

| 5,612,647    |               |         | Malec              |

| 5,814,878    |               |         | Hirakawa et al.    |

| 6,002,166    |               |         | Noda et al.        |

| 6,979,909    |               |         | Shinohara          |

| 2001/0048148 |               |         | Koyama et al.      |

| 2001/0048148 |               |         | Jeon et al.        |

|              |               |         |                    |

| 2003/0067065 | Al            | 4/2003  | Lee et al.         |

| 2003/0075783 | $\mathbf{A}1$ | 4/2003  | Yoshihara et al.   |

| 2005/0231925 | A1*           | 10/2005 | Fukuda H01L 21/565 |

|              |               |         | 257/E23.044        |

| 2005/0274982 | A1*           | 12/2005 | Ueda H01L 29/8611  |

|              |               | 12/200  | 257/E29.328        |

| 2000/0026055 |               | 0/0000  |                    |

| 2008/0036057 |               | _,      | Chou et al.        |

| 2008/0283978 | $\mathbf{A}1$ | 11/2008 | Aripin et al.      |

| 2009/0243061 | A1*           | 10/2009 | Yang H01L 25/162   |

|              |               |         | 257/E21.705        |

| 2012/0080297 | $\mathbf{A}1$ | 4/2012  | Takeuchi et al.    |

| 2012/0236503 | $\mathbf{A}1$ | 9/2012  | Asada et al.       |

| 2012/0236503 | Al            | 9/2012  | Asada et al.       |

#### FOREIGN PATENT DOCUMENTS

| JP | 2003-168769 | 6/2003  |

|----|-------------|---------|

| JP | 2007-311483 | 11/2007 |

| JP | 2008-101227 | 5/2008  |

| JP | 2009-105389 | 5/2009  |

| JP | 2009-302526 | 12/2009 |

| JP | 2010-272556 | 12/2010 |

## OTHER PUBLICATIONS

Japanese Office Action, issued in the corresponding Japanese patent application No. 2016-250437, dated Oct. 24, 2017, 23 pages.

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

x1(x) x2(x) y2(y)

FIG. 3

101

FIG. 5

FIG. 10

FIG. 11

A882

A882

FIG. 20

A7

A102

32

A7

FIG. 34

FIG. 39

FIG. 43

FIG. 44

FIG. 45

FIG. 47

FIG. 50

B991 **B**881

FIG. 54

B102 **B**812 B112 B111

FIG. 57

#### SEMICONDUCTOR DEVICE

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a Reissue Application of application Ser. No. 16/185,478, filed Nov. 9, 2018 (now U.S. Pat. No. 15) 10,679,927, issued Jun. 9, 2020), which is a Continuation of application Ser. No. 15/866,825, filed Jan. 10, 2018, (now U.S. Pat. No. 10,163,760, issued Dec. 25, 2018), which is a Continuation of application Ser. No. 15/265,176, filed Sep. 14, 2016 (now U.S. Pat. No. 9,892,996, issued Feb. 13, <sup>20</sup> 2018), which is a Continuation of application Ser. No. 14/549,920, filed Nov. 21, 2014 (now U.S. Pat. No. 9,484, 336, issued Nov. 1, 2016), which is a Continuation of application Ser. No. 13/606,581, filed Sep. 7, 2012 (now U.S. Pat. No. 8,921,999, issued Dec. 30, 2014), which is <sup>25</sup> based upon and claims the benefit of priority from Japanese Patent Application Nos. 2011-195828, 2011-195829 and 2011-195830, filed on Sep. 8, 2011 and 2012-142779, filed on Jun. 26, 2012, the entire contents of which are incorporated herein by reference.

#### TECHNICAL FIELD

The present disclosure relates to a semiconductor device, a semiconductor device manufacturing method, a semicon35 ductor device mounting structure and a power semiconductor device.

#### BACKGROUND

Various types of semiconductor devices are known. One of a semiconductor device is a device called an IPM (Intelligent Power Module). This semiconductor device includes a plurality of semiconductor chips, a plurality of die pad portions, a heat radiation plate, a joining layer and an 45 encapsulating resin. The semiconductor chips are respectively arranged in the die pad portions. The die pad portions are joined to the heat radiation plate through the joining layer. The encapsulating resin covers the semiconductor chips, the die pad portions, the heat radiation plate and the 50 joining layer. An IPM semiconductor device is known in the art.

Some semiconductor devices are mounted on a substrate (circuit substrate). When an IPM semiconductor device is mounted on a substrate, the heat radiation plate directly 55 faces a relatively large radiator existing outside the semiconductor device. In order to assure good heat transfer between the heat radiation plate and the radiator, heat radiating grease is often interposed between the heat radiation plate and the radiator. Therefore, each time the semiconductor device is mounted on the substrate, it is necessary to apply the heat radiating grease on the heat radiation plate or the radiator. This poses an impediment in efficiently mounting the semiconductor device.

It is costly to come by an adhesive agent that will become 65 the joining layer in the semiconductor device. In a manufacturing process of the semiconductor device, the die pad

2

portions and the heat radiation plate are joined together prior to forming a resin encapsulation portion. Forming the resin encapsulation portion and joining the die pad portions and the heat radiation plate together are performed independently of each other. This hampers manufacturing efficiency of the semiconductor device.

Different sorts of semiconductor devices are known in the art. As one example of the different semiconductor devices, a semiconductor device including a semiconductor chip, a die pad portion, an encapsulating resin and a heat sink is available. The semiconductor chip is arranged in the die pad portion. The heat sink is adhesively joined to the opposite surface of the die pad portion from the surface on which the semiconductor chip is arranged. The encapsulating resin covers the semiconductor chip, the die pad portion and the heat sink. The heat sink and the adhesive agent used in manufacturing the semiconductor device are relatively expensive. This makes it difficult to sufficiently reduce the manufacturing cost of the semiconductor device.

In a related art, an integrated circuit device (a semiconductor device) is configured to cover a lead frame with a resin having a high heat radiation property. In this related art, a heat sink is not joined to a die pad portion by an adhesive agent. This makes it possible to reduce the cost involved in providing a heat sink and an adhesive agent.

More specifically, the integrated circuit device disclosed in the related art includes a lead frame, a power element and a resin. The power element is mounted on the lead frame. The resin includes a low stress resin and a high heat 30 radiation resin. The low stress resin covers the power element and the lead frame. The high heat radiation resin covers the opposite surface of the lead frame from the surface on which the power element is arranged. In the integrated circuit device disclosed in the related art, an attempt is made to prevent exfoliation of the high heat radiation resin from the low stress resin. However, if the high-heat radiating resin and the lead frame are not strongly joined together, the high-heat radiating resin may be separated from the lead frame even though the high-heat radi-40 ating resin and the low stress resin are firmly bonded together.

## SUMMARY

The present disclosure provides some embodiments of a semiconductor device capable of being efficiently mounted on a substrate.

The present disclosure provides some embodiments of a semiconductor device manufacturing method capable of reducing manufacturing cost and assuring efficient manufacture of the semiconductor device.

The present disclosure provides some embodiments of a semiconductor device capable of suppressing exfoliation of a resin encapsulation portion and performing superior heat dissipation.

According to one aspect of the present disclosure, there is provided a semiconductor device, including a plurality of die pad sections, a plurality of semiconductor chips, a resin encapsulation portion, and a heat radiation layer. Each of semiconductor chips is arranged in each of the die pad sections. The resin encapsulation portion has a recess portion for exposing at least a portion of the die pad sections and is configured to cover the die pad sections and the semiconductor chips. The heat radiation layer is insulating and arranged in the recess portion. The heat radiation layer includes an elastic layer exposed toward a direction in which the recess portion is opened, and directly faces at least a

portion of the die pad sections. The elastic layer overlaps with at least a portion of the die pad sections when seen in a thickness direction of the heat radiation layer.

In one embodiment of the present disclosure, the resin encapsulation portion may include a resin bottom surface. 5 The recess portion may be depressed from the resin bottom surface. The heat radiation layer may have a section protruding beyond the resin bottom surface.

In some embodiments, the recess portion may have a recess bottom surface from which the die pad sections are 10 exposed, and the recess bottom surface may make direct contact with the heat radiation layer.

All the die pad sections may make direct contact with the heat radiation layer.

In some embodiments, the recess portion may have a recess side surface surrounding the heat radiation layer, and the recess side surface may be spaced apart from the heat radiation layer with a gap left therebetween.

In some embodiments, the recess portion may have a recess side surface surrounding the heat radiation layer, and the recess side surface may be spaced apart from the heat radiation layer with a gap left therebetween.

In some embodiments, the recess portion may have a recess side surface surrounding the heat radiation layer, and the recess side surface surrounding the heat radiation layer, and the recess side surface may be spaced apart from the heat radiation layer with a gap left therebetween.

In some embodiments, each of the die pad sections may have a die pad rear surface with which the heat radiation 20 layer makes direct contact, and the die pad rear surface may be an irregular surface.

In some embodiments, the recess bottom surface may make direct contact with the heat radiation layer, and the recess bottom surface may be an irregular surface.

In some embodiments, the heat radiation layer may overlap with all the die pad sections when seen in the thickness direction of the heat radiation layer.

In some embodiments, the heat radiation layer may be formed of only the elastic layer.

In some embodiments, the elastic layer may make contact with all the die pad sections.

In some embodiments, the Young's modulus of the elastic layer may be smaller than the Young's modulus of the resin encapsulation portion.

In some embodiments, the thickness of the heat radiation layer may be from 50  $\mu m$  to 500  $\mu m$ .

According to another aspect of the present disclosure, there is provided a semiconductor device manufacturing method. The semiconductor device manufacturing method 40 includes preparing a plurality of semiconductor chips and a lead frame having a plurality of die pad sections, arranging each of the semiconductor chips in each of the die pad sections, forming a resin encapsulation portion covering the die pad sections and the semiconductor chips, and forming 45 a heat radiation layer directly facing at least a portion of the die pad sections. Here, the heat radiation layer includes an elastic layer. A recess portion is formed when forming the resin encapsulation portion. The heat radiation layer is formed in the recess portion and the elastic layer is exposed 50 from the recess portion when forming the heat radiation layer.

In some embodiments, the resin encapsulation portion may have a resin bottom surface. The recess portion may be depressed from the resin bottom surface. The heat radiation 55 layer may protrude from the resin bottom surface when forming the heat radiation layer.

In some embodiments, the recess portion may have a recess side surface. The heat radiation layer may be spaced apart from the recess side surface with a gap left therebe- 60 tween when forming the heat radiation layer.

In some embodiments, the method may further include performing a blasting process to the die pad sections after forming the resin encapsulation portion and before forming the heat radiation layer.

In some embodiments, the recess portion may have a recess bottom surface from which the die pad sections are

4

exposed. The recess bottom surface may be subjected to the blasting process when performing the blasting process.

In some embodiments, the Young's modulus of the elastic layer may be smaller than the Young's modulus of the resin encapsulation portion.

In some embodiments, a heat radiation sheet may be embedded into the recess portion when forming the heat radiation layer.

According to still another aspect of the present disclosure, there is provided a semiconductor device mounting structure, including the semiconductor device provided by the above aspect of the present disclosure, a substrate to which the semiconductor device is mounted, and a heat radiator fixed to the substrate. In this configuration, the heat radiation member makes direct contact with the elastic layer.

According to yet another aspect of the present disclosure, there is provided a power semiconductor device, including a plurality of die pad sections, a plurality of power chips, and a LSI chip, a resin encapsulation portion, and a heat radiation layer. In this configuration, each of the power chips is arranged in each of the die pad sections and is provided with a heat generating portion. The LSI chip is configured to control the power chips. The resin encapsulation portion has a recess portion for exposing at least a portion of the die pad sections, and is configured to cover the die pad sections and the power chips. The heat radiation layer is insulating and is arranged in the recess portion. The heat radiation layer includes an elastic layer exposed toward a direction in which the recess portion is opened, and directly faces at least a 30 portion of the die pad sections. The elastic layer overlaps with at least a portion of the die pad sections when seen in a thickness direction of the heat radiation layer.

According to yet another aspect of the present disclosure, there is provided a semiconductor device manufacturing method includes preparing a semiconductor chip, a heat radiation plate and a lead frame having a die pad section, joining the semiconductor chip to the die pad section, setting the heat radiation plate to directly face the die pad section, and forming a resin encapsulation portion that covers the semiconductor chip, the heat radiation plate and the die pad section. Here, the heat radiation plate and the die pad section are joined by the resin encapsulation portion when forming the resin encapsulation portion.

In some embodiments, the die pad section may have a die pad major surface and a die pad rear surface. The semiconductor chip may be joined to the die pad major surface when joining the semiconductor chip. The heat radiation plate may be turned to directly face the die pad rear surface when setting the heat radiation plate to directly face the die pad section.

In some embodiments, the heat radiation plate may be exposed from the resin encapsulation portion when forming the resin encapsulation portion.

In some embodiments, the method may further include preparing a first mold and a second mold. Forming the resin encapsulation portion may include enclosing the heat radiation plate, the die pad section and the semiconductor chip with the first mold and the second mold, and after enclosing the heat radiation plate, injecting a resin material into a space surrounded by the first mold and the second mold. Here, the heat radiation plate and the die pad section may not be bonded to each other when the resin material is injected.

In some embodiments, the first mold may have a recess portion. Forming the resin encapsulation portion may include, before enclosing the heat radiation plate, arranging the heat radiation plate in the recess portion.

According to yet another aspect of the present disclosure, there is provided a semiconductor device, including a die pad section, a semiconductor chip joined to the die pad section, a heat radiation plate spaced apart from the die pad section, and a resin encapsulation portion configured to 5 cover at least semiconductor-chip-side regions of the die pad section, the semiconductor chip and the heat radiation plate. In this configuration, the resin encapsulation portion includes an intermediate section existing between the heat radiation plate and the die pad section, and the intermediate 10 section makes direct contact with the heat radiation plate and the die pad section.

According to yet another aspect of the present disclosure, there is provided a semiconductor device, including a die 15 chip configured to control the power chip. In this configupad section, a semiconductor chip joined to the die pad section, a heat radiation plate making direct contact with the die pad section, and an resin encapsulation portion configured to cover at least semiconductor-chip-side regions of the die pad section, the semiconductor chip and the heat radiation plate.

In some embodiments, the die pad section may have a die pad major surface and a die pad rear surface, and the semiconductor chip may be joined to the die pad major surface. The heat radiation plate may have a major surface 25 directly facing the die pad rear surface.

In some embodiments, the heat radiation plate may have a rear surface facing toward the direction opposite the major surface of the heat radiation plate. The rear surface of the heat radiation plate may be exposed from the resin encapsulation portion.

In some embodiments, the resin encapsulation portion may have a resin bottom surface facing toward the same direction as the facing direction of the rear surface of the heat radiation plate. The heat radiation plate may have a 35 section protruding in a direction facing the rear surface of the heat radiation plate beyond the resin bottom surface.

In some embodiments, the heat radiation plate may include a dropout prevention unit protruding from the rear surface of the heat radiation plate when seen in a thickness 40 direction of the die pad section. The dropout prevention unit may be positioned at the facing direction of the major surface of the heat radiation plate with respect to the resin encapsulation portion.

In some embodiments, the heat radiation plate may have 45 a side surface perpendicular to the rear surface of the heat radiation plate.

In some embodiments, the heat radiation plate may be made of an electrically conductive material.

In some embodiments, the electrically conductive mate- 50 of alumina, silicon dioxide or boron nitride. rial may be aluminum, copper, copper alloy or iron.

In some embodiments, the semiconductor device may further include a spacer existing between the die pad section and the heat radiation plate, the spacer made of an insulating material.

In some embodiments, the heat radiation plate may be made of an insulating material.

In some embodiments, the insulating material may be ceramic.

In some embodiments, the ceramic may be alumina, 60 aluminum nitride or silicon nitride.

In some embodiments, the heat radiation plate may include a concave-convex section or a groove formed in a peripheral portion of the major surface of the heat radiation plate.

In some embodiments, the semiconductor device may further include a joining layer existing between the semi-

conductor chip and the die pad section to join the semiconductor chip and the die pad section together.

According to still another aspect of the present disclosure, there is provided a semiconductor device mounting structure, including the semiconductor device provided by the above aspect of the present disclosure, a substrate to which the semiconductor device is mounted, and a heat radiation member which is fixed with respect to the substrate and configured to directly face the heat radiation plate.

According to yet another aspect of the present disclosure, there is provided an IPM semiconductor device. The IPM semiconductor includes the semiconductor chip as a power chip. The IPM semiconductor device further includes an LSI ration, the heat radiation plate is arranged at a rear surface side of the die pad section to which the power chip is mounted.

According to yet another aspect of the present disclosure, there is provided a semiconductor device, including an electrically conductive die pad section having a die pad major surface and a die pad rear surface, both of which face toward the opposite directions from each other, a semiconductor chip arranged in the die pad major surface, a first resin encapsulation portion covering the die pad major surface and the semiconductor chip, and a second resin encapsulation portion making direct contact with the first resin encapsulation portion. The second resin encapsulation portion has a resin bottom surface exposed toward a direction toward which the die pad rear surface faces. The resin bottom surface overlaps with the die pad section when seen in a thickness direction of the die pad section. The die pad rear surface has a concave-convex section with which the second resin encapsulation portion makes direct contact.

In some embodiments, the heat conductivity of a material making up the second resin encapsulation portion may be larger than the heat conductivity of a material making up the first resin encapsulation portion.

In some embodiments, the semiconductor device may further include a plurality of heat radiating fillers dispersed in the second resin encapsulation portion,

In some embodiments, the heat conductivity of a material making up the heat radiating fillers may be larger than the heat conductivity of a material making up the second resin encapsulation portion.

In some embodiments, the heat radiating fillers may be pulverized fillers.

In some embodiments, the pulverized fillers may be made

In some embodiments, the semiconductor device may further include a plurality of low-thermal-expansion fillers dispersed in the first resin encapsulation portion.

In some embodiments, the thermal expansion coefficient 55 of a material making up the low-thermal-expansion fillers may be smaller than the thermal expansion coefficient of a material making up the first resin encapsulation portion.

In some embodiments, the low-thermal-expansion fillers may be spherical fillers.

In some embodiments, the spherical fillers may be made of silicon dioxide.

In some embodiments, the first resin encapsulation portion may have a first resin surface with which the second resin encapsulation portion makes direct contact. The first 65 resin surface may have a concave-convex section.

In some embodiments, the first resin surface may be flush with the die pad rear surface.

In some embodiments, the first resin surface may be positioned between the die pad rear surface and the die pad major surface in the thickness direction of the die pad section.

In some embodiments, the first resin encapsulation portion may include a protrusion section extending into the second resin encapsulation portion.

In some embodiments, the second resin encapsulation portion may overlap with the entire die pad section when seen in the thickness direction of the die pad section.

In some embodiments, the first resin encapsulation portion may have a resin major surface facing the same direction as the die pad major surface faces. The resin major surface may overlap with the die pad section when seen in the thickness direction of the die pad section.

In some embodiments, the first resin encapsulation portion may have a resin side surface surrounding the semiconductor chip. The resin side surface may be inclined with respect to the resin major surface so as to form an obtuse angle with the resin major surface.

In some embodiments, the resin bottom surface may be  $100 \, \mu m$  to  $250 \, \mu m$  spaced apart from the die pad rear surface.

In some embodiments, the heat conductivity of the second resin encapsulation portion may be from 2 W/mK to 5 W/mK.

In some embodiments, the second resin encapsulation portion may have a resin wall surface shaped to surround the die pad section when seen in the thickness direction of the die pad section. The resin wall surface may be inclined with respect to the resin bottom surface so as to form an obtuse 30 angle with the resin bottom surface.

According to yet another aspect of the present disclosure, there is provided a semiconductor device mounting structure, including the semiconductor device provided by the above aspect of the present disclosure, a substrate to which 35 the semiconductor device is mounted, and a heat radiator directly facing the resin bottom surface.

According to yet another aspect of the present disclosure, there is provided a semiconductor device manufacturing method. The semiconductor device manufacturing method 40 includes preparing a semiconductor chip and a die pad section having a die pad major surface and a die pad rear surface, arranging the semiconductor chip in the die pad major surface, forming a first resin encapsulation portion covering the die pad major surface and the semiconductor 45 chip, forming a concave-convex section on the die pad rear surface, and forming a second resin encapsulation portion covering the concave-convex section of the die pad rear surface.

In some embodiments, the die pad rear surface may be 50 FIG. 12. subjected to a blasting process when forming the concave-convex section.

In some embodiments, forming the concave-convex section may be performed after forming the first resin encapsulation portion. Forming the second resin encapsulation 55 portion may be performed after forming the concave-convex section.

In some embodiments, the method may further include performing the blasting process to the first resin encapsulation portion at the same time when the die pad rear surface 60 is subjected to a blasting process.

According to yet another aspect of the present disclosure, there is provided a power semiconductor device, including a power chip having a heat generating portion, an LSI chip configured to control the power chip, the power chip and the 65 LSI chip encapsulated by a resin, a first resin encapsulation portion covering the power chip and the LSI chip, and a

8

second resin encapsulation portion making direct contact with the first resin encapsulation portion. The first resin encapsulation portion and the second resin encapsulation portion are provided with contact surfaces having concave-convex sections rougher than surfaces exposed to the outside.

Other features and advantages of the present disclosure will become more apparent from the following detailed description given in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

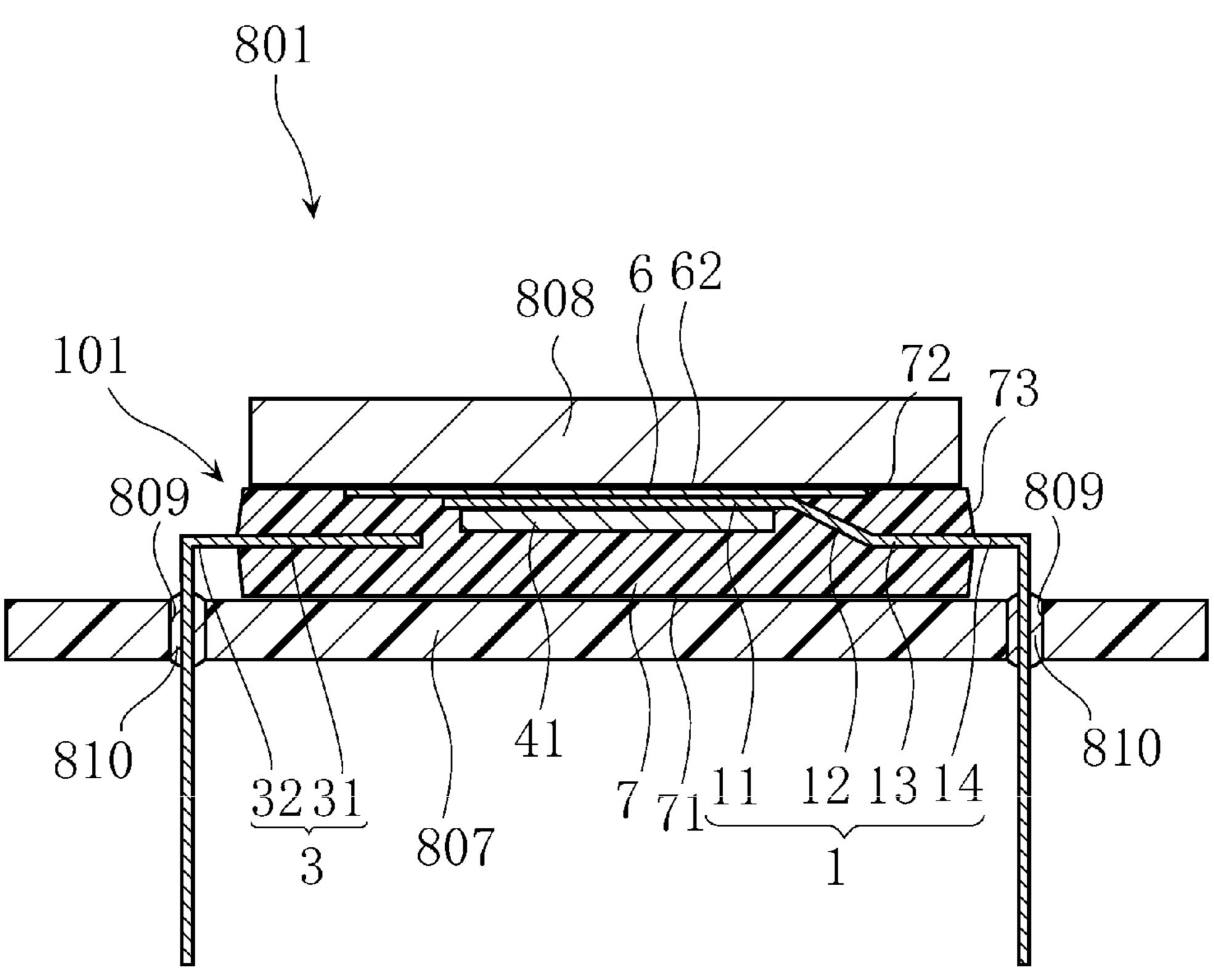

FIG. 1 is a section view illustrating a mounting structure of a semiconductor device according to a first embodiment of the present disclosure.

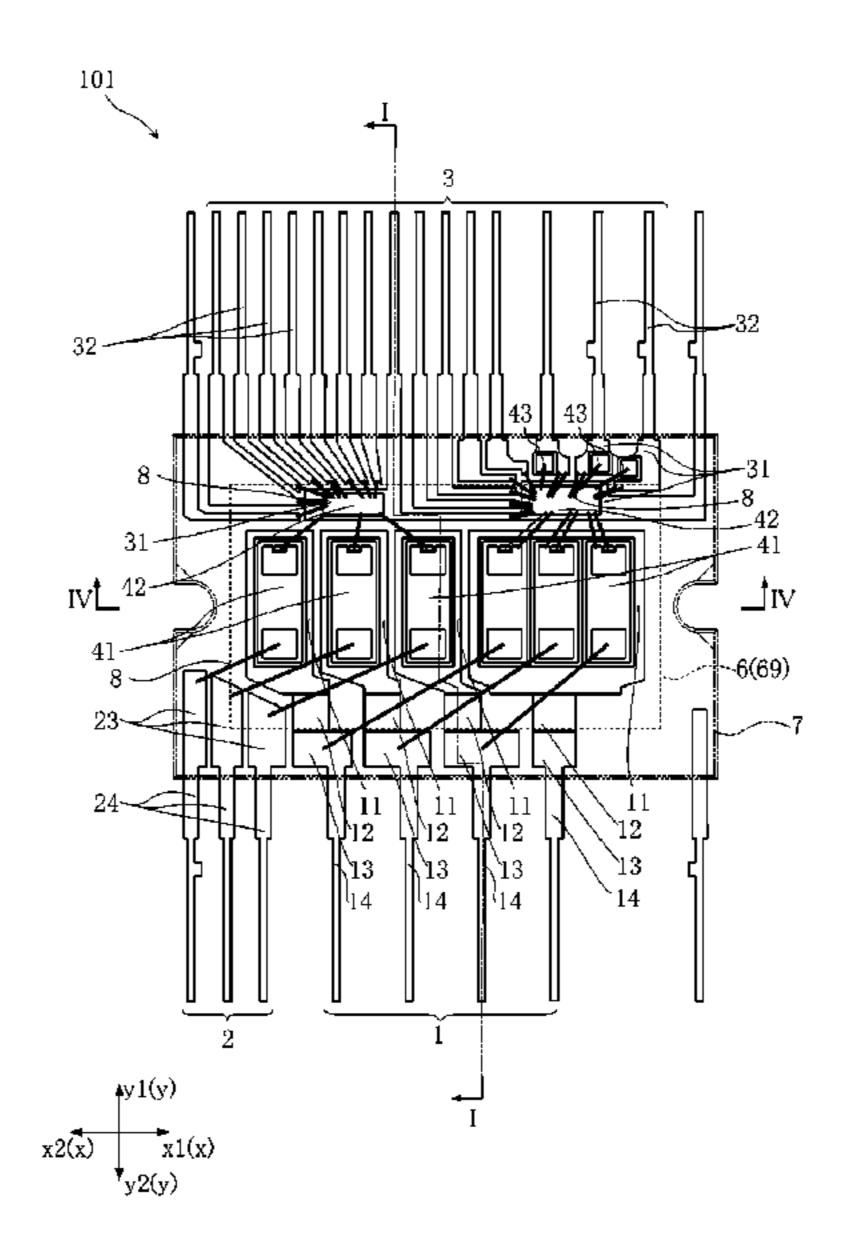

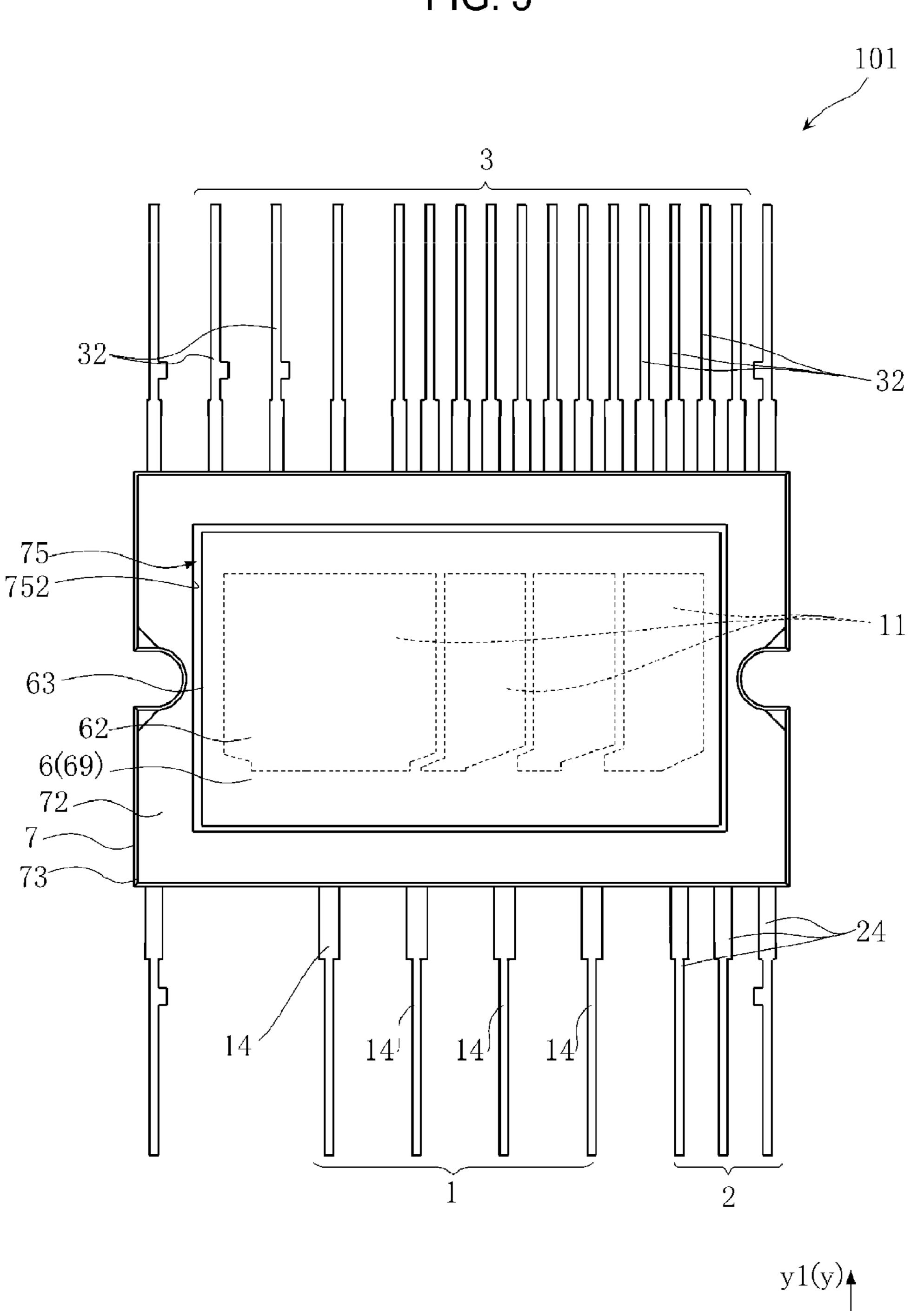

FIG. 2 is a (partially cut away) plan view of the semiconductor device according to the first embodiment of the present disclosure prior to bending the leads.

FIG. 3 is a bottom view of the semiconductor device according to the first embodiment of the present disclosure prior to bending the leads.

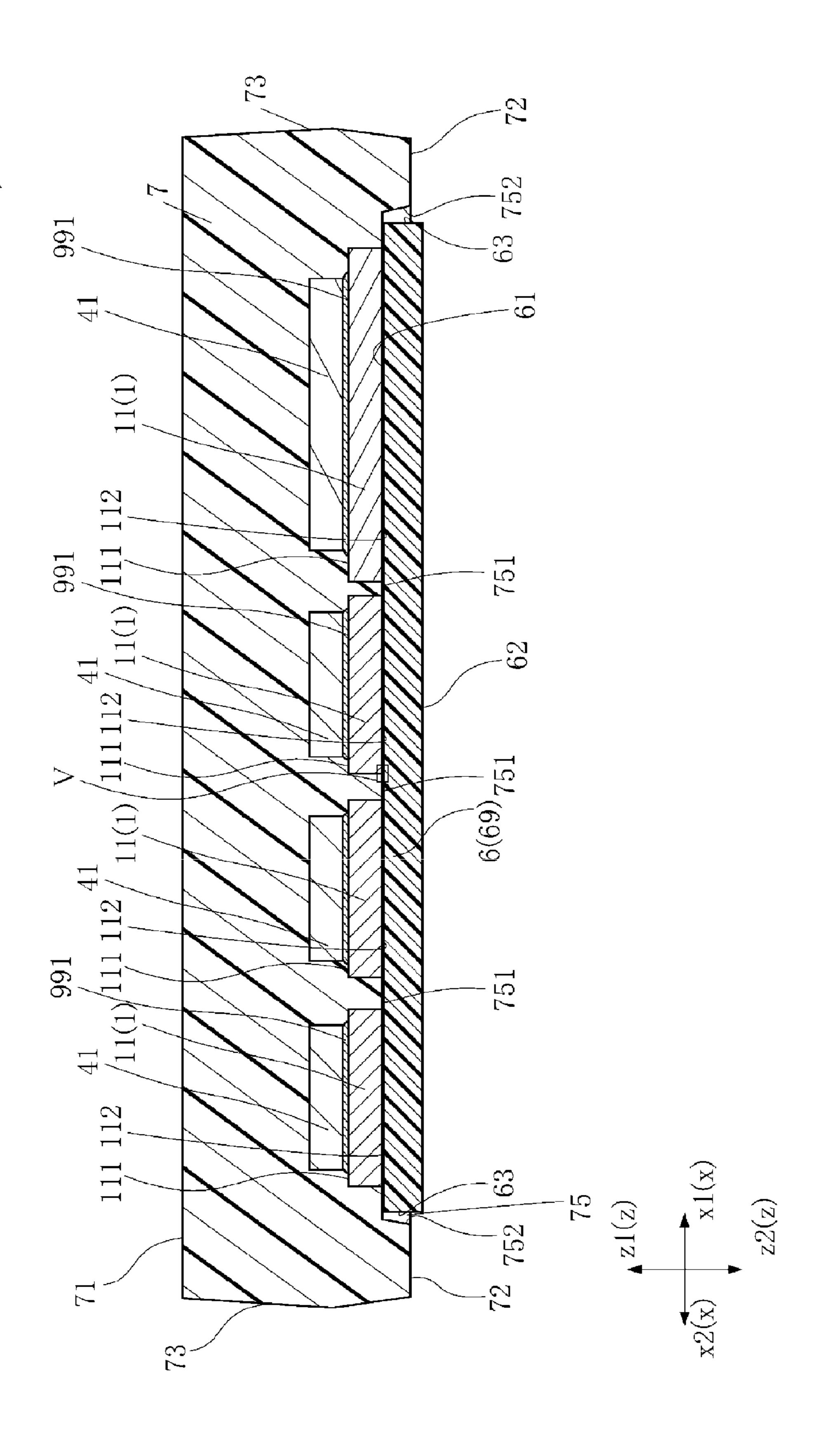

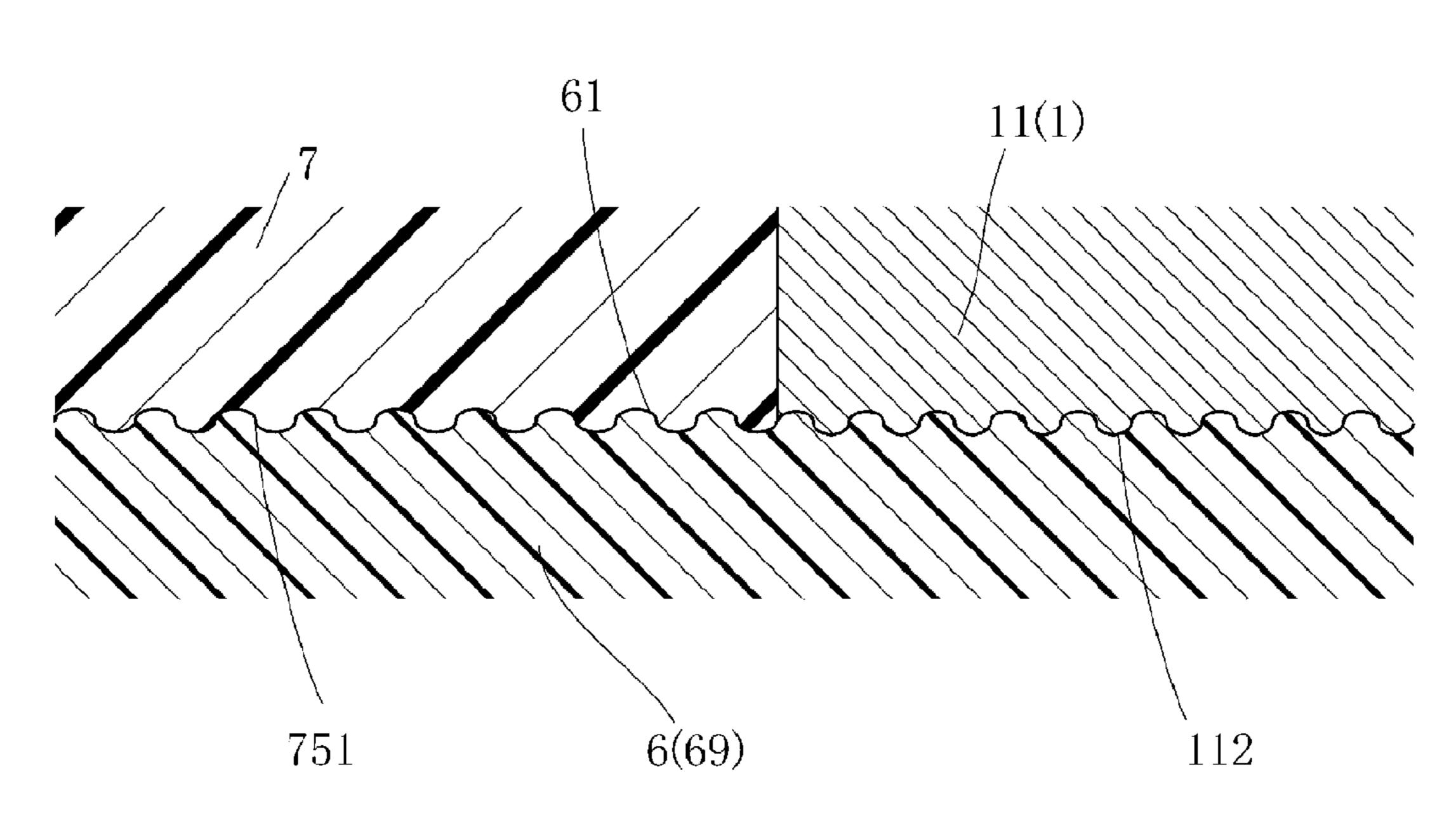

FIG. 4 is a section view taken along line IV-IV in FIG. 2. FIG. 5 is a partially enlarged view of the region V in FIG.

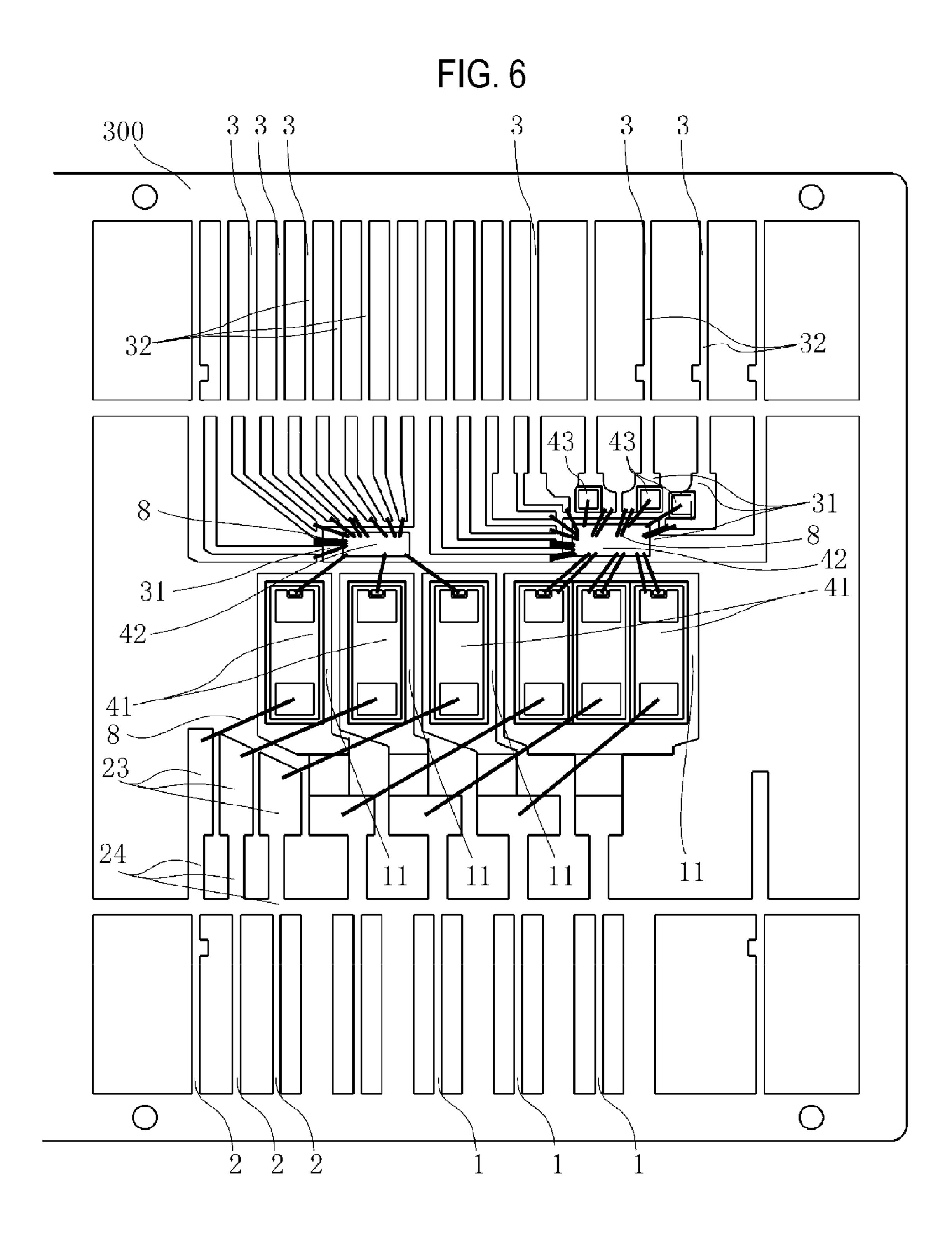

FIG. 6 is a plan view illustrating one process of a manufacturing method of the semiconductor device according to the first embodiment of the present disclosure.

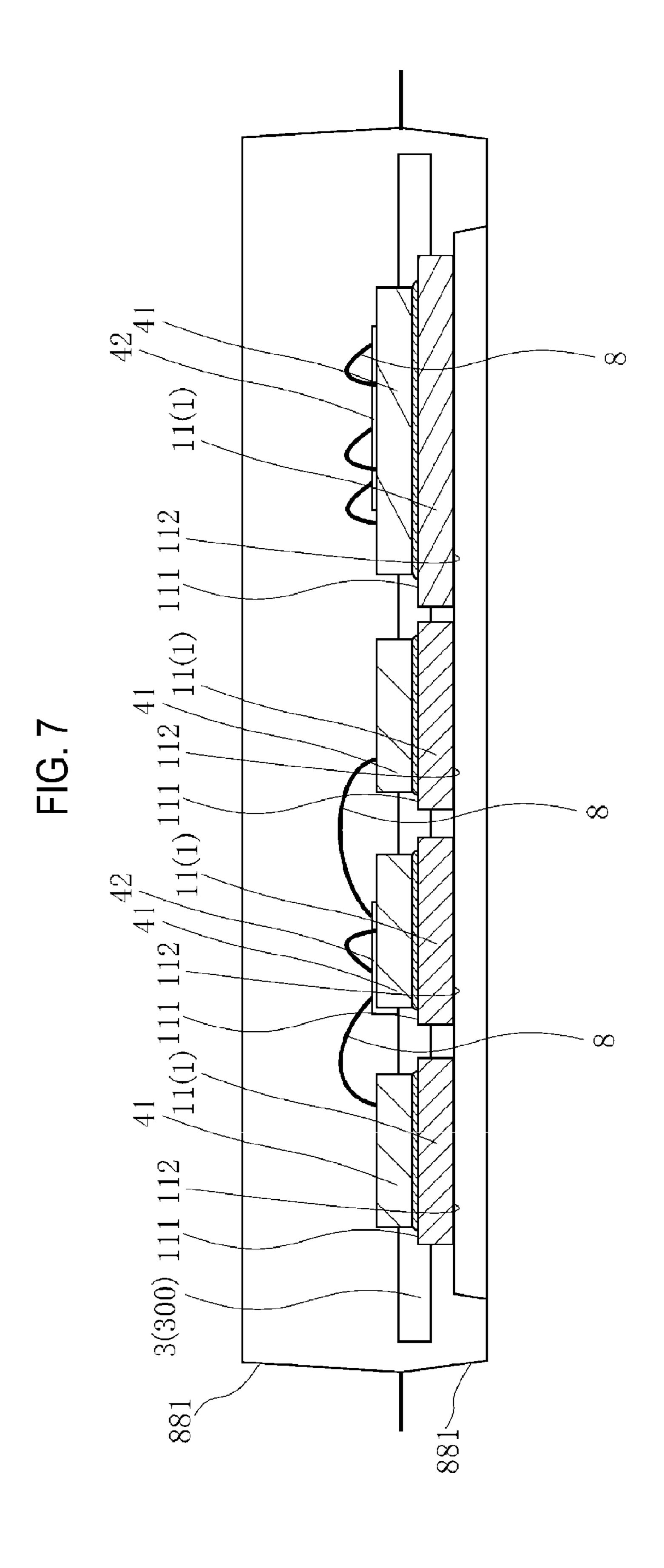

FIG. 7 is a section view illustrating a process subsequent to the process shown in FIG. 6.

FIG. 8 is a section view illustrating a process subsequent to the process shown in FIG. 7.

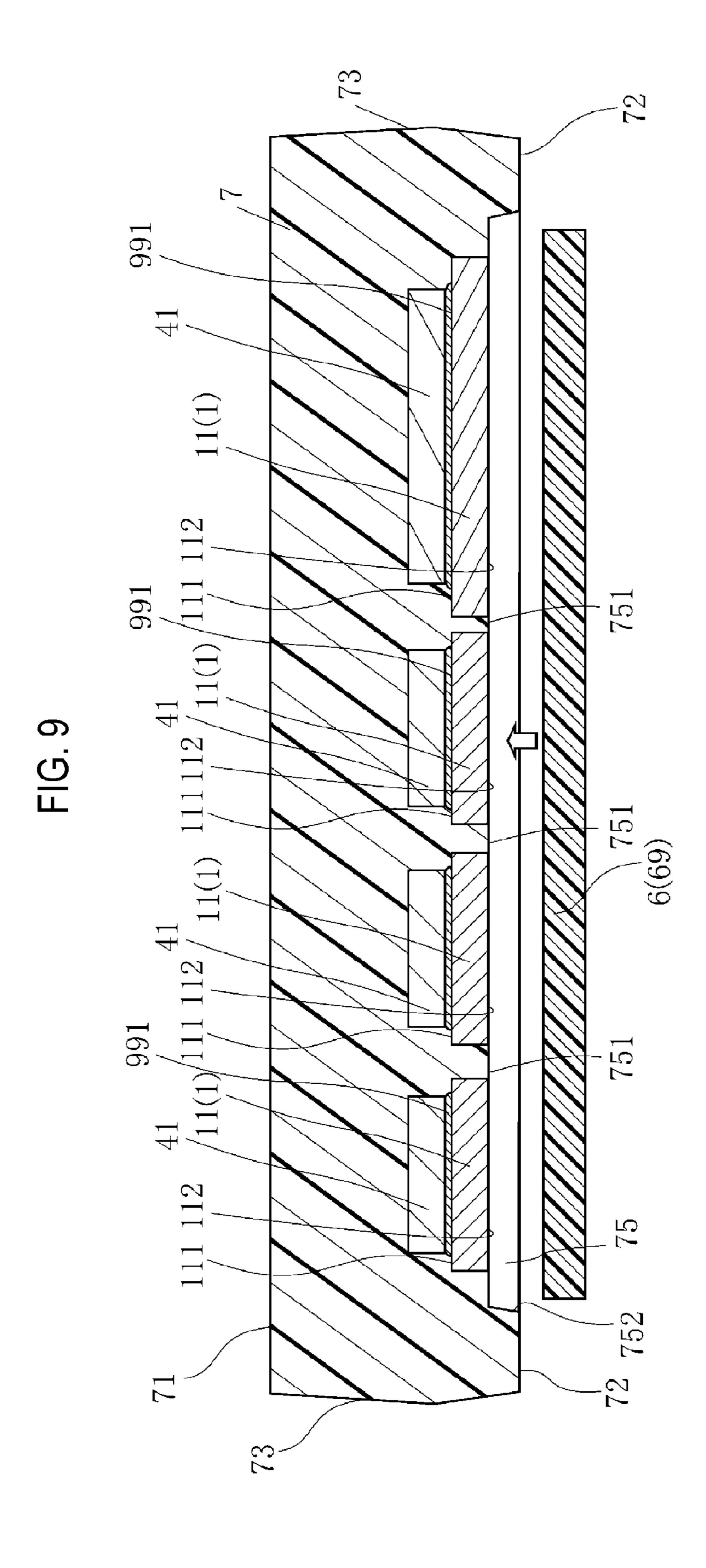

FIG. 9 is a section view illustrating a process subsequent to the process shown in FIG. 8.

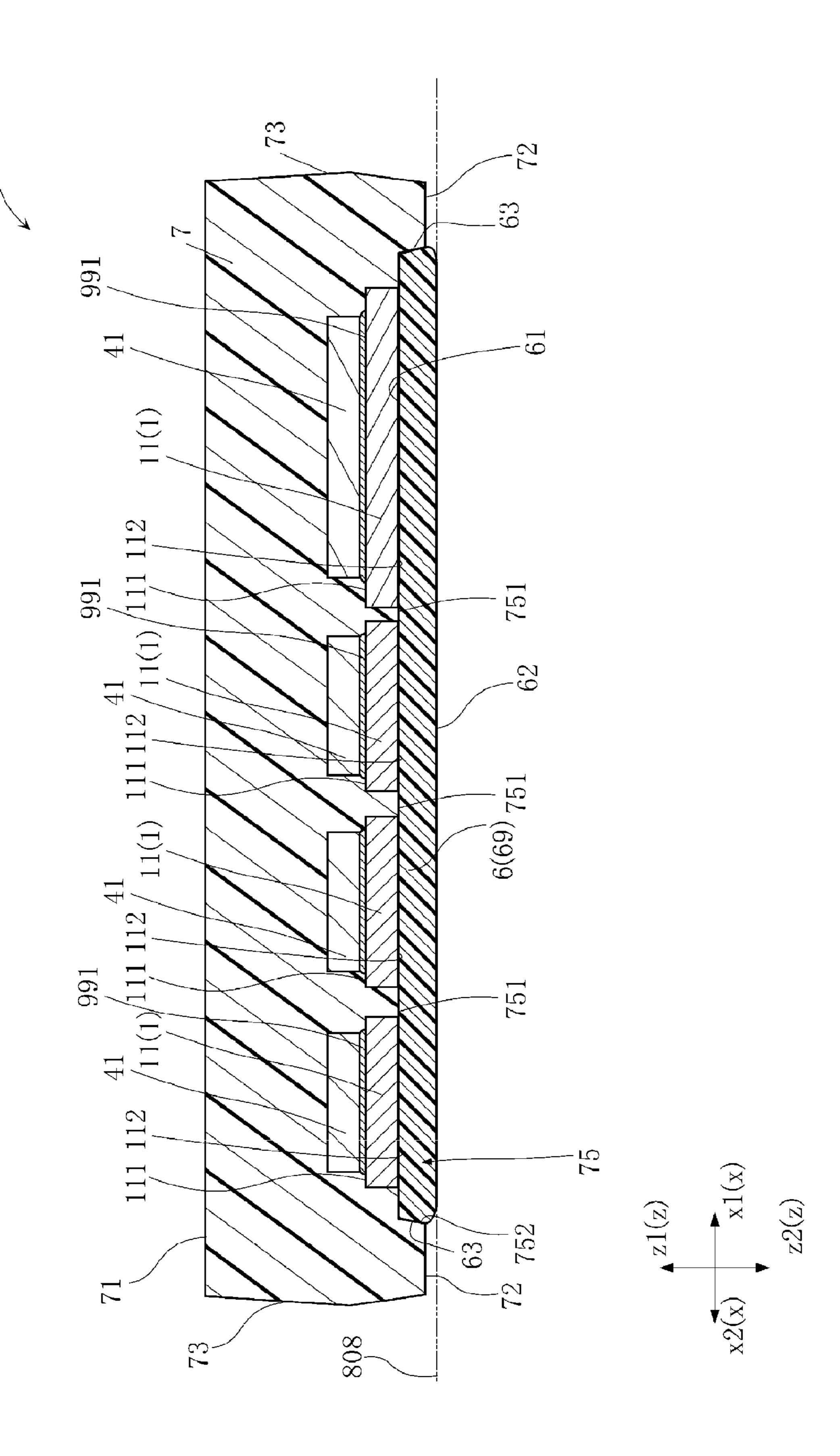

FIG. 10 is a section view of the mounting structure of the semiconductor device according to the first embodiment of the present disclosure.

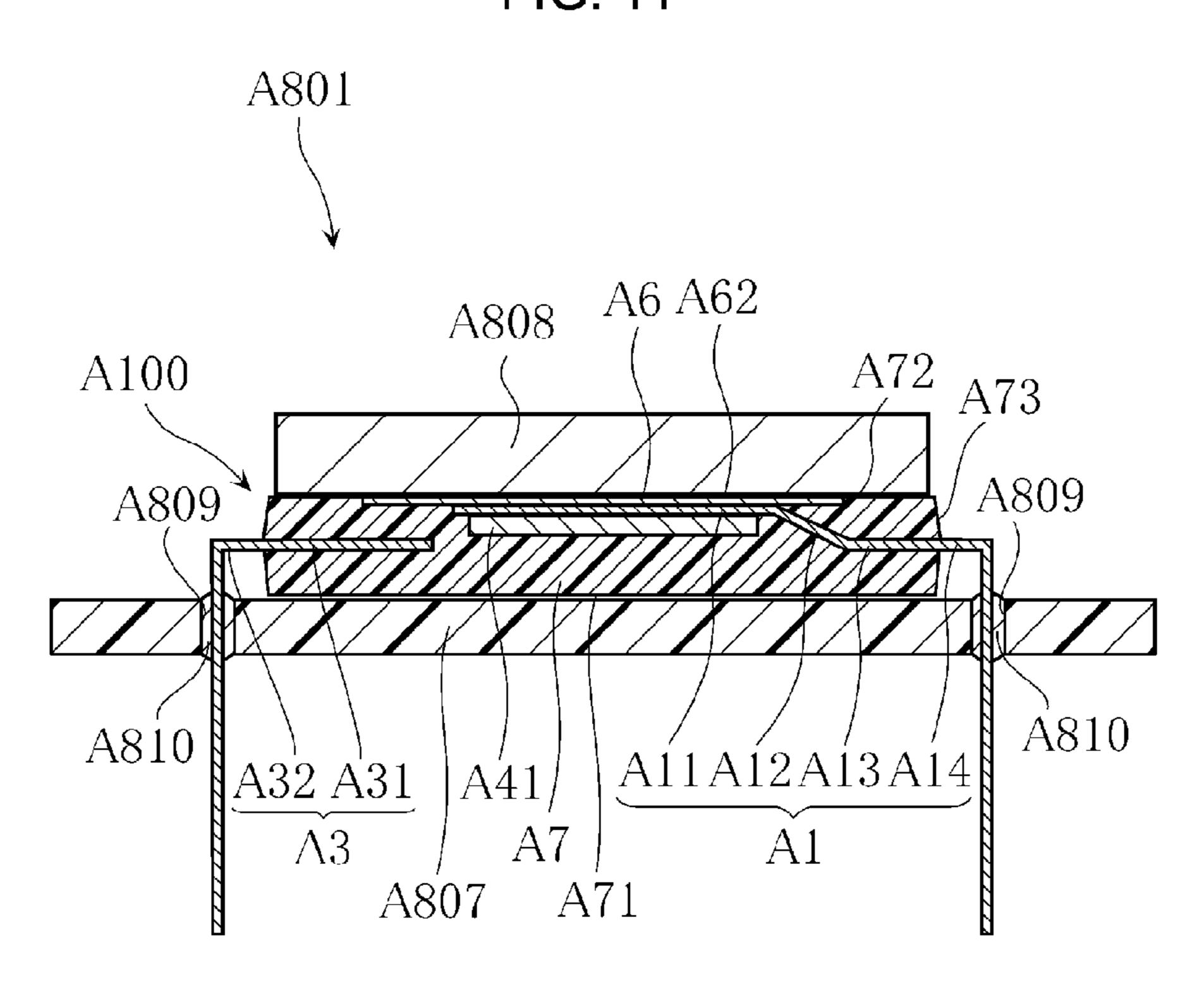

FIG. 11 is a section view illustrating a mounting structure of a semiconductor device according to a second embodiment of the present disclosure.

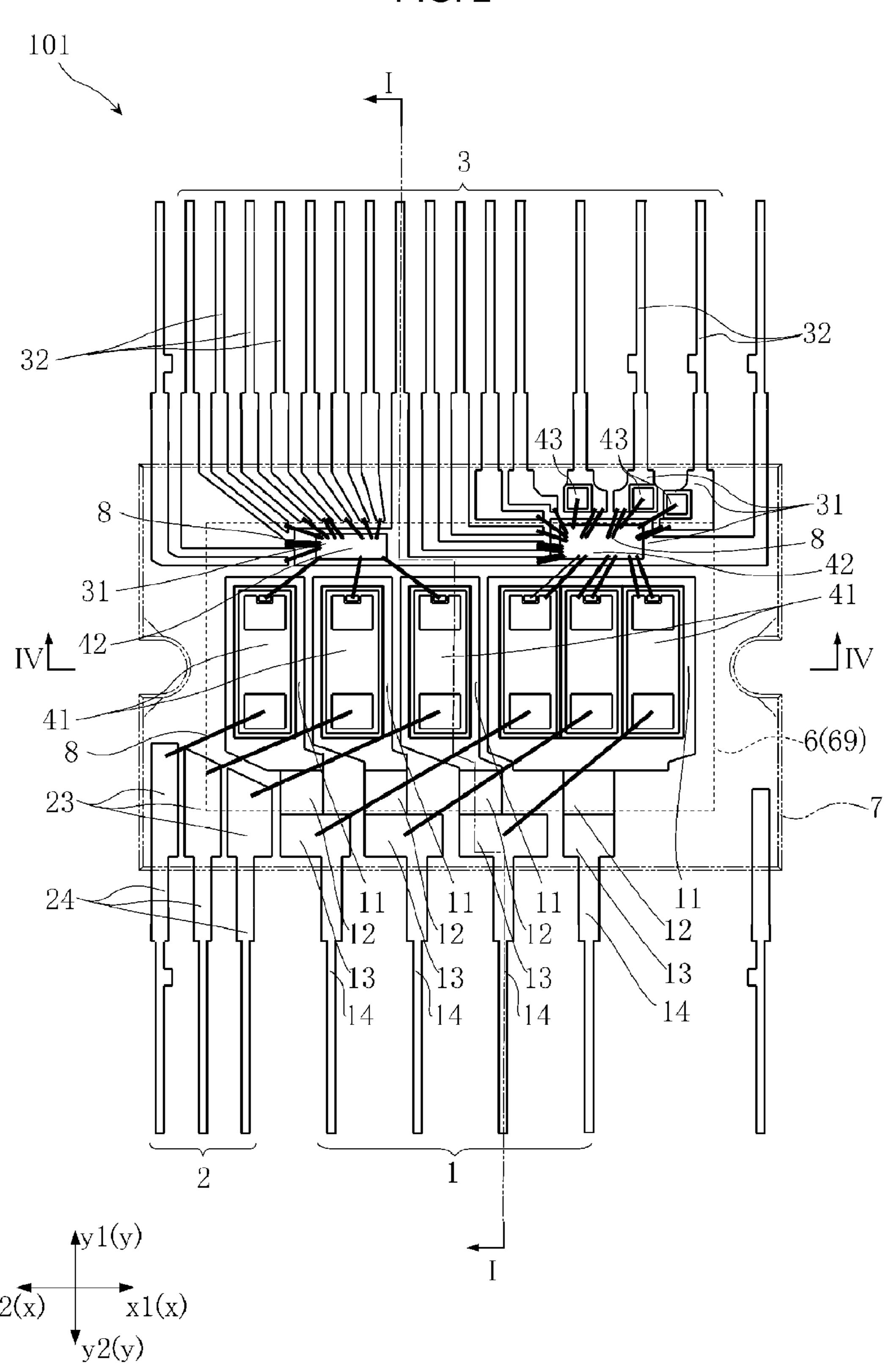

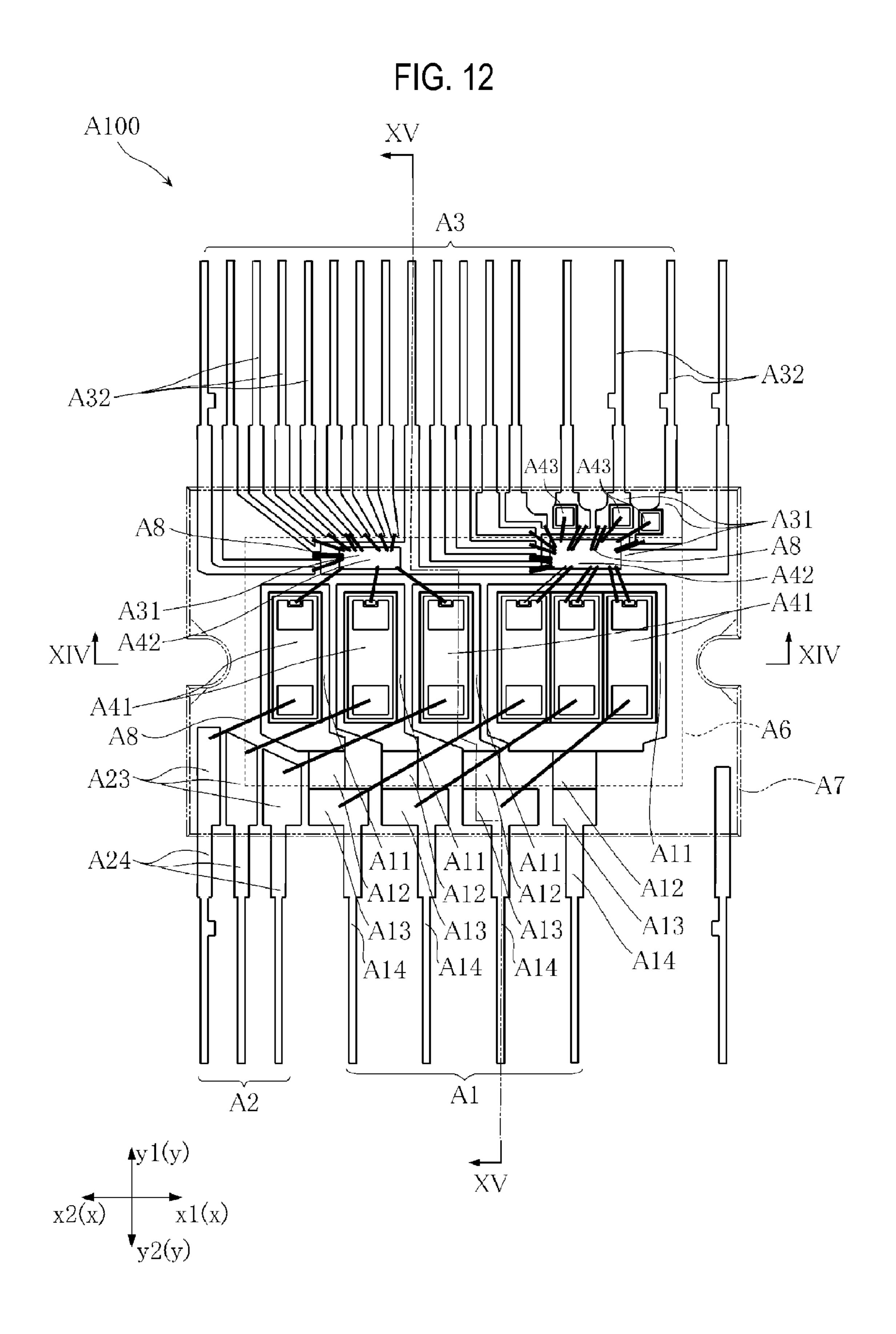

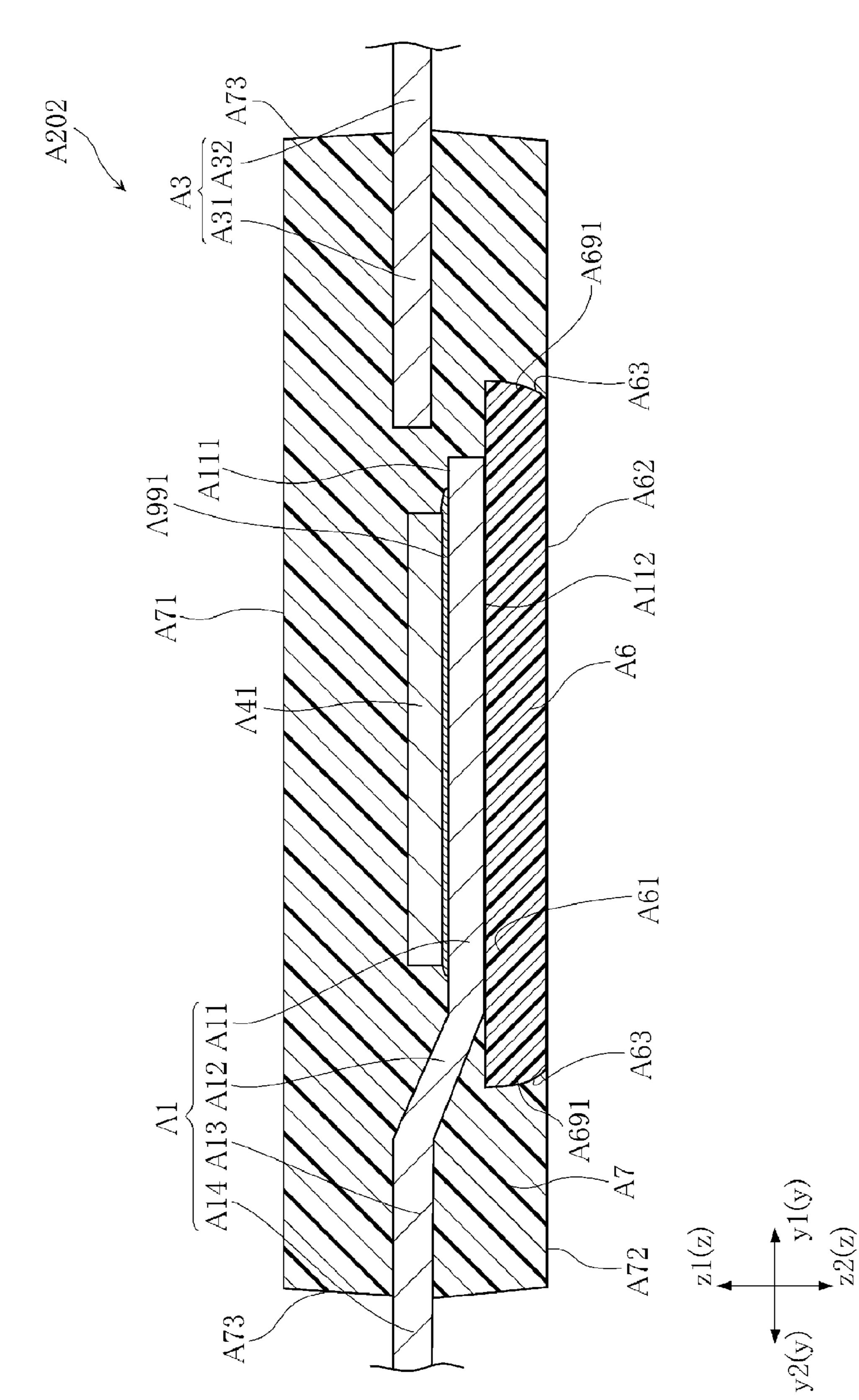

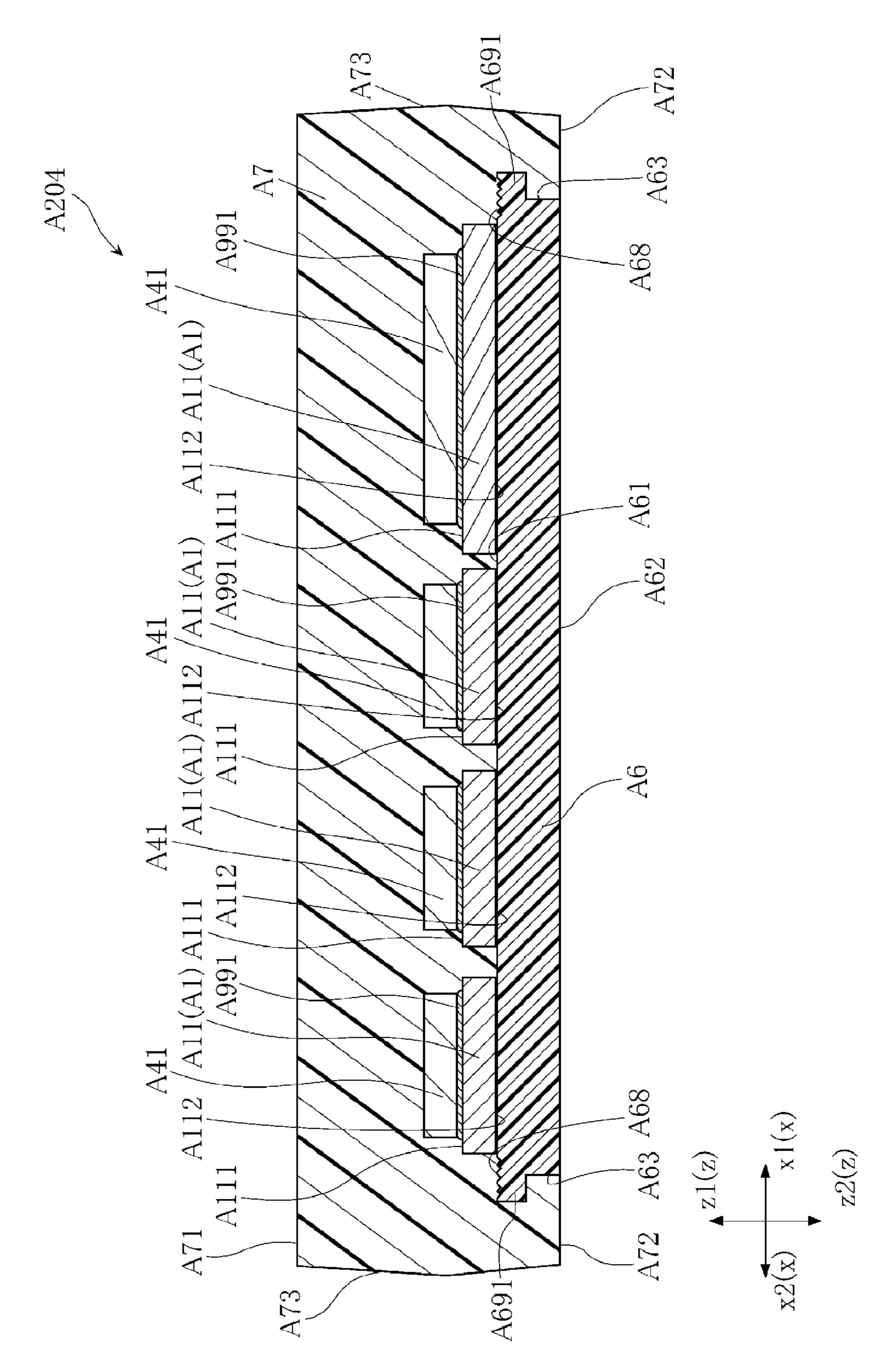

FIG. 12 is a (partially cut away) plan view of the semiconductor device according to the second embodiment of the present disclosure prior to bending the leads.

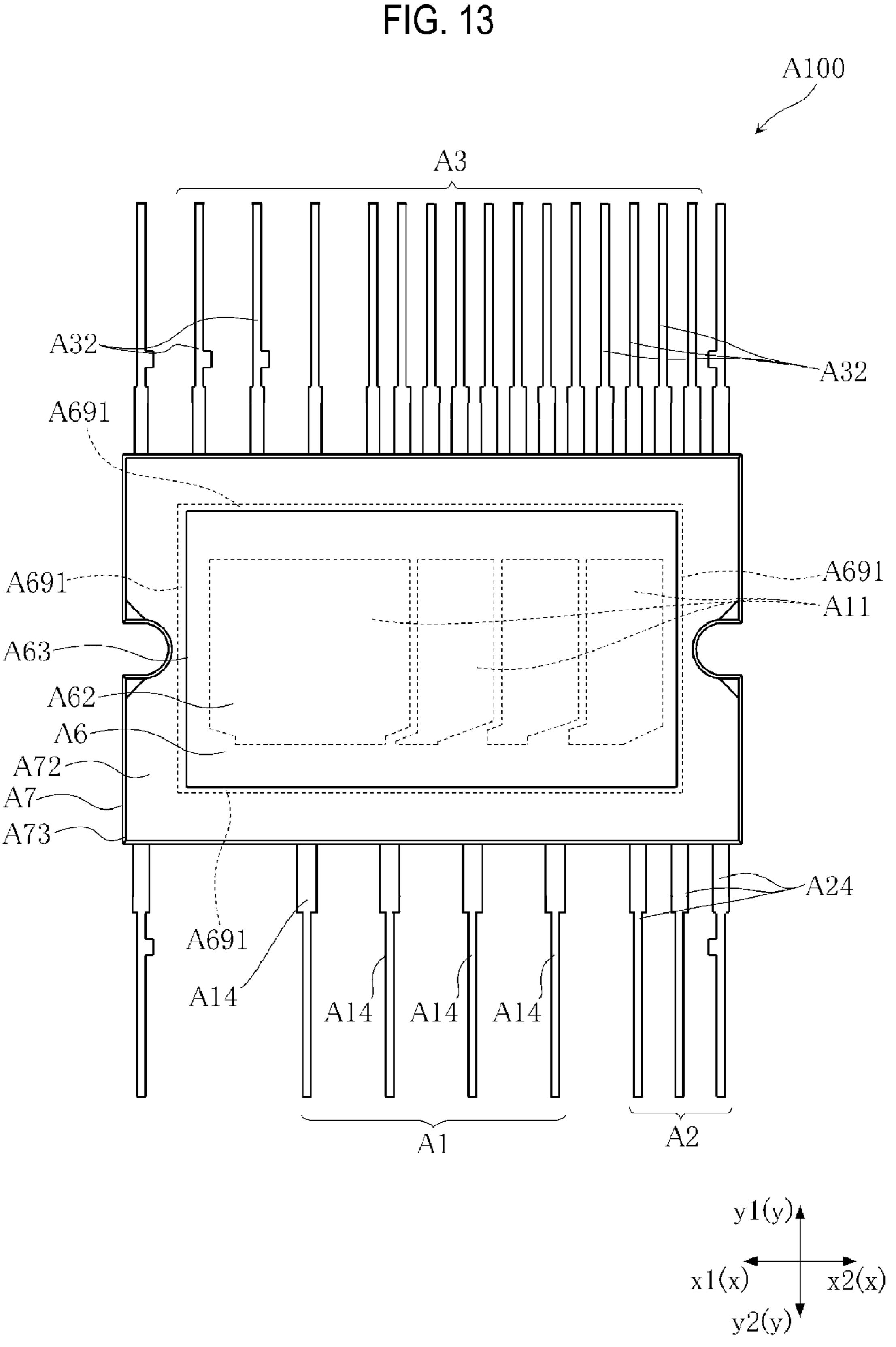

FIG. 13 is a bottom view of the semiconductor device according to the second embodiment of the present disclosure prior to bending the leads.

FIG. 14 is a section view taken along line XIV-XIV in FIG. 12.

FIG. **15** is a section view taken along line XV-XV in FIG. **12**.

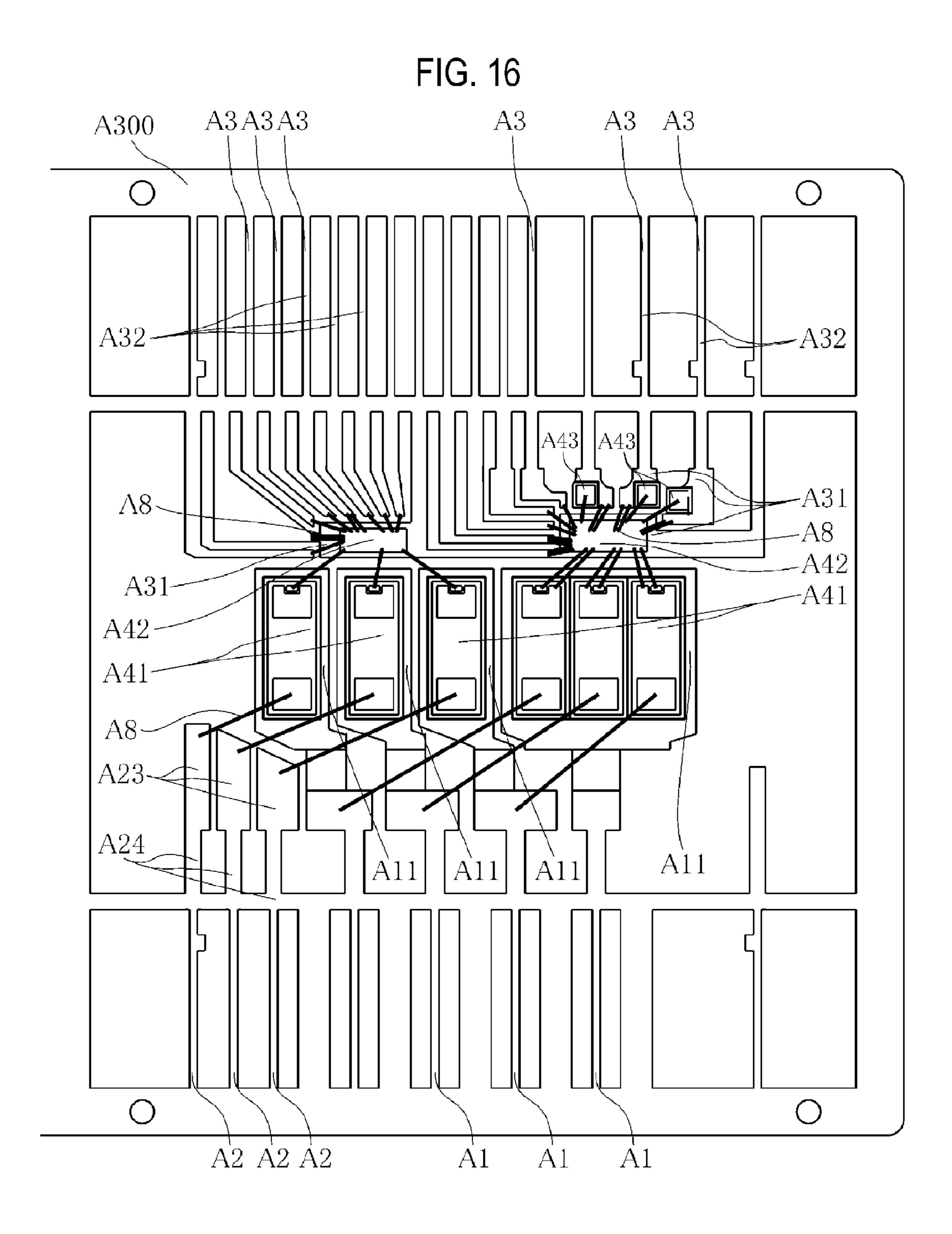

FIG. 16 is a plan view illustrating one process of a manufacturing method of the semiconductor device according to the second embodiment of the present disclosure.

FIG. 17 is a section view illustrating a process subsequent to the process shown in FIG. 16.

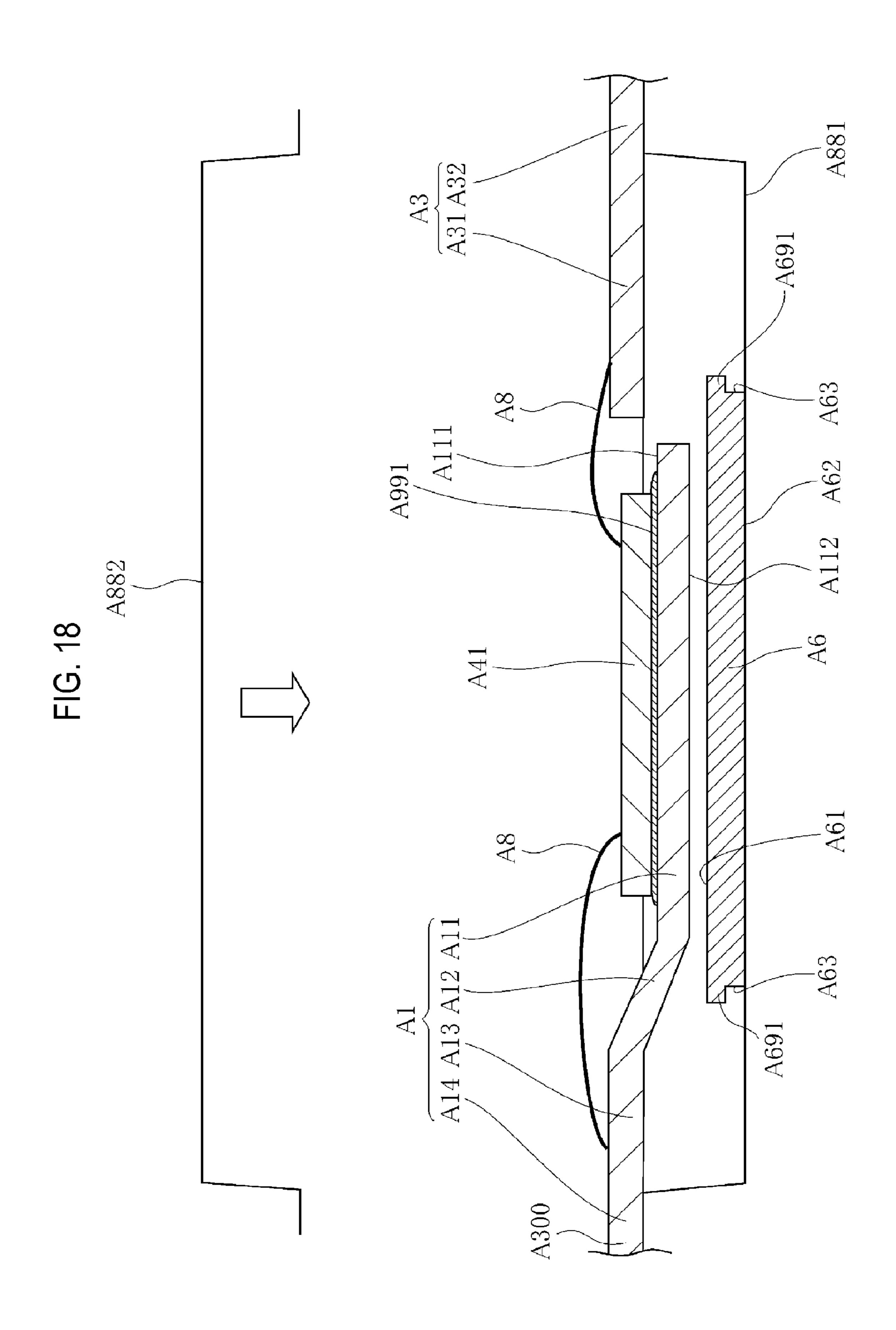

FIG. 18 is a section view illustrating a process subsequent to the process shown in FIG. 17.

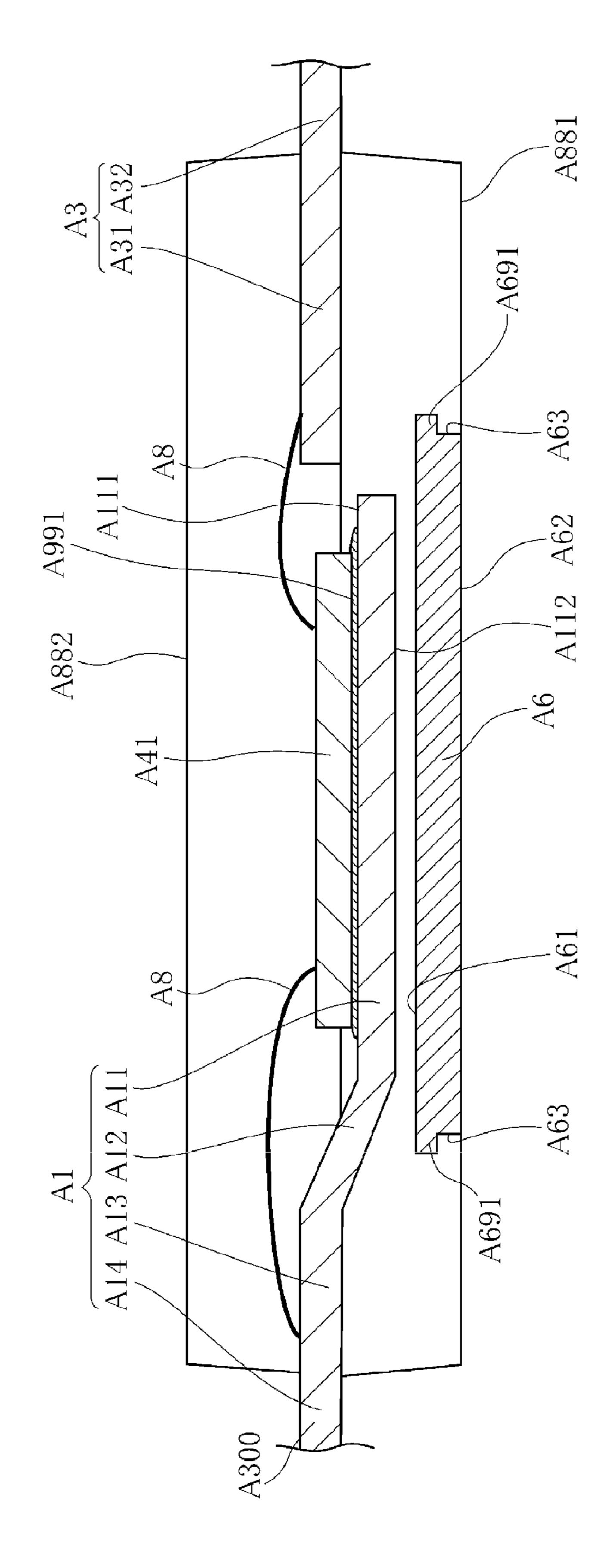

FIG. 19 is a section view illustrating a process subsequent to the process shown in FIG. 18.

FIG. 20 is a section view illustrating a process subsequent to the process shown in FIG. 19.

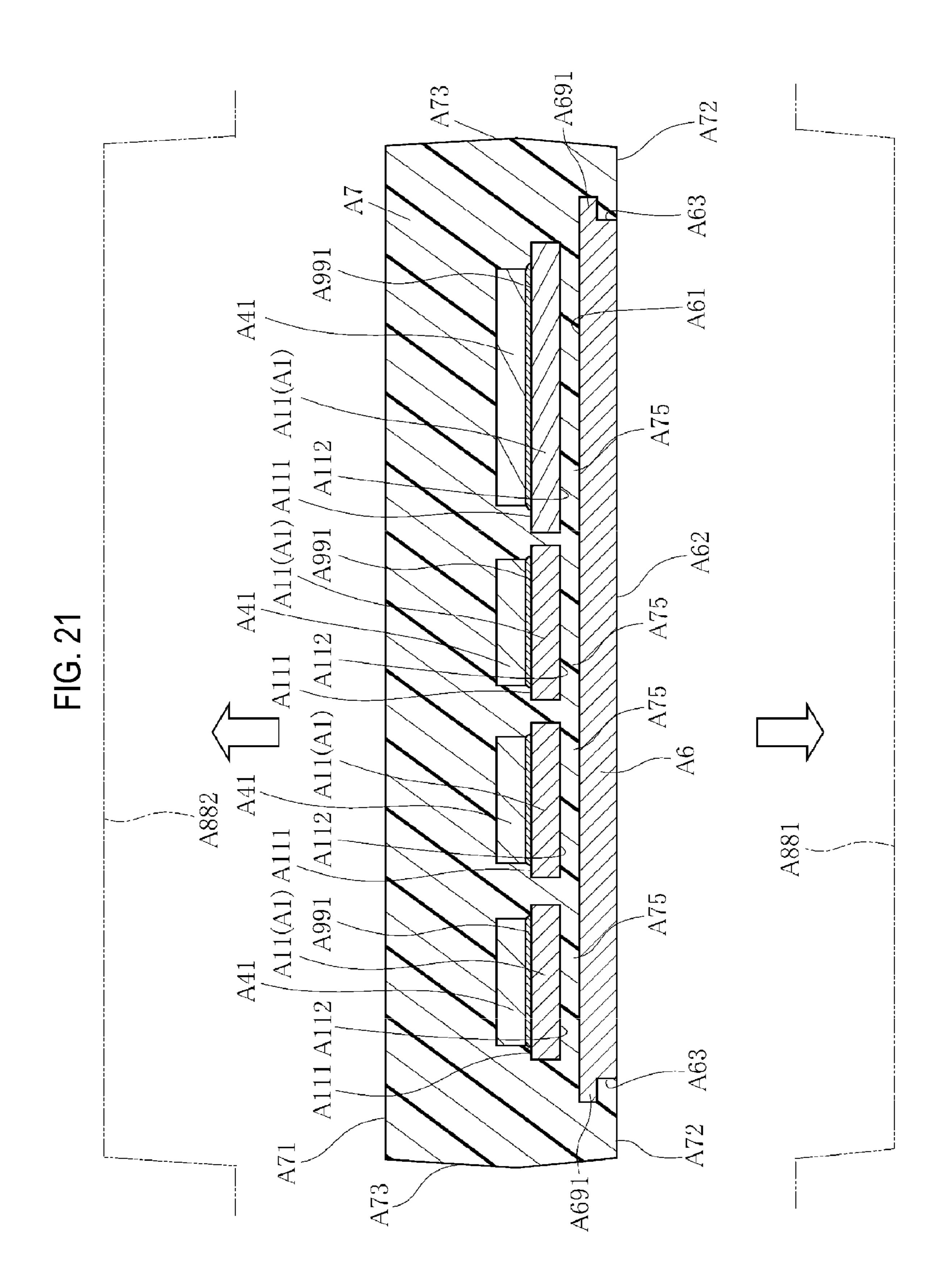

FIG. 21 is a section view illustrating a process subsequent to the process shown in FIG. 20.

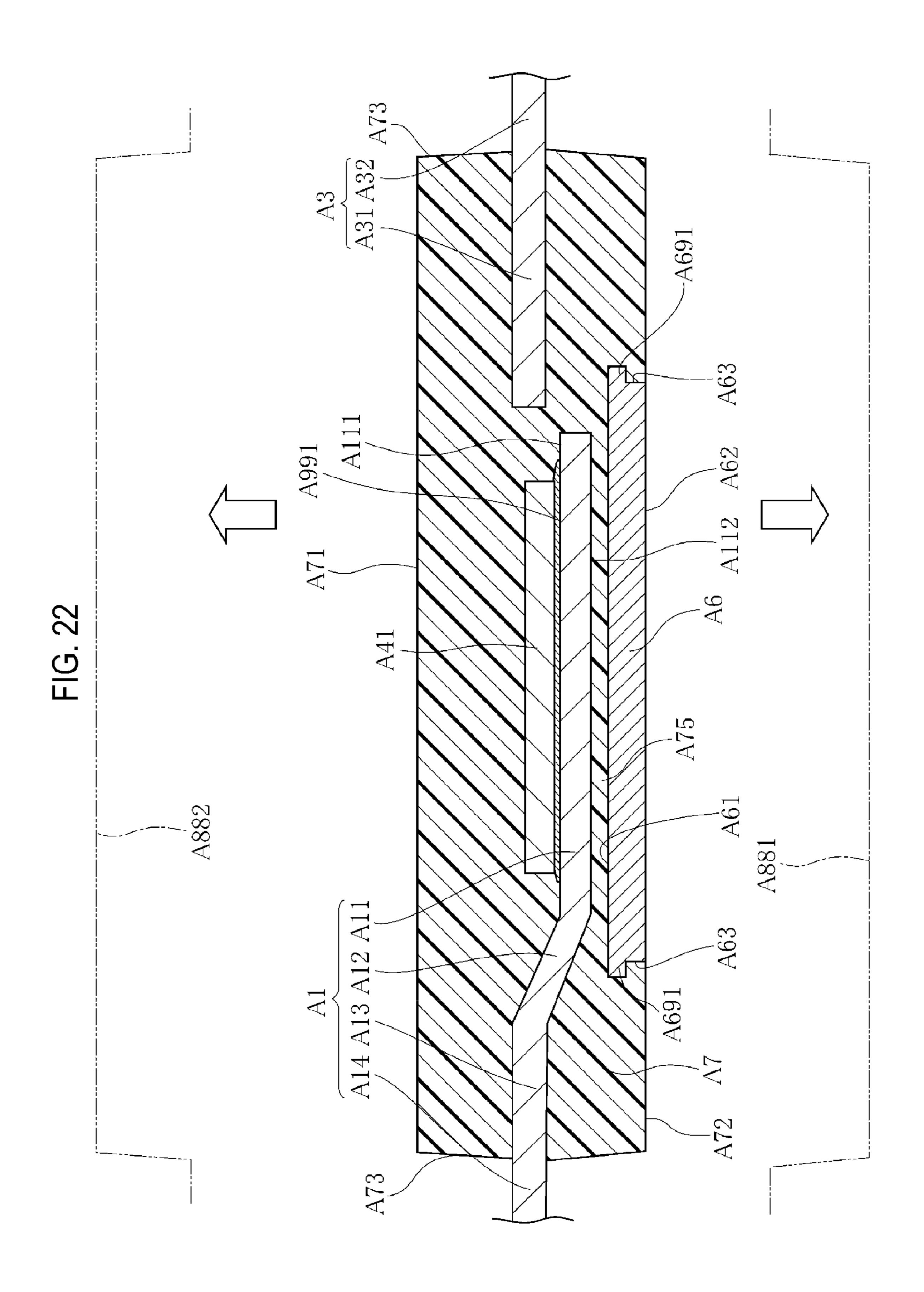

FIG. 22 is a section view illustrating a process subsequent to the process shown in FIG. 21.

- FIG. 23 is a section view illustrating a semiconductor device according to a first modified example of the second embodiment of the present disclosure.

- FIG. **24** is a section view illustrating the semiconductor device according to the first modified example of the second <sup>5</sup> embodiment of the present disclosure.

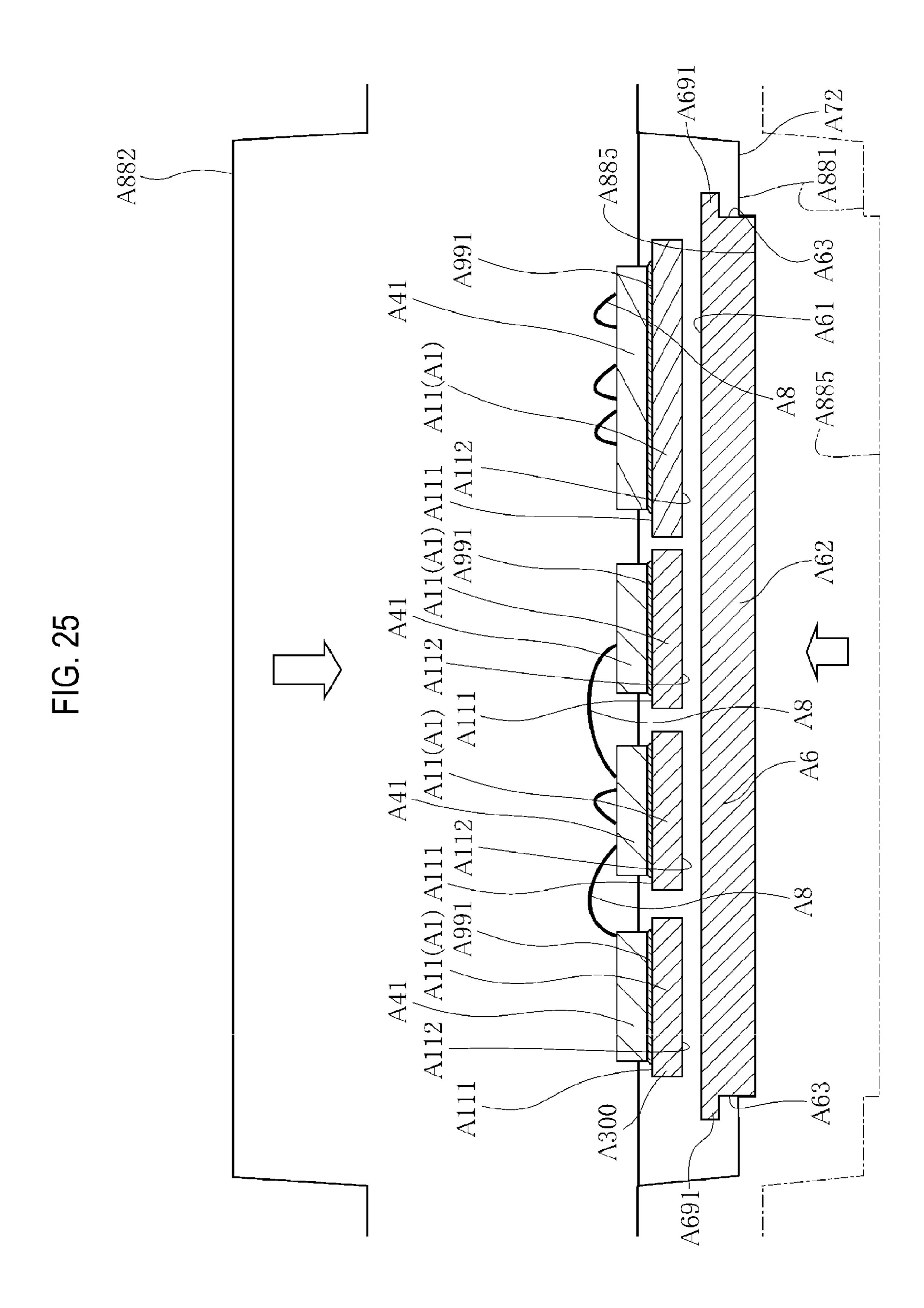

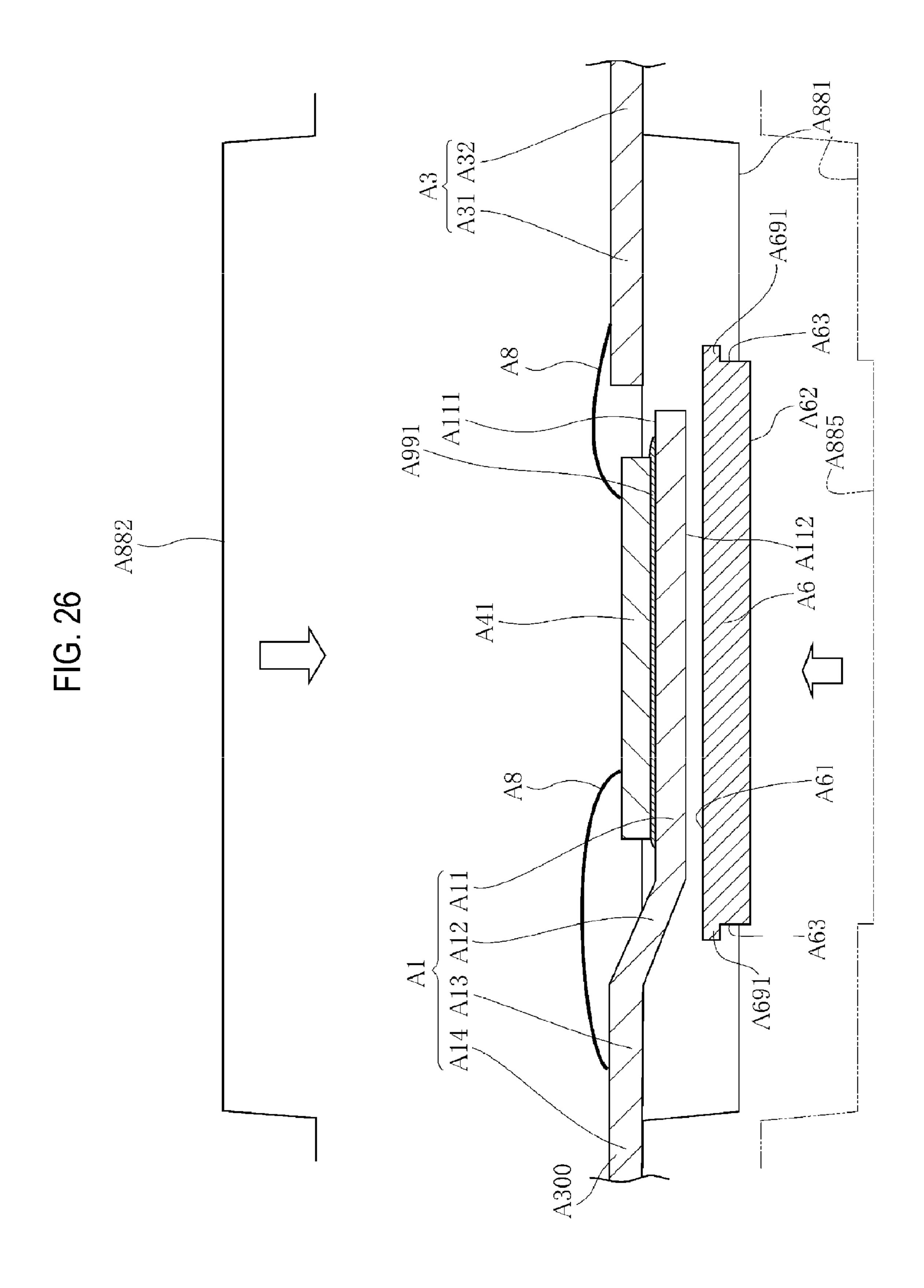

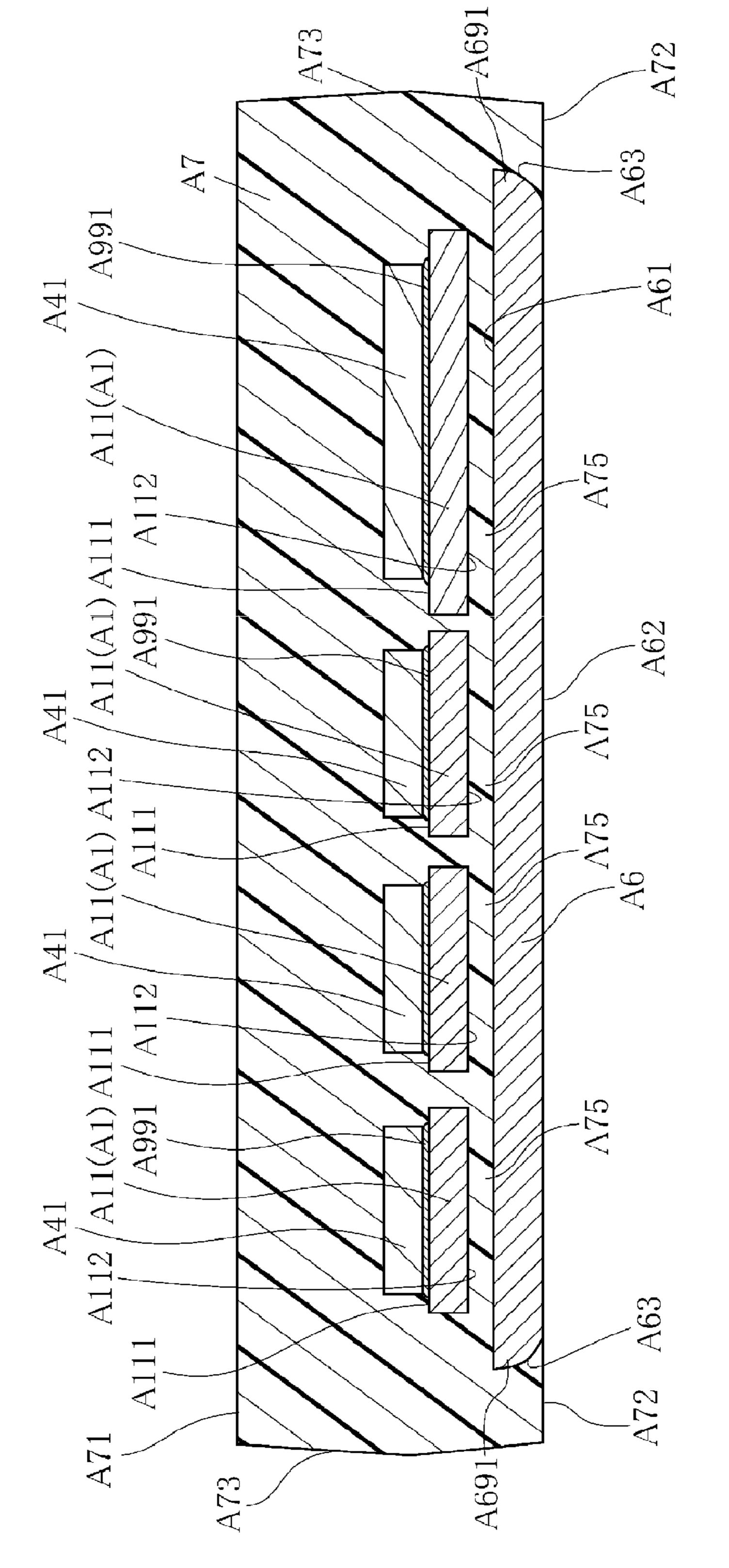

- FIG. 25 is a section view illustrating one process of a manufacturing method of the semiconductor device according to the first modified example of the second embodiment of the present disclosure.

- FIG. 26 is a section view illustrating one process of the manufacturing method of the semiconductor device according to the first modified example of the second embodiment of the present disclosure.

- FIG. 27 is a section view illustrating a semiconductor device according to a second modified example of the second embodiment of the present disclosure.

- FIG. 28 is a section view illustrating the semiconductor device according to the second modified example of the 20 second embodiment of the present disclosure.

- FIG. 29 is a section view illustrating a semiconductor device according to a third modified example of the second embodiment of the present disclosure.

- FIG. 30 is a section view illustrating the semiconductor <sup>25</sup> device according to the third modified example of the second embodiment of the present disclosure.

- FIG. 31 is a section view illustrating a semiconductor device according to a fourth modified example of the second embodiment of the present disclosure.

- FIG. 32 is a section view illustrating the semiconductor device according to the fourth modified example of the second embodiment of the present disclosure.

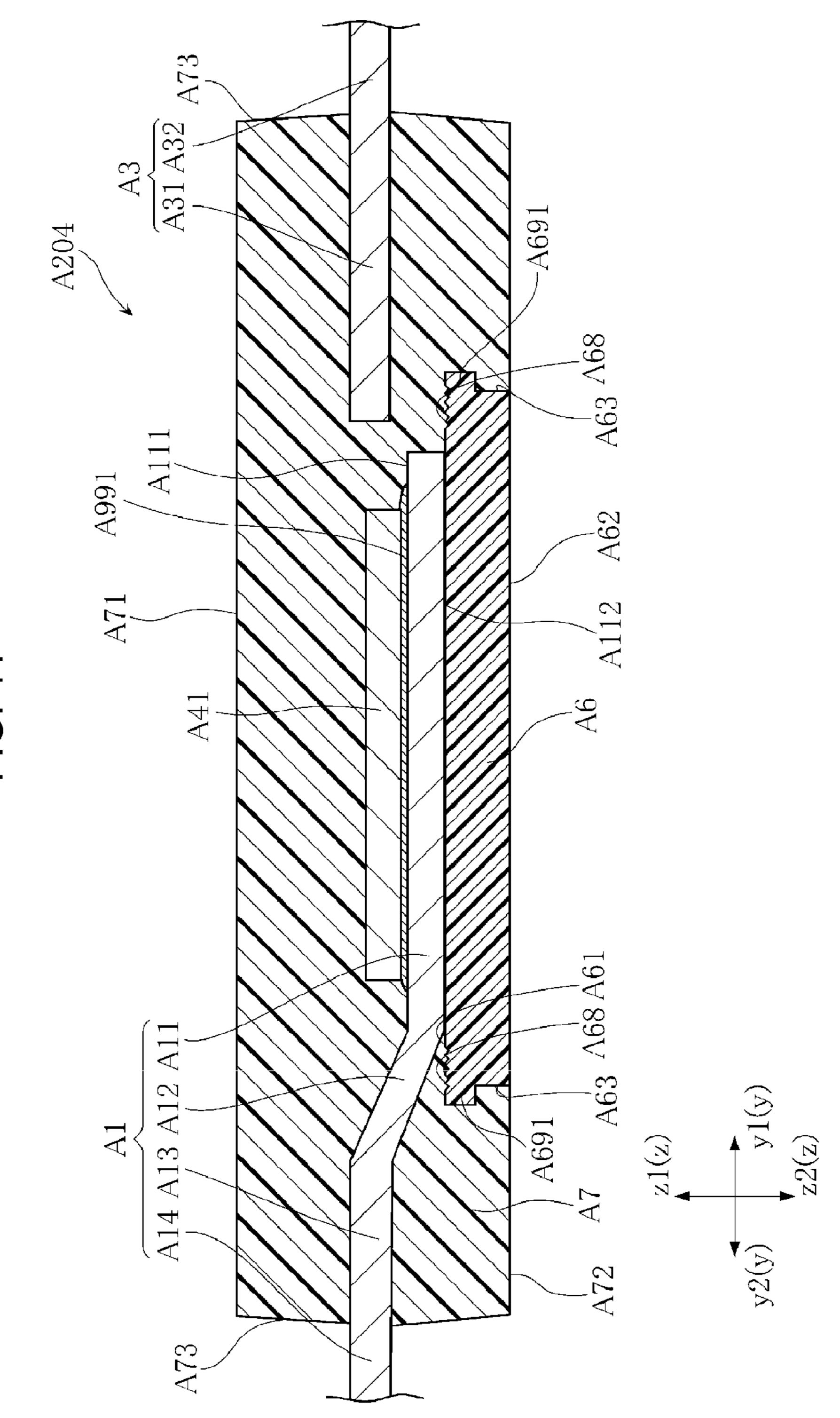

- FIG. 33 is a section view illustrating a semiconductor device according to a third embodiment of the present disclosure.

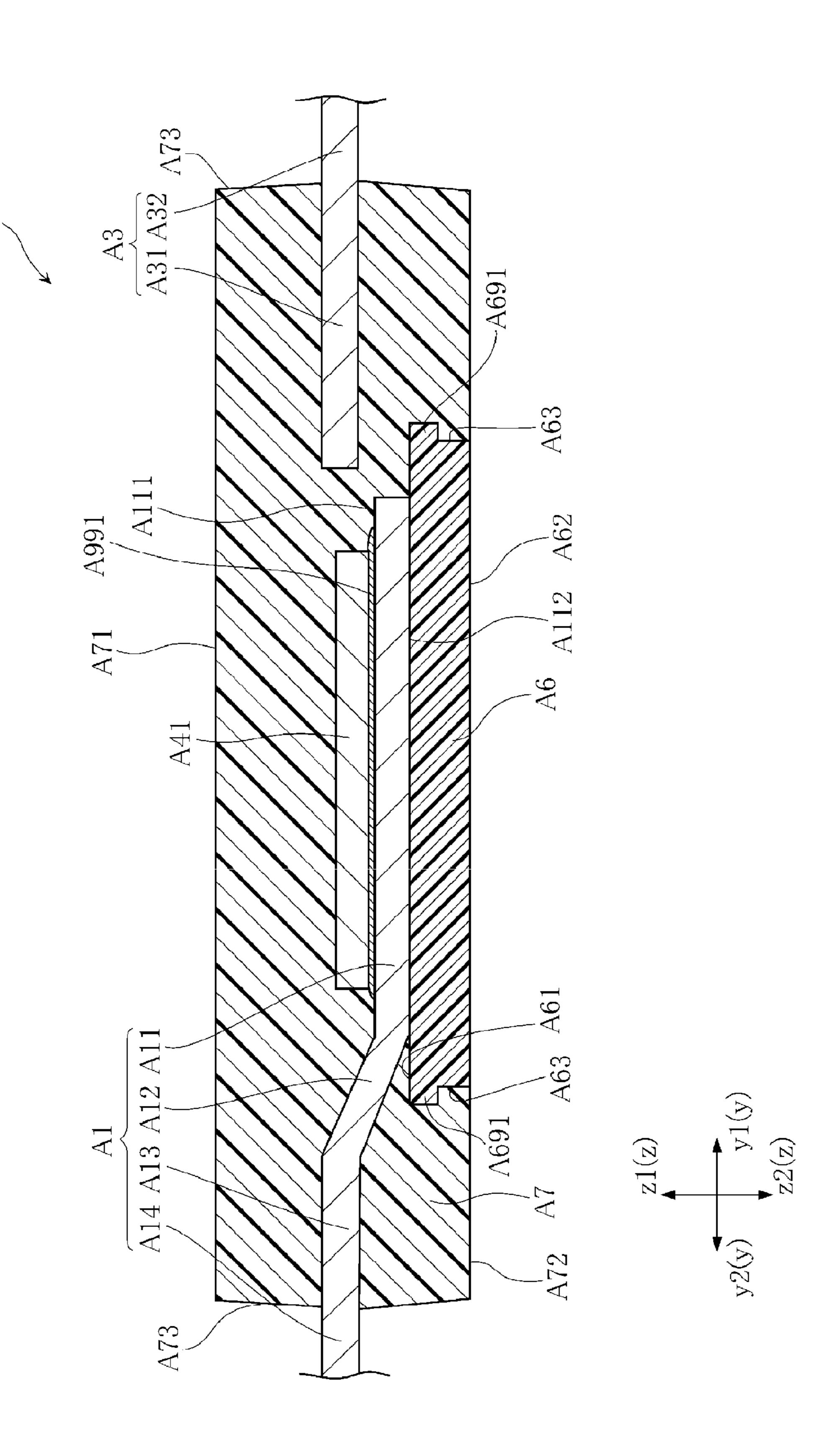

- FIG. 34 is a section view illustrating the semiconductor device according to the third embodiment of the present disclosure.

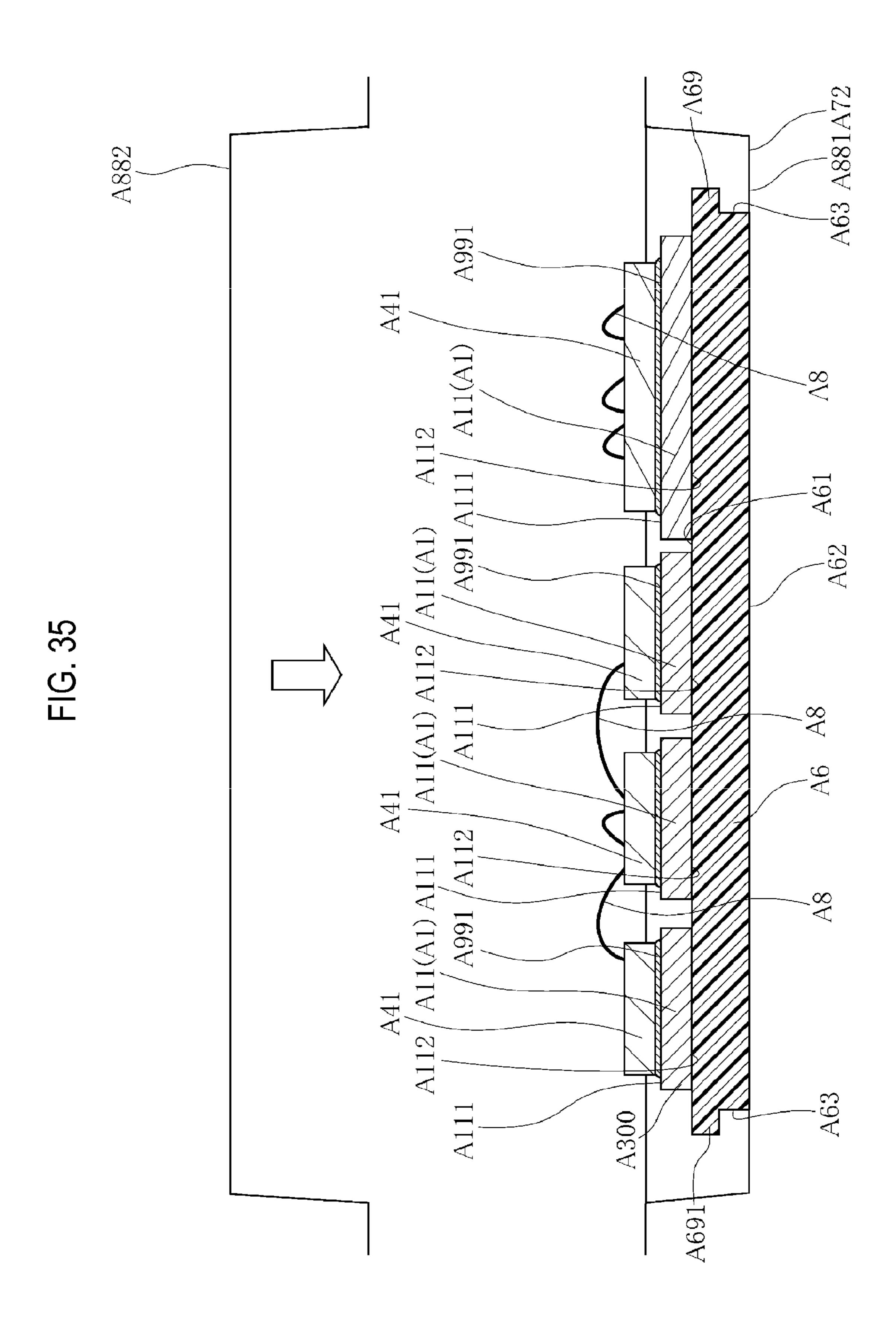

- FIG. 35 is a section view illustrating one process of a manufacturing method of the semiconductor device according to the third embodiment of the present disclosure.

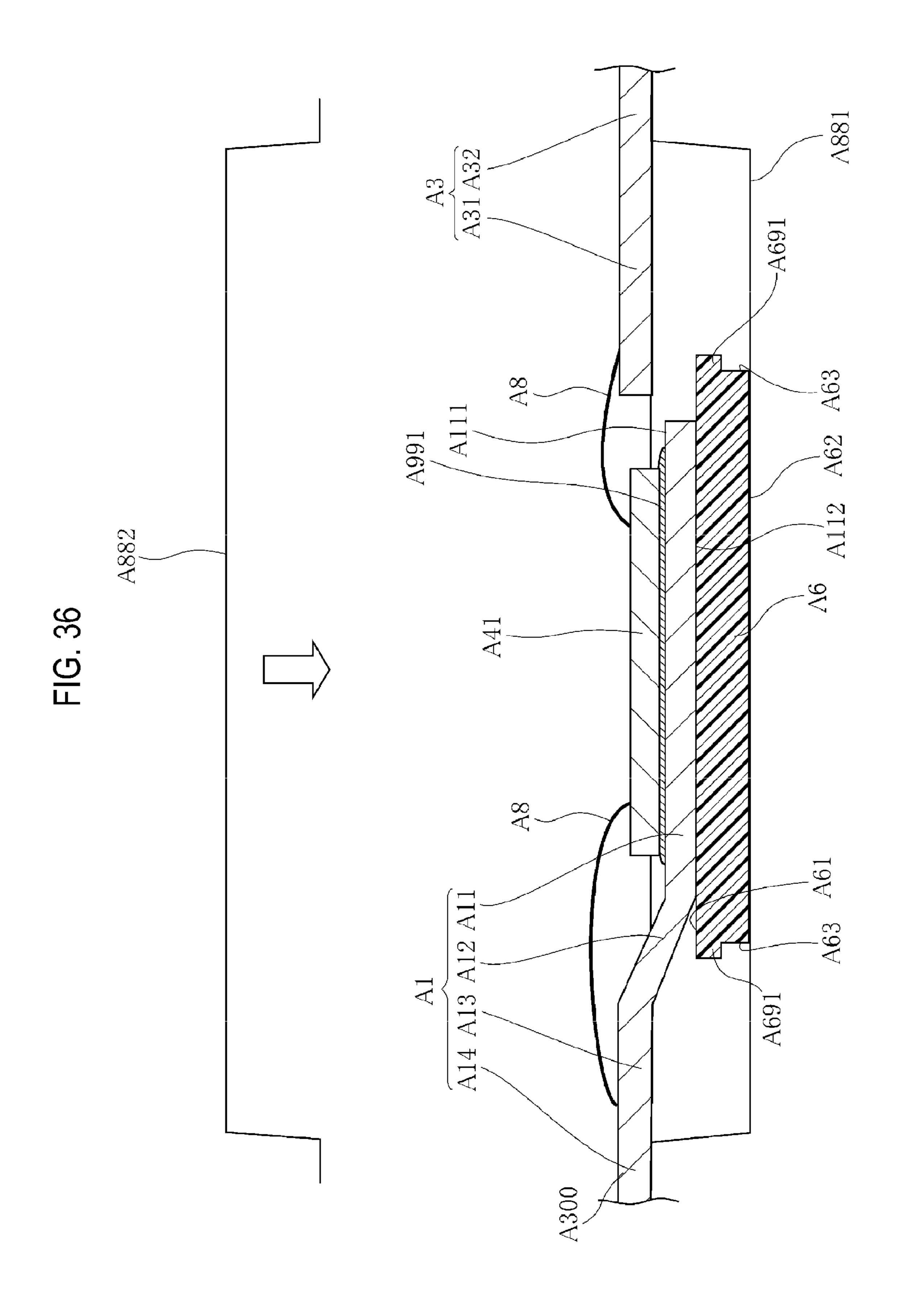

- FIG. 36 is a section view illustrating one process of the manufacturing method of the semiconductor device accord- 45 ing to the third embodiment of the present disclosure.

- FIG. 37 is a section view illustrating a semiconductor device according to a first modified example of the third embodiment of the present disclosure.

- FIG. 38 is a section view illustrating the semiconductor 50 device according to the first modified example of the third embodiment of the present disclosure.

- FIG. 39 is a section view illustrating a semiconductor device according to a second modified example of the third embodiment of the present disclosure.

- FIG. 40 is a section view illustrating the semiconductor device according to the second modified example of the third embodiment of the present disclosure.

- FIG. 41 is a section view illustrating a semiconductor device according to a third modified example of the third 60 embodiment of the present disclosure.

- FIG. 42 is a section view illustrating the semiconductor device according to the third modified example of the third embodiment of the present disclosure.

- FIG. **43** is a section view illustrating a semiconductor 65 device according to a fourth modified example of the third embodiment of the present disclosure.

**10**

- FIG. **44** is a section view illustrating the semiconductor device according to the fourth modified example of the third embodiment of the present disclosure.

- FIG. **45** is a section view illustrating a mounting structure of a semiconductor device according to a fourth embodiment of the present disclosure.

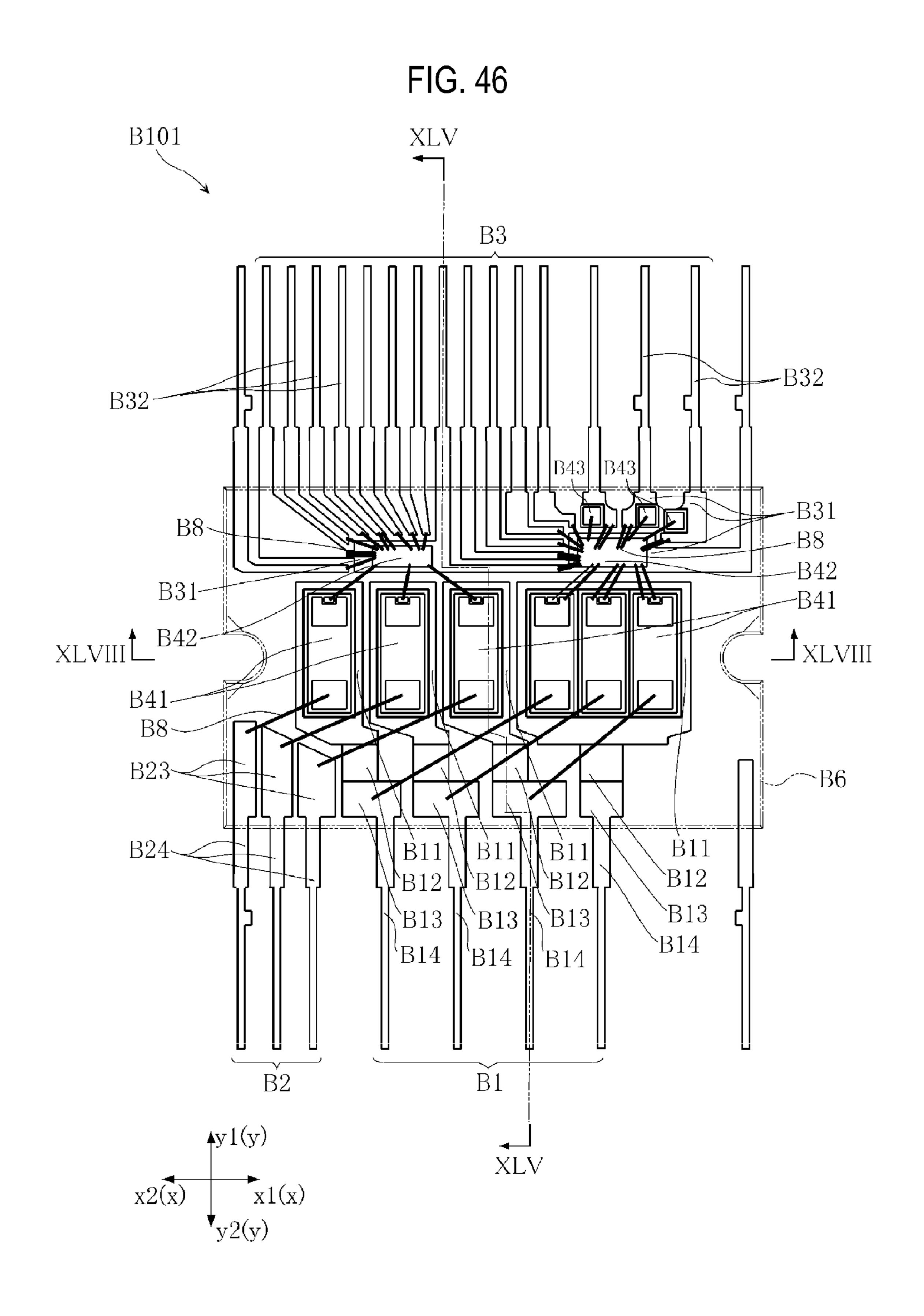

- FIG. 46 is a (partially cut away) plan view of the semiconductor device according to the fourth embodiment of the present disclosure prior to bending the leads.

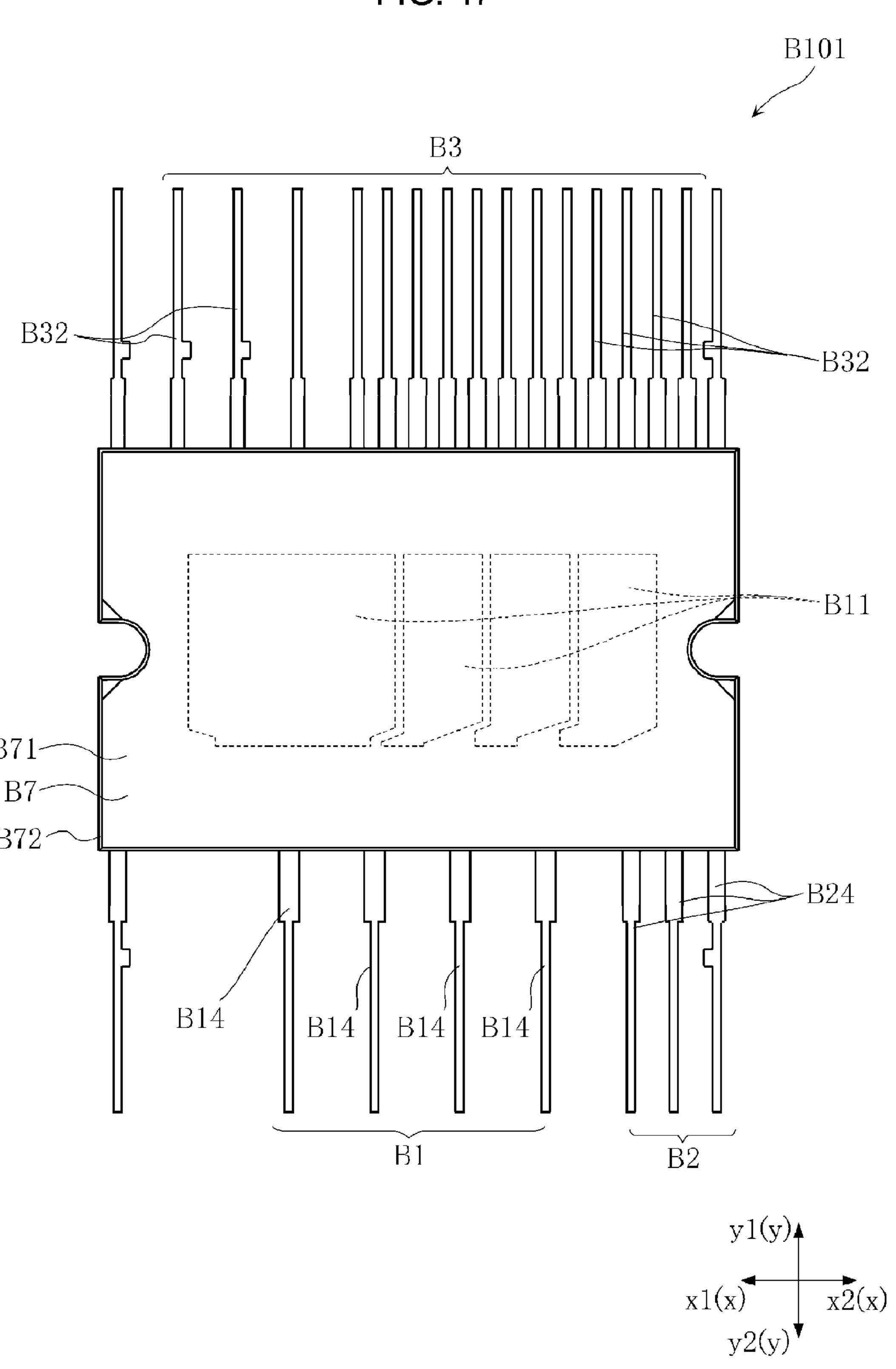

- FIG. 47 is a bottom view of the semiconductor device according to the fourth embodiment of the present disclosure prior to bending the leads.

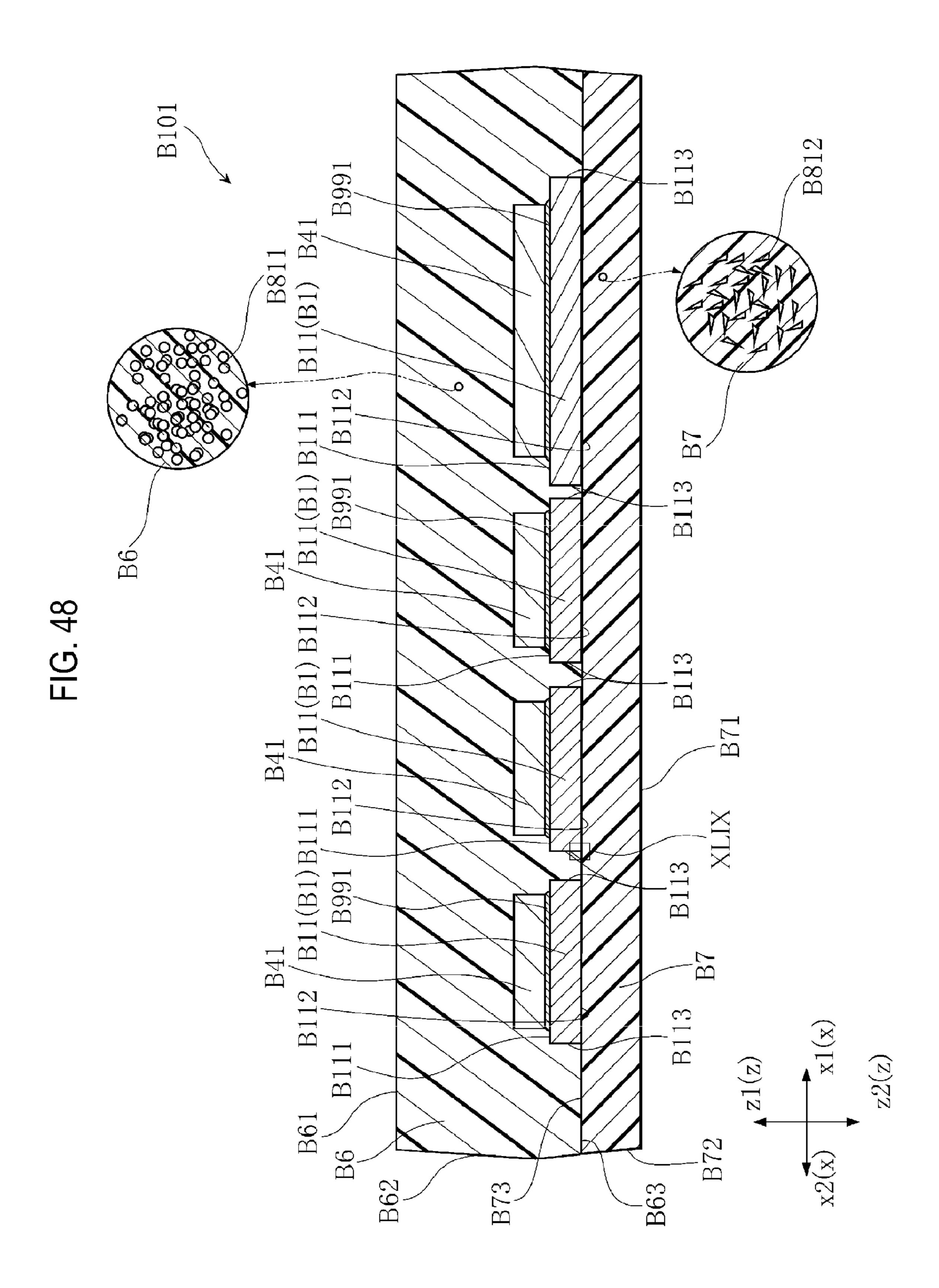

- FIG. **48** is a section view taken along line XLVIII-XLVIII in FIG. **46**.

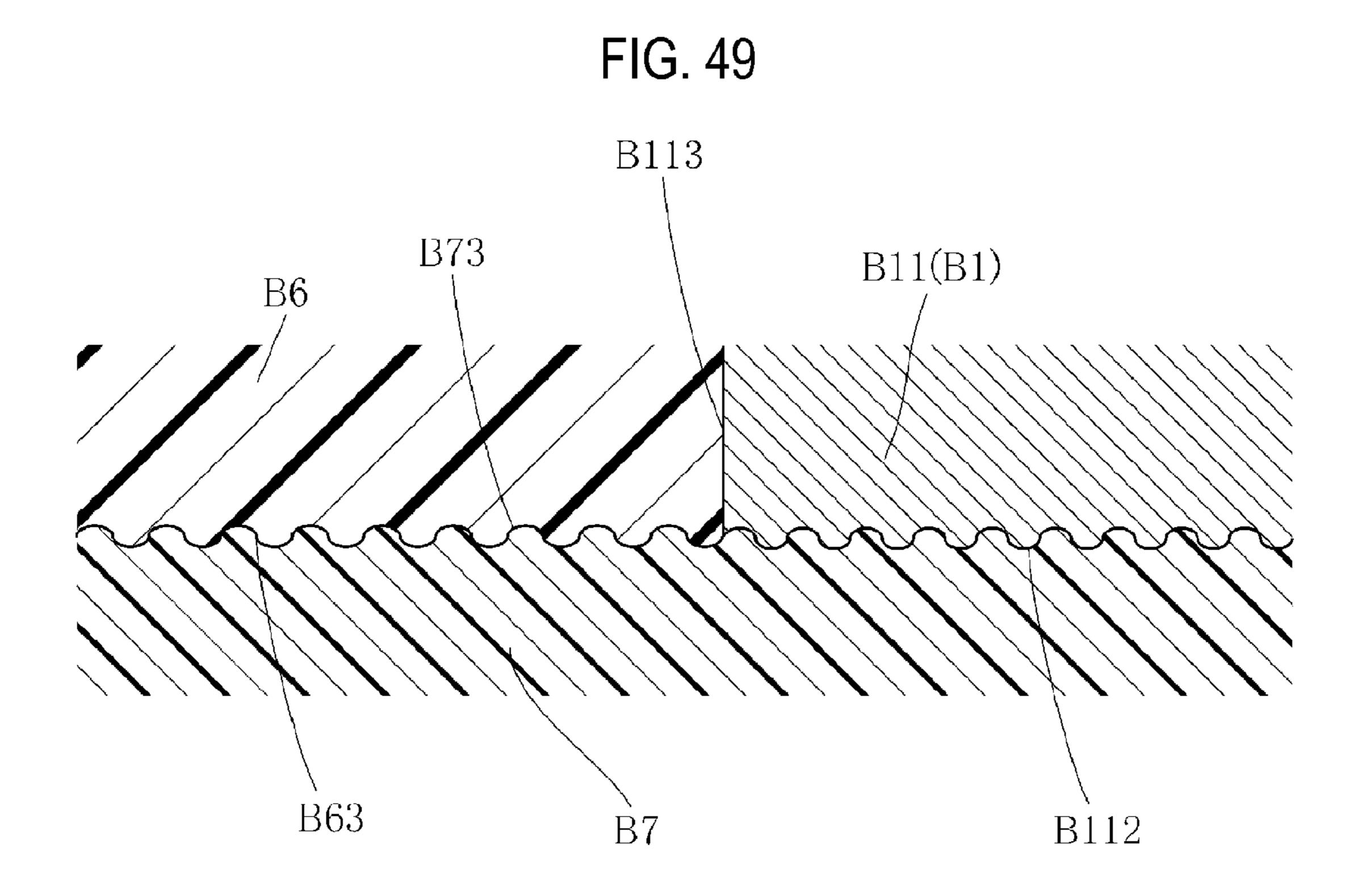

- FIG. **49** is a partially enlarged view of the region XLIX in FIG. **48**.

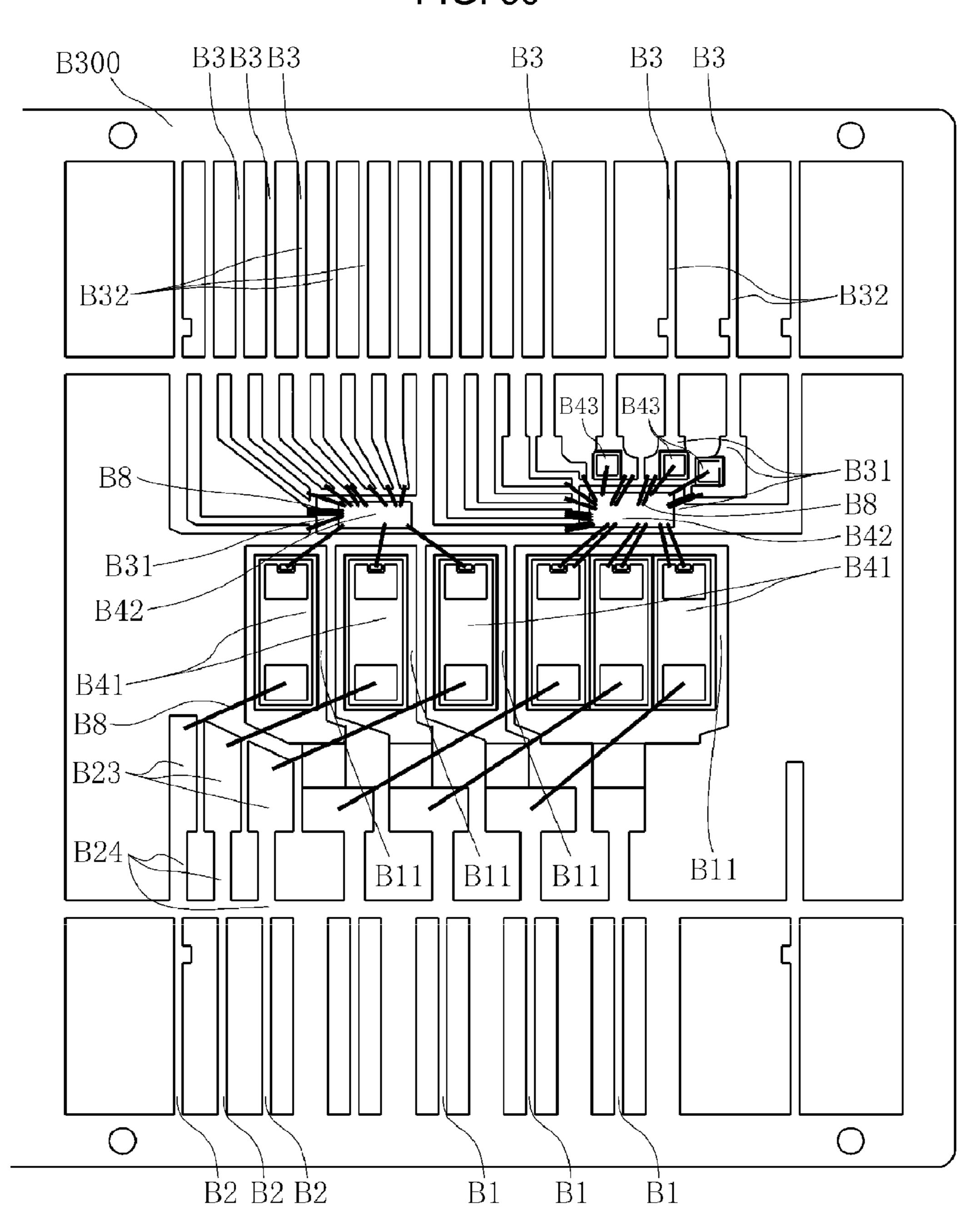

- FIG. **50** is a plan view illustrating one process of a manufacturing method of the semiconductor device according to the fourth embodiment of the present disclosure.

- FIG. **51** is a section view illustrating a process subsequent to the process shown in FIG. **50**.

- FIG. **52** is a section view illustrating a process subsequent to the process shown in FIG. **51**.

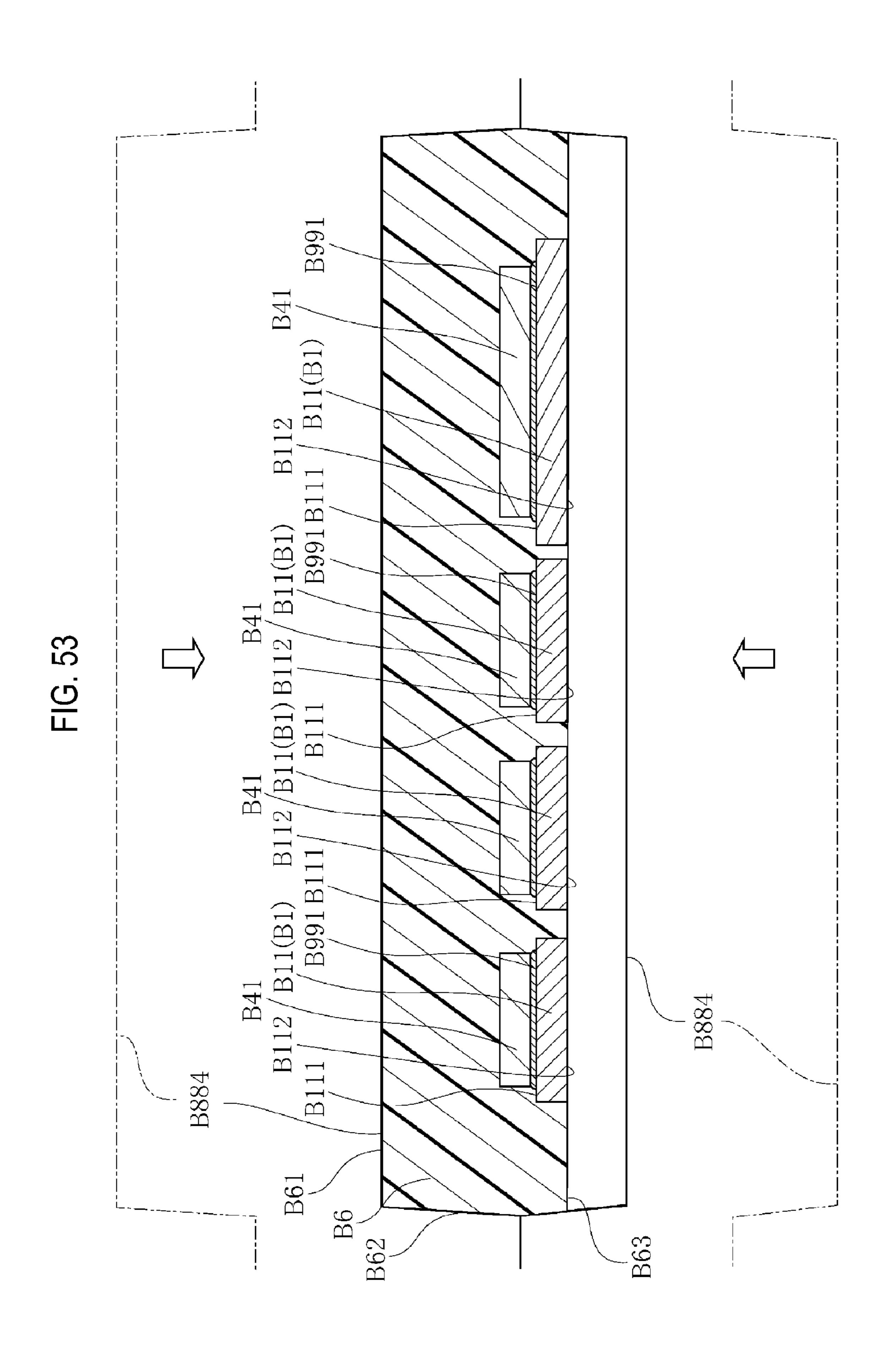

- FIG. **53** is a section view illustrating a process subsequent to the process shown in FIG. **52**.

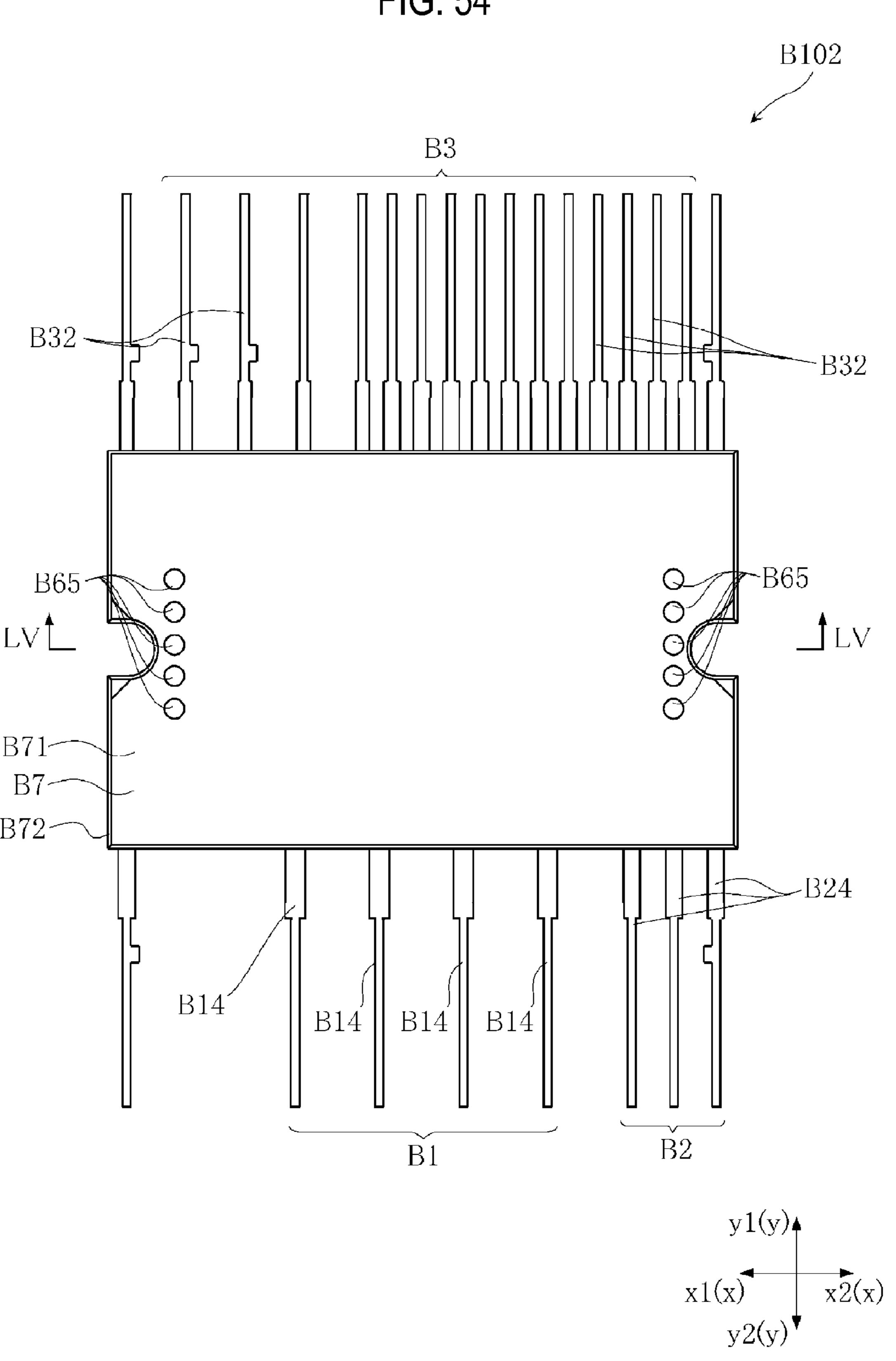

- FIG. **54** is a bottom view of a semiconductor device according to a fifth embodiment of the present disclosure prior to bending the leads.

- FIG. **55** is a section view taken along line LV-LV in FIG. **54**.

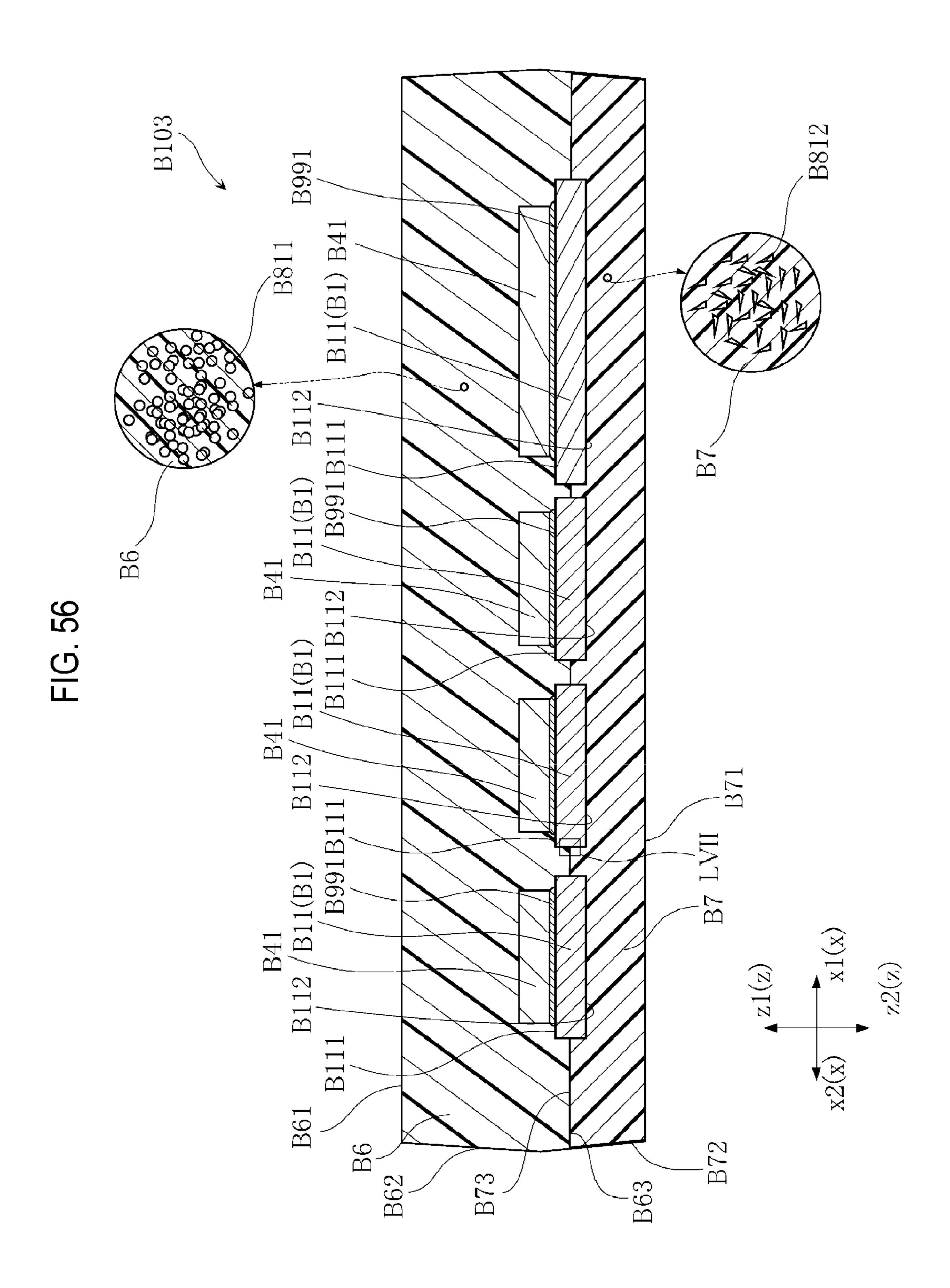

- FIG. **56** is a section view illustrating a semiconductor device according to a sixth embodiment of the present disclosure.

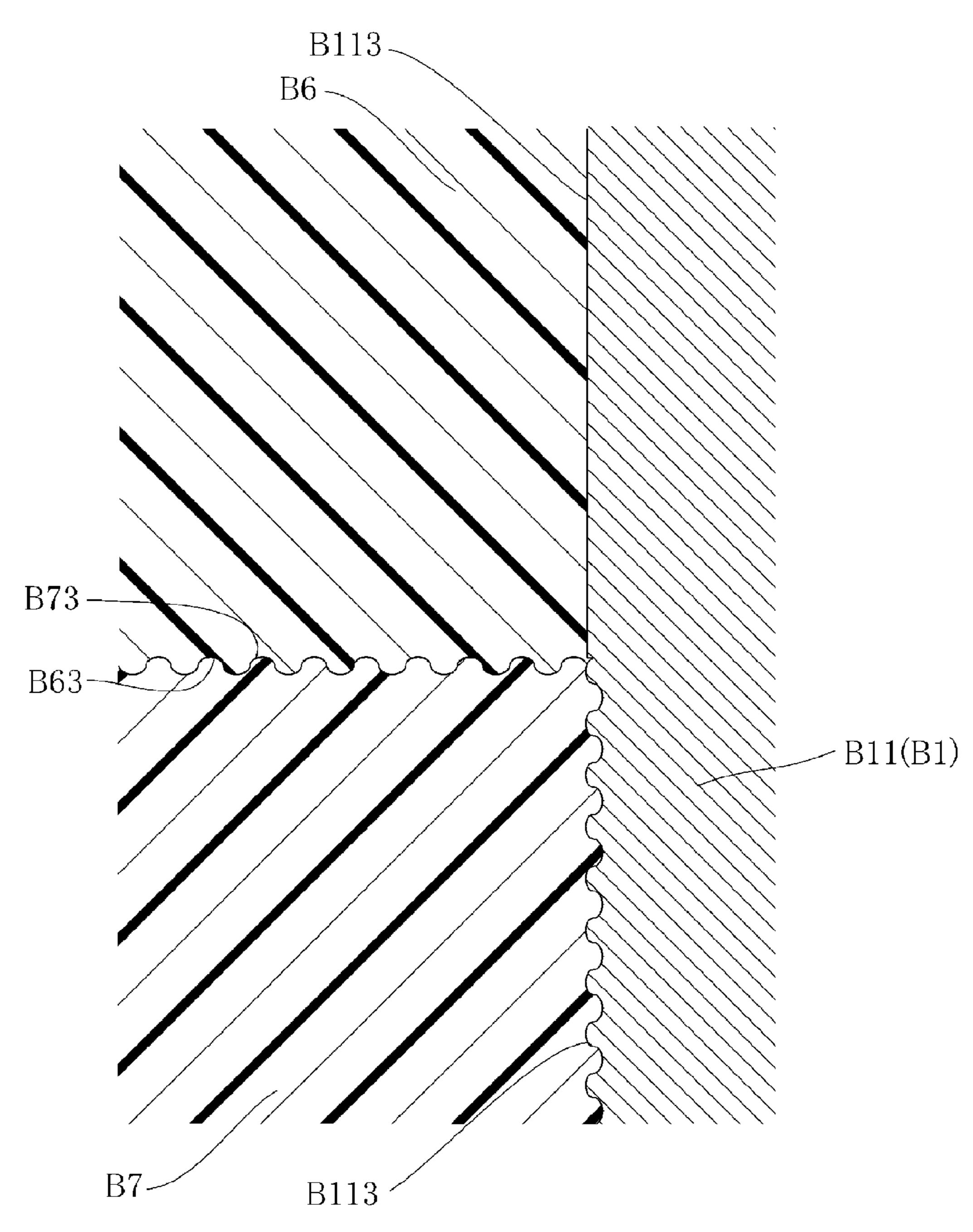

- FIG. **57** is a partially enlarged view of the region LVII in FIG. **56**.

#### DETAILED DESCRIPTION

Certain embodiments of the present disclosure will now be described in detail with reference to the drawings.

### First Embodiment

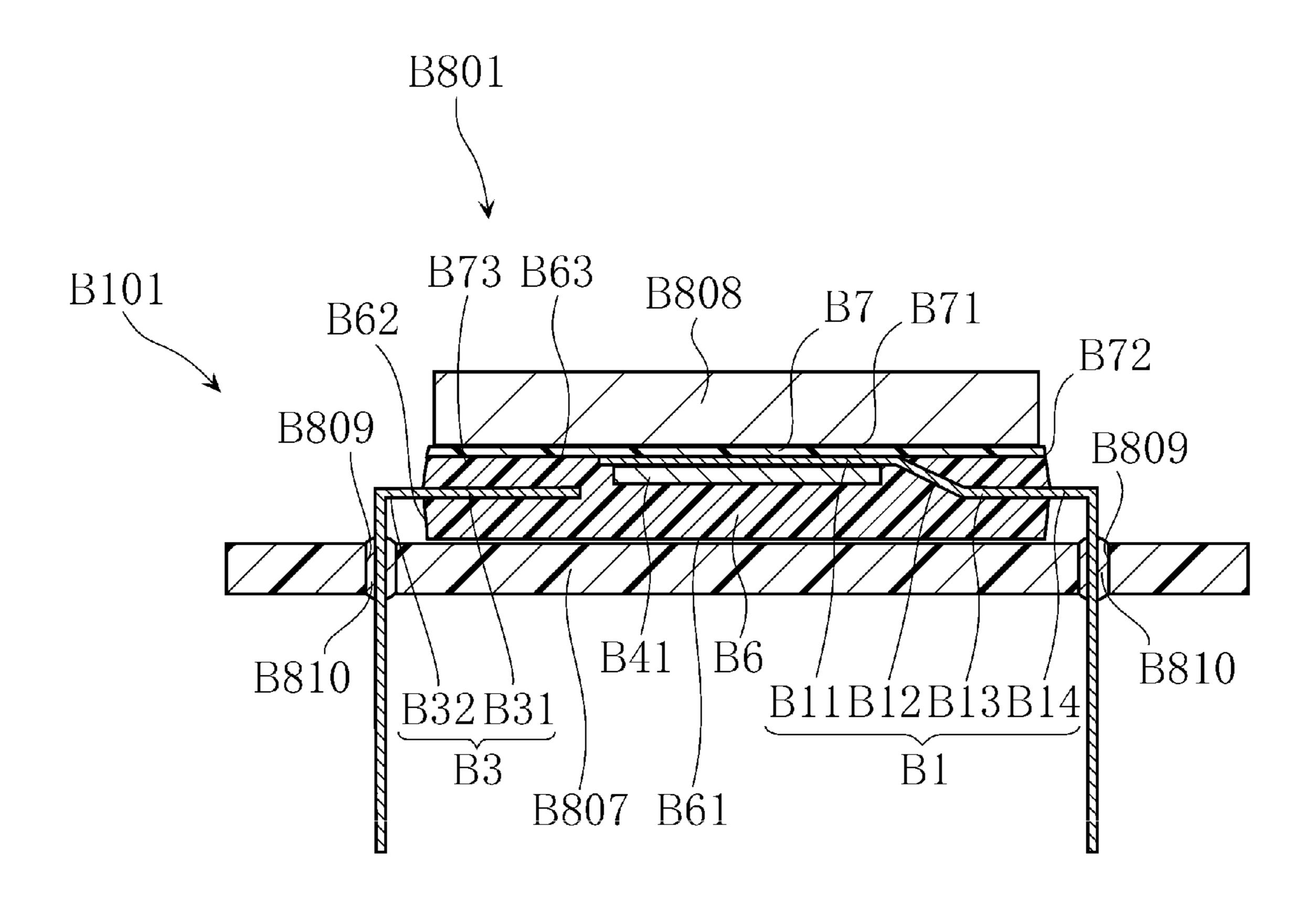

FIG. 1 is a section view illustrating a mounting structure of a semiconductor device according to a first embodiment of the present disclosure.

The mounting structure **801** of the semiconductor device shown in FIG. **1** includes a semiconductor device **101**, a substrate **807** and a heat radiation member **808**.

A plurality of electronic parts is mounted on the substrate 807. The substrate 807 is made of an insulating material. A wiring pattern not shown is formed in the substrate 807. A plurality of holes 809 is formed in the substrate 807. The heat radiation member 808 is made of a material having relatively high heat conductivity, e.g., a metal such as aluminum. The heat radiation member 808 is fixed with respect to the substrate 807 by a support member not shown. The semiconductor device 101 is mounted on the substrate 807. In the present embodiment, the semiconductor device 101 is an article called an IPM (Intelligent Power Module). The semiconductor device 101 has applications in, e.g., an air conditioner or a motor control device.

FIG. 2 is a (partially cut away) plan view of the semiconductor device according to the first embodiment of the present disclosure prior to bending the leads. FIG. 3 is a bottom view of the semiconductor device according to the first embodiment of the present disclosure prior to bending

the leads. FIG. 4 is a section view taken along line IV-IV in FIG. 2. FIG. 5 is a partially enlarged view of the region V in FIG. 4. FIG. 1 corresponds to the cross section taken along line I-I in FIG. 2. In FIG. 4, the respective components are schematically shown for the sake of understanding.

The semiconductor device 101 shown in these figures includes a plurality of first electrode portions 1, a plurality of second electrode portions 2, a plurality of third electrode portions 3, a plurality of semiconductor chips 41 and 42, a plurality of passive chips 43, a heat radiation layer 6, a resin 10 encapsulation portion 7 and wires 8. In FIG. 2, the heat radiation layer 6 is indicated by a dotted line and the resin encapsulation portion 7 is indicated by an imaginary line.

The resin encapsulation portion 7 covers the first electrode portions 1, the second electrode portions 2, the third 15 electrode portions 3, the semiconductor chips 41 and 42 and the passive chips 43. The resin encapsulation portion 7 is made of, e.g., a black epoxy resin. As shown in FIGS. 3 and 4, the resin encapsulation portion 7 has a resin major surface 71, a resin bottom surface 72 and a resin side surface 73.

The resin major surface 71 is a smooth surface facing in the direction z1 and extending along the x-y plane. The resin bottom surface 72 is a smooth surface facing in the direction z2 opposite to the direction z1 and extending along the x-y plane. The resin side surface 73 is shaped to surround the 25 semiconductor chips 41 and 42 and the passive chips 43 when seen in an x-y plane view. The resin side surface 73 is joined to the resin major surface 71 and the resin bottom surface 72.

As shown in FIG. 4, a recess portion 75 is formed in the resin encapsulation portion 7. The recess portion 75 is depressed from the resin bottom surface 72. The recess portion 75 has a recess bottom surface 751 and a recess side surface 752. The recess bottom surface 751 is shaped to extend along the x-y plane. In the present embodiment, as 35 shown in FIG. 5, the recess bottom surface 751 is an irregular surface having a fine concave-convex shape. The recess bottom surface 751 is converted to the irregular surface by subjecting the resin encapsulation portion 7 to a blasting process (to be described later). The height difference of the recess bottom surface 751 is in some embodiments, e.g., from 0.1  $\mu$ m to 1  $\mu$ m.

The recess side surface 752 is joined to the recess bottom surface 751 and the resin bottom surface 72. The recess side surface 752 is formed into a taper shape and is inclined with 45 respect to the z direction. The recess side surface 752 is inclined with respect to the z direction such that, as the recess side surface 752 extends in the direction z2, the recess side surface 752 goes away from the recess bottom surface 751 when seen in an x-y plane view.

As shown in FIG. 2, the semiconductor chips 41 and 42 and the passive chips 43 have a rectangular shape when seen in a plan view. The semiconductor chips 41 are, e.g., power chips such as an IGBT, a MOS and a diode. The semiconductor chips 42 are, e.g., LSI chips such as a control IC. The 55 passive chips 43 are, e.g., passives such as a resistor and a capacitor.

The first electrode portions 1, the second electrode portions 2 and the third electrode portions 3 shown in FIGS. 2 through 4 are all made of an electrically conductive material.

The electrode portions 3 shown in FIGS. 2 through 4 are all made of an electrically conductive material.

The electrode portion shown in the right lower region in FIG. 2 is connected to the ground.

The second electrode portion in FIGS. 2 through 4 are all made of an electrically conductive material.

The electrode portion shown in the right lower region in FIG. 2 is connected to the ground.

Each of the first electrode portions 1 (four first electrode portions 1 in the present embodiment) includes a die pad 65 section 11 (see FIGS. 1, 2 and 4), a connecting section 12 (see FIGS. 1 and 2), a wire bonding section 13 (see FIGS.

12

1 and 2) and a lead 14 (see FIGS. 1 through 3). The first electrode portions 1 are spaced apart from one another in the x direction.

Each of the die pad sections 11 is formed into a plate-like shape to extend along the x-y plane. Each of the semiconductor chips 41 is arranged in each of the die pad sections 11. As shown in FIG. 4, a joining layer 991 exists between each of the die pad sections 11 and each of the semiconductor chips 41. The joining layer 991 is made of an electrically conductive material. The electrically conductive material is, e.g., a solder or a silver paste. The solder is relatively high in heat conductivity. If the solder is used as the joining layer 991, it becomes possible to efficiently transfer heat from each of the semiconductor chips 41 to each of the die pad sections 11. The die pad sections 11 are all exposed from the recess bottom surface 751.

Each of the die pad sections 11 has a die pad major surface 111 and a die pad rear surface 112. The die pad major surface 111 faces in the direction z1. The die pad rear surface 112 faces in the direction z2. That is to say, the die pad major surface 111 and the die pad rear surface 112 face in opposite directions from each other. Each of the semiconductor chips 41 is arranged in the die pad major surface 111. The joining layer 991 exists between the die pad major surface 111 and each of the semiconductor chips 41. The die pad rear surface 112 is positioned in the same position as the recess bottom surface 751 in the thickness direction of the die pad sections 11 (in the z direction). The die pad rear surface 112 may be positioned at the open side of the recess portion 75 with respect to the recess bottom surface 751. In the present embodiment, as shown in FIG. 5, the die pad rear surface 112 is an irregular surface having a fine concave-convex shape. The die pad rear surface 112 is converted to the irregular surface by performing a blasting process to the die pad sections 11 (to be described later). The height difference of the die pad rear surface 112 (the height difference between the top and bottom ends of the concave portions) is in some embodiments, e.g., from 0.01 µm to 1 µm.

As shown in FIG. 2, each of the connecting sections 12 is positioned between each of the die pad sections 11 and each of the wire bonding sections 13 and is joined to each of the die pad sections 11 and each of the wire bonding sections 13. As shown in FIG. 1, each of the connecting sections 12 is shaped to extend along a surface inclined with respect to the x-y plane. Each of the connecting sections 12 is inclined with respect to the x-y plane such that each of the connecting sections 12 extends in the direction z1 as it goes away from each of the die pad sections 11.

Each of the wire bonding sections 13 shown in FIGS. 1 and 2 is shaped to extend along the x-y plane. Each of the wire bonding sections 13 is positioned in the z1 direction with respect to each of the die pad sections 11 in the z direction. The wires 8 are bonded to each of the wire bonding sections 13 and each of the semiconductor chips 41, whereby each of the wire bonding sections 13 and each of the semiconductor chips 41 are electrically connected to each other. Each of the leads 14 is joined to each of the wire bonding sections 13. Each of the leads 14 extends along the from the resin side surface 73 of the resin encapsulation portion 7. In the present embodiment, the leads 14 are used for an insertion-mounting purpose. As shown in FIG. 1, when the semiconductor device 101 is mounted on the substrate 807, each of the leads 14 is bent and inserted into each of the holes 809. A solder layer 810 fills each of the holes 809 in order to fix the leads 14 to the substrate 807.

As shown in FIG. 2, each of the second electrode portions 2 (three second electrode portions 2 in the present embodiment) includes a wire bonding section 23 and a lead 24. The second electrode portions 2 are spaced apart from one another in the x direction.

Each of the wire bonding sections 23 is shaped to extend along the x-y plane. Each of the wire bonding sections 23 is positioned in the z1 direction with respect to each of the die pad sections 11 in the z direction. The wires 8 are bonded to each of the wire bonding sections 23 and each of the 10 semiconductor chips 41, whereby each of the wire bonding sections 23 and each of the semiconductor chips 41 are electrically connected to each other. Each of the leads 24 is joined to each of the wire bonding sections 23. Each of the leads **24** extends along the y direction. Each of the leads **24** 15 has a section protruding from the resin side surface 73 of the resin encapsulation portion 7. In the present embodiment, the leads 24 are used for an insertion-mounting purpose. While not shown in the drawings, just like the leads 14, each of the leads 24 is inserted into each of the holes 809 when 20 the semiconductor device 101 is mounted on the substrate **807**.

The third electrode portions 3 shown in FIGS. 1 and 2 include a plurality of control die pad sections 31 and a plurality of leads 32. The control die pad sections 31 and the 25 leads 32 are all arranged in the same position in the z direction. The semiconductor chips 42 or the passive chips 43 are arranged in the respective control die pad sections 31. Joining layers (not shown) exist between the control die pad sections 31 and the semiconductor chips 42, and between the 30 control die pad sections 31 and the passive chips 43. The rear surfaces of the control die pad sections 31 may not face the heat radiation layer 6 and may not be exposed.

Each of the leads 32 has a section protruding from the resin side surface 73 of the resin encapsulation portion 7. In 35 the present embodiment, the leads 32 are used for the insertion-mounting purpose. As shown in FIG. 1, the leads 32 are inserted into the holes 809 when the semiconductor device 101 is mounted on the substrate 807. As described above with respect to the leads 14, a solder layer 810 fills the 40 holes 809 in order to fix the leads 32 to the substrate 807. The wires 8 are bonded to each of the leads 32 and each of the semiconductor chips 42, whereby each of the leads 32 and each of the semiconductor chips 42 are electrically connected to each other. The wires 8 are also bonded to each 45 of the semiconductor chips 42 and each of the passive chips 43.

The heat radiation layer 6 has an insulating property. As shown in FIG. 4, the heat radiation layer 6 is arranged in the recess portion 75 of the resin encapsulation portion 7. The 50 heat radiation layer 6 is surrounded by the recess side surface 752. In the present embodiment, the heat radiation layer 6 is formed into a plate-like shape to extend along the x-y plane. The heat radiation layer 6 makes direct contact with the die pad sections 11 on which the semiconductor 55 chips 41 are mounted. More specifically, the heat radiation layer 6 makes direct contact with the die pad rear surfaces 112 of the die pad sections 11. The heat radiation layer 6 makes direct contact with the recess bottom surface 751. On the other hand, the heat radiation layer **6** is spaced apart from 60 the recess side surface 752 (at least a portion of the recess side surface 752). In the present embodiment, the heat radiation layer 6 has a section protruding from the resin bottom surface 72.

The heat radiation layer 6 is provided to rapidly dissipate 65 the heat generated in the semiconductor chips 41 to the outside of the semiconductor device 101. In order to rapidly

14

dissipate the heat generated in the semiconductor chips 41 outside of the semiconductor device 101, it is preferred in some embodiments to have the heat conductivity of the material making up the heat radiation layer 6 become larger. The heat radiation layer 6 may be made of a material higher in heat conductivity than the material of which the resin encapsulation portion 7 is made. The heat radiation layer 6 directly faces all the die pad sections 11. As shown in FIG. 3, the heat radiation layer 6 overlaps with all the respective die pad sections 11 when seen in an x-y plane view (when seen in the thickness direction of the heat radiation layer 6).

The heat radiation layer 6 is called a heat radiation sheet (or a high-heat-conductivity sheet). The heat radiation layer 6 includes an elastic layer 69. The elastic layer 69 is made of an insulating material. In the present embodiment, the heat radiation layer 6 is formed of only the elastic layer 69. The elastic layer **69** is exposed in the direction (the direction z2) in which the recess portion 75 is opened. As shown in FIG. 3, the elastic layer 69 overlaps with all the die pad sections 11 when seen in the thickness direction z of the heat radiation layer 6 (when seen in an x-y plane view). The elastic layer 69 is a layer made of a material having a relatively small Young's modulus. The Young's modulus of the elastic layer 69 in some embodiments may be smaller than the Young's modulus of the resin encapsulation portion 7. The heat radiation layer 6 is, e.g., a relatively soft sheet available before a thermosetting resin sheet is cured. The elastic layer **69** is made of, e.g., an epoxy-based resin. The elastic layer 69 may be made of a silicon rubber. Unlike the present embodiment, the heat radiation layer 6 may be configured to include a base material and adhesive layers applied on the opposite surfaces of the base material. In that case, the adhesive layer makes up the elastic layer. Unlike the present embodiment, the heat radiation layer 6 may be formed by applying an insulating paste on the recess portion

As shown in FIGS. 3 and 4, the heat radiation layer 6 has a major surface 61, a rear surface 62 and a side surface 63. The major surface 61 faces in the direction z1. When seen in an x-y plane view, the major surface 61 overlaps with the die pad rear surface 112 of each of the die pad sections 11 and the recess bottom surface **751**. The major surface **61** of the heat radiation layer 6 makes direct contact with the die pad rear surface 112 and the recess bottom surface 751. As described above with reference to FIG. 5, the die pad rear surface 112 and the recess bottom surface 751 are irregular surfaces. For that reason, the major surface 61 making direct contact with the die pad rear surface 112 and the recess bottom surface 751 is also formed of an irregular surface. The rear surface 62 faces in the direction z2 opposite to the direction in which the major surface 61 faces. The rear surface 62 is not covered by the resin encapsulation portion 7 and is exposed. The side surface 63 faces in the direction perpendicular to the direction z, i.e., the thickness direction of the heat radiation layer 6. The side surface 63 of the heat radiation layer 6 is spaced apart from the recess side surface 752 (at least a portion of the recess side surface 752). This is to make sure that, as set forth later, the heat radiation sheet as the heat radiation layer 6 is easily embedded into the recess portion 75 after formation of the resin encapsulation portion 7. In the present embodiment, the heat radiation layer 6 is formed of only the elastic layer 69. Therefore, the major surface 61, the rear surface 62 and the side surface 63 of the heat radiation layer 6 are all made up of the elastic layer 69.

FIG. 10 is a section view illustrating the semiconductor device 101 mounted on the substrate 807 (see FIG. 1). As

shown in FIG. 10, the heat radiation layer 6 makes direct contact with the heat radiation member **808** in a state that the semiconductor device 101 is mounted on the substrate 807. The rear surface **62** of the heat radiation layer **6** is pressed by the heat radiation on member **808** toward the direction at 5 which the recess bottom surface 751 is positioned. Thus the heat radiation layer 6 is elastically deformed, thereby removing the gap between the heat radiation layer 6 and the recess side surface 752. Consequently, the heat radiation layer 6 makes direct contact with the recess side surface 752.

Next, description will be made on a manufacturing method of the semiconductor device 101. In the figures used in describing the manufacturing method, the same components as described above will be designated by like reference symbols.

As shown in FIG. 6, the lead frame 300 including the die pad sections 11, 31, the semiconductor chips 41 and 42 and the passive chips 43 are prepared first. Then, as shown in FIG. 6, each of the semiconductor chips 41 is arranged in one of the die pad sections 11 with the joining layer (not 20 101 to the substrate 807. shown) interposed therebetween. Similarly, each of the semiconductor chips 42 and each of the passive chips 43 are arranged in one of the control die pad sections 31 with the joining layer (not shown) interposed therebetween. Subsequently, as shown in FIG. 6, the wires 8 are bonded to the 25 respective semiconductor chips 41 and 42 and so forth.

Next, as shown in FIGS. 7 and 8, the resin encapsulation portion 7 is formed. As shown in FIG. 7, the resin encapsulation portion 7 is formed by a molding process using a mold **881**. As shown in FIG. 7, the die pad sections **11** are 30 pressed by the mold **881**. Then, a resin material is injected into the mold **881** and is cured. Once the resin material is cured, the mold **881** is removed from the die pad sections **11** and so forth as shown in FIG. 8. In this manner, the resin resin encapsulation portion 7, the recess portion 75 for exposing the die pad sections 11 is formed in the resin encapsulation portion 7. In order to easily remove the mold **881** from the resin encapsulation portion 7 after the resin is cured, the recess side surface 752 of the recess portion 75 is 40 formed into a taper shape as set forth above.

Thin resin burrs covering the die pad sections 11 are sometimes formed after formation of the resin encapsulation portion 7. In order to remove the resin burrs, the die pad sections 11 are subjected to a blasting process (not shown). 45 The blasting process refers to a method for roughening a surface by sputtering non-metallic particles, such as silica sands, or metallic particles at a high speed. As a consequence, the die pad rear surface 112 of each of the die pad sections 11 and the recess bottom surface 751 of the resin 50 encapsulation portion 7 become irregular surfaces having a fine concave-convex shape as shown in FIG. 5.

As shown in FIG. 9, the heat radiation layer 6 is formed in the recess portion 75 of the resin encapsulation portion 7. More specifically, the heat radiation sheet as the heat radia- 55 tion layer 6 is embedded into the recess portion 75. The formation of the recess portion 75 in the resin encapsulation portion 7 allows the heat radiation sheet to be easily positioned with respect to each of the die pad sections 11. Since the surface of the heat radiation sheet is relatively sticky, the 60 heat radiation sheet itself is joined to the recess bottom surface 751 and the die pad rear surface 112.

Thereafter, the lead frame 300 shown in FIG. 6 is appropriately diced to thereby manufacture the semiconductor device 101 shown in FIG. 2.

Next, description will be made on the operations and effects of the present embodiment.

**16**

In the semiconductor device 101, the heat radiation layer 6 includes the elastic layer 69. The elastic layer 69 is exposed in the direction (the direction z2) in which the recess portion 75 is opened. The elastic layer 69 overlaps with each of the die pad sections 11 when seen in an x-y plane view. With this configuration, as shown in FIG. 10, the elastic layer 69 is pressed by the heat radiation member 808 toward the recess bottom surface 751 when the semiconductor device 101 is mounted on the substrate 807. Thus the 10 elastic layer 69 undergoes elastic deformation and makes close contact with the heat radiation member 808. Since the elastic layer 69 and the heat radiation member 808 can be brought into close contact with each other, there is no need to interpose any heat radiating grease between the elastic 15 layer **69** and the heat radiation member **808**. Therefore, it is not necessary that heat radiating grease be applied on the heat radiation member 808 each time the semiconductor device 101 is mounted on the substrate 807. Accordingly, it is possible to efficiently mount the semiconductor device

The semiconductor device 101 is not provided with the heat radiation plate mentioned in the section of background. It is therefore possible to reduce the cost involved in providing the heat radiation plate. Moreover, the thickness of the semiconductor device 101 can be reduced just as much as the thickness of the heat radiation plate.

In the semiconductor device 101, as shown in FIG. 10, the resin encapsulation portion 7 has the resin bottom surface 72. The recess portion 75 is depressed from the resin bottom surface 72. The heat radiation layer 6 has a section protruding beyond the resin bottom surface 72. With this configuration, even if the heat radiation layer 6 is elastically deformed, it is hard for the heat radiation member 808 to make contact with the resin bottom surface 72. It is therefore encapsulation portion 7 can be formed. When forming the 35 possible to reliably bring the heat radiation layer 6 into close contact with the heat radiation member 808.

If the semiconductor device **101** is in such a state that it is mounted on the substrate 807 (see FIG. 1), the heat radiation layer 6 is elastically deformed. The gap between the heat radiation layer 6 and the recess side surface 752 is removed. The heat radiation layer 6 makes direct contact with recess side surface 752. With this configuration, the heat radiation layer 6 and the recess side surface 752 can be spaced apart from each other through a gap in order to easily arrange the heat radiation sheet as the heat radiation layer 6 in the recess portion 75. Moreover, the heat radiation layer 6 can be brought into close contact with the recess side surface 752 in such a state that the semiconductor device 101 is mounted on the substrate 807. Since the heat radiation layer 6 can be brought into close contact with the recess side surface 752, the heat transferred from the die pad sections 11 to the resin encapsulation portion 7 can be transferred to the heat radiation member 808 by way of the recess bottom surface **751** and the heat radiation layer **6**. This assists in enhancing the heat dissipation of the semiconductor device **101**.

In the semiconductor device 101, each of the die pad sections 11 has the die pad rear surface 112 with which the heat radiation layer 6 makes direct contact. As shown in FIG. 5, the die pad rear surface 112 is an irregular surface. With this configuration, it is possible to increase the joining area between the die pad rear surface 112 and the heat radiation layer 6. If the joining area between the die pad rear surface 112 and the heat radiation layer 6 grows larger, the die pad rear surface **112** and the heat radiation layer **6** are strongly joined together. Therefore, the heat radiation layer 6 is hardly separated from the die pad rear surface 112. In

addition, if the joining area between the die pad rear surface 112 and the heat radiation layer 6 grows larger, the heat transferred from the semiconductor chips 41 to the die pad sections 11 can be readily transferred from the die pad sections 11 to the heat radiation layer 6. For that reason, the 5 heat generated in the semiconductor chips 41 can be efficiently transferred outside of the semiconductor device 101 (to the heat radiation member 808 in the present embodiment) by way of the heat radiation layer 6. The semiconductor device 101 is superior in heat dissipation. With the 10 present embodiment, it is possible to provide the semiconductor device 101 capable of suppressing exfoliation of the heat radiation layer 6 and performing superior heat dissipation.

In the semiconductor device **101**, as shown in FIG. **5**, the recess bottom surface **751** is an irregular surface with which the heat radiation layer **6** makes direct contact. With this **17** configuration, it is possible to increase the joining area between heat radiation layer **6** and the resin encapsulation portion **7**. If the joining area between heat radiation layer **6** and the resin encapsulation portion **7** grows larger, it is possible to restrain the heat radiation layer **6** from being separated from the resin encapsulation portion **7**.

In the manufacturing method of the semiconductor device 101, the resin encapsulation portion 7 is subjected to a 25 blasting process, while a blasting process is performed on the die pad rear surface 112. With this configuration, it is not necessary to form a concave-convex section on the recess bottom surface 751 of the resin encapsulation portion 7 in addition to the formation of the concave-convex section on 30 the die pad rear surface 112. This assists in enhancing the manufacturing efficiency of the semiconductor device.

#### Second Embodiment

A second embodiment of the present disclosure will now be described with reference to FIGS. 11 through 22.

FIG. 11 is a section view illustrating a mounting structure of a semiconductor device according to a second embodiment of the present disclosure.

The mounting structure A801 of the semiconductor device shown in FIG. 11 includes a semiconductor device A100, a substrate A807 and a heat radiation member A808.

A plurality of electronic parts is mounted on the substrate A807. The substrate A807 is made of an insulating material. 45 A wiring pattern not shown is formed in the substrate A807. A plurality of holes A809 is formed in the substrate A807. The heat radiation member A808 is made of a material having relatively high heat conductivity, e.g., a metal such as aluminum. The heat radiation member A808 is fixed with 50 respect to the substrate A807 by a support member not shown. The semiconductor device A100 is mounted on the substrate A807. In the present embodiment, the semiconductor device A100 is an article called an IPM (Intelligent Power Module). The semiconductor device A100 can find its 55 application in, e.g., an air conditioner or a motor control device.

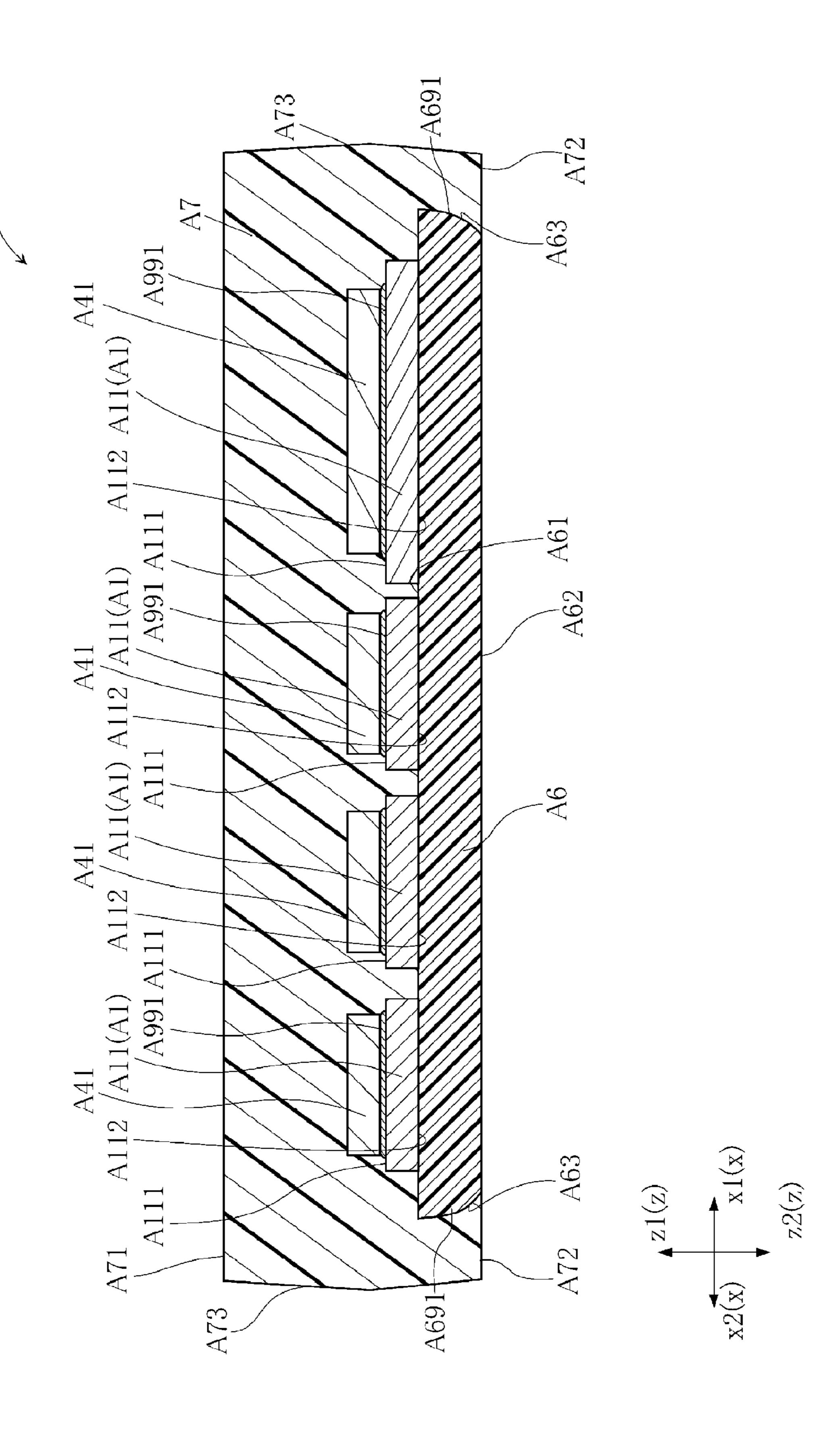

FIG. 12 is a (partially cut away) plan view of the semiconductor device according to the second embodiment of the present disclosure prior to bending the leads. FIG. 13 60 is a bottom view of the semiconductor device according to the second embodiment of the present disclosure prior to bending the leads. FIG. 14 is a section view taken along line XIV-XIV in FIG. 12. FIG. 15 is a section view taken along line XV-XV in FIG. 12.

The semiconductor device A100 shown in these figures includes first electrode portions A1, second electrode por-

**18**

tions A2, third electrode portions A3, semiconductor chips A41 and A42, passive chips A43, a heat radiation plate A6, a resin encapsulation portion A7, wires A8 and a joining layer A991. In FIG. 12, the resin encapsulation portion A7 is not shown and is indicated by a double-dot chain line.

The resin encapsulation portion A7 shown in FIGS. 13 through 15 covers the first electrode portions A1, the second electrode portions A2, the third electrode portions A3, the semiconductor chips A41 and A42, the passive chips A43, the heat radiation plate A6, the wires A8 and the joining layer A991. The resin encapsulation portion A7 is made of an insulating resin. The insulating resin may be, e.g., a black epoxy resin. As shown in FIGS. 14 and 15, the resin encapsulation portion A7 has a resin major surface A71, a resin bottom surface A72 and a resin side surface A73.

The resin major surface A71 is a smooth surface facing in the direction z1 and extends along the x-y plane. The resin bottom surface A72 is a smooth surface facing in the direction z2 opposite to the direction z1 and extends along the x-y plane. The resin side surface A73 is shaped to surround the semiconductor chips A41 and A42 and the passive chips A43 when seen in an x-y plane view. The resin side surface A73 is joined to the resin major surface A71 and the resin bottom surface A72.

In the present embodiment, the resin encapsulation portion A7 includes a plurality of intermediate sections A75. The intermediate sections A75 will be described later.

As shown in FIG. 12, the semiconductor chips A41 and A42 and the passive chips A43 have a rectangular shape when seen in a plan view. The semiconductor chips A41 are, e.g., power chips such as an IGBT, a MOS and a diode. The semiconductor chips A42 are, e.g., LSI chips such as a control IC. The passive chips A43 are, e.g., passives such as a resistor and a capacitor.

The first electrode portions A1, the second electrode portions A2 and the third electrode portions A3 shown in FIGS. 12 through 15 have electric conductivity. In other words, the first electrode portions A1, the second electrode portions A2 and the third electrode portions A3 are all made of an electrically conductive material. The electrically conductive material may be, e.g., copper. The electrode portion shown in the right lower region in FIG. 12 is connected to the ground.

Each of the first electrode portions A1 (four first electrode portions A1 in the present embodiment) includes a die pad section A11 (see FIGS. 11 through 14), a connecting section A12 (see FIGS. 11 and 12), a wire bonding section A13 (see FIGS. 11 and 12) and a lead A14 (see FIGS. 11 and 12). The first electrode portions A1 are spaced apart from one another in the x direction.

Each of the die pad sections A11 is formed into a plate-like shape to extend along the x-y plane. The semiconductor chips A41 are arranged in the die pad sections A11. More specifically, the semiconductor chips A41 which generate heat easily are joined to the die pad sections A11.

Each of the die pad sections A11 has a die pad major surface A111 and a die pad rear surface A112. The die pad major surface A111 faces in the direction z1. The die pad rear surface A112 faces in the direction z2. That is to say, the die pad major surface A111 and the die pad rear surface A112 face toward the opposite directions from each other. Each of the semiconductor chips A41 is arranged in the die pad major surface A111. More specifically, each of the semiconductor chips A41 is joined to the die pad major surface A111. The joining layer A991 (to be described later) exists between the die pad major surface A111 and each of the semiconductor chips A41.

As shown in FIGS. 11 and 12, each of the connecting sections A12 is positioned between each of the die pad sections A11 and each of the wire bonding sections A13 and is joined to each of the die pad sections A11 and each of the wire bonding sections A13. Each of the connecting sections 5 A12 is shaped to extend along a surface inclined with respect to the x-y plane. Each of the connecting sections A12 is inclined with respect to the x-y plane such that each of the connecting sections A12 extends in the direction z1 as it goes away from each of the die pad sections A11.

Each of the wire bonding sections A13 shown in FIGS. 11, **12** and **15** is shaped to extend along the x-y plane. Each of the wire bonding sections A13 is positioned in the z1 direction with respect to each of the die pad sections A11 in the direction z. The wires A8 are bonded to each of the wire 15 bonding sections A13 and each of the semiconductor chips A41, whereby each of the wire bonding sections A13 and each of the semiconductor chips A41 are electrically connected to each other. Each of the leads A14 is joined to each of the wire bonding sections A13. Each of the leads A14 20 extends along the direction y. Each of the leads A14 has a section protruding from the resin side surface A73 of the resin encapsulation portion A7. In the present embodiment, each of the leads A14 is used for an insertion-mounting purpose. As shown in FIG. 11, when the semiconductor 25 device A100 is mounted on the substrate A807, each of the leads A14 is bent and inserted into each of the holes A809. A solder layer A810 fills each of the holes A809 in order to fix the leads A14 to the substrate A807.

As shown in FIG. 12, each of the second electrode 30 portions A2 (three second electrode portions A2 in the present embodiment) includes a wire bonding section A23 and a lead A24. The second electrode portions A2 are spaced apart from one another in the x direction.

along the x-y plane. Each of the wire bonding sections A23 is positioned in the z1 direction with respect to each of the die pad sections A11 in the direction z. The wires 8 are bonded to each of the wire bonding sections A23 and each of the semiconductor chips A41, whereby each of the wire 40 bonding sections A23 and each of the semiconductor chips A41 are electrically connected to each other. Each of the leads A24 is joined to each of the wire bonding sections A23. Each of the leads A24 extends along the direction y. Each of the leads A24 has a section protruding from the resin side 45 surface A73 of the resin encapsulation portion A7. In the present embodiment, the leads A24 are used for an insertionmounting purpose. While not shown in the drawings, just like the leads 14, the leads A24 are inserted into the holes A809 when the semiconductor device A100 is mounted on 50 the substrate A807.

The third electrode portions A3 shown in FIGS. 11 and 12 include a plurality of control die pad sections A31 and a plurality of leads A32. The control die pad sections A31 and the leads A32 are all arranged in the same position in the z 55 direction. The semiconductor chips A42 or the passive chips A43 are arranged in the respective control die pad sections A31. A joining layer (not shown) exists between the control die pad sections A31 and the semiconductor chips A42, and between the control die pad sections A31 and the passive 60 chips A43. The rear surfaces of the control die pad sections A31 may not face the heat radiation plate A6 and may not be exposed.

Each of the leads A32 has a section protruding from the resin side surface A73 of the resin encapsulation portion A7. 65 In the present embodiment, the leads A32 are used for an insertion-mounting purpose. As shown in FIG. 11, the leads

**20**

A32 are inserted into the holes A809 when the semiconductor device A100 is mounted on the substrate A807. As described above with respect to the leads 14, a solder layer A810 fills the holes A809 in order to fix the leads A32 to the substrate A807. The wires A8 are bonded to each of the leads A32 and each of the semiconductor chips A42, whereby each of the leads A32 and each of the semiconductor chips A42 are electrically connected to each other. The wires A8 are also bonded to each of the semiconductor chips A42 and 10 each of the passive chips A43.

As shown in FIGS. 14 and 15, the joining layer A991 exists between each of the die pad sections A11 and each of the semiconductor chips A41. The joining layer A991 joins each of the semiconductor chips A41 to each of the die pad sections A11. The joining layer A991 is made of, e.g., an electrically conductive material. The electrically conductive material may be, e.g., a silver paste or a solder. The solder is relatively high in heat conductivity. If the solder is used as the joining layer A991, it becomes possible to efficiently transfer heat from each of the semiconductor chips A41 to each of the die pad sections A11. The joining layer A991 may be made of an insulating material instead of the electrically conductive material.

As shown in FIGS. 13 through 15, the heat radiation plate A6 directly faces the die pad sections A11. In the present embodiment, the heat radiation plate A6 is formed into a plate-like shape to extend along the x-y plane. The heat radiation plate A6 is spaced apart from the die pad sections A11. The intermediate sections A75 mentioned above exist between the heat radiation plate A6 and the die pad sections A11. The intermediate sections A75 make direct contact with the heat radiation plate A6 and the die pad sections A11. Therefore, the heat radiation plate A6 and the die pad sections A11 are joined by the resin encapsulation portion Each of the wire bonding sections A23 is shaped to extend 35 A7. Since the intermediate sections A75 are a portion of the resin encapsulation portion A7, the material making up the intermediate sections A75 is the same as the material making up the section of the resin encapsulation portion A7 that covers the semiconductor chips A41 and A42. The heat radiation plate A6 is exposed from the resin bottom surface A72 of the resin encapsulation portion A7.