US00RE49718E

# (19) United States

## (12) Reissued Patent

Iwasaka et al.

(10) Patent Number: US RE49,718 E

(45) Date of Reissued Patent: Oct. 31, 2023

## (54) MANUFACTURING METHOD OF SUBSTRATE FOR DISPLAY DEVICE AND MANUFACTURING METHOD OF DISPLAY DEVICE

- (71) Applicant: **Trivale Technologies**, Santa Clara, CA (US)

- (72) Inventors: **Toshihiko Iwasaka**, Kikuchi (JP); **Yusuke Yamagata**, Tokyo (JP); **Kazunori Inoue**, Kikuchi (JP)

- (73) Assignee: **Trivale Technologies**, Santa Clara, CA (US)

- (21) Appl. No.: 17/321,054

- (22) Filed: May 14, 2021

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 10,290,662

Issued: May 14, 2019

Appl. No.: 15/363,083

Filed: Nov. 29, 2016

#### (30) Foreign Application Priority Data

- (51) Int. Cl. H01L 27/12 (2006.01)

- (52) **U.S. Cl.**CPC ...... *H01L 27/127* (2013.01); *H01L 27/124* (2013.01); *H01L 27/1225* (2013.01)

- (58) Field of Classification Search

CPC .. H01L 27/1225; H01L 27/124; H01L 27/127

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 2003/0218222 | A1*           | 11/2003 | Wager, III H01L 29/7869 |

|--------------|---------------|---------|-------------------------|

| 2000/0025020 |               | 2/2000  | 257/E29.147             |

| 2008/0035920 |               |         |                         |

| 2013/0063675 | Al*           | 3/2013  | Misaki H01L 29/7869     |

|              |               |         | 349/46                  |

| 2015/0311233 | $\mathbf{A}1$ | 10/2015 | Hsin et al.             |

#### FOREIGN PATENT DOCUMENTS

| CN | 102938382     | A          | 2/2013  |                  |

|----|---------------|------------|---------|------------------|

| CN | 103995378     | A          | 8/2014  |                  |

| JP | 363-183482    | A          | 7/1988  |                  |

| JP | H05-088191    | A          | 4/1993  |                  |

| JP | H05-232496    | A          | 9/1993  |                  |

| JP | H11-190858    | A          | 7/1999  |                  |

| JP | 2008-040343   | A          | 2/2008  |                  |

| JP | 2008-235871   | A          | 10/2008 |                  |

| JP | 2009-290111   | A          | 12/2009 |                  |

| JP | 2011-187509   | A          | 9/2011  |                  |

| JP | 2015-211212   | A          | 11/2015 |                  |

| WO | WO-2008105347 | A1 *       | 9/2008  | <br>H01L 27/1225 |

| WO | 2016/068314   | A1         | 5/2016  |                  |

| WO | 2017002655    | <b>A</b> 1 | 1/2017  |                  |

<sup>\*</sup> cited by examiner

Primary Examiner — Elizabeth L McKane (74) Attorney, Agent, or Firm — Studebaker & Brackett PC

## (57) ABSTRACT

A substrate for a display device, includes: an insulation substrate; an insulation film, which is formed on the insulation substrate and is primarily made of one of silicon oxide and oxidized metal; an inorganic film, which is formed to be in direct contact with the insulation film and has an insulator part that is formed by changing oxide semiconductor into insulator; and a wiring film, which is formed to be in direct contact with the insulator part.

#### 95 Claims, 34 Drawing Sheets

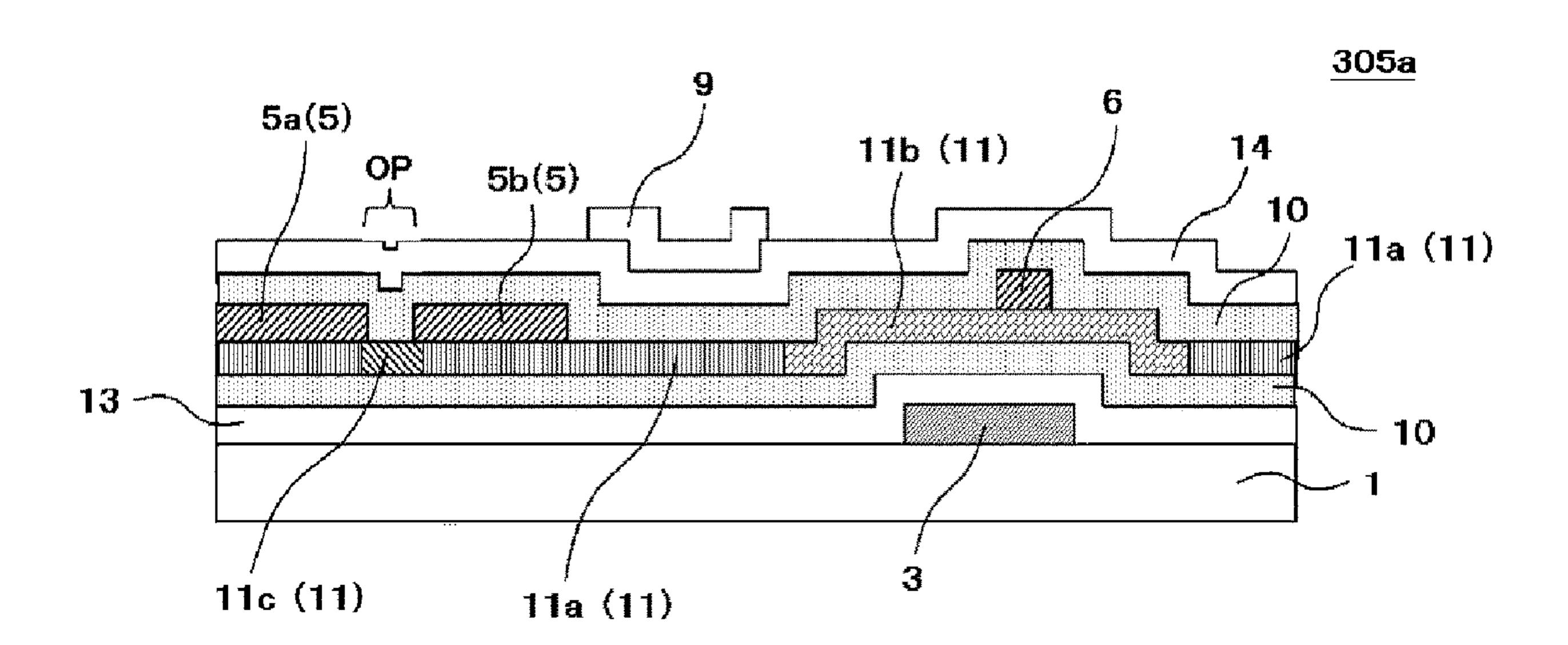

FIG.1

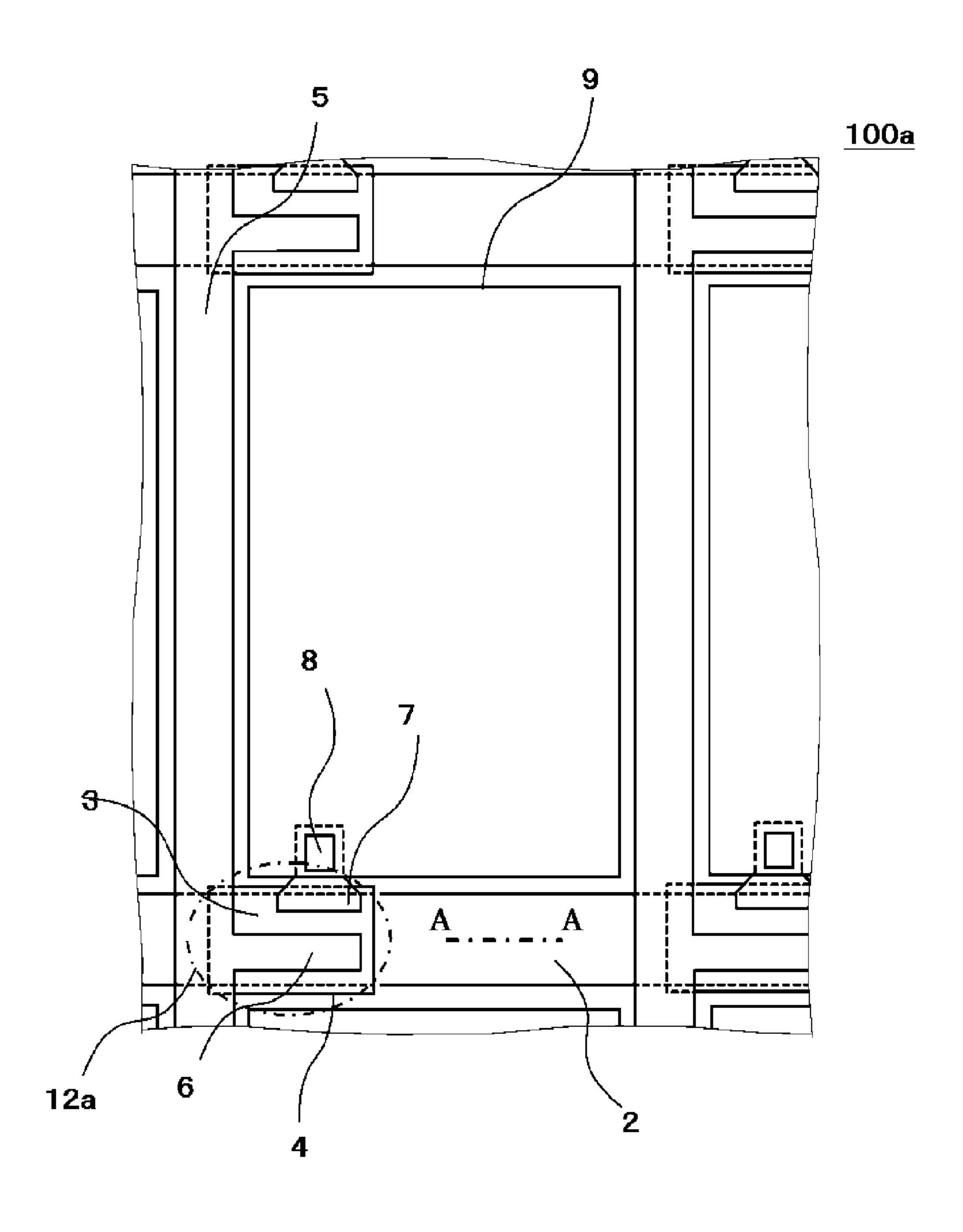

FIG.2

F/G.3

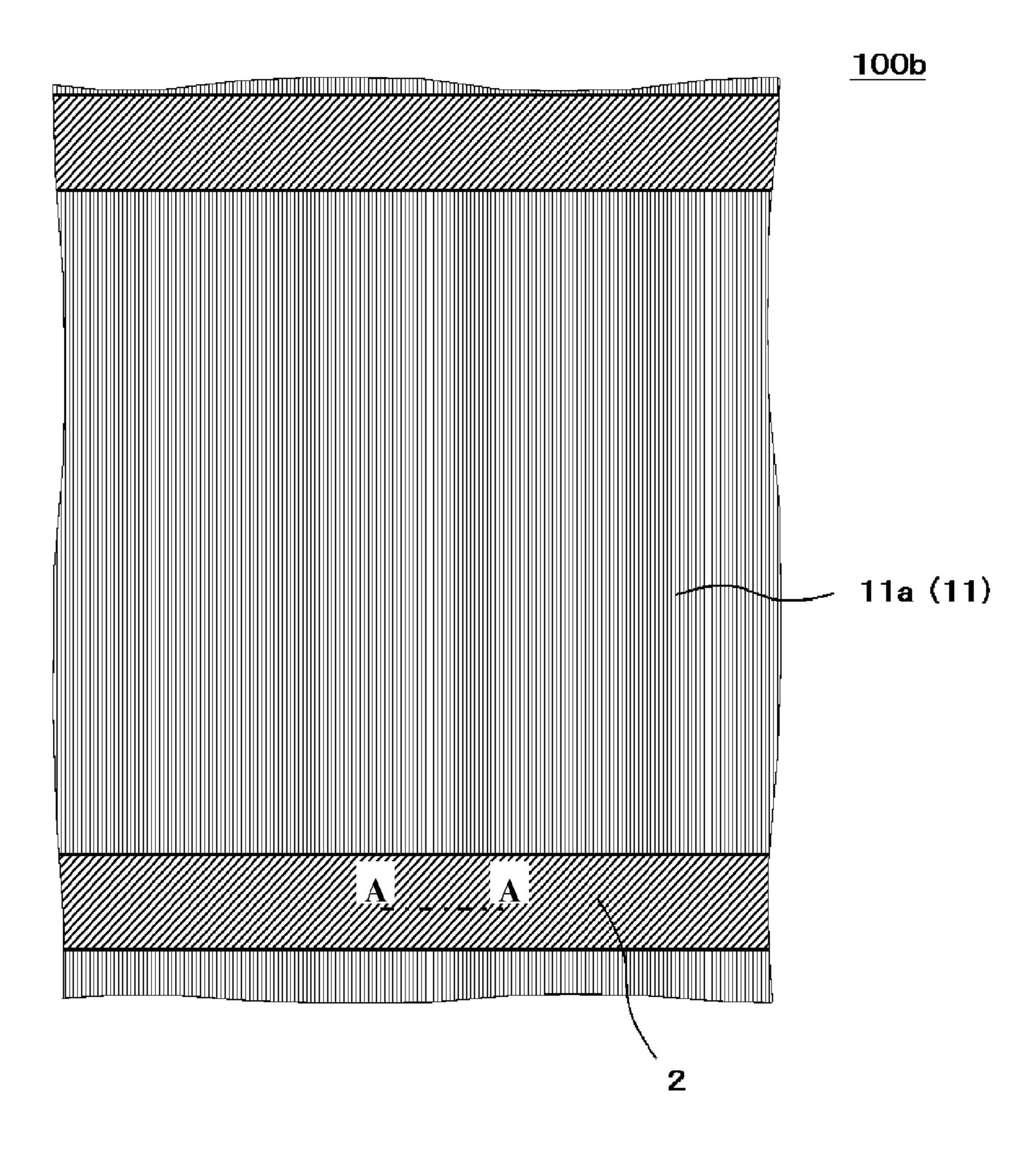

## 100b

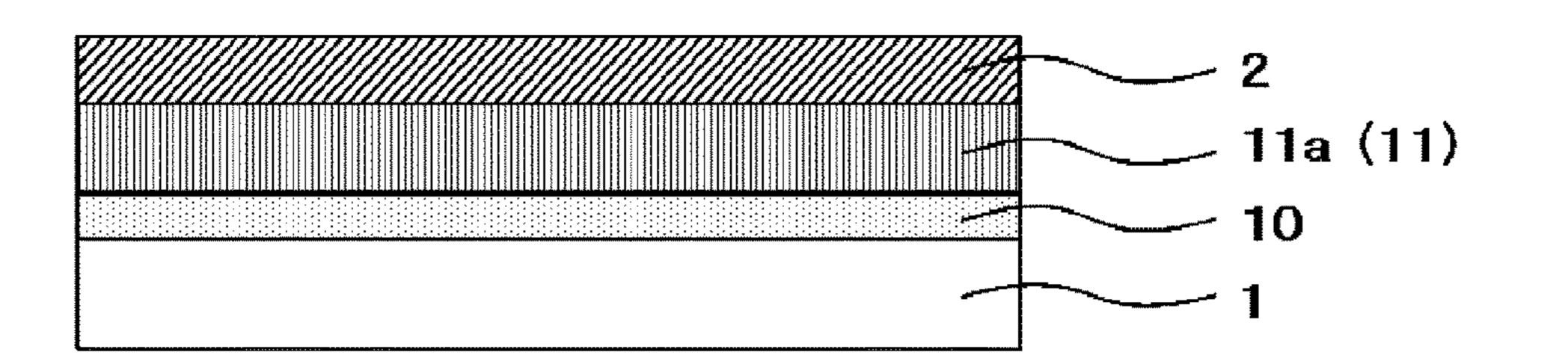

FIG.4

F/G.5

F/G.6A

F/G.6B P

FIG.7

FIG.8

F/G.9

F/G.10

F/G.11

US RE49,718 E

FIG. 12

F/G.13

US RE49,718 E

F/G.14

F/G.15

F/G.16

F/G.17

F/G.18

F/G.19

F/G.20

F/G.21

F/G.22

F/G.23

F/G.24

F/G.25

F/G.26

F/G.27

F/G.28

F/G.29

F/G.30

F/G.31

F/G.32

F/G.33

F/G.34

F/G.35

F/G.36

F/G.37

F/G.38

F/G.39

F/G.40

F/G.41

F/G.42

F/G.43

F/G.44

F/G.45

F/G.46

F/G.47

F/G.48

F/G.49

F/G.50

F/G.51

F/G.52

F/G.53

F/G.54

F/G.55

F/G.56

F/G.57

F/G.58

F/G.59

F/G.60

F/G.61

F/G.62

F/G.63

F/G.64

F/G.65

# F/G.66

F/G.67

F/G.68

F/G.69

FIG. 70

1

## MANUFACTURING METHOD OF SUBSTRATE FOR DISPLAY DEVICE AND MANUFACTURING METHOD OF DISPLAY DEVICE

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough 10 indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

# CROSS-REFERENCE TO RELATED APPLICATION

This application claims priority from Japanese Patent Application No. 2015-242365 filed on Dec. 11, 2015, the entire subject matter of which is incorporated herein by reference.

#### TECHNICAL FIELD

This disclosure relates to a substrate for a display device having a film formed by using oxide semiconductor, a 25 manufacturing method thereof, the display device and a manufacturing method thereof.

#### BACKGROUND

In recent years, a liquid crystal display device is often used as an example of a display device. The liquid crystal display device is includes a thin film transistor (hereinafter referred to as "TFT") array substrate, in which liquid crystal layer is interposed between a pair of translucent insulation 35 substrates. The TFT array substrate includes, on a liquid crystal layer face of one of the pair of translucent insulation substrates, a plurality of scanning wirings and a plurality of signal wirings arranged in a matrix with interposing an insulation film. TFTs are provided in the vicinity of cross 40 points between the scanning wirings and the signal wirings, and pixel electrodes apply image signals through the signal wirings.

Supplying of the image signals to the pixel electrodes is controlled by controlling turning on/off of the TFTs, based 45 on the scanning signals from the scanning wirings. Terminals for inputting the signals to the scanning wirings and the signal wirings are provided at the outer-side end portions of a display region of the TFT array substrate. Further, terminal wirings for coupling between the scanning wirings and the 50 corresponding terminals, and terminals wirings for coupling between the signal wirings and the corresponding terminals are provided.

Further, the liquid crystal display device includes a color filter (hereinafter referred to as "CF") substrate as the other 55 of the pair of translucent insulation substrates.

In the display device, while high precision and miniaturization is progressed, a demand for reducing failure in a manufacturing process is also increased. Failure of the display device is caused based on various reasons. One 60 example of the reasons is a disconnection failure in which a wiring such as the signal wiring, the scanning wiring or the terminal wiring is partially broken due to foreign particle incorporated in the manufacturing process, for example. If the disconnection failure occurs, an electrical signal flowing 65 through this wiring is broken, and thus a display failure such as a line-shaped image appears on a display screen.

2

For example, JP-A-H05-232496 discloses a technique so-called "connection repair" with respect to such the disconnection failure. According to the background art, a laser light is irradiated on two portions which sandwich the disconnection part of the wiring to partially remove the insulation film covering the wiring, and thus two contact holes each penetrating the insulation film are formed, so that a metal film is formed so as to bridge the two contact holes sandwiching the disconnection part, thereby electrically connecting the disconnection part to make this part conductive.

#### **SUMMARY**

However, according to the connection repair described above, shape of the inner wall of the contact hole becomes irregular when forming the contact hole in the insulation film. Accordingly, the coverage performance of the metal film formed as an upper layer becomes low, and sufficient electrical conductively cannot be obtained despite of the connection repair, and thus a conduction failure occurs.

This disclosure provides a substrate for a display device, a manufacturing method thereof, the display device and a manufacturing method thereof, each of which can reduce a conduction failure which occurs at a time of performing connection repair with respect to disconnection of a wiring.

The substrate for the display device and the display device according to this disclosure includes: an insulation substrate;

30 an insulation film, which is formed on the insulation substrate and is primarily made of one of silicon oxide and oxidized metal; an inorganic film, which is formed to be in direct contact with the insulation film and has an insulator part that is formed by changing oxide semiconductor into insulator; and a wiring film, which is formed to be in direct contact with the insulator part.

The method of manufacturing the substrate for the display device according to this disclosure includes: forming, on an insulation substrate, an insulation film, which is primarily made of one of silicon oxide and oxidized metal; forming an inorganic film, which has an insulator part that is formed by changing oxide semiconductor into insulator, to be in direct contact with the insulation film; and forming a wiring film to be in direct contact with the insulator part.

According to the substrate for the display device and the display device according to this disclosure, even if disconnection occurs in the wiring film, it is possible to reduce conduction failure occurring at a time of performing connection repair.

According to the method of manufacturing the substrate for the display device and the method of manufacturing the display device according to this disclosure, even if the disconnection occurs in the wiring film, the conduction failure occurring at the time of performing the connection repair can be reduced.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing and additional features and characteristics of this disclosure will become more apparent from the following detailed descriptions considered with the reference to the accompanying drawings, wherein:

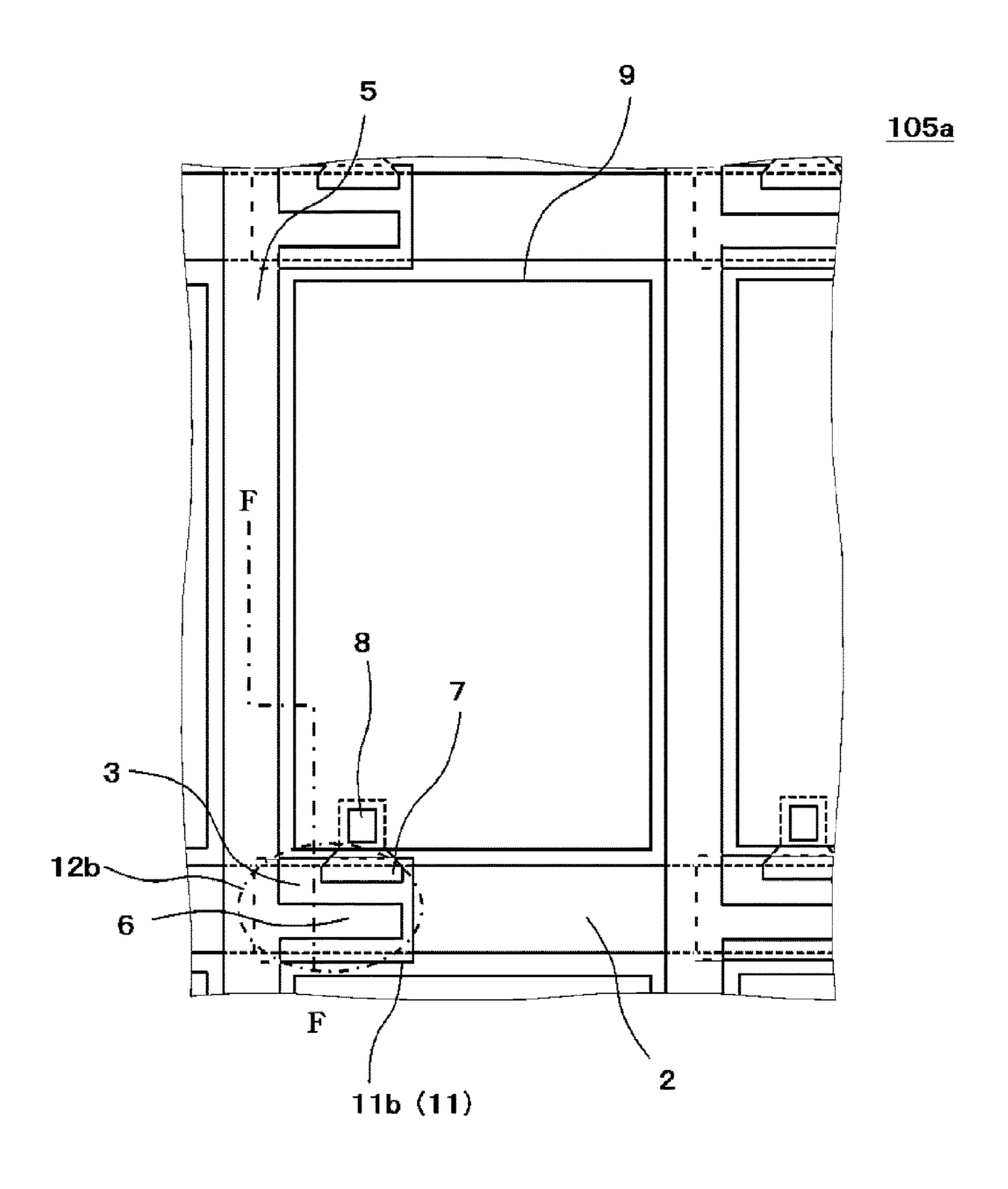

FIG. 1 is a top view illustrating a TFT array substrate according to a first embodiment of this disclosure;

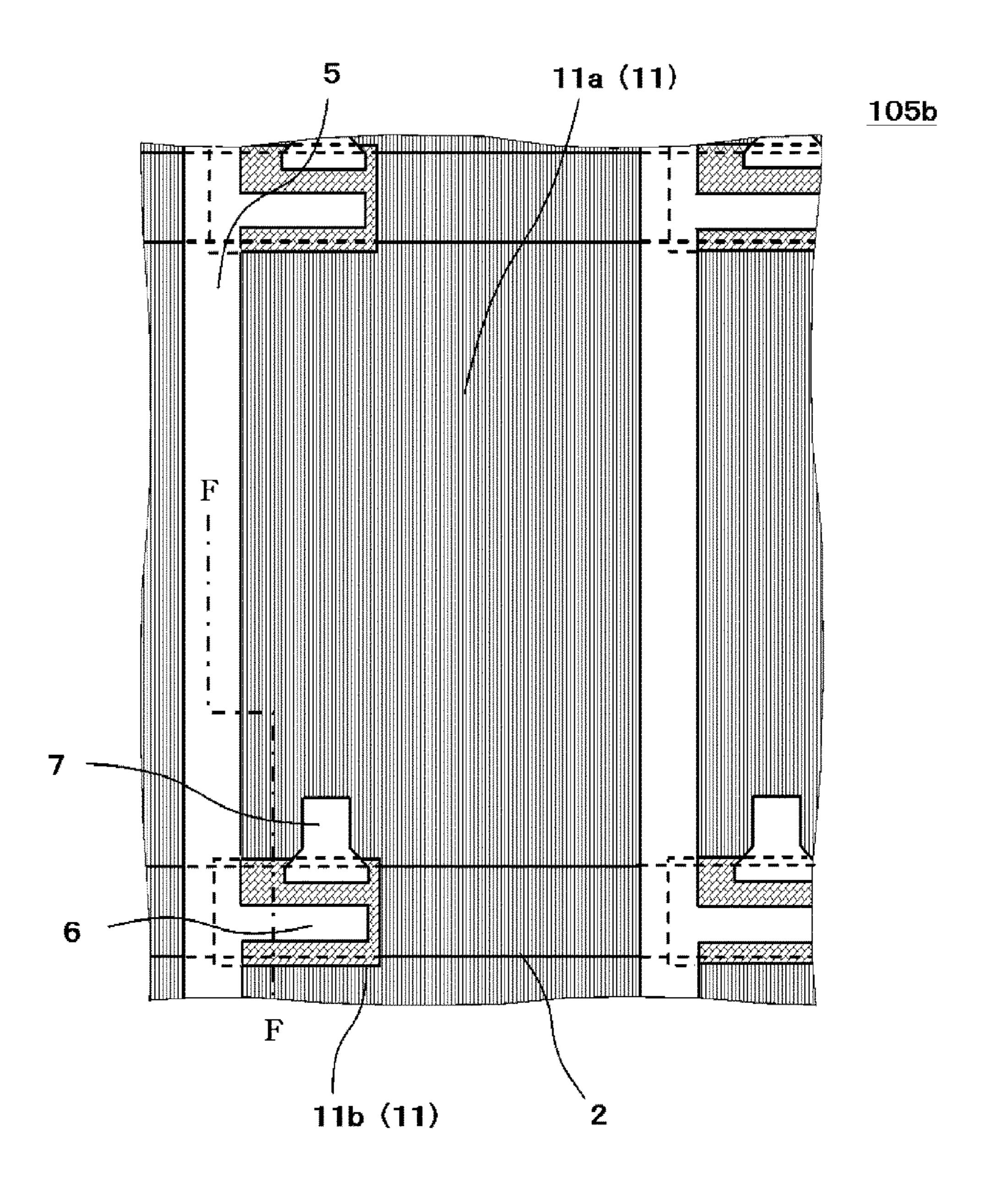

FIG. 2 is a top view illustrating a TFT array substrate according to the first embodiment of this disclosure;

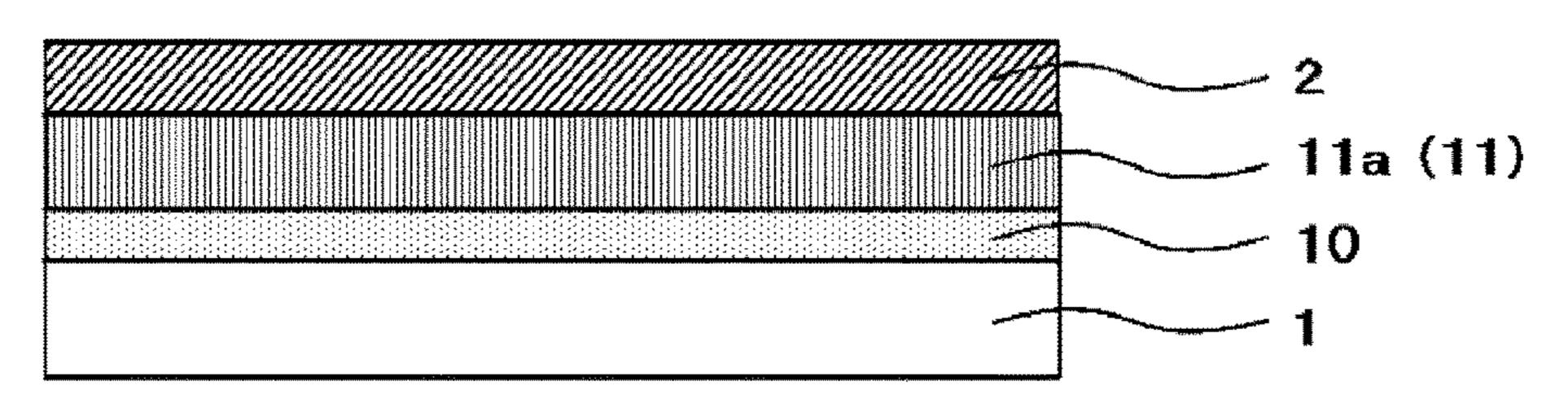

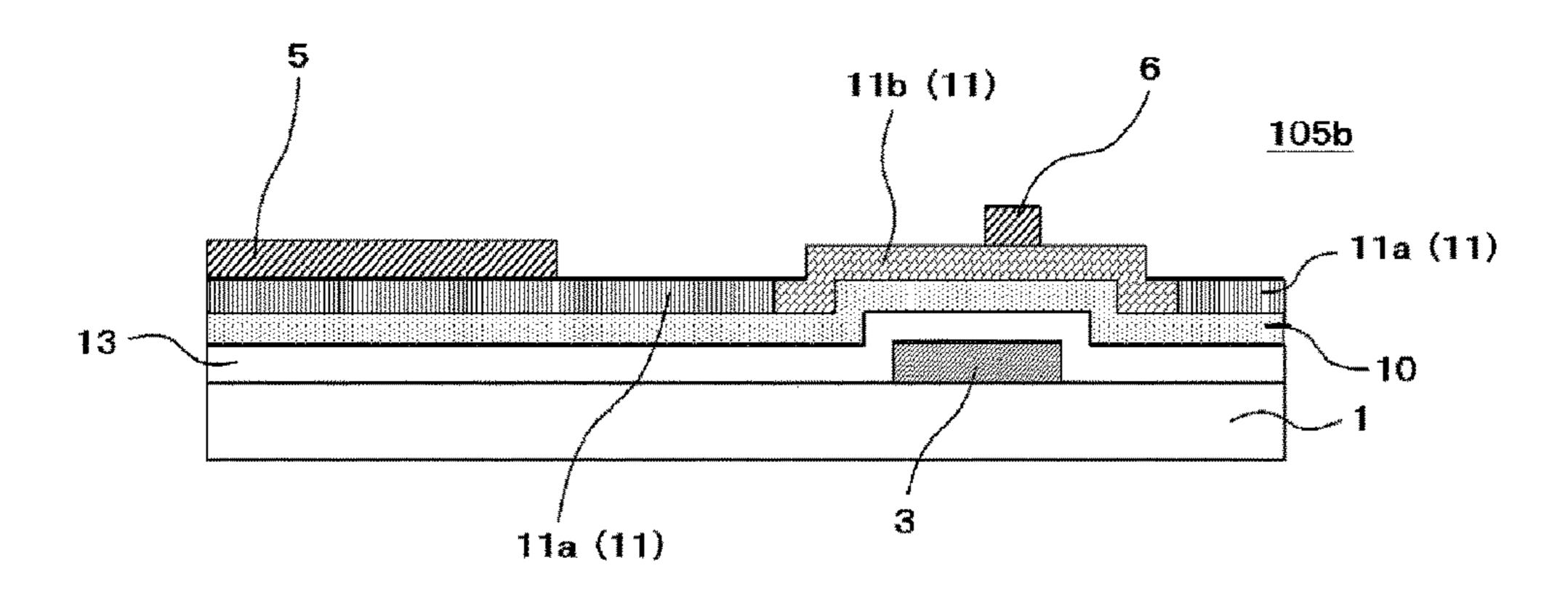

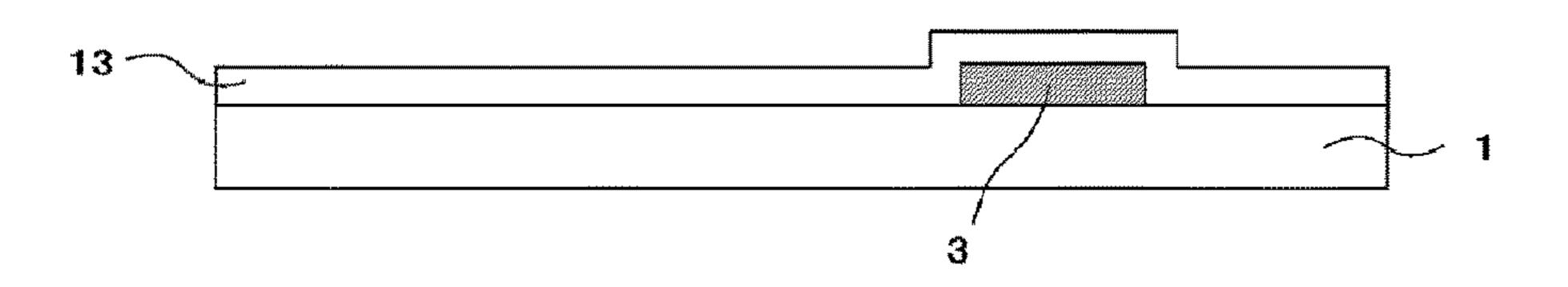

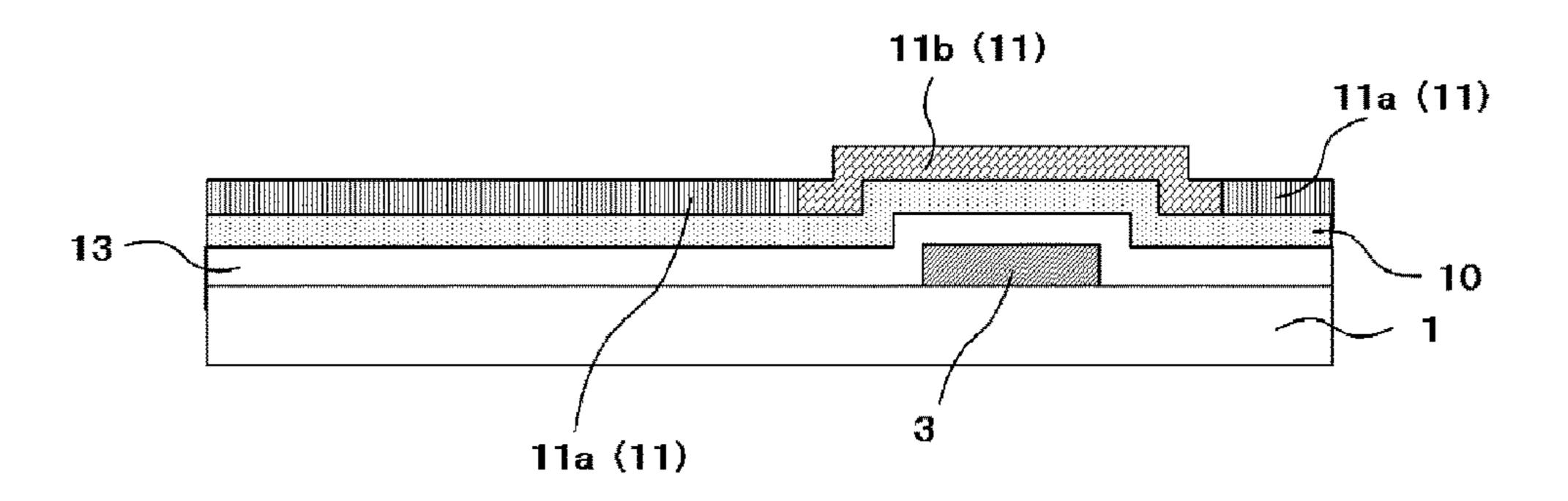

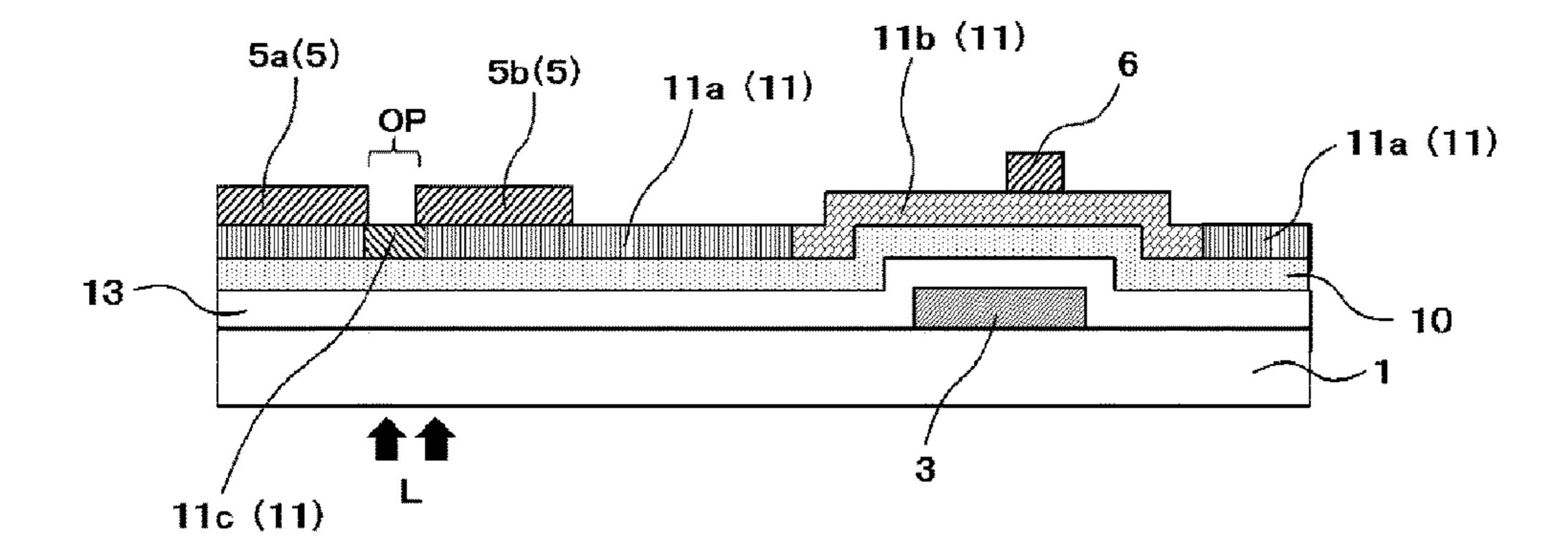

- FIG. 3 is a cross-sectional view illustrating the TFT array substrate according to the first embodiment of this disclosure;

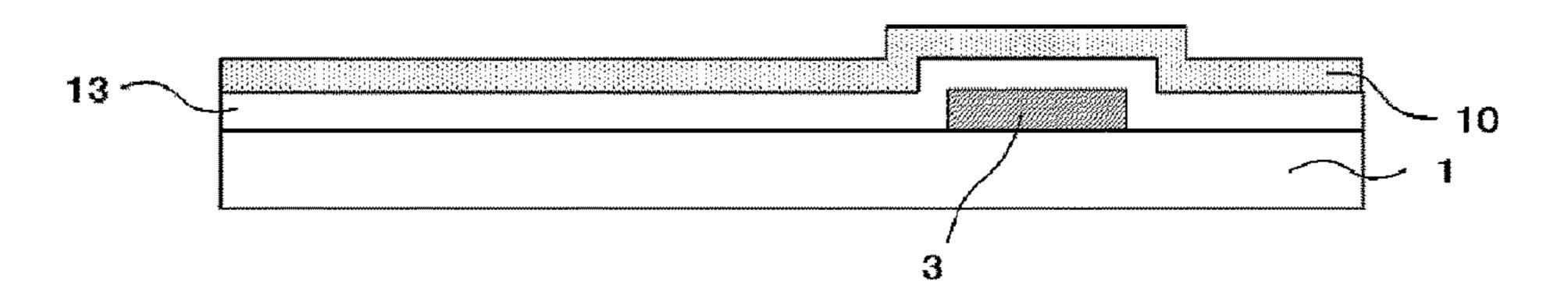

- FIG. 4 is a cross-sectional view illustrating a part of manufacturing process of the TFT array substrate according 5 to the first embodiment of this disclosure;

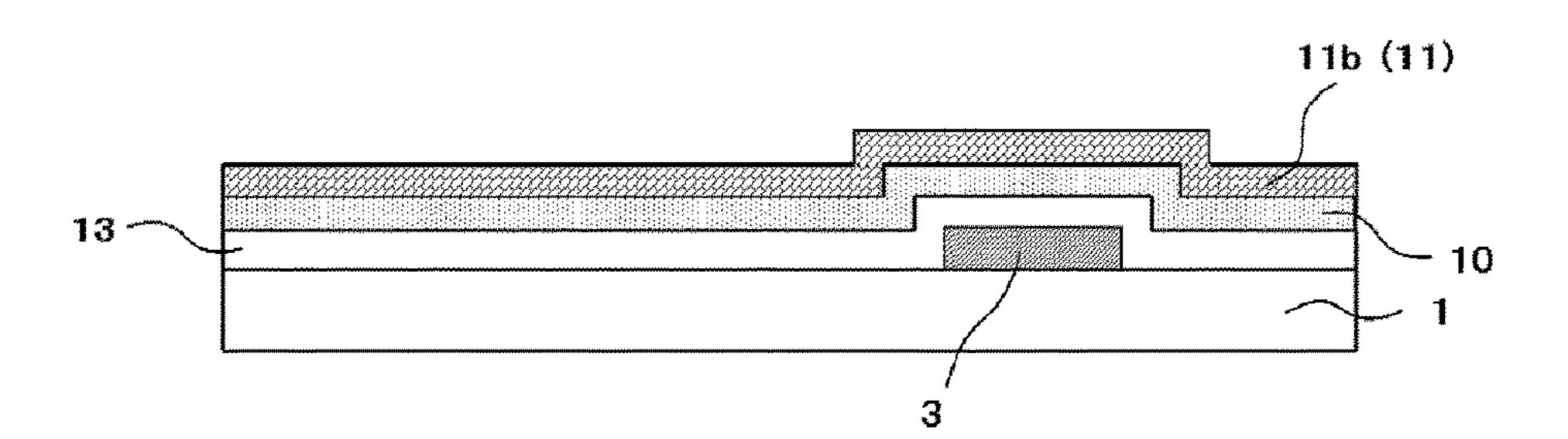

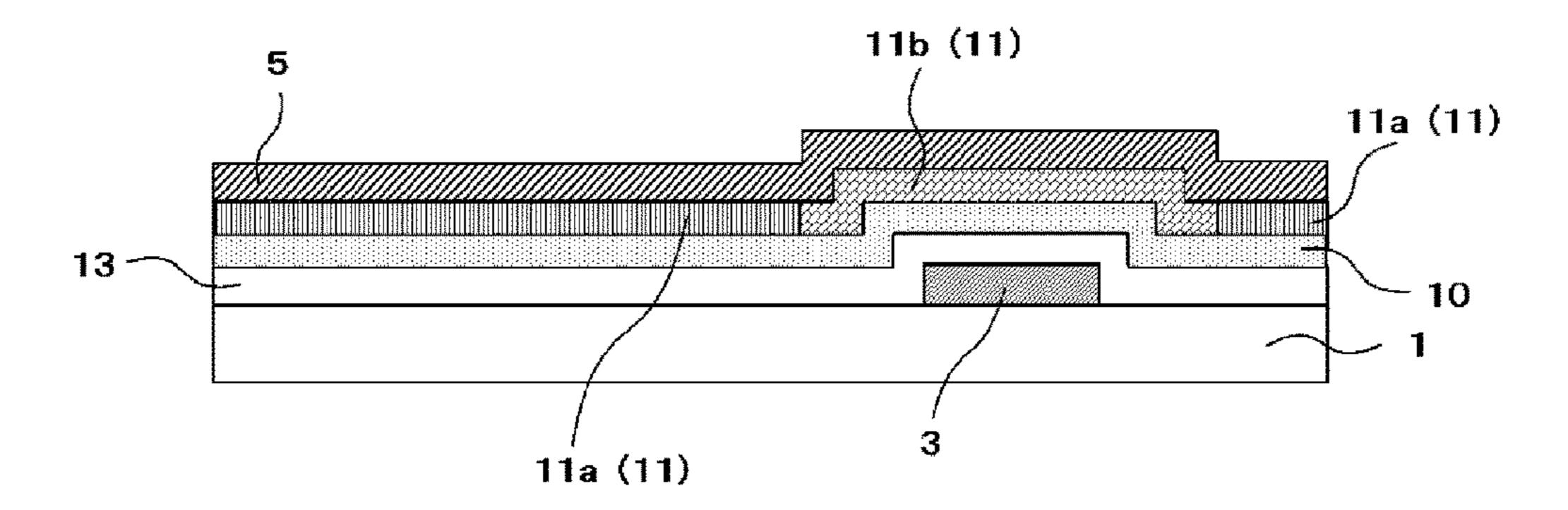

- FIG. **5** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the first embodiment of this disclosure;

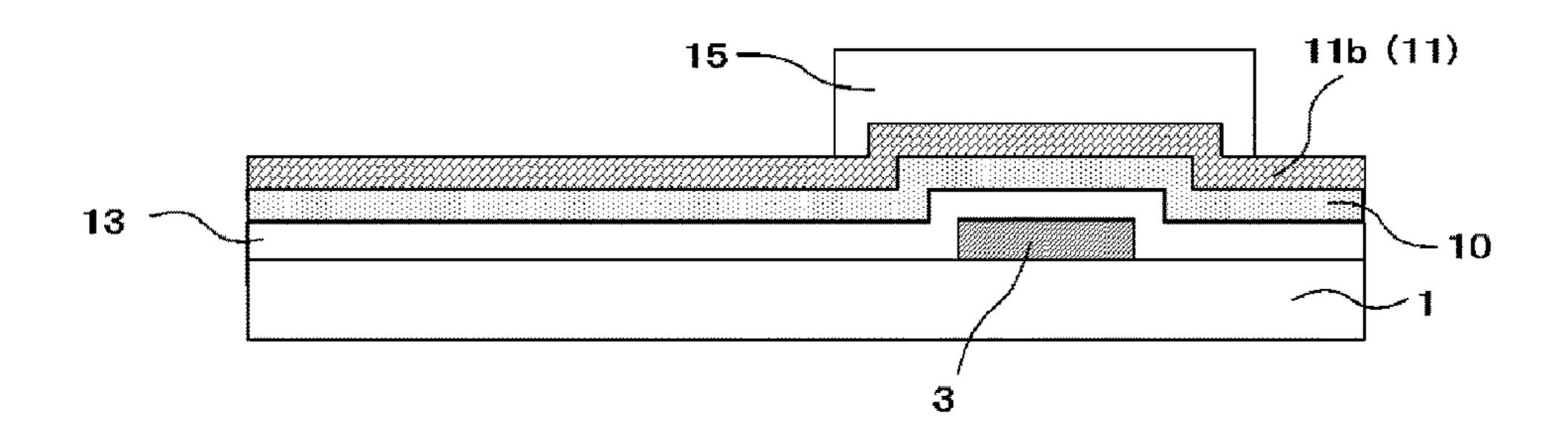

- FIGS. 6A and 6B are cross-sectional views illustrating a 10 part of the manufacturing process of the TFT array substrate according to the first embodiment of this disclosure;

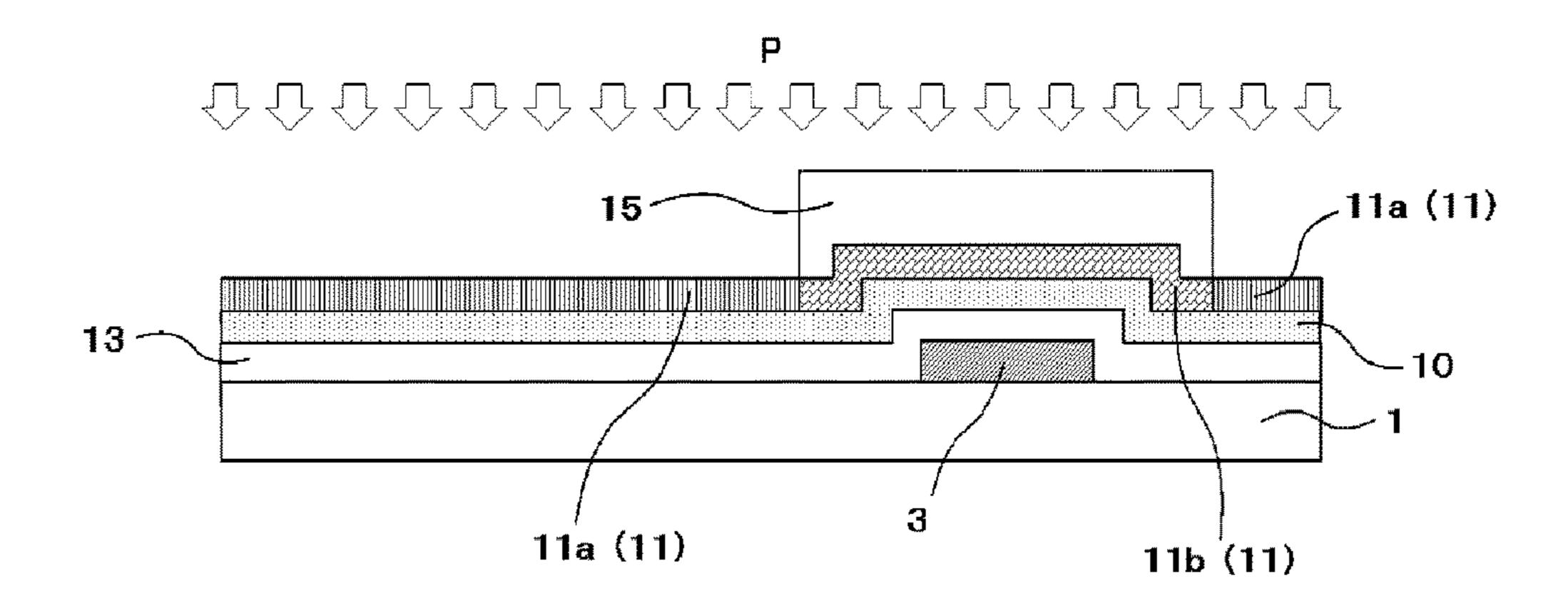

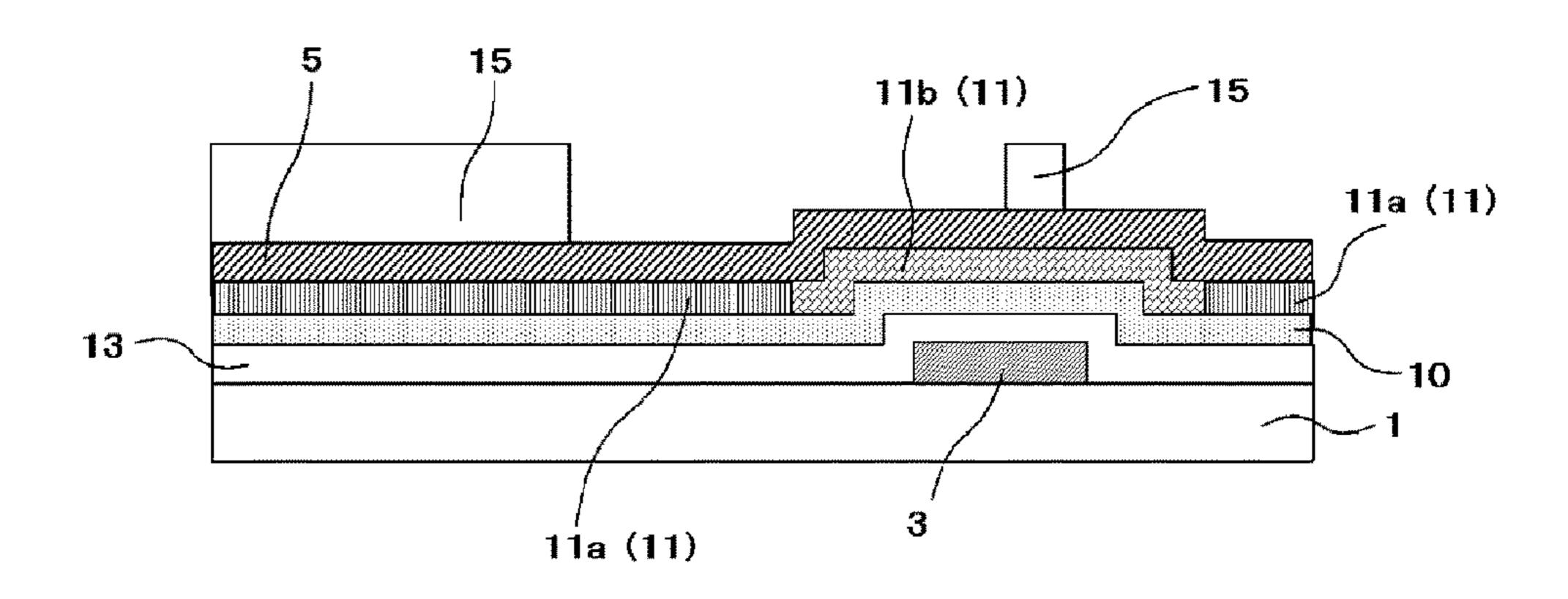

- FIG. 7 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the first embodiment of this disclosure;

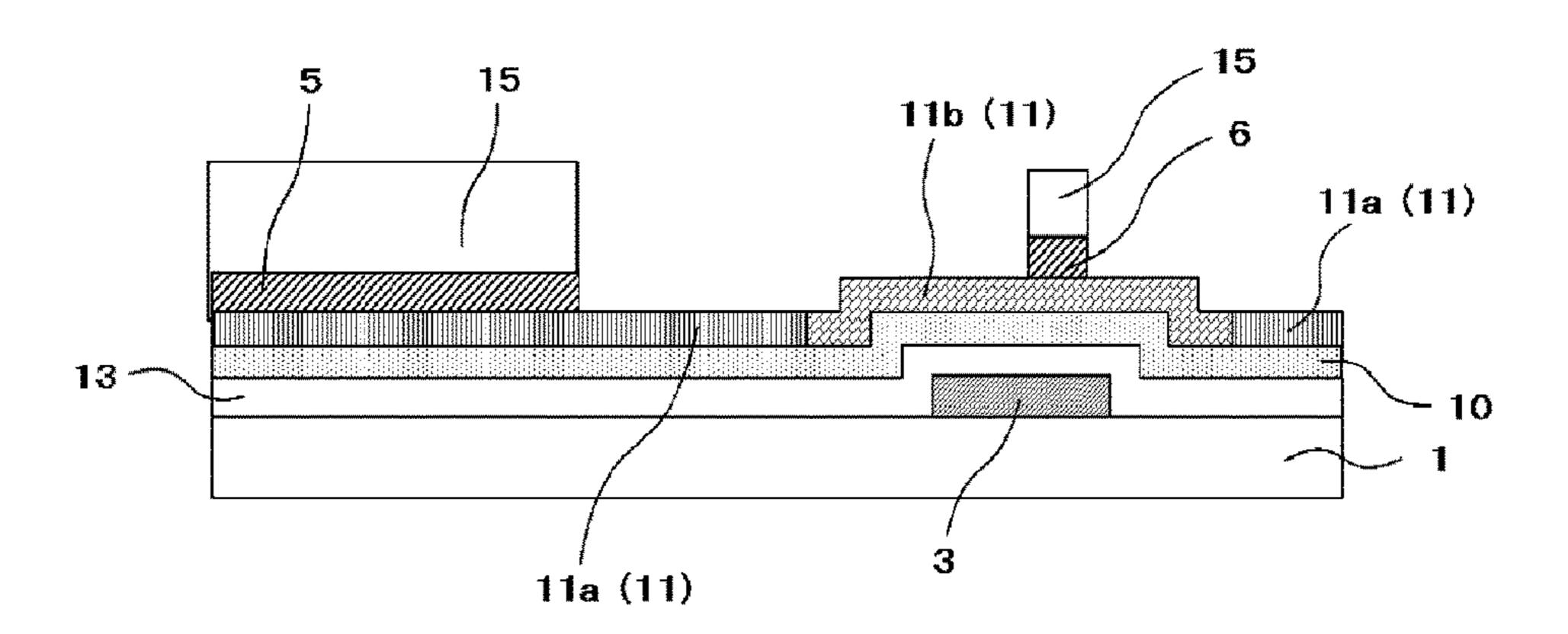

- FIG. 8 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the first embodiment of this disclosure;

- FIG. 9 is a top view illustrating a TFT array substrate according to the first embodiment of this disclosure;

- FIG. 10 is a top view illustrating a TFT array substrate according to the first embodiment of this disclosure;

- FIG. 11 is a top view illustrating a TFT array substrate according to the first embodiment of this disclosure;

- FIG. 12 is a top view illustrating a TFT array substrate 25 according to the first embodiment of this disclosure;

- FIG. 13 is a cross-sectional view illustrating the TFT array substrate according to the first embodiment of this disclosure;

- FIG. 14 is a cross-sectional view illustrating a part of 30 sure; manufacturing process of the TFT array substrate according FIG. to the first embodiment of this disclosure; manufacture.

- FIG. 15 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the first embodiment of this disclosure;

- FIG. **16** is a cross-sectional view illustrating the TFT array substrate according to the first embodiment of this disclosure;

- FIG. 17 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according 40 to the first embodiment of this disclosure;

- FIG. 18 is a top view illustrating the TFT array substrate according to the first embodiment of this disclosure;

- FIG. 19 is a cross-sectional view illustrating a liquid crystal display device according to the first embodiment of 45 this disclosure;

- FIG. 20 is a cross-sectional view illustrating a TFT array substrate according to a second embodiment of this disclosure;

- FIG. 21 is a cross-sectional view illustrating a TFT array 50 sure; substrate according to the second embodiment of this disclosure;

- FIG. 22 is a cross-sectional view illustrating a part of manufacturing process of the TFT array substrate according to the second embodiment of this disclosure;

- FIG. 23 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the second embodiment of this disclosure;

- FIG. **24** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according 60 to the second embodiment of this disclosure;

- FIG. 25 is a cross-sectional view illustrating the TFT array substrate according to the second embodiment of this disclosure;

- FIG. **26** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the second embodiment of this disclosure;

4

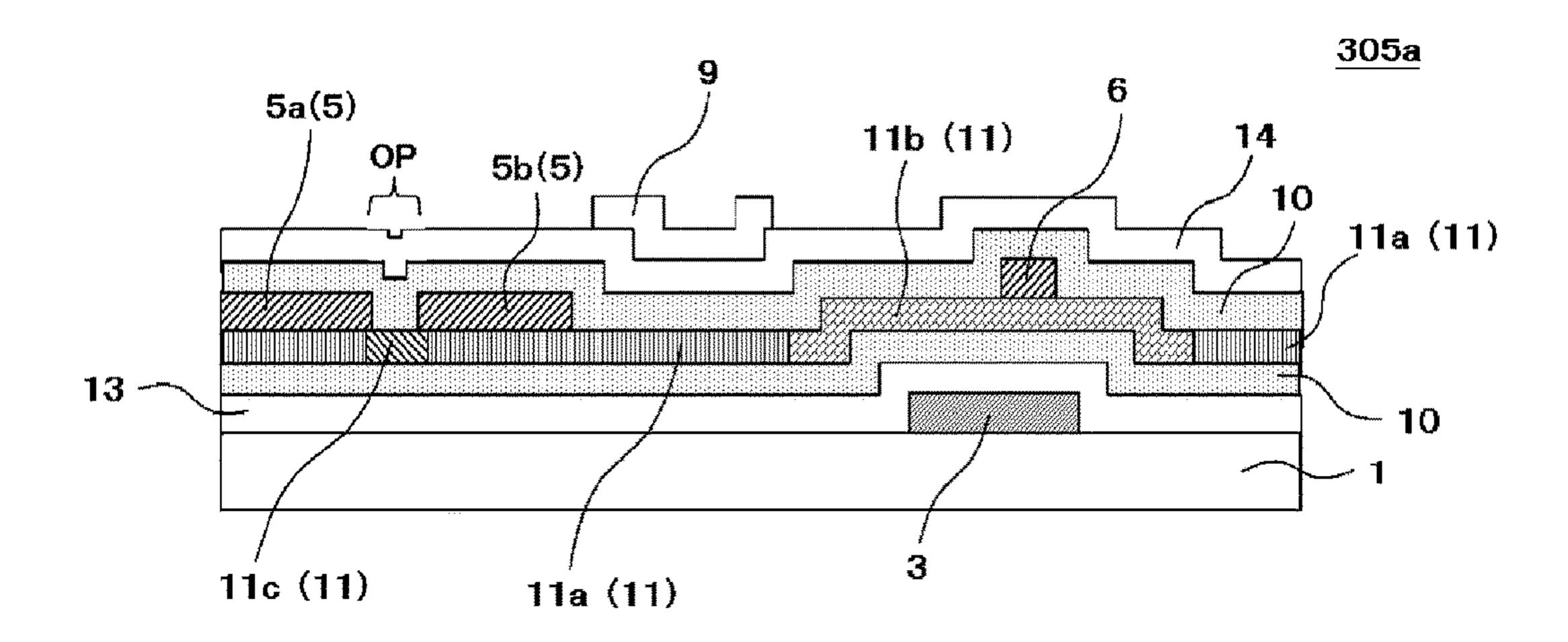

- FIG. 27 is a cross-sectional view illustrating a TFT array substrate according to a third embodiment of this disclosure;

- FIG. 28 is a cross-sectional view illustrating a TFT array substrate according to the third embodiment of this disclosure;

- FIG. 29 is a cross-sectional view illustrating a part of manufacturing process of the TFT array substrate according to the third embodiment of this disclosure;

- FIG. 30 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the third embodiment of this disclosure;

- FIG. 31 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the third embodiment of this disclosure;

- FIG. 32 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the third embodiment of this disclosure;

- FIG. **33** is a cross-sectional view illustrating a TFT array substrate according to the third embodiment of this disclosure;

- FIG. 34 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the third embodiment of this disclosure;

- FIG. **35** is a cross-sectional view illustrating a TFT array substrate according to a fourth embodiment of this disclosure;

- FIG. **36** is a cross-sectional view illustrating a TFT array substrate according to the fourth embodiment of this disclosure:

- FIG. 37 is a cross-sectional view illustrating a part of manufacturing process of the TFT array substrate according to the fourth embodiment of this disclosure;

- FIG. **38** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the fourth embodiment of this disclosure;

- FIG. 39 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the fourth embodiment of this disclosure;

- FIG. **40** is a cross-sectional view illustrating a TFT array substrate according to the fourth embodiment of this disclosure;

- FIG. **41** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the fourth embodiment of this disclosure;

- FIG. **42** is a cross-sectional view illustrating a TFT array substrate according to a fifth embodiment of this disclosure;

- FIG. **43** is a cross-sectional view illustrating a TFT array substrate according to the fifth embodiment of this disclosure;

- FIG. 44 is a cross-sectional view illustrating a part of manufacturing process of the TFT array substrate according to the fifth embodiment of this disclosure;

- FIG. **45** is a top view illustrating a TFT array substrate according to the fifth embodiment of this disclosure;

- FIG. **46** is a top view illustrating a TFT array substrate according to the fifth embodiment of this disclosure;

- FIG. 47 is a top view illustrating a TFT array substrate according to a sixth embodiment of this disclosure;

- FIG. 48 is a top view illustrating a TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **49** is a cross-sectional view illustrating the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **50** is a cross-sectional view illustrating a part of manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **51** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. 52 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according 5 to the sixth embodiment of this disclosure;

- FIG. **53** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **54** is a cross-sectional view illustrating a part of the 10 manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **55** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **56** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. 57 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according 20 to the sixth embodiment of this disclosure;

- FIG. **58** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **59** is a top view illustrating a TFT array substrate 25 according to the sixth embodiment of this disclosure;

- FIG. 60 is a top view illustrating a TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **61** is a top view illustrating a TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **62** is a top view illustrating a TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **63** is a cross-sectional view illustrating the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **64** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **65** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate according 40 to the sixth embodiment of this disclosure;

- FIG. **66** is a cross-sectional view illustrating the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **67** is a cross-sectional view illustrating a part of the 45 manufacturing process of the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **68** is a top view illustrating the TFT array substrate according to the sixth embodiment of this disclosure;

- FIG. **69** is a cross-sectional view illustrating the TFT array substrate according to the sixth embodiment of this disclosure; and

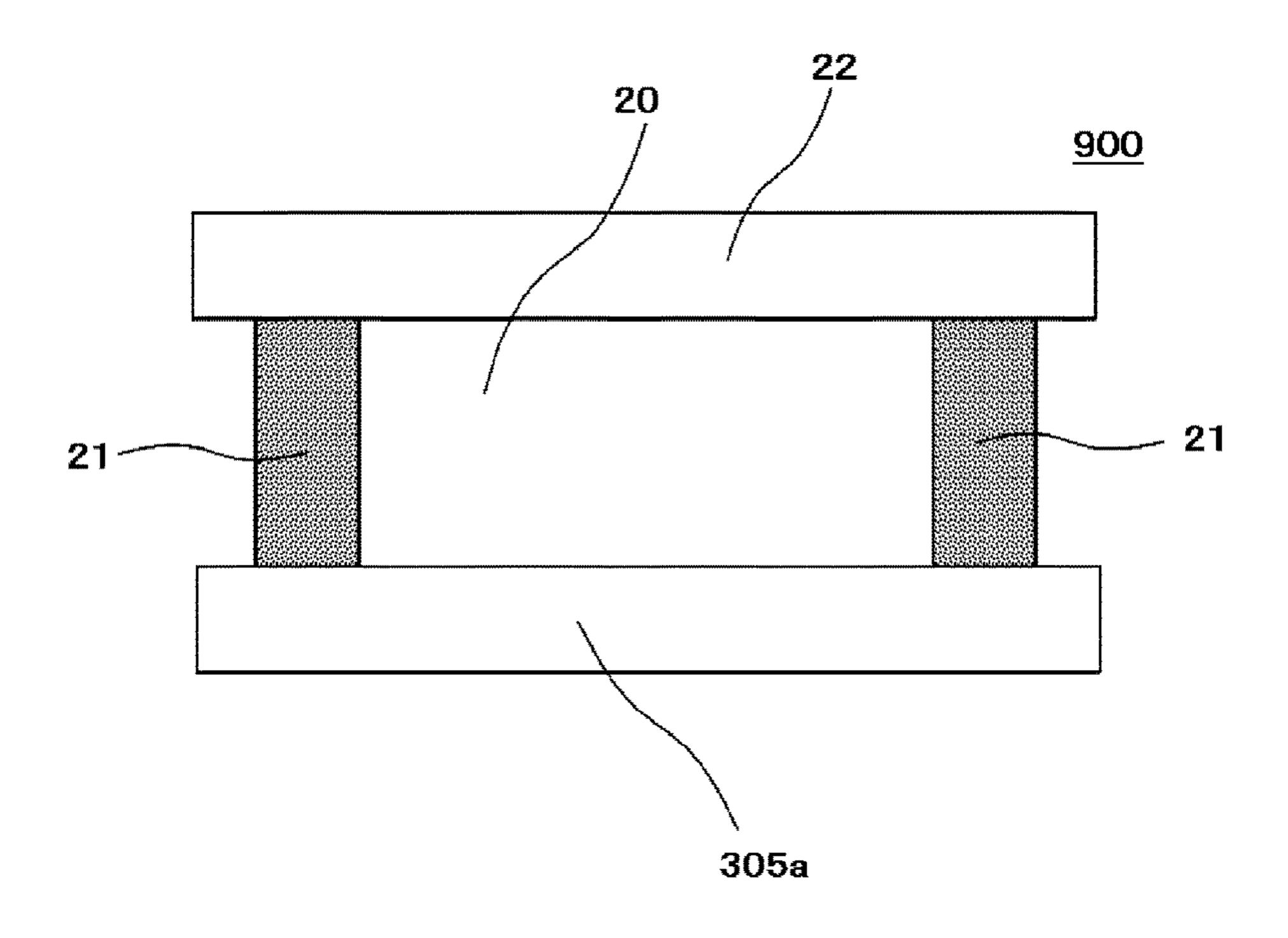

- FIG. 70 is a cross-sectional view illustrating a liquid crystal display device according to the sixth embodiment of this disclosure.

## DETAILED DESCRIPTION

First Embodiment

Firstly, configurations of TFT array substrates 100a, 100b 60 used as a substrate for a display device according to the first embodiment of this disclosure will be described. FIG. 1 is a top view illustrating the TFT array substrate 100a according to the first embodiment of this disclosure.

A display region of the TFT array substrate 100a of a 65 embodiment of this disclosure. liquid crystal display device will be described with reference to FIG. 1. In the display region, gate wiring films 2 as a

plurality of scanning wirings, and thusurce wiring films 5 as a plurality of signal wirings are arranged in a matrix.

A TFT 12a having an a-Si layer 4, a gate electrode 3, a source electrode 6 and a drain electrode 7 is provided in the vicinity of a cross point of the gate wiring film 2 and the source wiring film 5. The individual display region contains a pixel electrode 9 which is supplied with an image signal from the drain electrode 7 via a contact hole 8.

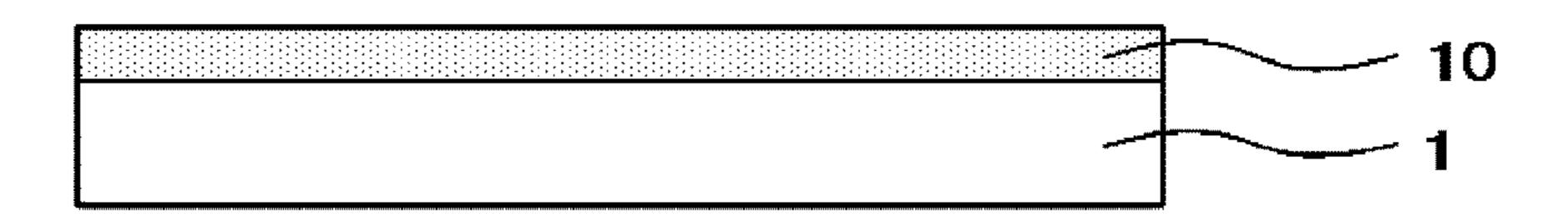

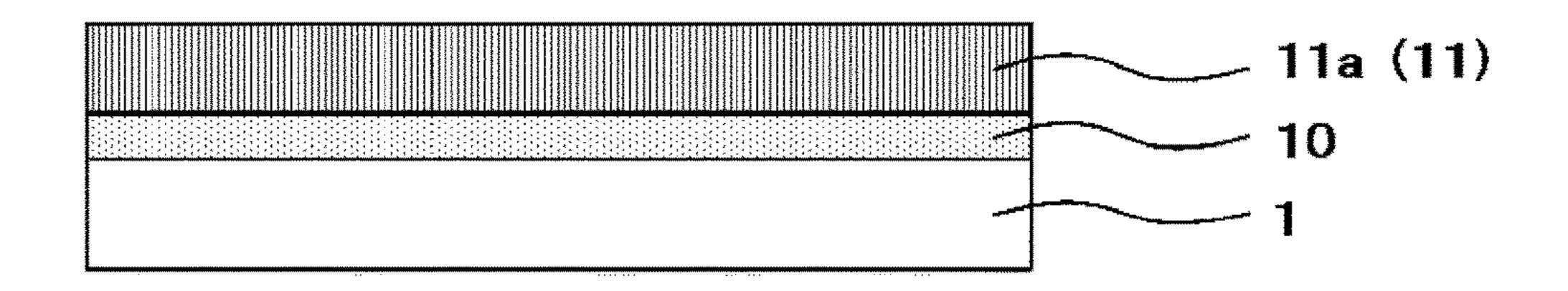

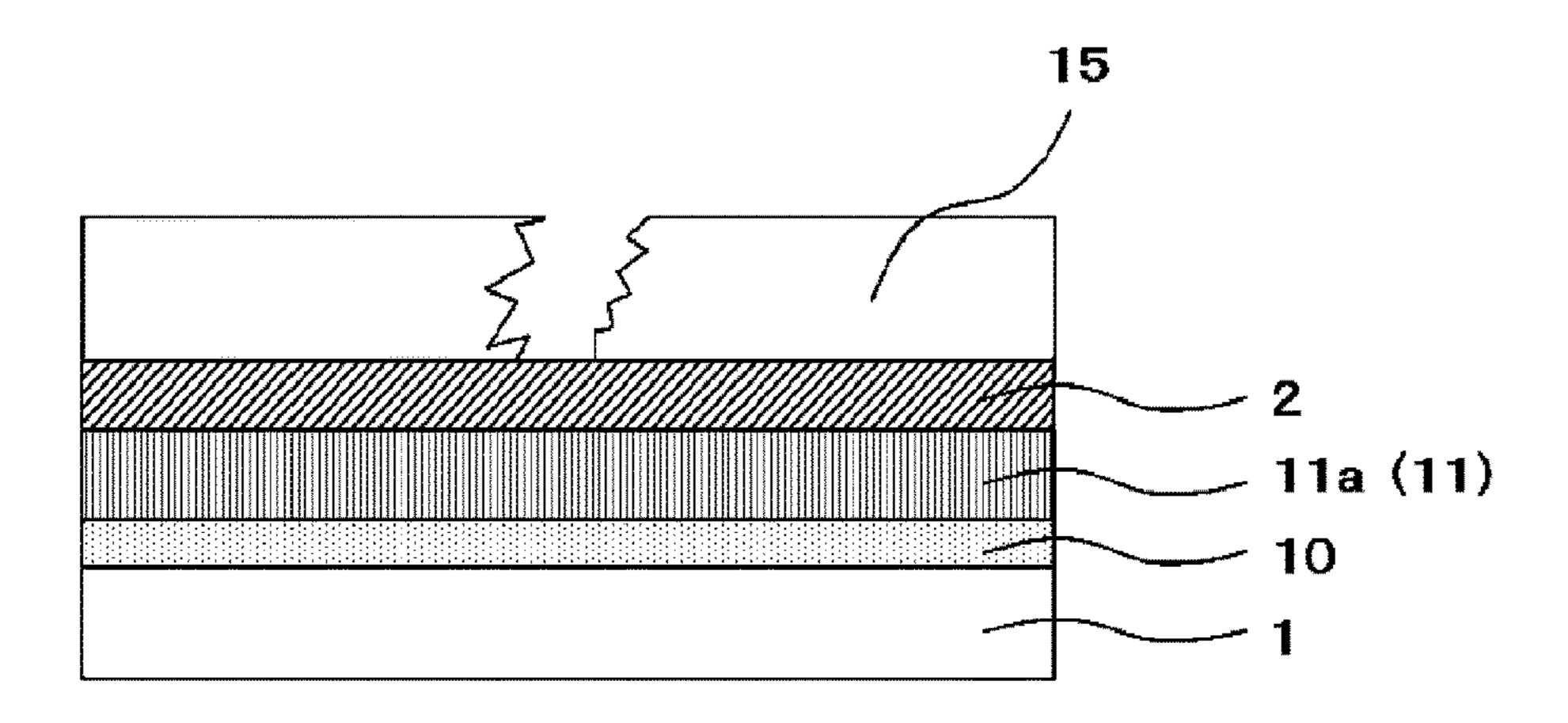

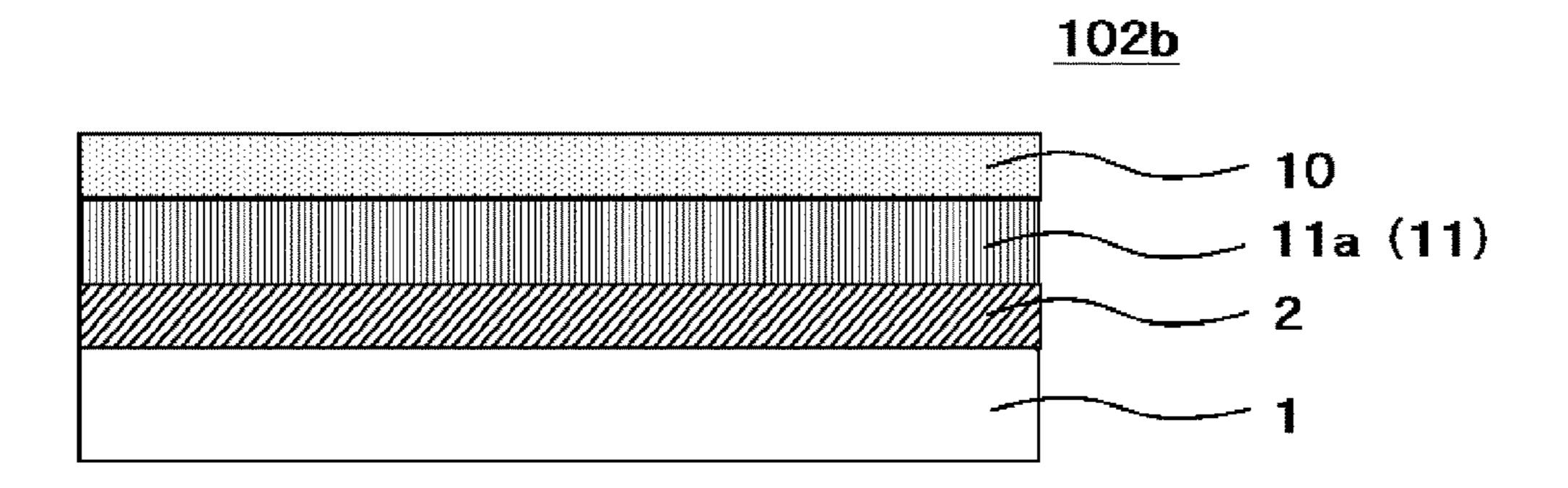

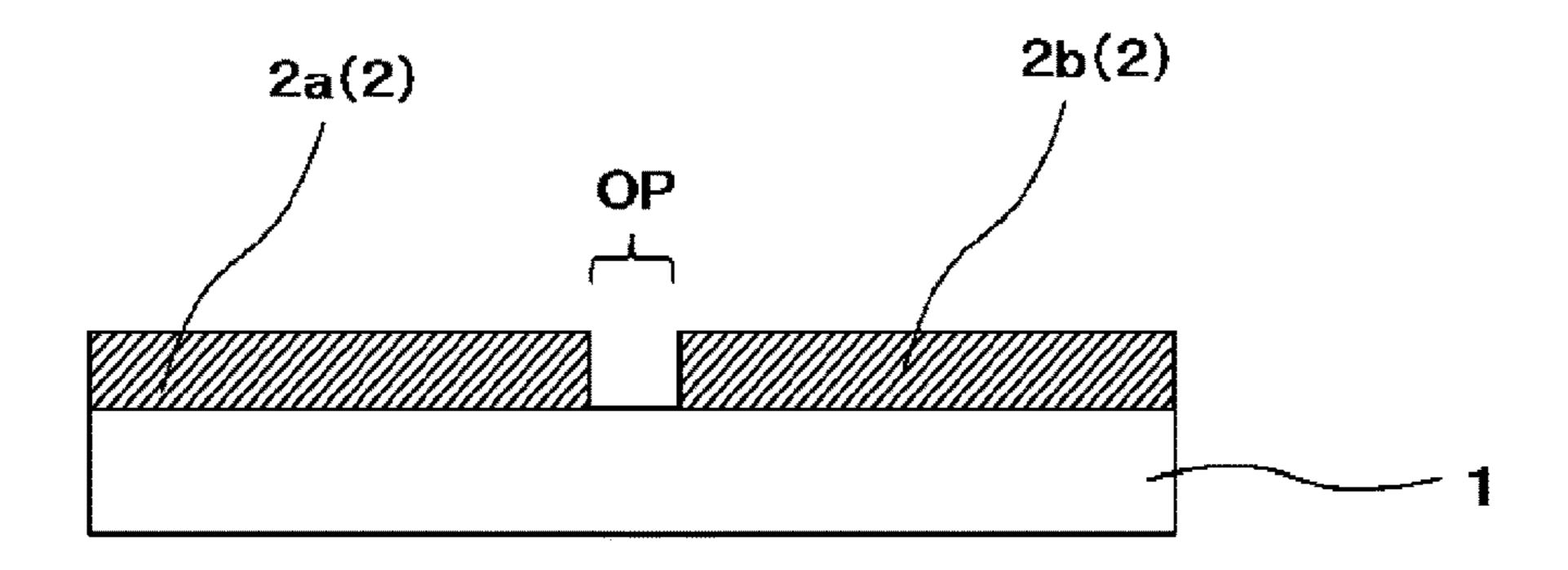

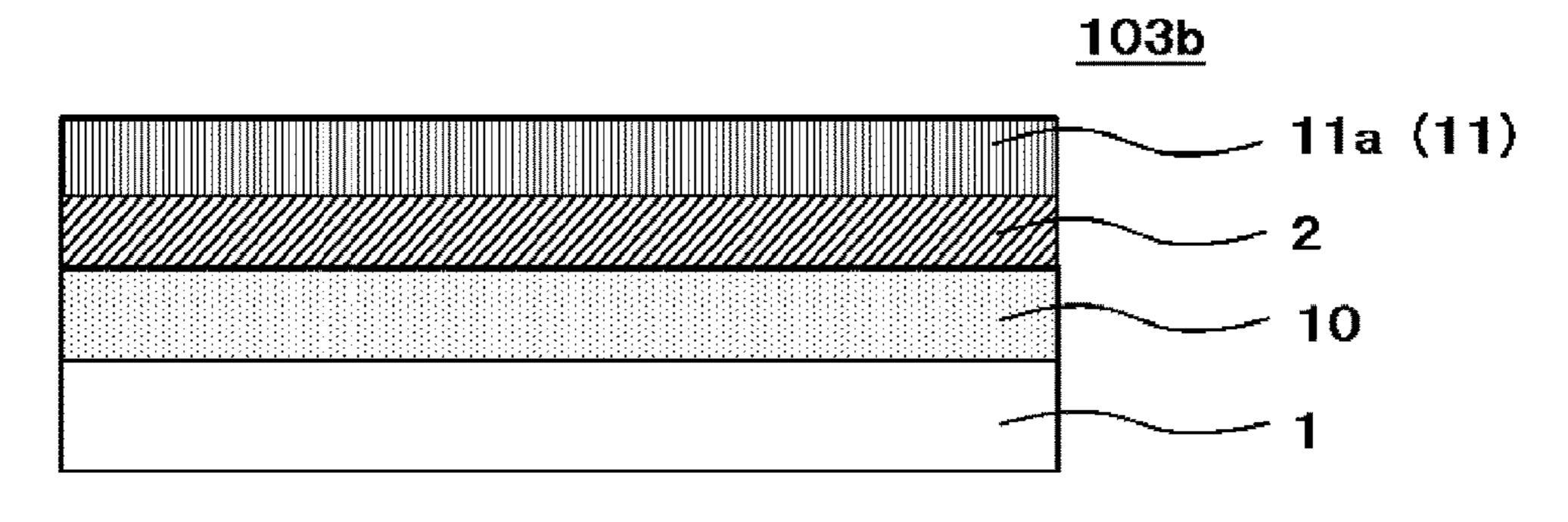

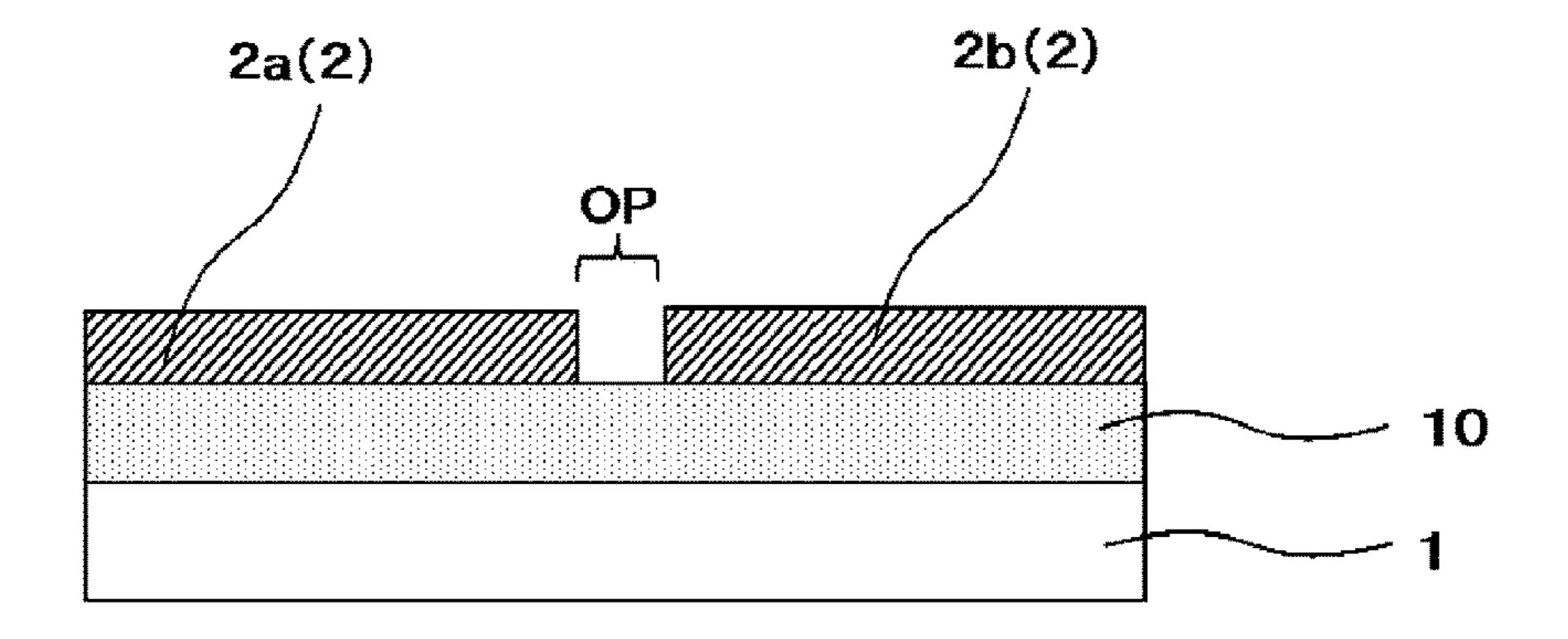

FIG. 2 is a top view illustrating the TFT array substrate 100b according to the first embodiment of this disclosure. FIG. 2 corresponds to the TFT array substrate 100a in a stage before forming the pixel electrode 9, the contact hole 8, an interlayer insulation film 14, the source electrode 6, the drain electrode 7, the source wiring film 5, the a-Si layer 4 and a 15 gate insulation film **13**. FIG. **3** is a cross-sectional view of the TFT array substrate 100b according to the first embodiment of this disclosure. FIG. 3 is the cross-sectional view taken along line A-A in parallel to a longitudinal direction of the gate wiring film 2 in FIG. 2.

In FIG. 3, an insulation film 10 is formed on a glass substrate 1 as a translucent insulation substrate. The insulation film 10 is primarily made of silicon oxide (SiOx) such as  $SiO_2$ .

For example, the insulation film 10 has a thickness of 1 nm to 1 μm. This film thickness is preferably 1 nm or more in a view point of forming a uniform film and obtaining a function of the insulation film. On the other hand, this film thickness is preferably 1 µm or less in a view point of productivity. More preferably, this film has the thickness of 30 10 nm to 500 nm.

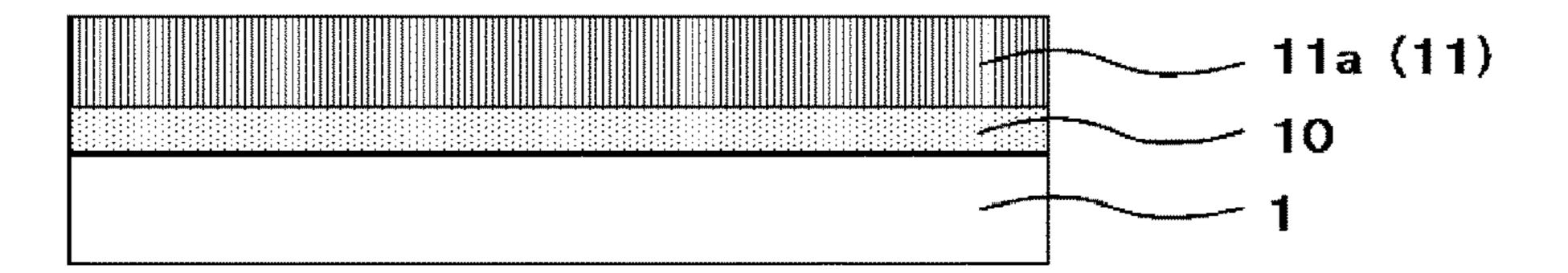

An inorganic film 11 is formed on the insulation film 10 to be in direct contact with the insulation film 10. The inorganic film 11 is formed by an insulator part 11a which is obtained by changing oxide semiconductor into insulator. 35 The insulator means that a specific resistance thereof is  $1\times10^{\circ}$   $\Omega$ ·cm or more. More preferably, the insulator has the specific resistance of  $1\times10^7~\Omega$ ·cm or more.

The inorganic film 11 is made of oxide semiconductor such as InGaZnO (indium gallium zinc oxide) under a condition to obtain property of the insulator.

For example, the inorganic film 11 has a thickness of 5 nm to 1 µm. This film thickness is preferably 5 nm or more in a view point of forming a uniform film. On the other hand, this film thickness is preferably 1 µm or less in a view point of productivity. More preferably, this film has the thickness of 10 nm to 500 nm.

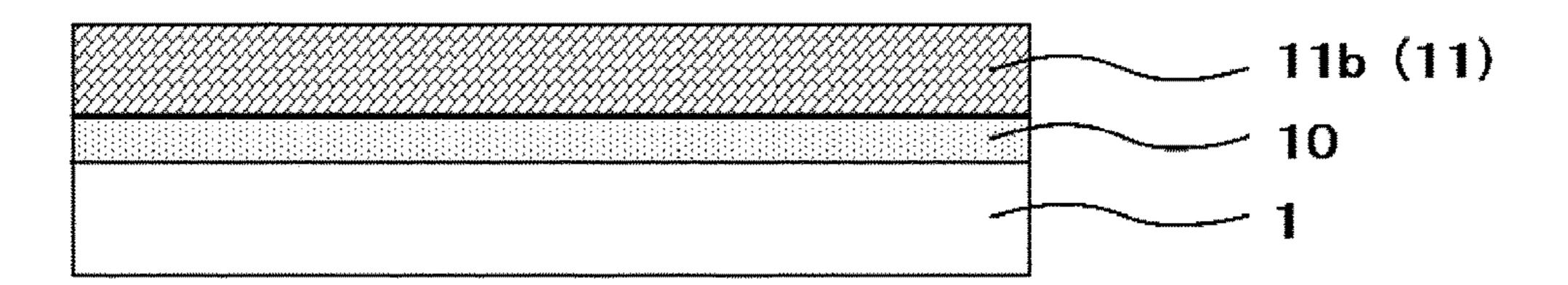

The gate wiring film 2, as a wiring film for forming a gate wiring, is formed on the insulator part 11a to be in direct contact with the insulator part 11a which is obtained by changing the oxide semiconductor into the insulator.

The gate wiring film 2 is formed of metal, for example, chrome (Cr), aluminum, aluminum alloy, molybdenum, molybdenum alloy or copper.

For example, the gate wiring film 2 has a thickness of 50 55 nm to 1 μm. This film thickness is preferably 50 nm or more in a view point of lowering a resistance value. On the other hand, this film thickness is preferably 1 µm or less in a view point of productivity. More preferably, this film has the thickness of 100 nm to 500 nm.

Secondly, a manufacturing method of the TFT array substrates 100a, 100b according to the first embodiment of this disclosure will be described. FIGS. 4 to 8 are crosssectional views illustrating parts of manufacturing process of the TFT array substrate 100b according to the first

At first, an SiO<sub>2</sub> film is formed to have a thickness of about 50 nm on the entire surface of the glass substrate 1 as

the translucent insulation substrate, by using a CVD device, whereby the insulation film 10 is formed (FIG. 4).

Next, an InGaZnO film as the oxide semiconductor film is formed to have a thickness of about 80 nm on the entire surface of the insulation film 10 under a condition to obtain 5 property of the insulator, by using a sputtering device, whereby the inorganic film 11 made of the insulator part 11a is formed (FIG. 5). Specifically, for example, this film is formed under a condition that a partial pressure of oxygen with respect to Ar (argon) is set to about 20% in the 10 sputtering.

In place of forming the InGaZnO film of the oxide semiconductor under the condition to obtain the property of insulator, the InGaZnO film may be formed under a condiconductor part 11b (FIG. 6A). Then the InGaZnO may be changed into insulator, that is, changed to the insulator from the semiconductor by implementing a plasma process (N<sub>2</sub>O plasma process) P with using nitrous oxide (N<sub>2</sub>O) gas, and thus the inorganic film 11 made of the insulator part 11a may 20 be formed (FIG. 6B). The semiconductor means that a specific resistance thereof is more than  $1\times10^{-2}~\Omega$ ·cm and less than  $1\times10^6~\Omega$ ·cm. More preferably, the semiconductor has the specific resistance of  $1 \times 10^2 \ \Omega \cdot \text{cm}$  to  $1 \times 10^5 \ \Omega \cdot \text{cm}$ .

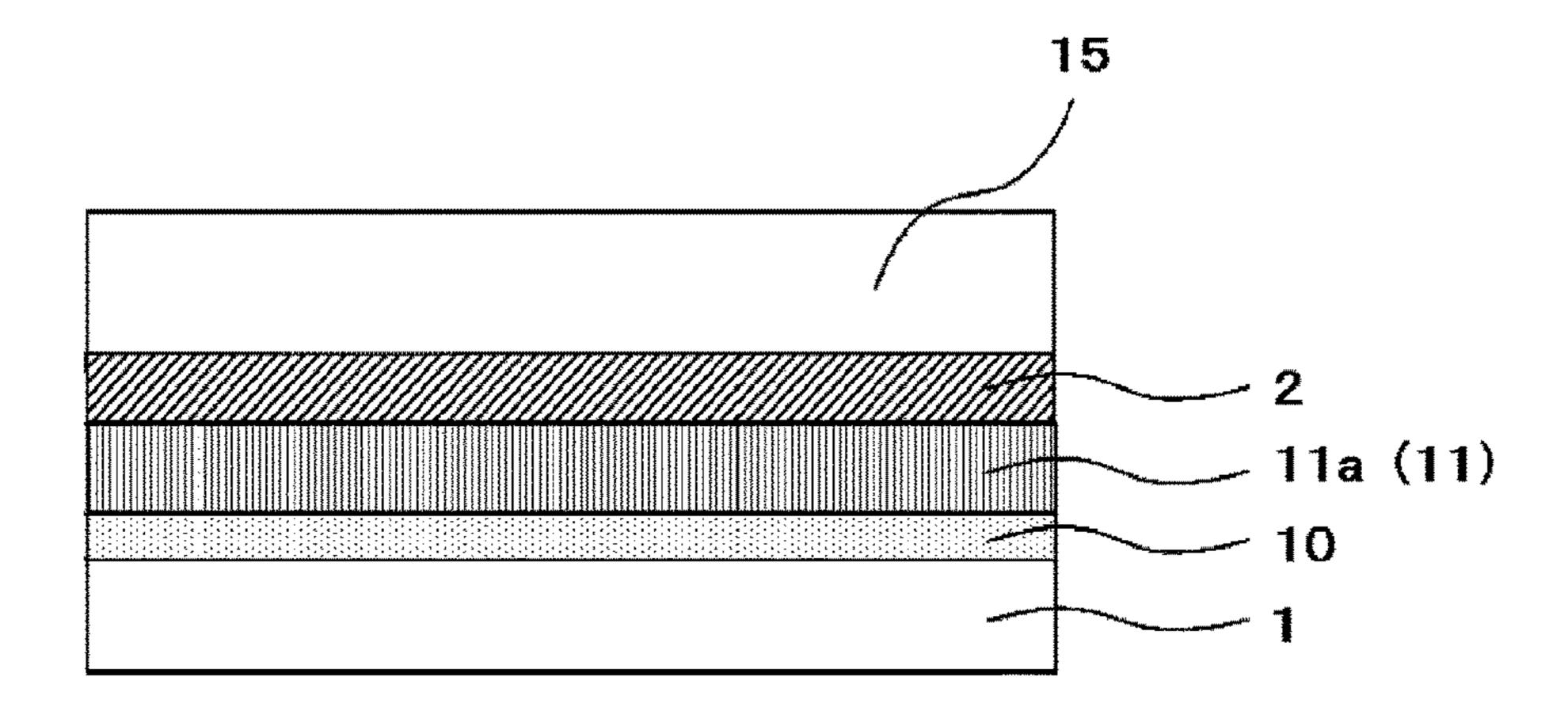

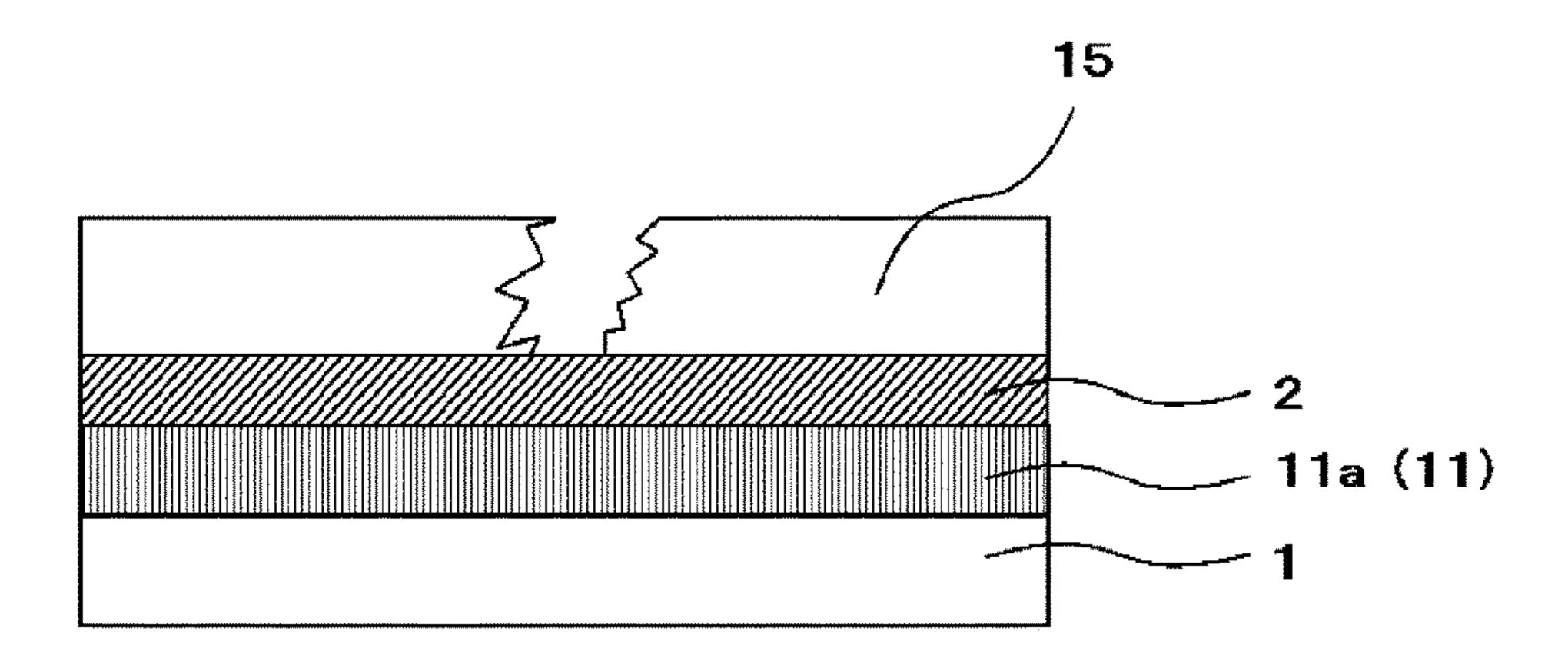

Next, a chrome film is formed to have a thickness of about 25 200 nm by using the sputtering device, whereby the gate wiring film 2 is formed on the insulator part 11a (FIG. 7). Thereafter, a photoengraving process for forming a wiring pattern, etc. is performed on the gate wiring film 2 by using resist 15, and an etching process for removing portions of 30 the gate wiring film 2 not covered by the resist 15 is performed (FIG. 8). Then the resist 15 is removed, and thus the TFT array substrate 100b shown in FIGS. 2 and 3 is obtained.

Thereafter, the gate insulation film 13, the a-Si layer 4, the source wiring film 5, the source electrode 6, the drain electrode 7, the interlayer insulation film 14, the contact hole 8 and the pixel electrode 9 are formed, and thus the TFT array substrate 100a shown in FIG. 1 is obtained.

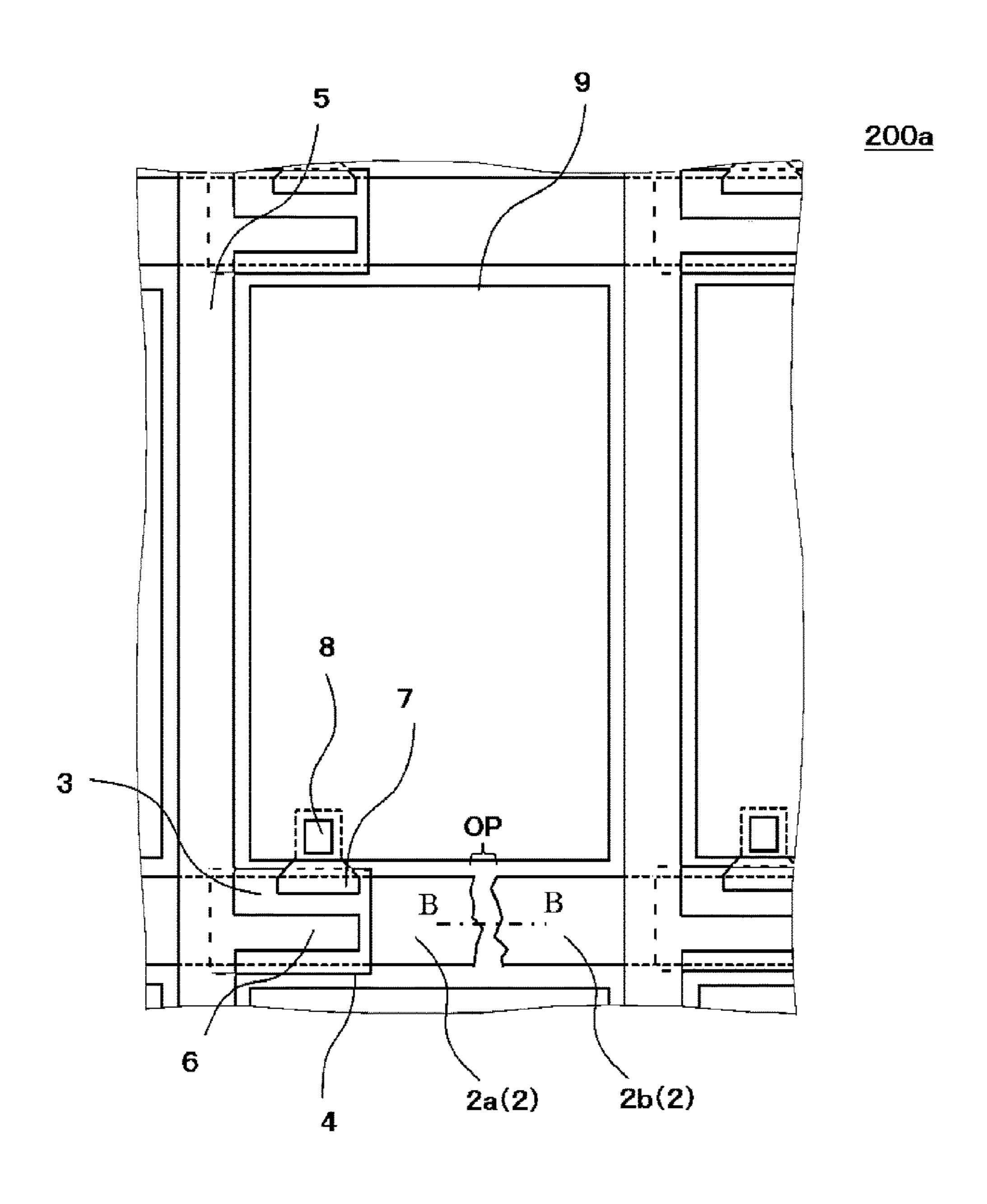

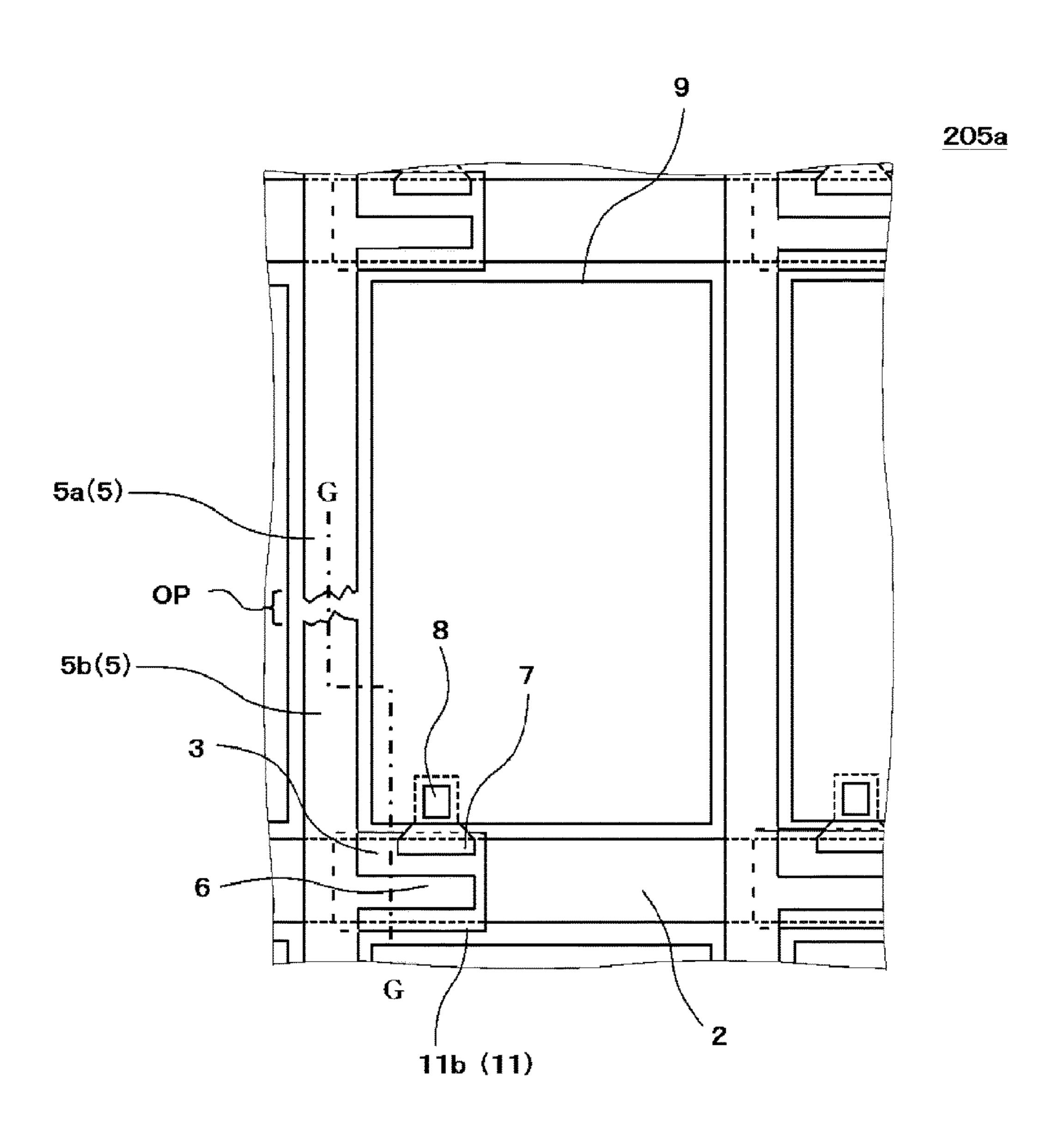

Thirdly, configurations of the TFT array substrates 100a, 40 100b according to the first embodiment of this disclosure in a case where the gate wiring film 2 has a disconnection part OP will be described. FIG. 9 is a top view illustrating a TFT array substrate 200a according to the first embodiment of this disclosure. In FIG. 9, the TFT array substrate 200a 45 according to the first embodiment of this disclosure has the disconnection part OP at the gate wiring film 2. The TFT array substrate 200a shown in FIG. 9 has the same configuration as the TFT array substrate shown in FIG. 1 except for that the gate wiring film 2 has the disconnection part OP.

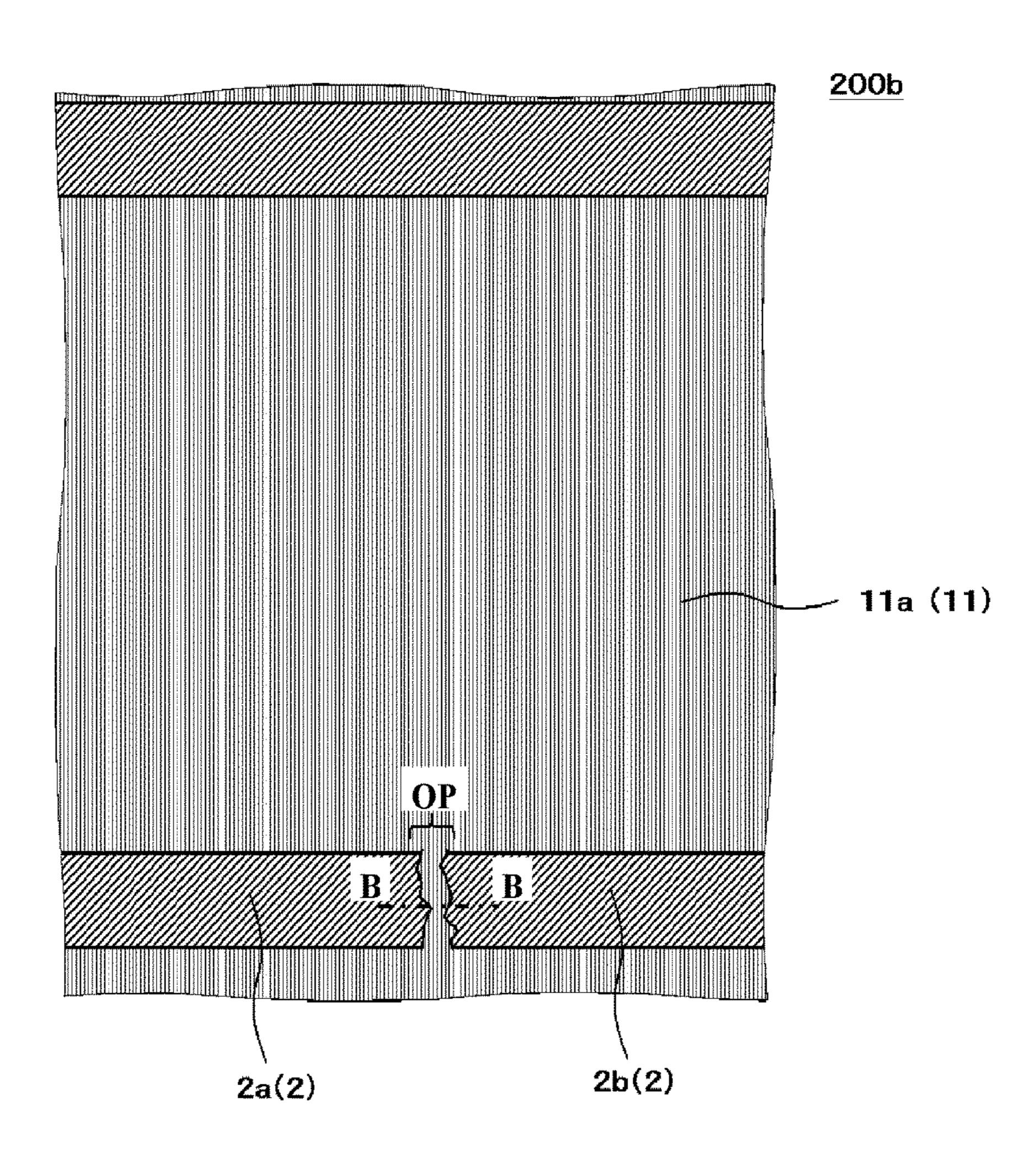

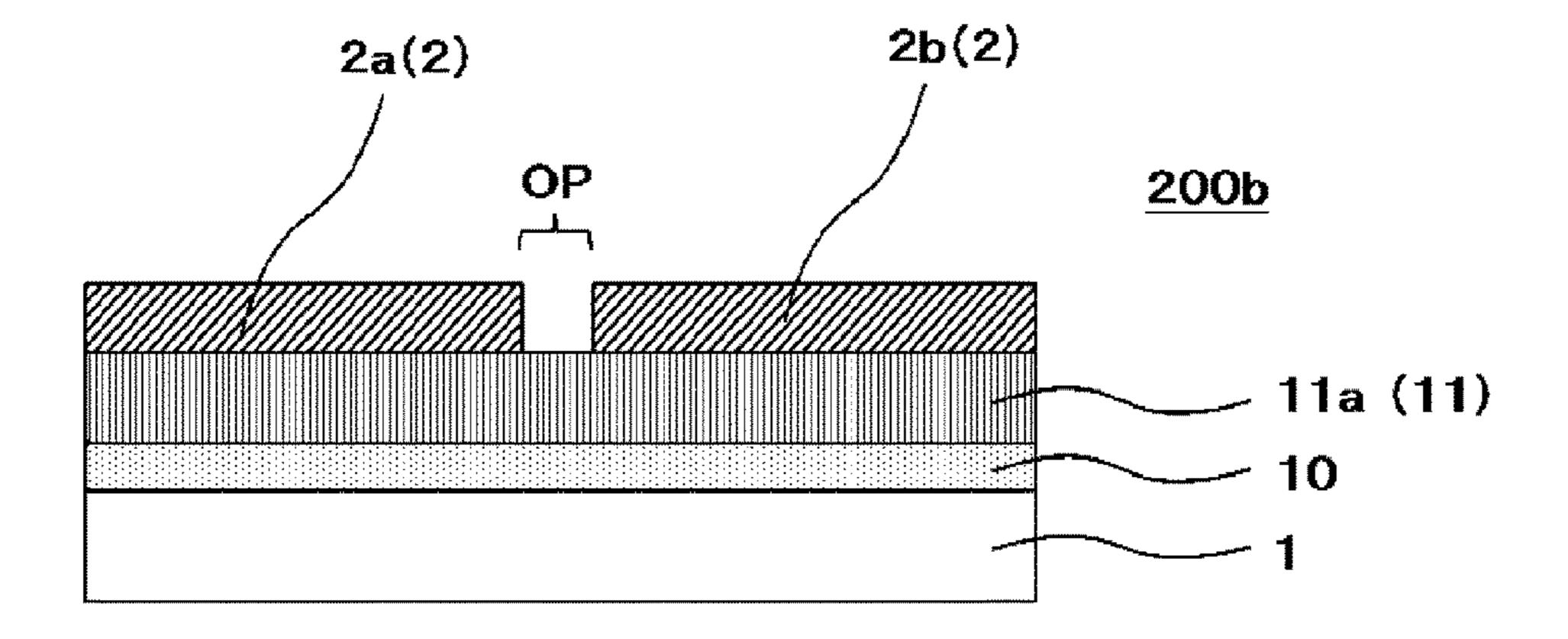

FIG. 10 is a top view illustrating a TFT array substrate 200b according to the first embodiment of this disclosure. FIG. 10 corresponds to the TFT array substrate 200a of FIG. 9 in a stage before forming the pixel electrode 9, the contact hole 8, the interlayer insulation film 14, the source electrode 55 **6**, the drain electrode **7**, the source wiring film **5**, the a-Si layer 4 and the gate insulation film 13.

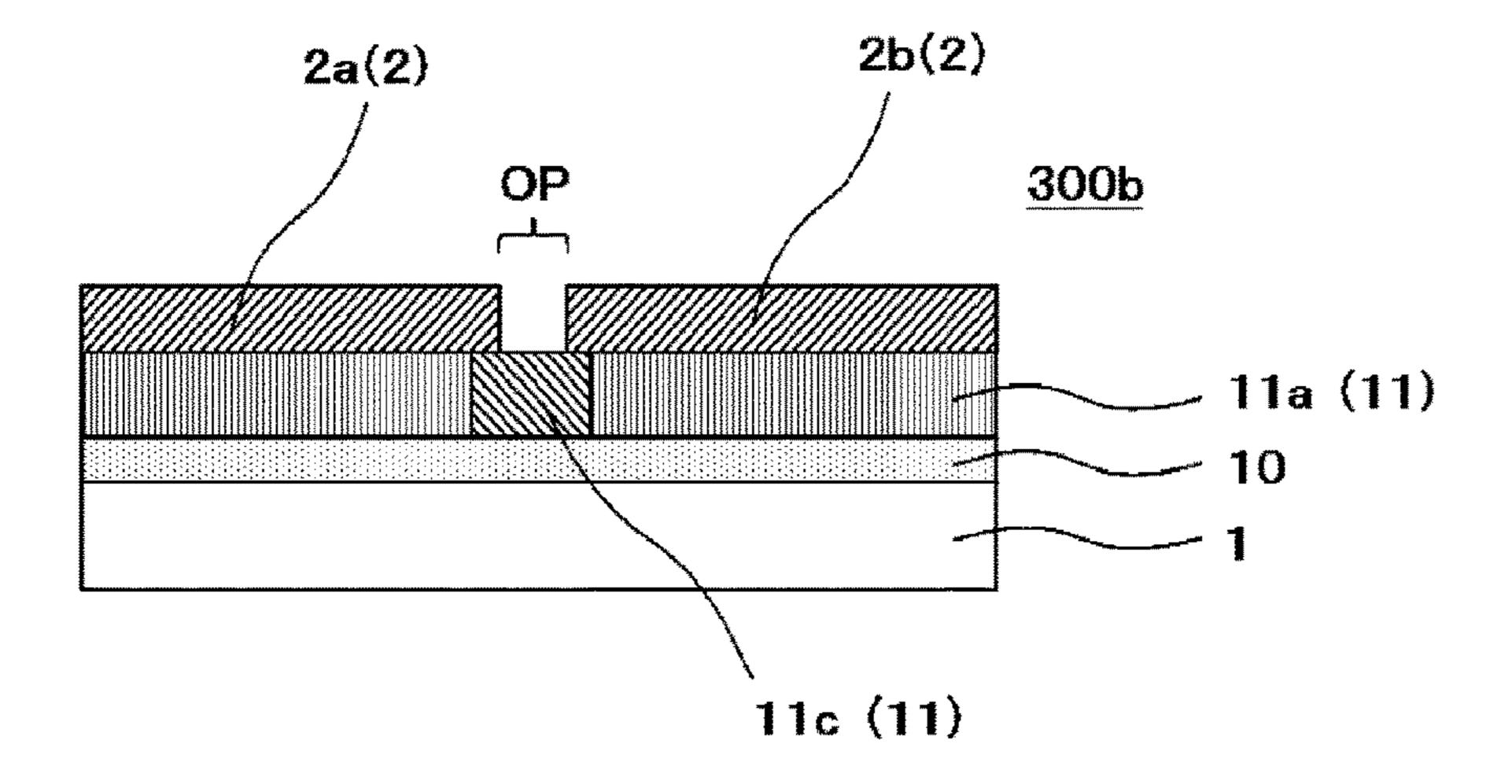

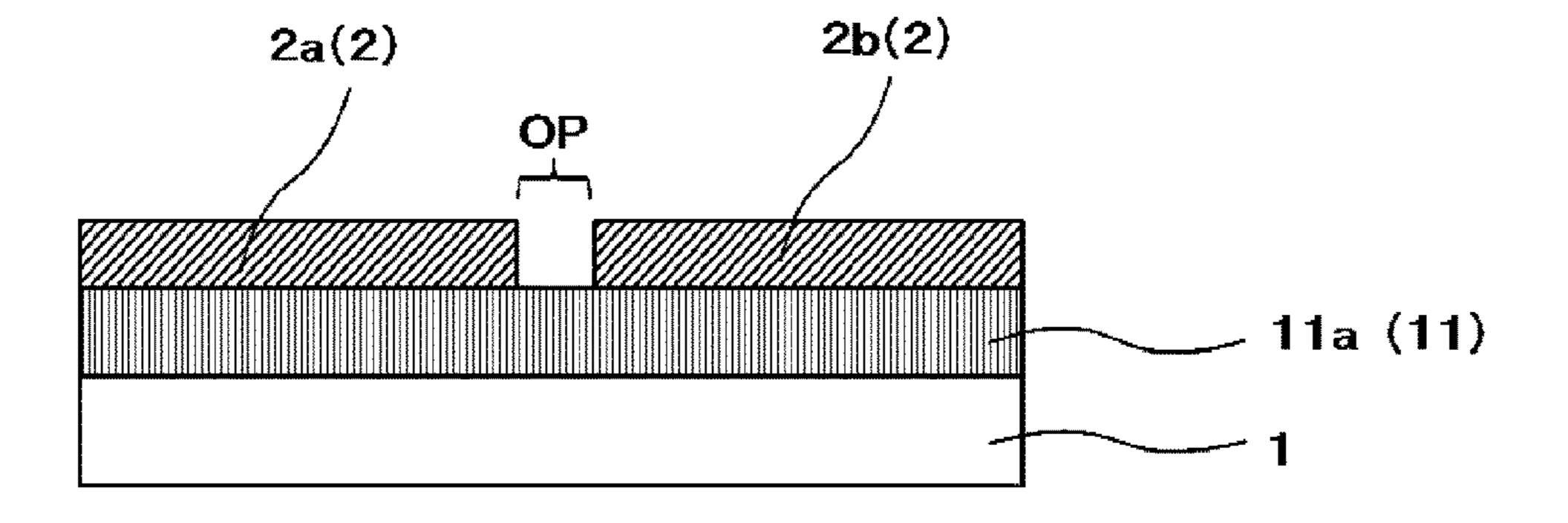

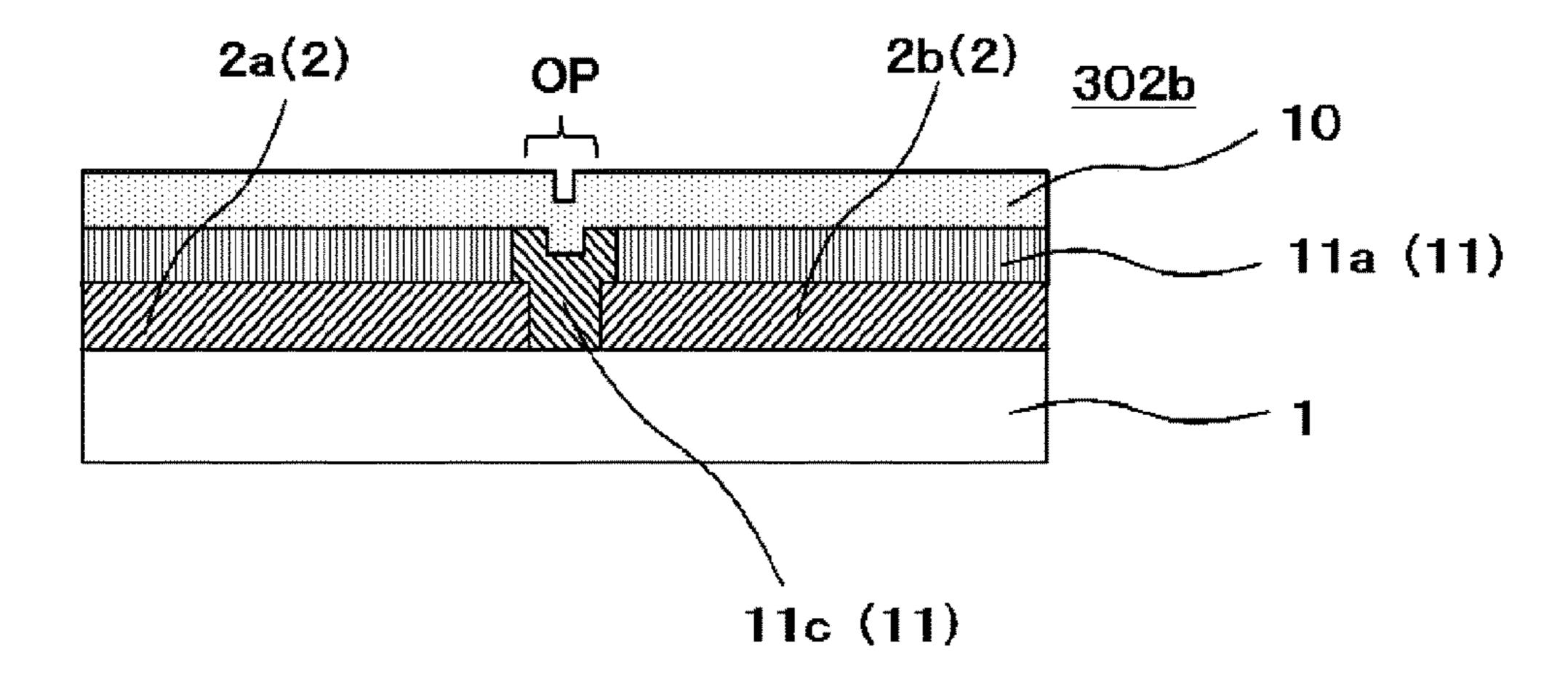

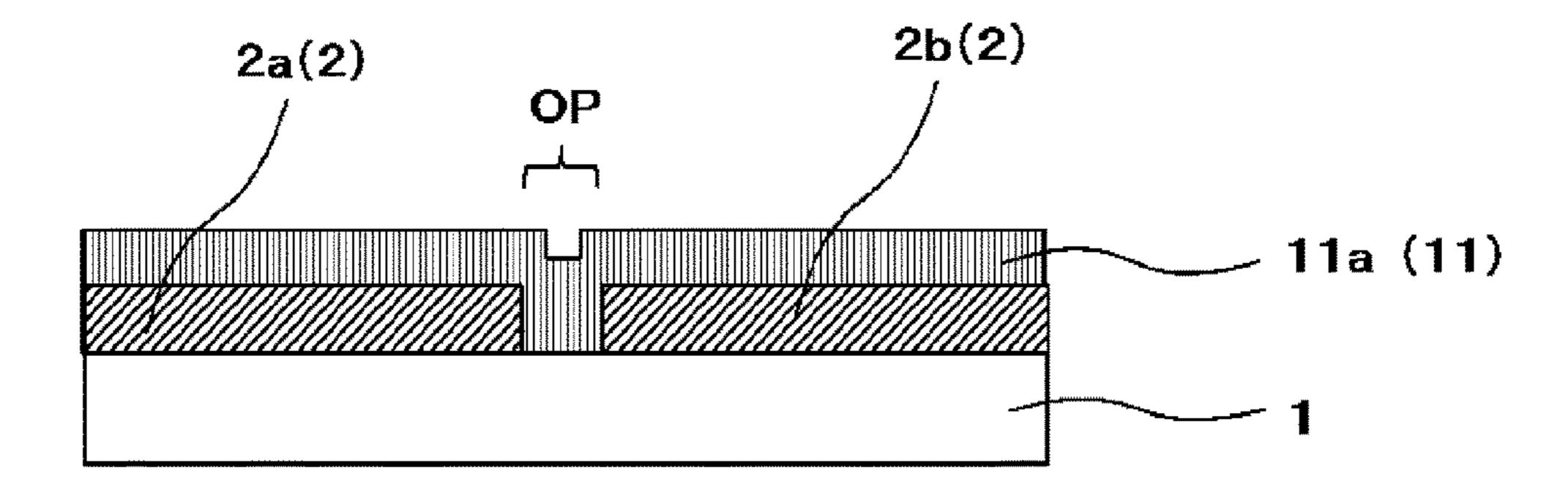

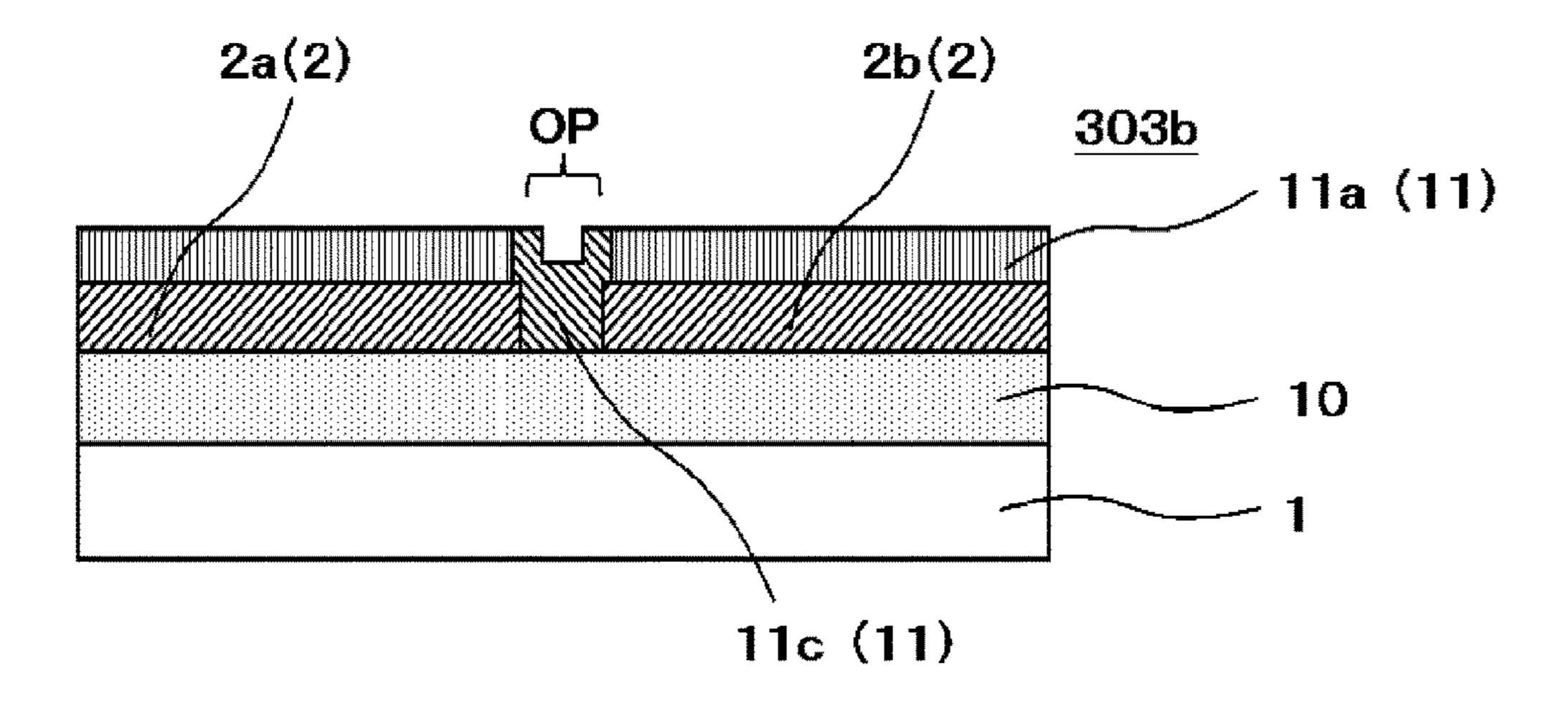

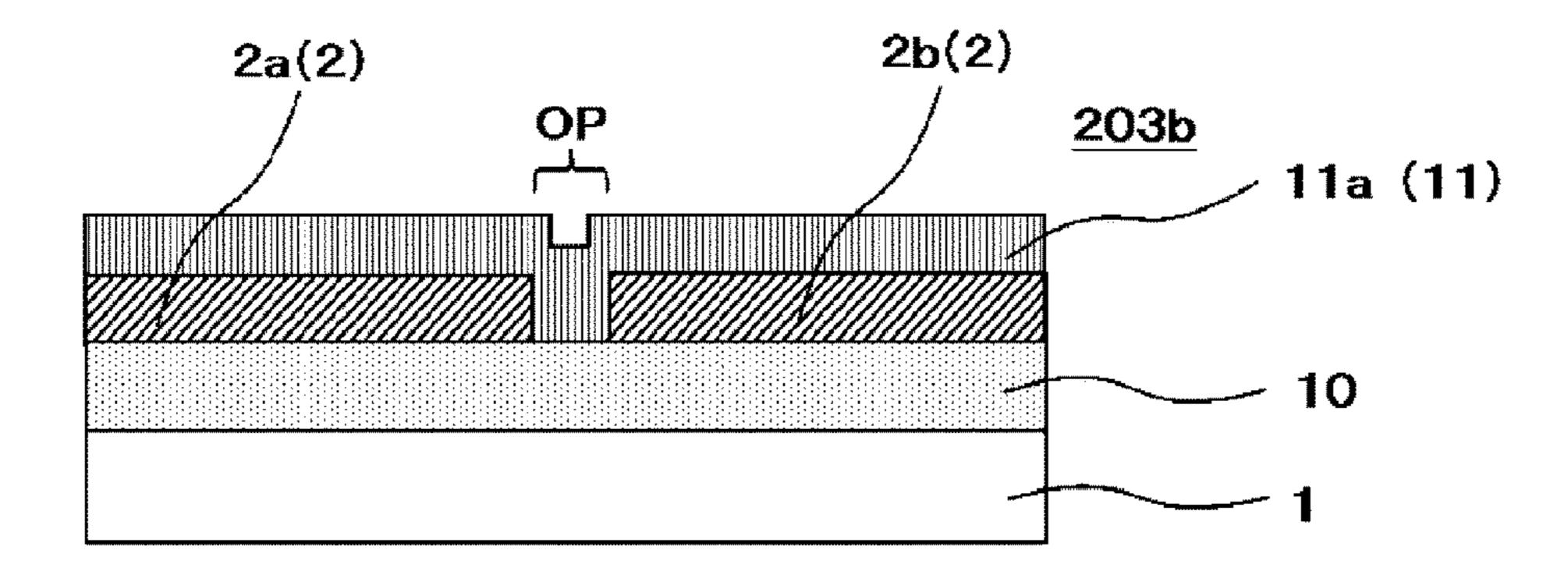

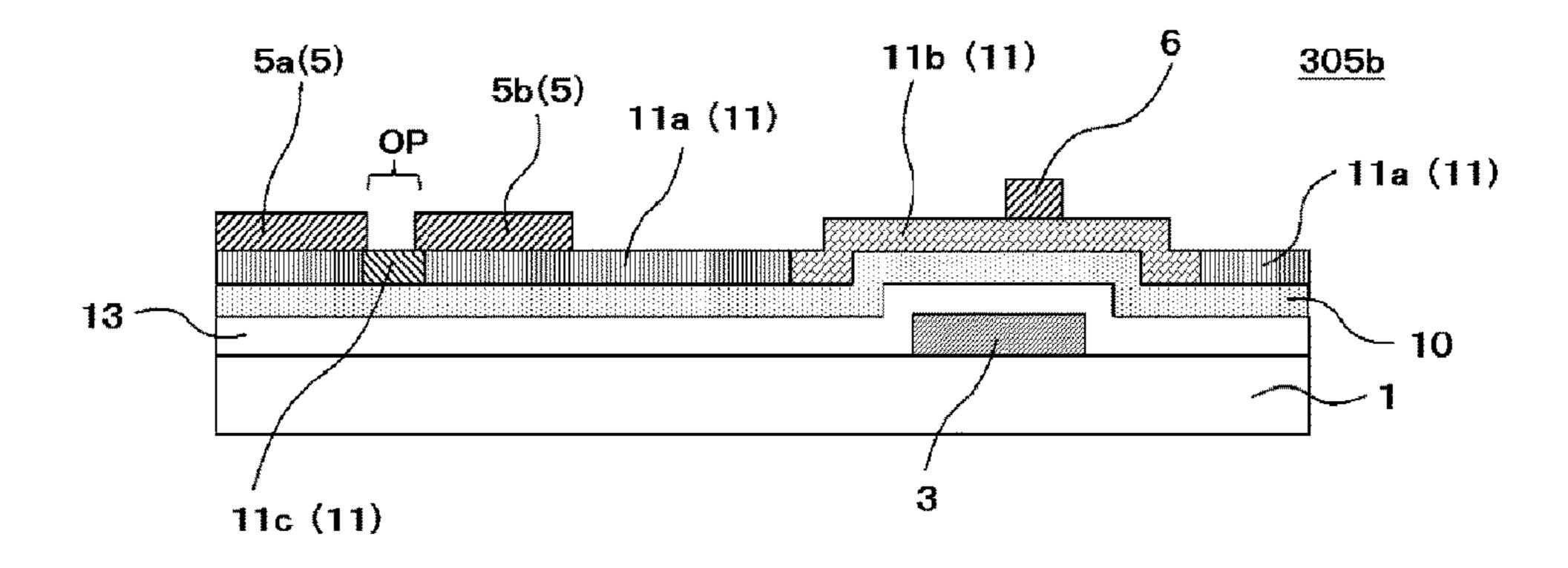

FIG. 16 is a cross-sectional view of the TFT array substrate 200b according to the first embodiment of this disclosure. FIG. 16 is the cross-sectional view taken along 60 line B-B in parallel to a longitudinal direction of the gate wiring film 2 in FIG. 10. In the configuration of the TFT array substrate according to the first embodiment of this disclosure in the case of having the disconnection part OP, as shown in FIG. 16, the gate wiring film 2 is separated in 65 the longitudinal direction in a manner of interposing the disconnection part OP. Thus, a first gate wiring film 2a and

a second gate wiring film 2b being not in direct contact with the first gate wiring film 2a are formed. Since the remaining configuration of this TFT array substrate is the same as that in the case where the disconnection part OP is not formed as shown in FIG. 3, descriptions thereof will be omitted.

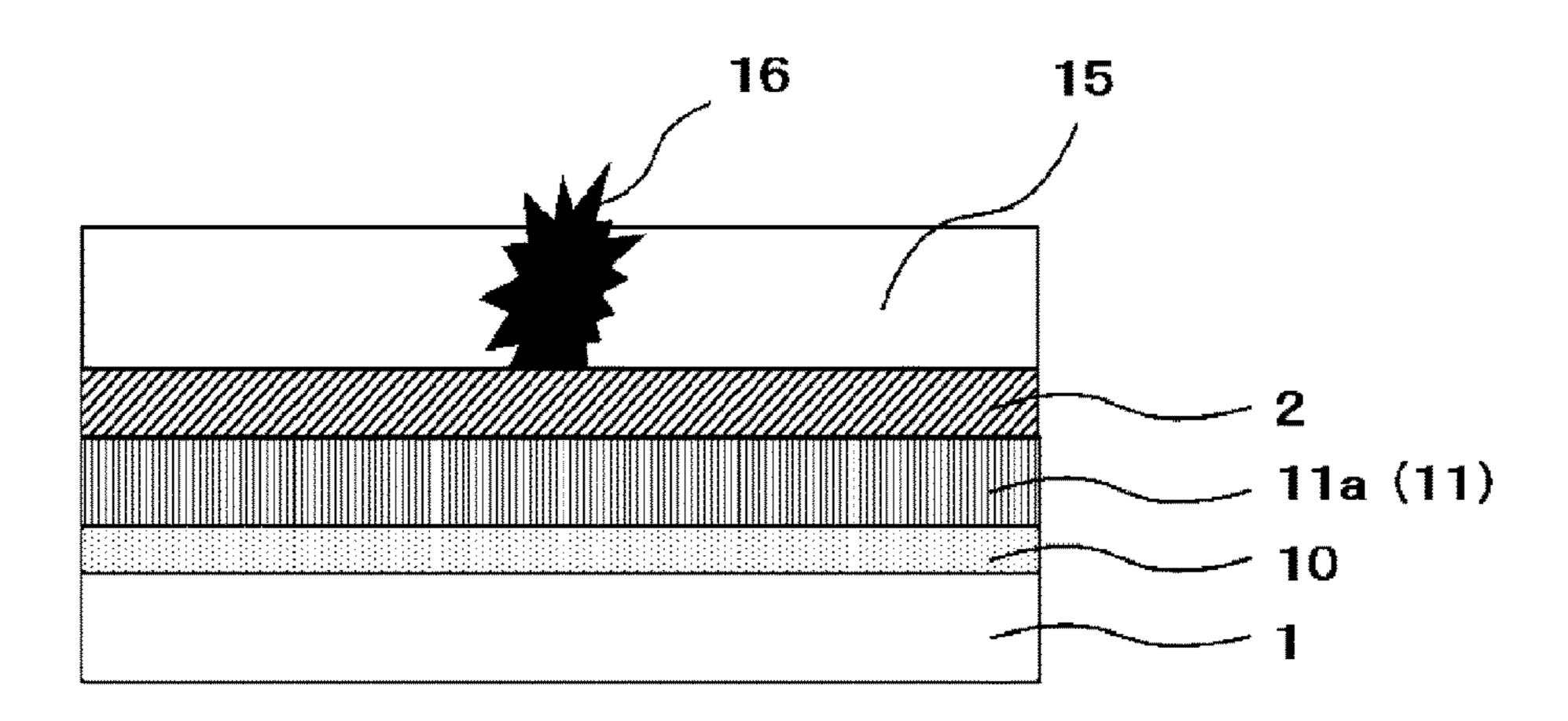

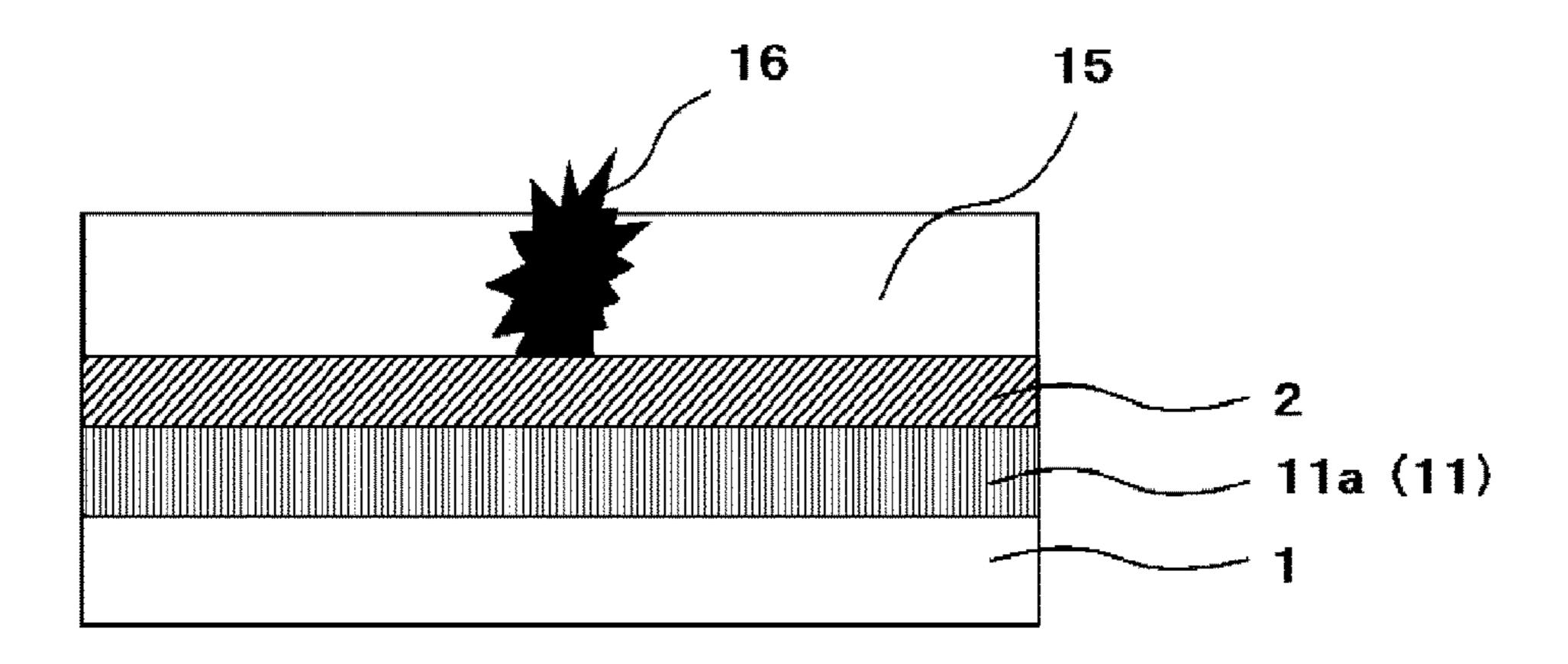

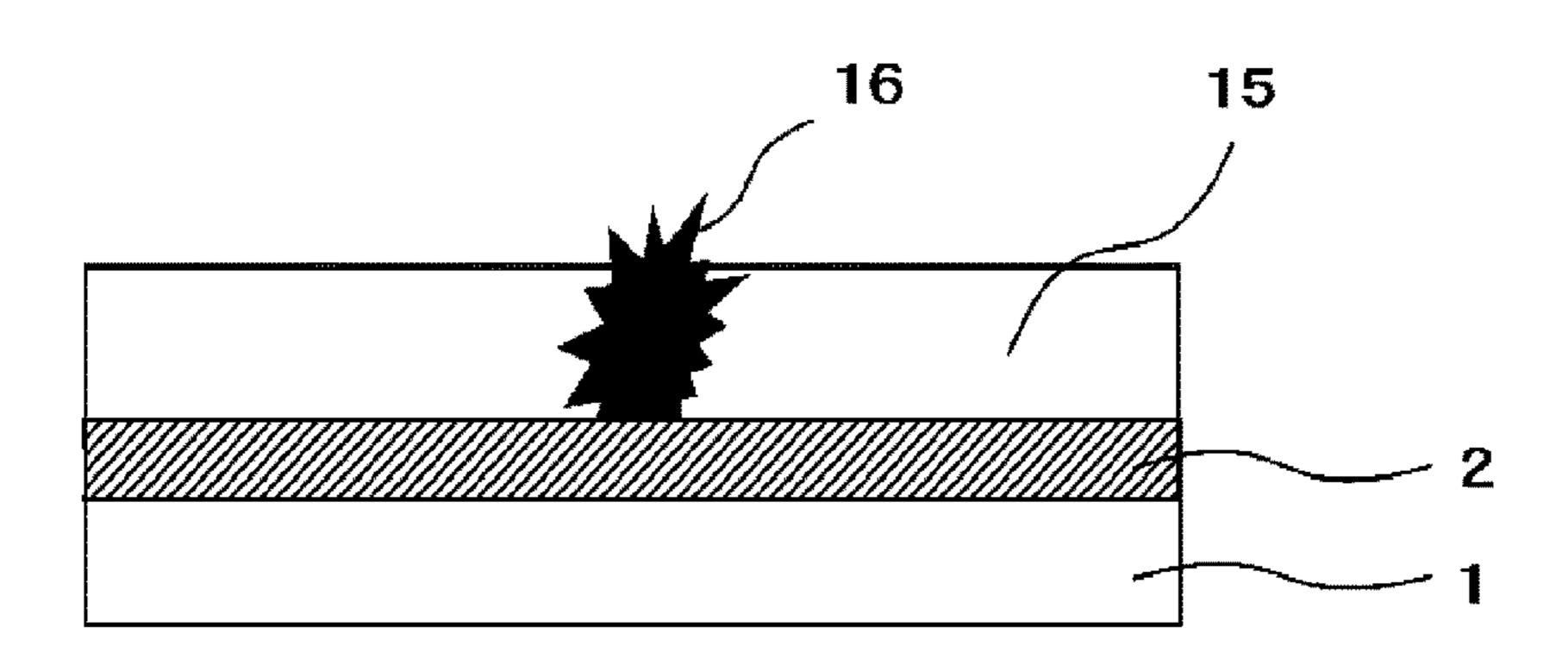

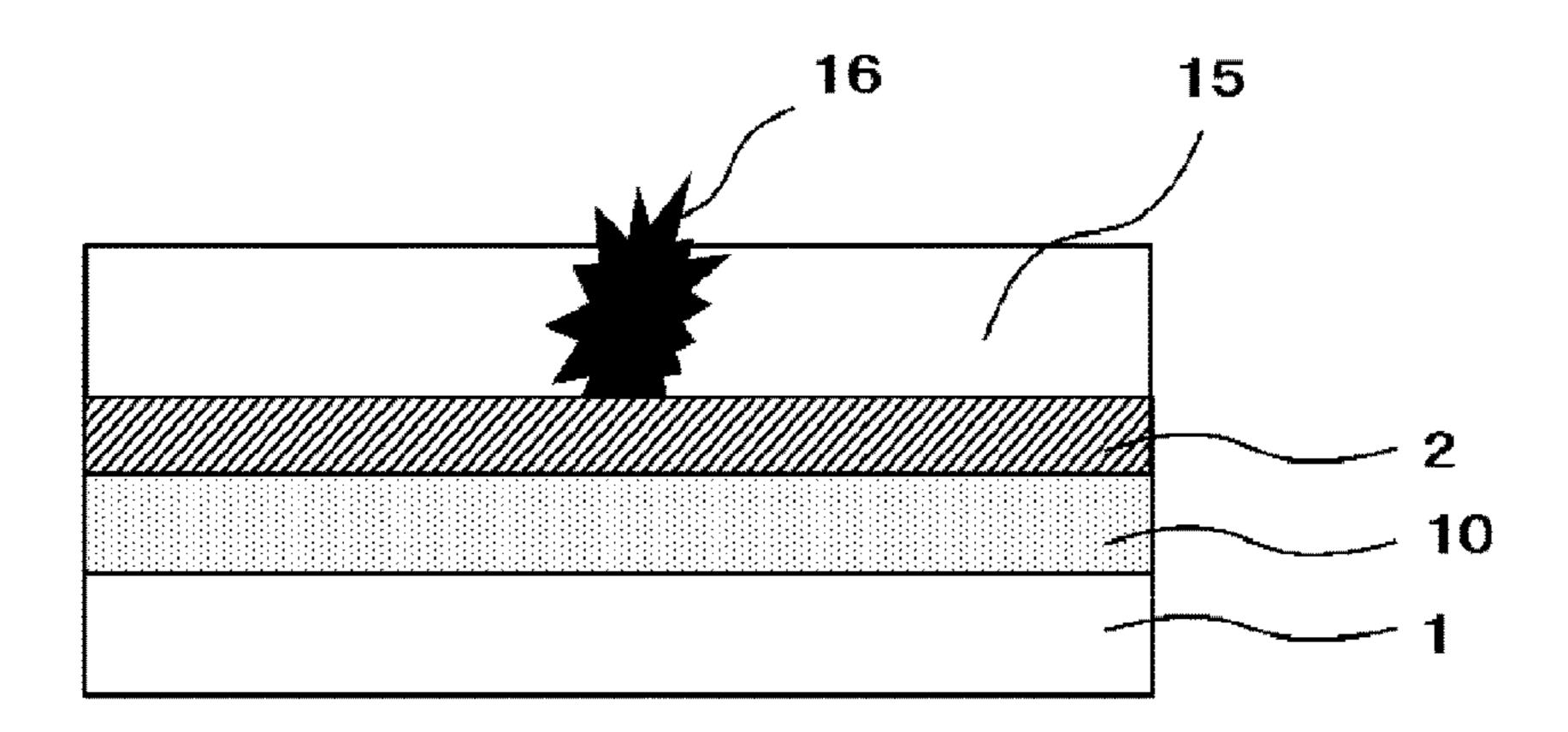

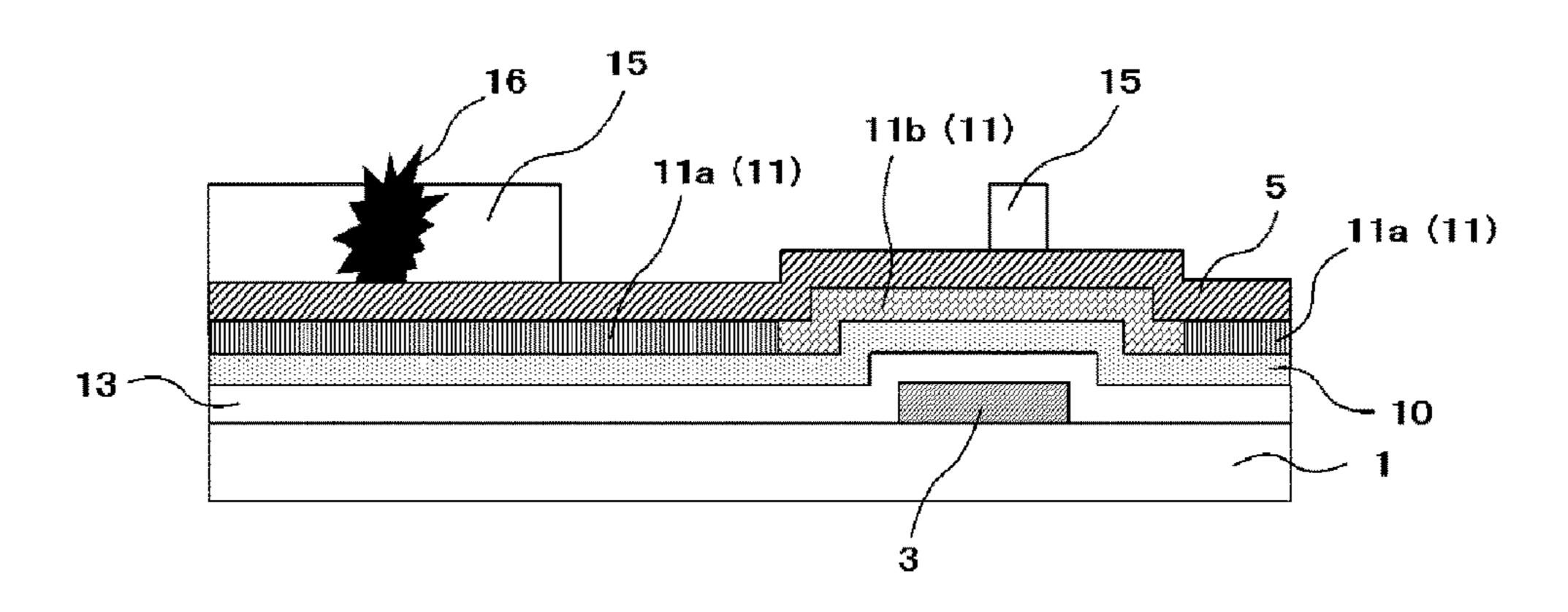

One example of mechanism of causing the disconnection part OP at the wiring will be described. If foreign particle 16 is incorporated on the surface of the substrate or the like, it arises various defects such as disconnection, short-circuit and insulation failure. Array manufacturing processes such as the photoengraving process, etc. are performed in a so-called "clean room" from which the foreign particle 16 is removed as much as possible.

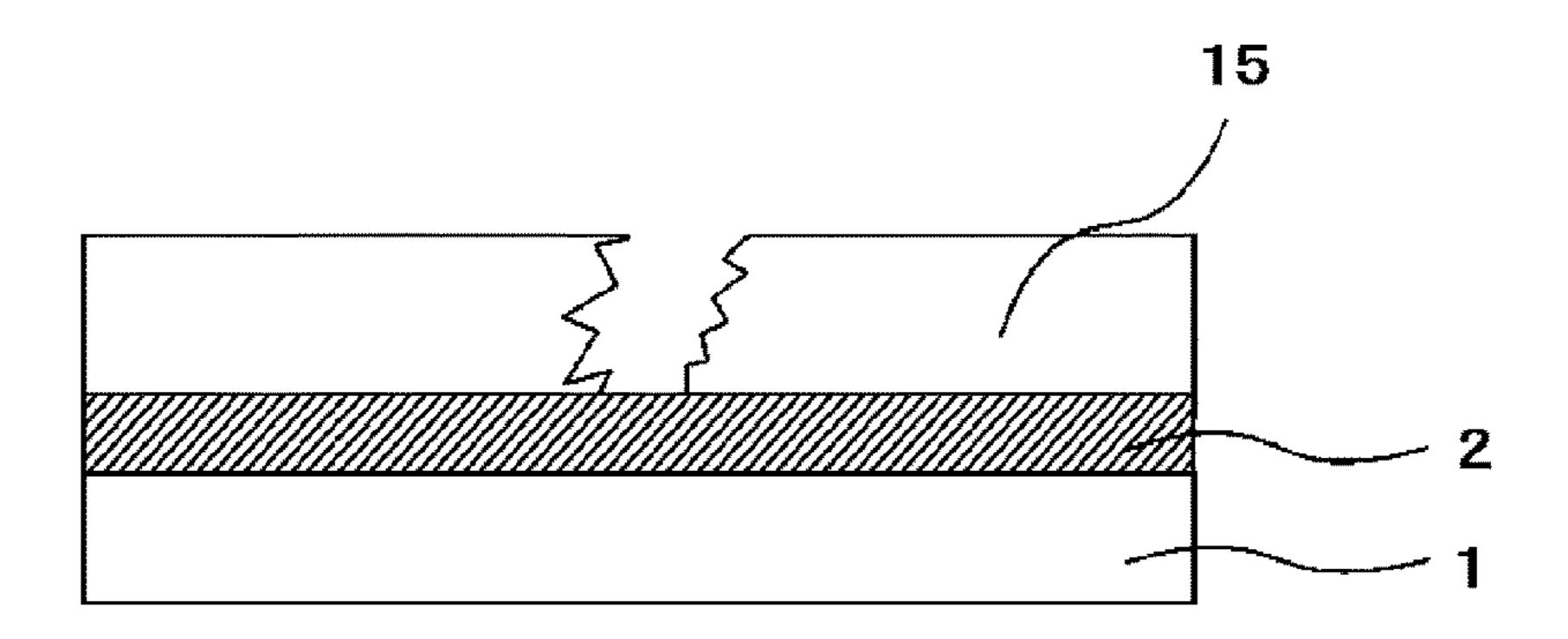

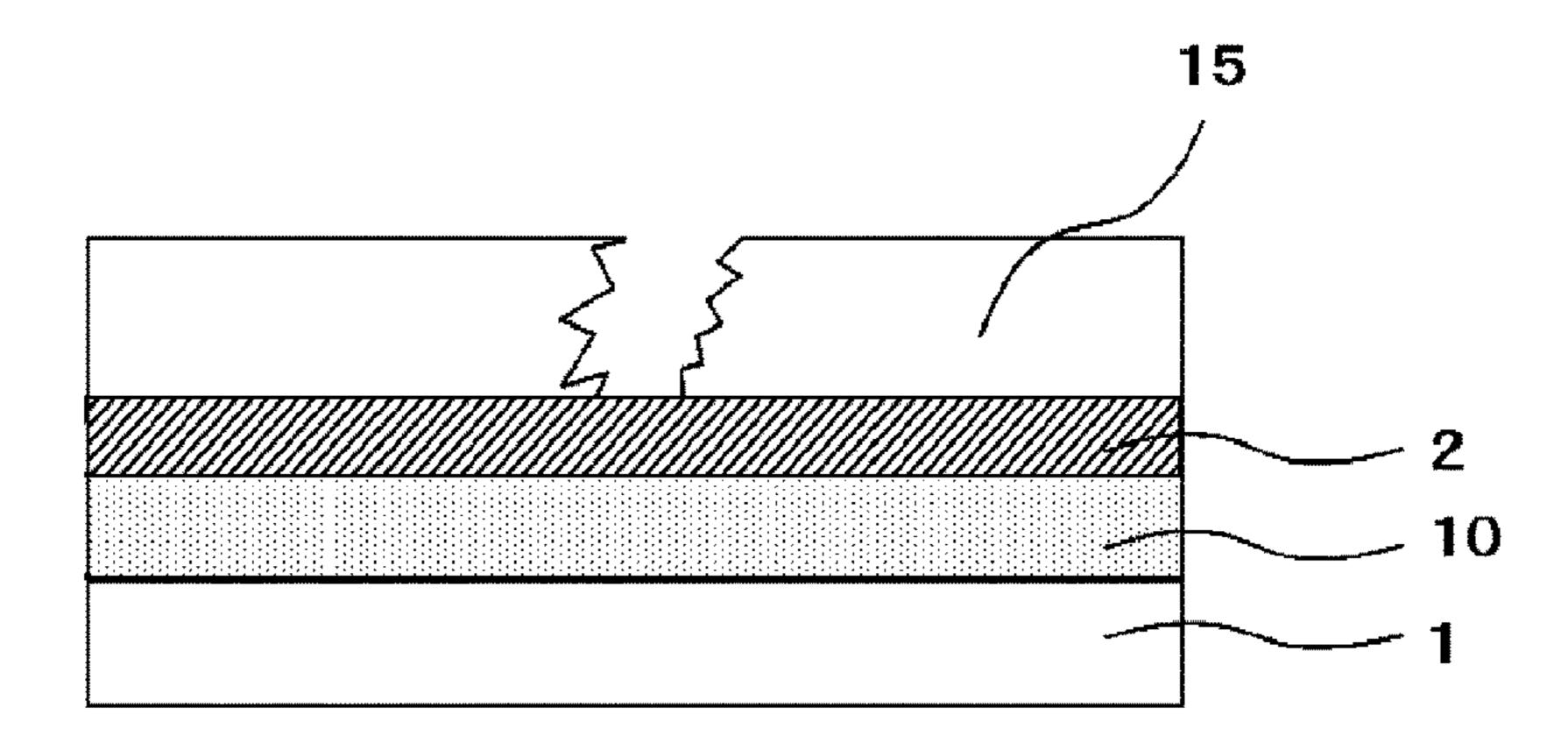

However, for example, the fine foreign particle 16 gention to obtain property of semiconductor to form a semi- 15 erated from a manufacturing device is sometimes incorporated on the surface of the substrate or the like. FIGS. 14 and 15 are cross-sectional views illustrating parts of the manufacturing process of the TFT array substrate 200b according to the first embodiment of this disclosure. FIG. 14 illustrates a case where the foreign particle 16 is incorporated into the resist 15 in the photoengraving process shown in FIG. 8. FIG. 15 is the cross-sectional view illustrating a state where the foreign particle 16 of FIG. 14 is peeled off.

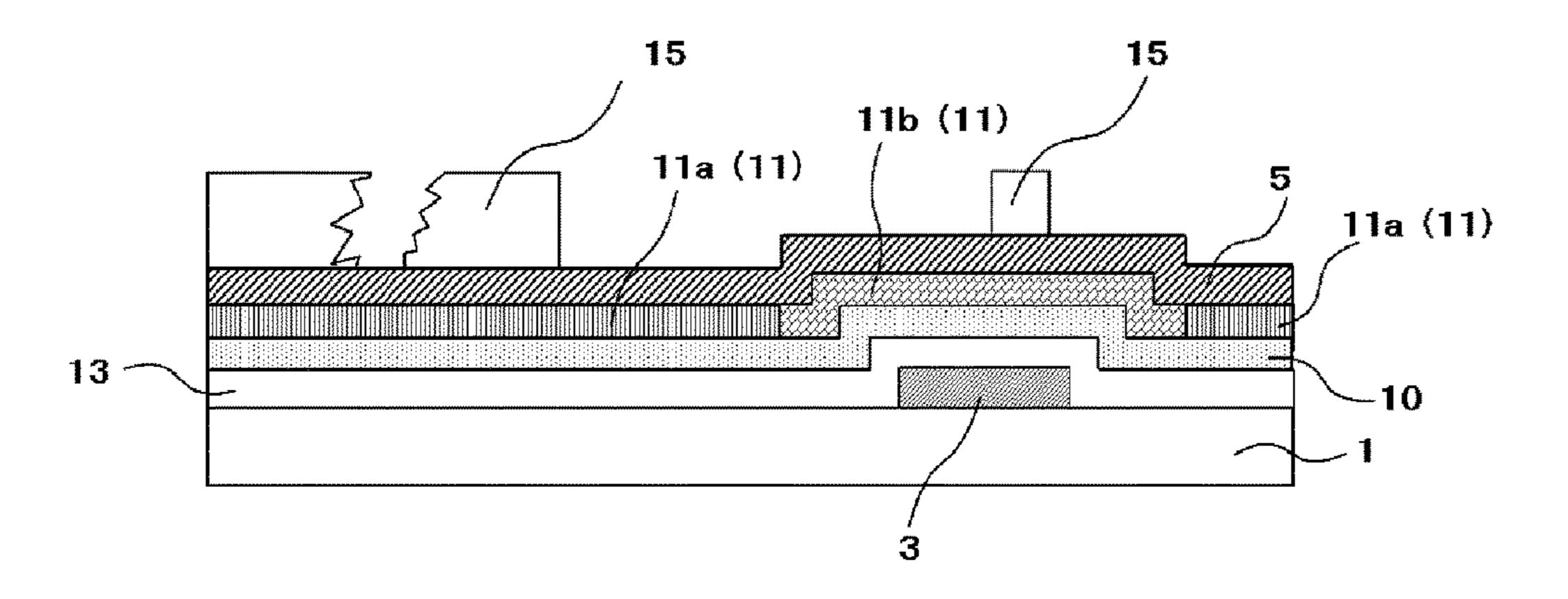

> As shown in FIG. 15, if the foreign particle 16 peels off, for example, in a resist developing step or a cleaning step before the etching step, an unintentional portion not covered by the resist 15 appears in the gate wiring film. As shown in FIG. 16, at this portion not covered by the resist 15, the gate wiring film 2 is etched away and the disconnection part OP appears. Even if the foreign particle 16 does not peel, etchant often enters into a boundary face between the gate wiring film 2 and the resist 15 and also a boundary face between the gate wiring film and the foreign particle 16, and thus a similar disconnection part OP is often generated.

> Fourthly, configurations of the TFT array substrate according to the first embodiment of this disclosure which is subjected to connection repair in a case where the disconnection part OP is generated at the gate wiring film 2 will be descried.

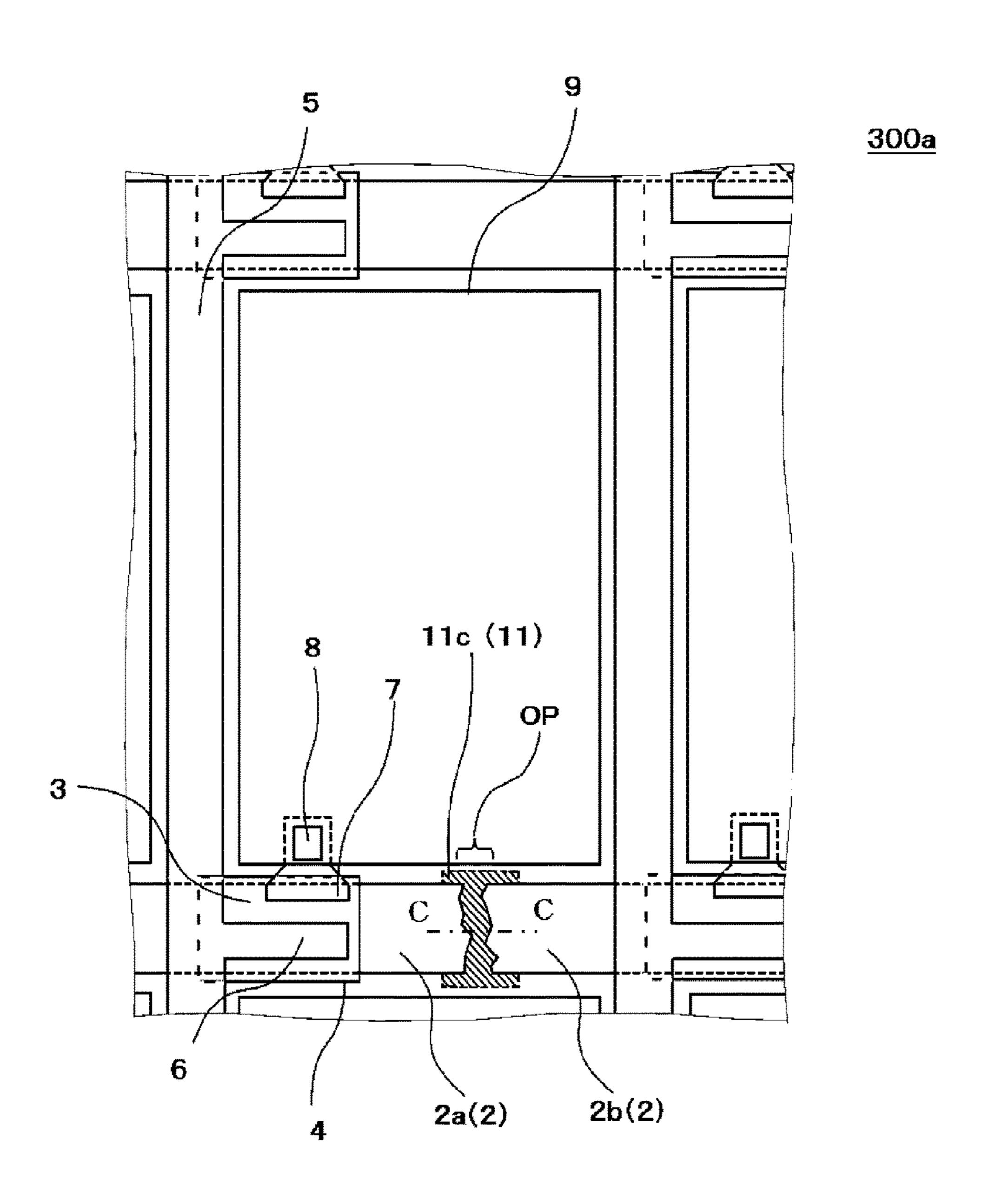

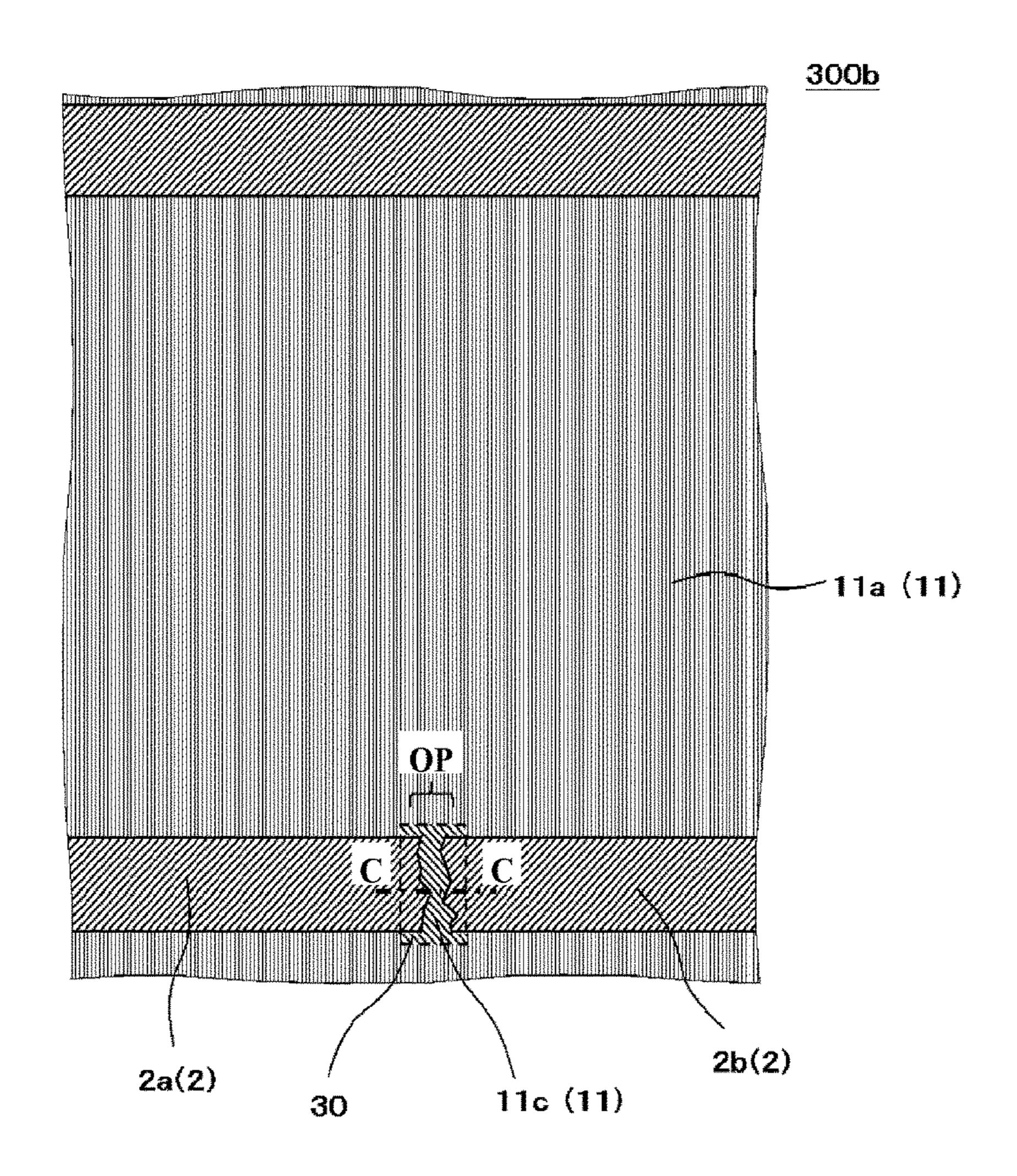

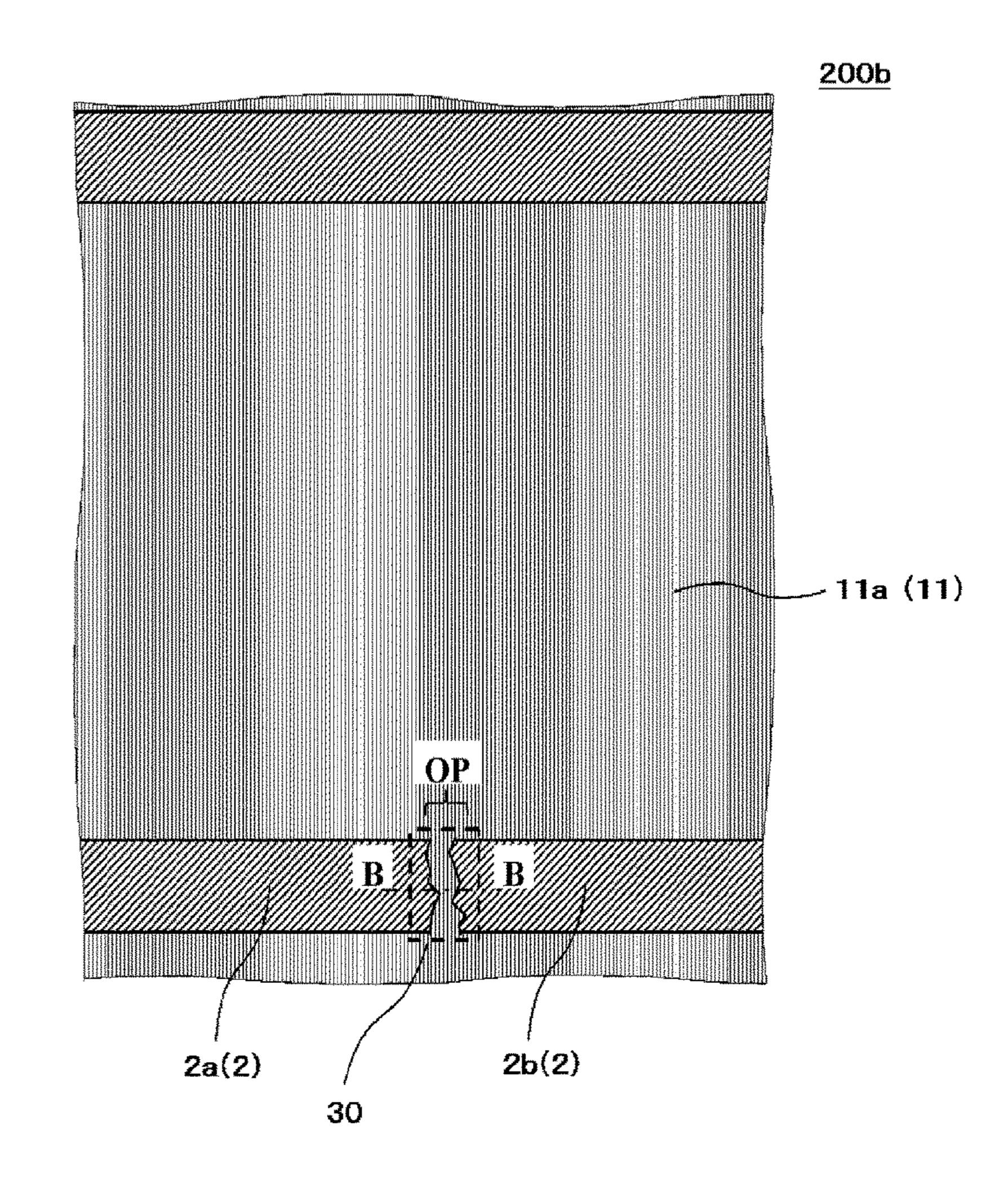

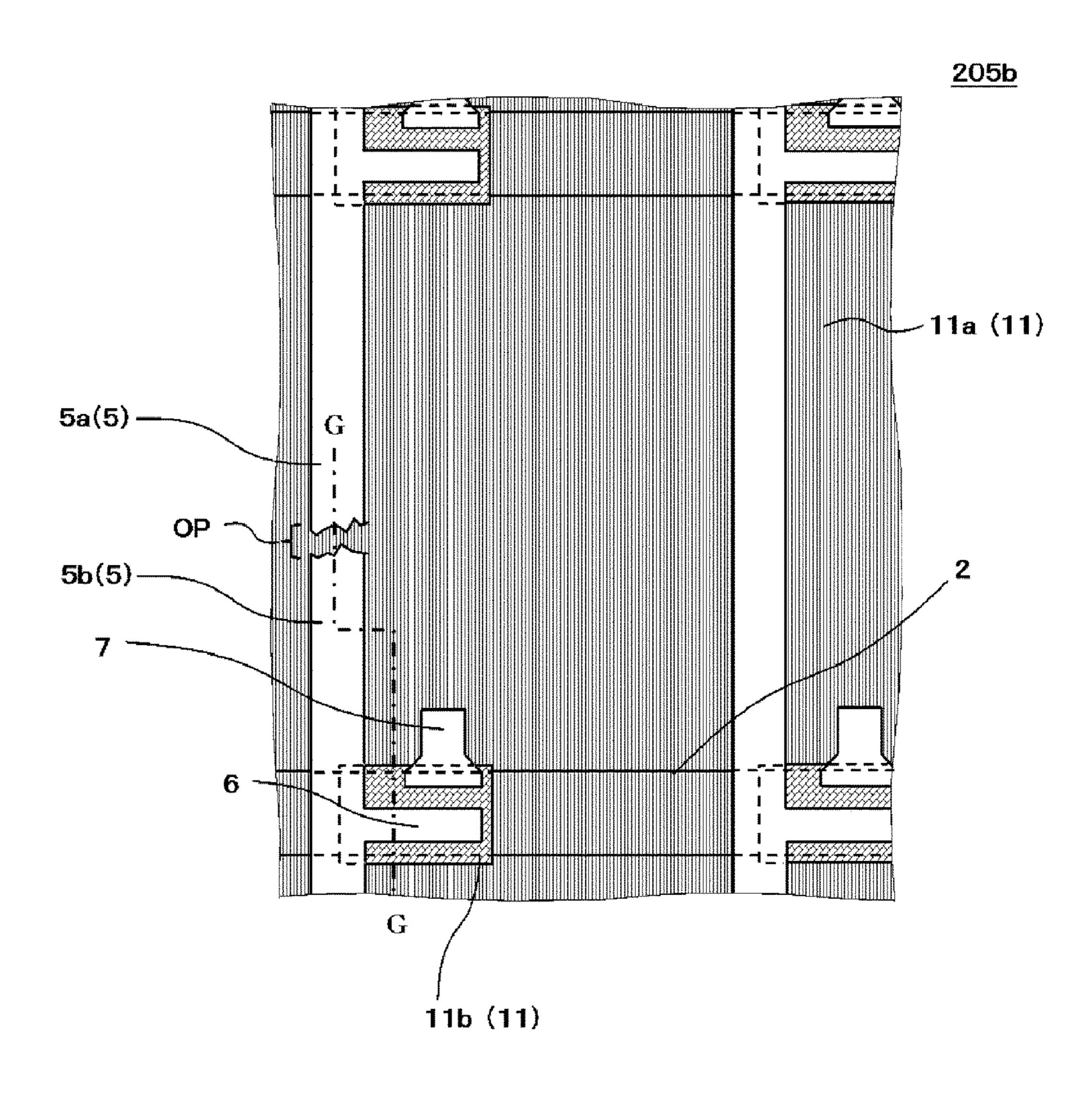

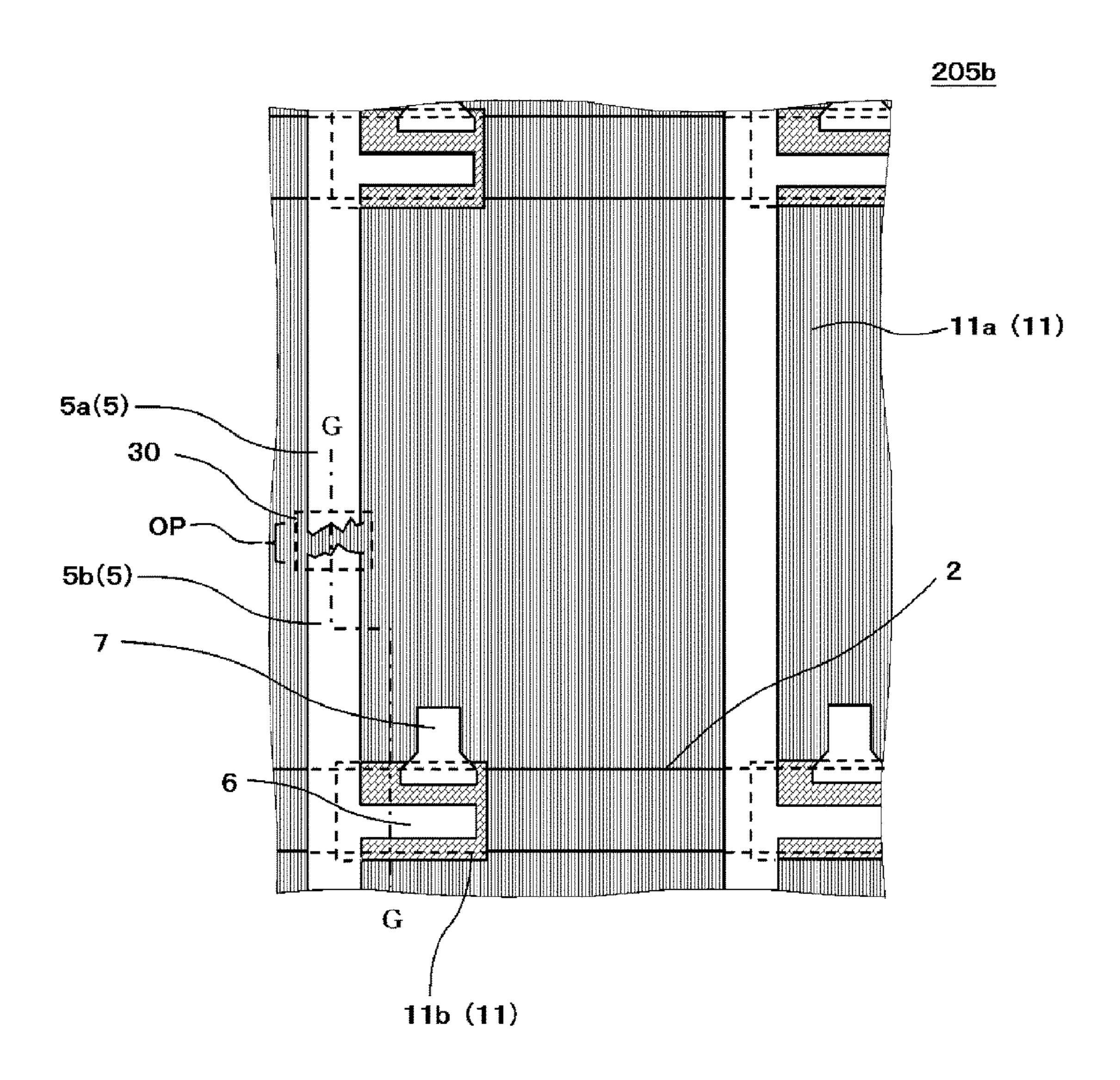

> FIG. 11 is a top view illustrating a TFT array substrate 300a according to the first embodiment of this disclosure. FIG. 12 is a top view illustrating a TFT array substrate 300b according to the first embodiment of this disclosure.

> FIG. 11 corresponds to a state where a conductor part 11c, which is formed by changing the oxide semiconductor film into conductor, is formed at the disconnection part OP of the gate wiring film 2 in FIG. 9. FIG. 12 corresponds to a state where the conductor part 11c, which is formed by changing the oxide semiconductor film into the conductor, is formed at the disconnection part OP of the gate wiring film 2 in FIG. **10**.

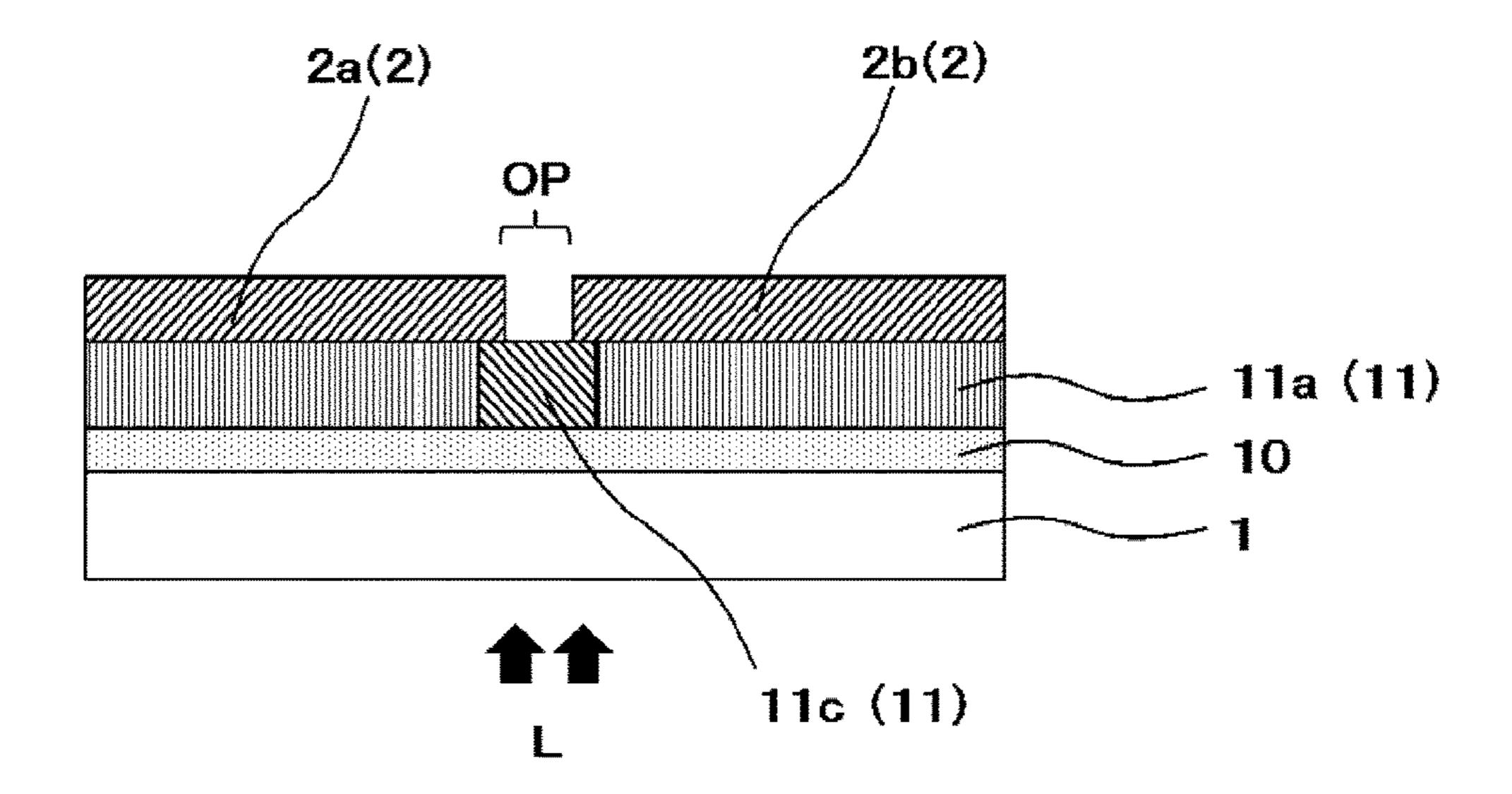

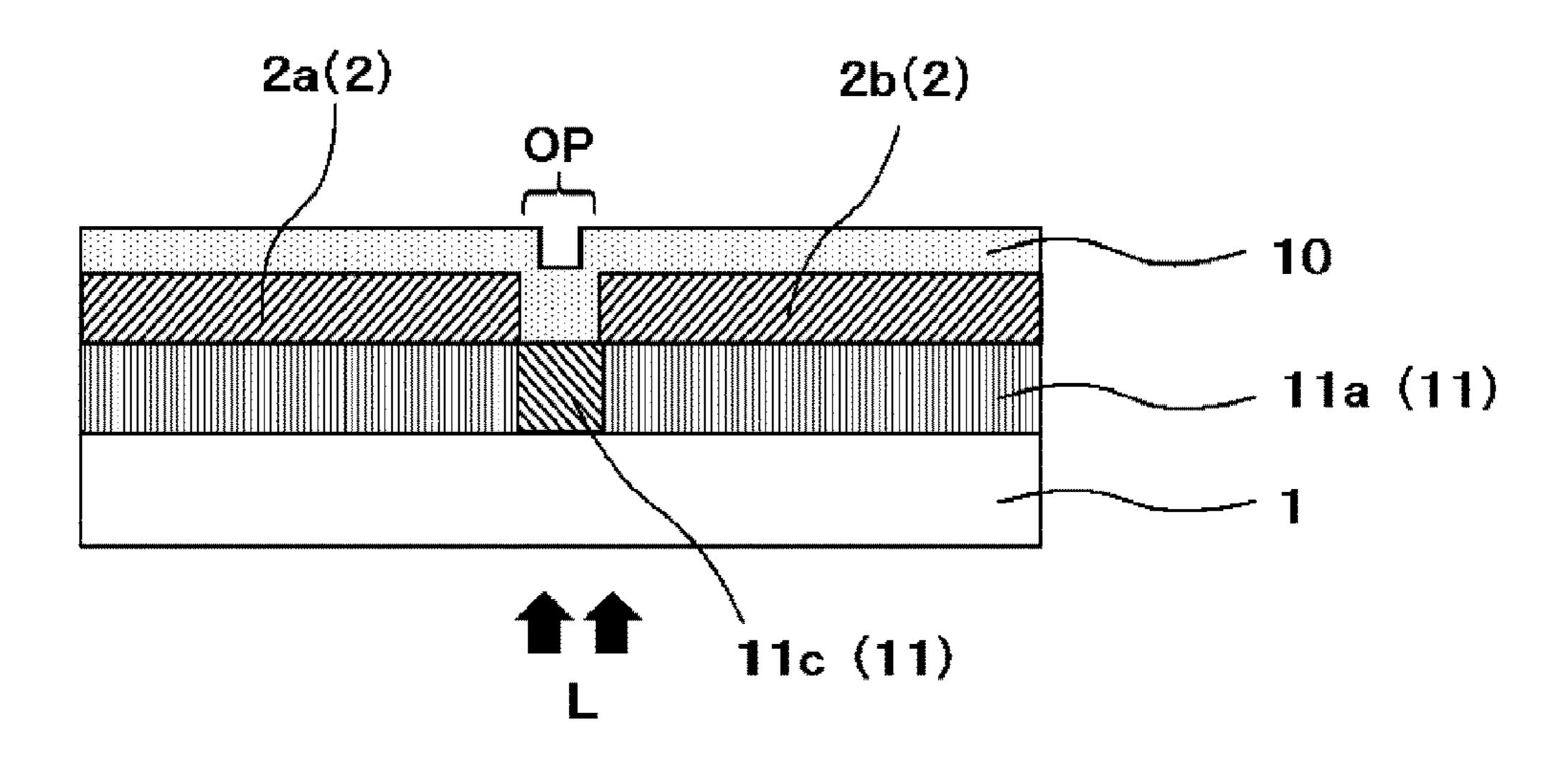

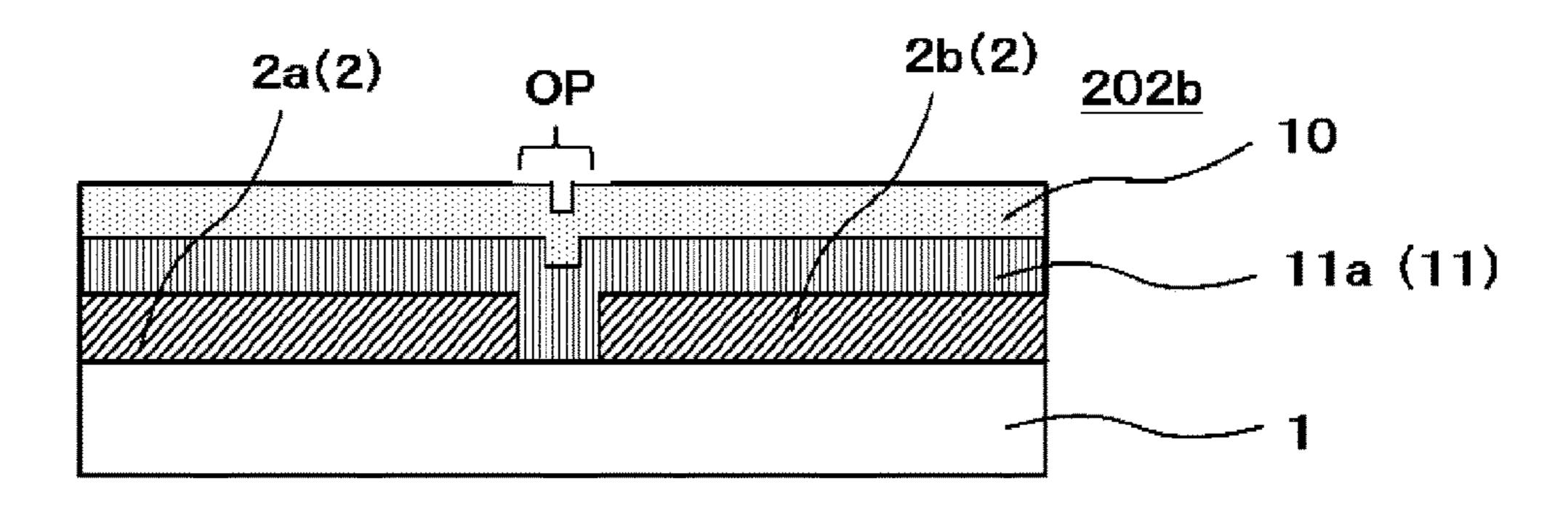

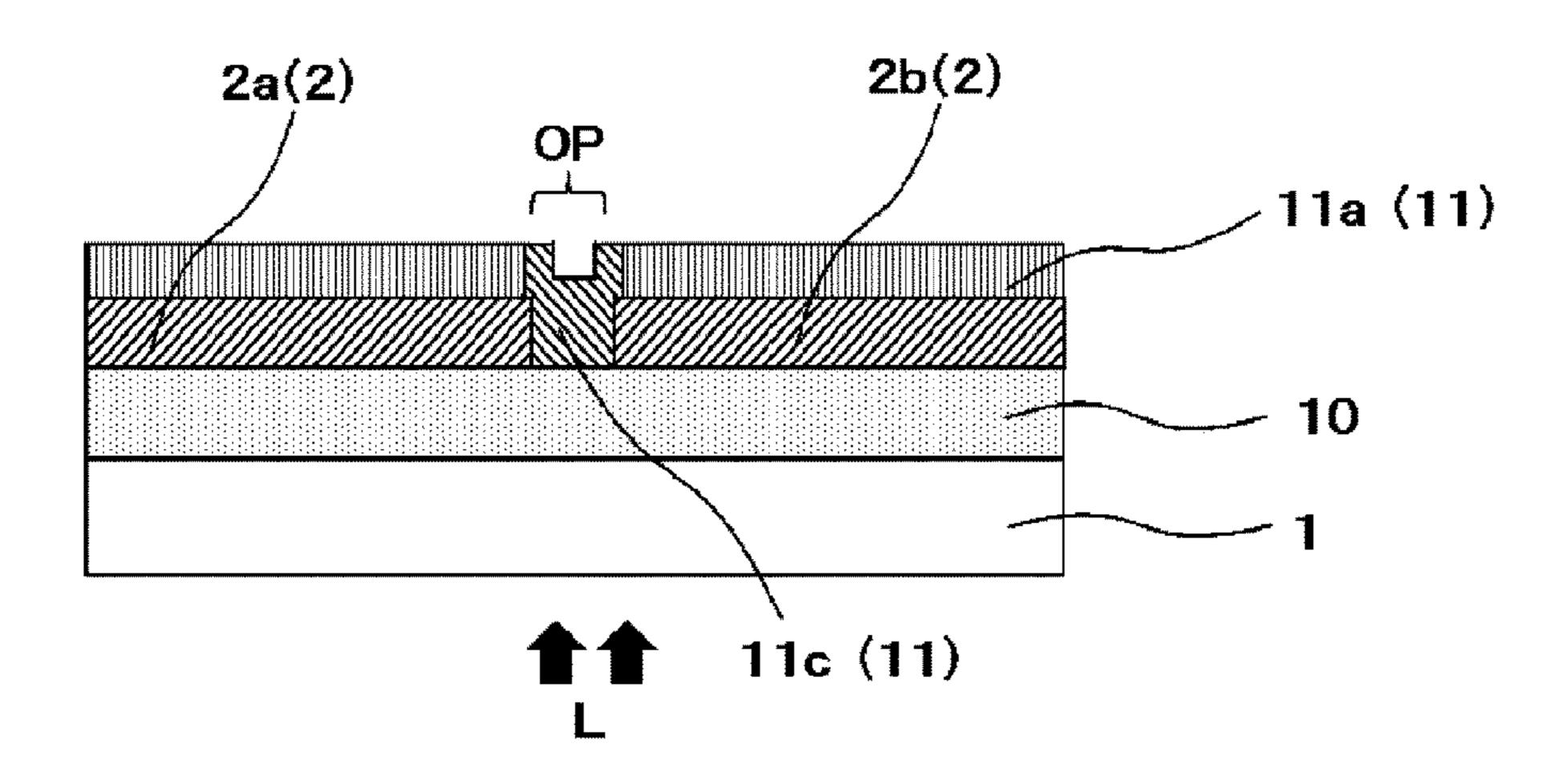

> FIG. 13 is a cross-sectional view of the TFT array substrate 300b according to the first embodiment of this disclosure. FIG. 13 is the cross-sectional view taken along line C-C in parallel to a longitudinal direction of the gate wiring film 2 in FIG. 12. In FIG. 13, the inorganic film 11 has the conductor part 11c formed by changing the oxide semiconductor into the conductor, and the conductor part 11c is in direct contact with both the first gate wiring film 2a and the second gate wiring film 2b. Since the remaining configuration of this TFT array substrate is the same as that of the TFT array substrate shown in FIG. 16, descriptions thereof will be omitted.

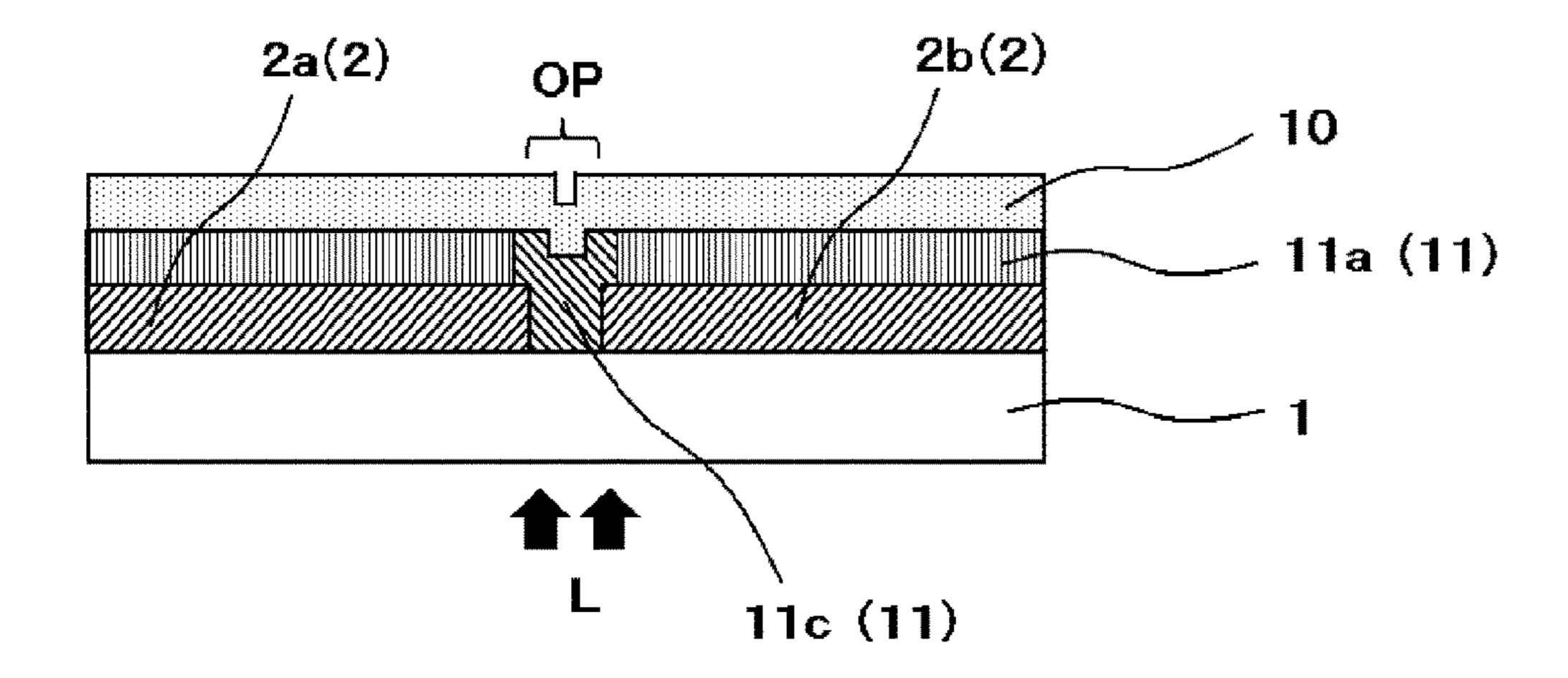

> Fifthly, a method of manufacturing the TFT array substrate 300b by subjecting the TFT array substrate 200b according to the first embodiment of this disclosure to the connection repair will be described. FIG. 17 is a cross-

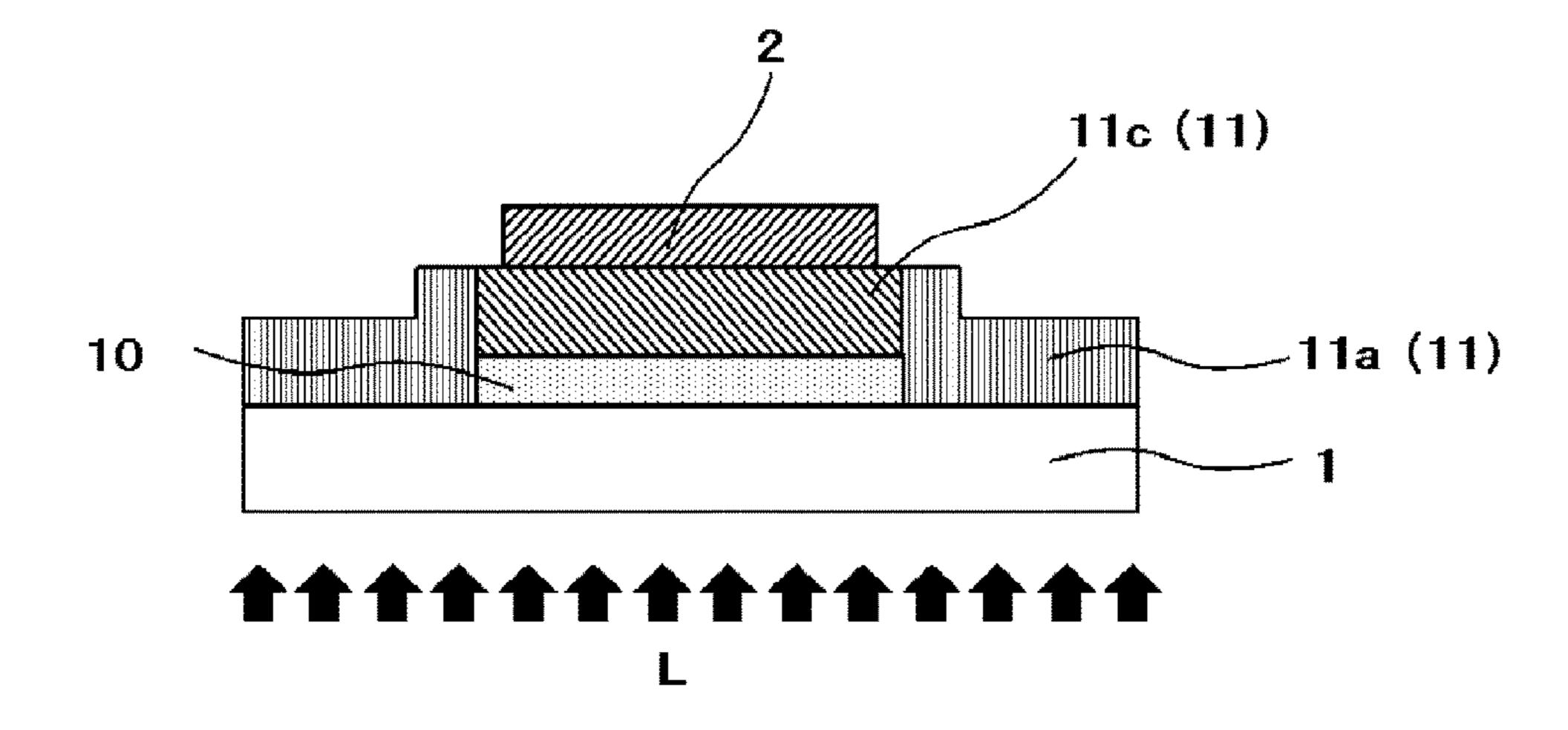

sectional view illustrating a part of the manufacturing process of the TFT array substrate 300b according to the first embodiment of this disclosure. FIG. 17 illustrates a process of irradiating the disconnection part OP with ultraviolet rays

At first, the disconnection part OP is detected by a defect inspection apparatus or the like and the ultraviolet rays L are irradiated on the disconnection part OP by using an ultraviolet laser. As shown in FIG. 17, the ultraviolet rays L are irradiated in a direction toward the inorganic film 11 from the glass substrate 1, that is, toward the disconnection part OP from the rear surface side of the glass substrate 1. The ultraviolet rays L transmit the glass substrate 1 and are irradiated on the insulation film 10 and the insulator part 11a of the inorganic film 11.

FIG. 18 is a top view illustrating the TFT array substrate 200b according to the first embodiment of this disclosure. FIG. 18 illustrates a range 30 on which the ultraviolet rays L are irradiated, at a time of manufacturing the TFT array substrate 300b by subjecting the TFT array substrate 200b 20 according to the first embodiment of this disclosure to the connection repair. The range 30 on which the ultraviolet rays L are irradiated is, for example, a range surrounding the disconnection part OP as shown in FIG. 18.

When the ultraviolet rays L are irradiated on a portion 25 where the insulator part 11a, which is formed by changing the oxide semiconductor film into the insulator, is in direct contact with the insulation film 10 made of the silicon oxide (SiO<sub>2</sub>) film, electronic carriers of the oxide semiconductor film are effectively excited, and thus a specific resistance 30 value of the oxide semiconductor film reduces. Therefore, the insulator part 11a is changed into the conductor, whereby the conductor part 11c is formed. Since the conductor part 11c formed by changing the oxide semiconductor into the conductor is in direct contact with both the first gate wiring 35 film 2a and the second gate wiring film 2b, the first gate wiring film 2a and the second gate wiring film 2b are electrically conducted to each other via the oxide semiconductor film that is changed into the conductor. As the connection repair is performed in this manner, the oxide 40 semiconductor film that is changed into the conductor directly fits to the first gate wiring film 2a and the second gate wiring film 2b. Thus, conduction failure can be reduced as compared with the conventional state (see FIGS. 12 and 13). The conductor means that a specific resistance thereof 45 is  $1\times10^{-2}$   $\Omega\cdot$ cm or less. More preferably, the conductor has the specific resistance of  $1\times10^{-3}~\Omega$ ·cm or less.

By performing the connection repair in this manner, the TFT array substrate 300b shown in FIGS. 12 and 13 is obtained. Thereafter, the gate insulation film 13, the a-Si 50 layer 4, the source wiring film 5, the source electrode 6, the drain electrode 7, the interlayer insulation film 14, the contact hole 8 and the pixel electrode 9 are formed, and thus the TFT array substrate 300a shown in FIG. 11 is obtained.

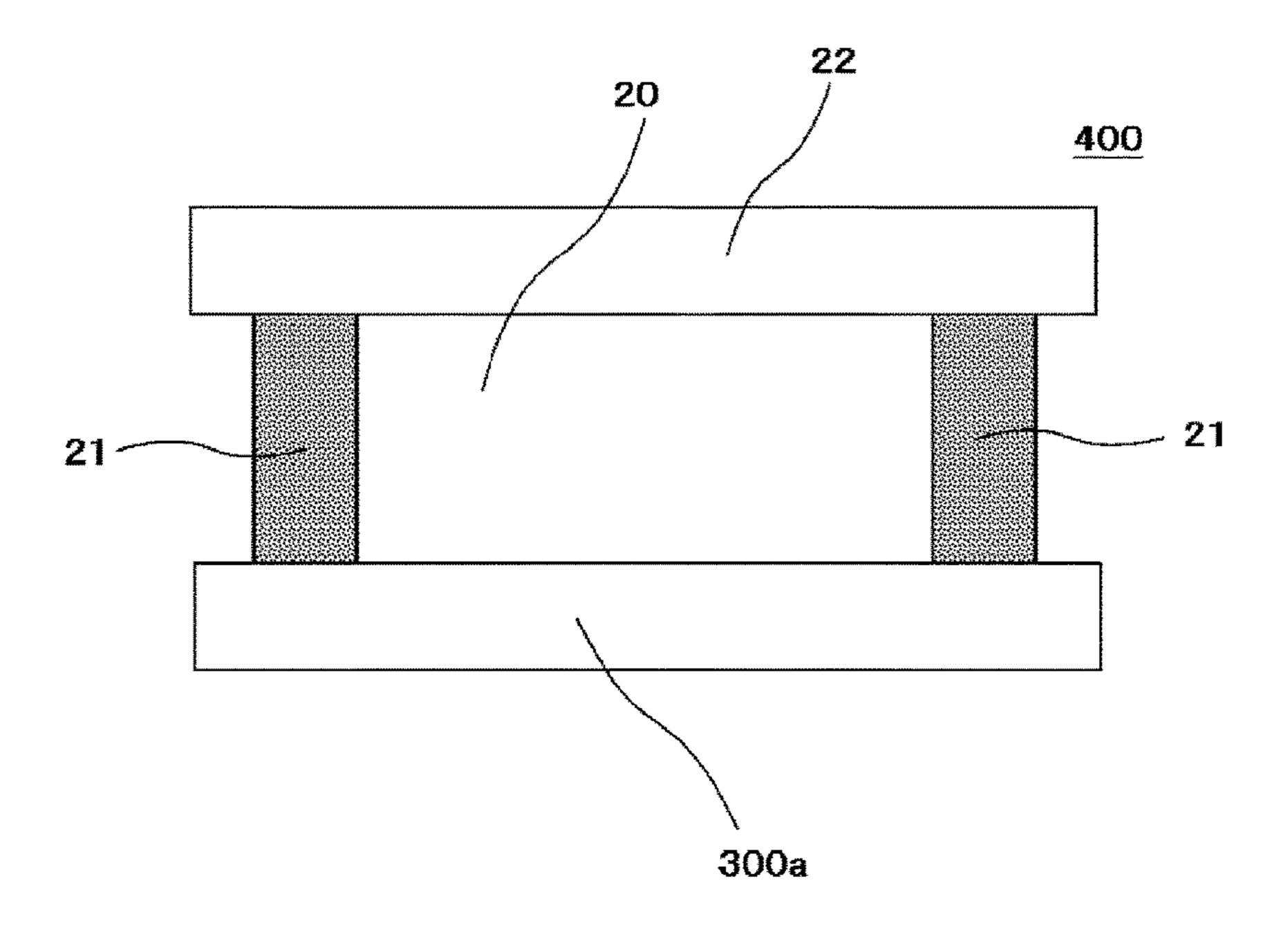

FIG. 19 is a cross-sectional view illustrating a liquid 55 crystal display device 400 according to the first embodiment of this disclosure. After forming an oriented film, etc., as shown in FIG. 19, a CF substrate 22 is laminated on the TFT array substrate 300a via a seal member 21, and liquid crystal 20 is filled in a region surrounded by the TFT array substrate 60 300a, the CF substrate 22 and the seal member 21, whereby the liquid crystal display device 400 as the display device is formed.

The TFT array substrate and the liquid crystal display device according to the first embodiment of this disclosure 65 includes: the insulation glass substrate 1; the insulation film 10 formed on the glass substrate 1 and is primarily made of

**10**

silicon oxide; the inorganic film 11 formed to be in direct contact with the insulation film 10 and having the insulator part 11a which is formed by changing the oxide semiconductor into the insulator; and the gate wiring film 2 formed to be in direct contact with the insulator part 11a. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

The TFT array substrate and the liquid crystal display device according to the first embodiment of this disclosure includes the insulator part 11a formed on the insulation film 10a to be in direct contact with the insulation film 10 and the gate wiring film 2 formed on the insulator part 11a to be in direct contact with the insulator part 11a. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

In the TFT array substrate and the liquid crystal display device according to the first embodiment of this disclosure, the gate wiring film 2 includes the first gate wiring film 2a and the second gate wiring film 2b being not in direct contact with the first gate wiring film 2a. Further, the inorganic film 11 has the conductor part 11c formed by changing the oxide semiconductor into the conductor, and the conductor part 11c is in direct contact with both the first gate wiring film 2a and the second gate wiring film 2b. Therefore, the conduction failure occurring at the time of performing the connection repair can be reduced.

The manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal display device according to the first embodiment of this disclosure includes: the step of forming the insulation film 10 primarily made of silicon oxide on the insulation glass substrate 1; the step of forming, to be in direct contact with the insulation film 10, the inorganic film 11 having the insulator part 11a which is formed by changing the oxide semiconductor into the insulator; and the step of forming the gate wiring film 2 to be in direct contact with the inorganic film 11. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

The manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal display device according to the first embodiment of this disclosure, the step of forming the inorganic film 11 is performed after the step of forming the insulation film 10, and the step of forming the gate wiring film 2 is performed after the step of forming the inorganic film 11. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

In the manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal display device according to the first embodiment of this disclosure, the step of forming the inorganic film 11 includes the step of forming the oxide semiconductor film, and the step of forming the insulator part 11a by changing the oxide semiconductor film into the insulator after the step of forming the oxide semiconductor film. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

In the manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal display device according to the first embodiment of this disclosure, the step of forming the gate wiring film 2 includes the step of forming the gate wiring film 2, which includes the first

gate wiring film 2a and the second gate wiring film 2b being not in direct contact with the first gate wiring film 2a, and forming the conductor part 11c which is formed by changing the oxide semiconductor into the conductor and directly in contact with both the first gate wiring film 2a and the second gate wiring film 2b. Thus, the conduction failure occurring at the time of performing the connection repair can be reduced.

In the manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal display device according to the first embodiment of this disclosure, the step of forming the conductor part 11c includes the step of forming the conductor part 11c by irradiating both the insulation film 10 and the inorganic film 11 with the ultraviolet rays L. Thus, the conduction failure occurring at the time of performing the connection repair can be reduced.

Although the first embodiment according to this disclosure employs the oxide semiconductor formed of InGaZnO as an example of the oxide semiconductor, the oxide semiconductor is not limited thereto. For example, the oxide semiconductor film such as InZnO-based, InGaO-based, InSnO-based, InSnO-based, InGaZnSnO-based, InAlZnO-based, InHf (hafnium) ZnO-based, InZr (zirconium) ZnO-based, InMg (magnesium) ZnO-based or InY 25 (yttrium) ZnO-based oxide semiconductor film may be used. Even when such the oxide semiconductor material is used, effects similar to the case of using the InGaZnO-based oxide semiconductor film in the first embodiment according to this disclosure can be achieved.

Although the first embodiment according to this disclosure employs the silicon oxide (SiO<sub>2</sub>) as an example of the insulation film 10, in place thereof, an insulation film primarily made of oxidized metal such as oxidized aluminum, oxidized titanium, oxidized zirconium, hafnium oxide, 35 tantalum oxide or tungsten oxide may be used. In this case, effects similar to the case of using the silicon oxide in the first embodiment according to this disclosure can be achieved.

Although the first embodiment according to this disclosure employs the ultraviolet laser in the step of irradiating with the ultraviolet rays L, in place thereof, an ultraviolet lamp such as a low-pressure mercury lamp, a high-pressure mercury lamp or an ultrahigh-pressure mercury lamp or an ultraviolet LED may be used. In this case, effects similar to 45 the effects of the first embodiment according to this disclosure can be achieved. For example, the ultraviolet lamp or the ultraviolet LED is only required to emit the ultraviolet rays of 480 nm or less.

The first embodiment according to this disclosure illustrates the case that, in the step of irradiating with the ultraviolet rays L shown in FIG. 12, the ultraviolet rays L are irradiated in the direction toward the inorganic film 11 from the glass substrate 1, that is, toward the disconnection part OP from the rear surface side of the glass substrate 1. In 55 contrast, the ultraviolet rays may be irradiated in a direction toward the glass substrate 1 from the inorganic film 11, that is, toward the disconnection part OP from the upper surface side of the glass substrate 1. In this case, effects similar to the effects of the first embodiment according to this disclosure can be achieved.

The first embodiment according to this disclosure illustrates the case that the  $N_2O$  plasma process P is performed in the step of forming the insulator part 11a by changing the oxide semiconductor film into the insulator. However, this disclosure is not limited thereto but another process may be performed so long as at least gas containing  $N_2O$  is used. In

12

this case, effects similar to the effects of the first embodiment according to this disclosure can be achieved.

Although the first embodiment according to this disclosure employs the glass substrate 1 as an example of the insulation substrate, in place thereof, a resin substrate formed of plastics or the like may be used. In this case, effects similar to the effects of the first embodiment according to this disclosure can be achieved. In particular, material having a high transmissivity in a wavelength range of the ultraviolet rays is more preferable because such the material can change the insulator part 11a made of the oxide semiconductor into the conductor with a high efficiency when the ultraviolet rays L are irradiated.

Although the first embodiment according to this disclo-15 sure illustrates the case where the disconnection occurs at the gate wiring film 2 as the wiring film, effects similar to the effects of the first embodiment according to this disclosure can also be achieved in a case where the disconnection occurs at the gate terminal, the gate electrode 3 or the gate terminal wiring. Further, effects similar to the effects of the first embodiment according to this disclosure can be achieved also in a case where the disconnection occurs at the source wiring film 5, the source terminal, the source terminal wiring, the source electrode 6 or the drain electrode 7, or in a case where the disconnection occurs at an upper electrode or a lower electrode of an in-plane switching type or an FFS (Fringe Field Switching) type liquid crystal display device as a liquid crystal display device of a transverse electric filed type, for example.

The first embodiment according to this disclosure illustrates the case of applying the invention to the liquid crystal device of transmissive structure. However, effects similar to the effects of the first embodiment according to this disclosure can also be achieved in a case of applying the invention to a display device such as a reflection type, a semitransmissive type or a field sequential type, or in a case of applying the invention to a display device such as a polysilicon TFT type or a low-temperature polysilicon TFT type.

Although the first embodiment according to this disclosure illustrates the case of applying the invention to the liquid crystal device, effects similar to the effects of the first embodiment according to this disclosure can also be achieved in a case of applying the invention to an electronic device having electric wirings such as a touch panel or an X-ray photodetector.

Second Embodiment

A TFT array substrate according to the second embodiment of this disclosure differs from the first embodiment according to this disclosure in an order of laminating the insulation film 10, the gate wiring film 2 and the inorganic film 11.

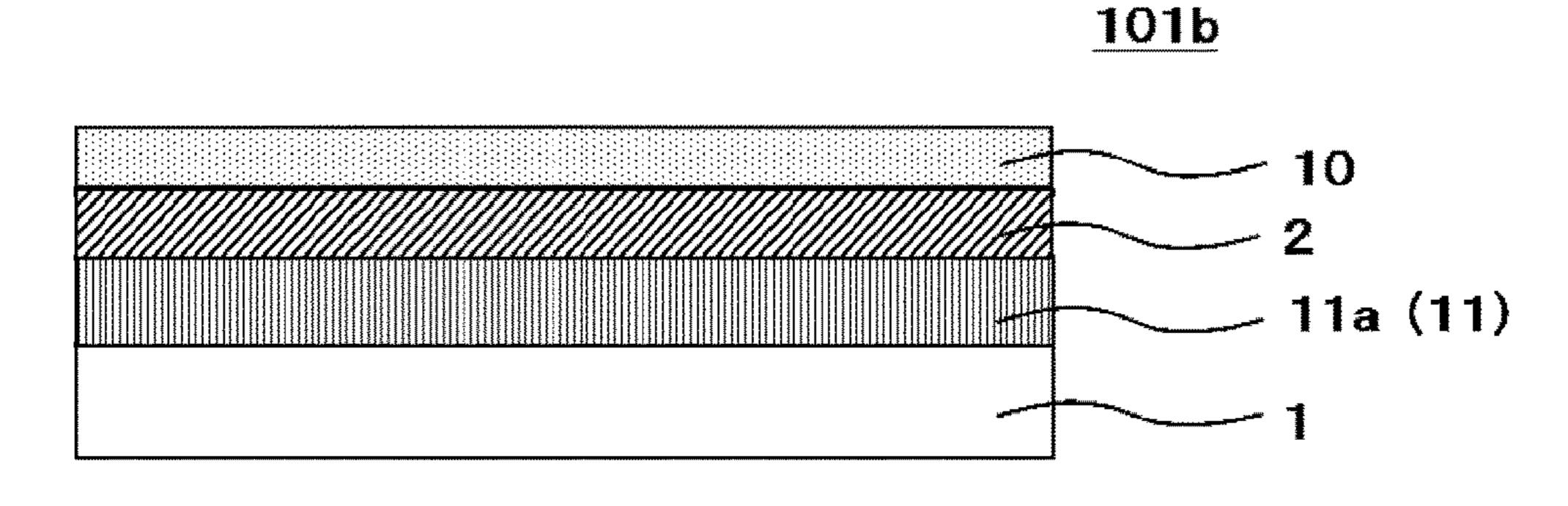

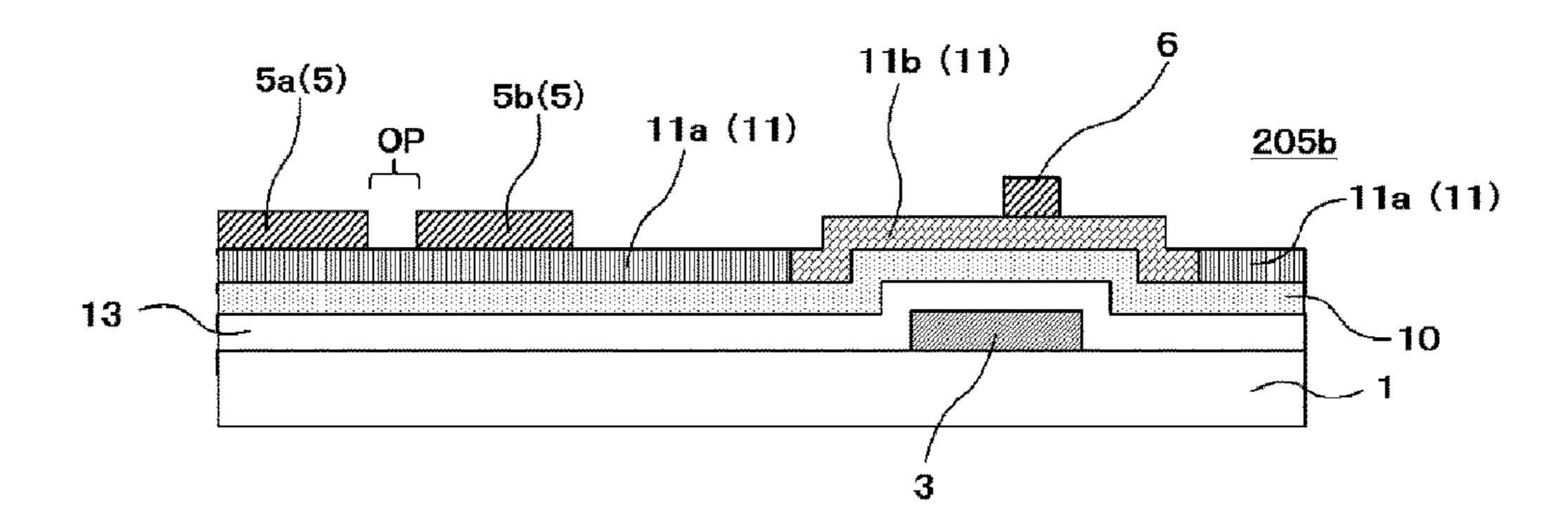

Configuration of a TFT array substrate 101b according to the second embodiment of this disclosure will be described. FIG. 20 is a cross-sectional view of the TFT array substrate 101b according to the second embodiment of this disclosure. In FIG. 20, portions identical or corresponding to those of FIG. 3 are referred to by the common symbols, and descriptions thereof will be omitted.

In FIG. 20, the inorganic film 11 made of the insulator part 11a, which is formed by changing the oxide semiconductor into the insulator, is formed on the glass substrate 1 as the translucent insulation substrate. The gate wiring film 2 is formed on the insulator part 11a to be in direct contact with the insulator part 11a which is obtained by changing the oxide semiconductor into the insulator. The insulation film 10 is formed on the gate wiring film 2 to be in direct contact with the gate wiring film 2.

Thereafter, the gate insulation film 13, the a-Si layer 4, the source wiring film 5, the source electrode 6, the drain electrode 7, the interlayer insulation film 14, the contact hole 8 and the pixel electrode 9 are formed, and thus the TFT array substrate 100a according to the second embodiment of 5 this disclosure is obtained.

Next, a manufacturing method of the TFT array substrate 101b according to the second embodiment of this disclosure will be described. At first, the inorganic film 11 having the insulator part 11a, which is formed by changing the oxide 10 semiconductor into the insulator, is formed on the glass substrate 1. After forming the inorganic film 11, the gate wiring film 2 is formed to be in direct contact with the inorganic film 11. After forming the gate wiring film 2, the insulation film 10 primarily made of silicon oxide is formed 15 on the gate wiring film 2 to be in direct contact with.

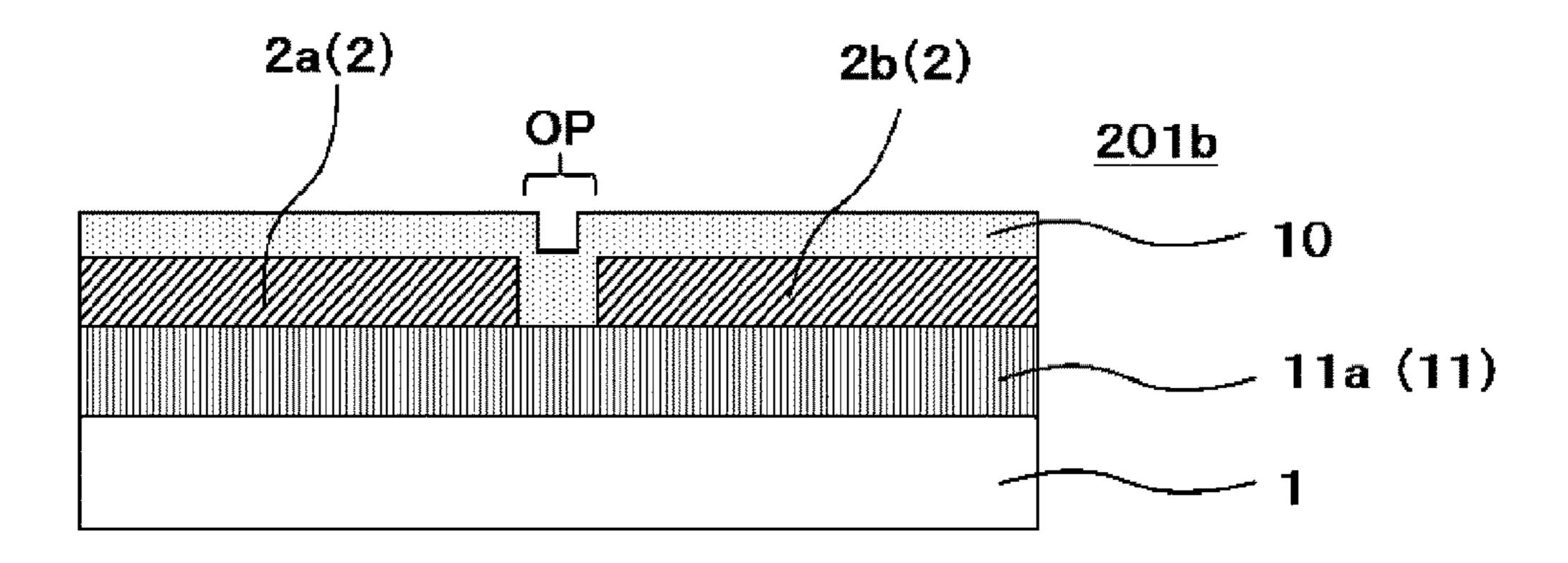

Explanation will be made as to the configuration of the TFT array substrate according to the second embodiment of this disclosure in a case where the gate wiring film 2 has a disconnection part OP. FIG. 25 is a cross-sectional view 20 illustrating a TFT array substrate 201b according to the second embodiment of this disclosure. In the configuration of the TFT array substrate according to the second embodiment of this disclosure in the case of having the disconnection part OP, as shown in FIG. 25, the gate wiring film 2 is 25 separated in the longitudinal direction in a manner of interposing the disconnection part OP. Thus, the first gate wiring film 2a and the second gate wiring film 2b being not in direct contact with the first gate wiring film 2a are formed. Since the remaining configuration of this TFT array sub- 30 strate is the same as that in the case where the disconnection part OP is not formed as shown in FIG. 20, descriptions thereof will be omitted.

Explanation will be made as to an example of mechanism that the disconnection part OP occurs at the wiring, in the 35 second embodiment according to this disclosure.

FIGS. 22 to 24 are cross-sectional views illustrating parts of manufacturing process of the TFT array substrate 201b according to the second embodiment of this disclosure. FIG. 22 illustrates a case where foreign particle 16 is incorporated into the resist 15 in the photoengraving process. FIG. 23 is the cross-sectional view illustrating a state where the foreign particle 16 of FIG. 22 peels.

As shown in FIG. 23, if the foreign particle 16 peels off, an unintentional portion not covered by the resist 15 appears 45 in the gate wiring film. As shown in FIG. 24, at this portion not covered by the resist 15, the gate wiring film 2 is etched away in the etching step and the disconnection part OP appears.

Next, explanation will be made as to configuration of the 50 TFT array substrate according to the second embodiment of this disclosure which is subjected to connection repair in a case where the disconnection part OP is generated at the gate wiring film 2.

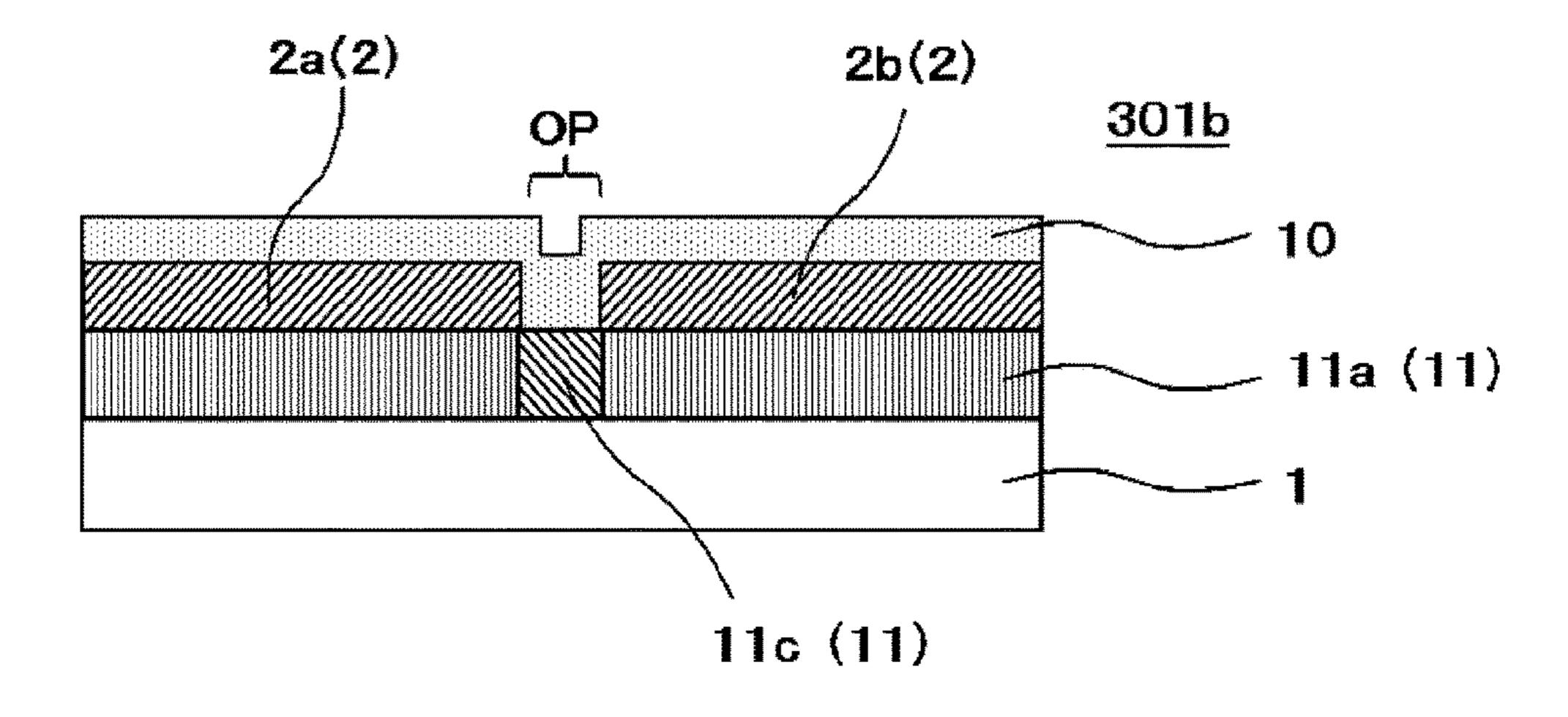

FIG. 21 is a cross-sectional view illustrating a TFT array 55 substrate 301b according to the second embodiment of this disclosure. FIG. 25 illustrates a state where the conductor part 11c, which is formed by changing the oxide semiconductor film into the conductor, is formed at the disconnection part OP of the gate wiring film 2 in FIG. 25.

In addition to the configuration explained with reference to FIG. 25, as shown in FIG. 21, the inorganic film 11 has the conductor part 11c formed by changing the oxide semiconductor into the conductor, and the conductor part 11c is in direct contact with both the first gate wiring film 2a and 65 the second gate wiring film 2b. Since the remaining configuration of this TFT array substrate is the same as that of

**14**

the TFT array substrate in the state before forming the conductor part 11c, which is obtained by changing the oxide semiconductor film into the conductor, shown in FIG. 25, descriptions thereof will be omitted.

Next, method of manufacturing the TFT array substrate 301b by subjecting the TFT array substrate 201b according to the second embodiment of this disclosure to the connection repair will be described. FIG. 26 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate 301b according to the second embodiment of this disclosure. FIG. 26 illustrates the step of irradiating the disconnection part OP with ultraviolet rays L.

The ultraviolet rays L are irradiated on the disconnection part OP, by using the ultraviolet laser. As shown in FIG, 26, the ultraviolet rays L are irradiated in a direction toward the inorganic film 11 from the glass substrate 1, that is, toward the disconnection part OP from the rear surface side of the glass substrate 1. The ultraviolet rays L transmit the glass substrate 1 and are irradiated on the insulation film 10 and the insulator part 11a of the inorganic film 11.

When the ultraviolet rays L are irradiated on a portion where the insulator part 11a, which is formed by changing the oxide semiconductor film into the insulator, is in direct contact with the insulation film 10 made of the silicon oxide (SiO<sub>2</sub>) film, electronic carriers of the oxide semiconductor film are effectively excited, and thus a specific resistance value of the oxide semiconductor film reduces. Thus, the insulator part 11a is changed into the conductor, whereby the conductor part 11c is formed. Since the conductor part 11c formed by changing the oxide semiconductor into the conductor is in direct contact with both the first gate wiring film 2a and the second gate wiring film 2b, the first gate wiring film 2a and the second gate wiring film 2b are electrically conducted to each other via the oxide semiconductor film that is changed into the conductor. As the connection repair is performed in this manner, the oxide semiconductor film that is changed into the conductor directly fits to the first gate wiring film 2a and the second gate wiring film 2b. Thus, conduction failure can be reduced as compared with the conventional art (see FIG. 21).

By performing the connection repair in this manner, the TFT array substrate 301b shown in FIG. 21 is obtained. Thereafter, the gate insulation film 13, the a-Si layer 4, the source wiring film 5, the source electrode 6, the drain electrode 7, the interlayer insulation film 14, the contact hole 8 and the pixel electrode 9 are formed, and thus the TFT array substrate 301a is obtained.

After forming the oriented film, etc., the CF substrate 22 is laminated on the TFT array substrate 301a via the seal member 21, and the liquid crystal 20 is filled in a region surrounded by the TFT array substrate 301a, the CF substrate 22 and the seal member 21, whereby a liquid crystal display device 500 as the display device is formed.

The TFT array substrate and the liquid crystal display device according to the second embodiment of this disclosure includes: the insulation glass substrate 1; the inorganic film 11 formed on the insulation glass substrate 1 and having the insulator part 11a which is formed by changing the oxide semiconductor into the insulator; the gate wiring film 2 formed to be in direct contact with the insulator part 11a; and the insulation film 10 formed to be in direct contact with the gate wiring film 2 and is primarily made of one of silicon oxide and oxidized metal. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

The TFT array substrate and the liquid crystal display device according to the second embodiment of this disclosure includes the gate wiring film 2 formed on the insulator part 11a to be in direct contact with the insulator part 11a and the insulation film 10 formed on the gate wiring film 2 to be 5 in direct contact with the gate wiring film 2. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

The manufacturing method of the TFT array substrate and 10 the manufacturing method of the liquid crystal display device according to the second embodiment of this disclosure includes: the step of forming, on the insulation glass substrate 1, the inorganic film 11 having the insulator part 11a which is formed by changing the oxide semiconductor 15 into the insulator; the step of forming the gate wiring film 2 to be in direct contact with the insulator part 11a; and the step of forming, on the gate wiring film 2 to be in direct contact, the insulation film 10 primarily made of one of silicon oxide and oxidized metal. Therefore, even if discon- 20 nection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

In the manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal display 25 device according to the second embodiment of this disclosure, the step of forming the gate wiring film 2 is performed after the step of forming the inorganic film 11, and the step of forming the insulation film 10 is performed after the step of forming the gate wiring film 2. Therefore, even if dis- 30 connection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

Third Embodiment

of this disclosure differs from the first embodiment according to this disclosure in an order of laminating the insulation film 10, the gate wiring film 2 and the inorganic film 11.

Configuration of a TFT array substrate **102**b according to the third embodiment of this disclosure will be described. 40 FIG. 27 is a cross-sectional view of the TFT array substrate **102**b according to the third embodiment of this disclosure. In FIG. 27, portions identical or corresponding to those of FIG. 3 are referred to by the common symbols, and descriptions thereof will be omitted.

In FIG. 27, the gate wiring film 2 is formed on the glass substrate 1 as the translucent insulation substrate. The inorganic film 11 made of the insulator part 11a, which is formed by changing the oxide semiconductor into the insulator, is formed on the gate wiring film 2 to be in direct contact with 50 the gate wiring film 2. The insulation film 10 is formed on the insulator part 11a to be in direct contact with the insulator part 11a which is obtained by changing the oxide semiconductor into the insulator.

source wiring film 5, the source electrode 6, the drain electrode 7, the interlayer insulation film 14, the contact hole 8 and the pixel electrode 9 are formed, and thus a TFT array substrate 102a according to the third embodiment of this disclosure is obtained.

Next, a manufacturing method of the TFT array substrate 102b according to the third embodiment of this disclosure will be described. At first, the gate wiring film 2 is formed on the glass substrate 1. After forming the gate wiring film 2, the inorganic film 11 having the insulator part 11a, which 65 is formed by changing the oxide semiconductor into the insulator, is formed to be in direct contact with the gate

**16**

wiring film 2. After forming the inorganic film 11, the insulation film 10 primarily made of silicon oxide is formed to be in direct contact with the inorganic film 11.

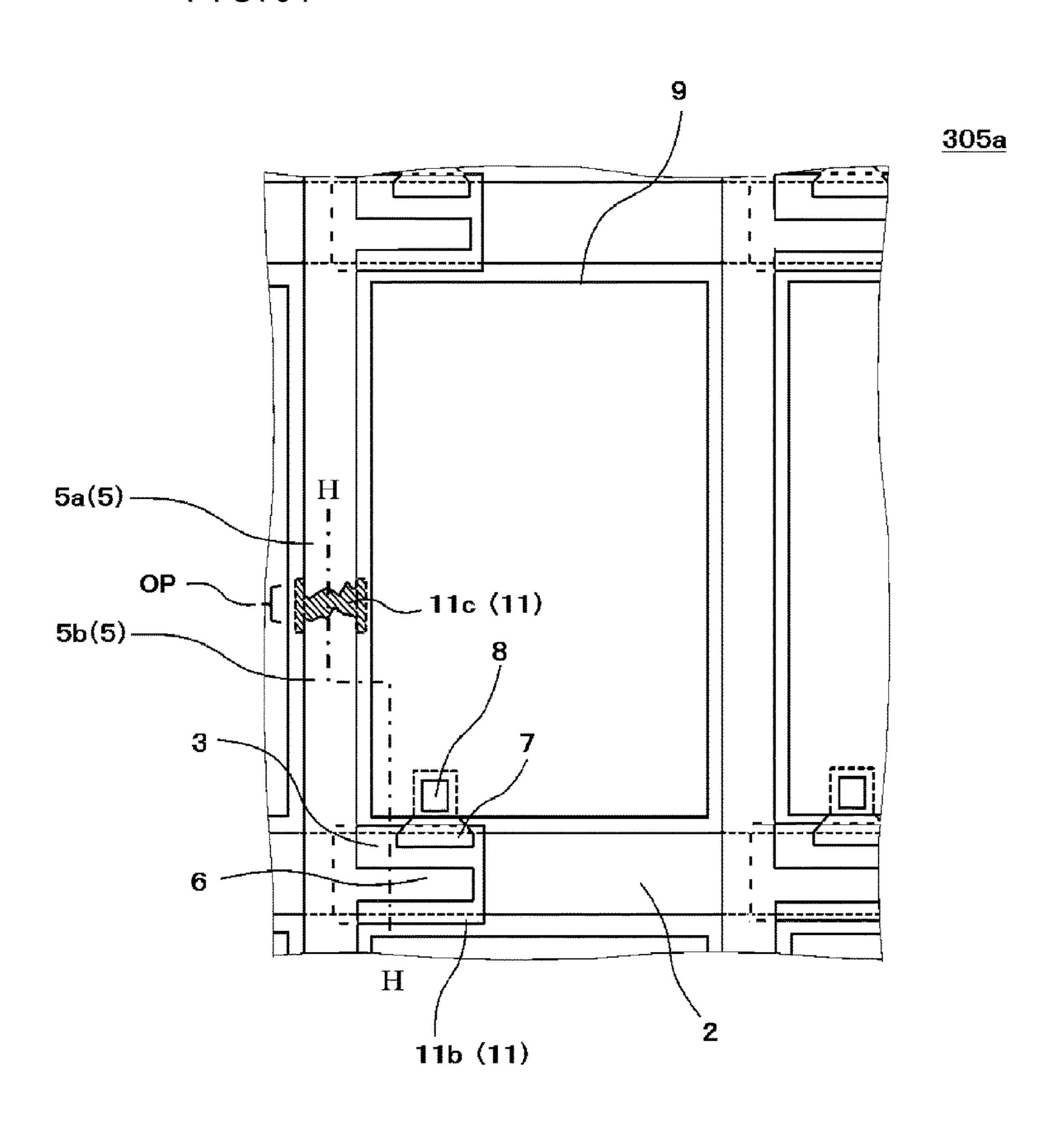

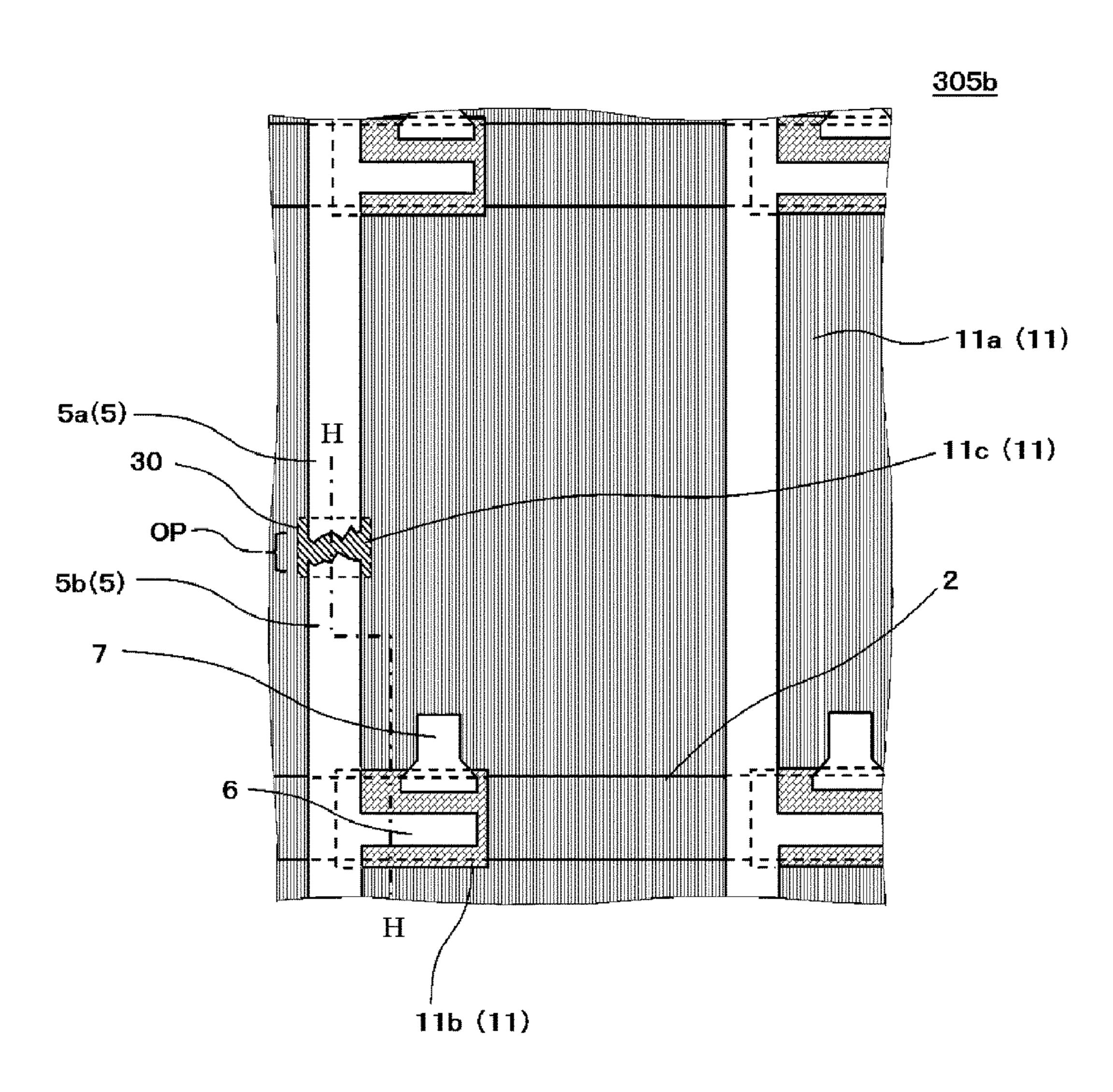

Explanation will be made as to the configuration of the TFT array substrate according to the third embodiment of this disclosure in a case where the gate wiring film 2 has a disconnection part OP. FIG. 33 is a cross-sectional view illustrating a TFT array substrate 202b according to the third embodiment of this disclosure. In the configuration of the TFT array substrate according to the third embodiment of this disclosure in the case of having the disconnection part OP, as shown in FIG. 33, the gate wiring film 2 is separated in the longitudinal direction in a manner of interposing the disconnection part OP. Thus, the first gate wiring film 2a and the second gate wiring film 2b being not in direct contact with the first gate wiring film 2a are formed. Since the remaining configuration of this TFT array substrate is the same as that in the case where the disconnection part OP is not formed as shown in FIG. 27, descriptions thereof will be omitted.

Explanation will be made as to an example of mechanism that the disconnection part OP occurs at the wiring, in the third embodiment according to this disclosure.

FIGS. 29 to 32 are cross-sectional views illustrating parts of manufacturing process of the TFT array substrate 202b according to the third embodiment of this disclosure. FIG. 29 illustrates a case where foreign particle 16 is incorporated into the resist 15 in the photoengraving process. FIG. 30 is the cross-sectional view illustrating a state where the foreign particle 16 of FIG. 29 peels.

As shown in FIG. 30, if the foreign particle 16 peels off, an unintentional portion not covered by the resist 15 appears in the gate wiring film. As shown in FIG. 31, at this portion A TFT array substrate according to the third embodiment 35 not covered by the resist 15, the gate wiring film 2 is etched away in the etching step and the disconnection part OP appears. Thereafter, as shown in FIG. 32, the inorganic film 11 having the insulator part 11a, which is formed by changing the oxide semiconductor into the insulator, is formed to be in direct contact with the gate wiring film 2.

> Next, configuration of the TFT array substrate according to the third embodiment of this disclosure which is subjected to connection repair in a case where the disconnection part OP is generated at the gate wiring film 2 will be described.

> FIG. 28 is a cross-sectional view illustrating a TFT array substrate 302b according to the third embodiment of this disclosure. FIG. 28 illustrates a state where the conductor part 11c, which is formed by changing the oxide semiconductor film into the conductor, is formed at the disconnection part OP of the gate wiring film 2 in FIG. 33.

In addition to the configuration explained with reference to FIG. 33, as shown in FIG. 28, the inorganic film 11 has the conductor part 11c formed by changing the oxide semiconductor into the conductor, and the conductor part 11c is Thereafter, the gate insulation film 13, the a-Si layer 4, the 55 in direct contact with both the first gate wiring film 2a and the second gate wiring film 2b. Since the remaining configuration of this TFT array substrate is the same as that of the TFT array substrate in the state before forming the conductor part 11c, which is obtained by changing the oxide semiconductor film into the conductor, shown in FIG. 33, descriptions thereof will be omitted.

> Next, a method of manufacturing the TFT array substrate 302b by subjecting the TFT array substrate 202b according to the third embodiment of this disclosure to the connection repair will be described. FIG. **34** is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate 302b according to the third embodiment of

this disclosure. FIG. **34** illustrates the step of irradiating the disconnection part OP with ultraviolet rays L.

The ultraviolet rays L are irradiated on the disconnection part OP, by using the ultraviolet laser. As shown in FIG. 34, the ultraviolet rays L are irradiated in a direction toward the inorganic film 11 from the glass substrate 1, that is, toward the disconnection part OP from the rear surface side of the glass substrate 1. The ultraviolet rays L transmit the glass substrate 1 and are irradiated on the insulation film 10 and the insulator part 11a of the inorganic film 11.

When the ultraviolet rays L are irradiated on a portion where the insulator part 11a, which is formed by changing the oxide semiconductor film into the insulator, is in direct contact with the insulation film 10 made of the silicon oxide (SiO<sub>2</sub>) film, electronic carriers of the oxide semiconductor 15 film are effectively excited, and thus a specific resistance value of the oxide semiconductor film reduces. Thus, the insulator part 11a is changed into the conductor, whereby the conductor part 11c is formed. Since the conductor part 11c formed by changing the oxide semiconductor into the con- 20 ductor is in direct contact with both the first gate wiring film 2a and the second gate wiring film 2b, the first gate wiring film 2a and the second gate wiring film 2b are electrically conducted to each other via the oxide semiconductor film that is changed into the conductor. As the connection repair 25 is performed in this manner, the oxide semiconductor film that is changed into the conductor directly fits to the first gate wiring film 2a and the second gate wiring film 2b. Thus, conduction failure can be reduced as compared with the conventional art (see FIG. 28).

By performing the connection repair in this manner, the TFT array substrate 302b shown in FIG. 28 is obtained. Thereafter, the gate insulation film 13, the a-Si layer 4, the source wiring film 5, the source electrode 6, the drain electrode 7, the interlayer insulation film 14, the contact hole 35 8 and the pixel electrode 9 are formed, and thus the TFT array substrate 302a is obtained.

After forming the oriented film, etc., the CF substrate 22 is laminated on the TFT array substrate 302a via the seal member 21, and the liquid crystal 20 is filled in a region 40 surrounded by the TFT array substrate 302a, the CF substrate 22 and the seal member 21, whereby a liquid crystal display device 600 as the display device is formed.

The TFT array substrate and the liquid crystal display device according to the third embodiment of this disclosure 45 includes the insulator part 11a formed on the gate wiring film 2 to be in direct contact with the gate wiring film 2, and the insulation film 10 formed on the insulator part 11a to be in direct contact with the insulator part 11a. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

In the manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal display device according to the third embodiment of this disclosure, 55 the step of forming the inorganic film 11 is performed after the step of forming the gate wiring film 2, and the step of forming the insulation film 10 is performed after the step of forming the inorganic film 11. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure 60 occurring at the time of performing the connection repair can be reduced.

Fourth Embodiment

ATFT array substrate according to the fourth embodiment of this disclosure differs from the first embodiment according to this disclosure in an order of laminating the insulation film 10, the gate wiring film 2 and the inorganic film 11.

18

Configuration of a TFT array substrate 103b according to the fifth embodiment of this disclosure will be described. FIG. 35 is a cross-sectional view of the TFT array substrate 103b according to the fourth embodiment of this disclosure. In FIG. 35, portions identical or corresponding to those of FIG. 3 are referred to by the common symbols, and descriptions thereof will be omitted.

In FIG. 35, the insulation film 10 is formed on the glass substrate 1 as the translucent insulation substrate. The gate wiring film 2 is formed on the insulation film 10 to be in direct contact with the insulation film 10. The inorganic film 11 made of the insulator part 11a, which is formed by changing the oxide semiconductor into the insulator, is formed on the gate wiring film 2, to be in direct contact with the gate wiring film 2.

Thereafter, the gate insulation film 13, the a-Si layer 4, the source wiring film 5, the source electrode 6, the drain electrode 7, the interlayer insulation film 14, the contact hole 8 and the pixel electrode 9 are formed, and thus a TFT array substrate 103a according to the fourth embodiment of this disclosure is obtained.

Next, a manufacturing method of the TFT array substrate 103b according to the fourth embodiment of this disclosure will be described. At first, the insulation film 10 primarily made of silicon oxide is formed on the glass substrate 1. After forming the insulation film 10, the gate wiring film 2 is formed to be in direct contact with the insulation film 10. After forming the gate wiring film 2, the inorganic film 11 having the insulator part 11a, which is formed by changing the oxide semiconductor into the insulator, is formed to be in direct contact with the gate wiring film 2.

The configuration of the TFT array substrate according to the fourth embodiment of this disclosure in a case where the gate wiring film 2 has a disconnection part OP will be described. FIG. 40 is a cross-sectional view illustrating a TFT array substrate 203b according to the fourth embodiment of this disclosure. In the configuration of the TFT array substrate according to the fourth embodiment of this disclosure in the case of having the disconnection part OP, as shown in FIG. 40, the gate wiring film 2 is separated in the longitudinal direction in a manner of interposing the disconnection part OP. Thus, the first gate wiring film 2a and the second gate wiring film 2b being not in direct contact with the first gate wiring film 2a are formed. Since the remaining configuration of this TFT array substrate is the same as that in the case where the disconnection part OP is not formed as shown in FIG. 35, descriptions thereof will be omitted.

Explanation will be made as to an example of mechanism that the disconnection part OP occurs at the wiring, in the fourth embodiment according to this disclosure.

FIGS. 37 to 39 are cross-sectional views illustrating parts of manufacturing process of the TFT array substrate 203b according to the fourth embodiment of this disclosure. FIG. 37 illustrates a case where foreign particle 16 is incorporated into the resist 15 in the photoengraving process. FIG. 38 is the cross-sectional view illustrating a state where the foreign particle 16 of FIG. 37 peels.

As shown in FIG. 38, if the foreign particle 16 peels off, an unintentional portion not covered by the resist 15 appears in the gate wiring film. As shown in FIG. 39, at this portion not covered by the resist 15, the gate wiring film 2 is etched away in the etching step and the disconnection part OP appears.

Next, the configuration of the TFT array substrate according to the fourth embodiment of this disclosure which is

subjected to connection repair in a case where the disconnection part OP is generated at the gate wiring film 2 will be described.

FIG. **36** is a cross-sectional view illustrating a TFT array substrate 303b according to the fourth embodiment of this 5 disclosure. FIG. 36 illustrates a state where the conductor part 11c, which is formed by changing the oxide semiconductor film into the conductor, is formed at the disconnection part OP of the gate wiring film 2 in FIG. 40.

In addition to the configuration explained with reference 10 to FIG. 40, as shown in FIG. 36, the inorganic film 11 has the conductor part 11c formed by changing the oxide semiconductor into the conductor, and the conductor part 11c is in direct contact with both the first gate wiring film 2a and the second gate wiring film 2b. Since the remaining con- 15 figuration of this TFT array substrate is the same as that of the TFT array substrate in the state before forming the conductor part 11c, which is obtained by changing the oxide semiconductor film into the conductor, shown in FIG. 40, descriptions thereof will be omitted.

Next, a method of manufacturing the TFT array substrate 303b by subjecting the TFT array substrate 203b according to the fourth embodiment of this disclosure to the connection repair will be described. FIG. 41 is a cross-sectional view illustrating a part of the manufacturing process of the TFT array substrate 303b according to the fourth embodiment of this disclosure. FIG. 41 illustrates the step of irradiating the disconnection part OP with ultraviolet rays L.

The ultraviolet rays L are irradiated on the disconnection part OP, by using the ultraviolet laser. As shown in FIG. 41, 30 the ultraviolet rays L are irradiated in a direction toward the inorganic film 11 from the glass substrate 1, that is, toward the disconnection part OP from the rear surface side of the glass substrate 1. The ultraviolet rays L transmit the glass substrate 1 and are irradiated on the insulation film 10 and 35 the insulator part 11a of the inorganic film 11.

When the ultraviolet rays L are irradiated on a portion where the insulator part 11a, which is formed by changing the oxide semiconductor film into the insulator, is in direct contact with the insulation film 10 made of the silicon oxide 40 (SiO<sub>2</sub>) film, electronic carriers of the oxide semiconductor film are effectively excited, and thus a specific resistance value of the oxide semiconductor film reduces. Thus, the insulator part 11a is changed into the conductor, whereby the conductor part 11c is formed. As the conductor part 11c 45 formed by changing the oxide semiconductor into the conductor is in direct contact with both the first gate wiring film 2a and the second gate wiring film 2b, the first gate wiring film 2a and the second gate wiring film 2b are electrically conducted to each other via the oxide semiconductor film 50 that is changed into the conductor. As the connection repair is performed in this manner, the oxide semiconductor film that is changed into the conductor directly fits to the first gate wiring film 2a and the second gate wiring film 2b. Thus, conventional art (see FIG. 36).

By performing the connection repair in this manner, the TFT array substrate 303b shown in FIG. 36 is obtained. Thereafter, the gate insulation film 13, the a-Si layer 4, the source wiring film 5, the source electrode 6, the drain 60 performed. electrode 7, the interlayer insulation film 14, the contact hole 8 and the pixel electrode 9 are formed, and thus the TFT array substrate 303a is obtained.

After forming the oriented film, etc., the CF substrate 22 is stacked on the TFT array substrate 302a via the seal 65 member 21, and the liquid crystal 20 is filled in a region surrounded by the TFT array substrate 303a, the CF sub**20**

strate 22 and the seal member 21, whereby a liquid crystal display device 700 as the display device is formed.

The TFT array substrate and the liquid crystal **20** display device according to the fourth embodiment of this disclosure includes the gate wiring film 2 formed on the insulation film 10 to be in direct contact with the insulation film 10 and the insulator part 11a formed on the gate wiring film 2 to be in direct contact with the gate wiring film 2. Therefore, even if disconnection occurs in the gate wiring film 2, the conduction failure occurring at the time of performing the connection repair can be reduced.

In the manufacturing method of the TFT array substrate and the manufacturing method of the liquid crystal 20 display device according to the fourth embodiment of this disclosure, the step of forming the gate wiring film 2 is performed after the step of forming the insulation film 10, and the step of forming the inorganic film 11 is performed after the step of forming the gate wiring film 2. Therefore, even if disconnection occurs in the gate wiring film 2, the 20 conduction failure occurring at the time of performing the connection repair can be reduced.

Fifth Embodiment

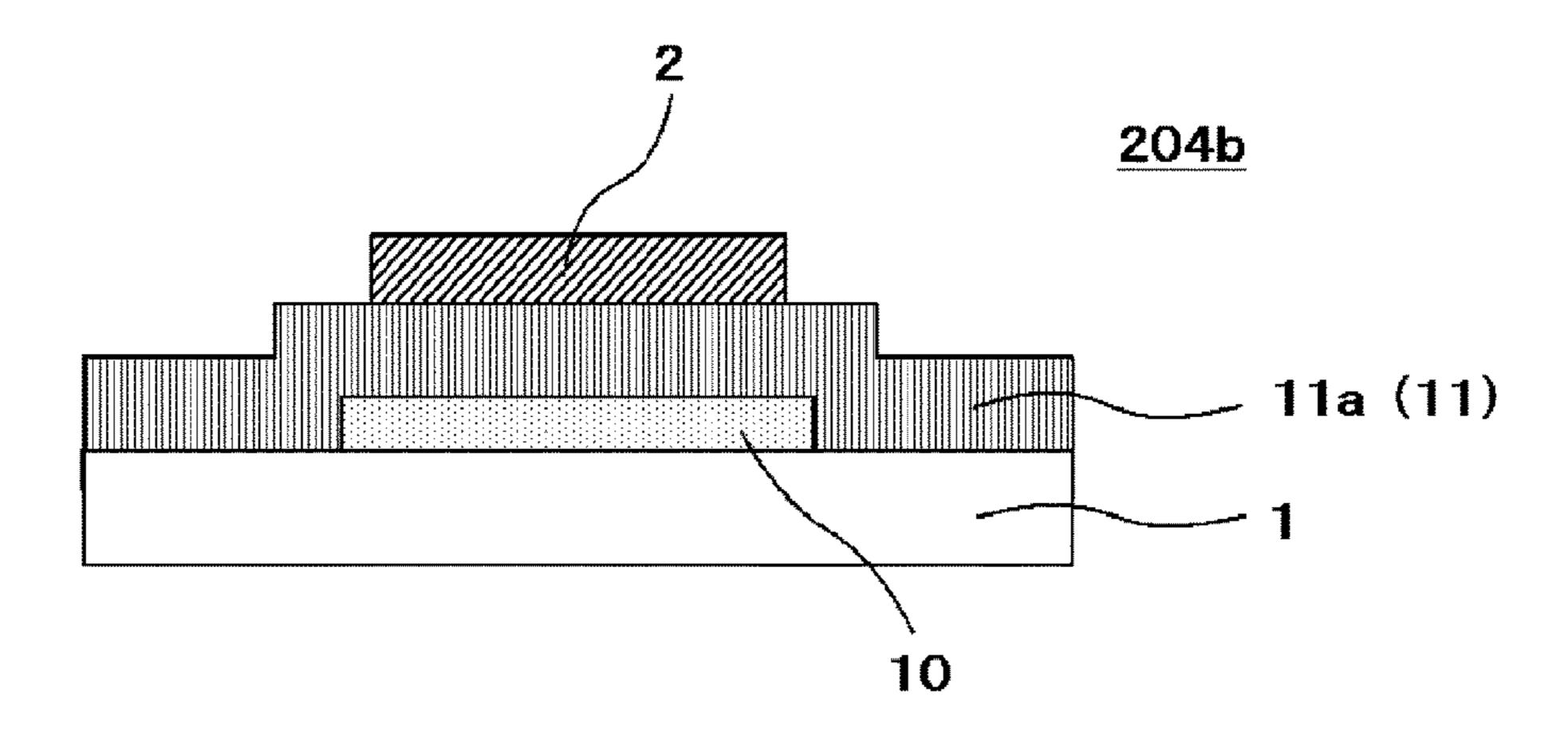

A TFT array substrate according to the fifth embodiment of this disclosure differs from the first embodiment according to this disclosure in that, in a planar view, the insulation film 10 contains the gate wiring film 2 in a transversal direction of the gate wiring film 2.

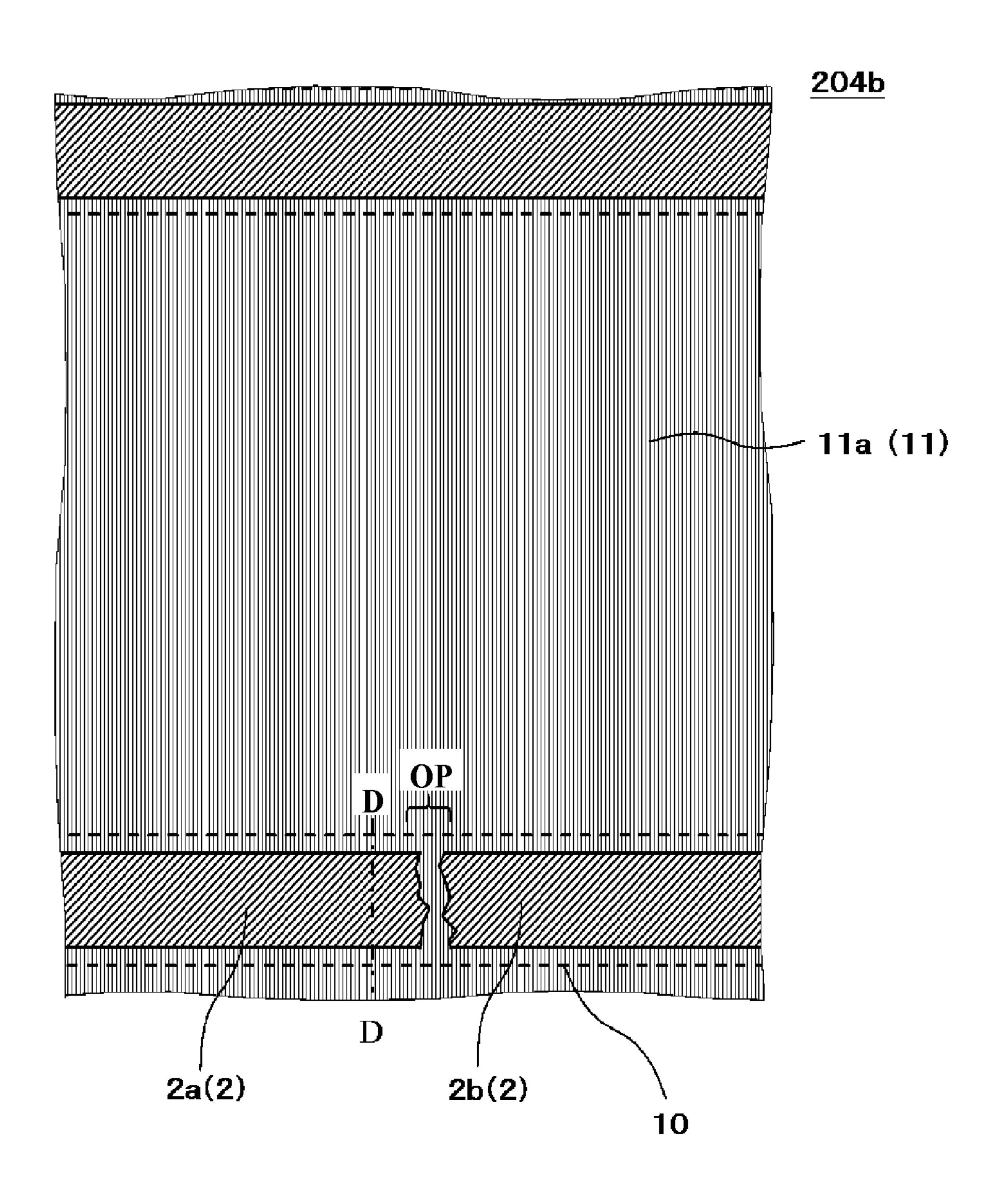

Firstly, explanation will be made as to configurations of a TFT array substrate 204b according to the fifth embodiment of this disclosure. FIG. **45** is a top view illustrating the TFT array substrate 204b according to the fifth embodiment of this disclosure. In FIG. 45, portions identical or corresponding to those of FIG. 10 are referred to by the common symbols, and descriptions thereof will be omitted.

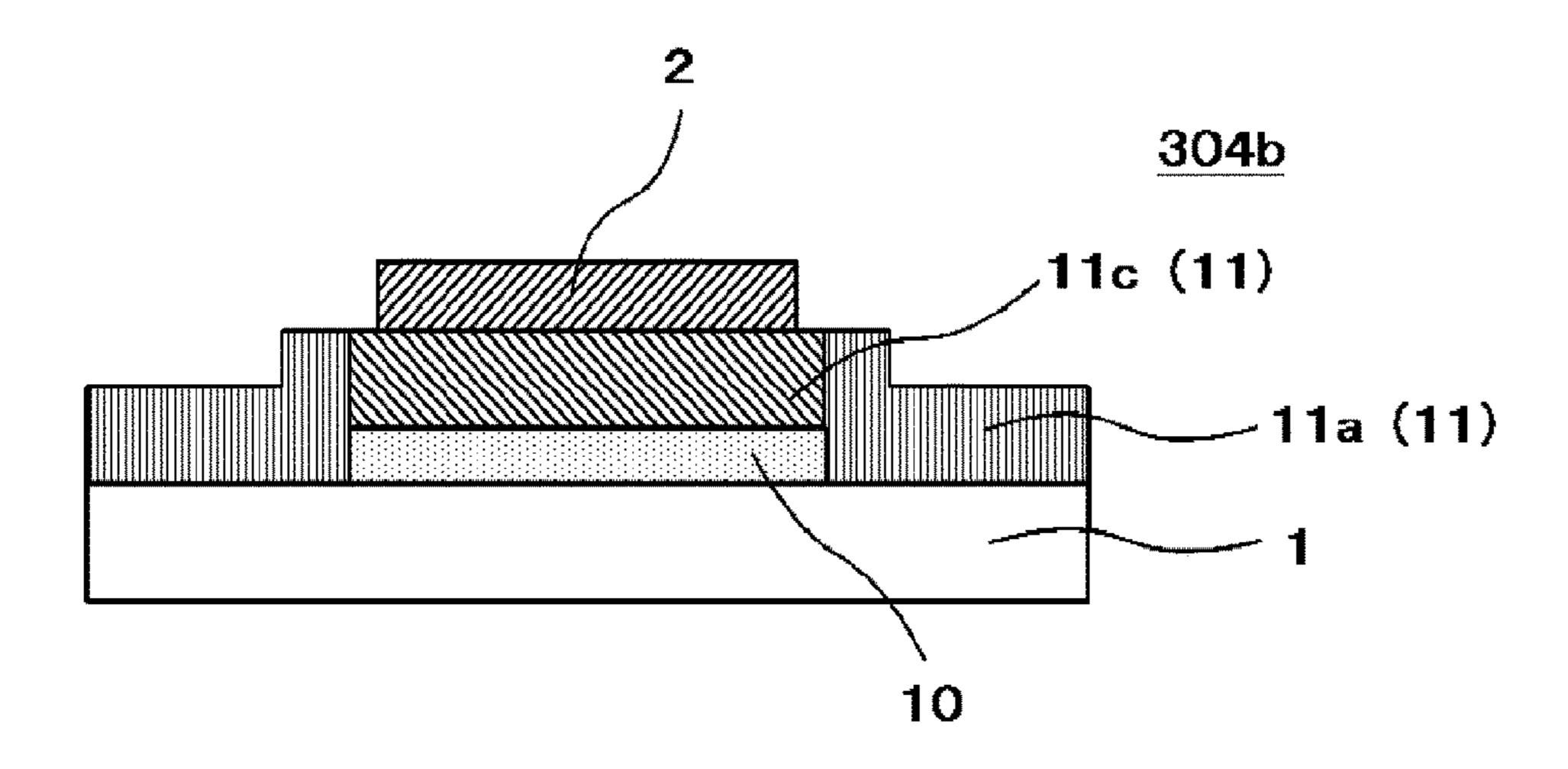

FIG. **42** is a cross-sectional view of the TFT array substrate 204b according to the fifth embodiment of this disclosure. FIG. 42 is the cross-sectional view taken along line D-D in the transversal direction of the gate wiring film 2 in the TFT array substrate 204b of FIG. 45.

In FIG. 42, the insulation film 10 is patterned on the glass substrate 1. As shown in FIGS. 42 and 45, in a planar view, the insulation film 10 contains the gate wiring film 2 in the transversal direction of the gate wiring film 2. Specifically the insulation film is larger than the gate wiring film by about 1 µm in the transversal direction of the gate wiring film **2**.

Secondly, a manufacturing method of the TFT array substrate 204b according to the fifth embodiment of this disclosure will be described. At first, an SiO<sub>2</sub> film is formed on the entire surface of the glass substrate 1 to have a thickness of about 50 nm by using the CVD device, whereby the insulation film 10 is formed

Thereafter, a photoengraving process for forming a resist pattern is performed on the insulation film 10 so that, in a conduction failure can be reduced as compared with the 55 planar view, the resist pattern contains an expected region of the gate wiring film 2 to be formed, in the transversal direction of the expected region of the gate wiring film 2 to be formed. Thereafter, a dry etching process for removing the insulation film 10 not covered by the resist 15 is

> Succeeding steps are the same as those of the manufacturing method of the TFT array substrate according to the first embodiment of this disclosure, descriptions thereof will be omitted.

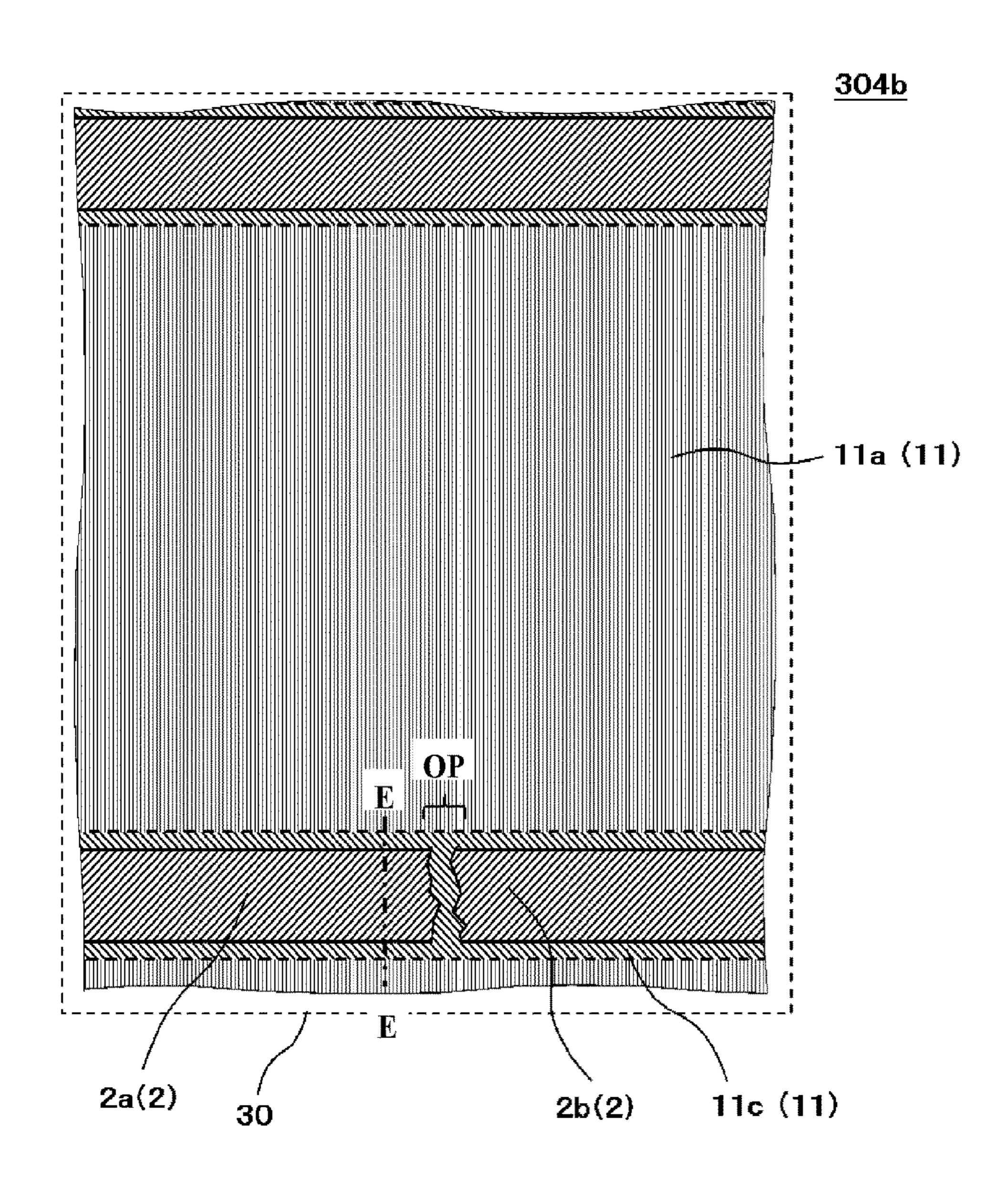

> Thirdly, explanation will be made as to configuration of the TFT array substrate according to the fifth embodiment of this disclosure which is subjected to connection repair. FIG.

46 is a top view illustrating a TFT array substrate 304b according to the fifth embodiment of this disclosure. In FIG. 46, portions identical or corresponding to those of FIG. 12 are referred to by the common symbols, and descriptions thereof will be omitted. FIG. **43** is a cross-sectional view of <sup>5</sup> the TFT array substrate 304b according to the fifth embodiment of this disclosure. FIG. 43 is the cross-sectional view taken along line E-E in the transversal direction of the gate wiring film 2 in the TFT array substrate 304b of FIG. 46.