#### US00RE49682E

## (19) United States

### (12) Reissued Patent

#### Fujimoto

### (10) Patent Number: US RE49,682 E

#### (45) Date of Reissued Patent: \*Oct. 3, 2023

# (54) SYSTEM, DEVICE, AND METHOD FOR INITIALIZING A PLURALITY OF ELECTRONIC DEVICES USING A SINGLE PACKET

- (71) Applicant: Kioxia Corporation, Tokyo (JP)

- (72) Inventor: Akihisa Fujimoto, Yamato (JP)

- (73) Assignee: Kioxia Corporation, Tokyo (JP)

- (\*) Notice: This patent is subject to a terminal dis

- claimer.

- (21) Appl. No.: 17/176,474

- (22) Filed: **Feb. 16, 2021**

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 9,141,398

Issued: Sep. 22, 2015

Appl. No.: 13/515,891

PCT Filed: Dec. 17, 2010

PCT No.: PCT/JP2010/073469

§ 371 (c)(1), (2) Date: **Jun. 14, 2012** PCT Pub. No.: **WO2011/074708** PCT Pub. Date: **Jun. 23, 2011**

U.S. Applications:

(63) Continuation of application No. 16/512,828, filed on Jul. 16, 2019, now Pat. No. Re. 48,495, which is a (Continued)

#### (30) Foreign Application Priority Data

| Dec. 17, 2009 | (JP) | ) | 2009-286791 |

|---------------|------|---|-------------|

| Feb. 2, 2010  | (JP  | ) | 2010-021569 |

(51) Int. Cl.

G06F 15/177

G06F 9/00

(2006.01) (2006.01)

(Continued)

(52) **U.S. Cl.**CPC ...... *G06F 9/4405* (2013.01); *G06F 1/26* (2013.01); *G06F 1/3287* (2013.01); *G06F 1/3/00* (2013.01);

(Continued)

(58) Field of Classification Search

CPC ..... G06F 9/4405; G06F 13/00; G06F 1/3287; G06F 1/26; G06F 1/26; Y02D 10/171 See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,792,269 A 12/1988 Engle 5,675,794 A 10/1997 Meredith (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 1451116 A 10/2003 CN 1457201 A 11/2003 (Continued)

#### OTHER PUBLICATIONS

Combined Office Action and Search Report dated Jan. 28, 2014 in Taiwanese Patent Application No. 099144561(w/English translation).

(Continued)

Primary Examiner — Robert L Nasser (74) Attorney, Agent, or Firm — Oblon, McClelland, Maier & Neustadt, L.L.P.

#### (57) ABSTRACT

According to one embodiment of the present disclosure, a semiconductor system may be disclosed. The semiconductor system according to the one embodiment may include, for example, a plurality of electronic devices and a host apparatus. The host apparatus may simultaneously initialize the plurality of electronic devices in units of group.

#### 4 Claims, 24 Drawing Sheets

#### Related U.S. Application Data

# continuation of application No. 15/464,041, filed on Mar. 20, 2017, now Pat. No. Re. 47,598, which is an application for the reissue of Pat. No. 9,141,398.

#### (51)Int. Cl. G06F 9/24 (2006.01)G06F 3/00 (2006.01)G06F 15/16 (2006.01)(2018.01)G06F 9/44 G06F 13/00 (2006.01)(2006.01)G06F 1/26 G06F 9/4401 (2018.01)G06F 1/3287 (2019.01)

####

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,018,690 A *    | 1/2000  | Saito et al 700/295    |

|------------------|---------|------------------------|

| 6,226,729 B1     | 5/2001  | Stevens et al.         |

| 6,233,625 B1     | 5/2001  | Vander Kamp et al.     |

| 6,301,674 B1*    | 10/2001 | Saito et al 713/340    |

| 6,820,148 B1     | 11/2004 | Cedar et al.           |

| 7,353,993 B2     | 4/2008  | Fujimoto               |

| 7,437,576 B2*    | 10/2008 | Makiyama et al 713/300 |

| 7,549,580 B2     | 6/2009  | Fujimoto               |

| 7,810,727 B2     | 10/2010 | Fujimoto               |

| 7,891,566 B2     | 2/2011  | Fujimoto               |

| 8,162,216 B2     | 4/2012  | Fujimoto               |

| 2003/0018763 A1  | 1/2003  | Doherty et al.         |

| 2003/0097422 A1  | 5/2003  | Richards et al.        |

| 2003/0163680 A1  | 8/2003  | Wang et al.            |

| 2005/0116754 A1  | 6/2005  | Ichikawa               |

| 2006/0236013 A1  | 10/2006 | Okeda                  |

| 2006/0248328 A1* | 11/2006 | Iszlai et al 713/2     |

| 2006/0282550 A1  | 12/2006 | Fujimoto               |

| 2007/0083779 A1  | 4/2007  | Misaka et al.          |

| 2007/0283139 A1  | 12/2007 | Kato                   |

| 2008/0201548 A1  | 8/2008  | Przybylski             |

| 2008/0263373 A1  | 10/2008 | Meier et al.           |

| 2009/0039927 A1  | 2/2009  | Gillingham             |

| 2009/0050943 A1  | 3/2009  | Nonomura               |

| 2009/0059943 A1  | 3/2009  | Nonomura               |

| 2009/0077400 A1  | 3/2009  | Enami et al.           |

| 2009/0198857 A1  | 8/2009  | Pyeon                  |

| 2010/0174866 A1  | 7/2010  | Fujimoto et al.        |

| 2012/0177050 A1  | 7/2012  | Fujimoto               |

| 2013/0067189 A1  | 3/2013  | Heinrich et al.        |

#### FOREIGN PATENT DOCUMENTS

| CN | 1567108 A       | 1/2005  |

|----|-----------------|---------|

| CN | 101377763 A     | 3/2009  |

| CN | 102906717 A     | 1/2013  |

| JP | 863408          | 3/1996  |

| JP | 10 500238       | 1/1998  |

| JP | 10 333783       | 12/1998 |

| JP | 2000-078561     | 3/2000  |

| JP | 2003-158526     | 5/2003  |

| JP | 2005/18329      | 1/2005  |

| JP | 2005 157883     | 6/2005  |

| JP | 2005/284468     | 10/2005 |

| JP | 2005 316594     | 11/2005 |

| JP | 2007-148828     | 6/2007  |

| JP | 2007-200220     | 8/2007  |

| JP | 2007 299227     | 11/2007 |

| JP | 2009-070301     | 4/2009  |

| JP | 2009-123141     | 6/2009  |

| JP | 2011-90349 A    | 5/2011  |

| KR | 10-2005-0048639 | 5/2005  |

| KR | 10-2009-0047545 | 5/2009  |

| TW | 200809593 A     | 2/2008  |

| TW | 200839785 A     | 10/2008 |

|    |                 |         |

#### OTHER PUBLICATIONS

Combined Office Action and Search Report dated Mar. 3, 2014 in in Chinese Patent Application No. 201080053410.2 (w/English translation and English translation of category of cited documents). International Preliminary Report on Patentability and Written Opinion dated Jun. 28, 2012, in International application No. PCT/JP2010/073469 (English translation only).

Combined Chinese Office Action and Search Report dated Jun. 30, 2017 in Chinese Patent Application No. 20150024061.6 (with English translation of Office Action and English translation of Category of Cited Documents).

Japanese Office Action issued Aug. 19, 2014 tn Patent Application No. 2013-212335 (w/English Translation).

Japanese Office Action issued May 21, 2013, in Japan Patent Application No. 2012-527940 (w/English translation).

Office Action dated Aug. 23, 2013 in Korean Application No. 10-2012-7013477 (w/English Translation).

Andrew S. Tanenbaum, "Computer Networks", 1996, Prentice-Hall Inc., third edition, pp. 370.\*

Office Action issued Aug. 23, 2013 in Korean Application No. 10-2012-7013477 (With English Translation).

International Search Report Issued Mar. 1, 2011 in PCT/JP10/73469 Filed Dec. 17, 2010.

U.S. Appl. No. 13/422,916, filed Mar. 16, 2012, Fujimoto.

U.S. Appl. No. 13/424,482, filed Mar. 20, 2012, Fujimoto.

<sup>\*</sup> cited by examiner

FIG. 1

F I G. 4

F I G. 5

F I G. 8

F 1 G. 9

F I G. 10

F I G. 11

F I G. 15

F I G. 16

F I G. 17

|                     | Device<br>4-1 | Device<br>4-2 | Device<br>4-3 | Device<br>4-4 |       | Device<br>4-15 | Host<br>apparatus<br>2 |

|---------------------|---------------|---------------|---------------|---------------|-------|----------------|------------------------|

| Operating frequency | f1            | f2            | f3//          | f4            | • • • | f15            | f0                     |

| Operation timing    | T1            | T2            | Т3            | T4            | • • • | T15            | TO                     |

|                     |               |               | •             | •             | • •   | •              |                        |

F I G. 19

F I G. 20

F I G. 22

F I G. 23

F1G. 25

F I G. 32

| VDD2ON | DIDA | Enumeration  | Capability setting |

|--------|------|--------------|--------------------|

| 0      | 0    | Executed     | Executed           |

| 1      | 0    | Executed     | Not executed       |

| 1      | 1    | Not executed | Not executed       |

F1G.33

**Sheet 23 of 24**

五 (2)

Oct. 3, 2023

F I G. 37

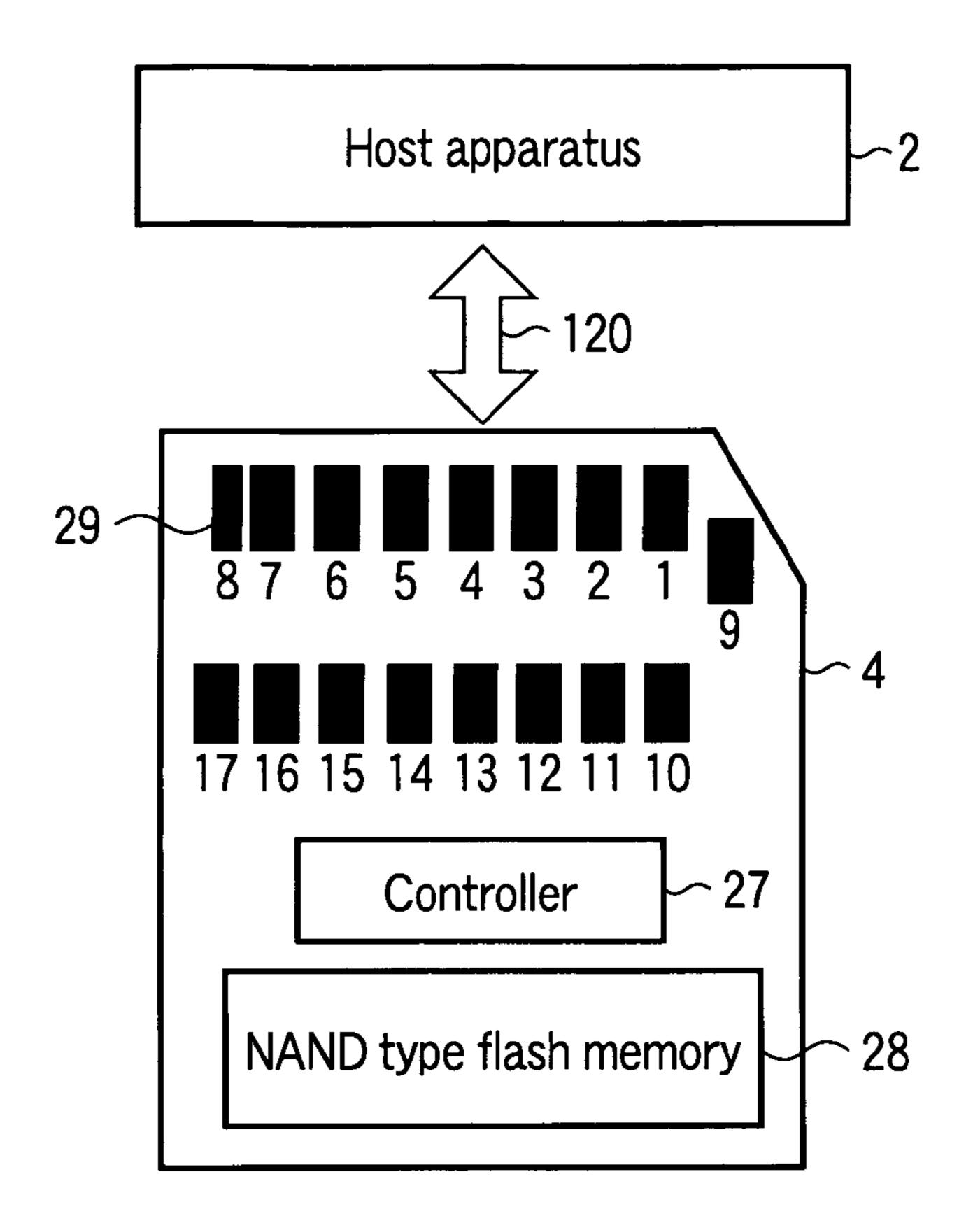

| Pin Number | Signal                          |

|------------|---------------------------------|

| Pin 1      | Card detection/data 3 (DAT3)    |

| Pin 2      | Command (CMD)                   |

| Pin 3      | GND                             |

| Pin 4      | Power supply voltage (VDD1)     |

| Pin 5      | Clock (CLK)                     |

| Pin 6      | GND                             |

| Pin 7      | Data 0 (DAT0)                   |

| Pin 8      | Data 1 (DAT1)                   |

| Pin 9      | Data 2 (DAT2)                   |

| Pin 10     | Power supply voltage (VDD2)/GND |

| Pin 11     | Data (D1+)                      |

| Pin 12     | Data (D1-)                      |

| Pin 13     | Power supply voltage (VDD2)/GND |

| Pin 14     | Power supply voltage (VDD2)/GND |

| Pin 15     | Data (D0-)                      |

| Pin 16     | Data (D0+)                      |

| Pin 17     | Power supply voltage (VDD2)/GND |

F1G.38

# SYSTEM, DEVICE, AND METHOD FOR INITIALIZING A PLURALITY OF ELECTRONIC DEVICES USING A SINGLE PACKET

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough 10 indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

# CROSS-REFERENCE TO RELATED APPLICATIONS

More than one reissue application has been filed for the reissue of U.S. Pat. No. 9,141,398. The reissue applications are application Ser. No. 17/176,474 (the present application), which is a continuation reissue of application Ser. No. 16/512,828, now RE48,495, which is a continuation reissue of application Ser. No. 15/464,041, now RE47,598, which is an application for reissue of U.S. Pat. No. 9,141,398.

This application is based upon and claims the benefit of priority from Japanese Patent Applications No. 2009- <sup>25</sup> 286791, filed Dec. 17, 2009; and No. 2010-021569, filed Feb. 2, 2010; the entire contents of both of which are incorporated herein by reference.

This application is further a U.S. national phase application under 35 U.S.C. §371 of international application <sup>30</sup> PCT/JP2010/073469 filed Dec. 17, 2010, and the entire contents of which are also incorporated herein by reference.

#### TECHNICAL FIELD

Embodiments described herein relate generally to a semiconductor system, a semiconductor device, and an electronic device initializing method. For example, the embodiments relate to a semiconductor system including plural electronic devices.

#### BACKGROUND ART

An SD<sup>TM</sup> card is well known as a memory system in which a NAND type flash memory is used. An SD interface 45 is well known as an interface between the SD card and a host apparatus. In the SD interface, plural devices can be connected to one bus. For example U.S. Pat. No. 6,820,148 discloses the above-described configuration.

However, in the conventional method, when more devices 50 are controlled by one host apparatus, it takes a long time to initialize the devices.

#### BRIEF DESCRIPTION OF DRAWINGS

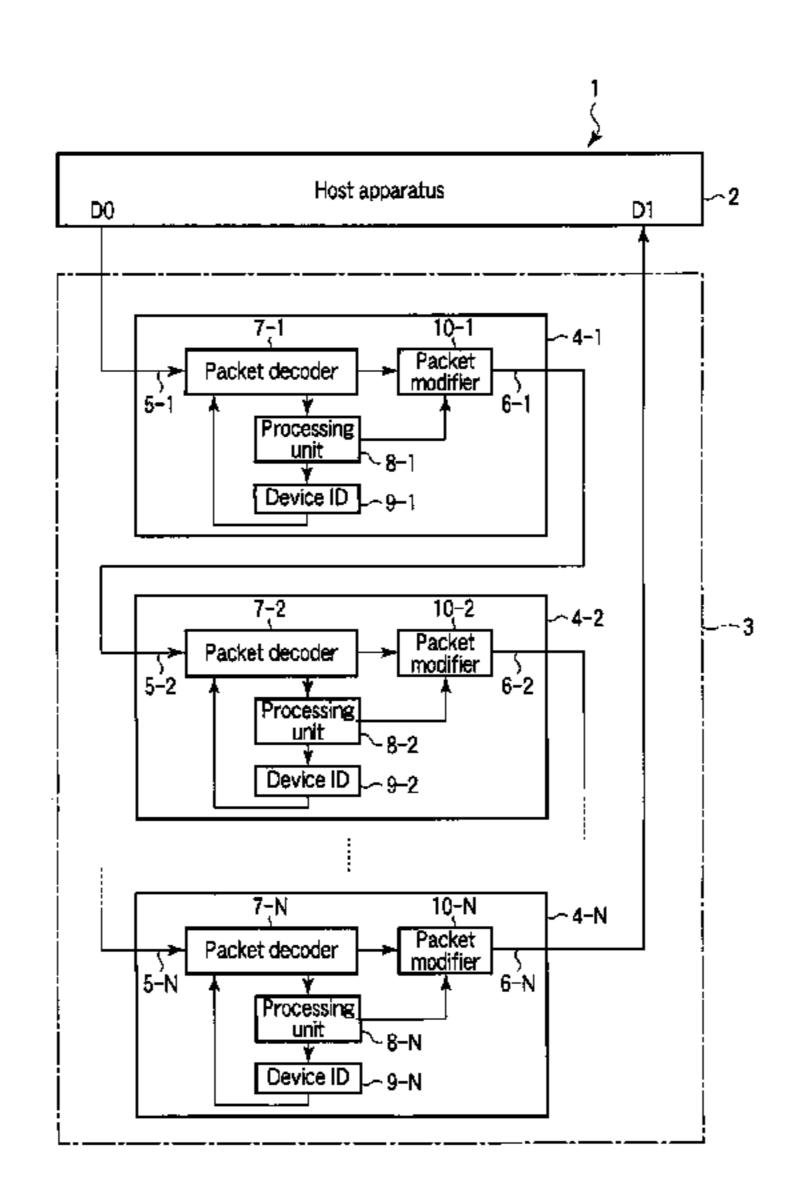

- FIG. 1 is a block diagram of a semiconductor system according to a first embodiment;

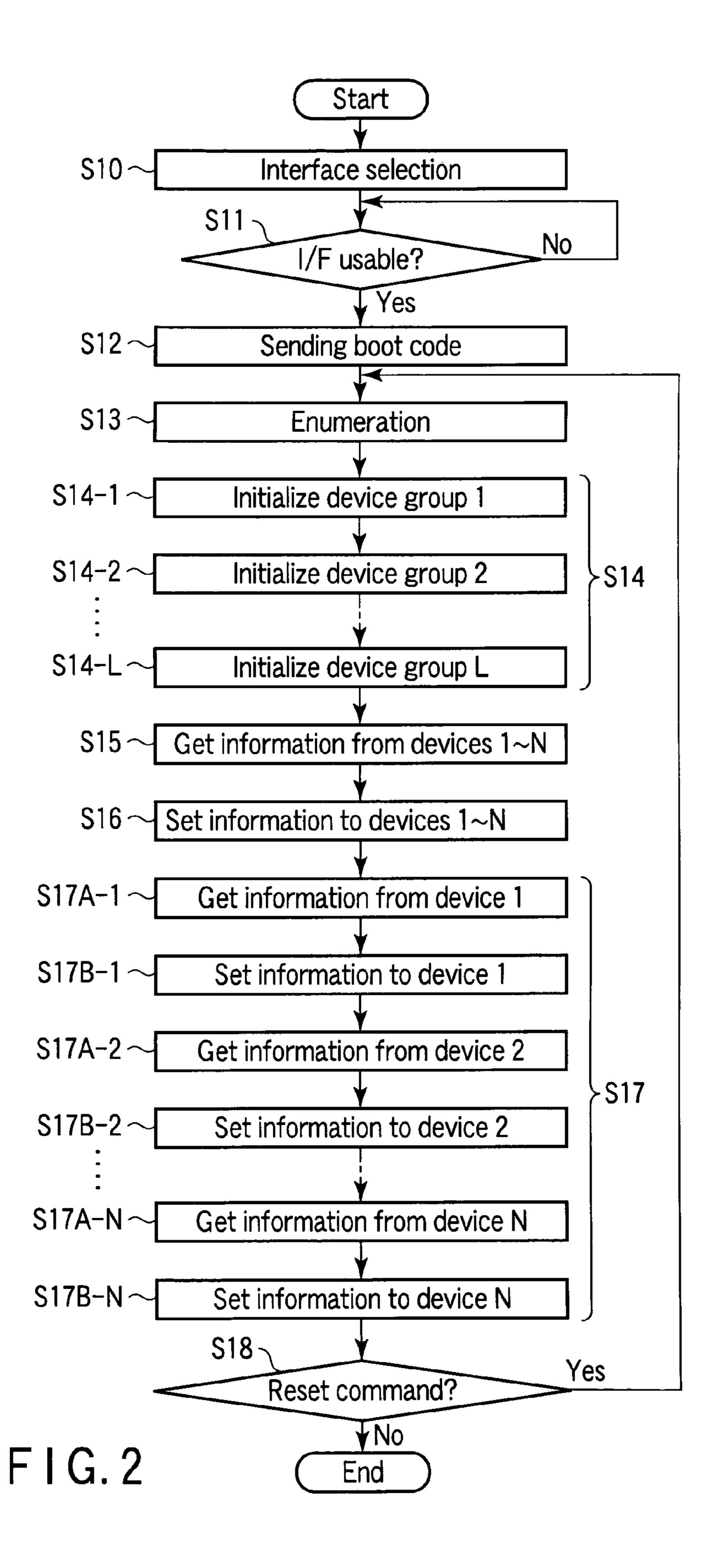

- FIG. 2 is a flowchart illustrating an operation of the semiconductor system of the first embodiment;

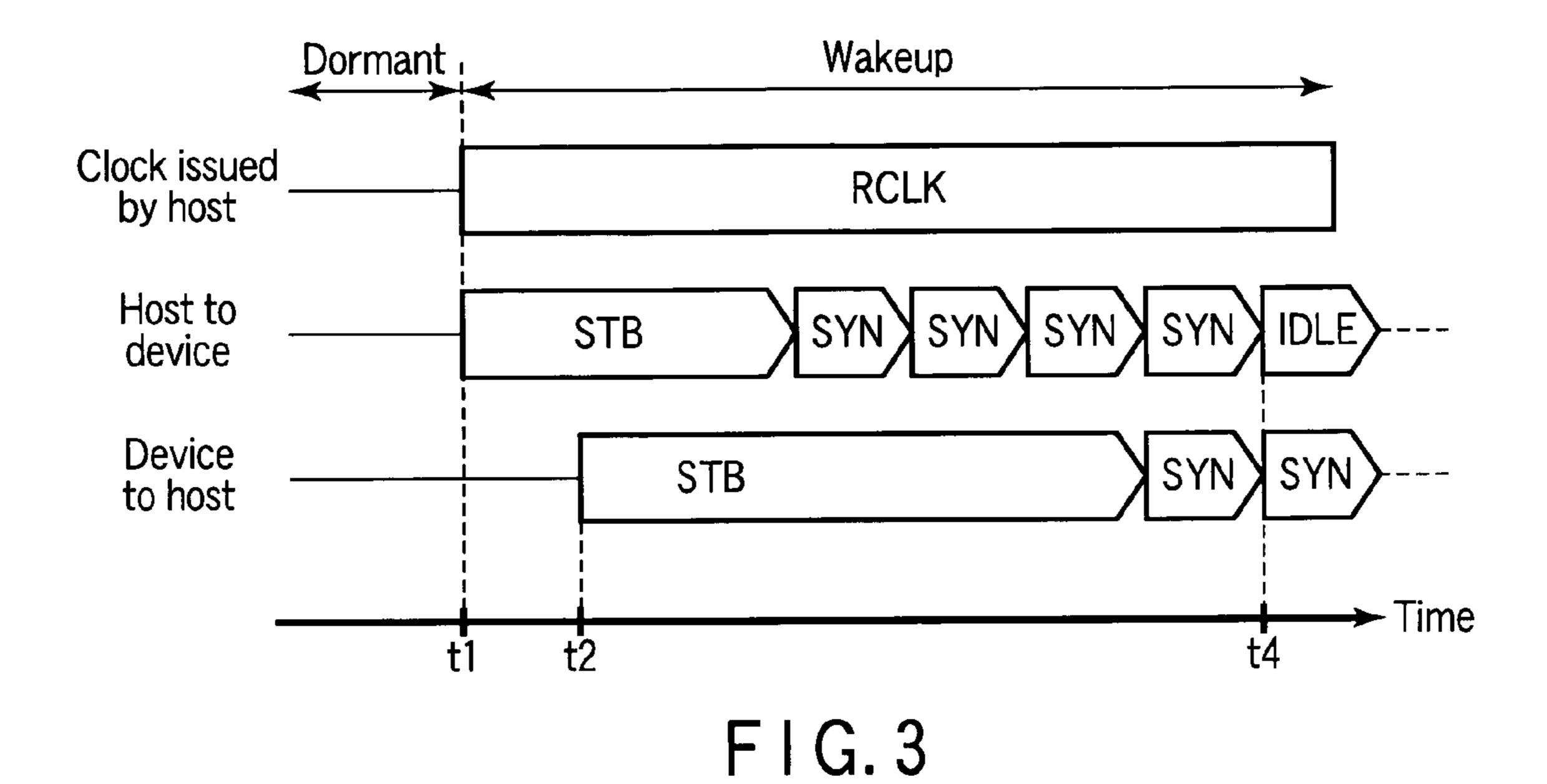

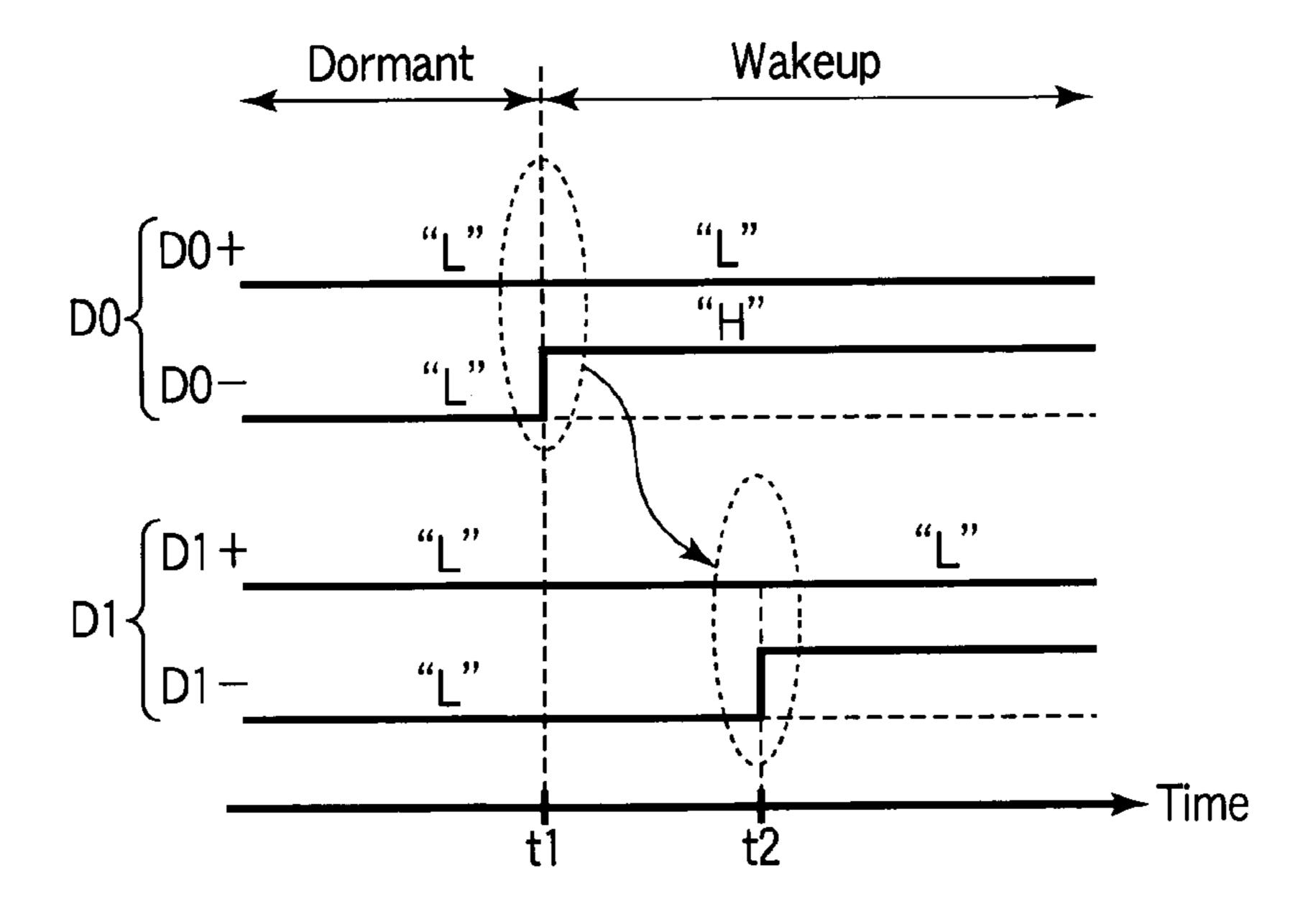

- FIG. 3 and FIG. 4 are timing charts of a symbol and a 60 signal of the first embodiment;

- FIG. **5** is a block diagram of the semiconductor system of the first embodiment;

- FIG. **6** is a block diagram of an electronic device of the first embodiment;

- FIG. 7 and FIG. 8 are conceptual views of a frame format of the first embodiment;

2

- FIG. 9 and FIG. 10 are flowcharts illustrating operations of a host apparatus and the electronic device of the first embodiment;

- FIG. 11 is a block diagram of the semiconductor system of the first embodiment;

- FIG. 12 is a conceptual view of the frame format of the first embodiment;

- FIG. 13 and FIG. 14 are flowcharts illustrating the electronic device of the first embodiment;

- FIGS. 15 to 18 are block diagrams of the semiconductor system of the first embodiment;

- FIG. 19 is a diagram illustrating capability of the electronic device of the first embodiment;

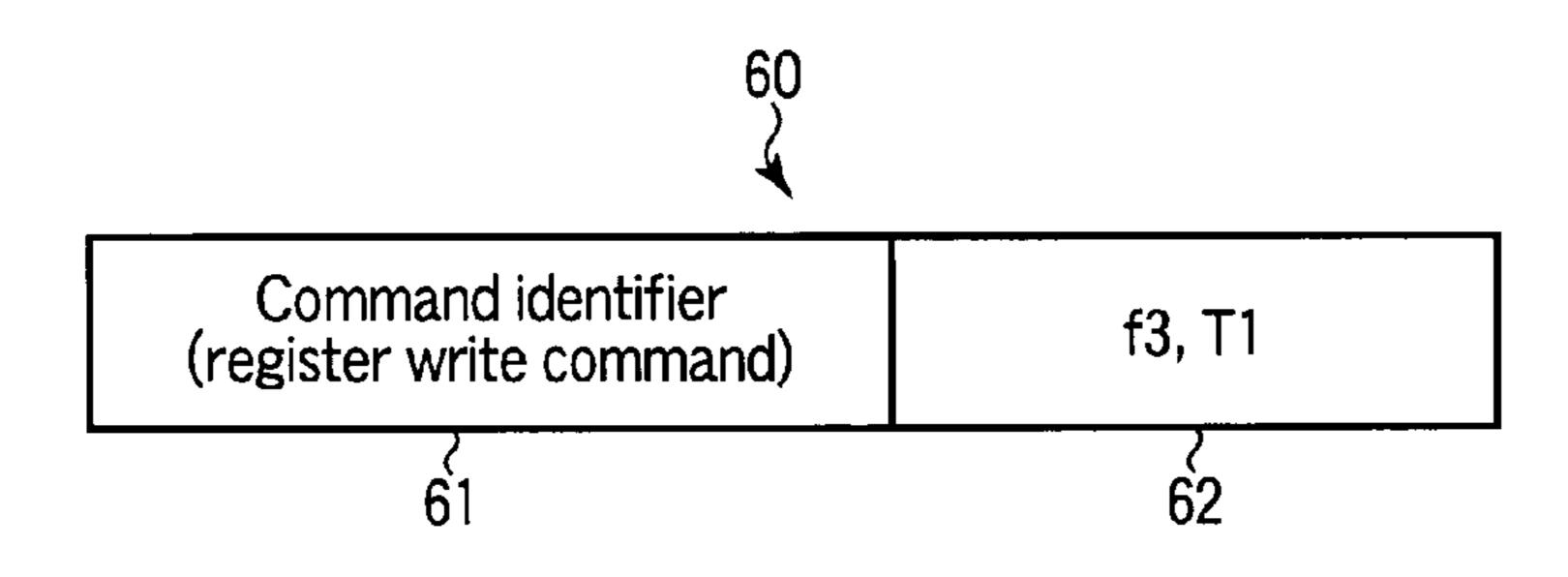

- FIG. **20** is a conceptual view of the frame format of the first embodiment;

- FIG. 21 is a conceptual view of a frame format according to a second embodiment;

- FIG. 22 and FIG. 23 are flowcharts illustrating operations of an electronic device and a host apparatus of the second embodiment;

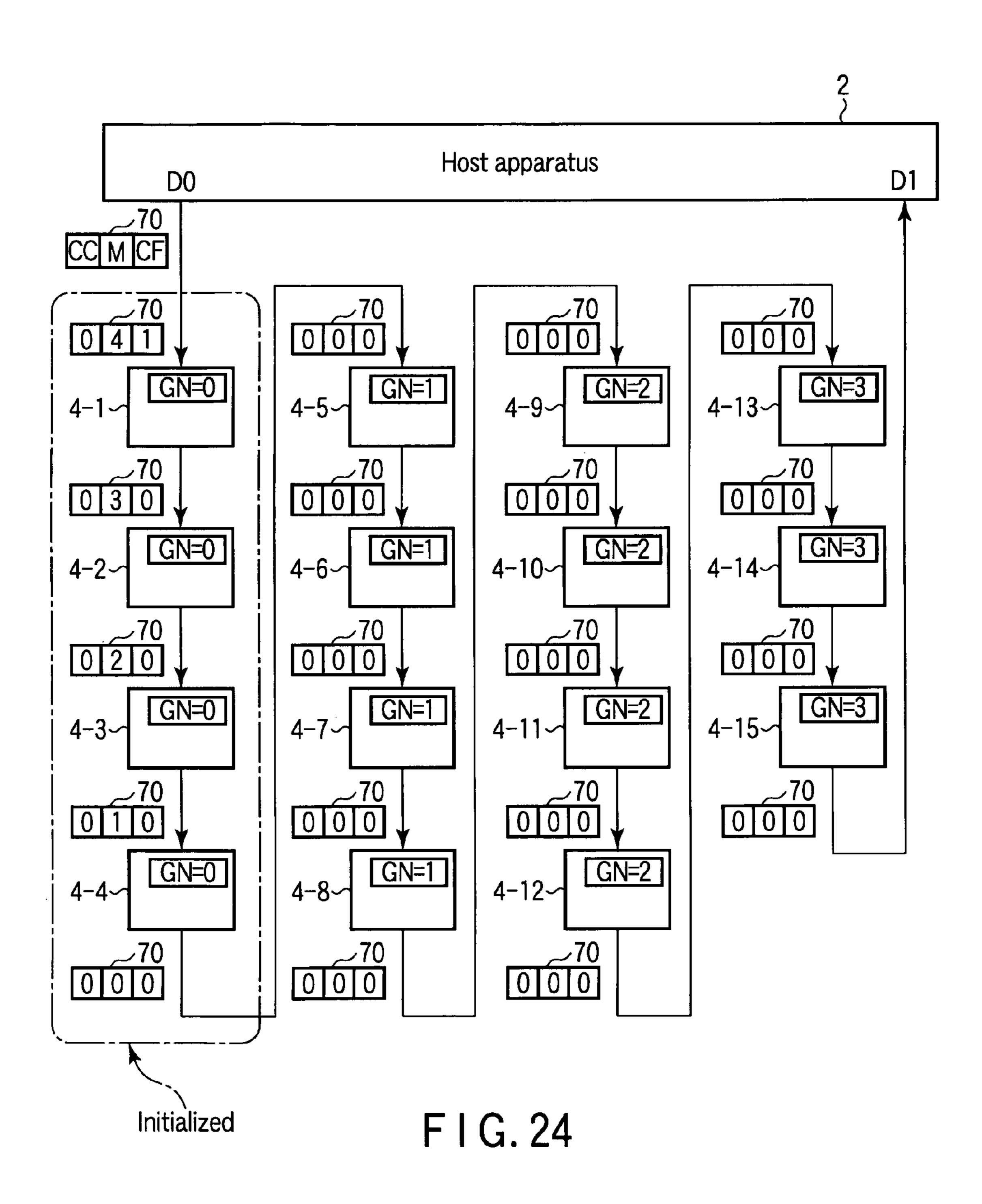

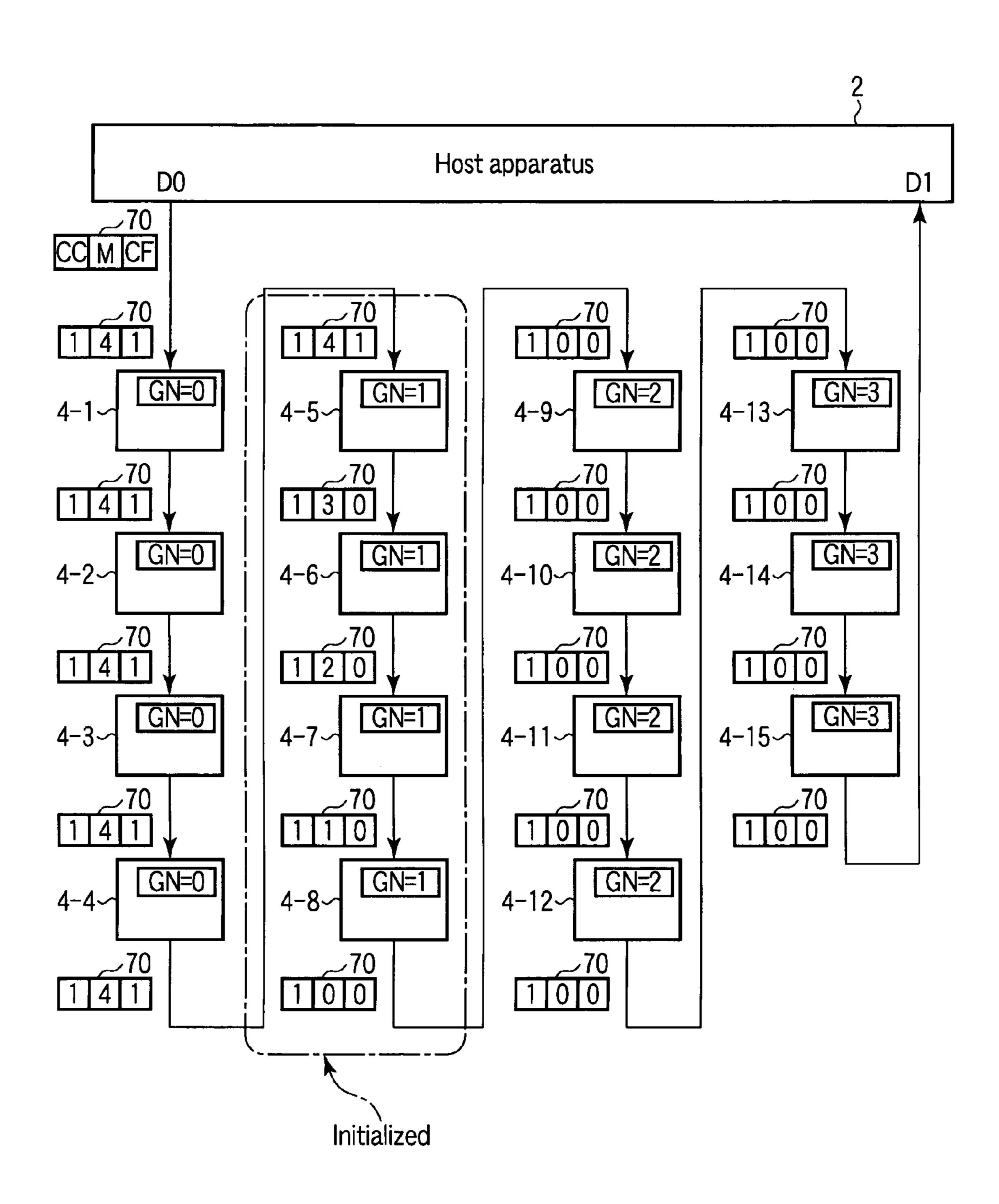

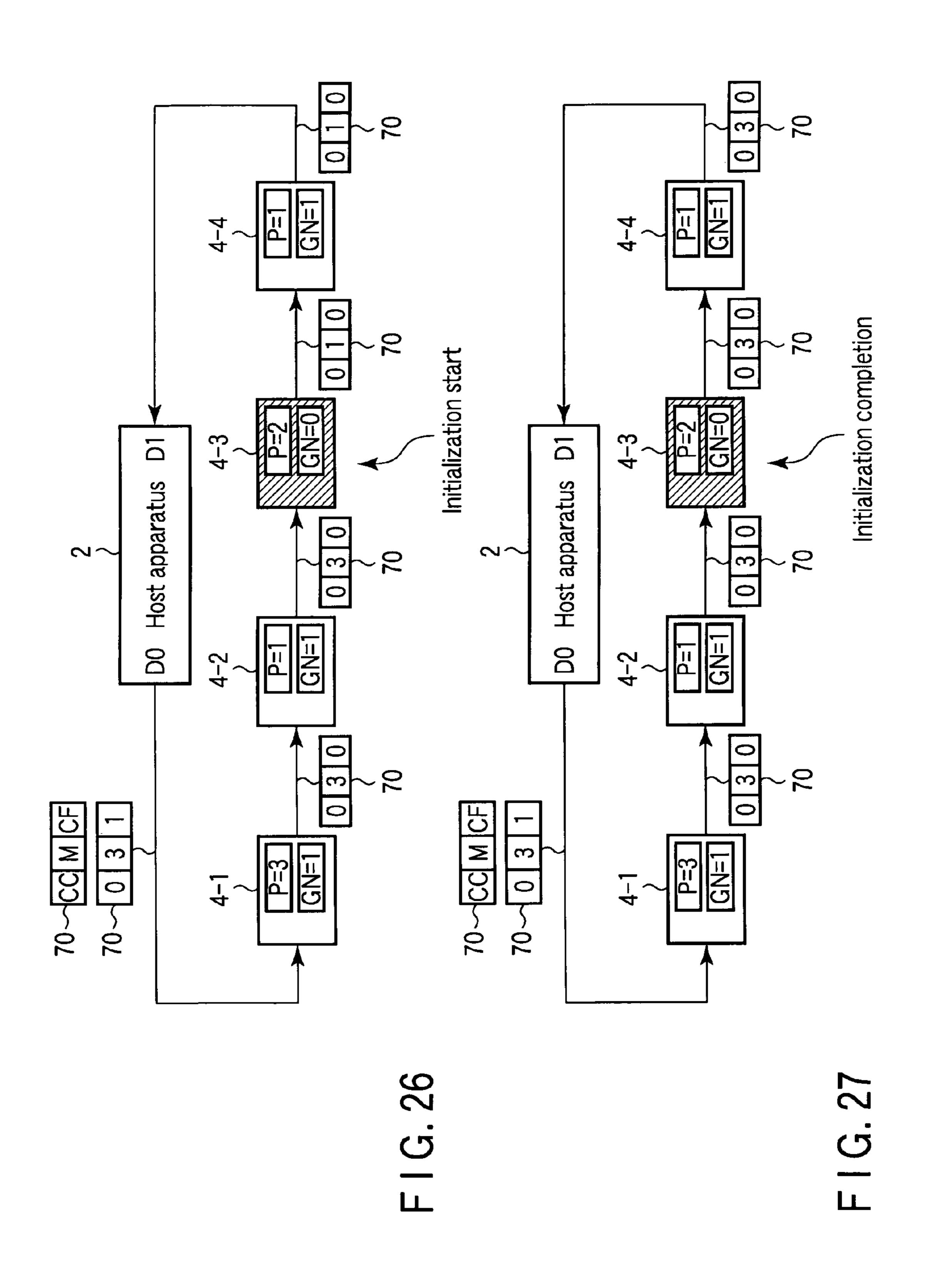

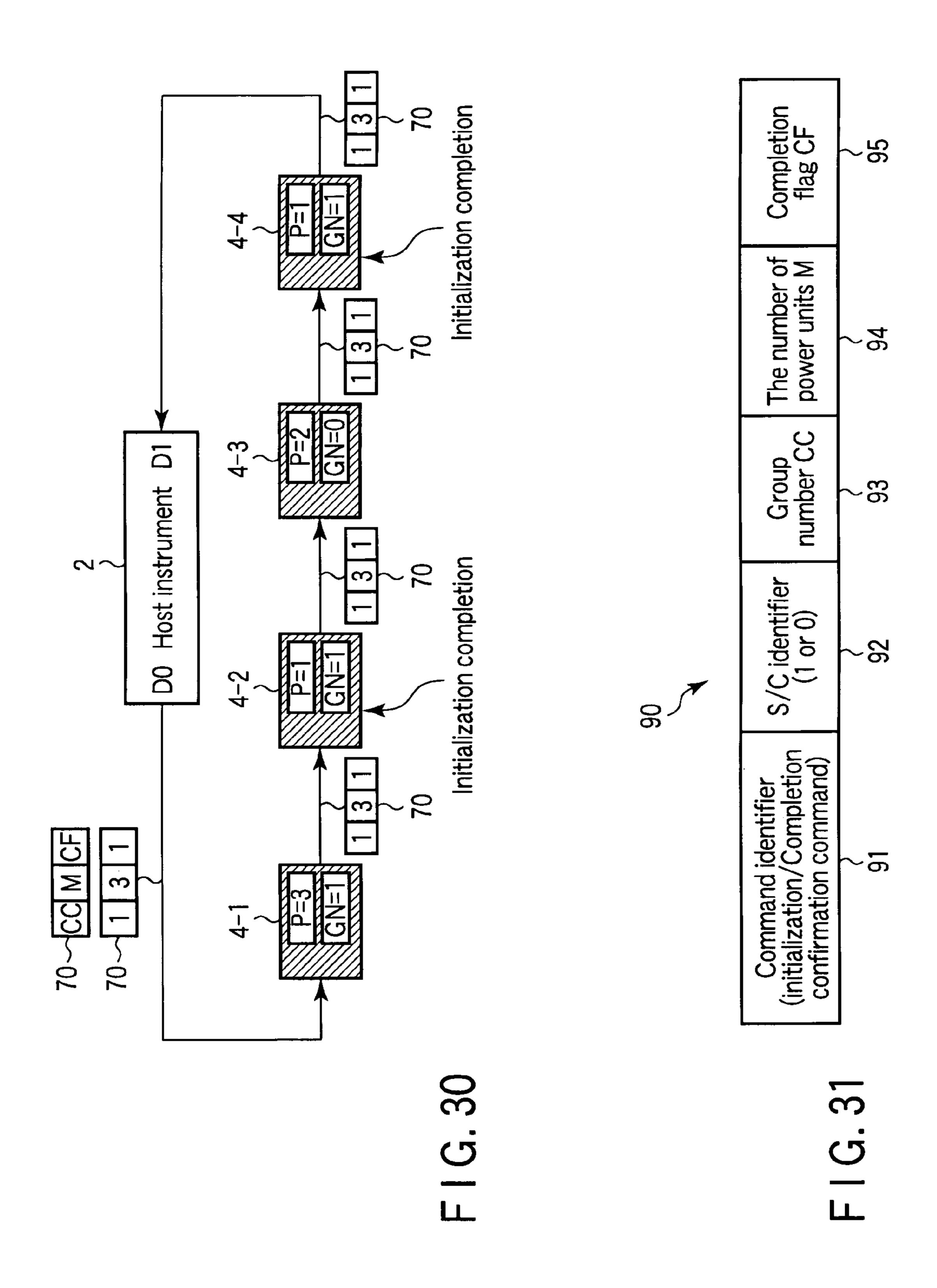

- FIGS. 24 to 30 are block diagrams of a semiconductor system of the second embodiment;

- FIG. 31 is a conceptual view of the frame format of the second embodiment;

- FIG. **32** is a block diagram of a semiconductor system according to a third embodiment;

- FIG. 33 is a diagram illustrating a flag and an operation of a host apparatus of the third embodiment;

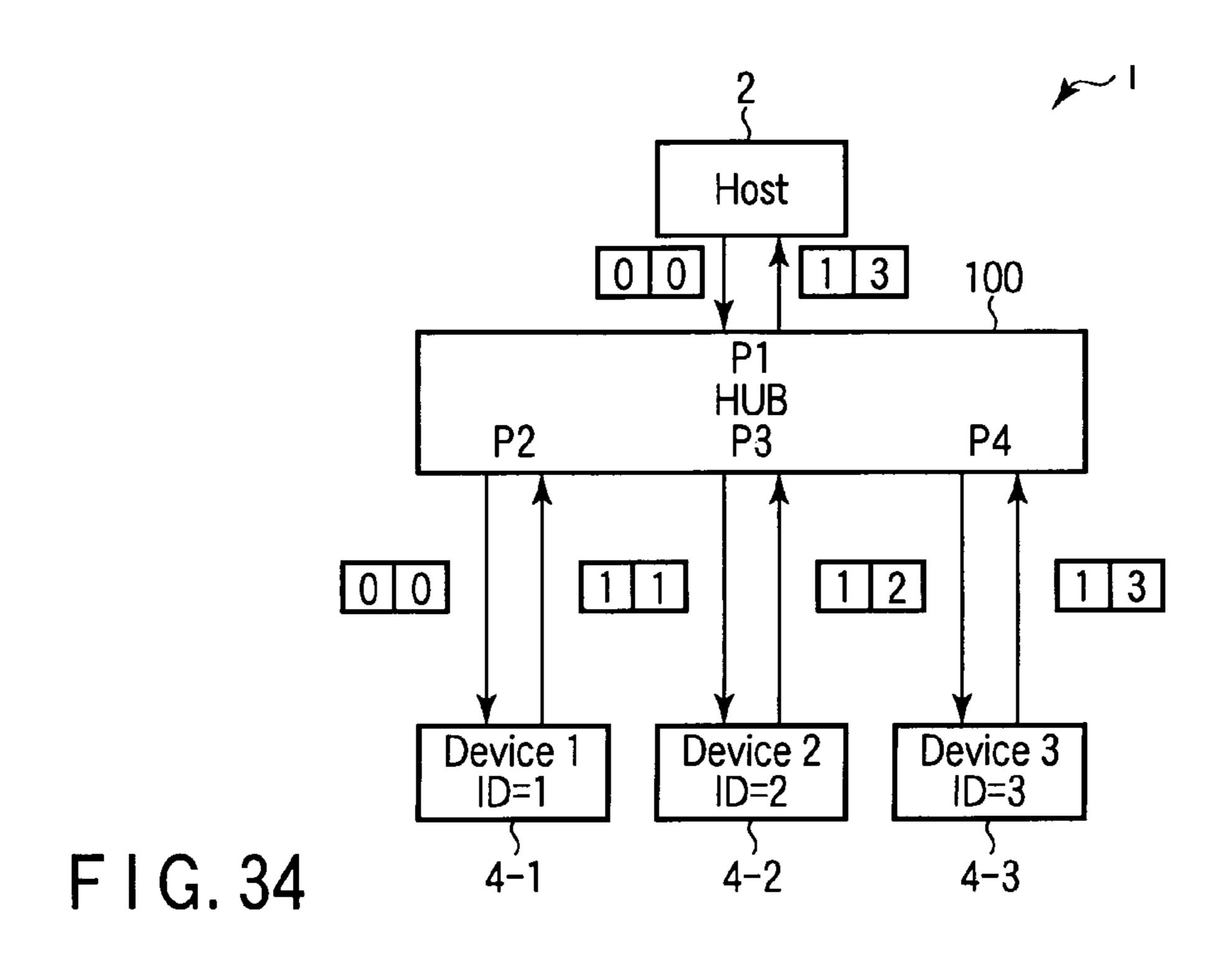

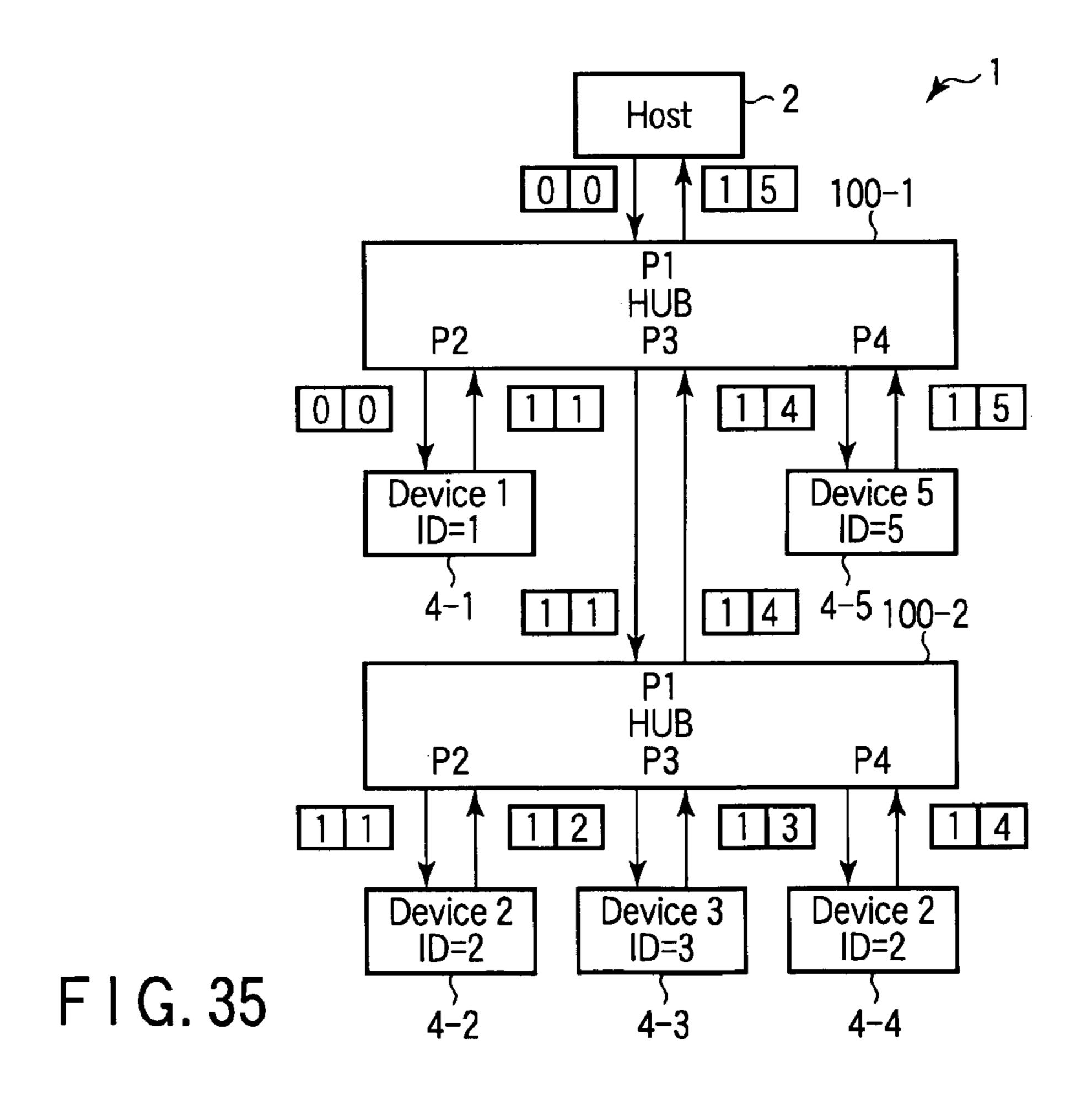

- FIG. **34** and FIG. **35** are block diagrams of a semiconductor system according to a fourth embodiment;

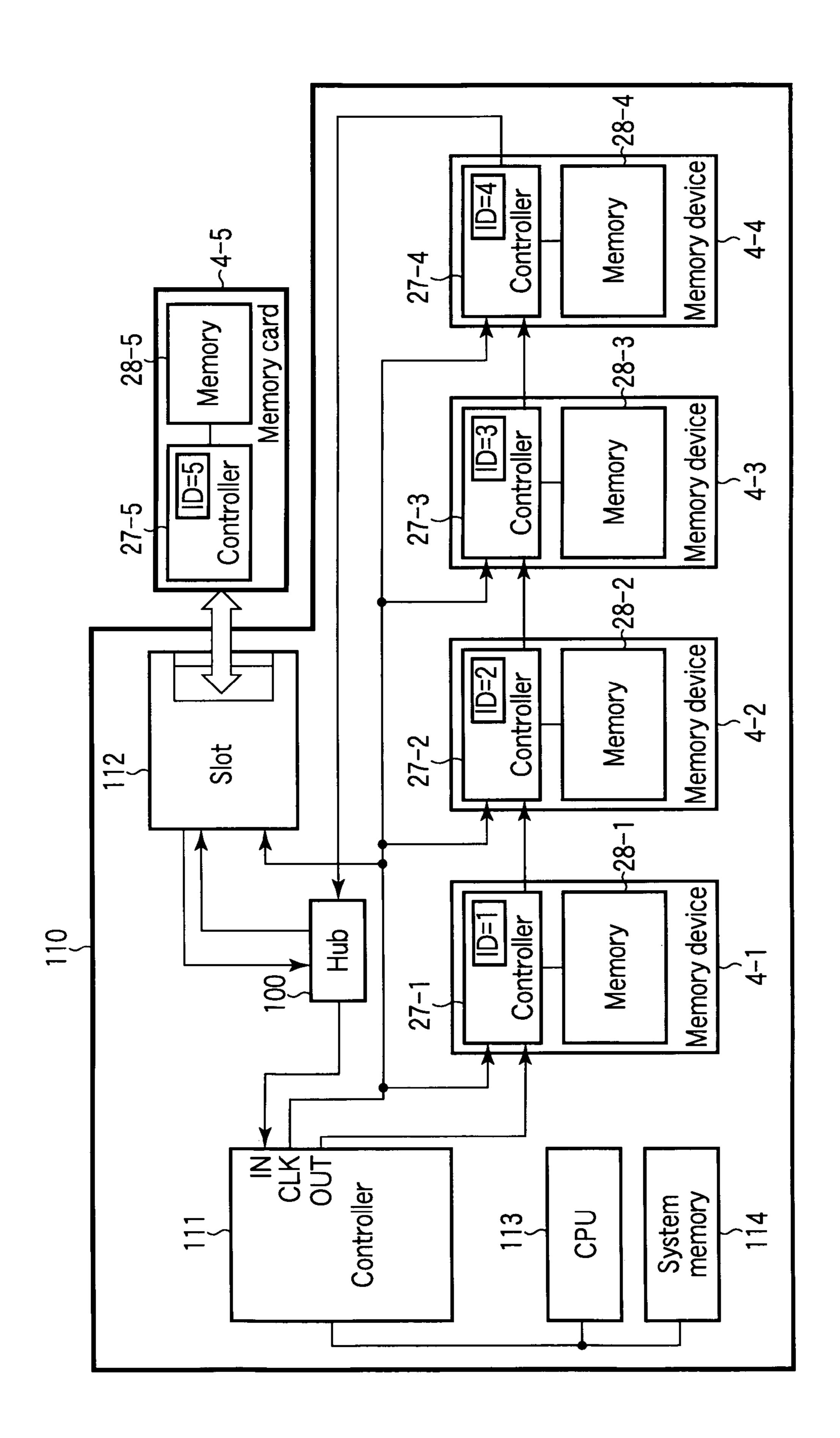

- FIG. **36** is a block diagram of a semiconductor system according to a fifth embodiment;

- FIG. 37 is a block diagram of a semiconductor system according to a sixth embodiment; and

- FIG. 38 is a diagram illustrating allocation of signals to signal pins of an electronic device of the sixth embodiment.

#### DETAILED DESCRIPTION

In general, according to one embodiment, a semiconductor system includes plural electronic devices and a host apparatus. The host apparatus initializes plural electronic devices in units of group.

#### First Embodiment

A semiconductor system and an electronic device initializing method according to a first embodiment will be described below. FIG. 1 is a block diagram illustrating an example of the semiconductor system of the first embodiment.

#### Configuration of Semiconductor System

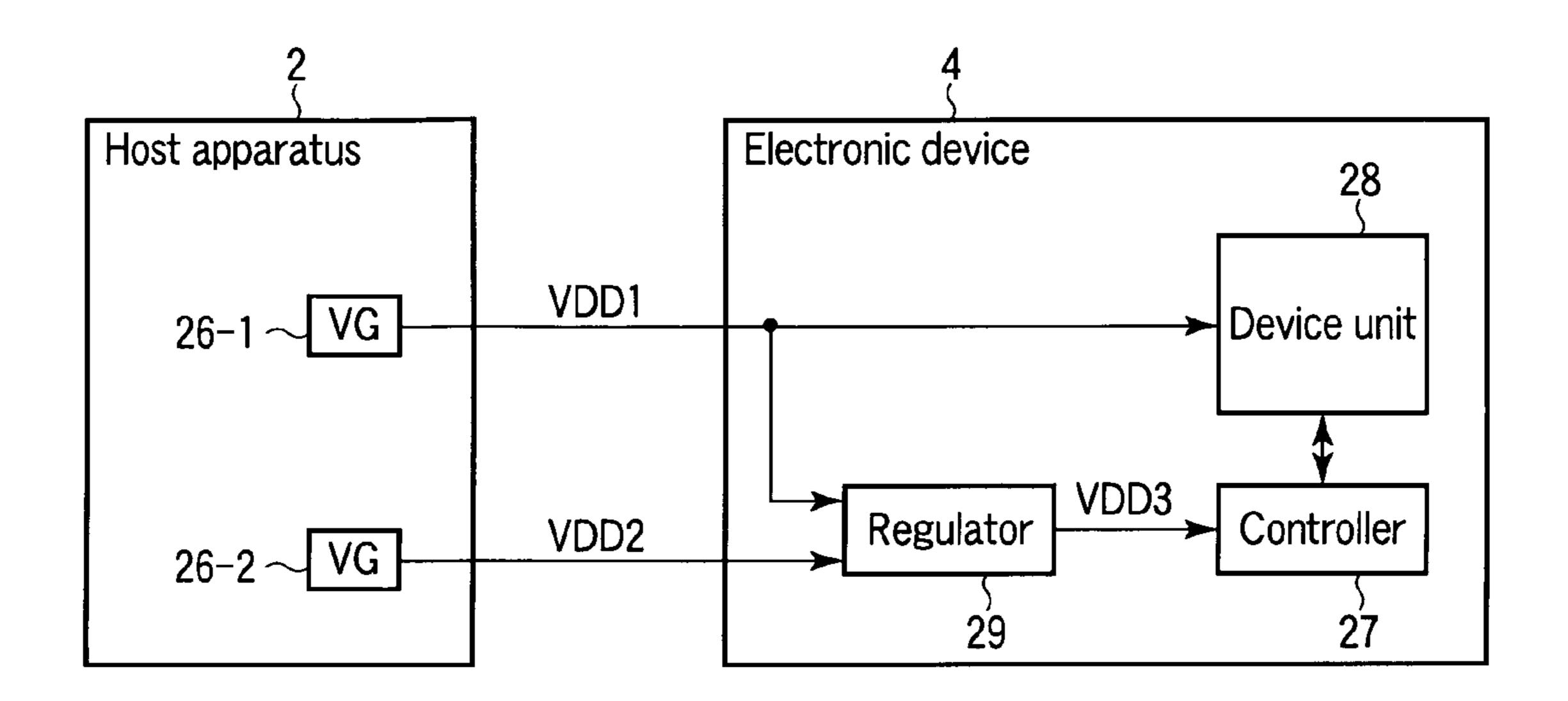

Referring to FIG. 1, a semiconductor system 1 includes a host apparatus 2 and a semiconductor devide 3.

The host apparatus 2 includes at least one input port and at least one output port. The host apparatus 2 controls an operation of the semiconductor device 3 through the ports to administer an operation of the semiconductor system 1. For example, each port is configured as a differential pair according to a LVDS (low voltage differential Signaling) method. Hereinafter, a signal output from the output port of the host apparatus 2 is referred to as a signal D0, and differential signals of the signal D0 are referred to as signals D0+ and D0-. A signal input to the output port of the host apparatus 2 is referred to as a signal D1, and differential

signals of the signal D1 are referred to as signals D1+ and D1-. The host apparatus 2 assembles a packet including a command and data, and the host apparatus 2 transmits the packet to the semiconductor device 3 to control the operation of the semiconductor device 3. The host apparatus 2 5 receives the packet transmitted from the semiconductor device 3 to perform the operation according to the received packet.

The semiconductor device 3 includes N (N is a natural number more than 1) electronic devices 4. Hereinafter, the N 10 electronic devices 4 are referred to as electronic devices 4-i (i is 1 to N) when distinguished from one another.

In the first embodiment, each of the electronic devices 4 includes an input signal pin 5, an output signal pin 6, a packet decoder 7, a processing unit 8, a register 9, and a 15 packet update circuit 10. Similarly, when the electronic devices 4-i are distinguished from one another, the units are referred to as an input signal pin 5-i, an output signal pin 6-i, a packet decoder 7-i, a processing unit 8-i, register 9-i, and a packet update circuit 10-i.

The input signal pin 5 including plural signals acts as at least one input port to receive the packet provided from the outside. The input signal pin 5 transfers the received packet to the packet decoder 7.

The packet decoder 7 is configured to be able to analyze 25 the packet transferred from the input signal pin 5. The packet decoder 7 distinguishes kinds of the packets using a command identifier in a packet header. The packet decoder 7 commands the processing unit 8 to perform a necessary calculation in response to the kind of the packet. The packet decoder 7 commands the packet update circuit 10 to update the received packet if needed.

The processing unit 8 is configured to be able to perform necessary processing in response to the command from the include initialization of the device and computation of a device ID. On computing the device ID, the processing unit 8 causes the register 9 to retain the device ID. The device ID means a number that is unique to each electronic device 4, and the host apparatus can identify each electronic device 4 40 using the device ID. When the received packet is not broadcast (for example, unicast or multicast), the packet decoder 7 compares the device ID that is included as address information in the packet with the device ID in the register 9, which allows the packet decoder 7 to determine whether 45 the packet is direct to the semiconductor device 3.

The packet update circuit 10 updates contents of a payload of the received packet, and the packet update circuit 10 outputs the packet to the outside from the output signal pin 6 that includes the plural signals to act as at least one output 50 port. For example, the packet update circuit 10 updates the contents of the payload according to calculation result of the processing unit 8. There are two kinds of timing in which the packet is output from the output signal pin 6, that is, the case in which the received packet is transmitted as soon as 55 possible irrespective of a processing status of the device to the received packet, and the case in which the packet is transmitted after the device performs the processing to the received packet. It depends on the command identifier of the packet and a state of the device.

The N electronic devices 4-1 to 4-N having the abovedescribed configuration are ring-connected (or chain-connected) to the host apparatus 2 as illustrated in FIG. 1. That is, the packet transmitted from the host apparatus 2 is received by the electronic device 4-1, transferred from the 65 electronic device 4-1 to the electronic device 4-2, and transferred from the electronic device 4-2 to the electronic

device 4-3. After that, similar steps are repeated. Then the packet output from the output signal pin 6-N of the electronic device 4-N is returned to the host apparatus 2. The semiconductor device 3 of FIG. 1 includes a configuration in which the semiconductor device 3 includes electronic devices 4-1 to 4-N and a hub (see a fourth embodiment). Almost all the pieces of communication conducted using the ring connection are used in the communication between the host and the electronic device and occasionally used in the communication between the electronic devices. For example, when the electronic device 4-2 does not correctly receive data, which is transmitted from electronic device 4-1 to the electronic device 4-2, due to a noise, the electronic device 4-2 can make a request to transmit the data again. At this point, the electronic device 4-1 is notifies of the retransmission request made by the electronic device 4-2 through the electronic devices 4-3 to 4-N and the host apparatus 2, which allows the electronic device 4-1 to retransmit the data.

#### Operation of Semiconductor System 1

An operation of the semiconductor system 1 having the above-described configuration in connecting the semiconductor device 3 to the host apparatus 2 will be described below with reference to FIG. 2. FIG. 2 is a flowchart illustrating an operation of the semiconductor system. First an entire flow will roughly be described.

As illustrated in FIG. 2, interface selection is performed (Step S10). In Step S10, the host apparatus 2 determines whether an interface connected to the semiconductor device 3 can be used, that is, whether the semiconductor device 3 is connected. When the interface can be used, that is, when the semiconductor device 3 is connected (YES in Step S11), one of the electronic devices 4 transmits a boot code to the packet decoder 7. Examples of the processing contents 35 host apparatus 2 (Step S12). The host apparatus 2 that receives the boot code performs the boot code and performs numbering of the electronic devices 4 (enumeration) (Step S13). That is, the device ID described above is allocated to each electronic device 4.

> After the allocation of the device ID, each electronic device 4 is initialized in response to the command from the host apparatus 2 (Step S14). Each electronic device 4 becomes a ready state by the initialization. The initialization is performed in units of a plurality of the electronic devices **4** in order to shorten a time necessary for the initialization. However, when the host apparatus 2 has a restriction to a power supply current that can be supplied to the electronic device 4, the number of simultaneously-initialized devices is restricted, and thus the initialization is separately performed.

Then, the host apparatus 2 obtains information on each electronic device 4 (Step S15). After Step S15, the host apparatus 2 determines an operating condition common to the electronic devices 4 based on the capabilities of the host apparatus 2 and electronic device 4, and the host apparatus 2 collectively sets the operating condition for the host apparatus 2 and the electronic devices 4 (Step S16). The capability set in this step is an item common to the whole system. Then the host apparatus 2 determines an individual operating condition of the electronic device 4, and the host apparatus 2 separately sets the individual operating condition for the electronic device 4 (Step S17).

A UHS-II card has a hierarchical structure. Therefore, when the semiconductor device 3 is the UHS-II card, the initialization is performed to a physical layer in Step S14. For example, the initialization is performed to a layer higher than the physical layer in Step S16 and Step S17B.

Each step will sequentially be described in detail.

#### Step S10

Step S10 will be described with reference to FIG. 3 and FIG. 4. FIG. 3 is a timing chart illustrating a clock and a symbol, transmitted from the host apparatus 2 to the semiconductor device 3 and a level and a symbol (the state is communicated in synchronization with the clock in the symbol, and the symbol includes plural bits and is encoded by 8b/10b coding), transmitted from the semiconductor device 3 to the host apparatus 2, immediately after the semiconductor device 3 is connected to the host apparatus 2. FIG. 4 is a timing chart of the signals D0 and D1 immediately after the semiconductor device 3 is connected to the host apparatus 2.

As illustrated in FIG. 3 and FIG. 4, before a time t1, the semiconductor system 1 is in a power-down state. In the power-down state, the host apparatus 2 does not generate the clock, and the host apparatus 2 does not transmit the symbol to the semiconductor device 3. The semiconductor device 3 does not transmit the symbol to the semiconductor device 3. Accordingly, either a level D0+=D0-=D1+=D1-="H" or a level D0+=D0-=D1+=D1-="L" can be taken before the time t1. FIG. 4 illustrates the level D0+=D0-=D1+=D1-="D1-="D1-="D1-="D1-="D1-="L".

Then, at the time t1, the host apparatus 2 transmits STB to the semiconductor device 3 using one of an "H" level or an "L" level of the differential signal in order to determine usability of the interface. At this point, it is assumed that the "H" level is STB. Therefore, a data link state transitions to a wakeup state. The host apparatus 2 outputs a clock RCLK to the semiconductor device 3. The clock RCLK is supplied to each of the electronic devices 4-0 to 4-n. Hereinafter the electronic device 4 performs the operation in synchronization with the clock RCLK. The level STB is sequentially transferred from the electronic device 4-0 to the electronic device 4-N. At a time t2, the electronic device 4 that receives the level STB returns the level STB to the host apparatus 2. The level STB is a signal that indicates that the host 40 apparatus 2 and the electronic device 4 are in a standby state before synchronized with each other.

The host apparatus 2 transmits the level STB, whereby the D0- changes from the "L" level to the "H" level while the signal D0 changes to the differential level. The semiconductor device 3 transmits the level STB, whereby the D1-changes from the "L" level to the "H" level while the signal D0 changes to the differential level. Thus, the host apparatus 2 recognizes that the interface can be used by detecting that the signals D0 and D1 change to the differential level.

Then processing is performed in order to synchronize the host apparatus 2 and the semiconductor device 3 with each other. That is, the host apparatus 2 transmits a symbol SYN to the semiconductor device 3, and the semiconductor device 3 returns the symbol SYN to the host apparatus 2 when a PLL is locked. When the PLL is locked with respect to all the semiconductor devices 3, the host apparatus 2 receives the symbol SYN. Because the reception clock of the host apparatus 2 differs from the transmission clock RCLK in a phase, it is necessary to lock another PLL for the 60 reception. The symbol SYN is one that is used for synchronization. The PLL is locked while the symbol SYN is received plural times, which allows synchronous communication to be conducted between the host apparatus 2 and the semiconductor device 3.

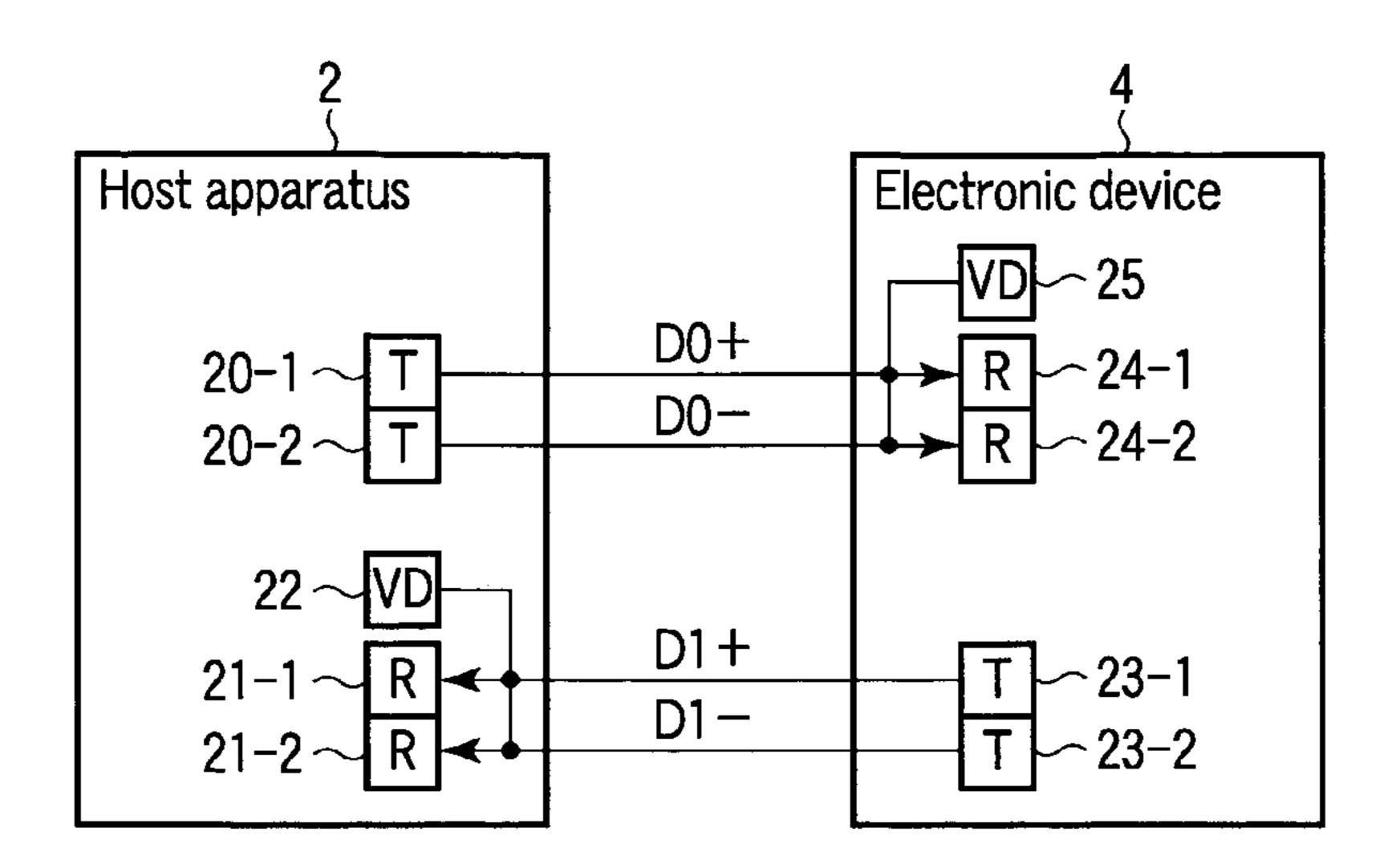

FIG. 5 is a block diagram of the host apparatus 2 and any one of the electronic devices 4, particularly illustrates a

6

configuration relating to data link. As illustrated in FIG. 5, the host apparatus 2 includes transmission I/Os 20-1 and 20-2 that transmit the signals D0+ and D0-, reception I/Os 21-1 and 21-2 that receive the differential signals D1+ and D1-, and a voltage level detection circuit 22. The voltage level detection circuit 22 detects a level change of the differential signal D1+ and D1-. A determination that the interface with the electronic device 4 can be used is made when the voltage level detection circuit 22 detects the change in signal level.

The electronic device 4 includes transmission I/Os 23-1 and 23-2 that transmit the differential signals D1+ and D1-, reception I/O 24-1 and 24-2 that receive the differential signals D0+ and D0-, and a voltage level detection circuit 25. The voltage level detection circuit 25 detects a level change of the differential signal D0+ and D0-. For example, when the host apparatus 2 is started up from the electronic device 4, the voltage level detection circuit 25 detects the change in signal level, which allows the host apparatus 2 to be started up.

#### Step S12

Step S12 of FIG. 2 will be described below. In the semiconductor device 3, any one of the electronic devices 4 is a memory device that retains the boot code. At this point, only by way of example, it is assumed that the electronic device 4-N is the memory device that retains the boot code. The boot code means a program code that is necessary to start up the system in the host apparatus 2. The boot code is transferred to a system memory of the host apparatus 2, and the boot code is executed by the host apparatus 2. A device driver and an OS (Operating System) are loaded on the system memory by a boot loader included in the boot code.

The electronic device 4-N receives the symbol STB from the host apparatus 2 and returns the symbol STB to the host apparatus 2. Then, the electronic device 4-N voluntarily reads the boot code without receiving the command from the host apparatus 2, and the electronic device 4-N transmits the boot code to the host apparatus 2.

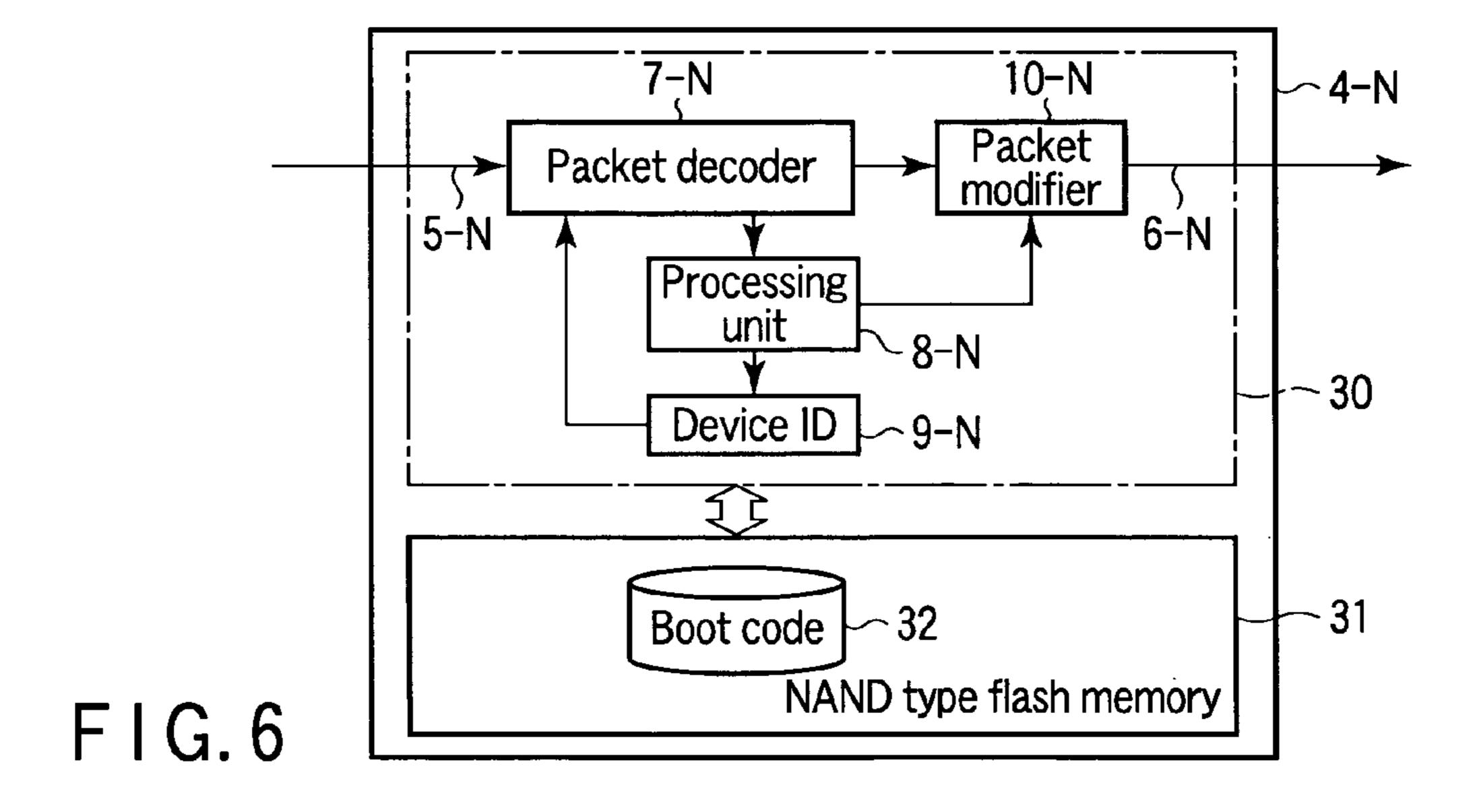

FIG. 6 is a block diagram of the electronic device 4-N, and FIG. 6 illustrates the detailed configuration of the electronic device 4-N rather than that of FIG. 1. As illustrated in FIG. 6, the electronic device 4-N includes a memory controller 30 and a NAND type flash memory 31. The memory controller 30 includes a packet decoder 7-N, a processing unit 8-N, register 9-N, and a packet update circuit 10-N. The NAND type flash memory 31 retains a boot code 32. After transmitting the level STB to the host apparatus 2, the processing unit 8-N reads the boot code 32 from the NAND type flash memory 31. The processing unit 8-N assembles the boot code 32 as the packet and transmits the packet from the output signal pin 6 to the host apparatus 2.

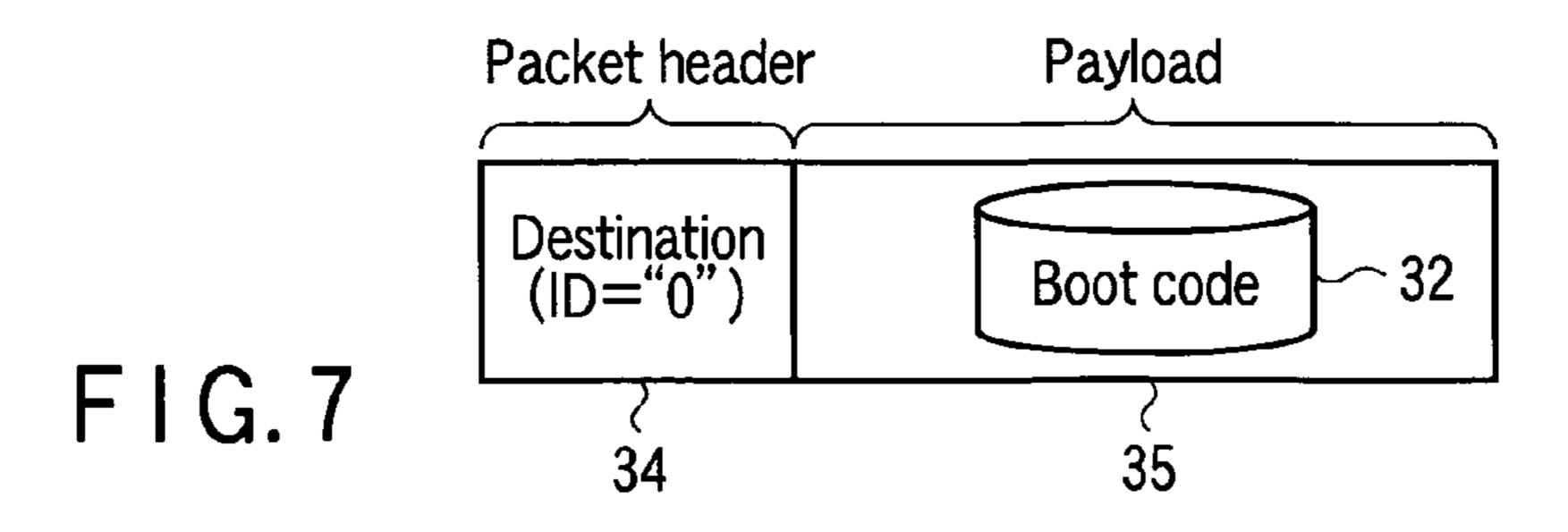

FIG. 7 is a schematic diagram illustrating a configuration of the packet. As illustrated in FIG. 7, the packet 33 includes a packet header 34 and a payload 35. The payload 35 includes the boot code 32 that is read from the NAND type flash memory 31. The packet header 34 includes a destination of the packet. The destination is indicated as an ID, and ID="0" is stored when the destination is host apparatus 2. Although a device ID of a boot device is not determined yet when the boot code is transmitted before the enumeration, for example, device ID=1 of the transmission source is tentatively allocated to the device ID of the boot device. A size of the boot code may be set as a preset value to the host

and the boot device, or a region indicating the size of the boot code may be secured in the packet header or a specific portion of the boot code.

The electronic device except the electronic device 4-N may be used as the electronic device including the boot 5 code. For example, the electronic device 4-(N-1) may be used as the electronic device including the boot code. In this case, at first the electronic device 4-(N-1) transmits the packet 33 to the electronic device 4-N. Because the destination of the packet 33 is the host apparatus 2, the electronic device 4-N transmits the packet 33 to the host apparatus 2 without change.

#### Step S13

Step S13 of FIG. 2 will be described below. In Step S13, the host apparatus 2 provides the device IDs to the electronic devices 4-0 to 4-N included in the semiconductor device 3. For example, a method disclosed in Japanese Patent Application No. 2009-221468 can be adopted in Step S13. FIG. 8 20 is a schematic diagram of the packet issued by the host apparatus 2 in performing Step S13.

As illustrated in FIG. 8, a packet header of a packet 40 includes at least fields 41-1 and 41-2. The device ID that indicates the destination of the packet 40 is stored in the field 25 41-1. A command identifier corresponding to a command to provide the device ID is stored in the field 41-2. A payload includes at least fields 42-1 and 42-2. The field 42-1 indicates a start device ID (start device number), and a value of the field **42-1** is determined by the electronic device **4-1** that 30 initially receives the packet 40 from the host apparatus 2. The number of electronic devices 4 to which the setting of the device ID is completed is stored in the field 42-2. The value of the field 42-1 is incremented in a process of transferring the packet among the electronic devices 4, 35 which allows the host apparatus 2 to recognize the total number of electronic devices 4. The host apparatus 2 can specify the device ID of each electronic device 4 from the values of the fields 42-1 and 42-2. A final device ID (final device number) may be indicated in the field **42-2** instead of 40 the number of electronic devices 4 to which the setting of the device ID is completed, because the number of devices can be computed by subtraction when the final device number and the initial device number are found.

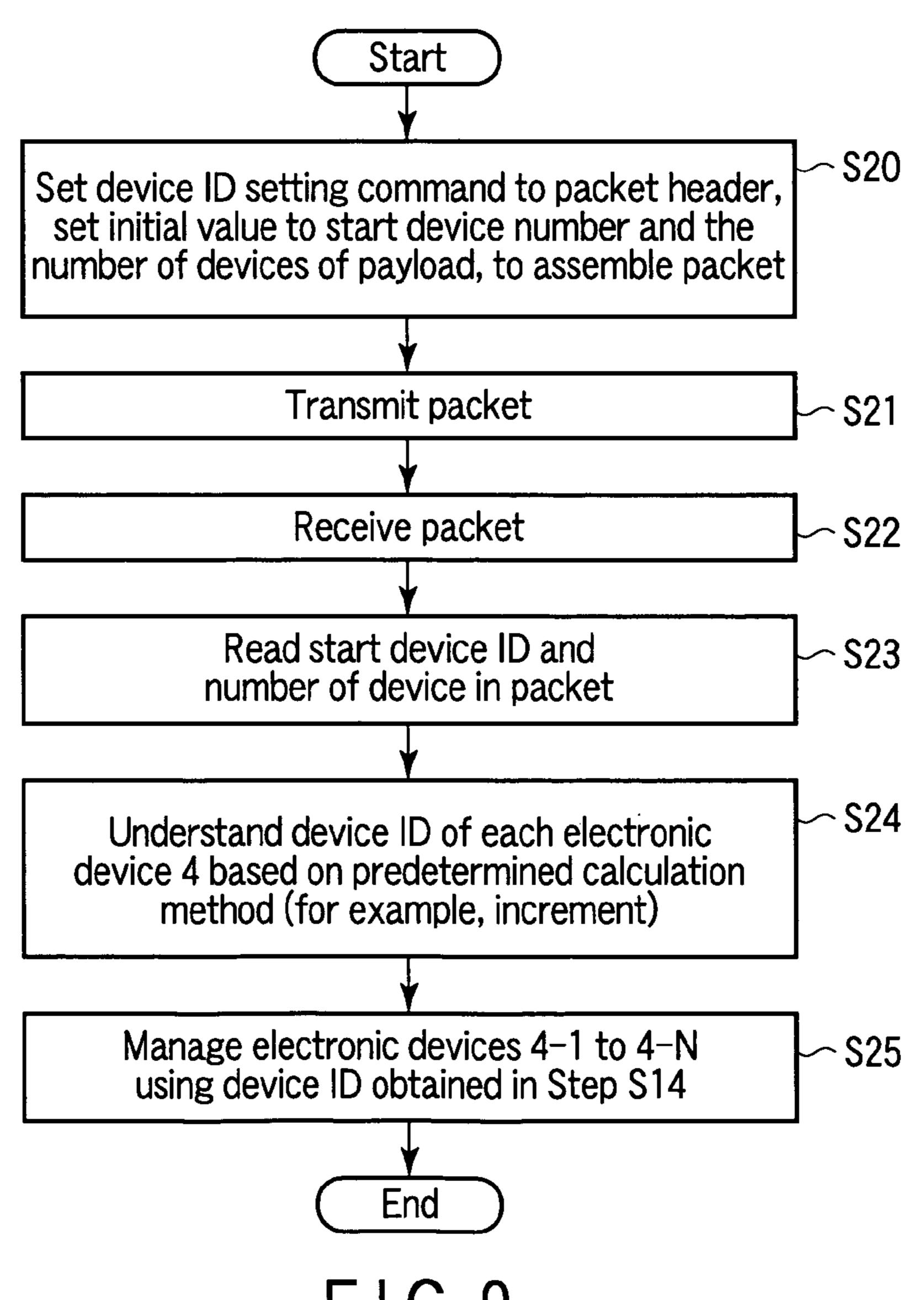

FIG. 9 is a flowchart illustrating the operation of the host apparatus 2 in providing the device ID. As illustrated in FIG. 9, the host apparatus 2 assembles the packet in order to specify the device ID (Step S20). That is, the command identifier (field 41-2) corresponding to the command (hereinafter referred to as ID providing command) to specify the 50 device ID is set to the packet header, and initial values (in the first embodiment, zero) are set to the values of the start device ID (field 42-1) and the number of devices (field 42-2) of the payload.

The host apparatus 2 transmits the packet assembled in 55 Step S20 to the semiconductor device 3 (Step S21). Whether the packet is transmitted in the form of the broadcast (multicast) or unicast is previously made in each command. The ID providing command is a broadcast command. Accordingly, the destination in the field 41-1 of the packet 60 header is ignored, and the packet is transmitted to the initial electronic device 4-1 of the ring connection in the case of the connection relationship in FIG. 1.

Then the host apparatus 2 receives the packet from the final electronic device 4-N of the ring connection (Step S22). 65 Therefore, the host apparatus 2 reads the initial device ID (field 42-1) and the number of devices (field 42-2) in the

8

received packet (Step S23). The value of the field 42-1 is the device ID of the initial electronic device 4-1 of the ring connection, and the value of the field 42-2 is the number N of ring-connected electronic devices 4-1 to 4-N.

The host apparatus 2 performs predetermined calculation using the values of the fields 42-1 and 42-2 to recognize the device ID and the total number of devices of the electronic devices 4-2 to 4-N (Step S24). The number of identifiable devices is determined by the number of bits of the device ID field. The predetermined calculation means a rule in which the electronic devices 4-2 to 4-N compute the IDs thereof with respect to the start device ID. For example, predetermined calculation means that the increment is performed by the number of devices. Accordingly, for example, the start device ID has a value "n (n is a natural number)" in the packet received from the electronic device 4-N, it is found that the electronic device 4-1 has the device ID "n", the electronic device 4-2 has the device ID "n+1", and the electronic device 4-N has the device ID "n+N".

The host apparatus 2 manages the electronic devices 4-1 to 4-3 using the device IDs obtained in Step S24.

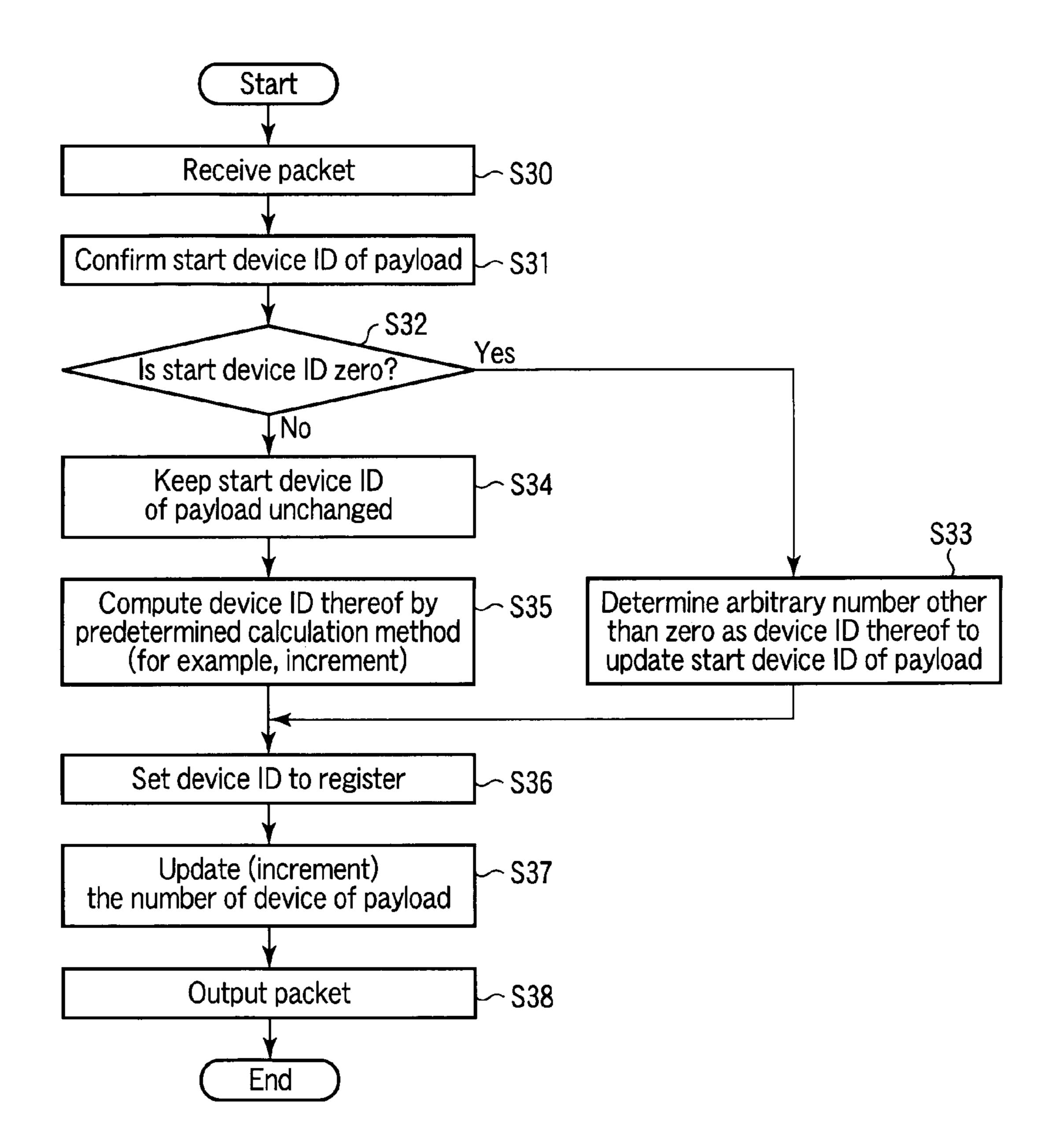

An operation of the electronic device 4 will be described below with reference to FIG. 10. FIG. 10 is a flowchart illustrating the operation of the electronic device 4 in receiving the packet including the ID providing command, and the flowchart of FIG. 10 is common to the electronic devices 4-1 to 4-N.

As illustrated in FIG. 10, the electronic device 4 receives the packet at the input signal pin 5 (Step S30). When recognizing that the received packet includes the ID providing command from the command number of the field 41-2 of the packet, the packet decoder 7 commands the processing unit 8 to compute the device ID thereof.

In response to the command, the processing unit 8 confirms whether the value (start device ID) of the field 42-1 of the received packet is a predetermined value (in the first embodiment, zero) set by the host apparatus 2 (Step S31). When the value of the field 42-1 is zero (YES in Step S32), the processing unit 8 determines any number except zero as the device ID thereof, and the processing unit 8 commands the packet update circuit 10 to update the value (start device ID) of the field 42-1 to the determined device ID. Therefore, the packet update circuit 10 updates the field 42-1. The reason for using the number other than zero is that zero has been already allocated to the device ID of the host apparatus 2

On the other hand, when the value of the field 42-1 is not the predetermined value set by the host apparatus 2 (NO in Step S32), the value of the field 42-1 is maintained (Step S34). That is, the processing unit 8 does not command the packet update circuit 10 to update the value of the field 42-1. The processing unit 8 performs the predetermined calculation using the field 42-1 to compute the device ID thereof (Step S35). The calculation in Step S35 is identical to the calculation in Step S24 of FIG. 9. For example, the calculation in Step S35 means that the field 42-1 (start device ID) is incremented by the number of times corresponding to the field 42-2 (the number of devices).

Then the processing unit 8 stores the device ID thereof determined in Step S33 or S35 in the register 9 (Step S36).

In response to the command from the packet decoder 7 or processing unit 8, the packet update circuit 10 updates (increments) the value of the field 42-2 of the received packet. The packet update circuit 10 outputs the packet in which the field 42-2 or both the fields 42-1 and 42-2 are updated.

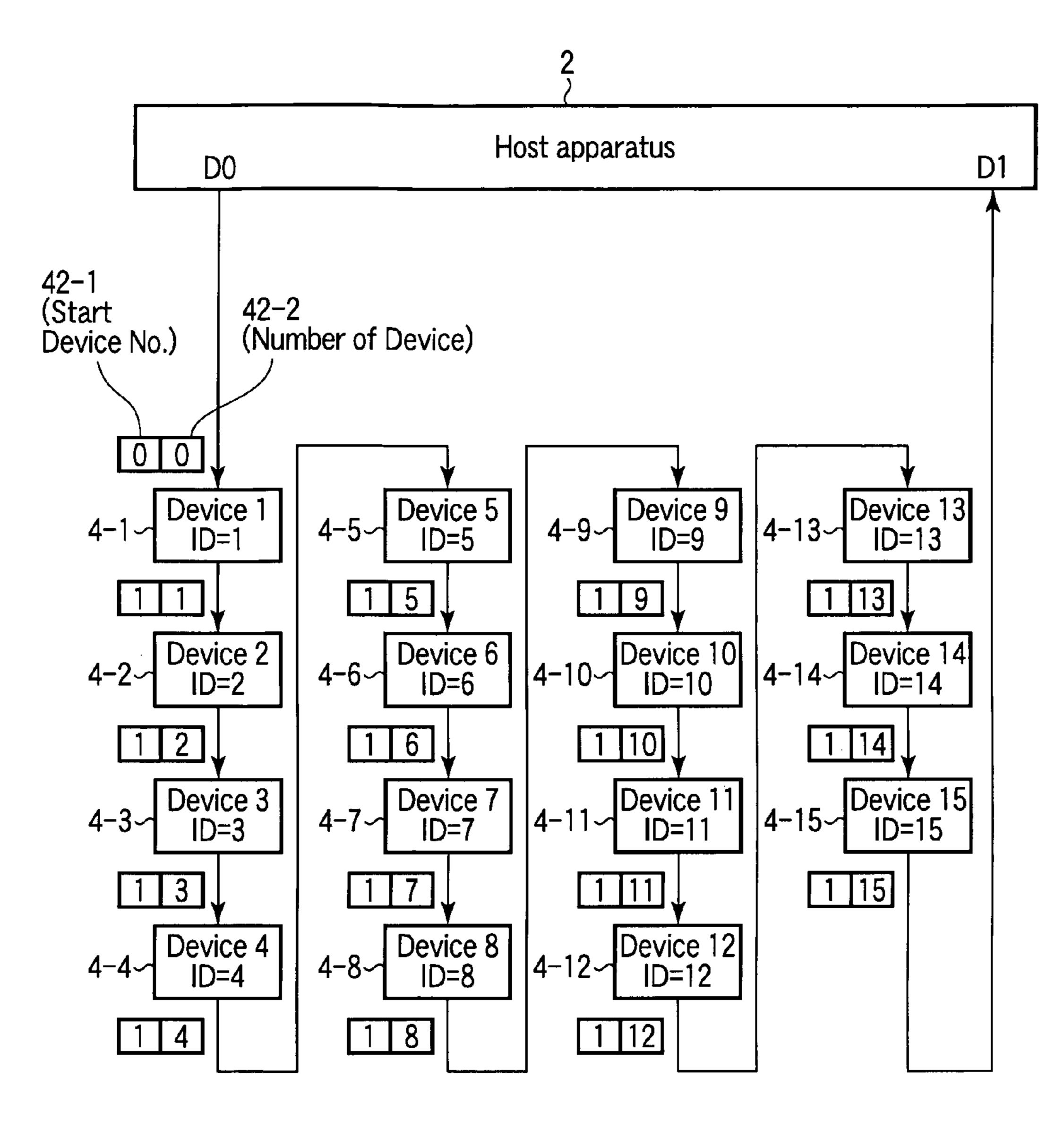

A specific example in Step S13 will be described with reference to FIG. 11. FIG. 11 is a block diagram of the semiconductor system 1, and FIG. 11 illustrates the case in which the 15 (N=15) electronic devices 4 are provided in the semiconductor device 3 by way of example. In FIG. 11, square marks added to a side of an arrow between the devices indicate payload contents of the packet, the left side of the square marks indicates the field 42-1 (start device ID), and the right side indicates the field 42-2 (the number of devices).

As illustrated in FIG. 11, at first the packet including the ID providing command is broadcasted from the host apparatus 2. At this point, the values of the fields 42-1 and 42-2 of the packet are the predetermined value (zero) set by the host apparatus 2 (Steps S20 and S21 of FIG. 9). The packet is initially received by the electronic device 4-1.

In the electronic device **4-1**, because the field **42-1** has the value "0" (YES in Step S32 of FIG. **10**), any number is determined as the device ID of the device **4-1**. In the 20 example illustrated in FIG. **11**, the device ID is the number "1". The field **42-1** is updated from "0" to "1" (Step S33 of FIG. **10**), the value of the field **42-2** is incremented and updated from "0" to "1" (Step S37 of FIG. **10**), and the updated value of the field **42-2** is output by the device **4-1**. <sup>25</sup>

The packet output from the electronic device 4-1 is received by the electronic device 4-2. In the electronic device 4-2, because the field 42-1 does not have the value "0" (NO in Step S32 of FIG. 10), the device ID of the device 4-2 is computed by the predetermined calculation method (Step S35 of FIG. 10). That is, the value of the field 42-1 is incremented by the value of the field 42-2 to determine the device ID of the electronic device 4-2 as "1"+"1"="2". While the value of the field 42-1 is maintained (Step S34 of FIG. 10), the value of the field 42-2 is incremented and updated from "1" to "2" (Step S37 of FIG. 10), and the updated value of the field 42-2 is output by the device 4-2.

Similarly, the device ID is allocated to the electronic device 4. That is, the device IDs "3" to "15" are allocated to 40 the electronic devices 4-3 to 4-15.

The packet output from the electronic device **4-15** is received by the host apparatus **2**. In the packet, the field **42-1** has the value "1" and the field **42-2** has the value "15". Accordingly, the host apparatus can recognize that the 45 electronic device **4-1** has the device ID "1" and the total number of electronic devices **4** is "15" (Step S**23** of FIG. **9**). Therefore, the host apparatus **2** understands that the electronic devices **4-1** to **4-15** have the device IDs "1" to "15", respectively.

#### Step S14

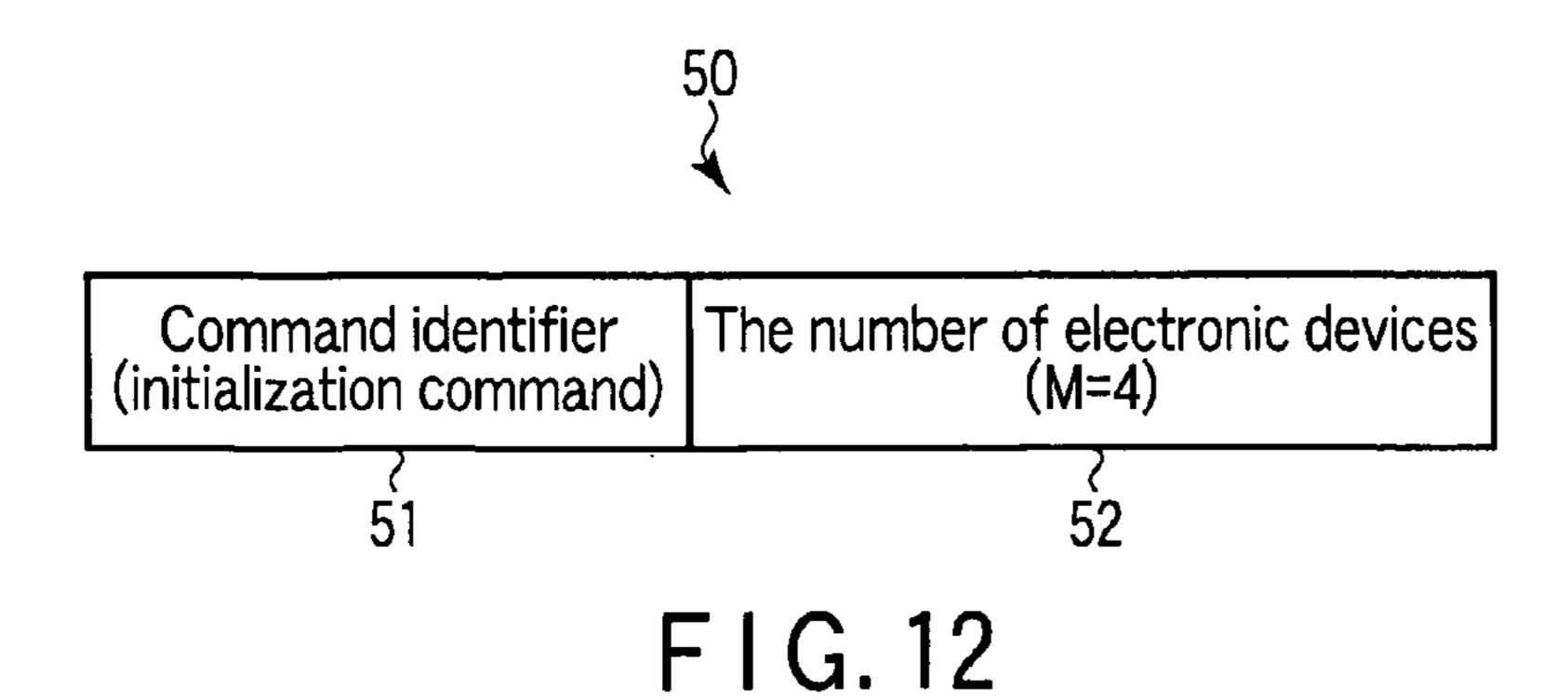

Step S14 of FIG. 2 will be described below. In Step S14, the host apparatus 2 initializes the electronic devices 4-0 to 55 4-N included in the semiconductor device 3. FIG. 12 is a schematic diagram of a packet issued by the host apparatus 2 in performing the initialization.

As illustrated in FIG. 12, a command identifier indicating an initialization command is included in a packet header 51 of a packet 50, and the maximum number of electronic devices M that can be initialized once by the host apparatus 2 is included in a payload 52. The initialization command is issued as the broadcast command. Whether the initialization command is the broadcast command may be determined by 65 the command identifier. Alternatively, the broadcast command may be defined by setting transmission source

**10**

ID=transmission destination ID="0". This means that the host apparatus 2 transmits the packet and the host apparatus 2 finally receives the packet.

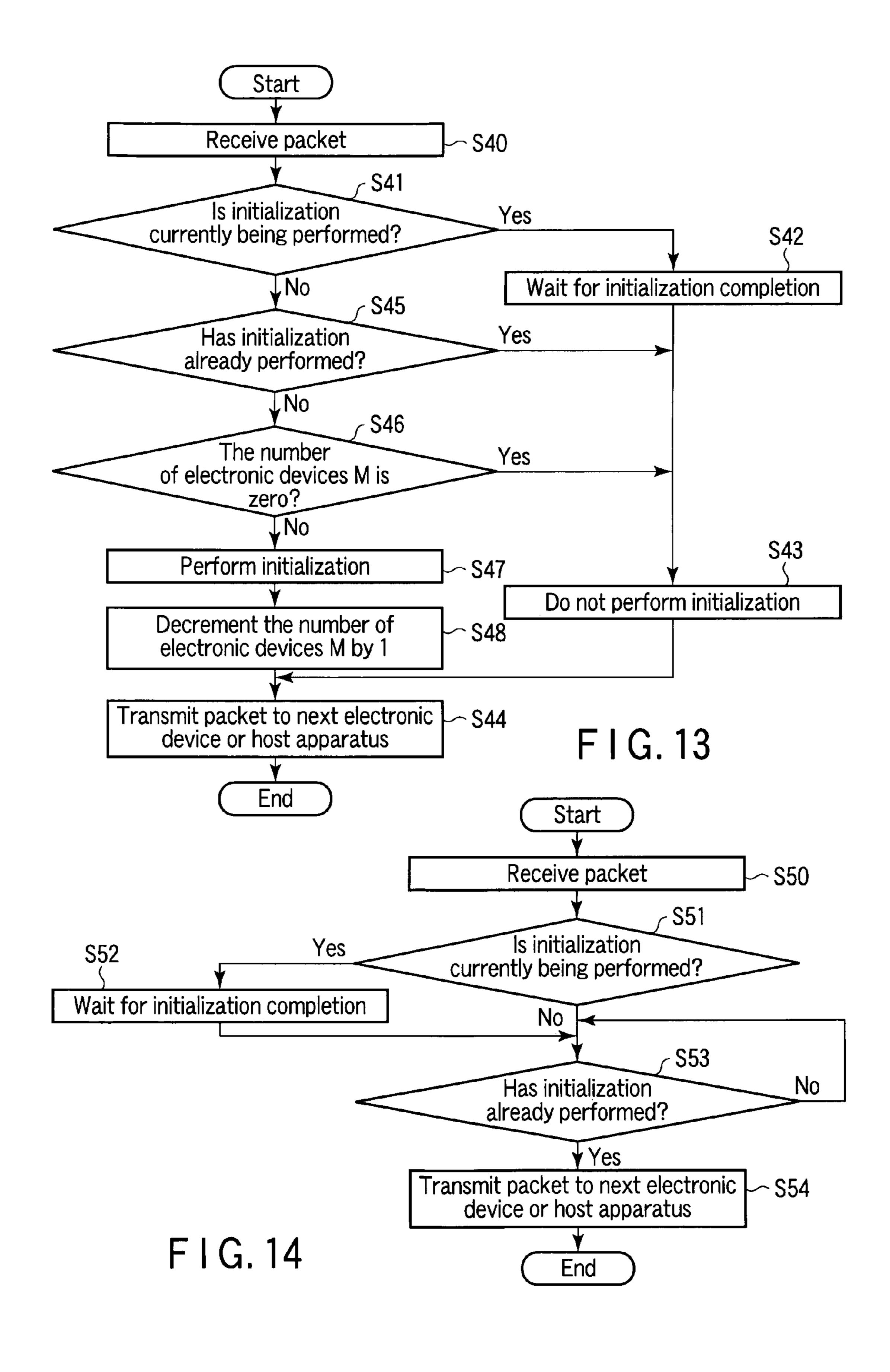

FIG. 13 is a flowchart illustrating an operation of the electronic device 4 in receiving the packet including the initialization command, and the flowchart of FIG. 13 is common to the electronic devices 4-1 to 4-N.

As illustrated in FIG. 13, the electronic device 4 receives the packet at the input signal pin 5 (Step S40). When 10 recognizing that the received packet includes the initialization command from the command identifier of the packet header 51 of the packet, the packet decoder 7 notifies the processing unit 8 of the initialization command included in the packet and the number of electronic devices M of the 15 payload **52**. The processing unit **8** determines whether the electronic device 4 is currently initializing. When the electronic device 4 is currently executing the initialization (YES) in Step S41), the processing unit 8 waits for the initialization completion (Step S42). After the initialization completion, the processing unit 8 does not perform the initialization again (Step S43), the processing unit 8 causes the packet update circuit 10 to transmit the received packet to the next electronic device 4 (in the case of the electronic device 4-N, to the host apparatus 2) with no change (Step S44).

When the electronic device 4 is not currently being initialized, the processing unit 8 determines whether the electronic device 4 has been already initialized. When the electronic device 4 has been already initialized (YES in Step S45), the processing unit 8 does not perform the initialization again (Step S43). The processing unit 8 causes the packet update circuit 10 to transmit the received packet to the next electronic device 4 (in the case of the electronic device 4-N, to the host apparatus 2) with no change (Step S44).

On the other hand, when the electronic device 4 is not initialized (NO in Step S45), the processing unit 8 confirms whether the number of electronic devices M of the payload 52 is "0" (Step S46). When the number of electronic devices M is "0" (YES in Step S46), the processing unit 8 goes to Step S43, and the processing unit 8 goes to Step S44 without performing the initialization.

When the number of electronic devices M is not "0" (NO in Step S46), the processing unit 8 performs the initialization (Step S47). The processing unit 8 commands the packet update circuit 10 to decrement the number of electronic devices of the payload 52 (Step S48). That is, the number of electronic devices M is updated to M-1. The packet update circuit 10 outputs the packet in which the number of electronic devices M of the payload 52 is updated (Step S44). At this point, in response to the start of the initialization in Step S47, the packet update circuit 10 executes the processing in Step S44 without waiting for the initialization completion of the electronic device 4.

The host apparatus 2 repeatedly issues the initialization packet 50 until the host apparatus 2 receives the initialization packet 50 in which the number of electronic devices M is not "0". The number of devices that can be initialized is reset at the same time as the initialization packet 50 is issued. In other words, the host apparatus 2 can confirm that the initialization is completed for all the electronic devices 4-1 to 4-N by receiving the packet 50 of  $M \neq "0$ ".

The confirmation whether the initialization is completed for all the electronic devices 4 can be made by transmitting an initialization completion confirming command. An operation of the electronic device 4 in receiving the initialization completion confirming command will be described with reference to FIG. 14. FIG. 14 is a flowchart illustrating the

operation of the electronic device 4 in receiving the packet including the initialization completion confirming command, and the flowchart of FIG. 14 is common to the electronic devices 4-1 to 4-N.

As illustrated in FIG. 14, the electronic device 4 receives 5 the packet at the input signal pin 5 (Step S50). When recognizing that the packet includes the initialization completion confirming command from the command identifier of the packet header of the received packet, the packet decoder 7 notifies the processing unit 8 that the packet includes the initialization completion confirming command The processing unit 8 determines whether the electronic device 4 is currently being initialized. When the electronic device 4 is currently being initialized (YES in Step S51), the 15 apparatus 2. processing unit 8 waits for the initialization completion (Step S52). After the initialization completion, the processing unit 8 causes the packet update circuit 10 to transmit the received packet to the next electronic device 4 (in the case of the electronic device 4-N, to the host apparatus 2) without 20 change (Step S54).

When the electronic device 4 is not currently being initialized, the processing unit 8 determines whether the electronic device 4 has been already initialized. When the electronic device 4 has been already initialized (YES in Step 25 S53), the processing unit 8 commands the packet update circuit 10 to transmit the received packet to the next electronic device 4 (in the case of the electronic device 4-N, to the host apparatus 2) without change (Step S54). Therefore, the packet is transferred to the next electronic device 4. On 30 the other hand, when the electronic device 4 is not initialized yet (NO in Step S53), the processing unit 8 does not transmit the packet to the next electronic device 4. That is, the packet stays in the electronic device 4.

electronic devices. In other words, the N electronic devices are divided into L=(N/M) groups, and the initialization is collectively performed to the electronic devices belonging to each group (Steps S14-1 to S14-L of FIG. 2).

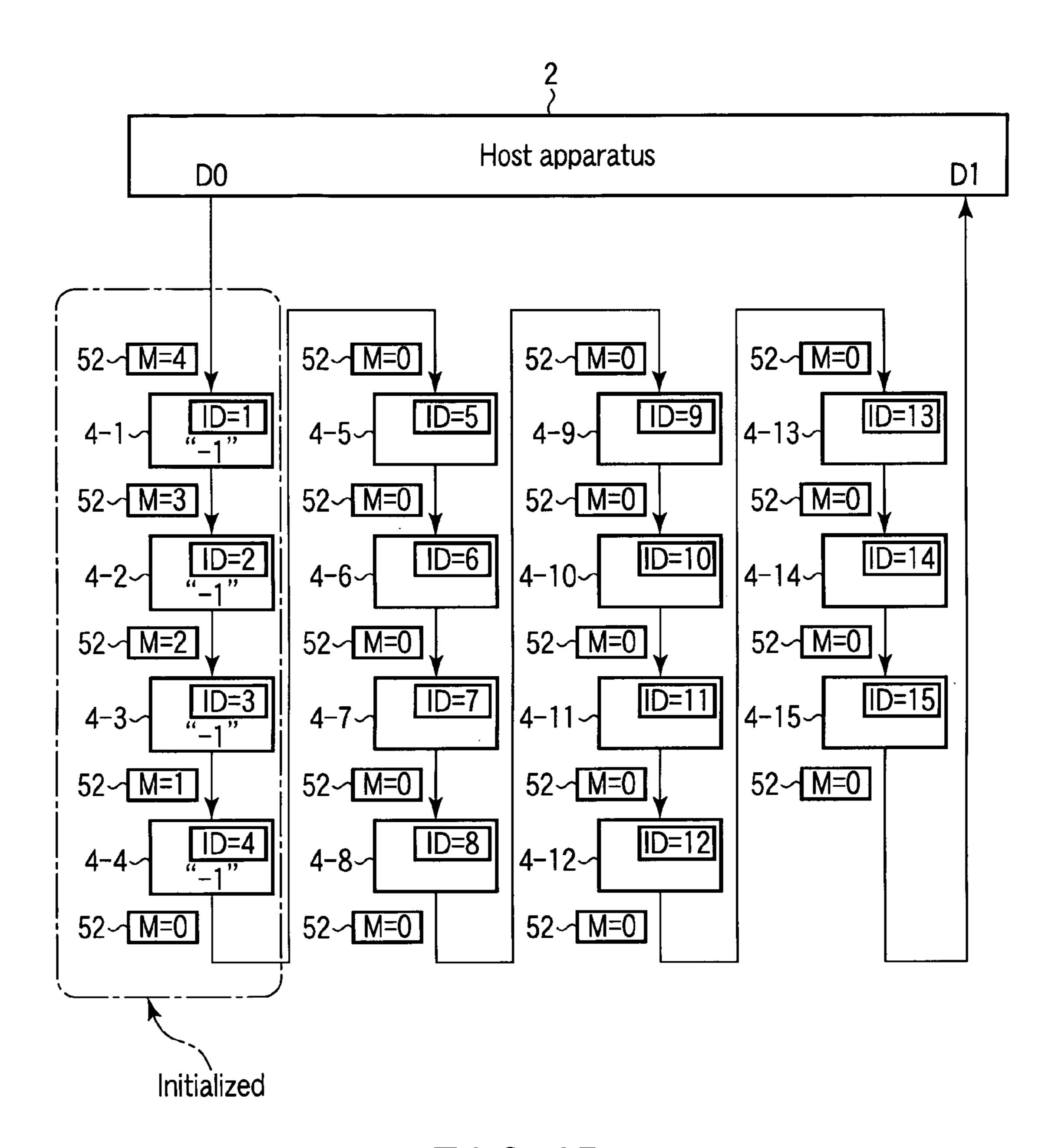

A specific example of Step S14 will be described with 40 reference to FIG. 15 to FIG. 18. FIG. 15 to FIG. 18 are block diagrams of the semiconductor system 1, and FIG. 15 to FIG. 18 illustrate the case in which the semiconductor system 1 includes 15 (N=15) electronic devices 4 similarly to the case of FIG. 11. In FIG. 15 to FIG. 18, square marks 45 added to the side of the arrow between the devices indicate the payload of the packet **50**, that is, the number of electronic devices M. Similarly to the case of FIG. 11, it is assumed that the device ID is provided to each electronic device 4.

FIG. 15 illustrates the state in which the initialization is 50 not performed yet to any electronic devices 4 while the initialization command is issued. As illustrated in FIG. 15, it is assumed that the host apparatus 2 issues the packet while the number of electronic devices M is set to "4". That is, the host apparatus 2 can initialize once up to four 55 electronic devices.

As illustrated in FIG. 15, the packet (M="4") including the initialization command is received by the electronic device 4-1. The electronic device 4-1 is not initialized yet is "4" (NO in Step S46). Therefore, the processing unit 8 performs the initialization (Step S47), the processing unit 8 updates the number of electronic devices M to M-1="3" (Step S48), and the processing unit 8 transmits the packet to the next electronic device **4-2**. In FIG. **15**, "-1" added to the electronic device 4 means that the number of electronic devices M is decremented.

Similarly to the electronic device 4-1, the electronic device 4-2 that receives the packet (M="3") including the initialization command performs the initialization, and the electronic device 4-2 decrements and updates the number of electronic devices M from "3" to "2", and transmits the packet to the electronic device 4-3. The electronic devices 4-3 and 4-4 perform the similar operation.

As a result of the decrement of the number of electronic devices M by the electronic device 4-4, the number of 10 electronic devices M becomes "0." Accordingly, the electronic devices 4-5 to 4-15 transfer the packet to the subsequent electronic devices 4-6 to 4-16 without performing the initialization. The final electronic device **4-16** of the ring connection transmits the packet with M="0" to the host

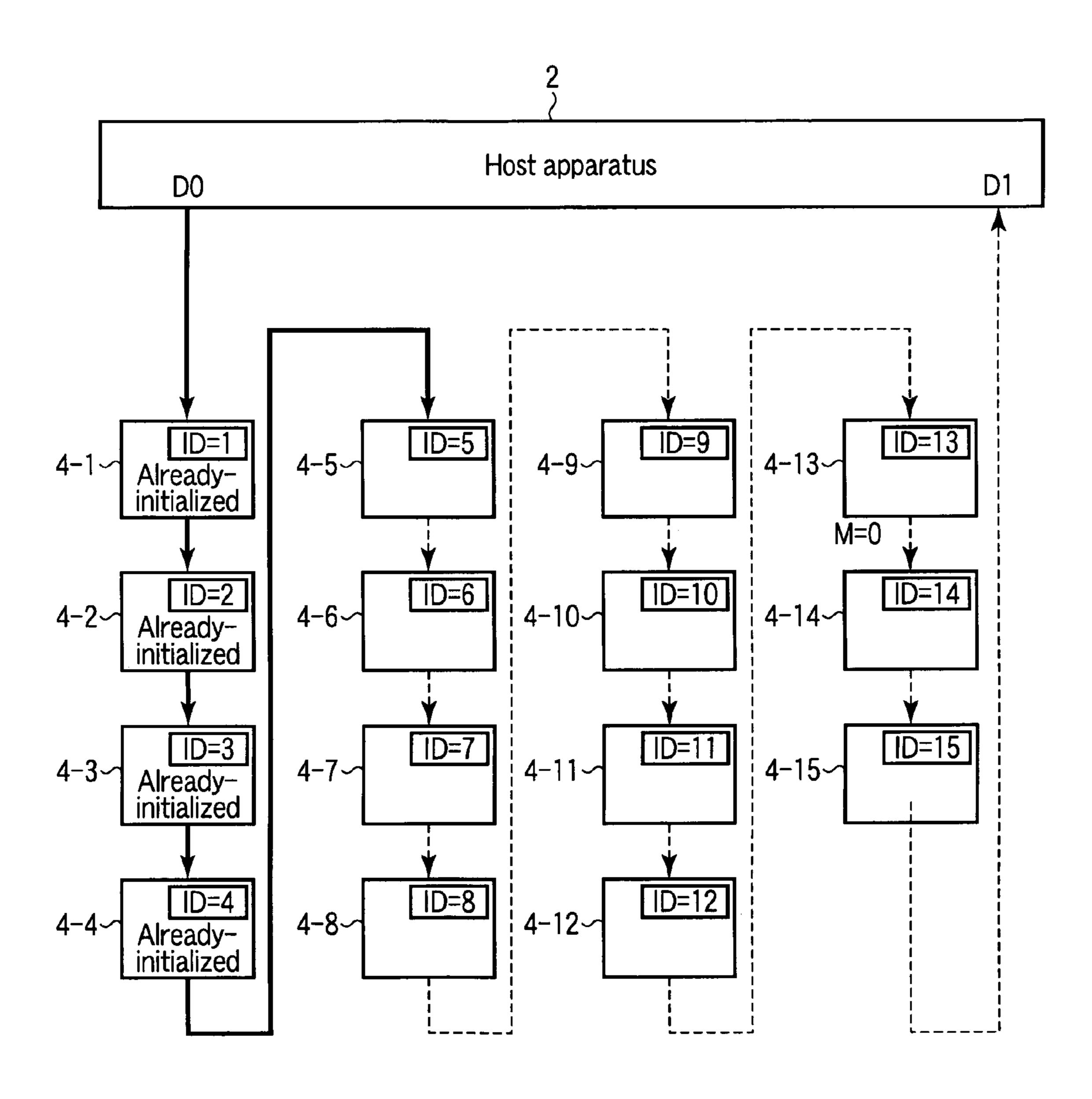

The host apparatus 2 repeatedly issues the initialization command until the host apparatus 2 receives the value except the value of M="0". Alternatively, after issuing the initialization command specific times, the host apparatus 2 issues the initialization completion confirming command in arbitrary timing to transmit the packet including the initialization completion confirming command to the semiconductor device 3. FIG. 16 illustrates the state in which the initialization completion confirming command is issued after the state in FIG. 15.

The packet including the initialization completion confirming command is received by the electronic device 4-1 (Step S50). Because the electronic device 4-1 has been already initialized (YES in Step S53), the electronic device 4-1 transfers the packet to the next electronic device 4-2 (Step S54). At this point, because the electronic devices 4-1 to 4-4 are initialized, the packet reaches the electronic device 4-5. However, the electronic device 4-5 is not initialized yet, the packet stays in the electronic device 4-5 but the packet Thus, the initialization is executed in each M of the 35 is not returned to the host apparatus 2. Therefore, the host apparatus 2 can recognize the existence of the electronic device 4 whose initialization is not completed.

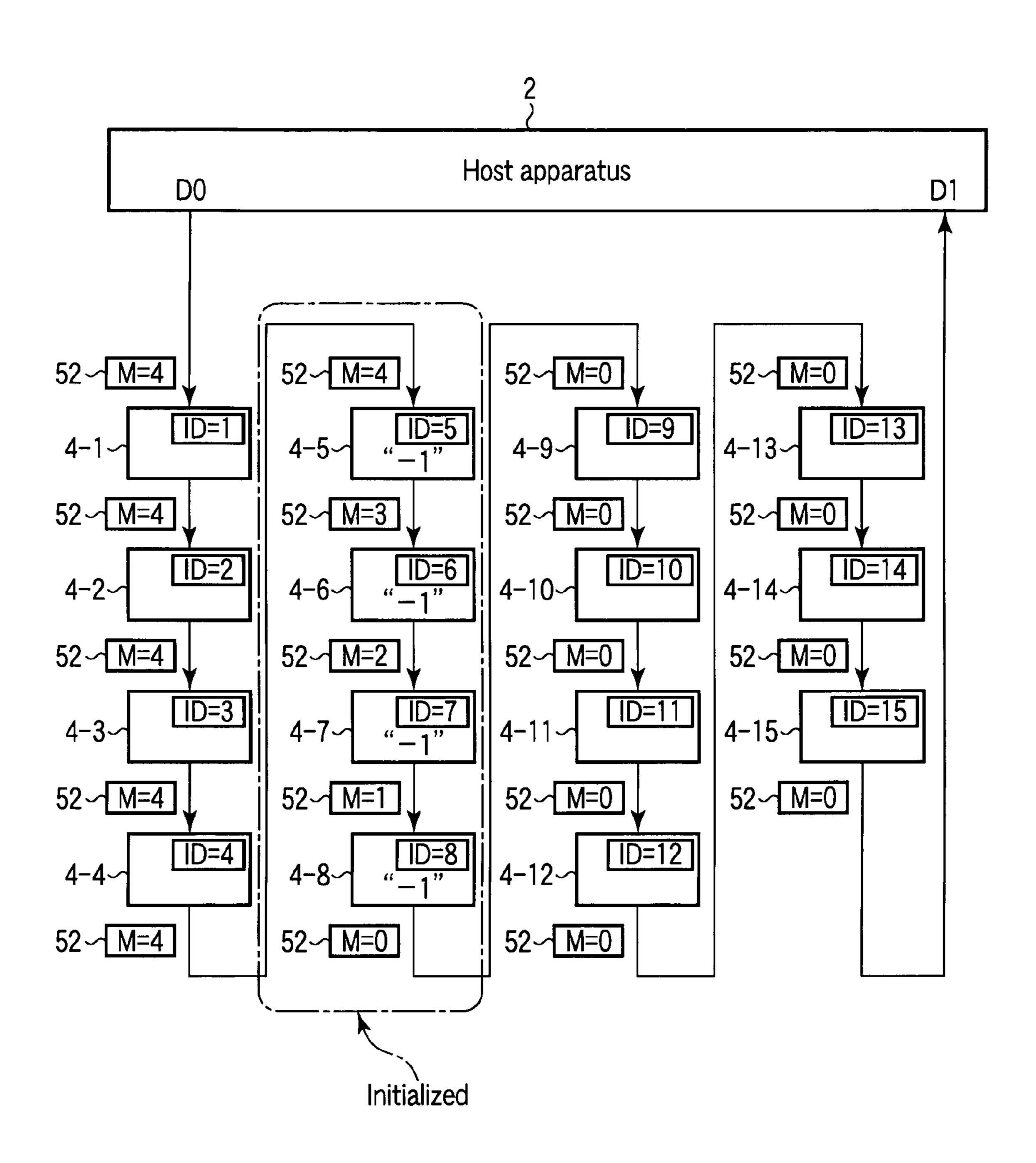

> Accordingly, the host apparatus 2 re-issues the packet including the initialization command to transmit the packet to the semiconductor device 3. FIG. 17 illustrates this state. As illustrated in FIG. 17, because the electronic devices 4-1 to 4-4 have been already initialized (YES in Step S41), the packet reaches the electronic device **4-5** without change. The electronic devices 4-5 to 4-8 are initialized in the manner similar to that of FIG. 15. The packet including the initialization completion confirming command reaches the electronic device 4-9.

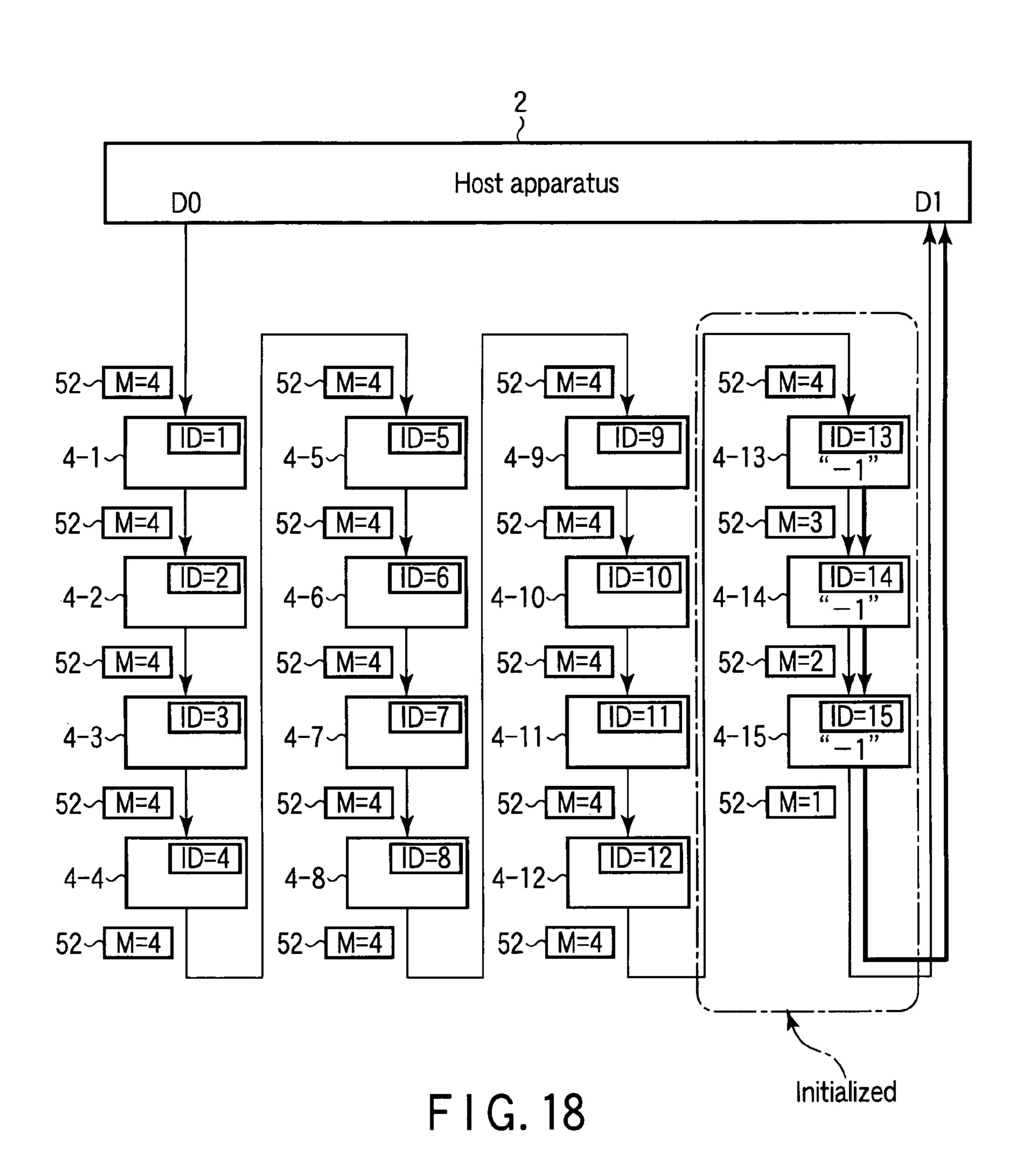

Then the host apparatus 2 issues the packet including the initialization command twice, thereby initializing all the electronic devices 4. FIG. 18 illustrates this state. When all the electronic devices 4 are initialized, the packet including the initialization completion confirming command is transmitted from the electronic device 4-16 to the host apparatus 2 (a bold-line arrow in FIG. 18 indicates a flow of the packet including the initialization completion confirming command). Therefore, the host apparatus 2 recognizes that all the electronic devices 4-1 to 4-16 are initialized. Obviously, even if the initialization completion confirming command is not issued, the host apparatus 2 receives the packet 50 of (NO in Step S45), and the number of electronic devices M 60 M="1" (M≠"0") from the electronic device 4-15 at the time of FIG. 18, whereby the host apparatus 2 can recognize that all the electronic devices 4 are initialized.

> The above initialization technique initializes the electronic devices by grouping the electronic devices to shorten the initialization for the plural electronic device, and to enable the initialization within a power supply current supported by the host. The method may be implemented by

defining an upper limit of an initialization current necessary for each electronic device. However, it is considered that sometimes the current necessary for the initialization depends on the electronic device. For example, it is considered that the initialization can be performed in a halftime <sup>5</sup> when the current necessary for the initialization becomes double. In an embedded system environment, sometimes the initialization time can further be shortened by previously designating the optimum initialization group in each electronic device. The further shortened initialization time can 10 be realized by setting a group number to each electronic device. The group number indicates that the initialization is performed to the electronic device in which times of initialization command. When the group number is set, the number of devices that can be initialized in the initialization com- 15 mand is ignored, each electronic device counts the number of received initialization commands, and each electronic device starts the initialization when the number of received initialization commands is matched with the group number. When the initialization is currently being performed, the <sup>20</sup> electronic device waits for the initialization completion to output the initialization command. The host system can select the optimum initialization procedure according to the feature of the electronic device. This point is described in detail in a second embodiment.

#### Step S15

Step S15 of FIG. 2 will be described below. In order to set a condition that all the electronic devices can be operated, the host apparatus 2 issues a command to read the setting value by broadcast. Parameters such as a maximum clock frequency range, time-out value, and various symbol lengths are indicated as an argument of the command, each electronic device does not update the argument that can be dealt therewith, and the electronic device updates the argument that cannot be dealt therewith to the parameter that can be dealt therewith. The parameter received by the host apparatus 2 includes the condition that all the electronic devices can be operated.

#### Step S16

Step S16 of FIG. 2 will be described below. Because the host apparatus 2 determines the operating condition common to the electronic devices 4 in Step S15, the same value is set to all the electronic devices 4 by a command to write the setting value by broadcast (the value is set to the register 9 of each electronic device 4).

This point will be described by taking a specific example. 50 FIG. 19 is a table illustrating the information read in Step S15, and FIG. 19 illustrates a maximum operating frequency and operation timing in the case of the 15 electronic devices by way of example.

As illustrated in FIG. 19, it is assumed that the electronic 55 devices 4-1 to 4-15 have the maximum operating frequencies f0 to f15, respectively, while the host apparatus has the maximum operating frequency f0. It is assumed that the lowest frequency is the maximum operating frequency f3 of the electronic device 4-3. From the information of FIG. 19, 60 the host apparatus 2 can recognize that all the electronic devices 4-1 to 4-15 and the host apparatus 2 can be operated at the frequency f3.

It is assumed that the electronic devices **4-1** to **4-15** have operation timings T1 to T15, respectively, while the host 65 apparatus **2** has operation timing T0. It is assumed that the worst timing is the operation timing T1 of the electronic

14

device 4-1. From the information of FIG. 19 the host apparatus 2 can recognize that all the electronic devices 4-1 to 4-15 and the host apparatus 2 can be operated in operation timing T1.

As a result of referring to the capabilities, the host apparatus 2 determines the operating frequencies of the electronic devices 4-1 to 4-15 as the operating frequency f3 and determines the operation timings of the electronic devices 4-1 to 4-15 as the operation timing T1. The host apparatus 2 writes the operating frequency f3 and operation timing T1 as the operating conditions in the register 9 of each electronic device 4. FIG. 20 illustrates a packet 60 that is issued by the host apparatus 2 at this point.

As illustrated in FIG. 20, in the packet 60, a command identifier corresponding to the register write command is stored in a packet header 61, and the operating frequency f3 and the operation timing T1 are stored in a payload 62. The operating frequency f3 and the operation timing T1 are sequentially written in the register of each electronic device 4 by transmitting the packet 60 (Steps S16-1 to S16-N). The packet 60 may be transmitted by the broadcast, unicast, or multicast.

The configuration set in Step S16 may include a length of a specific symbol, a kind of the packet supported, power control mode, and the number of retry times in addition to the maximum operating frequency and the operation timing.

#### Step S17

Step S17 of FIG. 2 will be described below. The operating conditions common to all the electronic devices 4 are determined in the sequences in Steps S15 and S16. Sometimes a transfer block size and the like depend on an individual I/O device. Accordingly, the host apparatus 2 reads the capability of the electronic devices 4 using the unicast command when the electronic device 4 has the parameter that should individually be set (Steps S17A-1, S17A-1, . . . , and S17A-N of FIG. 2), the host apparatus 2 determines the optimum value satisfying both the capability of the host apparatus 2 and the capability of the electronic device 4, and the host apparatus 2 sets the optimum value to the electronic device 4 using the unicast command (Steps S17B-1, S17B-1, . . . , and S17B-N of FIG. 2).

Examples of the parameter include a size of a buffer used in the data transfer and data transfer timing.

#### Effect

As described above, the speed enhancement of the initialization operation can be achieved in the semiconductor device of the first embodiment.

(1) In the configuration of the first embodiment, the host apparatus 2 determines the bus interface that can be connected to the electronic device 4 can be used by detecting the voltage level (Step S10 of FIG. 2). That is, the host apparatus 2 transmits the level STB to the electronic device 4, and the host apparatus 2 determines that the bus interface can be used when the level STB is returned from the electronic device 4. In other words, host apparatus 2 determines that the bus interface can be used by detecting that the signal D1 changes from the in-phase level to the differential level after the signal D0 changes from the in-phase level to the differential level.

The same holds true for the electronic device 4. When the host apparatus 2 transmits the level STB to the electronic device 4, the electronic device 4 detects that the signal D0

changes from the in-phase level to the differential level, and the electronic device 4 determines that the bus interface can be used.

Thus, the availability of the bus interface can be determined at high speed by detecting the voltage levels of the signals D0 and D1. When the bus interface can be used, the host apparatus 2 transmits the symbol SYN, whereby each electronic device 4 synchronizes the internal clock using the input symbol SYN. The electronic device 4 continuously output the level STB during the clock synchronization by the 10 internal PLL, and the electronic device 4 outputs the symbol SYN in synchronization with the clock when the clock synchronization is completed. When receiving the symbol SYN, the host apparatus 2 recognizes that the synchronization is completed for all the electronic devices 4.

The host apparatus 2 transmits a symbol IDLE after receiving the symbol SYN (time t4 of FIG. 3). The symbol IDLE is a symbol indicating that the host apparatus 2 is in an idle state.

(2) In the configuration of the first embodiment, when receiving the symbol IDLE, the electronic device 4 that retains the boot code voluntarily transmits the boot code to the host apparatus 2 without waiting for the command from the host apparatus 2 (Step S12 of FIG. 2).

Plural command procedures are required when the host apparatus 2 issues the command. Therefore, it takes a relatively long time to read the boot code. In the system that does not include the boot device, it is necessary to implement a dedicated boot ROM in order to read the program starting up the system from the memory device.

On the other hand, in the first embodiment, because the host controller directly loads the boot code from the boot device onto the system memory, it is not necessary that the host apparatus 2 generate the command, and the boot ROM is omitted, which allows the achievement of cost reduction. Accordingly, in the host apparatus 2, the system is quickly started up, and the speed enhancement of the initialization can be achieved in the electronic device 4.

- (3) In the configuration of the first embodiment, during the allocation of the device ID, the host apparatus 2 broadcasts the packet in order to make the request of the device ID of each electronic device 4 (Step S13 of FIG. 2). The packet is transferred among the electronic devices 4 in the 45 order of connection while the device ID is issued in each electronic device **4**. The device ID in the packet is updated every time the packet passes through the electronic device 4, and the updated value becomes the device ID of each electronic device 4. Accordingly, the device IDs do not 50 overlap each other. Therefore, it is not necessary that the host apparatus 2 confirm the presence or absence of the overlap between the device IDs, so that the initialization operation can be simplified.

- initialization is performed using the broadcast command similarly to the allocation of the device ID (Step S14). Accordingly, the speed enhancement of the initialization can be achieved.

Usually it maximally takes about one second to perform 60 the initialization. Accordingly, in the system that includes plural electronic devices, it takes a long time for the user to wait for the initialization completion by the method for issuing the command in each electronic device.

However, when the broadcast command is used, the 65 number of commands issued by the host apparatus 2 can be decreased to simplify the initialization sequence. The plural

**16**

electronic devices are simultaneously initialized by one command, which allows the shortening of the initialization time.

The host apparatus 2 determines the number of electronic devices 4 that are simultaneously initialized. Usually the current of 100 mA is maximally required to initialize one electronic device 4. However, there is a restriction to current supply ability of the host apparatus. Therefore, the host apparatus 2 stores the number of electronic devices that can be initialized in the packet including the initialization command, and the host apparatus 2 simultaneously initializes the electronic devices as many as the number of electronic devices stored in the packet. The electronic devices 4 are sequentially initialized in the numerical unit, which allows the initialization to be performed in a short time within the current supply ability of the host apparatus 2.

The method in which the group number is used can be adopted to further improve the initialization speed. In the 20 above example method, although the initialization current is restricted up to 100 mA, sometimes the initialization time can be shortened when the larger current is passed. In such cases, the electronic devices to be initialized are divided into groups to which the current can be supplied by the host 25 system, the group number is previously written in the electronic device, the number of issued initialization command is counted, and the electronic device starts the initialization when the count value is matched with the group number. Therefore, the host system can more efficiently 30 customize the initialization.

(5) In the configuration of the first embodiment, the common operating conditions satisfying both the host apparatus 2 and the electronic device 4 are determined based on the capabilities of the host apparatus 2 and electronic device 35 4 (Steps S15 and S16 of FIG. 2).

For example, in the conventional system, the maximum operating frequency is determined by specifications of the bus. When the bus frequency is extremely increased, the bus frequency is hardly supported on the electronic device side or the host apparatus side. Only the speed enhancement of the bus means very little for the memory device, and the data transfer rate should be determined according to write or read ability of the memory device. For example, because the ability of the memory device is restricted by memory ability, disadvantageously power consumption is increased even if the bus operating frequency is increased to enhance the bus interface speed.

On the other hand, in the first embodiment, the common operating conditions satisfying both the host apparatus 2 and the electronic device 4 are determined by referring to the capabilities of the host apparatus 2 and electronic device 4. Therefore, the optimum operating condition can be set to at least part of the operating ability, and the operating ability of the semiconductor system 1 can be improved. The operating (4) In the configuration of the first embodiment, the 55 condition is transmitted to the plural electronic devices 4 using the broadcast command, so that the speed enhancement of the initialization can be archived compared with the case in which the operating condition is determined in each electronic device 4.

(6) In the configuration of the first embodiment, the operating condition of the electronic device 4 is individually determined (Step S17 of FIG. 2). Accordingly, the electronic device 4 can sufficiently exert the operating ability. That is, while the operating conditions that should be communalized are determined in Step S15 and S16, the point that is not necessary to be communalized is determined in Step S17. The operating conditions are individually determined, which

allows each electronic device 4 to exert the excellent operating ability independently of the abilities of other electronic devices 4.

#### Second Embodiment

A semiconductor system and an electronic device initializing method according to a second embodiment will be described below. In the second embodiment, the processing in Step S14 of the first embodiment is performed by another 10 method. Because other configurations of the second embodiment are similar to those of the first embodiment, the description is omitted.

#### First Example

A first example will be described as another method for performing the processing in Step S14. In a host apparatus 2 of the first example, electronic devices 4-1 to 4-N are previously classified into groups. The group number is 20 provided to each group, and the group number is written in a register 9 of the electronic device 4. For example, the operation may be performed in Step S14 or Step S13, or the operation may previously be performed during production.

The number of power units M that can be used to initialize 25 the electronic device 4 by the host apparatus 2 is used instead of the maximum number of electronic devices M that can be initialized at one time. The number of power units M is a value that expresses power (electric power) that can be used for the initialization in a certain unit, and the host 30 apparatus 2 consumes the predetermined number of power units when each electronic device 4 is initialized.

An initialization completion flag CF (Completion Flag) is also used in addition to the group and the number of power when the initialization is completed for all the electronic devices 4, and, otherwise, the initialization completion flag CF is set to a value except "1" (for example, "0").

(Packet including Initialization Command)

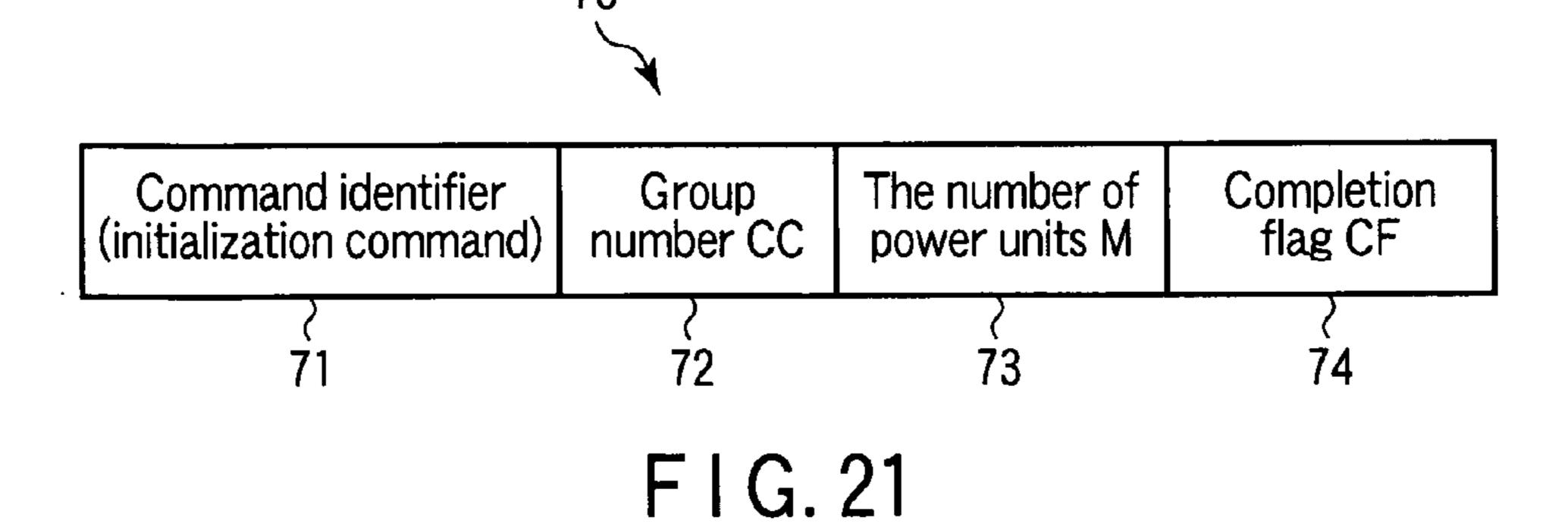

In Step S14, the host apparatus 2 produces a packet 70 40 illustrated in FIG. 21 to transmit the packet 70 to a semiconductor device 3. As illustrated in FIG. 21, the command identifier indicating the initialization command is included in a packet header 71 of the packet 70, and a group number CC, the number of power units M, and the initialization 45 completion flag CF are included as an argument in a payload. The packet 70 is issued as the broadcast command.

(Operation of Electronic Device 4)

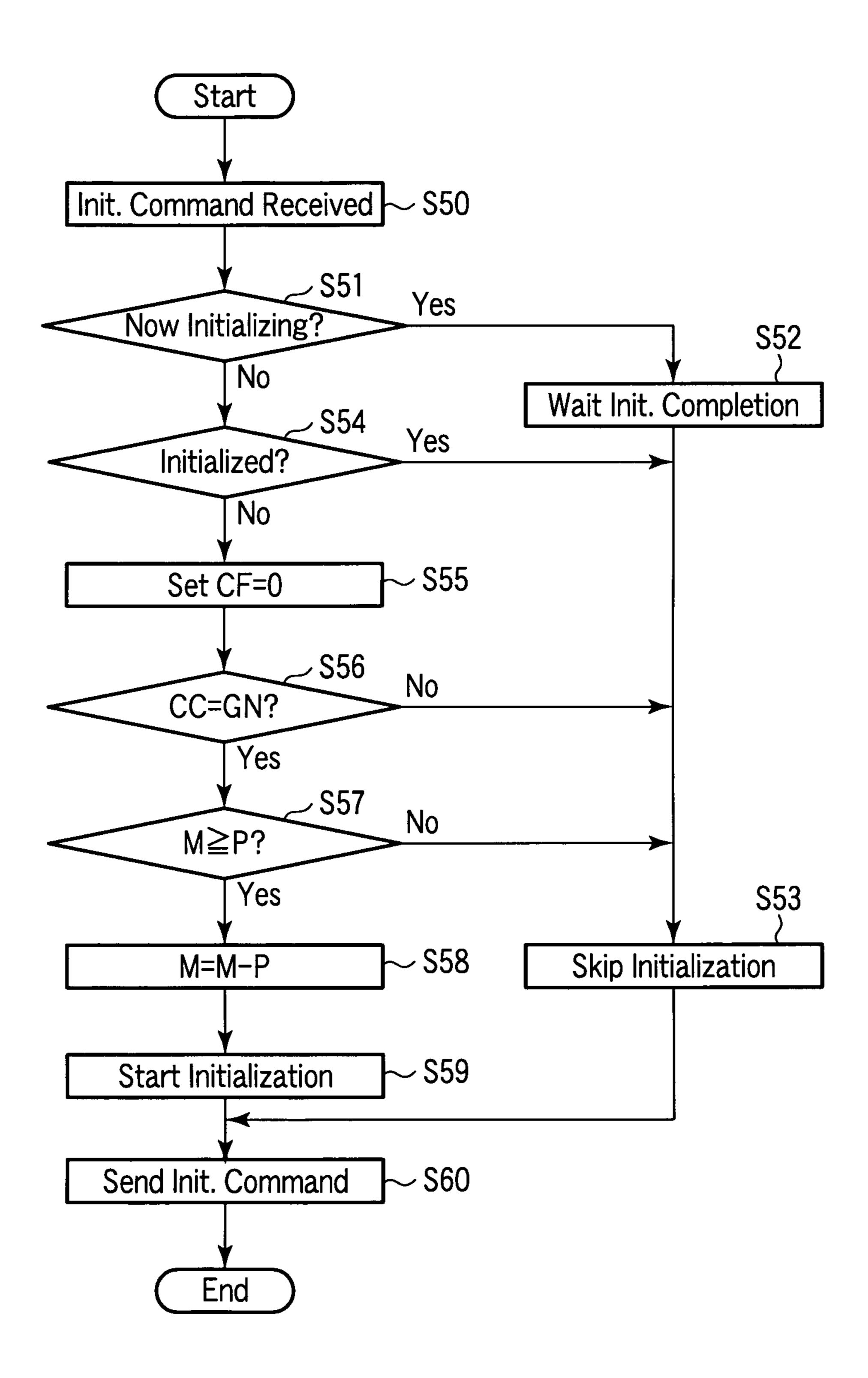

FIG. 22 is a flowchart illustrating an operation of the electronic device 4 in receiving the packet 70, and the 50 flowchart of FIG. 22 is common to the electronic devices 4-1 to 4-N. As illustrated in FIG. 22, the electronic device 4 receives the packet 70 at an input signal pin 5 (Step S50). When recognizing that the packet includes the initialization command from the command identifier of the packet header 55 71 of the received packet 70, a packet decoder 7 notifies a processing unit 8 that the packet includes the initialization completion confirming command, and the packet decoder 7 also notifies the processing unit 8 of the group number CC, the number of power units M, and the initialization completion flag CF in the payload. The processing unit 8 determines whether the electronic device 4 is currently being initialized (Step S51). When the electronic device 4 is currently being initialized (YES in Step S51), the processing unit 8 waits for the initialization completion (Step S**52**). The processing unit 65 8 does not perform the initialization (Step S53), and the processing unit 8 transmits the packet 70 to the next elec**18**

tronic device 4 (in the case of the electronic device 4-N, host apparatus 2) (Step S60). At this point, a packet update circuit 10 does not update the number of power units M and initialization completion flag CF in the packet 70.

When the electronic device 4 is not currently being initialized (NO in Step S51), and when the electronic device 4 has been already initialized (YES in Step S54), the flow goes to Steps S53 and S60. At this point, the number of power units M and initialization completion flag CF are not updated in the packet 70.

When the electronic device 4 is not currently being initialized (NO in Step S51), and when the electronic device has not been already initialized (NO in Step S54), the processing unit 8 commands the packet update circuit 10 to 15 clear the initialization completion flag CF in the payload to "0" (Step S55). When the initialization completion flag CF is cleared to "0", the host apparatus 2 recognizes that the issuance of the initialization command is continuously required (this point described later). The processing unit 8 also confirms the group number CC in the payload (Step S56). The processing unit 8 determines whether the group number CC is matched with its group number GN stored in a register 9.

When the group number CC is matched with the group number GN (YES in Step S56), the processing unit 8 compares the number of power units M in the payload and the number of power units P consumed in initializing the electronic device 4 (Step S57). For example, the number of power units P for each electronic device 4 may be written in the register 9 of each electronic device 4. In this case, the processing unit 8 compares the number of power units P in the register 9 and the number of power units M in the payload of the received packet. The number of power units P may be written in the register 9 in Step S14 or Step S13, units M. The initialization completion flag CF is set to "1" 35 or the processing may previously be performed during production.

> The processing unit 8 determines whether (M-P) is not lower than zero, that is, whether the number of power units M is not lower than the number of power units P. When (M–P) is not lower than zero, that is, when the number of power units M is not lower than the number of power units P (YES in Step S57), the processing unit 8 commands the packet update circuit 10 to update the number of power units M in the payload to (M-P) (Step S58). The value of (M-P) indicates a difference in which the power consumed by the electronic device 4 is subtracted from the power that can be supplied by the host apparatus 2, and the value of (M-P) also indicates the number of power units, which is necessary for other electronic devices to perform simultaneously the initialization. The processing unit 8 starts the initialization (Step S59). After the initialization is started, the processing unit 8 causes the packet update circuit 10 to transmit the packet 70 whose the number of power units M and completion flag are updated to the next electronic device 4 (in the case of the electronic device 4-N, to the host apparatus 2) without waiting for the initialization completion (Step S60).

> When the group numbers CC and GN are not matched with each other (NO in Step S56), the processing unit 8 goes to Step S60 without performing the initialization (Step S53). That is, the packet 70 is transmitted without updating the number of power units M. The processing unit 8 also goes to Step S60 without performing the initialization (Step S53), when (M-P) is lower than zero, that is, when the number of power units M is lower than the number of power units P (NO in Step S57).

> The plural numbers of power units P can be implemented in the electronic device 4. For example, the plural numbers

of implementable power units P are previously written in the register 9, and the pieces of processing in Steps S57 to S58 and the initialization can be performed using the numbers of power units P. Alternatively, the electronic device 4 can select the optimum number of power units P with respect to 5 a power unit M indicated in the initialization command

(Operation of Host apparatus 2)

An operation of the host apparatus 2 in performing the processing in Step S14 will be described below with reference to FIG. 23. FIG. 23 is a flowchart illustrating the 10 operation of the host apparatus 2.

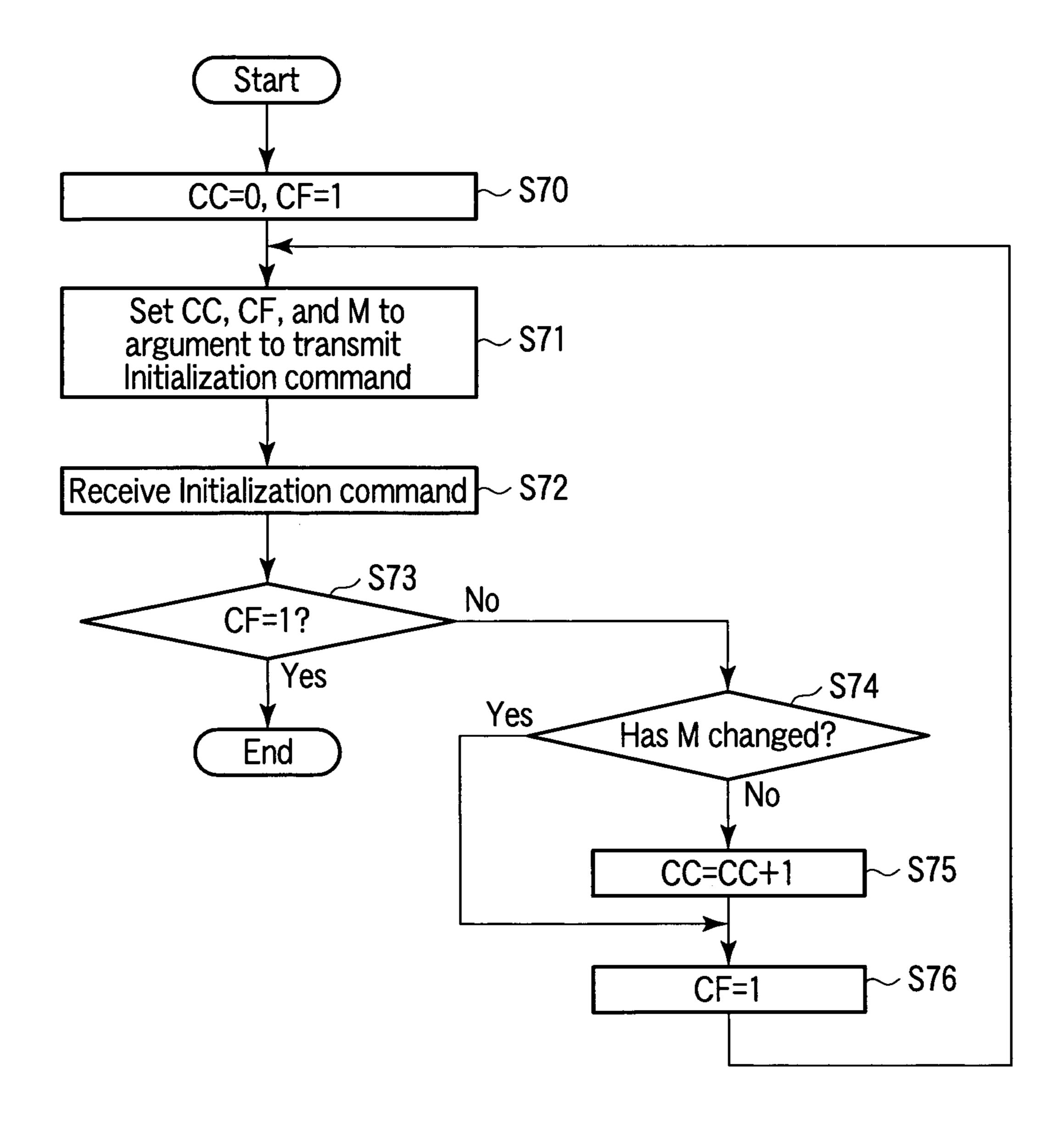

As illustrated in FIG. 23, the host apparatus 2 sets the group number initial value CC to zero while setting the initialization completion flag CF to 1 (Step S70). The host apparatus 2 sets the group number CC, the initialization 15 completion flag CF, and the number of power units M to the argument to assemble the packet 70, and the host apparatus 2 transmits the packet 70 by the broadcast command (Step S71).

passes through all the electronic devices 4 (Step S72). The host apparatus 2 confirms whether the initialization completion flag CF is 1 in the received packet 70 (Step S73). When the initialization completion flag CF is 1 (YES in Step S73), the host apparatus 2 determines that the initialization is 25 completed for all the electronic devices 4, and the initialization is ended.

On the other hand, when the initialization completion flag CF is not 1 (NO in Step S73), the host apparatus 2 confirms whether the number of power units M changes (Step S74). 30 That is, the host apparatus 2 determines whether the number of power units M included in the received packet 70 differs from the value of the transmission of the packet 70.

When the number of power units M does not change (NO in Step S74), the host apparatus 2 determines that all the 35 electronic devices 4 belonging to the group number CC have already started the initialization or that the initialization is completed for all the electronic devices 4, the host apparatus 2 increments the group number CC (Step S75), the host apparatus 2 sets the initialization completion flag CF to 1, 40 and the host apparatus 2 goes to Step S71 to issue the initialization command again.

When the number of power units M changes (YES in Step S74), the host apparatus 2 determines that possibly the electronic device 4 belonging to the group number does not 45 start the initialization yet, the host apparatus 2 sets the initialization completion flag CF to 1 while leaving the group number CC as it is (Step S76), and the host apparatus 2 goes to Step S71 to issue the initialization command again.

Thus, the host apparatus 2 can confirm whether the 50 initialization is completed for all the electronic devices 4 by checking the initialization completion flag CF of the received packet 70. In other words, it can be said that the initialization command to initialize the electronic device 4 and the initialization completion confirming command to 55 confirm whether the initialization is completed for all the electronic devices 4 are unified in the first example.

However, similarly to the first embodiment, a command to confirm the initialization completion of the electronic device 4 may separately be issued. For example, the packet illus- 60 trated in FIG. 21 is used as the initialization completion confirming command by setting the group number CC to a predetermined value. In this case, when the electronic device receives the command, the electronic device that is not currently being initialized instantaneously outputs the com- 65 mand, while the electronic device that is currently being initialized outputs the command after waiting for the ini**20**

tialization completion. When receiving the command, the host apparatus 2 recognizes that the initialization is completed for one group. The host apparatus 2 repeatedly transmits the packet 70 including the initialization command while changing the group number CC until all the electronic devices 4 are initialized.

The initialization command can also be issued before the device ID is allocated to the electronic device 4.

#### First Specific Example

A specific example of the processing in Step S14 of the first example will be described with reference to FIG. 24 and FIG. 25. FIG. 24 and FIG. 25 are block diagrams of the semiconductor system 1, and FIG. 24 and FIG. 25 illustrate that the semiconductor system 1 includes the 15 (N=15) electronic devices 4 similarly to FIG. 11. In FIG. 24 and FIG. 25, square marks added to the side of the arrow between the electronic devices indicate the payload 72 of the Then the host apparatus 2 receives the packet 70 that 20 packet 70, that is, group number CC, the number of power units M, and the initialization completion flag CF in the order from the left. In FIG. 23, GN=i (i=0 to 3) described in each electronic device 4 indicates the group number GN allocated to each electronic device 4.