#### US00RE49545E

## (19) United States

## (12) Reissued Patent

#### Kim et al.

### (10) Patent Number: US RE49,545 E

#### (45) Date of Reissued Patent: Jun. 6, 2023

## (54) SEMICONDUCTOR DEVICE INCLUDING POLYGON-SHAPED STANDARD CELL

(71) Applicant: SAMSUNG ELECTRONICS CO.,

LTD., Suwon-si (KR)

(72) Inventors: JinTae Kim, Daejeon (KR); Jaewan

Choi, Suwon-si (KR)

(73) Assignee: SAMSUNG ELECTRONICS CO.,

LTD., Suwon-si (KR)

- (21) Appl. No.: 17/175,381

- (22) Filed: Feb. 12, 2021

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 10,204,920

Issued: Feb. 12, 2019

Appl. No.: 15/095,579

Filed: Apr. 11, 2016

#### (30) Foreign Application Priority Data

| Apr. 9, 2015  | (KR) | <br>10-2015-0050150 |

|---------------|------|---------------------|

| Oct. 21, 2015 | (KR) | <br>10-2015-0146730 |

(51) **Int. Cl.**

*H01L 27/118* (2006.01) *H01L 27/02* (2006.01)

(52) U.S. Cl.

CPC .... *H01L 27/11807* (2013.01); *H01L 27/0207* (2013.01); *H01L 2027/11859* (2013.01); (Continued)

(58) Field of Classification Search

CPC ........... H01L 27/11807; H01L 27/0207; H01L 27/0886; H01L 27/088; H01L 29/0847; (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

6,054,872 A 4/2000 Fudanuki et al. 6,536,028 B1 3/2003 Katsioulas et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 101118909 A 2/2008 CN 101752368 A 6/2010 (Continued)

#### OTHER PUBLICATIONS

Notice of Allowance in U.S. Appl. No. 16/450,383, dated Feb. 24, 2021.

#### (Continued)

Primary Examiner — Tuan H Nguyen (74) Attorney, Agent, or Firm — Sughrue Mion, PLLC

#### (57) ABSTRACT

A semiconductor device including a standard cell for implementing a logic element includes a first active region and a second active region extending in a second direction on a substrate and spaced apart from each other in a first direction perpendicular to the second direction, gate electrodes intersecting the first active region and the second active region, and source regions and drain regions formed on the first and second active regions at both sides of each of the gate electrodes. A boundary of the standard cell has a polygonal shape, excluding a quadrilateral shape, when viewed in a plan view. As a result, an area of the standard cell may be reduced to reduce a size of the semiconductor device.

#### 64 Claims, 25 Drawing Sheets

# US RE49,545 E Page 2

| (52) | 2) <b>U.S. Cl.</b> CPC <i>H01L 2027/11874</i> (2013.01); <i>H01L</i> 2027/11881 (2013.01); <i>H01L 2027/11885</i> (2013.01) |            |                                                                             |                                    |                                          | 0155783<br>0187626<br>0196803<br>0199253<br>0049575 | A1<br>A1<br>A1   | 7/2010<br>8/2010<br>8/2010<br>3/2011                | Lu et al.<br>Cheng et al.<br>Tanaka             |            |           |

|------|-----------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------|------------------------------------|------------------------------------------|-----------------------------------------------------|------------------|-----------------------------------------------------|-------------------------------------------------|------------|-----------|

| (58) | Field of CPC                                                                                                                | L 29/41    | n <b>Search</b><br>791; H01L 2027/11874; H01L<br>885; H01L 2027/11859; H01L | 2011/<br>2011/                     | 0084312<br>0145775<br>0219341<br>0296366 | A1<br>A1                                            | 6/2011<br>9/2011 | Quandt et al.<br>Sano<br>Cao et al.<br>Arora et al. |                                                 |            |           |

|      | See appli                                                                                                                   | on file fo | 2027/11881 r complete search history.                                       | 2012/                              | 0167021<br>0241986<br>0249182            | A1                                                  | 9/2012           | Chen et al.<br>Sherlekar et al<br>Sherlekar         | •                                               |            |           |

| (56) |                                                                                                                             | Referen    | ces Cited                                                                   | 2013/                              | 0021026                                  | A1                                                  | 8/2013           | Ausserlechner<br>Becker et al.                      |                                                 |            |           |

|      | U.S. PATENT DOCUMENTS                                                                                                       |            |                                                                             |                                    |                                          | 0065728<br>0115546<br>0181774                       | A1               | 4/2014                                              | Agarwal et al.<br>Wang et al.<br>Hatamian et al | •          |           |

|      | 7,039,881 H                                                                                                                 |            | 5/2006                                                                      | _                                  | 2014/                                    | 0217513                                             | A1*              | 8/2014                                              | Hayashi                                         | Н01І       |           |

|      | 7,117,457 H                                                                                                                 |            | 10/2006                                                                     | Yoshida et al.                     | 2014/                                    | (0204671                                            | A 1              | 10/2014                                             | T4 -1                                           |            | 257/369   |

|      | 7,302,660 H                                                                                                                 |            |                                                                             | Shimamura                          |                                          | 0304671<br>0380256                                  |                  |                                                     | Lu et al.<br>Song et al.                        |            |           |

|      | 7,321,139 I                                                                                                                 |            |                                                                             | Chang et al.                       |                                          |                                                     |                  |                                                     | Park et al.                                     |            |           |

|      | 7,888,705 I                                                                                                                 |            |                                                                             | Becker et al.                      |                                          | 0095857                                             |                  |                                                     | Hsu et al.                                      |            |           |

|      | 7,919,792 H                                                                                                                 |            |                                                                             | Law et al.                         | 2016/                                    | 0056155                                             | A1*              | 2/2016                                              | Park                                            | H01I       |           |

|      | 7,943,998 H<br>7,989,849 H                                                                                                  |            |                                                                             | Sherlekar et al.                   | 2016/                                    | (0202624                                            | A 1              | 0/2016                                              | Wine at al                                      |            | 257/401   |

|      | 8,063,414 H                                                                                                                 |            | 11/2011                                                                     |                                    | 2010/                                    | 0283634                                             | Al               | 9/2010                                              | Kim et al.                                      |            |           |

|      | 8,173,491 I                                                                                                                 | B2         | 5/2012                                                                      | Law et al.                         |                                          | FO                                                  | RFIG             | N PATE                                              | NT DOCUME                                       | 2TM3       |           |

|      | 8,176,457 H                                                                                                                 |            |                                                                             | Kato et al.                        |                                          | 10                                                  | ILIO             | 1 1 1 2 1 1 1 2 .                                   | IVI DOCOIVIL                                    | 7115       |           |

|      | 8,220,696 H<br>8,239,807 H                                                                                                  |            |                                                                             | Kawada<br>Arora et al.             | CN                                       |                                                     | 103647           | '290 A                                              | 3/2014                                          |            |           |

|      | 8,255,837 I                                                                                                                 |            |                                                                             | Lu et al.                          | CN                                       |                                                     | 104425           | 509 A                                               | 3/2015                                          |            |           |

|      | 8,327,301 I                                                                                                                 |            |                                                                             | Cheng et al.                       | JP                                       |                                                     |                  | 466 A                                               | 8/1996                                          |            |           |

|      | 8,357,955 I                                                                                                                 |            | 1/2013                                                                      | . <del>-</del>                     | JP<br>ID                                 |                                                     |                  | 641 A                                               | 7/1997                                          |            |           |

|      | 8,513,978 I                                                                                                                 |            |                                                                             | Sherlekar                          | JP<br>JP                                 | 20                                                  |                  | 943 A<br>342 A                                      | 1/1999<br>9/2001                                |            |           |

|      | 8,584,052 H                                                                                                                 |            |                                                                             | Chen et al.                        | JP                                       |                                                     |                  | 210 A                                               | 9/2001                                          |            |           |

|      | 8,612,914 H<br>8,647,893 H                                                                                                  |            |                                                                             | Sherlekar et al.<br>Agarwal et al. | JP                                       |                                                     |                  | 5443 A                                              | 6/2004                                          |            |           |

|      | 8,661,392 H                                                                                                                 |            |                                                                             | Quandt et al.                      | JP                                       |                                                     |                  | 423 A                                               | 6/2011                                          |            |           |

|      | 8,729,606 H                                                                                                                 |            |                                                                             | Becker et al.                      | JР                                       | 2                                                   |                  | 8479 A                                              | 2/2012                                          |            |           |

|      | 8,732,628 I                                                                                                                 |            |                                                                             | Wu et al.                          | JP<br>JP                                 | 2                                                   |                  | 313 B2<br>3139 A                                    | 2/2013<br>4/2013                                |            |           |

|      | 8,739,095 H                                                                                                                 |            |                                                                             | Cao et al.                         | JP                                       |                                                     |                  | 5116 A                                              | 12/2013                                         |            |           |

|      | 8,788,998 H<br>8,863,063 H                                                                                                  |            |                                                                             | Hatamian et al.<br>Becker et al.   | JP                                       | 20                                                  |                  | 8815 B2                                             | 8/2015                                          |            |           |

|      | 8,935,639 I                                                                                                                 |            | 1/2015                                                                      |                                    | KR                                       | 1                                                   | 0-0846           | 5089 B1                                             | 7/2008                                          |            |           |

|      | 8,949,749 I                                                                                                                 |            |                                                                             | Wang et al.                        | KR                                       |                                                     |                  | 0004 A                                              | 5/2009                                          |            |           |

|      | 8,959,472 I                                                                                                                 | В1         | 2/2015                                                                      | Frederick, Jr. et al.              | KR<br>KR                                 |                                                     |                  | 6125 B1<br>688 A                                    | 1/2010<br>2/2013                                |            |           |

|      | 9,007,060 H                                                                                                                 |            |                                                                             | Ausserlechner                      | KR                                       |                                                     |                  | 6405 A                                              | 4/2015                                          |            |           |

|      | 9,098,670 H<br>0,242,985 H                                                                                                  |            |                                                                             | Song et al.<br>Shimbo              | KR                                       |                                                     |                  | 2858 B1                                             | 6/2015                                          |            |           |

|      | 2/0005572                                                                                                                   |            |                                                                             | Hatanaka                           | TW                                       |                                                     |                  | 486 A                                               | 6/2006                                          |            |           |

|      | 3/0084418 A                                                                                                                 |            | 5/2003                                                                      |                                    | WO                                       | 20                                                  | 015033           | 490 A1                                              | 3/2015                                          |            |           |

|      | 5/0198604                                                                                                                   |            |                                                                             | Yoshida et al.                     |                                          |                                                     |                  |                                                     |                                                 |            |           |

|      | 5/0138464 <i>A</i>                                                                                                          |            |                                                                             | Shimamura                          |                                          |                                                     | OTI              | HER PU                                              | BLICATIONS                                      |            |           |

| 2007 | 7/0111405 <i>A</i>                                                                                                          | A1*        | 5/2007                                                                      | Watanabe H01L 27/0207              | C .                                      | . 1 NT /*                                           | C 4              | . 11 1 111                                          | II.O. A                                         | 1 37 17    | (450, 202 |

| 2007 | 7/0234243 <i>A</i>                                                                                                          | <b>A</b> 1 | 10/2007                                                                     | 438/142<br>Kvoh                    |                                          |                                                     |                  |                                                     | ty in U.S. App                                  | 1. No. 16  | 0/430,383 |

|      | 7/0284618 <i>A</i>                                                                                                          |            |                                                                             | Chang et al.                       |                                          | d on Apr.                                           | •                |                                                     | ntimal 29 nm a                                  | nd 20      | Douting   |

|      | 7/0300202 A                                                                                                                 |            | 12/2007                                                                     |                                    | •                                        | ai Library<br>on 3.0), Ji                           | •                |                                                     | ptimal 28-nm a                                  | nu ZV-IIM  | Routing   |

|      | 8/0111158 A                                                                                                                 |            |                                                                             | Sherlekar et al.                   | `                                        | / /                                                 |                  |                                                     | 2017 issued by t                                | he U.S. P  | atent and |

|      | 8/0211056 <i>A</i>                                                                                                          |            |                                                                             | Kuroda et al.                      |                                          |                                                     |                  | •                                                   | U.S. Appl. No.                                  |            |           |

|      | 3/0223502 <i>A</i><br>3/0263500 <i>A</i>                                                                                    |            |                                                                             | Kawada<br>Kato et al.              |                                          |                                                     |                  | -                                                   | )ptimal 28-nm a                                 | •          |           |

|      | 9/0026503 A                                                                                                                 |            | 1/2009                                                                      |                                    | (Versio                                  | n 3.0)", I                                          | Router           | CAE, SY                                             | PNOSYS Accel                                    | erating In | novation, |

|      | 9/0032898                                                                                                                   |            |                                                                             | Becker et al.                      | Jul. 15.                                 | , 2013, p                                           | p. 1 <b>-</b> 63 |                                                     |                                                 |            |           |

|      | 9/0121208 A                                                                                                                 |            |                                                                             | Nagashima et al.                   |                                          | 1 1                                                 |                  |                                                     |                                                 |            |           |

| 2010 | )/0006896 <i>A</i>                                                                                                          | Al         | 1/2010                                                                      | Uemura                             | * cited                                  | d by exa                                            | ımıner           |                                                     |                                                 |            |           |

FIG. 1

FIG. 2

FIG. 3

FIG. 6

\$00000000 \$00000000

Š

000000000 000000000

\$00000000 \$00000000

\$00000000 \$00000000 \$00000000

FIG. 20A

Jun. 6, 2023

<u>S</u>

FIG. 21

# SEMICONDUCTOR DEVICE INCLUDING POLYGON-SHAPED STANDARD CELL

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

This is a reissue application of U.S. Pat. No. 10,204,920, which was filed as U.S. application Ser. No. 15/095,579 on Apr. 11, 2016 and issued on Feb. 12, 2019, the disclosure of <sup>15</sup> which is hereby incorporated by reference in its entirety.

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims priority from Korean Patent Application Nos. 10-2015-0050150 and 10-2015-0146730, filed on Apr. 9, 2015 and Oct. 21, 2015, respectively, in the Korean Intellectual Property Office. The disclosures of the above-listed applications are hereby incorporated by reference in their entireties.

#### BACKGROUND

Apparatuses and methods consistent with exemplary <sup>30</sup> embodiments to a semiconductor device including a standard cell having a polygonal shape.

Semiconductor devices have been highly integrated and circuits of semiconductor devices have been complicated. Thus, it may be very difficult to manually design a layout of a semiconductor device. Accordingly, in the related art, a semi-custom method of designing a layout of a semiconductor device using a computer may be used. In the semicustom method, standard cells for performing logic functions may be provided to a cell library of a design tool in advance and a layout may be designed using the same. For example, the standard cell may have a rectangular shape.

As circuit design techniques of semiconductor devices have been developed, relatively large-sized standard cells have been demanded. However, if a size of a standard cell 45 increases, an area of an unused region in the standard cell may also increase to cause an increase in size of a semiconductor device. Thus, reconfiguration of a standard cell may be needed to reduce a size of a semiconductor device.

#### **SUMMARY**

Exemplary embodiments address at least the above problems and/or disadvantages and other disadvantages not described above. Also, the exemplary embodiments are not 55 required to overcome the disadvantages described above, and may not overcome any of the problems described above.

One or more exemplary embodiments may provide a semiconductor device including a standard cell having a polygonal shape excluding a quadrilateral shape.

According to an aspect of an exemplary embodiment, a semiconductor device including a standard cell for implementing a logic element may include a first active region including a first PMOS region and a first NMOS region that extend in a first direction on a substrate and are spaced apart 65 from each other in a second direction perpendicular to the first direction, a second active region including a second

2

PMOS region and a second NMOS region that extend in the first direction on the substrate and are spaced apart from each other in the second direction, gate electrodes intersecting the first active region and the second active region, first source regions and first drain regions formed on the first active region at both sides of each of the gate electrodes, and second source regions and second drain regions formed on the second active region at both sides of each of the gate electrodes. A boundary of the standard cell, which includes a plurality of edges, may have a polygonal shape excluding a quadrilateral shape when viewed from a plan view.

The semiconductor device may further include a first power line extending in the first direction between the first active region and the second active region when viewed from a plan view, a second power line extending in the first direction, and a third power line extending in the first direction. The first active region may include one edge adjacent to the first power line and another edge opposite to the one edge, and the second power line may be adjacent to the another edge of the first active region. The second active region may include one edge adjacent to the first power line and another edge opposite to the one edge, and the third power line may be adjacent to the another edge of the second active region. The boundary of the standard cell may overlap with the first power line, the second power line, and the third power line.

The standard cell may include a first region having a quadrilateral shape and overlapping with the first power line, the second power line, and the third power line, and a second region having a quadrilateral shape and overlapping with the first power line and the third power line. The second region may be in contact with the first region.

The standard cell may further include a third region having a quadrilateral shape and overlapping with the first power line and the third power line. The first region may include a first edge being in contact with the second region and a second edge opposite to the first edge, and the third region may be in contact with the second edge of the first region.

The standard cell may further include a fourth region having a quadrilateral shape and overlapping with the first power line and the second power line. The first region may include a first edge being in contact with the second region and a second edge opposite to the first edge, and the fourth region may be in contact with the second edge of the first region.

The standard cell may further include a fifth region having a quadrilateral shape and overlapping with the first power line, the second power line, and the third power line. The second region may include a first edge being in contact with the first region and a second edge opposite to the first edge, and the fifth region may be in contact with the second edge of the second region.

The first PMOS region the second PMOS region may be adjacent to the first power line.

The semiconductor device may further include a third active region adjacent to the third power line on the substrate, the third active region including a third PMOS region and a third NMOS region that extend in the first direction and are spaced apart from each other in the second direction, the gate electrodes further extending to intersect the third active region, third source regions and third drain regions formed on the third active region at both sides of each of the gate electrodes, and a fourth power line extending in the first direction. The third active region may include one edge adjacent to the third power line and another edge opposite to the one edge, and the fourth power line may be adjacent to

the another edge of the third active region. The standard cell may further include a sixth region having a quadrilateral shape and overlapping with the third power line and the fourth power line. The sixth region may be in contact with the first region.

The second NMOS region and the third NMOS region ay be adjacent to the third power line.

According to an aspect of an exemplary embodiment, a semiconductor device including a standard cell for implementing a logic element may include an NMOS region and a PMOS region extending in a first direction on a substrate and spaced apart from each other in a second direction perpendicular to the first direction, gate electrodes intersecting the NMOS region and the PMOS region, and source regions and drain regions formed on the NMOS region and PMOS region at both sides of each of the gate electrodes. A boundary of the standard cell, which includes a plurality of edges, may have a polygonal shape excluding a quadrilateral shape.

The semiconductor device may further include a first power line extending in the first direction and adjacent to an edge of the NMOS region, and a second power line extending in the first direction and adjacent to an edge of the PMOS region. The NMOS region and the PMOS region may be 25 disposed between the first power line and the second power line when viewed from a plan view.

The standard cell may include a first region having a quadrilateral shape and overlapping with the first power line and the second power line; and a second region having a <sup>30</sup> quadrilateral shape and overlapping with the second power line and the PMOS region. The second region may be in contact with the first region.

The standard cell may further include a third region having a quadrilateral shape and overlapping with the second power line and the PMOS region. The first region may include a first edge being in contact with the second region and a second edge opposite to the first edge, and the third region may be in contact with the second edge of the first region.

The standard cell may further include a fourth region having a quadrilateral shape and overlapping with the first power line and the NMOS region. The first region may include a first edge being in contact with the second region and a second edge opposite to the first edge, and the fourth 45 region may be in contact with the second edge of the first region.

The standard cell may further include a fifth region having a quadrilateral shape and overlapping with the first power line and the second power line. The second region may include a first edge being in contact with the first region and a second edge opposite to the first edge, and the fifth region may be in contact with the second edge of the second region.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The above and/or other aspects will become more apparent by describing certain exemplary embodiments with reference to the accompanying drawings, in which:

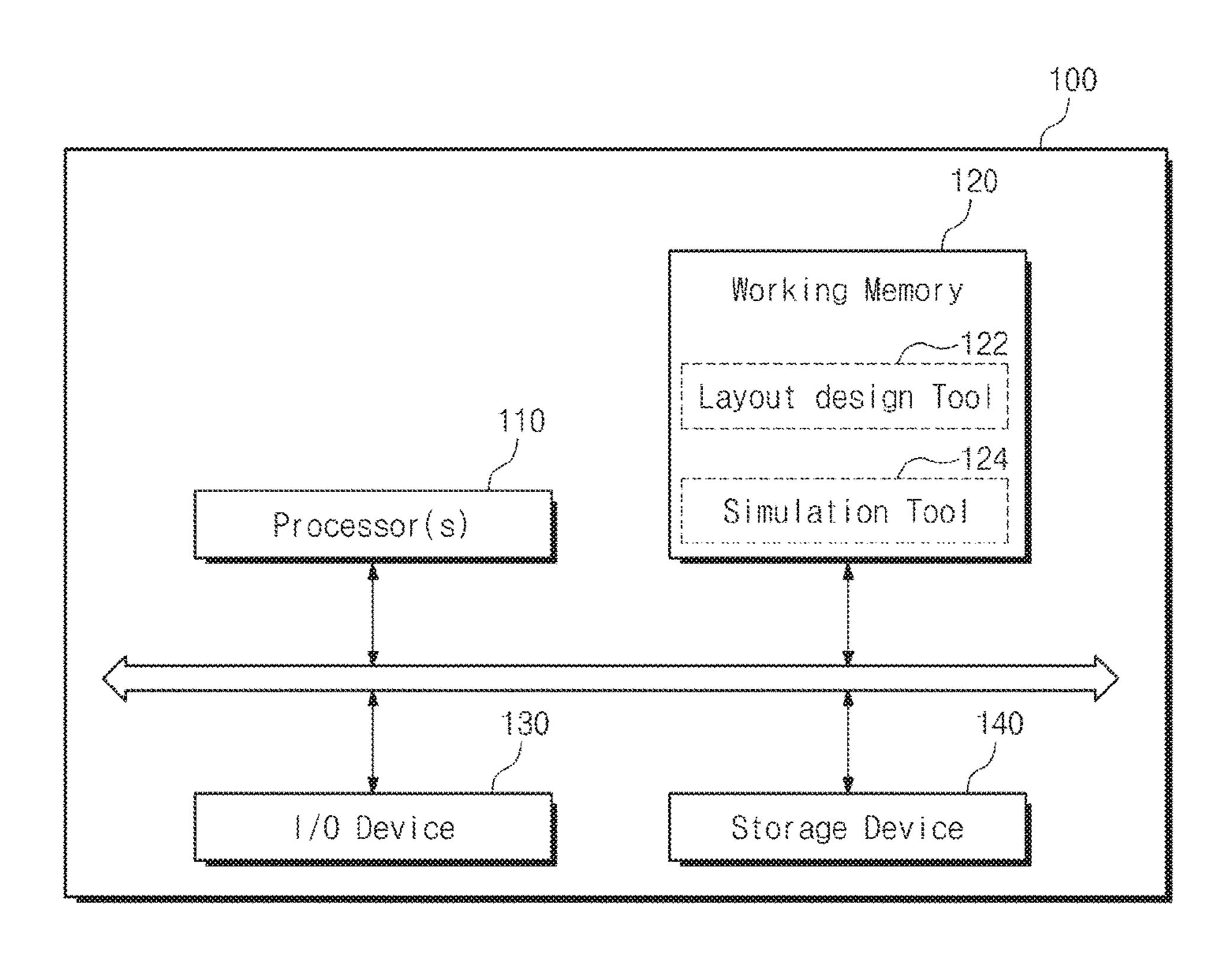

FIG. 1 is a schematic block diagram illustrating a computer system for designing a semiconductor device, according to an exemplary embodiment.

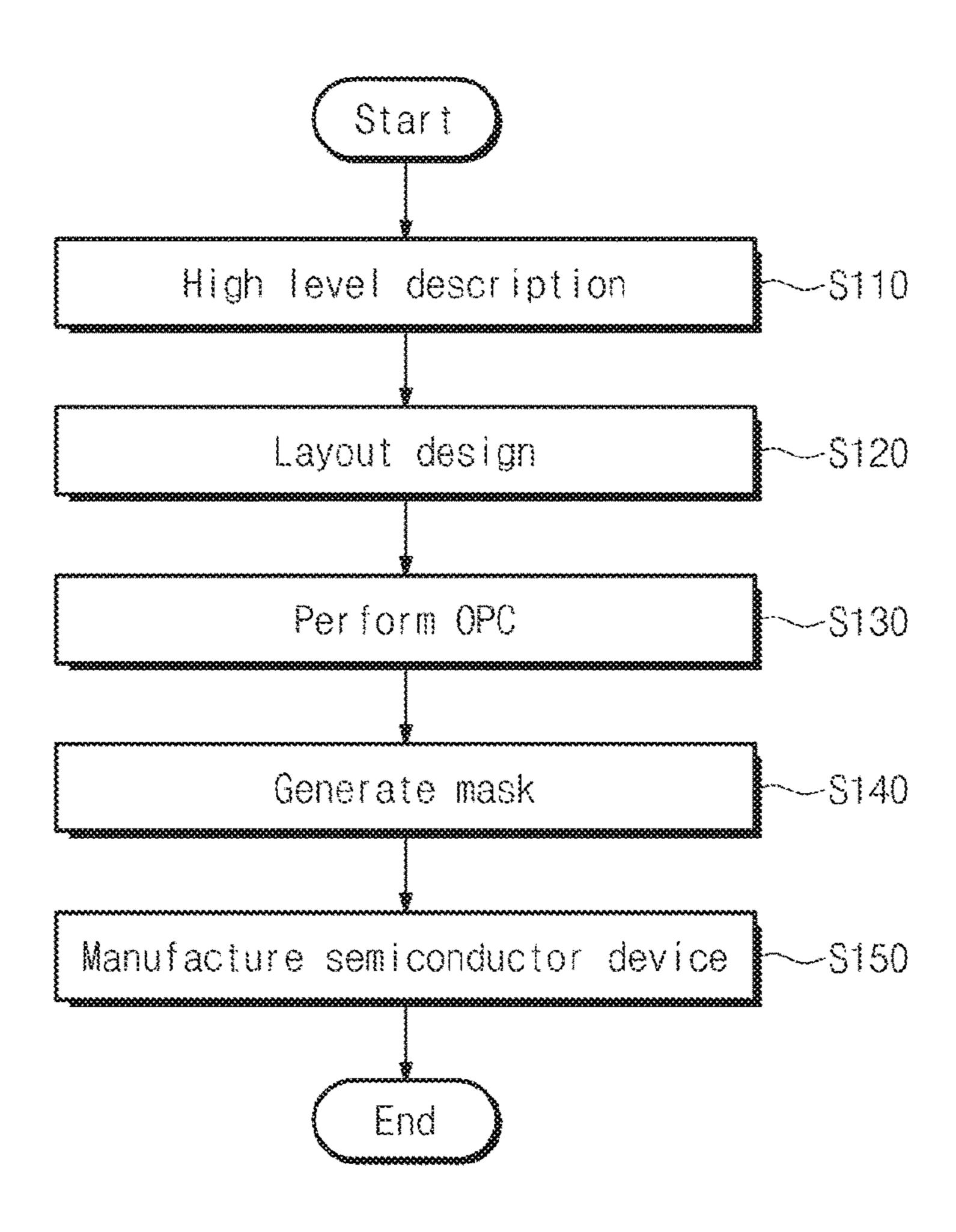

FIG. 2 is a flow chart illustrating a method for designing and manufacturing a semiconductor device, according to an exemplary embodiment.

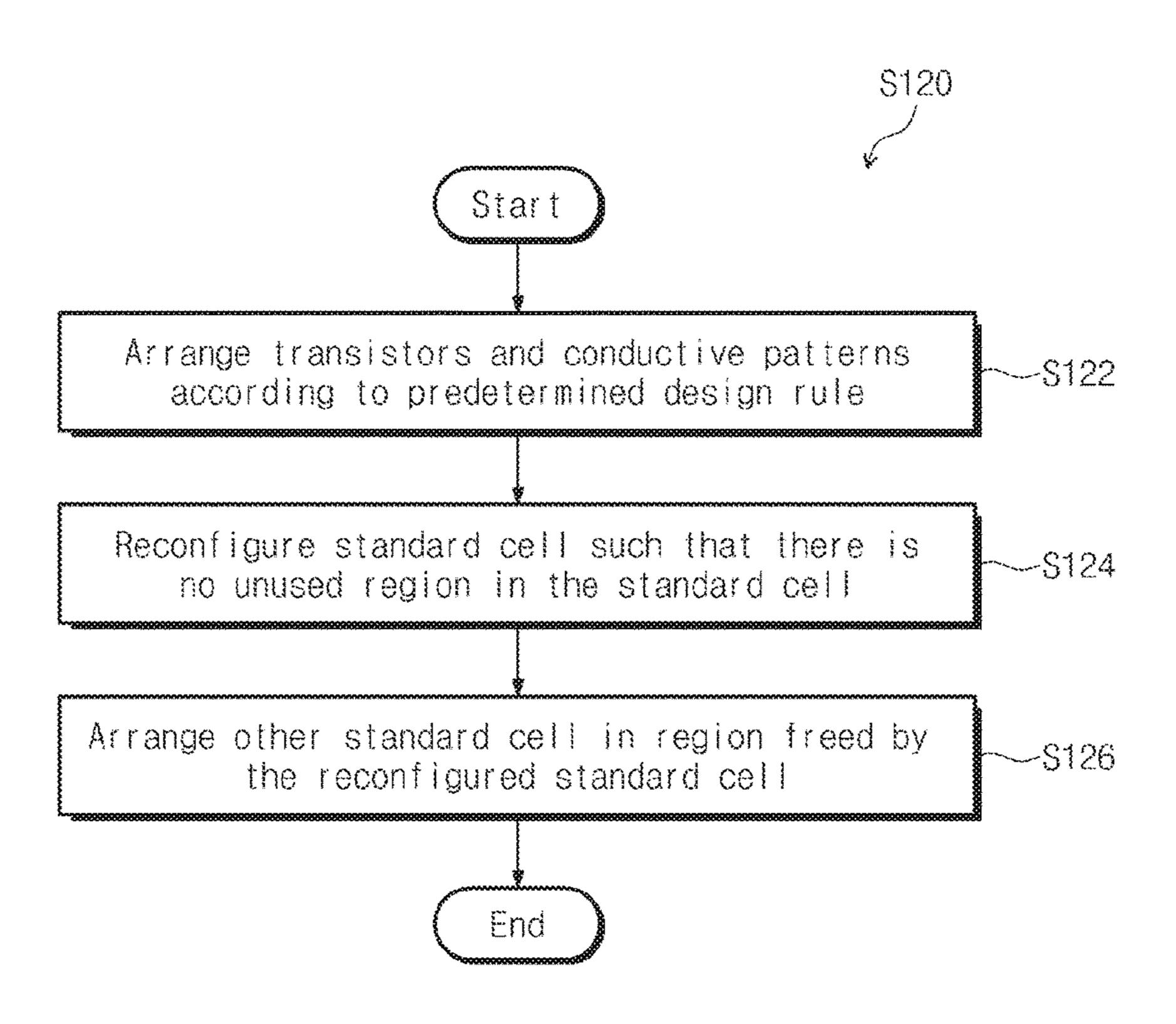

FIG. 3 is a flow chart illustrating an exemplary embodiment of operation S120 illustrated in FIG. 2.

4

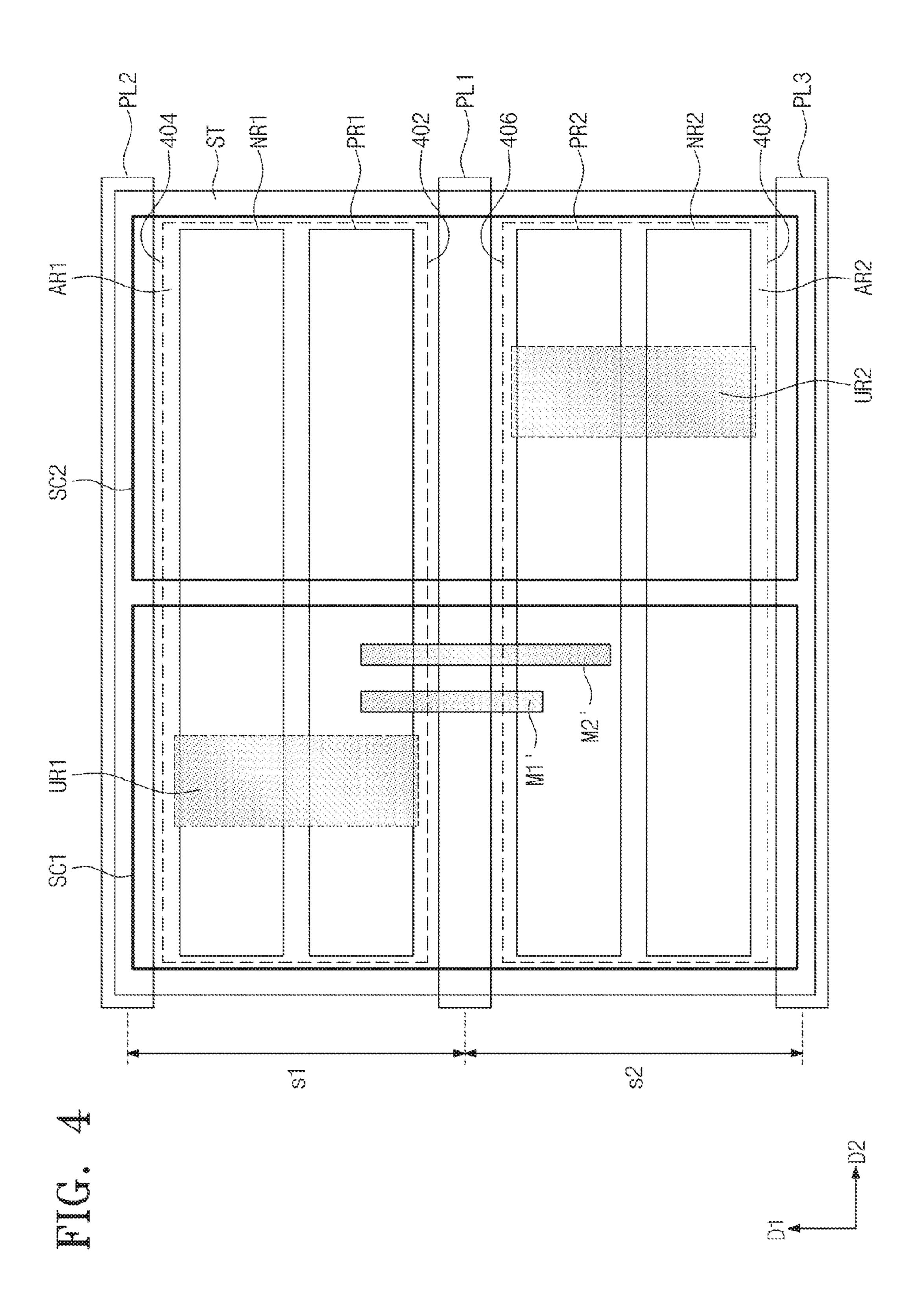

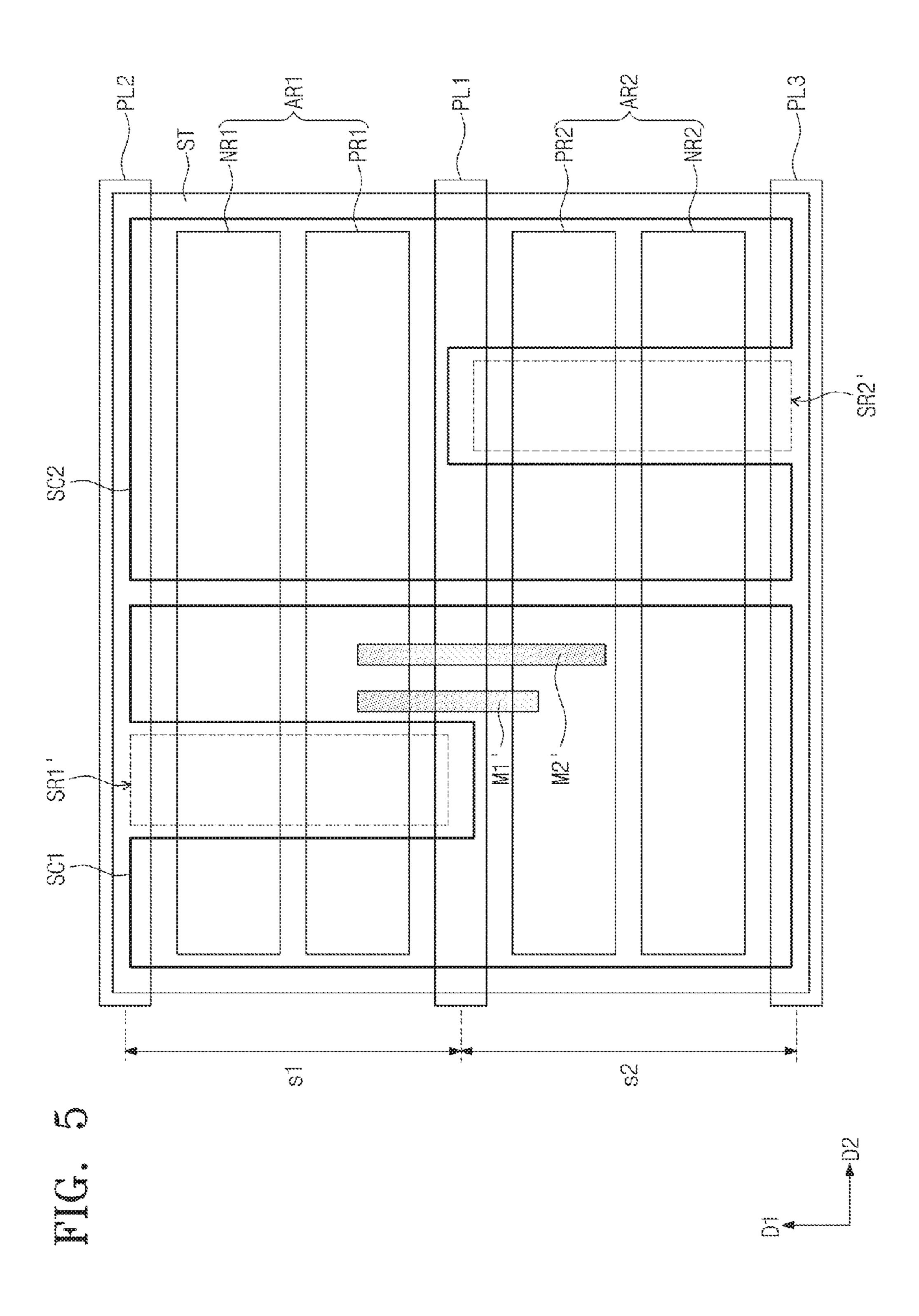

FIGS. 4 and 5 are plan views illustrating layout patterns to explain a method for designing a layout, according to an exemplary embodiment.

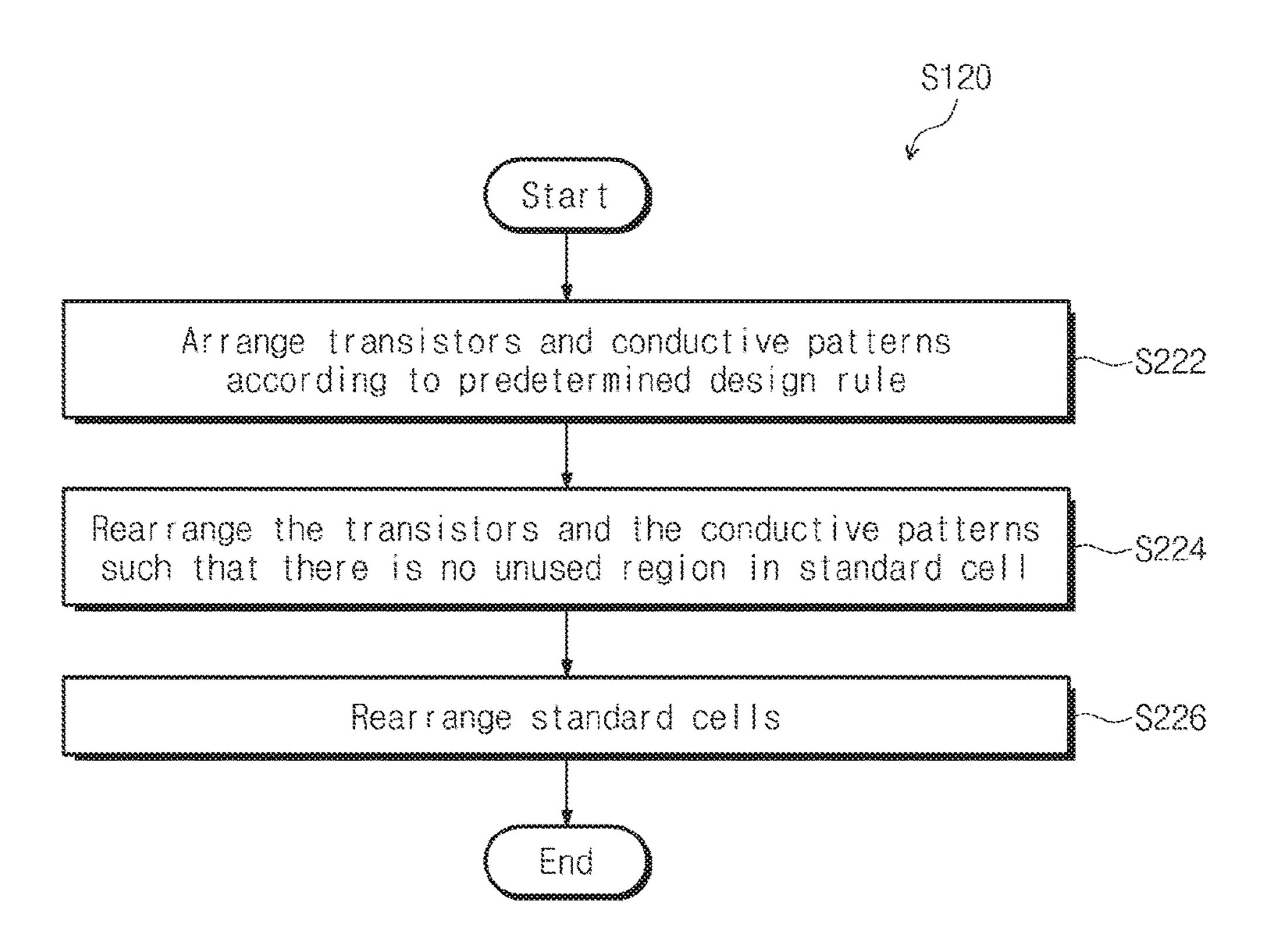

FIG. 6 is a flow chart illustrating an exemplary embodiment of operation S120 illustrated in FIG. 2.

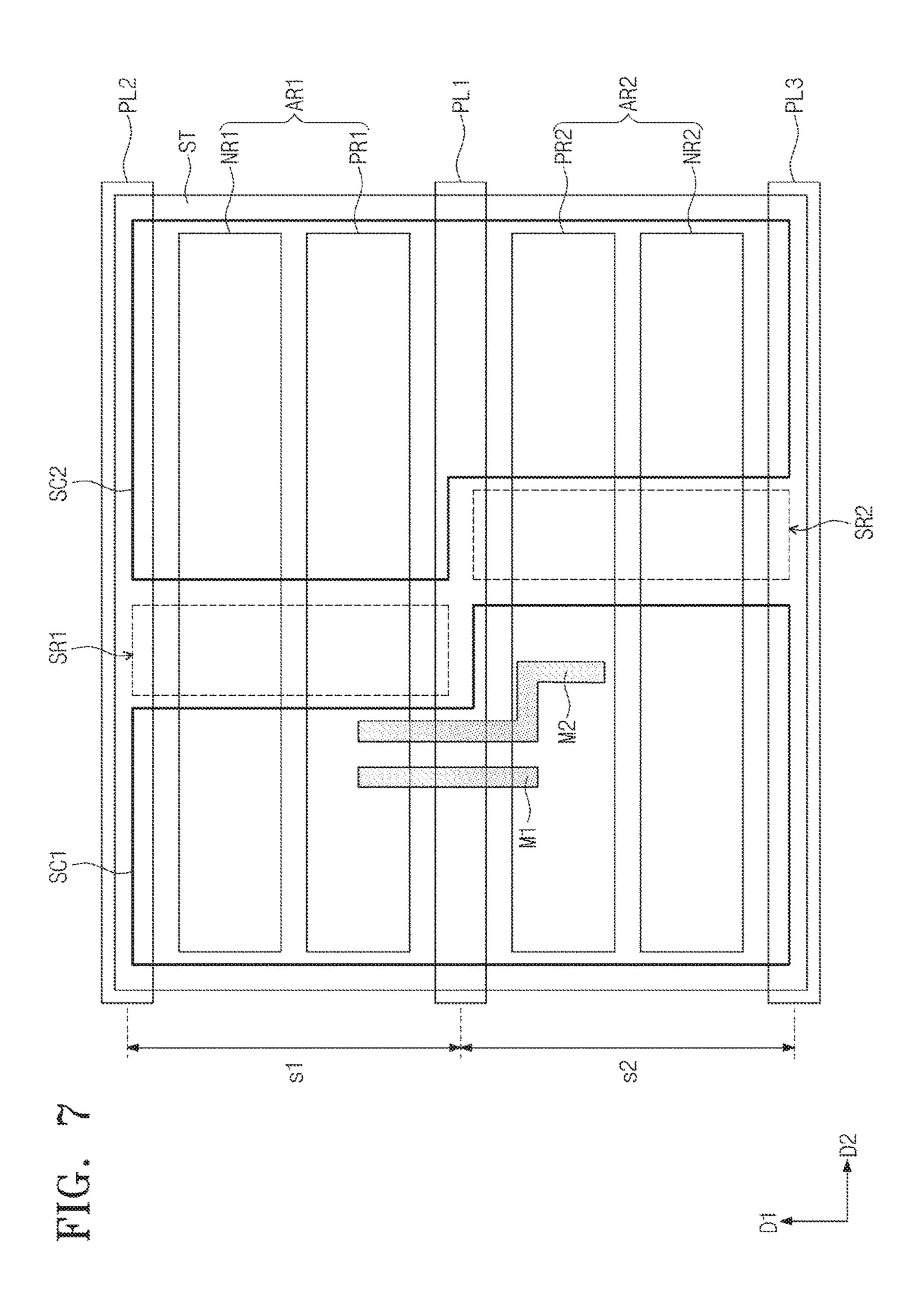

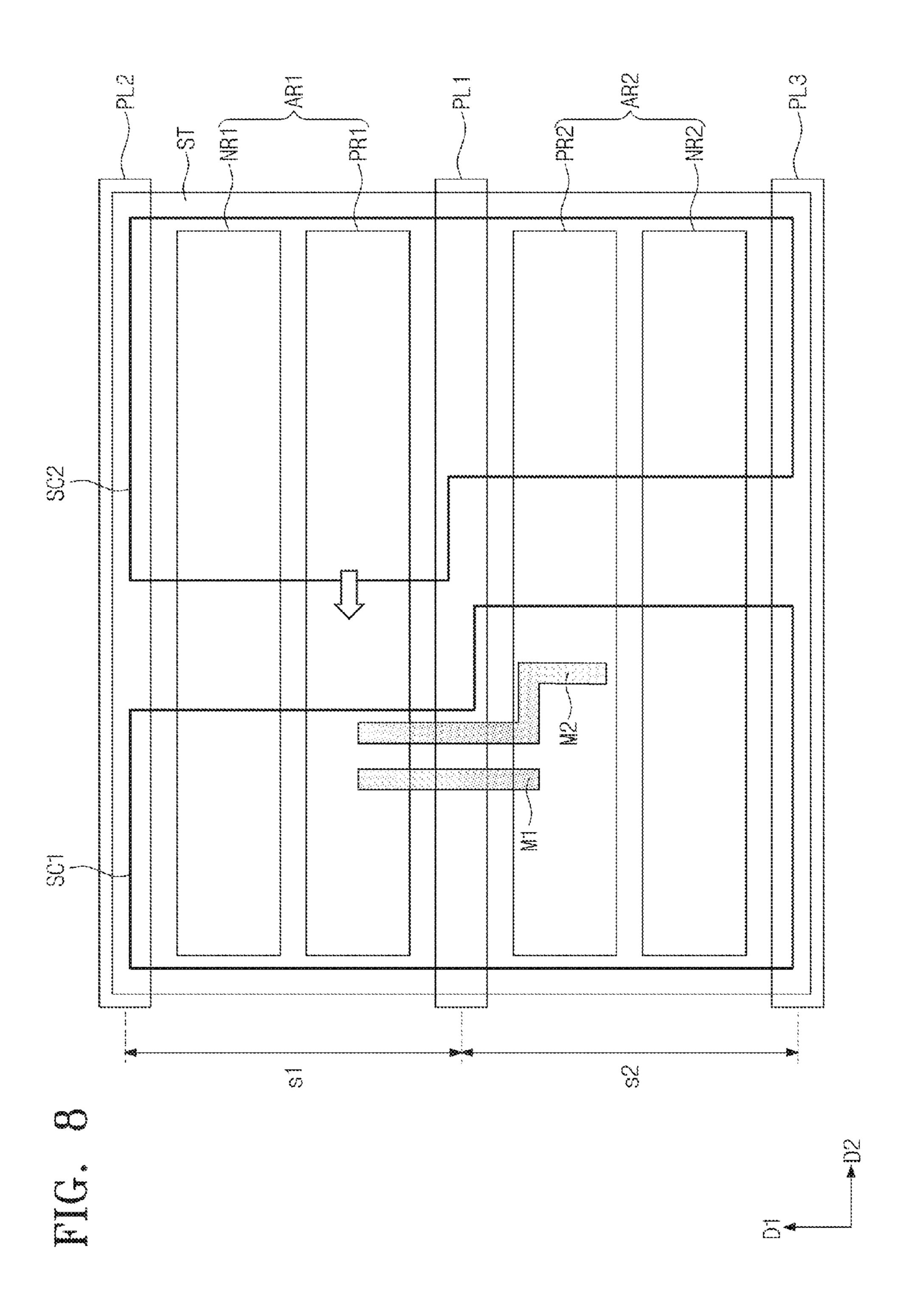

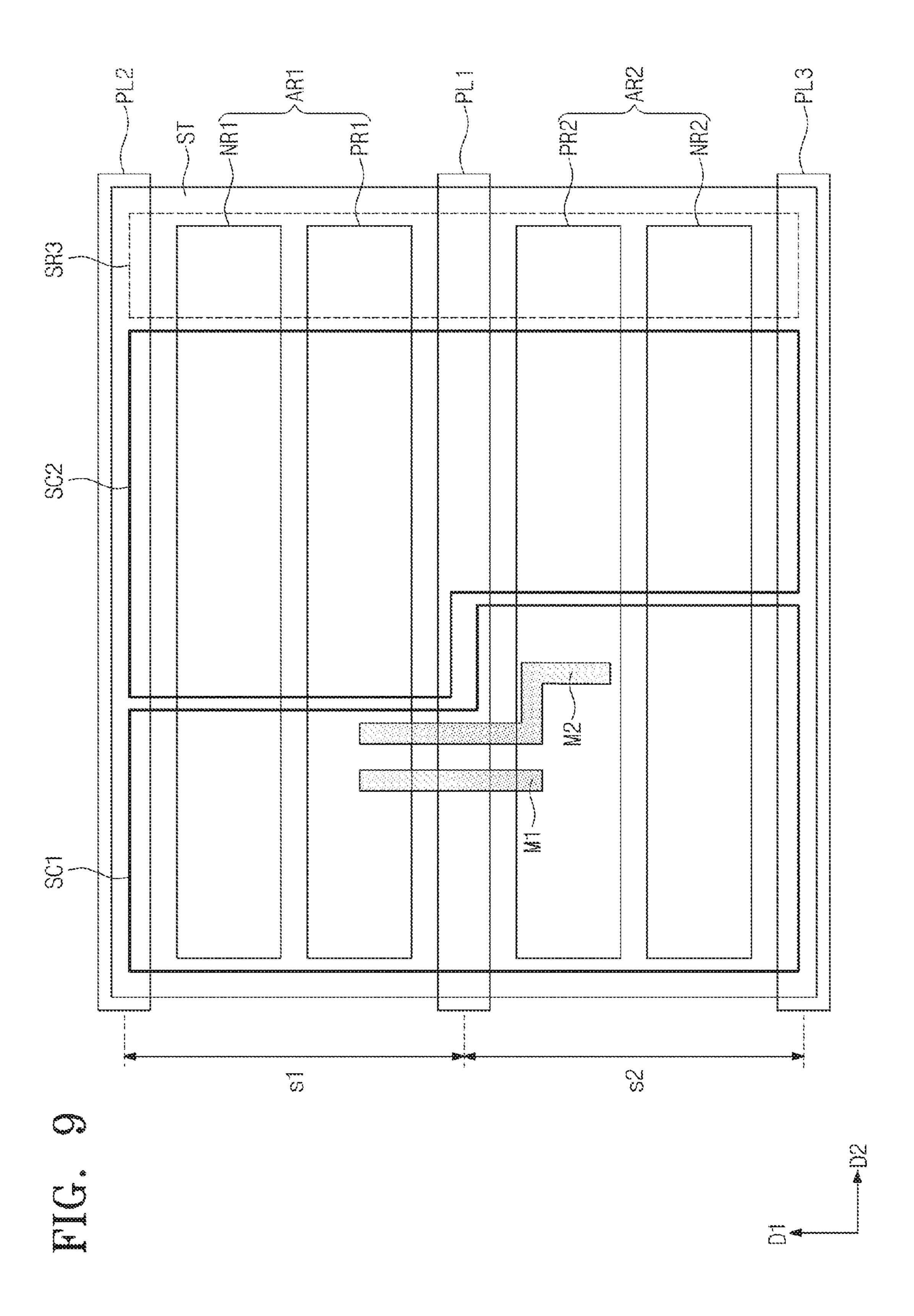

FIGS. 7, 8, and 9 are plan views illustrating layout patterns to explain a method for designing a layout, according to an exemplary embodiment.

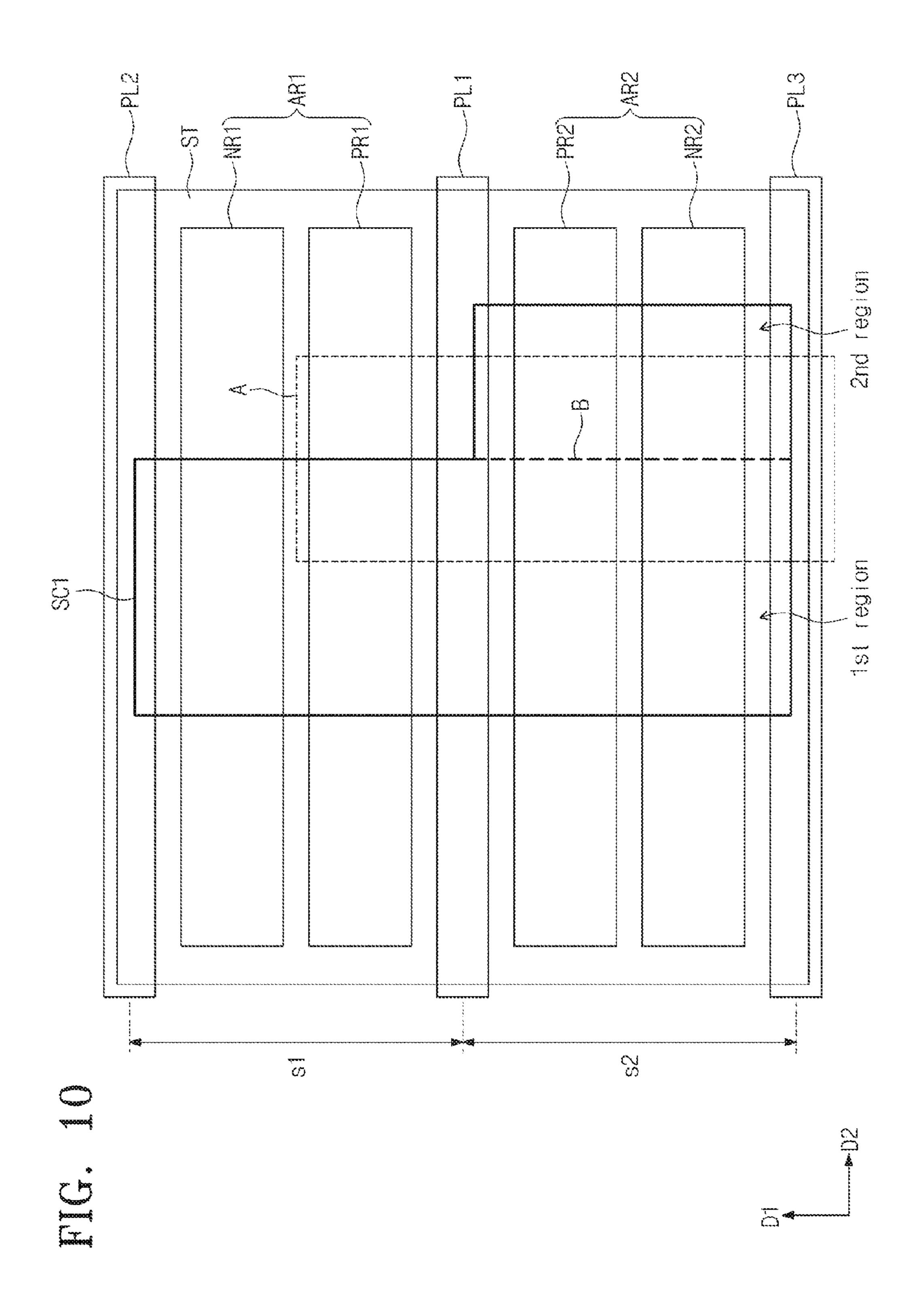

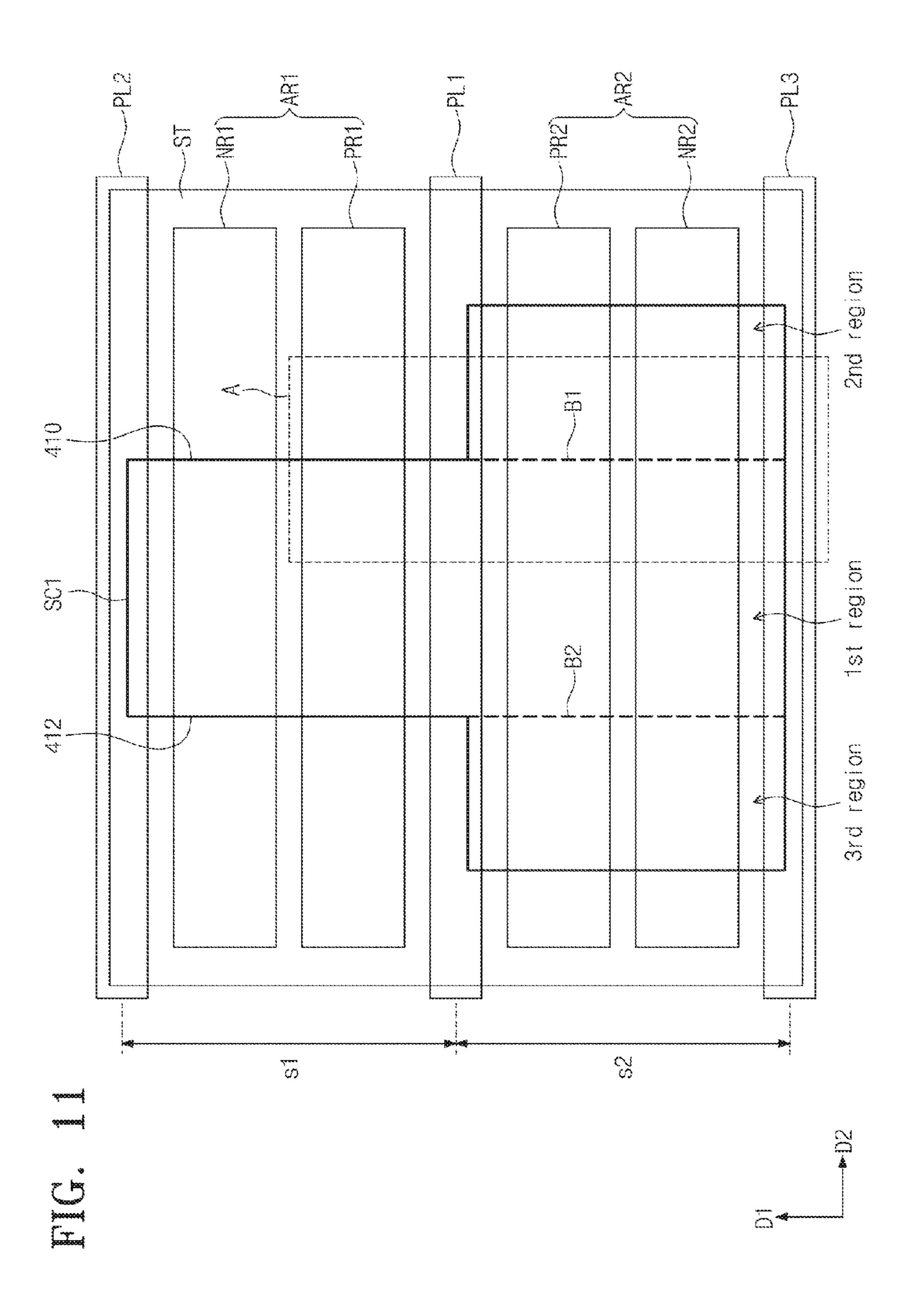

FIGS. 10, 11, 12, 13, and 14 are plan views illustrating standard cells according to an exemplary embodiment.

FIGS. 15, 16, 17, and 18 are plan views illustrating standard cells according to an exemplary embodiment.

FIG. 19 is a plan view illustrating a layout of a semiconductor device according to an exemplary embodiment.

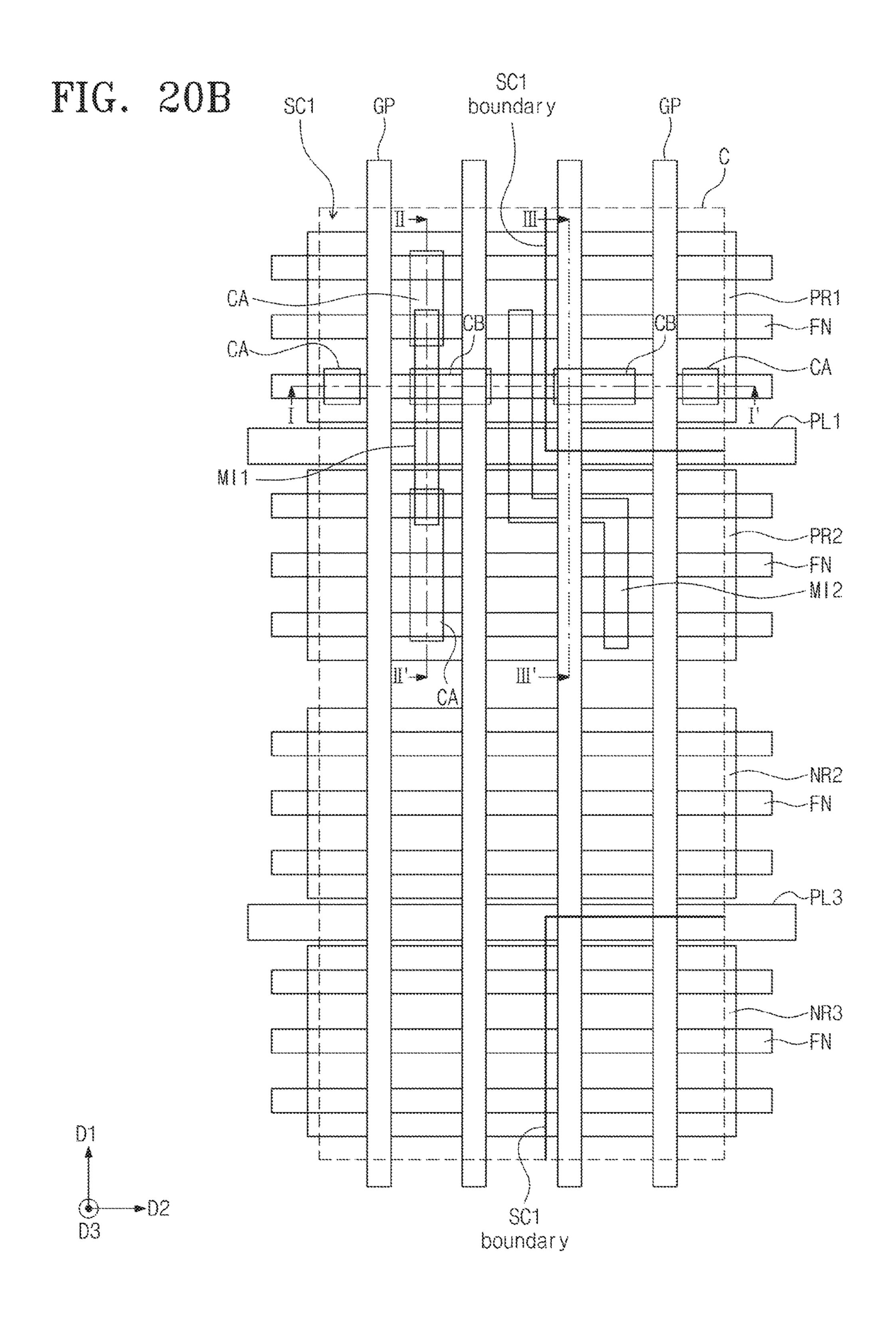

FIGS. 20A and 20B are plan views illustrating semiconductor devices including standard cells having polygonal shapes, according to an exemplary embodiment.

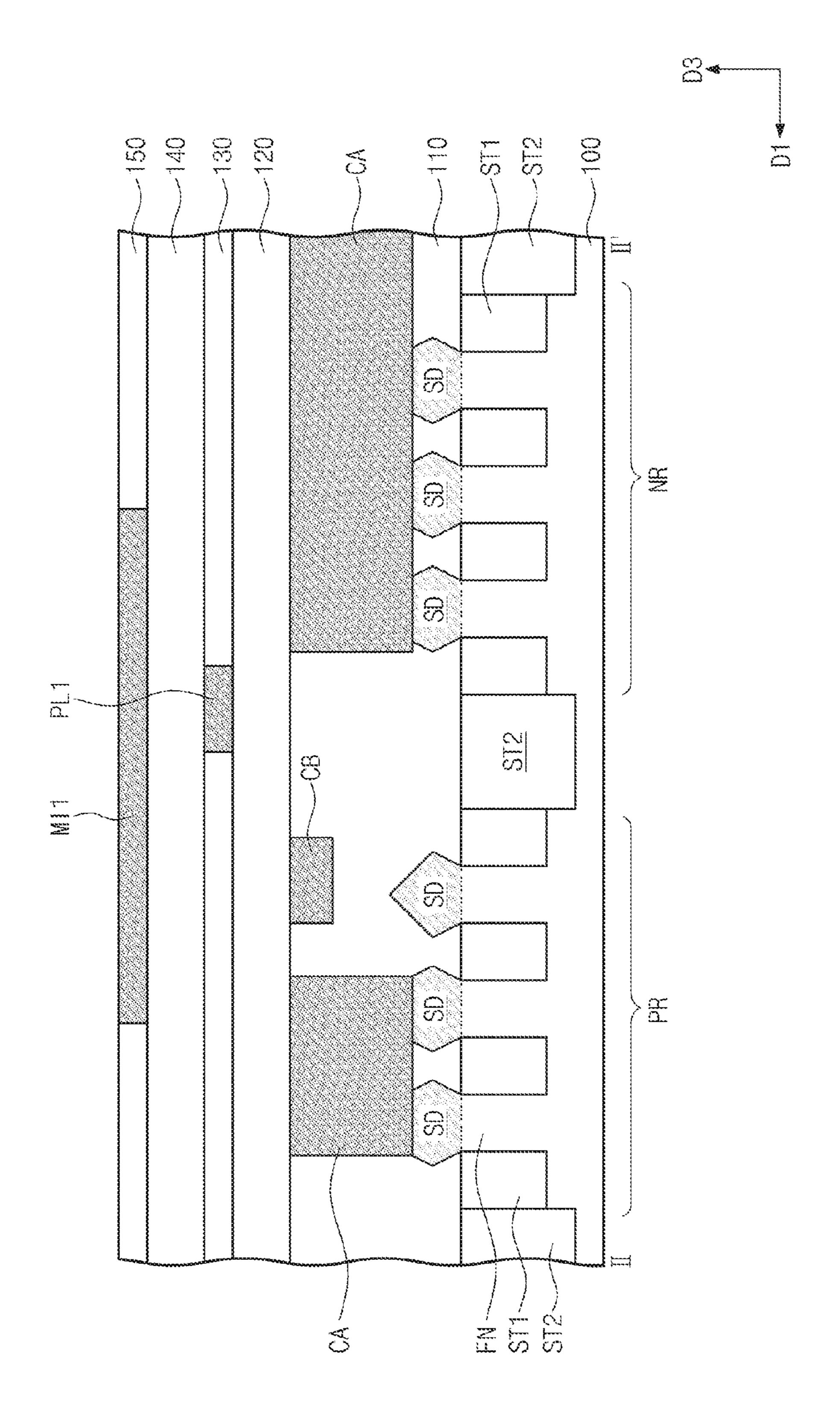

FIG. 20C is a cross-sectional view taken along a line I-I' of FIG. 20A or 20B.

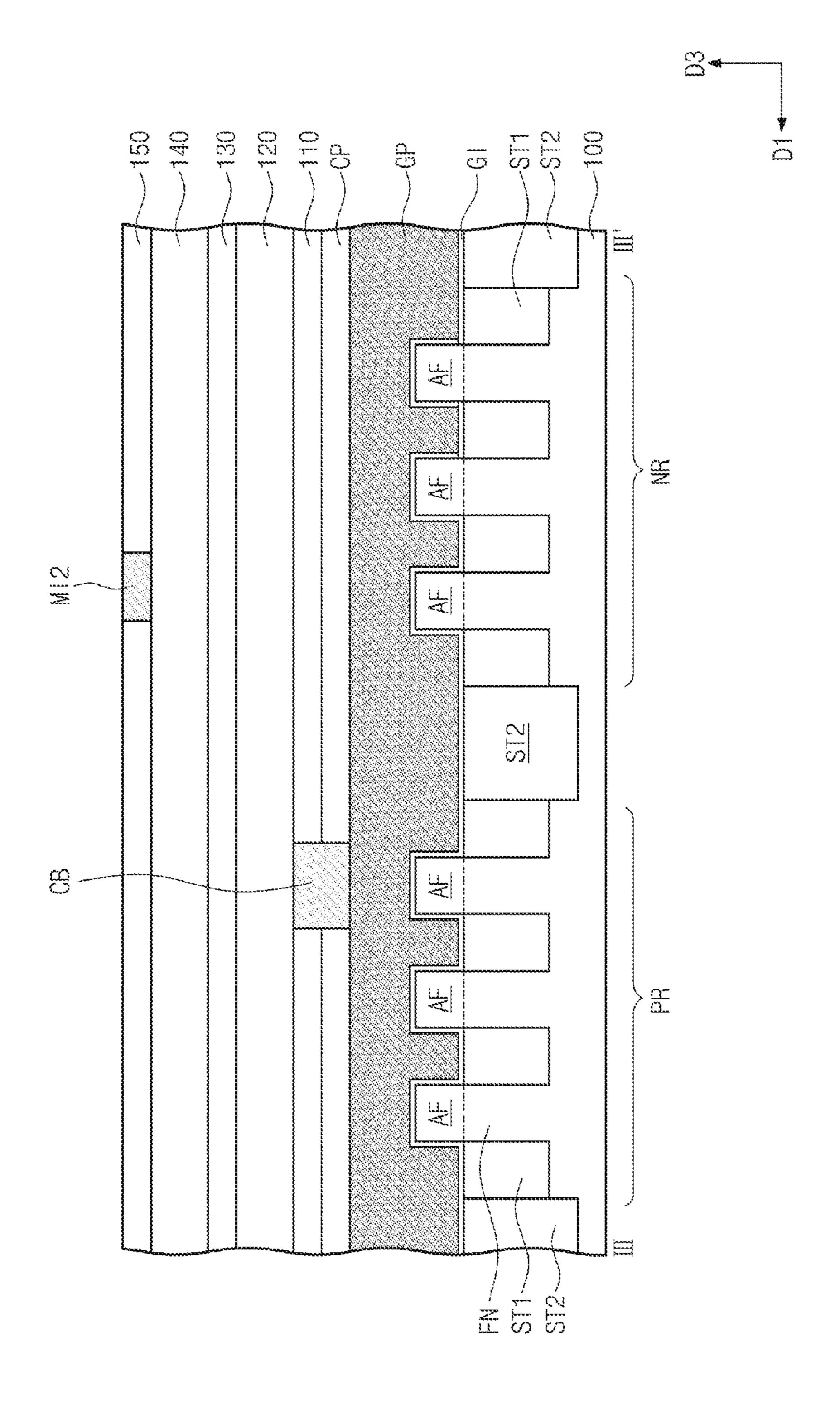

FIG. 20D is a cross-sectional view taken along a line II-II' of FIG. 20A or 20B.

FIG. 20E is a cross-sectional view taken along a line III-III' of FIG. 20A or 20B.

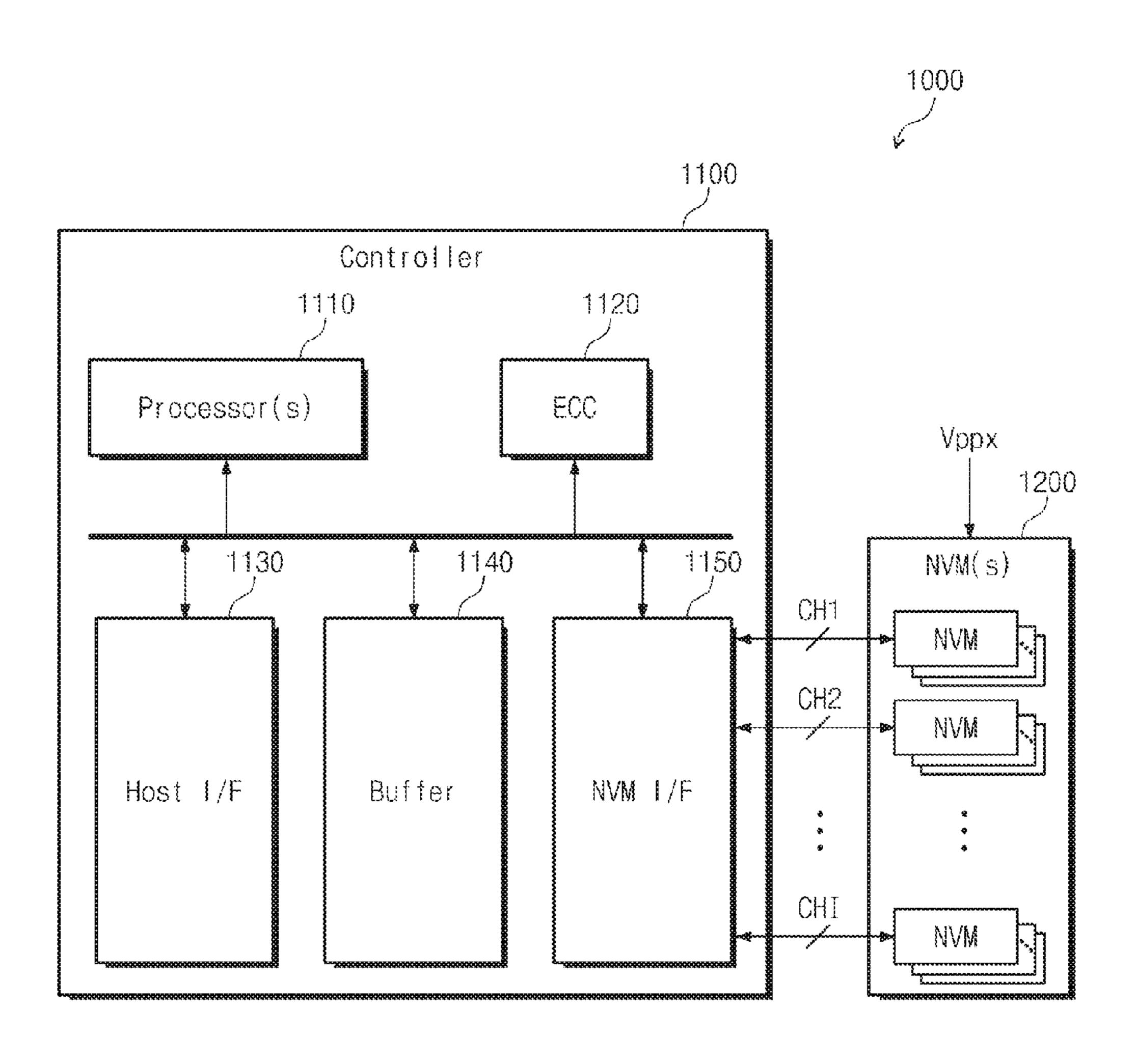

FIG. 21 is a schematic block diagram illustrating a solid state drive (SSD) implemented with a method for designing a layout of a semiconductor device, according to an exemplary embodiment.

#### DETAILED DESCRIPTION

Certain exemplary embodiments are described in greater detail below with reference to the accompanying drawings.

In the following description, like drawing reference numerals are used for like elements, even in different drawings. The matters defined in the description, such as detailed construction and elements, are provided to assist in a comprehensive understanding of the exemplary embodiments. However, it is apparent that the exemplary embodiments can be practiced without those specifically defined matters. Also, well-known functions or constructions are not described in detail since they would obscure the description with unnecessary detail.

It will be understood that when an element is referred to as being "connected", "coupled", or "adjacent" to another element, it may be directly connected or coupled to the other element or intervening elements may be present. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

It will be also understood that although the terms "first", "second", "third" etc. may be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another element. Thus, a first element in some embodiments could be termed a second element in other embodiments.

It will be understood that when an element such as a layer, region or substrate is referred to as being "beneath," "below," "above," "on," or "under" another element, it can be directly "beneath," "below," "above," "on," or "under" the other element or intervening elements may be present. In contrast, the term "directly" means that there are no intervening elements. Spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. It will be understood that the spatially relative terms are intended to encompass different

orientations of the device in use or operation in addition to the orientation depicted in the figures. For example, if the device in the figures is turned over, elements described as "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the exemplary term "below" can encompass both an orientation of above and below. The device may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein interpreted accordingly.

The terminology used herein is for the purpose of describing particular embodiments only and is not intended to limit the invention. As used herein, the singular terms "a," "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises", "comprising,", "includes" and/or "including", when used herein, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other 20 features, integers, steps, operations, elements, components, and/or groups thereof.

FIG. 1 is a schematic block diagram illustrating a computer system for designing a semiconductor device, according to an exemplary embodiment. Referring to FIG. 1, a 25 computer system 100 may include one or more processors 110, a working memory 120, an input/output (I/O) device 130, and a storage device 140. In an exemplary embodiment, the computer system 100 may be provided as a dedicated device for designing a layout according to an exemplary 30 embodiment. Moreover, the computer system 100 may be configured to drive various design and verification simulation programs.

The processor 110 may execute software (e.g., application computer system 100. The processor 110 may execute an operating system (not shown) loaded in the working memory 120. The processor 110 may execute various application programs to be driven based on the operating system. For example, the processor 110 may execute a layout design 40 tool 122 loaded in the working memory 120.

The operating system or application programs may be loaded in the working memory 120. When the computer system 100 is booted up, an OS image (not shown) stored in the storage device 140 may be loaded to the working 45 memory 120 according to a booting sequence. Overall input/output operations of the computer system 100 may be supported by the operating system. Likewise, application programs which are selected by a user or to provide a basic service may be loaded to the working memory 120. In an 50 exemplary embodiment, the layout design tool 122 prepared for a layout design process according to some embodiments may also be loaded from the storage device 140 to the working memory 120.

The layout design tool **122** may include a biasing function 55 for changing shapes and positions of specific layout patterns, which are defined by a design rule. In addition, the layout design tool 122 may perform a design rule check (DRC) in the changed biasing data condition. The working memory **120** may include a volatile memory device such as a static 60 random access memory (SRAM) device or a dynamic random access memory (DRAM) device. However, exemplary embodiments are not limited thereto. In an exemplary embodiment, the working memory 120 may include a nonvolatile memory device such as a phase-change random 65 access memory (PRAM) device, a magnetic random access memory (MRAM) device, a resistance random access

memory (ReRAM) device, a ferroelectric random access memory (FRAM) device, and/or a flash memory device.

A simulation tool **124** for performing an optical proximity correction (OPC) on designed layout data may be further loaded to the working memory 120.

The I/O device 130 may include various devices for receiving information from a designer and/or providing information to a designer. For example, the I/O device 130 may include a keyboard, a mouse, and/or a monitor. In an 10 exemplary embodiment, a processing procedure and a processing result of the simulation tool 124 may be shown through the I/O device 130.

The storage device 140 may be a storage medium of the computer system 100. The storage device 140 may store the 15 application programs, the OS image, and various kinds of data. For example, the storage device 140 may include an SSD, an embedded multimedia card (eMMC), and/or a hard disk drive (HDD). In an exemplary embodiment, the storage device 140 may include a NAND flash memory device. However, exemplary embodiments are not limited thereto. In an exemplary embodiment, the storage device 140 may include at least one of non-volatile memory devices such as a PRAM device, a MRAM device, a ReRAM device, a FRAM device, and a NOR flash memory device.

FIG. 2 is a flow chart illustrating a method for designing and manufacturing a semiconductor device, according to an exemplary embodiment.

In operation S110, a high-level design process of a semiconductor integrated circuit may be performed using the computer system 100 of FIG. 1. The high-level design process may mean that an integrated circuit corresponding to a design target is described with a high-level language of a hardware description language (HDL). For example, the high-level language such as C language may be used in the programs, operating system (OS), device drivers) in the 35 high-level design process. Circuits designed by the highlevel design process may be specifically expressed using a register transfer level (RTL) coding and a simulation. In addition, codes generated by the RTL coding may be converted into a netlist, and the netlist may be synthesized to describe an entire semiconductor device. The synthesized schematic circuit may be verified by the simulation tool 124, and an adjustment process may be performed based on the verified result.

> In operation S120, a layout design process may be performed to implement a logically completed semiconductor integrated circuit on a silicon substrate ST. For example, the layout design process may be performed based on the schematic circuit synthesized in the high-level design process or the netlist corresponding to the schematic circuit. The layout design process may include a routing process of placing and connecting various standard cells provided from a cell library, based on a prescribed design rule. The standard cell may mean a logic element (e.g., an inverter or a flip-flop) for performing a specific function. In other words, the standard cell may include a plurality of transistors and at least one interconnection connecting the transistors to each other, which are provided to constitute the logic element.

> According to a method for designing a layout in an exemplary embodiment, an unused space in the standard cell may be freed to reduce an area of a layout of a semiconductor device. In a layout design process, a related art standard cell may have a quadrilateral shape. However, to reduce the area of the layout, the standard cell according to an exemplary embodiment may have a polygonal shape, except a quadrilateral shape. That is, the standard cell according to exemplary embodiments does not have a boundary arranged as a quadrilateral shape, although the

boundary of the standard cell according to exemplary embodiments is arranged in a polygonal shape. This will be described later in more detail.

A cell library for expressing a specific gate-level circuit as a layout may be defined in the layout design tool. The layout 5 may be prepared to define or describe shapes and sizes of patterns constituting transistors and conductive lines which will be actually formed on a silicon substrate. For example, to actually form an inverter circuit on a silicon substrate, layout patterns (e.g., PMOS, NMOS, N-WELL, gate electrodes, and conductive lines to be disposed thereon) need to be properly placed. For this, suitable one(s) of inverters previously defined in the cell library may be searched and selected. In addition, a routing process may be performed on selected and placed standard cells. These processes may be 15 automatically or manually performed by the layout design tool.

After the routing process, a verification process may be performed on the layout to verify whether there is a portion violating the design rule. In an exemplary embodiment, the 20 verification process may include a DRC for verifying whether the layout meets the design rule, an electrical rule check (ERC) for verifying whether there is an issue of electrical disconnection in the layout, and a layout vs schematic (LVS) for recognizing whether the layout is 25 prepared to coincide with the gate-level netlist.

In operation S130, an optical proximity correction (OPC) process may be performed. The layout patterns obtained by the layout design process may be projected on a silicon substrate by a photolithography process. The OPC process 30 may be a technique for correcting an optical proximity effect occurring in the photolithography process. For example, the OPC process may correct the optical proximity effect which may occur by refraction or diffraction of light and/or a process side effect in an exposure process using the layout 35 patterns. The shapes and positions of the designed layout patterns may be slightly changed by the OPC process.

In operation S140, photomasks may be manufactured based on the layout changed by the OPC process. For example, the photomask may be manufactured by patterning 40 a chromium layer provided on a glass substrate based on the data of the layout patterns.

In operation S150, a semiconductor device may be manufactured using the photomasks. Various exposure processes and various etching processes may be repeatedly performed 45 in the process of manufacturing the semiconductor device, and thus, the patterns defined by the layout design process may be sequentially transferred to a silicon substrate.

FIG. 3 is a flow chart illustrating an exemplary embodiment of operation S120 illustrated in FIG. 2. FIGS. 4 and 5 50 are plan views illustrating layout patterns to explain a method for designing a layout, according to an exemplary embodiment.

Hereinafter, in terms used herein, 'a conductive pattern' may mean 'an imaginary conductive line' generated by the 55 layout design tool and 'a conductive line' may mean 'a real conductive line' formed by a photolithography process performed based on the conductive pattern.

Referring to FIGS. 3 and 4, in operation S122, transistors and conductive patterns may be arranged according to a 60 predetermined design rule. Here, the arrangement according to the predetermined design rule may mean that transistors and conductive patterns may be arranged to form a standard cell having a general rectangular shape.

A standard cell SC1 and a standard cell SC2 which have 65 rectangular shapes may be formed based on the predetermined design rule, as illustrated in FIG. 4. Boundaries of the

8

standard cells SC1 and SC2 are illustrated by thick solid lines in FIG. 4. Each of the standard cells SC1 and SC2 may include the first active region AR1 and the second active region AR2 and may include three power lines PL1, PL2, and PL3. A first power line PL1 may be disposed between a first active region AR1 and a second active region AR2 in a plan view and may be adjacent to one edge, i.e., a first edge **402**, of the first active region AR1 and one edge, i.e., a first edge 406, of the second active region AR2. The first power line PL1 may extend in a second direction D2. A second power line PL2 may extend in the second direction D2 and may be adjacent to another edge, i.e., a second edge 404, of the first active region AR1, as illustrated in FIG. 4. The third power line PL3 may extend in the second direction D2 and may be adjacent to another edge, i.e., a second edge 408, of the second active region AR2, as illustrated in FIG. 4. For example, the first active region AR1 may be disposed between the first power line PL1 and the second power line PL2 when viewed from a plan view, and the second active region AR2 may be disposed between the first power line PL1 and the third power line PL3 when viewed from a plan view. A distance between the first and second power lines PL1 and PL2 may be defined as a distance s1, and a distance between the first and third power lines PL1 and PL3 may be defined as a distance s2. The distance s1 may be equal to or different from the distance s2.

The first active region AR1 may include a first NMOS region NR1 and a first PMOS region PR1, and the second active region AR2 may include a second NMOS region NR2 and a second PMOS region PR2. Some of the conductive patterns M1' and M2' of the standard cell SC1 are illustrated in FIG. 4. The transistors (not shown) of the standard cell SC1 may be disposed on the active regions AR1 and AR2 adjacent to the conductive patterns M1' and M2'.

If standard cells are arranged based on a related art design rule, unused regions UR1 and UR2 may exist in the standard cells SC1 and SC2. Here, the unused regions UR1 and UR2 may mean regions in which a transistor is not disposed. The unused regions UR1 and UR2 of the standard cells SC1 and SC2 may be disposed at other various positions, unlike illustrated in FIG. 4, based on a layout design.

Referring to FIGS. 3 and 5, in operation S124, the standard cells may be reconfigured such that the unused region is eliminated in the standard cells. Since the standard cells SC1 and SC2 are reconfigured to have polygonal shapes, occupied areas of the standard cells SC1 and SC2 may be reduced. In some embodiments, the layout of the transistors and the conductive patterns of the standard cells SC1 and SC2 are not changed as illustrated in FIG. 5. In some exemplary embodiments, the arrangement of the transistors of the standard cells SC1 and SC2 is not changed, but the arrangement of the conductive patterns of the standard cells SC1 and SC2 may be changed by layouts of other standard cells to be arranged in regions SR1' and SR2' which are freed by reconfiguring standard cells SC1 and SC2.

Referring to FIGS. 3 and 5, in operation S126, other standard cells may be arranged in the freed regions SR1' and SR2'. For example, since each of the freed regions SR1' and SR2' includes two power lines and one NMOS region and one PMOS region, a simple circuit (e.g., an inverter manufactured based on a CMOS technique) may be disposed in each of the freed regions SR1' and SR2'.

FIG. 6 is a flow chart illustrating an exemplary embodiment of operation S120 illustrated in FIG. 2. FIGS. 7 to 9 are plan views illustrating layout patterns to explain a method for designing a layout, according to an exemplary embodiment.

Operation S222 of FIG. 6 may be the substantially same as operation S122 of FIG. 4, so the description to operation S222 will be omitted.

Referring to FIGS. 6 and 7, in operation S224, transistors and conductive patterns of the standard cells SC1 and SC2 5 may be rearranged such that there is no unused region in the standard cells SC1 and SC2. For example, the transistors and the conductive patterns of the standard cells SC1 and SC2 may be rearranged in such a way that the freed regions SR1' and SR2' illustrated in FIG. 5 are moved to positions of freed 10 regions SR1 and SR2 illustrated in FIG. 7. The rearranged conductive patterns M1 and M2 are illustrated in FIG. 7. In an exemplary embodiment, the transistors adjacent to the conductive patterns M1 and M2 may also be rearranged by the rearrangement of the conductive patterns M1 and M2.

Referring to FIGS. 6, 8, and 9, the standard cells SC1 and SC2 may be rearranged in operation S226. In FIGS. 8 and 9, the standard cell SC1 may include a first portion including the first active region AR1 and a second portion including the second active region AR2, and the standard cell SC2 may 20 include a first portion including the first active region AR1 and a second portion including the second active region AR2. Here, a width in the second direction D2 of the first portion of the standard cell SC1 may be smaller than a width in the second direction D2 of the second portion of the 25 standard cell SC1, but a width in the second direction D2 of the first portion of the standard cell SC2 may be greater than a width in the second direction D2 of the second portion of the standard cell SC2. The standard cells SC1 and SC2 may be rearranged similarly to putting together a puzzle.

Since the standard cells SC1 and SC2 are rearranged similarly to putting together the puzzle in FIGS. 8 and 9, a region SR3 may be freed. The freed region SR3 may overlap with the first power line PL1, the first active region AR1, the the third power line PL3, and thus, the freed region SR3 may be used to design a standard cell of which a size is greater than the size of a standard cell that may be disposed in the freed regions SR1 and SR2 illustrated in FIG. 7.

FIGS. 10 to 14 are plan views illustrating standard cells 40 according to an exemplary embodiment. Standard cells illustrated in FIGS. 10 to 14 may overlap with (i.e., at least partially include) at least two active regions. For example, the standard cells SC1 illustrated in FIGS. 10 to 13 may overlap with (i.e., at least partially include) first and second 45 active regions AR1 and AR2. The standard cell SC1 illustrated in FIG. 14 may overlap with (i.e., at least partially include) first, second and third active regions AR1, AR2, and AR3. The standard cell extending over at least two active regions may be defined as a multi-height cell.

FIG. 10 illustrates an exemplary embodiment of the standard cell SC1 having a polygonal shape. A boundary of the standard cell SC1 is illustrated by a thick solid line. For example, the standard cell SC1 may include a first region and a second region. A sub-boundary between the first 55 region and the second region is illustrated by a thick dotted line B. I.e., the sub-boundary B is shared by the first region and the second region and serves as a division line between an area of the first region and an area of the second region. The standard cell SC1 divided into the first and second 60 regions along a first direction D1 is illustrated only as an example in FIG. 10. However, in an exemplary embodiment, the standard cell SC1 may be divided along the second power line PL2. The first and second regions are not divided from each other based on their logical functions but are 65 divided from each other so that the standard cell SC1 has the polygonal shape, but does not have the quadrilateral shape

**10**

of the related art, although the individual regions included in the standard cell may have a quadrilateral shape. In FIG. 10, a region 'A' illustrated by a thin dotted line is used to describe a portion of a semiconductor device in more detail with reference to FIGS. 20A to 20E. This may be identically applied to the exemplary embodiments of FIGS. 11 to 18.

The first region may overlap with (i.e., at least partially include) the second power line PL2, the first active region AR1, the first power line PL1, the second active region AR2, and the third power line PL3. The first active region AR1 may include the first NMOS region NR1 and the first PMOS region PR1, and the second active region AR2 may include the second NMOS region and the second PMOS region PR2. The second region may overlap with (i.e., at least partially include) the first power line PL1, the second active region AR2, and the third power line PL3.

A basic logic element (e.g., a multi-bit flip-flop) performing a specific function may be formed using the transistors on the active regions AR1 and AR2 of the standard cell SC1.

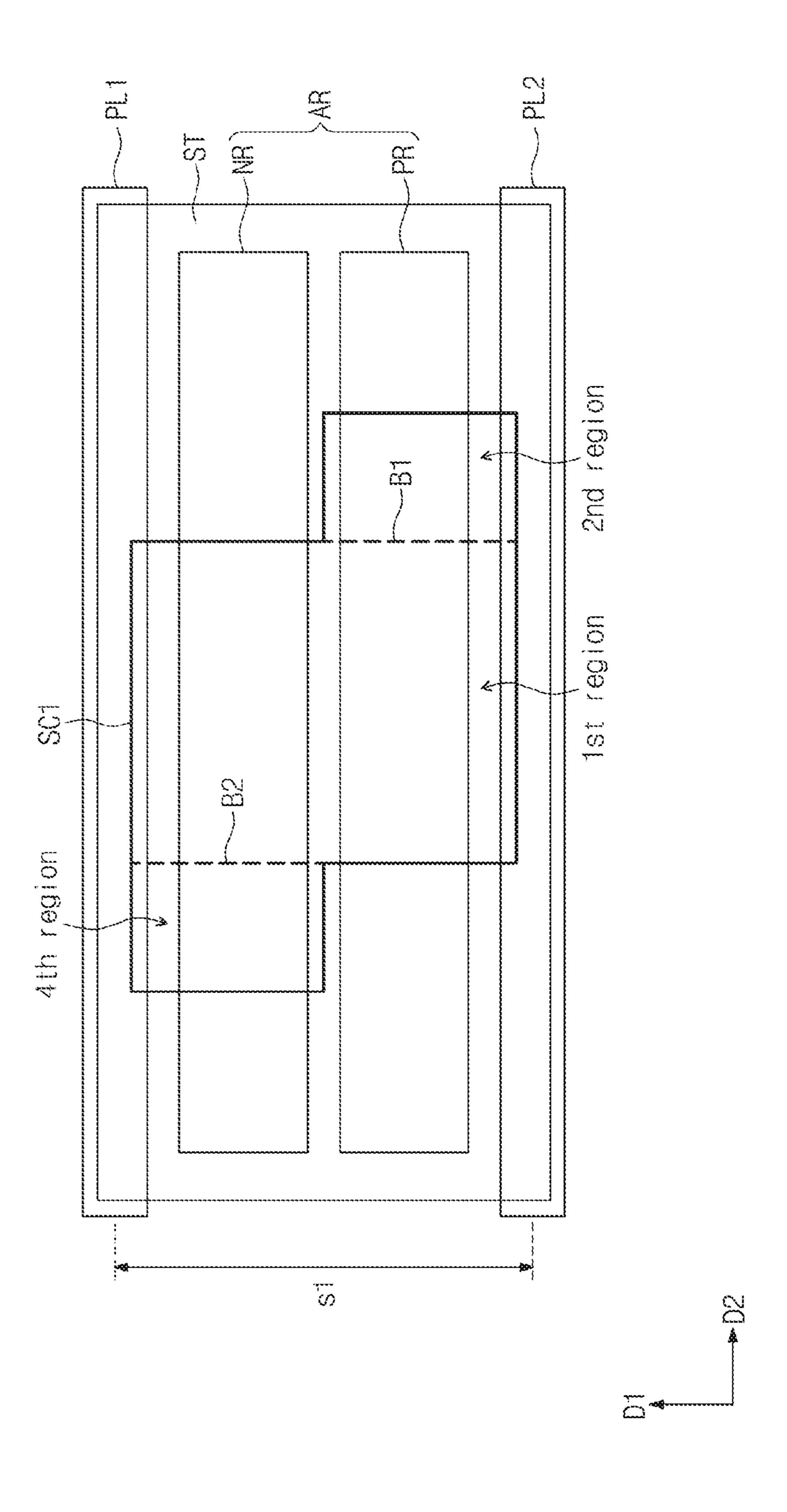

FIG. 11 illustrates an exemplary embodiment of the standard cell SC1 having a polygonal shape. For example, the standard cell SC1 may include a first region, a second region, and a third region. A thick dotted line B1 may be a boundary between the first region and the second region, and a thick dotted line B2 may be a boundary between the first region and the third region.

The first region may overlap with (i.e., at least partially include) the second power line PL2, the first active region AR1, the first power line PL1, the second active region AR2, and the third power line PL3. Each of the second and third regions may overlap with (i.e., at least partially include) the first power line PL1, the second active region AR2, and the third power line PL3. The second region may be in contact with one edge of the first region, and the third region may second power line PL2, the second active region AR2, and 35 be in contact with another edge, opposite to the one edge, of the first region.

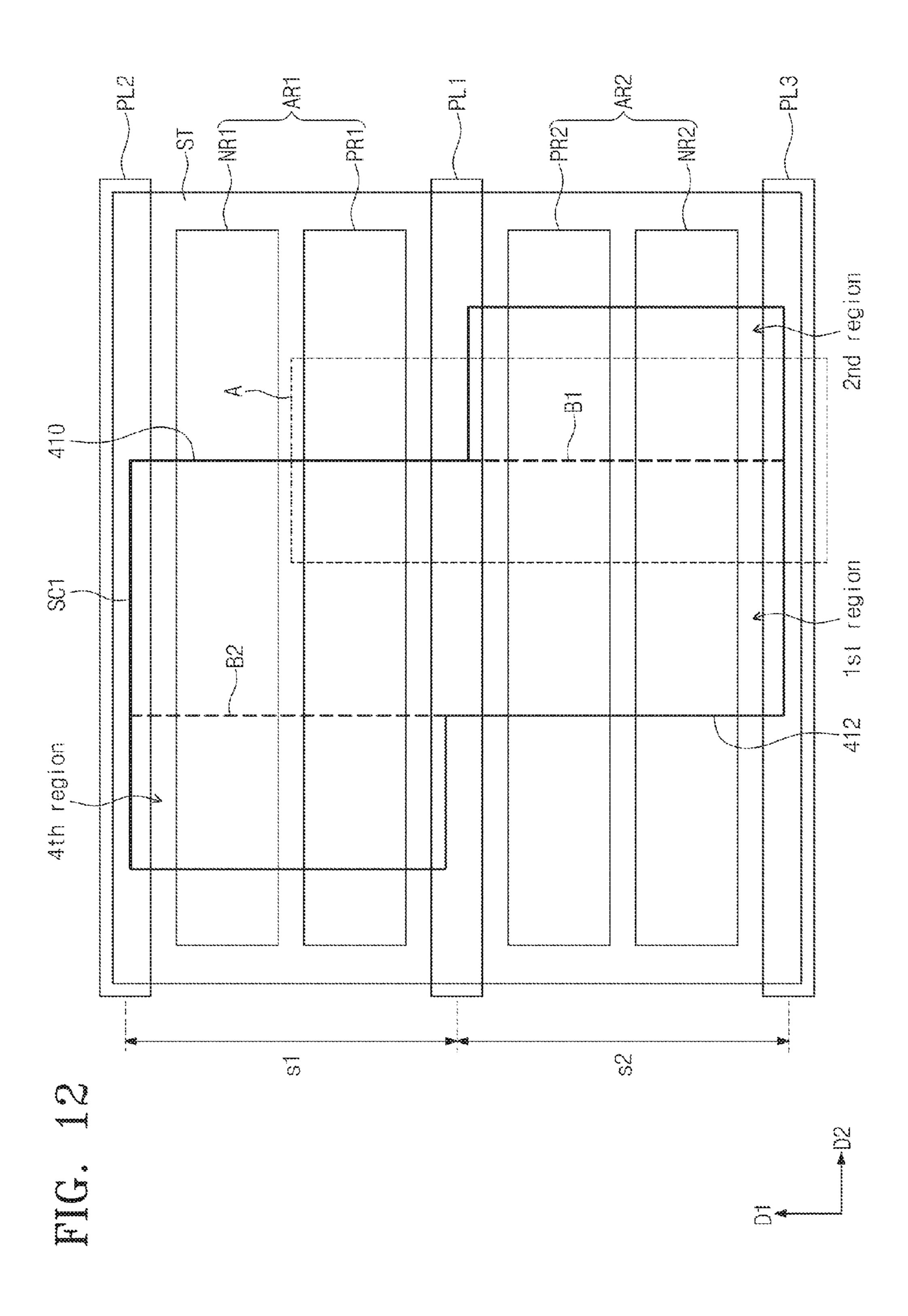

> FIG. 12 illustrates an exemplary embodiment of the standard cell SC1 having a polygonal shape. For example, the standard cell SC1 may include a first region, a second region, and a fourth region. A thick dotted line B1 may be a boundary between the first region and the second region, a thick dotted line B2 may be a boundary between the first region and the fourth region.

The first region may overlap with (i.e., at least partially include) the second power line PL2, the first active region AR1, the first power line PL1, the second active region AR2, and the third power line PL3. The second region may overlap with (i.e., at least partially include) the first power line PL1, the second active region AR2, and the third power 50 line PL3. The fourth region may overlap with (i.e., at least partially include) the second power line PL2, the first active region AR1, and the first power line PL1. The second region may be in contact with one edge of the first region, and the fourth region may be in contact with another edge, opposite to the one edge, of the first region.

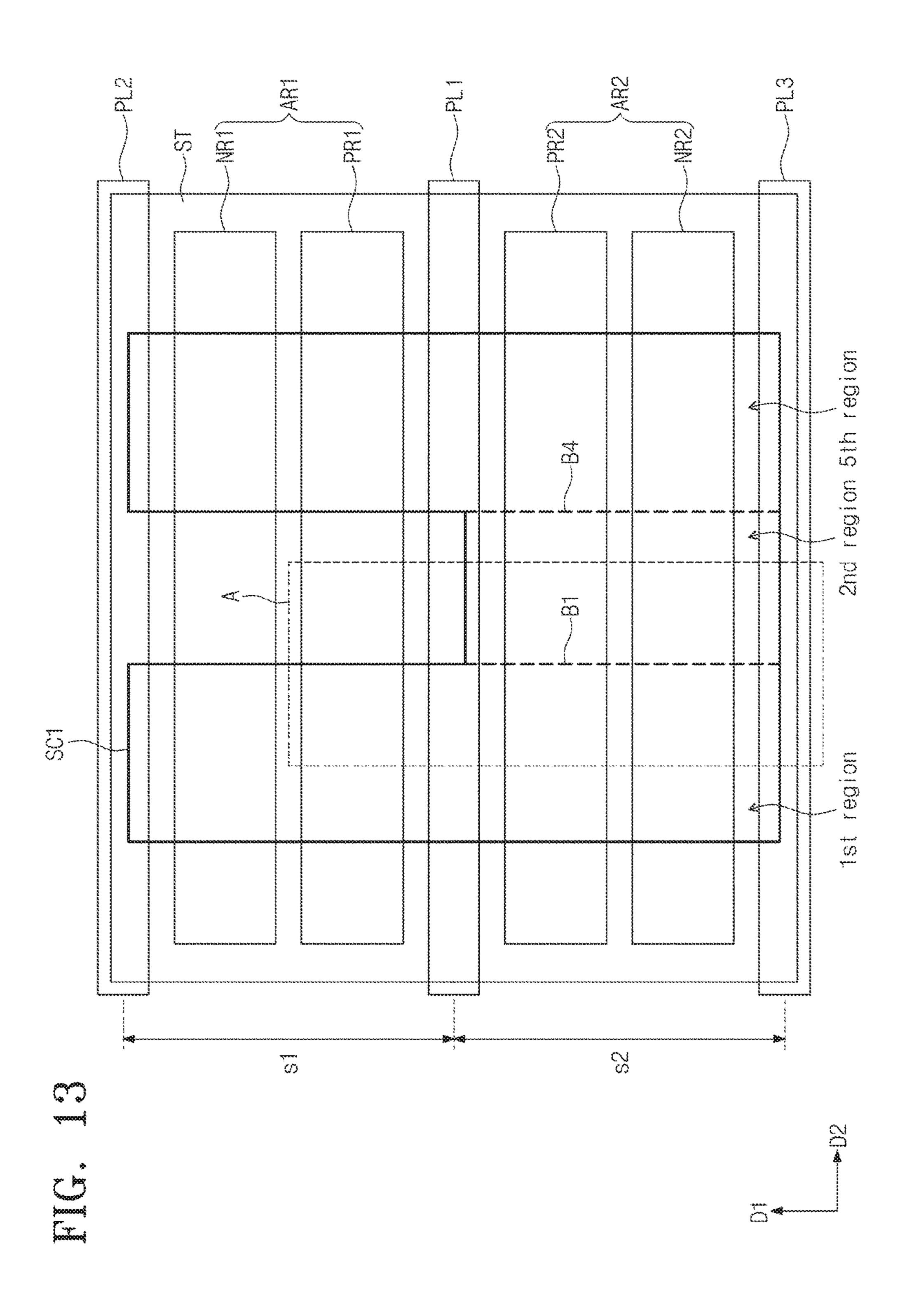

FIG. 13 illustrates an exemplary embodiment of the standard cell SC1 having a polygonal shape. For example, the standard cell SC1 may include a first region, a second region, and a fifth region. A thick dotted line B1 may be a boundary between the first region and the second region, and a thick dotted line B4 may be a boundary between the second region and the fifth region.

The first region may overlap with (i.e., at least partially include) the second power line PL2, the first active region AR1, the first power line PL1, the second active region AR2, and the third power line PL3. The second region may overlap with (i.e., at least partially include) the first power

line PL1, the second active region AR2, and the third power line PL3. The fifth region may overlap with (i.e., at least partially include) the second power line PL2, the first active region AR1, the first power line PL1, the second active region AR2, and the third power line PL3. The first region may be in contact with a first edge (illustrated by B1) of the second region, and the fifth region may be in contact with a second edge (illustrated by B4) that is opposite to the first edge, of the second region. In other words, the second region may be disposed between the first region and the fifth region.

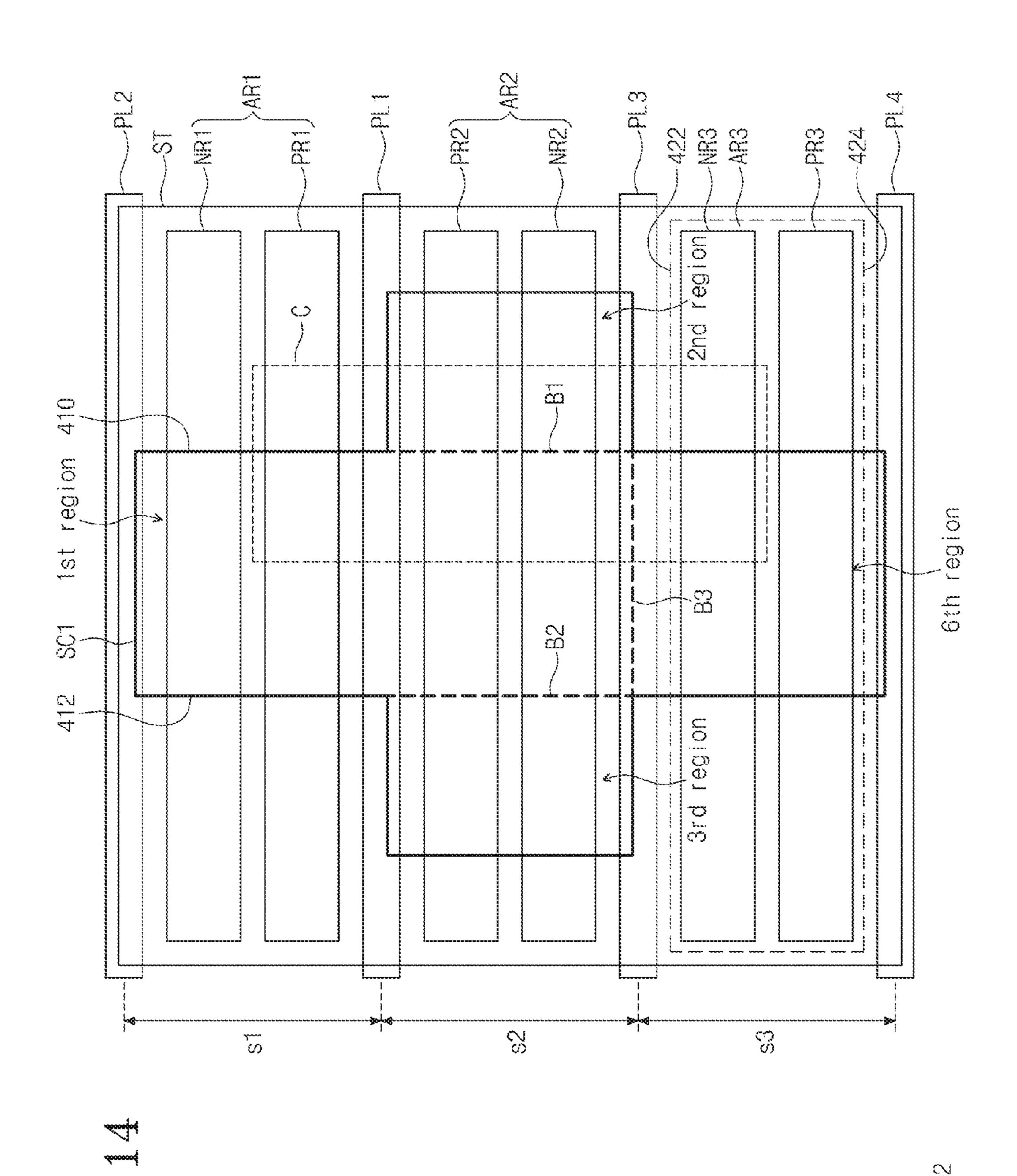

FIG. 14 illustrates an exemplary embodiment of the standard cell SC1 having a polygonal shape. For example, the standard cell SC1 may include a first region, a second region, a third region, and a sixth region. A thick dotted line B1 may be a boundary between the first region and the second region, a thick dotted line B2 may be a boundary between the first region and the third region, and a thick dotted line B3 may be a boundary between the first region and the sixth region.

The first region may overlap with (i.e., at least partially include) the second power line PL2, the first active region AR1, the first power line PL1, the second active region AR2, and the third power line PL3. Each of the second and third regions may overlap with (i.e., at least partially include) the 25 first power line PL1, the second active region AR2, and the third power line PL3. The second region may be in contact with a portion (illustrated by B1) of a first edge 410 of the first region, and the third region may be in contact with a portion (illustrated by B2) of a second edge 412, opposite to 30 the first edge, of the first region.

A third active region AR3 may be disposed at a side of the second active region AR2. The second active region AR2 may be disposed between the first active region AR1 and the third active region AR3. The third active region AR3 may 35 have a first edge 422 adjacent to the third power line PL3 and a second edge 424 opposite to the first edge. A fourth power line PL4 may be adjacent to the second edge 424 of the third active region AR3 and may extend in the second direction D2. The third active region AR3 may include a third NMOS 40 region NR3 and a third PMOS region PR3. The sixth region may overlap with (i.e., at least partially include) the third power line PL3, the third active region AR3, and the fourth power line PL4. The sixth region may be in contact with a third edge of the first region, which is not in contact with the 45 second and third regions.

The standard cells described above may have the polygonal shape and may have at least three power lines and at least two active regions. In addition, each of the active regions may include the NMOS region and the PMOS region. In particular, relatively large-sized standard cells have been demanded with the development of a circuit design technique. However, a layout area of the semiconductor device according to an exemplary embodiment may be reduced by the standard cell having the polygonal shape.

FIGS. 15 to 18 are plan views illustrating standard cells according to an exemplary embodiment. Standard cells of FIGS. 15 to 18 may have a polygonal shape overlapping with (i.e., at least partially including) two power lines and one active region. The standard cell overlapping with (i.e., 60 at least partially including) one active region may be defined as a single-height cell.

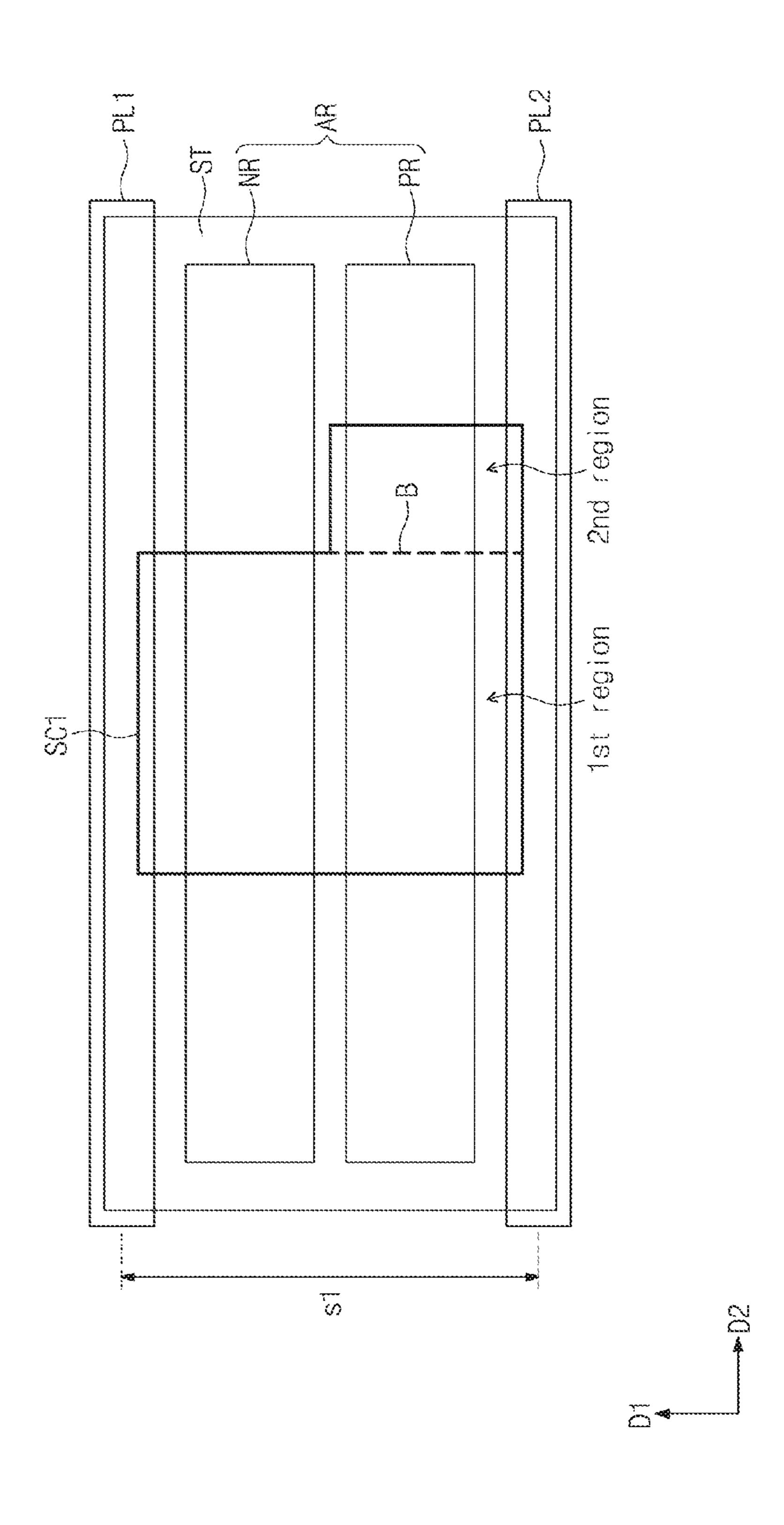

FIG. 15 illustrates an exemplary embodiment of the standard cell SC1 having the polygonal shape. For example, the standard cell SC1 may include a first region and a second 65 region. A thick dotted line B may be a boundary between the first region and the second region.

12

The first region may overlap with (i.e., at least partially include) a first power line PL1, an active region AR, and a second power line PL2. The active region AR may include an NMOS region NR and a PMOS region PR. The second region may overlap with (i.e., at least partially include) the PMOS region PR and the second power line PL2. Transistors for performing a specific function may be formed on the NMOS region NR and PMOS region PR of the standard cell SC1. In addition, conductive patterns for connecting the transistors to each other or connecting the transistors to another standard cell may also be disposed on the NMOS region NR and PMOS region PR of the standard cell SC1.

FIG. 16 illustrates an exemplary embodiment of the standard cell SC1 having the polygonal shape. For example, the standard cell SC1 may include a first region, a second region, and a third region. A thick dotted line B1 may be a boundary between the first region and the second region, and a thick dotted line B2 may be a boundary between the first region and the third region.

The first region may overlap with (i.e., at least partially include) the first power line PL1, the active region AR, and the second power line PL2. Each of the second and third regions may overlap with (i.e., at least partially include) the second power line PL2 and the PMOS region PR. The second region may be in contact with one edge of the first region, and the third region may be in contact with another edge, opposite to the one edge, of the first region.

FIG. 17 illustrates an exemplary embodiment of the standard cell SC1 having the polygonal shape. For example, the standard cell SC1 may include a first region, a second region, and a fourth region. A thick dotted line B1 may be a boundary between the first region and the second region, and a thick dotted line B2 may be a boundary between the first region and the fourth region.

The first region may overlap with (i.e., at least partially include) the first power line PL1, the active region AR, and the second power line PL2. The second region may overlap with (i.e., at least partially include) the PMOS region PR and the second power line PL2. The fourth region may overlap with (i.e., at least partially include) the first power line PL1 and the NMOS region NR. The second region may be in contact with one edge of the first region, and the fourth region may be in contact with another edge, opposite to the one edge, of the first region.

FIG. 18 illustrates an exemplary embodiment of the standard cell SC1 having the polygonal shape. For example, the standard cell SC1 may include a first region, a second region, and a fifth region. A thick dotted line B1 may be a boundary between the first region and the second region, and a thick dotted line B2 may be a boundary between the second region and the fifth region.

Each of the first and fifth regions may overlap with (i.e., at least partially include) the first power line PL1, the active region AR, and the second power line PL2. The second region may overlap with (i.e., at least partially include) the PMOS region PR and the second power line PL2. The second region may be in contact with one edge of the first region, and the fifth region may be in contact with another edge of the second region, which is not in contact with the first region.

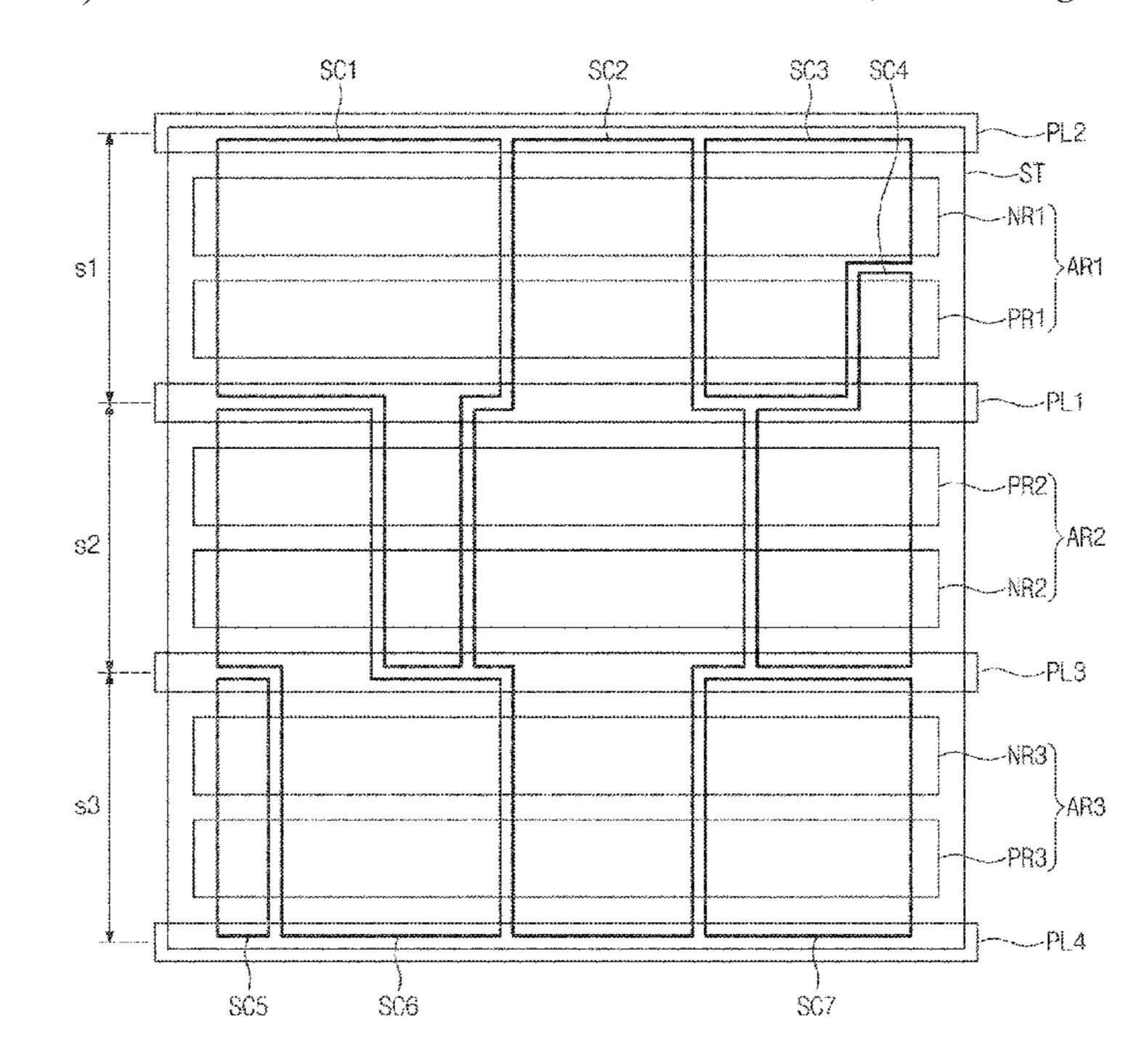

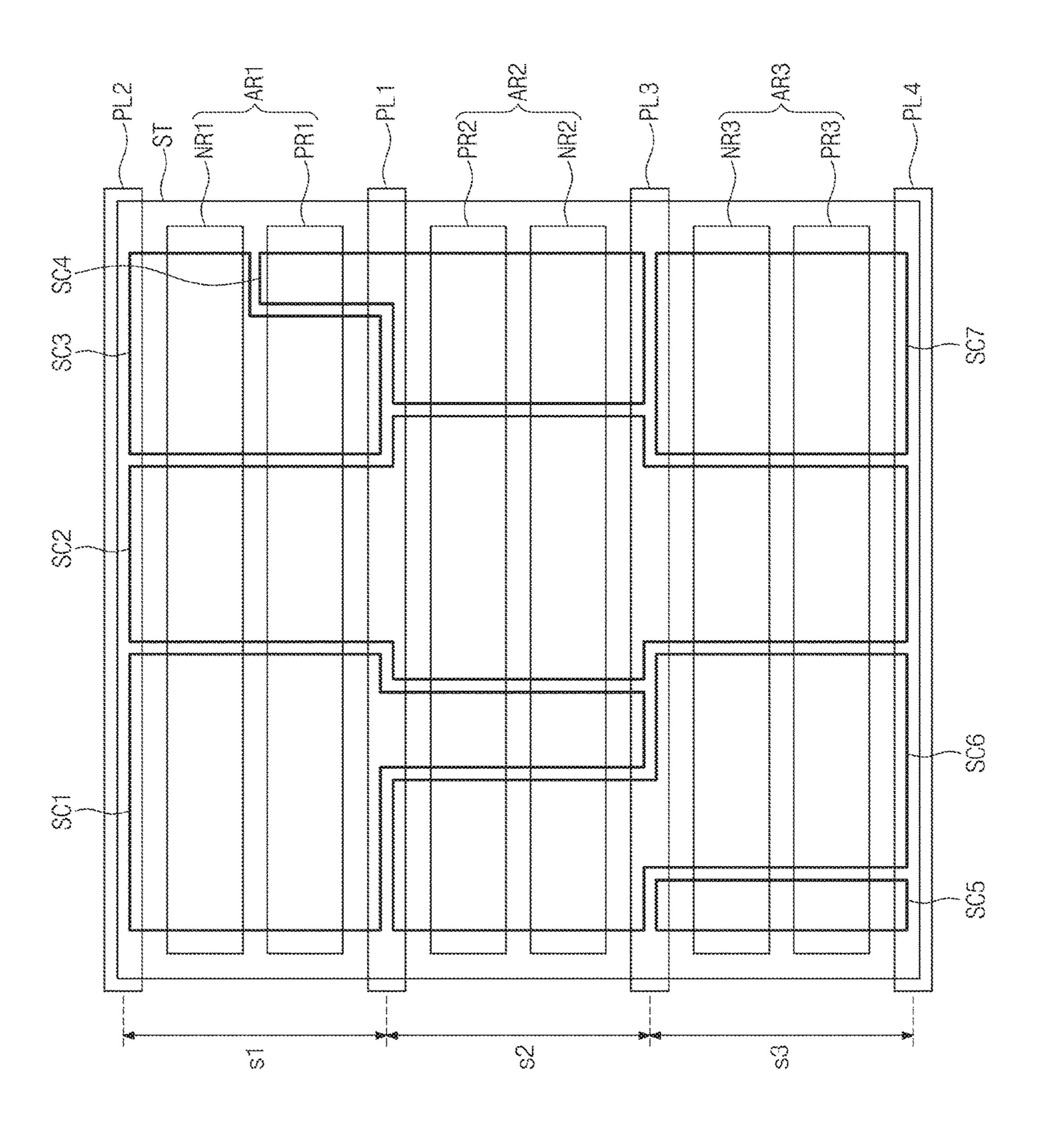

FIG. 19 is a plan view illustrating a layout of a semiconductor device according to an exemplary embodiment. FIG. 19 illustrates standard cells SC1 to SC7 designed according to an exemplary embodiment. As illustrated in FIG. 19, the standard cells SC1, SC2, SC4, and SC6 may be multi-height cells, and the standard cells SC3, SC5, and SC7 may be single-height cells. As described above, each of the standard

cells SC1 to SC7 may overlap with (i.e., at least partially include) at least one of the active regions AR1 to AR3. In FIG. 19, the standard cell SC2 overlaps with (i.e., at least partially include) three active regions AR1 to AR3. However, exemplary embodiments are not limited thereto. The standard cell may overlap with (i.e., at least partially include) four or more active regions.

Various standard cells having the polygonal shapes which are not a quadrilateral shape are described in the above embodiments. Since the layout of the semiconductor device 10 is designed using the standard cell having the polygonal shape which is not a quadrilateral shape, the occupied area of the layout of the semiconductor device may be reduced.

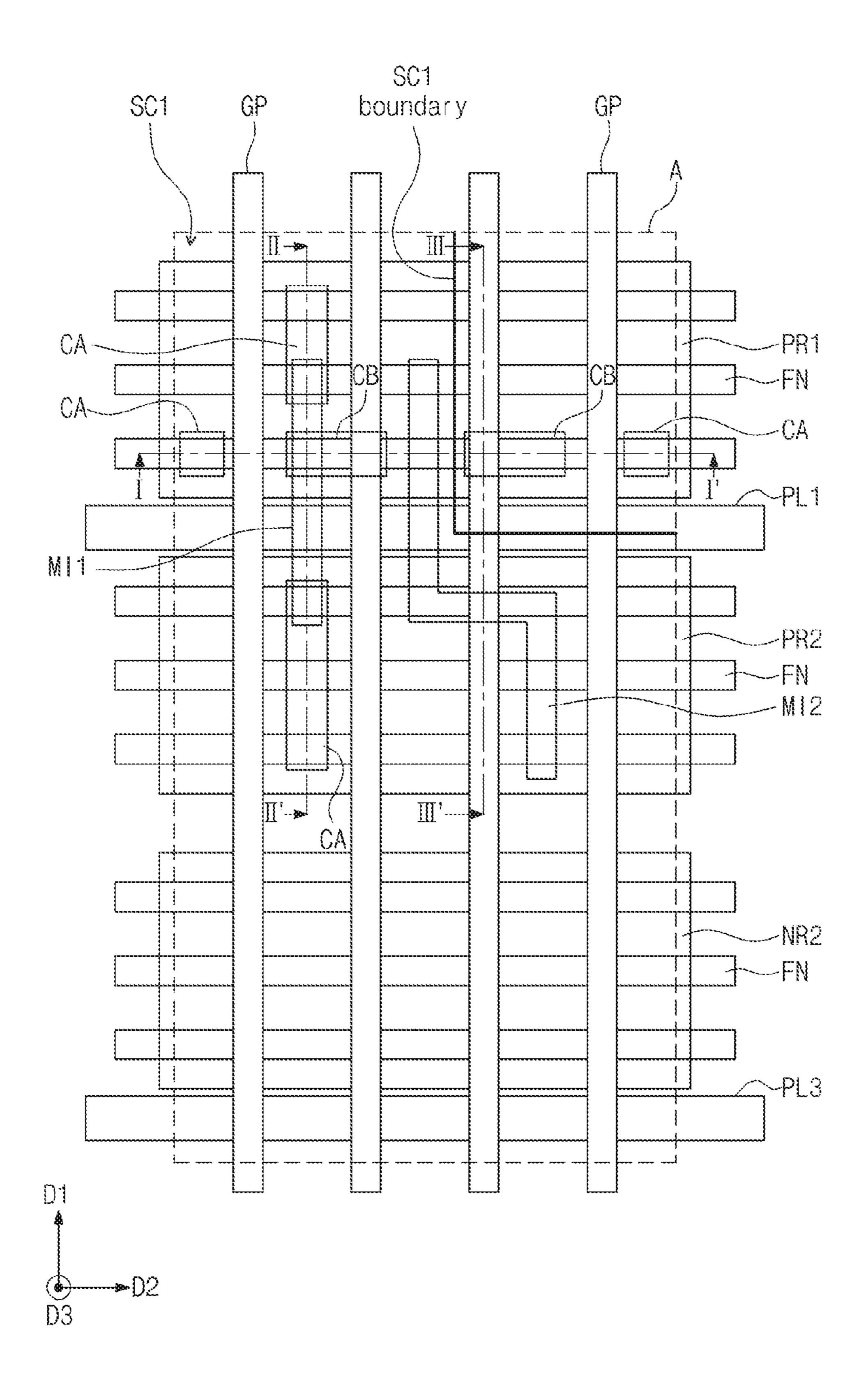

FIGS. 20A and 20B are plan views illustrating semiconductor devices including standard cells having polygonal 15 shapes, according to an exemplary embodiment. In detail, FIG. 20A illustrates the region 'A' of FIG. 10, 11, 12, or 13 in detail. FIG. 20B illustrates a region 'C' of FIG. 14 in detail. FIG. 20C is a cross-sectional view taken along a line I-I' of FIG. 20A or 20B. FIG. 20D is a cross-sectional view 20 taken along a line II-II' of FIG. 20A or 20B. FIG. 20E is a cross-sectional view taken along a line III-III' of FIG. 20A or 20B.

In the exemplary embodiments described with reference to FIGS. 10 to 13, the standard cell SC1 may overlap with 25 (i.e., at least partially include) the second power line PL2, the first NMOS region NR1, the first PMOS region PR1, the first power line PL1, the second PMOS region PR2, the second NMOS region NR2, and the third power line PL3. In the embodiment described with reference to FIG. 14, the 30 standard cell SC1 may overlap with (i.e., at least partially include) the second power line PL2, the first NMOS region NR1, the first PMOS region PR1, the first power line PL1, the second PMOS region PR2, the second NMOS region NR2, the third power line PL3, the third NMOS region NR3, the third PMOS region PR3, and the fourth power line PL4. The standard cell SC1 may have the polygonal shape. In FIGS. 20A and 20B, the boundary of the standard cell SC1 is illustrated by a polygonal line (SC1 boundary), not a straight line parallel to the first direction D1. Hereinafter, the 40 semiconductor device including the standard cell having the polygonal shape and a method for manufacturing the same will be described in detail.

Referring to FIGS. 20A to 20E, a substrate 100 may be provided. For example, the substrate 100 may be a silicon 45 substrate, a germanium substrate, or a silicon-on-insulator (SOI) substrate. Active fin patterns FN may be formed on the substrate 100. The active fin patterns FN may extend in a second direction D2 and may be spaced apart from each other in a first direction D1. First device isolation layers ST1 may be formed between the active fin patterns FN. Second device isolation layers ST2 may be formed in the substrate **100** to define PMOSFET regions PR1 and PR2 and NMOS-FET regions NR1 and NR2. In an exemplary embodiment, the first and second device isolation layers ST1 and ST2 may 55 be formed using a shallow-trench isolation (STI) technique. The active fin patterns FN may correspond to portions of the substrate 100 that are defined by the first device isolation layers ST1. For example, the first and second device isolation layers ST1 and ST2 may include silicon oxide.

The first and second device isolation layers ST1 and ST2 may have depths in a direction opposite to a third direction D3. The third direction D3 may be a direction perpendicular to a top surface of the substrate 100. In an exemplary embodiment, the depths of the first device isolation layers 65 ST1 may be shallower than those of the second device isolation layers ST2. The first device isolation layers ST1

**14**

may be formed by a process different from a process of forming the second device isolation layers ST2. In an exemplary embodiment, the first and second device isolation layers ST1 and ST2 may be formed at the same time, and the depths of the first device isolation layers ST1 may be substantially equal to those of the second device isolation layers ST2.

Gate electrodes GP may be formed on the active fin patterns FN. The gate electrodes GP may extend in the first direction D1 to intersect the active fin patterns FN. The gate electrodes GP may be spaced apart from each other in the second direction D2. A gate insulating pattern GI may be formed under each of the gate electrodes GP, and gate spacers GS may be formed on both sidewalls of each of the gate electrodes GP. The gate insulating pattern GI may be formed between each of the gate electrodes GP and the active fin patterns FN. In addition, a capping pattern CP may be formed to cover a top surface of each of the gate electrodes GP. A first interlayer insulating layer 110 may be formed to cover the gate electrodes GP.

For example, the gate electrodes GP may include at least one of a semiconductor material doped with dopants, a metal, or a conductive metal nitride. The gate insulating pattern GI may include at least one of silicon oxide, silicon oxynitride, or a high-k dielectric material. The high-k dielectric material may have a dielectric constant higher than that of silicon oxide. Each of the capping pattern CP and the gate spacer GS may include at least one of silicon oxide, silicon nitride, or silicon oxynitride. The first interlayer insulating layer 110 may include at least one of a silicon oxide layer or a silicon oxynitride layer.

Source/drain regions SD may be formed on the active fin patterns FN at both sides of each of the gate electrodes GP. The source/drain regions SD may be doped with P-type or N-type dopants. In an exemplary embodiment, the source/drain regions SD may be formed by performing an ion implantation process on the active fin patterns FN using the gate electrodes GP as an ion implantation mask.

In an exemplary embodiment, the source/drain regions SD may include epitaxial patterns formed by a selective epitaxial growth (SEG) process. The source/drain regions SD may include a different semiconductor element than that of the substrate 100. For example, the source/drain regions SD may include a semiconductor element of which a lattice constant is greater or smaller than that of the semiconductor element of the substrate 100. Since the source/drain regions SD include a different semiconductor element from the substrate 100, the source/drain regions SD may apply compressive stress or tensile stress to channel regions AF disposed between the source/drain regions SD. In an exemplary embodiment, when the substrate 100 is a silicon substrate, the source/drain regions SD of the PMOSFET regions PR1 and PR2 may include silicon-germanium (embedded SiGe) or germanium (Ge). The source/drain regions SD of the PMOSFET regions PR1 and PR2 may apply the compressive stress to the channel regions AF of the PMOS-FET regions PR1 and PR2. In an exemplary embodiment, when the substrate 100 is a silicon substrate, the source/drain regions SD of the NMOSFET regions NR1 and NR2 may 60 include silicon carbide (SiC). The source/drain regions SD of the NMOSFET regions NR1 and NR2 may apply the tensile stress to the channel regions AF of the NMOSFET regions NR1 and NR2. As a result, the mobility of carriers generated in the channel regions AF may be improved.

Source/drain contacts CA may be formed between the gate electrodes GP. The source/drain contacts CA may be electrically connected to the source/drain regions SD. The

source/drain contacts CA may be provided in the first interlayer insulating layer 110. At least one of the source/drain contacts CA may connect some source/drain regions SD arranged along the first direction D1 to each other.

Gate contacts CB may be formed in an upper portion of 5 the first interlayer insulating layer 110. Each of the gate contacts CB may penetrate the capping pattern CP so as to be directly connected to the gate electrode GP. Bottom surfaces of the gate contacts CB may be disposed at a higher level than bottom surfaces of the source/drain contacts CA. 10 In addition, the bottom surfaces of the gate contacts CB may be disposed at a higher level than top surfaces of the source/drain regions SD.