#### US00RE49484E

## (19) United States

## (12) Reissued Patent

Cho et al.

## (10) Patent Number:

## US RE49,484 E

### (45) Date of Reissued Patent:

Apr. 4, 2023

### ORGANIC LIGHT-EMITTING DISPLAY APPARATUS AND METHOD OF REPAIRING THE SAME

- Applicant: Samsung Display Co., Ltd., Yongin-si (KR)

- Inventors: Young-Jin Cho, Yongin-si (KR);

- Young-In Hwang, Yongin-si (KR); Dong-Gyu Kim, Yongin-si (KR)

- Assignee: Samsung Display Co., Ltd., Yongin-si (KR)

- Appl. No.: 16/807,126

- Filed: Mar. 2, 2020 (22)

#### Related U.S. Patent Documents

Reissue of:

9,911,799 (64) Patent No.: Issued: Mar. 6, 2018 Appl. No.: 14/231,618 Filed: Mar. 31, 2014

#### (30)Foreign Application Priority Data

(KR) ...... 10-2013-0057959 May 22, 2013 (KR) ...... 10-2013-0068638 Jun. 14, 2013

#### Int. Cl. (51)

H01L 27/32 (2006.01)G09G 3/3225 (2016.01)H01L 27/12 (2006.01)H01L 51/52 (2006.01)(2006.01)H01L 51/56

U.S. Cl. (52)

> CPC ...... *H01L 27/326* (2013.01); *G09G 3/3225* (2013.01); *H01L 27/1225* (2013.01); *H01L 27/3276* (2013.01); *H01L 51/5203* (2013.01); **H01L 51/56** (2013.01); G09G 2300/0426 (2013.01); G09G 2300/0465 (2013.01); G09G 2300/0819 (2013.01); G09G 2300/0852 (2013.01); G09G 2300/0861 (2013.01); G09G 2310/0245 (2013.01); G09G 2310/0251 (2013.01); G09G 2320/043 (2013.01); G09G 2320/045 (2013.01); G09G 2330/08 (2013.01); G09G 2330/10 (2013.01); H01L 2251/568 (2013.01)

#### Field of Classification Search (58)

27/3276; H01L 51/56; H01L 27/326; H01L 2251/568; H01L 27/3223; G09G 3/3225; G09G 2300/0861; G09G 2300/0465; G09G 2300/0426; G09G 2330/10; G09G 2300/0852; G09G 2320/043; G09G 2300/0819; G09G 2310/0251; G09G 2320/045; G09G 2310/0245; G09G 2330/08

See application file for complete search history.

#### **References Cited** (56)

#### U.S. PATENT DOCUMENTS

| 6,639,634 | В1 | 10/2003 | Zhang et al. |

|-----------|----|---------|--------------|

| 6,788,356 | B2 | 9/2004  | Song         |

| 6.979.956 | B2 | 12/2005 | Park et al.  |

| 7,248,324    | B2         | 7/2007  | Ono et al.            |  |  |  |  |

|--------------|------------|---------|-----------------------|--|--|--|--|

| 7,645,631    |            |         | Matsunaga             |  |  |  |  |

| 7,777,700    |            |         | Kwak et al.           |  |  |  |  |

| 7,884,785    |            |         | Yamashita et al.      |  |  |  |  |

| 7,978,165    |            |         | Kamada                |  |  |  |  |

| 8,258,692    |            |         | Hong et al.           |  |  |  |  |

| 8,436,956    |            |         | Kim G02F 1/133371     |  |  |  |  |

| , ,          |            |         | 349/43                |  |  |  |  |

| 8,922,461    | B2         | 12/2014 | Sagawa et al.         |  |  |  |  |

| 9,129,544    |            |         | Saitoh et al.         |  |  |  |  |

| 9,256,109    | B2         | 2/2016  | Kang et al.           |  |  |  |  |

| 9,911,385    | B2         | 3/2018  | •                     |  |  |  |  |

| 2001/0028429 | <b>A</b> 1 | 10/2001 | Wu                    |  |  |  |  |

| 2005/0173707 | <b>A</b> 1 | 8/2005  | Shiraki et al.        |  |  |  |  |

| 2005/0275352 | <b>A</b> 1 | 12/2005 | Sun                   |  |  |  |  |

| 2006/0017674 | <b>A</b> 1 | 1/2006  | Kamada                |  |  |  |  |

| 2006/0061524 | <b>A</b> 1 | 3/2006  | Suh et al.            |  |  |  |  |

| 2007/0046186 | <b>A</b> 1 | 3/2007  | Kim                   |  |  |  |  |

| 2007/0075944 | <b>A</b> 1 | 4/2007  | Shibusawa             |  |  |  |  |

| 2007/0120476 | <b>A</b> 1 | 5/2007  | Park et al.           |  |  |  |  |

| 2007/0152567 | <b>A</b> 1 | 7/2007  | Yao et al.            |  |  |  |  |

| 2008/0018636 | <b>A</b> 1 | 1/2008  | Chang                 |  |  |  |  |

| 2008/0024693 | <b>A</b> 1 | 1/2008  | Lee et al.            |  |  |  |  |

| 2008/0062096 | A1*        | 3/2008  | Yamashita G09G 3/3233 |  |  |  |  |

|              |            |         | 345/82                |  |  |  |  |

| 2009/0108763 | <b>A</b> 1 | 4/2009  | Han et al.            |  |  |  |  |

| 2009/0262049 | <b>A</b> 1 | 10/2009 | Yoon et al.           |  |  |  |  |

| 2010/0001941 | <b>A</b> 1 | 1/2010  | Shin et al.           |  |  |  |  |

| 2010/0026729 | A1*        | 2/2010  | Toyomura G09G 3/3233  |  |  |  |  |

|              |            |         | 345/690               |  |  |  |  |

| 2010/0200869 | <b>A</b> 1 | 8/2010  | Sekiya                |  |  |  |  |

| 2010/0207106 |            | 8/2010  | Lhee et al.           |  |  |  |  |

| 2010/0238149 | <b>A</b> 1 | 9/2010  | Kishi et al.          |  |  |  |  |

| (Continued)  |            |         |                       |  |  |  |  |

|              |            |         |                       |  |  |  |  |

#### FOREIGN PATENT DOCUMENTS

CN 1744181 A 3/2006 CN 101110204 A 1/2008 (Continued)

#### OTHER PUBLICATIONS

KIPO Notice of Allowance dated Sep. 29, 2015, for Korean priority Patent application 10 2013-0068638, (6 pages).

(Continued)

Primary Examiner — Ling X Xu

(74) Attorney, Agent, or Firm — Lewis Roca Rothgerber Christie LLP

#### (57)ABSTRACT

Provided is an organic light-emitting display apparatus and a method of repairing the same. The organic light-emitting display apparatus includes: an emission device comprising a plurality of sub-emission devices; an emission pixel circuit configured to supply a driving current to the emission device; a dummy pixel circuit configured to supply the driving current to the emission device; and a repair line coupling the emission device to the dummy pixel circuit, wherein the emission device is configured to receive the driving current from the emission pixel circuit or the dummy pixel circuit.

#### 54 Claims, 33 Drawing Sheets

# US RE49,484 E Page 2

| (56) References Cited    |               | JP                   | 2008-065200       | 3/2008                                               |                                     |  |

|--------------------------|---------------|----------------------|-------------------|------------------------------------------------------|-------------------------------------|--|

|                          |               | JP                   | 2008-262013       | 10/2008                                              |                                     |  |

| U.S. PATENT DOCUMENTS    |               |                      | JP<br>JP          | 2009-003473<br>4222396 B2                            | 1/2009<br>2/2009                    |  |

| 2011/0025656             | 2/2011        | TT 1 . 1             | JP                | 2009-151098 A                                        | 7/2009                              |  |

| 2011/0025659             |               | Kwak et al.          | JP                | 2009-131098 A<br>2009-288733 A                       | 12/2009                             |  |

| 2011/0069061             | 1 A1* 3/2011  | Nakamura G09G 3/3225 | JP                | 2009-288733 A<br>2009-288773 A                       | 12/2009                             |  |

| 2011(001105              |               | 345/214              | JP                | 2010-003880 A                                        | 1/2010                              |  |

| 2011/0014066             |               | Kim et al.           | JP                | 2010-003660 A<br>2011-209369                         | 10/2010                             |  |

| 2011/0146066             |               | Kim et al.           | JP                | 2011-203303<br>2012-247808 A                         | 12/2012                             |  |

| 2011/0175885             |               |                      | JP                | 2012-247000 A<br>2013-97093 A                        | 5/2013                              |  |

| 2012/0113077             |               | Kang                 | KR                | 10-2008-0000097 A                                    | 1/2008                              |  |

| 2012/0146034             |               | Hong et al.          | KR                | 10-2008-0024009 A                                    | 3/2008                              |  |

| 2012/0146999             |               | Hwang                | KR                | 10-2008-0059928 A                                    | 7/2008                              |  |

| 2012/0306840             |               |                      | KR                | 10-2008-0100533                                      | 11/2008                             |  |

| 2012/0326603             |               |                      | KR                | 10-0932989 B1                                        | 12/2009                             |  |

| 2013/0120230             |               | Chen et al.          | KR                | 10-2010-0091104                                      | 8/2010                              |  |

| 2013/0176194             |               | Jin et al.           | KR                | 10-1022156 B1                                        | 3/2011                              |  |

| 2013/0293236             |               | Lee et al.           | KR                | 10-1156447 B1                                        | 6/2012                              |  |

| 2015/0109189             | 9 A1" 4/2015  | Hwang G09G 3/3225    | KR                | 10-2012-0140489 A                                    | 12/2012                             |  |

|                          |               | 345/78               | TW                | 200540747 A                                          | 12/2005                             |  |

|                          |               |                      | WO                | WO 2004/068446                                       | 8/2004                              |  |

| FOREIGN PATENT DOCUMENTS |               | WO                   | WO 2012/001740 A1 | 1/2012                                               |                                     |  |

|                          |               |                      | WO                | WO 2012/137817                                       | 10/2012                             |  |

| CN                       | 101202014 A   | 6/2008               |                   |                                                      |                                     |  |

| CN                       | 101520560 A   | 9/2009               |                   |                                                      |                                     |  |

| CN                       | 101802900 A   | 8/2010               |                   | OTHER PU                                             | BLICATIONS                          |  |

| CN                       | 101989403 A   | 3/2011               |                   |                                                      |                                     |  |

| CN                       | 102437112 A   | 5/2012               | KIPO              | Office action dated Jul. 15                          | 5, 2014, for Korean priority Patent |  |

| CN                       | 102508384 A   | 6/2012               | applic            | application 10-2013-0068638, (5 pages).              |                                     |  |

| CN                       | 102983283 A   | 3/2013               |                   |                                                      | v. 2, 2022 issued in corresponding  |  |

| CN                       | 104103234 A   | 10/2014              |                   | cation No. CN 2019104978                             | •                                   |  |

| EP                       | 2 535 888 A1  |                      |                   |                                                      | n corresponding application No.     |  |

|                          | I 10-123563 A | 5/1998               |                   |                                                      | 1 0 11                              |  |

|                          | 001-305500 A  | 10/2001              |                   | 0497254.1, dated Jan. 31,                            | , I <del>C</del>                    |  |

|                          | 001-337349 A  | 12/2001              |                   | <b>-</b>                                             | 2015, for corresponding European    |  |

|                          | 003-050400    | 2/2003               | Patent            | application 14169289.7, (                            | (30 pages).                         |  |

|                          | 004-038188    | 2/2004               | Englis            | sh machine translation of In                         | nternational Publication WO 2012/   |  |

|                          | 006-030782    | 2/2007               | 00174             | 001740 dated Jan. 5, 2012, listed above, (12 pages). |                                     |  |

|                          | 007-047576    | 2/2007               |                   | · ·                                                  | d Sep. 30, 2014, corresponding to   |  |

|                          | 007-114477 A  | 5/2007               |                   | ean Patent application 141                           |                                     |  |

|                          | 007-149688    | 6/2007               | 20101             | Tari I acome application 1 11                        |                                     |  |

|                          | 007-316511 A  | 12/2007              | * oita            | d by examinar                                        |                                     |  |

| JP 2                     | 008-040478    | 2/2008               | · Cite            | ed by examiner                                       |                                     |  |

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

Apr. 4, 2023

FIG. 7

FIG. 8

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

CU1

CU2

CU1

RL

13 SN1 14 CM1 AD1' CN115 12 CN2 11 AD2' CM2

A

A

OL

AD1

OL

AD2

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28A

FIG. 28B

FIG. 29A

FIG. 29B

FIG. 30A

FIG. 30B

FIG. 31

FIG. 32

FIG. 33

FIG. 34

FIG. 35 EP3 ELVDD TC8 -2C N1 TC2 TC1 TC6\_ GW TC4 GW Vhold Vint Z OLEDn ELVSS

FIG. 36

FIG. 38

FIG. 39

FIG. 40

FIG. 41

FIG. 42

1

## ORGANIC LIGHT-EMITTING DISPLAY APPARATUS AND METHOD OF REPAIRING THE SAME

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held 10 invalid by a prior post-patent action or proceeding.

# CROSS-REFERENCE TO RELATED APPLICATIONS

[This application claims priority to and the benefit of Korean Patent Application Nos. 10-2013-0057959 and 10-2013-0068638, filed on May 22, 2013 and Jun. 14, 2013, respectively, in the Korean Intellectual Property Office, the disclosures of which are incorporated herein in their entirety by reference.] This application is a reissue application of U.S. Pat. No. 9,911,799, issued on Mar. 6, 2018, which claims priority to and the benefit of Korean Patent Application Nos. 10-2013-0057959 and 10-2013-0068638, filed on May 22, 2013 and Jun. 14, 2013, respectively, in the Korean Intellectual Property Office, the disclosures of which are incorporated herein in their entirety by reference.

#### BACKGROUND

#### 1. Field

Embodiments of the present invention relate to an organic light-emitting display apparatus and a method of repairing the same.

#### 2. Description of the Related Art

In an organic light-emitting display apparatus, when a pixel is defective, the pixel may emit light all the time or may display black (e.g., may not emit light), regardless of a scan signal and a data signal applied to the pixel. Pixels that emit light all the time, regardless of the scan or data signals, 40 are regarded as bright spots (or hot spots). By contrast, pixels that do not emit light (e.g., displayed in black), regardless of the scan or data signals, is regarded as a dark spot (or a black spot).

As a circuit in the pixel becomes more complex, bright 45 spots or dark spots due to circuit defects may not be easily solved or prevented.

#### **SUMMARY**

Embodiments of the present invention provide a display apparatus for forming a redundancy pattern in each column of pixels on a panel and normally driving a defective pixel by using the redundancy pattern.

According to an embodiment of the present invention, 55 there is provided An organic light-emitting display apparatus including: an emission device including a plurality of subemission devices; an emission pixel circuit configured to supply a driving current to the emission device; a dummy pixel circuit configured to supply the driving current to the 60 emission device; and a repair line coupling the emission device to the dummy pixel circuit, wherein the emission device is configured to receive the driving current from the emission pixel circuit or the dummy pixel circuit.

Each of the plurality of sub-emission devices may 65 include: a lower electrode among a plurality of separated lower electrodes; an upper electrode commonly facing the

2

plurality of separated lower electrodes; and an emission layer between the lower electrode and the upper electrode, wherein the plurality of separated lower electrodes are electrically coupled to each other through an electrode connection wiring.

The electrode connection wiring may include at least one of metal, amorphous silicon, crystalline silicon, and an oxide semiconductor.

The electrode connection wiring may be at a same layer and of a same material as an active layer of the emission pixel circuit.

The electrode connection wiring may be integrally formed with the plurality of separated lower electrodes.

The electrode connection wiring may include: a plurality of first connection units coupled to the plurality of separated lower electrodes; a second connection unit coupled to the emission pixel circuit; and a plurality of cut nodes between the first connection units and the second connection unit, wherein the cut nodes are cut to electrically isolate the plurality of separated lower electrodes from each other.

The electrode connection wiring may be coupled to the plurality of separated lower electrodes in each of the first connection units through a first contact hole and may be coupled to the emission pixel circuit through a second contact hole in the second connection unit.

The organic light-emitting display apparatus may further include at least one circuit wiring having one end coupled to the emission pixel circuit and another end coupled to the second connection unit, wherein the at least one circuit wiring may be configured to be cut to electrically isolate the emission pixel circuit from the emission device.

The organic light-emitting display apparatus may further include a first repair connection wiring having one end coupled to the repair line and another end overlapping with a first short wiring coupled to one of the first connection units; and an insulating layer between the first repair connection wiring and the first short wiring, wherein the first repair connection wiring is configured to be coupled to the first short wiring utilizing a laser beam.

Each of the first repair connection wiring and the first short wiring may be at a same layer and of a same material as respective conductive layers formed on different layers of the emission pixel circuit.

The dummy pixel circuit may be on at least one row among first and last rows of each column, or at least one column among first and last columns of each row.

The emission pixel circuit may be in a display area and the dummy pixel circuit is in a non-display area.

The emission pixel circuit and the dummy pixel circuit may have a same component structure and function.

The dummy pixel circuit may be coupled to the emission device through a second repair connection wiring having one end coupled to the repair line and another end overlapping with a second short wiring coupled to the dummy pixel circuit, wherein an insulating layer may be between the second repair connection wiring and the second short wiring.

The repair line may be coupled to a power voltage line through a power connection wiring and may be configured to be electrically isolated from the power voltage line by cutting the power connection wiring.

The repair line may be in each column or row.

The emission pixel circuit may include: a first transistor configured to transfer a data signal in response to a scan signal; a capacitor configured to be charged with a voltage corresponding to the data signal; and a second transistor

configured to transfer a driving current corresponding to the voltage charged in the capacitor to the emission device.

The emission pixel circuit may include: a first transistor configured to receive a data signal from a data line in response to a scan signal; a second transistor configured to 5 transfer a driving current corresponding to the data signal to the emission device; a third transistor configured to diodeconnect the second transistor; a first capacitor configured to be charged with a voltage corresponding to the data signal; and a second capacitor connected to one electrode of the first 10 capacitor and a gate electrode of the second transistor.

The emission pixel circuit may further include: a fourth transistor connected to between the first transistor and the one electrode of the first capacitor; a fifth transistor connected to between the data line and the one electrode of the 15 first capacitor; and a third capacitor having one electrode connected to a node between the first transistor and the fourth transistor and another electrode connected to a gate electrode of the fifth transistor.

The emission pixel circuit may include: a first transistor configured to receive a data signal from a data line in response to a scan signal; a second transistor configured to transfer a driving current corresponding to the data signal to the emission device; a third transistor configured to diodeconnect the second transistor; a fourth transistor connected to between the first transistor and the second transistor; a fifth transistor connected to between the second transistor and the emission device; a sixth transistor connected to between a gate electrode of the second transistor and an initial power; a first capacitor connected to between the gate 30 electrode of the second transistor and a first power source; and a second capacitor having one electrode connected to a node between the first transistor and the fourth transistor and another electrode connected to a second power source.

The dummy pixel circuit may be configured to supply the 35 driving current to the emission device at a predetermined time.

The dummy pixel circuit may be configured to supply a same data signal as that supplied by the emission pixel circuit to the emission device.

The plurality of sub-emission devices may include: a first sub-emission device including a first lower electrode, an upper electrode facing the first lower electrode, and a first emission layer between the first lower electrode and the upper electrode; and a second sub-emission device including 45 a second lower electrode, the upper electrode facing the second lower electrode, and a second emission layer between the second lower electrode and the upper electrode, wherein the first lower electrode and the second lower electrode are coupled to each other through an electrode 50 connection wiring.

The electrode connection wiring may include: a first connection unit coupled to the first lower electrode; a second connection unit coupled to the second lower electrode; a third connection unit coupled to the emission pixel circuit; 55 a first node between the first connection unit and the third connection unit and configured to be cut to electrically isolate the first sub-emission device from the emission pixel circuit; and a second node between the second connection unit and the third connection unit and configured to be cut 60 to electrically isolate the second sub-emission device from the emission pixel circuit.

The organic light-emitting display apparatus may further include a first repair connection wiring having one end coupled to the repair line and another end overlapping with 65 a first short wiring coupled to the first connection unit; a first insulating layer between the first repair connection wiring

4

and the first short wiring, wherein the first repair connection wiring is configured to be coupled to the first short wiring utilizing a laser beam; a second repair connection wiring having one end coupled to the repair line and another end overlapping with a second short wiring coupled to the dummy pixel circuit; and a second insulating layer between the second repair connection wiring and the second short wiring, wherein the second repair connection wiring is configured to be coupled to the second short wiring utilizing the laser beam.

According to another embodiment of the present invention there is provided a method of repairing a defective pixel in an organic light emitting display apparatus, the organic light emitting display apparatus including a plurality of emission pixels including an emission device including a plurality of sub-emission devices, the sub-emission devices being configured to receive a corresponding driving current from one of an emission pixel circuit and a dummy pixel circuit, the method including: connecting the defective pixel to the dummy pixel circuit through a repair line; and after connecting the defective pixel to the dummy pixel circuit, if the defective pixel does not normally emit light, separating the plurality of sub-emission devices.

The separating of the plurality of sub-emission devices may include: cutting between a connection unit of the emission pixel circuit and a connection unit of each of lower electrodes of the plurality of sub-emission devices in an electrode connection wiring that couples the lower electrodes to each other.

The method may further include after coupling the defective pixel to the dummy pixel circuit, if the defective pixel normally emits light, separating the emission pixel circuit and the emission device from each other.

The separating of the emission pixel circuit and the emission device may include: cutting at least one wiring coupled between the emission pixel circuit and the lower electrodes of the emission device.

The coupling of the defective pixel to the dummy pixel circuit may include: shorting a first short wiring coupled to the emission device and a second short wiring coupled to the dummy pixel circuit by: irradiating a laser beam onto a first repair connection wiring having one end coupled to the repair line and another end overlapping with the first short wiring, wherein a first insulating layer is between the first repair connection wiring and the first short wiring, and irradiating the laser beam onto a second repair connection wiring having one end coupled to the repair line and another end overlapping with the second short wiring with a second insulating layer between the second repair connection wiring and the second short wiring.

The method may further include separating a defective sub-emission device among a plurality of sub-emission devices of the defective pixel from the other sub-emission devices.

The separating of the defective sub-emission device among the plurality of sub-emission devices of the defective pixel from the other sub-emission devices may include: cutting between a connection unit of a lower electrode of the defective sub-emission device and a connection unit of the emission pixel circuit in an electrode connection wiring that couples lower electrodes of the plurality of sub-emission devices to each other.

## BRIEF DESCRIPTION OF THE DRAWINGS

The above and other features and aspects of the present invention will become more apparent by describing in detail exemplary embodiments thereof with reference to the attached drawings in which:

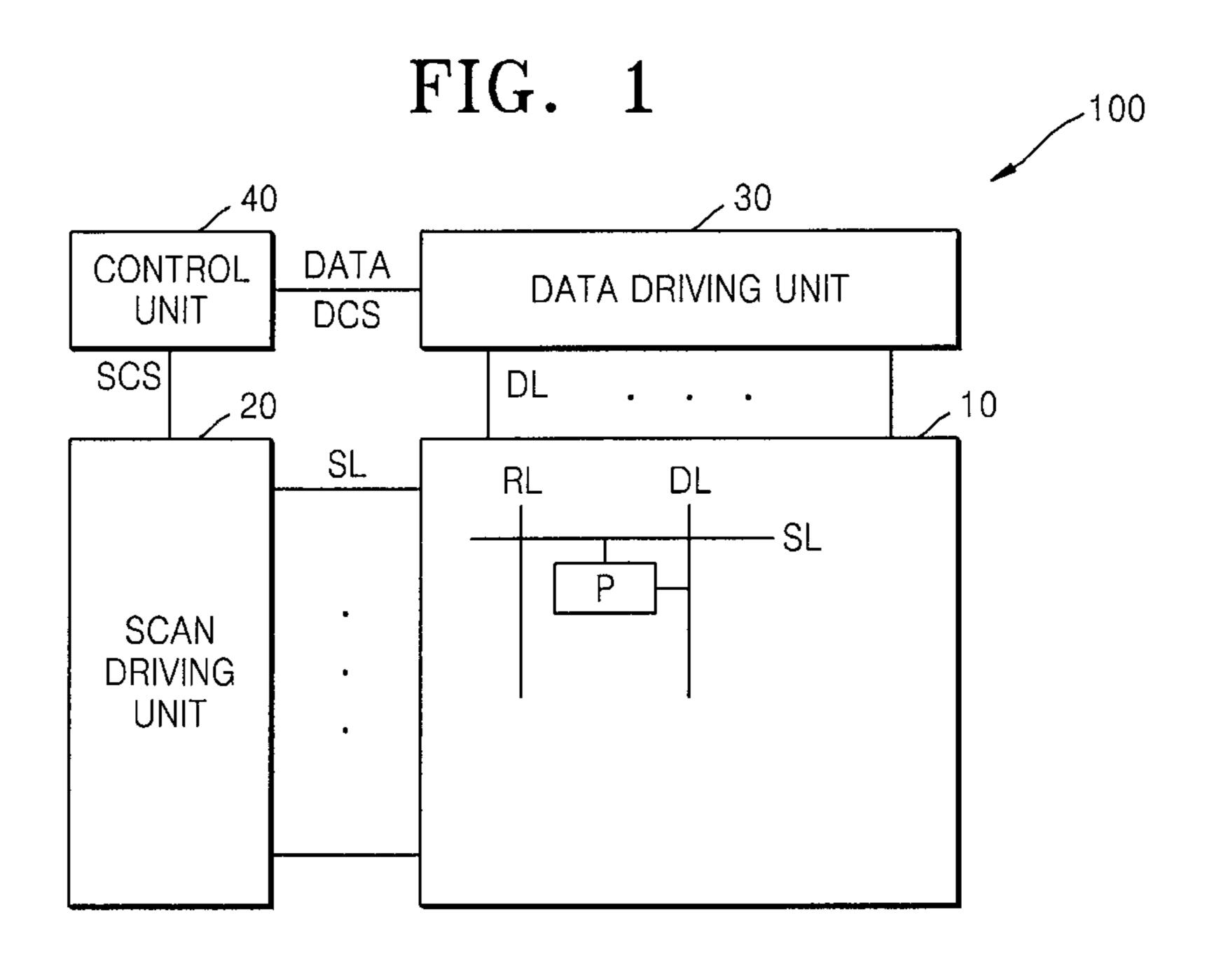

FIG. 1 is a block diagram of a display apparatus according to an embodiment of the present invention;

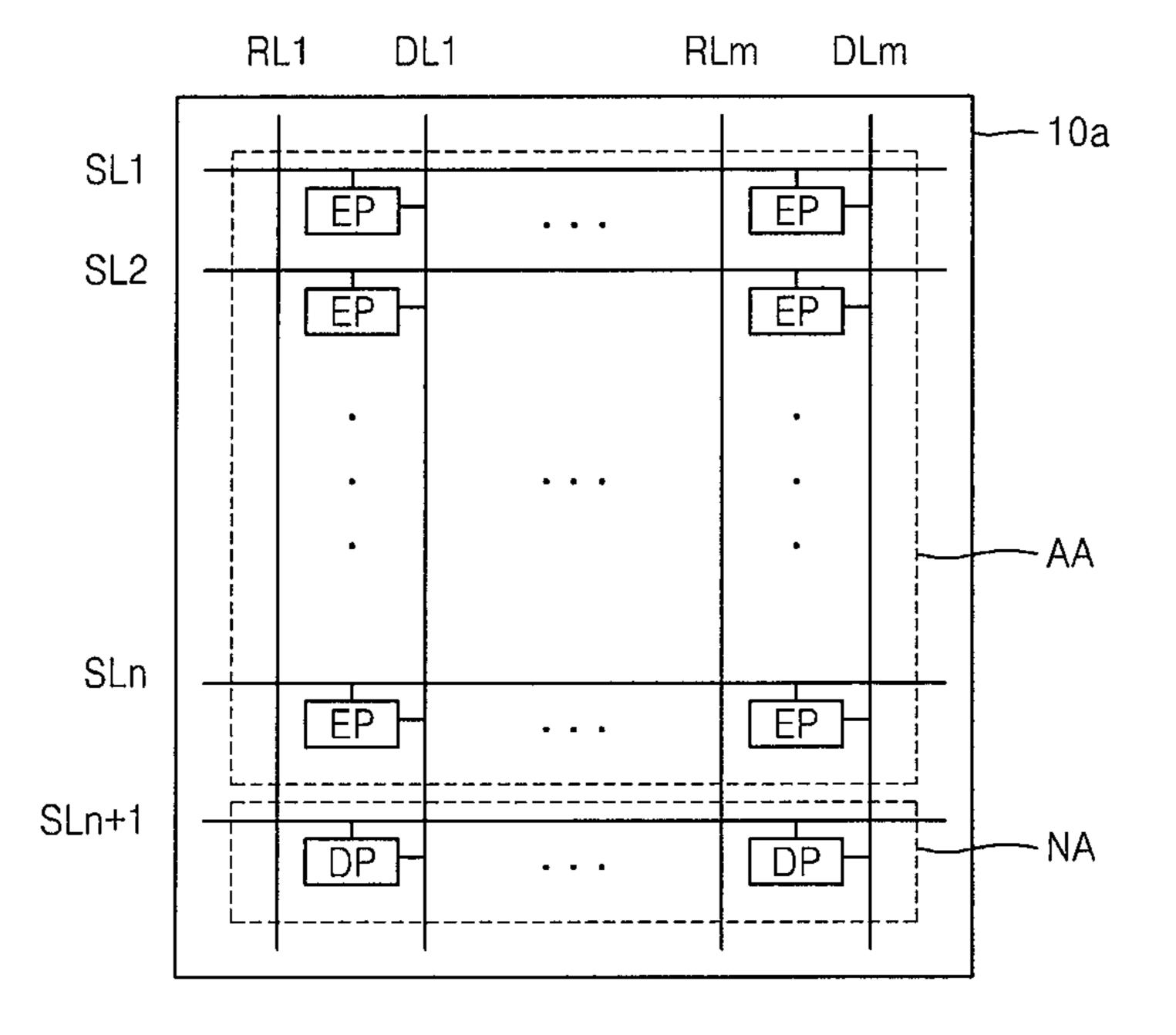

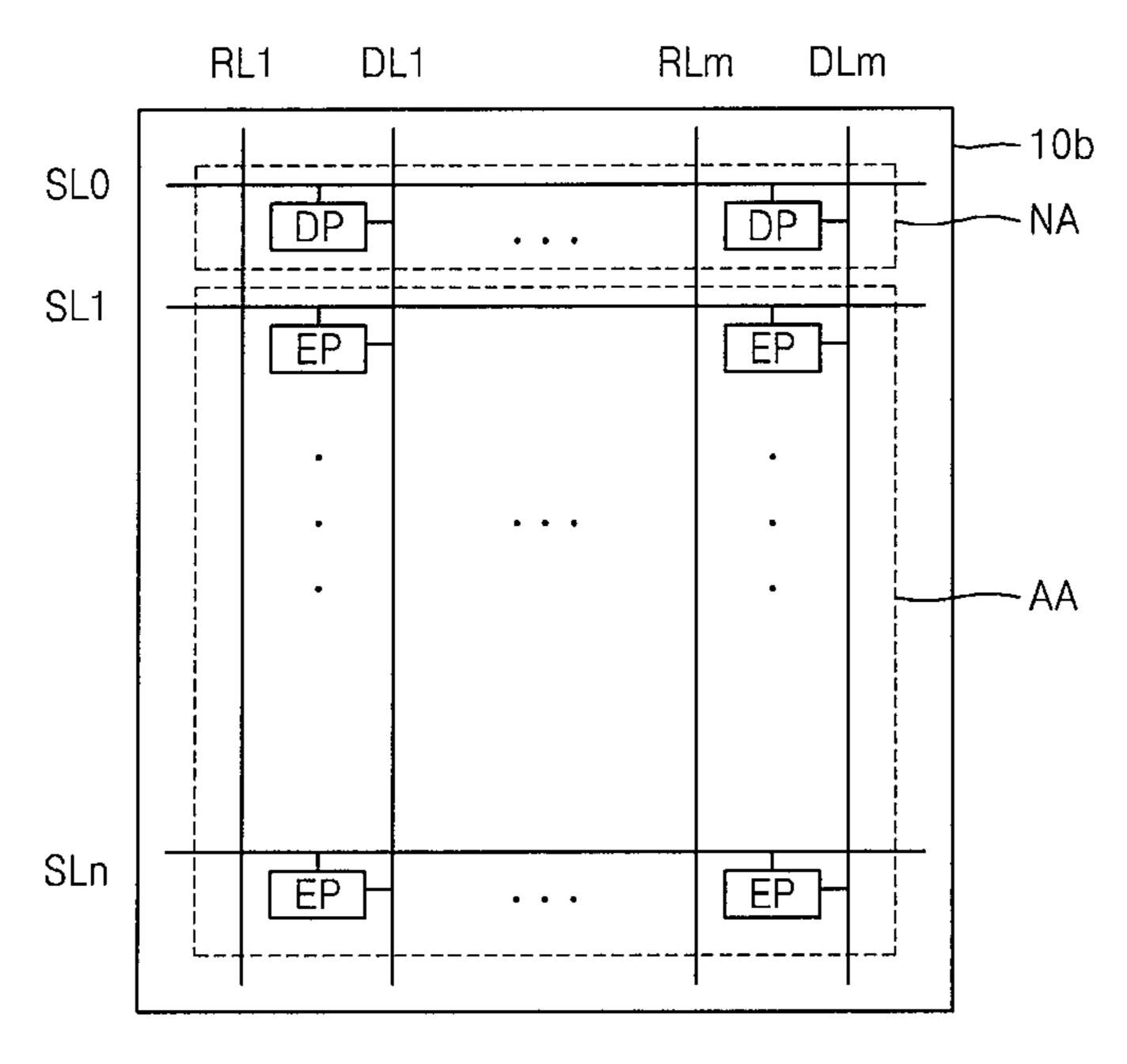

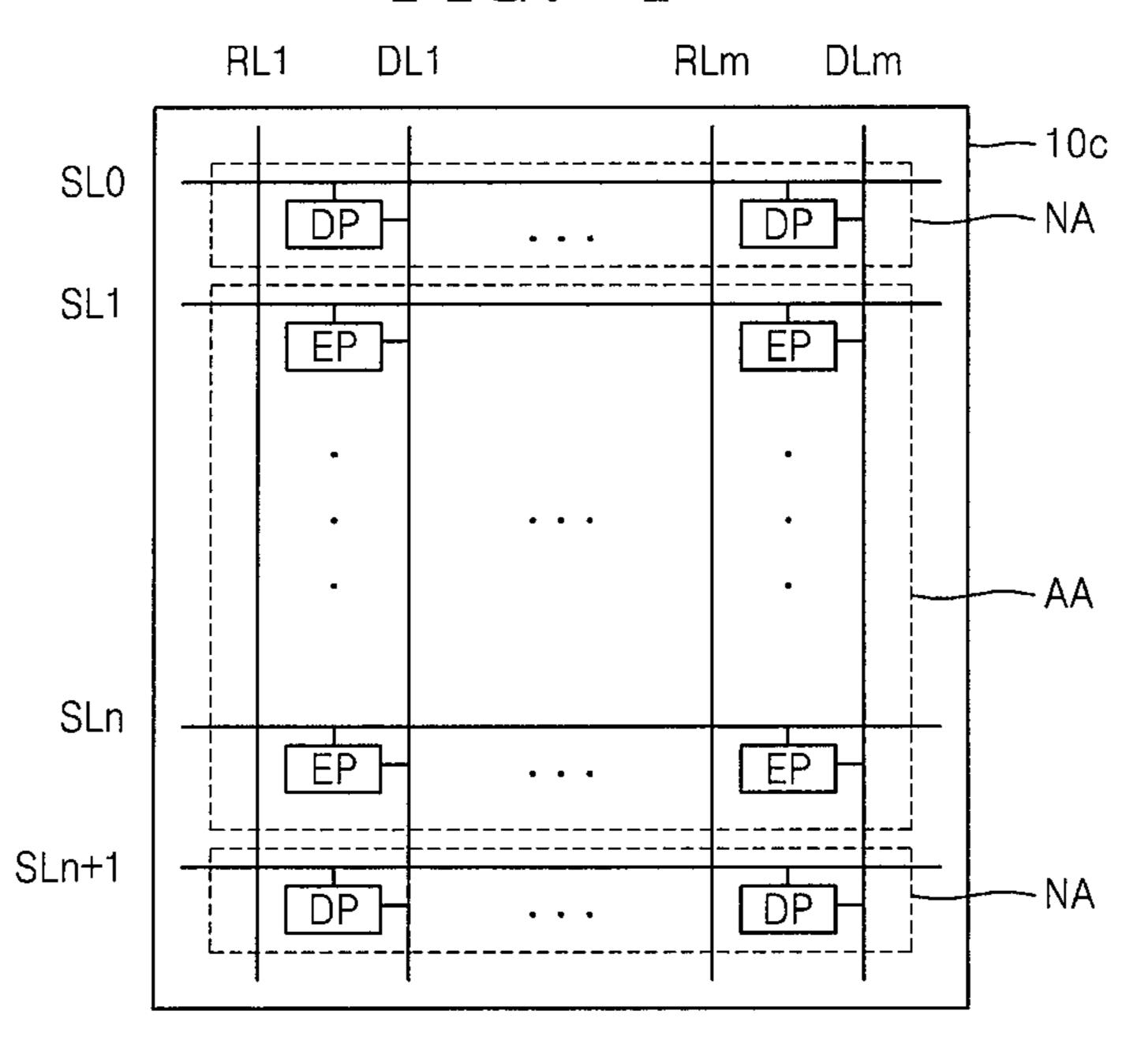

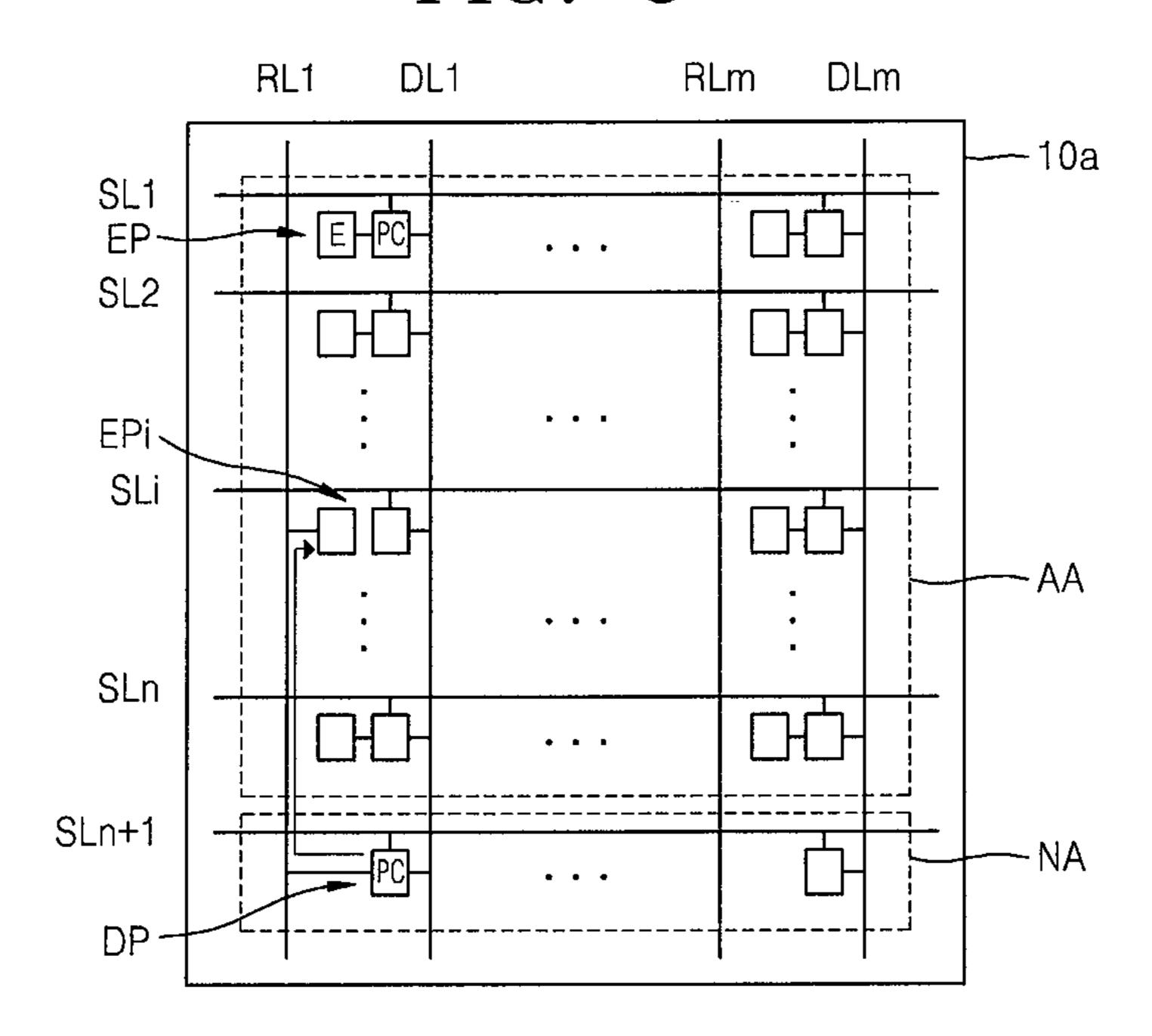

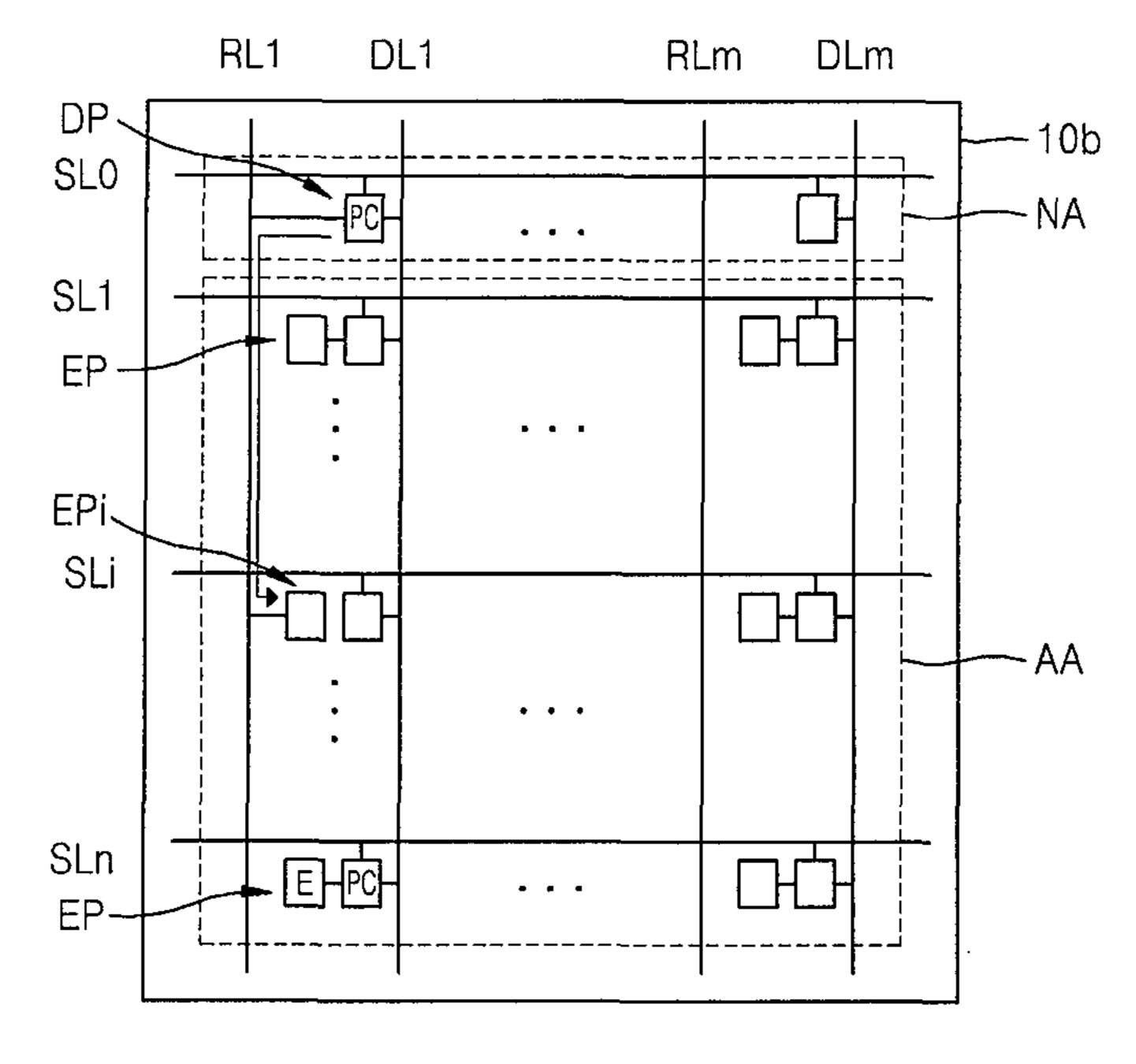

FIGS. 2 through 4 are schematic diagrams of examples of a display panel illustrated in FIG. 1;

FIG. 5 is a diagram for describing a method of repairing 5 a defective pixel by using a plurality of repair lines of the display panel of FIG. 2, according to an embodiment of the present invention;

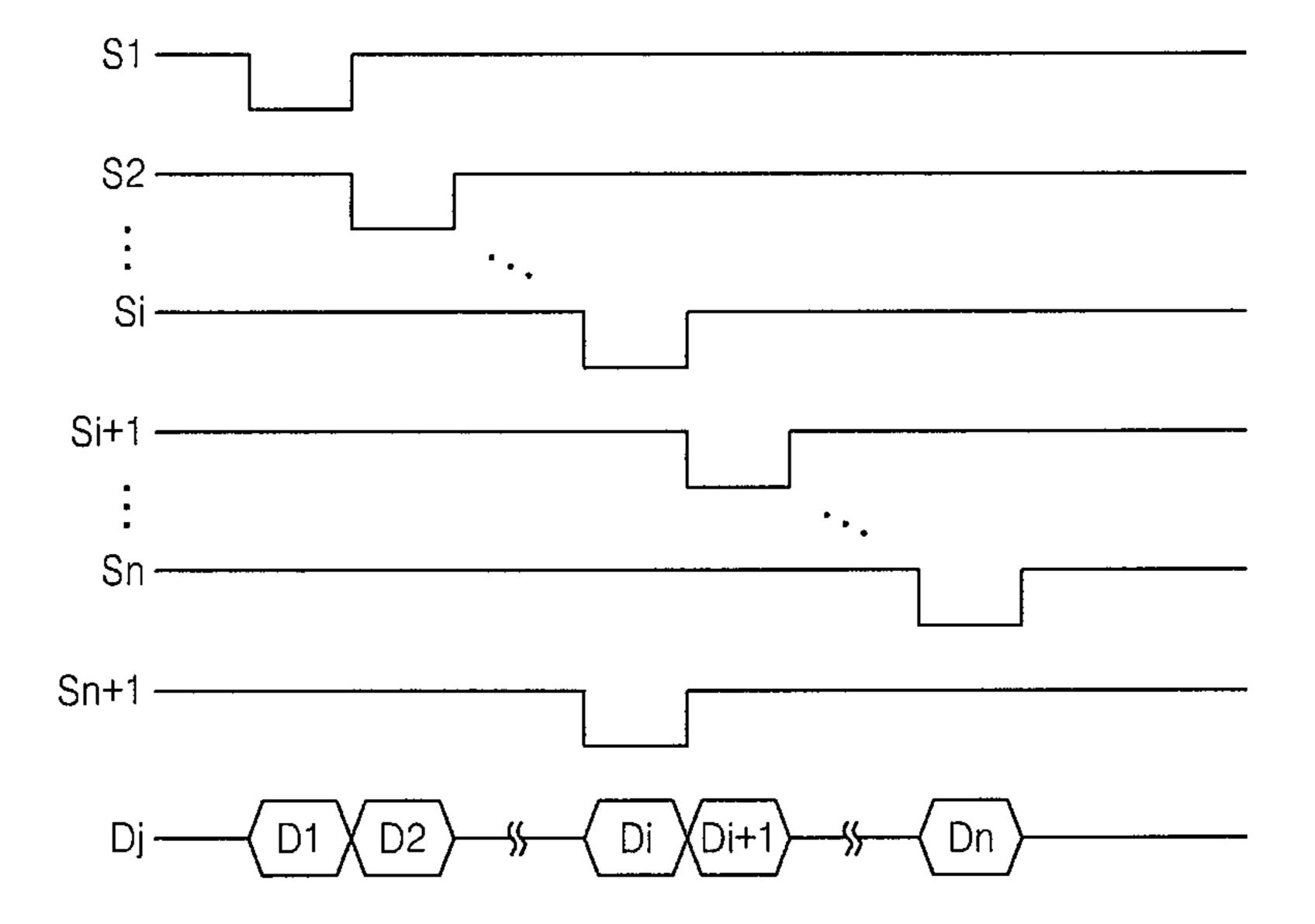

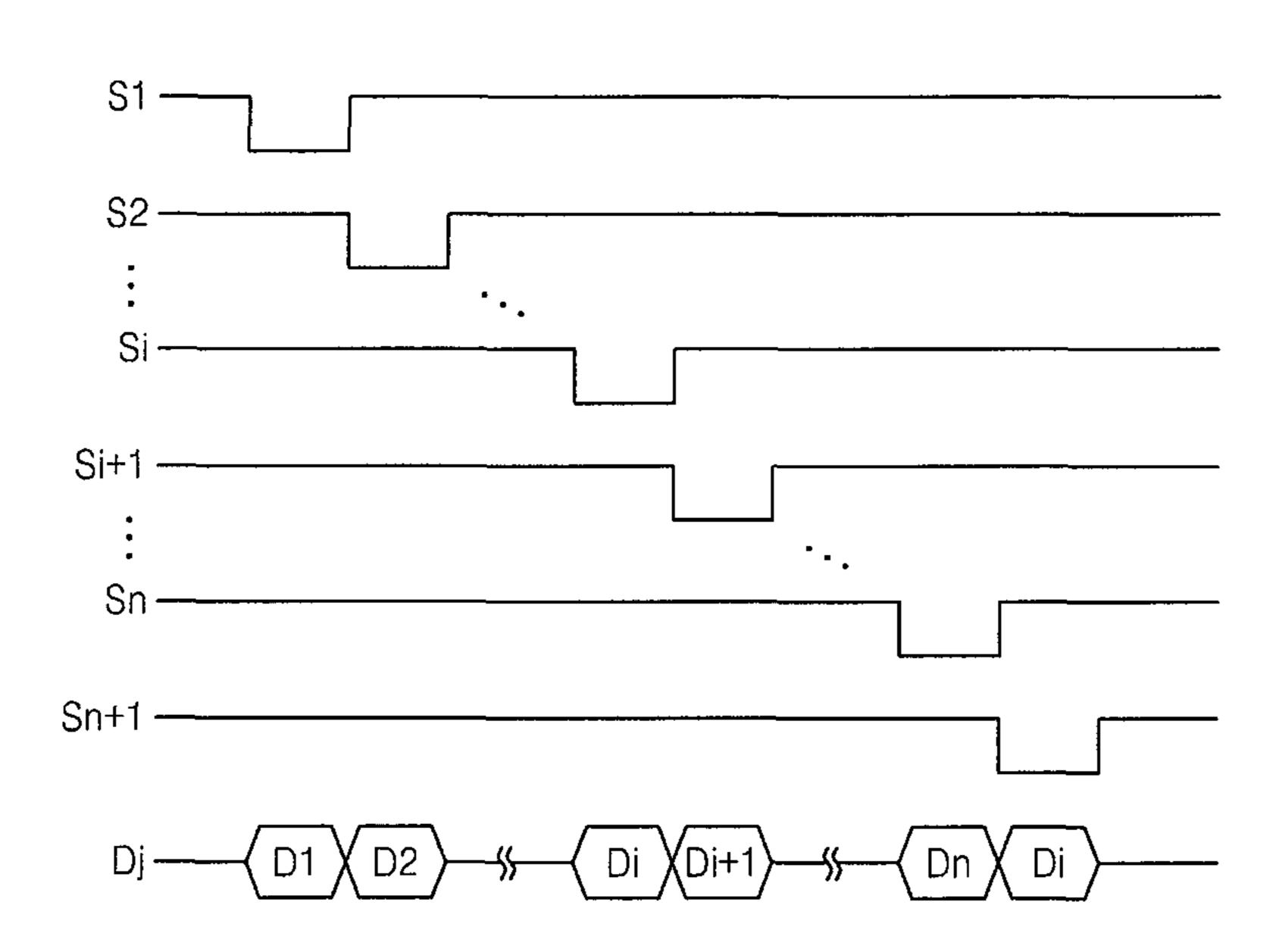

FIGS. 6 and 7 show waveforms of scan signals and data signals provided to the display panel repaired by using the method illustrated in FIG. 5;

FIG. 8 is a diagram for describing a method of repairing a defective pixel by using a plurality of repair lines of the display panel of FIG. 3, according to another embodiment of the present invention;

FIGS. 9 and 10 show waveforms of scan signals and data signals provided to the display panel repaired by using the method illustrated in FIG. 8;

FIG. 11 is a diagram for describing a method of repairing a defective pixel by using a plurality of repair lines of the 20 display panel of FIG. 4, according to another embodiment of the present invention;

FIGS. 12 and 13 show waveforms of scan signals and data signals provided to the display panel repaired by using the method illustrated in FIG. 11;

FIG. 14 is a schematic diagram of an emission pixel according to an embodiment of the present invention;

FIG. 15 is a plan view of an emission device of the emission pixel of FIG. 14;

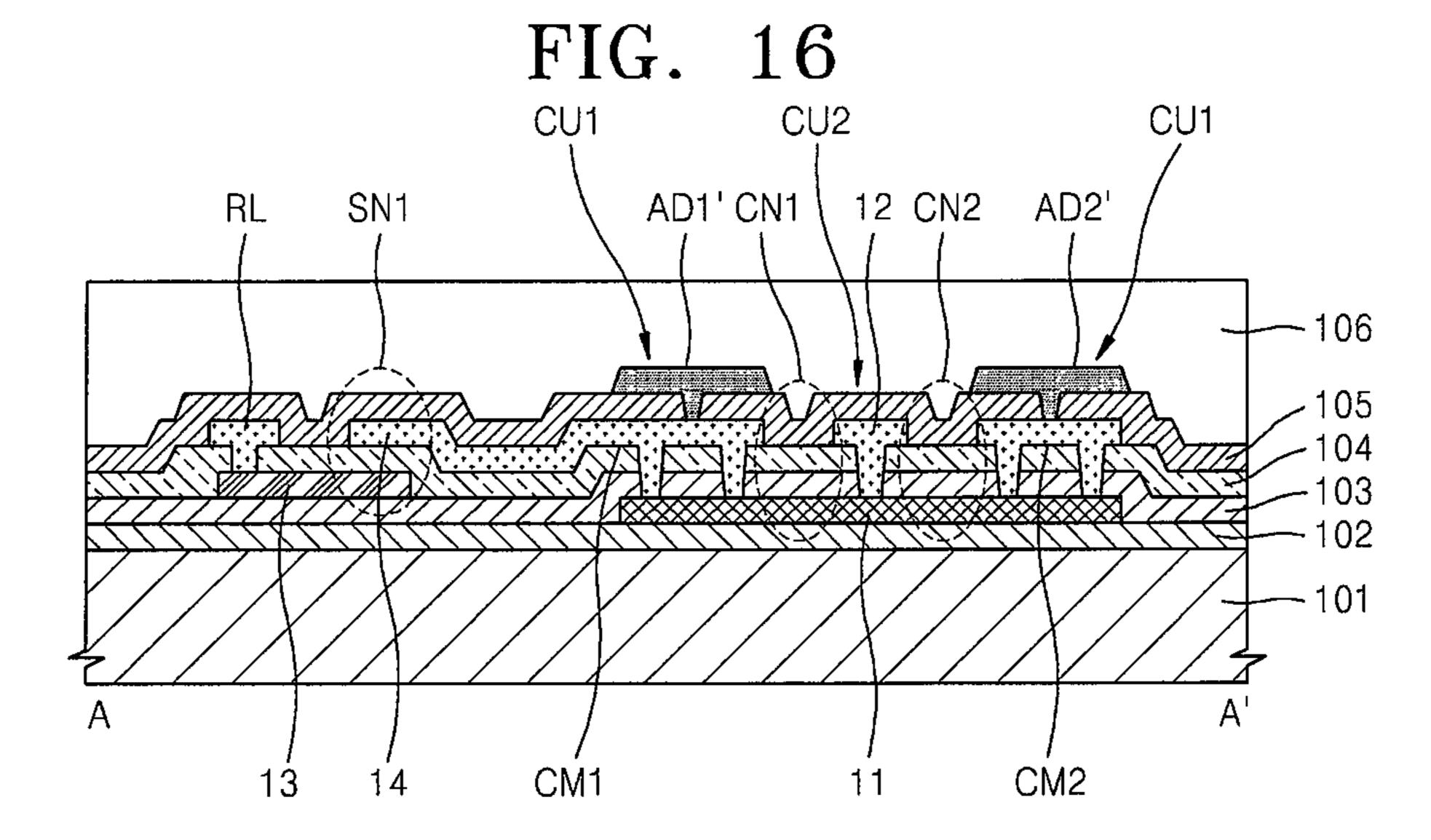

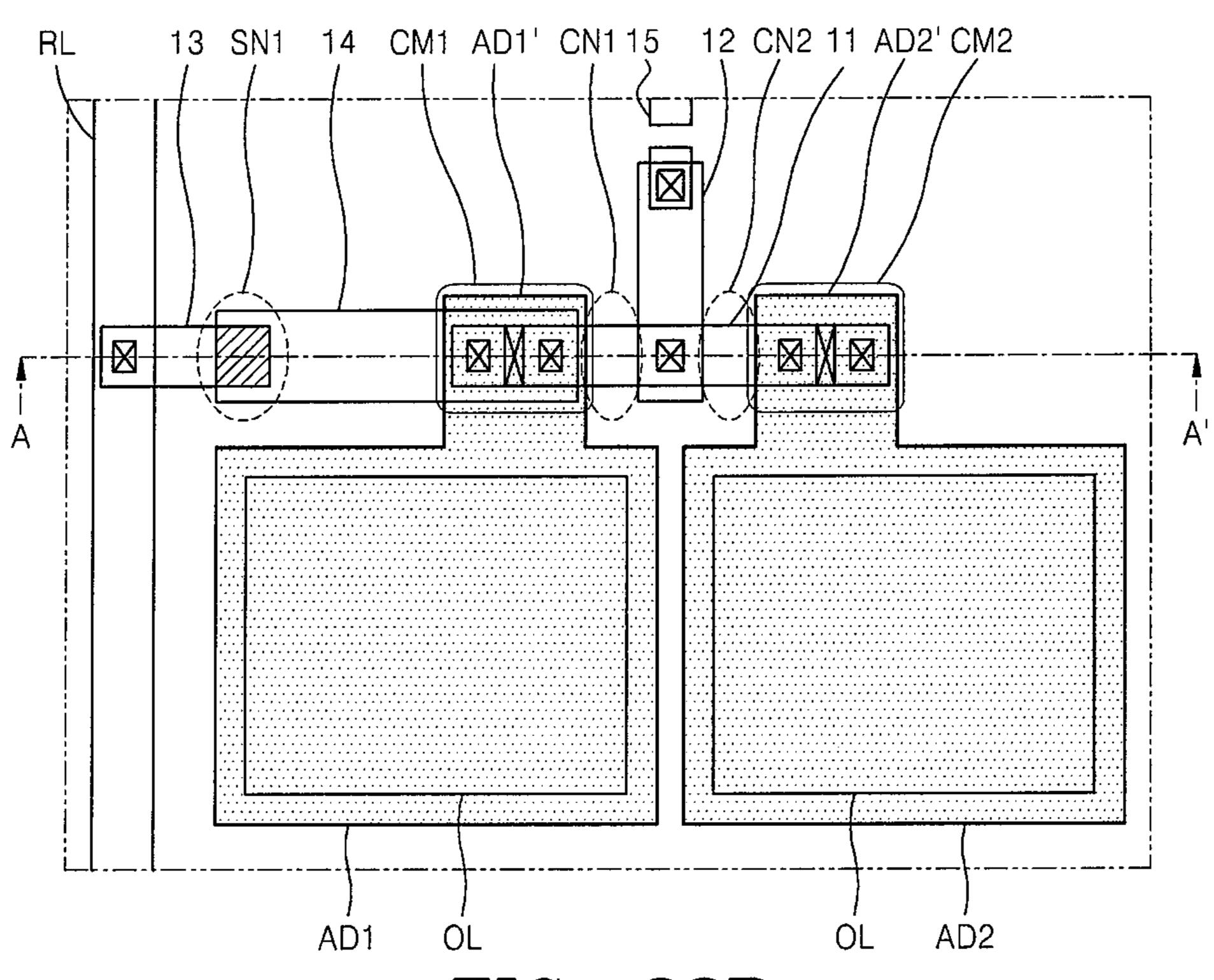

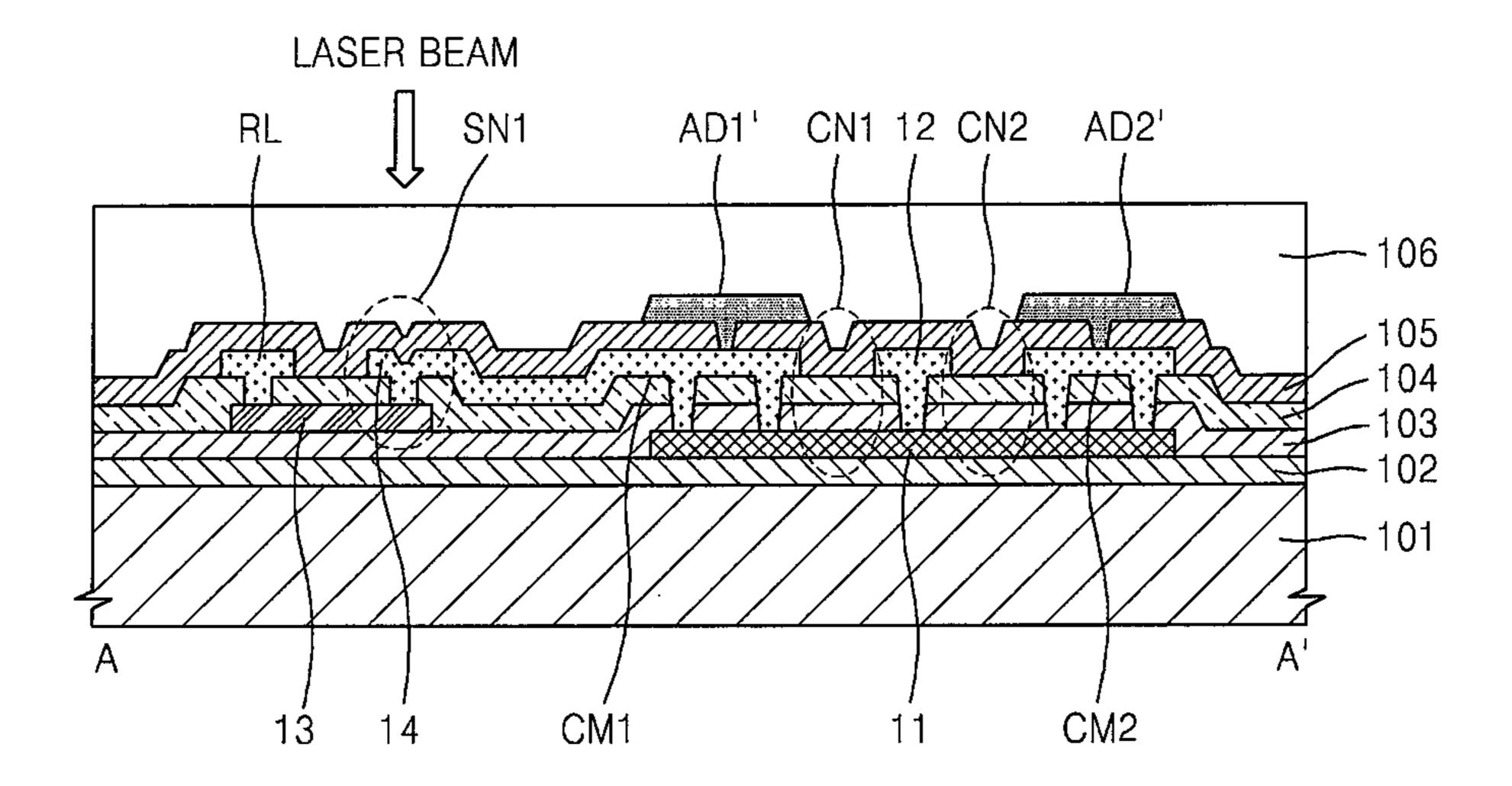

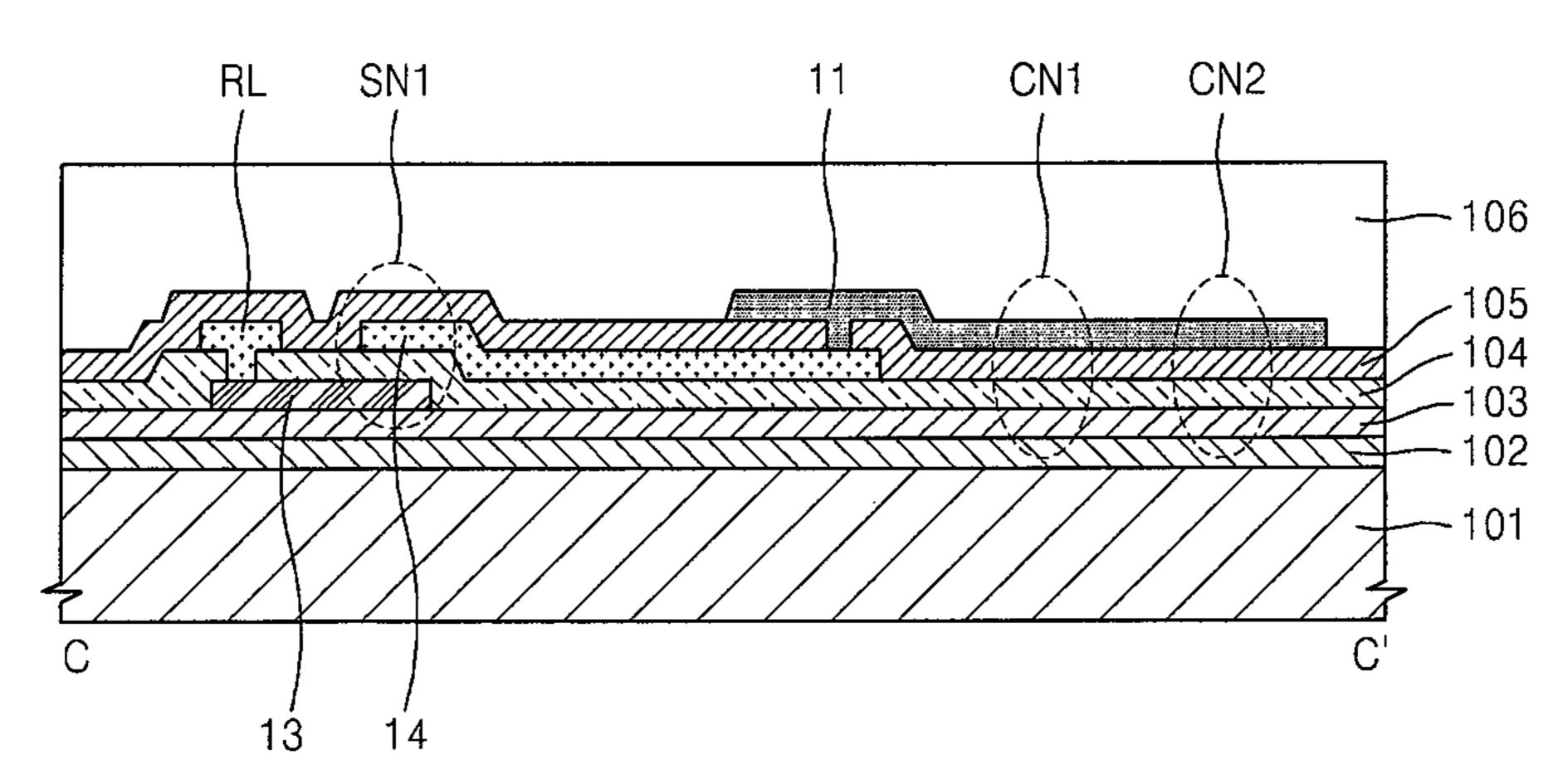

FIG. **16** is a cross-sectional view taken along the line A-A' 30 of FIG. **15**;

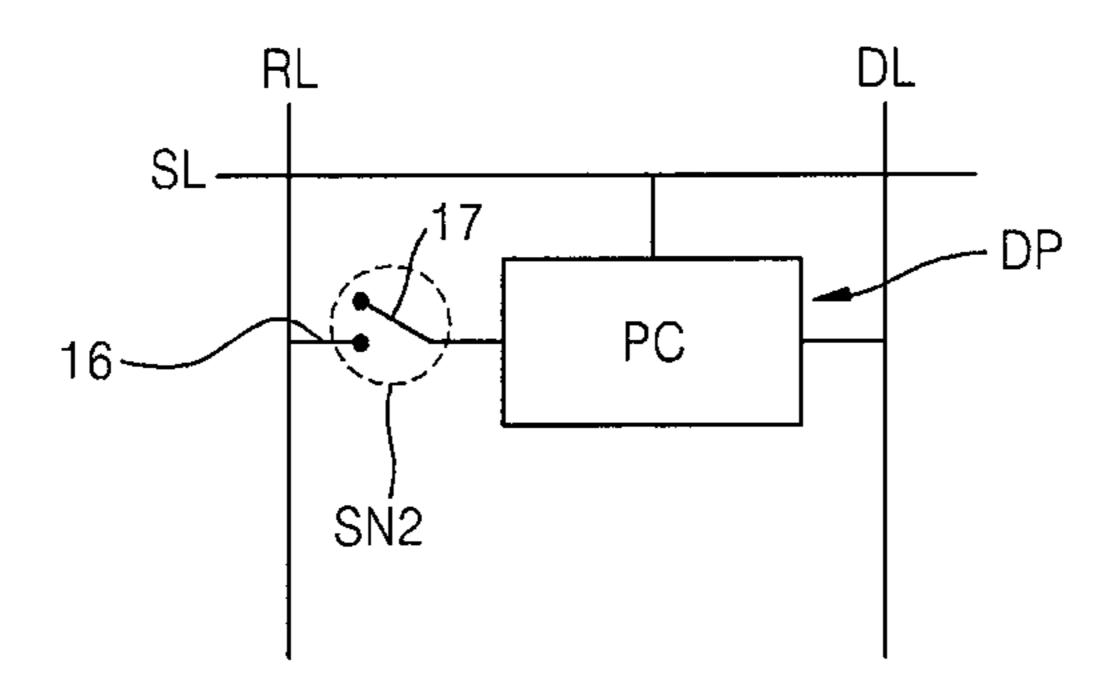

FIG. 17 is a schematic diagram of a dummy pixel according to an embodiment of the present invention;

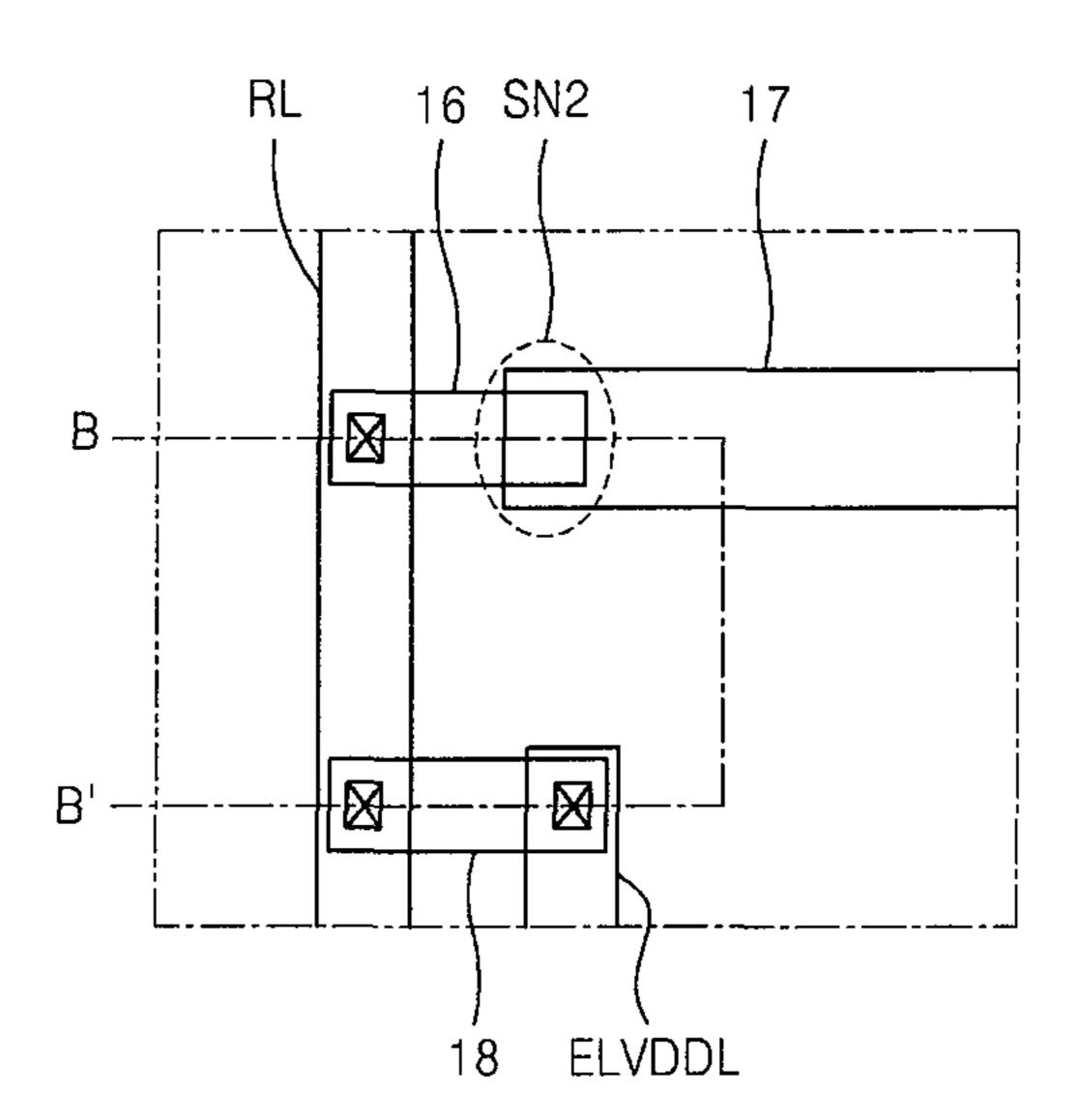

FIG. 18 is a plan view of a part of the dummy pixel of FIG. 17;

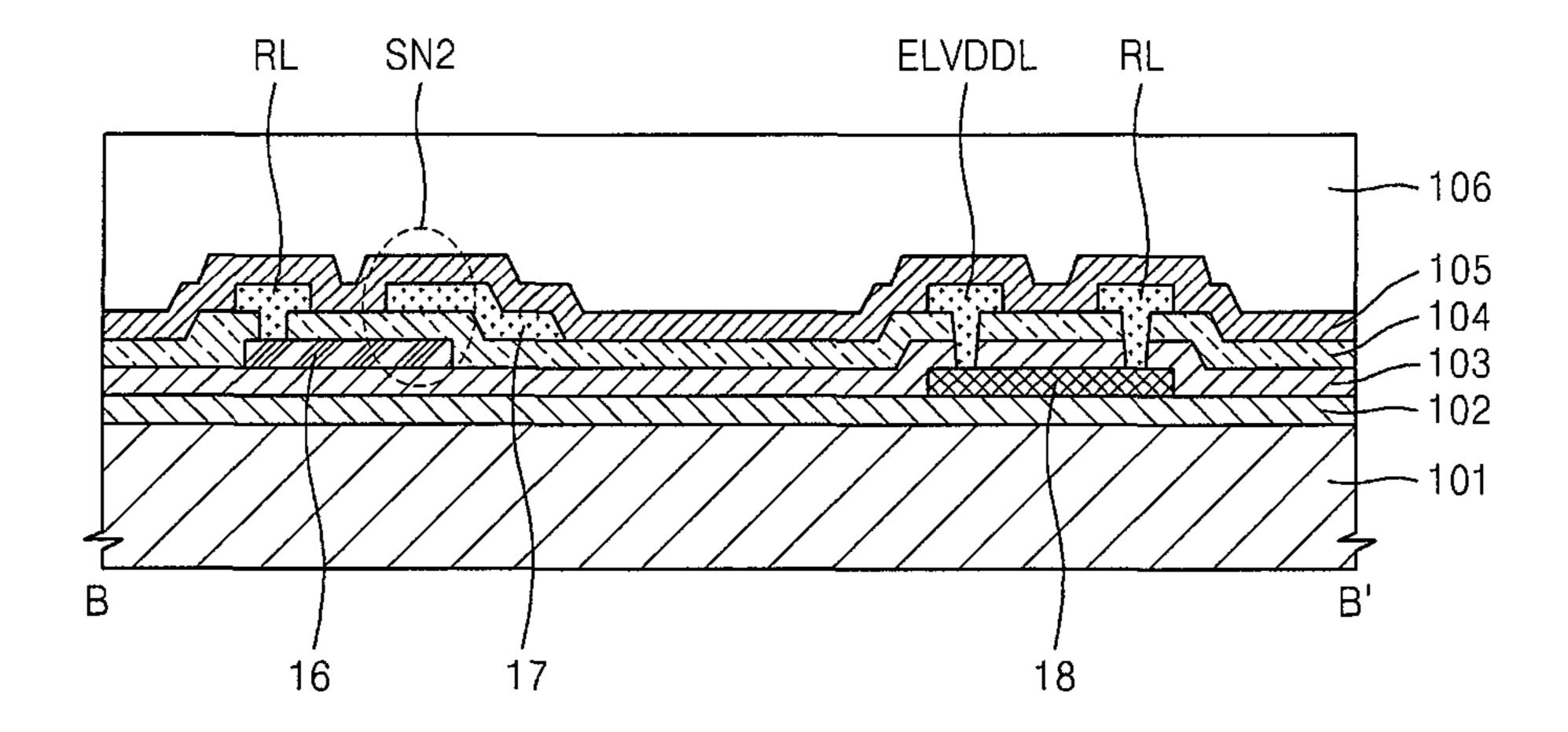

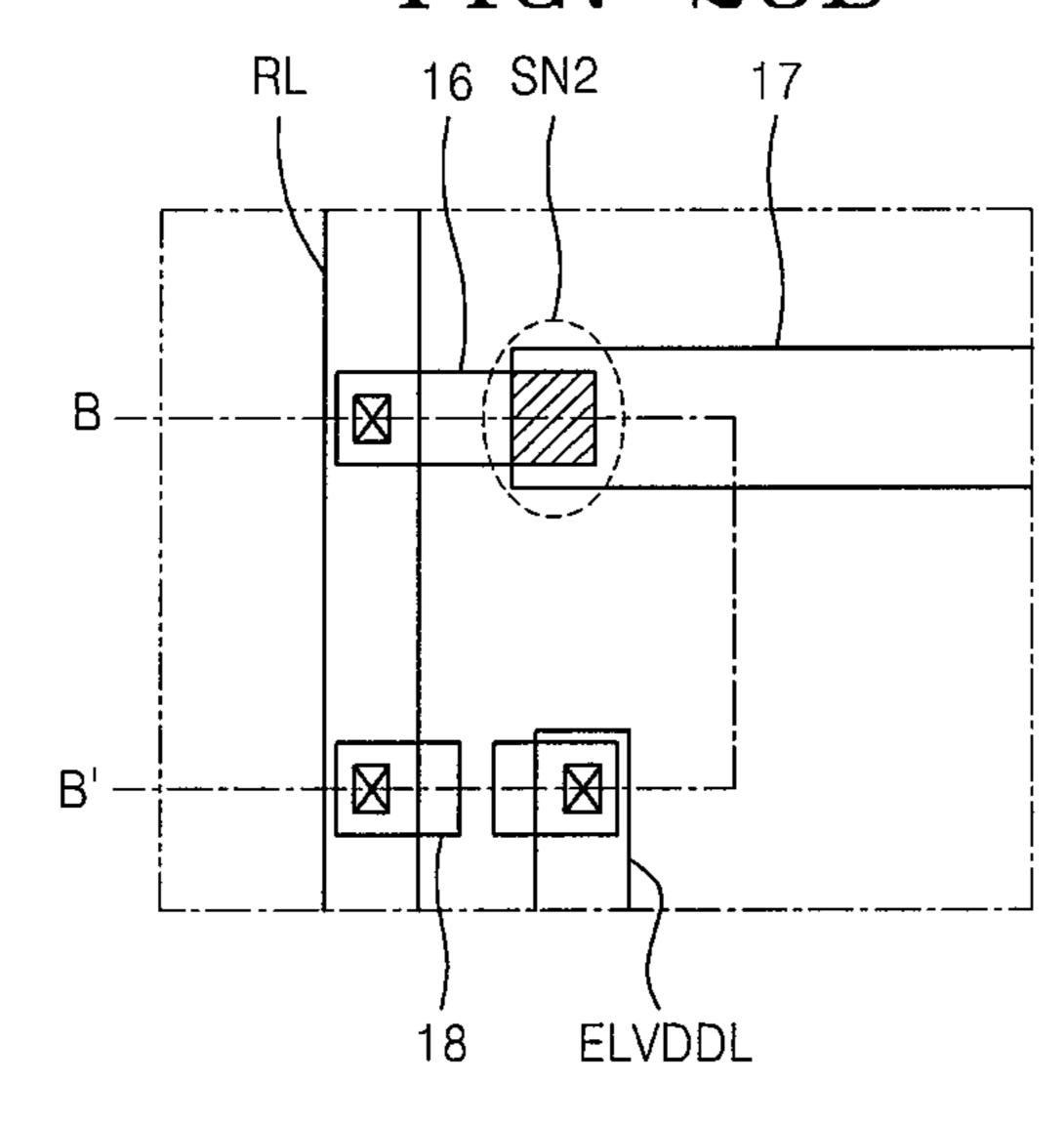

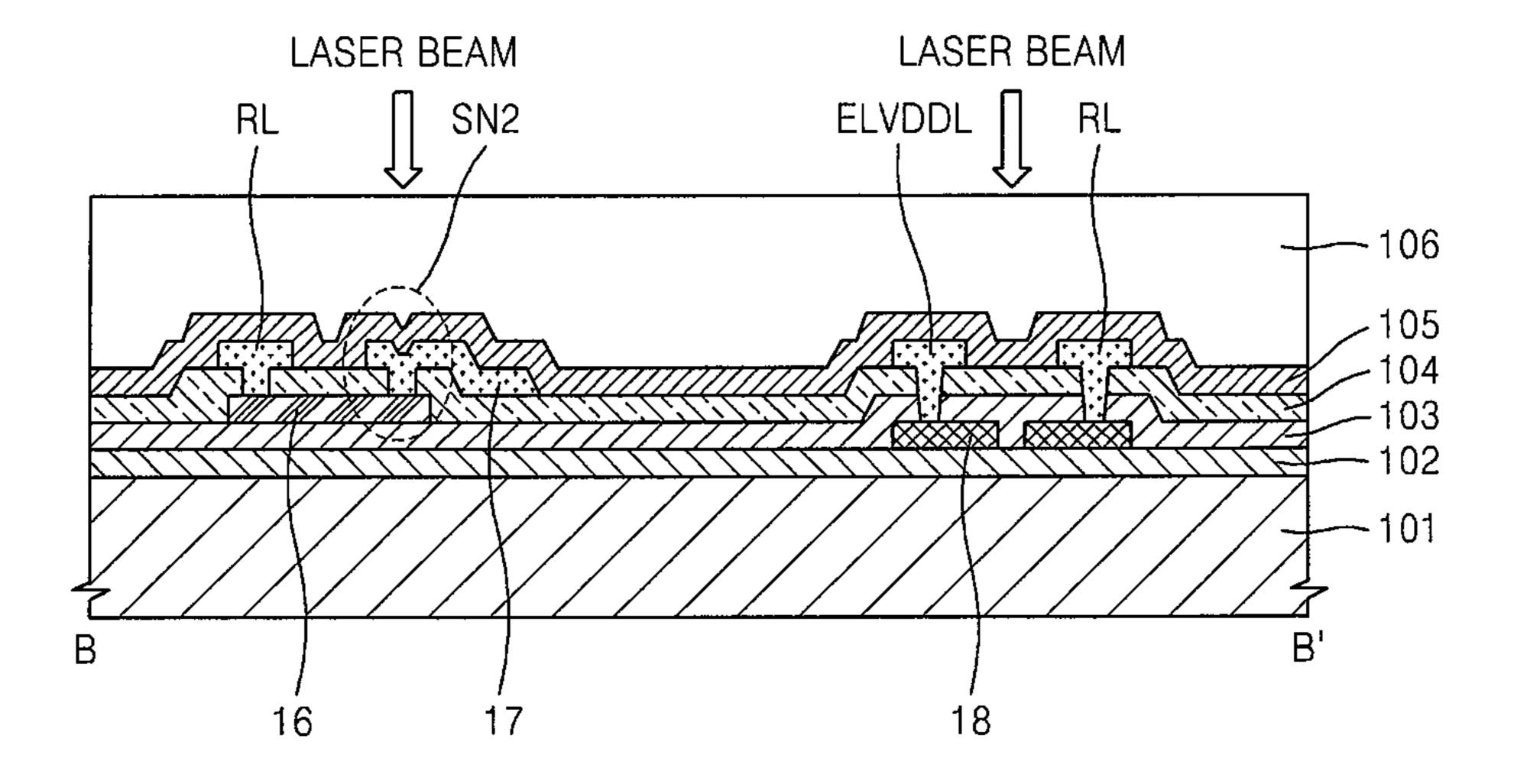

FIG. 19 is a cross-sectional view taken along the line B-B' of FIG. 18;

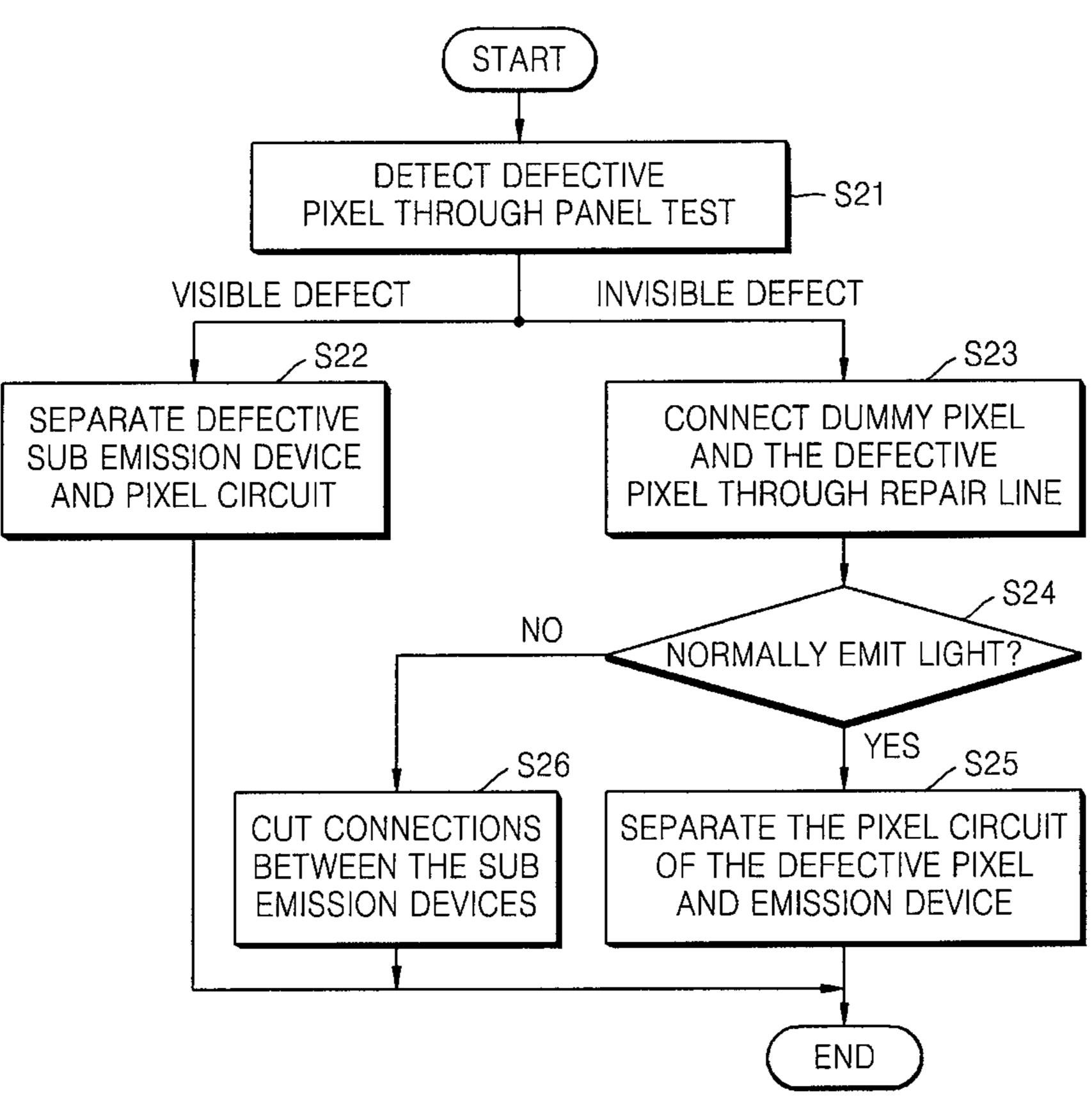

FIG. 20 is a flowchart for explaining a method of repairing a defective pixel, according to an embodiment of the present invention;

FIGS. 21 through 26 are diagrams for explaining a method of repairing a defective pixel in a case of a visible defect of FIG. 20, according to embodiments of the present invention;

FIGS. 27 through 29B are diagrams for explaining a 45 method of repairing a defective pixel in the case of the invisible defect of FIG. 20, according to embodiments of the present invention;

FIGS. 30A through 32 are diagrams for explaining a method of repairing a defective pixel in the case of the 50 invisible defect of FIG. 20, according to embodiments of the present invention;

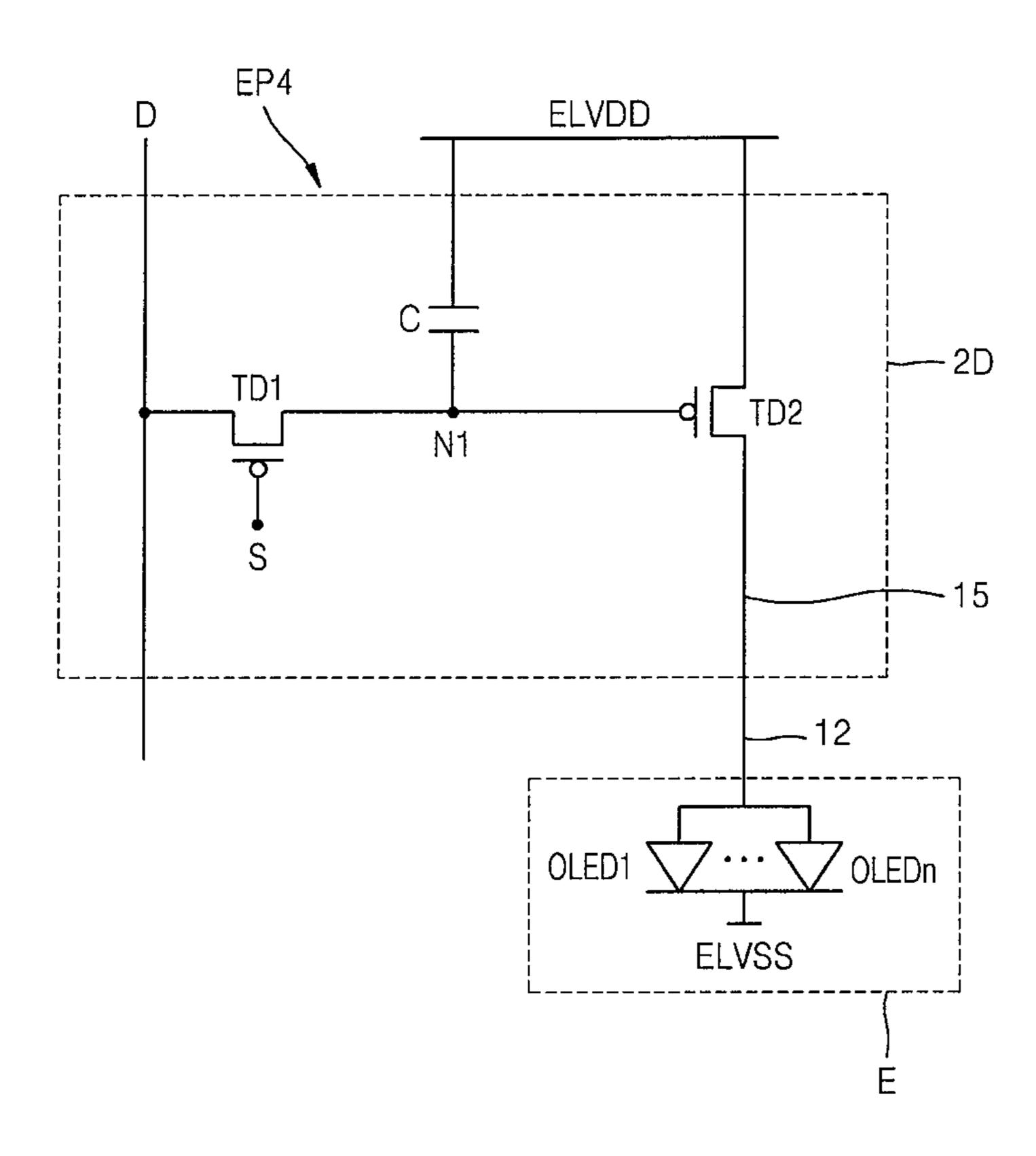

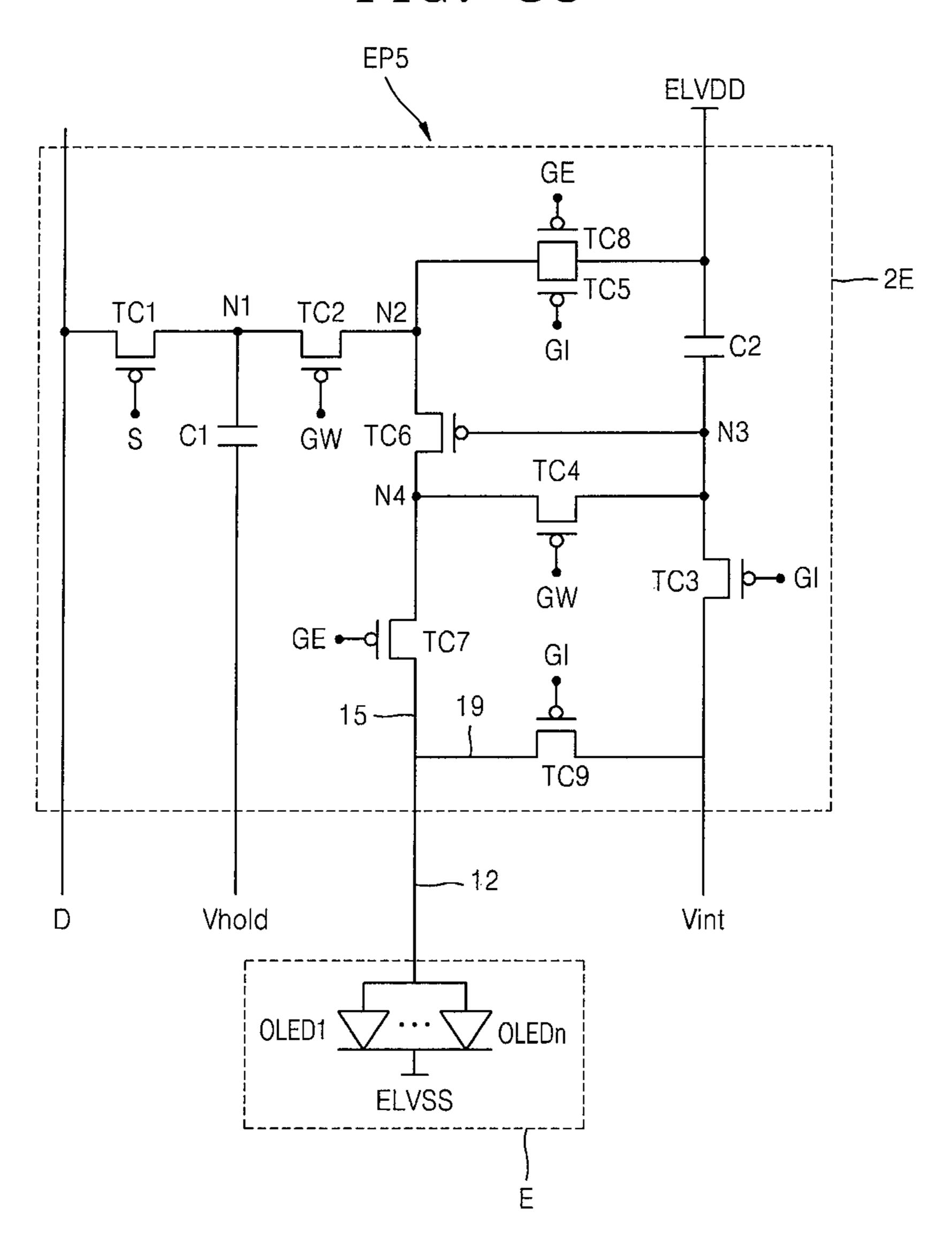

FIGS. 33 through 36 are circuit diagrams of an emission pixel according to embodiments of the present invention;

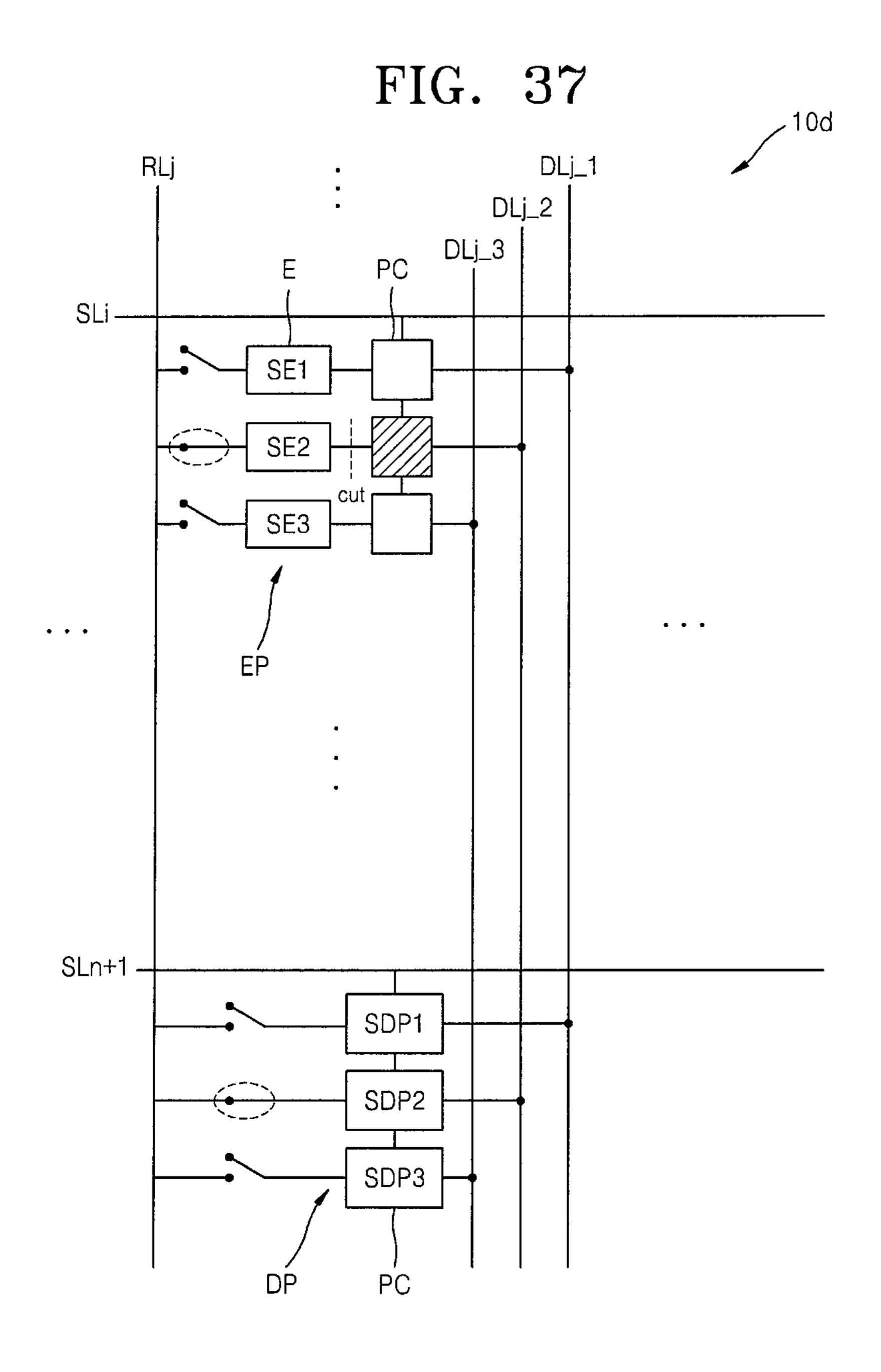

FIG. 37 is a schematic diagram of a display panel, 55 according to another embodiment of the present invention;

FIG. 38 is a circuit diagram of an emission pixel according to another embodiment of the present invention;

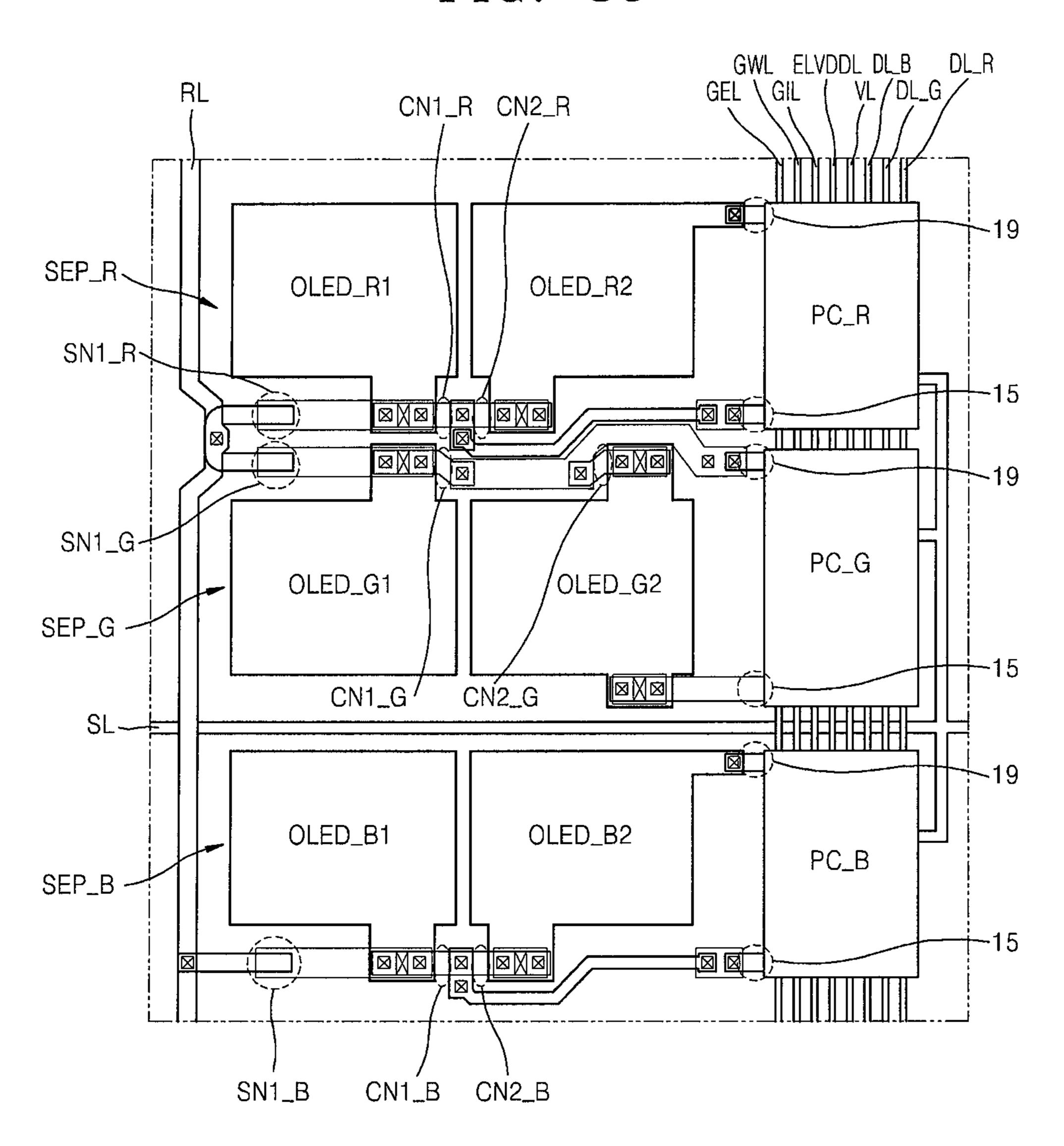

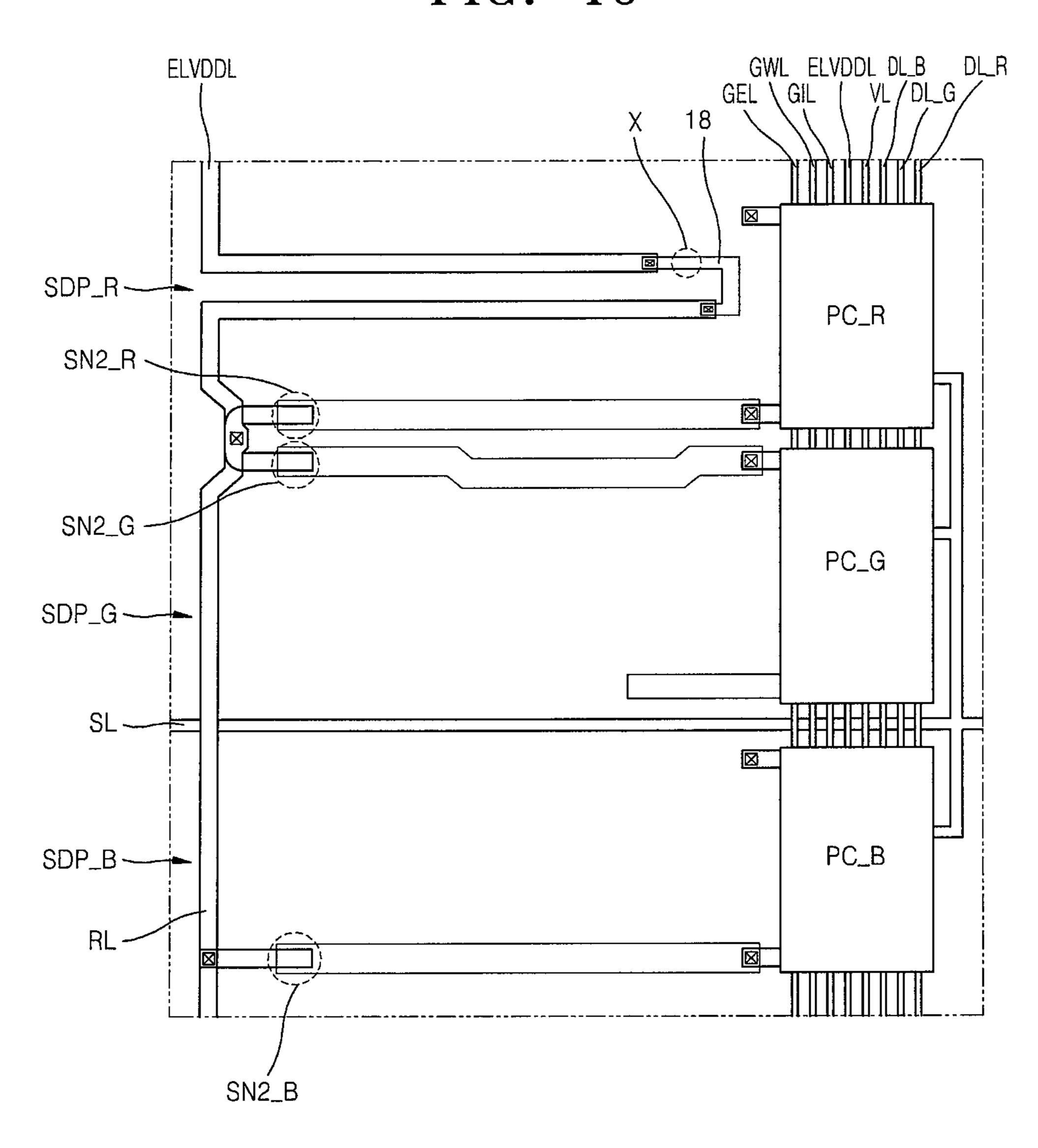

FIG. 39 is a plan view of an emission pixel including a pixel circuit of FIG. 38;

FIG. 40 is a plan view of a dummy pixel including a pixel circuit of FIG. 38;

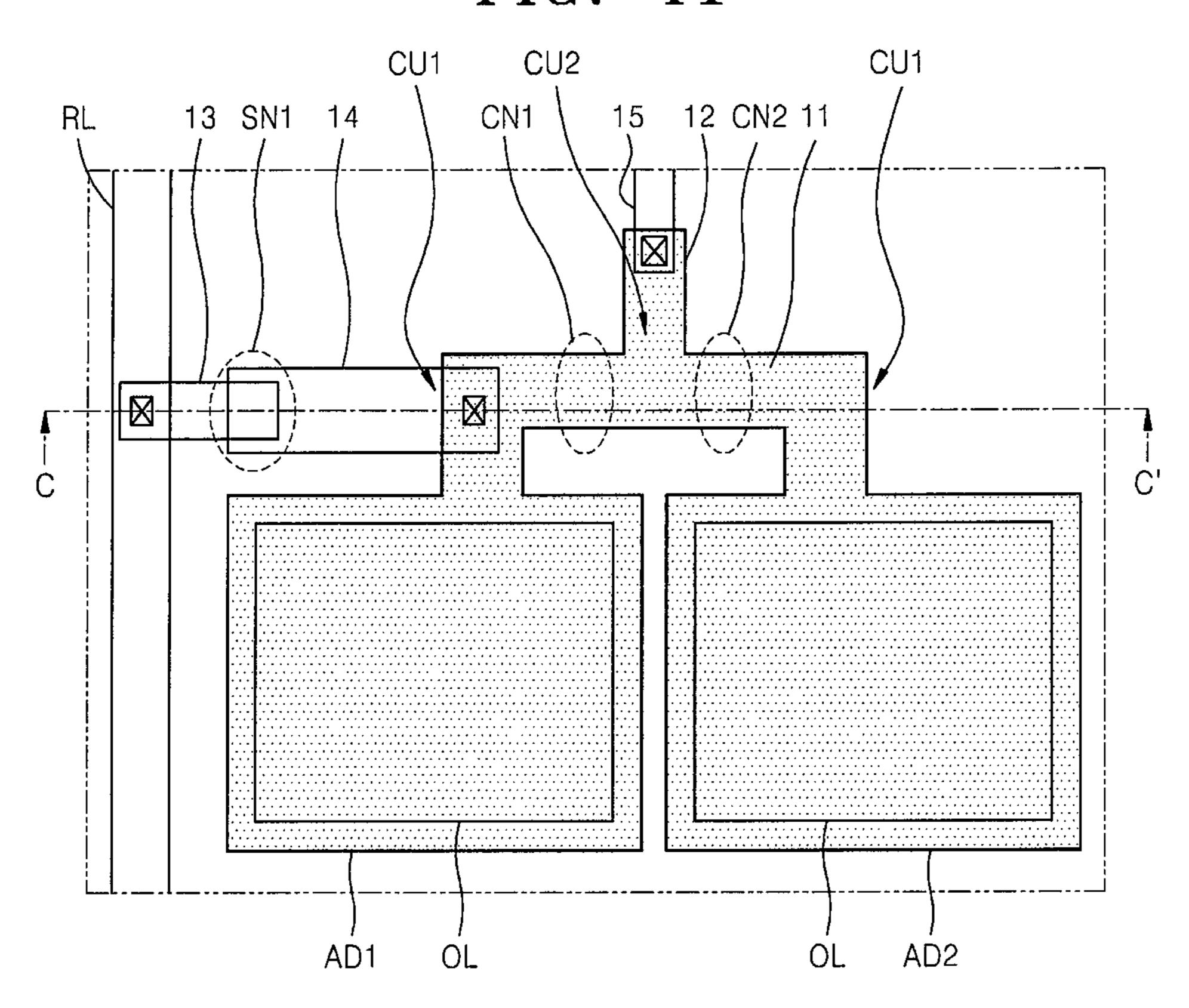

FIG. 41 is a plan view of an emission device of an emission pixel according to another embodiment of the present invention;

FIG. **42** is a cross-sectional view taken along a line C-C' of FIG. **41**; and

6

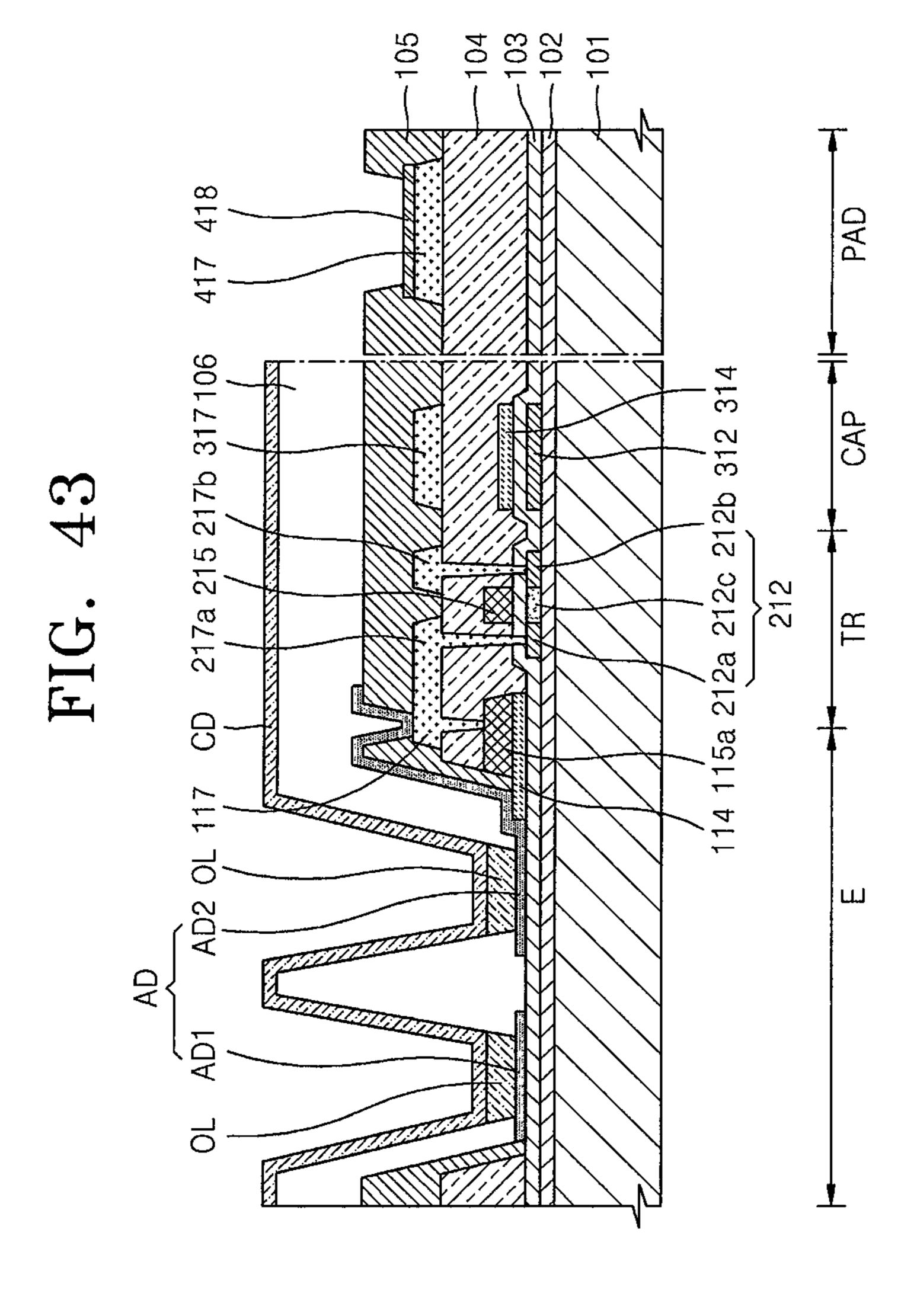

FIG. 43 is a cross-sectional diagram of an organic light emitting display apparatus including an emission pixel, according to an embodiment of the present invention.

## DETAILED DESCRIPTION

Hereinafter, embodiments of the present invention will be described in some detail by explaining embodiments of the invention with reference to the attached drawings. Like reference numerals in the drawings denote like elements. In the following description of the present invention, a detailed description of known functions and configurations incorporated herein will be omitted when it may make the subject matter of the present invention unclear.

In the drawings, the thicknesses of layers and regions are exaggerated for clarity. It will be understood that when a layer is referred to as being "on" another layer or substrate, it can be directly on the other layer or substrate, or intervening layers may also be present.

It will be further understood that the terms "comprises" and/or "comprising" when used in this specification, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. Also, the term "on" refers to an upper or lower side of a target and does not always mean an upper side in a direction of gravity.

It will be understood that, although the terms first, second, etc. may be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another. For example, a first element could be termed a second element, and, similarly, a second element could be termed a first element, without departing from the scope of the present invention.

As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items. Expressions such as "at least one of," when preceding a list of elements, modify the entire list of elements and do not modify the individual elements of the list.

FIG. 1 is a block diagram of a display apparatus 100 according to an embodiment of the present invention.

Referring to FIG. 1, the display apparatus 100 includes a display panel 10 including a plurality of pixels, a scan driving unit 20, a data driving unit 30, and a control unit 40. The scan driving unit 20, the data driving unit 30, and the control unit 40 may be separately formed on different semiconductor chips, or may be integrated on a single semiconductor chip. Also, the scan driving unit 20 may be formed on the same substrate as the display panel 10.

A plurality of scan lines SL extending in a horizontal direction and a plurality of the data lines DL extending in a vertical direction and perpendicularly crossing the scan lines SL are formed on the display panel 10. Also, a plurality of repair lines RL extending almost parallel or substantially parallel with and spaced apart from the data lines DL and perpendicularly crossing the scan lines SL are formed on the display panel 10. A plurality of pixels P aligned in a matrix-like shape are formed where the scan lines SL, the data lines DL, and the repair lines RL cross each other.

Although the data line DL is formed at a right side of the pixel P and the repair line RL is formed at a left side of the pixel P in FIG. 1, the present invention is not limited thereto.

For example, the positions of the data line DL and the repair line RL may be switched according to the design and function of the display panel 10. One or more repair lines RL

may be formed in each pixel column. The one or more repair lines RL may be formed or arranged in parallel to the scan lines SL according to a pixel design so that the one or more repair lines RL may be formed or arranged in each pixel row. Although not shown in FIG. 1, additional signal or voltage lines such as a plurality of emission control lines for providing an emission control signal, an initialization voltage line for providing an initialization voltage, and a driving voltage line for providing a power voltage may be additionally formed or arranged on the display panel 10.

The scan driving unit 20 may generate and sequentially provide scan signals via the scan lines SL to the display panel 10.

The data driving unit 30 may sequentially provide data signals via the data lines DL to the display panel 10. The data 15 driving unit 30 transforms input image data DATA, input from the control unit 40 and having a grayscale (e.g., grey levels), into a voltage or current data signal.

The control unit **40** generates and transmits a scan control signal SCS and a data control signal DCS respectively to the 20 scan driving unit 20 and the data driving unit 30. As such, the scan driving unit 20 sequentially provides or activates scan signals to the scan lines SL, and the data driving unit 30 provides data signals to the pixels P. Additional voltage or control signals such as a first power voltage ELVDD, a 25 second power voltage ELVSS, an emission control signal EM, and an initialization voltage Vint may be provided to the pixels P under the control of the control unit 40. The control unit 40 may control a time when the scan driving unit **20** provides a scan signal to a dummy pixel and may control 30 the data driving unit 30 to provide a data signal that is the same as the data signal provided or to be provided to a defective signal, to the dummy pixel when the scan signal is provided to the dummy pixel.

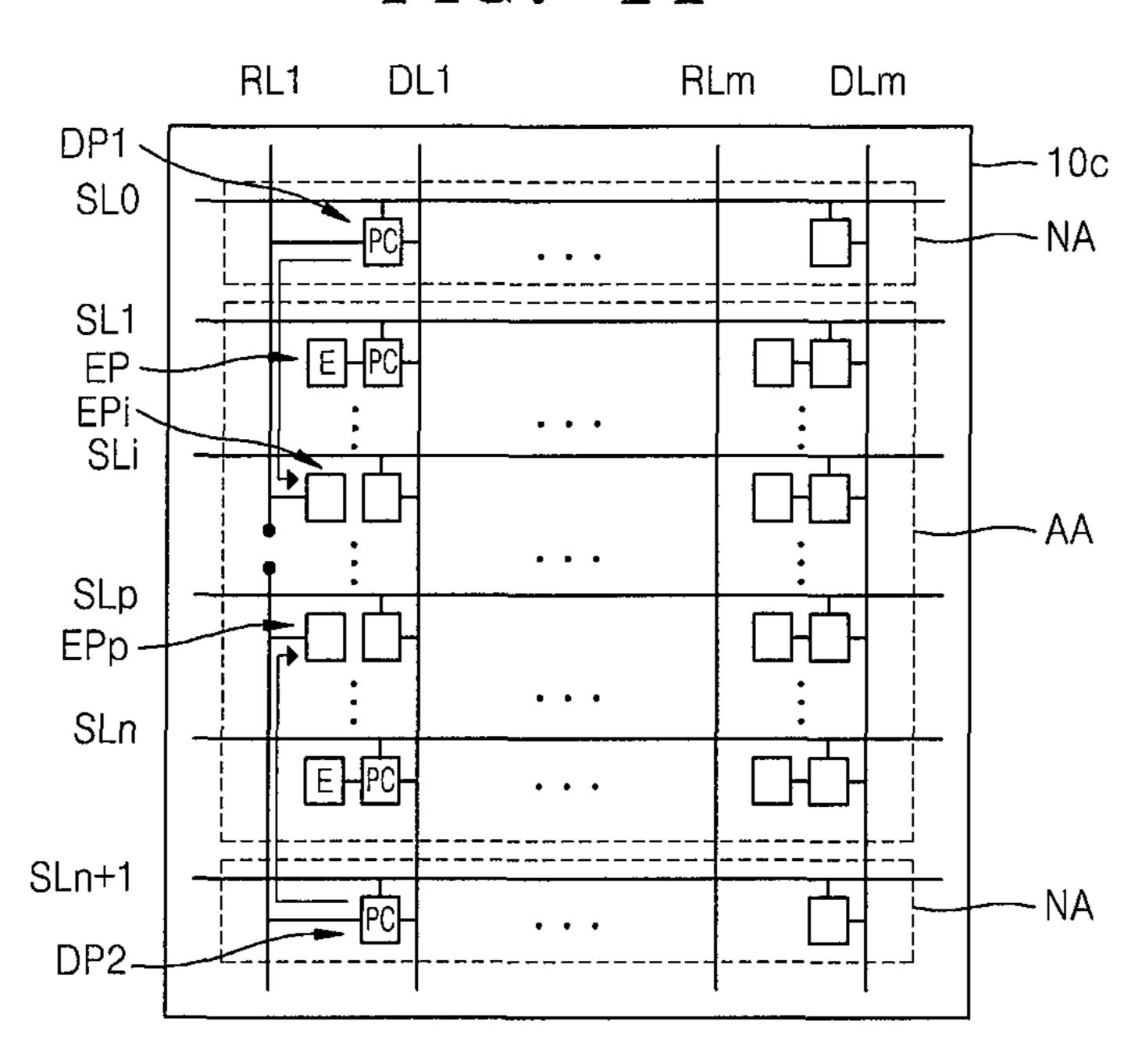

FIGS. 2 through 4 are schematic diagrams of examples of the display panel 10 illustrated in FIG. 1.

Referring to FIGS. 2 through 4, a plurality of pixels P aligned in a matrix-like shape are formed where a plurality of scan lines SL, a plurality of data lines DL, and a plurality of repair lines RL cross each other, on a display panel 10a, 40 10b, or 10c. The pixels P include emission pixels EP formed on a display area AA and dummy pixels DP formed on a non-display area NA. The non-display area NA may be formed on at least one of top and bottom regions or left and right regions of the display area AA. As such, one or more 45 dummy pixels DP may be formed in each pixel column on at least one of top and bottom regions of the pixel column, or one or more dummy pixels DP may be formed in each pixel row on at least one of left and right regions of the pixel row. An example of forming the dummy pixels DP in the 50 pixel column of the non-display area NA on the top and bottom regions of the display area AA is explained with respect to FIGS. 2 through 4. This may apply to a case where the dummy pixels DP are formed in the pixel row of the non-display area NA on the left and right regions of the 55 display area AA.

Referring to FIG. 2, the display panel 10a includes a display area AA and a non-display area NA formed below the display area AA. From among first through (n+1)th scan lines SL1 through SLn+1, the first through nth scan lines 60 SL1 through SLn are formed on the display area AA, and the (n+1)th scan line SLn+1 is formed on the non-display area NA. First through mth data lines DL1 through DLm and first through mth repair lines RL1 through RLm are formed separately in pixel columns in the display area M and 65 extending into the non-display area NA. A plurality of emission pixels EP coupled to the first through nth scan lines

8

SL1 through SLn and the first through mth data lines DL1 through DLm are formed in the display area AA, and a plurality of dummy pixels DP coupled to the (n+1)th scan line SLn+1 and the first through mth data lines DL1 through DLm are formed in the non-display area NA.

Referring to FIG. 3, the display panel 10b includes a display area AA and a non-display area NA above the display area AA. From among zeroth through nth scan lines SL0 through SLn, the first through nth scan lines SL1 through SLn are formed on the display area AA, and the zeroth scan line SL0 is formed on the non-display area NA. First through mth data lines DL1 through DLm and first through mth repair lines RL1 through RLm are formed separately in pixel columns in the display area AA and extending into the non-display area NA. A plurality of emission pixels EP coupled to the first through nth scan lines SL1 through SLn and the first through mth data lines DL1 through DLm are formed in the display area AA, and a plurality of dummy pixels DP coupled to the zeroth scan line SL0 and the first through mth data lines DL1 through DLm are formed in the non-display area NA.

Referring to FIG. 4, the display panel 10c includes a display area AA and a non-display area NA formed above and below the display area AA. From among zeroth through (n+1)th scan lines SL0 through SLn+1, the first through nth scan lines SL1 through SLn are formed on the display area AA, and the zeroth and (n+1)th scan lines SL0 and SLn+1 are formed on the non-display area NA. First through mth data lines DL1 through DLm and first through mth repair lines RL1 through RLm are formed separately in pixel columns on the display area AA and the non-display area NA. A plurality of emission pixels EP coupled to the first through nth scan lines SL1 through SLn and the first through mth data lines DL1 through DLm are formed on the display area AA, and a plurality of dummy pixels DP coupled to the zeroth and (n+1)th scan lines SL0 and SLn+1 and the first through mth data lines DL1 through DLm are formed on the non-display area NA.

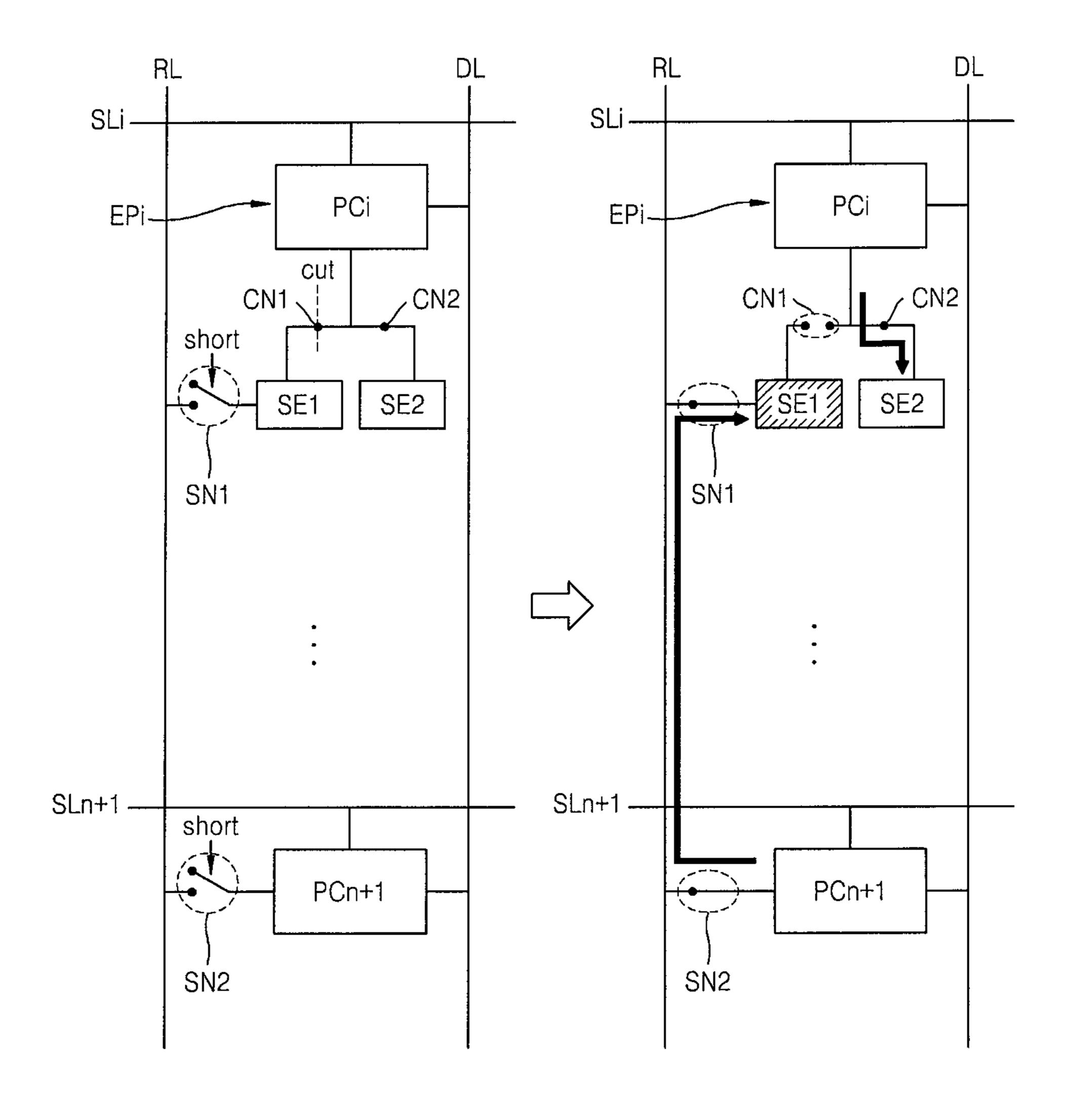

FIG. 5 is a diagram for describing a method of repairing a defective pixel by using repair lines of the display panel 10a of FIG. 2, according to an embodiment of the present invention.

Referring to FIG. 5, the emission pixels EP formed in the display area AA may include pixel circuits PC that are coupled to the first through nth scan lines SL1 through SLn and the first through mth data lines DL1 through DLm, and emission devices E that emit light by receiving a driving current from the pixel circuits PC. The dummy pixels DP formed in the non-display area NA may include only the pixel circuits PC that are coupled to the (n+1)th scan line SLn+1 and the first through mth data lines DL1 through DLm.

When an emission pixel EPi coupled to an ith scan line SLi of a first column is defective, the emission device E of the defective emission pixel EPi is disconnected from the corresponding pixel circuit PC, and the disconnected emission device E is coupled to the pixel circuit PC of the dummy pixel DP that is coupled to the (n+1)th scan line SLn+1 through the repair line RL. The disconnection of the emission device E and the corresponding pixel circuit PC, the coupling of the repair line RL and the emission device E, and the coupling of the repair line RL and the dummy pixel DP may be performed by cutting or shorting by irradiating a laser beam from a substrate side or from an opposite side of a substrate.

FIGS. 6 and 7 show waveforms of scan signals and data signals provided to the display panel repaired by using the method illustrated in FIG. 5.

Referring to FIG. 6, the scan driving unit 20 sequentially provides or activates the first through nth scan signals S1 5 through Sn to first through nth scan line SL1 through SLn and provides the (n+1)th scan signal Sn+1 to the (n+1)th scan line SLn+1 at the same time as the scan signal Si is provided to the repaired emission pixel EPi.

The data driving unit 30 sequentially provides or activates 10 the first through nth data signals D1 through Dn to the data line DL1 in synchronization with the first through (n+1)th scan signals S1 through Sn+1. In this regard, a data signal Di that is the same as the data signal Di provided to the defective emission pixel EPi is concurrently provided to the 15 dummy pixel DP. Accordingly, the emission device E of the defective emission pixel EPi may receive a current corresponding to the data signal Di via the pixel circuits PC of the dummy pixels DP and the repair lines RL1, thereby suppressing or reducing generation of a bright spot or a dark 20 spot of the defective emission pixel EPi.

Referring to FIG. 7, the scan driving unit 20 sequentially provides or activates the first through (n+1)th scan signals S1 through Sn+1 to the first through (n+1)th scan lines SL1 through SLn+1.

The data driving unit 30 sequentially provides or activates the first through nth data signals D1 through Dn to the data line DL1 in synchronization with the first through (n+1)th scan signals S1 through Sn+1. In this regard, a data signal Di that is the same as the data signal Di provided to the 30 defective emission pixel EPi is again provided to the dummy pixel DP. Accordingly, the emission device E of the defective emission pixel EPi may receive a current corresponding to the data signal Di via the pixel circuits PC of the dummy reducing generation of a bright spot or a dark spot of the defective emission pixel EPi.

Although a width of the first through (n+1)th scan signals S1 through Sn+1 may be provided as one horizontal period (1H) in FIGS. 6 and 7, a width of a scan signal may be 40 provided as two horizontal periods (2H), and widths of adjacent scan signals, for example, widths of the (n-1)th scan signal Sn-1 and the nth scan signal Sn, may be provided to overlap by 1H or less. Accordingly, a lack of charges due to a resistive-capacitive (RC) delay of signal 45 lines caused by a large-sized display area may be solved or reduced.

FIG. 8 is a diagram for describing a method of repairing a defective pixel by using the repair lines of the display panel 10b of FIG. 3, according to another embodiment of the 50 present invention.

Referring to FIG. 8, the emission pixels EP formed in the display area AA may include the pixel circuits PC and the emission devices E that emit light by receiving a driving current from the pixel circuits PC. The dummy pixels DP formed in the non-display area NA may include only the pixel circuits PC.

When the emission pixel EPI coupled to the ith scan line SLi of a first column is defective, the emission device E of the defective emission pixel EPi is disconnected from the 60 pixel circuit PC, and the disconnected emission device E is coupled to the pixel circuit PC of the dummy pixel DP that is coupled to the zeroth scan line SL0 through the repair line RL1. The disconnection of the emission device E and the pixel circuit PC, the coupling of the repair line RL and the 65 emission device E, and the coupling of the repair line RL and the dummy pixel DP may be performed by cutting or

**10**

shorting by irradiating a laser beam from a substrate side or from an opposite side of a substrate.

FIGS. 9 and 10 show waveforms of scan signals and data signals provided to the display panel 10b repaired by using the method illustrated in FIG. 8.

Referring to FIG. 9, the scan driving unit 20 sequentially provides or activates the first through nth scan signals S1 through Sn to the first through nth scan line SL1 through SLn and provides the zeroth scan signal S0 to the zeroth scan line S0 at the same time as the scan signal Si is provided to the repaired emission pixel EPi.

The data driving unit 30 sequentially provides or activates the first through nth data signals D1 through Dn to the data line DL1 in synchronization with the zeroth through nth scan signals S0 through Sn. In this regard, the data signal Di that is the same as the data signal Di provided to the defective emission pixel EPi is concurrently provided to the dummy pixel DP. Accordingly, the emission device E of the defective emission pixel EPi may receive a current corresponding to the data signal Di via the pixel circuits PC of the dummy pixels DP and the repair lines RL1, thereby suppressing or reducing generation of a bright spot or a dark spot of the defective emission pixel EPi.

Referring to FIG. 10, the scan driving unit 20 sequentially provides or activates the zeroth through nth scan signals S0 through Sn to the zeroth through nth scan lines SL0 through SLn.

The data driving unit 30 sequentially provides or activates the first through nth data signals D1 through Dn to the data line DL1 in synchronization with the zeroth through nth scan signals S0 through Sn. In this regard, the data signal Di that is the same as the data signal Di that is to be provided to the defective emission pixel EPi is first provided to the dummy pixel DP. Accordingly, the emission device E of the defecpixels DP and the repair lines RL1, thereby suppressing or 35 tive emission pixel EPi may receive a current corresponding to the data signal Di via the pixel circuits PC of the dummy pixels DP and the repair lines RL1, thereby suppressing or reducing generation of a bright spot or a dark spot of the defective emission pixel EPi.

> Although a width of the zeroth through nth scan signals S0 through Sn may be provided as one horizontal period (1H) in FIGS. 9 and 10, a width of a scan signal may be provided as two horizontal periods (2H), and widths of adjacent scan signals, for example, widths of the (n-1)th scan signal Sn-1 and the nth scan signal Sn, may be provided to overlap by 1H or less. Accordingly, a lack of charges due to a RC delay of signal lines caused by a large-sized display area may be solved or reduced.

> FIG. 11 is a diagram for describing a method of repairing a defective pixel by using repair lines of the display panel 10C of FIG. 4, according to another embodiment of the present invention.

> Referring to FIG. 11, the emission pixels EP formed in the display area AA may include the pixel circuits PC and the emission devices E that emit light by receiving a driving current from the pixel circuits PC. The dummy pixels DP formed in the non-display area NA may include only the pixel circuits PC.

> When the emission pixel EPi coupled to the ith scan line SLi of a first column and an emission pixel EPp coupled to a pth scan line SLp of the first column are defective, the repair line RL1 between the defective emission pixels EPi and EPp is disconnected, the emission devices E of the defective emission pixels EPi and EPp are disconnected from the pixel circuits PC, and the disconnected emission devices E are coupled to the pixel circuits PC of a first dummy pixel DP1 and a second dummy pixie DP2 that are

respectively coupled to the zeroth scan line SL0 and the (n+1)th scan line SLn+1 through the repair lines RL1. The disconnection of the emission devices E and the pixel circuits PC, the coupling of the repair lines RL and the emission devices E, and the coupling of the repair lines RL 5 and the dummy pixels DP may be performed by cutting or shorting by irradiating a laser beam from a substrate side or from an opposite side of a substrate.

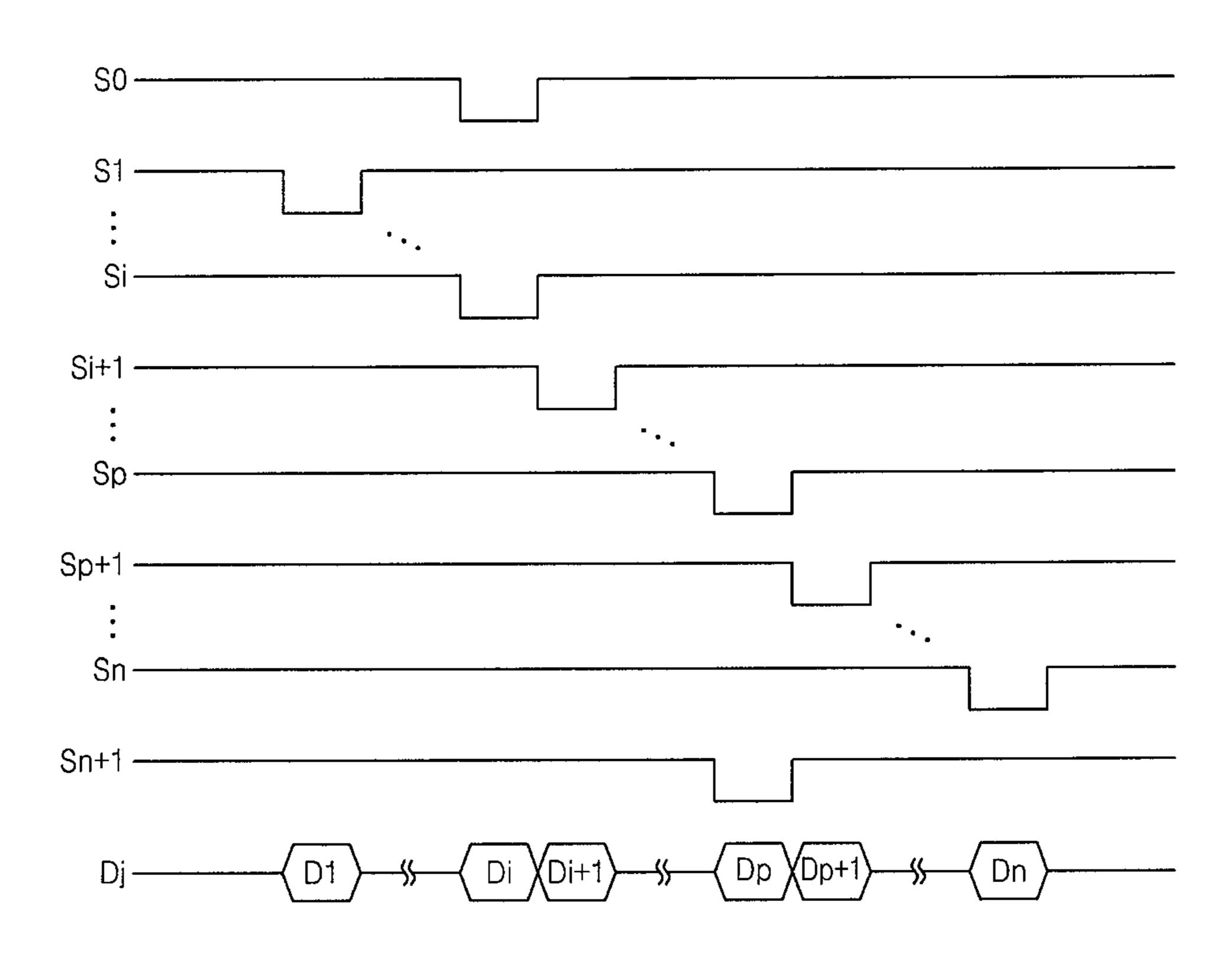

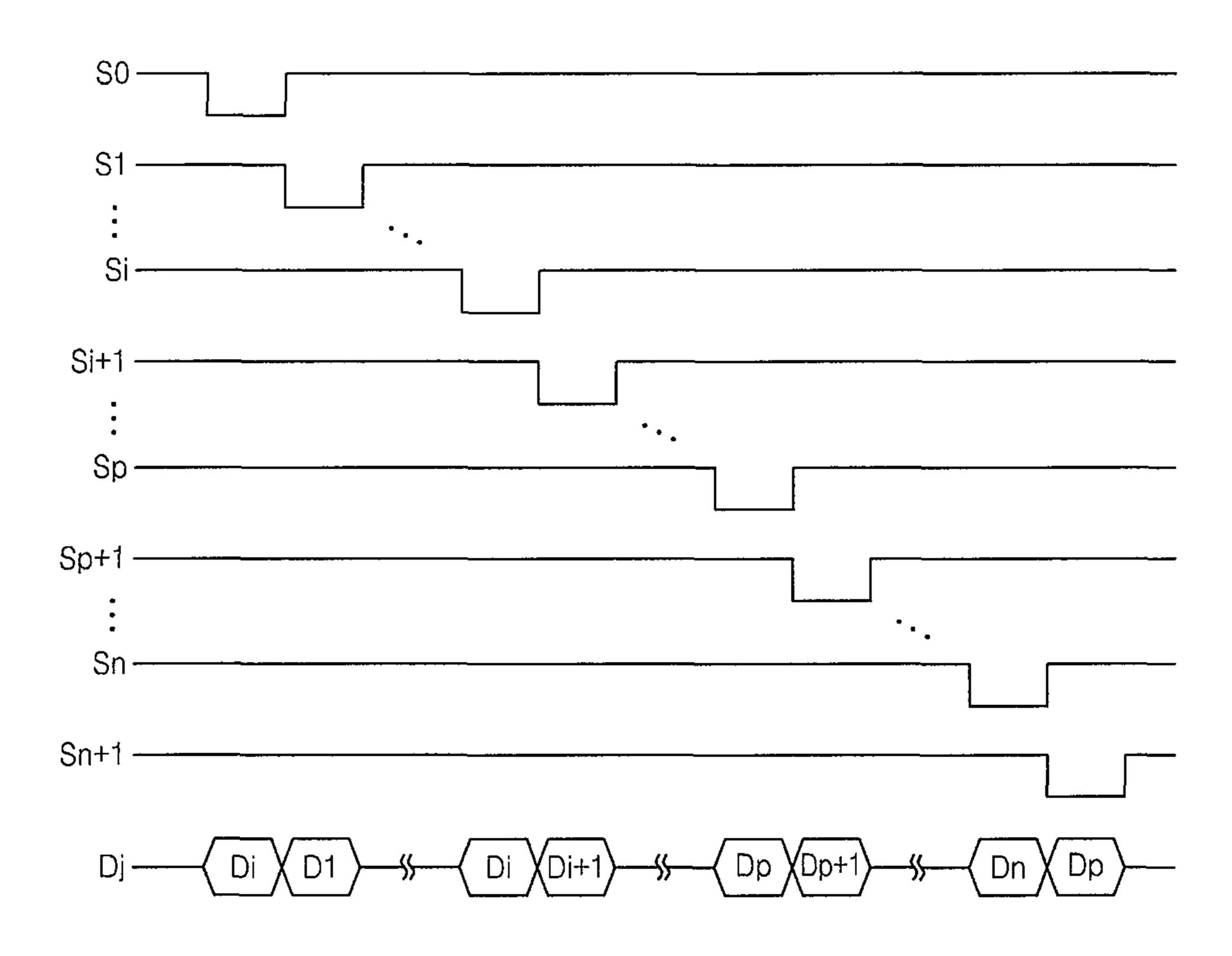

FIGS. 12 and 13 show waveforms of the scan signals and the data signals provided to the display panel 10c repaired by using the method illustrated in FIG. 11.

Referring to FIG. 12, the scan driving unit 20 sequentially provides or activates the first through nth scan signals S1 through Sn to the first through nth scan line SL1 through SLn and respectively provides the zeroth and (n+1)th scan 15 signals S0 and Sn+1 to the zeroth and (n+1)th scan line SL0 and SLn+1 at the same time as the scan signals Si and Sp are respectively provided to the repaired emission pixels EPi and EPp.

The data driving unit **30** sequentially provides or activates 20 the first through nth data signals D1 through Dn to the data line DL1 in synchronization with the zeroth through (n+1)th scan signals S0 through Sn+1. In this regard, the data signals Di and Dp that are the same as the data signals Di and Dp provided to the defective emission pixels EPi and EPp are 25 concurrently provided to the first and second dummy pixels DP1 and DP2. Accordingly, the emission devices E of the defective emission pixels EPi and EPp may receive current corresponding to the data signals Di and Dp via the pixel circuits PC of the first and second dummy pixels DP1 and 30 DP2 and the repair lines RL1, thereby suppressing or reducing generation of a bright spot or a dark spot of the defective emission pixels EPi and EPp.

Referring to FIG. 13, the scan driving unit 20 sequentially provides or activates the zeroth through (n+1)th scan signals 35 S0 through Sn+1 to the zeroth through (n+1)th scan line SL0 through SLn+1.

The data driving unit 30 sequentially provides or activates the first through nth data signals D1 through Dn to the data line DL1 in synchronization with the zeroth through (n+1)th 40 scan signals S0 through Sn+1. In this regard, the data signal Di that is the same as the data signal Di that is to be provided to the defective emission pixel EPi is first provided to the first dummy pixel DP1. The data signal Dp that is the same as the data signal Dp provided to the defective emission 45 pixel EPp is again provided to the second dummy pixel DP2. Accordingly, the emission devices E of the defective emission pixels EPi and EPp may receive current corresponding to the data signals Di and Dp via the pixel circuits PC of the first and second dummy pixels DP1 and DP2 and the repair 50 lines RL1, thereby suppressing or reducing generation of a bright spot or a dark spot of the defective emission pixels EPi and EPp.

Although a width of the zeroth through (n+1)th scan signals S0 through Sn+1 may be provided as one horizontal 55 period (1H) in FIGS. 12 and 13, a width of a scan signal may be provided as two horizontal periods (2H), and widths of adjacent scan signals (for example, widths of the (n-1)th scan signal Sn-1 and the nth scan signal Sn) may be provided to overlap by 1H or less. Accordingly, a lack of 60 charges due to a RC delay of signal lines caused by a large-sized display area may be solved.

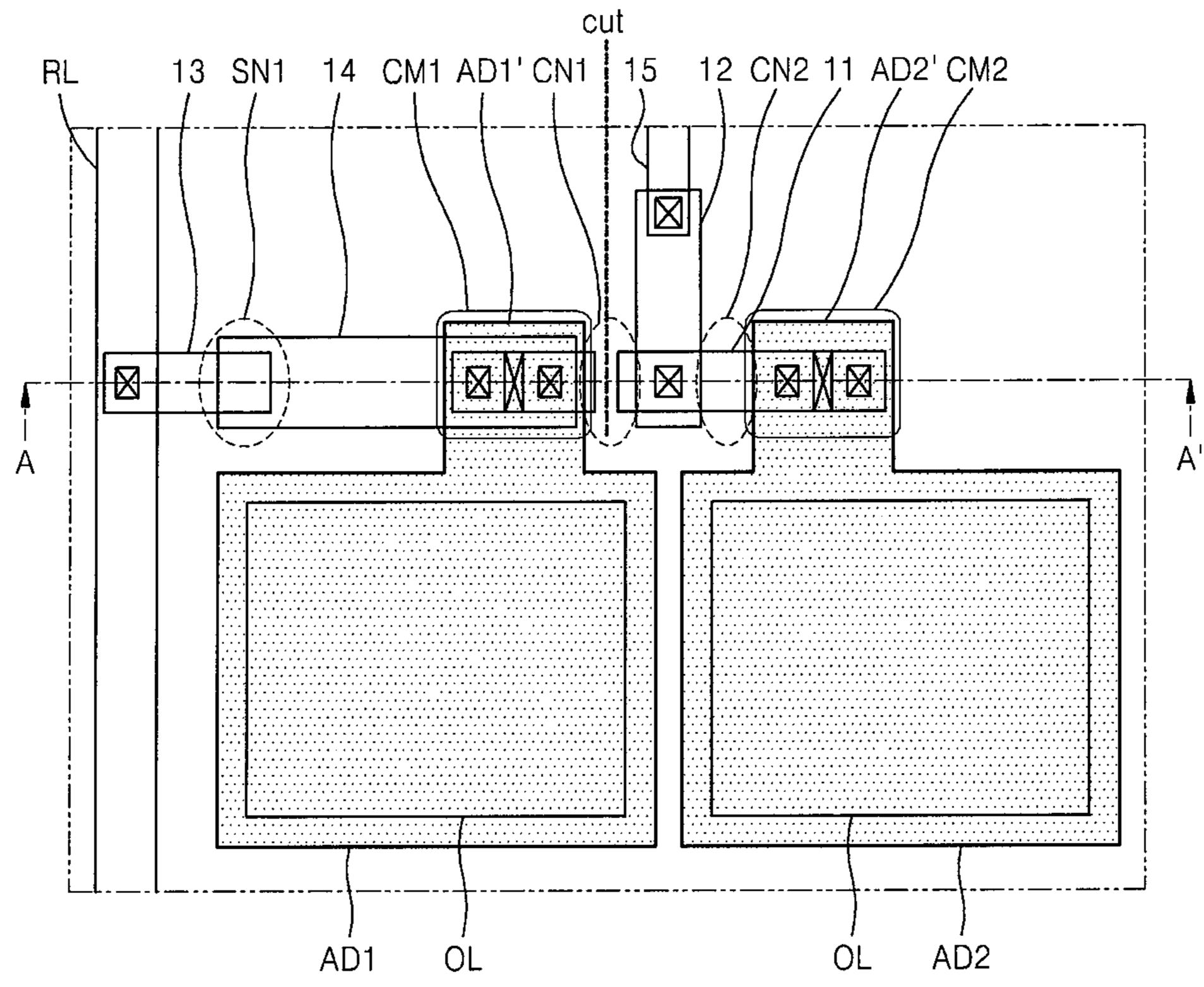

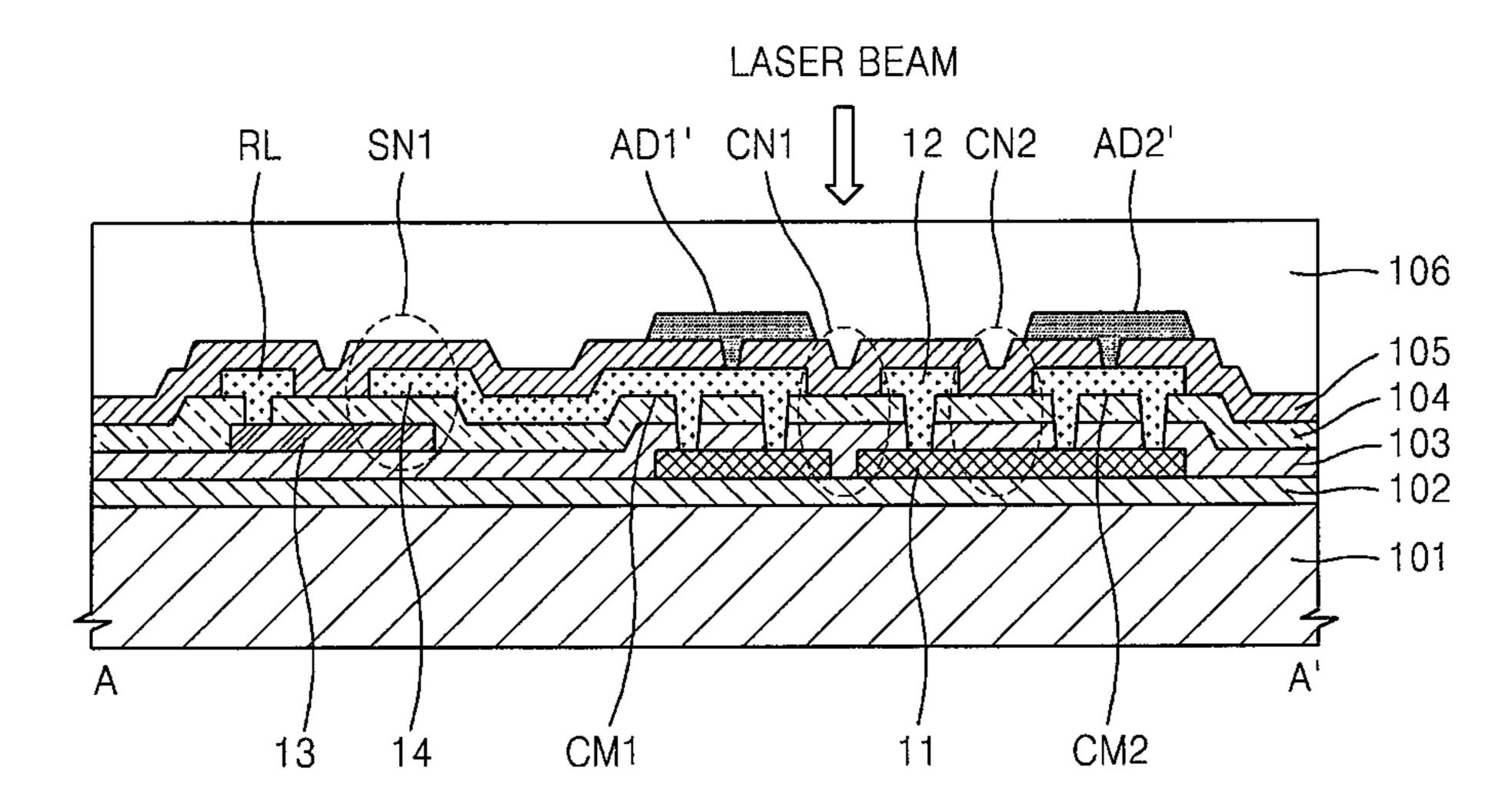

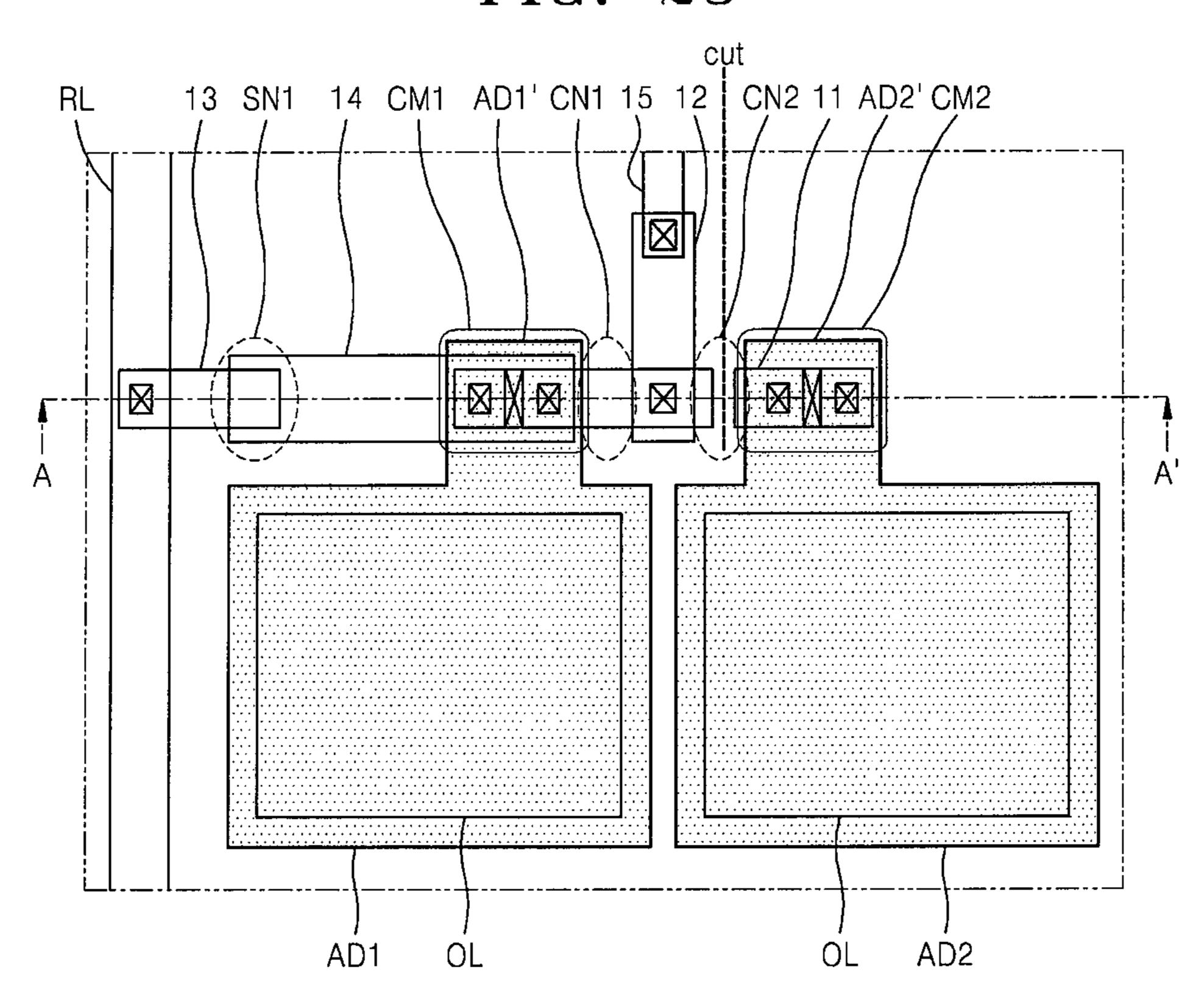

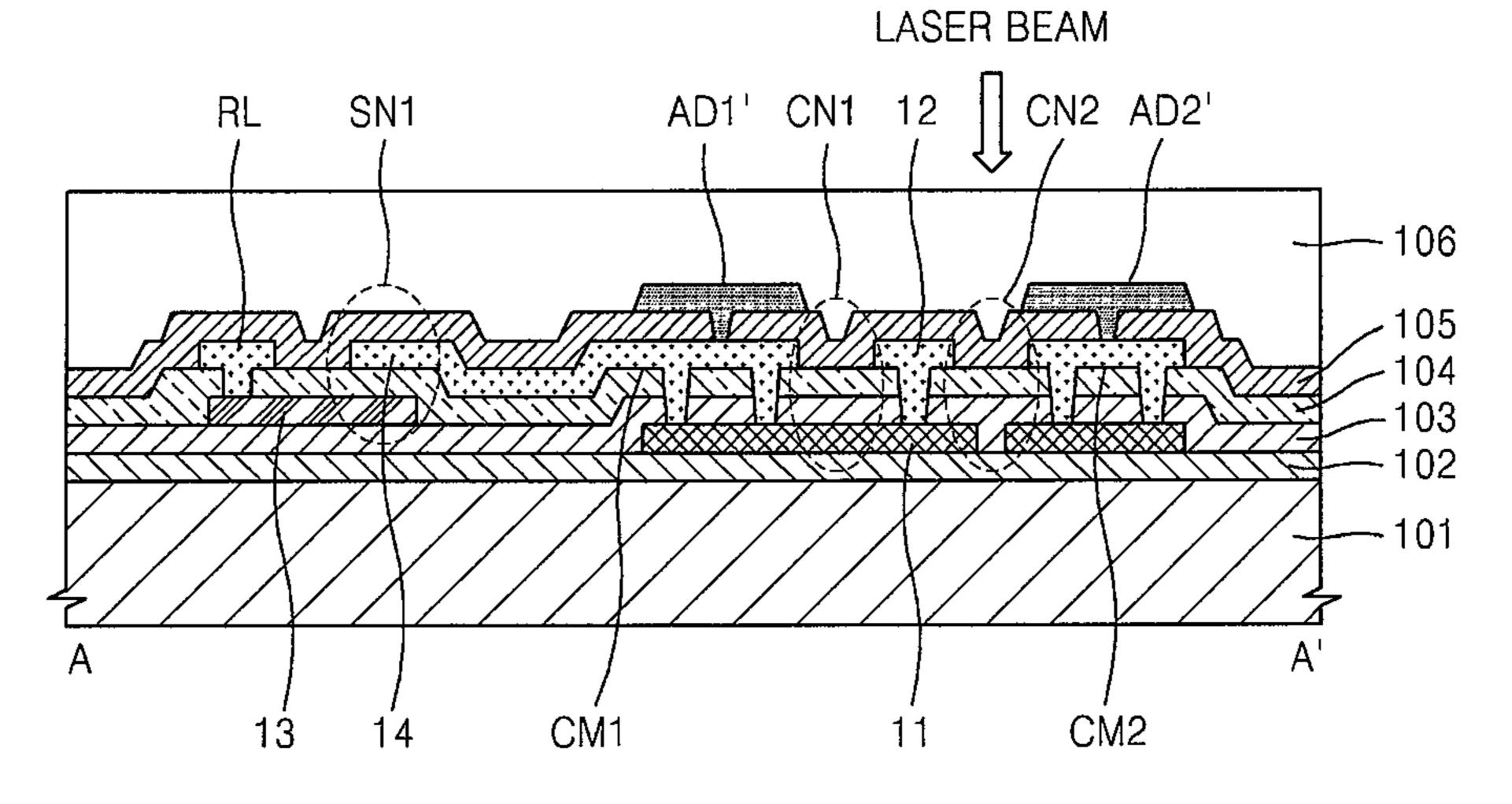

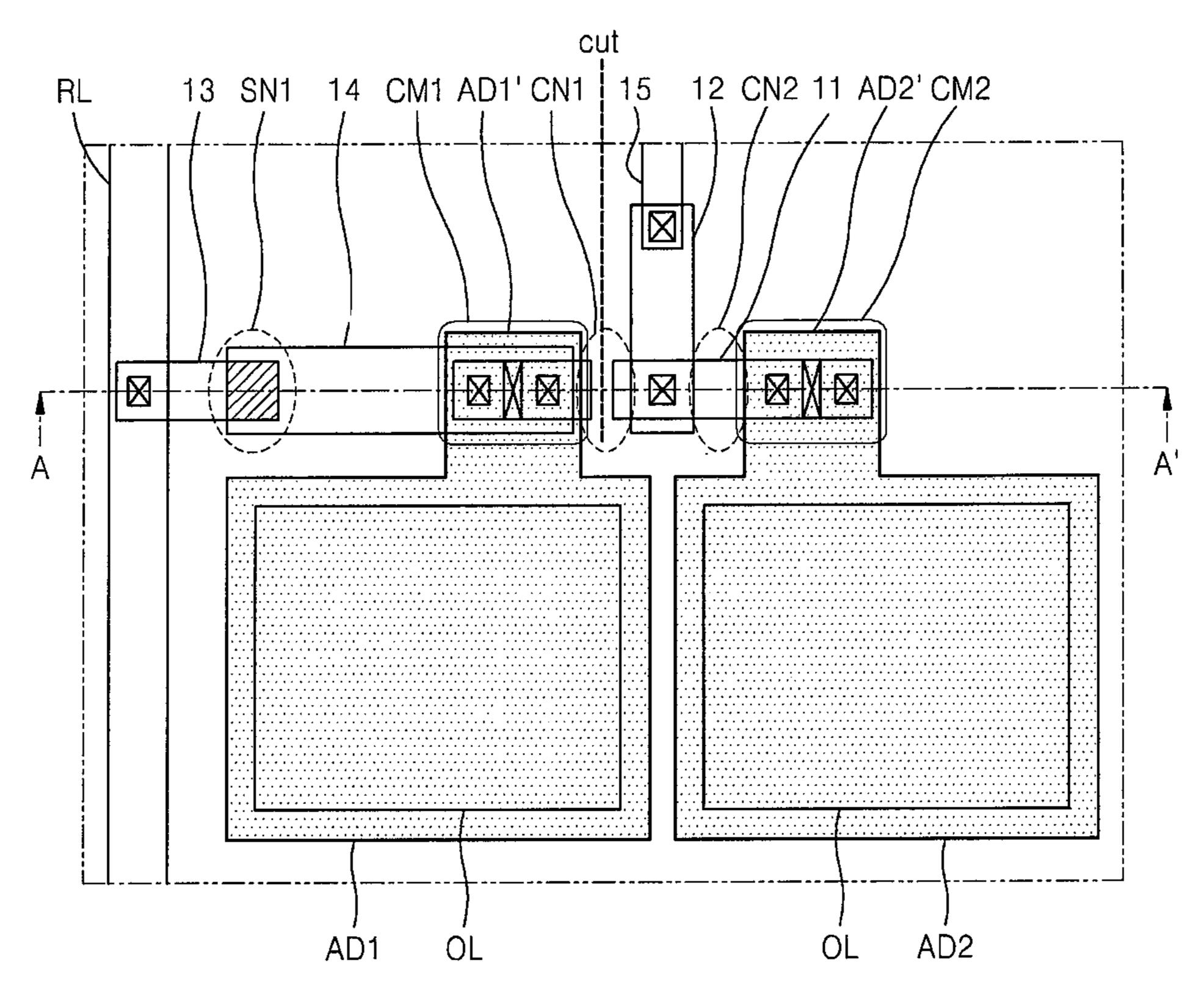

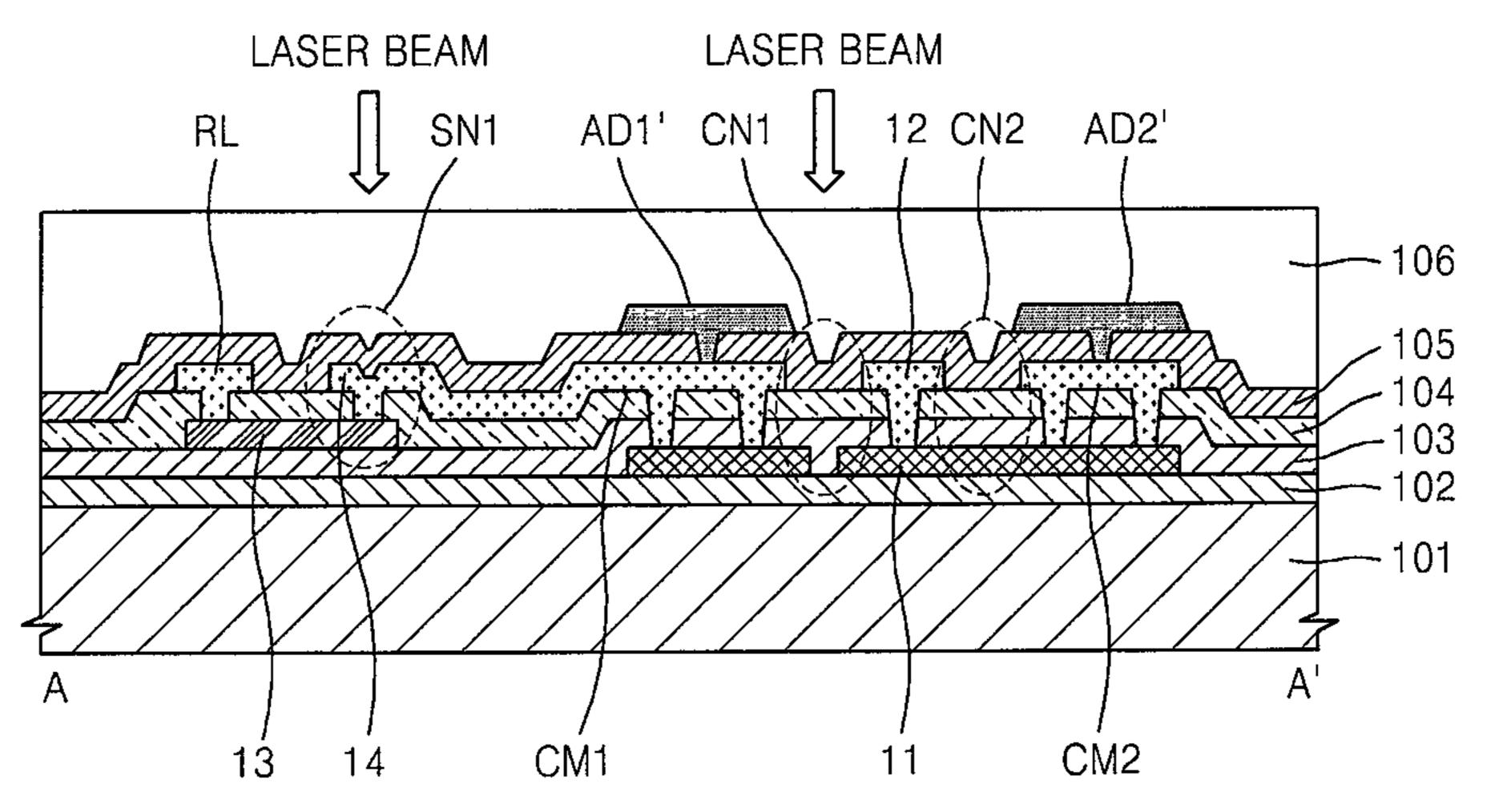

FIG. 14 is a schematic diagram of the emission pixel EP according to an embodiment of the present invention. FIG. 15 is a plan view of an emission device of the emission pixel 65 EP of FIG. 14. FIG. 16 is a cross-sectional view taken along a line A-A' of FIG. 15.

12

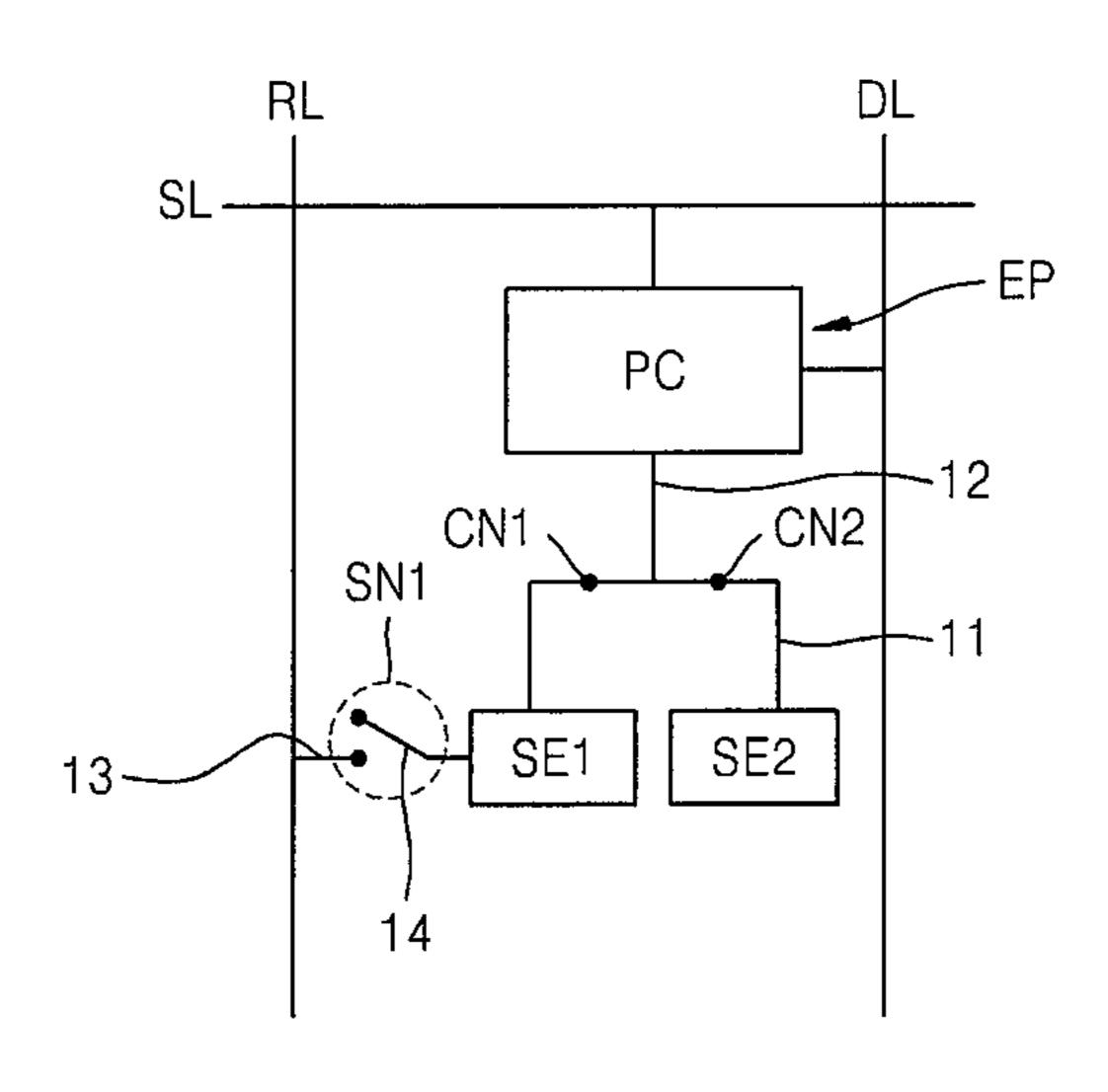

Referring to FIG. 14, the emission pixel EP that is coupled to the scan line SL and the data line DL may include the pixel circuit PC and the emission device E that emits light by receiving a driving current from the pixel circuit PC. The pixel circuit PC may include at least one thin film transistor (TFT) and at least one capacitor. The emission device E may be an organic light emitting diode (OLED) including an anode, a cathode, and an emission layer formed or located between the anode and the cathode. The anode of the emission device E may be split or separated (e.g., physically separated by a gap or space) into at least two anodes so that the emission device E may include at least two sub-emission devices SE1 and SE2.

Referring to FIGS. 15 and 16, the first sub-emission device SE1 includes a first anode AD1, an organic layer OL including an emission layer, and a cathode (not shown). The second sub-emission device SE2 includes a second anode AD2, the organic layer OL including the emission layer, and a cathode. The organic layer OL may be separately or commonly formed in the first and second sub-emission devices SE1 and SE2. The cathode may be commonly formed in the first and second sub-emission devices SE1 and SE2, and may be formed on an entire surface of a substrate 101 so that the cathode may be commonly formed in the first anode AD1 and the second anode AD2 to face each other.

An electrode connection wiring 11 is formed on the substrate 101 and a buffer layer 102. The electrode connection wiring 11 may be formed of a conductive material. For example, the electrode connection wiring 11 may be formed of amorphous silicon, crystalline silicon, or an oxide semiconductor. In this case, the electrode connection wiring 11 may be formed on the same layer and of the same material as an active layer included in the TFT of the pixel circuit PC. The electrode connection wiring 11 may be formed of metal. In this case, the electrode connection wiring 11 may have a single layer structure including metal, semitransparent metal, or a transparent conductive oxide or a three layer structure including the semitransparent metal and the transparent conductive oxide formed on top and bottom portions of the semitransparent metal and protecting the semitransparent metal. The semitransparent metal may include silver (Ag) or a silver alloy. The transparent conductive oxide may include at least one selected from the group consisting of indium tin oxide (ITO), indium zinc oxide (IZO), zinc oxide (ZnO), indium oxide ( $In_2O_3$ ), indium gallium oxide (IGO), and aluminum zinc oxide (AZO). A first insulating film 103 is formed on the electrode connection wiring 11. A repair connection wiring 13 is formed on the first insulating film **103**.

The repair connection wiring 13 may be formed on the same layer and of the same material as a conductive electrode included in the TFT of the pixel circuit PC, for example, a gate electrode. A second insulating layer 104 is formed on the repair connection wiring 13. In a first connection unit CU1, a first contact metal CM1 and a second contact metal CM2 formed on the second insulating layer 104 are coupled to the electrode connection wiring 11 through contact holes. A circuit connection wiring 12, that is coupled to a circuit wiring 15 coupled to the pixel circuit PC, is coupled to the electrode connection wiring 11 through a contact hole, in a second connection unit CU2. The circuit wiring 15, along with the active layer included in the TFT of the pixel circuit PC, may be formed of amorphous silicon, crystalline silicon, or an oxide semiconductor or may be formed on the same layer and of the same material as a source electrode and a drain electrode that are included in the TFT. The circuit connection wiring 12 is coupled to the

electrode connection wiring 11 between the first connection units CU1 so that a first cut node CN1 and a second cut node CN2 are formed in the electrode connection wiring 11. A short wiring 14 extending from the first contact metal CM1 overlaps with a part of the repair connection wiring 13 in a 5 first short node SN1 and is provisionally coupled to the repair connection wiring 13. The repair line RL is coupled to the repair connection wiring 13 through a contact hole. The repair line RL, the circuit connection wiring 12, the first and second contact metals CM1 and CM2, and the short 10 wiring 14 may be formed on the same layer and of the same material as a conductive electrode included in the TFT of the pixel circuit PC, for example, the source electrode and the drain electrode. A third insulating layer 105 is formed on the  $_{15}$  present invention. repair line RL, the first and second contact metals CM1 and CM2, and the short wiring 14. The first anode AD1 and the second anode AD2 are formed on the third insulating layer **105**.

A first protrusion unit AD1' extending from the first anode 20 AD1 is coupled to the electrode connection wiring 11 through the first contact meal CM1 in the first connection unit CU1. A second protrusion unit AD2' extending from the second anode AD2 is coupled to the electrode connection wiring 11 through the second contact meal CM2 in the first 25 connection unit CU1. Accordingly, the first anode AD1 and the second anode AD2 are electrically coupled to each other by the electrode connection wiring 11. A fourth insulating layer 106 that covers edges of the first anode AD1 and the second anode AD2 is formed on the first anode AD1 and the 30 second anode AD2.

FIG. 17 is a schematic diagram of the dummy pixel DP according to an embodiment of the present invention. FIG. 18 is a plan view of a part of the dummy pixel DP of FIG. 17. FIG. 19 is a cross-sectional view taken along a line B-B' 35 of FIG. 18.

Referring to FIG. 17, the dummy pixel DP that is coupled to the zeroth scan line SL0 and/or the (n+1)th scan line SLn+1 and the data line DL may include only the pixel circuit PC. The pixel circuit PC of the dummy pixel DP may 40 be the same (e.g., the same design, structure, and/or function) as the pixel circuit PC of the emission pixel EP.

Referring to FIGS. 18 and 19, a power connection wiring 18 is formed on the substrate 101 and the buffer layer 102. The power connection wiring 18 may be formed of amorphous silicon, crystalline silicon, or an oxide semiconductor. The power connection wiring 18 may be formed on the same layer and of the same material as an active layer included in the TFT of the pixel circuit PC. The first insulating layer 103 is formed on the power connection wiring 18. A repair 50 connection wiring 16 is formed on the first insulating layer 103.

The repair connection wiring 16 may be formed on the same layer and of the same material as a conductive electrode included in a TFT of the pixel circuit PC, for example, 55 a gate electrode. The second insulating layer 104 is formed on the repair connection wiring 16. On the second insulating layer 104, a short wiring 17 coupled to the pixel circuit PC overlaps with a part of the repair connection wiring 16 in the first short node SN2 and is provisionally coupled to the forepair connection wiring 16. The repair line RL is coupled to the repair connection wiring 16 through a contact hole. The repair line RL and a power voltage line ELVDDL in a boundary of the display panel 10 are coupled to the power connection wiring 18 so that the repair line RL and the 65 power voltage line ELVDDL are electrically coupled to each other. When the repair line RL is used to repair the emission

14

pixel EP, the power voltage line ELVDDL is disconnected from the repair line RL by cutting the power connection wiring 18.

The repair line RL, the short wiring 17, and the power voltage line ELVDDL may be formed on the same layer and of the same material as a conductive electrode included in the TFT of the pixel circuit PC, for example, a source electrode and a drain electrode. The third insulating layer 105 and the fourth insulating layer 106 are sequentially formed on the repair line RL, the short wiring 17, and the power voltage line ELVDDL.

FIG. 20 is a flowchart for explaining a method of repairing a defective pixel, according to an embodiment of the present invention.

Referring to FIG. 20, after the display panel 10 is manufactured, the defective pixel of the display area AA is detected through a panel test performed on the display panel 10 (operation S21). The panel test may include, for example, a lighting test, an aging test, etc. The defective pixel is an emission pixel recognized as a bright spot or a dark spot. The bright spot or the dark spot may be generated due to a defective pixel circuit or a defective emission device. When an anode and a cathode of an emission device are shorted due to a defect present therebetween, and when a value of a resistance Rdef formed in parallel with the anode and the cathode is small, a driving current generated in the pixel circuit PC flows from the anode to the cathode through the resistance Rdef, and thus a voltage of the anode is not sufficiently higher than a turn-on voltage of the emission device, which causes the dark spot in which the emission device does not emit light.

A pixel that is visibly recognized as a bright spot or a dark spot of the display panel 10 may be detected through an optical microscope of a lighting inspection apparatus.

In a case of a visible defect in which a sub-emission device that is the bright spot or the dark spot is visibly recognized among a plurality of sub-emission devices, the sub-emission device having the defect of the bright spot or the dark spot is separated or electrically isolated from the pixel circuit PC (operation S22).

In a case of an invisible defect in which a defective sub-emission device is not visibly recognized among a plurality of sub-emission devices, an emission device of the defective pixel is coupled to the repair line RL and the pixel circuit PC of the dummy pixel DP is coupled to the repair line RL so that the defective pixel is coupled to the dummy pixel DP (operation S23). It is determined whether the defective pixel normally emits light (operation S24).

When the defective pixel normally emits light by the coupling of the defective pixel and the dummy pixel DP, the defective pixel is determined to have resulted from the defective pixel circuit. Thus, in order to completely insulate the defective pixel circuit from the emission device, the pixel circuit PC of the defective pixel may be selectively separated or electrically isolated from the emission device (operation S25). Operation S25 may be selectively performed.

When the defective pixel does not normally emit light by the coupling of the defective pixel and the dummy pixel DP, the defective pixel is determined to have resulted from the short defect of the emission device, and the sub-emission devices are disconnected from each other (operation S26).

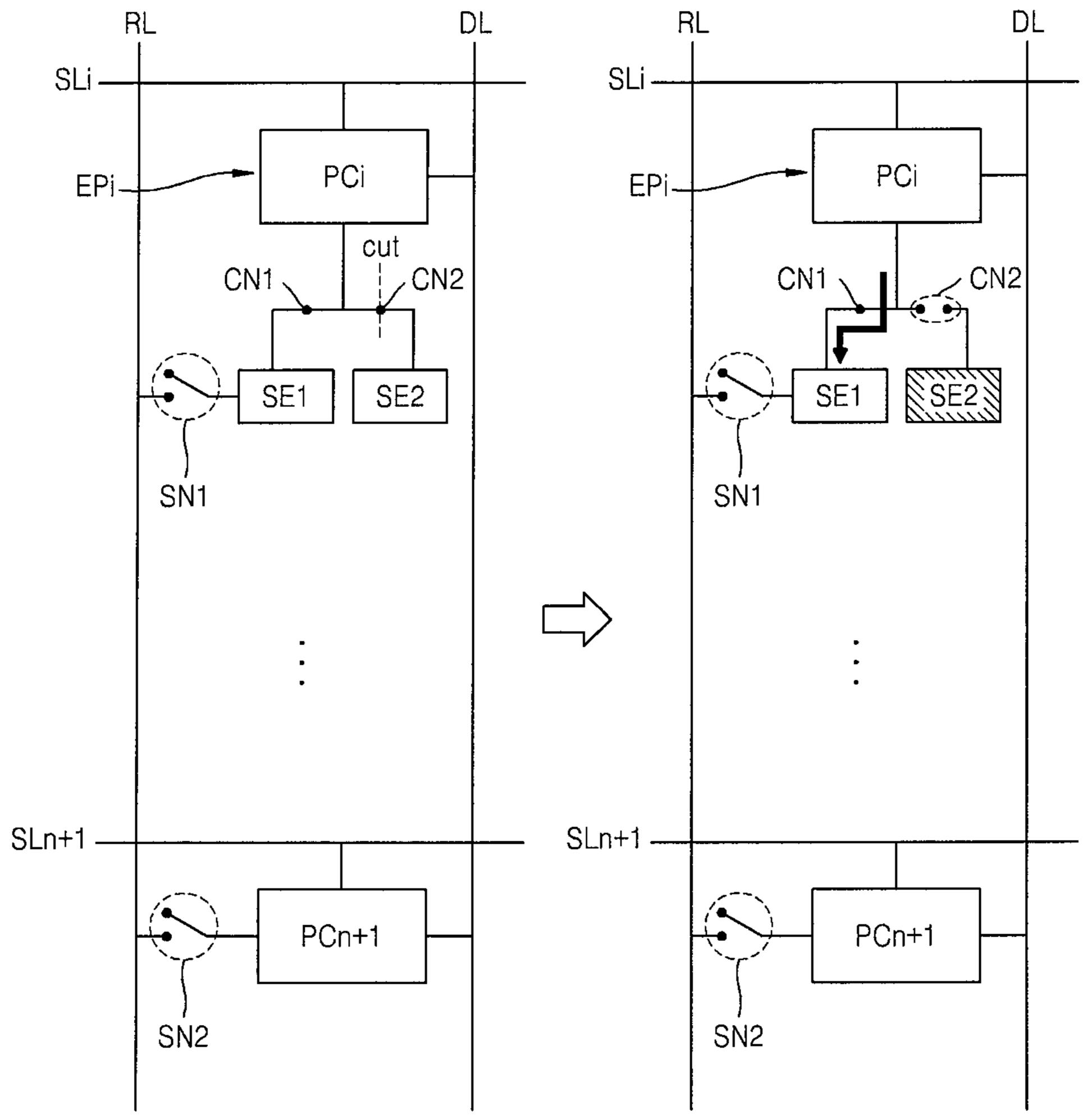

FIGS. 21 through 26 are diagrams for explaining a method of repairing a defective pixel (operation S22) in a case of a visible defect of FIG. 20, according to embodiments of the present invention.

The repairing method of FIGS. 21 through 26 describes an example of the dummy pixel DP coupled to the (n+1)th scan line SLn+1 among the first through (n+1)th scan lines SL1 through SLn+1 like the display panel 10a of FIG. 2. This may apply to the display panels 10b and 10c of FIGS. 3 and 5

Referring to FIGS. 21 through 23, when the first subemission device SE1 of the defective emission pixel ER is visibly recognized to have a short defect, the first subemission device SE1 is disconnected from the second subemission device SE2. In this regard, the first cut node CN1 of the electrode connection wiring 11 is cut by irradiating a laser beam. Accordingly, the first sub-emission device SE1 becomes a dark spot and a driving current flows from an emission pixel circuit PCi to the second sub-emission device 15 SE2 so that the second sub-emission device SE2 may emit light without any perceivable brightness reduction.

Referring to FIGS. 24 through 26, when the second sub-emission device SE2 of the defective emission pixel EPi is visibly recognized to have a short defect, the second sub-emission device SE1 is disconnected from the first sub-emission device SE1. In this regard, the second cut node cN2 of the electrode connection wiring 11 is cut by irradiating the laser beam. Accordingly, the second sub-emission device SE2 becomes the dark spot, and the driving current and defection device SE1 so that the first sub-emission device SE1 may emit light without any perceivable brightness reduction.

SL1 through 26, when the second SL1 through 20 is and 4.

Referring to FIGS. 24 through 26, when the second SL1 through 20 is and 4.

In the embodiments described with reference to FIGS. 21 30 through 26, the emission pixel EPi has a short defect, and the emission pixel circuit PCi is normal, and thus the emission pixel EPi is not necessarily coupled to the dummy pixel DP through the repair line RL.

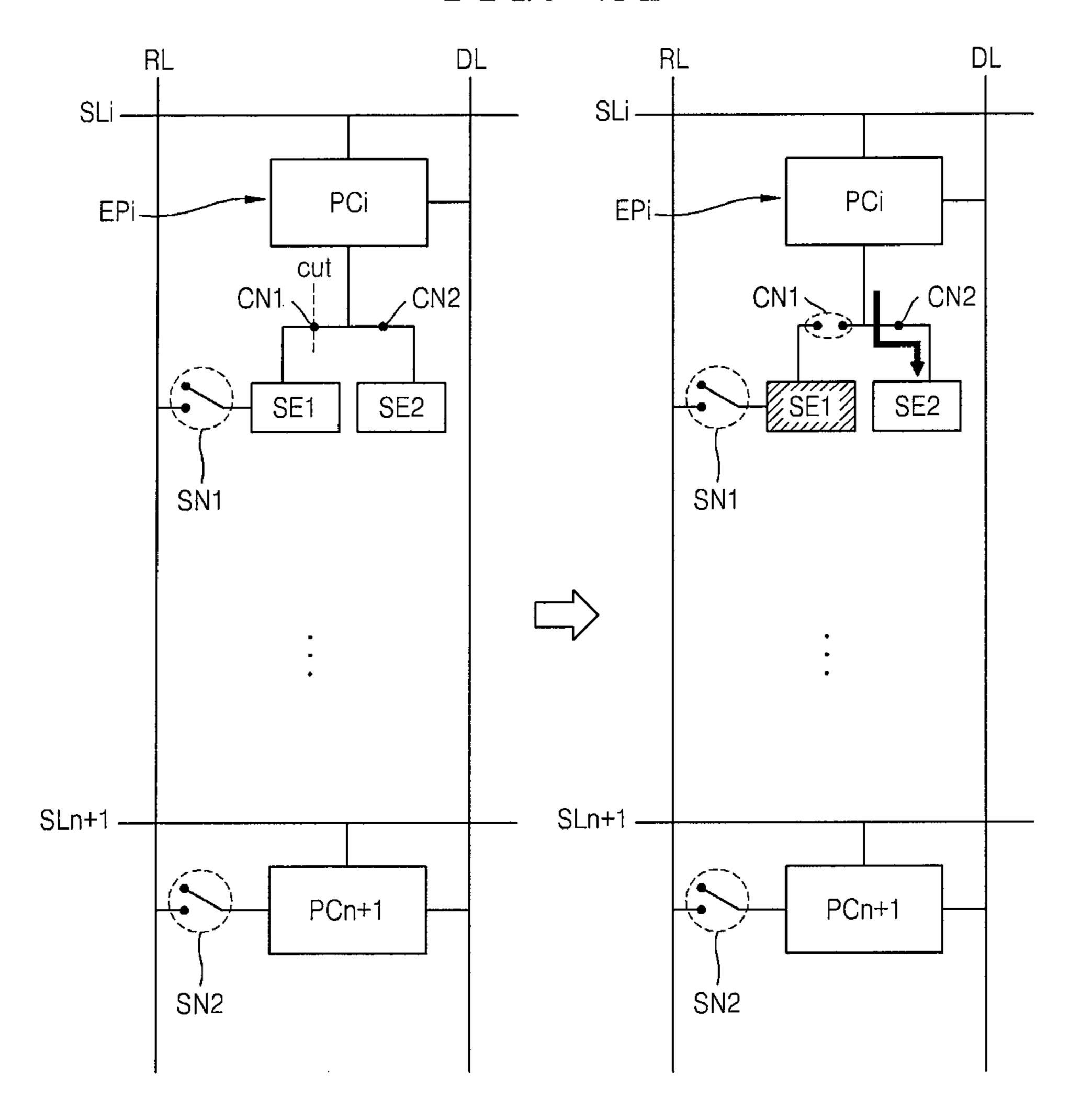

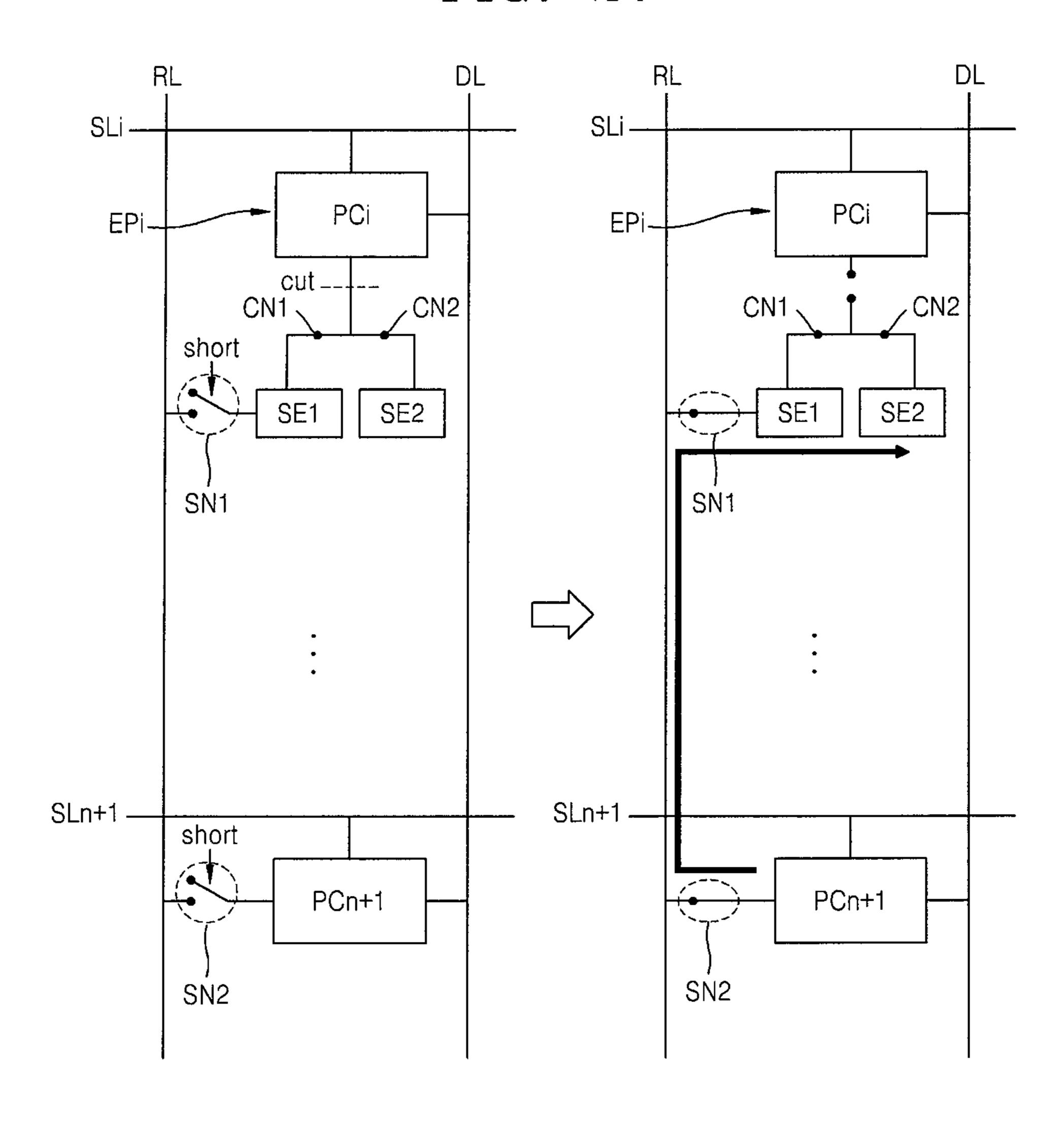

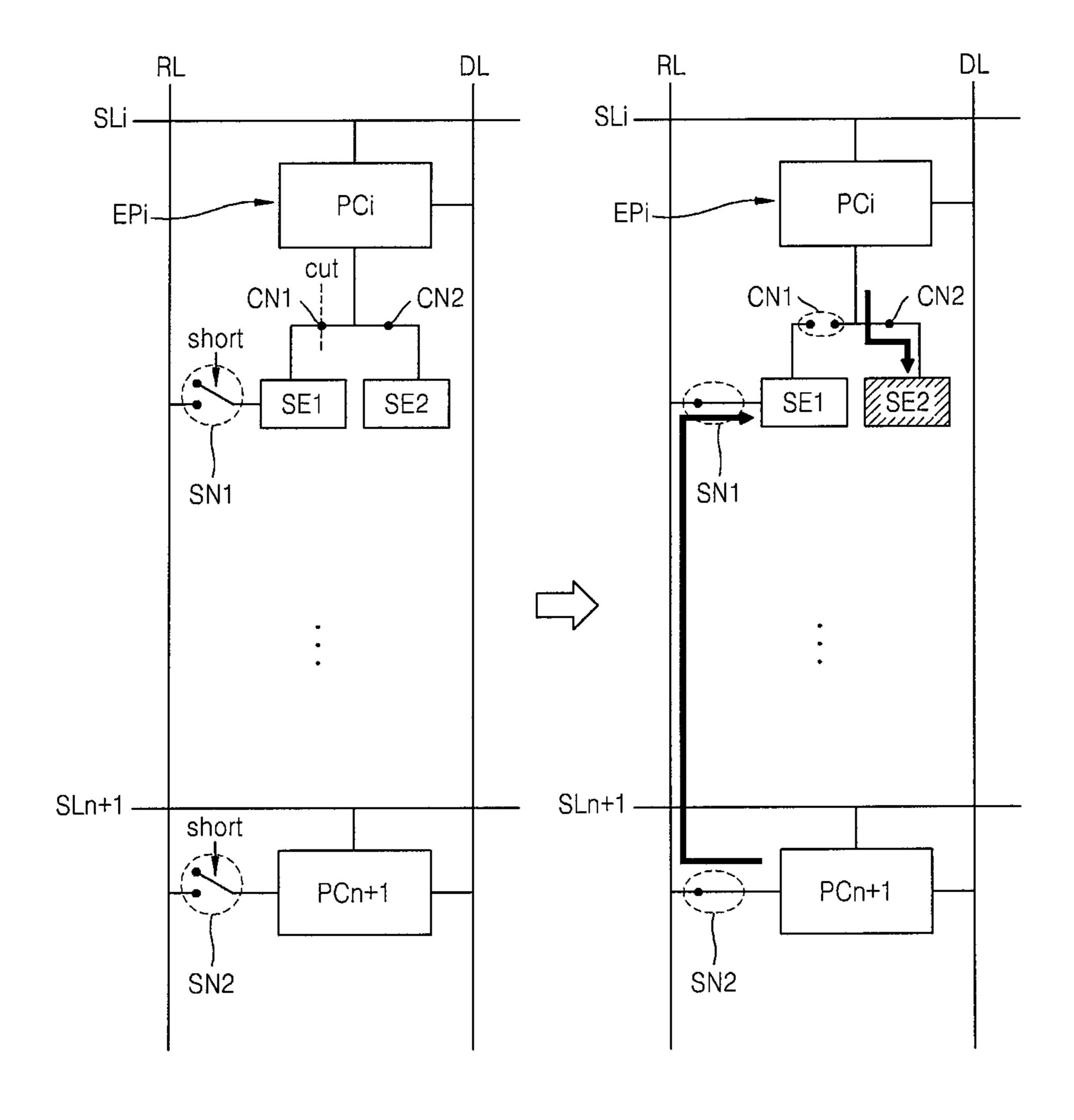

FIGS. 27 through 29B are diagrams for explaining a 35 onto the power connection wiring 18. method of repairing a defective pixel (operations S23 and S25) in the case of an invisible defect of FIG. 20, according to embodiments of the present invention.

After the coupling of the repair line in DP, and the emission pixel EPi, when to device SE1 and the second sub-emission

The repairing method of FIGS. 27 through 29B describes an example of the dummy pixel DP coupled to the (n+1)th 40 scan line SLn+1 among the first through (n+1)th scan lines SL1 through SLn+1 like the display panel 10a of FIG. 2. This may apply to the display panels 10b and 10c of FIGS. 3 and 4.

Referring to FIGS. 27 through 29B, although the emission 45 pixel EPi coupled to the ith scan line SLi is determined to be defective, when it is not determined whether the defective emission pixel EPi has resulted from a defective pixel circuit or a defective emission device, the provisionally coupled repair connection wiring 13 and the short wiring 14 are 50 shorted by irradiating a laser beam onto the first short node SN1, and then the provisionally coupled repair connection wiring 16 and the short wiring 17 are shorted by irradiating the laser beam onto the second short node SN2, and thus the emission pixel EPi and the dummy pixel DP are electrically 55 coupled to each other (operation S23). The power voltage line ELVDDL and the repair line RL are disconnected from each other by irradiating the laser beam onto the power connection wiring 18.

After the coupling of the repair line RL and the dummy 60 pixel DP and defective emission pixel EPi, when the first sub-emission device SE1 and the second sub-emission device SE2 normally emit light, because the defective emission pixel EPi is determined to have resulted from the defective emission pixel circuit PCi, to completely insulate 65 the defective emission pixel circuit PCi from the defective emission pixel EPi, the circuit connection wiring 12 and the

**16**

circuit wiring 15 are separated or electrically isolated from each other by cutting the circuit wiring 15 by irradiating the laser beam onto the circuit wiring 15, and thus the emission pixel circuit PCi is separated or electrically isolated from the emission pixel EPi (operation S25).

Accordingly, a driving current flows from a dummy pixel circuit PCn+1 to the first sub-emission device SE1 and the second sub-emission device SE so that the emission pixel EPi may emit light without any perceivable brightness reduction.

FIGS. 30A through 32 are diagrams for explaining a method of repairing a defective pixel (operations S23 and S26) in the case of the invisible defect of FIG. 20, according to embodiments of the present invention.

The repairing method of FIGS. 30A through 32 describes an example of the dummy pixel DP coupled to the (n+1)th scan line SLn+1 among the first through (n+1)th scan lines SL1 through SLn+1 like the display panel 10a of FIG. 2. This may apply to the display panels 10b and 10c of FIGS. 3 and 4.

Referring to FIGS. 28B and 30A through 32, although the emission pixel EPi coupled to the ith scan line SL1 is determined to be defective, when it is not determined whether the defective emission pixel EPI has resulted from a defective pixel circuit or a defective emission device, the provisionally coupled repair connection wiring 13 and the short wiring 14 are shorted by irradiating a laser beam onto the first short node SN1, and the provisionally coupled repair connection wiring 16 and the short wiring 17 are shorted by irradiating the laser beam onto the second short node SN2, and thus the emission pixel EPi and the dummy pixel DP are electrically coupled to each other (operation S23). The power voltage line ELVDDL and the repair line RL are disconnected from each other by irradiating the laser beam onto the power connection wiring 18.

After the coupling of the repair line RL, the dummy pixel DP, and the emission pixel EPi, when the first sub-emission device SE1 and the second sub-emission device SE2 do not normally emit light, because the defective emission pixel EPi is determined to have resulted from the defective emission device E, the first cut node CN1 of the electrode connection wiring 11 is cut by irradiating the laser beam onto the electrode connection wiring 11 (operation S26). Thus, the first sub-emission device SE1 and the second sub-emission device SE2 are separated or electrically isolated from each other, the first sub-emission device SE1 receives a driving current from the dummy pixel circuit PCn+1, and the second sub-emission device SE2 receives a driving current from the emission pixel circuit PCi.

If the defective emission pixel EPi is determined to have resulted from a short defect of the first sub-emission device SE1, as shown in FIG. 30A, the first sub-emission device SE1 becomes a dark spot, and the second sub-emission device SE2 may emit light by the driving current from the emission pixel circuit PCi without any perceivable brightness reduction.

If the defective emission pixel EPi is determined to have resulted from a short defect of the second sub-emission device SE2, as shown in FIG. 30B, the second sub-emission device SE2 becomes the dark spot, and the first sub-emission device SE1 may emit light by the driving current from the dummy pixel circuit PCn+1 without any perceivable brightness reduction.

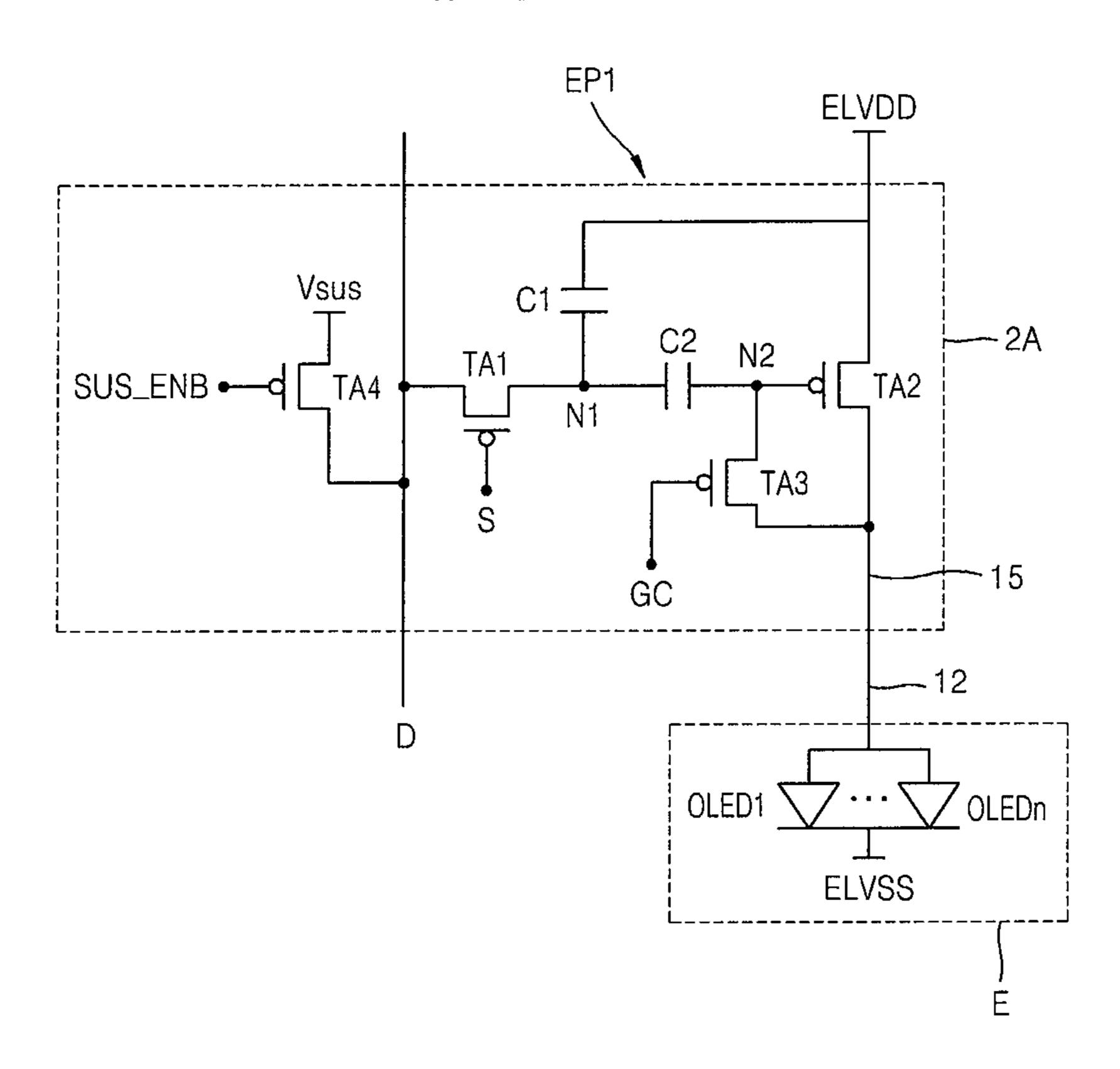

FIG. 33 is a circuit diagram of an emission pixel EP1 according to an embodiment of the present invention.

Referring to FIG. 33, the emission pixel EP1 includes the emission device E and a pixel circuit 2A for supplying a

current to the emission device E. The dummy pixel DP includes the pixel circuit 2A excluding the emission device E. The emission device E includes an anode, a cathode, and an emission layer formed or located between the anode and the cathode, and may be an OLED having a structure in 5 which the anode is split or separated into a plurality of anodes. The emission device E may include first through nth OLEDs OLED1 through OLEDn that are coupled in parallel to each other by the plurality of anodes resulting from the splitting of the anode. Accordingly, a driving current of the 10 pixel circuit 2A is separately provided to the first through nth OLEDs OLED1 through OLEDn. If a defective OLED is separated or electrically isolated from the corresponding pixel circuit, because the driving current is separately provided to the other OLEDs, the OLEDs may emit light 15 without any perceivable brightness loss. The circuit connection wiring 12 coupled to the emission device E is disconnected from the circuit wiring 15 coupled to the pixel circuit 2A by cutting the circuit wiring 15, and thus the pixel circuit 2A and the emission device E may be separated or electri- 20 cally isolated from each other.

The pixel circuit 2A may include first through fourth transistors TA1 through TA4, and first and second capacitors C1 and C2.

A gate electrode of the first transistor TA1 receives a scan 25 signal S from a scan line. A first electrode of the first transistor TA1 receives a data signal D from a data line. A second electrode of the first transistor TA1 is coupled to a first node N1.

A gate electrode of the second transistor TA2 is coupled 30 to a second node N2. A first electrode of the second transistor TA2 receives a first power voltage ELVDD from a first power source. A second electrode of the second transistor TA2 is coupled to the anode of the OLED. The second transistor TA2 functions as a driving transistor.

The first capacitor C1 is coupled between the first node N1, and the second electrode of the second transistor TA2 and the first power source. The second capacitor C2 is coupled between the first node N1 and the second node N2.

A gate electrode of the third transistor TA3 receives a first 40 control signal GC. A first electrode of the third transistor TA3 is coupled to the gate electrode of the second transistor TA2. A second electrode of the third transistor TA3 is coupled to the anode of the OLED and the second electrode of the second transistor TA2.

A gate electrode of the fourth transistor TA4 receives a second control signal SUS\_ENB. A first electrode of the fourth transistor TA4 receives an auxiliary voltage Vsus. A second electrode of the fourth transistor TA4 is coupled to the data line and receives the data signal D.

In an initialization period, the scan signal S having a low level is provided to the scan line, and a second control signal SUS\_ENB having a low level is provided to the gate electrode of the fourth transistor TA4. In this case, the data line is in a high impedance (Hi-Z) state. As such, the first 55 transistor TA1 and the fourth transistor TA4 are turned on and thus the auxiliary voltage Vsus having a high level is provided to the first node N1, a voltage of the second node N2 is reduced, and the second node N2 is maintained at an initialization voltage (e.g., a predetermined initialization 60 voltage).

In a compensation period, the auxiliary voltage Vsus having a high level is provided to the first node N1 through the data line. The first control signal GC is provided at a low level and thus the third transistor TA3 is turned on. As such, 65 the second transistor TA2 is diode-connected and thus a current flows until a voltage corresponding to a threshold

18

voltage of the second transistor TA2 is stored in the second capacitor C2. After that, the second transistor TA2 is turned off.

In a scan/data input period, the scan signal S having a low level is provided to the scan line and thus the first transistor TA1 is turned on, and the data signal D is provided through the data line. As such, a voltage difference between the driving voltage ELVDD and a voltage of the first node N1 is stored in the first capacitor C1.

In an emission period, the first power voltage ELVDD is provided at a high level, and the second power voltage ELVSS is provided at a low level. A current path from the first power voltage ELVDD to the cathode of the OLED is formed via the second transistor TA2, and the emission devices E of all the emission pixels EP1 emit light at a brightness corresponding to the data signal.

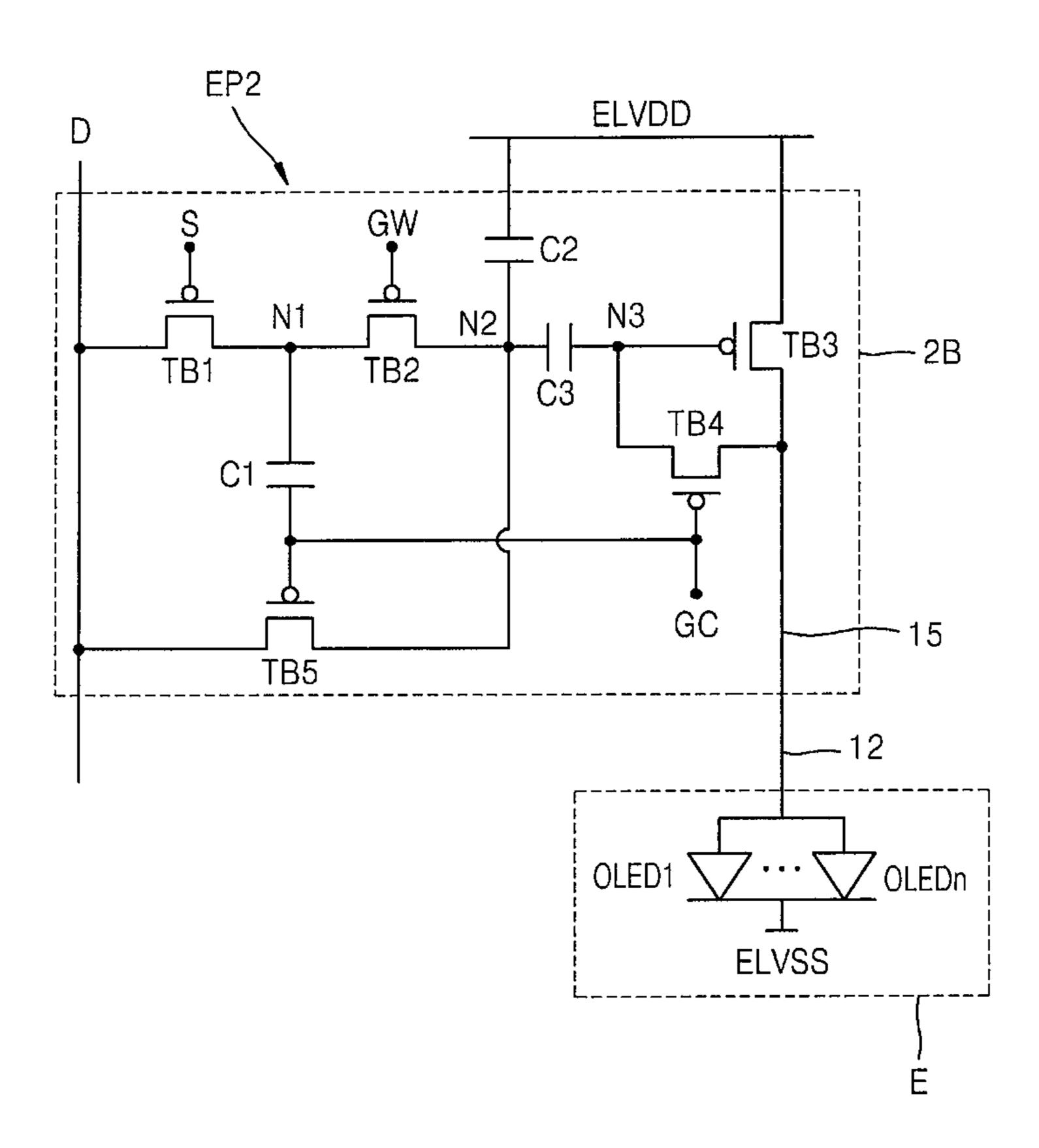

FIG. **34** is a circuit diagram of an emission pixel EP**2** according to another embodiment of the present invention.