### US00RE49389E

# (19) United States

# (12) Reissued Patent

Chaji et al.

# (10) Patent Number: US RE49,389 E

## (45) Date of Reissued Patent: \*Jan. 24, 2023

## (54) METHOD AND SYSTEM FOR DRIVING LIGHT EMITTING DISPLAY

- (71) Applicant: Ignis Innovation Inc., Waterloo (CA)

- (72) Inventors: Gholamreza Chaji, Waterloo (CA);

Kongning Li, Toronto (CA); Vasudha

Gupta, Cupertino, CA (US); Arokia

Nathan, Cambridge (CA)

- (73) Assignee: Ignis Innovation Inc., Waterloo (CA)

- (\*) Notice: This patent is subject to a terminal dis-

claimer.

- (21) Appl. No.: 15/687,017

- (22) Filed: Aug. 25, 2017

### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: **8,471,875**Issued: **Jun. 25, 2013**Appl. No.: **12/510,780**Filed: **Jul. 28, 2009**

U.S. Applications:

(63) Continuation of application No. 14/477,037, filed on Sep. 4, 2014, now Pat. No. Re. 46,561, which is an application for the reissue of Pat. No. 8,471,875.

### (30) Foreign Application Priority Data

| Jul. 29, 2008 | (CA) | <br>CA2637343 |

|---------------|------|---------------|

| Iul 24 2009   | (CA) | CA2672590     |

(51) Int. Cl.

G09G 5/10 (2006.01)

G09G 3/36 (2006.01)

(Continued)

(52) **U.S. Cl.**CPC ...... *G09G 3/3696* (2013.01); *G09G 3/20* (2013.01); *G09G 3/3677* (2013.01); (Continued)

(58) Field of Classification Search

CPC ..... G09G 3/20; G09G 3/3688; G09G 3/3696; G09G 3/3266; G09G 3/3275; (Continued)

### (56) References Cited

### U.S. PATENT DOCUMENTS

3,506,851 A 4/1970 Polkinghom et al. 8/1973 Gobel (Continued)

#### FOREIGN PATENT DOCUMENTS

AU 729652 6/1997 AU 764896 12/2001 (Continued)

### OTHER PUBLICATIONS

Ahnood et al.: "Effect of threshold voltage instability on field effect mobility in thin film transistors deduced from constant current measurements", dated Aug. 2009.

(Continued)

Primary Examiner — Woo H Choi (74) Attorney, Agent, or Firm — Stratford Group Ltd.

## (57) ABSTRACT

A display system includes a driver for operating a panel having a plurality of pixels arranged by a plurality of first lines and at least one second line The driver includes a driver output unit for providing to the panel a single driver output for activating the plurality of first lines, the single driver output being demultiplexed on the panel to activate each first line.

# 5 Claims, 19 Drawing Sheets

# US RE49,389 E Page 2

| (51)        | Int. Cl.                                  |                                           | 6,388,653              |    |                   | Goto et al 345/98                 |

|-------------|-------------------------------------------|-------------------------------------------|------------------------|----|-------------------|-----------------------------------|

|             | G09G 3/20                                 | (2006.01)                                 | 6,392,617              |    |                   | Gleason                           |

|             | G09G 3/3266                               | (2016.01)                                 | 6,396,469              |    |                   | Miwa et al.                       |

|             | G09G 3/3275                               |                                           | 6,414,661              |    | 7/2002            | _                                 |

| / <b></b> > |                                           | (2016.01)                                 | 6,417,825              |    |                   | Stewart et al.                    |

| (52)        | U.S. Cl.                                  |                                           | 6,430,496              |    |                   | Smith et al.                      |

|             | CPC <i>G09G 3/3</i>                       | <b>8688</b> (2013.01); <i>G09G 3/3266</i> | 6,433,488<br>6,473,065 |    | 8/2002<br>10/2002 |                                   |

|             | (2013.01): $G($                           | 09G 3/3275 (2013.01); G09G                | 6,475,845              |    | 11/2002           |                                   |

|             | ` ''                                      | 52 (2013.01); G09G 2310/027               | 6,501,098              |    |                   | Yamazaki                          |

|             |                                           |                                           | 6,501,466              |    |                   | Yamagashi et al.                  |

|             | ` //                                      | <i>2310/0218</i> (2013.01); <i>G09G</i>   | 6,522,315              |    |                   | Ozawa et al.                      |

|             |                                           | 7 (2013.01); G09G 2310/0286               | 6,535,185              | B2 | 3/2003            | Kim et al.                        |

|             | (2013.01); G09G                           | <i>2310/0294</i> (2013.01); <i>G09G</i>   | 6,542,138              | B1 | 4/2003            | Shannon et al.                    |

|             | 2310/0297                                 | 7 (2013.01); G09G 2320/0276               | 6,559,839              | B1 | 5/2003            | Ueno et al.                       |

|             |                                           | ); G09G 2320/0673 (2013.01)               | 6,580,408              |    |                   | Bae et al.                        |

| (50)        | ` '                                       |                                           | 6,583,398              |    | 6/2003            | _                                 |

| (58)        | Field of Classification                   |                                           | 6,618,030              |    |                   | Kane et al.                       |

|             |                                           | 276; G09G 2310/0297; G09G                 | 6,639,244              |    |                   | Yamazaki et al.                   |

|             |                                           | 452; G09G 2310/2118; G09G                 | 6,680,580<br>6,686,699 |    | 1/2004            | Yumoto                            |

|             | 2310                                      | /0267; G09G 2310/27; G09G                 | 6,690,000              |    |                   | Muramatsu et al.                  |

|             | 2310/02                                   | 286; G09G 2310/0294; G09G                 | 6,693,610              |    |                   | Shannon et al.                    |

|             |                                           | 2320/0673                                 | 6,694,248              |    |                   | Smith et al.                      |

|             | See application file for                  | complete search history.                  | 6,697,057              |    |                   | Koyama et al.                     |

|             | occ application inc for                   | complete search mistory.                  | 6,724,151              |    | 4/2004            |                                   |

| (56)        | Deference                                 | es Cited                                  | 6,734,636              | B2 | 5/2004            | Sanford et al.                    |

| (30)        | Reference                                 | cs Citeu                                  | 6,753,655              | B2 |                   | Shih et al.                       |

|             | HS PATENT                                 | DOCUMENTS                                 | 6,753,834              |    |                   | Mikami et al.                     |

|             | O.D. ITTILITI                             | DOCOMENTS                                 | 6,756,741              |    | 6/2004            |                                   |

|             | 3,774,055 A 11/1973                       | Bapat et al.                              | 6,777,888              |    | 8/2004            |                                   |

|             | 4,090,096 A 5/1978                        | <b>-</b>                                  | 6,781,567              |    |                   | Kimura                            |

|             | 4,354,162 A 10/1982                       | •                                         | 6,788,231              |    |                   |                                   |

|             | 4,996,523 A 2/1991                        |                                           | 6,809,706<br>6,828,950 |    |                   | Shimoda<br>Koyama                 |

|             | 5,134,387 A * 7/1992                      | Smith et al 345/83                        | 6,858,991              |    |                   | Miyazawa                          |

|             | 5,153,420 A 10/1992                       | Hack et al.                               | 6,859,193              |    |                   | Yumoto                            |

|             | 5,170,158 A 12/1992                       |                                           | , ,                    |    |                   | Anzai et al.                      |

|             | 5,204,661 A 4/1993                        |                                           | 6,900,485              |    | 5/2005            |                                   |

|             | 5,266,515 A 11/1993                       |                                           | 6,903,734              |    | 6/2005            |                                   |

|             |                                           | Smith et al 345/690                       | 6,911,960              | B1 | 6/2005            | Yokoyama                          |

|             | 5,408,267 A 4/1995                        |                                           | 6,911,964              |    |                   | Lee et al.                        |

|             | 5,498,880 A 3/1996<br>5,572,444 A 11/1996 | Lee et al.<br>Lentz et al.                | 6,914,448              |    | 7/2005            |                                   |

|             | 5,589,847 A 12/1996                       |                                           | 6,919,871              |    | 7/2005            |                                   |

|             |                                           | Weisfield                                 | 6,924,602              |    |                   | Komiya                            |

|             |                                           | Hara et al.                               | 6,937,220              |    |                   | Kitaura et al.                    |

|             |                                           | Bassetti et al.                           | 6,940,214<br>6,954,194 |    |                   | Komiya et al.<br>Matsumoto et al. |

|             | 5,691,783 A 11/1997                       | Numao et al.                              | 6,970,149              |    |                   | Chung et al.                      |

|             | 5,701,505 A 12/1997                       | Yamashita et al.                          | 6,975,142              |    |                   | Azami et al.                      |

|             | 5,714,968 A 2/1998                        |                                           | , ,                    |    |                   | Arnold et al.                     |

|             |                                           | Kousai et al.                             | 6,995,519              |    |                   | Arnold et al.                     |

|             | 5,745,660 A 4/1998                        | <b>-</b>                                  | 7,027,015              | B2 | 4/2006            | Booth, Jr. et al.                 |

|             |                                           | Shieh et al.                              | 7,034,793              | B2 | 4/2006            | Sekiya et al.                     |

|             |                                           | Gray et al. Smith et al.                  | 7,038,392              |    |                   | Libsch et al.                     |

|             | 5,870,071 A 2/1999                        |                                           | 7,057,588              |    |                   | Asano et al.                      |

|             |                                           | Garbuzov et al.                           | 7,061,451              |    |                   | Kimura                            |

|             | 5,880,582 A 3/1999                        |                                           | 7,071,932              |    |                   | Libsch et al.                     |

|             | 5,903,248 A 5/1999                        |                                           | 7,106,285<br>7,112,820 |    | 9/2006<br>9/2006  | Chang et al.                      |

|             | 5,917,280 A 6/1999                        | Burrows et al.                            | 7,112,820              |    |                   | Smith et al.                      |

|             | 5,949,398 A 9/1999                        | Kim                                       | 7,122,835              |    |                   | Ikeda et al.                      |

|             | , , , ,                                   | Stewart et al.                            | 7,129,914              |    |                   | Knapp et al.                      |

|             |                                           | Yamada et al.                             | 7,164,417              |    |                   | * * ·                             |

|             |                                           | Howard et al.                             | 7,224,332              | B2 | 5/2007            | Cok                               |

|             |                                           | Chow et al.                               | 7,248,236              | B2 | 7/2007            | Nathan et al.                     |

|             | 6,091,203 A 7/2000<br>6,097,360 A 8/2000  | Kawashima et al.                          | 7,259,737              |    |                   | Ono et al.                        |

|             | 6,100,868 A 8/2000                        |                                           | 7,262,753              |    |                   | Tanghe et al.                     |

|             | 6,144,222 A 11/2000                       |                                           | 7,274,363              |    |                   | Ishizuka et al.                   |

|             |                                           | Dawson et al.                             | 7,310,092              |    |                   | Imamura                           |

|             | 6,229,508 B1 5/2001                       |                                           | 7,315,295              |    | 1/2008            |                                   |

|             |                                           | Nishigaki                                 | , ,                    |    |                   | Lan et al.                        |

|             |                                           | Sano et al.                               | 7,321,348              |    |                   | Cok et al.                        |

|             |                                           | Cairns et al.                             | 7,327,357              |    | 2/2008            |                                   |

|             |                                           | Holloman                                  | 7,333,077              |    |                   | Koyama et al.                     |

|             |                                           | Dawson et al.                             | 7,343,243              |    |                   | Smith et al.                      |

|             | 6,310,962 B1 10/2001                      | $\mathcal{L}$                             | , ,                    |    |                   | Nathan et al.                     |

|             | 6,323,631 B1 11/2001                      | •                                         |                        |    |                   | Date et al.                       |

|             | 0,333,729 B1 T 12/2001                    | Ha 345/98                                 | 7,493,301              | DZ | Z/ZUU9            | Iwabuchi et al.                   |

# US RE49,389 E Page 3

| (56)                                         | Referer            | ices Cited                     | 2003/0112208 A1                     |                    | Okabe et al.                              |

|----------------------------------------------|--------------------|--------------------------------|-------------------------------------|--------------------|-------------------------------------------|

| IIS                                          | PATENT             | DOCUMENTS                      | 2003/0117348 A1<br>2003/0122474 A1  | 6/2003<br>7/2003   | Knapp et al.<br>Lee                       |

| 0.5.                                         | 17111111           | DOCOMENTS                      | 2003/0122747 A1                     |                    | Shannon et al.                            |

| 7,502,000 B2                                 | 3/2009             | Yuki et al.                    | 2003/0128199 A1                     |                    | Kimura                                    |

| 7,515,124 B2                                 |                    | Yaguma et al.                  | 2003/0151569 A1<br>2003/0156104 A1  |                    | Lee et al.<br>Morita                      |

| 7,535,449 B2<br>7,554,512 B2                 | 5/2009<br>6/2009   | Miyazawa<br>Steer              | 2003/0150104 A1*                    |                    | LeChevalier 345/204                       |

| 7,569,849 B2                                 |                    | Nathan et al.                  | 2003/0169247 A1                     | 9/2003             | Kawabe et al.                             |

| 7,595,776 B2*                                |                    | Hashimoto et al 345/76         | 2003/0179626 A1                     |                    | Sanford et al.                            |

| 7,604,718 B2                                 |                    | <del>-</del>                   | 2003/0185438 A1<br>2003/0189535 A1  |                    | Osawa et al.<br>Matsumoto et al.          |

|                                              | 10/2009<br>11/2009 | Yumoto et al.                  | 2003/0197663 A1                     |                    |                                           |

| 7,619,594 B2                                 |                    |                                | 2003/0214465 A1                     |                    |                                           |

| 7,619,597 B2                                 |                    |                                | 2003/0227262 A1<br>2003/0230141 A1  | 12/2003            |                                           |

| 7,639,211 B2<br>7,683,899 B2                 |                    | Miyazawa<br>Hirakata et al.    | 2003/0230980 A1                     |                    | _                                         |

| 7,688,289 B2                                 |                    |                                | 2004/0004589 A1                     |                    |                                           |

| 7,692,641 B2                                 |                    |                                | 2004/0032382 A1<br>2004/0041750 A1  |                    |                                           |

| 7,760,162 B2<br>7,808,008 B2                 |                    |                                | 2004/0066357 A1                     |                    | Kawasaki                                  |

| 7,859,520 B2                                 |                    | <del>-</del>                   | 2004/0070557 A1                     |                    | Asano et al.                              |

|                                              |                    | Nathan et al.                  | 2004/0129933 A1<br>2004/0130516 A1* |                    | Nathan et al 345/82                       |

| , ,                                          |                    | Kwon                           | 2004/0135749 A1                     |                    |                                           |

| ·                                            |                    | Shirasaki et al.               | 2004/0145547 A1                     | 7/2004             |                                           |

| 7,978,170 B2                                 |                    |                                | 2004/0150595 A1<br>2004/0155841 A1  | 8/2004<br>8/2004   |                                           |

| 7,989,392 B2<br>7,995,008 B2                 |                    | Crockett et al.<br>Miwa        | 2004/0133641 A1<br>2004/0171619 A1  |                    | Libsch et al.                             |

| 8,063,852 B2                                 |                    |                                | 2004/0174349 A1                     |                    | Libsch                                    |

| 8,102,343 B2                                 |                    |                                | 2004/0174354 A1<br>2004/0183759 A1  | 9/2004             | Ono<br>Stevenson et al.                   |

| 8,144,081 B2<br>8,159,007 B2                 |                    | Mıyazawa<br>Barna et al.       | 2004/0183739 A1<br>2004/0189627 A1  |                    |                                           |

| 8,242,979 B2                                 |                    | Anzai et al.                   |                                     | 10/2004            |                                           |

| 8,253,665 B2                                 |                    |                                |                                     | 11/2004<br>12/2004 |                                           |

| 8,319,712 B2<br>2001/0002703 A1              |                    | Nathan et al.                  | 2004/0259696 A1<br>2004/0251844 A1  |                    |                                           |

|                                              |                    | Koyama<br>Arao et al.          | 2004/0252085 A1                     | 12/2004            | Miyagawa                                  |

| 2001/0026257 A1                              |                    | Kimura                         | 2004/0252089 A1<br>2004/0256617 A1  |                    | Ono et al.<br>Yamada et al.               |

| 2001/0030323 A1<br>2001/0040541 A1           | 10/2001            | Ikeda<br>Yoneda et al.         |                                     |                    | Imamura et al.                            |

| 2001/0040341 A1<br>2001/0043173 A1           |                    | Troutman                       | 2004/0257355 A1                     | 12/2004            | Naugler                                   |

| 2001/0045929 A1                              | 11/2001            |                                | 2004/0263437 A1<br>2005/0007357 A1  | 1/2004             | Hattori<br>Yamashita et al.               |

| 2001/0052940 A1<br>2002/0000576 A1           |                    | Hagihara et al.<br>Inukai      | 2005/0007337 A1<br>2005/0052379 A1* |                    | Waterman 345/87                           |

| 2002/0000376 A1<br>2002/0011796 A1           |                    | Koyama                         | 2005/0057459 A1                     | 3/2005             | Miyazawa                                  |

| 2002/0011799 A1                              |                    | Kimura                         | 2005/0067970 A1<br>2005/0067971 A1  | 3/2005<br>3/2005   | Libsch et al.                             |

| 2002/0012057 A1<br>2002/0030190 A1           |                    | Kimura<br>Ohtani et al.        | 2005/0007971 A1<br>2005/0083270 A1  |                    | Miyazawa                                  |

| 2002/0030130 A1<br>2002/0047565 A1           |                    | Nara et al.                    | 2005/0110420 A1                     | 5/2005             | Arnold et al.                             |

| 2002/0052086 A1                              |                    | Maeda                          | 2005/0110727 A1*<br>2005/0123193 A1 |                    | Shin 345/76<br>Lamberg et al.             |

| 2002/0080108 A1<br>2002/0084463 A1           | 6/2002<br>7/2002   | Wang<br>Sanford et al.         | 2005/0123193 A1<br>2005/0140610 A1  |                    | Smith et al.                              |

| 2002/0001103 AT                              | 8/2002             |                                | 2005/0145891 A1                     | 7/2005             |                                           |

| 2002/0117722 A1                              |                    | Osada et al.                   | 2005/0156831 A1<br>2005/0168416 A1* |                    | Yamazaki et al.<br>Hashimoto et al 345/76 |

| 2002/0140/12 A1*<br>2002/0158587 A1          |                    | Ouchi et al 345/690<br>Komiya  | 2005/0106410 A1<br>2005/0206590 A1  |                    |                                           |

| 2002/0158666 A1                              |                    |                                |                                     |                    | Kawabe et al 345/94                       |

| 2002/0158823 A1                              |                    | •                              | 2005/0243037 A1<br>2005/0248515 A1  |                    | Eom et al.<br>Naugler et al               |

| 2002/01/1613 A1 <sup>a</sup> 2002/0186214 A1 |                    | Goto et al 345/87<br>Siwinski  | 2005/0218313 711<br>2005/0258867 A1 |                    | •                                         |

| 2002/0190971 A1                              |                    |                                |                                     |                    | Eom et al.                                |

| 2002/0195967 A1                              |                    |                                | 2006/0012311 A1<br>2006/0038750 A1  |                    | Ogawa<br>Inoue et al.                     |

| 2002/0195968 A1<br>2003/0001828 A1           |                    | Santord et al.<br>Asano        | 2006/0038758 A1                     |                    | Routley et al.                            |

| 2003/0020413 A1                              |                    | Oomura                         | 2006/0038762 A1                     | 2/2006             | _                                         |

| 2003/0030603 A1                              |                    | Shimoda                        | 2006/0044236 A1<br>2006/0066533 A1  | 3/2006<br>3/2006   | Sato et al.                               |

| 2003/0062524 A1<br>2003/0062844 A1           |                    | Kimura<br>Miyazawa             | 2006/0077077 A1*                    |                    | Kwon                                      |

| 2003/0076048 A1                              |                    | Rutherford                     | 2006/0092185 A1                     |                    | Jo et al.                                 |

| 2003/0090445 A1                              |                    | Chen et al.                    | 2006/0125408 A1                     |                    | Nathan et al.                             |

| 2003/0090447 A1<br>2003/0090481 A1           |                    | Kimura<br>Kimura               | 2006/0139253 A1<br>2006/0145964 A1  |                    | Choi et al.<br>Park et al.                |

| 2003/0095087 A1                              |                    | Libsch                         | 2006/01/13/30 A1                    | 8/2006             | Sempel et al.                             |

| 2003/0098829 A1                              |                    | Chen et al.                    | 2006/0209012 A1*                    | 9/2006             | Hagood 345/109                            |

| 2003/0107560 A1<br>2003/0107561 A1           |                    | Yumoto et al.<br>Uchino et al. | 2006/0214888 A1<br>2006/0221009 A1  | 9/2006<br>10/2006  | Schneider et al.                          |

| 2003/010/361 A1<br>2003/0111966 A1           |                    | Mikami et al.                  |                                     |                    | Ogata et al.                              |

| 2003/0112205 A1                              |                    | Yamada                         |                                     |                    | Roy et al.                                |

|                                              |                    |                                |                                     |                    |                                           |

# US RE49,389 E Page 4

| (56)                                | Referen          | ces Cited                                | CA                     | 2 438 363                              | 2/2005                                     |

|-------------------------------------|------------------|------------------------------------------|------------------------|----------------------------------------|--------------------------------------------|

| IISI                                | PATENT           | DOCUMENTS                                | CA<br>CA               | 2 443 206<br>2 519 097                 | 3/2005<br>3/2005                           |

| 0.5.1                               | AILINI           | DOCUMENTS                                | $\mathbf{C}\mathbf{A}$ | 2 472 671                              | 12/2005                                    |

| 2006/0244391 A1                     |                  | Shishido et al.                          | CA<br>CA               | 2 523 841<br>2 567 076                 | 1/2006<br>1/2006                           |

| 2006/0244697 A1<br>2006/0261841 A1  | 11/2006          | Lee et al.<br>Fish                       | CA                     | 2 495 726                              | 7/2006                                     |

| 2006/0290614 A1                     | 12/2006          | Nathan et al.                            | CA                     | 2 557 713<br>2 526 782 C               | 11/2006                                    |

| 2007/0001939 A1*<br>2007/0001945 A1 | 1/2007<br>1/2007 | Hashimoto et al 345/76<br>Yoshida et al. | CA<br>CA               | 2 526 782 C<br>2 651 893               | 8/2007<br>11/2007                          |

| 2007/0001343 A1                     | 1/2007           | Kohno et al.                             | CA                     | 2651893 A1                             | 11/2007                                    |

| 2007/0008297 A1<br>2007/0035489 A1  | 1/2007<br>2/2007 | Bassetti                                 | CA<br>CA               | 2 672 590<br>2672590 A1                | 10/2009<br>10/2009                         |

| 2007/0035489 A1<br>2007/0035707 A1  |                  | Margulis                                 | CN                     | 1601594 A                              | 3/2005                                     |

| 2007/0040773 A1*<br>2007/0040782 A1 | 2/2007<br>2/2007 | Lee et al 345/77                         | CN<br>DE               | 1886774<br>202006007613                | 12/2006<br>9/2006                          |

| 2007/0040782 A1<br>2007/0063932 A1  |                  | Woo et al.<br>Nathan et al.              | EP                     | 0 478 186                              | 4/1992                                     |

| 2007/0080908 A1                     |                  | Nathan et al.                            | EP<br>EP               | 1 028 471 A<br>1 130 565 A1            | 8/2000<br>9/2001                           |

| 2007/0085801 A1<br>2007/0109232 A1  |                  | Park et al.<br>Yamamoto et al.           | EP                     | 1 194 013                              | 4/2002                                     |

| 2007/0128583 A1                     |                  | Miyazawa                                 | EP<br>EP               | 1 321 922<br>1 335 430 A1              | 6/2003<br>8/2003                           |

| 2007/0164941 A1<br>2007/0182671 A1  |                  | Park et al.<br>Nathan et al.             | EP                     | 1 381 019                              | 1/2004                                     |

| 2007/0236430 A1                     | 10/2007          | Fish                                     | EP<br>EP               | 1 429 312 A<br>1 439 520 A2            | 6/2004<br>7/2004                           |

| 2007/0241999 A1<br>2007/0242008 A1  | 10/2007          | Lin<br>Cummings                          | EP                     | 1 439 320 A2<br>1 465 143 A            | 10/2004                                    |

| 2008/0001544 A1                     | 1/2008           | Murakami et al.                          | EP                     | 1 473 689 A                            | 11/2004                                    |

| 2008/0043044 A1*<br>2008/0048951 A1 |                  | Woo et al 345/690<br>Naugler et al.      | EP<br>EP               | 1 517 290 A2<br>1 521 203 A2           | 3/2005<br>4/2005                           |

| 2008/0045531 A1                     |                  | Li et al.                                | GB                     | 2 399 935                              | 9/2004                                     |

| 2008/0088549 A1                     |                  | Nathan et al.                            | GB<br>JP               | 2 460 018<br>09 090405                 | 11/2009<br>4/1997                          |

| 2008/0094426 A1<br>2008/0122819 A1  |                  | Kimpe<br>Cho et al.                      | JP                     | 10-254410                              | 9/1998                                     |

| 2008/0074360 A1                     |                  | Lu et al.                                | JP<br>JP               | 11 231805<br>2002-278513               | 8/1999<br>9/2002                           |

| 2008/0129906 A1<br>2008/0228562 A1  |                  | Lin et al.<br>Smith et al.               | JP                     | 2003-076331                            | 3/2003                                     |

| 2008/0231641 A1                     |                  | Miyashita                                | JP<br>JP               | 2003-099000<br>2003-173165             | 4/2003<br>6/2003                           |

| 2008/0265786 A1<br>2008/0290805 A1  | 10/2008          | Koyama<br>Yamada et al.                  | JP                     | 2003-175105                            | 7/2003                                     |

| 2009/0009459 A1                     | 1/2009           | Miyashita                                | JP<br>ID               | 2003-195809                            | 7/2003<br>9/2003                           |

| 2009/0015532 A1<br>2009/0058789 A1  |                  | Katayama et al.<br>Hung et al.           | JP<br>JP               | 2003-271095<br>2003-308046             | 10/2003                                    |

| 2009/0121988 A1                     | 5/2009           | Feng et al.                              | JP                     | 2004-054188                            | 2/2004                                     |

| 2009/0146926 A1<br>2009/0153448 A1  |                  | Sung et al.<br>Tomida et al.             | JP<br>JP               | 2004-226960<br>2005-004147             | 8/2004<br>1/2005                           |

| 2009/0153459 A9                     | 6/2009           | Han et al.                               | JP                     | 2005-099715                            | 4/2005                                     |

| 2009/0174628 A1<br>2009/0201230 A1  | 7/2009<br>8/2009 | Wang et al.                              | JP<br>JP               | 2005-258326<br>2005-338819             | 9/2005<br>12/2005                          |

| 2009/0201230 A1<br>2009/0201281 A1  |                  | Routley et al.                           | TW                     | 569173                                 | 1/2004                                     |

| 2009/0251486 A1<br>2009/0278777 A1  |                  | Sakakibara et al.<br>Wang et al.         | TW<br>TW               | 200526065<br>1239501                   | 8/2005<br>9/2005                           |

| 2009/02/8/// A1<br>2009/0289964 A1  |                  | Miyachi                                  | WO                     | WO 98/11554                            | 3/1998                                     |

| 2010/0039451 A1<br>2010/0039453 A1  | 2/2010           | <u> </u>                                 | WO<br>WO               | WO 99/48079<br>WO 01/27910 A1          | 9/1999<br>4/2001                           |

| 2010/0039433 A1<br>2010/0207920 A1  |                  | Nathan et al.<br>Chaji et al.            | WO                     | WO 02/067327 A                         | 8/2002                                     |

| 2010/0225634 A1                     |                  | Levey et al.                             | WO<br>WO               | WO 03/034389<br>WO 03/063124           | 4/2003<br>7/2003                           |

| 2010/0251295 A1<br>2010/0269889 A1  |                  | Amento et al.<br>Reinhold et al.         | WO                     | WO 03/075256                           | 9/2003                                     |

|                                     | 11/2010          | . •                                      | WO<br>WO               | WO 2004/003877<br>WO 2004/015668 A1    | 1/2004<br>2/2004                           |

| 2010/0315319 A1<br>2011/0050741 A1  | 3/2010           | Cok et al.<br>Jeong                      | WO                     | WO 2004/034364                         | 4/2004                                     |

| 2011/0069089 A1                     | 3/2011           | Kopf et al.                              | WO<br>WO               | WO 2005/022498<br>WO 2005/055185       | 3/2005<br>6/2005                           |

| 2012/0299976 A1                     | 11/2012          | Chen et al.                              | WO                     | WO 2005/055185<br>WO 2005/055186 A1    | 6/2005                                     |

| FOREIG                              | N PATE           | NT DOCUMENTS                             | WO<br>WO               | WO 2005/069267<br>WO 2005/122121       | 7/2005<br>12/2005                          |

| C A 1 20 4                          | 024              | 1 (1000                                  | WO                     | WO 2005/122121<br>WO 2006/063448       | 6/2006                                     |

| CA 1 294<br>CA 2 249                |                  | 1/1992<br>7/1998                         | WO                     | WO 2006/128069                         | 11/2006                                    |

| CA 2 303                            | 302              | 3/1999                                   | WO<br>WO               | WO 2008/057369<br>WO 2008/0290805      | 5/2008<br>11/2008                          |

| CA 2303<br>CA 2 368                 | 3302 A1<br>386   | 3/1999<br>9/1999                         | WO                     | WO 2009/059028                         | 5/2009                                     |

| CA 2 242                            | 720              | 1/2000                                   | WO<br>WO               | WO 2009/127065<br>WO 2010/066030       | 10/2009<br>6/2010                          |

| CA 2 354<br>CA 2 432                |                  | 6/2000<br>7/2002                         | WO                     | WO 2010/120733                         | 10/2010                                    |

| CA 2 432<br>CA 2 436                |                  | 8/2002                                   |                        |                                        | NT TO LOUIS TO                             |

| CA 2 507<br>CA 2 463                |                  | 8/2002<br>1/2004                         | Alexa                  |                                        | BLICATIONS ical Measurement Technology for |

| CA 2 403<br>CA 2 498                |                  | 3/2004                                   |                        | —————————————————————————————————————— | rocess Diagnostics of AMOLED               |

| CA 2 522 3                          | 3 96             | 11/2004                                  | HDTV                   | "; dated May 2010 (4 pag               | ges).                                      |

### (56) References Cited

### OTHER PUBLICATIONS

Chaji et al.: "A fast settling current driver based on the CCII for AMOLED displays"; dated Dec. 2009 (6 pages).

Chaji et al.: "Driving scheme for stable operation of 2-IFT a-Si AMOLED pixel"; dated Apr. 2005 (2 pages).

Chaji et al.: "eUTDSP: a design study of a new VLIW-based DSP architecture"; dated May 2003 (4 pages).

Chaji et al.: "Stable RGBW AMOLED display with OLED degradation compensation using electrical feedback"; dated Feb. 2010 (2 pages).

Chaji et al.: "Thin-Film Transistor Integration for Biomedical Imaging and AMOLED Displays"; dated May 2008 (177 pages). Chapter 3: Color Spaces" Keith Jack: "Video Demystified: "A Handbook for the Digital Engineer" 2001 Referex ORD-0000-00-00 USA EP040425529 ISBN: 1-878707-56-6 pp. 32-33.

Chapter 8: Alternative Flat Panel Display 1-25 Technologies; Willem den Boer: "Active Matrix Liquid Crystal Display: Fundamentals and Applications" 2005 Referex ORD-0000-00-00 U.K.; XP040426102 ISBN: 0-7506-7813-5 pp. 206-209 p. 208.

European Partial Search Report Application No. 12 15 6251.6 European Patent Office dated May 30, 2012 (7 pages).

European Patent Office Communication Application No. 05 82 1114 dated Jan. 11, 2013 (9 pages).

European Patent Office Communication with Supplemental European Search Report for EP Application No. 07 70 1644.2 dated Aug. 18, 2009 (12 pages).

European Search Report Application No. 10 83 4294.0-1903 dated Apr. 8, 2013 (9 pages).

European Search Report Application No. EP 05 80 7905 dated Apr. 2, 2009 (5 pages).

European Search Report Application No. EP 05 82 1114 dated Mar. 27, 2009 (2 pages).

European Search Report Application No. EP 07 70 1644 dated Aug. 5, 2009.

European Search Report Application No. EP 10 17 5764 dated Oct. 18, 2010 (2 pages).

European Search Report Application No. EP 10 82 9593.2 European Patent Office dated May 17, 2013 (7 pages).

European SearchReport Application No. EP 12 15 6251.6 European Patent Office dated Oct. 12, 2012 (18 pages).

European Search Report Application No. EP. 11 175 225.9 dated Nov. 4, 2011 (9 pages).

European Supplementary Search Report Application No. EP 09 80 2309 dated May 8, 2011 (14 pages).

European Supplementary Search Report Application No. EP 09 83 1339.8 dated Mar. 26, 2012 (11 pages).

Extended European Search Report Application No. EP 06 75 2777.0 dated Dec. 6, 2010 (21 pages).

Extended European Search Report Application No. EP 09 73 2338.0 dated May 24, 2011 (8 pages).

Extended European Search Report Application No. EP 11 17 5223., 4 dated Nov. 8, 2011 (8 pages).

Extended European Search Report Application No. EP 12 17 4465.0 European Patent Office dated Sep. 7, 2012 (9 pages).

Fan et al. "LTPS\_TFT Pixel Circuit Compensation for TFT Threshold Voltage Shift and IR-Drop On the Power Line For Amolded Displays" 5 pages copyright 2012.

Goh et al. "A New a-Si:H Thin-Film Transistor Pixel Circuit for Active-Matrix Organic Light-Emitting Diodes" IEEE Electron Device Letters vol. 24 No. Sep. 9, 2003 pp. 583-585.

International Search Report Application No. PCT/CA2005/001844 dated Mar. 28, 2006 (2 pages).

International Search Report Application No. PCT/CA2006/000941 dated Oct. 3, 2006 (2 pages).

International Search Report Application No. PCT/CA2007/000013 dated May 7, 2007.

International Search Report Application No. PCT/CA2009/001049 dated Dec. 7, 2009 (4 pages).

International Search Report Application No. PCT/CA2009/001769 dated Apr. 8, 2010.

International Search Report Application No. PCT/IB2010/002898 Canadian Intellectual Property Office dated Jul. 28, 2009 (5 pages). International Search Report Application No. PCT/IB2010/055481 dated Apr. 7, 2011 (3 pages).

International Search Report Application No. PCT/IB2011/051103 dated Jul. 8, 2011 3 pages.

International Search Report Application No. PCT/IB2012/052651 5 pages dated Sep. 11, 2012.

International Searching Authority Written Opinion Application No. PCT/IB2010/055481 dated Apr. 7, 2011 (6 pages).

International Searching Authority Written Opinion Application No. PCT/IB2012/0526516 pages dated Sep. 11, 2012.

International Searching Authority Written Opinion Application No. PCT/IB2011/051103 dated Jul. 8, 2011 6 pages.

International Searching Authority Written Opinion Application No. PCT/IB2010/002898 Canadian Intellectual Property Office dated Mar. 30, 2011 (8 pages).

International Searching Authority Written Opinion Application No. PCT/CA2009/001769 dated Apr. 8, 2010 (8 pages).

Jafarabadiashtiani et al.: "A New Driving Method for a-Si AMOLED Displays Based on Voltage Feedback"; dated May 2005 (4 pages). Lee et al.: "Ambipolar Thin-Film Transistors Fabricated by PECVD Nanocrystalline Silicon"; dated May 2006 (6 pages).

Ma e y et al.: "Organic Light-Emitting Diode/Thin Film Transistor Integration for foldable Displays" Conference record of the 1997 International display research conference and international workshops on LCD technology and emissive technology. Toronto Sept. 15-19, 1997 (6 pages).

Matsueda y et al.: "35.1: 2.5-in. AMOLED with Integrated 6-bit Gamma Compensated Digital Data Driver"; dated May 2004 (4 pages).

Nathan et al. "Amorphous Silicon Thin Film Transistor Circuit Integration for Organic LED Displays on Glass and Plastic" IEEE Journal of Solid-State Circuits vol. 39 No. Sep. 9, 2004 pp. 1477-1486.

Nathan et al.: "Backplane Requirements for Active Matrix Organic Light Emitting Diode Displays"; dated Sep. 2006 (16 pages).

Nathan et al.: "Call for papers second international workshop on compact thin-film transistor (TFT) modeling for circuit simulation"; dated Sep. 2009 (1 page).

Nathan et al.: "Invited Paper: a-Si for AMOLED—Meeting the Performance and Cost Demands of Display Applications (Cell Phone to HDTV)"; dated Jun. 2006 (4 pages).

Nathan et al.: "Thin film imaging technology on glass and plastic"; dated October 31-Nov. 2, 2000 (4 pages).

Ono et al. "Shared Pixel Compensation Circuit for AM-OLED Displays" Proceedings of the 9<sup>th</sup> Asian Symposium on Information Display (ASID) pp. 462-465 New Delhi dated Oct. 8-12, 2006 (4 pages).

Philipp: "Charge transfer sensing" Sensor Review vol. 19 No. 2 Dec. 31, 1999 (Dec. 31, 1999) 10 pages.

Smith, Lindsay I., "A tutorial on Principal Components Analysis," dated Feb. 26, 2001 (27 pages).

Stewart M. et al. "Polysilicon TFT technology for active matrix OLED displays" IEEE transactions on electron devices vol. 48 No. 5 May 2001 (7 pages).

Vygranenko et al.: "Stability of indium-oxide thin-film transistors by reactive ion beam assisted deposition"; dated Feb. 2009.

Yi He et al. "Current-Source a-Si:H Thin Film Transistor Circuit for Active-Matrix Organic Light-Emitting Displays" IEEE Electron Device Letters vol. 21 No. 12, Dec. 2000 pp. 590-592.

International Search Report Application No. PCT/IB2013/059074, dated Dec. 18, 2013 (5 pages).

International Searching Authority Written Opinion Application No. PCT/IB2013/059074, dated Dec. 18, 2013 (8 pages ).

Supplementary European Search Report for EP 09 80 2309, dated May 8, 20011 (14 pages).

Alexander et al.: "Pixel circuits and drive schemes for glass and elastic AMOLED displays"; dated Jul. 2005 (9 pages).

Ashtiani et al.: "AMOLED Pixel Circuit With Electronic Compensation of Luminance Degradation"; dated Mar. 2007 (4 pages).

Chaji et al.: "A Current-Mode Comparator for Digital Calibration of Amorphous Silicon AMOLED Displays"; dated Jul. 2008 (5 pages).

### (56) References Cited

#### OTHER PUBLICATIONS

Chaji et al.: "A Low-Cost Stable Amorphous Silicon AMOLED Display with Full V~T- and V~O~L~E~D Shift Compensation"; dated May 2007 (4 pages).

Chaji et al.: "A low-power driving scheme for a-Si:H active-matrix organic light-emitting diode displays"; dated Jun. 2005 (4 pages). Chaji et al.: "A low-power high-performance digital circuit for deep submicron technologies"; dated Jun. 2005 (4 pages).

Chaji et al.: "A novel a-Si:H AMOLED pixel circuit based on short-term stress stability of a-Si:H TFTs"; dated Oct. 2005 (3 pages).

Chaji et al.: "A Novel Driving Scheme and Pixel Circuit for AMOLED Displays"; dated Jun. 2006 (4 pages).

Chaji et al.: "A novel driving scheme for high-resolution large-area a-Si:H AMOLED displays"; dated Aug. 2005 (4 pages).

Chaji et al.: "A Stable Voltage-Programmed Pixel Circuit for a-Si:H AMOLED Displays"; dated Dec. 2006 (12 pages).

Chaji et al.: "A Sub-µA fast-settling current-programmed pixel circuit for AMOLED displays"; dated Sep. 2007.

Chaji et al.: "An Enhanced and Simplified Optical Feedback Pixel Circuit for AMOLED Displays"; dated Oct. 2006.

Chaji et al.: "Compensation technique for DC and transient instability of thin film transistor circuits for large-area devices"; dated Aug. 2008.

Chaji et al.: "Driving scheme for stable operation of 2-TFT a-Si AMOLED pixel"; dated Apr. 2005 (2 pages).

Chaji et al.: "Dynamic-effect compensating technique for stable a-Si:H AMOLED displays"; dated Aug. 2005 (4 pages).

Chaji et al.: "Electrical Compensation of OLED Luminance Degradation"; dated Dec. 2007 (3 pages).

Chaji et al.: "Fast and Offset-Leakage Insensitive Current-Mode Line Driver for Active Matrix Displays and Sensors"; dated Feb. 2009 (8 pages).

Chaji et al.: "High Speed Low Power Adder Design With A New Logic Style: Pseudo Dynamic Logic (SDL)"; dated Oct. 2001 (4 pages).

Chaji et al.: "High-precision, fast current source for large-area current-programmed a-Si flat panels"; dated Sep. 2006 (4 pages). Chaji et al.: "Low-Cost AMOLED Television with IGNIS Compensating Technology"; dated May 2008 (4 pages).

Chaji et al.: "Low-Cost Stable a-Si:H AMOLED Display for Portable Applications"; dated Jun. 2006 (4 pages).

Chaji et al.: "Low-Power Low-Cost Voltage-Programmed a-Si:H AMOLED Display"; dated Jun. 2008 (5 pages).

Chaji et al.: "Merged phototransistor pixel with enhanced near infrared response and flicker noise reduction for biomolecular imaging"; dated Nov. 2008 (3 pages).

Chaji et al.: "Parallel Addressing Scheme for Voltage-Programmed Active-Matrix OLED Displays"; dated May 2007 (6 pages).

Chaji et al.: "Pseudo dynamic logic (SDL): a high-speed and low-power dynamic logic family"; dated 2002 (4 pages).

Chaji et al.: "Stable a-Si:H circuits based on short-term stress stability of amorphous silicon thin film transistors"; dated May 2006 (4 pages).

Chaji et al.: "Stable Pixel Circuit for Small-Area High- Resolution a-Si:H AMOLED Displays"; dated Oct. 2008 (6 pages).

Chaji et al.: "Thin-Film Transistor Integration for Biomedical Imaging and AMOLED Displays"; dated 2008 (177 pages).

Jafarabadiashtiani et al.: "A New Driving Method for a-Si AMOLED Displays Based on Voltage Feedback"; dated 2005 (4 pages).

Lee et al.: "Ambipolar Thin-Film Transistors Fabricated by PECVD Nanocrystalline Silicon"; dated 2006 (6 pages).

Nathan et al.: "Driving schemes for a-Si and LTPS AMOLED displays"; dated Dec. 2005 (11 pages).

Rafati et al.: "Comparison of a 17 b multiplier in Dual-rail domino and in Dual-rail D L (D L) logic styles"; dated 2002 (4 pages).

Safavaian et al.: "Three-TFT image sensor for real-time digital X-ray imaging"; dated Feb. 2, 2006 (2 pages).

Safavian et al.: "3-TFT active pixel sensor with correlated double sampling readout circuit for real-time medical x-ray imaging"; dated Jun. 2006 (4 pages).

Safavian et al.: "A novel current scaling active pixel sensor with correlated double sampling readout circuit for real time medical x-ray imaging"; dated May 2007 (7 pages).

Safavian et al.: "A novel hybrid active-passive pixel with correlated double sampling CMOS readout circuit for medical x-ray imaging"; dated May 2008 (4 pages).

Safavian et al.: "Self-compensated a-Si:H detector with current-mode readout circuit for digital X-ray fluoroscopy"; dated Aug. 2005 (4 pages).

Safavian et al.: "TFT active image sensor with current-mode readout circuit for digital x-ray fluoroscopy [5969D-82]"; dated Sep. 2005 (9 pages).

Vygranenko et al.: "Stability of indium-oxide thin-film transistors by reactive ion beam assisted deposition"; dated 2009.

Wang et al.: "Indium oxides by reactive ion beam assisted evaporation: From material study to device application"; dated Mar. 2009 (6 pages).

\* cited by examiner

FIG. 1A

FIG. 2

FIG. 3A

FIG. 3B

FIG. 4

FIG. 5

US RE49,389 E

| Rad  | Graan | Rlug      | Rod            | Green              | Blue                     |

|------|-------|-----------|----------------|--------------------|--------------------------|

| IXCU |       | Dide      | I VE           | Oreen              | Diac                     |

|      |       |           |                |                    |                          |

|      |       |           |                |                    |                          |

|      | Red   | Red Green | Red Green Blue | Red Green Blue Red | Red Green Blue Red Green |

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 11

FIG. 12

FIG. 13 (Prior Art)

FIG. 14

FIG. 15

FIG. 16A

15

10

5

FIG. 16B

FIG. 17

FIG. 18

<u>660</u>

FIG. 19

## METHOD AND SYSTEM FOR DRIVING LIGHT EMITTING DISPLAY

Matter enclosed in heavy brackets [] appears in the 5 original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

Notice: More than one reissue application has been filed for the reissue of U.S. Pat. No. 8,471,875. This application is a reissue continuation of application Ser. No. 14/477,037, which is an application for reissue of U.S. Pat. No. 8,471, *875*.

### FIELD OF INVENTION

The present invention relates to a display system, more specifically to a method and system for driving light emitting displays.

### BACKGROUND OF THE INVENTION

A display device having a plurality of pixels (or subpixels) arranged in a matrix has been widely used in various applications. Such a display device includes a panel having the pixels and peripheral circuits for controlling the panels. 30 Typically, the pixels are defined by the intersections of scan lines and data lines, and the peripheral circuits include a gate driver for scanning the scan lines and a source driver for supplying image data to the data lines. The source driver may include gamma corrections for controlling gray scale of 35 each pixel. In order to display a frame, the source driver and the gate driver respectively provide a data signal and a scan signal to the corresponding data line and the corresponding scan line. As a result, each pixel will display a predetermined brightness and color.

In recent years, the matrix display has been widely employed in small electronic devices, such as handheld devices, cellular phones, personal digital assistants (PDAs), and cameras. However, the conversional scheme and structure of the source driver and the gate driver demands the 45 large number of elements (e.g., resistors, switchers, and operational amplifiers), resulting that the layout area of the peripheral circuits is still large and expensive.

Therefore there is a need to provide a display driver that can reduce a driver die area and thus cost, without reducing 50 the driver performance.

### SUMMARY OF THE INVENTION

It is an object of the invention to provide a method and 55 a panel for a display system; system that obviates or mitigates at least one of the disadvantages of existing systems.

According to an embodiment of this disclosure, there is provided a display system, which includes: a driver for operating a panel having a plurality of pixels arranged by a 60 plurality of first lines and at least one second line, the driver having: a driver output unit for providing to the panel a single driver output for activating the plurality of first lines, the single driver output being demultiplexed on the panel to activate each first line.

According to an embodiment of this disclosure, there is provided a display system, which includes: a driver for

operating a panel having a plurality of pixels arranged by a plurality of data lines and at least one scan line, the driver having: a shift register unit including a plurality of shift registers; a latch and shift register unit including a plurality of latch and shift circuits for the plurality of shift registers, each storing an image signal from the corresponding shift register or shifting the image signal to a next latch and shift circuit; and a decoder unit including at least one decoder coupled to one of the latch and shift circuits, for decoding 10 the image signal latched in the one of the latch and shift circuit to provide a driver output.

According to an embodiment of this disclosure, there is provided a display system, which includes: a driver for operating a panel having a plurality of pixels, the driver having: a plurality of multiplexers for a plurality of offset gamma curve sections, each offset gamma curve section having a first range less than a second range of a main gamma curve, at least one of offset gamma curve sections being offset by a predetermined voltage from a correspond-20 ing section of the main gamma curve; a plurality of decoders for the plurality of multiplexers; and an output buffer for providing a driver output based on the output from the decoder and the predetermined voltage.

### BRIEF DESCRIPTION OF THE DRAWINGS

These and other features of the invention will become more apparent from the following description in which reference is made to the appended drawings wherein:

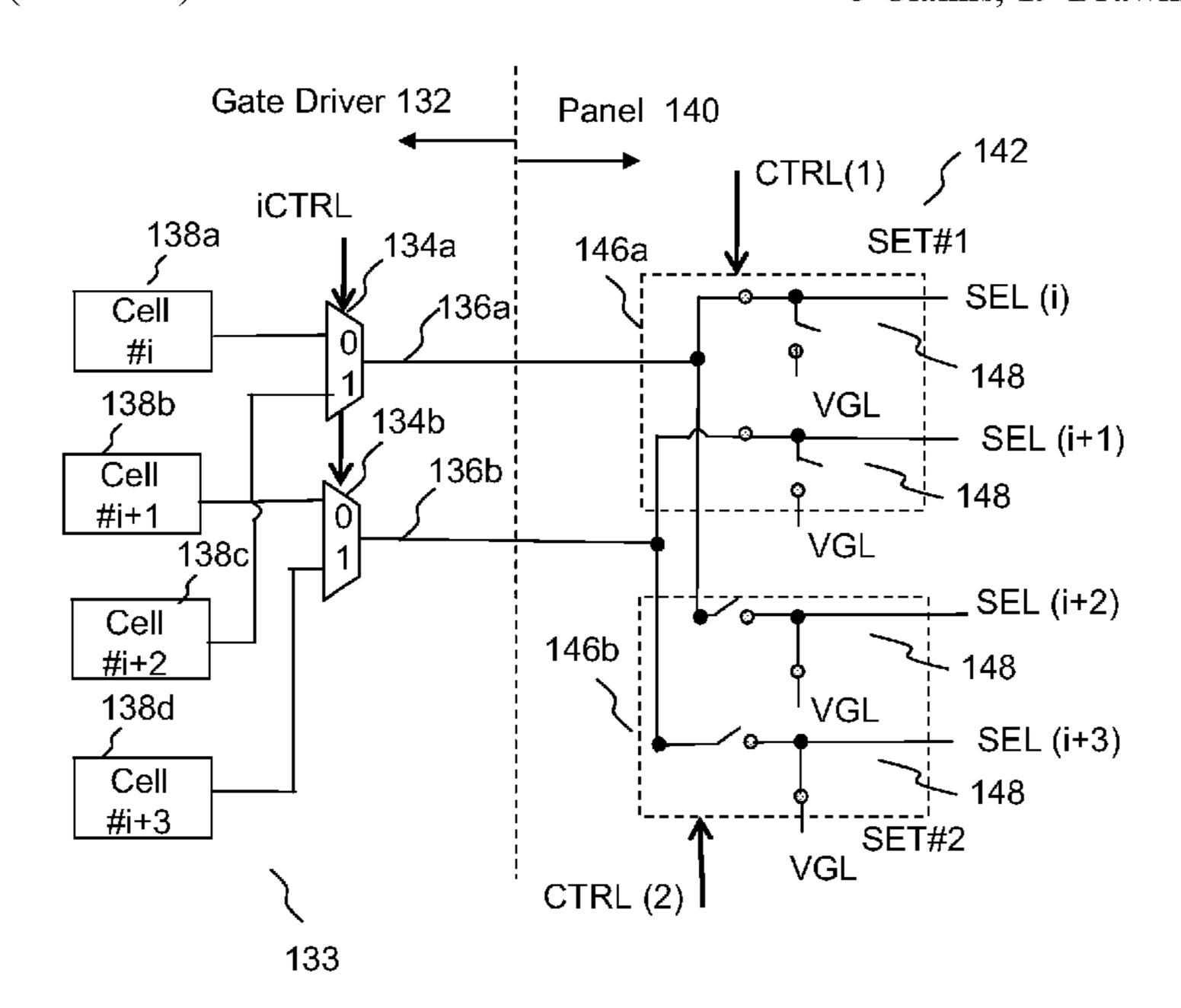

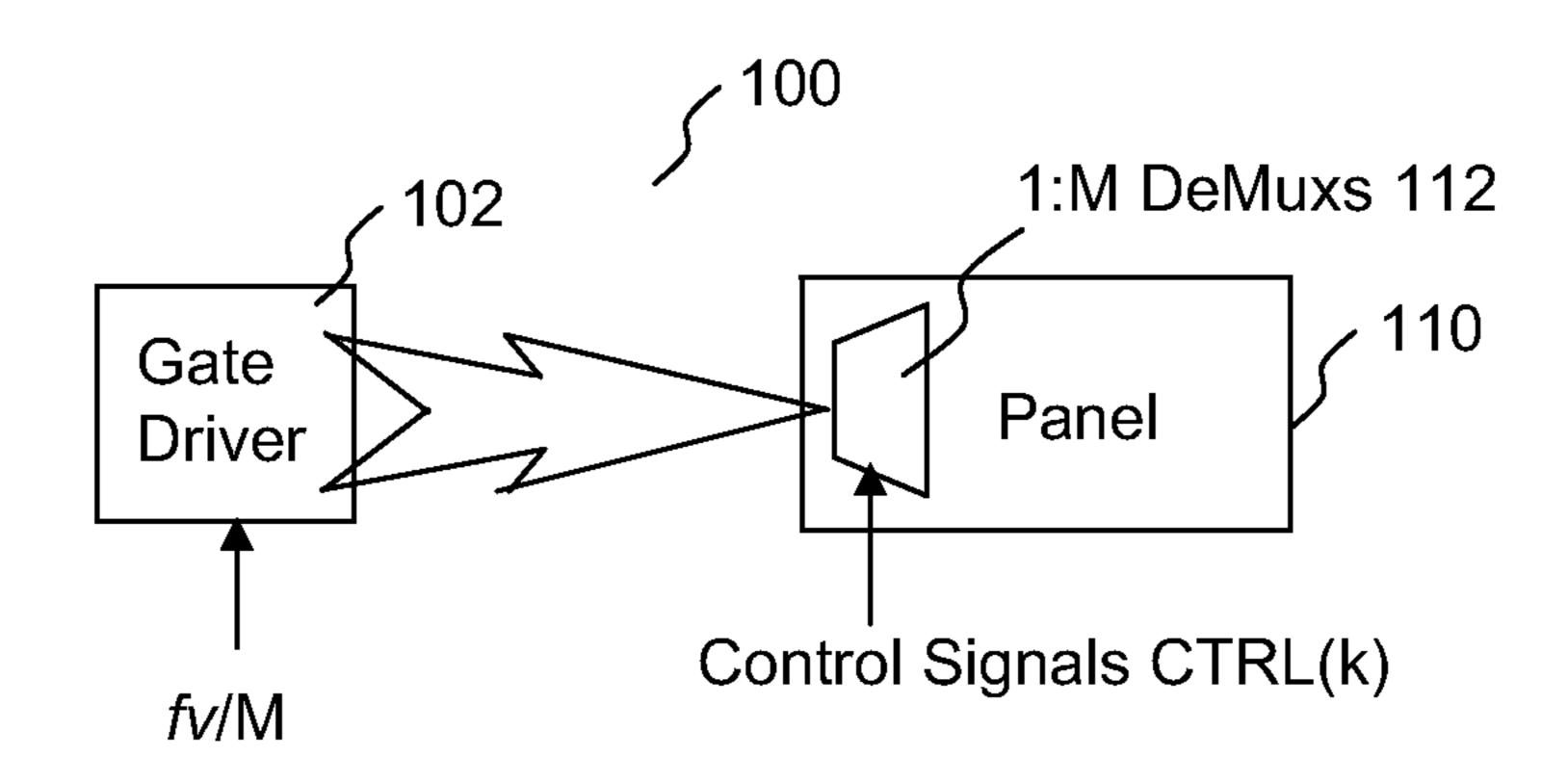

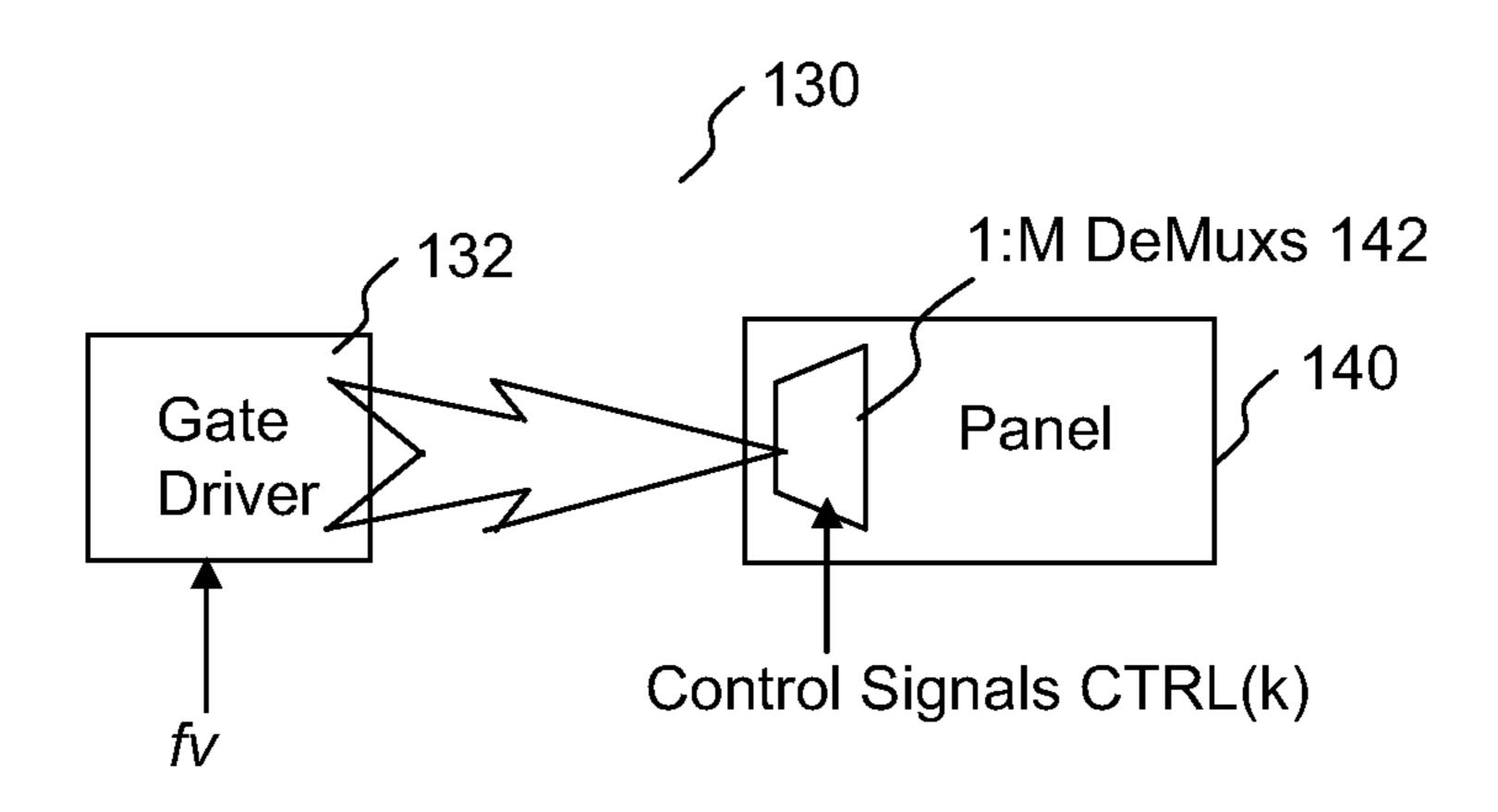

FIG. 1A illustrates a gate driver and a panel for a display system;

FIG. 1B illustrates an example of the gate driver and the panel of FIG. 1A;

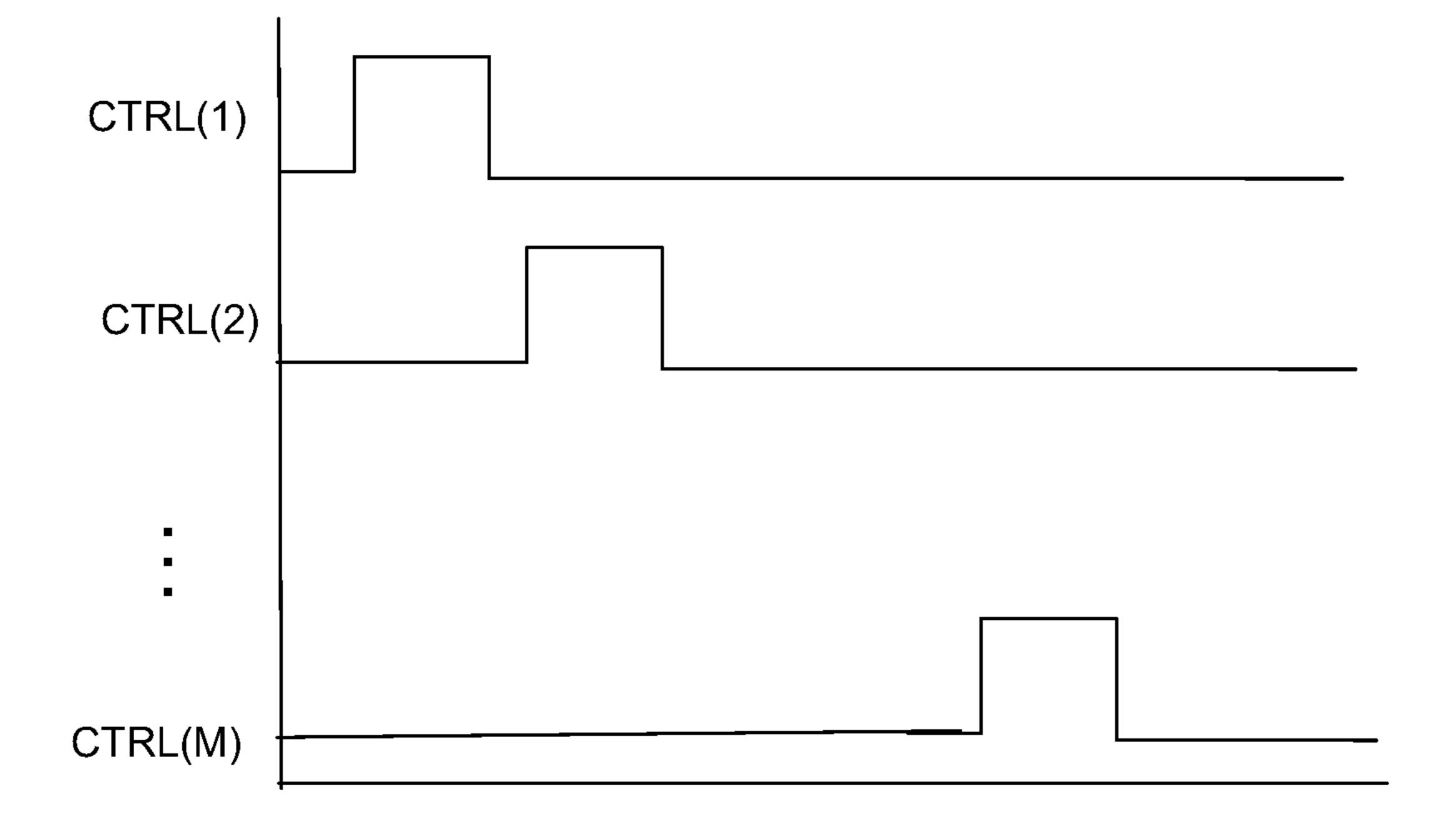

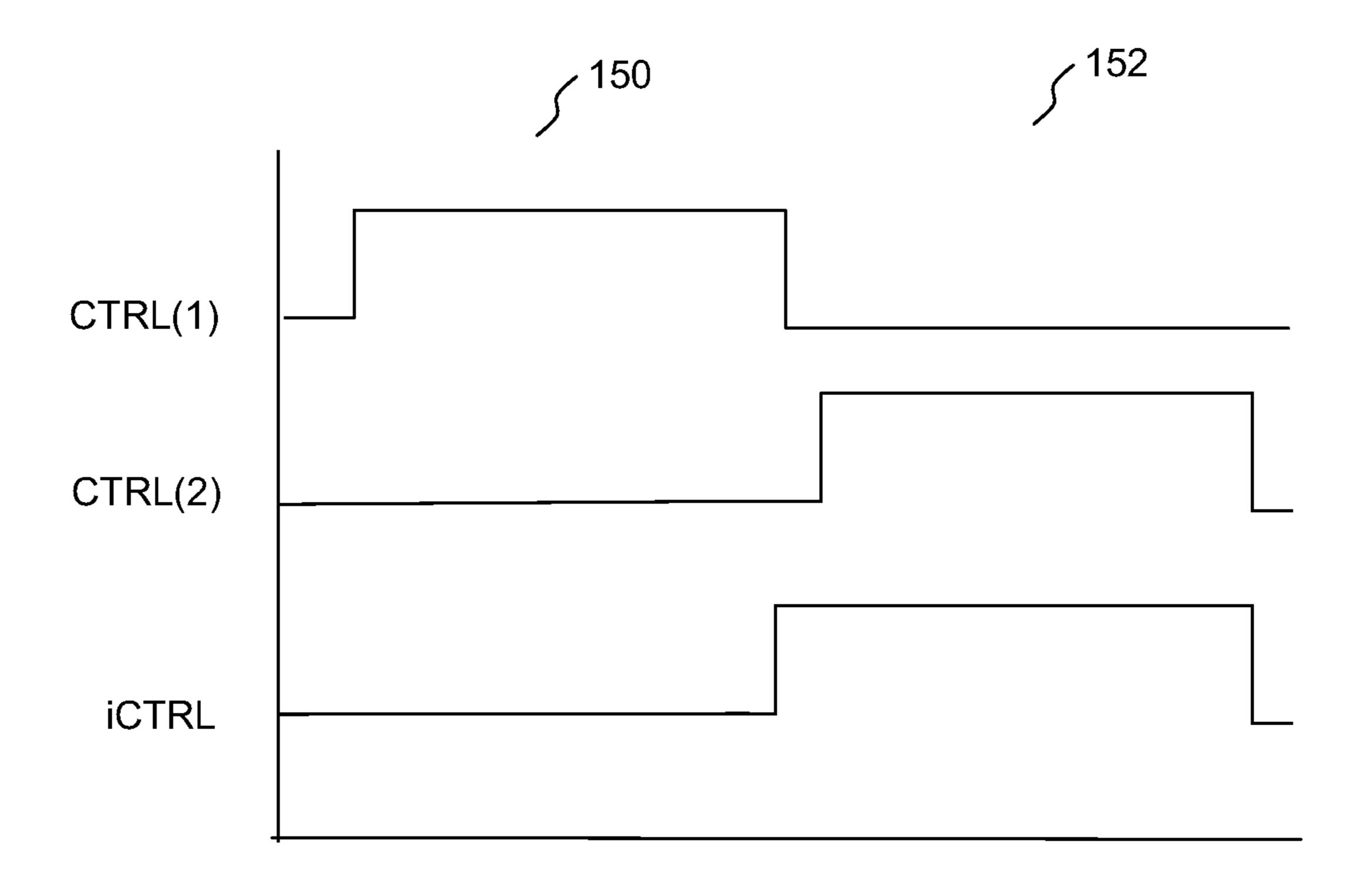

FIG. 2 illustrates a timing chart for operating the display system of FIGS. 1A-1B;

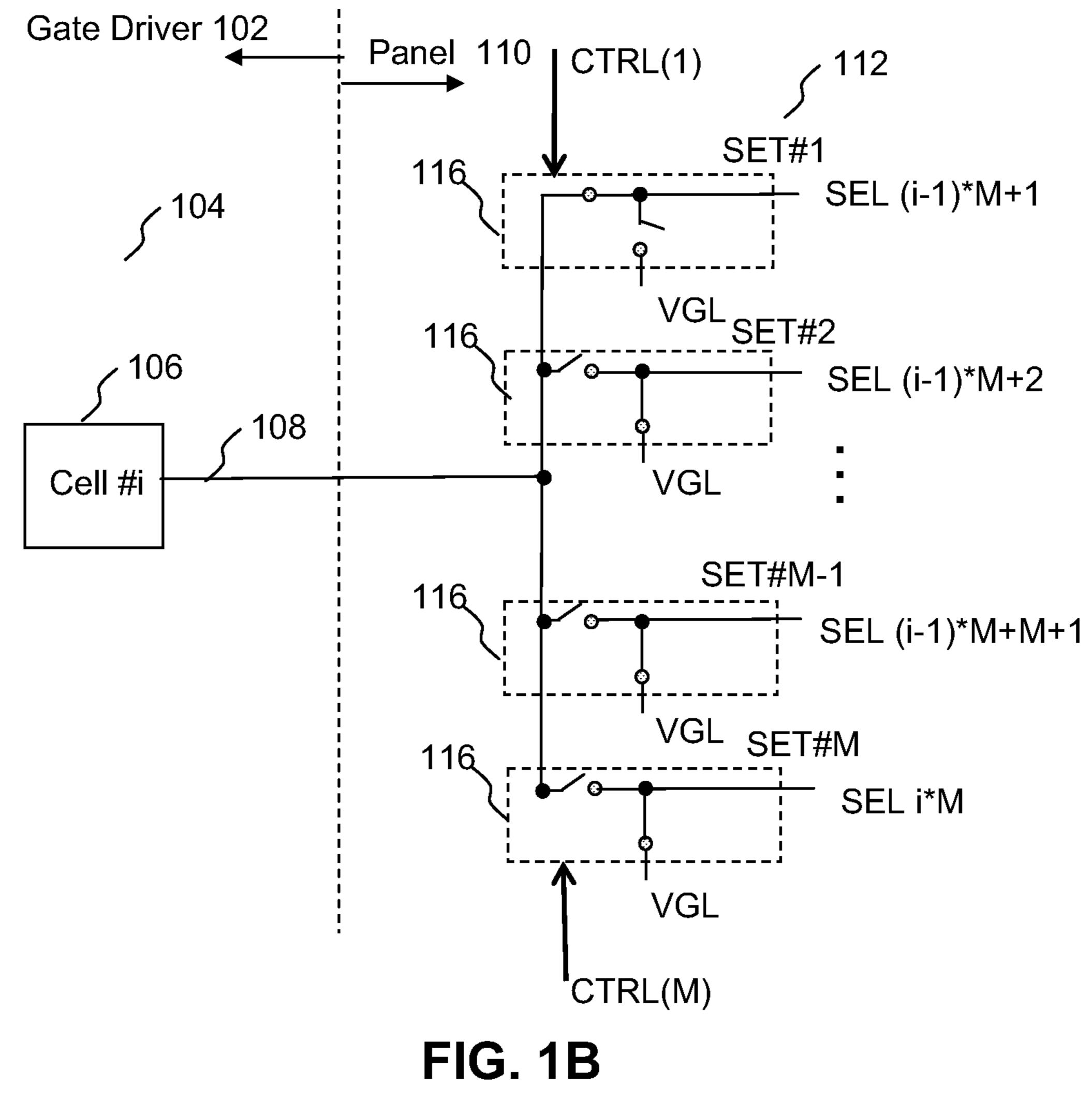

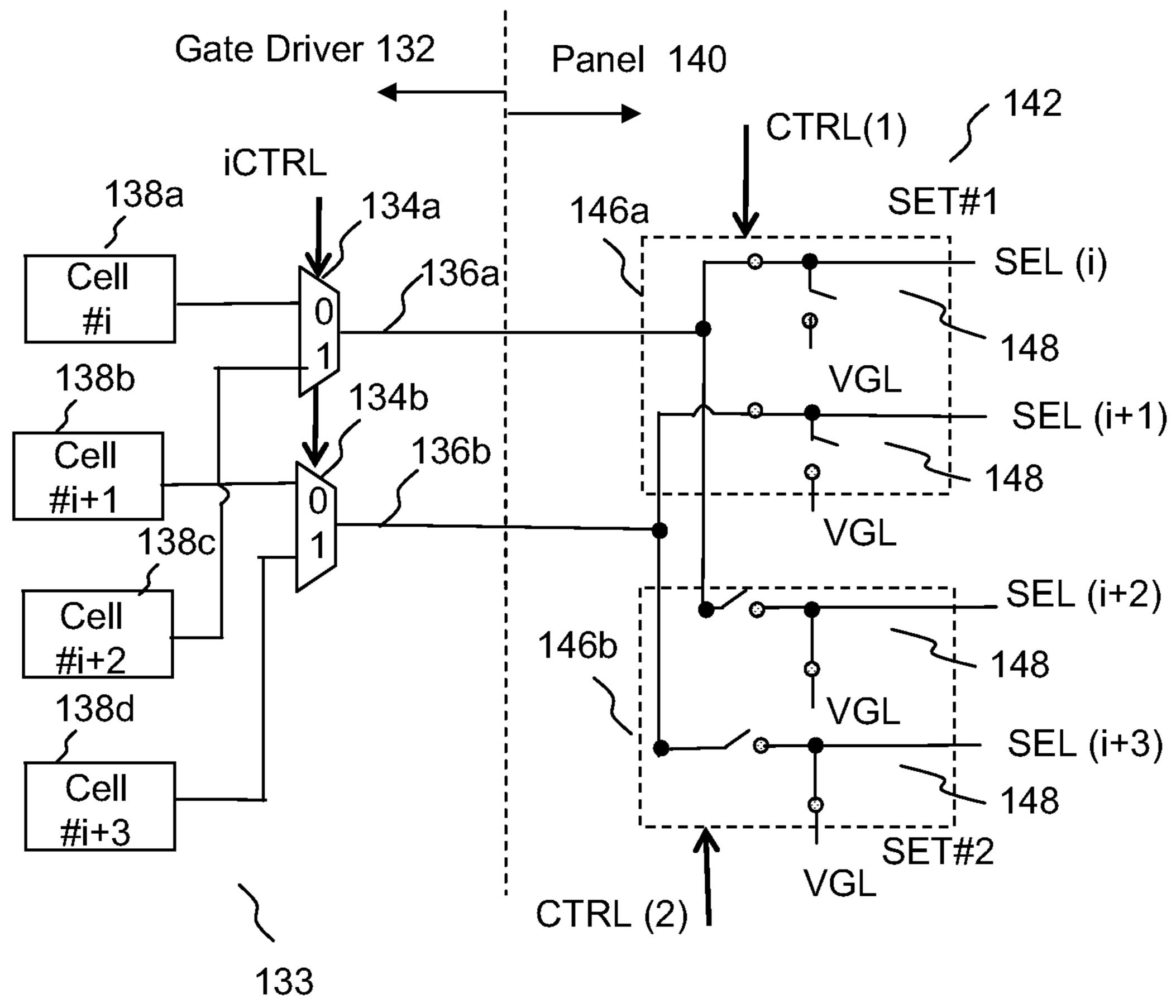

FIG. 3A illustrates another example of a gate driver and a panel for a display system;

FIG. 3B illustrates an example of the gate driver and the panel of FIG. 3A;

FIG. 4 illustrates a timing chart for operating the display system of FIGS. 3A-3B;

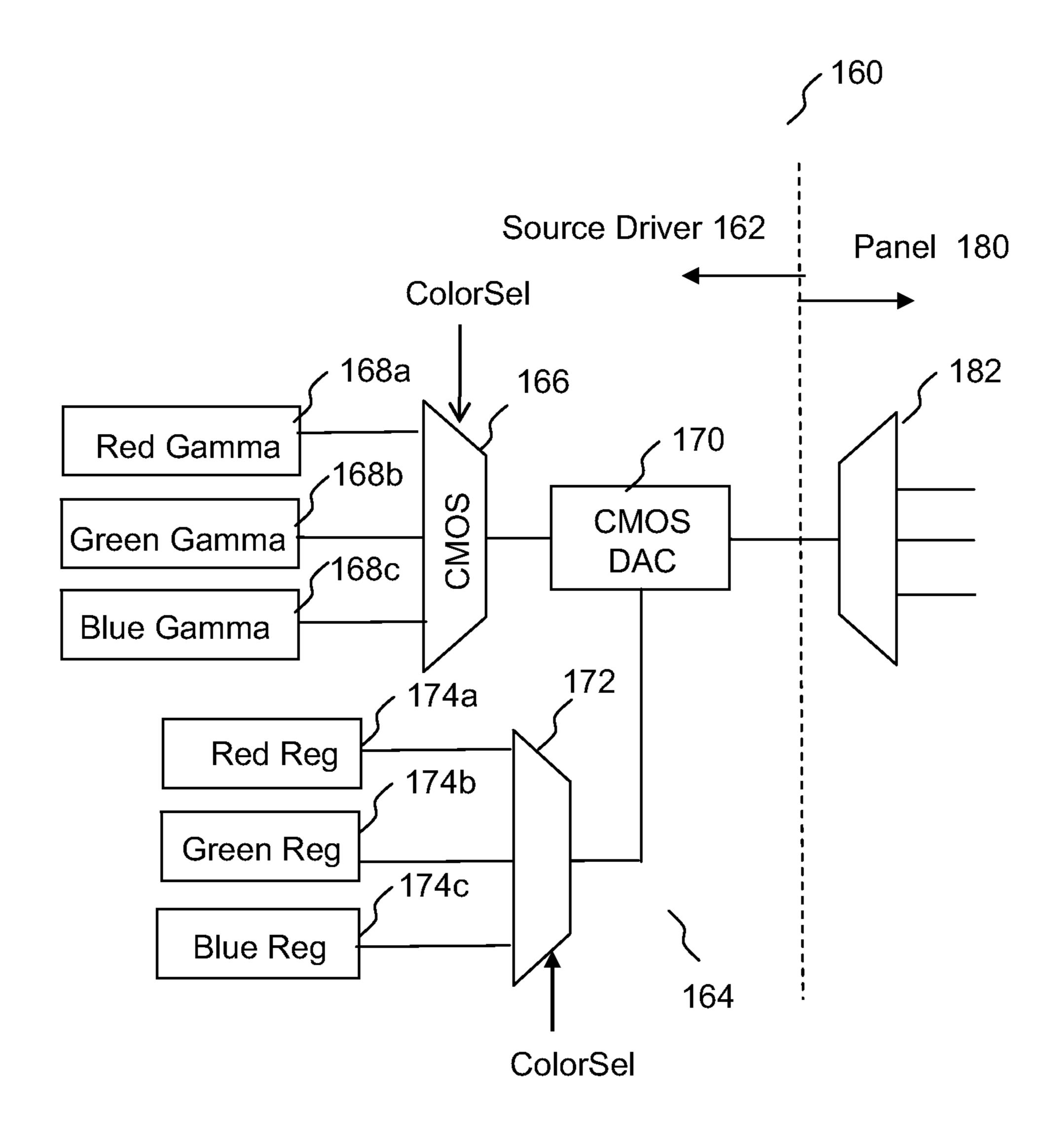

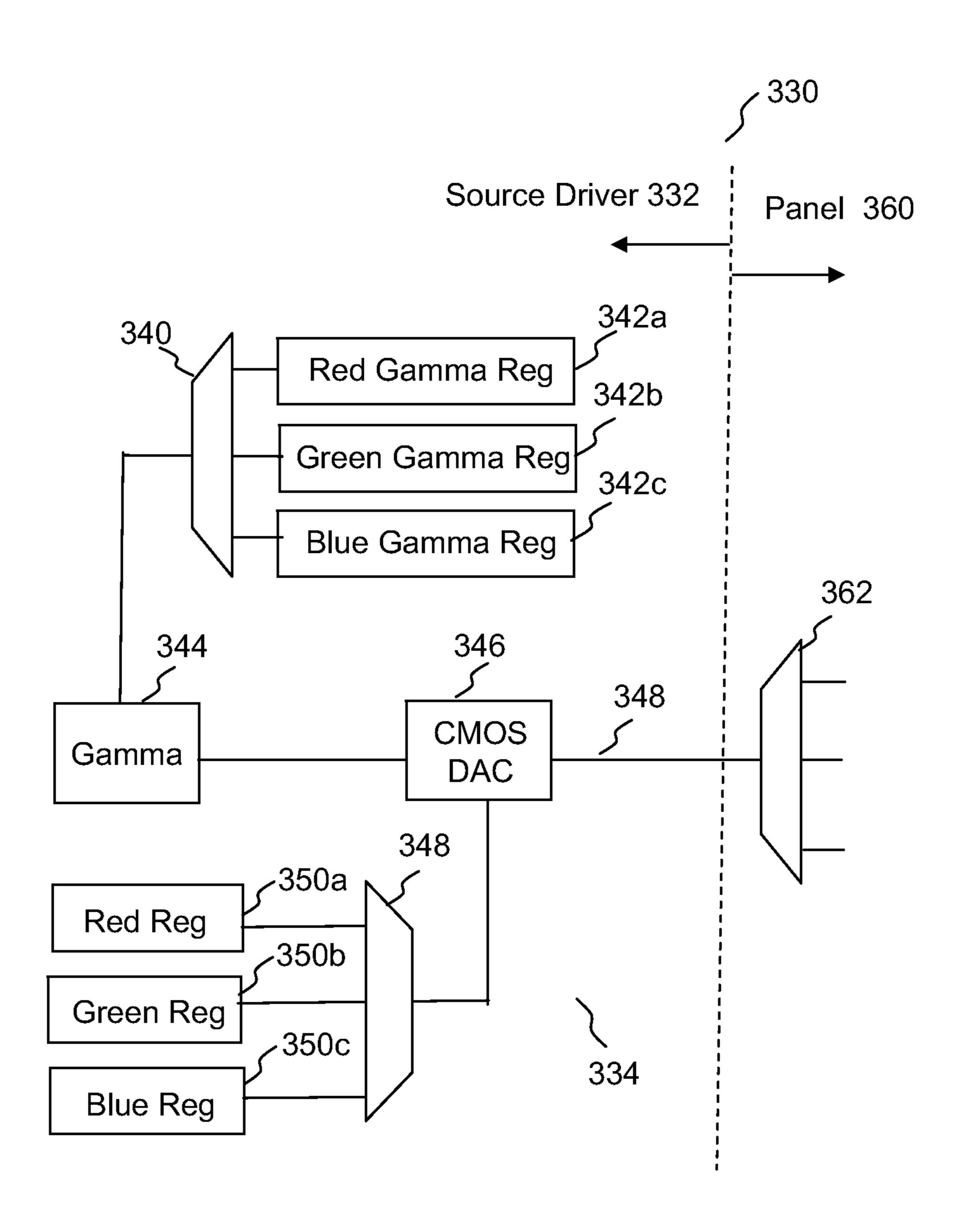

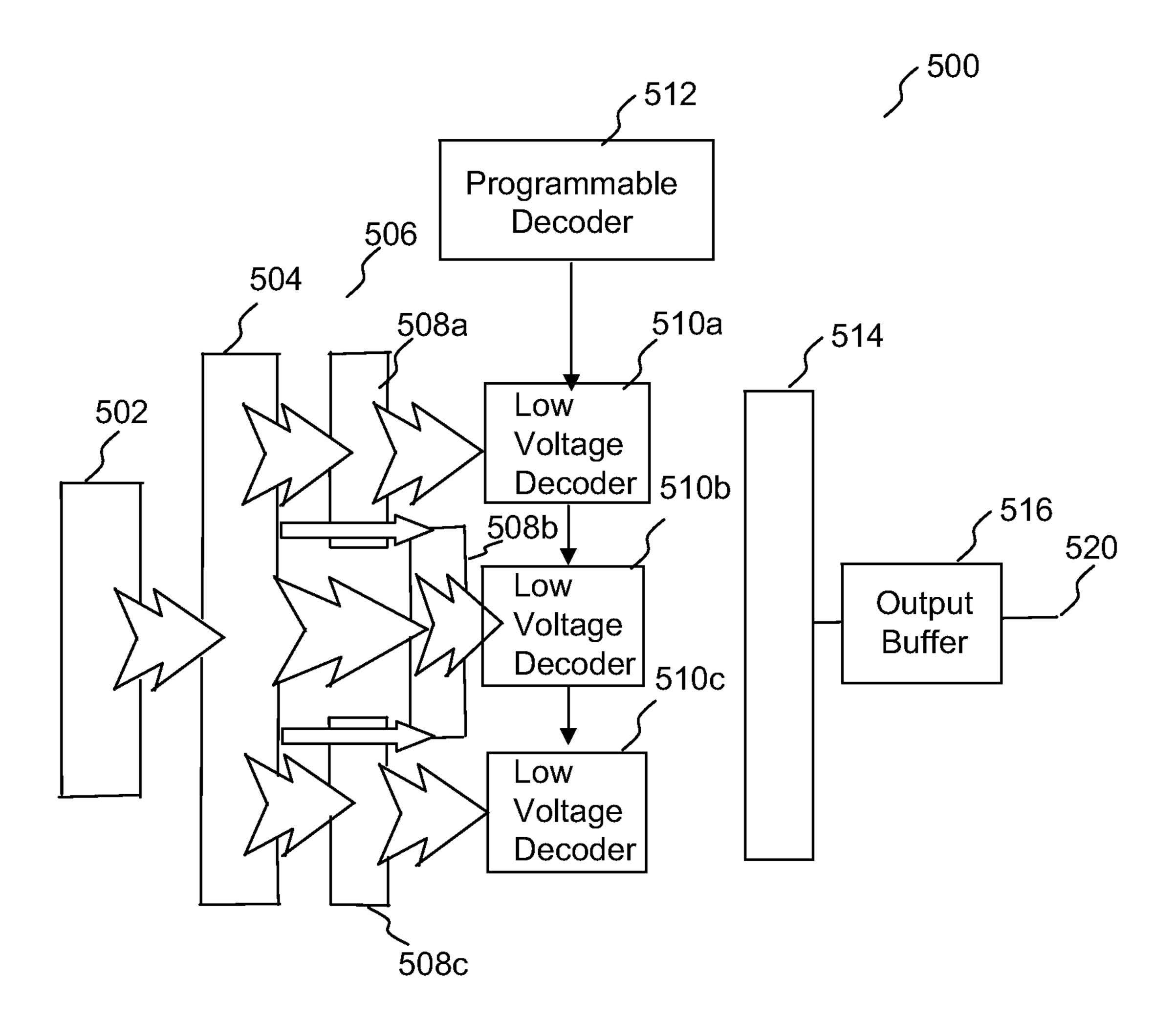

FIG. 5 illustrates an example of a source driver and a panel for a display system;

FIG. 6 illustrates an example of operation for the display system having RGB pixel structure;

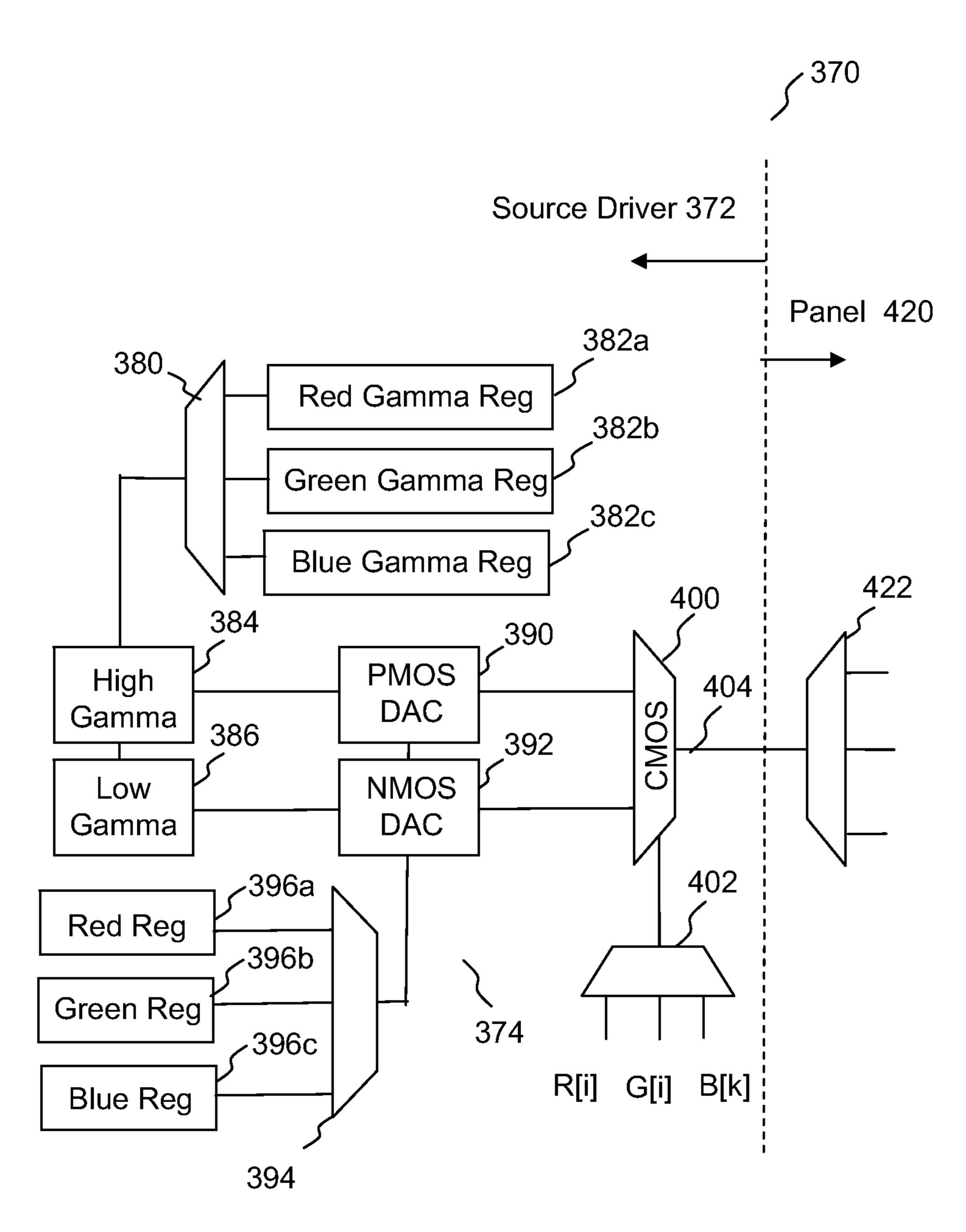

FIG. 7 illustrates a further example of a source driver and a panel for a display system;

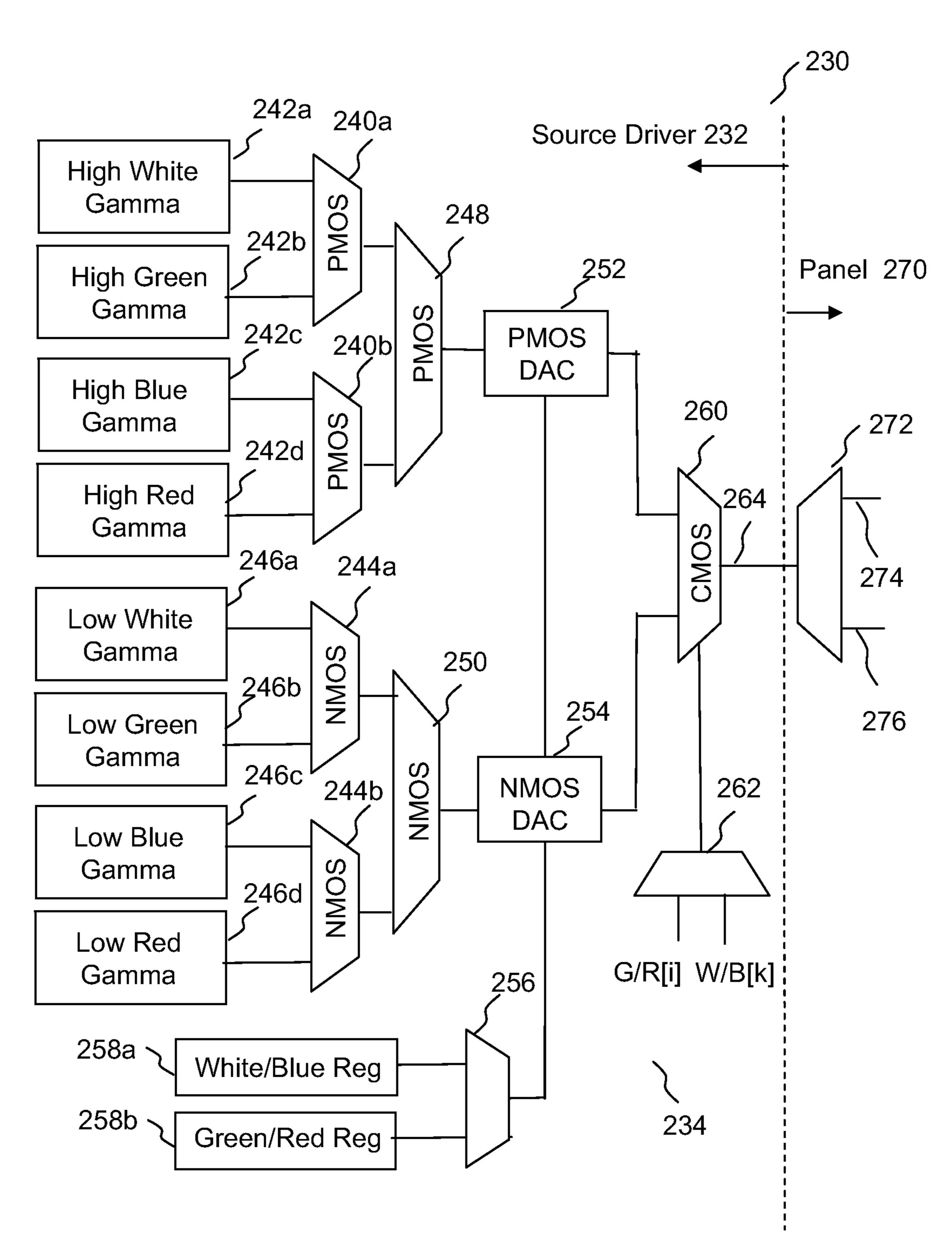

FIG. 8 illustrates a further example of a source driver and a panel for a display system having RGBW pixel structure;

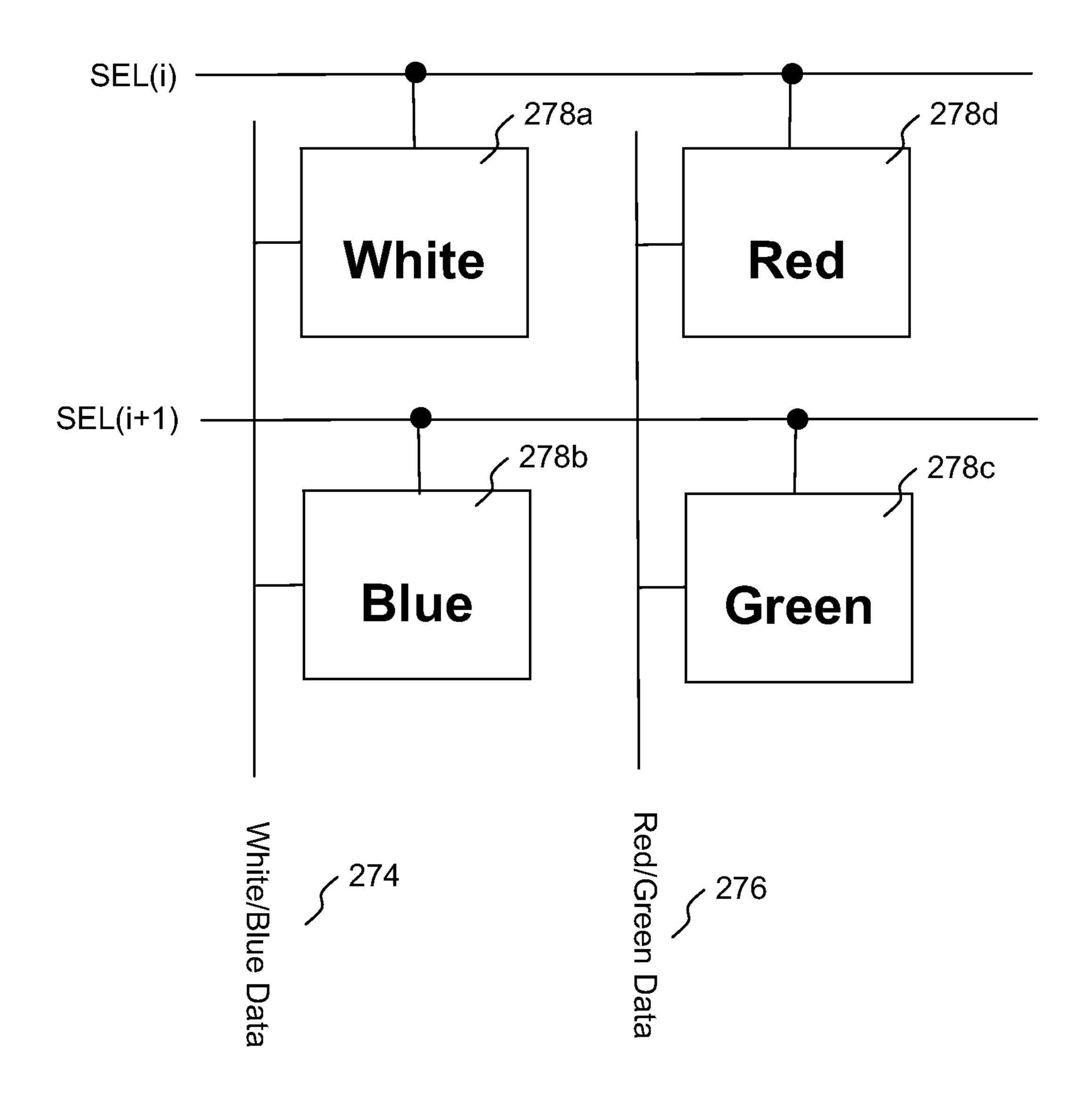

FIG. 9 illustrates an example of subpixel configuration for RGBW pixel stricture;

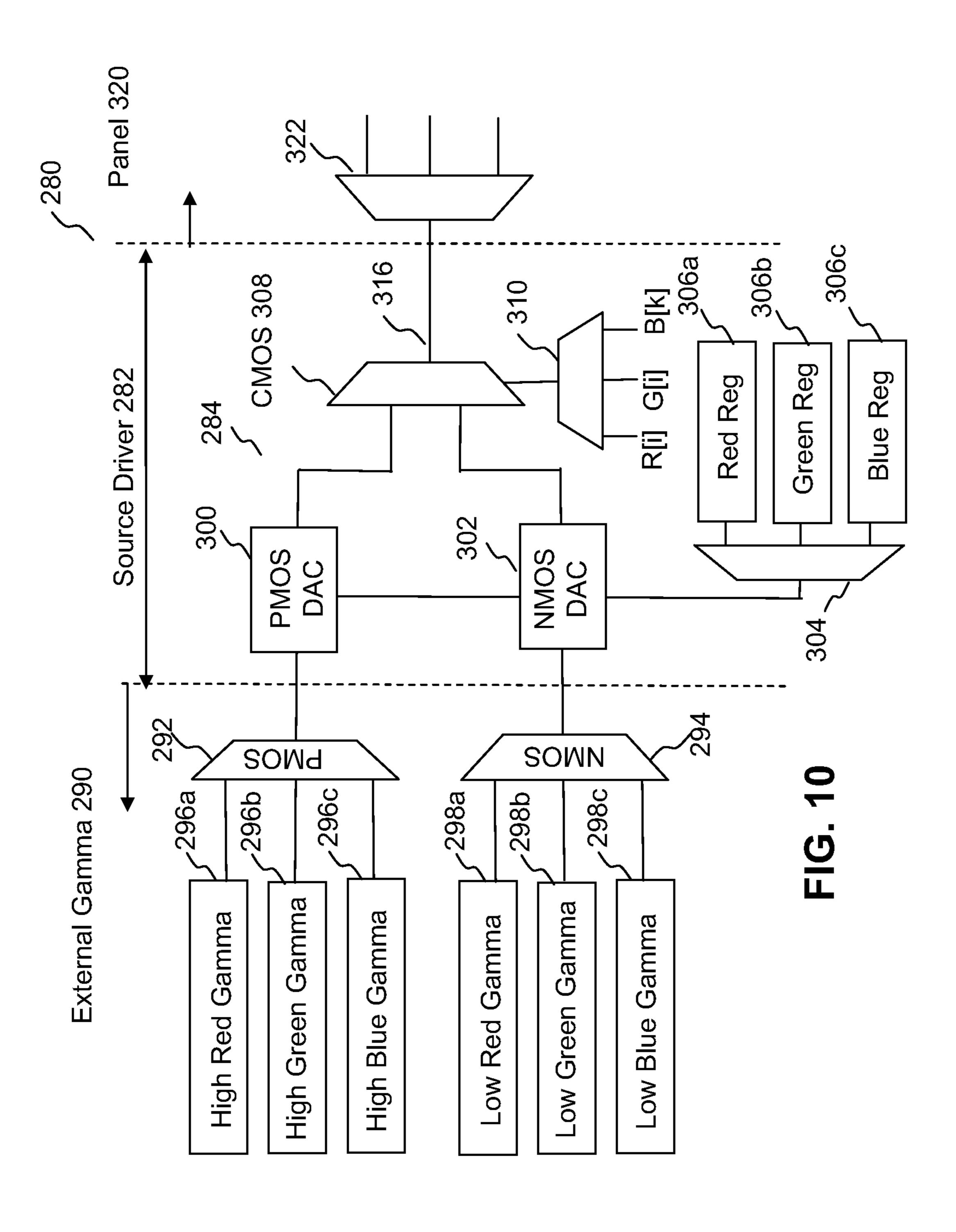

FIG. 10 illustrates a further example of a source driver, external gamma and a panel for a display system;

FIG. 11 illustrates a further example of a source driver and

FIG. 12 illustrates a further example of a source driver and a panel for a display system;

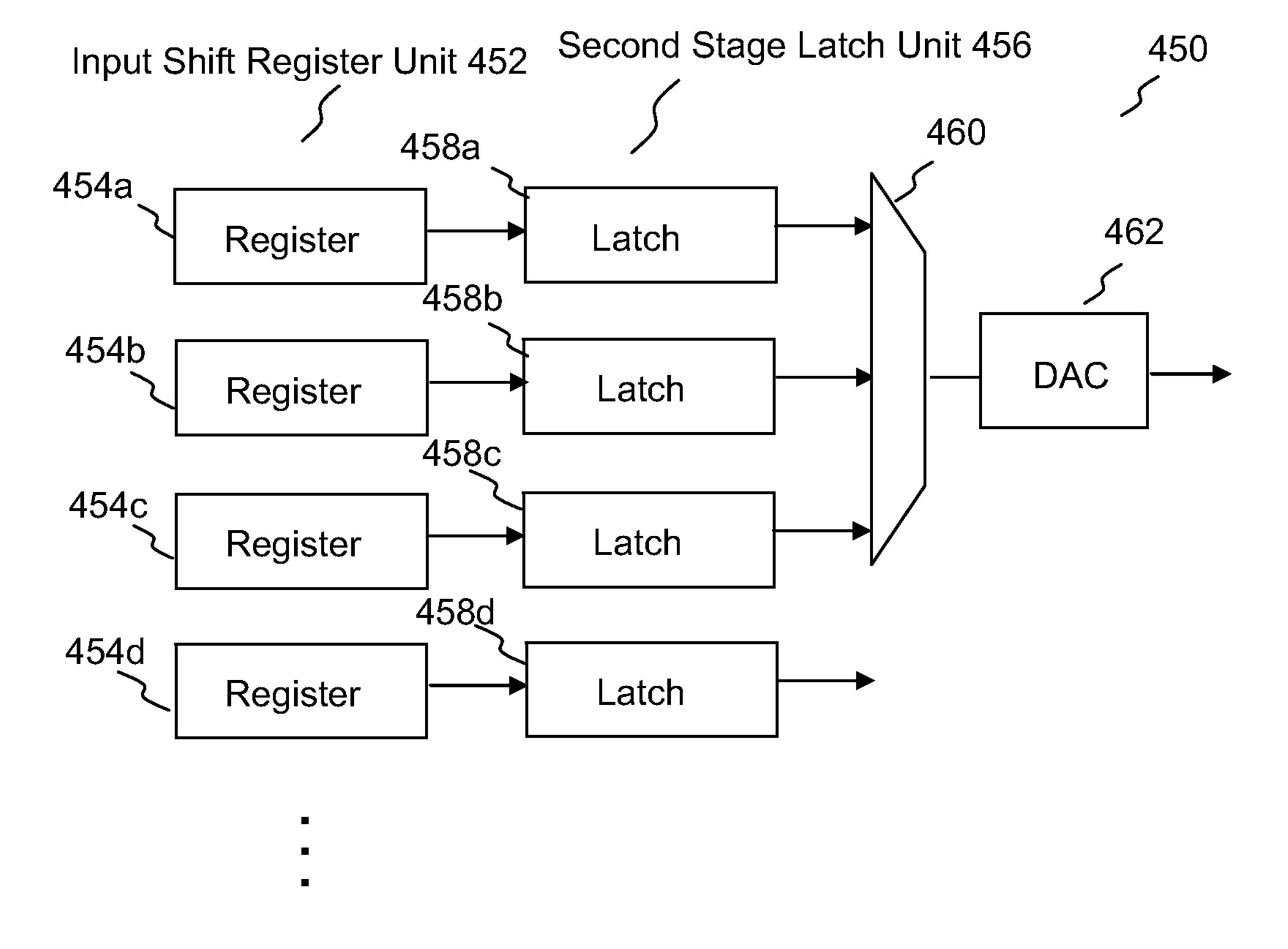

FIG. 13 illustrates a source driver for a conventional display system;

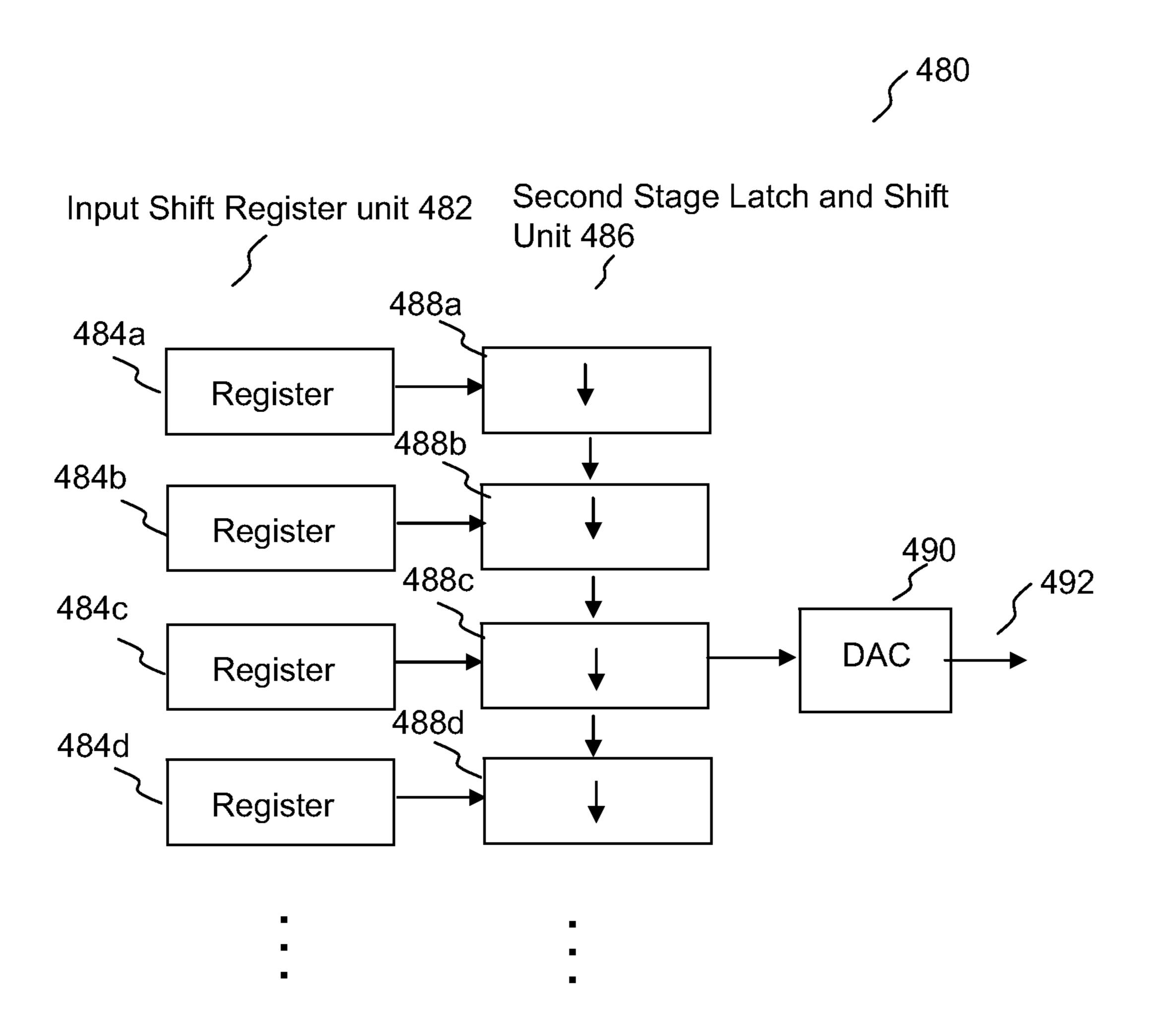

FIG. 14 illustrates a further example of a source driver for a display system;

FIG. 15 illustrates a further example of a source driver for a display system;

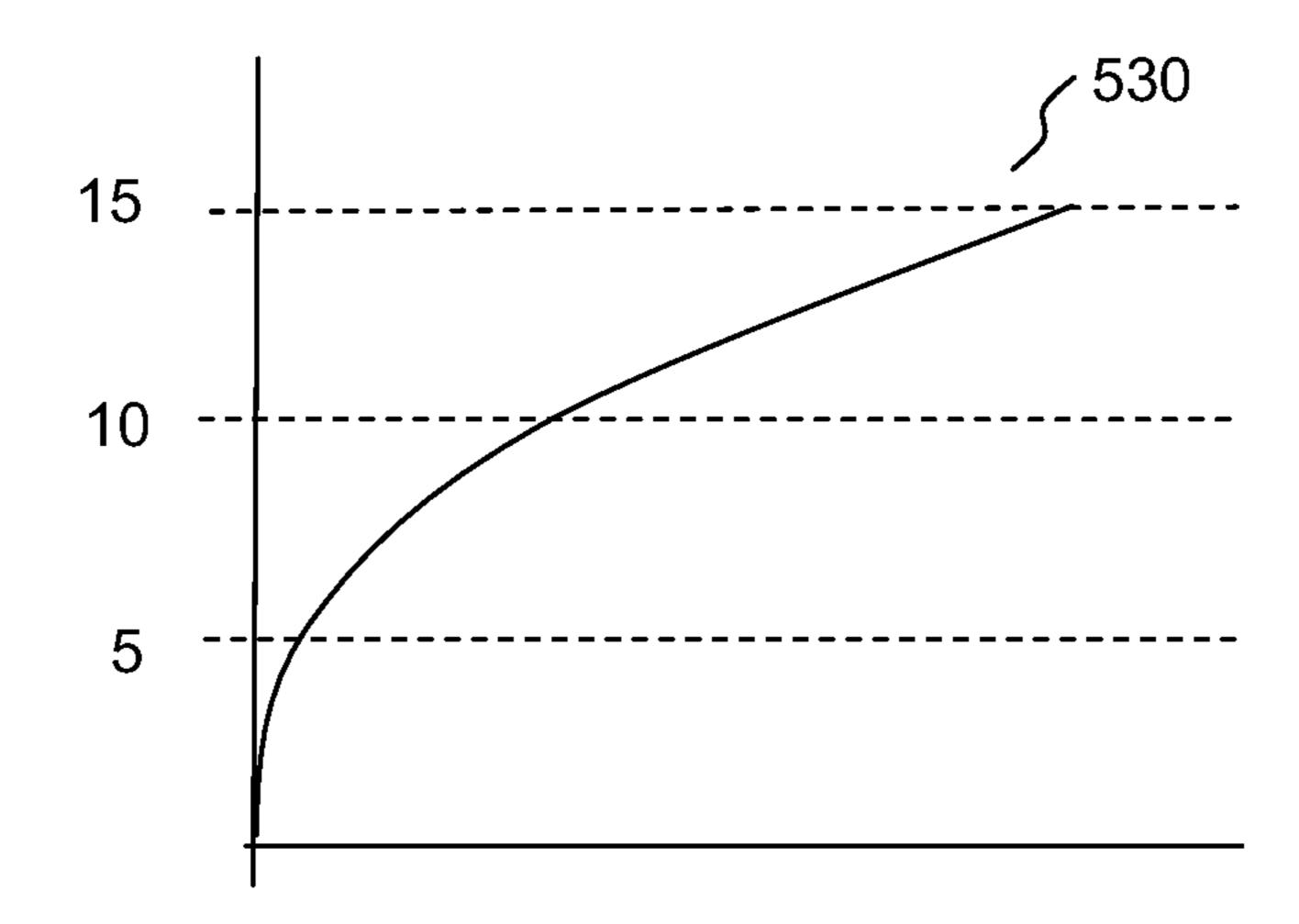

FIG. 16 illustrates an example of a gamma curve and 65 segmented offset gamma curves;

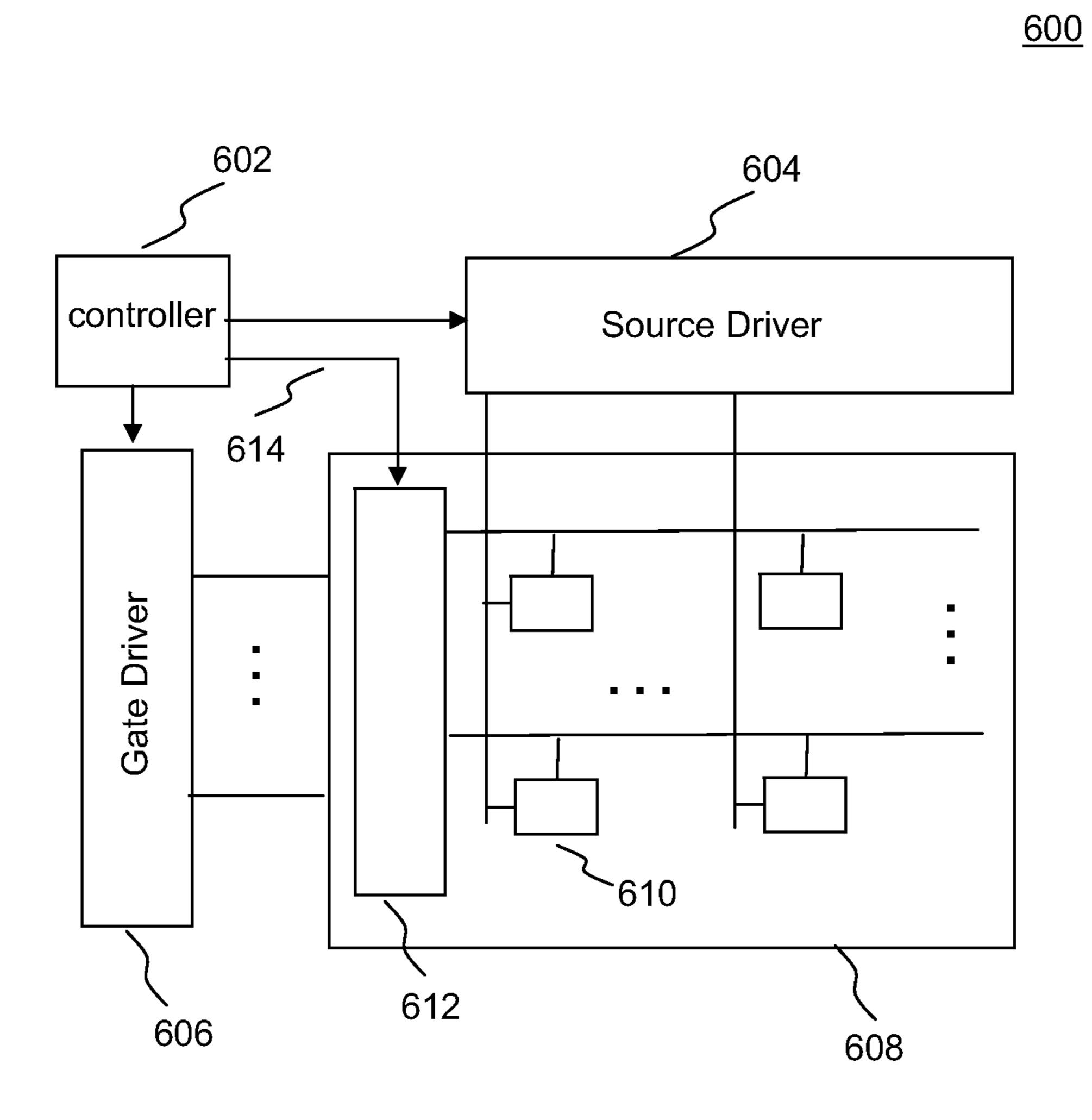

FIG. 17 illustrates an example of a display system having the gate driver of FIG. 1A or 3A;

FIG. 18 illustrates an example of a display system having the source driver of FIGS. 5-12; and

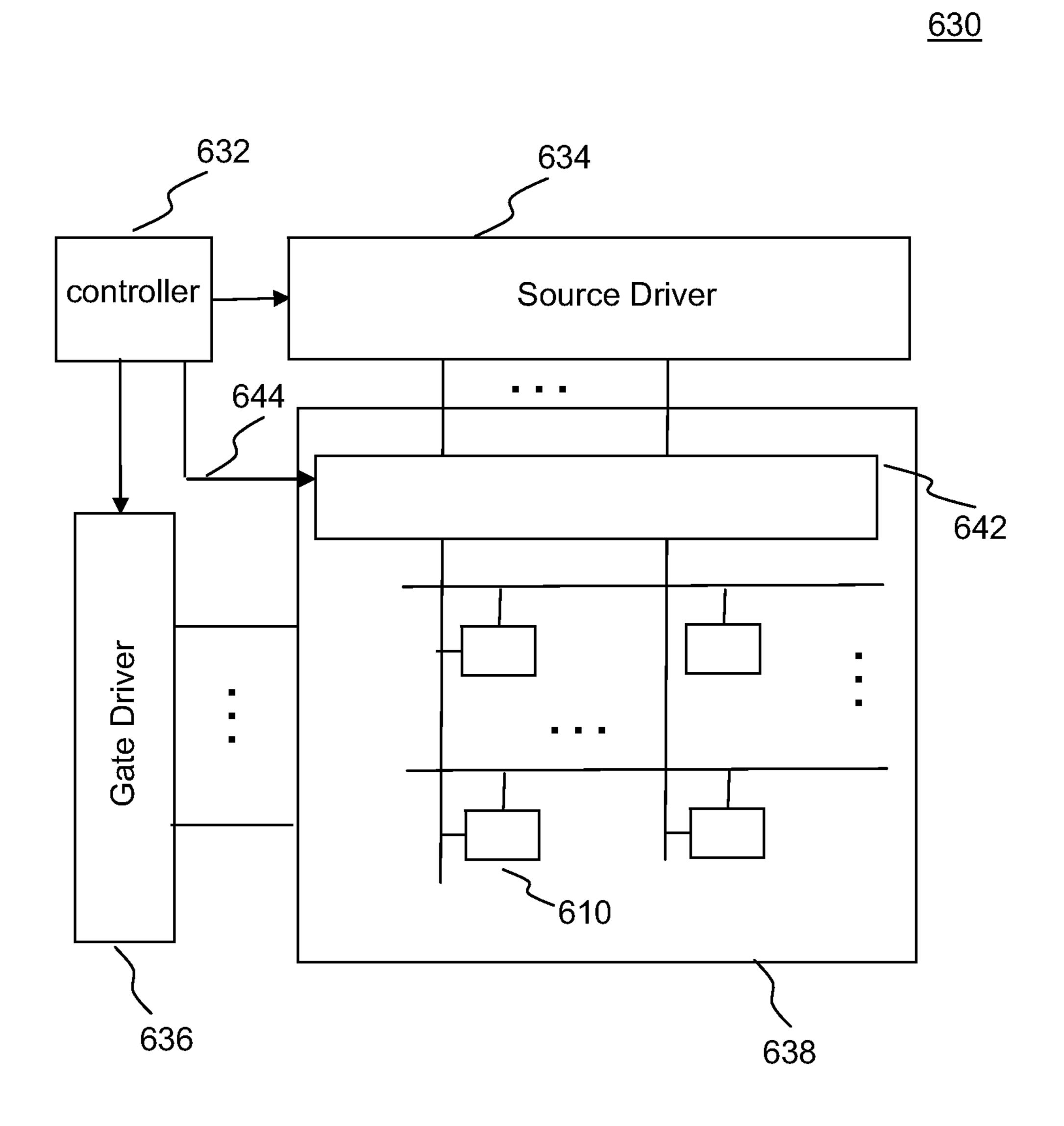

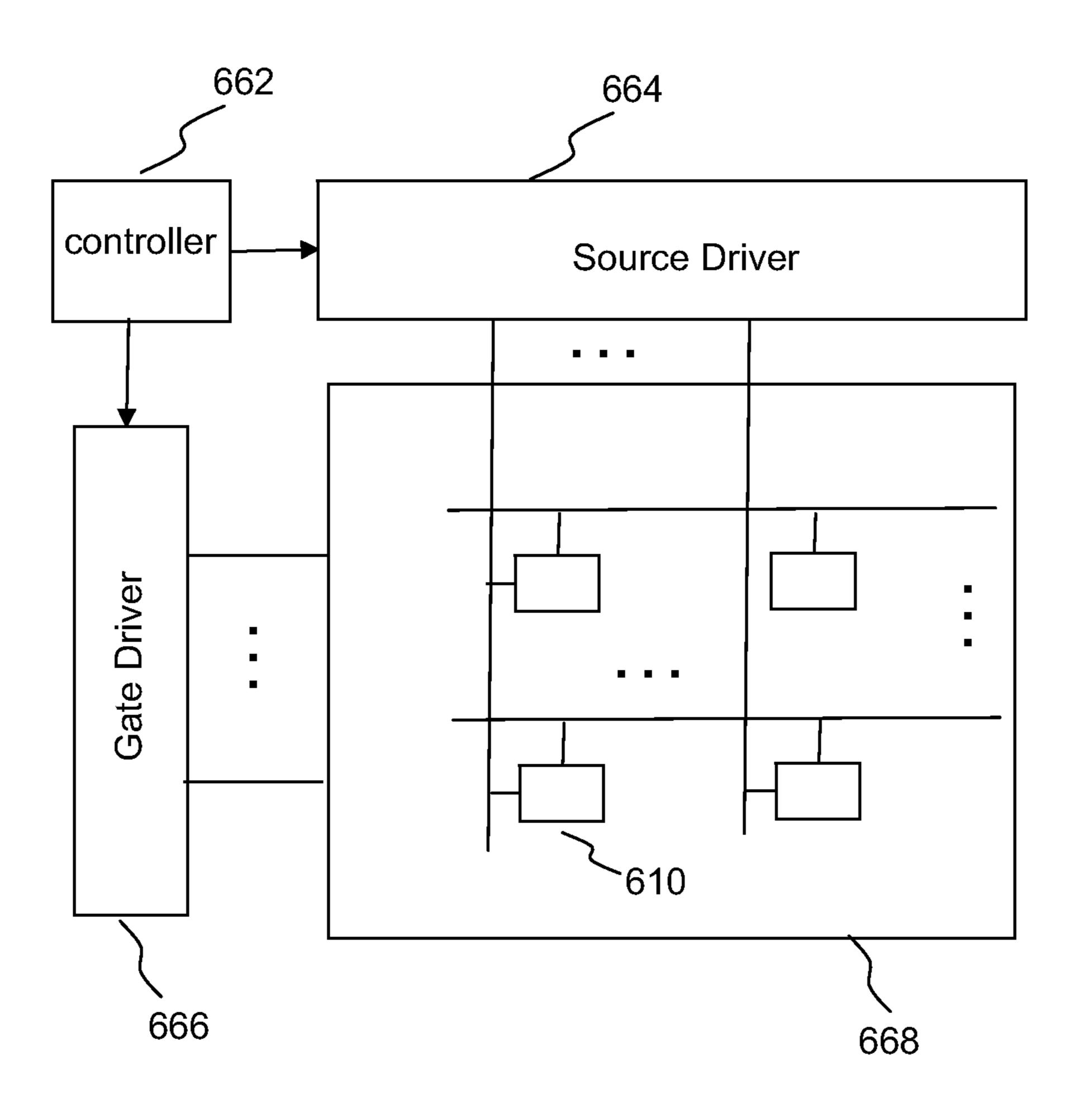

FIG. 19 illustrates an example of a display system having the source driver of FIGS. 14-15.

### DETAILED DESCRIPTION

One or more currently preferred embodiments have been described by way of example. It will be apparent to persons skilled in the art that a number of variations and modifica- 10 tions can be made without departing from the scope of the invention as defined in the claims.

Embodiments in this disclosure are described using a panel having pixels that are coupled to at least first line and at least one second line (e.g., scan lines and data lines) and 15 being operated by a driver. The driver may be a driver IC having a plurality of pins, e.g., source driver ICs, gate driver ICs. The panel may be, for example, but not limited to, a LCD or LED panel. The panel may be a color panel or a monochrome panel.

In the description below, the terms "source driver" and "data driver" are used interchangeably, and the terms "gate" driver" and "address driver" are used interchangeably. In the description below, the terms "row", "scan line" and "address line" may be used interchangeably. In the description below, 25 the terms "column", "data line" and "source line" may be used interchangeably. In the description below, the terms "pixel" and "subpixel" may be used interchangeably.

Referring to FIGS. 1A-1B, there is illustrated a system 100 having a gate driver 102 and a panel 110 having pixels 30 arranged in rows and columns. The system 100 includes a mechanism for multiplexing (muxing) gate driver outputs based on frequency reduction. In FIG. 1A, "fv" represents the vertical frequency of the display (or row frequency), and represents an address cell 106, and "SEL k" (k=(i-1)\*M+1,(i-1)\*M+2, ..., (i-1)\*M+M+1, i\*M) represents a row or a scan line coupled to the row of the panel 110. A pixel in the row is selected by the scan line. The address cell 106 may be a logic or a flip-flop in a shift register chain to output 40 a gate output.

The gate driver 102 includes a driver output unit 104 having at least one address cell **106** (Cell #i). The address cell 106 provides a single gate driver output 108 which is shared by M rows. An individual gate driver output 108 from 45 the gate driver 102 is active for M rows. On the panel side 110, a demultiplexer 112 ("1:M Demuxs" in FIG. 1A) is employed for M rows. The input of the demultiplexer 112 is coupled to the gate driver output 108, and the outputs of the demultiplexer 112 are coupled to M rows. In this example, 50 the demultiplexer 112 is coupled to scan lines SEL (i-1) \*M+1, SEL (i-1)\*M+2, . . . , and SEL i\*M. The activated gate driver output 108 from the address cell 106 (Cell #i) is assigned to each individual row in sequence, via the demultiplexer 112.

The demultiplexer 112 is implemented using, for example, thin film transistors, on the panel 110. The demultiplexer 112 includes a plurality of switch blocks for activating M rows. In FIG. 1B, switches 116 (SET #1, SET #2, . . . , SET #M) are shown as an example of the 60 components of the demultiplexer 112. The switch block 116 (SET #k: k=1, 2, ..., M) is employed for the scan line SEL (i-1)\*M+k. Each switch block 116 includes a pair of switches, one being capable of connecting the gate driver output 108 to the corresponding scan line and the other being 65 capable of connecting VGL to the corresponding scan line. VGL may be a ground level voltage. Each scan line SEL

(i−1)\*M+k turns to be on the VGL level or the activated gate driver output 108 via the corresponding switch block 116 (SET #k). Each switch block 116 (SET #k) is controlled by the corresponding control signal CTRL (k). In FIG. 3B, the scan line SEL (i-1)\*M+k is selected (becomes active) by the control signal CTRL (k). By operating the demultiplexer 112 with the control signals CTRL (1)-CTRL (M), the number of the gate driver outputs and address cells is reduced by a factor of M.

In FIG. 1B, one address cell 116 is shown as an element of the driver output unit 104; however, the number of the address cells may vary. In FIG. 1B, M rows (scan lines) are shown; however, the panel 110 may include a plurality of groups of rows where the ith group has M rows and is operated by the ith address cell (Cell #i). One of ordinary skill in the art would appreciate that the gate driver 102 and the panel 110 may include components not shown in the FIGS. **1A-1**B.

Referring to FIGS. 1A, 1B and 2, the operation of a 20 display having the gate driver 102 and the panel 110 is described. Each of the controlling signals CTRL (1)-CTRL (M) for controlling the demultiplexing on the panel 110 works at the normal gate frequency. When the display programming reaches the row SEL (i-1)\*M+1, the control signal CTRL (1) for that row is high, resulting that the address cell 106 for the ith block (Cell #i) of rows is connected to SEL (i-1)\*M+1. Thus, that row SEL (i-1)\*M+1\*M+1 is selected and the image data can be written in the pixels of the row.

After the programming of the row SEL (i-1)\*M+1, the next control signal CTRL (2) is high, resulting that the next row SEL (i-1)\*M+2 becomes active. This continues till the entire display is programmed (end of a frame).

If a row is not active, the control signal related to that row "M" is the number of muxing blocks. In FIG. 1B, "Cell #i" 35 is low or the address cell related to that row is not active. Thus, the row is connected to VGL which will disconnect the pixels in that row from the gate driver 102.

Referring to FIGS. 3A-3B, there is illustrated a system 130 having a gate driver 132 and a panel 140 having pixels arranged in rows and columns. The system 130 has a mechanism for reducing the number of gate driver outputs and reducing the operation frequency of demultiplexing control signals on the panel side. In FIG. 3A, "fv" represents the vertical frequency of the display (or row frequency). In FIG. 3B, "Cell #j" (j=i, i+1, i+2, i+3) represents an address cell, and "SEL k" (k=i, i+1, i+2, i+3) represents a row or a scan line coupled to the row of the panel 140. A pixel in the row is selected by the scan line. The address cell may be a logic or a flip-flop in a shift register chain to output a gate output.

In the system 130, gate driver output signals are multiplexed on the gate driver 132 side, and the outputs from the gate driver 132 are demultiplexed on the panel 140 side.

The gate driver 132 includes a driver output unit 133 55 having a plurality of multiplexers for a plurality of address cells. Each address cell provides a gate driver signal, and each multiplexer multiplexing the gate driver signals and outputs a single gate driver output. In FIG. 3B, four address cells 138a-138d (Cell #i, Cell #i+1, Cell #i+2, and Cell #i+3) are shown as an example of the address cells in the gate driver 132. In FIG. 3B, two multiplexers 134a and 134b are shown as an example of multiplexing the gate driver signals. The multiplexers 134a and 134b are controlled by a control signal iCTRL. The multiplexer 134a is coupled to the address cells 138a and 138c (Cell #i and Cell #i+2) and outputs a gate output signal 136a that corresponds to either address cell 138a or 138c (Cell #i or Cell #i+2). The

multiplexer 134b is coupled to the address cells 138b and 138d (Cell #i+1 and Cell #i+3) and outputs a gate output signal 136b that corresponds to either address cell 138b or 138d (Cell #i+1 or Cell #i+3).

The panel **140** includes a multiplexer **142** ("1:M Demuxs" in FIG. **3A**) coupling to the gate driver outputs and a plurality of rows. The demultiplexer **142** is implemented using, for example, thin film transistors, on the panel **140**. The demultiplexer **142** includes a plurality of switch group blocks, each coupling to the gate driver multiplexers. In FIG. **3B**, two switch group blocks **146**a and **146**b (SET #1 and SET #2) are shown as an example of the components of the demultiplexer **142**. On the panel side **140**, the activated gate driver outputs **136**a and **136**b are assigned of the switch group blocks **146**a and **146**b.

Each switch group block in the panel 140 includes a plurality of switch blocks 148. In FIG. 3B, each of the switch group blocks 146a and 146b includes two switch blocks 148, one being capable of coupling one gate driver output 136a 20 to one scan line and the other being capable of coupling the other gate driver output 136b to the other scan line. The switch block 148 includes a pair of switches, one being capable of coupling the gate driver output to the corresponding scan line and the other being capable of coupling VGL 25 to the corresponding scan line. VGL may be a ground level voltage. The switch block 148 in the switch group block (SET #k: k=1, 2, ...) is controlled by the corresponding control signal CTRL (k). Each scan line turns to be on the VGL level or the corresponding activated gate driver output 30 136a or 136b via the corresponding switch block 148. In FIG. 3B, the scan lines SEL (i) and SEL (i+1) are selected (become active) by the control signal CTRL (1), and the scan lines SEL (i+2) and SEL (i+3) are selected (become active) by the control signal CTRL (2).

In FIG. 3B, the multiplexing (muxing) and demultiplexing (demuxing) operations are executed for two rows, however, the multiplexing and demultiplexing operations may be executed for more than two rows. In FIG. 3B, four address cells are shown as an element of the driver output unit 133; 40 however, the number of the address cells is not limited to four and may vary. In FIG. 3B, rows (scan lines) are divided into two groups, each having two rows; however, the number of groups and the number of rows in each group are not limited to two and may vary. One of ordinary skill in the art 45 would appreciate that the gate driver 132 and the panel 140 may include components not shown in the FIGS. 3A-3B.

In this structure, the physical multiplexing is used at the gate driver side 132. As a result, the number of address cells remains the same while the number of gate driver outputs is reduced by a factor of multiplexing blocks. The number of rows in each set (SET #k) can be increased for further reduction in output of the gate driver and the frequency of the control signals. Since multiple gate driver outputs can be active, the operation frequency of the demultiplexing control signals is reduced.

Referring to FIGS. 3A, 3B and 4, the operation of a display having the gate driver 132 and the panel 140 is described. When the display programming reaches the rows SEL (i) and SEL (i+1), the control signal CTRL (1) for those 60 rows is high (150), resulting that the gate driver output 136a is coupled to the row SEL (i) and the gate driver output 136b is coupled to the row SEL (i+1). At this period (150), the control signal iCTRL is in one state (e.g., low). The gate driver output 136a corresponds to the output from the 65 address cell 138a (Cell #i) and the gate driver output 136b corresponds to the output from the address cell 138b (Cell

6

#i+1). The image data can be written in the pixels of the selected rows SEL (i) and SEL (i+1).

After the programming of the rows SEL (i) and SEL (i+1), the next control signal CTRL (2) is high (152), resulting that the next rows SEL (i+2) and SEL (i+3) become active. At this period (152), the control signal iCTRL is in the other state (e.g., high). The gate driver output 136a corresponds to the output from the address cell 138c (Cell #i+2) and the gate driver output 136b corresponds to the output from the address cell 138d (Cell #i+3). The image data can be written in the pixels of the selected rows SEL (i+2) and SEL (i+3). This continues till the entire display is programmed (end of a frame).

If a row is not active, the control signal related to that row is low or the address cell related to that row is not active. Thus, the row is connected to VGL which will disconnect the pixels in that row from the gate driver 132.

Referring to FIG. 5, there is illustrated a system 160 having a source driver 162 and a panel 180 having subpixels for RGB. Most of light emitting displays employ different gammas (or gamma corrections) for different subpixels, which use different decoders for different outputs. In the system 160, gammas (gamma corrections, gamma voltages) are multiplexed on the source driver 162 side. In the description, the terms "gamma", "gamma correction" and "gamma voltages" may be used interchangeably. One of ordinary skill in the art would appreciate that the source driver 162 and the panel 180 may include components not shown in FIG. 5.

The source driver 162 includes a driver output unit 164 having a CMOS multiplexer 166 and a CMOS digital to analog converter (DAC) 170. The multiplexer 166 multiplexes a Red gamma correction 168a, a Green gamma correction 168b and a Blue gamma correction 168c. The DAC 170 includes a decoder. In the description, the terms "DAC" and "DAC decoder" may be used interchangeably.

Each of the gamma corrections 168a, 168b and 168c provides a reference voltage to the DAC 170. The reference voltage is selected based on the dynamic range of the DAC decoder 170. The reference voltage at the gamma correction block may be generated using, for example, resistors, or be stored using, for example, registers.

The output from the multiplexer 166 is provided to the DAC 170. The multiple gammas share one decoder in the DAC 170. The DAC decoder 170 operates on an output from a multiplexer 172. The multiplexer 172 multiplexes a Red register (reg) 174a for storing image data for Red, a Green register (reg) 174b for storing image data for Green, and a Blue register (reg) 174c for storing image data for Blue. The CMOS DAC 170 provides a single source driver output 174.

A demultiplexer 182 is employed on the panel 180 side to demultiplex the driver output 174 from the source driver 162. The demultiplexer 182 is implemented using, for example, thin film transistors, on the panel 180. The outputs from the demultiplexer 182 are couples to three data lines. The driver output 174 is demultiplexed 182 on the panel 180 side and goes to different subpixels (i.e., Red subpixel, Blue subpixel and Green subpixel).

In the system 160, the output of the source driver 162 is multiplexed to reduce the number of driver pins and demultiplexed at the panel 180. To further improve the size of the driver area, the multiplexing is executed at few stage earlier at the gamma selection and DAC inputs. For example, when, the Red pixels are being programmed at the panel 180, the Red data (Red register 174a) and the red gamma 168a are assigned to the DAC 170.

The multiplexers 166 and 172 may be controlled by a color selection control signal ColorSel. The demultiplexer 182 may be controlled by the control signal ColorSel or a control signal associated with the multiplexing control signal ColorSel.

As shown in FIG. 6, the Red pixels, Green pixels and Blue pixels may be programmed sequentially. It will be appreciated by one of ordinary skill in the art that the programming sequence is not limited to that of FIG. 6, and is changeable by using the color selection control signal.

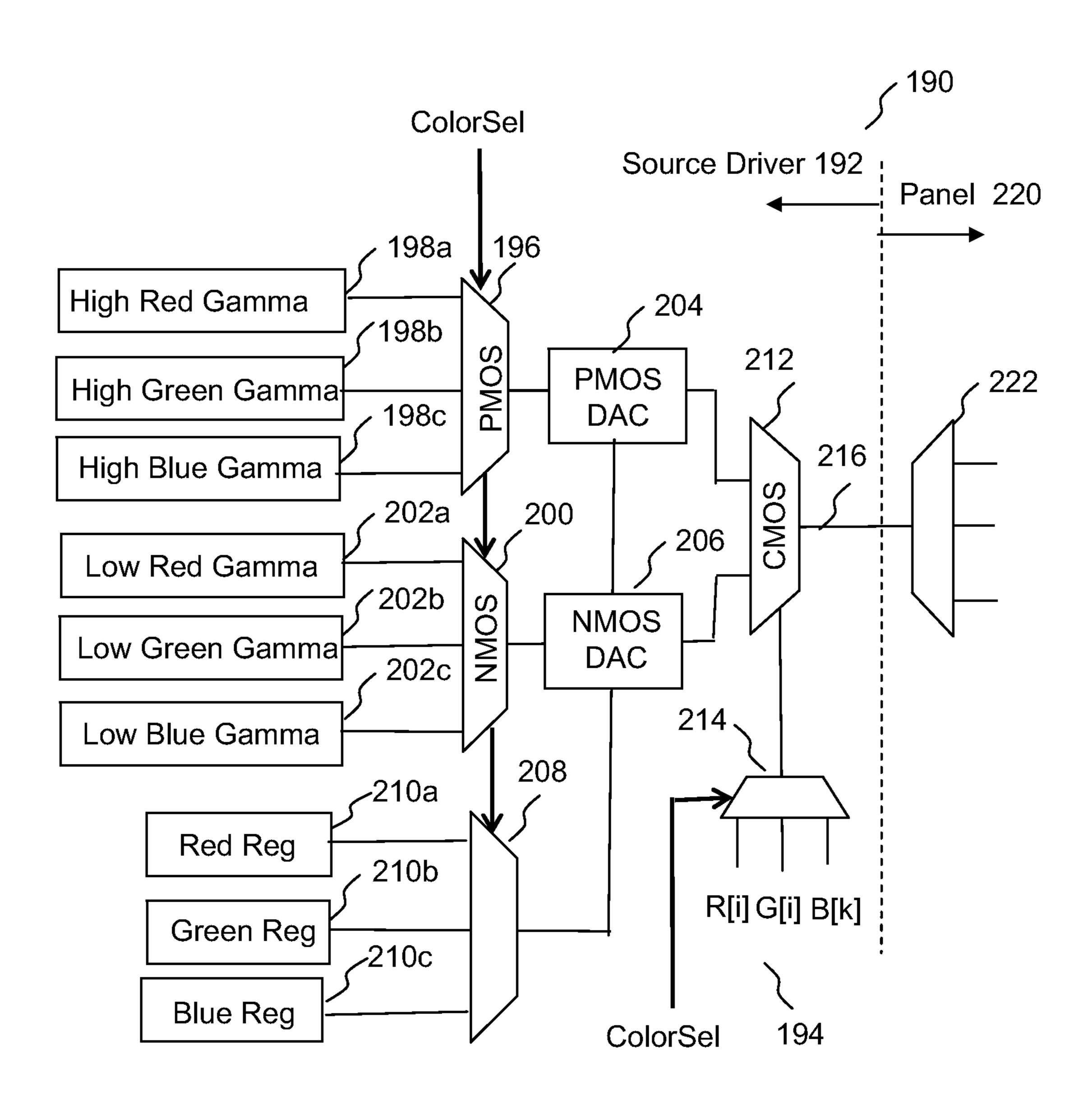

Generally, the output range of the voltage required for the light emitting displays is high and thus source drivers are to be a rail-to-rail design for the power. Currently, this results in using multiple CMOS decoders, leading to a larger area source driver. Referring to FIG. 7, there is illustrated a 15 system 190 having a source driver 192 and a panel 220 having sub-pixels for RGB. In this system 190, multiple gammas (gamma corrections, gamma voltages) are multiplexed and a DAC is divided into separate NMOS and PMOS components, resulting in that the source driver 192 20 area is reduced. One of ordinary skill in the art would appreciate that the source driver 192 and the panel 220 may include components not shown in FIG. 7.

The source driver 192 includes gamma corrections for Red, Blue and Green, each providing a reference voltage to 25 a DAC decoder. The reference voltage is selected based on the dynamic range of the decoder. The reference voltage may be generated using, for example, resistors, or be stored using, for example, registers. Each gamma correction has a high voltage level gamma correction (high voltage level of 30 gamma corrections) and a low voltage level gamma correction (low voltage level of gamma corrections). The high voltage level of gamma corrections is a level from a predefined reference voltage to the high point of the driver level from the predetermined reference voltage to the beginning of the gamma voltage. The predetermined reference voltage may be at the middle for the driver output range. For example, if the driver range is 10V, the predetermined reference voltage is 5V; the high voltage level of gamma 40 corrections is 5 to 10V; and the low voltage level of gamma corrections is 0 to 5V.