#### US00RE49125E

## (19) United States

## (12) Reissued Patent

Hung et al.

#### (10) Patent Number:

US RE49,125 E

#### (45) Date of Reissued Patent:

\*Jul. 5, 2022

# (54) METHOD AND SYSTEM FOR A SERIAL PERIPHERAL INTERFACE

- (71) Applicant: MACRONIX INTERNATIONAL CO., LTD., Hsinchu (TW)

- (72) Inventors: Chun-Hsiung Hung, Hsinchu (TW);

Kuen-Long Chang, Taipei (TW);

Chia-He Liu, Taoyuan (TW)

- (73) Assignee: MACRONIX INTERNATIONAL CO., LTD., Hsinchu (TW)

- (\*) Notice: This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 16/734,882

- (22) Filed: Jan. 6, 2020

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: 8,630,128

Issued: Jan. 14, 2014

Appl. No.: 13/523,060

Filed: Jun. 14, 2012

#### U.S. Applications:

- (60) Continuation of application No. 14/995,059, filed on Jan. 13, 2016, now Pat. No. Re. 47,803, which is an application for the reissue of Pat. No. 8,630,128, which is a continuation of application No. 13/282, 116, filed on Oct. 26, 2011, now Pat. No. 8,223,562, which is a division of application No. (Continued)

- (51) Int. Cl.

G11C 7/10 (2006.01)

G11C 7/22 (2006.01)

# (52) **U.S. Cl.**CPC ...... *G11C* 7/1072 (2013.01); *G11C* 7/1045 (2013.01); *G11C* 7/22 (2013.01)

(58) Field of Classification Search

CPC ....... G11C 7/22; G11C 7/1045; G11C 7/1072

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

#### (Continued)

Primary Examiner — William H. Wood (74) Attorney, Agent, or Firm — Andrew L. Dunlap; Haynes Beffel & Wolfeld LLP

#### (57) ABSTRACT

An integrated circuit includes a serial peripheral interface memory device. In an embodiment, the memory device includes a clock signal, a plurality of pins, and a configuration register. In an embodiment, the configuration register includes a wait cycle count. The method includes transmitting a read address to the memory device using a first input/output pin and a second input/output pin concurrently. In an embodiment, the read address includes at least a first address bit and a second address bit, the first address bit being transmitted using the first input/output pin, and the second address bit being transmitted using the second input/ output pin. The method includes accessing the memory device for data associated with the address and waiting a predetermined number clock cycles associated with the wait cycle count. The method includes transferring the data from the memory device using the first input/output pin and the second input/output pin concurrently.

#### 11 Claims, 24 Drawing Sheets

### Fast Dual I/O SARSDR Page Read

# US RE49,125 E Page 2

|      | Related U.S.            | Application Data                              |                                |              | Bhakta et al.                               |

|------|-------------------------|-----------------------------------------------|--------------------------------|--------------|---------------------------------------------|

|      | 12/564 789 filed on     | Sep. 22, 2009, now Pat. No.                   | 7,397,717 B2*                  | 7/2008       | Chen et al G11C 7/1075<br>365/185.33        |

|      | -                       | continuation of application No.               | 7 475 174 R2 *                 | 1/2009       | Chow et al G06F 13/1684                     |

|      |                         | Jan. 4, 2008, now Pat. No.                    | 7,773,177 102                  | 1/2005       | 710/10                                      |

|      | 7,613,049.              | Jan. 4, 2000, now 1 at. 110.                  | 7,515,471 B2 *                 | 4/2009       | Oh et al G06F 1/12                          |

|      | 7,013,049.              |                                               |                                |              | 365/185.11                                  |

| (60) | Provisional application | on No. 60/884,000, filed on Jan.              | 7,519,751 B2                   | 4/2009       | Perroni et al.                              |

| ` /  | 8, 2007.                |                                               | 7,532,537 B2                   |              | Solomon et al.                              |

|      |                         |                                               | 7,558,900 B2 *                 | 7/2009       | Jigour et al G11C 7/1045                    |

| (56) | Refere                  | nces Cited                                    | 7.500.205. D2                  | 10/2000      | 710/105                                     |

| ` /  |                         |                                               | 7,599,205 B2                   | 10/2009      | 3                                           |

|      | U.S. PATENT             | DOCUMENTS                                     | 7,613,049 B2<br>7,652,922 B2   |              | Kim et al G11C 5/066                        |

|      |                         |                                               | 7,032,322 132                  | 1/2010       | 365/185.11                                  |

|      | ·                       | Wright et al.                                 | 7,660,177 B2                   | 2/2010       | Lee et al.                                  |

|      | 5,923,899 A 7/1999      |                                               | 7,685,343 B2 *                 |              | Hou et al G06F 13/4291                      |

|      | 5,966,723 A * 10/1999   | James et al G11C 16/10                        |                                |              | 710/105                                     |

|      | 5,966,724 A 10/1999     | 711/103<br>Ryan                               | 7,788,438 B2*                  | 8/2010       | Kuo et al G06F 13/404                       |

|      | 5,970,069 A 10/1999     | •                                             | 0.054.050.70                   | 4.4 (2.0.4.4 | 710/305                                     |

|      | , ,                     | Baker et al G06F 13/28                        | 8,064,268 B2                   |              | ~                                           |

|      |                         | 710/113                                       | 8,072,819 B2*                  | 12/2011      | Rai et al G11C 7/1078                       |

|      | 5,991,194 A * 11/1999   | Jigour et al G11C 5/06                        | 8 120 710 B2 *                 | 2/2012       | 365/189.02<br>Swartz H04N 7/0115            |

|      |                         | 365/185.04                                    | 0,120,710 DZ                   | 2/2012       | 348/700                                     |

|      | 6,243,797 B1 6/2001     |                                               | 8,223,562 B2                   | 7/2012       |                                             |

|      | 6,310,596 B1* 10/2001   | Takasugi G09G 3/3644                          | 8,250,287 B1*                  |              | Mirichigni G06F 13/28                       |

|      | 6 419 050 D1 7/2002     | 345/98<br>Vraifala et al                      |                                |              | 711/103                                     |

|      | *                       | Kreifels et al.<br>Kitamura et al G06F 11/364 | 8,270,244 B2*                  | 9/2012       | Kim G11C 7/20                               |

|      | 0,001,712 D1 10,2001    | 710/312                                       |                                | 4.0 (0.0.4.0 | 365/226                                     |

|      | 6,892,269 B2 * 5/2005   | Polizzi et al G11C 7/1075                     | 8,341,330 B2*                  | 12/2012      | Hung et al G06F 3/0673                      |

|      |                         | 710/71                                        | DE 47 202 E                    | 1/2020       | 711/103                                     |

|      | 7,088,132 B1* 8/2006    | Tang et al H03K 19/17748                      | RE47,803 E<br>2006/0067123 A1* |              | Jigour G11C 7/1045                          |

|      |                         | 326/39                                        | 2000/0007123 711               | 3/2000       | 365/185.05                                  |

|      | 7,095,247 B1 * 8/2006   | Tang et al H03K 19/17748                      | 2006/0123164 A1*               | 6/2006       | Rai G11C 7/24                               |

|      | 7 120 059 D2* 10/2006   | Chan et al. C11C 16/10                        |                                |              | 710/62                                      |

|      | 7,130,938 BZ * 10/2006  | Chou et al G11C 16/10<br>711/103              | 2006/0143366 A1*               | 6/2006       | Yang G11C 16/102                            |

|      | 7 151 705 B2* 12/2006   | Polizzi et al G06F 13/4234                    |                                |              | 711/103                                     |

|      | 7,131,703 DZ 12/2000    | 365/201                                       | 2006/0239104 A1*               | 10/2006      | Lee G11C 8/06                               |

|      | 7,197,590 B2 * 3/2007   | Chiu                                          | 2007/00/12/42 4.1 *            | 2/2007       | 365/230.01                                  |

|      |                         | 710/100                                       |                                |              | Magdeburger G06F 13/385<br>Wen G06F 13/4291 |

|      | 7,259,702 B2* 8/2007    | Rai et al G11C 7/1006                         | Z007/013030Z A17               | 0/200/       | 710/110                                     |

|      |                         | 341/100                                       |                                |              | /10/110                                     |

|      | 7,277,973 B2 10/2007    |                                               | <b>.</b> • , 1 1 •             |              |                                             |

|      | 7,281,082 B1 10/2007    | Knapp                                         | * cited by examine             | r            |                                             |

|      |                         |                                               |                                |              |                                             |

| mast mead              |        |

|------------------------|--------|

|                        |        |

| Quad 10 read           | 22 Tex |

| East Feat              |        |

| Chad Wo DER read       |        |

| Dual 1/0 page read     |        |

| Dual 160 DER page read |        |

| £                      |        |

|                        |        |

|                        |        |

|                        |        |

Simultaneously Read Write op

Coming the second

TOOOM PESS ACCEPTED TO THE SECOND TO THE SEC

FOR THE FOLKING PARTICIES TO THE STATE OF TH

Come of the control o

Figure 13

THE STATE OF THE SET OF THE SET ASSET

THE PROBLEM OF THE SEE

The state of the s

| );;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | Purpase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Cestrintia                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                        | AND THE REPORT OF THE PROPERTY OF A PARTY OF THE PARTY OF | 1869. I dummy cycle, 20010. 2 dummy cycles, 8811. 3 dummy cycles.     |

|                                        | Bunny eyele countilling dummy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ignes, a dumany cycles, bidle S dumany cycles, bills 6 dumany cycles, |

| 17 m                                   | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | eyeles, 1669: 8 dummy v                                               |

|                                        | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                       |

| δγ                                     | **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | vontiuusus durst (default)                                            |

|                                        | Wran around                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8: Wear ground, 1: No werd around (default)                           |

Figure 17

\* Burst length 4 dries with wrap around and program 3 bytes were show

Sing some

" Burst length 4 hytes with wrap around and program 3 bytes were shown

mode:

Han Emul

Pirms Si

Direct Holling

read mode;

Pinks solstor

Jul. 5, 2022

Pinas Susio Pinas Wina

Pink? HOLDA

x4 read mode:

DEFOS 28411

Pinks Werksion

Dies Sies

HO! D#SIO3

PagaiBurst read mode: Pinks Sosson

\*\*\*\*\*\*

# METHOD AND SYSTEM FOR A SERIAL PERIPHERAL INTERFACE

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

# CROSS-REFERENCES TO RELATED APPLICATIONS

This application is a continuation reissue of application <sup>15</sup> Ser. No. 14/995,059 filed on 13 Jan. 2016, and is an application for reissue of U.S. Pat. No. 8,630,128, issued from U.S. application Ser. No. 13/523,060, filed 14 Jun. 2012, which is a continuation of U.S. patent application Ser. No. 13/282,116, filed 26 Oct. 2011, which is a divisional of <sup>20</sup> U.S. Pat. No. 8,064,268, which is a continuation of U.S. Pat. No. 7,613,049, which claims the benefit of U.S. Provisional Patent Application No. 60/884,000, titled "METHOD AND SYSTEM FOR A SERIAL PERIPHERAL INTERFACE PROTOCOL", filing date Jan. 8, 2007, all of which are <sup>25</sup> incorporated by reference herein.

#### BACKGROUND OF THE INVENTION

The present invention is directed to integrated circuits and their operation. More particularly, this invention provides a method and system for serial peripheral interface protocol for an integrated circuit which include memory device. Merely by way of example, the invention has been applied to serial memory devices for fast data transfer rate and for enabling simultaneously read/write operations. But it would be recognized that the invention has a much broader range of applicability. For example, the invention can be applied to other stand-alone or embedded memory devices such DRAM, SRAM, parallel flash, or other non-volatile memories.

Flash memories are used in a variety of applications in electronics. These memory devices often include a large number of input and output pins to accommodate data and addresses required to access the memory cells. In response 45 to increasing space and wiring demands, serial flash memories have been developed to provide reduced pin counts, often requiring only one or two data pins. These serial flash memories provide a storage solution for systems with limited space, pin connections, and power supplies. Serial flash 50 memories can be used for code download applications, as well as for storage of voice, video, text, and data, etc. However, conventional serial flash memory devices have many limitations. For example, a conventional serial peripheral interface flash memory device transfers data or address 55 bits in a sequential and serial fashion, limiting the speed of the memory device.

From the above, it is seen that an improved technique for design of semiconductor memory devices is desired.

#### BRIEF SUMMARY OF THE INVENTION

The present invention is directed to integrated circuit memory devices and their operation. More particularly, this invention provides a method and system for serial peripheral 65 interface protocol for integrated circuits which include memory devices. Merely by way of example, the invention

2

has been applied to serial flash memory devices for improved data transfer rate and for enabling simultaneously read and write operations. But it would be recognized that the invention has a much broader range of applicability. For example, the invention can be applied to other stand-alone or embedded memory devices such DRAM, SRAM, parallel flash, or other non-volatile memories.

According to an embodiment of the present invention, a method is provided for dual I/O data read in an integrated 10 circuit which includes a memory device. In a specific embodiment, the integrated circuit includes a flash memory device. In other embodiments, the method can be applied to integrated circuits which include other types of memory devices. In an embodiment, the integrated circuit includes a serial peripheral interface pin out configuration and a configuration register. In an embodiment, the configuration register includes a wait cycle count. The serial peripheral interface pin out configuration typically includes pin #1 (CS#), pin #2 (SO/SIO1), pin #3 (WP#), pin #4 (GND), pin #5 (SI/SIO0), pin #6 (SCLK), pin #7 (HOLD#), and pin #8 (VCC). The method includes applying a chip select signal coupled to pin #1 and transferring a dual I/O read instruction to the memory device using pin #5. The method includes transferring a read address to the memory device using pin #5 and pin #2 concurrently. The read address is associated with a location in the memory and includes at least a first address bit and a second address bit. The first address bit is transmitted using pin #5, and the second address bit is transmitted using pin #2. In a specific embodiment, the method uses a same clock edge to transmit the first address bit and the second address bit. The method also includes accessing data associated with the read address and waiting for a predetermined number of clock cycles. In an embodiment, the predetermined number of clock cycles is associated with the wait cycle count. The method includes transferring the data from the memory device using pin #5 and pin #2 concurrently. The data is associated with the read address and includes at least a first data bit and a second data bit. The first data bit is transmitted using pin #5, and the second data bit is transmitted using pin #2. According to embodiments of the invention, the transferring of the read address concurrently reduces address transfer clock cycles by one half. In an embodiment, the method also includes using a falling edge or a rising edge or both edges of a clock signal from pin #6 to trigger data transfer. In another embodiment, the method uses a falling edge or a rising edge or both edges of a first clock signal from pin #6 to trigger address transfer. In yet another embodiment, the method uses a falling edge or a rising edge or both edges of a first clock signal from pin #6 to trigger address transfer; and uses a falling edge or a rising edge or both edges of a second clock signal from pin #6 to trigger data transfer.

According to another embodiment, the present invention provides a method for quadruple I/O data read an integrated circuit which includes a memory device. In a specific embodiment, the integrated circuit includes a flash memory device. In other embodiments, the method can be applied to integrated circuits which include other types of memory devices. In an embodiment, the integrated circuit includes a serial peripheral interface pin out configuration and a configuration register. The configuration register includes a wait cycle count. The serial peripheral interface pin out configuration including pin #1 (CS#), pin #2 (SO/SIO1), pin #3 (WP#/SIO2), pin #4 (GND), pin #5 (SI/SIO0), pin #6 (SCLK), pin #7 (HOLD#/SIO3), and pin #8 (VCC). The method includes applying a chip select signal coupled to pin #1, and transferring a quadruple I/O read instruction to the

memory device using pin #5. The method also includes transmitting a read address to the memory device using pin #5, pin #2, pin #3, and pin #7 concurrently. The read address is associated with a location in the memory and includes at least a first address bit, a second address bit, a third address 5 bit, and a fourth address bit. The first address bit is transmitted using pin #5, the second address bit is transmitted using pin #2, the third address bit is transmitted using pin #3, and the fourth address bit is transmitted using pin #7. In an embodiment, the transferring of the read address concur- 10 rently further includes using a same clock edge to transmit the first, second, third, and fourth address bits. In a specific embodiment, the transferring of the read address concurrently reduces address transfer clock cycles by 3/4. The method then accesses data bits associated with the address in 15 the memory device, and waits for a predetermined number of clock cycles, which is associated with the wait cycle count, and then transfers the data bits from the memory device using pin #5, pin #2, pin #3, and pin #7, concurrently. In a specific embodiment, the method uses a falling edge of 20 a clock signal from pin #6 to trigger address transfer. In another embodiment, the method uses a falling edge or a rising edge or both edges of a first clock signal from pin #6 to trigger address transfer. In yet another embodiment, the method uses a falling edge or a rising edge or both edges of 25 a first clock signal from pin #6 to trigger address transfer, and uses a falling edge or a rising edge or both edges of a second clock signal from pin #6 to trigger data transfer.

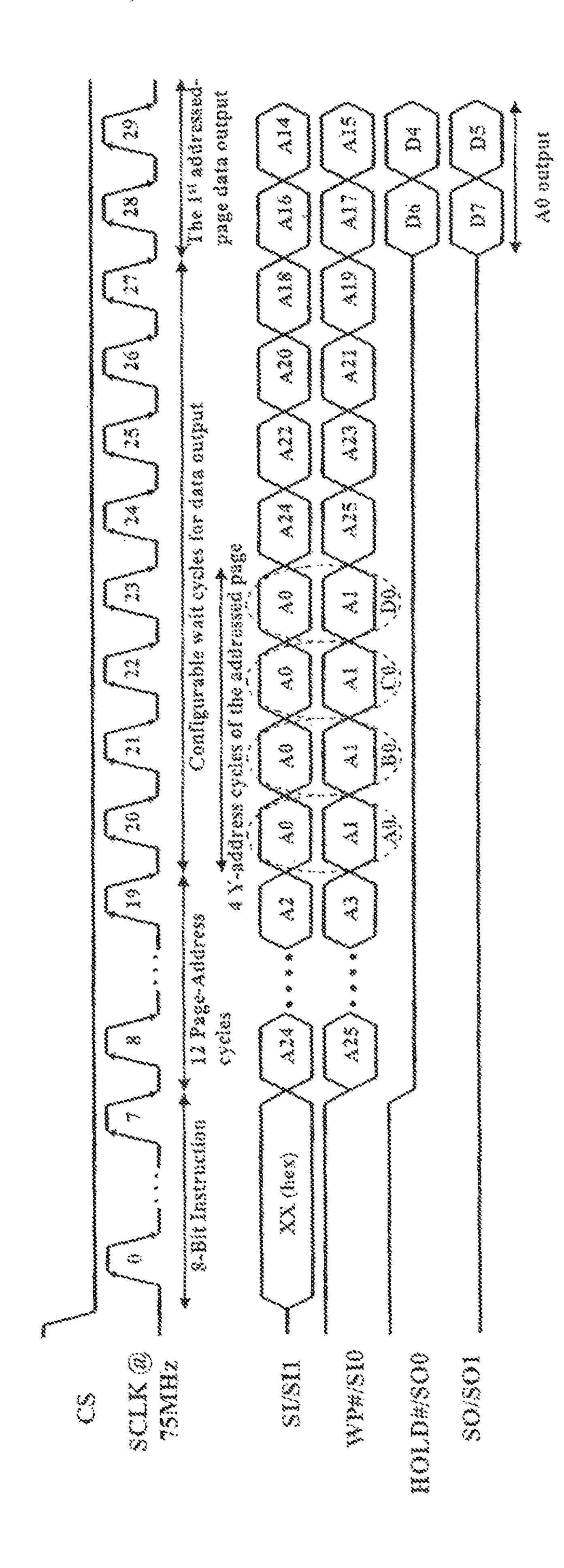

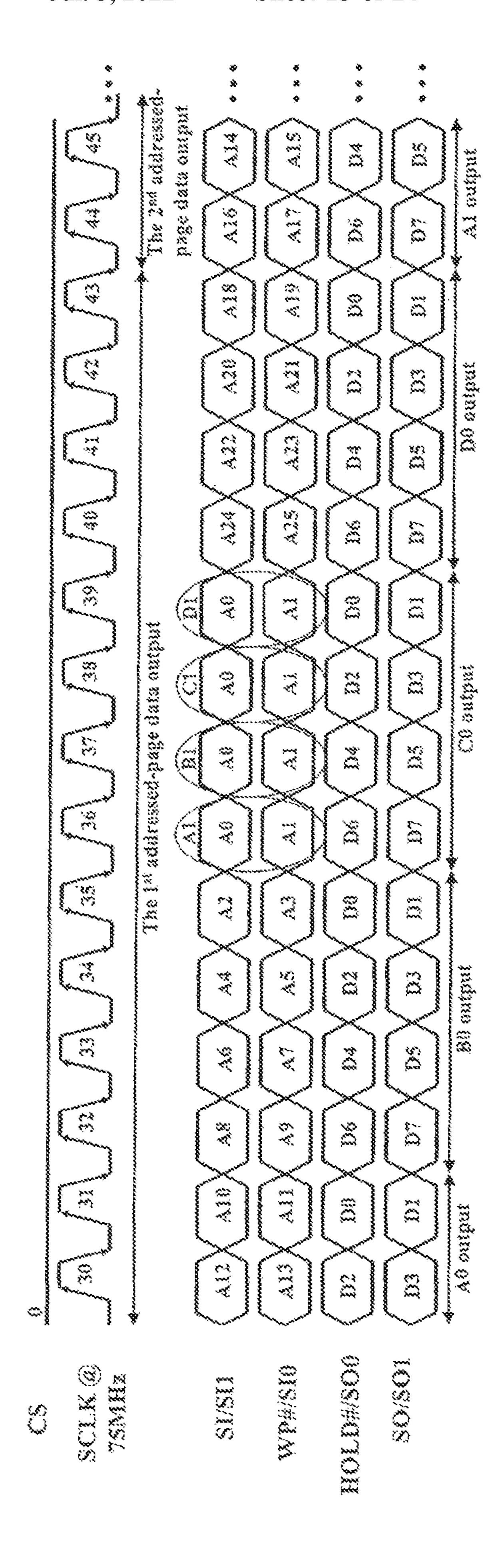

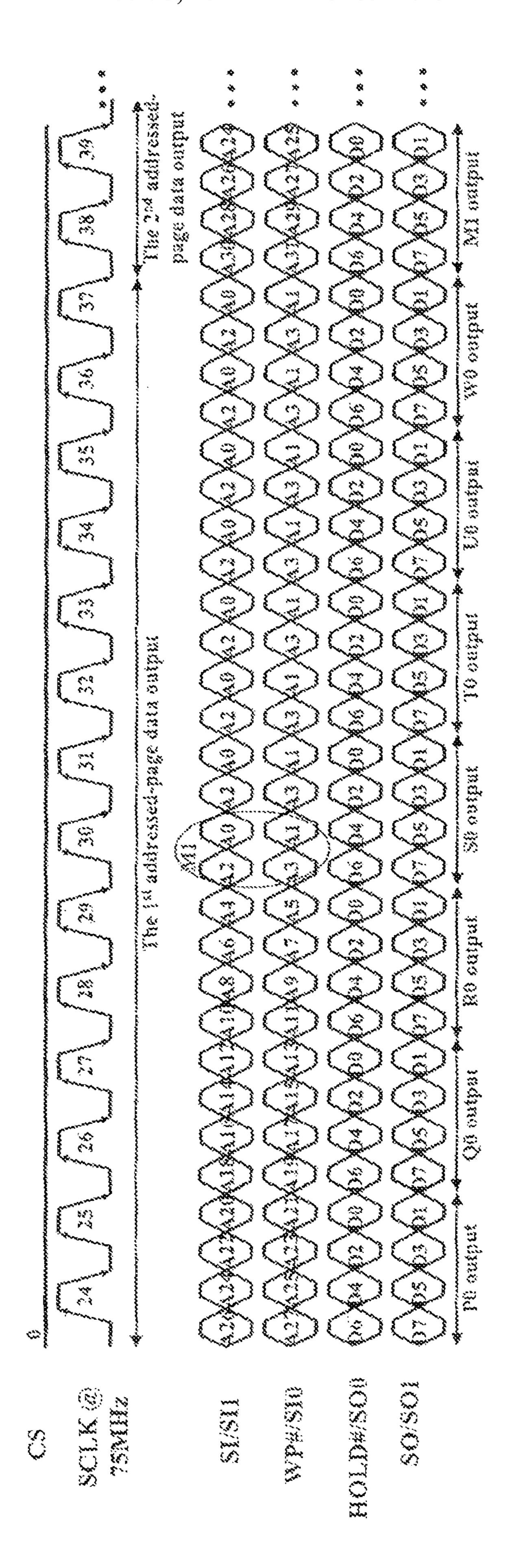

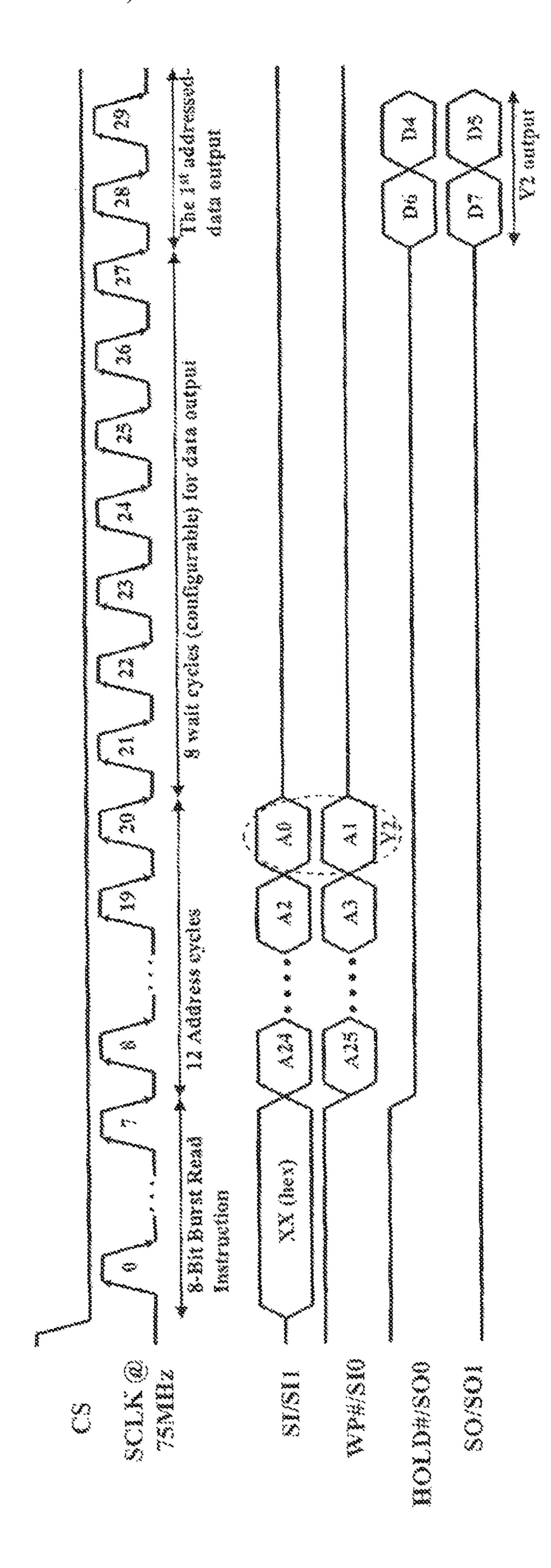

According to an alternative embodiment, the invention provides a method for dual I/O page read in an integrated 30 circuit which includes a memory device. In a specific embodiment, the integrated circuit includes a flash memory device. In other embodiments, the method can be applied to integrated circuits which include other types of memory devices. In an embodiment, the integrated circuit includes a 35 serial peripheral interface pin out configuration and a configuration register. The configuration register includes a wait cycle count. The serial peripheral interface pin out configuration includes pin #1 (CS#), pin #2 (SO/SO1), pin #3 (WP#/SI0), pin #4 (GND), pin #5 (SI/SI1), pin #6 (SCLK), 40 pin #7 (HOLD#/SO0), and pin #8 (VCC). The method includes applying a chip select signal coupled to pin #1 and transferring a dual I/O page read instruction to the memory device using pin #5. The method includes transferring a page address to the memory device using pin #5 and pin #3 45 concurrently. The page addresses includes a first part and a second part. The first part is associated with a page of data in the memory device, whereas the second part includes a plurality of byte addresses, each of which pointing to a corresponding byte in the page of data. The method includes 50 accessing data associated with the page address in the memory device and waiting for a predetermined number of clock cycles, which is determined by the wait cycle count. The method then transfers the data in page mode from the memory device using pin #7 and pin #2 concurrently. In an 55 embodiment, in one or more clock cycles, pin #5 and pin #3 are transferring address into the memory and pin #7 and pin #2 are transferring data out of the memory. In a specific embodiment, in one or more clock cycles, the method uses a falling edge or a rising edge or both edges of clock signal 60 from pin #6 to trigger address transfer and data transfer.

According to another alternative embodiment, the inventions provides a method for dual I/O simultaneous read/write operation an integrated circuit which includes a memory device. In a specific embodiment, the integrated circuit 65 includes a memory device. In other embodiments, the method can be applied to integrated circuits which include

4

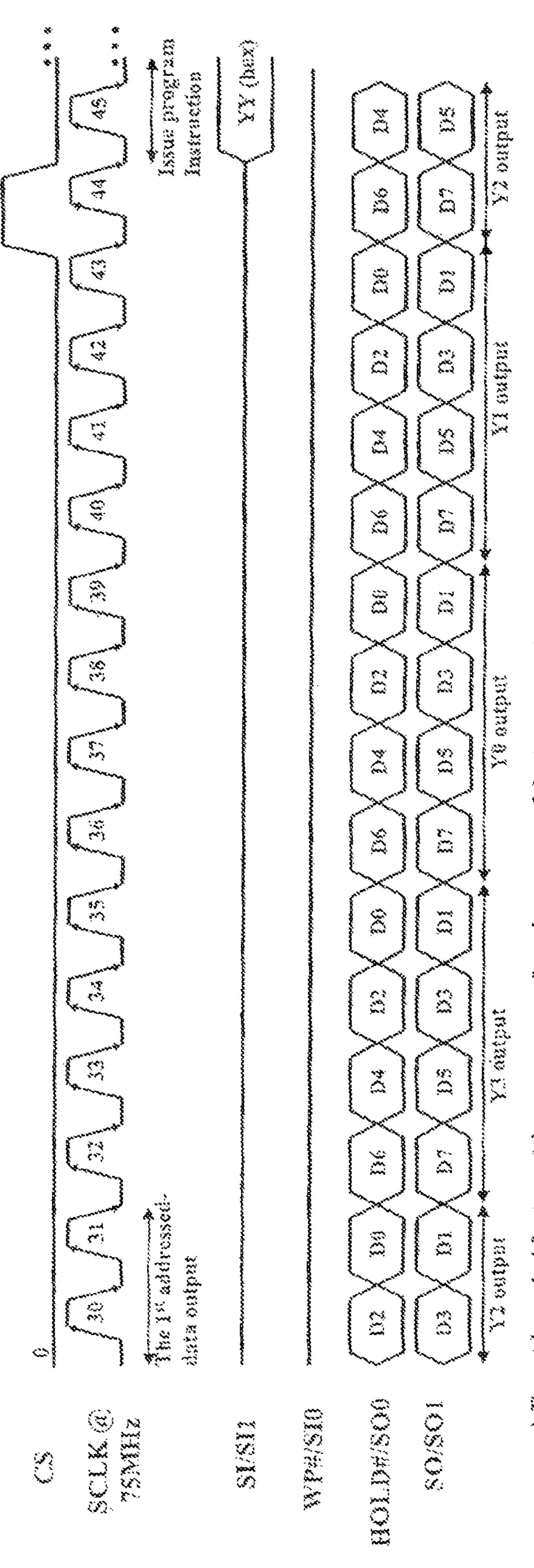

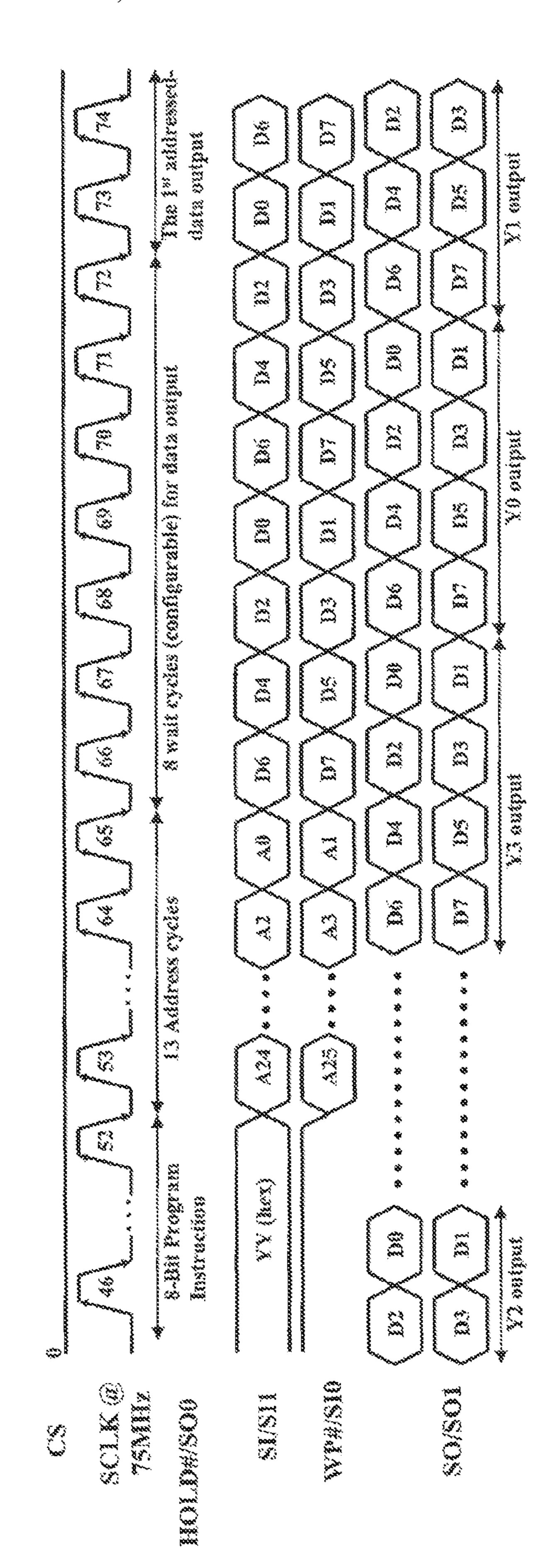

other types of memory devices. In an embodiment, the integrated circuit includes a serial peripheral interface pin out configuration and a configuration register. The configuration register includes a wait cycle count, a burst read length, and a wrap around indicator, and the serial peripheral interface pin out configuration includes pin #1 (CS#), pin #2 (SO/SO1), pin #3 (WP#/SI0), pin #4 (GND), pin #5 (SI/SI1), pin #6 (SCLK), pin #7 (HOLD#/SO0), and pin #8 (VCC). The method includes applying a chip select signal coupled to pin #1, and performing a read operation. The read operation including the following processes.

transferring a read instruction to the memory device using pin #5;

transferring an address to the memory device using pin #5 and pin #3 concurrently;

accessing data associated with the address in the memory device; and

transferring the data in burst mode from the memory device using pin #7 and pin #2 concurrently, a length of the data being determined by the burst read length.

The method also includes performing a write operation while the transferring of the data is being carried out using pin #7 and pin #2. The write operation includes the following processes.

transferring a write instruction to the memory device using pin #5;

transferring a write address to the memory device using pin #5 and pin #3 concurrently;

transferring write data to the memory device using pin #5 and pin #3 concurrently; and

writing data to the memory device in memory locations associated with the write address.

In a specific embodiment, the method also includes repeating the transferring of the read data associated with the location in the memory if the wrap around indicator is set. In an embodiment, the method includes waiting for a predetermined number of cycles associated with the wait cycle count before transferring the read data in from the memory device. In a specific embodiment, in one or more clock cycles, the method uses a falling edge or a rising edge or both edges of clock signal from pin #6 to trigger address transfer and data transfer.

In yet another embodiment, the invention provides a method for dual I/O data read an integrated circuit which includes a memory device. In a specific embodiment, the integrated circuit includes a memory device. In other embodiments, the method can be applied to integrated circuits which include other types of memory devices. In an embodiment, the integrated circuit includes a clock signal, a plurality of pins, and a configuration register. The configuration register includes a wait cycle count, among other parameters. The method includes transmitting a read address to the memory device using a first pin and a second pin concurrently. The read address is associated with a location in the memory and includes at least a first address bit and a second address bit. In an embodiment, the first address bit is transmitted using the first pin, the second address bit is transmitted using the second pin. In a specific embodiment, the transferring of the read address concurrently further includes using a same clock edge to transmit the first address bit and the second bit. The method includes accessing the memory device for data associated with the address and waiting a predetermined number clock cycles. The predetermined number is associated with the wait cycle count. The method also includes transferring the data from the memory device using the first pin and the second pin concurrently. In an embodiment, the method uses a falling

edge or a rising edge or both edges of the clock signal to trigger data transfer. In a specific embodiment, method uses a falling edge or a rising edge or both edges of the clock signal to trigger address transfer. In some embodiments, the method uses a first falling edge or a first rising edge or first both edges of the clock signal to trigger address transfer, and using a second falling edge or a second rising edge or second both edges of the clock signal to trigger data transfer.

In still another embodiment, the invention provides a method for quadruple I/O data read in an integrated circuit which includes a memory device. In a specific embodiment, the integrated circuit includes a memory device. In other embodiments, the method can be applied to integrated embodiment, the integrated circuit includes a clock signal, a plurality of pins, and a configuration register. The configuration register includes a wait cycle count, among other parameters. The method includes transmitting a read address to the memory device using a first pin, a second pin, a third 20 pin, and a fourth pin concurrently. The read address is associated with a location in the memory device, and includes at least a first address bit, a second address bit, a third address bit, and a fourth address bit. These address bits are transmitted concurrently, e.g., the first address bit being 25 transmitted using the first pin, the second address bit being transmitted using the second pin, the third address bit being transmitted using the third pin, and the fourth address bit being transmitted using the fourth pin. The method includes accessing data associated with the read address in the memory device and waiting a predetermined number of clock cycles which is associated with the wait cycle count. The method includes transferring the data from the memory device using the first pin, the second pin, the third pin, and the fourth pin concurrently. In an embodiment, the transferring of the read address concurrently includes using a same clock edge to transmit the first, second, third, and fourth address bits. In a specific embodiment, the method uses a falling edge or a rising edge or both edges of the clock signal 40 to trigger data transfer. In an embodiment, the method uses a falling edge or a rising edge or both edges of the clock signal to trigger address transfer. In some embodiments, the method uses a first falling edge or a first rising edge or first both edges of the clock signal to trigger address transfer, and 45 using a second falling edge or a second rising edge or second both edges of the clock signal to trigger data bit transfer.

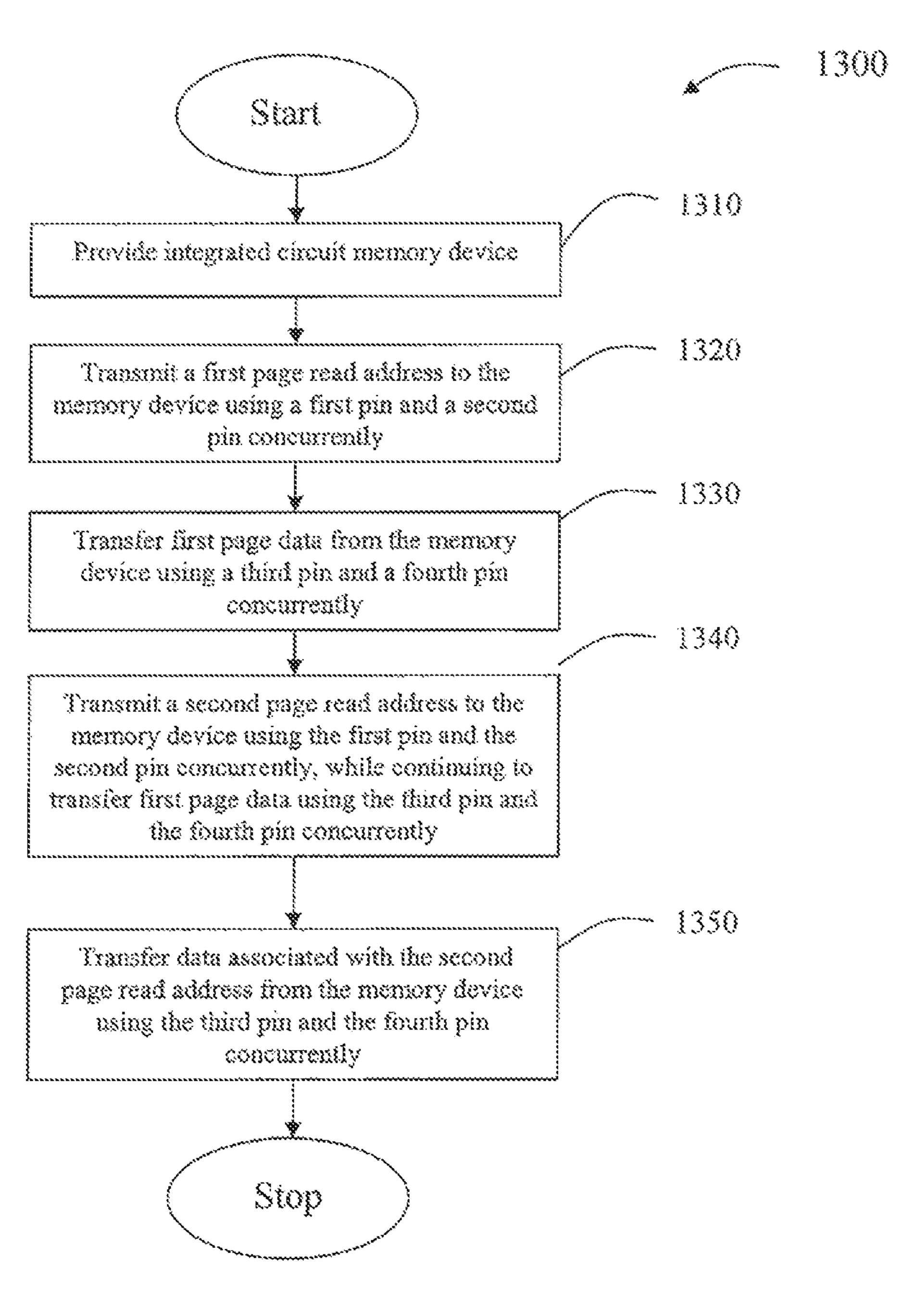

According to an alternative embodiment of the invention, a method is provided for dual I/O page read an integrated circuit which includes a memory device. In a specific 50 embodiment, the integrated circuit includes a memory device. In other embodiments, the method can be applied to integrated circuits which include other types of memory devices. In an embodiment, the integrated circuit includes a clock signal and a plurality of pins. The method includes 55 transmitting a first page read address to the memory device using a first pin and a second pin concurrently. The first page read address is associated with a location in the memory device. The method includes transferring data from the memory device using a third pin and a fourth pin concur- 60 rently. The data is associated with the first page read address in the memory device. The method includes transmitting a second page read address to the memory device using the first pin and the second pin concurrently, while continuing to transfer the data associated with the first page read address 65 from the memory device using the third pin and the fourth pin concurrently. The method includes transferring data

associated with the second page read address from the memory device using the third pin and the fourth pin concurrently.

In a specific embodiment of the method for page read, the first page read address includes a first part and a second part. The first part is associated with a page of data in the memory device, and the second part includes a plurality of byte addresses. Each of the byte addresses is associated with a corresponding byte in the page of data. In an embodiment, the first page read address includes at least a first address bit and a second address bit, the first address bit being transmitted using the first pin, the second address bit being transmitted using the second pin. In a specific embodiment, the integrated circuit memory device includes a configuracircuits which include other types of memory devices. In an 15 tion register which includes a wait cycle count, and the method includes waiting for a predetermined number of clock cycles before transferring data from the memory device. The predetermined number of clock cycles is associated with the wait cycle count. In an embodiment, the method uses a falling edge or a rising edge or both edges of the clock signal to trigger address transfer. In a specific embodiment, method uses a falling edge or a rising edge or both edges of the clock signal to trigger data transfer. In some embodiments, the method uses a falling edge or a rising edge or both edges of a clock signal to trigger address transfer and data transfer.

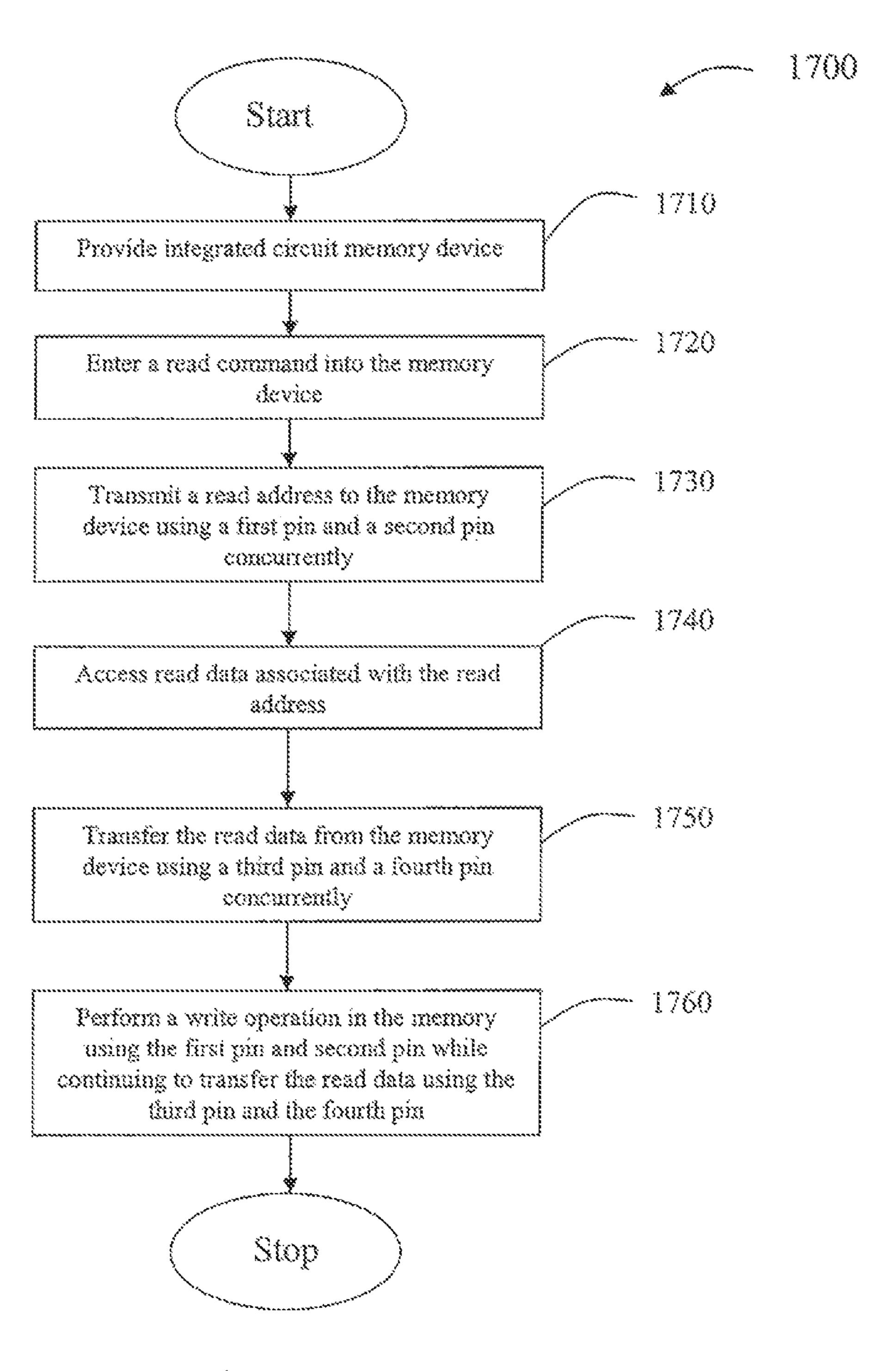

> In still another embodiment, the invention provides a method for dual I/O simultaneous read/write operation an integrated circuit which includes a memory device. In a specific embodiment, the integrated circuit includes a memory device. In other embodiments, the method can be applied to integrated circuits which include other types of memory devices. In an embodiment, the integrated circuit includes a clock signal, a plurality of pins, and a configu-35 ration register. The configuration register includes a wait cycle count, a burst read length, and a wrap around indicator. The method includes entering a read command into the memory device using a first pin and transmitting a read address to the memory device using the first pin and a second pin concurrently. The read address is associated with a location in the memory device, and includes at least a first address bit and a second address bit. The first address bit is transmitted using the first pin, and the second address bit is transmitted using the second pin. The method includes accessing read data associated with the read address in the memory device. The method includes transferring the read data in burst mode from the memory device using a third pin and a fourth pin concurrently. The length of the read data is provided in the burst read length field of the configuration register. The method includes performing a write operation in the memory using the first pin and second pin while continuing to transfer the read data in burst mode using the third pin and the fourth pin. The write operation includes at least one of the following processes:

entering a write command into the memory device using the first pin;

transferring a write address to the memory device using the first pin and the second pin concurrently;

transferring write data to the memory device using the first pin and the second pin concurrently; and

writing data to the memory device in the memory location associated with the write address.

In a specific embodiment of the method for simultaneous read/write operation, the method includes repeating the transferring of the read data associated with the location in the memory if the wrap around indicator is set. In an embodiment, the method includes waiting for a predeter-

mined number of cycles before transferring the read data in from the memory device. In an example, the predetermined number of cycles is associated with the wait cycle count. In specific embodiments, the method uses a falling edge or a rising edge or both edges of a clock signal to trigger address transfer and data transfer.

Many benefits can be achieved by way of the present invention over conventional techniques. For example, in an embodiment, the present technique provides an easy to use method that relies upon conventional serial peripheral interface pin out technology. In certain embodiments, the data and address transfer rates are increased. In some embodiments, the method provides high speed and random read operation, for example, the page read method accessing 15 present invention; individual bytes in a page. In certain embodiments, the invention provides methods for simultaneously read and program or erase operation. Depending upon the embodiment, one or more of these benefits may be achieved. These and other benefits will be described in more detail through- 20 out the present specification and more particularly below.

Various additional objects, features and advantages of the present invention can be more fully appreciated with reference to the detailed description and accompanying drawings that follow.

#### BRIEF DESCRIPTION OF THE DRAWINGS

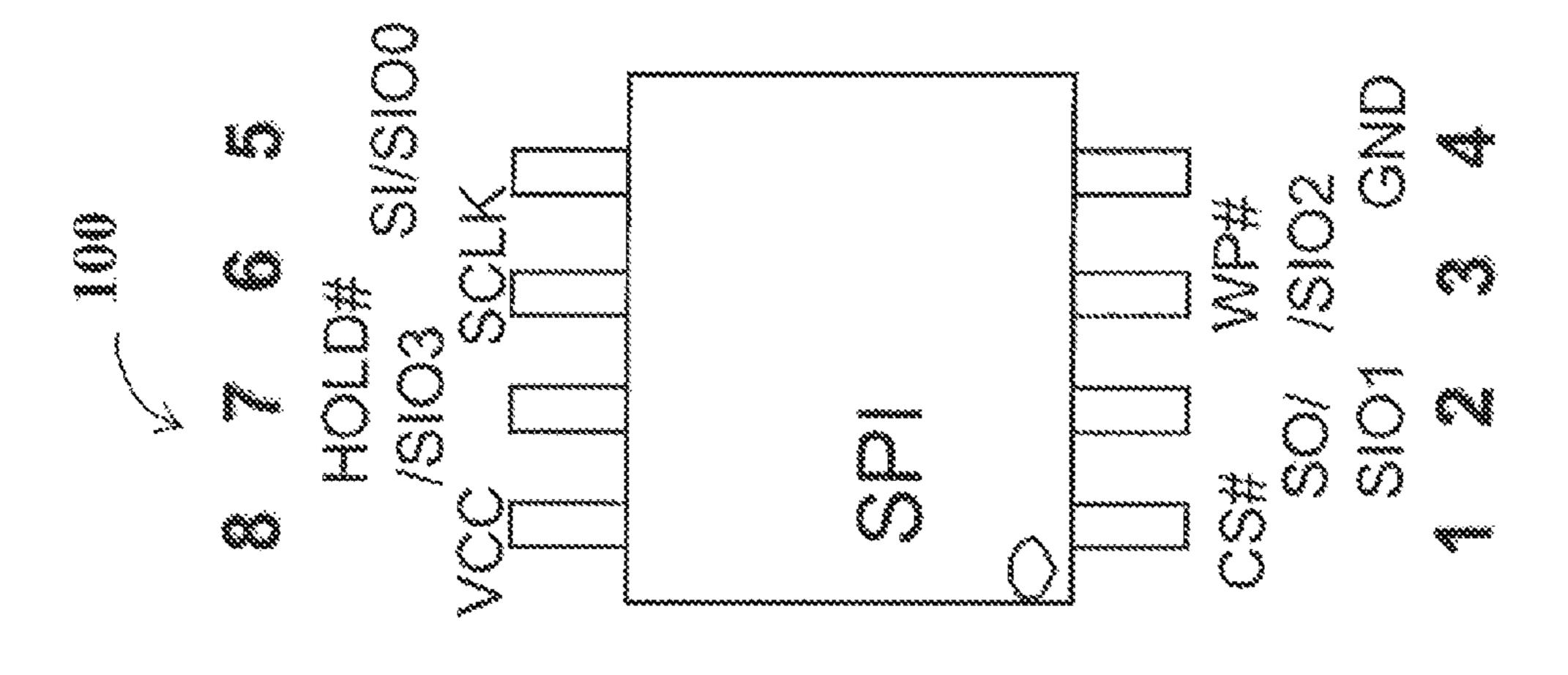

- FIG. 1A is a simplified pin out diagram for an integrated circuit which includes a serial peripheral interface I/O 30 according to an embodiment of the present invention;

- FIG. 1B is a simplified view diagram of read mode command set according to an embodiment of the present invention;

- circuit which includes a memory device according to an embodiment of the present invention;

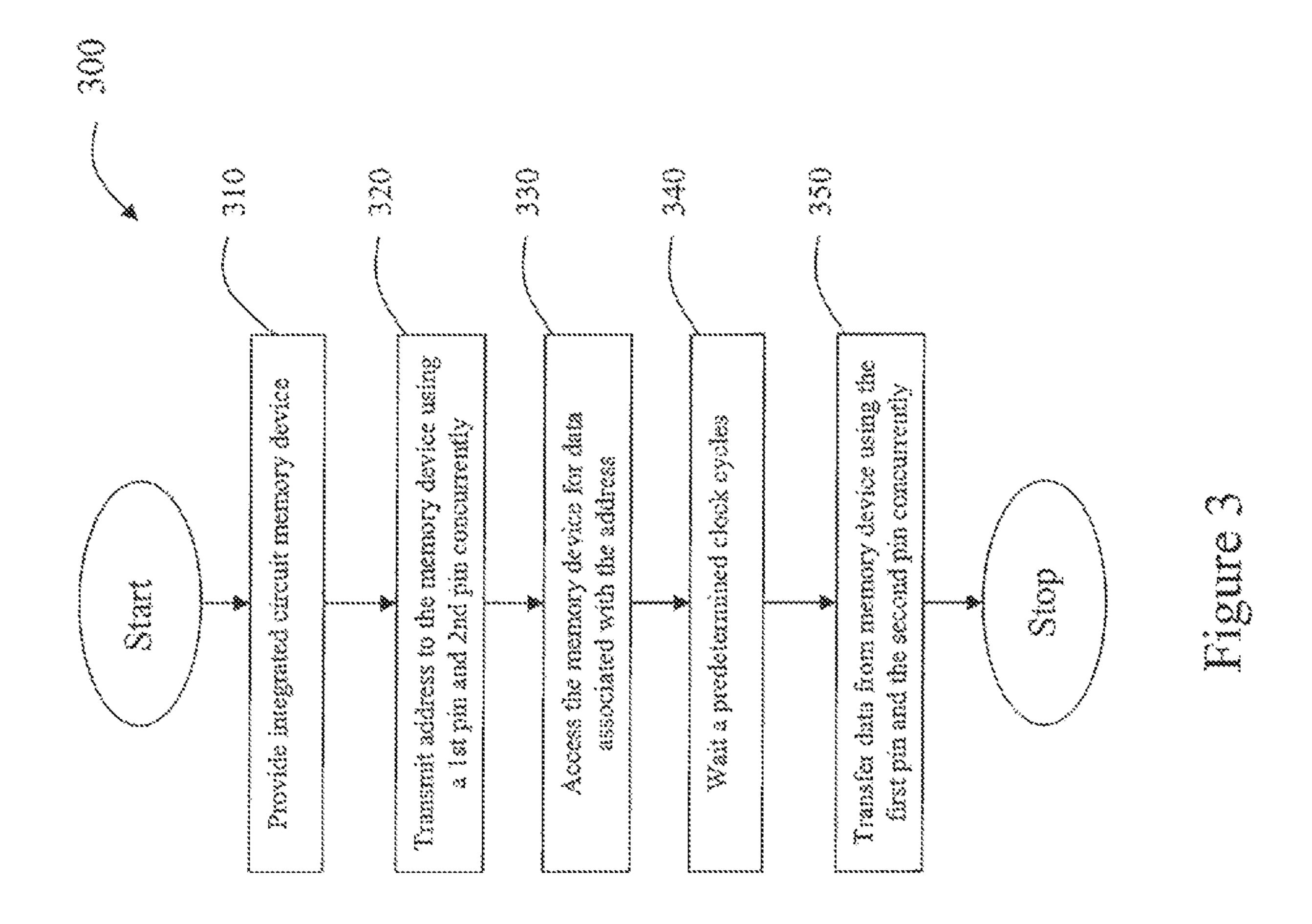

- FIG. 3 is a simplified flow chart for a dual I/O memory read method according to an embodiment of the present invention;

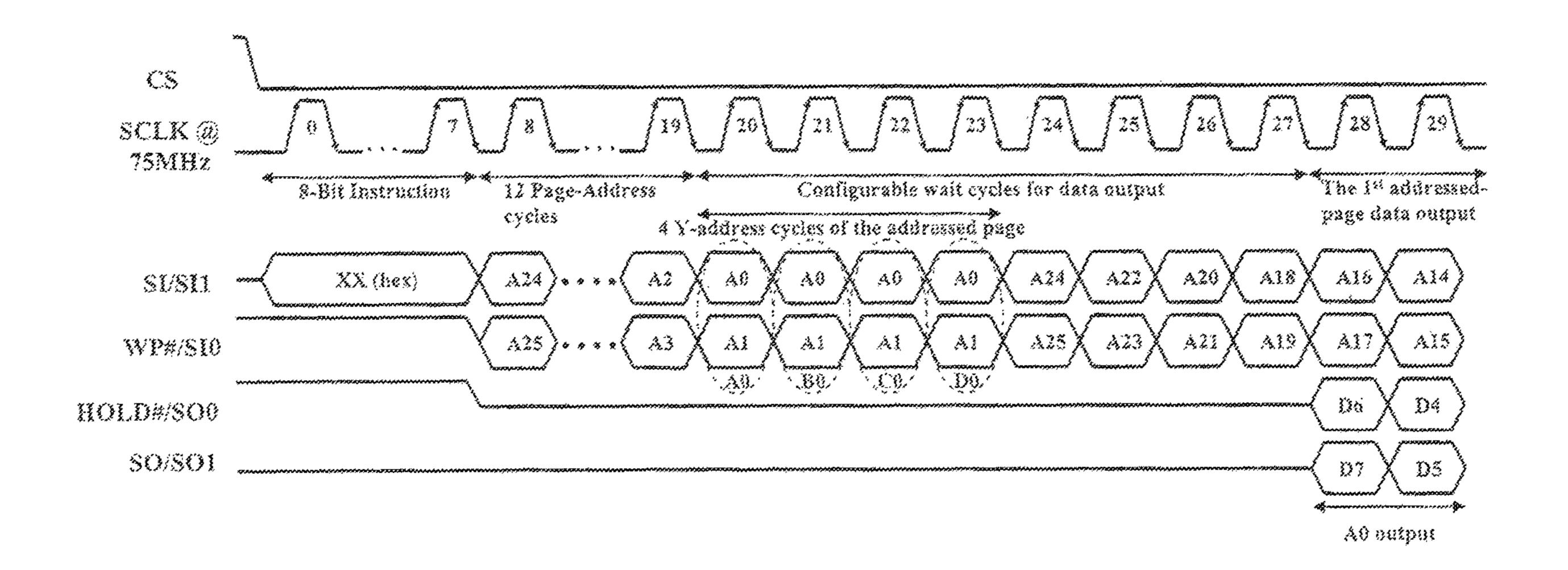

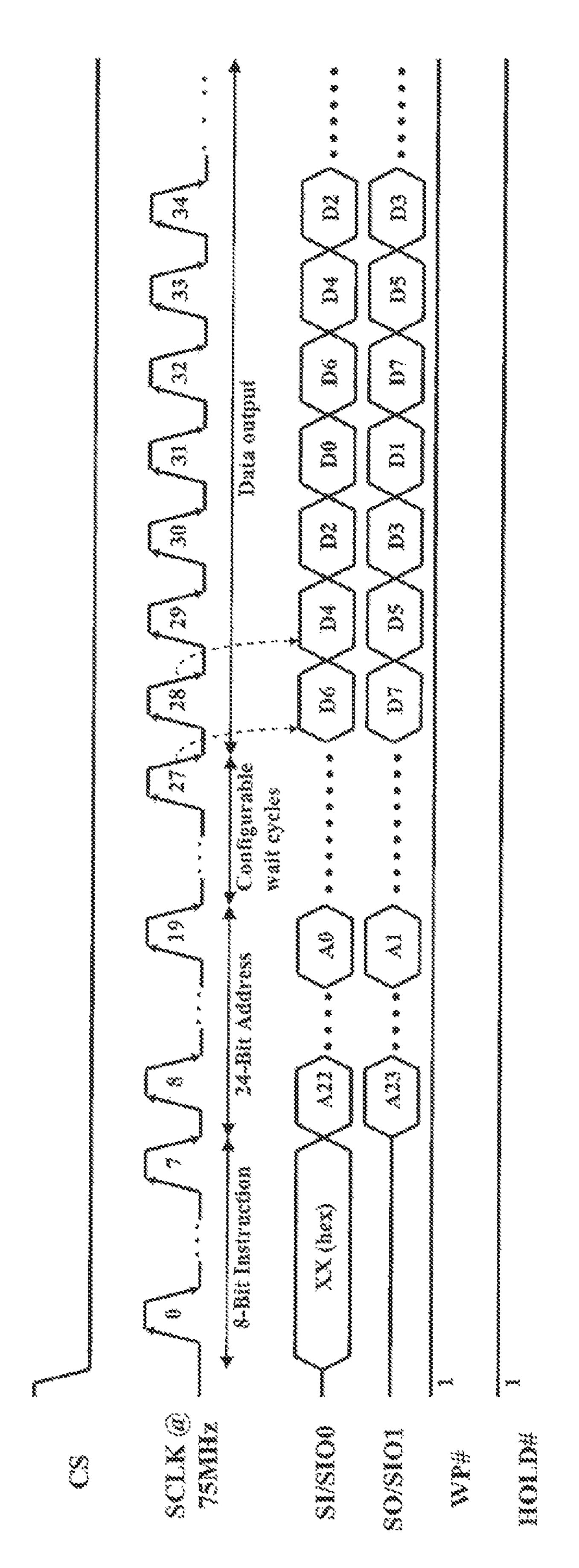

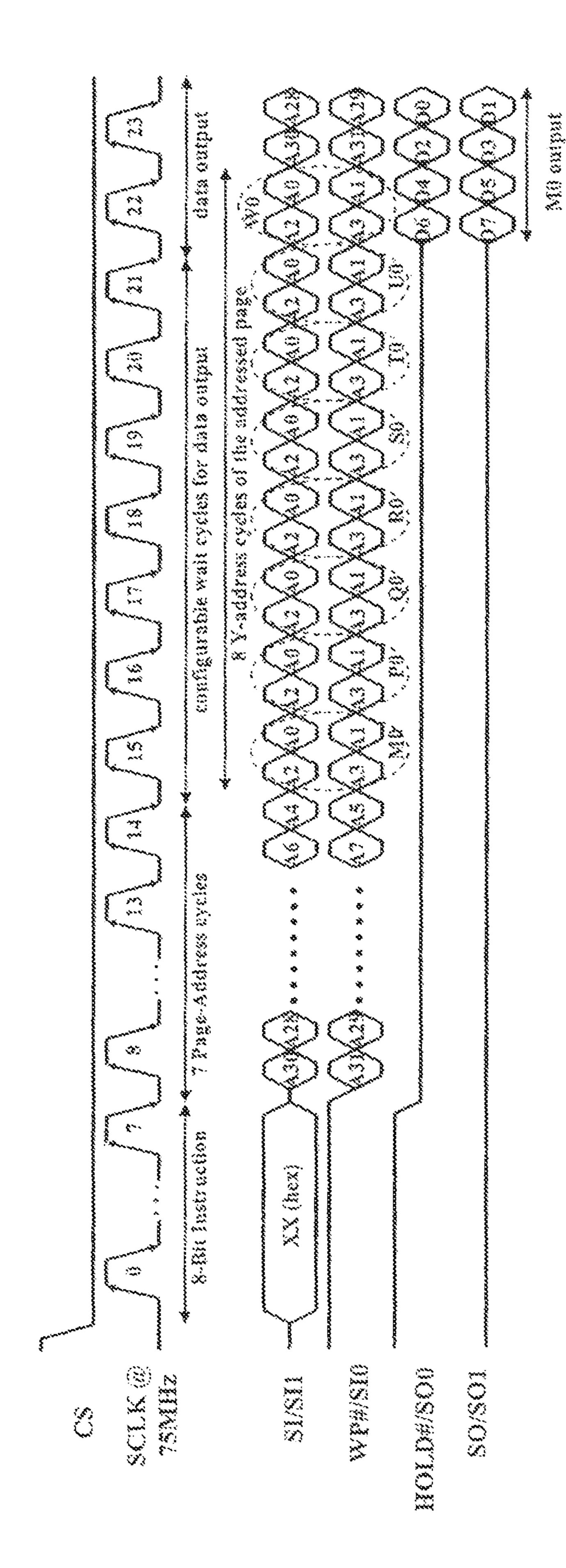

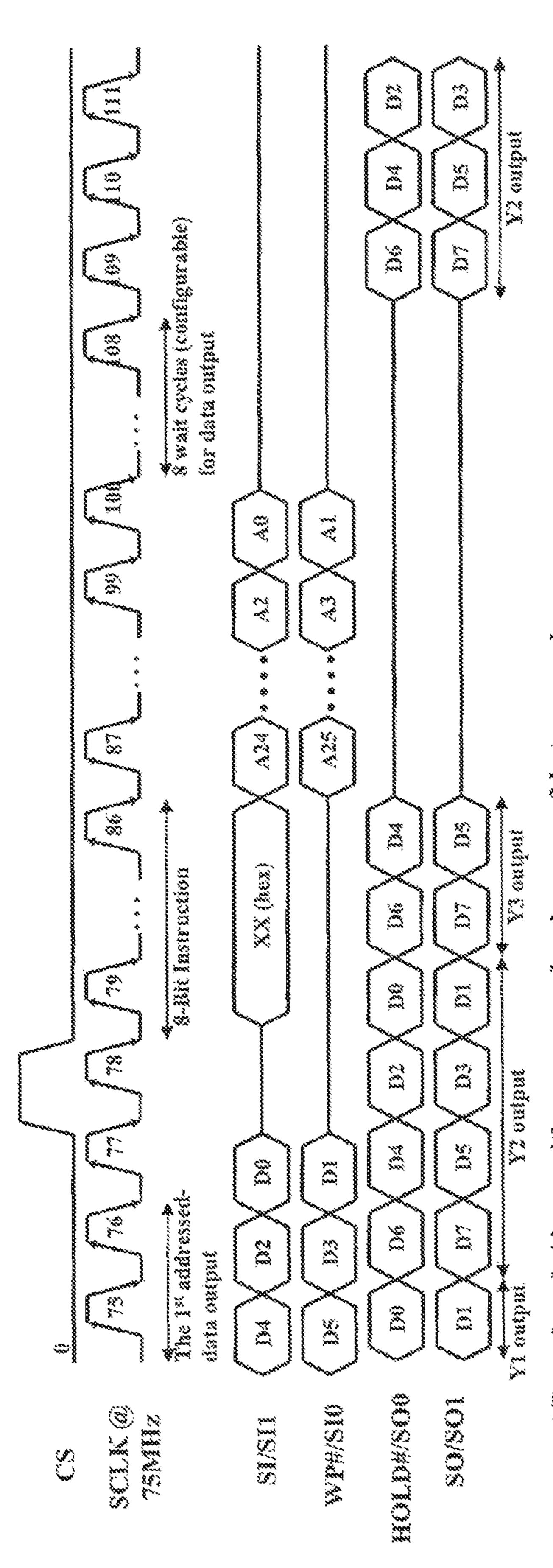

- FIG. 4 is a simplified timing diagram for a fast Dual I/O SARSDR Read method according to an embodiment of the present invention;

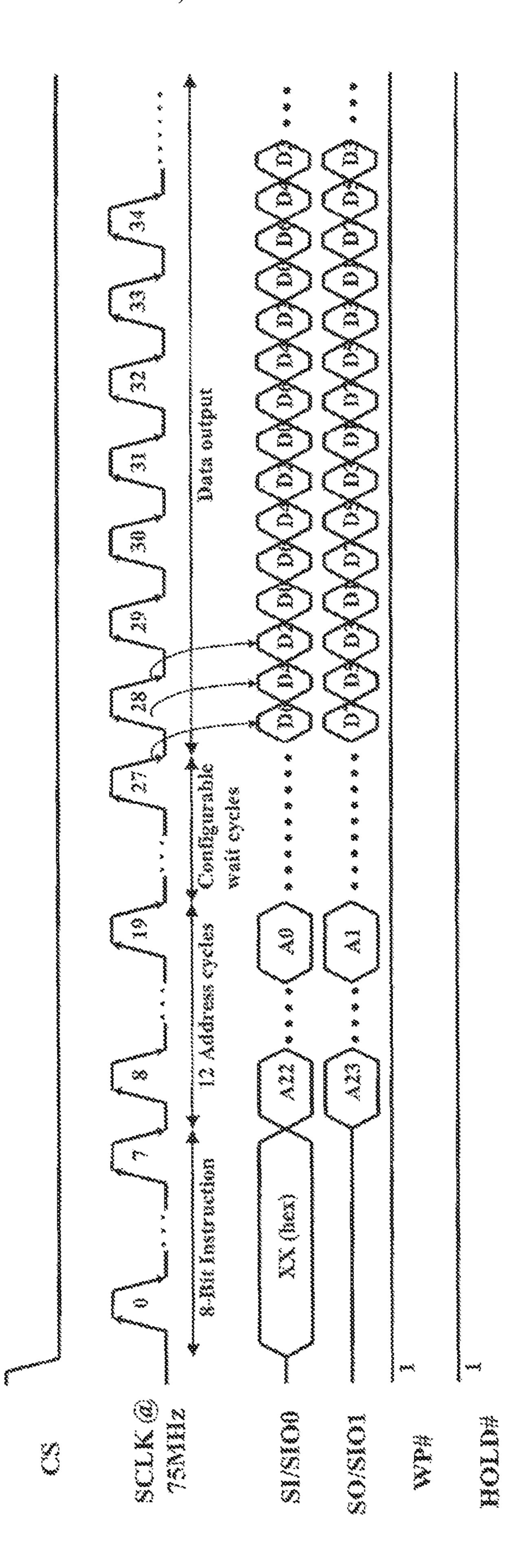

- FIG. **5** is a simplified timing diagram for a fast Dual I/O SARDDR Read method according to an embodiment of the 45 present invention;

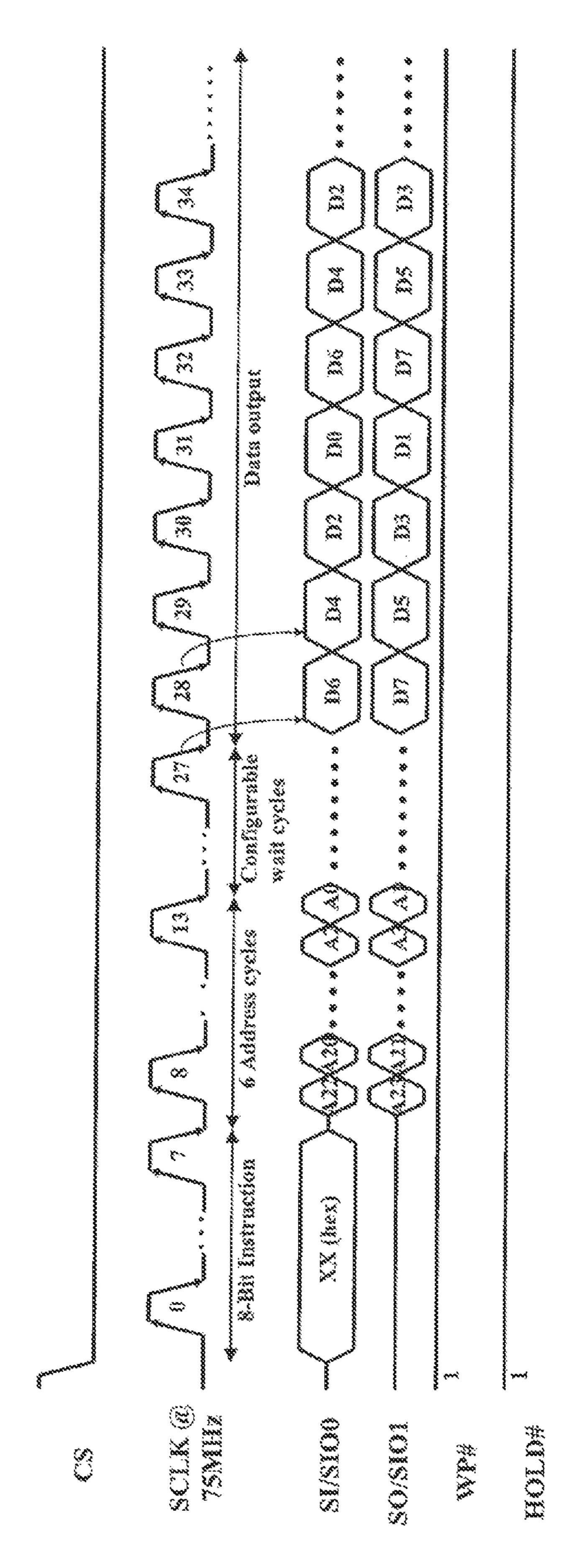

- FIG. 6 is a simplified timing diagram for a fast Dual I/O DARSDR Read according to an embodiment of the present invention;

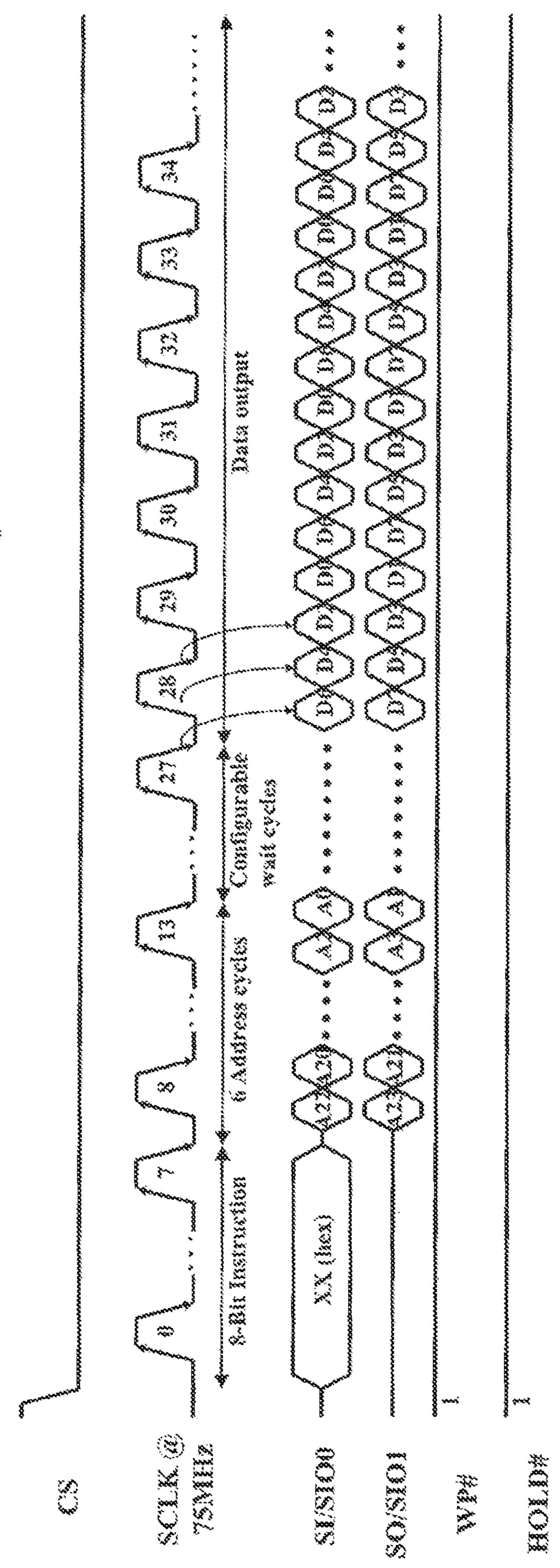

- FIG. 7 is a simplified timing diagram for a fast Dual I/O 50 DARDDR Read according to an embodiment of the present invention;

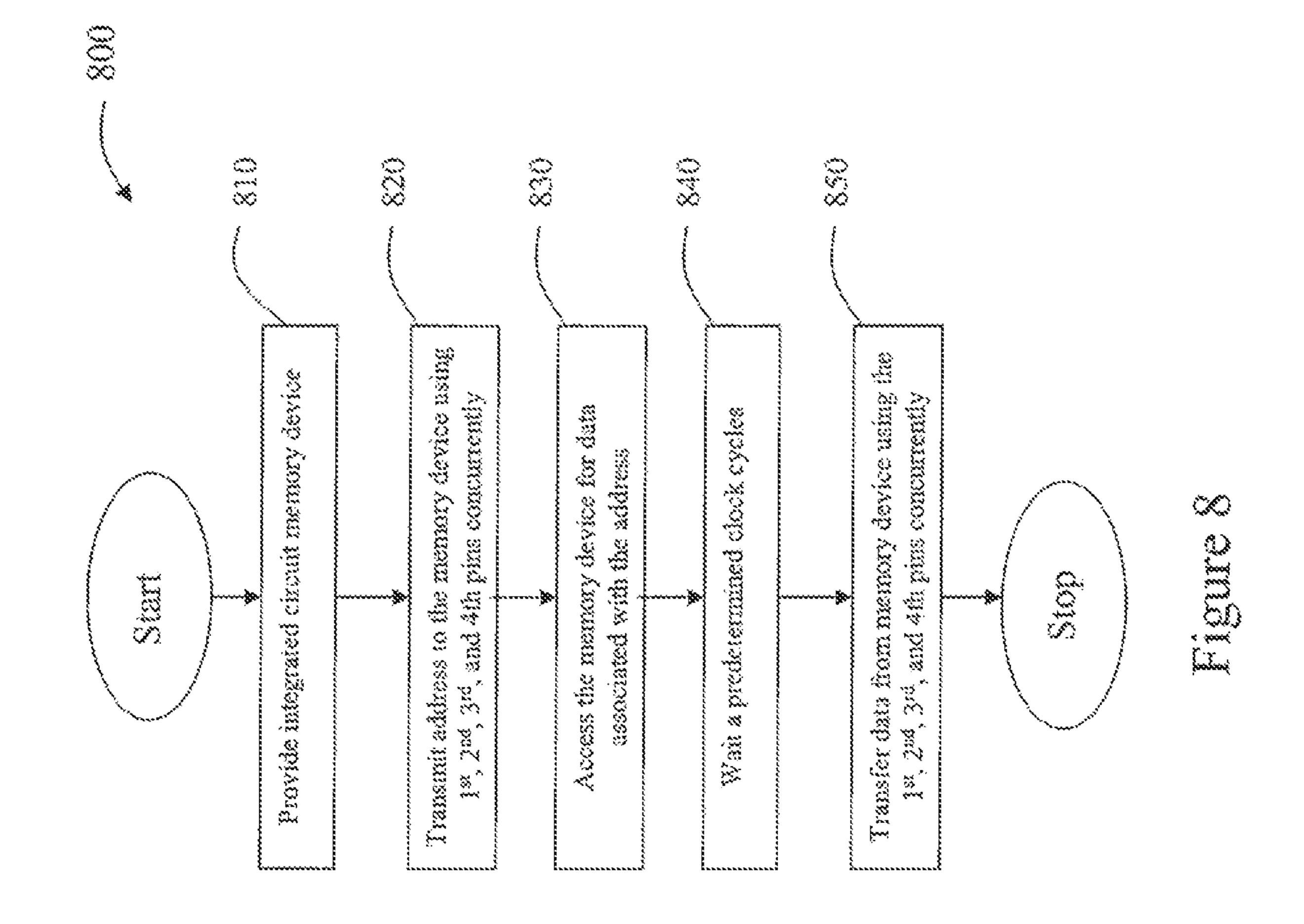

- FIG. 8 is a simplified flow chart for a quadruple I/O memory read method according to an embodiment of the present invention;

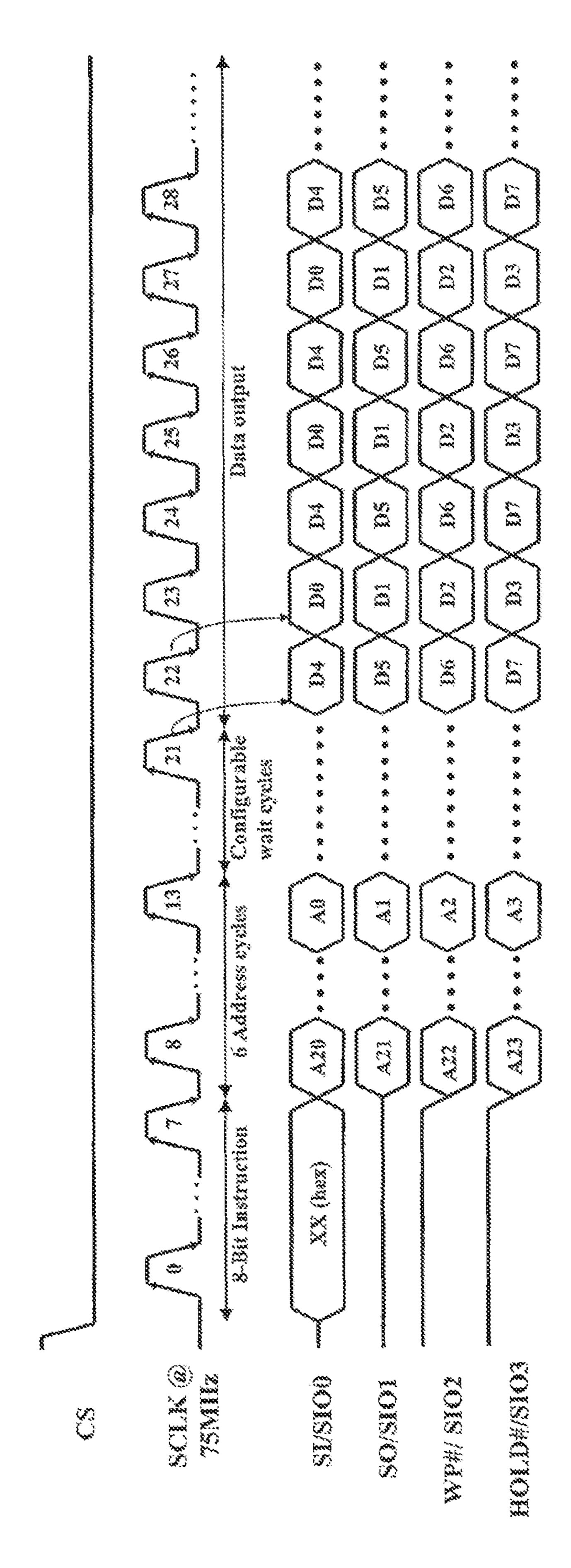

- FIG. 9 is a simplified timing diagram for a fast Quadruple I/O SARSDR Read method according to an embodiment of the present invention;

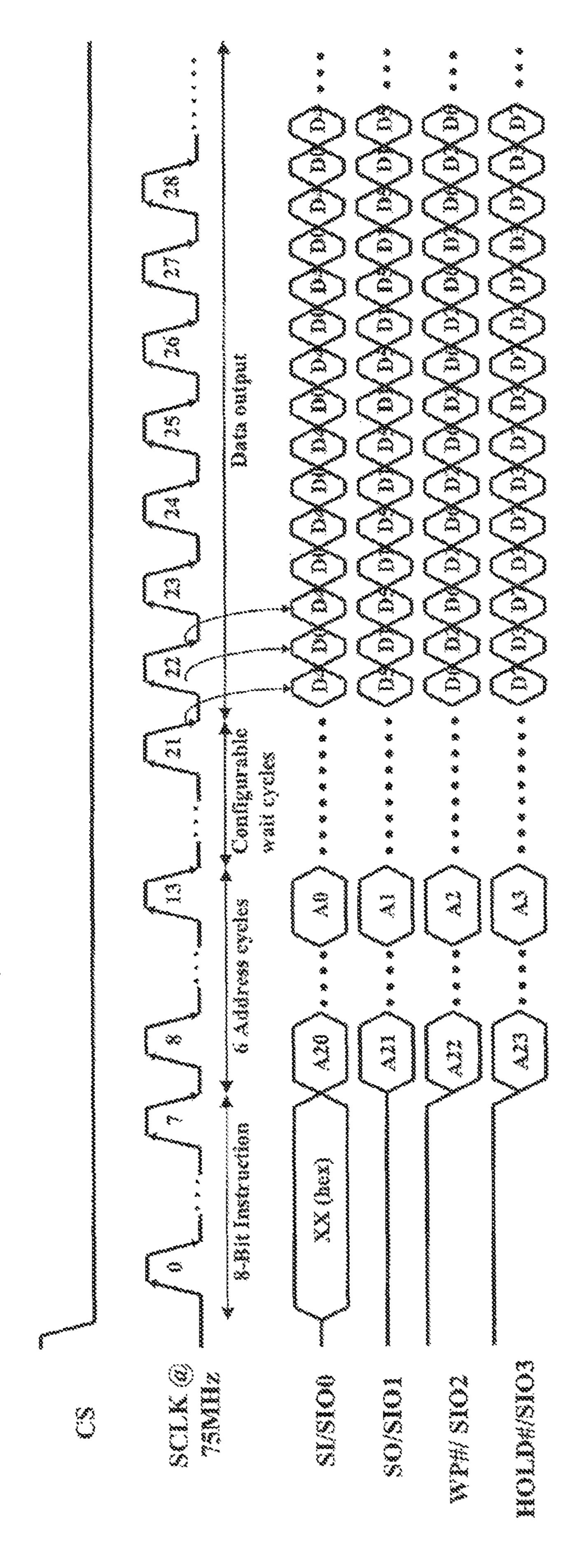

- FIG. 10 is a simplified timing diagram for a fast Quadruple I/O SARDDR Read method according to an embodi- 60 ment of the present invention;

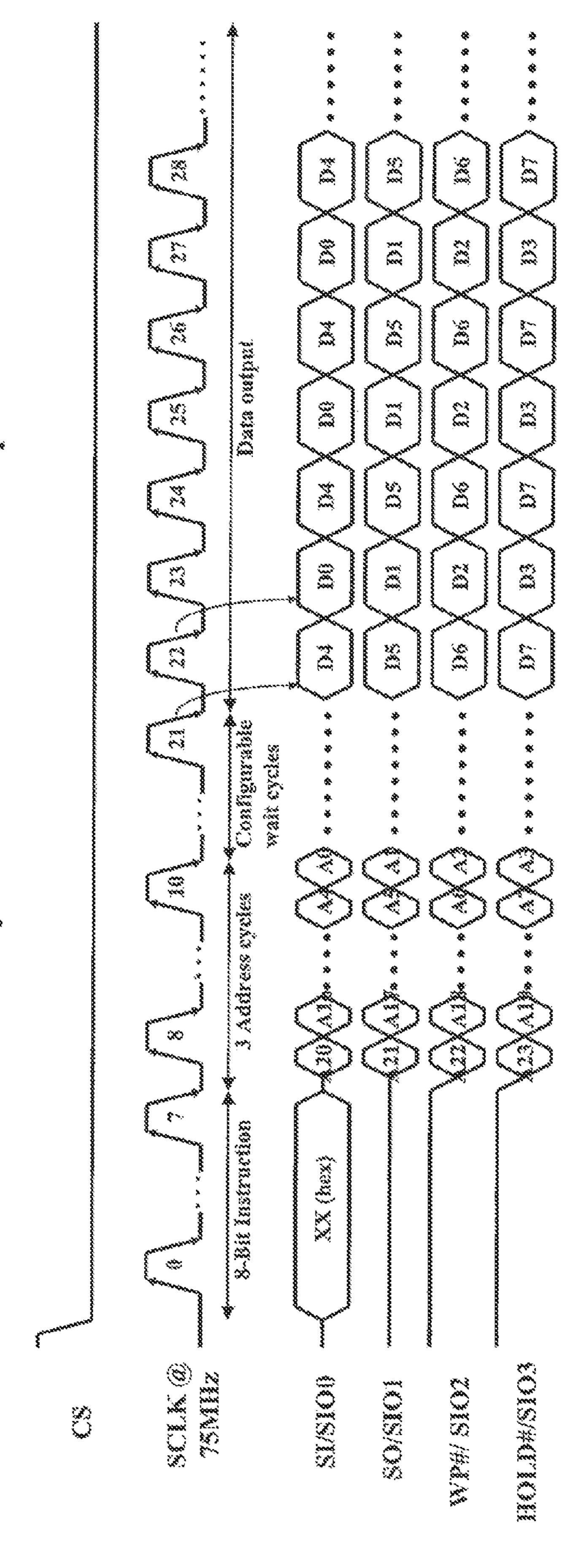

- FIG. 11 is a simplified timing diagram for a fast Quadruple I/O DARSDR Read method according to an embodiment of the present invention;

- FIG. 12 is a simplified timing diagram for a fast Qua- 65 druple I/O DARDDR Read method according to an embodiment of the present invention;

8

- FIG. 13 is a simplified flow chart for a dual I/O memory page read method according to an embodiment of the present invention;

- FIGS. 14A and 14B are simplified timing diagrams for a fast Dual I/O SARSDR Page Read method according to an embodiment of the present invention;

- FIGS. 15A and 15B are simplified timing diagrams for a fast Dual I/O DARDDR Page Read method according to an embodiment of the present invention;

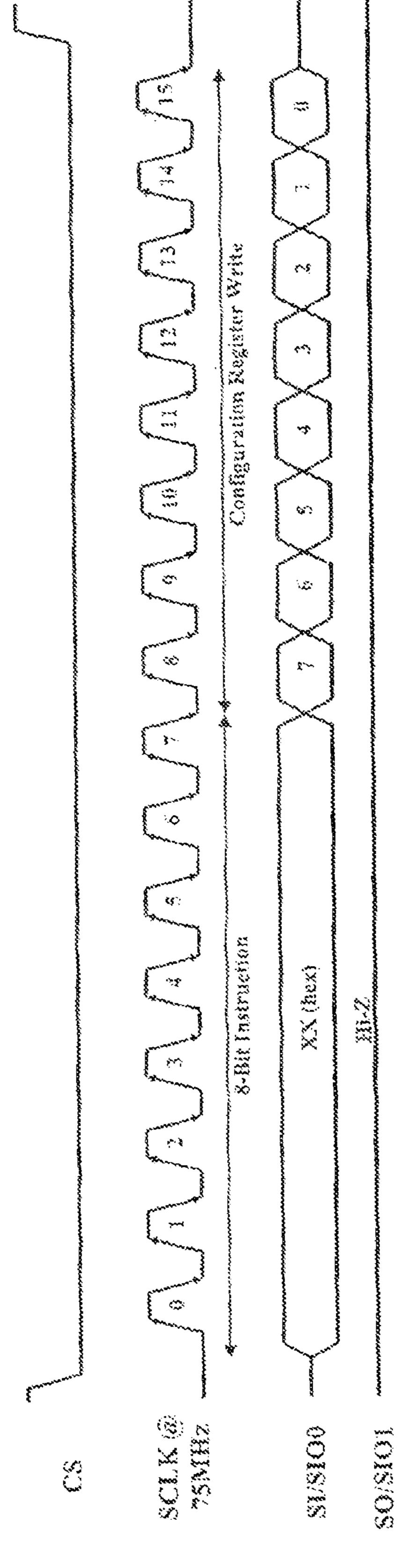

- FIG. 16A is a simplified timing diagram of Configuration Register write method according to an embodiment of the present invention;

- FIG. 16B is a simplified diagram of a configuration register bit assignment according to an embodiment of the

- FIG. 17 is a simplified flow chart for a method for dual I/O memory burst read with simultaneous read/write (SRW) according to an embodiment of the present invention;

- FIGS. 18A, 18B, 18C and 18D are simplified timing diagrams of a method for fast Dual I/O Burst Read with SRW according to an embodiment of the present invention;

- FIG. 19A is a simplified pin out diagram for an integrated circuit which includes a serial peripheral interface I/O according to an embodiment of the present invention; and

- FIG. 19B is a simplified list of pin assignments for an integrated circuit which includes a serial peripheral interface I/O according to an embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

The present invention is directed to integrated circuits and their operation. More particularly, this invention provides a method and system for serial peripheral interface protocol FIG. 2 is a simplified block diagram of an integrated 35 for integrated circuits which include memory devices. Merely by way of example, the invention has been applied to serial flash memory devices for improved data transfer rate and for enabling simultaneously read/write operations. But it would be recognized that the invention has a much 40 broader range of applicability. For example, the invention can be applied to other stand-alone or embedded memory devices such as DRAM, SRAM, parallel flash, or other non-volatile memories.

> Depending upon the embodiment, the present invention includes various features, which may be used. These features include the following:

- A high performance serial peripheral interface that has a higher data transmission rate;

- Random read operation by using the conventional serial peripheral interface pin-out;

- Simultaneously read/write operation by using the conventional serial peripheral interface pin-out;

- The address input and data output are simultaneously in operation in order to achieve higher data throughput and random read operation in the conventional serial peripheral interface pin-out;

- Configurable wait cycles are provided for different applications;

- Several read methods are defined to achieve high performance read. For example, the random read can be single bit random read, page mode random read or burst mode random read operation; and

- These high performance methods are applicable to low pin count application to flash memories, DRAM, SRAM, and other non-volatile memories.

As shown, the above features may be in one or more of the embodiments to follow. These features are merely

examples, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize many variations, modifications, and alternatives.

FIG. 1A is a simplified pin out diagram for an integrated circuit which includes a serial peripheral interface I/O 5 according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. As shown, according to a specific embodiment 10 of the invention, integrated circuit device 100 includes pin #1 CS# (chip select), pin #2 SO (serial data out), pin #3 WP# (write protect), pin #4 GND (ground), pin #5 DI (serial data in), pin #6 SCLK (clock), pin #7 HOLD# (hold), and pin #8 VCC (power supply). In certain embodiments, pin #2 is 15 designated at SO/SIO1, pin #3 is designated as WP#/SIO2, pin 5 is designated as SI/SIO0, and pin #7 is designated as HOLD#/SIO3. In other embodiments, pin #2 is designated at SO/SO1, pin #3 is designated as WP#/SI0, pin 5 is designated as SI/SI1, and pin #7 is designated as HOLD#/SO0. In 20 the discussion below, these I/O pins are used in address and data transfers in various methods according to embodiments of the present invention.

FIG. 1B is a simplified view diagram of read mode command set according to an embodiment of the present <sup>25</sup> invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. As shown, the read mode command set includes the commands listed below in Table <sup>30</sup> I according to a specific embodiment of the invention.

TABLE I

| Read                           | 03 Hex |

|--------------------------------|--------|

| Fast Read                      | 0B Hex |

| Dual I/O read                  | BB Hex |

| Quad I/O read                  | 32 Hex |

| Dual I/O DDR read              | BA hex |

| Quad I/O DDR read              | 33 Hex |

| Dual I/O page read             | BC Hex |

| Dual I/O DDR page read         | BD Hex |

| Dual I/O read with SRW         | AE Hex |

| Dual I/O program with SRW      | CE Hex |

| Dual I/O sector erase with SRW | CD Hex |

| Configuration register write   | D1 Hex |

|                                |        |

It is noted that SRW is used here to mean simultaneous read and write. Of course, there can be other variations, modifications, and alternatives. Various features will be discussed below.

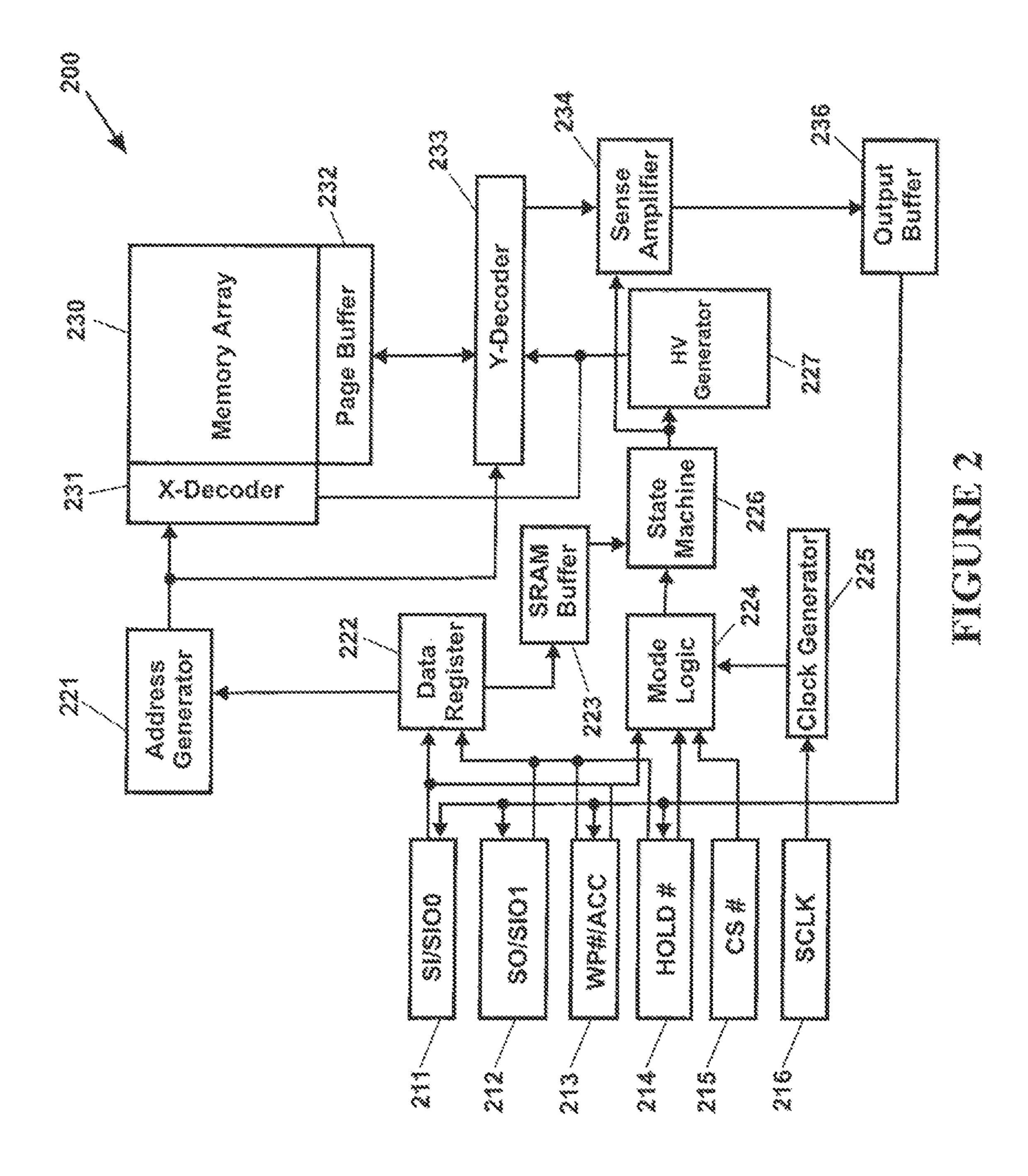

FIG. 2 is a simplified block diagram of an integrated 50 circuit which includes a memory device according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. 55 As shown, integrated circuit device 200 includes several input blocks coupled to respective input/output pins. In a specific embodiment, the integrated circuit device includes I/O pins consistent with the serial peripheral interface pin assignment. For example, device 200 may include I/O pins 60 coupled to the following input/output circuit blocks. SI/SIO0 pin coupled to SI/SIO0 block 211;

SO/SIO1 pin coupled to SO/SIO1 block 212, WP#/ACC pin coupled to WP#/ACC block 213, HOLD# pin coupled to HOLD# block 214, CS# pin coupled to CS# block 215, and SCLK pin coupled to SCLK block 216.

**10**

As shown in FIG. 2, device 200 also includes the following circuit blocks associated with the memory array 230.

Memory Array 230,

X-Decoder 231,

Page Buffer 232,

Y-decoder 233,

Sense Amplifier 234, and

Output Buffer 236.

Device 200 also includes the following control and support circuit blocks.

Address Generator 221,

Data Register 222,

SRAM Buffer 223,

Mode Logic 224,

Clock Generator 225,

State Machine 226, and

HV Generator 227.

Merely as examples, certain operations of device 200 are now discussed according to a specific embodiment of the present invention. System clock signal SCLK on input terminal 216 is coupled to Clock Generator 225, which in turn is coupled to Mode Logic 224. Mode Logic 224 is operably coupled to receive a chip select signal CS# on CS# input terminal 215. Commands or instructions may be input through input SI/SIO0 block 211 and then transferred to Data Register 222 and Mode Logic 224. Mode Logic 224, in combination with State Machine 226, interprets and executes the command such as a read, erase, or program operation. In an embodiment, Mode Logic 224 also receives a signal from WP#/ACC block 213 to perform a write protect function, and a signal from HOLD# block 214 to keep a clock signal from entering the State Machine 226.

According to a specific embodiment, data may be input through SI/SIO0 block 211, SO/SIO1 block 212, WP#/ACC 35 block 213, and HOLD# block 214, which are coupled to Data Register 222. Data Register 222 is coupled to SRAM Buffer 223 for temporary storage. Data may be output through SI/SIO0 block 211, SO/SIO1 block 212, WP#/ACC block 213, and HOLD# block 214, which are coupled the 40 Output Buffer **236**. An address corresponding to a location in memory array 230 may be supplied from Data Register 222 to Address Generator 221. The address is then decoded by X-decoder 231 and Y-decoder 233. Page Buffer 232 is coupled to memory array 230 to provide temporary storage 45 for memory operation. In a read operation, the data is transferred from memory array 230 through Sense Amplifier 234 to the Output Buffer 236. For write operation, data is transferred from Data Register to Page Buffer 232 and then written into Memory Array 230. For high voltage operation, e.g., for a write operation, High Voltage Generator 227 is activated.

Although the above has been shown using a selected group of components for the integrated circuit device, there can be many alternatives, modifications, and variations. For example, some of the components may be expanded and/or combined. Other components may be inserted to those noted above. Depending upon the embodiment, the arrangement of components may be interchanged with others replaced. Further details of these components are found throughout the present specification and more particularly below.

FIG. 3 is a simplified flow chart for a dual I/O memory read method according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. As shown, the method for the dual I/O memory read can be briefly outlined below.

- 1. (Process 310) Provide an integrated circuit memory device;

- 2. (Process 320) Transmit a read address to the memory device using a first pin and a second pin concurrently;

- 3. (Process **330**) Access the memory device for data asso- 5 ciated with the address;

- 4. (Process 340) Wait a predetermined number of clock cycles; and

- 5. (Process **350**) Transfer the data from the memory device using the first pin and the second pin concurrently.

The above sequence of processes provides a dual I/O read method for a memory device according to an embodiment of the present invention. As shown, the method uses a combination of processes including a way of transmitting address information using two pins concurrently, and transferring 15 data using two pins concurrently. Other alternatives can also be provided where processes are added, one or more processes are removed, or one or more processes are provided in a different sequence without departing from the scope of the claims herein. Further details of the present method can 20 be found throughout the present specification and more particularly below with reference to FIGS. 4-7.

FIG. 4 is a simplified timing diagram for a fast Dual I/O SARSDR Read method according to an embodiment of the present invention. This diagram is merely an example, 25 which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. FIG. 4 includes timing diagrams for a fast dual I/O SARSDR read method for single address rate and single data rate read operation for 30 an integrated circuit according to a specific embodiment of the invention. In this specific example, a clock rate of 75 MHz is used. In other embodiments, the clock rate may vary depending on the application. As shown, the CS# (chip select) signal is set to low, and an 8-bit instruction, designated as XX(hex), is transferred using the SI/SIO0 pin. In a specific embodiment, a 24-bit address A0, . . . , A23 is transferred using pin SI/SIO0 and pin SO/SIO1 simultaneously. In an embodiment, a number of configurable wait cycles are provided. The number of wait cycles is specified 40 in a configuration register and can be selected according to the application. In FIG. 4, the configurable wait cycles are shown in clock cycles 20-27. In an embodiment, the memory device obtains data bits associated with the address. In an embodiment, data bits, for example, D0, . . . , D7 are 45 transferred using pins SI/SIO0 and SO/SIO1 simultaneously at falling edges of the clock signal SCLK. For example, at the falling edge of clock pulse 27, data bit D6 is transferred at pin SI/SIO0 and data bit D7 is transferred at pin SO/SIO1 simultaneously. In a particular embodiment, the WP# pin 50 and HOLD# pin are held at "1" as shown in FIG. 4. Of course, there can be other variations, modifications, and alternatives. For example, the address and data bits can be transferred on either a rising or falling edge of the clock.

Many benefits can be achieved by the embodiment shown in FIG. 4. For example, the transfer rate is doubled for both the address and the data. Referring to FIG. 4, after the chip select (CS#) signal is issued, the 24-bit address are transmitted into the memory device using two pins, SI/SIO0 and pin SO/SIO1, concurrently, in clock cycles 8-19. In this 60 specific example, 12 clock cycles are used to transfer 24 bits of address information. A number of configurable wait cycles are elapsed, which allow the memory to process the command and prepare for receiving the input data. Data are then transmitted into the memory using two pins, SI/SIO0 65 and pin SO/SIO1, concurrently. In contrast, conventional serial peripheral interface devices do not use multiple bits to

12

transmit both address and data, and 24 clock cycles are needed to transfer a 24-bit address.

In an embodiment, a configurable wait period is provided after the transfer of address information. As an example, a wait cycle is shown as clock cycles 20-27 in FIG. 4. In a specific embodiment, the configurable wait period is provided in a configuration register. For example, in FIGS. 16A and 16B, bits 4-7 of the configuration register are used to designate the number of clock cycles for the wait cycles. In the specific embodiment shown in FIG. 16B, dummy cycles range from 1-8 clock cycles are provides. Depending on the embodiments, bits 4-7 of the configuration register can be used to specify 16 different clock cycles for the wait cycles or dummy cycles. Of course, other variations, modifications, and alternatives can be envisioned b one skilled in the art in view of this disclosure.

FIG. 5 is a simplified timing diagram for a fast Dual I/O SARDDR Read method according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. As shown, FIG. 5 includes timing diagrams for a fast dual I/O SARDDR read method for single address rate and double data rate read operation for an integrated circuit device according to a specific embodiment of the invention. In this specific example, a clock rate of 75 MHz is used. In other embodiments, the clock rate may vary depending on the application. As shown, the CS# (chip select) signal is set to low, and an 8-bit instruction, designated as XX(hex), is transferred using the SI/SIO0 pin. In a specific embodiment, a 24-bit address A0, . . . , A23 is transferred using pin SI/SIO0 and pin SO/SIO1 simultaneously. In an embodiment, a number of configurable wait cycles are provided. The number of wait cycles is specified in a configuration register and can be selected according to the application. In FIG. 5, the configurable wait cycles are shown in clock cycles 20-27. In an embodiment, the memory device obtains data bits associated with the address. In an embodiment, data bits are transferred using pins SI/SIO0 and SO/SIO1 simultaneously at falling and rising edges of the clock signal SCLK. For example, at the falling edge of clock pulse 27, data bit D6 is transferred at pin SI/SIO0 and data bit D7 is transferred at pin SO/SIO1. At the rising edge of clock pulse 28, data bit D4 is transferred at pin SI/SIO0 and data bit D5 is transferred at pin SO/SIO1. At the falling edge of clock pulse 28, data bit D2 is transferred at pin SI/SIO0 and data bit D3 is transferred at pin SO/SIO1. Of course, there can be other variations, modifications, and alternatives.

FIG. 6 is a simplified timing diagram for a fast Dual I/O DARSDR Read according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. As shown, FIG. 6 includes timing diagrams for a fast dual I/O DARSDR read method for double address rate and single data rate read operation for a serial peripheral interface memory device according to a specific embodiment of the invention. In this specific example, a clock rate of 75 MHz is used. In other embodiments, the clock rate may vary depending on the application. As shown, the CS# (chip select) signal is set to low, and an 8-bit instruction, designated as XX(hex), is transferred using the SI/SIO0 pin. In a specific embodiment, a 24-bit address A0, . . . , A23 is transferred using pin SI/SIO0 and pin SO/SIO1 simultaneously, using both rising and falling edges of clock signal SCLK. The double address rate operation

allows the address information to be transferred at a fast rate. For example, a 24-bit address information can be transferred in 6 clock cycles using both the rising edge and falling edge of the clock signal in the embodiment as shown in FIG. 6, whereas using only the rising edge or only the falling edge of the clock signal, the 24-bit address information is transferred in 24 clock cycles. Thus the number of clock cycles needed for address transfer can be reduced from 24 to 6, a reduction of 75%.

In an embodiment, a number of configurable wait cycles 10 are provided. The number of wait cycles is specified in a configuration register and can be selected according to the application. In FIG. 6, the configurable wait cycles are shown in clock cycles 14-27. In an embodiment, the memory device obtains data bits associated with the address. 15 In an embodiment, the memory device obtains data bits associated with the address. In an embodiment, data bits, for example, D0, . . . , D7 are transferred using pins SI/SIO0 and SO/SIO1 simultaneously at falling edges of the clock signal SCLK. For example, at the falling edge of clock pulse 27, 20 data bit D6 is transferred at pin SI/SIO0 and data bit D7 is transferred at pin SO/SIO1. In a particular embodiment, the WP# pin and HOLD# pin are held at "1" as shown in FIG. **6**. Of course, there can be other variations, modifications, and alternatives.

FIG. 7 is a simplified timing diagram for a fast Dual I/O DARDDR Read according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, 30 modifications, and alternatives. As shown, FIG. 7 includes timing diagrams for a fast dual I/O DARSDR read method for double address rate and double data rate read operation for a serial peripheral interface memory device according to a specific embodiment of the invention. In this specific 35 example, a clock rate of 75 MHz is used. In other embodiments, the clock rate may vary depending on the application. As shown, the CS# (chip select) signal is set to low, and an 8-bit instruction, designated as XX(hex), is transferred using the SI/SIO0 pin. In a specific embodiment, a 24-bit address 40 A0, . . . , A23 is transferred using pin SI/SIO0 and pin SO/SIO1 simultaneously, using both rising and falling edges of clock signal SCLK. In an embodiment, the memory device obtains data bits associated with the address. In an embodiment, data bits are transferred using pins SI/SIO0 45 and SO/SIO1 simultaneously at falling and rising edges of the clock signal SCLK. For example, at the falling edge of clock pulse 27, data bit D6 is transferred at pin SI/SIO0 and data bit D7 is transferred at pin SO/SIO1. At the rising edge of clock pulse 22, data bit D4 is transferred at pin SI/SIO0 50 and data bit D5 is transferred at pin SO/SIO1. At the falling edge of clock pulse 28, data bit D2 is transferred at pin SI/SIO0 and data bit D3 is transferred at pin SO/SIO1. In an embodiment, a number of configurable wait cycles are provided. The number of wait cycles is specified in a 55 configuration register and can be selected according to the application. In FIG. 7, the configurable wait cycles are shown in clock cycles 14-27. Of course, there can be other variations, modifications, and alternatives.

memory read method according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. As shown, the 65 method for the quadruple I/O memory read can be briefly outlined below.

14

- 1. (Process 810) Provide an integrated circuit memory device;

- 2. (Process **820**) Transmit a read address to the memory device using a first pin, a second pin, a third pin, and a fourth pin concurrently;

- 3. (Process 830) Access data associated with the read address in the memory device;

- 4. (Process 840) Wait a predetermined number of clock cycles; and

- 5. (Process **850**) Transfer the data from the memory device using the first pin, the second pin, the third pin, and the fourth pin concurrently.

The above sequence of processes provides a quadruple I/O page read method for a memory device according to an embodiment of the present invention. As shown, the method uses a combination of processes including a way of transmitting address information using four pins concurrently, and transferring data using four pins concurrently. Other alternatives can also be provided where processes are added, one or more processes are removed, or one or more processes are provided in a different sequence without departing from the scope of the claims herein. Further details of the present method can be found throughout the present specification and more particularly below with reference to FIGS. 25 **9-12**.

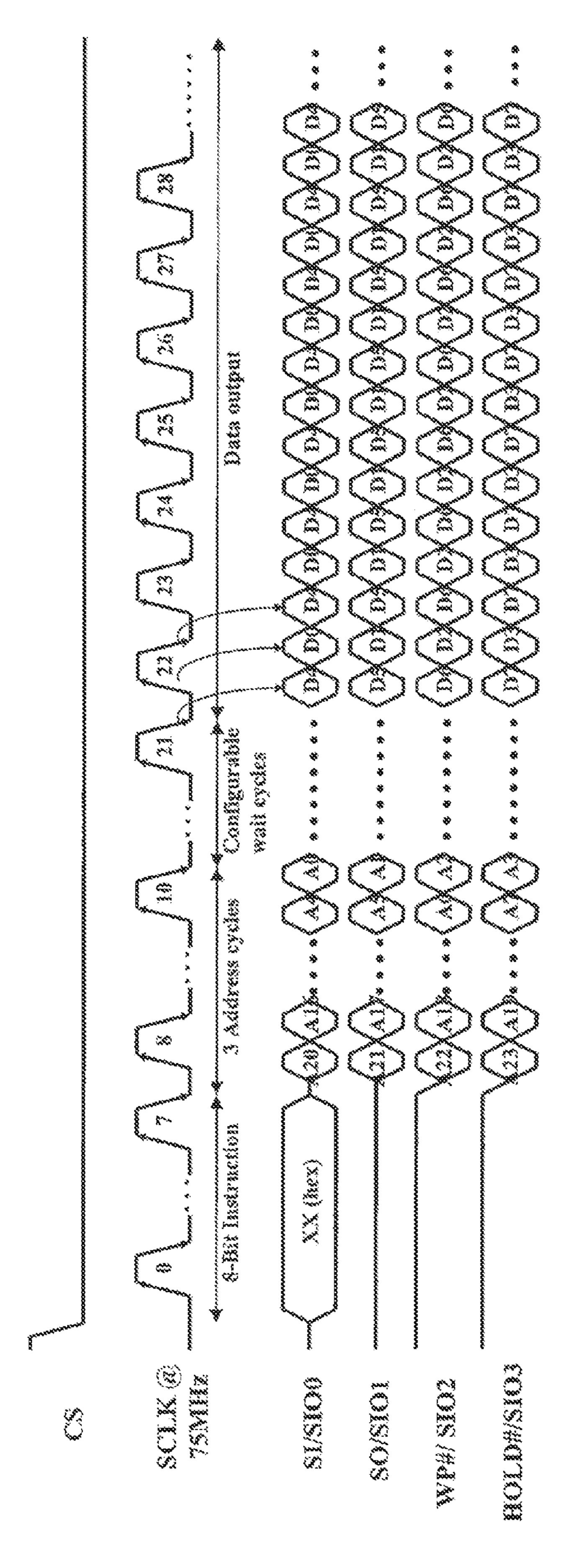

FIG. 9 is a simplified timing diagram for a fast Quadruple I/O SARSDR Read method according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. As shown, FIG. 9 includes timing diagrams for a fast quadruple I/O SARSDR read method for single address rate and single data rate read operation for a serial peripheral interface memory device according to a specific embodiment of the invention. In this specific example, a clock rate of 75 MHz is used. In other embodiments, the clock rate may vary depending on the application. As shown, the CS# (chip select) signal is set to low, and an 8-bit instruction, designated as XX(hex), is transferred using the SI/SIO0 pin. In a specific embodiment, a 24-bit address A0, . . . A23 is transferred using pin SI/SIO0, pin SO/SIO1, pin WP#/SIO2, and pin HOLD#/ SIO3 simultaneously, using rising edges of clock signal SCLK. For example, at the rising edge of clock pulse 8, address bit A20 is transferred at pin SI/SIO0, address bit A21 is transferred at pin SO/SIO1, address bit A22 is transferred at pin WP#/SIO2, and address bit A23 is transferred at pin HOLD#/SI03. In an embodiment, the memory device obtains data bits associated with the address. In an embodiment, data bits are transferred using pins SI/SIO0, SO/SIO1, WP#/SIO2, and HOLD#/SIO3 simultaneously at falling edges of the clock signal SCLK. For example, at the falling edge of clock pulse 21, data bit D4 is transferred at pin SI/SIO0, data bit D5 is transferred at pin SO/SIO1, data bit D6 is transferred at pin WP#/SIO2, and data bit D7 is transferred at pin HOLD#/SIO3. In a specific embodiment, a 24-bit address can be transferred in six address clock cycles. Similarly, a byte of data, for example D0-D7, can be transferred in two data clock cycles. In an embodiment, a FIG. 8 is a simplified flow chart for a quadruple I/O 60 number of configurable wait cycles are provided. The number of wait cycles is specified in a configuration register and can be selected according to the application. In FIG. 9, the configurable wait cycles are shown in clock cycles 14-21. Of course, there can be other variations, modifications, and alternatives.

FIG. 10 is a simplified timing diagram for a fast Quadruple I/O SARDDR Read method according to an embodi-