#### US00RE47816E

# (19) United States

## (12) Reissued Patent Rhie

US RE47,816 E (10) Patent Number:

(45) Date of Reissued Patent: Jan. 14, 2020

## THREE-DIMENSIONAL NONVOLATILE MEMORY CELL STRUCTURE WITH UPPER **BODY CONNECTION**

Applicant: Conversant Intellectual Property

**Management Inc.**, Ottawa (CA)

Inventor: **Hyoung Seub Rhie**, Ottawa (CA)

Assignee: Conversant Intellectual Property **Management Inc.**, Ottawa (CA)

Appl. No.: 15/869,245

Jan. 12, 2018 (22)Filed:

#### Related U.S. Patent Documents

Reissue of:

9,236,394 (64) Patent No.: Jan. 12, 2016 Issued: Appl. No.: 14/532,048 Filed: Nov. 4, 2014

U.S. Applications:

Provisional application No. 61/901,830, filed on Nov. 8, 2013.

Int. Cl. (51)

G11C 16/00 (2006.01)G11C 16/26 (2006.01)

(Continued)

U.S. Cl. (52)

CPC .... *H01L 27/11556* (2013.01); *G11C 16/0408* (2013.01); *G11C 16/0483* (2013.01);

(Continued)

Field of Classification Search (58)

> 27/10864; H01L 27/11551; H01L 27/11556; H01L 27/11565; H01L 27/1157; H01L 27/11578; H01L

27/11582; H01L 21/28282; H01L 27/11573; G06F 21/79; G11C 7/062; G11C 11/5628; G11C 16/02; (Continued)

#### **References Cited** (56)

#### U.S. PATENT DOCUMENTS

| 5,907,170 A  | * 5/1999  | Forbes H01L 27/10864 |  |  |  |  |  |  |

|--------------|-----------|----------------------|--|--|--|--|--|--|

|              |           | 257/296              |  |  |  |  |  |  |

| 6,643,159 B2 | * 11/2003 | Fricke G11C 5/025    |  |  |  |  |  |  |

|              |           | 257/E21.614          |  |  |  |  |  |  |

| (Continued)  |           |                      |  |  |  |  |  |  |

OTHER PUBLICATIONS

Y. Fukuzumi et al., Optimal Integration and Characteristics of Vertical Array Devices for Ultra-High Density, Bit-Cost Scalable Flash Memory, IEEE International Electron Devices Meeting, 2007, Dec. 10-12, 2007, pp. 449-452.

(Continued)

Primary Examiner — Christopher E. Lee (74) Attorney, Agent, or Firm — Conversant IP Management Corp.

#### **ABSTRACT** (57)

A three-dimensional integrated circuit non-volatile memory array includes a memory array of vertical channel NAND flash strings connected between a substrate source line and upper layer connection lines which each include n-type drain regions and p-type body line contact regions alternately disposed on each side of undoped or lightly doped string body regions so that each NAND flash string includes a vertical string body portion connected to a horizontal string body portion formed from the string body regions of the upper body connection lines.

## 26 Claims, 14 Drawing Sheets

100 🚤 BITLINES<0:M> SOURCE LINE 102 -SUBSTRATE 101 103D/104D 103C/104C Y DIRECTION X DIRECTION

| (51) | Int. Cl.                                |                   |                                      | 2011/0147824      | A1*        | 6/2011                      | Son                                    | G11C 16/0483             |

|------|-----------------------------------------|-------------------|--------------------------------------|-------------------|------------|-----------------------------|----------------------------------------|--------------------------|

|      | H01L 29/79                              | 02                | (2006.01)                            | 2011/0157090      | A 1 *      | 6/2011                      | Transfer                               | 257/324<br>C11C 16/0482  |

|      | H01L 27/11                              | 15                | (2017.01)                            | 2011/0157989      | Al         | 0/2011                      | Iwata                                  | 365/185.17               |

|      | G11C 16/04                              | į.                | (2006.01)                            | 2011/0216597      | A1*        | 9/2011                      | Higashi H                              |                          |

|      | G11C 16/14                              | į.                | (2006.01)                            |                   |            |                             | C                                      | 365/185.18               |

|      | H01L 27/11                              | 556               | (2017.01)                            | 2011/0284946      | A1*        | 11/2011                     | Kiyotoshi H                            |                          |

|      | H01L 27/11                              | 524               | (2017.01)                            | 2011/0200012      | A 1 🕸      | 12/2011                     | TT T                                   | 257/324                  |

|      | H01L 27/11                              | 1582              | (2017.01)                            | 2011/0298013      | A1*        | 12/2011                     | Hwang H                                | 257/208                  |

|      | H01L 27/11                              | 157               | (2017.01)                            | 2012/0033503      | A1*        | 2/2012                      | Kim                                    |                          |

| (52) | U.S. Cl.                                |                   |                                      | 2012,000000       |            | 2,2012                      | 121111                                 | 365/185.33               |

|      |                                         | <b>G11C</b>       | 16/14 (2013.01); G11C 16/26          | 2012/0043673      | A1*        | 2/2012                      | Chang H                                |                          |

|      |                                         |                   | 101L 27/1157 (2013.01); H01L         | 2012(0122001      |            | <b>=</b> ( <b>- - - - -</b> | _                                      | 257/786                  |

|      |                                         | / /               | 524 (2013.01); H01L 27/11582         | 2012/0132981      | Al*        | 5/2012                      | Imamura H                              |                          |

|      |                                         |                   | .01); <i>H01L 29/7926</i> (2013.01)  | 2012/02/8525      | A 1 *      | 10/2012                     | Lee H                                  | 257/321<br>1011 27/11582 |

| (58) | Field of Cla                            | `                 |                                      | 2012/0240323      | A1         | 10/2012                     |                                        | 257/354                  |

| ()   |                                         |                   | ; G11C 16/0483; G11C 16/16;          | 2013/0016561      | <b>A</b> 1 | 1/2013                      | Nam                                    | 231,331                  |

|      |                                         |                   | G11C 5/025                           | 2013/0069141      | A1*        | 3/2013                      | Pan                                    | G11C 5/02                |

|      | USPC                                    | 257/66.           | 296, 302, 314, 315, 321, 324,        |                   |            | - /                         |                                        | 257/324                  |

|      |                                         | ,                 | 1, 786, 208, E21.614; 365/130,       | 2013/0248974      | Al*        | 9/2013                      | Alsmeier                               |                          |

|      | 3                                       |                   | 85.02, 185.03, 185.17, 185.18,       | 2013/0264631      | A 1        | 10/2013                     | Alsmeier et al.                        | 257/321                  |

|      |                                         |                   | 365/185.33, 185.29; 713/193          |                   |            |                             | Hwang H                                | IO1L 27/11551            |

|      | See applicat                            | tion file fo      | or complete search history.          |                   |            | 10,2010                     |                                        | 365/185.05               |

|      | arpina.                                 |                   |                                      | 2014/0047246      | A1*        | 2/2014                      | Seo1                                   | G06F 21/79               |

| (56) |                                         | Referen           | ices Cited                           |                   |            | _ /                         |                                        | 713/193                  |

| · /  |                                         |                   |                                      | 2014/0252363      | A1*        | 9/2014                      | Liu H                                  |                          |

|      | U.S                                     | . PATENT          | DOCUMENTS                            | 2014/0307508      | A 1 *      | 10/2014                     | Rhie                                   | 257/66<br>G11C 16/0483   |

| ,    | 7.602.050 D2:                           | * 4/2010          | D1: IIO1I 07/101                     | 2014/0307308      | AI         | 10/2014                     | Kille                                  | 265/185.17               |

|      | 7,692,950 B2 <sup>3</sup>               | * 4/2010          | Rhie H01L 27/101 365/148             | 2015/0115344      | A1*        | 4/2015                      | Lai H                                  |                          |

| ,    | 7,852,676 B2                            | 12/2010           | Maejima 303/148                      |                   |            |                             |                                        | 257/314                  |

|      | 7,994,011 B2                            |                   | · ·                                  |                   |            |                             |                                        |                          |

| 1    | 8,188,530 B2                            | * 5/2012          | Tanaka H01L 27/11573                 |                   | OTF        | HER PU                      | BLICATIONS                             |                          |

|      | 0 100 550 DO                            | 6/2012            | 257/314                              |                   |            |                             |                                        |                          |

|      | 8,199,573 B2<br>8,427,881 B2 °          |                   | Fukuzumi et al.<br>Jang G11C 16/0483 | •                 |            |                             | y using TCAT(Tera                      | •                        |

| '    | 0,727,001 DZ                            | 7/2013            | 365/185.02                           | /                 | ~          |                             | High Density NAND                      | • •                      |

|      | 8,531,901 B2 <sup>3</sup>               | * 9/2013          | Ogiwara G11C 16/30                   | • •               |            |                             | nology Digest of Tec                   | chnical Papers,          |

|      |                                         |                   | 365/185.17                           | Jun. 16-18, 2009, |            |                             | ed BiCS Flash Me                       | many with 16             |

| ;    | 8,587,998 B2 <sup>3</sup>               | * 11/2013         | Hung G11C 16/0483                    |                   | •          |                             | el-Cell Operation for                  | •                        |

|      | 0 001 200 D2:                           | * 11/201 <i>4</i> | 365/130                              |                   |            |                             | Symposium on VLS                       | •                        |

|      | 8,891,300 BZ                            | * 11/2014         | Oh                                   | •                 |            |                             | 16-18, 2009, pp. 13                    |                          |

|      | 9,070,442 B2 <sup>3</sup>               | * 6/2015          | Yip G11C 16/02                       | •                 |            |                             | NAND Flash Archi                       | •                        |

|      | 9,076,879 B2                            |                   | Yoo H01L 27/1157                     | •                 | •          |                             | cked ARray, IEEE T                     | ransactions on           |

| 2006 | 5/0138522 A1 <sup>3</sup>               | * 6/2006          | Kim H01L 27/115                      | Electron Devices  | ,          | ,                           | l, Jan. 2012.<br>Iash Memory due t     | o High Roost             |

|      |                                         |                   | 257/315                              |                   | •          |                             | d Optimal Memory                       | •                        |

| 2006 | /0237851 A1 <sup>3</sup>                | * 10/2006         | Ko H01L 23/485                       | _                 |            |                             | vice, IEEE Internat                    |                          |

| 2000 | 0/0173981 A1°                           | * 7/2000          | 257/774<br>Nitta H01L 21/84          | •                 | •          | ~                           | 17, 2008 pp. 1-4.                      |                          |

| Z003 | 70173301 AI                             | 112003            | 257/302                              | •                 | _          | •                           | le 8-Layer 3D Verti                    | ` /                      |

| 2010 | 0/0208511 A1 <sup>3</sup>               | * 8/2010          | Rhie G11C 7/062                      |                   |            | _                           | ction-Free Buried                      |                          |

|      |                                         |                   | 365/148                              | ·                 |            | • •                         | m on VLSI Techno                       | logy Digest of           |

| 2010 | /0224928 A1 <sup>3</sup>                | * 9/2010          | Fukuzumi H01L 21/28282               | Technical Papers, | •          | •                           | <b>.</b> .                             | nunch and Di             |

| 2010 | V0065000 + 1                            | 10/2010           | 257/324                              | ·                 |            |                             | e Technology with Plash Memory, 2007 S | •                        |

|      | /0265773 A1<br>/0024816 A1 <sup>*</sup> |                   | Lung et al.<br>Moon H01L 27/11578    |                   | _          | •                           | nical Papers, Jun. 12                  |                          |

| ∠U11 | 70024010 AT                             | Z/ZU11            | 257/314                              | 14-15.            | 17150      | ot of fool                  | anvar i apers, sum 12                  | z i i, 2007, pp.         |

| 2011 | /0051527 A13                            | * 3/2011          |                                      |                   |            |                             |                                        |                          |

\* cited by examiner

365/185.29

2011/0051527 A1\* 3/2011 Kirisawa ........... G11C 16/0483

Jan. 14, 2020

10A -

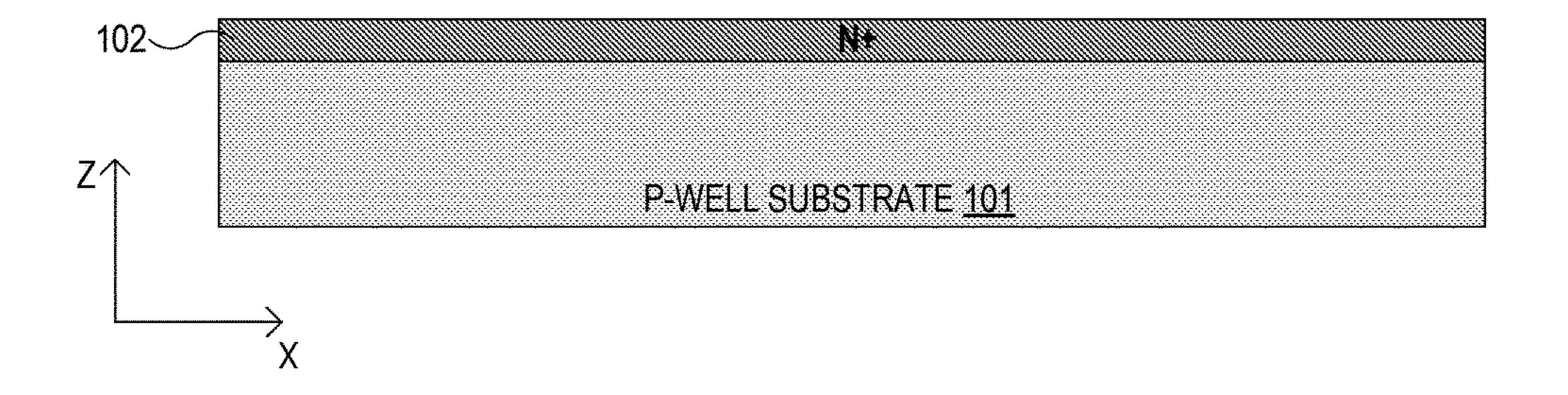

Figure 1a

10B 🚤

Figure 1b

30 🛶

Figure 3

40 -

Figure 4

Figure 5

100 ---

Figure 6

Figure 7

Figure 8

100C -

Figure 9

100D 🚤

Figure 10

Jan. 14, 2020

100E -

Figure 11

100F -

Figure 12

Figure 13

Figure 14

Figure 15

# THREE-DIMENSIONAL NONVOLATILE MEMORY CELL STRUCTURE WITH UPPER BODY CONNECTION

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

# CROSS REFERENCE TO RELATED APPLICATIONS

This application is a Reissue of U.S. patent application Ser. No. 14/532,048 filed Nov. 4, 2014, now issued as U.S. Pat. No. 9,236,394, this application claims the benefit to Provisional Application No. 61/901,830, filed Nov. 8, 2013, all of which are incorporated by reference herein.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention is directed in general to integrated circuit devices and methods for manufacturing same. In one aspect, the present invention relates to nonvolatile memory devices, such as NAND flash memory and other types of flash memory.

#### 2. Description of the Related Art

With the increasing demand for nonvolatile data storage in consumer electronics having mass storage, such as video or audio players, digital cameras, and other computerized devices, there continues to be interest in having nonvolatile 35 memory devices progress over time towards having smaller sizes, larger memory capacity, and improved performance. Flash memory is a commonly used type of nonvolatile memory which can take the form of memory cards or USB type memory sticks, each having at least one memory device and a memory controller formed therein. For example, the need to reduce manufacturing costs per data bit is driving the NAND flash industry to continuously reduce the size of the cell transistors. But as fabrication process limitations (for example, limitations imposed by photolithography tools) limit the ability to reduce physical transistor sizes, there have been structural and/or design schemes proposed to increase memory density, such as, for example, stacking NAND cells in a direction perpendicular to the chip surface, thereby reducing the effective chip area per data bit without requiring shrinkage of the physical cell transistor size. However, there continue to be challenges associated with designing, fabricating, and operating vertical NAND flash memory devices.

## BRIEF DESCRIPTION OF THE DRAWINGS

The present invention may be understood, and its numerous objects, features and advantages obtained, when the 60 following detailed description is considered in conjunction with the following drawings, in which:

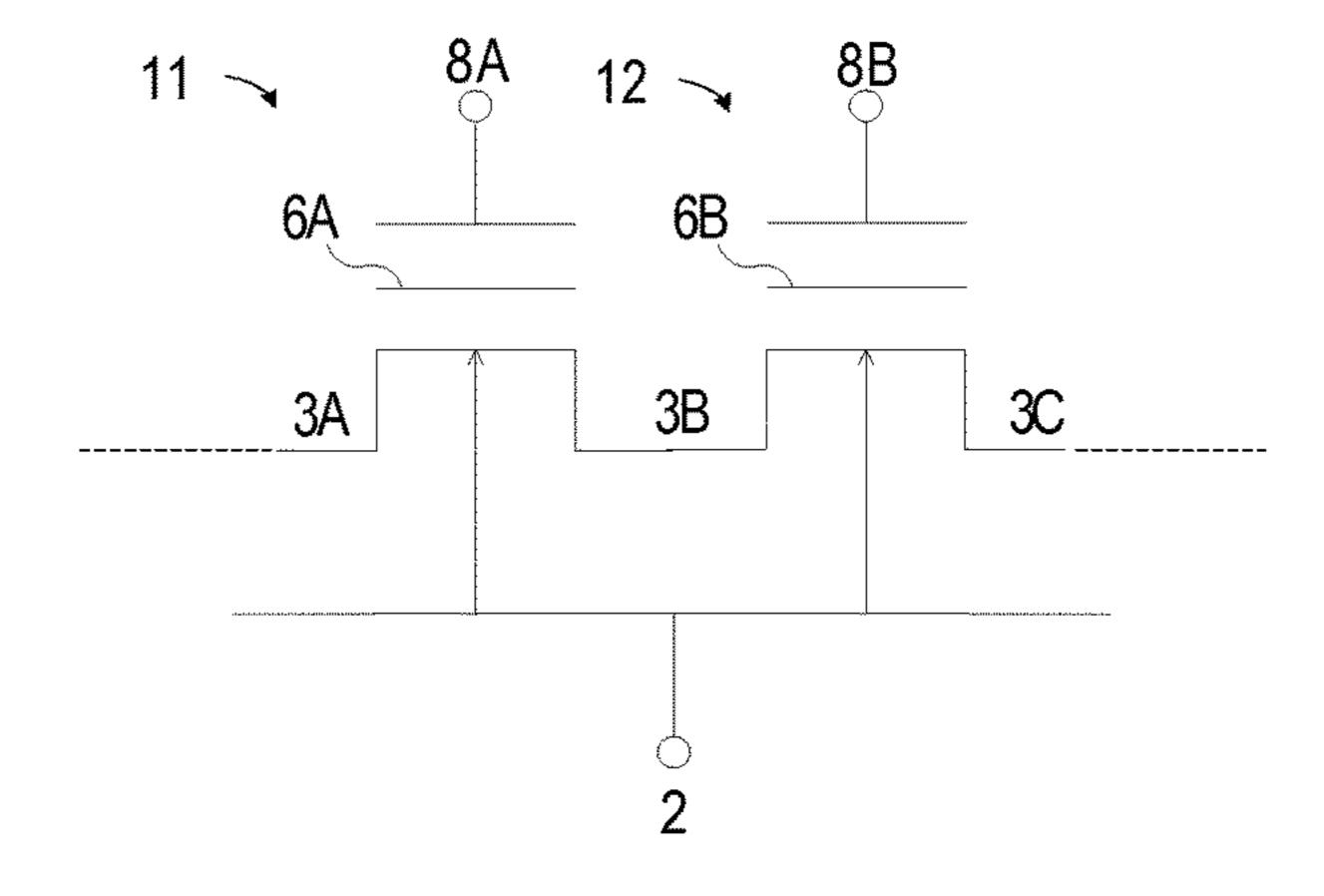

FIG. 1a illustrates a simplified circuit schematic representation of two serially-connected NAND flash memory cell transistors;

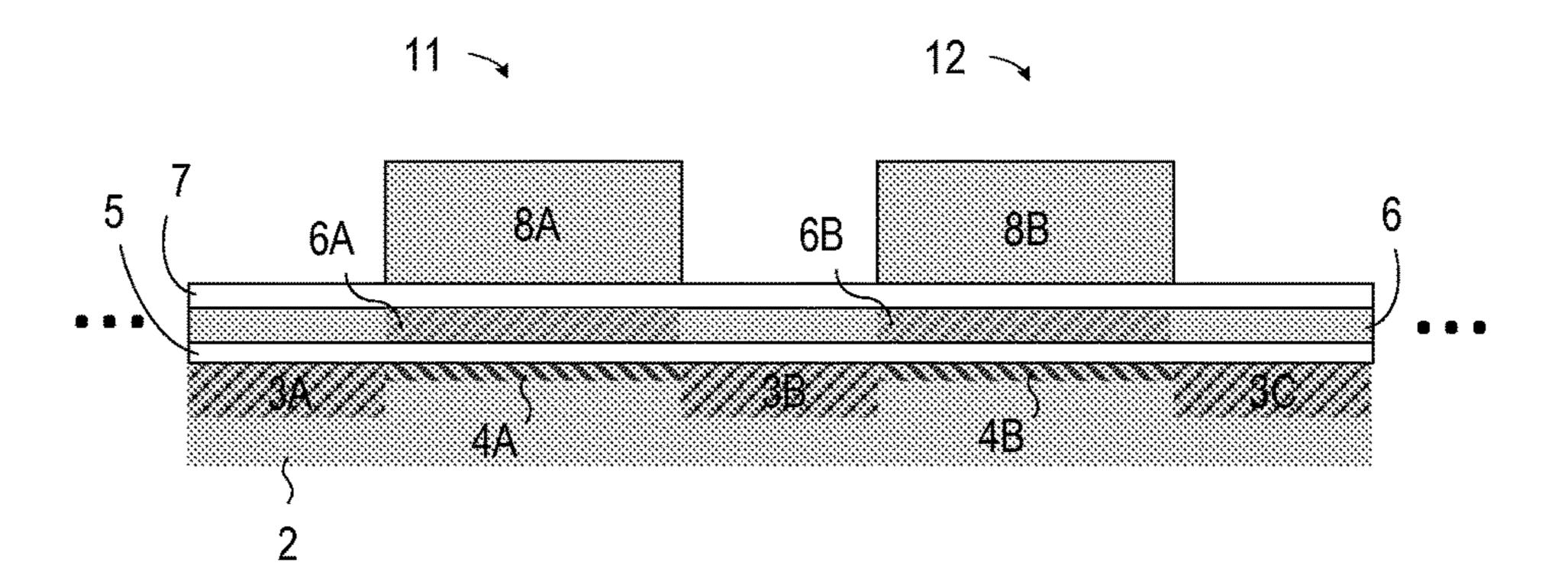

FIG. 1b illustrates a simplified cross sectional view of the NAND flash memory cell transistors shown in FIG. 1a;

2

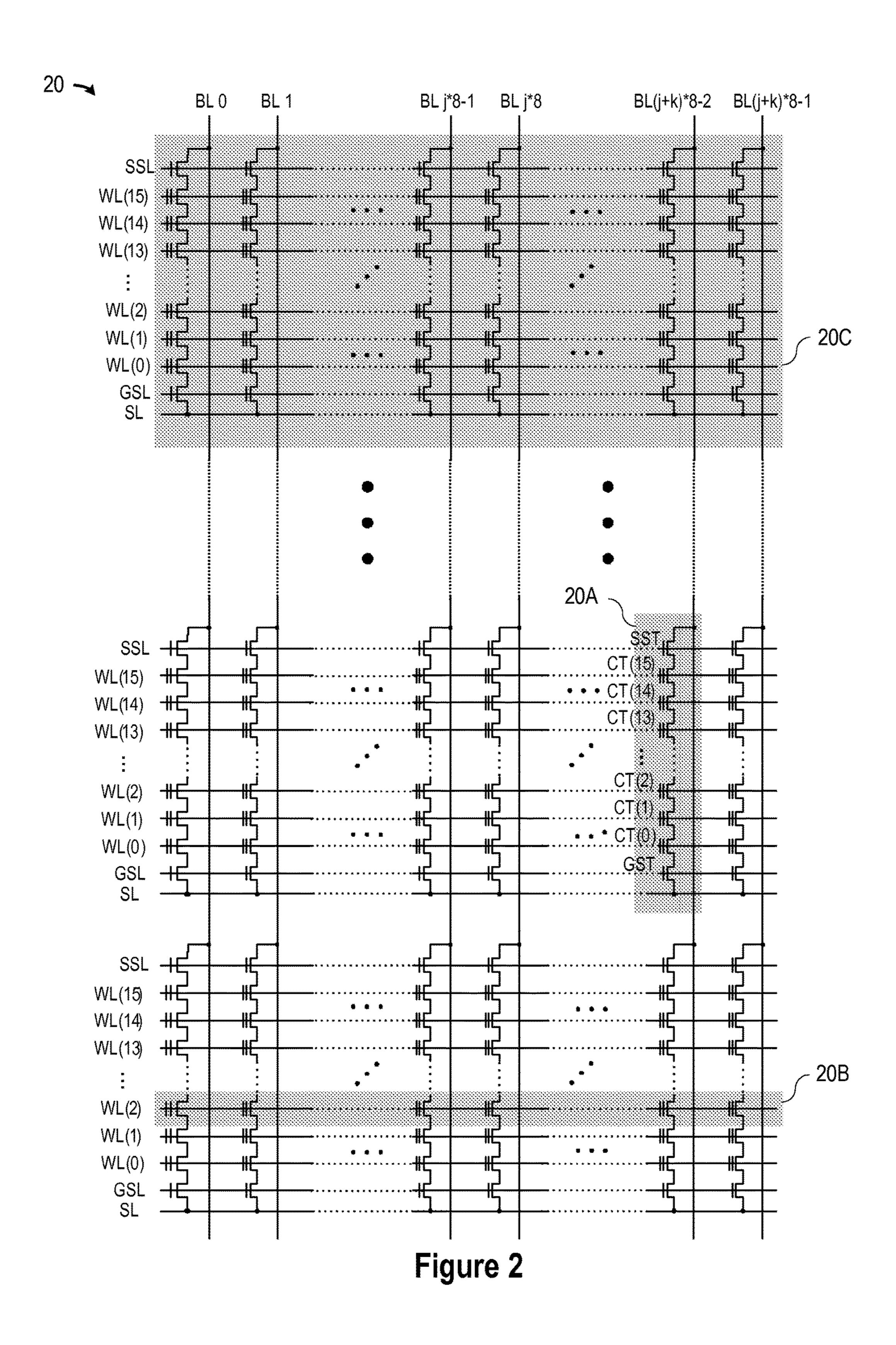

- FIG. 2 illustrates a simplified circuit schematic representation of a NAND flash memory cell array in which a string, page, and block of data are identified;

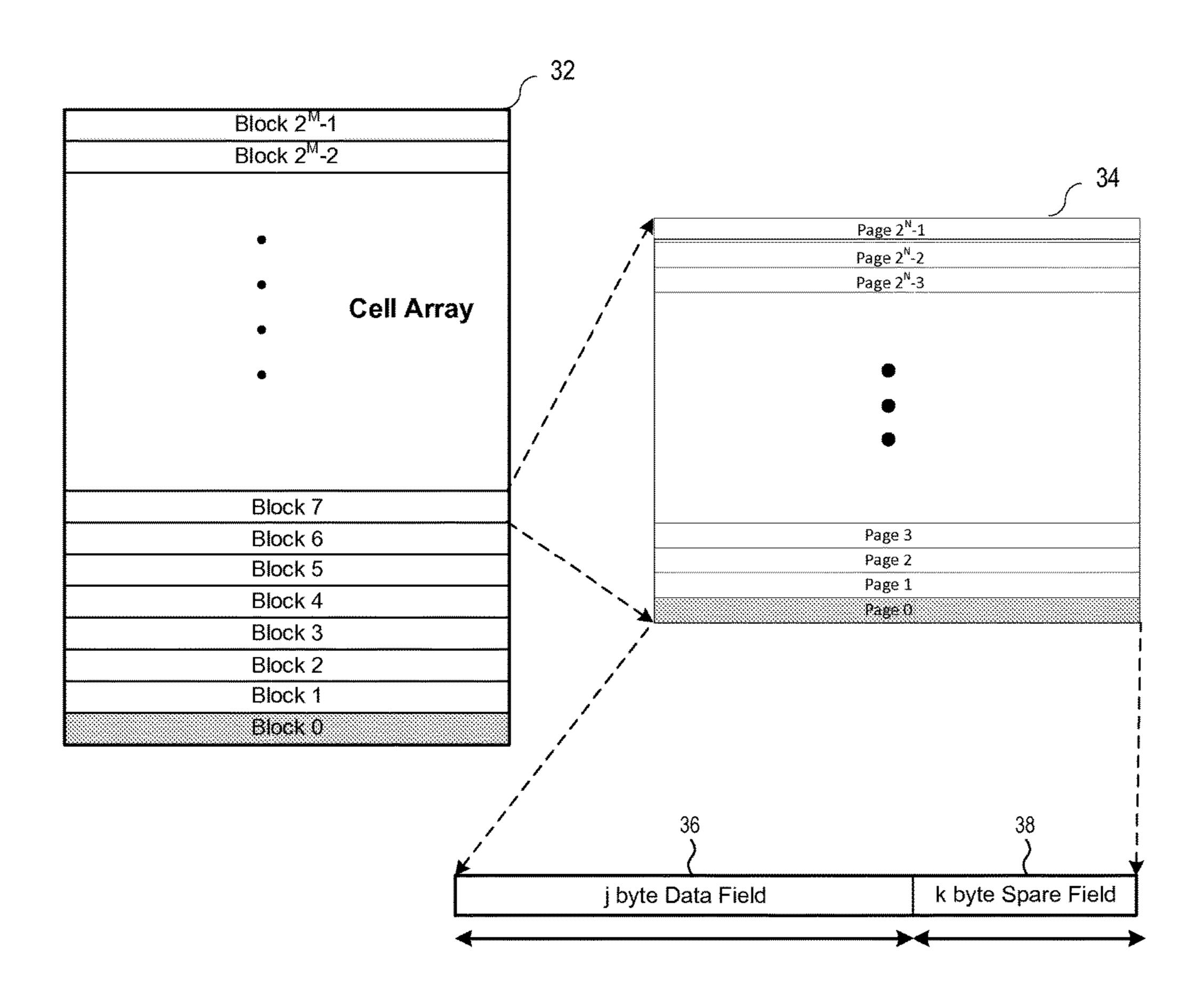

- FIG. 3 illustrates a multi-block NAND flash cell array memory using block and page addressing to support read, program, and erase operations;

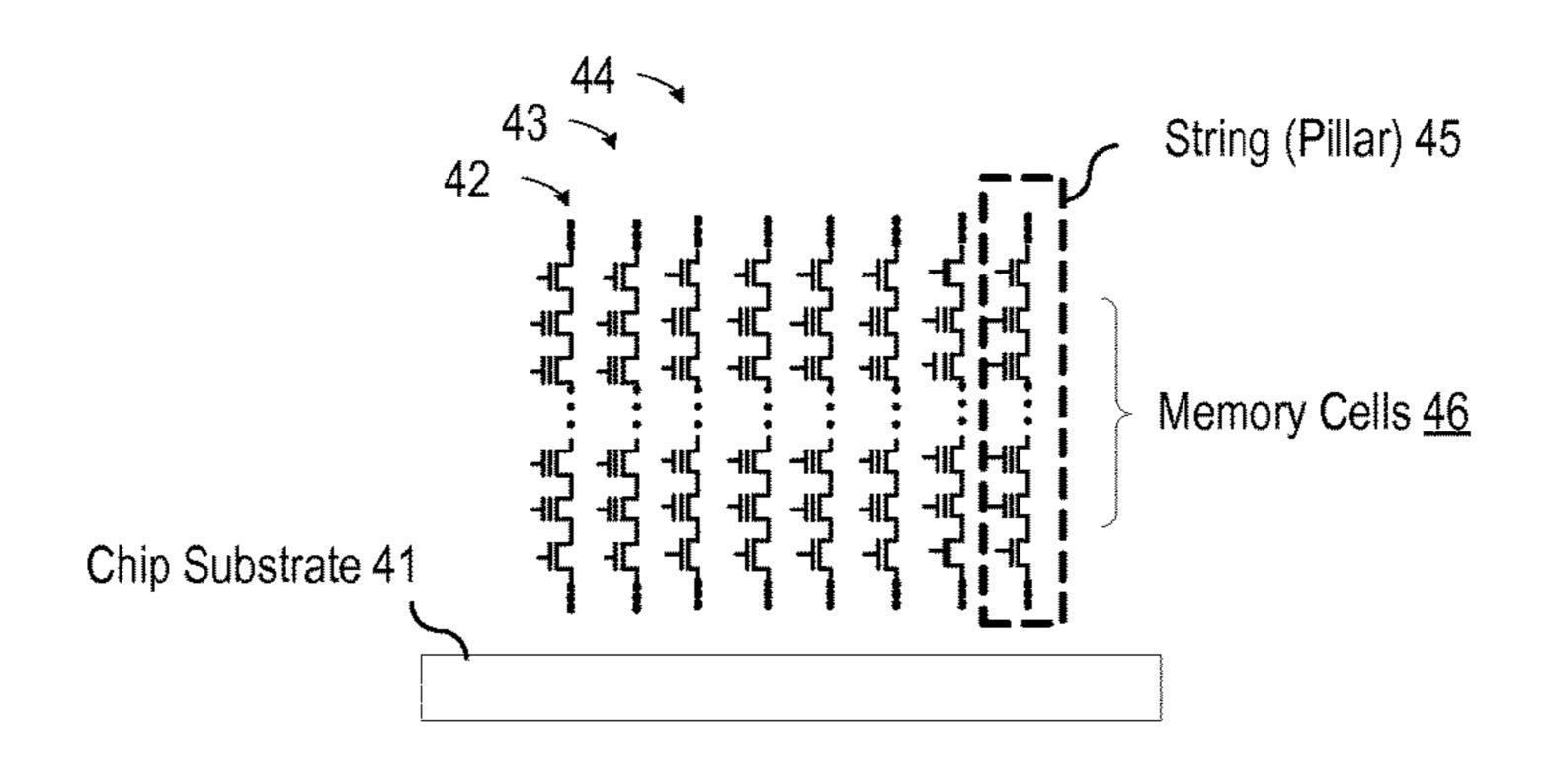

- FIG. 4 illustrates a simplified cross-sectional schematic representation of a vertically stacked array of vertical channel NAND flash cell strings formed over a substrate;

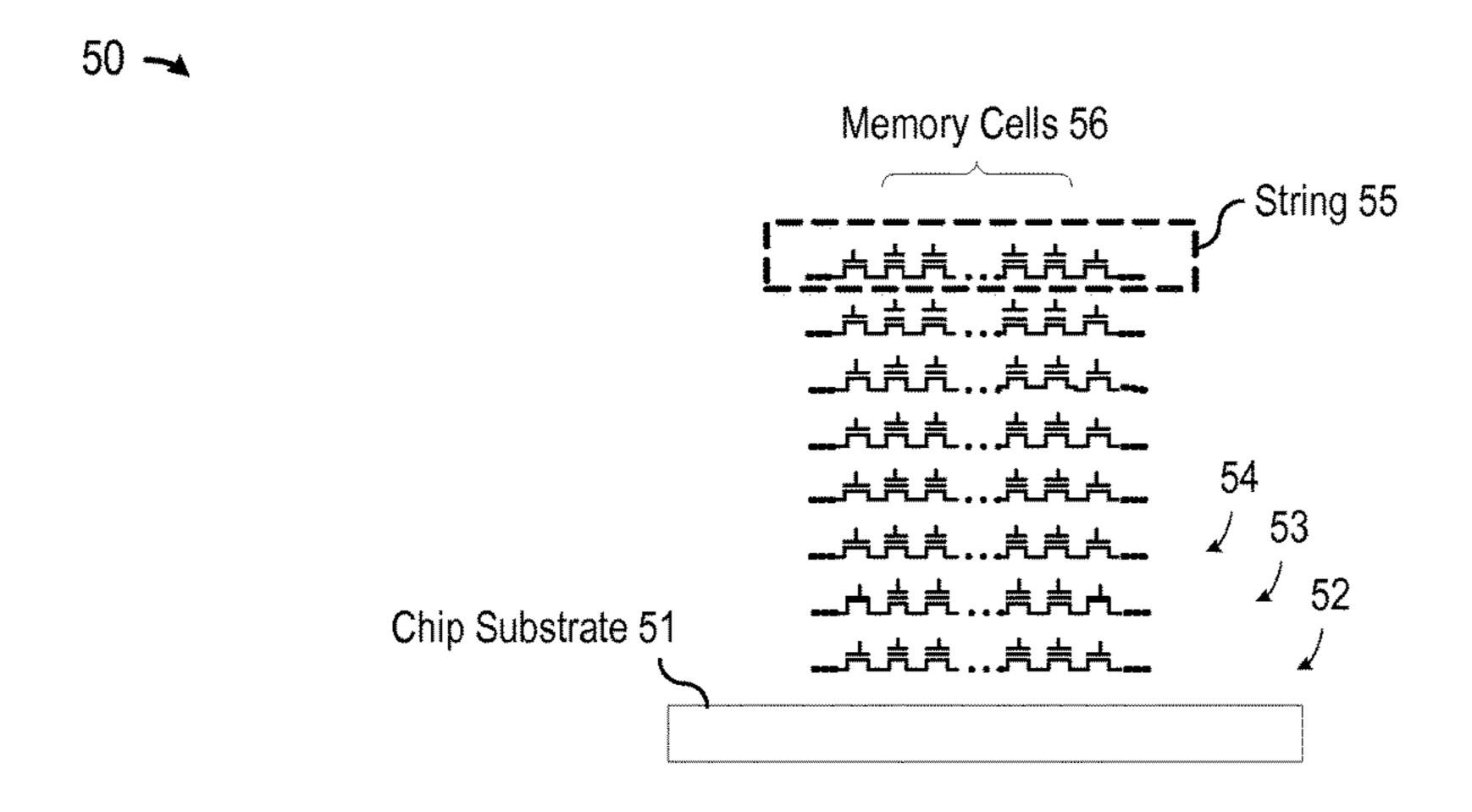

- FIG. 5 illustrates a simplified cross-sectional schematic representation of a vertically stacked array of vertical gate NAND flash cell strings formed over a substrate;

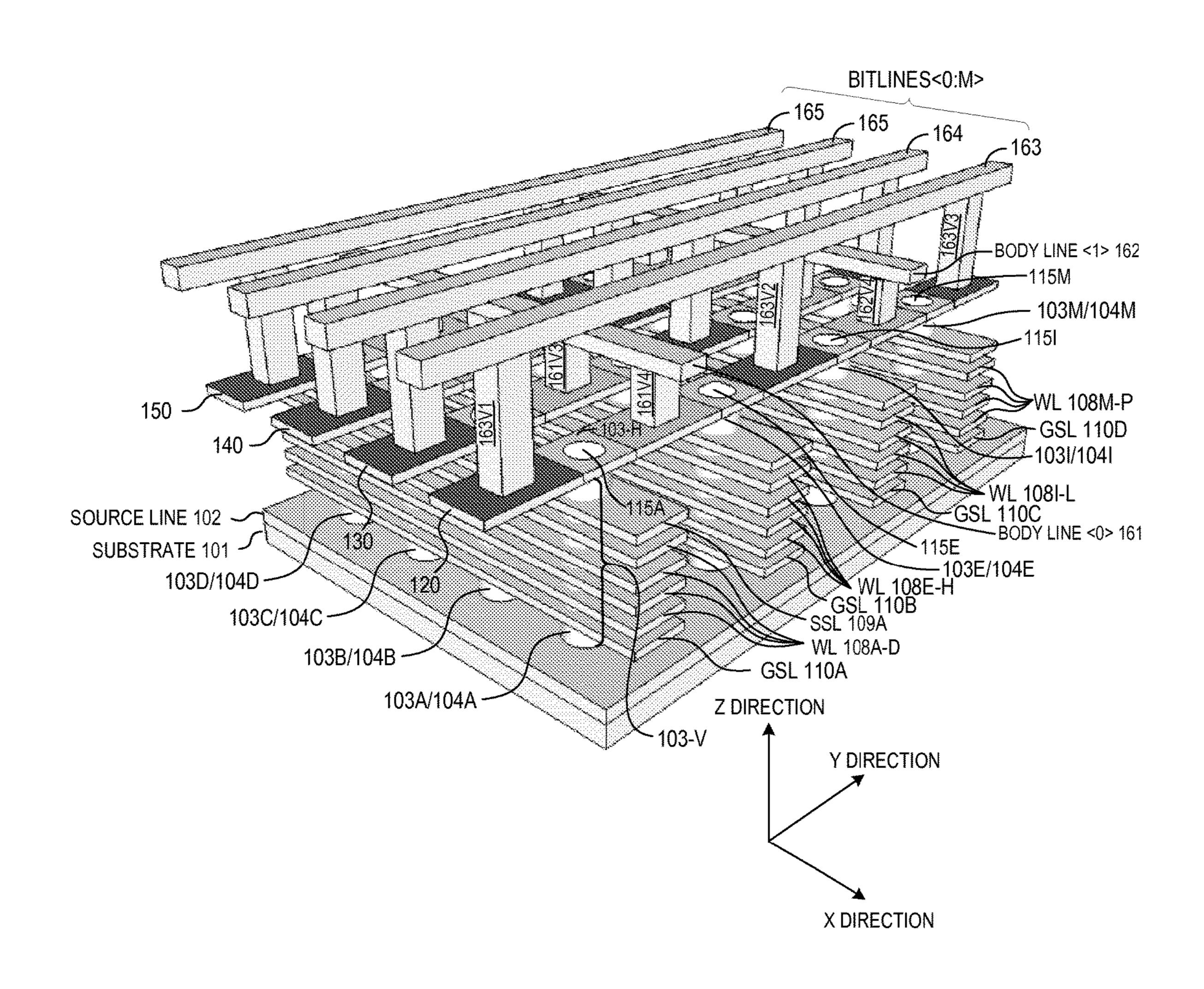

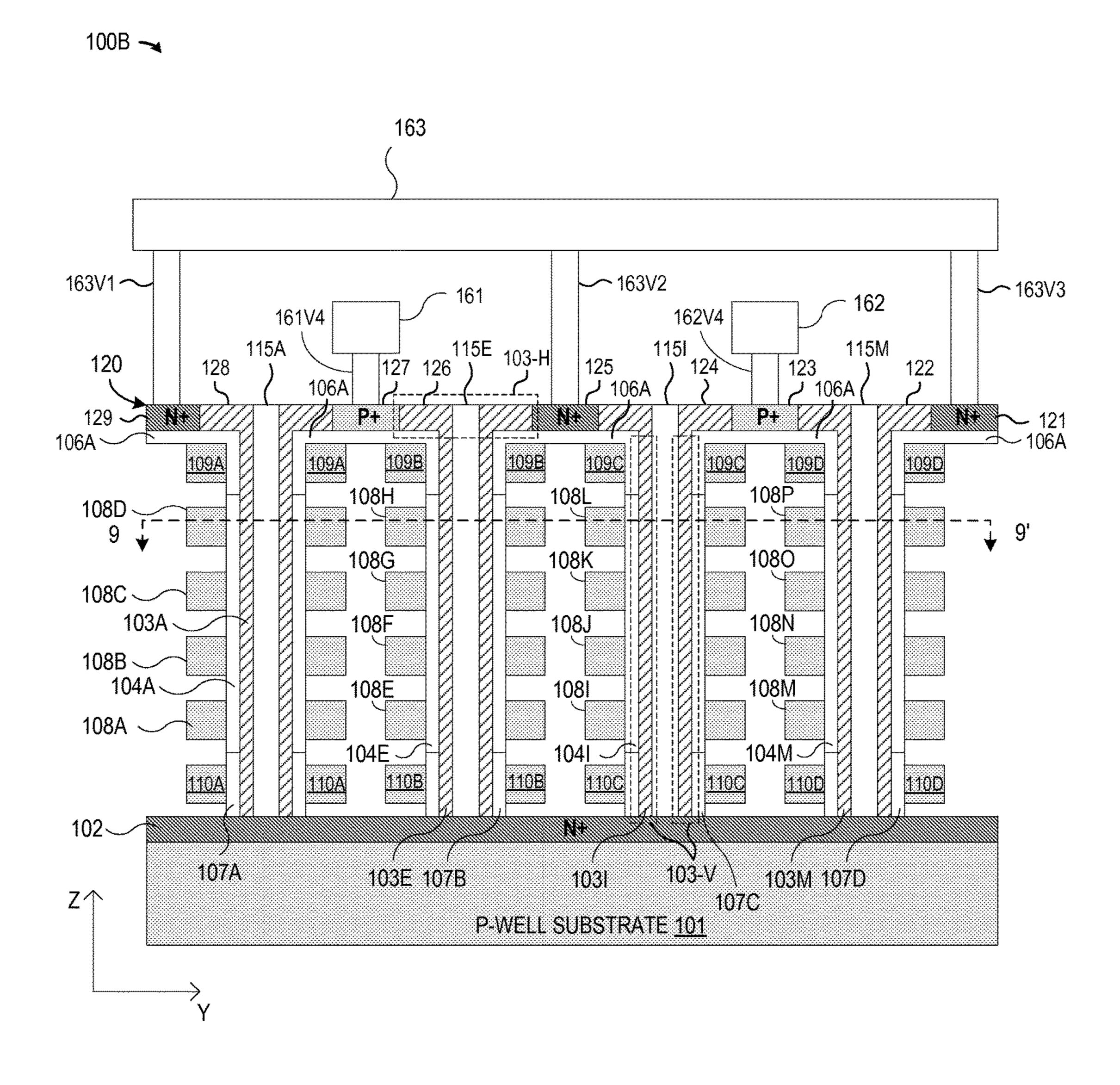

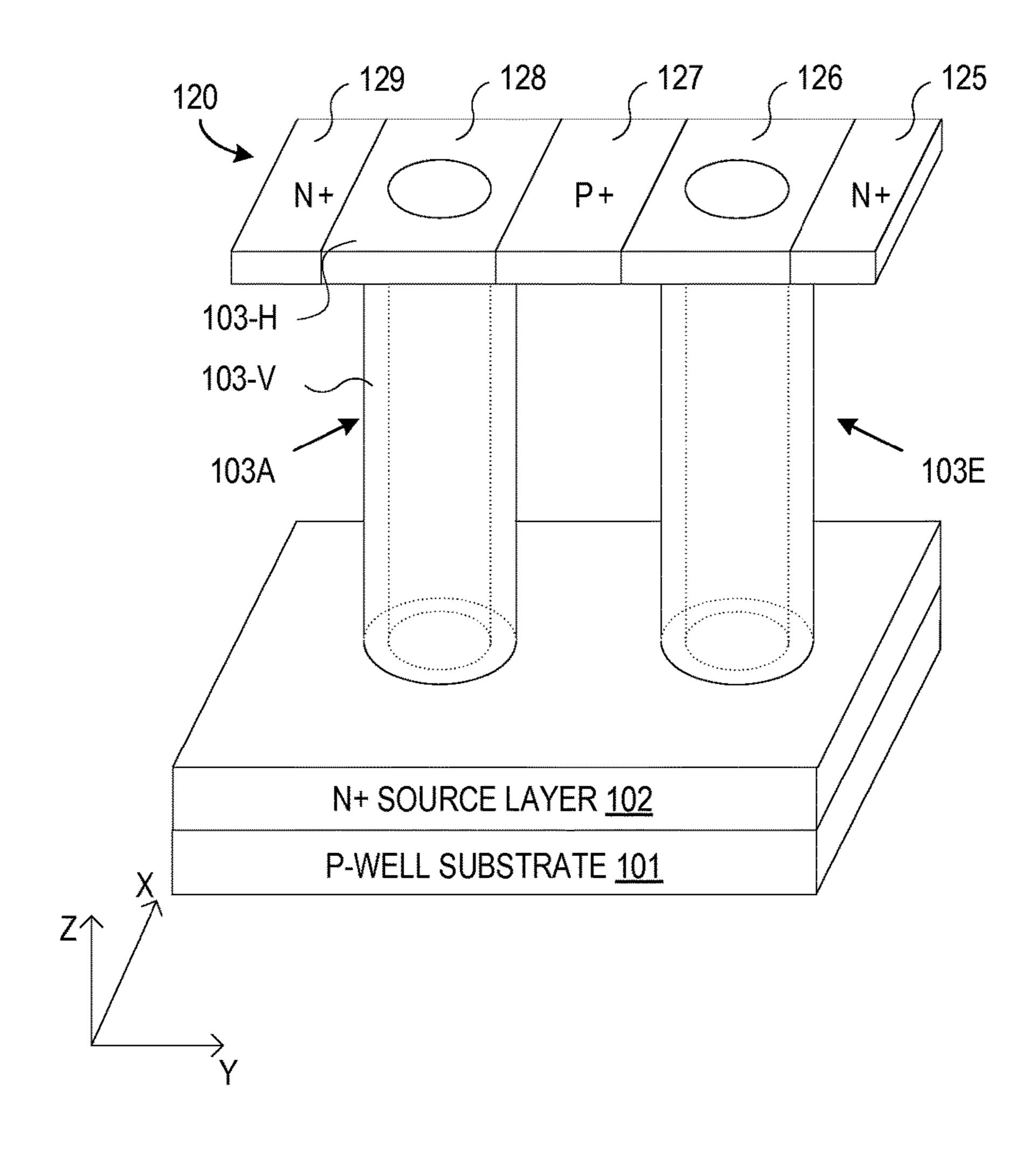

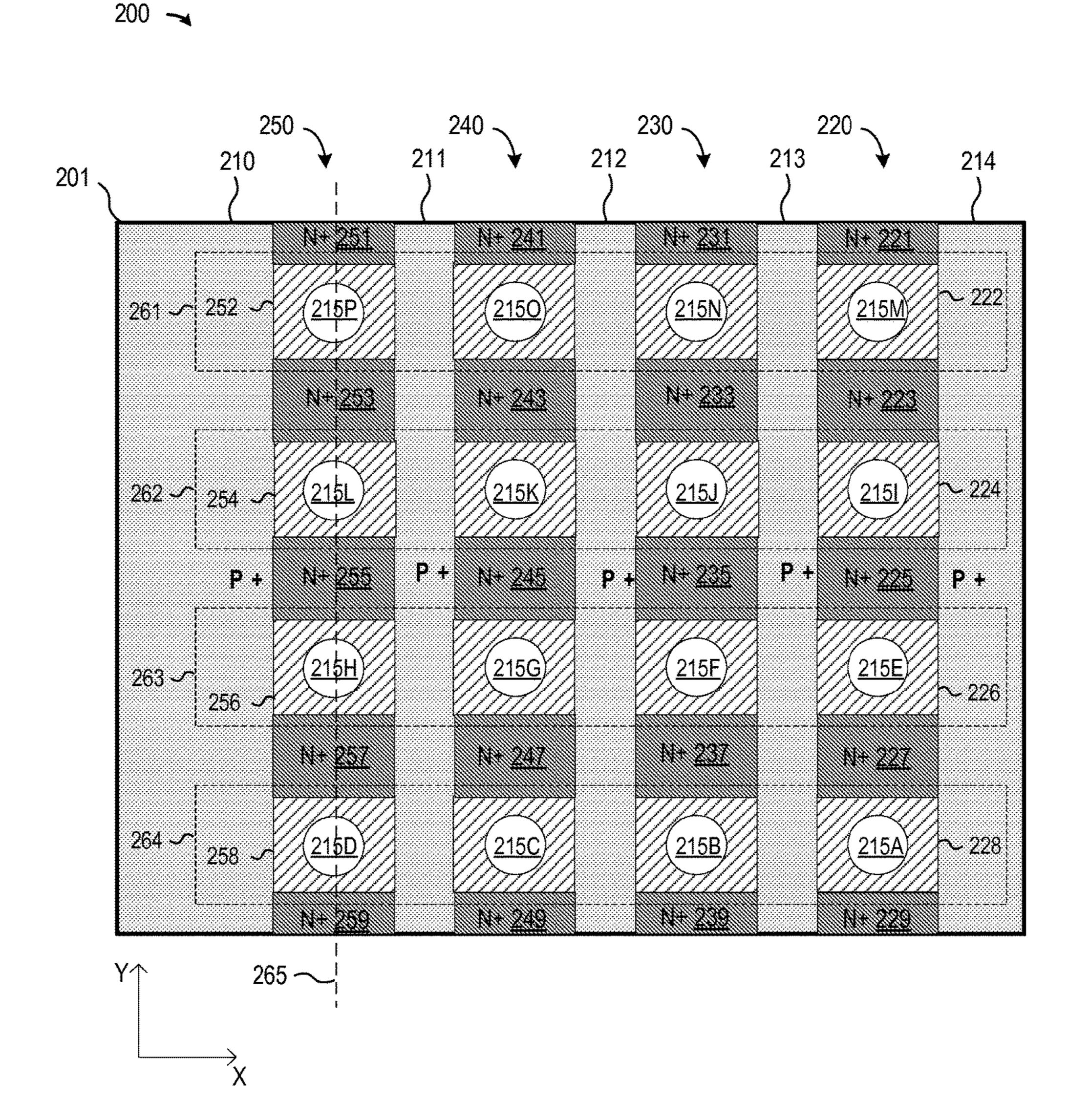

- FIG. 6 illustrates a simplified perspective view of a three-dimensional vertical channel NAND flash memory array architecture using upper layer connection lines with n-type bit line nodes and p-type body nodes for stacks of vertical channel NAND flash cell strings;

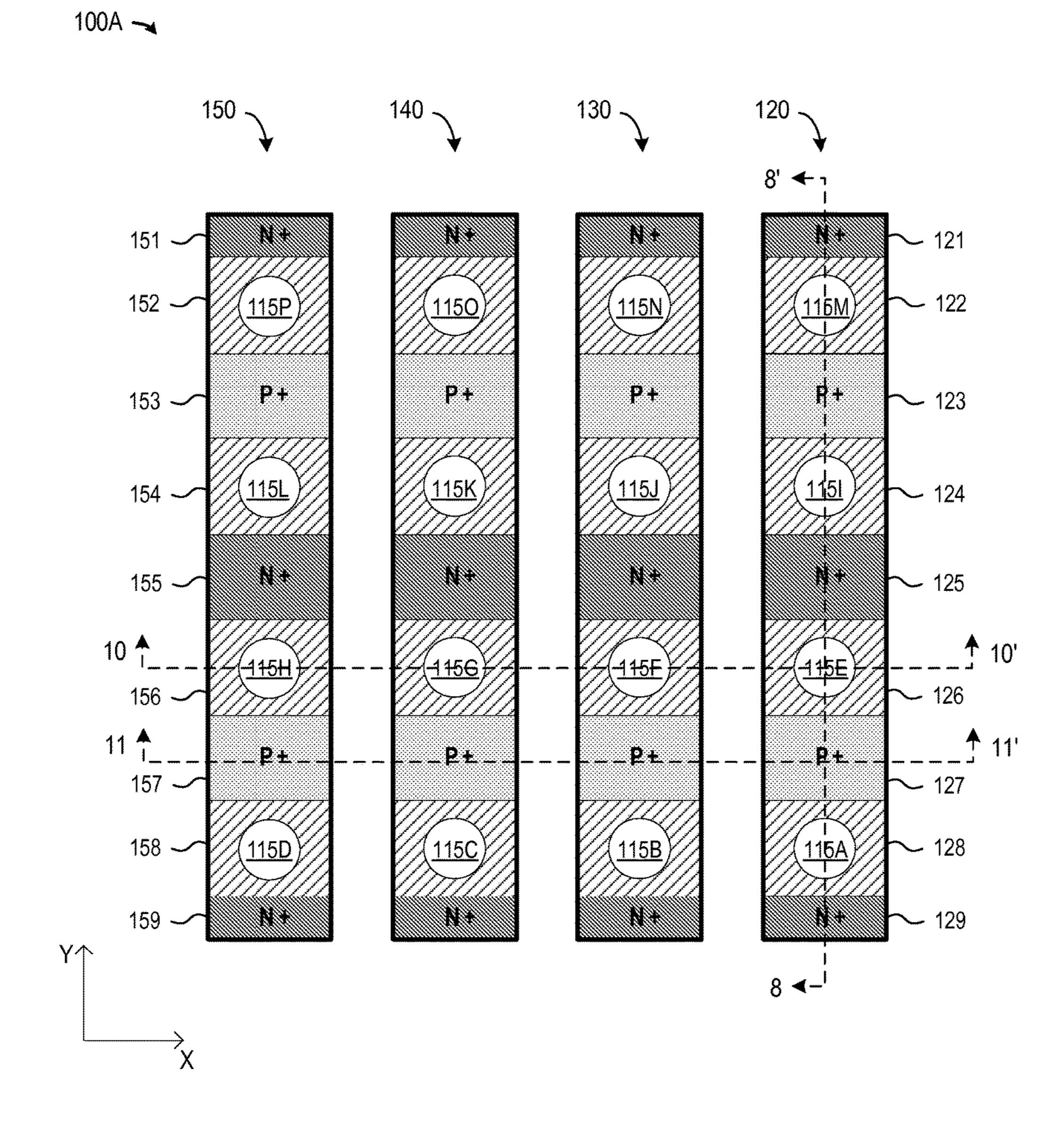

- FIG. 7 illustrates a plan view of upper layer connection lines in the vertical channel NAND flash memory structure shown in FIG. 6 in accordance with selected embodiments of the present disclosure;

- FIG. 8 illustrates a partial cross-sectional view of the vertical channel NAND flash memory structure shown in FIG. 6 cut in a bit line direction through an upper layer connection line;

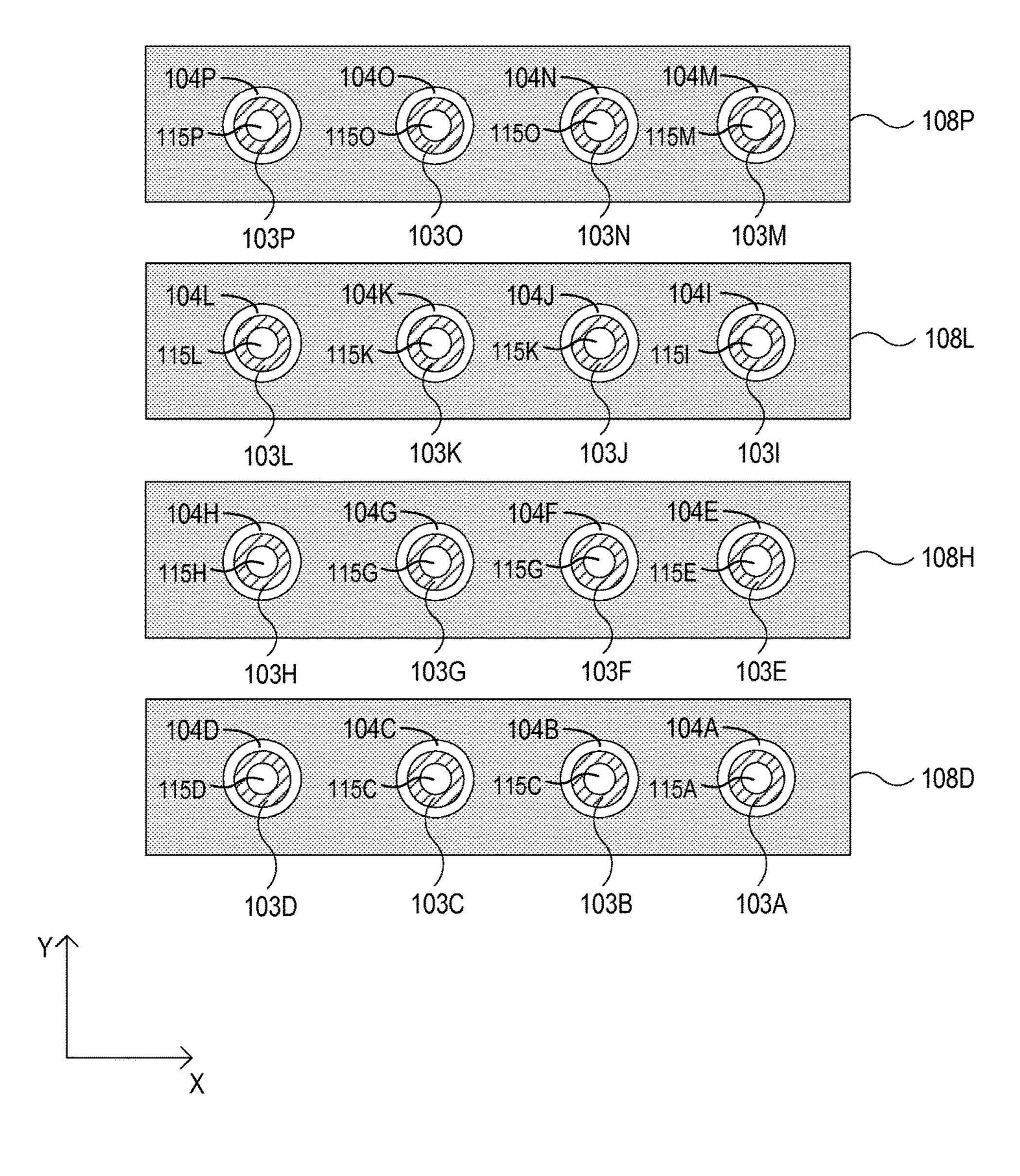

- FIG. 9 illustrates a plan view of transistor gate lines in a single lateral plane to show additional structural details of the flash cell strings in the vertical channel NAND flash memory structure shown in FIG. 6;

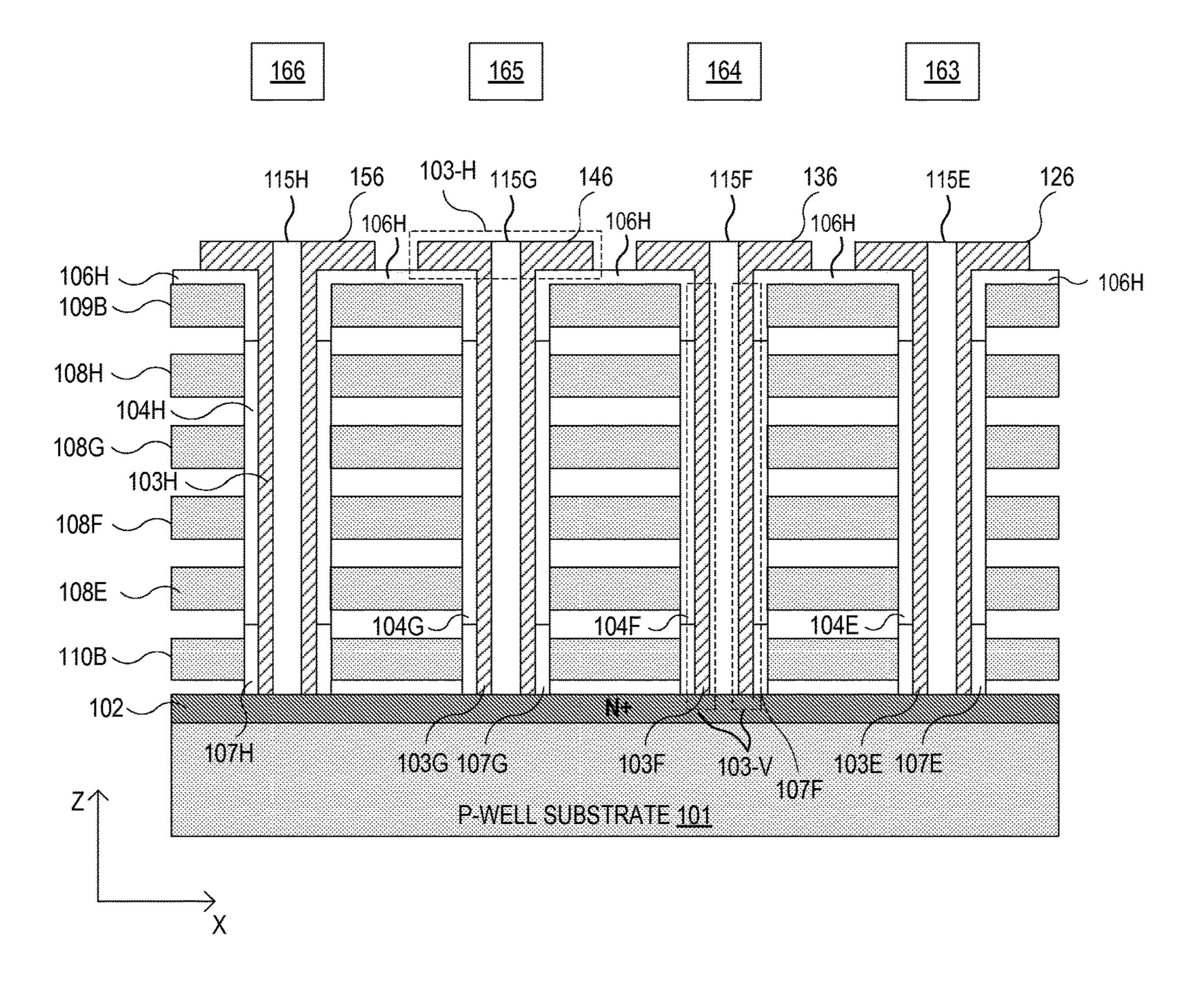

- FIG. 10 illustrates a partial cross-sectional view of the vertical channel NAND flash memory structure shown in FIG. 6 cut in a word line direction through a row of flash cell strings;

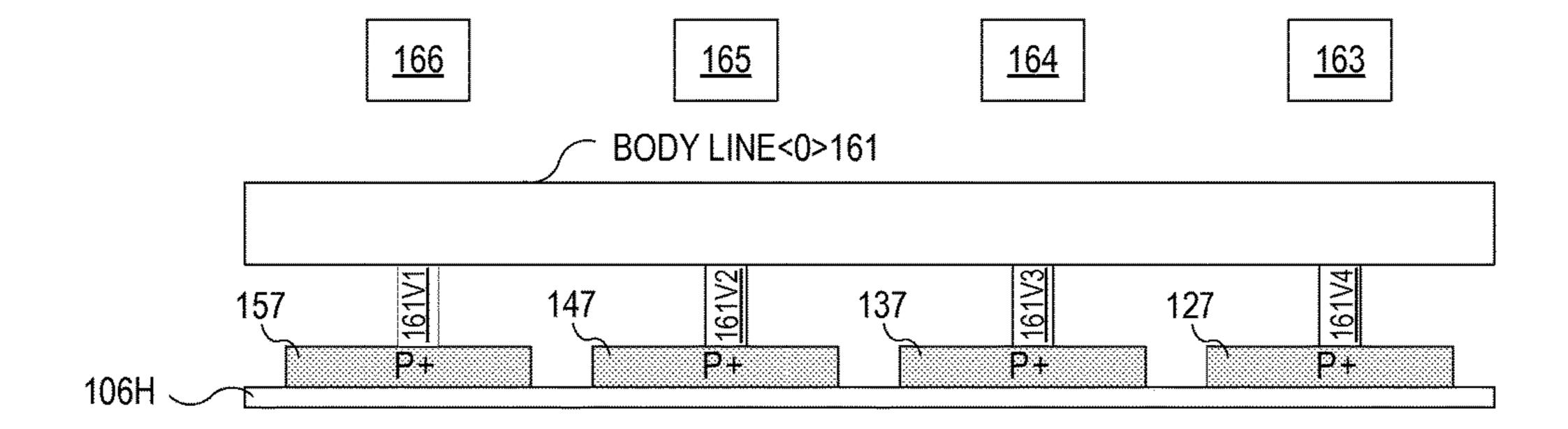

- FIG. 11 illustrates a partial cross-sectional view of the vertical channel NAND flash memory structure shown in FIG. 6 cut in a word line direction between adjacent rows of flash cell strings;

- FIG. 12 illustrates a simplified perspective view of a portion of the vertical channel NAND flash memory structure shown in FIG. 6 to show the connection of the semiconductor string bodies between the substrate and upper layer connection line;

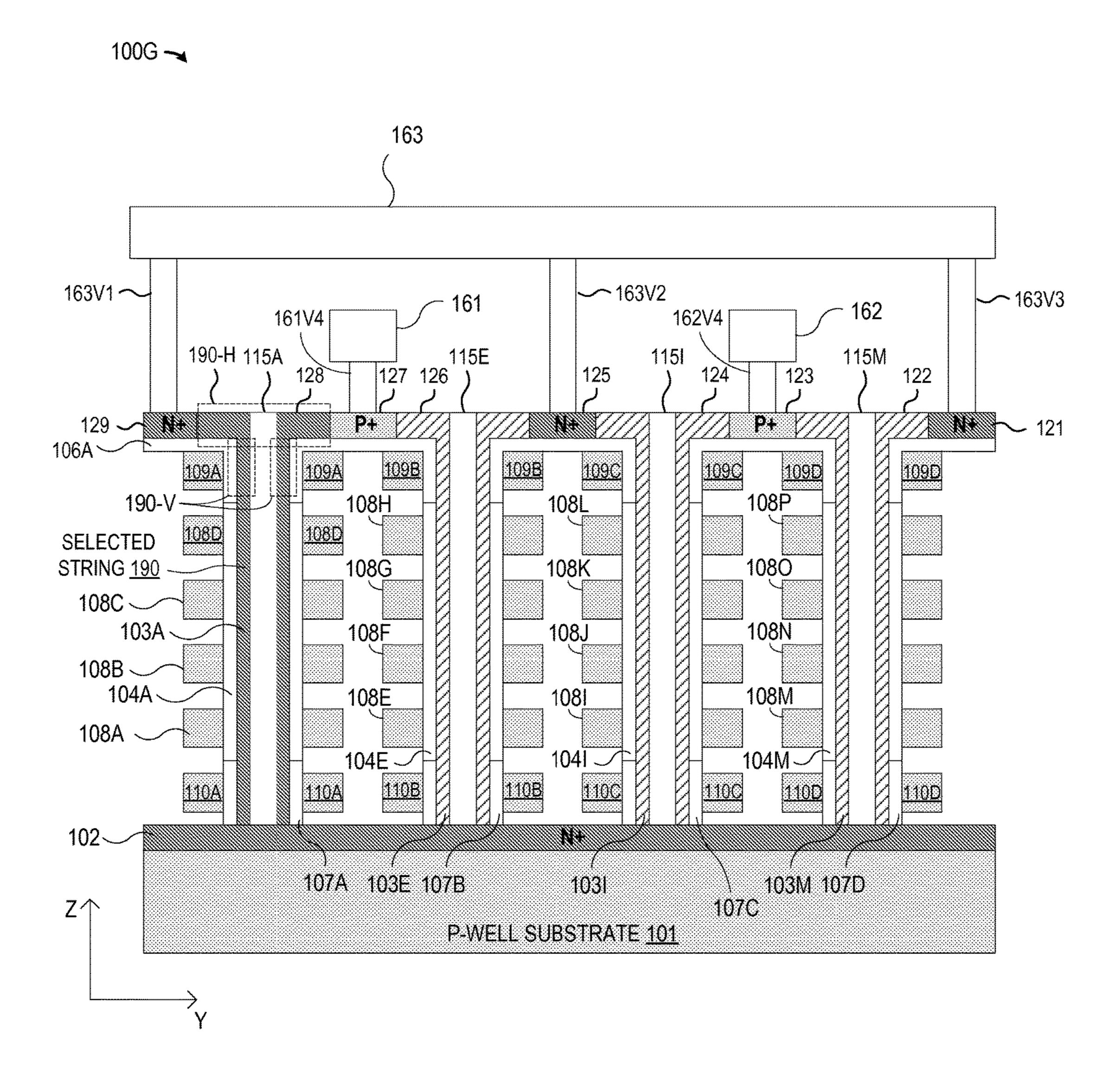

- FIG. 13 illustrates a partial cross-sectional view of the vertical channel NAND flash memory structure shown in FIG. 8 during selection of a flash cell string for a read operation;

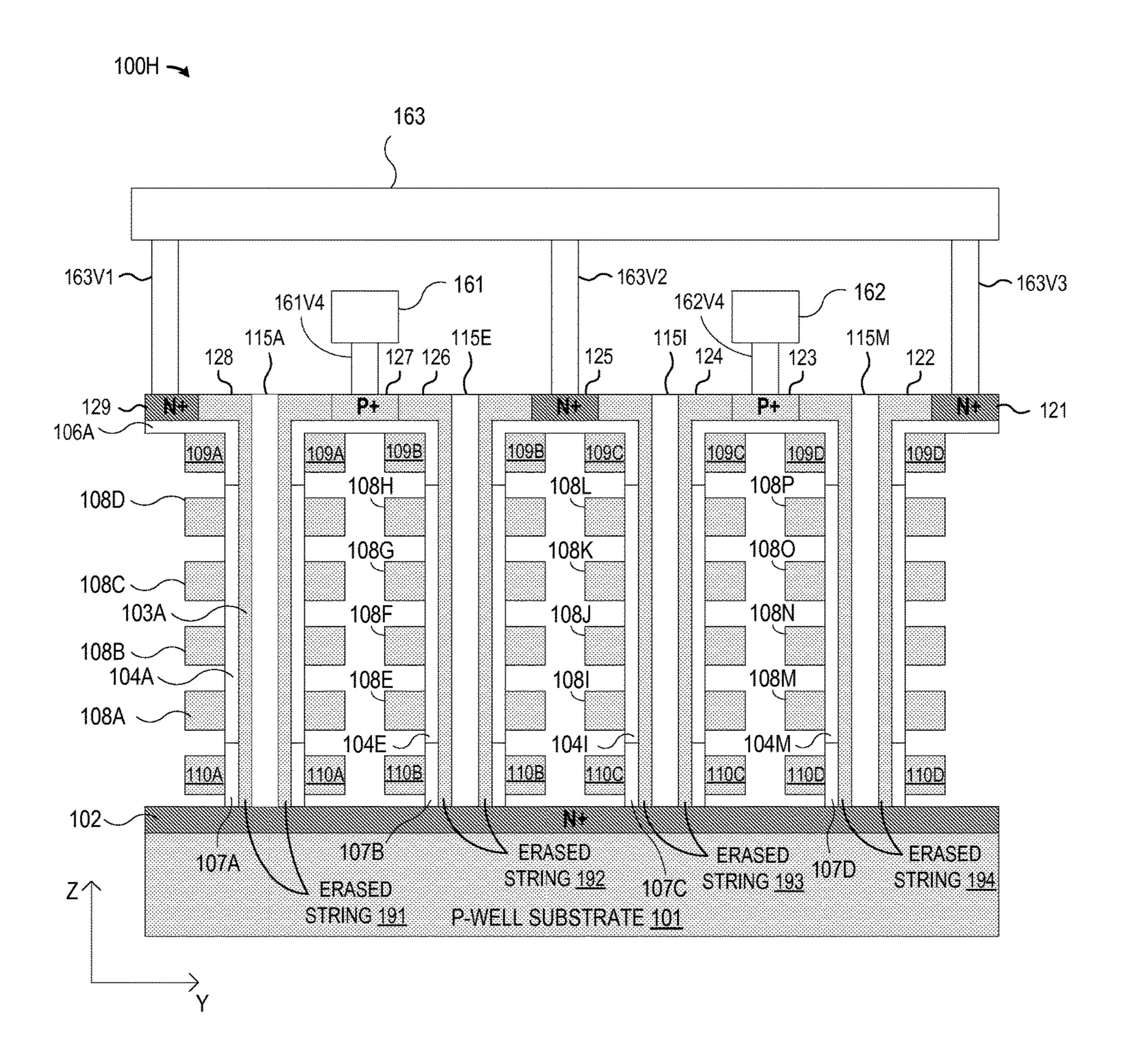

- FIG. 14 illustrates a partial cross-sectional view of the vertical channel NAND flash memory structure shown in FIG. 8 during erasure of a block of flash cell strings; and

- FIG. 15 illustrates a plan view of an upper body connection layer in a vertical channel NAND flash memory structure in accordance with selected embodiments of the present disclosure wherein n-type and p-type regions in the upper body connection layer separate the horizontal semiconductor body portions of the flash cell strings.

It will be appreciated that for simplicity and clarity of illustration, elements illustrated in the drawings have not necessarily been drawn to scale. For example, the dimensions of some of the elements are exaggerated relative to other elements for purposes of promoting and improving clarity and understanding. Further, where considered appropriate, reference numerals have been repeated among the drawings to represent corresponding or analogous elements.

#### DETAILED DESCRIPTION

In a three-dimensional vertical channel NAND flash memory device, a stacked memory architecture and cell

array structure are provided with upper connection lines formed with semiconductor strips or in a single semiconductor layer. The upper connection lines include n-type bit line nodes for connection to vertical string channels through horizontal string body portions. The upper connection lines 5 also include p-type body nodes for direct electrical connection to vertical string bodies through horizontal string body portions to provide direct charging through a common body node during erase operations. By connecting the flash cell strings between the upper connection lines and an n-type 1 source line formed in the substrate, the transistors on each string may include a plurality of series-connected transistors, including a string select transistor having a drain which is electrically connected to an n-type bit line node of the upper connection line and a source which is connected to 15 one out of multiple cell transistors connected in series through a ground select transistor to the n-type source line in the substrate. In selected embodiments, a plurality of upper connection lines running in the bit line direction is formed over a stacked array of vertical gate NAND flash cell 20 strings, such as by depositing, patterning, and etching a polysilicon layer to form the plurality of upper connection lines, and then selectively implanting the upper connection lines to define alternating n-type bit line contact regions and p-type body contact regions which are laterally spaced apart 25 from vertical string body portions of the underlying flash cell strings by horizontal string body portions formed in the upper connection lines. In other embodiments, the upper connection lines may be formed by depositing, patterning, and selectively implanting a polysilicon layer to form upper connection lines having implanted n-type bit line contact regions and p-type body contact regions which surround horizontal string body portions formed around vertical string body portions of the underlying flash cell strings. By forming and positioning each upper connection line to include a 35 horizontal string body portion in direct electrical contact with a corresponding vertical string body portion, each semiconductor body of the cell array transistors is not confined to a straight pillar structure, and is connected to an n-type bit line contact region and p-type body contact region 40 in a corresponding upper connection line. In addition, by forming n-type and p-type node regions in the upper connection lines after fabrication of the stacked cell structures to be laterally spaced apart from the vertical string bodies by the horizontal string body portions, the risk of dopant ion 45 diffusion into the vertical string bodies may be reduced or eliminated.

In this disclosure, an improved system, apparatus, and fabrication method are described for fabricating vertical channel NAND flash memory devices with upper connec- 50 tion line structures and substrate source line regions positioned on opposing ends of adjacent NAND strings that address various problems in the art where various limitations and disadvantages of conventional solutions and technologies will become apparent to one of skill in the art after 55 reviewing the remainder of the present application with reference to the drawings and detailed description provided herein. For example, there are performance limitations with performing erase operations in conventional floating-body directly charging cell bodies in such memories. There are also manufacturing challenges that can impair device performance, such as when source lines are implanted into the substrate through the stacked cell structures, resulting in increased resistance due to limited implantation area and/or 65 dopant concentration. While there have been attempts to address such limitations, such solutions typically include

doped n-type drain contact regions formed on top of the vertical string bodies, resulting in other technical challenges when dopants diffuse into the string body structures during high-temperature fabrication processing used to make stacked cell structures. Various illustrative embodiments of the present invention will now be described in detail with reference to the accompanying figures. While various details are set forth in the following description, it will be appreciated that the present invention may be practiced without these specific details, and that numerous implementationspecific modifications may be made to the invention described herein to achieve the device designer's specific goals, such as compliance with process technology or design-related constraints, which will vary from one implementation to another. While such a development effort might be complex and time-consuming, it would nevertheless be a routine undertaking for those of ordinary skill in the art having the benefit of this disclosure. For example, selected aspects are depicted with reference to simplified drawings and representations of a flash memory device without including every device feature, geometry, or circuit detail in order to avoid limiting or obscuring the present invention. Such descriptions and representations are used by those skilled in the art to describe and convey the substance of their work to others skilled in the art. In addition, although specific example materials are described herein, those skilled in the art will recognize that other materials with similar properties can be substituted without loss of function. It is also noted that, throughout this detailed description, certain materials will be formed and removed to fabricate the semiconductor structure. Where the specific procedures for forming or removing such materials are not detailed below, conventional techniques to one skilled in the art for growing, depositing, removing or otherwise forming such layers at appropriate thicknesses shall be intended. Such details are well known and not considered necessary to teach one skilled in the art how to make or use the present invention.

To provide a contextual framework for selected embodiments of the present disclosure, reference is now made to FIG. 1a which illustrates a simplified circuit schematic representation 1 of two serially connected NAND Flash cell transistors 11, 12. Each of the transistors 11, 12 includes a control gate 8A, 8B and a floating node (or storage nodes) 6A, 6B. Source/drain nodes 3A, 3B, 3C and the cell body node 2 are also shown. The NAND flash memory cell transistors 11, 12 can perform erase, program, and read operations by applying appropriate voltages to the indicated nodes, thereby trapping electrons in the charge storage nodes **6A**, **6B** to modify the threshold voltage of each cell transistor to different levels, depending on the data (0 or 1) stored in the cell. The threshold voltage of each cell transistor determines the resistance of the corresponding channel 4A, 4B. In selected embodiments where each NAND Flash memory cell stores two logic states (data '1' and data '0'), each memory cell corresponds to one bit, but in other embodiments where NAND Flash memory cells can be programmed to four or more threshold levels, multiple bits can be stored in each physical cell, which is referred to as a type stacked NAND flash memories due to difficulties with 60 multi-level cell (MLC). With NAND flash memory cells, data is typically erased and programmed using Fowler-Nordheim (F-N) tunneling to deliver or remove charge from the floating gate/charge storage nodes 6A, 6B by applying a suitably large voltage to the control gate 8A, 8B (for example, 20V) while holding the substrate 2 and source/ drain regions 3 to a lower voltage (for example, ground or 0V) to induce the formation of a channel 4A, 4B under the

tunnel dielectric 5 which injects electrons into the floating gate/charge storage nodes 6A, 6B. As a result, the cell threshold voltage Vth of the programmed cell is shifted in the positive direction.

In order to read cell data, the control gate **8A**, **8B** is biased 5 to a lower voltage (for example, Vss=0V). If the cell is in an erased state, the erased cell has a negative threshold voltage so that the cell current (Icell) from the drain 3B to the source 3A flows under the given read bias condition. On the other hand, if the cell is in a programmed state, the programmed 10 cell has a positive threshold voltage so that there is no cell current from the drain 3B to the source 3A under read bias condition. An erased cell (on-cell) is thus read or sensed as data '1' and a programmed cell (off-cell) is read or sensed as data '0'.

During an erase operation, the control gate 8A, 8B of a cell is biased to a low voltage (for example, Vss=0V) while the cell body 2 is biased to an erase voltage V\_erase (for example 18 V) and the source and drain 3A/3B of the cell are floated. In the erase bias conditions, no conductive 20 inversion layer channel 4A, 4B exists because the cell transistors are strongly turned off, in which case the trapped electrons in the floating node 6A, 6B are emitted uniformly to the substrate 2 through the tunnel dielectric 5. As a result, the cell threshold voltage (Vth) of the erased cell becomes 25 negative. In other words, the erased cell transistor is in an on-state if the gate bias of the control gate is 0V. Because of the cell body bias requirement for erase bias conditions, erase operations are not applied to individual NAND Flash memory cells, but are instead applied to erase entire blocks 30 of cells.

To further illustrate the contextual framework for selected embodiments of the present disclosure, reference is now made to FIG. 1b which illustrates a simplified cross sectional shown in FIG. 1a formed in a semiconductor substrate or string structure. The illustrated NAND Flash cell includes a semiconductor body or well layer 2 formed with an appropriate semiconductor material (for example, monocrystalline or polycrystalline silicon) having a first polarity type 40 (for example, p-type silicon), such as a bulk semiconductor substrate, semiconductor-on-insulator (SOI) substrate, or a polysilicon layer. Multiple semiconductor substrate or string structures can be vertically stacked over a bulk or SOI substrate and separated from one another by interlayer 45 dielectric layers.

On or around the semiconductor body or well layer 2, a multi-layered memory film structure 5-7 is formed for each transistor 11, 12, including a tunnel dielectric layer 5 that is formed (for example, deposited or grown) on the semiconductor body/well layer 2, a charge storage layer 6 that is formed on the tunnel dielectric 5, and a coupling dielectric 7 (a.k.a., blocking dielectric) that is formed (for example, deposited) on the charge storage layer 6. Sandwiched between the tunnel dielectric layer 5 and the coupling 55 dielectric layer 7, the charge storage layer 6 performs a charge trap function by including charge storage nodes or locations 6A, 6B where electrons are trapped. In selected embodiments, the charge storage nodes 6A, 6B may be formed as a SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) 60 structure, though other charge storage node structures may be used. As will be appreciated, the charge storage nodes 6A, 6B are formed to prevent unintentional charge flow between adjacent cells, such as by forming the charge storage layer 6 with dielectric charge trapping material or with conductive 65 material in each cell which is isolated from adjacent cells (e.g., by patterned dielectric layers between adjacent floating

gates). In selected floating gate embodiments (not shown), the charge storage layer 6 is patterned into separate floating gates that are isolated from one another. However, in embodiments where the charge storage layer 6 and storage nodes 6A, 6B are formed as a single continuous layer, the multi-layered memory film structure 5-7 may be fabricated as a continuous thin film without patterned, isolated segments. On the multi-layered memory film structure 5-7, patterned control gates 8A, 8B are formed, such as by depositing a polysilicon layer or other conductive control gate layer on the coupling dielectric 7.

In the semiconductor body/well layer 2, source/drain regions 3A-3C are formed using any desired technique. For example, the source/drain regions 3 may be formed by 15 implanting or diffusing regions with appropriate polarity dopants (for example, n-type doping). In other embodiments, the source/drain regions 3 are not formed through ion implantation as permanently conducting implant regions, but instead have their conductivity controlled by applying electric fringe-fields from the control gates 8A, 8B. For example, a large bias applied at the control gates 8A, 8B can induce conductive inversion layers in the source/drain regions 3A-3C in the same manner as a channel inversion layer forms when a transistor is turned on. These types of cells are called "junction-free" or "junctionless" cells. In such junction-free cells, the channel regions 4A, 4B and the source/drain regions 3A, 3B, 3C are only conductive if the electric field between the charge storage node 6A, 6B and the substrate 2 is sufficiently large to induce an inversion layer. This electric field is caused by a combination of the charge stored in the charge storage layer 6A, 6B and the external bias that is applied to the control gate 8A, 8B.

Turning now to FIG. 2, there is shown a simplified circuit schematic of a plurality of NAND flash memory cells view of the NAND flash memory cell transistors 11, 12 35 organized and arrayed into multiple rows and columns, where each column is connected to a respective bit line conductor (for example, BL0-BL(j+k)\*8-1) and each row is connected to a respective word line conductor (for example, WL(0)-WL (15)). As depicted, the NAND flash memory cell array 20 can be subdivided into data strings, data pages, and data blocks, as illustrated by examples of a data string 20A, data page 20B, and data block 20C.

In the depicted NAND string 20A, the cells are connected in series in a group of a predetermined numbers of cells (for example, 16, 32 or 64). To connect each string to its corresponding source line (SL) and bit line (for example, BL(j+k)\*8-2), selection transistors are placed at the edges of the string. For example, the NAND cell string 20A includes at least one string select transistor (SST, SSL gate or SSL transistor) and at least one ground select transistor (GST, GSL gate or GSL transistor). The gate of the string select transistor (SST) is connected to a string select line (SSL), while the drain of a string select transistor (SST) is connected to a bit line for the string (for example, BL(j+k) \*8–2). The gate of a ground select transistor (GST) is connected to a ground select line (GSL), while the source of the ground select transistor (GST) is connected to a source line (SL or CSL) for the string. Connected in series between the string select transistor SST and ground select transistor GST is a plurality of memory cell transistors CT(i), each having a control gate connected to a respective word line WL(i). In the depicted configuration, the NAND string 20A shares the bit line contact with another string, and any desired number of memory cell transistors may be connected in a string so that the number of cells per string may vary with 4 cells per string, 8 cells per string, 16 cells per string, 32 cells per string, 64 cells per string, 128 cells per string,

and so on. To specify a direction within the string **20**A, the direction towards the string select line SSL of a string is referred to as "drain direction" or "drain side," and the direction towards the ground select line GSL of a string is referred to as "source direction" or "source side."

In the depicted NAND page 20B, the cells are addressed by a row address to specify the smallest unit of cells for which a read or program operation can be performed. In selected embodiments, the page 20B includes the cells connected to the same word line (for example, WL(2)). In 10 other embodiments, the number of pages per word line depends upon the storage capabilities of the memory cell. For example, the cells connected to a certain word line may be subdivided into multiple subgroups so that the array 20 the multiple pages in one word line has a different row address. In the case of multiple bit storage in one physical cell, different bits can belong to different pages although they are physically located in the same cell transistor and thus connected to the same word line.

The NAND Flash array 20 may also be grouped into a series of blocks (for example, 20C). For example, the depicted NAND flash block 20C includes all strings which share the same word lines, string select lines, and ground select lines. Stated another way, a block 20C includes all 25 pages sharing the same string select lines and ground select lines. In other embodiments, different groupings of NAND flash cells may be used for the flash erase blocks. In selected embodiments, the smallest unit for which an erase operation is performed is one cell block, which is therefore often 30 named "erase block."

To illustrate the block-base erase operations for a NAND flash array, reference is now made to FIG. 3 which shows a multi-block NAND flash memory 30 which uses block and page addressing to support read, program, and erase operations. As depicted, the flash memory 30 is organizationally divided in blocks 32 and pages 34. The depicted flash memory 30 includes  $2^{M}$  blocks, though more generally, there may be power of two blocks within any flash memory. Each block (for example, Block 7) contains multiple pages 34 40 which are typically 64, 128 or more generally,  $2^N$  pages in each block. Again, a page is the smallest addressable unit for reading and writing, and may include a main area for storing data and a spare area for error correction, system pointers, and/or other information relating to the data stored in the 45 main area. Assuming that the row address contains M bits for the block address and N bits for the page address, the multi-block NAND flash memory 30 includes  $2^{M}$  erase blocks, with each block subdivided into  $2^N$  programmable pages. Each page (for example, Page 0) includes (j+k) bytes 50 (times 8 bits) which are divided into a j-byte data storage region or data field 36 and a separate k-byte area or spare field 38 which is typically used for error management functions. As seen in the embodiment of FIG. 3, one page=(j+k) bytes, one block= $2^{M}$  pages=(j+k) bytes\* $2^{M}$ , and 55 the total memory array size= $2^N$  blocks=(j+k) bytes\* $2^{M+N}$ .

As memory array sizes increase, the need to reduce manufacturing costs per data bit is driving the NAND Flash industry to continuously reduce the size of the cell transistors. Due to the limitations imposed by photolithography 60 tools and the limits of shrinking the physical transistor size, schemes have been proposed whereby NAND cells are stacked in a direction perpendicular to the chip surface. Thereby, the effective chip area per data bit can be reduced without relying on the shrinkage of the physical cell tran- 65 sistor size. Generally speaking, there are two main types of stacked NAND flash memory device architectures. First, and

as illustrated in simplified cross-sectional schematic form in FIG. 4, a vertically stacked array 40 may be fabricated with vertical channel NAND flash cell strings **42-45** formed over a substrate 41 to run in a direction that is perpendicular or orthogonal to the chip substrate 41. In the vertical channel NAND architecture, the memory cells 46 belonging to the same string are stacked vertically on top of each other, and different strings 42-45 are arranged as pillars that are laterally positioned next to one another. By convention, the device architecture for the vertically stacked array 40 may be referred to as Vertical Channel NAND or VC NAND. Second, and as illustrated in simplified cross-sectional schematic form in FIG. 5, a vertically stacked array 50 may be fabricated with vertical gate NAND flash cell strings 52-55 includes multiple pages per word line, whereby each one of 15 formed over a substrate 51 to run in a direction that is parallel to the chip substrate **51**. In this architecture, memory cells 56 belonging to the same string (for example, 52) are aligned in a direction parallel to the chip surface as in conventional planar NAND cells, but additional strings (for 20 example, **53-55**) are stacked vertically on top of each other. By convention, the device architecture for the vertically stacked array 50 may be referred to as Vertical Gate NAND or VG NAND.

> FIG. 6 illustrates a simplified perspective view of a three-dimensional vertical channel NAND flash memory array architecture 100 having upper layer connection lines 120, 130, 140, 150 formed over a plurality of vertical channel NAND flash cell strings 103 with surrounding multilayered memory film structures 104 and stacked cell and select gate structures 108-110, where each upper layer connection line includes n-type bit line nodes and p-type body nodes for connection to the underlying flash cell strings 103. In the VC NAND flash memory 100, the plurality of NAND flash cell strings (e.g., 103A-D) are arranged in a matrix of rows (e.g., 103A/104A, 103B/104B, 103C/104C, 103D/104D) and columns (e.g., 103A/104A, 103E/104E, 103I/104I, 103M/104M). As formed, the NAND flash cell strings 103 extend vertically from a source diffusion layer 102 in a chip substrate 101 and through separate stacks of conductive layers (e.g., 108A-D, 109A, 110A) separated from one another by insulating layers (not shown) for direct connection to upper layer connection lines 120, 130, 140, 150. As described hereinbelow, each NAND string may be formed with a cell body layer (for example, a cylindrical polysilicon layer 103A) in which channels are formed to run in a vertical direction that is perpendicular to the chip surface, with different NAND strings (for example, cylindrical polysilicon layers 103B, 103C) being laterally separated from each other and arranged in a matrix shape when viewed from a top plan view. In addition, each cell string includes a bottom or vertical pillar portion 103-V and a top or horizontal cap portion 103-H. The bottom pillar portion 103-V is directly connected to the source diffusion layer 102 in the chip substrate 101, is shaped like a tube that wraps around a non-conductive dielectric core 115, and is surrounded by a multilayered memory film structure 104. The horizontal cap portion 103-H is directly connected to the bottom pillar portion 103-V and is formed as part of an upper layer connection line (e.g., 120) to make direct electrical connection to a bit line contact region and body line contact region formed therein.

> In the illustrated example, the cell transistors formed along each silicon flash cell string (for example, 103A-D) are formed as gate-all-around devices by forming stacked word line gate structures 108A-D with multi-layered memory film structure 104A-D to surround the silicon flash cell string with cell transistor gates where each cell channel

is formed. In addition, separate stacks of word line gate structures 108E-H, 108I-L, 108M-P may be formed around other groups of flash cell strings (e.g., 103E/104E, 103I/ 104I, 103M/104M). Though not separately shown, it will be appreciated that each multi-layered memory film structure 5 104 formed around each string 103 for each memory cell transistor may include a tunnel dielectric layer formed to surround the channel region of the silicon strip, a charge storage layer (for example, silicon nitride) formed around the tunnel dielectric layer, and a coupling dielectric formed 10 around the charge storage layer. Around each multi-layered memory film structure (e.g., 104A-D), a stack of word line gate structures (e.g., 108A-D) may be formed with one or more patterned polysilicon layers to extend across multiple strings (e.g., 103A-D). While the transistors formed in each 15 silicon string may include implanted and/or diffused source/ drain regions (for example, n+ regions) for each defined transistor cell, in other embodiments, the transistors formed in at least the bottom or vertical pillar portion 103-V may be formed as junction-free cells with virtual source/drain 20 regions formed to have conductivity that depends on the existence of electric fringe fields between gates adjacent to the source/drain regions and the source/drain silicon itself.

In addition to the stacked word line gate structures (e.g., **108**A-D) defining multiple memory cells, each string may 25 also include additional gate structures on each end of the string to define ground and string select line transistors. For example, ground select line transistors may be formed as a lower select gate at the bottom of each string with separate poly gate structures (e.g., 110A) which connect the source 30 node of each vertical flash cell string (e.g., 103A-D) to a shared or common source line diffusion 102 formed in the substrate 101. In addition, string select transistors may be formed as an upper select gate at the top of each vertical flash cell string (e.g., 103A-D) with separate poly gate 35 structures (e.g., 109A) which connect the drain nodes of each vertical flash cell string (e.g., 103A-D) to a corresponding drain region formed in the upper layer connection line (e.g., 120) which is electrically connected to a bit line (e.g., **163**) of the cell array under control of a string select signal. 40 In this way, the source nodes of all strings in a designated block are connected to the shared source line 102 in the substrate 101, but the drain nodes of each string (e.g., 103A) is shared only horizontally with other strings in a first lateral direction (e.g., 103E, 103I, 103M) via a shared bitline (e.g., 45 163), but not with strings in a second lateral direction. If desired, the ground and string select transistors may be formed as gate-all-around devices substantially as described above. For example, the string select transistor at the drain node of each string may be formed with a poly gate structure 50 (for example, 109A-D) formed around a multi-layered memory film structure (e.g., 104A, 104E, 104I, 104M), while the ground select transistor at the source node of each string may be formed with a poly gate structure (e.g., 110A-D) formed around the corresponding multi-layered 55 memory film structure.

As depicted in FIG. 6, the vertical channel NAND flash memory array 100 includes NAND flash strings 103 which run in the z-direction, where each string includes string select transistors formed with string select gates/lines 109, 60 cell transistors formed with cell control gates 108, and ground select transistors formed with ground select gates 110. In each NAND flash string, the transistors are serially connected with the string select transistor located at the top, the cell transistors in the middle, and the ground select 65 transistor at the bottom of the string. As described more fully hereinbelow, each string select transistor includes a drain

**10**

region (shown in dark grey) formed in the upper layer connection line (e.g., 120) which is electrically connected to a bit line (e.g., 163) of the cell array, and a source which is connected to one of the multiple series-connected cell transistors in the associated NAND flash string. In addition, each ground select transistor has a source that is directly electrically connected to the source line region 102, and a drain which is connected to one of the multiple series-connected cell transistors in the associated NAND flash string. String select transistors, cell transistors and ground select transistors have gates connected to string select lines 109, word lines 108, and ground select lines 110, respectively, each running in the x-direction.

Each NAND flash string is formed with a semiconductor body 103 which is shared by the string select, cell, and ground select transistors belonging to that string 103. In selected embodiments, each NAND flash string has a shape which resembles a cylinder or vertical pillar so that the string body or channel runs along the long axes of the cylinders in the z-direction. As shown more clearly in FIG. 12, each transistor may include a semiconductor body 103 having a near-circular or elliptical cross section so that each gate electrode forms a gate-all-around type gate structure. In selected embodiments, such strings can be fabricated within vertical, cylinder-shaped memory "holes" cutting through stacked alternating layers of conductive gate material 108-110 and interlayer dielectrics by sequentially forming layers inside the "memory hole," including a gate dielectric or multi-layered memory film structure 104, semiconducting string body thin film 102 (e.g., polysilicon), and dielectric filler material 115 (e.g., silicon oxide). In selected embodiments, the memory film structure 104 may be formed with an outermost blocking (or coupling) dielectric, an inner charge storage layer, and an innermost tunnel dielectric. In addition, the string select transistors and ground select transistors may have the same basic structure as the cell transistors, though a gate dielectric layer may replace the memory film structure 104 in the case of the string select transistor and/or ground select transistor since these transistors do not store any data.

When a transistor is turned on, a conductive channel of a first conductivity type (for example n-type) is formed in the transistor body 103. When all transistors of a string are turned on during a read or program operation, a continuous conductive channel of the first conductivity type forms throughout the entire string 103 from the string drain to the string source, thereby forming a conductive path from a bit line to a source line node. During an erase operation, the string body 103 is charged with a high positive voltage (e.g., 18V-20V), thereby inducing a second, opposite conductivity type (for example p-type). To control the different read, program, and erase modes, each cell string has four different terminals to which external voltages can be applied: a drain terminal (bit line node) in the upper layer connection line, a source terminal (source line node) in the substrate, a body terminal (body line) in the upper layer connection line, and multiple gate terminals 108-110 which are the gate terminals of string select transistors, cell transistors and ground select transistors.

By forming each word line gate structure (e.g., 108A) to extend horizontally across separate multi-layered memory film structures (e.g., 104A-D) surrounding the vertical channel NAND flash cell strings (e.g., 103A-D), separate word line (WLi) signals may be connected across the word line gate structure 108A to cell transistors in the adjacent flash cell strings in a first horizontal or lateral direction that share the poly gate node 108A. Bit lines can also be shared by one

or more adjacent flash cell strings formed in a second horizontal or lateral direction (for example, 103E, 103I, 103M) by connecting the strings through bit line contact regions in the upper layer connection line (e.g., 120) to a shared bit line (for example, 163) which is used to establish 5 electrical connection from the connected strings to the common bit line through one or more via contacts or conductors 163V1-3. As illustrated, each of the bit line conductors 163-165 is connected to bit line contact regions in a corresponding upper layer connection line 120, 130, 10 140, 150) through via contacts or conductors. By the same token, separate body charging voltages may be connected to adjacent flash cell strings in a first horizontal or lateral direction that share a body line conductor (e.g., 161) by connecting the strings through body contact regions in the 15 upper layer connection lines (e.g., 120, 130, 140, 150) to the shared body line (for example, 161) through one or more via contacts or conductors (e.g., 161V3-4) which apply a voltage for holding the body nodes of the connected strings at a predetermined or low voltage.

The depicted vertical channel NAND flash memory 100 illustrates selected example embodiments of a three-dimensional vertical channel NAND flash memory array which allows individual pages to be selected for read and program operation and which may erase selected blocks in a VG 25 NAND structure using the upper layer connection lines 120, 130, 140, 150 to connect bit line and erase voltages to the flash cell strings. However, it will be appreciated that a vertical channel NAND flash memory may be implemented with different features and structures. For example, the cell 30 string structures are described has having a dielectric filler at the core of the vertical pillar structures, but such structures are not functionally required in all embodiments. In addition, the different semiconductor structures, such as the flash strings or transistor gates, may be formed with polysilicon or 35 with any desired semiconductor material. There are also numerous variations in the charge storage structures used to store charge in NAND flash devices, such as, for example, floating gate devices, charge-trap devices, etc. And while the string bodies may be formed with implanted p-type semi- 40 conductor material, selected embodiments may form the string bodies with undoped or even lightly n-type doped semiconductor material, such as silicon. Even in these cases, the conductivity type may be controlled during read/program or erase operation by way of external biasing condi- 45 tions. It will also be appreciated that the vertical channel NAND flash memory 100 shown in FIG. 6 shows conductive elements, such as interconnections, contacts, string bodies and gate material, to highlight the connectivity of the constituting elements, but not isolating materials such as 50 gate dielectrics, interlayer dielectrics, intermetal dielectrics, etc. Persons skilled in the art will understand that dielectric layers are located around the conductor elements to provide electrical isolation.

Turning now to FIGS. 7-14, there are provided various 55 plan and cross-sectional views of the cell structures in the vertical channel NAND flash memory array 100 shown in FIG. 6 which reference x, y, and z axis directions. In these figures, a direction along an x-axis refers to a direction parallel to the word lines 108, a direction along a y-axis 60 refers to a direction parallel to bit lines 163-165, and a direction along a z-axis refers to a direction perpendicular to the surface of the chip substrate 101. For example, FIG. 7 illustrates a plan view 100A of a plurality of upper layer connection lines 120, 130, 140, 150 shown in FIG. 6 in 65 accordance with selected embodiments of the present disclosure. For ease of illustration, the contact vias and metal

12

lines which connect to these regions are not shown. The illustrated top view 100A of the stacked cell array structure shows that each upper layer connection line includes a plurality of semiconductor regions having different conductivity types. For example, a first upper layer connection line 120 includes drain regions 121, 125, 129 of a first conductivity type (e.g., N+) and body line regions 123, 127 of a second, opposite conductivity type (e.g., P+) which are alternately disposed on each side of undoped or lightly doped string body regions 122, 124, 126, 128. In similar fashion, the other upper layer connection lines 130, 140, 150 likewise include first conductivity type drain regions (e.g., 151, 155, 159) and second conductivity type body line regions (e.g., 153, 157) alternately disposed on each side of string body regions (e.g., 152, 154, 156, 158).

In selected embodiments, the upper layer connection lines 120, 130, 140, 150 may be formed with different polysilicon film regions (e.g., 121-129) which each include lightly 20 doped (or undoped) string body cap regions (shown in cross-hatch), string drain regions (shown in dark grey), and body line contact regions (shown in light gray). The string body cap regions (e.g., 122, 124, 126, 128, 152, 154, 156, 158) are positioned and aligned for connection to underlying vertical flash cell strings (e.g., 103M, 103I, 103E, 103A, **103**P, **103**L, **103**H, **103**D), and may be formed with a lightly doped or undoped semiconductor material (e.g., polysilicon) that is not permanently n-type or p-type conductive or permanently insulating, and may include either n-type or p-type sub-regions depending on externally applied voltage conditions. For example, the string body cap regions (e.g., 122, 124, 126, 128, 152, 154, 156, 158) may be lightly doped with p-type dopants and may therefore be of p-type conductivity at times when transistors are in a turned-off state. In similar fashion, the string drain regions (e.g., 121, 125, 129, 151, 155, 159) may be formed with polysilicon film regions having permanent n-type conductivity to form string drains for underlying vertical flash cell strings connected thereto (e.g., 103M, 103I, 103E, 103A, 103P, 103L, 103H, 103D). In addition, the body line contact regions (e.g., 123, 127, 153, 157) to form body line contact regions for underlying vertical flash cell strings connected thereto (e.g., 103M, 103I, 103E, 103A, 103P, 103L, 103H, 103D). The conductivity type and concentrations for the string body cap regions, string drain regions, and body line contact regions may be controlled by using patterning mask and implantation techniques to selectively implant ions of the desired conductivity type and amount into the target regions.

To illustrate additional structural details of the vertical channel NAND flash memory shown in FIG. 6, reference is now made to FIG. 8, which illustrates a vertical crosssectional view 100B taken in a bit line direction through an upper layer connection line 120 indicated with the 8-8' view line shown in FIG. 7. As illustrated, a row of NAND flash strings 103A, 103E, 103I, 103M and surrounding multilayered memory film structures 104A, 104E, 104I, 104M extend from the substrate source line 102, through the stacked cell and select gate structures 108-110, and to the upper layer connection line 120. In particular, a first NAND flash string 103A is surrounded by a gate dielectric layer 107A, memory film structure 104A, and upper gate dielectric layer 106A and extends through stacked gate structures 110A, 108A, 108B, 108C, 108D, and 109A. Likewise, NAND flash strings 103E, 103I, 103M and surrounding gate dielectric layers 106A, memory film structures 104E, 104I, 104M, and upper gate dielectric layer 106A extend through stacked gate structures 110B/108E-H/109B, 110C/108I-L/

**109**C, and **110**D/**108**M-P/**109**D. Each NAND flash string includes a first vertical portion 103-V and a second horizontal portion 103-H.

The first vertical portion of each string 103A, 103E, 103I, 103M may be shaped as a hollow (or optionally filled) 5 cylindrical semiconductor tube surrounding a dielectric fill layer 115A, 115E, 115I, 115M, that is directly electrically connected to the n-type source line region 102 formed in the substrate 101. Each vertical string portion runs between the string source line 102 and the uppermost vertical portion 10 adjacent to the string select transistor gates 109A, 109B, 109C, 109D. The uppermost part of the first vertical portion 103-V is therefore controlled by the sidewall-facing portion of the corresponding string select transistor 109A, 109B, 109C, 109D.

The second horizontal portion 103-V of each string 103A, 103E, 103I, 103M is formed with the string body regions **122**, **124**, **126**, **128** in the upper layer connection line **120** to be located above the string stack and facing the upper side of the corresponding string select transistor 109A, 109B, 20 **109**C, **109**D. The second horizontal portion faces the corresponding string select transistor gate 109A, 109B, 109C, 109D across the gate dielectric 106A, and is therefore controlled by the upward-facing portion of the string select transistor 109A, 109B, 109C, 109D in the same way the 25 vertical portions of the string select transistor channels are controlled. Formed as part of the upper layer connection line 120, the second horizontal portion 103-V of each string 103A, 103E, 103I, 103M is directly connected to a corresponding drain region 121, 125, 129 (shown in dark grey) 30 having a permanent first conductivity type (e.g., N+) to function as a string drain region. In read and program operations for the strings 103A, 103E, 103I, 103M, each drain region 121, 125, 129 is connected to a shared bit line 163V1-3. The second horizontal portion 103-V of each string 103A, 103E, 103I, 103M is also directly electrically connected to a corresponding body line region 123, 127 of a second, opposite conductivity type (e.g., P+) (shown in light grey). During erase operations for the strings 103A, 40 103E, 103I, 103M, each body line region 123, 127 is connected to a corresponding body line 161, 162 through one or more corresponding interconnect or via structures 161V4, 162V4.

To illustrate additional structural details of the vertical 45 channel NAND flash memory shown in FIG. 6, reference is now made to FIG. 9, which illustrates a lateral crosssectional view 100C taken in the x-y plane through a plurality of transistor gate word lines 108D, 108H, 108L, **108**P indicated with the **9-9**' view line shown in FIG. **8**. As 50 illustrated, each word line may be formed with a patterned layer of conductive material, such as doped polysilicon, which is shared by a plurality of NAND flash strings aligned in the x-axis direction. In particular, a first transistor gate word line 108D extends horizontally across a row of NAND 55 flash strings 103A-D, each of which is formed around a corresponding dielectric core 115A-D and surrounded by a corresponding multi-layered memory film structure 104A-D, thereby forming a gate-all-around type gate electrode 108D. In the same layer, a second, separate transistor gate 60 word line 108H extends horizontally across another row of NAND flash string structures 103E-H/115E-H/104E-H. In addition, a third transistor gate word line 108L extends horizontally across another row of NAND flash string structures 103I-L/115I-L/104I-L, and a fourth transistor gate 65 word line 108P extends horizontally across another row of NAND flash string structures 103M-P/115M-P/104M-P. As

14

will be appreciated, the same layout and arrangement of transistor gate word lines shown in FIG. 9 could be used for other levels in the stacked array, including other transistor gate word lines, ground select transistor lines, and/or string select transistor lines.

To illustrate additional structural details of the vertical channel NAND flash memory shown in FIG. 6, reference is now made to FIG. 10, which illustrates a vertical crosssectional view 100D taken in a word line direction through a row of NAND flash strings 103E-H indicated with the 10-10' view line shown in FIG. 7. As illustrated, a row of NAND flash strings 103E-H and surrounding multi-layered memory film structures 104E-H aligned in the x-axis direction extend from the substrate source line 102, through the 15 stacked cell and select gate structures 110B, 108E-H, 109B, and to the string body regions 126, 136, 146, 156 in the upper layer connection lines 120, 130, 140, 150. In particular, a first NAND flash string 103E is surrounded by a gate dielectric layer 107E, memory film structure 104E, and upper gate dielectric layer 106H, and extends through stacked gate structures 110B, 108E-H, 109B. Likewise, NAND flash strings 103F, 103G, 103H and surrounding gate dielectric layers 106H, memory film structures 104F, 104G, 104H, and upper gate dielectric layer 106H extend through stacked gate structures 110B, 108E-H, 109B. Again, each NAND flash string 103E-H includes a first vertical portion 103-V and a second horizontal portion 103-H formed with the string body regions 126, 136, 146, 156 from the upper layer connection lines 120, 130, 140, 150.

To illustrate additional structural details of the vertical channel NAND flash memory shown in FIG. 6, reference is now made to FIG. 11, which illustrates a vertical crosssectional view 100E taken in a word line direction indicated with the 11-11' view line shown in FIG. 7. As illustrated, 163 through one or more interconnect or via structures 35 body line regions 127, 137, 147, 157 from the upper layer connection lines 120, 130, 140, 150 are formed over the substrate 101 and source line region 102, and are connected across interconnect or via structures 161V1-3 to an associated body line (e.g., Body Line <0> 161) which runs orthogonally in the x-axis direction below the bit lines 163-166. The body line regions 127, 137, 147, 157 are aligned in the x-axis direction between the adjacent rows of NAND flash strings 103A-D, 103E-H (not shown), and are used to connect the adjacent strings to the associated body line (e.g., Body Line <0> 161). For example, the body line region 127 from upper layer connection line 120 is directly electrically connected to the string body regions 128, 126 for NAND flash strings 103A, 103E to function as an active body line during erase operations when an erase voltage from the body line 161 is applied through one or more interconnect or via structures 163V4. The same erase voltage from the body line 161 may be applied through one or more additional interconnect or via structures 161V1-3 to body line regions 137, 147, 157 in other upper layer connection lines 130, 140, 150, and in turn to the NAND flash strings 103B-D, 103F-H respectively connected thereto.

To give a clearer understanding of the three-dimensional shape of the portions of the device which consist of semiconducting material, reference is now made to FIG. 12, which shows a partial perspective view 100F of the semiconductor portions of the vertical channel NAND flash memory structure shown in FIG. 6 to show the connection of the semiconductor string bodies 103A, 103E between the substrate 101 and upper layer connection line 120. In particular, the upper layer connection line 120 includes n-type conductivity regions 125, 129 which are electrically connected to contact vias and metal bit lines (not shown). In

addition, the upper layer connection line 120 includes p-type conductivity regions 127 that are electrically connected to contact vias and metal body lines (not shown) which are different from the bit lines. Finally, the upper layer connection line 120 includes undoped or lightly doped string body 5 regions 126, 128 which are formed between the n-type conductivity regions 125, 129 and p-type conductivity regions 127 as a top or horizontal cap portion 103-H of each string. Extending down form the horizontal cap portions 126, 128, each string 103A, 103E includes a vertical cylinder shaped portion 103-V which is connected directly to the N+ source layer 102 in the substrate 101. Although the n-type regions, p-type regions, and lightly doped (or undoped) regions have been described as separate entities, it will be appreciated that they may be connected with each 15 other in a continuous thin polysilicon film 125-129 which may be deposited in the same fabrication step, and then doped with different doping type ions to delineate separate regions of different conductivity types. For example, selected example embodiments of each upper layer connec- 20 tion line may include horizontal portions that are laterally patterned along semiconductor strips formed over the stacked array to have a long axis along the bit line direction (y-axis) and a short axis along the word line direction (x-axis) so as to be electrically isolated from each other. In 25 this way, the n-type conductivity drain regions 125, 129 formed in the upper layer connection line 120 are isolated from adjacent n-type drain regions (e.g., 139, 135) in the x-direction. However, multiple n-type drain regions belonging to the same strip 120 are connected to the same bit line 30 (not shown), while the n-type drain regions belonging to different strips (in other words have different x-coordinates) are connected to different bit lines. Therefore, strings share bit lines in the y-direction as in most known NAND Flash devices, but not in the x-direction.

In operation, selected embodiments of the vertical channel NAND flash memory array 100 described herein are operative to perform basic read, program, and erase operations using the cell structures disclosed herein. Examples of such operations will now be provided with reference to 40 FIGS. 13 and 14 which illustrate selected examples of device operation. However, the following description is not intended to be an exhaustive description of the device operation including all possible scenarios, but is instead provided to illustrate example read/program and erase 45 operations to illustrate ways in which electrical paths are formed in the VC NAND flash memory array 100.

Turning now to FIG. 13, there is shown a partial crosssectional view 100G of the vertical channel NAND flash memory shown in FIG. 8 during selection of a flash cell 50 string for a read operation. As illustrated, the leftmost string 103A is selected as the string 190 from which data will be read by applying appropriate voltages to the string terminals. In particular, a positive read voltage (e.g., Vcc=1.8V) is applied to the bit line 163, and a positive read pass voltage 55 (e.g., 4.5V) is applied to the gates of all string select, memory cell, and ground select transistors on the selected string 190, except for the one cell transistor which is intended to be read. In addition, a read voltage (e.g., 0V) is applied to the word line gate for the cell transistor to be read, 60 and a holding voltage (e.g., 0V) is applied to body line 161 for the selected string 190 to hold the body node 103A of the string at a low voltage. Since the uppermost select transistor of the selected string 190 (a.k.a., string select transistor) is turned ON by application of the read pass voltage to gate 65 conductor 190A, its channel is in an n-type conductive state. As described hereinabove, the channel of the uppermost

**16**

string select transistor includes a vertical conducting portion 190-V and a horizontal conducting portion 190-H since the conductive n-type inversion layer is induced by the gate conductor 190A in both the horizontal and vertical portions of the string body 103A. The horizontal portion of the induced n-type channel **190**-H is electrically connected to a drain region 129 of permanent n-type impurity, and thus also to the bit line 163 across the interconnect/via structure(s) 163V1. As a result, all transistors in the selected string 190 are turned ON to establish a continuous conducting channel throughout the selected string 190 from the bit line 163 to the source line **102**. This conduction state is indicated by the darker grey color of the selected string 190. In other read scenarios, it will be appreciated that the conductive n-type string channel may extend only partway down the string 103 from the string drain/bit line node 129 to the cell intended to be read. Thus, the illustrated example serves only to show that the conductive string channel connects through the vertical and horizontal portions of the string select transistor to the permanent n-type drain region 129 in the upper layer connection line 120. In similar fashion, program operations for a selected string (e.g., 190) may form a conductive string channel from the n-type drain region 129 in the upper layer connection line 120 through the horizontal and vertical channel portions of the string select transistor in the same manner as during read operation.

Turning now to FIG. 14, there is shown a partial crosssectional view 100H of the vertical channel NAND flash memory shown in FIG. 8 during erasure of a block of flash cell strings 191-194. As illustrated, the strings are erased by applying external biasing voltages to the string terminals. In particular, the bodies of all strings 191-194 may be charged with a high positive erase voltage V\_erase (e.g., 18-20 V) that is applied from the body line conductors 161, 162 and associated interconnect/via structures 161V4, 162V4 and through the body line contact regions 127, 123 in the upper layer connection line 120. In addition, the word lines of cell blocks intended to be erased may be held at a low voltage (e.g., 0V) while the bit lines (e.g., 163) and source lines (e.g., 102) may be left floating, but may nonetheless passively charge up through forward biased p-n junctions at the boundaries between string source/drains and string bodies up to a certain voltage (e.g., V\_erase reduced by the built-in junction potential). By applying the erase voltage V\_erase to the string bodies 191-194 using body lines 161, 162 which are connected to the permanently p-type conductive regions 127, 123 of the upper layer connection line 120, the p-type conductive string bodies during erase operation are in direct contact with the permanently p-type conductive regions 127, 123, thereby forming a single node with the string bodies without any n-p junction in between. As a result, the application of the erase voltage V\_erase to the body lines 161, 162 charges the string bodies 191-194 with the erase voltage V\_erase at the same time.

While any desired fabrication sequence may be used to form the vertical channel NAND flash memory structures disclosed herein, the manufacturing process may include an initial step of forming a NAND flash memory cell array in which transistors are vertically stacked on NAND flash strings arranged in a matrix pattern to extend up from a substrate. For example, alternating layers of polysilicon and dielectric insulator layers may be deposited, patterned, and selectively etched to define a laminated stack of patterned gate conductor layers over a substrate. In the laminated stack, a matrix pattern of memory holes may be selectively etched down to the substrate, and then sequentially filled with memory film structure layers and semiconductor body

layers to thereby form the vertical channel NAND flash strings. Over the VC NAND flash strings, a plurality of body connection layer strips may then be formed with alternating n-type drain and p-type body contact regions surrounding undoped or lightly doped string body regions which are 5 positioned and connected to underlying vertical string structures. Subsequently, additional interconnect structures are formed to connect bit line conductors to the n-type drain contact regions, and to connect body line conductors to the p-type body contact regions.