## US00RE47456E

# (19) United States

## (12) Reissued Patent

## Kobayashi

## (10) Patent Number:

US RE47,456 E

## (45) Date of Reissued Patent:

Jun. 25, 2019

# (54) PATTERN TRANSFER APPARATUS AND METHOD FOR FABRICATING SEMICONDUCTOR DEVICE

- (71) Applicant: **Toshiba Memory Corporation**, Tokyo (JP)

- (72) Inventor: Yuji Kobayashi, Mie (JP)

- (73) Assignee: Toshiba Memory Corporation, Tokyo

(JP)

- (21) Appl. No.: 15/143,264

- (22) Filed: Apr. 29, 2016

## Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 8,709,955

Issued: Apr. 29, 2014

Appl. No.: 13/422,942

Filed: Mar. 16, 2012

## (30) Foreign Application Priority Data

(51) **Int. Cl.**

G03F 7/00 (2006.01) B82Y 10/00 (2011.01) B82Y 40/00 (2011.01) H01L 21/302 (2006.01)

(52) **U.S. Cl.**

CPC ...... *G03F 7/0002* (2013.01); *B82Y 10/00* (2013.01); *B82Y 40/00* (2013.01)

(58) Field of Classification Search

CPC ...... G03F 7/0002; B82Y 10/00; B82Y 40/00 See application file for complete search history.

## (56) References Cited

### U.S. PATENT DOCUMENTS

| 7,802,978    | B2         | 9/2010  | Sreenivasan et al.        |

|--------------|------------|---------|---------------------------|

| 7,878,791    | B2 *       | 2/2011  | Simon et al 425/345       |

| 2005/0230346 | <b>A</b> 1 | 10/2005 | Kasumi et al.             |

| 2006/0192928 | A1*        | 8/2006  | Kasumi et al 355/30       |

| 2008/0018875 | <b>A</b> 1 | 1/2008  | Schram et al.             |

| 2008/0254626 | A1*        | 10/2008 | Kasumi et al 438/689      |

| 2009/0047606 | <b>A</b> 1 | 2/2009  | Schram et al.             |

| 2010/0078840 | A1*        | 4/2010  | Kawakami et al B82Y 10/00 |

|              |            |         | 264/40.1                  |

| 2010/0233377 | A1*        | 9/2010  | Aoki et al 427/355        |

| 2010/0244326 | A1*        | 9/2010  | Tokue B29C 43/021         |

|              |            |         | 264/409                   |

|              |            |         |                           |

## (Continued)

## FOREIGN PATENT DOCUMENTS

| JP | 08-051052   | 2/1996  |

|----|-------------|---------|

| JP | 8-51052     | 2/1996  |

| JP | 2005-286061 | 10/2005 |

|    |             |         |

(Continued)

Primary Examiner — Carlos N Lopez (74) Attorney, Agent, or Firm — Finnegan, Henderson, Farabow, Garrett & Dunner, L.L.P.

## (57) ABSTRACT

A pattern transfer apparatus according to one embodiment includes a transfer region selecting part that performs operation in which when performing pattern transfer from a template provided with N transfer regions (N is an integer of 2 or larger) to a transferring substrate a plurality of times, 1 to N-1 transfer regions, which are to be used to perform the transfer to regions of the transferring substrate corresponding to part of the N transfer regions, are selected such that the number of the transfer to be performed using each of the N transfer regions is evened out.

## 51 Claims, 5 Drawing Sheets

## US RE47,456 E

Page 2

## (56) References Cited

## U.S. PATENT DOCUMENTS

2011/0189329 A1 8/2011 Miller et al. 2014/0072202 A1\* 3/2014 Ogawa ....... G01N 21/956 382/145

## FOREIGN PATENT DOCUMENTS

| JP | 2010-041050 | 2/2010 |

|----|-------------|--------|

| JP | 2010-41050  | 2/2010 |

| JP | 2010-145785 | 7/2010 |

<sup>\*</sup> cited by examiner

FIG.3A

FIG.3B

FIG.4A

FG4B

FIG.5A

# PATTERN TRANSFER APPARATUS AND METHOD FOR FABRICATING SEMICONDUCTOR DEVICE

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held 10 invalid by a prior post-patent action or proceeding.

# CROSS-REFERENCE TO RELATED APPLICATIONS

This [application] is a reissue of U.S. Pat. No. 8,709,955, issued on Apr. 29, 2014 from U.S. patent application Ser. No. 13/422,942, which is based upon and claims the benefit of priority from Japanese Patent Application No. 2010-189465, filed on Aug. 31, 2011[; the]. The entire contents of [which] the above-identified applications are incorporated herein by reference.

#### **FIELD**

Embodiments described herein relate generally to a pattern transfer apparatus and methods for fabricating a semiconductor device.

### BACKGROUND

Attention is being given to a nanoimprinting method in which a pattern formed at an original plate is transferred to transferring substrates in a semiconductor device fabrication process. The nanoimprinting method is a method in which an original plate at which a pattern to be transferred is formed (i.e., a template) is pressed on a resist layer of an imprinting material applied on a substrate, and then the resist layer is cured to transfer the pattern to the resist layer. In the nanoimprinting pattern formation method, breakage and defects sometimes occur at templates since imprinting is done by firmly pressing the templates to wafers.

## BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a schematic perspective view of a pattern transfer apparatus according to a first embodiment;

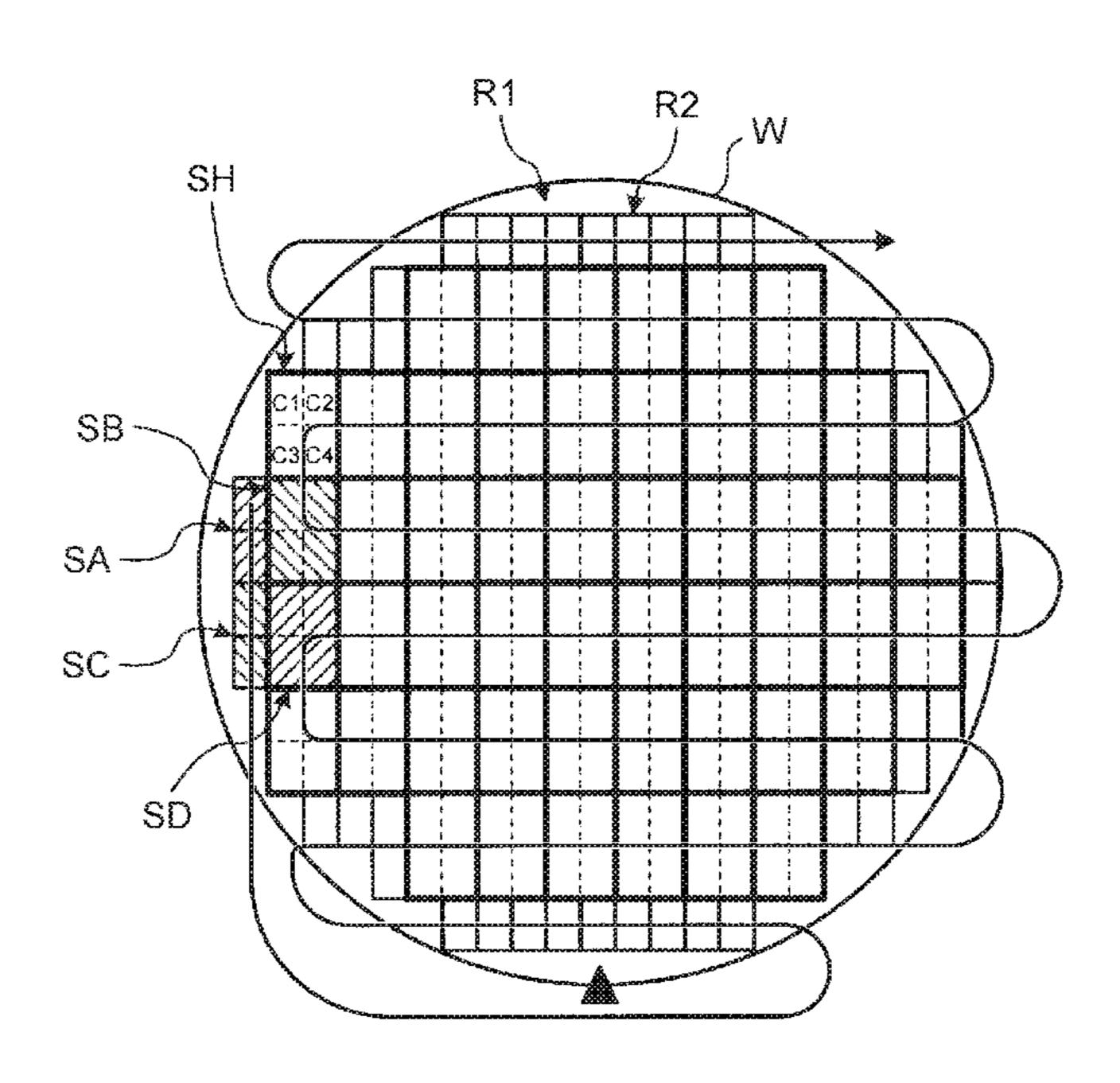

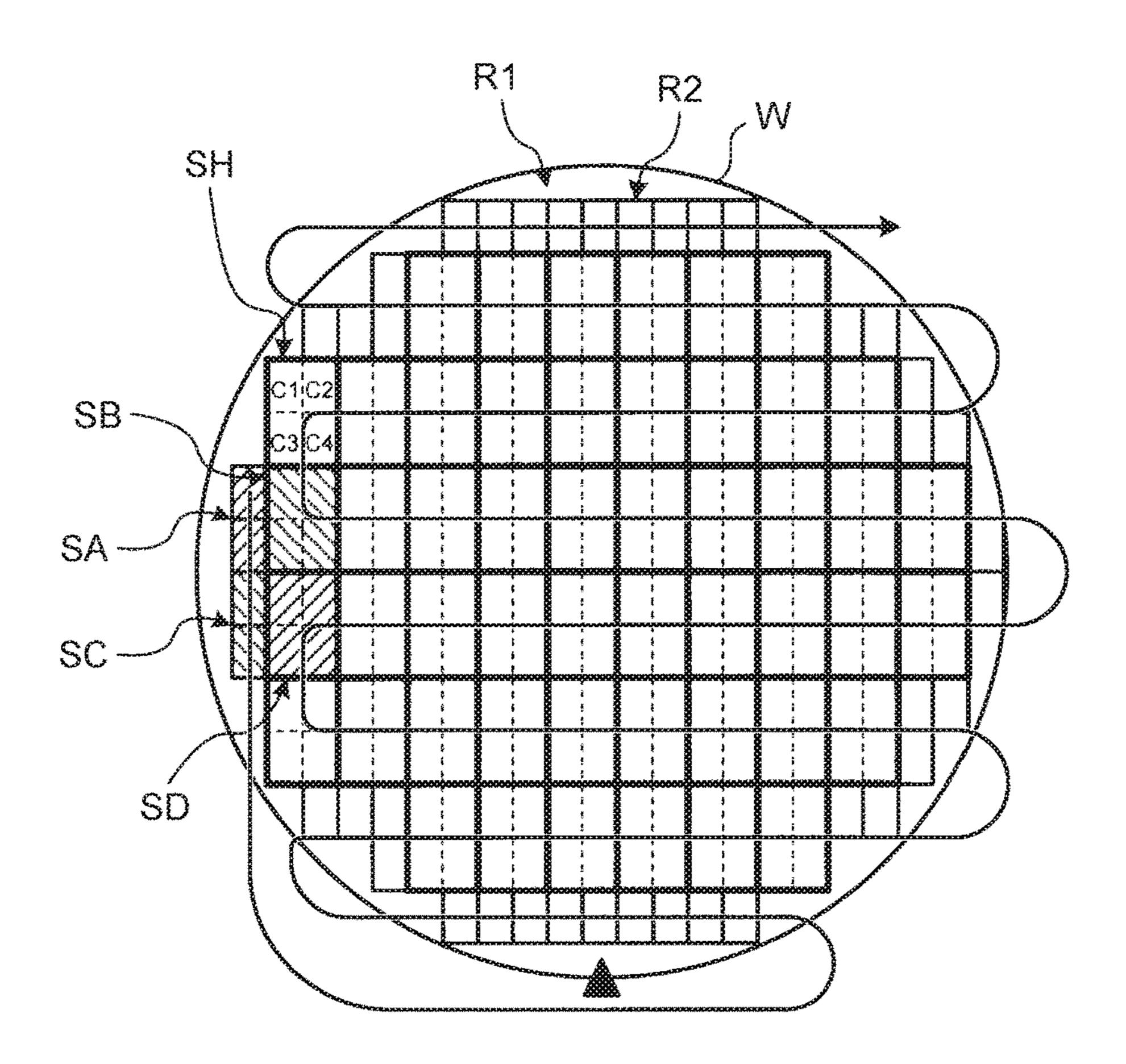

FIGS. 2A and 2B are plan views of a template and a wafer in the pattern transfer apparatus of FIG. 1 illustrating the relationship between the template and the shot regions of the wafer;

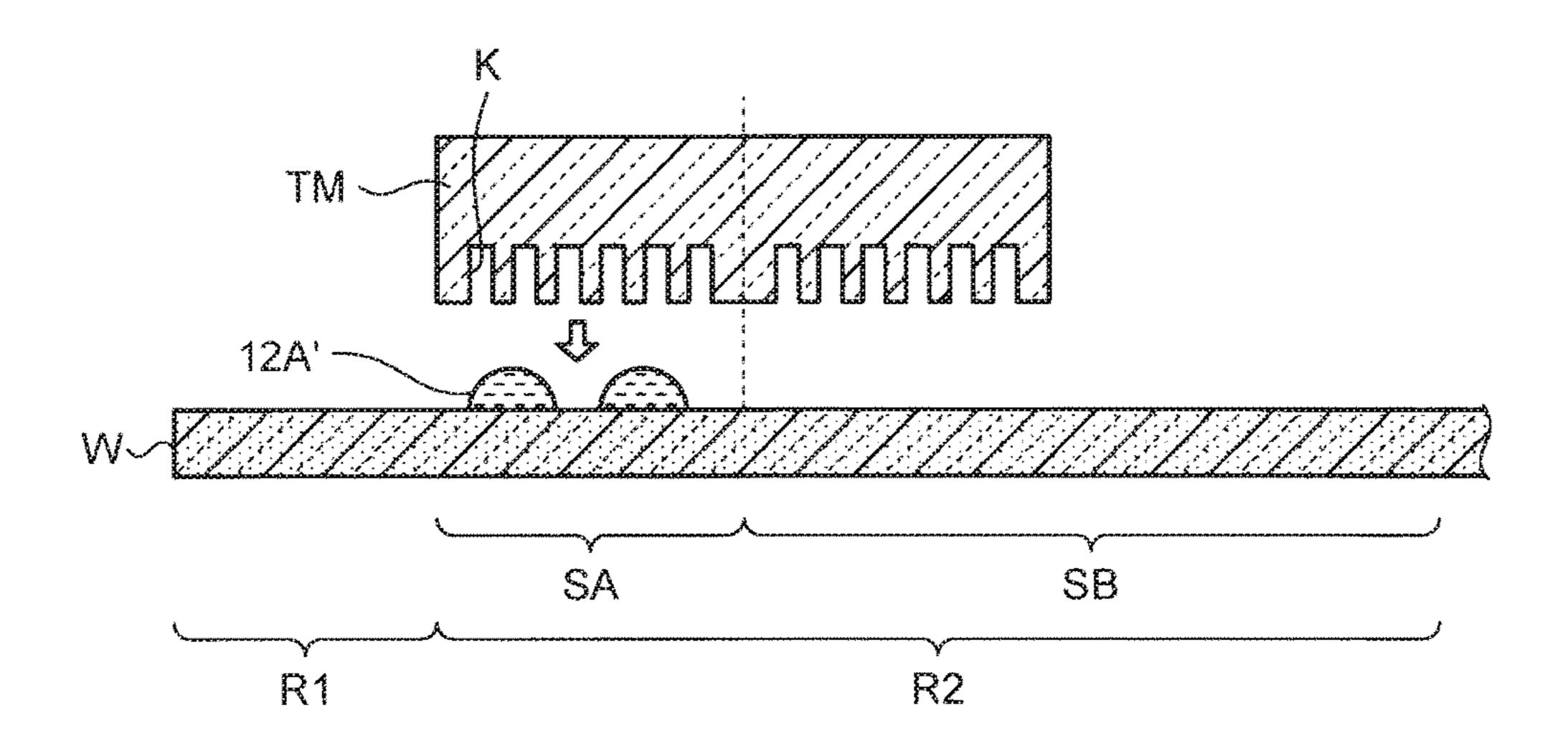

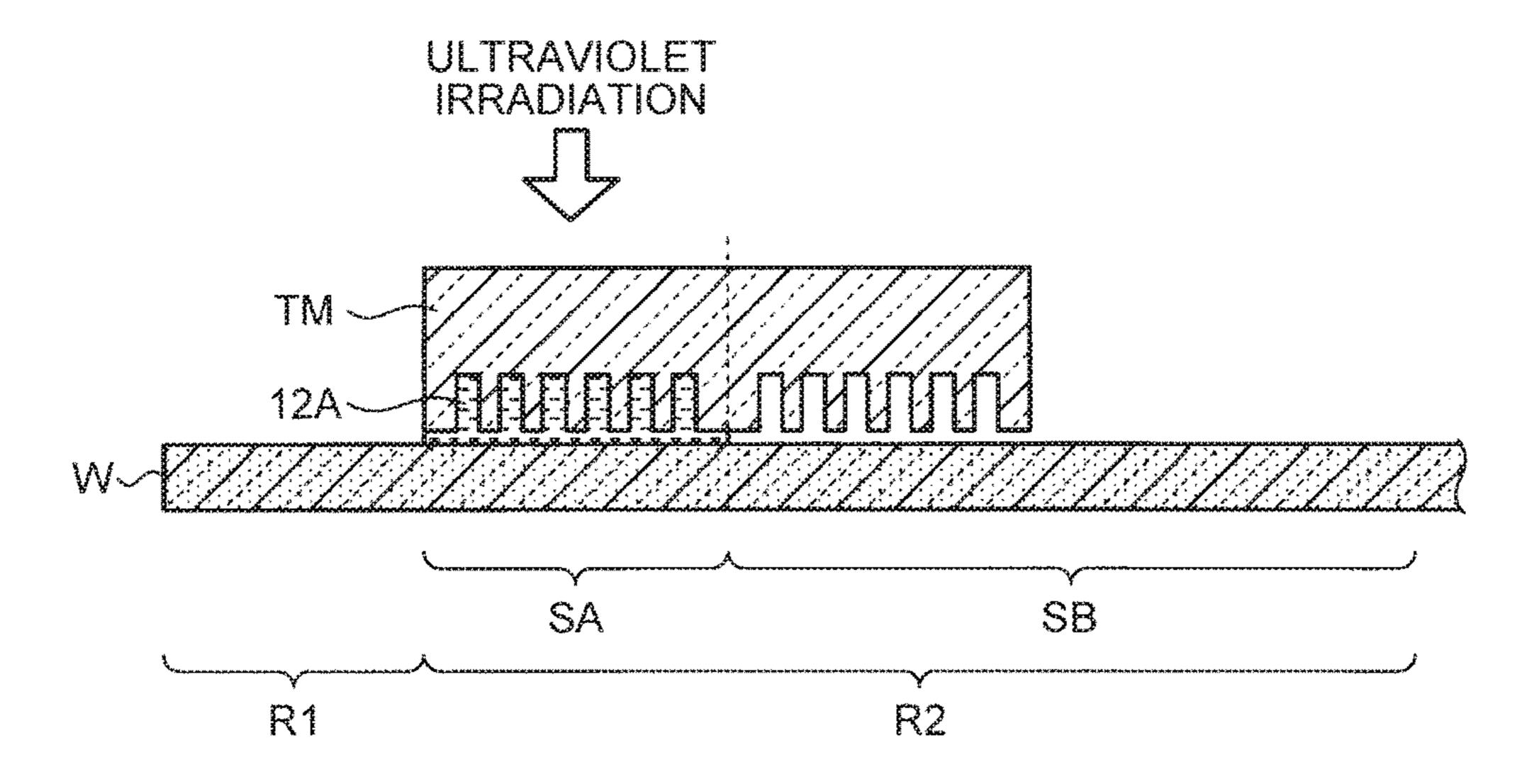

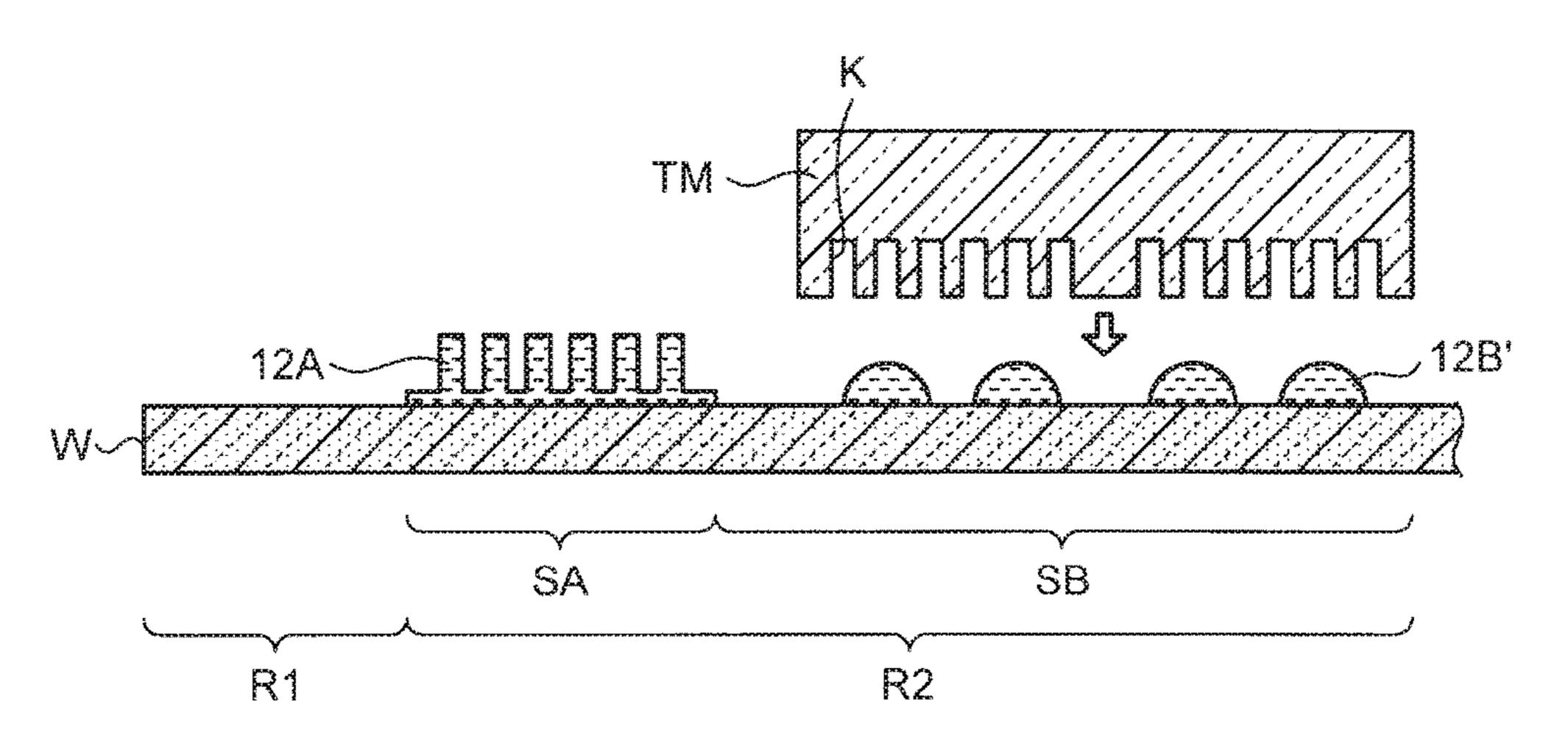

FIGS. 3A and 3B are cross-sectional views illustrating an imprinting method employed at the shot region SA of FIG. 2A;

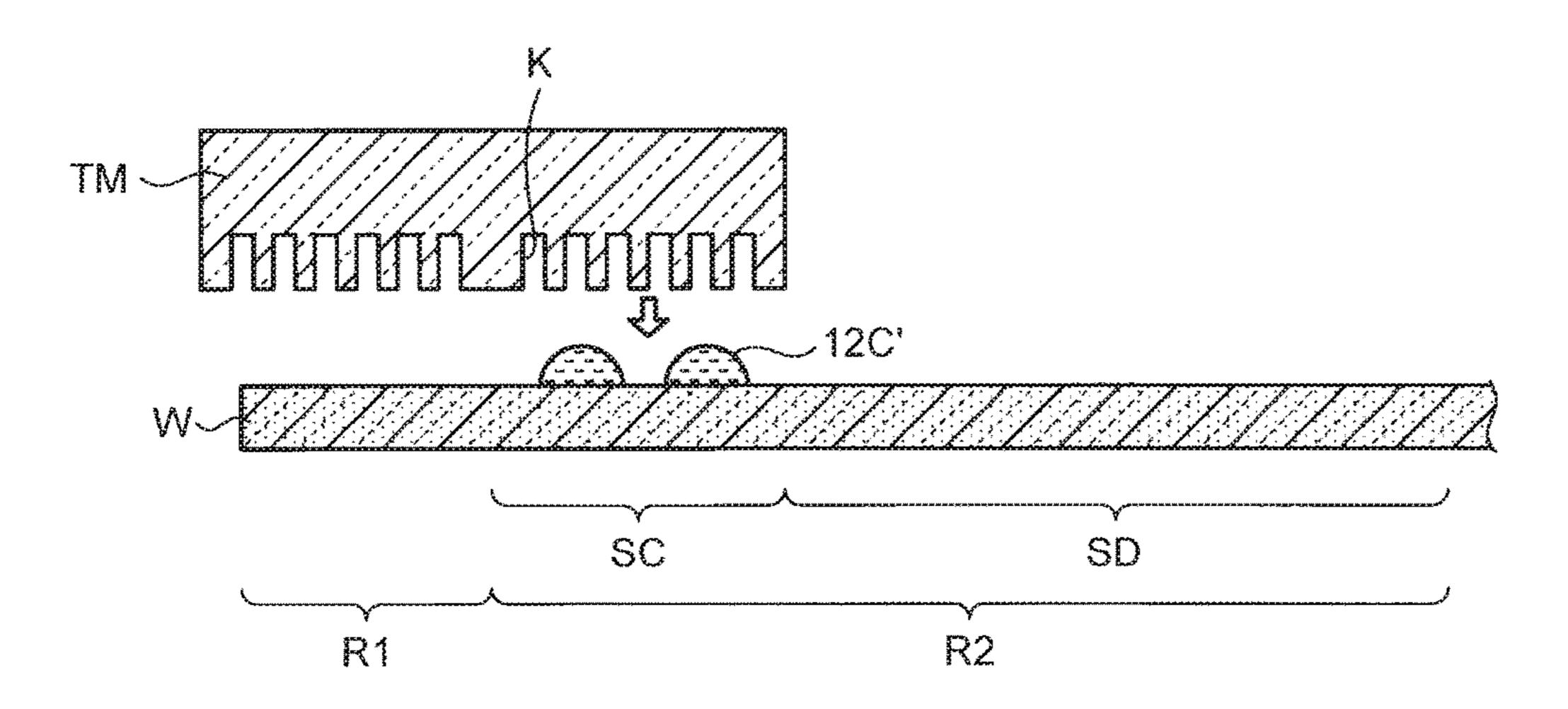

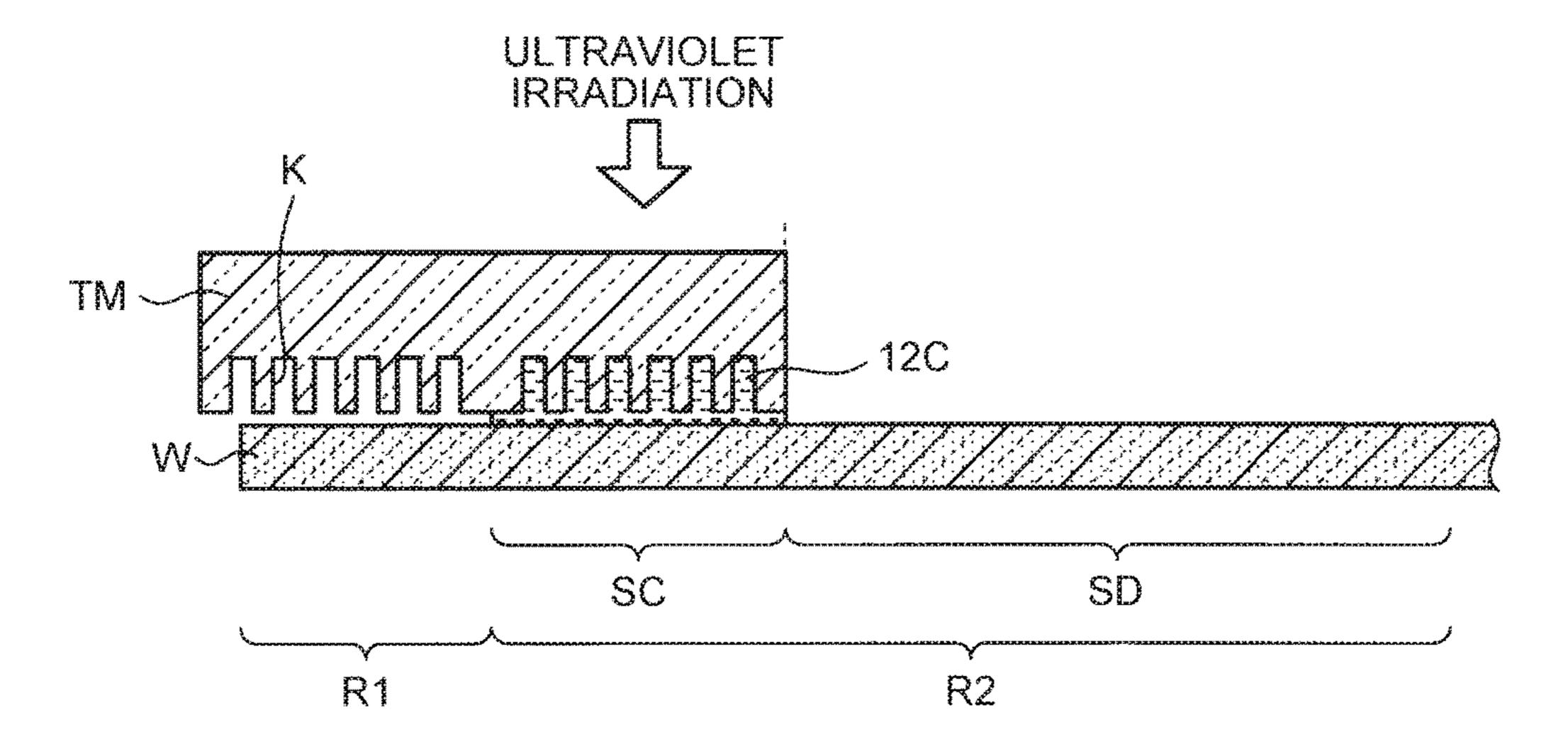

FIGS. 4A and 4B are cross-sectional views illustrating an 55 imprinting method employed at the shot region SC of FIG. 2A; and

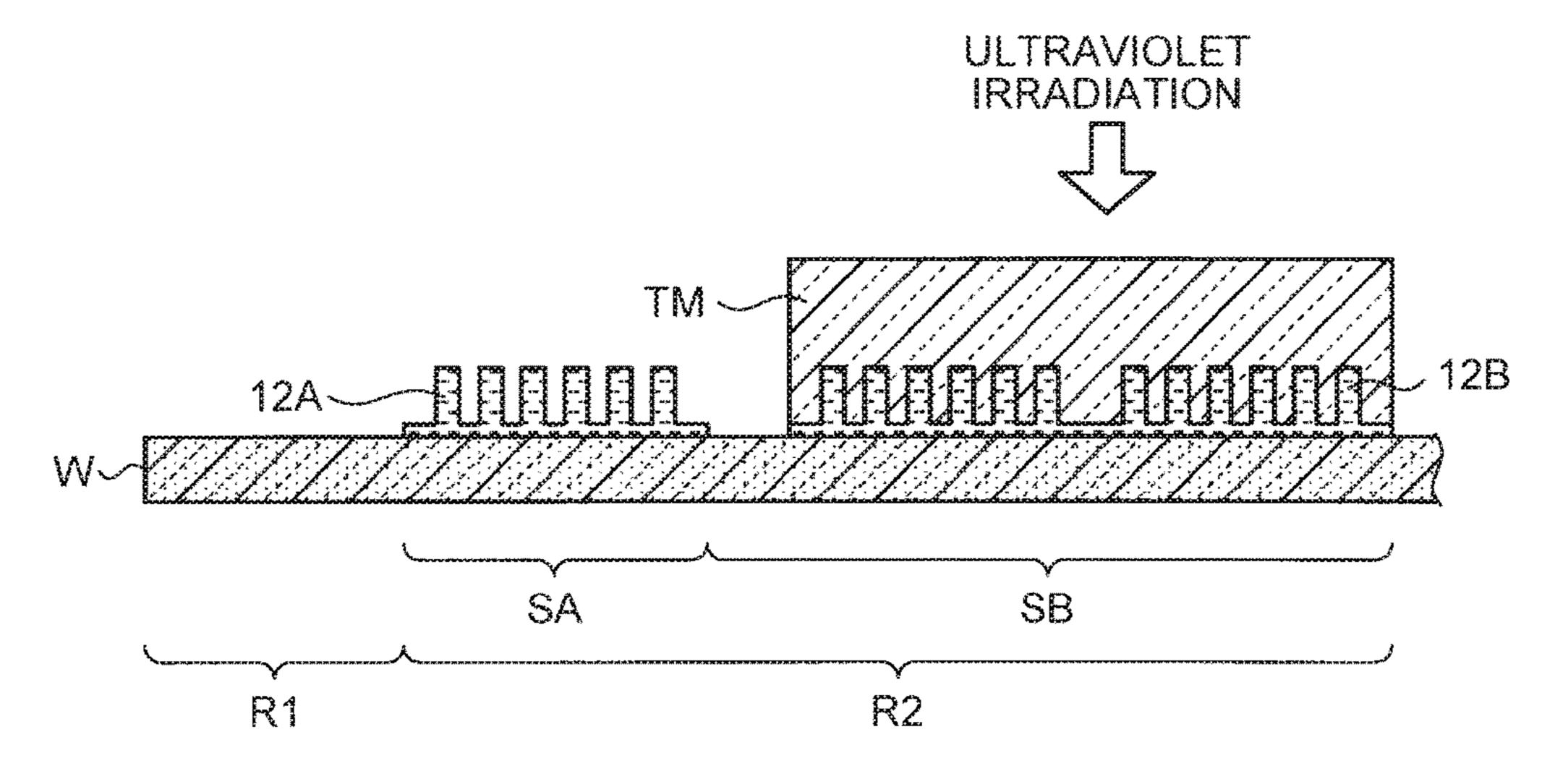

FIGS. **5**A and **5**B are cross-sectional views illustrating an imprinting method employed at the shot region SB of FIG. **2**A.

## DETAILED DESCRIPTION

A pattern transfer apparatus according to the present embodiment is provided with a transfer region selecting 65 part. When performing pattern transfer from a template provided with N transfer regions (N is an integer of 2 or 2

larger) to a transferring substrate a plurality of times, the transfer region selecting part selects 1 to N-1 transfer regions to be used to perform the transfer to regions of the transferring substrate corresponding to part of the N transfer regions such that the number of the transfer to be performed using each of the N transfer regions is evened out.

The pattern transfer apparatus and methods for fabricating a semiconductor device according to the present embodiments will be described below with reference to the accompanying drawings; however, note that the present invention is not limited to these embodiments.

#### First Embodiment

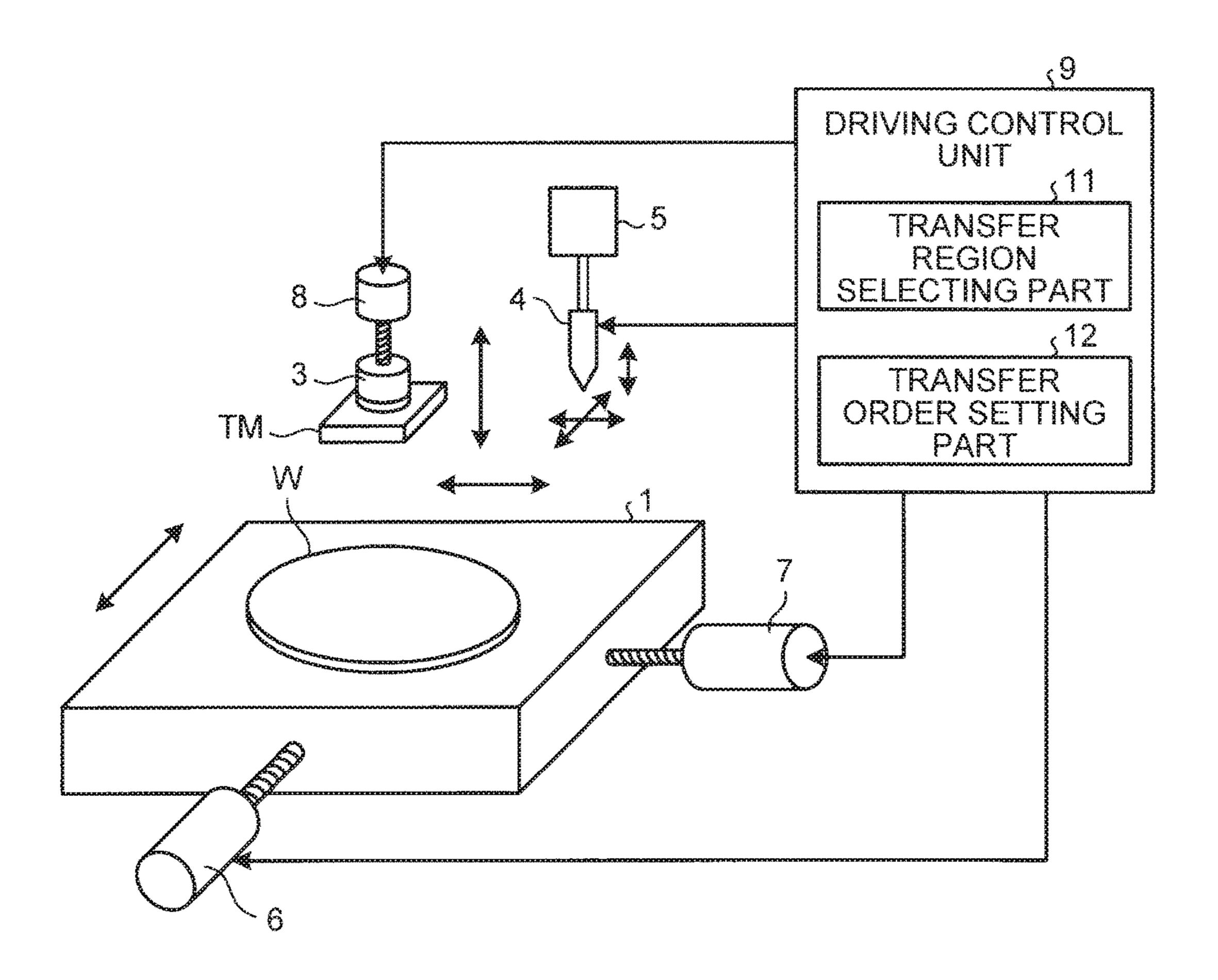

FIG. 1 is a schematic perspective view of a pattern transfer apparatus according to a first embodiment.

As illustrated in FIG. 1, the pattern transfer apparatus is provided with a stage 1 that holds a wafer W used as a transferring substrate, a template TM to be used for imprinting, a nozzle 4 that delivers an imprinting material onto the wafer W, and an ultraviolet irradiating unit 3 that irradiates the imprinting material on the wafer W with ultraviolet light via the template TM.

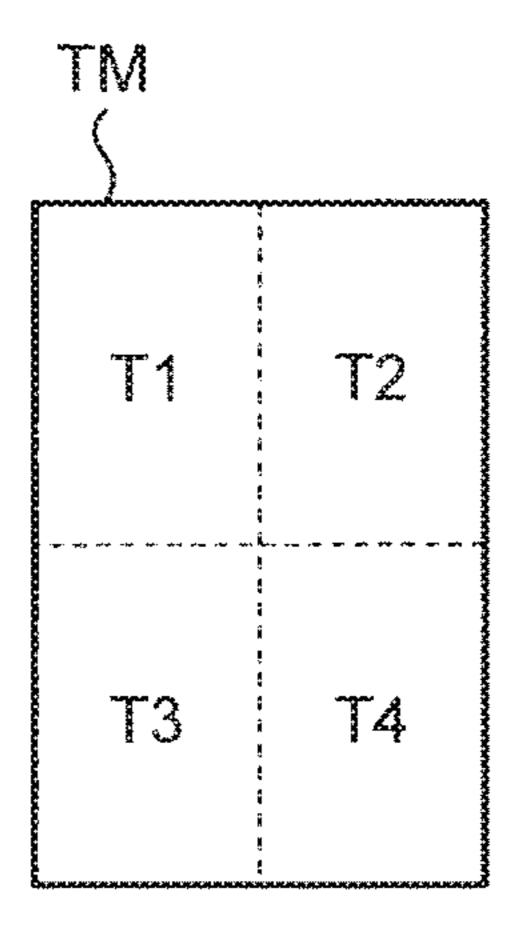

The template TM is provided with N transfer regions (N is an integer of 2 or larger). The transfer regions can be provided such that a one-to-one correspondence is established between the transfer regions and the chip regions of the wafer W. The nozzle 4 is coupled to a tank 5 that stores the imprinting material, and can be moved above the wafer W back and forth, right and left, and up and down.

The stage 1 can be moved back and forth, and right and left. The template TM can be moved up and down. The stage 1 is provided with driving parts 6 and 7 that move the stage 1 back and forth, and right and left. The template TM is provided with a driving part 8 that moves the template TM up and down.

The pattern transfer apparatus is further provided with a driving control unit 9 which drivingly controls the driving parts 6 to 8 so that the number of pattern transfer to be performed using each of the N transfer regions of the template TM is evened out. The driving control unit 9 is provided with a transfer region selecting part 11 and a transfer order setting part 12. The transfer region selecting part 11 can select the 1 to N-1 transfer regions from among the N transfer regions to even out the number of pattern transfer to be performed using each of the N transfer regions of the template TM. The transfer order setting part 12 can set the order of pattern transfer from the template TM to the wafer W such that nonselected one(s) of the transfer regions of the template TM does not collide with transfer-performed region(s) of the wafer W.

FIGS. 2A and 2B are plan views in the pattern transfer apparatus of FIG. 1 illustrating the relationship between the template and the shot regions of the wafer.

As illustrated in FIG. 2B, the template TM is provided with four transfer regions T1 to T4; as illustrated in FIG. 2A, the wafer W is provided with a pattern nonforming region R1 and a pattern forming region R2. The pattern forming region R2 is provided with shot regions SH. Each shot region SH is provided with chip regions C1 to C4. The transfer regions T1 to T4 of the template TM are allowed to respectively correspond to the chip regions C1 to C4 of the wafer W.

To begin with, an imprinting material is applied through the nozzle 4 onto the wafer W every shot region SH. Next, the ultraviolet irradiation unit 3 irradiates the imprinting material with ultraviolet light with the template TM pressed

on the imprinting material to cure the imprinting material, and then the above processing is repeated from one of the shot regions SH to another, whereby imprinting patterns can be formed on the entire pattern forming region R2 of the wafer W.

In that case, however, at the perimeter of the pattern forming region R2, imperfect shots result. At the imperfect shots, only part of the four transfer regions T1 to T4 of the template TM is used. That is, at the imperfect shots, certain regions of the transfer regions T1 to T4 are frequently used, 10 and thus the number of the transfer performed using the transfer regions T1 to T4 becomes unbalanced.

For example, since there are only two chip regions at shot regions SA and SC, imperfect shots result. In the case where it is assumed that at that time, the transfer to the shot regions 15 SA and SC has been repeated using the transfer regions T2 and T4 of the template TM along an arrow on the wafer W, the number of the transfer performed using the transfer regions T1 and T3 of the template TM comes to 59 times, and the number of the transfer performed using the transfer 20 regions T2 and T4 of the template TM comes to 62 times.

When the number of the transfer performed using the transfer regions T1 to T4 has become unbalanced like the above, the possibility of occurrence of breakage and defects increases at the transfer regions T2 and T4 with which the 25 transfer has been frequently performed. And further, in the case where breakage and defects have been caused even at part of the transfer regions T1 to T4, the use of the entire template TM becomes impossible.

On the other hand, in the case where it is assumed that 30 pattern transfer to the shot region SA has been performed using the transfer regions T1 and T3 of the template TM and pattern transfer to the shot region SC has been performed using the transfer regions T2 and T4 of the template TM, the number of the transfer performed using the transfer regions 35 T1 and T3 of the template TM comes to 60 times, and the number of the transfer performed using the transfer regions T2 and T4 of the template TM comes to 61 times.

Therefore, when compared with the case where the transfer to the shot regions SA and SC has been performed using 40 the transfer regions T2 and T4 of the template TM, the number of the transfer performed using the transfer regions T1 to T4 of the template TM are evened out, and thus the number of the transfer performed using the transfer regions T2 and T4 decreases. Hence it becomes possible to prevent 45 breakage and defects from readily occurring at the transfer regions T2 and T4 of the template TM, and the life of the template TM can, therefore, be lengthened.

However, in the case where pattern transfer to the shot region SA has been performed using the transfer regions T1 50 and T3 of the template TM as described above, the transfer regions T2 and T4 of the template TM overlap into the shot region SB; therefore, in the case where pattern transfer to the shot region SB has already been performed, the shot region SB as a transfer-performed region collides with the transfer 55 regions T2 and T4 of the template TM, and thus an imprinting pattern formed at the transfer-performed shot region SB is damaged.

Hence the order of pattern transfer to the shot region SA is set so that the transfer to the shot region SA is performed 60 before the transfer to the shot region SB is performed.

FIGS. 3A and 3B are cross-sectional views illustrating an imprinting method employed at the shot region SA of FIG. 2A.

As illustrated in FIG. 3A, the shot region SB adjoins the 65 shot region SA. To begin with, an imprinting material 12A' is delivered through the nozzle 4 onto the shot region SA of

4

the wafer W by using a method such as an inkjet method. Incidentally, as the imprinting material 12A', an ultraviolet cure resist, for example, can be used.

Next, as illustrated in FIG. 3B, the template TM is pressed on the imprinting material 12A' to form an imprinting pattern 12A on the wafer W. Incidentally, the template TM can be made of quartz, for example. In this embodiment, in the template TM are formed concave portions K corresponding to the imprinting pattern 12A; that is, by pressing the template TM on the imprinting material 12A', the imprinting material 12A' is sucked up into the concave portions K by a capillary phenomenon, whereby the imprinting pattern 12A corresponding to the shape of the concave portions K is formed.

Thereafter, by irradiating the imprinting pattern 12A with ultraviolet light through the template TM with the template TM pressed on the imprinting pattern 12A, the imprinting pattern 12A cures.

In the example of FIG. 3B, an ultraviolet cure resist may be used as the imprinting material 12A' to cure the imprinting pattern 12A, but a thermosetting resist may be used.

When forming the imprinting pattern 12A at the shot region SA, the transfer regions T1 and T3 of the template TM can be pressed on the imprinting material 12A'. And further, before forming an imprinting pattern 12B (see FIG. 5B) at the shot region SB, the imprinting pattern 12A can be formed at the shot region SA. Therefore, in the case where the transfer regions T2 and T4 of the template TM also overlap into the shot region SB when forming the imprinting pattern 12A at the shot region SA, it is possible to prevent the imprinting pattern 12B at the shot region SB from being damaged.

FIGS. 4A and 4B are cross-sectional views illustrating an imprinting method employed at the shot region SC of FIG. 2A.

As illustrated in FIG. 4A, the shot region SD adjoins the shot region SC. To begin with, an imprinting material 12C' is delivered through the nozzle 4 onto the shot region SC of the wafer W by using a method such as an inkjet method.

Next, as illustrated in FIG. 4B, by pressing the template TM on the imprinting material 12C', an imprinting pattern 12C is formed on the wafer W.

Thereafter, by irradiating the imprinting pattern 12C with ultraviolet light through the template TM with the template TM pressed on the imprinting pattern 12C, the imprinting pattern 12C cures.

When forming the imprinting pattern 12C at the shot region SC, the transfer regions T2 and T4 of the template TM can be pressed on the imprinting material 12C'. Therefore, at the shot region SA, the transfer regions T1 and T3 of the template TM can be used; at the shot region SC, the transfer regions T2 and T4 of the template TM can be used. Thus, in the case where imperfect shots result at the shot regions SA and SC too, the number of the transfer performed using the shot regions T1 to T4 of the template TM can be evened out, whereby the life of the template TM can be lengthened.

FIGS. **5**A and **5**B are cross-sectional views illustrating an imprinting method employed at the shot region SB of FIG. **2**A.

As illustrated in FIG. 5A, an imprinting material 12B' is delivered through the nozzle 4 onto the shot region SB by using a method such as an inkjet method.

Next, as illustrated in FIG. 5B, the template TM is pressed on the imprinting material 12B' to form an imprinting pattern 12B on the wafer W.

Thereafter, by irradiating the imprinting pattern 12B with ultraviolet light through the template TM with the template TM pressed on the imprinting pattern 12B, the imprinting pattern 12B cures.

In this case, by forming the imprinting pattern 12B at the shot region SB after the formation of the imprinting pattern 12A at the shot region SA, it is possible to prevent the imprinting pattern 12B at the shot region SB from being damaged.

After the formation of the imprinting patterns at all the shot regions SH of the wafer W, the wafer W is processed via the imprinting patterns, whereby semiconductor devices can be made on the wafer W. Incidentally, as a method for processing the wafer W, etching processing may be performed, or ion implantation processing may be performed. 15

Although the case where the template TM is provided with the four transfer regions T1 to T4 has been taken as an example in this embodiment, the template TM can be provided with N transfer regions. And further, although the case where the transfer regions T1 to T4 correspond respectively to the chip regions C1 to C4 of the wafer W has been taken as an example in FIGS. 2A and 2B, the transfer regions T1 to T4 may correspond to circuit blocks and so on. Furthermore, although the case where the wafer W is used as an underlying layer for the imprinting pattern formation 25 has been described as an example in the first embodiment, a conductive layer or an insulating layer may be formed on the wafer W as the underlying layer for the imprinting pattern formation.

### Second Embodiment

In the first embodiment has been described the method in which pattern transfer to the shot region SA is performed using the transfer regions T1 and T3 of the template TM, and 35 pattern transfer to the shot region SC is performed using the transfer regions T2 and T4 of the template TM; however even in this method, the number of the transfer performed using the transfer regions T1 and T3 of the template TM comes to 60 times, and the number of the transfer performed 40 using the transfer regions T2 and T4 of the template TM comes to 61 times, that is, there is a difference in the number of the transfer between the transfer regions T1 and T3 and the transfer regions T2 and T4.

On the other hand, at a first wafer W used in a second 45 embodiment, pattern transfer to the shot region SA is performed using the transfer regions T1 and T3 of the template TM, and pattern transfer to the shot region SC is performed using the transfer regions T2 and T4 of the template TM. Then, at a second wafer W, pattern transfer to the shot 50 regions SA and SC can be performed using the transfer regions T1 and T3 of the template TM.

In that case, at the first wafer W, the number of the transfer performed using the transfer regions T1 and T3 of the template TM comes to 60 times, and the number of the 55 transfer performed using the transfer regions T2 and T4 of the template TM comes to 61 times. At the second wafer W, the number of the transfer performed using the transfer regions T1 and T3 of the template TM comes to 61 times, and the number of the transfer performed using the transfer regions T2 and T4 of the template TM comes to 60 times. Therefore, at the two wafers W, the total number of the transfer performed using the transfer regions T1 to T4 of the template TM comes to 121 times, and thus a correspondence is seen between the number of the transfer performed using 65 the transfer regions T1 and T3 and the number of the transfer performed using the transfer regions T2 and T4. That is, by

6

selecting the transfer regions T1 to T4 such that the number of pattern transfer performed using the transfer regions T1 to T4 is evened out with respect to the M wafers W (M is a positive integer), the correspondence between the number of the transfer performed using the transfer regions T1 to T4 can be implemented.

While certain embodiments have been described, these embodiments have been presented by way of example only, and are not intended to limit the scope of the inventions. Indeed, the novel embodiments described herein may be embodied in a variety of other forms; furthermore, various omissions, substitutions and changes in the form of the embodiments described herein may be made without departing from the spirit of the inventions. The accompanying claims and their equivalents are intended to cover such forms or modifications as would fall within the scope and spirit of the inventions.

### What is claimed is:

- 1. A pattern transfer apparatus comprising a transfer region selecting part that performs *an* operation in which when performing pattern transfer from a template provided with N transfer regions (N is an integer of 2 or larger) to a transferring substrate a plurality of times, 1 to N-1 transfer regions, which are to be used to perform the *pattern* transfer to regions of the transferring substrate corresponding to part of the N transfer regions, are selected such that [the] *a* number of [the transfer] *pattern transfers* to be performed using each of the N transfer regions is evened out.

- 2. The pattern transfer apparatus according to claim 1, further comprising a transfer order setting part which sets *an* order of the pattern transfer to the transferring substrate such that the transfer regions that have not been selected when selecting the 1 to N-1 transfer regions do not collide with each of transfer-performed regions of the transferring substrate.

- 3. The pattern transfer apparatus according to claim 1, wherein the transfer region selecting part selects the transfer regions such that [the] a number of [the transfer] pattern transfers to M transferring substrates (M is a positive integer) to be performed using each of the N transfer regions is evened out.

- 4. The pattern transfer apparatus according to claim 1, wherein each of the transfer regions corresponds to a chip region of a wafer used as the transferring substrate.

- 5. The pattern transfer apparatus according to claim 4, wherein a pattern forming region of the wafer is provided with a shot region corresponding to the N transfer regions, there is a region where imperfect shot will result at a perimeter of the pattern forming region, and only part of the N transfer regions of the template is used when performing pattern transfer to the region where the imperfect shot will result.

- 6. The pattern transfer apparatus according to claim 5, further comprising a transfer order setting part that sets *an* order of pattern transfer to the shot region of the pattern forming region and to the region where the imperfect shot will result of the wafer such that an unused transfer region of the N transfer regions does not collide with an adjacent pattern-transferred shot region when performing pattern transfer to the region where the imperfect shot will result.

- 7. A pattern transfer apparatus comprising:

- a stage that holds a wafer used as a transferring substrate; driving parts that move the stage back and forth, and right and left;

- a nozzle that delivers an imprinting material onto the wafer;

- an ultraviolet irradiating unit that irradiates the imprinting material on the wafer with ultraviolet light via a template provided with N transfer regions (N is an integer of 2 or larger); and

- a driving control unit that controls the driving parts so as 5 to even out [the] a number of pattern [transfer] transfers to be performed using each of the N transfer regions.

- 8. The pattern transfer apparatus according to claim 7, wherein the driving control unit comprises a transfer region 10 selecting part that performs operation in which when performing pattern transfer from the template provided with the N transfer regions to the transferring substrate a plurality of times such that [the] a number of [the transfer] pattern 15 transfers to be performed using each of the N transfer regions is evened out, 1 to N-1 transfer regions, which are to be used to perform the *pattern* transfers to regions of the transferring substrate corresponding to part of the N transfer regions, are selected.

- **9**. The pattern transfer apparatus according to claim **8**, wherein the driving control unit further comprises a transfer order setting part that sets an order of pattern transfer to the transferring substrate such that the transfer regions, which have not been selected when selecting the 1 to N-1 transfer 25 regions, do not collide with each of transfer-performed regions of the transferring substrate.

- 10. The pattern transfer apparatus according to claim 8, wherein the transfer region selecting part selects the transfer regions such that the number of the transfer to M transferring 30 substrates (M is a positive integer) to be performed using each of the N transfer regions is evened out.

- 11. The pattern transfer apparatus according to claim 7, wherein the each of transfer regions corresponds to a chip region of the wafer used as the transferring substrate.

- 12. The pattern transfer apparatus according to claim 11, wherein a pattern forming region of the wafer is provided with a shot region corresponding to the N transfer regions, there is a region where imperfect shot will result at a perimeter of the pattern forming region, and only part of the 40 N transfer regions of the template is used when performing pattern transfer to the region where the imperfect shot will result.

- 13. The pattern transfer apparatus according to claim 12, wherein the driving control unit comprises a transfer order 45 setting part that sets an order of pattern transfer to the shot region of the pattern forming region and to the region where the imperfect shot will result [of the wafer] such that when performing pattern transfer to the region where the imperfect shot will result, an unused transfer region of the N transfer 50 regions does not collide with an adjacent pattern-transferred shot region.

- 14. A method for fabricating a semiconductor device comprising:

when performing pattern transfer to regions of a transferring substrate corresponding to part of N transfer regions (N is an integer of 2 or larger) provided at a template, 1 to N-1 transfer regions are selected such that [the] a number of [the transfer] pattern transfers to 60 be performed using each of the N transfer regions is evened out, and the pattern transfer is performed by applying an imprinting material onto an underlying layer of the transferring substrate and pressing the template on the imprinting material; and

processing the underlying layer via the imprinting patterns formed on the underlying layer.

8

- 15. The method for fabricating a semiconductor device according to claim 14, wherein concave portions corresponding to the imprinting patterns are formed in the template, and the imprinting patterns are irradiated with ultraviolet light through the template with the template pressed on the imprinting material to cure the imprinting patterns.

- 16. The method for fabricating a semiconductor device according to claim 14, wherein an order of [the] pattern transfer to the transferring substrate is set such that the transfer regions, which have not been selected when selecting the 1 to N-1 transfer regions, do not collide with each of transfer-performed regions of the transferring substrate.

- 17. The method for fabricating a semiconductor device according to claim 14, wherein the transfer regions are selected such that [the] a number of [the transfer] pattern transfers to the M transferring substrates (M is a positive integer) performed using each of the N transfer regions is evened out.

- 18. The method for fabricating a semiconductor device according to claim 14, wherein each of the transfer regions corresponds to a chip region of a wafer used as the transferring substrate.

- 19. The method for fabricating a semiconductor device according to claim 18, wherein a pattern forming region of the wafer is provided with a shot region corresponding to the N transfer regions.

- 20. The method for fabricating a semiconductor device according to claim 19, wherein there is a region where imperfect shot will result at a perimeter of the pattern forming region, and only part of the N transfer regions of the template is used when performing pattern transfer to the region where the imperfect shot will result.

- 21. A method for fabricating a semiconductor device 35 comprising:

forming, sequentially using a template, a plurality of patterns on one or more substrates, the template including a first template region with a first template pattern and a second template region with a second template pattern, the plurality of patterns including a first chip pattern and a second chip pattern respectively corresponding to the first template pattern and the second template pattern; and

processing the one or more substrates based on the plurality of patterns formed on the one or more substrates;

wherein the first chip pattern is formed on the one or more substrates a first number of times;

wherein the second chip pattern is formed on the one or more substrates a second number of times; and

wherein the first number and the second number are equal.

- 22. The method of claim 21, wherein each of the first template region and the second template region corresponds forming imprinting patterns by repeating process wherein 55 to a chip region to be formed on the one or more substrates.

- 23. The method of claim 21, wherein the forming of a plurality of patterns on one or more substrates comprises: forming the first chip pattern on a first chip region of one substrate of the one or more substrates; and

- after forming the first chip pattern on the first chip region, forming the first chip pattern and the second chip pattern on a second chip region of the one substrate.

- 24. The method of claim 23, wherein the forming the first chip pattern on a first chip region of one substrate of the one 65 or more substrates comprises:

- depositing, by a nozzle, an imprinting material on the first chip region; and

- moving, by a driver, the template to cause the first template region to press on the imprint material deposited on the first chip region.

- 25. The method of claim 24, wherein when the first template region is pressed on the imprint material on the 5 first chip region, the second template region overlaps with at least a part of a non-pattern forming region of the one substrate.

- 26. The method of claim 24, wherein when the first template region is pressed on the imprint material on the first chip region, the second chip pattern region overlaps with at least a part of a chip pattern forming region of the one substrate.

- 27. The method of claim 24, wherein when the first template region is pressed on the imprint material on the first chip region, the second chip pattern region overlaps with at least a part of the second chip region.

- 28. The method of claim 21, wherein the forming of the first chip pattern and the second chip pattern on a second <sub>20</sub> chip region of the one substrate comprises:

- controlling a nozzle to deposit an imprinting material on the second chip region; and

- controlling one or more drivers to move at least one of the template and the one substrate to cause the first tem- <sup>25</sup> plate region and the second template region to press on the imprint material deposited on the second chip region.

- 29. The method of claim 21, wherein the first chip pattern and the second chip pattern are identical.

- 30. The method of claim 21, wherein the processing of the one or more substrates based on the plurality of patterns formed on the one or more substrates comprises:

- irradiating, by an irradiation unit through the template, 35 the plurality of patterns on the one or more substrates with ultraviolet light.

- 31. The method of claim 21, wherein the plurality of patterns are formed on two substrates; and wherein the first number and the second number are equal.

- 32. The method of claim 31, wherein the forming of the plurality of patterns comprises:

- forming a first chip pattern on a first chip region of a first substrate of the two substrates;

- forming a second chip pattern on a second chip region of 45 the first substrate;

- forming the first chip pattern on a third chip region and on a fourth chip region of a second substrate of the two substrates;

- wherein the first chip region corresponds to the third chip 50 region, and wherein the second chip region corresponds to the fourth chip region.

- 33. The method of claim 31,

- wherein the first chip pattern is formed on the first substrate a third number of times;

- wherein the first chip pattern is formed on the second substrate a fourth number of times;

- wherein the second chip pattern is formed on the second substrate a fifth number of times; and

- wherein the second chip pattern is formed on the second 60 substrate a sixth number of times.

- 34. The method of claim 33, wherein the third number and the fourth number are different; wherein the fifth number and the sixth number are different.

- 35. The method of claim 33, wherein the third number and 65 the fourth number are equal; wherein the fifth number and the sixth number are equal.

- 36. A pattern transfer apparatus comprising:

- a driving control unit configured to use a template to, sequentially, form a plurality of patterns on one or more substrates, the template including a first template region with a first template pattern and a second template region with a second template pattern, the plurality of patterns including a first chip pattern and a second chip pattern respectively corresponding to the first template pattern and the second template pattern; and

- an irradiating unit configured to process the one or more substrates based on the plurality of patterns formed on the one or more substrates;

- wherein the first chip pattern is formed on the one or more substrates for a first number of times;

- wherein the second chip pattern is formed on the one or more substrates for a second number of times; and

- wherein the first number and the second number are equal.

- 37. The pattern transfer apparatus of claim 36, wherein each of the first template region and the second template region corresponds to a chip region to be formed on the one or more substrates.

- 38. The pattern transfer apparatus of claim 36, wherein the forming of a plurality of patterns on one or more substrates comprises the driving control unit being configured to cause the template to:

- form the first chip pattern on a first chip region of one substrate of the one or more substrates; and

- after forming the first chip pattern, form the first chip pattern and the second chip pattern on a second chip region of the one substrate.

- 39. The pattern transfer apparatus of claim 38, wherein the forming of a first chip pattern on a first chip region of one substrate of the one or more substrates comprises the driving control unit being configured to:

- control a nozzle to deposit an imprint material on the first chip region; and

- control one or more drivers to move at least one of the template and the one substrate to cause the first template region to press on the imprint material on the first chip region.

- 40. The pattern transfer apparatus of claim 39, wherein when the first template region is pressed on the imprint material on the first chip region, the second template region overlaps with at least a part of a non-pattern forming region of the one substrate.

- 41. The pattern transfer apparatus of claim 39, wherein when the first template region is pressed on the imprint material on the first chip region, the second chip pattern region overlaps with at least a part of a pattern forming region of the one substrate.

- 42. The pattern transfer apparatus of claim 39, wherein when the first template region is pressed on the imprint material on the first chip region, the second chip pattern region overlaps with at least a part of the second chip region.

- 43. The pattern transfer apparatus of claim 36, wherein the forming of the first chip pattern and the second chip pattern on a second chip region of the one substrate comprises the driving control unit being configured to:

- control a nozzle to deposit an imprint material on the second chip region; and

- control one or more drivers to move at least one of the template and the one substrate to cause the first tem-

plate region and the second template region to press on the imprint material deposited on the second chip region.

44. The pattern transfer apparatus of claim 36, wherein the first chip pattern and the second chip pattern are 5 identical.

45. The pattern transfer apparatus of claim 36, wherein the processing the one or more substrates based on the plurality of patterns formed on the one or more substrates comprises the ultraviolet irradiation unit being configured to:

irradiate, through the template, the plurality of patterns formed on the one or more substrates with ultraviolet light.

46. The pattern transfer apparatus of claim 36, wherein the plurality of patterns are formed on two substrates of the 15 one or more substrates; and wherein the first number and the second number are equal.

47. The pattern transfer apparatus of claim 46, wherein the forming of the plurality of patterns comprises the driving control unit being configured to cause the template to:

form a first chip pattern on a first chip region of a first substrate of the two substrates;

form a second chip pattern on a second chip region of the first substrate;

form the first chip pattern on a third region and on a 25 fourth region of a second substrate of the two substrates;

12

wherein the first chip region corresponds to the third chip region, and wherein the second chip region corresponds to the fourth chip region.

48. The pattern transfer apparatus of claim 46,

wherein the first chip pattern is formed on the first substrate a third number of times;

wherein the first chip pattern is formed on the second substrate a fourth number of times;

wherein the second chip pattern is formed on the second substrate a fifth number of times; and

wherein the second chip pattern is formed on the second substrate a sixth number of times.

49. The pattern transfer apparatus of claim 48, wherein the third number and the fourth number are different; and wherein the fifth number and the sixth number are different.

50. The pattern transfer apparatus of claim 48, wherein the third number and the fourth number are equal; and wherein the fifth number and the sixth number are equal.

51. The pattern transfer apparatus of claim 36, further comprising a stage adapted to hold a wafer that includes one substrate of the one or more substrates; wherein the driver control unit is configured to control one or more drivers to move at least one of the stage and the template to sequentially form the plurality of patterns on the one substrate.

\* \* \* \* \*