#### US00RE47420E

### (19) United States

### (12) Reissued Patent

Altmejd et al.

#### (10) Patent Number:

US RE47,420 E

#### (45) Date of Reissued Patent:

Jun. 4, 2019

# (54) PERFORMANCE AND POWER OPTIMIZATION VIA BLOCK ORIENTED PERFORMANCE MEASUREMENT AND CONTROL

(71) Applicant: Advanced Micro Devices, Inc.,

Sunnyvale, CA (US)

(72) Inventors: Morrie Altmejd, Austin, TX (US);

Evandro Menezes, Austin, TX (US); Dave Tobias, Pflugerville, TX (US)

(73) Assignee: Advanced Micro Devices, Inc.,

Sunnyvale, CA (US)

(21) Appl. No.: 15/217,563

(22) Filed: Jul. 22, 2016

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 6,895,520

Issued: May 17, 2005

Appl. No.: 09/798,176

Filed: Mar. 2, 2001

(51) Int. Cl. G06F 1/32 G06F 1/3234

(2019.01) (2019.01)

(Continued)

(52) **U.S. Cl.**

CPC ...... *G06F 1/3234* (2013.01); *G06F 1/3203* (2013.01); *G06F 1/324* (2013.01);

(Continued)

(58) Field of Classification Search

CPC ..... G06F 1/324; G06F 1/3234; G06F 1/3287; G06F 1/3296; G06F 1/3203; G06F 1/329; G06F 1/3228; Y02D 10/24

(Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,544,950 A 10/1985 Tu 4,745,402 A 5/1988 Auerbach (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 1154629 A 7/1997 EP 0594240 A2 4/1994 (Continued)

#### OTHER PUBLICATIONS

IBM Technical Disclosure Bulletin "Power Management Clock Change for 603 Processor", vol. 38, No. 12, Dec. 1995; 5 pages. (Continued)

Primary Examiner — Matthew E Heneghan (74) Attorney, Agent, or Firm — Sterne, Kessler, Goldstein & Fox P.L.L.C.

#### (57) ABSTRACT

An integrated circuit includes a plurality of functional blocks. Utilization information for the various functional blocks is generated. Based on that information, the power consumption and thus the performance levels of the functional blocks can be tuned. Thus, when a functional block is heavily loaded by an application, the performance level and thus power consumption of that particular functional block is increased. At the same time, other functional blocks that are not being heavily utilized and thus have lower performance requirements can be kept at a relatively low power consumption level. Thus, power consumption can be reduced overall without unduly impacting performance.

#### 21 Claims, 3 Drawing Sheets

# US RE47,420 E Page 2

| (51) <b>I</b>      | Int. Cl.                      |          |                                         | 5,781,78              | 3 A * | 7/1998  | Gunther G06F 1/3228                    |

|--------------------|-------------------------------|----------|-----------------------------------------|-----------------------|-------|---------|----------------------------------------|

| ` /                | G06F 1/3287                   |          | (2019.01)                               |                       |       |         | 700/295                                |

|                    | G06F 1/3296                   |          | (2019.01)                               | 5,784,62              |       |         | Reneris                                |

|                    | G06F 1/324                    |          | (2019.01)                               | 5,784,63              |       |         | Saito et al.                           |

|                    | G06F 1/329                    |          | (2019.01)                               | 5,790,87              |       |         | Nishiyama et al.                       |

|                    | G06F 1/3228                   |          | (2019.01)                               | 5,793,98<br>5,798,66  |       |         | Glaser et al.<br>Herbert               |

|                    | G06F 1/3203                   |          | (2019.01)                               | 5,808,69              |       | 9/1998  |                                        |

|                    |                               |          | (2019.01)                               | 5,812,86              |       |         | Horden et al 395/750.04                |

| \ /                | U.S. Cl.                      | 0.417 1  | (/200 (2010 01)                         | 5,828,37              | 0 A   | 10/1998 | Moeller et al.                         |

| (                  |                               |          | //329 (2013.01); G06F 1/3228            | 5,828,89              |       |         | Chan et al.                            |

|                    | •                             |          | 606F 1/3287 (2013.01); G06F             | 5,832,28              |       |         | Michail et al.                         |

|                    |                               | •        | 13.01); Y02D 10/24 (2018.01)            | ·                     |       | 11/1998 | Walsh et al.                           |

| $(58)  \mathbf{I}$ | Field of Classifi             | cation   | n Search                                | 5,850,21              |       |         | LaJoie et al.                          |

| J                  | USPC                          | •••••    | 713/300, 320, 322, 324                  | 5,850,47              |       |         | Kung et al.                            |

| S                  | See application f             | file for | r complete search history.              | 5,852,73              |       |         | Bikowsky 395/750.05                    |

|                    |                               | _        |                                         | 5,873,00<br>5,881,24  |       |         | Lin et al 395/892                      |

| (56)               | Re                            | feren    | ces Cited                               | 5,881,24<br>5,881,29  |       |         | Thompson Cathey 395/750.06             |

|                    | II C DAT                      | TENT     | DOCLIMENTS                              | 5,884,04              |       |         | Atkinson                               |

|                    | U.S. PAI                      |          | DOCUMENTS                               | 5,886,69              |       |         | Pond et al.                            |

| 4 9                | 821,261 A 4/                  | /1989    | Pommier                                 | 5,887,17              |       |         | Halahmi et al 395/750.06               |

| /                  | ,                             |          | Barlow et al.                           | 5,898,84              |       | 4/1999  |                                        |

|                    | 843,568 A 6/                  |          |                                         | 5,920,57<br>5,923,75  |       |         | Washington et al.<br>Birch             |

| /                  | •                             |          | Vea 714/1                               | 5,925,13              |       |         | Buxton et al 713/323                   |

|                    | -                             |          | Groezinger 702/182                      | 5,930,44              |       |         | Camhi et al.                           |

| ,                  | •                             |          | Perry et al.<br>Heberle                 | 5,940,78              | 5 A * | 8/1999  | Georgiou G06F 1/206                    |

| ,                  | ,                             |          | Goldwasser et al.                       |                       |       |         | 702/132                                |

| ,                  | ·                             |          | Trew et al.                             | ·                     |       |         | Evoy et al                             |

| 5,3                | 307,003 A 4/                  | 1994     | Fairbanks et al.                        | / /                   |       |         | Barrus 713/320<br>Whittaker et al.     |

| ,                  | /                             |          | Asher                                   | , ,                   |       |         | Nishiumi et al.                        |

| ,                  | ,                             |          | Bouchard et al.                         | , ,                   |       |         | Thomas et al.                          |

| ,                  | •                             |          | Fung<br>Matsuzaki et al.                | 5,978,86              | 4 A   | 11/1999 | Hetherington et al.                    |

| ,                  | 423,045 A 6/                  |          |                                         | / /                   |       |         | Kou 713/323                            |

| ,                  | ,                             |          | Arai et al.                             | , ,                   |       |         | Kau et al.                             |

| /                  | <i>'</i>                      |          | Pint et al.                             | 6,014,61              |       |         | Gupta et al.  Arai et al 702/132       |

| _ ′                | ·                             |          | Tsumori et al.                          | 6,020,91              |       |         | De Lang                                |

| ,                  | <i>'</i>                      |          | Bailey<br>Mahalingaiah et al.           | 6,026,18              |       | 2/2000  | •                                      |

| ,                  | · ·                           |          | Kikinis                                 | 6,047,24              |       |         | Georgiou et al.                        |

| _ ′                | /                             |          | Wisor et al 395/750                     | 6,073,24              |       |         | Iwazaki 713/322                        |

| /                  | ,                             |          | Kannan et al.                           | 6,076,17<br>RE36,83   |       |         | Kawata 713/501<br>Simmons et al 326/93 |

| /                  | ·                             |          | Hoogenboom et al.                       | 6,105,12              |       |         | Kimura et al.                          |

| _ ′                | ,                             |          | Dunn et al.<br>Fujinami et al.          | 6,105,14              |       |         | Goff et al.                            |

| ,                  | •                             |          | Platzker et al.                         | 6,108,03              |       |         | Ito et al.                             |

| /                  | 528,304 A 6/                  |          |                                         | 6,111,51              |       |         | Atick et al.                           |

| •                  | ,                             |          | Kamei et al.                            | 6,111,58<br>6,119,24  |       |         | Murphy<br>Michail et al.               |

| ,                  | ,                             |          | Buchner et al.                          | 6,122,67              |       |         | Brief et al.                           |

|                    | · ·                           |          | MacDougall Lee et al.                   | 6,128,65              |       |         | del Val et al.                         |

| •                  | ,                             |          | Maes et al.                             | 6,128,74              |       |         | Anderson et al 713/323                 |

| ,                  | <i>'</i>                      |          | McLaughlin et al.                       | 6,141,00              |       |         | Chor et al.                            |

| ,                  | •                             |          | Gaughan et al.                          | 6,141,76<br>6,147,71  |       |         | Nicol et al.<br>Terasawa et al.        |

| ,                  | · ·                           |          | Yung                                    | 6,151,05              |       |         | Schein et al.                          |

| ,                  | /                             | _        | Freeman et al.<br>Van Meerbergen et al. | 6,151,68              |       |         | Roden et al 713/322                    |

| /                  | ·                             |          | Florin et al.                           | 6,184,87              |       |         | Dodson et al.                          |

| ,                  | ,                             |          | Matthews, III et al.                    | 6,185,31              |       |         | Crabtree et al.                        |

| /                  | ,                             |          | Bullock et al.                          | 6,185,64<br>6,191,77  |       |         | Dunnihoo<br>Maruno et al.              |

|                    | 682,511 A 10/                 |          | <b>-</b>                                | 6,195,75              |       |         | Nakamura                               |

| ·                  | 696,985 A 12/<br>713,030 A 1/ |          | <u>.</u>                                | 6,208,36              |       |         | Gossett                                |

| ·                  | •                             |          | Mittal et al 713/321                    | 6,219,72              |       |         | Hetherington et al 710/18              |

| ,                  | 721,829 A 2/                  |          |                                         | 6,226,44              |       |         | Sasaki et al.                          |

| /                  | ,                             |          | Inoue et al.                            | 6,233,38<br>6,239,81  |       |         | Barton et al.<br>Van Hook et al.       |

| /                  | ,                             |          | Ohkura et al.                           | 6,252,59              |       |         |                                        |

| ,                  | ′                             |          | Reinhardt et al 364/492                 | 6,252,87              |       |         | Locklear et al 370/401                 |

| /                  | •                             |          | Ohyama et al.<br>Walsh et al.           | 6,256,74              | 3 B1  | 7/2001  | Lin                                    |

| ,                  | ,                             |          | Walsh et al.                            | 6,266,71              |       |         | Loyer et al.                           |

| 5,7                | 774,591 A 6/                  | 1998     | Black et al.                            | 6,275,78              |       | 8/2001  |                                        |

| ,                  | 774,704 A 6/                  |          |                                         | 6,295,32<br>6,311,28  |       |         | -                                      |

| •                  | ,                             |          | Yamamoto et al.<br>Wehmeyer et al.      | ·                     |       |         | Dischler et al.<br>Schein et al.       |

| ·                  | •                             |          | Walsh et al.                            | ,                     |       | 12/2001 |                                        |

| ٠,٠                | ,                             |          |                                         | - ,~ <b>- · · · ·</b> |       |         |                                        |

## US RE47,420 E Page 3

| (56)                       | Referen                  | ces Cited                                      | •                                     | 2,298 B1             |                    | Lang et al.                                                            |

|----------------------------|--------------------------|------------------------------------------------|---------------------------------------|----------------------|--------------------|------------------------------------------------------------------------|

| U                          | S. PATENT                | DOCUMENTS                                      | ,                                     | 3,706 B2<br>1,369 B2 |                    | Williams et al.<br>Wyatt et al.                                        |

|                            |                          |                                                |                                       | 7,369 B2             |                    | Morein et al.                                                          |

| 6,345,362 B                | 31 2/2002                | Bertin et al.                                  | ,                                     | 3,472 B2             |                    | Stuttard et al.                                                        |

| 6,353,628 B                |                          | Wallace et al 375/220                          | ,                                     | 6,407 B2             |                    | Hallberg et al.                                                        |

| 6,363,490 B                |                          | Senyk                                          | ŕ                                     | 6,848 B2<br>8,645 B2 | 5/2008<br>9/2008   | O'Connor et al.                                                        |

| 6,397,000 B<br>6,407,595 B |                          | Hatanaka et al.                                | · · · · · · · · · · · · · · · · · · · | 7,581 B2             |                    | Grochowski et al.                                                      |

| 6,421,463 B                |                          | Huang et al.<br>Poggio et al.                  | ,                                     | 5,175 B2             |                    | Klein et al.                                                           |

| 6,425,086 B                |                          | Clark G06F 1/3203                              | 7,502                                 | 2,948 B2             | 3/2009             | Rotem et al.                                                           |

| -,,                        |                          | 713/322                                        | ,                                     | 6,334 B2             |                    | Suzuoki et al.                                                         |

| 6,442,700 B                | 81 * 8/2002              | Cooper 713/320                                 | ,                                     | 9,465 B2             |                    | Barton et al.                                                          |

| , ,                        | 31 10/2002               |                                                | ŕ                                     | 7,262 B1<br>6,863 B2 | 12/2009            | 11                                                                     |

| 6,490,000 B                |                          | Schaefer et al.                                | ,                                     | 4,971 B2             | 2/2010             |                                                                        |

| 6,510,400 B<br>6,513,124 B |                          | Moriyama<br>Furuichi et al.                    | ,                                     | 3,304 B2             |                    | Gosalia et al.                                                         |

| 6,535,798 B                |                          | Bhatia et al.                                  | ,                                     | 2,053 B2             |                    | Lefebvre et al.                                                        |

| 6,535,905 B                |                          | Kalafatis et al.                               |                                       | 6,511 B2             |                    | Naveh et al.                                                           |

| 6,542,621 B                |                          | Brill et al.                                   |                                       | 3,184 E<br>5,109 B2  |                    | Lee et al.<br>Sasaki et al.                                            |

| 6,545,683 B                |                          | Williams                                       | ,                                     | 3,110 B2             |                    | O'Connor                                                               |

| 6,564,328 B<br>6,564,329 B |                          | Grochowski et al 713/320<br>Cheung G06F 1/3203 | ,                                     | 03206 A1             |                    | Pole, II et al.                                                        |

| 0,504,525                  | J1 3/2003                | 713/322                                        |                                       | 54146 A1             | 5/2002             | Fukumoto et al.                                                        |

| 6,573,900 B                | 6/2003                   | Lindholm et al.                                |                                       | 2193 A1              |                    | Altman et al.                                                          |

| , ,                        |                          | O'Connor et al.                                |                                       | 30326 A1<br>30012 A1 |                    | Shenai et al.<br>Orenstien et al.                                      |

| 6,608,476 B                | 81 * 8/2003              | Mirov G06F 1/08                                |                                       | 22429 A1             |                    | Zhang et al.                                                           |

| C C20 025 D                | 10/2002                  | 324/103 R                                      |                                       | 88208 A1             | 10/2003            | •                                                                      |

| 6,630,935 B                | 31 10/2003<br>32 10/2003 | Taylor et al.                                  | 2003/018                              | 38212 A1             |                    | Kahn et al.                                                            |

|                            |                          | Grochowski et al 713/320                       |                                       |                      | 1/2004             |                                                                        |

| , ,                        | 31 10/2003               |                                                |                                       | 7678 A1<br>50958 A1  |                    | Soltis, Jr. et al.<br>Issa et al.                                      |

| , ,                        | 31 11/2003               |                                                |                                       | 6400 A1              | 3/2005             |                                                                        |

|                            | 31 11/2003               | · ·                                            |                                       |                      |                    |                                                                        |

| 6,711,447 B<br>6,717,599 B |                          |                                                |                                       | FOREIG               | N PATE             | NT DOCUMENTS                                                           |

| 6,724,825 B                |                          | Nemiroff et al.                                |                                       |                      |                    |                                                                        |

| 6,724,915 B                |                          | Toklu et al.                                   | EP                                    |                      | 2360 A1            | 1/1995                                                                 |

| 6,728,862 B                |                          | Wilson                                         | EP                                    |                      | 7006 B2            | 10/1996<br>10/1006                                                     |

| 6,731,289 B<br>6,762,797 B |                          | Peercy et al.<br>Pelletier                     | EP<br>EP                              |                      | 7007 A2<br>2769 B1 | 10/1996<br>3/1997                                                      |

| 6,784,879 B                |                          |                                                | EP                                    |                      | 0504 A1            | 5/1998                                                                 |

| 6,788,710 B                |                          | Knutson et al.                                 | EP                                    | 059                  | 4240 B1            | 1/2000                                                                 |

| 6,789,037 B                |                          | Gunther et al.                                 | EP                                    |                      | 9750 A2            | 9/2000                                                                 |

| 6,804,632 B                |                          | Orenstien et al.                               | JP<br>JP                              | 05-25<br>06-15       |                    | 9/1993<br>5/1994                                                       |

| 6,825,843 B                |                          | Allen et al. Cooper et al 713/320              | JP                                    | 06-13                |                    | 8/1994                                                                 |

| 6,845,456 B                |                          | Menezes et al.                                 | JP                                    | 07-15                | 4626               | 6/1995                                                                 |

| 6,859,882 B                |                          |                                                | JP                                    | 07-22                |                    | 8/1995                                                                 |

| 6,889,332 B                |                          | Helms et al.                                   | JP<br>ID                              | 07-28                |                    | 10/1995<br>4/1996                                                      |

| 6,897,871 B<br>6,901,522 B |                          | Morein et al.                                  | JP<br>JP                              | 08-10<br>08-32       |                    | 12/1996                                                                |

| 6,922,783 B                |                          | Knee et al.                                    | JP                                    | 08-33                |                    | 12/1996                                                                |

| 6,928,559 B                |                          |                                                | JP                                    | 0832                 |                    | 12/1996                                                                |

| 6,952,520 B                |                          | •                                              | JP                                    | 09-00                |                    | 1/1997                                                                 |

| 6,954,204 B<br>6,976,182 B |                          | Zatz et al.                                    | JP<br>JP                              | 09-16°<br>2000-10    | 7260<br>0673 A     | 6/1997<br>1/2000                                                       |

| 6,978,389 B                |                          | * *                                            | KR                                    | 10018                |                    | 12/1998                                                                |

| 7,015,913 B                |                          | Lindholm et al.                                | KR                                    | 10019                |                    | 1/1999                                                                 |

| 7,024,100 B                |                          | Furuyama                                       | KR                                    | 10030                |                    | 6/2001<br>5/1007                                                       |

| 7,028,196 B<br>7,038,685 B |                          | Soltis, Jr. et al.                             | WO<br>WO                              | WO 9719<br>WO 9919   |                    | 5/1997<br>4/1999                                                       |

| 7,038,083 B                |                          | Lindholm<br>Helms                              | ****                                  | 11 0 001             | 7005               |                                                                        |

| 7,051,306 B                |                          | Hoberman et al.                                |                                       | ОТ                   | HED DIE            | DI ICATIONIC                                                           |

| 7,081,895 B                |                          | Papakipos et al.                               |                                       | OI                   | HEK PUI            | BLICATIONS                                                             |

| 7,085,945 B                |                          | Silvester                                      | "Analogue                             | Dialogue a           | a forum foi        | r the exchange of circuits, systems,                                   |

| 7,095,945 B<br>7,100,056 B |                          | Kovacevic<br>Barr et al.                       | •                                     | •                    |                    |                                                                        |

| 7,100,030 B                |                          | Cai et al.                                     |                                       |                      | _                  | nal processing," vol. 34, Analog                                       |

| 7,100,061 B                | 8/2006                   | Halepete et al.                                | ,                                     | nc., 2000; 5         | 1 0                | Somon Erropetion for I D                                               |

| 7,134,031 B                |                          | Flautner Pugn et el                            |                                       |                      | -                  | ogram Execution for Low Power in                                       |

| 7,144,152 B<br>7,174,194 B |                          | Rusu et al.<br>Chauvel et al.                  | -                                     |                      | •                  | rsity of Maryland, Department of                                       |

| 7,174,194 B                |                          | Helms et al.                                   |                                       | -                    | •                  | ering, Oct. 1999; 13 pages.                                            |

| 7,197,229 B                |                          | Hatanaka et al.                                | ·                                     | •                    |                    | ottling of Processor Activity for chnical Report, Friedrich-Alexander- |

| 7,206,966 B                |                          | Barr et al.                                    | •                                     | ·                    | ŕ                  | <b>L</b> '                                                             |

| 7,216,064 B<br>7,233,335 B |                          | Pippin<br>Moreton et al.                       | •                                     | · •                  |                    | epartment, Jun. 1999; 7 pages.<br>ower-efficient Design, New York:     |

| 7,233,333 B<br>7,249,268 B |                          | Bhandarkar                                     |                                       | 2010; pp. 11         |                    | ondi dindicine izosign, inow ioik.                                     |

| · ,_ · ,_ · ,_ ·           |                          |                                                | -r, 2                                 | , rr,                | _ <del>-</del> •   |                                                                        |

#### OTHER PUBLICATIONS

Horowitz, et al., "Low-Power Digital Design," IEEE Symposium on Low Power Electronics, 1994; pp. 8-11.

Excerpt from the IBM Dictionary of Computing, International Business Machines Corporation, 1994; p. 108.

Wagner, K, "Clock System Design," IEEE Design & Text of Computers, vol. 5, Issue 5, Oct. 1988; pp. 9-27.

Excerpt from the Authoritative Dictionary of IEEE Standards Terms, Seventh Edition, 2000; pp. 458-459.

Benini, et al., "A Survey of Design Techniques for System-Level Dynamic Power Management," IEEE Transaction on Very Large Scale Integration (VLSI) Systems, vol. 8, No. 3, Jun. 2000; pp. 299-316.

Lu, et al., "Operating-System Directed Power Reduction," Proceedings of the 2000 International Symposium on Low Power Electronics and Design, 2000; pp. 37-42.

Microprocessor Quick Reference Guide, Intel Corporation, accessible at http://www.intel.com/pressroom/kits/quickrefyr.htm, last accessed Aug. 4, 2016; 34 pages.

Intel Corporation 1990 Annual Report, Order No. 240946-001, Intel Corporation, 1990; 34 pages.

Lewis, P., "Personal Computers; Innovative Portables From Zenith," New York Times, May 21, 1991; 3 pages.

EPC-21/22 Hardware Reference, Radisys Corporation, Aug. 1993; 55 pages.

Laird, D., "Crusoe Processor Products and Technology," PowerPoint Presentation, Transmeta Corporation, Jan. 19, 2000; 23 pages.

"Transmeta Breaks the Silence, Unveils Smart Processor to Revolutionize Mobile Internet Computing," Crusoe Press Release, Jan. 19, 2000, archived by the Internet Archive on Aug. 17, 2000 at https://web.archive.org/web/20000817082320/http://www.transmeta.com/press/011900-1.html; 3 pages.

"Notebooks with Transmeta chip arrive in U.S.," CNET, Jan. 2, 2002, accessible at http://www.cnet.com/news/notebooks-with-transmeta-chip-arrive-in-u-s; 6 pages.

Quan, M., "Notebooks try on Crusoe processor at PC Expo," EE Times, Jun. 30, 2000, accessible at http://www.eetimes.com/document.asp?doc\_id=1141693&print=yes; 3 pages.

Klaiber, A., "The Technology Behind Crusoe Processors, Low-Power x86-Compatible Processors Implemented with Code Morphing Software," Transmeta Corporation, Jan. 2000; 18 pages.

Fleischmann, M., "LongRung Power Management, Dynamic Power Management for Crusoe Processors," Transmeta Corporation, Jan. 17, 2001; 18 pages.

Halfhill, T., "Top PC Vendors Adopt Crusoe," Cahners Microprocessor Report, Jul. 10, 2000; 6 pages.

Geppert, et al., "Transmeta's Magic Show," IEEE Spectrum, May 2001; 8 pages.

Halfhill, T., "Transmeta Breaks x86 Low-Power Barrier," Cahners Microprocessor Report, Feb. 14, 2000; 11 pages.

Fleischmann, M., "Crusoe Power Management: Cutting x86 Operating Power Through LongRun," PowerPoint Presentation, 12th Hot Chips Symposium, Aug. 15, 2000; 21 pages.

Gervasi, B., "DDR SDRAM, the Memory of Choice for Mobile Computing," PowerPoint Presentation, Computex 2000 Conference, Jun. 2000; 22 pages.

"Our History," AMD, Inc., accessible at http://www.amd.com/en-us/who-we-are/corporate-information/history, last accessed Aug. 4, 2016; 16 pages.

"AMD PowerNow! Technology Dynamically Manages Power and Performance," AMD, Inc., Informational White Paper, Publication No. 24404, Rev. A, Nov. 2000; 18 pages.

"AMD Introduces 0.18 Micron Mobile AMD-K6-III+ and Mobile AMD-K6-2+ Processors," AMD, Inc., Press Release, Apr. 18, 2000, archived by the Internet Archive on Jun. 17, 2000, at https://web.archive.org/web/20000617082528/http://www.amd.com/news/prodpr/20083.html; 2 pages.

"AMD Boosts Battery Life for Notebook Computers with AMD PowerNow! Technology," AMD, Inc., Press Release, Jun. 26, 2000,

archived by the Internet Archive on Aug. 15, 2000, at https://web.archive.org/web/20000815210041/http://www.amd.com/news/prodpr/20119.html; 2 pages.

"AMD Introduces Powerful and Power Friendly AMD-K6-2E+, AMD-K6-IIIE+ Embedded Processors," AMD, Inc., Press Release, Sep. 25, 2000, archived by the Internet Archive on Oct. 17, 2000, at https://web.archive.org/web/20001017162155/http://www.amd.com/news/prodpr/20138.html; 3 pages.

Fleischmann, M., "Crusoe Power Management: Cutting x86 Operating Power Through LongRun," PowerPoint Presentation, Nikkei Electronics Design Conference 2000, May 30, 2000; 18 pages.

"Introduction to the Intel386 SL Microprocessor SuperSet Technical Overview," Intel Corporation, Order No. 2408952-002, 1991; 99 pages.

Crusoe Processor Model TM5400, Transmeta Corporation, Jan. 18, 2000; 7 pages.

"AMD PowerNow! Technology Platform Design Guide for Embedded Processors, Application Note," AMD, Inc., Publication No. 24267, Rev. A, Dec. 2000.

Technical Reference Guide, Compaq LTE Lite Family of Personal Computers, Nov. 1992, Part No. 140097-001; 343 pages.

"AMD-K6-IIIE+ Embedded Processor Data Sheet," AMD, Inc., Publication No. 23543, Rev. A, Sep. 2000; 370 pages.

"Mobile AMD-K6-2+ Processor Data Sheet," AMD, Inc., Publication No. 23446, Rev. B, Jul. 2000; 332 pages.

"Intel 386 SL Microprocessor SuperSet Programmer's Reference Manual," Order No. 240815-001, Intel Corporation, 1990; 468 pages.

"Advanced Power Configuration and Power Interface Specification," Revision 2.0, Compaq Computer Corporation, Intel Corporation, Microsoft Corporation, Phoenix Technologies, Ltd., Toshiba Corporation, Jul. 27, 2000; 481 pages.

Burd, et al., "WA 17.4 A Synamic Voltage Scaled Microprocessor System," IEEE International Solid-State Circuits Conference, 2000; 3 pages.

"AMD-762 System Controller Data Sheet," AMD, Inc., Publication No. 24416, Rev. C, Dec. 2001; 122 pages.

Marculescu, D., "Application-Driven Processor Design Exploration for Power-Performance Trade-off Analysis," IEEE International Conference on Computer-Aided Design, 2001; pp. 306-313.

Iyer, et al., "Power Aware Microarchitecture Resource Scaling," Proceedings of the Conference and Exhibition on Design, Automation, and Test in Europe, Mar. 13-16, 2001; pp. 190-196.

Pering, et al., "The Simulation and Evaluation of Dynamic Voltage Scaling Algorithms," Proceedings of the International Symposium on Low Power Electronics and Design, Aug. 10-12, 1998; pp. 76-81.

Crusoe Processor Model TM5800, Transmeta Corporation, Jul. 5, 2001; 8 pages.

Pering, et al., "Voltage Scheduling in the IpARM Microprocessor System," Proceedings of the International Symposium on Low Power Electronics and Design, Jul. 26-27, 2000; pp. 96-101.

Curriculum Vitae for Bill Gervasi, available at http://www.discobolusdesigns.com/personal/resume.html, last accessed Aug. 26, 2016; 3 pages.

"Intel Announces New Microarchitecture for Wireless and Internet Infrastructure Applications," Intel Corporation Press Release, Aug. 23, 2000, archived by the Internet Archive at <a href="http://web.archive.org/web/20001208135800/http://www.intel.com/pressroom/archive/releases/em082300.htm">http://www.intel.com/pressroom/archive/releases/em082300.htm</a>; 3 pages.

"Intel Demonstrates 'Geyserville' Technology—Bringing Near Desktop Performance to Mobile PCs," Intel Corporation Press Release, Feb. 24, 1999, archived by the Internet Archive at <a href="http://web.archive.org/http://developer.intel.com/pressroom/archive/releases/mp022499.htm">http://developer.intel.com/pressroom/archive/releases/mp022499.htm</a>; 3 pages.

"Intel Pentium II Processor Mobile Module: Mobile Module Connector 2 (MMC-2)," Intel Corporation, Order No. 243668-002, Aug. 1998; 56 page.

Intel Xscale Microarchitecture Technical Summary, Intel Corporation, 2000; 14 pages.

Halfhill, T., "Top PC Vendors Adopt Crusoe," Microprocessor Report, Jul. 10, 2000; 6 pages.

#### OTHER PUBLICATIONS

Halfhill, T., "Transmeta Breaks x86 Low-Power Barrier," Microprocessor Report, Feb. 14, 2000; 11 pages.

"Mobile Intel Pentium III Processor in BGA2 and Micro-PGA2 Packages," Intel Corporation Data Sheet, Order No. 249562-001, 2001; 84 pages.

English-language Abstract of Japanese Patent Application Publication No. 2000-10673 A, published Jan. 14, 2000; 2 pages.

Advanced Configuration and Power Interface Specification, Revision 1.0b, Intel Corporation, Microsoft, and Toshiba, Feb. 2, 1999; 397 pages.

Hong, et al., "Power Optimization of Variable-Voltage Core-Based Systems," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 18, No. 12, Dec. 1999; 13 pages. Advanced Configuration and Power Interface Specification, Revision 2.0, Intel Corporation, Microsoft Corporation, Phoenix Technologies Ltd., Toshiba Corporation, Jul. 27, 2000; 481 pages.

Duarte, et al., "Evaluating Run-Time Techniques for Leakage Power Reduction," VLSI Design/ASPDAC 2002; 30 pages.

Iyer, et al., "Power Efficiency of Voltage Scaling in Multiple Clock, Multiple Voltage Cores," IEEE International Conference on Computer Aided Design, 2002; 8 pages.

Katz, et al., "Dynamic Power Management Optimizes Performance vs. Power in Embedded Applications of Blackfin Processors," Analog Dialogue, vol. 36, No. 4, Jul.-Aug. 2002; 7 pages.

Kim, et al., "Long-Term Power Minimization of Dual-VT CMOS Circuits," IBM Thomas J. Watson Research Center, Jun. 20, 2002; 5 pages.

Advanced Configuration and Power Interface Specification, Revision 2.0c, Compaq Computer Corporation, Intel Corporation, Microsoft Corporation, Phoenix Technologies Ltd., Toshiba Corporation, Aug. 25, 2003; 518 pages.

Hu, et al., "Microarchitectural Techniques for Power Gating of Execution Units," Proceedings of the International Symposium on Low Power Electronics and Design, 2004; pp. 32-37.

Advanced Configuration and Power Interface Specification, Revision 3.0, Compaq Computer Corporation, Intel Corporation, Microsoft Corporation, Phoenix Technologies Ltd., Toshiba Corporation, Sep. 2, 2004; 618 pages.

Chapman, M., "The Benefits of Dual-Core Processors in High-Performance Computing," IBM Systems and Technology Group, Jun. 2005; 18 pages.

Semeraro, et al. "Dynamic Frequency and Voltage Control for a Multiple Clock Domain Architecture" Department of Electrical and Computer Engineering and Department of Computer Science University of Rochester, 2002; 12 pages.

Zorian, et al., "Testing Embedded-Core Based System Chips" IEEE Computer, vol. 32, No. 6, 1999; 9 pages.

Turk, et al., "Eigenfaces for Recognition," Journal of Cognitive Neuroscience, vol. 3, No. 1, 1991; pp. 71-86.

Yuille, et al., "Feature Extraction from Faces Using Deformable Templates," International Journal of Computer Vision, 8:2, 99-111, 1992; pp. 99-111.

Montera, D., "Object Tracking Through Adaptive Correlation," Master's Thesis, School of Engineering of the Air Force Institute of Technology, Dec. 17, 1992; 164 pages.

Maes, et al., "The Alive System: Wireless, Full-body Interaction with Autonomous Agents," M.I.T. Media Laboratory Perceptual Computing Technical Report No. 257, Nov. 1995; 17 pages.

Beymer, D., "Pose-Invariant Face Recognition Using Real and Virtual Views", Massachusetts Institute of Technology Artificial Intelligence Laboratory, A.I. Technical Report No. 1574, Mar. 1996; 186 pages.

Jebara, T., "3D Pose Estimation and Normalization for Face Recognition," Bachelor's Thesis, Department of Electrical Engineering, McGill University, May 1996; 138 pages.

Jebara, et al., "Parametrized Structure from Motion for 3D Adaptive Feedback Tracking of Faces," MIT Media Laboratory, Perceptual Computing Technical Report No. 401, Nov. 28, 1996; 8 pages.

Oliver, et al., "LAFTER: Lips and Face Real Time Tracker," Proceedings of the Computer Vision and Pattern Recognition Conference, 1997; 11 pages.

Raja, et al., "Colour Model Selection and Adaptation in Dynamic Scenes," Proceedings European Conference Computer Vision, 1998; 15 pages.

Haritaoglu, I., "A Real Time System for Detection and Tracking of People and Recognizing Their Activities," European Conference on Computer Vision, Oct. 1998; 35 pages.

Darrell, et al., "Integrated Person Tracking Using Stereo, Color, and Pattern Detection," Conference on Computer Vision and Pattern Recognition, Jun. 23-25, 1998; pp. 601-609.

Gavrilla, et al., "Real-Time Object Detection for 'Smart' Vehicles," Proceedings of the International Conference on Computer Vision, 1999; 7 pages.

Jepson, et al., "Robust Online Appearance Models for Visual Tracking" IEEE Transactions on Pattern Analysis and Machine Intelligence, vol. 25, No. 10, Oct. 2003; 16 pages.

Bolt, R., "Put-That-There': Voice and Gesture at the Graphics Interface," Architecture Machine Group, Massachusetts Institute of Technology, 1980; 9 pages.

Krueger, et al., "Videoplace—An Artificial Reality," Proceedings of the SIGCHI Conference on Human Factors in Computing Systems, Apr. 1985; pp. 35-40.

Sturman, et al., "A Survey of Glove-based Input," IEEE Computer Graphics and Applications, 1994; 10 pages.

Kjeldsen, F., "Visual Interpretation of Hand Gestures as a Practical Interface Modality," Columbia University, Doctoral Dissertation, 1997; 178 pages.

Hand, C., "A Survey of 3D Interaction Techniques," Computer Graphics Forum, vol. 16, No. 5, 1997; pp. 269-281.

Hammond, et al., "Next Generation Itanium Processor Overview," Intel Developer's Forum, Aug. 27-30, 2001; 27 pages.

Quan, M., "Notebooks try on Crusoe processor at PC Expo," EE Times, Jun. 30, 2000; 3 pages.

Intel® Microprocessor Quick Reference Guide, 1990; 34 pages. Lewis, P., "Personal Computers; Innovative Portables From Zenith", The New York Times, May 21, 1991; 3 pages.

"Transmeta Breaks the Silence, Unveils Smart Processor to Revolutionize Mobile Internet Computing," Crusoe, Jan. 19, 2000, archived by the Internet Archive at https://web.archive.org/web/20000817082320/http://www.transmeta.com/press/011900-1.html; 3 pages.

Fried, J., "Notebooks with Transmeta chip arrive in U. S.," CNET News, Oct. 25, 2000, archived by the Internet Archive at http://web.archive.org/web/20011101161522/http://news.cnet.com/news/0-1006-200-3294237.html; 2 pages.

Owens, et al., "Polygon Rendering on a Stream Architecture," 2000 SIGGRAPH Eurographics Workshop on Graphics Hardware, Aug. 2000; 10 pages.

McConnell, R., "Massively Parallel Computing on the Fuzion Chip," PixelFusion PLC, 2000; 23 pages.

"i860 64-Bit Microprocessor Hardware Design Guide," Intel Corporation, Feb. 1989; 219 pages.

Ellsworth, D., "Polygon Rendering for Interactive Visualization on Multicomputers," the University of North Carolina at Chapel Hill, Doctoral Dissertation, 1996; 236 pages.

Stokes, J., "Introduction to Multithreading, Superthreading and Hyperthreading," Ars Technica, Oct. 3, 2002; 10 pages.

Segal, et al., "The OpenGL Graphics System: A Specification, Version 1.4," Silicon Graphics, Inc., Jul. 24, 2002; 312 pages.

Boleyn, et al., "A Split Data Cache for Superscalar Processors", Proceedings of the IEEE International Conference on Computer Design: VLSI in Computers & Processors, Oct. 1993; 8 pages.

Lenoski, et. al., "The DASH Prototype: Implementation and Performance," ACM, 1992; pp. 418-429.

"PERMEDIA Testimonials Oct. 95", Oct. 1995, available at http://www.thefreelibrary.com/PERMEDIA+ Testimonials+Oct+95.-a017424284; 5 pages.

Saavedra, et al., "Measuring Cache and TLB Performance and Their Effect on Benchmark Run Times," IEEE Transactions on Computers, vol. 44, No. 10, Oct. 1995; pp. 1223-1235.

#### OTHER PUBLICATIONS

"SL-11 USB Controller Technical Reference," Scanlogic Corporation (now Cypress Semiconductor Corporation), Dec. 1996; 56 pages.

"SL11-R-USB RISC Processor Product Information, Revision 1.0," ScanLogic Corporation (now Cypress Semiconductor Corporation), Aug. 1997; 2 pages.

"USBN9602 (Universal Serial Bus) Full Speed Function Controller with DMA Support," National Semiconductor Corporation (now Texas Instruments), Nov. 1998; 47 pages.

"ST72671 Product Preview," SGS-Thomson Microelectronics (now STMicroelectronics), Rev. 1.1, Mar. 1998; 101 pages.

"PowerPC MPC823 Users Manual, The Microprocessor for Mobile Computing," Motorola, Inc. (now Freescale Semiconductor, Inc.), Apr. 1998; 1357 pages.

"Universal Serial Bus Specification", Revision 1.0, Compaq Computer Corporation, Digital Equipment Corporation, IBM PC Company, Intel Corporation, Microsoft Corporation, NEC, Northern Telecom, Jan. 15, 1996; 268 pp.

"Am186TMED/EDLV High Performance, 80C186- and 80C188-Compatible, 16-Bit Embedded Microcontrollers," Advanced Micro Devices, Inc., May 1997; 88 pp.

"SL11RUSB Hardware Specification Technical Reference," Revision 1.20, Scanlogic Corporation, Jul. 14, 1998; 47 pp.

"USB Products Keep Rollin," EDN Network Magazine, Nov. 7, 1996; 2 pp.

"USB97C100 Advance Information, Multi-Endpoint USB Peripheral Controller," Standard Microsystems Corporation, Feb. 11, 1998; 80 pp.

"USBFC (USB Function Controller) EIFUFAL501 User's Manual," Revision 2.0, Seiko Epson Corporation, Mar. 24, 1998; 35 pp.

Freeman, et al., "Television Control by Hand Gestures," Mitsubishi Electric Research Laboratories, Dec. 1994; 7 pp.

"Hardware Maintenance Service for Service Level I, Machine Types 2144 and 2168 and IBM Monitors," IBM Corporation, Dec. 1995; 246 pp.

"IBM Aptiva" Wikipedia, available at http://en.wikipedia.org/wiki/IBM\_Aptiva, accessed Sep. 24, 2014; 3 pp.

Dalal, et al., "48-bit Absolute Internet and Ethernet Host Numbers," Xerox Corporation, Jul. 1981; 18 pp.

"RFC: 793, Transmission Control Protocol, Darpa Internet Program Protocol Specification," Information Sciences Institute University of Southern California, Sep. 1981; 90 pages.

Saltzer, J., "Request for Comments: 1498, On the Naming and Binding of Network Destinations," Network Working Group, Aug. 1993; 10 pages.

Podgorny, et al., "Video on Demand Technologies and Demonstrations," Air Force Research Laboratory Information Directorate, May 1998; 393 pages.

Murhammer, et al., "TCP/IP Tutorial and Technical Overview," IBM, Oct. 1998; 738 pages.

Cortes, et al., "The SICMA Teleteaching Trial on ADSL and Intranet Networks," 4th European Conference on Multimedia Applications, Services, and Techniques, 1999; 14 pages.

"RealPlayer 5.0, Release Notes," RealNetworks Inc., 1996, available at http://service.real.com/help/player/free5.0/notes.htm; 7 pages. "NetShow," Wikipedia, available at http://en.wikipedia.org/wiki/NetShow, accessed Sep. 24, 2014; 2 pages.

"History," TiVo, archived on Aug. 7, 2013 by the Internet Archive at http://www3.tivo.com/jobs/questions/history-of-tivo/index.html; 2 pages.

"Philips HDR110", Tivopedia.com, archived on Feb. 28, 2014 by the Internet Archive at https://web.archive.org/web/20140228205013/http://www.tivopedia.com/model-philips-hdr110.php; 3 pages.

Mutoh, et al., "1-V Power Supply High-Speed Digital Circuit Technology with Multithreshold-Voltage CMOS," IEEE Journal of Solid-State Circuits, vol. 30, No. 8, Aug. 1995; 8 pages.

Lackey, et al., "Managing Power and Performance for System-on-Chip Designs using Voltage Islands" ("Lackey"), IBM Microelectronics Division, IEEE/ACM International Conference, 2002; 8 pages.

Semeraro, et al., "Energy-Efficient Processor Design Using Multiple Clock Domains with Dynamic Voltage and Frequency Scaling," High Performance Computer Architecture, 2002; 12 pages.

Lefurgy, et al., "Energy Management for Commercial Servers", vol. 36, Issue 12, IBM Austin Research Lab, 2003; 10 pages.

Wu, et al., "Voltage and Frequency Control with Adaptive Reaction Time in Multiple-Clock-Domain Processors," IEEE Computer Society, Feb. 2005; 12 pages.

Gruian, F., "System-Level Design Methods for Low-Energy Architectures Containing Variable Voltage Processors," Department of Computer Science, Lund University, 2001; 7 pages.

Rosenfeld, et al. "Coarse-Fine Template Matching", vol. 7, No. 2, IEEE Systems, Feb. 1977; 4 pages.

Lee, et al. "An Intelligent Real-Time Multiple Moving Object Tracker" ("Lee 1988"), SPIE vol. 937, Applications of Artificial Intelligence VI, 1988; 8 pages.

Yuille A., "Deformable Templates for Face Recognition," Massachusetts Institute of Technology, Journal of Cognitive Neuroscience, vol. 3, No. 1, 1991; 12 pages.

Harvey, A., et al., "Software Speedup Techniques for Binary Image Object Recognition," vol. 3, IEEE, 1991; 5 pages.

Rauterberg, et al., "A gesture based interaction technique for a planning tool for construction and design," IEEE International Workshop on Robot and Human Communication, 1997; 6 pages. Kjeldsen, et al., "Interaction with On-Screen Objects using Visual Gesture Recognition," IEEE Computer Society, Jun. 1997; 6 pages. Crockett, et al., "Parallel Polygon Rendering for Message-Passing

Crockett, et al., "Parallel Polygon Rendering for Message-Passing Architectures," vol. 2, No. 2, IEEE Parallel & Distributed Technology, 1994; 12 pages.

Araki, et al., "Video DSP Architecture for MPEG 2 Codec," Proceedings of 1994 IEEE International Conference on Acoustics, Speech, and Signal Processing, vol. 2, Apr., 1994; 4 pages.

Wirthlin, et al., "The Nano Processor: a Low Resource Reconfigurable Processor," 1994; 8 pages.

Wazlowski M. "A Reconfigurable Architecture Superscalar Coprocessor", Brown University, 1992; 128 pages.

Crockett, et al., "A MIMD Rendering Algorithm for Distributed Memory Architectures," IEEE, Oct. 1993; 8 pages.

Whitman, S., "A Task Adaptive Parallel Graphics Renderer," IEEE Oct. 1993; 8 pages.

Smith, A., "Cache Memory Design: An Evolving Art," IEEE Spectrum, vol. 24, No. 12, Dec. 1987; 6 pages.

"SL-11 USB Controller Technical Reference, Revision 1.11," ScanLogic Corporation (now Cypress Semiconductor Corporation), Jan. 1997; 57 pages.

USS-620 USB Device Controller with DMA Bridge Advance Data Sheet, Revision 4, Lucent Technologies (now Alcaltel-Lucent), Oct. 1997; 1 page.

"8237/8237-2 High Performance Programmable DMA Controller," Component Data Catalog, Intel Corporation, Jan. 1981; 23 pages. "SN54153, SN54LS153, SN54S153 SN74153, SN74LS153, SN74S153 Dual 4-Line to 1-Line Data Selectors/Multiplexers," Texas Instruments, Mar. 1988; 4 pages.

"Standard Microsystems Corporation Reports Net Income from Continuing Operations for the Third Quarter of Fiscal 1998," Business Wire, Dec. 16, 1997; 5 pages.

Fredlund, et al., "Film-to-Video Imaging; Concepts and Applications," Consumer Electronics 1990, IEEE 1990 International Conference, Jun. 1990; 8 pages.

Kinghorn, J.R., "Enhanced On-Screen Displays for Simpler TV Control," IEEE Transactions on Consumer Electronics, vol. 38, No. 3, Aug. 1992; 9 pages.

Miller, E., "Standardization of Set Top Box Design for Interactive Television," Consumer Electronics 1994, Jun. 1994; 2 pages.

Lee, et al., "Point & Pick User Interface for Projection Television," Consumer Electronics 1995, Jun. 1995; 2 pages.

Perry, T., "The Trials and Travails of Interactive TV,", IEEE Spectrum, vol. 33, No. 4, Apr. 1996; 7 pages.

#### OTHER PUBLICATIONS

Usui, et al., "Multimedia Services in the HDTV MUSE System", IEEE Transactions and Broadcasting, vol. 42, No. 3, Sep. 1996; 6 pages.

Sakamoto, et al., "An MPEG-1 & 2 Decoder and GUI System for a Multimedia Home Terminal (STB)," Consumer Electronics 1996, Jun. 1996; 2 pages.

Kalva, et al., "Implementing Multiplexing, Streaming and Server Interaction for MPEG-4," IEEE Transactions on Curcuits and Systems for Video Technology, vol. 9, No. 8, Dec. 1999; 14 pages. Lohan, et al., "Broadband Network Set-Top Box System," Tampere University of Technology, Oct. 25, 2000; 7 pages.

England, N., "Graphics System Architecture for Interactive Application-Specific Display Functions," 1986.

England, N., "Graphics-Intensive Applications Get a Boost, Application Acceleration: Development of the TAAC-1," 1988;.

Owens, J., "Computer Graphics on a Stream Architecture," Stanford University, Doctoral Dissertation, Nov. 2002; 178 pages.

Boyd, C., "Chapter 5: DirectX," SIGGRAPH 2002; 50 pages. Olano, M., "SGI OpenGL Shader," Level-of-Detail White Paper, SIGGRAPH 2002; 22 pages.

Weber, et al., "Exploring the Benefits of Multiple Hardware Contexts in a Multiprocessor Architecture: Preliminary Results," Proceedings of the 16th Annual International Symposium on Computer Architecture, Jun. 1989; 8 pages.

Rost, R., "Course 17: State-of-the-Art in Hardware Rendering, The OpenGL Shading Language," SIGGRAPH 2002.

Rost, R., "Course 17: State-of-the-Art in Hardware Rendering, Chapter 6: The OpenGL Shading Language," SIGGRAPH 2002 Course Notes, Aug. 5, 2002; 56 pages.

"Microsoft DirectX 8.1 (C++) Programmers Guide," Microsoft Corporation, Jun. 17, 2002; 406 pages.

Hirata, et al., "An Elementary Processor Architecture with Simultaneous Instruction Issuing from Multiple Threads," Proceedings of the 19th Annual Symposium on Computer Architecture, May 1992; 10 pages.

McCool, M. "Smash: A Next-Generation API for Programmable Graphics Accelerators," University of Waterloo, Technical Report CS-2000-14, Apr. 20, 2001; 31 pages.

i860 Microprocessor Family Programmer's Reference Manual, 1991. Bajaj, et al., "Parallel Multi-PC Volume Rendering System," University of Texas at Austin, 2002; 6 pages.

McConnell, R., "Massively Parallel Computing on the Fuzion Chip," PixelFusion plc, Presentation slides, Aug. 25, 1999; 24 pages.

Meissner, et al., "Parallel volume rendering on a single-chip SIMD architecture," Proceedings of the IEEE 2001 Symposium on Parallel and Large-Data Visualization and Graphics; 8 pages.

Rixner, et al., "A Bandwidth-Efficient Architecture for Media Processing," Proceedings of the 31st Annual ACM/IEEE International Symposium on Microarchitecture, 1998; 11 pages.

Rixner, R., "Stream Processor Architecture," Rice University, Aug. 1, 2001; 134 pages.

Kapasi, et al., "Stream Scheduling," Stanford University Concurrent VLSI Architecture Memo 122, Proceedings of the 3rd Workshop on Media and Stream Processors, Dec. 2, 2001; 11 pages.

Khailany, et al., "Imagine: Media Processing with Streams," IEEE Micro, Mar.-Apr. 2001; 12 pages.

Rixner, S., "A Bandwidth-efficient Architecture for a streaming Media Processor," Massachusetts Institute of Technology, Doctoral Dissertation, Apr. 24, 2001; 146 pages.

Mattson, P., "A programming System for the Imagine Media Processor," Stanford . . . University, Doctoral Dissertation, Mar. 2002; 210 pages.

Tullsen, et al., "Simultaneous Multithreading: Maximizing On-Chip Parallelism," Proceedings of the 22nd Annual International Symposium on Computer Architecture, Jun. 1995; 12 pages.

Ungerer, et al., "Multithreaded Processors," The Computer Journal, vol. 45, No. 3, 2002; 29 pages.

Eggers, et al., "Simultaneous Multithreading: A Platform for Next-Generation Processors," WRL Technical Note TN-52, Digital Western Research Laboratory; 26 pages.

Patel, et al., "Architectural Features of the i860™-Microprocessor RISC Core and On-Chip Caches," Proceedings of the IEEE International conference on Computer Design: VLSI in Computers and Processors, Oct. 2-4, 1989; 6 pages.

Kohn, et al., "Introducing the Intel i860 64-Bit Microprocessor," IEEE Micro, vol. 9, Issue 4, Jul. 1989; pp. 15-30.

Grimes, et al., "The Intel i860 64-Bit Processor: A General-Purpose CPU with 3D Graphics Capabilities," IEEE Computer Graphics and Applications, vol. 9, Issue 4, Jul. 1989; pp. 85-94.

Definition of "live", Merriam-Webster's Online Dictionary, available at http://www.merriam-webster.com/dictionary/live; 3 pages. English-language Abstract of Chinese Patent Application Publication No. 1154629 A, published Jul. 16, 1997; 1 page.

English-language Abstract of European Patent Application Publication No. 0762769 A1, published Mar. 12, 1997; 1 page.

English-language Abstract of Japanese Patent Application Publication No. 05-252439, published Sep. 28, 1993; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 06-153017, published May 31, 1994; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 06-217271, published Aug. 5, 1994; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 07-154626, published Jun. 16, 1995; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 07-222027, published Aug. 18, 1995; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 07-281666, published Oct. 27, 1995; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 08-106421, published Apr. 23, 1996; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 08-331415, published Dec. 13, 1996; 2 pages.

English-language Abstract of Japanese Patent Application Publication No. 09-006947, published Jan. 10, 1997; 2 pages.

\* cited by examiner

FIG. 1

FIG. 3

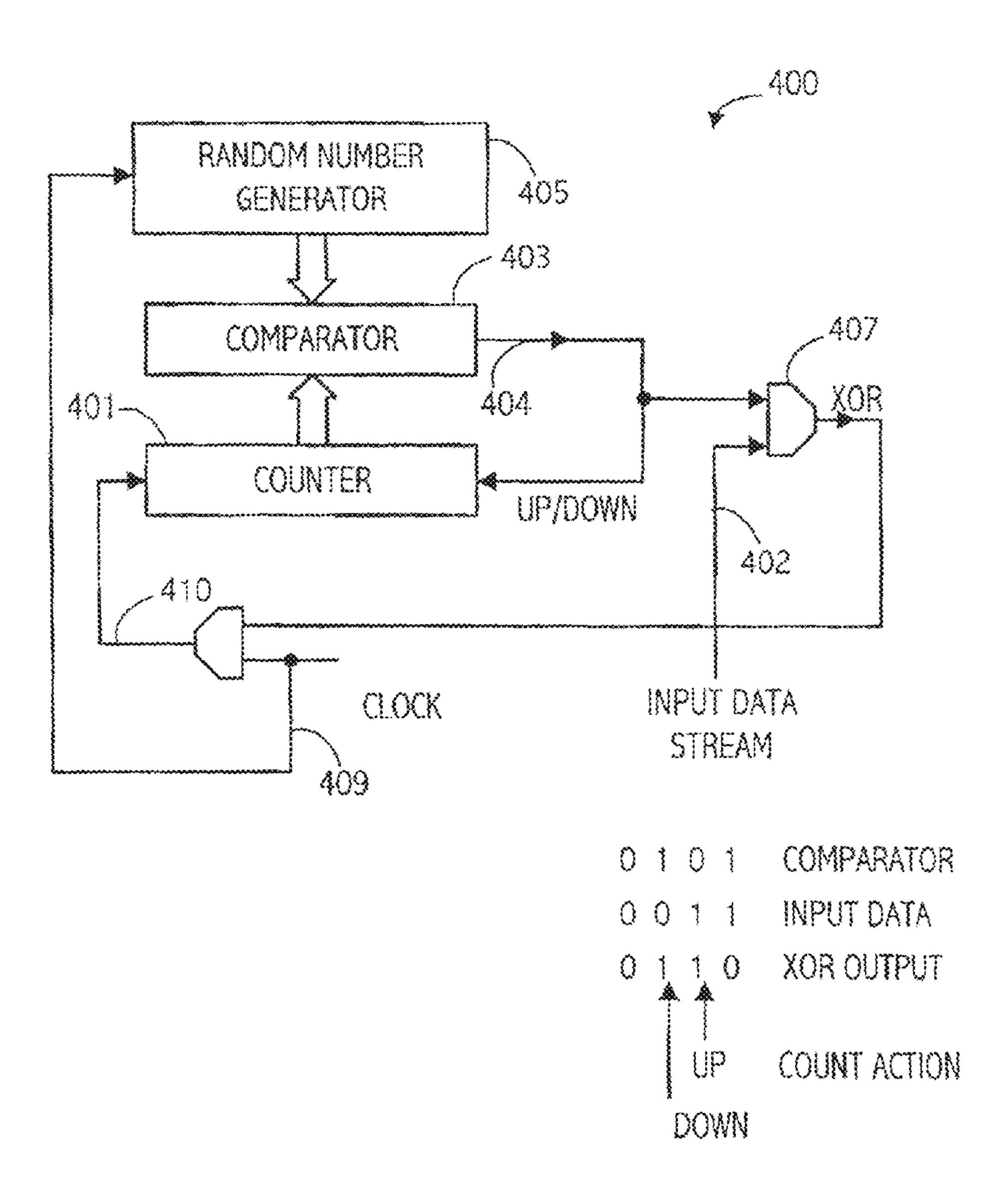

FIG. 4

# PERFORMANCE AND POWER OPTIMIZATION VIA BLOCK ORIENTED PERFORMANCE MEASUREMENT AND CONTROL

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This invention relates to integrated circuits and more particularly to power management in integrated circuits.

#### 2. Description of the Related Art

Large computational devices, e.g., current microprocessors, include many functional units such as one or more 20 fixed point units, load/store units, floating point units (FPU), vector arithmetic units, barrel shifters, instruction and data cache memories, bridge or tunnel circuits, memory controllers, first in first out (FIFO) buffers, and various input/output interface units (e.g., interfaces for universal asynchronous receiver/transmitters (UART), serializer/deserializer (SER- <sup>25</sup> DES), HyperTransport<sup>TM</sup>, Infiniband<sup>TM</sup>, PCI bus). In a portable computing environment, where power conservation is particularly important, power management techniques have been implemented to conserve power based on when, e.g., a period of inactivity occurs. The power conservation typi- <sup>30</sup> cally includes stopping clocks for a period of time. However, the clocks are controlled globally, and thus in situations where one part of a processor is being heavily used but another part is being lightly utilized, all the functional blocks in the processor are configured for heavy use. Thus, power 35 may be wasted in situations where, e.g., the fixed point unit is being used but the floating point unit is not being utilized heavily or at all.

In a prior art power savings approach, disclosed in U.S. Pat. No. Re 37,839, functional blocks are deactivated to save power. The activation and deactivation of the functional blocks is controlled by the flow of data within the integrated circuit. Thus, as data flows through the integrated circuit, those functional blocks are turned on and off as necessary to accommodate that data flow.

The amount of power consumed by a functional block is directly related to its performance. In order to allocate power resources more effectively, it would be desirable to be able to dynamically match performance and thus control power consumed by individual functional blocks according to the utilization requirements of the functional blocks. However, 50 current designs generally do not provide information about utilization of the individual functional blocks, and power consumption is not tuned to match the loading of the individual functional blocks. A possible disadvantage to turning clocks on and off based on data flow is that ineffi- 55 ciencies may result due to the time it takes to turn clocks on and off to the various functional blocks. Accordingly, it would be desirable to dynamically adjust the power consumed by functional blocks of an integrated circuit according to the utilization or loading of those functional blocks 60 and thus achieve power savings while maintaining performance.

#### SUMMARY OF THE INVENTION

The present invention monitors the utilization of the functional blocks in an integrated circuit. Based on that

2

information, the power consumption and thus the performance levels of the functional blocks can be tuned. When a functional block is heavily loaded by an application, the performance level and power consumption of that particular functional block can be increased. At the same time, other blocks that may not be loaded by that application and have lower performance requirements can be kept at a relatively low power consumption level. Thus, power consumption can be reduced overall without unduly impacting performance.

In one embodiment, the invention provides a method for controlling power consumption in an integrated circuit that includes a plurality of functional blocks. The functional blocks generate block utilization information. The power consumption of the respective functional blocks is managed according to respective block utilization information. The power consumption can be managed by adjusting dispatch rate of operations through the particular functional block, adjusting the clock frequency of clocks being supplied to the functional circuit and/or adjusting the voltage along with the clock frequency. In an embodiment, utilization information may be kept on a task basis.

In another embodiment, the invention provides a computer system that includes an integrated circuit that has a plurality of functional blocks. Utilization circuits that are respectively associated with the functional blocks provide block utilization information of the functional blocks. A computer program includes an instruction sequence executable by the integrated circuit to adjust power consumption levels of the functional blocks according to the block utilization information.

In another embodiment an integrated circuit includes a plurality of functional blocks. Utilization circuits respectively associated with the functional blocks provide block utilization information of the functional blocks. The integrated circuit is responsive to the block utilization information to independently adjust power consumption levels of the functional blocks.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention may be better understood, and its numerous objects, features, and advantages made apparent to those skilled in the art by referencing the accompanying drawings.

- FIG. 1 shows a block diagram of an exemplary integrated circuit incorporating the present invention.

- FIG. 2 illustrates a representative functional block and associated detection and counting registers.

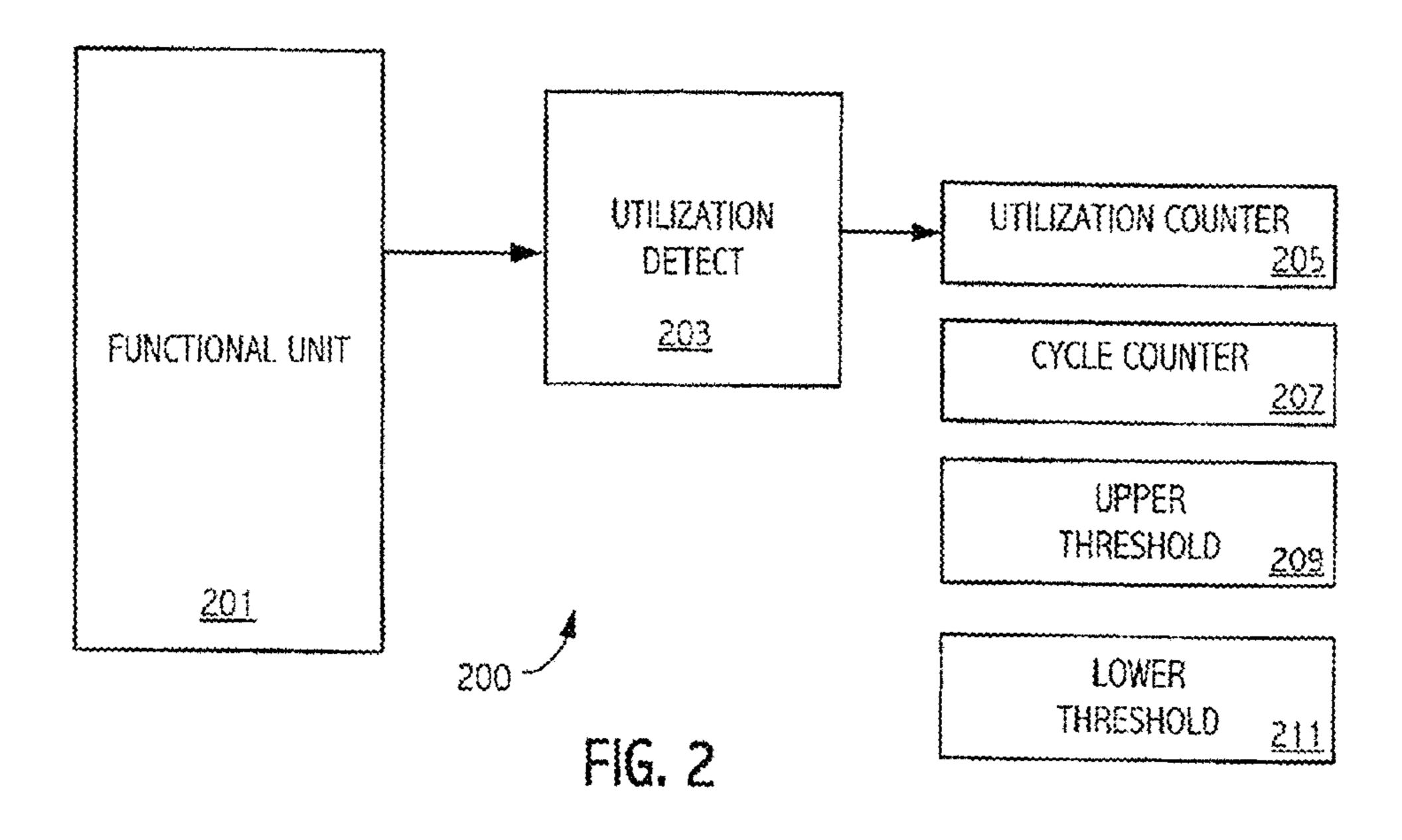

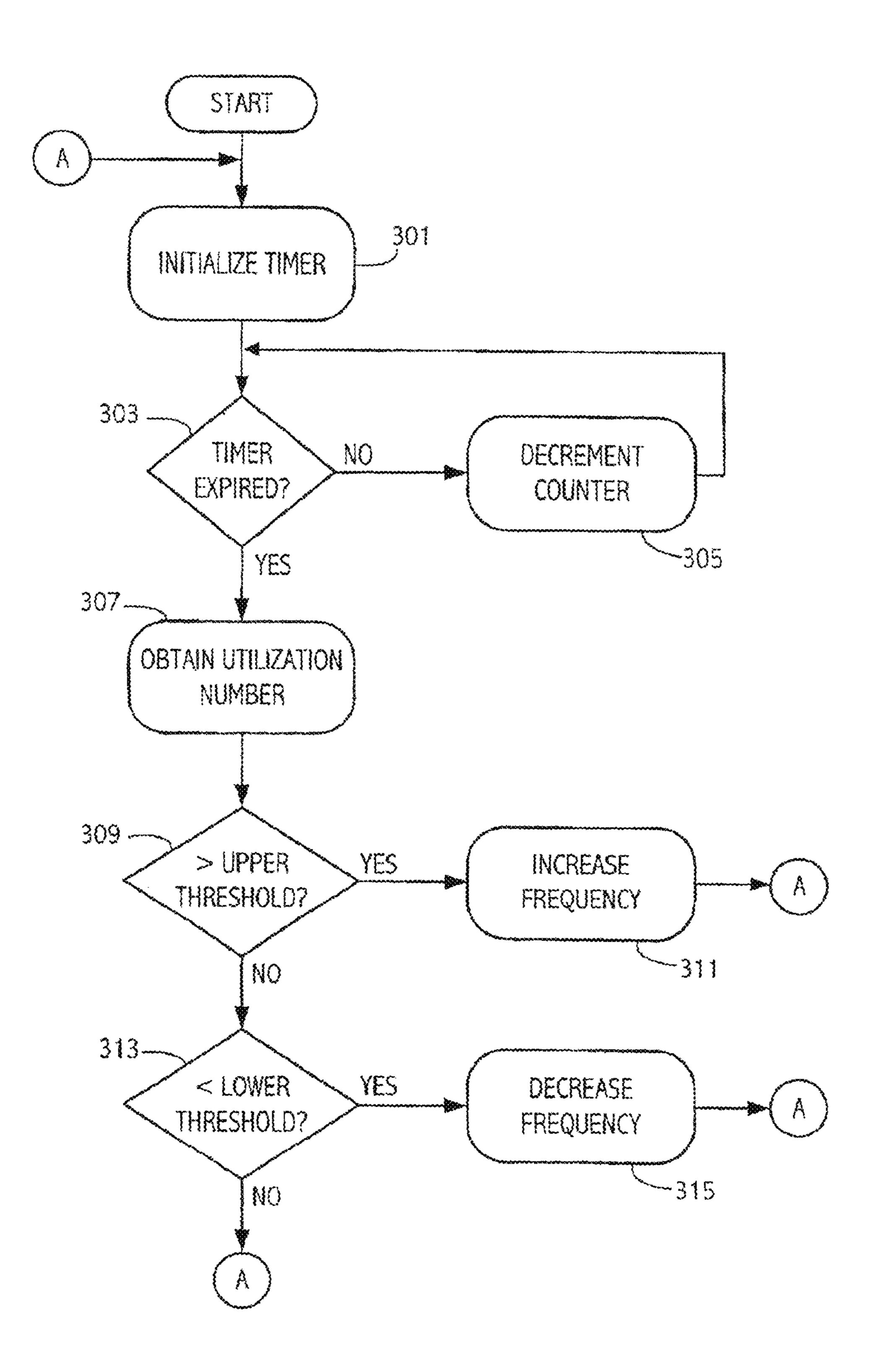

- FIG. 3 illustrates a flow diagram of operation of an embodiment of the present invention utilizing threshold values to determine when to adjust the power consumption of a functional block.

- FIG. 4 illustrates a detection circuit that can be utilized to provide a statistical utilization value that provides a rolling average of prior utilizations.

The use of the same reference symbols in different drawings indicates similar or identical items.

## DESCRIPTION OF THE PREFERRED EMBODIMENT(S)

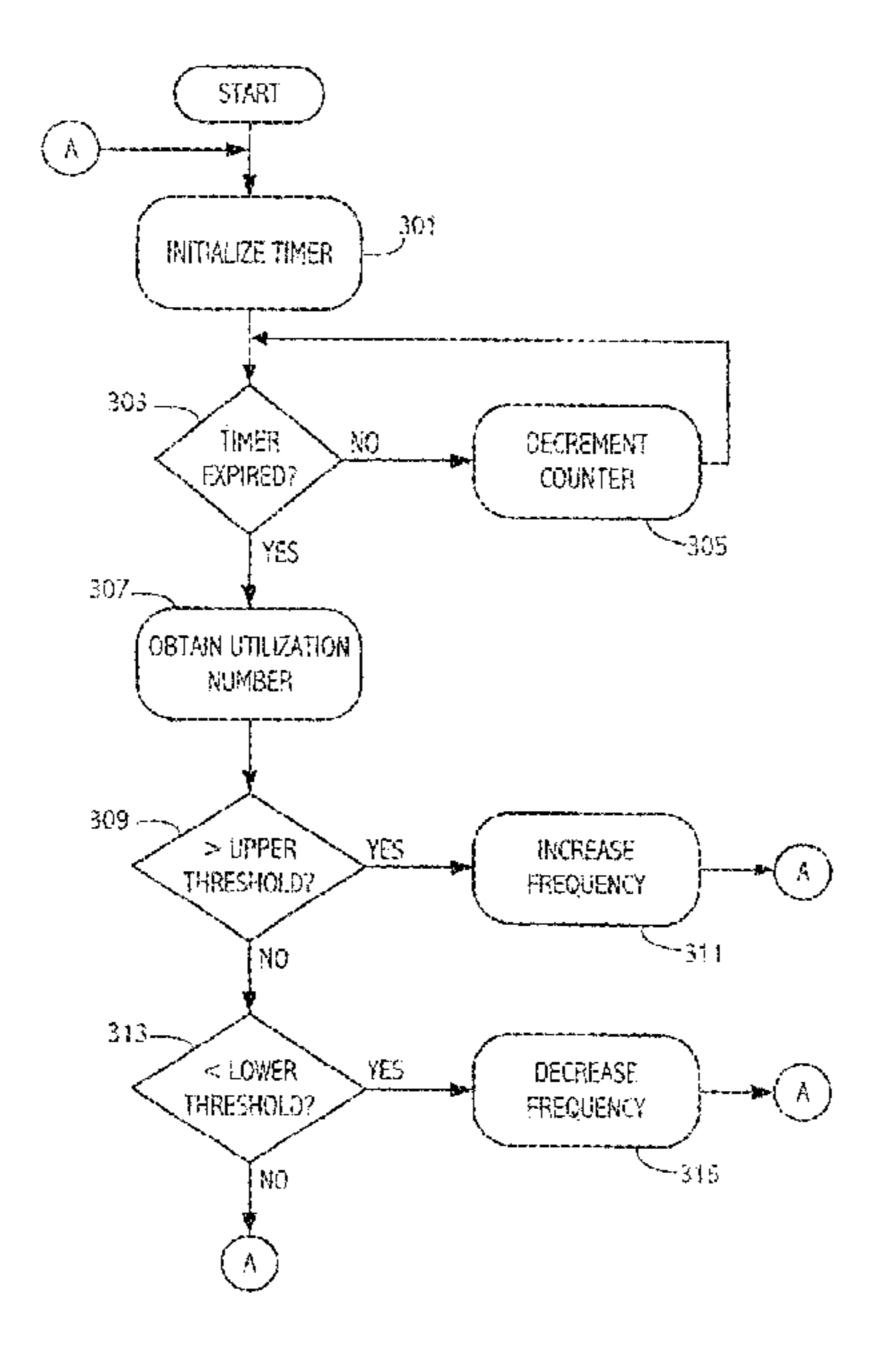

Referring to FIG. 1, a block diagram of an exemplary integrated circuit incorporating an embodiment of the present invention is illustrated. Exemplary processor 100 includes fixed point unit (ALU) 102, a floating point unit (FPLU) 104, a load/store unit 106, instruction/data cache

108, input/output units 110 and a power management unit 112. In one embodiment, power management unit 112 supplies clock signals 111, 113, 115, 117, and 119 to the individual functional blocks. In an embodiment, power management unit 112 adjusts the frequency of the clocks 5 according to the utilization of the functional units. The functional units shown in FIG. 1 are general in nature. Other functional units may be included in addition to or in place of those illustrated.

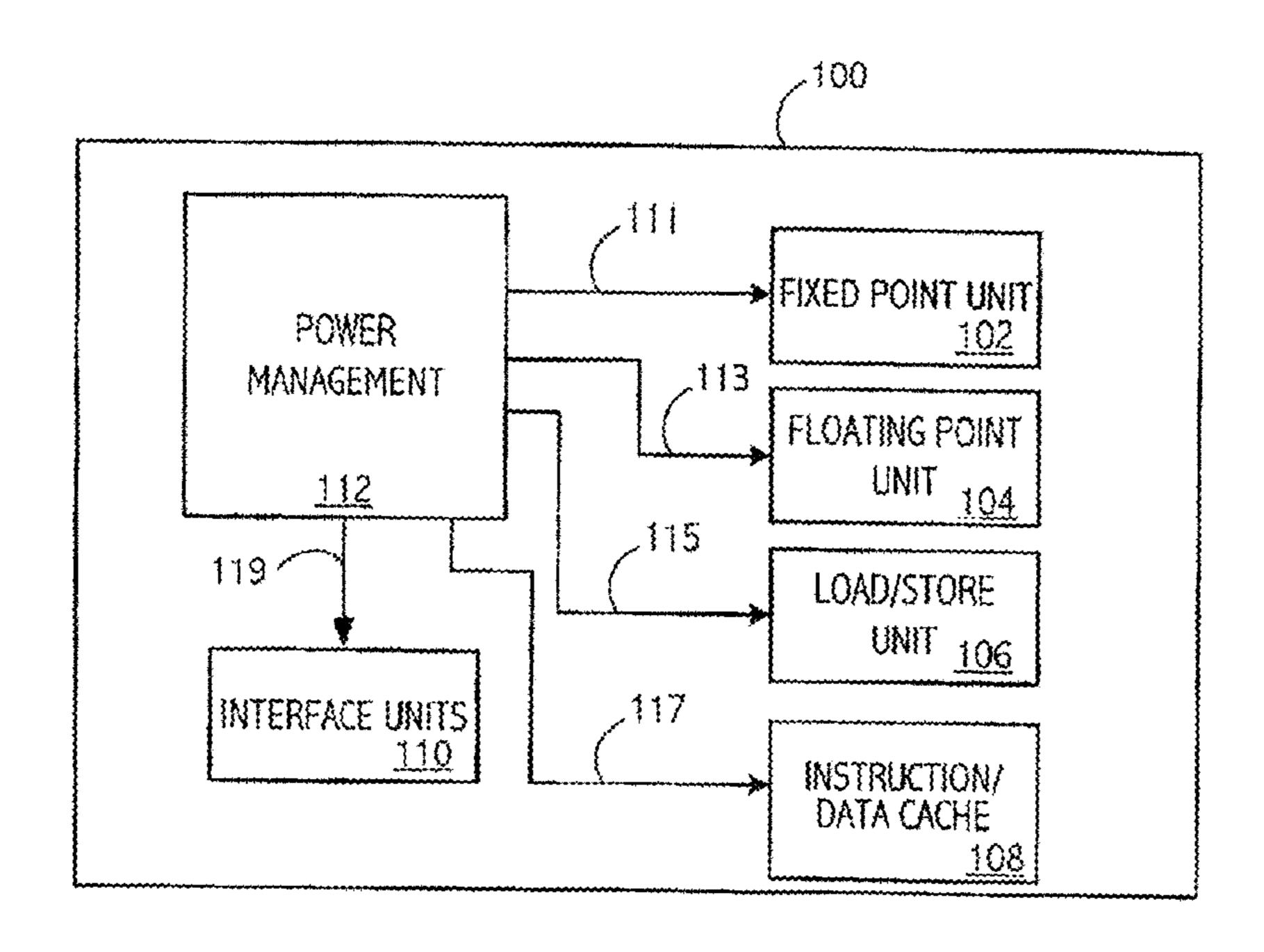

An exemplary functional block 200 is shown in FIG. 2. 10 The "function" provided by the functional block **200** shown in FIG. 2 can vary. For example, the functional block 200 may be a floating point unit or a cache memory. Functional block 200 includes the functional unit 201 that performs the "function." Functional unit 100 also includes a utilization 15 detect circuit 203. The functional block 200 generates information indicating the utilization of the block. That information may be a percentage of time that the block is used or conversely, the percentage of time the block is idle. The utilization information can be generated in a number of 20 ways. For example, the utilization of a cache memory may be determined according to the number of cache accesses that occur over a predetermined period of time. Alternately, the cache access utilization may be determined by the percentage of memory accesses that are directed to the 25 cache. In another example, floating point (FPU) utilization may be determined by detecting when the FPU is requested to perform a floating point operation. The number of FPU requests may be counted over a period of time to determine utilization. For an execution unit of a processor, the measured value used to determine utilization may be the number of instructions that are dispatched over a period of time.

Thus, as shown in FIG. 2, a utilization detection circuit 203 is provided that detects when the functional unit is being utilized in the manner described above according to the type 35 of functional unit and the particular information desired. Assume that the utilization detection circuit 203 detects a utilization event, e.g., when an FPU receives a request to perform a floating point operation. That detection causes a utilization counter 205 to increment a count value to indicate 40 that a utilization occurred. The size of the utilization counter depends upon how often the system checks utilization of the functional block, e.g., every 10 microseconds, as well as the number of utilization events that counter 205 is expected to count. The longer the period between checking of block 45 utilization, and/or the more events to be counted, the bigger the counter size required.

In addition to counting the utilization events, a measure may be needed to indicate the period of time over which the counted utilizations occurred. In the exemplary embodiment 50 shown in FIG. 2, cycle counter 207 counts the number of cycles that occurs to provide that information. Cycle counter 207 may be a global counter or a counter local to the functional block. Note that cycle counter 207 may count more slowly than the actual clock rate. For example, cycle 55 counter 207 may count at 100 MHz when the rated processor speed is one GHz. It is sufficient that cycle counter 207 provide an indication of a time period over which utilization counter 205 can be evaluated.

Software, which may reside in the operating system or 60 elsewhere in the electronic system can periodically read utilization counter 205 and cycle counter 207 and determine whether the power consumption and thus the performance of the functional unit matches the load of the functional unit, i.e., its utilization. The power consumption of a functional 65 unit can be adjusted in a number of ways including increasing or decreasing a dispatch rate of instructions into an

4

execution unit (or floating point operations into an FPU), adjusting clock frequency up or down as well as adjusting voltage up or down to match the clock rate. If the functional unit is set for low performance operations and thus has a low power consumption setting and the latest utilization information indicates that the functional unit is heavily loaded, the power consumption and thus performance of the functional unit can be increased to match the performance requirements indicated by the utilization information. In order to increase performance, clock frequency, voltage, and dispatch rate can all be increased. Note that voltage is typically changed only with clock frequency.

If on the other hand, the utilization information indicates that the functional unit is lightly loaded, the clock frequency and/or other power management parameters can be decreased to match the loading. If a particular functional unit is unused or very lightly used, its clocks may even be turned off for a period of time.

In an embodiment, thresholds are provided to determine whether a current power consumption and performance level is appropriate. In order to determine whether current performance levels are adequate as indicated by the utilization information in counter 205, the utilization level can be checked periodically at a predetermined time interval determined by counter 207. Thus, a timer may be provided for each functional unit that indicates how often the utilization counter should be read and the power usage adjusted according to loading factors. When the timer expires, appropriate power management software is notified. The timers could be set differently for different functional units so that each functional unit can be checked at a different time. Alternatively, the operating system or other power management software can read all of the utilization information periodically, with the period being determined by a single timer for all of the functional units.

Alternatively, the value in the utilization counter can be divided by the cycle counter to obtain a utilization per unit time. If that is done, then the utilization counter has to be read before the utilization counter 205 overflows. In either case, the utilization level is compared to upper threshold level 209. If the utilization level is above the upper threshold level 209, clock frequency and/or other performance parameters are increased to provide increased performance. The amount of that increase may be based upon the magnitude of the difference between the calculated utilization level and the upper threshold level. For example, a 10% difference may result in a 10% increase. Alternatively, the increase may occur in fixed steps, e.g., from ¼ of a base clock to ½ of a base clock frequency regardless of the difference between the calculated utilization level and the upper threshold level.

The utilization level may also be compared to the lower threshold value and if the calculated utilization is below the lower threshold level, the clock speed is adjusted downward. Again, the adjustment may be based on the magnitude of the difference between the calculated utilization value and the lower threshold value. Or the adjustment may be fixed between a current level and a next lower level, e.g., from full clock speed in the functional unit to <sup>3</sup>/<sub>4</sub> clock speed. In addition, voltage can be adjusted up or down to match the clock speed for additional power savings.

The threshold registers can be implemented as registers in the functional units or integrated circuit (e.g., model specific registers), system memory, or any other suitable memory that can be used by the software performing the power management function. The values for the threshold registers may be supplied by BIOS, application software or some other initialization source. For example, the values for the

threshold registers for each functional block may be calculated empirically by the operating system. Each functional unit would typically have associated with it unique threshold registers.

FIG. 3 illustrates a flow diagram of operation of an 5 exemplary embodiment utilizing thresholds. The embodiment shown in FIG. 3 could be implemented entirely in hardware, software or a combination, according to the needs of the particular system. On power up, a timer is initialized in 301. The initialization routine may, e.g., load a down 10 counter with a predetermined value. In 303 a comparison is made to see if the counter is expired. If not, the counter is decremented in 305 and the loop continues until the timer has counted down to zero. Once that occurs, a utilization number is obtained in 307. The timer assures that the 15 utilization counter has not overflowed. In other embodiments as described further herein, the utilization counter may be implemented to provide a probability (a rolling average) of the utilization event, and thus there is no risk of utilization counter overflow.