### US00RE46784E

# (19) United States

## (12) Reissued Patent

Lin

US RE46,784 E (10) Patent Number:

(45) Date of Reissued Patent: Apr. 10, 2018

## INTEGRATED CIRCUIT DEVICE HAVING PADS STRUCTURE FORMED THEREON AND METHOD FOR FORMING THE SAME

Applicant: REALTEK SEMICONDUCTOR

CORPORATION, Hsinchu (TW)

Inventor: Ying-Hsi Lin, Hsinchu (TW)

Assignee: REALTEK SEMICONDUCTOR CORPORATION, Hsinchu (TW)

Appl. No.: 14/743,421

Jun. 18, 2015 (22)Filed:

## Related U.S. Patent Documents

Reissue of:

6,787,928 Patent No.: (64)Sep. 7, 2004 Issued: 10/425,973 Appl. No.: Filed: Apr. 30, 2003

#### (30)Foreign Application Priority Data

(TW) ...... 92104606 A Feb. 26, 2003

Int. Cl. (51)

> H01L 23/48 (2006.01)H01L 23/485 (2006.01)H01L 23/00 (2006.01)

(2013.01); **H01L 24/48** (2013.01); H01L 2224/02166 (2013.01); H01L 2224/04042 (2013.01); H01L 2224/05093 (2013.01); H01L 2224/05095 (2013.01); H01L 2224/05558 (2013.01); H01L 2224/05599 (2013.01); H01L 2224/48463 (2013.01); H01L 2224/85399 (2013.01); H01L 2924/00014 (2013.01); H01L 2924/01004 (2013.01); H01L 2924/01005

(2013.01); H01L 2924/01006 (2013.01); H01L 2924/14 (2013.01); H01L 2924/30105 (2013.01)

(58)Field of Classification Search

CPC ..... H01L 2924/14; H01L 24/03; H01L 24/05; H01L 24/48; H01L 2924/00014; H01L 2924/30105; H01L 2924/01006; H01L 2924/01005; H01L 2224/85399; H01L 2224/02166; H01L 2224/04042; H01L 2224/05093; H01L 2224/05095; H01L 2224/05558; H01L 2224/05599; H01L 2224/48463; H01L 2224/45099

See application file for complete search history.

#### **References Cited** (56)

## U.S. PATENT DOCUMENTS

5,736,791 A \* (Continued)

## FOREIGN PATENT DOCUMENTS

JP 2000299319 A 10/2000

Primary Examiner — Norca L Torres Velazquez (74) Attorney, Agent, or Firm — Sughrue Mion, PLLC

#### ABSTRACT (57)

The invention is to provide a structure of IC pad and its forming method. The structure is arranged in an insulation layer and is comprised of a lower electric-conduction layer, a compound layer structure and a pad layer. The lower electric-conduction layer is arranged at an appropriate position in the insulation layer and is connected to an electric potential. The compound layer structure is arranged on the insulation layer and is composed of at least one electricconduction layer and at least one electric-conduction connecting layer, both are inter-overlapped to each other. The pad layer is arranged on the compound layer structure.

## 40 Claims, 5 Drawing Sheets

# US RE46,784 E Page 2

#### **References Cited** (56)

## U.S. PATENT DOCUMENTS

| 5,923,088 A    | * 1        | 7/1999  | Shiue et al       | 257/758 |

|----------------|------------|---------|-------------------|---------|

| , , ,          |            |         | Chittipeddi et al |         |

| 6,023,095 A    | 4          | 2/2000  | Hirabayashi       |         |

| 6,163,074 A    | * 1        | 12/2000 | Lee et al         | 257/734 |

| 6,163,075 A    | 4          | 12/2000 | Okushima          |         |

| 6,313,537 E    | 31*        | 11/2001 | Lee et al         | 257/758 |

| 6,465,337 E    | 31*        | 10/2002 | Lee et al         | 438/612 |

| 2001/0000928 A | <b>11*</b> | 5/2001  | Lee et al         | 257/786 |

| 2001/0010407 A | <b>A</b> 1 | 8/2001  | Ker et al.        |         |

| 2002/0145206 A | <b>A</b> 1 | 10/2002 | Park et al.       |         |

<sup>\*</sup> cited by examiner

FIG. 1

(PRIOR ART)

FIG. 2

(PRIOR ART)

(PRICE ART)

FIG. 6

1

# INTEGRATED CIRCUIT DEVICE HAVING PADS STRUCTURE FORMED THEREON AND METHOD FOR FORMING THE SAME

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held 10 invalid by a prior post-patent action or proceeding.

This application and its continuation application, U.S. patent application Ser. No. 15/253,539, filed Aug. 31, 2016, <sup>15</sup> are reissue applications of U.S. patent application Ser. No. 10/425,973, filed Apr. 30, 2003, now U.S. Pat. No. 6,787, 928, issued Sep. 7, 2004, which claims priority from Taiwanese Patent Application No. 92104606, filed on Feb. 26, 2003, the disclosure of which is incorporated herein by <sup>20</sup> reference in its entirety.

## FIELD OF THE INVENTION

The invention relates to a structure of IC pad and its 25 forming method, in particular to a structure and method that are adapted to form a pad of integrated circuit of high frequency and low noise; not only the noise from the semiconductor substrate be separated effectively and the value of equivalent electric capacitance of the pad be low-30 ered, but also the bonding adherence be further enhanced.

## BACKGROUND OF THE INVENTION

Recently, since the requirement of transceiver of low 35 power and low cost is steadily on the increase, so the technology of mainstream IC competitively concentrates on how to realize further more functions of radio frequency on one single chip. Except making integrated circuit be able to arrange on the package substrate, the external circuit con- 40 nected by the external legs of package substrate must be electrically connected to the integrated circuit. So, when packaging the integrated circuit, the technology of pad has become an important factor that influences the yield and quality of a product. This pad adapted for providing electric 45 connection between the integrated circuit and the external circuit is usually arranged in the metal zone around the IC die. When the pad is formed, the metal connecting wire must contact with the pad accurately and connect to the external legs of the IC packaging substrate. Because of the limitation 50 of the prior arts and the characteristics of metal connecting wire and pad, the area of pad is sometimes too large to occupy too much area of chip. Furthermore, during high frequency, the performance of the integrated circuit is influenced because the equivalent electric capacitance is too 55 large.

Additionally, because of the market growth of communication IC recently, the operational frequency of integrated circuit is also growing in indexing type. The low noise and low loss of high frequency signal are always the pursuing 60 goals for communication IC.

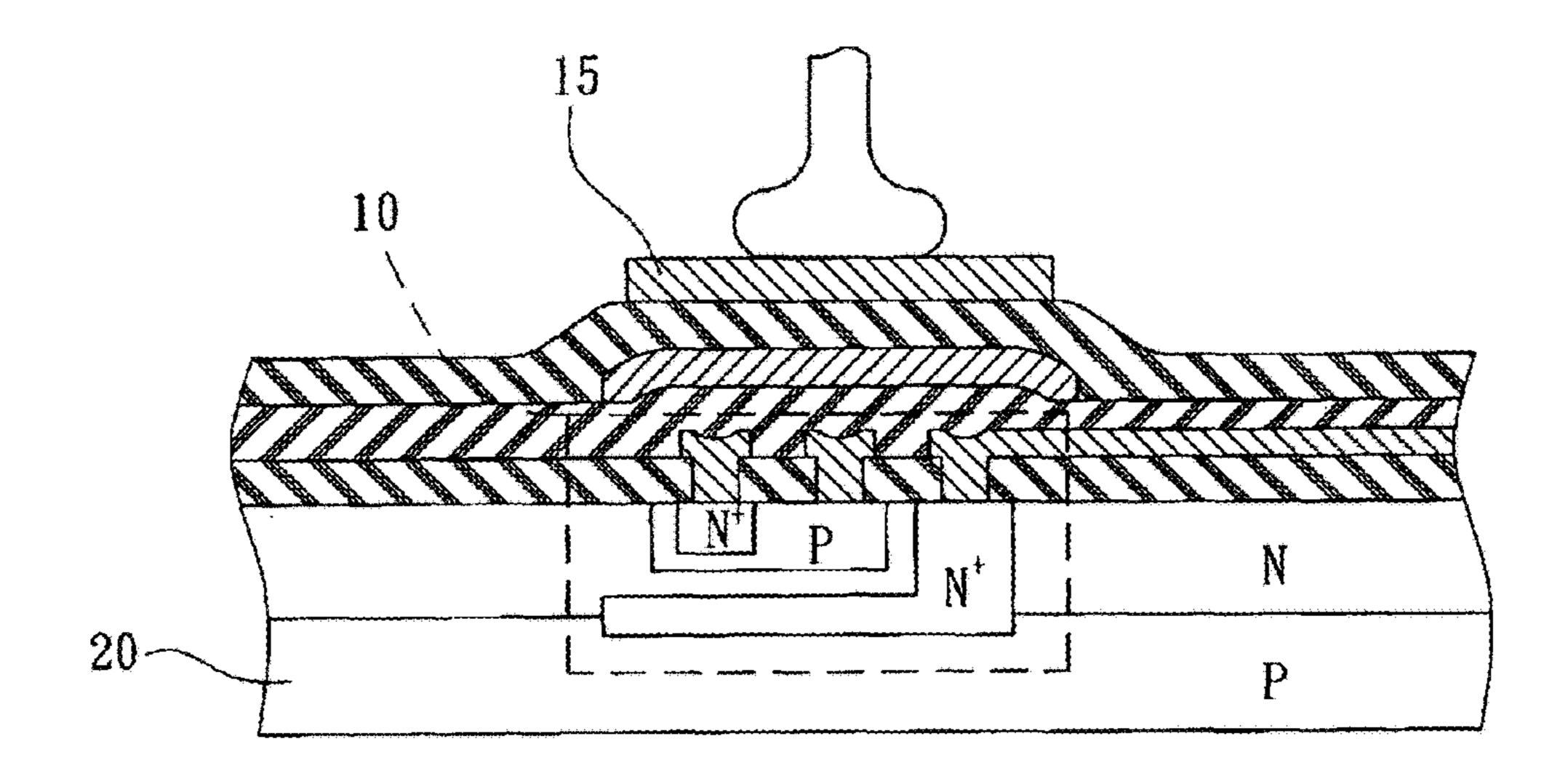

In 1987, the U.S. Pat. No. 4,636,832 "Semiconductor device with an improved bonding section" proposed a design method of the pad of integrated circuit. Please refer to FIG. 1, which is a cross-sectional diagram of the IC 65 and a pad layer. The lower electric-coacteristic of this prior art is that the semiconductor element insulation layer and a pad layer.

2

10 is arranged below the pad 15. Although it may reduce the area of layout, this kind of pad can not be adapted to high frequency circuit with low noise because the noise coming from the semiconductor substrate 20 will directly influence the signal of high frequency when it passes through the pad.

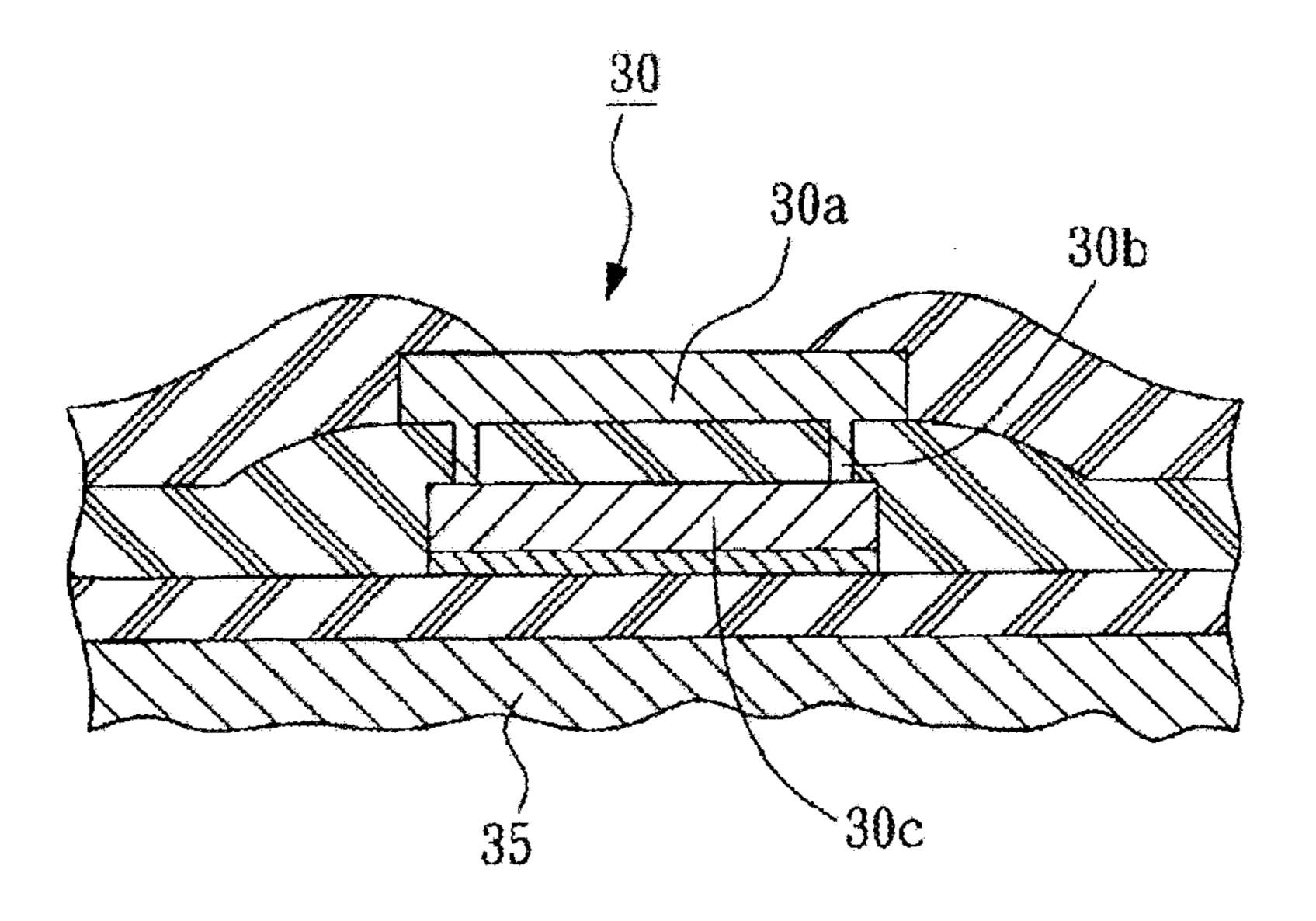

To overcome the tensile and tension of bonding, the U.S. Pat. No. 5,248,903 "Composite pads for semiconductor devices" proposed a kind of pad. Please refer to FIG. 2, which is the cross-sectional diagram of the IC device disclosed in the U.S. Pat. No. 5,248,903. Wherein, the pad 30 has at least two layers of electric-conduction layer 30a and 30c and a connection layer 30b. But, this kind of pad is not adapted for the signals of high frequency and low noise because the noise of semiconductor substrate 35 will directly influence the quality of signal.

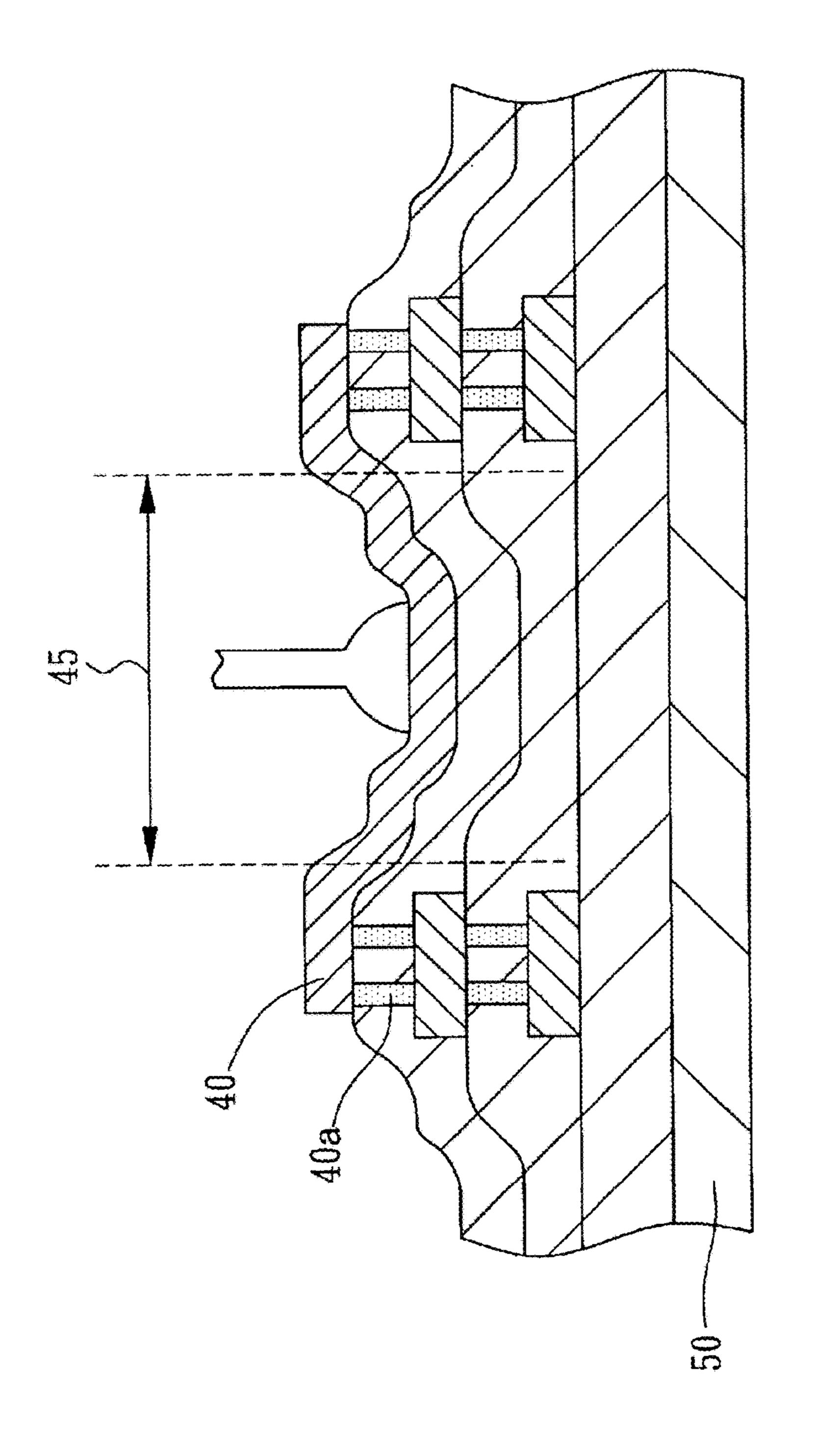

The U.S. Pat. No. 5,502,337 "Semiconductor device structure including multiple interconnection layers with interlayer insulating films" proposed a different designing method for pad. Please refer to FIG. 3, which is a crosssectional diagram for the IC device disclosed in the U.S. Pat. No. 5,502,337, which arranges the connection layer 40a in the pad 40 around the bonding zone 45. When the integrated circuit is manufactured, a bonding zone of arc shape will be formed on the pad 40 to thereby enhance the bonding adherence. However, the technology of current integrated circuit has stepped into the levels of sub micrometer or deep sub micrometer, and CMP (Chemical-Mechanical Polish) is already a standard procedure for current semiconductor process. So, this kind of prior art no longer generates original effectiveness in current semiconductor process, besides this technique has the same drawback as that of previous techniques; i.e., it can not separate the noise coming from the semiconductor substrate 50.

From above discussion, we know that the prior arts described there are unable to propose an effective solution that aims for the high frequency, low noise and bonding adherence. Therefore, the emphasis of the invention is to provide a pad structure adapted for a integrated circuit of high frequency and low noise to lower down the equivalent electric capacitance and enhance the bonding adherence, such that it can prevent the entire pad from being drawn out of the semiconductor chip by the tension generated in the bonding procedure.

## SUMMARY OF THE INVENTION

The main objective of the present invention is to provide a structure of IC pad and its forming method, which are adapted for the structure of the pad of an integrated circuit of high frequency and low noise, such that the effective area of the pad may be reduced effectively to thereby reduce its value of equivalent electric capacitance.

The second objective of the present invention is to provide a structure of IC pad and its forming method effectively separate the noise coming from the semiconductor substrate.

The further objective of the present invention is to provide a structure of IC pad and its forming method effectively enhance the bonding adherence, such that it prevent the entire pad from being drawn out of the semiconductor chip by the tension generated in the bonding procedure.

To achieve above objectives, the invention provides an IC pad structure arranged in an insulation layer comprises a lower electric-conduction layer, a compound layer structure and a pad layer.

The lower electric-conduction layer is arranged in the insulation layer and is connected to an electric potential.

3

The compound layer structure arranged on the insulation layer comprises at least one electric-conduction layer and at least one electric-conduction connecting layer, each of the electric-conduction layer are connected to each other.

The pad layer is arranged on the compound layer structure.

To achieve above objectives, the invention further presents method for forming IC pad structure, comprising the following steps of:

Step (a): providing a substrate arranged with an insulation layer.

Step (b): forming a lower electric-conduction layer which prepared connect to an electric potential.

Step (c): forming a compound layer structure composed by inter-overlapping or connect at least one electric-conduction layer and at least one electric-conduction connecting layer on the insulation layer.

Step (d): forming a pad layer on the compound layer structure, of which area is larger than that of the electric-conduction layer of the compound layer structure.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a cross-sectional diagram for the IC device disclosed in the U.S. Pat. No. 4,636,832.

FIG. 2 is a cross-sectional diagram for the IC device disclosed in the U.S. Pat. No. 5,248,903.

FIG. 3 is a cross-sectional diagram for the IC device disclosed in the U.S. Pat. No. 5,502,337.

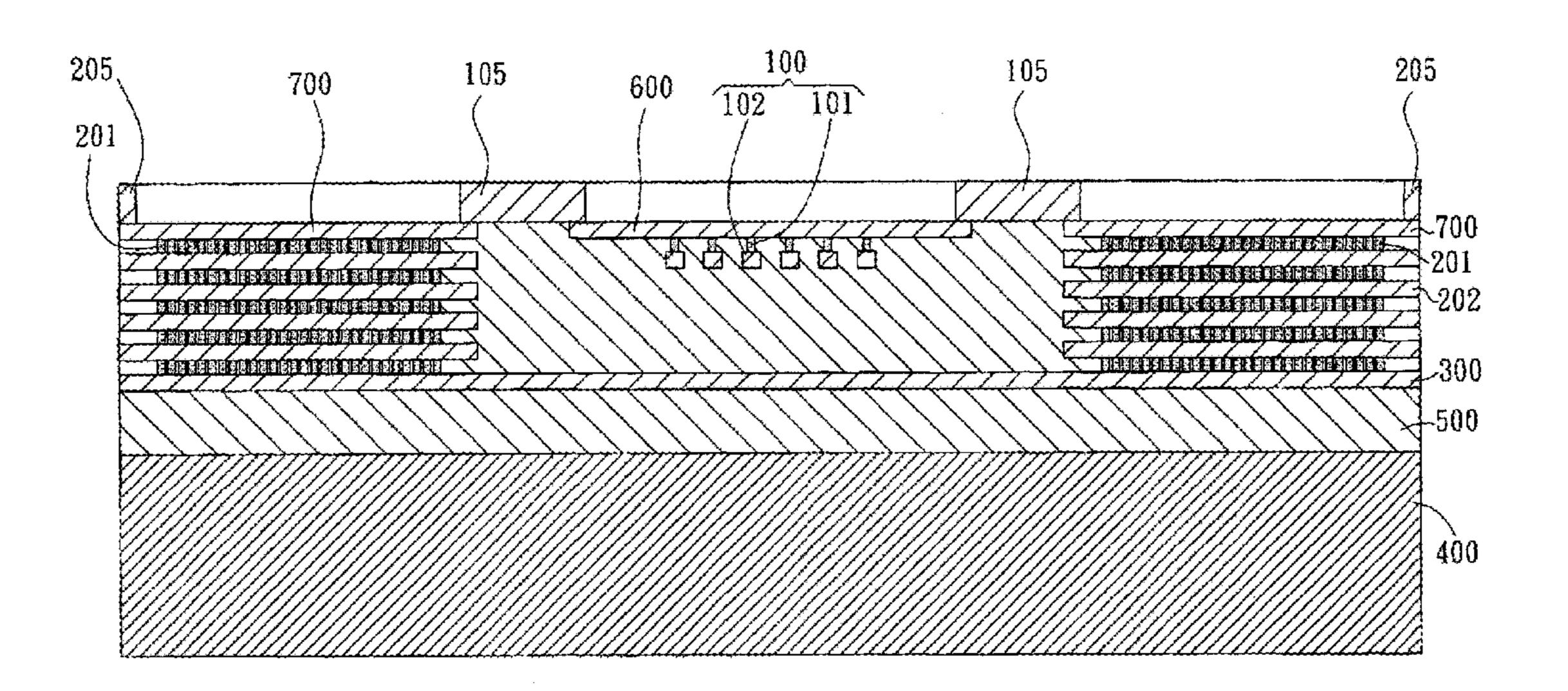

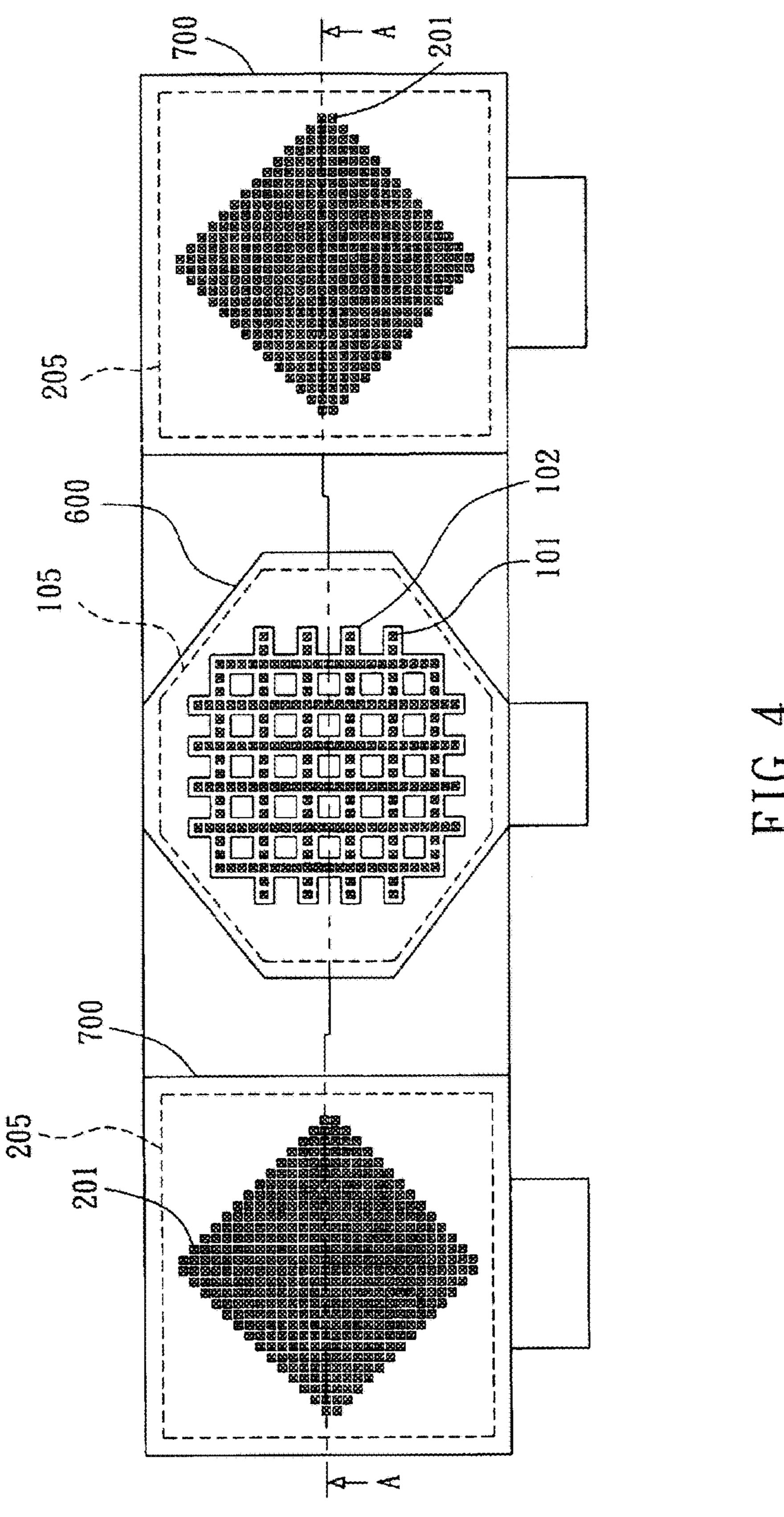

FIG. 4 is an upper side view for the structural illustration 30 herein. of a preferable embodiment of the IC pad according to the invention.

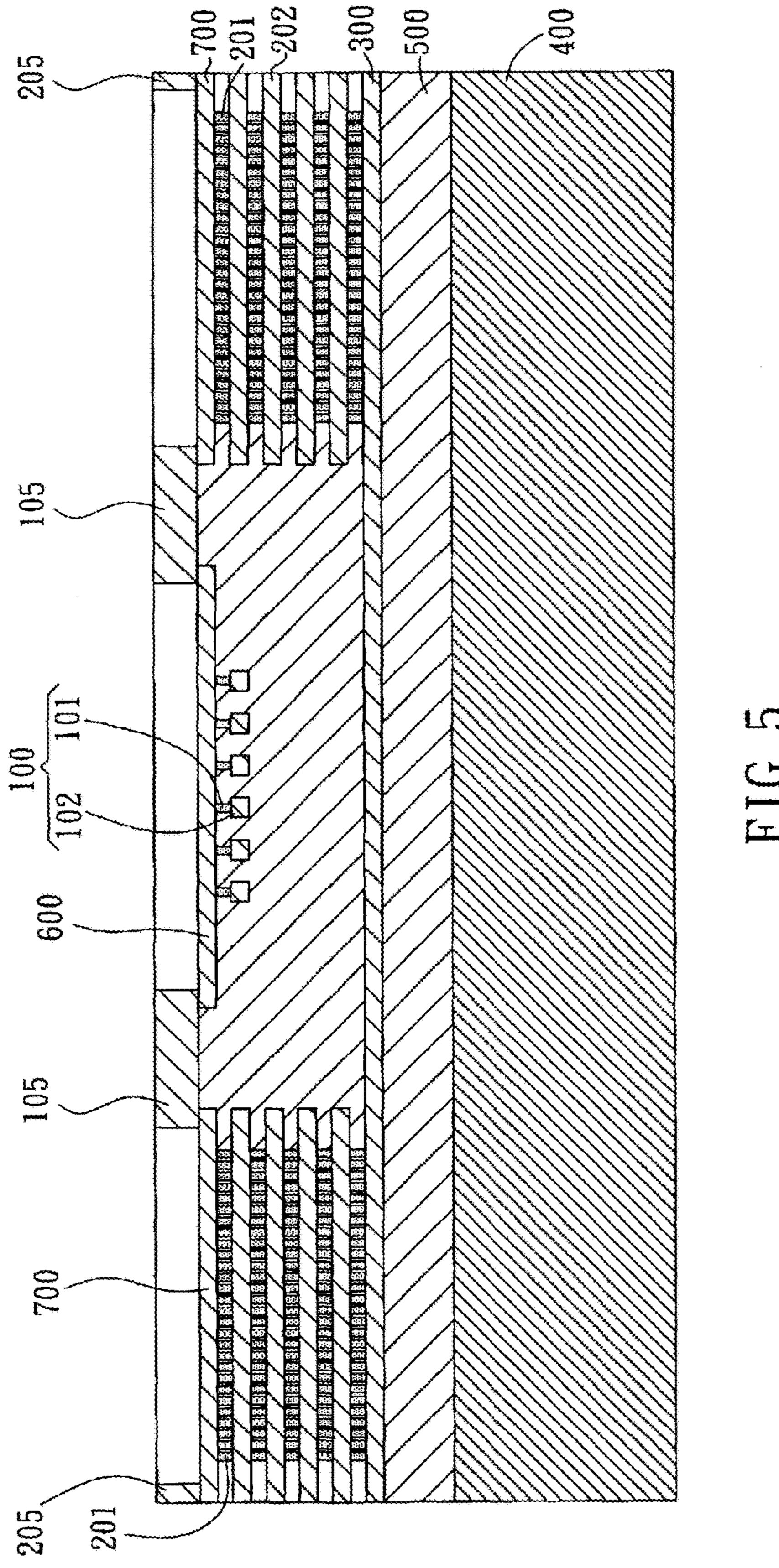

FIG. **5** is a cross-sectional view along the A-A line cutting through FIG. **4** illustrating the preferable embodiment of the IC pad according to the invention.

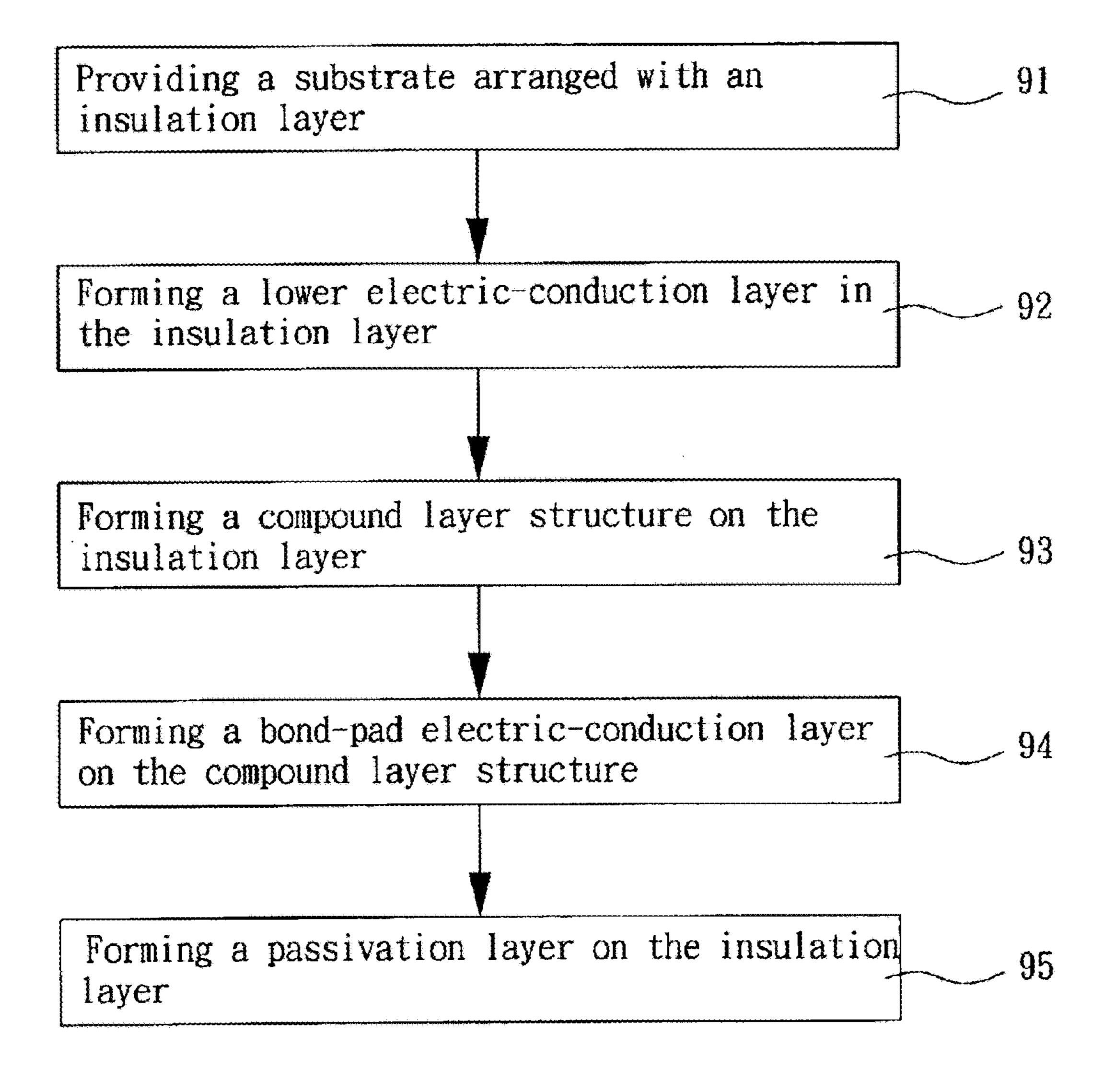

FIG. 6 is a flowchart illustrating the preferable embodiment of the method forming the IC pad according to the invention.

# DETAILED DESCRIPTION OF THE INVENTION

For your esteemed member of reviewing committee to further recognize and understand the characteristics, objectives, and functions of the present invention, a detailed 45 description together with corresponding drawings are presented thereinafter.

The invention discloses a structure of IC pad and its forming method. Its embodiments are described according to referential drawings, in which similar referential numbers 50 represent similar elements.

Please refer to FIG. 4 and FIG. 5, which are structural illustrations for the preferable embodiments of the IC pad according to the present invention. The IC pad structure includes a lower electric-conduction layer 300, a compound 55 layer structure 100, and a first pad layer 600. The lower electric-conduction layer 300 formed at an appropriate position in the insulation layer 500 is coupled with plural electric-conduction layers 202 and plural electric-conduction connecting layers 201, shown in FIG. 5, such that the 60 lower electric-conduction layer 300 may a voltage signal from a second pad layer 700 formed on the upper surface exposing on the insulation layer 500 through provide electric-conduction layers 202 and electric-conduction connecting layers 201 shown in FIG. 5, which further provides a 65 connection to a device providing the voltage signal (not shown in the drawings). The second pad layer 700 further

4

forms a bonding zone with a chip passivation layer 205 and 105. The noise transferred from the substrate [40] 400 will be kept away by the lower electric-conduction layer 300 which may be connected to a power source or voltage signal by the second pad layer 700.

The compound layer structure 100 is arranged on the insulation layer 500 and is composed of at least one electricconduction layer 102 and at least one electric-conduction connecting layer 101, both which are inter-overlapped to each other. The pad layer 600 is arranged on the compound layer structure 100 and is adjacent to the top face side of the insulation layer 500. In the preferable embodiments according to the invention and in order to lower down the value of the effective capacitance of the entire pad, the pad layer 600 is realized by the structuring method of polygon shape and the area of the electric-conduction layer 102 is designed to be smaller than that of the pad layer 600, such that the value of the equivalent electric capacitance to the lower electricconduction layer 300 may be further effectively lowered down. The electric-conduction layer **102** may be realized by the methods of railing structure or honeycomb structure that may reduce the area of electric-conduction layer 102. The electric-conduction connecting layer 101 further includes plural vias and plural via plugs. The structure of this 25 electric-conduction connecting layer 101 may be modified and implemented by those who are skilled in such art according to above disclosure, but it still possesses the merits of the invention and is also within the spirit and scope of the invention, so repetitious description is not presented

In the preferable embodiments according to the invention, the IC pad structure further includes a passivation layer 105, which is arranged on the insulation layer 500 and is partially connected to the pad layer 600. From above design, the compound layer structure 100 is signally connected and structured to the pad layer 600, and a steady bonding zone is thereby formed, such that it may enhance the boding tension and effectively raise the bonding adherence. Therefore, the tension generated during the bonding procedure to draw the entire structure of the IC pad out of the semiconductor chip may be prevented.

In order to further recognize and understand the characteristics, objectives and functions of the present invention, please refer to FIG. 6, which is a flowchart illustrating the preferable embodiment of the method forming the IC pad according to the invention, wherein the numbers 91, 92, 93, 94 and 95 shown in the drawing respectively illustrate the steps from (a) to (e) of the method forming the IC pad according to the invention.

Step (a): providing a substrate that is arranged with an insulation layer thereon.

Step (b): forming a lower electric-conduction layer at an appropriate position in the insulation layer; the lower electric-conduction layer is composed of plural electric-conduction layers and plural electric-conduction connecting layers. In this embodiment, each of the electric-conduction layer is interlaced-connected to the corresponding electric-conduction connecting layers, as shown in FIG. 5, such that a signal connection may be provided to a bond-pad electric-connection layer, which further forms a bonding zone with a passivation layer, such that the pad layer may be connected to a potential of cleaner power source or electric potential.

Step (c): a compound layer structure formed on the insulation layer is composed of at least one electric-conduction layer and at least one electric-conduction connecting layer, each of the electric-conduction layer is interlaced-connected to the corresponding electric-conduction connect-

ing layers, as shown in FIG. 5, and the area of the electricconduction layer can be reduced by the methods of railing structure or honeycomb structure, and the electric-conduction connecting layer further includes the structure of plural vias and plural via plugs.

Step (d): forming a pad layer on the compound layer structure, wherein the area of the former is larger than that of the electric-conduction layer of the latter, and the pad layer is structured as a polygon shape.

Step (e): forming a passivation layer on the insulation 10 layer, such that the pad layer may form a bonding zone with the passivation layer.

Accordingly, the structure of an IC pad and its forming method according to the invention may indeed reduce the 15 value of equivalent electric capacitance of the entire pad, separate the noise coming from the semiconductor substrate, and increase the bonding adherence, so this kind of designing method may be adapted to integrated circuit of high frequency and fulfill the requirement of high frequency and 20 the IC device comprising: low noise.

What is claimed is:

- 1. An integrated circuit (IC) device having a pad structure formed thereon, the IC device comprising:

- a) a substrate;

- b) an insulation layer formed on the substrate;

- c) a plurality of electric-conduction layers formed in the insulation layer, including a lower electric-conduction layer [formed in the insulation layer], each electric- 30 conduction layer having a thickness;

- d) a plurality of connecting layers, each connecting layer having a thickness, the connecting layers interposed between the electric-conduction layers, the plurality of connecting layers selectively coupling one or more of 35 the electric-conduction layers;

- [d] e) a compound layer structure formed in the insulation layer;

- [e] f) a first pad layer formed on the insulation layer and coupled to the compound layer structure, wherein the 40 first pad layer and the compound layer structure are spaced apart [from the lower electric-conduction] and substantially above from the lower electric-conduction layer, wherein the compound layer structure and the lower electric-conduction layer are spaced apart by the 45 thickness of at least one electric-conduction layer and the thickness of at least one connecting layer, wherein the first pad layer is designated for signal transmission; and

- [f] g) a second pad layer formed on the insulation layer 50 and coupled to the lower electric-conduction layer, wherein the second pad layer is designated to be coupled to a power source;

- h) at least one second connecting layer for coupling the second pad layer to the lower electric-conduction 55 layer; and

- i) at least one second electric-conduction layer coupled between the second pad layer and the lower electricconduction layer with the second connecting layer.

- 2. The IC device according to claim 1, wherein the 60 compound layer structure comprises a first electric-conduction layer and a first connecting layer to couple the first electric-conduction layer to the first pad layer.

- 3. The IC device according to claim 2, wherein the first connecting layer comprises a plurality of via plugs.

- 4. The IC device according to claim 2, wherein the first electric-conduction layer is shaped like a webbed railing.

- 5. The IC device according to claim 2, wherein the area of the first electric-conduction layer is smaller than that of the first pad layer.

- **6**. The IC device according to claim **1**, wherein the first pad layer is shaped like a polygon.

- 7. The IC device according to claim 1, further comprising a passivation layer formed on the insulation layer to cover a part of the outer rim of at least one of the first and second pad layers.

- [8. The IC device according to claim 1, further comprising at least one second connecting layer for coupling the second pad layer to the lower electric-conduction layer.]

- [9. The IC device according to claim 8, further comprising least one second electric-conduction layer coupled between the second pad layer and the lower electric-conduction layer with the second connecting layer.

- 10. [The IC device according to claim 1,] An integrated circuit (IC) device having a pad structure formed thereon,

- a) a substrate;

- b) an insulation layer formed on the substrate;

- c) a lower electric-conduction layer formed in the insulation layer;

- d) a compound layer structure formed in the insulation layer;

- e) a first pad layer formed on the insulation layer, substantially formed above the lower electric-conduction layer and coupled to the compound layer structure, wherein the first pad layer and the compound layer structure are spaced apart from the lower electricconduction layer, wherein the first pad layer is designated for signal transmission;

- f) a second pad layer formed on the insulation layer and coupled to the lower electric-conduction layer, wherein the second pad layer is designated to be coupled to a power source;

- g) at least one second connecting layer for coupling the second pad layer to the lower electric-conduction layer; and

- h) at least one second electric-conduction layer coupled between the second pad layer and the lower electricconduction layer with the second connecting layer and disposed lower than the compound layer structure;

- wherein a noise from the substrate is kept away from the first pad layer by the lower electric-conduction layer.

- 11. An integrated circuit (IC) device having a pad structure formed thereon, the IC device comprising:

- a) a substrate;

- b) an insulation layer formed on the substrate;

- c) a lower electric-conduction layer formed in the insulation layer;

- d) a compound layer structure formed in the insulation layer; [and]

- e) a first pad layer formed on the insulation layer and coupled to the compound layer structure, wherein the first pad layer and the compound layer structure are spaced apart from the lower electric-conduction layer, wherein the first pad layer is designated for signal transmission:

- f) a second pad layer formed on the insulation layer and coupled to the lower electric-conduction layer, wherein the second pad layer is designated to be coupled to a power source;

- g) at least one second connecting layer for coupling the second pad layer to the lower electric-conduction layer; and

55

7

- h) at least one second electric-conduction layer coupled between the second pad layer and the lower electricconduction layer with the second connecting layer and disposed lower than the compound layer structure.

- 12. The IC device according to claim 11, wherein the compound layer structure comprises a first electric-conduction layer and a first connecting layer to couple the first electric-conduction layer to the first pad layer.

- [13. The IC device according to claim 11, further comprising a second pad layer formed on the insulation layer and coupled to the lower electric-conduction layer.]

- [14. The IC device according to claim 13, further comprising at least one second connecting layer for coupling the second pad layer to the lower electric-conduction layer; and at least one second electric-conduction layer coupled between the second pad layer and the lower electric-conduction layer with the second connecting layer.]

- 15. The IC device according to claim [14] 11, wherein, the area of the first electric-conduction layer is smaller than that 20 of the first pad layer.

- 16. The IC device according to claim 11, wherein the first pad layer is shaped like a polygon.

- 17. The IC device according to claim 11, further comprising a passivation layer formed on the insulation layer to cover a part of the outer rim of at least one of the first and second pad layers.

- 18. The IC device according to claim 11, wherein a noise from the substrate is kept away from the first pad layer by the lower electric-conduction layer.

- 19. A method for fabricating an IC device having a pad structure formed thereon, the method comprising:

- a) providing a substrate;

- b) forming an insulation layer formed on the substrate;

- c) forming a lower electric-conduction layer formed in the insulation layer, at least a part of the lower electric-conduction layer being covered by the insulation layer;

- d) forming a compound layer structure formed in the insulation layer, the compound layer structure being 40 spaced apart from and not connected to the lower electric-conduction layer; [and]

- e) forming a first pad layer formed on the insulation layer, [the first pad layer being] coupled to the compound layer,

- wherein [in the forming a first pad layer step e)] the first pad layer and the compound layer are spaced apart from the lower electric-conduction layer;

- f) forming a second pad layer formed on the insulation layer and coupled to the lower electric-conduction 50 layer, wherein the second pad layer is designated to be coupled to a power source;

- g) forming at least one second connecting layer for coupling the second pad layer to the lower electric-conduction layer; and

- h) forming at least one second electric-conduction layer coupled between the second pad layer and the lower electric-conduction layer with the second connecting layer.

- 20. The method according to claim 19, wherein a noise 60 from the substrate is kept away [form] *from* the first pad layer by the lower electric-conduction layer.

- 21. The method according to claim 19, wherein the forming a compound layer structure step d) further comprises the steps of:

forming at least one first electric-conduction layer on the insulation layer; and

8

- forming at least one first connecting layer on the insulation layer, wherein the first connecting layer is to couple the first electric-conduction layer to the first pad layer.

- 22. The method according to claim 21, wherein the area of the first electric-conduction layer is smaller than that of the first pad layer.

- 23. The IC device according to claim 1, wherein the lower electric-conduction layer is lowest in depth of the plurality of electric-conduction layers.

- 24. The IC device according to claim 1, wherein the at least one electric-conduction layer is not substantially disposed between the first pad layer and an area of the lower electric-conduction layer beneath the first pad layer.

- 25. The IC device according to claim 1, wherein the lower electric-conduction layer is disposed such that an area of the first pad layer substantially intersects the lower electric-conduction layer when superimposed on the lower electric-conduction layer.

- 26. The IC device according to claim 25, wherein the lower electric-conduction layer is comprised of a plurality of sub-layers disposed at the same depth.

- 27. The IC device according to claim 1, wherein the second pad layer is designated to be coupled to a ground potential.

- 28. The IC device according to claim 1, wherein the second pad layer is designated to be coupled to a voltage potential.

- 29. The IC device according to claim 1, wherein the first pad layer is designated to be coupled to a high frequency signal.

- 30. The IC device according to claim 10, wherein the compound layer structure comprises a first electric-conduction layer and a first electric-conduction connecting layer for coupling the first electric-conduction layer to the first pad layer.

- 31. The IC device according to claim 30, further comprising:

- a second electric-conduction layer, comprised of a first and second sub-layers at the same depth,

- a second electric-conduction connecting layer, comprised of first and second sub-layers at the same depth,

- wherein the first sub-layer of the second electric-conduction layer and the first sub-layer of the second electricconduction connecting layer couple the second pad layer with a first portion of the lower electric-conduction layer.

- 32. The IC device according to claim 31, further comprising:

- a third electric-conduction layer, comprised of a first and second sub-layers at the same depth,

- a third electric-conduction connecting layer, comprised of a first and second sub-layers at the same depth;

- wherein the second sub-layer of the third electric-conduction layer and the second sub-layer of the third electric-conduction connecting layer couple a third pad layer with a second portion of the lower electricconduction layer.

- 33. The IC device according to claim 31, wherein the second pad layer is designated to be coupled to a ground potential.

- 34. The IC device according to claim 31, wherein the second pad layer is designated to be coupled to a voltage potential.

- 35. The IC device according to claim 31, wherein the first pad layer is designated to be coupled to a high frequency signal.

- 36. The IC device according to claim 29, wherein the compound layer structure and the lower electric-conduction layer are spaced apart by at least one electric-conduction layer and at least one connecting layer.

- 37. The IC device according to claim 36, further comprising multiple second electric-conduction layers, multiple second electric-conduction connecting layers, multiple third electric-conduction layers; wherein the multiple second electric-conduction layers and the multiple second electric-conduction connecting layers are used to couple the second pad layer with one side of the lower electric-conduction layer, and the multiple third electric-conduction layers and the multiple third electric-conduction layers are used to couple the other second pad layer with the other side of the lower electric-conduction layer.

- 38. The IC device according to claim 37, wherein the multiple second electric-conduction layers, multiple second electric-conduction connecting layers, multiple third electric-conduction layers, multiple third electric-conduction connecting layers and the lower electric-conduction layer 20 are formed as a U-shaped structure.

- 39. The IC device according to claim 38, further comprising a passivation layer formed on the insulation layer, wherein the bonding zone of the passivation layer is smaller than the area of first and second pad layers.

- 40. The IC device according to claim 39, wherein the second pad layer and the other second pad layer are coupled to a power source.

- 41. The IC device according to claim 10, wherein the noise from the substrate is generated by an integrated circuit.

- 42. The IC device according to claim 10, further comprising multiple second electric-conduction layers, multiple second electric-conduction connecting layers, multiple third electric-conduction connecting layers; wherein the multiple second electric-conduction connecting layers and the multiple second electric-conduction connecting layers are used to couple the second pad layer with one side of the lower electric-conduction layer, and the multiple third electric-conduction layers are used to couple their deverse and the multiple third electric-conduction connecting layers are used to couple the other second pad layer with the other side of the lower electric-conduction layer.

- 43. The IC device according to claim 42, wherein the multiple second electric-conduction layers, multiple second electric-conduction connecting layers, multiple third electric-conduction layers, multiple third electric-conduction connecting layers and the lower electric-conduction layer are formed as a U-shaped structure.

- 44. The IC device according to claim 10, wherein first pad layer is designated to be coupled to a high frequency signal and the second pad layer is designated to be coupled to a voltage potential or ground potential.

\* \* \* \* \*

# UNITED STATES PATENT AND TRADEMARK OFFICE

## CERTIFICATE OF CORRECTION

PATENT NO. : RE46,784 E

ADDITION NO. : 14/742421

APPLICATION NO. : 14/743421 DATED : April 10, 2018

INVENTOR(S) : Lin

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

In the Specification

At Column 1, please replace Lines 14-18 (approx.), with the following:

--CROSS REFERENCE TO RELATED APPLICATIONS

NOTICE: More than one reissue application has been filed for the reissue of U.S. Patent No. 6,787,928 B1. The reissue applications are U.S. Reissue Patent Application Serial Nos. 15/253,539, filed on August 31, 2016, now U.S. Reissue Patent No. RE47,171 E, issued December 18, 2018, which is a continuation reissue application of U.S. Patent Application Serial No. 14/743,421 (the present application), filed on June 18, 2015, now U.S. Reissue Patent No. 46,784 E, issued April 10, 2018, which is a reissue application of U.S. Patent Application Serial No. 10/425,973, filed on April 30, 2003, now U.S. Patent No. 6,787,928 B1, issued September 7, 2004, which claims foreign priority under 35 U.S.C. § 119 from Tai---

Signed and Sealed this

Eighteenth Day of October, 2022

VONOVIVA KULA VIDA

Katherine Kelly Vidal

Director of the United States Patent and Trademark Office