#### US00RE46448E

## (19) United States

## (12) Reissued Patent

Anderson et al.

### (10) Patent Number: US RE46,448 E

(45) Date of Reissued Patent: Jun. 20, 2017

## (54) ISOLATION REGION FABRICATION FOR REPLACEMENT GATE PROCESSING

(71) Applicant: Samsung Electronics Co., Ltd., Suwon-si, Gyeonggi-do (KR)

(72) Inventors: **Brent A. Anderson**, Jericho, VT (US); **Edward J. Nowak**, Shelburne, VT (US)

(73) Assignee: Samsung Electronics Co., Ltd. (KR)

(21) Appl. No.: 15/015,546

(22) Filed: Feb. 4, 2016

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: **8,643,109**Issued: **Feb. 4, 2014**Appl. No.: **13/771,275**Filed: **Feb. 20, 2013**

U.S. Applications:

(62) Division of application No. 13/213,713, filed on Aug. 19, 2011, now Pat. No. 8,546,208.

(51) Int. Cl.

H01L 27/12 (2006.01)

H01L 29/66 (2006.01)

H01L 21/28 (2006.01)

H01L 21/84 (2006.01)

H01L 21/762 (2006.01)

(52) **U.S. Cl.**

CPC .. *H01L 29/66545* (2013.01); *H01L 21/28123* (2013.01); *H01L 21/76283* (2013.01); *H01L 21/84* (2013.01); *H01L 27/1203* (2013.01)

(58) Field of Classification Search

CPC ....... H01L 29/66545; H01L 21/28123; H01L 27/1203; H01L 21/76283; H01L 21/84 USPC ...... 257/E27.112, 347, E21.703, E21.409, 257/369, 374, 446, 501, 506, 510, 257/E29.02, E21.545, E21.564, E20.018,

257/E21.426, E21.445, E21.453; 438/183, 400, 587, 368, 671, 926

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,803,278    | B2         | 10/2004 | Tran                    |  |  |

|--------------|------------|---------|-------------------------|--|--|

| 6,812,149    | B1         | 11/2004 | Wang et al.             |  |  |

| 7,049,185    | B2         | 5/2006  | Ito                     |  |  |

| 7,052,937    | B2 *       | 5/2006  | Clevenger H01L 21/76264 |  |  |

|              |            |         | 257/717                 |  |  |

| 7,525,173    | B2         | 4/2009  | Yang et al.             |  |  |

| 7,569,887    | B2         | 8/2009  | Otsuki                  |  |  |

| 7,671,469    | B2         | 3/2010  | Lee et al.              |  |  |

| 8,502,316    | B2         | 8/2013  | Fung et al.             |  |  |

| 2005/0169052 | <b>A</b> 1 | 8/2005  | Hsu et al.              |  |  |

| (Continued)  |            |         |                         |  |  |

#### OTHER PUBLICATIONS

Hirose Shingo, JP2004288685, Oct. 14, 2004, Abstract. Shinohara Tsuneo, JP2005340461, Dec. 8, 2005, Abstract.

Primary Examiner — Kenneth J Whittington (74) Attorney, Agent, or Firm — Ward and Smith, P.A.

#### (57) ABSTRACT

A semiconductor structure includes a silicon-on-insulator (SOI) substrate, the SOI substrate comprising a bottom silicon layer, a buried oxide (BOX) layer, and a top silicon layer; a plurality of active devices formed on the top silicon layer; and an isolation region located between two of the active devices, wherein at least two of the plurality of active devices are electrically isolated from each other by the isolation region, and wherein the isolation region extends through the top silicon layer to the BOX layer.

#### 21 Claims, 9 Drawing Sheets

# US RE46,448 E Page 2

#### **References Cited** (56)

#### U.S. PATENT DOCUMENTS

| 2005/0239242 | A1*        | 10/2005 | Zhu H01L 21/845         |

|--------------|------------|---------|-------------------------|

|              |            |         | 438/199                 |

| 2006/0125024 | <b>A</b> 1 | 6/2006  | Ishigaki                |

| 2007/0176235 | A1*        | 8/2007  | Tsujiuchi et al 257/347 |

| 2007/0178660 | A1*        | 8/2007  | Miller et al 438/424    |

| 2008/0020515 | A1*        | 1/2008  | White et al 438/118     |

| 2008/0079074 | A1*        | 4/2008  | Icel et al 257/347      |

| 2008/0079088 | <b>A</b> 1 | 4/2008  | Kudo                    |

| 2008/0197424 | A1*        | 8/2008  | Haensch H01L 21/26586   |

|              |            |         | 257/407                 |

| 2009/0114995 | A1*        | 5/2009  | Suzuki H01L 21/26506    |

|              |            |         | 257/369                 |

| 2010/0148248 | <b>A</b> 1 | 6/2010  | Mikasa                  |

| 2010/0193877 | <b>A</b> 1 | 8/2010  | Liaw et al.             |

| 2011/0147765 | <b>A</b> 1 | 6/2011  | Huang et al.            |

<sup>\*</sup> cited by examiner

FIG. 2/

<u>円</u>

FIG. 4

HG.

FIG. 6

. Б

五 (C) (S)

# ISOLATION REGION FABRICATION FOR REPLACEMENT GATE PROCESSING

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

## CROSS-REFERENCE TO RELATED APPLICATION

This application is a divisional of U.S. application Ser. <sup>15</sup> No. 13/213,713, filed on Aug. 19, 2011, which is herein incorporated by reference in its entirety.

#### BACKGROUND

This disclosure relates generally to the field of integrated circuit (IC) manufacturing, and more specifically to isolation region fabrication for electrical isolation between semiconductor devices on an IC.

ICs are formed by connecting isolated active devices, 25 which may include semiconductor devices such as field effect transistors (FETs), through specific electrical connection paths to form logic or memory circuits. Therefore, electrical isolation between active devices is important in IC fabrication. Isolation of FETs from one another is usually provided by shallow trench isolation (STI) regions located between active silicon islands. An STI region may be formed by forming a trench in the substrate between the active devices by etching, and then filling the trench with an insulating material, such as an oxide. After the STI trench is 35 filled with the insulating material, the surface profile of the STI region may be planarized by, for example, chemical mechanical polishing (CMP).

However, use of raised (or regrown) source/drain structures, which may be employed to achieve lower series  $^{40}$  resistances of the IC or to strain FET channels, may exhibit significant growth non-uniformities at the boundary between a gate and an STI region, or when the opening in which the source/drain structure is formed is of variable dimensions. This results in increased variability in FET threshold voltage  $^{45}$  ( $V_t$ ), delay, and leakage, which in turn degrades over-all product performance and power. One solution to such boundary non-uniformity is to require all STI regions to be bounded by isolation regions. However, inclusion of such isolation region structures may limit space available for  $^{50}$  wiring, device density, and increase the load capacitance, thereby increasing switching power of the IC.

#### **BRIEF SUMMARY**

In one aspect, a semiconductor structure includes a silicon-on-insulator (SOI) substrate, the SOI substrate comprising a bottom silicon layer, a buried oxide (BOX) layer, and a top silicon layer; a plurality of active devices formed on the top silicon layer; and an isolation region located between 60 two of the active devices, wherein at least two of the plurality of active devices are electrically isolated from each other by the isolation region, and wherein the isolation region extends through the top silicon layer to the BOX layer.

Additional features are realized through the techniques of the present exemplary embodiment. Other embodiments are 2

described in detail herein and are considered a part of what is claimed. For a better understanding of the features of the exemplary embodiment, refer to the description and to the drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Referring now to the drawings wherein like elements are numbered alike in the several FIGURES:

FIG. 1 illustrates a flowchart of an embodiment of a method of isolation region fabrication for replacement gate processing.

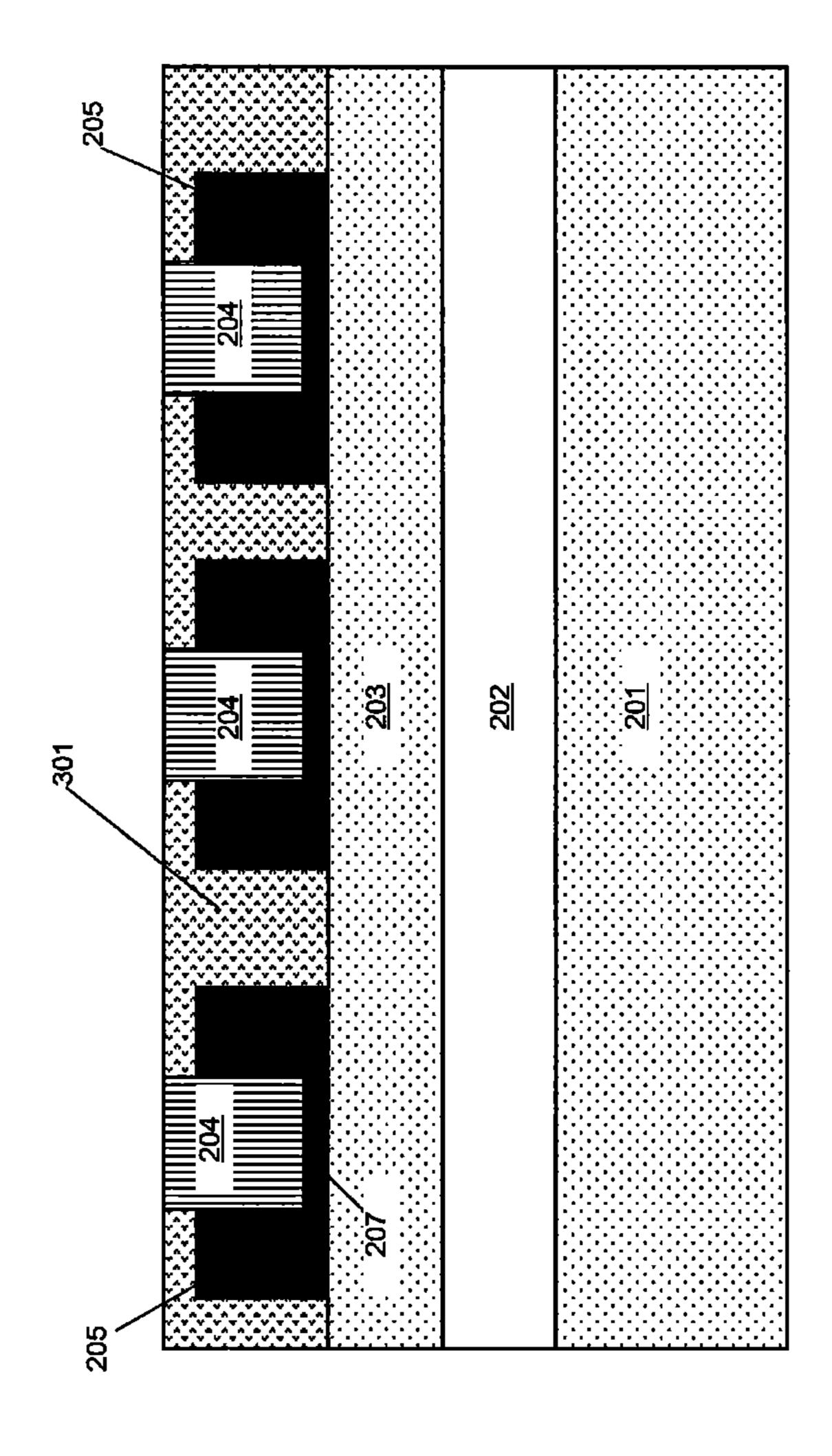

FIG. 2A is a cross sectional view illustrating an embodiment of a semiconductor structure including dummy gates on a silicon-on-insulator (SOI) substrate.

FIG. 2B is a top view illustrating an embodiment of the semiconductor structure of FIG. 2A that comprises fins for formation of fin field effect transistors (finFETs).

FIG. 3 is a cross sectional view illustrating the semiconductor structure of FIG. 2A after formation of an interlevel dielectric layer (ILD) over the dummy gates.

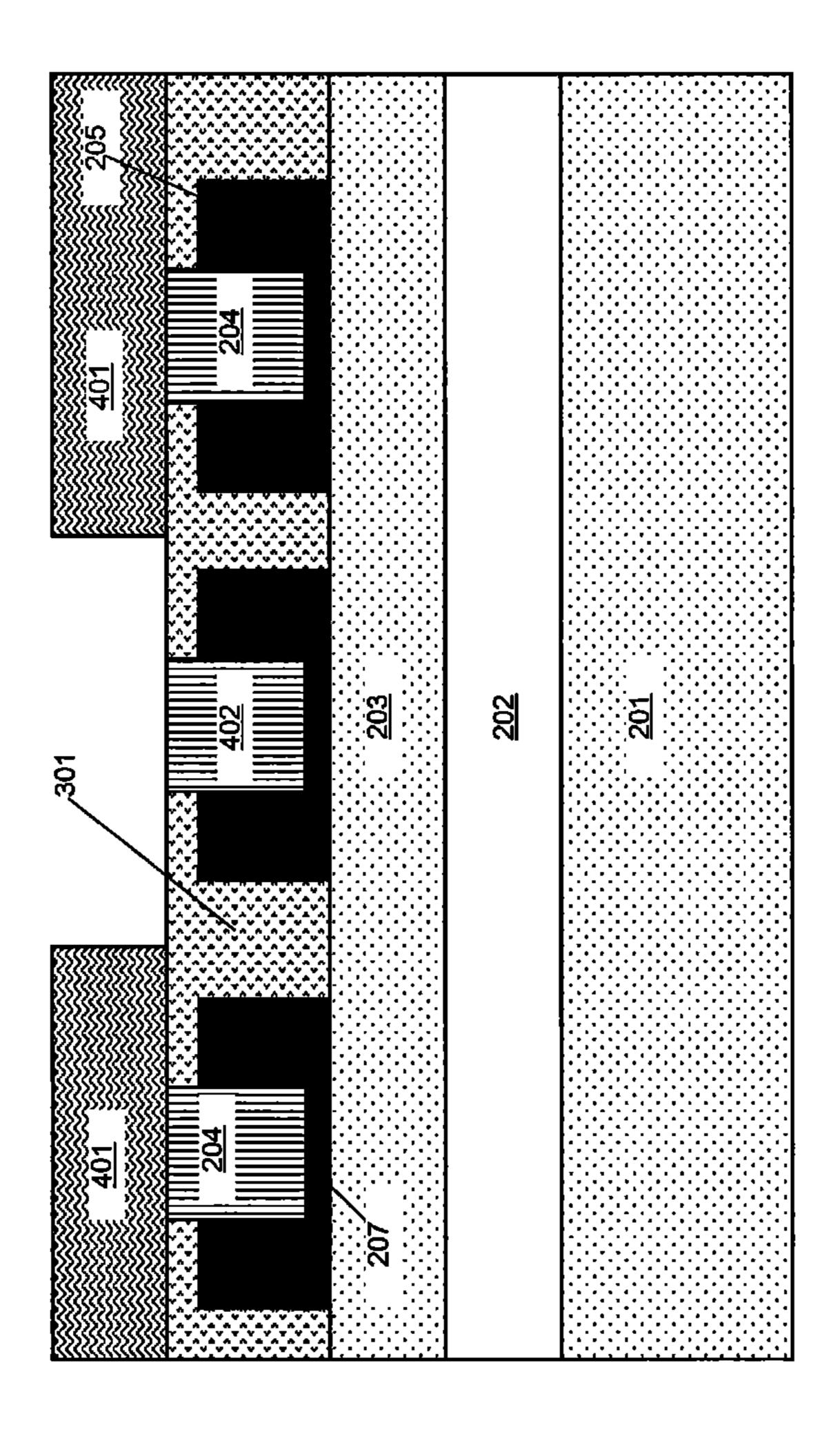

FIG. 4 is a cross sectional view illustrating the semiconductor structure of FIG. 3 after application and patterning of photoresist.

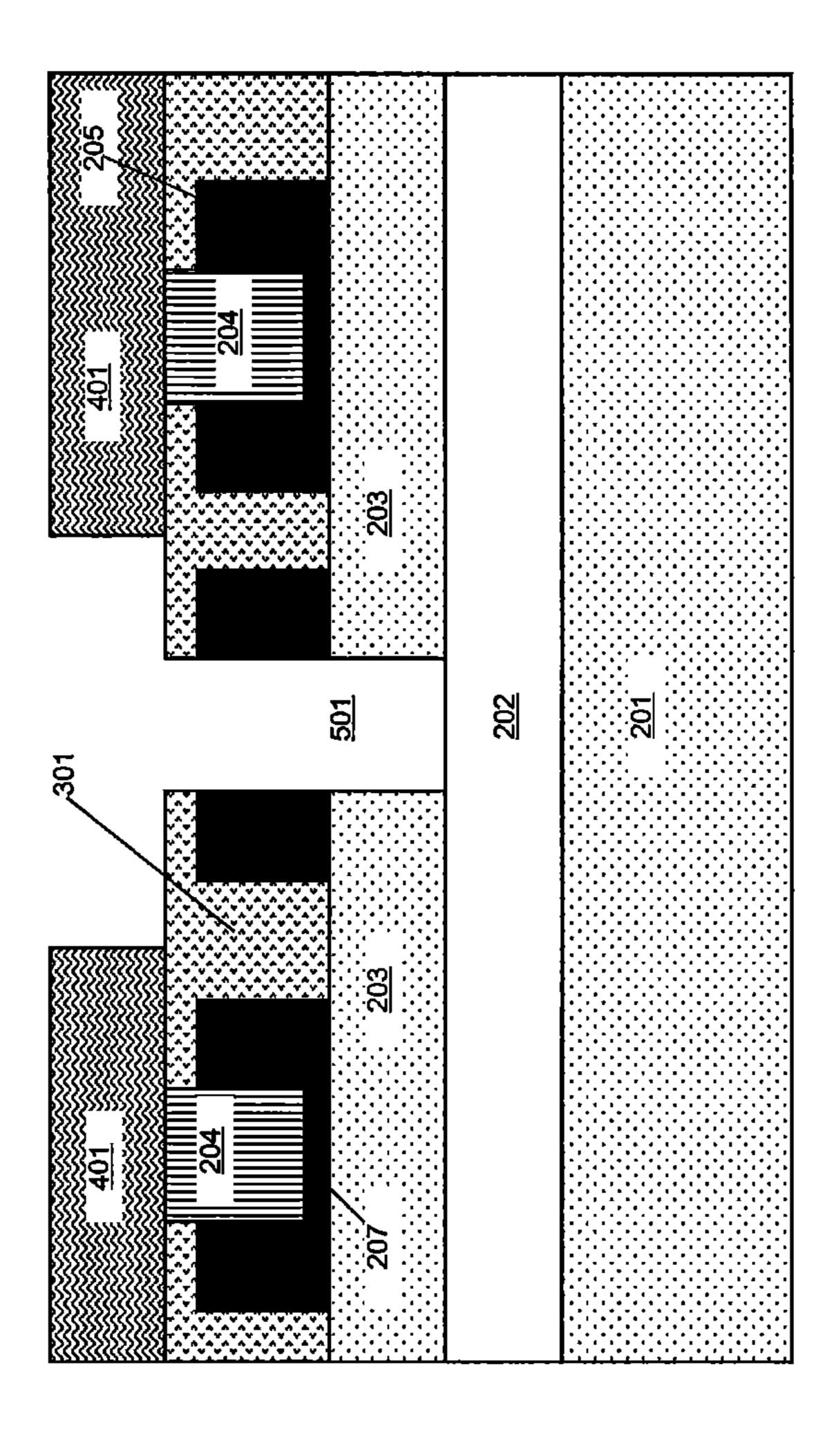

FIG. 5 is a cross sectional view illustrating the semiconductor structure of FIG. 3 after removal of an exposed dummy gate to form an isolation region trench.

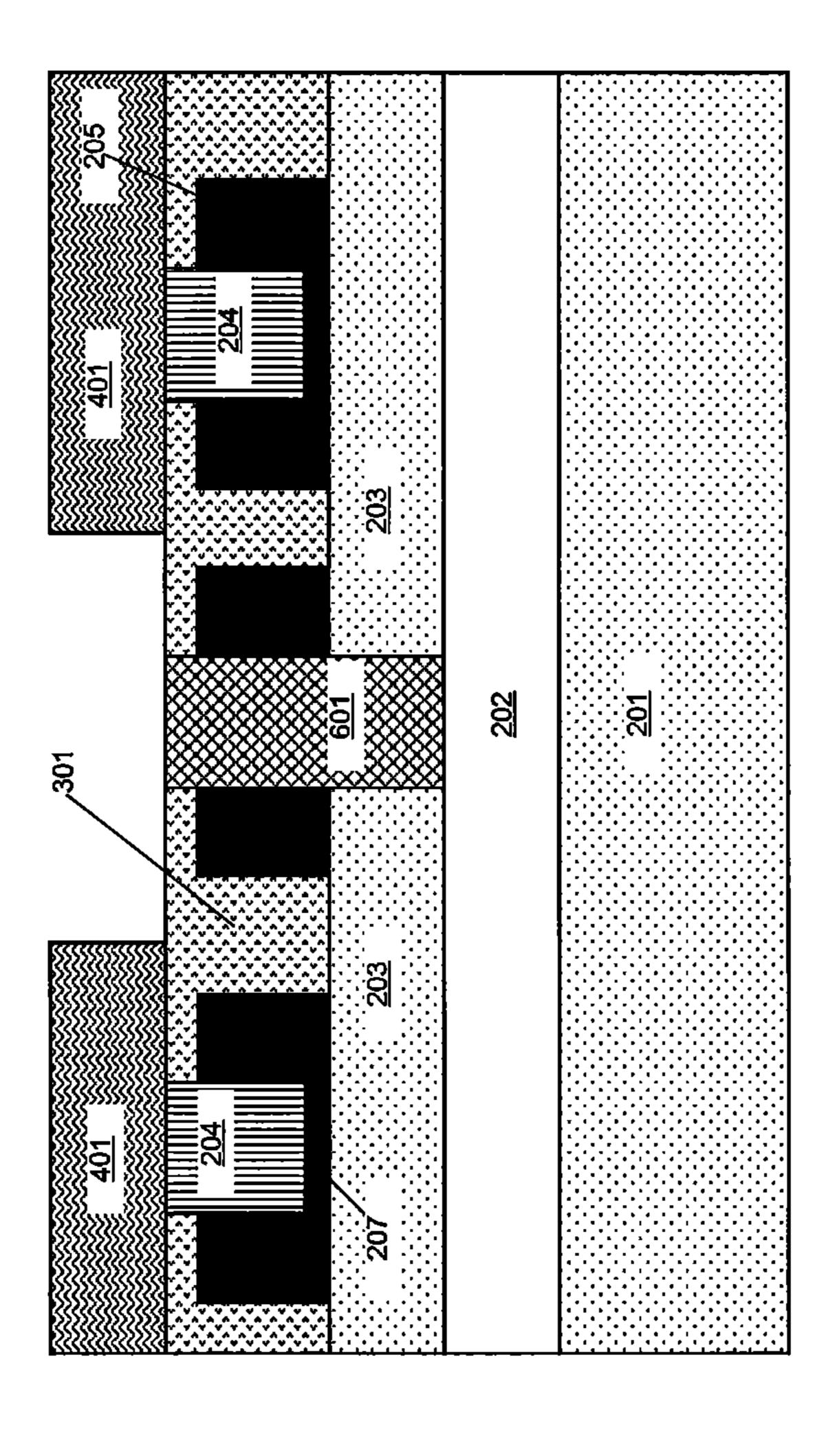

FIG. 6 is a cross sectional view illustrating the semiconductor structure of FIG. 4 after removal filling the isolation region trench with an isolation dielectric.

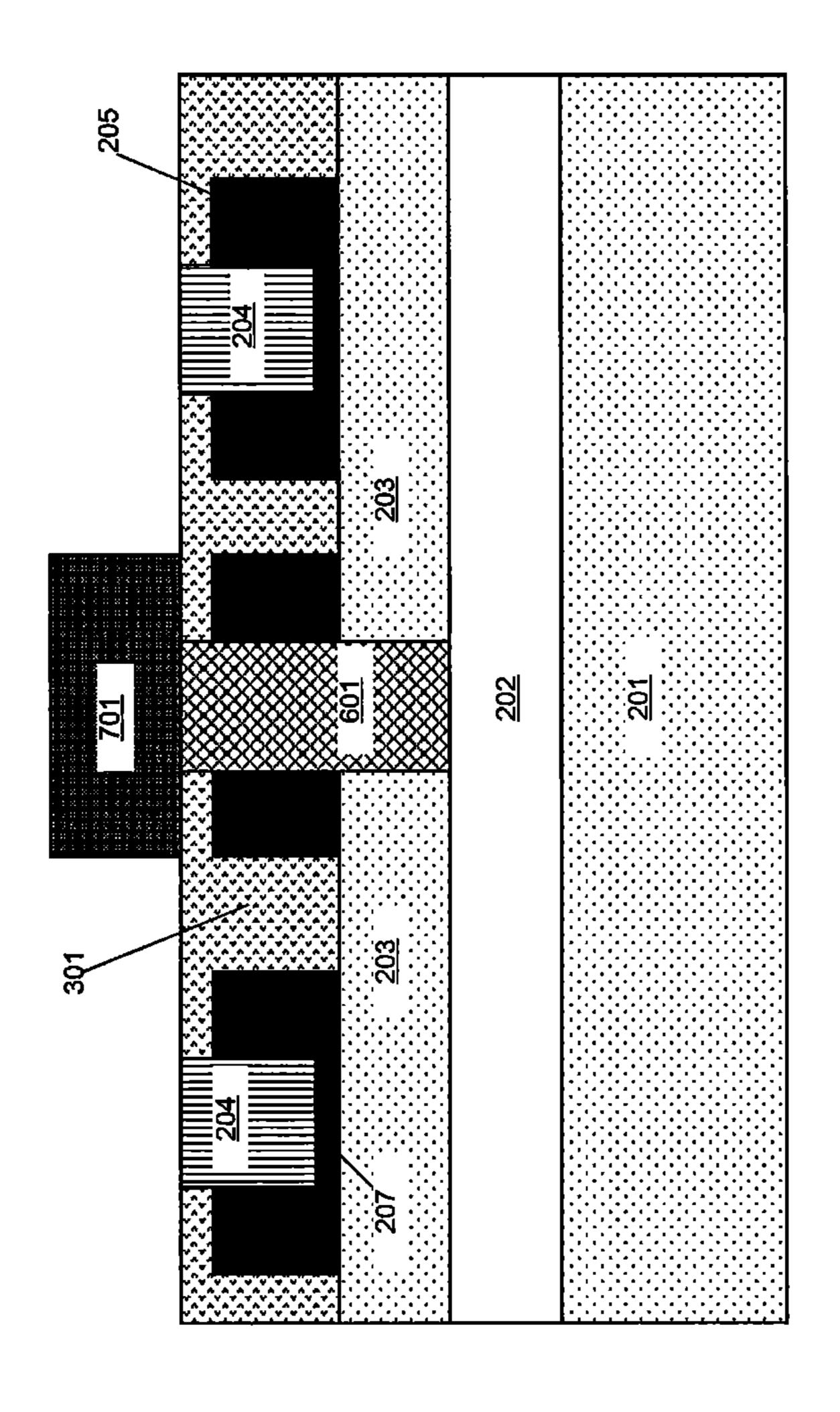

FIG. 7 is a cross sectional view illustrating the semiconductor structure of FIG. 5 after formation of a hardmask layer over the isolation region trench.

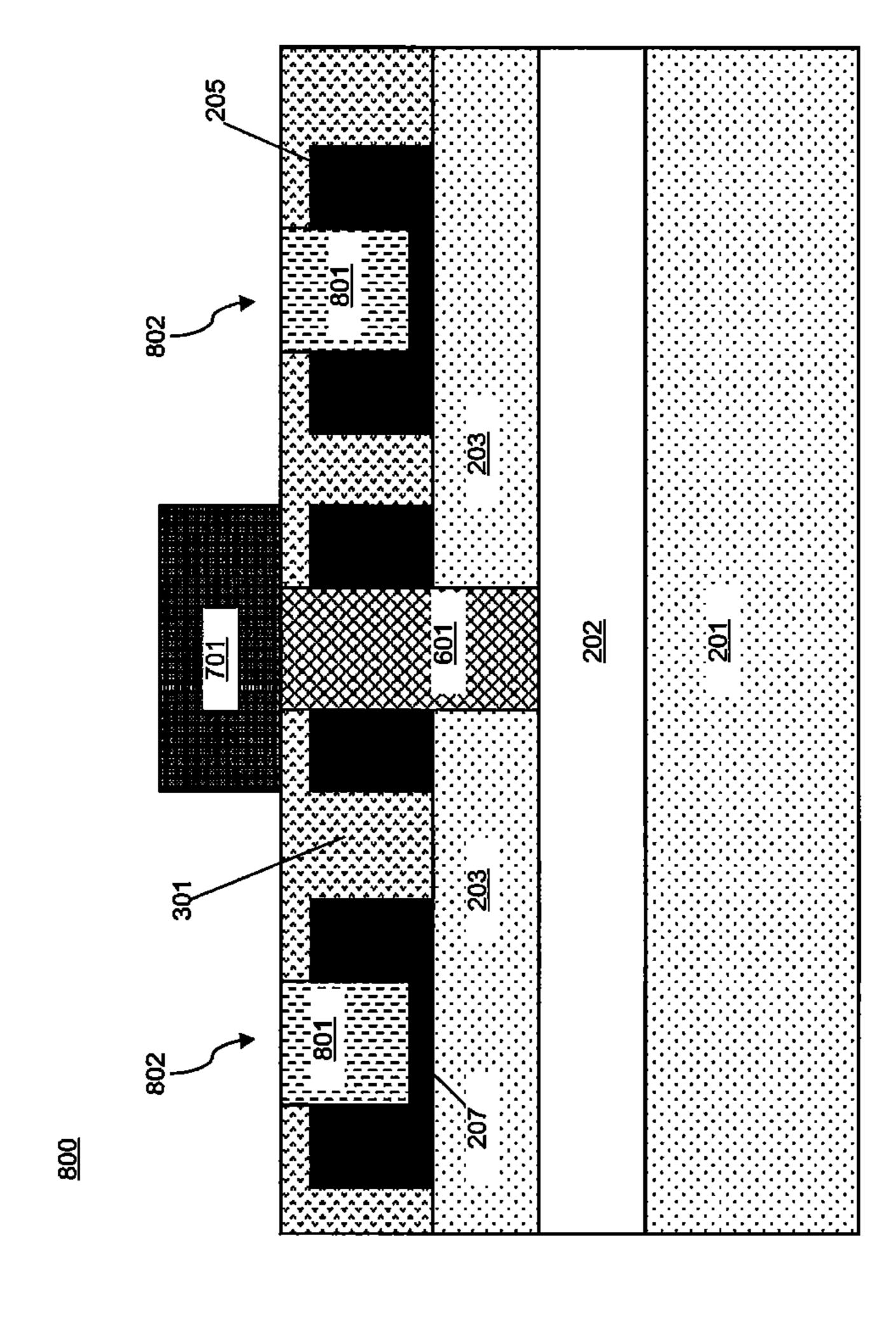

FIG. 8 is a cross sectional view illustrating the semiconductor structure of FIG. 6 after replacement gate processing.

#### DETAILED DESCRIPTION

Embodiments of a method for isolation region fabrication for replacement gate processing, and an IC including isolation regions, are provided, with exemplary embodiments being discussed below in detail. Instead of placing isolation regions at STI region boundaries, isolation regions may replace STI regions, as is described in U.S. patent application Ser. No. 12/951,575 (Anderson et al.), filed Nov. 22, 2010, which is herein incorporated by reference in its entirety. A relatively dense, low-capacitance IC may be formed by replacement gate (i.e., gate-last) processing through use of a block mask that selectively allows removal of active silicon in a gate opening to form an isolation region. The active silicon is removed in a manner that is self-aligned to the dummy gate, such that there is no overlap of gate to active area and hence minimal capacitance penalty.

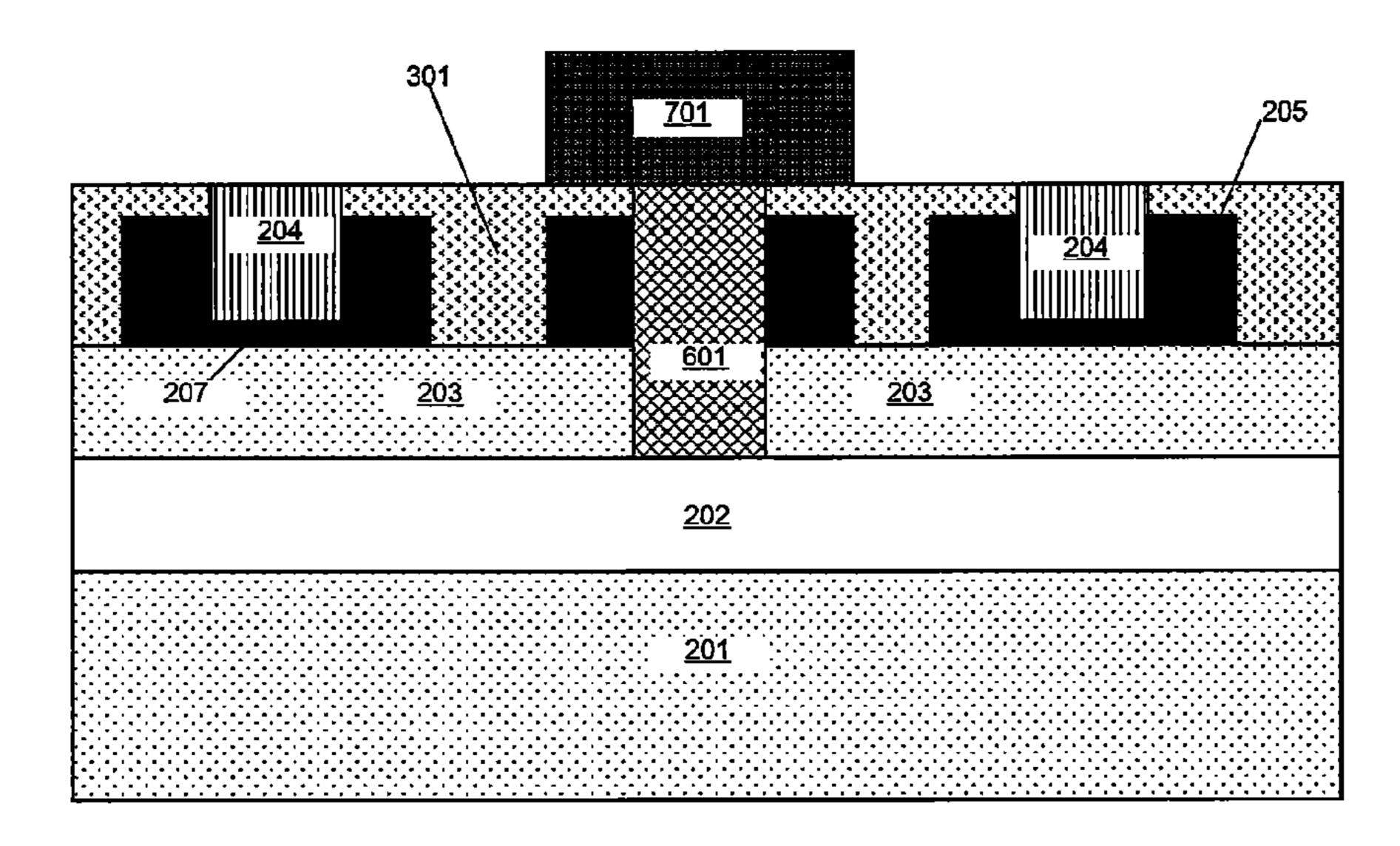

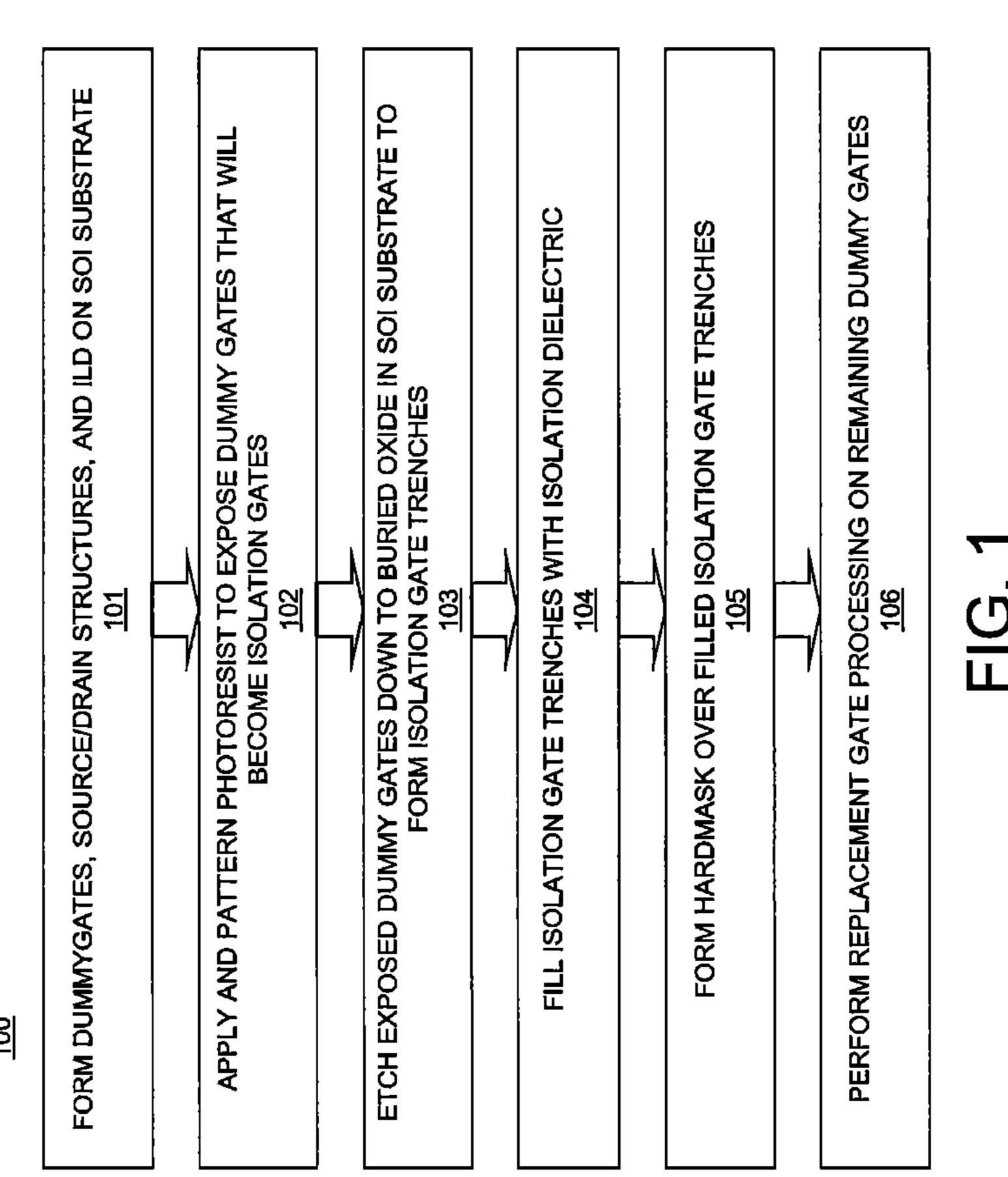

FIG. 1 shows a flowchart of an embodiment of a method 100 of isolation region fabrication for replacement gate processing. FIG. 1 is discussed with reference to FIGS. 2-7. First, in block 101 of FIG. 1, a semiconductor structure including dummy gates, source/drain regions, spacers, is formed on a substrate using regular semiconductor processing techniques, and an interlevel dielectric layer (ILD) is formed over the dummy gates. The semiconductor structure may also include raised source/drain regions located on either side of the dummy gates underneath the spacers is some embodiments. The semiconductor structure may include any appropriate semiconductor structure that includes dummy gates, including but not limited to a fin field

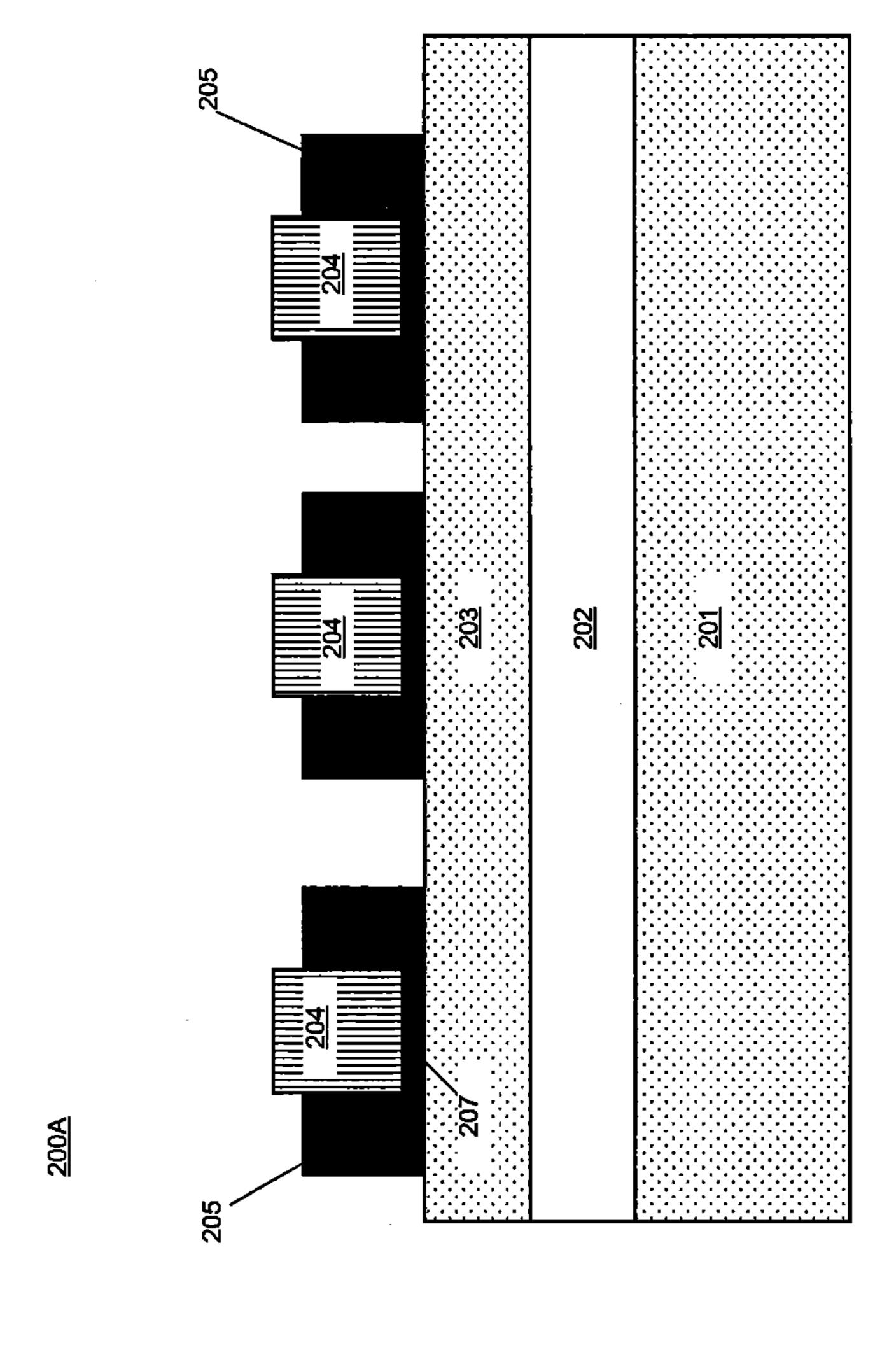

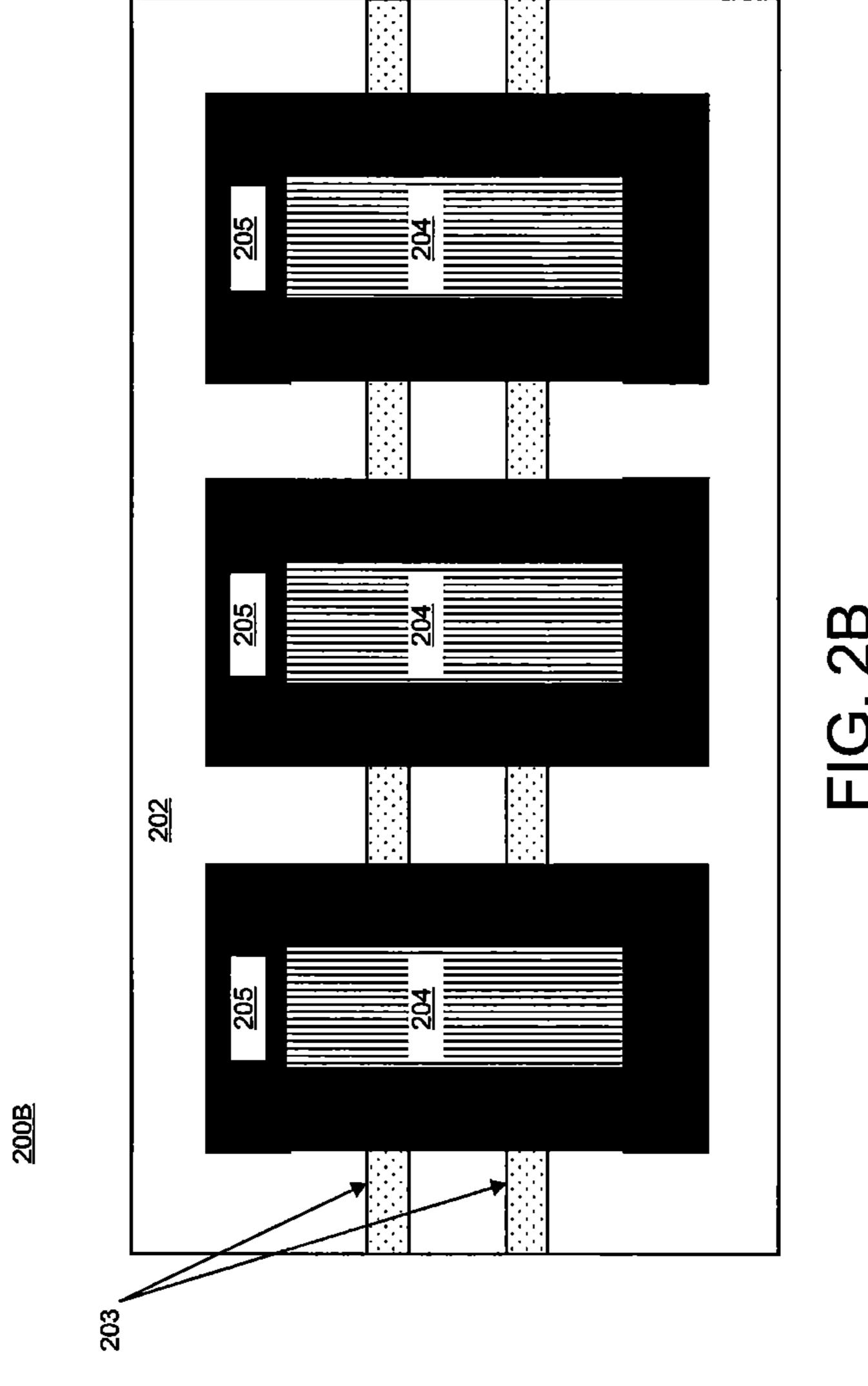

effect transistor (finFET) structure. An embodiment of such a semiconductor structure 200A is shown in FIG. 2A. The substrate is a silicon-on-insulator substrate, including bottom silicon layer 201, buried oxide (BOX) layer 202, and top silicon layer 203. Dummy gates 204 are located on top 5 silicon layer 203. In some embodiments, a gate dielectric layer 207 is formed underneath each dummy gate 204. The dummy gate structure 204 may be polysilicon in some embodiments. The gate dielectric layer 207 may be any appropriate dielectric material, and in some embodiments 10 may include a bottom dielectric layer and a top metal layer. Spacers 205 are formed on either side of the dummy gates **204**. FIG. **2**B shows a top view of an embodiment of the semiconductor structure 200A of FIG. 2A in which the top silicon layer 203 has been patterned to form fins for finFETs. 15 In the semiconductor structure 200B of FIG. 2B, the dummy gates 204 wrap around and cover the fins that comprise top silicon layer 203. After formation of the dummy gates 204, as shown in FIG. 3, ILD 301 is formed over the dummy gates 204 and spacers 205, and ILD 301 is planarized such 20 that the top surfaces of dummy gates **204** are exposed.

Returning to method 100, in block 102, a block mask is applied to the top surface of the dummy gates and the ILD, and the block mask is patterned to selectively expose the dummy gates that are to become isolation regions. The block 25 mask may comprise, for example, photoresist. FIG. 4 shows an embodiment of the semiconductor structure 200A after application and patterning of photoresist 401 to form the block mask, which exposes a dummy gate 402. Then, turning again to method 100, in block 103, the exposed 30 dummy gate is removed, and the portion of the top silicon layer located underneath the removed dummy gate is etched down to the BOX layer to form an isolation region recess. FIG. 5 shows an embodiment of a device including an isolation region recess **501**. The etch used to remove 35 exposed dummy gate 402 and its respective gate dielectric layer 207, and to form the recess 501 in top silicon layer 203, may be a sequential multistage etch. The sequential multistage etch may have 3 or 4 different stages depending on the materials that make up dummy gate 204 and gate dielectric 40 layer 207. In embodiments in which the dummy gate 402 is polysilicon, dummy gate 402 may be removed using a dry etch such as a bromine-based etch. The respective gate dielectric layer 207 may next be removed using a wet etch, such as a hydrofluoric etch for example. In embodiments in 45 which respective gate dielectric layer 207 includes a bottom dielectric layer and a top metal layer, the etch to remove the gate dielectric layer 207 may be a 2-stage etch. Then, the recess 501 may be formed in the top silicon layer 203 using a dry etch such as a bromine-based etch to etch down to 50 BOX layer 202.

Next, in method 100 of FIG. 1, in block 104, the recess that was formed during the etch performed in block 103 is filled with an insulating material to form the isolation region, and the top surface of the insulating material is planarized 55 such as is shown in FIG. 6. In FIG. 6, the recess 501 is filled with an insulator, and the top surface of the insulator is planarized, to form isolation region 601. The insulator that comprises isolation region 601 may include silicon dioxide or silicon nitride in various embodiments. Then, flow of 60 method 100 proceeds to block 105, in which a hardmask layer is formed over the isolation region and the photoresist is removed. FIG. 7 shows an embodiment of a hardmask layer 701 formed over the isolation region 601. The hardmask layer 701 may be silicon nitride. The photoresist 401 65 is also removed to expose the top surfaces of the remaining dummy gates 204.

4

Lastly, in block 106 of method 100 of FIG. 1, replacement gate processing is performed on the remaining dummy gates, resulting in an IC device including electrical devices separated by isolation regions. An example of an IC device 800 including an isolation region 601 between two active devices is shown in FIG. 7. Dummy gates 204 have been replaced with gate stacks 801 to form active FETs 802, including gate stacks 801, gate dielectric layer 207, spacers 205, and source/drain and channel regions located underneath the devices in the top silicon layer 203. The active FETs 802 may include raised source/drain regions (not shown) located under the spacers 205 in some embodiments. The active FETs 802 are separated by the isolation region 601, which extends down to BOX layer 202, preventing electrical leakage between active FETs 802. The hardmask layer 701 acts to protect the isolation region 601 during the replacement gate processing. The hardmask layer 701 may be left on the device 800 in some embodiments, or in other embodiments the hardmask layer 701 may be removed after replacement gate processing is completed. FIGS. 2A-8 are shown for illustrative purposes only; a device formed using method 100 may include any appropriate number, type, and layout of FETs separated by any appropriate number and layout of isolation regions. For example, in some embodiments, two active devices in a semiconductor structure may have two isolation regions located between the two active devices. Also, in some embodiments, the gate dielectric layer that is initially formed underneath the dummy gate may be replaced during the replacement gate processing. The finished active devices may comprise finFETs in some embodiments, or any other appropriate type of active device that may be formed by replacement gate processing in other embodiments.

The technical effects and benefits of exemplary embodiments include formation of an IC having relatively high device density and low capacitance through replacement gate processing.

The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of the invention. As used herein, the singular forms "a", "an", and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises" and/or "comprising," when used in this specification, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof.

The corresponding structures, materials, acts, and equivalents of all means or step plus function elements in the claims below are intended to include any structure, material, or act for performing the function in combination with other claimed elements as specifically claimed. The description of the present invention has been presented for purposes of illustration and description, but is not intended to be exhaustive or limited to the invention in the form disclosed. Many modifications and variations will be apparent to those of ordinary skill in the art without departing from the scope and spirit of the invention. The embodiment was chosen and described in order to best explain the principles of the invention and the practical application, and to enable others of ordinary skill in the art to understand the invention for various embodiments with various modifications as are suited to the particular use contemplated.

The invention claimed is:

- 1. A semiconductor structure, comprising:

- a silicon-on-insulator (SOI) substrate, the SOI substrate comprising a bottom silicon layer, a buried oxide (BOX) layer, and a top silicon layer;

- a plurality of active devices formed on the top silicon layer; and

- an isolation region located between two of the plurality of active devices, wherein [at least] the two of the plurality of active devices are electrically isolated from each other by the isolation region, wherein the isolation region extends through the top silicon layer to the BOX layer, wherein the isolation region further extends between a pair of spacers that are located on the top silicon layer on either side of the isolation region to provide an inactive device between the two of the plurality of active devices, and wherein the isolation region further extends through an interlevel dielectric (ILD) layer that is located over the pair of spacers of the inactive device.

- 2. The semiconductor structure of claim 1, further comprising a hardmask layer located over the isolation region.

- 3. The semiconductor structure of claim 2, wherein the hardmask layer comprises silicon nitride.

- 4. A semiconductor structure, comprising: a substrate;

a plurality of active devices on the substrate; and

- an isolation region located between two of the plurality of active devices, wherein the two of the plurality of active devices are electrically isolated from each other by the isolation region, wherein the isolation region extends into the substrate, wherein the isolation region further extends between a pair of spacers that are located on the substrate on either side of the isolation region to provide an inactive device between the two of the plurality of active devices, and wherein the isolation region further extends through an interlevel dielectric (ILD) layer that is located over the pair of spacers of 40 the inactive device.

- 5. The semiconductor structure of claim 4 further comprising:

- a plurality of pairs of gate spacers, wherein each of the plurality of active devices comprises a respective gate 45 electrode and a respective one of the plurality of pairs of gate spacers on opposing sides of the respective gate electrode.

- 6. The semiconductor structure of claim 5 wherein a distance between each of the plurality of pairs of gate 50 spacers through the respective gate electrode is about equal to a distance between the pair of spacers that are located on the substrate on either side of the isolation region.

- 7. The semiconductor structure of claim 14 wherein the pair of spacers absent from between the isolation region and 55 the substrate.

- 8. The semiconductor structure of claim 4 wherein the ILD layer and isolation region are separate structures.

- 9. The semiconductor structure of claim 4 wherein the pair of spacers comprise replacement gate spacers.

- 10. The semiconductor structure of claim 4 wherein the ILD layer surrounds the isolation region.

- 11. The semiconductor structure of claim 4 wherein the plurality of active devices comprise finFET active devices.

- 12. The semiconductor structure of claim 11 wherein the 65 finFET active devices comprise respective gate electrodes surrounded by respective gate spacers.

6

- 13. The semiconductor structure of claim 12 wherein an uppermost surface of the isolation region is above a lowest portion of a gate electrode included in the plurality of active devices.

- 14. The semiconductor structure of claim 4 wherein the isolation region penetrates the pair of spacers into the substrate.

- 15. A semiconductor structure, comprising: a substrate;

- a plurality of active fins extending parallel to one another in a first direction on the substrate, wherein at least one of the plurality of active fins is included in a plurality of respective finFET active devices spaced apart in the first direction on the substrate;

- a plurality of adjacent insulation regions in the substrate, respective ones of which are located between adjacent ones of the plurality of fins; and

- an isolation region located between two of the plurality of respective finFET active devices spaced apart in the first direction, wherein the two of the plurality of respective finFET active devices are electrically isolated from each other by the isolation region, wherein the isolation region extends into the substrate, wherein the isolation region further extends between a pair of spacers that are located on the substrate on first and second sides the isolation region to provide an inactive finFET device between the two of the plurality of respective finFET active devices, and wherein the isolation region further extends through a interlevel dielectric (ILD) layer that is located over the pair of spacers of the finFET inactive device.

- 16. The semiconductor structure of claim 15 wherein the isolation region penetrates the pair of spacers into the substrate.

- 17. The semiconductor structure of claim 15 wherein the ILD layer surrounds the isolation region.

- 18. A semiconductor structure, comprising: a substrate;

- a plurality of fins extending parallel to one another in a first direction on the substrate and spaced apart on the substrate in a second direction, at least one of the plurality of fins being segmented by an isolation region into a plurality of respective finFET active devices spaced apart in the first direction on the substrate; and

- a plurality of adjacent insulation regions in the substrate, respective ones of which are located between adjacent ones of the plurality of fins,

- wherein the isolation region is located between two of the plurality of respective finFET active devices spaced apart in the first direction, wherein the two of the plurality of respective finFET active devices are electrically isolated from each other by the isolation region, wherein the isolation region extends into the substrate, wherein the isolation region further extends between a pair of spacers that are located on the substrate on first and second sides of the isolation region to provide an finFET inactive device between the two of the plurality of respective finFET active devices, and wherein the isolation region further extending through an interlevel dielectric (ILD) layer that is located over the pair of spacers of the finFET inactive device.

- 19. The semiconductor structure of claim 18 wherein the ILD layer surrounds the isolation region.

- 20. The semiconductor structure of claim 18 wherein the isolation region penetrates the pair of spacers into the substrate.

21. A semiconductor structure, comprising: a substrate;

- a first active device on the substrate, the first active device having a first gate electrode and first spacers on opposing sides of the first gate electrode;

- a second active device on the substrate, the second active device having a second gate electrode and second spacers on opposing sides of the second gate electrode; and

- an isolation region located on the substrate between the first and second active devices, wherein the first and second active devices are electrically isolated from each other by the isolation region, wherein the isolation region extends into the substrate, wherein the isolation region further extends between third spacers that are 15 located on the substrate on either side of the isolation region to provide an inactive device between the first and second active devices, and wherein the isolation region further extends through an interlevel dielectric (ILD) layer that is located over the third spacers.

\* \* \* \* \*