US00RE46279E

# (19) United States

## (12) Reissued Patent

### Mokhlesi

## (10) Patent Number: US RE46,279 E

### (45) Date of Reissued Patent: Jan. 17, 2017

# (54) READ OPERATION FOR NON-VOLATILE STORAGE WITH COMPENSATION FOR COUPLING

(71) Applicant: SANDISK TECHNOLOGIES INC.,

Plano, TX (US)

(72) Inventor: Nima Mokhlesi, Los Gatos, CA (US)

(73) Assignee: SANDISK TECHNOLOGIES LLC,

Plano, TX (US)

(21) Appl. No.: 14/290,938

(22) Filed: May 29, 2014

### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: **8,199,571**Issued: Jun. 12, 2012

Appl. No.: 13/028,674

Filed: Feb. 16, 2011

U.S. Applications:

(60) Continuation of application No. 12/622,966, filed on Nov. 20, 2009, now Pat. No. 7,911,838, which is a (Continued)

(51) **Int. Cl.**

G11C 16/04 (2006.01) G11C 16/34 (2006.01) G11C 11/56 (2006.01)

(52) **U.S. Cl.**

CPC ..... *G11C 16/3418* (2013.01); *G11C 11/5642* (2013.01); *G11C 16/0483* (2013.01)

(58) Field of Classification Search

(Continued)

### (56) References Cited

### U.S. PATENT DOCUMENTS

### FOREIGN PATENT DOCUMENTS

DE 10164149 12/2000 EP 01271553 1/2003 (Continued)

### OTHER PUBLICATIONS

Argument and Amendment filed Jun. 1, 2012, Japanese Patent Application No. 2009-544243.

(Continued)

Primary Examiner — Ovidio Escalante (74) Attorney, Agent, or Firm — Vierra Magen Marcus LLP

### (57) ABSTRACT

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). The problem occurs most pronouncedly between sets of adjacent memory cells that have been programmed at different times. To account for this coupling, the read process for a particular memory cell will provide compensation to an adjacent memory cell in order to reduce the coupling effect that the adjacent memory cell has on the particular memory cell.

### 29 Claims, 21 Drawing Sheets

#### 10/2008 Mokhlesi Related U.S. Application Data 7,436,733 B2 10/2008 Mokhlesi 7,440,324 B2 continuation of application No. 12/357,368, filed on 11/2008 Mokhlesi 7,450,421 B2 7,495,962 B2 2/2009 Mokhlesi Jan. 21, 2009, now Pat. No. 7,778,106, which is a 3/2009 Mokhlesi 7,499,319 B2 division of application No. 11/384,057, filed on Mar. 7,561,473 B2 7/2009 Mokhlesi 17, 2006, now Pat. No. 7,499,319. 7,613,068 B2 11/2009 Mokhlesi 8,199,571 B2 6/2012 Mokhlesi Provisional application No. 60/778,857, filed on Mar. (60)2002/0126532 A1 9/2002 Matsunaga 10/2002 Noguchi 3, 2006. 2002/0159315 A1 2004/0047182 A1 3/2004 Cernea Field of Classification Search (58)2004/0057283 A1 3/2004 Cernea 2004/0057285 A1 3/2004 Cernea See application file for complete search history. 2004/0057287 A1 3/2004 Cernea 2004/0057318 A1 3/2004 Cernea 2004/0060031 A1 3/2004 Cernea (56)**References Cited** 2004/0079988 A1 4/2004 Harari 2004/0109357 A1 6/2004 Cernea U.S. PATENT DOCUMENTS 2004/0153826 A1 8/2004 Hazama 8/2004 Mokhlesi 2004/0156241 A1 5,532,962 A 7/1996 Auclair 2004/0179404 A1 9/2004 Quader 7/1996 Talreja 5,539,690 A 2004/0190337 A1 9/2004 Chen 5,657,332 A 8/1997 Auclair 2004/0213031 A1 10/2004 Hosono 6/1998 Hammick 5,764,572 A 3/2005 Khalid 2005/0057967 A1 5,862,074 A 1/1999 Park 2005/0157564 A1 7/2005 Hosono 2/1999 Chen 5,867,429 A 2005/0162913 A1 7/2005 Chen 8/1999 Hirakawa 5,943,260 A 8/2005 Hemink 2005/0174852 A1 8/1999 Endoh 5,946,231 A 11/2005 Noguchi 2005/0254302 A1 11/1999 Chen 5,995,417 A 6/2006 Confalonieri 2006/0120161 A1 6,044,019 A 3/2000 Cernea 10/2006 Hemink 2006/0221660 A1 4/2000 Takeuchi 6,046,935 A 2006/0221692 A1 10/2006 Chen 8/2000 Itoh 6,107,658 A 12/2006 Cernea ..... 2006/0285391 A1\* G11C 7/02 11/2000 Murray 6,144,580 A 365/185.22 11/2000 Wong 6,154,157 A 2007/0047314 A1 3/2007 Goda 12/2000 Wong 6,160,739 A 2007/0121383 A1 5/2007 Chen 1/2001 Fang 6,175,522 B1 10/2007 Hermink 2007/0242510 A1 1/2001 Gongwer 6,181,599 B1 1/2008 Li ..... G11C 8/10 2008/0019188 A1\* 4/2001 Guterman 6,222,762 B1 365/185.22 7/2001 Khouri 6,259,632 B1 2009/0129160 A1 5/2009 Mokhlesi 9/2001 Wong 6,285,593 B1 2010/0074018 A1 3/2010 Mokhlesi 2/2002 Wong 6,345,000 B1 6,349,055 B1 2/2002 Murray FOREIGN PATENT DOCUMENTS 6,363,014 B1 3/2002 Fastow 7/2002 Kitazaki 6,418,061 B1 EP 01329898 7/2003 6,456,528 B1\* KR 1/2003 2003-0009090 6,462,988 B1 10/2002 Harari WO WO03025512 3/2003 1/2003 Harari 6,504,762 B1 WO 11/2005 2/2003 Chen WO2005104135 6,522,580 B2 WO 10/2006 2/2003 Kurihara WO2006107731 6,525,969 B1 3/2003 Wong WO WO2007078793 7/2007 6,532,556 B1 3/2003 Trivedi WO WO2007089370 8/2007 6,535,423 B2 4/2003 Chen 6,542,407 B1 5/2003 Mangan 6,570,785 B1 OTHER PUBLICATIONS 5/2003 Harari 6,570,790 B1 9/2003 6,614,070 B1 Hirose European Search Report dated Jan. 27, 2010, European Patent 11/2003 6,643,188 B2 Tanaka et al. 6,657,891 B1 12/2003 Shibata Application No. 09 01 5112.7. 4/2004 Chen 6,717,847 B2 European Office Action dated Jan. 11, 2010, European Patent 4/2004 Mangan 6,717,851 B2 Application No. 07 751 706.8. 7/2004 Petropoulos et al. 6,760,068 B2 Taiwan Office Action dated Jan. 22, 2010, Taiwan Patent Applica-7/2004 Huang 6,760,257 B2 tion No. 096107259. 8/2004 Li 6,771,536 B2 Notice of Allowance dated Dec. 10, 2010, U.S. Appl. No. 6,781,877 B2 8/2004 Cernea 10/2004 Chen 6,807,095 B2 12/622,966. 6,847,553 B2 1/2005 Chen Aritome, "Reliability Issues of Flash Memory Cells," Proceedings 2/2005 Lutze 6,859,397 B2 of the IEEE, IEEE. New York, vol. 81, No. 5, May 1, 1993. 3/2005 Cho 6,870,766 B2 Notice of Allowance dated Mar. 27, 2008, U.S. Appl. No. 6,870,768 B2 3/2005 Cernea 11/377,972, filed Mar. 17, 2006. 5/2005 Mangan 6,888,752 B2 Notice of Allowance dated Jun. 27, 2008, U.S. Appl. No. 5/2005 Hemink 6,888,758 B1 11/377,972, filed Mar. 17, 2006. 5/2005 Chien 6,898,121 B2 6,914,817 B2 7/2005 Harari Office Action dated Feb. 6, 2008, U.S. Appl. No. 11/384,057, filed 10/2005 Khalid 6,956,770 B2 Mar. 17, 2006. 6,967,872 B2 11/2005 Quader Response to Office Action dated Apr. 1, 2008, U.S. Appl. No. 12/2005 Abedifard 6,975,538 B2 11/384,057, filed Mar. 17, 2006. 6,987,694 B2 1/2006 Lee Office Action dated Apr. 29, 2008, U.S. Appl. No. 11/384,057, filed 7,009,881 B2 3/2006 Noguchi Mar. 17, 2006. 3/2006 Chen 7,020,017 B2 Response to Office Action dated Aug. 14, 2008, U.S. Appl. No. 1/2007 Wan 7,170,788 B1

11/384,057, filed Mar. 17, 2006.

12/2007 Mokhlesi

7,310,272 B1

#### (56)**References Cited**

### OTHER PUBLICATIONS

Notice of Allowance dated Oct. 17, 2008, U.S. Appl. No. 11/384,057, filed Mar. 17, 2006.

Office Action dated Jun. 11, 2009, U.S. Appl. No. 12/357,364, filed Jan. 21, 2009.

Response to Office Action dated Jul. 10, 2009, U.S. Appl. No. 12/357,364, filed Jan. 21, 2009.

Notice of Allowance dated Aug. 31, 2009, U.S. Appl. No. 12/357,364, filed Jan. 21, 2009.

Office Action dated May 27, 2009, U.S. Appl. No. 12/357,368, filed Jan. 21, 2009.

Response to Office Action dated Aug. 18, 2009, U.S. Appl. No. 12/357,368, filed Jan. 21, 2009.

Notice of Allowance dated Oct. 8, 2009, U.S. Appl. No. 12/357,368, filed Jan. 21, 2009.

International Search Report and Written Opinion of the International Searching Authority dated Jul. 26, 2007, PCT Patent Appl. PCT/US2007/004967, filed Feb. 27, 2007.

European Office Action dated Mar. 9, 2009, European Patent Appl. No. 07751706.8.

Office Action dated Sep. 24, 2007, U.S. Appl. No. 11/421,871, filed Jun. 2, 2006.

Response to Office Action dated Oct. 17, 2007, U.S. Appl. No. 11/421,871, filed Jun. 2, 2006.

Notice of Allowance dated May 19, 2008, U.S. Appl. No. 11/421,871, filed Jun. 2, 2006.

Office Action dated Jul. 12, 2007, U.S. Appl. No. 11/421,884, filed Jun. 2, 2006.

Response Office Action dated Jul. 30, 2007, U.S. Appl. No. 11/421,884, filed Jun. 2, 2006.

Notice of Allowance dated Aug. 23, 2007, U.S. Appl. No. 11/421,884, filed Jun. 2, 2006.

Notice of Allowance dated Sep. 24, 2007, U.S. Appl. No. 11/421,884, filed Jun. 2, 2006.

Notice of Allowance dated Oct. 22, 2007, U.S. Appl. No. 11/421,884, filed Jun. 2, 2006.

Preliminary Amendment dated Feb. 1, 2008, U.S. Appl. No. 11/933,632, filed Nov. 1, 2007.

Office Action dated Aug. 4, 2008, U.S. Appl. No. 11/933,632, filed Nov. 1, 2007.

Response to Office Action dated Aug. 22, 2008, U.S. Appl. No. 11/933,632, filed Nov. 1, 2007.

Office Action dated Oct. 8, 2008, U.S. Appl. No. 11/933,632, filed Nov. 1, 2007.

Response to Office Action dated Jan. 8, 2009, U.S. Appl. No. 11/933,632, filed Nov. 1, 2007.

Notice of Allowance dated Mar. 20, 2009, U.S. Appl. No. 11/933,632, filed Nov. 1, 2007.

Preliminary Amendment dated Feb. 1, 2008, U.S. Appl. No.

11/933,649, filed Nov. 1, 2007. Office Action dated Apr. 1, 2008, U.S. Appl. No. 11/933,649, filed

Nov. 1, 2007.

International Search Report and Written Opinion of the International Searching Authority dated Jan. 28, 2008, PCT Patent Appl. PCT/US2007/069590, filed May 23, 2007.

International Preliminary Report and Written Opinion of the International Searching Authority dated Dec. 18, 2008, PCT Patent Appl. PCT/US2007/069590, filed May 23, 2007.

Office Action dated May 14, 2008, U.S. Appl. No. 11/618,569, filed Dec. 29, 2006.

Response to Office Action dated Aug. 14, 2008, U.S. Appl. No. 11/618,569, filed Dec. 29, 2006.

Notice of Allowance dated Oct. 14, 2008, U.S. Appl. No. 11/618,569, filed Dec. 29, 2006.

Notice of Allowance dated Mar. 25, 2008, U.S. Appl. No. 11/618,578, filed Dec. 29, 2006.

Notice of Allowance dated May 12, 2008, U.S. Appl. No. 11/618,578, filed Dec. 29, 2006.

Notice of Allowance dated Jun. 4, 2008, U.S. Appl. No. 11/618,578, filed Dec. 29, 2006.

International Search Report and Written Opinion of the International Searching Authority dated May 28, 2008, PCT Patent Appl. PCT/US2007/088787, filed Dec. 24, 2007.

International Preliminary Report and Written Opinion of the International Searching Authority dated Jun. 30, 2009, PCT Patent Appl. PCT/US2007/088787, filed Dec. 24, 2007.

Amendment and Amended Claims filed Mar. 5, 2010 in European Patent Application No. 09015112.7.

Notice of Allowance dated Apr. 9, 2010, U.S. Appl. No. 12/357,368, filed Jan. 21, 2009.

Korean Office Action dated Apr. 28, 2010, Korean Patent Application No. 10-2008-7023384.

Response to Taiwan Office Action dated May 4, 2010, Taiwan Patent Application No. 096107259.

English translation of Amended Claims and Drawings filed with Response to Taiwan Office Action dated May 4, 2010, Taiwan Patent Application No. 096107259.

Response to European Office Action dated Jun. 22, 2010, European Patent Application No. 07 751 706.8.

Response to Korean Office Action dated Aug. 30, 2010, Korean Patent Application No. 7023384/2008.

Chinese Office Action dated Dec. 3, 2010, Chinese Patent Appl. No.

200780007206.5. Notification of Reasons for Rejection dated Nov. 22, 2011, Japanese

Patent Application No. 2008-557330. Notice of Reasons for Rejection dated Mar. 8, 2011, Japanese Patent

Application No. 2008-557330. Argument and Claim Amendments, dated May 31, 2011, Japanese

Patent Application No. 2008-557330. Japanese Argument and Claim Amendments dated Jan. 19, 2012, Japanese Patent Application No. 2008-557330.

Chinese Office Action dated Dec. 7, 2011, Chinese Patent Application No. 200780050890.5.

Notice of Reasons for Rejection dated Mar. 13, 2012, Japanese Patent Application No. 2009-544243.

<sup>\*</sup> cited by examiner

Fig. 1

126

120CG

100FG

100CG

102FG

104CG

106FG

106CG

122CG

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 9

Fig. 12

Fig. 10

| Wordline | all bit lines |

|----------|---------------|

| WL3      | Pare 3        |

| W12      | Page 2        |

| Wilji    | 7440 i        |

| WLO      | Page ()       |

Fig. 14A

| Wordline | Even Bit<br>Lines | Odd Bit<br>Lines |

|----------|-------------------|------------------|

| WL3      | Page 6            | Page 7           |

| WL2      | Page 4            | Page 5           |

| WL       | Page 2            | Page 3           |

| WLO      | Page ()           | Page             |

Fig. 14B

| Wordline | Lower Page | All Bit Lines |

|----------|------------|---------------|

|          |            | Page 7        |

|          |            | Page6         |

|          |            | Page 5        |

|          | lower      | Page 4        |

|          |            | 124223        |

|          | lower      | Page 2        |

|          |            | Page i        |

|          | lower      | Page 0        |

Fig. 14C

| Wordline | Lower Page | Even Bit<br>Lines | Odd Bit<br>Lines |

|----------|------------|-------------------|------------------|

|          |            |                   |                  |

|          | lower      | Page 12           | Page 13          |

| WL2      |            | Page 10           |                  |

|          |            | Pa208             | Page 9           |

| WLi      |            | Page 6            | 74267            |

|          |            | Page 4            | Page5            |

|          |            | Page 2            | 12age 3          |

|          | lower      | Pare              | Pagel            |

Fig. 14D

| Wordline                               | Upper/<br>Lower Page | Even Bit<br>Lines | Odd Bit<br>Lines |

|----------------------------------------|----------------------|-------------------|------------------|

|                                        |                      |                   |                  |

|                                        |                      | Page 12           | Page 14          |

|                                        |                      | Page 9            |                  |

| ************************************** |                      |                   |                  |

|                                        |                      |                   |                  |

|                                        |                      |                   |                  |

|                                        |                      |                   |                  |

|                                        | lower                | Page ()           |                  |

1 Fig. 14E

| Wordline     | Lower Page | All Bit Lines |

|--------------|------------|---------------|

|              | upoer -    |               |

|              | lower      | Page 5        |

| <b>W</b> 1_2 |            |               |

|              |            |               |

|              |            |               |

|              |            |               |

|              |            | 20222         |

|              | lower      | Page          |

Fig. 14F

| Wordline    | Upper/<br>Lower Page | Even Bit<br>Lines | Odd Bit<br>Lines |

|-------------|----------------------|-------------------|------------------|

|             |                      | Page 14           |                  |

|             | lover                |                   |                  |

|             |                      | Page 12           |                  |

| <b>W1.2</b> | lower                |                   |                  |

|             |                      |                   |                  |

|             |                      |                   |                  |

|             |                      |                   |                  |

|             |                      |                   |                  |

Fig. 14G

Fig. 16

Fig. 17

Fig. 20

Fig. 25

|                      | State E | State B | Sigis |

|----------------------|---------|---------|-------|

| (1) Read at Vra      |         |         |       |

| (2) Read at Vrb      |         |         | 0     |

| (3) (Invert 2) XOR 1 |         |         |       |

| (4) Read at Vrc      |         |         |       |

| (5) 4 AND 3          |         |         |       |

Fig. 23 1150 upper page? 1170 ,1152 lower apply Vrb to word line upper page read 1154 sense bit lines 1156 store result 1158 No flag? ,4,71160 apply Vra to word line Yes 1162 sense bit lines ,1164 store result ,1166 determine data values ,1168 store data values in latches

Fig. 24

Fig. 27

# READ OPERATION FOR NON-VOLATILE STORAGE WITH COMPENSATION FOR COUPLING

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held 10 invalid by a prior post-patent action or proceeding.

### CLAIM OF PRIORITY

This application is a continuation application of U.S. 15 patent application Ser. No. 12/622,966, "Read Operation For Non-Volatile Storage With Compensation For Coupling," filed Nov. 20, 2009, by Mokhlesi, which is a continuation application of U.S. patent application Ser. No. 12/357,368, "Read Operation For Non-Volatile Storage With Compensation For Coupling," filed Jan. 21, 2009, by Mokhlesi, which is a divisional application of U.S. patent application Ser. No. 11/384,057, "Read Operation For Non-Volatile Storage With Compensation For Coupling," filed on Mar. 17, 2006 by Mokhlesi, now U.S. Pat. No. 7,499,319, which claims the benefit of U.S. Provisional Application No. 60/778,857, filed Mar. 3, 2006. All of these applications are incorporated herein by reference.

# CROSS-REFERENCE TO RELATED APPLICATIONS

The following U.S. patent and U.S. patent application are cross-referenced and incorporated by reference herein in its 35 entirety:

U.S. Pat. No. 7,436,733, issued Oct. 14, 2008, entitled "System for Performing Read Operation On Non-volatile Storage with Compensation for Coupling," by Nima Mokhlesi, and

U.S. Pat. No. 7,613,068, issued Nov. 3, 2009, entitled "Read Operation For Non-Volatile Storage With Compensation For Coupling," by Nima Mokhlesi.

### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to technology for non-volatile memory.

### 2. Description of the Related Art

Semiconductor memory has become more popular for use in various electronic devices. For example, non-volatile semiconductor memory is used in cellular telephones, digital cameras, personal digital assistants, mobile computing devices, non-mobile computing devices and other devices. 55 Electrical Erasable Programmable Read Only Memory (EE-PROM) and flash memory are among the most popular non-volatile semiconductor memories.

Both EEPROM and flash memory utilize a floating gate that is positioned above and insulated from a channel region 60 in a semiconductor substrate. The floating gate is positioned between the source and drain regions. A control gate is provided over and insulated from the floating gate. The threshold voltage of the transistor is controlled by the amount of charge that is retained on the floating gate. That 65 is, the minimum amount of voltage that must be applied to the control gate before the transistor is turned on to permit

2

conduction between its source and drain is controlled by the level of charge on the floating gate.

When programming an EEPROM or flash memory device, such as a NAND flash memory device, typically a program voltage is applied to the control gate and the bit line is grounded. Electrons from the channel are injected into the floating gate. When electrons accumulate in the floating gate, the floating gate becomes negatively charged and the threshold voltage of the memory cell is raised so that the memory cell is in a programmed state. More information about programming can be found in U.S. Pat. No. 6,859,397, titled "Source Side Self Boosting Technique for Non-Volatile Memory;" and in U.S. Pat. No. 6,917,542, titled "Detecting Over Programmed Memory;" both patents are incorporated herein by reference in their entirety.

Some EEPROM and flash memory devices have a floating gate that is used to store two ranges of charges and, therefore, the memory cell can be programmed/erased between two states (an erased state and a programmed state). Such a flash memory device is sometimes referred to as a binary flash memory device.

A multi-state flash memory device is implemented by identifying multiple distinct allowed/valid programmed threshold voltage ranges separated by forbidden ranges. Each distinct threshold voltage range corresponds to a predetermined value for the set of data bits encoded in the memory device.

Shifts in the apparent charge stored on a floating gate can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates. This floating gate to floating gate coupling phenomena is described in U.S. Pat. No. 5,867,429, which is incorporated herein by reference in its entirety. An adjacent floating gate to a target floating gate may include neighboring floating gates that are on the same bit line, neighboring floating gates on the same word line, or floating gates that are diagonal from the target floating gate because they are on both a neighboring bit line and neighboring word line.

The floating gate to floating gate coupling phenomena occurs most pronouncedly between sets of adjacent memory cells that have been programmed at different times. For example, a first memory cell is programmed to add a level of charge to its floating gate that corresponds to one set of data. Subsequently, one or more adjacent memory cells are programmed to add a level of charge to their floating gates that correspond to a second set of data. After the one or more of the adjacent memory cells are programmed, the charge level read from the first memory cell appears to be different than programmed because of the effect of the charge on the adjacent memory cells being coupled to the first memory cell. The coupling from adjacent memory cells can shift the apparent charge level being read a sufficient amount to lead to an erroneous reading of the data stored.

The effect of the floating gate to floating gate coupling is of greater concern for multi-state devices because in multi-state devices the allowed threshold voltage ranges and the forbidden ranges are narrower than in binary devices. Therefore, the floating gate to floating gate coupling can result in memory cells being shifted from an allowed threshold voltage range to a forbidden range.

As memory cells continue to shrink in size, the natural programming and erase distributions of threshold voltages are expected to increase due to short channel effects, greater oxide thickness/coupling ratio variations and more channel dopant fluctuations, reducing the available separation between adjacent states. This effect is much more significant for multi-state memories than memories using only two

states (binary memories). Furthermore, the reduction of the space between word lines and of the space between bit lines will also increase the coupling between adjacent floating gates.

Thus, there is a need to reduce the effect of coupling <sup>5</sup> between floating gates.

### SUMMARY OF THE INVENTION

To account for the coupling between floating gates, the read process for a particular memory cell will provide compensation to an adjacent memory cell in order to reduce the coupling effect that the adjacent memory cell has on the particular memory cell. Various embodiments are disclosed.

One embodiment includes applying a read voltage to a selected non-volatile storage element during a read process for a selected non-volatile storage element, using a particular voltage during the read process for a neighbor of the selected non-volatile storage element based on a current condition of the neighbor, and sensing a condition of the selected non-volatile storage element during the read process. Another embodiment includes applying a read compare voltage to a selected word line connected to a non-volatile storage element being read, applying a first pass voltage to a first set of unselected word lines, applying a second pass voltage to 25 neighbor unselected word line, and sensing a condition of the non-volatile storage element being read.

One example implementation comprises a plurality of non-volatile storage elements and one or more managing circuits in communication with the plurality of non-volatile <sup>30</sup> storage elements for performing the processes discussed herein.

### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a top view of a NAND string.

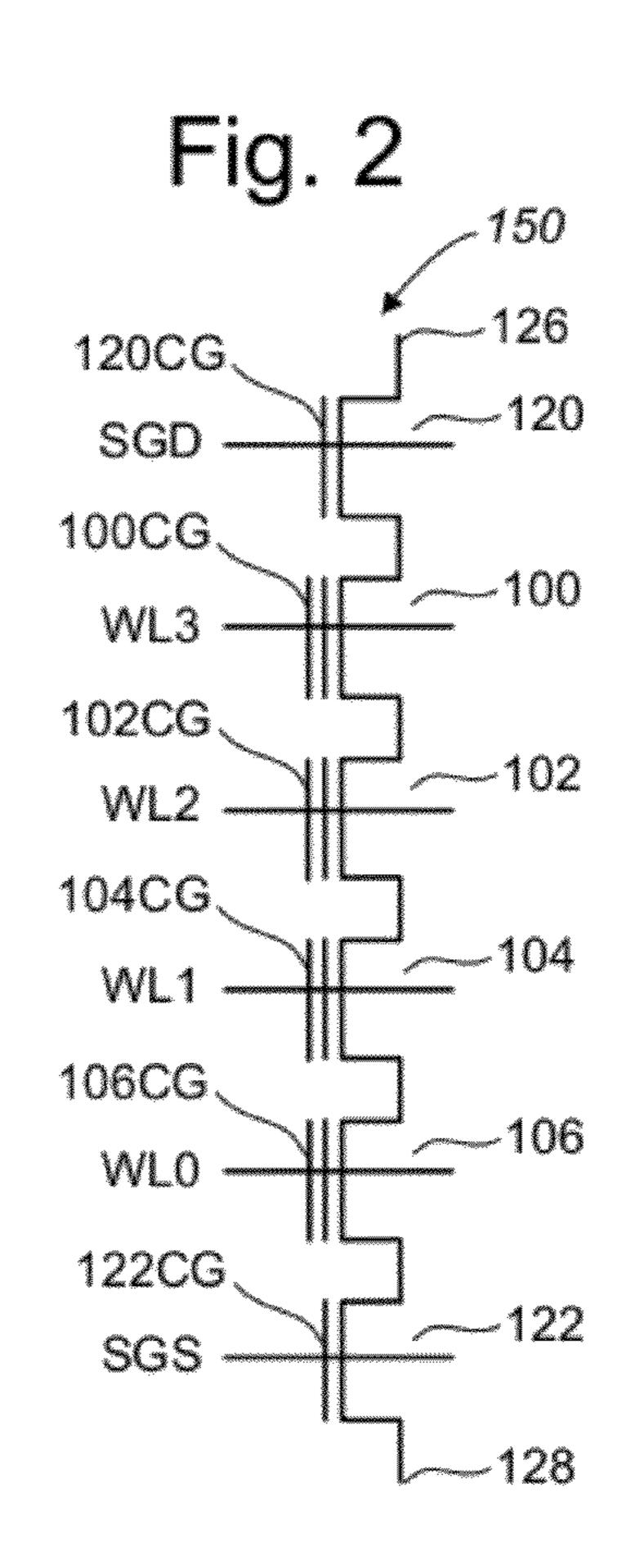

- FIG. 2 is an equivalent circuit diagram of the NAND string.

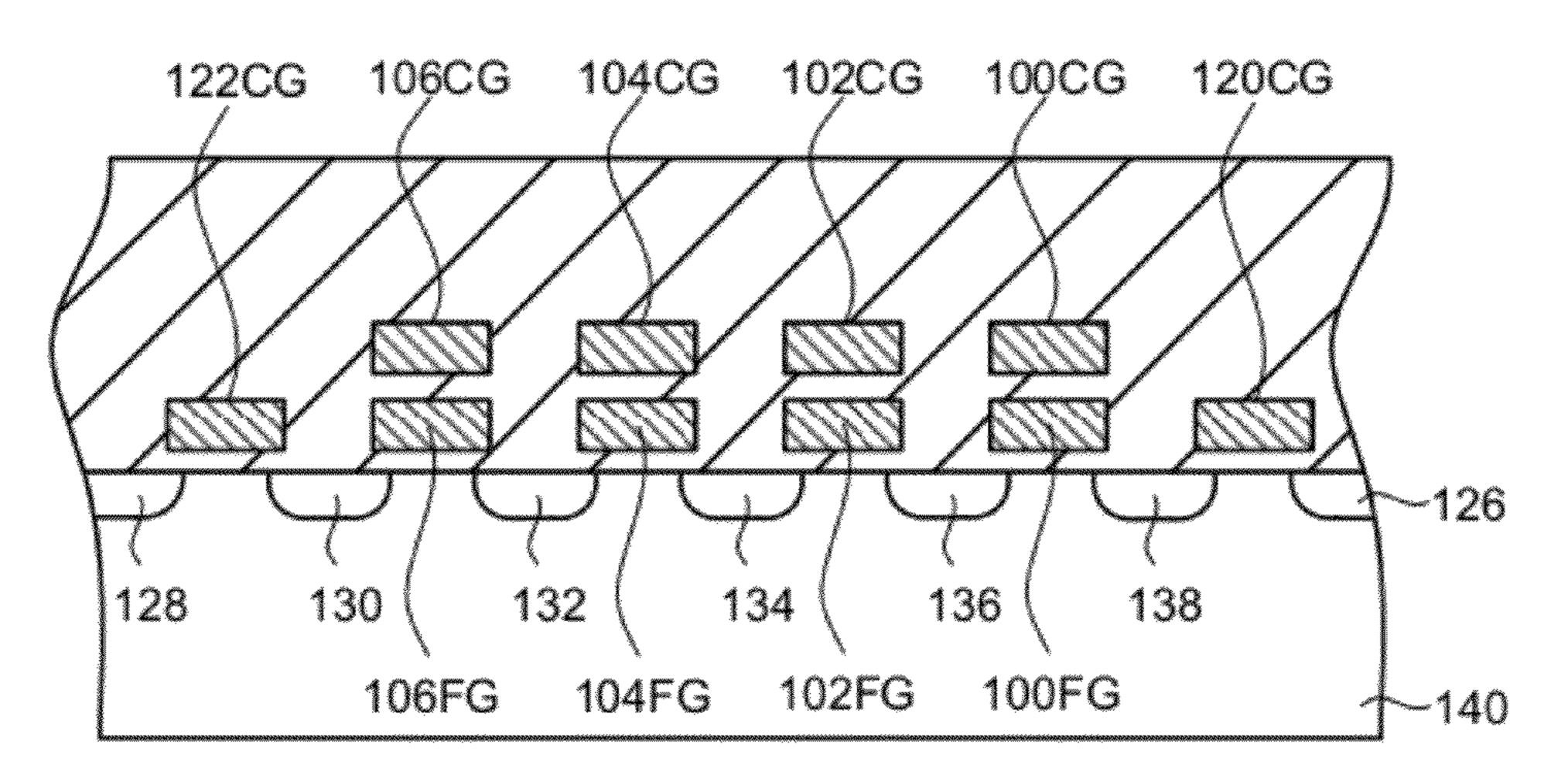

- FIG. 3 is a cross-sectional view of the NAND string.

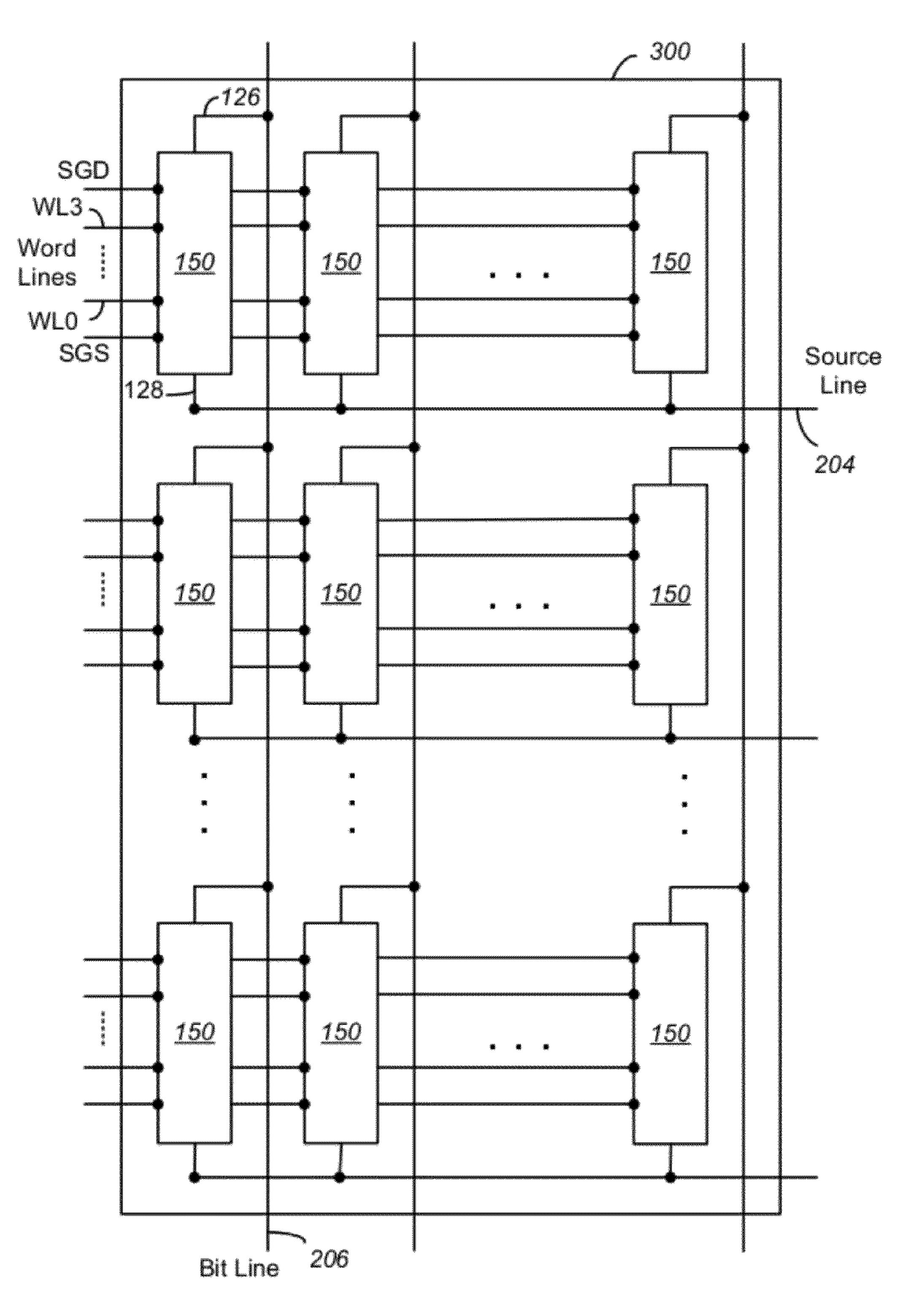

- FIG. 4 is a block diagram of an array of NAND flash 40 memory cells.

- FIG. 5 is a block diagram of a non-volatile memory system.

- FIG. 6 is a block diagram of a non-volatile memory system.

- FIG. 7 is a block diagram depicting one embodiment of the sense block.

- FIG. 8 is a flow chart describing one embodiment of a process for programming non-volatile memory.

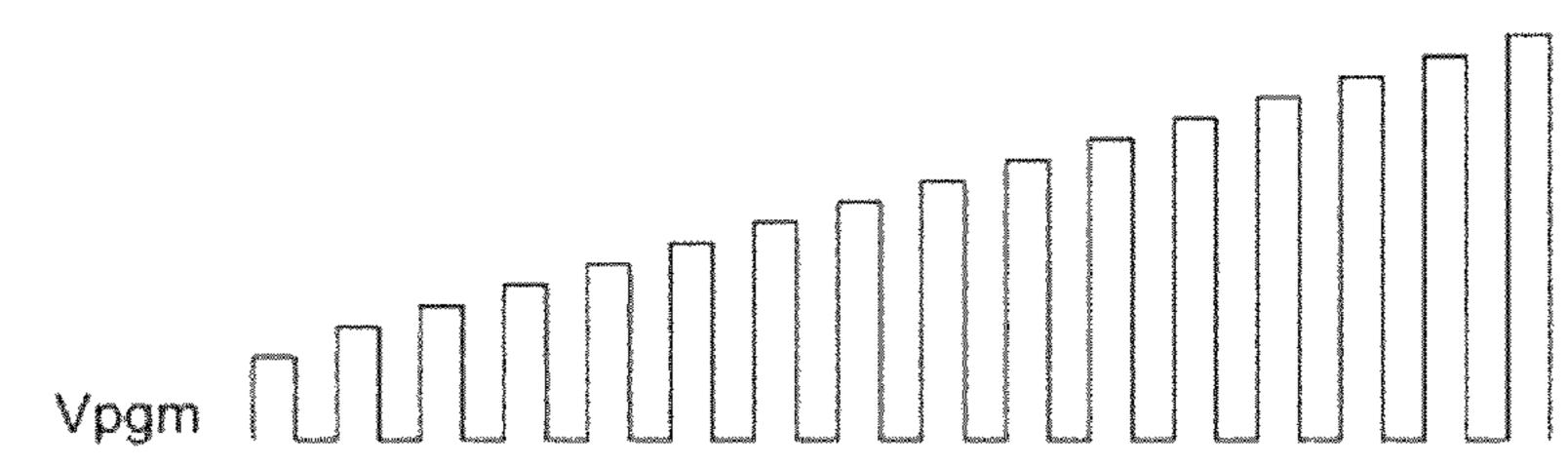

- FIG. 9 is an example wave form applied to the control 50 gates of non-volatile memory cells.

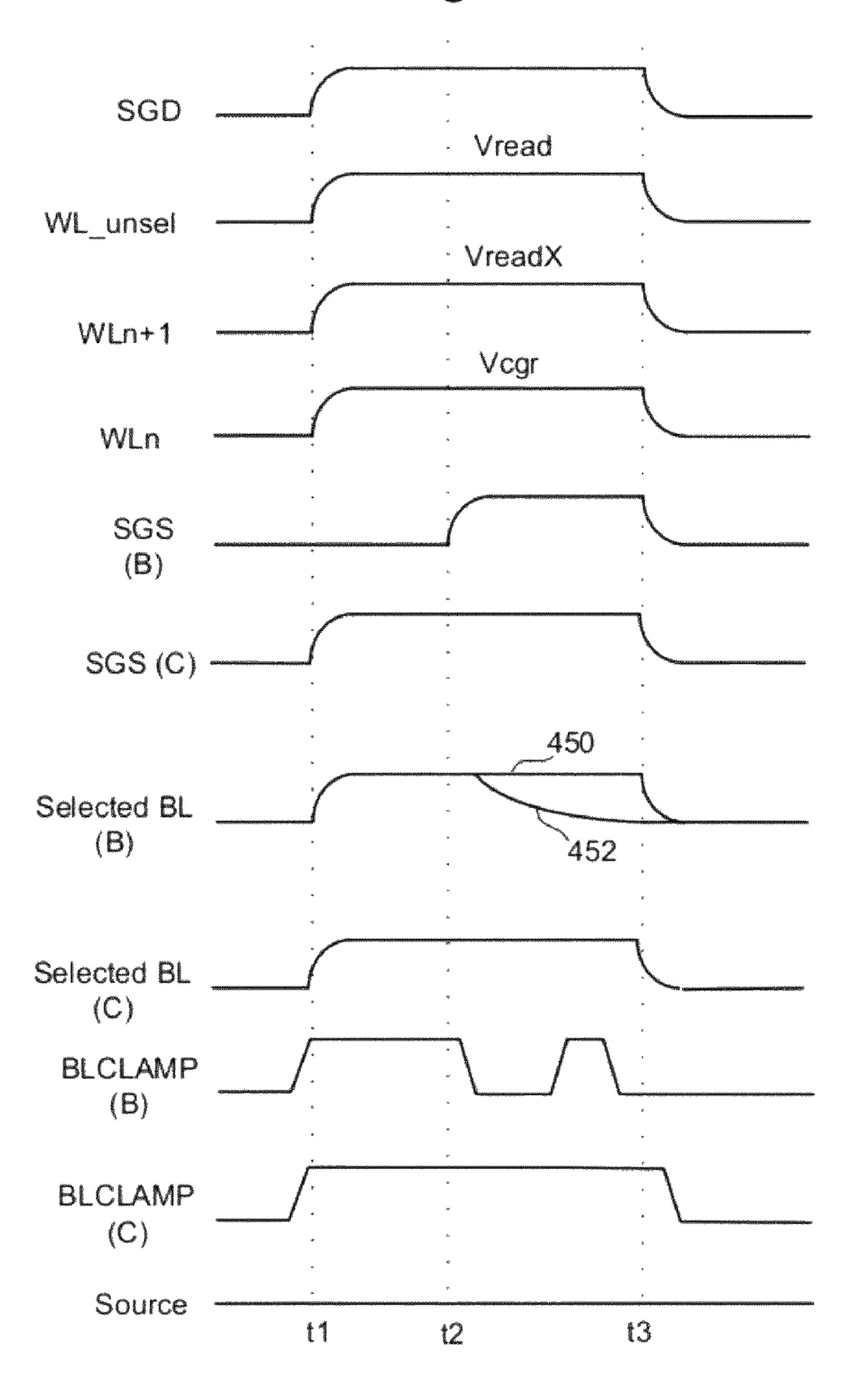

- FIG. 10 is a timing diagram that explains the behavior of certain signals during read/verify operations.

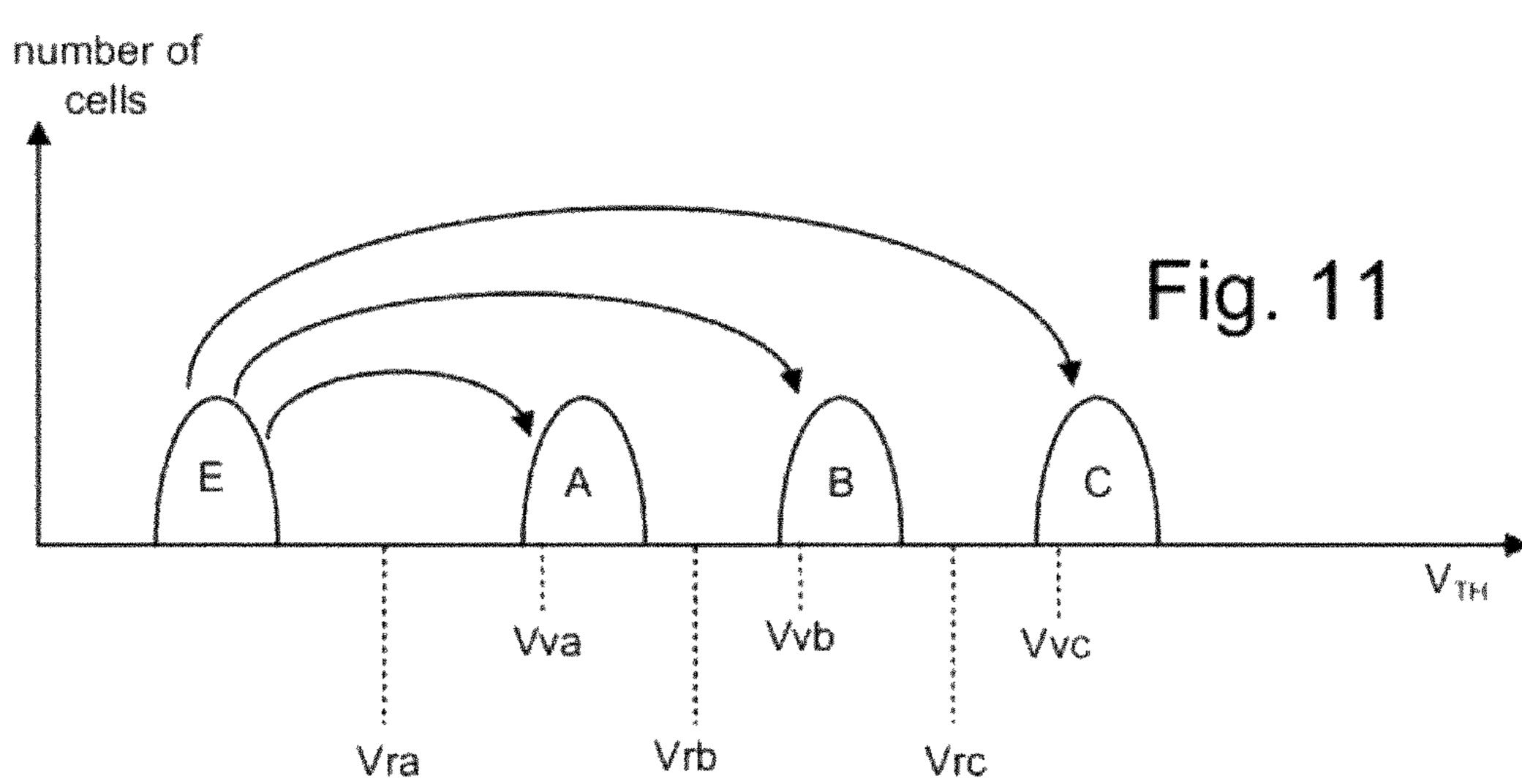

- FIG. 11 depicts an example set of threshold voltage distributions.

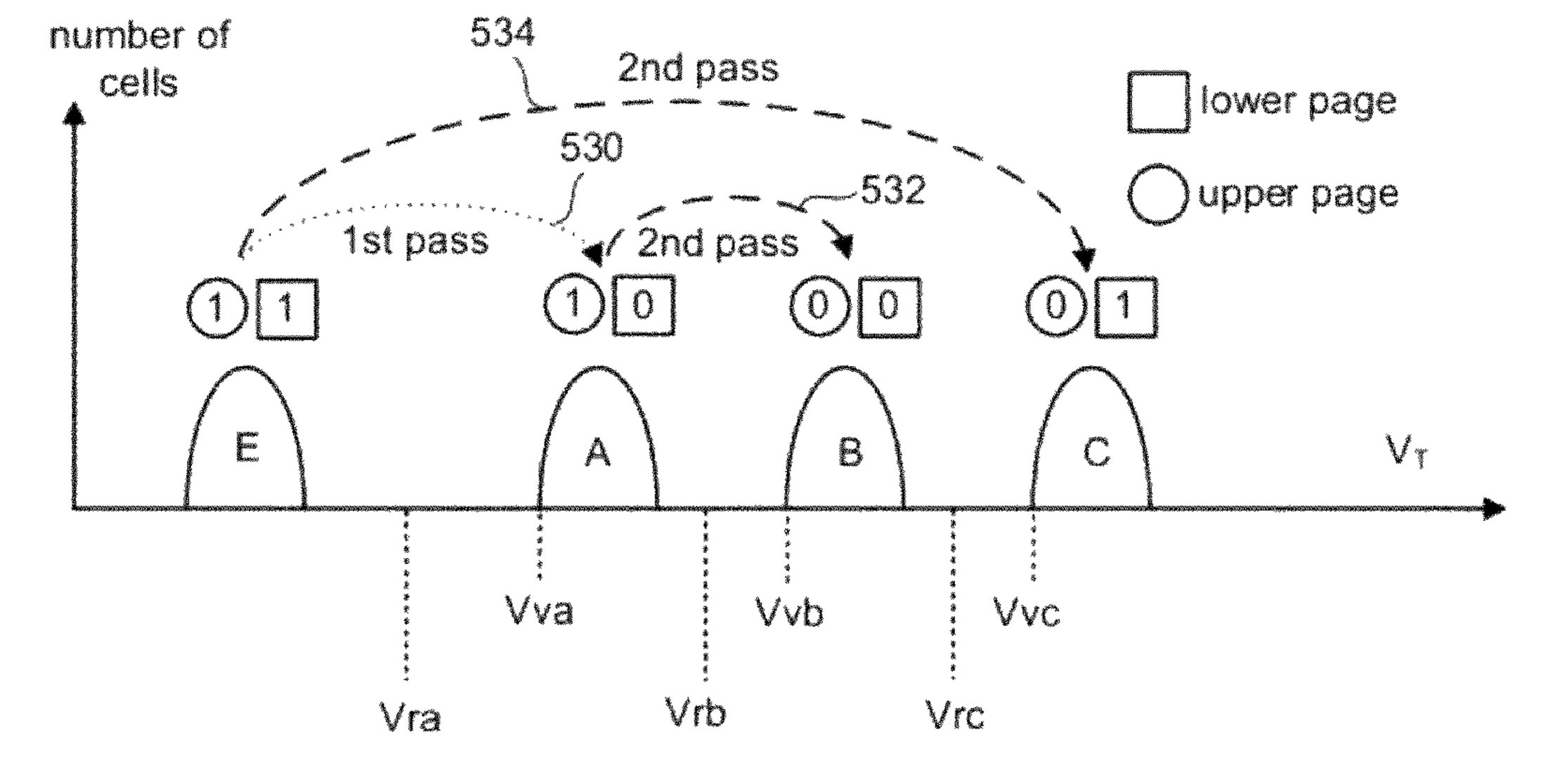

- FIG. 12 depicts an example set of threshold voltage distributions.

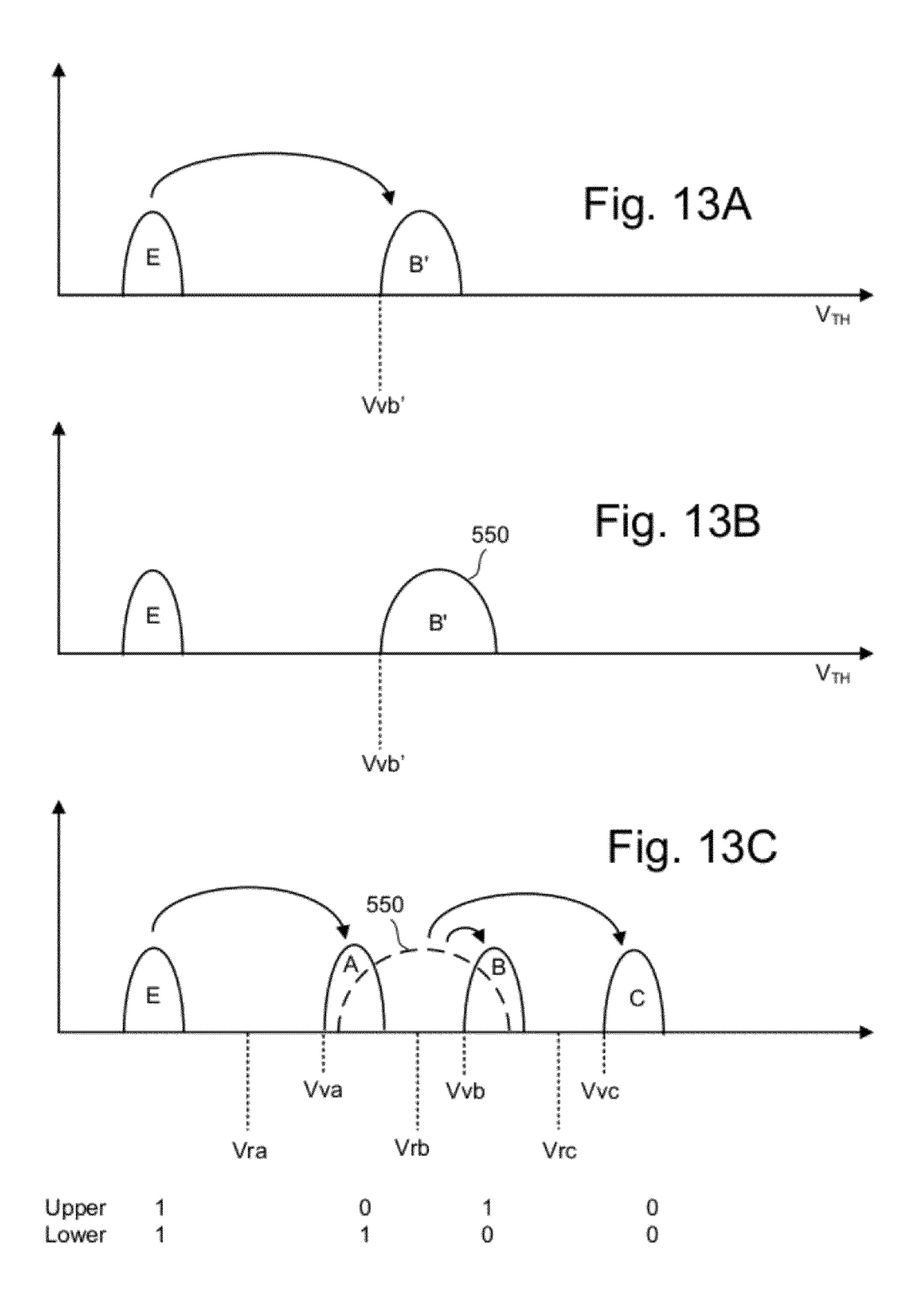

- FIGS. 13A-C show various threshold voltage distributions and describe a process for programming non-volatile memory.

- FIGS. 14A-G are tables depicting the order of programming non-volatile memory in various embodiments.

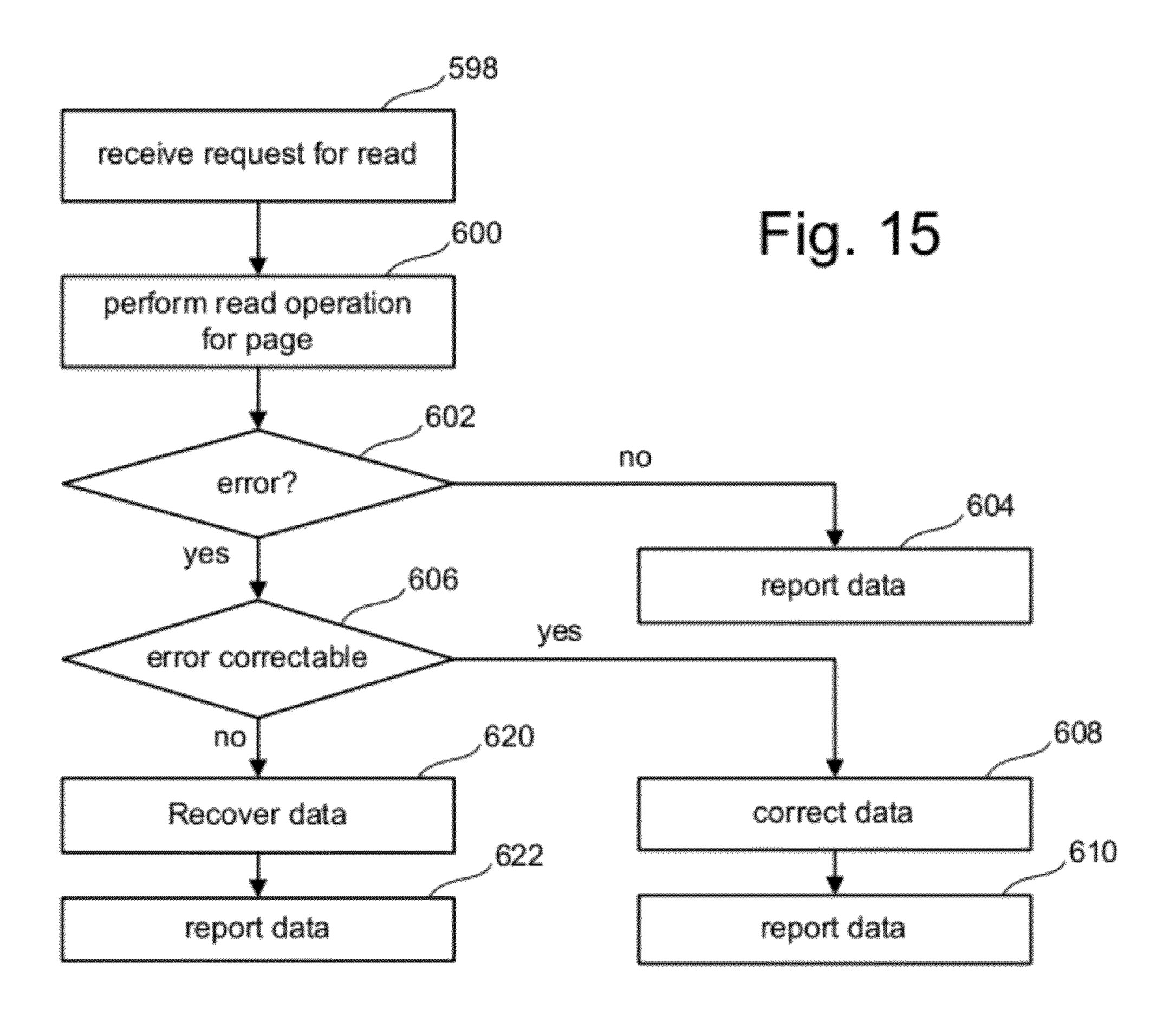

- FIG. 15 is a flow chart describing one embodiment of a process for reading non-volatile memory.

- FIG. **16** is a flow chart describing one embodiment of a 65 process for performing a read operation for non-volatile memory.

4

- FIG. 17 is a flow chart describing one embodiment of a process for recovering data.

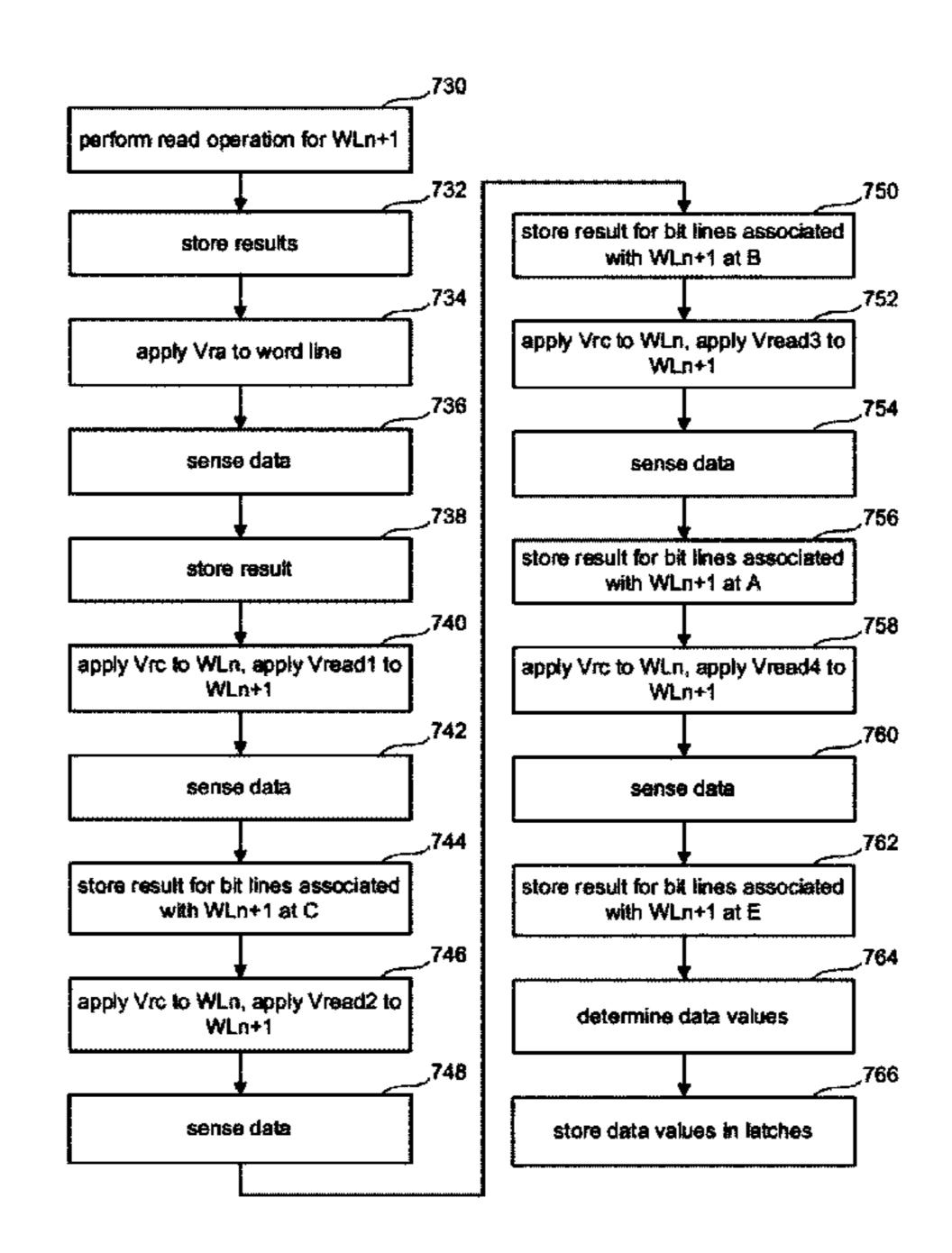

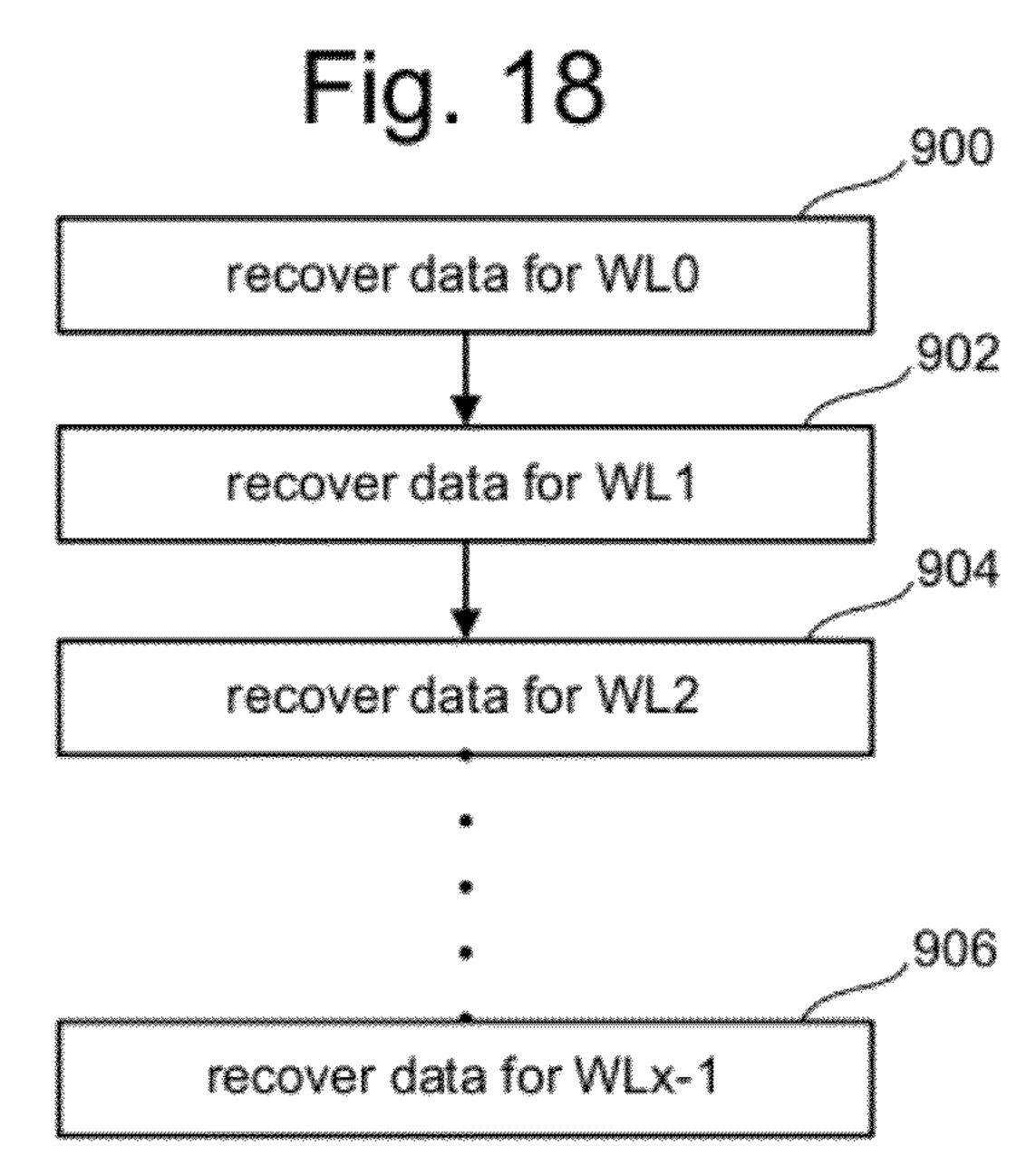

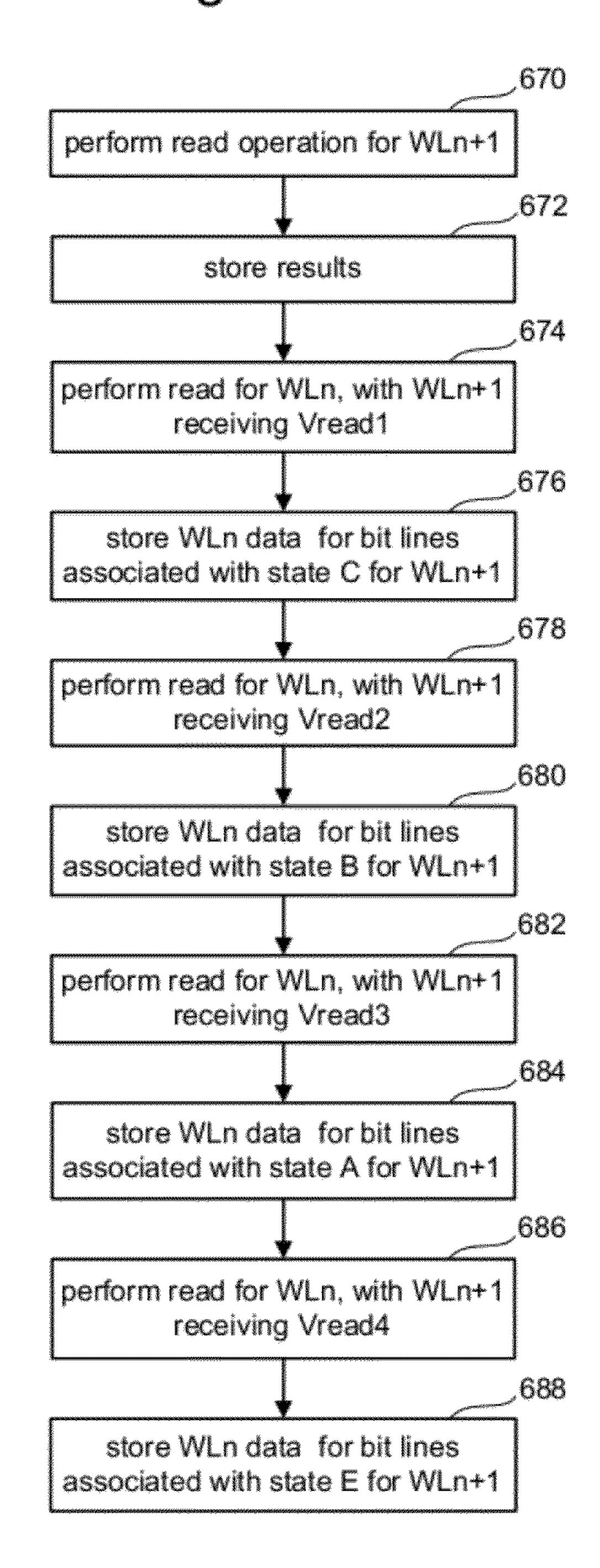

- FIG. 18 is a flow chart describing one embodiment of a process for recovering data from multiple word lines.

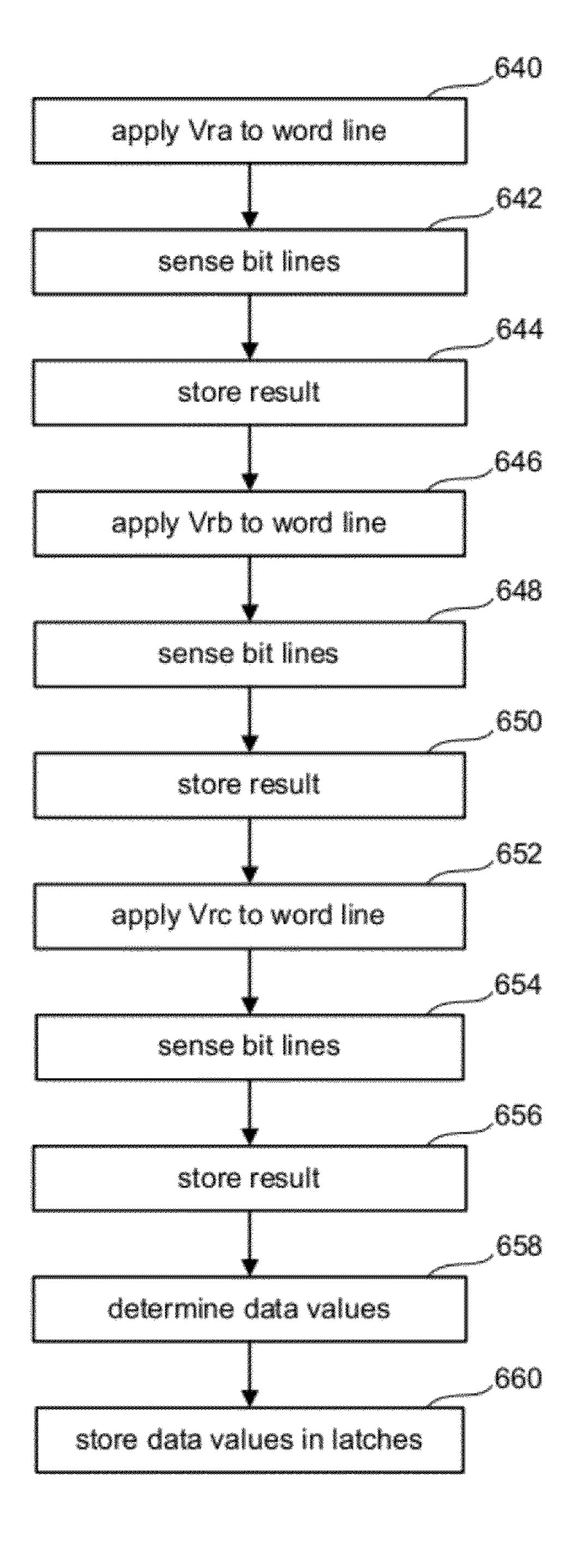

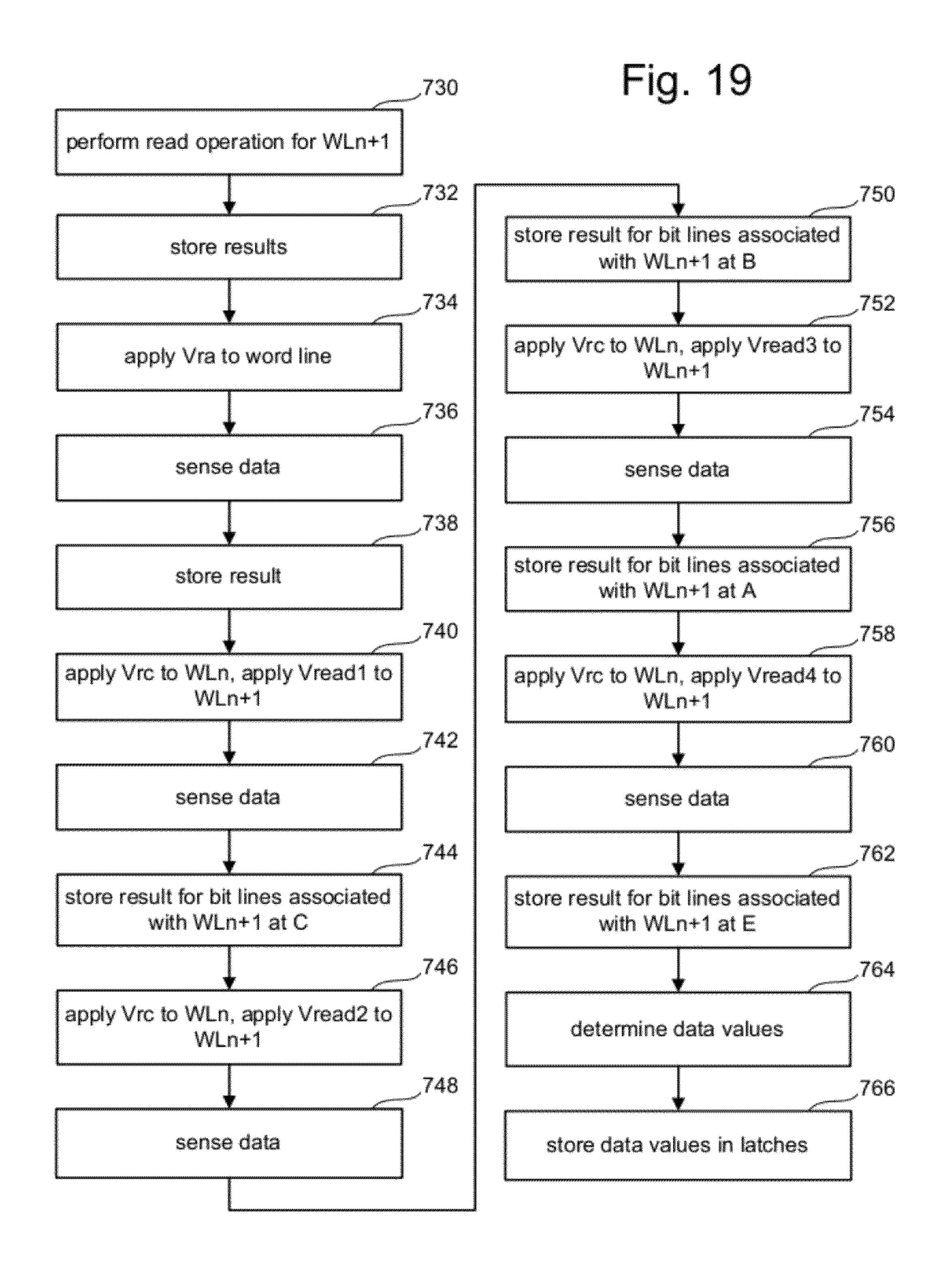

- FIG. 19 is a flow chart describing one embodiment of a process for reading data from a lower page.

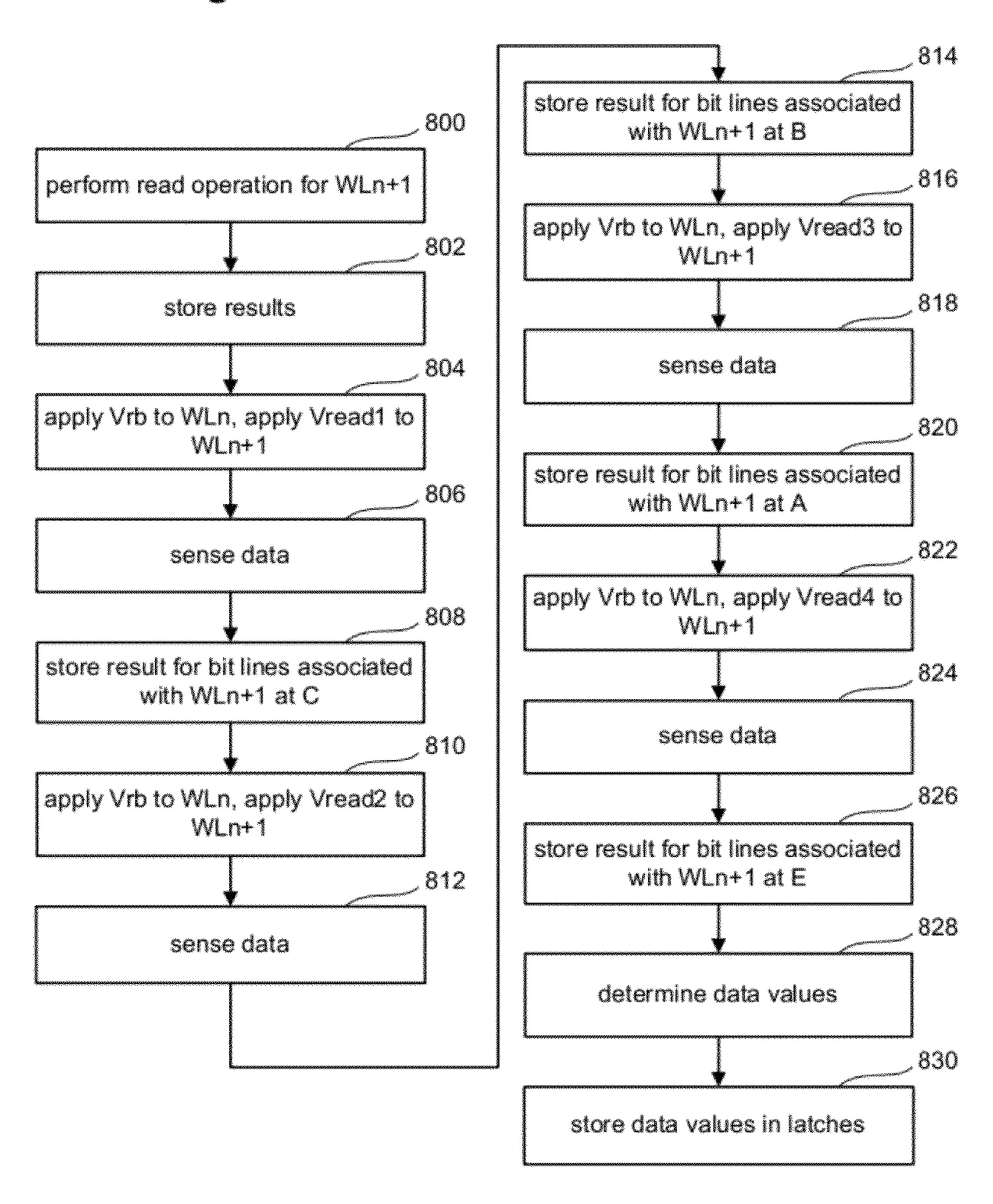

- FIG. 20 is a flow chart describing one embodiment of a process of reading data from an upper page.

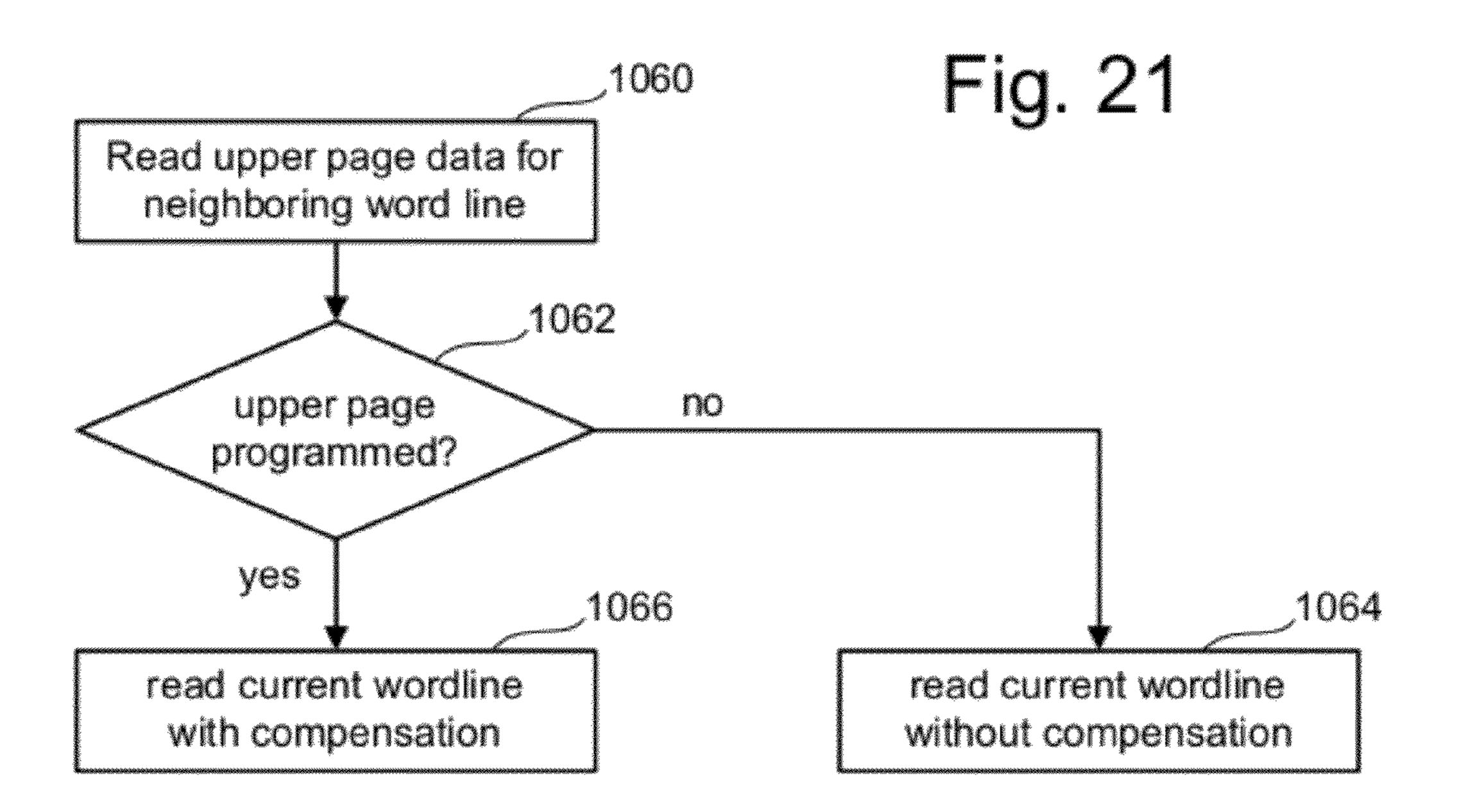

- FIG. 21 is a flow chart describing one embodiment of a process for reading data.

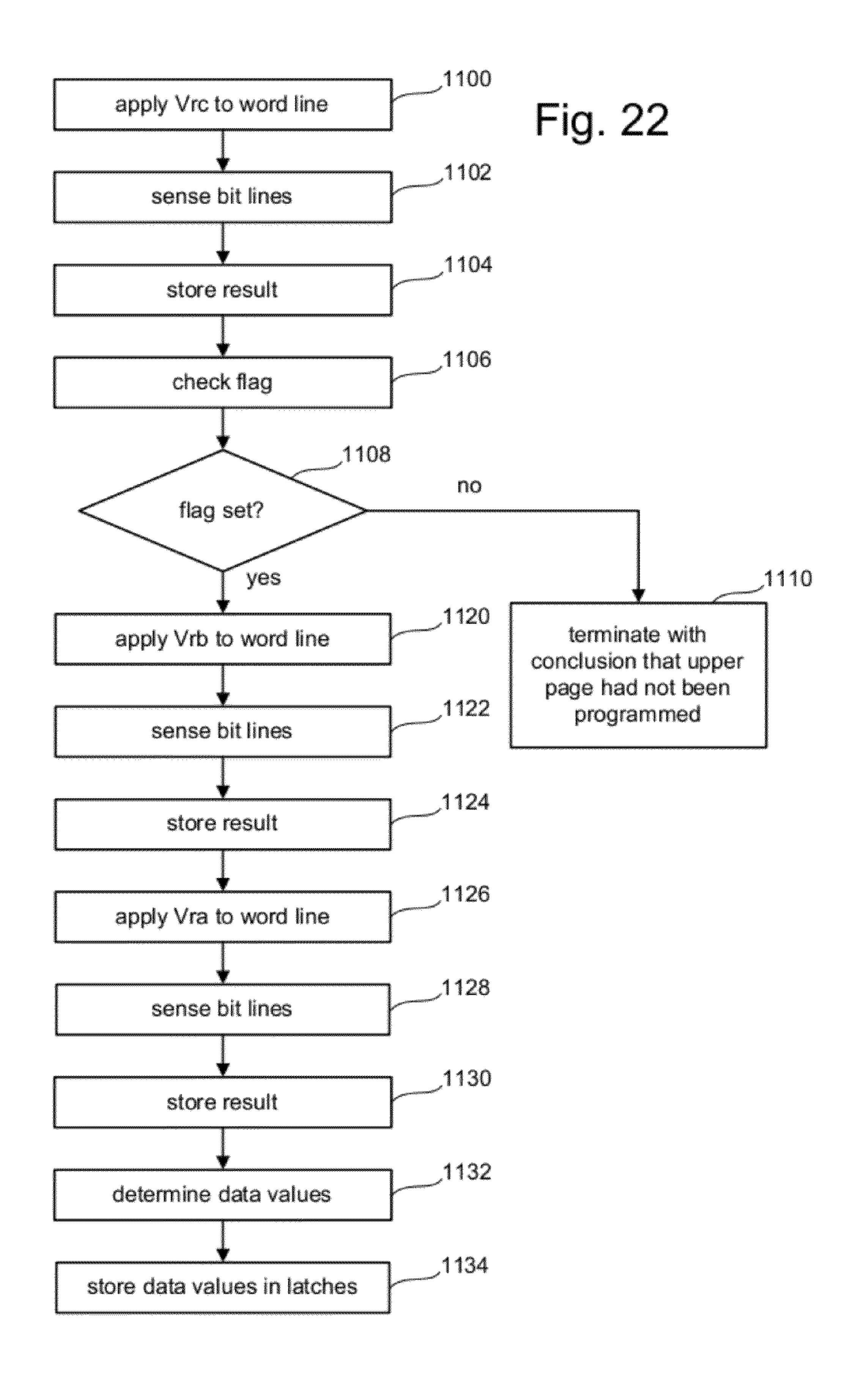

- FIG. 22 is a flow chart describing one embodiment of a process for reading data from an upper page.

- FIG. 23 is a flow chart describing one embodiment of a process for reading data without using compensation.

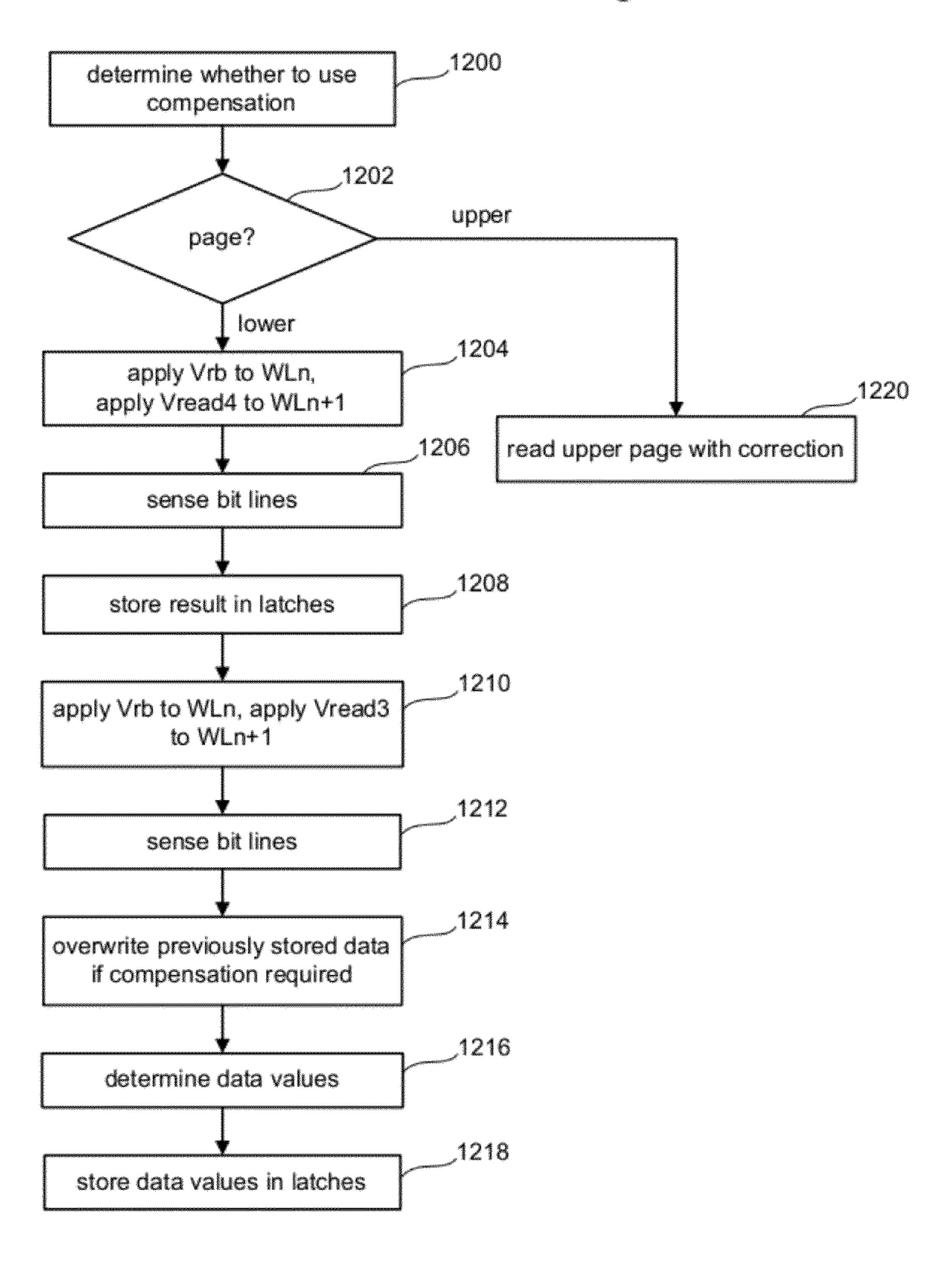

- FIG. 24 is a flow chart describing one embodiment of a process for reading data while compensating for floating gate to floating gate (or dielectric region to dielectric region) coupling.

- FIG. **25** is a table depicting a process for determining data values.

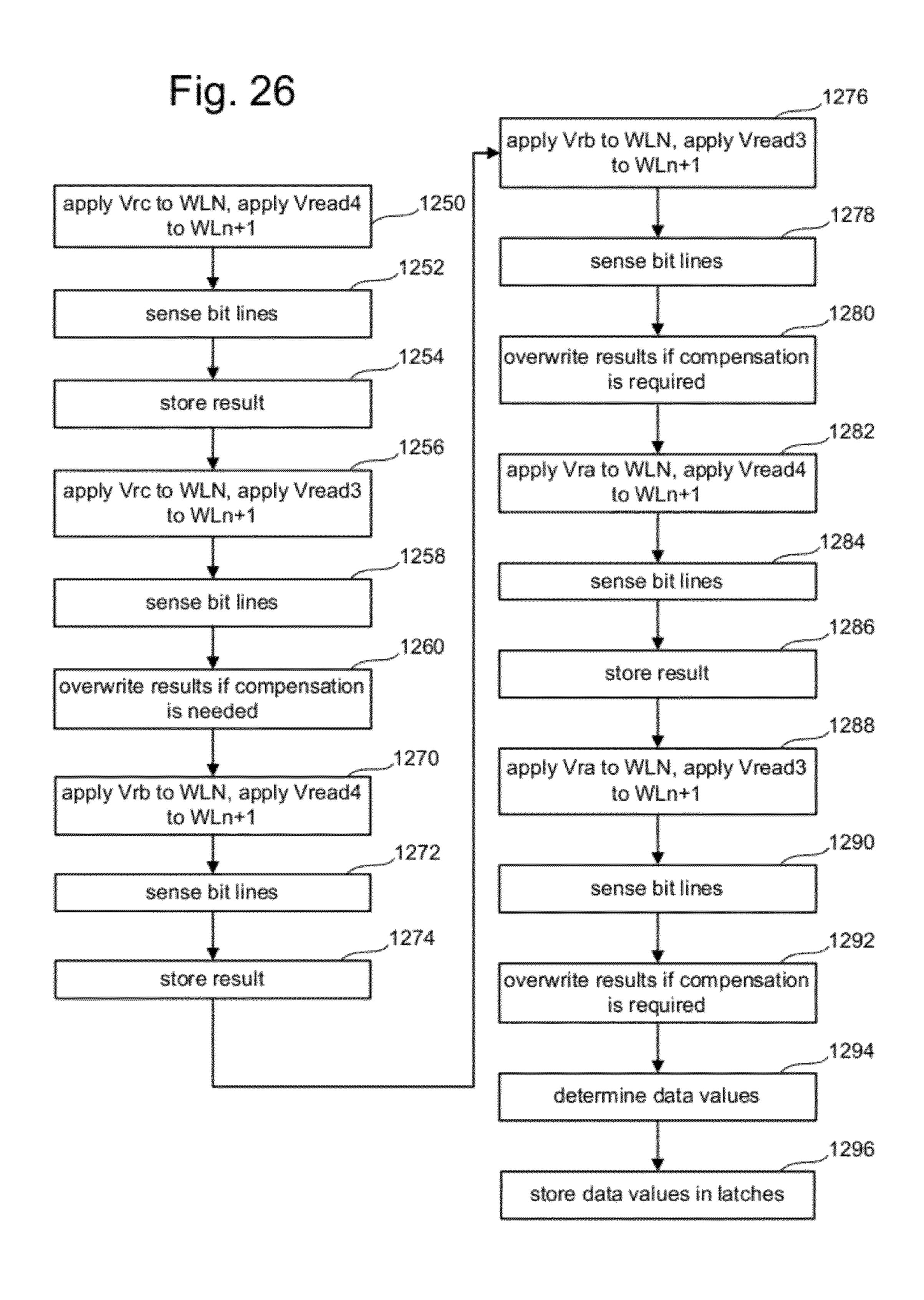

- FIG. 26 is a flow chart describing one embodiment of a process for reading upper page data using a correction.

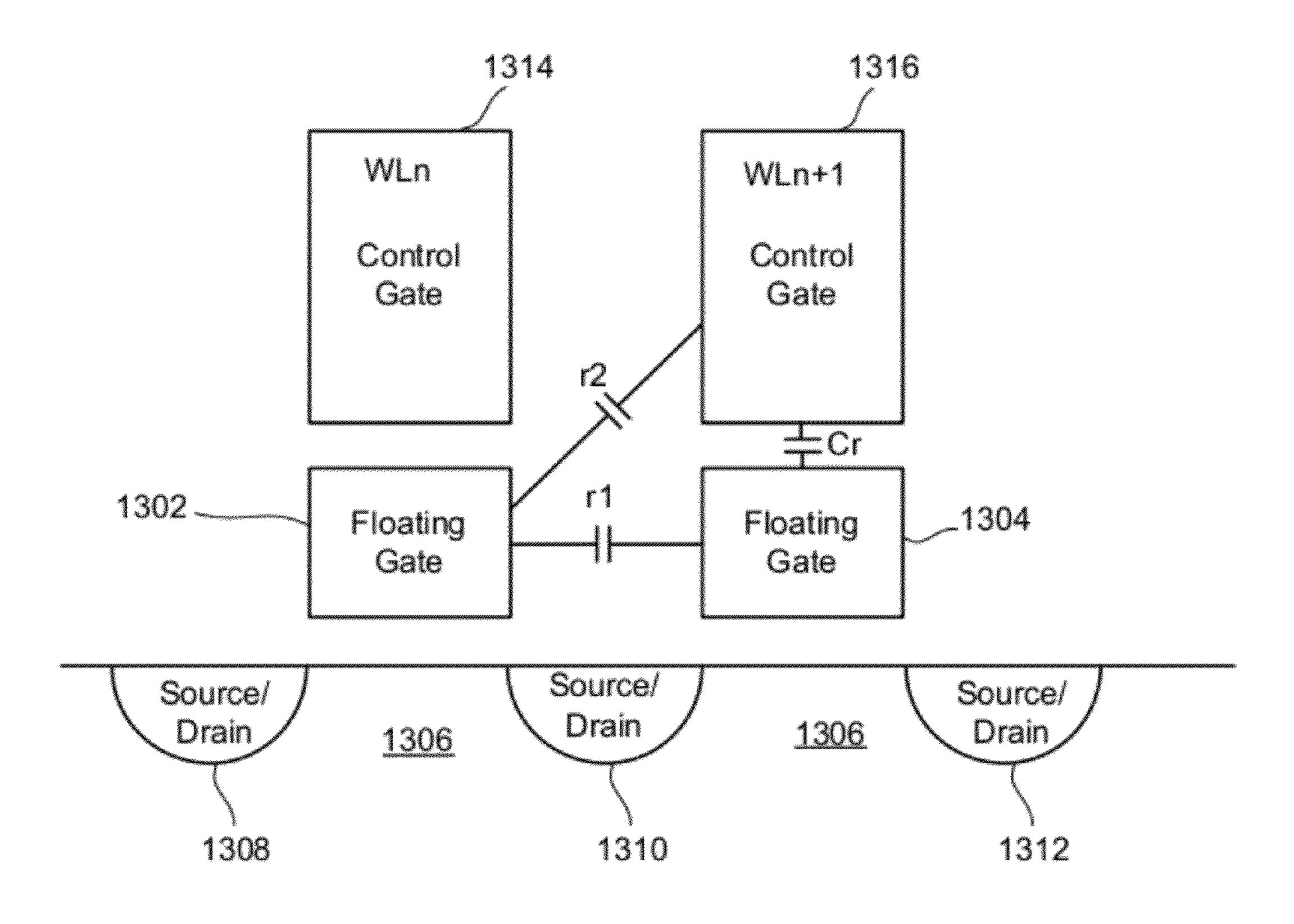

- FIG. 27 is a block diagram showing capacitive coupling between two neighboring memory cells.

### DETAILED DESCRIPTION

One example of a memory system suitable for implementing the present invention uses the NAND flash memory structure, which includes arranging multiple transistors in series between two select gates. The transistors in series and the select gates are referred to as a NAND string. FIG. 1 is a top view showing one NAND string. FIG. 2 is an equivalent circuit thereof. The NAND string depicted in FIGS. 1 and 2 includes four transistors, 100, 102, 104 and 106, in series and sandwiched between a first select gate 120 and a second select gate 122. Select gate 120 gates the NAND string connection to bit line 126. Select gate 122 gates the NAND string connection to source line 128. Select gate 120 is controlled by applying the appropriate voltages to control gate 120CG. Select gate 122 is controlled by applying the appropriate voltages to control gate 122CG. Each of the transistors 100, 102, 104 and 106 has a control gate and a floating gate. Transistor 100 has control gate 100CG and 45 floating gate 100FG. Transistor 102 includes control gate 102CG and floating gate 102FG. Transistor 104 includes control gate 104CG and floating gate 104FG. Transistor 106 includes a control gate 106CG and floating gate 106FG. Control gate 100CG is connected to (or is) word line WL3, control gate 102CG is connected to word line WL2, control gate 104CG is connected to word line WL1, and control gate **106**CG is connected to word line WL0. In one embodiment, transistors 100, 102, 104 and 106 are each memory cells. In other embodiments, the memory cells may include multiple 55 transistors or may be different than that depicted in FIGS. 1 and 2. Select gate 120 is connected to select line SGD. Select gate 122 is connected to select line SGS.

FIG. 3 provides a cross-sectional view of the NAND string described above. As depicted in FIG. 3, the transistors of the NAND string are formed in p-well region 140. Each transistor includes a stacked gate structure that consists of a control gate (100CG, 102CG, 104CG and 106CG) and a floating gate (100FG, 102FG, 104FG and 106FG). The control gates and the floating gates are typically formed by depositing polysilicon layers. The floating gates are formed on the surface of the p-well on top of an oxide or other dielectric film. The control gate is above the floating gate,

with an inter-polysilicon dielectric layer separating the control gate and floating gate. The control gates of the memory cells (100, 102, 104 and 106) form the word lines. N+ doped diffusion regions 130, 132, 134, 136 and 138 are shared between neighboring cells, through which the cells are 5 connected to one another in series to form a NAND string. These N+ doped regions form the source and drain of each of the cells. For example, N+ doped region 130 serves as the drain of transistor 122 and the source for transistor 106, N+ doped region 132 serves as the drain for transistor 106 and 10 the source for transistor 104, N+ doped region 134 serves as the drain for transistor 104 and the source for transistor 102, N+ doped region 136 serves as the drain for transistor 102 and the source for transistor 100, and N+ doped region 138 serves as the drain for transistor 100 and the source for 15 transistor 120. N+ doped region 126 connects to the bit line for the NAND string, while N+ doped region 128 connects to a common source line for multiple NAND strings.

Note that although FIGS. **1-3** show four memory cells in the NAND string, the use of four transistors is provided only 20 as an example. A NAND string used with the technology described herein can have less than four memory cells or more than four memory cells. For example, some NAND strings will include 8 memory cells, 16 memory cells, 32 memory cells, 64 memory cells, etc. The discussion herein 25 is not limited to any particular number of memory cells in a NAND string.

Each memory cell can store data represented in analog or digital form. When storing one bit of digital data, the range of possible threshold voltages of the memory cell is divided 30 into two ranges, which are assigned logical data "1" and "0." In one example of a NAND-type flash memory, the voltage threshold is negative after the memory cell is erased, and defined as logic "1." The threshold voltage is positive after a program operation, and defined as logic "0." When the 35 threshold voltage is negative and a read is attempted by applying 0 volts to the control gate, the memory cell will turn on to indicate logic one is being stored. When the threshold voltage is positive and a read operation is attempted by applying 0 volts to the control gate, the 40 memory cell will not turn on, which indicates that logic zero is stored.

A memory cell can also store multiple states, thereby storing multiple bits of digital data. In the case of storing multiple states of data, the threshold voltage window is 45 divided into the number of states. For example, if four states are used, there will be four threshold voltage ranges assigned to the data values "11," "10," "01," and "00." In one example of a NAND-type memory, the threshold voltage after an erase operation is negative and defined as "11." 50 Positive threshold voltages are used for the states of "10," "01," and "00." In some implementations, the data values (e.g., logical states) are assigned to the threshold ranges using a Gray code assignment so that if the threshold voltage of a floating gate erroneously shifts to its neighboring 55 physical state, only one bit will be affected. The specific relationship between the data programmed into the memory cell and the threshold voltage ranges of the cell depends upon the data encoding scheme adopted for the memory cells. For example, U.S. Pat. No. 6,222,762 and U.S. patent 60 application Ser. No. 10/461,244, "Tracking Cells For A Memory System," filed on Jun. 13, 2003, both of which are incorporated herein by reference in their entirety, describe various data encoding schemes for multi-state flash memory cells.

Relevant examples of NAND-type flash memories and their operation are provided in the following U.S. patents/

6

patent applications, all of which are incorporated herein by reference in their entirety: U.S. Pat. No. 5,570,315; U.S. Pat. No. 5,774,397; U.S. Pat. No. 6,046,935; U.S. Pat. No. 5,386,422; U.S. Pat. No. 6,456,528; and U.S. patent application Ser. No. 09/893,277 (Publication No. US2003/0002348). Other types of non-volatile memory in addition to NAND flash memory can also be used with the present invention.

Another type of memory cell useful in flash EEPROM systems utilizes a non-conductive dielectric material in place of a conductive floating gate to store charge in a non-volatile manner. Such a cell is described in an article by Chan et al., "A True Single-Transistor Oxide-Nitride-Oxide EEPROM Device," IEEE Electron Device Letters, Vol. EDL-8, No. 3, March 1987, pp. 93-95. A triple layer dielectric formed of silicon oxide, silicon nitride and silicon oxide ("ONO") is sandwiched between a conductive control gate and a surface of a semi-conductive substrate above the memory cell channel. The cell is programmed by injecting electrons from the cell channel into the nitride, where they are trapped and stored in a limited region. This stored charge then changes the threshold voltage of a portion of the channel of the cell in a manner that is detectable. The cell is erased by injecting hot holes into the nitride. See also Nozaki et al., "A 1-Mb EEPROM with MONOS Memory Cell for Semiconductor Disk Application," IEEE Journal of Solid-State Circuits, Vol. 26, No. 4, April 1991, pp. 497-501, which describes a similar cell in a split-gate configuration where a doped polysilicon gate extends over a portion of the memory cell channel to form a separate select transistor. The foregoing two articles are incorporated herein by reference in their entirety. The programming techniques mentioned in section 1.2 of "Non-volatile Semiconductor Memory Technology," edited by William D. Brown and Joe E. Brewer, IEEE Press, 1998, incorporated herein by reference, are also described in that section to be applicable to dielectric charge-trapping devices. The memory cells described in this paragraph can also be used with the present invention. Thus, the technology described herein also applies to coupling between dielectric regions of different memory cells.

Another approach to storing two bits in each cell has been described by Eitan et al., "NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell," IEEE Electron Device Letters, vol. 21, no. 11, November 2000, pp. 543-545. An ONO dielectric layer extends across the channel between source and drain diffusions. The charge for one data bit is localized in the dielectric layer adjacent to the drain, and the charge for the other data bit localized in the dielectric layer adjacent to the source. Multi-state data storage is obtained by separately reading binary states of the spatially separated charge storage regions within the dielectric. The memory cells described in this paragraph can also be used with the present invention.

FIG. 4 illustrates an example of an array of NAND cells, such as those shown in FIGS. 1-3. Along each column, a bit line 206 is coupled to the drain terminal 126 of the drain select gate for the NAND string 150. Along each row of NAND strings, a source line 204 may connect all the source terminals 128 of the source select gates of the NAND strings. An example of a NAND architecture array and its operation as part of a memory system is found in U.S. Pat. Nos. 5,570,315; 5,774,397; and 6,046,935.

The array of memory cells is divided into a large number of blocks of memory cells. As is common for flash EEPROM systems, the block is the unit of erase. That is, each block contains the minimum number of memory cells that are erased together. Each block is typically divided into

a number of pages. A page is a unit of programming. In one embodiment, the individual pages may be divided into segments and the segments may contain the fewest number of cells that are written at one time as a basic programming operation. One or more pages of data are typically stored in one row of memory cells. A page can store one or more sectors. A sector includes user data and overhead data. Overhead data typically includes an Error Correction Code (ECC) that has been calculated from the user data of the sector. A portion of the controller (described below) calculates the ECC when data is being programmed into the array, and also checks it when data is being read from the array. Alternatively, the ECCs and/or other overhead data are stored in different pages, or even different blocks, than the user data to which they pertain.

A sector of user data is typically 512 bytes, corresponding to the size of a sector in magnetic disk drives. Overhead data is typically an additional 16-20 bytes. A large number of pages form a block, anywhere from 8 pages, for example, up to 32, 64, 128 or more pages. In some embodiments, a row 20 of NAND strings comprises a block.

Memory cells are erased in one embodiment by raising the p-well to an erase voltage (e.g., 20 volts) for a sufficient period of time and grounding the word lines of a selected block while the source and bit lines are floating. Due to 25 capacitive coupling, the unselected word lines, bit lines, select lines, and c-source are also raised to a significant fraction of the erase voltage. A strong electric field is thus applied to the tunnel oxide layers of selected memory cells and the data of the selected memory cells are erased as 30 electrons of the floating gates are emitted to the substrate side, typically by Fowler-Nordheim tunneling mechanism. As electrons are transferred from the floating gate to the p-well region, the threshold voltage of a selected cell is lowered. Erasing can be performed on the entire memory 35 array, separate blocks, or another unit of cells.

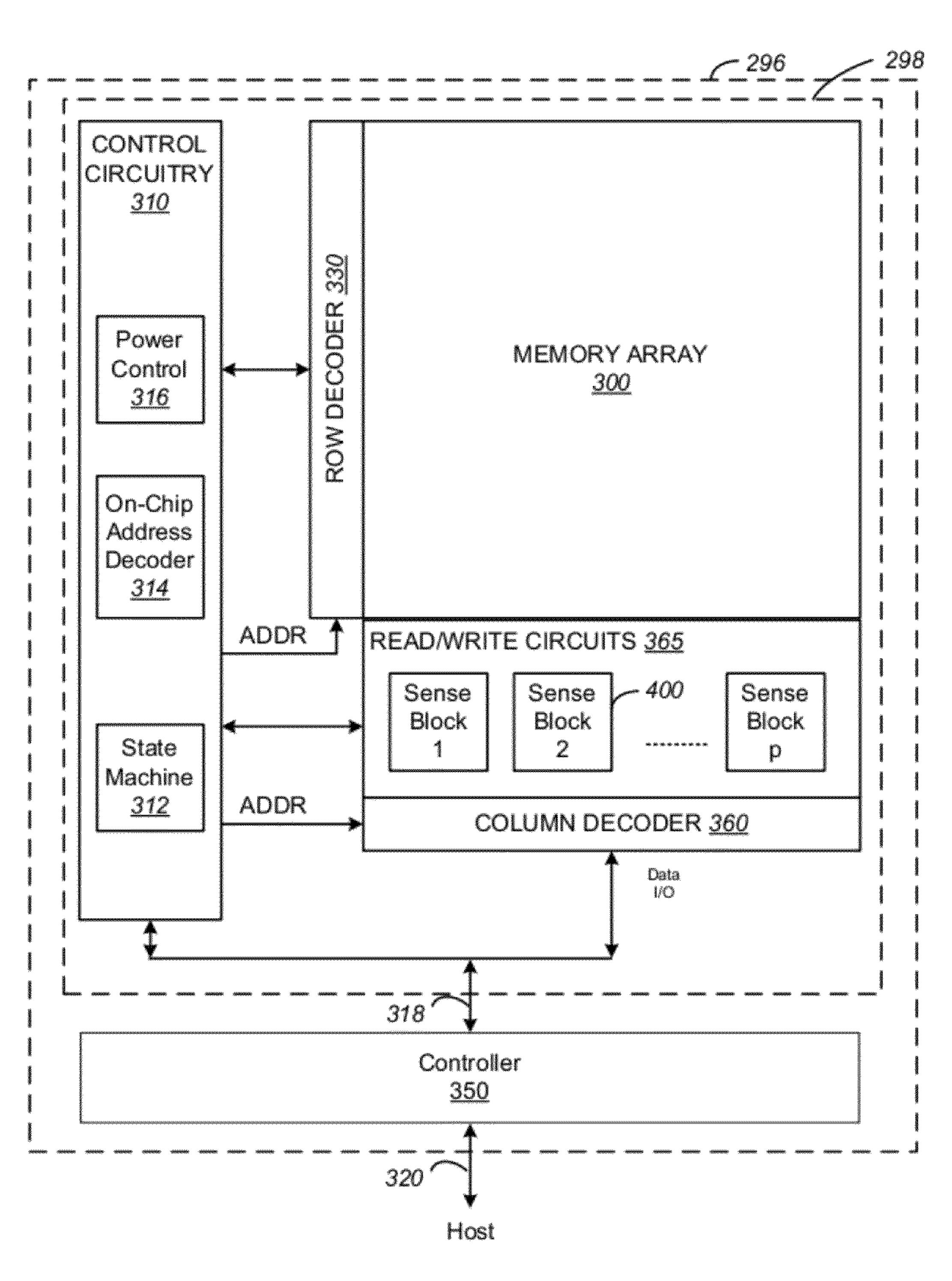

FIG. 5 illustrates a memory device 296 having read/write circuits for reading and programming a page of memory cells in parallel, according to one embodiment of the present invention. Memory device 296 may include one or more 40 memory die 298. Memory die 298 includes a two-dimensional array of memory cells 300, control circuitry 310, and read/write circuits 365. In some embodiments, the array of memory cells can be three dimensional. The memory array 300 is addressable by word lines via a row decoder 330 and 45 by bit lines via a column decoder 360. The read/write circuits 365 include multiple sense blocks 400 and allow a page of memory cells to be read or programmed in parallel. Typically a controller 350 is included in the same memory device 296 (e.g., a removable storage card) as the one or 50 more memory die **298**. Commands and Data are transferred between the host and controller 350 via lines 320 and between the controller and the one or more memory die 298 via lines 318.

The control circuitry 310 cooperates with the read/write 55 circuits 365 to perform memory operations on the memory array 300. The control circuitry 310 includes a state machine 312, an on-chip address decoder 314 and a power control module 316. The state machine 312 provides chip-level control of memory operations. The on-chip address decoder 60 314 provides an address interface between that used by the host or a memory controller to the hardware address used by the decoders 330 and 360. The power control module 316 controls the power and voltages supplied to the word lines and bit lines during memory operations.

In some implementations, some of the components of FIG. 5 can be combined. In various designs, one or more of

8

the components of FIG. 5 (alone or in combination), other than memory cell array 300, can be thought of as a managing circuit. For example, one or more managing circuits may include any one of or a combination of control circuitry 310, state machine 312, decoders 314/360, power control 316, sense blocks 400, read/write circuits 365, controller 350, etc.

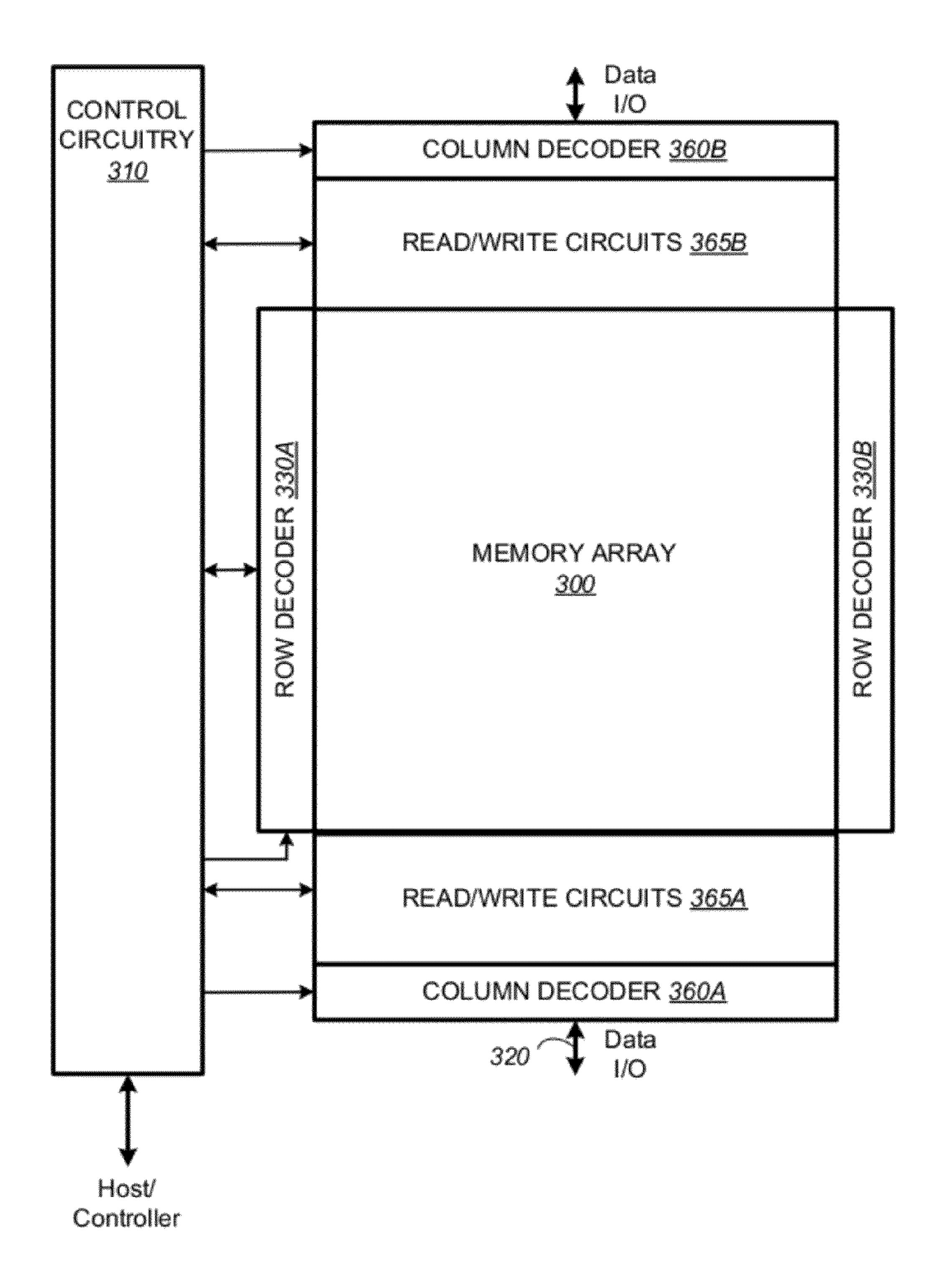

FIG. 6 illustrates another arrangement of the memory device 296 shown in FIG. 5. Access to the memory array 300 by the various peripheral circuits is implemented in a symmetric fashion, on opposite sides of the array, so that the densities of access lines and circuitry on each side are reduced by half. Thus, the row decoder is split into row decoders 330A and 330B and the column decoder into column decoders 360A and 360B. Similarly, the read/write circuits are split into read/write circuits 365A connecting to bit lines from the bottom and read/write circuits 365B connecting to bit lines from the top of the array 300. In this way, the density of the read/write modules is essentially reduced by one half. The device of FIG. 6 can also include a controller, as described above for the device of FIG. 5.

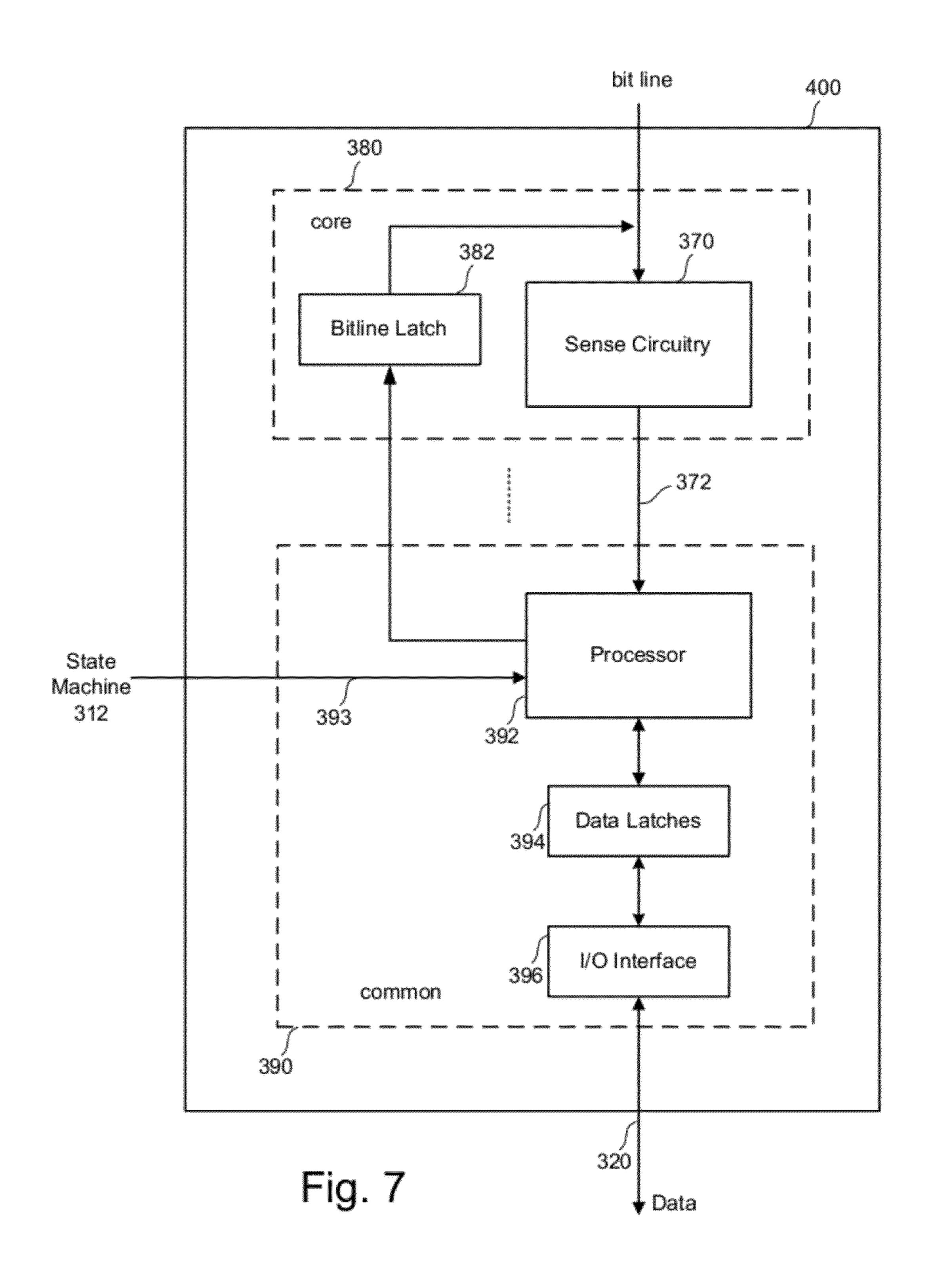

FIG. 7 is a block diagram of an individual sense block 400 partitioned into a core portion, referred to as a sense module 380, and a common portion 390. In one embodiment, there will be a separate sense module 380 for each bit line and one common portion 390 for a set of multiple sense modules 380. In one example, a sense block will include one common portion 390 and eight sense modules 380. Each of the sense modules in a group will communicate with the associated common portion via a data bus 372. For further details refer to U.S. patent application Ser. No. 11/026,536 "Non-Volatile Memory & Method with Shared Processing for an Aggregate of Sense Amplifiers" filed on Dec. 29, 2004, which is incorporated herein by reference in its entirety.

p-well region, the threshold voltage of a selected cell is lowered. Erasing can be performed on the entire memory array, separate blocks, or another unit of cells.

FIG. 5 illustrates a memory device 296 having read/write circuits for reading and programming a page of memory cells in parallel, according to one embodiment of the present invention. Memory device 296 may include one or more memory die 298. Memory die 298 includes a two-dimensiste.

Sense module 380 comprises sense circuitry 370 that determines whether a conduction current in a connected bit line is above or below a predetermined threshold level. Sense module 380 also includes a bit line latch 382 that is used to set a voltage condition on the connected bit line latch 382 will result in the connected bit line being pulled to a state designating program inhibit (e.g., Vdd).

Common portion 390 comprises a processor 392, a set of data latches 394 and an I/O Interface 396 coupled between the set of data latches 394 and data bus 320. Processor 392 performs computations. For example, one of its functions is to determine the data stored in the sensed memory cell and store the determined data in the set of data latches. The set of data latches 394 is used to store data bits determined by processor 392 during a read operation. It is also used to store data bits imported from the data bus 320 during a program operation. The imported data bits represent write data meant to be programmed into the memory. I/O interface 396 provides an interface between data latches 394 and the data bus 320.

During read or sensing, the operation of the system is under the control of state machine 312 that controls the supply of different control gate voltages to the addressed cell. As it steps through the various predefined control gate voltages corresponding to the various memory states supported by the memory, the sense module 380 may trip at one of these voltages and an output will be provided from sense module 380 to processor 392 via bus 372. At that point, processor 392 determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 393. It then computes a binary encoding for the memory state and stores the

resultant data bits into data latches **394**. In another embodiment of the core portion, bit line latch 382 serves double duty, both as a latch for latching the output of the sense module 380 and also as a bit line latch as described above.

It is anticipated that some implementations will include 5 multiple processors 392. In one embodiment, each processor 392 will include an output line (not depicted in FIG. 7) such that each of the output lines is wired-OR'd together. In some embodiments, the output lines are inverted prior to being connected to the wired-OR line. This configuration enables 10 a quick determination during the program verification process of when the programming process has completed because the state machine receiving the wired-OR can determine when all bits being programmed have reached the desired level. For example, when each bit has reached its 15 load" command is issued by the controller and input desired level, a logic zero for that bit will be sent to the wired-OR line (or a data one is inverted). When all bits output a data 0 (or a data one inverted), then the state machine knows to terminate the programming process. Because each processor communicates with eight sense 20 modules, the state machine needs to read the wired-OR line eight times, or logic is added to processor 392 to accumulate the results of the associated bit lines such that the state machine need only read the wired-OR line one time. Similarly, by choosing the logic levels correctly, the global state 25 machine can detect when the first bit changes its state and change the algorithms accordingly.

During program or verify, the data to be programmed is stored in the set of data latches 394 from the data bus 320. The program operation, under the control of the state 30 machine, comprises a series of programming voltage pulses applied to the control gates of the addressed memory cells. Each programming pulse is followed by a read back (verify) to determine if the cell has been programmed to the desired memory state relative to the desired memory state. When the two are in agreement, the processor 222 sets the bit line latch 214 so as to cause the bit line to be pulled to a state designating program inhibit. This inhibits the cell coupled to the bit line from further programming even if programming 40 pulses appear on its control gate. In other embodiments the processor initially loads the bit line latch 382 and the sense circuitry sets it to an inhibit value during the verify process.

Data latch stack 394 contains a stack of data latches corresponding to the sense module. In one embodiment, 45 there are three data latches per sense module 380. In some implementations (but not required), the data latches are implemented as a shift register so that the parallel data stored therein is converted to serial data for data bus 320, and vice versa. In the preferred embodiment, all the data latches 50 corresponding to the read/write block of m memory cells can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of r read/write modules is adapted so that each of its set of data latches will shift data in to or out of 55 the data bus in sequence as if they are part of a shift register for the entire read/write block.

Additional information about the structure and/or operations of various embodiments of non-volatile storage devices can be found in (1) United States Patent Application 60 Pub. No. 2004/0057287, "Non-Volatile Memory And Method With Reduced Source Line Bias Errors," published on Mar. 25, 2004; (2) United States Patent Application Pub No. 2004/0109357, "Non-Volatile Memory And Method with Improved Sensing," published on Jun. 10, 2004; (3) 65 U.S. patent application Ser. No. 11/015,199 titled "Improved" Memory Sensing Circuit And Method For Low Voltage

**10**

Operation," Inventor Raul-Adrian Cernea, filed on Dec. 16, 2004; (4) U.S. patent application Ser. No. 11/099,133, titled "Compensating for Coupling During Read Operations of Non-Volatile Memory," Inventor Jian Chen, filed on Apr. 5, 2005; and (5) U.S. patent application Ser. No. 11/321,953, titled "Reference Sense Amplifier For Non-Volatile Memory, Inventors Siu Lung Chan and Raul-Adrian Cernea, filed on Dec. 28, 2005. All five of the immediately abovelisted patent documents are incorporated herein by reference in their entirety.

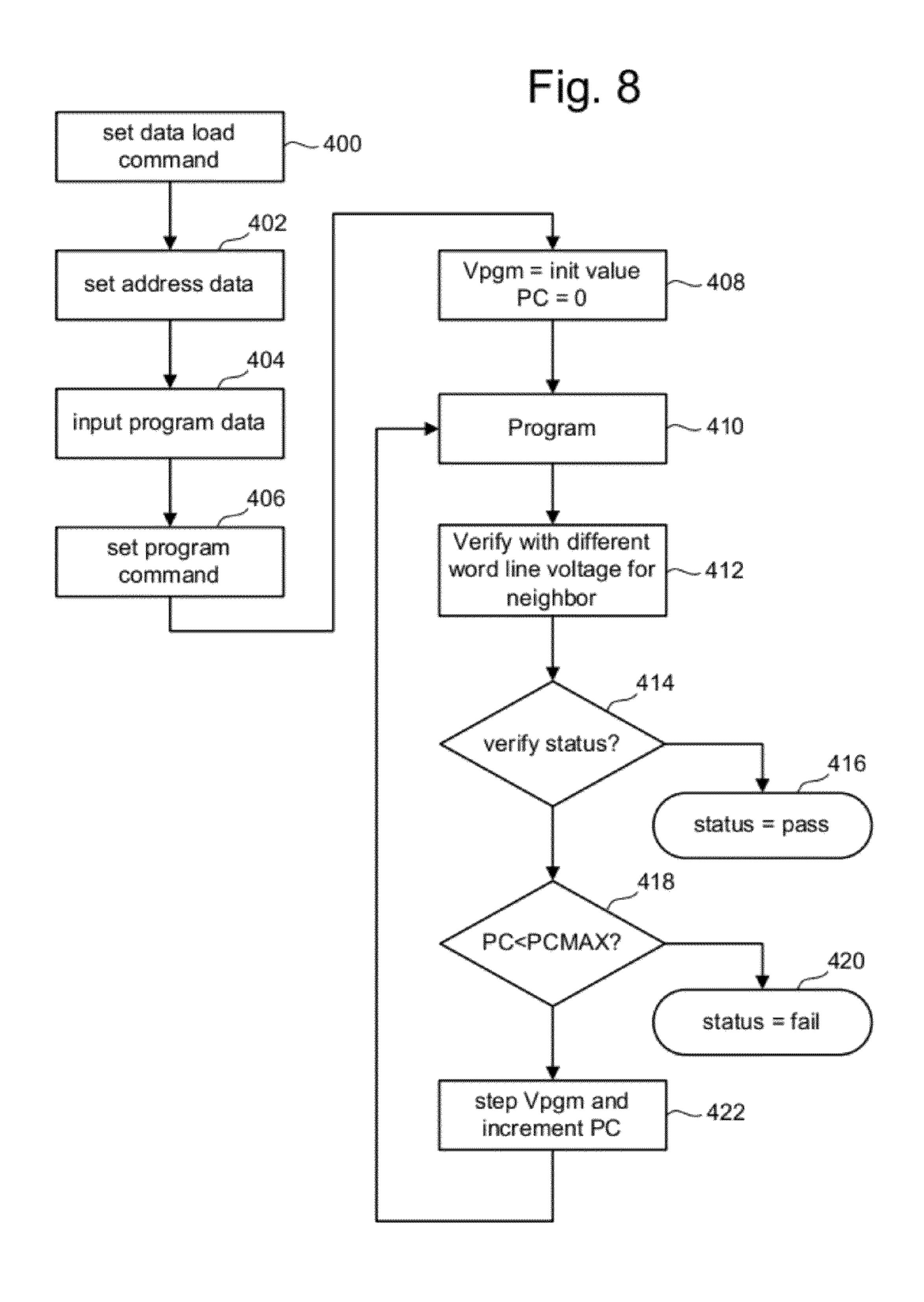

FIG. 8 is a flow chart describing one embodiment of a method for programming non-volatile memory. In one implementation, memory cells are erased (in blocks or other units) prior to programming. In step 400 of FIG. 8, a "data received by control circuitry 310. In step 402, address data designating the page address is input to decoder 314 from the controller or host. In step 404, a page of program data for the addressed page is input to a data buffer for programming. That data is latched in the appropriate set of latches. In step 406, a "program" command is issued by the controller to state machine 312.

Triggered by the "program" command, the data latched in step 404 will be programmed into the selected memory cells controlled by state machine 312 using the stepped pulses of FIG. 9 applied to the appropriate word line. In step 408, the program voltage Vpgm is initialized to the starting pulse (e.g., 12V or other value) and a program counter PC maintained by state machine **312** is initialized at 0. In step 410, the first Vpgm pulse is applied to the selected word line. If logic "0" is stored in a particular data latch indicating that the corresponding memory cell should be programmed, then the corresponding bit line is grounded. On the other hand, if logic "1" is stored in the particular latch indicating that the memory state. Processor 392 monitors the read back 35 corresponding memory cell should remain in its current data state, then the corresponding bit line is connected to Vdd to inhibit programming.

In step 412, the states of the selected memory cells are verified. If it is detected that the target threshold voltage of a selected cell has reached the appropriate level, then the data stored in the corresponding data latch is changed to a logic "1." If it is detected that the threshold voltage has not reached the appropriate level, the data stored in the corresponding data latch is not changed. In this manner, a bit line having a logic "1" stored in its corresponding data latch does not need to be programmed. When all of the data latches are storing logic "1," the state machine (via the wired-OR type mechanism described above) knows that all selected cells have been programmed. In step **414**, it is checked whether all of the data latches are storing logic "1." If so, the programming process is complete and successful because all selected memory cells were programmed and verified. A status of "PASS" is reported in step 416. In one embodiment, the verification of step 412 includes providing a different one or more voltages to memory cells adjacent to the memory cells being programmed than that which is provided to the other unselected memory cells. For example, if memory cells on word line WLn are being programmed, then the voltage applied to memory cells on word lines WLn+1 will be different than the voltage applied to other unselected word lines. This compensation will be discussed in more detail below with respect to FIG. 10.

If, in step 414, it is determined that not all of the data latches are storing logic "1," then the programming process continues. In step 418, the program counter PC is checked against a program limit value PCMAX. One example of a program limit value is 20; however, other numbers can also

be used. If the program counter PC is not less than 20, then the program process has failed and a status of "FAIL" is reported in step 420. If the program counter PC is less than 20, then the Vpgm level is increased by the step size and the program counter PC is incremented in step 422. After step 5422, the process loops back to step 410 to apply the next Vpgm pulse.

FIG. 9 shows a series of program pulses that are applied to the word line selected for programming. In between program pulses are a set of verify pulses (not depicted). In 10 some embodiments, there can be a verify pulse for each state that data is being programmed into. In other embodiments, there can be more or less verify pulses.

In one embodiment, data is programmed to memory cells along a common word line. Thus, prior to applying the 15 program pulses of FIG. 9, one of the word lines is selected for programming. This word line will be referred to as the selected word line. The remaining word lines of a block are referred to as the unselected word lines. The selected word line may have one or two neighboring word lines. If the 20 selected word line has two neighboring word lines, then the neighboring word line on the drain side is referred to as the drain side neighboring word line and the neighboring word line on the source side is referred to as the source side neighboring word line. For example, if WL2 of FIG. 2 is the 25 selected word line, then WL1 is the source side neighboring word line.

Each block of memory cells includes a set of bit lines forming columns and a set of word lines forming rows. In one embodiment, the bit lines are divided into odd bit lines and even bit lines. Memory cells along a common word line and connected to the odd bit lines are programmed at one time, while memory cells along a common word line and connected to even bit lines are programmed at another time ("odd/even programming"). In another embodiment, 35 memory cells are programmed along a word line for all bit lines in the block ("all bit line programming"). In other embodiments, the bit lines or block can be broken up into other groupings (e.g., left and right, more than two groupings, etc.).

FIG. 10 is a timing diagram depicting the behavior of various signals during one iteration of a read or verify process. For example, if the memory cells are binary memory cells, the process of FIG. 10 may be performed once for each memory cell during an iteration of step 412. If the memory cells are multi-state memory cells with four states (e.g., E, A, B, and C), the process of FIG. 10 may be performed three times for each memory cell during an iteration of step 412.

In general, during the read and verify operations, the 50 selected word line is connected to a voltage, a level of which is specified for each read and verify operation in order to determine whether a threshold voltage of the concerned memory cell has reached such level. After applying the word line voltage, the conduction current of the memory cell is 55 measured to determine whether the memory cell turned on in response to the voltage applied to the word line. If the conduction current is measured to be greater than a certain value, then it is assumed that the memory cell turned on and the voltage applied to the word line is greater than the 60 threshold voltage of the memory cell. If the conduction current is not measured to be greater than the certain value, then it is assumed that the memory cell did not turn on and the voltage applied to the word line is not greater than the threshold voltage of the memory cell.

There are many ways to measure the conduction current of a memory cell during a read or verify operation. In one 12

example, the conduction current of a memory cell is measured by the rate it discharges a dedicated capacitor in the sense amplifier. In one embodiment, a memory array that uses all bit line programming can measure the conduction current of a memory cell by the rate it discharges a dedicated capacitor in the sense amplifier. In another example, the conduction current of the selected memory cell allows (or fails to allow) the NAND string that included the memory cell to discharge the bit line. The charge on the bit line is measured after a period of time to see whether it has been discharged or not. In one embodiment, a memory array that uses odd/even programming can measure the conduction current of a memory cell by determining whether the bit line has discharged. FIG. 10 explains both examples.

FIG. 10 shows signals SGD, WL\_unsel. WLn+1, WLn, SGS, Selected BL, BLCLAMP, and Source starting at Vss (approximately 0 volts). SGD represents the gate of the drain side select gate. SGS is the gate of the source side select gate. WLn is the word line selected for reading/verification. WLn+1 is the unselected word line that is the drain side neighboring word line to WLn. WL\_unsel represents the unselected word lines other than the drain side neighboring word line. Selected BL is the bit line selected for reading/ verification. Source is the source line for the memory cells (see FIG. 4). BLCLAMP is an analog signal that sets the value of the bit line when charged from the sense amplifier. Note that there are two versions of SGS, Selected BL and BLCLAMP depicted. One set of these signals SGS (B), Selected BL (B) and BLCLAMP (B) depict a read/verify operation for an array of memory cells that measure the conduction current of a memory cell by determining whether the bit line has discharged. Another set of these signals SGS (C), Selected BL (C) and BLCLAMP (C) depict a read/ verify operation for an array of memory cells that measure the conduction current of a memory cell by the rate it discharges a dedicated capacitor in the sense amplifier.

First, the behavior of the sensing circuits and the array of memory cells that are involved in measuring the conduction current of a memory cell by determining whether the bit line 40 has discharged will be discussed with respect to SGS (B), Selected BL (B), and BLCLAMP (B). At time t1 of FIG. 10, SGD is raised to Vdd (e.g., approximately 3.5 volts), the unselected word lines (WL\_unsel) are raised to Vread (e.g., approximately 5.5 volts), the drain side neighboring word line (WLn+1) is raised to VreadX, the selected word line WLn is raised to Vcgr (e.g., Vra, Vrb, or Vrc of FIG. 11) for a read operation or a verify level (e.g., Vva, Vvb, or Vvc of FIG. 11) for a verify operation, and BLCLAMP (B) is raised to a pre-charging voltage to pre-charge the selected bit line Selected BL(B) (e.g., to approximately 0.7 volts). The voltages Vread and VreadX act as pass voltages because they cause the unselected memory cells to turn on and act as pass gates. At time t2, BLCLAMP (B) is lowered to Vss so the NAND string can control the bit line. Also at time t2, the source side select gate is turned on by raising SGS (B) to Vdd. This provides a path to dissipate the charge on the bit line. If the threshold voltage of the memory cell selected for reading is greater than Vcgr or the verify level applied to the selected word line WLn, then the selected memory cell will not turn on and the bit line will not discharge, as depicted by signal line 450. If the threshold voltage in the memory cell selected for reading is below Vcgr or below the verify level applied to the selected word line WLn, then the memory cell selected for reading will turn on (conduct) and the bit line of voltage will dissipate, as depicted by curve 452. At some point after time t2 and prior to time t3 (as determined by the particular implementation), the sense amplifier will deter-

mine whether the bit line has dissipated a sufficient amount. In between t2 and t3, BLCLAMP (B) is raised to let the sense amplifier measure the evaluated BL voltage and then lowered, as depicted in FIG. 10. At time t3, the depicted signals will be lowered to Vss (or another value for standby or recovery). Note that in other embodiments, the timing of some of the signals can be changed (e.g. shift the signal applied to the neighbor).

Next, the behavior of the sensing circuits and the array of memory cells that measure the conduction current of a 10 memory cell by the rate it discharges a dedicated capacitor in the sense amplifier will be discussed with respect to SGS (C), Selected BL (C) and BLCLAMP (C). At time t1 of FIG. 10, SGD is raised to Vdd (e.g., approximately 3.5 volts), the unselected word lines (WL\_unsel) are raised to Vread (e.g., 15 approximately 5.5 volts), the drain side neighboring word line (WLn+1) is raised to VreadX, the selected word line WLn is raised to Vcgr (e.g., Vra, Vrb, or Vrc of FIG. 11) for a read operation or a verify level (e.g., Vva, Vvb, or Vvc of FIG. 11) for a verify operation, and BLCLAMP (C) is raised. 20 In this case, the sense amplifier holds the bit line voltage constant regardless of what the NAND sting is doing, so the sense amplifier measures the current flowing with the bit line "clamped" to that voltage. Therefore, BLCLAMP (C) rises at t1 and does not change from t1 to t3. At some point after 25 time t1 and prior to time t3 (as determined by the particular implementation), the sense amplifier will determine whether the capacitor in the sense amplifier has dissipated a sufficient amount. At time t3, the depicted signals will be lowered to Vss (or another value for standby or recovery). Note that in 30 other embodiments, the timing of some of the signals can be changed.

As discussed above, shifts in the apparent threshold voltage of a floating gate (or other charge storing element) of a non-volatile memory cell as measured from the control 35 gate can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). The problem occurs most pronouncedly between sets of adjacent memory cells that have been programmed at different times. To account for 40 this coupling, the read process for a particular memory cell will provide compensation to an adjacent memory cell in order to reduce the coupling effect that the adjacent memory cell has on the particular memory cell. One embodiment also includes setting up, during the verification process, the 45 required conditions for the later application of compensation to the adjacent memory cell. In such an embodiment the overdrive/bypass voltage, otherwise known as VREAD, applied to WLn+1 is reduced from a typical value of, for example, 6V down to, for example, 3V. The compensation 50 will consist of application of higher voltage, as compared to that voltage that was used during the verify phase of program/verify operations, to WLn+1 during the read operation performed on WLn. In other words the compensation consists of a change/delta: ΔVREAD={[VREAD(WLn+1] during read of WLn)]-[VREAD(WLn+1 during verify of WLn)]}. The advantage of using a lower VREAD value during verify is that it allows the application of nominal values of VREAD later during read operations, while maintaining the required  $\Delta VREAD$ . Had it not been for the use 60 of a smaller than nominal value of VREAD during verify, the necessary value of VREAD during read that would allow the application of sufficient  $\Delta VREAD$  would have been, for example, 6+3=9V which would have been too high a voltage as such high VREAD voltage lead to read disturb conditions. 65 One example of such setting up for later compensation is depicted in FIG. 10 as the application of VreadX to the drain

**14**

side neighboring word line while the other unselected word lines receive Vread. In many prior art devices, all of the unselected word lines would receive Vread. In the embodiment of FIG. 10, all of the unselected word lines, except for the drain side neighbor, receive Vread; while the drain side neighbor receives VreadX.

For the verify process where memory cells are programmed from the source side to the drain side, it is guaranteed (in one embodiment) that when writing to word line WLn, all memory cells on word lines WLn+1 are in the erased state (e.g., state E) (Note: This is true for full sequence and not for LM mode. Please see above explanation). Word line WLn+1 will receive a voltage level VreadX, where VreadX=Vread4 (discussed below). In one embodiment, Vread4 is equal to 3.7 v. In another embodiment, VreadX=Vread. In other embodiment, other values can also be used. In different implementations, different values of Vread4 or VreadX can be determined based on device characterization, experimentation and/or simulation.

At the end of a successful program process, the threshold voltages of the memory cells should be within one or more distributions of threshold voltages for programmed memory cells or within a distribution of threshold voltages for erased memory cells, as appropriate. FIG. 11 illustrates example threshold voltage distributions for the memory cell array when each memory cell stores two bits of data. FIG. 11 shows a first threshold voltage distribution E for erased memory cells. Three threshold voltage distributions, A, B and C for programmed memory cells, are also depicted. In one embodiment, the threshold voltages in the E distribution are negative and the threshold voltages in the A, B and C distributions are positive.

Each distinct threshold voltage range of FIG. 11 corresponds to predetermined values for the set of data bits. The specific relationship between the data programmed into the memory cell and the threshold voltage levels of the cell depends upon the data encoding scheme adopted for the cells. For example, U.S. Pat. No. 6,222,762 and U.S. patent application Ser. No. 10/461,244, "Tracking Cells For A Memory System," filed on Jun. 13, 2003, both of which are incorporated herein by reference in their entirety, describe various data encoding schemes for multi-state flash memory cells. In one embodiment, data values are assigned to the threshold voltage ranges using a Gray code assignment so that if the threshold voltage of a floating gate erroneously shifts to its neighboring physical state, only one bit will be affected. One example assigns "11" to threshold voltage range E (state E), "10" to threshold voltage range A (state A), "00" to threshold voltage range B (state B) and "01" to threshold voltage range C (state C). However, in other embodiments, Gray code is not used. Although FIG. 11 shows four states, the present invention can also be used with other multi-state structures including those that include more or less than four states.

FIG. 11 also shows three read reference voltages, Vra, Vrb and Vrc, for reading data from memory cells. By testing whether the threshold voltage of a given memory cell is above or below Vra, Vrb and Vrc, the system can determine what state the memory cell is in.

FIG. 11 also shows three verify reference voltages, Vva, Vvb and Vvc. When programming memory cells to state A, the system will test whether those memory cells have a threshold voltage greater than or equal to Vva. When programming memory cells to state B, the system will test whether the memory cells have threshold voltages greater than or equal to Vvb. When programming memory cells to

state C, the system will determine whether memory cells have their threshold voltage greater than or equal to Vvc.

In one embodiment, known as full sequence programming, memory cells can be programmed from the erase state E directly to any of the programmed states A, B or C. For 5 example, a population of memory cells to be programmed may first be erased so that all memory cells in the population are in erased state E. The process depicted in FIG. 18, using the control gate voltage sequence depicted in FIG. 9, will then be used to program memory cells directly into states A, 10 B or C. While some memory cells are being programmed from state E to state A, other memory cells are being programmed from state E to state B and/or from state E to state C. When programming from state E to state C on WLn, the amount of parasitic coupling to the adjacent floating gate 1 under WLn-1 is a maximized since the change in amount of charge on the floating gate under WLn is largest as compared to the change in voltage when programming from state E to state A or state E to state B. When programming from state E to state B the amount of coupling to the adjacent floating 20 gate is reduced but still significant. When programming from state E to state A the amount of coupling is reduced even further. Consequently the amount of correction required to subsequently read each state of WLn-1 will vary depending on the state of the adjacent cell on WLn.

FIG. 12 illustrates an example of a two-pass technique of programming a multi-state memory cell that stores data for two different pages: a lower page and an upper page. Four states are depicted: state E (11), state A (10), state B (00) and state C (01). For state E, both pages store a "1." For state A, 30 the lower page stores a "0" and the upper page stores a "1." For state B, both pages store "0." For state C, the lower page stores "1" and the upper page stores "0." Note that although specific bit patterns have been assigned to each of the states, different bit patterns may also be assigned.

In a first programming pass, the cell's threshold voltage level is set according to the bit to be programmed into the lower logical page. If that bit is a logic "1," the threshold voltage is not changed since it is in the appropriate state as a result of having been earlier erased. However, if the bit to 40 be programmed is a logic "0," the threshold level of the cell is increased to be state A, as shown by arrow **530**. That concludes the first programming pass.

In a second programming pass, the cell's threshold voltage level is set according to the bit being programmed into 45 the upper logical page. If the upper logical page bit is to store a logic "1," then no programming occurs since the cell is in one of the states E or A, depending upon the programming of the lower page bit, both of which carry an upper page bit of "1." If the upper page bit is to be a logic "0," then the 50 threshold voltage is shifted. If the first pass resulted in the cell remaining in the erased state E, then in the second phase the cell is programmed so that the threshold voltage is increased to be within state C, as depicted by arrow **534**. If the cell had been programmed into state A as a result of the 55 first programming pass, then the memory cell is further programmed in the second pass so that the threshold voltage is increased to be within state B, as depicted by arrow 532. The result of the second pass is to program the cell into the state designated to store a logic "0" for the upper page 60 without changing the data for the lower page. In both FIG. 11 and FIG. 12 the amount of coupling to the floating gate on the adjacent word line depends on the final state.

In one embodiment, a system can be set up to perform full sequence writing if enough data is written to fill up an entire 65 page. If not enough data is written for a full page, then the programming process can program the lower page program-

**16**

ming with the data received. When subsequent data is received, the system will then program the upper page. In yet another embodiment, the system can start writing in the mode that programs the lower page and convert to full sequence programming mode if enough data is subsequently received to fill up an entire (or most of a) word line's memory cells. More details of such an embodiment are disclosed in U.S. patent application titled "Pipelined Programming of Non-Volatile Memories Using Early Data," Ser. No. 11/013,125, filed on Dec. 14, 2004, inventors Sergy Anatolievich Gorobets and Yan Li, incorporated herein by reference in its entirety.

FIGS. 13A-C disclose another process for programming non-volatile memory that reduces the effect of floating gate to floating gate coupling by, for any particular memory cell, writing to that particular memory cell with respect to a particular page subsequent to writing to adjacent memory cells for previous pages. In one example of an implementation of the process taught by FIGS. 13A-C, the nonvolatile memory cells store two bits of data per memory cell, using four data states. For example, assume that state E is the erased state and states A, B and C are the programmed states. State E stores data 11. State A stores data 01. State B stores data 10. State C stores data 00. This is an example of 25 non-Gray coding because both bits change between adjacent states A & B. Other encodings of data to physical data states can also be used. Each memory cell stores two pages of data. For reference purposes these pages of data will be called upper page and lower page; however, they can be given other labels. With reference to state A for the process of FIGS. 13A-C, the upper page stores bit 0 and the lower page stores bit 1. With reference to state B, the upper page stores bit 1 and the lower page stores bit 0. With reference to state C, both pages store bit data 0.

The programming process of FIGS. 13A-C is a two-step process. In the first step, the lower page is programmed. If the lower page is to remain data 1, then the memory cell state remains at state E. If the data is to be programmed to 0, then the threshold of voltage of the memory cell is raised such that the memory cell is programmed to state B'. FIG. 13A therefore shows the programming of memory cells from state E to state B'. State B' depicted in FIG. 13A is an interim state B; therefore, the verify point is depicted as Vvb', which is lower than Vvb.

In one embodiment, after a memory cell is programmed from state E to state B', its neighbor memory cell (WLn+1) in the NAND string will then be programmed with respect to its lower page. For example, looking back at FIG. 2, after the lower page for memory cell 106 is programmed, the lower page for memory cell 104 would be programmed. After programming memory cell 104, the floating gate to floating gate coupling effect will raise the apparent threshold voltage of memory cell 106 if memory cell 104 had a threshold voltage raised from state E to state B'. This will have the effect of widening the threshold voltage distribution for state B' to that depicted as threshold voltage distribution 550 of FIG. 13B. This apparent widening of the threshold voltage distribution will be remedied when programming the upper page.

FIG. 13C depicts the process of programming the upper page. If the memory cell is in erased state E and the upper page is to remain at 1, then the memory cell will remain in state E. If the memory cell is in state E and its upper page data is to be programmed to 0, then the threshold voltage of the memory cell will be raised so that the memory cell is in state A. If the memory cell was in intermediate threshold voltage distribution 550 and the upper page data is to remain

at 1, then the memory cell will be programmed to final state B. If the memory cell is in intermediate threshold voltage distribution 550 and the upper page data is to become data 0, then the threshold voltage of the memory cell will be raised so that the memory cell is in state C. The process 5 depicted by FIGS. 13A-C reduces the effect of floating gate to floating gate coupling because only the upper page programming of neighbor memory cells will have an effect on the apparent threshold voltage of a given memory cell. An example of an alternate state coding is to move from 10 distribution 550 to state C when the upper page data is a 1, and to move to state B when the upper page data is a 0.

Although FIGS. 13A-C provide an example with respect to four data states and two pages of data, the concepts taught by FIGS. 13A-C can be applied to other implementations 15 with more or less than four states and different than two pages.

FIGS. 14A-F depict various tables that describe the order of programming according to various embodiments for the methods described by FIGS. 11, 12 and 13A-C.

FIG. 14A is a table which describes the order for programming memory cells along a bit line for all bit line programming. In this embodiment, the block with four word lines includes four pages (page 0-3). Page 0 is written first, followed by page 1, followed by page 2 and then followed 25 by page 3. The data in page 0 includes the data stored by all the memory cells connected to word line WL0. The data in page 1 includes the data stored by the memory cells connected to word line WL1. The data in page 2 includes the data stored by memory cells connected to WL2. The data in 30 page 3 includes the data stored by memory cells connected to word line WL3. The embodiment of FIG. 14A assumes full sequence programming, as described above with respect to FIG. 11.