### US00RE46014E

# (19) United States

# (12) Reissued Patent

Sakai et al.

# (10) Patent Number:

US RE46,014 E

# (45) Date of Reissued Patent:

May 24, 2016

### (54) DEFECTIVE WORD LINE DETECTION

# (71) Applicant: SANDISK TECHNOLOGIES, INC.,

Milpitas, CA (US)

# (72) Inventors: Manabu Sakai, Kanagawa (JP); Toru

Miwa, Kanagawa (JP)

# (73) Assignee: SanDisk Technologies Inc., Plano, TX

(US)

### (21) Appl. No.: 14/285,459

# (22) Filed: May 22, 2014

# Related U.S. Patent Documents

### Reissue of:

| (64) | Patent No.: | 8,630,118     |

|------|-------------|---------------|

|      | Issued:     | Jan. 14, 2014 |

|      | Appl. No.:  | 13/292,556    |

|      | Filed:      | Nov. 9, 2011  |

### (51) **Int. Cl.**

| G11C 16/04 | (2006.01) |

|------------|-----------|

| G11C 29/02 | (2006.01) |

| G11C 11/56 | (2006.01) |

| G11C 29/12 | (2006.01) |

# (52) U.S. Cl.

CPC ...... *G11C 29/025* (2013.01); *G11C 11/5628* (2013.01); *G11C 16/0483* (2013.01); *G11C 2029/1202* (2013.01); *G11C 2211/5621* (2013.01)

# (58) Field of Classification Search

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 5,673,223 A | 4  | 9/1997  | Park            |

|-------------|----|---------|-----------------|

| 5,936,890 A | 4  | 8/1999  | Yeom            |

| 5,996,041 A | 4  | 11/1999 | Kim             |

| 6,278,632 H | 31 | 8/2001  | Chevallier      |

| 6,601,191 H | 31 | 7/2003  | Norman et al.   |

| 6,907,497 E | 32 | 6/2005  | Hosono et al.   |

| 6,914,823 H | 32 | 7/2005  | Chen et al.     |

| 6,917,542 H | 32 | 7/2005  | Chen et al.     |

| 7,117,296 E | 32 | 10/2006 | Hosono et al.   |

| 7,120,051 E | 32 | 10/2006 | Gorobets et al. |

| 7,206,230 H | 32 | 4/2007  | Li et al.       |

| 7,304,893 H | 31 | 12/2007 | Hemink          |

| 7,345,928 E | 32 | 3/2008  | Li              |

|             |    |         |                 |

### (Continued)

### OTHER PUBLICATIONS

Response to Office Action dated Jan. 9, 2015, European Patent Application No. 12798079.5.

(Continued)

Primary Examiner — Ovidio Escalante

(74) Attorney, Agent, or Firm — Vierra Magen Marcus LLP

# (57) ABSTRACT

Methods and non-volatile storage systems are provided for detecting defects in word lines. A "broken" word line defect may be detected. Information may be maintained as to which storage elements were intended to be programmed to a tracked state. Then, after programming is complete, the storage elements are read to determine which storage elements have a threshold voltage below a reference voltage level associated with the tracked state. By tracking which storage elements are in the tracked state, elements associated with other states may be filtered out such that an accurate assessment may be made as to which storage elements were under-programmed. From this information, a determination may be made whether the word line is defective. For example, if too many storage elements are under-programmed, this may indicate a broken word line.

### 30 Claims, 26 Drawing Sheets

# Program a group of non-volatile storage elements associated with a word line Maintain information after programming is complete that indicates which elements were intended to be programmed to a tracked data state Apply reference voltage associated with tracked data state to first end of word line Determine results of applying the reference voltage Determine whether word line has a defect based on the results and the maintained information

# US RE46,014 E

Page 2

### **References Cited** (56)OTHER PUBLICATIONS Notice of Allowance for U.S. Appl. No. 13/292,556, filed Nov. 9, U.S. PATENT DOCUMENTS 2011, mailed Apr. 4, 2013. 6/2008 Keays 7,392,436 B2 Office Action for U.S. Appl. No. 13/292,556, filed Nov. 9, 2011, 9/2008 Li 7,420,847 B2 mailed May 16, 2013. 3/2009 Li 7,502,260 B2 Response to Office Action mailed May 16, 2013 for U.S. Appl. No. 7,508,721 B2 3/2009 Li et al. 13/292,556, filed Jul. 30, 2013. Tu et al. ...... 365/185.22 7,599,223 B2\* 10/2009 Notice of Allowance for U.S. Appl. No. 13/292,556, filed Nov. 9, 7,623,388 B2 11/2009 Chen et al. 2011, mailed Sep. 20, 2013. 8,014,205 B2\* Response to Office Action mailed Jun. 4, 2013 for U.S. Appl. No. 1/2014 Sakai ...... G11C 29/025 8,630,118 B2\* 13/292,569, filed Aug. 20, 2013. 365/185.17 Final Office Action for U.S. Appl. No. 13/292,569, filed Nov. 9, 2011, 2003/0214853 A1 11/2003 Hosono et al. mailed Sep. 12, 2013. 2005/0024939 A1 2/2005 Chen et al. Notice of Allowance for U.S. Appl. No. 13/292,569, filed Nov. 9, 2006/0221690 A1 10/2006 Rehm 2011, mailed Apr. 15, 2014. 9/2007 Mokhlesi 2007/0206426 A1 Amendment Under 37 CFR 1.312 for U.S. Appl. No. 13/292,569, Hemink 2007/0279985 A1 12/2007 filed Jul. 8, 2014. G11C 29/028 2008/0062770 A1 3/2008 Tu et al. ..... International Search Report and Written Opinion of the International 365/185.28 Searching Authority dated Feb. 6, 2013, PCT Application No. PCT/ 2008/0127104 A1 5/2008 Li et al. US2012/064150 filed Nov. 8, 2012, 12 pages. 2008/0225597 A1 9/2008 Park International Search Report and Written Opinion of the International 11/2008 Pyeon 2008/0273386 A1 Searching Authority dated Jul. 15, 2013, PCT Application No. PCT/ 2009/0175097 A1 7/2009 Chen et al. US2012/064152, filed Nov. 8, 2012, 13 pages. 2009/0262578 A1 10/2009 Li et al. Partial International Search Report dated May 28, 2013, PCT Appli-2010/0002514 A1 1/2010 Lutze et al. cation No. PCT/US2012/064152, filed Nov. 8, 2012, 4 pages. 2/2010 Kang et al. 2010/0034019 A1 Office Action dated Jun. 4, 2013, U.S. Appl. No. 13/292,569, filed 12/2010 Yun et al. 2010/0329029 A1 Nov. 9, 2011, 26 pages. 12/2010 Chen et al. 2010/0329052 A1 Response A to Office Action dated Aug. 20, 2013, U.S. Appl. No. 5/2011 Dutta et al. 2011/0110153 A1 13/292,569, filed Nov. 9, 2011, 15 pages. 7/2011 Dutta et al. 2011/0182121 A1 Response to Final Office Action dated Dec. 3, 2013, U.S. Appl. No. G11C 13/0007 2013/0021838 A1\* 1/2013 Tomotani .......... 13/292,569, filed Nov. 9, 2011, 13 pages. 365/148 2013/0031430 A1\*

714/719

\* cited by examiner

May 24, 2016

Fig. 4 BL0 BL1 BL2 BL3 BL4 BL5 BL6 BL7 BL8 BL9 BL10 BL11 BL12 BL13 400 \ SGD WL3 WL2 WL1 WLO SGS 400 \ SGD WL63 -I WL3 WL2 I WL1 I WLO SGS

Fig. 6B

May 24, 2016

Fig. 8

# <u>1000</u>

Fig. 10

|       | Er      | Α       | В       | С       | D       | Ε       | F       | G       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| State | Lockout | Program |

| CDL   | 1       | 0       | 1       | 0       | 1       | 0       | 1       | 0       |

| BDL   | 1       | 1       | 0       | 0       | 1       | 1       | 0       | 0       |

| ADL   | 1       | 1       | 1       | 1       | 0       | 0       | 0       | 0       |

| DDL   | 1       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

Fig. 13A

|       | Er      | А       | В       | С       | D       | E       | F       |         | j       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| State | Lockout | Program | Lockout |

| CDL   | 1       | 0       | 1       | 0       | 1       | 0       | 1       | 0       | 1       |

| BDL   | 1       | 1       | 0       | 0       | 1       | 1       | 0       | 0       | 1       |

| ADL   | 1       | 1       | 1       | 1       | 0       | 0       | 0       | 0       | 1       |

| DDL   | 1       | QPW     | QPW     | QPW     | QPW     | QPW     | QPW     | 0       | 0       |

Fig. 13B

|       | Er      | Α         | В       | С       | D       | E       | F       |         | j       |  |  |

|-------|---------|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|

| State | Lockout | Lockout   | Lockout | Lockout | Lockout | Program | Program | Program | Lockout |  |  |

| CDL   | 1       | 1         | 1       | 1       | 1       | 0       | 1       | 0       | 1       |  |  |

| BDL   | 1       | 1         | 1       | 1       | 1       | 1       | 0       | 0       | 1       |  |  |

| ADL   |         | Available |         |         |         |         |         |         |         |  |  |

| DDL   | 1       | 1         | 1       | 1       | 1       | QPW     | QPW     | 0       | 0       |  |  |

Fig. 13C

|       | Er      | Α         | В       | С       | D         | E       | F       | (       | }       |  |

|-------|---------|-----------|---------|---------|-----------|---------|---------|---------|---------|--|

| State | Lockout | Lockout   | Lockout | Lockout | Lockout   | Lockout | Lockout | Program | Lockout |  |

| CDL   | 1       | 1         | 1       | 1       | 1         | 1       | 1       | 0       | 1       |  |

| BDL   |         |           |         |         | Available |         |         |         |         |  |

| ADL   |         | Available |         |         |           |         |         |         |         |  |

| DDL   | 1       | 1         | 1       | 1       | 1         | 1       | 1       | 0       | 0       |  |

Fig. 13D

**1 1 4**

May 24, 2016

Fig. 15A

|       | Er      | Α       | В       | С       | D       | E       | F       | G       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| State | Lockout |

| CDL   | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 0/1     |

| DDL   | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 0       |

| SDL   | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     |

Fig. 15B

|       | Er      | Α       | В       | C       | D       | E       | F       | G       |

|-------|---------|---------|---------|---------|---------|---------|---------|---------|

| State | Lockout |

| CDL   | 0       | 0/1     | 0       | 0       | 0       | 0       | 0       | 0       |

| DDL   | 0       | 1       | 0       | 0       | 0       | 0       | 0       | 0       |

| SDL   | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     | 0/1     |

Fig. 15C

# <u>1600</u>

Fig. 16

Fig. 17

7 0 7

May 24, 2016

| G  | Program | 0   | 0   | 0   | 0   | 0   |

|----|---------|-----|-----|-----|-----|-----|

|    |         |     |     |     |     |     |

| Щ  | Program | 1   | 0   | 0   | 0   | 0   |

| Э  | Program | 0   | ļ   | 0   | 0   | 0   |

| D  | Program |     |     | 0   | 0   | 0   |

| C  | Program | 0   | 0   | 1   | 0   | 0   |

| В  | Program | 1   | 0   | 1   | 0   | 0   |

| Y  | Program | 0   |     | _   | 0   | 0   |

| Εr | Lockout | 1   | 1   |     | 1   | _   |

|    | State   | CDL | BDL | ADL | DDL | XDL |

|    | 1                                           | ,   |     | -   | -   |     |

|----|---------------------------------------------|-----|-----|-----|-----|-----|

| ν. | Lockout                                     | 0   | 0   | 0   | 1   | 1   |

| G  | Program                                     | 0   | 0   | 0   | 0   | 0   |

|    | Lockout                                     | 1   | 0   | 0   | 1   | 1   |

|    | Lockout Program                             | ļ   | 0   | 0   | QPW | 0   |

|    | Lockout                                     | 0   | 1   | 0   | 1   | 1   |

| ш  | Program                                     | 0   | 1   | 0   | QPW | 0   |

| )  | Program Lockout Progran                     | 1   | 1   | 0   | 1   | 1   |

|    | Program                                     | 1   | 1   | 0   | QPW | 0   |

| S  | Lockout                                     | 0   | 0   | 1   | 1   | 1   |

| )  | ram Lockout Program Lockout Program Lockout | 0   | 0   | 1   | QPW | 0   |

| 3  | Lockout                                     | 1   | 0   | 1   | 1   | 1   |

| B  | Program                                     | 1   | 0   | 1   | QPW | 0   |

| 7  | Lockout                                     | 0   | 1   | 1   | 1   | ļ   |

| /  | Prog                                        | 0   | 1   | 1   | QPW | 0   |

| Er | Lockout                                     | 1   | 1   | 1   | 1   | 1   |

|    | State                                       | CDL | BDL | ADL | DDL | XDL |

| 9  | Lockout | 0   | 0   | 0   | l     | 1     | 0 / 1 |

|----|---------|-----|-----|-----|-------|-------|-------|

| Щ  | Lockout | 1   | 0   | 0   | 1     | 1     | 0/1   |

| Ш  | Lockout | 0   | 1   | 0   | 0 / 1 | 0 / 1 | 0/1   |

| Ο  | Lockout | 1   | 1   | 0   | 1     | 1     | 0 / 1 |

| C  | Lockout | 0   | 0   | 1   | 1     | 1     | 0 / 1 |

| В  | Lockout | 1   | 0   | 1   | 1     | 1     | 0 / 1 |

| А  | Lockout | 0   | 1   |     |       | 1     | 0/1   |

| Er | Lockout |     |     |     |       |       | 0 / 1 |

|    | State   | CDL | BDL | ADL | DDL   | XDL   | SDL   |

**Fig.** 22B

Fig. 23

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

### **BACKGROUND**

The present disclosure relates to technology for non-volatile memory.

Semiconductor memory has become increasingly popular 15 for use in various electronic devices. For example, non-volatile semiconductor memory is used in cellular telephones, digital cameras, personal digital assistants, mobile computing devices, non-mobile computing devices and other devices. Electrically Erasable Programmable Read Only 20 Memory (EEPROM) and flash memory are among the most popular non-volatile semiconductor memories. With flash memory, also a type of EEPROM, the contents of the whole memory array, or of a portion of the memory, can be erased in one step, in contrast to the traditional, full-featured 25 EEPROM. The array of storage elements may be divided into a large number of blocks of storage elements.

Both the traditional EEPROM and the flash memory utilize a floating gate that is positioned above and insulated from a channel region in a semiconductor substrate. The floating gate is positioned between the source and drain regions. A control gate is provided over and insulated from the floating gate. The threshold voltage (Vth) of the transistor thus formed is controlled by the amount of charge that is retained on the floating gate. That is, the minimum amount of voltage that must be applied to the control gate before the transistor is turned on to permit conduction between its source and drain is controlled by the level of charge on the floating gate. Thus, a storage element may be read by applying a reference voltage to it control gate and sensing the magnitude of the current that 40 flows between its drain and source.

A storage element may be programmed by applying suitable programming voltages to its control gate. Typically, a program voltage Vpgm applied to the control gate during a program operation is applied as a series of pulses that increase 45 in magnitude over time.

For some architecture, the control gates of many storage elements are electrically connected. Typically, the term "word line" is used to refer to this electrical connection of many storage elements. Therefore, a common voltage may be applied to many storage elements at the same time. One end of the word line is driven by a read reference voltage in order to read many storage elements at once. Likewise, one end of the word line is driven by a programming voltage in order to program many storage elements at once.

However, if the word line has some sort of a defect, then the read reference voltage or the programming voltage may not be properly applied to each of the storage elements on the selected word line. Therefore, errors may occur when programming or reading the storage elements.

### BRIEF DESCRIPTION OF THE DRAWINGS

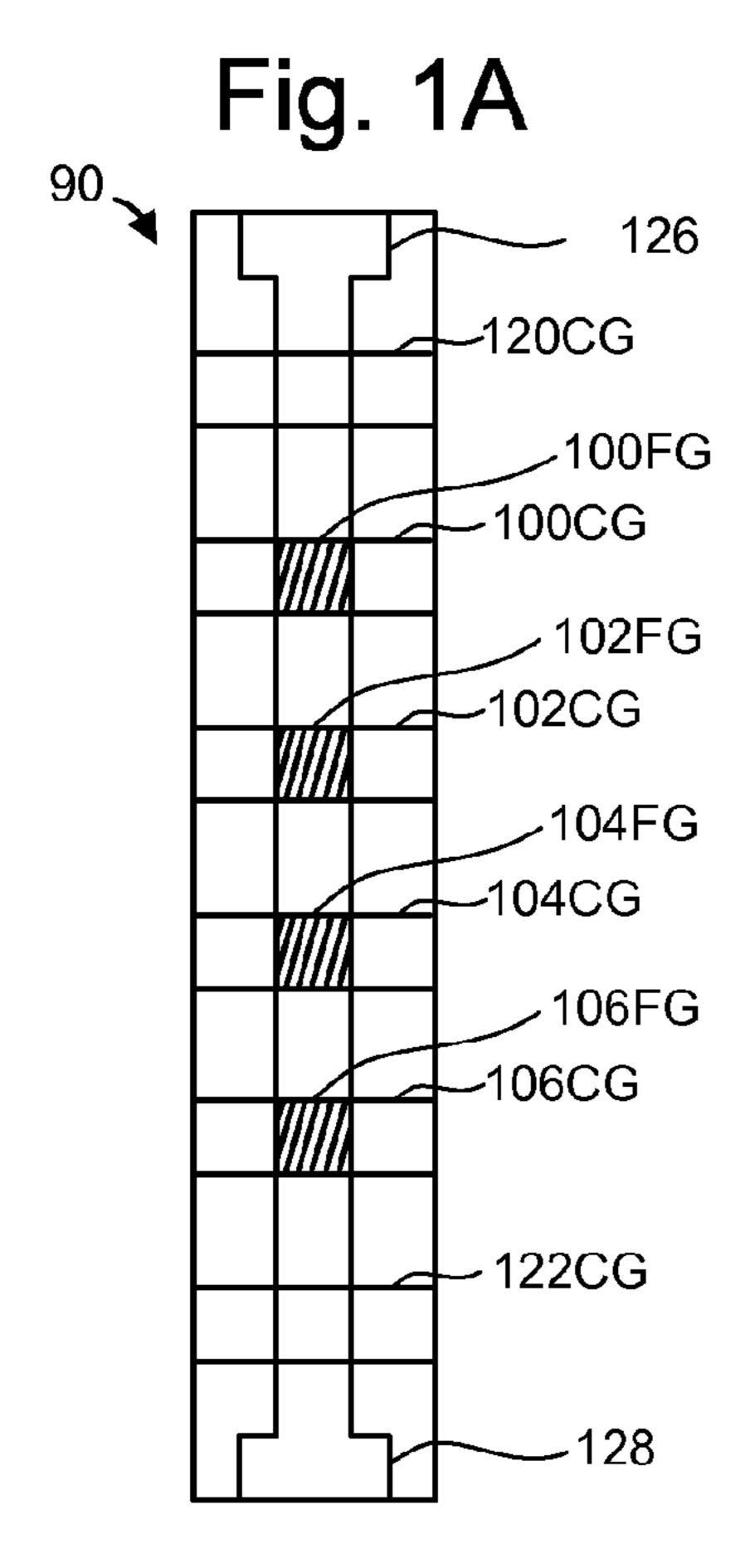

- FIG. 1A is a top view of one embodiment of a NAND string.

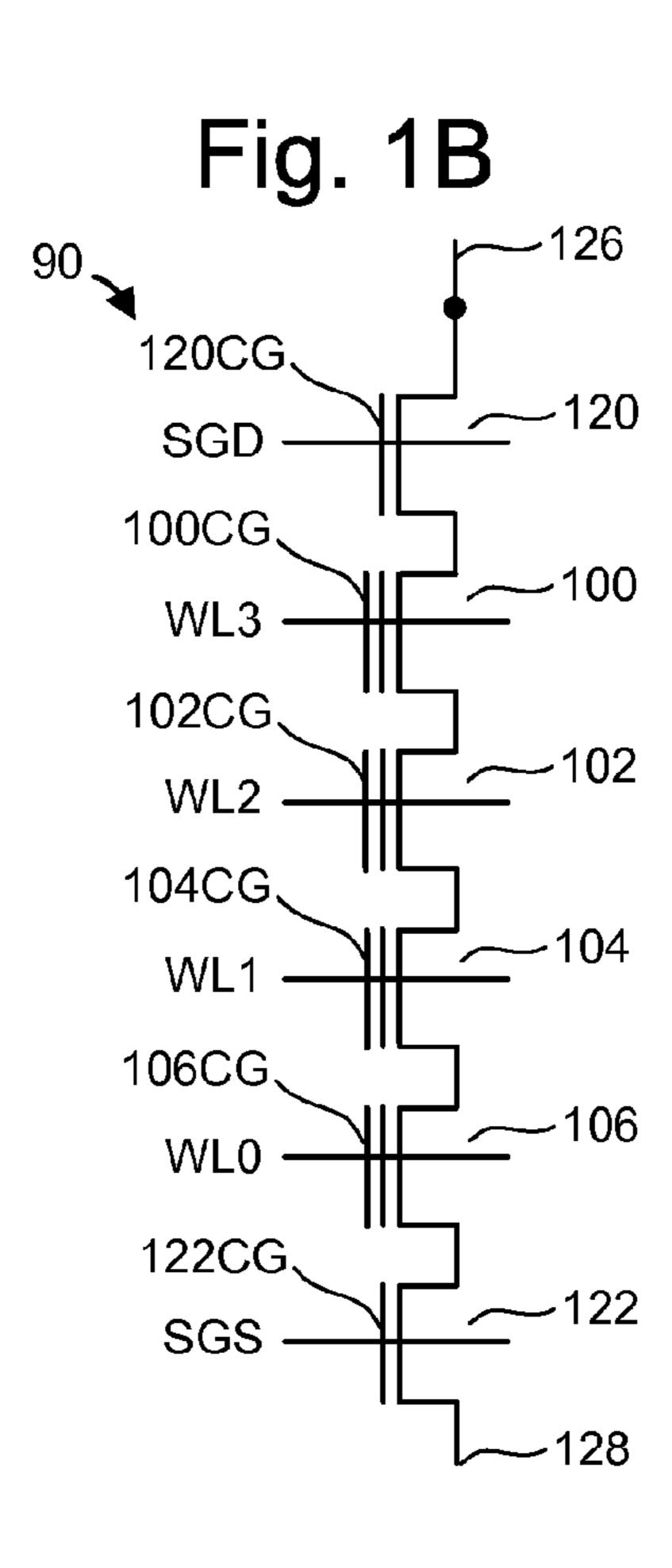

- FIG. 1B is an equivalent circuit diagram of the NAND string.

2

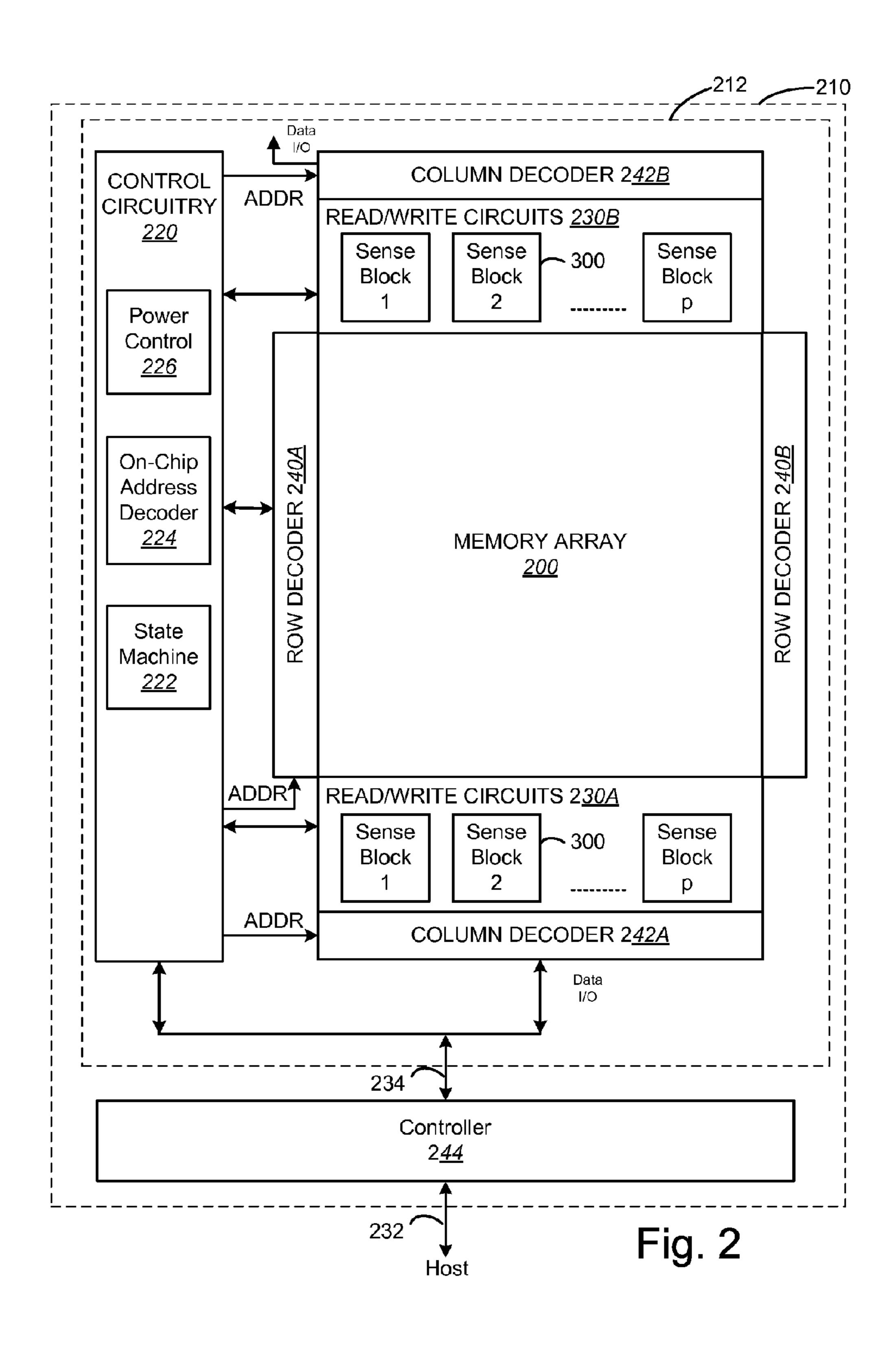

- FIG. 2 illustrates a non-volatile storage device that may include one or more memory die or chips.

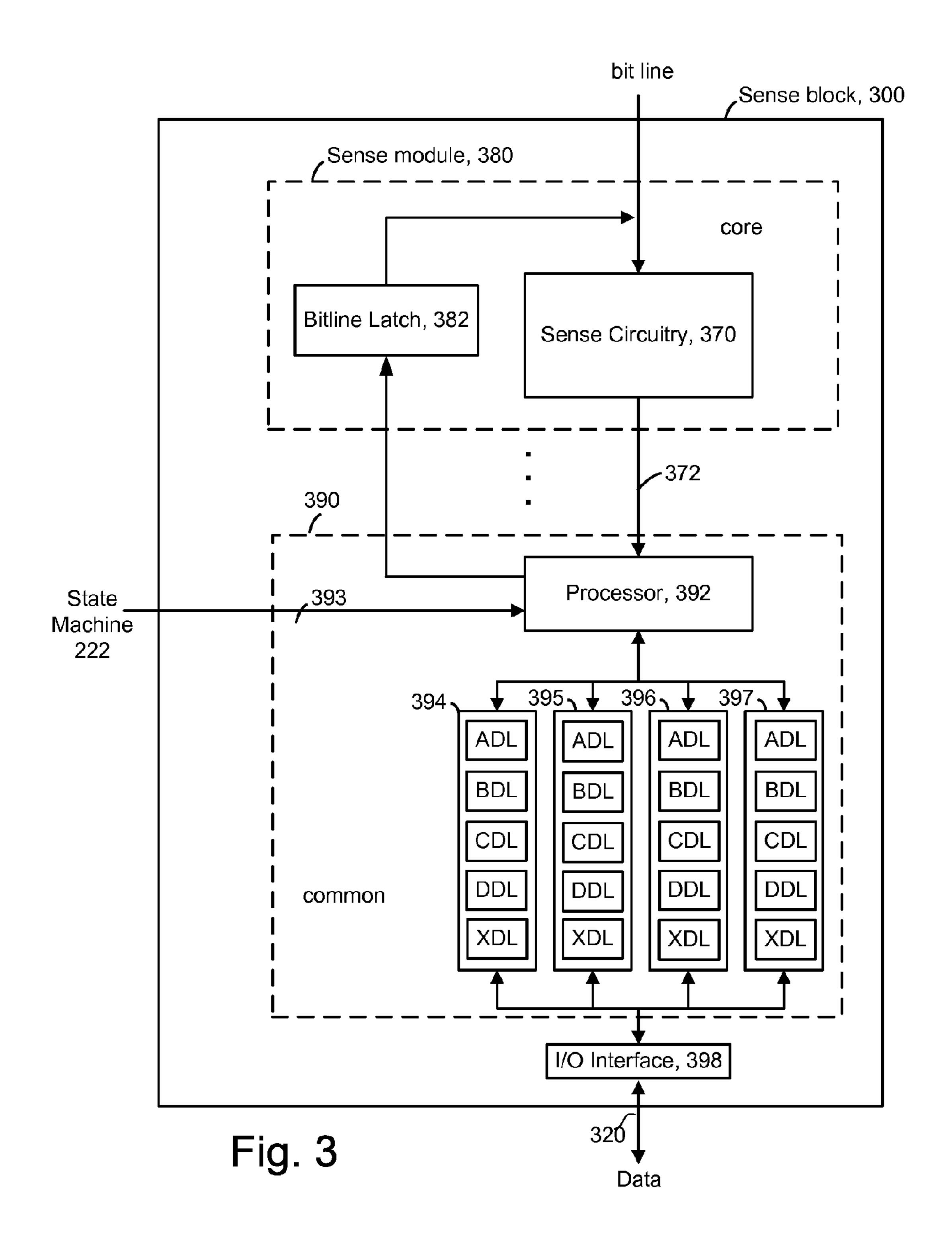

- FIG. 3 is a block diagram depicting one embodiment of a sense block.

- FIG. 4 depicts blocks of NAND flash memory cells in the memory array of FIG. 2.

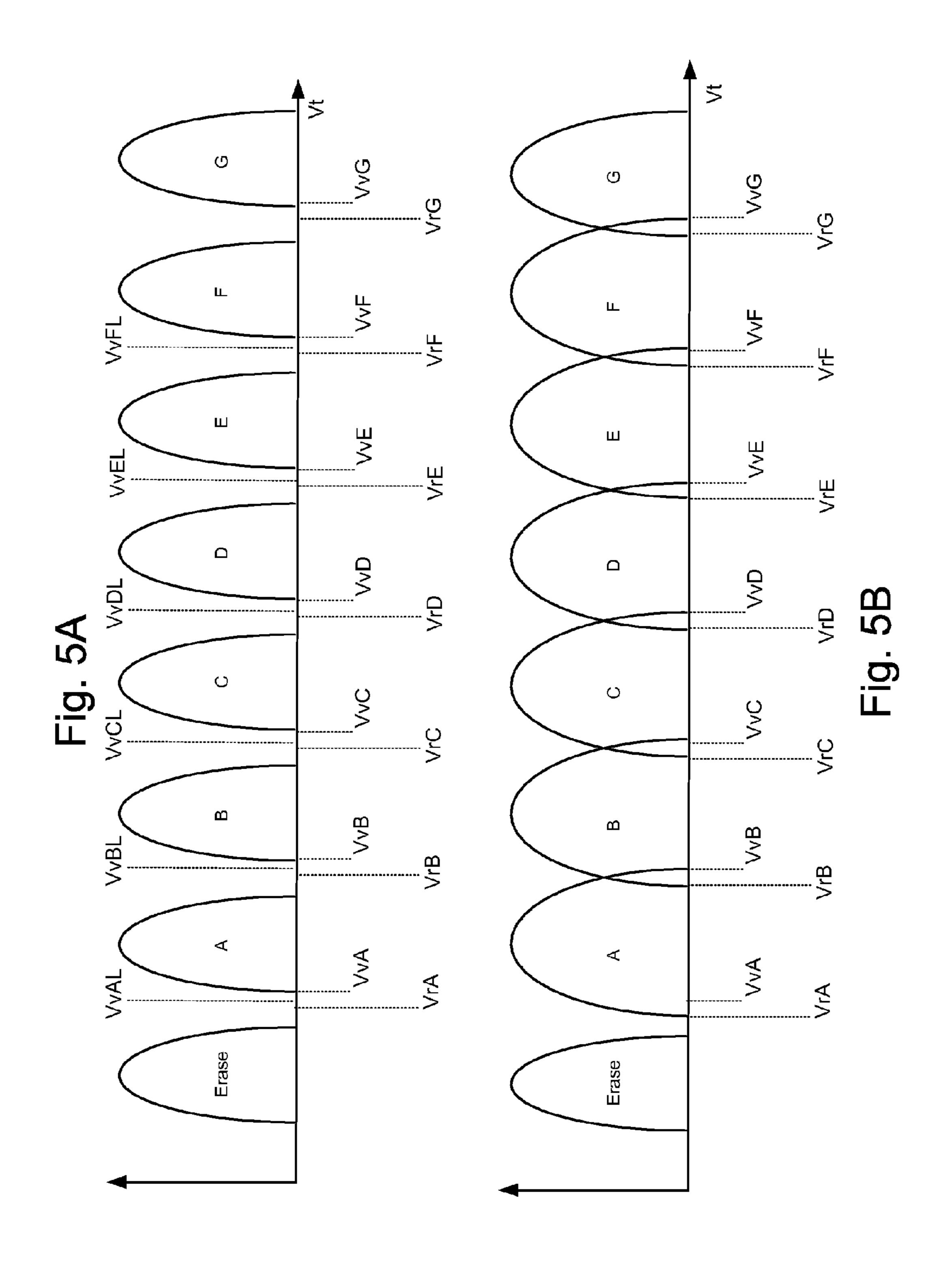

- FIG. **5**A depicts an example set of threshold voltage distributions for an eight-state memory device in which each storage element stores three bits of data.

- FIG. **5**B illustrates that Vt distributions can partially overlap.

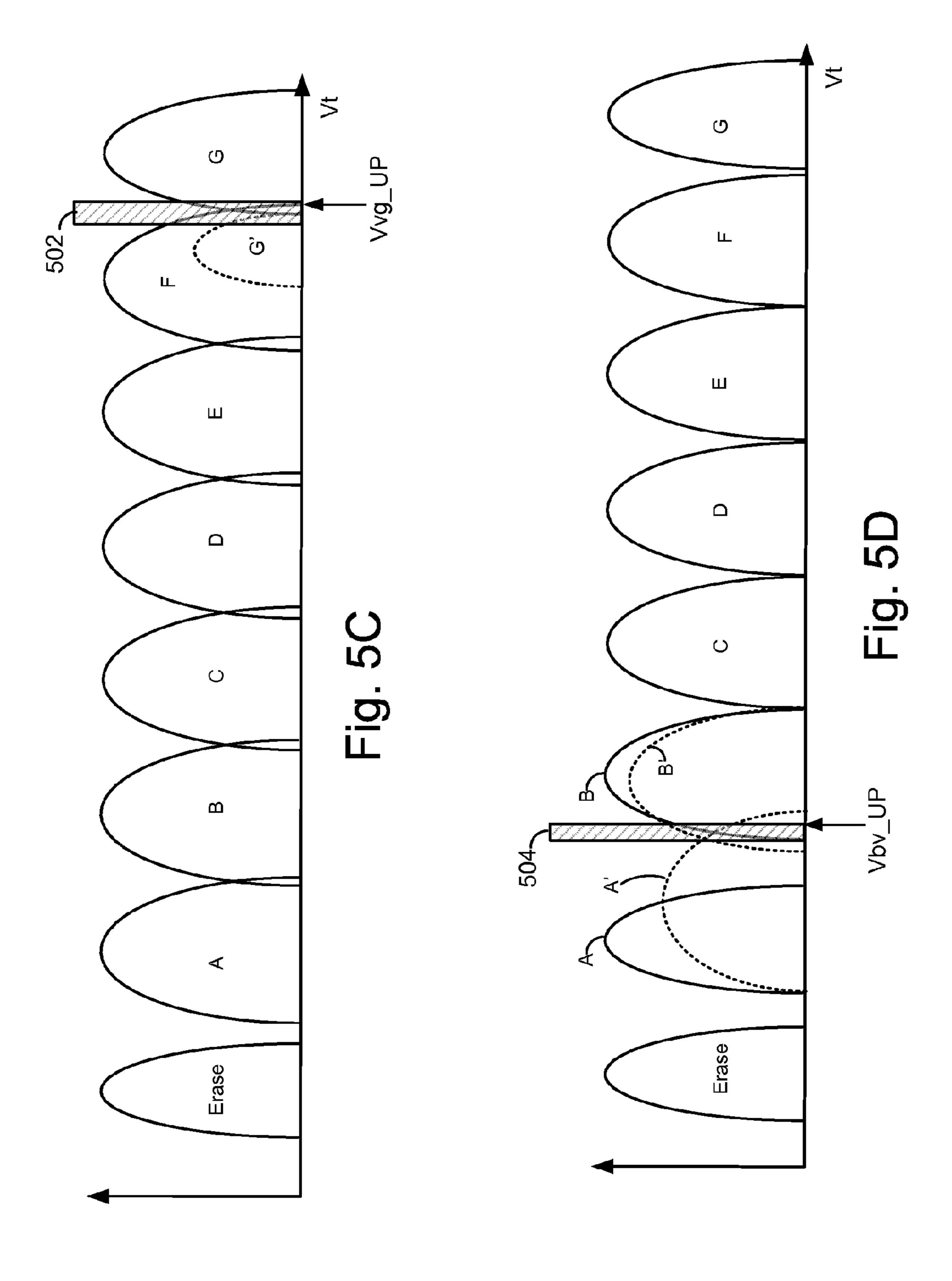

- FIG. 5C illustrates that Vt distributions with a region for detecting mis-programmed cells, and a reference voltage used in one embodiment for detecting defects.

- FIG. **5**D illustrates that Vt distributions with a region for detecting mis-programmed cells, and a reference voltage used in one embodiment for detecting defects.

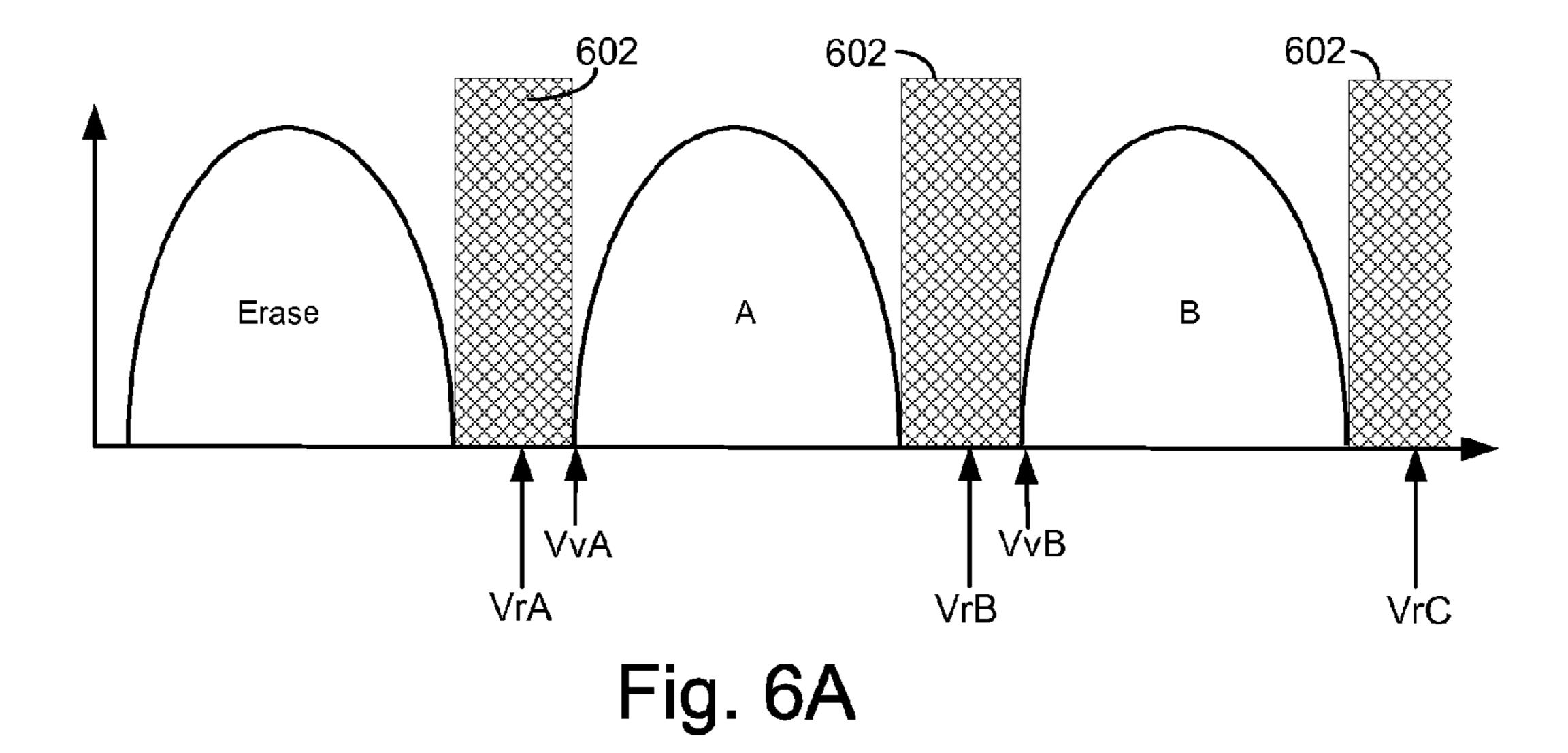

- FIG. **6**A depicts several Vt distributions to illustrate reference voltages in accordance with one embodiment.

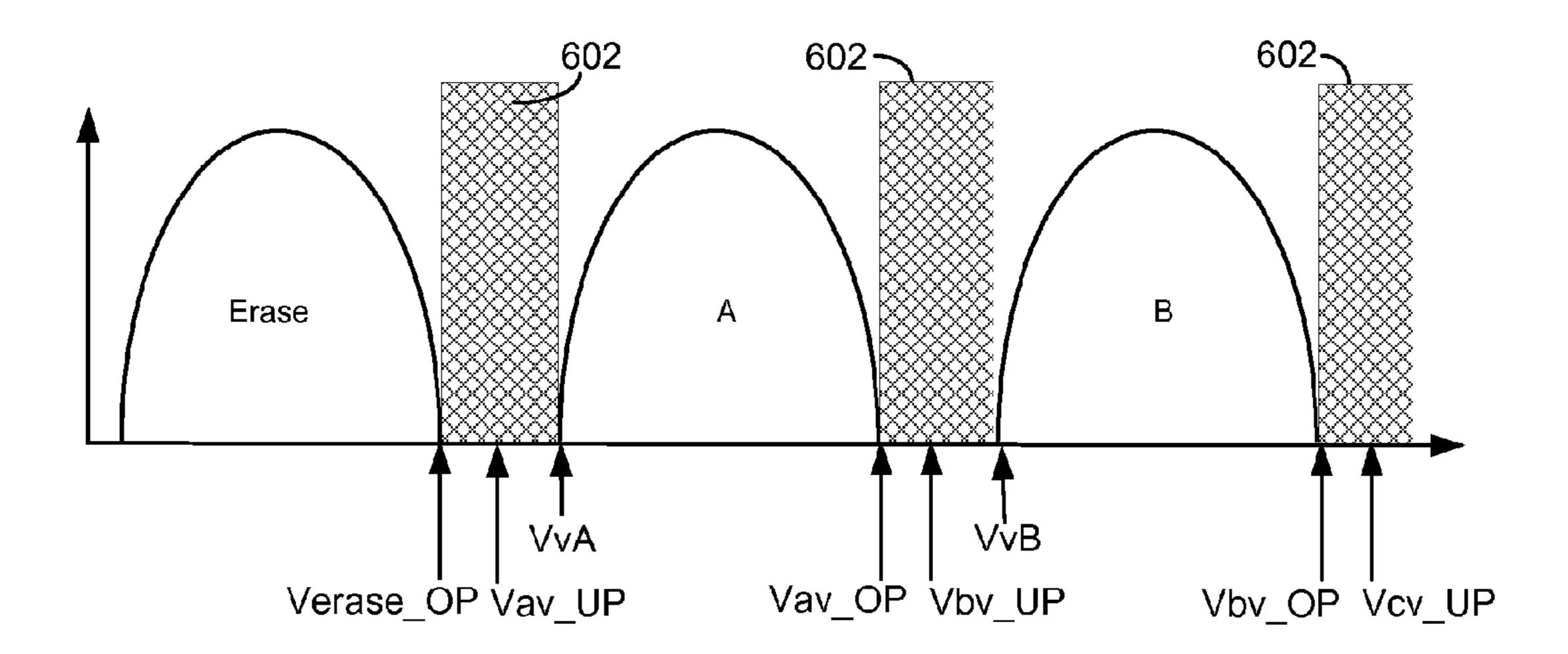

- FIG. **6**B depicts several Vt distributions to illustrate underand over-program reference voltages in accordance with one embodiment.

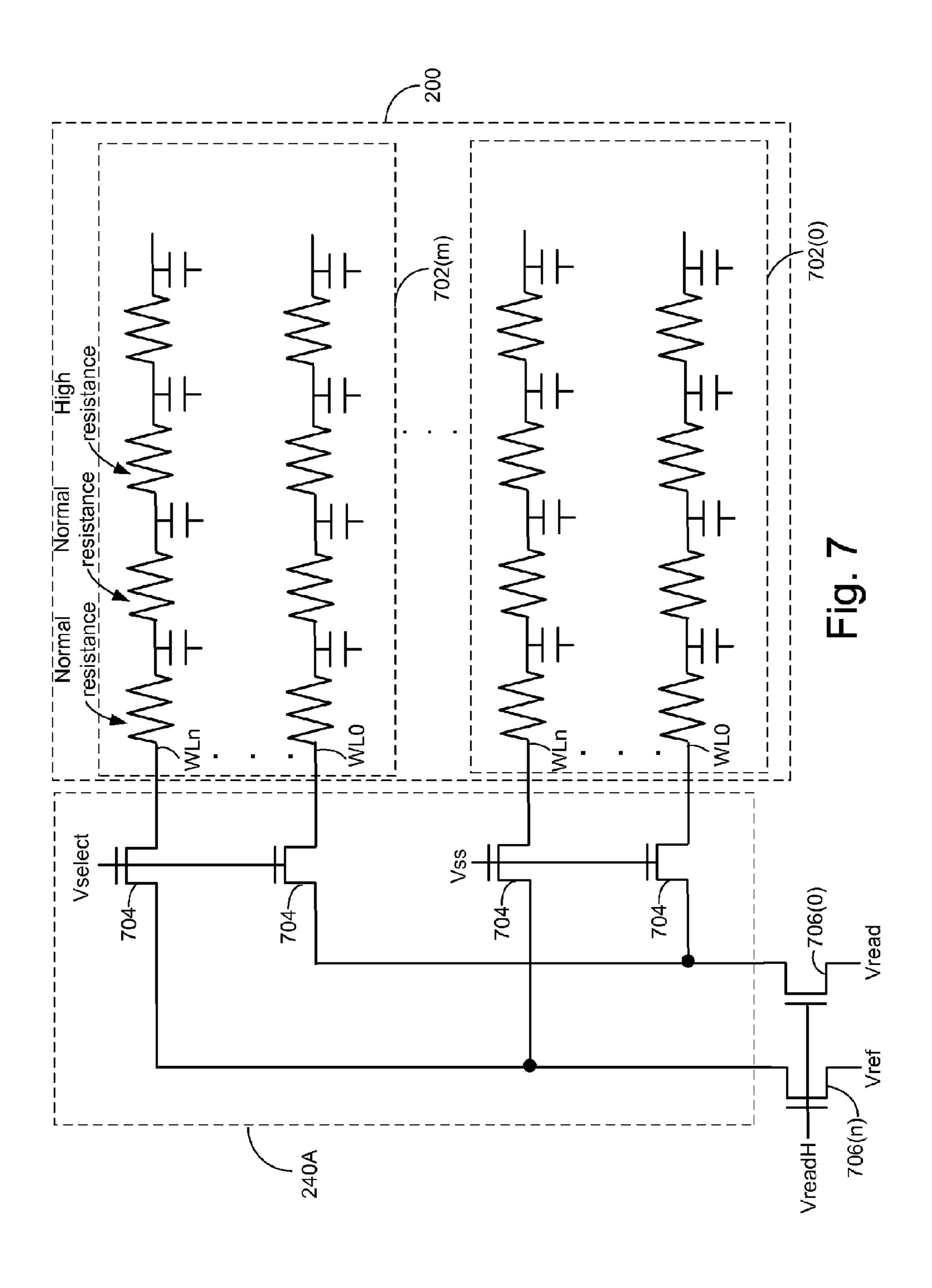

- FIG. 7 depicts a schematic diagram of a portion of one embodiment of a memory array.

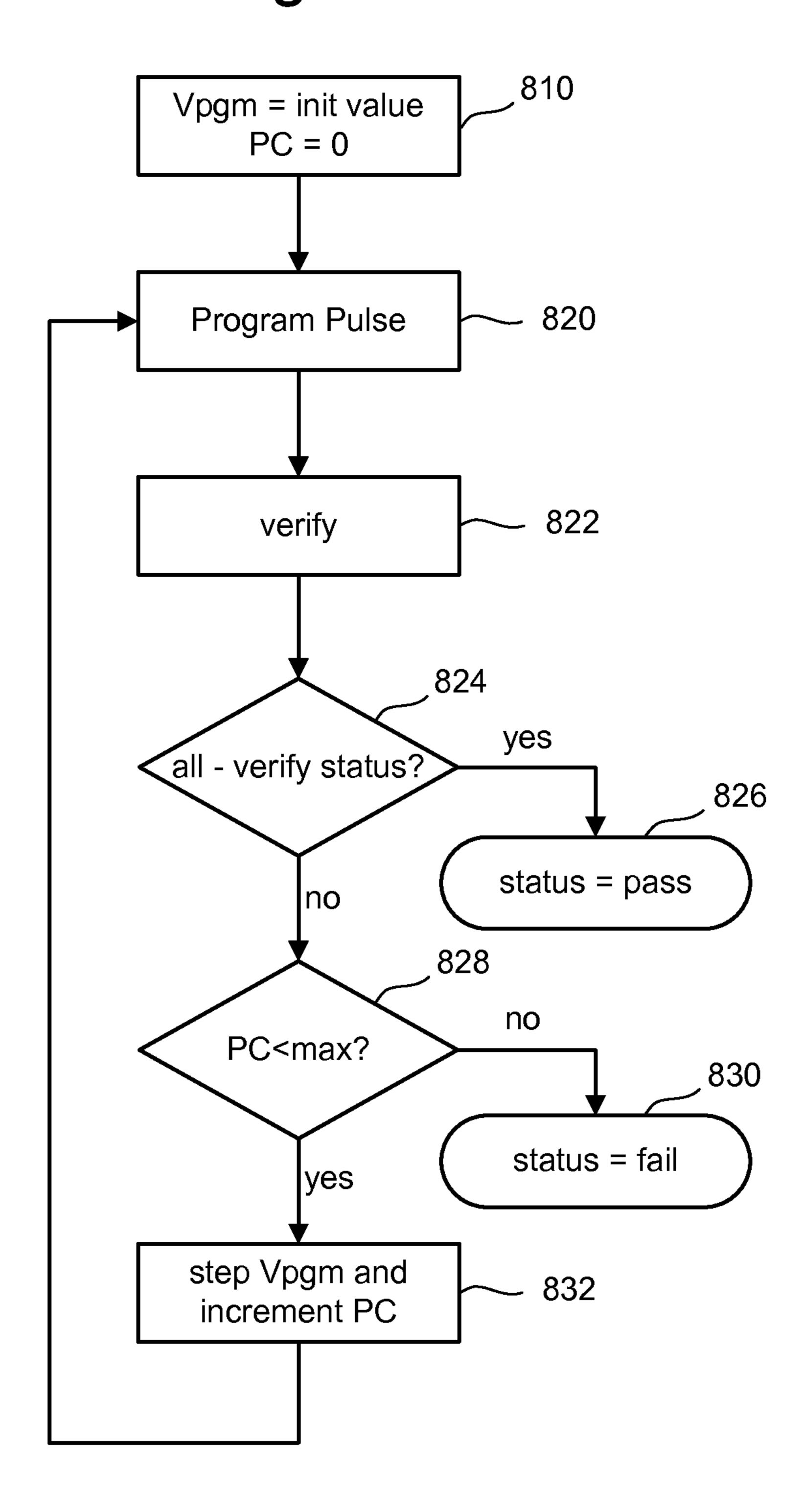

- FIG. 8 is a flowchart describing one embodiment of a programming process, which includes one or more verification steps.

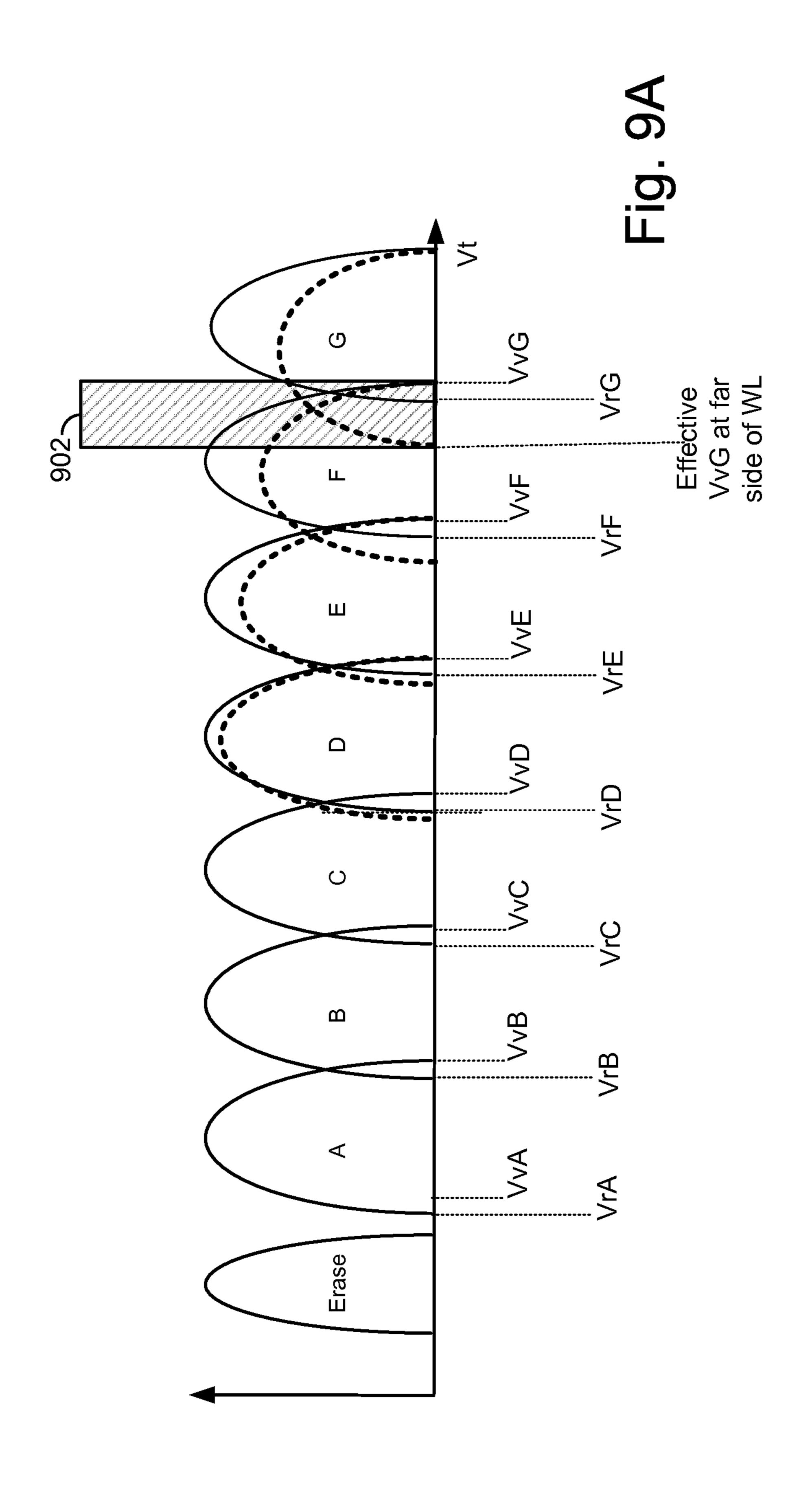

- FIG. 9A depicts threshold voltage distributions to help illustrate a possible word line defect that may show up as under-programmed states.

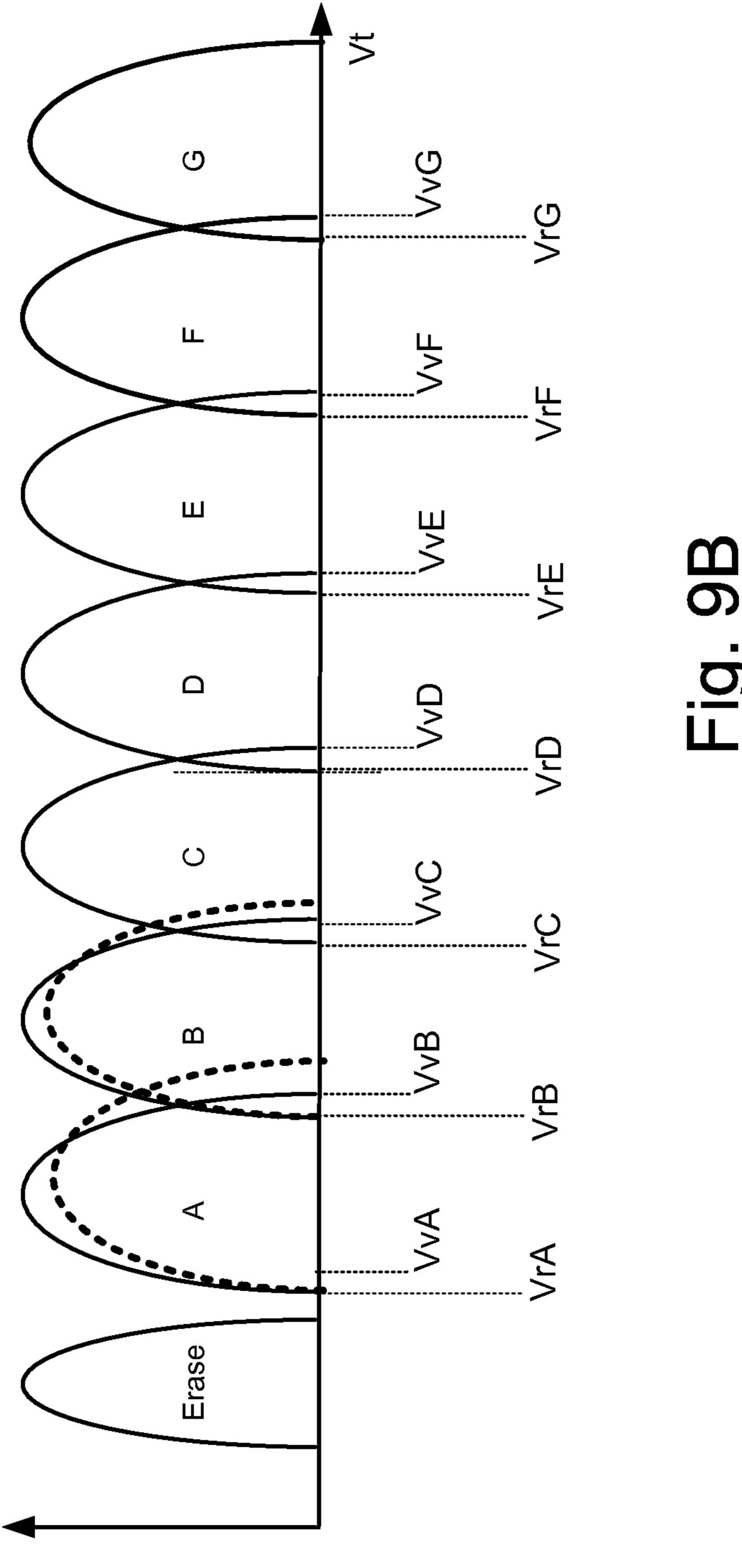

- FIG. 9B depicts threshold voltage distributions to help illustrate a possible word line defect that may show up as over-programmed states.

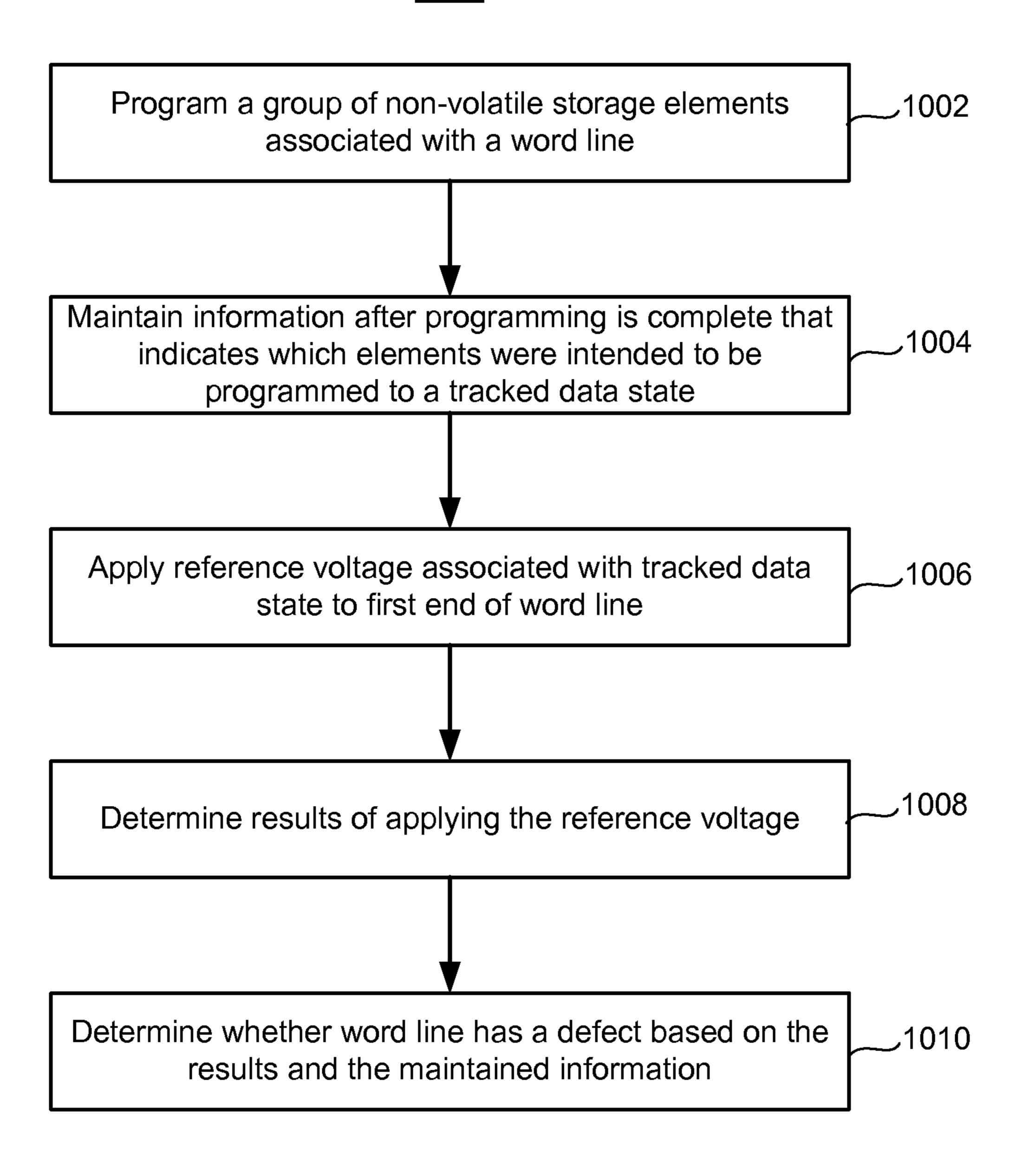

- FIG. 10 is a flowchart of one embodiment of a process of determining whether a word line is defective following programming of non-volatile storage.

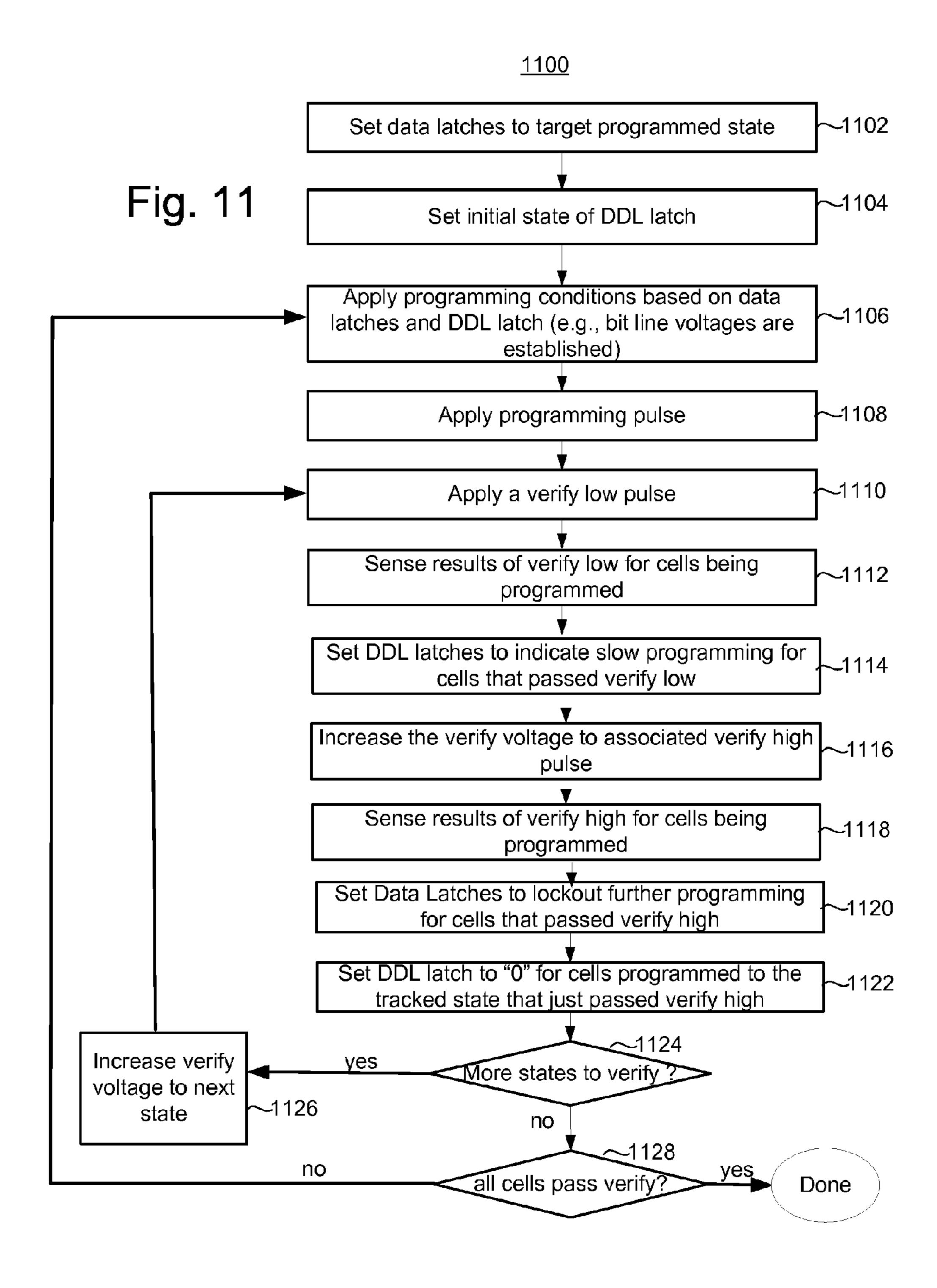

- FIG. 11 is a flowchart of one embodiment of a process of operating data latches while programming and verifying non-volatile storage.

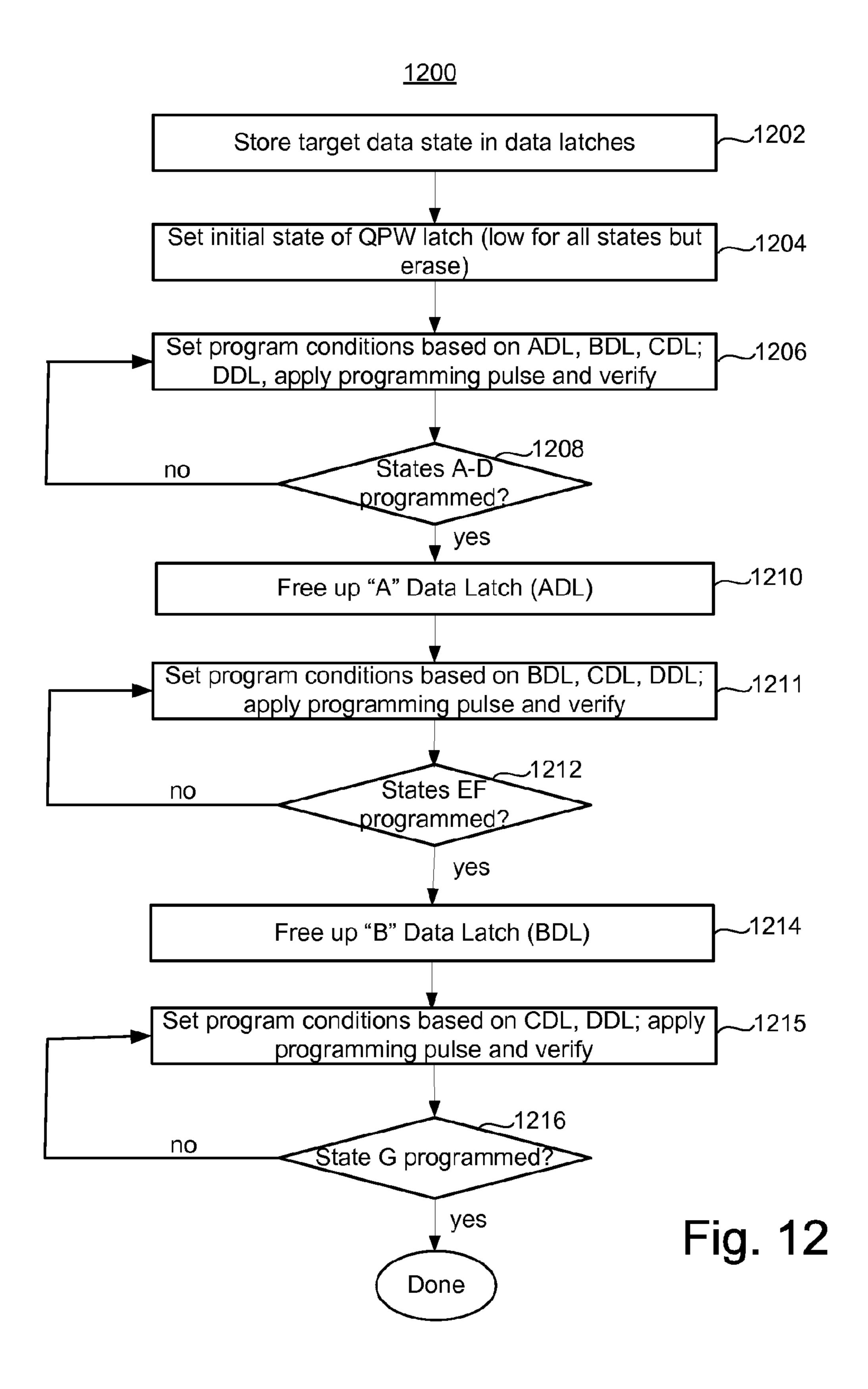

- FIG. 12 is a flowchart of one embodiment of a process of operating data latches while programming and verifying non-volatile storage.

- FIG. 13A, FIG. 13B, FIG. 13C, and FIG. 13D are tables that show status of data latches ADL, BDL, CDL, and DDL throughout various stages of the process of FIG. 12.

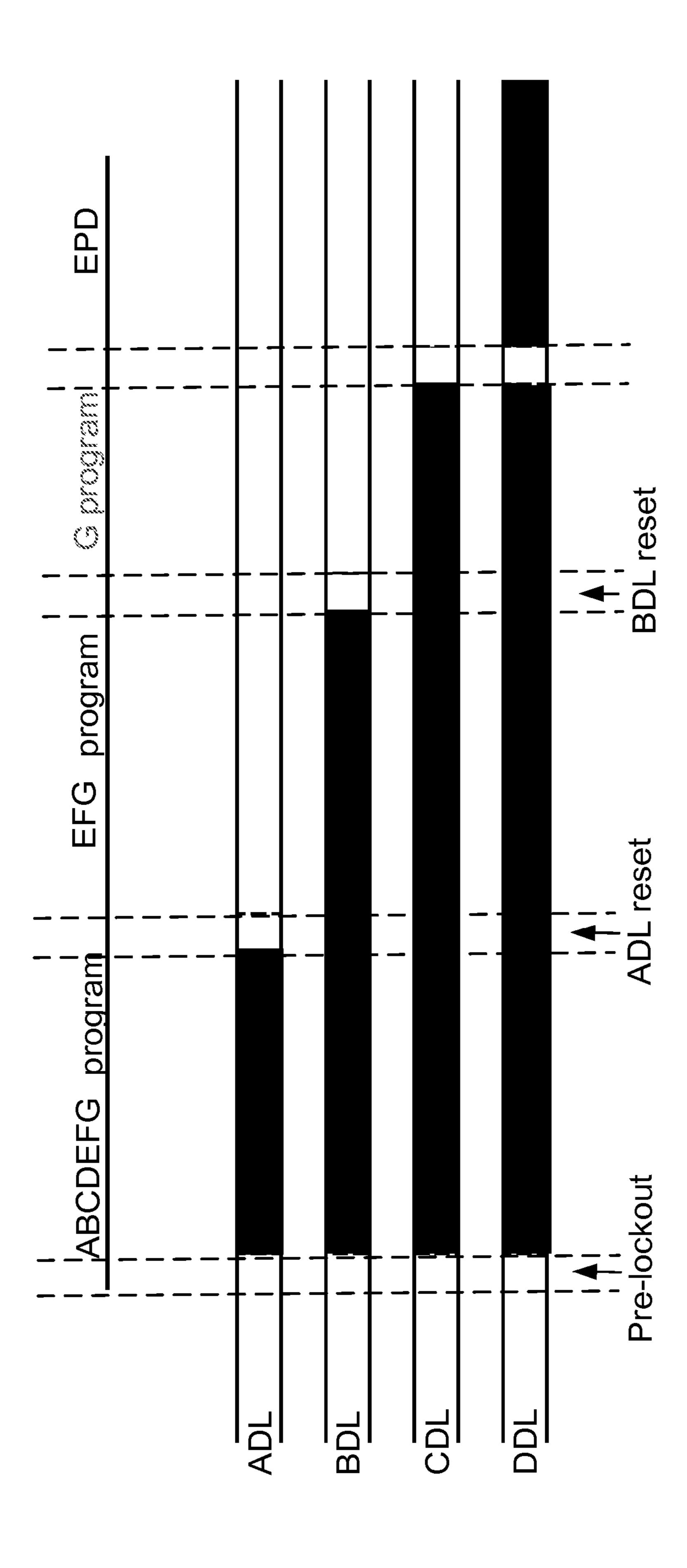

- FIG. 14 shows latch usage during various stages of one embodiment of programming.

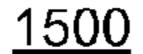

- FIG. 15A is a flowchart of one embodiment of a process of determining whether a word line has a defect.

- FIG. 15B is a table of one embodiment of data latch use during the process of FIG. 15A.

- FIG. 15C is a table of one embodiment of data latch use during the process of FIG. 15A.

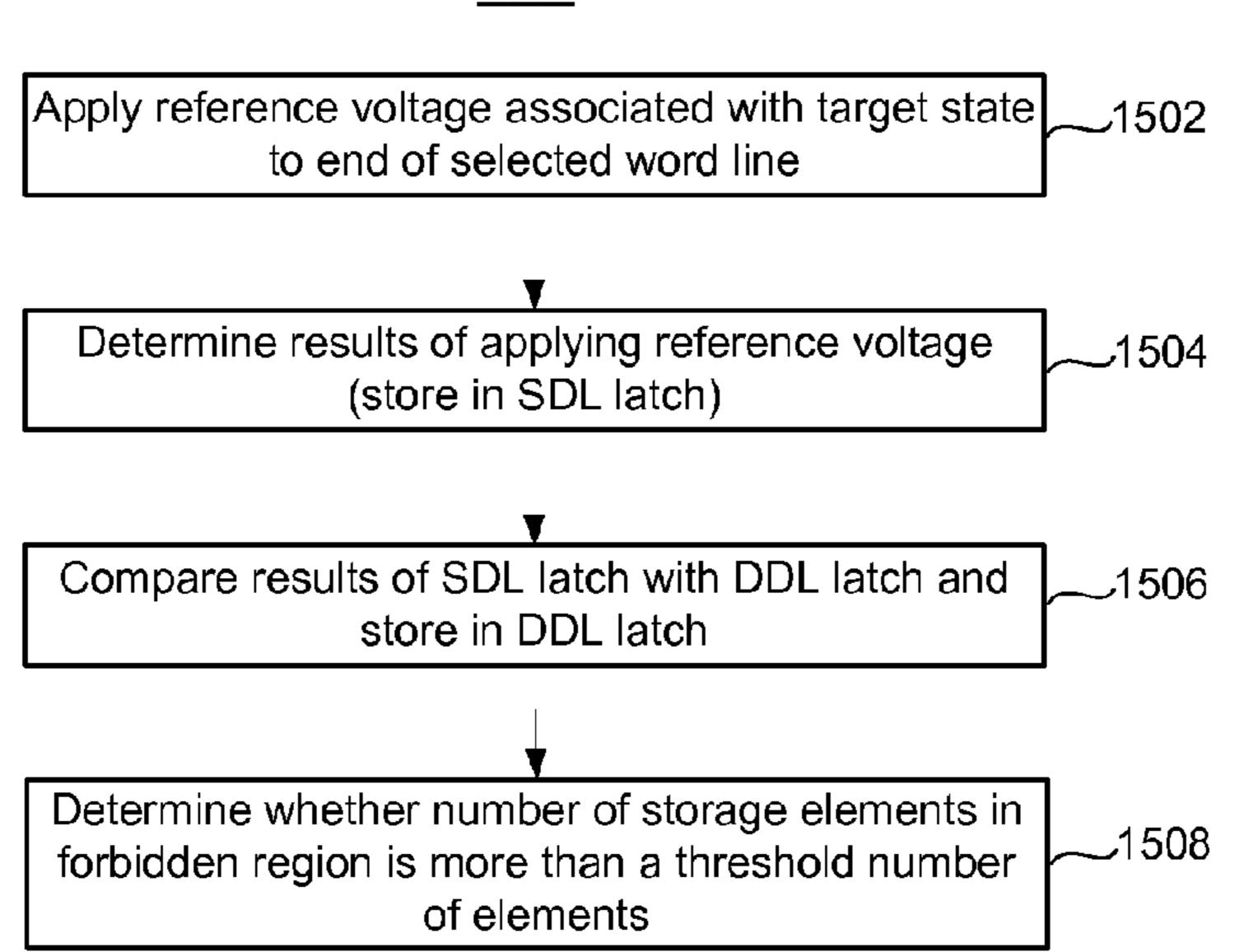

- FIG. 16 is a flowchart of one embodiment of a process of determining broken word lines during device qualification.

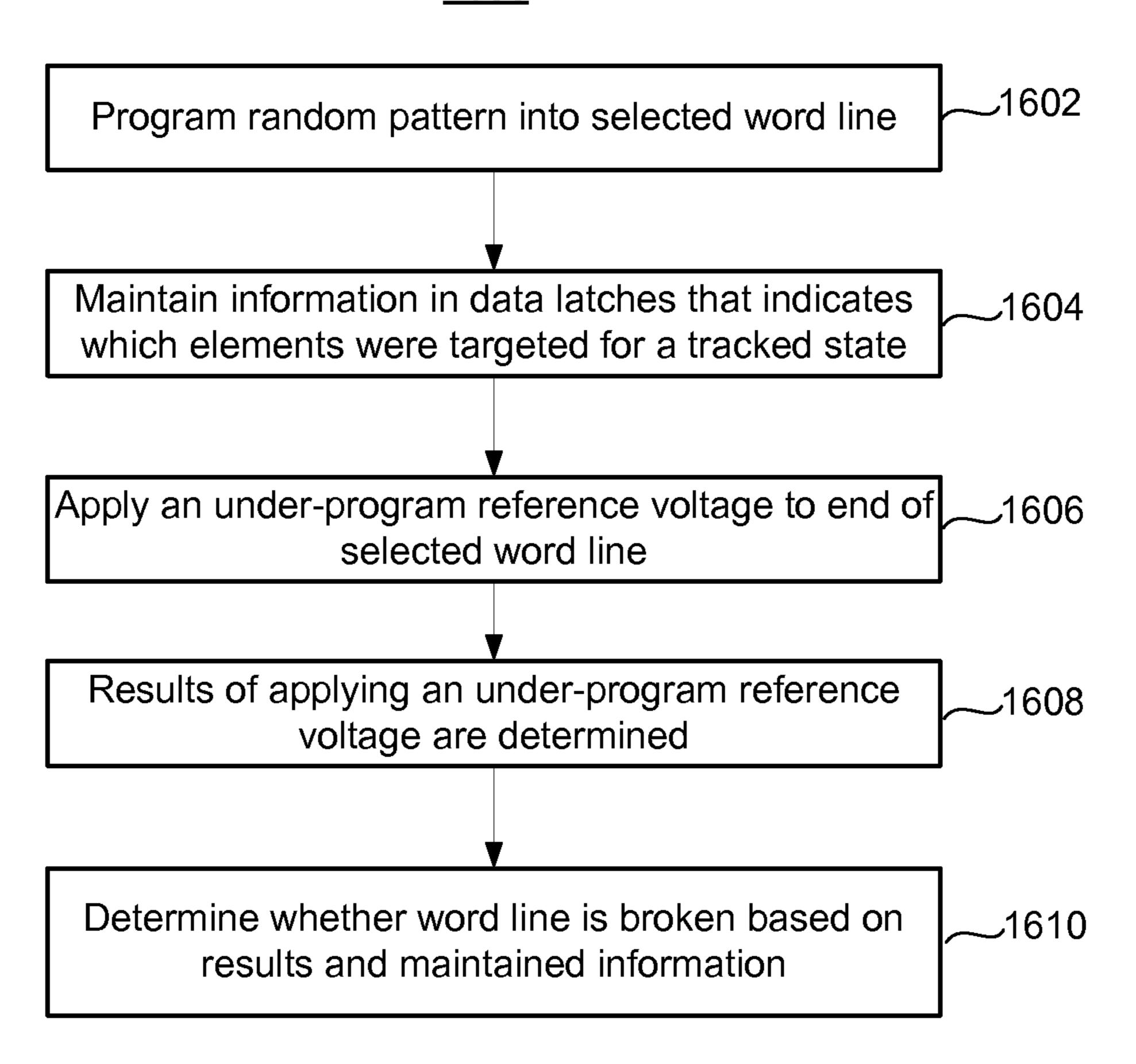

- FIG. 17 is a flowchart of one embodiment of a method of detecting erratically programmed storage elements.

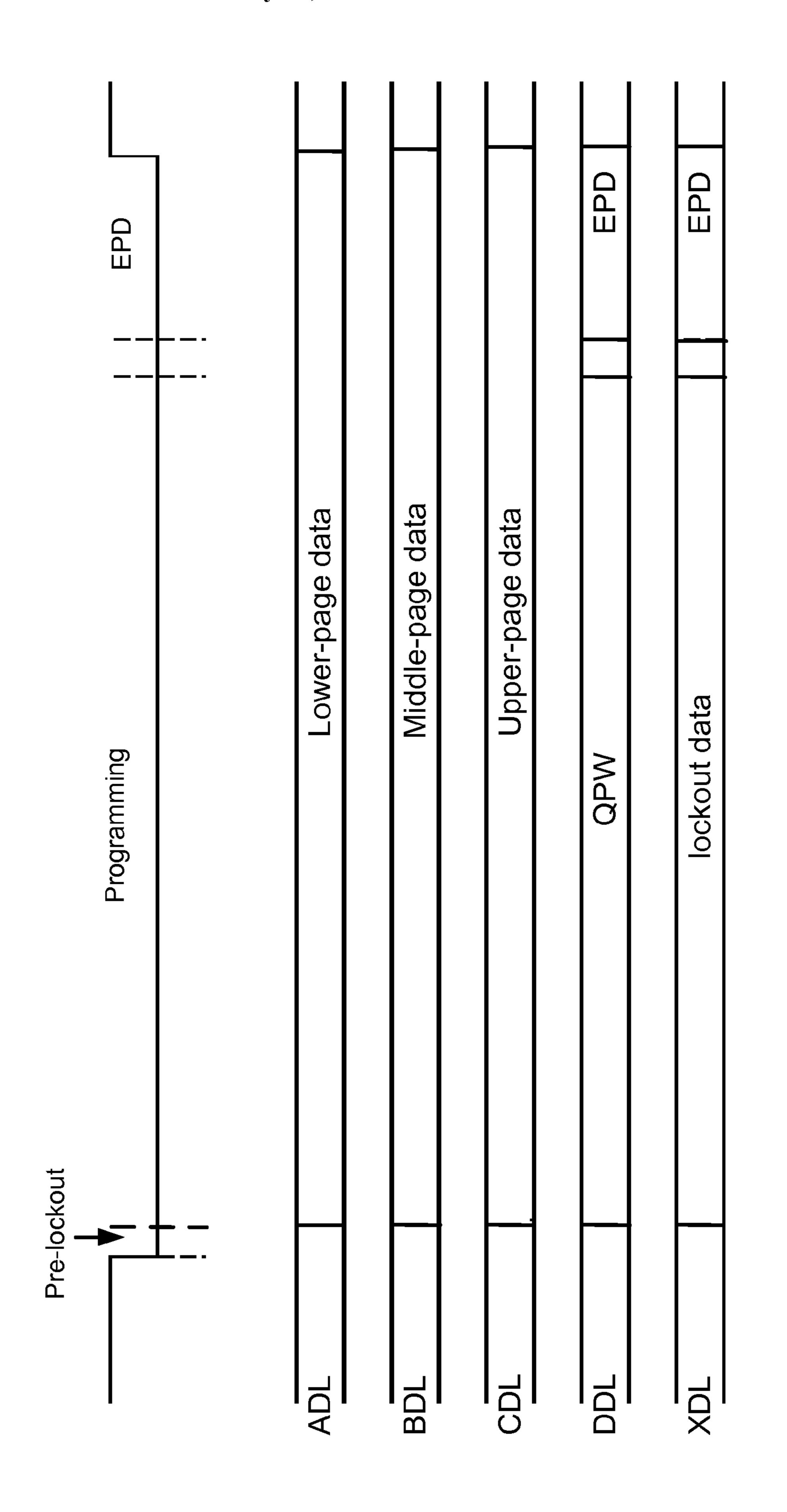

- FIG. **18** is a diagram that illustrates how latches are used during one embodiment of programming and erratic program detection (EPD).

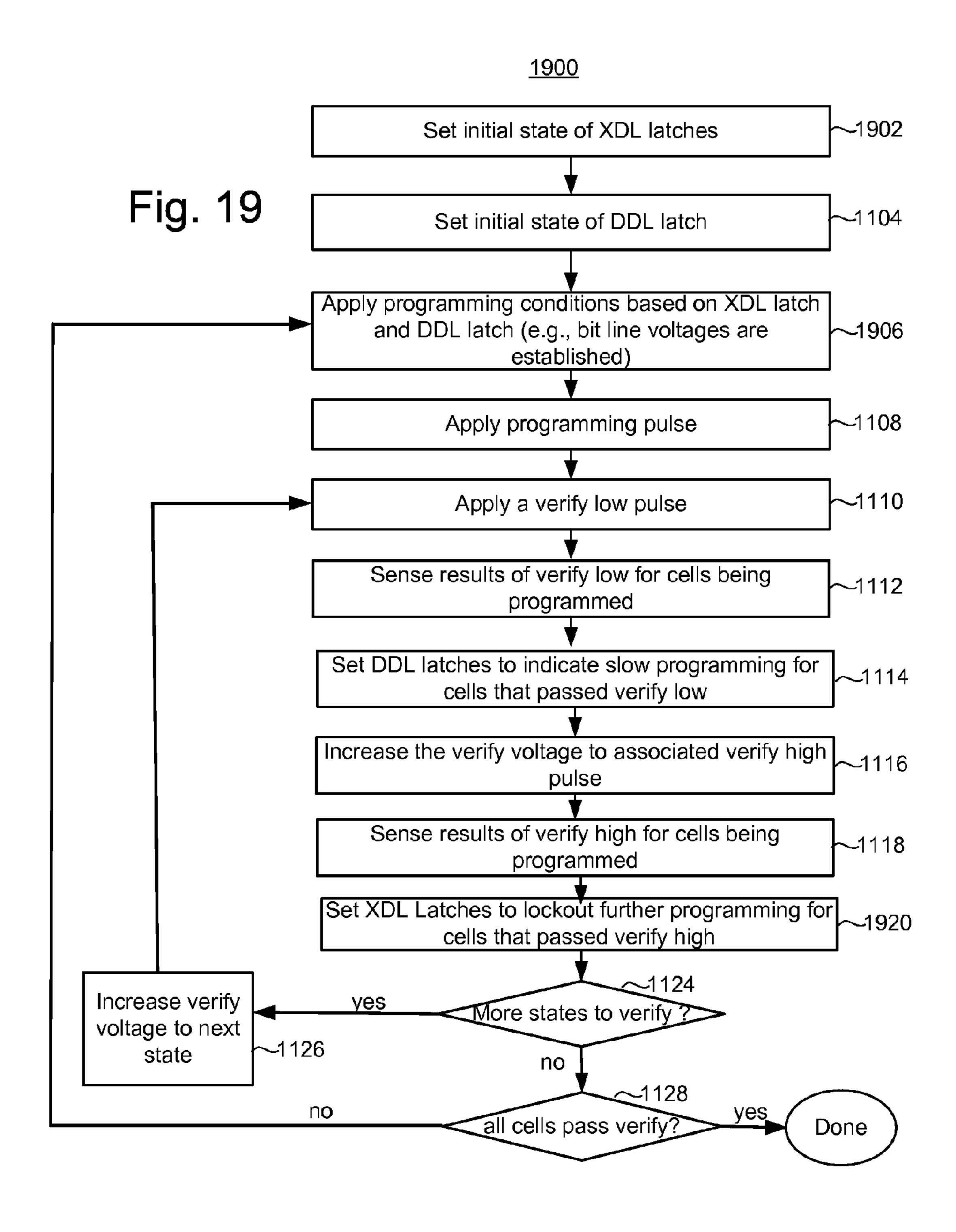

- FIG. 19 is a flowchart of one embodiment of a process for programming storage elements and maintaining program data in latches.

- FIG. **20**A depicts one example of how latches may be used during one embodiment of programming.

- FIG. 20B shows a table that demonstrates how latches may be used during one embodiment of programming.

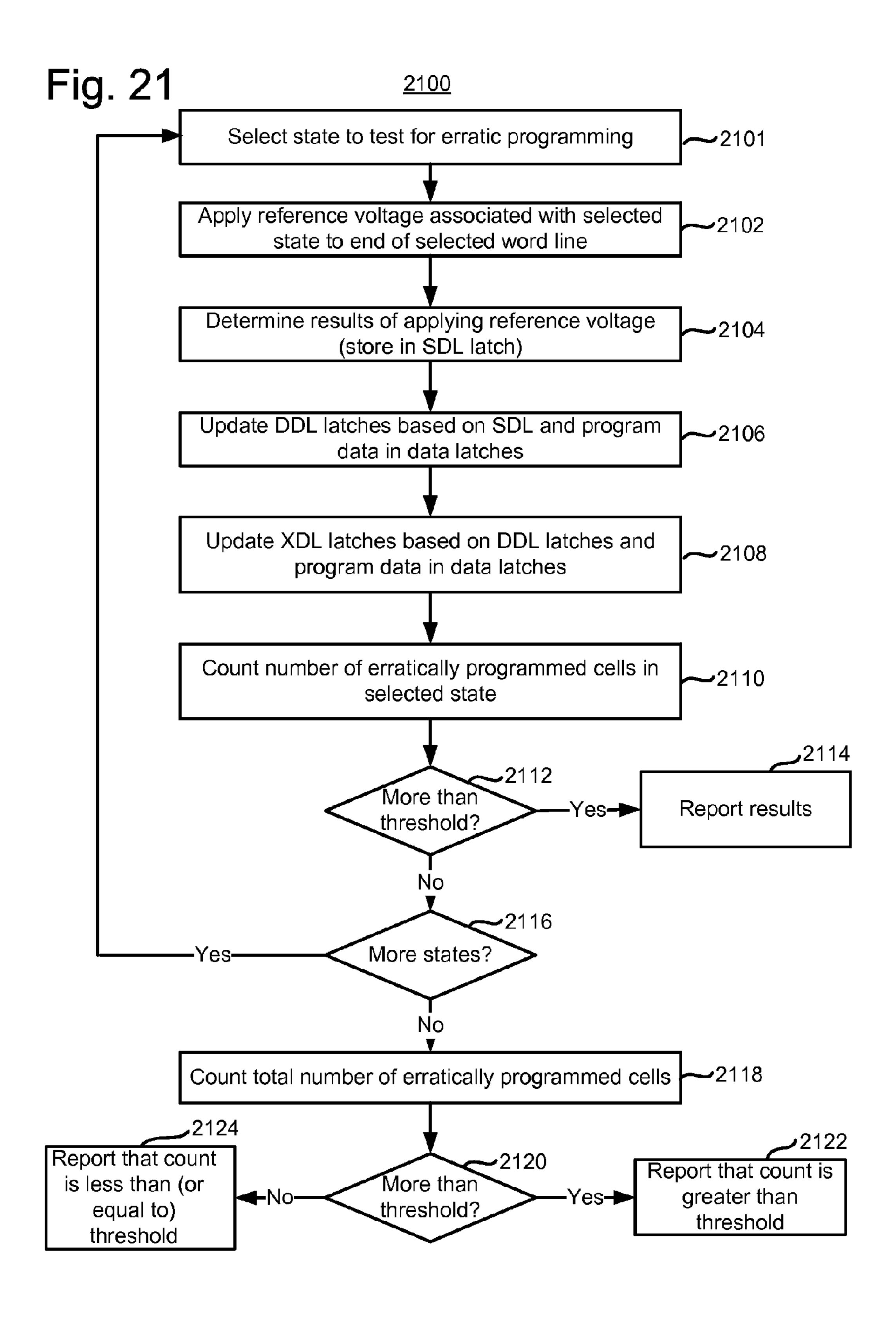

FIG. 21 is a flowchart of one embodiment of a process of erratic program detection for non-volatile storage elements.

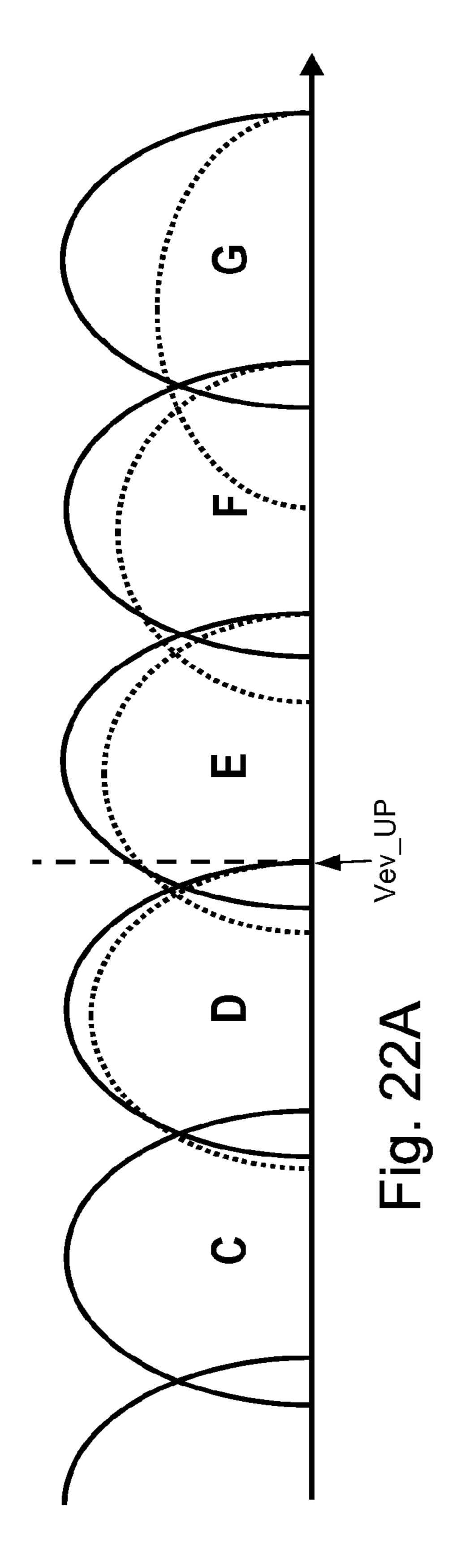

FIG. 22A shows nominal threshold voltage distributions and erratic distributions.

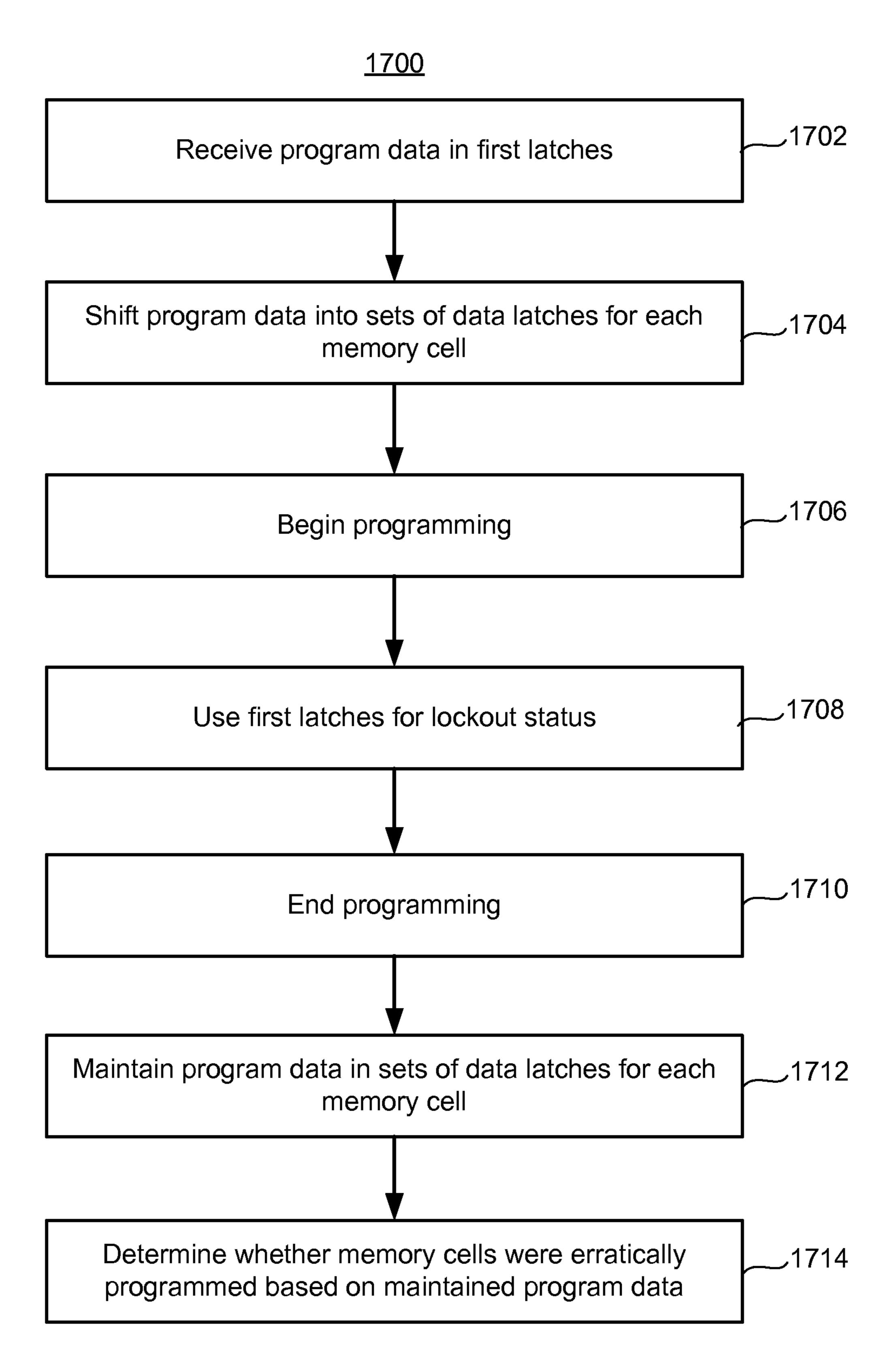

FIG. 22B shows a table that demonstrates how the latches may be used during one embodiment of erratic program detection.

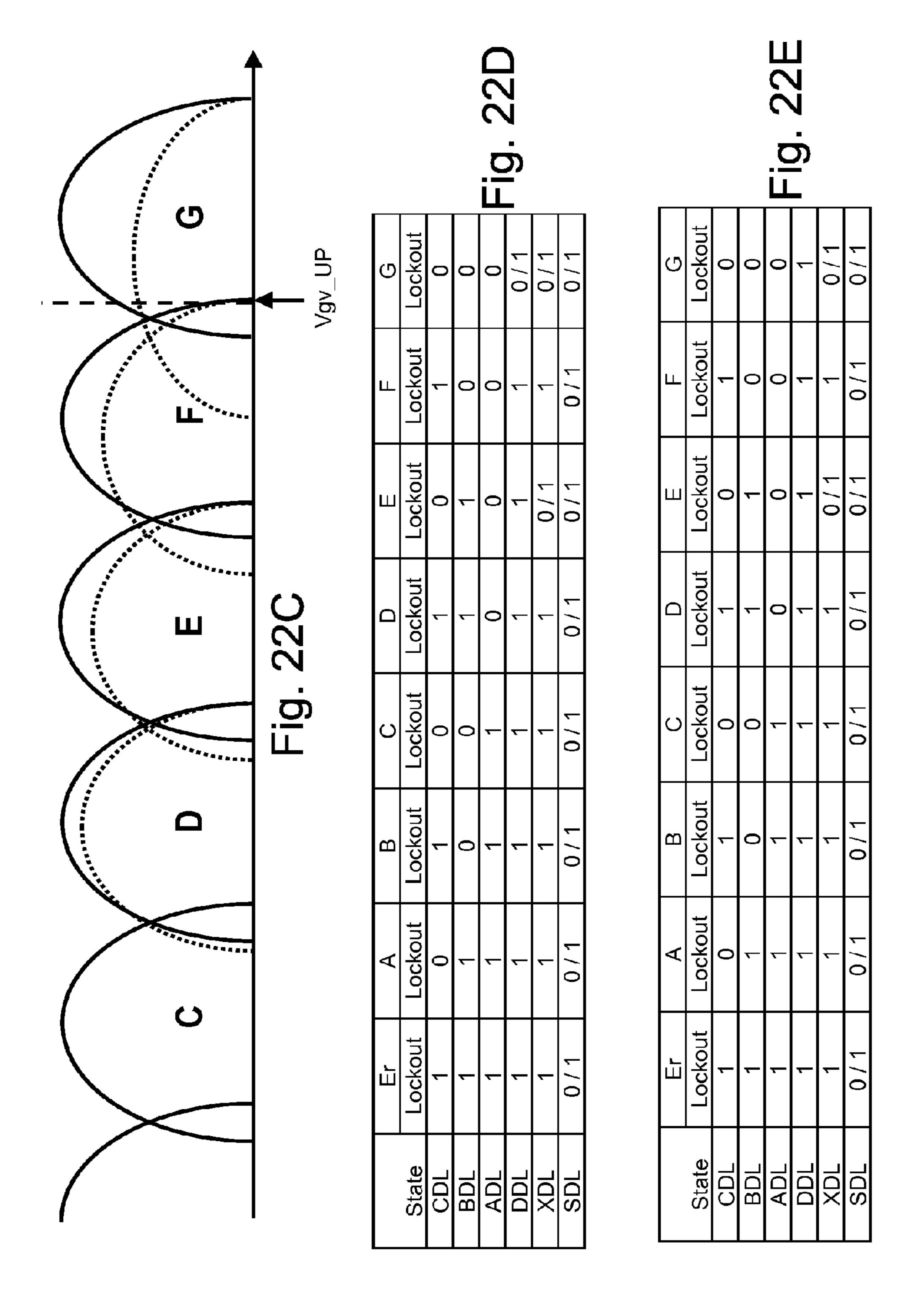

FIG. 22C depicts threshold voltage distributions and an under-programmed reference voltage for determining whether storage elements intended for the G-state are under- programmed.

FIG. 22D shows a table that demonstrates how latches may be used during one embodiment of erratic program detection.

FIG. 22E shows a table that demonstrates how latches may be used during one embodiment of erratic program detection. 15

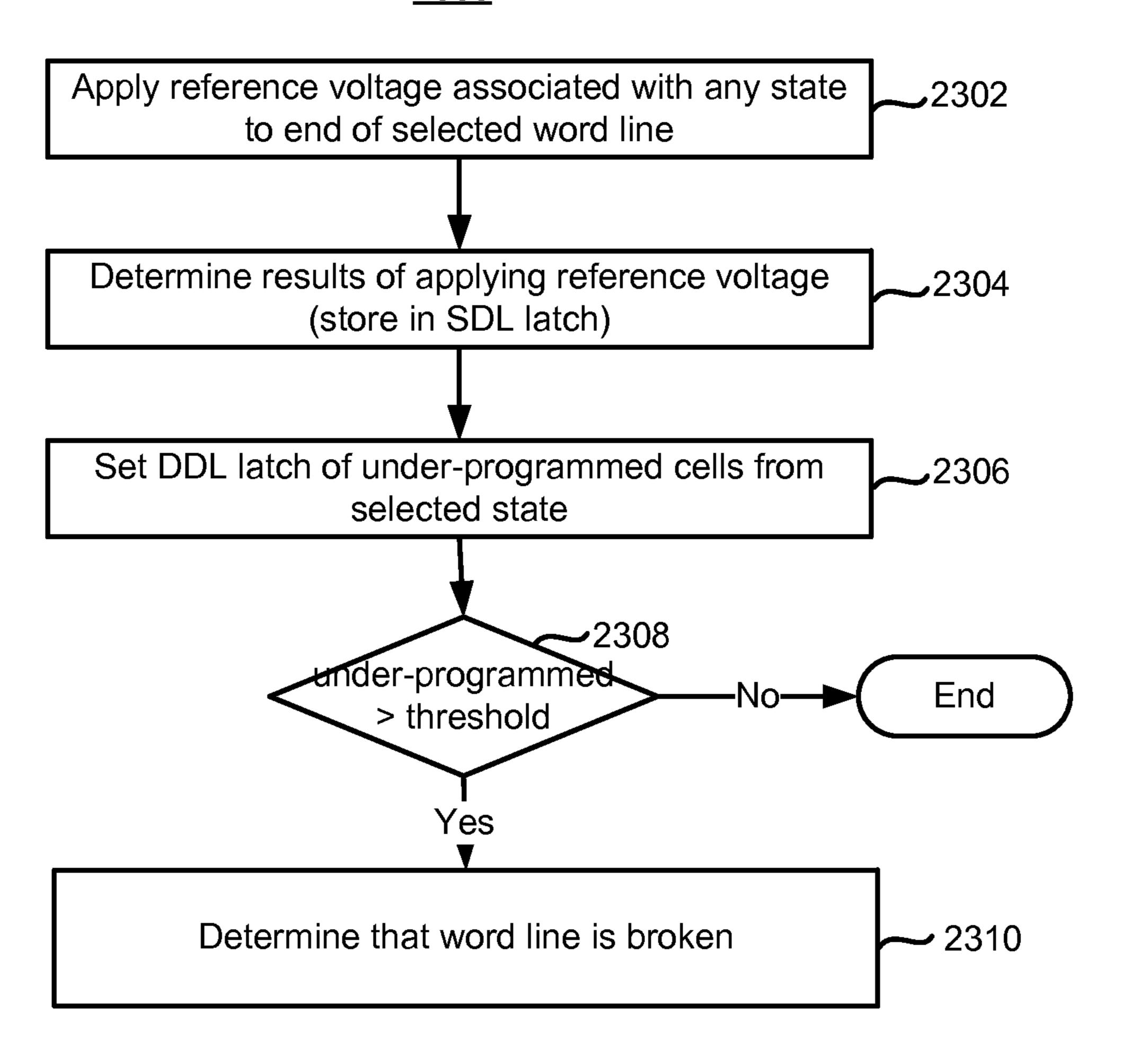

FIG. 23 is a flowchart of one embodiment of a process for detecting a broken word line.

### DETAILED DESCRIPTION

Methods and non-volatile storage systems are provided for detecting defects in word lines. In one embodiment, a "broken" word line defect is detected. Note that the term "broken" word line refers to a portion of the word line that has an abnormally high resistance. Some broken word lines may 25 result in under-programmed storage elements. However, the storage elements may not show up as being under-programmed during the verify stage of programming. For example, if the resistance is only slightly higher than normal, then this may not show up during programming as a program 30 defect. On the other hand, if the resistance is extremely high, it might get detected during programming. Embodiments disclosed herein are able to detect cases in which the resistance is higher than normal (such that it causes under-programmed cells), even though the resistance is not high enough such that 35 it is detected during programming as an error. Embodiments disclosed herein detect broken word lines and other defects after programming has completed.

Note that it can be very difficult to detect such conditions. Each storage element could store one, two, three, four, or 40 more bits. In one approach, storage elements are programmed to 2" states to store "n" bits. Referring briefly to FIG. 5A, each state (erase and A-G) may be assigned a unique range of threshold voltages. In the example of FIG. 5A, there is a considerable gap between states. In one possible approach, 45 the gap between threshold voltage distributions may be used to define a "forbidden area." In one possible approach, a storage element with a threshold voltage in the forbidden region is either over- or under-programmed.

In one possible approach, two reads (one each at two reference voltages) could be performed to count the number of storage elements that fall within the two reference voltages.

This may be used to count under-programmed storage elements, if there is considerable gap between states. However, as more bits are stored per storage element, the gap between states shrinks. A possible reason for the gap to shrink is floating gate to floating gate coupling. It is even possible for there to be some overlap between threshold voltage distributions, as in FIG. 5C. Therefore, it can be difficult to define a forbidden region between states. Thus, even if reads at two reference voltage are made, it might not be possible to tell whether the storage elements that fall within the two reference voltages are either over- or under-programmed.

Referring to FIG. **5**C, it is possible for there to be a separate threshold voltage distribution G' for memory cells that were 65 intended to be programmed to the G-state, but that were under-programmed as a result of being past a "break" in the

4

word line. If a read were to be made to count the total number of memory cells in a "forbidden region" **502**, this count could miss most of the memory cells in the G' distribution. Note that the width and height of the G' region could vary considerably depending on the location of the break along the word line, as well as the nature of the break (e.g., its resistance).

However, in one embodiment, a read is performed at Vgv\_UP (e.g., an under-program reference voltage), to determine which memory cells have a threshold voltage below Vgv\_UP. This may be performed during an erratic program detection (EPD), after programming has completed. Also, information is maintained as to which storage elements were intended to be programmed to, in this example, the G-state. Therefore, the memory cells in the G' distribution can be identified. Therefore, a broken word line may be detected.

In one embodiment, information is maintained as to which storage elements were intended to be programmed to a tracked state. This information may be maintained without 20 adding any additional data latches. Also, at least some of the data latches used during programming may be freed during the programming operation. Then, after programming is complete, the storage elements are read to determine which storage elements have a threshold voltage below a reference voltage level associated with the tracked state. However, those elements could include storage elements from any state below the tracked state, as well as under-programmed elements from the tracked state. By tracking which storage elements are in the tracked state, elements associated with other states may be filtered out such that an accurate assessment may be made as to which storage elements were under-programmed. From this information, a determination may be made whether the word line is defective. For example, if too many storage elements are under-programmed, this may indicate a broken word line. Further details are discussed below.

Another problem that may occur is A-state widening on a heavily cycled block. Even a word line without a break may show massive upper tail widening of the A-state for a heavily cycled block. This is depicted by the widened A' threshold distribution in FIG. 5D. However, note that a fresh (e.g., low cycled) block may not have nearly as much A-state widening.

Also note that memory cells that were intended to be programmed to the B-state may be under-programmed. The B' distribution represents that case with some under-programmed cells. One possible way to detect under-programmed B-state cells is to count the memory cells having a threshold voltage in region 504. However, this would count over-programmed A-state cells. An assumption might be made as to how many A-state cells are expected to be in region 504, such that the number of under-programmed B-state cells may be deduced from the total in region 504. However, the assumption of the number of A-state cells in region 504 may be inaccurate. As one example, for a fresh block the total number of cells in region 504 might not reach a failure criteria

However, in one embodiment, a read is performed at Vbv\_UP (e.g., an under-program reference voltage for the B-state). This counts all cells with a threshold voltage less than Vbv\_UP. This may be performed during an erratic program detection after programming is complete. Note that B-state cells that are below region 504 will be counted. Moreover, the memory cells that were intended to be programmed to the B-state are tracked. Therefore, A-state (and erase state) cells can be subtracted from the initial count. Therefore, the under-programmed B-state cells can be accurately counted. Note that this may allow detection of word line defects even for a fresh block.

One example of a suitable memory system for implementing embodiments uses the NAND flash memory structure, which arranges multiple transistors in series between two select gates. The transistors in series and the select gates are referred to as a NAND string. FIG. 1A is a top view showing one NAND string 90. FIG. 1B is an equivalent circuit thereof. The NAND string depicted includes four transistors, 100, 102, 104 and 106, in series and sandwiched between a first select gate 120 and a second select gate 122. Select gate 120 connects the NAND string to bit line 126. Select gate 122 connects the NAND string to source line 128. Select gates 120 and 122 are controlled by applying the appropriate voltages to control gates 120CG and 122CG, respectively. Each of the transistors 100, 102, 104 and 106 has a control gate and a floating gate. Transistor 100 has control gate 100CG and floating gate 100FG. Transistor 102 includes control gate **102**CG and floating gate **102**FG. Transistor **104** includes control gate 104CG and floating gate 104FG. Transistor 106 includes a control gate 106CG and floating gate 106FG. Con-20 trol gates 100CG, 102CG, 104CG and 106CG are connected to word lines WL3, WL2, WL1 and WL0, respectively. In one embodiment, transistors 100, 102, 104 and 106 are each memory cells. In other embodiments, the memory cells may include multiple transistors or may be different than that 25 depicted. Select gates 120 and 122 are connected to drain-side select line SGD and source-side select line SGS, respectively. Other types of non-volatile memory in addition to NAND flash memory can also be used.

FIG. 2 illustrates a non-volatile storage device 210 that 30 is further discussed below. may include one or more memory die or chips 212. Memory die 212 includes an array (two-dimensional or three dimensional) of memory cells 200, control circuitry 220, and read/ write circuits 230A and 230B. In one embodiment, access to the memory array 200 by the various peripheral circuits is 35 implemented in a symmetric fashion, on opposite sides of the array, so that the densities of access lines and circuitry on each side are reduced by half The read/write circuits 230A and 230B include multiple sense blocks 300 which allow a page of memory cells to be read or programmed in parallel. The 40 memory array 200 is addressable by word lines via row decoders 240A and 240B and by bit lines via column decoders 242A and 242B. In a typical embodiment, a controller 244 is included in the same memory device 210 (e.g., a removable storage card or package) as the one or more memory die 212. 45 Commands and data are transferred between the host and controller 244 via lines 232 and between the controller and the one or more memory die 212 via lines 234. One implementation can include multiple chips 212.

Control circuitry 220 cooperates with the read/write circuits 230A and 230B to perform memory operations on the memory array 200. The control circuitry 220 includes a state machine 222, an on-chip address decoder 224 and a power control module 226. The state machine 222 provides chiplevel control of memory operations. The on-chip address 55 decoder 224 provides an address interface to convert between the address that is used by the host or a memory controller to the hardware address used by the decoders 240A, 240B, 242A, and 242B. The power control module 226 controls the power and voltages supplied to the word lines and bit lines during memory operations. In one embodiment, power control module 226 includes one or more charge pumps that can create voltages larger than the supply voltage.

In one embodiment, one or any combination of control circuitry 220, power control circuit 226, decoder circuit 224, 65 state machine circuit 222, decoder circuit 242A, decoder circuit 242B, decoder circuit 240A, decoder circuit 240B,

6

read/write circuits 230A, read/write circuits 230B, and/or controller 244 can be referred to as one or more managing circuits.

FIG. 3 is a block diagram depicting one embodiment of a sense block 300. An individual sense block 300 is partitioned into a core portion, referred to as a sense module 380, and a common portion 390. In one embodiment, there is a separate sense module 380 for each bit line and one common portion 390 for a set of multiple sense modules 380. In one example, a sense block 300 will include one common portion 390 and eight sense modules 380. Each of the sense modules in a group will communicate with the associated common portion via a data bus 372.

Sense module **380** comprises sense circuitry **370** that deternines whether a conduction current in a connected bit line is above or below a predetermined threshold level. Sense module **380** also includes a bit line latch **382** that is used to set a voltage condition on the connected bit line. For example, a predetermined state latched in bit line latch **382** will result in the connected bit line being pulled to a state designating program inhibit (e.g., 1.5-3 V). As an example, a flag=0 can inhibit programming, while flag=1 does not inhibit programming.

Common portion 390 comprises a processor 392, five example sets of data latches 394 and an I/O Interface 398 coupled between the sets of data latches 394 and data bus 320. One set of data latches can be provide for each sense module, and five data latches identified by ADL, BDL, CDL, DDL, XDL may be provided for each set. The use of the data latches is further discussed below.

Processor 392 performs computations. For example, one of its functions is to determine the data stored in the sensed storage element and store the determined data in the set of data latches. At least some of the data latches in a set of data latches (e.g., 394) are used to store data bits determined by processor 392 during a read operation. At least some of the data latches in a set of data latches are also used to store data bits imported from the data bus 320 during a program operation. The imported data bits represent write data meant to be programmed into the memory. I/O interface 398 provides an interface between data latches 394-397 and the data bus 320.

In one embodiment, a user is able to stream data to be programmed into a storage element into the XDL latch. This program data may be transferred to the ADL, BDL, and CDL latches at the beginning of the program operation. Note this describes programming three bits per memory cell. In one embodiment, during a read operation, the ADL, BDL and CDL latch are used to store the three bits that are read from the memory cell. The user is able to toggle the read data out through the XDL latch in one embodiment.

In one embodiment, the user has access to the XDL latch, but not to the ADL, BDL, or CDL latches. For example, the user may be able to access the XDL latch to perform background caching during a program operation. Background caching is discussed in more detail below. In one embodiment, the user has limited access to the XDL during a program operation. For example, the user may be able to stream program data into the XDL latch prior to the programming operation. However, the user may not have access to the XDL latch during one embodiment of programming. In one embodiment, the XDL latch is used to store "lockout data" for the memory cell during a program operation. Briefly, the lockout data may indicate that a storage element is locked out from further programming. Further details are discussed below.

During reading or other sensing, the state machine 222 controls the supply of different control gate voltages to the addressed storage element. As it steps through the various

control gate voltages corresponding to the various memory states supported by the memory, the sense module 380 may trip at one of these voltages and an output will be provided from sense module 380 to processor 392 via bus 372. At that point, processor 392 determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 393. It then computes a binary encoding for the memory state and stores the resultant data bits into data latches (e.g., 394). In another embodiment of the core portion, bit line latch 382 serves both as a latch for latching the output of the sense module 380 and as a bit line latch as described above.

392. In one embodiment, each processor 392 will include an output line (not depicted) such that each of the output lines is wired-OR'd together. In some embodiments, the output lines are inverted prior to being connected to the wired-OR line. This configuration enables a quick determination during the 20 program verification process of when the programming process has completed because the state machine receiving the wired-OR can determine when all bits being programmed have reached the desired level. For example, when each bit has reached its desired level, a logic zero for that bit will be 25 sent to the wired-OR line (or a data one is inverted). When all bits output a data 0 (or a data one inverted), then the state machine knows to terminate the programming process. Because each processor communicates with eight sense modules, the state machine needs to read the wired-OR line eight 30 times, or logic is added to processor 192 to accumulate the results of the associated bit lines such that the state machine need only read the wired-OR line one time. Similarly, by choosing the logic levels correctly, the global state machine can detect when the first bit changes its state and change the 35 algorithms accordingly.

During program or verify, the data to be programmed is stored in the set of data latches 394-397 from the data bus 320. The program operation, under the control of the state machine, comprises a series of programming voltage pulses 40 applied to the control gates of the addressed storage elements. Each program pulse is followed by a read back (verify) to determine if the storage element has been programmed to the desired memory state. Processor 392 monitors the read back memory state relative to the desired memory state. When the 45 two are in agreement, the processor 392 sets the bit line latch **382** so as to cause the bit line to be pulled to a state designating program inhibit. This inhibits the storage element coupled to the bit line from further programming even if program pulses appear on its control gate. In other embodiments, the proces- 50 sor initially loads the bit line latch 382 and the sense circuitry sets it to an inhibit value during the verify process.

Each set of data latch stacks 394-397 contains a stack of data latches corresponding to the sense module 380, in one embodiment. In one embodiment, there are five data latches per sense module 380. The ADL, BDL, and CDL data latches can be implemented as a shift register so that the parallel data stored therein is converted to serial data in the XDL latch for transfer across data bus 320, and vice-versa. All the ADL, BDL, and CDL data latches corresponding to the read/write 60 block of m storage elements can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of read/write modules may be adapted so that each of its set of ADL, BDL, and CDL data latches will shift data in to or out of the XDL 65 latch in sequence as if they are part of a shift register for the entire read/write block.

8

In one embodiment, one purpose of the ADL, BDL, and CDL latches is to store data that is to be programmed into a storage element. For example, the storage elements may store three bits per storage element. In one embodiment, the storage elements store four bits per storage element. In this case, there may be an additional data latch (not depicted in FIG. 3) for storing the fourth bit of data that is to be programmed into a storage element. In one embodiment, the storage elements store only two bits per storage element, in which case one of the ADL, BDL, and CDL latches is not needed. The storage elements could store more than four bits per storage element, in which case there may be one data latch for each bit.

In one embodiment, the ADL, BDL, and CDL latches may also be used to store status information during programming. For example, after the storage element has reached its target threshold voltage, each latch (ADL, BDL, CDL) could be set to "1" to indicate that programming is complete for this storage element. In one embodiment, the latches are used differently as programming process has completed because the state machine receiving the ired-OR can determine when all bits being programmed

In one embodiment, the DDL latch is used to store status information during programming. In one embodiment, programming is slowed as the storage element nears the target threshold level. For example, the DDL latch may identify that a storage element's Vth is above a lower verify level (e.g., VvaL or VvbL in FIG. 5A). If that storage element is not yet locked out, then it may receive slower programming. If the DDL latch indicates the storage element's Vth is below the lower verify level, then it may be in a fast programming mode. Further details are discussed below.

In one embodiment, the XDL latch is used to store status information during programming. After the data from the XDL latch has been shifted in to the ADL, BDL, and CDL data latches, the XDL latch may be set to an initial state (e.g., "0"). After a memory cell has reached its target threshold voltage, the XDL latch may be set to another state (e.g., "1"). Thus, the XDL latch may store "lockout status." Therefore, the program data in the ADL, BDL, and CDL latches may be preserved both during and after the program operation. Further details are discussed below.

FIG. 4 depicts blocks of NAND flash memory cells in the memory array 200 of FIG. 2. The memory array can include many blocks 400. Two example blocks 400 are depicted in FIG. 4. Each block 400 includes a number of NAND strings. A set of bit lines, e.g., BL0, BL1, . . . may be shared among the blocks. Thus, each NAND string is associated with one bit line. Each NAND string is connected at one end to a drain select gate (SGD), and the control gates of the drain select gates are connected via a common SGD line. The NAND strings are connected at their other end to a source select gate which, in turn, is connected to a common source line 420. Sixty-four word lines, for example, WL0-WL63, extend between the source select gates and the drain select gates.

Other types of non-volatile memory in addition to NAND flash memory can also be used. For example, another type of memory cell useful in flash EEPROM systems utilizes a non-conductive dielectric material in place of a conductive floating gate to store charge in a non-volatile manner. A triple layer dielectric formed of silicon oxide, silicon nitride and silicon oxide ("ONO") is sandwiched between a conductive control gate and a surface of a semi-conductive substrate above the memory cell channel. The cell is programmed by injecting electrons from the cell channel into the nitride, where they are trapped and stored in a limited region. This stored charge then

changes the threshold voltage of a portion of the channel of the cell in a manner that is detectable. The cell is erased by injecting hot holes into the nitride. A similar cell can be provided in a split-gate configuration where a doped polysilicon gate extends over a portion of the memory cell channel to form a separate select transistor.

In another approach, NROM cells are used. Two bits, for example, are stored in each NROM cell, where an ONO dielectric layer extends across the channel between source and drain diffusions. The charge for one data bit is localized 10 in the dielectric layer adjacent to the drain, and the charge for the other data bit localized in the dielectric layer adjacent to the source. Multi-state data storage is obtained by separately reading binary states of the spatially separated charge storage regions within the dielectric. Other types of non-volatile 15 memory are also known.

Note that there may be thousands, or tens of thousands of bit lines. Therefore, a single word line may be used by tens of thousands of storage elements. Typically, there is a driver at one and of the word line that provides the read reference 20 voltages or the programming voltages.

FIG. 5A depicts an example set of threshold voltage distributions for an eight-state memory device in which each storage element stores three bits of data. A first threshold voltage (Vth) distribution is provided for erased (Er-state) 25 storage elements. Seven Vth distributions represent programmed states A through G. In one embodiment, the threshold voltages in the Er-state are negative and the threshold voltages in the A-G distributions are positive. However, all or a part of the threshold distribution in the Er-state may be 30 positive. Also, all or a part of the threshold distribution of the A-state may be negative (likewise for other data states).

Read reference voltages, Vra, Vrb, Vrc, etc. are also provided for reading data from storage elements. By testing whether the threshold voltage of a given storage element is above or below Vra, Vrb Vrc, etc. the system can determine the state, e.g., programming condition, the storage element is in.

ments on WLn are raised such that the storage element is programmed to an intermediate state. This intermediate state could have a lower tail just below VvD. In the second programming pass of one embodiment, the middle page is programmed for a selected word line WLn. This results in the creation of two more threshold voltage distributions (one

Further, verify reference voltages, Vva, Vvb Vvc, etc. are provided. When programming storage elements to the 40 A-state, B-state, C-state, etc. the system will test whether those storage elements have a threshold voltage greater than or equal to Vva, Vvb Vvc, etc.

In one embodiment, known as full sequence programming, storage elements can be programmed from the Er-state 45 directly to any of the programmed states A-G. For example, a population of storage elements to be programmed may first be erased so that all storage elements in the population are in the Er-state. A series of program pulses will then be used to program storage elements into their respective target states 50 A-G. While some storage elements are being programmed from the Er-state to the A-state, other storage elements are being programmed from the Er-state to the B-state, etc.

FIG. **5**A also shows verify low reference voltages VvAL, VvBL, VvCL, etc. These reference voltages may be used 55 during a program verify operation to determine whether a storage element is near its intended target threshold. If so, then programming speed may slow down. In one embodiment, Vdd is applied to bit lines that have reached their target state and are inhibited from further programming. Bit lines of 60 storage elements that are still below the verify low level may be grounded to allow for fast programming. However, when between the verify low level and the normal verify level, the bit line may receive an intermediate voltage (e.g., between ground and Vdd) to cause slow or moderate speed programming. As one example, the intermediate voltage could be about 0.6V to 0.8V. However, the intermediate voltage could

10

be either below or above this range. In one embodiment, the DDL latch indicates where the storage element is in this programming sequence. Further details are discussed below. In one embodiment, storage elements being programmed to the G-state do not receive the slow (or moderate) speed programming. Hence, no verify low reference voltage is depicted in FIG. 5A for the G-state. However, there may be a VvGL for the G-state, if desired.

In one embodiment, multiple passes may be used to program the storage elements. For example, one pass may be used to program each bit. Thus, in the case of storing three bits per memory cell, there may be three passes. In the case of storing two bits per memory cell, there may be two passes. In one embodiment, a multi-state storage element stores data for three different pages: a lower page, a middle page, and an upper page. The eight states, and the bits they represent, may be: Er-state (111), A-state (011), B-state (101), C-state (001), D-state (110), E-state (010), F-state (100), and G-state (000). For Er-state, all pages store a "1." For A-state, the lower page stores a "0", the middle page stores a "1" the upper page stores a "1." Other states can be deduced in a similar manner. Note that although specific bit patterns have been assigned to each of the states, different bit patterns may also be assigned. Also note that this bit and page assignment may be used for other programming sequences, such as the fast/slow programming described above.

In the first programming pass of one embodiment, the lower page is programmed for a selected word line WLn. If the lower page is to remain data 1, then the storage element state remains at the Erased state. If the data is to be programmed to 0, then the threshold voltage of the storage elements on WLn are raised such that the storage element is programmed to an intermediate state. This intermediate state could have a lower tail just below VvD. In the second programming pass of one embodiment, the middle page is programmed for a selected word line WLn. This results in the creation of two more threshold voltage distributions (one additional from each of the former distributions). In the third programmed for a selected word line WLn. This results in the creation of four more threshold voltage distributions (one additional from each of the former four distributions).

Although the programming examples depict eight data states and three pages of data, the concepts taught can be applied to other implementations with more or fewer than eight states and more or fewer than three pages. Moreover, in the example programming techniques discussed, the Vth of a storage element is raised gradually as it is programmed to a target data state. However, programming techniques can be used in which the Vth of a storage element is lowered gradually as it is programmed to a target data state. Programming techniques which measure storage element current can be used as well. The concepts herein can be adapted to the different programming techniques.

FIG. 5B illustrates that Vt distributions can partially overlap since the error correction algorithm can handle a certain percentage of cells that are in error. Note that in some embodiments, at one point in time the threshold voltage distribution may resemble FIG. 5A and at another time the threshold voltage distributions may overlap, as in FIG. 5B. For example, just after programming, the threshold voltage distribution may resemble FIG. 5A. However, over time, the threshold voltages of memory cells may shift, such that there may be overlap.

However, there may be overlap between at least some neighboring threshold distributions immediately after pro-

gramming. Note that it can be very difficult to detect word line defects when there is overlap between neighboring Vt thresholds.

Also note that contrary to the equal spacing/width of the depicted threshold voltage distributions, various distributions 5 may have different widths/spacings in order to accommodate varying amounts of susceptibility to data retention loss.

FIG. **6**A depicts several Vt distributions to further illustrate reference voltages in accordance with one embodiment. Only the erase, A-, and B-state are depicted. It will be understood that there are more states. For example, there may be eight states, as depicted in FIG. **5**A. Each data state is budgeted a range of threshold voltage, as indicated by the width of each individual Vt distribution.

A forbidden region **602** may be defined between the upper tail of a distribution and the verify reference level of the next highest state. In one embodiment, any storage element having a threshold voltage in the forbidden region may be classified as a type of error. For example, storage elements in the forbidden region **602** may be classified as either over-programmed, or under-programmed. Note that over- and underprogrammed may be defined differently from this example. Also note that a forbidden region **602** is not required to be at the exact location as in this example.

FIG. 6B shows over-programmed reference voltages, as 25 well as under-programmed reference voltages, in accordance with one embodiment. The over-programmed reference voltages may be at or lower than the lower boundary of one of the forbidden regions 602, in this embodiment. For example, Verase\_OP may be at or below the lower boundary of the 30 forbidden region 602 just above the erased state. Thus, storage elements that were intended to be in the erased state, but that have a Vt above Verase\_OP may be classified as over-programmed. Likewise, storage elements that were intended to be in the A-state, but that have a Vt above Vav\_OP may be 35 classified as over-programmed. Note that FIG. 6B depicts just one possible location for the over-programmed reference voltages.

The under-programmed reference voltages may be lower than or equal to the verify reference voltage for their respective state, in this embodiment. For example, Vav\_UP may be equal to or lower than VvA. Thus, storage elements that were intended to be in the A-state, but that have a Vt below Vav\_UP may be classified as under-programmed. Likewise, storage elements that were intended to be in the B-state, but that have 45 a Vt below Vbv\_OP may be classified as under-programmed. Note that FIG. 6B depicts just one possible location for the under-programmed reference voltages. Finally, please note that FIG. 6B does not depict any representative under-programmed or over-programmed storage elements.

As noted above, it is possible for word line defects to exist. Such defects may be present when the memory device is manufactured, or may develop over time. One example of a word line defect is referred to as a "broken" word line. A "broken word line" is one in which the resistance is higher than normal at some point along the word line. For a broken word line, the resistance higher than normal resistance may cause memory cells to fail to program properly; however, this may not show up during programming as a program defect. Note that if the resistance is extremely high, it might get 60 detected during programming due to a programming defect. Embodiments disclosed herein are able to detect cases in which the resistance is higher than normal (such that it causes under-programmed cells), even though the resistance is not high enough such that it is detected during programming as an 65 error. Embodiments disclosed herein detect broken word lines and other defects after programming has completed.

12

Note that typically the voltage on the word line is able to pass through the break to at least some extent. However, the signal may be impaired at the break. One possible reason for this impairment is due to the RC constant being higher at the break.

FIG. 7 depicts a schematic diagram of a portion of one embodiment of a memory array 200. FIG. 7 provides more details of one embodiment of the memory array 200 and associated row decoders 240A. The memory array has blocks 702(0)-702(m). Two blocks are depicted in FIG. 7, although there typically may be many more blocks 702. The word lines (WL0 . . . WLn) in a block 702 are modeled as having some resistance and some capacitance. The row decoders 240A include a block select transistor connected 704 to each word line. The voltage Vselect is applied to each block select transistor 704 in block 702(n) to select that block 702(n). The voltage Vss is applied to each block select transistor 704 in other blocks (e.g., block 702(0)), such that that other blocks are un-selected. Typically, there is one selected block and many unselected blocks. There may be one word line voltage transistor 706(0)-706(n) coupled to each word line. For example, transistor 706(0) is coupled to WL0 of each block 702 through one of the word line select transistors 704. Likewise, transistor 706(n) is coupled to WLn of each block 702 through one of the word line select transistors **704**. Note that a given word line voltage transistor 706 may be shared by different blocks. For example, if there are **64** word lines per block, there may be 64 word line voltage transistors 706.

Suitable voltages for a read or verify operation are being applied. A reference voltage (Vref) is applied to word line voltage transistor 706(n). The reference voltage may be a verify reference voltage, read reference voltage, etc. Vread is applied to word line voltage transistor 706(0). The voltage Vread may also be applied to other word line voltage transistors (not depicted in FIG. 7) in order to apply Vread to other un-selected word lines of the selected block 702(m). Because Vss is applied to the block select transistors 704 in the non-selected blocks, the voltages Vref and Vread do not pass to the word lines in the un-selected blocks. Note that other configurations could be used to provide the voltages to the word lines.

Because there is some resistance and some capacitance associated with the word lines (both selected and un-selected), the voltages that are applied to the word lines take some time to propagate to the far end of the word lines. Note that a word line may have many memory cells associated with it. For example, there may be thousands, tens of thousands or even more memory cells associated with a single word line. In some cases, bit lines of memory cells along the entire word line may be sensed during a sensing operation. For example, all memory cells on a word line might be sensed together, or every other memory cell might be sensed together. Even if fewer memory cells are being sensed, the selected word line voltage should be at its target reference voltage level before sensing the selected memory cell.

If the pulse width of the read reference voltage is long enough, relative to the RC time constant along the selected word line, then the reference voltage should be able to ramp up to its intended value at both the near and far ends of the selected word line. However, if there is a high resistance portion of the selected word line (e.g., a "break"), then the RC time constant may be so high that the reference voltage cannot ramp up to its intended value. Therefore, storage elements on the far side of the break (relative to the drive transistors 704) may receive a lower reference voltage than intended. Therefore, results of the read of verify cannot be trusted. Note that this may cause some storage elements to be under-pro-

grammed in that they may pass a program verify even though their Vt is below its target level.

Note that in some embodiments, the resistance of the control lines outside of the memory array 200 may be lower than the resistance of the word lines. Also, the control lines may, in 5 some cases, be spaced further apart than word lines in the memory array 200 are spaced. Therefore, capacitive coupling between control lines outside the memory array 200 may be less than for word lines. Due to this lower resistance and/or the lower capacitive coupling, the RC time constant for the 10 control lines may be lower than that of the word lines. Thus, the signal propagation delay along the control lines may be less of a problem than the delay along word lines.

FIG. 8 is a flowchart describing one embodiment of a programming process, which includes one or more verification steps. In step 810, the program voltage (Vpgm) is set to an initial value. Also, in step 810, a program counter (PC) is initialized to zero. In step 820, a program pulse is applied.

In step 822, a verification process is performed. In one embodiment, the verification is a concurrent coarse/fine 20 verify. Referring to FIG. 5A, some memory cells that are being programmed to the A-state are verified for the VvaL level, while others that are being programmed to the A-state are verified for the Vva level. During the initial programming steps in which the memory cell's threshold is well below the 25 final level (Vva), course programming is applied. However, after the memory cell's threshold voltage reaches VvaL, fine programming is used. Thus, while some memory cells are being verified for coarse programming, other memory cells are being verified for fine programming. Note that with 30 course/fine programming, some memory cells are being verified for one state (e.g., A-state), while others are being verified for another state (e.g., B-state). Note that when a particular memory cell has been verified as being programmed to its intended state, it may be locked out from further program- 35 sible. ming.

However, note that if there is a break on the selected word line being programmed, then the verification may produce an erroneous result. As noted above, a break in the word line could result in storage elements on the far side of the break 40 receiving a reference voltage that is smaller than intended. For example, storage elements that are intended to be programmed to the G-state should receive the reference voltage VvG (see FIG. 5A) at their control gate. However, they may in fact receive a lower voltage due to the break. Under normal 45 circumstances, if a storage element has not yet reached its target state (e.g., its actual Vt is below the reference voltage), the storage element will turn on in response to the verify voltage. On the other hand, if a storage element has reached its target state (e.g., its actual Vt is at or above the reference 50 voltage) it should not turn on. For example, consider the case of a storage element being targeted for the G-state. This storage element will be verified by applying VvG to the selected word line. If its actual Vt is below VvG it will conduct a current. After its actual Vt is above VvG it will no 55 longer turn on, indicating it has reached its target state.

However, since storage elements beyond the break receive too low of a verify voltage, they may fail to turn on when their actual Vt is below the target Vt. A storage element past the break might see a lower verify voltage than intended. For 60 example, a storage element that is targeted for the G-state might should see a verify voltage of VvG, but might experience a lower voltage at its control gate. As one particular example, the storage example might only see a verify voltage of VvF, if it is past the break. Therefore, in this particular example, when its actual Vt is greater than VvF it will pass the verify test. In general, the storage element past the break

14

could pass the verify test if its actual threshold voltage is below VvG. Therefore, programming will stop for that storage element. However, it may in fact be under-programmed.

In step 824, it is determined whether all of the memory cells have verified that their threshold voltages are at the final target voltage for that memory cell. If so, the programming process is completed successfully (status=pass) in step 826. If all of the memory cells are not all verified, then it is determined whether the program counter (PC) is less than a maximum value such as 20. If the program counter (PC) is not less than max (step 828), then the program process has failed (step 830). If the program counter (PC) is less than a maximum value (e.g., 20), then the program counter (PC) is incremented by 1 and the program voltage is stepped up to the next pulse in step 832. Subsequent to step 832, the process loops back to step 820 and the next program pulse is applied to the memory cells.

FIG. 9A depicts threshold voltage distributions to help illustrate a possible word line defect. The solid line represents desired threshold voltage distributions for each state. The dashed lines for states D-G represent possible threshold voltages if the word line has a defect, such as a break. As was noted during description of the programming operation (see FIG. 8), storage elements could be under-programmed if there is a word line break. Specifically, those storage elements beyond the break might be under-programmed. However, storage elements that are between the word line drive and the break should not be affected by the break. This is depicted in FIG. 9A by some storage elements being under-programmed. Of course, the location of the break (e.g., how near it is to the word line driver) may impact how much under-programming occurs. In one possible scenario, the G-state may experience more under-programming than the F-state, which experience more than the E-state, etc. However, other scenarios are pos-

In FIG. 9A, the under-programmed storage elements for the G-state are represented by region 902. The under-programmed region lies between the effective verify voltage at the far end of the selected word line and the VvG that was applied to the selected word line. Note that the effective VvG at the far end of the word line may be a function of the RC time constant due to the break and the shape (e.g., duration) of the verify pulse. Similar under-programmed regions are not depicted for other states, so as to not obscure the diagram. However, such regions could be defined.

Note that it is also possible for some states to have memory cells that are over-programmed, as a result of a defect such as a broken word line. As one example, some memory cells in the A-state, B-state, etc. might be over-programmed. FIG. 9B depicts a case in which lower states are over-programmed due to a defective word line. In this example, the A-state and B-state are over-programmed. However, other states may be affected, as well. In one embodiment, a broken word line is detected during an erratic program process by looking for over-programmed memory cells in lower states.

A possible cause for this is coupling between adjacent word lines and/or signals running above the word line and the far end of the broken word line. For example, during program verify the far end of broken word line could be floating (at least to some extent), if the resistance is high enough at the break. If the far end of a selected word line is floating, its voltage level could be significantly affected by its neighbors. As one example, this could cause the A-state verify voltage VvA to shift to the right, as compared to the correct level depicted in FIG. 9B. When verifying, a voltage Vread is typically applied to unselected neighbor word lines. As one example, Vread could be around 6-7 volts and an A verify

voltage around 0V. Therefore, the voltage at the far end of a broken word line could be higher than intended, especially when verifying lower voltage states. Note that the voltage at the far end of the broken word line may settle down after some period of time. However, it might not settle down in time prior to sensing the bit lines.

FIG. 10 is a flowchart of one embodiment of a process 1000 of determining whether a word line is defective following programming of non-volatile storage. In one embodiment, process 1000 determines whether the word line is broken (e.g., has an abnormally high resistance portion).

Step 1002 is programming non-volatile storage elements associated with a selected word line. FIG. 8 shows one embodiment of programming non-volatile storage. In one embodiment, when performing the verify operations the width of the voltage pulses has a first duration. This first duration may not be sufficient to allow the verify voltage to fully develop at the end of the selected word line past a break (if a break exists). Therefore, it is possible that storage elements that are past the break could be under-programmed. It is also possible that the first duration may not be long enough for the voltage at the far end to settle down to the correct verify voltage in the event its voltage is coupled up by neighbor word lines (especially for lower voltage states). Therefore, it is possible that storage elements that are past the break could be over-programmed.

Note that steps 1004-1010 may be performed after a programming operation. Step 1004 is to maintain information after the programming operation is complete that indicates 30 which elements were intended to be programmed to a tracked data state. Any of the data states may be tracked. In one embodiment, one of the data latches (e.g., 394-397) that was used during programming is used to maintain this information. Further details are discussed below. Note that at least 35 some of the data latches may be freed up during programming, in one embodiment. Therefore, these free latches may be used for other purposes.

Step 1006, a reference voltage that is associated with the tracked data state is applied to the selected word line. This 40 reference voltage might have the same magnitude as the verify reference voltage for the tracked state. However, that is not required. In one embodiment, the reference voltage of step 1006 is an under-program voltage for the tracked state. The under-program voltage may be equal to or less than the 45 verify voltage. Examples were discussed with respect to FIG. 6B. For example, the voltage Vbv\_UP might be used if the B-state is the first state in question.

In one embodiment, the reference voltage in step **1006** has a longer duration than the verify voltages used during programming. The reference voltage may be long enough to increase the probability that the applied reference voltage will reach the storage elements past a break in the word line. However, it may not be possible to guarantee that the reference voltage will in fact reach the storage elements past the break. For example, if the RC time constant is too high, then a pulse of reasonable duration may not reach the steady state value at the end of the word line. However, in this case it is likely that the program operation fails, in one embodiment. That is, if the RC time constant is too high, then the program operation of one embodiment fails.

The reference voltage of step **1006** may be long enough to increase the probability that far end of the word line will settle down to the intended reference voltage. However, it may not be possible to guarantee that the far end will settle down to the 65 intended reference voltage. However, in this case it is likely that the program operation fails, in one embodiment.

**16**

In step 1008, results of applying the reference voltage are determined. For example, the results indicate which storage elements have a threshold voltage greater than the reference voltage. Note that applying the reference voltage may cause the selected storage element to turn on and have a "conduction current." There are numerous ways to perform step 1008. In one embodiment, the conduction current (if any) of the storage element cell is measured to determine whether the storage element turned on in response to the voltage applied to the word line. If the conduction current is measured to be greater than a certain value, then it is assumed that the storage element turned on and the voltage applied to the word line is greater than the threshold voltage of the storage element. If the conduction current is not measured to be greater than the 15 certain value, then it is assumed that the storage element did not turn on and the voltage applied to the word line is not greater than the threshold voltage of the storage element.

In one embodiment, the conduction current of a storage element is measured by the rate it discharges a dedicated capacitor in the sense amplifier. In one embodiment, the conduction current of the selected storage element allows (or fails to allow) the NAND string that included the storage element to discharge the bit line. The charge on the bit line is measured after a period of time to see whether it has been discharged or not.

In step 1010, a determination is made whether the word line has a defect based on the results from step 1008 and the maintained information. In one embodiment, step 1010 includes determining whether the non-volatile storage elements that were both intended to be programmed to the first data state and conducted a current in response to the first reference voltage is greater than a threshold number of the non-volatile storage elements.

For example, referring to FIG. 9, step 1010 may determine which storage elements were intended to be programmed to the G-state (based on the maintained information), but have a threshold voltage below VvG (note that a different reference voltage maybe used). In effect, one embodiment of step 1010 may determine which storage elements are in region 902.

Two aspects are to be noted. First, note that storage elements that were intended to be programmed to the any state but the G-state are not included in the count of step 1010. Second, only a single read (at step 1006) is needed. Performing only a single read saves time. This is in contrast with techniques that need to read at at least two points to count how many total cells are in a region such as region 902. Note that if two reads were to be performed at say, Vfv\_OP and Vgv\_UP, then a count could be made of how many cells are in this region. However, because there may be overlap between the F-state and G-state, it may not be possible to tell how many of those cells are F-state and how many are G-state. Thus, such techniques may not be able to accurately determine how many G-state memory cells were under-programmed. Moreover, referring to FIG. 9, there may be a substantial number of under-programmed G-state cells having threshold voltages between the effective VvG at the far side of the word line and VvG. However, the effective VvG could be any value, and is unlikely to correspond to Vfv\_OP. Therefore, reading at Vfv\_OP and Vgv\_UP is not likely to count G-state cells in region 902.

In one embodiment, step 1010 determines which memory cells that were intended to be programmed to the A-state were over-programmed. In this case, an over-program reference voltage (e.g., Vav\_OP, FIG. 6B) may be used as a reference voltage. The tracked state may be the A-state in this example.

FIG. 11 is a flowchart of one embodiment of a process 1100 of operating data latches while programming and verifying

non-volatile storage. Process 1100 provides details of maintaining information that indicates which storage elements were programmed to a particular state. Note that data latches that initially indicate which state that a storage element is to be programmed to may be freed up during programming. Therefore, this information may be lost during the programming process. In one embodiment, the process 1100 "tracks" or maintains information for one state. By tracking a state, it is meant that the process 1100 maintains information after the programming is over as to which storage elements were 10 intended to be programmed to a particular (tracked) state. Note that this may be the erased state, as well as any of the programmed states.

Process 1100 provides further details of one embodiment 15 one embodiment, the current of the bit line is sensed. of steps 1002 and 1004 from FIG. 10. Reference will be made to a set of data latches **394** in FIG. **3**. As noted above, three data latches ADL, BDL, and CDL initially store the data to be programmed into the storage element. Thus, the storage element stores three bits, in one embodiment. The fourth data 20 latch, DDL, is used for what is referred to herein as "quick" pass write" (QPW) status. Note that there could be more or fewer than four latches.

In step 1102, data latches are set to their target program state. In one embodiment, ADL, BDL, and CDL latches are 25 set as indicated in FIG. 13A. Note that a different bit assignment may be used.

In step 1104, the DDL latch is set to an initial state. In one embodiment, the DDL latch is set as indicated in FIG. 13A. In that embodiment, the DDL latch for all storage elements is set 30 to "0" except for those that are to remain in the erase-state. In one embodiment, every DDL latch is set to "0". In one embodiment, setting the DDL latch for all states to "0" is used when tracking the erased state.

In step 1106, programming conditions are applied based at 35 least in part on the data latches. In one embodiment, bit line voltages are set. In one embodiment, three categories are used. One for storage elements that are locked out (or inhibited) from any further programming, one is for storage elements that are still undergoing fast programming, and one is 40 for storage elements that are to receive slower programming because they are near their target threshold voltages.

In one embodiment, bit lines for storage elements locked out or inhibited storage elements are set to Vdd, bit lines for storage elements undergoing nominal (or fast) programming 45 are set to ground (e.g., Vss), bit lines for the third category are set to an intermediate voltage between ground and Vdd. This intermediate voltage slows down the programming to some extent.

In step 1108, one or more programming pulses are applied 50 to the selected word line. A pass voltage (e.g., Vpass) may be applied to unselected word lines.

In step 1110, a verify low pulse is applied to the selected word line. Referring to FIG. 5A, VvAL may be applied. In step 1112, sensing is performed to determine whether storage 55 elements that were intended to be programmed to the state associated with the verify low pulse have reached the verify low point. For example, storage elements intended to be programmed to the A-state (as indicated in ADL, BDL, CDL) are sensed to determine whether their threshold voltage is at or 60 above VvAL. In one embodiment, the current of the bit line is sensed.

In step 1114, the DDL latches are set based on the results of step 1112. Note that the DDL latches in question are those associated with the state that was just verified. In one embodi- 65 ment, the DDL latch is set to "1" to indicate that slow programming is to be performed. For example, storage elements

**18**

intended to be programmed to the A-state that have a threshold voltage above VvAL have their DDL latch set to "1".

In step 1116, the verify reference voltage is increased to the associated verify high reference voltage for the present state being verified. For example, the reference voltage is set to VvA (see, FIG. 5A). In one embodiment, step 1116 involves increasing the voltage on the selected word line.

In step 1118, sensing is performed to determine whether storage elements that were intended to be programmed to the state associated with the nominal verify pulse have reached the nominal verify point. For example, storage elements intended to be programmed to the A-state are sensed to determine whether their threshold voltage is at or above VvA. In

In step 1120, the ADL, BDL, and CDL latches are set based on the results of step 1120. Note that the latches in question are those associated with the state that was just verified. In one embodiment, one or more of the ADL, BDL, and CDL latches are set to "1" to indicate that programming is to be inhibited. For example, storage elements intended to be programmed to the A-state that have a threshold voltage above VvA have their ADL, BDL, and CDL latches set to "1".