#### US00RE45989E

## (19) United States

## (12) Reissued Patent

#### Morita et al.

### (10) Patent Number: US RE45,989 E

#### (45) Date of Reissued Patent: Apr. 26, 2016

# (54) SEMICONDUCTOR DEVICE AND METHOD FOR DRIVING THE SAME

- (71) Applicant: PANASONIC CORPORATION, Osaka (JP)

- (72) Inventors: **Tatsuo Morita**, Kyoto (JP); **Manabu Yanagihara**, Osaka (JP); **Hidetoshi Ishida**, Osaka (JP); **Yasuhiro Uemoto**,

Toyama (JP); **Hiroaki Ueno**, Osaka (JP); **Tsuyoshi Tanaka**, Osaka (JP); **Daisuke**

**Ueda**, Osaka (JP)

- (73) Assignee: PANASONIC CORPORATION, Osaka (JP)

- (21) Appl. No.: 14/301,066

- (22) Filed: Jun. 10, 2014

#### Related U.S. Patent Documents

#### Reissue of:

| (64) | Patent No.: | 8,203,376     |

|------|-------------|---------------|

|      | Issued:     | Jun. 19, 2012 |

|      | Appl. No.:  | 12/445,390    |

|      | PCT Filed:  | Nov. 20, 2007 |

PCT No.: PCT/JP2007/072476

§ 371 (c)(1),

(2) Date: **Apr. 13, 2009**PCT Pub. No.: **WO2008/062800**PCT Pub. Date: **May 29, 2008**

#### (30) Foreign Application Priority Data

| Nov. 20, 2006 | (JP) | 2006-312502 |

|---------------|------|-------------|

| Dec. 12, 2006 | (JP) | 2006-334094 |

| Jun. 8, 2007  | (JP) | 2007-153031 |

(51) **Int. Cl.**

| H03K 17/687 | (2006.01) |

|-------------|-----------|

| H01L 29/778 | (2006.01) |

| H01L 27/06  | (2006.01) |

(52) **U.S. Cl.** CPC ...... *H01L 29/7787* (2013.01); *H01L 27/0605* (2013.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,903,091 A 2/1990 Baba et al. 5,111,256 A 5/1992 Ohata et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

EP 1 128 443 A1 8/2001 JP 52-072185 6/1977

(Continued)

#### OTHER PUBLICATIONS

Notice of Allowance issued in U.S. Appl. No. 12/445,390 with Date Mailed Mar. 5, 2012.

(Continued)

Primary Examiner — Linh M Nguyen (74) Attorney, Agent, or Firm — McDermott Will & Emery LLP

#### (57) ABSTRACT

A semiconductor device includes a semiconductor layer stack 13 formed on a substrate 11 and having a channel region, a first electrode 16A and a second electrode 16B formed spaced apart from each other on the semiconductor layer stack 13, a first gate electrode 18A formed between the first electrode 16A and the second electrode 16B, and a second gate electrode 18B formed between the first gate electrode 18A and the second electrode 16B. A first control layer 19A having a p-type conductivity is formed between the semiconductor layer stack 13 and the first gate electrode 18A.

#### 84 Claims, 23 Drawing Sheets

# US RE45,989 E Page 2

| (56)                                                                                                                                         | Referen                                                                                               | ces Cited                     |                                                                  | FOREIGN PA                                              | TEN                   | T DOCUMENTS                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------|---------------------------------------------------------|-----------------------|--------------------------------------------------|

| U                                                                                                                                            | J.S. PATENT                                                                                           | DOCUMENTS                     | JP                                                               | 52-072185 A                                             | A                     | 6/1977                                           |

|                                                                                                                                              |                                                                                                       |                               | JP                                                               | 61-230379 A                                             |                       | 10/1986                                          |

| 6,111,273 A                                                                                                                                  | A 8/2000                                                                                              | Kawai                         | JP                                                               | 2-254762                                                |                       | 10/1990                                          |

| , ,                                                                                                                                          |                                                                                                       | Ishiguro et al H01L 27/1214   | JP                                                               | 02-254762 A                                             | A                     | 10/1990                                          |

| , ,                                                                                                                                          |                                                                                                       | 257/E21.413                   | JP                                                               | 4-80957 A                                               | A                     | 3/1992                                           |

| 6,586,766 B                                                                                                                                  | 32 * 7/2003                                                                                           | Yamazaki H01L 27/1237         | JP                                                               | 9-199452 A                                              | A                     | 7/1997                                           |

|                                                                                                                                              |                                                                                                       | 257/57                        | JP                                                               | 11-261053                                               |                       | 9/1999                                           |

| 6,600,192 B                                                                                                                                  | 31 7/2003                                                                                             | Sugawara et al.               | JP                                                               | 11-261053 A                                             | A                     | 9/1999                                           |

| 7,038,252 B                                                                                                                                  |                                                                                                       | Saito et al.                  | JP                                                               | 2000-349095 A                                           | A                     | 12/2000                                          |

| 7,576,373 B                                                                                                                                  | 8/2009                                                                                                | Hikita et al.                 | JP                                                               | 2003-059946 A                                           | A                     | 2/2003                                           |

| 7,595,680 B                                                                                                                                  | 32 * 9/2009                                                                                           | Morita et al 327/427          | JP                                                               | 2003-228320                                             |                       | 8/2003                                           |

| 7,852,137 B                                                                                                                                  | 32 * 12/2010                                                                                          | Machida et al 327/427         | JP                                                               | 2003-228320 A                                           | A                     | 8/2003                                           |

| 7,982,240 B                                                                                                                                  | 32 * 7/2011                                                                                           | Machida 257/133               | JP                                                               | 2004-273486                                             |                       | 9/2004                                           |

| 2002/0017648 A                                                                                                                               | $\lambda 1 = 2/2002$                                                                                  | Kasahara et al.               | JP                                                               | 2004-273486 A                                           | A                     | 9/2004                                           |

| 2002/0024057 A                                                                                                                               | $\lambda 1 = 2/2002$                                                                                  | Inokuchi et al.               | WO                                                               | 2005/070007 A                                           | <b>A</b> 2            | 8/2005                                           |

| 2005/0189559 A                                                                                                                               | A1 9/2005                                                                                             | Saito et al.                  | WO                                                               | 2005/070009 A                                           | <b>A</b> 2            | 8/2005                                           |

| 2005/0189561 A                                                                                                                               | A1* 9/2005                                                                                            | Kinzer et al 257/192          | WO                                                               | 2005/079370 A                                           | <b>A</b> 2            | 9/2005                                           |

| 2006/0033480 A                                                                                                                               | A1 2/2006                                                                                             | Soldano                       | WO                                                               | 2006/020921 A                                           | <b>A</b> 2            | 2/2006                                           |

| 2006/0060871 A                                                                                                                               | A1 3/2006                                                                                             | Beach                         | WO                                                               | 2006/061942 A                                           | <b>A</b> 1            | 6/2006                                           |

| 2006/0062032 A                                                                                                                               | A1 3/2006                                                                                             | Soldano                       |                                                                  | OTHER I                                                 | DI IDI                |                                                  |

| 2006/0145746 A                                                                                                                               | A1* 7/2006                                                                                            | Metzler 327/427               |                                                                  | OTHER                                                   | PORI                  | LICATIONS                                        |

| 2006/0273347 A                                                                                                                               | A1 12/2006                                                                                            | Hikita et al.                 |                                                                  | 4                                                       |                       |                                                  |

| 2007/0102727 A                                                                                                                               | A1 5/2007                                                                                             | Twynam                        | European Search Report issued in European Patent Application No. |                                                         |                       |                                                  |

| 2007/0131968 A                                                                                                                               | A1 6/2007                                                                                             | Morita et al.                 | 07832206.2-2203, mailed Nov. 19, 2010.                           |                                                         |                       |                                                  |

| 2009/0121775 A                                                                                                                               |                                                                                                       | Ueda et al.                   |                                                                  |                                                         |                       |                                                  |

| 2009/0154210 A                                                                                                                               |                                                                                                       | Fujikawa                      | * cited by e                                                     | examiner                                                |                       |                                                  |

| 2006/0033480 A<br>2006/0060871 A<br>2006/0062032 A<br>2006/0145746 A<br>2006/0273347 A<br>2007/0102727 A<br>2007/0131968 A<br>2009/0121775 A | A1 3/2006<br>A1 3/2006<br>A1 3/2006<br>A1 7/2006<br>A1 12/2006<br>A1 5/2007<br>A1 6/2007<br>A1 5/2009 | Soldano Beach Soldano Metzler | WO European Se 07832206.2-                                       | 2006/061942 A OTHER I arch Report issue 2203, mailed No | A1<br>PUBI<br>ed in 1 | 6/2006 LICATIONS European Patent Application No. |

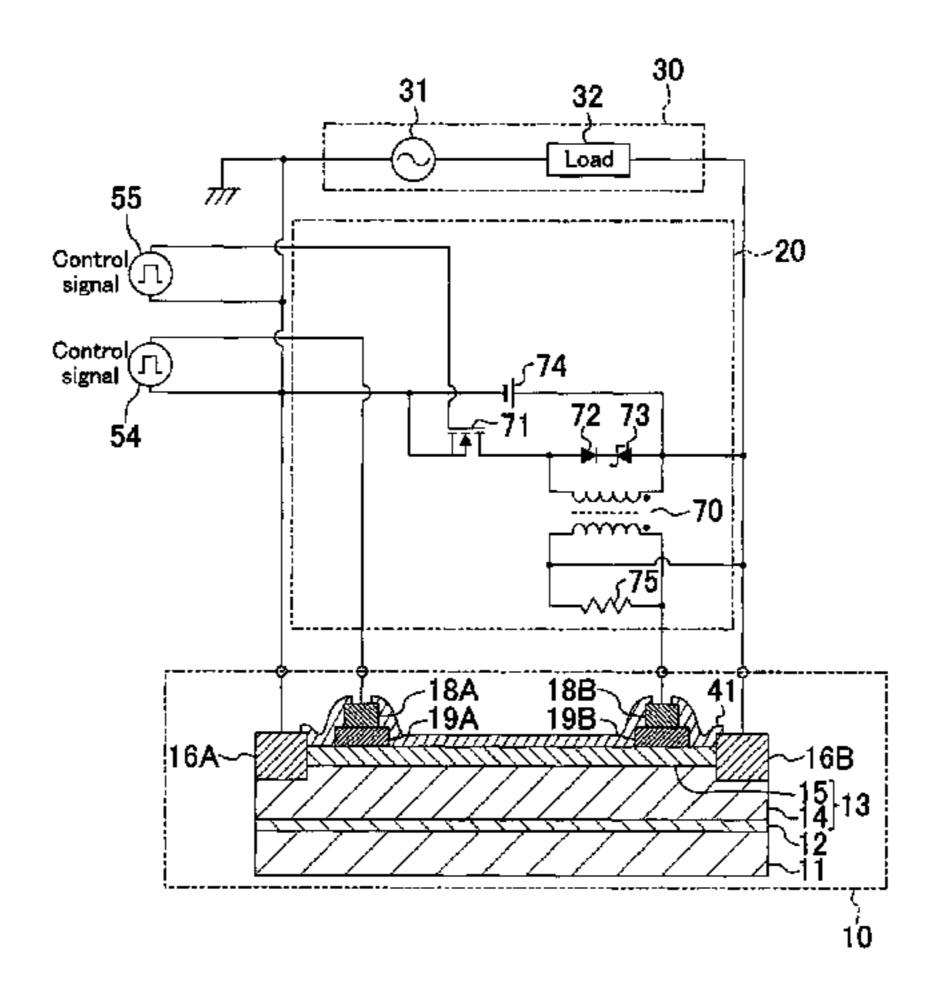

FIG.1

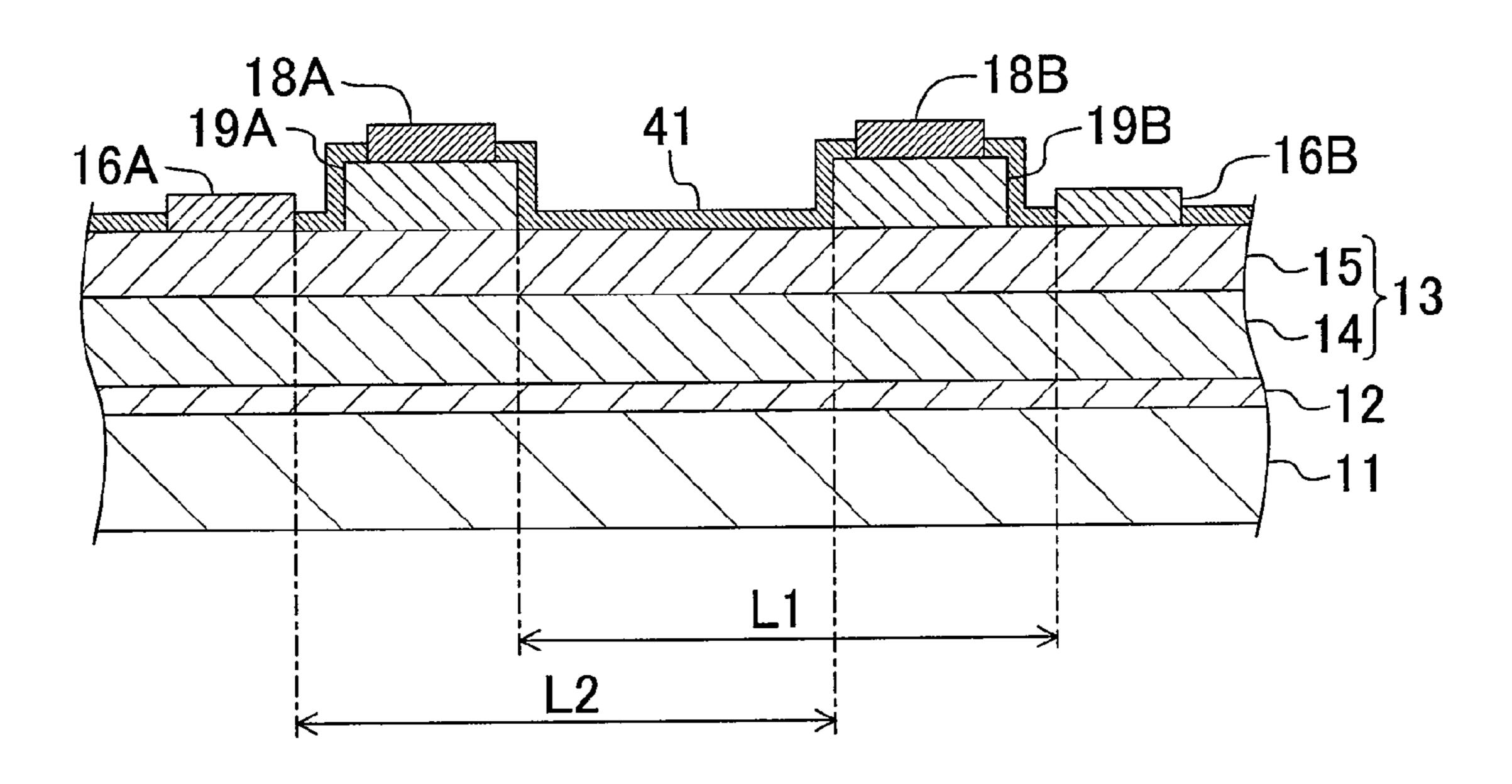

FIG.2

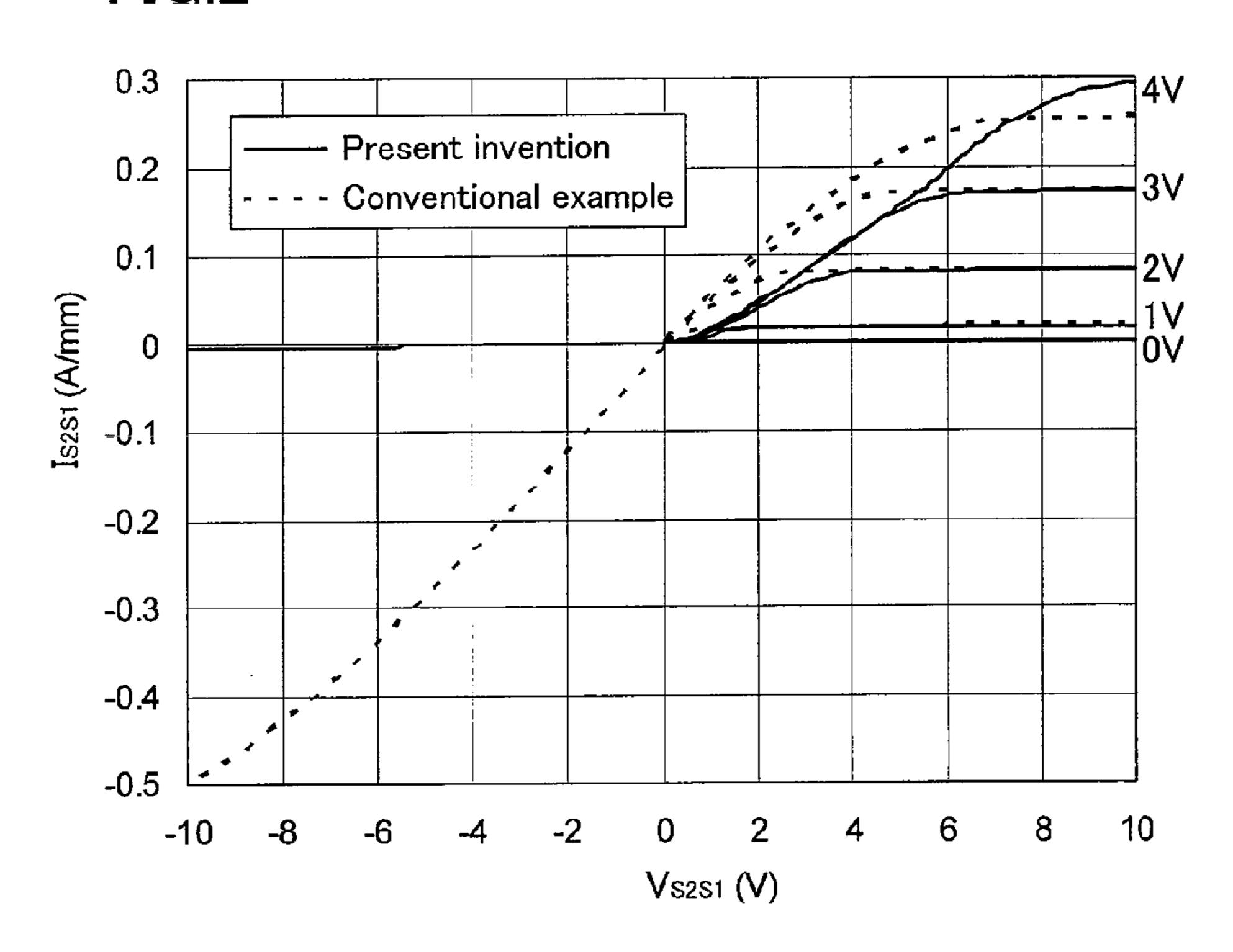

FIG.3

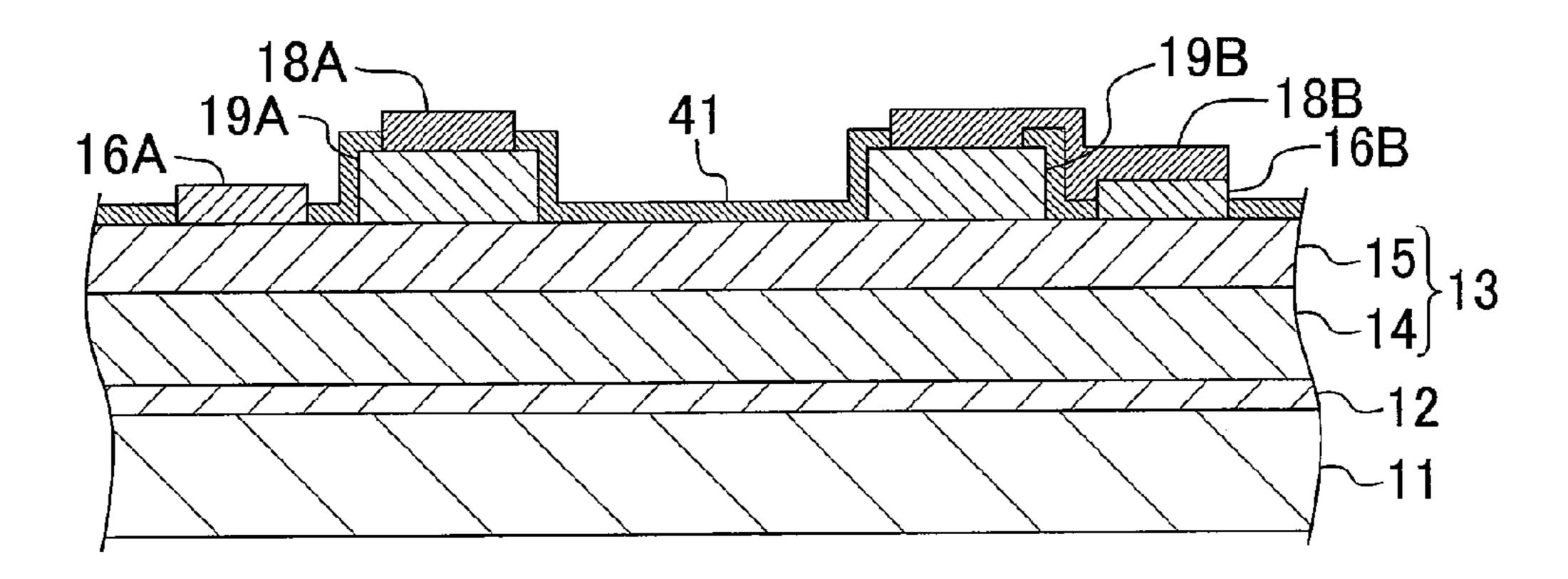

FIG.4

FIG.5

FIG.6

FIG.7

FIG.8

FIG.9

FIG.10

FIG.11

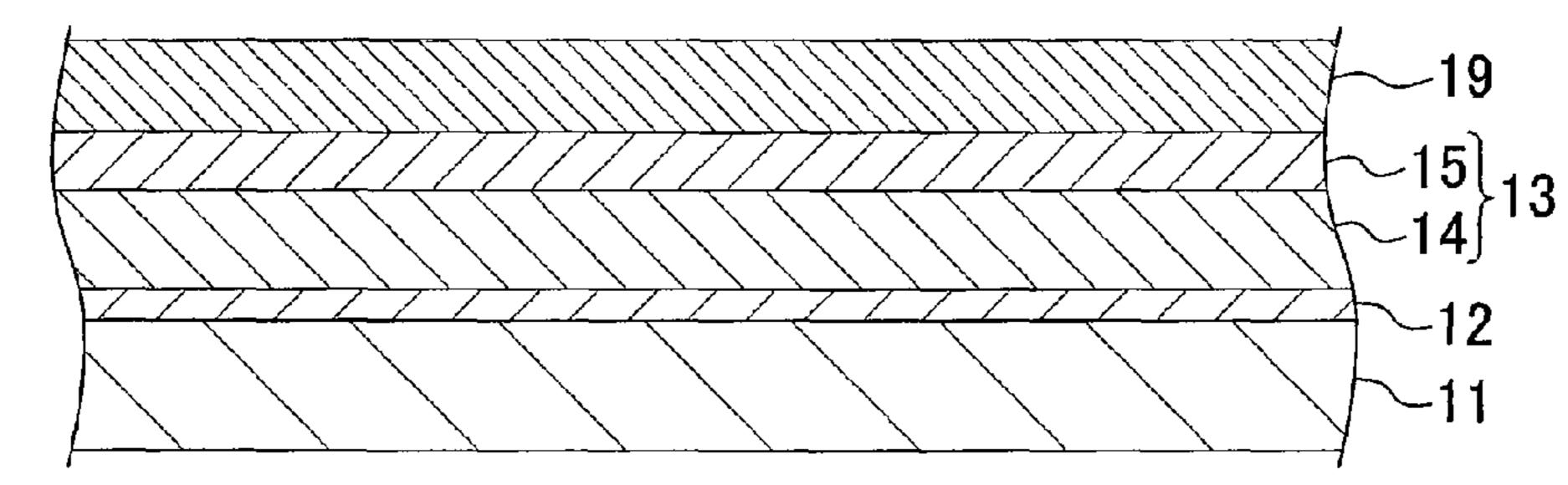

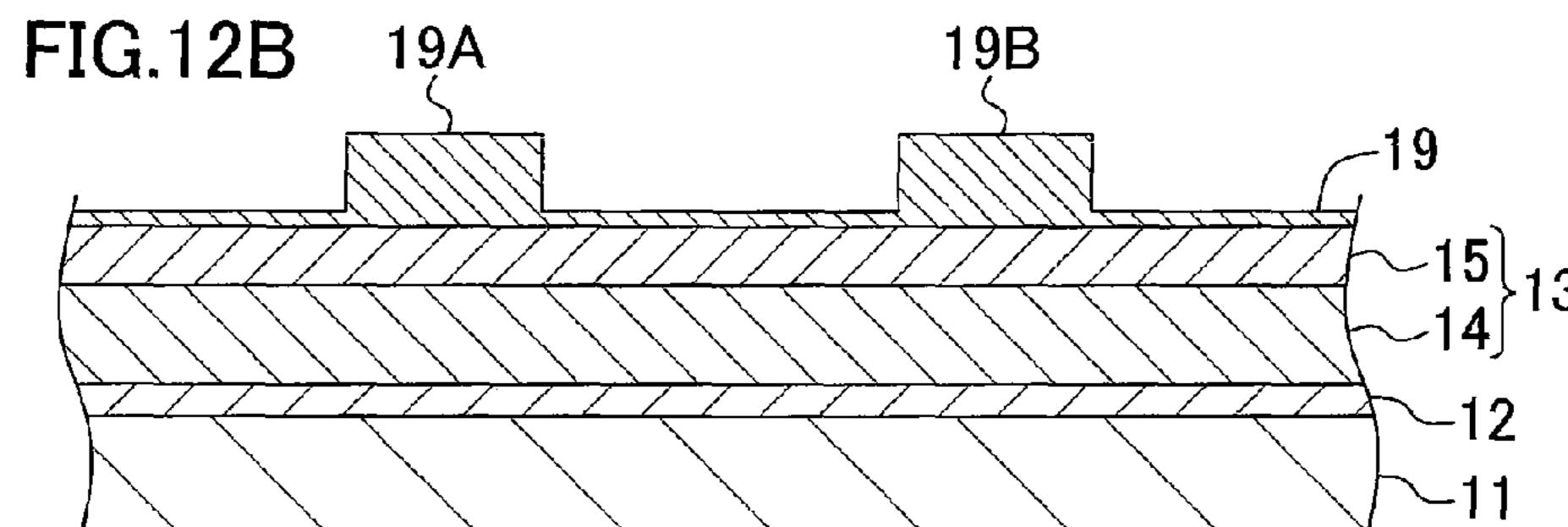

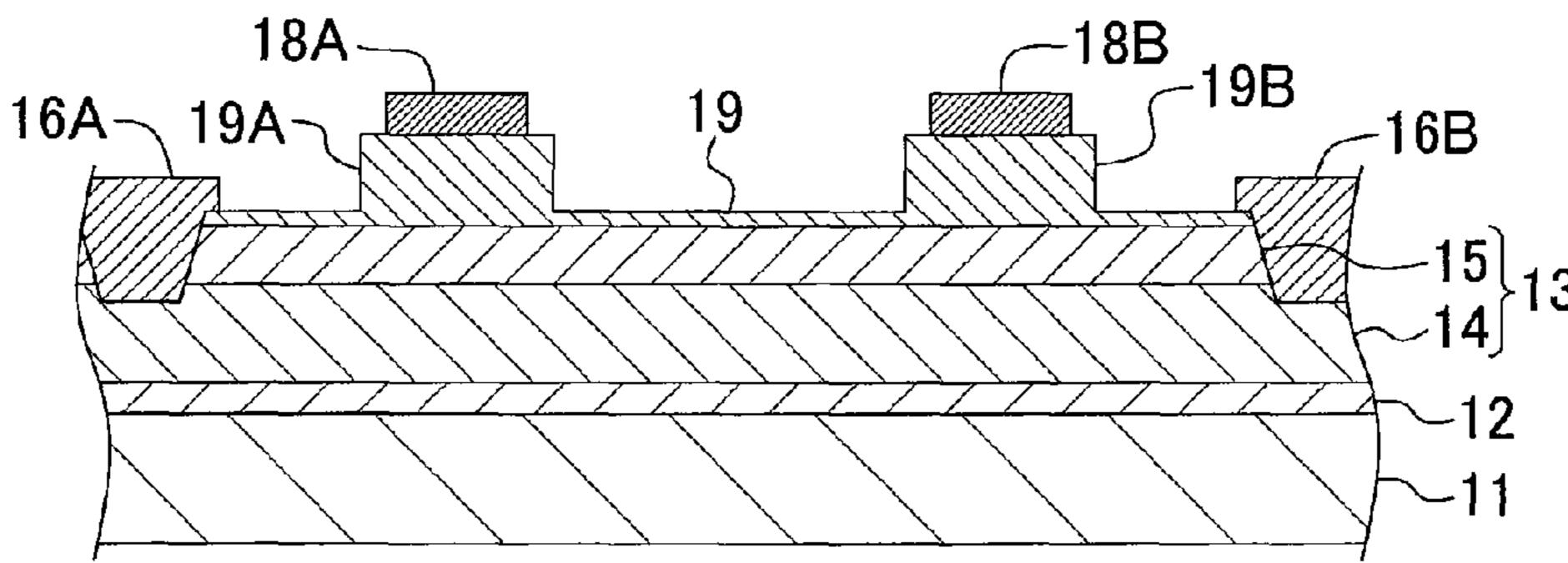

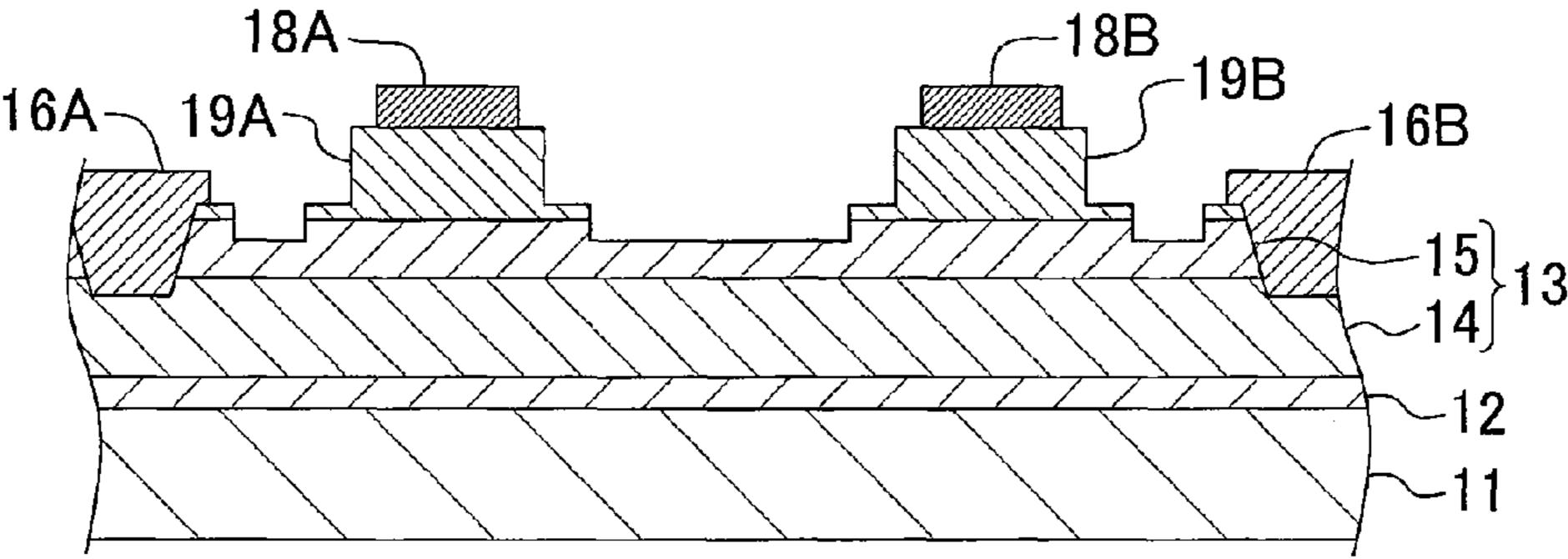

FIG.12A

FIG.12C

FIG.12D

FIG.13

FIG.14

FIG. 15

FIG.16A

FIG.16B

FIG.16C

FIG.17

FIG.18A

FIG.18B

FIG.18C

FIG.19

FIG.20A

FIG.20B

FIG.20C

FIG.21A

FIG.21B

FIG.21C

FIG.22

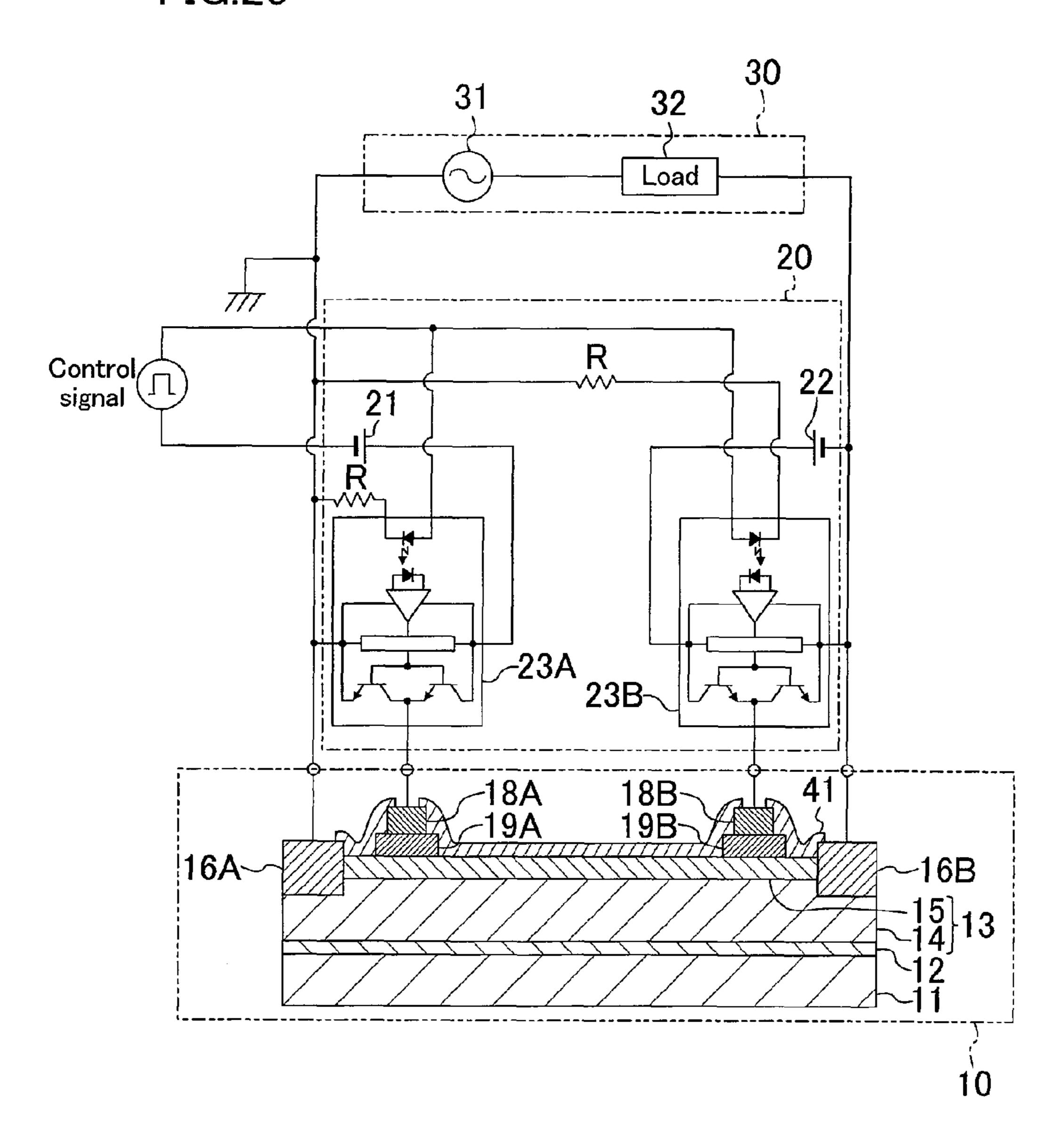

FIG.23

FIG.24

FIG.25

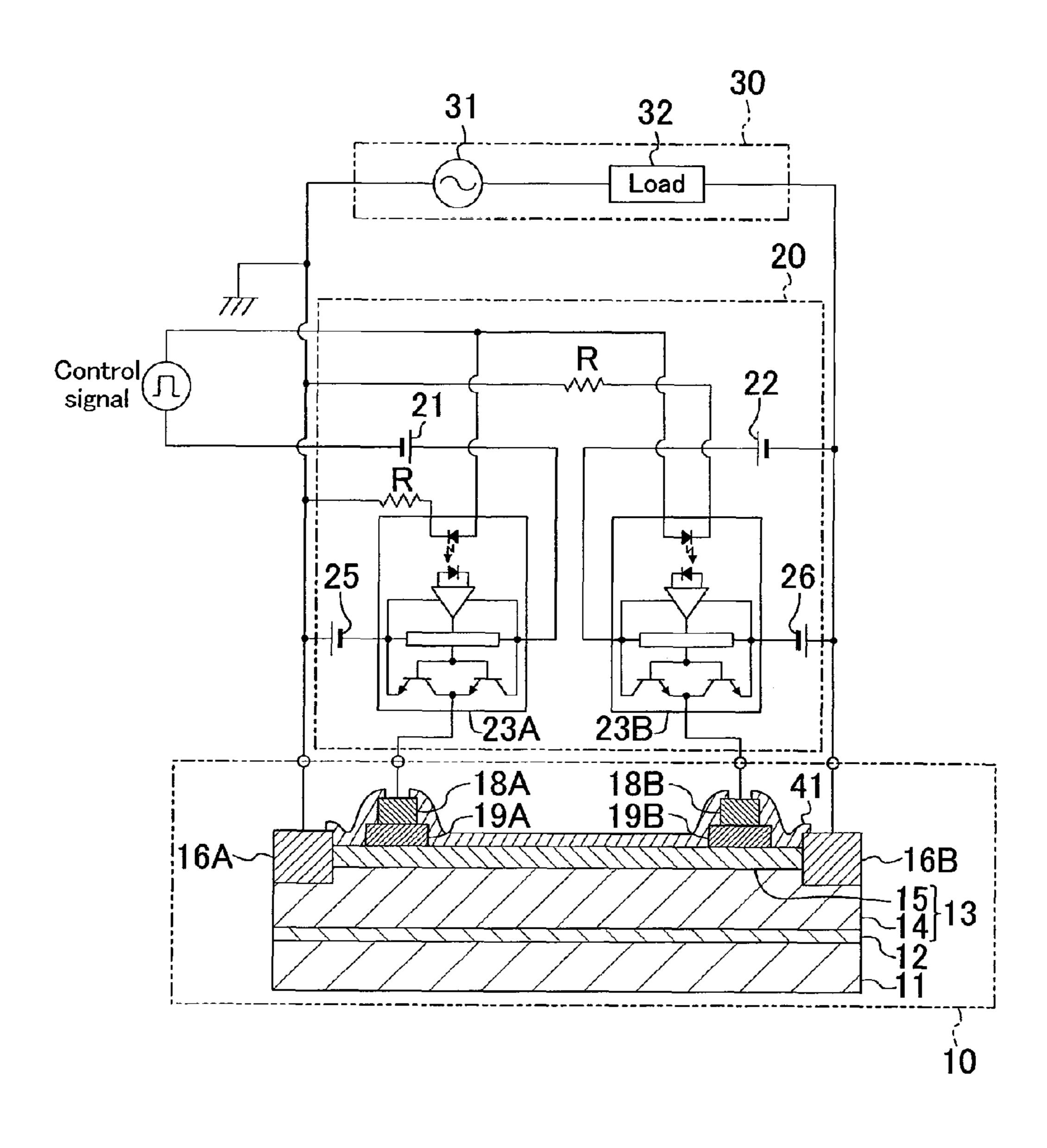

FIG.26

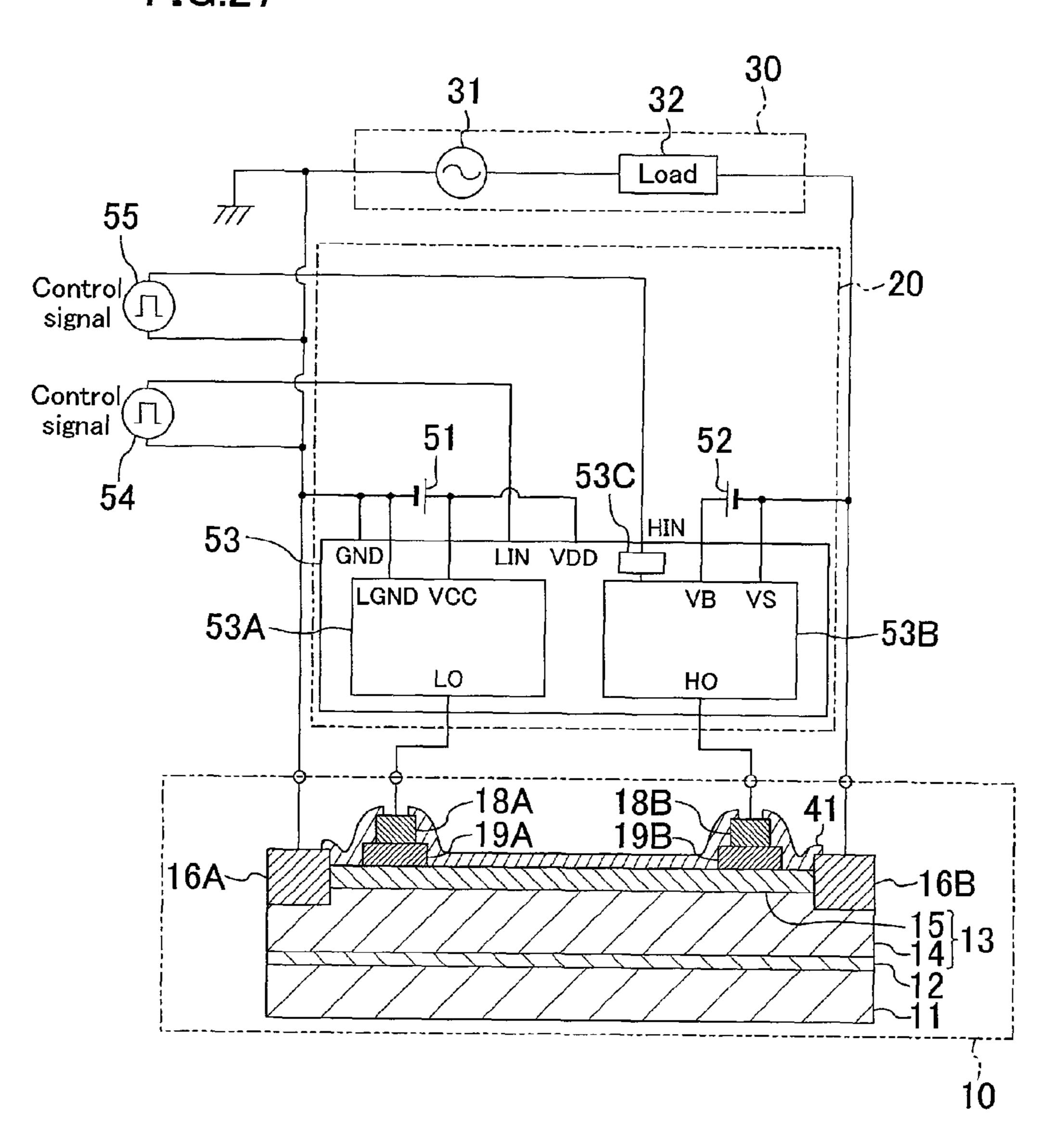

FIG.27

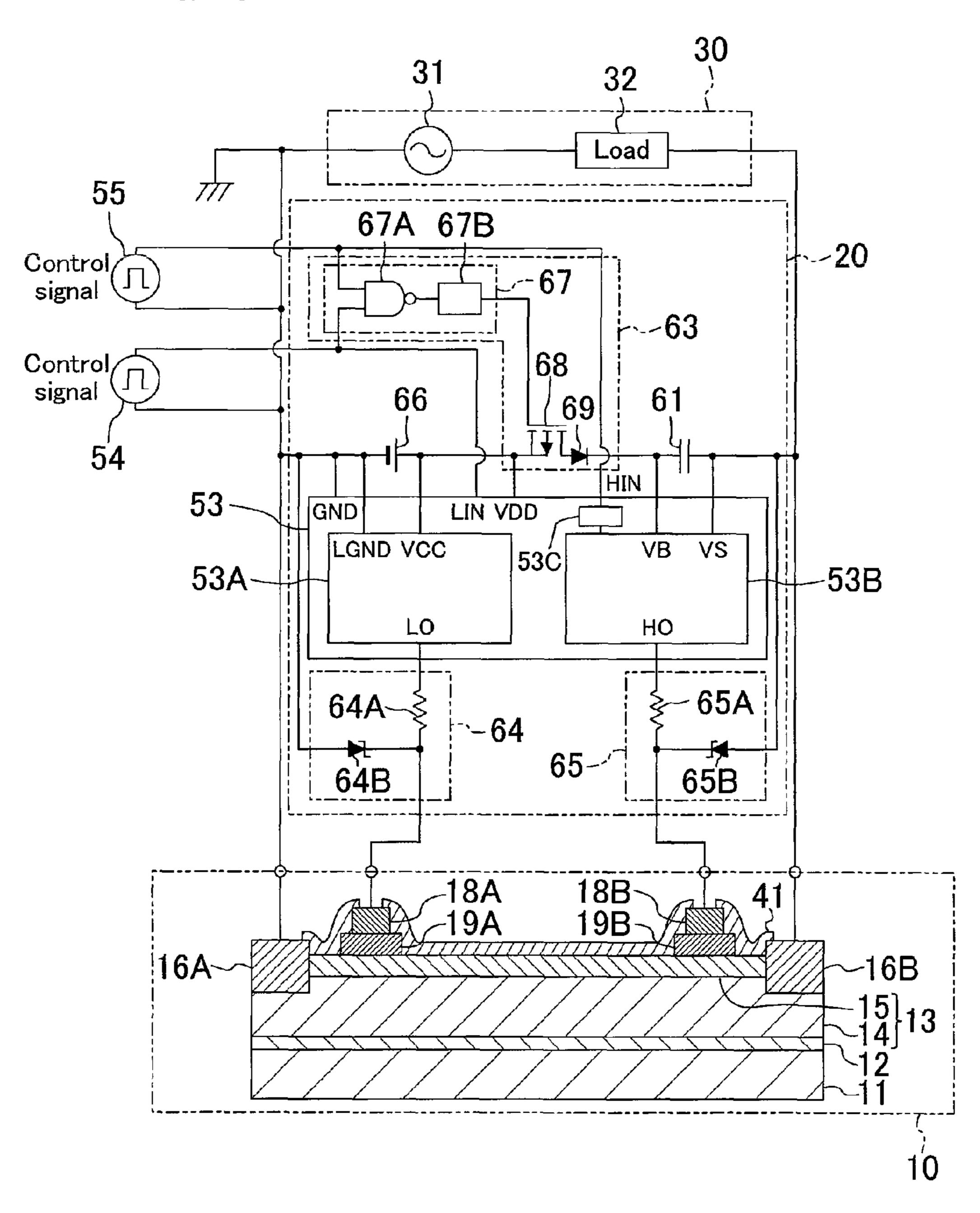

FIG.28

FIG.29

FIG.30

FIG.31

# SEMICONDUCTOR DEVICE AND METHOD FOR DRIVING THE SAME

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

#### RELATED APPLICATIONS

This application *is a reissue application of U.S. Pat. No.* 8,203,376 issued on Jun. 19, 2012 issued from U.S. patent <sup>15</sup> application Ser. No. 12/445,390 filed on Apr. 13, 2009, which is the U.S. National Phase under 35 U.S.C. §371 of International Application No. PCT/JP2007/072476, filed on Nov. 20, 2007, which in turn claims the benefit of Japanese Application Nos. 2006-312502, filed on Nov. 20, 2006, 2006-334094, <sup>20</sup> filed on Dec. 12, 2006, and 2007-153031, filed on Jun. 8, 2007, the disclosures of which Applications are incorporated by reference herein.

#### TECHNICAL FIELD

The present invention relates to a semiconductor device, and more particularly to a semiconductor device capable of a bidirectional switching operation used for power control, and a method for driving the same.

#### BACKGROUND ART

In recent years, field effect transistors (FETs) using a nitride semiconductor such as gallium nitride (GaN) have 35 been widely researched as power switching devices. Since GaN can form various compound materials with aluminum nitride (AlN) and indium nitride (InN), nitride semiconductors can form heterojunctions as do arsenic-based semiconductors such as gallium arsenide (GaAs). Therefore, they can 40 be used for forming heterojunction field effect transistors (HFETs) with heterojunctions.

For most of devices currently used in the field of power electronics, normally-off type devices are strongly desired for ensuring safety in the event of a failure. However, even if a 45 nitride semiconductor is undoped, spontaneous polarization and piezoelectric polarization produce a high concentration of carriers at the heterojunction interface. Therefore, when an FET is produced by using a nitride semiconductor, it is likely to be of the depression type (normally-on type), and it is 50 difficult to obtain characteristics of the enhancement type (normally-off type) (see, for example, Patent Document 1).

Structures of normally-off type FETs using nitride semi-conductors include, but not limited to: a structure in which the thickness and/or the Al composition ratio of an AlGaN layer 55 being the barrier layer in the AlGaN/GaN heterojunction is reduced; a structure in which a recessed portion is provided in the gate portion to thereby shift the threshold voltage in the positive direction; a structure in which an FET is produced on the (10-12) plane of a sapphire substrate to prevent a polarization electric field from being generated in the crystal growth direction of the nitride semiconductor.

Junction field effect transistors (JFETs) having a p-type GaN layer formed in a gate portion have also been proposed (see, for example, Patent Document 2). A JFET employs, for 65 the gate thereof, a pn junction having a larger built-in potential than that of a Schottky junction. Therefore, the gate turn-

2

ON voltage can be increased, and the gate leakage current can be suppressed even when a positive gate voltage is applied.

Moreover, in the field of power electronics, there is a demand for a bidirectional switch capable of bidirectional current control, and a bidirectional switch using a GaN semiconductor has been proposed. (Patent Document 3)

Patent Document 1: Japanese Laid-Open Patent Publication No. 2004-273486

Patent Document 2: Japanese Laid-Open Patent Publication No. 2003-228320

Patent Document 3: United States Patent Application Publication No. 2005/189561

#### DISCLOSURE OF THE INVENTION

#### Problems to be Solved by the Invention

However, the following problem will be encountered when one attempts to realize a bidirectional switching operation required for power control, or the like, by using a normally-off type FET using a conventional nitride semiconductor as described above. The bidirectional switching operation as used herein refers to a switching operation with which a current can be conducted in at least one direction and with which the current can be blocked in both directions.

First, since a conventional FET has a small breakdown voltage (reverse voltage) to a negative bias; a bidirectional switch product capable of conducting and blocking a current cannot be realized unless a plurality of elements are combined together. Moreover, where operated as a bidirectional switch, control from external equipment will be complicated. Moreover, it is difficult to realize a control in four quadrants and to operate it as a diode, i.e., a reverse-blocking switch.

A conventional normally-off type FET has a narrow margin for the voltage that can be applied to the gate electrode. Therefore, a gate voltage higher than about 1 V cannot be applied, and an erroneous operation may therefore occur due to noise.

It is an object of the present invention to solve the problems in the prior art and to realize a semiconductor device which has excellent reverse voltage characteristics, which as a single element constitutes a bidirectional switch product, and which allows for the application of a high gate voltage.

#### Means for Solving the Problems

Specifically, a semiconductor device of the present invention includes: a semiconductor layer stack formed on a substrate and having a channel region; a first electrode and a second electrode formed spaced apart from each other on the semiconductor layer stack; a first gate electrode formed between, and spaced apart from, the first electrode and the second electrode, and a second gate electrode formed between the first gate electrode and the second electrode; and a first control layer having a p-type conductivity formed between the semiconductor layer stack and the first gate electrode.

The semiconductor device of the present invention includes the first control layer having a p-type conductivity. Therefore, it is possible to inject holes into the channel region by applying a forward bias from the first gate electrode to the channel region. Since the holes injected into the channel region act like donor ions, the carrier concentration can be modulated in the channel region. As a result, it is possible to realize a normally-off type nitride semiconductor transistor having a large operating current.

In a semiconductor device of the present invention, the semiconductor device has a mode of operation in which a positive voltage with reference to a potential of the first electrode is applied to the first gate electrode to thereby inject holes into the channel region.

In a semiconductor device of the present invention, a threshold voltage of the first gate electrode and that of the second gate electrode are different from each other.

In a semiconductor device of the present invention, the second gate electrode is in a Schottky junction with the semiconductor layer stack.

In a semiconductor device of the present invention, the semiconductor layer stack includes a depressed portion; and the second gate electrode is in contact with a bottom surface of the depressed portion.

A semiconductor device of the present invention further includes a second control layer having a p-type conductivity formed between the semiconductor layer stack and the second gate electrode.

In a semiconductor device of the present invention, an 20 uppermost layer of the semiconductor layer stack includes a first portion, and a second portion having a thickness smaller than that of the first portion; and the first control layer and the second control layer are formed on the first portion.

In a semiconductor device of the present invention, the first 25 portion surrounds a third portion having a thickness less than or equal to that of the second portion; and the first control layer and the second control layer is formed on the first portion and the third portion.

In a semiconductor device of the present invention, the 30 semiconductor layer stack includes a first semiconductor layer, a second semiconductor layer having a bandgap larger than that of the first semiconductor layer, and an etching absorbing layer having a bandgap smaller than that of the second semiconductor layer, wherein the layers are formed in 35 this order from bottom; and the etching absorbing layer is the uppermost layer of the semiconductor layer stack.

In a semiconductor device of the present invention, the first control layer and the second control layer have a protruding portion.

A semiconductor device of the present invention further includes a high resistance layer formed on the semiconductor layer stack in a region between the first control layer and the second control layer, the high resistance layer having a resistance higher than that of the first control layer and the second 45 control layer.

In a semiconductor device of the present invention, the high resistance layer is of a gallium oxide or is a layer containing boron ions.

A semiconductor device of the present invention further 50 includes an undoped semiconductor layer formed on the semiconductor layer stack, wherein the first control layer and the second control layer are p-type impurity-diffused regions selectively formed in the undoped semiconductor layer.

A semiconductor device of the present invention further 55 includes an oxide film layer having an opening formed on the semiconductor layer stack, wherein the first control layer and the second control layer are formed so as to be in contact with the semiconductor layer stack exposed through the opening.

In a semiconductor device of the present invention, an 60 silicon carbide semiconductor. interval between the first gate electrode and the second gate electrode is larger than that between the first electrode and the first gate electrode, and is larger than that between the second electrode and the second gate electrode.

In a semiconductor device of the present invention, the 65 semiconductor device has a mode of operation in which a voltage greater than or equal to a built-in potential of a pn

junction formed by the first control layer and the semiconductor layer stack is applied between the first gate electrode and the first electrode.

In a semiconductor device of the present invention, a potential greater than a threshold voltage of the first gate electrode with reference to a potential of the first electrode is applied to the first gate electrode and a potential less than or equal to a threshold voltage of the second gate electrode with reference to a potential of the second electrode is applied to the second gate electrode, whereby the semiconductor device is brought to a reverse-blocking state in which a current flows from the second electrode to the first electrode but not from the first electrode to the second electrode; and a potential less than or equal to the threshold voltage of the first gate electrode is applied to the first gate electrode with respect to the potential of the first electrode and a potential less than or equal to the threshold voltage of the second gate electrode is applied to the second gate electrode with respect to the potential of the second electrode, whereby the semiconductor device is brought to a non-conductive state in which a current does not flow in either direction between the first electrode and the second electrode.

In a semiconductor device of the present invention, the second electrode and the second gate electrode are electrically shorted with each other.

In a semiconductor device of the present invention, a potential greater than the threshold voltage of the first gate electrode with reference to the potential of the first electrode is applied to the first gate electrode and a potential greater than the threshold voltage of the second gate electrode with reference to the potential of the second electrode is applied to the second gate electrode, whereby the semiconductor device is brought to a conductive state in which a current flows in both directions between the first electrode and the second electrode; and a potential less than or equal to the threshold voltage of the first gate electrode is applied to the first gate electrode with respect to the potential of the first electrode and a potential less than or equal to the threshold voltage of the second gate electrode is applied to the second gate electrode with respect to the potential of the second electrode, whereby the semiconductor device is brought to a non-conductive state in which a current does not flow in either direction between the first electrode and the second electrode.

A semiconductor device of the present invention further includes a third control layer having a p-type conductivity formed on the semiconductor layer stack and spaced apart from the first control layer, wherein the second gate electrode and the second electrode are formed integrally on the third control layer.

In a semiconductor device of the present invention, the semiconductor layer stack includes a first semiconductor layer and a second semiconductor layer which are layered in this order from a side of the substrate; the second semiconductor layer has a bandgap larger than that of the first semiconductor layer; and the channel region is an interface region between the first semiconductor layer and the second semiconductor layer.

In a semiconductor device of the present invention, the semiconductor layer stack is of a nitride semiconductor or a

In a semiconductor device of the present invention, the nitride semiconductor contains at least one of gallium nitride and aluminum gallium nitride.

A semiconductor device of the present invention further includes a control section for controlling a voltage applied to the first gate electrode and second gate electrode, wherein: in a conductive state in which a current flows in both directions

between the first electrode and the second electrode, the control section applies, to the first gate electrode, a voltage higher than a threshold voltage of the first gate electrode with respect to a potential of the first electrode, and applies, to the second gate electrode, a voltage higher than a threshold voltage of the second gate electrode with reference to a potential of the second electrode; in a non-conductive state in which a current does not flow in either direction between the first electrode and the second electrode, the control section applies, to the first gate electrode, a voltage less than or equal to the threshold voltage of the first gate electrode with reference to the potential of the first electrode, and applies, to the second gate electrode, a voltage less than or equal to the threshold voltage of the second gate electrode with reference to the potential of the second gate electrode with reference to the potential of the second electrode.

In a semiconductor device of the present invention, the control section includes: a first power supply for applying a voltage between the first electrode and the first gate electrode; and a second power supply for applying a voltage between the second electrode and the second gate electrode.

In a semiconductor device of the present invention, an output voltage of the first power supply and that of the second power supply are equal to each other.

In a semiconductor device of the present invention, the first power supply and the second power supply are each a variable 25 power supply capable of varying the output voltage thereof.

In a semiconductor device of the present invention, the control section includes: a first control terminal receiving a first control signal for controlling a voltage applied to the first gate electrode; a second control terminal receiving a second 30 control signal for controlling a voltage applied to the second gate electrode; a first gate driving circuit driven by the first control signal for switching between a first state in which a voltage higher than the threshold voltage of the first gate electrode is applied between the first electrode and the first 35 gate electrode, and a second state in which a voltage less than or equal to the threshold voltage of the first gate electrode is applied between the first electrode and the gate electrode; and a second gate driving circuit driven by the second control signal for switching between a third state in which a voltage 40 higher than the threshold voltage of the second gate electrode is applied between the second electrode and the second gate electrode, and a fourth state in which a voltage less than or equal to the threshold voltage of the second gate electrode is applied between the second electrode and the second gate 45 electrode, wherein: in the conductive state, the first gate driving circuit is set to the first state and the second gate driving circuit is set to the third state; and in the non-conductive state, the first gate driving circuit is set to the second state and the second gate driving circuit is set to the fourth state.

In a semiconductor device of the present invention, the first gate driving circuit and the second gate driving circuit are controlled by control signals whose reference potentials are different from each other.

In a semiconductor device of the present invention, the semiconductor element is of a normally-off type; the control section includes: a first power supply for applying a voltage higher than the threshold voltage of the first gate electrode between the first electrode and the first gate electrode; and a second power supply for applying a voltage higher than the 60 threshold voltage of the second gate electrode between the second electrode and the second gate electrode; the first gate driving circuit connects the first power supply between the first electrode and the first gate electrode with each 65 other in the second state; and the second gate driving circuit connects the second power supply between the second elec-

6

trode and the second gate electrode in the third state, and shorts the second electrode and the second gate electrode with each other in the fourth state.

In a semiconductor device of the present invention, the semiconductor element is of a normally-on type; the control section includes: a third power supply for applying a voltage less than or equal to the threshold voltage of the first gate electrode between the first electrode and the first gate electrode; and a fourth power supply for applying a voltage less than or equal to the threshold voltage of the second gate electrode between the second electrode and the second gate electrode; the first gate driving circuit shorts the first electrode and the first gate electrode with each other in the first state, and connects the third power supply between the first electrode and the first gate electrode in the second state; and the second gate driving circuit shorts the second electrode and the second gate electrode with each other in the third state, and connects the fourth power supply between the second electrode and the second gate electrode in the fourth state.

In a semiconductor device of the present invention, the control section includes: a first power supply for applying a voltage higher than the threshold voltage of the first gate electrode between the first electrode and the first gate electrode; a second power supply for applying a voltage higher than the threshold voltage of the second gate electrode between the second electrode and the second gate electrode; a third power supply for applying a voltage less than or equal to the threshold voltage of the first gate electrode between the first electrode and the first gate electrode; and a fourth power supply for applying a voltage less than or equal to the threshold voltage of the second gate electrode between the second electrode and the second gate electrode; the first gate driving circuit connects the first power supply between the first electrode and the first gate electrode in the first state, and connects the third power supply between the first electrode and the first gate electrode in the second state; and the second gate driving circuit connects the second power supply between the second electrode and the second gate electrode in the third state, and connects the fourth power supply between the second electrode and the second gate electrode in the fourth state.

In a semiconductor device of the present invention, the control section includes: a driver power supply for supplying a power to the first gate driving circuit; a capacitor for supplying a power to the second gate driving circuit; and a charging circuit for charging the capacitor; and the charging circuit includes a charging switch circuit connected between the driver power supply and the capacitor and charging the capacitor by the driver power supply.

In a semiconductor device of the present invention, the charging switch circuit includes a semiconductor switch, and a diode connected in series with the semiconductor switch.

In a semiconductor device of the present invention, the semiconductor element is of a normally-off type; the control

In a semiconductor device of the present invention, the semiconductor switch is a p-channel MOSFET, a p-channel IGBT or a PNP transistor.

In a semiconductor device of the present invention, the charging circuit charges the capacitor when a current flows between the second electrode and the first electrode.

In a semiconductor device of the present invention, the control section includes a first step-down circuit connected between the first gate driving circuit and the first gate electrode; and a second step-down circuit connected between the second gate driving circuit and the second gate electrode.

In a semiconductor device of the present invention, the first step-down circuit and the second step-down circuit each include a resistor element and a Zener diode.

In a semiconductor device of the present invention, the second gate driving circuit includes a photocoupler for electrically insulating the second control signal from the potential of the second electrode.

In a semiconductor device of the present invention, the second gate driving circuit includes a level shift circuit for converting a signal level of the second control signal.

In a semiconductor device of the present invention, the control section includes a delay circuit for delaying the first control signal and inputting the delayed signal to the first control terminal; and a delay time of the delay circuit is equal to that of the level shift circuit.

In a semiconductor device of the present invention, the second gate driving circuit includes a transformer whose primary side is connected between the first electrode and the 15 second electrode, whose secondary side is connected between the second gate electrode and the second control terminal, and wherein a voltage and a phase of an output from the secondary side are equal to those of an input to the primary side.

In a semiconductor device of the present invention, the second gate driving circuit includes: a transformer whose primary side is connected between the first electrode and the second electrode, whose secondary side is connected between the second gate electrode and the second control 25 terminal, and wherein a voltage of an output from the secondary side is equal to that of an input to the primary side, and a phase of the output from the secondary side is shifted from that of the input to the primary side; and a phase compensation circuit for compensating for a phase shift between the 30 primary side and the secondary side.

In a semiconductor device of the present invention, the phase compensation circuit includes a capacitor.

In a semiconductor device of the present invention, the second gate driving circuit includes a transformer whose pri- 35 mary side receives the second control signal, and whose secondary side is connected to the second electrode and the second gate electrode.

In a semiconductor device of the present invention, the second gate driving circuit includes a pulsed current generating section connected to the primary side of the transformer for generating a pulsed current; and the second control signal is input to the transformer via the pulsed current generating section.

In a semiconductor device of the present invention, the first gate driving circuit directly applies the first control signal between the first electrode and the first gate electrode.

In a semiconductor device of the present invention, the first control signal and the second control signal are a same signal.

A method for driving a semiconductor device of the present 50 invention is a method for driving a semiconductor device including a semiconductor element, the semiconductor element including a first electrode, a first gate electrode, a second gate electrode and a second electrode formed in this order while being spaced apart from one another on a semiconduc- 55 tion. tor layer stack, which is formed on a substrate, the method including the steps of: applying a voltage higher than a threshold voltage of the first gate electrode between the first electrode and the first gate electrode and applying a voltage higher than a threshold voltage of the second gate electrode between 60 the second electrode and the second gate electrode, whereby the semiconductor device is brought to a conductive state in which a current flows in both directions between the first electrode and the second electrode; and applying a voltage less than or equal to the threshold voltage of the first gate 65 electrode between the first electrode and the first gate electrode and applying a voltage less than or equal to the threshold

8

voltage of the second gate electrode between the second electrode and the second gate electrode, whereby the semiconductor device is brought to a non-conductive state in which a path between the first electrode and the second electrode is blocked.

The method for driving a semiconductor device of the present invention includes the step of applying a voltage less than or equal to the threshold voltage of the first gate electrode between the first electrode and the first gate electrode and applying a voltage less than or equal to the threshold voltage of the second gate electrode between the second ohmic electrode and the second gate electrode, whereby the semiconductor device is brought to a non-conductive state in which a path between the first ohmic electrode and the second ohmic electrode is blocked. Therefore, even if the potential of the second ohmic electrode, the channel region is pinched off under the second gate electrode. Thus, it is possible to block the current flow in either direction between the first ohmic electrode and the second ohmic electrode, thus realizing a bidirectional switch.

#### Effects of the Invention

With the semiconductor device of the present invention and the method for driving the same, it is possible to realize a semiconductor device which has excellent reverse voltage characteristics, which as a single element constitutes a bidirectional switch product, and which allows for the application of a high gate voltage, and a method for driving the same.

#### BRIEF DESCRIPTION OF THE DRAWINGS

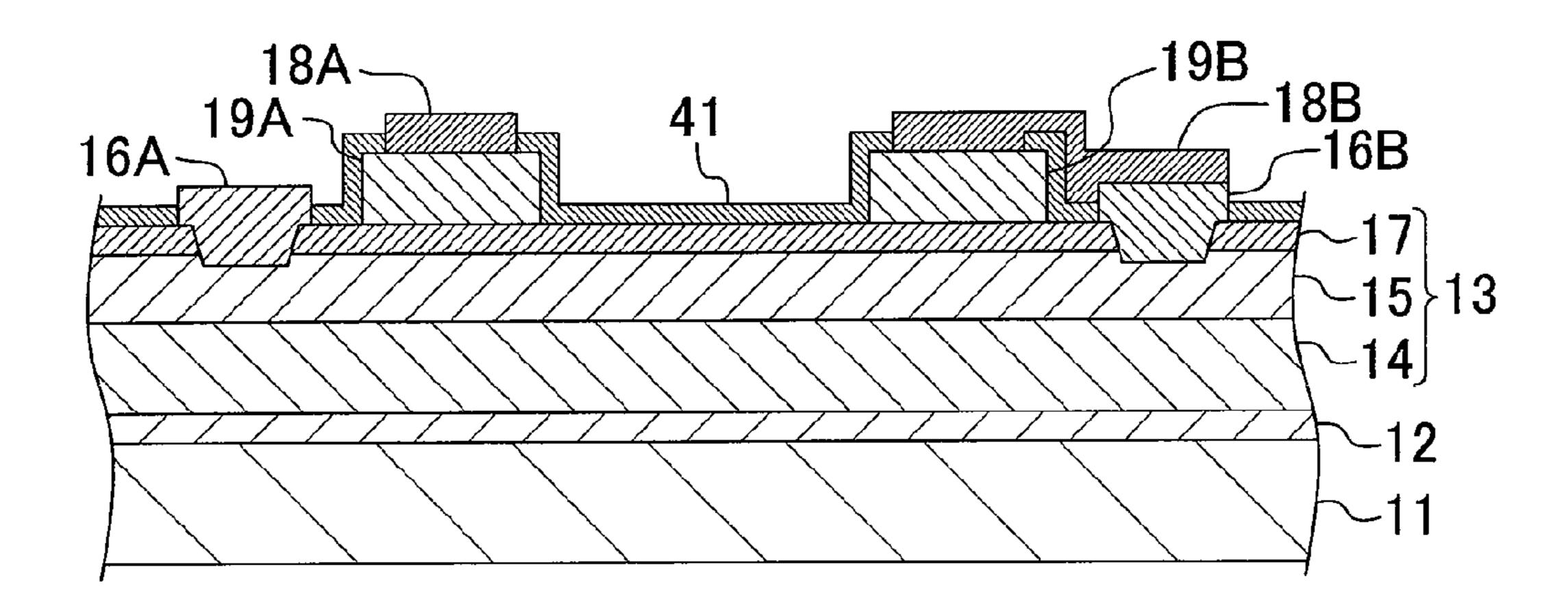

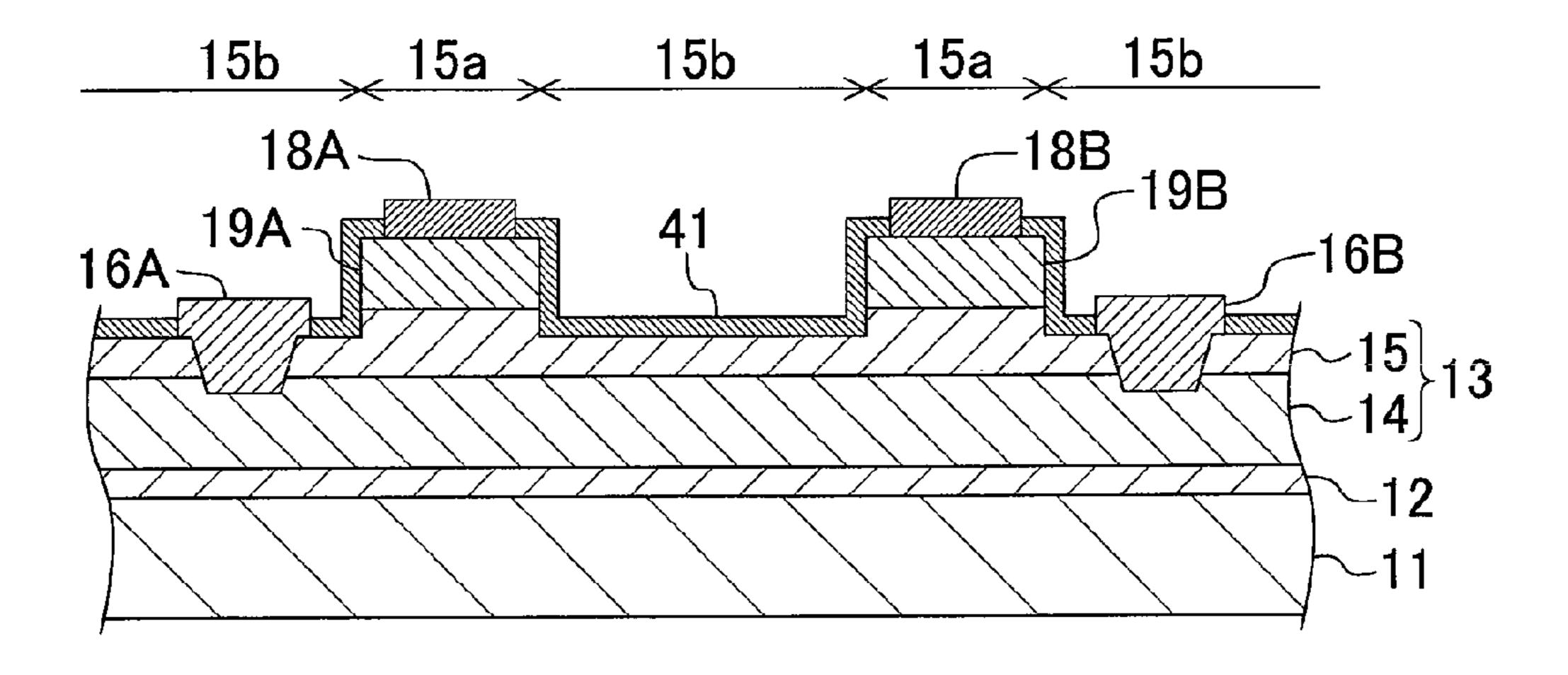

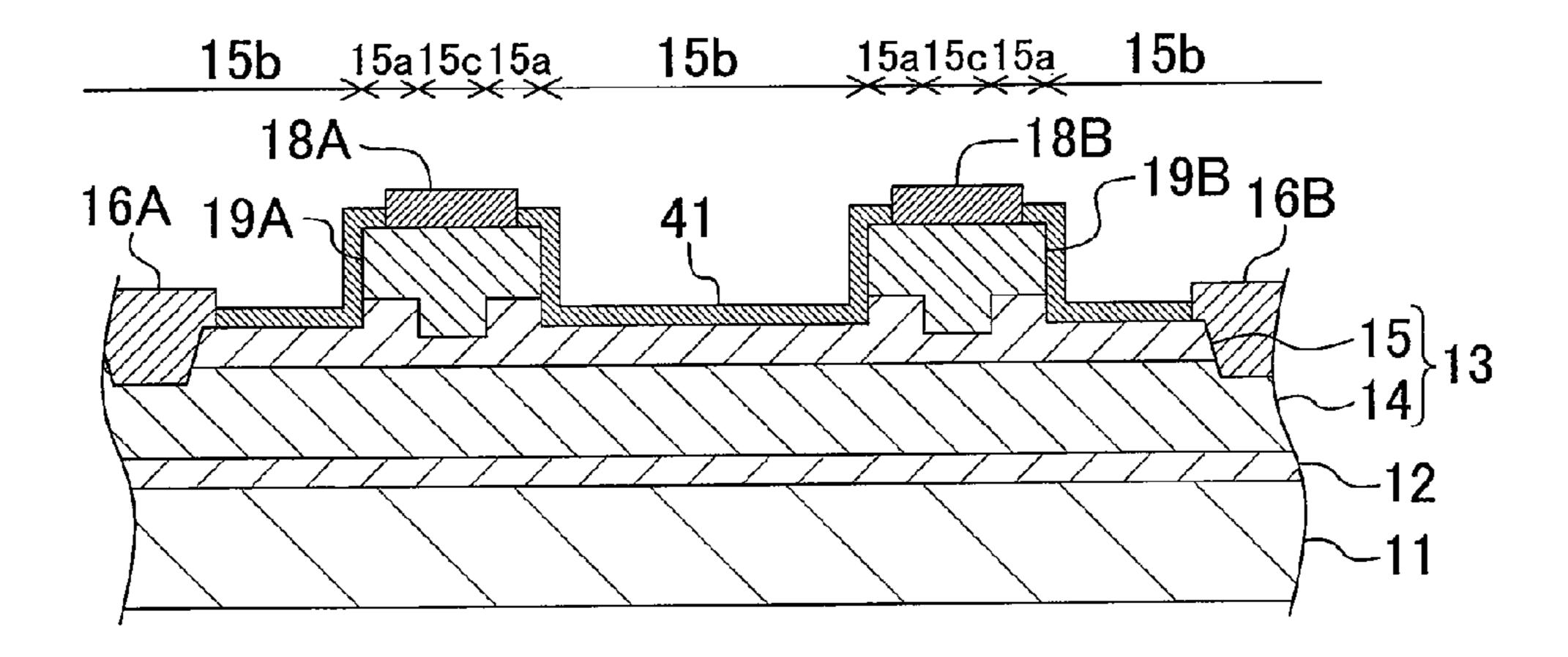

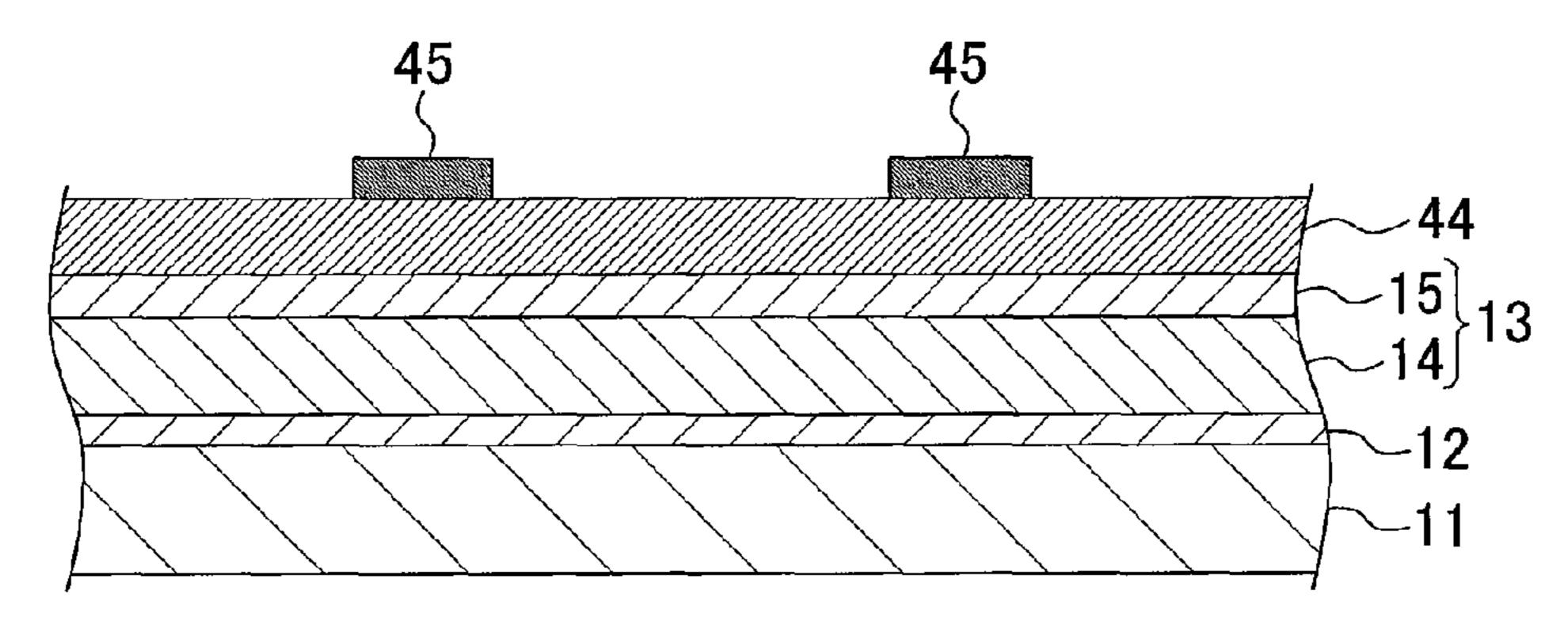

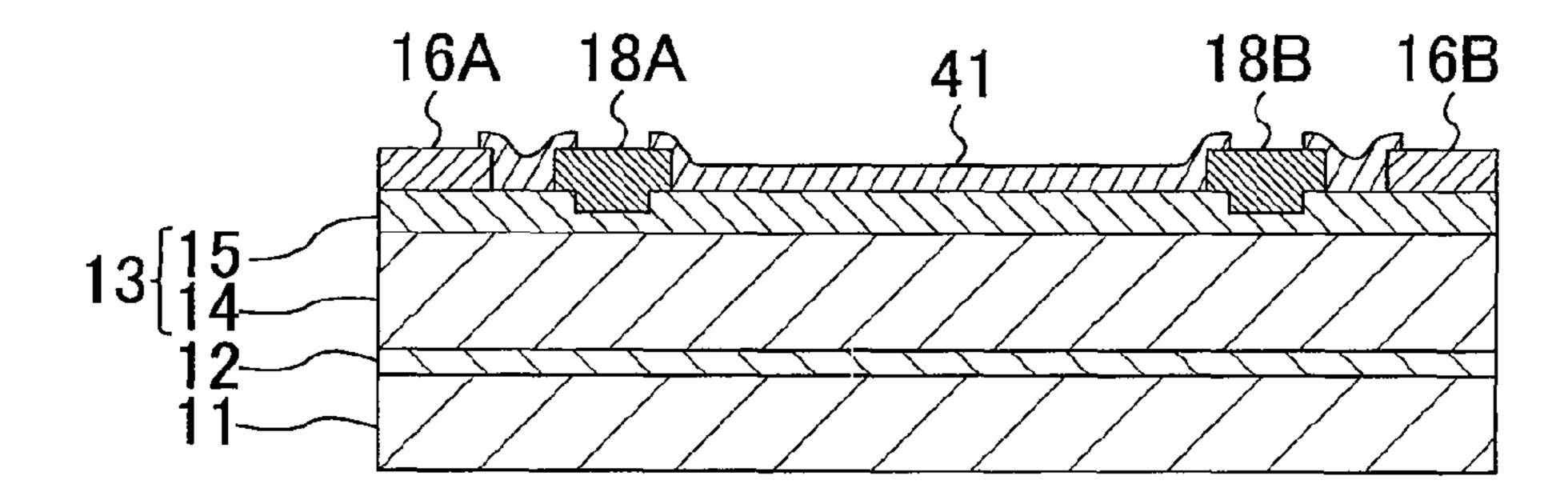

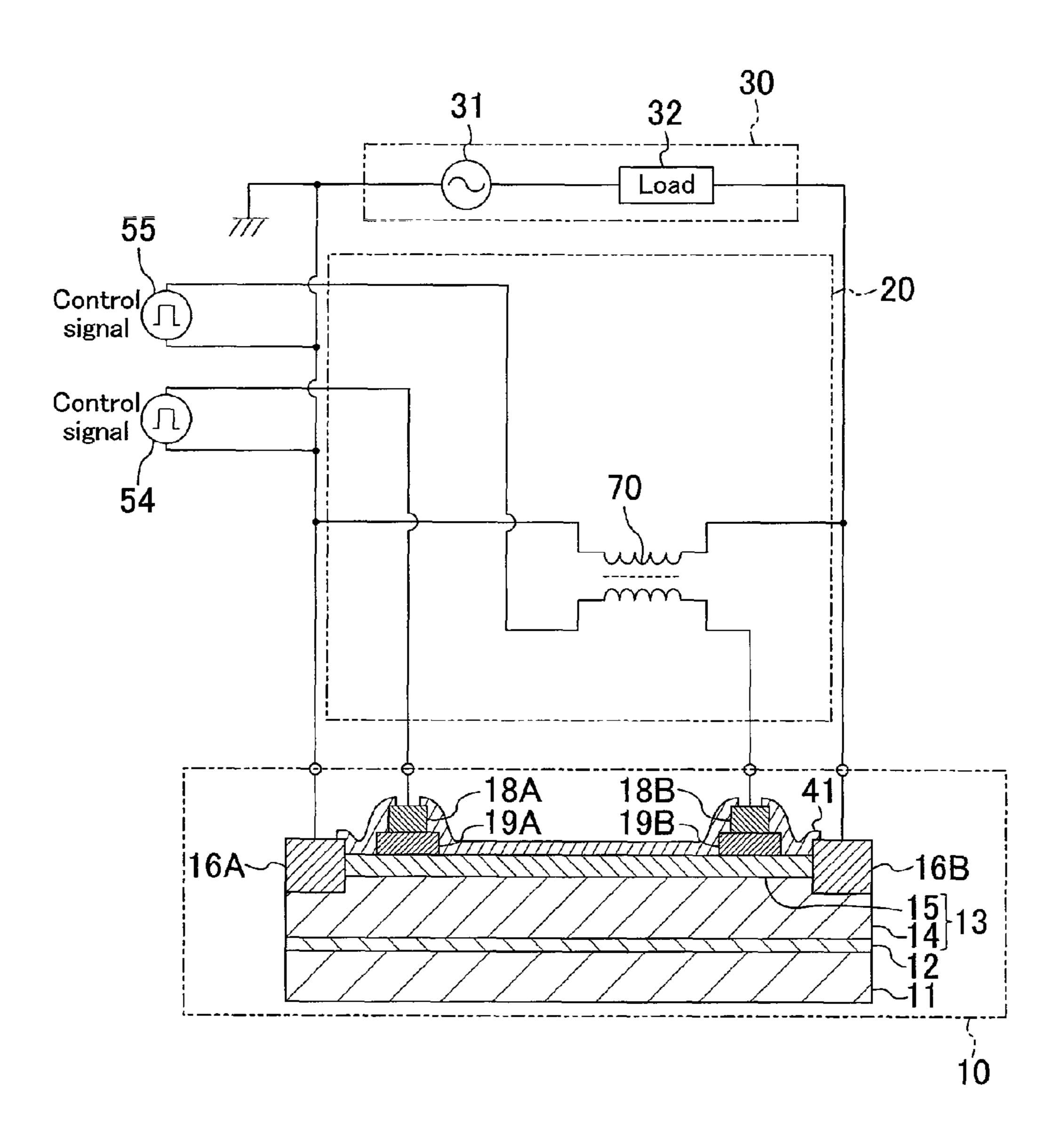

- FIG. 1 A cross-sectional view showing a semiconductor device according to a first embodiment of the present invention.

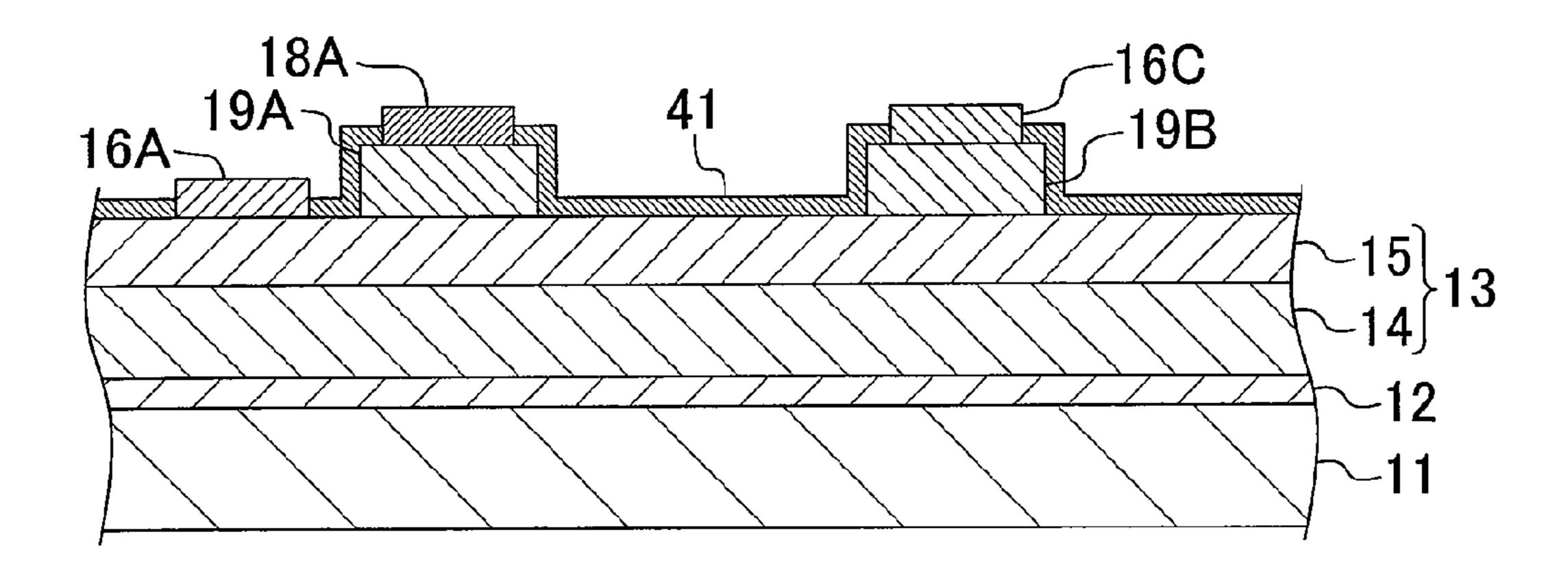

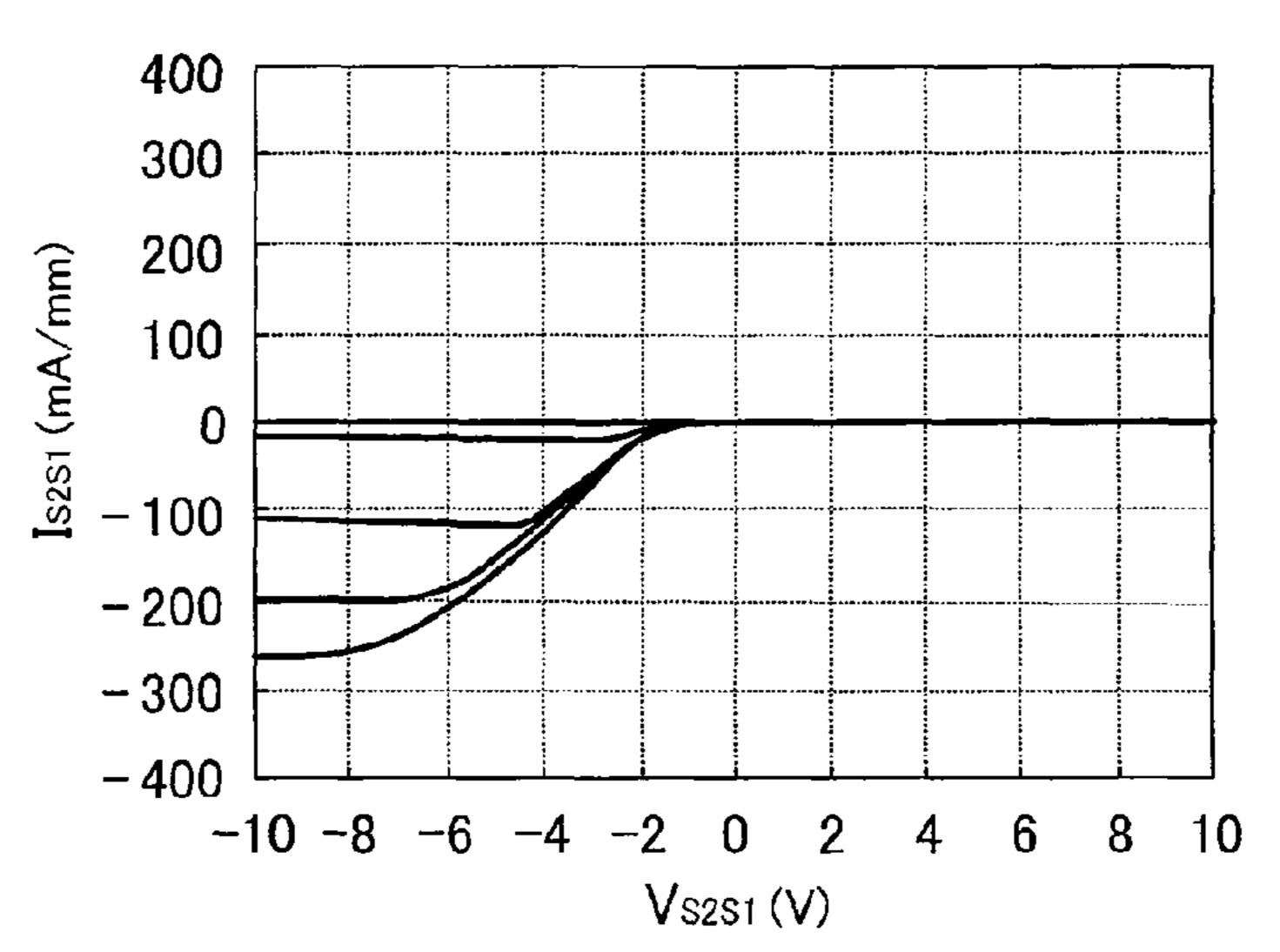

- FIG. 2 A graph showing current-voltage characteristics of the semiconductor device according to the first embodiment of the present invention.

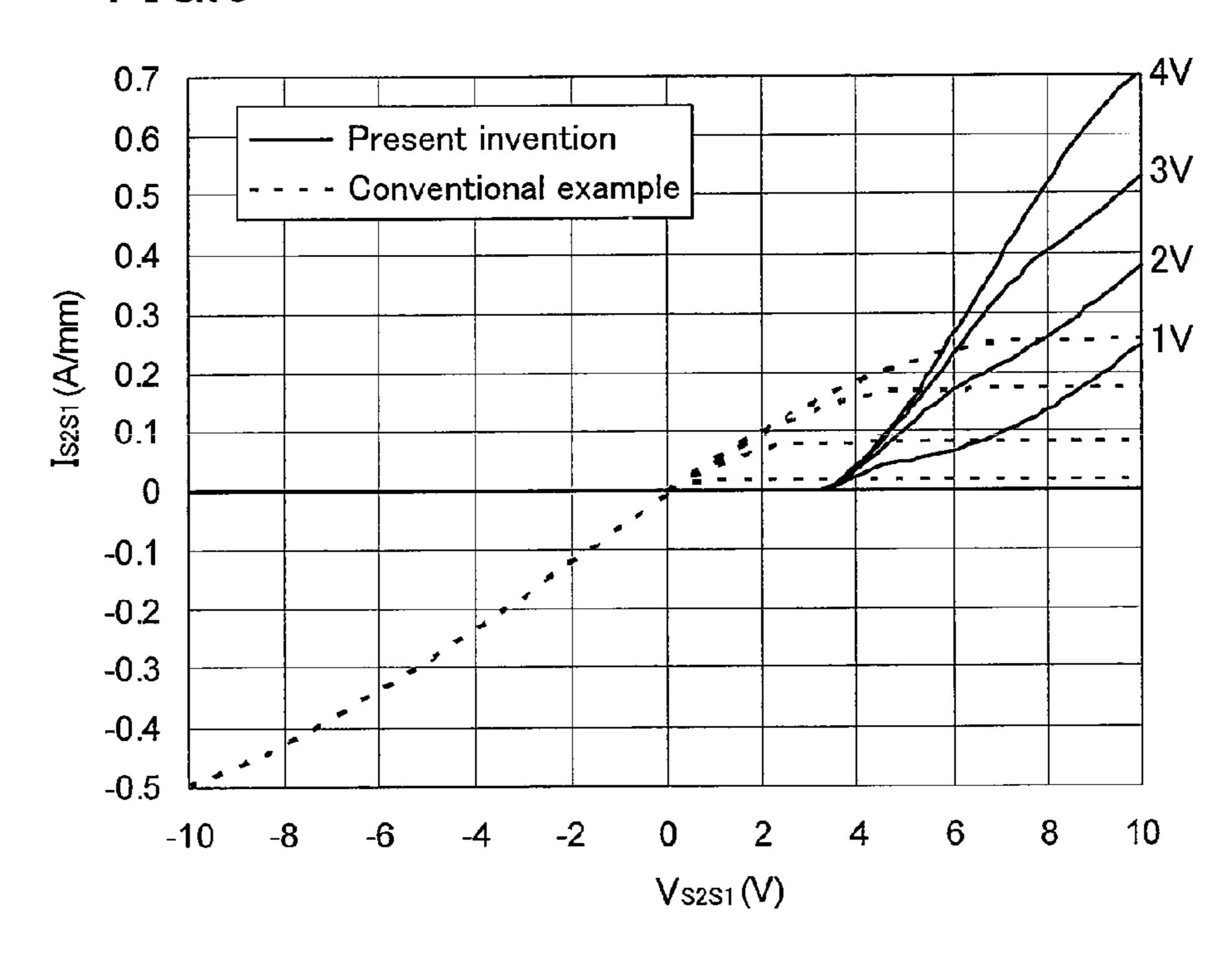

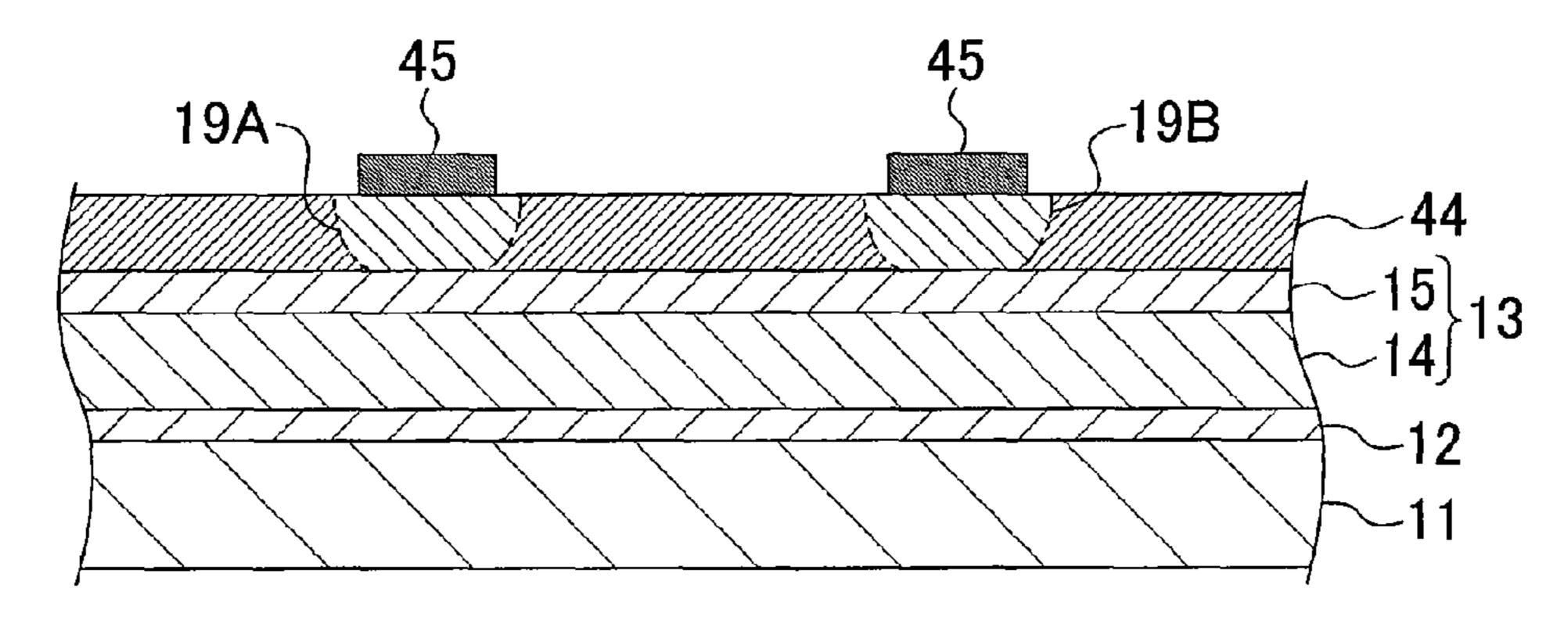

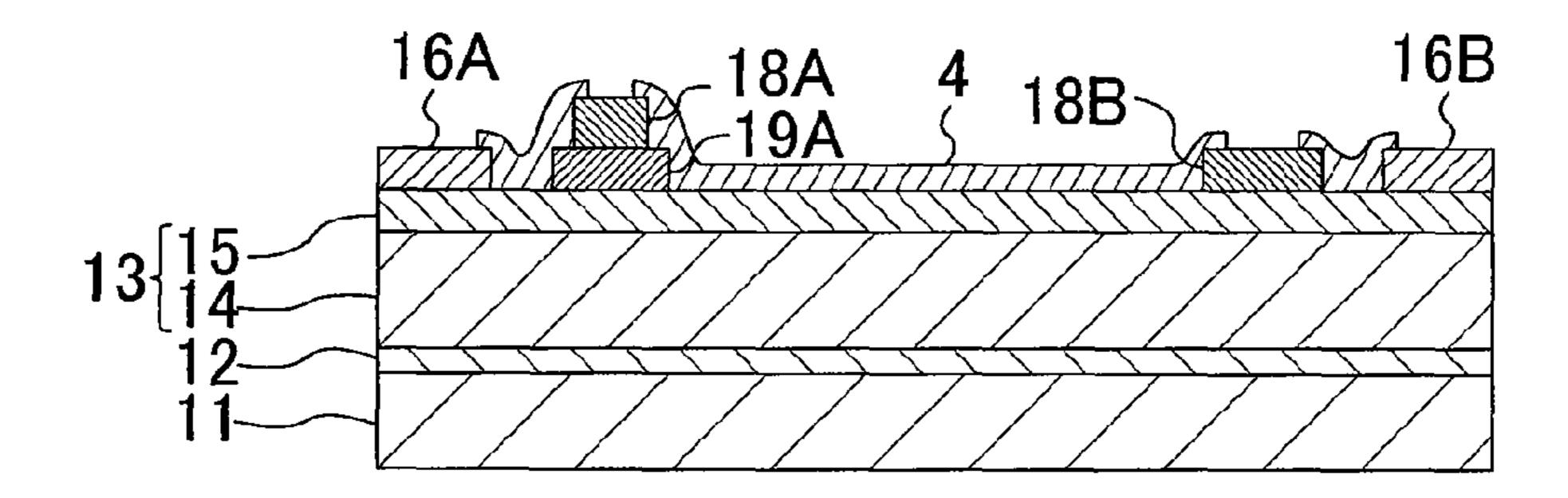

- FIG. 3 A cross-sectional view showing a variation of the semiconductor device according to the first embodiment of the present invention.

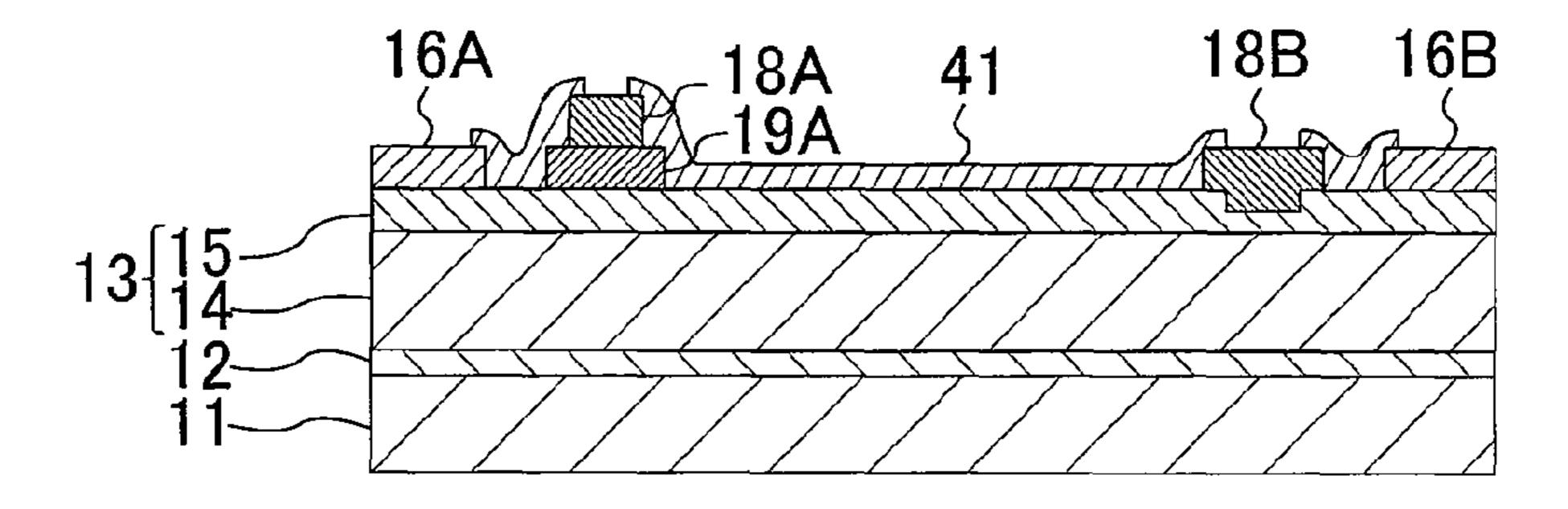

- FIG. 4 A cross-sectional view showing a semiconductor device according to a second embodiment of the present invention.

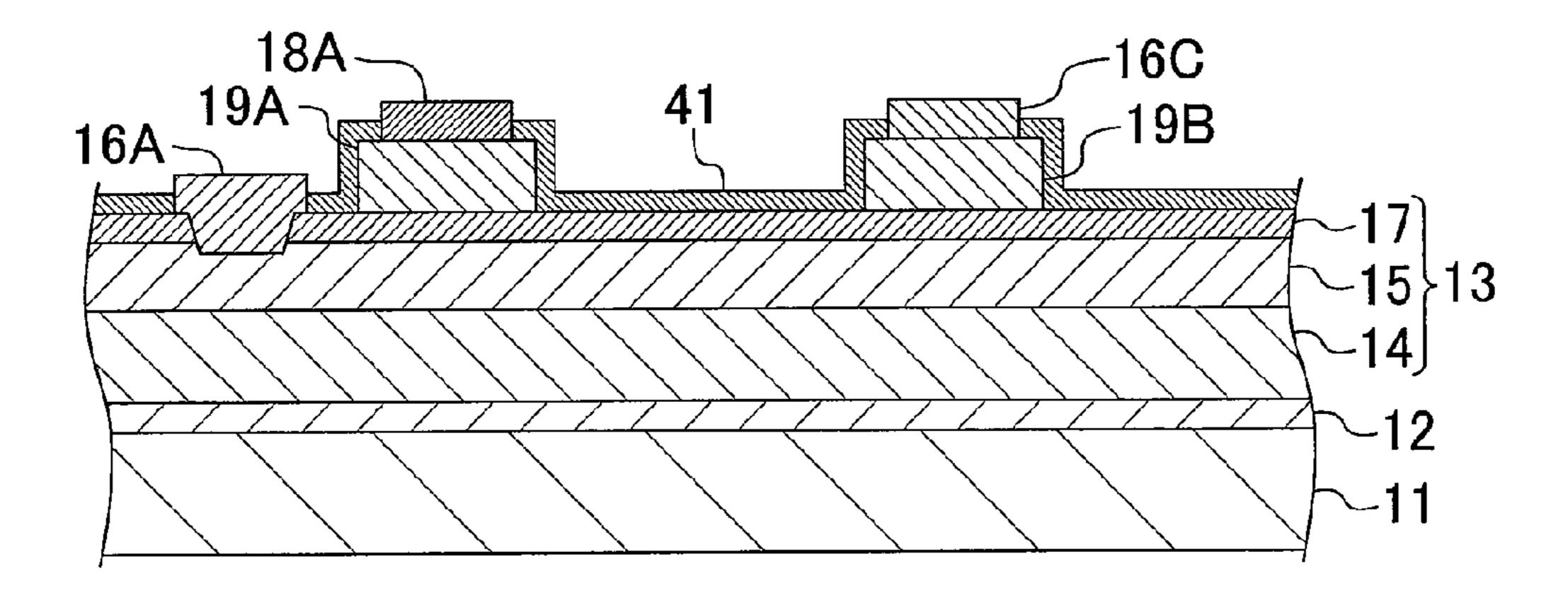

- FIG. **5** A cross-sectional view showing a semiconductor device according to a third embodiment of the present invention.

- FIG. 6 A graph showing current-voltage characteristics of the semiconductor device according to the third embodiment of the present invention.

- FIG. 7 A cross-sectional view showing a variation of the semiconductor device according to the third embodiment of the present invention.

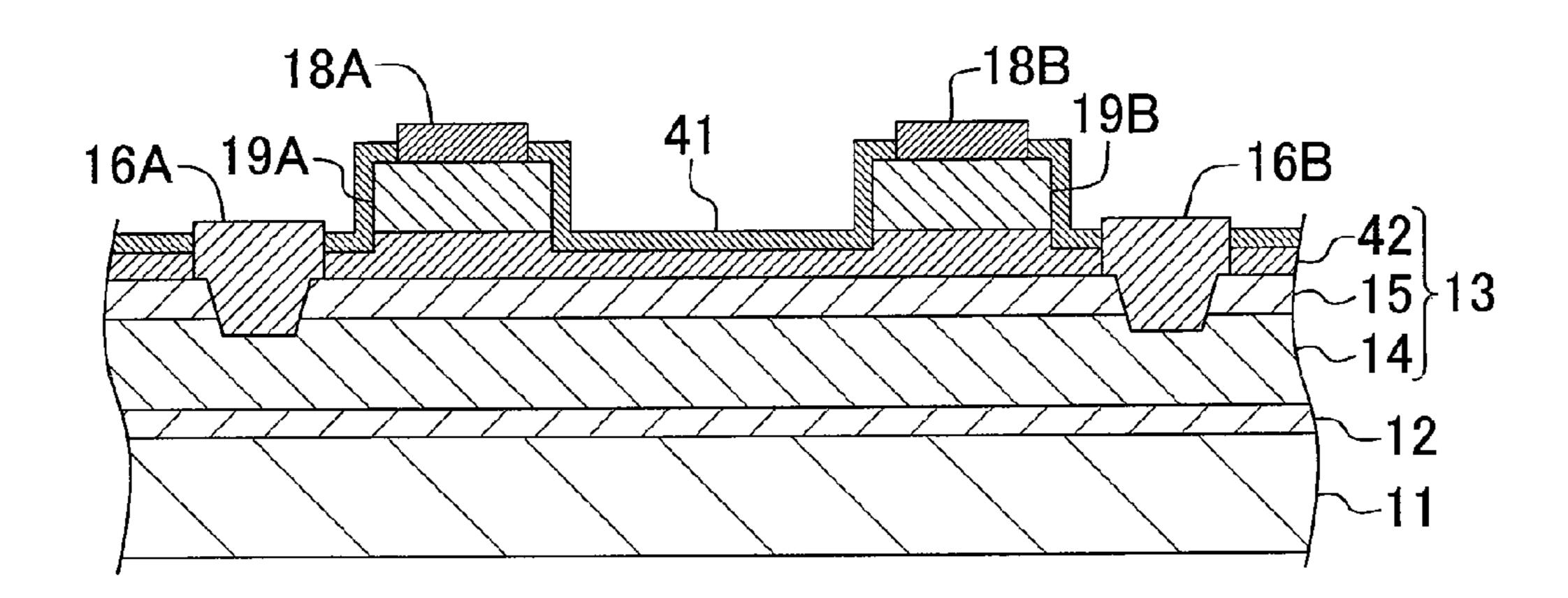

- FIG. **8** A cross-sectional view showing a semiconductor device according to a fourth embodiment of the present invention.

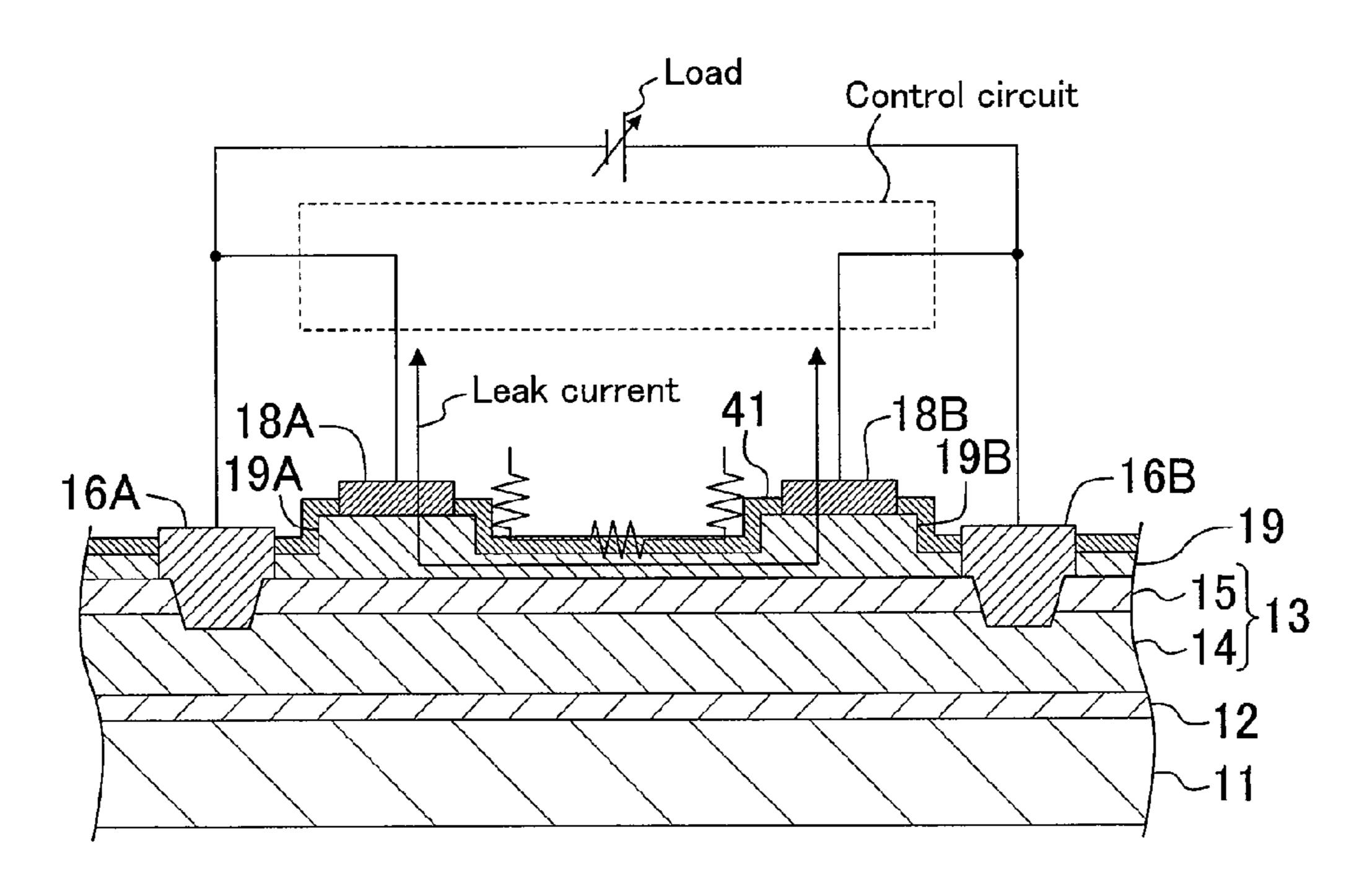

- FIG. 9 A cross-sectional view illustrating problems with a dual-gate semiconductor device.

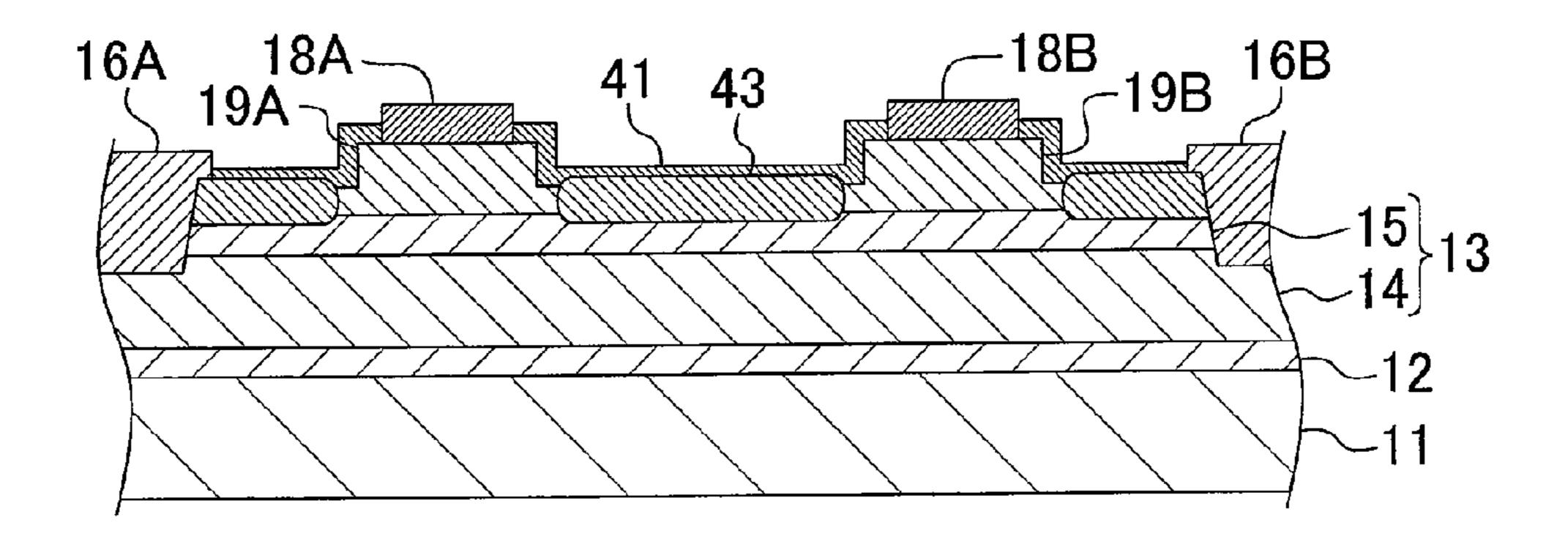

- FIG. 10 A cross-sectional view showing a semiconductor device according to a first variation of the fourth embodiment of the present invention.

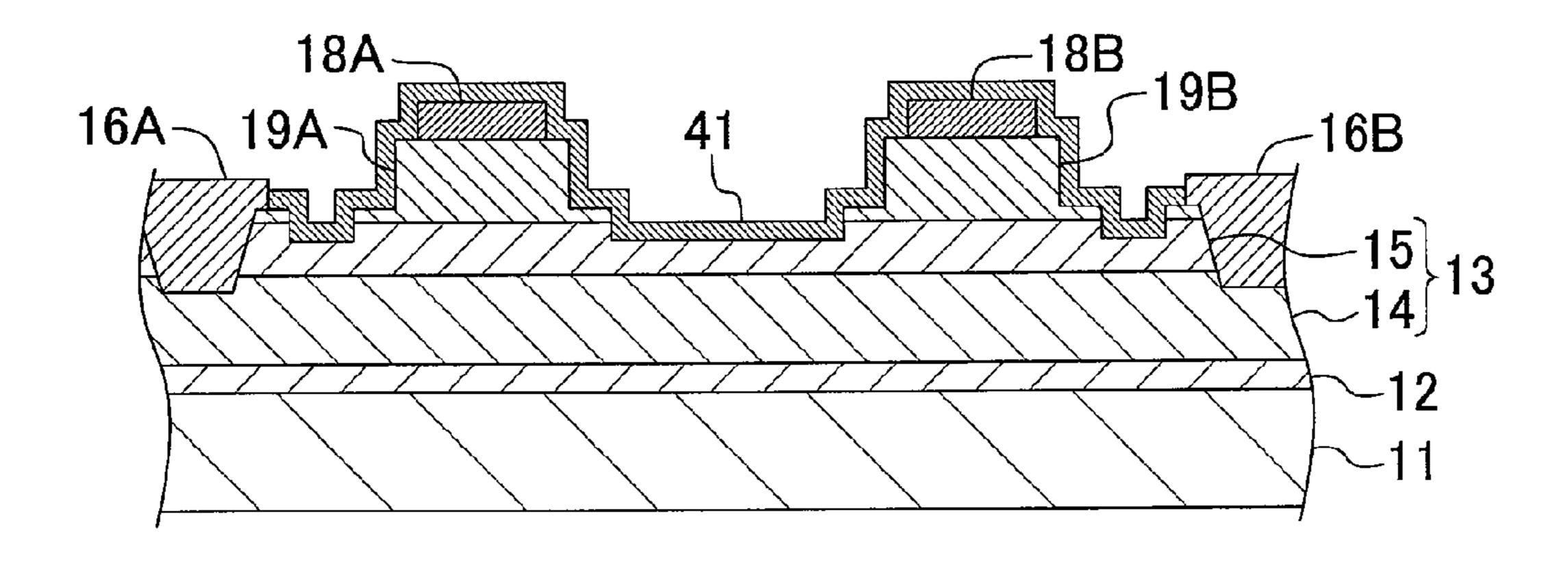

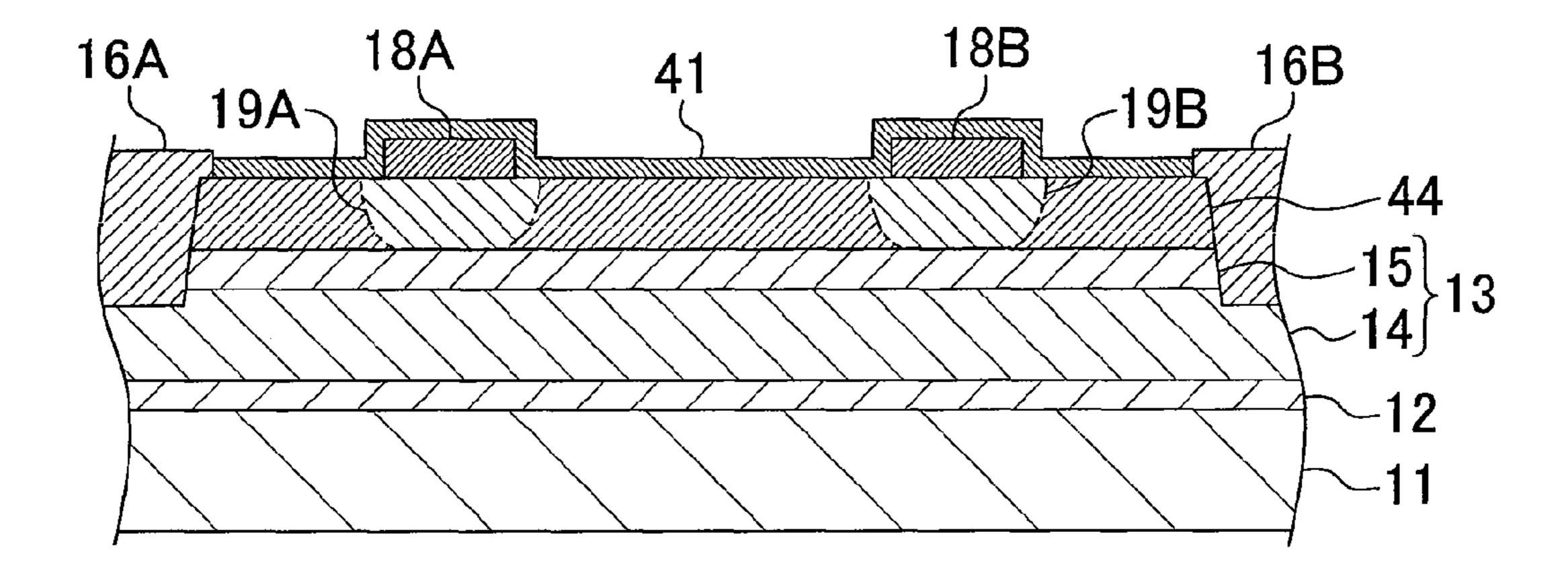

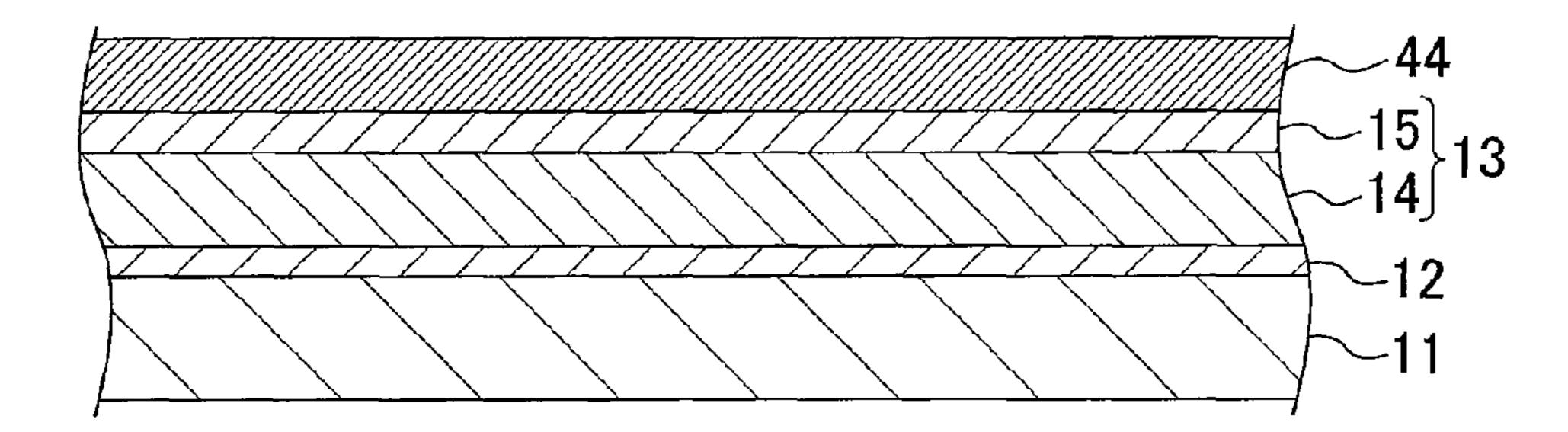

- FIG. 11 A cross-sectional view showing a semiconductor device according to a second variation of the fourth embodiment of the present invention.

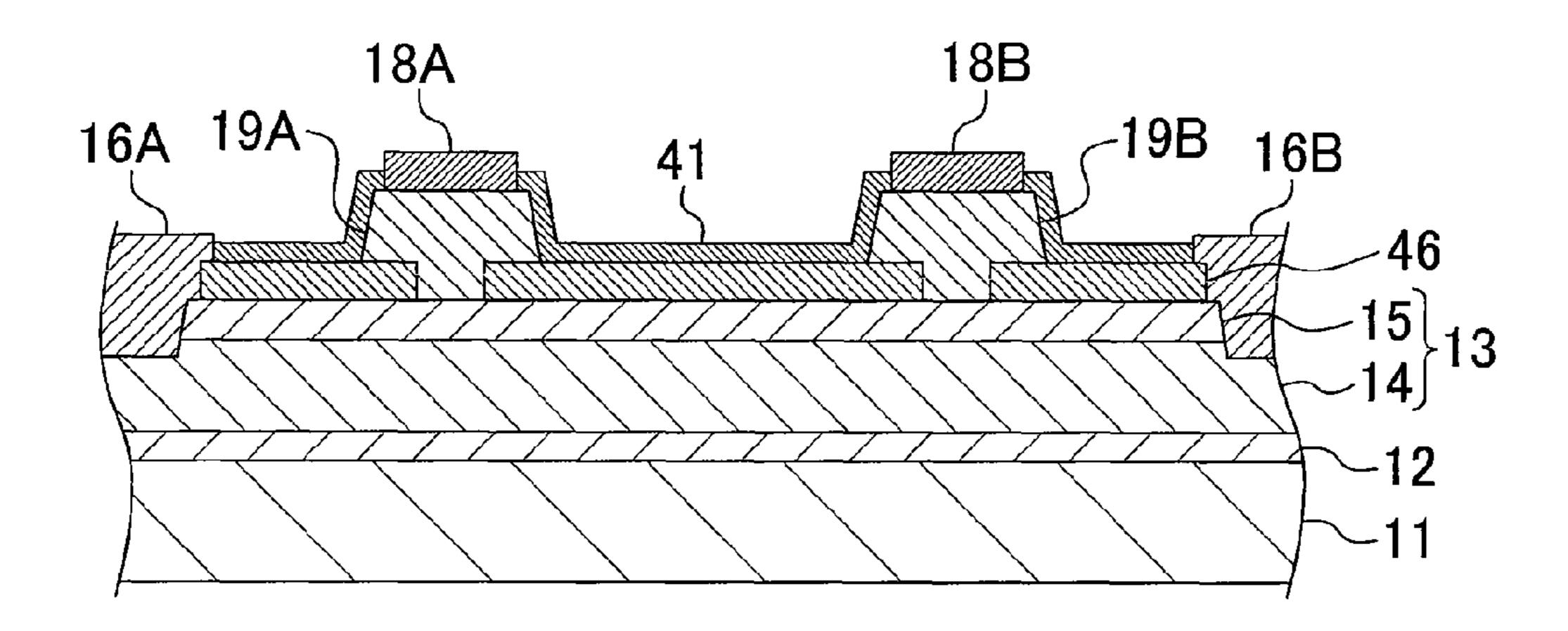

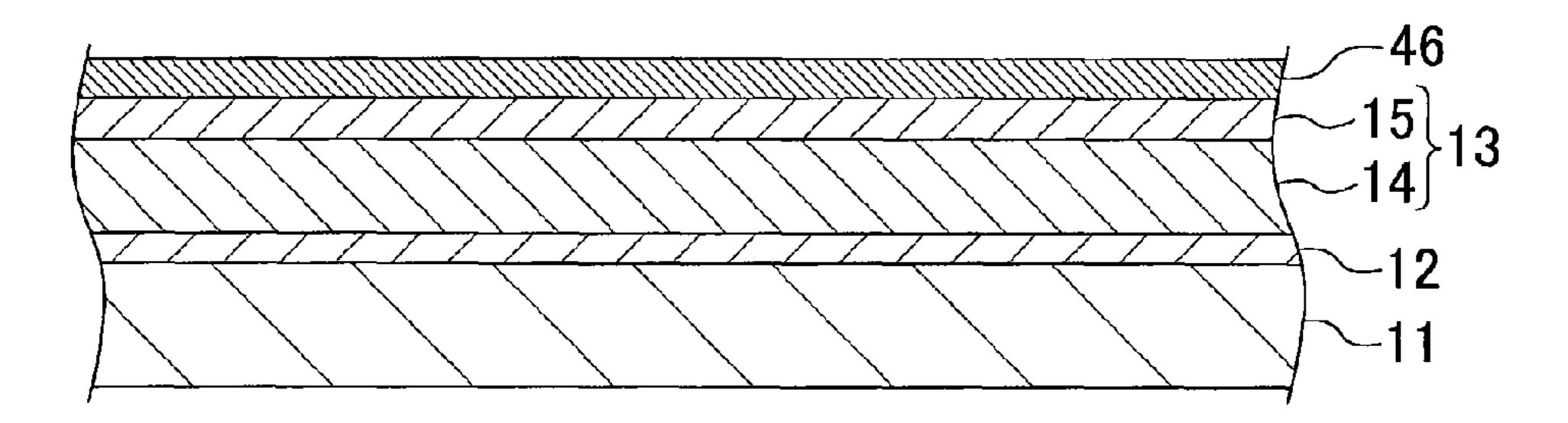

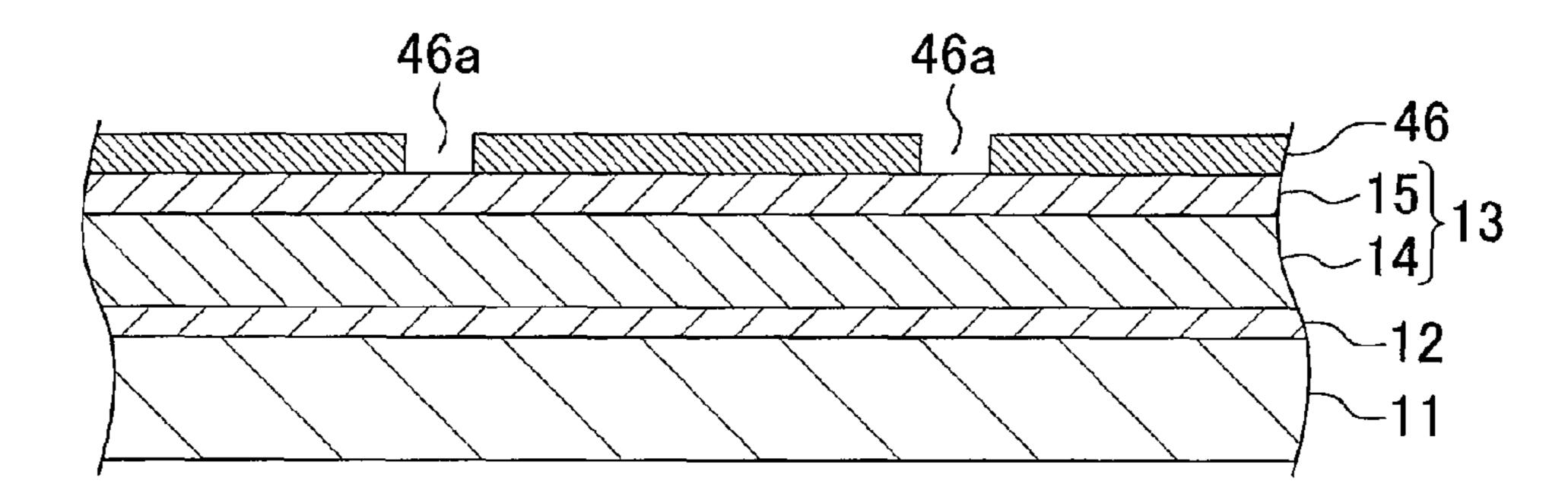

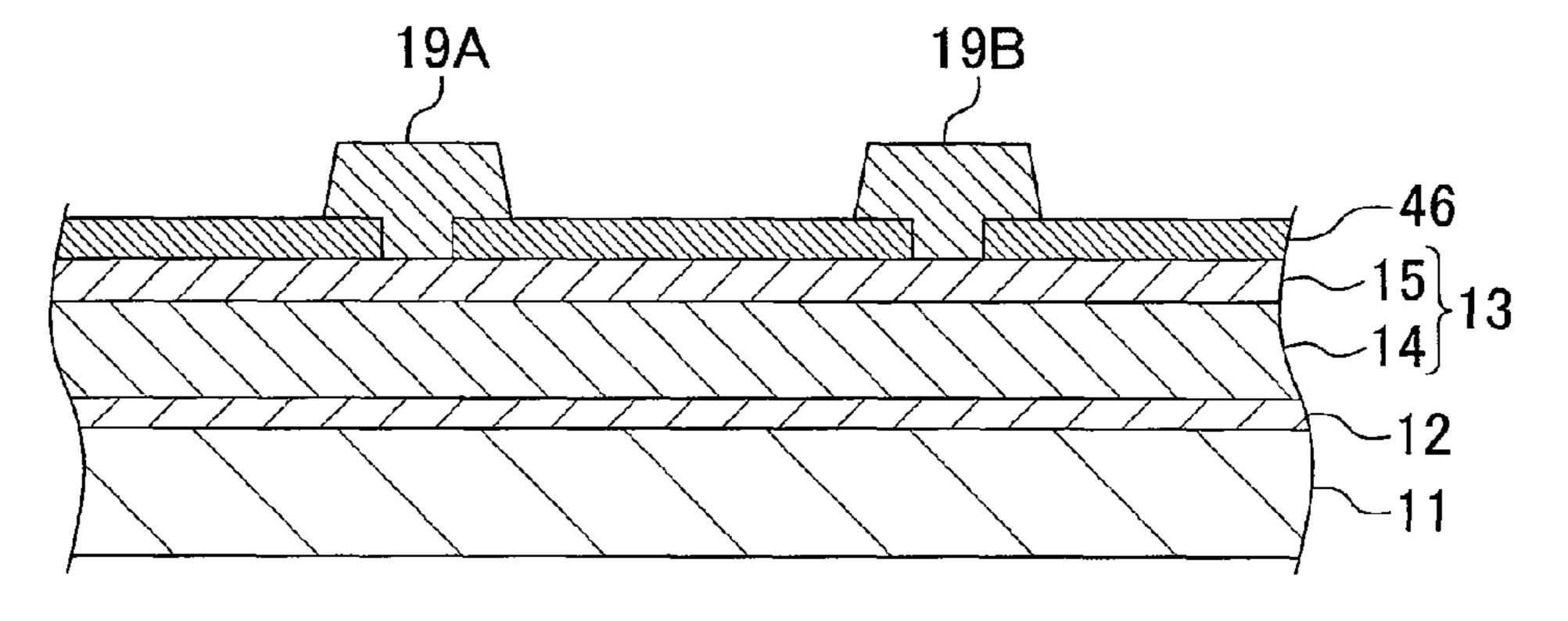

- FIG. 12 Cross-sectional views showing a sequence of steps for producing the semiconductor device according to the second variation of the fourth embodiment of the present invention.

55

9

FIG. 13 A cross-sectional view showing a semiconductor device according to a third variation of the fourth embodiment of the present invention.

FIG. 14 A cross-sectional view showing a semiconductor device according to a fourth variation of the fourth embodi- 5 ment of the present invention.

FIG. 15 A cross-sectional view showing a semiconductor device according to a fifth variation of the fourth embodiment of the present invention.

FIG. 16 Cross-sectional views showing a sequence of steps 10 for producing the semiconductor device according to the fifth variation of the fourth embodiment of the present invention.

FIG. 17 A cross-sectional view showing a semiconductor device according to a sixth variation of the fourth embodiment of the present invention.

FIG. 18 Cross-sectional views showing a sequence of steps for producing the semiconductor device according to the sixth variation of the fourth embodiment of the present invention.

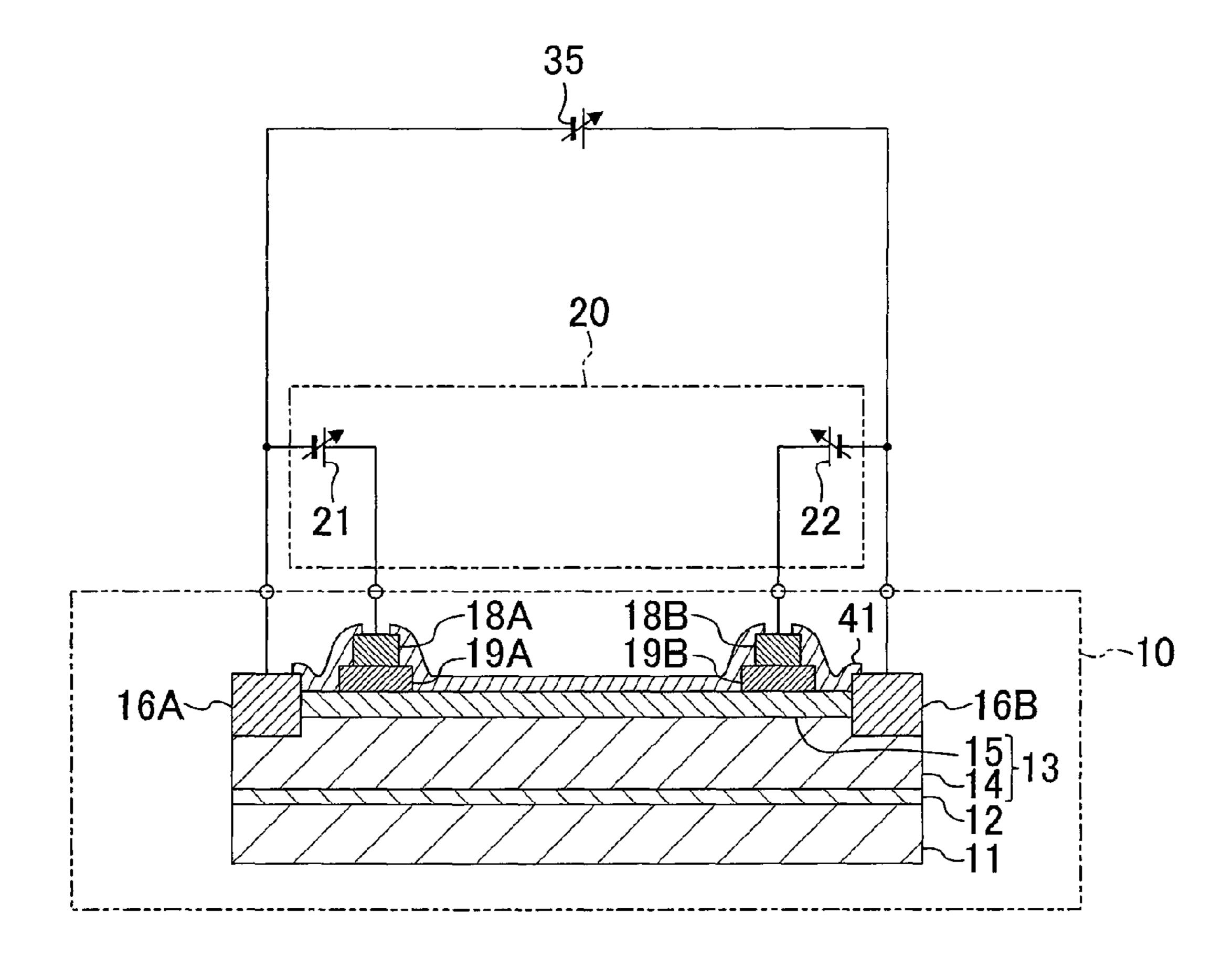

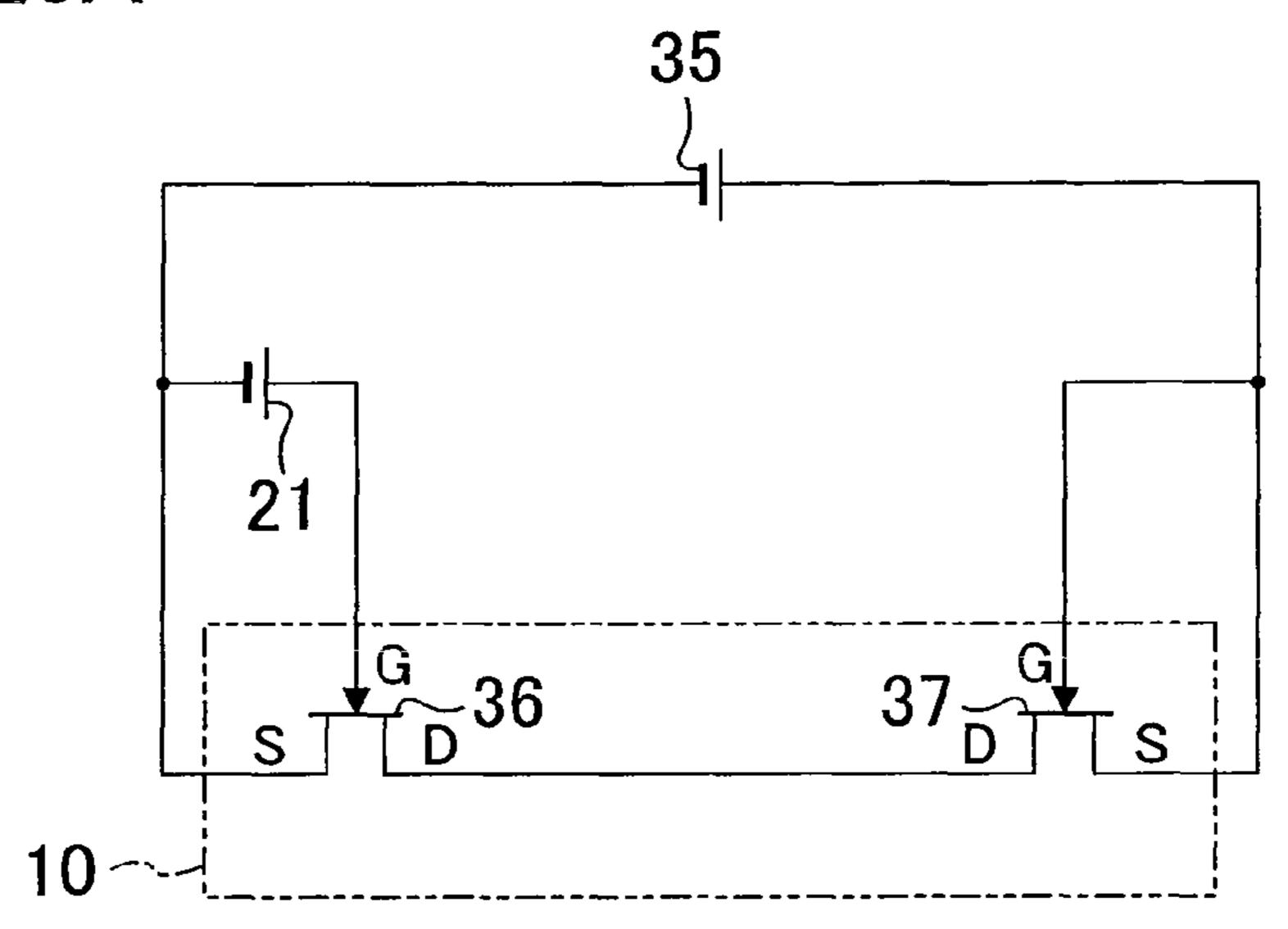

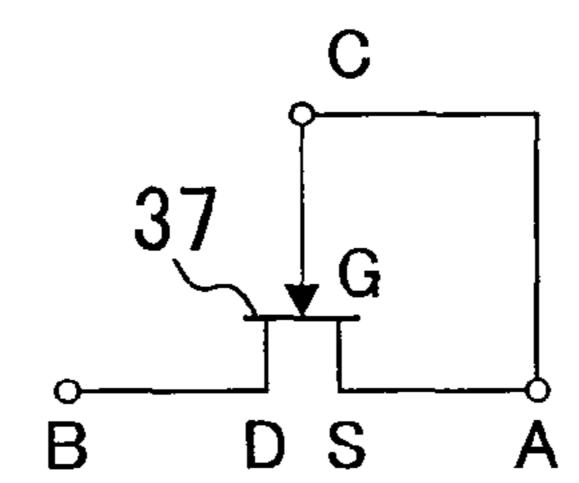

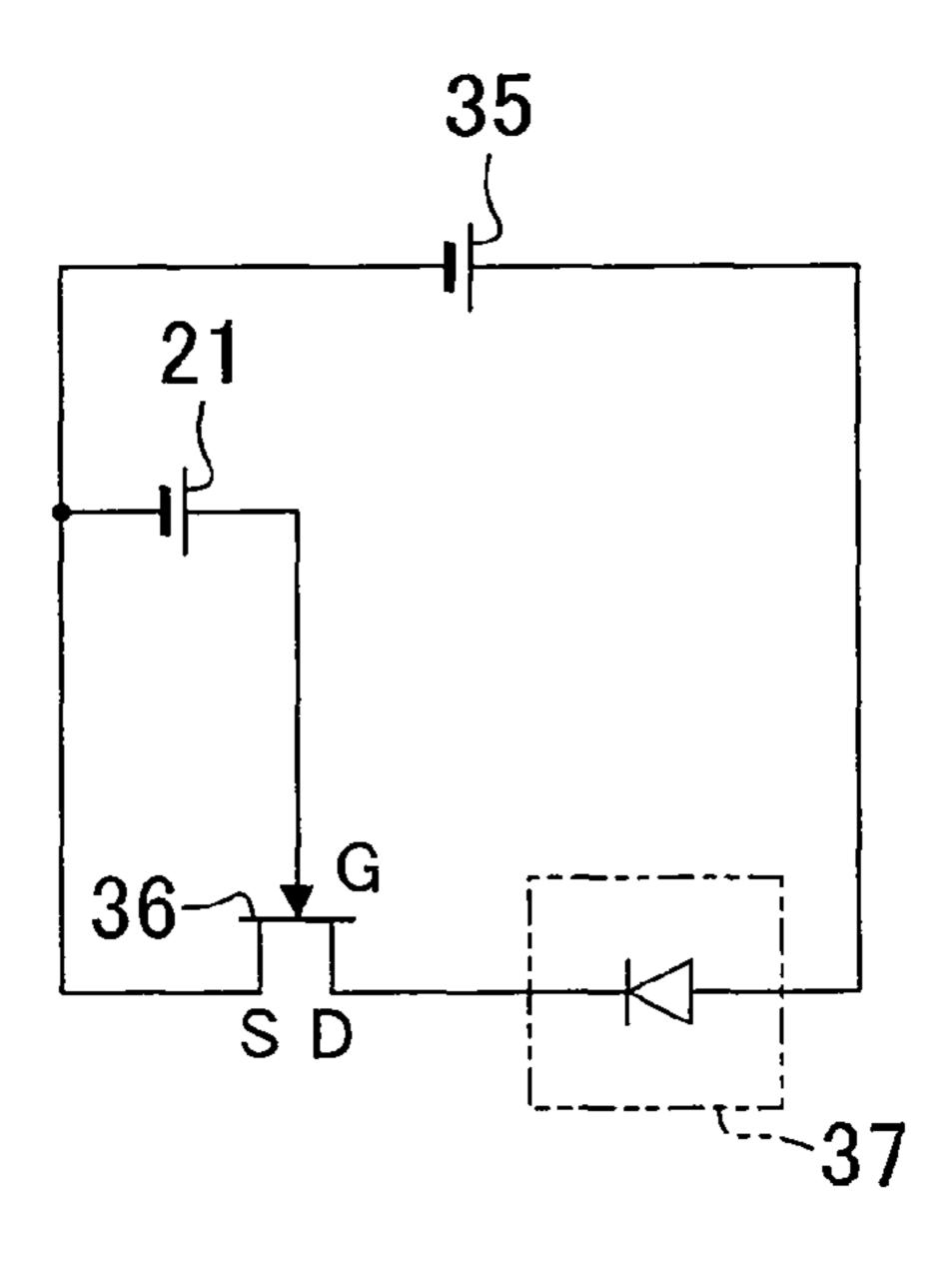

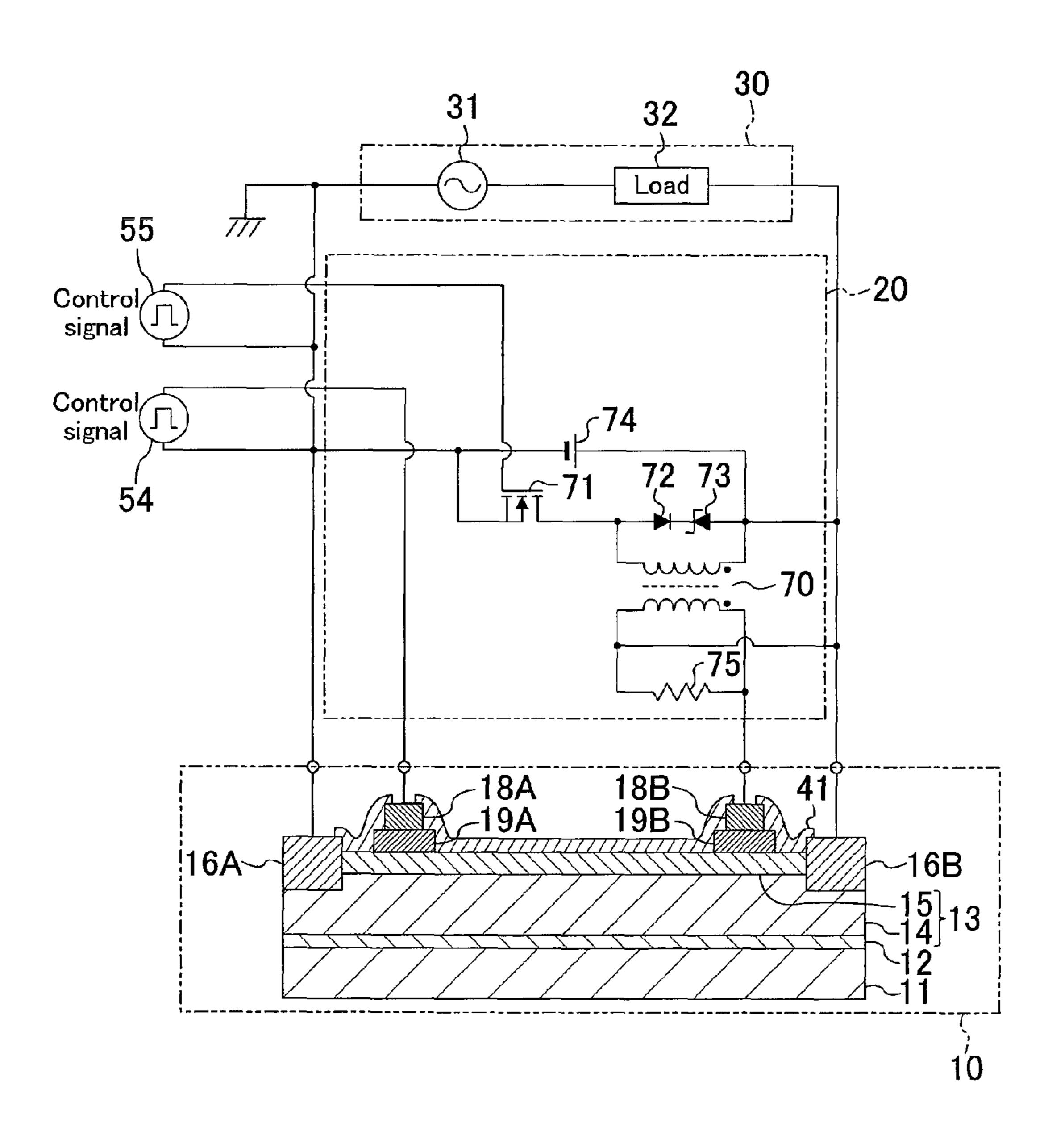

FIG. 19A circuit diagram showing a semiconductor device according to a fifth embodiment of the present invention.

FIG. 20 Circuit diagrams showing an equivalent circuit of the semiconductor device according to the fifth embodiment of the present invention.

FIG. 21 Graphs each showing current-voltage characteristics of the semiconductor device according to the fifth 25 embodiment of the present invention.

FIG. 22 A cross-sectional view showing semiconductor elements used in a semiconductor device according to a sixth embodiment of the present invention.

FIG. 23 A cross-sectional view showing semiconductor 30 elements used in a semiconductor device according to a seventh embodiment of the present invention.

FIG. 24 A cross-sectional view showing a variation of the semiconductor elements used in the semiconductor device according to the seventh embodiment of the present inven- 35 tion.

FIG. 25 A circuit diagram showing a semiconductor device according to an eighth embodiment of the present invention.

FIG. **26** A circuit diagram showing a semiconductor device according to a ninth embodiment of the present invention.

FIG. 27 A circuit diagram showing a semiconductor device according to a tenth embodiment of the present invention.

FIG. 28 A circuit diagram showing a semiconductor device according to an eleventh embodiment of the present invention.

FIG. 29 A circuit diagram showing a semiconductor device according to a twelfth embodiment of the present invention.

FIG. 30 A circuit diagram showing a semiconductor device according to a thirteenth embodiment of the present invention.

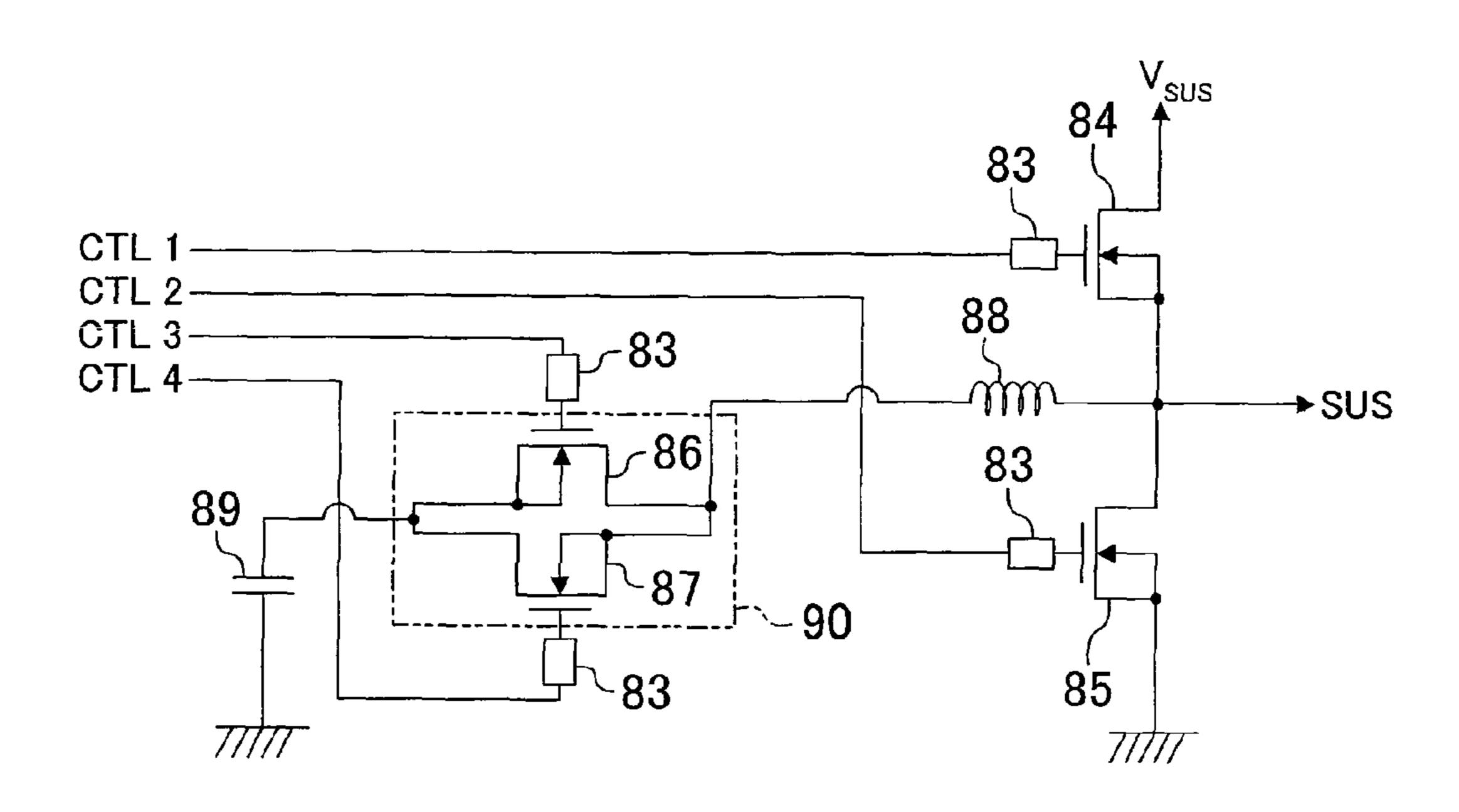

FIG. 31 A circuit diagram showing a sustain circuit according to a fourteenth embodiment of the present invention.

| DESCRIPTION OF REFERENCE NUMERALS |                            |  |

|-----------------------------------|----------------------------|--|

| 10                                | Semiconductor element      |  |

| 11                                | Substrate                  |  |

| 12                                | Buffer layer               |  |

| 13                                | Semiconductor layer stack  |  |

| 14                                | First semiconductor layer  |  |

| 15                                | Second semiconductor layer |  |

| 16A                               | First electrode            |  |

| 16B                               | Second electrode           |  |

| 16C                               | Integral electrode         |  |

| 17                                | Third semiconductor layer  |  |

| 18A                               | First gate electrode       |  |

| 18B                               | Second gate electrode      |  |

| 19                                | P-type GaN layer           |  |

10 -continued

| DESCRIPTION OF REFERENCE NUMERALS |                                            |  |

|-----------------------------------|--------------------------------------------|--|

| 19A                               | First control layer                        |  |

| 19B                               | Second control layer                       |  |

| 20                                | Control section                            |  |

| 21                                | First power supply                         |  |

| 22                                | Second power supply                        |  |

| 23A                               | First switch circuit                       |  |

| 23B                               | Second switch circuit                      |  |

| 25D<br>25                         | Third power supply                         |  |

| 26                                | Fourth power supply                        |  |

| 30                                | Load circuit                               |  |

| 31                                |                                            |  |

| 35                                | Load power supply<br>Variable power supply |  |

| 36                                | First transistor                           |  |

|                                   |                                            |  |

| 37                                | Second transistor                          |  |

| 41                                | Passivation film                           |  |

| 42                                | Etching absorbing layer                    |  |

| 43                                | High resistance layer                      |  |

| 44                                | Fourth semiconductor layer                 |  |

| 45                                | Impurity layer                             |  |

| 46                                | Oxide film layer                           |  |

| 51                                | First power supply                         |  |

| 52                                | Second power supply                        |  |

| 53                                | Driver element                             |  |

| 53A                               | Low-side gate driving circuit              |  |

| 53B                               | High-side gate driving circuit             |  |

| 53C                               | Level shift circuit                        |  |

| 54                                | First signal source                        |  |

| 55                                | Second signal source                       |  |

| 61                                | Capacitor                                  |  |

| 63                                | Charging circuit                           |  |

| 64                                | First step-down circuit                    |  |

| 64A                               | Resistor                                   |  |

| 64B                               | Zener diode                                |  |

| 65<br>65 <b>A</b>                 | Second step-down circuit                   |  |

| 65A                               | Resistor                                   |  |

| 65B                               | Zener diode                                |  |

| 66                                | Driver power supply                        |  |

| 67                                | Logic circuit                              |  |

| 67A                               | NAND circuit                               |  |

| 67B                               | Delay circuit                              |  |

| 68                                | Semiconductor switch Diode                 |  |

| 69<br>70                          | Transformer                                |  |

| 70                                | N-channel MOSFET                           |  |

| 72                                | Diode                                      |  |

| 73                                | Zener diode                                |  |

| 7 <i>3</i><br>74                  | First power supply                         |  |

| 7 <del>-1</del><br>75             | Resistor element                           |  |

| 83                                | Gate driving circuit                       |  |

| 84                                | First switching element                    |  |

| 85                                | Second switching element                   |  |

| 86                                | Third switching element                    |  |

| 87                                | Fourth switching element                   |  |

| 88                                | Inductor                                   |  |

| 89                                | Capacitor                                  |  |

| 90                                | Bidirectional switching circuit            |  |

|                                   |                                            |  |

## BEST MODE FOR CARRYING OUT THE INVENTION

#### First Embodiment

A first embodiment of the present invention will be described with reference to the drawings. FIG. 1 shows a cross section of a nitride semiconductor device according to the first embodiment of the present invention. As shown in FIG. 1, the semiconductor device of the present embodiment is a dual-gate semiconductor element. Specifically, a buffer layer 12 of AlN having a thickness of 100 nm is formed on a substrate 11 of sapphire in which the orientation of the principal plane is (0001), and a semiconductor layer stack 13 is formed thereon. The semiconductor layer stack 13 includes a first semiconductor layer 14 of undoped GaN having a thick-

ness of 1  $\mu$ m and a second semiconductor layer 15 of undoped Al<sub>0.15</sub>Ga<sub>0.85</sub>N having a thickness of 25 nm, which are formed in this order from the bottom.

A first electrode 16A and a second electrode 16B are formed from a stack of titanium (Ti) and aluminum (Al) so as to be spaced apart from each other on the second semiconductor layer 15, wherein one of the first electrode 16A and the second electrode 16B is to be the source electrode and the other the drain electrode. A first control layer 19A and a second control layer 19B each of p-type doped GaN having a thickness of 200 nm are formed spaced apart from each other on a region of the second semiconductor layer 15 between the first electrode 16A and the second electrode 16B. A first gate electrode 18A of nickel (Ni) is formed on the first control layer 19A. A second gate electrode 18B of Ni is formed on the second control layer 19B. A passivation film 41 of silicon nitride is formed on the second semiconductor layer 15, the first control layer 19A and the second control layer 19B.

The first control layer 19A and the second control layer 19B are formed in a stripe pattern having a width of 1.5  $\mu$ m, 20 for example, on the second semiconductor layer 15, and the first gate electrode 18A and the second gate electrode 18B are formed in a stripe pattern having a width of 1  $\mu$ m. In order to realize a sufficiently large drain breakdown voltage, the distance L1 from a side end of the first control layer 19A to a side 25 end of the second electrode 16B is preferably 5  $\mu$ m or more. The distance L2 from a side end of the second control layer 19B to a side end of the first electrode 16A is preferably 5  $\mu$ m or more.

Operation principles of the semiconductor device of the 30 first embodiment will now be described. The transistor of the first embodiment includes the first gate electrode 18A formed on the first control layer 19A having the p-type conductivity. Therefore, by applying a forward bias from the first gate electrode 18A to a channel region that is produced in an 35 interface region between the first semiconductor layer 14 and the second semiconductor layer 15, holes can be injected into the channel region. Since hole mobility is much lower than electron mobility in a nitride semiconductor, holes injected into the channel region hardly contribute as a current carrier. 40 The holes injected from the first gate electrode **18**A generate the same amount of electrons in the channel region. Accordingly, the holes have an increased effect of generating electrons in the channel region, and thus act like donor ions. In other words, since a carrier concentration can be modulated in 45 the channel region, a normally-off type nitride semiconductor transistor having a large operating current can be realized.

The present invention is similar in structure to a JFET, but the carrier injection is done intentionally and the present invention is therefore totally different in operation principles 50 from a JFET, which realizes carrier modulation in the channel region by means of the gate electric field. Specifically, it operates as a JFET up to a gate voltage of 3 V, but where there is applied a gate voltage of 3 V or more, exceeding the built-in potential of the pn junction, holes are injected into the gate, 55 thus increasing the current by the above-described mechanism, thereby realizing an operation with a large current and a low ON-resistance.

When a voltage exceeding the forward turn-ON voltage, e.g., a voltage exceeding about 1 V, is applied to a conventional FET using a nitride, a large gate current flows in, and it is no longer possible to realize a normal switching operation. Therefore, a gate voltage of only about 0.8 V can be applied, and an erroneous operation may therefore occur due to noise. With the semiconductor device of the present embodiment, 65 however, it is possible to apply a high gate voltage, making it unlikely that an erroneous operation occurs due to noise.

12

In the semiconductor device of the present embodiment, the second control layer 19B is formed near the second electrode 16B, and the second gate electrode 18B is formed on the second control layer 19B. The second gate electrode 18B can also control the channel region, as can the first gate electrode **18**A. Therefore, the electrical conductivity between the first electrode **16A** and the second electrode **16B** is controlled by the second gate electrode 18B, and by applying a potential less than or equal to that of the second electrode 16B to the second gate electrode 18B at least when the potential of the second electrode 16B is lower than that of the first electrode **16**A, it is possible to pinch off the channel region under the second control layer 19B. As a result, unlike with the conventional FET, no current flows between the first electrode 16A and the second electrode 16B, thus exhibiting excellent reverse voltage characteristics.

When the second gate electrode 18B and the second electrode 16B are electrically connected with each other, the second gate electrode 18B has the same potential as that of the second electrode 16B. Therefore, when a positive bias is applied to the second electrode 16B, a positive bias is applied also to the second gate electrode 18B, and the electrical conductivity between the first electrode 16A and the second electrode 16B is controlled by the first gate electrode 18A. On the other hand, when a negative bias is applied to the second electrode 16B, a negative bias is applied also to the second gate electrode **18**B. Therefore, a depletion layer expands in a region of the first semiconductor layer 14 and the second semiconductor layer 15 under the second control layer 19B, thereby pinching off the channel region. As a result, unlike the conventional FET, no current flows between the first electrode 16A and the second electrode 16B when a negative bias is applied to the second electrode 16B, thus exhibiting excellent reverse voltage characteristics.

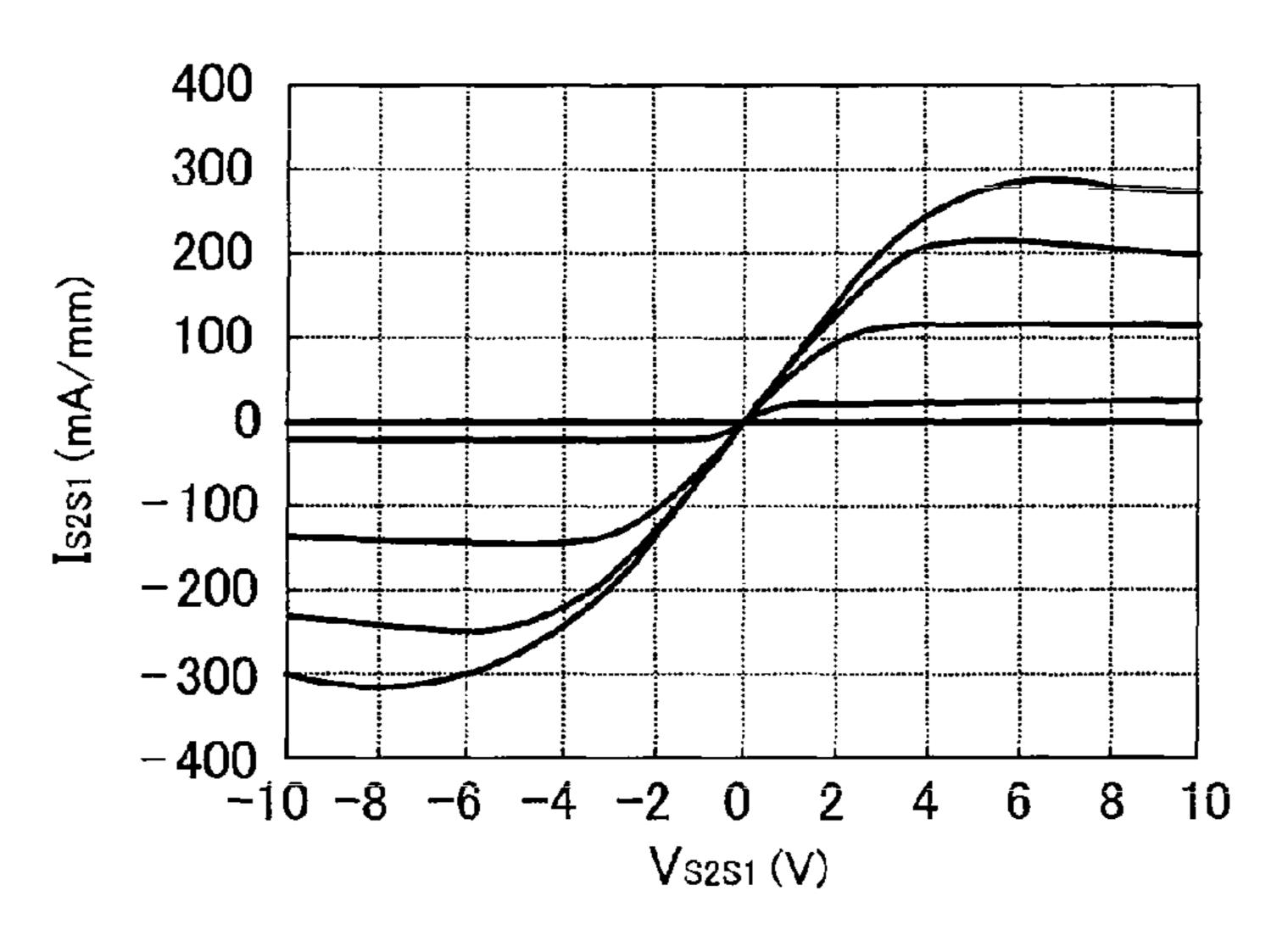

FIG. 2 shows the  $V_{S2S1}$ - $I_{S2S1}$  characteristics where the second gate electrode 18B and the second electrode 16B are electrically connected (shorted) with each other, with the first electrode 16A being the source electrode and the second electrode 16B being the drain electrode.  $V_{S2S1}$  is the voltage between the second electrode 16B and the first electrode 16A, and corresponds to the drain voltage Vds of an ordinary FET.  $I_{S2S1}$  is the current between the second electrode 16B and the first electrode 16A, and corresponds to the drain current Ids of an ordinary FET.  $V_{S2S1}$  along the horizontal axis in FIG. 2 is a voltage with respect to the first electrode 16A, and  $I_{52.51}$ along the vertical axis is plotted assuming that the positive direction is the direction of a current flow from the second electrode 16B toward the first electrode 16A. The figure shows cases where voltages of 0 V, 1 V, 2 V, 3 V and 4 V are applied to the first gate electrode 18A.

The conventional semiconductor device with no second gate electrode 18B, denoted by a broken line in FIG. 2, has a negative  $I_{S2S1}$  (drain current) flowing therethrough when  $V_{S2S1}$  (drain voltage) is negative, regardless of the gate voltage, clearly indicating that the conventional semiconductor device does not have reverse voltage characteristics.

On the other hand, the semiconductor device of the present embodiment does not have  $I_{S2S1}$  flowing therethrough even if  $V_{S2S1}$  is negative, regardless of the voltage applied to the first gate electrode 18A, clearly indicating that the semiconductor device has excellent reverse voltage characteristics.

With such excellent reverse voltage characteristics, it is possible to realize a control in four quadrants, which cannot be realized with the conventional semiconductor device.

In the semiconductor device of the present embodiment, the first control layer 19A and the second control layer 19B may be doped with about  $1\times10^{19}$  cm<sup>-3</sup> of magnesium (Mg), in

which case the carrier concentration is about  $1 \times 10^{18}$  cm<sup>-3</sup>. Portions of the second semiconductor layer 15 under the first control layer 19A and the second control layer 19B may contain impurities thermally diffused from the first control layer 19A and the second control layer 19B. While GaN is used herein for the first control layer 19A and the second control layer 19B, AlGaN may be used.

While the material of the first gate electrode **18**A and the second gate electrode **18**B is herein Ni, it may be any material as long as it exhibits desirable ohmic characteristics with the first control layer **19**A and the second control layer **19**B, and may be palladium (Pd), or the like.

While the first electrode **16**A and the second electrode **16**B are herein formed on the second semiconductor layer **15**, any structure may be used as long as they can be electrically connected through a tunneling current to the two-dimensional electron gas that is produced at the heterojunction interface between the first semiconductor layer **14** and the second semiconductor layer **15** to form an ohmic junction. For example, impurities such as silicon (Si) may be selectively diffused into regions of the second semiconductor layer **15** under the first electrode **16**A and the second electrode **16**B.

While a sapphire substrate is used herein, a substrate of SiC, GaN, Si, or the like, may be used, and the orientation of the principal plane is not limited to (0001) as long as a desir- 25 able crystal can be grown.

While the description of the present embodiment is directed to a single semiconductor device, there may be a plurality of semiconductor devices formed with the provision of device isolation regions. The device isolation regions may <sup>30</sup> be formed by, for example, selectively increasing the resistance of a first device isolation region and that of a second device isolation region by implanting boron (B) ions into these regions.

As shown in FIG. 3, the second gate electrode 18B may be formed so as to cover the top of the second electrode 16B, thereby shorting the second electrode 16B and the second gate electrode 18B with each other. This simplifies the wiring process. Conversely, the second electrode 16B may be formed so as to cover the second gate electrode 18B.

#### Second Embodiment

A second embodiment of the present invention will now be described with reference to the drawings. FIG. 4 shows a 45 cross section of a semiconductor device of the second embodiment. In FIG. 4, like elements to those of FIG. 3 are denoted by like reference numerals and will not be further described below.

As shown in FIG. 4, the semiconductor device of the 50 present embodiment includes a third semiconductor layer 17 of p-type doped Al<sub>0.2</sub>Ga<sub>0.8</sub>N having a thickness of 15 nm between the second semiconductor layer 15 and the first control layer 19A and the second control layer 19B.

The first control layer 19A and the second control layer 55 19R are typically formed by forming a nitride semiconductor layer of p-type GaN on the second semiconductor layer 15 and then selectively etching the p-type nitride semiconductor layer by dry etching using a chlorine gas, for example. However, it is very difficult to completely remove by etching only 60 the p-type nitride semiconductor layer to be the first control layer and the second control layer without etching the second nitride semiconductor layer. As a result, the structure may be overetched wherein the second semiconductor layer 15 is etched, or underetched wherein the p-type nitride semiconductor layer partly remains on the second semiconductor layer 15. With overetching, the thickness of the second semi-

14

conductor layer 15 is reduced, and the concentration of the two-dimensional electron gas (2DEG) generated by polarization is reduced, thereby lowering the maximum current (Imax). With underetching, the first electrode 16A and the second electrode 16B, being n-type ohmic electrodes, are formed on the portion of the p-type nitride semiconductor layer remaining through the etching process, thereby increasing the contact resistance of the first electrode 16A and the second electrode **16**B. However, the semiconductor device of the present embodiment includes the third semiconductor layer 17 of the p-type conductivity having a lower etching rate than that of the first control layer 19A and the second control layer 19B, whereby the p-type nitride semiconductor layer can be completely etched away except for portions thereof to be the first control layer 19A and the second control layer 19B. As a result, it is possible to obtain, with desirable reproducibility, a semiconductor device having excellent device characteristics.

In the present embodiment, the first electrode 16A and the second electrode 16B are formed in the opening formed in the third semiconductor layer 17 and are in contact with the second semiconductor layer 15. However, the first electrode 16A and the second electrode 16B may have any other structure as long as they can form an ohmic contact with the channel region, and an even more desirable ohmic contact may be realized by forming these electrodes so as to run through the second semiconductor layer 15 to be in contact with the first semiconductor layer 14.

While the second gate electrode **18**B is formed so as to cover the top of the second electrode **16**B in the illustrated example, the second gate electrode **18**B and the second electrode **16**B may be shorted with each other by a wire.

#### Third Embodiment

A third embodiment of the present invention will now be described with reference to the drawings. FIG. 5 shows a cross section of a semiconductor device of the third embodiment. In FIG. 5, like elements to those of FIG. 1 are denoted by like reference numerals and will not be further described below. As shown in FIG. 5, the semiconductor device of the present embodiment includes an integral electrode 16C of Ni on the second control layer 19B, wherein the integral electrode 16C is an integration of the second gate electrode and the second electrode.

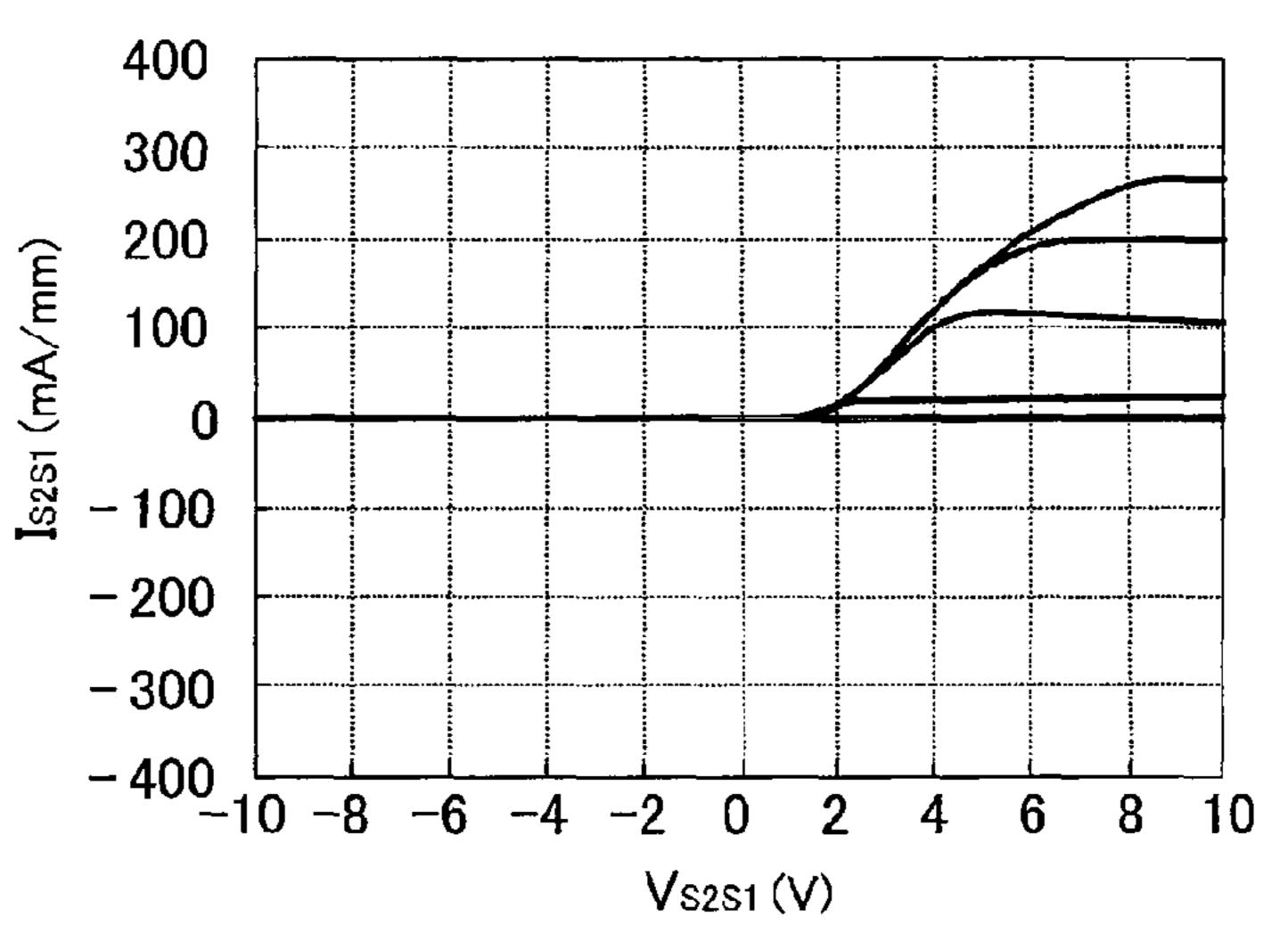

FIG. 6 shows the  $V_{S2S1}$ - $I_{S2S1}$  characteristics of the semiconductor device of the present embodiment, in comparison with those of the conventional semiconductor device with no second control layer. In FIG. 6,  $V_{S2S1}$  is a voltage with respect to the first electrode 16A, and  $I_{S2S1}$  along the vertical axis is plotted assuming the positive direction is the direction of a current flow from the second electrode 16B toward the first electrode 16A. For the conventional semiconductor device,  $V_{S2S1}$  denotes the drain voltage Vds and  $I_{S2S1}$  the drain current Ids. FIG. 6 shows cases where the gate voltage is 0 V, 1 V, 2 V, 3 V and 4 V.

The conventional semiconductor device, denoted by a broken line in FIG. 6, has a negative  $I_{S2S1}$  (drain current) flowing therethrough when  $V_{S2S1}$  (drain voltage) is negative even if the gate voltage is 0 V, clearly indicating that the conventional semiconductor device does not have reverse voltage characteristics. With the semiconductor device of the present embodiment, on the other hand,  $I_{S2S1}$  does not flow regardless of the gate voltage when  $V_{S2S1}$  is negative, clearly indicating that the semiconductor device has excellent reverse voltage characteristics. A pn junction is formed by the second control layer 19B and the channel region. Therefore, in an operation

region where a positive bias is applied to the integral electrode 16C, a current suddenly starts flowing when the drain voltage becomes 3V or higher which is the forward ON voltage of a GaN-based pn junction, thus showing an operation as if it were an IGBT. As a result, the degree of conductivity is 5 modulated, and a large drain current can be obtained.

While the material of the integral electrode **16**C is Ni in the present embodiment, any material may be used as long as it exhibits desirable ohmic characteristics with the second control layer **19**B, and may be Pd, or the like, for example.

As shown in FIG. 7, the third semiconductor layer 17 may be formed between the second semiconductor layer 15 and the first control layer 19A and the second control layer 19B, as in the second embodiment. However, the first electrode 16A may have any other structure as long as it can form an ohmic contact with the channel region, and an even more desirable ohmic contact may be realized by forming the electrode so as to run through the second semiconductor layer 15 to be in contact with the first semiconductor layer 14.

#### Fourth Embodiment

A fourth embodiment of the present invention will be described with reference to the drawings. FIG. 8 shows a cross section of a semiconductor device of the fourth embodiment. In FIG. 8, like elements to those of FIG. 1 are denoted by like reference numerals and will not be further described below. As shown in FIG. 8, in the semiconductor device of the present embodiment, the second semiconductor layer 15 includes first portions 15a having a larger thickness, and 30 second portions 15b having a smaller thickness than the first portions 15a. The first control layer 19A and the second control layer 19B are formed on the first portions 15a. In other words, the first control layer 19A and the second control layer 19B are formed on protruding portions of the second semi-35 conductor layer 15.

The first control layer 19A and the second control layer **19**B are formed by forming a p-type GaN layer on the second semiconductor layer 15 and then selectively removing the p-type GaN layer. In such a case, if the p-type GaN layer is 40 underetched as shown in FIG. 9, the p-type GaN layer partly remains between the first control layer 19A and the second control layer 19B, resulting in a state where the first control layer 19A and the second control layer 19B are electrically connected with each other with a resistor therebetween. In a 45 normally-off type dual-gate semiconductor element, the first gate electrode 18A and the second gate electrode 18B are in an ohmic contact with the first control layer 19A and the second control layer 19B, respectively. Thus, there is a nonnegligible current flowing between the first gate electrode 50 **18**A and the second gate electrode **18**B via the remaining portion of the p-type GaN layer. Especially, when there is formed a bidirectional switch device as shown in FIG. 9, a leak path may be formed between the first electrode 16A and the second electrode 16B, whereby a non-conductive state 55 cannot be sustained.

In the semiconductor device of the present embodiment, in the formation of the first control layer 19A and the second control layer 19B, the p-type GaN layer is overetched so as to remove even a portion of the second semiconductor layer 15. 60 Therefore, it is possible to reliably remove the p-type GaN layer except for the first control layer 19A and the second control layer 19B. Then, the second semiconductor layer 15 has a larger thickness in areas where the first control layer 19A and the second control layer 19B are formed.

The amount by which the second semiconductor layer 15 is overetched may be determined in view of the thickness of the

**16**

second semiconductor layer 15 when grown, the threshold voltage, variations in the amount of etching, etc. For example, where the second semiconductor layer 15 is grown to 60 nm and the p-type GaN layer to 300 nm, the amount of overetching may be 40 nm. Then, the thickness of the first portion 15a will be 60 nm and that of the second portion 15b 20 nm. Thus, it is possible to substantially completely remove an unnecessary portion of the p-type GaN layer. The thickness of the second semiconductor layer 15 substantially influences the 10 current characteristics between the first electrode **16A** and the second electrode **16**B. Therefore, the thickness of the second semiconductor layer 15 cannot be made excessively small. However, with the semiconductor device of the present embodiment, a thickness of 20 nm can be ensured for the second semiconductor layer 15 even in the overetched second portion 15b, thereby suppressing the current characteristics deterioration.

The thickness of the first portion **15**a may be even larger, e.g., about 100 nm, as long as it allows for epitaxy on the first semiconductor layer **14** of undoped GaN and it allows for a normally-off operation. As for the lower limit, the thickness can be reduced as long as it is possible to completely remove the residue of the p-type GaN layer remaining between the first control layer **19**A and the second control layer **19**B. For example, where the amount of overetching is 5 nm, the thickness may be about 25 nm. The thickness of the second portion **15**b may be even larger, e.g., about 95 nm, as long as it is possible to completely remove the residue of the p-type GaN layer remaining between the first control layer **19**A and the second control layer **19**B. As for the lower limit, the thickness can be reduced, e.g., to about 5 nm, as long as the element is operative.

FIG. 8 shows an example where portions of the second semiconductor layer 15 are removed and the first semiconductor layer 14 is dug down by about 40 nm so that the first electrode 16A and the second electrode 16B are in contact with the interface between the second semiconductor layer 15 and the first semiconductor layer 14, in order to reduce the contact resistance Alternatively first electrode 16A and the second electrode 16R may be formed on the second semiconductor layer 15.

#### First Variation of Fourth Embodiment

A first variation of the fourth embodiment of the present invention will now be described with reference to the drawings. FIG. 10 shows a cross section of a semiconductor device according to the first variation of the fourth embodiment. In FIG. 10, like elements to those of FIG. 8 are denoted by like reference numerals and will not be further described below.