#### US00RE45953E

# (19) United States

## (12) Reissued Patent

Dong et al.

## (10) Patent Number:

US RE45,953 E

#### (45) Date of Reissued Patent:

Mar. 29, 2016

#### (54) MITIGATING CHANNEL COUPLING EFFECTS DURING SENSING OF NON-VOLATILE STORAGE ELEMENTS

(71) Applicant: SANDISK TECHNOLOGIES INC.,

Milpitas, CA (US)

(72) Inventors: Yingda Dong, San Jose, CA (US); Yan

Li, Milpitas, CA (US); Cynthia Hsu,

San Jose, CA (US)

(73) Assignee: SanDisk Technologies Inc., Plano, TX

(US)

(21) Appl. No.: 14/285,446

(22) Filed: May 22, 2014

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: **8,208,310**Issued: **Jun. 26, 2012**Appl. No.: **12/773,701**Filed: **May 4, 2010**

(51) **Int. Cl.**

G11C 16/06 (2006.01) G11C 11/56 (2006.01) G11C 16/34 (2006.01)

(52) **U.S. Cl.**

CPC ...... *G11C 11/5642* (2013.01); *G11C 16/3418* (2013.01)

(58) Field of Classification Search

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

6,956,770 B2 10/2005 Khalid et al. 7,064,980 B2 6/2006 Cernea et al.

| 7,206,235    | В1   | 4/2007  | Lutze et al.              |

|--------------|------|---------|---------------------------|

| 7,215,574    |      | 5/2007  | Khalid et al.             |

| 7,508,721    | B2 * | 3/2009  | Li et al                  |

| 2006/0221660 | A1*  | 10/2006 | Hemink et al 365/100      |

| 2007/0070704 | A1*  | 3/2007  | Ho et al 365/185.22       |

| 2008/0056005 | A1*  | 3/2008  | Aritome                   |

| 2008/0158986 | A1*  | 7/2008  | Elmhurst et al 365/185.21 |

| 2010/0202216 | A1*  | 8/2010  | Byeon                     |

#### FOREIGN PATENT DOCUMENTS

| CN | 1926635       | A            | 3/2007 |

|----|---------------|--------------|--------|

| CN | 101263560     | $\mathbf{A}$ | 9/2008 |

| WO | WO2004/029975 | <b>A</b> 1   | 4/2004 |

| WO | 2010017013    | <b>A</b> 1   | 2/2010 |

#### OTHER PUBLICATIONS

Chinese Office Action dated Jan. 12, 2015, Chinese Patent Application No. 201180022609.3.

(Continued)

Primary Examiner — Ovidio Escalante

(74) Attorney, Agent, or Firm — Vierra Magen Marcus LLP

#### (57) ABSTRACT

Channel coupling effects during verify and read of non-volatile storage are mitigated by matching the amount of channel coupling that occurs during read with channel coupling that occurred during verify. All bit lines may be read together during both verify and read. In one embodiment, first bias conditions are established on bit lines when verifying each of a plurality of programmed states. A separate set of first bias conditions may be established when verifying each state. Biasing a bit line may be based on the state to which a non-volatile storage elements on the bit line is being programmed. A separate set of second bias conditions are established for each state being read. The second bias conditions for a given state substantially match the first bias conditions for the given state.

#### 30 Claims, 19 Drawing Sheets

#### (56) References Cited

#### OTHER PUBLICATIONS

Response to Office Action dated May 14, 2015, Chinese Patent Application No. 201180022609.3.

English translation of the claims filed in Response to Office Action dated May 14, 2015, Chinese Patent Application No. 201180022609.

English Abstract of Chinese Publication No. CN1926635 published on Mar. 7, 2007.

English Abstract of Chinese Publication No. CN101263560 published on Sep. 10, 2008.

Notice of Allowance U.S. Appl. No. 12/773,701, filed May 4, 2010, mailed Mar. 16, 2012.

International Search Report and Written Opinion of the International Searching Authority dated Aug. 17, 2011, PCT Application No. PCT/US2011/034951, filed May 3, 2011, 8 pages.

\* cited by examiner

Fig. 1

Fig. 2

Fig. 6D

Fig. 7A

Fig. 7B

#### <u>1000</u>

## <u>1040</u>

## <u>1100</u>

## <u>1200</u>

## <u>1220</u>

Fig. 13

Mar. 29, 2016

<u> 1400</u>

| VerifyA                    | Er | Α   | Aq | Ain | В   | Bq | Bin | С   | Cq | Cin |

|----------------------------|----|-----|----|-----|-----|----|-----|-----|----|-----|

| Data Latch =<br>Erase (Er) | 1  | 0   | 0  | 1   | 0   | 0  | 1   | 0   | 0  | 1   |

| QPW (VvaL)                 | 0  | 0/1 | 1  | 1   | 0/1 | 1  | 1   | 0/1 | 1  | 1   |

| QPW OR ~Er                 | 0  | 1   | 1  | 1   | 1   | 1  | 1   | 1   | 1  | 1   |

Fig. 14A

## <u>1420</u>

| VerifyA                           | Er | Α | Aq | Ain | В   | Bq | Bin | С   | Cq | Cin |

|-----------------------------------|----|---|----|-----|-----|----|-----|-----|----|-----|

| Data Latch = Erase<br>OR A (Er A) | 1  | 1 | 1  | 1   | 0   | 0  | 1   | 0   | 0  | 1   |

| QPW (VvbL)                        | 0  | 0 | 0  | 0   | 0/1 | 1  | 1   | 0/1 | 1  | 1   |

| QPW OR ~(Er A)                    | 0  | 0 | 0  | 0   | 1   | 1  | 1   | 1   | 1  | 1   |

Fig. 14B

## <u> 1440</u>

| VerifyA                                  | Er | Α | Aq | Ain | В | Bq | Bin | С   | Cq | Cin |

|------------------------------------------|----|---|----|-----|---|----|-----|-----|----|-----|

| Data Latch = Erase<br>OR A OR B (Er A B) | 1  | 1 | 1  | 1   | 1 | 1  | 1   | 0   | 0  | 1   |

| QPW (VvcL)                               | 0  | 0 | 0  | 0   | 0 | 0  | 0   | 0/1 | 1  | 1   |

| QPW OR ~(Er A B)                         | 0  | 0 | 0  | 0   | 0 | 0  | 0   | 1   | 1  | 1   |

Fig. 14C

Fig. 16

#### MITIGATING CHANNEL COUPLING EFFECTS DURING SENSING OF NON-VOLATILE STORAGE ELEMENTS

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held 10 invalid by a prior post-patent action or proceeding.

#### BACKGROUND

1. Field of the Invention

This disclosure relates to non-volatile storage.

2. Description of the Related Art

Semiconductor memory has become more popular for use in various electronic devices. For example, non-volatile semiconductor memory is used in personal navigation devices, 20 cellular telephones, digital cameras, personal digital assistants, mobile computing devices, non-mobile computing devices and other devices. Electrical Erasable Programmable Read Only Memory (EEPROM) and flash memory are among the most popular non-volatile semiconductor memories.

In both EEPROM and flash memory, a memory cell includes a transistor with a floating gate that is positioned above and insulated from a channel region in a semiconductor substrate. The floating gate and channel regions are positioned between the source and drain regions. A control gate is 30 provided over and insulated from the floating gate. The threshold voltage of the transistor is controlled by the amount of charge that is retained on the floating gate. That is, the minimum amount of voltage that must be applied to the control gate before the transistor is turned on to permit conduction of current between its source and drain is controlled by the level of charge on the floating gate. The memory cell may connected to a bit line to allow the conduction current to be sensed.

When programming a memory cell in an EEPROM or flash 40 memory device, such as a NAND flash memory device, typically a program voltage is applied to the control gate and the bit line is grounded. Electrons from the channel are injected into the floating gate. When electrons accumulate in the floating gate, the floating gate becomes negatively charged and the 45 threshold voltage of the memory cell is raised so that the memory cell is in a programmed state. More information about programming can be found in U.S. Pat. No. 6,859,397, titled "Source Side Self Boosting Technique for Non-Volatile Memory;" U.S. Pat. No. 6,917,542, titled "Detecting Over 50 Programmed Memory;" and U.S. Pat. No. 6,888,758, titled "Programming Non-Volatile Memory," all three cited patents are incorporated herein by reference in their entirety.

In many cases, the program voltage is applied to the control gate as a series of pulses (referred to as programming pulses), 55 with the magnitude of the pulses increasing at each pulse. Between programming pulses, a set of one or more verify operations are performed to determine whether the memory cell(s) being programmed have reached their target level. If a memory cell has reached its target level, programming stops 60 for that memory cell. If a memory cell has not reached its target level, programming will continue for that memory cell.

Memory cells in some EEPROM and flash memory devices have a floating gate that is used to store two ranges of charges and, therefore, the memory cell can be programmed/ 65 erased between two states (an erased state and a programmed state).

2

A multi-state memory device stores multiple bits of data per memory cell by identifying multiple distinct valid threshold voltage (Vt) distributions (or data states). Each distinct Vt distribution corresponds to a predetermined value for the set of data bits encoded in the memory device. For example, a memory cell that stores two bits of data uses four valid Vt distributions. A memory cell that stores three bits of data uses eight valid Vt distributions.

One factor that affects the reading of memory cell's Vt is the channel potential of its neighbor memory cell (or cells). For example, if the neighbor's drain side channel potential is 0.4 volts, the apparent Vt of a memory cell may be different than if the neighbor's drain side channel potential is 0 volts.

Once a non-volatile storage element has been programmed, it is important that its programmed state can be read back with a high degree of reliability. However, differences in the neighbor's channel potential between when the memory cell was verified and later read can impact the apparent Vt of the memory cell. Hence, the memory cell might be read incorrectly.

One technique for reducing the differences between program verify and read conditions such as differences in channel potential is to sense only every other bit line during program verify and read. This keeps the neighbor's channel potential at 0V during both during program verify and read. However, by only reading every other bit line at a time, the time to verify and read may double. Because many program cycles may be needed, each with its own verify operations, doubling the number of verify operations for each program cycle can be detrimental to performance.

#### BRIEF DESCRIPTION OF THE DRAWINGS

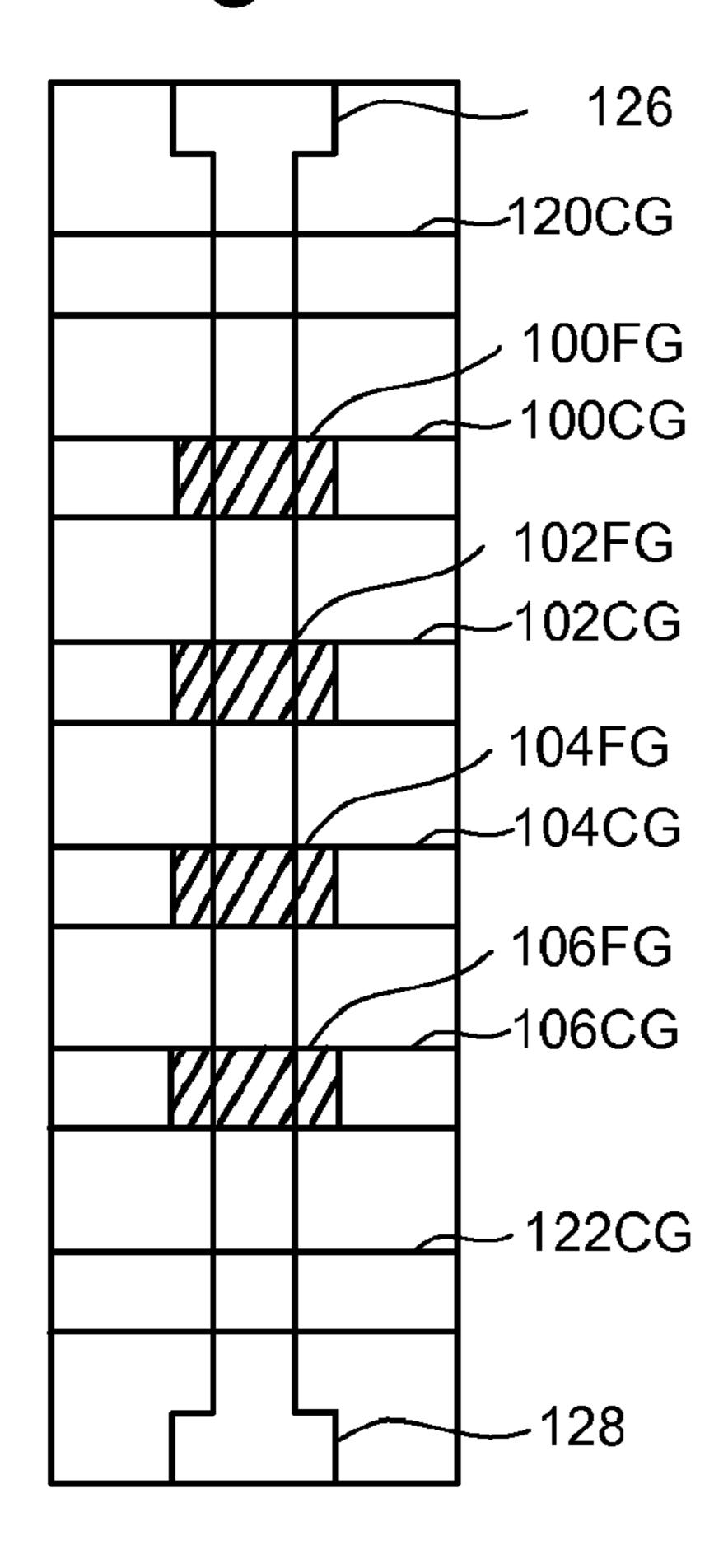

FIG. 1 is a top view of a NAND string.

FIG. 2 is an equivalent circuit diagram of the NAND string.

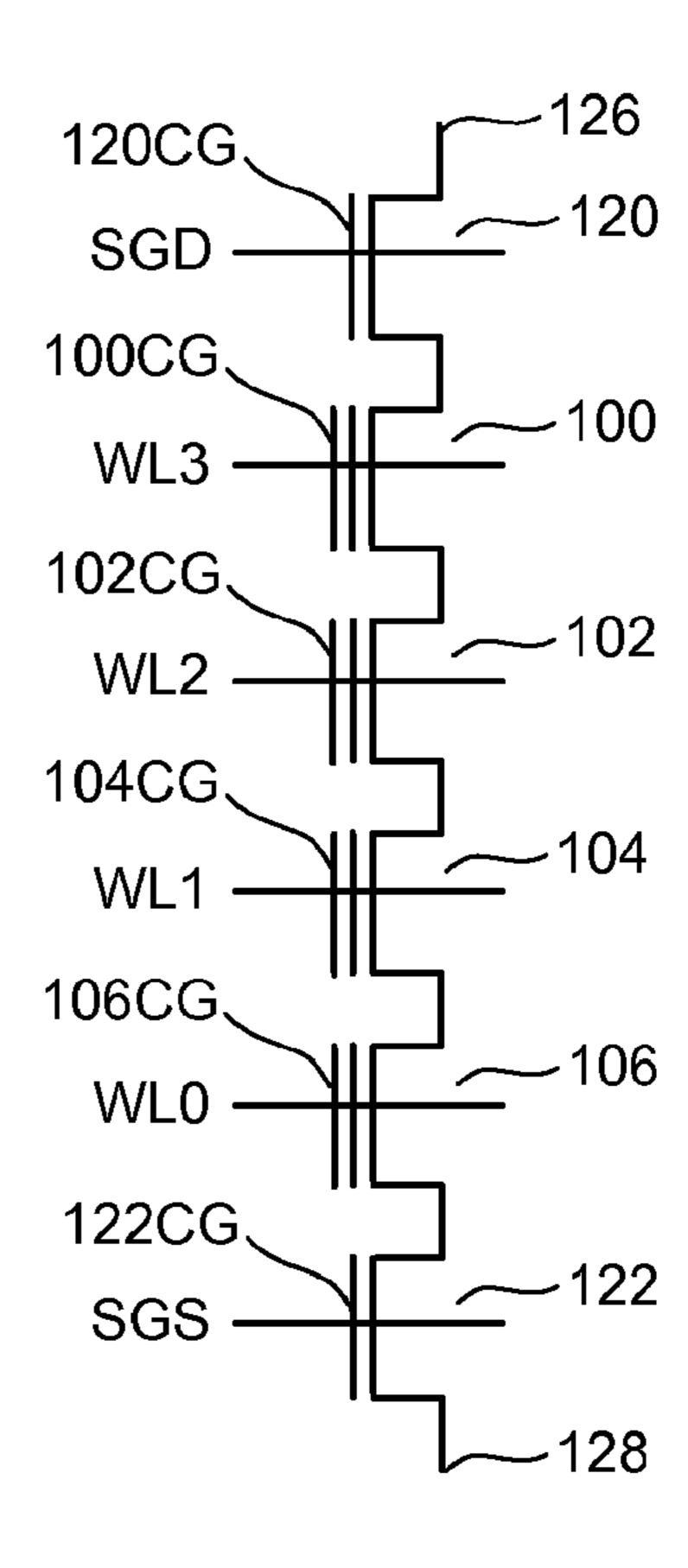

FIG. 3 is a block diagram of a non-volatile memory system.

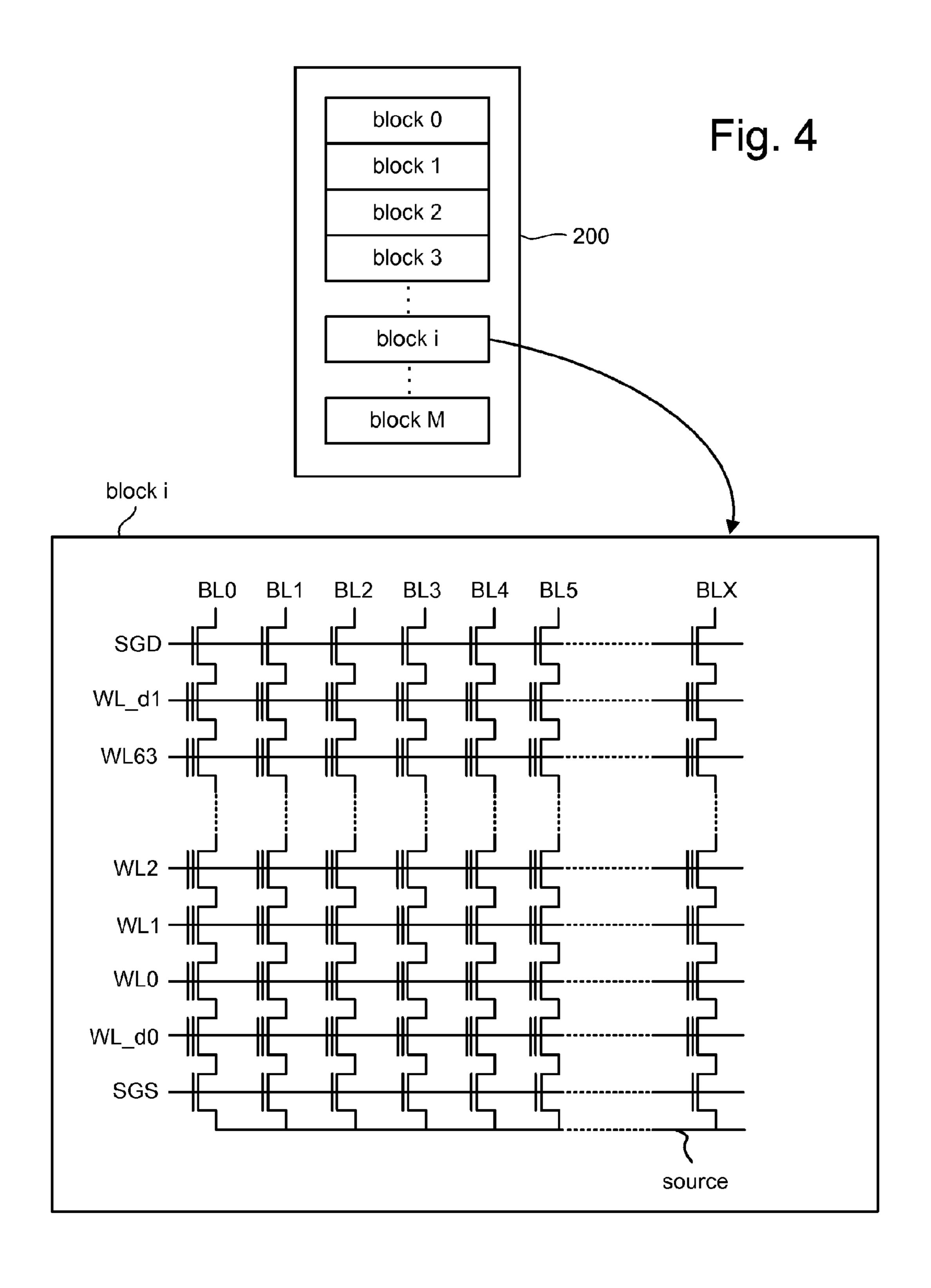

FIG. 4 is a block diagram depicting one embodiment of a memory array.

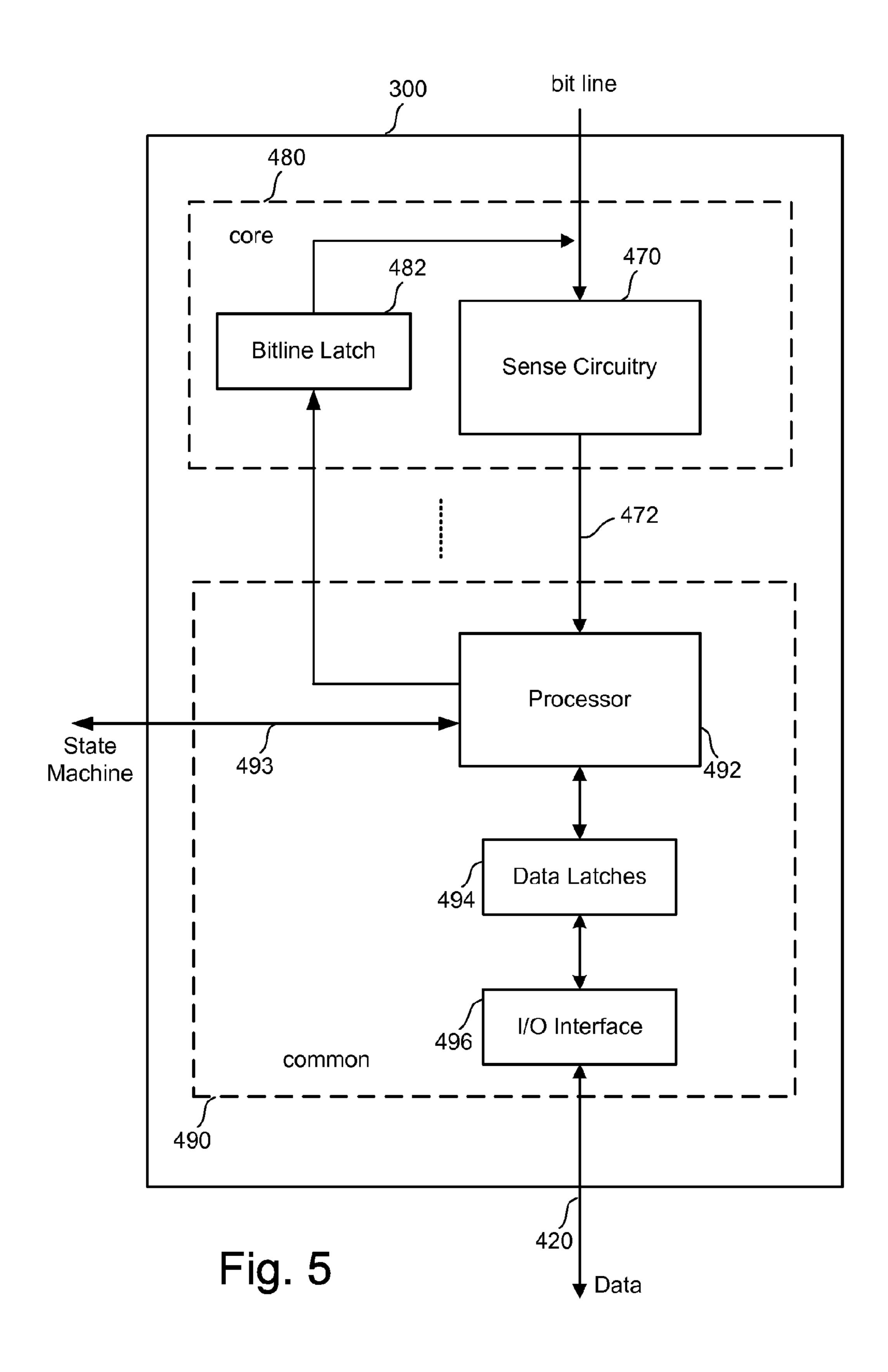

FIG. 5 is a block diagram depicting one embodiment of a sense block.

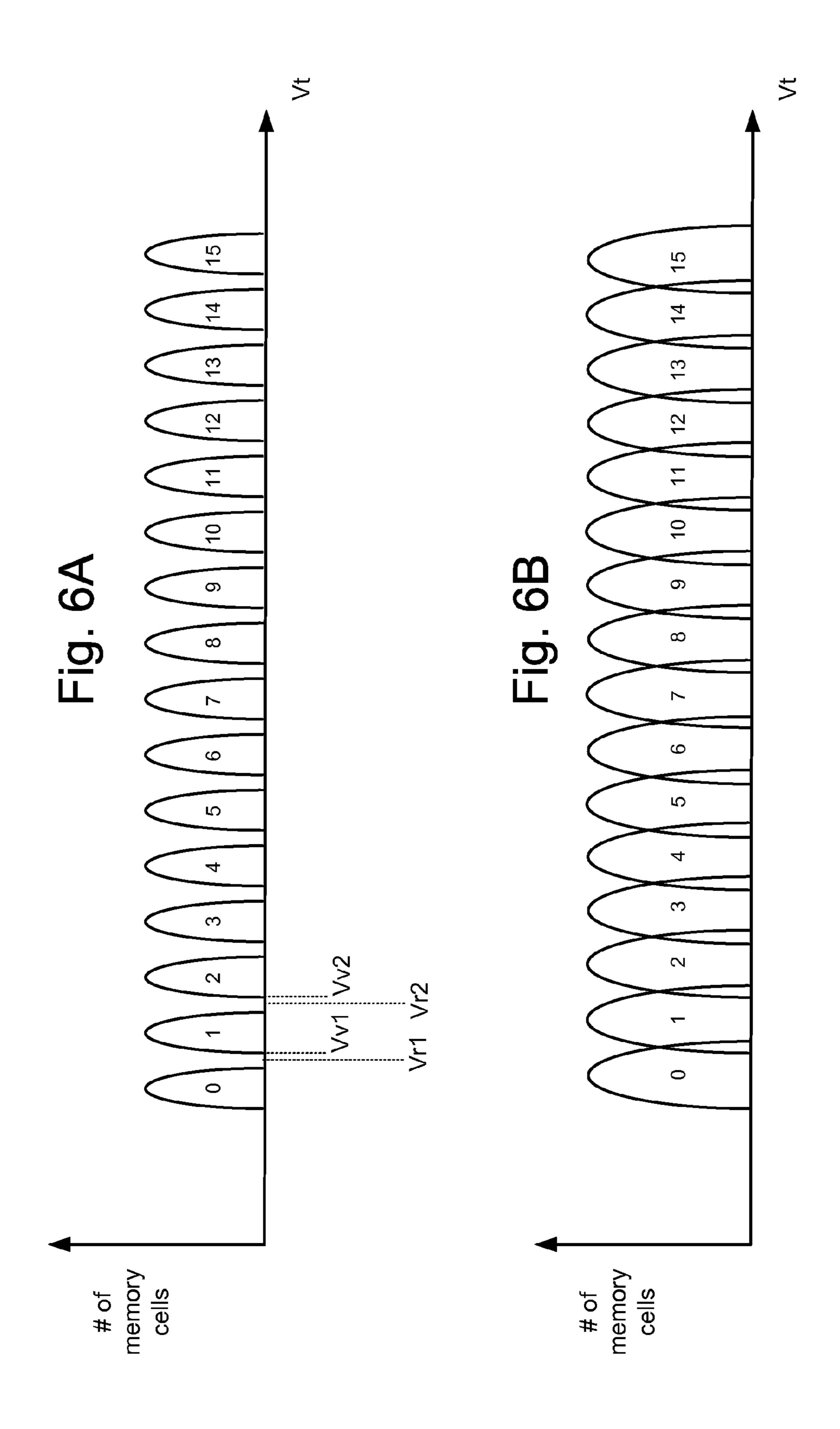

FIG. 6A depicts an example set of Vt distributions.

FIG. 6B depicts an example set of Vt distributions.

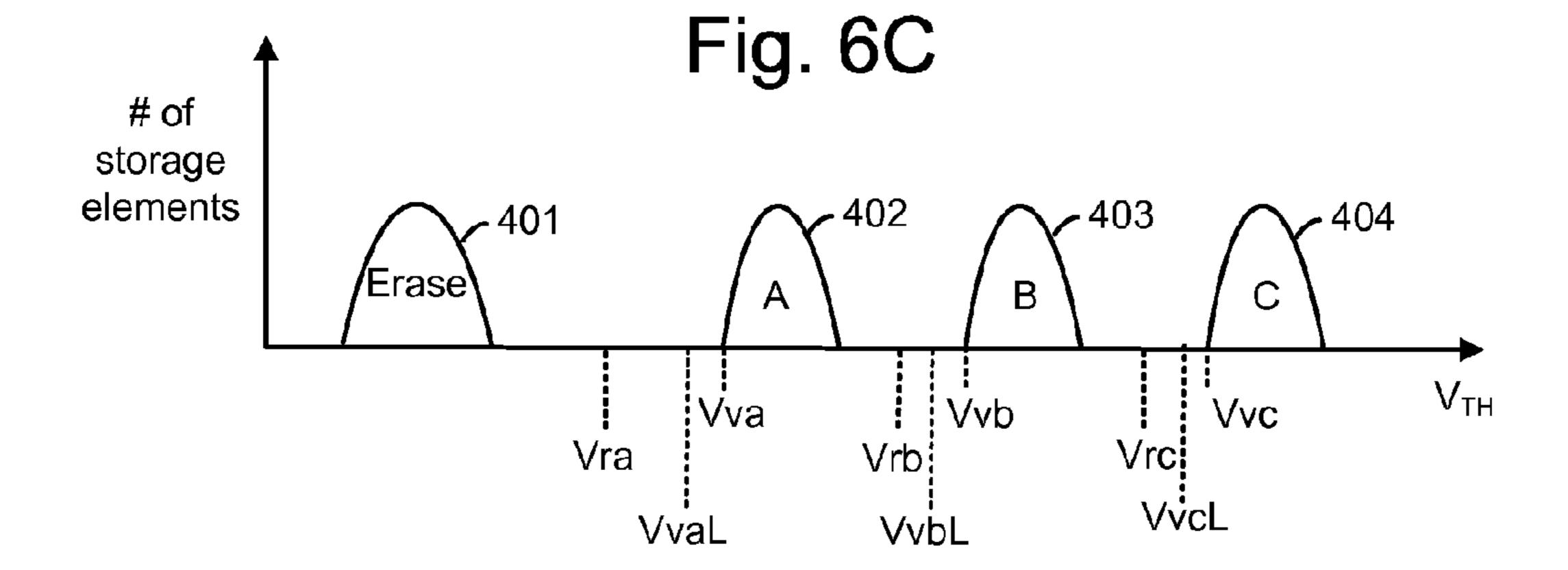

FIG. 6C depicts an example set of threshold voltage distributions for a four-state memory device in which each storage element stores two bits of data.

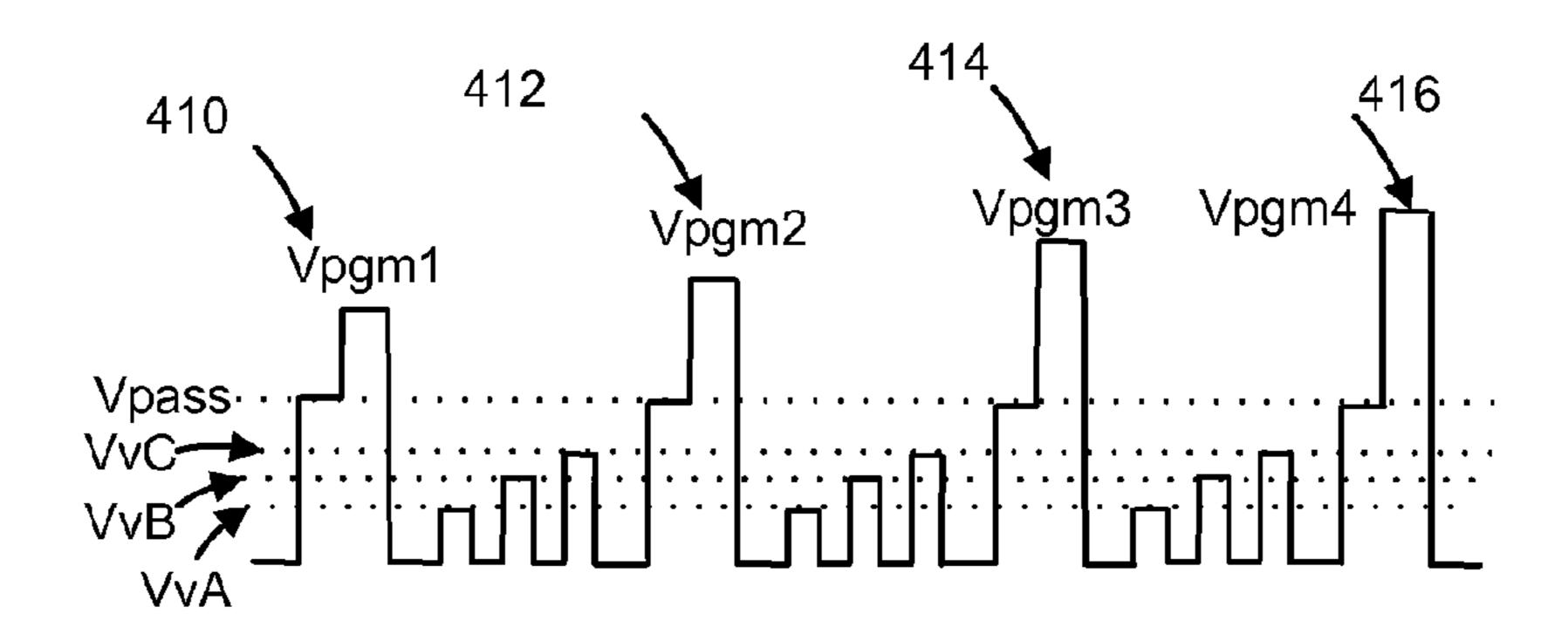

FIG. **6**D depicts a series of program and verify pulses which are applied to a selected word line during a programming operation.

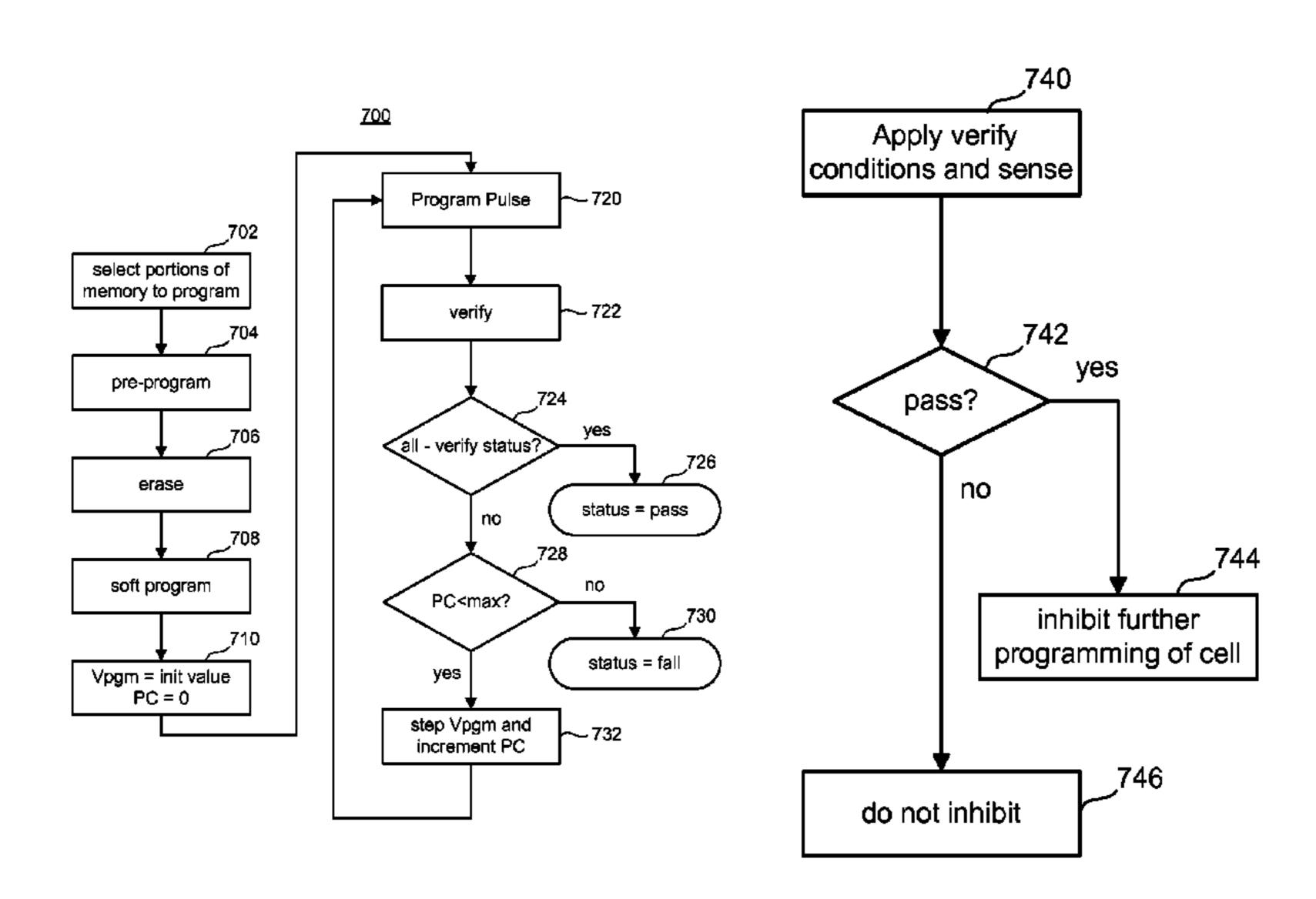

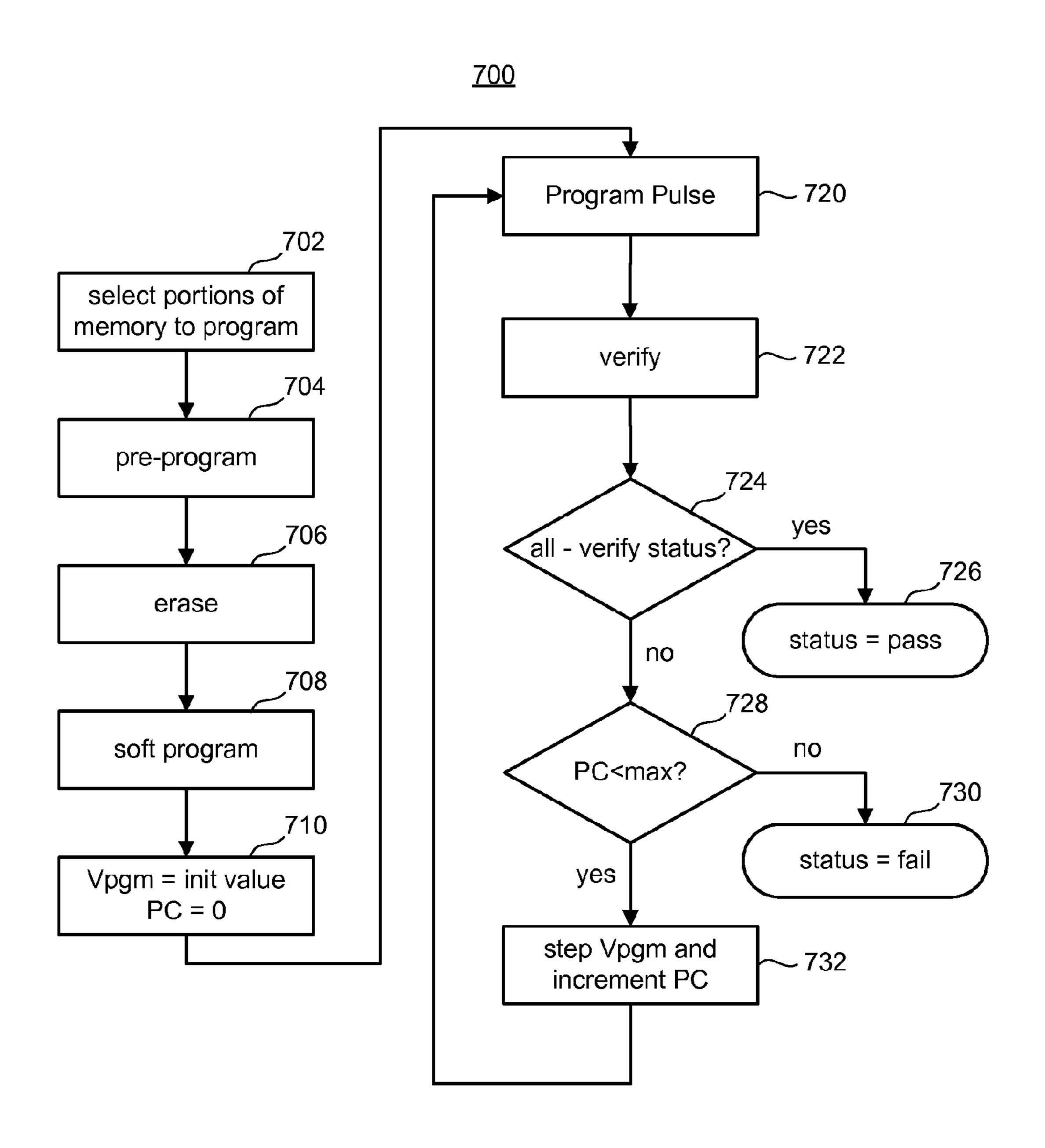

FIG. 7A is a flowchart describing one embodiment of a programming process, which includes one or more verification steps.

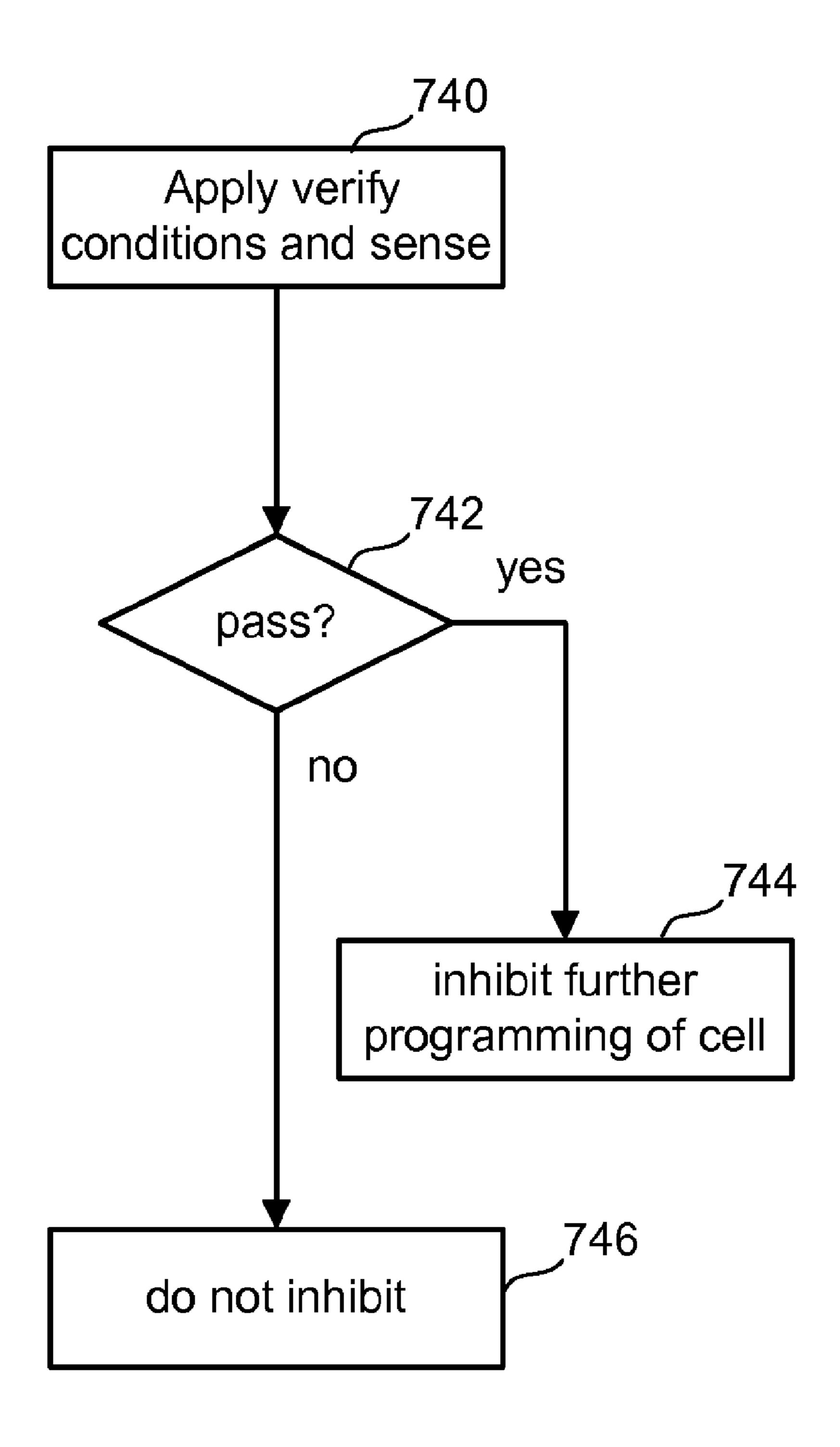

FIG. 7B provides a flow chart describing one embodiment of a process of performing verification without coarse/fine programming.

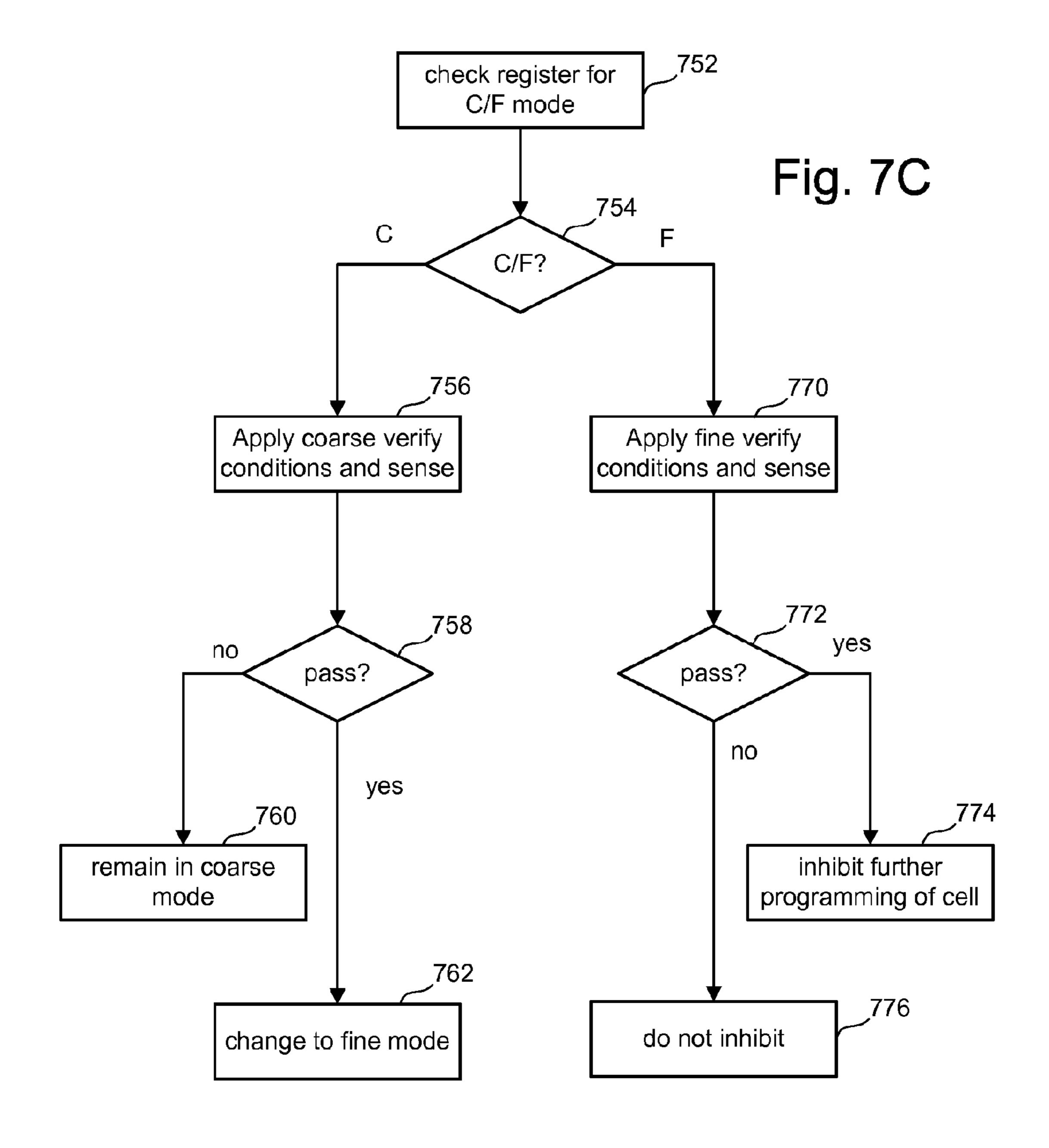

FIG. 7C provides a flow chart describing one embodiment of a process of verifying in which coarse/fine programming is used.

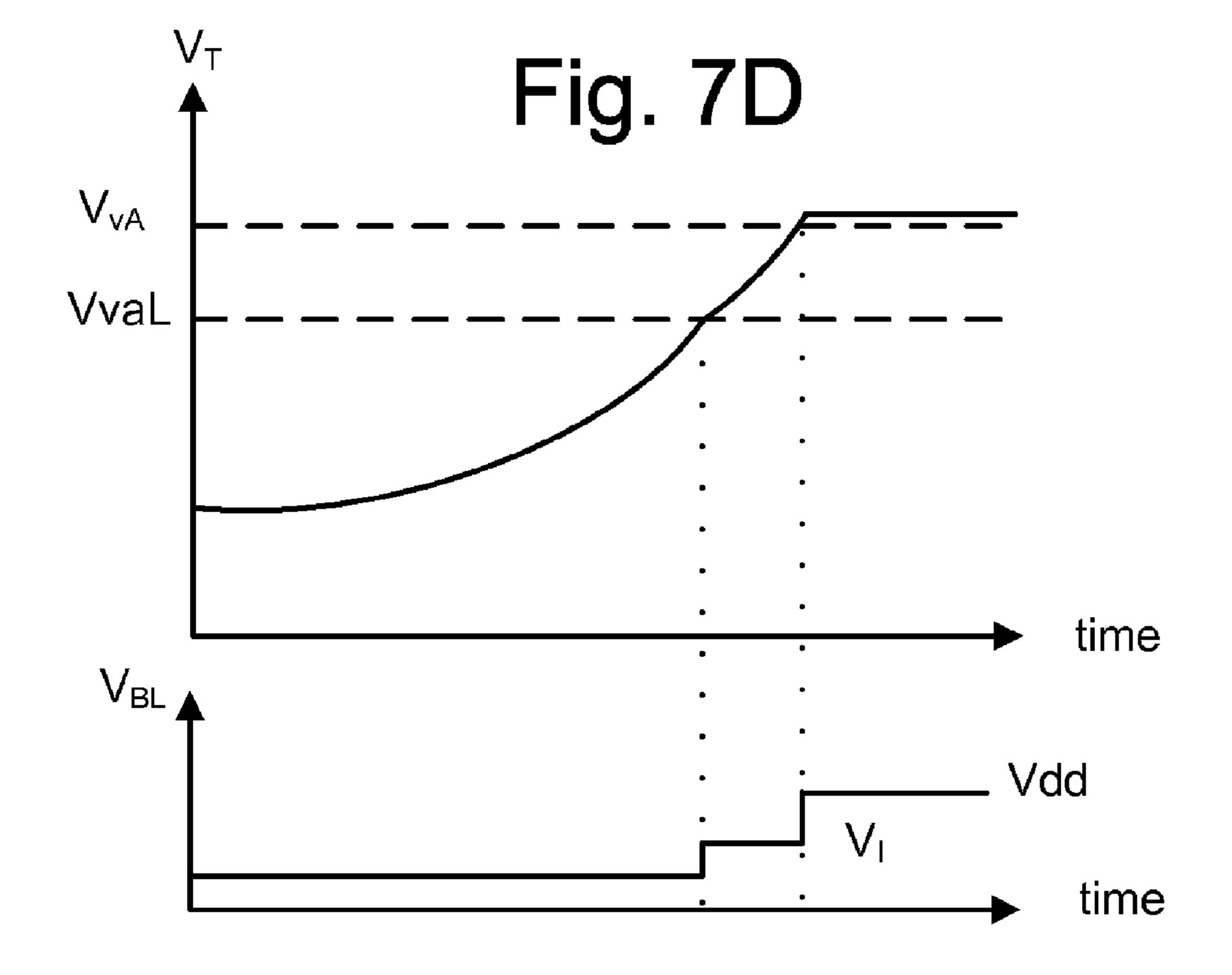

FIG. 7D provides graphs of threshold voltage  $(V_T)$  versus time and bit line voltage  $(V_{BL})$  versus time to indicate how one example of a coarse/fine programming process is performed.

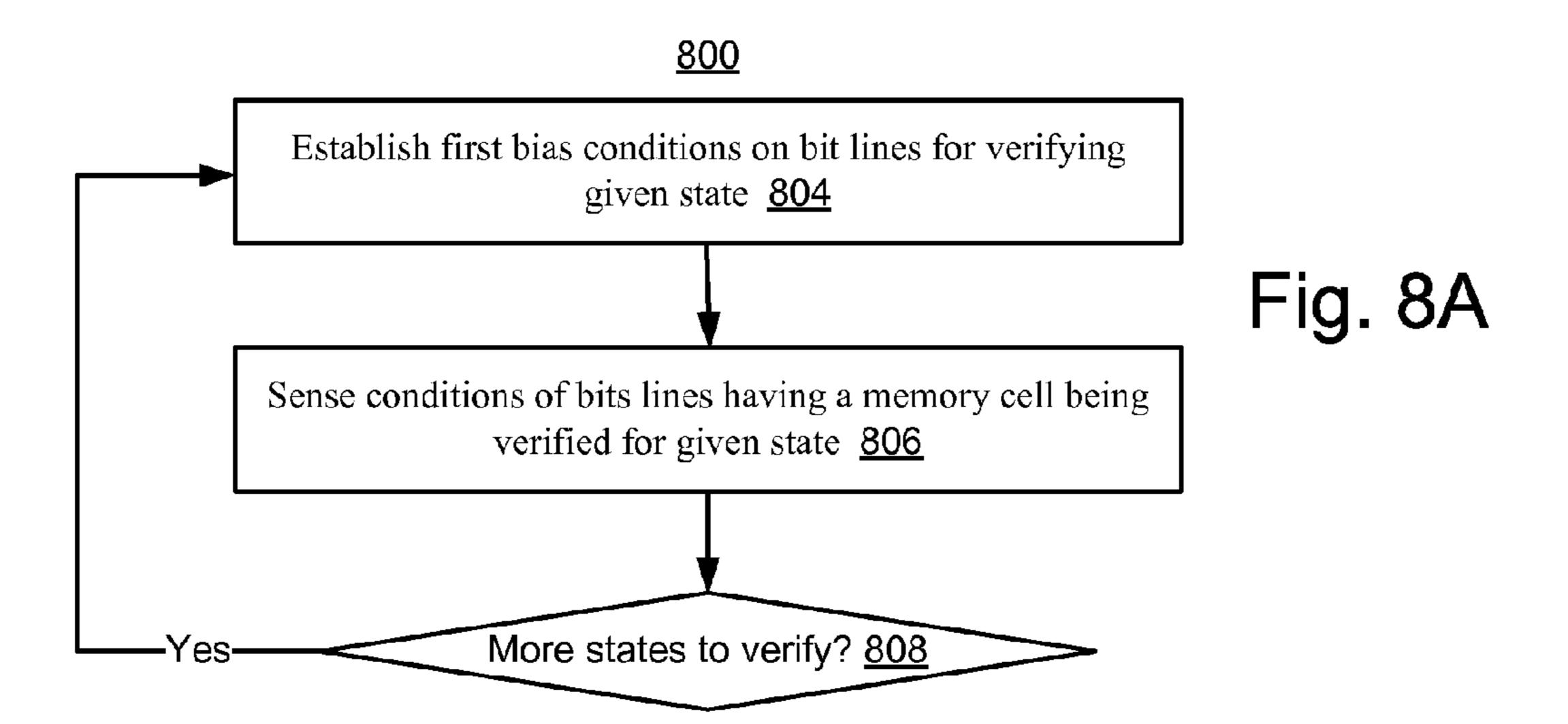

FIG. 8A is flowchart of one embodiment of a process for verifying memory cells during a programming process.

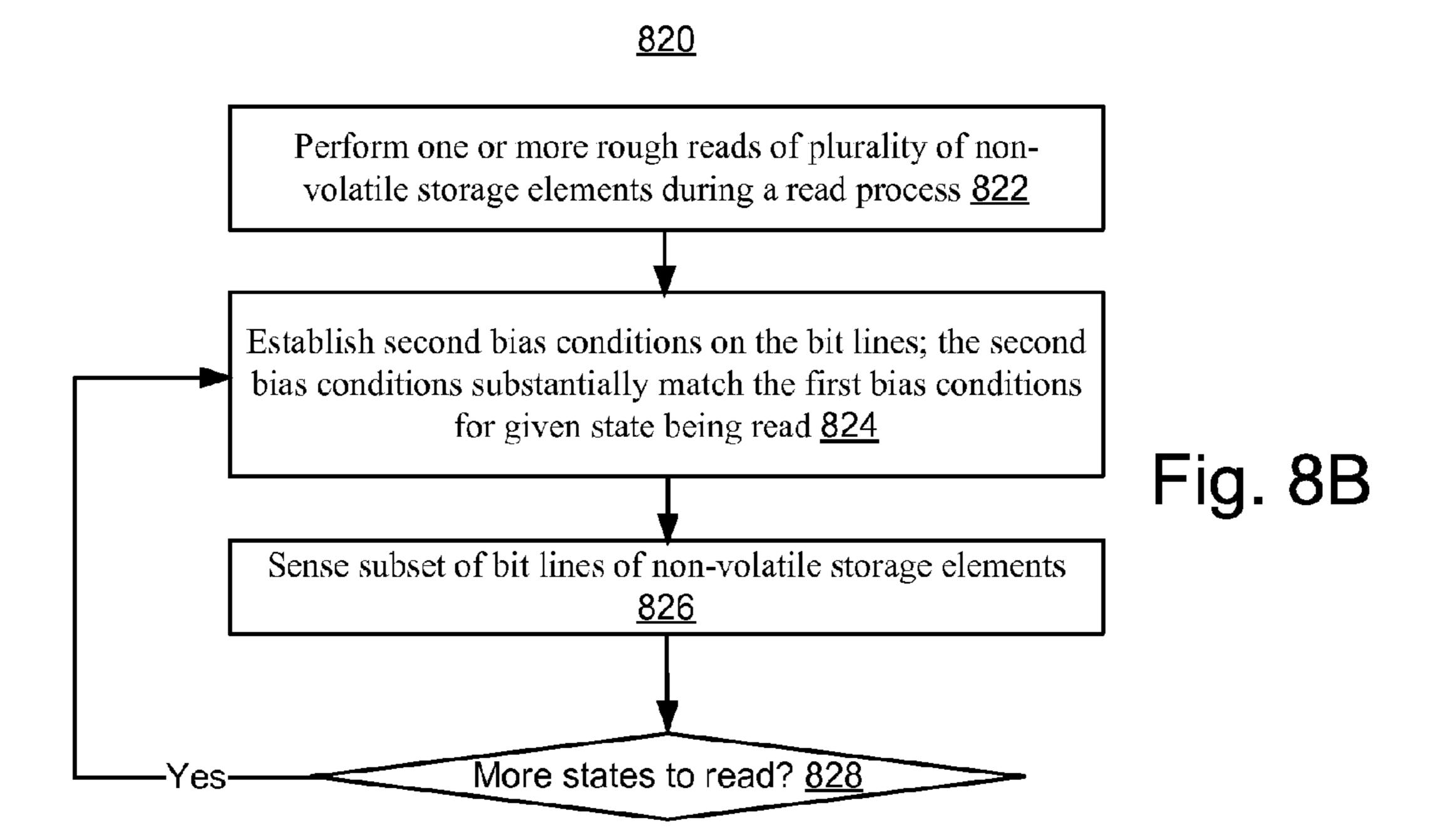

FIG. 8B depicts a flowchart of one embodiment of a process for reading memory cells.

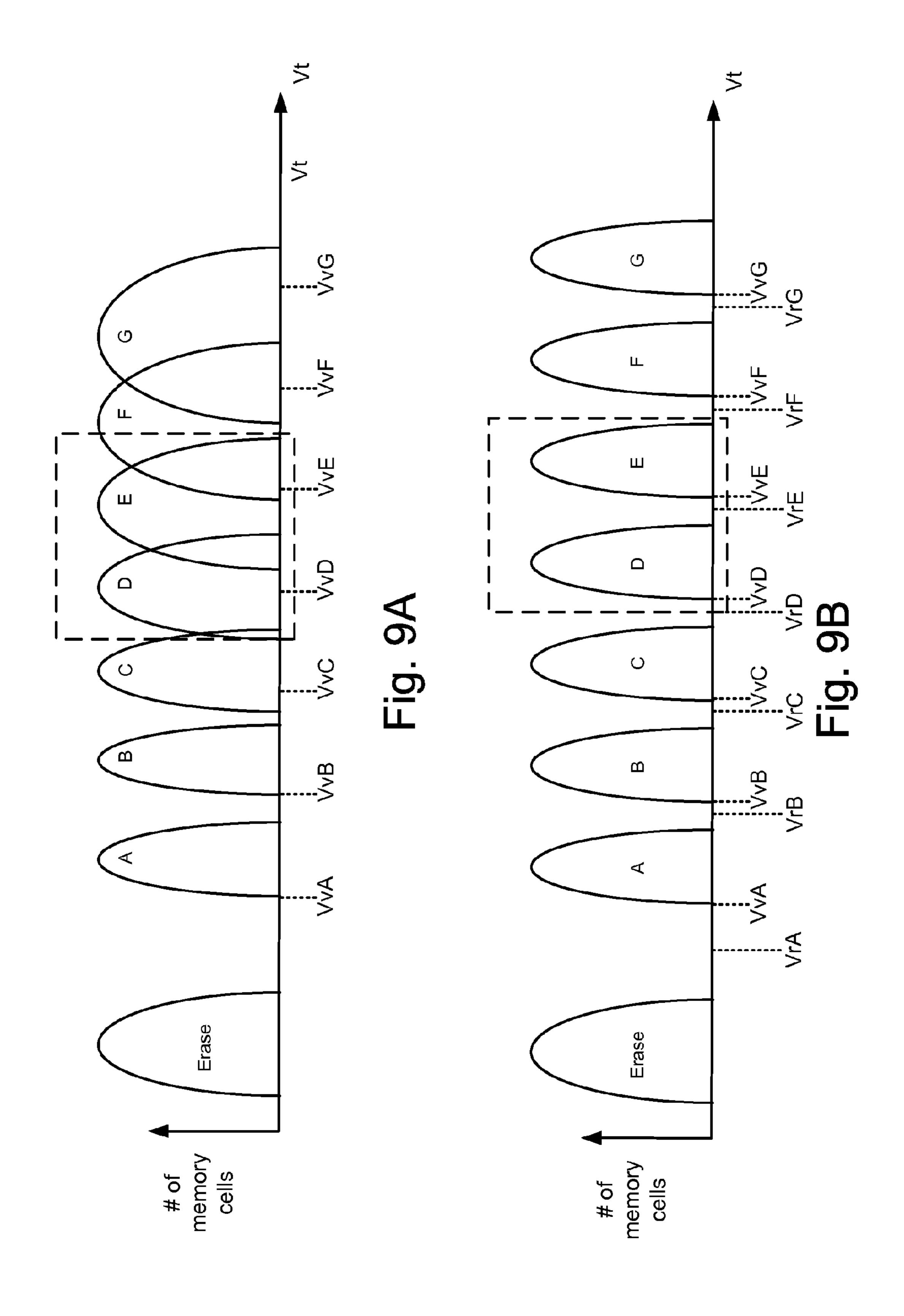

FIG. 9A depicts an example of threshold voltage distributions during programming.

FIG. 9B depicts an example of threshold voltage distributions after programming is complete.

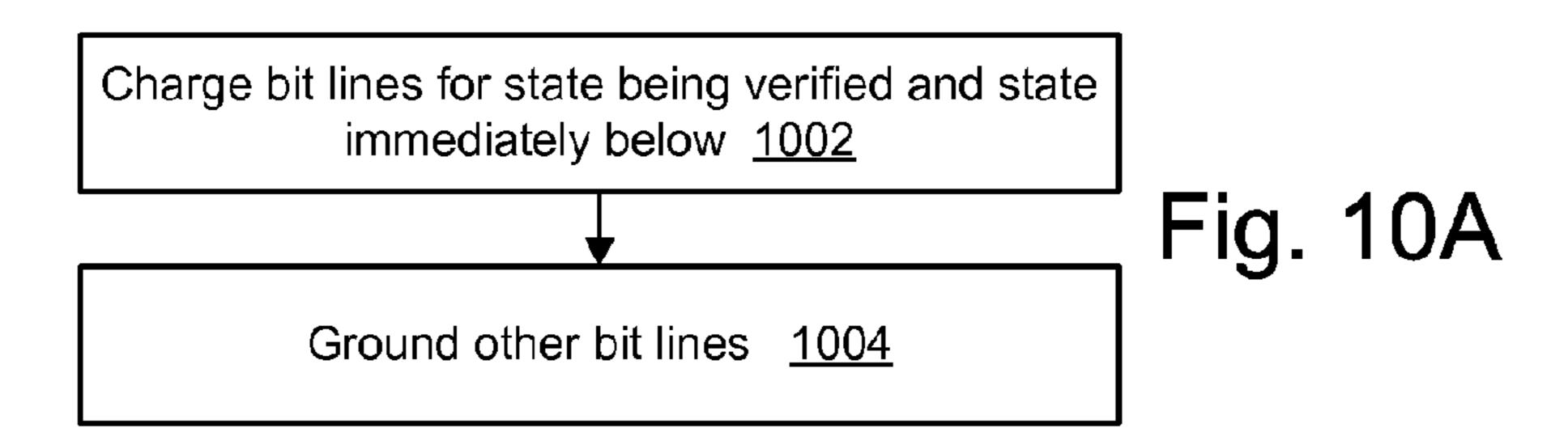

FIG. 10A is a flowchart of one embodiment of a process for establishing first bias conditions during verify.

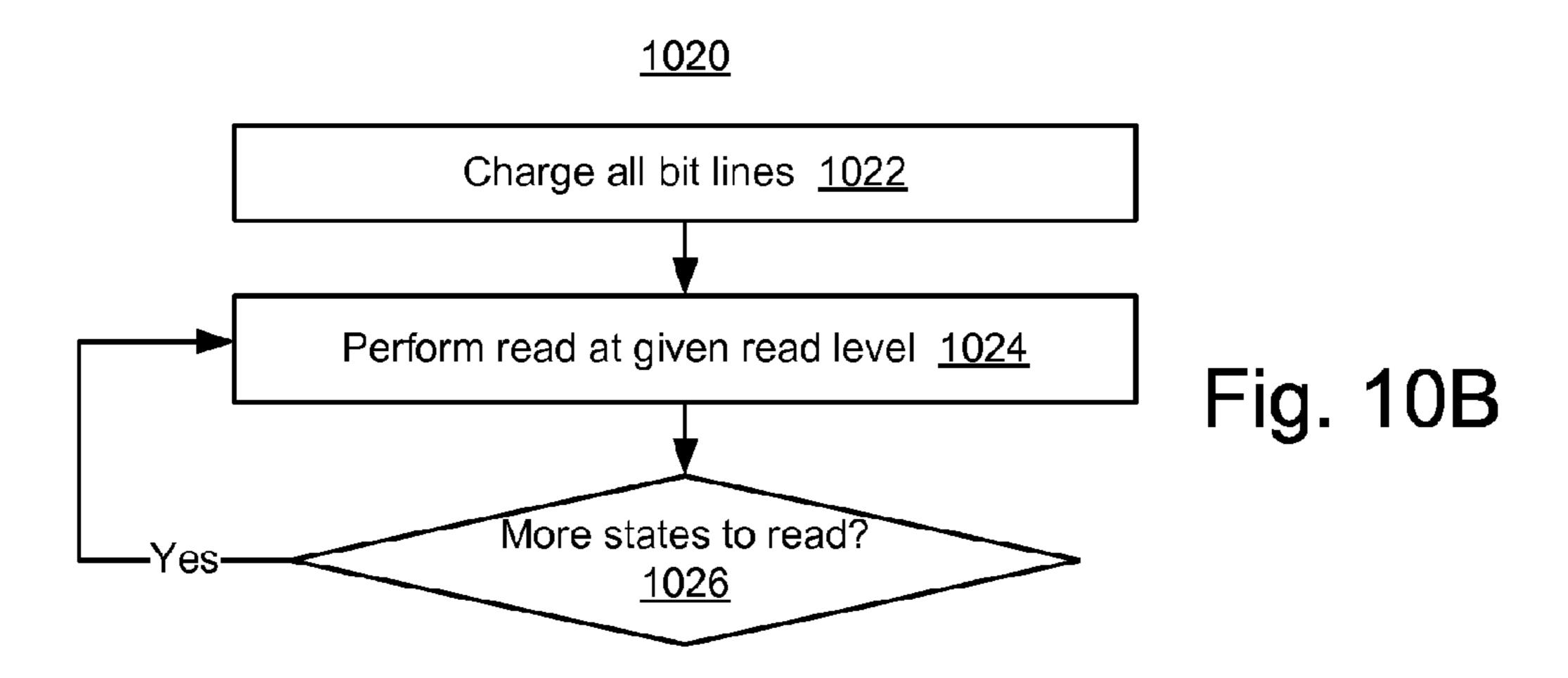

FIG. 10B is a flowchart of one embodiment of a process for 5 performing rough reads.

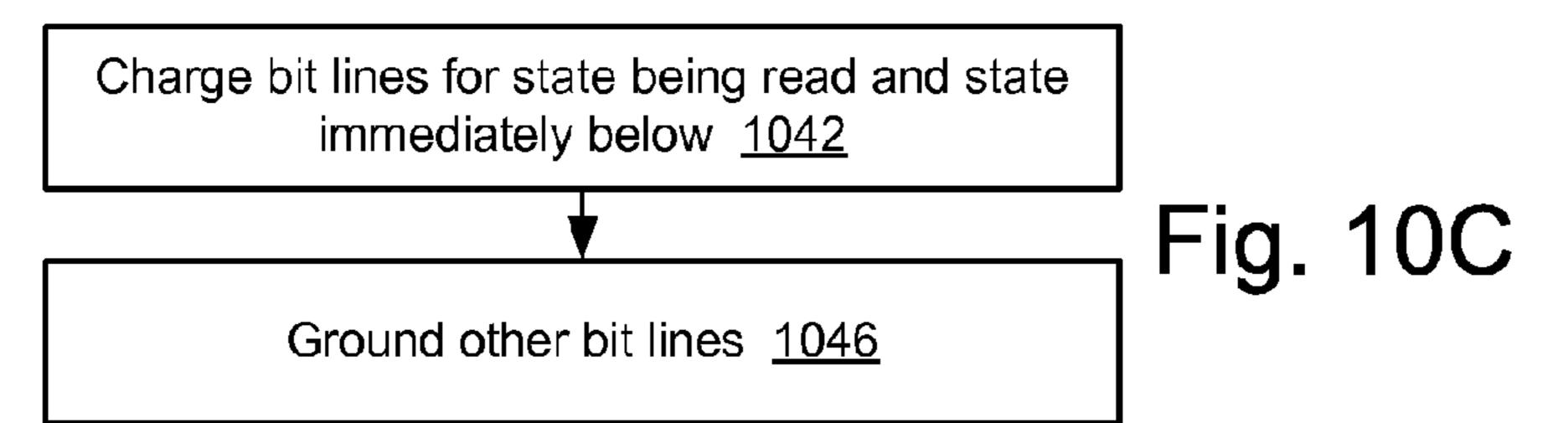

FIG. 10C is a flowchart of one embodiment of a process for establishing second bit line bias conditions based on rough reads.

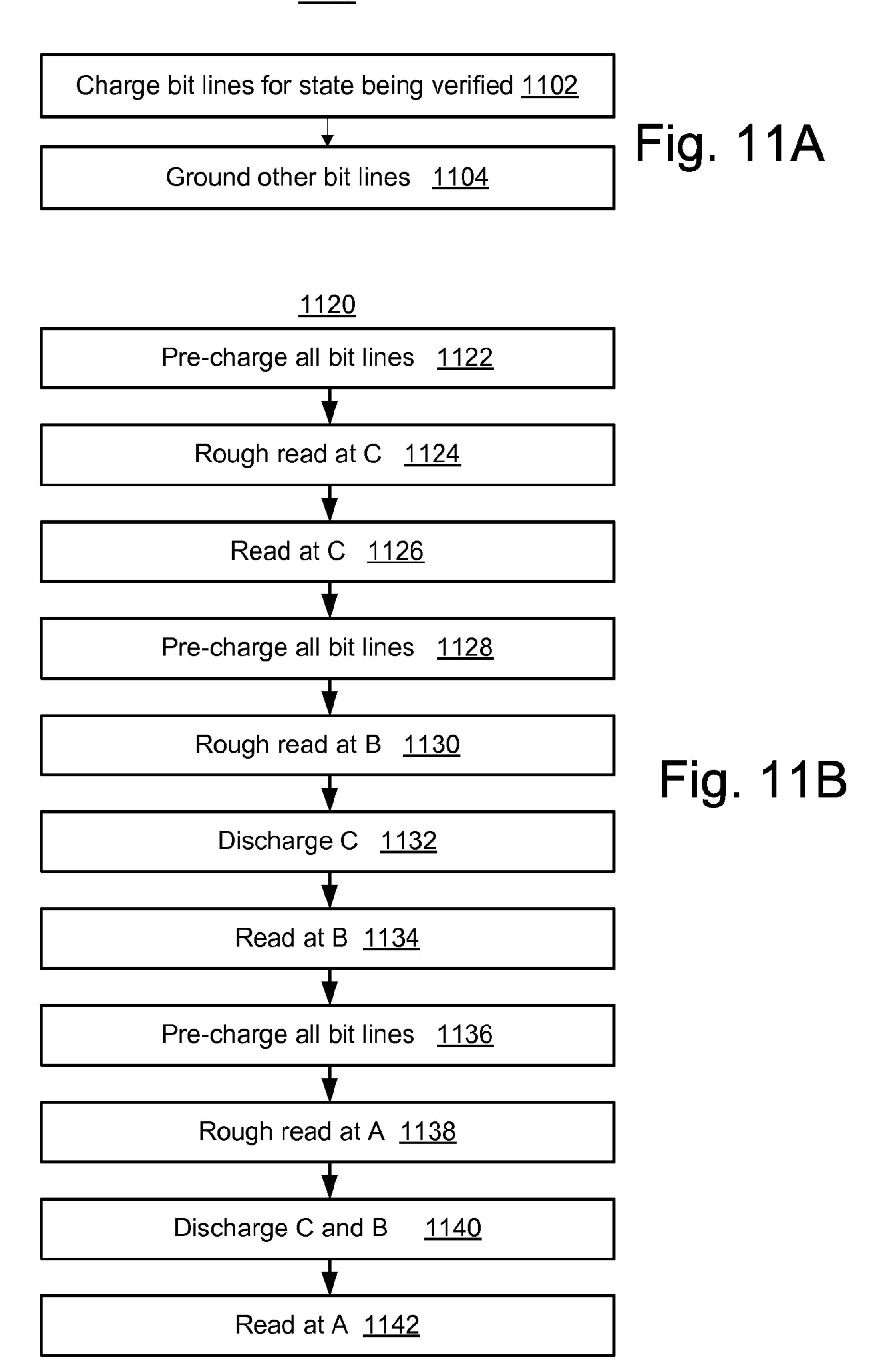

FIG. 11A is a flowchart of one embodiment of a process for establishing first bias conditions during verify.

FIG. 11B is a flowchart of one embodiment of a process for reading memory cells.

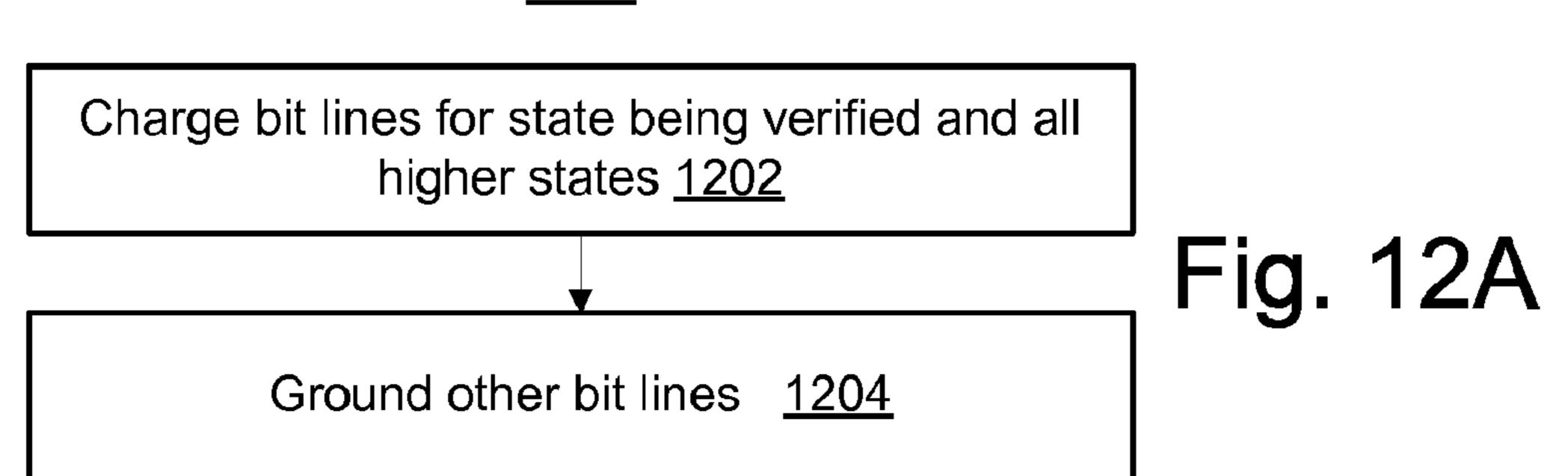

FIG. 12A is a flowchart of one embodiment of a process for establishing first bias conditions during verify.

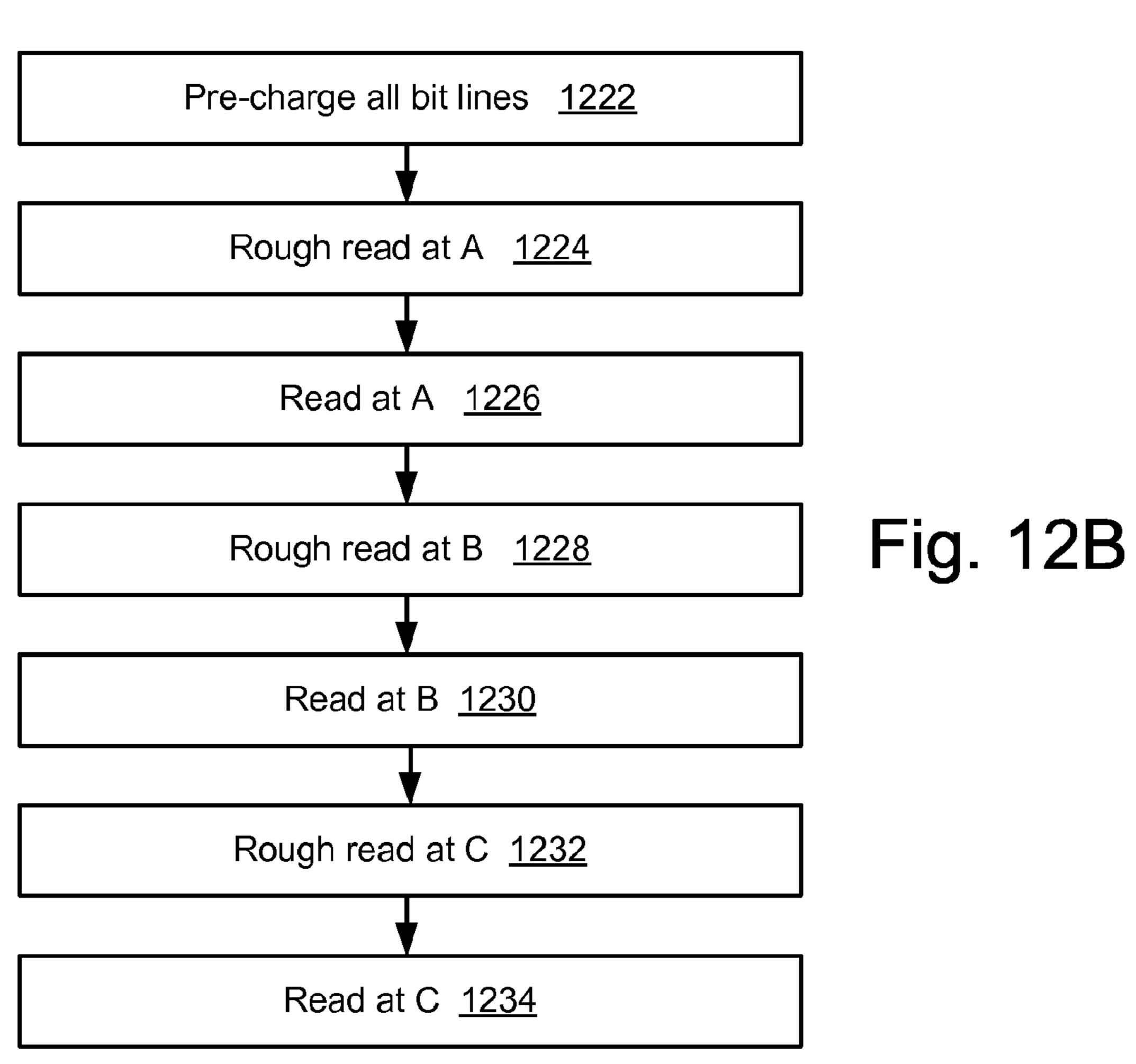

FIG. 12B is a flowchart of one embodiment of a process for 15 performing rough reads and establishing second bit line conditions during read.

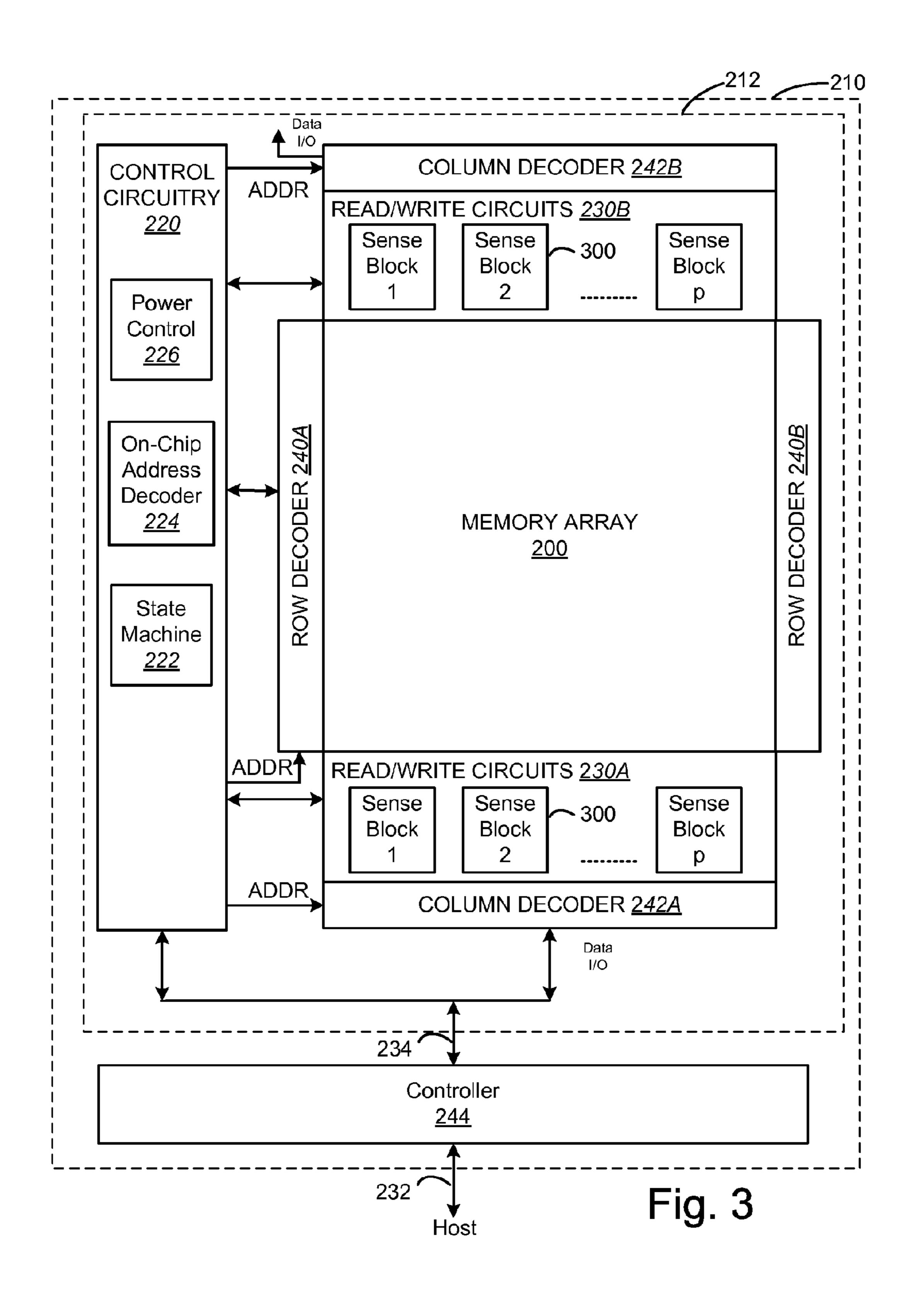

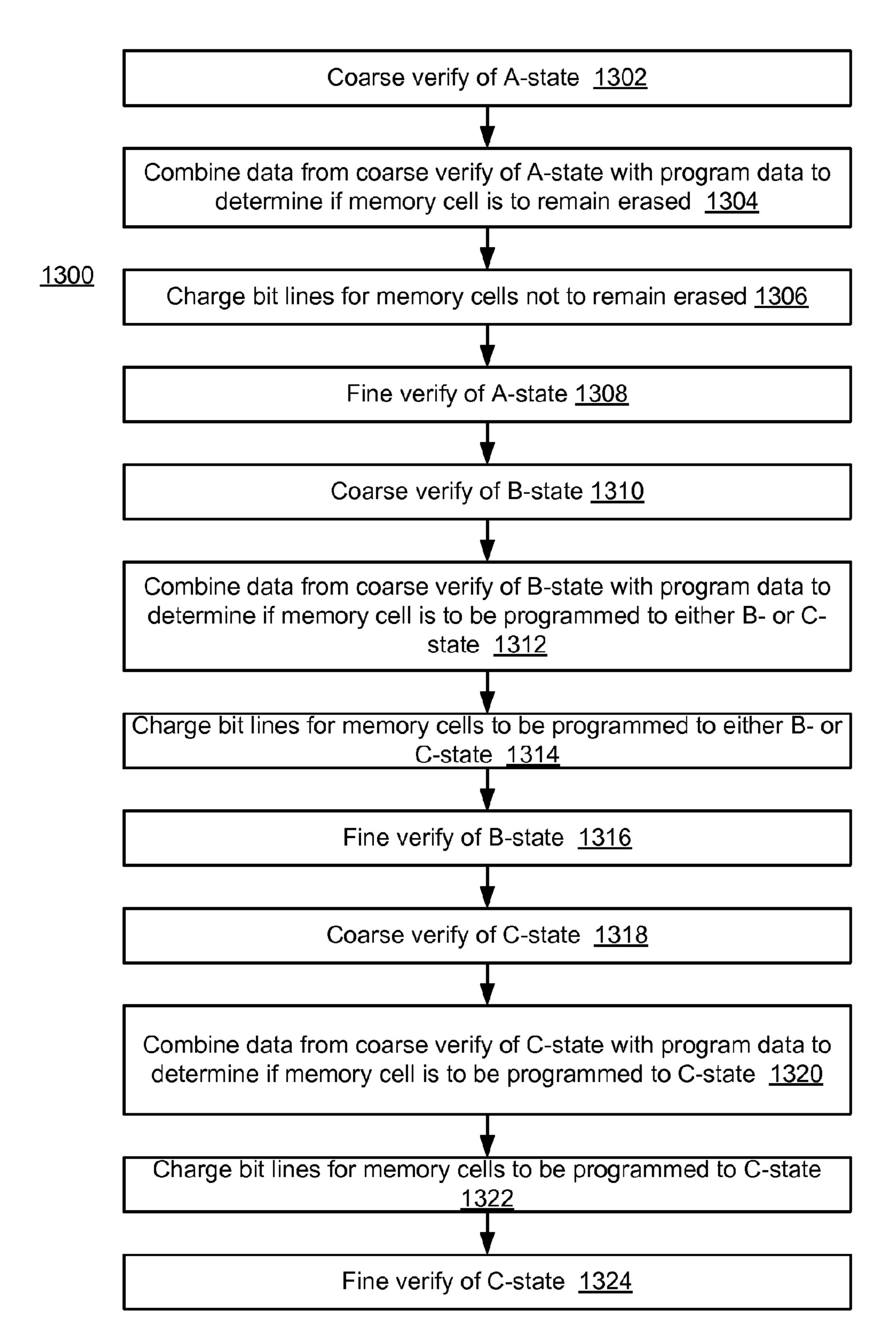

FIG. 13 is a flowchart of one embodiment of a process of verifying memory cells.

FIG. 14A, FIG. 14B, and FIG. 14C depict tables that summarize conditions to illustrate one embodiment of how data from latches may be used to determine bit line bias conditions for verify.

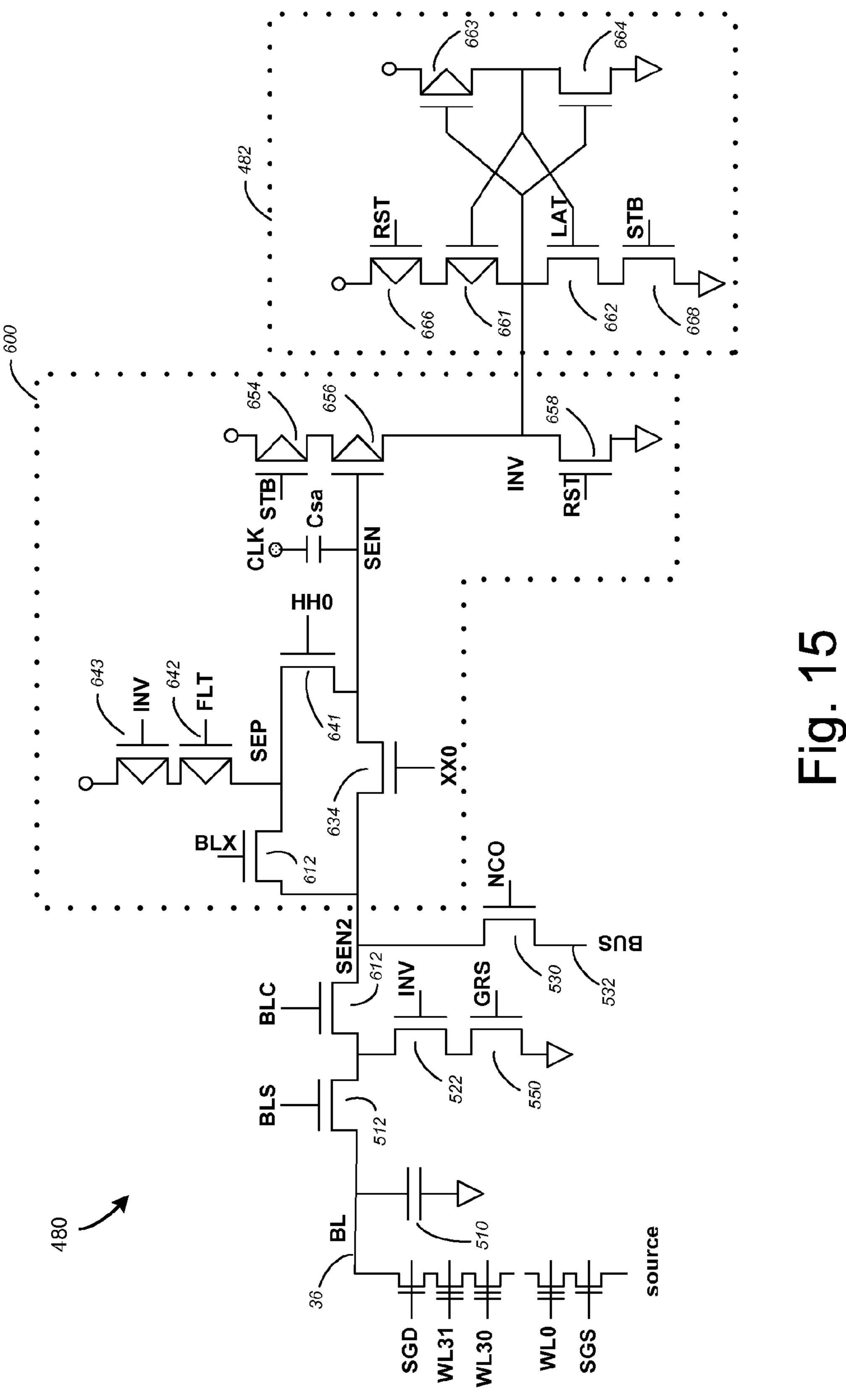

FIG. 15 illustrates an example of sense module.

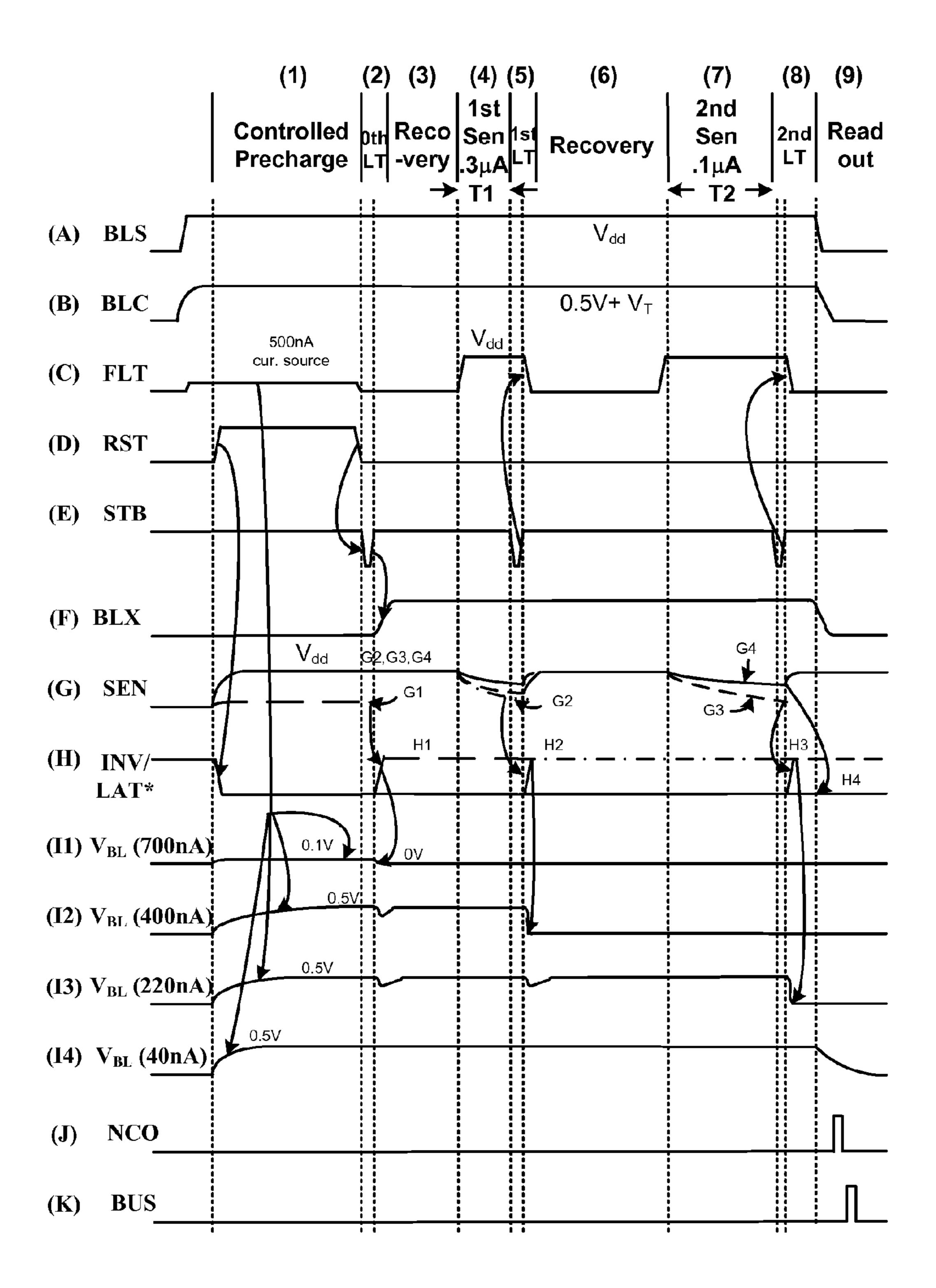

FIG. 16 depicts a timing diagram of one embodiment of 25 sensing during a read or verify using the sense amplifier of FIG. **15**.

#### DETAILED DESCRIPTION

Techniques are disclosed for improvements in operating non-volatile storage devices. The amount of channel coupling that a specific memory cell experiences from one or more neighbor memory cells during read may be matched to the neighbor(s) during verify. Therefore, differences in channel coupling between program verify and read are reduced or eliminated.

Note that the threshold voltage of the target memory cell being sensed may depend on the bit line bias of the neighbor 40 memory cells. For example, if the neighbor's bit line is grounded, the threshold voltage of the target memory may be higher than if the neighbor's bit line is biased at Vbl (where Vbl may be, for example, 0.4V). On the other hand, if the neighbor's bit line is biased at Vbl, the threshold voltage of 45 the target memory cell may be lower than if the neighbor's bit line is grounded. Embodiments include methods and devices that match the bit line bias conditions of neighbor bit lines during read of the target memory cell to the neighbor bit line bias conditions that were used during verify of the target 50 memory cell. This may help to mitigate channel coupling effects.

Reducing such differences in channel coupling may improve accuracy in determining the memory cell's threshold voltage. Moreover, all of the bit lines can be read together during both verify and read. Therefore, verify are read are efficient. Note that during programming, one or more verify operations may be performed for each programming pulse. Therefore, reducing the number of verify operations following each programming pulse by sensing all bit lines together 60 during verify may be quite beneficial. Furthermore, at least some of the bit lines may be grounded during at least some verify and read operations, which may save power. Also, the peak amount of current that is consumed may be reduced.

In some embodiments, the non-volatile storage elements 65 are within a flash memory array. One example of a flash memory system uses the NAND structure, which includes

arranging multiple transistors in series, sandwiched between two select gates. The transistors in series and the select gates are referred to as a NAND string. The NAND structure will be described as one example architecture; however, techniques described herein are not limited to the NAND architecture.

FIG. 1 is a top view showing one NAND string. FIG. 2 is an equivalent circuit thereof. The NAND string depicted in FIGS. 1 and 2 includes four transistors 100, 102, 104 and 106 in series and sandwiched between a first (or drain side) select gate 120 and a second (or source side) select gate 122. Select gate 120 connects the NAND string to a bit line via bit line contact 126. Select gate 122 connects the NAND string to source line 128. Select gate 120 is controlled by applying the appropriate voltages to select line SGD. Select gate 122 is controlled by applying the appropriate voltages to select line SGS. Each of the transistors 100, 102, 104 and 106 has a control gate and a floating gate. For example, transistor 100 has control gate 100CG and floating gate 100FG. Transistor 102 includes control gate 102CG and a floating gate 102FG. Transistor 104 includes control gate 104CG and floating gate 104FG. Transistor 106 includes a control gate 106CG and a floating gate 106FG. Control gate 100CG is connected to word line WL3, control gate 102CG is connected to word line WL2, control gate 104CG is connected to word line WL1, and control gate 106CG is connected to word line WL0.

Note that although FIGS. 1 and 2 show four memory cells in the NAND string, the use of four transistors is only provided as an example. A NAND string can have fewer than four memory cells or more than four memory cells. For example, 30 some NAND strings will include eight memory cells, 16 memory cells, 32 memory cells, 64 memory cells, 128 memory cells, etc. The discussion herein is not limited to any particular number of memory cells in a NAND string.

A typical architecture for a flash memory system using a amount of channel coupling that occurred from the 35 NAND structure will include many NAND strings. Each NAND string is connected to the source line by its source select gate controlled by select line SGS and connected to its associated bit line by its drain select gate controlled by select line SGD. Each bit line and the respective NAND string(s) that are connected to that bit line via a bit line contact comprise the columns of the array of memory cells. Bit lines are shared with multiple NAND strings. Typically, the bit line runs on top of the NAND strings in a direction perpendicular to the word lines and is connected to one or more sense amplifiers.

> Each memory cell can store data (analog or digital). When storing one bit of digital data, the range of possible threshold voltages of the memory cell is divided into two ranges which are assigned logical data "1" and "0." In one example of a NAND type flash memory, the threshold voltage is negative after the memory cell is erased, and defined as logic "1." The threshold voltage after programming is positive and defined as logic "0." When the threshold voltage is negative and a read is attempted by applying 0 volts to the control gate, the memory cell will turn on to indicate logic one is being stored. When the threshold voltage is positive and a read operation is attempted by applying 0 volts to the control gate, the memory cell will not turn on, which indicates that logic zero is stored.

> In the case of storing multiple levels of data, the range of possible threshold voltages is divided into the number of levels of data. For example, if four levels of information is stored (two bits of data), there will be four threshold voltage ranges assigned to the data values "11", "10", "01", and "00." In one example of a NAND type memory, the threshold voltage after an erase operation is negative and defined as "11". Positive threshold voltages may be used for the data states of "10", "01", and "00." If eight levels of information

(or states) are stored (e.g. for three bits of data), there will be eight threshold voltage ranges assigned to the data values "000", "001", "010", "011" "100", "101", "110" and "111."

The specific relationship between the data programmed into the memory cell and the threshold voltage levels of the cell depends upon the data encoding scheme adopted for the cells. In one embodiment, data values are assigned to the threshold voltage ranges using a Gray code assignment so that if the threshold voltage of a floating gate erroneously shifts to its neighboring physical state, only one bit will be affected. In some embodiments, the data encoding scheme can be changed for different word lines, the data encoding scheme can be changed over time, or the data bits for random word lines may be inverted to reduce data pattern sensitivity and even wear on the memory cells.

Relevant examples of NAND type flash memories and their operation are provided in the following U.S. Patents/Patent Applications, all of which are incorporated herein by reference: U.S. Pat. Nos. 5,570,315; 5,774,397; 6,046,935; 6,456, 528; and U.S. Pat. Publication No. US2003/0002348. The 20 discussion herein can also apply to other types of flash memory in addition to NAND as well as other types of nonvolatile memory.

Other types of non-volatile storage devices, in addition to NAND flash memory, can also be used. For example, a so 25 called TANOS structure (consisting of a stacked layer of TaN—Al<sub>2</sub>O<sub>3</sub>—SiN—SiO<sub>2</sub> on a silicon substrate), which is basically a memory cell using trapping of charge in a nitride layer (instead of a floating gate), can also be used with embodiments. Another type of memory cell useful in flash 30 EEPROM systems utilizes a non-conductive dielectric material in place of a conductive floating gate to store charge in a non-volatile manner. Such a cell is described in an article by Chan et al., "A True Single-Transistor Oxide-Nitride-Oxide EEPROM Device," IEEE Electron Device Letters, Vol. EDL- 35 8, No. 3, March 1987, pp. 93-95. A triple layer dielectric formed of silicon oxide, silicon nitride and silicon oxide ("ONO") is sandwiched between a conductive control gate and a surface of a semi-conductive substrate above the memory cell channel. The cell is programmed by injecting 40 electrons from the cell channel into the nitride, where they are trapped and stored in a limited region. This stored charge then changes the threshold voltage of a portion of the channel of the cell in a manner that is detectable. The memory cell is erased by injecting hot holes into the nitride. See also Nozaki 45 et al., "A 1-Mb EEPROM with MONOS Memory Cell for Semiconductor Disk Application," IEEE Journal of Solid-State Circuits, Vol. 26, No. 4, April 1991, pp. 497-501, which describes a similar memory cell in a split-gate configuration where a doped polysilicon gate extends over a portion of the 50 memory cell channel to form a separate select transistor. The foregoing two articles are incorporated herein by reference in their entirety. The programming techniques mentioned in section 1.2 of "Nonvolatile Semiconductor Memory Technology," edited by William D. Brown and Joe E. Brewer, IEEE 55 be used. Press, 1998, incorporated herein by reference, are also described in that section to be applicable to dielectric chargetrapping devices. Other types of memory devices can also be used.

FIG. 3 illustrates a non-volatile storage device 210 that 60 may include one or more memory die or chips 212. Memory die 212 includes an array (two-dimensional or three dimensional) of memory cells 200, control circuitry 220, and read/write circuits 230A and 230B. In one embodiment, access to the memory array 200 by the various peripheral circuits is 65 implemented in a symmetric fashion, on opposite sides of the array, so that the densities of access lines and circuitry on each

6

side are reduced by half. The read/write circuits 230A and 230B include multiple sense blocks 300 which allow a page of memory cells to be read or programmed in parallel. The memory array 100 is addressable by word lines via row decoders 240A and 240B and by bit lines via column decoders 242A and 242B. In a typical embodiment, a controller 244 is included in the same memory device 210 (e.g., a removable storage card or package) as the one or more memory die 212. Commands and data are transferred between the host and controller 244 via lines 232 and between the controller and the one or more memory die 212 via lines 234. One implementation can include multiple chips 212.

Control circuitry 220 cooperates with the read/write circuits 230A and 230B to perform memory operations on the memory array 200. The control circuitry 220 includes a state machine 222, an on-chip address decoder 224 and a power control module 226. The state machine 222 provides chiplevel control of memory operations. The on-chip address decoder 224 provides an address interface to convert between the address that is used by the host or a memory controller to the hardware address used by the decoders 240A, 240B, 242A, and 242B. The power control module 226 controls the power and voltages supplied to the word lines and bit lines during memory operations. In one embodiment, power control module 226 includes one or more charge pumps that can create voltages larger than the supply voltage.

In one embodiment, one or any combination of control circuitry 220, power control circuit 226, decoder circuit 224, state machine circuit 222, decoder circuit 242A, decoder circuit 242B, decoder circuit 240A, decoder circuit 240B, read/write circuits 230A, read/write circuits 230B, and/or controller 244 can be referred to as one or more managing circuits.

FIG. 4 depicts an exemplary structure of memory cell array **200**. In one embodiment, the array of memory cells is divided into M blocks of memory cells. As is common for flash EEPROM systems, the block is the unit of erase. That is, each block contains the minimum number of memory cells that are erased together. Each block is typically divided into a number of pages. A page is a unit of programming. One or more pages of data are typically stored in one row of memory cells. A page can store one or more sectors. A sector includes user data and overhead data. Overhead data typically includes an Error Correction Code (ECC) that has been calculated from the user data of the sector. A portion of the controller (described below) calculates the ECC when data is being programmed into the array, and also checks it when data is being read from the array. Alternatively, the ECCs and/or other overhead data are stored in different pages, or even different blocks, than the user data to which they pertain. A sector of user data is typically 512 bytes, corresponding to the size of a sector in magnetic disk drives. A large number of pages form a block, anywhere from 8 pages, for example, up to 32, 64, 128 or more pages. Different sized blocks and arrangements can also

In another embodiment, the bit lines are divided into odd bit lines and even bit lines. In an odd/even bit line architecture, memory cells along a common word line and connected to the odd bit lines are programmed at one time, while memory cells along a common word line and connected to even bit lines are programmed at another time.

FIG. 4 shows more details of block i of memory array 200. Block i includes X+1 bit lines and X+1 NAND strings. Block i also includes 64 data word lines (WL0-WL63), 2 dummy word lines (WL\_d0 and WL\_d1), a drain side select line (SGD) and a source side select line (SGS). One terminal of each NAND string is connected to a corresponding bit line via

a drain select gate (connected to select line SGD), and another terminal is connected to the source line via a source select gate (connected to select line SGS). Because there are sixty four data word lines and two dummy word lines, each NAND string includes sixty four data memory cells and two dummy memory cells. In other embodiments, the NAND strings can have more or less than 64 data memory cells and two dummy memory cells. Data memory cells can store user or system data. Dummy memory cells are typically not used to store user or system data. Some embodiments do not include 10 dummy memory cells.

FIG. 5 is a block diagram of an individual sense block 300 partitioned into a core portion, referred to as a sense module 480, and a common portion 490. In one embodiment, there will be a separate sense module 480 for each bit line and one 15 common portion 490 for a set of multiple sense modules 480. In one example, a sense block will include one common portion 490 and eight sense modules 480. Each of the sense modules in a group will communicate with the associated common portion via a data bus 472. For further details, refer 20 to U.S. Patent Application Publication 2006/0140007, which is incorporated herein by reference in its entirety.

Sense module **480** comprises sense circuitry **470** that determines whether a conduction current in a connected bit line is above or below a predetermined threshold level. In some 25 embodiments, sense module **480** includes a circuit commonly referred to as a sense amplifier. Sense module **480** also includes a bit line latch **482** that is used to set a voltage condition on the connected bit line. For example, a predetermined state latched in bit line latch **482** will result in the 30 connected bit line being pulled to a state designating program inhibit (e.g., Vdd). In some embodiments, the voltage condition on each bit line during verify of a particular programmed state is matched to the voltage condition on each bit line during read of that particular programmed state.

Common portion 490 comprises a processor 492, a set of data latches **494** and an I/O Interface **496** coupled between the set of data latches 494 and data bus 420. Processor 492 performs computations. For example, one of its functions is to determine the data stored in the sensed memory cell and store 40 the determined data in the set of data latches. In some embodiments, the processor 492 determines what voltage should be applied to the bit line during verify and read. During verify, the processor 492 may make this determination based on the state to which the memory cell on the bit line is (or has been) 45 programmed. During read, the processor 492 may make this determination based on a rough read of the memory cell to roughly determine what state is has been programmed to. The set of data latches 494 is used to store data bits determined by processor 492 during a read operation. It is also used to store 50 data bits imported from the data bus 420 during a program operation. The imported data bits represent write data meant to be programmed into the memory. I/O interface 496 provides an interface between data latches **494** and the data bus **420**.

During read or sensing, the operation of the system is under the control of state machine 222 that controls the supply of different control gate voltages to the addressed cell. As it steps through the various predefined control gate voltages corresponding to the various memory states supported by the memory, the sense module 480 may trip at one of these voltages and an output will be provided from sense module of read determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 493. It then computes a binary encoding for the

8

memory state and stores the resultant data bits into data latches **494**. In another embodiment of the core portion, bit line latch **482** serves double duty, both as a latch for latching the output of the sense module **480** and also as a bit line latch as described above.

It is anticipated that some implementations will include multiple processors 492. In one embodiment, each processor **492** will include an output line (not depicted in FIG. 5) such that each of the output lines is wired-OR'd together. In some embodiments, the output lines are inverted prior to being connected to the wired-OR line. This configuration enables a quick determination during the program verification process of when the programming process has completed because the state machine receiving the wired-OR line can determine when all bits being programmed have reached the desired level. For example, when each bit has reached its desired level, a logic zero for that bit will be sent to the wired-OR line (or a data one is inverted). When all bits output a data 0 (or a data one inverted), then the state machine knows to terminate the programming process. In embodiments where each processor communicates with eight sense modules, the state machine may (in some embodiments) need to read the wired-OR line eight times, or logic is added to processor 492 to accumulate the results of the associated bit lines such that the state machine need only read the wired-OR line one time.

During program or verify, the data to be programmed is stored in the set of data latches 494 from the data bus 420. The program operation, under the control of the state machine, comprises a series of programming voltage pulses (with increasing magnitudes) applied to the control gates of the addressed memory cells. Each programming pulse is followed by a verify process to determine if the memory cell has been programmed to the desired state. Processor 492 monitors the verified memory state relative to the desired memory state. When the two are in agreement, processor 492 sets the bit line latch 482 so as to cause the bit line to be pulled to a state designating program inhibit. This inhibits the cell coupled to the bit line from further programming even if it is subjected to programming pulses on its control gate. In other embodiments the processor initially loads the bit line latch **482** and the sense circuitry sets it to an inhibit value during the verify process. In some embodiments, even if the memory cell is inhibited from further programming, the bit line may be charged normally during the verify operation. In other words, even though verify is no longer needed for the cell on the bit line, the bit line is charged in a way that would allow a verify to be performed. This may allow the channel potential of a neighbor of a target memory cell being verified to match the neighbor's channel potential during read of the target memory cell.

Data latch stack **494** contains a stack of data latches corresponding to the sense module. In one embodiment, there are 3-5 (or another number) data latches per sense module **480**. In one embodiment, the latches are each one bit. In some implemented as a shift register so that the parallel data stored therein is converted to serial data for data bus **420**, and vice versa. In one embodiment, all the data latches corresponding to the read/write block of m memory cells can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of read/write modules is adapted so that each of its set of data latches will shift data in to or out of the data bus in sequence as if they are part of a shift register for the entire read/write

Additional information about the read operations and sense amplifiers can be found in (1) U.S. Pat. No. 7,196,931, "Non-

Volatile Memory And Method With Reduced Source Line Bias Errors,"; (2) U.S. Pat. No. 7,023,736, "Non-Volatile Memory And Method with Improved Sensing,"; (3) U.S. Patent Application Pub. No. 2005/0169082; (4) U.S. Pat. No. 7,196,928, "Compensating for Coupling During Read Operations of Non-Volatile Memory," and (5) United States Patent Application Pub. No. 2006/0158947, "Reference Sense Amplifier For Non-Volatile Memory," published on Jul. 20, 2006. All five of the immediately above-listed patent documents are incorporated herein by reference in their entirety.

At the end of a successful programming process (with verification), the threshold voltages of the memory cells should be within one or more distributions of threshold voltthreshold voltages for erased memory cells, as appropriate. FIG. 6A illustrates example threshold voltage distributions corresponding to data states for the memory cell array when each memory cell stores four bits of data. Other embodiment, however, may use more or less than four bits of data per 20 memory cell. FIG. 6A shows 16 threshold voltage distributions corresponding to data states 0-15. In one embodiment, the threshold voltages in state 0 are negative and the threshold voltages in the states 1-15 are positive. However, the threshold voltages in one or more of states 1-15 may be negative.

Between each of the data states 0-15 are read reference voltages used for reading data from memory cells. For example, FIG. 6A shows read reference voltage Vr1 between data states 0 and 1, and Vr2 between data states 1 and 2. By testing whether the threshold voltage of a given memory cell 30 is above or below the respective read reference voltages, the system can determine what state the memory cell is in.

At or near the lower edge of each data state 0-15 are verify reference voltages. For example, FIG. 6A shows Vv1 for state 1 and Vv2 for state 2. When programming memory cells to a 35 given state, the system will test whether those memory cells have a threshold voltage greater than or equal to the verify reference voltage. In some embodiments, one data state (e.g., the lowest data state) is referred to as an erased state and all other data states are referred to as "programmed states."

FIG. **6**B illustrates that another embodiment of threshold voltage distributions corresponding to data states 0-15 can partially overlap since the correction algorithm can handle a certain percentage of cells that are in error.

Also note that the threshold voltage axis may be offset from 45 actual voltages applied to the control gates as body effect through source or body biasing is used to shift negative threshold voltage into the measurable positive range. Another point to note is that contrary to the equal spacing/width of the depicted sixteen states, various states may have different 50 widths/spacings in order to accommodate varying amounts of susceptibility to data retention loss. In some embodiments, states 0 and/or 15 are wider than the other states.

In the example implementations of FIGS. 6A and 6B, the non-volatile storage elements store four bits of data per stor- 55 age element, using four data states. FIG. 6C depicts an example set of threshold voltage distributions for a four-state memory device in which each storage element stores two bits of data. A first threshold voltage distribution 401 is provided for erased (Erased-state) storage elements. Three threshold 60 voltage distributions 402, 403 and 404 represent programmed states A, B and C, respectively. In one embodiment, the threshold voltages in the Erased-state are negative, and the threshold voltages in the A-, B- and C-states are positive.

Read reference voltages, Vra, Vrb and Vrc, are also pro- 65 vided for reading data from storage elements. By testing whether the threshold voltage of a given storage element is

**10**

above or below Vra, Vrb and Vrc, the system can determine the state, e.g., programming condition, the storage element is ın.

Further, verify reference voltages, Vva, Vvb, and Vvc are provided. When programming storage elements to the A-state, B-state or C-state, the system will test whether those storage elements have a threshold voltage greater than or equal to Vva, Vvb or Vvc, respectively. In one embodiment, "verify low" reference voltages, Vval, Vvbl, and Vvcl are provided. Similar "verify low" reference voltages could also be used in embodiments with a different number of states. The verify low levels may be used during a "coarse verify," which will be described below.

In full sequence programming, storage elements can be ages for programmed memory cells or within a distribution of 15 programmed from the Erased-state directly to any of the programmed states A, B or C. For example, a population of storage elements to be programmed may first be erased so that all storage elements in the population are in the Erased-state. A series of program pulses such as depicted in FIG. 6D may be used to program storage elements directly into the A-, Band C-states. While some storage elements are being programmed from the Erased-state to the A-state, other storage elements are being programmed from the Erased-state to the B-state and/or from the Erased-state to the C-state. Note that using a full sequence programming is not required.

One example of a slow programming mode uses low (offset) and high (target) verify levels for one or more programmed states. For example, VvaL and Vva are offset and target verify levels, respectively, for the A-state, and VvbL and Vvb are offset and target verify levels, respectively, for the B-state. During programming, when the threshold voltage of a storage element which is being programmed to the A-state as a target state (e.g., an A-state storage element) exceeds VvaL, its programming speed is slowed, such as by raising the bit line voltage to a level, e.g., 0.6-0.8 V, which is between a nominal program or non-inhibit level, e.g., 0 V and a full inhibit level, e.g., 2-3 V. This provides greater accuracy by avoiding large step increases in threshold voltage. When the threshold voltage reaches Vva, the storage element is 40 locked out from further programming. Similarly, when the threshold voltage of a B-state storage element exceeds VvbL, its programming speed is slowed, and when the threshold voltage reaches Vvb, the storage element is locked out from further programming. In one approach, a slow programming mode is not used for the highest state since some overshoot is typically acceptable. Instead, the slow programming mode can be used for the programmed states below the highest state.

Moreover, in the example programming techniques discussed, the threshold voltage of a storage element is raised as it is programmed to a target programmed state. However, programming techniques can be used in which the threshold voltage of a storage element is lowered as it is programmed to a target programmed state. Programming techniques which measure storage element current can be used as well. The concepts herein can be adapted to different programming techniques.

FIG. 6D depicts a series of program and verify pulses which are applied to a selected word line during a programming operation. A programming operation may include multiple programming iterations, where each iteration applies one or more program pulses (voltages) followed by one or more verify voltages, to a selected word line. In one possible approach, the program voltages are stepped up in successive iterations. Moreover, the program voltages may include a first portion which has a pass voltage (Vpass) level, e.g., 6-8 V, followed by a second portion at a program level, e.g., 12-25 V. For example, first, second, third and fourth program pulses

410, 412, 414 and 416 have program voltages of Vpgm1, Vpgm2, Vpgm3 and Vpgm4, respectively, and so forth. A set of one or more verify voltages may be provided after each program pulse.

In FIG. 6D, three verify pulses are depicted between each 5 program pulse. For example, verify pulse VvA may be used to verify whether memory cells that are targeted for the A-state have reached Vva, VvB may be used to verify whether memory cells that are targeted for the B-state have reached VvB, and VvC may be used to verify whether memory cells 10 that are targeted for the C-state have reached VvC. In some cases, one or more initial program pulses are not followed by verify pulses because it is not expected that any storage elements have reached the lowest program state (e.g., A-state). Subsequently, program iterations may use verify pulses for 15 the A-state, followed by program iterations which use verify pulses for the A- and B-states, followed by program iterations which use verify pulses for the B- and C-states, for instance. The voltage pulses depicted in FIG. **6**D are for the final verify levels. There may also be pulses for the low verify levels of 20 VvaL, VvbL, and VvcL.

FIG. 7A is a flowchart describing one embodiment of a programming process 700, which includes one or more verification steps. In step 702, the portion of the memory to be programmed is selected. In one embodiment, this can be one 25 or more write units appropriate to the memory structure. One example of a write unit is referred to as a page. In other embodiments, other units and/or structures can also be used. In step 704, a pre-programming process is sometimes used wherein the addressed memory cells are given non-data 30 dependent programming to level out storage element wear and provide a more uniform starting point for the subsequent erase. In step 706, an erase process is performed, as appropriate for the type of storage element being used. One Pat. No. 5,095,344, incorporated herein by reference in its entirety. Step 708 includes a soft programming process designed to put the threshold voltages of erased memory cells into a more uniform starting range for the actual write phase. In one embodiment, if any of the memory cells fail to verify 40 during erase (or during soft programming), they can be mapped out of the logical address space. At this point the memory is ready for the data conditional programming phase.

In step 710, the program voltage (Vpgm) is set to an initial value. Also, in step 710, a program counter (PC) is initialized 45 to zero. In step 720, a program pulse is applied.

In step 722, a verification process is performed. In one embodiment, the verification is a concurrent coarse/fine verify. During the initial programming steps in which the memory cell's threshold is well below the final level (Vva), 50 course programming is applied. However, after the memory cell's threshold voltage reaches VvaL, fine programming is used. Thus, while some memory cells are being verified for coarse programming, other memory cells are being verified for fine programming. Note that when a particular memory 55 cell has been verified as being programmed to its intended state, it may be locked out from further programming. More details of step 722 are described below.

In step 724, it is determined whether all of the memory cells have verified that their threshold voltages are at the final target 60 voltage for that memory cell. If so, the programming process is completed successfully (status=pass) in step 726. If all of the memory cells are not all verified, then it is determined whether the program counter (PC) is less than a maximum value, such as **20**. If the program counter (PC) is not less than 65 max (step 728), then the program process has failed (step 730). If the program counter (PC) is less than 20, then the

program counter (PC) is incremented by 1 and the program voltage is stepped up to the next pulse in step 732. Subsequent to step 732, the process loops back to step 720 and the next program pulse is applied to the memory cells.

In some embodiments, programming has a coarse mode and a fine mode. In general, a coarse programming mode may attempt to program a memory cell faster when it is further from its target threshold voltage, and program more slowly when the memory cell is closer to its target threshold voltage. However, using both a coarse programming mode and a fine programming mode is not required. The coarse and fine program can also be executed in one program sequence as in FIG. 7B. The verify process in 722 can be done to execute both coarse and fine verify. The program pulse step 720 can also be executed with differentiation of fast program for coarse and slow program for fine program. First, a verify process will be discussed for the case in which coarse/fine programming is not used. FIG. 7B provides a flow chart describing one embodiment of a process of performing verification without coarse/fine programming (see step 722 of FIG. 7A). The process describes verification of a single memory cell. The process may be performed concurrently on many memory cells.

Verify conditions are applied and sensing is performed in step 740. For example, looking at FIG. 6A, if the A-state is being verified, then the threshold voltage of the memory cell can be compared to the final target threshold voltage for the A-state VvA. Further details of step 740 are discussed below. If the memory cell's threshold voltage is greater than the target voltage VvA (step 742), then the verification test has passed and the memory cell will be inhibited from programming in step 744. One embodiment for inhibiting a memory cell from further programming is to raise the bit line to Vdd, which causes the NAND chain channel to be cut off from the example of a suitable smart erase process is described in U.S. 35 bitline bias. A high voltage may be formed in the isolated channel as the wordline voltage rises to high voltage due to coupling when the program pulse is applied. Other means for inhibiting a memory cell from further programming can also be used. If, in step 742, it is determined that the verification test did not pass (e.g., because the threshold voltage of the memory cell is less than target voltage VvA), then the memory cell will not be inhibited from further programming (step **746**).

> FIG. 7C provides a flow chart describing one embodiment of a process of verifying in which coarse/fine programming is used. The process performs coarse and fine verification. The process describes verification of a single memory cell. The process may be performed concurrently on many memory cells. In step 752, the system will check a register (or other storage device) to determine whether the particular memory cell is in a coarse programming mode or a fine programming mode. If the memory cell is in the coarse programming mode (step 754), then a coarse verification is performed in step 756. For example, referring to FIG. 6C, if the A-state is being verified, then the memory cell could have its threshold voltage compared to voltage VvaL. Further details of step 756 are discussed below. If the threshold voltage of the memory cell is above VvaL (step 758), then the memory cell has passed the coarse verification test. If the threshold voltage of the memory cell is less VvaL, then the memory cell has not passed the verification test. If the memory cell has not passed the coarse verification test, then the memory cell remains in the coarse programming mode (step 760). If the memory cell passes the coarse verification test, the memory cell will change programming modes to the fine programming mode (step 762). Note that the programming mode can be changed in a different program pass or changed in the same program pass. One

program pass is described in FIG. 7A from step 702 to step 726 or 730. Applying coarse verify and fine verify can be done together regardless of whether bits pass the coarse Vt target VvaL or the fine Vt target VvA.

If, in step 754, it is determined that the memory cell was in 5 the fine programming mode, then a fine verification conditions are applied and sensing will be performed in step 770. For example, looking at FIG. 6C, the threshold voltage of the memory cell can be compared to the final target threshold voltage VvA. Further details of step 754 are discussed below. 10 If the memory cell's threshold voltage is greater than the target voltage VvA (step 772), then the fine verification test has passed and the memory cell will be inhibited from programming in step 774. One embodiment for inhibiting a memory cell from further programming is to raise the bit line 15 to Vdd, at least when the program pulse is applied. Other means for inhibiting a memory cell from further programming can also be used. If, in step 772, it is determined that the verification test did not pass (e.g., because the threshold voltage of the memory cell is less than target voltage VvA), then 20 the memory cell will not be inhibited from further programming (step 776). In some embodiments, even after the memory cell is inhibited from further programming, its bit line may be charged during verify of step 770. Further details of biasing bit lines during verify are discussed below.

FIG. 7D provides graphs of threshold voltage  $(V_T)$  versus time and bit line voltage  $(V_{BL})$  versus time in a program pulse to indicate how one example of a coarse/fine programming process is performed. Threshold voltage levels for verifying the A-state are depicted (VvaL and VvA). Other levels may be 30 used for verifying other states. Various alternatives and embodiments of the coarse/fine programming methodology can also be used. The signals in the graphs begin with the coarse phase of the programming process. Thus, the threshold voltage of the memory cell Vt is relatively low. When the 35 threshold voltage of the memory cell reaches voltage of VvaL, then the memory cell enters a fine programming phase by raising the bit line voltage of the cell to a value of  $V_{\tau}$  in order to slow down the programming. During the fine programming phase, programming is slowed, as compared to the 40 coarse programming phase. Therefore, the change in threshold voltage per program step is likely to be smaller during the fine programming phase. The memory cell will remain in the fine programming phase until the threshold voltage of the memory cell has reached the target threshold voltage level of 45 VvA. When the threshold voltage of the memory cell reaches VvA, the memory cell's bit line voltage may be raised to Vdd to inhibit further programming of that cell. In one embodiment, VvaL is one  $V_{pgm}$  step size below VvA. In other embodiments, the difference between VvaL and VvA is 50 smaller or greater. Note that FIG. 7D depicts bit line voltages when program pulses are applied, as opposed to the bit line voltages during verify. Bit line voltages during verify are further discussed below.

FIG. 8A is flowchart of one embodiment of a process 800 for verifying memory cells during a programming process. When verifying the memory cells, certain bias conditions are applied to the bit lines. For example, some bit lines are precharged and other are grounded. In one embodiment, the biasing of the bit lines depends on the state to which each 60 memory cell is being programmed to (or already has been programmed to). FIG. 8B depicts a flowchart of one embodiment of a process 820 for reading memory cells. When reading a particular state, the bit lines are biased in way that substantially matches the bit line biasing used during verify of 65 that state. Therefore, the channel potential of most of the memory cells that neighbor the memory cells being read

**14**

matches the channel potential of the neighbor memory cell during verify of that state. This reduces or eliminates channel coupling effects.

Process 800 of FIG. 8A may be used during verify step 740 of FIG. 7B, coarse verify step 756 of FIG. 7C or fine verify step 770 of FIG. 770. Note for some embodiments, process 800 is used for the fine verify step 770 of FIG. 7C, but is not used for the coarse verify step 756 of FIG. 7C. Also, note that process 800 is not required to be performed for every iteration of the programming process. Therefore, process 800 does not need to be performed for each verify operation. For example, process 800 is not required to be used for every iteration of step 740 of FIG. 7B. Therefore, it is not an absolute requirement that the neighbor's channel potential during verify of every iteration of programming process 700 of FIG. 7A match the neighbor's channel potential during read. In one embodiment, process 800 is used at least the final time that a given memory cell is being verified.

Note that process **800** repeats once for each state that is being verified. Thus, with each iteration a different state may be verified. For example, those memory cells that are being programmed to the A-state have their threshold voltage compared to VvA during a certain iteration. In step **804**, first bias conditions for verifying a given state are established on bit lines. The term "first bias conditions" is used herein to refer to the bit line bias conditions used during verify. The term "second bias conditions" will be used herein to refer to the bit line bias conditions used during read. A separate set of first bias conditions may be established when verifying each programmed state. Biasing a bit line may be based on the state to which a non-volatile storage elements on the bit line is being programmed.

In one embodiment, a first voltage is applied to a first group of bit lines that contain at least those bits lines having a memory cell that is being programmed to the state being verified. The first group may include bit lines that have memory cells not being programmed to the state being verified. In one embodiment, the first group of non-volatile storage elements have a first channel potential during the verify operation. In one embodiment, all bit lines of memory cells that are not in the first group are in a second group. The second group of bit lines may include at least some bit lines that have a non-volatile storage element that is to be programmed to a programmed state other than the state being verified. The second group of memory cells may be grounded. By grounding the bit lines power may be saved. Also, the peak current may be reduced.

In step 806, a condition of each bit line having a memory cell being verified is tested in order to verify whether each memory cell is programmed to the given programmed state. For example, a sense amplifier may measure the bit line current in order to measure the conduction current of the selected memory cell on that bit line after the first bias conditions are established. Note that only those bit lines having a memory cell being verified need to be tested. The first bias conditions may impact the channel potential of the memory cells that are neighbors to the ones being verified. For example, the neighbor's bit line might be either charged to some voltage or grounded. In one embodiment, the neighbor's bit line might be either charged to 0.4 volts or grounded. However, other voltages could be used. As already noted, the bit line biasing may depend on the state to which the memory cell on that bit line is being (or already has been) programmed. As one example, if the neighbor memory cell is being programmed to (or has already been programmed to) either the state presently being verified or the state below the state presently being verified, then the neighbor's bit line may

be pre-charged. Otherwise, the neighbor's bit line may be grounded. Therefore, non-volatile storage elements that are neighbors of non-volatile storage elements being programmed to a given state may have a channel potential during verify of the given state that depends on the state to which the neighbor non-volatile storage element was programmed or is being programmed. Many other bit line biasing schemes are possible including, but not limited to, those discussed below.

If there are more states to verify (step 808), then step 804 may be performed again to establish another set of first bias 1 conditions. However, this time the first bias conditions are for the next state being verified. Note that these bit line bias conditions may be different from the previous ones. Therefore, the first bias conditions may depend on the state that is being verified. Once all states have been verified, process 800 15 concludes. After performing process 800, a step may be performed for each bit line to determine whether verification passed on an individual memory cell basis. For example, one of steps 742 of FIG. 7B, 758 or 770 of FIG. 7C may be performed. After completing the process of FIG. 7B or 7C, 20 step 724 of FIG. 7A may be performed to determine whether all memory cells have passed verify. If not, then one or more additional program pulses may be applied in step **720** of FIG. 7A. Eventually, programming completes with memory cells verified.

At some later point in time, the programmed memory cells may be read to access the stored data. The process 820 of FIG. 8B may be performed to read the memory cells. As mentioned, the term "second bias conditions" will be used to refer to bit line bias conditions during read. Process **820** may 30 substantially match the second bit line bias conditions to the first line bias conditions. Therefore, the channel potential that most of the neighbor memory cell's have during read of a target memory cell may be matched to the channel potential nates differences in channel coupling effects between verify and read. Note that it is not a requirement that all neighbor memory cells have the same channel potential during verify and read.

In step 822, at least one rough read of the non-volatile 40 storage elements associated with the selected word line is performed during a read process. Note that when performing the rough read, the bit line conditions are not necessarily matched to the first bit line conditions used during verify. For example, in some embodiments, all bit lines are charged to 45 some voltage when performing the rough read. Also note that while step 822 is depicted as occurring prior to other steps as a matter of convenience of explanation, one or more rough reads may occur at other points in process 820. Further details of performing rough reads are discussed below.

Steps 824-828 form a loop that is repeated once for each state being read during the read process. For example, referring to FIG. 6C, one iteration may be performed for each read voltage VrA-VrC. Note that the term "reading a state" is used herein to refer to determining whether a memory cell has a 55 threshold voltage of at least a voltage level associated with the state (such as VrA). To finally determine whether a memory cell is actually in the A-state, the memory cell's threshold voltage should be compared to VrB also.

In step **824**, second bias conditions are established for the 60 present state being read=during the read process. A separate set of second bias conditions nay established for each state being read during the read process. The second bias conditions for a given state may substantially match the first bit line bias conditions used during verify of the given state. For 65 example, if the A-state is being read, then the second bit line bias conditions may substantially match the first bit line bias

**16**

conditions used when verifying the A-state. In some embodiments, the second set of bias conditions are based on the one or more rough reads of step 822. As already mentioned, verifying may be performed multiple times for a given memory cell. In some embodiments, the second bit line bias conditions substantially match the first bit line bias conditions used for at least the final time a memory cell is verified. Note that establishing the second bias conditions when reading a given state may cause substantially all non-volatile storage elements that are neighbors of non-volatile storage elements that were programmed to the given state to have a channel potential that matches the channel potential of the neighbor when verifying the given state.

In some embodiments, data from the rough reads is used to determine what voltage should be applied to each bit line. For example, the second bias conditions may be based on what state the rough reads indicate that the selected memory cell on a bit line was programmed to. In some embodiments, the rough read itself may help to establish the second bit line bias. For example, the rough read may discharge a bit line to establish the bit line potential at a desired level. In some embodiments, establishing the second bias conditions includes pre-charging a first group of bit lines to a certain voltage and grounding a second group of bit lines.

In step 826, bit lines are sensed after establishing the second bias conditions during the read process. Note that not all bit lines need to be sensed. In one embodiments, bit lines that were pre-charged are sensed and those that were grounded are not. Sensing the bit lines determines whether the memory cell on the bit line has a threshold voltage above or below the voltage level for the state being read. For example, when reading the A-state, the sensing determines whether the memory cell has a Vt above or below VrA.

Note that there may not be an exact correspondence that the neighbor's had during verify. This reduces or elimi- 35 between the bit lines that had the voltage applied during verify of the present state and those that had the voltage applied during read of the present state. Also note that there may not be an exact correspondence between the bit lines that were grounded during verify and those that were grounded during read. However, no bit line having a memory cell being either verified or read should be grounded. Even if there is not an exact correspondence between bit line voltages during verify and read, for most memory cells the neighboring bit lines should be at the same potential during read and verify. Therefore, the channel potential of the neighbors of most of the target memory cells being read should be the same during verify and read. Consequently, differences in channel coupling effects between verify and read are mitigated.

> The term "first group of memory cells" will be used to refer to those that had their bit lines charged during one embodiment of verify. In one embodiment, the first group of memory cells during verify are those that are being programmed to the state being verified and those memory cells being programming to the state immediately below the state being verified. FIG. 9A depicts an example of threshold voltage distributions during programming. There are eight different threshold distribution curves in FIG. 9A. Each curve corresponds to one of the data states (e.g., erase state and programmed states A-G). Verify voltages VvA-VvG are depicted on the Vt axis. Note that programming is complete for some of the lower states. For example, all memory cells being programmed to the A-state are above VvA and all memory cells being programmed to the B-state are above VvB. However, for the other states at least some of the memory cells are still below the corresponding verify level.

FIG. 9A shows a dashed box to represent that memory cells being programmed to either the D- or E-state have their bit

lines charged during verify of the E-state. However, bit lines for memory cells being programmed to any other state are grounded when verifying the E-state in this embodiment. Note that memory cells being programmed to either the C- or F-state do not have their bit lines charged during verify of the 5 E-state.

FIG. 9B depicts an example of threshold voltage distributions after programming is complete. The read reference voltages Vra-VrG are depicted on the Vt axis. When reading the E-state, first a rough read is performed to roughly determine which memory cells have a Vt between VrD and VrF. The read roughly determines which memory cells are in either the D-state or the E-state. Then, a fine read is performed in which the bit lines for those memory cells that were roughly determined to be in either the D-state or the E-state are charged up. 15 However, bit lines for other memory cells are grounded. Therefore, the neighbor's channel potential for memory cells being read should match what the neighbor's channel potential was during verify.

FIG. 10A is a flowchart of one embodiment of a process 1000 for establishing first bias conditions during verify. Process 1000 is one embodiment of step 804 of verify process 800. In process 1000, bit lines of memory cells being verified and those in the state immediately below are charged and other bit lines are not charged. Thus, process 1000 may use 25 the scheme depicted in FIG. 9A. In step 1002, bit lines memory cells being verified and those in the state immediately below are charged. For example, bit lines of memory cells being programmed to the A-state and those to stay erased are charged. The bit lines may be charged to a suitable level to 30 allow the threshold voltage of memory cells to be compared to VvA. In step 1004, other bit lines are grounded.

After establishing the bit line bias conditions, memory cells being programmed to the state being verified are sensed to determine if their Vt is at the verify level, as described in step 806 of process 800. For example, memory cells being programmed to the A-state are sensed. Memory cells that reach the verify level may be locked out from further programming. Process 1000 may then be repeated to verify another state. For example, when the B-state is being verified, bit lines of memory cells being programmed to the B-state and those programmed to the A-state are charged. Other bit lines are grounded in step 1004.

being read. Therefore, match the bit line bit verifying the A-state.

After establishing to example, an appropriate selected word line to above/below VrA. The establish the second because if the B-state memory cells that the verifying the A-state.

After establishing to verify an appropriate selected word line to above/below VrA. The establish the second because is the verify and the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the bit line bit verifying the A-state.

After establishing the A-state.

FIG. 10B is a flowchart of one embodiment of a process 1020 for performing rough reads. In this embodiment, the 45 rough reads are used to roughly determine what state each memory cells is in. This may be referred to as a rough read because later the reading will be refined based on information learned from the rough read. For example, the information will be used to determine which bit lines to charge when 50 reading at each state. Process 1020 describes one embodiment of step 822 from process 820. FIG. 10C is a flowchart of one embodiment of a process 1040 for establishing second bit line bias conditions based on rough reads. Process 1040 describes one embodiment of step 824 from process 820. Processes 1020 and 1040 are typically used together when reading memory cells and may be used if process 1000 of FIG. 10A was used to verify the memory cells during programming.

In step 1022 of FIG. 10B, all bit lines are pre-charged to a 60 voltage that is suitable to sense the memory cells. For example, 0.4 volts may be applied to all bit lines. In step 1024 of FIG. 10B, a read of the memory cells is performed at given level. For example, a read is performed to determine which memory cells have a Vt above VrA. To perform the read, the 65 voltage of VrA may be applied to the selected word line. Then, a conduction current of each bit line may be sensed.

**18**

Results of the sensing operation may be stored in a latch or other storage unit. In one embodiment, the reading is "all bit line" ("ABL") reading. In ABL reading, both the even and odd bit lines are sensed together. However, ABL sensing is not a requirement. For example, the even and odd bit lines may be read separately. Further details of one embodiment reading memory cells are discussed below.

If there are more states to read, the process 1020 returns to step 1022 to read the next state. In one embodiment, the reading proceeds from the A-state upwards. In some embodiments, reading causes bit lines that have memory cells with a Vt below the read compare level to discharge. For example, reading at VrA may cause the bit lines of erased memory cells to discharge. However, bit lines of other memory cells may not discharge as a result of the read. Therefore, the bit lines may not need to be re-charged again if reading proceeds from the A-state upwards. However, reading is not required to be performed in any specific order. Moreover, reading is not required to be performed in a way that prevents certain bit lines from discharging. After all states have been read, the process 1020 concludes.

After completion of process 1020, process 1040 of FIG. 10C may be performed. As mentioned, process 1040 establishes the second bias conditions on the bit lines for reading a certain state. Recall that a different set of second bias conditions may be established for each state that is read. In step 1024 of FIG. 10C bit lines for a state being read and the state immediately below are charged. For example, based on the information from the rough read of process 1020, bit lines of memory cells roughly determined to be in the A-state and the erased state are charged. All other bit line may be grounded in step 1046. The foregoing assumes that the A-state is presently being read. Therefore, the bit line bias conditions may closely match the bit line bias conditions that were applied when verifying the A-state.

After establishing the bit line bias conditions, step **826** of FIG. **8**B may performed for the present state being read. For example, an appropriate read voltage may be applied to the selected word line to test whether memory cells have a Vt above/below VrA. Then, process **1040** may be repeated to establish the second bit line conditions for another state. For example, if the B-state is the next to be read, then bit lines of memory cells that were roughly determined to be programmed to the B-state and those roughly determined to be programmed to the A-state may be charged. Note that process **1020** of roughly reading all of the states does not need to be performed again. Instead, data that was previously read may be used.

FIG. 11A is a flowchart of one embodiment of a process 1100 for establishing first bias conditions during verify. Process 1100 is one embodiment of step 804 of verify process 800. In process 1100, bit lines of memory cells being verified are charged and other bit lines are not charged. In step 1102, bit lines memory cells being verified are charged. For example, bit lines of memory cells being programmed to the A-state are charged. The bit lines may be charged to a suitable level to allow the threshold voltage of memory cells to be compared to VvA. In step 1104, all other bit lines may be grounded.

After establishing the bit line bias conditions in process 1100, memory cells being programmed to the state being verified are sensed to determine if their Vt is at the verify level, as described in step 806 of process 800. For example, memory cells being programmed to the A-state are sensed. Memory cells that reach the verify level may be locked out from further programming. Thus, when the B-state is being verified, memory cells being programmed to the B-state may

be charged and all other bit lines may be grounded. Process 1100 may be repeated for each state that is verified.

FIG. 11B is a flowchart of one embodiment of a process 1120 for reading memory cells. Process 1120 describes one embodiment of steps 822-828 from process 820 of FIG. 8B. Process 1120 may be used when process 1100 was used when verifying memory cells in order to mitigate effects of channel coupling. Process 1120 describes an embodiment with four states: erase, A, B, and C. However, the process 1120 may be extended to more or fewer states. In general, the process 1120 involves reading states in an order from highest state to lowest state. For example, the C-state is read, then the B-state, then the A-state.

In step **1122**, all bit lines are pre-charged. Note that charging all bit lines is not required. However, charging all bit lines allows all bit lines (odd and even) to be read together, which saves time.

In step 1124, a rough read at the C-state is performed. Performing the rough read at the C-state may discharge the bit 20 lines of memory cells that are in any state below the C-state. For example, memory cells having a threshold level that is less than the read level for the C-state (e.g., VrC) may conduct a large current, whereas memory cells having a threshold level that is greater than VrC will conduct only a very small 25 current or no current. A large conduction current may discharge the bit line. Alternatively, bit lines with large conduction currents may be detected and shut down by, for example, grounding those bit lines. However, bit lines for memory cells in the C-state should not be discharged. Therefore, after the rough read, only the bit lines of memory cells that are programmed to the C-state remain charged. The rough read at the C-state therefore establishes the second bit line conditions. Note that the second bit line conditions match the first bit line conditions that were established during the verify of the 35 C-state when using the process 1100 of FIG. 11A. Thus, steps 1122 and 1124 are one embodiment of step 824 of establishing second bit line conditions.

Note that it is not required that the rough read at the C-state save the results of the read. Therefore, it is not required to 40 determine which memory cells have a Vt above VrC. In one embodiment, the rough read is a first strobe of a two-strobe read. Further details of one embodiment of a two-strobe read are discussed below. In one embodiment, the rough read includes all but the final strobe of a multi-strobe read.

In step 1124, another read is performed at the C-state. For example, a read is performed at VrC. For example, the voltage VrC is applied to the selected word line after the second bit line conditions were established. Step 1124 determines which memory cells have a threshold voltage of at least VrC. 50 Because the C-state is the highest state in this example, the memory cells that are in the C-state are thus determined. In one embodiment, the read of step 1124 is the second strobe of the two-strobe read used in step 1122. In one embodiment, the read of step 1124 is the final strobe of the multi-strobe read 55 used in step 1122.

In step 1128, all of the bit lines may be charged again. In step 1130, a rough read at the B-state is performed. Performing the rough read at the B-state may discharge the bit lines of memory cells that are in any state below the B-state. For 60 example, memory cells having a threshold level that is less than the read level for the B-state (e.g., VrB) will conduct a large current, whereas memory cells having a threshold level that is greater than VrB will not conduct a large current. Therefore, after the rough read at the B-state, only the bit lines 65 of memory cells that are programmed to either the B- or C-state remain charged.

**20**