#### US00RE45781E

## (19) United States

## (12) Reissued Patent

Hedrick et al.

#### (10) Patent Number:

US RE45,781 E

#### (45) Date of Reissued Patent:

Oct. 27, 2015

# (54) TOUGHNESS, ADHESION AND SMOOTH METAL LINES OF POROUS LOW K DIELECTRIC INTERCONNECT STRUCTURES

(71) Applicants: Jeffrey C. Hedrick, Montvalle, NJ (US); Kang-Wook Lee, Yorktown Heights, NY (US); Kelly Malone, Newburgh, NY (US); Christy S. Tyberg, Mahopac, NY

(US)

(72) Inventors: **Jeffrey C. Hedrick**, Montvalle, NJ (US); **Kang-Wook Lee**, Yorktown Heights, NY

(US); Kelly Malone, Newburgh, NY (US); Christy S. Tyberg, Mahopac, NY

(US)

(73) Assignee: GLOBALFOUNDRIES, INC., Grand

Cayman (KY)

(21) Appl. No.: 14/176,526

(22) Filed: Feb. 10, 2014

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 6,783,862

Issued: Aug. 31, 2004

Appl. No.: 10/290,682

Filed: Nov. 8, 2002

(51) **Int. Cl.**

H01L 21/02 (2006.01) H01L 23/532 (2006.01)

(Continued)

(52) **U.S. Cl.**

CPC ....... *H01L 21/22* (2013.01); *H01L 21/02126* (2013.01); *H01L 21/02203* (2013.01); *H01L 21/02362* (2013.01); *H01L 21/31695* (2013.01); *H01L 21/31695* (2013.01);

(Continued)

#### (58) Field of Classification Search

CPC C04B 41/009; C09D 183/04; H01L 23/5329; H01L 22/22; H01L 21/76802; H01L 23/53271; H01L 2924/01079

USPC ...... 428/447–448; 257/756, 775; 438/6, 438/623, 634 See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

| WO | WO00/24050 A | 4/2000 |

|----|--------------|--------|

| WO | WO 00/31183  | 6/2000 |

| WO | WO 00/40637  | 7/2000 |

#### OTHER PUBLICATIONS

Application No. 02797318.9 Filed: Dec. 13, 2002 EPO Office Action dated Jan. 9, 2009.

Primary Examiner — Terrence Till (74) Attorney, Agent, or Firm — Yuanmin Cai; Hoffman Wanrnick LLC

#### (57) ABSTRACT

A structure useful for electrical interconnection comprises a substrate; a plurality of porous dielectric layers disposed on the substrate; an etch stop layer disposed between a first of the dielectric layers and a second of the dielectric layers; and at least one thin, tough, non-porous dielectric layer disposed between at least one of the porous dielectric layers and the etch stop layer. A method for forming the structure comprising forming a multilayer stack of porous dielectric layers on the substrate, the stack including the plurality of porous dielectric layers, and forming a plurality of patterned metal conductors within the multilayer stack. Curing of the multilayer dielectric stack may be in a single cure step in a furnace. The application and hot plate baking of the individual layers of the multi layer dielectric stack may be accomplished in a single spin-coat tool, without being removed, to fully cure the stack until all dielectric layers have been deposited.

#### 65 Claims, 1 Drawing Sheet

# US RE45,781 E Page 2

| (51) | Int. Cl.                                          |                                                                                                                                                                                                                           | (56)                    |                                                                                                      |                                                                  | Referen                                                                                                     | ces Cited                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | H01L 21/70<br>H01L 23/52                          | (2006.01)<br>(2006.01)                                                                                                                                                                                                    |                         | U.S. PATENT DOCUMENTS                                                                                |                                                                  |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (52) | (2013.01); <i>I</i><br>21/76829 (2013<br>H01L 21/ | (2006.01)<br>(2006.01)<br>(2006.01)<br>(2006.01)<br>(7682 (2013.01); H01L 21/76801<br>H01L 21/76807 (2013.01); H01L<br>(3.01); H01L 21/76832 (2013.01);<br>(76835 (2013.01); H01L 23/5222<br>H01L 23/5329 (2013.01); H01L | 2003/<br>2003/<br>2003/ | 5,177,199<br>5,218,020<br>5,358,842<br>5,362,091<br>5,383,920<br>5,472,306<br>5,593,211<br>5,603,204 | B1<br>B1*<br>B1*<br>B1*<br>B1<br>B2*<br>B2*<br>B2*<br>A1*<br>A1* | 1/2001<br>4/2001<br>3/2002<br>3/2002<br>5/2002<br>10/2002<br>7/2003<br>8/2003<br>9/2004<br>1/2003<br>4/2003 | Yonehara       428/446         Hacker et al.       428/447         Hacker et al.       428/447         Zhou et al.       438/633         Andideh et al.       438/624         Wang et al.       438/639         Lee et al.       438/623         Sato       438/455         Gates et al.       257/760         Goh et al.       438/622         Steiner et al.       257/760         Tsai et al.       438/633         Thomas et al.       427/384 |

|      | ()                                                | <i>23/53295</i> (2013.01)                                                                                                                                                                                                 | * cited                 | d by exan                                                                                            | niner                                                            |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### TOUGHNESS, ADHESION AND SMOOTH METAL LINES OF POROUS LOW K DIELECTRIC INTERCONNECT **STRUCTURES**

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held 10 invalid by a prior post-patent action or proceeding.

#### CROSS REFERENCE TO RELATED APPLICATION

This application claims priority, under 35 U.S.C. 119(e), from provisional patent application serial No. 60/339,734 filed on Dec. 13, 2001.

This application is related to application serial number Dielectric Interconnects with Improved Adhesion Produced by Partial Burnout of Surface Porogens, assigned to the same assignee as the present application, and filed of even date herewith.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This invention relates to interconnect structures for highspeed microprocessors, application specific integrated circuits (ASICs), and other high speed IC's. The invention pro- 30 vides ultra low dielectric constant (low-k) interconnect structures having enhanced circuit speed, precise values of conductor resistance, and improved mechanical integrity. The structures of this invention have improved toughness and adhesion along with improved control over the metal line 35 resistance compared to conventional structures. The present invention also provides many additional advantages which shall become apparent as described below.

#### 2. Background Art

This application is related to application Ser. No. 09/795, 40 431, entitled Low-k Dielectric Interconnect Structure Comprised of a Multi Layer of Spin-On Porous Dielectrics, assigned to the same assignee as the present application, and filed on Feb. 28, 2001, the contents of which are incorporated herein by reference.

Many low-k dielectric plus copper interconnect structures of the dual damascene type are known. For example, reference is made to U.S. Pat. No. 6,383,920, which is assigned to the same assignee as the present invention, and is incorporated in its entirety by reference, as if fully set forth herein. 50 However, in order to achieve the necessary reduction in the RC delay in the future generations, porous materials must be used as the dielectric. In addition, due to the 5-20 nanometer pore sizes of porous organic materials, a buried etch stop layer is necessary to give smooth metal line bottoms. These struc- 55 tures undergo several processing steps including chemical mechanical polishing (CMP) of the copper, which create stresses within the dielectric stack that can lead to delamination. Delamination can occur due to poor adhesion at the etch stop to dielectric interfaces, or within the dielectric due to 60 decreased toughness of the porous dielectric and increased stress near the interfaces.

#### SUMMARY OF THE INVENTION

It is an object of this invention to provide an ultra low-k dielectric plus copper interconnect structure of the dual

damascene type with precise and uniform control over the copper conductor resistance with increased toughness and adhesion to prevent delaminations during CMP.

It is an object of this invention to provide a porous dielec-5 tric stack with a buried RIE stop with improved toughness and adhesion that is based on a multilayer of spin coated dielectrics.

It is an object of this invention to provide a low-k dielectric plus copper interconnect structure with precise and uniform control over the copper conductor resistance that is based on a multilayer of spin coated dielectric layers, with improved toughness and adhesion and decreased line roughness.

It is another object of this invention to provide a method for making the inventive structure.

The structures of this invention are unique in that they have an ultra-thin non-porous tough dielectric layer between the porous dielectric and the buried etch stop layer. This tough, thin non-porous dielectric layer serves several purposes: it improves toughness, adhesion and reliability of the intercon-10/290,616 (currently allowed), entitled Porous Low-k 20 nect structure. To improve adhesion, the non-porous layer is a version of the porous dielectric with a fracture toughness of greater than 0.3 MPa-m<sup>1/2</sup> which will covalently bond with the porous dielectric to create one network, while increasing the surface area of contact with the etch stop layer by elimi-25 nating pores at the surface. Increased toughness is achieved by incorporating a tough material near the interface in the area of increased stress in the structure. This type of tough material does not have the necessary properties to support the very small pores required by the porous dielectric and therefore generally cannot be used as the matrix for the porous dielectric. Finally, by incorporating a non-porous dielectric layer between the etch stop layer and the porous dielectric layer, smoother lines can be achieved by eliminating pores at the bottom of the etch stop.

> Thus, the present invention is directed to a metal wiring plus porous low dielectric constant (low-k) interconnect structure having improved toughness and adhesion, of the dual damascene type with a spin-on buried RIE stop. The inventive structure is comprised of: a) a multilayer of all spin-on dielectric materials which are applied sequentially in a single tool, and then cured in a single furnace cure step, and b) a plurality of patterned metal conductors within the dielectric multilayer. The improved toughness and adhesion is obtained by incorporating a thin, non-porous dielectric layer, which has a fracture toughness greater than 0.3 MPa-m<sup>1/2</sup>, between the porous dielectric and the etch stop, between the etch stop and the porous dielectric, or both.

> In accordance with the invention, a structure, and in particular an electrical interconnect structure, comprises a substrate; a plurality of porous dielectric layers disposed on the substrate; an etch stop layer disposed between a first of the dielectric layers and a second of the dielectric layers; and at least one thin, non-porous dielectric layer disposed between at least one of the porous dielectric layers and the etch stop layer. The thin, non-porous dielectric layer may have a thickness of substantially 25 to 150 Angstroms. Preferably, the thin, non-porous dielectric layer has a composition with reactive functionalities identical to those of the porous dielectric layers and in particular a composition which forms a covalent bond with the composition of the porous dielectric layers. The thin, non-porous dielectric layer may be comprised of a material selected from the group consisting of SiLK<sup>TM</sup>, GX-3<sup>TM</sup>, or other low k dielectric materials that exhibit fracture toughness values greater than 0.3 MPa-m<sup>1/2</sup>, preferably greater than  $0.35 \text{ MPa-m}^{1/2}$ , and will covalently bond to the porous dielectric layer. Materials of this kind are described in Patent Cooperation Treaty International Patent Application WO

00/40637 entitled Low Dielectric Constant Polymers Having Good Adhesion and Toughness and Articles Made With Such Polymers of Edward O. Shaffer II et al. which is assigned to The Dow Chemical Company.

At least one of the porous dielectric layers is comprised of 5 a material selected from the group consisting of porous SiLK<sup>TM</sup>, GX-3p<sup>TM</sup>, or other porous low-k dielectric layers. Materials of this kind are described in Patent Cooperation Treaty International Patent Application WO 00/31183 entitled A composition containing a cross-linkable matrix precursor and a porogen, and a porous matrix prepared therefrom of Kenneth, J. Bruza et al. which is assigned to The Dow Chemical Company, the contents of which are incorporated herein in their entirety by reference. It may have a thickness of  $_{15}$  RIE and metallization. substantially 600-5000 Angstroms. In general, at least one of the porous dielectric layers has the same chemical composition as another of the porous dielectric layers. At least one of the porous dielectric layers may be of substantially the same thickness as another of the porous dielectric layers and have a 20 thickness of substantially 600-5000 Angstroms.

The etch stop layer may be comprised of HOSP<sup>TM</sup>, HOSP BESt<sup>TM</sup>, Ensemble<sup>TM</sup> Etch Stop, Ensemble<sup>TM</sup> Hard Mask, organo silsesquioxanes, hydrido silsesquioxanes, hydridoorgano silsesquioxanes, siloxanes, or other spin-on material 25 with etch selectivity to the porous dielectric. Materials of this kind are described in U.S. Pat. No. 6,218,020 entitled Dielectric films from organohydridosiloxane resins with high organic content of Nigel P. Hacker et al. which is assigned to AlliedSignal Inc., and U.S. Pat. No. 6,177,199 entitled 30 Dielectric films from organohydridosiloxane resins with low organic content of Nigel P. Hacker et al. which is assigned to AlliedSignal Inc., the contents of which are incorporated herein in their entirety by reference. It may have a thickness of substantially 200-600 Angstroms.

The structure may further comprise a plurality of patterned metal conductors formed within a multilayer stack of porous dielectric layers on the substrate, the stack including the plurality of porous dielectric layers. At least one of the patterned metal conductors may be an electrical via or a line 40 connected to the via.

The invention is also directed to a method for forming an electrical interconnect structure on a substrate, the structure having a plurality of porous dielectric layers disposed on the substrate and an etch stop layer between a first of the dielec- 45 tric layers and a second of the dielectric layers. The method comprises forming at least one thin, non-porous dielectric layer between at least one of the porous dielectric layers and the etch stop layer. The method further comprising forming a multilayer stack of porous dielectric layers on the substrate, 50 the stack including the plurality of porous dielectric layers, and forming a plurality of patterned metal conductors within the multilayer stack. At least one of the patterned metal conductors may be formed as an electrical via. At least one of the patterned metal conductors may be a line connected to the via. 55

The multilayer dielectric stack is applied to the substrate by spin coating. The method may further comprise baking the individual layers of the multilayer dielectric stack on a hot plate. The method may further comprise curing the multilayer dielectric stack. The curing of the multiplayer dielectric stack 60 may be accomplished using a furnace in a single step.

The method also includes applying a miltilayer dielectric stack to the substrate and baking the multilayer dielectric stack, so that the applying and baking are accomplished in a added, and dual damascene conductors may be formed in the additional layers.

Other and further objects, advantages and features of the present invention will be understood by reference to the following specification in conjunction with the annexed drawings, wherein like parts have been given like numbers.

#### BRIEF DESCRIPTION OF THE DRAWINGS

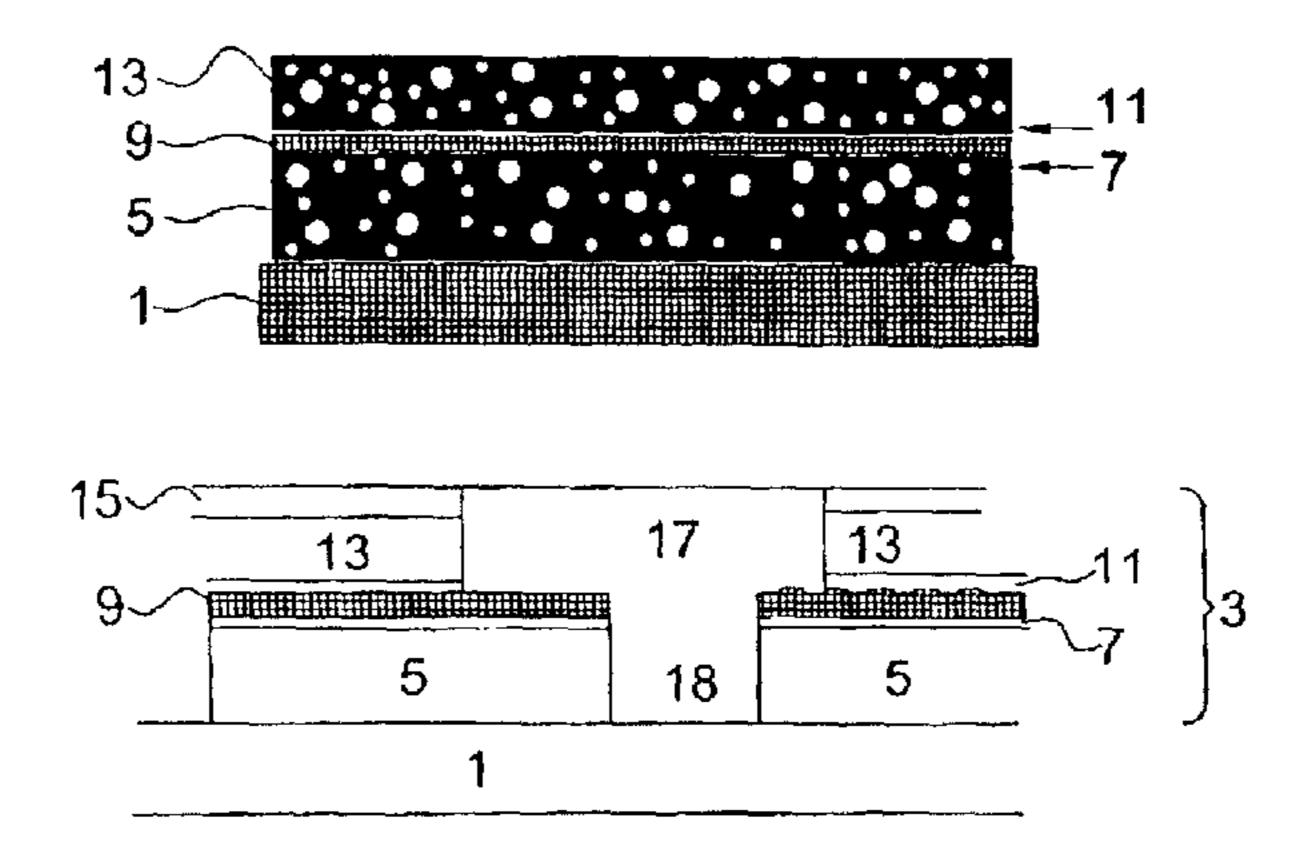

FIG. 1 is a schematic drawing of a porous dielectric with a buried etch stop in accordance with the prior art, before RIE and metallization.

FIG. 2A is a schematic drawing of a structure in accordance with the invention with a thin layer below the etch stop before

FIG. 2B is a schematic drawing of a structure in accordance with the invention with a thin layer above the etch stop before RIE and metallization.

FIG. 2C is a schematic drawing of a structure in accordance with the invention with a thin layer both above and below the etch stop before RIE and metallization.

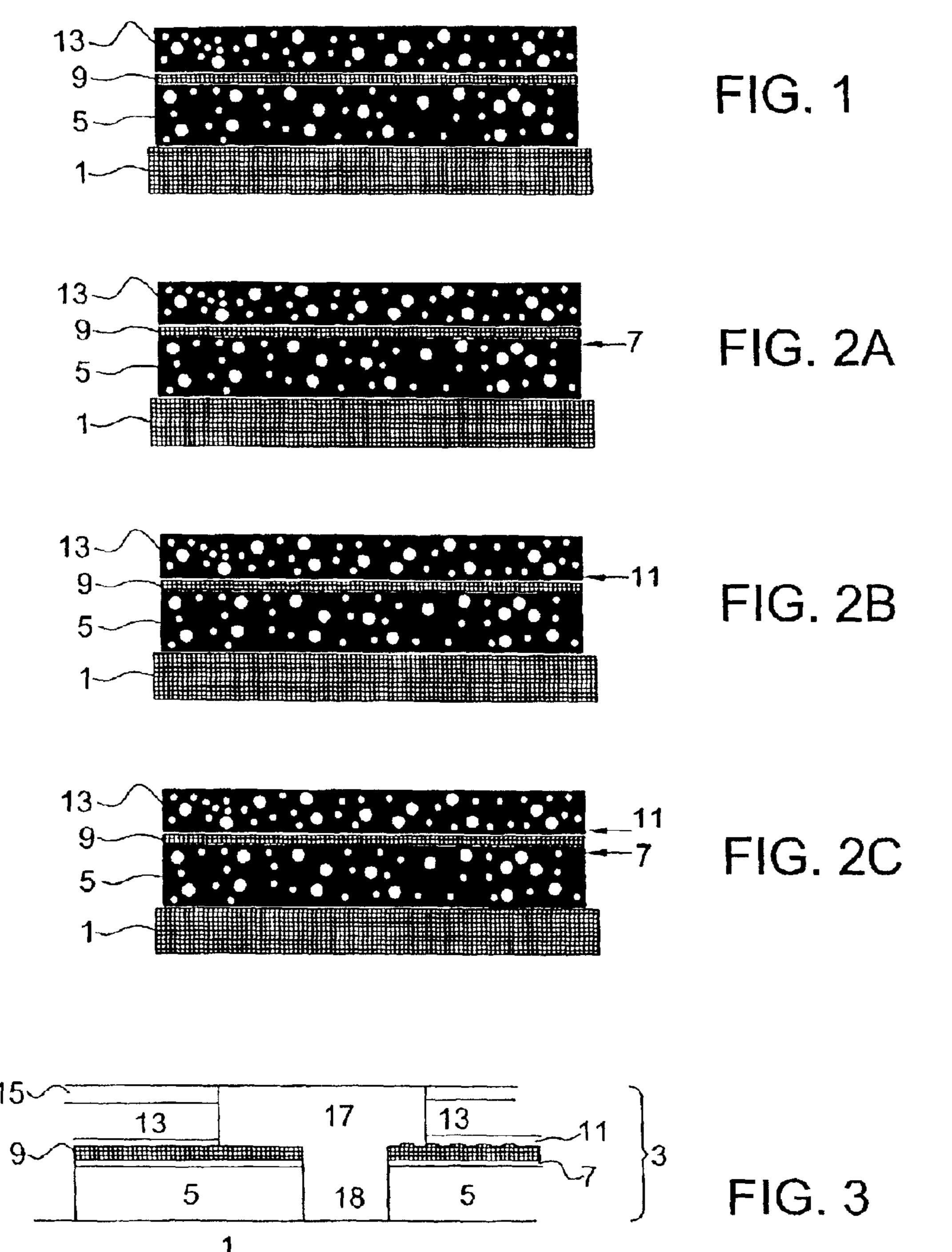

FIG. 3 is a schematic drawing of a structure in accordance with the invention, after RIE and metallization.

#### DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Referring to FIG. 1, a structure on which, for example, an integrated circuit may be fabricated includes a substrate 1, a first porous dielectric layer 5, and a second porous dielectric layer 13. As is well known in the art, an etch stop layer 9 may be disposed between dielectric layers 5 and 13. Substrate 1 is generally comprised of silicon, and may include a dielectric, a metal region, an adhesion promoter, or any combination thereof. Substrate 1 may be a semiconductor wafer of a different composition, porous dielectic layers 5 and 13 may be comprised of a material sold under the trademark porous SiLK(TM) (a Dow Chemical Company proprietary organic ultra low-k interlayer dielectric resin). Other possible materials include GX-3p<sup>TM</sup>, or other porous low k dielectric materials.

Referring to FIG. 2A, in accordance with the invention, a non-porous dielectric layer with a fracture toughness greater than 0.3 MPa-m<sup>1/2</sup> 7 is provided between porous dielectric layer 5 and etch stop layer 9. Dielectric layer 7 may have a thickness of approximately 25-150 Angstroms. Dielectric layer 7 has increased fracture toughness compared to porous SiLK<sup>TM</sup> due to a decreased network density, as described in above mentioned International Patent Application WO 00/40637. This structure has the same reactive functionalities as a porous SiLK<sup>TM</sup> layer and can crosslink with a porous SiLK<sup>TM</sup> layer. Layer 7 preferably has a highly aromatic structure, which is thermally stable to approximately 425° C. with a glass transition temperature above 430° C., and a low dielectric constant of approximately 2.65.

The structure of FIG. 2B is similar to that of FIG. 2A, but does not include layer 7. Instead, the structure of FIG. 2B includes a layer 11 disposed between etch stop layer 9 and porous dielectric layer 13. Layer 11 may be, in all respects except location, similar to layer 7.

Referring to FIG. 2C, the structure shown therein includes single spin-coat tool. Additional dielectric layers may be 65 both a layer 7 and a layer 11, having the characteristics described above. A more specific example is described below with respect to FIG. 3.

Substrate/Porous SiLK<sup>TM</sup>/thin SiLK<sup>TM</sup> layer/HOSP BESt<sup>TM</sup> /thin SiLK<sup>TM</sup> layer/Porous SiLK<sup>TM</sup>

FIG. 3 schematically illustrates a specific embodiment of 5 the invention. A substrate 1 may contain transistors and an array of conductor elements. An interconnect structure 3, in accordance with the invention, is disposed on the substrate 1. Structure 3 is comprised of a first porous SiLK<sup>TM</sup> dielectric layer 5, having a thickness of 600-5000 Angstroms and having a highly aromatic structure which is thermally stable to approximately 425° C., with a glass transition temperature above approximately 450° C., and a low dielectric constant of approximately 2.2.

A thin non porous SiLK<sup>TM</sup> layer 7, having a fracture tough- 15 ness greater than 0.30 MPa-m<sup>1/2</sup> and having a thickness of approximately 25-150 Angstroms, is disposed on the first porous SiLK layer 5. As noted above, layer 7 has increased fracture toughness compared to porous SiLK due to a decreased network density. This structure has the same reactive functionalities as the porous SiLK layer 5 and can crosslink with porous SiLK layer 5. Layer 7 is a highly aromatic structure which is thermally stable to approximately 425° C. with a glass transition temperature above approximately 430° C., and a low dielectric constant of approxi- 25 mately 2.65.

A HOSP BESt<sup>TM</sup> (a spin-on hybrid organic-inorganic low-k dielectric) etch stop layer 9 of thickness 200-600 Angstroms (more preferably 200-300 Angstroms), and having an atomic composition that gives etch selectivity of at least 10:1 to the porous dielectric is disposed on the thin SiLK<sup>TM</sup> layer 7. The material of layer 9 has good adhesion to SiLK<sup>TM</sup>, thermal stability to approximately 450° C., and a low dielectric constant of approximately 2.7.

ness greater than 0.30 MPa-m<sup>1/2</sup> and having a thickness of approximately 25-150 Angstrom, is disposed on the etch stop layer 9. Layer 11 has increased fracture toughness compared to porous SiLK<sup>TM</sup> due to a decreased network density. Layer 11 has the same reactive functionalities as a porous SiLK<sup>TM</sup> 40 layer and can crosslink with a porous SiLK<sup>TM</sup> layer. Layer 11 has a highly aromatic structure which is thermally stable to approximately 425° C. with a glass transition temperature above approximately 430° C., and a low dielectric constant of approximately 2.65.

A second porous SiLK dielectric layer 13 having a thickness of approximately 600-5000 Angstroms, and having a highly aromatic structure which is thermally stable to approximately 425° C. with a glass transition temperature above approximately 450° C., and a low dielectric constant of 50 approximately 2.2, is disposed on the thin SiLK<sup>TM</sup> layer 11.

Patterned metal lines 17 and vias 18, formed by a dual damascene process, such as that described in the above referenced U.S. Pat. No. 6,383,920, are formed within the dielectric multilayer of FIG. 3.

As is known by one skilled in the art, other low-k spin coated dielectric materials may be used for dielectric layers 5 and 13, for etch stop layer 9, and for the thin toughening layers 7 and 11.

Invention

Steps in the General Method

A. The stack of dielectric layers is applied

The inventive interconnect structure 3 is applied to the substrate 1 by spin on techniques. The first layer 5 in the 65 structure is preferably a porous low k dielectric with a desired thickness of 600-5000 Å. This low k dielectric is applied by a

spin-on technique with a spin speed of 1000-4000 rpm. After spinning the low k dielectric is hot plate baked to dry the solvent and render the film insoluble at 200-400° C. for 1-2 minutes. This time and temperature is sufficient to render the film insoluble without eliminating the porogen. After cooling a thin layer of a dielectric having a fracture toughness greater than 0.30 MPa-m<sup>1/2</sup> 7 capable of crosslinking with the bottom porous dielectric layer, and having a thickness of approximately 25-150 Angstroms is applied by spin coating. After spinning the dielectric is hot plate baked to dry the solvent and render the film insoluble at 200-400° C. for 1-2 minutes. After cooling, the buried RIE etch stop layer 9, with a desired thickness of approximately 200-600 Angstroms, is applied by a spin-on technique with a spin speed of 1000-4000 rpm. The etch stop layer is hot plate baked to dry the solvent and render the film insoluble at 200-400° C. for 1-2 minutes. This time promotes sufficient crosslinking to render the film insoluble. After cooling, a second thin layer of a dielectric having a fracture toughness greater than 0.30 MPa-m<sup>1/2</sup> 11 capable of crosslinking with the top porous dielectric layer, and having a thickness of 25-150 Angstroms is applied by spin coating. After spinning the low k dielectric is hot plate baked to dry the solvent and render the film insoluble at 200-400° C. for 1-2 minutes. After cooling, the top dielectric layer 13 is applied in a similar fashion. Layer 13 may be of the same composition as layer 5, but with a slightly higher thickness. The desired thickness of the top low k dielectric layer 13 is approximately 600-5000 Angstroms. This layer is spun at 1000-4000 rpm, then hot plate baked at approximately 100-400° C. for approximately 30-120 seconds to partially- dry the solvent.

B. The stack of dielectric layers is cured in a single cure step

At this point the wafer is placed in a furnace in an atmosphere of pure  $N_2$  (with very low  $O_2$  and  $H_2O$  concentrations) A thin non-porous SiLK layer 11, having a fracture tough- 35 and cured at approximately 300-450° C. for approximately 15 minutes to 3 hours to crosslink the stack and burn out the sacrificial porogen.

> C. Additional dielectric layers are added for dual damascene patterning (distributed hard mask)

For this step and the next, reference is made to the above mentioned U.S. Pat. No. 6,383,920.

D. The dual damascene structure of FIG. 3 is completed (using standard process steps)

A Method for Making the Preferred Embodiment)

(Porous SiLK<sup>TM</sup>/Thin SiLK<sup>TM</sup> layer/HOSP BESt<sup>TM</sup>/Thin SiLK<sup>TM</sup> layer/Porous SiLK<sup>TM</sup>)

A. The stack of dielectric layers is applied

The first layer of low k dielectric porous SiLK<sup>TM</sup> is applied to the substrate by spin coating (layer 5, FIG. 3). After spinning, the wafer is placed on a 250° C. hot plate for 2 minute to partially dry the solvent. It is then transferred to a 310° C. hot plate for 2 minutes and a 400° C. hot plate for 2 minutes. This time and temperature are sufficient to render the film insoluble.

A solution of SiLK<sup>TM</sup> such as, for example, the composition specified in International Patent Application WO 00/40637 on page 17, Table II, resin I diluted to achieve a film thickness of about 100 Å at a spin speed of 3000 rpm, is applied to the wafer and spun at 3000 rpm for 30 seconds, to A General Method for Fabricating the Structure of the 60 produce layer 7 (FIG. 3). After spinning, the wafer is placed on a hot plate at 310° C. for 1 minute to dry the solvent. It is then moved to a 400° C. hot plate for 2 minutes to partially crosslink the film. This time and temperature are sufficient to render the film insoluble.

> A solution of HOSP BESt<sup>TM</sup> diluted to achieve a film thickness of 250 Angstroms at a spin speed of 3000 rpm, is applied to the wafer and spun at 3000 rpm for 30 seconds, to

7

produce layer 9 (FIG. 3). After spinning, the wafer is placed on a hot plate at 310° C. for 2 minutes to dry and partially crosslink the film. This time and temperature is sufficient to render the film insoluble.

The solution of SiLK<sup>TM</sup> diluted to achieve a film thickness of 100 Angstroms, at a spin speed of 3000 rpm, is applied to the wafer and spun at 3000 rpm for 30 seconds to produce layer 11 (FIG. 3). After spinning, the wafer is placed on a hot plate at 310° C. for 1 minute to partially dry the solvent. It is then moved to a 400° C. hot plate for 2 minutes to partially 10 crosslink the film. This time and temperature are sufficient to render the film insoluble. The wafer is then allowed to cool and is returned to the spinner.

The second layer of porous SiLK<sup>TM</sup> is applied in a manner similar to that for the first layer to produce layer **13** (FIG. **3**). 15 Porous SiLK<sup>TM</sup> is applied to the wafer and the wafer is spun at 3000 rpm for 30 seconds. The wafer is placed on a 250° C. hot plate for 2 minute to partially dry the solvent.

At this point the wafer is placed in an oxygen controlled oven and cured at 430° C. for 80 minutes to cure the SILK and 20 etch stop layers, to promote crosslinking between the layers, and to thermally degrade and burn out the porogen.

C. Additional dielectric layers are added for dual damascene patterning (distributed hard mask)

The cured wafer containing the layers described above was 25 placed in a PE CVD reactor and a 350 Angstrom layer of silicon nitride **15** was deposited at 350° C., and then a 1500 Angstrom layer of SiO<sub>2</sub> was deposited at 350° C. This completes the formation of the dielectric multilayer of Example 1.

D. The dual damascene structure of FIG. 3 is completed

Lithography and etching processes are then performed as described in the above referenced U.S. Pat. Na. 6,383,920. The dual damascene structure is then completed using standard process methods known in the industry (the etched trench and via opening are filled with a liner and then with 35 copper, and the copper is planarized by CMP).

During the final CMP process, silicon dioxide layer deposited in step C. is removed, leaving the structure shown in FIG. 3. It should be noted that all the dielectric layers (5, 7, 9, 11 and 13) shown in FIG. 3 have been cured in a single furnace 40 cure step after sequential application of the 5 layers in a single spin/apply tool.

Thus, The structure of the invention has improved adhesion over conventional buried etch stop structures because the non-porous layer will increase the surface area of contact with 45 the etch stop layer by eliminating pores at the surface, and form covalent bonds with the porous dielectric to create one network.

Increased toughness is achieved by incorporating a tough material near the interface in the area of increased stress in the 50 dielectric stack. This type of tough material may not have the necessary properties to support very small pores required by the porous dielectric and therefore cannot be used as the matrix for the porous dielectric.

Incorporating a non-porous dielectric layer between the etch stop and the porous dielectric layer allows for smoother lines by eliminating pores at the bottom of the etch stop. Specifically, in a dual damascene process, the last step of the RIE process that includes the cap open step, may result in the line bottoms etching through the etch stop and landing on the top of the dielectric that is directly below the etch stop. Incorporation of the thin dense dielectric between the via level porous dielectric and the etch stop will result in decreased line roughness compared with the conventional structure that has the porous dielectric directly below the etch stop.

While we have shown and described several embodiments in accordance with our invention, it is to be clearly understood

8

that the same are susceptible to numerous changes apparent to one skilled in the art. Therefore, we do not wish to be limited to the details shown and described but intend to show all changes and modifications which come within the scope of the appended claims.

What is claimed is:

- 1. A structure comprising:

- a substrate;

- a plurality of porous dielectric layers disposed on said substrate;

- an etch stop layer disposed between a first of said *porous* dielectric layers and a second of said *porous* dielectric layers; and

- at least one thin, non-porous dielectric layer disposed between at least one of said porous dielectric layers and said etch stop layer,

- wherein said thin, non-porous dielectric layer and said porous dielectric layers are associated with an identical reactive functionality.

- 2. The structure of claim 1, wherein a thin, non-porous dielectric layer is disposed between only one of said porous dielectric layers and said etch stop layer.

- 3. The structure of claim 1, wherein a thin, non-porous dielectric layer is disposed between each of two of said porous dielectric layers and said etch stop layer.

- 4. The structure of claim 1, wherein a thin, non-porous dielectric layer is disposed above one of said porous dielectric layers and below said etch stop layer.

- 5. The structure of claim 1, wherein a thin, non-porous dielectric layer is disposed below one of said porous dielectric layers and above said etch stop layer.

- 6. The structure of claim 1, wherein said thin, non-porous dielectric layer has a thickness of substantially 25 to 150 Angstroms.

- 7. The structure of claim 1, wherein said thin, non-porous dielectric layer has a composition with reactive functionalities identical to those of said porous dielectric layers.

- 8. The structure of claim 1, wherein said thin, non-porous dielectric layer has a composition which forms a covalent bond with [the] a composition of said porous dielectric layers.

- 9. The structure of claim 1, wherein said thin, non-porous dielectric layer is comprised of a material selected from low k dielectric materials that exhibit fracture toughness values greater than 0.30 MPa-m1/2 and will covalently bond to the porous dielectric layer.

- 10. The structure of claim 1, wherein at least one of said porous dielectric layers is comprised of a material selected from porous low k dielectric materials.

- 11. The structure of claim 1, wherein at least one of said porous dielectric layers has a thickness of substantially 600-5000 Angstroms.

- 12. The structure of claim 1, wherein said at least one of said porous dielectric layers has [the] a same chemical composition as another of said porous dielectric layers.

- 13. The structure of claim 1, wherein said at least one of said porous dielectric layers has substantially the same thickness as another of said porous dielectric layers.

- 14. The structure of claim 1, wherein said etch stop layer has a chemical composition comprising silicon, carbon, oxygen, and hydrogen.

- 15. The structure of claim 1, wherein said etch stop layer is selected from [the] a group consisting of organo silsesquioxanes, hydrido silsesquioxanes, hydrido-organo silsesquioxanes, and siloxanes[, and other spin-on material with etch selectivity to the porous dielectric].

- 16. The structure of claim 1, wherein said etch stop layer has a thickness of substantially 200-600 Angstroms.

- 17. The structure of claim 1, further comprising a plurality of patterned metal conductors formed within a multilayer stack of porous dielectric layers on the substrate, said stack including said plurality of porous dielectric layers.

- **18**. The structure of claim **17**, wherein at least one of the patterned metal conductors is an electrical via.

- 19. The structure of claim [17] 18, wherein at least one of the patterned metal conductors is a line connected to said via.

- 20. The structure of claim 17, wherein the first porous dielectric layer has a metal via formed therein.

- 21. The structure of claim 17, wherein the second porous dielectric layer has a metal line formed therein.

- 22. A method for forming an electrical interconnect structure on a substrate, the structure having a plurality of porous 15 dielectric layers disposed on said substrate and an etch stop layer between a first of said dielectric layers and a second of said dielectric layers comprising:

- forming at least one thin, non-porous dielectric layer between at least one of said porous dielectric layers and 20 said etch stop layer,

- wherein said thin, non-porous dielectric layer and said at least one of said porous dielectric layers are formed such that each is associated with an identical reactive functionality.

- 23. The method of claim 22, wherein a thin, non-porous dielectric layer is formed between only one of said porous dielectric layers and said etch stop layer.

- 24. The method of claim 22, wherein a thin, non-porous dielectric layer is formed between each of two of said porous 30 dielectric layers and said etch stop layer.

- 25. The method of claim 22, wherein a thin, non-porous dielectric layer is formed above one of said porous dielectric layers and below said etch stop layer.

- 26. The method of claim [23] 22, wherein a thin, non- 35 porous dielectric layer is formed below one of said porous dielectric layers and above said etch stop layer.

- 27. The method of claim 22, wherein said thin, non-porous dielectric layer is formed to a thickness of substantially 25 to 150 Angstroms.

- 28. The method [structure] of claim 22, wherein said thin, non-porous dielectric layer is formed to have a composition with reactive functionalities identical to those of said porous dielectric layers.

- 29. The method of claim 22, wherein said thin, non-porous 45 dielectric layer is formed to have a composition which forms a covalent bond with [the] a composition of said porous dielectric layers.

- 30. The method of claim 22, wherein said thin, non-porous dielectric layer is comprised of a material selected from low k 50 dielectric materials that exhibit fracture toughness values greater than 0.3 MPa-m<sup>1/2</sup> and covalently bond to the porous dielectric layer.

- 31. The [structure] *method* of claim 22, wherein at least one of said porous dielectric layers is comprised of a material 55 functionality in said porous dielectric layers. selected from porous low k dielectric materials.

- 32. The method of claim 22, wherein at least one of said porous dielectric layers is formed to have a thickness of substantially 600-5000 Angstroms.

- 33. The method of claim 22, wherein said at least one of 60 said porous dielectric layers is formed with [the] a same chemical composition as another of said porous dielectric layers.

- **34**. The method of claim **22**, wherein said at least one of substantially [the] same thickness as another of said porous dielectric layers.

**10**

- 35. The method of claim 22, wherein said etch stop layer is selected from [the] a group consisting of organo silsesquioxanes, hydride silsesquioxanes, hydrido-organo silsesquioxanes, and siloxanes, and other spin-on material with etch selectivity to the porous dielectric.

- **36**. The method of claim **22**, wherein said etch stop layer has a chemical composition comprising silicon, oxygen, carbon, and hydrogen.

- 37. The method of claim 22, wherein said etch stop layer is formed to have a thickness of substantially 200-600 Angstroms.

- **38**. The method of claim **22**, further comprising forming a multilayer stack of porous dielectric layers on the substrate, said stack including said plurality of porous dielectric layers, and forming a plurality of patterned metal conductors within said multilayer stack.

- **39**. The method of claim **38**, wherein at least one of the patterned metal conductors is formed as an electrical via.

- 40. The method of claim [38] 39, wherein at least one of the patterned metal conductors is a line connected to said via.

- 41. The method of claim 38, wherein the first porous dielectric layer has a metal via formed therein.

- **42**. The method of claim **38**, wherein the second porous 25 dielectric layer has a metal line formed therein.

- **43**. The method of claim **38**, wherein said multilayer dielectric stack is applied to said substrate by spin coating.

- 44. The method of claim 38, further comprising baking each layer of said multilayer dielectric stack.

- 45. The method of claim 44, wherein said baking is accomplished on a hot plate.

- **46**. The method of claim **38**, further comprising curing said multilayer dielectric stack in a single cure step.

- 47. The method of claim [38] 46, wherein said curing of the multilayer stack is a furnace curing process that is carried out at a temperature from about 300° C. to about 450° C. for a time period of from about 15 minutes to about 3 hours.

- **48**. The method of claim **47**, wherein said curing step 40 crosslinks [the] films and burns out sacrifical porogen from the porous dielectric layers.

- 49. The method of claim 22, further comprising applying a miltilayer dielectric stack to said substrate and baking said multilayer dielectric stack, said applying and baking being accomplished in a single spin-coat tool.

- 50. The method of claim 22, further comprising adding additional dielectric layers, and forming dual damascene conductors in said additional layers.

- **51**. The method of claim **22**, wherein said substrate is a dielectric, a metal region, an adhesion promoter, a semiconductor wafer or any combination thereof.

- 52. The structure according to claim 1, wherein said thin, non-porous dielectric layer has more than one reactive functionality identical to, respectively, more than one reactive

- 53. The structure according to claim 1, wherein said thin, non-porous dielectric layer has two reactive functionalities that are respectively identical to two reactive functionalities in said porous dielectric layers.

- 54. The structure according to claim 1, wherein said thin, non-porous dielectric layer has two distinct reactive functionalities that are respectively identical to two distinct reactive functionalities in said porous dielectric layers.

- 55. The structure according to claim 8, wherein said comsaid porous dielectric layers is formed to [be of] have a 65 position of said thin non-porous dielectric layer and said composition of said porous dielectric layers forms a covalent bond network.

11

- 56. The structure according to claim 1, wherein said thin, non-porous dielectric layer has a composition which forms a covalent bond network with a composition of said at least one porous dielectric layer.

- 57. The structure according to claim 56, wherein said thin, non-porous dielectric layer and said composition of said porous dielectric layers are such that said formed covalent bond network increases adhesion between said thin, non-porous dielectric layer and said at least one porous dielectric layer.

- 58. The method according to claim 22, wherein both said thin, non-porous dielectric layer and at least one of said porous dielectric layers are formed such that each comprises more than one reactive functionality that are identical to each other.

- 59. The method according to claim 22, wherein both said thin, non-porous dielectric layer and at least one of said porous dielectric layers are formed such that each comprises two reactive functionalities that are identical to each other 20 respectively.

- 60. The method according to claim 22, wherein both said thin, non-porous dielectric layer and at least one of said porous dielectric layers are formed such that each comprises two distinct reactive functionalities that are identical to each 25 other respectively.

- 61. The method according to claim 22, wherein said thin, non-porous dielectric layer has a composition which forms a covalent bond network with a composition of said porous dielectric layers.

- 62. The method according to claim 22, further comprising: increasing adhesion between said thin, non-porous dielectric layer and a composition of at least one of said porous dielec-

12

tric layers by forming a covalent bond network between said thin, non-porous dielectric layer and said at least one porous dielectric layer.

- 63. The structure according to claim 1, wherein during the formation of the structure there was at least one reactive functionality in a composition of said thin, non-porous dielectric layer that is identical to that in said porous dielectric layers.

- 64. The method according to claim 22 further comprising: selecting materials for said thin, non-porous dielectric layer and said porous dielectric layers such that reactive functionalities between said thin, non-porous dielectric layer and said porous dielectric layers react to covalently bond said thin, non-porous dielectric layer and said porous dielectric layers, forming a covalent bond network there-between, and wherein at least one reactive functionality of said thin, non-porous dielectric layer and at least one reactive functionality of said porous dielectric layers is identical.

- 65. A structure comprising:

a substrate;

- a plurality of porous dielectric layers disposed on said substrate;

- an etch stop layer disposed between a first of said porous dielectric layers and a second of said porous dielectric layers; and

- at least one thin, non-porous dielectric layer disposed between at least one of said porous dielectric layers and said etch stop layer,

- wherein said thin, non-porous dielectric layer has a composition which forms a covalent bond with a composition of said porous dielectric layers.

\* \* \* \* \*