### US00RE45697E

## (19) United States

### (12) Reissued Patent

Lin et al.

### US RE45,697 E (10) Patent Number: Sep. 29, 2015

### (45) Date of Reissued Patent:

### SYSTEM, METHOD AND MEMORY DEVICE PROVIDING DATA SCRAMBLING COMPATIBLE WITH ON-CHIP COPY **OPERATION**

Applicant: SanDisk Technologies Inc., Plano, TX

(US)

Inventors: Jason T Lin, Santa Clara, CA (US);

Steven S Cheng, Sunnyvale, CA (US); Shai Traister, San Jose, CA (US)

Assignee: SanDisk Technologies Inc., Plano, TX (73)

(US)

Appl. No.: 14/242,610

(22)Filed: Apr. 1, 2014

### Related U.S. Patent Documents

Reissue of:

8,301,912 Patent No.: (64)Oct. 30, 2012 Issued: Appl. No.: 12/345,921 Filed: Dec. 30, 2008

U.S. Applications:

Provisional application No. 61/018,096, filed on Dec. 31, 2007.

Int. Cl. (51)G11B 20/00

(2006.01)U.S. Cl. (52)

Field of Classification Search

<u>150</u>

CPC ............. G11B 20/0021; G06F 12/0246; G06F 12/1408; G06F 21/72; G06F 21/725; G06F 21/79; G06F 2212/1032; G06F 2221/2107; G11C 11/5628; G11C 16/0483; G11C 16/3418; G11C 16/3427; G11C 7/1006

See application file for complete search history.

#### **References Cited** (56)

#### U.S. PATENT DOCUMENTS

5,587,959 A 12/1996 Tsukude 5,592,436 A 1/1997 Toda 5,689,473 A 11/1997 Toda

### (Continued)

#### OTHER PUBLICATIONS

International Search Report and Written Opinion for App. No. PCT/ US2008/088625, dated Mar. 19, 2009, 7 pages.

(Continued)

Primary Examiner — Jason Proctor

(74) Attorney, Agent, or Firm — Brinks Gilson & Lione

#### ABSTRACT (57)

Data scrambling techniques implemented externally to a flash memory device are disclosed which can be used in concert with flash memory on-chip copy functionality operating internally to the flash device, thus supporting high performance copying operations. All the data stored in the flash may be scrambled, including headers and control structures. Robust file system operation may be achieved, including the capability to tolerate a power loss at any time, and yet be able to relocate data internally within the flash without having to de-scramble and then re-scramble the data. An exemplary hardware based solution has little or no impact on overall system performance, and may be implemented at very low incremental cost to increase overall system reliability. The data scrambling technique preferably uses a logical address, such as logical block address or logical page address, rather than a physical address, to determine a seed scrambling key.

### 71 Claims, 15 Drawing Sheets

### Data Pattern Scrambler/Descrambler Block Diagram

Scrambler

# US RE45,697 E Page 2

| (56)                                                                                                                                                                                                                                                                                                                                                                                             | Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | eferen                                                                                                                                                                                    | ces Cited                                       | 2007/0217608                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                    |                                                                                                                                                                                                            | Shimasaki                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                  | U.S. PAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ΓENT                                                                                                                                                                                      | DOCUMENTS                                       | 2007/0220197<br>2008/0151618<br>2008/0158948                                                                                                                                                                                                                                                                                                                                        | A1 6                                                                                                                                                                               | 5/2008                                                                                                                                                                                                     | Lasser Sharon et al. Sharon et al. |

| 5,706,248<br>5,911,062<br>5,915,025<br>5,943,283<br>6,094,368<br>6,307,776<br>6,549,468<br>6,621,745<br>6,684,289<br>6,856,572<br>6,917,539<br>6,977,855<br>7,012,835<br>7,012,835<br>7,139,864<br>7,177,169<br>7,349,267<br>7,464,216<br>7,512,813<br>8,187,936<br>2003/0126451<br>2005/0141329<br>2005/0144365<br>2005/0201401<br>2005/0213393<br>2006/0026341<br>2006/0156189<br>2006/0156189 | A 1/A 6/A * 6/A * 6/A A 7/B1 10/B2 4/B1 9/B1 1/B2 2/B2 11/B2 12/B2 3/B2 11/B2 2/B2 3/B2 11/B2 2/B2 3/B2 11/B2 2/A1 * 7/A1 6/A1 * 7/A1 6/A1 6/A1 6/A1 6/A1 6/A1 6/A1 6/A1 6 | /1998<br>/1999<br>/1999<br>/2000<br>/2003<br>/2003<br>/2005<br>/2005<br>/2006<br>/2006<br>/2007<br>/2008<br>/2008<br>/2009<br>/2005<br>/2005<br>/2005<br>/2006<br>/2006<br>/2006<br>/2006 | Toda Taki Taguchi et al                         | 2008/0158948 2008/0215798 2008/0317246 2009/0083485 2009/0150596  European Supple App. No. 088695 Application as Fi 2013, 121 pages. Application as Fi 2013, 56 pages. Jang et al., "Ver Transistor) Tech Memory," 2009 S Papers, pp. 192-1 Arya, P., "A Surv ate Program, Nan Nowak, E. et al. Memories", 2012 cal Papers, 2012 International Sea 2009 for App. No Europena Supple | A1 9 A1 12 A1 3 A1 3 A1 6 OTHE mentary 63.0, data iled for U intrins 2 Symposia 7 Symposia 7 Symposia 8 Symposia 9 OF TOTHE | 7/2008<br>9/2008<br>3/2009<br>5/2009<br>5/2009<br>ER PUH<br>Search<br>ted Mar<br>J.S. Ap<br>J.S. Ap<br>J.S. Ap<br>J.S. Ap<br>Mand H<br>mao Tur<br>sic Fluction on<br>22.<br>ort and<br>JS2008/<br>y Search |                                    |

| 2007/0089034<br>2007/0124652<br>2007/0208905                                                                                                                                                                                                                                                                                                                                                     | A1 5/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | /2007                                                                                                                                                                                     | Litsyn et al.<br>Litsyn et al.<br>Litsyn et al. | * cited by exan                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                    | <b>r r</b>                                                                                                                                                                                                 |                                    |

FIG. 1 (prior art)

Data Pattern Scrambler/Descrambler Block Diagram

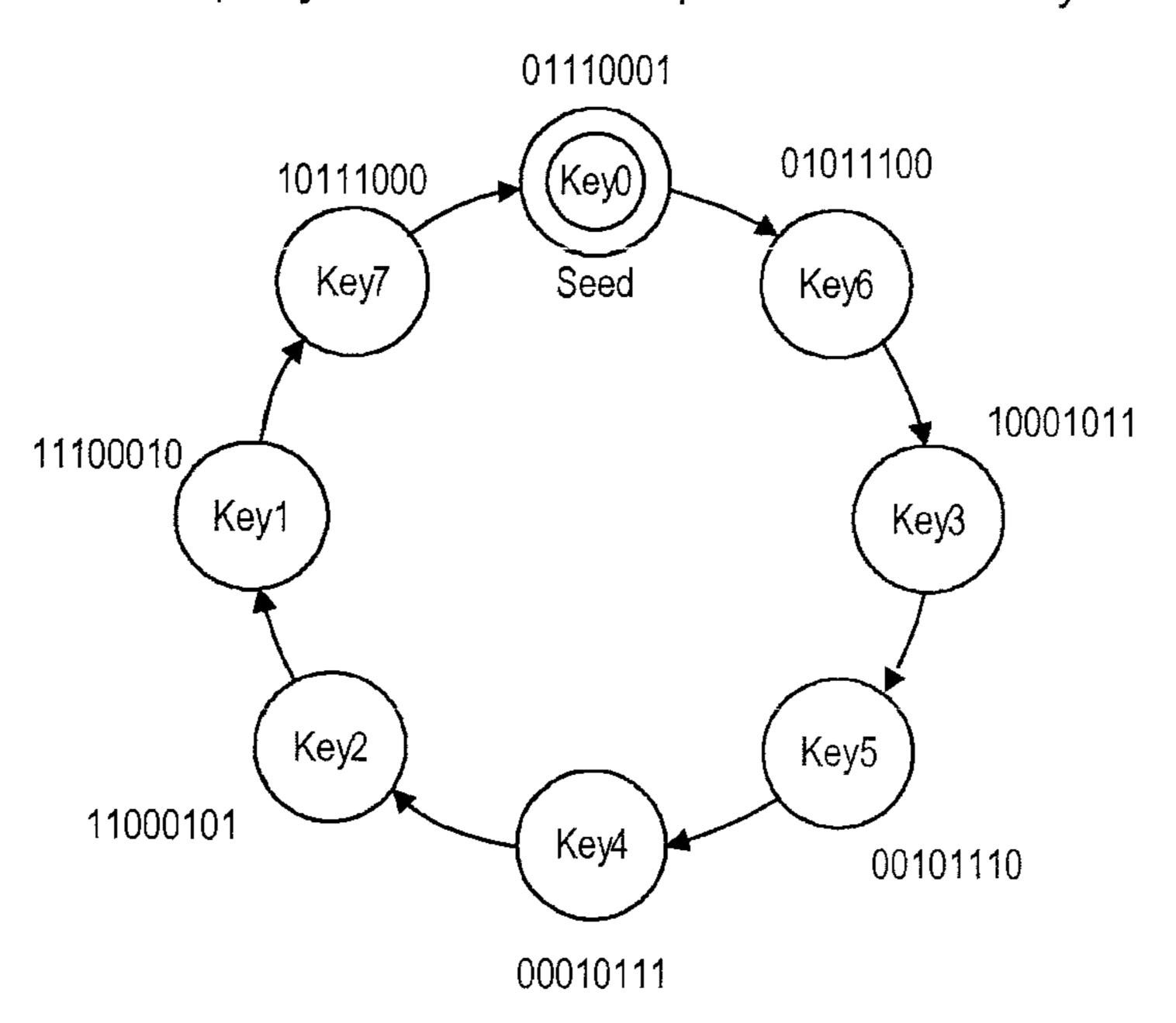

# Exemplary Sequence based on Seed of 0x71 rotating left with 8-bit shifter

Sep. 29, 2015

# Exemplary Sequence based on Seed of 0x695334C6 rotating left with Shifter size of 32

Rotation Length: 32 Rotation Direction: Left

| # of | Cnt |

|------|-----|

| 0's  | 16  |

| 1's  | 16  |

| Key        | Key |                  | Shifter  | Output   | <u></u>  |

|------------|-----|------------------|----------|----------|----------|

| Sequence   | #   | Byte 3           | Byte 2   | Byte 1   | Byte 0   |

| 0x69C734C6 | 0   | 01101001         | 11000111 | 00110100 | 11000110 |

| 0xD38E698C | 1   | 11010011         | 10001110 | 01101001 | 10001100 |

| 0xA71CD319 | 2   | 10100111         | 00011100 | 11010011 | 00011001 |

| 0x4E39A633 | 3   | 01001110         | 00111001 | 10100110 | 00110011 |

| 0x9C734C66 | 4   | 10011100         | 01110011 | 01001100 | 01100110 |

| 0x38E698CD | 5   | 00111000         | 11100110 | 10011000 | 11001101 |

| 0x71CD319A | 6   | 01110001         | 11001101 | 00110001 | 10011010 |

| 0xE39A6334 | 7   | 11100011         | 10011010 | 01100011 | 00110100 |

| 0xC734C669 | 8   | 11000111         | 00110100 | 11000110 | 01101001 |

| 0x8E698CD3 | 9   | 10001110         | 01101001 | 10001100 | 11010011 |

| 0x1CD319A7 | 10  | 00011100         | 11010011 | 00011001 | 10100111 |

| 0x39A6334E | 11  | 00111001         | 10100110 | 00110011 | 01001110 |

| 0x734C669C | 12  | 01110011         | 01001100 | 01100110 | 10011100 |

| 0xE698CD38 | 13  | 11100110         | 10011000 | 11001101 | 00111000 |

| 0xCD319A71 | 14  | 11001101         | 00110001 | 10011010 | 01110001 |

| 0x9A6334E3 | 15  | 10011010         | 01100011 | 00110100 | 11100011 |

| 0x34C669C7 | 16  | 00110100         | 11000110 | 01101001 | 11000111 |

| 0x698CD38E | 17  | 01101001         | 10001100 | 11010011 | 10001110 |

| 0xD319A71C | 18  | 11010011         | 00011001 | 10100111 | 00011100 |

| 0xA6334E39 | 19  | 10100110         | 00110011 | 01001110 | 00111001 |

| 0x4C669C73 | 20  | 01001100         | 01100110 | 10011100 | 01110011 |

| 0x98CD38E6 | 21  | 10011000         | 11001101 | 00111000 | 11100110 |

| 0x319A71CD | 22  | 00110001         | 10011010 | 01110001 | 11001101 |

| 0x6334E39A | 23  | 01100011         | 00110100 | 11100011 | 10011010 |

| 0xC669C734 | 24  | <b>110</b> 00110 | 01101001 | 11000111 | 00110100 |

| 0x8CD38E69 | 25  | 10001100         | 11010011 | 10001110 | 01101001 |

| 0x19A71CD3 | 26  | 00011001         | 10100111 | 00011100 | 11010011 |

| 0x334E39A6 | 27  | 00110011         | 01001110 | 00111001 | 10100110 |

| 0x669C734C | 28  | 01100110         | 10011100 | 01110011 | 01001100 |

| 0xCD38E698 | 29  | 11001101         | 00111000 | 11100110 | 10011000 |

| 0x9A71CD31 | 30  | 10011010         | 01110001 | 11001101 | 00110001 |

| 0x34E39A63 | 31  | 00110100         | 11100011 | 10011010 | 01100011 |

FIG. 5

# Byte Offset Number Example with 32-bit Keys and Sector 0 size of 518 Bytes

FIG. 8

### Exemplary "calculated" sequence of 8-bit keys

FIG. 9

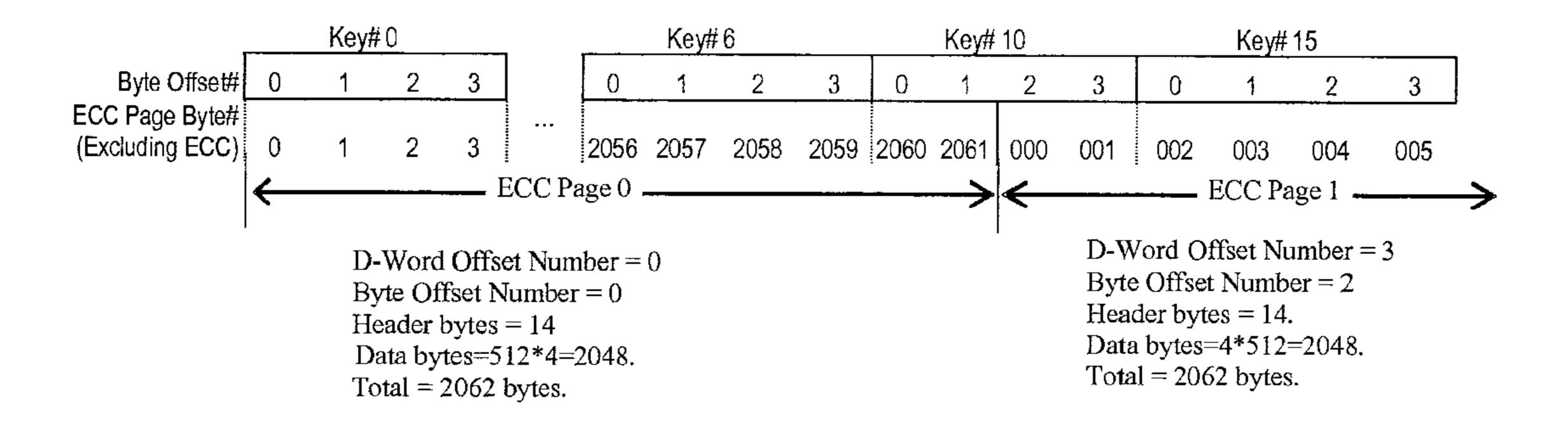

# Byte Offset Number example with 32-bit keys and 2062-byte ECC pages

FIG. 10

D-Word Offset and Byte Offset Register Values for Exemplary 2062-byte ECC Pages

| Z G | .U. |

|-----|-----|

| S   | X   |

| e y | C   |

| X   | Z   |

| j     | User |

|-------|------|

| bytes | keys |

| 4     | 32   |

| ECC F   | ge    | Format<br>User | ECC Page<br>Size | Column<br>Start | Column<br>End | #Keysper<br>ECC Page |             | Byte<br>Offset |

|---------|-------|----------------|------------------|-----------------|---------------|----------------------|-------------|----------------|

| [הבת]   | [הפת] | - 11           | l luec]          | Luexi           | lnexj         | Loecl                | )<br>0<br>1 | [DeC]          |

| 14 2048 | 2048  |                | 2062             | 0               | 080D          | 0                    | 00          | 0              |

| 14 2048 | 2048  |                | 2062             | 80E             | 101B          | 515 2/4              | 03          | 7              |

| 14 2048 | 2048  |                | 2062             | 101C            | 1829          | 1031                 | 20          | 0              |

| 14 2048 | 2048  |                | 2062             | 182A            | 2037          | 1546 2/4             | 10          | 2              |

FIG. 11

SKN Register Values for Exemplary 2062-byte ECC Pages

| Page Offset | ECC    | ECC    | ECC    | ECC    |

|-------------|--------|--------|--------|--------|

| No.         | Page 0 | Page 1 | Page 2 | Page 3 |

| 0           | 0      | 6      | 28     | 23     |

| 1           | 1      | 0      | 18     | 6      |

| 2           | 2      | 1      | 17     | 4      |

| 3           | 3      | 7      | 27     | 21     |

| 4           | 4      | 6      | 3      | 30     |

| 5           | 5      | 14     | 15     | 14     |

| 6           | 6      | 24     | 28     | 1      |

| 7           | 7      | 17     | 17     | 17     |

| 8           | 8      | 9      | 31     | 19     |

| 9           | 9      | 12     | 8      | 31     |

| 10          | 10     | 25     | 25     | 20     |

| 11          | 11     | 8      | 12     | 9      |

| 12          | 12     | 23     | 31     | 0      |

| 13          | 13     | 8      | 20     | 23     |

| 14          | 14     | 27     | 11     | 17     |

| 15          | 15     | 31     | 20     | 29     |

| 16          | 16     | 6      | 30     | 12     |

| 17          | 17     | 21     | 17     | 0      |

| 18          | 18     | 18     | 18     | 4      |

| 19          | 19     | 9      | 13     | 2      |

| 20          | 20     | 0      | 9      | 0      |

| 21          | 21     | 24     | 5      | 31     |

| 22          | 22     | 18     | 2      | 0      |

| 23          | 23     | 14     | 2      | 2      |

| 24          | 24     | 8      | 31     | 3      |

| 25          | 25     | 1      | 16     | 8      |

| 26          | 26     | 29     | 9      | 0      |

| 27          | 27     | 30     | 13     | 6      |

| 28          | 28     | 12     | 1      | 27     |

| 29          | 29     | 12     | 4      | 7      |

| 30          | 30     | 14     | 10     | 16     |

| 31          | 31     | 14     | 12     | 16     |

FIG. 12

Sep. 29, 2015

### Exemplary Header Format, including 5-bit Page Offset Field (e.g., for a single-sector ECC page)

| LBA     | Data Structure ID | Page Offset | Application Byte |

|---------|-------------------|-------------|------------------|

| 4 Bytes | 6 Bits            | 5 Bits      | 5 Bits           |

### FIG. 13

### Exemplary 2K Byte ECC Page Header Format, including 5-bit Page Offset Field (e.g., for each of four Sectors in an ECC Page)

ECC Page Header Layout (14 Bytes)

| <u> </u> | 1 23 Wy O GEV (1 1 25 ) 10 | <del>"</del> " |          |                     |         |

|----------|----------------------------|----------------|----------|---------------------|---------|

| Sector 0 | Sector 1                   | Sector 2       | Sector 3 | Page Header Data    |         |

| Header   | Header                     | Header         | Header   | (LBA or Other Data) | Unused  |

| 2 Bytes  | 2 Bytes                    | 2 Bytes        | 2 Bytes  | 4 Bytes             | 2 Bytes |

The Page Header Data field holds either the LBA or other parameters related to sector 0.

Sector Header Layout (2 Bytes)

| Page Offset | SD Application | Sector Id |

|-------------|----------------|-----------|

| 5 Bits      | 5 Bits         | 6 Bits    |

| Bits 11-15  | Bits 6-10      | Bits 0-5  |

FIG. 14

Page Offset Value Reverse mapping physical ASH) stored in FL 作任化化すららて伤水物 **ABT%KMOEF代化HS** PAGE CODE (actually Mapped page 010 MAPPED OFFSET ( (FROM XOR Table, 0x69C734C6 Ω Scrambling Pattern of bytes 0-3 [Bina S Seed Key Scrambling Default and <u>§</u> Page ģ Code "written" Page (value Reverse mapping Table Page Offset Value 33838383838385838

Sep. 29, 2015

F/G. 16

SKN Values (showing the exemplary ECC Page crossing boundaries)

|             | Š                        |             |            |        |          |          | _        | •        |               |             |        |              | •             |       |                 |          |                       |          |          |      |                       |          |              |       |              | <del> •</del> |              |          | ·        |       |                |        |             |                                         |           |

|-------------|--------------------------|-------------|------------|--------|----------|----------|----------|----------|---------------|-------------|--------|--------------|---------------|-------|-----------------|----------|-----------------------|----------|----------|------|-----------------------|----------|--------------|-------|--------------|---------------|--------------|----------|----------|-------|----------------|--------|-------------|-----------------------------------------|-----------|

| Offset = 2  | 78. 78. 60<br>78. 60     | 1 2         |            | 27     | <u>~</u> | <b>т</b> |          | m<br>    |               | <b>о</b>    | 52     |              |               | 23    | 16              | <b>о</b> | <b>α</b>              |          |          | 0    |                       |          |              |       | m            |               | <del>-</del> |          | 4        | 30    |                | ~      |             | 30                                      | 28        |

| Page 3 Byte | 6+943<br>6-83            |             |            | ς,,,,  | <u>0</u> | 4        | m        | 4        | 30            | <del></del> | m      | φ            | 20            | <br>თ | <u></u>         | 23       | 16                    | 9        | 24       | _    | 28                    | ·····    | ·····        | 34    | 0            | ·····         | 4            | ω        | <u>3</u> | ω     | ÷              | <br>თ  | بي.         | 26                                      | 27        |

| ECO         |                          | 7.7         | •          | 23     | <br>છ    | √        | 77       |          | <u>4</u>      |             |        | <del>0</del> | <u>س</u>      | 8     | <br>ი           |          | 23                    | 17       | 83       | 12   | Ο<br>                 | 4        | ν            |       |              | 0             | ~~           | co.      |          |       | φ              | 27     |             | 16                                      | 16        |

| 0 ÷ 1381#   |                          |             |            | 3      |          |          |          |          |               |             |        |              |               | ····· | ,<br>O          |          |                       |          |          |      |                       |          | .,,,,,       | ~~~   |              | ·····         |              | *****    |          |       |                |        |             |                                         |           |

| Jan Saga    |                          |             |            | *****  | ·····    |          |          | ,,,,,,,  | ·····         | 53 b 5 3 1  | ,,,,,, | an e e e     | to to see a t |       | *****           | ,12111   | ***                   | .,,,,,   | *****    | **** | 137133                | *****    | *****        | ***** | *****        | ****          | *1***        | *****    | *****    | ***** | . 5 5 7 7 7    | *****  | *****       | ·····                                   | ****      |

| HOOL        |                          |             |            | 28     | <u>D</u> | 17       | 27       | m        | <u>.</u><br>ک | 28          | 17     |              |               |       |                 |          |                       |          |          |      |                       |          |              |       |              |               |              |          |          |       |                |        |             | 9                                       |           |

| Offset = 2  |                          |             | <b>©</b>   | 21     |          | 7        | 22       | 83       | <del>-</del>  | 13          | on.    |              |               |       |                 |          |                       |          |          |      |                       |          |              |       |              |               |              |          |          |       |                |        |             |                                         |           |

| Byte        | i<br>G                   |             |            | ****** | *****    | ****     | *****    | *****    | *****         | ****        | *****  |              | ****          | ***** | * > * * * * * * | ****     | (7 <b>7 1 7 1</b> 7 1 | *****    |          | **** | <b>16 2 2 2 2 2</b> 1 |          | ·** * ** * * | ***** | *****        | ****          | ****         | *****    | *****    | ****  | 5 To 50 4 70 1 | *****  |             | ******                                  | . 3 7 % 7 |

| CO Proper   |                          | ## <b>5</b> |            | 10     | ιΩ       | _        | <br>4    | 4        | 23            | Ν           | 28     | 27           | 52            | ω     | 23              | ω        | 25                    | 4        | 6        | 26   | <del></del>           | <u>თ</u> | 0            | 24    | <del>-</del> | 13            | 10           |          | 30       | 28    | 30             | 43     | 4           | <u> </u>                                | 18        |

| 3           | 060 <b>  2082</b>   2081 | 515         | <b>C19</b> | 9      | 0        | •        | 7        | ယ        | 14            | 24          | 17     | တ            | 12            | 25    | ω               | 23       | œ                     | 27       | 31       | 9    | 21                    | 18       | တ            | 0     | 24           | 18            | 14           | 80       | •        | 29    | <u>%</u>       | 12     | 5           | 14                                      | 14        |

|             | 5 2058 2<br>2057 2059    | 514         |            | თ      | <br>58   | 788      | ····     | <br>S    | φ             | 15          | ·····  | 53           | 31            | 12    | 25              | ∞        | 23                    | 10       | 13       |      | ····                  |          | ₩            | თ     |              | 24            | 19           | 12       | <b>ب</b> |       |                | 12     | <del></del> | 12                                      | 11        |

| et = 0      | 202                      |             |            | ****   |          | *****    |          |          |               |             | ,,,,   |              | ****          |       |                 | ردددر    | *****                 | ,,,,,,,  |          | **** | *****                 |          | *1***        |       |              | *****         | ****         |          |          | ***** |                |        | *****       | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |           |

| 0 Byte Offs | F 0, 6 8                 | S.          | ( C)       | က      | 9        | ග        | 12       | <u>τ</u> | 18            | 21          | 24     | 27           | 30            | _     | ស               | ω        | ₹~                    | 4        | 17       | 20   | 23                    | 26       | 53           | 0     | 4            | 7             | 6            | 13       | 16       | 19    | 22             | 22     | 28          | 31                                      | -         |

| ECC Page 0  | ٠.<br>د                  |             |            | •      | m        | ιŷ       | <b>~</b> | an.      | <del>-</del>  | <u>e</u>    | ਨ      | 4            | <u>0</u>      | 2     | 23              | <br>22   | 27                    | 53       | <u>ب</u> | N    | <b>4</b>              | 9        | œ.           |       | 12           | 4             | 16           | <u>4</u> | 8        | 23    | 24             | <br>20 | 28          | <br>OS                                  | 0         |

|             |                          | 0           | 0          | 0      |          | C)       | m        | 4        | ı۵            | φ           |        | <b>6</b> 0   | <br>O)        | 5     | <del>-</del>    | 12       | <u>\$</u>             | 4        | 15       | 16   | 17                    | 18       | 6            | 20    | 77           | 22            | 23           | 24       | 25       | 56    | 27             | 78     | 59          | 30                                      | 31        |

|             | Column_St<br>art         | 4 byte col. | D_Word Of  | 0      | ·        | 23       | m        | 4        | 5             | ယ           | _      | တ            | 6             | 9     | <del></del>     | 12       |                       | 98]<br>4 |          |      |                       | 18       | 91           | 50    | 24           | 22            | 23           | 24       | 25       | 26    | 27             | 28     | <u>5</u>    | 30                                      | 31        |

SKN

FIG. 17

FIG. 18

Sep. 29, 2015

Exemplary memory cell states of unscrambled repeating 0xFF data (showing first 16 bytes of each word line)

|           | Щ            | <u>Ц</u>    | щ          | <u>س</u> ِ | ш          | Щ        | سِ         | ļļļ.       | ļŲ.        | ш          | щ          | щ.         | <u>щ</u>   | Щ          | ببر        | <u> </u> | Ш            | لب           | Щ        | ļļ.          | <u></u>   | بب       | щ            |             | ببر          | Щ.       | بب         | Щ          | Щ          | щ            | <u> </u>            | Ļ                     |

|-----------|--------------|-------------|------------|------------|------------|----------|------------|------------|------------|------------|------------|------------|------------|------------|------------|----------|--------------|--------------|----------|--------------|-----------|----------|--------------|-------------|--------------|----------|------------|------------|------------|--------------|---------------------|-----------------------|

| Byte 16   | HEEEEEE      | EEEEEEE     | EEEEEEE    | EEEEEE     | EEEEEE     |          | EEEEEE     | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEE     | EEEEEEE    | EEEEEEE    | EEEEEEE  | EEEEEE       | EEEEEEE      | EEEEEEE  |              | EEEEEE    | EEEEEEE  |              | EEEEEE      | EEEEEE       | EEEEEEE  | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEE       | EFFFEFF             | F                     |

| Byte 15   | 3333333      | EEEEE       | FEFFEE     |            | EEEEEEEE   | EEEEEEE  | EEEEEEE    | EEEEEEE    | EEEEEEE    |            | EEEEEEE    | HEEEEEEE   |            |            | EEEEEEE    | EEEEEEEE | EEEEEEEE     | EEEEEEE      | EEEEEE   | EEEEEEI      | EEEEEEE   | EEEEEEE  |              | EEEEEEE     | EEEEEEE      | EEEEEE   | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEEE      | EEEEEEE             |                       |

| Byte 14   | EEEEEEE      | ш           | H<br>H     | щ          | Щ          | Щ        | IJĴ        | Щ          | Ш          | Ш          | EE         | Щ          | Ш          | Щ          | Ш<br>Щ     | Ш        | Ш            | ш            | Ш        |              | Ш         | Ш        | EEEEE        | Ш           | ш            | Щ        | Щ          | ш          | Щ          |              | EEEEEEE             | 1                     |

| Byte 13   | EEEEEEE      | EEEEEE      | FEF        | EEEEEEE    | EEEEEE     | EEEEE    | EEEEE      | EEEEEI     | EEEEI      |            | FE         | EEEEE      |            | FEFEE      | EEEEE      | EEEEEE   |              | EEE          | 出出       |              | EFEEE     | EEEE     | EEEEE        | EEEEE       | EEEEE        | EEEEEE   | EEE        | EEEEE      | Ш          | 田            | EEEEEEE             | 1                     |

| yte 12    |              | EEEEEE      | EEEEEEE    | EEEEEE     | EFFEEE     | EEEEEE   | EEEEEEE    | EEEEEE     |            | FEEFFEE    | EEEEEE     | EFFEEE     |            |            | 3333333    | EEEEEE   |              | EEEEEE       | EEEEEE   |              | EEEEEEE   | EEEEEE   |              |             | EEEEEE       | EEEEEE   | EEEEEE     | EEEEEE     | EEEEEE     |              | 3333333             | \<br>\<br>\<br>!      |

| Byte 11 B | EEEEE        | EEEEEE      | EEEEEE     | EEEEEE     | EEEEEEE    | EEEEEE   | EEEEEE     | EEEEEE     | EEEEEEE    | EEEEEE     | EEEEEE     | EEEEEE     |            | EEEEEE     | EEEEEEE    | EEEEEE   | EEEEEE       | EEEEEE       | EEEEEEE  |              | EEEEEE    | EEEEEE   |              | EEEEEEE     | EEEEEE       | EEEEEE   | EEEEE      | EEEEEE     | EEEEEE     |              | EEEEEEE             |                       |

| e 10      | EEEEEE       | EEEEEE      | EEEEEE     | EFFEFF     | EEEEEE     | EEEEE    | EEEEEEE    | EEEEEE     | EEEEEE   | FEFFE        | EEEEEE       | EEEEE    |              | EEEEEE    | EEEEEEE  |              |             |              | EEEEEE   | EEEEEE     | EEEE       | EEE EE     | EEEEE        | 3 <u> </u> 33333333 |                       |

| Byte 9    | EEEEEE       | EEEEEEE     | EEEEEE     | EEEEEEE    |            | EEEEEEE  | EEEEEE     | EEEEEE     | EEEEEE     | EEEEEE     | EFEEEE     | EEEEEE     | FEEEEE     |            | EEEEEEE    | EEEEEE   |              |              |          |              | EEEEEE    | EEEEEEE  | EEEEEE       | EEEEEE      | EEEEEE       | EEEEEE   |            | EEEEE      | EEEEEEE    | Ш            | )<br>  33333333     | ]<br>]<br>[           |

| Byte 8    | EEEEEEE E    |             | EEEE       | EEE        | EEEEEE     | EEEEEE   | EEEE       | EEE        | EEEEEE     | EEEE       | EE         | EEEEEE     | EFF        | FEE        | EEEE       | EEEEEEE  |              | EEEE         | EEEE     |              | EEEE      | EEEEEE   | EEEEEE       |             | EEEE         | EEE      | EEEE       | EEEE       | EEEEEE     | EEEEEE       | EEEEEEE             | 1                     |

| Byle 7    | EE           | EEEEEEE (   | Ш          | EEEEEEE    | EEEEEE     | EEEEEEE  | EEEEEEE    | EEEEEEE    | FEE        | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEEE    | EEEEEEE    |          | H<br>H       | EEEEE        | EEEEE    |              | EEEEEEE   | EEEEEEE  | EEEEEEE      |             | EEEEE        | EE EE    | EEEEEEE    | EEEEEEEE   | EEEEEEE    | EEEEEEE      |                     | ;<br>;<br>;<br>;<br>; |

| Byte 6    | BEEBBBB      | Beebbabb (1 | BEEBBBBB 1 | BEEBBBB    | BEEBBBBB 1 | BEEBBBBB | BEEBBBBB   | BEEBBBBB ( | BEEBBBBB 1 | BEEBBBBB   | BEEBBBB    | BEEBBBBB   | BEEBBBBB   | BEEBBBBB   | BEEBBBBB   | EBBBBB   | EBBBBB       | BEEBBBB   1  | BEEBBBBB | EBBBBB       | BEEBBBBB  | BEEBBBBB | BEEBBBBB     | EBBBBB      | BEEBBBBB     | BEEBBBBB | BEEBBBB    | BEEBBBBB   | EBBBBB     | BEEBBBBB     | BEEBBBBB            |                       |

| Byte 5    | BBBBBBB      | 8888888 [E  | BBBBBBE E  | BBBBBBE    | ш          | ш        | BBBBBBBE E | BBBBBBB    |            | BBBBBBE E  | BBBBBBBE E |            | BBBBBBE [  | BBBBBBBE   | BBBBBBE [  |          |              | BBBBBBBE E   | BBBBE    | <u>.</u>     | 888888E [ |          | BBBE         | BBBE        | BBBBBBE I    | ш        | BBBBBBBE [ | BBBBBBE 1  | BBBBE      | BBBBBBBE [   | BBBBBBE             |                       |

| Byte 4    | BBCBBBB E    | BCBABBBB E  | BCEABBBB E | CABABBBB E |            | m        | ECEABBBB E | ABBBB      | AAEABBBB E | BCBABBBB E | BCEABBBB E |            | CAEABBBB E | ECBABBBB E | ECEABBBB E | ·        | AAEABBBB   E | BCBABBBB   E |          |              |           |          | ECEABBBB   E | AABABBBB  E | AAEABBBB   I | മ        | BCEABBBB E | CABABBBB E | CAEABBBB E | ECBABBBB   E | ECEABBBB E          |                       |

| Byte 3    | BBBBBBBB     | BBBBBBBB [E | BBBBBBBB I | BBBBBBB (  | BBBBBBB (  | BBBBBBBB | BBBBBBBB   | BBBBBBC /  | BBBBBBC /  | BBBBBBE E  | BBBBBBE    | BBBBBBBE ( | BBBBBBE (  | BBBBBBE    | BBBBBBBE   | <<       | BBBBBBCA /   |              |          |              | BBBBBEB ( | BBBBBEB  | BBBBBBEB [   | BBBBBEC /   | BBBBBEC /    | Щ        | BBBBBBEE [ | BBBBBBEE ( | BBBBBBEE ( | BBBBBBEE [   | BBBBBEE             | -                     |

| Byte 2    | 88888888   E | BBBBBBBB    | BBBBBBBB   | BBBBBBB    |            |          | BBBBBBBB   |            | _          | BBBBBBBB   | BBBBBBBB   |            | BBBBBBBB   | BBBBBBBB   | BBBBBBBB   | BBBBBBBB | BBBBBBB      | B888888      |          | BBBBB        | BBBBBBBB  |          |              |             | BBBBBBBB     |          |            | 88888888   | BBBBBBBB   | BBBBBBBB     | 88888888            | _                     |

| Byte 1    | BBBBBBBB     | BBBBBBBB    | BBBBBBBB   | BBBBBBBB   | B8888888   | BBBBBBBB | BBBBBBBB   | BBBBBBBB   | BBBBBBBB   | BBBBBBBB   | BBBBBBBB   | BBBBBBBBB  | BBBBBBBB   | BBBBBBBB   | 88888888   | BBBBBBBB | BBBBBBB      | BBBBBBB      | _        | <del>-</del> | BBBBBBBB  | BBBBBBBB | BBBBBBBB     | BBBBBBBB    | BBBBBBBB     | BBBBBBBB | BBBBBBBB   | BBBBBBBB   | BBBBBBBB   | BBBBBBBB     | 88888888            |                       |

.1G. 19

Exemplary memory cell states of scrambled repeating 0xFF (showing first 16 bytes of each word line)

| Byte 1   | Byte 2   | Byte 3   | Byte 4          |                      | Byte 6         | Byte 7         | Byte 8       | Byte 9   | Byte 10  | Byte 11  | Byte 12  | Byte 13  | Byte 14  | Byte 15  | Byte 16              |

|----------|----------|----------|-----------------|----------------------|----------------|----------------|--------------|----------|----------|----------|----------|----------|----------|----------|----------------------|

| AABCCAAC | CCAEBACC | AABCCEAA | CAABACCE        | ABCCAACA             | CCBBACCA       | CEAABCCA       | CBECAABC     | EAACCAAC | CBECAACC | EAABCCAA | BECAABCC | AACCAACB | BECAACCE | AABCCAAC | ECAABCCE             |

| CAACCAEB | BACCAABC | CEAACCAE | ABCCAABC        | BC                   | AAAAABCC       | BCCAACBE )     | AABCCEAA     | CAACBECA | AACCEAAC | CCAACBEC | ABCCEAAB | AACBECAA | ACCEAACC | CAACBECA | BCCEAABC             |

| CAEBACCE | AABCCAAC | CCAEBACC | AEEECEAA        | AEBACCEC             | EACAACC        | ACBECAAC       | EAABCCA      | BECAABCC | EAACCAAC | CBECAACC | EAABCCAA | ECAABCCE | AACCAACB | BECAACCE | AABCCAAC             |

| ACCEAABC | CAACCAEB | BACCAABC | BCABCCAE        | AABCA                | Æ              | EA             | AACBE        | ABCCEAAB | CAACBECA | AACCEAAC | CCAACBEC | BCCEAABC | AACBECAA | ACCEAACC | CAACBECA             |

| AABCCEAA | CAEBACCE | AABCCAAC | BECCBACC        | ABCCEAAA             | ABEACCEA       | CEAACCAA       | ACBECAAC     | EAABCCAA | BECAABCC | EAACCAAC | CBECAACC | AABCCAAC | ECAABCCE | AACCAACB | BECAACCE             |

| CEAACCAE | ACCEAABC | CAACCAEB | EECEAABC        | Щ                    | CABAABCC       |                | CAACCEAA     | CCAACBEC | ABCCEAAB | CAACBECA | AACCEAAC | CAACBECA | BCCEAABC | AACBECAA | ACCEAACC             |

| CCAEBACC | AABCCEAA | CAEBACCE | CEEECAAC        | CAEBACCC             | AEACEAAC       | CBECAABC       | ₹            | CBECAACC | EAABCCAA | BECAABCC | EAACCAAC | BECAACCE | AABCCAAC | ECAABCCE | AACCAACB             |

| BACCAABC | CEAACCAE | ACCEAABB | EBAECAEB        | ACCAABCA             | ECCCCAEB       | AABCCEAA       | CCAACBEC     | AACCEAAC | CCAACBEC | ABCCEAAB | CAACBECA | ACCEAACC | CAACBECA | BCCEAABC | AACBECAA             |

| AABCCAAC | CCAEBACC | AABCCEAE | EBBAACCE        | ABCCAACA             | CCBBACCA       | CEAABCCA       | ن            | EAACCAAC | CBECAACC | EAABCCAA | BECAABCC | AACCAACB | BECAACCE | AABCCAAC | ECAABCCE             |

| CAACCAEB | BACCAABC | CEAACCAB | ABCCAABC        | CAEBC                | AAAAABCC       | BCCAACBE       | AABCCEAA (   | CAACBECA | AACCEAAC | CCAACBEC | ABCCEAAB | AACBECAA | ACCEAACC | CAACBECA | BCCEAABC             |

| BEECABBE | EABCCAEB | BBEEBABA | EAEACEAE        | EECABBEB             | AEACAEBB       |                | BEEABCBE     | BACEEBBB | EAACBEEB | BBECEABC | EEABCBEE | ACEEBBBE | AACBEEBB | BECEABCE | EABCBEE              |

| ACCEAABC | CAACCAEB | BACCAABA | BCABCCAE        | $\overline{\forall}$ | ACACAEBA       | CAACCEAA       | BCCAACBE .   | ABCCEAAB | CAACBECA | AACCEAAC | CCAACBEC | BCCEAABC | AACBECAA | ACCEAACC | CAACBECA             |

| AABCCEAA | CAEBACCE | AABCCAAA | BECCBACC        | ◁                    | ABEACCEA       | CEAACCAA /     | ACBECAAC     | EAABCCAA | BECAABCC | EAACCAAC | CBECAACC | AABCCAAC | ECAABCCE | AACCAACB | BECAACCE             |

| CEAACCAE | ACCEAABC | CAACCAEE | EECEAABC        | EAACCAEE             | CABAABCC       | CCAACBEC       | CCEAA        | CCAACBEC | ABCCEAAB | CAACBECA | AACCEAAC | CAACBECA | BCCEAABC | AACBECAA | ACCEAACC             |

| CCAEBACC | AABCCEAA | CAEBACCB | CEEECAAC        | Ö                    | AEACEAAC       | O              | 4CCAA        | CBECAACC | EAABCCAA | BECAABCC | EAACCAAC | BECAACCE | AABCCAAC | ECAABCCE | AACCAACE             |

| BACCAABC | CEAACCAE | ACCEAACE | EBAECAEB        | 4                    | ECCCCAEB       | <u></u>        | $\ddot{o}$   | AACCEAAC | CCAACBEC | ABCCEAAB | CAACBECA | ACCEAACC | CAACBECA | BCCEAABC | AACBECA <sup>A</sup> |

| AABCCAAC | CCAEBACC | < _      | EBBAACCE        |                      | CCBBACCA       | EAABCCA        | CAABC        | EAACCAAC | CBECAACC | EAABCCAA | BECAABCC | AACCAACB | BECAACCE | AABCCAAC | ECAABCCE             |

| CAACCAEB | BACCAABC | CEAACCCE | ABCCAABC        | ن                    | AAAAABCC       | BCCAACBE       | ⋖            | CAACBECA | AACCEAAC | CCAACBEC | ABCCEAAB | AACBECAA | ACCEAACC | CAACBECA | BCCEAABC             |

| CAEBACCE | AABCCAAC | CCAEBAAC | AEEECEAA        |                      | AEACAACC       | $\overline{O}$ | EAABCCA      | BECAABCC | EAACCAAC | CBECAACC | EAABCCAA | ECAABCCE | AACCAACB | BECAACCE | AABCCAAC             |

| ACCEAABC | CAACCAEB | BACCAAEC | <b>BCABCCAE</b> | ⋖                    | ACACAEBA       | AACCEAA        | BCCAACBE     | ABCCEAAB | CBECA    | AACCEAAC | CCAACBEC | BCCEAABC | AACBECAA | ACCEAACC | CAACBECA             |

| AABCCEAA | CAEBACCE | AABCCACC | BECCBACC        | ABCCEAAA             | ABEACCEA       | ₹              | CAAC         | EAABCCAA | BECAABCC | EAACCAAC | CBECAACC | AABCCAAC | ECAABCCE | AACCAACB | BECAACCI             |

| CEAACCAE | ACCEAABC | CAACCABB | EECEAABC        | EAACCAEE             | $\overline{C}$ | CCAACBEC       | CAACCEAA     | CCAACBEC | ABCCEAAB | CAACBECA | AACCEAAC | CAACBECA | BCCEAABC | AACBECAA | ACCEAACC             |

| CCAEBACC | AABCCEAA | CAEBACAE | CEEECAAC        | CAEBACCC             | AEACEAAC       | ਹ              | <b>ACCAA</b> | CBECAACC | EAABCCAA | <b>₹</b> | EAACCAAC | BECAACCE | AABCCAAC | ECAABCCE | AACCAACE             |

| BACCAABC | CEAACCAE | ACCEAAEB | EBAECAEB        | 4                    | ECCCCAEB       | AABCCEAA       | CCAACBEC (   | AACCEAAC | CCAACBEC | ABCCEAAB | CAACBECA | ACCEAACC | CAACBECA | BCCEAABC | AACBECA/             |

| AABCCAAC | CCAEBACC | AABCCECE | EBBAACCE        | ABCCAACA             | CCBBACCA       | ⋖              | CBECAABC     | EAACCAAC | CBECAACC | EAABCCAA | BECAABCC | AACCAACB | BECAACCE | AABCCAAC | ECAABCC              |

| CAACCAEB | BACCAABC | CEAACCCB | ABCCAABC        | AACCAEBC             | AAAAABCC       | BCCAACBE       | BCCEAA       | CAACBECA | AACCEAAC | CCAACBEC | ABCCEAAB | AACBECAA | ACCEAACC | CAACBECA | BCCEAABC             |

| CAEBACCE | AABCCAAC | CCAEBAAA | AEEECEAA        | AEBACCEC             | AEACAACC       | ACBECAAC       | CEAABCCA     | BECAABCC | EAACCAAC | CBECAACC | EAABCCAA | ECAABCCE | AACCAACB | BECAACCE | AABCCAAC             |

| ACCEAABC | Щ        | BACCAAEA | BCABCCAE        | CCEAABCA             | ACACAEBA       | CAACCEAA       | CBE          | ABCCEAAB | ACBECA   | AACCEAAC | CCAACBEC | BCCEAABC | AACBECAA | ACCEAACC | CAACBEC/             |

| AABCCEAA | CAEBACCE | AABCCACA | BECCBACC        | <u>~1</u>            | ABEACCEA       | CEAACCAA       | ACBECAAC     | EAABCCAA | BECAABCC | EAACCAAC | CBECAACC | AABCCAAC | ECAABCCE | AACCAACB | BECAACCE             |

| CEAACCAE | ACCEAABC | CAACCABE | EECEAABC        | EAACCAEE             | CABAABCC       | CCAACBEC       | \$           | CCAACBEC | ABCCEAAB | CAACBECA | AACCEAAC | CAACBECA | BCCEAABC | AACBECAA | ACCEAACC             |

| CCAEBACC | AABCCEAA | CAEBACAB | CEEECAAC        |                      | AEACEAAC       | CBECAABC       | CEAACCAA     | CBECAACC | EAABCCAA | BECAABCC | EAACCAAC | BECAACCE | AABCCAAC | ECAABCCE | AACCAACE             |

| BACCAABC | CEAACCAE | ACCEAAEA | ACEACAEB        | ACCAABCA             | ECCCCAEB       | AABCCEAA       | CCAACBEC     | AACCEAAC | CCAACBEC | ABCCEAAB | CAACBECA | ACCEAACC | CAACBECA | BCCEAABC | AACBECAA             |

# SYSTEM, METHOD AND MEMORY DEVICE PROVIDING DATA SCRAMBLING COMPATIBLE WITH ON-CHIP COPY OPERATION

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

# CROSS-REFERENCE TO RELATED APPLICATION(S)

This application claims the benefit under 35 U.S.C. §119 (e) of U.S. Provisional Application No. 61/018,096 filed on Dec. 31, 2007 and entitled "System, Apparatus, and Method for Memory Device Data Scrambling Usable with On-Chip 20 Copy Operation" by Jason T. Lin, Steven S. Cheng, and Shai Traister, which application is incorporated herein by reference in its entirety.

### **BACKGROUND**

The present invention relates generally to flash memory storage systems, and more specifically to such a system in which data to be written to the flash memory is scrambled to help reduce certain data pattern-dependent sensitivities and 30 disturbance effects.

A "flash file system" provides a system of data storage and manipulation on a flash memory device that allows the device to emulate a magnetic disk. A flash file system enables applications or operating systems to interact with a flash memory 35 device not using physical addresses but rather using logical addresses (sometimes called virtual addresses). An intermediate software layer between the software application and the physical memory system provides a mapping between logical addresses and physical addresses. Some systems that implement logical-to-physical address mapping are described in U.S. Pat. No. 5,404,485 to Ban, in U.S. Pat. No. 5,937,425 to Ban, and in U.S. Pat. No. 6,591,330 to Lasser, all three of which patents are incorporated herein by reference in their entirety.

NAND flash memories are inherently susceptible to specific data patterns. For example, programming many cells on the same bit line to the same data state, or many cells on the same word line to the same data state, may cause program disturb effects which may alter the cell charge distribution 50 and shift one or more cells to a different data state. Such fixed repetitive data patterns are not uncommon in bit patterns frequently written to flash memories, particularly those written to certain blocks, such as control blocks, within a flash file system. Such control blocks are used by the file system, for 55 example, to keep track of logical-to-physical address mapping information, and other information about the various data blocks. At times, programming even a few word lines to specific data states may also cause such disturb effects. These disturb effects, as well as others, are particularly problematic 60 in memory arrays storing multiple bits per cell (i.e., MBC) arrays), also known as "multiple level cell" (MLC) arrays, and these effects can cause one or more cells to generate a read error as a function of specific user data patterns. Certain program disturb effects are described in U.S. Pat. No. 7,023, 65 739 to Chen, et al., (the '739 patent), the disclosure of which is incorporated herein by reference in its entirety.

2

To address this issue, techniques have been devised using system level data scrambling or randomization to eliminate the particularly problematic data patterns in the user data and control blocks before programming into a flash device. In this context, the act of scrambling or randomizing data refers to breaking up the bit patterns associated with the memory cell states along memory bit-lines and word-lines. However, such data scrambling techniques implemented outside the NAND memory are incompatible with the use of Flash Memory On-Chip-Copy or Copy-Back operations, and cannot achieve the system performance that would otherwise be attainable. Such an on-chip-copy operates on chunks of data to autonomously relocate data from one physical memory location to another physical memory location. This provides higher per-15 formance and requires less power consumption than is achievable without using on-chip copy operation, in which data is read from the device and communicated off-chip to a companion device (e.g., a flash controller device), then rewritten into a different physical location of the NAND memory. However, an on-chip copy operation performed on data that is scrambled based on a physical memory address will unintentionally associate the scrambled data with a new key/seed, and results in the inability to properly descramble the data using the incorrect new key/seed to retrieve the 25 original intended data.

#### **SUMMARY**

The present invention provides for data scrambling techniques implemented externally to a flash memory device which can be used in concert with flash memory on-chip copy functionality operating internally to the flash device, thus supporting high performance copying operations. Many modern flash memory sub-systems implement "flash file systems" which frequently utilize garbage collection techniques, and can benefit greatly from such on-chip copy functionality. In addition, the techniques may be implemented to provide, for example, a hardware based solution which has little or no impact on overall system performance, and which may be implemented at very low incremental cost, to provide a cost-effective solution for increasing overall system reliability.

The data scrambling technique preferably uses a logical address, such as a logical page address, rather than a physical page address, to determine a seed scrambling key. The logical page address is determined from the logical block address of the data, and thus does not restrict the physical placement of the scrambled data in memory. As a result, on-chip copy operations may be used. Since the logical page address of the data remains unchanged even if the data is relocated by an on-chip copy operation, the same seed scrambling key may be used to descramble the data. This seed scrambling key is used to scramble the user data in a particular portion of the block, but as additional data is written across a single word line, and as additional data is written along bit lines, the scrambling key is deterministically varied to generally "randomize" the data states.

The invention also provides for robust file system operation, including the capability to tolerate a power loss at any time, and be able to re-initialize a flash memory and reconstruct the mapping of the various blocks stored therewithin, to properly descramble and read back data in order to identify data types and data relocations due to on-chip-copy operations. All the data stored in the flash may be scrambled, including headers and control structures. The scrambling key information may be stored in the page headers to enable extraction of the scrambling key itself, from the scrambled data, during initialization. In some embodiments, different

scrambling methods are used to scramble information in control structures to support initialization and debug processes.

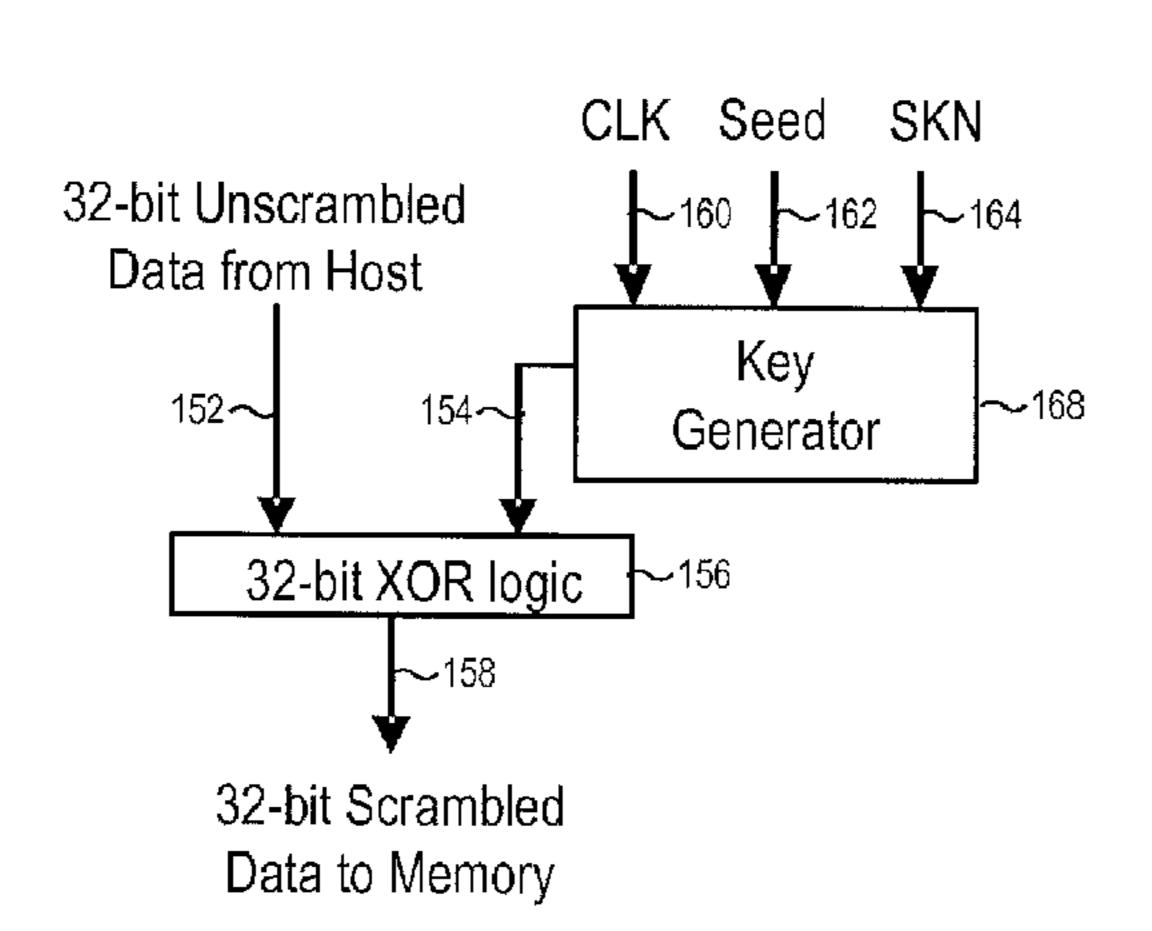

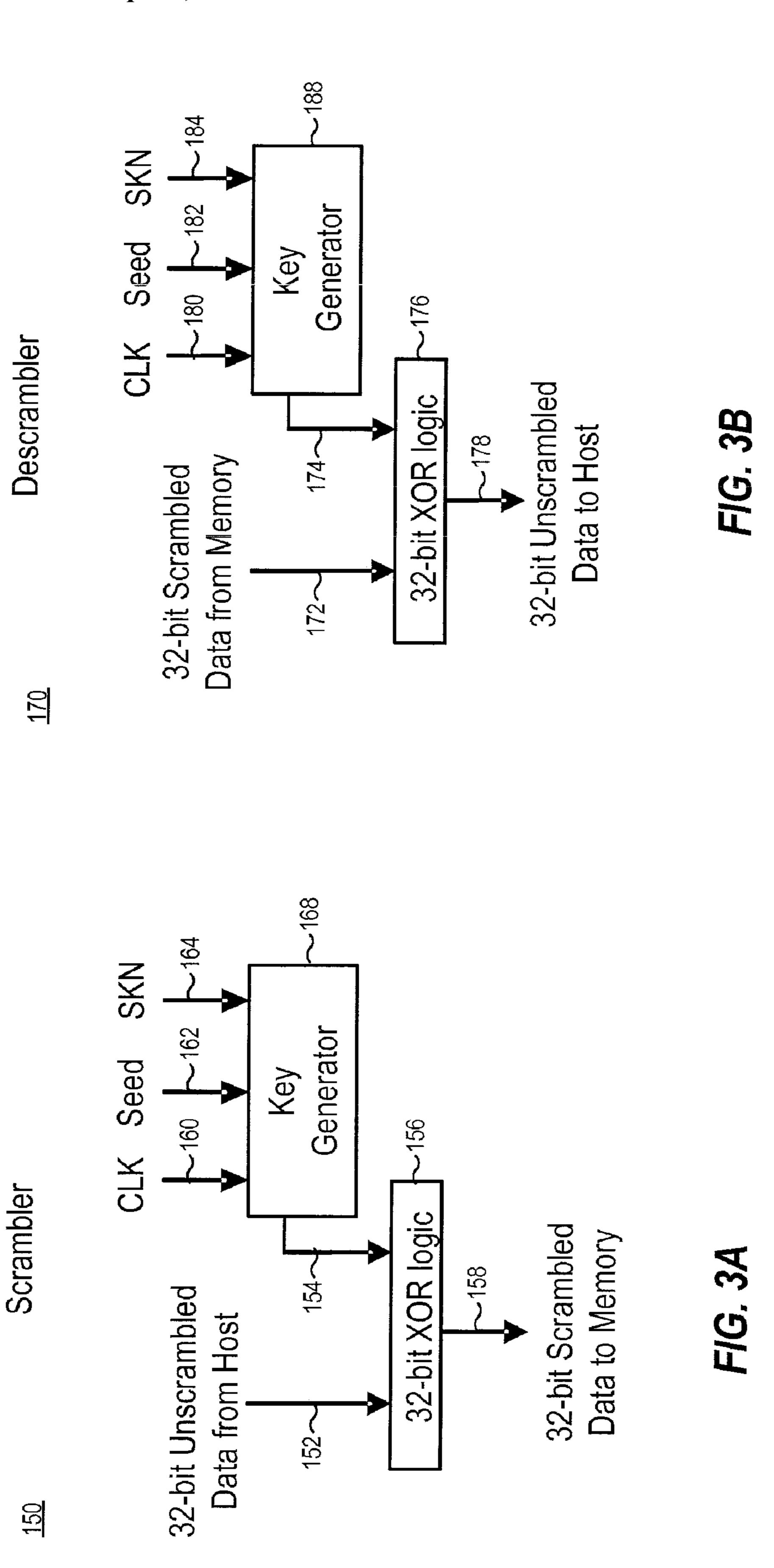

In certain embodiments, the data scrambling can be done effectively by hardware, firmware, or software using a simplistic method involving XOR logic and a deterministic number of Scrambling Keys by bitwise rotating a predetermined initial Scrambling Key Seed, thereby creating a sequence of revolving scrambling keys, each with an assigned key number. The scrambling keys (i.e., "scrambler" keys) can be deduced for any logical group of data with knowledge of the first scrambling key number used in the logical group, which may be referred to as the Starting Key Number (SKN).

SKN's can be associated with the logical group memory address and used for scrambling data. The SKN itself, as well as other header (or overhead) information, can be scrambled in the same method as user data bits. In some embodiments, the Flash Controller Firmware (FW) or System Host Software need only set the SKN at the beginning of each memory transaction. Within the transaction, the scrambler may be configured to automatically generate subsequent Scrambling Keys as additional groups of data are written or read.

ECC encoding can be applied to the scrambled SKN bits separately or applied together with the associated scrambled user data bits. ECC encoded scrambled SKN bits and ECC 25 encoded scrambled user data bits may be then stored in the Flash Memory. ECC generation/correction can be done either before or after scrambling/descrambling. The ECC parity bytes may or may not be scrambled, even though the header and data portions are scrambled.

In some embodiments, the Flash Controller Firmware or System Host Software having prior knowledge of Scrambler Key generation mechanism and data scrambling method can: (a) mimic the Data Scrambler operations; (b) efficiently build a table (e.g., 32 entries) forward mapping desired scrambled SKN's to logical addresses (e.g., using the default seed); and (c) efficiently build a table with reverse mapping of logical addresses to desired scrambled SKN's.

During system initialization, an exemplary system may 40 perform the following to identify the data types and logical grouping locations stored in Flash Memory: (a) Flash Controller Firmware (FW) or System Host Software generates the forward and reverse mapping tables for the desired scrambled SKN's; (b) with the Hardware Scrambler disabled, the first 45 sector of each memory block is scanned to extract the first scrambled SKN stored in that memory block (e.g., within the first several bytes of each sector); (c) using the extracted scrambled SKN, the Flash Controller Firmware or System Host Software looks up the reverse mapping table to deter- 50 mine the unscrambled SKN; (d) with the Hardware Scrambler enabled, the first sector is read again but descrambled using the unscrambled SKN as the key (alternatively, the FW) may use the SKN and perform the descrambling of the header without reading the data again); and (e) the memory block 55 type is identified and stored in the Flash Controller RAM.

4

chip-copy operation(s) at any time. The controller is aware when an on-chip copy is performed, and can re-map the data accordingly.

In one aspect the invention provides a method for storing information in a non-volatile memory which, in an exemplary embodiment, includes determining a starting key based upon a seed key and a logical page address associated with a group of data; randomizing the group of data using a deterministic sequence of keys corresponding to the starting key; and storing the randomized group of data into a physical page of the non-volatile memory.

In another aspect the invention provides a method for storing information in a non-volatile memory which, in an exemplary embodiment, includes determining a page offset number using a logical block address of a memory page; determining a starting key based upon a seed key and the page offset number; scrambling page data using a deterministic sequence of scrambling keys corresponding to the starting key; storing into a header of a physical page of the non-volatile memory an identifier corresponding to the page offset number; and storing the scrambled page data into the physical page.

In another aspect the invention provides an apparatus which, in an exemplary embodiment, includes a non-volatile memory, and a memory controller configured to determine a starting key based upon a seed key and a logical page address associated with a group of data; randomize the group of data using a deterministic sequence of keys corresponding to the starting key; and store the randomized group of data into a physical page of the non-volatile memory.

The methods of the present invention may be implemented by software, by hardware, or by a combination of both. Such software may be software executed on a host computer which reads and writes the data (e.g., within a software device driver supporting the storage device), or may be firmware executed within a memory controller that interacts with the host computer and controls the memory media. Such hardware may be implemented either within the memory controller or within the memory media, irrespective of whether the memory controller and the memory media reside on two separate dies or reside on a common die. All of the above configurations and variations are within the scope of this invention.

The foregoing summary is intended to help introduce the invention, and should not be viewed as limiting, as the invention is defined by the claims. Moreover, the inventive concepts and embodiments described herein are specifically contemplated to be used alone as well as in various combinations. Accordingly, other embodiments, variations, and improvements not described herein are not necessarily excluded from the scope of the invention.

### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention may be better understood, and its numerous objects, features, and advantages made apparent to those skilled in the art by referencing the accompanying drawings.

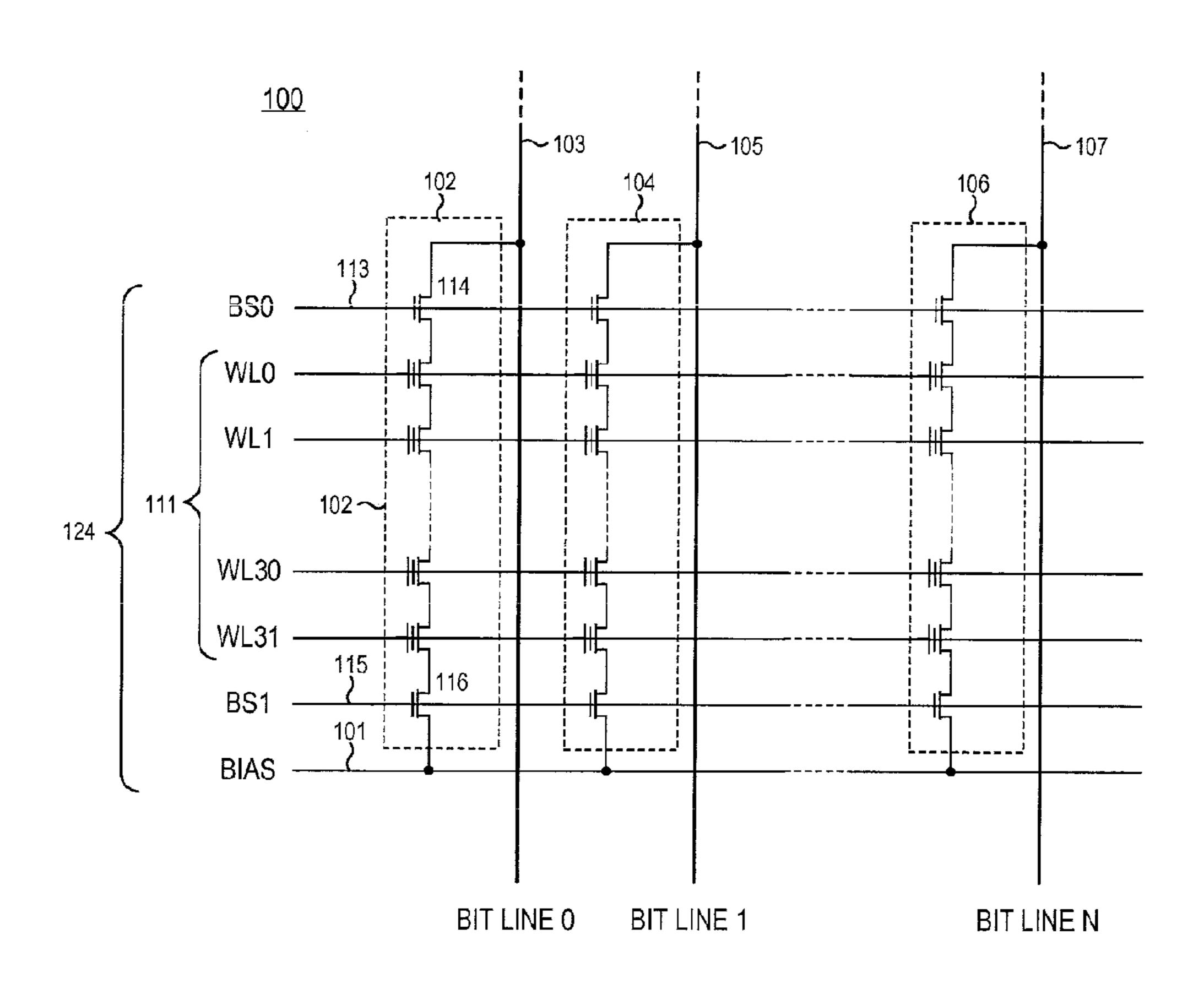

FIG. 1, labeled prior art, is a schematic diagram of a NAND memory array.

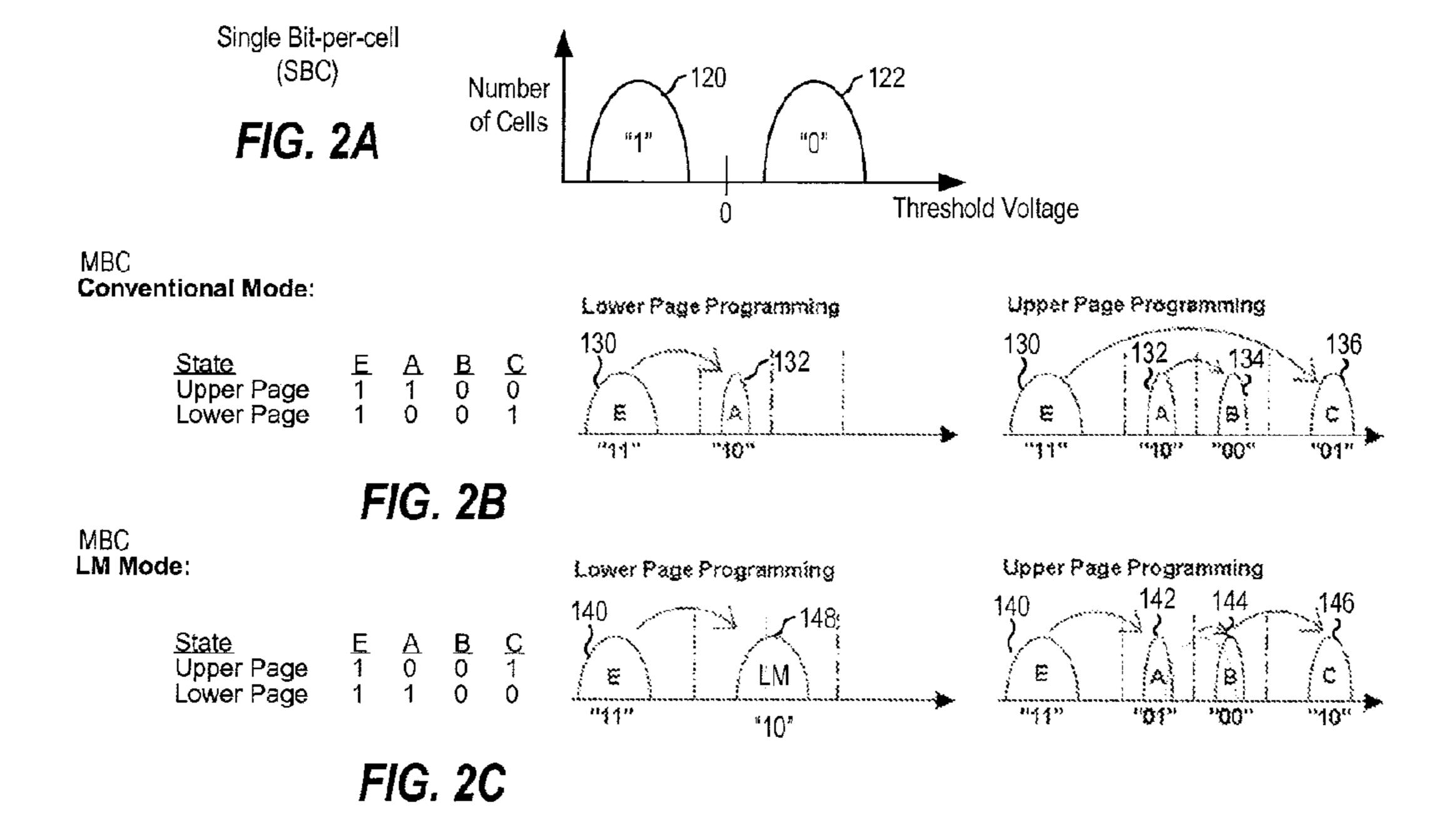

FIGS. 2A, 2B, and 2C are diagrams depicting various programmed memory states in a single-bit-per-cell memory, and in a multiple-bit-per-cell memory.

FIGS. 3A and 3B depict conceptually a scrambler block and a descrambler block in accordance with the present invention.

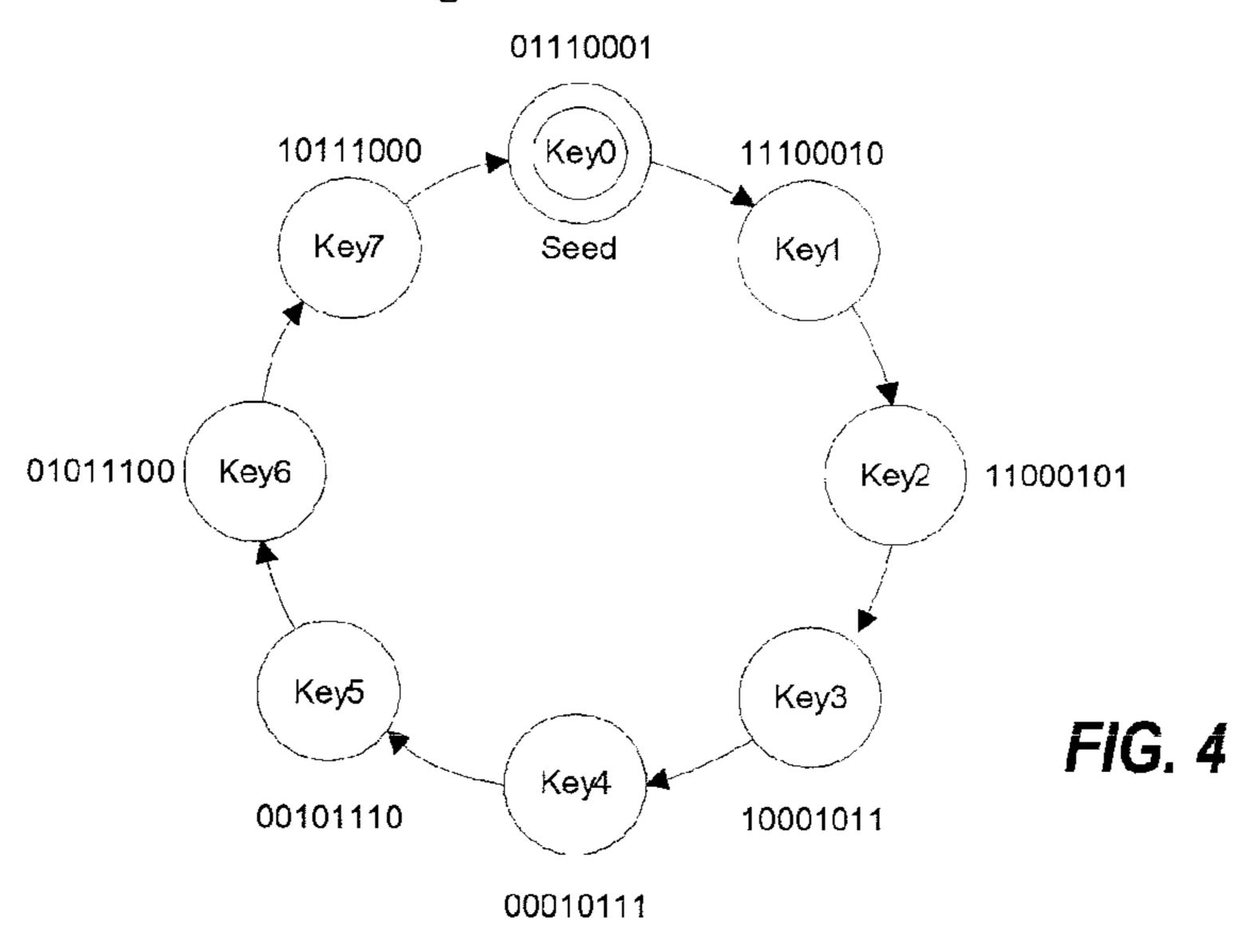

FIG. 4 is a diagram of an exemplary sequence of 8-bit scrambling keys.

FIG. **5** is a table depicting an exemplary sequence of 32-bit scrambling keys.

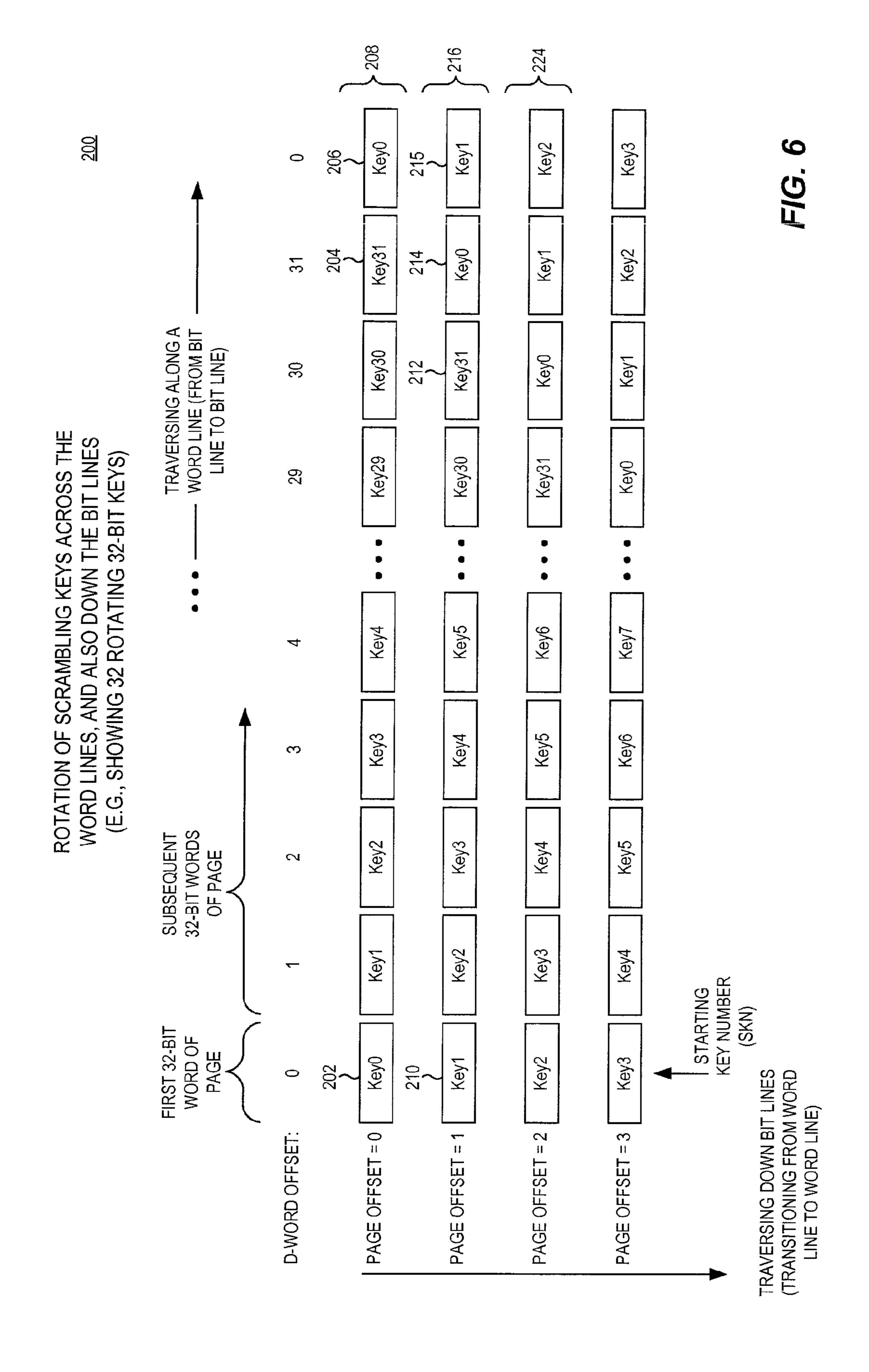

FIG. 6 is a diagram depicting the use of different scrambling keys for different words of a page, and for different pages.

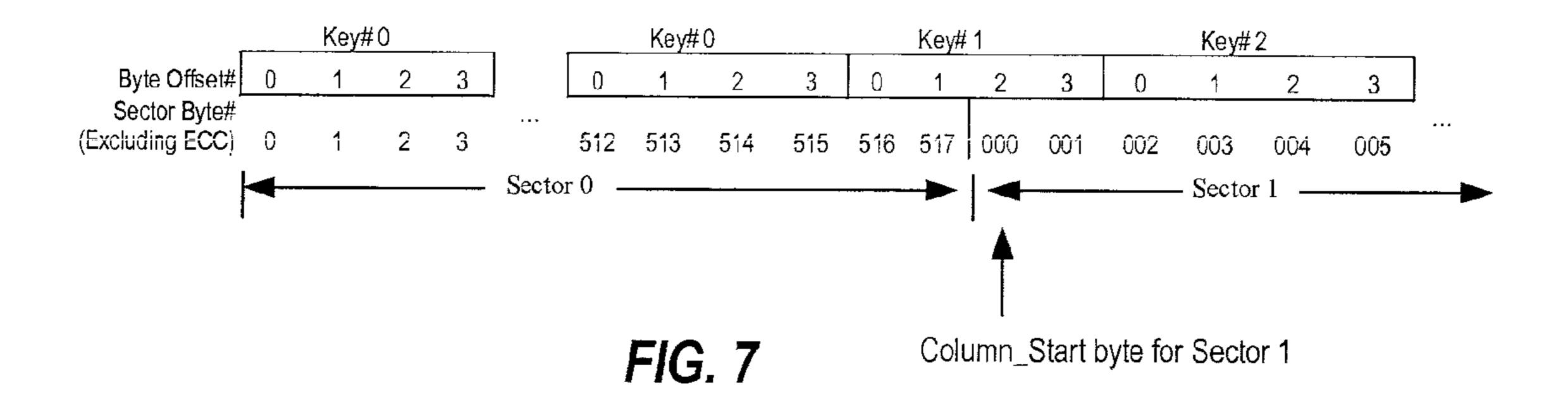

FIG. 7 is a diagram illustrating a sector boundary falling in the middle of a scrambling key.

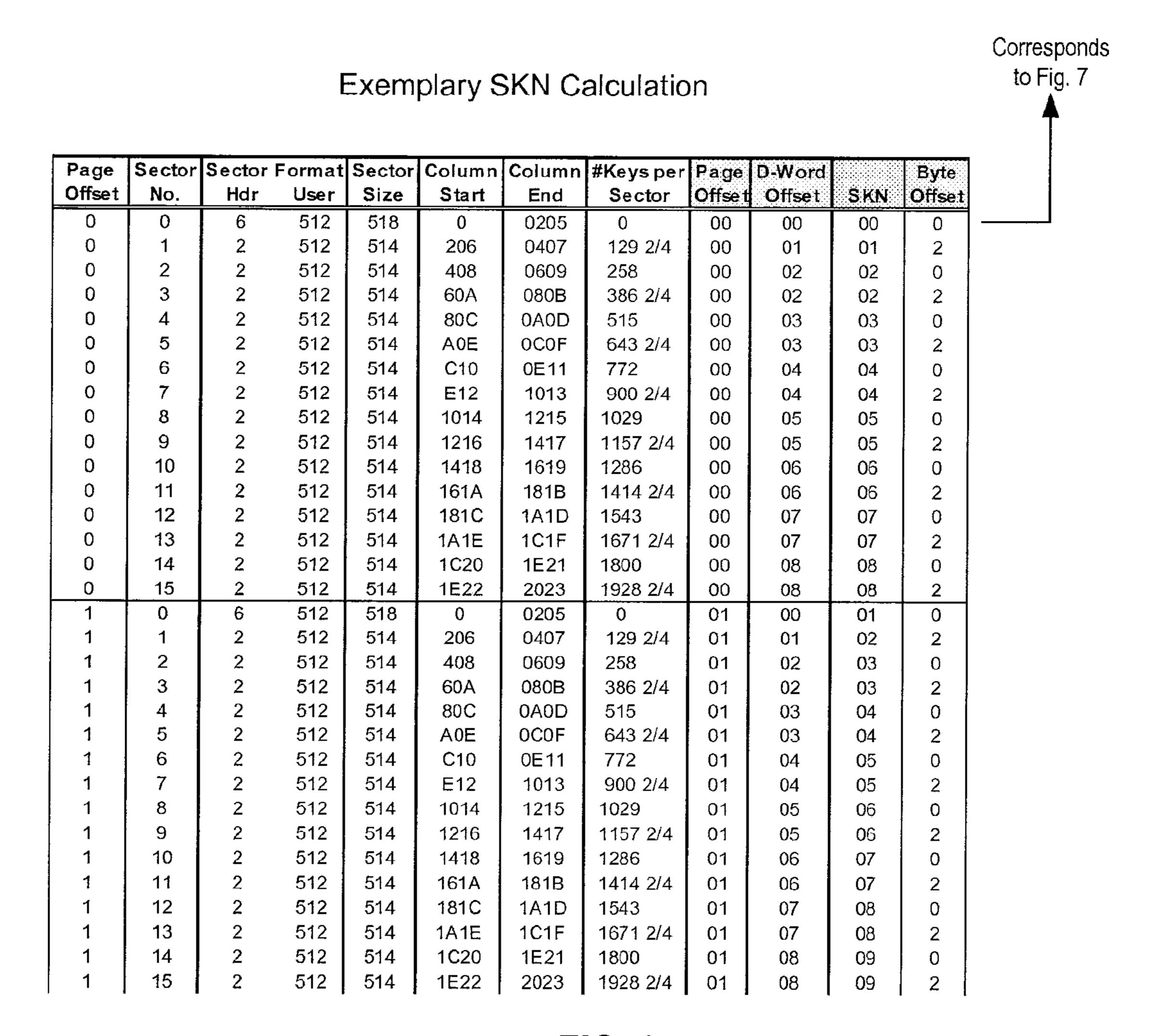

FIG. 8 is a table illustrating exemplary values of several scrambling parameters relevant to each of 16 sectors within a physical page.

FIG. 9 is a diagram of another exemplary sequence of 8-bit scrambling keys.

FIG. 10 is another diagram illustrating a sector boundary falling in the middle of a scrambling key.

FIG. 11 is a table illustrating exemplary values of several 15 scrambling parameters relevant to each of 4 ECC pages within a physical page.

FIG. 12 is a table illustrating exemplary SKN values for each of 4 ECC pages within a physical page, and for each of 32 physical pages.

FIG. 13 is a diagram depicting an exemplary header format for a single-sector ECC page.

FIG. 14 is a diagram depicting another exemplary header format for a 2K Byte ECC page.

FIG. **15** is an exemplary page mapping table in accordance 25 with some embodiments of the present invention.

FIG. 16 is an exemplary SKN table in accordance with some embodiments of the present invention.

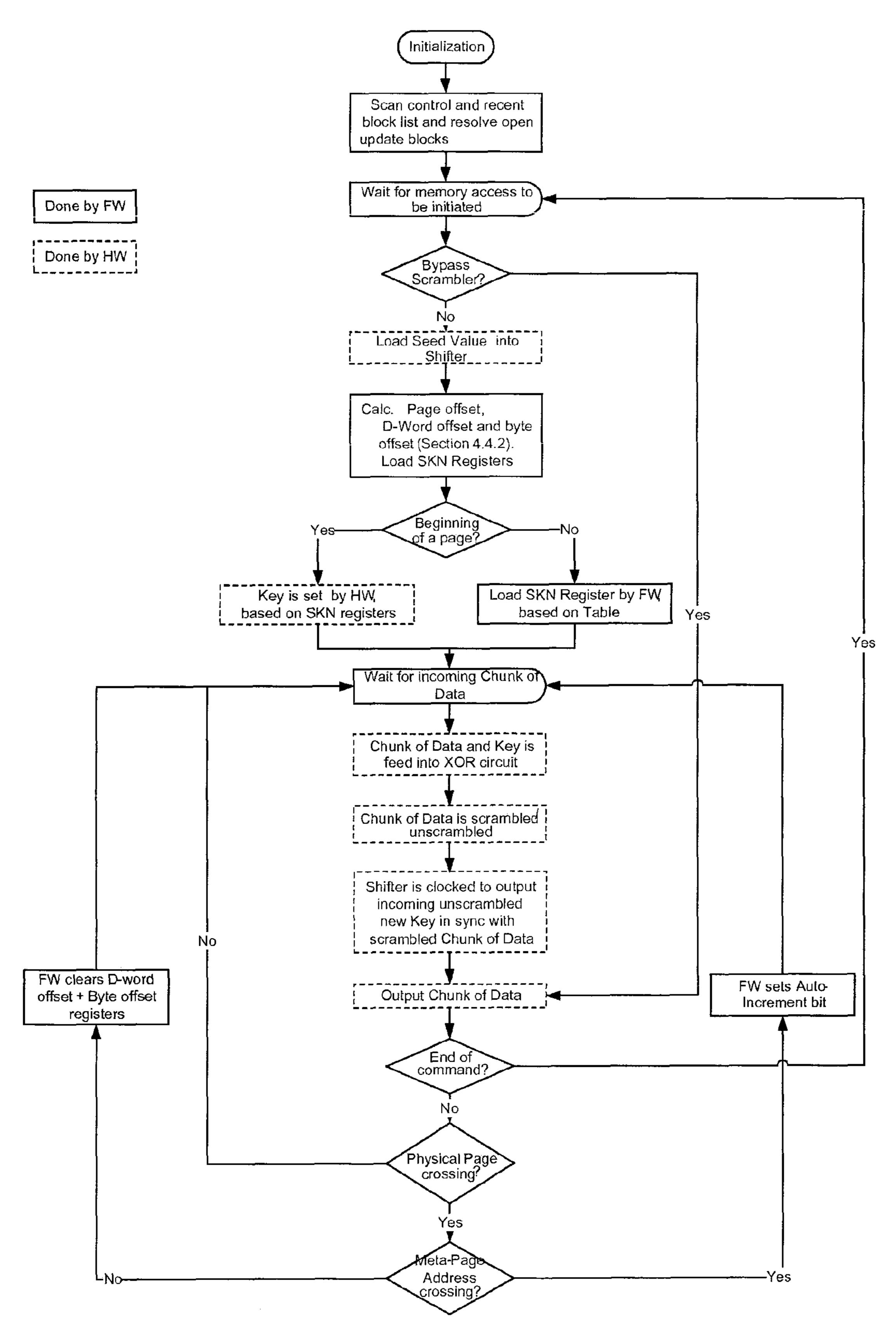

FIG. 17 is a flowchart of exemplary operation of a scrambler in accordance with some embodiments of the present 30 invention.

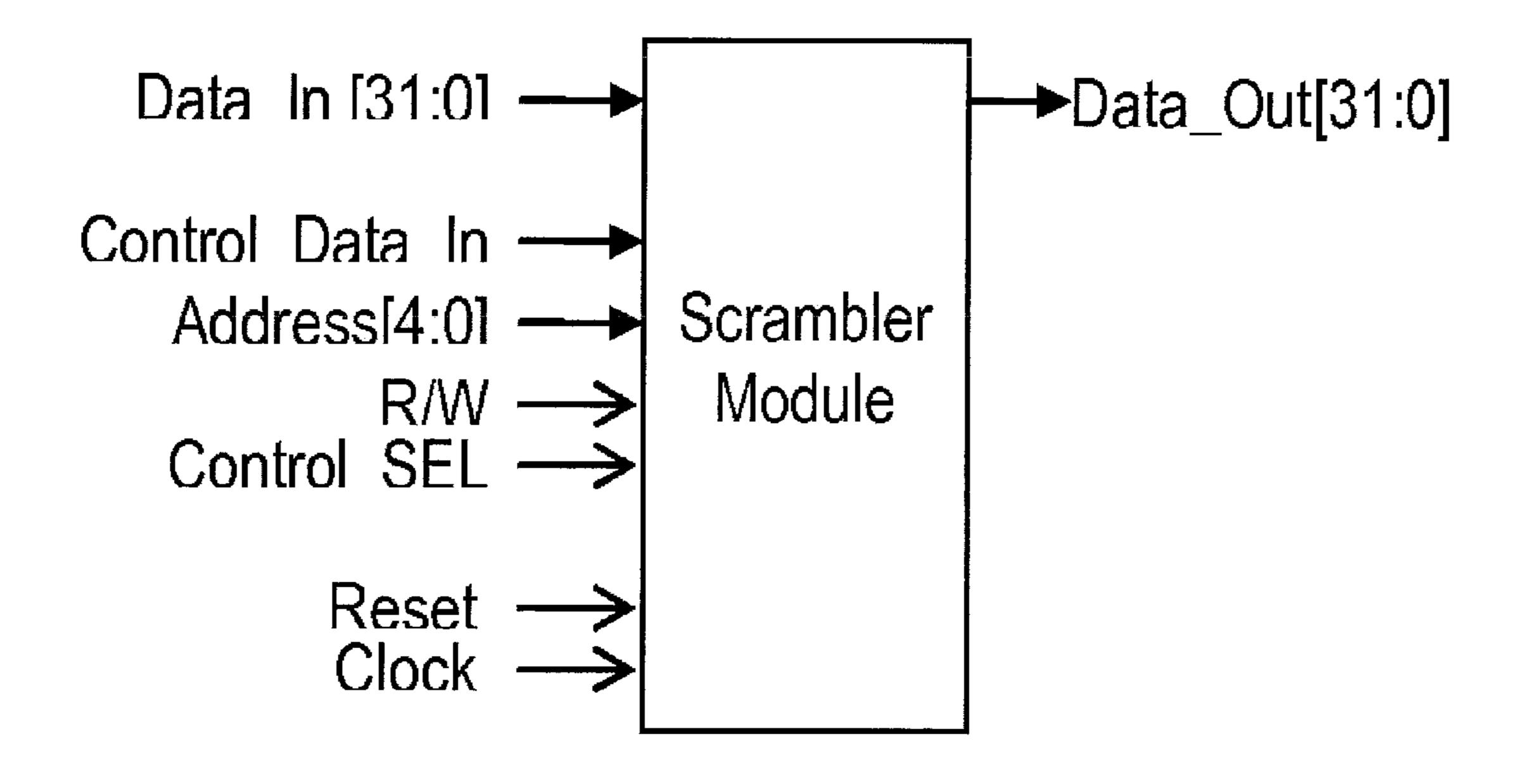

FIG. 18 is a diagram of an exemplary scrambler block in accordance with some embodiments of the present invention.

FIG. 19 is a table depicting memory cell states of unscrambled repeating 0×FF data patterns.

FIG. 20 is a table depicting memory cell states of scrambled data corresponding to that shown in FIG. 19, after scrambling in accordance with certain embodiments of the present invention.

The use of the same reference symbols in different draw- 40 ings indicates similar or identical items.

# DESCRIPTION OF THE PREFERRED EMBODIMENT(S)

Referring now to FIG. 1, a schematic diagram is shown representing a portion of a typical NAND memory array 100. The portion shown may represent a two-dimensional array having only one plane of memory cells, or may represent one level of three-dimensional memory array having more than 50 one plane of memory cells stacked on top of each other. The exemplary NAND string 102 includes thirty-two memory cell transistors connected in series, each gated by a respective one of a plurality of thirty-two word lines 111 (individually labeled WL0, WL1, . . . , WL30, WL31). The NAND string 55 102 also includes a block select device 114 for coupling one end of the NAND string to a bit line 103 in accordance with a block select signal BS0 conveyed on node 113, and further includes a second block select device 116 for coupling the other end of the NAND string to a shared bias node **101** in 60 accordance with a block select signal BS1 conveyed on node **115**.

Each NAND string 102, 104, 106 is disposed within the same block 124 within the memory array, and each is respectively coupled to its associated bit line 103, 105, 107. The 65 memory cells in the NAND strings (i.e., those gated by one of the word lines) typically incorporate a floating gate structure,

6

or may incorporate a charge storage dielectric layer between the gate and the underlying channel, so that the threshold voltage of the memory cell device may be altered by programming and erasure. The various block select devices (e.g., 114, 116) are typically normal MOS devices (i.e., non-programmable), but in certain memory technologies may be fabricated identically to the memory cell devices. While this exemplary NAND array 100 shows thirty-two word lines in a NAND block, other numbers of word lines per block are possible, such as 16, 64, 88, or any other value, although a number equal to an integral power of two is typically implemented.

Thus, a typical NAND memory cell array may be generalized as having a memory cell represented by the intersection of each bit-line and word-line. Traditionally, each memory cell stores one bit of information, which is accomplished by supporting two states of the memory cell. One state represents a logical "0" and the other state represents a logical "1". Frequently, the two states may be implemented by having a 20 floating gate situated above the cell's channel (the area connecting the source and drain elements of the cell's transistor), and having two valid states for the amount of charge stored within the floating gate. Typically, one state is with zero charge in the floating gate and is the initial unwritten state of the cell after being erased (commonly defined to represent the "1" state) and another state is with some amount of negative charge in the floating gate (commonly defined to represent the "0" state). Having negative charge in the gate causes the threshold voltage of the cell's transistor (i.e. the voltage that has to be applied to the transistor's control gate in order to cause the transistor to conduct) to increase. It is then possible to read the stored bit by checking the threshold voltage of the cell—if the threshold voltage is in the higher state then the bit value is "0" and if the threshold voltage is in the lower state 35 then the bit value is "1". Actually there is no need to accurately read the cell's threshold voltage—all that is needed is to correctly identify in which of the two states the cell is currently located. For that purpose it is enough to make a comparison against a reference voltage value that is in the middle between the two states, and thus to determine if the cell's threshold voltage is below or above this reference value.

FIG. 2A shows graphically how this works. Specifically, FIG. 2A shows the distribution of the threshold voltages of a large population of cells. Because the cells in a flash device are not exactly identical in their characteristics and behavior (due, for example, to small variations in impurities concentrations or to defects in the silicon structure), applying the same programming operation to all the cells does not cause all of the cells to have exactly the same threshold voltage. (Note that, for historical reasons, writing data to a flash memory is commonly referred to as "programming" the flash memory.) Instead, the threshold voltage is distributed. Cells storing a value of "1" typically have a negative threshold voltage, such that most of the cells have a threshold voltage close to the value shown by the left peak 120, with some smaller numbers of cells having lower or higher threshold voltages. Similarly, cells storing a value of "0" typically have a positive threshold voltage, such that most of the cells have a threshold voltage close to the value shown by the right peak 122, with some smaller numbers of cells having lower or higher threshold voltages.

It is increasingly common for memory cells to store more than 1 bit of information, using a technique conventionally called "Multi Level Cells" or MLC for short. However, this nomenclature is misleading, because the previous type of flash cells also has more than one level: they have two levels, as described above. Therefore, the two kinds of flash cells are

referred to herein as "Single Bit Cells" (SBC) and "Multi-Bit Cells" (MBC). The improvement brought by the MBC flash is the storing of two (or more) bits in each cell. In order to simplify the explanations, the two-bit case is emphasized herein. It should however be understood the present invention is equally applicable to flash memory devices that support any number of bits per cell. In order for a single memory cell to store two bits of information, the memory cell must be able to be programmed in one of four different states. As the cell's "state" is represented by its threshold voltage, it is clear an 10 MBC cell should support four different valid ranges for its threshold voltage. FIG. 2B shows an exemplary threshold voltage distribution for a typical MBC cell. As expected, FIG. 2B has four peaks 130, 132, 134, 136, each corresponding to one state. As for the SBC case, each state is actually a range 1 and not a single number. When reading the cell's contents, all that must be guaranteed is that the range that the cell's threshold voltage falls within is correctly identified. An example of an MBC flash device is described in U.S. Pat. No. 5,434,825 to Harari, the disclosure of which is incorporated herein by 20 reference in its entirety.

When encoding two bits in an MBC cell by the four states, it is common to have the left-most state, peak 130, (typically having a negative threshold voltage) represent the case of both bits having a value of "1". In the discussion below, the 25 following notation is used—the two bits of a cell are called the "lower bit" and the "upper bit". An explicit value of the bits is written in the form ["upper bit" "lower bit"], with the lower bit value on the right. So the case of the lower bit being "0" and the upper bit being "1" is written as "10". It should be 30 understood that the selection of this terminology and notation is arbitrary, and other names and encodings are possible. Using this notation, the left-most state represents the case of "11". The other three states are typically assigned by the following order from left to right—"10", "00", "01". An 35 example of MBC NAND flash device using such encoding is described in U.S. Pat. No. 6,522,580 to Chen, the disclosure of which is incorporated herein by reference in its entirety. See in particular FIG. 8 of the Chen patent. The four such states may be referred to simply as E, A, B, and C. It should be 40 noted though that there is nothing limiting about this assignment of the states, and that any other ordering can be used. When reading an MBC cell's content, the range that the cell's threshold voltage falls within must be identified correctly; but in this case this cannot be achieved by comparing to one 45 reference voltage, and several comparisons may be necessary.

Another state assignment is depicted in FIG. 2C, which may be referred to as LM Mode. In this mode, there are four peaks 140, 142, 144, 146 (in order from left to right) corresponding respectively to memory states "11", "01", "00", 50 "10". These four states may again be referred to simply as E, A, B, and C. The lower page is typically programmed first, and if a "0" is to be programmed, results in an intermediate LM state, labeled as peak 148. When the upper page is to be programmed, if the upper bit is a "0", either the E state 140 is 55 programmed to the A state 142, or the LM state 148 is programmed to the B state 144. If the upper bit is a "1", then the LM state 148 is programmed to the C state 146.

This LM Mode provides several advantages over the Conventional mode. First, there may be less programming stress 60 since the programming time in the LM mode may be less than in the conventional mode (e.g., programming a memory cell in the conventional mode from the E state 130 to the C state 136 requires a long time to shift the threshold voltage of the memory cell, and stresses neighboring cells the entire time, 65 whereas each of the threshold shifts in the LM mode are smaller in magnitude), and therefore less program disturb,

8

and greater reliability. In addition, if using only the lower page, the separation between the E state 140 and the intermediate LM state 148 is larger than the separation between the E state 130 and A state 132 in the conventional mode, thereby resulting in greater signal margins in the memory cell. Lastly, the width of peak 148 can be wider than the width of peak 132 in the conventional mode, which allows lower page programming to occur more quickly since the resulting final threshold value need not be controlled as exactingly as in the conventional mode.

MBC devices provide a great advantage of cost—using a similarly sized cell an MBC device stores two bits rather than one. However, there may also some drawbacks to using MBC flash—the average read and write times of MBC memories are longer than of SBC memories, resulting in lower performance. Also, the reliability of MBC is lower than SBC. This can easily be understood—the differences between the threshold voltage ranges in MBC are much smaller than in SBC. Thus, a disturbance in the threshold voltage (e.g. leaking of the stored charge causing a threshold voltage drift, interference from operations on neighboring cells, etc.) that may have gone unnoticed in SBC because of the large gap between the two states, might cause an MBC cell to move from one state to another, resulting in an erroneous bit. The end result is a lower quality specification of MBC cells in terms of data retention time or the endurance of the device to many write/erase cycles. Thus there may be advantages to using both MBC cells and SBC cells, depending on the application's requirements.

While the above explanations deal with floating-gate flash memory cells, there are other types of flash memory technologies. For example, in the NROM flash memory technology there is no conductive floating gate but an insulating layer trapping the electric charge. The present invention is equally applicable for all flash memory types, even though the explanations are given in the context of floating-gate technology. Program Disturb

There are several sources of errors in flash memory devices. One specific source of error is typically called "Program Disturb" or "PD" for short. The PD effect causes cells that are not intended to be written, to unintentionally move from their initial left-most state to some other state. (The explanations herein assume the common practice, also used in FIGS. 2A, 2B, and 2C, of drawing the threshold voltage axis such that its left direction represents lower values. This is an arbitrary practice and should not be construed to limit the scope of the invention in any way). Referring to the two-bitper-cell example of FIG. 2C, cells that are in the leftmost state corresponding to bit values of "11" (or in other words, to the cell's erased state) and which are supposed to remain in such state, are found to be in the next-to-leftmost state of "10", resulting in one bit out of the two bits stored in the cell to be incorrect. In some cases, especially in cells storing more than two bits per cell and having more than four states, PD effects might turn out not only as a move from the leftmost state to its immediately adjacent state, but also as a move from the leftmost state to more distant states, and also as a move from a state that is not the leftmost state to another state to its right (i.e. having a higher threshold voltage). However, the case described first above of moving from the leftmost state to its immediately adjacent neighboring state is the most common, and will be used herein for all examples and explanations without limiting the generality of the methods of the present invention.

The reason for the PD effect is easy to understand when reviewing the voltages applied to the cells of a NAND flash device when programming a page. When programming a

page of cells, a relatively high voltage is applied to the word line connected to the control gates of the cells of the page. What decides whether a certain cell threshold voltage is increased as a result of this control gate voltage is the voltage applied to the bit line connected to that cell. Cells that are not 5 to be written with data have their bit line connected to a relatively high voltage level that minimizes the voltage difference across the cell. Cells that are to be written have their bit line connected to low voltage, causing a large voltage difference across the cell, and resulting in the cell's threshold 10 voltage getting increased, thus moving the cell to the right on the voltage axis of FIG. 2C and causing the cell's state to change.

However, even though cells that are not meant to be written have a lower voltage difference across them than cells that are 15 meant to be written, they still have some voltage difference them. To reduce the voltage across these non-programmed cells even more, their channels may be "boosted" to a voltage closer in magnitude to the programming voltage applied to the selected word line, and thereby reduce the voltage differ- 20 ence across such memory cell devices. This is done by biasing other non-selected word lines in the memory block to an intermediate voltage closer to the "relatively high" bit line voltage corresponding to the cells that are not meant to be written. This biases the channel of these cells to a higher 25 voltage, which is boosted to an even higher voltage when the selected word line is pulsed to a high programming voltage. However, since the charge trapped in the programmed cells along the selected word line partially negates the voltage applied to those non-selected word lines, and the overall 30 boosting depends on the data (i.e., memory state) programmed to previous cells along the same bit line. For example, cells programmed to the "C" state (i.e., maximum charge stored in the memory cell) have the highest threshold voltage of such memory cell devices. If other cells along the 35 bit line were previously programmed to the "C" state, this reduces the boosted voltage that is achieved, thus increasing the voltage across the memory device that is not to be written, and which causes unintentional programming.