## US00RE45291E

# (19) United States

# (12) Reissued Patent

Nathan et al.

# (10) Patent Number: US

US RE45,291 E

(45) Date of Reissued Patent: Dec. 16, 2014

# (54) VOLTAGE-PROGRAMMING SCHEME FOR CURRENT-DRIVEN AMOLED DISPLAYS

(71) Applicant: Ignis Innovation Inc., Waterloo (CA)

(72) Inventors: Arokia Nathan, Cambridge (GB);

Richard I-Heng Huang, Waterloo (CA);

Stefan Alexander, Elmira (CA)

(73) Assignee: Ignis Innovation Inc., Waterloo (CA)

(21) Appl. No.: 14/090,320

(22) Filed: Nov. 26, 2013

# Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 8,232,939

Issued: Jul. 31, 2012

Appl. No.: 13/396,375

Filed: Feb. 14, 2012

# U.S. Applications:

(63) Continuation of application No. 11/571,480, filed as application No. PCT/CA2005/001007 on Jun. 28, 2005, now Pat. No. 8,115,707.

## (30) Foreign Application Priority Data

(51) Int. Cl. G09G 3/30

(2006.01)

(52) U.S. Cl.

(58) Field of Classification Search

See application file for complete search history.

## (56) References Cited

#### U.S. PATENT DOCUMENTS

| 3,506,851 A | 4/1970  | Polkinghorn et al. |

|-------------|---------|--------------------|

| 3,774,055 A | 11/1973 | Bapat et al.       |

| 4,090,096 A | 5/1978  | Nagami             |

| 4,160,934 A | 7/1979  | Kirsch             |

| 4,354,162 A | 10/1982 | Wright             |

| 4,758,831 A | 7/1988  | Kasahara et al.    |

| 4,943,956 A | 7/1990  | Noro               |

|             | (Con    | tinued)            |

|             | (       |                    |

# FOREIGN PATENT DOCUMENTS

CA 1 294 034 1/1992 CA 2 109 951 11/1992

(Continued)

### OTHER PUBLICATIONS

Ahnood et al.: "Effect of threshold voltage instability on field effect mobility in thin film transistors deduced from constant current measurements"; dated Aug. 2009 (3 pages).

## (Continued)

Primary Examiner — Dmitriy Bolotin

(74) Attorney Agent or Firm — Nixon Peabod

(74) Attorney, Agent, or Firm — Nixon Peabody LLP

# (57) ABSTRACT

A system and method for driving an AMOLED display is provided. The AMOLED display includes a plurality of pixel circuits. A voltage-programming scheme, a current-programming scheme or a combination thereof is applied to drive the display. Threshold shift information, and/or voltage necessary to obtain hybrid driving circuit may be acquired. A data sampling may be implemented to acquire a current/voltage relationship. A feedback operation may be implemented to correct the brightness of the pixel.

# 70 Claims, 23 Drawing Sheets

| (56)                   |              | Referen          | ces Cited                   | 6,373,454<br>6,384,427 |    |                  | Knapp et al.<br>Yamazaki et al.     |

|------------------------|--------------|------------------|-----------------------------|------------------------|----|------------------|-------------------------------------|

|                        | II S         | PATENT           | DOCUMENTS                   | 6,392,617              |    |                  | Gleason 345/82                      |

|                        | 0.5.         | IAILINI          | DOCOMENTS                   | 6,399,988              |    |                  | Yamazaki                            |

| 4,963,860              | Δ            | 10/1990          | Stewart                     | 6,414,661              |    |                  | Shen et al.                         |

| 4,975,691              |              | 12/1990          |                             | 6,417,825              | B1 | 7/2002           | Stewart et al.                      |

| 4,996,523              |              |                  | Bell et al.                 | 6,420,758              | B1 |                  | Nakajima                            |

| 5,051,739              | $\mathbf{A}$ | 9/1991           | Hayashida et al.            | 6,420,834              |    |                  | Yamazaki et al.                     |

| 5,153,420              |              |                  | Hack et al.                 | 6,420,988              |    |                  | Azami et al.                        |

| 5,198,803              |              |                  | Shie et al.                 | 6,433,488<br>6,437,106 |    | 8/2002           | Stoner et al.                       |

| , ,                    |              |                  | Hack et al.                 | 6,445,369              |    |                  | Yang et al.                         |

| 5,222,082<br>5,266,515 |              | 6/1993           | Robb et al.                 | 6,445,376              |    |                  | •                                   |

| , ,                    |              | 2/1996           |                             | , ,                    |    |                  | Jacobsen et al.                     |

| , ,                    |              |                  | Lee et al.                  | 6,475,845              | B2 | 11/2002          | Kimura                              |

| , ,                    |              |                  | Lentz et al.                | , ,                    |    |                  | Tanaka et al.                       |

| 5,589,847              | $\mathbf{A}$ | 12/1996          | Lewis                       | , ,                    |    |                  | Yamazaki                            |

| 5,619,033              |              |                  | Weisfield                   |                        |    |                  | Yamagishi et al.                    |

| 5,648,276              |              |                  | Hara et al.                 | , ,                    |    |                  | Yamazaki et al.<br>Nakajima et al.  |

| 5,670,973              |              |                  | Bassetti et al.             | 6,522,315              |    |                  | Ozawa et al.                        |

| 5,686,935<br>5,691,783 |              |                  | Weisbrod<br>Numao et al.    | 6,524,895              |    |                  | Yamazaki et al.                     |

| 5,712,653              |              |                  | Katoh et al.                | 6,525,683              | B1 | 2/2003           | Gu                                  |

| 5,714,968              |              | 2/1998           |                             | 6,531,713              |    |                  | Yamazaki                            |

| 5,723,950              |              |                  | Wei et al.                  | /                      |    |                  | Kawashima                           |

| 5,744,824              | $\mathbf{A}$ | 4/1998           | Kousai et al.               | 6,542,138              |    |                  | Shannon et al.                      |

| 5,745,660              |              |                  | Kolpatzik et al.            | 6,559,594              |    |                  | Fukunaga et al.                     |

| 5,747,928              |              |                  | Shanks et al.               | 6,573,195<br>6,573,584 |    |                  | Yamazaki et al.<br>Nagakari et al.  |

| 5,748,160              |              |                  | Shieh et al.                | 6,576,926              |    |                  | Yamazaki et al.                     |

| 5,784,042<br>5,790,234 |              |                  | Ono et al.<br>Matsuyama     | 6,580,408              |    |                  | Bae et al.                          |

| 5,815,303              |              | 9/1998           |                             | 6,580,657              |    |                  | Sanford et al.                      |

| 5,870,071              |              |                  | Kawahata                    | 6,583,398              | B2 | 6/2003           | Harkin                              |

| 5,874,803              |              |                  | Garbuzov et al.             | 6,583,775              |    |                  | Sekiya et al.                       |

| 5,880,582              | $\mathbf{A}$ | 3/1999           | Sawada                      | 6,583,776              |    |                  | Yamazaki et al.                     |

| 5,903,248              |              | 5/1999           |                             | 6,587,086              |    |                  | Koyama<br>Nichi et el               |

| 5,917,280              |              |                  | Burrows et al.              | 6,593,691<br>6,594,606 |    | 7/2003           | Nishi et al.                        |

| 5,923,794<br>5,045,072 |              |                  | McGrath et al.              | 6,597,203              |    | 7/2003           |                                     |

| 5,945,972<br>5,949,398 |              | 8/1999<br>9/1999 | Okumura et al.              | 6,611,108              |    |                  |                                     |

| 5,952,789              |              |                  | Stewart et al.              | , ,                    |    |                  | Yamazaki et al.                     |

| , ,                    |              |                  | Akiyama et al.              | 6,618,030              | B2 | 9/2003           | Kane et al.                         |

| 5,982,104              |              |                  | Sasaki et al.               | 6,639,244              |    |                  | Yamazaki et al.                     |

| 5,990,629              | Α            | 11/1999          | Yamada et al.               | , ,                    |    |                  | Yamazaki et al.                     |

| 6,023,259              |              |                  | Howard et al.               | 6,661,180              |    |                  | Koyama<br>Mikami et al.             |

| 6,069,365              |              |                  | Chow et al.                 | , ,                    |    |                  | Gilmour et al.                      |

| 6,081,131<br>6,091,203 |              | 6/2000<br>7/2000 | Kawashima et al.            |                        |    |                  | Yamazaki et al.                     |

| 6,097,360              |              |                  | Holloman                    | 6,677,713              |    |                  |                                     |

| 6,144,222              |              | 11/2000          |                             | 6,680,577              | B1 | 1/2004           | Inukai et al.                       |

| , ,                    |              |                  | Starnes et al.              | 6,680,580              |    |                  | ~                                   |

| 6,166,489              | $\mathbf{A}$ | 12/2000          | Thompson et al.             | 6,687,266              |    |                  | Ma et al.                           |

| 6,177,915              |              |                  | Beeteson et al.             | 6,690,000<br>6,690,344 |    |                  | Muramatsu et al.<br>Takeuchi et al. |

| 6,225,846              |              |                  | Wada et al.                 | 6,693,388              |    |                  | Oomura                              |

| 6,229,506<br>6,229,508 |              | 5/2001           | Dawson et al.               | 6,693,610              |    |                  | Shannon et al.                      |

| 6,232,939              |              |                  | Saito et al.                | 6,697,057              | B2 | 2/2004           | Koyama et al.                       |

| 6,246,180              |              |                  | Nishigaki                   | 6,720,942              |    |                  | Lee et al.                          |

| 6,252,248              | B1           |                  | Sano et al.                 | 6,724,151              |    | 4/2004           |                                     |

| 6,259,424              | B1           | 7/2001           | Kurogane                    | 6,734,636              |    |                  | Sanford et al.                      |

| 6,262,589              |              |                  | Tamukai                     | 6,738,034              |    |                  | Kaneko et al.                       |

| 6,271,825              |              |                  | Greene et al.               | 6,738,035<br>6,753,655 |    | 5/2004<br>6/2004 | Shih et al.                         |

| 6,274,887              |              |                  | Yamazaki et al.<br>Holloman | , ,                    |    |                  | Mikami et al.                       |

| 6,300,928              |              | 10/2001          |                             | 6,756,741              |    | 6/2004           |                                     |

| 6,303,963              |              |                  | Ohtani et al.               | 6,756,952              | B1 | 6/2004           | Decaux et al.                       |

| 6,304,039              |              |                  | Appelberg et al.            | 6,756,985              |    |                  | Hirotsune et al.                    |

| 6,306,694              |              |                  | Yamazaki et al.             | 6,771,028              |    |                  | Winters                             |

| 6,307,322              |              |                  | Dawson et al.               | 6,777,712              |    |                  | Sanford et al.                      |

| 6,310,962              |              |                  | Chung et al.                | 6,777,888              |    | 8/2004<br>8/2004 |                                     |

| , ,                    |              |                  | Mueller et al.              | 6,780,687<br>6,781,567 |    | 8/2004<br>8/2004 | Nakajima et al.<br>Kimura           |

| 6,320,325              |              |                  | Cok et al.                  | 6,806,497              |    | 10/2004          |                                     |

| 6,323,832              |              |                  | Nishizawa et al.            | 6,806,638              |    |                  | Lih et al.                          |

| 6,345,085              |              |                  | Yeo et al.                  | 6,806,857              |    |                  | Sempel et al.                       |

| 6,348,835              |              |                  | Sato et al.                 | 6,809,706              |    |                  | Shimoda                             |

| 6,356,029              |              | 3/2002           |                             | , ,                    |    |                  | Nara et al.                         |

| 6,365,917              |              |                  | Yamazaki                    | 6,828,950              |    |                  |                                     |

| •                      |              |                  | Yudasaka                    |                        |    |                  | Miyajima et al.                     |

|                        |              |                  |                             |                        |    |                  |                                     |

| (56)                   |      | Referen          | ces Cited                          | 7,402,467 B1                        |                    | Kadono et al.                       |

|------------------------|------|------------------|------------------------------------|-------------------------------------|--------------------|-------------------------------------|

|                        | U.S. | PATENT           | DOCUMENTS                          | 7,411,571 B2<br>7,414,600 B2        | 8/2008<br>8/2008   | Nathan et al.                       |

|                        | 0.2. |                  | DOCOME                             | 7,423,617 B2                        |                    | Giraldo et al.                      |

| 6,859,193              |      |                  | Yumoto                             | 7,432,885 B2<br>7,474,285 B2        | 10/2008            | Asano et al.                        |

| 6,861,670<br>6,873,117 |      |                  | Ohtani et al.<br>Ishizuka          | 7,485,478 B2                        |                    | Yamagata et al.                     |

| 6,873,320              | B2   | 3/2005           | Nakamura                           | 7,502,000 B2                        |                    | Yuki et al.                         |

| 6,876,346<br>6,878,968 |      |                  | Anzai et al.<br>Ohnuma             | 7,528,812 B2<br>7,535,449 B2        |                    | Tsuge et al.<br>Miyazawa            |

| 6,885,356              |      |                  | Hashimoto                          | 7,554,512 B2                        | 6/2009             | Steer                               |

| 6,900,485              |      | 5/2005           |                                    | 7,569,849 B2<br>7,576,718 B2        |                    | Nathan et al.<br>Miyazawa           |

| 6,903,734<br>6,909,114 |      | 6/2005<br>6/2005 | Eu<br>Yamazaki                     | 7,570,718 B2<br>7,580,012 B2        |                    | Kim et al.                          |

| 6,909,243              |      | 6/2005           |                                    | 7,589,707 B2                        | 9/2009             |                                     |

| 6,909,419              |      |                  | Zavracky et al.                    | 7,609,239 B2<br>7,619,594 B2        | 10/2009<br>11/2009 | •                                   |

| 6,911,960<br>6,911,964 |      |                  | Yokoyama<br>Lee et al.             | 7,619,597 B2                        |                    | Nathan et al.                       |

| 6,914,448              | B B2 | 7/2005           | Jinno                              | 7,633,470 B2                        |                    |                                     |

| 6,919,871<br>6,924,602 |      | 7/2005<br>8/2005 | Kwon<br>Komiya                     | 7,656,370 B2<br>7,697,052 B1        |                    | Schneider et al.<br>Yamazaki et al. |

| 6,937,215              |      | 8/2005           | •                                  | 7,800,558 B2                        | 9/2010             | Routley et al.                      |

| 6,937,220              |      |                  | Kitaura et al.                     | 7,825,419 B2<br>7,847,764 B2        |                    | Yamagata et al.                     |

| 6,940,214<br>6,943,500 |      |                  | Komiya et al.<br>LeChevalier       | 7,859,492 B2                        |                    |                                     |

| / /                    |      |                  | McCartney                          | 7,868,859 B2                        |                    | Tomida et al.                       |

| 6,954,194              |      |                  | Matsumoto et al.                   | 7,876,294 B2<br>7,924,249 B2        |                    | Sasaki et al.<br>Nathan et al.      |

| 6,936,347<br>6,975,142 |      |                  | Bae et al 345/77<br>Azami et al.   | 7,932,883 B2                        |                    | Klompenhouwer et al.                |

| 6,975,332              | 2 B2 | 12/2005          | Arnold et al.                      | 7,948,170 B2                        |                    | Striakhilev et al.                  |

| 6,995,510<br>6,995,519 |      |                  | Murakami et al.<br>Arnold et al.   | 7,969,390 B2<br>7,978,187 B2        |                    | Yoshida<br>Nathan et al.            |

| 7,022,556              |      |                  | Adachi                             | 7,994,712 B2                        | 8/2011             | Sung et al.                         |

| 7,023,408              |      | 4/2006           | Chen et al.                        | 7,995,010 B2<br>8,026,876 B2        |                    | Yamazaki et al.<br>Nathan et al.    |

| 7,027,015<br>7,027,078 |      | 4/2006<br>4/2006 | Booth, Jr. et al. Reihl            | 8,020,870 B2<br>8,044,893 B2        |                    | Nathan et al.                       |

| 7,027,076              |      |                  | Sekiya et al.                      | 8,049,420 B2                        |                    | Tamura et al.                       |

| 7,038,392              |      |                  | Libsch et al.                      | 8,077,123 B2<br>8,115,707 B2        |                    | Naugler, Jr.<br>Nathan et al.       |

| 7,057,359<br>7,061,451 |      |                  | Hung et al.<br>Kimura              | 8,223,177 B2                        |                    | Nathan et al.                       |

| 7,064,733              | B2   | 6/2006           | Cok et al.                         | 8,232,939 B2                        |                    | Nathan et al.                       |

| 7,071,932<br>7,088,051 |      |                  | Libsch et al. Cok                  | 8,259,044 B2<br>8,264,431 B2        |                    | Nathan et al.<br>Bulovic et al.     |

| 7,088,051              |      |                  | Kimura                             | 8,279,143 B2                        | 10/2012            | Nathan et al.                       |

| 7,102,378              |      |                  | Kuo et al.                         | 8,339,386 B2<br>8,378,362 B2        |                    | Leon et al.<br>Heo et al.           |

| 7,106,285<br>7,112,820 |      |                  | Naugler<br>Chang et al.            | 8,493,295 B2                        |                    | Yamazaki et al.                     |

| 7,116,058              |      |                  | Lo et al.                          | 8,497,525 B2                        |                    | Yamagata et al.                     |

| 7,119,493              |      |                  | Fryer et al.                       | 2001/0002703 A1<br>2001/0004190 A1  |                    | Koyama<br>Nishi et al.              |

| 7,122,835<br>7,127,380 |      |                  | Ikeda et al.<br>Iverson et al.     | 2001/0009283 A1                     | 7/2001             | Arao et al.                         |

| 7,129,914              | B2   | 10/2006          | Knapp et al.                       | 2001/0013806 A1<br>2001/0015653 A1  |                    | Notani<br>Do Jong et al             |

| 7,129,917<br>7 141 821 |      |                  | Yamazaki et al.<br>Yamazaki et al. | 2001/0013033 A1<br>2001/0020926 A1  | 9/2001             | De Jong et al.<br>Kuijk             |

| 7,141,621              |      | 1/2007           | _                                  | 2001/0024181 A1                     | 9/2001             | Kubota                              |

| 7,193,589              |      |                  | Yoshida et al.                     | 2001/0024186 A1<br>2001/0026127 A1  |                    | Kane et al.<br>Yoneda et al.        |

| 7,199,516<br>7,220,997 |      | 5/2007           | Seo et al.<br>Nakata               | 2001/0026179 A1                     |                    |                                     |

| 7,224,332              | 2 B2 | 5/2007           | Cok                                | 2001/0026257 A1<br>2001/0030323 A1  |                    |                                     |

| 7,227,519<br>7,235,810 |      | _                | Kawase et al.<br>Yamazaki et al.   | 2001/0030323 A1<br>2001/00333199 A1 |                    |                                     |

| 7,245,277              |      |                  | Ishizuka 345/78                    | 2001/0038098 A1                     |                    | Yamazaki et al.                     |

| 7,248,236              |      |                  | Nathan et al.                      | 2001/0040541 A1<br>2001/0043173 A1  |                    |                                     |

| 7,262,753<br>7,264,979 |      |                  | Tanghe et al.<br>Yamagata et al.   | 2001/0045929 A1                     |                    |                                     |

| 7,274,345              | B2 * | 9/2007           | Imamura et al 345/76               | 2001/0052606 A1                     |                    | -                                   |

| 7,274,363<br>7,279,711 |      |                  | Ishizuka et al.<br>Yamazaki et al. | 2001/0052898 A1<br>2001/0052940 A1  |                    | Osame et al.<br>Hagihara et al.     |

| 7,279,711              |      |                  | Oomori et al.                      | 2002/0000576 A1                     | 1/2002             | Inukai                              |

| 7,310,092              | 2 B2 | 12/2007          | Imamura                            | 2002/0011796 A1                     |                    | Koyama                              |

| , ,                    |      | 1/2008<br>1/2008 | Kimura<br>Shirasaki et al.         | 2002/0011799 A1<br>2002/0011981 A1  | 1/2002             | Kimura<br>Kuijk                     |

| 7,317,425              |      |                  | Mikami et al.                      | 2002/0012057 A1                     |                    | Kimura                              |

| 7,321,348              |      |                  | Cok et al.                         | 2002/0014851 A1                     |                    | Tai et al.                          |

| 7,339,560<br>7,339,636 |      | 3/2008<br>3/2008 | Sun<br>Voloschenko et al.          | 2002/0015031 A1<br>2002/0015032 A1  |                    | Fujita et al.<br>Koyama et al.      |

| 7,355,574              |      |                  | Leon et al.                        | 2002/0013032 A1<br>2002/0018034 A1  |                    | Ohki et al.                         |

| 7,358,941              |      |                  | Ono et al.                         | 2002/0030190 A1                     |                    | Ohtani et al.                       |

| 7,368,868              | 8 B2 | 5/2008           | Sakamoto                           | 2002/0030528 A1                     | 3/2002             | Matsumoto et al.                    |

| (56)                                | Referer | ices Cited                         | 2004/0100427 A1<br>2004/0108518 A1  | 5/2004<br>6/2004   | Miyazawa                                |

|-------------------------------------|---------|------------------------------------|-------------------------------------|--------------------|-----------------------------------------|

| U.S.                                | PATENT  | DOCUMENTS                          | 2004/0113903 A1                     | 6/2004             | Mikami et al.                           |

| 2002/0020647 4.1                    | 2/2002  | TT1_4_1                            | 2004/0129933 A1<br>2004/0130516 A1  |                    | Nathan et al.<br>Nathan et al.          |

| 2002/0030647 A1<br>2002/0036463 A1  |         | Hack et al.<br>Yoneda et al.       | 2004/0130310 A1                     |                    | Kondakov et al.                         |

| 2002/0047565 A1                     |         | Nara et al.                        | 2004/0145547 A1                     | 7/2004             |                                         |

| 2002/0047852 A1                     |         | Inukai et al.                      | 2004/0150592 A1*<br>2004/0150594 A1 |                    | Mizukoshi et al 345/76<br>Koyama et al. |

| 2002/0048829 A1<br>2002/0050795 A1  |         | Yamazaki et al.<br>Imura           | 2004/0150595 A1                     | 8/2004             |                                         |

| 2002/0052086 A1                     | 5/2002  | Maeda                              | 2004/0155841 A1<br>2004/0174347 A1* | 8/2004             | Kasai<br>Sun et al 345/204              |

| 2002/0053401 A1<br>2002/0067134 A1  |         | Ishikawa et al.<br>Kawashima       | 2004/01/434/ A1<br>2004/0174349 A1  |                    | Libsch                                  |

| 2002/0007134 A1<br>2002/0070909 A1  |         | Asano et al.                       | 2004/0174354 A1                     |                    | Ono et al.                              |

| 2002/0080108 A1                     | 6/2002  |                                    | 2004/0178743 A1<br>2004/0183759 A1  |                    | Miller et al.<br>Stevenson et al.       |

| 2002/0084463 A1<br>2002/0101172 A1  | 8/2002  | Sanford et al.<br>Bu               | 2004/0189627 A1                     |                    | Shirasaki et al.                        |

| 2002/0101433 A1                     | 8/2002  | McKnight                           | 2004/0196275 A1                     | 10/2004            |                                         |

| 2002/0105279 A1<br>2002/0113248 A1  |         | Kimura<br>Yamagata et al.          | 2004/0201554 A1<br>2004/0207615 A1  | 10/2004<br>10/2004 |                                         |

| 2002/0113248 A1<br>2002/0117722 A1  |         | Osada et al.                       |                                     |                    | Ono et al 345/76                        |

| 2002/0122308 A1*                    |         | Ikeda 362/259                      | 2004/0252089 A1<br>2004/0257313 A1  |                    | Ono et al.<br>Kawashima et al.          |

| 2002/0130686 A1<br>2002/0154084 A1  |         | Forbes<br>Tanaka et al.            | 2004/0257353 A1                     |                    |                                         |

| 2002/0158587 A1                     | 10/2002 | Komiya                             | 2004/0257355 A1                     | 12/2004            | $\sim$                                  |

| 2002/0158666 A1<br>2002/0158823 A1  |         |                                    | 2004/0263437 A1<br>2004/0263444 A1  | 12/2004<br>12/2004 |                                         |

| 2002/0138823 A1<br>2002/0163314 A1  |         | •                                  | 2004/0263445 A1                     | 12/2004            | Inukai et al.                           |

|                                     |         | Everitt 345/76                     | 2004/0263541 A1<br>2005/0007355 A1  |                    | Takeuchi et al.<br>Miura                |

| 2002/0167474 A1<br>2002/0180369 A1  |         |                                    | 2005/0007353 A1                     |                    |                                         |

| 2002/0180721 A1                     |         | •                                  | 2005/0014891 A1                     |                    |                                         |

| 2002/0186214 A1                     |         |                                    | 2005/0017650 A1<br>2005/0024081 A1  |                    | Fryer et al.<br>Kuo et al.              |

| 2002/0190332 A1<br>2002/0190924 A1  |         |                                    | 2005/0024393 A1                     | 2/2005             | Kondo et al.                            |

| 2002/0190971 A1                     |         |                                    | 2005/0030267 A1<br>2005/0035709 A1  |                    | Tanghe et al.<br>Furuie et al.          |

| 2002/0195967 A1<br>2002/0195968 A1  |         |                                    | 2005/0055709 A1<br>2005/0057484 A1  |                    | Diefenbaugh et al.                      |

| 2003/0020413 A1                     |         | Oomura                             | 2005/0057580 A1                     | 3/2005             | Yamano et al.                           |

| 2003/0030603 A1                     |         | Shimoda  Death at al               | 2005/0067970 A1<br>2005/0067971 A1  | 3/2005<br>3/2005   | Libsch et al.<br>Kane                   |

| 2003/0043088 A1<br>2003/0057895 A1  |         | Booth et al.<br>Kimura             | 2005/0068270 A1*                    |                    | Awakura et al 345/76                    |

| 2003/0058226 A1                     | 3/2003  | Bertram et al.                     | 2005/0068275 A1<br>2005/0073264 A1  | 3/2005             | Kane<br>Matsumoto                       |

| 2003/0062524 A1<br>2003/0063081 A1* |         | Kimura<br>Kimura et al 345/211     | 2005/0073204 A1<br>2005/0083323 A1  |                    | Suzuki et al.                           |

| 2003/0003001 A1<br>2003/0071821 A1  |         | Sundahl et al.                     | 2005/0088103 A1*                    |                    | Kageyama et al 315/169.3                |

| 2003/0076048 A1                     |         | Rutherford Chan at al              | 2005/0110420 A1<br>2005/0110807 A1  |                    | Arnold et al.<br>Chang                  |

| 2003/0090445 A1<br>2003/0090447 A1  |         | Chen et al.<br>Kimura              | 2005/0117096 A1                     |                    | Voloschenko et al.                      |

| 2003/0090481 A1                     | 5/2003  | Kimura                             | 2005/0140598 A1*<br>2005/0140610 A1 |                    | Kim et al 345/76<br>Smith et al.        |

| 2003/0095087 A1<br>2003/0107560 A1  |         | Libsch<br>Yumoto et al.            | 2005/0140010 A1<br>2005/0145891 A1  | 7/2005             |                                         |

| 2003/0107366 A1                     |         | Mikami et al.                      | 2005/0156831 A1                     |                    | Yamazaki et al.                         |

| 2003/0122745 A1                     |         | Miyazawa                           | 2005/0168416 A1*<br>2005/0179626 A1 |                    | Hashimoto et al 345/76<br>Yuki et al.   |

| 2003/0122813 A1<br>2003/0140958 A1  |         | Ishizuki et al.<br>Yang et al.     | 2005/0179628 A1                     | 8/2005             | Kimura                                  |

| 2003/0142088 A1                     | 7/2003  | LeChevalier                        | 2005/0185200 A1<br>2005/0200575 A1  | 8/2005<br>9/2005   | Tobol<br>Kim et al.                     |

| 2003/0151569 A1<br>2003/0156101 A1  |         | Lee et al.<br>LeChevalier          | 2005/02005/5 A1<br>2005/0206590 A1  |                    | Sasaki et al.                           |

| 2003/0169219 A1                     |         | LeChevalier                        | 2005/0219184 A1                     |                    | Zehner et al.                           |

| 2003/0174152 A1                     |         | Noguchi<br>Sanford et al           | 2005/0225686 A1<br>2005/0248515 A1  |                    | Brummack et al.<br>Naugler et al.       |

| 2003/0179626 A1<br>2003/0197663 A1  |         | Sanford et al.<br>Lee et al.       | 2005/0260777 A1                     | 11/2005            | Brabec et al.                           |

| 2003/0206060 A1                     |         |                                    |                                     |                    | Uchino et al. Ono et al                 |

| 2003/0210256 A1<br>2003/0230141 A1  |         | Mori et al.<br>Gilmour et al.      |                                     |                    | Cok et al                               |

| 2003/0230980 A1                     |         | Forrest et al.                     |                                     |                    | Johnson et al.                          |

| 2003/0231148 A1<br>2004/0027063 A1  |         | Lin et al.                         |                                     |                    | Reddy et al.<br>Eom et al.              |

| 2004/002/003 A1<br>2004/0032382 A1  |         | Nishikawa<br>Cok et al.            | 2006/0001613 A1                     |                    | Routley et al.                          |

| 2004/0056604 A1                     | 3/2004  | Shih et al.                        | 2006/0007072 A1                     |                    | Character 1                             |

| 2004/0066357 A1<br>2004/0070557 A1  |         | Kawasaki<br>Asano et al.           | 2006/0012310 A1<br>2006/0012311 A1  |                    | Chen et al.<br>Ogawa                    |

| 2004/0070565 A1                     |         | Nayar et al.                       | 2006/0012311 A1<br>2006/0027807 A1  |                    | Nathan et al.                           |

| 2004/0080262 A1                     |         | Park et al.                        | 2006/0030084 A1*                    |                    | Young 438/149                           |

| 2004/0080470 A1<br>2004/0090186 A1  |         | Yamazaki et al.<br>Kanauchi et al. | 2006/0038758 A1<br>2006/0038762 A1  | 2/2006<br>2/2006   | Routley et al.<br>Chou                  |

| 2004/0090180 A1*                    |         | Yoo 345/76                         | 2006/0050702 A1*                    |                    | Gunner et al 345/82                     |

| 2004/0095297 A1                     | 5/2004  | Libsch et al.                      | 2006/0066527 A1                     | 3/2006             | Chou                                    |

| (56)                         |            | Referen            | ces Cited                          |         | 2010/0165002<br>2010/0194670 |                    | 7/2010<br>8/2010 |                                |

|------------------------------|------------|--------------------|------------------------------------|---------|------------------------------|--------------------|------------------|--------------------------------|

| ]                            | U.S. I     | PATENT             | DOCUMENTS                          |         | 2010/0207960                 |                    |                  | Kimpe et al.                   |

| 2005(00555                   |            | a (a a a a         | ~ · · · •                          |         | 2010/0277400<br>2010/0315319 |                    | 11/2010          | Jeong<br>Cok et al.            |

| 2006/0066533<br>2006/0077135 |            |                    | Sato et al.<br>Cok et al.          |         | 2010/0313319                 |                    |                  | Sasaki et al.                  |

| 2006/007/133                 |            |                    | Guo et al.                         |         | 2011/0069051                 |                    |                  | Nakamura et al.                |

| 2006/0092185                 |            |                    | Jo et al.                          |         | 2011/0069089                 |                    |                  | Kopf et al.                    |

| 2006/0097628                 | <b>A</b> 1 | 5/2006             | Suh et al.                         |         | 2011/0074750                 |                    |                  | Leon et al.                    |

| 2006/0097631                 |            | 5/2006             |                                    |         | 2011/0090210<br>2011/0149166 |                    |                  | Sasaki et al.<br>Botzas et al. |

| 2006/0103611<br>2006/0149493 |            | 5/2006<br>7/2006   | Choi<br>Sambandan et al.           |         | 2011/0145100                 |                    |                  | Chaji et al.                   |

| 2006/0149493                 |            |                    | Nathan et al.                      | 345/82  | 2011/0273399                 |                    | 11/2011          | 3                              |

| 2006/0170623                 |            |                    | Naugler, Jr. et al.                |         | 2011/0293480                 |                    |                  | Mueller                        |

| 2006/0176250                 |            |                    | Nathan et al.                      |         | 2012/0056558                 |                    |                  | Toshiya et al.                 |

| 2006/0208961                 |            |                    | Nathan et al.                      | 245/76  | 2012/0062565<br>2012/0299978 |                    | 11/2012          | Fuchs et al.                   |

| 2006/0208971<br>2006/0232522 |            |                    | Deane                              | 343/70  | 2012/0255576                 |                    |                  | Nathan et al.                  |

| 2006/0232322                 |            |                    | Lee et al.                         |         | 2013/0032831                 |                    |                  | Chaji et al.                   |

| 2006/0261841                 | <b>A</b> 1 | 11/2006            | Fish                               |         | 2013/0057595                 | <b>A</b> 1         | 3/2013           | Nathan et al.                  |

| 2006/0264143                 |            |                    | Lee et al.                         |         |                              |                    |                  |                                |

| 2006/0273997<br>2006/0284801 |            |                    | Nathan et al.<br>Yoon et al.       |         | FC                           | PREIG              | N PATE           | NT DOCUMENTS                   |

| 2006/0284895                 |            |                    | Marcu et al.                       |         |                              | 2 240              | 503              | 7/1000                         |

| 2006/0290618                 |            | 12/2006            |                                    |         | CA<br>CA                     | 2 368              | 592<br>386       | 7/1998<br>9/1999               |

| 2007/0001937                 |            |                    | Park et al.                        |         | CA                           | 2 242              |                  | 1/2000                         |

| 2007/0001939                 |            |                    | Hashimoto et al                    | 345/76  | ČA                           | 2 354              |                  | 6/2000                         |

| 2007/0008268<br>2007/0008297 |            |                    | Park et al.<br>Bassetti            |         | CA                           | 2 432              |                  | 7/2002                         |

| 2007/0008297                 |            |                    | Uchino et al.                      |         | CA                           | 2 436              |                  | 8/2002                         |

| 2007/0069998                 |            |                    | Naugler et al.                     |         | CA<br>CA                     | 2 438 · 2 483 ·    |                  | 8/2002<br>12/2003              |

| 2007/0075727                 | <b>A</b> 1 |                    | Nakano et al.                      |         | CA                           | 2 463              |                  | 1/2003                         |

| 2007/0076226                 |            |                    | Klompenhouwer et al.               | 0.45/56 | CA                           | 2 498              |                  | 3/2004                         |

| 2007/0080905<br>2007/0080906 |            | 4/2007<br>4/2007   | Takahara                           | 345/76  | CA                           | 2 522              | 396              | 11/2004                        |

| 2007/0080908                 |            |                    | Tanabe<br>Nathan et al.            |         | CA                           | 2 443              |                  | 3/2005                         |

| 2007/0080918                 |            |                    | Kawachi et al.                     |         | CA<br>CA                     | 2 472 (<br>2 567 ( |                  | 12/2005<br>1/2006              |

| 2007/0097038                 | <b>A</b> 1 | 5/2007             | Yamazaki et al.                    |         | CA                           | 2 526              |                  | 4/2006                         |

| 2007/0097041                 |            |                    | Park et al.                        |         | CA                           | 2 550              |                  | 4/2008                         |

| 2007/0103419<br>2007/0115221 |            |                    | Uchino et al.<br>Buchhauser et al. |         | CN                           | 1 381              |                  | 11/2002                        |

| 2007/0113221                 |            |                    | Nathan et al.                      |         | CN                           | 1 448 9            |                  | 10/2003                        |

| 2007/0236517                 |            | 10/2007            |                                    |         | CN<br>DE 20 20               | 1 760 1<br>106 005 |                  | 4/2006<br>6/2006               |

| 2007/0241999                 |            | 10/2007            |                                    |         | EP 2020                      | 0 158              |                  | 10/1985                        |

| 2007/0273294                 |            |                    | Nagayama                           |         | EP                           | 0 940              |                  | 9/1999                         |

| 2007/0285359<br>2007/0290958 |            | 12/2007<br>12/2007 |                                    |         | EP                           | 1 028              |                  | 8/2000                         |

| 2007/0296572                 |            |                    | Kim et al.                         |         | EP                           | 1 103 9            |                  | 5/2001                         |

| 2008/0001525                 |            |                    | Chao et al.                        |         | EP<br>EP                     | 1 111 .            | 565 A1           | 6/2001<br>9/2001               |

| 2008/0001544                 |            |                    | Murakami et al.                    | /       | EP                           | 1 184              |                  | 3/2002                         |

| 2008/0036708                 |            |                    | Shirasaki et al                    |         | EP                           | 1 194              |                  | 3/2002                         |

| 2008/0042942<br>2008/0042948 |            |                    | Takahashi Yamashita et al.         | 343/77  | EP                           | 1 194              |                  | 4/2002                         |

| 2008/0042948                 |            |                    | Naugler, Jr. et al.                |         | EP<br>EP                     | 1 310 9            |                  | 5/2003<br>8/2003               |

| 2008/0055209                 |            | 3/2008             | •                                  |         | EP                           | 1 333              | 430 A1<br>136    | 8/2003<br>12/2003              |

| 2008/0074413                 |            | 3/2008             |                                    |         | EP                           | 1 381              |                  | 1/2004                         |

| 2008/0088549<br>2008/0088648 |            |                    | Nathan et al.<br>Nathan et al.     |         | $\mathbf{EP}$                | 1 418              |                  | 5/2004                         |

| 2008/0088048                 |            |                    | Nakano et al.                      |         | EP                           |                    | 312 A            | 6/2004                         |

| 2008/0150847                 |            |                    | Kim et al.                         |         | EP<br>EP                     | 1 439              | 520<br>143 A     | 7/2004<br>10/2004              |

| 2008/0158115                 | <b>A</b> 1 | 7/2008             | Cordes et al.                      |         | EP                           | 1 467              |                  | 10/2004                        |

| 2008/0231558                 |            |                    | Naugler                            |         | EP                           |                    | 448 A            | 10/2004                        |

| 2008/0231562<br>2008/0252571 |            | 9/2008             | Kwon<br>Hente et al.               |         | EP                           | 1 517              |                  | 3/2005                         |

| 2008/0232371                 |            | 11/2008            |                                    |         | EP                           |                    | 203 A2           | 4/2005                         |

| 2008/0297055                 |            |                    | Miyake et al.                      |         | EP<br>EP                     | 1 594 3            | 347<br>055 A2    | 11/2005<br>5/2007              |

| 2009/0032807                 | <b>A</b> 1 |                    | Shinohara et al.                   |         | EP                           |                    | 338 A1           | 11/2007                        |

| 2009/0058772                 |            | 3/2009             |                                    |         | EP                           |                    | 169 A1           | 1/2008                         |

| 2009/0160743<br>2009/0174628 |            |                    | Tomida et al.                      |         | EP                           | 1 879              |                  | 1/2008                         |

| 2009/01/4028                 |            | 7/2009             | Wang et al.<br>Kwon                |         | GB<br>GB                     | 2 205 4            |                  | 12/1988                        |

| 2009/0195483                 |            |                    | Naugler, Jr. et al.                |         | GB<br>JP                     | 2 389 9<br>12-72   |                  | 12/2003<br>10/1989             |

| 2009/0201281                 |            | 8/2009             | Routley et al.                     | _       | JP                           | 4-042              |                  | 2/1992                         |

| 2009/0213046                 |            |                    |                                    | 345/76  | JP                           | 6-314              |                  | 11/1994                        |

| 2010/0004891                 |            |                    | Ahlers et al.                      |         | JP                           | 8-340              |                  | 12/1996                        |

| 2010/0026725<br>2010/0039422 |            | 2/2010<br>2/2010   |                                    |         | JP<br>ID                     | 9 0904             |                  | 4/1997<br>6/1008               |

| 2010/0039422                 |            |                    | Marcu et al.                       |         | JP<br>JP                     | 10-153°<br>10-254  |                  | 6/1998<br>9/1998               |

| 2010/0079711                 |            | 4/2010             |                                    |         | JP                           | 11-202             |                  | 7/1999                         |

|                              |            |                    |                                    |         |                              |                    |                  |                                |

| (56)       | Referen                             | ces Cited         | OTHER PUBLICATIONS                                                                                                  |

|------------|-------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------|

|            | FOREIGN PATE                        | NT DOCUMENTS      | Alexander et al.: "Unique Electrical Measurement Technology for                                                     |

| JP         | 11-219146                           | 8/1999            | Compensation, Inspection, and Process Diagnostics of AMOLED                                                         |

| JP         | 11 231805                           | 8/1999            | HDTV"; dated May 2010 (4 pages).                                                                                    |

| JP         | 11-282419                           | 10/1999           | Chaji et al.: "A Current-Mode Comparator for Digital Calibration of                                                 |

| JP         | 2000-056847                         | 2/2000            | Amorphous Silicon AMOLED Displays"; dated Jul. 2008 (5 pages).                                                      |

| JP<br>ID   | 2000-077192                         | 3/2000            | Chaji et al.: "A fast settling current driver based on the CCII for                                                 |

| JP<br>JP   | 2000-81607<br>2000-089198           | 3/2000<br>3/2000  | AMOLED displays"; dated Dec. 2009 (6 pages).                                                                        |

| JP         | 2000-352941                         | 12/2000           | Chaji et al.: "A Low-Cost Stable Amorphous Silicon AMOLED Display with Full V~T- and V~O~L~E~D Shift Compensation"; |

| JP         | 2001-134217                         | 5/2001            | dated May 2007 (4 pages).                                                                                           |

| JP         | 2001-195014                         | 7/2001            | Chaji et al.: "A novel a-Si:H AMOLED pixel circuit based on short-                                                  |

| JP<br>JP   | 2002-055654<br>2002-91376           | 2/2002<br>3/2002  | term stress stability of a-Si:H TFTs"; dated Oct. 2005 (3 pages).                                                   |

| JP         | 2002-51370                          | 5/2002            | Chaji et al.: "A Sub-µA fast-settling current-programmed pixel cir-                                                 |

| JP         | 2002-268576                         | 9/2002            | cuit for AMOLED displays"; dated Sep. 2007.                                                                         |

| JР         | 2002-278513                         | 9/2002            | Chaji et al.: "An Enhanced and Simplified Optical Feedback Pixel                                                    |

| JP<br>JP   | 2002-333862<br>2003-022035          | 11/2002<br>1/2003 | Circuit for AMOLED Displays"; dated Oct. 2006.                                                                      |

| JP         | 2003-022033                         | 3/2003            | Chaji et al.: "Compensation technique for DC and transient instabil-                                                |

| JP         | 2003-124519                         | 4/2003            | ity of thin film transistor circuits for large-area devices"; dated Aug.                                            |

| $_{ m JP}$ | 2003-150082                         | 5/2003            | 2008.                                                                                                               |

| JP<br>JP   | 2003-177709<br>2003-271095          | 6/2003<br>9/2003  | Chaji et al.: "Fast and Offset-Leakage Insensitive Current-Mode Line                                                |

| JP         | 2003-271093                         | 10/2003           | Driver for Active Matrix Displays and Sensors"; dated Feb. 2009 (8                                                  |

| JP         | 2003-317944                         | 11/2003           | pages).<br>Chail at all, "Lawy Coat AMOLED Talayidian with ICNIS Common                                             |

| JP         | 2004-145197                         | 5/2004            | Chaji et al.: "Low-Cost AMOLED Television with IGNIS Compensating Technology"; dated May 2008 (4 pages).            |

| JP<br>ID   | 2004-287345                         | 10/2004           | Chaji et al.: "Low-Power Low-Cost Voltage-Programmed a-Si:H                                                         |

| JP<br>JP   | 2005-157217<br>4-158570             | 6/2005<br>10/2008 | AMOLED Display"; dated Jun. 2008 (5 pages).                                                                         |

| KR         | 2004-0100887                        | 12/2004           | Chaji et al.: "Merged phototransistor pixel with enhanced near infra-                                               |

| TW         | 342486                              | 10/1998           | red response and flicker noise reduction for biomolecular imaging";                                                 |

| TW         | 473622                              | 1/2002            | dated Nov. 2008 (3 pages).                                                                                          |

| TW<br>TW   | 485337<br>502233                    | 5/2002<br>9/2002  | Chaji et al.: "Stable Pixel Circuit for Small-Area High- Resolution                                                 |

| TW         | 538650                              | 6/2003            | a-Si:H AMOLED Displays"; dated Oct. 2008 (6 pages).                                                                 |

| TW         | 569173                              | 1/2004            | Chaji et al.: "Stable RGBW AMOLED display with OLED degrada-                                                        |

| TW         | 1221268                             | 9/2004            | tion compensation using electrical feedback"; dated Feb. 2010 (2                                                    |

| TW<br>TW   | 1223092<br>2007-27247               | 11/2004<br>7/2007 | pages).                                                                                                             |

| WO         | WO 94/25954                         | 11/1994           | European Search Report and Written Opinion for Application No.                                                      |

| WO         | WO 98/48403                         | 10/1998           | 08865338 mailed Nov. 2, 2011 (7 pages).                                                                             |

| WO         | WO 99/48079                         | 9/1999            | European Search Report for European Application No. 10000421.7 mailed Mar. 26, 2012 in corresponding (6 pages).     |

| WO<br>WO   | WO 01/06484<br>WO 01/27910 A1       | 1/2001<br>4/2001  | European Search Report for European Application No. 10834294.0-                                                     |

| WO         | WO 01/27510 A1<br>WO 01/63587 A2    | 8/2001            | 1903, dated Apr. 8, 2013, (9 pages).                                                                                |

| WO         | 03/063124                           | 3/2002            | European Search Report for European Application No. EP                                                              |

| WO         | WO 02/067327 A                      | 8/2002            | 011122313 dated Sep. 14, 2005 (4 pages).                                                                            |

| WO<br>WO   | WO 03/001496 A1<br>03/034389        | 1/2003<br>4/2003  | European Search Report for European Application No. EP 04786661                                                     |

| WO         | WO 03/034389 A                      | 4/2003            | dated Mar. 9, 2009.                                                                                                 |

| WO         | WO 03/058594 A1                     | 7/2003            | European Search Report for European Application No. EP 05759141                                                     |

| WO         | WO 03/063124                        | 7/2003            | dated Oct. 30, 2009.                                                                                                |

| WO<br>WO   | WO 03/077231<br>WO 03/105117        | 9/2003<br>12/2003 | European Search Report for European Application No. EP 05819617                                                     |

| WO         | WO 2004/003877                      | 1/2003            | dated Jan. 30, 2009.  European Search Benert for European Application No. ED 05221114                               |

| WO         | WO 2004/025615 A                    | 3/2004            | European Search Report for European Application No. EP 05821114                                                     |

| WO         | WO 2004/047058                      | 4/2004<br>6/2004  | dated Mar. 27, 2009 (2 pages).<br>European Search Report for European Application No. EP 06705133                   |

| WO<br>WO   | WO 2004/047058<br>WO 2004/104975 A1 | 6/2004<br>12/2004 | dated Jul. 18, 2008.                                                                                                |

| WO         | WO 2005/022498                      | 3/2005            | European Search Report for European Application No. EP 06721798                                                     |

| WO         | WO 2005/022500 A                    | 3/2005            | dated Nov. 12, 2009 (2 pages).                                                                                      |

| WO         | WO 2005/029455                      | 3/2005            | European Search Report for European Application No. EP                                                              |

| WO<br>WO   | WO 2005/029456<br>WO 2005/055185    | 3/2005<br>6/2005  | 07710608.6 dated Mar. 19, 2010 (7 pages).                                                                           |

| WO         | WO 2006/000101 A1                   | 1/2006            | European Search Report for European Application No. EP 07719579                                                     |

| WO         | WO 2006/053424                      | 5/2006            | dated May 20, 2009.<br>European Search Report for European Application No. EP 07815784                              |

| WO         | 2006/063448                         | 6/2006            | dated Jul. 20, 2010 (2 pages).                                                                                      |

| WO<br>WO   | WO 2006/063448 A<br>WO 2006/084360  | 6/2006<br>8/2006  | European Search Report for European Application No. EP                                                              |

| WO         | WO 2006/084300<br>WO 2006/137337    | 12/2006           | 10166143, dated Sep. 3, 2010 (2 pages).                                                                             |

| WO         | WO 2007/003877 A                    | 1/2007            | European Search Report for European Application No. EP                                                              |

| WO         | WO 2007/079572                      | 7/2007            | 11739485.8-1904 dated Aug. 6, 2013, (14 pages).                                                                     |

| WO         | WO 2007/120849 A2                   | 10/2007           | European Search Report for European Application No. PCT/                                                            |

| WO<br>WO   | WO 2009/055920<br>WO 2010/023270    | 5/2009<br>3/2010  | CA2006/000177 dated Jun. 2, 2006. European Supplementary Search Report for European Application                     |

| WO         | WO 2010/023270<br>WO 2011/041224 A1 | 3/2010<br>4/2011  | No. 04786662 dated Jan. 19, 2007 (2 pages).                                                                         |

| 110        | 11 0 2011/071227 A1                 | 1/2011            | 110. 0 1700002 dated sam. 19, 2007 (2 pages).                                                                       |

# (56) References Cited

### OTHER PUBLICATIONS

Extended European Search Report for European Application No. .09733076.5 mailed Apr. 27, 2011 issued during prosecution (13 pages).

Extended European Search Report for European Application No. 11168677.0 mailed Nov. 29, 2012, (13 page).

Extended European Search Report for European Application No. 11191641.7 mailed Jul. 11, 2012 (14 pages).

Fossum, Eric R.. "Active Pixel Sensors: Are CCD's Dinosaurs?" SPIE: Symposium on Electronic Imaging. Feb. 1, 1993 (13 pages). Goh et al., "A New a-Si:H Thin-Film Transistor Pixel Circuit for Active-Matrix Organic Light-Emitting Diodes", IEEE Electron Device Letters, vol. 24, No. 9, Sep. 2003, pp. 583-585.

International Preliminary Report on Patentability, PCT/CA2005/001007 dated Oct. 16, 2006, 4 pages.

International Search Report, PCT/CA02/00180 dated Jul. 31, 2002 (3 pages).

International Search Report, PCT/CA2004/001741 dated Feb. 21, 2005.

International Search Report, PCT/CA2004/001742, Canadian Patent Office, dated Feb. 21, 2005 (2 pages).

International Search Report, PCT/CA2005/001007 dated Oct. 18, 2005.

International Search Report, PCT/CA2005/001844 dated Mar. 28, 2006 (2 pages).

International Search Report, PCT/CA2005/001897 mailed Mar. 21, 2006 (2 pages).

International Search Report, PCT/CA2007/000652 dated Jul. 25, 2007.

International Search Report, PCT/CA2008/002307, mailed Apr. 28, 2009 (3 pages).

International Search Report, PCT/CA2009/000501 mailed Jul. 30, 2009 (4 pages).

International Search Report, PCT/CA2009/001769, dated Apr. 8, 2010 (3 pages).

International Search Report, PCT/IB2010/055481, dated Apr. 7, 2011, 3 pages.

International Search Report, PCT/IB2010/055486, Dated Apr. 19, 2011, 5 pages.

International Search Report, PCT/IB2010/055541 filed Dec. 1, 2010, dated May 26, 2011; 5 pages.

International Search Report, PCT/IB2011/050502, dated Jun. 27, 2011 (6 pages).

International Search Report, PCT/IB2011/051103, dated Jul. 8, 2011, 3 pages.

International Search Report, PCT/IB2011/055135, Canadian Patent Office, dated Apr. 16, 2012 (5 pages).

International Search Report, PCT/IB2012/052372, mailed Sep. 12, 2012 (3 pages).

International Search Report, PCT/IB2013/054251, Canadian Patent Office, dated Sep. 11, 2013; (4 pages).

International Search Report, PCT/JP02/09668 mailed Dec. 3, 2002, (4 pages).

International Written Opinion, PCT/CA2004/001742, Canadian Patent Office, dated Feb. 21, 2005 (5 pages).

International Written Opinion, PCT/CA2005/001897 mailed Mar. 21, 2006 (4 pages).

International Written Opinion, PCT/CA2009/000501 Application No. PCT/CA2009/000501 mailed Jul. 30, 2009 (6 pages).

International Written Opinion, PCT/CA2009/000501 mailed Jul. 30, 2009 for International Application No. PCT/CA2009/000501 (6 pages).

International Written Opinion, PCTAB2010/055486, Dated Apr. 19, 2011, 8 pages.

International Written Opinion, PCTAB2010/055541, dated May 26, 2011; 6 pages.

International Written Opinion, PCT/IB2011/050502 dated Jun. 27, 2011 (7 pages).

International Written Opinion, PCT/IB2011/051103, dated Jul. 8, 2011, 6 pages.

International Written Opinion, PCT/IB2011/055135, Canadian Patent Office, dated Apr. 16, 2012 (5 pages).

International Written Opinion, PCT/IB2012/052372, mailed Sep. 12, 2012 (6 pages).

International Written Opinion, PCT/IB2013/054251, Canadian Intellectual Property Office, dated Sep. 11, 2013; (5 pages).

Jafarabadiashtiani et al.: "A New Driving Method for a-Si AMOLED Displays Based on Voltage Feedback"; dated 2005 (4 pages).

Kanicki, J., et al. "Amorphous Silicon Thin-Film Transistors Based Active-Matrix Organic Light-Emitting Displays." Asia Display: International Display Workshops, Sep. 2001 (pp. 315-318).

Karim, K. S., et al. "Amorphous Silicon Active Pixel Sensor Readout Circuit for Digital Imaging." IEEE: Transactions on Electron Devices. vol. 50, No. 1, Jan. 2003 (pp. 200-208).

Ma e y et al: "Organic Light-Emitting Diode/Thin Film Transistor Integration for foldable Displays" Conference record of the 1997 International display research conference and international workshops on LCD technology and emissive technology. Toronto, Sep. 15-19, 1997 (6 pages).

Machine English translation of JP 2002-333862, 49 pages.

Matsueda y et al.: "35.1: 2.5-in. AMOLED with Integrated 6-bit Gamma Compensated Digital Data Driver"; dated May 2004.

Mendes E., et al. "A High Resolution Switch-Current Memory Base Cell." IEEE: Circuits and Systems. vol. 2, Aug. 1999 (pp. 718-721). Nathan A. et al., "Thin Film imaging technology on glass and plastic" ICM 2000, proceedings of the 12 international conference on microelectronics, dated Oct. 31, 2001 (4 pages).

Nathan et al., "Amorphous Silicon Thin Film Transistor Circuit Integration for Organic LED Displays on Glass and Plastic", IEEE Journal of Solid-State Circuits, vol. 39, No. 9, Sep. 2004, pp. 1477-1486. Nathan et al.: "Backplane Requirements for active Matrix Organic Light Emitting Diode Displays,"; dated 2006 (16 pages).

Nathan et al.: "Call for papers second international workshop on compact thin-film transistor (TFT) modeling for circuit simulation"; dated Sep. 2009 (1 page).

Nathan et al.: "Invited Paper: a -Si for AMOLED—Meeting the Performance and Cost Demands of Display Applications (Cell Phone to HDTV)", dated 2006 (4 pages).

Office Action in Japanese patent application No. JP2006-527247 dated Mar. 15, 2010. (8 pages).

Office Action in Japanese patent application No. JP2007-545796 dated Sep. 5, 2011. (8 pages).

Office Action issued in Chinese Patent Application 200910246264.4 Dated Jul. 5, 2013; 8 pages.

Partial European Search Report mailed Mar. 20, 2012 which issued in corresponding European Patent Application No. EP 11191641.7 (8 pages).

Partial European Search Report mailed Sep. 22, 2011 corresponding to European Patent Application No. EP 11168677.0 (5 pages).

Patent Abstracts of Japan, vol. 1997, No. 08, Aug. 29, 1997, & JP 09 090405 A, Apr. 4, 1997 Abstract.

Patent Abstracts of Japan, vol. 1999, No. 13, Nov. 30, 1999, & JP 11 231805 A, Aug. 27, 1999 Abstract.

Patent Abstracts of Japan, vol. 2000, No. 09, Oct. 13, 2000—JP 2000 172199 A, Jun. 3, 2000, abstract.

Patent Abstracts of Japan, vol. 2002, No. 03, Apr. 3, 2002 (Apr. 4, 2004 & JP 2001 318627 A (Semiconductor EnergyLab DO Ltd), Nov. 16, 2001, abstract, paragraphs '01331-01801, paragraph '01691, paragraph '01701, paragraph '01721 and figure 10.

Safavian et al.: "A novel hybrid active-passive pixel with correlated double sampling CMOS readout circuit for medical x-ray imaging"; dated May 2008 (4 pages).

Safavian et al.: "Self-compensated a-Si:H detector with current-mode readout circuit for digital X-ray fluoroscopy"; dated Aug. 2005 (4 pages).

Safavian et al.: "Three-TFT image sensor for real-time digital X-ray imaging"; dated Feb. 2, 2006 (2 pages).

Sanford, James L., et al., "4.2 TFT AMOLED Pixel Circuits and Driving Methods", SID 03 Digest, ISSN/0003, 2003, pp. 10-13.

Search Report for Taiwan Invention Patent Application No. 093128894 dated May 1, 2012. (1 page).

Search Report for Taiwan Invention Patent Application No. 94144535 dated Nov. 1, 2012. (1 page).

#### **References Cited** (56)

#### OTHER PUBLICATIONS

Singh, et al., "Current Conveyor: Novel Universal Active Block", Samriddhi, S-JPSET vol. I, Issue 1, 2010, pp. 41-48.

Spindler et al., System Considerations for RGBW OLED Displays, Journal of the SID 14/1, 2006, pp. 37-48.

Stewart M. et al., "polysilicon TFT technology for active matrix oled displays" IEEE transactions on electron devices, vol. 48, No. 5, dated May 2001 (7 pages).

Tatsuya Sasaoka et al., 24.4L; Late-News Paper: a 13.0-inch AM-Oled Display with Top Emitting Structure and Adaptive Current Mode Programmed Pixel Circuit (TAC), SID 01 Digest, (2001), pp. 384-387.

Vygranenko et al.: "Stability of indium-oxide thin-film transistors by reactive ion beam assisted deposition"; dated 2009.

Wang et al.: "Indium oxides by reactive ion beam assisted evaporation: From material study to device application"; dated Mar. 2009 (6) pages).

Yi He et al., "Current-Source a-Si:H Thin Film Transistor Circuit for Active-Matrix Organic Light-Emitting Displays", IEEE Electron Device Letters, vol. 21, No. 12, Dec. 2000, pp. 590-592.

Yu, Jennifer: "Improve OLED Technology for Display", Ph.D. Dissertation, Massachusetts Institute of Technology, Sep. 2008 (151 pages).

Zhiguo Meng et al; "24.3: Active-Matrix Organic Light-Emitting Diode Display implemented Using Metal-Induced Unilaterally Crystallized Polycrystalline Silicon Thin-Film Transistors", SID 01Digest, (2001), pp. 380-383.

Alexander et al.: "Pixel circuits and drive schemes for glass and elastic AMOLED displays"; dated Jul. 2005 (9 pages).

Ashtiani et al.: "AMOLED Pixel Circuit With Electronic Compensation of Luminance Degradation"; dated Mar. 2007 (4 pages).

Chahi et al.: "An Enhanced and Simplified Optical Feedback Pixel Circuit for AMOLED Displays"; dated Oct. 2006.

Chaji et al.: "A low-power driving scheme for a-Si:H active-matrix organic light-emitting diode displays"; dated Jun. 2005 (4 pages).

Chaji et al.: "A low-power high-performance digital circuit for deep submicron technologies"; dated Jun. 2005 (4 pages).

Chaji et al.: "A Novel Driving Scheme and Pixel Circuit for AMOLED Displays"; dated Jun. 2006 (4 pages).

Chaji et al.: "A novel driving scheme for high-resolution large-area a-Si:H AMOLED displays"; dated Aug. 2005 (4 pages).

Chaji et al.: "A Stable Voltage-Programmed Pixel Circuit for a-Si:H AMOLED Displays"; dated Dec. 2006 (12 pages).

Chaji et al.: "Driving scheme for stable operation of 2-TFT a-Si AMOLED pixel"; dated Apr. 2005 (2 pages).

Chaji et al.: "Dynamic-effect compensating technique for stable a-Si:H AMOLED displays"; dated Aug. 2005 (4 pages).

Chaji et al.: "Electrical Compensation of OLED Luminance Degra-

dation"; dated Dec. 2007 (3 pages).

Chaji et al.: "eUTDSP: a design study of a new VLIW-based DSP architecture"; dated May 2003 (4 pages).

Chaji et al.: "High Speed Low Power Adder Design With A New Logic Style: Pseudo Dynamic Logic (SDL)"; dated Oct. 2001 (4) pages).

Chaji et al.: "High-precision, fast current source for large-area current-programmed a-Si flat panels"; dated Sep. 2006 (4 pages).

Chaji et al.: "Low-Cost Stable a-Si:H AMOLED Display for Portable Applications"; dated Jun. 2006 (4 pages).

Chaji et al.: "Parallel Addressing Scheme for Voltage-Programmed Active-Matrix OLED Displays"; dated May 2007 (6 pages).

Chaji et al.: "Pseudo dynamic logic (SDL): a high-speed and lowpower dynamic logic family"; dated 2002 (4 pages).

Chaji et al.: "Stable a-Si:H circuits based on short-term stress stability of amorphous silicon thin film transistors"; dated May 2006 (4) pages).

Chaji et al.: "Stable Pixel Circuit for Small-Area High-Resolution a-Si:H AMOLED Displays"; dated 2008 (7 pages).

Chaji et al.: "Thin-Film Transistor Integration for Biomedical Imaging and AMOLED Displays"; dated 2008 (177 pages).

He et al., "Current-Source a-Si:H Thin Film Transistor Circuit for Active-Matrix Organic Light-Emitting Displays", IEEE Electron Device Letters, vol. 21, No. 12, Dec. 2000, pp. 590-592.

Goh et al., "A New a-Si:H Thin Film Transistor Pixel Circul for Active-Matrix Organic Light-Emitting Diodes", IEEE Electron Device Letters, vol. 24, No. 9, Sep. 2003, 4 pages.

Jafarabadiashtiani et al.: "A New Driving Method for a-Si AMOLED Displays Based on Voltage Feedback"; May 27, 2005 (4 pages).

Lee et al.: "Ambipolar Thin-Film Transistors Fabricated by PECVD Nanocrystalline Silicon"; dated 2006 (6 pages).

Matsueda y et al.: "35.1: 2.5-in. AMOLED with Integrated 6-bit Gamma Compensated Digital Data Driver"; dated May 2004 (4) pages).

Nathan et al., "Amorphous Silicon Thin Film Transistor Circuit Integration Oganic LED Displays on Glass and Plastic", IEEE Journal of Solid-State Circuits, vol. 39, No. 9, Sep. 2004, 12 pages.

Nathan et al.: "Driving schemes for a-Si and LTPS AMOLED displays"; dated Dec. 2005 (11 pages).

Philipp: "Charge transfer sensing" Sensor Review, vol. 19, No. 2, Dec. 31, 1999, 10 pages.

Rafati et al.: "Comparison of a 17 b multiplier in Dual-rail domino and in Dual-rail D L (D L) logic styles"; dated 2002 (4 pages).

Safavian et al.: "3-TFT active pixel sensor with correlated double sampling readout circuit for real-time medical x-ray imaging"; dated Jun. 2006 (4 pages).

Safavian et al.: "A novel current scaling active pixel sensor with correlated double sampling readout circuit for real time medical x-ray imaging"; dated May 2007 (7 pages).

Safavian et al.: "Self-compensated a-Si-H detector with currentmode readout circuit for digital X-ray fluoroscopy"; dated Aug. 2005 (4 pages).

Safavian et al.: "TFT active image sensor with current-mode readout circuit for digital x-ray fluoroscopy [5969D-82]"; dated Sep. 2005 (9 pages).

International Preliminary Report on Patentability for International Application No. PCT/CA2005/001007 dated Oct. 16, 2006, 4 pages.

<sup>\*</sup> cited by examiner

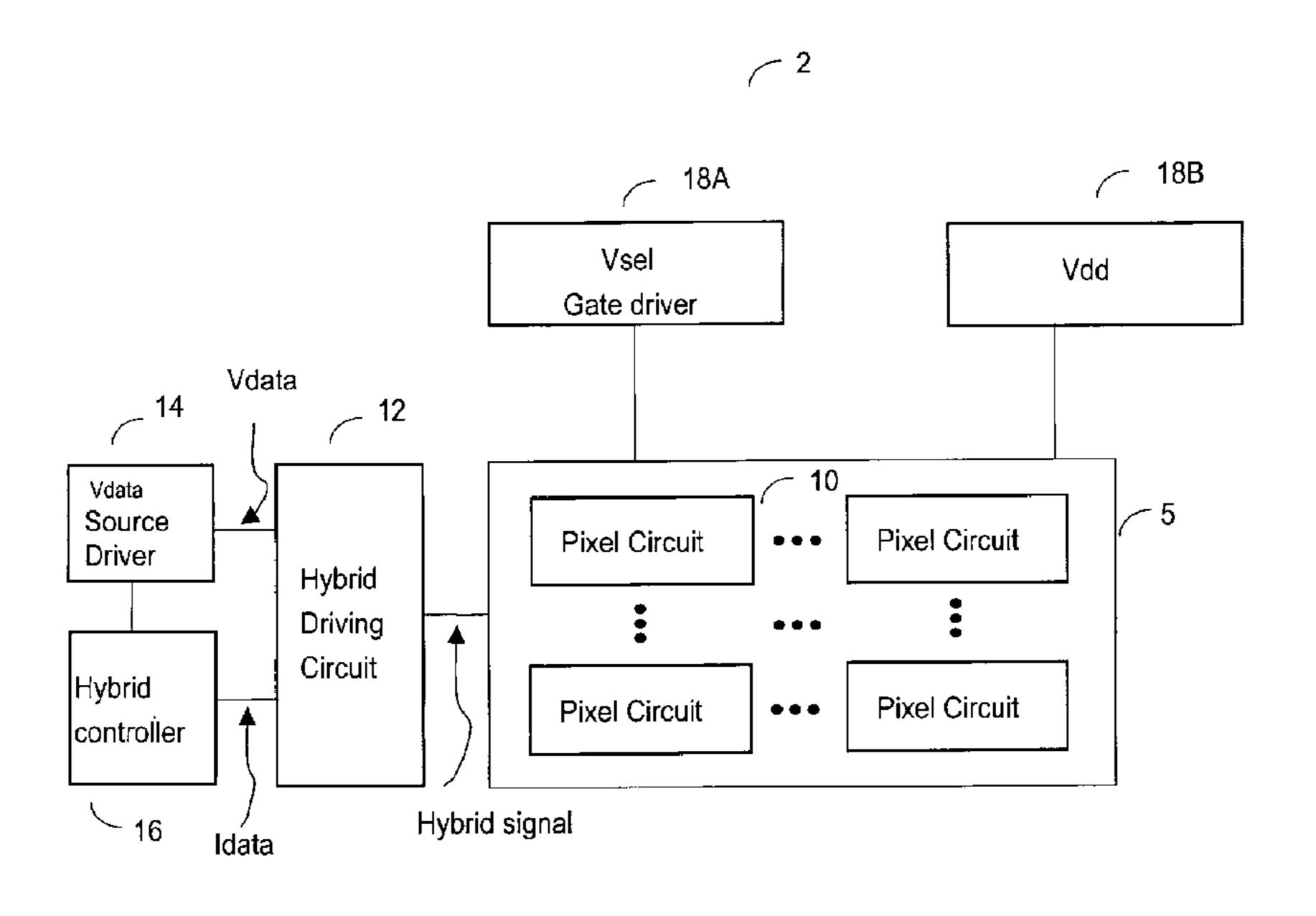

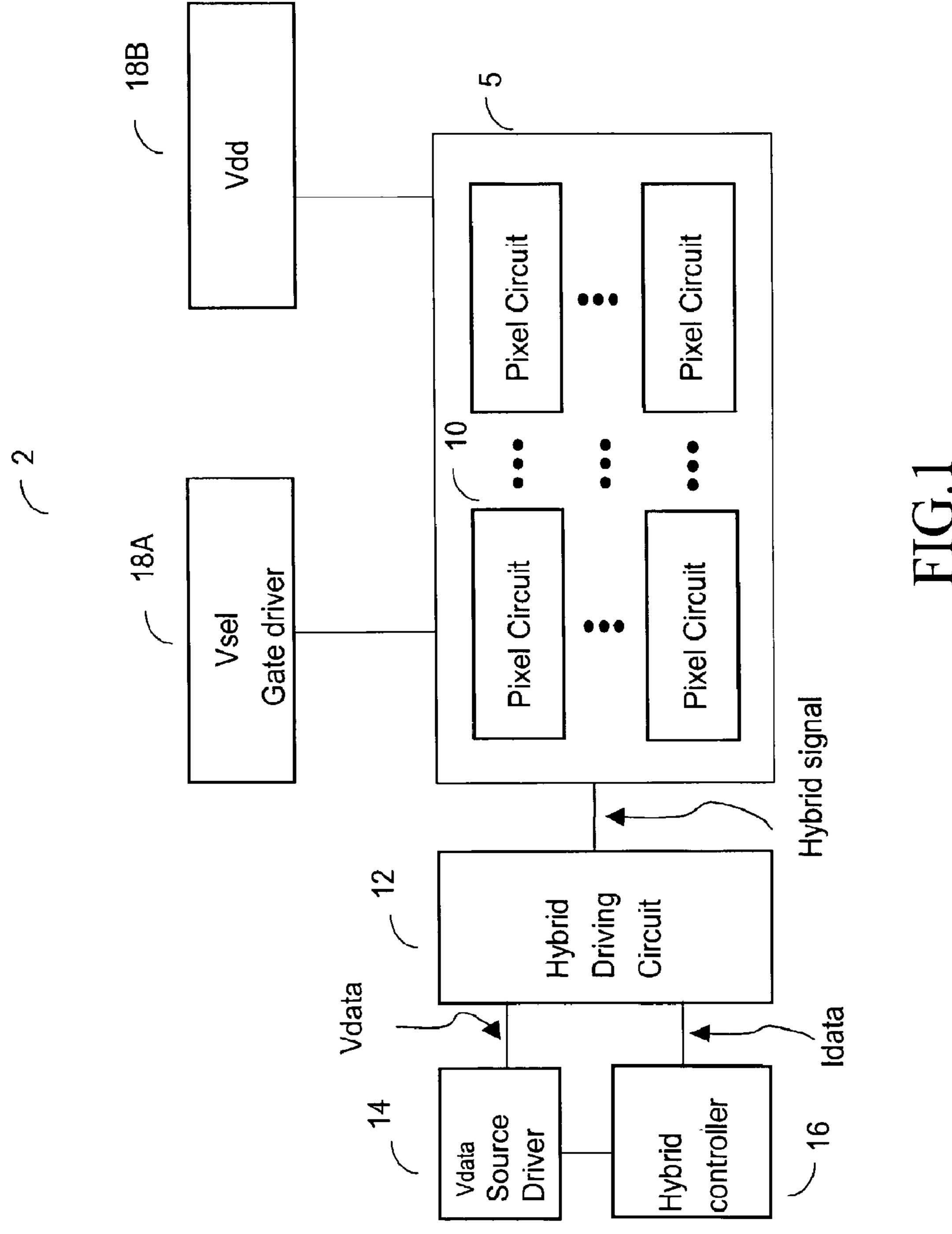

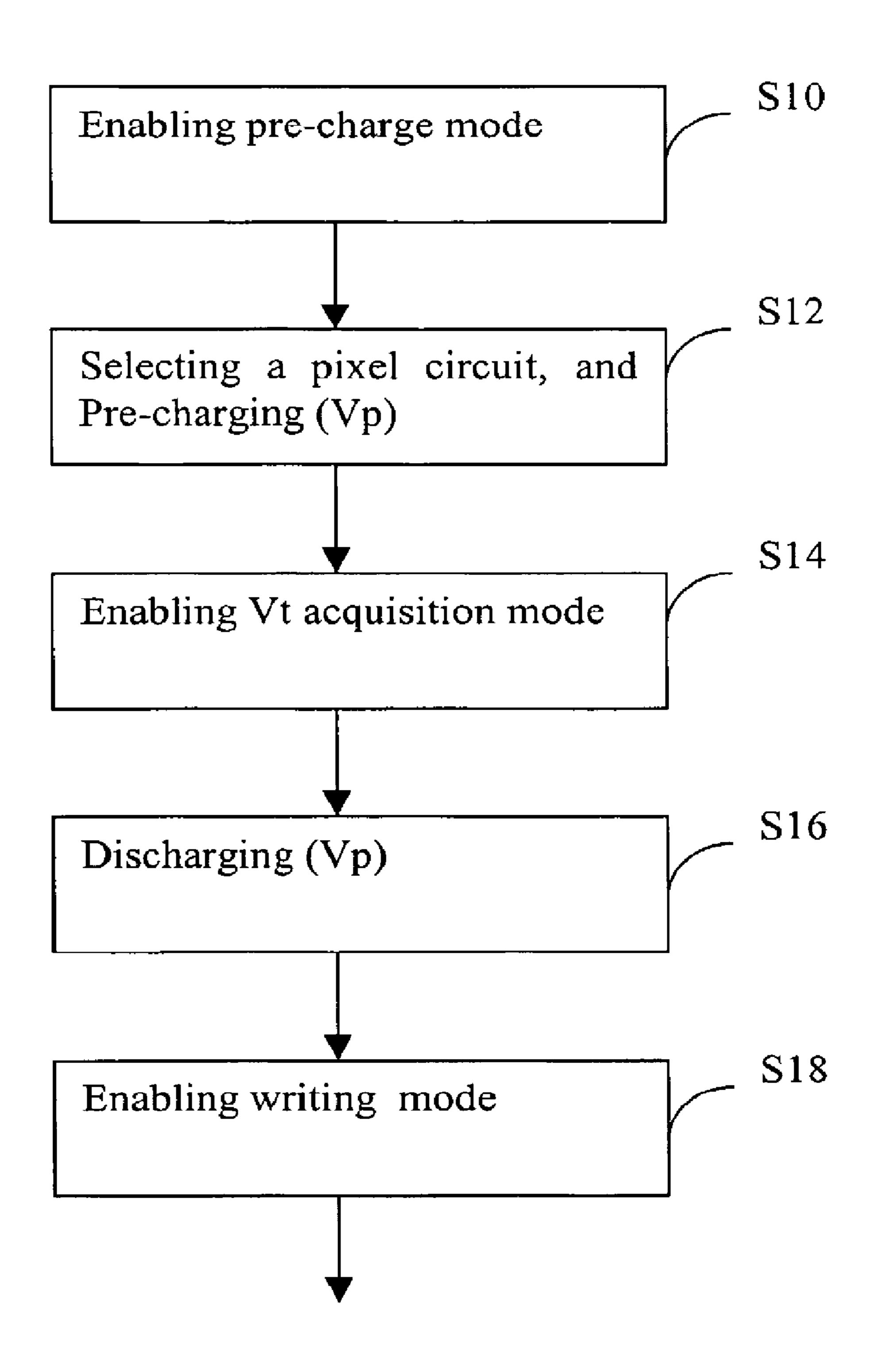

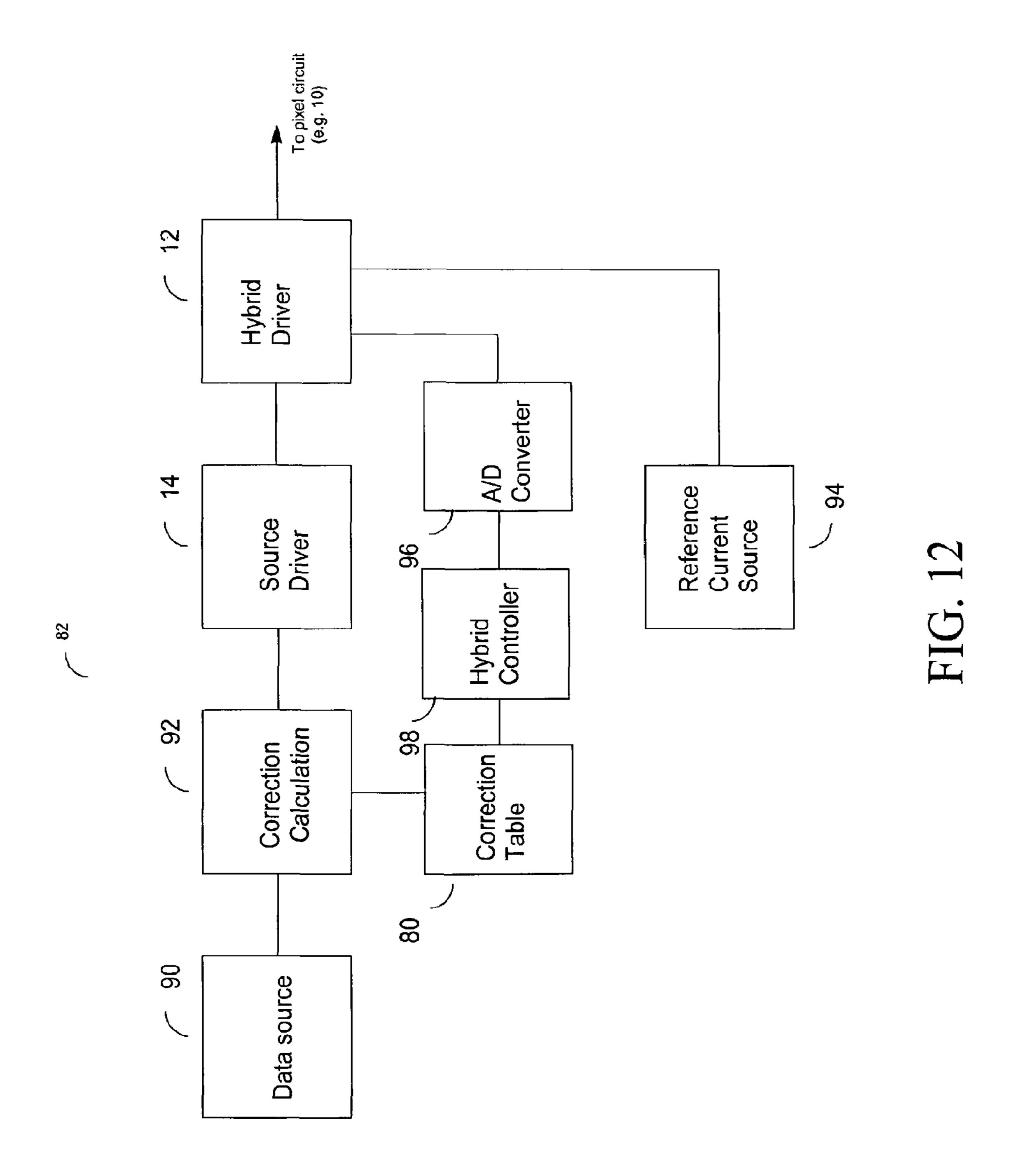

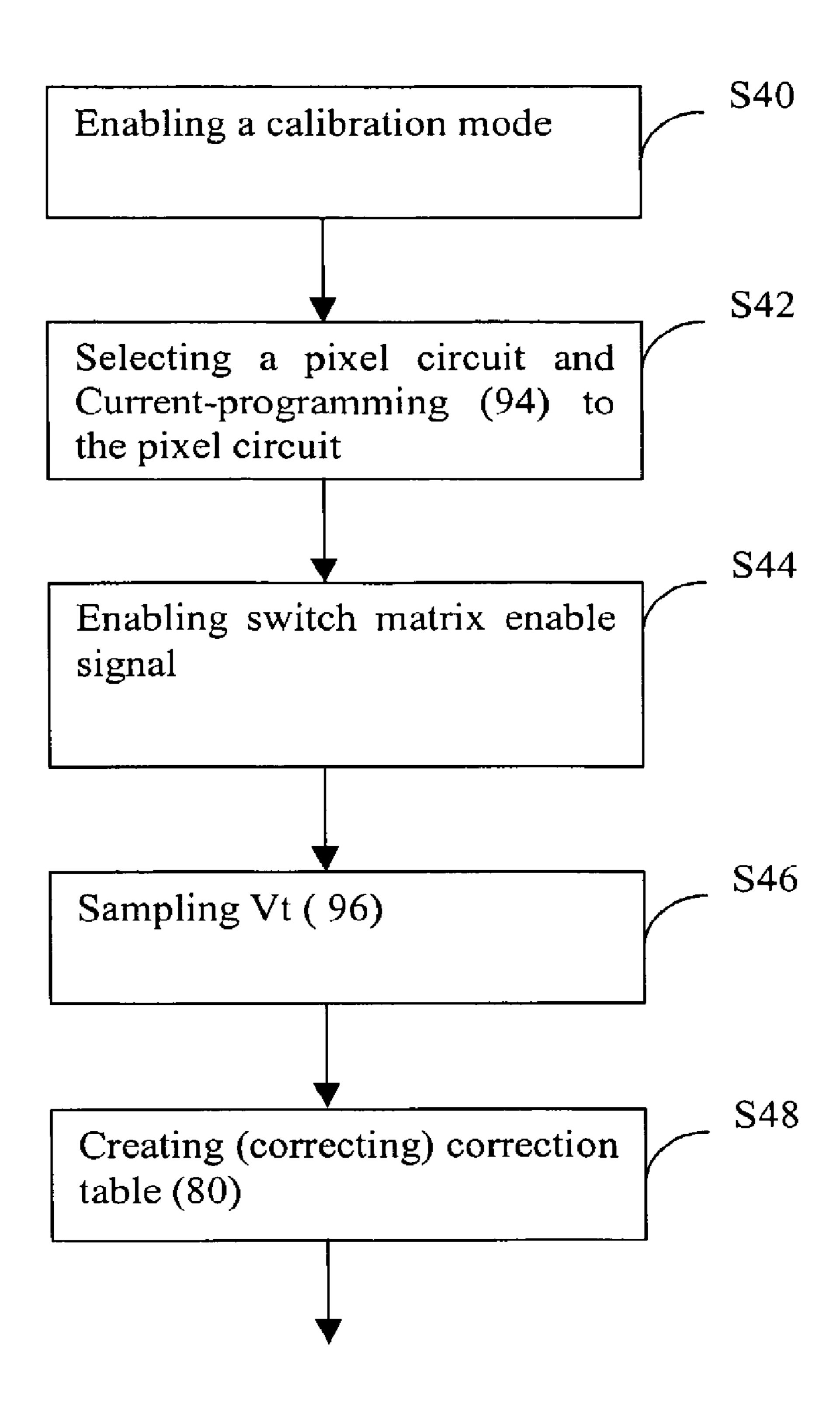

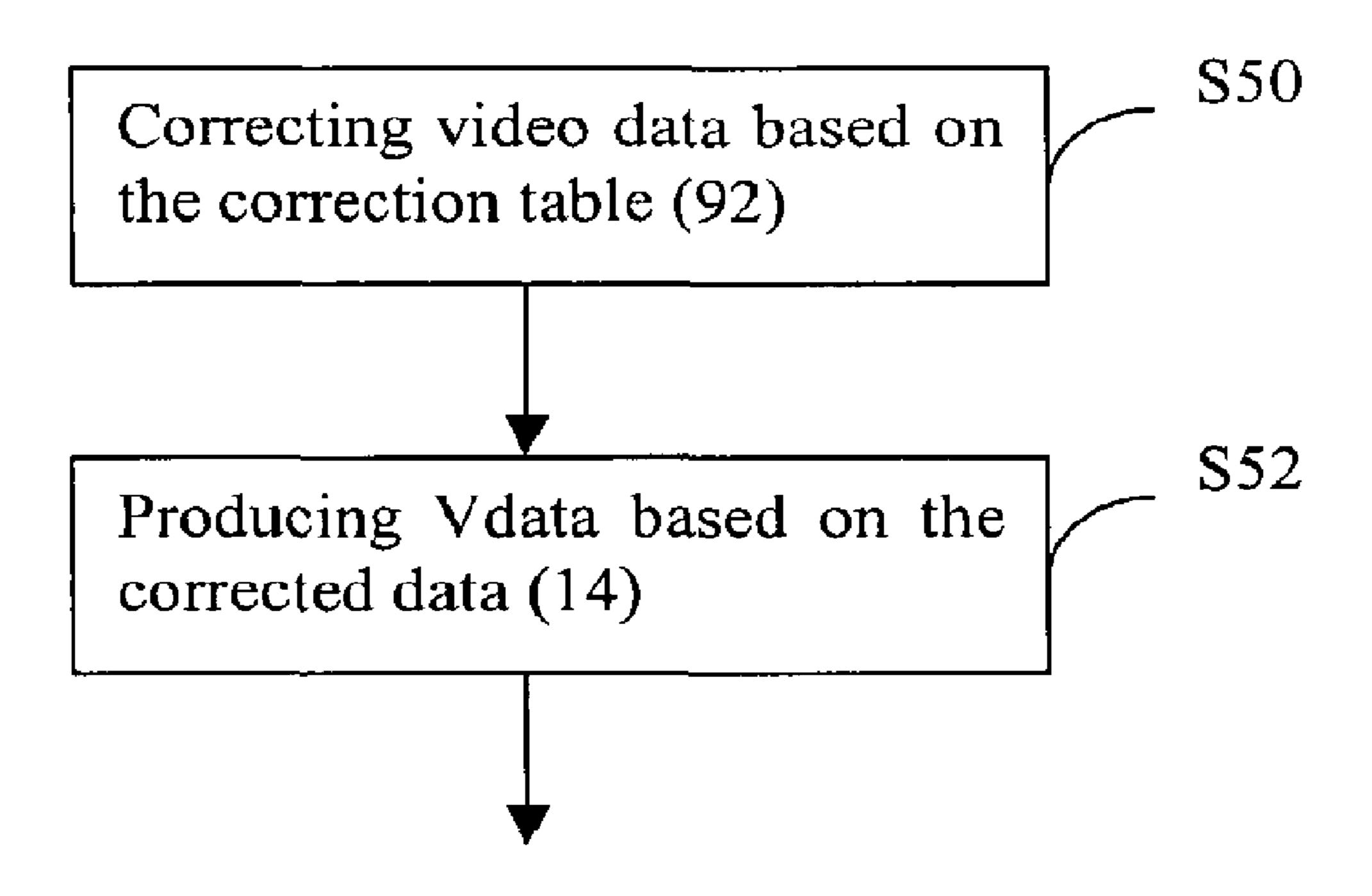

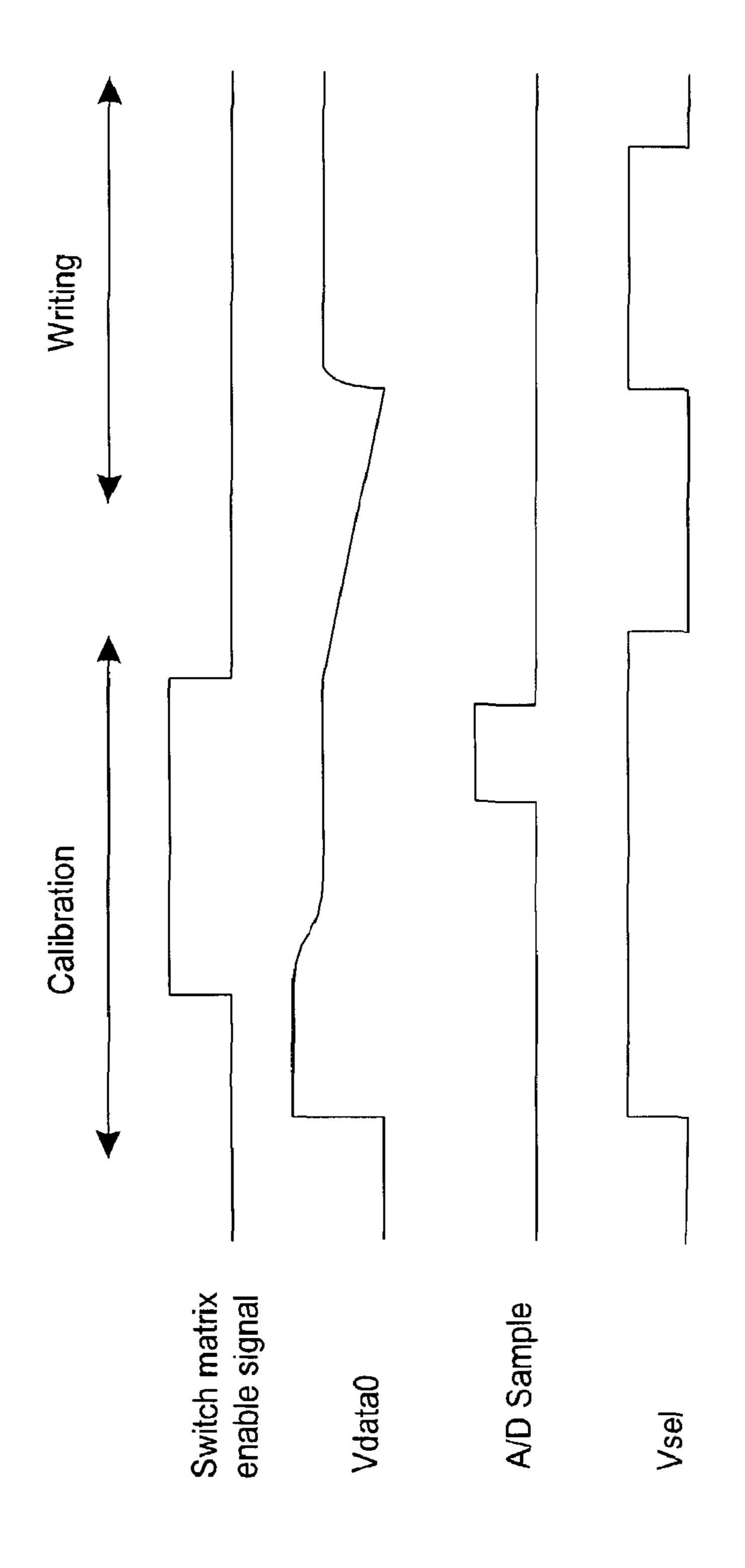

FIG.2