#### US00RE44632E

## (19) United States

# (12) Reissued Patent

Oh et al.

(10) Patent Number:

US RE44,632 E

(45) Date of Reissued Patent:

Dec. 10, 2013

# (54) SEMICONDUCTOR MEMORY DEVICE AND DRIVING METHOD THEREOF

(75) Inventors: Young-Hoon Oh, Kyoungki-do (KR);

Kwang-Myoung Rho, Kyoungki-do

(KR)

(73) Assignee: **658868 N.B. Inc.**, St. John, NB (CA)

(21) Appl. No.: 13/538,130

(22) Filed: **Jun. 29, 2012** (Under 37 CFR 1.47)

## Related U.S. Patent Documents

Reissue of:

(64) Patent No.: **7,746,723**

Issued: Jun. 29, 2010 Appl. No.: 12/354,158

U.S. Applications:

Filed:

(63) Continuation of application No. 11/647,402, filed on Dec. 29, 2006, now Pat. No. 7,489,586.

Jan. 15, 2009

### (30) Foreign Application Priority Data

Jun. 29, 2006 (KR) ...... 10-2006-0059735

(51) **Int. Cl.**

G11C 8/00 (2006.01)

(52) U.S. Cl.

(58) Field of Classification Search

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,859,404 B1* | 2/2005 | Kim 365/194           |

|---------------|--------|-----------------------|

| 6,990,042 B2* | 1/2006 | Stark 365/233.1       |

| 6,996,026 B2* | 2/2006 | Brox et al 365/189.15 |

| 7,171,321 B2* | 1/2007 | Best 702/106          |

| 7.397.725 B2* | 7/2008 | Stark 365/233.1       |

#### FOREIGN PATENT DOCUMENTS

| KR | 10-2005-0020359 | 3/2005  |

|----|-----------------|---------|

| KR | 10-2005-0048755 | 5/2005  |

| KR | 10-2005-0109813 | 11/2005 |

<sup>\*</sup> cited by examiner

Primary Examiner — David Lam

(74) Attorney, Agent, or Firm — Harvey Auerback

#### (57) ABSTRACT

A semiconductor memory device includes: a variable delay for delaying a delay locked loop (DLL) clock by a predetermined delay time to output a delayed DLL clock; an output driver for outputting data and data strobe signal in response to the delayed DLL clock; and a calibration controller for controlling the predetermined delay time of the variable delay in response to output AC parameters.

### 39 Claims, 4 Drawing Sheets

FIG. 1

(RELATED ART)

FIG. 2

(RELATED ART)

FIG. 3

FIG. 4

FIG. 5

FIG. 6

# SEMICONDUCTOR MEMORY DEVICE AND DRIVING METHOD THEREOF

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

#### RELATED APPLICATIONS

This application is Continuation of U.S. application Ser. No. 11/647,402, filed on Dec. 29, 2006 and issued as U.S. Pat. No. 7,489,586 on Feb. 10, 2009, claiming priority of Korean Application No. 10-2006-0059736 filed on Jun. 29, 2006, the entire contents of each of which are hereby incorporated by reference.

#### FIELD OF THE INVENTION

The present invention relates to a semiconductor memory device, and more particularly, to a synchronous semiconductor device and a method for controlling output AC parameters thereof.

#### DESCRIPTION OF RELATED ART

A synchronous semiconductor memory device shares a system clock output from a clock generator with a chipset and receives or transfers command, address and data in synchronization with the system clock.

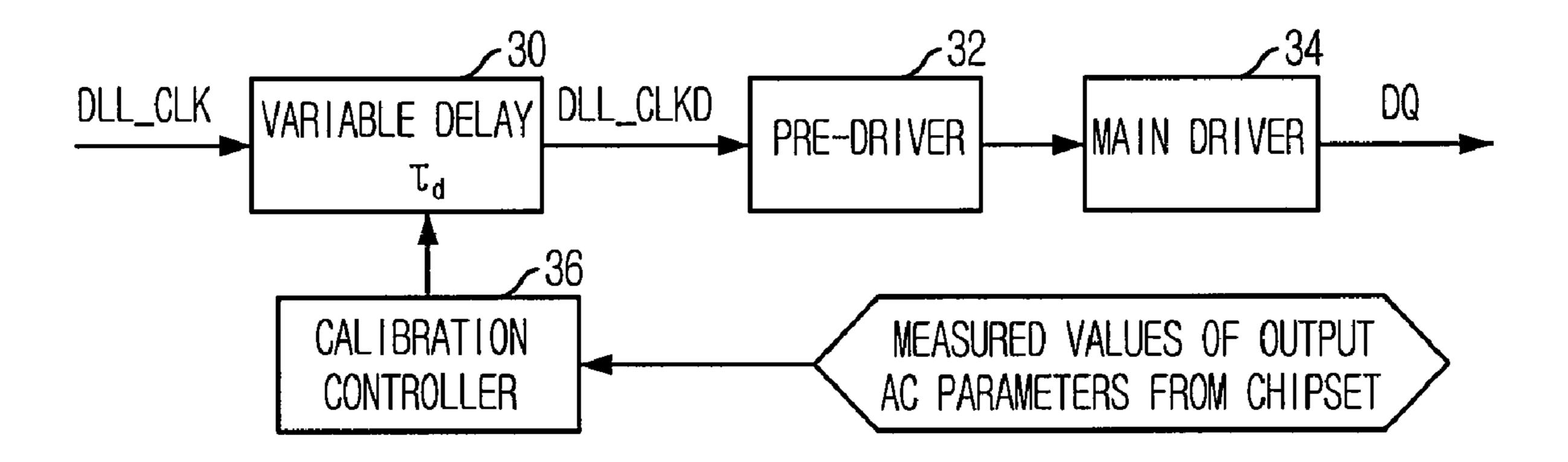

FIG. 1 is a block diagram of a communication scheme between a synchronous dynamic random access memory (DRAM) and a chipset.

In a write operation, the chipset transfers command CMD, 35 address ADD, and data DQ to the DRAM. The chipset also transfers a data strobe signal DQS to the DRAM together with the data DQ.

In a read operation, the DRAM receives the command CMD and the address ADD from the chipset and transfers the 40 corresponding data DQ to the chipset together with the data strobe signal DQS.

The chipset transfers the data strobe signal DQS to the DRAM in the write operation, while the DRAM transfers the data strobe signal DQS to the chipset in the read operation. 45

The data strobe signal DQS is used for source synchronization and is also called "echo clock". If the data DQS is strobed in synchronization with the data strobe signal DQS, skew between the clock CLK and the data DQS can be reduced.

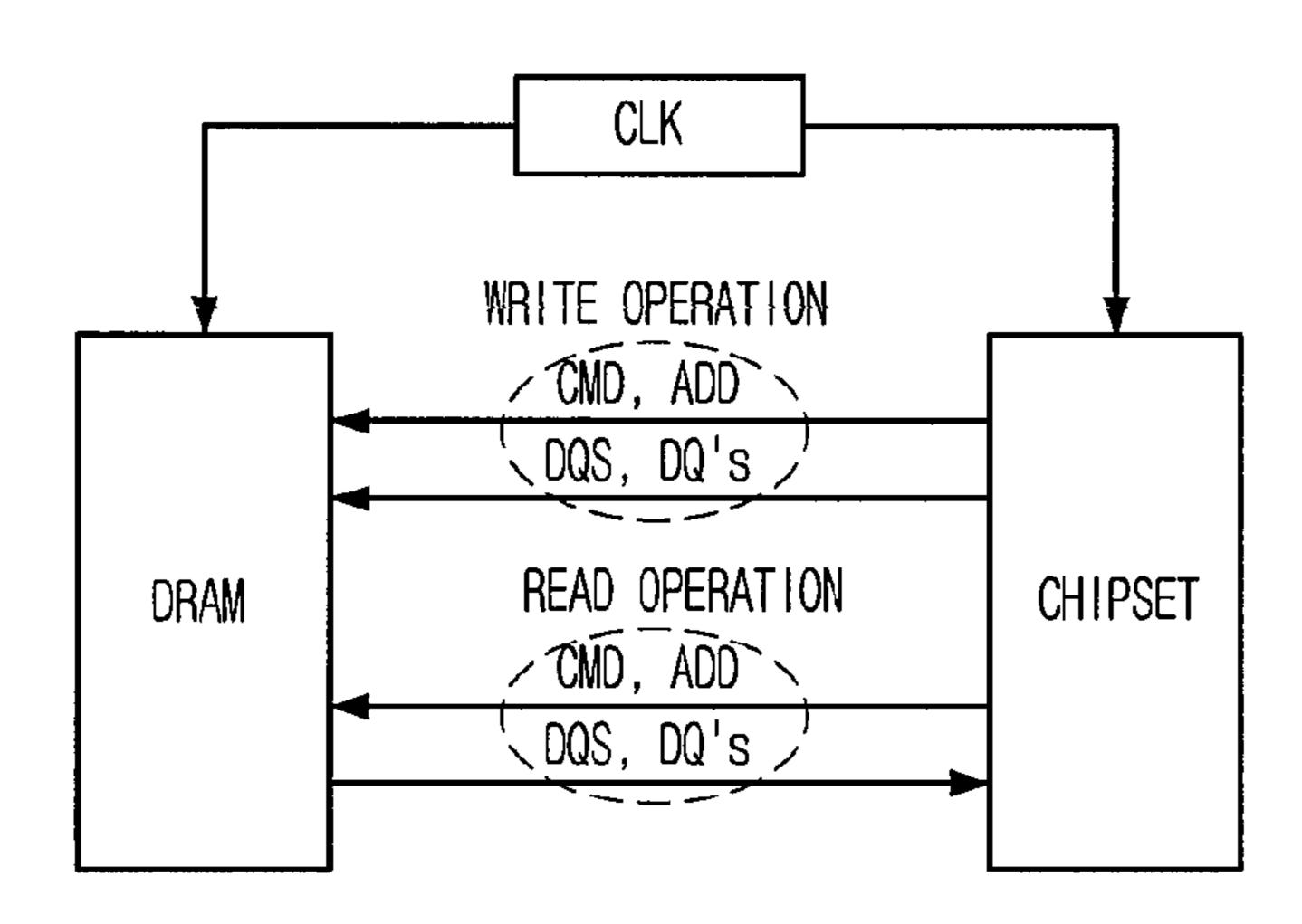

FIG. 2 is a diagram relating AC parameters in a read operation of a DDR SDRAM.

Timing of data DQ and data strobe signal DQS is illustrated in FIG. 2. In FIG. 2, "tDQSQ" is a parameter representing skew between the data strobe signal DQS and the data DQ, 55 "tDQSCK" is a parameter representing skew between the data strobe signal DQS and clock CLK, and "tAC" is a parameter representing skew between the data DQ and the clock CLK.

In order to enable a chipset to receive the data DQ, a 60 DRAM sets the data strobe signal DQS to a low-Z state during tRPRE (read DQS preamble time). When data (DQ) transmission is completed, the DRAM sets the data strobe signal DQS to a high-Z state after tRPST (read DQS postamble time). In this manner, the read operation is completed. 65

If any one of the above-described parameters does not meet the specification, operation error will occur because the 2

chipset receives incorrect data. However, the conventional DRAM module and chipset do not actively control the output AC parameters, e.g., tDQSQ, tDQSCK, etc. Thus, the system will shut down when the output AC parameters are distorted by fluctuation of a board power supply or ambient temperature characteristic. Moreover, as the operation speed of the DRAM increases, the specification requirements of the output AC parameters become narrower. Consequently, the development of high-speed DRAMs becomes increasingly more difficult.

#### SUMMARY OF THE INVENTION

It is, therefore, an object of the present invention to provide a semiconductor memory device that can actively control the output AC parameters, and a driving method thereof.

In accordance with an aspect of the present invention, a semiconductor memory device includes: a variable delay for delaying a delay locked loop (DLL) clock by a predetermined delay time to output a delayed DLL clock; an output driver for outputting data and data strobe signal in response to the delayed DLL clock; and a calibration controller for controlling the predetermined delay time of the variable delay in response to output AC parameters.

In accordance with another aspect of the present invention, a method for driving a semiconductor memory device includes: measuring output AC parameters; setting a delay value with respect to a delay locked loop (DLL) clock in response to the measured values of the output AC parameters; delaying the DLL clock by the delay value to output a delayed DLL clock; and outputting data strobe signal and data having calibrated output AC parameters in response to the delayed DLL clock.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The above and other objects and features of the present invention will become apparent from the following description of the preferred embodiments given in conjunction with the accompanying drawings, in which:

FIG. 1 is a block diagram of a communication scheme between a Synchronous DRAM and a chipset;

FIG. 2 is a diagram relating AC parameters in a read operation of a DDR SDRAM;

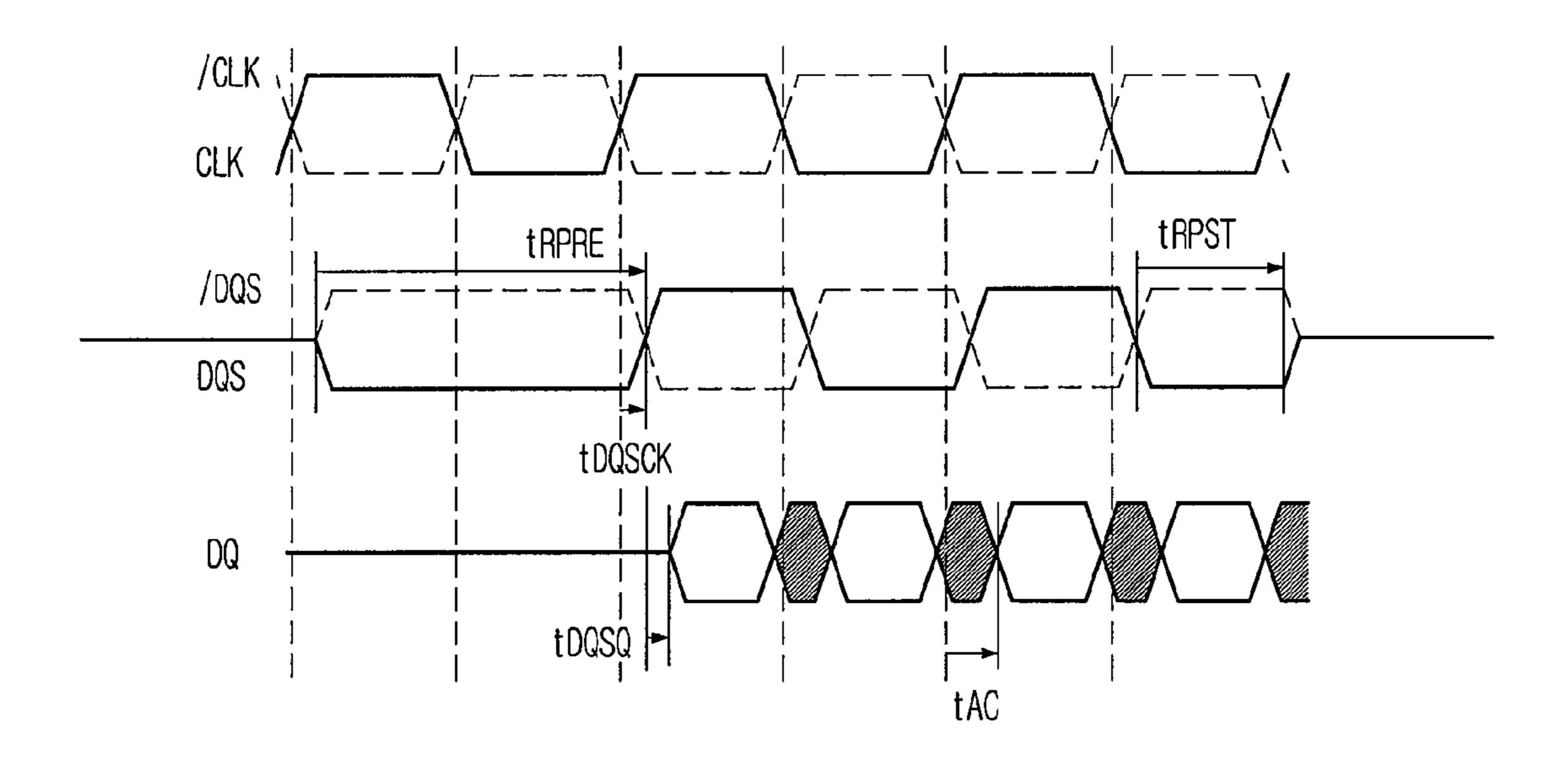

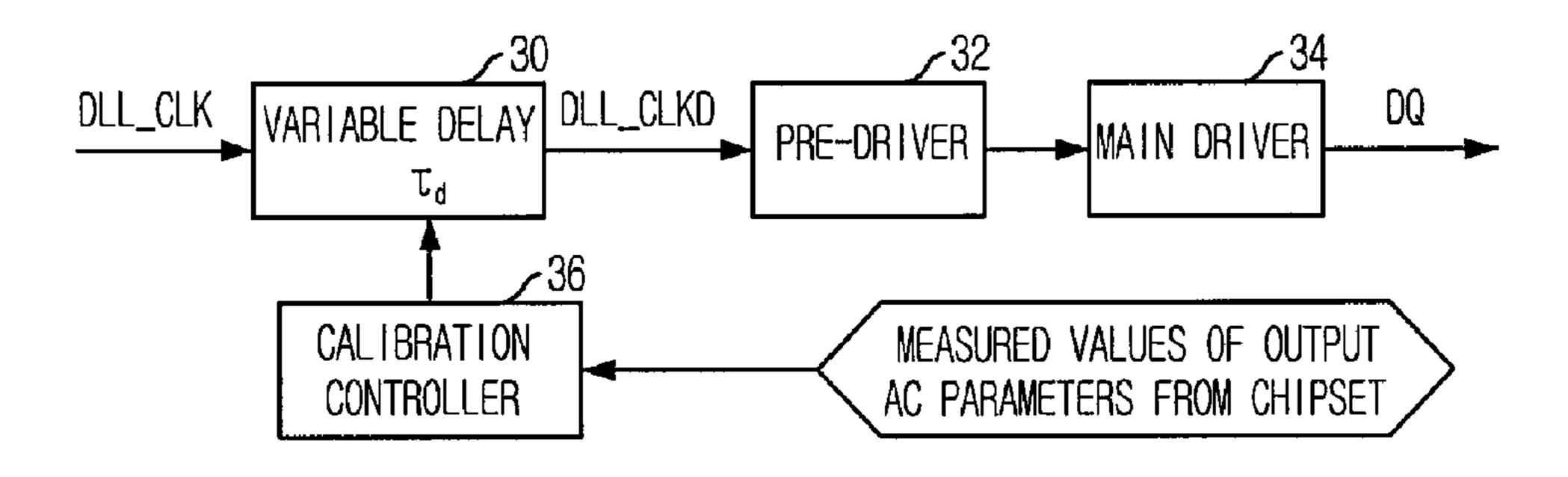

FIG. 3 is a block diagram of a DRAM in accordance with a first embodiment of the present invention;

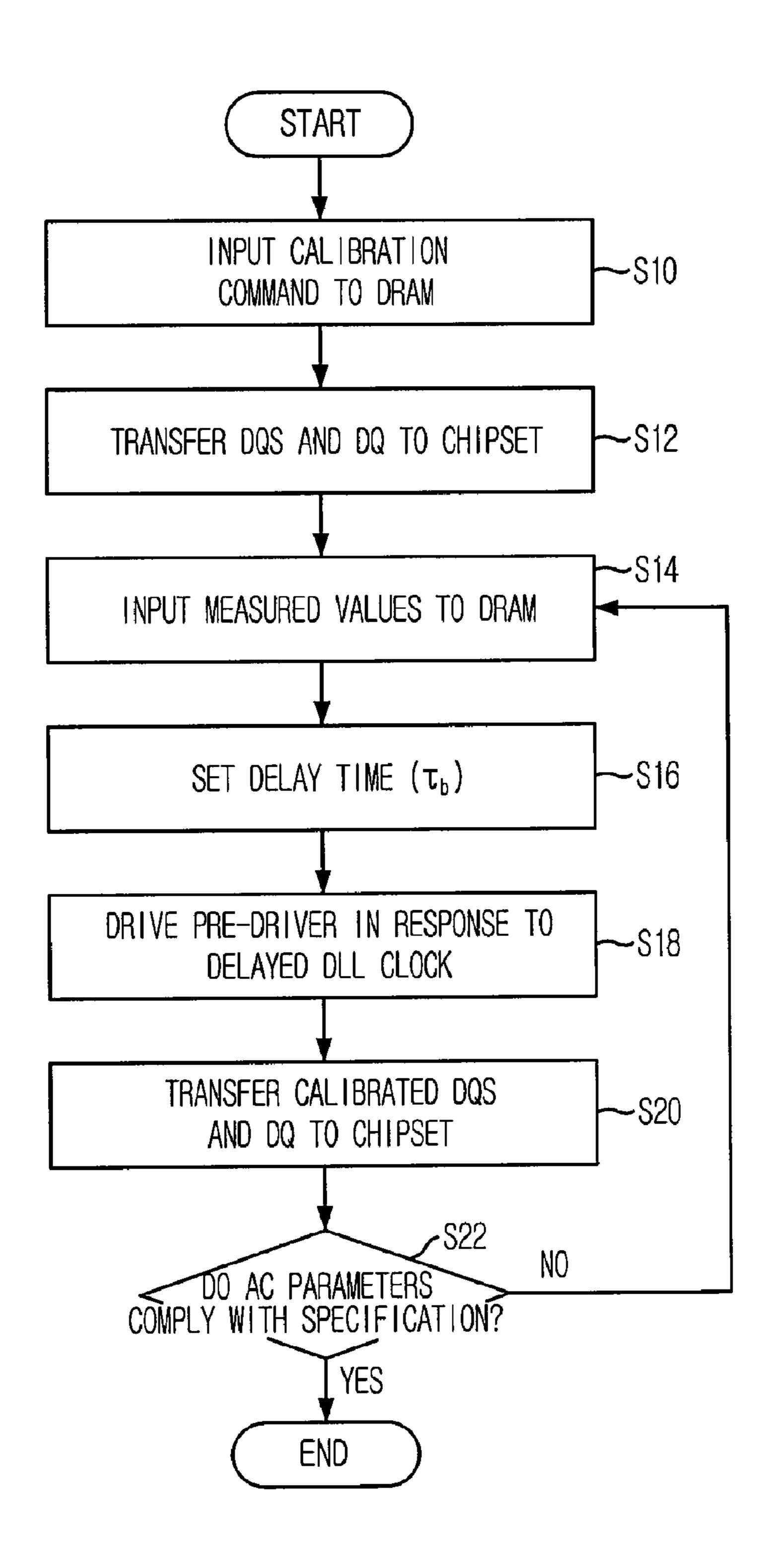

FIG. 4 is a flow chart of a calibration operation of the DRAM of FIG. 3;

FIG. **5** is a block diagram of a DRAM in accordance with a second embodiment of the present invention; and

FIG. 6 is a block diagram of a DRAM in accordance with a third embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

A semiconductor memory device and a driving method thereof in accordance with exemplary embodiments of the present invention will be described in detail with reference to the accompanying drawings.

FIG. 3 is a block diagram of a DRAM in accordance with a first embodiment of the present invention.

The DRAM in accordance with the first embodiment of the present invention includes a variable delay 30, a pre-driver 32, a main driver 34, and a calibration controller 36. The variable delay 30 delays a delay locked loop (DLL) clock DLL\_CLK to output a delayed DLL clock DLL\_CLKD, and the pre-driver 32 pre-drives an output data signal in response to the

delayed DLL clock DLL\_CLKD. The main driver 34 drives a data output terminal DQ in response to an output signal of the pre-driver 32. The calibration controller 36 controls a delay time  $(\tau_d)$  of the variable delay 30 in response to measured values of output AC parameters. The measured values of the 50 output AC parameters are received from a chipset.

FIG. 4 is a flow chart of a calibration operation of the DRAM of FIG. 3.

When the chipset inputs a calibration command to the DRAM in step S10, the DRAM transfers data strobe signal 10 DQS and data DQ to the chip set in step S12.

In step S14, the chipset measures the output AC parameters (e.g., tDQSCK, tDQSQ, etc.) in the data strobe signal DQS and the data DQ, and transfers the measured values of the output AC parameters to the DRAM. In step S16, the calibration controller 36 sets the delay time ( $\tau_d$ ) of the variable delay 30 in response to the measured values.

In this case, the variable delay 30 delays the DLL clock DLL\_CLK by  $+\tau_d$  or  $-\tau_d$ , and the pre-driver 32 is driven in response to the delayed DLL clock DLL\_CLKD in step S18. 20 In step S20, the calibrated data strobe signal DQS and the calibrated data DQ are transferred to the chipset.

In step S22, the chipset remeasures the output AC parameters, based on the calibrated data strobe signal DQS and the calibrated data DQ, and determines if the AC parameters comply with the specification. When the AC parameters comply with the specification, the calibration operation is completed. When the AC parameters do not comply with the specification, the process returns to step S14 to transfer the remeasured values to the DRAM. This loop is repeated until 30 the AC parameters comply with the specification. Since steps subsequent to step S22 are a verify operation, they can be omitted.

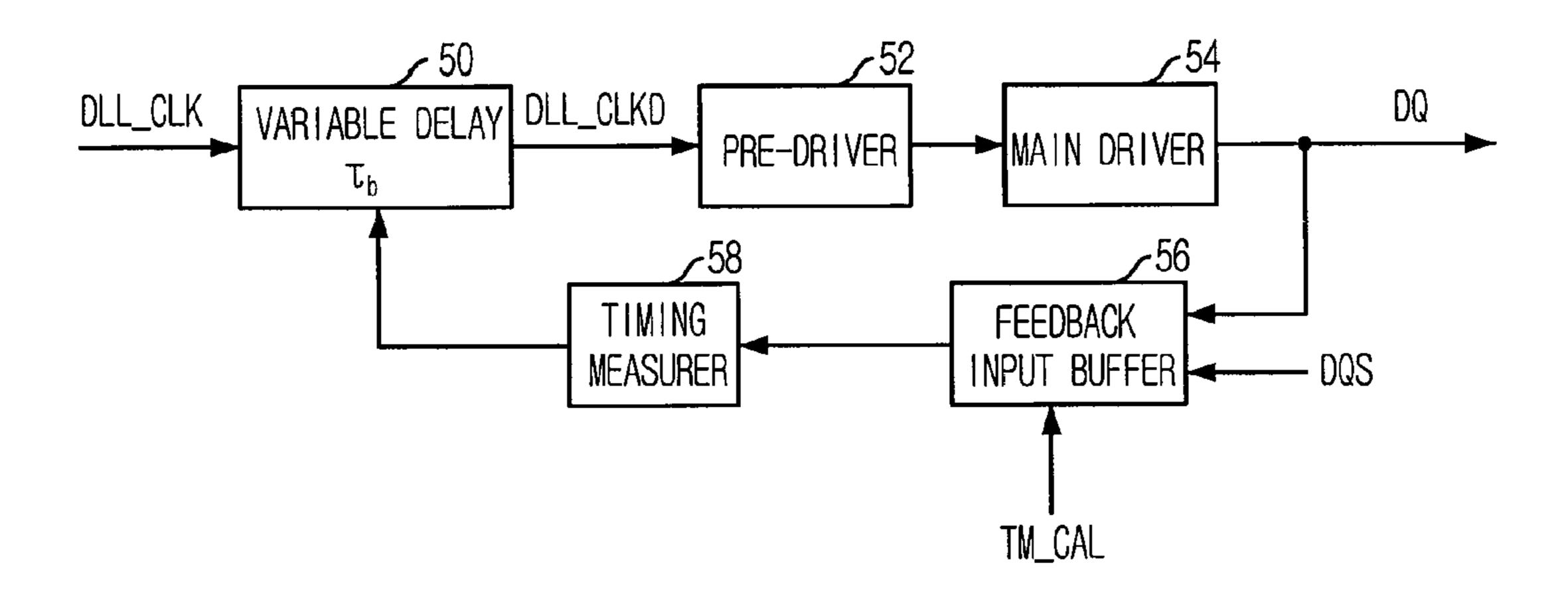

FIG. **5** is a block diagram of a DRAM in accordance with a second embodiment of the present invention.

The DRAM in accordance with the second embodiment of the present invention includes a variable delay 50, a pre-driver **52**, a main driver **54**, a feedback input buffer **56**, and a timing measurer 58. The variable delay 50 delays a DLL clock DLL\_CLK to output a delayed DLL clock DLL\_CLKD, and 40 the pre-driver 52 pre-drives an output data signal in response to the delayed DLL clock DLL\_CLKD. The main driver **54** drives a data output terminal DQ in response to an output signal of the pre-driver 52. The feedback input buffer 56 feeds back data DQ and data strobe signal DQS to the timing 45 measurer 58 in response to a calibration test mode signal TM\_CAL. The timing measurer **58** measures output AC parameters (e.g., tDQSCK, tDQSQ, etc.) of the data DQ and the data strobe signal DQS, and controls the delay time  $(\tau_d)$  of the variable delay **30** in response to the measurement values 50 of the output AC parameters.

When a calibration command is input from the chipset, the DRAM activates the calibration test mode signal TM\_CAL in response to the calibration command. When the calibration to the test mode signal TM\_CAL is activated, the feedback input 55 tions buffer  $\bf 56$  is enabled to receive the data DQ and the data strobe signal DQS. The timing measurer  $\bf 58$  measures skew between the data DQ and the data strobe signal DQS and controls the delay time ( $\tau_d$ ) of the DLL clock DLL\_CLK according to the measured skew. When the calibration test mode signal 60 ing: TM\_CAL is deactivated after the calibration operation is completed, the DRAM transfers a calibration test mode exit signal to the chipset.

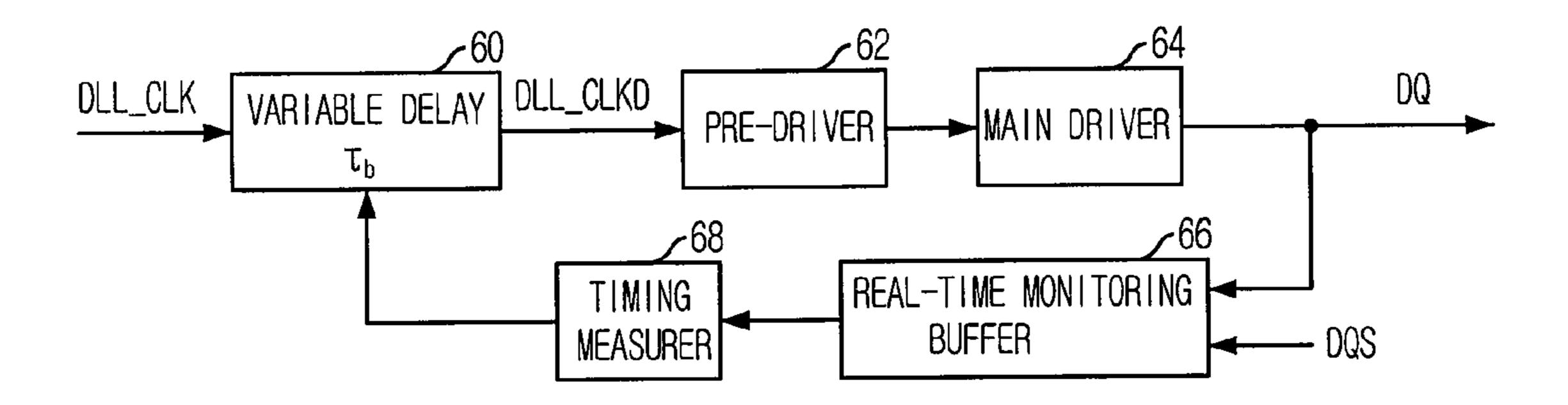

FIG. 6 is a block diagram of a DRAM in accordance with a third embodiment of the present invention.

The DRAM in accordance with the third embodiment of the present invention includes a variable delay **60**, a pre-driver

4

**62**, a main driver **64**, a real-time monitoring buffer **66**, and a timing measurer **68**. The variable delay **60** delays a DLL clock DLL\_CLK to output a delayed DLL clock DLL\_CLKD, and the pre-driver **62** pre-drives an output data signal in response to the delayed DLL clock DLL\_CLKD. The main driver **64** drives a data output terminal DQ in response to an output signal of the pre-driver **62**. The real-time monitoring buffer **66** monitors data DQ and data strobe signal DQS, which is being transferred to the chipset. The timing measurer **68** measures output AC parameters (e.g., tDQSCK, tDQSQ, etc.) in data DQ and data strobe signal DQS received from the real-time monitoring buffer **66**, and controls the delay time  $(\tau_d)$  of the variable delay **60** in response to the measured values.

In this embodiment, the DRAM itself performs the calibration without calibration command provided from the chip set. Although the real-time monitoring buffer **66** must be embedded into the DRAM, it is possible to omit time taken to perform the calibration through the communication between the DRAM and the chipset.

If undesired skew occurs during the operation of the DRAM, the skew can be immediately adjusted to meet the specification without time loss because the DRAM monitors the skew in real time.

As described above, the embodiments of the present invention provide the timing control methods that can actively adjust the output AC parameters in the memory device. In the first method, the chipset transfers the calibration command and the measured values of the output AC parameters to the memory device, and the memory device performs the calibration operation. In the second method, when the chipset transfers the calibration command to the memory device, the memory device measures the output AC parameters and performs the calibration operation. In the third method, the memory device transfers the data strobe signal DQS and the data DQ to the chipset while monitoring them in real time, without calibration command of the chipset.

Therefore, the memory device can actively control the output AC parameters, thus providing the decreased failure rate and the improved reliability. In addition, the memory device can cope with the narrowed specification requirements of the AC parameters, attributing to the developments of high-speed memory devices.

Although the DRAM has been described, the present invention is not limited to the DRAM. That is, the present invention can also be applied to any memory device that communicates the chipset using data strobe signal.

The present application contains subject matter related to Korean patent application No. 2006-59735, filed in the Korean Intellectual Property Office on Jun. 29, 2006, the entire contents of which are incorporated herein by reference.

While the present invention has been described with respect to certain preferred embodiments, it will be apparent to those skilled in the art that various changes and modifications may be made without departing from the scope of the invention as defined in the following claims.

What is claimed is:

- 1. A [semiconductor] memory [device] *system*, comprising:

- a variable delay configured to delay a clock;

- an output driver configured to transfer data to a chipset in response to a calibration command received from the chipset and the delayed clock;

- an output buffer configured to transfer a data strobe signal to the chipset in response to the calibration command and the [delayed] clock; and

- a calibration controller configured to control the delay time of the variable delay according to *an* output AC [parameters] *parameter* measured by the chipset.

- 2. The [semiconductor] memory [device] *system* of claim 1, wherein the output driver comprises:

- a pre-driver configured to pre-drive an output data signal; and

- a main driver configured to drive a data output terminal in response to an output signal of the pre-driver.

- 3. The [semiconductor] memory [device] *system* of claim 1, wherein the output AC [parameters include at least] *parameter is a selected* one of a parameter representing skew between the data strobe signal and the data, a parameter representing skew between the data strobe signal and a clock, and a parameter representing skew between the data and the clock.

- 4. A [semiconductor] memory [device] *system*, comprising:

- a variable delay configured to delay a clock;

- an output driver configured to receive and output data in response to the delayed clock; and

- a calibration controller configured to measure *an* AC [parameters] *parameter* of data and data strobe signal [received from a chipset] in response to a calibration 25 command received from the chipset, and control the delay time of the variable delay according to measured values of the output AC [parameters] *parameter*.

- 5. The [semiconductor] memory [device] system of claim

- 4, wherein the calibration controller comprises:

- a feedback input buffer configured to feed back the data and the data strobe signal, which are transferred to the chipset, in response to a calibration test mode signal generated when the calibration command is received; and

- a timing measurer configured to receive the data and the data strobe signal from the feedback input buffer, measure the AC [parameters] *parameter* of data and data strobe signal, and control the delay time of the variable delay according to measured values of the output AC 40 [parameters] *parameter*.

- 6. The [semiconductor] memory [device] *system* of claim 4, wherein the calibration controller comprises:

- a real-time monitor configured to monitor the data and the data strobe signal being transferred to the chipset; and

- a timing measurer configured to receive the data and the data strobe signal from the real-time monitor, measure the AC [parameters] *parameter* of data and data strobe signal, and control the delay time of the variable delay according to measured values of the output AC [parameter.]

- 7. The [semiconductor] memory [device] *system* of claim 4, wherein the output driver comprises:

- a pre-driver configured to pre-drive an output data signal; and

- a main driver configured to drive a data output terminal in response to an output signal of the pre-driver.

- 8. The [semiconductor] memory [device] *system* of claim 4, wherein the output AC [parameters include at least] *parameter is a selected* one of a parameter representing skew 60 between the data strobe signal and the data, a parameter representing skew between the data strobe signal and the clock, and a parameter representing skew between the data and the clock.

- 9. A method for driving a [semiconductor] memory 65 [device] system, comprising:

receiving a calibration command from a chipset;

6

transferring a first data and a first data strobe signal to the chipset in response to the calibration command;

receiving a measured [values] value of an output AC [parameters] parameter from the chipset, wherein the measured [values] value of an output AC [parameters are] parameter is measured at the chipset by using the first data and the first data strobe signal;

setting a delay value with respect to a clock in response to the measured values of the output AC [parameters] parameter;

delaying the clock by the delay value to output a delayed clock; and

transferring a second data [and a second data strobe signal] having a calibrated output AC [parameters] parameter to the chipset in response to the delayed clock and transferring a second data strobe signal to the chipset in response to the clock.

10. The method of claim 9, further comprising:

after transferring the second data and the second data strobe signal, remeasuring the output AC [parameters] parameter at the chipset based on the second data and the second data strobe signal having the calibrated output AC [parameters] parameter; and

when the remeasured output AC [parameters] *parameter* comply with a specification, completing a calibration operation.

11. A method for driving a [semiconductor] memory [device] *system*, comprising:

receiving a calibration command from a chipset;

receiving a first data and a first data strobe signal from the chipset;

measuring an AC [parameters] parameter of the first data and the first data strobe signal in response to the calibration command;

controlling the delay time of a clock according to measured values of the AC [parameters] parameter; and

- transferring a second data [and a second data strobe signal] having a calibrated output AC [parameters] parameter to the chipset in response to the delayed clock and transferring a second data strobe signal to the chipset in response to the clock.

- 12. The memory system of claim 1, wherein the memory system is a synchronous memory system.

- 13. The memory system of claim 1, wherein the memory system is a synchronous DDR memory system.

- 14. The memory system of claim 1, further comprising a DLL configured to provide the clock.

- 15. The memory system of claim 1, further comprising a plurality of output drivers configured to transfer data to a chipset in response to a calibration command received from the chipset.

- 16. The memory system of claim 15, further comprising a plurality of variable delays corresponding to respective output drivers configured to delay the clock in response to the calibration controller to control the delay time of the plurality of variable delays according to the output AC parameter measured by the chipset.

- 17. The memory system of claim 15, wherein the output AC parameter measured by the chipset is a parameter representing skew between two signals.

- 18. The memory system of claim 17, wherein the output AC parameter measured by the chipset is a selected one of a skew between the data strobe signal and the data, a skew between the data strobe signal and a system clock, and a skew between data and the system clock.

- 19. The memory system of claim 4, wherein the memory system is a synchronous memory system.

- 20. The memory system of claim 4, wherein the memory system is a synchronous DDR memory system.

- 21. The memory system of claim 4, further comprising a DLL configured to provide the clock.

- 22. The memory system of claim 4, further comprising a 5 plurality of output drivers configured to transfer data to a chipset in response to a calibration command received from the chipset.

- 23. The memory system of claim 22, further comprising a plurality of variable delays corresponding to respective out- 10 put drivers configured to delay the clock in response to the calibration controller to control the delay time of the plurality of variable delays according to the output AC parameter measured by the chipset.

- 24. The memory system of claim 22, wherein the output AC 15 parameter measured by the chipset is a parameter representing skew between two signals.

- 25. The memory system of claim 24, wherein the output AC parameter measured by the chipset is a selected one of a skew between the data strobe signal and the data, a skew between 20 the data strobe signal and a system clock, and a skew between data and the system clock.

- 26. The method of claim 9, wherein the memory system is a synchronous memory system.

- 27. The method of claim 9, wherein the memory system is a 25 synchronous DDR memory system.

- 28. The method of claim 9, wherein setting a delay value with respect to a clock comprises setting a delay value with respect to a DLL.

- 29. The method of claim 9, wherein:

- transferring a first data and a first data strobe signal to the chipset comprises transferring a plurality of first data and first data strobe signals to the chipset; and

- receiving a measured value of an output AC parameter from the chipset comprises receiving a plurality of mea- 35 sured values of output AC parameters from the chipset corresponding to the plurality of first data and first data strobe signals.

- 30. The method of claim 29, wherein:

setting a delay value with respect to a clock in response to 40 the measured values of the output AC parameter comprises setting a plurality of delay values with respect to the clock in response to the measured values of the output AC parameters corresponding to the plurality of first data and first data strobe signals; and

8

- delaying the clock by the delay value to output a delayed clock comprises delaying the clock by the plurality of delay values to output a plurality of delayed clocks corresponding to the plurality of first data and first data strobe signals.

- 31. The method of claim 29, wherein receiving a measured value of an output AC parameter from the chipset comprises receiving a parameter representing skew between two signals.

- 32. The method of claim 31, wherein the output AC parameter measured by the chipset is a selected one of a skew between the data strobe signal and the data, a skew between the data strobe signal and a system clock, and a skew between data and the system clock.

- 33. The method of claim 11, wherein the memory system is a synchronous memory system.

- 34. The method of claim 11, wherein the memory system is a synchronous DDR memory system.

- 35. The method of claim 11, wherein controlling the delay time of a clock comprises controlling the delay time of a DLL.

- 36. The method of claim 11, wherein: receiving a first data and a first data strobe signal from the chipset comprises receiving a plurality of first data and

- first data strobe signals from the chipset; and measuring an AC parameter of the first data and the first data strobe signal in response to the calibration command comprises measuring a plurality of AC parameters corresponding to the plurality of first data and first data strobe signals.

- 37. The method of claim 36, wherein controlling the delay time of a clock according to measured values of the AC parameter comprises controlling a plurality of delay times of a clock in response to the measured values of the AC parameters corresponding to the plurality of first data and first data strobe signals.

- 38. The method of claim 36, wherein measuring an AC parameter of the first data and the first data strobe signal in response to the calibration command comprises measuring a parameter representing skew between two signals.

- 39. The method of claim 38, wherein the measured AC parameter is a selected one of a skew between the data strobe signal and the data, a skew between the data strobe signal and a system clock, and a skew between data and the system clock.

\* \* \* \* \*