### US00RE44420E

# (19) United States

# (12) Reissued Patent

Yokokawa et al.

# (10) Patent Number:

US RE44,420 E

# (45) Date of Reissued Patent:

Aug. 6, 2013

# DECODING APPARATUS, DECODING METHOD, AND PROGRAM TO DECODE LOW DENSITY PARITY CHECK CODES

Inventors: **Takashi Yokokawa**, Tokyo (JP);

Toshiyuki Miyauchi, Tokoy (JP);

Yasuhiro Iida, Tokyo (JP)

Assignee: **Sony Corporation**, Tokyo (JP)

Appl. No.: 12/611,227

(22)Filed: Nov. 3, 2009

## Related U.S. Patent Documents

### Reissue of:

(64)Patent No.: 7,299,397 Issued: Nov. 20, 2007 Appl. No.: 10/521,054 PCT Filed: Apr. 19, 2004

PCT No.: PCT/JP2004/005562

§ 371 (c)(1),

(2), (4) Date: Jan. 12, 2005 PCT Pub. No.: **WO2004/102811** PCT Pub. Date: **Nov. 25, 2004**

#### (30)Foreign Application Priority Data

| May 13, 2003  | (JP) | ) | 2003-133941 |

|---------------|------|---|-------------|

| Aug. 18, 2003 | (JP  | ) | 2003-294383 |

Int. Cl. (51)H03M 13/00

(2006.01)

U.S. Cl. (52)

Field of Classification Search (58)

> See application file for complete search history.

#### **References Cited** (56)

### U.S. PATENT DOCUMENTS

3/2003 Blanksby et al. 6,539,367 B1 10/2003 Richardson et al. 6,633,856 B2

|   | 6,785,863    | B2            | 8/2004  | Blankenship et al. |

|---|--------------|---------------|---------|--------------------|

|   | 6,938,196    | B2            | 8/2005  | Richardson et al.  |

|   | 6,957,375    | B2            | 10/2005 | Richardson         |

|   | 6,961,888    | B2            | 11/2005 | Jin et al.         |

| 2 | 2002/0116677 | $\mathbf{A}1$ | 8/2002  | Morelos-Zaragoza   |

| 2 | 2002/0186759 | $\mathbf{A}1$ | 12/2002 | Goldstein et al.   |

| 2 | 2003/0023617 | $\mathbf{A}1$ | 1/2003  | Hunt et al.        |

| 2 | 2004/0019845 | <b>A</b> 1    | 1/2004  | Eroz et al.        |

| 2 | 2004/0034828 | $\mathbf{A}1$ | 2/2004  | Hocevar            |

| 2 | 2004/0187129 | $\mathbf{A}1$ | 9/2004  | Richardson         |

| - | 2005/0278606 | <b>A</b> 1    | 12/2005 | Richardson et al.  |

### FOREIGN PATENT DOCUMENTS

| EP | 1 158 682       | 11/2001 |

|----|-----------------|---------|

| JP | 2002-33670      | 1/2002  |

| JP | 2003-269302     | 9/2003  |

| WO | WO 02/103631    | 12/2002 |

| WO | WO 03-021440 A1 | 3/2003  |

### OTHER PUBLICATIONS

Robert G. Gallager, Low-Density Parity Check Codes (M. I. T. Press 1963).

# (Continued)

Primary Examiner — Sam Rizk

(74) Attorney, Agent, or Firm—Finnegan, Henderson, Farabow, Garrett & Dunner, LLP

#### ABSTRACT (57)

The present invention relates to a decoding apparatus and a decoding method for realizing the decoding of LDPC codes, in which, while the circuit scale is suppressed, the operating frequency can be suppressed within a sufficiently feasible range, and control of memory access can be performed easily, and to a program therefor. A check matrix of LDPC codes is formed by a combination of a (P×P) unit matrix, a matrix in which one to several 1s of the unit matrix are substituted with 0, a matrix in which they are cyclically shifted, a matrix, which is the sum of two or more of them, and a  $(P \times P)$  0-matrix. A check node calculator 313 simultaneously performs p check node calculations. A variable node calculator 319 simultaneously performs p variable node calculations.

# 63 Claims, 35 Drawing Sheets

### OTHER PUBLICATIONS

David J. C. MacKay, "Good Error-Correcting Codes Based on Very Sparse Matrices," *IEEE Transactions on Information Theory*, vol. 45, No. 2, pp. 399-431, Mar. 1999.

Michael G. Luby, Michael Mitzenmacher, M. Amin Shokrollahi & Daniel A. Spielman, "Analysis of Low Density Codes and Improved Design Using Irregular Graphs," *Proceedings of ACM Symposium on Theory of Computing*, pp. 249-258 (1998).

C. Howland & A. Blanksby, "Parallel Decoding Architectures for Low Density Parity Check Codes," *Symposium on Circuits and Systems*, part IV, pp. 742-745 (2001).

Engling Yeo, Payam Pakzad, Borivoje Nikolic & Venkat Anantharam, "VLSI Architectures for Iterative Decoders in Magnetic Recording Channels," *IEEE Transactions on Magnetics*, vol. 37, No. 2, pp. 748-755, Mar. 2001.

M.M. Mansour, "Memory-Efficient Turbo Decoder Architectures for LDPC Codes," *Proc. IEEE Workshop on Signal Processing Systems*, Oct. 16, 2002, pp. 159-164.

Y. Chen, "High Throughput Overlapped Message Passing for Low Density Parity Check Codes," *Proc. of the 2003 ACM Great Lates Symposium on VLSI*, Apr. 28, 2003, pp. 245-248.

E. Yeo, "VLSI Architectures for Iterative Decoders in Magnetic Recording Channels," *IEEE Transactions on Magnetics*, vol. 37, No. 2, Mar. 2001, pp. 748-755.

M. M. Mansour, "Low Power VLSI Decoder Architectures for LDPC Codes," *Proc. Internat. Symposium on Low Power Electronics and Design*, Aug. 12-14, 2002, pp. 284-289.

English-language Summons to attend oral hearing pursuant to Rule 115 (1) EPC dated Feb. 22, 2012, from the European Patent Office in counterpart European Application No. 04 728 265.2.

S. Kim et al, 'Parallel VSLI Architectures for a Class of LD PC Codes', IEEE International Symposium on Circuits and Systems, 2002, ISCAS 2002, vol. 2, Nov. 2002, p. 26-29.

FIG. 1 - Prior Art

FIG. 2 - Prior Art

FIG. 3 - Prior Art

FIG. 4 - Prior Art

FIG. 5 - Prior Art

FIG. 6 - Prior Art

FIG. 7 - Prior Art

FIG. 8 - Prior An

FIG. 9 - Prior Ar

CLOCK DEI 9 CLOCK DELAY 127 O 130 S D106

FIG. 11 - Prior Art

FIG. 12A - Prior Art

D2071 MEMORY FOR EDGES A TOTAL OF 45 NODES OF 3 INPUTS AND OUTPUTS AND OUTPUTS 02061 ro∐ nco9 (3) - A TOTAL OF 5 INPUTS AN VARIABLE NODE CALCULATOR 02051 EDGE INTERCHANGE DEVICE D203<sub>1</sub> X OUANTIZATION BITS OF EDGES MEMORY FOR EDGES D202<sub>1</sub> CALCULATOR 202 AND S ATOR CALCULATOR CALCULATOR OF ATION BITS CALCUL NODE CALCUL AND ONE NODE INPUTS AND LENGTH NODE NODE CHECK NODE CHECK 2011 D2011 EDGE INTERCHANGE DEVICE

STI8 NOITASITNAUD OF EDGES **WEMORY FOR EDGES** S നൃ S VARIABLE NODE CALCULATOR VARIABLE NODE CALCULATOR 21 INPUT VARIABLE NODE CALCULATOR AND OUTPU 2 D20588 020 EDGE INTERCHANGE DEVICE D20330 OUMBER OF STIGN BITS TOTAL NUMBER **WEWORY FOR EDGES** O), യർ ATOR CALCULATOR CALCULATOR CALCULATOR 20130 20126 NODE Y CHECK NODE Y CHECK NODE 0 EDGE INTERCHANGE DEVICE N

FIG. 12C - Prior Art

FIG. 13 - Prior Art

FIG. 14 - Prior Art

315 3,132 D3116 5-0 4-0 3.0 2-0 1.0 0-0 0-7 0-6 0-5 0-4 0-3 0-2 0-1 1-8 1-7 1-6 1-5 1-4 1-3 1-2 1-1 12-8 2-7 2-6 2-5 2-4 2-3 2-2 2-1 3-8 3-7 3-6 3-5 3-4 3-3 3-2 3-1 4-8 4-7 4-6 4-5 4-4 4-3 4-2 4-1 5-8 5-7 5-6 5-5 5-4 5-3 5-2 5-1 3115

3195 3191

FIG. 17

52 4154 D421 D416 4122 MEMORY FOR STORING DECODING IN-PROGRESS RESULTS **D418**

(0) 155 0151 0) O), 407 10 60)

| 1-PROGRESS RESULTS           | READING OF 1ST | WRITING INTO 1ST | READING OF 11TH  |

|------------------------------|----------------|------------------|------------------|

|                              | TO 5TH ROWS    | TO 5TH ROWS      | TO 15TH ROWS     |

| RAM 503 FOR STORING DECODING |                | READING OF 6TH   | WRITING INTO 6TH |

| IN-PROGRESS RESULTS          |                | TO 10TH ROWS     | TO 10TH ROWS     |

FIG. 25

D615 D617 **D621** D616 6123 612 61 611 610

6 YOU

D610 D702

| -PROGRESS RESULTS            | TO 5TH COLUMNS | TO 5TH COLUMNS   | TO 15TH COLUMNS  |

|------------------------------|----------------|------------------|------------------|

| RAM 703 FOR STORING DECODING |                | READING OF SIXTH | WRITING INTO 6TH |

| IN-PROGRESS RESULTS          |                | TO 10TH COLUMNS  | TO 10TH COLUMNS  |

FIG. 33

**BUS 901** UT INTERFACE INPUT/OUTP

# DECODING APPARATUS, DECODING METHOD, AND PROGRAM TO DECODE LOW DENSITY PARITY CHECK CODES

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

#### TECHNICAL FIELD

The present invention relates to a decoding apparatus, a decoding method, and a program. More particularly, the present invention relates to a decoding apparatus and a decoding method for decoding codes on which coding is performed using low density parity check codes (LDPC codes), and to a program therefor.

#### **BACKGROUND ART**

In recent years, research in, for example, communication fields such as mobile communication and deep space communication, and broadcasting fields such as terrestrial-wave or satellite digital broadcasts has progressed remarkably. 25 Along with this situation, research on coding theories for making error correction coding and decoding efficient has been actively carried out.

As a theoretical limit of code performance, the Shannon limit implied by the so-called Shannon's (C. E. Shannon) 30 channel coding theorem is known. Research on coding theories has been carried out for the purpose of developing codes exhibiting performance near this Shannon limit. In recent years, as a coding method exhibiting performance near the Shannon limit, for example, techniques for what is commonly 35 called "turbo coding", such as parallel concatenated convolutional codes (PCCC) and serially concatenated convolutional codes (SCCC), have been developed. Furthermore, whereas this turbo coding has been developed, low density parity check codes (hereinafter referred to as "LDPC codes"), 40 which is a coding method that has been known for a long time, have attracted attention.

LDPC codes were proposed first in R. G. Gallager, "Low Density Parity Check Codes", Cambridge, Mass.: M. I. T. Press, 1963. Thereafter, LDPC codes reattracted attention in 45 D. J. C. MacKay, "Good error correcting codes based on very sparse matrices", submitted to IEEE Trans. Inf. Theory, IT-45, pp. 399-431, 1999, and M. G. Luby, M. Mitzenmacher, M. A. Shokrollahi and D. A. Spielman, "Analysis of low density codes and improved designs using irregular graphs", 50 in Proceedings of ACM Symposium on Theory of Computing, pp. 249-258, 1998.

It is beginning to be known from this recent research that, for the LDPC codes, as the code length increases, performance close to the Shannon limit can be obtained, similarly to 55 turbo coding. Furthermore, since the LDPC codes have the property that the minimum length is proportional to the code length, they have the advantages that the block error probability characteristics are good, and a so-called error floor phenomenon, which is observed in decoding characteristics 60 of turbo coding, hardly occurs.

Such LDPC codes will now be described in detail below. The LDPC codes are linear codes and do not always need to be two-dimensional, but here, a description is given assuming that the LDPC codes are two-dimensional.

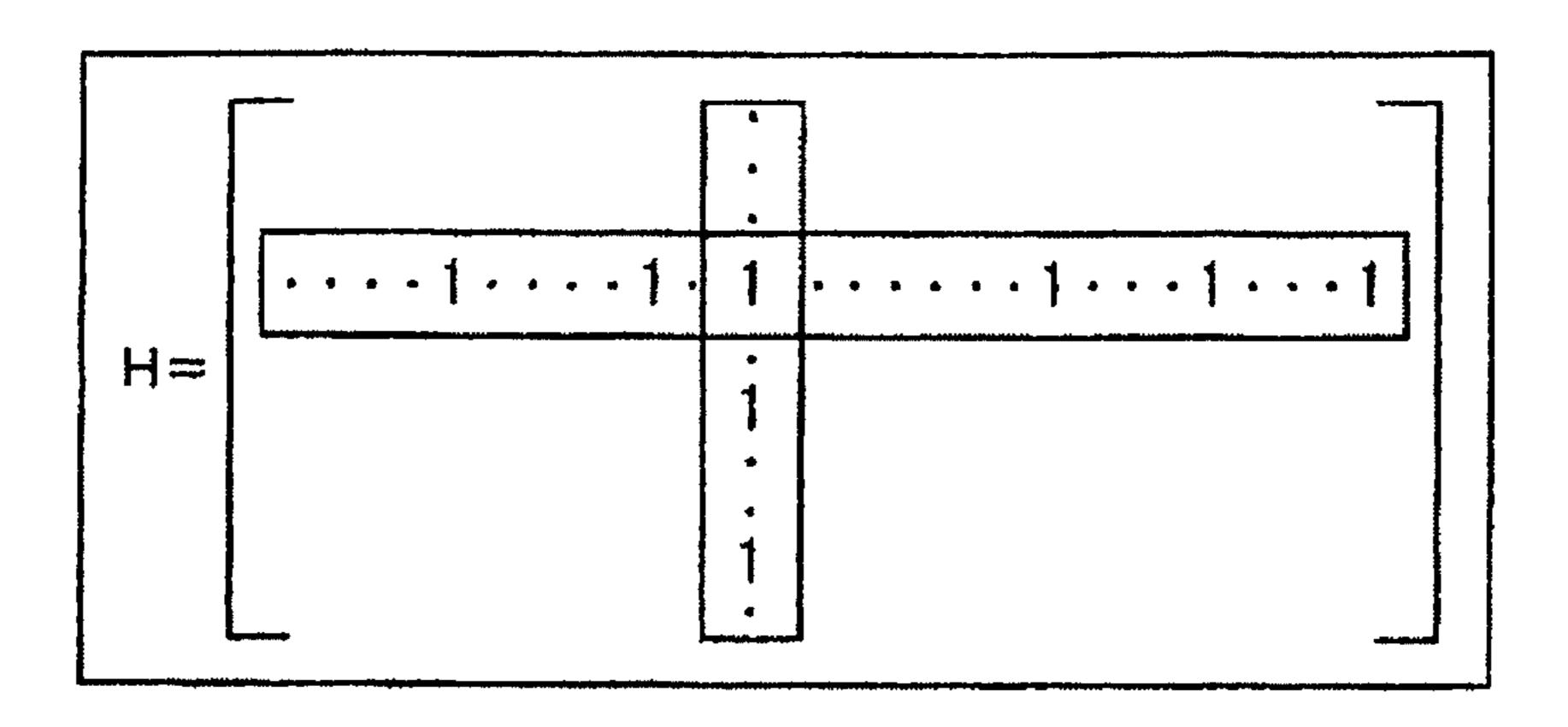

The greatest features of the LDPC codes are that the parity check matrix that defines the LDPC codes are sparse. Here, a

2

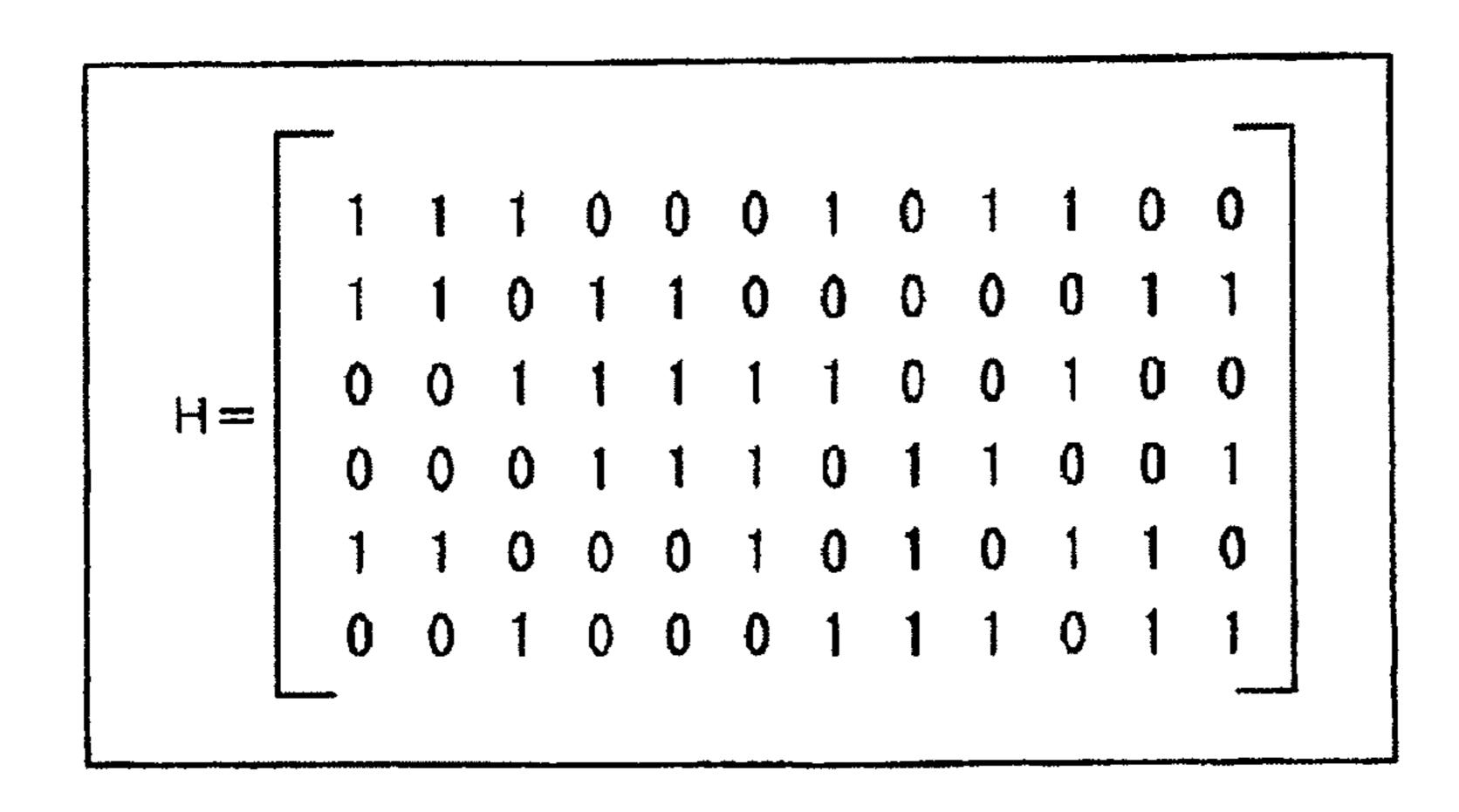

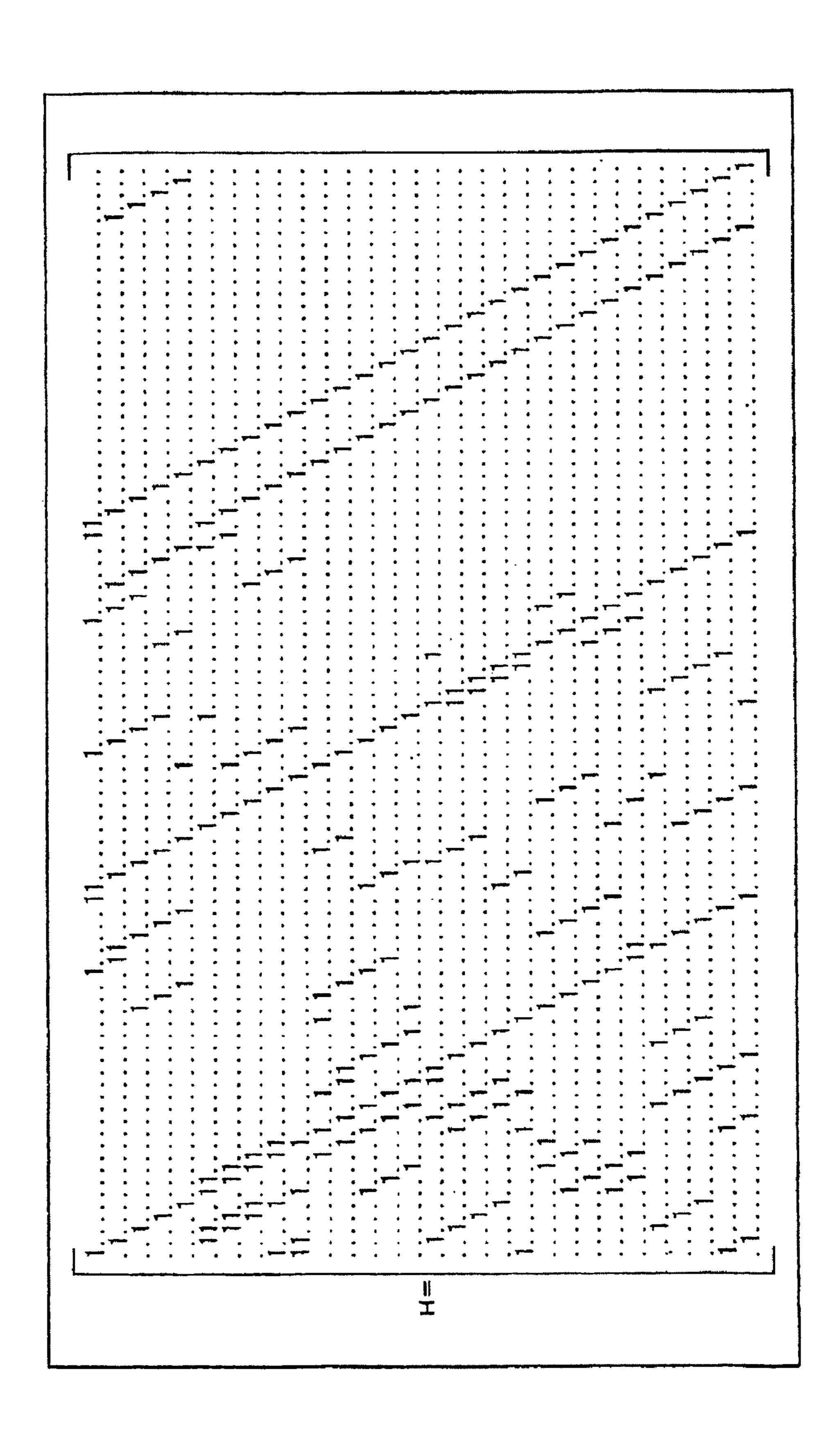

sparse matrix is formed in such a manner that the number of 1s in the elements of the matrix is very small. If the sparse check matrix is denoted as H, examples thereof include a check matrix in which, as shown in FIG. 1, the Hamming weight of each column (number of 1s; weight) is "3", and the Hamming weight of each row is "6".

As described above, the LDPC codes defined by the check matrix H in which the Hamming weight of each row and each column is fixed are called "regular LDPC codes". On the other hand, the LDPC codes defined by a check matrix H in which the Hamming weight of each row and each column is not fixed are called "irregular LDPC codes".

Coding by such LDPC codes is realized by generating a generation matrix G on the basis of the check matrix H and by generating a code word by multiplying this generation matrix G by a two-dimensional information message. More specifically, a coding apparatus for performing coding by LDPC codes computes a generation matrix G in which the equation GH<sup>T</sup>=0 holds with a transpose matrix H<sup>T</sup> of the check matrix H. Here, when the generation matrix G is a k×n matrix, the coding apparatus multiplies the generation matrix G by a k-bit information message (vector u), and generates an n-bit codeword c (=uG). The codeword generated by this coding apparatus is transmitted with the code bit whose value is "0" being mapped to "+1" and the code bit whose value is "1" being mapped to "-1", and is received at the reception side via a predetermined communication channel.

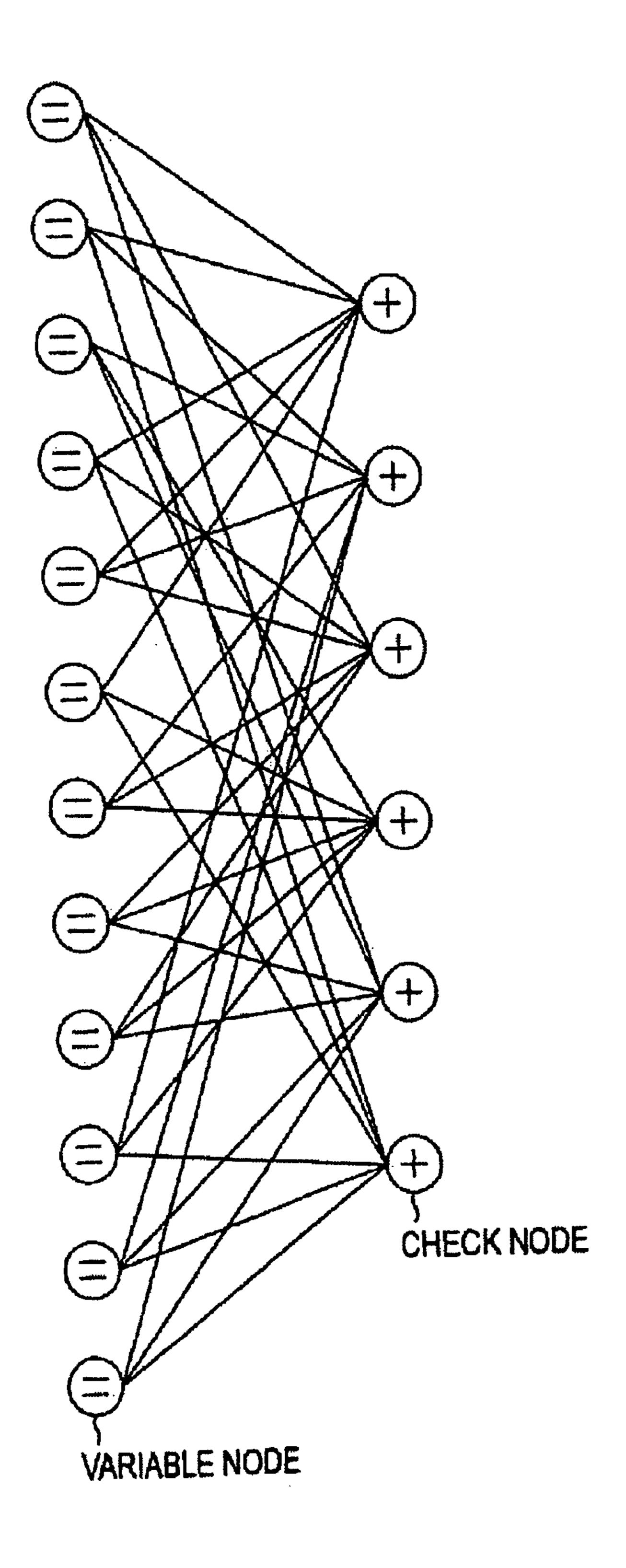

On the other hand, decoding of the LDPC codes can be performed by a message passing algorithm by belief propagation on a so-called Tanner graph, which is formed of a variable node (also called a message node) and a check node; this message passing algorithm was proposed by Gallager and is known as "probabilistic decoding". Hereafter, the variable nodes and the check nodes are also referred to simply as nodes where appropriate.

However, in probabilistic decoding, since messages exchanged between nodes are real-number values, in order to find an analytical solution, it is necessary to trace the probability distribution of the message that takes a continuous value. This necessitates analysis involving a large degree of difficulty. Accordingly, Gallager has proposed an algorithm A or an algorithm B as an algorithm for decoding LDPC codes.

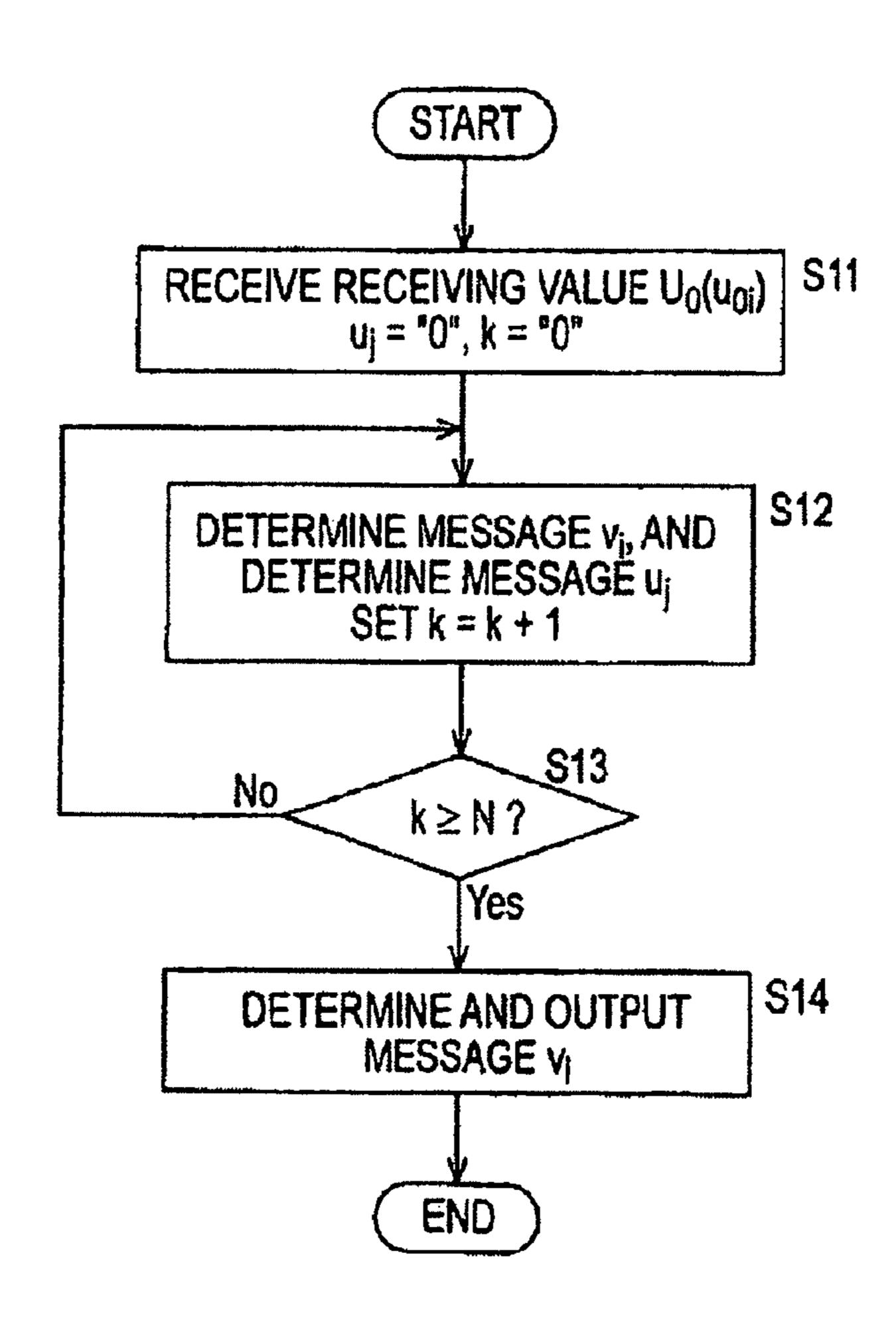

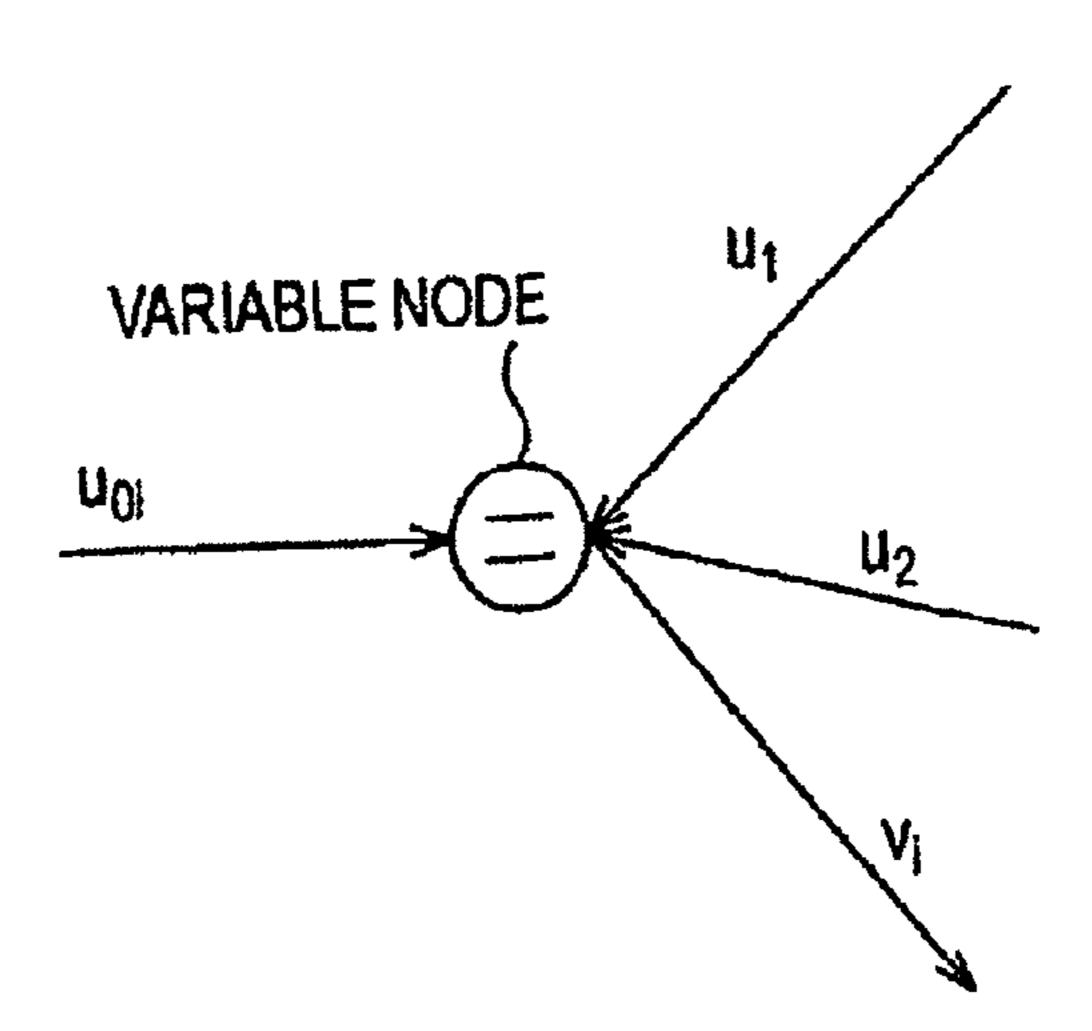

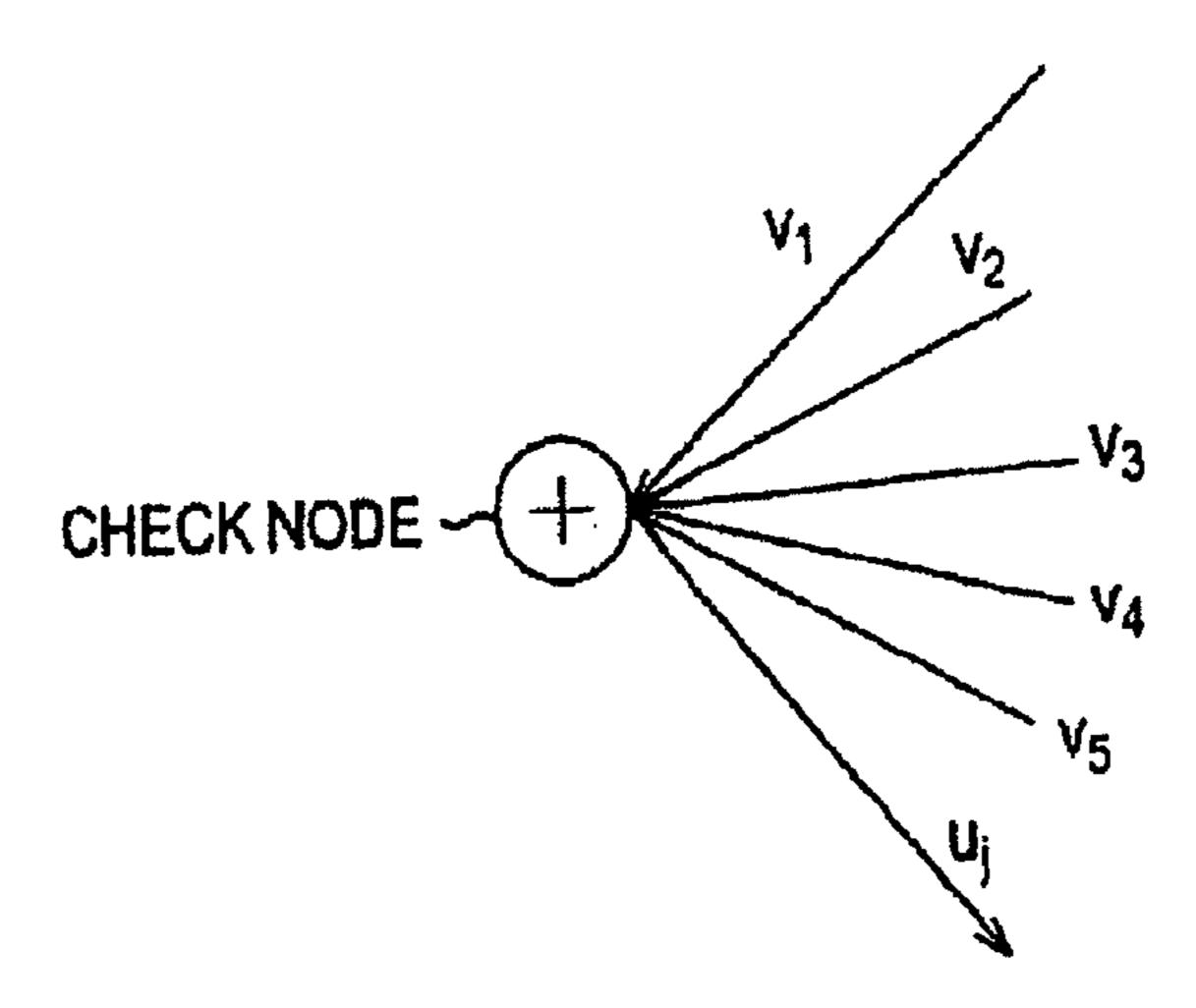

In general, decoding of the LDPC codes is performed in accordance with the procedure shown in FIG. 2. Here, the receiving value is denoted as  $U_0$  ( $u_{0i}$ ), the message output from the check node is denoted as  $u_j$ , and the message output from the variable node is denoted as  $v_i$ . Here, the message is a real-number value such that the "0"-likeness of the value is represented by a so-called log likelihood ratio.

In the decoding of the LDPC codes, initially, as shown in FIG. 2, in step S11, the receiving value  $U_0(u_{0i})$  is received, the message  $u_j$  is initialized to 0, and a variable k that takes an integer as a counter for an iterative process is initialized to 0. The process then proceeds to step S12. In step S12, based on the received value  $U_0(u_{0i})$ , a message  $v_i$  is determined by performing a computation shown in equation (1). Furthermore, based on this message  $v_i$ , a message  $u_j$  is determined by performing a computation shown in equation (2).

$$\mathbf{v}_{i} = \mathbf{u}_{0i} + \sum_{j=1}^{d_{v}-1} \mathbf{u}_{j} \tag{1}$$

$$\tanh\left(\frac{\mathbf{u}_{j}}{2}\right) = \prod_{i=1}^{d_{c}-1} \tanh\left(\frac{\mathbf{v}_{i}}{2}\right) \tag{2}$$

Here,  $d_v$  and  $d_c$  in equations (1) and (2) are parameters respectively that indicate the number of 1s in the vertical direction (in the row direction) and in the horizontal direction (in the column direction) of the check matrix H and that can be selected as desired. For example, in the case of a (3, 6) code,  $d_v$ =3 and  $d_c$ =6.

In the computation of each of equations (1) and (2), since the message input from an edge from which a message is to be output is not used as a parameter for a sum or product computation, the range of the sum or product computation is from 1 to  $d_v$ -1 or 1 to  $d_c$ -1. In practice, the computation shown in equation (2) is performed by creating in advance a table of a function  $R(v_1, v_2)$ , shown in equation (3), that is defined by one output with respect to two inputs  $v_1$  and  $v_2$  and by using this table continuously (recursively), as shown in equation (4).

$$x=2 \tan h^{-1} \{ \tan h(v_1/2) \tan h(v_2/2) \} = R(v_1, v_2)$$

(3)

$$u_j = R(v_1, R(v_2, R(v_3, \dots R(v_{d_c} - 2, v_{d_c} - 1))))$$

(4)

In step S12, furthermore, the variable k is incremented by 1, and the process then proceeds to step S13. In step S13, it is determined whether or not the variable k is greater than or equal to a predetermined number N of iterative decodings. When it is determined in step S13 that the variable k is not greater than or equal to N, the process returns to step S12, and the identical processing is performed again.

When it is determined in step S13 that the variable k is greater than or equal to N, the process proceeds to step S14, where the message v serving as the decoded result, which is finally output as a result of performing the computation shown in equation (5), is determined and output. This completes the decoding process of the LDPC codes.

$$\mathbf{v}_i = \mathbf{u}_{0i} + \sum_{j=1}^{d_v} \mathbf{u}_j \tag{5}$$

Here, unlike the computation of equation (1), the computation of equation (5) is performed using the input messages from all the edges connected to the variable nodes.

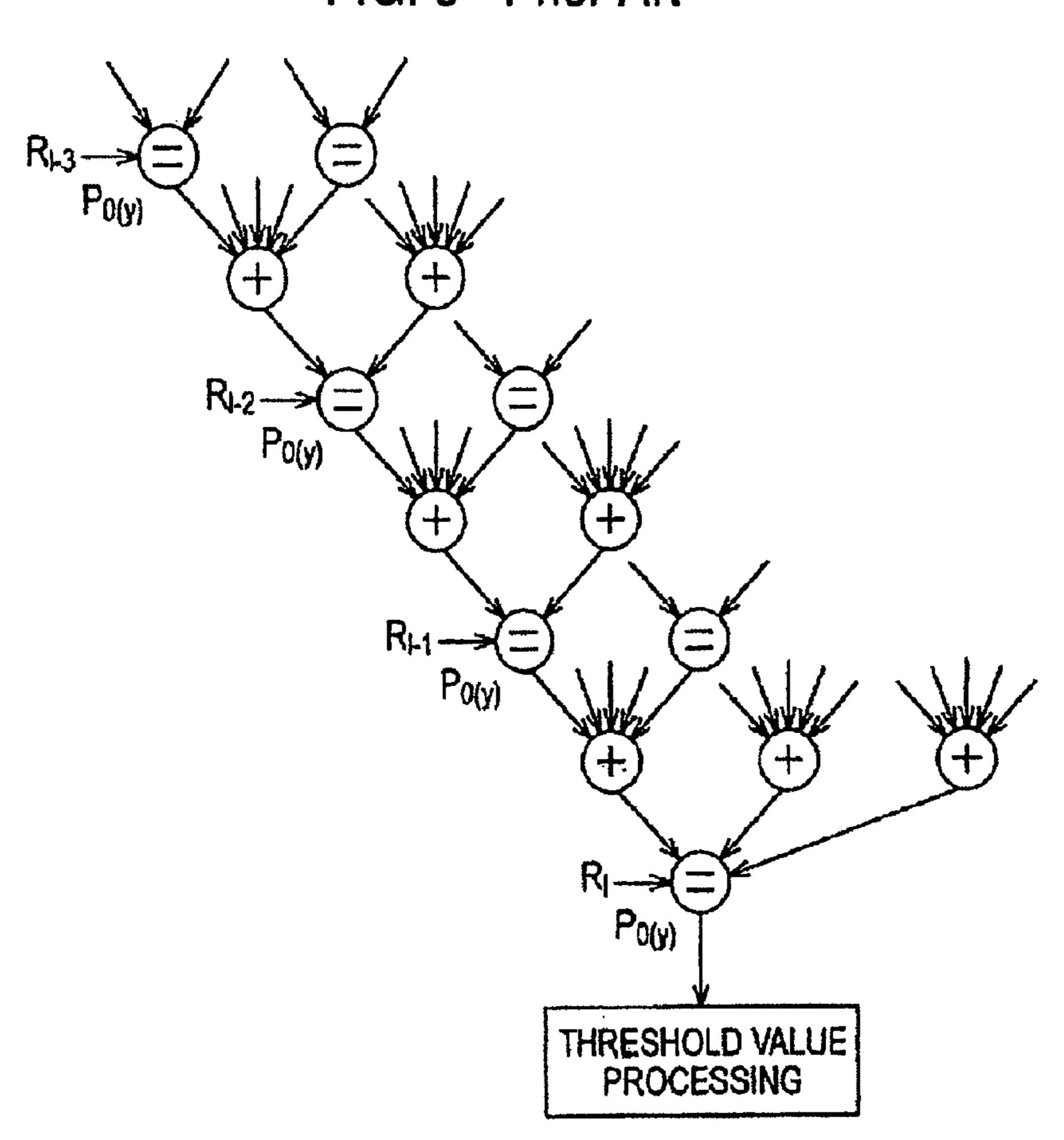

In such LDPC code decoding, for example, in the case of (3, 6) code, as shown in FIG. 3, messages are exchanged 50 between nodes. In the node (variable node) indicated by "=" in FIG. 3, the computation shown in equation (1) is performed. In the node indicated by "+" (check node), the computation shown in equation (2) is performed. In particular, in the algorithm A, the message is formed to be two-dimensional; in the node indicated by "+", an exclusive OR computation of  $d_c$ –1 input messages is performed; and in the node indicated by "=", with respect to the received value R, when all the  $d_v$ –1 input messages are different bit values, the sign is inverted and output.

Furthermore, in recent years, research on an implementation method of the decoding of LDPC codes has been carried out. Before describing the implementation method, the decoding of LDPC codes is described in a schematic form.

FIG. 4 shows an example of a parity check matrix of (3,6) 65 LDPC codes (a coding rate of ½, a code length of 12). The parity check matrix of LDPC codes can be written by using a

4

Tanner graph, as shown in FIG. 5. In FIG. 5, nodes indicated by "+" are check nodes, and nodes indicated by "=" are variable nodes. The check nodes and the variable nodes correspond to the rows and the columns of the parity check matrix, respectively. The connecting line between the check node and the variable node is an edge and corresponds to "1" of the check matrix. That is, when the element of the j-th row and the i-th column of the check matrix is 1, in FIG. 5, the i-th variable node (node of "=") from the top and the j-th check node (node of "+") from the top are connected to each other by an edge. The edge indicates that the sign bit corresponding to the variable node has a constraint condition corresponding to the check node. FIG. 5 shows a Tanner graph of the check matrix of FIG. 4.

In the sum product algorithm, which is a method of decoding LDPC codes, the computation of the variable node and the computation of the check node are repeatedly performed.

In the variable node, as shown in FIG. 6, the computation of equation (1) is performed. That is, in FIG. 6, the message  $v_i$  corresponding to the edge to be calculated is calculated by using the messages  $u_1$  and  $u_2$  from the remaining edges connected to the variable node, and the received information  $u_{0i}$ . The messages corresponding to the other edges are also calculated similarly.

Before describing the check node computation, equation (2) is rewritten as shown in equation (6) by using the equation  $a \times b = \exp\{\ln(|a|) + \ln(|b|)\} \times \operatorname{sign}(a) \times \operatorname{sign}(b)$ , where  $\operatorname{sign}(x)$  is 1 when  $x \ge 0$  and is -1 when x < 0.

$$u_{j} = 2\tanh^{-1}\left(\prod_{i=1}^{d_{c}-1}\tanh\left(\frac{\mathbf{v}_{i}}{2}\right)\right)$$

$$= 2\tanh^{-1}\left[\exp\left\{\sum_{i=1}^{d_{c}-1}\ln\left(\left|\tanh\left(\frac{\mathbf{v}_{i}}{2}\right)\right|\right)\right\} \times \prod_{i=1}^{d_{c}-1}\operatorname{sign}\left(\tanh\left(\frac{\mathbf{v}_{i}}{2}\right)\right)\right]$$

$$= 2\tanh^{-1}\left[\exp\left\{-\left(\sum_{i=1}^{d_{c}-1}-\ln\left(\tanh\left(\frac{|\mathbf{v}_{i}|}{2}\right)\right)\right)\right\} \times \prod_{i=1}^{d_{c}-1}\operatorname{sign}(\mathbf{v}_{i})$$

Furthermore, in the case of  $x \ge 0$ , when the definition  $\phi(x) = \ln(\tan h(x/2))$  is made, since  $\phi^{-1}(x) = 2 \tan h^{-1}(e^{-x})$ , equation (6) can be written as equation (7).

$$\mathbf{u}_{j} = \phi^{-1} \left( \sum_{i=1}^{d_{c}-1} \phi(|\mathbf{v}_{i}|) \right) \times \prod_{i=1}^{d_{c}-1} \operatorname{sign}(\mathbf{v}_{i})$$

(7)

In the check node, as shown in FIG. 7, the computation of equation (7) is performed. That is, in FIG. 7, the message  $u_j$  corresponding to the edge for which a calculation is to be performed is calculated by using the messages  $v_1, v_2, V_3, V_4$ , and  $v_5$  from the remaining edges connected to the check node. The messages corresponding to the other edges are also calculated similarly.

The function  $\phi(x)$  can also be expressed as  $\phi(x)=\ln((e^x+1)/(e^x-1))$  and when x>0,  $\phi(x)=\phi^{-1}(x)$ . When the functions  $\phi(x)$  and  $\phi^{-1}(x)$  are implemented as hardware, there are cases in which they are implemented using an LUT (Look-Up Table), and both of them are the same LUT.

When the sum product algorithm is implemented as hardware, it is necessary to repeatedly perform the variable node computation expressed by equation (1) and the check node computation expressed by equation (7) with an appropriate circuit scale and at an appropriate operating frequency.

As an example of the implementation of the decoding apparatus, a description is given first of an implementation method in a case where decoding is performed by simply performing the computation of each node one-by-one in sequence (full serial decoding).

It is assumed here that, for example, codes (a coding rate of <sup>2</sup>/<sub>3</sub>, and a code length of 90) represented by a 30 (rows)×90 (columns) check matrix of FIG. 8 are decoded. The number of 1s of the check matrix of FIG. 8 is 269; therefore, in the Tanner graph, the number of edges becomes 269. Here, in the 10 check matrix of FIG. 8, 0 is represented by "."

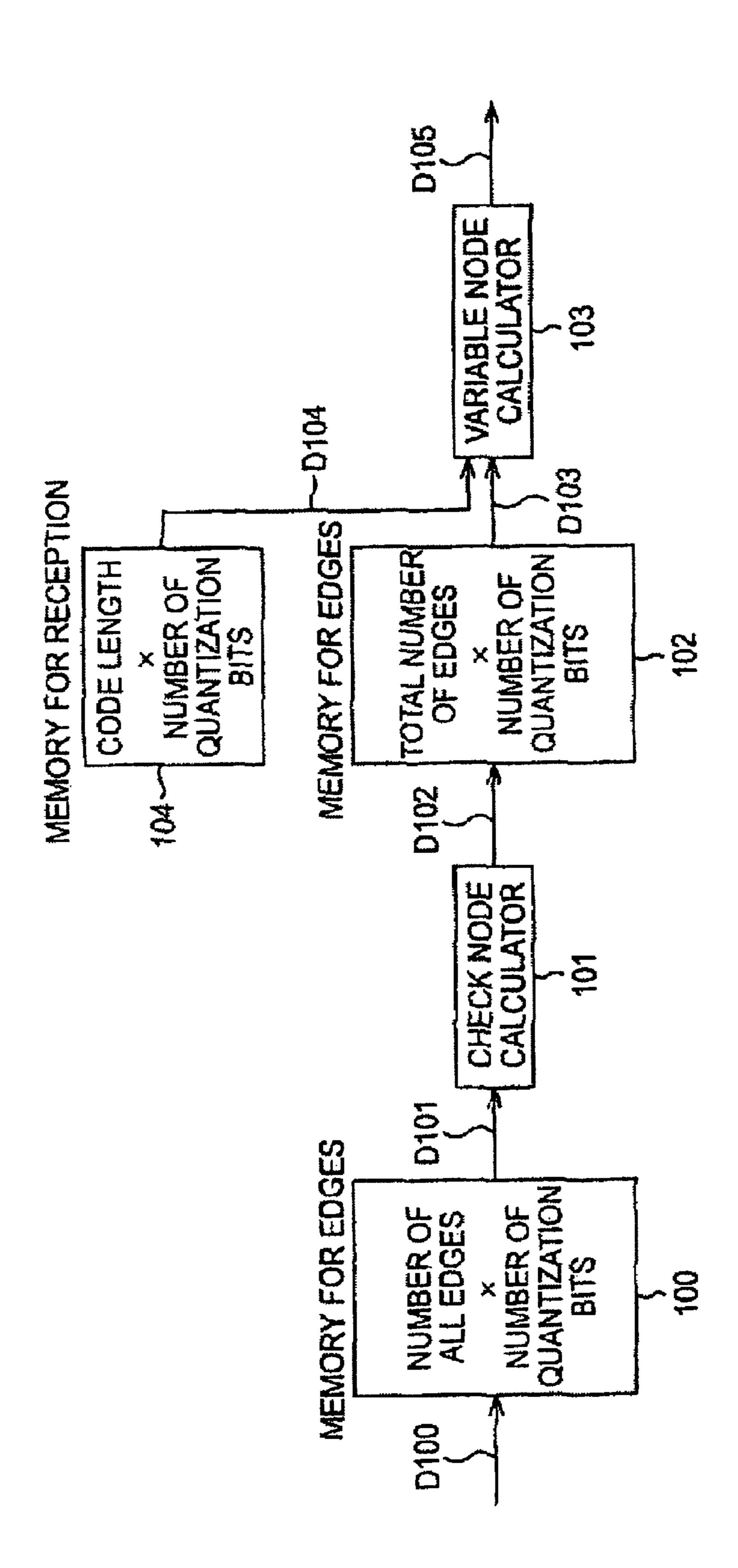

FIG. 9 shows an example of the configuration of a decoding apparatus for decoding LDPC codes once.

In the decoding apparatus of FIG. 9, a message corresponding to one edge is calculated for each clock at which it operates.

More specifically, the decoding apparatus of FIG. 9 includes two memories 100 and 102 for edges, one check node calculator 101, and one variable node calculator 103, one memory 104 for reception, and one control section 105.

In the decoding apparatus of FIG. 9, message data is read one-by-one from the memory 100 or 102 for edges, and by using the message data, the message data corresponding to the desired edge is calculated. Then, the message data determined by that calculation is stored one-by-one in the memory 25 100 or 102 for edges at a subsequent stage. When iterative decoding is to be performed, the iterative decoding is realized by serially concatenating a plurality of the decoding apparatuses of FIG. 9 for decoding LDPC codes once or by repeatedly using the decoding apparatus of FIG. 9. Here, it is 30 assumed that, for example, a plurality of the decoding apparatuses of FIG. 9 are connected.

The memory 100 for edges stores messages D100 supplied from the variable node calculator 103 of the decoding apparatus (not shown) at a previous stage in the order in which the 35 check node calculator 101 at a subsequent stage reads them. Then, at the phase of the check node calculation, the memory 100 for edges supplies, to the check node calculator 101, the messages D100 as a message output D101 in the order in which they are stored.

Based on the control signal D106 supplied from the control section 105, the check node calculator 101 performs a computation in accordance with equation (7) by using the message D101 supplied from the memory 100 for edges, and supplies a message D102 determined by that computation to 45 the memory 102 for edges at a subsequent stage.

The memory 102 for edges stores the messages D102 supplied from the check node calculator 101 at a previous stage in the order in which the variable node calculator 103 at a subsequent stage reads them. Then, at the phase of the variable node calculation, the memory 102 for edges supplies the message D102 as a message D103 to the variable node calculator 103 in the order in which they are stored.

Furthermore, a control signal D107 is supplied to the variable node calculator 103 from the control section 105, and 55 received data D104 is supplied thereto from the memory 104 for reception. Based on a control signal D107, the variable node calculator 103 performs a computation in accordance with equation (1) by using the message D103 supplied from the memory 100 for edges and the received data D104 supplied from the memory 100 for reception, and supplies a message D105 obtained as a result of the computation to the memory 100 for edges, of the decoding apparatus (not shown) at a subsequent stage.

In the memory 104 for reception, received data (LDPC 65 codes) that are converted into LDPC codes are stored. The control section 105 supplies a control signal D106 for con-

6

D107 for controlling a check node computation to the check node calculator 101 and the variable node calculator 103, respectively. The control section 105 supplies the control signal D106 to the check node calculator 101 when the messages of all the edges are stored in the memory 100 for edges, and the control section 105 supplies the control signal D107 to the variable node calculator 103 when the messages of all the edges are stored in the memory 102 for edges.

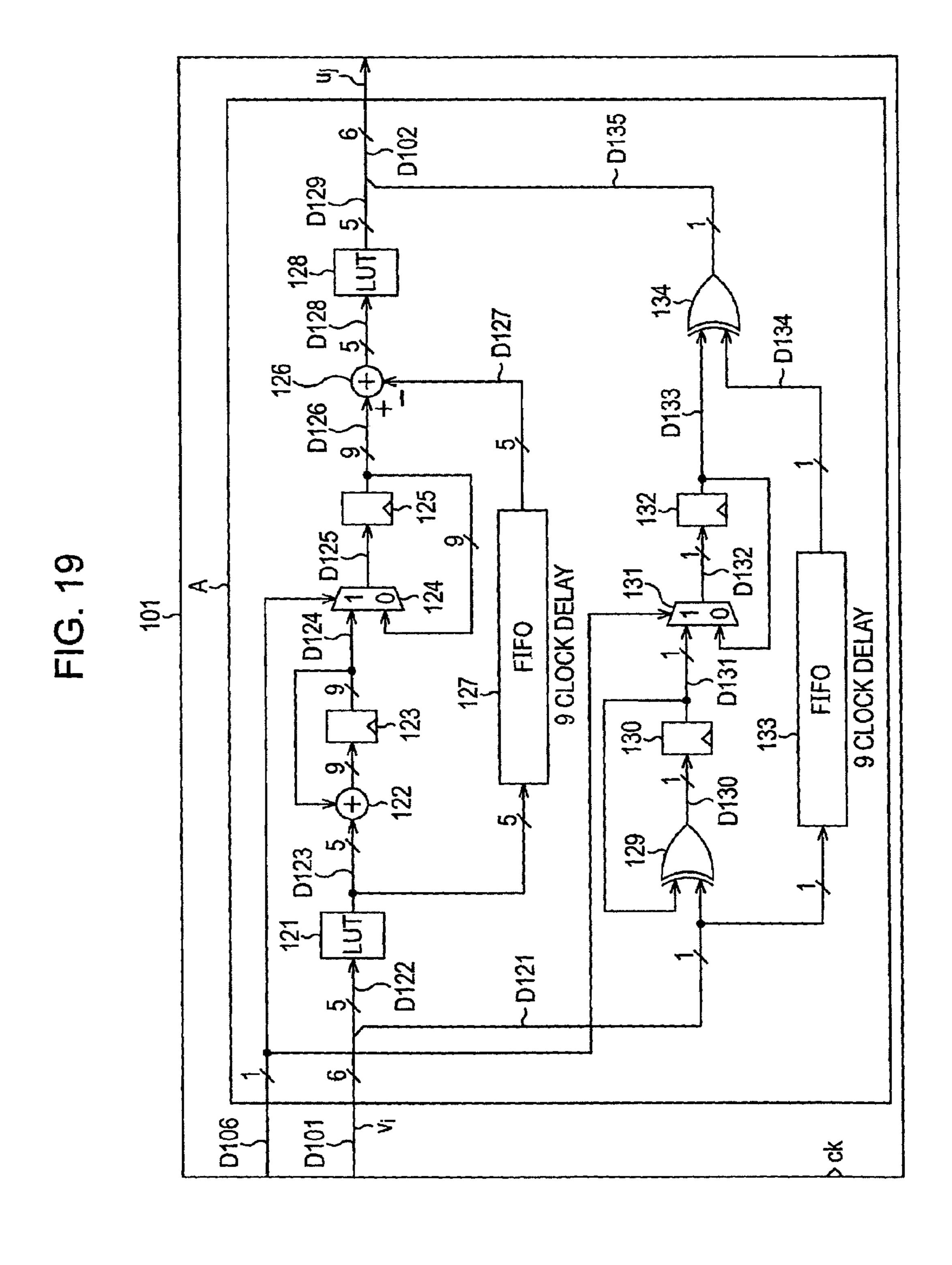

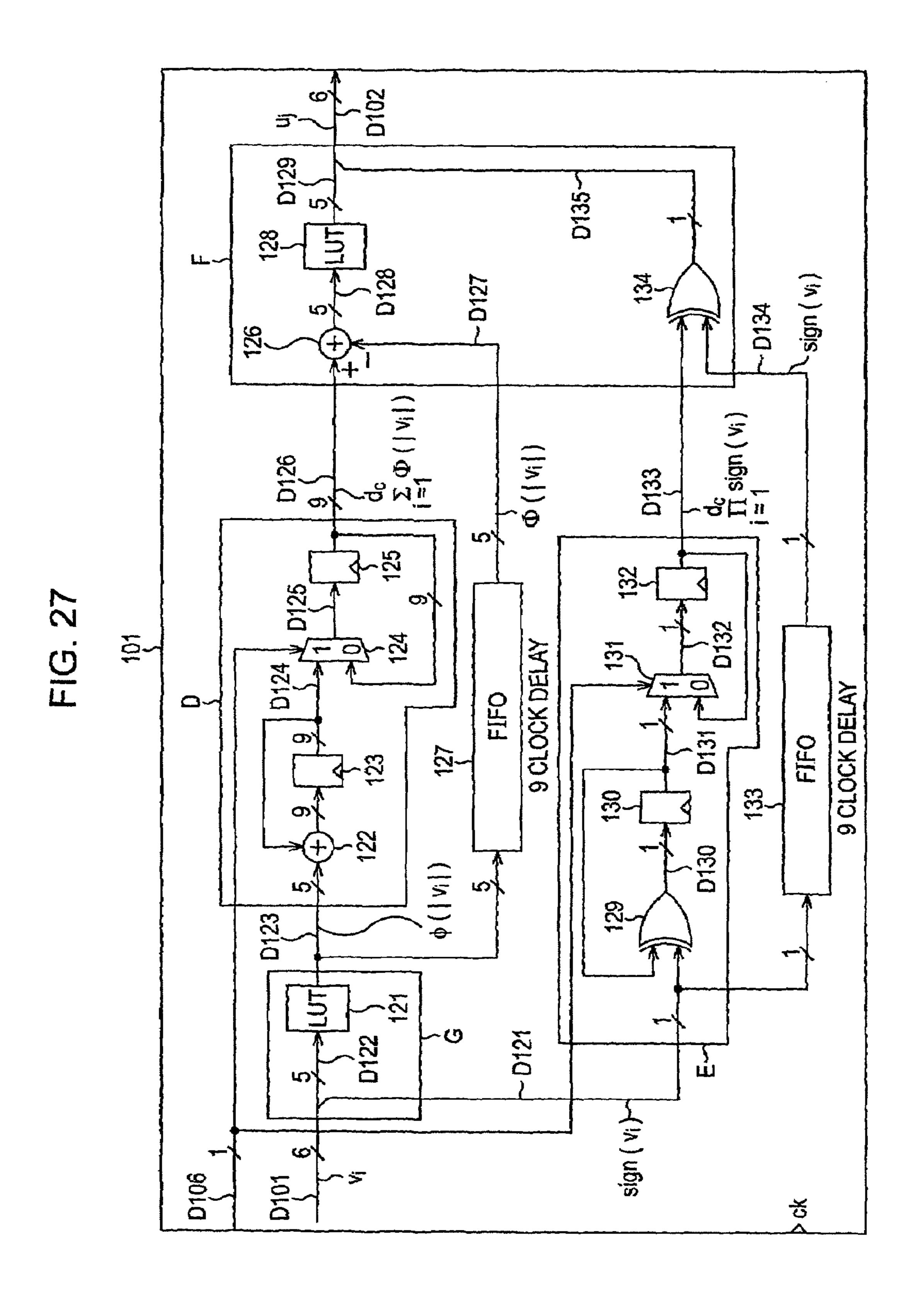

FIG. 10 shows an example of the configuration of the check node calculator 101 of FIG. 9 for performing check node computations one-by-one.

In FIG. 10, the check node calculator 101 is shown by assuming that each message, together with the sign bit, is quantized into a total of six bits. Furthermore, in FIG. 10, a check node computation of LDPC codes represented by the check matrix of FIG. 8 is performed. Furthermore, a clock ck is supplied to the check node calculator 101 of FIG. 10, this clock ck being supplied to necessary blocks. Each block performs processing in synchronization with the clock ck.

Based on, for example, a 1-bit control signal D106 supplied from the control section 105, the check node calculator 101 of FIG. 10 performs computations in accordance with equation (7) by using the messages D101 that are read one-by-one from the memory 100 for edges.

More specifically, in the check node calculator 101, 6-bit messages D101 (messages  $v_i$ ) from the variable node, corresponding to each column of the check matrix, are read one-by-one, the absolute value D122 ( $|v_i|$ ), which is the lower-order bits thereof, is supplied to the LUT 121, and a sign bit D121, which is the highest bit thereof, is supplied to an EXOR circuit 129 and an FIFO (First In First Out) memory 133, respectively. Furthermore, the control signal D106 is supplied to the check node calculator 101 from the control section 105, and the control signal D106 is supplied to a selector 124 and a selector 131.

The LUT **121** reads a 5-bit computation result D**123**  $(\phi(|v_i|))$  such that the computation of  $\phi(|v_i|)$  in equation (7) is performed on the absolute value D**122**  $(|v_i|)$ , and supplies it to an adder **122** and an FIFO memory **127**.

The adder 122 integrates the computation results D123 by adding together the computation results D123 ( $\phi(|v_i|)$ ) and a 9-bit value D124 stored in a register 123, and stores the 9-bit integration value obtained thereby in the register 123 again. When the computation results for the absolute values D122 ( $|v_i|$ ) of the messages D101 from all the edges over one row of the check matrix are integrated, the register 123 is reset.

When the messages D101 over one row of the check matrix are read one-by-one and the integrated value such that the computation results D123 for one row is stored in the register 123, the control signal D106 supplied from the control section 105 changes from 0 to 1. For example, when the row weight is "9", the control signal D106 is "0" at the first to eighth clocks, and is "1" at the ninth clock.

When the control signal D106 is "1", the selector 124 selects the value stored in the register 123, that is, the 9-bit value D124 ( $\Sigma \phi(|v_i|)$  from i=1 to i=d<sub>c</sub>) such that  $\phi(|v_i|)$  determined from the messages D101 (messages  $v_i$ ) from all the edges over one row of the check matrix, and outputs the value as a value D125 to a register 125, whereby it is stored. The register 125 supplies the stored value D125 as a 9-bit value D126 to the selector 124 and the adder 126. When the control signal D106 is "0", the selector 124 selects the value D126 supplied from the register 125, and outputs the value to the selector 124, whereby it is stored again. That is, until  $\phi(|v_i|)$  determined from the messages D101 (messages  $v_i$ ) from all the edges over one row of the check matrix are integrated, the

register 125 supplies the previously integrated  $\phi(|v_i|)$  to the selector 124 and the adder 126.

On the other hand, the FIFO memory 127 delays the computation results D123 ( $\phi(|\langle v_i|\rangle)$ ) output by the LUT 121 until a new value D126 ( $\Sigma \phi(|v_i|)$  from i=1 to i=d<sub>c</sub>) is output from the register 125, and supplies them as a 5-bit value D127 to a subtractor 126. The subtractor 126 subtracts, from the value D126 supplied from the register 125, the value D127 supplied from the FIFO memory 127, and supplies the subtracted result as a 5-bit subtracted value D128 to the LUT 128. That is, the subtractor 126 subtracts  $\phi(|v_i|)$  determined from the messages D101 (messages  $v_i$ ) from the edge to be determined, from the integrated value of  $\phi(|v_i|)$  determined from the messages D101 (messages  $v_i$ ) from all the edges over one  $v_i$ row of the check matrix, and supplies the subtracted value  $(\Sigma \phi(|v_i|))$  from i=1 to i=d<sub>c</sub>-1) as a subtracted value D128 to the LUT **128**.

The LUT **128** outputs the 5-bit computation results D**129**  $(\phi^{-1}(\Sigma\phi(|v_i|)))$  such that the computation of  $\phi^{-1}(\Sigma\phi(|v_i|))$  in 20 equation (7) is performed on the subtracted value D128 ( $\Sigma \phi$  $(|\mathbf{v}_i|)$  from i=1 to  $i=d_c-1$ ).

In parallel with the above processing, the EXOR circuit 129 performs a multiplication of sign bits by computing the exclusive OR of a 1-bit value D131 stored in a register 130 25 and the sign bit D121, and stores the 1-bit multiplication result D130 in the register 130 again. When the sign bits D121 of the messages D101 from all the edges over one row of the check matrix are multiplied, the register 130 is reset.

When the multiplied results D130 ( $\Pi$ sign ( $v_i$ ) from i=1 to 30 d<sub>c</sub>) such that the sign bits D121 of the messages D101 from all the edges over one row of the check matrix are multiplied are stored, the control signal D106 supplied from the control section 105 changes from "0" to "1".

selects the value stored in the register 130, that is, the value D131 ( $\Pi$ sign ( $v_i$ ) from i=1 to i= $d_c$ ) such that the sign bits D121 of the messages D101 from all the edges over one row of the check matrix are multiplied, and outputs the value as a 1-bit value D133 to a register 132, whereby it is stored. The register 132 supplies the stored value D132 as a 1-bit value D132 to the selector 131 and the EXOR circuit 134. When the control signal D106 is "0", the selector 131 selects a value D133 supplied from the register 132, and outputs the value to the register 132, whereby it is stored again. That is, until the 45 sign bits D121 of the messages D101 (messages v<sub>i</sub>) from all the edges over one row of the check matrix are multiplied, the register 132 supplies the value stored at the previous time to the selector 131 and the EXOR circuit 134.

On the other hand, the FIFO memory **133** delays the sign 50 bits D121 until a new value D133 ( $\Pi$ sign ( $v_i$ ) from i=1 to i= $d_c$ ) is supplied from the register 132 to the EXOR circuit 134, and supplies the result as a 1-bit value D134 to the EXOR circuit 134. The EXOR circuit 134 divides the value D133 by the value D134 by computing the exclusive OR of the value D133 supplied from the register 132 and the value D134 supplied from the FIFO memory 133, and outputs a 1-bit divided result as a divided value D135. That is, the EXOR circuit 134 divides the multiplication value of the sign bits D121 (sign  $(|v_i|)$ ) of the messages D101 from all the edges over one row 60 of the check matrix by the sign bits D121 (sign (|v<sub>i</sub>|)) of the messages D101 from the edge to be determined, and outputs the divided value ( $\Pi$ sign ( $|v_i|$ ) from i=1 to i= $d_c$ -1) as a divided value D135.

In the check node calculator 101, a total of six bits such that 65 the 5-bit computation result D129 output from the LUT 128 is the lower-order 5 bits and the 1-bit divided value D135 output

8

from the EXOR circuit **134** is the highest-order bit is output as a message D102 (message  $u_i$ ).

As described above, in the check node calculator 101, the computation of equation (7) is performed, and a message  $u_i$  is determined.

Since the maximum of the row weight of the check matrix of FIG. 8 is 9, that is, since the maximum number of the messages supplied to the check node is 9, the check node calculator 101 has an FIFO memory 127 and the FIFO memory 133 for delaying nine messages ( $\phi(|v_i|)$ ). When a message of the row whose weight is less than 9 is to be calculated, the amount of delay in the FIFO memory 127 and the FIFO memory 133 is reduced to the value of the row weight.

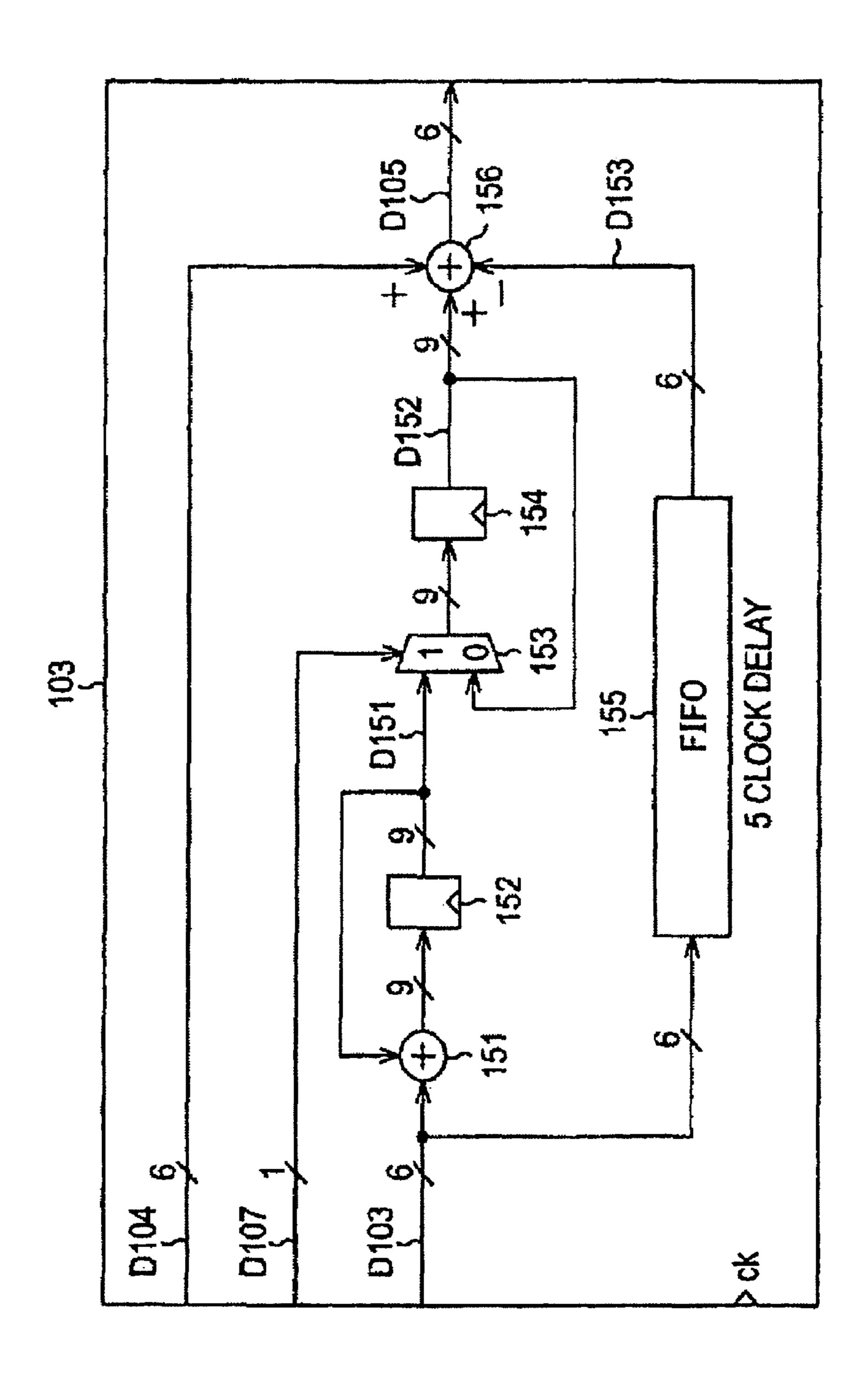

FIG. 11 shows an example of the configuration of the variable node calculator 103 of FIG. 9, for performing variable node calculations one-by-one.

In FIG. 11, the variable node calculator 103 is shown by assuming that each message, together with the sign bit, is quantized into a total of six bits. In FIG. 11, the variable node computation of LDPC codes represented by the check matrix of FIG. 8 is performed. Furthermore, a clock ck is supplied to the variable node calculator 103 of FIG. 11, and the clock ck is supplied to necessary blocks. Each block performs processing in synchronization with the clock ck.

Based on, for example, a 1-bit control signal D107 supplied from the control section 105, the variable node calculator 103 of FIG. 11 performs computations in accordance with equation (1) by using the messages D103 that are read one-by-one from the memory 102 for edges and the received data D104 that is read from the memory 104 for reception.

More specifically, in the variable node calculator 103, 6-bit messages D103 (messages  $u_i$ ) from the check node corresponding to each row of the check matrix is read one-by-one, When the control signal D106 is "1", the selector 131 35 and the messages D103 are supplied to the adder 151 and the FIFO memory **155**. Furthermore, in the variable node calculator 103, 6-bit received data D104 are read one-by-one from the memory 104 for reception, and is supplied to the adder **156**. Furthermore, a control signal D107 is supplied to the variable node calculator 103 from the control section 105, and the control signal D107 is supplied to a selector 153.

> The adder 151 integrates the messages D103 by adding together the messages D103 (messages  $u_i$ ) and a 9-bit value D151 stored in the register 152, and stores the 9-bit integrated value in the register 152 again. When the message D103 from all the edges over one row of the check matrix are integrated, the register 152 is reset.

> When the messages D103 from all the edges over one row of the check matrix are read one-by-one, and the value such that the messages D103 for one column are integrated is stored in the register 152, the control signal D107 supplied from the control section 105 changes from "0" to "1". For example, when the column weight is "5", the control signal D107 is "0" at the first clock up to the fourth clock and is "0" at the fifth clock.

> When the control signal D107 is "1", the selector 153 selects the value stored in the register 152, that is, a 9-bit value D151 ( $\Sigma u_i$  from j=1 to  $d_v$ ) such that the messages D103 (messages  $u_i$ ) from all the edges over one row of the check matrix are integrated, and outputs the value to the register 154, whereby it is stored. The register 154 supplies the stored value D151 as a 9-bit value D152 to the selector 153 and the adder-subtractor 156. When the control signal D107 is "0", the selector 153 selects a value D152 supplied from the register 154, and outputs the value to a register 154, whereby it is stored again. That is, until the messages D103 (messages  $u_i$ ) from all the edges over one row of the check matrix are

integrated, the register 154 supplies the previously integrated value to the selector 153 and the adder-subtractor 156.

On the other hand, the FIFO memory 155 delays the message D103 from the check node until a new value D152 ( $\Sigma u_i$ from j=1 to d<sub>v</sub>) is output from the register **154**, and supplies it 5 as a 6-bit value D153 to the adder-subtractor 156. The addersubtractor 156 subtracts the value D153 supplied from the FIFO memory 155, from the value D152 supplied from the register 154. That is, the adder-subtractor 156 subtracts the message  $u_i$  from the edge to be determined, from the inte- 10 grated value of the messages D103 (messages  $u_i$ ) from all the edges over one row of the check matrix, and determines the subtracted value ( $\Sigma u_j$  from j=1 to  $d_v$ -1). Furthermore, the adder-subtractor 156 adds the received data D104 supplied from the memory 104 for reception to the subtracted value 15  $(\Sigma u_i \text{ from } j=1 \text{ to } d_v 1)$ , and outputs the 6-bit value obtained thereby as a message D105 (message  $v_i$ ).

As described above, in the variable node calculator 103, the computation of equation (1) is performed, and the message  $v_i$ is determined.

Since the maximum of the column weight of the check matrix of FIG. 8 is 5, that is, since the maximum number of the messages supplied to the variable node is 5, the variable node calculator 103 has an FIFO memory 155 for delaying five messages  $(u_i)$ . When a message of a column whose 25 weight is less than 5 is to be calculated, the amount of delay in the FIFO memory **155** is reduced to the value of the column weight.

In the decoding apparatus of FIG. 9, a control signal is supplied from the control section **105** in accordance with the 30 weight of the check matrix. According to the decoding apparatus of FIG. 9, if only the capacities of the memories for edges 100 and 102 and the FIFO memories 127, 133, and 155 of the check node calculator 101 and the variable node calmatrices can be decoded by changing only the control signal.

Although not shown, in the decoding apparatus of FIG. 9, at the final stage of the decoding, instead of the variable node calculation of equation (1), the computation of equation (5) is performed, and the computation result is output as the final 40 decoded result.

When LDPC codes are decoded by repeatedly using the decoding apparatus of FIG. 9, the check node computation and the variable node computation are alternately performed. That is, in the decoding apparatus of FIG. 9, a variable node 45 computation is performed by the variable node calculator 103 by using the result of the check node computation by the check node calculator 101, and a check node computation is performed by the check node calculator 101 by using the result of the variable node computation by the variable node 50 calculator 103.

Therefore, for performing one decoding using the check matrix having 269 edges of FIG. 8, 269×2=538 clocks are required. For example, in order to perform 50 iterative decodings,  $538\times50=26900$  clock operations are necessary while 55 to  $201_{30}$ . one frame in which 90 codes (received data) are set as one frame, which is the code length, is received, and thus, a high-speed operation approximately 300 (≈26900/90) times as high as the receiving frequency becomes necessary. If the receiving frequency is assumed to be several tens of MHz, 60 operation at a speed of GHz or higher is required.

Furthermore, in a case where, for example, 50 decoding apparatuses of FIG. 9 are concatenated to decode LDPC codes, a plurality of variable node calculations and check node calculations can be performed simultaneously. For 65 example, while a variable node computation of the first frame is being performed, a check node computation of the second

**10**

frame is performed, and a variable node computation of the third frame is performed. In this case, while 90 codes are received, since 269 edges need to be calculated, the decoding apparatus needs to operate at a frequency approximately 3 (≈269/90) times as high as the receiving frequency, and thus realization is sufficiently possible. However, in this case, the circuit scale becomes, in simple terms, 50 times as large as the decoding apparatus of FIG. 9.

Next, a description is given of the implementation method of the decoding apparatus in a case where decoding is performed by simultaneously performing computations of all the nodes (full parallel decoding).

This implementation method is described in, for example, C. Howland and A. Blanksby, "Parallel Decoding Architectures for Low Density Parity Check Codes", Symposium on Circuits and Systems, 2001.

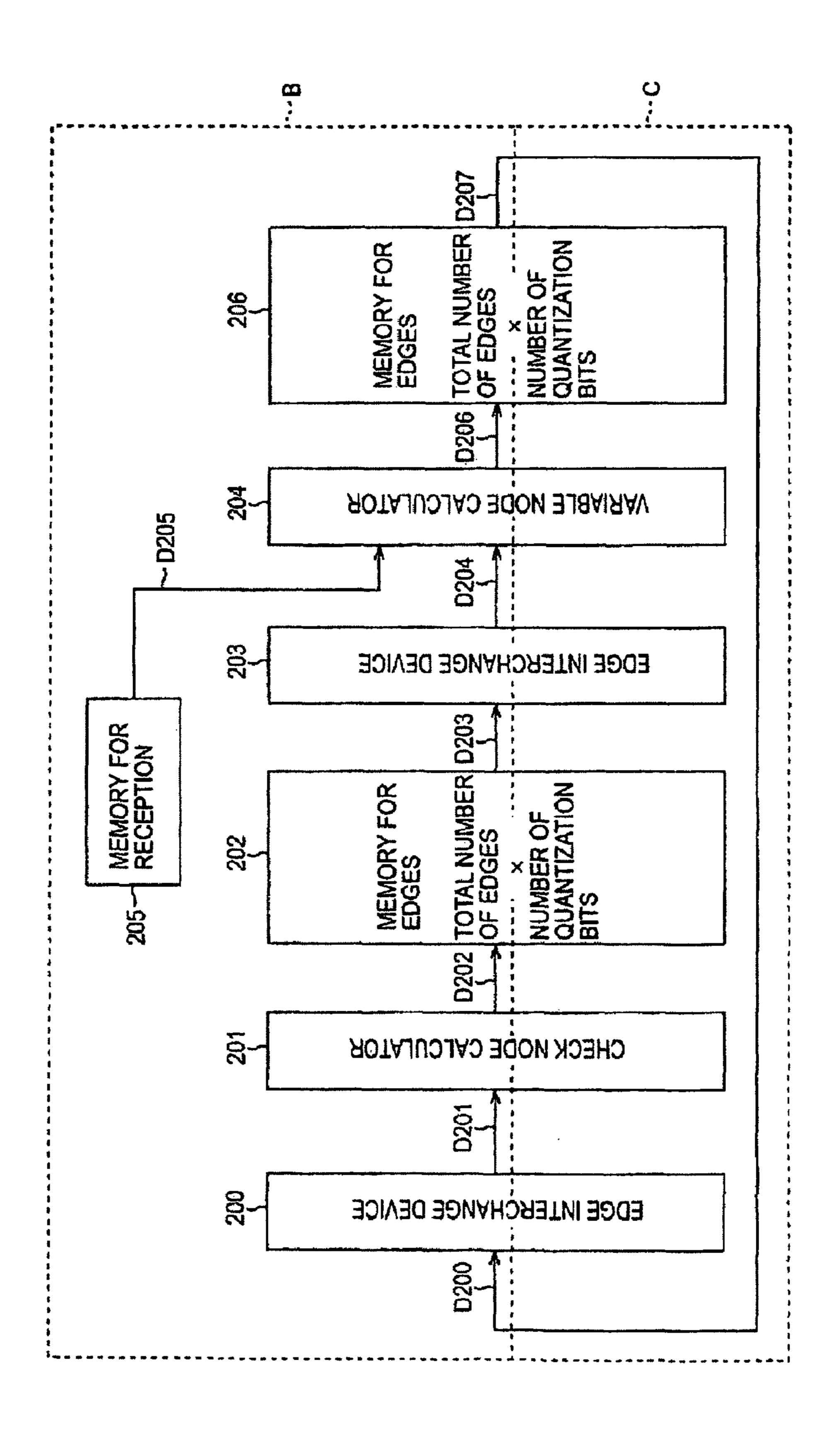

FIGS. 12A to 12C show the configuration of examples of the decoding apparatus for decoding the codes (a coding rate of <sup>2</sup>/<sub>3</sub>, and a code length of 90) represented by the check matrix of FIG. 8. FIG. 12A shows the overall configuration of the decoding apparatus. FIG. 12B shows the detailed configuration of the upper portion in the figure surrounded by the dotted line B, of the decoding apparatus of FIG. 12A. FIG. 12C shows the detailed configuration of the lower portion in the figure surrounded by the dotted line C, of the decoding apparatus of FIG. 12A.

The decoding apparatus of FIGS. 12A to 12C includes one memory 205 for reception, two edge interchange devices 200 and 203, two memories 202 and 206 for edges, a check node calculator 201 made up of 30 check node calculators 201, to 201<sub>30</sub>, and a variable node calculator 204 made up of 90 variable node calculators  $204_1$  to  $204_{90}$ .

In the decoding apparatus of FIGS. 12A to 12C, all the culator 103 are sufficient, LDPC codes of various check 35 message data corresponding to 269 edges is read simultaneously from the memory 202 or 206 for edges, and by using the message data, new message data corresponding to the 269 edges is computed. Furthermore, all the new message data determined as a result of the computation is simultaneously stored in the memory 206 or 202 for edges at a subsequent stage. By repeatedly using the decoding apparatus of FIGS. **12**A to **12**C, iterative decoding is realized. Each section will now be described below in detail.

> The memory 206 for edges simultaneously stores all the messages D206<sub>1</sub> to D206<sub>90</sub> from the variable node calculators 204<sub>1</sub> to 204<sub>90</sub> at a previous stage, reads the messages D206<sub>1</sub> to  $D206_{90}$  as messages  $D207_1$  to  $D207_{90}$  at the next clock (the timing of the next clock), and supplies them as messages  $D200 (D200_1 \text{ to } D200_{90})$  to the edge interchange device 200 at the subsequent stage. The edge interchange device 200 rearranges (interchanges) the order of the messages  $D200_1$  to D200<sub>90</sub> supplied from the memory 206 for edges in accordance with the check matrix of FIG. 8, and supplies them as messages D201<sub>1</sub> to D201<sub>30</sub> to the check node calculators 201<sub>1</sub>

> The check node calculators  $201_1$  to  $201_{30}$  perform a computation in accordance with equation (7) by using the messages  $D201_1$  to  $D201_{30}$  supplied from the edge interchange device 200, and supplies the messages D202<sub>1</sub> to D202<sub>30</sub> obtained as a result of the computation to the memory 202 for edges.

> The memory 202 for edges simultaneously stores all the messages D202<sub>1</sub> to D202<sub>30</sub> supplied from the check node calculators  $201_1$  to  $201_{30}$  at the previous stage, and at the next time, supplies all the messages  $D202_1$  to  $D202_{30}$ , as messages D203<sub>1</sub> to D203<sub>30</sub>, to the edge interchange device 203 at the subsequent stage.

The edge interchange device 203 rearranges the order of the messages  $D203_1$  to  $D203_{30}$  supplied from the memory 202 for edges in accordance with the check matrix of FIG. 8, and supplies them as messages  $D204_1$  to  $D204_{90}$  to the variable node calculators  $204_1$  to  $204_{90}$ .

The variable node calculators  $204_1$  to  $204_{90}$  perform a computation in accordance with equation (1) by using the messages  $D204_1$  to  $D204_{90}$  supplied from the edge interchange device 203 and the received data  $D205_1$  to  $D205_{90}$  supplied from the memory 205 for reception, and supplies messages  $D206_1$  to  $D206_{90}$  obtained as a result of the computation to the memory 206 for edges at the subsequent stage.

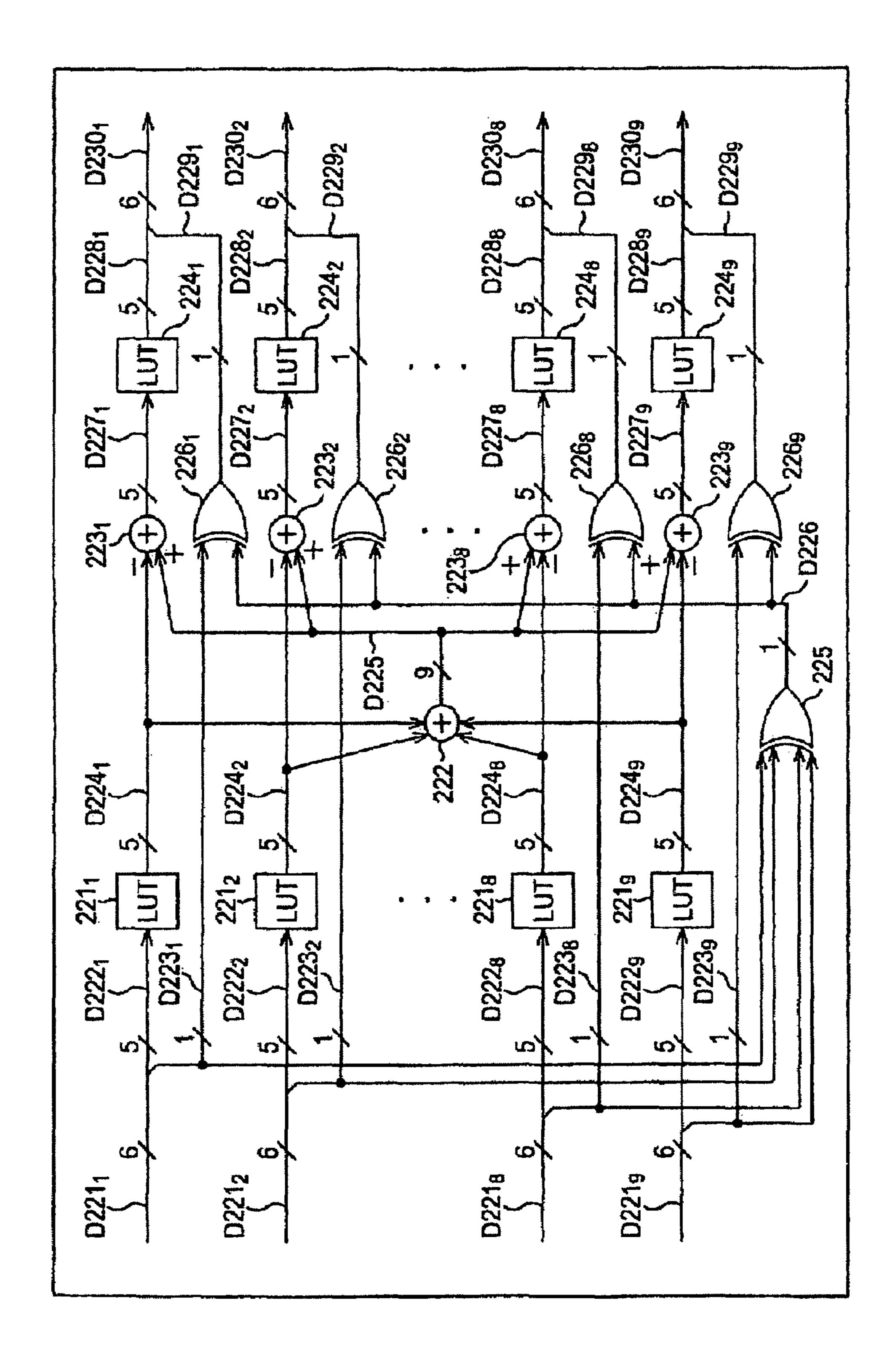

FIG. 13 shows an example of the configuration of a check node calculator  $201_m$  (m=1, 2, ..., 30) of FIGS. 12A to 12C for simultaneously performing check node calculations.

In the check node calculator  $201_m$  of FIG. 13, similarly to the check node calculator 101 of FIG. 10, the check node computation of equation (7) is performed, and the check node calculations are simultaneously performed for all the edges. 20

More specifically, in the check node calculator  $201_m$  of FIG. 13, all the messages  $D221_1$  to  $D221_9$  ( $v_i$ ) from the variable node corresponding to each row of the check matrix of FIG. 8, which are supplied from the edge interchange device 200, are read simultaneously, and the absolute values  $D222_1$  25 to  $D222_9$  ( $|v_i|$ ) which are the respective lower-order 5 bits thereof, are supplied to the LUTs  $221_1$  to  $221_9$ , respectively. 1-bit sign bits  $D223_1$  to  $D223_9$ , which are the highest-order bits of the message  $D221_1$  to  $D221_9(v_i)$ , are supplied to the EXOR circuits  $226_1$  to  $226_9$ , respectively, and are also supplied to the EXOR circuit 225.

The LUTs  $221_1$  to  $221_9$  read 5-bit computation results D224<sub>1</sub> to D224<sub>9</sub> ( $\phi(|v_i|)$ ) such that the computation of  $\phi(|v_i|)$  in equation (7) is performed, respectively, on the absolute values D222<sub>1</sub> to D222<sub>9</sub> ( $|v_i|$ ), respectively, and supplies them 35 to the respective subtractors  $223_1$  to  $223_9$ . The LUTs  $221_1$  to  $221_9$  supply the computation results D224<sub>1</sub> to D224<sub>9</sub> ( $\phi(|v_i|)$ ) to an adder 222.

The adder 222 computes the total sum of the values of the computation results D224<sub>1</sub> to D224<sub>9</sub> ( $\phi(|v_i|)$ ) (the total sum of 40 the computation results for one row), and supplies the 9-bit computation results D225 ( $\Sigma \phi(|v_i|)$  from i=1 to 9) to the subtractors 223<sub>1</sub> to 223<sub>9</sub>. The subtractors 223<sub>1</sub> to 223<sub>9</sub> subtract the computation results D224<sub>1</sub> to D224<sub>9</sub> ( $\phi(|v_i|)$ ) from the computation results D225, respectively, and supply the 45 5-bit subtracted value D227<sub>1</sub> to D227<sub>9</sub> to the LUTs 224<sub>1</sub> to 224<sub>9</sub>. That is, the subtractors 223<sub>1</sub> to 223<sub>9</sub> subtract  $\phi(|v_i|)$ determined from the message v<sub>i</sub> from the edge to be determined, from the integrated value of  $\phi(|v_i|)$  determined from the message v, from all the edges, and supply the subtracted 50 values D227<sub>1</sub> to D227<sub>9</sub> ( $\Sigma \phi(|v_i|)$  from i=1 to 8) to the LUTs 224<sub>1</sub> to 224<sub>9</sub>, respectively. The LUTs 224<sub>1</sub> to 224<sub>9</sub> read the 5-bit computation results D228<sub>1</sub> to D228<sub>9</sub> such that the computation of  $\phi^{-1}(\Sigma\phi(|v_i|))$  in equation (7) is performed on the subtracted values D227<sub>1</sub> to D227<sub>9</sub>, and outputs them.

On the other hand, the EXOR circuit 225 performs a multiplication of the sign bits  $D223_1$  to  $D223_9$  by computing the exclusive OR of all the sign bits  $D223_1$  to  $D223_9$ , and supplies a 1-bit multiplication value D226 (multiplication value of the sign bits for one row ( $\Pi$ sign ( $v_i$ ) from i=1 to 9)) to the exclusive OR of the multiplication value D226 and the sign bits  $D223_1$  to  $D223_9$ , respectively, the EXOR circuits  $226_1$  to  $226_9$  determine 1-bit divided values  $D229_1$  to  $D229_9$  ( $\Pi$ sign ( $v_i$ ) from i=1 to 8) such that the multiplication value D226 is divided by the sign bits  $D223_1$  to  $D223_9$ , respectively, and output them.

12

In the check node calculator  $201_m$ , a total of six bits such that the 5-bit computation results  $D228_1$  to  $D228_9$  output from the LUTs  $224_1$  to  $224_9$  are each made to be the five lower-order bits and the divided values  $D229_1$  to  $D229_9$  output from the EXOR circuits  $226_1$  to  $226_9$  are each made to be the highest-order bit is output as messages  $D230_1$  to  $D230_9$  obtained as a result of the check node computation.

In the manner described above, in the check node calculator  $201_m$ , the computation of equation (7) is performed, and the message  $u_i$  is determined.

In FIG. 13, the check node calculator  $201_m$  is shown by assuming that each message, together with the sign bit, is quantized to a total of six bits. The circuit of FIG. 13 corresponds to one check node. For the check matrix to be processed here in FIG. 8, since check nodes of 30 rows, which is the number of the rows thereof, exist, the decoding apparatus of FIGS. 12A to 12C has 30 check node calculators  $201_m$  shown in FIG. 13.

In the check node calculator  $201_m$  of FIG. 13, nine messages can be calculated simultaneously. For the row weight of the check matrix to be processed here in FIG. 8, the weight of the first row is 8, and the weight of the second row is 9, that is, there is one case in which the number of messages supplied to the check node is 8 and there are nine cases in which the number of messages is 9. Therefore, the check node calculator  $201_1$  has a circuit configuration capable of simultaneously calculating eight messages similarly to the circuit of FIG. 13, and the remaining check node calculators  $201_2$  to  $201_{30}$  are configured in the same way as for the circuit of FIG. 13.

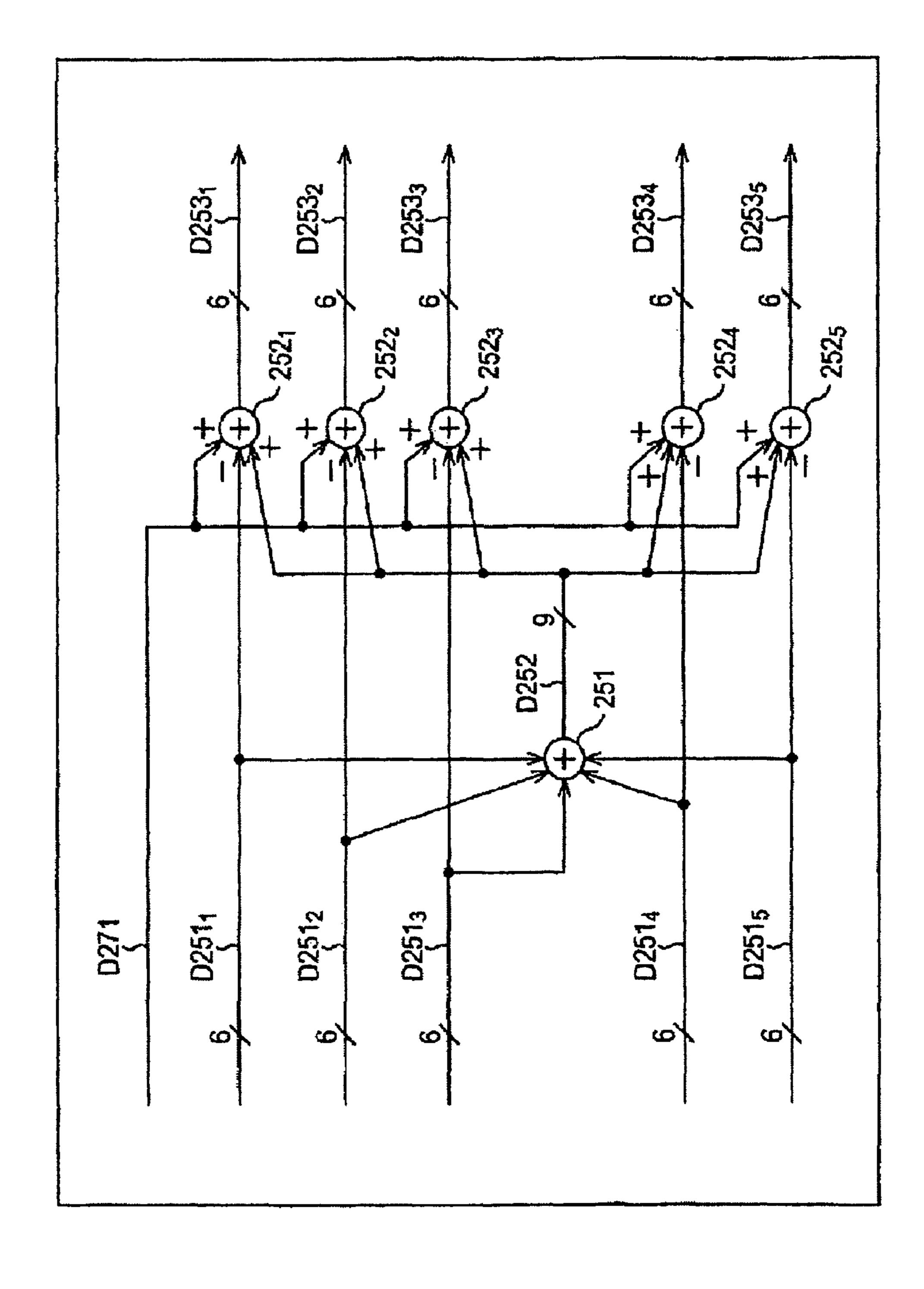

FIG. 14 shows an example of the configuration of a variable node calculator  $204_p$  (p=1, 2, ..., 90) of FIGS. 12A to 12C for simultaneously performing variable node computations.

In the variable node calculators  $204_p$  of FIG. 14, similarly to the variable node calculator 103 of FIG. 11, the variable node computations of equation (1) are performed, and the variable node computations are simultaneously performed for all the edges.

More specifically, in the variable node calculators  $204_p$  of FIG. 14, all the 6-bit messages D251<sub>1</sub> to D251<sub>5</sub> (messages  $u_j$ ) from the check node corresponding to each row of the check matrix, which are supplied from the edge interchange device 203, are read simultaneously, and these messages are supplied to the respective adders  $252_1$  to  $252_5$  and are also supplied to the adder 251. Furthermore, received data D271 is supplied to the variable node calculator  $204_p$  from the memory 205 for reception and the received data D271 is supplied to the adders-subtractors  $252_1$  to  $252_5$ .

The adder **251** integrates all the messages D**251**<sub>1</sub> to D**251**<sub>5</sub> (messages u<sub>j</sub>), and supplies a 9-bit integrated value D**252** (the total sum value of messages for one column (Σu<sub>j</sub> from j=1 to 5)) to the adders-subtractors **252**<sub>1</sub> to **252**<sub>5</sub>. The adders-subtractors **252**<sub>1</sub> to **252**<sub>5</sub> subtract the messages D**251**<sub>1</sub> to D**251**<sub>5</sub> (messages u<sub>j</sub>) from the added value D**252**, respectively. That is, the adders-subtractors **252**<sub>1</sub> to **252**<sub>5</sub> subtract the messages D**251**<sub>1</sub> to D**251**<sub>5</sub> (messages u<sub>j</sub>) from the edge to be determined, from the integrated value D**252** of the messages u<sub>j</sub> from all the edges, respectively, and determine the subtracted value (Σu<sub>j</sub> from j=1 to 4).

Furthermore, the adders-subtractors  $252_1$  to  $252_5$  add the received data D271 ( $u_{0i}$ ) to the subtracted value ( $\Sigma u_j$  from j=1 to 4), and output 6-bit added values D253<sub>1</sub> to D253<sub>5</sub> as the results of the variable node computations.

In the manner described above, in the variable node calculator  $204_p$ , the computation of equation (1) is performed, and the message  $v_i$  is determined.

In FIG. 14, the variable node calculators  $204_p$  is shown by assuming that each message, together with the sign bit, is quantized to six bits. The circuit of FIG. 14 corresponds to one variable node. For the check matrix to be processed here in FIG. 8, since variable nodes of 90 columns, which is the number of the columns thereof, exist, the decoding apparatus of FIGS. 12A to 12C has 90 circuits shown in FIG. 14.

In the variable node calculators  $204_p$  of FIG. 14, it is possible to simultaneously calculate five messages. The check matrix to be processed here in FIG. 8 has 15, 45, 29, and 1 columns having weights of 5, 3, 2, and 1, respectively. Therefore, 15 variable node calculators out of the variable node calculators  $204_1$  to  $204_{90}$  have the same circuit configuration as that of the circuit of FIG. 14. The remaining 45, 29, and 1 variable node calculators have the circuit configuration capable of simultaneously calculating 3, 2, and 1 messages similarly to the circuit of FIG. 14.

Although not shown, also, in the decoding apparatus of FIGS. 12A to 12C, similarly to the case of FIG. 9, at the final stage of the decoding, instead of the variable node calculation of equation (1), the computation of equation (5) is performed, and the computation result is output as the final decoded result.

According to the decoding apparatus of FIGS. 12A to 12C, 25 it is possible to simultaneously calculate all the messages corresponding to 269 edges at one clock.

When decoding is performed by repeatedly using the decoding apparatus of FIGS. 12A to 12C, the check node computation and the variable node computation are alternately performed, and one decoding can be performed at two clocks. Therefore, for example, in order to perform 50 decodings, the decoding apparatus needs to operate at 2×50=100 clocks while received data in which codes having a code length of 90 are one frame is received, and thus, approximately the same operating frequency as the receiving frequency may be used. In general, since the code length of the LDPC codes is as great as several thousands to several tens of thousands, if the decoding apparatus of FIGS. 12A to 12C is used, the number of decodings can be greatly increased, and 40 the improvement in the error correction performance can be expected.

However, in the decoding apparatus of FIGS. 12A to 12C, since computations of messages corresponding to all the edges of a Tanner graph are performed in parallel, the circuit scale increases in proportion to the code length. When the decoding apparatus of FIGS. 12A to 12C is configured as an apparatus for performing the decoding of LDPC codes having a particular coding rate, it is difficult for the decoding apparatus of FIGS. 12A to 12C to deal with the decoding of various codes even if the control signal is changed only, and the dependence on codes is high.

In addition to the decoding apparatus of FIG. 9 and FIGS. 12A to 12C, the implementation method for simultaneously calculating messages in units of four messages rather than one message or all messages is described in, for example, E. 60 Yeo, P. Pakzad, B. Nikolic and V. Anantharam, "VLSI Architectures for Iterative Decoders in Magnetic Recording Channels", IEEE Transactions on Magnetics, Vol. 37, No. 2, March 2001. In this case, there are problems in that, generally, it is not easy to avoid simultaneous read-out from or simultaneous writing to different addresses of the memory, and memory access control is difficult.

**14**

Furthermore, a method of implementation by approximating the sum product algorithm has also been proposed. However, in this method, the deterioration of performance is caused to occur. For implementing the sum product algorithm as hardware, there are, as described above, a method in which computations of messages corresponding to the edges (a check node computation and a bit node computation) are serially performed one-by-one, a method in which all the computations of messages are performed in parallel (full parallel), and a method in which the computations of messages are performed in units of several computations in parallel (parallel).

However, in the method in which computations of messages corresponding to the edges are performed one-by-one, a high operating frequency is required. Accordingly, as a method for increasing throughput, a method for arranging the apparatus in a pipeline structure is known. In this case, the circuit scale, in particular, (the capacity of) the memory, increases.

In the method in which all the computations of messages are performed in parallel, the circuit scale for logic increases, and the dependence on codes is high.

In the method in which the computations of messages are performed in units of several computations in parallel, control of memory access is difficult.

#### DISCLOSURE OF INVENTION

The present invention has been made in view of such circumstances. An object of the present invention is to suppress the operating frequency to a sufficiently realizable range while suppressing the circuit scale for both logic and memory, and to be capable of easily controlling memory access.

The decoding apparatus of the present invention, when using as a sub-matrix, a (P×P) unit matrix, a quasi-unit matrix in which one or more 1s, which are elements of the unit matrix, are substituted with 0, a shift matrix in which the unit matrix or the quasi-unit matrix is cyclically shifted, a sum matrix, which is the sum of two or more of the unit matrix, the quasi-unit matrix, and the shift matrix, or a (P×P) 0-matrix, a check matrix of the LDPC codes is represented by a combination of a plurality of the sub-matrices, includes: first computation means for simultaneously performing p check node computation means for simultaneously performing p variable node computations for decoding the LDPC codes.

The first computation means may have p check node calculators for performing check node computations, and the second computation means may have p variable node calculators for performing variable node computations.

The decoding apparatus may further include message storage means for simultaneously reading and writing message data corresponding to p edges, which is obtained as a result of the p check node computations or the p variable node computations.

The message storage means may store message data corresponding to the edges, which is read during the check node computation in such a manner that 1s of the check matrix are packed closer in the row direction.

The message storage means may store message data corresponding to edges, which is read during the variable node computations in such a manner that 1s of the check matrix are packed closer in the column direction.

The message storage means may store, at the same address, messages corresponding to p edges belonging to a unit matrix whose weight is 1, a quasi-unit matrix, or a shift matrix when the sub-matrices whose weight is 2 or more from among the

sub-matrices representing the check matrix are represented in the form of the sum of the unit matrix whose weight is 1, the quasi-unit matrix, or the shift matrix.

The message storage means may include number-of-rows/p FIFOs and number-of-columns/p FIFOs, and the number-of-columns/p FIFOs each have a number of words corresponding to the row weight and the column weight of the check matrix, respectively.

The message storage means may include a RAM (Random Access Memory), and the RAM may store the message data in the read-out sequence in such a manner as to be packed closer and reads the message data in the storage position sequence.

The decoding apparatus may further include received information storage means for storing received information of LDPC codes and for simultaneously reading p pieces of the received information.

The received information storage means may store the 20 received information in such a manner that the received information can be read in the sequence necessary for the variable node computation.

The decoding apparatus may further include rearranging means for rearranging messages obtained as a result of the p 25 check node computations or the p variable node computations.

The rearranging means may include a barrel shifter.

The first computation means and the second computation means may determine messages corresponding to p edges.

The first computation means may perform some of the p check node computations and the p variable node computations, and the second computation means may perform some of the others of the p variable node computations.

The first computation means may include p calculators for 35 performing some of the p check node computations and the p variable node computations, and the second computation means may include p calculators for performing some of the others of the p variable node computations.

The decoding apparatus may further include first decoding in-progress result storage means for simultaneously reading and writing first decoding in-progress results corresponding to p edges, which are obtained by the first computation means by performing some of the p check node computations and the p variable node computations.

The first decoding in-progress result storage means may store the first decoding in-progress results corresponding to the edges, which are read when some of the others of the p variable node computations are performed, in such a manner that 1s of the check matrix are packed closer in the row 50 direction.

The first decoding in-progress result storage means may be two single-port RAMs (Random Access Memories).

The two single-port RAMs may alternately store the first decoding in-progress results in units of p of the first decoding 55 in-progress results.

The two single-port RAMs (Random Access Memories) each may read the first decoding in-progress results stored at the same address.

The first decoding in-progress result storage means may 60 store, at the same address, the first decoding in-progress results corresponding to p edges belonging to a unit matrix whose weight is 1, a quasi-unit matrix, or a shift matrix when the sub-matrices whose weight is 2 or more from among the sub-matrices representing the check matrix are represented in 65 the form of the sum of the unit matrix whose weight is 1, the quasi-unit matrix, or the shift matrix.

**16**

The decoding apparatus may further include second decoding in-progress result storage means for simultaneously reading and writing the second decoding in-progress results corresponding to p edges, which are obtained by the second computation means by performing some of the others of the p variable node computations.

The decoding apparatus may further include received information storage means for storing received information of LDPC codes and simultaneously reading p pieces of the received information.

The received information storage means may store the received information in such a manner that the received information can be read in the sequence necessary for some of the others of the p variable node computations.

The decoding apparatus may further include rearranging means for rearranging first decoding in-progress results obtained by the first computation means by performing some of the p check node computations and the p variable node computations, or second decoding in-progress results obtained by the second computation means by performing some of the others of the p variable node computations.

The rearranging means may include a barrel shifter.

The first computation means may perform some of the p check node computations, and the second computation means may perform some of the others of the p check node computations, and the p variable node computations.

The first computation means may include p calculators for performing some of the p check node computations, and the second computation means may include p calculators for performing some of the others of the p check node computations, and the p variable node computations.

The decoding apparatus may further include first decoding in-progress result storage means for simultaneously reading and writing first decoding in-progress results corresponding to p edges, which are obtained by the first computation means by performing some of the p check node computations.

The decoding apparatus may further include second decoding in-progress result storage means for simultaneously reading and writing second decoding in-progress results corresponding to p edges, which are obtained by the second computation means by performing some of the others of the p check node computations, and the p variable node computations.

The second decoding in-progress result storage means may store the second decoding in-progress results corresponding to edges, which are read when some of the others of the p check node computations, and the p variable node computations are performed, in such a manner that 1s of the check matrix are packed closer in the column direction.

The second decoding in-progress result storage means may be two single-port RAMs (Random Access Memories).

The two single-port RAMs may alternately store the second ond decoding in-progress results in units of p of the second decoding in-progress results.

The two single-port RAMs (Random Access Memories) each may read the second decoding in-progress results stored at the same address.

The second decoding in-progress result storage means may store, at the same address, the second decoding in-progress results corresponding to p edges belonging to a unit matrix whose weight is 1, a quasi-unit matrix, or a shift matrix when the sub-matrices whose weight is 2 or more from among the sub-matrices representing the check matrix are represented in the form of the sum of the unit matrix whose weight is 1, the quasi-unit matrix, or the shift matrix.

The decoding apparatus may further include received information storage means for storing received information of LDPC codes and for simultaneously reading p pieces of the received information.

In the decoding apparatus according to claim 36, the 5 received information storage means may store the received information in such a manner that the received information can be read in the sequence necessary for some of the others of the p check node computations, and the p variable node computations.

The decoding apparatus may further include rearranging means for rearranging first decoding in-progress results obtained by the first computation means by performing some of the p check node computations, or second decoding inprogress results obtained by the second computation means by performing some of the others of the p check node computations, and the p variable node computations.

The rearranging means may include a barrel shifter.

The decoding method of the present invention, when using 20 as a sub-matrix, a (P×P) unit matrix, a quasi-unit matrix in which one or more 1s, which are elements of the unit matrix, are substituted with 0, a shift matrix in which the unit matrix or the quasi-unit matrix is cyclically shifted, a sum matrix, which is the sum of two or more of the unit matrix, the 25 quasi-unit matrix, and the shift matrix, or a  $(P \times P)$  0-matrix, a check matrix of LDPC codes is represented by a combination of a plurality of the sub-matrices, includes a first computation step of simultaneously performing p check node computations for decoding the LDPC codes; and a second computa- 30 tion step of simultaneously performing p variable node computations for decoding the LDPC codes.

The program of the present invention includes a first computation step of simultaneously performing p check node computations for decoding LDPC codes; and a second computation step of simultaneously performing p variable node computations for decoding the LDPC codes.

In the present invention, when using as a sub-matrix, a (P×P) unit matrix, a quasi-unit matrix in which one or more 1s, which are elements of the unit matrix, are substituted with 40 0, a shift matrix in which the unit matrix or the quasi-unit matrix is cyclically shifted, a sum matrix, which is the sum of two or more of the unit matrix, the quasi-unit matrix, and the shift matrix, or a (P×P) 0-matrix, a check matrix of the LDPC codes is represented by a combination of a plurality of the 45 sub-matrices, p check node computations for decoding the LDPC codes are simultaneously performed, and p variable node computations for decoding the LDPC codes are simultaneously performed.

## BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 illustrates a check matrix H of LDPC codes.

- FIG. 2 is a flowchart illustrating a procedure for decoding LDPC codes.

- FIG. 3 illustrates the flow of messages.

- FIG. 4 shows an example of a check matrix of LDPC codes.

- FIG. 5 shows a Tanner graph of the check matrix.

- FIG. 6 shows a variable node.

- FIG. 7 shows a check node.

- FIG. 8 shows an example of a check matrix of LDPC codes.

- FIG. 9 is a block diagram showing an example of the configuration of an LDPC code decoding apparatus for performing node computations one-by-one.

- FIG. 10 is a block diagram showing an example of the 65 RAM for storing decoding in-progress results of FIG. 31. configuration of a check node calculator for calculating messages one-by-one.

**18**

- FIG. 11 is a block diagram showing an example of the configuration of a variable node calculator for calculating messages one-by-one.

- FIG. 12A is a block diagram showing an example of the configuration of an LDPC code decoding apparatus for simultaneously performing all node computations.

- FIG. 12B is a block diagram showing an example of the configuration of the LDPC code decoding apparatus for simultaneously performing all node computations.

- FIG. 12C is a block diagram showing an example of the configuration of the LDPC code decoding apparatus for simultaneously performing all node computations.

- FIG. 13 is a block diagram showing an example of the configuration of a check node calculator for simultaneously calculating messages.

- FIG. 14 is a block diagram showing an example of the configuration of a variable node calculator for simultaneously calculating messages.

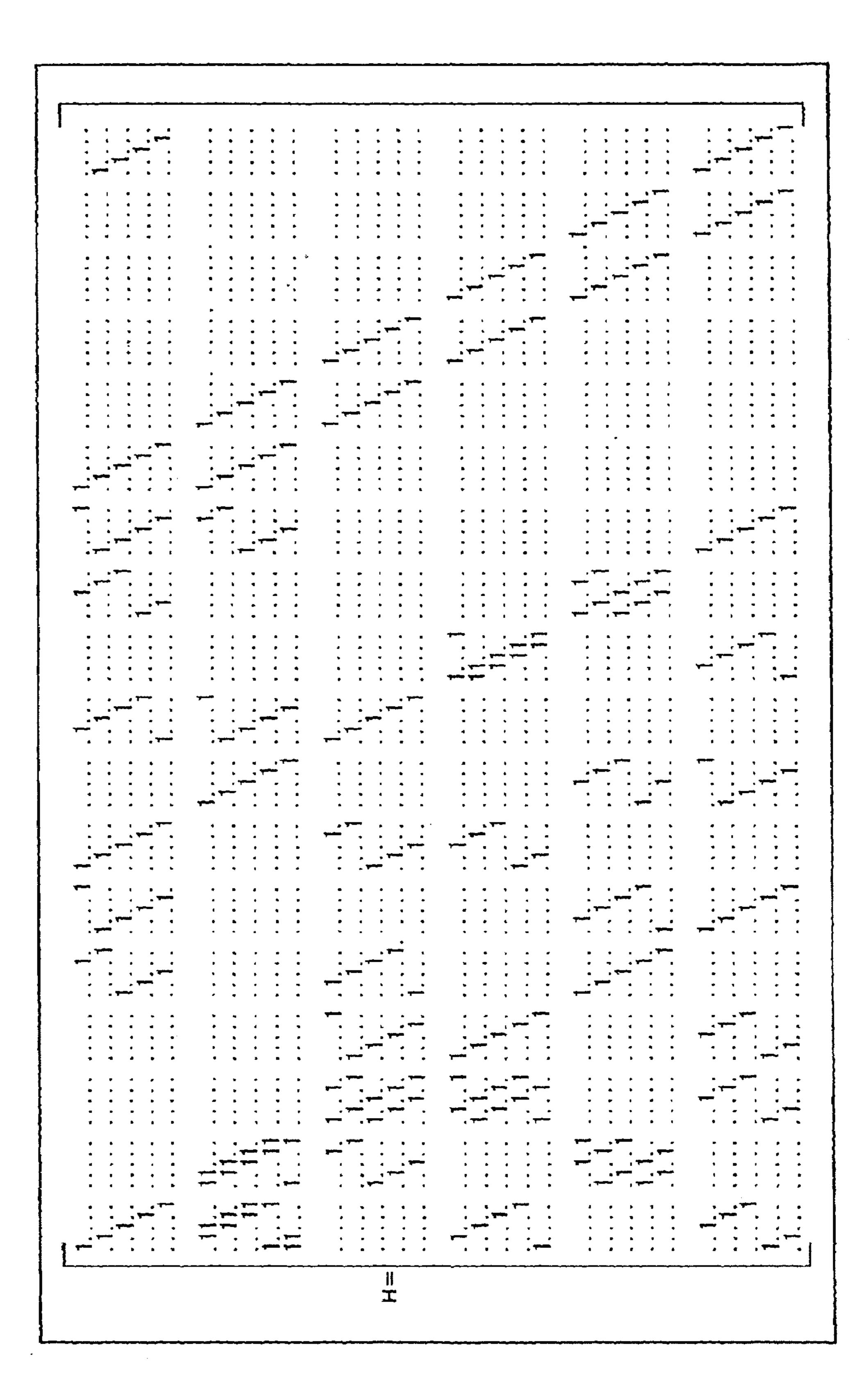

- FIG. 15 shows a matrix, which is divided into  $5 \times 5$  units.

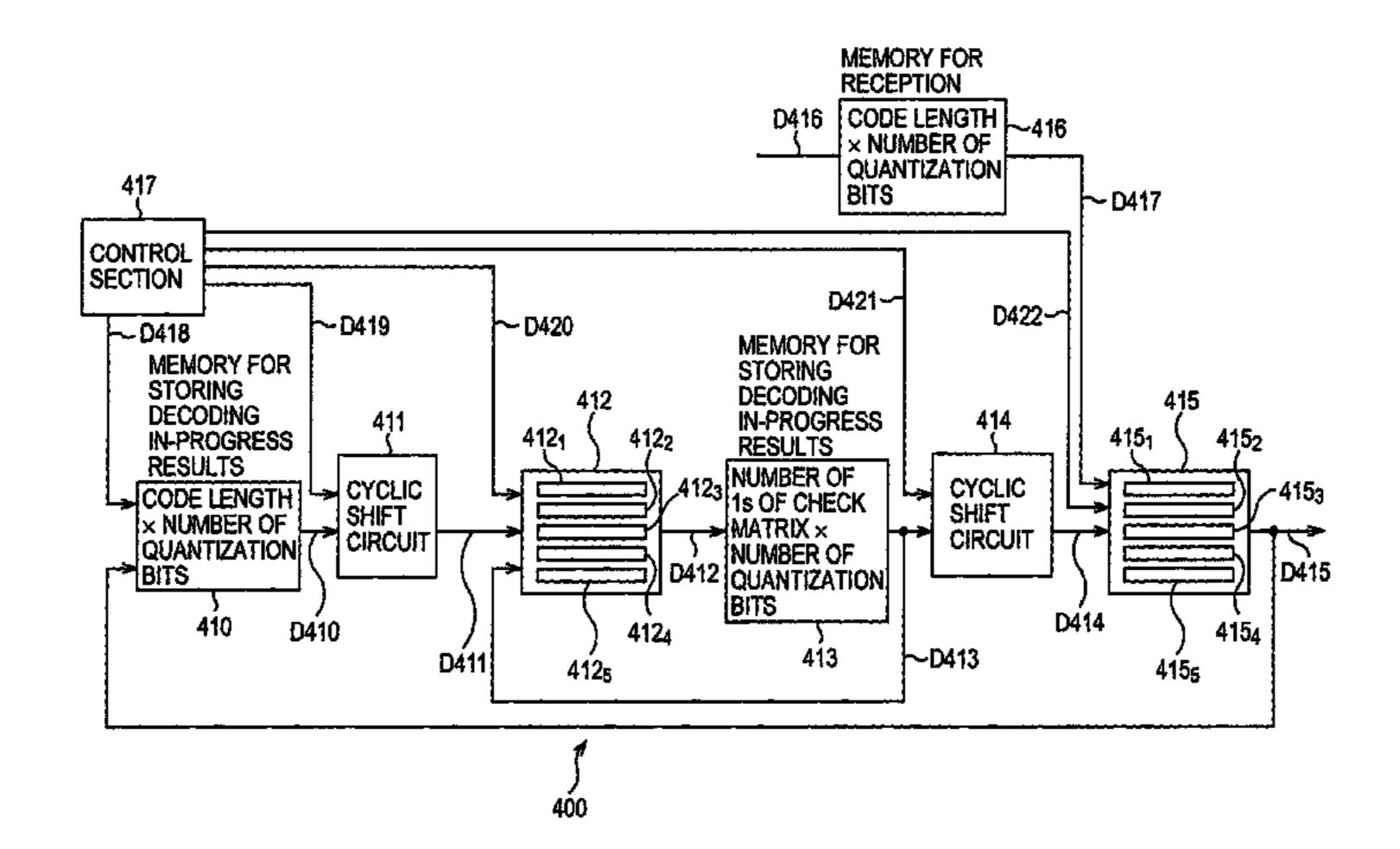

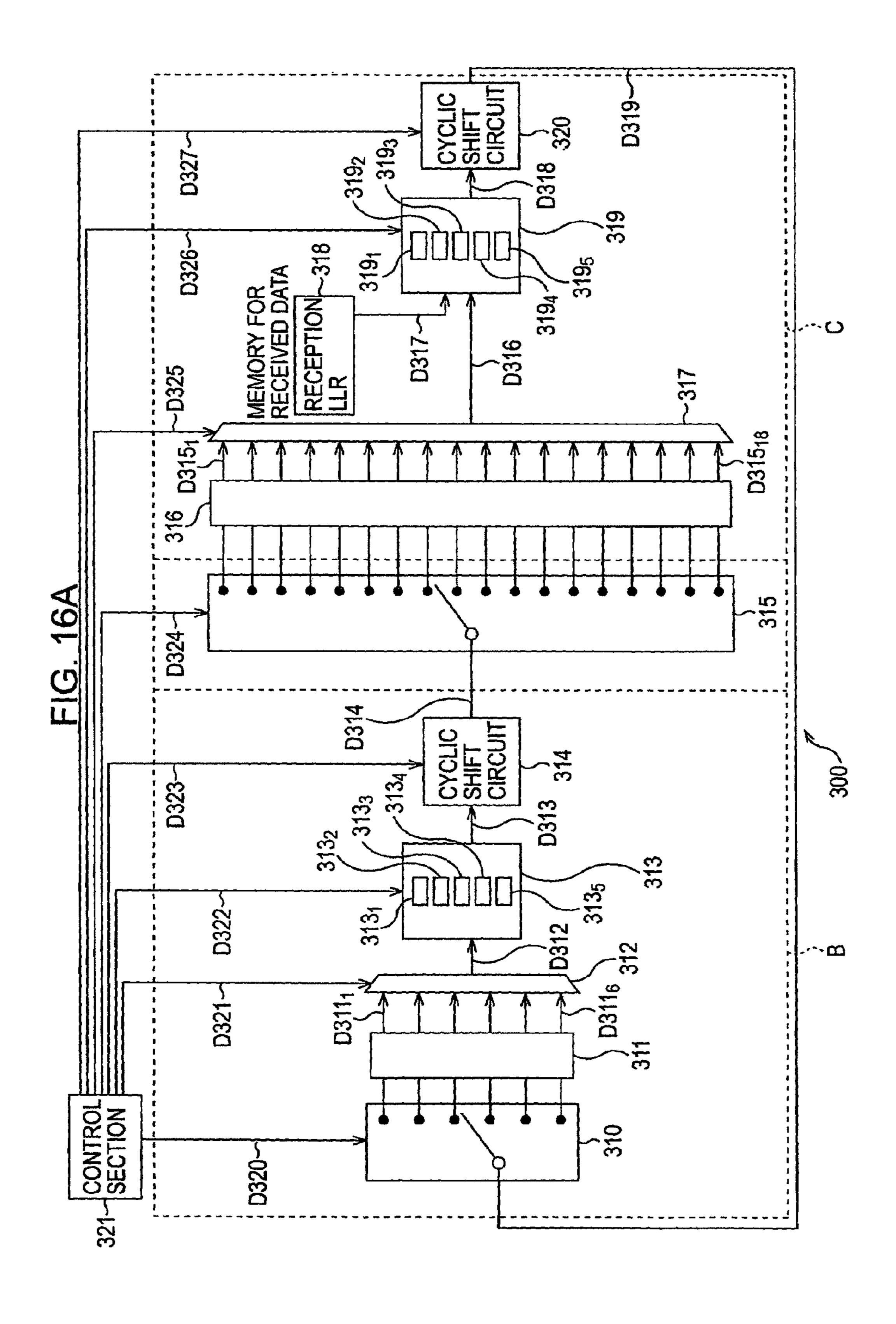

- FIG. 16A is a block diagram showing an example of the configuration of an embodiment of a decoding apparatus to which the present invention is applied.

- FIG. 16B is a block diagram showing an example of the configuration of the embodiment of the decoding apparatus to which the present invention is applied.

- FIG. 16C is a block diagram showing an example of the configuration of the embodiment of the decoding apparatus to which the present invention is applied.

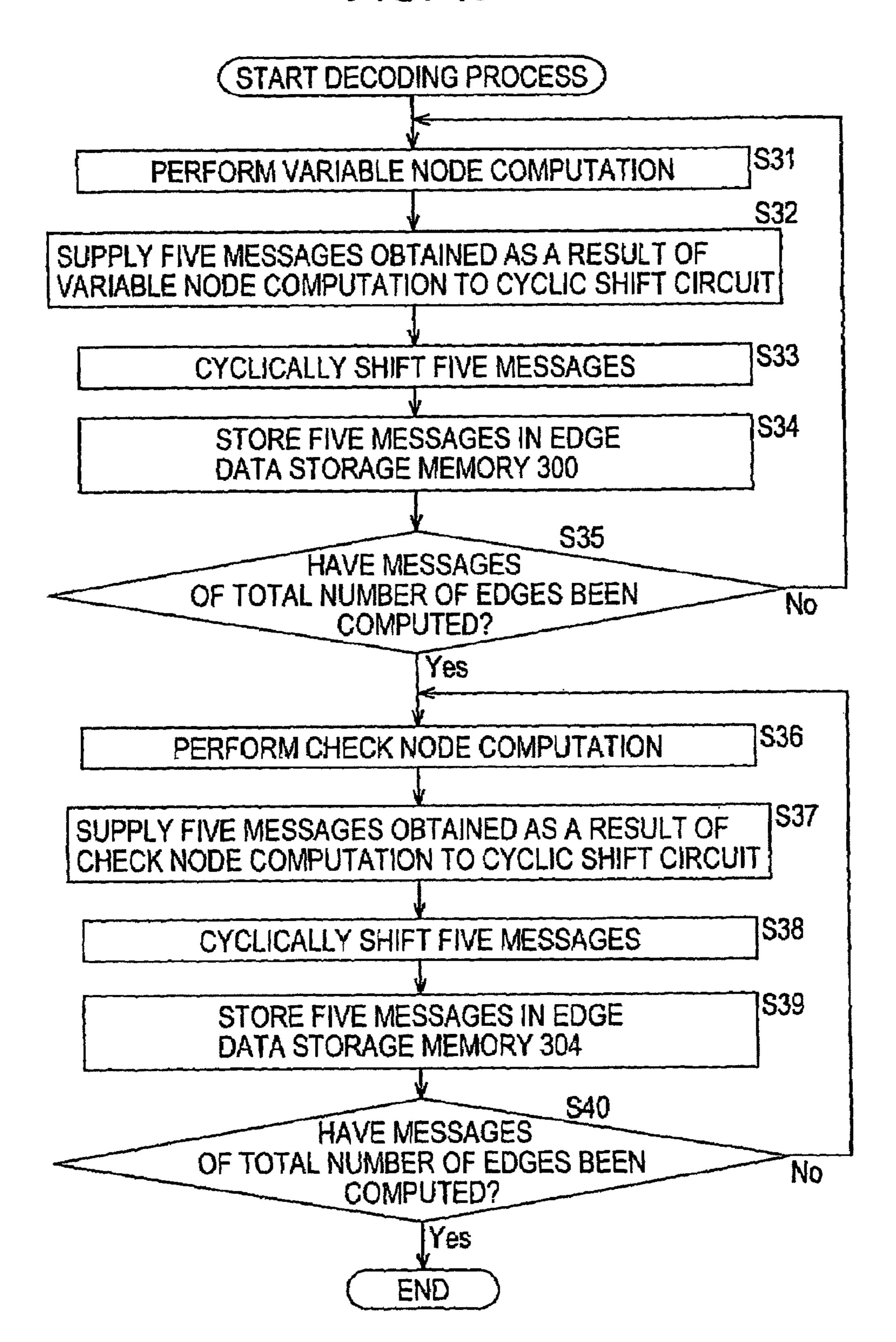

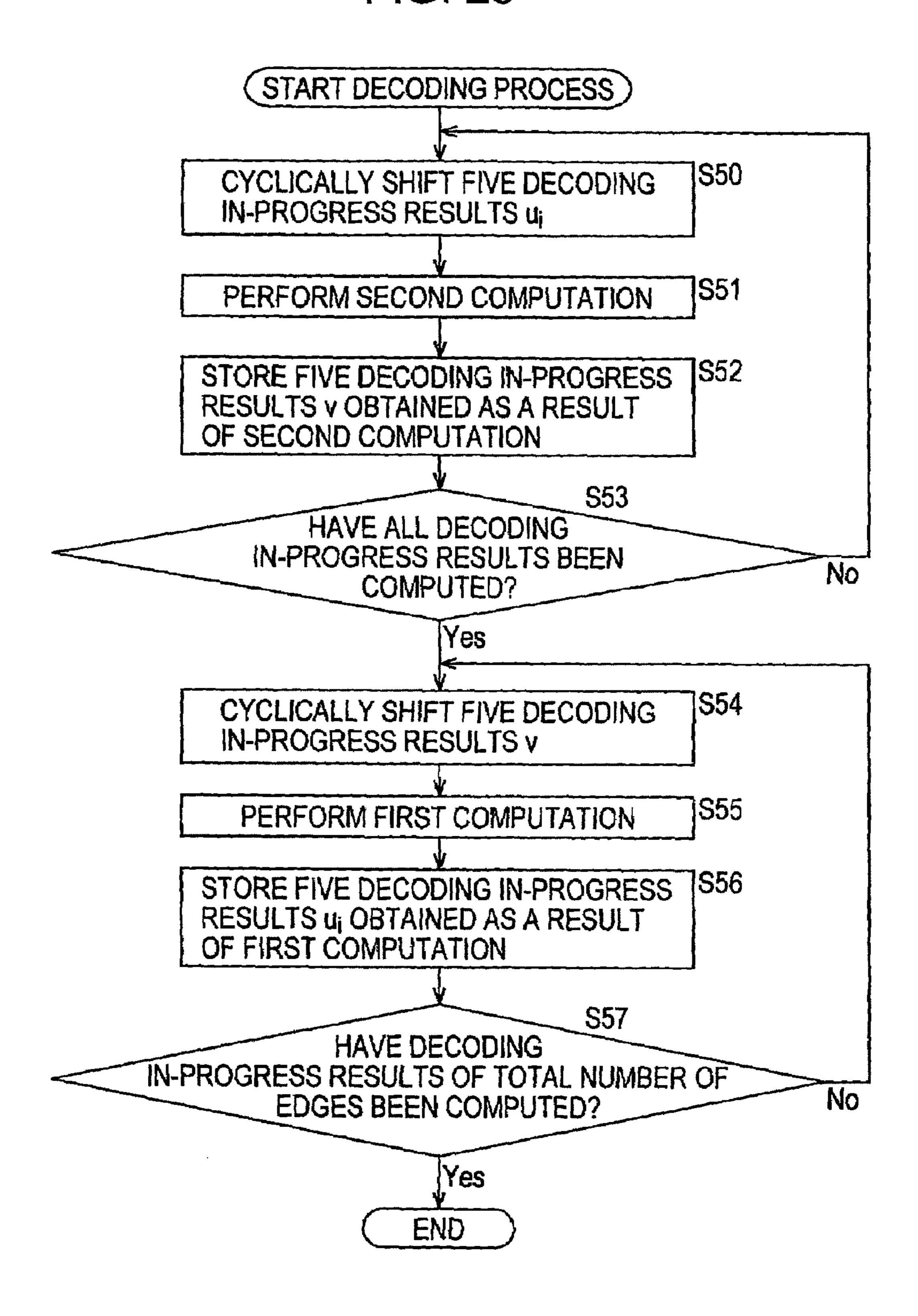

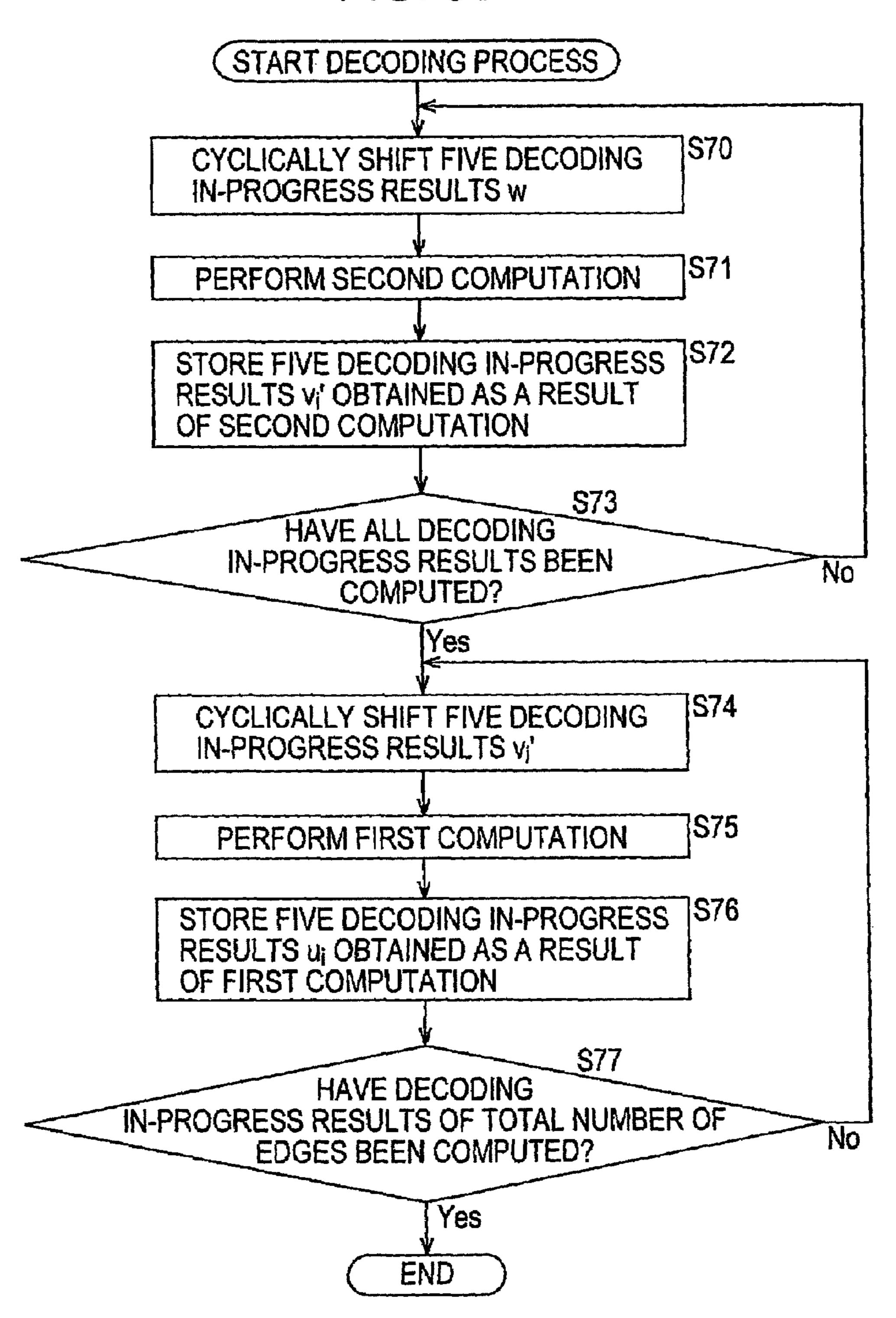

- FIG. 17 is a flowchart illustrating the decoding process of the decoding apparatus of FIGS. 16A to 16C.

- FIG. 18 is a block diagram showing an example of the configuration of an embodiment of the decoding apparatus to which the present invention is applied.

- FIG. 19 is a block diagram showing an example of the configuration of a check node calculator.

- FIG. 20 is a block diagram showing an example of the configuration of a variable node calculator.

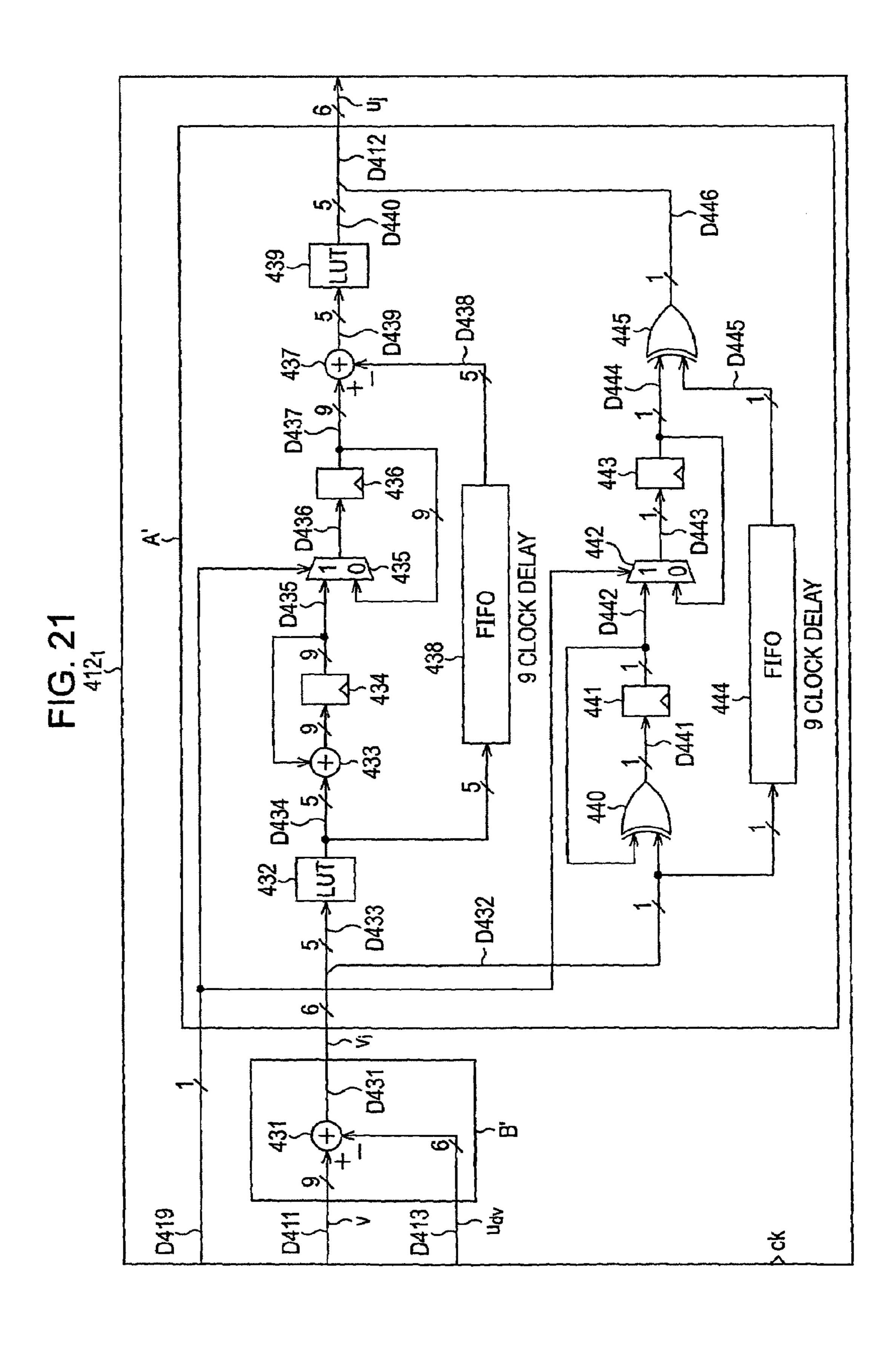

- FIG. 21 is a block diagram showing an example of the configuration of a calculator of FIG. 18.

- FIG. 22 is a block diagram showing an example of the configuration of the calculator of FIG. 18.

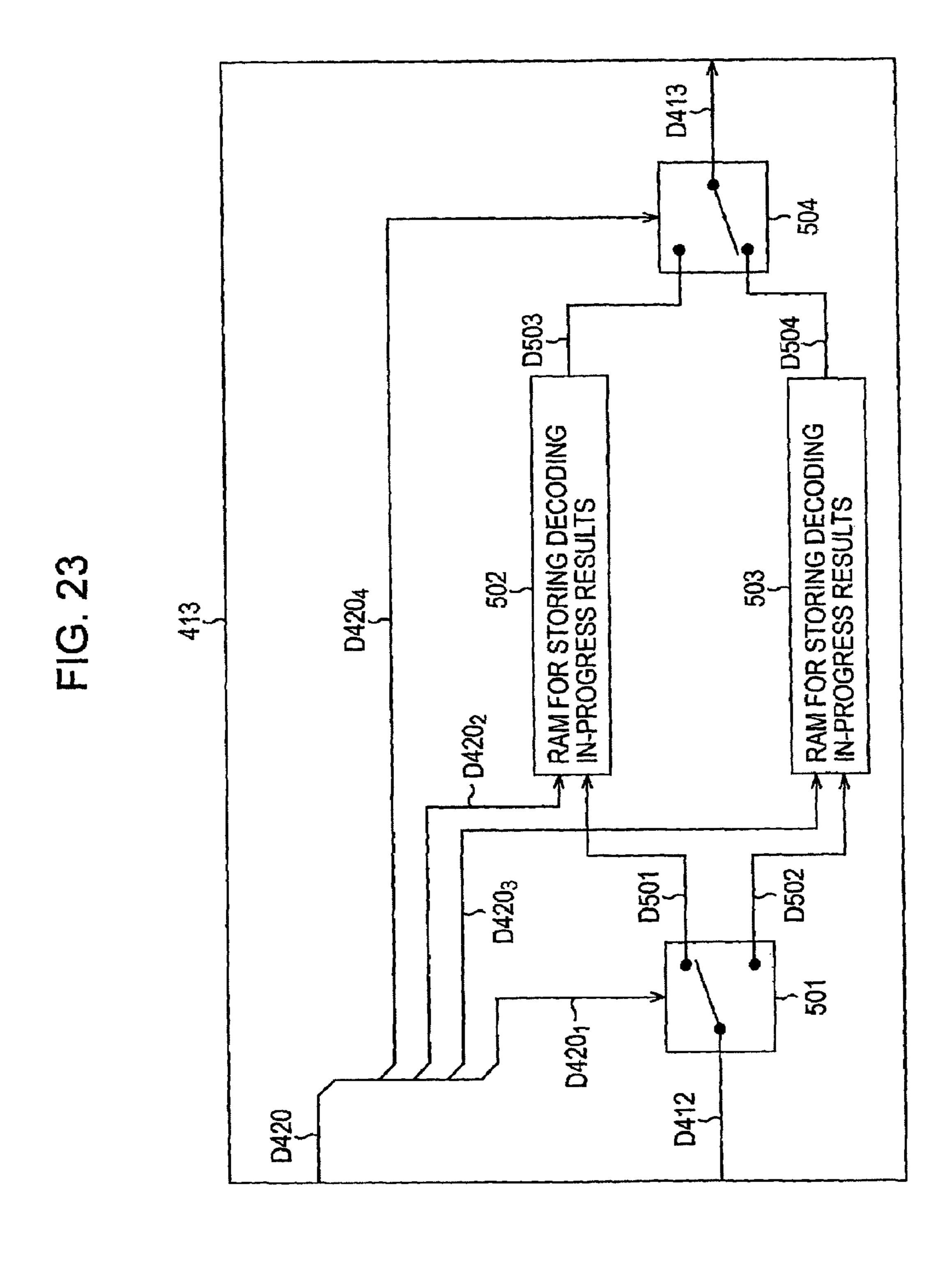

- FIG. 23 is a block diagram showing an example of the configuration of a memory for storing decoding in-progress results of FIG. 18.

- FIG. 24 is a timing chart illustrating the operation of a RAM for storing decoding in-progress results of FIG. 18.

- FIG. 25 is a flowchart illustrating the decoding process of the decoding apparatus of FIG. 18.

- FIG. 26 is a block diagram showing an example of the configuration of an embodiment of the decoding apparatus to which the present invention is applied.

- FIG. 27 is a block diagram showing an example of the configuration of a check node calculator.

- FIG. 28 is a block diagram showing an example of the configuration of a variable node calculator.

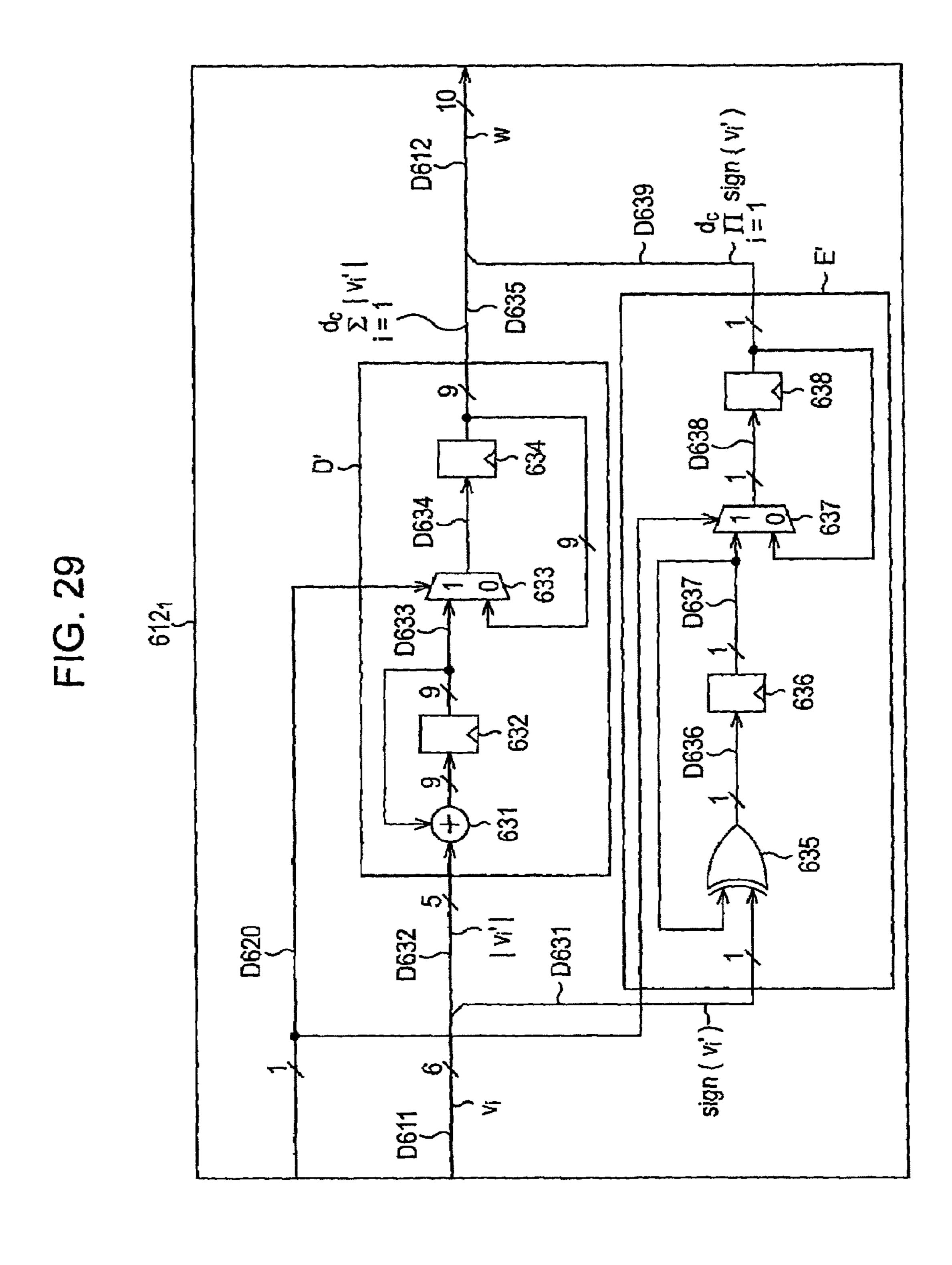

- FIG. 29 is a block diagram showing an example of the configuration of a calculator of FIG. 26.

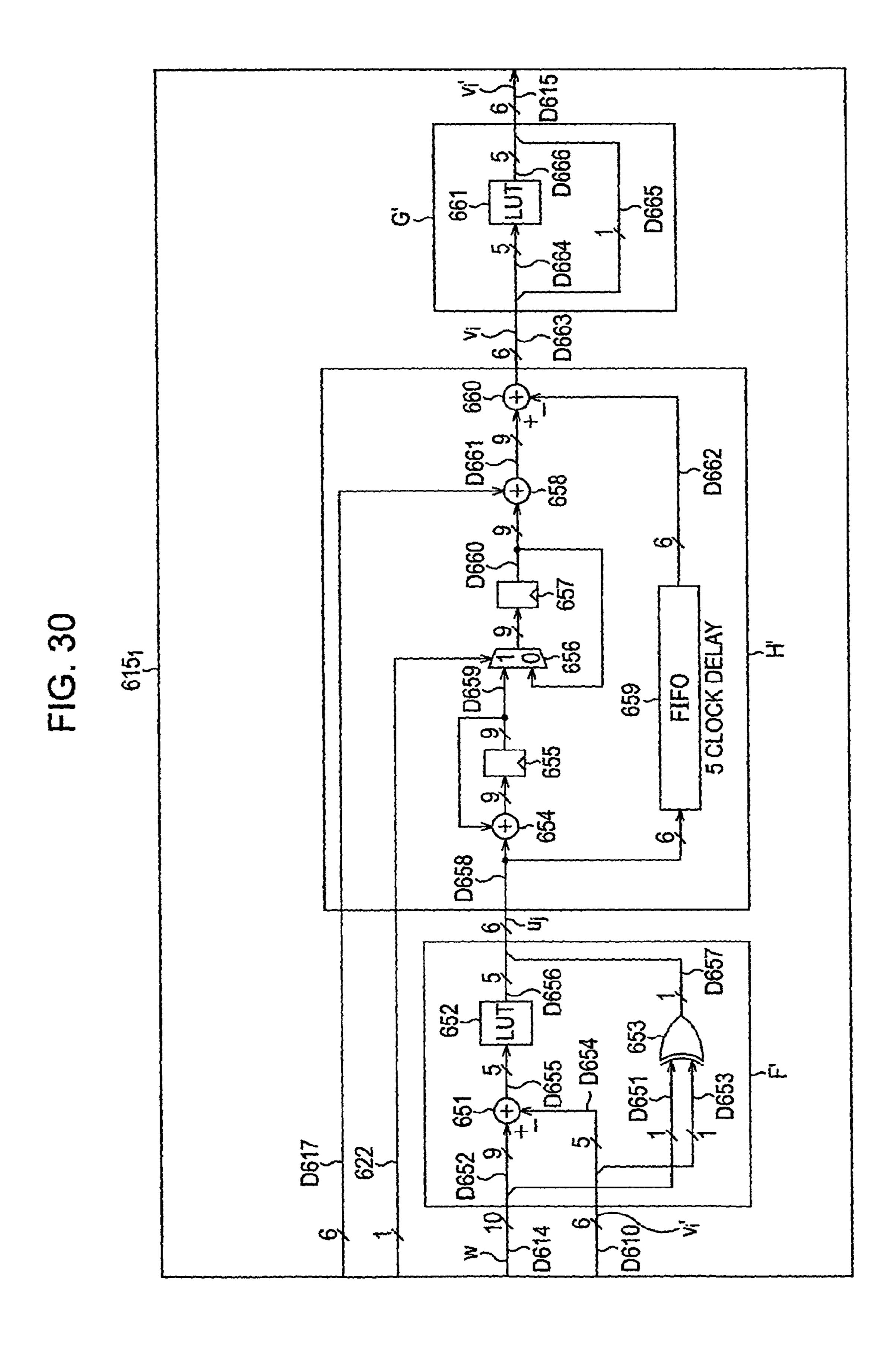

- FIG. 30 is a block diagram showing an example of the 60 configuration of the calculator of FIG. 26.

- FIG. 31 is a block diagram showing an example of the configuration of a memory for storing decoding in-progress results of FIG. 26.

- FIG. 32 is a timing chart illustrating the operation of a

- FIG. 33 is a flowchart illustrating the decoding process of the decoding apparatus of FIG. 26.

FIG. 34 is a block diagram showing an example of the configuration of an embodiment of a computer to which the present invention is applied.

### BEST MODE FOR CARRYING OUT THE INVENTION

Specific embodiments to which the present invention is applied will be described below in detail with reference to the drawings.

FIG. 15 shows an example of a 30×9 check matrix, which are divided in units of  $5\times5$  matrices. The check matrix of FIG. 15 is the same as the check matrix shown in FIG. 8.

In FIG. 15, the check matrix is represented by a combination of a 5×5 unit matrix, a matrix in which one or more 1s, 15 which are elements of the unit matrix, are substituted with 0 (hereinafter referred to as a "quasi-unit matrix" where appropriate), a matrix in which the unit matrix or the quasi-unit matrix is cyclically shifted (hereinafter referred to as a "shift matrix" where appropriate), a sum of two or more (plural) of 20 the unit matrix, the quasi-unit matrix, and the shift matrix (hereinafter referred to as a "sum matrix" where appropriate), and a 5×5 0-matrix. The LDPC codes represented by the check matrix of FIG. 15 have a coding rate of <sup>2</sup>/<sub>3</sub> and a code length of 9.

It may be said that the check matrix of FIG. 15 is formed of a  $5\times5$  matrix, a quasi-unit matrix, a shift matrix, a sum matrix, and a 0-matrix. Therefore, these  $5\times5$  matrices, which form the check matrix, will be hereinafter referred to as "sub-matrices" where appropriate.

FIGS. 16A to 16C show an example of the configuration of an embodiment of a decoding apparatus for decoding LDPC codes represented by the check matrix of FIG. 15. FIGS. 16A to 16C are block diagrams showing an example of the configuration of an embodiment of such a decoding apparatus. 35 FIG. 16A shows the overall configuration of the decoding apparatus. FIG. 16B shows the detailed configuration of the left portion in the figure surrounded by the dotted line B, of the decoding apparatus of FIG. 16A. FIG. 16C shows the detailed configuration of the right portion in the FIG. 5 sur- 40 rounded by the dotted line C, of the decoding apparatus of FIG. **16**A.

A decoding apparatus 300 of FIGS. 16A to 16C includes switches 310 and 315, an edge data storage memory 311 made up of six FIFOs  $311_1$  to  $311_6$ , a selector 312, a check 45 node calculator 313 made up of five check node calculators 313<sub>1</sub> to 313<sub>5</sub>, two cyclic shift circuit 314 and 320, an edge data storage memory 316 made up of 18 FIFOs 316<sub>1</sub> to 316<sub>18</sub>, a selector 317, a received data memory 318 for storing received information, a variable node calculator **319**, and a control 50 section 321.

Before describing in detail each section of the decoding apparatus 300, the method of storing data in the edge data storage memories 311 and 316 will be described first.

311, to 3116, the number being such that 30, the number of rows, of the check matrix is divided by 5, the number of rows. The FIFO  $311_v$  (y=1, 2, ..., 6) is formed in such a manner that messages corresponding to five edges, which is the number of the rows and the columns of the sub-matrix, can be read or 60 written simultaneously. The length (the number of stages) thereof is 9, which is the maximum number of 1s (Hamming weight) in the row direction of the check matrix.

In the FIFO 311, the data corresponding to the positions of 1s from the first row up to the fifth row of the check matrix of 65 FIG. 15 is stored in such a manner that 1s are packed closer (in a manner in which 0s are ignored) in the horizontal direction

**20**