### US00RE44350E

## (19) United States

### (12) Reissued Patent

Yoshida et al.

(10) Patent Number: US RE44,350 E

(45) Date of Reissued Patent: Jul. 9, 2013

(54) NONVOLATILE SEMICONDUCTOR

MEMORY INCLUDING MULTI-THRESHOLD

VOLTAGE MEMORY CELLS INCLUDING

VOLTAGE RANGES INDICATING EITHER AN

ERASE STATE OR A TWO OR MORE

PROGRAM STATE

(75) Inventors: Keiichi Yoshida, Tokyo (JP); Shooji

Kubono, Ome (JP)

(73) Assignee: Renesas Electronics Corporation,

Kanagawa (JP)

(21) Appl. No.: **12/794,905**

(22) Filed: Jun. 7, 2010

### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 6,906,952

Issued: Jun. 14, 2005

Appl. No.: 10/394,050

Filed: Mar. 24, 2003

U.S. Applications:

(63) Continuation of application No. 09/984,833, filed on Oct. 31, 2001, now abandoned, which is a continuation of application No. 09/679,867, filed on Oct. 5, 2000, now Pat. No. 6,320,785, which is a continuation of application No. 09/342,223, filed on Jun. 29, 1999, now Pat. No. 6,525,960, which is a continuation of application No. 08/890,396, filed on Jul. 9, 1997, now Pat. No. 5,959,882.

### (30) Foreign Application Priority Data

Jul. 10, 1996 (JP) ...... 8-180859

(51) Int. Cl.

G11C 11/34 (2006.01)

G11C 16/04 (2006.01)

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,435,786 | A |   | 3/1984  | Tickle | <br>365/154    |

|-----------|---|---|---------|--------|----------------|

| 4,707,809 | A | * | 11/1987 | Ando   | <br>365/189.05 |

|           |   |   | . ~     |        |                |

### (Continued)

### FOREIGN PATENT DOCUMENTS

JP 59-121696 7/1984 JP 62-6493 1/1987

(Continued)

### OTHER PUBLICATIONS

IEEE International Solid-State Circuits Conference, "A 3.3V 128 Mb Multi-Level NAND Flash Memory for Mass Storage Applications", T. Jung, et al., Feb. 8, 1996, (7 pp.).

(Continued)

Primary Examiner — Vanthu Nguyen (74) Attorney, Agent, or Firm — Antonelli, Terry, Stout & Kraus, LLP.

### (57) ABSTRACT

In a nonvolatile semiconductor memory device wherein a plurality of threshold voltages are set so as to store multivalued information in one memory cell, data is first written into the memory cell whose threshold voltage is the lowest as a written state from the erase level, and data is successively written into memory cells whose threshold voltages are higher.

### 4 Claims, 11 Drawing Sheets

| <del></del>                              | INITIAL STATE                                                                                    | WRITE #1                                                   |

|------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| CHANGE IN<br>Vih<br>DISTRIBUTION         | FREQUENCY A'0'A                                                                                  |                                                            |

| MEMORY BIAS<br>CONDITIONS                | bi b2 b3 b4<br> (11) (11) (11) (11)<br> (11) (11) (11)<br> (11) (11)                             | 5V b1 b2 b3 b4 Vwg1=  (01)  (11)  (11)  (11) -11V (=)      |

| WRITE DATA<br>MEMORY DATA<br>DISTURBANCE | 01 00 10 11<br>11 11 11 11<br><br>WRITE #2                                                       | 01 00 10 11<br>01 11 11 11<br>0 1 1 1 1<br>WRITE #3        |

| CHANGE IN VIIIN DISTRIBUTION             | FREQUENCY Section 1975                                                                           | HEQUENCY 10" "11" Vwv3=3.3V Vth                            |

| MEMORY BIAS<br>CONDITIONS                | 5V<br>b1 b2 b3 b4<br>Vwg2=  (01)  (00)  (11)  (11)<br>-10.5V   (11)  (11)<br>(01) (00) (10) (11) | 5V<br>b1 b2 b3 b4<br>Vwg3=  (01)  (00)  (10)  (11)<br>-10V |

| WRITE DATA                               | 01 00 10 11                                                                                      | 01 00 10 11<br>01 00 10 11                                 |

| MEMORY DATA DISTURBANCE                  | 01 00 11 11<br>1 0 2 2                                                                           | 01 00 10 11<br>2 1 20 3                                    |

### US RE44,350 E

Page 2

| U.S. PATENT DO                    | OCUMENTS                    |

|-----------------------------------|-----------------------------|

| 4,860,258 A 8/1989 Fr             | ruhauf et al 365/194        |

| 4,964,079 A 10/1990 D             | evin                        |

| · ·                               | owalski et al 365/185.25    |

| 5,163,021 A 11/1992 M             | Iehrotra et al 365/185      |

| 5,200,920 A 4/1993 No             | orman et al 365/185         |

| 5,218,569 A * 6/1993 Ba           | anks 365/185.21             |

| 5,365,486 A 11/1994 Sc            | chreck 365/222              |

| 5,440,505 A * 8/1995 Fa           | azio et al 365/45           |

| 5,450,363 A 9/1995 CI             | hristopherson et al 365/205 |

| 5,487,036 A 1/1996 A              | kaogi et al 365/189.09      |

| 5,539,688 A 7/1996 Yi             | iu et al 365/185.14         |

| , ,                               | ara 365/185.19              |

| 5,555,204 A 9/1996 E <sub>1</sub> | ndoh et al 365/189.01       |

|                                   | azio et al 365/45           |

| , ,                               | anaka et al 365/185.22      |

| , ,                               | ndoh et al 365/201          |

|                                   | iu et al 365/185.19         |

| , , ,                             | anzawa et al 365/185.03     |

| , , ,                             | hoi et al 365/185.17        |

| , ,                               | anaka et al 365/185.17      |

| , ,                               | ill et al 365/185.22        |

| , ,                               | akahashi et al 365/185      |

| , ,                               | azio et al 365/185.03       |

|                                   | han 365/185.03              |

| , , ,                             | Iori 365/185.03             |

| 5,748,533 A 5/1998 D              | unlap et al 365/185.19      |

|                                   | oh 365/185.17               |

| 5,754,469 A 5/1998 H              | ung et al 365/185.03        |

| 5,754,475 A 5/1998 Bi             | ill et al 365/185.25        |

| 5,757,699 A 5/1998 Ta             | akeshima et al 365/185.24   |

| 5,761,150 A * | 6/1998  | Yukutake et al 365/233     |

|---------------|---------|----------------------------|

| 5,768,188 A   | 6/1998  | Park et al 365/185.03      |

| 5,768,191 A   | 6/1998  | Choi et al 365/185.22      |

| 5,768,193 A   | 6/1998  | Lee et al 365/185.25       |

| 5,796,652 A   | 8/1998  | Takeshima et al 365/185.03 |

| 5,825,690 A   | 10/1998 | Saitoh 365/185.22          |

| 5,864,569 A   | 1/1999  | Roohparvar 365/185.09      |

| 5,870,218 A   | 2/1999  | Jyouno et al 365/185.03    |

| 5,889,698 A   | 3/1999  | Miwa et al 365/185.03      |

| 5,960,458 A * | 9/1999  | Kametani                   |

| 6,166,950 A   | 12/2000 | Yamada et al 365/185.03    |

### FOREIGN PATENT DOCUMENTS

| JP | 1-134793   |   | 5/1989 |

|----|------------|---|--------|

| JP | 3-59886    |   | 3/1991 |

| JP | 4-57294    |   | 2/1992 |

| JP | 4-238196   |   | 8/1992 |

| JP | 7-93979    |   | 4/1995 |

| JP | 9-091971   |   | 9/1995 |

| JP | 08087876 A | * | 4/1996 |

### OTHER PUBLICATIONS

1994 Symposium on VLSI Circuits Digest of Technical Papers, "High-Speed Programming and Program—Verify Methods Suitable for Low-Voltage Flash Memories", T. Tanaka, et al., pp. 61-62. IEEE Journal of Solid-State Circuits, vol. 31, No. 11, "A117 mm<sup>2</sup> 3.3-V Only 128-Mb Multilevel NAND Flash Memory for Mass Storage Applications", T. Jung, et al., Nov. 1996, pp. 1575-1583.

<sup>\*</sup> cited by examiner

FIG. 1

|                                    | INITIAL STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WRITE #1                                                                                               |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| CHANGE IN VIH DISTRIBUTION         | FREQUENCY 11., And                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FREQUENCY VW1=1.5V Vth                                                                                 |  |  |

| MEMORY BIAS<br>CONDITIONS          | b1 b2 b3 b4<br> (11) (11) (11) (11)<br> (11) (11) (11)<br> (11) (11) (11)<br> (11) (11) (11) (11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5V<br>b1 b2 b3 b4<br>Vwg1=  (01)  (11)  (11)  (11)<br>-11V                                             |  |  |

| WRITE DATA MEMORY DATA DISTURBANCE | 01 00 10 11<br>11 11 11 11<br>WRITE #2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01 00 10 11<br>01 11 11 11<br>0 1 1 1<br>WRITE #3                                                      |  |  |

| CHANGE IN VIh DISTRIBUTION         | FREQUENCY (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (11), (1 | FREQUENCY (10, 11, 11) (10, 11) (11) (11) (11) (11) (11) (11) (11)                                     |  |  |

| MEMORY BIAS<br>CONDITIONS          | b1 b2 b3 b4<br>Vwg2=  (01) (00) (11) (11)<br>-10.5V 点 点 点<br>(01) (00) (10) (11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5V   5V   5V   50   52   53   54   (01)   (00)   (10)   (11)   (11)   10   11   11   11   11   11   11 |  |  |

| WRITE DATA MEMORY DATA DISTURBANCE | 01     00     10     11       01     00     11     11       1     0     2     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01     00     10     11       01     00     10     11       2     1     0     3                        |  |  |

FIG. 2 DLT DLT Qs1 **WL11** MCC MCC MC1 MC1 LDL ~ LDL-WELL LSL -LSL WL1n MCn MCn MCn SS1 Qs2 Qs2 O 0V/-4V ĊSL Qs1 Qst WL21 MCC MCC MC1 MC1 LDL LDL-WELL -LSL -- LSL WL2n MCn MCn SS2 Qs2 -0.0VI - 4VQs2 DL11 ~ DL21 ~ DATA LINE

MEMORY 123 MEMORY CONVERSION 22 87 83

F/G. &

FIG.

# F/G. 10

F/G. 11

FIG. 12 PRIOR ART

|                                    | INITIAL STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | WRITE #1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CHANGE IN VIA DISTRIBUTION         | FREQUENCY A10. A10. Ath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FREQUENCY (10, 11, 10) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11) (10, 11 |  |  |

| MEMORY BIAS<br>CONDITIONS          | b1 b2 b3 b4<br> (11)  (11)  (11)  (11)<br>OV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5V 5V 5V<br>b1 b2 b3 b4<br>Vwg1= (10) (10) (10) (11)<br>-11V (計) (計) (計)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| WRITE DATA MEMORY DATA DISTURBANCE | 01 00 10 11<br>11 11 11 11<br>WRITE #2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 01 00 10 11<br>10 10 10 11<br>0 1<br>WRITE #3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| CHANGE IN Vth DISTRIBUTION         | FREQUENCY Approximation of the content of the conte | FREQUENCY Name of the Name of  |  |  |

| MEMORY BIAS<br>CONDITIONS          | 5V 5V<br>b1 b2 b3 b4<br>Vwg= (00) (00) (10) (11)<br>-11V (声) 声, 声, (01) (00) (10) (11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5V<br>b1 b2 b3 b4<br>Vwg=  (01)  (00)  (10)  (11)<br>-11V (声) 声, 声, 声, (01) (00) (10) (11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| WRITE DATA MEMORY DATA DISTURBANCE | 01     00     10     11       00     00     10     11       -     0     1     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01     00     10     11       01     00     10     11       0     1     2     3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

### NONVOLATILE SEMICONDUCTOR MEMORY INCLUDING MULTI-THRESHOLD VOLTAGE MEMORY CELLS INCLUDING **VOLTAGE RANGES INDICATING EITHER AN** ERASE STATE OR A TWO OR MORE **PROGRAM STATE**

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specifica- 10 tion; matter printed in italics indicates the additions made by reissue.

### CROSS-REFERENCE TO RELATED REISSUE *APPLICATIONS*

More than one reissue application has been filed for the reissue of U.S. Pat. No. 6,906,952. The reissue applications are application numbers Ser. No. 12/794,905 (the present divisional reissue application), filed Jun. 7, 2010, and Ser. No. 11/812,099 (the parent application), both of which are reissues of U.S. Pat. No. 6,906,952.

This application is a continuation of U.S. application Ser. No. 09/984,833 now abandoned, filed Oct. 31, 2001, which, 25 in turn is a continuation of U.S. application Ser. No. 09/679, 867, filed Oct. 5, 2000, now U.S. Pat. No. 6,320,785; which is a continuation of U.S. application Ser. No. 09/342,223, filed Jun. 29, 1999, now U.S. Pat. No. 6,525,960; and which, in turn, is a continuation of U.S. application Ser. No. 08/890, 30 396, filed Jul. 9, 1997, and now U.S. Pat. No. 5,959,882; and the entire disclosures of which are incorporated herein by reference.

### BACKGROUND OF THE INVENTION

The present invention relates to a semiconductor memory device, and to a technique which is particularly effective when applied to a memory system for multivalued information in a nonvolatile semiconductor memory device. By way 40 of example, the technique is effective when utilized for a nonvolatile memory device (hereinafter referred to simply as a flash memory) in which a plurality of pieces of stored information can be electrically erased all at once.

In a flash memory, nonvolatile memory elements each hav- 45 ing a control gate and a floating gate are used as memory cells, and each memory cell can be constructed of a single transistor. In such a flash memory, when a write operation is executed, as illustrated in FIG. 10, the drain region of the nonvolatile memory element is set at, for example, about 5 V 50 (volts), while a word line with the control gate CG connected thereto is set at, for example, about -11 V, whereby electric charges are extracted from the floating gate FG by means of a tunnel current so as to render the threshold voltage of the memory element low (logical value "0"). When an erase 55 operation is executed, as illustrated in FIG. 11, a well region, the drain region and a source region are set at about –4 V, by way of example, while the control gate CG is set at a high voltage, such as 12 V, whereby negative charges are injected into the floating gate FG by the generation of a tunnel current 60 present invention will become more apparent from the so as to render the threshold voltage high (logical value "1"). Thus, data of 1 (one) bit is stored in one memory cell.

There has been proposed the concept of a so-called "multivalued" memory wherein data of 2 or more bits is stored in one memory cell for the purpose of enlarging the memory 65 capacity. An invention concerning such a multivalued memory is disclosed in, for example, PCT/JP95/02260.

### SUMMARY OF THE INVENTION

In the multivalued memory disclosed in PCT/JP95/02260, data is written in three stages, as shown in FIG. 12. More specifically, from the starting point of an erase level (threshold voltage of about 5 V), a memory cell whose threshold voltage is nearest to the erase level is first subjected to a write operation, and memory cells whose threshold voltages are farther from the erase level are thereafter subjected to a write operation. This is intended to shorten the time period taken to write multivalued data. In a write operation in a flash memory, however, a high voltage is applied not only to the control gate of the selected memory cell, but also to the control gates of nonselected memory cells which are coupled with a word line 15 common to that of the selected memory cell. As is known, accordingly, each of the nonselected memory cells is brought into a weak written (disturbed) state, so that the threshold voltage thereof may fluctuate to change stored data. This phenomenon is known as word line disturbance.

Besides, the inventors have found that the memory cell whose threshold voltage is nearer to the erase level is more susceptible to the fluctuation of the threshold voltage attributed to the word line disturbance, than the memory cell whose threshold voltage is farther. It is considered that this is because the initial threshold voltage of each memory cell at the time of manufacture of a memory chip is much lower than the erase level, and the memory cells have a tendency of reverting to their initial threshold voltage when subjected to a disturbance.

However, it has been found that the data writing system disclosed in PCT/JP95/02260 is subject to a problem in that the fluctuations of the threshold voltages attributed to word line disturbance are great because the write operation is performed from the memory cell of a threshold voltage nearest to 35 the erase level, as compared to the memory cells having more distant threshold voltages. More specifically, the data writing method, as shown in FIG. 12, has a drawback in that the memory cell (of data "01") having a threshold voltage (lower than 1.5 V) farthest from the erase level does not undergo word line disturbance even once, whereas the memory cell (of data "10") having a threshold voltage (about 3.2 V) nearest to the erase level, being most susceptible to the word line disturbance, undergoes the disturbance twice on the average.

Further, it has been found that the data writing method disclosed in PCT/JP95/02260 has a drawback in that, since a write pulse is fed to all the memory cells whose threshold voltages are to be shifted in the write operation of the first stage, the peak current in the write operation increases and the average power consumption also increases.

An object of the present invention is to provide a multivalued memory type nonvolatile semiconductor memory device wherein the fluctuations in the threshold voltages of memory cells attributed to word line disturbance can be minimized.

Another object of the present invention is to provide a nonvolatile semiconductor memory device whose peak current and average power consumption in a write operation can be decreased.

The above and other objects and novel features of the description of this specification taken in conjunction with the accompanying drawings.

A typical aspect of the present invention will be briefly outlined below.

In a nonvolatile semiconductor memory device wherein a plurality of threshold voltages are determined so as to store multivalued information in one memory cell, data is first

written into a memory cell whose threshold voltage is the farthest from the erase level, and data is thereafter written into memory cells whose threshold voltages are nearer to the erase level, in succession. In other words, with the erase level used as a written state, data is first written into a memory cell having the lowest threshold voltage, and data is thereafter successively written into memory cells having higher threshold voltages.

Thus, the number of word line disturbances which affect the memory cell having a threshold voltage nearest to the <sup>10</sup> erase level and being most influenced by word line disturbance can be decreased, and the fluctuation of the threshold voltages attributed to word line disturbance can be minimized.

Moreover, owing to this feature, the number of data lines which must be precharged by one writing operation and the total number of data lines which must be precharged from the start of a write operation to the end thereof can be made smaller than conventional, thereby to reduce the peak current and average power consumption in a write operation.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is an explanatory diagram showing the outline of a data writing method for a multivalued flash memory accord- 25 ing to the present invention;

FIG. 2 is a circuit diagram showing an example of the construction of a memory array of a multivalued flash memory according to the present invention;

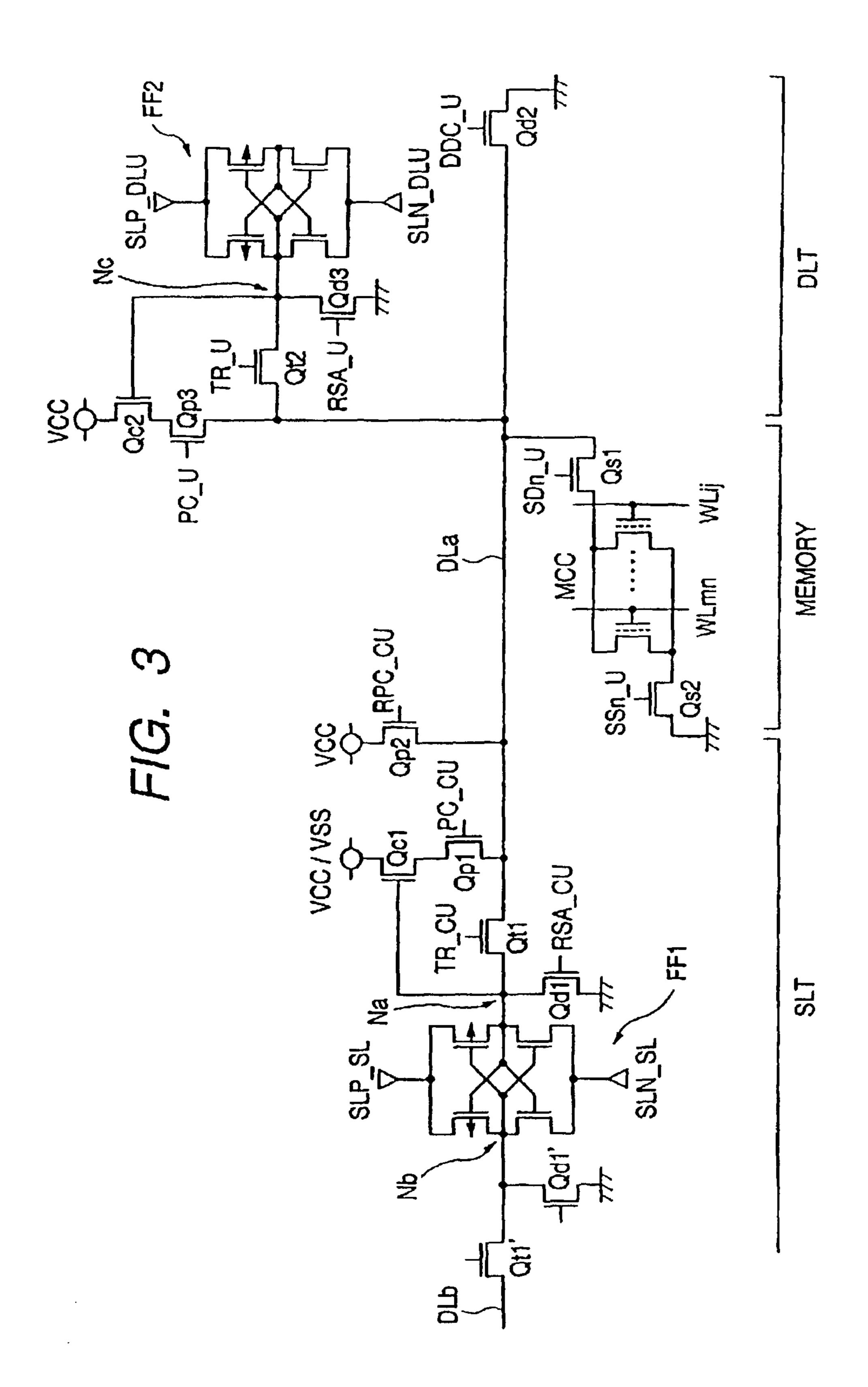

FIG. 3 is a circuit diagram showing practical examples of a 30 sense latch circuit (SLT) and a data latch circuit (DLT);

FIG. 4 is a logic circuit diagram showing an embodiment of a data conversion circuit according to the present invention, which converts write data of 2 bits into quaternary data;

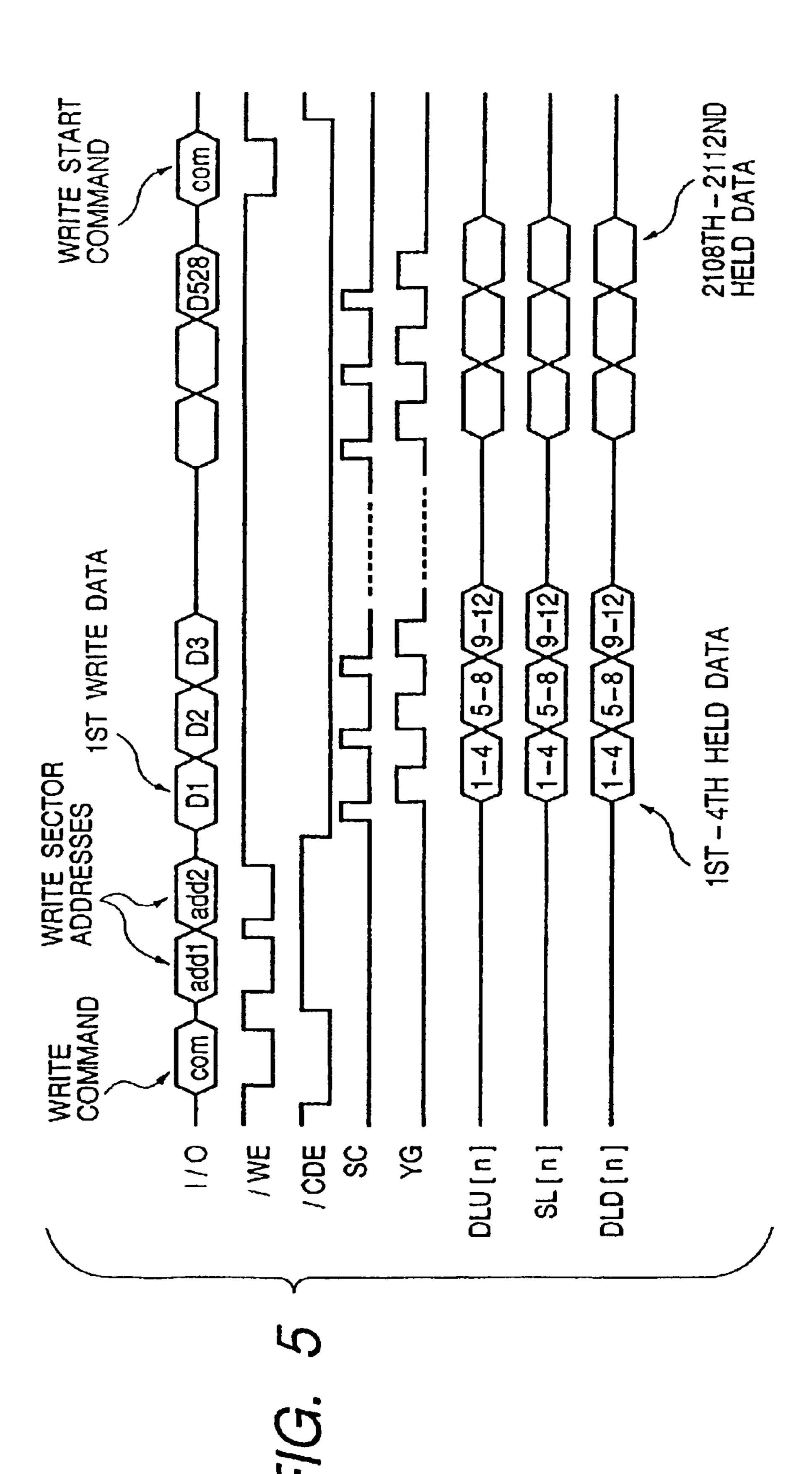

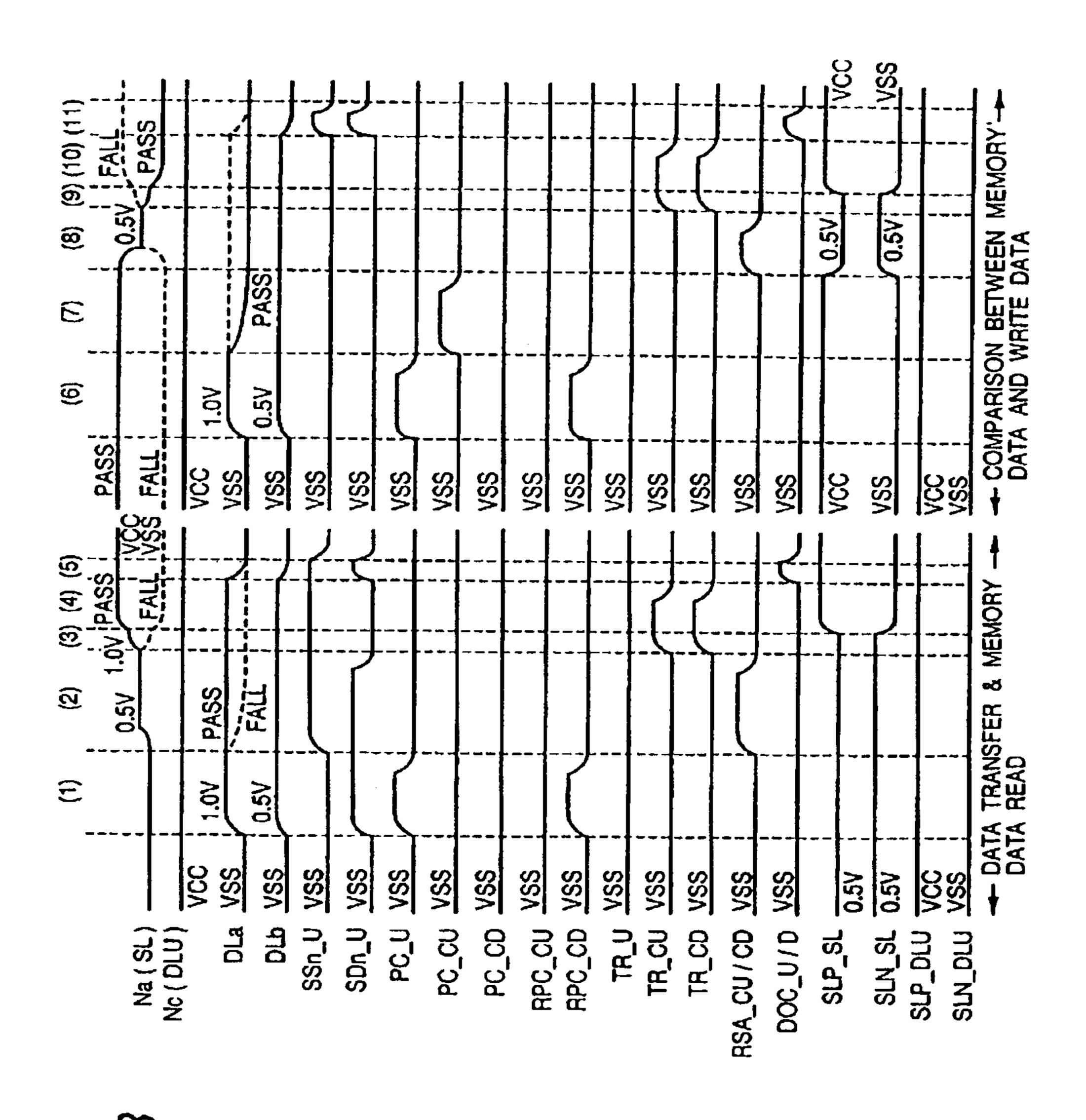

FIG. **5** is a timing chart showing the data input timings of the write operation of the multivalued flash memory of the embodiment;

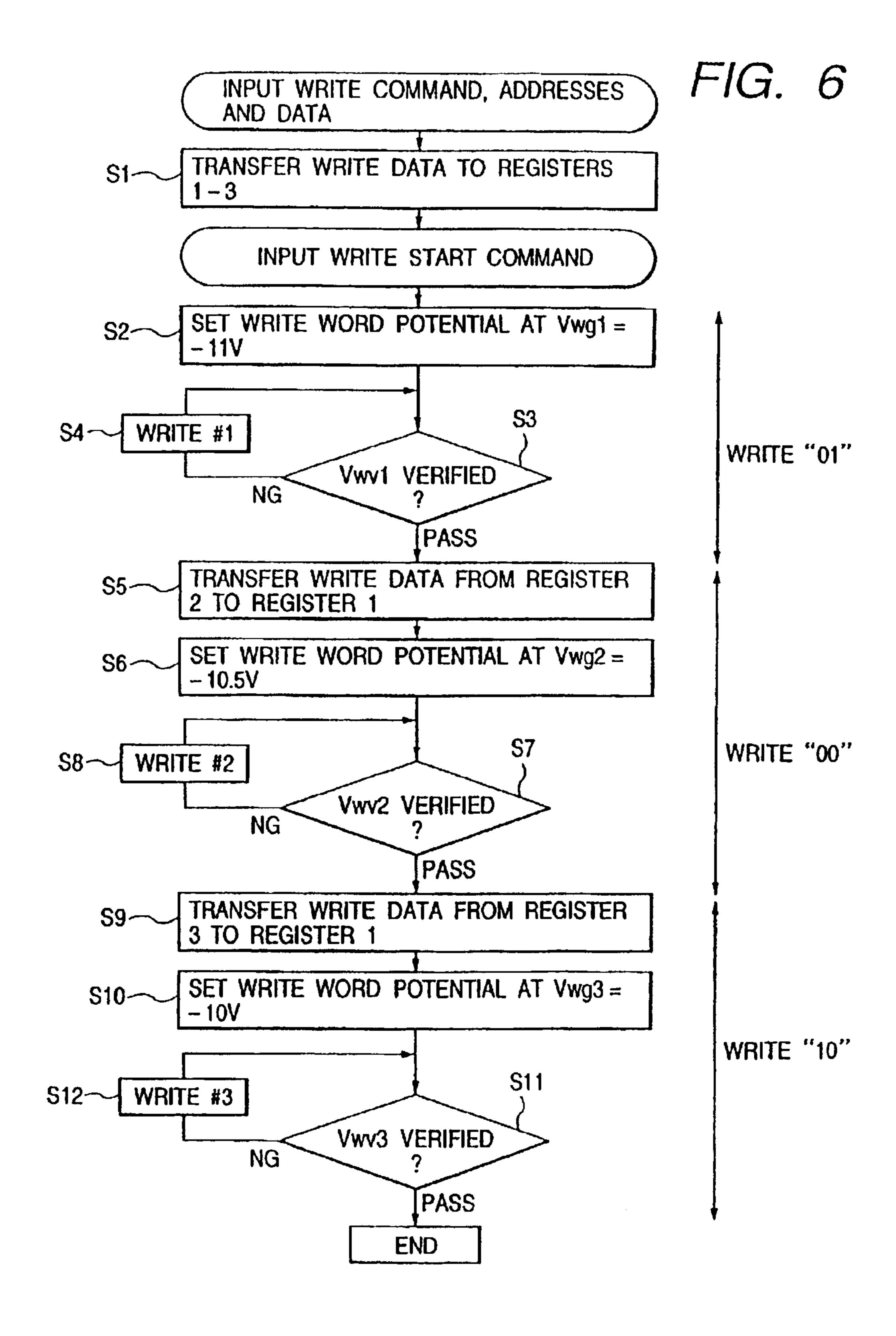

FIG. 6 is a flowchart showing the write procedure of the multivalued flash memory of the embodiment;

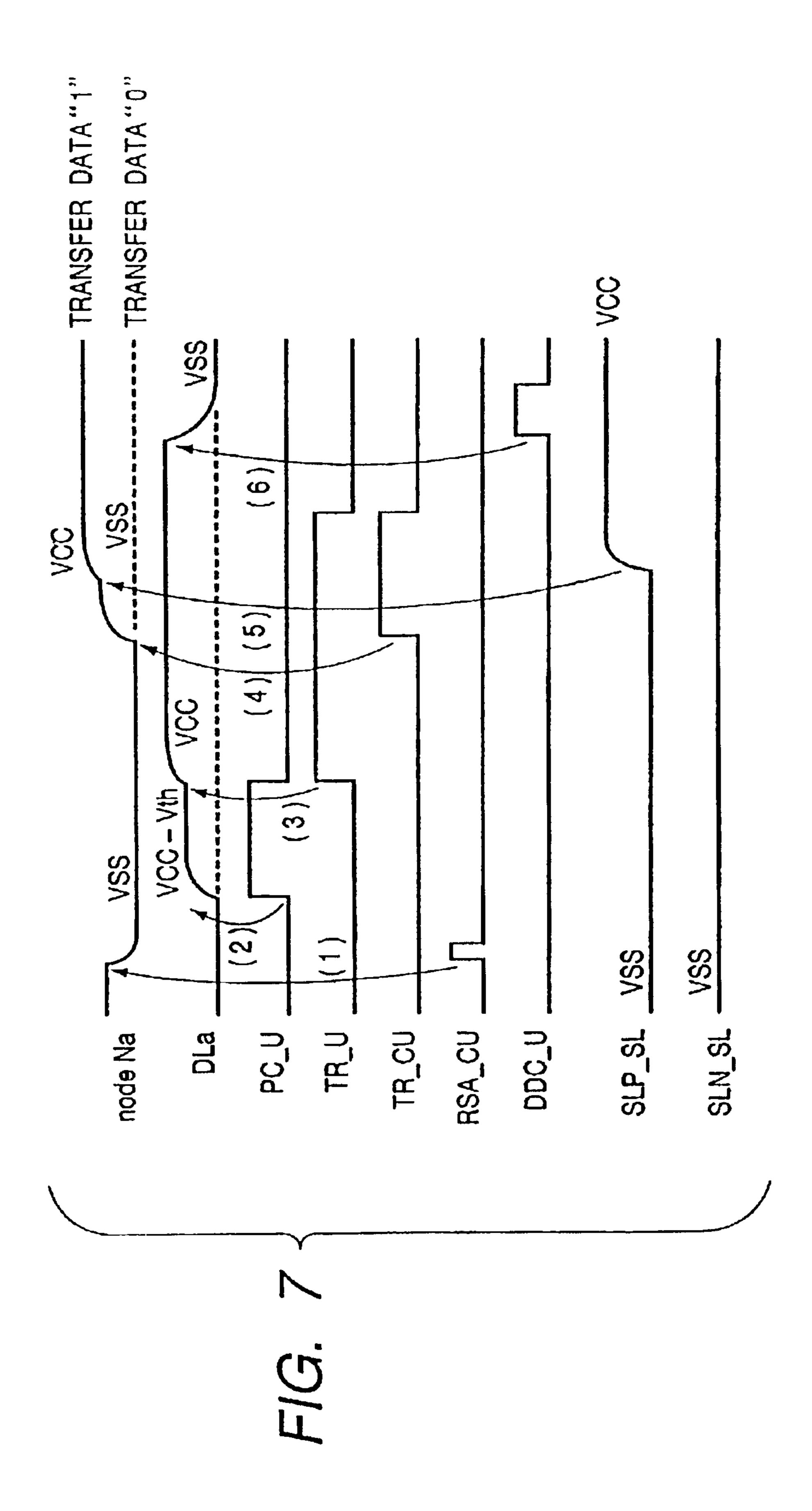

FIG. 7 is a timing chart showing the signal timings in 40 transferring data from the data latch circuit (DLT) to the sense latch circuit (SLT);

FIG. 8 is a timing chart showing the timings of the practical procedure of the detection of an erratic bit;

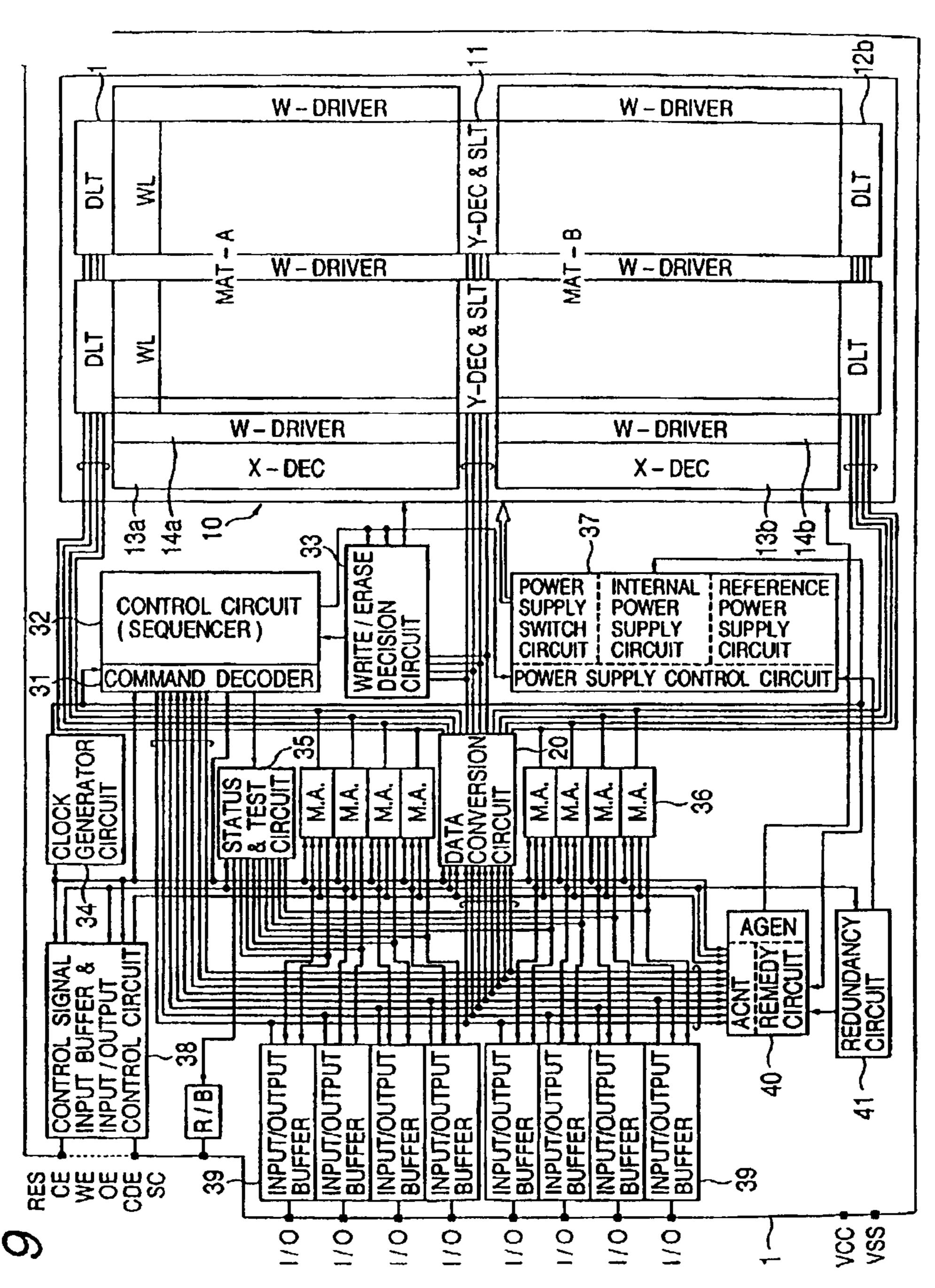

FIG. 9 is a schematic block diagram showing the whole of 45 the embodiment of the multivalued flash memory according to the present invention;

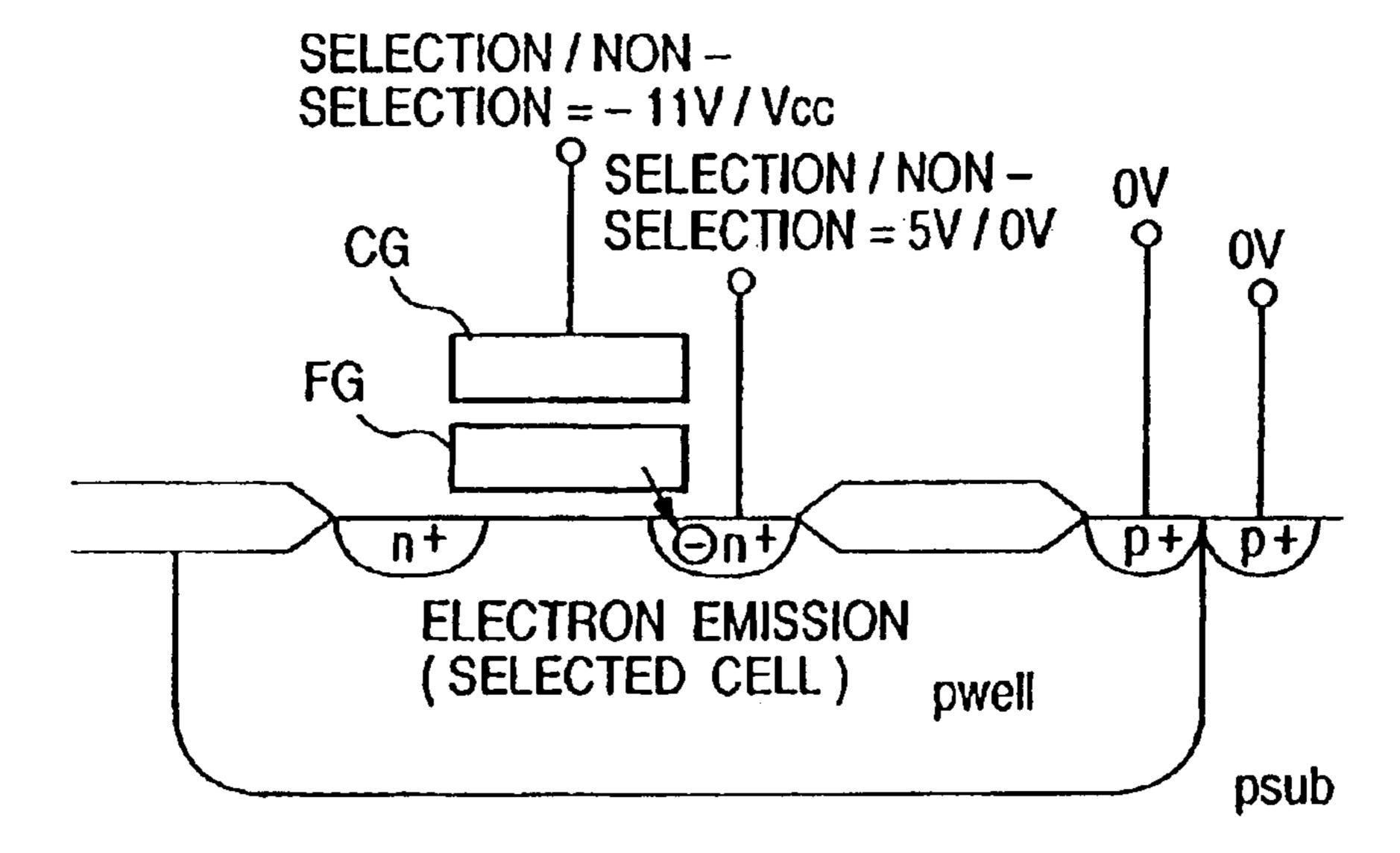

FIG. 10 is a schematic diagram showing the structure of a memory cell for use in the flash memory of the embodiment, and the voltage state in data writing operation of the memory cell;

FIG. 11 is a schematic diagram showing the voltage state of the erasing operation of the memory cell for use in the flash memory of the embodiment; and

FIG. 12 is an explanatory diagram showing the outline of a 55 data writing method for a multivalued flash memory according to a prior application.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

Now, various embodiments of the present invention will be described with reference to the drawings in relation to the case where the invention is applied to a flash memory which is capable of storing a quaternary value in one memory cell. 65

FIG. 1 illustrates the data writing sequence of a flash memory in one embodiment of the present invention. In this

4

embodiment, all the memory cells thereof are brought into the threshold voltage region (the threshold voltages are at least 4 V and the stored data is "11") of the erase level prior to the writing operation. Subsequently, as shown in FIG. 1, data is written into the memory cell (stored data is "01") whose threshold voltage region (the threshold voltage is higher than 0 V and not higher than 1.4 V) is the farthest (lowest) from the erase level. Thereafter, the data is written into the memory cell (stored data is "00" whose threshold voltage region (the threshold voltage is not lower than 1.6 V and not higher than 2.4 V) is the second farthest (second lowest) from the erase level. Lastly, the data is written into the memory cell (stored data is "10") whose threshold voltage region (the threshold voltage is not lower than 2.6 V and not higher than 3.2 V) is the nearest to the erase level.

Thus, the number of word line disturbances affecting the memory cell (the stored data is "01"), whose threshold voltage region is the farthest from the erase level and is little affected by the word line disturbance, becomes 2, but the number of the word line disturbances affecting the memory cell (the stored data "10"), whose threshold voltage region is the nearest to the erase level and is most affected by the word line disturbance, can be reduced to zero. Accordingly, compared with the method shown in FIG. 12 in which data is written from the memory cell nearest to the erase level, the method of this embodiment can suppress to smaller values the fluctuation of the threshold voltages attributed to word line disturbance.

FIG. 2 illustrates a practical example of a memory array 10, which will be explained later with reference to FIG. 9. The memory array 10 of this embodiment comprises two memory mats, one (the upper one) of which is illustrated in FIG. 2. As seen from the drawing, each memory mat comprises memory cell columns MCC disposed in the row direction (in the direction of word lines WL) and in the column direction (in the direction of data lines DL), and each of which includes n parallelly-connected memory cells (MOSFETs, each having a floating gate) MC1-MCn that are arrayed in the column direction and that have their sources and drains connected in common. In each memory cell column MCC, the drains and sources of the n memory cells MC1-MCn are respectively connected to a common local drain line LDL formed of a diffused layer and to a common local source line LSL formed of a diffused layer. The local drain line LDL is connected through a switching MOSFET Qs1 to the data line DL which is formed of a metallic interconnection layer made of, for example, aluminum. The local source line LSL is connected through a switching MOSFET Qs2 to a common source line CSL, which also is formed of a metallic interconnection layer made of, for example, aluminum, and which is fed with the ground potential or a negative voltage.

Those of the plurality of memory cell columns MCC which are disposed in the word line direction are formed within the same well region WELL on a semiconductor substrate. In the data erasing operation of the flash memory, the negative voltage of, e.g., -4 V is applied to the well region, and a voltage of, e.g., 12 V is applied to the word lines associated with the common well region, whereby the all-at-a-time erasure of the flash memory is realized. By the way, in the data erasing operation, all the switching MOSFETs Qs1 and Qs2 formed in the common well region are brought into ON states so as to apply the negative voltage of -4 V to the sources and drains of the memory cells.

On the other hand, in the data writing operation of the flash memory, a negative voltage of, e.g., -11 V is applied to the word line to which a selected one of the memory cells is connected, the data line DL corresponding to the selected

memory cell is set at a potential of, e.g., 5 V, and the switching MOSFET Qs1 on the local drain line LDL to which the selected memory cell is connected is brought into an ON state so as to apply the voltage of 5 V to the drain of the selected memory cell. In this case, however, the switching MOSFET Qs2 on the pertinent local source line LSL is held in an OFF state. Further, in the data reading operation of the flash memory, a voltage of, e.g., 1.5 V, 2.5 V or 3.3 V is applied to the word line to which the selected memory cell is connected, the data line DL corresponding to the selected memory cell is 10 precharged to a potential of, e.g., 1 V, and the switching MOSFET Qs1 on the local drain line LDL to which the selected memory cell is connected is brought into the ON state. At this time, the switching MOSFET Qs2 on the local source line LSL is brought into the ON state and the ground 15 potential of 0 V is applied thereto.

Connected to one end of each data line DL (on the center side of the memory array) is a sense latch circuit SLT which detects the level of the data line in the read operation and which impresses a potential corresponding to write data in the write operation, while the other end of each data line DL is connected to a data latch circuit DLT which holds the write data and read data. Since the memory array of this embodiment is configured of two mats, a memory mat similar to the one described above is also arranged on the opposite side to the sense latch circuits SLT, that is, on the bottom side of the drawing, and respective data lines DL in the lower memory mat are connected to the other input/output terminals of the corresponding sense latch circuits SLT in the upper memory mat.

FIG. 3 illustrates examples of the specific circuits of the sense latch circuit SLT and the data latch circuit DLT. Since the circuit of the memory array is symmetric with respect to the sense latch circuits SLT, a part of the circuit in relation to only one data line DL included in one memory mat is shown. 35 In addition, only one of the memory cell columns MCC connected to the data line DL is shown for convenience, but actually the plurality of memory cell columns MCC are connected. As shown in the drawing, the sense latch circuit SLT includes a flip-flop circuit FF1 in which the input/output 40 terminals of two CMOS (complementary MOS) inverters each consisting of a P-channel MOSFET and an N-channel MOSFET are cross-coupled to each other. One end of the data line DLa within one memory mat is connected to one input/ output node Na of the sense latch circuit SLT through a data 45 transfer MOSFET Qt1. Similarly, one end of the data line DLb within the other memory mat is connected to the other input/output node Nb of the sense latch circuit SLT through a data transfer MOSFET Qt1'.

Further, discharging MOSFETs Qd1 and Qd1' are respectively connected to the input/output nodes Na and Nb of the sense latch circuit SLT, and a discharging MOSFET Qd2 is connected also to the other end of the data line DLa. The precharging MOSFETs Qp1 and Qp2 are connected to each data line DL, and one Qp1 of them is connected through 55 another MOSFET Qc1 to a terminal which is fed with a supply voltage Vcc or the ground potential Vss. Write data can be input from a data conversion circuit, which will be described later, to the input/output nodes Na and Nb of the sense latch circuit SLT through a common input/output line 60 not shown.

Similarly to the sense latch circuit SLT, the data latch circuit DLT includes a flip-flop circuit FF2 in which the input/output terminals of two CMOS inverters each consisting of a P-channel MOSFET and an N-channel MOSFET are 65 cross-coupled to each other. The data line DLa within the memory mat is connected to one input/output node Nc of the

data latch circuit DLT through a data transfer MOSFET Qt2. A discharging MOSFET Qd3 is connected to the input/output node Nc of the data latch circuit DLT, and MOSFETs Qp3 and Qc2 which are turned on/off, depending upon the level of a precharge signal PC\_U and the potential of the input/output node Nc, are connected in series between the data line DLa and the supply voltage Vcc.

Further, the write data can be input from the data conversion circuit, which will be described later, to the input/output node Nc of the data latch circuit DLT through the common input/output line not shown. Although not depicted in FIG. 3, the data latch circuit DLT constructed of a flip-flop circuit for holding the write data transmitted from the data conversion circuit is arranged also at the other end of the data line DLb which is connected to the input/output node Nb of the sense latch circuit SLT.

FIG. 4 illustrates the data conversion circuits 20, by which externally inputted data to be stored is converted into multivalued data to be stored in the memory cells, and the relations of the data conversion circuits 20 with a sense latch array 11 and data latch arrays 12a and 12b, which are included in the memory array 10. Each data conversion circuit 20 is constituted by an input buffer unit 21 and a data conversion unit 22, and data of 8 bits can be input in parallel in pairs of 2 bits. One set of an input buffer unit 21 and a data conversion unit 22 is shown in detail in FIG. 4, and will be described below.

The input buffer unit 21 of one data conversion circuit 20 includes two clocked inverters INV1 and INV2, and two latch circuits LT1 and LT2. The data conversion unit 22 includes inverters INV11 and INV12, which are respectively connected to the relevant latch circuits LT1 and LT2, three NAND gate circuits G1, G2 and G3, which receive the outputs of the two inverters INV11 and INV12 and the outputs of the latch circuits LT1 and LT2 as input signals, inverters INV21, INV22 and INV23, which invert the outputs of the respective gate circuits G1, G2 and G3, and transfer gates TG1, TG2 and TG3, which are made up of MOSFETs connected to the respective inverters TG1, TG2 and TG3. Thus, the input data of 2 bits is converted into data of 3 bits, and data of 3 bits×4 is outputted as a whole.

Table 1 below shows an example of data conversion by the data conversion circuit **20**.

TABLE 1

| Write Data | <b>I/O</b> 0 | I/O 1 | DLU [1] | SL [1] | DLD [1] |

|------------|--------------|-------|---------|--------|---------|

| 01         | 0            | 1     | 0       | 1      | 0       |

| 00<br>10   | 1            | 0     | 0       | 0      | 1       |

| <br>11     | 1            | 1     | 0       | 0      | 0       |

As listed in Table 1, write data "01" is converted into 3-bit data "010", write data "00" is converted into 3-bit data "100", write data "10" into 3-bit data "001", and write data "11" is converted into 3-bit data "000". After the conversion, the data is written into only the memory cell which corresponds to the bit corresponding to "1", and no data is written into the memory cells which correspond to the bits corresponding to "0".

Data of 3 bits, obtained by converting two bits out of the 8 bits of the write data, which is received by the data conversion circuit 20 and supplied through the external terminals I/O 0 and I/O 1, are respectively transferred to and held in the first latch circuits (DLU1, SL1 and DLD1) of the data latch arrays 12a and 12b which are arranged at both ends of the memory array 10 (at the top and bottom of FIG. 4) and the sense latch arrays 11 which is arranged at the center of the memory array

10. Data of 3 bits, obtained by converting two bits of the 8-bit write data supplied through the external terminals I/O 2 and I/O 3, are respectively transferred to and held in the second latch circuits (DLU2, SL2 and DLD2) of the data latch arrays 12a and 12b of the memory array 10 and the sense latch array 5 11 thereof.

Similarly to the above, 3-bit data, obtained by converting the two bits of the 8-bit write data supplied through the external terminals I/O 4 and I/O 5, are respectively transferred to and held in the third latch circuits (DLU3, SL3 and DLD3) 10 of the data latch arrays 12a and 12b and the sense latch array 11. Also, 3-bit data, obtained by converting the two bits of the 8-bit supplied through the external terminals I/O 6 and I/O 7, are respectively transferred to and held in the fourth latch circuits of the data latch arrays 12a and 12b and the sense 15 latch array 11. The 8-bit write data subsequently input are respectively converted by the data conversion circuits 20, and the resulting 3-bit data are respectively transferred to and held in the fifth-eighth latch circuits of the data latch arrays 12a and 12b and the sense latch array 11.

When all the write data has been stored in all the latch circuits of the data latch arrays 12a and 12b and the sense latch array 11 by repeating the operations described above, a control circuit which will be described later, and which is included in the memory, starts a write sequence in which the 25 data held in the sense latch array 11 is first written, the data held in the data latch array 12a is subsequently written, and the data held in the data latch array 12b is thereafter written. Incidentally, the control circuit is so constructed as to perform controls in compliance with commands which are input from, 30 e.g., a CPU outside the flash memory.