#### US00RE43404E

## (19) United States

## (12) Reissued Patent

#### DiStefano et al.

#### (10) Patent Number:

### US RE43,404 E

#### (45) Date of Reissued Patent: May 22, 2012

# (54) METHODS FOR PROVIDING VOID-FREE LAYER FOR SEMICONDUCTOR ASSEMBLIES

(75) Inventors: **Thomas H. DiStefano**, Monte Sereno,

CA (US); Joseph Fjelstad, Maple

Valley, WA (US)

(73) Assignee: Tessera, Inc., San Jose, CA (US)

(21) Appl. No.: 12/728,630

(22) Filed: **Mar. 22, 2010**

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: 6,458,681

Issued: Oct. 1, 2002

Appl. No.: 09/638,079

Filed: Aug. 14, 2000

#### U.S. Applications:

- (60) Continuation of application No. 09/188,599, filed on Nov. 9, 1998, now Pat. No. 6,107,123, which is a division of application No. 08/610,610, filed on Mar. 7, 1996, now Pat. No. 5,834,339.

- (51) Int. Cl. *H01L 21/44* (2006.01)

(56) References Cited

#### U.S. PATENT DOCUMENTS

3,390,308 A 6/1968 Marley 3,413,713 A 12/1968 Helda et al. 3,614,832 A 10/1971 Chance et al.

| 3,811,183 A | 5/1974  | Celling et al.  |

|-------------|---------|-----------------|

| 3,868,724 A | 2/1975  | Perrino         |

| 3,906,144 A | 9/1975  | Wiley et al.    |

| 4,012,766 A | 3/1977  | Phillips et al. |

| 4,017,495 A | 4/1977  | Jaffe et al.    |

| 4,143,456 A | 3/1979  | Inoue et al.    |

| 4,163,072 A | 7/1979  | Soos            |

| 4,300,153 A | 11/1981 | Hayakawa et al. |

| 4,312,116 A | 1/1982  | Moser et al.    |

| 4,366,187 A | 12/1982 | Gabriel         |

| 4,374,080 A | 2/1983  | Schroeder       |

| 4,381,602 A | 5/1983  | McIver          |

| 4,536,469 A | 8/1985  | Adlerstein      |

| 4,566,184 A | 1/1986  | Higgins et al.  |

| 4,604,644 A | 8/1986  | Beckham et al.  |

|             | (Can    | tinuad)         |

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

JP 53-139468 12/1978 (Continued)

#### OTHER PUBLICATIONS

Adamson, S., "Underfill Design and Process Considerations", Proc. SMTA Int'l., Chicago, IL, Aug. 2000, p. 69.

#### (Continued)

Primary Examiner — Phuc Dang (74) Attorney, Agent, or Firm — Lerner, David, Littenberg, Krumholz & Mentlik, LLP

#### (57) ABSTRACT

A method of providing a substantially void free layer for one or more flip chip assemblies, or one or more microelectronic components, utilizing a curable encapsulant. Also disclosed is a method of injecting an encapsulant into an assembly and a method of treating a microelectronic component to form a void free layer.

#### 11 Claims, 9 Drawing Sheets

| TIC DATENTED                                   | NOCH IN AUDITUU                           | 6.049.656 A 4/2000 Alamom et el                                                                                                    |

|------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| U.S. PATENT D                                  |                                           | 6,048,656 A 4/2000 Akram et al.<br>6,207,478 B1 3/2001 Chung et al.                                                                |

| 4,605,153 A 8/1986 V<br>4,616,412 A 10/1986 S  | Van Den Brekel et al.<br>Schroeder        | 6,221,697 B1 4/2001 Su et al.                                                                                                      |

| 4,658,332 A 4/1987 E                           |                                           | FOREIGN PATENT DOCUMENTS                                                                                                           |

| 4,697,203 A 9/1987 S<br>4,701,999 A 10/1987 P  |                                           | JP 55-011361 1/1980                                                                                                                |

| 4,707,724 A 11/1987 S                          | Suzuki et al.                             | JP 55-117254 9/1980                                                                                                                |

|                                                | Marcantonio et al.                        | JP 59-143333 8/1984<br>JP 60-077446 5/1985                                                                                         |

|                                                | Hoppe et al.<br>Gazdik et al.             | JP 63-239826 10/1988                                                                                                               |

| 4,825,284 A 4/1989 S                           | <u> </u>                                  | JP 63-241955 10/1988<br>JP 63241955 A * 10/1988                                                                                    |

| 4,829,666 A 5/1989 H<br>4,847,146 A 7/1989 Y   | laginii-ichani ci ai.                     | JP 1-170027 7/1989                                                                                                                 |

|                                                | Steffen et al.                            | JP 1-191457 8/1989                                                                                                                 |

|                                                | Smith et al.                              | JP 1-278755 11/1989<br>JP 1-293528 11/1989                                                                                         |

|                                                | Saeki et al.<br>Shyr 438/463              | JP 2-056941 2/1990                                                                                                                 |

| 4,913,930 A 4/1990 C                           | Getson                                    | JP 4-137641 5/1992<br>D 52 21673 0/1003                                                                                            |

|                                                | Medders et al.<br>Eichelberger et al.     | JP 52-31673 9/1993<br>WO 89/10005 10/1989                                                                                          |

|                                                | Shimizu et al.                            |                                                                                                                                    |

|                                                | Juskey, Jr. et al.                        | OTHER PUBLICATIONS                                                                                                                 |

|                                                | Ootsuki et al.<br>Fujitsu et al.          | Babiarz, A.J., et al.; "Process Notes for Successful Encapsulation and                                                             |

|                                                | Ozawa et al.                              | Underfilling in MCM Assembly;" Electronic Packaging & Produc-                                                                      |

|                                                | Ackermann et al.                          | tion; pp. 20-22 (Nov. 1994).                                                                                                       |

|                                                | Hamano et al.<br>Christie et al.          | Bascom et al., "Air Entrapment in the Use of Structural Adhesive                                                                   |

|                                                | Juskey et al 174/527                      | Films," J. Adhesion, 1972, vol. 4, pp. 193-209, Copyrgt. 1972 Gordon and Breach Science Publishers Ltd.                            |

|                                                | Whalley et al.<br>Matumoto et al.         | Bouras, C.E., "Adhesive Dispensing for Flip Chip-on-Board;" Elec-                                                                  |

| 5,052,357 A 10/1991 L                          |                                           | tronic Packaging & Production; pp. S9-S11 (Oct. 1995).                                                                             |

|                                                |                                           | Clementi et al., "Flip-Chip Encapsulation on Ceramic Substrates",                                                                  |

|                                                | Nakashima et al.<br>Christie et al.       | 1993 Proceedings, 43rd Electronic Components and Technology                                                                        |

| 5,120,678 A 6/1992 N                           | Moore et al.                              | Conference, IEEE, New York, NY, pp. 175-181 Jun. 1, 1993. Salmon, Edward R., Encapsulation of Electronic Devices and Com-          |

| , , ,                                          | Hsiao et al.<br>Kovac et al.              | ponents (Marcel Dekker, Inc. 1987).                                                                                                |

| ·                                              | Eichelberger                              | IBM Tech Disclosure Bull., vol. 23, No. 5, Oct. 1980, pp. 1877-1878.                                                               |

| 5,148,265 A 9/1992 K                           | Khandros et al.                           | IBM Tech Disclosure Bull., vol. 29, No. 11, Apr. 1987, pp. 4718-                                                                   |

|                                                | Khandros et al.<br>Higgins, III           | 4719. IBM Tech Disclosure Bull., vol. 32, No. 10B, Mar. 1990, p. 480.                                                              |

|                                                | Bechtel et al.                            | Tummala et al., Microelectronics Packaging Handbook, 1989, pp.                                                                     |

|                                                | Interrante et al.                         | 420-423, 1132.                                                                                                                     |

|                                                | Papathomas et al.<br>Banerji et al 29/840 | Nakano, F. et al., "Resin-Insertion Effect on Thermal Cycle Resistivity of Flip-Chip Mounted LSI Devices", ISHM '87 Proceedings,   |

| 5,203,706 A 4/1993 Z                           | Zamir et al.                              | pp. 536-541, 1987.                                                                                                                 |

| 5,218,234 A 6/1993 T<br>5,249,101 A 9/1993 F   | I hompson et al.                          | Park et al., "Evaluation of Epoxy Underfill Materials for Use in                                                                   |

| 5,252,784 A 10/1993 A                          |                                           | Chip-on-Board Method of Packaging Silicon Integrated Circuits",                                                                    |

|                                                | Khandros et al.                           | Annual Tech. Conf. Proceedings, pp. 2871-2876 1995.<br>Suryanarayana et al., "Encapsulants Used in Flip-Chip Packages",            |

|                                                | Bronson et al.<br>Carey et al.            | 1993 Proceedings, 43rd Electronic Components and Technology                                                                        |

| 5,296,738 A 3/1994 F                           | Freyman et al.                            | Conference, IEEE, New York, NY, pp. 193-198 Jun. 1, 1993.                                                                          |

|                                                |                                           | Suryanarayana, D. et al., "Enhancement of Flip-Chip Fatigue Life by                                                                |

| 5,304,512 A 4/1994 A                           |                                           | Encapsulation", IEEE Transactions on Components and Hybrids, and Manufacturing Technology, vol. 14, No. 1, Mar. 1991, pp. 218-     |

|                                                | Banerji et al.                            | 223.                                                                                                                               |

|                                                | Juskey et al.<br>Marrs et al.             | Wang, D. And K. Papathomas, "Encapsulant For Fatigue Life                                                                          |

| , , , , , , , , , , , , , , , , , , , ,        | Yoshida et al                             | Enhancement of Controlled Collapse Chip Connection (C4)", Proc. Of 43rd Electronic Components & Technology Conference, Orlando,    |

| 5,385,869 A 1/1995 L<br>5,394,009 A 2/1995 L   | iu et ai.                                 | FL, Jun. 1993, p. 780.                                                                                                             |

| 5,394,009 A 2/1995 1<br>5,409,362 A 4/1995 N   |                                           | Excerpts from Response of Acer Inc. And Acer America Corp. To                                                                      |

| 5,409,865 A 4/1995 K                           |                                           | Complaint And Notice Of Investigation Under Section 337 Of the                                                                     |

| 5,409,866 A 4/1995 S<br>5,473,512 A 12/1995 E  |                                           | Tariff Act Of 1930, As Amended, dated Feb. 15, 2008, In the Matter of Certain Semiconductor Chips With Minimized Chip Package Size |

| 5,473,814 A 12/1995 V                          | White                                     | and Products Containing Same (III), ITC Investigation No. 337-TA-                                                                  |

| 5,477,611 A 12/1995 S<br>5,483,106 A 1/1996 E  | Sweis et al.<br>Echigo et al.             | 630.                                                                                                                               |

| •                                              | Echigo et al.<br>Fsukada 174/261          | Excerpts from Response of Nanya Technology Corp. And Nanya Technology Corp. U.S.A. To Complaint and Notice Of Investigation        |

| 5,563,445 A 10/1996 I                          | ijima et al.                              | Technology Corp. U.S.A. To Complaint and Notice Of Investigation Under Section 337 Of The Tariff Act of 1930, As Amended, dated    |

| , ,                                            | Rostoker et al.<br>Doi et al              | Feb. 15, 2008, In the Matter of Certain Semiconductor Chips With                                                                   |

| 5,710,071 A 1/1998 E                           | Beddingfield et al.                       | Minimized Chip Package Size and Products Containing Same (III),                                                                    |

| 5,720,100 A 2/1998 S<br>5,817,545 A 10/1998 V  | Skipor et al.<br>Wang et al               | ITC Investigation No. 337-TA-630. Excerpts from Response of Powerchip Semiconductor Corp. To                                       |

| 5,817,343 A 10/1998 V<br>5,834,339 A 11/1998 E | ~                                         | Complaint And Notice Of Investigation Under Section 337 Of The                                                                     |

| 5.834.340 A 11/1998 S                          |                                           | Tariff Act of 1930. As Amended, with 22 attachments dated Feb. 15.                                                                 |

Tariff Act of 1930, As Amended, with 22 attachments dated Feb. 15,

5,834,340 A 11/1998 Sawai et al.

### US RE43,404 E

Page 3

2008, In the Matter of Certain Semiconductor Chips With Minimized Chip Package Size and Products Containing Same (III), ITC Investigation No. 337-TA-630.

Excerpts from Response of Respondents Elpida Memory, Inc. and Elpida Memory (USA) Inc. To The Complaint And Notice Of Investigation, dated Feb. 15, 2008, In the Matter of Certain Semiconductor Chips With Minimized Chip Package Size and Products Containing Same (III), ITC Investigation No. 337-TA-630.

Request for Inter Partes Reexamination and Exhibits of U.S. Patent 6,458,681, dated Apr. 2, 2008, Control No. 95/001,035.

Office Action in Inter Partes Reexamination, dated Jun. 6, 2008, Control No. 95/001,035.

Order Granting/Denying Request for Inter Partes Reexamination, dated Jun. 6, 2008, Control No. 95/001,035.

Response to Official Action, dated Aug. 6, 2008, Control No. 95/001,035.

Action Closing Prosecution, dated Sep. 21, 2009, Control No. 95/001,035.

Third Party Requestor's Comments to Patent Owner's Response to Action Closing Prosecution, dated Nov. 20, 2009, Control No. 95/001,035.

Third Party's Requestor's Comments to Patent Owner's Response to Official Action, dated Oct. 10, 2008, Control No. 95/001,035.

Response to Action Closing Prosecution, dated Oct. 21, 2009, Control No. 95/001,035.

Inter Partes Reexamination Certificate, dated Oct. 26, 2010, Control No. 95/001,035.

\* cited by examiner

FIG. 2K

FIG. 2L

FIG. 3A

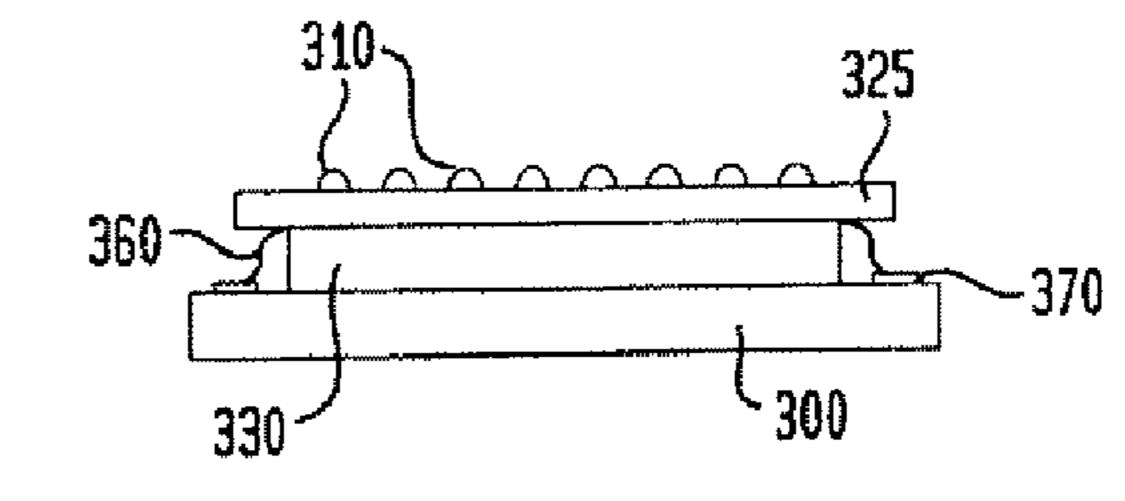

FIG. 3B

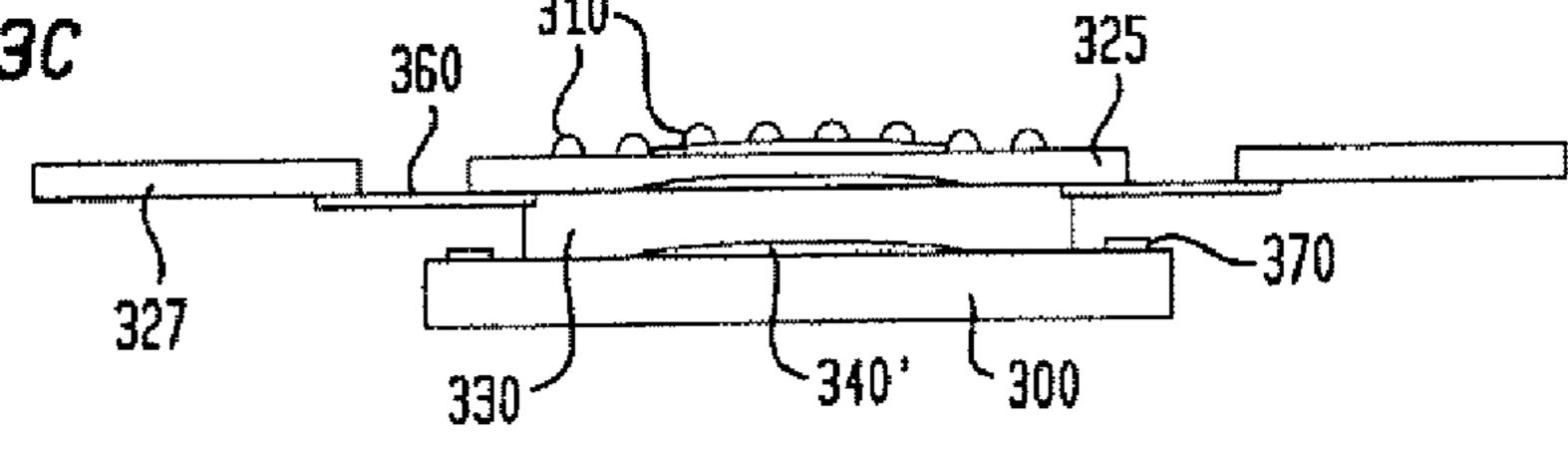

FIG. 3C

FIG. 3D

FIG. 3E

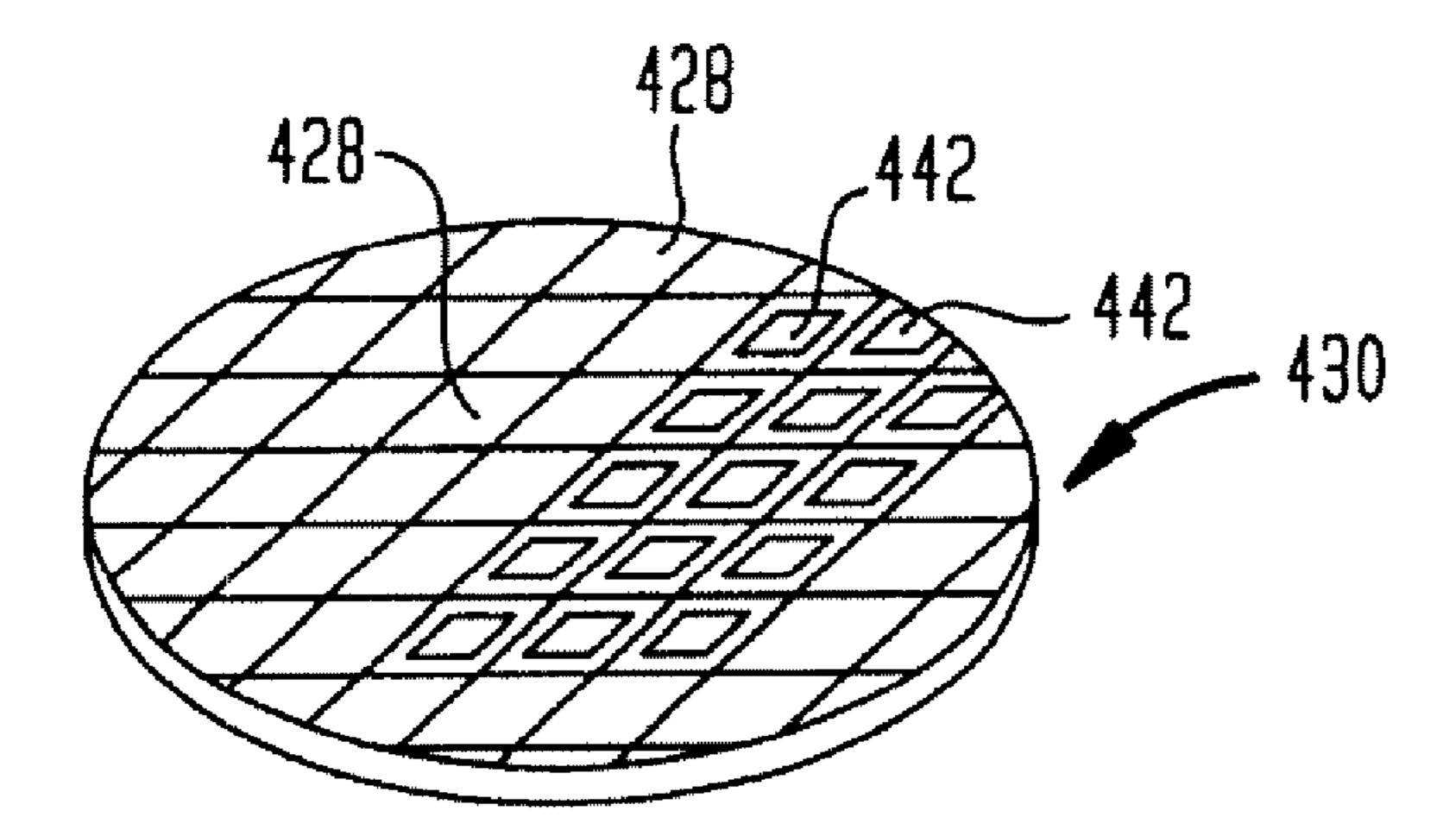

FIG. 4A

FIG. 4B

# METHODS FOR PROVIDING VOID-FREE LAYER FOR SEMICONDUCTOR ASSEMBLIES

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

# CROSS-REFERENCE TO RELATED APPLICATIONS

This is a continuation application of application Ser. No. 09/188,599 filed Nov. 9, 1998, now U.S. Pat. No. 6,107,123, which is a divisional application of application Ser. No. 08/610,610 filed Mar. 7, 1996, now U.S. Pat. No. 5,834,339.

#### FIELD OF THE INVENTION

The present invention relates to the field of semiconductor chip packaging.

#### BACKGROUND OF THE INVENTION

In the construction of semiconductor chip assemblies, it has been found desirable to interpose encapsulating material between and/or around elements of the semiconductor assemblies in an effort to reduce and/or redistribute the strain and strain on the connections between the semiconductor chip 30 and a supporting circuitized substrate during operation of the chip, and to seal the elements against corrosion.

Ball grid array ("BGA") packaged and chip scale packaged ("CSP") semiconductor chips and flip chip attachment solutions are connected to external circuitry through contacts on a 35 surface of the chip. To save area on a supporting substrate, such as a printed wiring board ("PWB"), these chips are directly connected/soldered to the substrates and from there connected to external circuitry on other parts of the substrate. The chip contacts are either disposed in regular grid array 40 patterns, substantially covering the face surface of the chip (commonly referred to as an "area array") or in elongated rows extending parallel to and adjacent each edge of the chip front surface. Many of the techniques for attachment run into problems because of the thermal expansion mismatch 45 between the material the chip is composed of and the material the supporting circuitized substrate is made of, such as a PWB. In other words, when the chip is in operation, the chip heats up and also heats its supporting substrate thereby causing both the chip and the substrate to expand. When the heat 50 is removed, the chip and substrate both contract. This heating and cooling process is referred to as "thermal cycling". Since the heat is being generated in the chip, the chip will heat up more quickly and will typically get hotter than its supporting substrate. The materials comprising both the chip and the 55 substrate have inherent expansion and contraction rates, referred to as their coefficients of thermal expansion ("CTE"), which causes them to expand and contract at different rates and in different degrees when subjected to the same thermal conditions. This thermal expansion mismatch between the 60 chips and the substrate places considerable mechanical stress and strain on the connections between the chip contacts and corresponding bond pads on the substrate.

BGA and CSP technology refers to a large range of semiconductor packages which use interconnection processes 65 such as wirebonding, beam lead, tape automated bonding ("TAB") or the like as an intermediate connection step to 2

interconnect the chip contacts to the exposed package terminals. This results in a device which can be tested prior to mechanical attachment to the bond pads on supporting substrate. The BGA or CSP packaged chips are then typically interconnected with their supporting substrates using standard tin-lead solder connections. In most such packaged devices, the mechanical stress/strain due to thermal cycling is almost completely placed on the solder connections between the chip and the substrate. However, solder was never intended to undergo such forces and commonly under-goes significant elastic solder deformation causing the solder to crack due to fatigue brought on by the thermal cycling. When the solder connections have smaller diameters, thermal cycling has an even more profound fatiguing affect on the solder. This has driven efforts in the packaging art to modify the solder and other elements of the packages so that they may better withstand the thermal cycling forces.

As the features of semiconductor chip packages continue to be reduced in size, as in the case of CSPs, the number of chips packed into a given area will be greater and thus the heat dissipated by each of these chips will have a greater effect on the thermal mismatch problem. Further, the solder cracking problem is exacerbated when more than one semiconductor chip is mounted in a package, such as in a multichip module.

25 As more chips are packaged together, more heat will be dissipated by each package which, in turn, means the interconnections between a package and its supporting substrate will encounter greater mechanical stress due to thermal cycling. Further, as more chips are integrated into multichip modules, each package requires additional interconnections thereby increasing the overall rigidity of the connection between the module and its supporting substrate.

Certain designs have reduced solder connection fatigue by redistributing the thermal cycling stress into a portion of the chip package itself. An example of such a design is shown in U.S. Pat. Nos. 5,148,265 and 5,148,266, the disclosure of which is incorporated herein by reference. One disclosed embodiment of these patents shows the use of a chip carrier in combination with a compliant layer to reduce the CTE mismatch problems. Typically, the compliant layer includes an elastomeric layer which, in the finished package, is disposed between the chip carrier and the face surface of the chip. The compliant layer provides resiliency to the individual terminals, allowing each terminal to move in relation to its electrically connected chip contact to accommodate CTE mismatch as necessary during testing, final assembly and thermal cycling of the device.

In some arrangements used heretofore, the compliant layer was formed by stenciling a thermoset resin onto the chip carrier and then curing the resin. Next, additional resin was applied to the exposed surface of the cured layer, this additional resin was partially cured, and the resulting tacky adhesive surface was used to bond the elastomeric layer to the chip and chip carrier. Once attached, the entire structure was heated and fully cured. Although this process is effective, further improvement would be desirable. The ambient gas can be occasionally entrapped when the chip carrier and die are affixed to the compliant layer. The entrapped gas can create voids and gas bubbles in the encapsulation of the surface of the die by the encapsulation material. These voids/bubbles allow moisture and other contamination to come into direct contact with the surface of the die. Accordingly, care must be taken to prevent such entrapment. This adds to the expense of the process.

In the flip-chip mounting technique, the contact bearing face surface of the chip opposes a bond pad bearing supporting substrate. Each contact on the device is joined by a solder

3

connection to a corresponding bond pad on the supporting substrate, as by positioning solder balls on the substrate or device, juxtaposing the device with the substrate in the frontface-down orientation and momentarily reflowing the solder. The flip-chip technique yields a compact assembly, which occupies an area of the substrate no larger than the area of the chip itself. However, flip-chip assemblies suffer from significant problems when encountering thermal cycling stress because the sole thermal cycling stress bearing elements are the solder connections, as described above in relation to the 10 BGA and CSP packages. In the case of flip chip devices, there is no package to redistribute the thermal cycling stress. Because of this, significant work has been done in the art to make the flip chip solder connections more reliable. However, to keep the chip's standoff from the substrate to a minimum, 15 the solder connections have a typical diameter of between about five and eight thousandths of an inch ("mils"), too small to provide much real mechanical compliance. In an attempt to solve this problem, a curable liquid underfill is flowed between the chip and its attached substrate, enclosing the 20 solder connections. The underfill is then cured into a rigid form which has a CTE that is closely matched to the solder material. The aim of the underfill is to reduce the stress caused by CTE mismatch by redistributing the stress more uniformly over the entire surface of the chip, supporting substrate and 25 solder balls. Examples of the use of underfill materials may be found in U.S. Pat. Nos. 5,120,678, 5,194,930, 5,203,076 and 5,249,101. All of these prior art solutions are aimed at reducing the shear stress endured by the interconnections caused by thermal cycling. However, each of these solutions also 30 encounters significant problems such as insufficient compliancy, voids and process cost. Most significant among these costs is reducing the voiding problem which occurs when the underfill flows between the chip and the substrate and traps gas therebetween. If this gas is not removed, it will typically 35 quickly expand during a heating cycle of the chip. The force associated with the expanding gas can cause the solder connections to crack or otherwise become unreliable. Yet, presently, the underfill process involves a very costly and timeconsuming process of allowing the underfill to flow very 40 slowly between the chip and the substrate to try to avoid voids. After the underfill has flowed completely between the chip and the substrate, the assembly will then be subjected to one or more vacuuming steps in a further attempt to remove any voids in the underfill material.

Despite these and other efforts in the art, still further improvements in interconnection technology would be desirable.

#### SUMMARY OF THE INVENTION

The present invention provides a method of eliminating voids and gas bubbles within the encapsulation used in attaching and packaging microelectronic devices which solves the aforementioned problems in the art. The present invention 55 further provides an effective method of filling cavities and channels during encapsulation of a plurality of semiconductor chips formed on a semiconductor wafer.

In one embodiment, the method includes providing a substantially void and bubble free underfill for a semiconductor 60 wafer having a plurality of flip chip assemblies. Typically, a flip chip device is electrically and mechanically attached to a circuitized substrate, such as a PWB, by a plurality of conductive members, which are most typically a plurality of solder balls. These solder balls provide an electrical path from 65 each chip contact to a respective bond pad on the substrate. The solder balls further provide a gap or stand-off between

4

the wafer and hence each flip chip device and its substrate. This gap is then sealed on all sides of the flip chip device with a curable liquid encapsulant so that either a void (vacuum) or an area containing a first gas is thereby created. An isostatic or hydrostatic pressure is then applied to the semiconductor wafer assembly causing the encapsulant to flow into the gap and around the solder balls. An energy is applied to cure the encapsulant once the void/bubble has been completely removed thereby ensuring that new voids and/or bubbles do not re-occur between the flip chip device and the substrate. Typically, heat and/or ultra-violet radiation are used as the applied energy.

In another embodiment of the present invention, the method includes creating a substantially void/bubble free interposer layer between a semiconductor wafer having a plurality of microelectronic components and a sheet-like substrate. According to this method, an interposer layer is injected into a gap between each of the microelectronic components and the substrate such that any voids or gas bubbles are sealed within the gap. Isostatic or hydrostatic pressure is then applied to the entire semiconductor wafer assembly which causes the total volume for the voids/bubbles to be reduced to the point where they are substantially eliminated from the interposer layer. A further step of applying energy, such as heat, is employed to cure the interposer layer thereby ensuring that future voids/bubbles do not occur.

The injecting step may include providing a curable, liquid encapsulant at each edge of the gap between the microelectronic components and the substrate prior to the step of applying pressure, effectively sealing the space between the component and the substrate. When the pressure is then applied, it causes the sealed volume to be reduced thereby allowing the encapsulant to flow into the gap and form a substantially void/bubble free interposer layer.

A still further embodiment of the present invention includes a method of treating an interposer layer for a semiconductor wafer assembly to provide a substantially void/bubble free interposer layer. An interposer layer is first disposed between a semiconductor wafer having a plurality of semiconductor chips and a sheet-like substrate such that any voids within or at the boundaries of the interposer are sealed within the assembly. An isostatic or hydrostatic pressure is then applied to the assembly thereby reducing the volume of the voids/bubbles and substantially eliminating them from the interposer layer.

The foregoing and other objects and advantages of the present invention will be better understood from the following Detailed Description of a Preferred Embodiment, taken together with the attached Figures.

#### BRIEF DESCRIPTION OF THE DRAWINGS

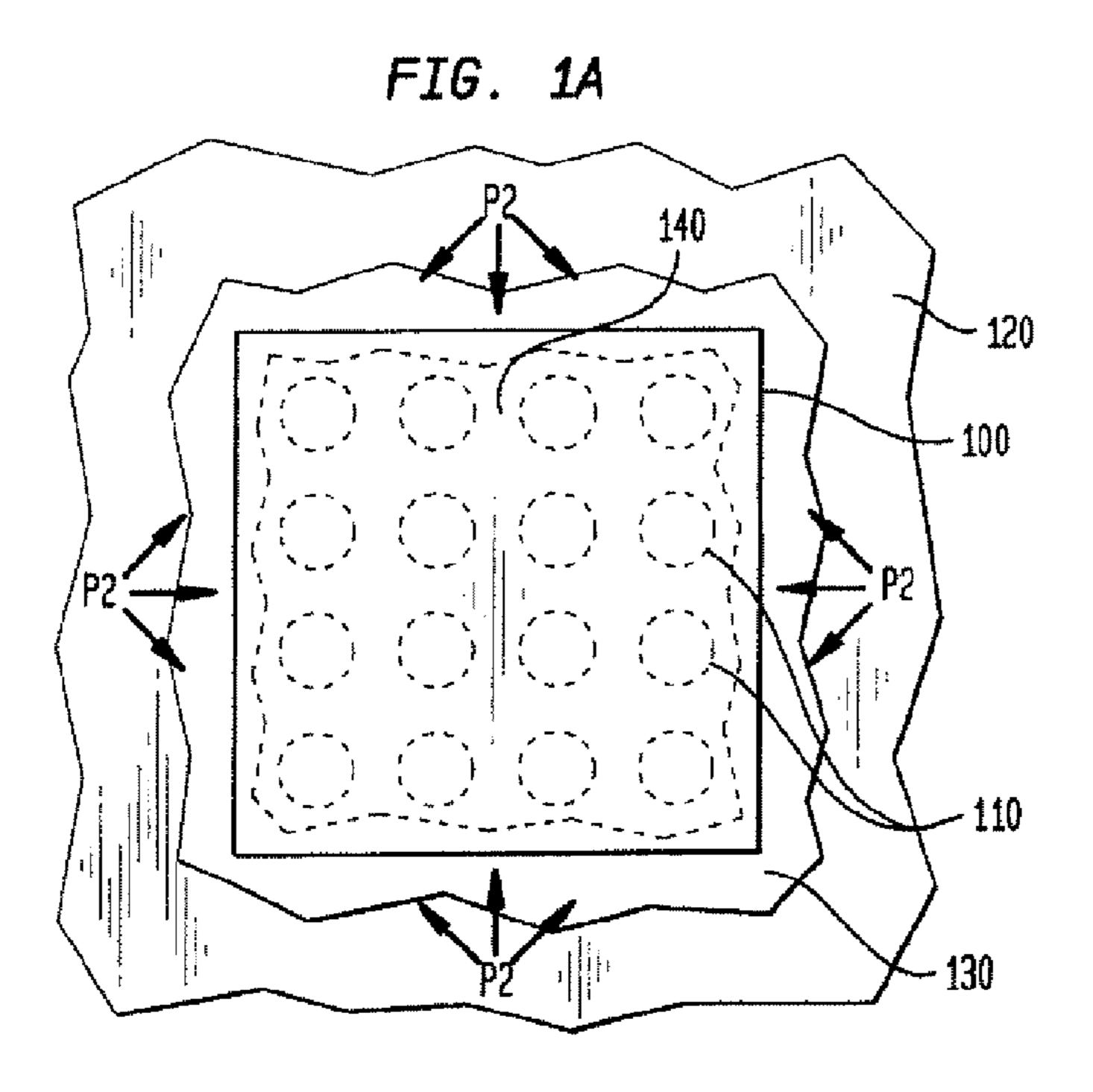

FIG. 1A shows a top plan view of a flip chip device attached to a circuitized substrate having encapsulant sealing the edges therebetween, according to the present invention.

FIG. 1B shows a fragmentary side view of the elements shown in FIG. 1A, according to the present invention.

FIG. 1C shows a bottom plan view of the elements shown in FIG. 1A with the substrate removed from view, according to the present invention.

FIG. 1D shows a bottom plan view of the elements shown in FIG. 1A with the substrate removed from view and after full encapsulation, according to the present invention.

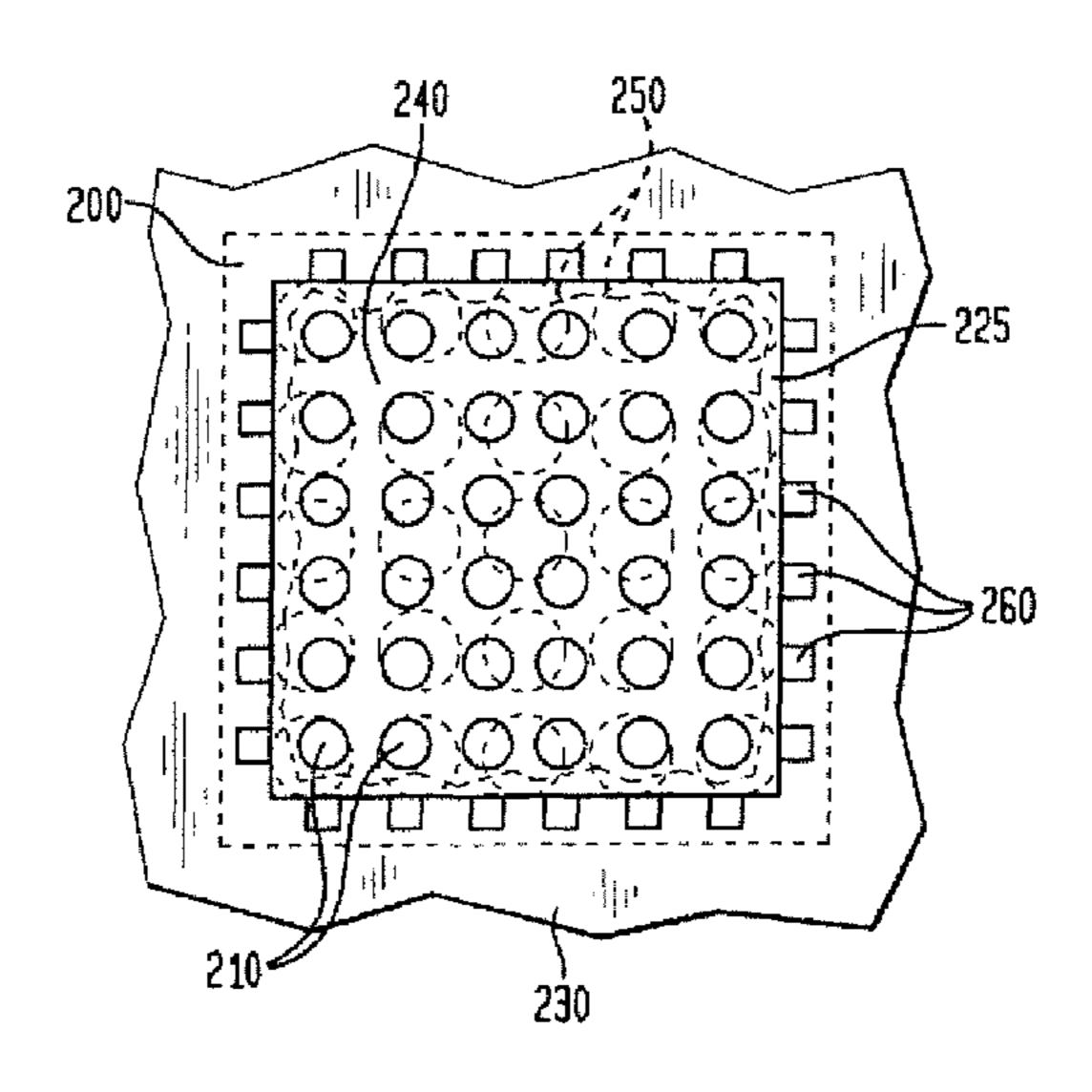

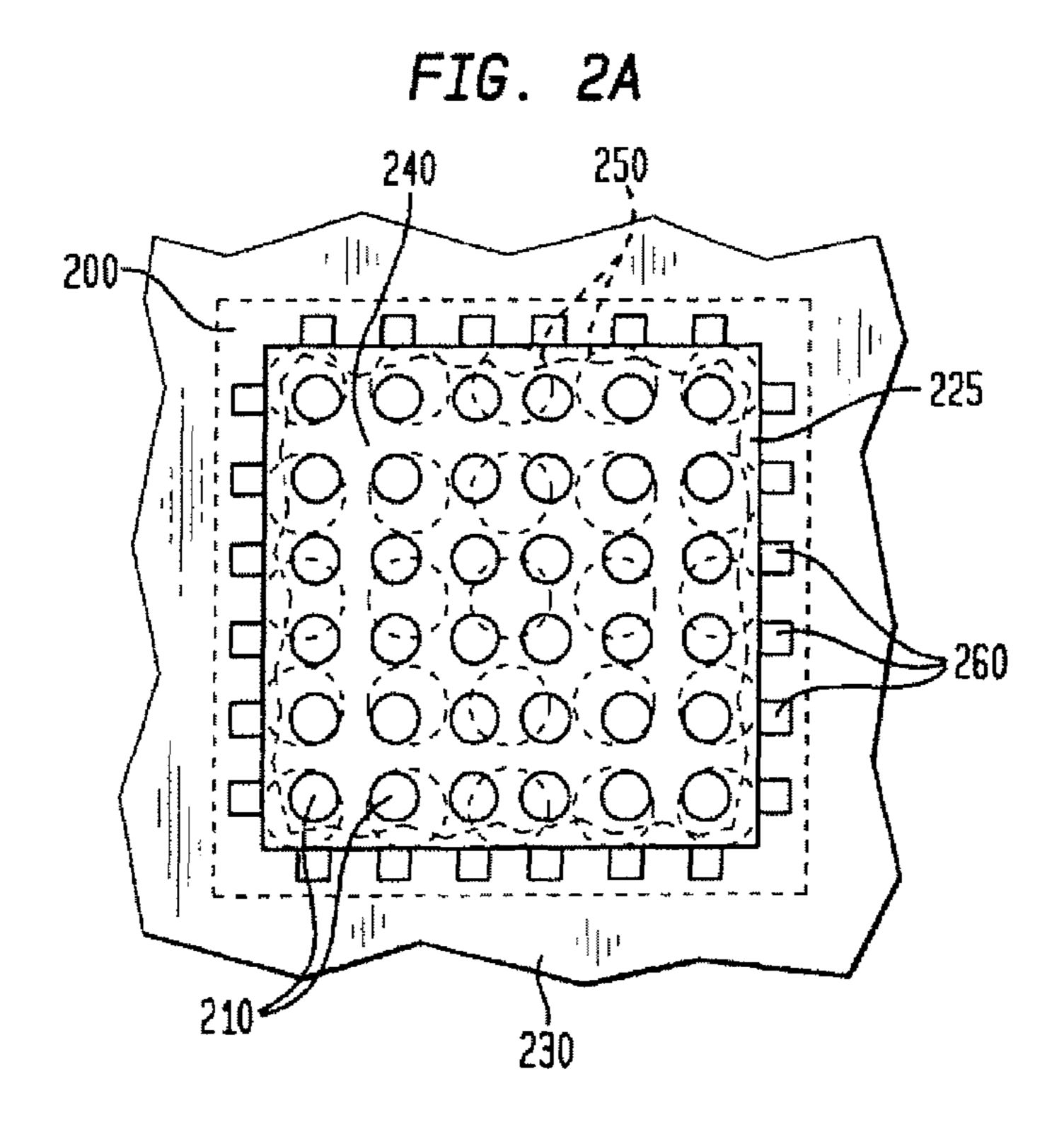

FIG. 2A shows a top plan view of a semiconductor package assembly having an encapsulation sealing the edges of a gap between a sheet-like substrate and a semiconductor chip, according to the present invention.

FIG. 2B shows a fragmentary side view of the elements shown in FIG. 2A, according to the present invention.

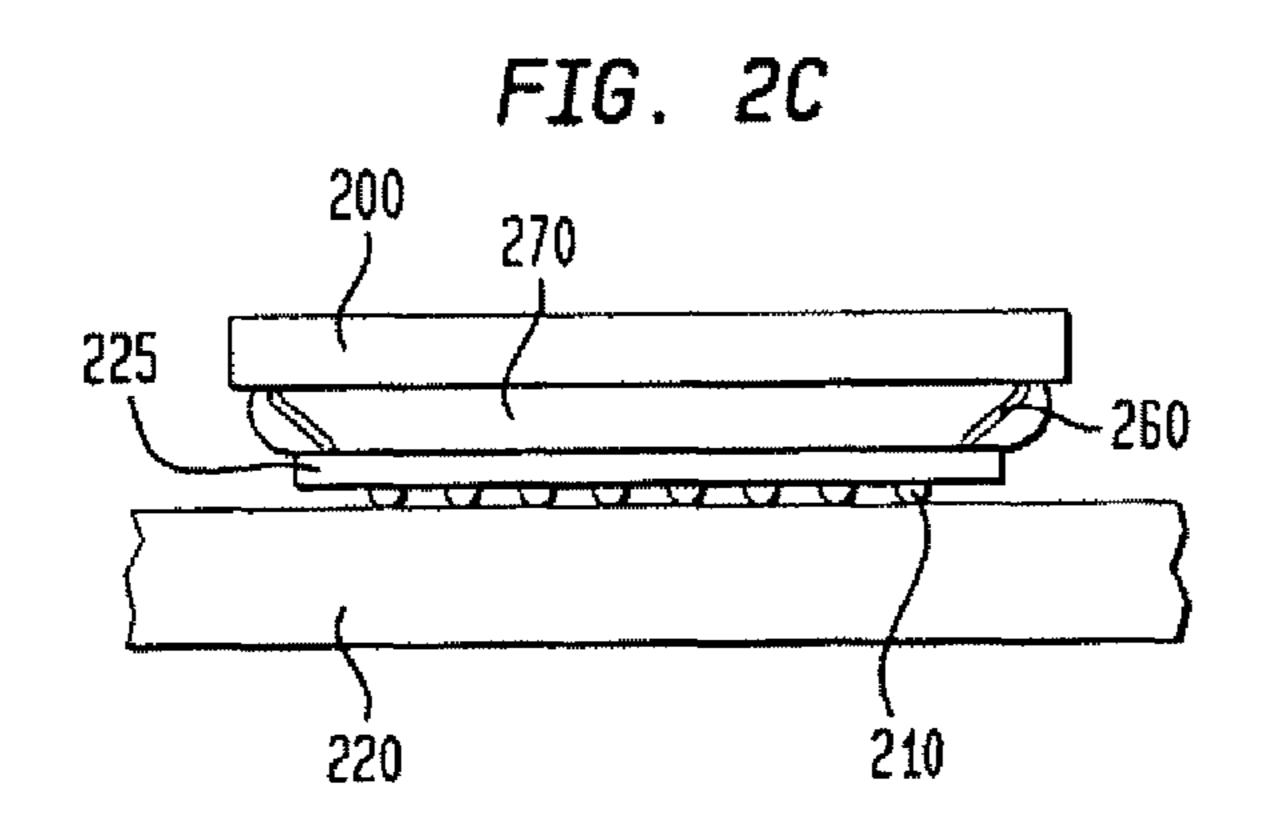

FIG. 2C shows a fragmentary side view of the elements shown in FIG. 2A after full encapsulation, according to the present invention.

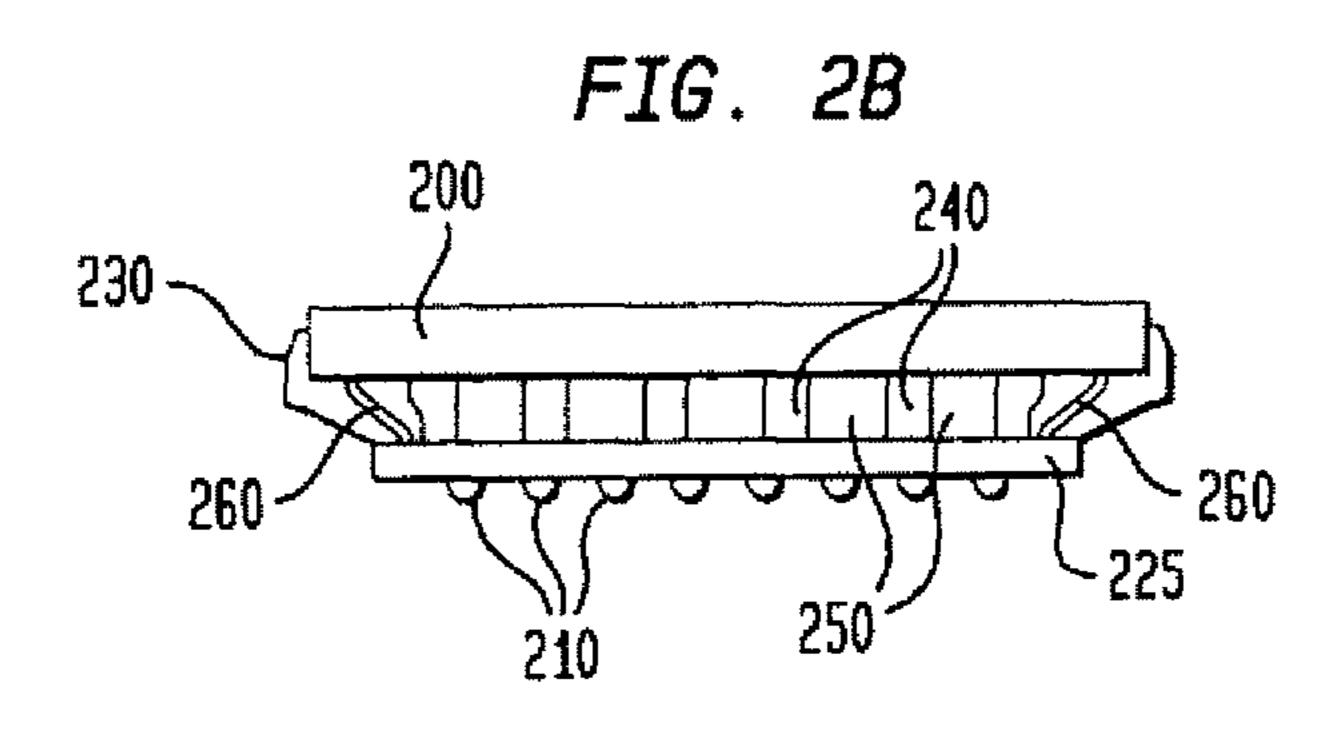

FIG. 2D shows a perspective view of a plurality of chips attached to a substrate which is connected to a frame to support the substrate, according to the present invention.

FIG. **2**E shows a side view of a nozzle for depositing the encapsulant around the edges of the gap between the chips and the substrate in FIG. **2**D so as to seal the voids.

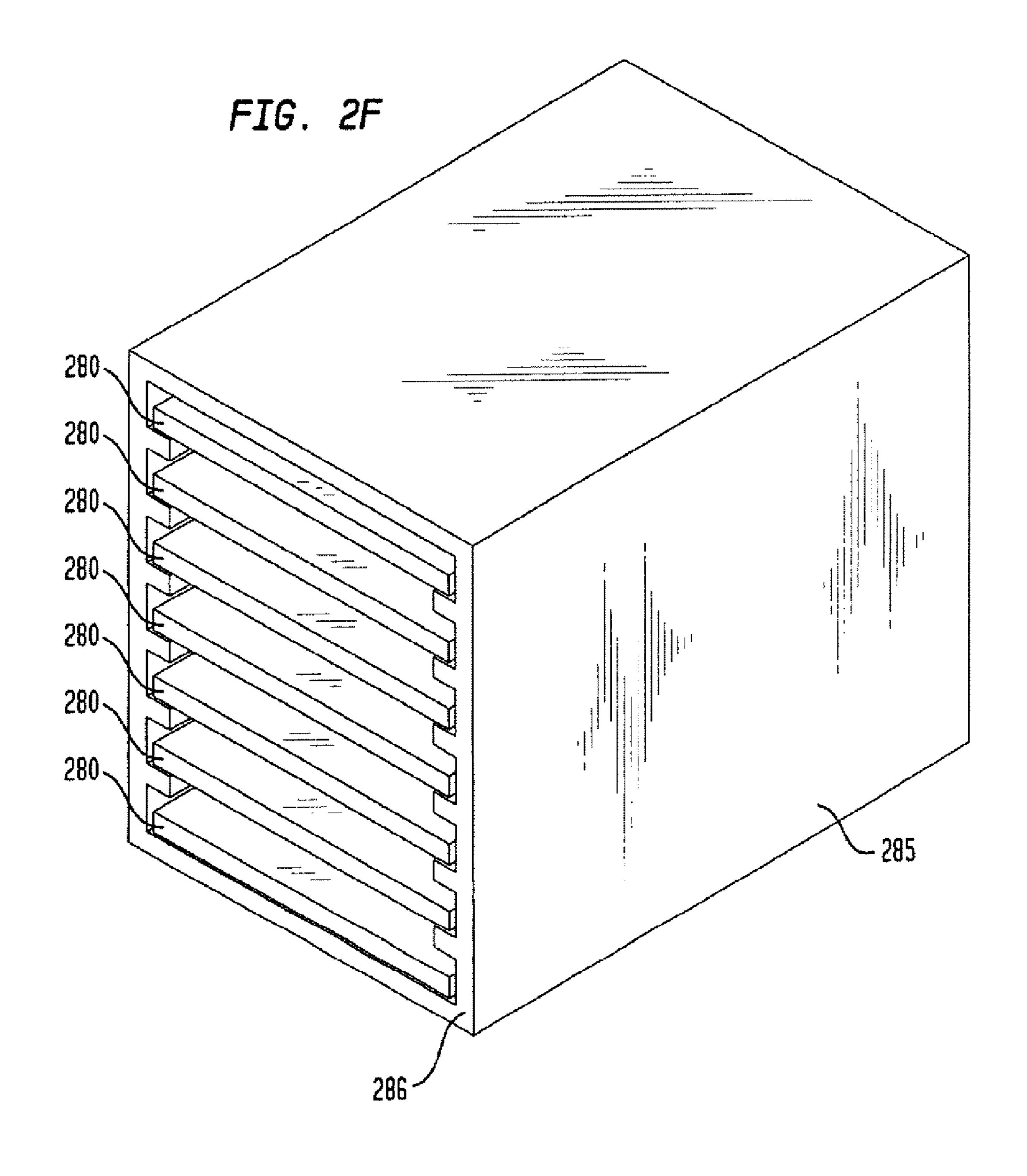

FIG. 2F shows a perspective view of a plurality of the frames shown in FIG. 2D placed within a single carrier.

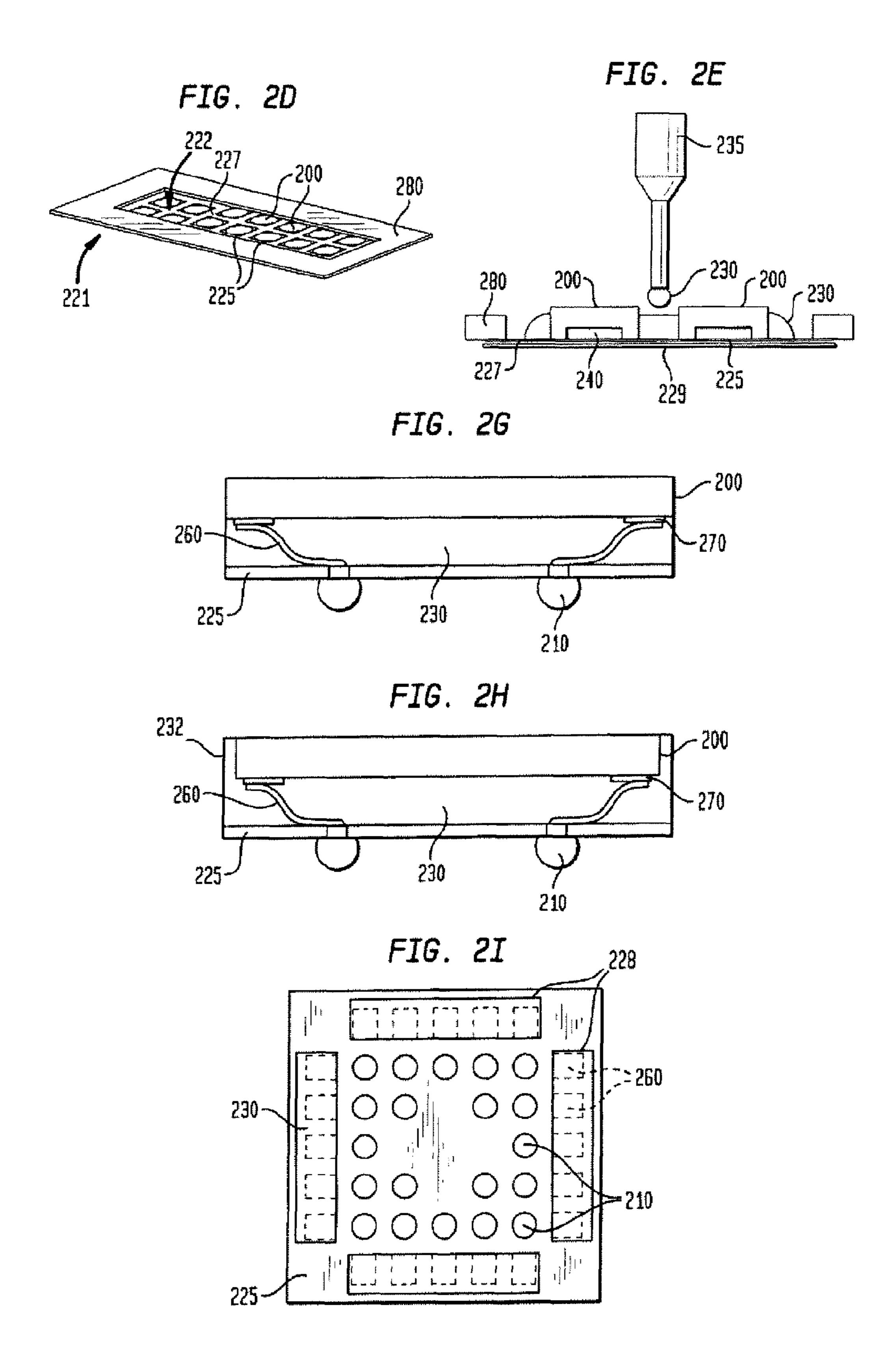

FIGS. 2G and 2H show cross sectional side views of two packaged devices, according to the present invention.

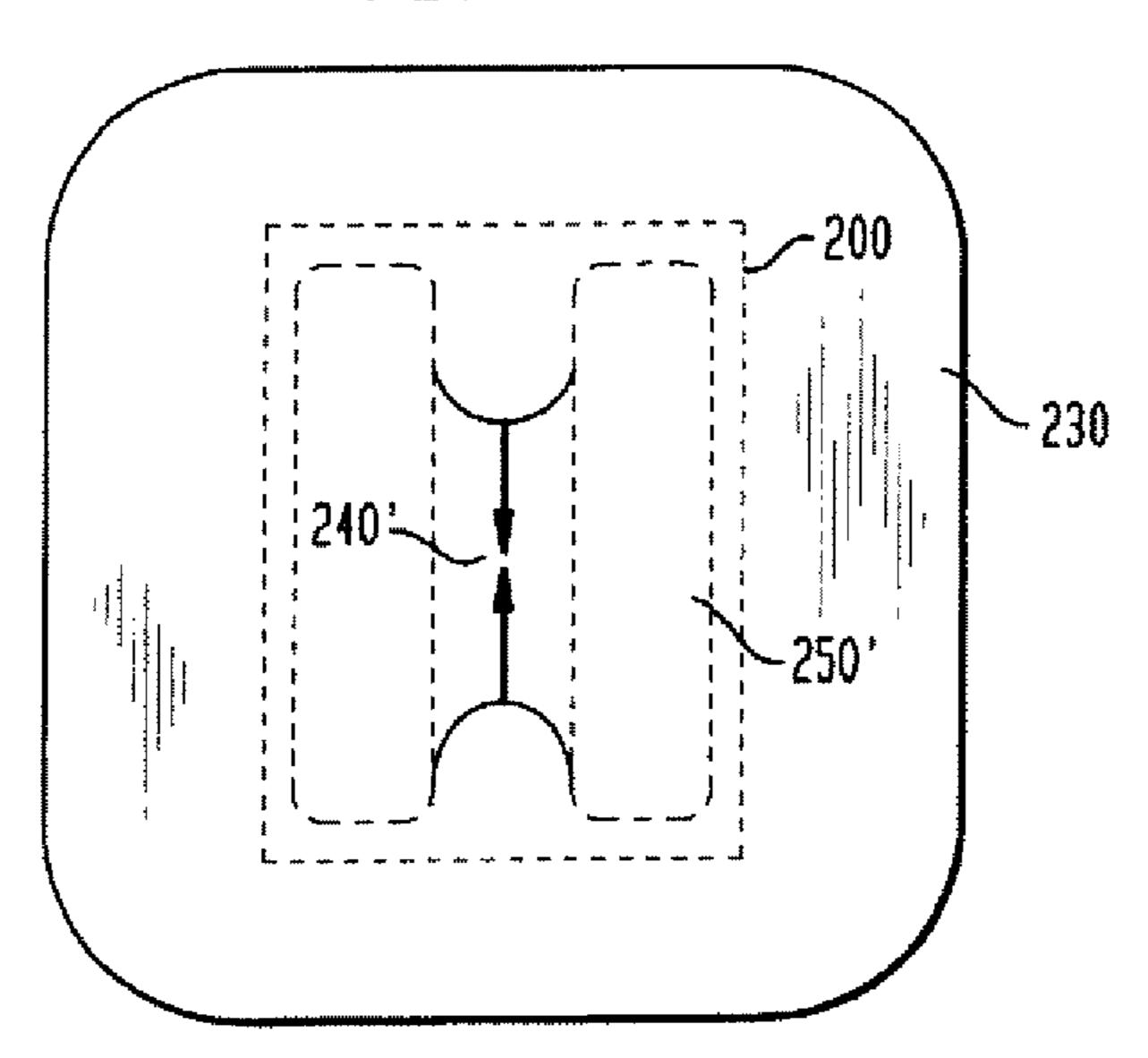

FIG. 2I shows a face view of the chip package described in FIGS. 2G and 2H, according to the present invention.

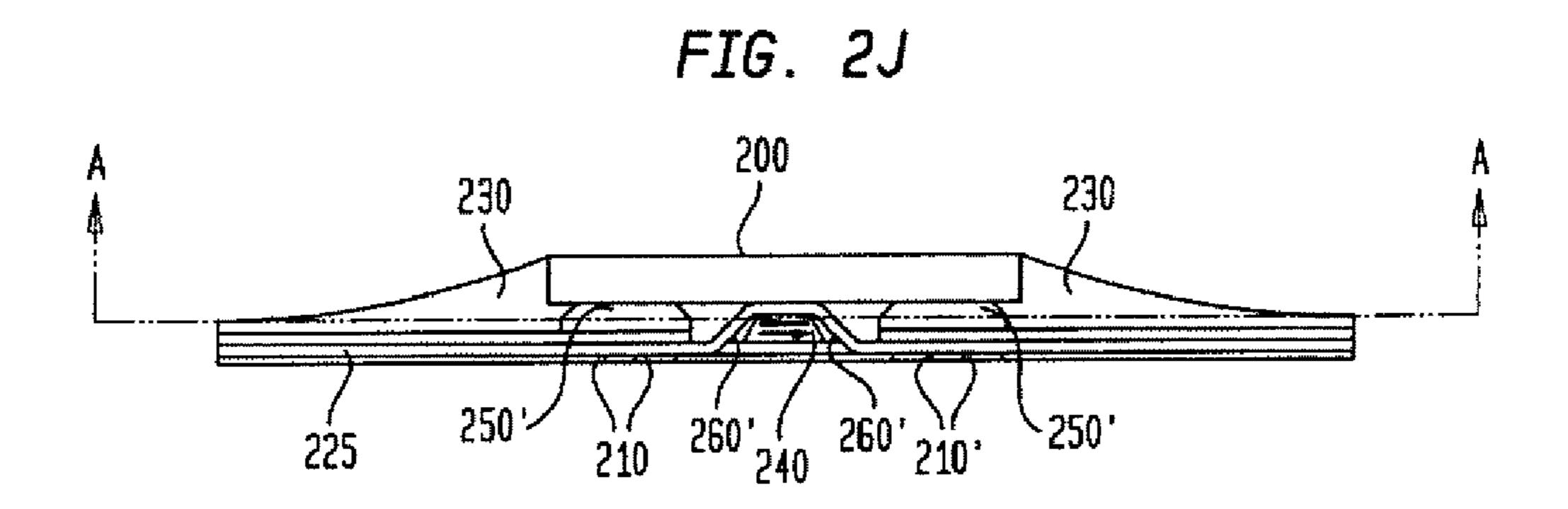

FIG. 2J shows a cross sectional view of a center bonded package as the void is being diffused into the encapsulation 20 material, according to the present invention.

FIG. 2K shows cut-away cross section A from FIG. 2J depicting the collapsing of the void in response to isostatic pressure, according to the present invention.

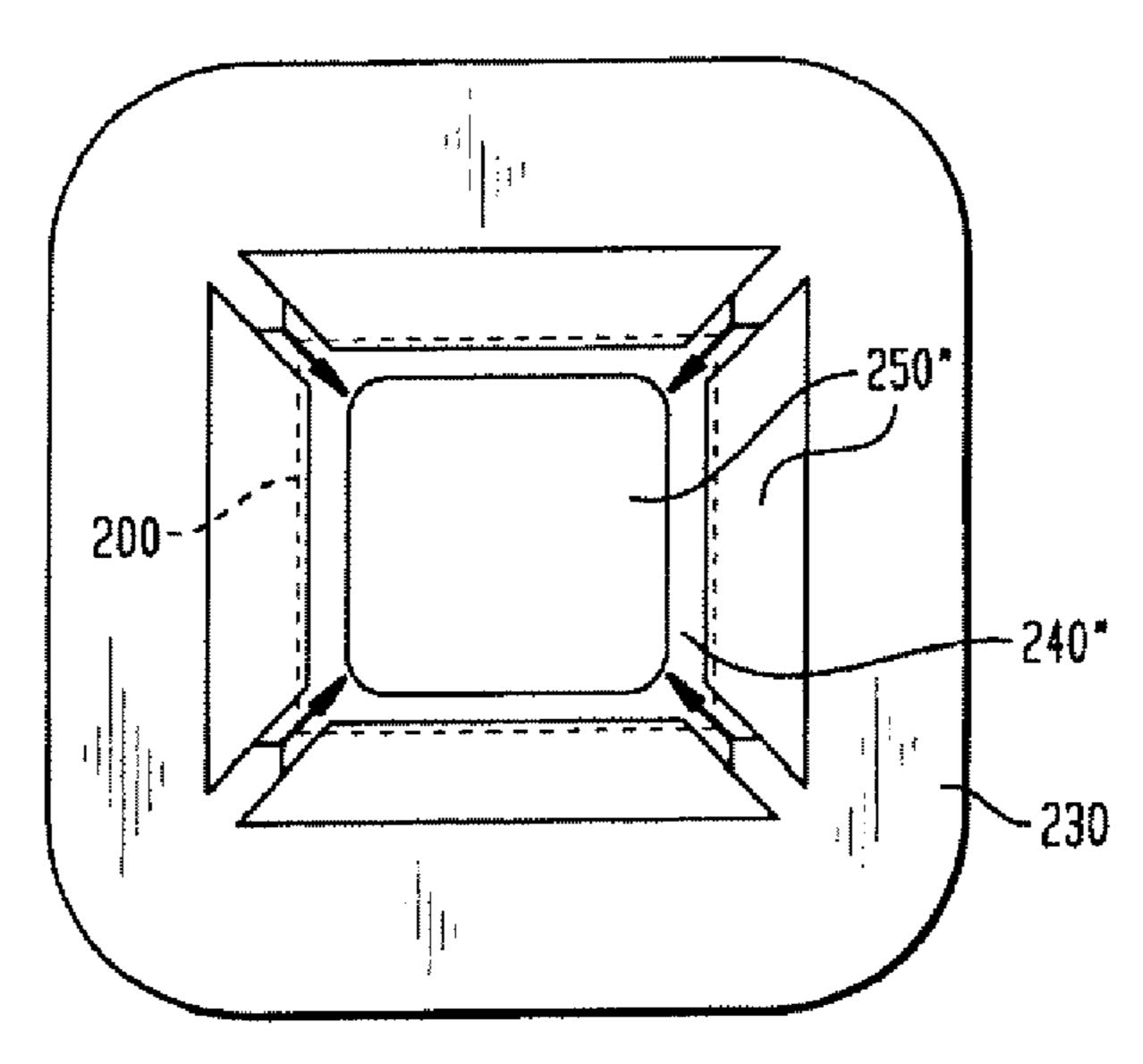

FIG. 2L shows a cut-away cross sectional view of a fan-in/fan-out embodiment, according to the present invention.

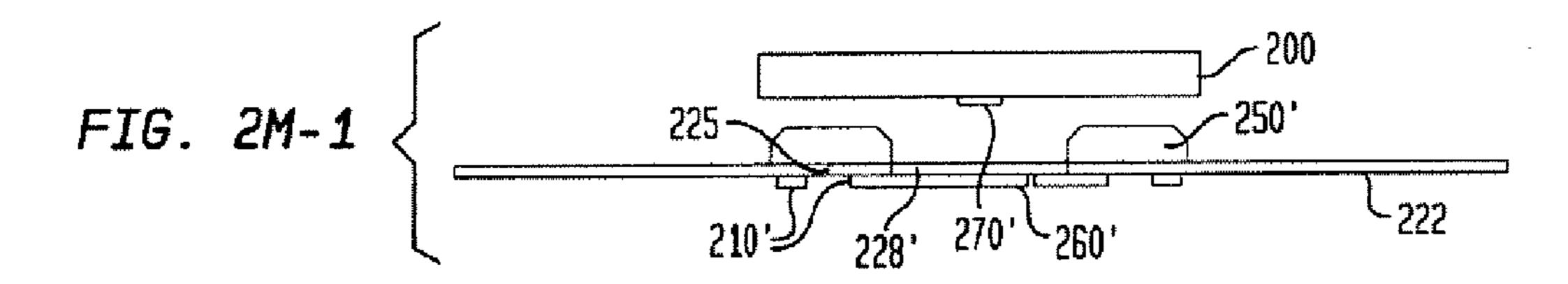

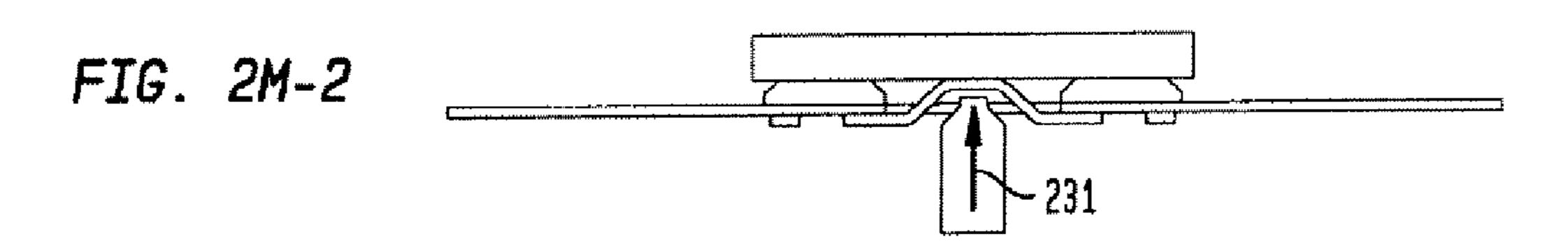

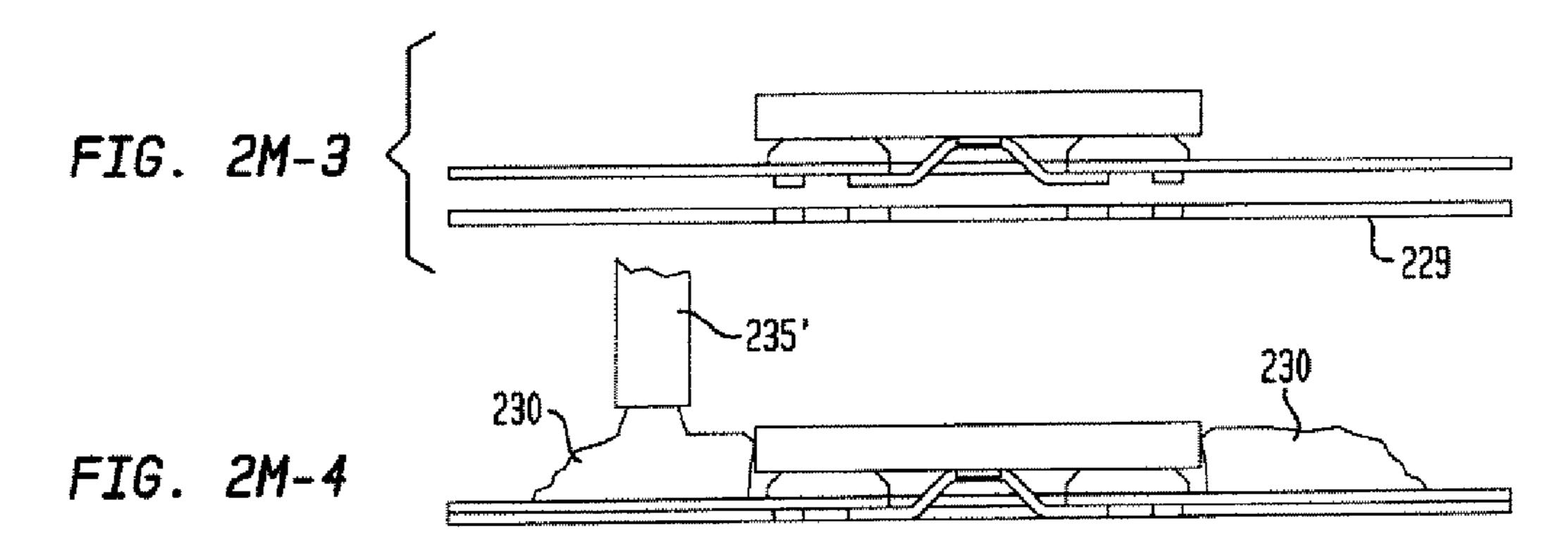

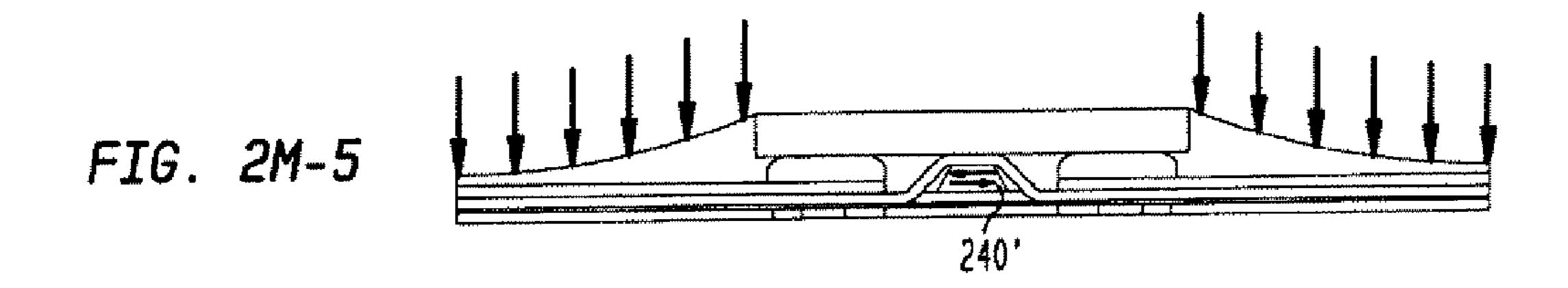

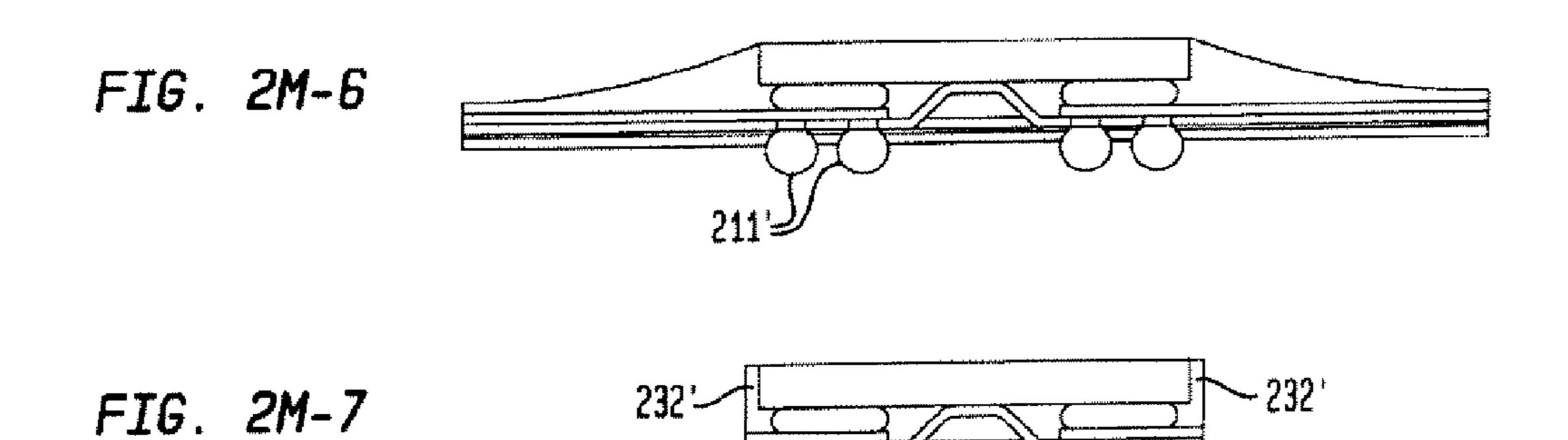

FIGS. 2M-1 through 2M-7 show the process of creating a void free layer by injection using the center bonded package shown in FIG. 2J, according to the present invention.

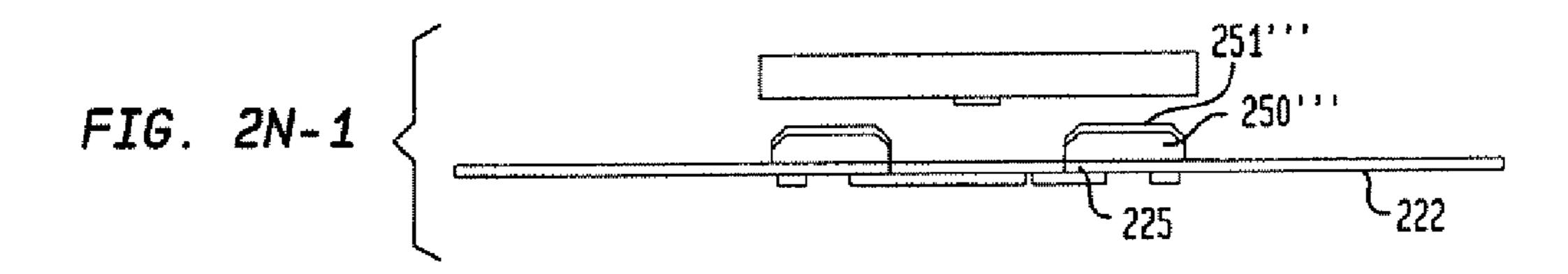

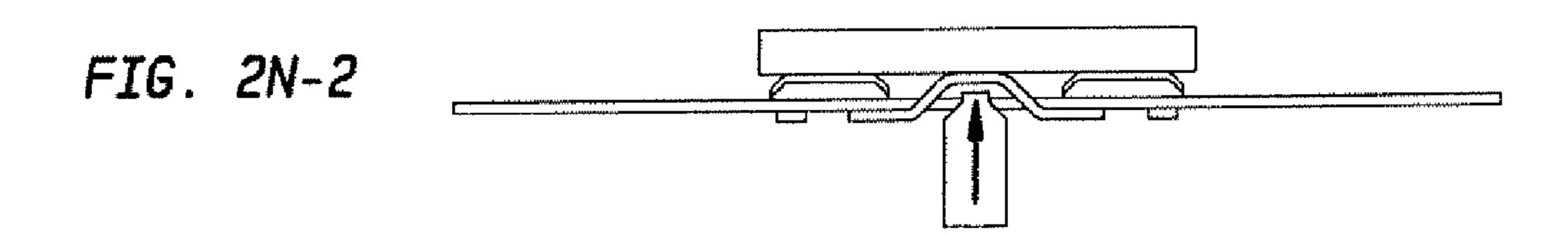

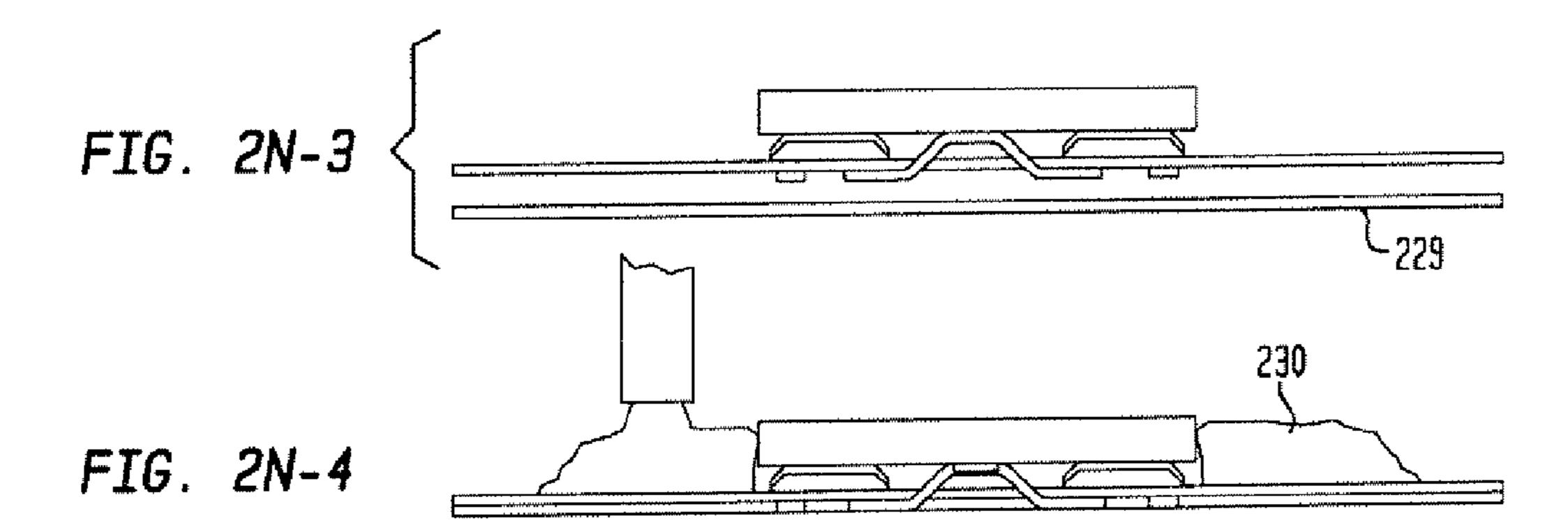

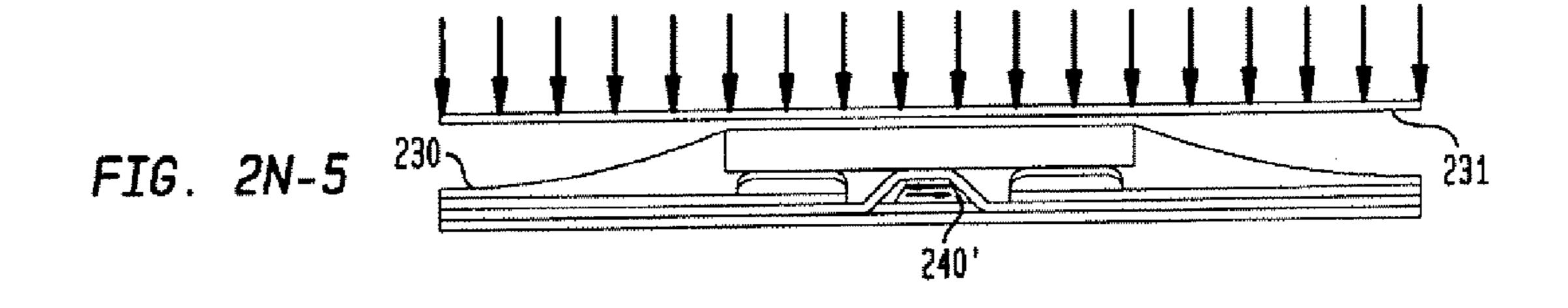

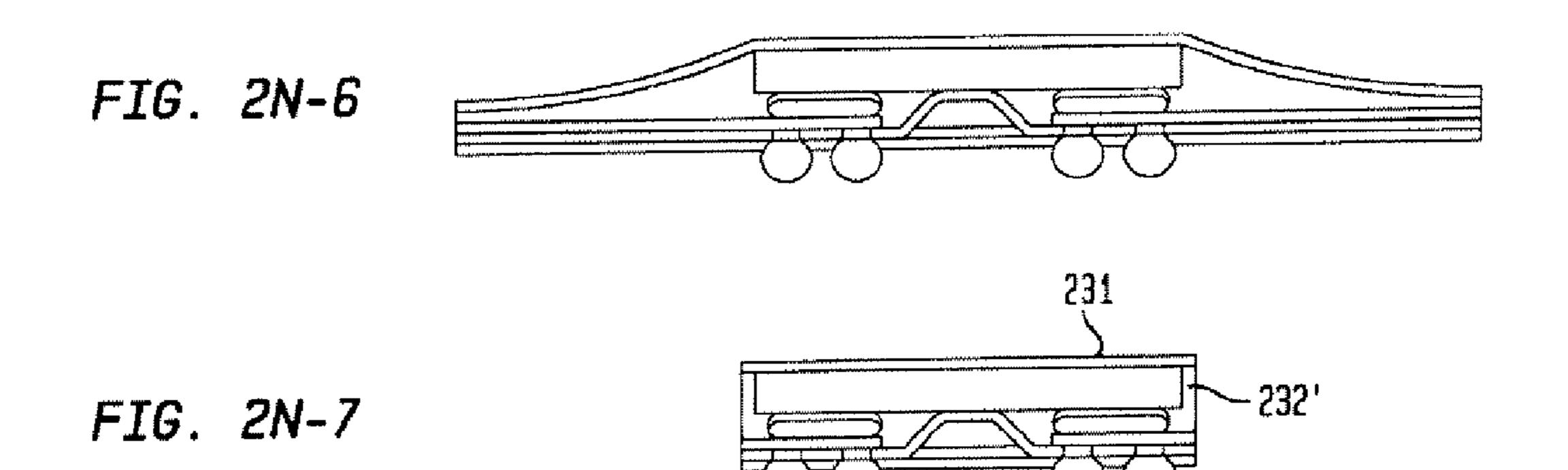

FIGS. 2N-1 through 2N-7 show the process of creating a <sup>30</sup> void free layer by injection using the center bonded package having a peelable compliant layer, according to the present invention.

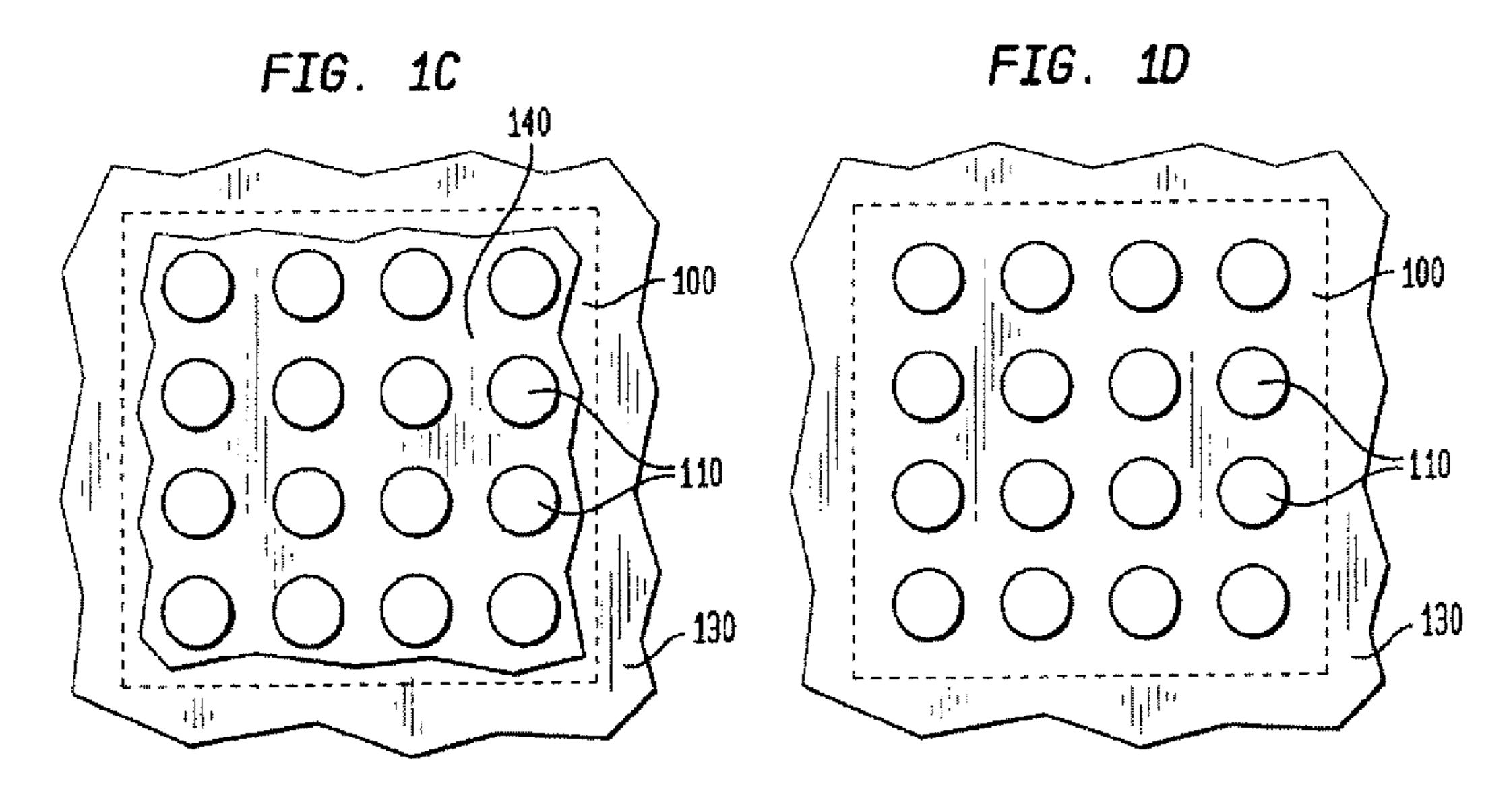

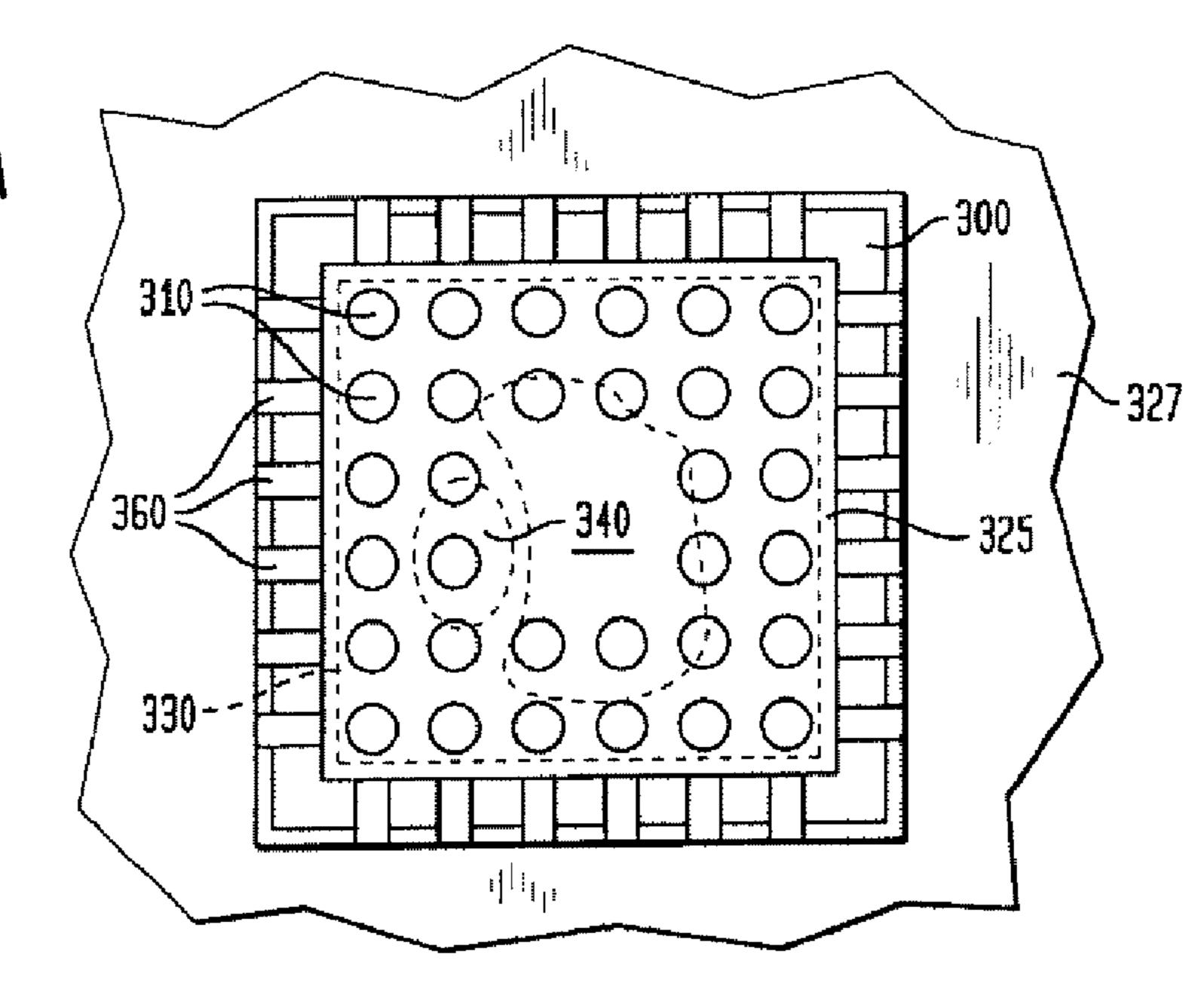

FIG. 3A shows a top plan view of a semiconductor package assembly having an interposer layer disposed between a sheet-like substrate and a semiconductor chip, according to the present invention.

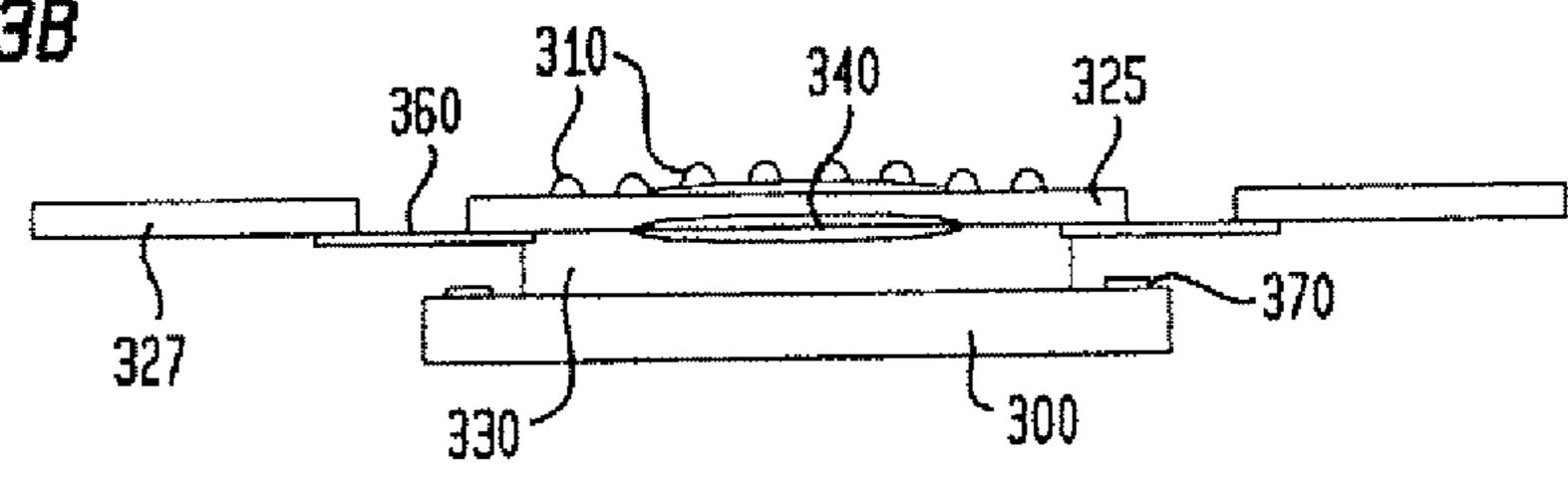

FIGS. 3B and 3C show fragmentary side views of the elements shown in FIG. 3A, according to the present invention.

FIG. 3D shows a fragmentary side view of the elements shown in FIG. 3A after the voids/bubbles have been removed, according to the present invention.

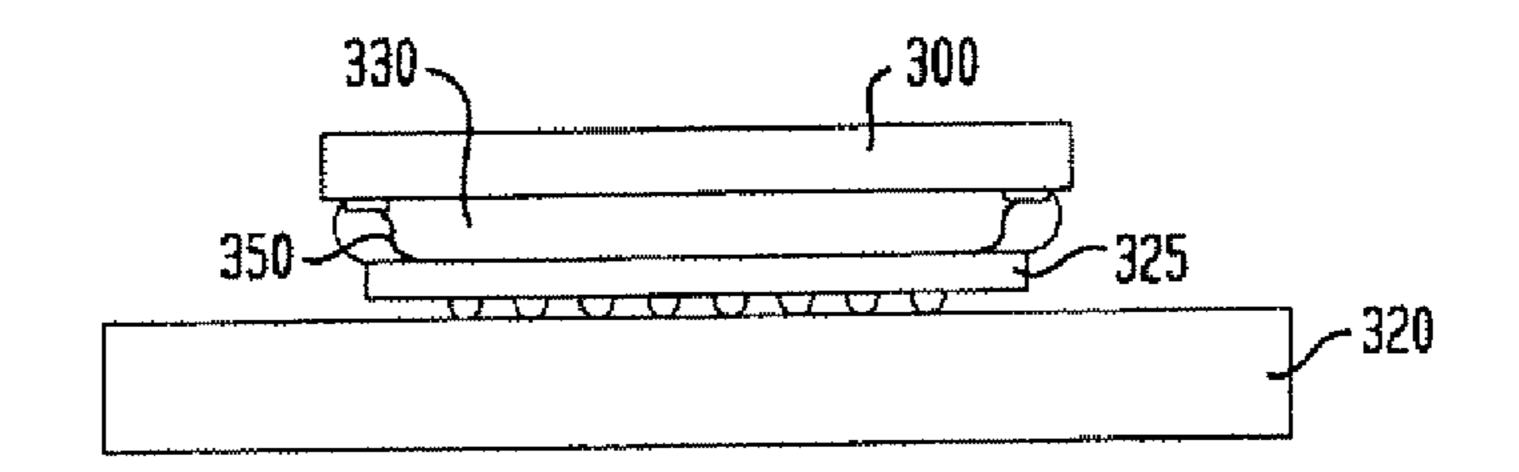

FIG. 3E shows a fragmentary side view of the elements shown in FIG. 3A after the package's leads have been encapsulated and the package is connected to a circuitized substrate, according to the present invention.

FIG. 4A shows a perspective illustration of a semiconductor wafer having a plurality of chips for encapsulation in accordance with one embodiment of the present invention.

FIG. 4B shows a perspective illustration of a semiconductor wafer having a plurality of chips for encapsulation in accordance with another embodiment of the present invention.

# DETAILED DESCRIPTION OF A PREFERRED EMBODIMENT

The present invention is directed toward the pressure injection of encapsulants into cavities and gaps in micro-electronic 60 structures and the simultaneous removal of voids and gas bubbles within encapsulants and adhesive/chip attach layers. As described below, the present inventive methods may be used as a method for underfilling attached flip chip devices, for injecting encapsulant and for removing voids and gas 65 bubbles within encapsulants. As will be appreciated by one skilled in the art, each of the embodiments described below

6

could and preferably would be performed on more than one assembly at a time to facilitate the mass production of finished parts.

I. Flip Chip Underfill Encapsulation

FIGS. 1A-D show a preferred method of providing a substantially gas bubble/void free underfill for a flip chip assembly, according to the present invention. FIG. 1A shows top fragmentary view of a flip chip type assembly including a semiconductor chip 100, a supporting substrate 120 (such as a PWB), a plurality of electrical connections 110 interconnecting corresponding chip contacts (not shown) and bond pads (not shown) on the substrate 120. The solder connections both electrically and mechanically interconnect the chip contacts to the bond pads and, as best shown in FIG. 1B, provide a "stand-off" or gap between the chip 100 and the substrate 120. Although many metals, conductive composites and alloys would be suitable to act as the electrical connections 110, the electrical connections 110 are typically comprised of an alloy of tin and lead, referred to generically in the semiconductor packaging industry as "solder balls". FIG. 1C shows a bottom view of the assembly shown in FIG. 1A with the substrate **120** removed from view.

As shown in FIGS. 1A-B and the side fragmentary view of FIG. 1B, a curable, liquid encapsulant material 130 is deposited at each of the edges of the chip 100 so as to seal the gap between the chip 100 and the substrate 120 creating a sealed void or gas bubble 140 therebetween (depending on whether the surrounding environment has been evacuated prior to the sealing step). For the sake of simplicity, this void/bubble 140 will generically be referred to in this specification and in the claims as a "void". Typically, in flip chip embodiments, the encapsulant is comprised of a curable thermoset resin material. Since it is desired in a flip chip mounted device to have the encapsulant rigid after it is cured, an example of a suitable resin would include an epoxy resin, such as Hysol® epoxy sold by Dexter Corporation of Pittsburg, Pa.

Isostatic pressure is then applied to the outside of the assembly. This step of applying more pressure on the assembly after the void **140** has been sealed will cause a pressure differential between the compressive, ambient gas applied to the outside of the assembly and any first gas trapped within the void 140. The average diameter of the void 140 will thus be reduced allowing the encapsulant to begin encapsulating the outermost solder connections 110 on all four sides of the chip 100. This pressure differential further causes the encapsulant 130 to flow between the chip and the substrate and around the connections. The amount of pressure required to collapse the void 140 depends on the type of encapsulant 130 used and on the desired time period to entirely collapse the void 140. Typically, if more pressure is used, less time is required to collapse the void 140. The amount of pressure applied may also depend on how the pressure is applied, i.e. all at once in a virtual pressure "step" or gradually in progres-55 sively increasing pressure steps. While either pressure application method may be used, using one virtual pressure step increases the rate of collapse of the void 140. By way of example, the applied ambient gas pressure may be approximately between 10 and 1000 pounds per square inch ("psi") and will be applied for between thirty minutes to several hours; although typically no harm will come to the assembly if it is allowed to remain within the pressurized environment beyond this specified time frame. Such pressure may be supplied by an autoclave device such as has been used in the aerospace industry; although the required size of an autoclave for the removal of voids within encapsulation is typically much smaller than required for the aerospace industry. An

example of a possible autoclave device is the Mini-bonder autoclave manufactured by United McGill of Westerville, Ohio.

Eventually, the trapped first gas in the void 140 will begin to reach an equilibrium state with the ambient pressure 5 applied to the outside of the assembly, i.e. the pressure of the first gas (P<sub>1</sub>) will be approximately the same as the ambient pressure (P<sub>2</sub>). At this time, the added pressure due to the surface tension (P<sub>t</sub>) of the void 140 begins to play a more dominant role. As the void 140 gets smaller, the surface 10 tension induced pressure acting on any first gas within the void 140 gets larger. At some point, during a second time period, the sum of the pressures within the void  $140 \, (P_1)$  will become greater than the ambient pressure (P<sub>2</sub>) acting on the outside of the assembly. At or near this point, the first gas 15 within the void 140 will slowly diffuse into the encapsulant 130. Since the gas within the void 140 is under higher pressure, during the second time period, than the ambient gas acting on the outside of the assembly, the rate of diffusion of the first gas into the encapsulant 130 will be greater than the 20 rate of diffusion of the ambient gas into the encapsulant 130 causing the void 140 to get smaller still. As the diameter of the void 140 gets smaller and smaller, the pressure due to the surface tension (P<sub>t</sub>) of the void **140** will progressively grow greater and greater, up until the point where the gas within the 25 void is completely diffused within the encapsulant, as shown in FIG. 1D, and the void implodes.

If the area around the flip chip device has been evacuated prior to the sealing step, there will of course be virtually no first gas within the void 140. This being the case, the combination of the ambient pressure  $(P_2)$  and the surface tension pressure  $(P_t)$  push the encapsulant in to the void 140 while aided by a "pulling effect" created by the vacuum within the void 140 pulling the encapsulation into the void 140. Thus, an evacuation step prior to the sealing step will cause any voids 35 140 to collapse more quickly.

Typically, the next step includes applying energy to cure the encapsulant 130. The object of applying the curing energy is to fully cure (cross-link) the encapsulant 130 so that new voids will not reoccur such as may happen when the ambient 40 gas pressure  $(P_2)$  is released quickly. The type of applied energy will depend on what encapsulant is used and how that particular encapsulant cures. Examples of possible sources of energy include heat, ultra-violet radiation, catalysis and combinations thereof. When an epoxy, such as Hysol®, is used as 45 the encapsulant, heat is typically applied as the curing energy. An appropriate temperature range will again depend on the type of encapsulant 130 used and the length of time desired to fully cure the encapsulant 130. A fully cured, thermoset encapsulant 130 will maintain its structural integrity without 50 allowing new voids to occur. It has also been found that the step of applying energy may occur after the ambient gas pressure  $(P_2)$  is removed from the assembly without the reoccurrence of voids 140 if the ambient gas pressure (P<sub>2</sub>) is released slowly enough so as to allow any dissolved gases within the encapsulant 130 to come to equilibrium with the surrounding ambient gas.

In a variation of this process, a first gas within the void 140 and an ambient gas may be comprised of different gases to facilitate the diffusion of the first gas into and through the 60 encapsulant 130 at a greater rate than the rate of diffusion of the ambient gas into the encapsulant. After the step of sealing the gap between the chip 100 and the substrate 120, the first gas surrounding the assembly may be evacuated and another ambient gas may take its place. In such an embodiment, the 65 first gas contained within the void 140 may have smaller molecules than the ambient gas accelerating first gas' diffu-

8

sion into the encapsulant 130. Choosing the correct sealed first gas will necessarily entail choosing the correct ambient gas and vice-versa. Examples of sealed first gases include helium, hydrogen, H<sub>2</sub>O vapor, etc. Examples of ambient gases when compared with the first gases listed above include argon, air, nitrogen, carbon dioxide and Krypton.

In a further variant of this process, hydrostatic pressure could be used instead of the isostatic pressure discussed above to compress the voids/bubbles. Typically in such a process, inert fluids would be used to compress the voids/bubbles.

#### II. Injection of an Encapsulant

As shown in FIGS. 2A-C, the methods described above in connection with encapsulating flip chip device may also be used to inject a fluid encapsulant between a first intermediate substrate 225 and a chip 200 as well. One such embodiment where injection of encapsulation is described is in U.S. patent application Ser. No. 08/365,699 filed Dec, 12, 1994, which is hereby incorporated by reference. In brief, as shown in part in FIGS. 2A-C, the '699 application describes a method and structure for disposing a plurality of compliant pads 250 which provide a stand-off or gap between a first sheet-like support structure 225, and a contact bearing face surface of a semiconductor chip 200. The first substrate 225 may be rigid, semi-rigid or flexible. For added CTE compensation, preferably the first substrate 225 is a substantially inextensible dielectric film, such as polyimide having a thickness of between 0.5 mils and 3 mils.

As described above, the adjacent compliant pads 250 provide the structure for the gap between the chip 200 and the first substrate 225 and provide and define channels therebetween for the encapsulant 230 to eventually flow; however other alternatives could be used instead, such as cellular foam, loosely woven non-conductive strands, etc. It is only important that a gap be provided between the chip 200 and the first substrate 225 while holding the two items in a substantially coplanar relationship. The compliant pad embodiment will be described in this example. As described in the '669 application, the compliant pads 250 are typically deposited, as by stenciling, and cured so that the chip 200 and the first substrate 225 are attached to each other in a substantially coplanar relationship. A curable liquid encapsulant 230 may then be deposited completely around the perimeter of the gap between the chip 200 and the first substrate 225 so as to seal the pads 250 and create a sealed void (void/gas bubble) 240 out of the network of the channels therewithin, very much like the sealed assembly described in the flip chip embodiment above. Typically, a curable, compliant thermoset resin is used as an encapsulant, such as silicone and flexiblized epoxy. Alternately, thermoplastic materials may be used if they are specially formulated to undergo a phase change such that they go liquid under certain conditions and not under others, such as at a temperature which would be typically higher than the normal operating temperature of the resulting device.

An isostatic pressure is then applied to the assembly causing the encapsulant to flow between the chip 200 and the first substrate 225 and into the channels within the void 240. Again, the ambient gas pressure applied will depend on the encapsulant material selected and the amount of time desired for the process of removing the void 240; and further on whether the pressure is applied in a virtual step or is applied gradually. The typical applied ambient gas pressure here will be approximately between 10 and 450 pounds per square inch ("psi"), and preferably between about 30 and 200 psi, for a time period of between about thirty minutes and several hours (the time period also depends on the volume to be encapsu-

lated). A virtual step of ambient gas pressure is preferred in order to increase the rapidity of the void removal.

As described above, the step of applying pressure on the assembly after the void 240 has been sealed will cause a pressure differential between the compressive, ambient gas applied to the outside of the assembly and any first gas trapped within the void 240. The average diameter of the void 240 will thus be reduced allowing the encapsulant to begin encapsulating the outermost compliant pads 250 on all four sides of the chip 200.

The pressure from the ambient gas combined with the pressure from the surface tension of the void 240 itself will cause the void to grow smaller. If there is a first gas trapped the pressure due to the ambient gas pressure, the first gas will begin to diffuse into the encapsulant 230. Since any first gas within the void 240 is under higher pressure, during the second time period, than the ambient gas acting on the outside of the assembly, the rate of diffusion of the first gas into the 20 encapsulant will be greater than the rate of diffusion of the ambient gas into the encapsulant. As the diameter of the void **240** gets smaller and smaller, the pressure due to the surface tension of the void **240** will progressively grow greater and greater, up until the point where the void **240** is completely 25 removed from the encapsulant, as shown in FIG. 2C.

As described in the last section, energy is typically applied to cure the encapsulant 230. The type of energy applied depends on the encapsulant 230 selected and under what conditions the selected encapsulant 230 cures. If a silicone is used as the encapsulant, the energy applied is typically heat. The amount of heat and the length of time the heat is applied is again dependent upon the selected encapsulant material and the volume of material that needs to be cured. As described above, the application of energy will typically 35 occur prior to the termination of the step of applying pressure so that no new voids are allowed to develop in the encapsulant by the reduction of the ambient pressure. A fully cured, thermoset encapsulant 130 will maintain its structural integrity so that gas bubbles and voids do not reenter the encapsulant. The 40 above mentioned variations and embodiments listed in the Flip Chip Underfill Encapsulation section, above, would also facilitate this injection process.

Thus, in the configuration shown in FIG. 2C, the internal high stress zones in the chip package assembly are reduced by 45 the substantial removal of the voids and bubbles in the cured compliant layer 270. This method of injection also works where the encapsulant is injected between a first substrate and a second substrate, such as in a fan-out chip package embodiment where at least some of the terminals 210 are disposed 50 above a second support structure such as a thermal spreader or ring, as described more fully in the '669 application.

As described above and shown in FIGS. 2D-2G, the above injection methods are preferably performed on more than one assembly at a time to facilitate the mass production of finished 55 parts. FIG. 2D shows a perspective view of a plurality of chips 200 attached to a substrate 222, which includes the first substrate 225 and a sacrificial outer portion 227. An outer portion of the substrate 222 is also attached to a rigid or semi-rigid frame 280 to support the typically flexible substrate 222 such 60 that it is stretched taut across the frame and further to better ensure the dimensional stability of the substrate. Since the combined thickness of the chips 200 and the substrate 222 is fairly thin, the thickness of the frame 280 is also typically thin so that a plurality of such assembled frames 221 may be 65 placed in the same pressure/temperature vessel after the encapsulant has been deposited, as described above.

**10**

FIG. 2E shows a nozzle 235 for depositing the encapsulant 230 around the edges of the gap between the chips 200 and the first substrate 225 so as to seal the voids 240. A CAM/ALOT programmable dispensing machine manufactured by Camelot Systems, Inc. in Haverhill, Mass. could be used to perform such a task. In this configuration, the encapsulant 230 is deposited from the chip side of the frame assembly 221. A layer of sheet-like material 229, such as a coverlay or solder mask material, is attached to the terminal 210 side of the substrate 222 so that the encapsulant is bounded and does not escape through the bonding apertures 228 (FIG. 21) such that it could contaminate the terminals and thus impede any subsequent electrical connection of the terminals to the bond pads on the circuitized substrate 220. The frame 280 also acts within the void, as the first gas pressure becomes greater than 15 as a barrier to provide a side boundary for the deposited encapsulant should the need arise. However, preferably, the encapsulant 230 has a thick enough consistency such that it substantially maintains its shape through the surface tension of the material. Most preferably, the encapsulant 230 is deposited such that it does not flow onto the back surface (non-contact bearing surface) of the chip 200. This allows the back surface of the chip to subsequently be connected to a heat sink or thermal spreader without an insulative material impeding the dissipation of heat from the chip 200 during thermal cycling.

After the gap has been sealed, the frame assembly 222 is placed within a pressure chamber, such as the aforementioned autoclave chamber, and an isostatic pressure is applied to collapse the voids and/or gas bubbles 240 thereby causing the encapsulant to engulf the supports 250 and provide a substantially void free interposer layer, as described above. Preferably, a plurality of frames 280 are placed within a frame assembly carrier 285 so that the frames 280 may be more easily stacked together and placed within the pressure chamber. In the embodiment shown in FIG. 2F, the frames are placed within the carrier 285 such that the opposite edges of the frames rest upon small shelves or projections 286 extending from the side walls of the carrier **285**. In another example, the frames 280 may simply be optimized such that a plurality of such frames 280 may be stacked one on top of the other such that the individual frames do not come into contact with the substrate 222 or chips 200 on an adjacent frame 280. Energy is then applied to cure the encapsulant, as described above.

The fully encapsulated semiconductor chip packages within the frame assemblies 221 are next separated (or "diced") from their respective frame/substrate into single packaged chips, such as that shown in FIG. 2G, or the packaged chip may be diced into multi-chip modules. The dicing operation is typically performed by laser cutting, stamping or sawing (such as with a water saw). The component in FIG. 2G has some benefits when compared with the embodiment depicted in FIG. 2C. First, the first substrate 225 is extended to be the same size as the contact 270 bearing surface of the chip 200. This allows the cured encapsulant layer 230 (interposer layer) to have a substantially uniform thickness at every point between the chip 200 and the first substrate 225, even at the periphery of the package. This provides added support for the leads 260 during thermal cycling of the component us well as added physical and environmental protection for the metallurgy of the connection between the leads 260 and the contacts 270.

FIG. 2H shows a side view of an alternate embodiment which is similar to the embodiment shown in FIG. 2G. However, in FIG. 2H, the first substrate 225 is juxtaposed with the contact 270 bearing surface of the chip, but is larger than the surface of the chip 200 such that it uniformly extends beyond

the perimeter of the chip 200. The interposer layer 230 correspondingly extends beyond the chip perimeter to form a bumper of encapsulant material 232. This structure may be created by dicing the packaged chips a short distance beyond the periphery of the chip 200 itself. The bumper 232 further protects the chip and the metallurgy of the connection of the leads 260 to the contacts 270.

FIG. 2I shows a face surface view of the chip package described in FIGS. 2G and 2H. The bonding windows 228 allow the leads 260 to be detached from the sacrificial sub- 10 strate 227 and be bonded to respective chip contacts 270.

FIG. 2J shows a cross section view of a center bonded package as the void **240** is being diffused into the encapsulation material 230. The package in this FIG. is similar to the package shown in FIGS. 2A and 2B except that in FIG. 2J the 15 die 200 is rectangular and the plurality of compliant pads 250 have been replaced by two compliant pads 250' which create a single center channel 240' therebetween instead of rows and columns of channels 240. Also, the leads 260' in FIG. 2J are chip contacts which are located in a central portion of the 20 contact bearing surface of the chip such that the leads 260' extend from either side of channel 240' and are bonded to the contacts in somewhat of an interleaving pattern, instead of being bonded to contacts which are peripherally positioned on the chip. The encapsulant **230** is again deposited at the 25 edges of the gap created by the compliant pads 250' sealing void within channel 240'. FIG. 2K shows cross section A from FIG. 2J depicting the collapsing of the void 240' in response to isostatic pressure and any first gas contained within the void being diffused into the encapsulant, as described in the 30 above embodiments. FIG. 2L shows the same type of void 240" collapse described above except that the compliant pads 250" define a differently shaped void 240". In this Figure, the compliant pads 250" are located in the central portion of the chip 200 and beyond the periphery of the chip 200 (typically 35) there is a support structure surrounding the chip to support the peripheral pads). This arrangement allows for a so-called "fan-out" or "fan-in/fan-out" semiconductor package embodiment in which the terminals 210 on the substrate 225 may be located above the chip surface or beyond the chip's 40 periphery or both, as described above.

FIGS. 2M-1 through 2M-7 graphically show the above described method (discussed in relation to FIGS. 2D through 21) with respect to the center bonded embodiment of FIG. 2J. In this embodiment, the chip 200 is attached to the compliant 45 pads 250' attached to the tape 225. The tape has a bonding window so that the leads 260' may extend and typically be detachably held in place thereacross. As shown in FIG. 2M-2, the leads are detached from the substrate 225, guided and bonded to respective chip contacts 270' using a bonding tool 231 which typically bonds the leads to the contacts using ultrasonic or thermosonic or thermocompression means or some combination thereof, as shown. FIG. 2M-3 shows a protective sheet-like layer 229, such as a coverlay or solder mask layer, attached to the terminal 210 side of the substrate 55 222 so that the encapsulant may be bounded and will not escape through the bonding apertures 228' so that it does not contaminate the terminals and impede any subsequent electrical connection of the terminals 210 to the bond pads on the circuitized substrate.

FIG. 2M-4 shows a nozzle 235 depositing encapsulation material 230 around the chip 200 on the chip/compliant pad bearing surface of the substrate 222 so as to seal the gap/void 240' between the chip 200 and the substrate 225, as described in more detail above. It is evident from this that the protective 65 layer 229 is performing the function of sealing any apertures in the substrate 225, such as the bonding aperture 228'. FIG.

12

2M-5 shows the application of isostatic force and the resulting collapse of the void 240'. At this point, any gas which may be within the void **240**' diffuses into the encapsulation material 230 at a rate which is faster than the rate of gas diffusion from outside the sealed area causing the voids 240' to reduce in size and further causing the eventual removal of the voids 240', as shown in FIG. 2M-6. FIG. 2M-6 further shows the application of solder-balls **211** to the terminal sites **210**. FIG. 2M-7 shows a finished semiconductor package after it has been cut away (or "diced") from the frame assembly, shown in FIG. 2D, by laser cutting, stamping or sawing (such as with a water saw). In this particular embodiment, the package is diced such that a bumper 232 of encapsulation material is left along the side edges of the chip 200, similar to the embodiment shown in FIG. 2H. In a variation, the package may be diced such that there is no bumper 232. In a further variation, a final step may be added in which a thermoset or thermoplastic resin sheet-like layer is vacuum laminated onto the back of the chip 200 and around each of the sides of the package to add further protection and durability to the package.

FIGS. 2N-1 through 2N-7 show a further variation on the processes and structures shown in FIGS. 2M-1 through 2M-7 in which a reworkable package structure is disclosed. In FIG. 2N-1, a compliant layer 250" is attached to the substrate 225 by means of a peelable tacky surface 251". This peelable compliant layer must be compliant enough to accommodate the CTE mismatch problems in thermal cycling of the finished device, yet have the ability to be removed (or peeled off) from the substrate 225 or allow the chip 200 to be removed after attachment without substantial residue on the substrate or chip. Examples of possible materials for the peelable compliant layer 230 include structures which have inherent releasable adhesive properties, such as pressure sensitive adhesives, and structures which may be "impregnated" so that they have such releasable adhesive properties, such as cured silicone pads impregnated with pressure sensitive adhesives or fully cured pads of tacky silicone gel, or fully cured compliant pad structures which have releasable adhesive on the major opposing surfaces.

As shown in FIG. 2N-2 and described above, the chip 200 is then attached to the tacky surface 251" and the leads are bonded. If there is a problem or defect with the package up to this point, the chip 200 may be removed and reused hereby providing a cost saving to chip manufacturers. Further, if the problem is with the pad 230 and the lead bonding function has not occurred, the pad may be removed from the substrate 225 and a new pad 250" may be used in its place.

Such a releasable package structure would encounter durability problems in use of the finished package due to the possibility of the pads 250"'/251"' peeling away from either the substrate 225 or the chip 200 or both unless, at some point before the package is shipped to a customer, the peelable nature of the pad is neutralized. FIG. 2N-4 shows the encapsulant 230 being deposited on the substrate 222 at the periphery of the chip 200 so as to seal the area between the chip 200 and the substrate 225, as explained earlier. Isostatic pressure is placed on the assembly so as to reduce the volume of the void 240. As explained above, during this step, any first gas trapped within the void 240 diffuses into the encapsulant until the void 240 has been completely removed, as shown in FIG. 2N-6. At this point, the encapsulant completely surrounds the peelable compliant pad 250" thereby providing the needed means to bind the chip 200 to the substrate 225 prior to shipment to an end user, as shown in FIG. 2N-7.

In a variation to this process, a pressure sealed membrane 231 may be applied or deposited in a sheet form atop the

assembly, as shown in FIGS. 2N-5 and 2N-6, prior to the application of pressure thereby, in effect, laminating the membrane to the structure (back surface of the chip 200 and exposed surface of the encapsulant 230). Such a membrane 231 may be permanently sealed to the back of the chip 200 5 protecting the chip 200 and further binding the bumper portions 232 so that they do not de-laminate from the side edges of the chip 200 after the package has been diced, as shown in FIG. 2N-7. Alternately, the membrane 231 may be removed from the back of the die leaving the back surface of the chip 10 200 bare to be subsequently attached to a cooling surface or heat sink.

In a still further variant of this process, hydrostatic pressure could be used instead of the isostatic pressure discussed above to compress the voids/bubbles. Typically in such a 15 process, inert fluids would be used to compress the voids/bubbles.

Treating an Interposer Layer

FIGS. 3A-E show a similar design to that shown in FIGS. 2A-C; however, in this embodiment, an interposer layer, such 20 as a compliant pad 330, is disposed between the first substrate 325 and the semiconductor chip 300. The present invention provides a method of treating the pad 330 to provide a substantially void free layer. Typically, the compliant pad 330 is comprised of a curable thermoset resin, such as silicone, 25 flexiblized epoxy, urethane elastomer or polyimide foam. In the embodiments shown in FIGS. 3A-E, the first substrate 325 is typically comprised of a substantially inextensible sheet-like material, such as polyimide, which may be substantially rigid, semi-rigid or flexible.

The pad 330 may be positioned and attached as a solid piece, as with adhesive on opposing sides thereof, or it may be stenciled or screened onto the face surface of the chip 300 or onto the opposing surface of the first substrate 325. Typically, it is stenciled onto the first substrate 325 prior to the leads 360 35 being detached from a sacrificial outer portion 327 of the first substrate and formed and bonded to respective chip contacts 370. The stenciled pad 330 is then at least partially cured. If a thicker compliant pad 330 is desired or if added adhesive properties are required a chip attach layer (not shown) may 40 then be deposited on top of a typically fully cured pad 330, as by a stenciling step. The chip attach layer may then be left either uncured or may be partially cured ("B-staged") prior to the attachment of the chip 300. Preferably, the chip is attached using a heated collet placement system so that the chip is 45 relatively hot when it is pressed against the chip attach layer so as to minimize the number and size of any voids (or gas bubbles) 340/340'. Typically, these voids will occur at the boundary between the different materials in the assembly, e.g. first substrate/compliant pad, compliant pad/chip or even 50 compliant pad/chip attach layer depending upon the materials chosen for those two materials. Even using a hot chip placement system, gas bubbles or voids 340/340' are difficult to avoid in the uncured chip attach layer whether from the entrapment of gas when the chip is attached (FIG. 3B) or 55 when the pad 330 is stenciled (FIG. 3C).

After the chip 300 has been attached and the voids 340/340' have been sealed within the package assembly, the assembly is placed under isostatic pressure for a given amount of time to remove the voids 340/340'. As in the embodiments 60 described above, the step of applying an isostatic ambient gas to the outside of the assembly is used to create a pressure gradient between the lower pressure first gas/vacuum within the voids 340/340' and the ambient gas pressure be applied to the outside of the assembly. This has the effect of compressing any first gas in the voids 340/340' thereby reducing the volume of the void and increasing the pressure therewith. If

14

there is a sealed first gas within the voids 340/340', the pressure within each void 340/340' is the sum of the pressure from the compressed first gas and the pressure from the surface tension of the void. As the void volume decreases, the pressure from the surface tension of the void will increase dramatically. At some point during a second time period, the sum of the pressures within the void **340** will become greater than the ambient pressure acting on the outside of the assembly. Because of the greater pressure within the void in relation to the pressure outside the assembly during second time period, the first gas within the void will begin to diffuse into the compliant pad/chip attach layer 330 faster than the ambient gas diffuses into the compliant pad/chip attach layer 330. The greater rate of diffusion of the first gas combined with the increased pressure of the first gas will cause the first gas to completely diffuse into the compliant pad/chip attach layer 330 such that the bubble has been removed.

As described in the above sections, the pressure which is needed to remove the voids will depend on the materials used as the compliant pad and the hip attach layer and will also depend on the time allotted for their removal and the total volume of the voids to be removed. An example of a suitable pressure/time range where both the compliant pad and the chip attach layers are comprised of silicone resin includes between about 10 and 1000 psi for anywhere over approximately one hour. The assembly may be kept under pressure for more than the specified amount of time, without harm coming to it.

Any first gas sealed within the void 340 may be comprised of the same gas as the ambient gas; however, the first gas and the ambient gas may also be different in order to facilitate a greater rate of diffusion of the sealed first gas. After the step of sealing the first gas by attaching the chip to the compliant pad/chip attach layer 330, the first gas present on the outside of the assembly may be evacuated and replaced with a different pressurized ambient gas. Desirably, the second ambient gas should have an inherent rate of diffusivity with respect to the chip attach layer material that is less than the rate of diffusivity of the first gas into the same chip attach material. If the chip attach material is a curable thermoset resin material, suitable examples of possible first gases include: helium, hydrogen, H<sub>2</sub>O vapor, methane and fluorinated hydrocarbons. Examples of suitable second ambient gases in such a situation include: argon, air, nitrogen, and carbon dioxide.

Typically, after the voids 340/340' have been removed from the compliant pad/chip attach layer 330, the assembly is heated in order to cure (or fully cross link) the chip attach layer to ensure that the voids 340/340' do not return prior to the removal of the ambient gas pressure being applied to the assembly. As described above, other types of energy may be used to cause the chip attach layer to cure depending upon what the material is comprised.

As shown in FIG. 3D, after the voids 340/340' have been removed and the compliant pad is cured, the leads 350 are typically detached from the sacrificial outer portion 327 and coupled to respective chip contacts 370. These leads are then encapsulated, as shown in FIG. 3E, to protect them from corrosion and to support them during thermal cycling of the finished chip package assembly. If voids are present in the lead encapsulant material, the voids may be removed by using the aforementioned methods. The encapsulation of the leads may also be performed using the same techniques described in the "back-side encapsulation" embodiment of FIGS. 2D-2H if the user desires to simultaneously produce a plurality of components.

In a further variant of this process, hydrostatic pressure could be used instead of the isostatic pressure discussed

above to compress the voids/bubbles. Typically in such a encapsulant between a face process, inert fluids would be used to compress the voids/bubbles.

The method of the present invention has thus far been described with respect to individual semiconductor chips. 5 However, it is contemplated that the method of encapsulation may be employed with a plurality of chips simultaneously provided on a semiconductor wafer. As illustrated in FIG. 4A, chips 428 may be provided in the form of a semiconductor wafer 430 incorporating a plurality of such chips, all of the  $_{10}$ same design or of differing designs. Individual interposers 442 may be positioned on the individual chips 428 constituting wafer 430, and the interposers may be assembled to the chips as discussed above. In this operation, the contacts on each chip 428 are secured to the leads and terminals of each interposer. The encapsulation of the interposer **442** and chips <sup>15</sup> 428 can be accomplished in accordance with the methods of the present invention as thus far described with respect to individual semiconductor chips. In addition, where an interposer 442 is omitted, encapsulation of the plurality of chips **428** on the semiconductor wafer can be achieved in accordance with the previously described process, for example, flip chip underfill encapsulation and injection of the encapsulant.

After the interposers 442 and chips 428 are encapsulated, the individual chips are separated from the wafer 430 and from one another, as by cutting the wafer using conventional 25 wafer severing or "dicing" equipment commonly utilized to sever individual chips without interposers. This procedure yields a plurality of encapsulated chips and interposer subassemblies, each of which may be secured to an individual substrate.

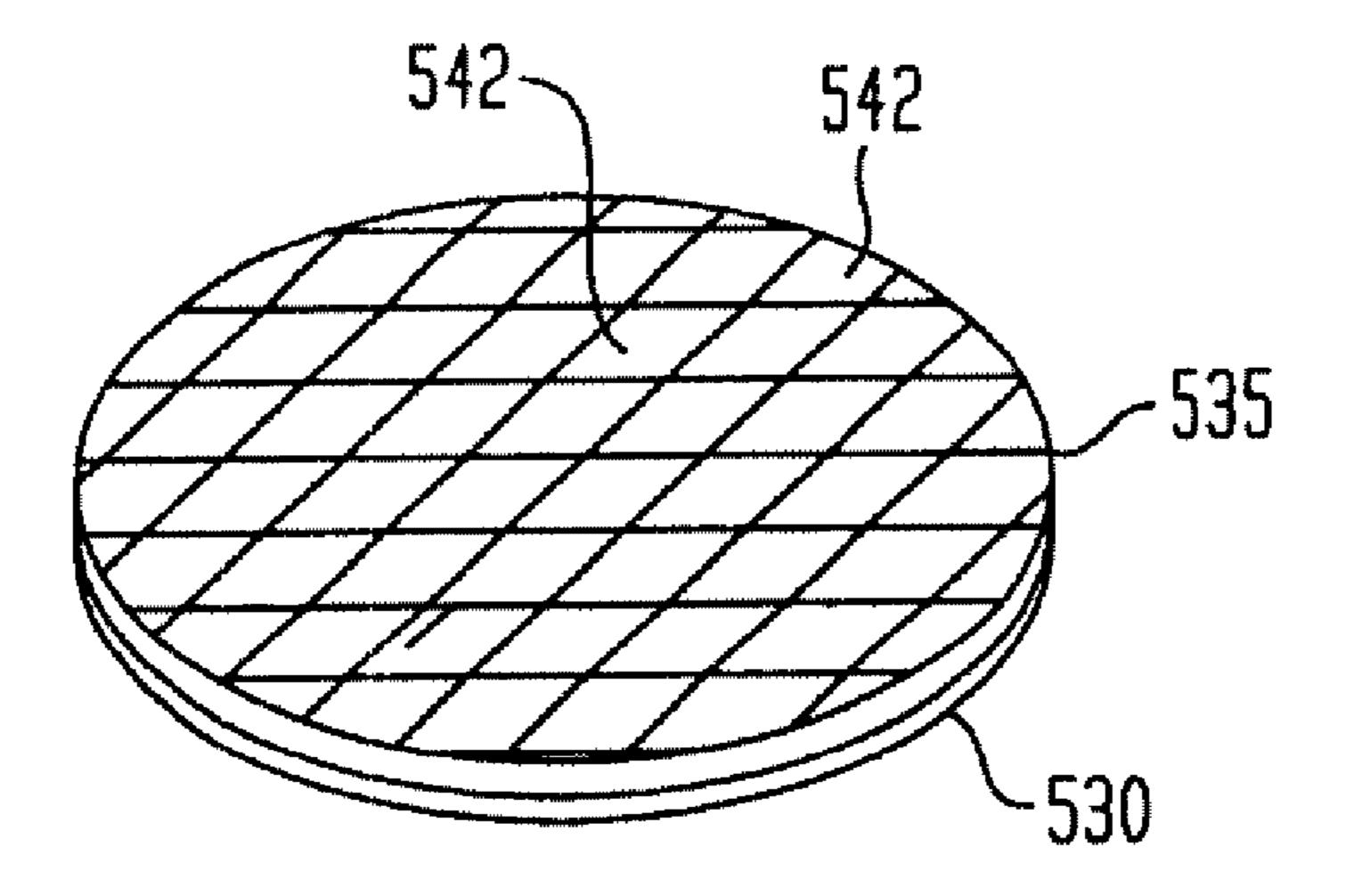

As illustrated in FIG. 4B, a wafer 530 incorporates a plurality of interposers **542**. Again, the contacts on each chip are secured to the terminals and leads of one individual interposer overlying the particular chip. The encapsulation of the chip and interposer may be accomplished in using any of the methods as thus far described. The wafer **530** and the sheet <sup>35</sup> 535 are severed after this operation, and desirably after encapsulating, so as to provide individual subassemblies each including a chip and an interposer.

Having fully described several embodiments of the present invention, it will be apparent to those of ordinary skill in the 40 art that numerous alternatives and equivalents exist which do not depart from the invention set forth above. It is therefore to be understood that the present invention is not to be limited by the foregoing description, but only by the appended claims.

What is claimed is:

1. A method of providing a substantially void free underfill for a flip chip assembly, comprising:

electrically connecting a plurality of contact pads on a surface of a semiconductor chip to corresponding bond pads on a circuitized substrate such that the connections 50 create a gap between the chip and the substrate, wherein the substrate is rigid;

sealing the gap between the chip and the substrate with a fluid, curable encapsulant so that there is a void therebetween;

applying pressure to the assembly causing the encapsulant to flow into the gap and around the connections; and

applying energy to the assembly in order to cure the encapsulant.

- 2. The method as claimed in claim 1, wherein the pressure 60 applying step is conducted for a time period that is between 30 minutes to several hours.

- [3. The method as claimed in claim 1, wherein the pressure applying includes gradually increasing the applied pressure.

- [4. A method of injecting an encapsulant between a face 65] surface of a semiconductor chip and a juxtaposed substrate, comprising:

**16**

providing a gap between the face surface of the chip and the substrate, wherein the substrate is rigid;

sealing each edge of the gap with a curable fluid encapsulant so that there is a void between the chip and the substrate;

applying pressure to cause the encapsulant to flow between the chip and the substrate; and

applying energy to cure the encapsulant.

[5. The method as claimed in claim 4, wherein the pressure applying step is conducted for a time period that is between 30 minutes to several hours.

**[6**. The method as claimed in claim **4**, wherein the pressure applying includes gradually increasing the applied pressure.]

[7. The method as claimed in claim 4, wherein the applied pressure is between about 10 and 450 pounds per square inch.]

[8. The method as claimed in claim 4, wherein the applied pressure is between about 30 and 200 pounds per square inch.]

9. [The method as claimed in claim 4] A method of injecting an encapsulant between a face surface of a semiconductor chip and a juxtaposed substrate, comprising:

providing a gap between the face surface of the chip and the substrate, wherein the substrate is rigid;

sealing each edge of the gap with a curable fluid encapsulant so that there is a void between the chip and the substrate; applying pressure to cause the encapsulant to flow between the chip and the substrate;

and applying energy to cure the encapsulant,

wherein the gap providing step includes: providing compliant pads on the substrate, wherein each of the compliant pads includes a peelable tacky surface to which the face surface of the chip is releasably attached.

[10. A method of providing a substantially void free underfill for a semiconductor wafer having a plurality of flip chip assemblies, comprising:

electrically connecting a plurality of contact pads of flip chip assemblies disposed on a surface of a semiconductor wafer to corresponding bond pads on a circuitized substrate such that the connections create a gap between the flip chip assemblies and the substrate, wherein the substrate is rigid;

sealing the gap between the flip chip assemblies and the substrate with a fluid, curable encapsulant so that there is a void therebetween;

applying pressure to cause the encapsulant to flow into the gap and around the connections; and

applying energy to cure the encapsulant.

[11. The method as claimed in claim 10, wherein the pressure applying step is conducted for a time period that is between 30 minutes to several hours.

[12. The method as claimed in claim 10, wherein the pres-55 sure applying includes gradually increasing the applied pressure.

[13. A method of injecting an encapsulant between a face surface of a semiconductor wafer and a juxtaposed substrate, comprising:

providing a gap between the face surface of the wafer and the substrate, wherein the substrate is rigid;

sealing each edge of the gap with a curable fluid encapsulant so that there is a void between the wafer and the substrate;

applying pressure to cause the encapsulant to flow between the wafer and the substrate; and applying energy to cure the encapsulant.

- [14. The method as claimed in claim 13, wherein the pressure applying step is conducted for a time period that is between 30 minutes to several hours.

- 15. The method as claimed in claim 13, wherein the pressure applying includes gradually increasing the applied pres- 5 sure.

- **16**. The method as claimed in claim **13**, wherein the applied pressure is between about 10 and 450 pounds per square inch.

- 17. The method as claimed in claim 13, wherein the 10 applied pressure is between about 30 and 200 pounds per square inch.

**18**. [The method as claimed in claim **13**,] A method of injecting an encapsulant between a face surface of a semiconductor wafer and a juxtaposed substrate, comprising: