#### US00RE43171E

# (19) United States

# (12) Reissued Patent

Chu

# (10) Patent Number:

# US RE43,171 E

# (45) Date of Reissued Patent:

\*Feb. 7, 2012

# (54) DATA SECURITY METHOD AND DEVICE FOR COMPUTER MODULES

- (75) Inventor: William W. Y. Chu, Los Altos, CA (US)

- (73) Assignee: ACQIS LLC, McKinney, TX (US)

- (\*) Notice: This patent is subject to a terminal dis-

claimer.

- (21) Appl. No.: 11/545,056

- (22) Filed: Oct. 6, 2006

#### Related U.S. Patent Documents

#### Reissue of:

- (64) Patent No.: 6,643,777

Issued: Nov. 4, 2003

Appl. No.: 09/312,199

Filed: May 14, 1999

- (51) **Int. Cl.**

| G06F 7/04  | (2006.01) |

|------------|-----------|

| G06F 11/30 | (2006.01) |

See application file for complete search history.

# (56) References Cited

## U.S. PATENT DOCUMENTS

| 3,996,585 | A |   | 12/1976 | Hogan          |       |

|-----------|---|---|---------|----------------|-------|

| 4,141,068 | A |   | 2/1979  | Mager et al.   |       |

| 4,228,496 | A |   | 10/1980 | Katzman et al. |       |

| 4,453,215 | A |   | 6/1984  | Reid           |       |

| 4,623,964 | A | * | 11/1986 | Getz et al     | 705/1 |

| 4,670,837 | A |   | 6/1987  | Sheets         |       |

| 4,680,674 | A |   | 7/1987  | Moore          |       |

| 4,700,362 | A |   | 10/1987 | Todd et al.    |       |

|           |   |   |         |                |       |

| 4,760,276 A | 7/1988    | Lethellier        |  |  |

|-------------|-----------|-------------------|--|--|

| 4,769,764 A | 9/1988    | Levanon           |  |  |

| 4,791,524 A | 12/1988   | Teigen et al.     |  |  |

| 4,799,258 A | 1/1989    | Davies            |  |  |

| 4,872,091 A | 10/1989   | Maniwa et al.     |  |  |

| 4,890,282 A | 12/1989   | Lambert et al.    |  |  |

| 4,918,572 A | 4/1990    | Tarver et al.     |  |  |

| 4,939,735 A | 7/1990    | Fredericks et al. |  |  |

| 5,056,141 A | * 10/1991 | Dyke 340/5.27     |  |  |

| 5,086,499 A | 2/1992    | Mutone            |  |  |

| 5,103,446 A | 4/1992    | Fischer           |  |  |

| 5,187,645 A | 2/1993    | Spalding et al.   |  |  |

| 5,191,581 A |           | Woodbury et al.   |  |  |

| 5,251,097 A |           | Simmons et al.    |  |  |

| (Continued) |           |                   |  |  |

## FOREIGN PATENT DOCUMENTS

EP 722138 A1 7/1996 (Continued)

# OTHER PUBLICATIONS

PC Magazine Online. "Think Modular" (Jun. 10, 1997).

(Continued)

Primary Examiner — Eleni Shiferaw Assistant Examiner — Ali S Abyaneh (74) Attorney, Agent, or Firm — Cooley LLP

## (57) ABSTRACT

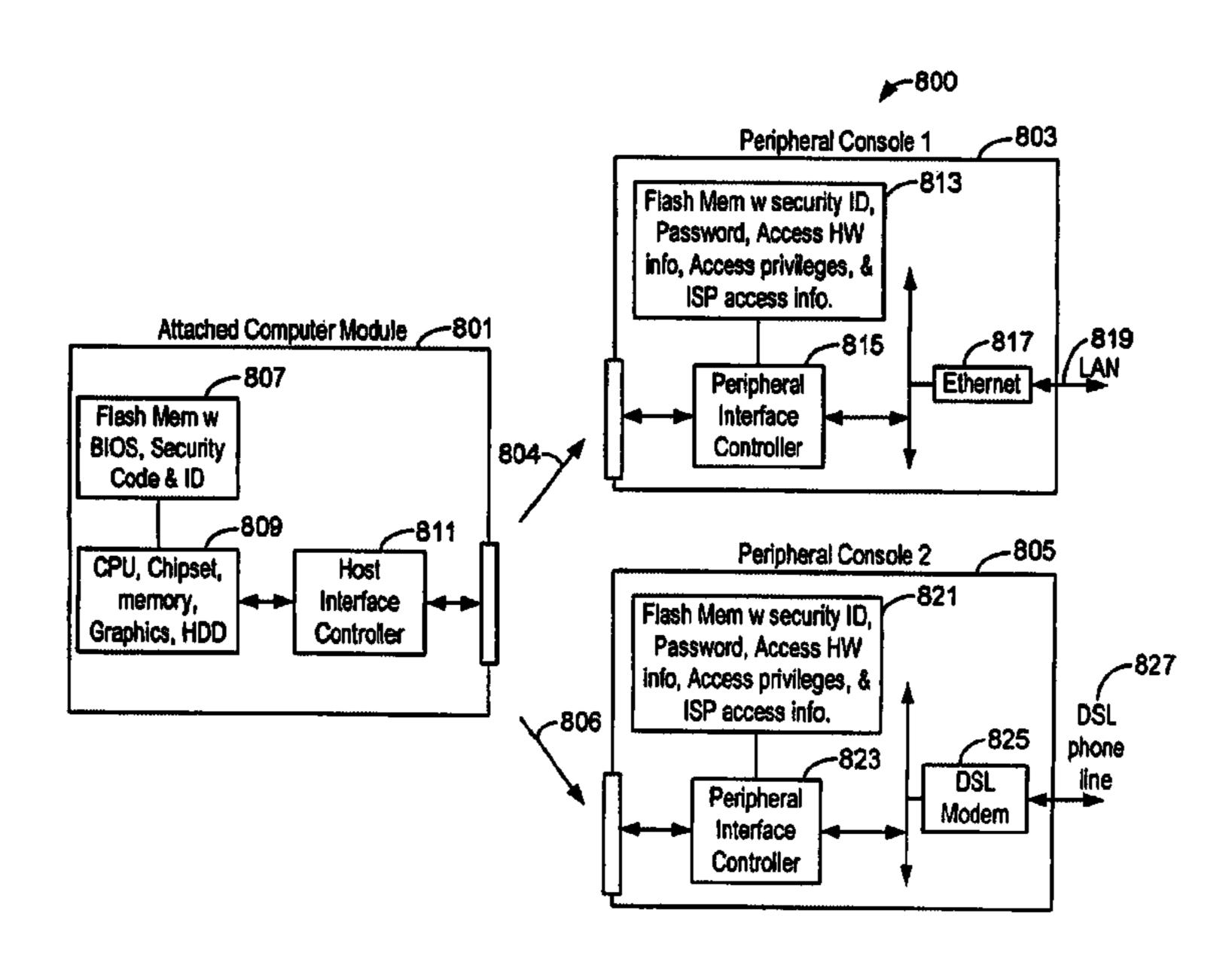

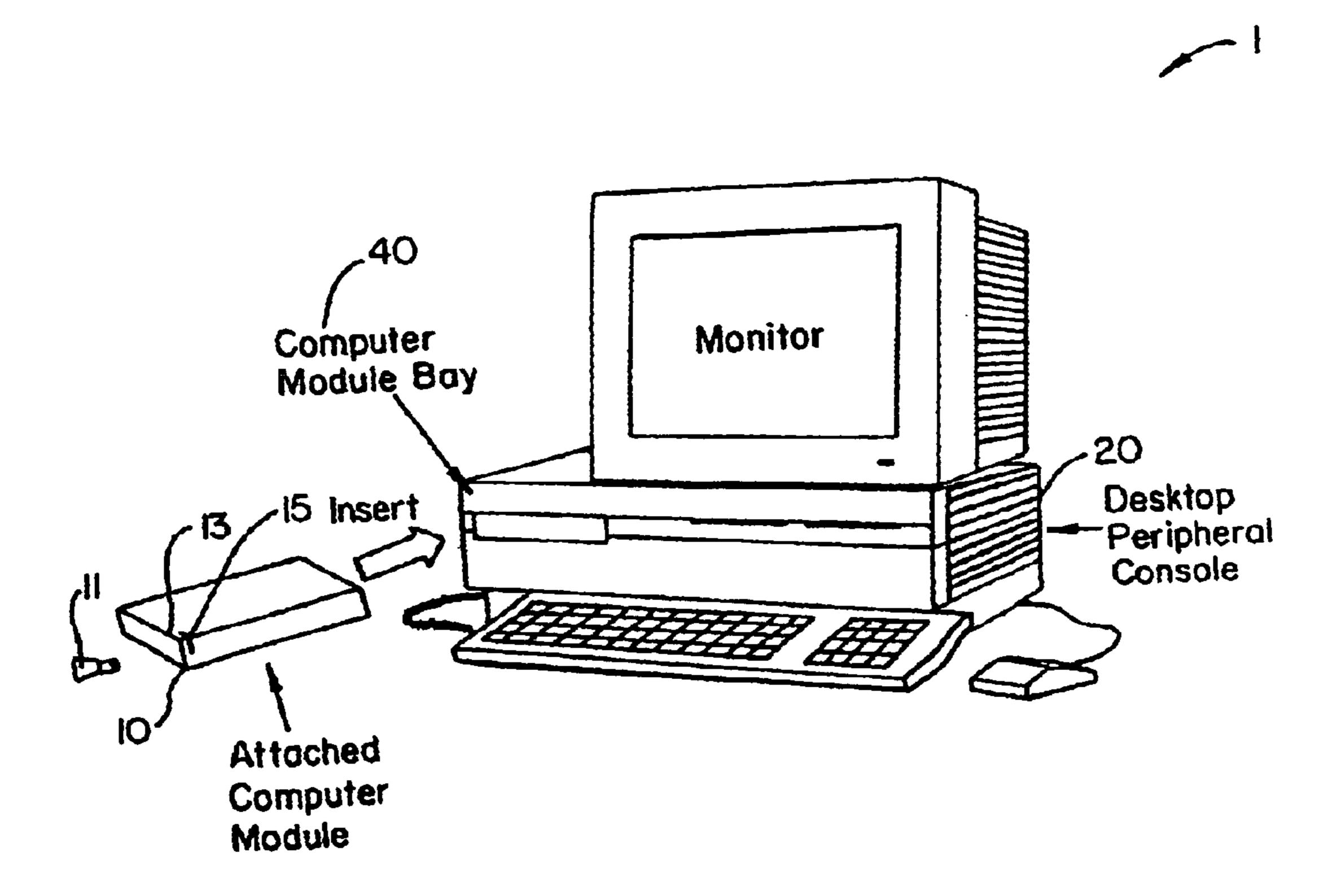

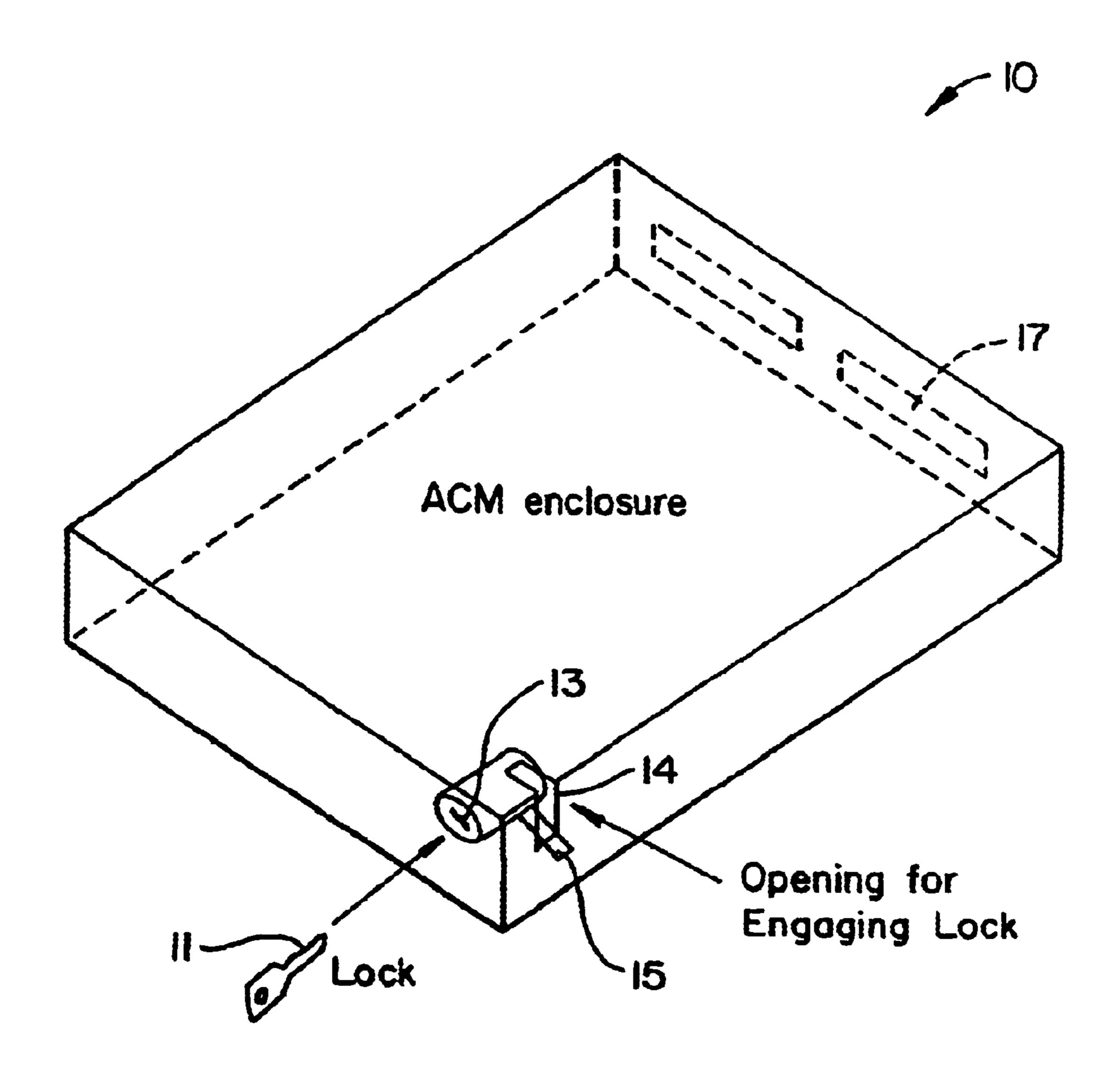

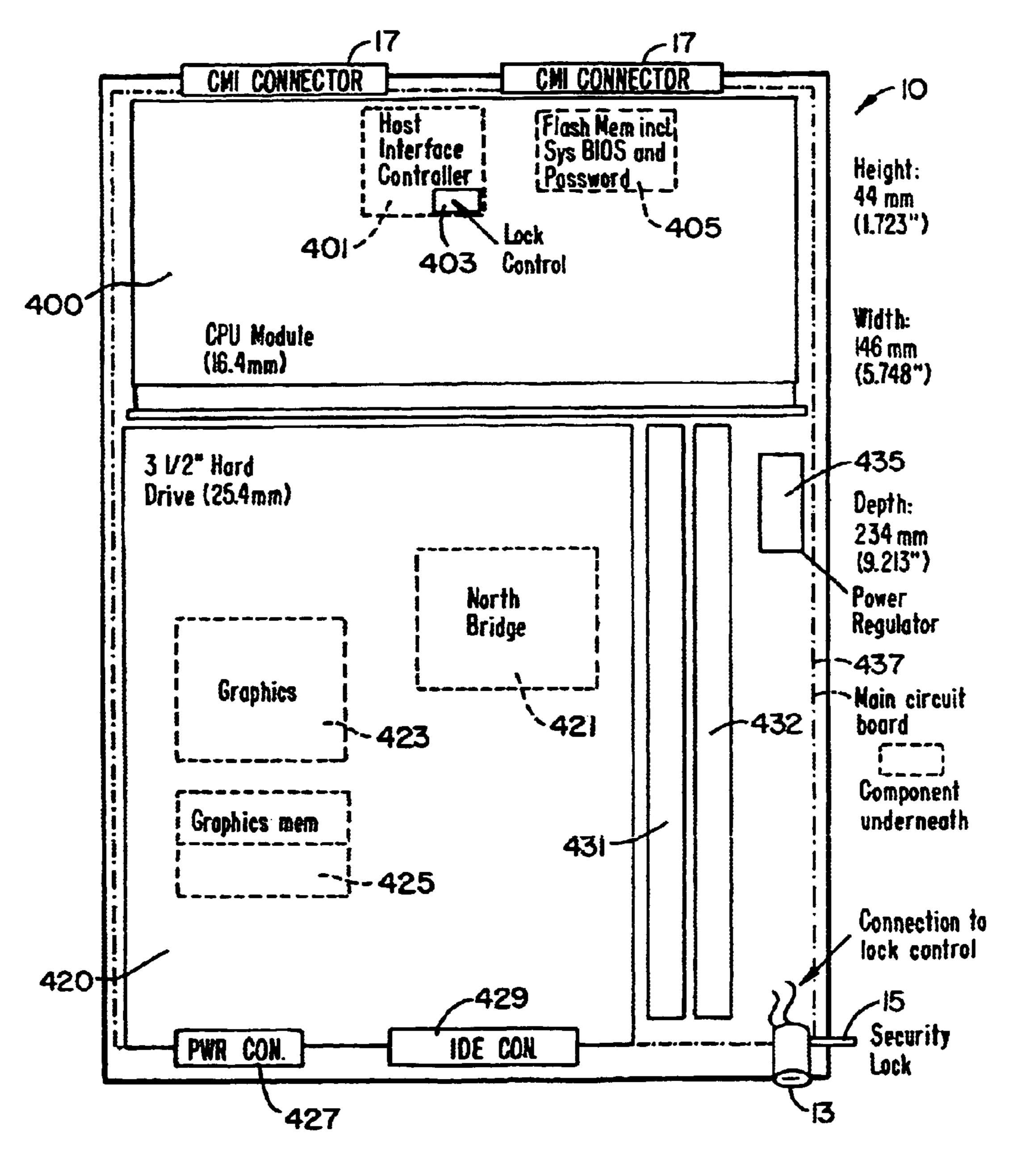

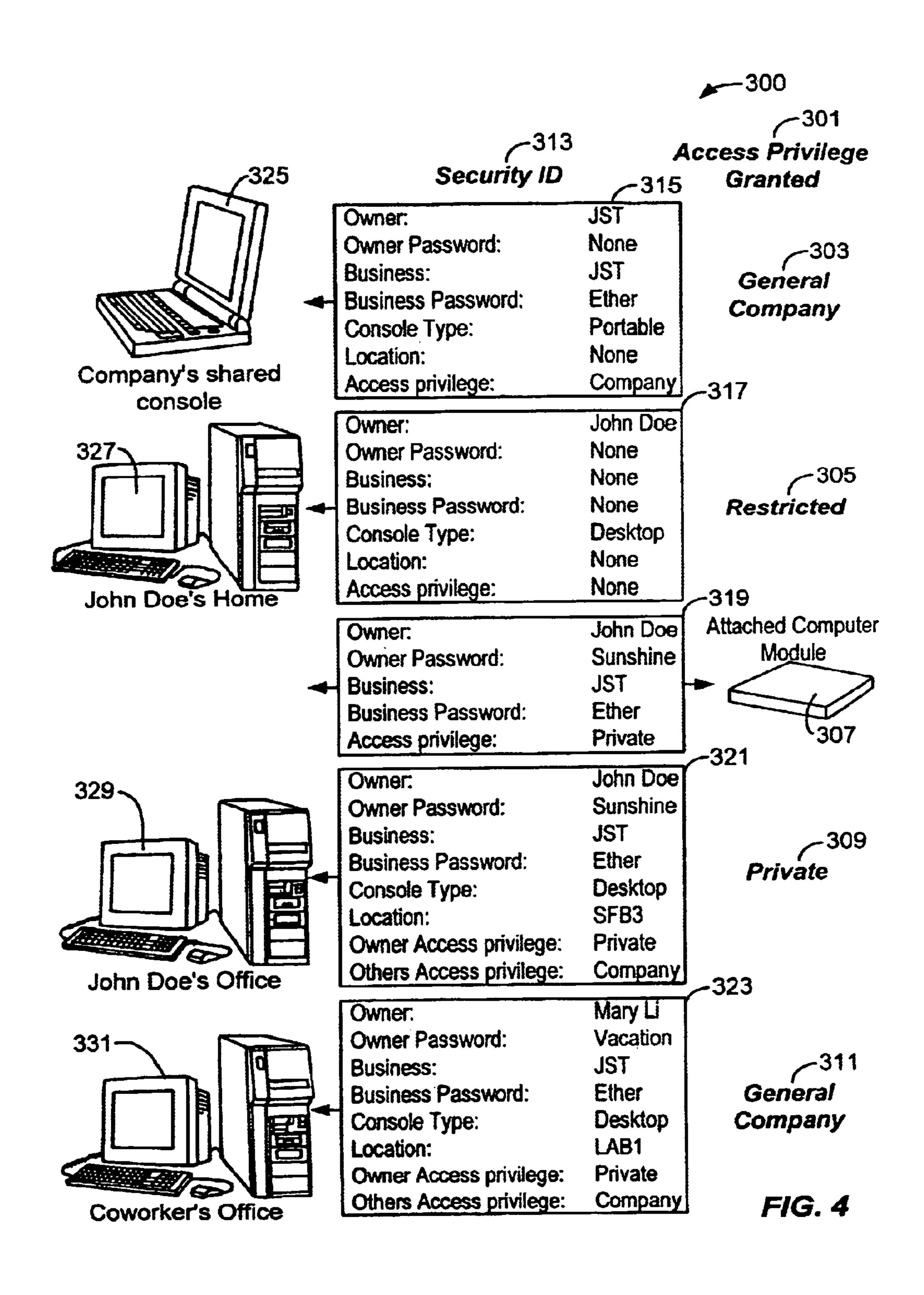

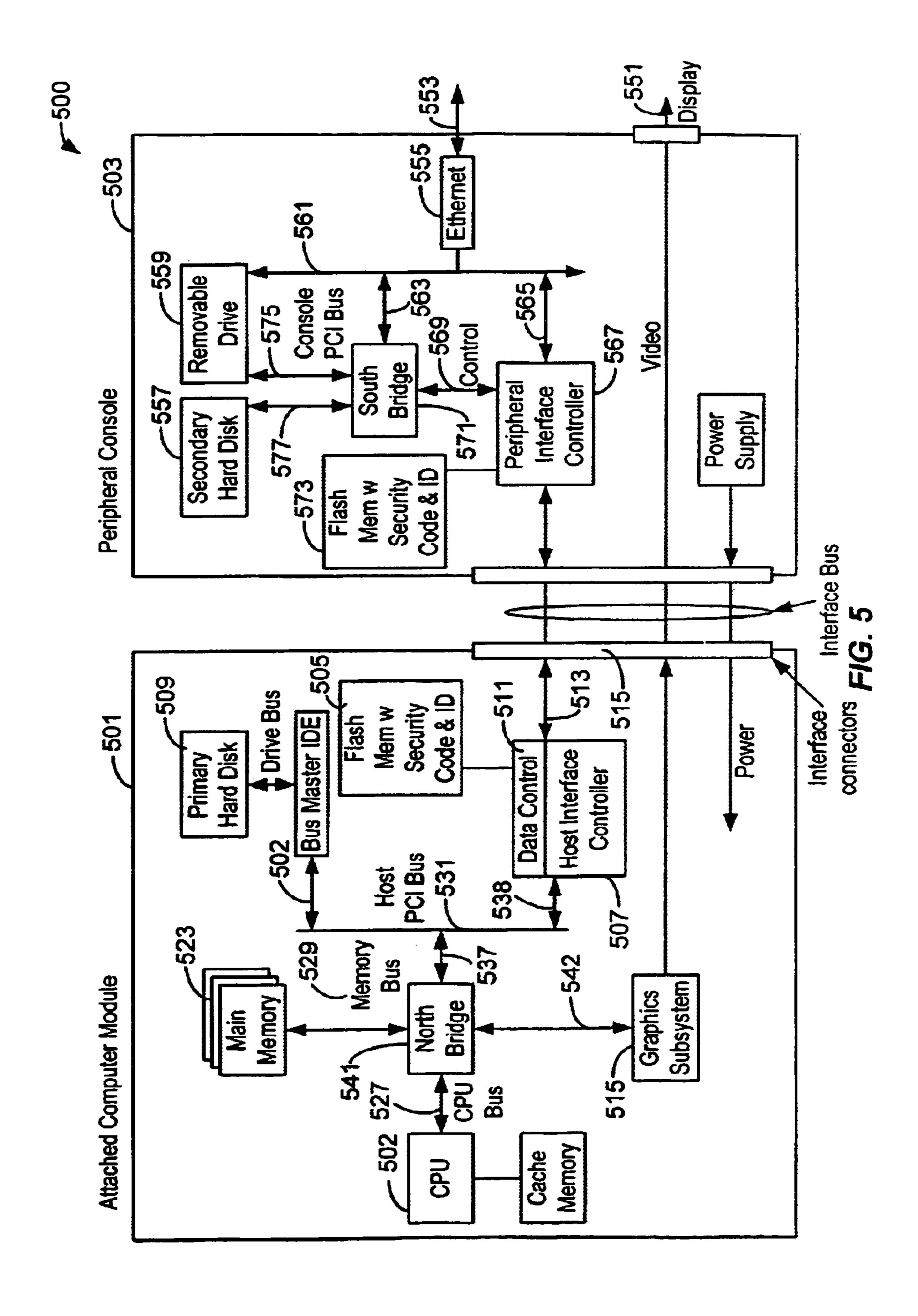

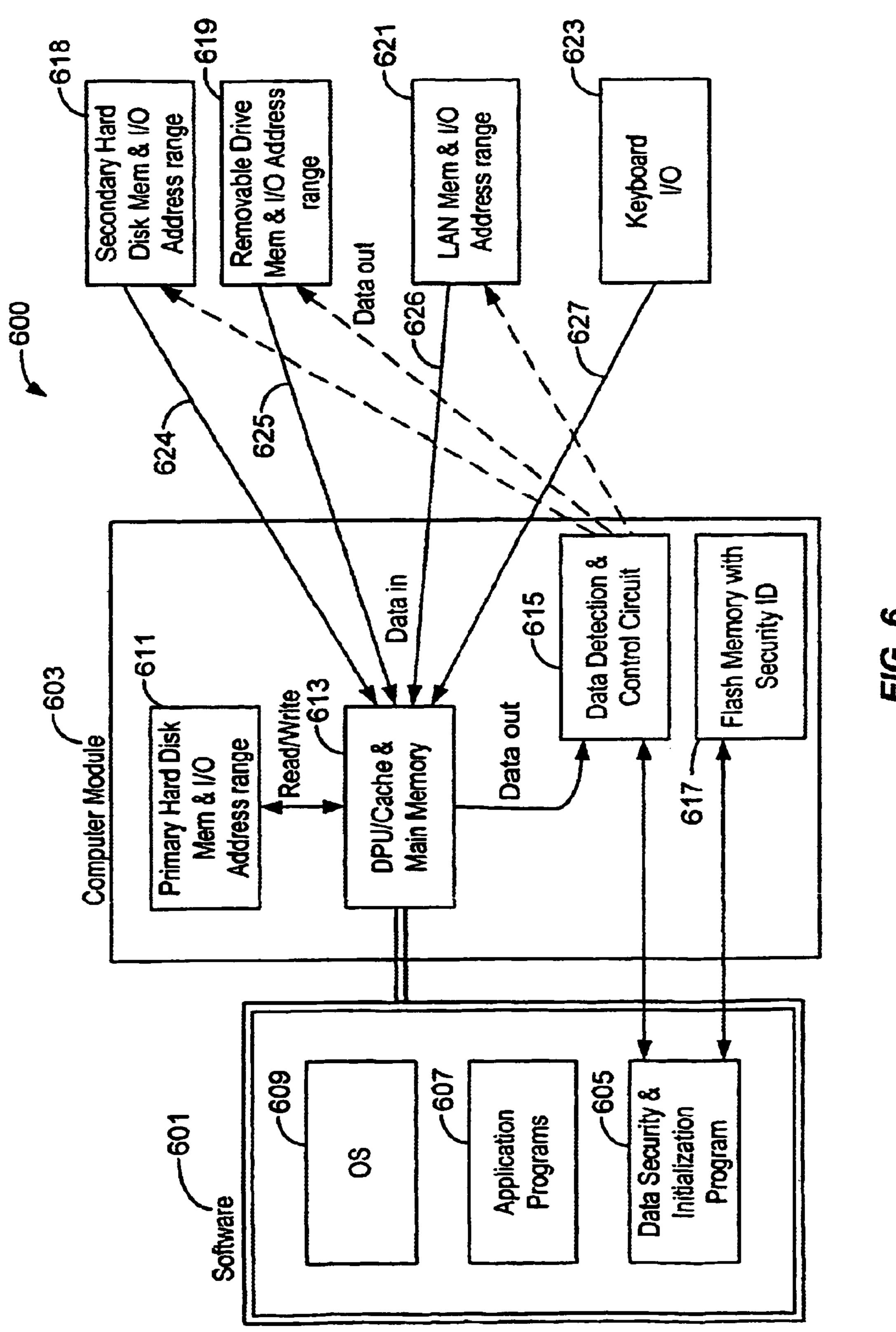

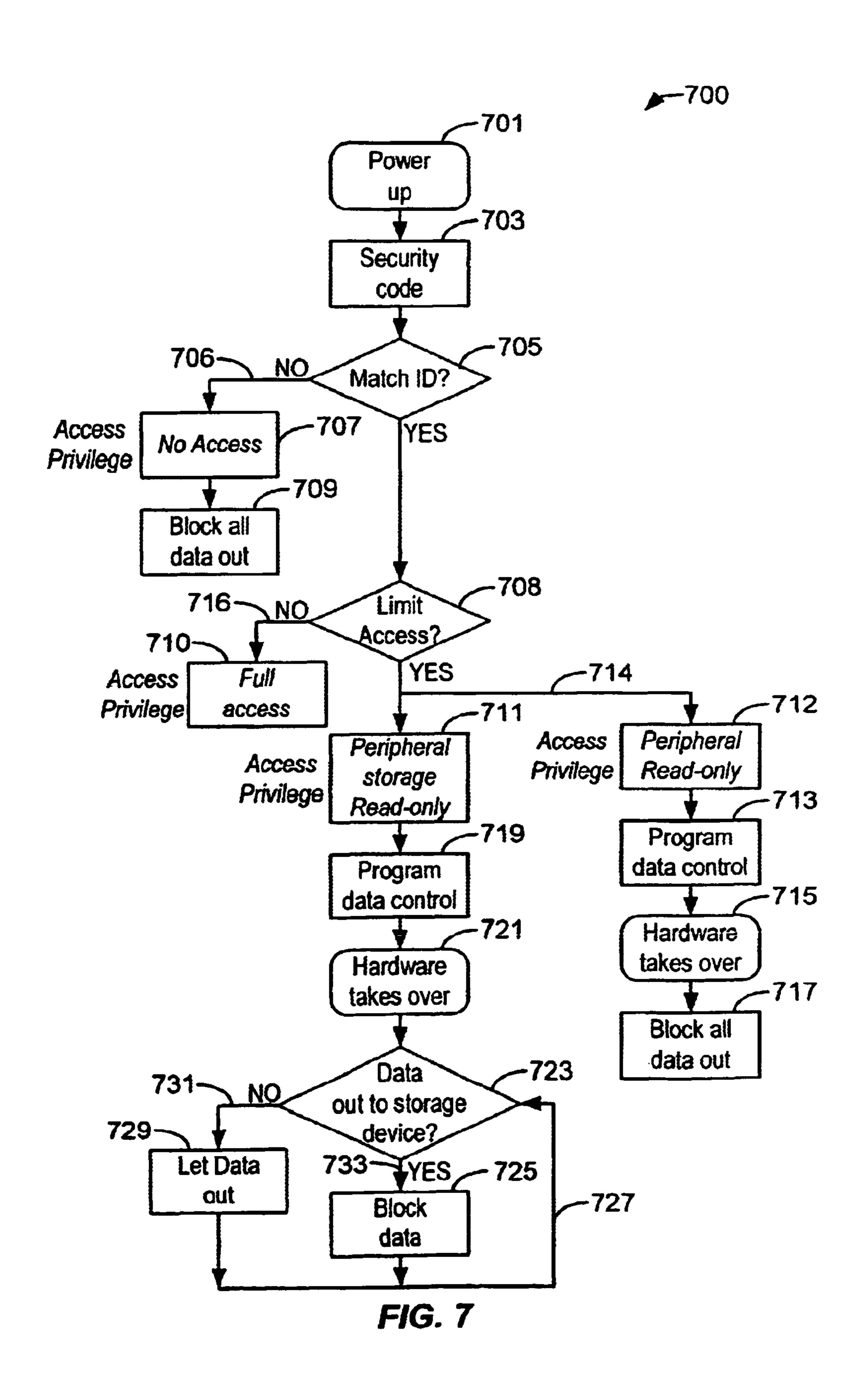

A security method for an attached computer module in a computer system. The security method reads a security identification number in an attached computer module and compares it to a security identification number in a console, which houses the attached computer module. Based upon a relationship between these numbers, a security status is selected. The security status determines the security level of operating the computer system.

# 53 Claims, 14 Drawing Sheets

# US RE43,171 E Page 2

| II C DATENIT                             | DOCUMENTS                             | 5,933,609 A                  | 8/1000  | Walker et al.                               |

|------------------------------------------|---------------------------------------|------------------------------|---------|---------------------------------------------|

|                                          |                                       | 5,933,009 A<br>5,941,965 A   | 8/1999  |                                             |

|                                          | Haynes et al.                         | 5,948,047 A                  |         | Jenkins et al.                              |

|                                          | Kikinis<br>Mal can at al              | 5,960,213 A                  | 9/1999  | Wilson                                      |

|                                          | McLean et al.<br>Russo et al.         | 5,965,957 A                  |         | Bourgeois                                   |

| 5,293,497 A 3/1994                       |                                       | , ,                          |         | Walker et al.                               |

| , ,                                      | Harshberger et al.                    | · ·                          |         | Gallagher et al.                            |

|                                          | Sidman                                | 5,974,486 A<br>5,977,989 A   |         | Siddappa<br>Lee et al                       |

| 5,317,477 A 5/1994                       | Gillett                               | 5,978,821 A                  |         |                                             |

|                                          | Takeda                                | 5,978,919 A                  |         |                                             |

|                                          | Baker et al.                          | 5,982,363 A                  |         |                                             |

| 5,331,509 A 7/1994<br>5,339,408 A 8/1994 | Kikinis<br>Bruckert et al             | , ,                          | 11/1999 |                                             |

| 5,355,391 A 10/1994                      |                                       | 5,991,163 A                  |         |                                             |

| 5,428,806 A 6/1995                       |                                       | 5,991,844 A                  |         | <u> </u>                                    |

| 5,430,607 A 7/1995                       |                                       | 6,002,442 A                  |         | Jenkins et al 708/100                       |

|                                          | Blackledge, Jr. et al.                | 6,003,105 A                  |         |                                             |

|                                          | Nelson et al.                         | 6,006,243 A                  |         |                                             |

|                                          | McNamara et al.                       | 6,009,488 A                  | 12/1999 | Kavipurapu                                  |

|                                          | Kobayashi<br>Moran et al.             | 6,011,546 A                  |         |                                             |

|                                          | Bensimon et al.                       | 6,012,145 A *                |         | Mathers et al 726/17                        |

| * *                                      | Morisawa et al.                       | 6,016,252 A<br>6,025,989 A   |         | Pignolet et al.<br>Ayd et al.               |

| 5,539,616 A 7/1996                       | Kikinis                               | 6,028,643 A                  |         | Jordan et al.                               |

| , ,                                      | Caputo et al.                         | 6,029,183 A                  |         | Jenkins et al.                              |

| , , ,                                    | Rahamim et al.                        | 6,038,621 A                  |         | Gale et al.                                 |

|                                          | Chan et al.<br>Wade et al.            | 6,040,792 A                  | 3/2000  | Watson et al.                               |

| 5,572,441 A 11/1996                      |                                       | 6,046,571 A                  |         | Bovio et al.                                |

| 5,577,205 A 11/1996                      |                                       | 6,049,823 A                  |         | Hwang                                       |

| 5,578,940 A 11/1996                      |                                       | 6,052,513 A<br>6,069,615 A   |         | McLaren<br>Abraham et al.                   |

| 5,588,850 A 12/1996                      | Pan et al.                            | 6,070,211 A                  | 5/2000  |                                             |

| 5,590,377 A 12/1996                      |                                       | 6,070,211 A                  | 5/2000  | -                                           |

| , ,                                      | Kikinis et al.                        | 6,078,503 A                  |         | Gallagher et al.                            |

| 5,603,044 A 2/1997<br>5,606,717 A 2/1997 | Annapareddy et al.<br>Farmwald et al. | 6,088,224 A                  |         | Gallagher et al.                            |

|                                          | Flint et al.                          | 6,088,620 A                  |         | Ninomiya et al.                             |

|                                          | Jones et al.                          | 6,088,752 A                  | 7/2000  |                                             |

| 5,630,057 A 5/1997                       | Hait                                  | 6,091,737 A<br>6,104,921 A   |         | Hong et al.<br>Cosley et al.                |

|                                          | Buchala et al.                        | , ,                          |         | Tran et al.                                 |

|                                          | Kikinis                               | , ,                          |         | Gallagher et al.                            |

|                                          | Ichimura et al 726/34                 | , ,                          |         | Akbarian et al.                             |

| 5,659,773 A 8/1997<br>5,663,661 A 9/1997 | Dillon et al.                         | 6,163,464 A                  |         | Ishibashi et al.                            |

|                                          | Hastings et al.                       | 6,175,490 B1                 |         | ±                                           |

|                                          | Hamirani                              | 6,188,602 B1                 |         | Alexander et al.                            |

| 5,680,126 A 10/1997                      | Kikinis                               | 6,202,169 B1<br>6,208,522 B1 |         | Razzaghe-Ashrafi et al.<br>Manweiler et al. |

|                                          | Tyuluman                              | 6,216,185 B1*                |         | Chu 710/303                                 |

| 5,689,654 A 11/1997                      |                                       | 6,256,689 B1                 |         | Khosrowpour                                 |

|                                          | Kikinis et al.<br>Kikinis             | 6,256,691 B1                 | 7/2001  | Moroz et al.                                |

| · · · · · · · · · · · · · · · · · · ·    | Beasley et al.                        | 6,260,155 B1                 |         | Dellacona                                   |

|                                          | Hara et al.                           | 6,266,539 B1                 | 7/2001  |                                             |

| · · · · · · · · · · · · · · · · · · ·    | Hopkins et al.                        | 6,289,376 B1<br>6,297,955 B1 |         | Frank, Jr. et al.                           |

| 5,737,524 A 4/1998                       | Cohen et al.                          | , ,                          |         | Krull et al.                                |

| · · · · · · · · · · · · · · · · · · ·    | Robinson                              | , ,                          |         | Schneider et al.                            |

|                                          | Sakaue                                | 6,311,268 B1                 | 10/2001 | Chu                                         |

| 5,752,080 A 5/1998<br>5,764,924 A 6/1998 |                                       | , ,                          |         | Dischler et al.                             |

|                                          | Weiss et al.                          | 6,314,522 B1                 |         |                                             |

|                                          | Williams                              | 6,317,329 B1                 |         |                                             |

|                                          | Trumbull                              | , ,                          | 11/2001 | Rafferty et al.                             |

|                                          | Hwang                                 | 6,325,636 B1                 |         |                                             |

| 5,805,903 A 9/1998                       |                                       | ·                            |         | Kauffman et al.                             |

|                                          | Potter                                | 6,345,330 B2                 | 2/2002  | Chu                                         |

| * *                                      | Pollmann<br>Kikinis                   | 6,366,951 B1                 |         | Schmidt                                     |

| , ,                                      | Boehling et al.                       | 6,378,009 B1                 |         | Pinkston, II et al.                         |

|                                          | Dempsey et al.                        | 6,381,602 B1*                |         | Shoroff et al                               |

| 5,838,932 A 11/1998                      | Alzien                                | 6,393,561 B1 * 6,401,124 B1  |         | Hagiwara et al 713/100                      |

| 5,848,249 A 12/1998                      | _                                     | 6,401,124 B1<br>6,411,506 B1 |         | Yang et al.<br>Hipp et al.                  |

|                                          | Prentice                              | 6,425,033 B1                 |         | Conway                                      |

| , ,                                      | Coulson<br>Advani et al.              | 6,452,789 B1                 |         | Pallotti et al.                             |

| · · · · · · · · · · · · · · · · · · ·    | Delagrange et al 726/34               | 6,452,790 B1                 |         | Chu et al.                                  |

|                                          | Atkinson                              | 6,453,344 B1                 |         | Ellsworth                                   |

| 5,884,053 A 3/1999                       | Clouser                               | , ,                          |         | Kim et al 361/683                           |

|                                          | Benson et al 714/798                  |                              |         | Osann, Jr.                                  |

| 5,930,110 A 7/1999                       | Nishigaki et al.                      | 6,549,966 B1                 | 4/2003  | Dickens et al.                              |

|                                          |                                       |                              |         |                                             |

| 6,564,274    | B1         | 5/2003  | Heath et al.     |

|--------------|------------|---------|------------------|

| 6,567,877    | B1         | 5/2003  | Lewis et al.     |

| 6,578,103    | B1         | 6/2003  | Hill             |

| 6,581,125    | B1         | 6/2003  | Lange            |

| 6,606,253    | B2         | 8/2003  | Jackson et al.   |

| 6,643,777    | B1         | 11/2003 | Chu              |

| 6,664,377    | B1         | 12/2003 | Xu               |

| 6,715,100    | B1         | 3/2004  | Hwang            |

| 6,718,415    | B1         | 4/2004  | Chu              |

| 6,725,317    | B1         | 4/2004  | Bouchier et al.  |

| 6,742,068    | B2         | 5/2004  | Gallagher et al. |

| 6,747,878    | B1         | 6/2004  | _                |

| 6,757,748    | B1         | 6/2004  | Hipp             |

| 6,948,047    | B2         | 9/2005  | Maruska et al.   |

| 6,985,967    | B1         | 1/2006  | Hipp             |

| 7,017,001    | B2         |         | Hill et al.      |

| 7,020,735    | B2         | 3/2006  | Kikinis          |

| 7,099,981    | B2         | 8/2006  | Chu              |

| 7,146,446    | B2         | 12/2006 | Chu              |

| 7,328,297    | B2         | 2/2008  | Chu              |

| 7,339,786    | B2         | 3/2008  | Bottom et al.    |

| 7,363,415    | B2         | 4/2008  | Chu              |

| 7,363,416    | B2         | 4/2008  | Chu              |

| 7,376,779    | B2         | 5/2008  | Chu              |

| RE41,076     | E          | 1/2010  | Chu              |

| RE41,092     | E          | 1/2010  | Chu              |

| 7,676,624    | B2         | 3/2010  | Chu              |

| RE41,294     | E          | 4/2010  | Chu              |

| 7,818,487    | B2         | 10/2010 | Chu              |

| RE41,961     | E          | 11/2010 | Chu              |

| 2001/0011312 | A1         | 8/2001  | Chu              |

| 2005/0182882 | <b>A1</b>  | 8/2005  | Chu              |

| 2009/0157939 | <b>A1</b>  | 6/2009  | Chu              |

| 2010/0174844 | <b>A</b> 1 | 7/2010  | Chu              |

|              |            |         |                  |

#### FOREIGN PATENT DOCUMENTS

| JP | 6-289953    | 10/1994 |

|----|-------------|---------|

| JP | 6-289956    | 10/1994 |

| JP | 7-64672     | 3/1995  |

| JP | 7-84675     | 3/1995  |

| WO | WO 92/18924 | 10/1992 |

| WO | WO 94/00097 | 1/1994  |

| WO | WO 94/00970 | 1/1994  |

| WO | WO 95/13640 | 5/1995  |

| WO | W097/00481  | 1/1997  |

| WO | WO 97/05618 | 2/1997  |

|    |             |         |

# OTHER PUBLICATIONS

Spang. "Component House: Design Technology for 'PCs in a snap'—NeoSystems Offers Building Blocks". Techweb, 2 pp. (Apr. 21, 1997) No. 732:Channel Assembly.

Faegre, et al. "Unisys' Best-Kept Secret Is An Operating System Built For Distributed Business Applications." Core Technologies / CTOS Revealed, 6 pp. (Dec. 1994).

Boyd-Merritt. "Upgradable-PC Effort Takes Divergent Paths." EE Times Headline News, 3 pp. (1997). http://techweb.cmp.com/eet/news/97/949new/effort.html.

Berst. "Hope For The Modular PCs We all Really Want." ZDNet, 3 pp. (Dec. 5, 1997). http://www.zdnet.com/anchordesk/story/story\_1504.html.

Liquorman. "Convergent Technologies Had This Idea." Talkback to Jesse Berst, 1 pp. (Dec. 5, 1997).

U.S. Appl. No. 12/322,858, filed Feb. 5, 2009, Chu.

Part 3: Carrier sense multiple access with collision detertion (CSMA/CD) access method and physical layer specifications, IEEE Standard 802.3z, The Institute of Electrical and Electronics Engineers, Inc., Jul. 1998, 1262 pages.

Microsoft Cluster Service Center, "MSCS Basics", <<http://www.networks.com/mscsbasics.htm>>, downloaded from web on Feb. 7, 2005, 6 pgs.

Intel Corporation, Intel 82559 Fast Ethernet Controller, [retrieved on Mar. 14, 2011], Retrieved from the Internet: <URL: http://www.intel.com/design/network/products/lan/controllers/82559.htm>, 1 page. Gruener, J., "Vendors Pack in More Servers," PC Week, vol. 14, No. 1, Mar. 17, 1997, 2 pages.

Microsoft Press Computer User's Dictionary, pp. 82 and 232, Kim Fryer ed., Microsoft Press, 1998, 5 pages.

IBM Thinkpad Product Information Guide, IBM PC Company, Apr. 28, 1998, 26 pages.

The American Heritage Dictionary, pp. 536, 607 and 770, Dell Publishing, 1994, 5 pages.

The New IEEE Standard Dictionary of Electrical and Electronics Terms, Fifth Ed., p. 1236, The Institute of Electrical and Electronics Engineers, Inc., 1993, 3 pages.

Microsoft Press Computer Dictionary, Third Ed., pp. 96, 313, and 355, Kim Fryer ed., Microsoft Press, 1997, 5 pages.

IBM Dictionary of Computing, Tenth Ed., pp. 139, 439, 480 and 629, George McDaniel ed., McGraw-Hill, Inc., Aug. 1993, 16 pages.

IEEE 100: The Authoritative Dictionary of IEEE Standards Terms, Seventh Ed., pp. 703, 704, 856 and 1064, The Institute of Electrical and Electronics Engineers, Inc., 2000, 13 pages.

Microsoft Press Computer Dictionary, Second Edition, pp. 82, 92, 93 and 260, Alice Smith ed., Microsoft Press, 1994, 13 pages.

Microsoft Press Computer User's Dictionary, pp. 232, 262, and 275, Kim Fryer ed., Microsoft Press, 1998, 12 pages.

Feibel, W., Encyclopedia of Networking, Third Edition, p. 265, The Network Press, 2000, 4 pages.

IEEE Standard for a High Performance Serial Bus, IEEE Std 1394-1995, The Institute of Electrical and Electronics Engineers, Inc., 1996, 392 pages.

RLX System 324 Hardware Installation Guide, RLX Technologies, Inc., 2001, 80 pages.

RLX System 324 Platform Guide: RLX Linux Web Server, RLX Technologies, Inc., 2001, 73 pages.

RLX System 324 Technical Guide: RLX Control Tower SNMP Implementation, RLX Technologies, 2001, 32 pages.

RLX System 324 Technical Guide: RLX Control Tower SNMP Implementation, Supplementary Document, Draft, RLX Techologies, May 26, 2001, 48 pages.

RLX System 324 Technical Guide: RLX Control Tower Backup/ Restore, Draft, RLX Techologies, May 18, 2001, 8 pages.

"RocketLogix Passive I/O Board Topology," RocketLogix, Inc., Revision 6, May 24, 2000, 1 page.

"RocketLogix Switched I/O Board Topology," RocketLogix, Inc., Revision 6, May 24, 2000, 1 page.

"Redefining Server Economics—Take Control," RLX Technologies, 2001, 2 pages.

RLX Technologies Presentation, RLX Technologies, Inc., Apr. 27, 2001, 44 pages.

"Engineering Design Proposal for RocketLogix, Inc.," Anigma, Inc., Apr. 19, 2000, 35 pages.

RLX Blade, RLX Technologies, 2001, 2 pages.

"RLX System 324 Technical Guide: RLX Red Hat Installation," RLX Technologies, Inc., 2001, 22 pages.

"Firmware Interface Specification, Orbiter 1680, Orbiter 3360," Anigma, Inc., Aug. 17, 2000, 16 pages.

Board Specifications for DataModule Board, DataStation Backplane, DataStation Front Bezel, and BaseStation Backplane, Rev. E, Anigma, Inc., Mar. 2, 2000, 5 pages.

"Logical Management Process," RocketLogix, Rev. 5, Apr. 5, 2000, 1 page.

Eversys Corporation Business Plan, Eversys Corporation, Mar. 21, 1997, 53 pages.

System 8000 Web Product Brief, Eversys Corporation, [retrieved on Oct. 22, 2009], Retrieved from the Internet: <URL: http://www.web.archive.org/web/1997052509465/www.eversys.com/Products/S8000/Brief/Index/htm, 6 pages.

Nicholls, T., "9800 First level design," White Cross Systems Limited, Mar. 26, 1997, 26 pages.

Nicholls, T., "9800 System Architecture," White Cross Systems Limited, Mar. 27, 1997, 28 pages.

Feakes. L., "Fast Ethernet Switch Card Design Specification," Revision 4.00, White Cross Systems Limited, Jul. 27, 2010, 23 pages. Phillips, J., "9800 Power System Backplane Design Specification,"

Revision 1.00, White Cross Systems Limited, Oct. 22, 1997, 11 pages.

Phillips, J., "9800 Auxiliary PSU Design Specification," Revision

1.00, White Cross Systems Limited, Oct. 27, 1997, 13 pages.

"Narus and Whitecross Join Forces to Deliver Comprehensive Usage Pattern Analysis Applications for IP Service Providers," Press Release, Palo Alto, CA, Mar. 27, 2000, 4 pages.

"P6000 Fault-Tolerant Multiprocessor Application Server," Powerstation Technologies, Inc., 1996, 3 pages.

Network Engines P6000 System Guide, Revision C, Network Engines, Inc., Jul. 1998, 89 pages.

Network Engines P6000EXP System Guide, Revision A, Network Engines, Inc., Jan. 1998, 106 pages.

Powerstation Technologies P6000 System Guide, Powerstation Technologies, Inc., 1996, 65 pages.

Network Engines<sup>TM</sup> SBC2000ST Reference Guide, Rev. A, Network Engines, Inc., Oct. 1998, 178 pages.

Network Engines<sup>TM</sup> SBC2000S Reference Guide, Rev. 1.0, Network Engines, Inc., Sep. 1998, 156 pages.

Network Engines<sup>TM</sup> SBC2000 User's Manual, Rev. 1.0, Network Engines, Inc., Jul. 1998, 140 pages.

Network Engines<sup>TM</sup> SBC1000 User's Manual, Rev. E Draft, Network Engines, Inc., Jun. 1998, 78 pages.

Pentium Processor<sup>TM</sup> Network Engines<sup>TM</sup> P586 Guide, Issue 0.0.20 Preliminary, Network Engines, Inc., Nov. 10, 1997, 58 pages.

"PTI Fault Tolerant System Working Document Specification," Rev 0, Feb. 26, 1996, 2 pages.

Network Engines Network, Network Engines, Inc., Jun. 22, 1999, 20 pages.

"HMU—586 Card Guide (Mustang) Pentium PCI," Issue 0.0.14 Preliminary, HM Systems, Inc., Nov. 18, 1996, 57 pages.

"TLD Queries Complete Call Detail Record Database with WhiteCross Data Exploration Server," Data Mining Product Reviews, Feb. 2000, 1 page.

"WhiteCross Data Exploration Announces ExplorationSTUDIO™," Press Release, New York, NY, Sep. 2, 1999, 2 pages.

"WhiteCross Introduces 'World's Most Powerful Exploration Warehouse System," Press Release, New York, NY, Sep. 2, 1999, 2 pages. Charlesworth, I., "Technology Audit, Data Exploration Server," Butler Group, Sep. 1999, 8 pages.

Groom, P., "WhiteCross 9800 pre-release configuration details and USA Pricing Information," WhiteCross Systems Limited, Nov. 3, 1998, 4 pages.

"Kognitio—Infrastructure Partners," Retrieved from the Internet on Sep. 8, 2010, Retrieved at URL: www.kognito.com/partners/infrastructure.php, 2 pages.

RocketLogix Presentation, RocketLogix, Inc., Apr. 6, 2000, 84 pages.

"Expanding the Reach of the Internet with a New Breed of Web Server Appliances," RocketLogix, Inc., May 2000, 10 pages.

Radigan, J., "A Solution to the Power Shortage?" CFO.com, Jan. 17, 2001, [online] Retrieved from the Internet on Dec. 14, 2007, Retrieved at URL: www.cfo.com/article.cfm/2991376?f=singlepage, 3 pages.

Goldman, A, "ISP Profiles: RLX Technologies," ISP-Planet, May 17, 2001, retrieved from the Internet on Jul. 26, 2001, Retrieved at URL: www.isp-planet.com/profiles/2001/rlx.html, 3 pages.

Rosencrance, L., "IBM agrees to resell RLX high-density servers," Computerworld, May 8, 2001, retrieved from the Internet on Jul. 25, 2001, Retrieved at URL: www.itworld.com/Comp/1362/CWD010508STO60353/pfindex.html, 3 pages.

"ChatCom, Inc. Announces Results for the Dec. 31, 1996 Quarter," ChatCom, Inc., Press Release, Feb. 12, 1997, 2 pages.

"ChatCom Defines Specification for Future Consolidated Server Products, RAINS<sup>TM</sup> Concept to Accelerate the Adoption of Consolidated Servers," ChatCom, Inc., Press Release, Mar. 31, 1997, 2 pages. "ChatCom, Inc. Announces PentiumPro/200 MHz Server Module, Server Module Offers Scalability and High Availability for File Server Environments," ChatCom, Inc., Press Release, Mar. 24, 1997, 3 pages.

"ChatCom Strengthens Sales Management Team, Three New Sales Directors to Address Growing Demand for ChatCom's ChatterBox<sup>TM</sup>," ChatCom, Inc., Press Release, Mar. 18, 1997, 2 pages. "ChatCom Announces Major Push into International Markets, Significant International Sales Opportunities for ChatCom's Consolidated Server Technology," ChatCom, Inc., Press Release, Mar. 18, 1997, 2 pages.

"ChatCom Receives Product Award From LAN Times Magazine, Consolidated Server Product Comparison Puts ChatCom on Top," ChatCom, Inc., Press Release, Feb. 20, 1997, 2 pages.

"Astro Sciences Corporation Shareholders Elect Two New Directors, and Vote to Change Corporate Name to ChatCom, Inc.," Astro Sciences Corporation, Press Release, Feb. 12, 1996, 2 pages.

"ChatCom, Inc., (Formerly Astro Sciences Corporation) Trades Under New Symbol—NASDAQ/NMS: Chat," ChatCom, Inc., New Release, Feb. 22, 1996, 1 page.

"ChatCom Names James B. Mariner President/CEO," ChatCom, Inc., Press Relase, Mar. 7, 1996, 2 pages.

"ChatCom Selected as Partner in Anixter Race '96 Program and Completes First Part of Financing," ChatCom, Inc., Press Release, Mar. 26, 1996, 2 pages.

"Astro Sciences Corporation Announces Results for The Third Quarter," Astro Sciences Corporation, Press Release, Feb. 8, 1996, 2 pages.

"Telecom Australia to Receive Astro Sciences/J&L 486 Services," Astro Sciences Corporatoin, Press Release, Jan. 4, 1996, 1 page.

"Astro Sciences Receives Microsoft Certification and Announces New Director," Astro Sciences Corporation, Press Release, Nov. 21, 1995, 2 pages.

"Astro Sciences Corp. Announces Results for Second Quarter," Astro Sciences Corporation, Press Release, Nov. 17, 1995, 2 pages.

"Astro Sciences Corp. Signs Agreement With Storage Computer Corp.," Astro Sciences Corporation, Press Release, Nov. 7, 1995, 2 pages.

"Astro Sciences Corporation Appoints Interim President/CEO Board Expanded by Two Seats," Astro Sciences Corporation, Press Release, Aug. 17, 1995, 1 page.

"Astro Sciences Corporation Announces Results for the First Quarter of the Fiscal Year," Astro Sciences Corporation, Press Release, Aug. 3, 1995, 1 page.

"Astro Sciences Corporation Retains Technology Strategies and Alliance Partners," Astro Sciences Corporation, News Release, Jun. 29, 19951 page.

"Astro Sciences Corporation Receives Patent For Network Security and Management," Astro Sciences Corporation, News Release, Jun. 6, 1995, 2 pages.

"Astro Sciences Corporation Introduces New Generation of Products at PC Expo Show," Astro Sciences Corporation, Press Release, Jun. 23, 1995, 1 page.

"Astro Sciences Corporation Announces Results for the Fourth Quarter and the Fiscal Yeart," Astro Sciences Corporation, News Release, Jun. 26, 1995, 1 page.

"Astro Sciences Corporation Announces Signing of \$4 Million Credit Facility With Deutsche Financial Services," Astro Sciences Corporation, News Release, May 19, 1995, 1 page.

"Astro Sciences Corporation to Strengthen Management Team Board," Astro Sciences Corporation, News Release, Apr. 21, 1995, 1 page.

"J&L Announces their ChatExpress—P75Applications Server at Networks Expo," J&L Information Systems, Press Release, Feb. 13, 1994, 3 pages.

"J&L Information Systems Announces two DX4 for their ChatterBox Family of Remote Access Servers," J&L Information Systems, Press Release, Feb. 13, 1994, 2 pages.

"J&L Announces the NRS-T10RS<sup>TM</sup> a Fault Tolerant Applications Server Platform at FOSE," J&L Information Systems, Press Release, Mar. 20, 1994, 2 pages.

"J&L Announces their ChatAccess™ Family of Remote LAN Node Servers at Networld+Intertop Las Vegas," J&L Information Systems, Press Release, Mar. 27, 1994, 2 pages.

"J&L Announces ChatExpress—P120 Rackmounted Applications Server at PC Expo, New York," J&L Information Systems, Press Release, Jun. 19, 1994, 2 pages.

"ChatCom Books Additional Orders with Major Facilities—Based Carrier Companies, ChatCom Products Provide Internet Platforms for Carrier's Customers Worldwide," ChatCom, Inc., Press Release, Mar. 12, 1997, 2 pages.

"ChatCom Announces Comprehensive VAR Program, Commitment to VARs is Key to Corporate Strategy," ChatCom, Inc., Press Release, Jan. 13, 1997, 1 page.

"ChatCom, Inc. Reports Completion of \$2.5 Million Private Placement," ChatCom, Inc., Press Release, Jan. 9, 1997, 2 pages.

"ChatCom Announces Mass Storage Subsystem, ChatRAID to Address Application Server Market," ChatCom, Inc., Press Release, Aug. 12, 1996, 1 page.

"ChatCom, Inc. Announces Commitment to ISO 9001 Quality Certification, ISO 9001 Quality Control Programs are High Priority Company Imperative," ChatCom, Inc., Press Release, Aug. 1, 1996, 1 page.

"ChatCom Adds New Senior Management Team Members," ChatCom, Inc., Press Release, Jul. 2, 1996, 1 page.

"ChatCom Announces Mass Storage Subsystem, ChatRAID to Address Application Server Market," ChatCom, Inc., Press Release, Aug. 14, 1996, 2 pages.

"ChatCom Announces Complete Line of Scaleable Application and Communication Servers," ChatCom, Inc., Press Release, Aug. 30, 1996, 4 pages.

"ChatCom, Inc. Announces Highly Adaptable Intranet and Web Servers, Servers reduce costs associated with radical change," Press Release, Sep. 3, 1996, 1 page.

J&L Introduces Twin Pentium for ChatterBox Systems, J&L Information Systems, Press Release, Jan. 29, 1996, 1 page.

"ChatterBox/SAS<sup>TM</sup>—Scaleable Access Server<sup>TM</sup>," J&L Information Systems, Networks Expo—Boston '96, Dec. 22, 1995, 1 page. "J&L Information Systems Announces ChatPower-Plus<sup>TM</sup> a Revolutionary Redundant Power Supply System," J&L Information Systems, Press Release, Jun. 19, 1995, 2 pages.

"J&L Announces ChatAccess/PCTM, a PCMCIA Based Remote LAN Node Server," J&L Information Systems, Press Release, Jun. 19, 1995, 2 pages.

"J&L Announces Two Patents," J&L Information Systems, Press Release, Feb. 9, 1995, 1 page.

"J&L Announces their ChatExpress—P100 Rackmounted Applications Server at Networks Expo. Boston," J&L Information Systems, Press Release, Feb. 13, 1994, 3 pages.

"J&L Doubles the Rack-Mounted Communications Server Density with ChatVantage/486<sup>TM</sup>," J&L Information Systems, Press Release, Sep. 11, 1995, 2 pages.

"ChatCom, Inc. Announces Results for the Jun. 30 Quarter," ChatCom, Inc., News Release, Aug. 16, 1996, 2 pages.

"Introducing the new ChatterBox<sup>TM</sup> Corporate and Office Series . . . the Power Behind Your Network," ChatCom, Inc., May 31, 1996, 15 pages.

"ChatterBox Communications and Server Solutions," ChatCom, Inc., Mar. 7, 1996, 12 pages.

"ChatterBox Communications and Server Solutions Products," ChatCom, Inc., Apr. 24, 1996, 7 pages.

Lazik, G., "Remote Access—a Historical Perspective," Network News, vol. 3, No. 7, NPA The Network Professional Association, Jul. 1994, 6 pages.

Lazik, G., "Remote Access—Part II, Cost Analysis," Network News, vol. 3, No. 8, NPA The Network Professional Association, Sep. 1994, 5 pages.

"Plexnet<sup>TM</sup> Product Overview," Plexcom, Inc., 1992, 8 pages.

"Thin Client Servers High-Speed Data Switching Technical Summary," QuantumNet, Inc., Aug. 29, 2010, 28 pages.

Facsimile from Procrass to Paunovich attaching "QuantumNet Network Computing Systems," Aug. 30, 2010, 8 pages.

World Wide System Price Guide, Network Engines, Inc., Sep. 26, 1997, 10 pages.

P6000 System Price Guide, Network Engines, Inc., Feb. 24, 1998, 9 pages.

"Venture financing is fuel for Powerstation's Growth Plans," Mass High Tech Communications, Inc., Jun. 2, 1997, 1 page.

Grigonis, R., "Life-Saving Computers: Network Engines," Computer Telephony, Sep. 1997, 1 page.

Rodgers, A., "NT Clustering Hardware Readied, Vendor Racks up Windows NT Clustering Options at NetWorld+Interop," Internetweek, Oct. 20, 1997, 1 page.

"Network Engines Awarded Best of Show at Networld + Interop 97, New company debuts product and wins," Network Engines, Inc., Press Release, Oct. 14, 1997, 2 pages. Network Engines Website, Network Engines, Inc., [retrieved on Feb. 27, 1998], Retrieved from the Internet: <URL: http://www.networkengines.com/>, 12 pages.

Network Engines, Inc., Company Overview, Aug. 26, 2010, 21 pages. Network Engines ClusterDirector Users' Manual, Revision B, Network Engines, Inc., Jun. 1998, 88 pages.

Network Engines ClusterDirector Users' Manual, Network Engines, Inc., Jan. 1998, 52 pages.

MP700 User Guide, Issue 0.0.89, Network Engines, Inc., Oct. 16, 1997, 29 pages.

"ClusterDirector<sup>TM</sup> Product Description, Fault Tolerance for Industry Standard Processors, Operating Systems, and Applications," Network Engines, Inc., 1998, 4 pages.

"Network Engines Announces New Clustered Application Servers for Web, Thin-Client and Windows NT Enterprise Environments," Network Engines, Inc., Press Release, Oct. 8, 1997, 3 pages.

"Network Engines Announces Partnership With Telegration Associates, Inc.," Network Engines, Inc., Press Release, Dec. 10, 1997, 2 pages.

"Network Engines Debuts ClusterDirector in Internet/Intranet Load Balanced Environment," Network Engines, Inc., Press Release, Jan. 27, 1998, 3 pages.

Stallings, W., "Computer Organization and Architecture—Designing for Performance," Sixth Edition, Pearson Education, Inc., 2003, pp. 69-89.

Hill, Goff (editor), "The Cable and Telecommunications Professional's Reference: vol. 1," Third Edition, Focal Press, 2007, pp. 225-229, 7 pages.

Dell, Inc., White Paper, "PCI Express Technology," Feb. 2004, pp. 1-11.

Athavale, A., "How to Lower the Cost of PCI Express Adoption by Using FPGAs," EETimes Design [online] Apr. 26, 2006, [retrieved on May 3, 2011]. Retrieved from the Internet at <URL: http://www.eetimes.com/General/

DisplayPrintViewContent?contentItemID=4014824>, 6 pages.

Thoms, I., "IBM Hit with \$9M Judgment in Server Patent Suit," Law360 [online], [retrieved on May 3, 2011], Retrieved from the Internet at <URL: http://www.law360.com/articles/229575/print?section=ip>, 2 pages.

McKenzie, L., "Fujitsu Reaches Deal in Acqis Blade Server IP Spat," Law360 [online], [retrieved on Jun. 16, 2010], Retrieved from the Internet at <URL: http://ip.law360.com/print\_article/175004>, 2 pages.

PCI Local Bus Specification, Rev. 2.1, The PCI Special Interest Group, Jun. 1, 1995, 298 pages.

"National Semiconductor Design Guide," LVDS Owner's Manual, Spring 1997, 65 pages.

Intel Corporation, "PCI Express\* to PCI-X\* Bridge Architecture: Where Interface Standards Meet," 2003, 8 pages.

Desai, D.M. et al., "BladeCenter system overview," IBM Journal of Research and Development, vol. 49, No. 6, Nov. 2005, pp. 809-821, 13 pages.

Spring, Tom, "Top of the News—Broadband Users Still Sing the Blues," PC World, Jun. 2011, pp. 42-54, 13 pages.

San Jose Mercury News, "Business & Stocks—Top Stories from The Mercury News," Jun. 28, 2001, [online], [retrieved on Jun. 30, 2001], Retrieved from the Internet at <URL: http://www0.mercurycenter.com/premium/business/docs technews28.htm>, 5 pages.

"iMod Pad," Wired Magazine, Mar. 2001, 1 page.

"Amended Invalidity Chart For Base Reference Network Engines P6000 Server," submitted by the Defendants in connection with Case No. 6:09-cv-148-LED on Jun. 4, 2010, 64 pages.

Email from Emanuel to Juarez including Invalidity Chart for Base Reference IBM BladeCenter, submitted by the Defendants in connection with Case No. 6:09-cv-148-LED, dated Aug. 20, 2010, 54 pages.

Letter from Martiniak to Byers regarding Proposed Amendment to the Invalidity Contentions based on products from RLX Systems and a description of RLX products, dated Jul. 15, 2010, 2 pages.

Defendant's Invalidty Chart for Base Reference RLX System 324, proposed in connection with Case No. 6:09-cv-148-LED on Jul. 15, 2010, 58 pages.

"Disclosure of Asserted Claims and Infringement Contentions," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED, served on Sep. 14, 2009, 5 pages.

"Exhibit 1, Disclosure of Asserted Claims and Infringement Contentions for Defendant Appro International, Inc.," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED, served on Sep. 14, 2009, 105 pages.

"Exhibit 2, Disclosure of Asserted Claims and Infringement Contentions for Defendant ClearCube Technology, Inc.," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED, served on Sep. 14, 2009, 163 pages.

"Exhibit 3, Disclosure of Asserted Claims and Infringement Contentions for Defendant Dell Inc.," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED, served on Sep. 14, 2009, 184 pages.

"Exhibit 4, Disclosure of Asserted Claims and Infringement Contentions for Defendant Fujitsu America, Inc.," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED, served on Sep. 14, 2009, 210 pages.

"Exhibit 7, Disclosure of Asserted Claims and Infringement Contentions for Defendant NEC Corp. of America," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED, served on Sep. 14, 2009, 166 pages.

"Exhibit 9, Disclosure of Asserted Claims and Infringement Contentions for Defendant Super Micro Computer, Inc.," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED, served on Sep. 14, 2009, 220 pages.

"Disclosure of Plaintiff's Reduced List of Asserted Claims," submitted by the Plaintiff in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-00148-LED, served on Jul. 30, 2010, 6 pages.

"Memorandum Opinion and Order Construing Claim Terms and Denying Defendants' Motion for Partial Summary Judgment," Issued by the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED on Aug. 2, 2010, 18 pages.

"Jury Verdict Form," Returned by the Jury in the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED on Februrary 23, 2011, 2 pages.

"Final Judgement," Issued by the U.S. District Court for the Eastern District of Texas, Case No. 6:09-cv-148-LED on Mar. 1, 2011, 1 page.

"Complaint for Patent Infringement," Acqis v. Appro Int'l, Inc. et al., Case No. 6:09-cv-00148, filed Apr. 2, 2009, 13 pages.

"First Amended Complaint for Patent Infringement," *Acqis* v. *Appro Int'l, Inc. et al.*, Case No. 6:09-cv-00148, filed May 18, 2009, 14 pages.

"Defendant Clearcube Technology, Inc.'s Answer, Counterclaims to Acqis LLC's First Amended Complaint for Patent Infringement, and Jury Demand," Case No. 6:08-cv-00148, filed Jul. 2, 2009, 28 pages. "Defendant Nex Computers Technology, Inc.'s Answer to Acqis LLC's First Amended Complaint for Patent Infringement, and Jury Demand," Case No. 6:09-cv-00148-LED, filed Jul. 8, 2009, 16 pages. "Defendant Hitachi Ameirca, Ltd.'s, Answer to Acqis LLC's First Amended Complaint for Patent Infringement, and Affirmative Defenses and Counterclaims," Case No. 6:09-cv-00148-LED, filed Jul. 8, 2009, 22 pages.

"Defendant International Business Machines Corp.'s Answer to Acqis LLC's First Amended Complaint, Affirmative Defenses, and Counterclaims," Case No. 6:09-cv-148-LED, filed Jul. 8, 2009, 22 pages.

"Second Amended Complaint for Patent Infringement," *Acqis* v. *Appro Int'l, Inc. et al.*, Case No. 6:09-cv-00148, filed Jul. 22, 2009, 49 pages.

"Defendant Appro's Answer, Affirmative Defenses, and Counterclaims to Acqis LLC's Second Amended Complaint for Patent Infringement," Case No. 6:09-cv-148, filed Aug. 5, 2009, 43 pages. "Defendant International Business Machines Corp.'s Answer to Acqis LLC's Second Amended Complaint, Affirmative Defenses, and Counterclaims," Case No. 6:09-cv-148-LED, filed Aug. 10, 2009, 28 pages.

"Defendant Super Micro Computer, Inc.'s Answer and Counterclaims to Acqis LLC's Second Amended Complaint for Patent Infringement," Case No. 6:09-cv-148, filed Aug. 10, 2009, 96 pages. "Defendant Sun Microsystems, Inc.'s Answer and Counterclaims to Acqis LLC's Second Amended Complaint for Patent Infringement," Case No. 6:09-cv-148, filed Aug. 10, 2009, 95 pages.

"NEC Corporation of America's Answer, Affirmative Defenses, and Counterclaims to Acqis LLC's Second Amended Complaint for Patent Infringement," Case No. 6:09-cv-00148-LED, filed Aug. 10, 2009, 38 pages.

"Answer to Plaintiff's Second Amended Complaint and Counter-claims of Defendant Fujitsu Computer Systems Corp., n/k/a/ Fujitsu America, Inc. to Acqis LLC's Second Amended Complaint for Patent Infringement," Case No. 6:09-cv-00148-LED, filed Aug. 10, 2009, 34 pages.

"Answer, Affirmative Defenses, and Counterclaims of Defendant Hewlett-Packard Company to Acqis LLC's Second Amended Complaint for Patent Infringement," Case No. 6:09-cv-148-LED, filed Aug. 10, 2009, 40 pages.

"Defendant Clearcube Technology, Inc.'s Answer, Counterclaims to Acqis LLC's Second Amended Complaint for Patent Infringement, and Jury Demand," Case No. 6:08-cv-00148, filed Aug. 10, 2009, 39 pages.

"Dell's Answer and Counterclaims to Acqis LLC's Second Amended Complaint," Case No. 6:09-cv-00148-LED, filed Aug. 10, 2009, 36 pages.

"Defendant Nex Computers Technology, Inc.'s Answer to Acqis LLC's Second Amended Complaint for Patent Infringement, and Jury Demand," Case No. 6:09-cv-00148-LED, filed Aug. 10, 2009, 28 pages.

"Defendant Clearcube Technology, Inc.'s First Amended Answer, Counterclaims to Acqis LLC's Second Amended Complaint for Patent Infringement and Jury Demand," Case No. 6:09-cv-00148, filed Aug. 11, 2009, 39 pages.

"Plaintiff Acqis LLC's Answer to Defendant Appro International, Inc.'s Counterclaims," Case No. 6:09-00148-LED, filed Aug. 28, 2009, 16 pages.

"Defendant Clearcube Technology, Inc.'s Second Amended Answer Counterclaims to Acqis LLC's Second Amended Complaint for Patent Infringement and Jury Demand," Case No. 6:09-CV-00148, filed Aug. 31, 2009, 45 pages.

"Plaintiff Acqis LLC's Answer to Defendant International Business Machines Corp.'s Counterclaims," Case No. 6:09-00148-LED, filed Sep. 2, 2009, 11 pages.

"Plaintiff Acqis LLC's Answer to Defendant Super Micro Computer, Inc.'s Counterclaims," Case No. 6:09-00148-LED, filed Sep. 2, 2009, 15 pages.

"Plaintiff Acqis LLC's Answer to Defendant Sun Microsystems, Inc.'s Counterclaims," Case No. 6:09-cv-00148-LED, filed Sep. 2, 2009, 14 pages.

"Plaintiff Acqis LLC's Answer to Defendant Dell Inc.'s Counterclaims," Case No. 6:09-00148-LED, filed Sep. 2, 2009, 16 pages.

"Plaintiff Acqis LLC's Answer to Defendant Fujitsu Computer Systems Corp., N/K/A Fujitsu America, Inc.'s Counterclaims," Case No. 6:09-00148-LED, filed Sep. 16, 2009, 7 pages.

"Plaintiff Acqis LLC's Answer to Defendant Hewlett-Packard Company's Counterclaims," Case No. 6:09-00148-LED, filed Sep. 16, 2009, 14 pages.

"Plaintiff Acqis LLC's Answer to Defendant NEC Corporation of America's Counterclaims," Case No. 6:09-00148-LED, filed Sep. 16, 2009, 8 pages.

"Defendant Clearcube Technology, Inc.'s Third Amended Answer to Acqis LLC's Second Amended Complaint for Patent Infringement and Jury Demand," Case No. 6:09-cv-00148, filed Nov. 11, 2009, 26 pages.

"Defendant Clearcube Technology, Inc.'s Fourth Amended Answer to Acqis LLC's Second Amended Complaint for Patent Infringement and Jury Demand," Case No. 6:09-cv-00148, filed Jan. 8, 2010, 26 pages.

"Dell's First Amended Answer and Counterclaims to Plaintiff's Second Amended Complaint," Case No. 6:09-cv-00148-LED, filed Apr. 22, 2010, 38 pages.

"Plaintiff Acqis LLC's Answer to Defendant Dell Inc.'s First Amended Counterclaims," Case No. 6:09-00148-LED, filed May 10, 2010, 16 pages.

"Affidavit of Timothy P. Cremen in Support of NEC Corporation of America's Opposition to Plaintiff's Motion to Dismiss and Strike," Case No. 6:09-cv-00148-LED, filed Oct. 9, 2009, 4 pages.

"Comparison [by NEC] of Rejected Elements in Office Action and Elements of Exemplary Claims of Acqis's Patents," Case No. 6:09-cv-00148-LED, filed Oct. 9, 2010, 7 pages.

"Defendant NEC Corporation of America's Opposition to Plaintiffs Motion to Dismiss and Motion to Strike," Case No. 6:09-cv-00148-LED, filed Oct. 9, 2010, 36 pages.

"Motion to Dismiss Counterclaim Pursuant to Rule 12(b)(6) and Motion to Strike Affirmative Defense Pursuant to Rule 12(f)," Case 6:09-00148-LED, filed Sep. 16, 2009, 18 pages.

"Transcript of Videotaped Deposition of William Mangione-Smith," taken by the Defendants in connection with Case No. 6:09-cv-148-LED in the U.S. District Court for the Eastern District of Texas, Sep. 9, 2010, 192 pages.

"Defendant Sun Microsystems, Inc.'s Responses and Objections to Plaintiff Acqis LLC's Second Set of Common Interrogatories," Case No. 6:09-cv-00148-LED, filed May 12, 2010, 9 pages.

"Plaintiff Acqis LLP's Objections and Responses to Defendants' First Set of Interrogatories," Case No. 6:09-cv-00148-LED, filed Aug. 5, 2010, 21 pages.

"Plaintiff Acqis LLP's Objections and Responses to Defendants' Third Set of Interrogatories," Case No. 6:09-cv-00148-LED, filed Aug. 5, 2010, 13 pages.

"Plaintiff Acqis LLP's First Supplemental Objections and Responses to Defendants' Third Set of Interrogatories," Case No. 6:09-cv-00148-LED, filed Aug. 5, 2010, 14 pages.

"Declaration of Jennifer Chen in Support of Defendants' Motion for Leave to Amend Defendants' Invalidity Contentions," Case No. 6:09cv-00148-LED, Aug. 5, 2010, 3 pages.

Excerpts of Transcript of "Videotaped Deposition of William W.Y. Chu," taken by the Defendants in connection with Case No. 6:09-cv-148-LED in the U.S. District Court for the Eastern District of Texas, Jun. 7, 2010, 20 pages.

"Declaration of Monty McGraw in Support of Defendants' Motion for Leave to Amend Defendants' Invalidity Contentions," Case No. 6:09-cv-00148-LED, Aug. 5, 2010, 3 pages.

"Plaintiff's Opening Brief Regarding Claim Construction," Case No. 6:09-cv-00148-LED, filed Jun. 1, 2010, 35 pages.

"Declaration of Carolyn V. Juarez in Support of Plaintiff Acqis LLC's Opening Brief Regarding Claim Construction," Case No. 6:09-cv-00148-LED, filed Jun. 1, 2010, 3 pages.

"Defendant's Brief in Response to Plaintiff's Opening Brief Regarding Claim Construction," Case No. 6:09-cv-00148-LED, filed Jun. 15, 2010, 40 pages.

"Proposed Claim Construction Statement," Case No. Case No. 6:09-cv-00148-LED, filed Jun. 15, 2010, 39 pages.

"Claim Chart for International Business Machines Corp.," Case No. 6:09-cv-00148-LED, filed Jun. 15, 2010, 12 pages.

"Acqis LLC's Disclosure of Proposed Terms and Claim Elements For Construction Pursuant to Patent Rule 4-1," Case No. 6:09-cv-00148-LED, filed Mar. 5, 2010, 3 pages.

"Defendant's List of Proposed Terms and Claim Elements for Construction," Case No. 6:09-cv-00148-LED, filed Mar. 5, 2010, 15 pages.

"Defendant's Amended List of Proposed Terms and Claim Elements for Construction," Case No. 6:09-cv-00148-LED, filed Mar. 31, 2010, 11 pages.

"Defendant's Corrected List of Proposed Terms and Claim Elements for Construction," Case No. 6:09-cv-00148-LED, filed Apr. 2, 2010, 9 pages.

"Acqis, LLC's P.R.-4-2 Disclosure of Preliminary Claim Constructions and Extrinsic Evidence," Case No. 6:09-cv-00148-LED, filed Apr. 14, 2010, 10 pages.

"Defendant's P.R.-4-2 Disclosure of Preliminary Claim Constructions and Extrinsic Evidence," Case No. 6:09-cv-00148-LED, filed Apr. 14, 2010, 16 pages.

"Joint Claim Construction Statement," Case No. 6:09-cv-00148-LED, filed Apr. 30, 2010, 46 pages. "Corrected p. 13 of Plaintiff's Opening Brief Concerning Claim Construction (D.I. 261)," Case No. 6:09-cv-00148-LED, filed Jun. 2, 2010, 2 pages.

"Plaintiffs Reply Brief Regarding Claim Construction," Case No. 6:09-cv-00148-LED, filed Jun. 28, 2010, 14 pages.

Final Office Action for U.S. Appl. No. 12/561,138, mailed Mar. 17, 2011, 5 pages.

Agerwala, T. et al., "SP2 System Architecture", IBM Systems Journal, vol. 34, No. 2 (1995).

Bernal, Carlos, product brochure entitled: "PowerSMP Series 4000", (Mar. 1998) <<a href="http://www/winnetmag.com/Windows/Article/ArticleID/3095//3095.html">http://www/winnetmag.com/Windows/Article/ArticleID/3095//3095.html</a>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cragle, Jonathan, "Density System 1100", (May 1999) << http://www.winnetmag.com/Windows/Article/ArtideID/5199/5199.

html>>, downloaded from web on Jun. 21, 2004, 3 pgs.

Feldman, Jonathan, "Rack Steady: The Four Rack-Mounted Servers That Rocked Our Network", <<a href="http://www.networkcomputing.com/shared/printArtide.jhtml?article=/910/910r3sidel.htm...>> Jun. 23, 2004, 3 pgs.

Fetters, Dave, "Cubix High-Density Server Leads the Way With Standout Management Software", (Feb. 8. 1999) << http://www.nwc.com/shared/printArticle.jhtml?article=/1003/1003r3full.html

&pub=nwc>>, downloaded from web on Jun. 23, 2004, 5 pgs.

Gardner, Michael and Null, Christopher, "A Server Condominium", <<http://www.lantimes.com/testing/98jun/806a042a.html>>, Jun. 23, 2004, 3 pgs.

Harrison, Dave, "VME in the Military: The M1A2 Main Battle Tank Upgrade Relies on COTS VME" <<ht>http://www.dy4.com>>, (Feb. 9, 1998), pp. 1-34.

Williams, Dennis, "Consolidated Servers", (Feb. 17, 1997) << http://www.lantimes.com/testing/97compare/pcconsol.html>> down-loaded from web on Jun. 23, 2004, 2 pgs.

Williams, Dennis, "Executive Summary: Consolidate Now", (Feb. 17, 1997) <<a href="http://www.lantimes.com/testing/97feb/702b064a">http://www.lantimes.com/testing/97feb/702b064a</a>. html>> downloaded from web on Jun. 23, 2004, 2 pgs.

Williams, Dennis, "Top "Scores for Useability and Openness", (Feb. 17, 1997) <<a href="http://www.lantimes.com/testing/97feb/702b064a">http://www.lantimes.com/testing/97feb/702b064a</a>. html>> downloaded from web on Jun. 23, 2004, 2 pgs.

Williams, Dennis, "ChatCom Inc. Chatterbox", (Feb. 17, 1997) <<a href="http://www.lantimes.com/testing/97feb/702b066a.html">http://www.lantimes.com/testing/97feb/702b066a.html</a>> downloaded from web on Jun. 23, 2004, 3 pgs.

Williams, Dennis, "Eversys Corp. System 8000", (Feb. 17, 1997) <<ht>http://www.lantimes.com/testing/97feb/702b070b.html>> downloaded from web on Jun. 22, 2004, 4 pgs.

Williams, Dennis, "Cubix Corp. ERS/FT II", (Feb. 17, 1997) <<a href="http://www.lantimes.com/testing/97feb/702b068b.html">http://www.lantimes.com/testing/97feb/702b068b.html</a>> downloaded from web on Jun. 23, 2004, 4 pgs.

Crystal Group, "Rackmount Computers", (© 2000-2004) <<a href="http://www.crystalpc.com/products/roservers.asp">http://www.crystalpc.com/products/roservers.asp</a>, downloaded from web on Jun. 17, 2004, 8 pgs.

Crystal Group, "QuickConnect® Cable Management", (© 2000-2004) <<a href="http://www.crystalpc.com/products/quickconnect.asp">http://www.crystalpc.com/products/quickconnect.asp</a>> downloaded from web on Jun. 17, 2004, 4 pgs.

Cubix Product Brochure entitled, "Density System", (© 2000) <<a href="http://64.173.211.7/support/techinfo/system/density/density10.">http://64.173.211.7/support/techinfo/system/density/density10.</a> htm>> downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix Product Brochure entitled, "Density System, Technical Specifications", (©2000) << http://64.173.211.7/support/techinfo/system/density/info/spec.htm>> downloaded from web on Jun. 22, 2004, 2

Cubix Product Manual entitled, "Density System", Chapter 1—Introduction, (© 2000) <<a href="http://64.173.211.7/support/techinfo/manuals/density/Chap-1.htm">http://64.173.211.7/support/techinfo/manuals/density/Chap-1.htm</a> downloaded from web on Jun. 22, 2004, 5 pgs.

Cubix, "Click on the front panel that matches your system", (© 2000) <<a href="http://64.173.211.7/support/techinfo/system/density/density/">http://64.173.211.7/support/techinfo/system/density/density/</a>.

htm>>, downloaded from web on Jun. 22, 2004, 1 pg.

Cubix Product Manual entitled, "Density System", Chapter 2—Installation, (© 2000) <<a href="http://64.173.211.7/support/techinfo/manuals/density/Chap-2.htm">http://64.173.211.7/support/techinfo/manuals/density/Chap-2.htm</a> downloaded from web on Jun. 22, 2004, 9 pgs.

Cubix Product Manual entitled, "Density System", Chapter 3—Operation, (© 2000) <<a href="http://64.173.211.7/support/techinfo/manuals/density/Chap-3.htm">http://64.173.211.7/support/techinfo/manuals/density/Chap-3.htm</a> downloaded from web on Jun. 22, 2004, 4 pgs.

Cubix Product Manual entitled, "Density System", Chapter 4—Maintenance and Repair, (© 2000) <<a href="http://64.173.211.7/sup-port/techinfo/manuals/density/Chap-4.htm">http://64.173.211.7/sup-port/techinfo/manuals/density/Chap-4.htm</a> downloaded from web on Jun. 22, 2004, 5 pgs.

Cubix, "What are Groups?", (© 2000) <<a href="http://64.173.211.7/sup-port/techinfo/system/density/info/groups.htm">http://64.173.211.7/sup-port/techinfo/system/density/info/groups.htm</a>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "SP 5200XS Series Plug-in Computers", (© 2000) <<a href="http://64.173.211.7/support/techinfo/bc/sp5200xs/intro.htm">http://64.173.211.7/support/techinfo/bc/sp5200xs/intro.htm</a>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "SP 5200XS Series Technical Specifications", (© 2000) << http://64.173.211.7/support/techinfo/bc/sp5200xs/spec.htm>>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "SP 5200 Series" Chapter 1—Introduction, (© 2000) <<http://64.173.211.7/support/techinfo/manuals/s 5200/chap-1. htm>>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "SP 5200 Series" Chapter 2—Switches & Jumpers, (© 2000) <<a href="http://64.173,211.7/support/techinfo/manuals/sp5200/chap-2">http://64.173,211.7/support/techinfo/manuals/sp5200/chap-2</a>.

htm>>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "SP 5200 Series" Chapter 3—Installation, (© 2000) << http://64.173.211.7/support/techinfo/manuals/sp5200/chap-3.htm>>, downloaded from web on Jun. 22, 2004, 4 pgs.

Cubix, "SP 5200 Series" Chapter 4—Technical Reference, (© 2000) << http://64.173.211.7/support/techinfo/manuals/sp5200/chap-4.

htm>>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "DP 6200 'D' Series Plug-in Computers" <<http://64.173. 211.7/support/techinfo/bc/dp/6200d/intro.htm>>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "Installing DP or SP Series Boards" (© 2000) <<a href="http://64.173.211.7/support/techinfo/bc/dp/6200d/intro.htm">>>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "Powering On/Off or Resetting Plug-in Computers in an Density System", (© 2000) <<a href="http://64.173.211.7/support/techinfo/system/density/info/power.htm">http://64.173.211.7/support/techinfo/system/density/info/power.htm</a>>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "Multiplexing Video, Keyboard & Mouse with Multiple Density Systems", (© 2000) << http://64.173.211.7/support/techinfo/system/density/info/vkm-mux.htm>>, downloaded from web on Jun. 22, 2004, 2 pgs.

eBay Advertisement for "Total IT Group Network Engines", <<a href="http://cgi.ebay.com/we/eBayISAPI.dll?ViewItem">http://cgi.ebay.com/we/eBayISAPI.dll?ViewItem</a>

&item=5706388046

&sspagename+STRK%3AMDBI%3AMEBI3AIT&rd=1>>, downloaded from web on Jun. 25, 2004, 1 pg.

"Features Chart", (Feb. 1, 1997) <<a href="http://lantimes.com/testing/97feb/702b072a.html">http://lantimes.com/testing/97feb/702b072a.html</a>>, downloaded from web on Jun. 23, 2004, 3 pgs.

Internet Telephony Roundup, "Industrial Computers" << http://www.tmcnet.com/articles/itmag/0499/0499roundup.htm>>, downloaded from web on Jun. 23, 2004, pp. 1-5.

Press Release: "Crystal Group Products Offer Industrial PCs with Built-in Flexibility", Hiawatha, Iowa, (Mar. 1, 1997) <<a href="http://www.crystalpc.com/news/pressreleases/prodpr.asp">http://www.crystalpc.com/news/pressreleases/prodpr.asp</a>>, downloaded from web on May 14, 2004, 2 pgs.

Press Release: "Enhanced COTS SBC from DY 4 Systems features 166MHz Pentium<sup>TM</sup> Processor" Kanata, Ontario, Canada, (Apr. 1998) <<a href="http://www.realtime-info.be/">http://www.realtime-info.be/</a> VPR/layout/display/pr.asp-?PRID=363>>, 2 pgs.

DY 4 Systems, Inc., SVME/DM-192 Pentium® II Single Board Computer (Jun. 1999) pp. 1-9.

Bomara Associates, "System 8000", <<http://www.bomara.com/ Eversys/briefDefault.htm>>, downloaded from web on Jun. 22, 2004, 4 pgs.

Cubix, "ERS/FT II System", (© 2000) <<a href="http://64.173.211.7/sup-port/techinfo/system/ersft2/ersft2.htm">http://64.173.211.7/sup-port/techinfo/system/ersft2/ersft2.htm</a>, downloaded from web on Jun. 22, 2004, 4 pgs.

Cubix, "ERS II and ERS/ FT II", Chap. 3, System Components, <<a href="http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c3">http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c3</a>.

htm>>, downloaded from web on Jun. 22, 2004, 21 pgs.

Product Manual entitled: "ERS II and ERS/FT II", Chap. 6, Component Installation, <<a href="http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c6.htm">http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c6.htm</a>>, downloaded from web on Jun. 22, 2004, 18 pgs. Windows Magazine, "Cubix PowerSMP Series 4000", Nov. 1997, <a href="http://www.techweb.com/winmag/library/1997/1101/ntent008">http://www.techweb.com/winmag/library/1997/1101/ntent008</a>.

htm>> downloaded from the web on Jun. 22, 2004, p. NT07.

CETIA Brochure "CETIA Powerengine CVME 603e" pp. 1-6 downloaded from the internet @ http://www.cetia.com/Products\_Addons/wp-47-01.pdf. on Feb. 15, 2006.

MPL Brochure, "The First Rugged AI in One Industrial 486FDX-133 Mhz PC", (1998), pp. 53.

MPL Brochure "IPM 486 Brochure/IPM5 User Manual", pp. 1-9, downloaded from the internet @ http://www.mplch/DOCS./u48600xd.pdf on Feb. 15, 2006.

Snyder, Joel, "Better Management Through Consolidation," pp. 1-6 http://www.opus1.com/www/jms/nw-con-0818rev.html. (Aug. 18, 1997).

Eversys Corporation, "Eversys System 8000 Consolidated Network Server Market and Product Overview," Slide presentation, downloaded from <a href="http://eversys.com">http://eversys.com</a>, product to be released Mar. 1, 1997, 20 pages (no date on document).

"SQL Server and NT Cluster Manager Availability Demo," Microsoft Server Programmer Developers Conference, Nov. 1996, 15 pages.

HP: HDMP-1636, Gigabit Ethernet Transceiver Chip, Preliminary Technical Data (May 1997) (No. 123.pdf).

ACCTON, Gigabit Ethernet PCI Adapter (1999) (2 pp) (No. 122. pdf).

Intel, 82559 Fast Ethernet Multifunction PCI/Cardbus Controller (Jan. 1999) (56 pp.) (No. 128.pdf).

Intel, 21143 PCl/CardBus 10/100Mb/s Ethernet LAN Controller, Product Datasheet (Oct. 1998) (8 pp.) (No. 127.pdf).

KTI Networks, Installation Guide 10/100 Dual-speed Fast Ethernet PCI Adapters (1999) (24 pp.) (No. 126.pdf).

Micronet SP2500R Series Etherfast 10/100 MBPS Adapter, User's Guide (1999) (10 pp.) (No. 136.pdf).

PCI Local Bus Specification (Rev. 2.2, Dec. 1998) (322 pp.) (No. 135.pdf).

EIA-422A—Standard (Superseded), Electrical Characteristics of Balanced Voltage Digital Interface Circuits (Dec. 1978) (20 pp) (No. 118a.pdf).

TIA/EIA (644) Standard Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits (Mar. 1996) (42 pp) (No. 118c.pdf).

Huq et al. "An Overview of LVDS Technology" National Semiconductor Corp. (Jul. 1998) (6 pp.) (No. 118d.pdf).

Ziatech Corporation—Ketris9000 Product Manual (2000) (159 pp.) (No. 18.pdf).

Ziatech Corp. ZT 8907 Product Description (1998) (4 pp) (No. 19b. pdf).

Ziatech Corp. ZT 8908 Product Description (1998)+A249 (6 pp) (No. 19c.pdf).

Ziatech Corp. System Designer's Guide: Hot Swap Capability on STD 32 Computers (Jan. 1996) (6 pp) (No. 19e.pdf).

Ziatech Corp. Press Release (Feb. 1996) (2 pp.) (No. 19i.pdf).

Ziatech Corp. Industrial BIOS for CompacktPCI and STD 32 Systems Software Manual (Jul. 1998) (134 pp) No. 19h.pdf).

Ziatech Corp.System Designers Guide: Expanding STD Bus Performance Through Multiprocessing. (Apr. 1996) (6 pp.) (No. 19d.pdf). Network Engines: P6000EXP Fault—Tolerant Load—Balanced Cluster Server (NEI00095) (1997) (4 pp.) (No. 22a.pdf).

Whitecross Data Exploration Configuration and Maintenance Manual. Draft. (Jul. 2000) (699 pp.) (No. 26e.pdf).

Whitecross WX-DES Hardware Maintenance (2000) (284 pp) (No. 26g.pdf).

Whitecross WX-DES Technical Overview (2000) (211 pp) (No. 26h. pdf).

8260 ATM Product Architecture, IBM International Technical Support Organization, Raleigh Center, Sep. 1997, First Edition, International Business Machines Corporation, 220 pages.

8265 Nways ATM Switch, Product Description, Sep. 1998, Fifth Edition, International Business Machines Corporation, 141 pages.

Origin2000 Rackmount Owner's Guide, Document No. 007-3456-003, 1997, Silicon Graphics, Inc., 146 pages.

QuantumNet, Inc., QuantumNet Product Overview [online], 1996 [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19971011194003/www.quantumnet.com/product.htm>, 1 page.

QuantumNet, Inc., QuantumNet: The Next Generation Computing and Networking Environment [online], 1996 [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19971011194123/www.quantumnet.com/qnetovw.htm>, 7 pages.

QuantumNet, Inc., QuantumNet 6500 Processor Modules [online], 1996 [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL:http://web.archive.org/web/19971011194317/www.

quantumnet.com/ds6500.htm>, 4 pages.

QuantumNet, Inc., QuantumServer Chassis [online], 1996 [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19971011194309/www.quantumnet.com/dsq6000. htm> 3 pages.

Cubix Corporation, White Paper: Benefits of High-Density Servers [online], 1997 [retrieved on Jul. 31, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19970716204215/www.cubix.com/coporate/whitep/densit.htm>, 6 pages.

Cubix Corporation, Datasheet: Single—Board Computers with Pentium Processors [online], 1997 [retrieved on Jul. 31, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19970716204717/www.cubix.com/corporate/data/bcp5t.htm>, 5 pages.

Cubix Corporation, Datasheet:ERS/FT II Server Chassis [online], 1997 [retrieved on Jul. 31, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19970716204623/www.cubix.com/corporate/data/ersft2.htm>, 3 pages.

Cubix Corporation, Cubix ERS/FT II Systems [online], 1997 [retrieved on Jul. 31, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19980124213320/www.cubix.com/sup-port/steps/ers-ft2/intro.htm>, 5 pages.

Cubix Corporation, Cubix Product Catalog, Summer 1995, 56 pages. Cubix Corporation, BC Series, Processor Boards Installation Guide, DOC 800A, Aug. 1994, 149 pages.

Cubix Corporation, ERS/FT II—Enhanced Resource Subsystem/Fault Tolerant II, Nov. 1994, 4 pages.

Cubix Corporation, Density Series Plug-In Servers, Plug-In Computers for Managed Server Farms, Sep. 15, 1998, 2 pages.

Cubix Corporation, Cubix Pentium II Plug-In Computers for Density Series Systems, Sep. 15, 1998, 1 page.

Cubix Corporation, Density Series Multi-Server Systems, Sep. 10, 1999, 4 pages.

Compaq Computer Corporation, White Paper, "Order and Configuration Guide for Compaq ProLiant Cluster Series F Model 100," Sep. 1998, pp. 1-8.

Compaq Computer Corporation, QuickSpecs, Compaq ProLiant Cluster Series F Model 100, (undated), pp. 8-36 to 8-37.

Compaq Computer Corporation, Compaq Performance Brief, ProLiant 1600 ServerBench Performance Summary, Aug. 1998, pp. 1-7.

Compaq Computer Corporation, Compaq ActiveAnswers Installation Guide, Installation and Configuration Guide for Linux and Apache Web Server on Compaq Prosignia and ProLiant Servers, May 1999, pp. 1-40.

Compaq Computer Corporation, Compaq White Paper, "Microsoft Internet Information Server 4.0 on the Compaq ProLiant 6500," Aug. 1998, pp. 1-14.

Compaq Computer Corporation, Compaq White Paper, "Accelerating Financial Spreadsheet Simulations with Workstation Clusters," Oct. 1998, pp. 1-14.

Compaq Computer Corporation, ProLiant 6500-PDC/O1000 C/S with 4 ProLiant 1850R, TPC-C Rev. 3.4, Report Date: Dec. 22, 1998, pp. 1-3.

Black Box Corporation, Black Box Network Services, Black Box ServSwitch Duo, Jul. 1998, 52 pages.

Compaq Computer Corporation, Compaq White Paper, "ServerNet—A High Bandwith, Low Latency Cluster Interconnection," Sep. 1998, pp. 1-9.

JL ChatCom, Inc.—Web Site, JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], 1996 [retrieved on Dec. 2, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104221841/www.jlchatcom.com/>, 1 page.

JL ChatCom, Inc.—Scaleable Application and Communication Servers, "ChatCom, Inc. Announces Complete Line of Scaleable Application and Communication Servers," Aug. 30, 1996 [retrieved on Dec. 2, 2009], JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104221932/www.jlchatcom.com/cpofrel.htm>, 4 pages.

JL ChatCom, Inc.—Highly Adaptable Intranet and Web Servers, "ChatCom, Inc. Announces Highly Adaptable Intranet and Web Servers," Sep. 3, 1996 [retrieved on Dec. 2, 2009], JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104221941/www.jlchatcom.com/chat4int.htm>, 2 pages.

JL ChatCom, Inc., "ChatPower Plus," 1996 [retrieved on Dec. 2, 2009], JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104222122/www.jlchatcom.com/chatplus.htm>, 3 pages.

JL ChatCom, Inc., "ChatterBox ChatPower Plus," (undated) [retrieved on Dec. 2, 2009], JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104222556/www.jlchatcom.com/cpp1.gif>, 1 page.

JL ChatCom, Inc., "ChatExpress PB5 Series P166 Pentium PCI/ISA CPU Card," 1996 [retrieved on Dec. 2, 2009], JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104222157/www.jlchatcom.com/chat599.htm>, 2 pages.

JL ChatCom, Inc., "ChatExpress—2 Slot," [retrieved on Dec. 2, 2009], JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104222644/www.jlchatcom.com/exp2ill.gif>, 1 page.

Intel Corporation, Intel 82559 Fast Ethernet Multifunction PCI/Cardbus Controller, Networking Silicon, Preview Datasheet, Jan. 1999, 56 pages.

Ziatech Corporation, STD 32 zVID2 Local Bus Super VGA/FPD Adapter, Apr. 1996, 2 pages.

Wolfpack or Microsoft Cluster Services on Star System, (undated), 3 pages.

Network Engines, Inc., Network Engines ClusterDirector User's Manual, Jun. 1998, 32 pages.

Eversys Corporation, System 8000 Consolidated Network Server Product Brief, (undated), 2 pages.

Eversys Corporation, System 8000 Consolidated Server, (undated), [retrieved on Nov. 9, 2009], Retrieved from C: drive <path: file://C:\Documents and Settings\Daniel\M Documents\Eversys\Eversys Web Site Master...>, 6 pages.

Eversys Corporation, System 8000 Consolidated Server Presentation, (undated), 23 pages.

Eversys Corporation, System 8000 Consolidated Network Server, Pentium II Processor Module User's Guide for Module version P2D-BXT, Jan. 1998, 49 pages.

Eversys Corporation, Eversys System 8000 Peripheral Sharing Switch (PSS) User's Guide, 1st Edition—Jun. 1997, 2nd Edition—Jan. 1998, 17 pages.

Eversys Corporation, WebView 8000 version 1.1 User's Guide, Web-Based Management Software fo the Eversys System 8000 Consolidated Server, Revision A—Nov. 1998, Revision B—Dec. 1998, 56 pages.

Eversys Corporation, S8000 Single Module Body Assemby, Oct. 9, 1998, 9 pages.

Eversys CAPserver Product Brief [online], (undated), [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19961104093115/www.eversys.com/CAPbrief. htm>, 10 pages.

Eversys CAPcard 9500/sa Product Brief [online], (undated), [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archive.org/web/19961104093144/www.eversys.com/cc95sa\_Brief.htm>, 3 pages.

Evergreen Systems, Inc., "CAPserver, The Communication/Application server for local area networks," Product Guide, (undated), 18 pages.

Phillips, J., "9800 Disk Card Design Specification," May 26, 1998, White Cross Systems Limited, pp. 1-44.

Phillips, J., "9800 Disk Card Layout Specification," Apr. 6, 1998, White Cross Systems Limited, pp. 1-22.

Feakes, L., "Disk Connector Card Functional Requirement Specification," Jan. 14, 1998, White Cross Systems Limited, pp. 1-4.

Feakes, L., "Disk Connector Card Layout Specification," Jan. 14, 1998, White Cross Systems Limited, pp. 1-6.

Burrow, M., WhiteCross Data Exploration, "A Technical Overview of the WXDES/9800," Mar. 2, 1999, Revision 2.00, White Cross Systems Limited, pp. 1-90.

Burrow, M., WhiteCross Data Exploration, "A Technical Overview of the WXDES/9800," Apr. 21, 1999, White Cross Systems Limited, 222 pages.

Khan, M. F., "Ethernet Switch Card Design Specification," Mar. 8, 2001, White Cross Systems Limited, pp. 1-32.

Khan, M. F., "Ethernet Switch Card Layout Specifications," Mar. 8, 2001, pp. 1-31.

Smith, B., Processor Backplane Functional Requirement Specification, Jul. 31, 1997, White Cross Systems Limited, pp. 1-11.

Smith, B., "Processor Backplane Design Specification," Feb. 3, 1998, White Cross Systems Limited, pp. 1-16.

Smith, B., "Processor Backplane Layout Specification," Nov. 12, 1997, White Cross Systems Limited, pp. 1-7.

Phillips, J., "9800 Processor Card Design Specification," Feb. 25, 1998, White Cross Systems Limited, pp. 1-41.

Phillips, J., "9800 Processor Card Layout Specification," Sep. 29, 1997, White Cross Systems Limited, pp. 1-13.

Miastkowski, S. (Editor), "A Whale of a System," Byte, Aug. 1991, 4 pages, vol. 16, No. 8.

Advanced Micro Devices, Inc., "AMD-K6-III Processor Data Sheet," 21918B/0, Oct. 1999, 326 pages.

Black Box Corporation, "Black Box Serve Switch Duo," Black Box Network Services Manual, Jul. 1998, 52 pages.

Cisco Systems, Inc., "Cisco AS5800 Universal Access Server Dial Shelf Controller Card Installation and Replacement," Doc. No. 78-4653-02, 1997, 28 pages.

Digital Equipment Corporation, "Digital AlphaServer 4000 and 4100 systems," [Brochure], 1998, 4 pages.

Eversys, "CAPserver Product Brief" [online], [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archieve.org/web/19961104093115/www.eversys.com/CAPbrief.htm>, 10 pages.

Eversys, "CAPcard 9500/sa Product Brief," [online], [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archieve.org/web/19961104093144/www.eversys.com/cc95sa\_Brief.htm>, 3 pages.

Evergreen Systems, Inc., "CAPserver, The Communication/Application server for local area networks," Product Guide, (undated), 18 pages.

Grow, R. et al., "Gigabit Media Independent Interface Proposal," Nov. 11, 1996, IEEE 802.3Z, Vancouver, 22 pages.

Intel, "Pentium® II Processor at 350 MHz, 400 MHz, and 450 MHz, Datasheet," Order No. 243657-003, Aug. 1998, 83 pages.

Ellis, S., "IRIS FailSafe™ Administrator's Guide," Document No. 007-3109-003, Apr. 6, 1997, 212 pages.

NEC, "Server HX4500 User's Guide," PN: 456-00005-000, Dec. 1998, 160 pages.

Novell, Inc., "Novell's NetWare 4.1 Momentum Continues—NetWare 4 Now World's Best-Selling Network Operating System," [online], Mar. 21, 1996, [retrieved on Nov. 16, 2009]. Retrieved from the Internet: <URL: http://www.novell.com/news/press/archive/1996/03/pr96056.html>, 2 pages.

Chapter 7: Maintaining the NetWare Server, "Supervising the Network," (undated), pp. 514-517.

Chapter 7: Designing a Data Protection Plan, (undated), pp. 170-171.

Concepts, Disk Driver and Disk Duplexing, (undated), pp. 82-83. Network Engines, "P6000EXP Fault-tolerant Load-balanced Clustered Server," 1997, 3 pages.

Sun Microsystems Computer Company, "Sun<sup>TM</sup> Enterprise<sup>TM</sup> 250 Server Owner's Guide," Jun. 1998, Part No. 805-5160-10, Revision A, 324 pages.

Sun Microsystems, Inc., "UltraSPARCTM—II CPU Module, Datasheet 400 MHz CPU, 2.0 MP E-Cache," Jul. 1999, 28 pages. Sun Microsystems, Inc., White Paper, "Netra<sup>TM</sup> ft 1800," Apr. 1999, Revision 09, 50 pages.

Compaq Computer Corporation, et al., "Universal Serial Bus Specification," Sep. 23, 1998, Revision 1.1, 327 pages.

Compaq Computer Corporation, et al., "Universal Serial Bus Specification," Apr. 27, 2000, Revision 2.0, 650 pages.

Silicon Graphics International, "Additional Information for: IRIS FailSafe Administrator's Guide (IRIX 6.4)," [online], Document No. 007-3109-003, Published Apr. 6, 1997, [retrieved on Nov. 5, 2009], Retrieved from the Internet: <URL: http://techpubs.sgi.com/library/tpl/cgi-bin/summary.cgi?coll=0640&db=bks&docnumber=...>, 2 pages.

Origin and Onyx Theory of Operations Manual, Document No. 007-3439-002, 1997, Silicon Graphics, Inc., 124 pages.

QuantumNet, Inc., QuantumNet 6000 Sharing Modules [online], 1996 [retrieved on Nov. 16, 2009], Retrieved from the Internet: <a href="http://web.archive.org/web/19971011194326/www.guantumnet.com/dsq60xx.htm">http://web.archive.org/web/19971011194326/www.guantumnet.com/dsq60xx.htm</a>, 3 pages.

JL ChatCom, Inc., "ChatTwin," [retrieved on Dec. 2, 2009], JL ChatCom, Inc., ChatterBox Communications and Server Solutions [online], Retrieved from the Internet: <URL: http://web.archive.org/web/19970104222644/www.jlchatcom.com/chattwin.htm>, 2 pages.

Eversys, "Welcome to EverSys" [online], [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archieve.org/web/19961.104092834/www.eversys.com/index2.htm>, 1 page.

Eversys, "Products" [online], [retrieved on Nov. 16, 2009], Retrieved from the Internet: <URL: http://web.archieve.org/web/19961104093103/www.eversys.com/prodinfo.htm>, 2 pages.

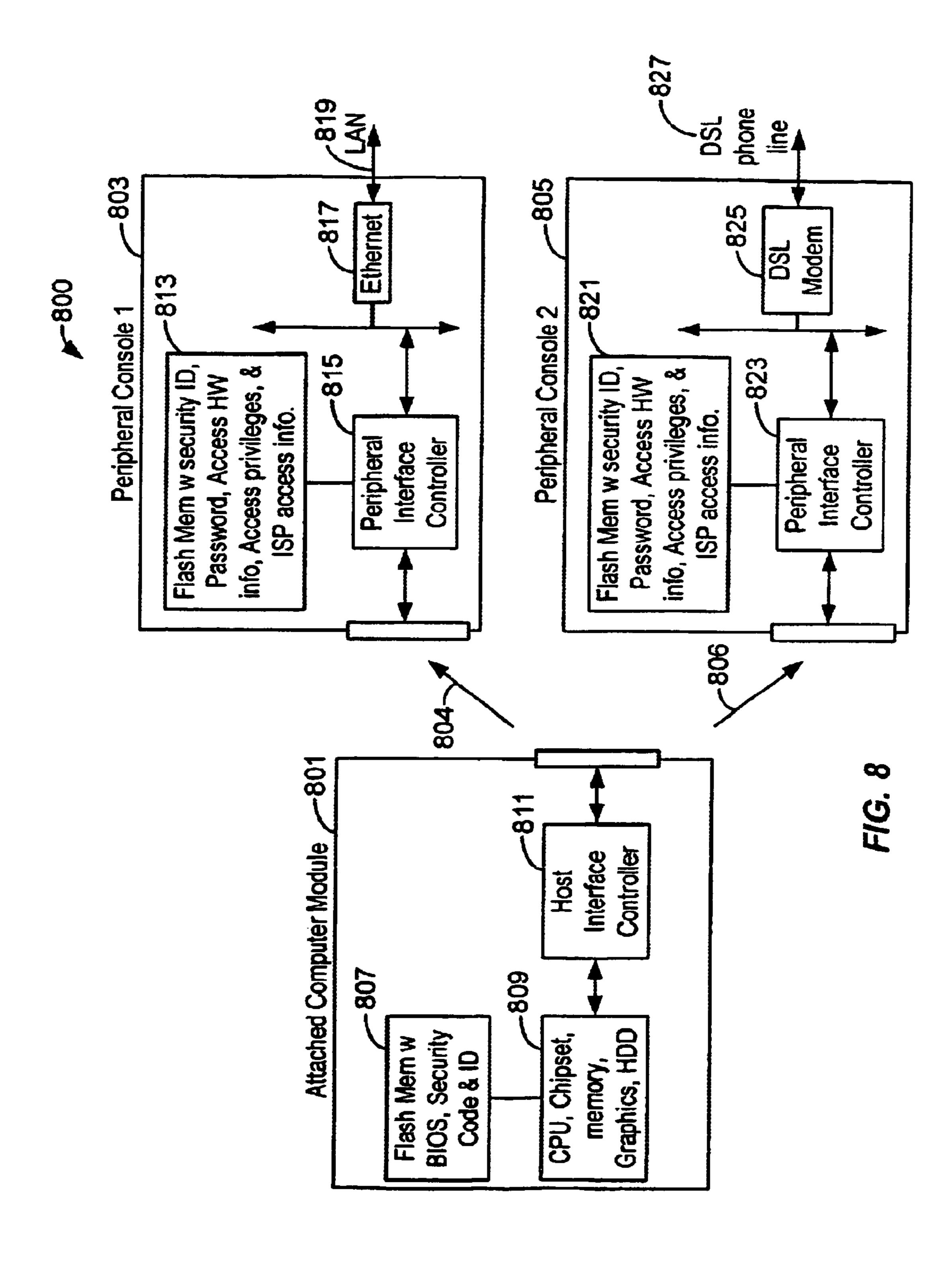

"Microsoft Press Computer Dictionary, Third Edition," Microsoft Press, 1997, pp. 199 and 332, Kim Fryer ed.

Excerpt from "Microsoft Computer Dictionary, 5th Edition", Microsoft Press, 2002, pp. 96 and 547.

Excerpt from IEEE 100: The Authoritative Dictionary of IEEE Standards Terms (7th Ed., 2000), pp. 78, 79 and 128.