#### US00RE42976E

## (19) United States

## (12) Reissued Patent

Ahn et al.

#### (10) Patent Number:

US RE42,976 E

#### (45) Date of Reissued Patent:

Nov. 29, 2011

## (54) SEMICONDUCTOR MEMORY DEVICE WITH REDUCED DATA ACCESS TIME

(75) Inventors: **Jin-Hong Ahn**, Kyoungki-do (KR);

Sang-Hoon Hong, Kyoungki-do (KR); Se-Jun Kim, Kyoungki-do (KR); Jae-Bum Ko, Kyoungki-do (KR)

(73) Assignee: Hynix Semiconductor, Inc. (KR)

(21) Appl. No.: 11/897,516

(22) Filed: Aug. 29, 2007

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: 6,937,535

Issued: Aug. 30, 2005

Appl. No.: 10/696,144

Filed: Oct. 28, 2003

#### (30) Foreign Application Priority Data

| Oct. 29, 2002 | (KR) | 10-2002-0066269 |

|---------------|------|-----------------|

| Feb. 21, 2003 | (KR) | 10-2003-0011121 |

(51) **Int. Cl.**

G11C 7/00 (2006.01) G11C 7/10 (2006.01) G11C 8/00 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,210,723 A   | 5/1993 | Bates et al.            |

|---------------|--------|-------------------------|

| 5,299,157 A * | 3/1994 | Kimura et al 365/189.02 |

| 5,555,529 A   | 9/1996 | Hose, Jr. et al.        |

| 5,625,602   | A            | * | 4/1997  | Hasegawa et al 365/222     |

|-------------|--------------|---|---------|----------------------------|

| 5,715,423   | $\mathbf{A}$ | * |         | Levy 711/103               |

| 5,892,724   | A            |   |         | Hasegawa et al.            |

| 5,917,745   | A            |   | 6/1999  | Fujii                      |

| 5,996,041   | A            | * | 11/1999 | Kim 711/103                |

| 6,023,423   | A            | * | 2/2000  | Aritome 365/185.11         |

| 6,058,065   | A            | * | 5/2000  | Lattimore et al 365/230.03 |

| 6,125,071   | A            |   | 9/2000  | Kohno et al.               |

| (Continued) |              |   |         |                            |

#### FOREIGN PATENT DOCUMENTS

JP 02-143982 6/1990

### OTHER PUBLICATIONS

(Continued)

Park, Y.K., "Highly Manufacturable 90 nm DRAM Technology", 2002 IEEE, pp. 819-822.

(Continued)

Primary Examiner — Son L Mai (74) Attorney, Agent, or Firm — Blakely, Sokoloff, Taylor &

#### (57) ABSTRACT

Zafman

A memory device includes at least two cell blocks connected to a global bit line for outputting data in response to an instruction; at least one global bit line connection unit for selectively connecting the global bit line to each cell block under control of a control block, one global bit line connection unit being allocated between the two cell blocks; and said control block for controlling output of data stored in each cell block to the global bit line and restoration of the outputted data of the global bit line to the original cell block or another cell block which is determined by depending upon whether data in response to a next instruction is outputted from the original cell block or another cell block.

#### 7 Claims, 37 Drawing Sheets

# US RE42,976 E Page 2

| U.S. PATENT            | DOCUMENTS                                     | 2003/0051148 A1 3/2003 Garney                                    |  |

|------------------------|-----------------------------------------------|------------------------------------------------------------------|--|

| 6,191,988 B1 2/2001    | Tanaka                                        | 2003/0076719 A1* 4/2003 Byeon et al                              |  |

|                        | Ohshima et al.<br>Yoo et al.                  | FOREIGN PATENT DOCUMENTS                                         |  |

| , ,                    | Kawai et al 365/185.12                        | JP 03-127144 5/1991<br>JP 06-131867 5/1994                       |  |

| 6,768,692 B2 * 7/2004  | Luk et al 365/205                             | JP 07-169295 7/1995<br>JP 11-306751 11/1999                      |  |

| 7,248,538 B2 * 7/2007  | Ko et al                                      | JP 11-339466 12/1999<br>JP 2002-334579 11/2002                   |  |

|                        | Kameda et al 365/189.09<br>Kang et al 365/145 | JP 2002-334580 11/2002                                           |  |

| , ,                    | Gorobets                                      | OTHER PUBLICATIONS                                               |  |

| 2002/0016967 A1 2/2002 | Carlile                                       | Marc Haberland, "Synchrone laufen schneller", Funktionsweise und |  |

|                        | Yabe et al 365/189.05<br>Perner               | Technologie synchroner DRAMs, Elektronik, 19/1995, pp. 113-119.  |  |

|                        | Kirihata et al.                               | * cited by examiner                                              |  |

(PRIOR ART)

FIG. 3 (PRIOR ART)

FIG. 4

(PRIOR ART)

59 BAK GLOBAL BIT LENE 619 정수 BLOCK FIRST CELL BLOCK 以 SECOND DECODER ADDRESS ADDRESS £0€ COMTROL SIGNALS SOUSE PODESS ADDRESS 意 CONTROL 8.00 9.00 9.00 SEGMENT INSTRUCTION! SGNWES 器

-1G. 5

FIG. 6 **CELL AREA** 610 FIRST CELL BLOCK 1612A BIT LINE LOCAL SENSE AMPLIFIER UNIT 505 161AA LOCAL SENSE AMPLIFIER CONNECTION UNIT /BL BL <u>∠</u>616 **CELL ARRAY** /BL <u>√580</u> LOCAL SENSE AMPLIFIER CONNECTION UNIT CONTROL ∠612B BLOCK LOCAL SENSE AMPLIFIER UNIT **∠550** GLOBAL BIT LINE CONNECTION UNIT SECOND CELL BLOCK √622B LOCAL SENSE AMPLIFIER UNIT **CELL ARRAY** LOCAL SENSE AMPLIFIER UNIT

FIG. 7

五 (2)

SINTRA CELL BLOCK DATA ACCESSY

五 6 9

< NITER CELL BLOCK DATA ACCESS>

FIG. 10

FIG. 13A

FIG. 138

FIG. 13C

FIG. 130

FIG. 14

FIG. 15

FIG. 16

FIG. 18

FIG. 19

FIG. 22

FIG. 23

b<sub>4</sub> + b<sub>5</sub>: ROW CYCLE TIME OF THE PRIOR ART a<sub>4</sub> + b<sub>6</sub>: ROW CYCLE TIME OF THE PRESENT INVENTION

FIG. 24

TWING PERIOD JOAN JOAN PAGE CELT CCUPAHING POATING MG BLOCK \$/ORO CELL AREA OPERATING SET PREDETERMENT CELL BLOCK HRST TIMING REPROD COMPARING LAG BLOCK CELL BECGESS ADORESS TAG BLOCK OPERATING SET ENSING ETERMINED CRO LINE

FIG. 27

E OF THE PRIOR ART OUT AND SAY EBT\_U WE3 핌 1220年125日第1 ROW CYCLE 田 OUT AND RES D2 (BLD, W[3] 园. WEZ *anni* 2 W120F EBT\_UP5 贸 NET NET 띪 핌 **M** FS 0 DI OF 0年1年 8 (BL0,WL2) min 经 NIWB 85 BT UP4 SEL WL1 OUT D1 M/C **RES DO** THE BLI 8 OF BL1 (BLO, WLI) 哥 SEC SEC の記号 EBI\_UPS 8 WED T SELW13 IT AND RES D3 일을 第一条 豆 (BLO, WLD) 28 dinini. WL3 RES CO TBI UP3 80 3 D2 0F THE BEO INVENTION 出る (BLD, WA3) 2 台 **2**]系 ROW CYCLE THE OF THE PRESENT 8 SEL W12 OUT 02 8 RES DI の諸の問題 INTWA 当ませ 報 (BLO, ML2) mm. 3 WLi EBT\_UP1 SEL XI FES DO ALOOF BLD (BLO,WL1) SEL WIO SEL PB **SIM** 9 8 (BLO,WLO) **1** :15:1111 MORD LINE OF SELECTED

UNIT CRL BLOCK) INT CELL BLCCK **COUTAINTED DATA** INSTRUCTION OPERATING PERIOD II CELL BLOCK (BEQ) (BEI)

: A CONYERSION TIME OF THE CELL BLOCK ADDRESS AND A FORCED PRECHARGE TIME 11111

FIG. 30

FIG. 31

FIG. 32

: CONVERSION TIME OF CELL BLOCK ADDRESS : FORCED PRECHARGE

FIG. 33

3320 出 DATA LATCH BLO 田 9TH UNIT BTH UNIT FIRST 3410 3420 ED INSTRUCTION ROLLING THE POPERATIONS) CONTROL UNIT (CONVERTING ADDRESS AND CONTROLLING FORCED PRECHARGE) N DATA ACCESS CONTROL UNIT INSTRUCTION TIMING CONTROL CELL BLOCK ADDR ESS CONVERT UNIT -3430 INSTRUCTION

FIG. 34

FIG. 36

## SEMICONDUCTOR MEMORY DEVICE WITH REDUCED DATA ACCESS TIME

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

#### FIELD OF THE INVENTION

The present invention relates to a semiconductor memory device; and, more particularly, to the semiconductor memory device capable of providing a reduced data access time.

### DESCRIPTION OF RELATED ART

Generally, a semiconductor memory device is classified as a random access memory (RAM) and a read only memory (ROM).

The RAM includes a Dynamic RAM (DRAM) and a Static RAM (SRAM). One cell of the dynamic RAM has one transistor and one capacitor and that of the static RAM does four transistors and two load resistances. The DRAM is used more widespread than the SRAM because the DRAM is more 25 efficient than SRAM in a chip integration and a manufacturing process.

Today, an operation speed of a central processing unit (CPU) is more dramatically advanced than that of the DRAM. As a result, many problems may arise because the operation 30 speed of the memory device is slower than that of CPU. For overcoming these problems, several kinds of scheme in the memory device have been developed for a high speed data transmission.

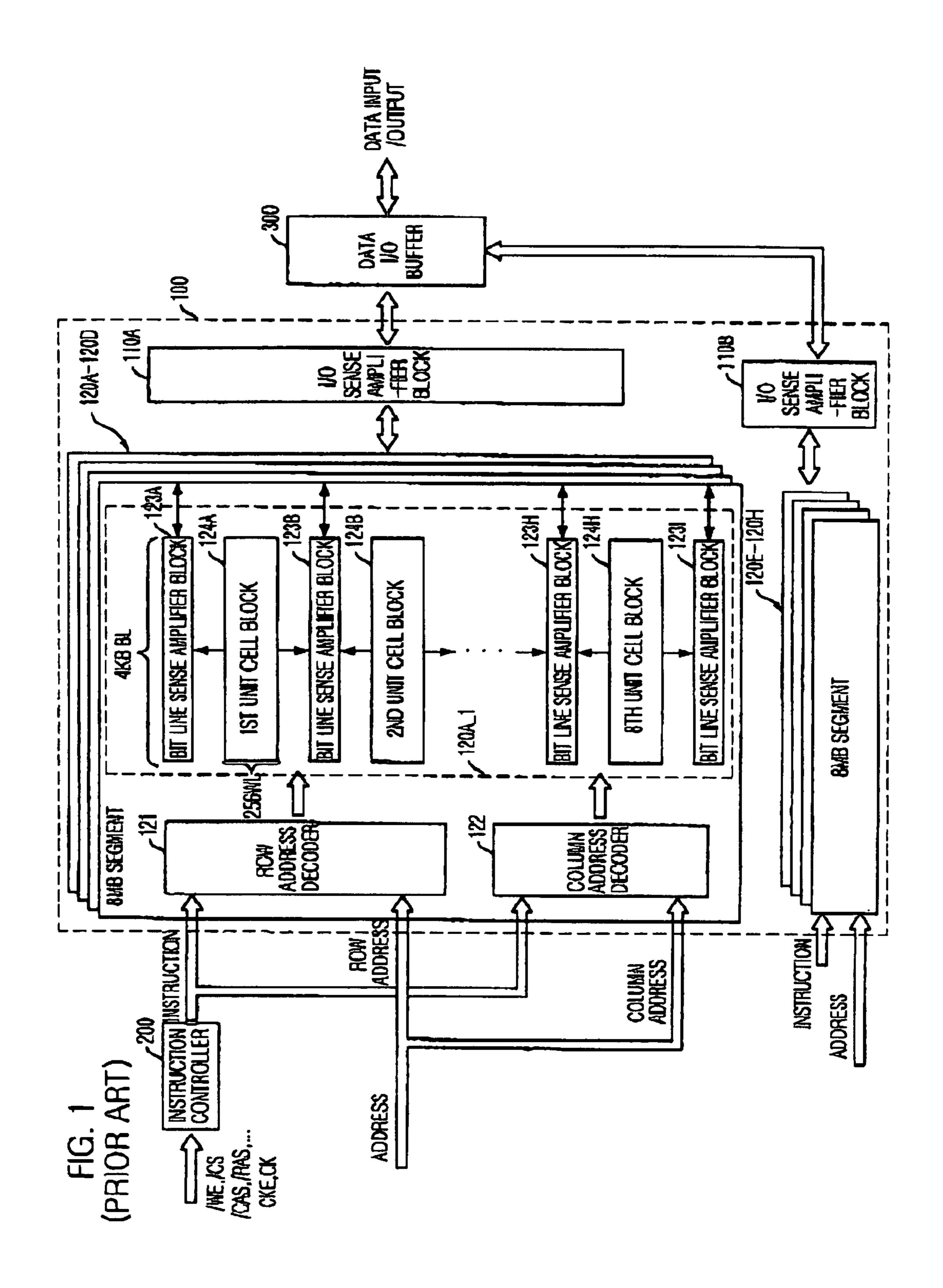

device.

As shown, the memory device is provided with an instruction controller 200, more than one banks 100, and a data input-output buffer 300. The instruction controller 200 controls the bank 100 in various operation modes, e.g., read, write 40 and refresh execution mode, in response to a plurality of the instructions /RAS, /CAS, /WE, /CS, CKE, CK and the like, inputted from an external part (not shown). The bank 100 has a number of segments 120A to 120H, each segment includes a row address decoder 121 and a column address decoder 122 45 so that data stored in a unit cell block read out in response to an inputted address or an inputted data is written in the unit cell block of the segment 120A. The data input-output buffer 300 serves to buffering the inputted or the outputted data for the unit cell block of the bank 100.

Typically, the memory device has, e.g., four banks. However, FIG. 1 describes only one bank 100 in detail, because each of the banks has the same structure. Although, for the sake of convenience, elements of the conventional memory device are simplified in FIG. 1, another element may be 55 contained in the conventional memory device.

One bank has input/output (I/O) sense amplifier blocks 110A and 110B for amplifying sensed data outputted from, e.g., eight segments 120A to 120D and 120E to 120H to provide the amplified data to the data input/output (I/O) 60 buffer 300. Each segment is constituted of several unit cell blocks. Furthermore, the I/O sense amplifier blocks 110A and 110B supplies the data inputted from the data input/output (I/0) buffer 300 to the first to eighth segments 120A to 120H.

The first segment 120A includes the row address decoder 65 121, the column address decoder 122 and a cell area 120A\_1. The row address decoder 121 decodes a row address to output

the decoded row address to the cell area 120A\_1. The column address decoder 122 decodes a column address to output the decoded column address to the cell area 120A 1.

The cell area 120A\_1 is constituted of a plurality of unit cell blocks, each having a number of unit cells. One unit cell block 124A is coupled to a pair of the bit line sense amplifier block, e.g., 123A and 123B, for sensing and amplifying the data outputted from the unit cell block, e.g., 124A.

For example, the 256 Mb memory device includes typically, four 64 Mb banks. In this case, a size of the segment is 8 Mb because each bank 100 includes eight segments 120A to **120**H. Each segment, e.g., **120**A has eight unit cell blocks 124A to 124H and each unit cell block, e.g., 124A has 256 word lines and 4 Kb( $4\times1024$ ) bit lines. Thus, each unit cell 15 block, e.g., 124A has 256×4 Kb unit cells. Hereinafter, it is assumed that the size of the segment is 8 Mb and each unit cell block has 256 word lines.

As mentioned, if each unit cell block, e.g., 124A is coupled to two sense amplifier blocks, e.g., 123A and 123B, it is 20 needed that the segment 120A having eight unit cell blocks 124A to 124H should have sixteen bit line sense amplifier blocks. However, the segment 120A of the conventional memory device is implemented by using nine bit line sense amplifier blocks 123A to 123I. Each bit line sense amplifier block, e.g., 123B is commonly connected to the two neighboring unit cell blocks, e.g., 124A and 124B. Namely, two neighboring unit cell blocks, e.g., 124A and 124B commonly hold one bit line sense amplifier block, e.g., 123B for efficiency of chip integration. In this case, the bit line sense amplifier block, e.g., 123B may be selectively coupled to the unit cell blocks 124A and 124B under control of the instruction controller 200.

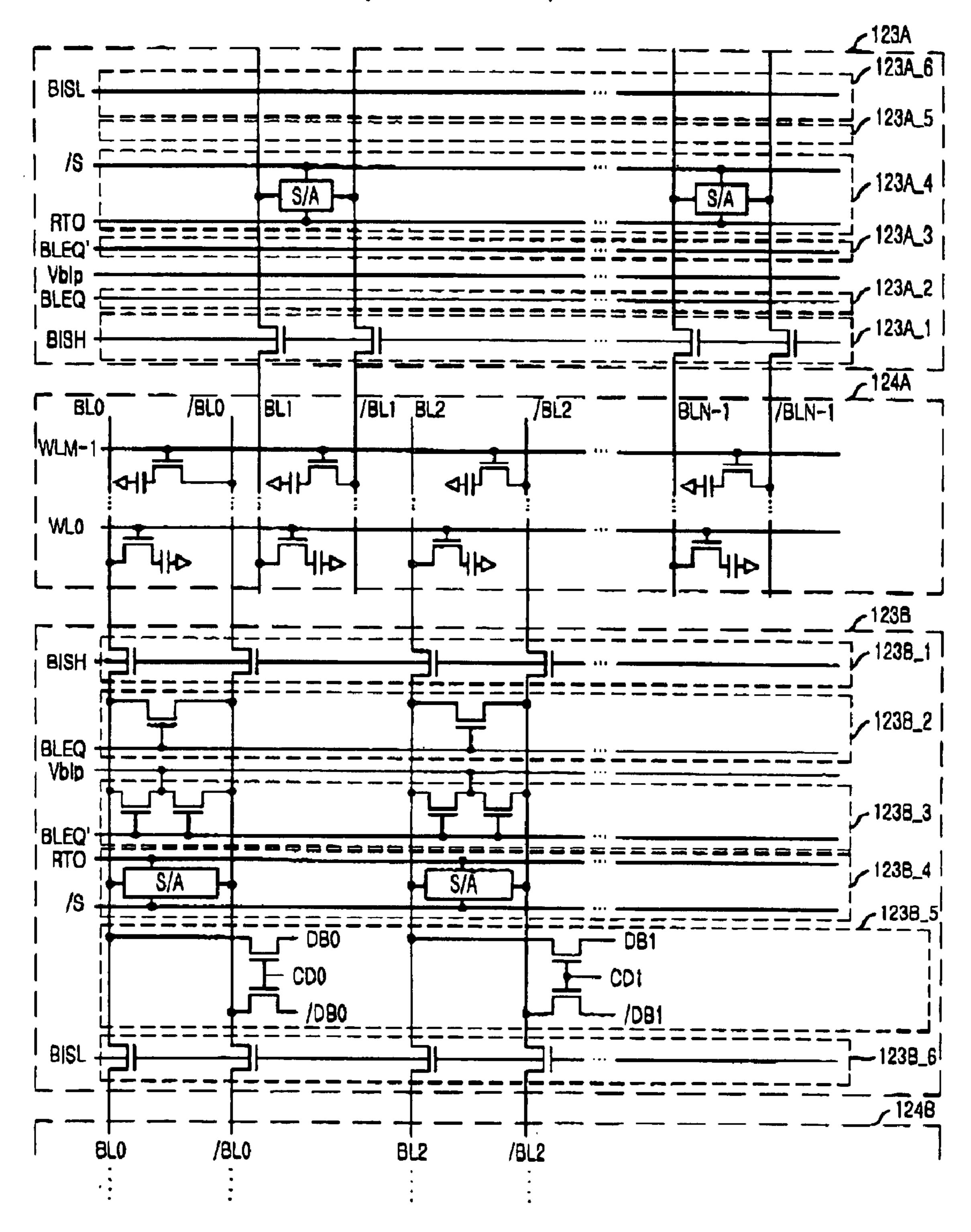

FIG. 2 is a schematic circuit diagram demonstrating a bit line sense amplifier block and a unit cell block shown in FIG. FIG. 1 is a block diagram showing a conventional memory 35 1. That is, the partial structure of two unit cell blocks 124A and 124B and the bit line sense amplifier block 123B is described.

> As shown, the first unit cell block 124A has 256×4 Kb unit cells, each having one MOS transistor and one capacitor, wherein a word line is coupled to the gate of the MOS transistor and each of bit lines BL and /BL is coupled to the drain of the MOS transistor. The source of the MOS transistor is coupled to one electrode of the capacitor and the other electrode of the capacitor is coupled to a cell plate supplier, e.g., a ground voltage. For the sake of convenience, since the structure of the second unit cell block 124B is identical to first unit cell blocks 124A, the structure of the second unit cell block **124**B is not described in detail.

The bit line sense amplifier block **123**B is provided with a 50 bit line sense amplifier 123B\_4, a precharge block 123B\_3, an equalization block 123B\_2, a data output block 123B\_5 and first and second bit line sense amplifier connection units **123**B\_**1** and **123**B\_**6**.

The bit line sense amplifier 123B\_4 is enabled by bit line sense amplifier enable signals RTO and /S for amplifying the difference between two voltage levels supplied to the bit line pair BL0 and /BL0 as a sensed data. The precharge block 123B\_3 precharge the bit line pair BL0 and /BL0 up to a bit line precharge voltage Vblp in response to a precharge enable signal BLEQ'. The precharge enable signal BLEQ' is enabled if the bit line sense amplifier 123B\_4 is disabled. The equalization block 123B\_2 is enabled by an equalization signal BLEQ so as to equalize voltage levels appearing on the bit line pair BL0 and BL1 connected to the first cell unit block 124A. The data output block 123B\_5 outputs the data sensed and amplified by the bit line senses amplifier 123B\_4 to a data line pair DB0 and/DB0 by a column control signal, e.g., CD0,

generated by using a column address. If the first connection unit 123B\_1 is enabled by a first sense amplifier connection signal BISH, the bit line sense amplifier 123B\_4 is connected to the first unit cell block 124A. Otherwise, if the second sense bit line sense amplifier connection unit 123B\_6 is 5 enabled by a second connection signal BISL, the bit line sense amplifier 123B\_4 is connected to the second unit cell block 124B.

Herein, the first unit cell block 124A is provided with a plurality of unit cells coupled to N number of bit line pairs, e.g., BL0 and/BL0,..., BLN-1 and/BLN-1, and M number of word lines e.g., WL0,..., WLM-1. Namely, a size of the first unit cell block is N×M bits. Herein, M and N are positive integers. Since the first unit cell block 124A is coupled to the first and second bit line sense amplifier blocks 123A and line sense amplifier block 123A or 123B is N/2. So, in the first unit cell block 124A, some of the data coupled to some bit line pairs, e.g., BL1 and /BL1, ..., BLN-1 and /BLN-1, in response to an instruction is outputted to the first bit line sense amplifier block 123A; and others coupled to other bit line pairs, e.g., BL0 and/BL0, BL2 and/BL2,..., is outputted to the second bit line sense amplifier block 123B.

Moreover, the second bit line sense amplifier block 123B is selectively connected to one of the first and second unit cell 25 blocks 124A and 124B in response to the first and second sense amplifier connection signals BISH and BISL.

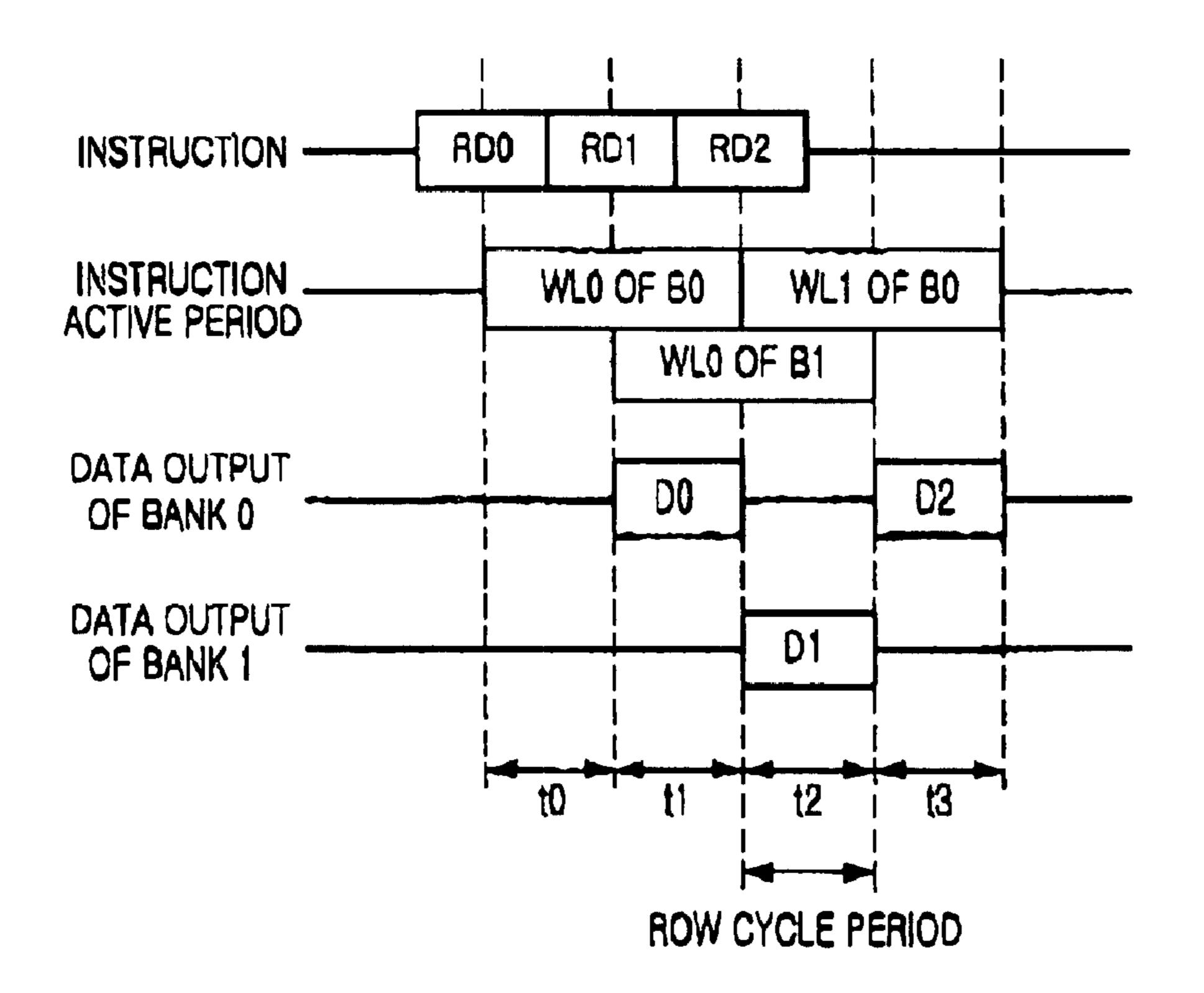

FIGS. 3 and 4 are timing diagrams describing operation of the conventional memory device described in FIGS. 1 and 2.

Hereinafter, referring FIGS. 1 to 4, the operation of the 30 conventional memory device is described in detailed.

First, when an address is inputted to the memory device, the inputted address is classified into a bank address, a row address and a column address. Furthermore, the row address is split into a cell block address and a local address. The bank 35 address is used for selecting one among four banks. One segment and one unit cell block in the selected bank are selected by the cell block address. The local address is used for selecting one word line in the selected unit cell block, and the column address is used for selecting one unit cell in 4 Kb 40 unit cells selected by the word line.

Continuously, it is described the operation of the memory device in a read mode.

First of all, one bank, e.g., 100, is selected by a bank address in response to a read instruction RD0. Herein, a row 45 address is then inputted to a row address decoder 121, included in each segment of the selected bank 100.

Then, the row address decoder 121 decodes the cell block address and the local address included in the inputted row address and one unit cell block 124A in a selected segment 50 tor. 120A of the bank 100 is selected by using the cell block address and the local address.

Next, a word line, e.g., WL0, of 256 word lines in the first unit cell block **124**A, is activated by the local address outputted from the row address decoder **121** when the bit line pairs 55 BL0 and /BL0, . . . , BLN-1 and /BLN-1 included in the first unit cell block is typically precharged with a half of a supply voltage by the precharge blocks **123**A\_3 and **123**B\_3 shown in FIG. **2**.

After that, each bit of 4 Kb data stored in unit cells connected to the activated word line WL0 is individually supplied to each of bit line pairs BL0 and /BL0, . . . , BLN-1 and /BLN-1. At this time, if the first sense amplifier connection signal BISH shown in FIG. 2 is enabled and the second sense amplifier connection signal BISL is disabled, the bit line 65 sense amplifier blocks 123A and 123B are connected to the selected first unit cell block 124A.

4

Next, the bit line sense amplifiers  $123A_4$  and  $123B_4$  senses and amplifies the data supplied at the bit line pairs BL0 and /BL0, . . . , BLN-1 and /BLN-1.

That is, the bit line sense amplifier 123B senses and amplifies data supplied to some bit line pairs BL0 and /BL0, BL2 and /BL2, . . . , BLN-2 and /BLN-2. Simultaneously, the bit line sense amplifier 123B senses and amplifies data supplied to other bit line pairs BL1 and /BL1, BL3 and /BL3, . . . , BLN-1 and /BLN-1. Of course, the bit line sense amplifier block 123B allocated between two unit cell blocks 124A and 124B is selectively connected to the two neighboring unit cell blocks 124A and 124B at a preferred timing scheme determined by the instructions /RAS, /CAS, /WE, /CS, CKE, and CK etc, for obtaining a high integration and a high operation speed of the memory device.

And then, the column address decoder 122 decodes the inputted column address in response to the read instruction RD0 to output the column select signal, e.g., CD0, CD1, CD2, . . . The 4 Kb data is amplified by the bit line sense amplifier blocks 123A and 123B; and the selected data by the column select signal is outputted to the I/O sense amplifier block 110A shown in FIG. 1 through the use of the data line pair DB and /DB.

The I/O sense amplifier block, e.g., 110A, amplifies the selected data signal for compensating a loss occurred in a relatively long data line pair DB and /DB and outputs the amplified data signal to the data I/O buffer 300. The data input-output buffer 300 temporarily stores and outputs the amplified data outputted from each bank to an external part (not shown) at predetermined data output timing scheme.

In the meanwhile, selected 4 Kb data latched after sensed and amplified by the bit line sense amplifier blocks 123A and 123B should be restored in selected 4 Kb unit cells connected to the word line WL0 activated by the read instruction RD0.

In the conventional memory device, a capacitance of the capacitor included in the unit cell is a few femto-farad and charge amount stored in the capacitor is very small. As a result, after the charge stored in the capacitor of the cell-unit is discharged to the bit line as sensed data, the sense data is amplified by the sense amplifier and should be restored in the capacitor. Typically, the capacitor can be recharged over 90 percentages of a charging capability of the capacitor by using the above restoration operation.

Furthermore, since a small amount of charges stored in the capacitor may be lost with lapse of time, the memory device needs a refresh operation for periodically recharging the capacitor. Therefore, it is necessary that the memory device spends an additional time for the refresh or the data restoration operation in order to prohibit the data loss in the capacitor.

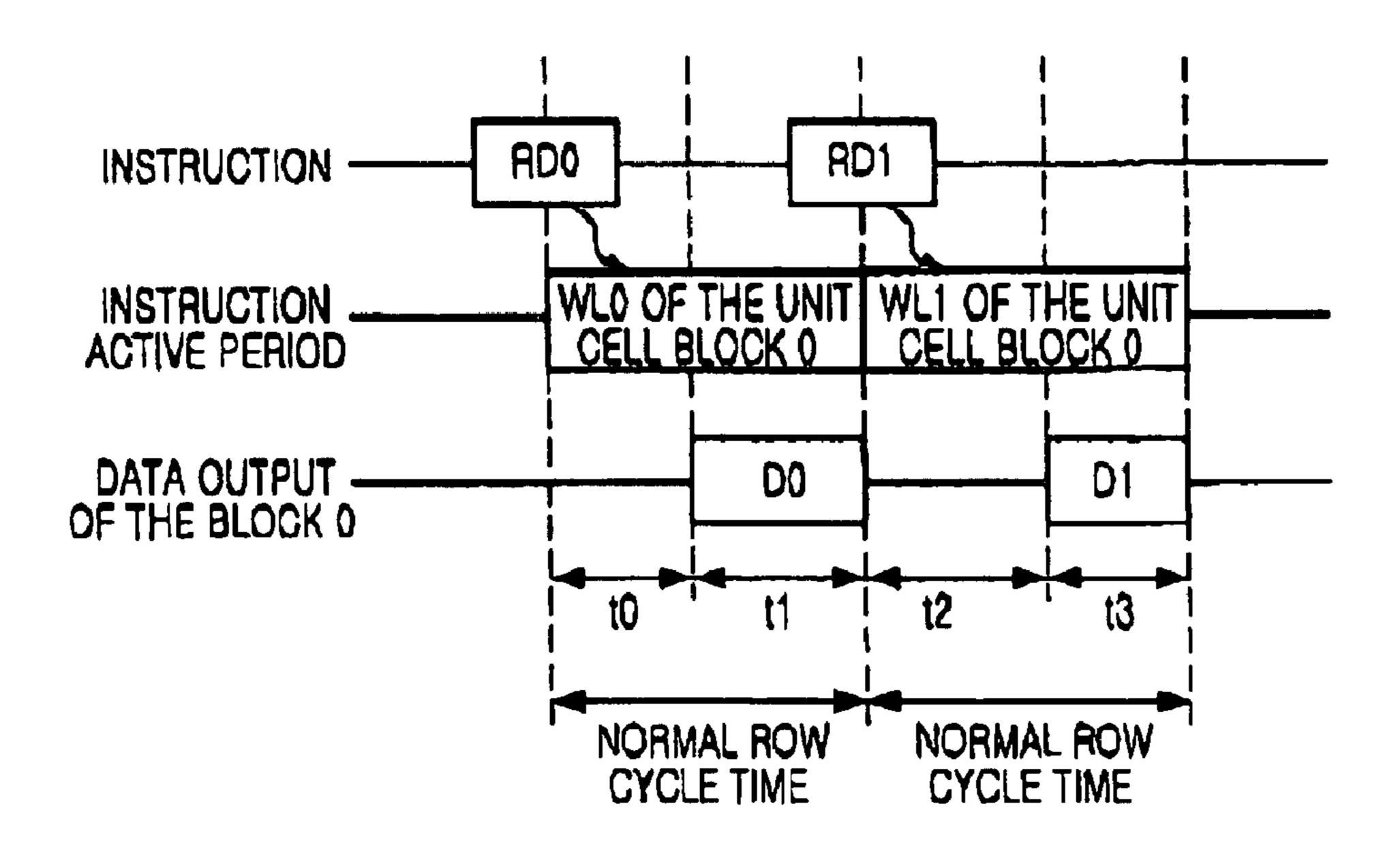

FIG. 3 is a timing diagram showing the operation of continuously and sequentially accessing at least two data in one bank of the memory device shown in FIG. 1. Hereinafter, the operation of continuously and sequentially retrieving at least two data in one bank is referred as a intra bank data access.

As shown, if the first read instruction RD0 is inputted to the memory device, the inputted row address is divided into the cell block address and the local address at a first timing period t0. Herein, the cell block address and local address are individually used for selecting one unit cell block and one word line, e.g., the first unit cell block 124A and the word line WL0. Then, at the first timing period t0, 4 Kb data stored in unit cells are sensed and amplified in response to the activated word line WL0 by the bit line sense amplifier blocks 123A and 123B connected to the first unit cell block 124A.

Next, in a second timing period t1, a selected data D0 of the amplified 4 Kb data is selected and outputted by the column

select signal CD0 generated from the inputted column address and, at the same time, the amplified 4 Kb data are restored in the original unit cells coupled to the activated word line WL0. As above described, one read operation is completed during two timing periods t0 and t1.

Likewise, after the two timing periods t0 and t1, if a second read instruction RD1 is inputted, the second read operation by the second read instruction RD1 is then executed during two timing periods t2 and t3.

The normal row cycle time shown in FIG. 3 is defined as a 10 time period since a word line is activated in response to a current row address or an instruction until a next word line is activated by a next row address or a next instruction.

Hereinafter, in detail, operation of a data writing mode is described.

Like the data reading mode, the writing operation also includes the step that 4 Kb data are sensed and amplified by the bit line sense amplifier blocks after a selected word line is activated.

In a first timing period t0, one word line is activated by the 20 row address; and, then, 4 Kb data in response to the activated word line are sensed and amplified by the bit line sense amplifiers blocks, e.g., 123A and 123B.

In a second timing period t1, data inputted from external-part is latched in a bit line sense amplifier selected in response 25 to a column select signal, e.g., CD0. Herein, the column select signal CD0 used for storing the new data is decoded from the column address. Then, 4 Kb data are stored in unit cells selected by the activated word line. Herein, it may be unnecessary to sense and amplify the inputted data which is latched 30 in the bit line sense amplifier because voltage level of the inputted data are enough high to be sensed and stored. As above described, the writing operation is also carried out during the two timing periods t0 and t1.

As mentioned above, the memory device having a capacitor which is served as a storage element needs two timing periods for completing one data reading r writing operation. First, a data stored in the unit cells is sensed and amplified, or an inputted data is sensed at the first timing period t0. Second, the amplified data is outputted to external part, or the inputted data from external part is stored in each unit cell at the second timing period.

In a high integrated memory device, the quantity of stored charge stored as a data signal is relatively small because the size of the capacitor is very small. As a result, if the charge 45 stored in the capacitor is not amplified periodically, the charge stored in the capacitor may be lost to thereby allow the stored data to be corrupted. Namely, the refresh operation including the data restoration operation should be periodically carried out for preserving the data of the unit cell after 50 the reading or writing operation as described.

In the conventional memory device, after the data are accessed by one instruction, the next data can not be accessed immediately, since the initially accessed data should be restored to the original unit cells.

On the other hand, the conventional memory device employs a bank interleaving mode for reducing the data restoration time in a inter bank data access, i.e., to thereby improve the operation speed of the memory device. The inter bank data access means that at least two data stored in different banks are continuously and sequentially accesses.

In the bank interleaving mode, the conventional memory device may continuously output data to the external part in response to the inputted instructions, without any additional data access time for a restoration operation. Namely, the next data may be accessed and outputted from the neighboring bank, during the current data is restored in the original bank.

6

FIG. 4 is a timing diagram describing a bank interleaving mode of the conventional memory device shown FIG. 1.

As shown, in the bank interleaving mode of the memory device, a first word line of a first bank, e.g., WL0 of B0, is activated by a first read instruction RD0 at a first timing period t0 and a first data D0 in response to the first activated word line WL0 is outputted and restored at a second timing period t1. Simultaneously, at the second timing period t1, a next read instruction RD1 is continuously inputted in a second bank B1.

And, a second word line of the second bank, e.g., WL0 of B1, is activated; and a second data D1 in response to the second activated word line WL0 is outputted at the second timing period t1. Thus, in the bank interleaving mode, the first to third data D0, D1 and D2 are continuously outputted in response to the continuously first to third read instructions RD0, RD1 and RD2.

As describe above, if the data outputted from the neighboring bank are sensed and amplified by the next inputted instruction in neighboring bank while the present data are restored in the current bank, the data access time may be reduced.

However, as mentioned above, it is difficult to apply the bank interleaving mode in the intra bank data access of the conventional memory device and, to obtain higher data access time in the convention memory device. That is, in the intra bank data access of the convention memory device, the conventional memory device should receive the next instruction after the current data outputted in response to the present instruction are restored in the original unit cell.

Therefore, even though the conventional memory device may use the bank interleaving mode, the data access speed in the memory device is greatly depend on a data access pattern, i.e., the inter bank data access or the intra bank data access.

If a system uses the conventional memory device whose data access speed is seriously affected by the data access pattern, there may be occurred some critical problems about the operation reliability of the system because the operation speed of the system may not be stable.

Therefore, it is necessary to develop a memory device which can access the data on high speed less sensitive to the data access pattern.

# SUMMARY OF THE INVENTION

It is, therefore, an object of the present invention to provide a method and an apparatus of a memory device for accessing data on high speed so that the data restoration time does not affect seriously the data access time.

In addition, there is provided a method and a apparatus of the memory device for high speed data access unrelated a data access pattern by using inter or intra cell block interleaving mode which can make the memory device operate on high speed without reduction of data access time when at least two data accesses are sequentially occurred in the same bank.

In accordance with an aspect of the present invention, there is provided a memory device including at least two cell blocks connected to a global bit line for outputting data in response to an instruction; at least one global bit line connection unit for selectively connecting the global bit line to each cell block under control of a control block, one global bit line connection unit being allocated between the two cell blocks; and said control block for controlling output of data stored in each cell block to the global bit line and restoration of the outputted data of the global bit line to the original cell block or another cell block which is determined by depending upon whether data in response to a next instruction is outputted from the original cell block or another cell block.

In accordance with another aspect of the present invention, there is provided a memory device including a plurality of unit cell blocks, each having a plurality of unit cells, a first local bit line sense amplifier block for sensing and amplifying data from a unit cell, and a second local bit line sense amplifier block for sensing and amplifying data from another cell unit; a first global bit line sense amplifier block for latching data sensed and amplified from the first local bit line sense amplifier block; a second global bit line sense amplifier block for latching data sensed and amplified from the second local 10 bit line sense amplifier block; a first global bit line connection unit, in response to a first control signal, for selectively connecting either the second local bit line sense amplifier block of a first unit cell block to the second global bit line sense amplifier block or the first local bit line sense amplifier block 15 of a second unit cell block to the first global bit line sense amplifier block; a second global bit line connection unit, in response to a second control signal, for selectively connecting either the second local bit line sense amplifier block of a third unit cell block to the second global bit line sense amplifier block or the first local bit line sense amplifier block of a forth unit cell block to the first global bit line sense amplifier block; and a control unit for generating the control signals to thereby control a storing operation of the data latched in the first and the second global bit line sense amplifier block.

In accordance with another aspect of the present invention, there is provided a memory device including a plurality of first unit cell blocks, each having a plurality of unit cells, a first local bit line sense amplifier block for sensing and amplifying data from a unit, and a second local bit line sense amplifier block for sensing and amplifying data from another unit cell; a first global bit line sense amplifier block for latching data sensed and amplified by the first local bit line sense amplifier block; a second global bit line sense amplifier block for latching data sensed and amplified by the second local bit line sense amplifier block; and a control unit for controlling a restoration execution of data latched in the first and the second global bit lines.

In accordance with another aspect of the present invention, there is provided a memory device including a plurality of 40 unit cell blocks, each including a local bit line sense amplifier block for sensing and amplifying data stored in a plurality of unit cell and having the plurality of th unit cells; a global bit line sense amplifier block for latching data sensed and amplified by the plurality of the local bit line sense amplifier block; 45 and a control unit for controlling the use of the latched data in a restoration execution.

In accordance with another aspect of the present invention, there is provided a memory device including a cell area including N+1 number of unit cell blocks, each having M 50 number of word lines for responding to inputted row address; and a control unit for controlling the cell area to thereby restoring data accessed in a first unit cell block selected out of the N+1 number of the unit cell blocks either in the first unit cell block or in a second unit cell block.

In accordance with another aspect of the present invention, ther is provided a memory device including a cell area having N+1 number of unit cell blocks, each including M number of word lines for responding to an inputted row address; a predetermined cell block table for storing information wherein at least more than one word line among the (N+1)×M number of the word lines is assigned as a predetermined restorable word line by using the information; a tag block for sensing an input logical cell block address for designating a unit cell block to be accessed to converting the input logical cell block address for designating a unit cell block to be restored; and a control unit for controlling the tag

8

block and the predetermined cell block table for activating one word line of the unit cell block selected by the physical cell block address.

In accordance with another aspect of the present invention, there is provided a memory device including a cell area including N+1 number of unit cell blocks adding N number of the unit cell blocks individually having M number of word lines for responding to an inputted row address and an additional unit cell block having M number of the word lines; a data access control unit for controlling operation that data accessed in a first unit cell block selected in the N+1 number of the unit cell blocks are restored either in the first unit cell block or in a second unit cell block; and an instruction control unit for controlling an operation that a cell block address in response to a second instruction being at an active next timing period is conversed and a bit line in response to a first Instruction is precharged during accessing data in response to the first present active instruction.

In accordance with another aspect of the present invention,

there is provided a method for operating a memory device

having first and second cell blocks, each having a number of

cell units including the steps of: (A) sensing and amplifying a

first data in the first cell block; (B) restoring the first data in the

second cell block; and (C) sensing and amplifying a second

data in the first unit block, wherein both the step (B) and the

step (C) are performed at a substantially simultaneous timing

period.

In accordance with another aspect of the present invention, there is provided a method for operating a memory device having an N+1 number of unit cell blocks adding an N number of unit cell blocks and an additional unit cell block individually both corresponding to an inputted row address and having an M number of word lines, N and M being positive integers including steps of: (A) sensing and amplifying a first data in a first unit cell block selected out of the N+1 number of the unit cell blocks; (B) restoring the first data in a second unit cell block selected out of the N+1 number of the unit cell blocks; and (C) sensing and amplifying a second data in the first unit cell block, wherein both the step (B) and the step (C) are performed at a substantially simultaneous timing period.

In accordance with another aspect of the present invention, there is provided 67. A method for operating a memory device including an N+1 number of unit cell blocks, adding a N number of unit cell blocks and an additional unit cell block, both corresponding to an inputted row address and having a M number of word lines, N and M being positive integers, comprising the steps of: (A) activating a first word line of a first unit cell block selected out of the N+1 number of the unit cell blocks; (B) sensing and amplifying a K number of data in response to the first word line; (C) moving the K number of the sensed and amplified date in response to the first word line to the other unit cell block having a predetermined word line in response to the first word line and restoring thereof; (D) activating a second word line of the first unit cell block; (E) sensing and amplifying a K number of data in response to the second word line, wherein the steps (C) and (E) are performed at substantially simultaneous timing period.

In accordance with another aspect of the present invention, there is provided a method for operating a memory device having a cell area containing an N+1 number of unit cell blocks, adding an N number of unit cell blocks and an additional unit cell block, both corresponding to an inputted row address and having an M number of word lines, N and M being positive integers including the steps of: (A) sensing data by both a logical cell block address for selecting a N number of logical unit cell blocks by receiving the row address and a local address for selecting one out of the M

number of word lines included in the s lected unit cell block; (B) converting the logical cell block address to a physical cell block address for selecting one out of a N+1 number of the physical cell block addresses; (C) activating a first word line in response to the local address in a first unit cell block selected in response to the converted physical cell block address; (D) sensing and amplifying the data in response to the first word line; (E) moving the first data to a second unit cell block of which a predetermined word line is assigned in response to the first unit cell block in response to the local address inputted for a next instruction; and (G) sensing and amplifying a second data in response to the second word line, wherein the steps E and G are occurred at a substantially simultaneous timing period.

In accordance with another aspect of the present invention, there is provided a method for operating a memory device including a cell area having an N+1 number of unit cell blocks, adding an N number of unit cell blocks and an addi- 20 tional unit cell block, individually both corresponding to an inputted logical cell block address and having an M number of word lines, N and M being positive integers including the steps of: (A) receiving a first logical cell block address in response to a first instruction and thereof converting to a first 25 physical cell block address for selecting one out of a N+1 number of the physical cell block addresses; (B) sensing and amplifying a first data in a first unit cell block in response to the first physical cell block address; (C) moving the first data and latching thereof; (D) precharging the first data sensed and amplified in the first unit cell block; (E) converting to a second physical cell block address after receiving a second logical cell block address in response to a second instruction; (F) moving the first latched data to the second unit cell block 35 selected out of the N+1 number of the unit cell blocks and restoring thereof; and (G) of sensing and amplifying the second data in the second unit cell block in response to the second physical cell block address, wherein the steps F and G are occurred at a substantially simultaneous timing period.

## BRIEF DESCRIPTION OF THE DRAWINGS

The above and other objects and features of the instant invention will become apparent from the following descrip- 45 tion of preferred embodiments taken in conjunction with the accompanying drawings, in which:

- FIG. 1 is a block diagram showing a conventional memory device;

- FIG. 2 is a schematic circuit diagram demonstrating a bit 50 line sense amplifier block and a unit cell block shown in FIG. 1.

- FIGS. 3 and 4 are timing diagrams describing data access operations of the conventional memory device described in FIG. 1;

- FIG. 5 is a block diagram describing a semiconductor memory device in accordance with a preferred embodiment of the present invention.

- FIG. 6 is a block diagram showing a segment in the semiconductor memory device in accordance with an embodiment 60 of the present invention;

- FIG. 7 is a block diagram describing a segment in the semiconductor memory device in accordance with another embodiment of the present invention;

- FIGS. 8 and 9 are timing diagrams depicting operation of 65 the semiconductor memory device, depending upon a data access pattern;

**10**

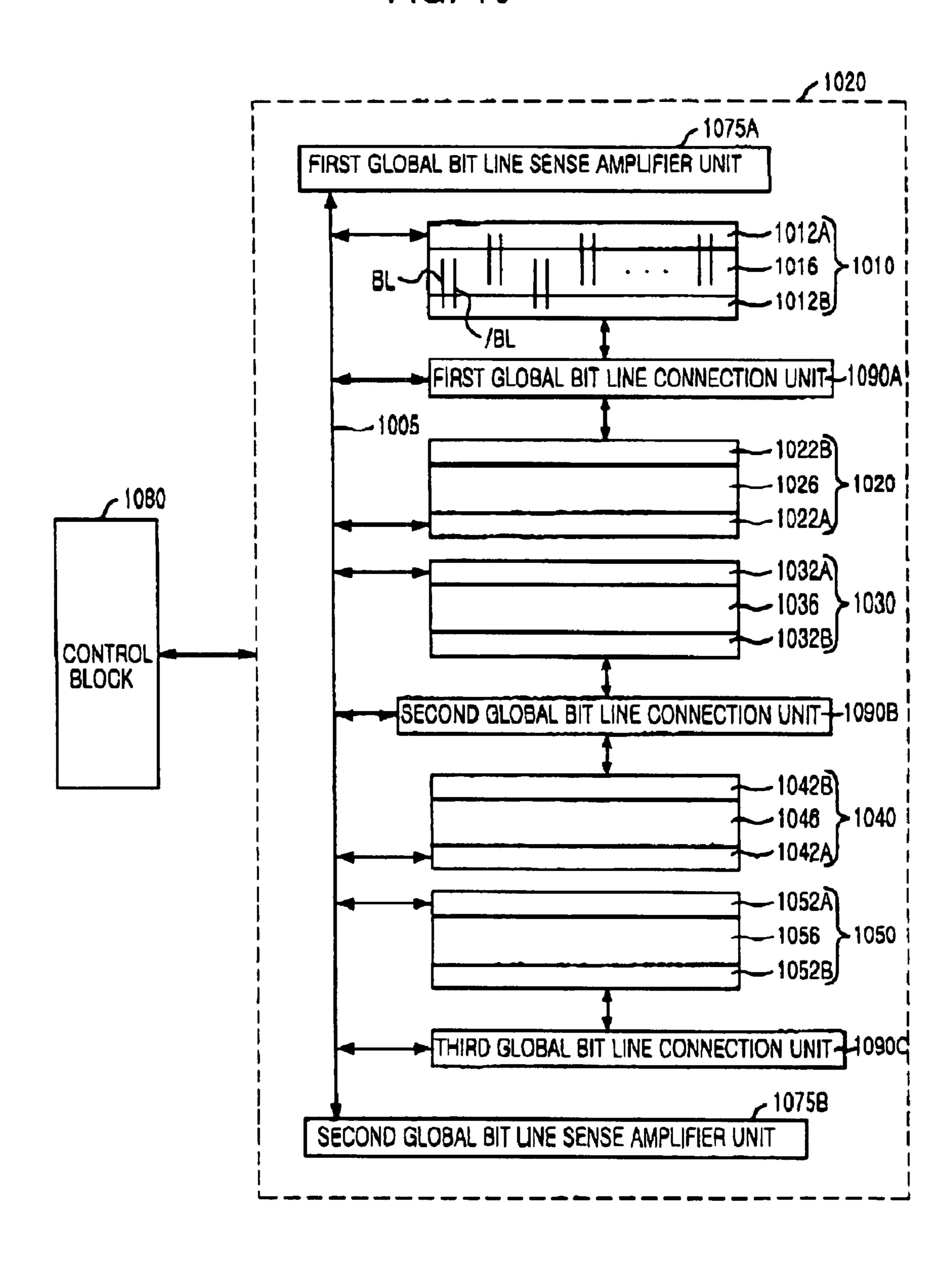

- FIG. 10 is a block diagram describing a segment in the memory device in accordance with another embodiment of the present invention;

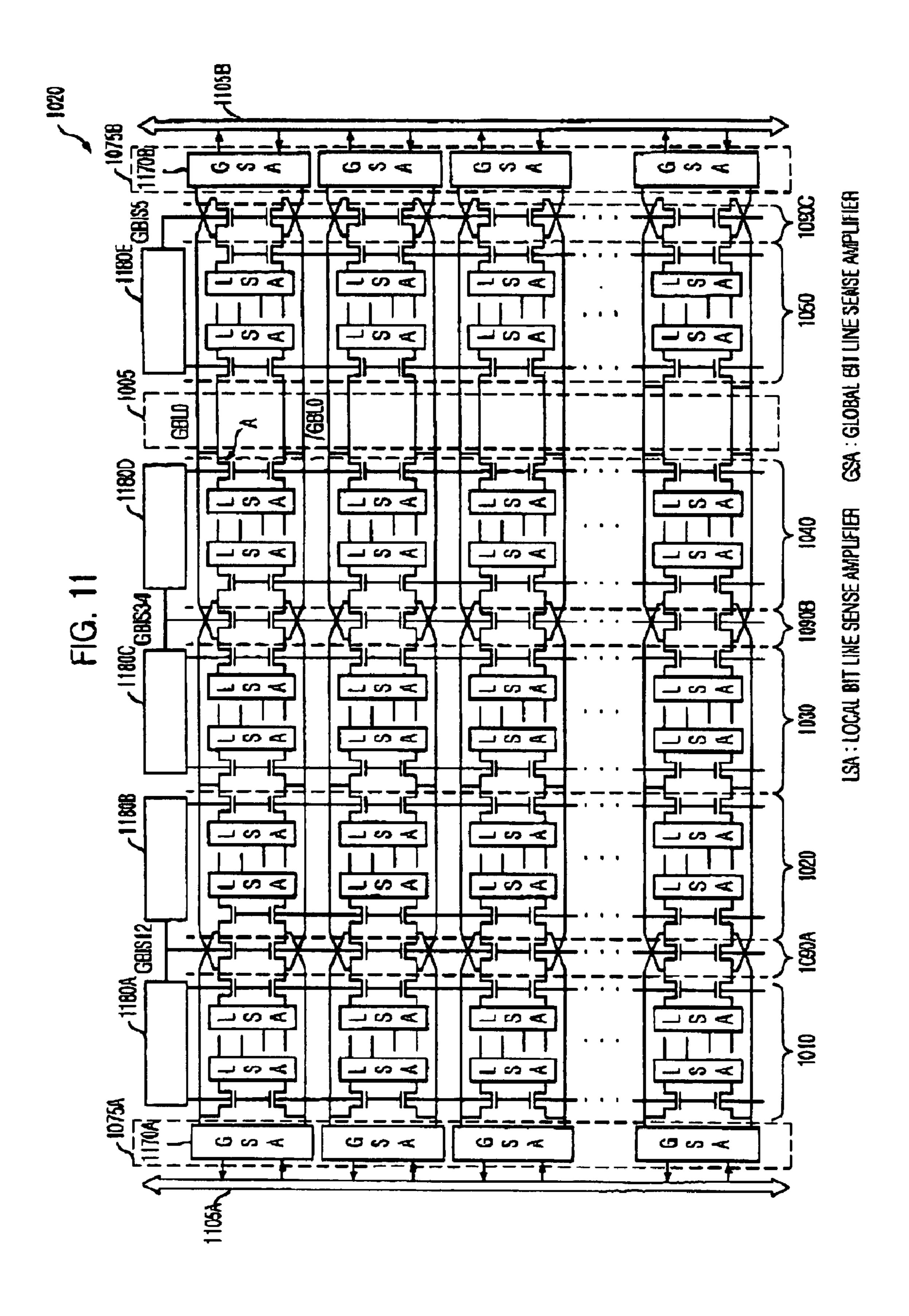

- FIG. 11 is a schematic circuit diagram showing a cell area shown in FIG. 10;

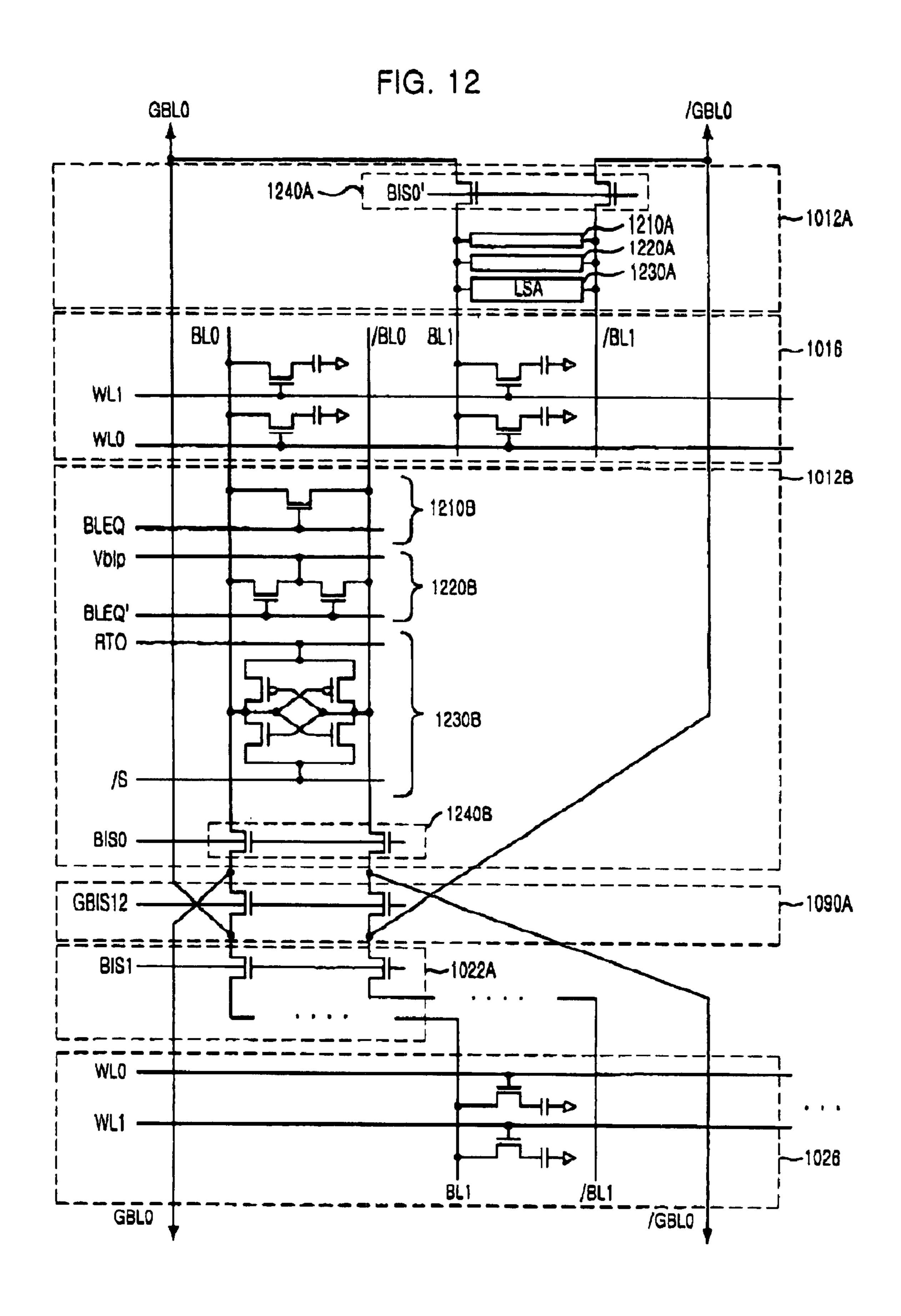

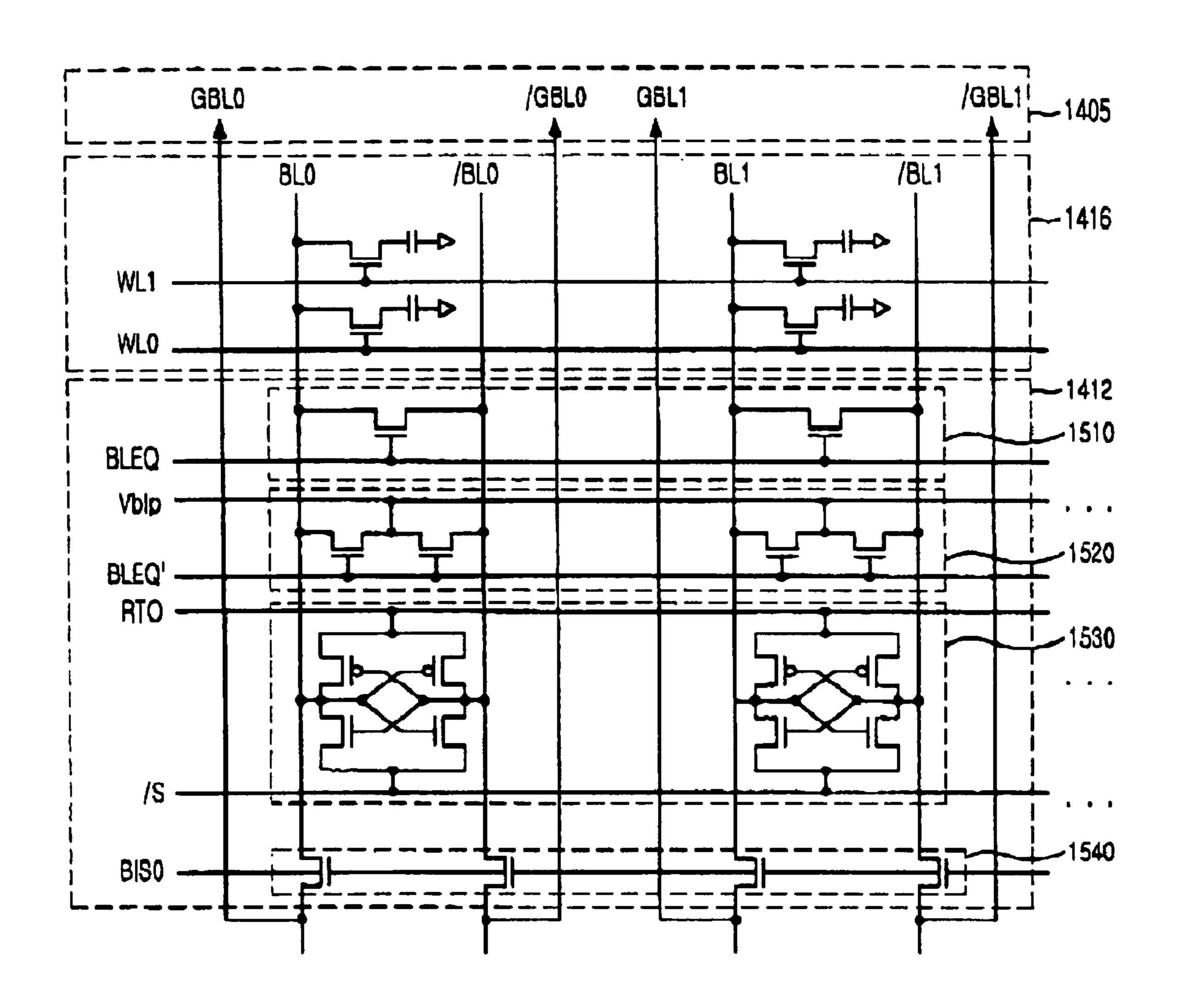

- FIG. 12 is a schematic circuit diagram describing a cell block of the cell area shown in FIG. 11;

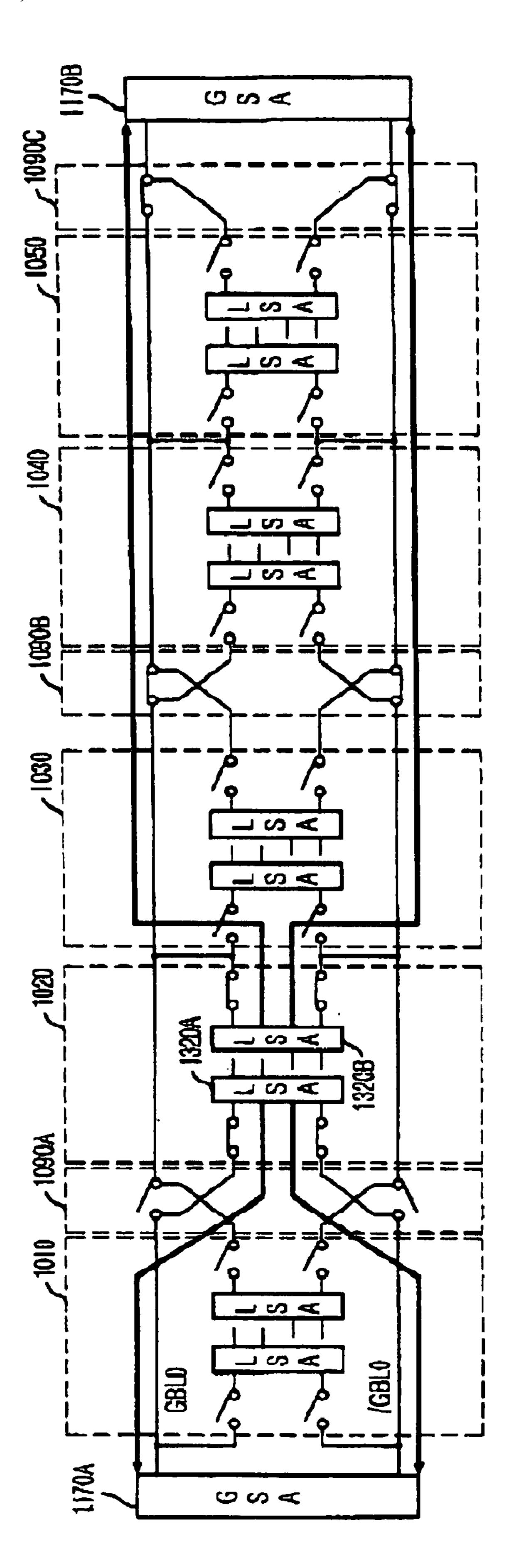

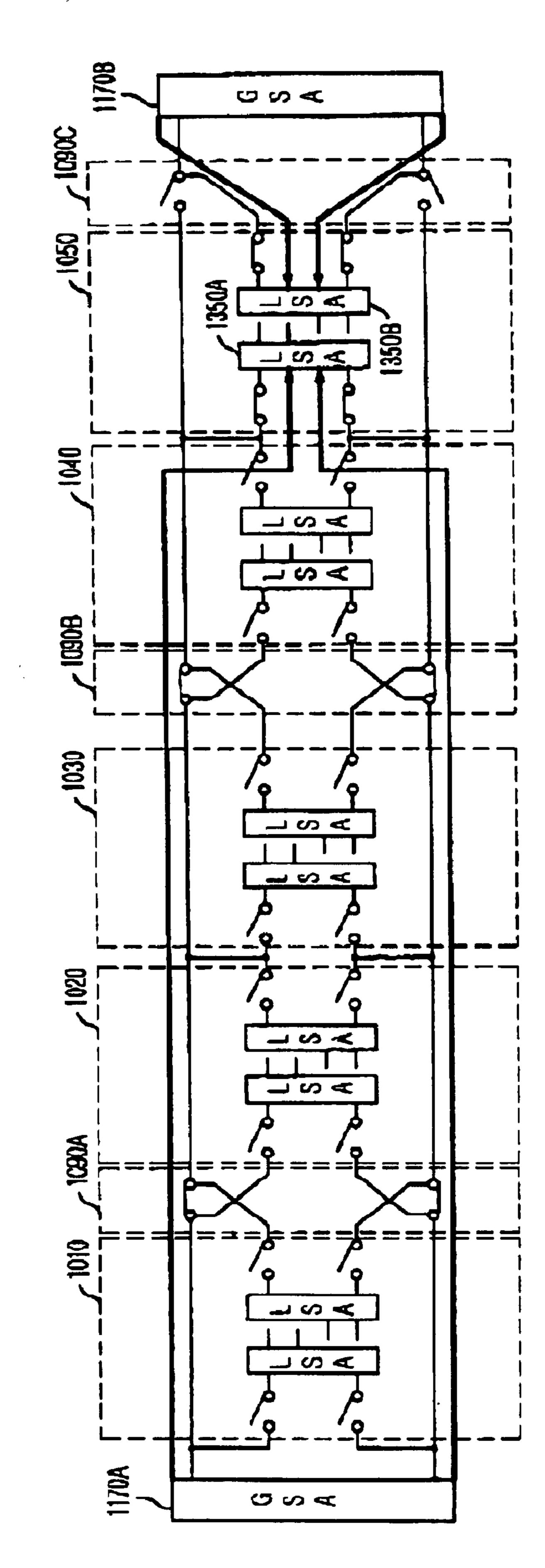

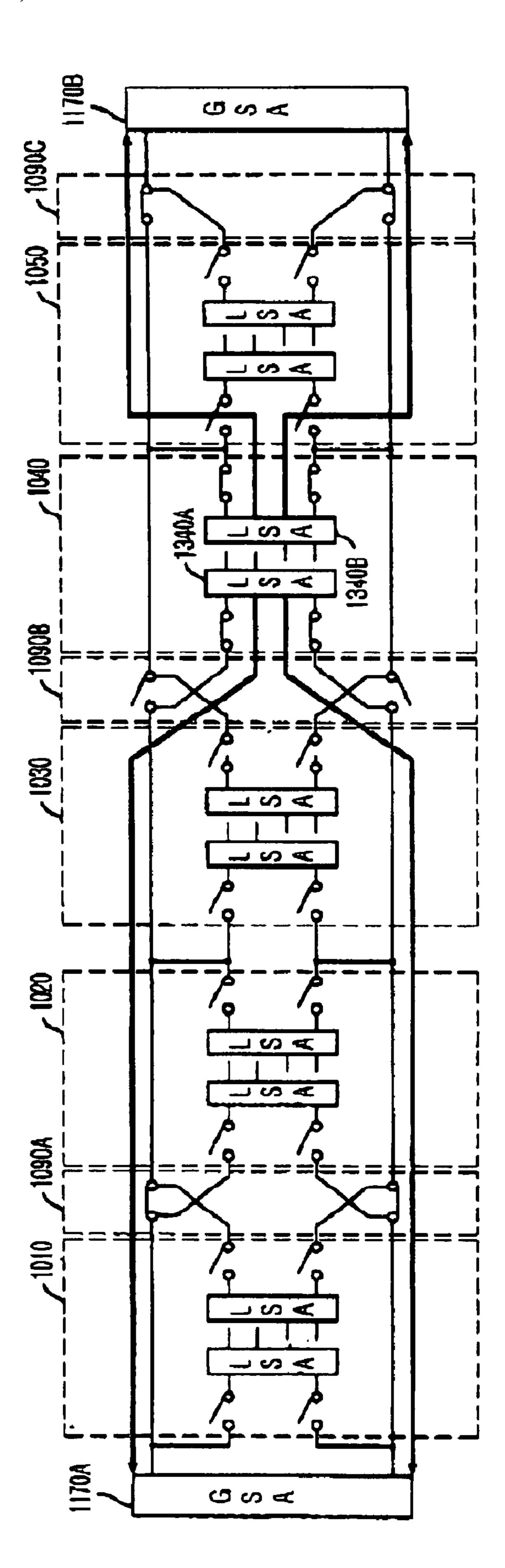

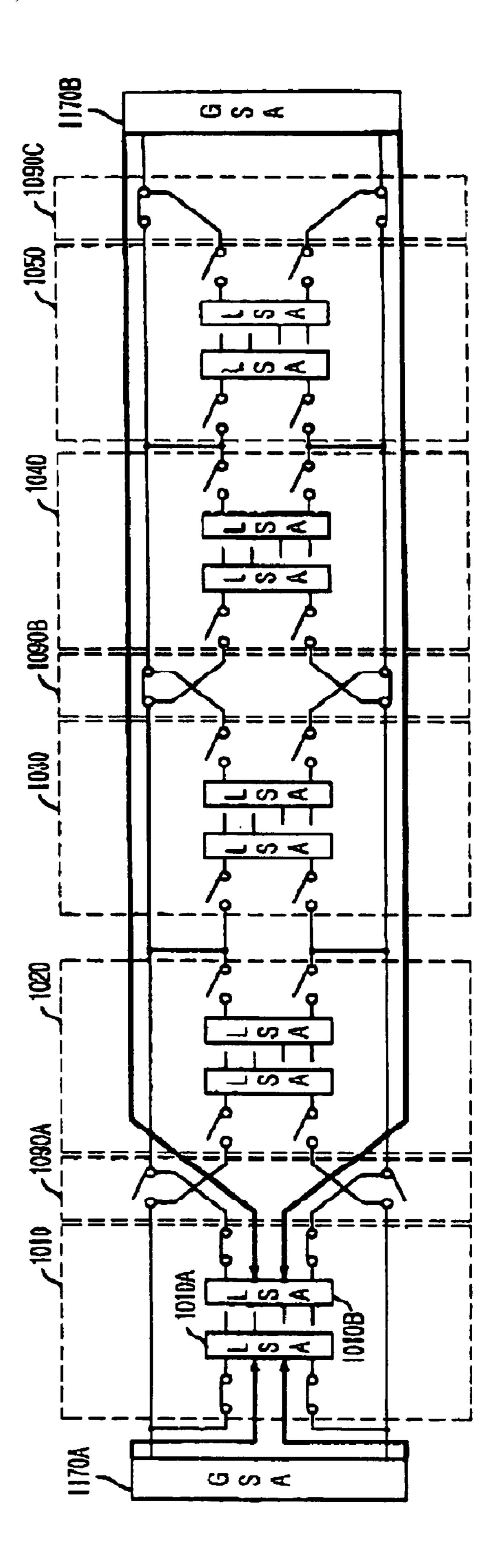

- FIGS. 13A to 13D are explanatory diagrams depicting the operation of the cell area shown in FIG. 11;

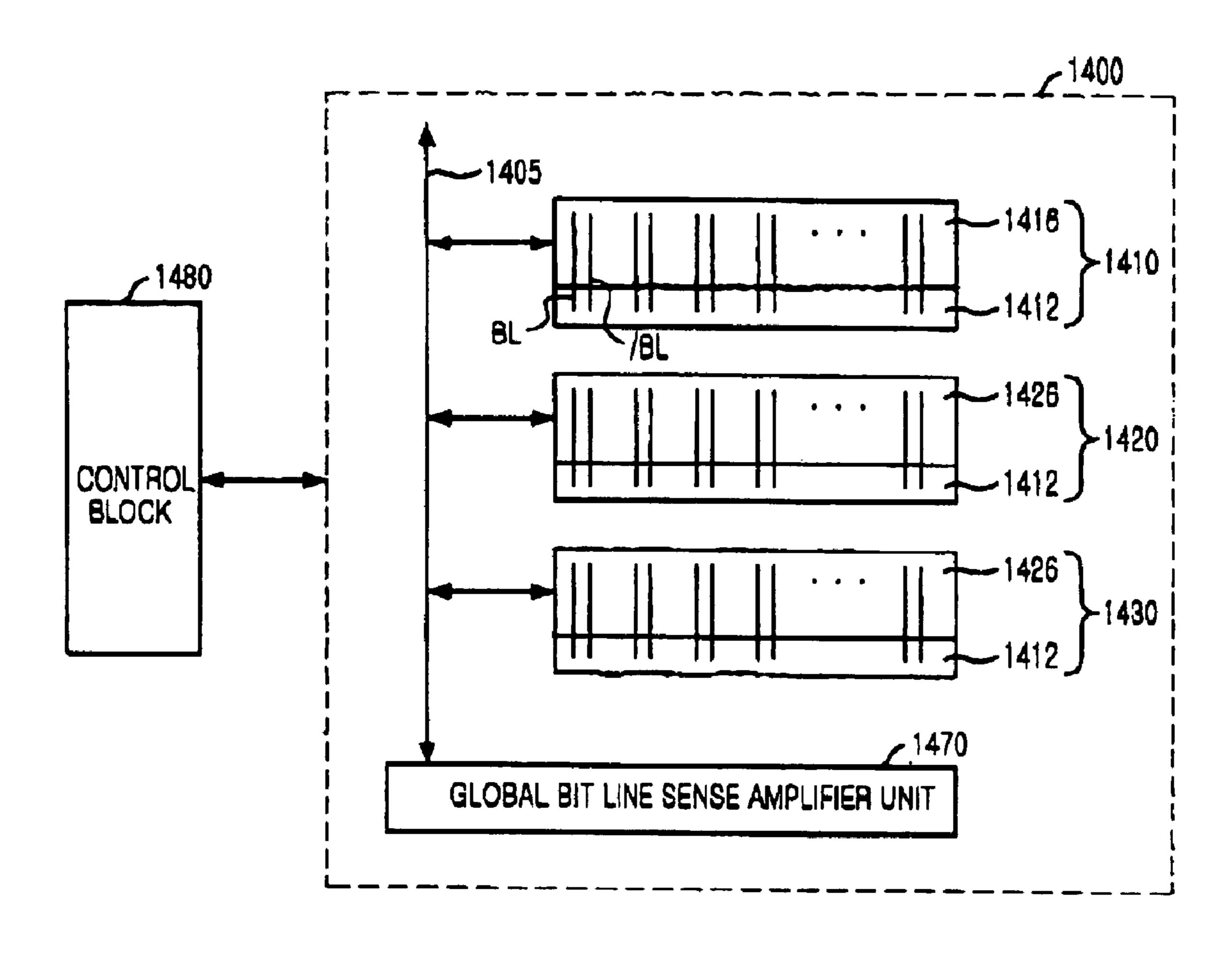

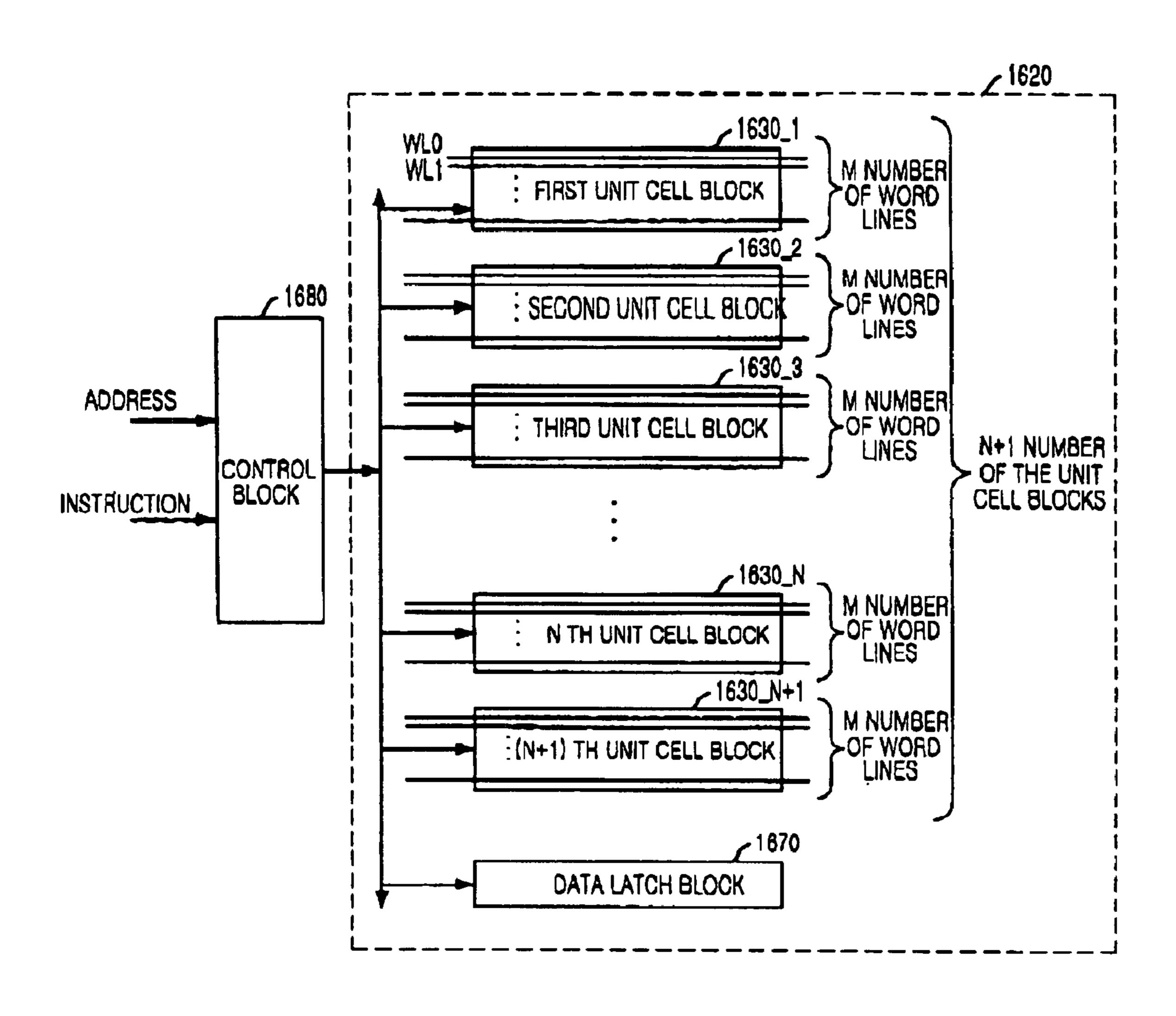

- FIG. 14 is a block diagram showing a segment in the memory device in accordance with another embodiment of the present invention;

- FIG. 15 is a schematic circuit diagram describing a cell block of the bank shown in FIG. 14;

- FIG. 16 is a block diagram showing a segment in the memory device in accordance with another embodiment of the present invention;

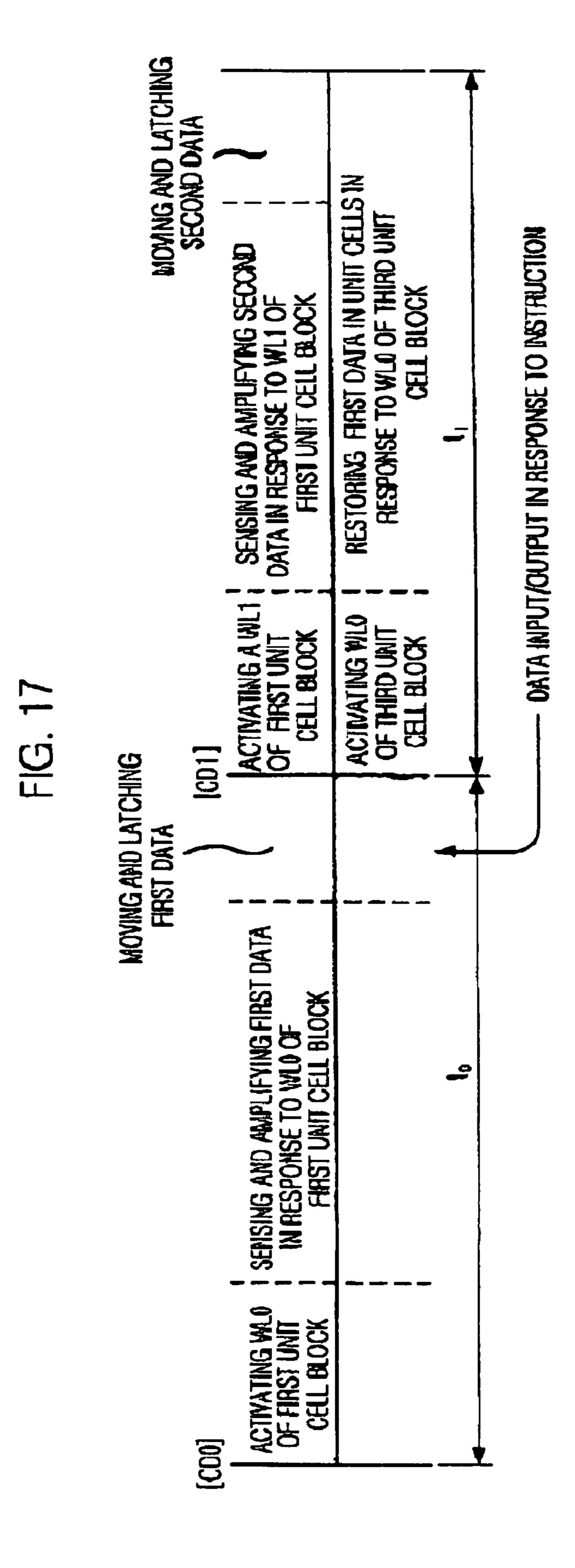

- FIG. 17 is a timing diagram describing the operation of the memory device described in FIG. 16;

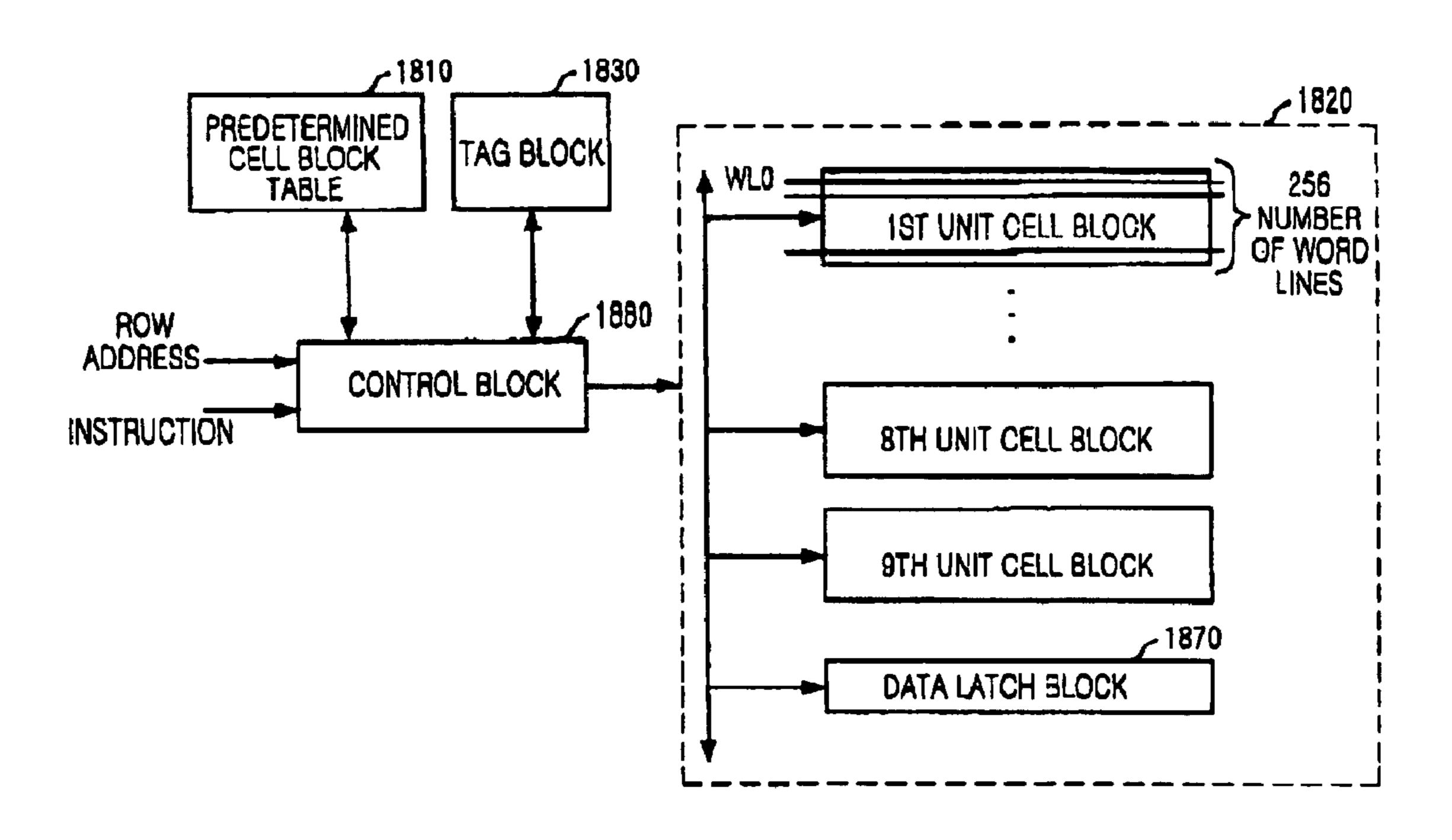

- FIG. 18 is a block diagram showing a segment in the inventive memory device in accordance with another embodiment of the present invention;

- FIG. 19 is an exemplary block diagram describing a predetermined cell block table shown in FIG. 18;

- FIG. 20 is an exemplary block diagram depicting a tag block shown in FIG. 18;

- FIG. 21 is a block diagram showing a part of a control block shown in FIG. 18;

- FIGS. **22** and **23** describe explanatory diagrams of the tag block shown in FIG. **20** in detail;

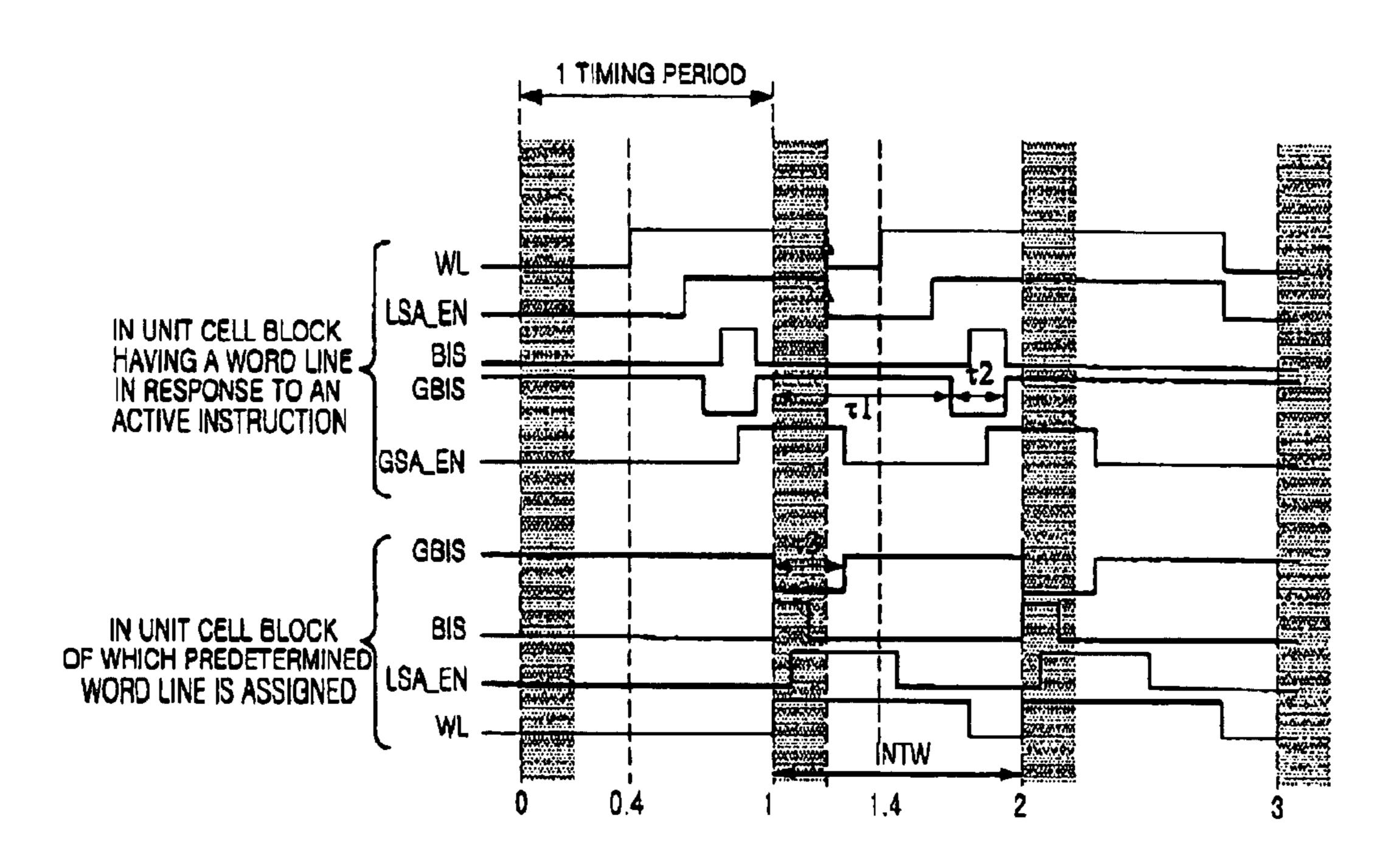

- FIG. **24** is a timing diagram depicting operation of the memory device shown in FIG. **18**;

- FIG. 25 is a timing diagram describing the operation of the memory device employing the tag block shown in FIG. 18;

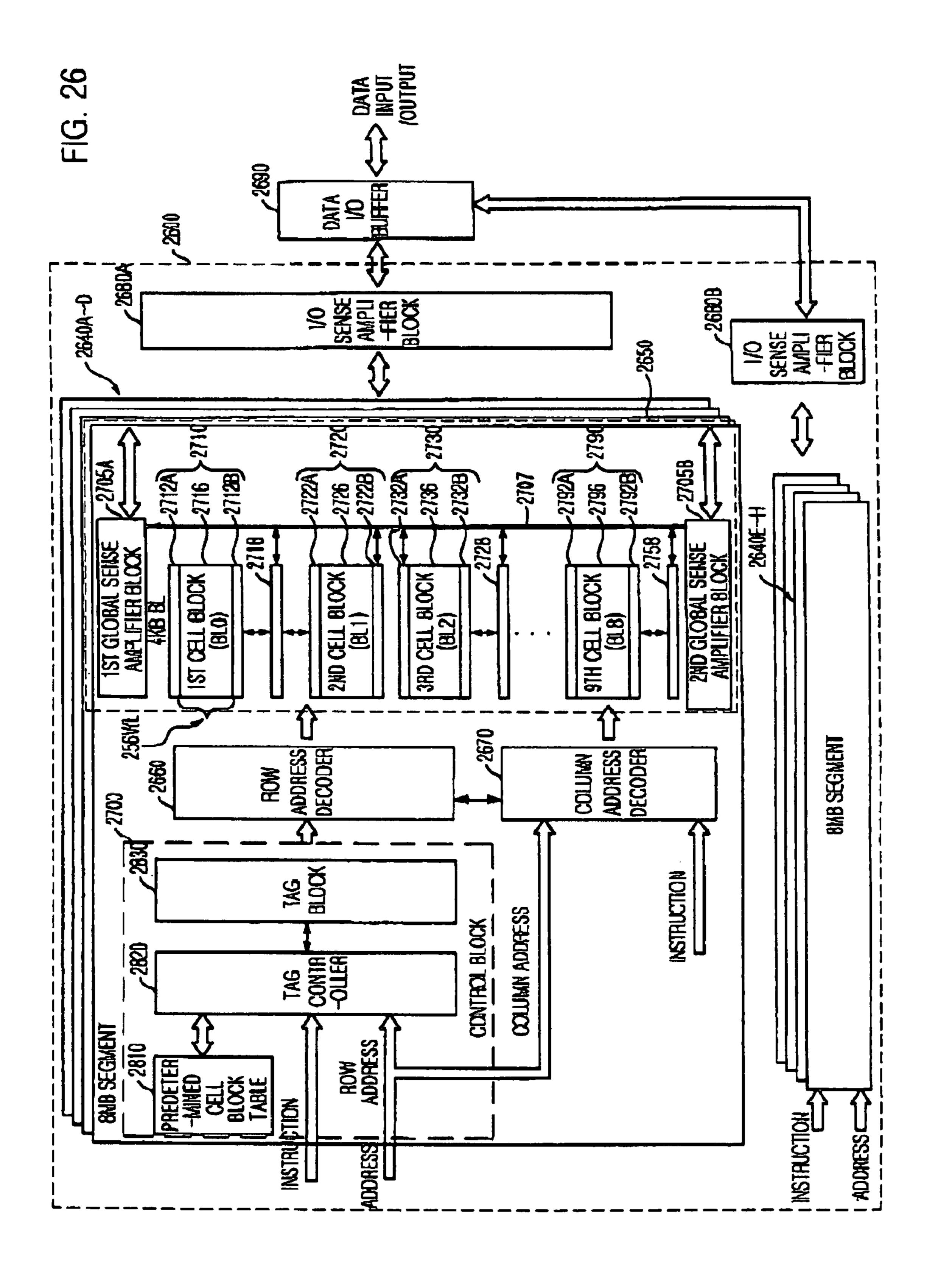

- FIG. 26 is a block diagram showing a semiconductor memory device in accordance with another preferred embodiment of the present invention;

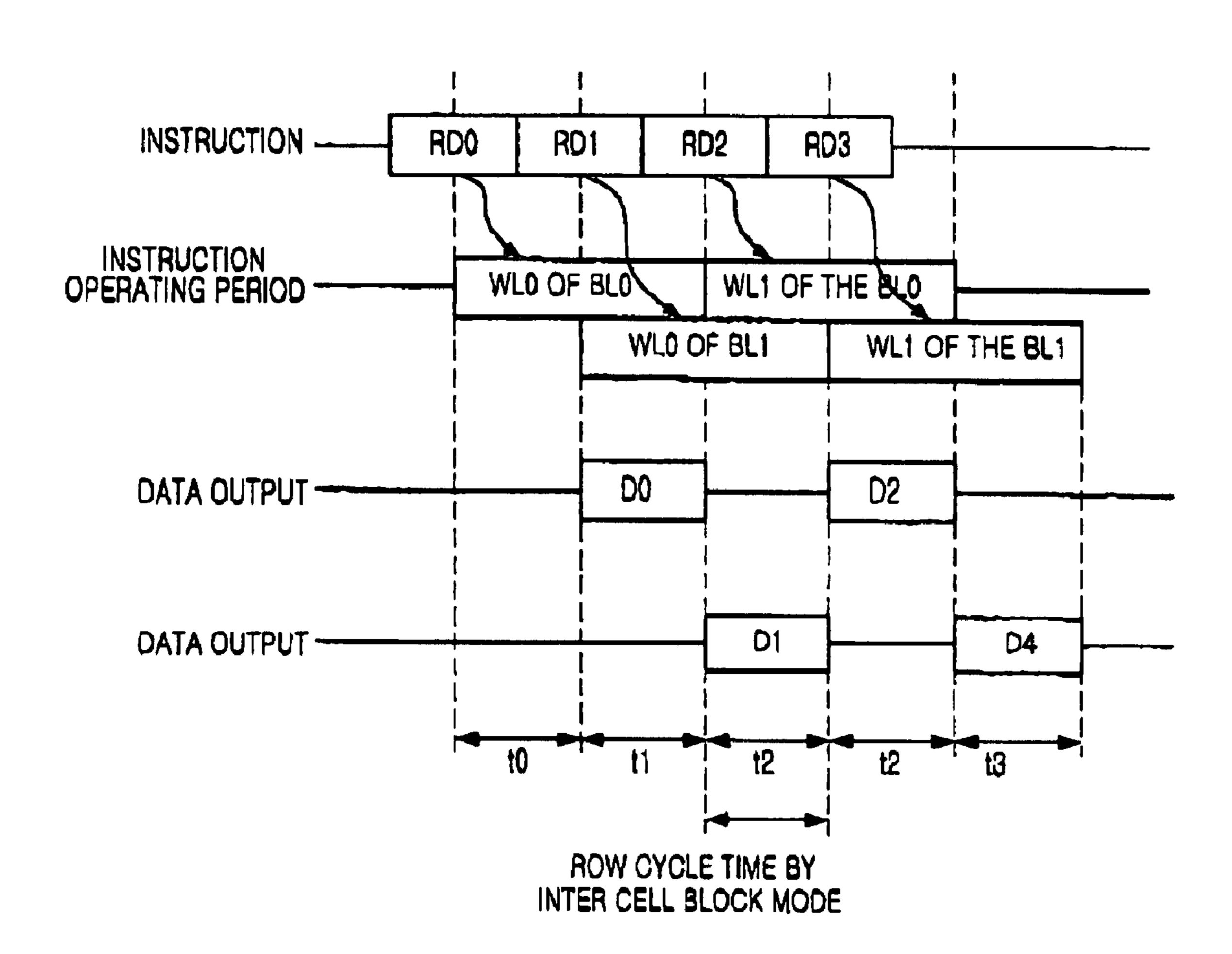

- FIG. 27 is a timing diagram depicting an inter cell block interleaving mode in the memory device shown in FIG. 26;

- FIG. 28 is a timing diagram depicting operation of the memory device shown in FIG. 26 in a read mode;

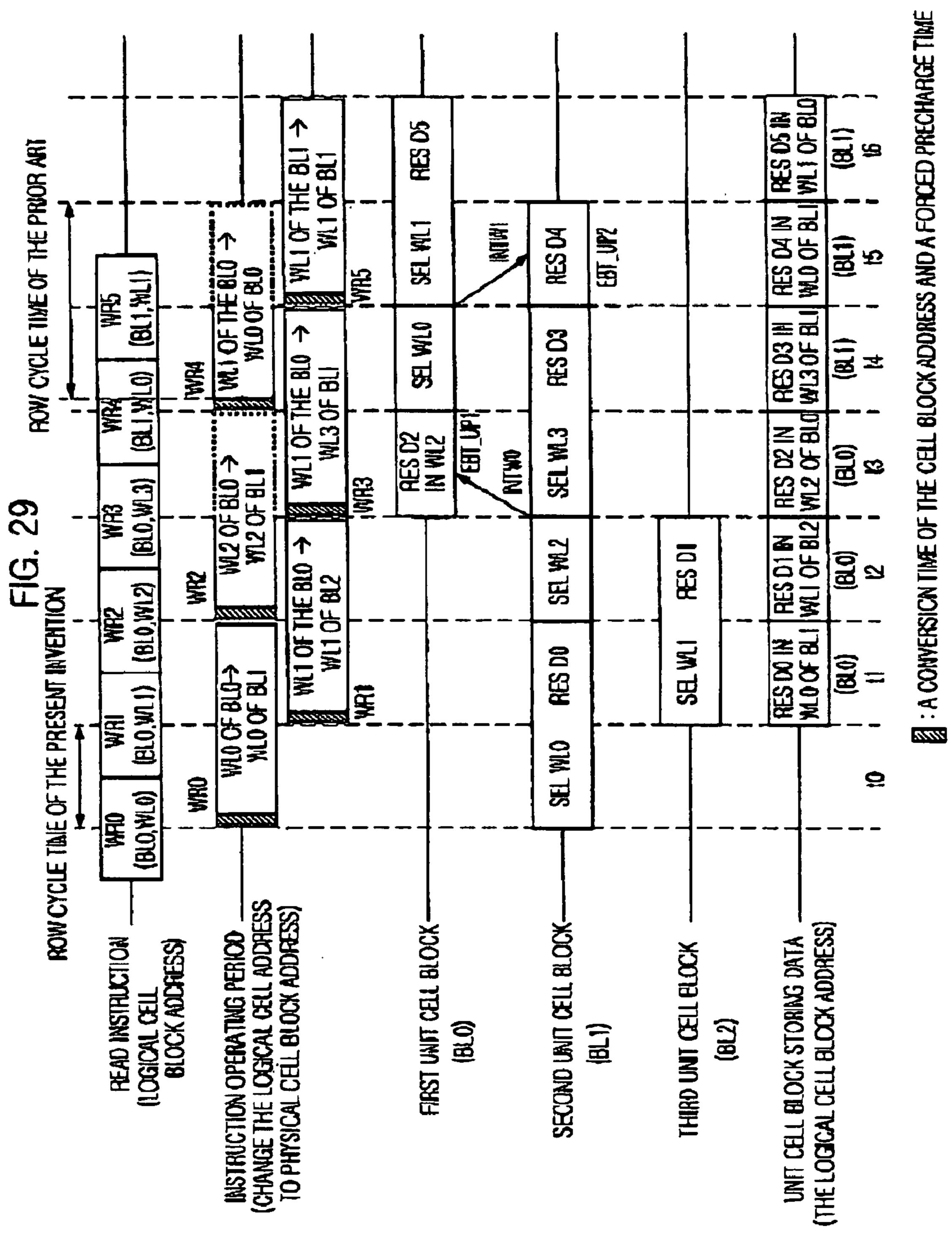

- FIG. 29 is a timing diagram depicting operation of the memory device shown in FIG. 26 in a write mode;

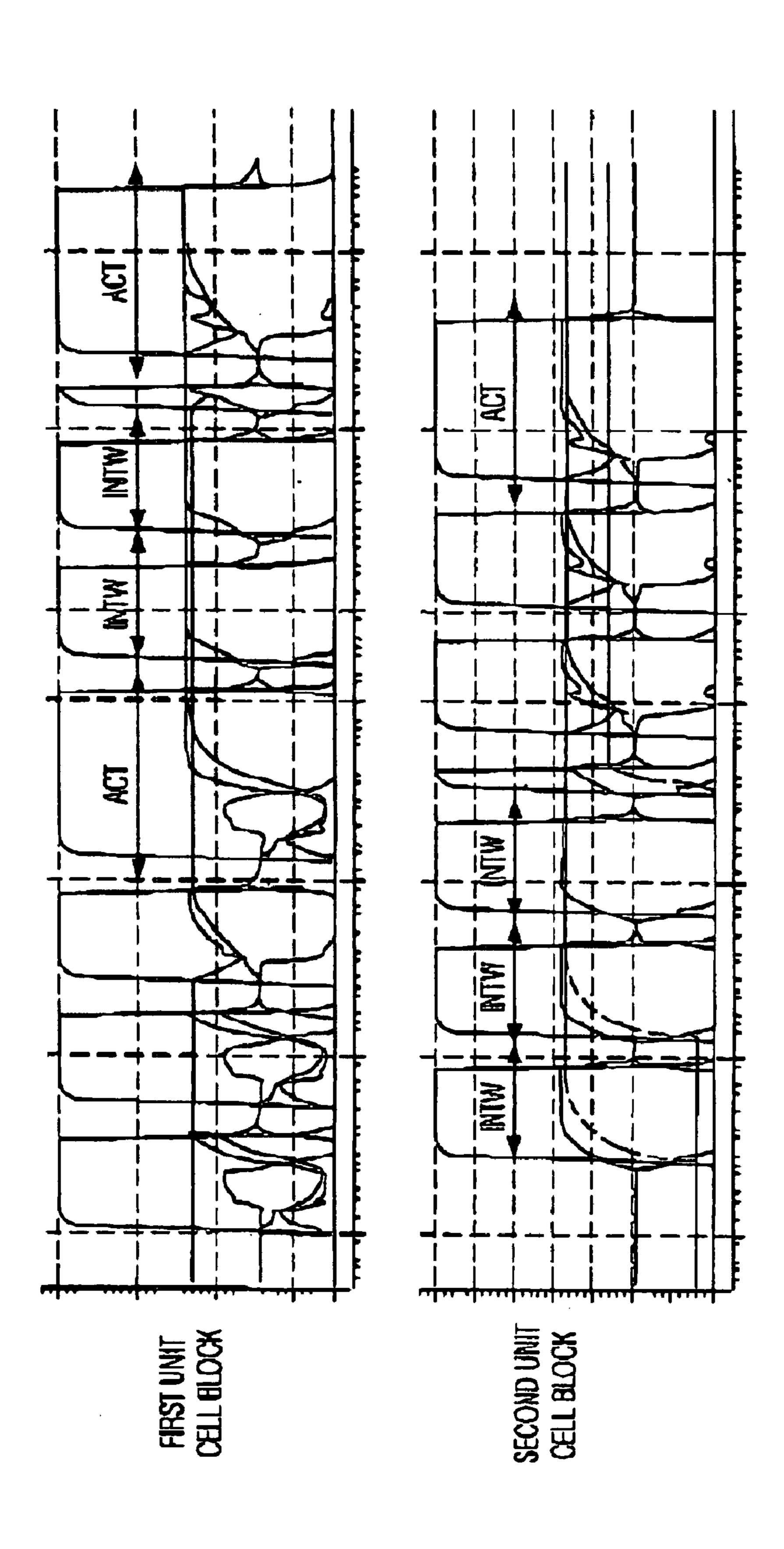

- FIG. **30** is a simulation waveform showing operation of the memory device shown in FIG. **26** in the read mode;

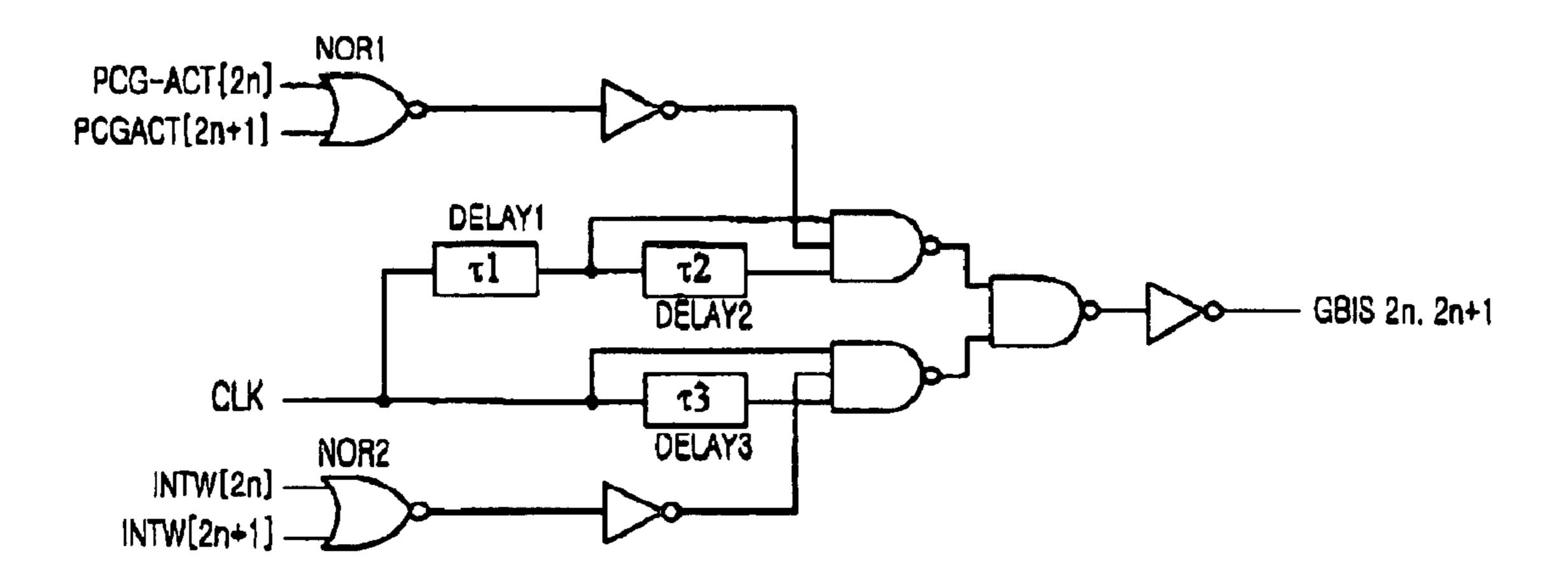

- FIG. 31 is a schematic circuit diagram describing a circuit for generating signals used for a global bit line connection unit shown in FIG. 24;

- FIG. 32 is a timing diagram showing operation of the memory device in response to the signals generated from th circuit shown in FIG. 31;

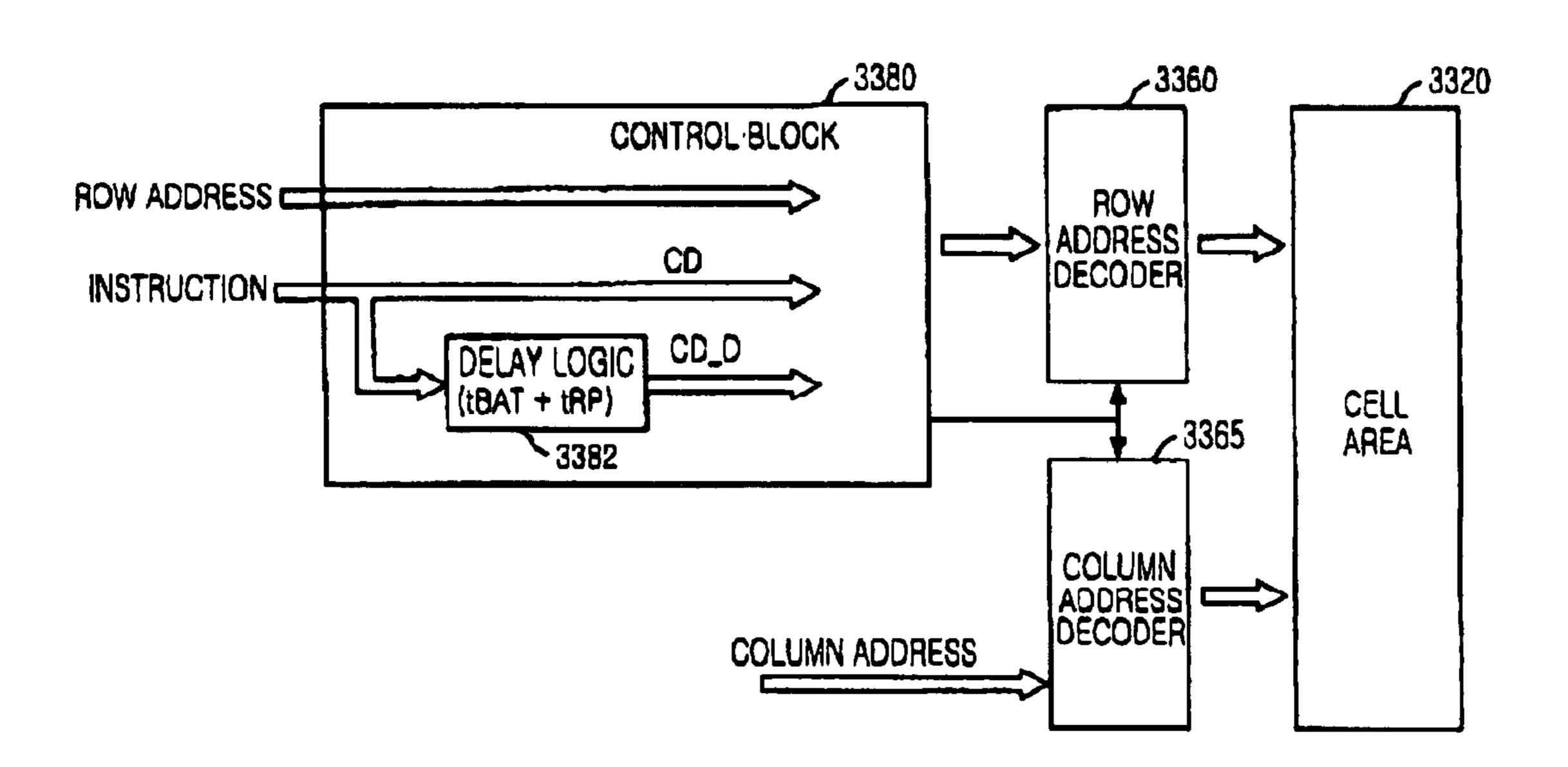

- FIG. 33 is a block diagram depicting a memory device having a reduced row cycle time;

- FIG. **34** is a block diagram describing the memory device shown in FIG. **33** in detail;

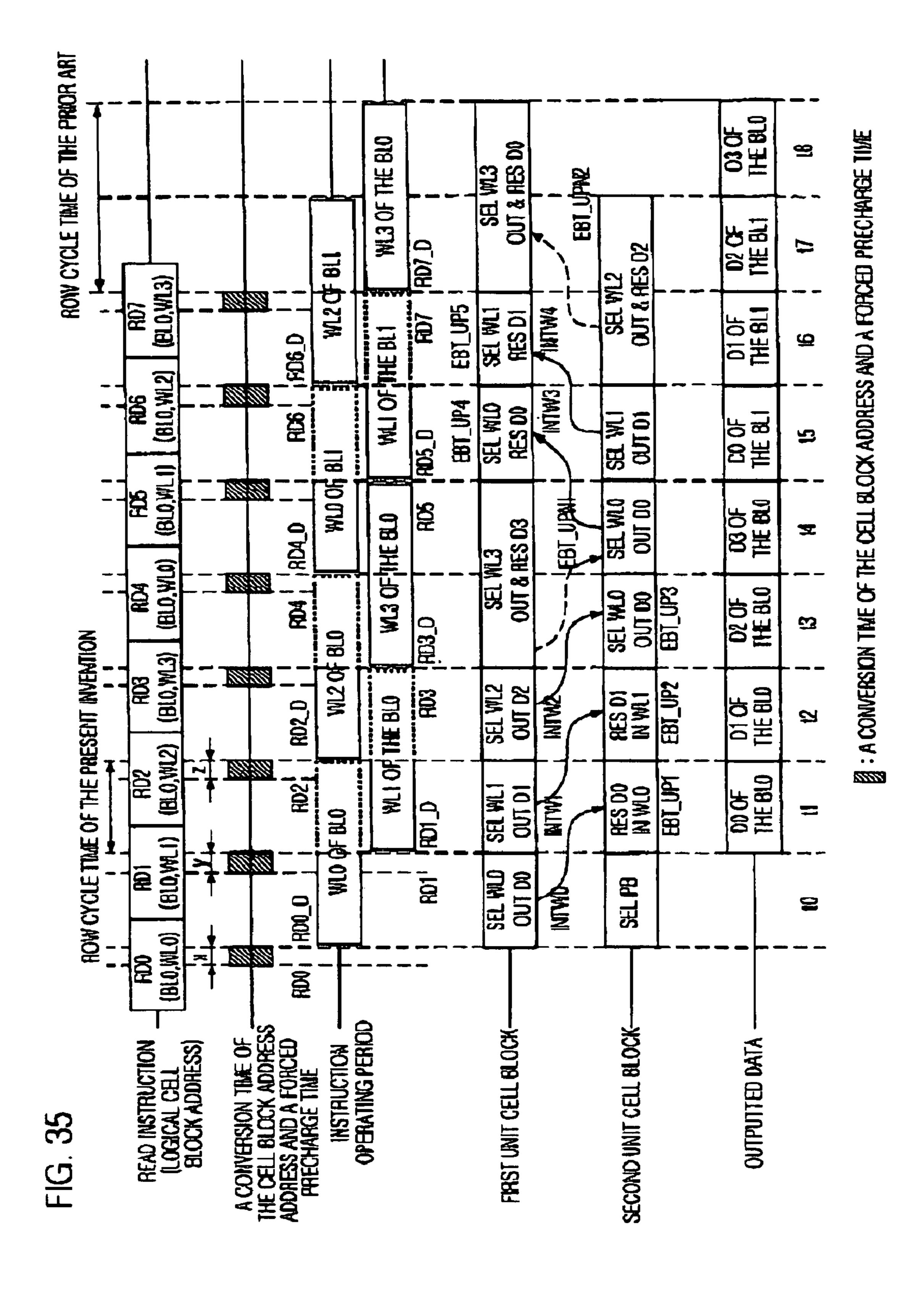

- FIG. 35 is a timing diagram depicting operation of the memory device shown in FIG. 34 in response to continuously inputted reed instructions; and

- FIG. 36 is a timing diagram showing operation of the memory device shown in FIG. 34 in comparison with that of the memory device shown in FIG. 18.

## DETAILED DESCRIPTION OF THE INVENTION

Hereinafter, a semiconductor memory device in accordance with the present invention will be described in detail referring to the accompanying drawings.

Referring to FIG. 5, there is shown a block diagram showing a semiconductor memory device in accordance with a preferred embodiment of the present invention.

As shown, the semiconductor memory device includes a plurality of banks. Each bank has at least one segment 510A to 510D and an input/output (I/O) sense amplifier block 590. The segment, e.g., 510A, includes a cell area 520, a control block 580, a row address decoder 560 and a column address decoder 565. Herein, because the row and column address decoder 560 and 565 are similar to those of the conventional memory device as shown in FIG. 1, detailed descriptions about operation of the row and column address decoder 560 and 565 is omitted for the sake of convenience.

Referring to FIG. 6, the cell area 520 includes at least two cell blocks, e.g., 610 and 620, at least one global bit line connection unit, e.g., 550. The cell block, e.g., 610, outputs data through the use of a global bit line 505 in response to an instruction. The global bit line connection unit 550 allocated between the two cell blocks, e.g., 610 and 620, serves to selectively connect the global bit line 505 to each cell block, e.g., 610 or 620. For the sake of convenience, the row address decoder and the column address decoder identical to those shown in FIG. 5 does not described in the segment embodiment, hereinafter.

15 shown in FIG. 6.

Each of the first a plurality of unit 722. The connection unit 550 allocated block 710 and 720 temporary latched in mode.

The control block ing mode.

For supporting 25 control block 780

The memory device can support an "intra cell block interleaving mode". Hereinafter, the inter cell block interleaving mode is defined as an operation that during a current data in response to a current instruction is restored in the original cell block or in another cell block, a next data in response to a next 30 instruction is simultaneously outputted from the same cell block.

For implementing the intra cell block interleaving mode, the control block **580** controls the cell area in a manner that a first data is restored into the original cell block, e.g., **610** and 35 a second data is simultaneously outputted from the same cell block, e.g., **610** in response to a next instruction, after the cell block, e.g., **610** outputs the first data to the global bit line **505** in response to an instruction.

In detail, a first cell block **610** includes a first cell array **616**, 40 a first local sense amplifier unit **612**A and a first local sense amplifier connection unit **614**A. The first cell block **610** further includes a second local sense amplifier unit **612**B and a second local sense amplifier connection unit **614**B.

The first cell array 616 has a plurality of unit cells and is 45 coupled to the first and the second local sense amplifier units 612A and 612B through the first and second local sense amplifier connection units 614A and 614B. The first local sense amplifier block 612A amplifies and outputs a first data outputted from the first cell array 616 to the global bit line 50 505. The first local sense amplifier connection unit 614A serves to selectively connect the first cell array 616 to the first local sense amplifier block 612A. As soon as the first data from the first cell array 616 is supplied to the first local sense amplifier unit 612A, the first cell array 616 is isolated from 55 the first local sense amplifier block 612A by the first local sense amplifier connection unit 614A.

After the first data is coupled to the input/output sense amplifier block **590**, the first data should be restored. Thus, the global bit line connection unit **550** connects the global bit 60 line **505** to the second local sense amplifier unit **612**B. Then, the first data is amplified by the second local sense amplifier unit **612**B; and the amplified first data is restored in the original cells. Simultaneously, a second data in response to the next instruction can be outputted from the same cell array 65 **616** or another cell array, e.g., **626** after amplified by the local sense amplifier unit, e.g., **612**A or **622**A.

12

Thus, a data access time of the inventive memory device is not depended upon whether the first and second data are accessed on the same cell blocks or each different cell block in the intra cell block data access. Namely, the inventive memory device can guarantee stable operation speed without depending on a data access pattern.

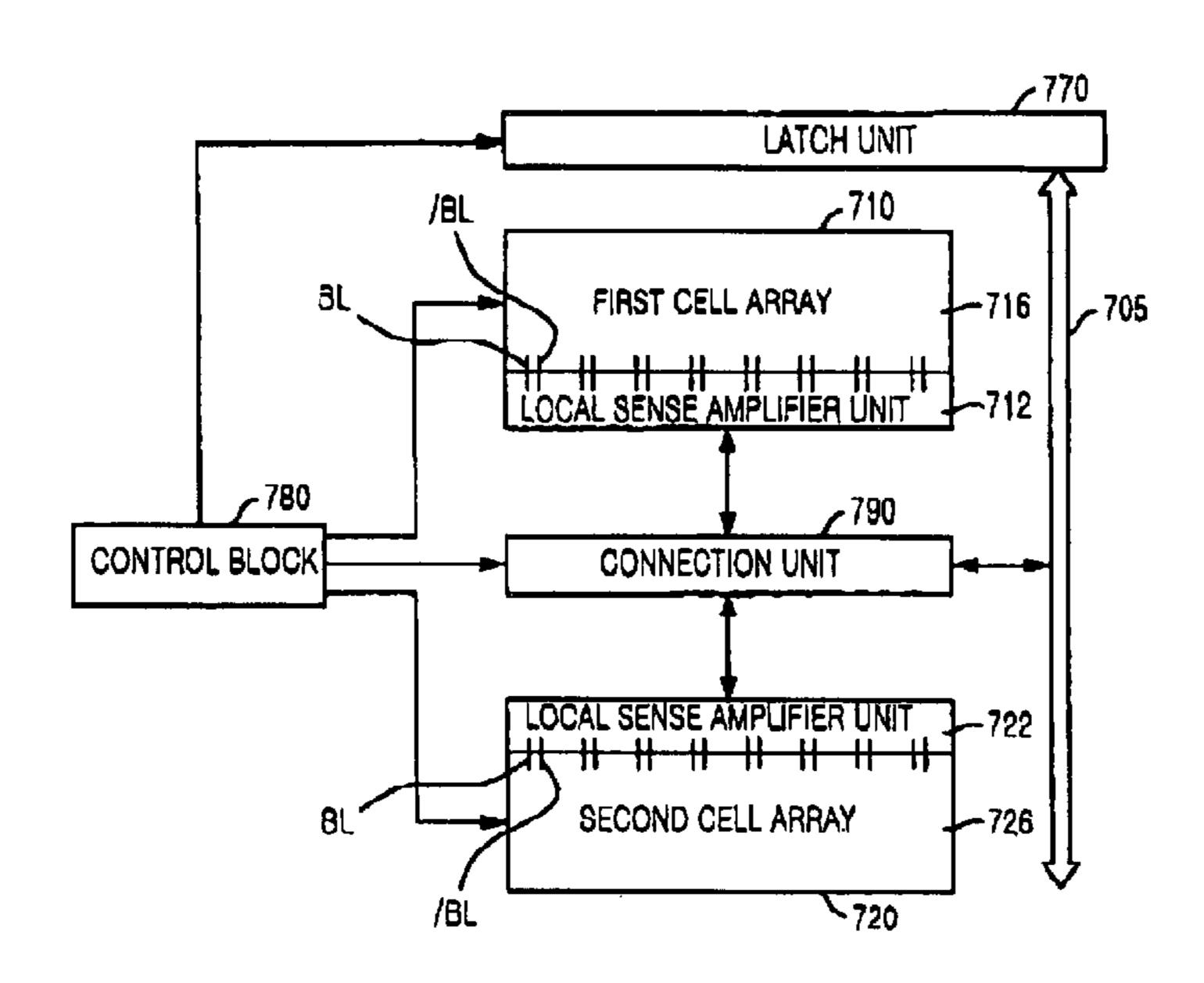

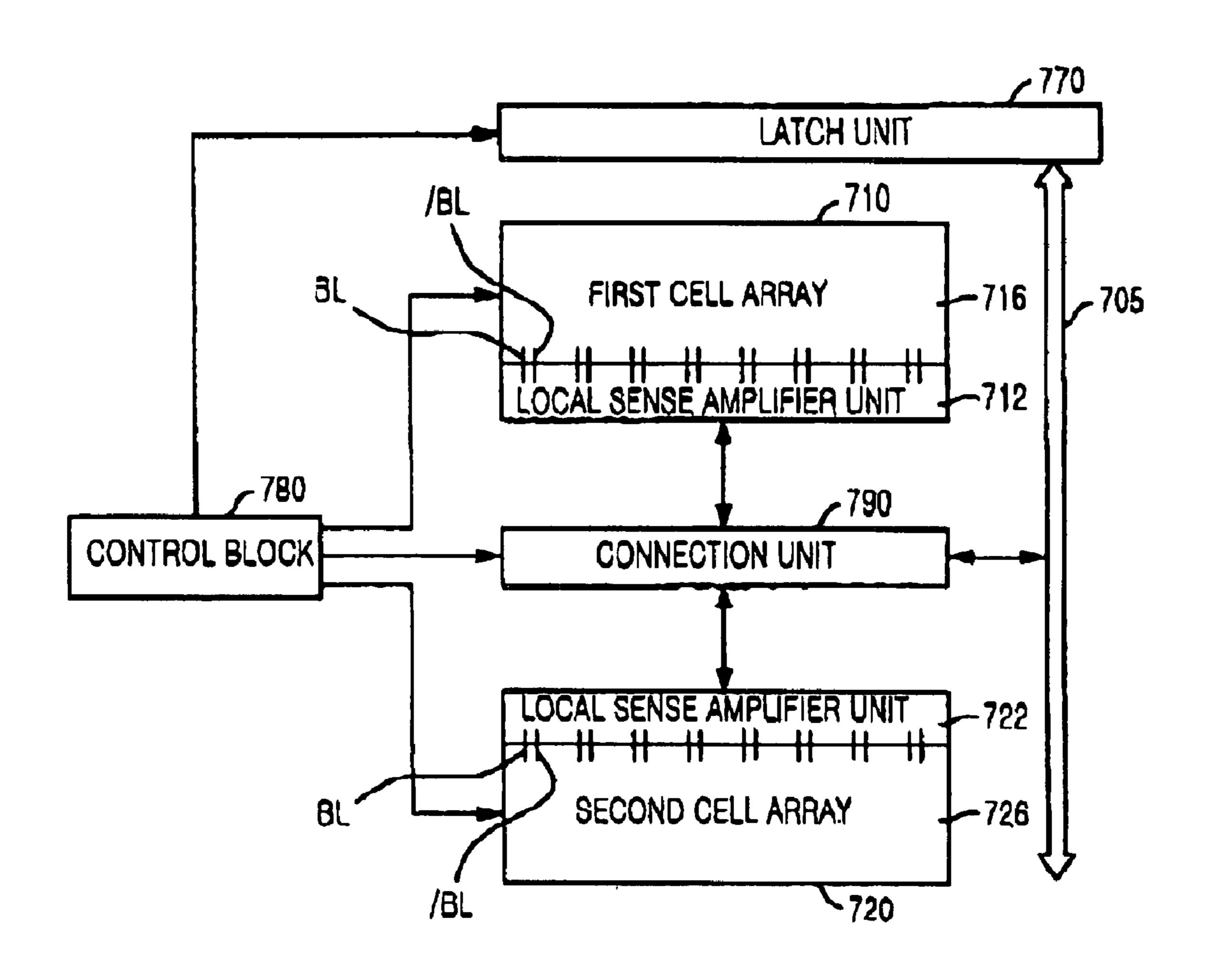

FIG. 7 is a block diagram describing a segment in the semiconductor memory device in accordance with another embodiment of the present invention.

As shown, the segment of the semiconductor memory device includes a first cell block 710, a second cell block 720, a connection unit 790 and a control block. And the segment further includes a latch unit 770 and the cell area is couple to a control block 780 which is similar to the control block shown in FIG. 6.

Each of the first and the second cell blocks 710 and 720 has a plurality of unit cells and a local sense amplifier unit 712 or 722. The connection unit 790 is used for selectively connecting or disconnecting an alternative of the first and second cell block 710 and 720 to a global bit line 705. The latch unit 770 temporary latches a data supplied in the global bit line 705. The control block 780 supports an intra cell block interleaving mode.

For supporting the inter cell block interleaving mode, the control block **780** controls the cell area in a manner that a first data from the first cell block **710** is restored into the other cell block, e.g., **720**, and a second data is simultaneously outputted from the same cell block, e.g., **710** in response to a next instruction, after a first cell block, e.g., **710** outputs a first data to the global bit line **705** in response to a instruction.

In detail, if the second data in response to the next instruction is sequentially accessed in the first cell block 710 after the first data in response to the current instruction is accessed in the same cell block 710, the first data is restored not in the original cell block 710 but in the second cell block 720. At this time, the latch unit 770 is used for temporarily latching the first data supplied to the global bit line 705.

Namely, first of all, the connection unit 790 connects the first cell block 710 to the global bit line 705 for outputting the first data. The first data is outputted to an external circuit and latched in the latch unit 770. Then, the connection unit 790 connects the second cell block 720 to the global bit line 705 for restoring the latch d first data, while the second data is accessed and amplified by the local sense amplifier unit 712 of the first cell block 710.

If the second data is accessed and outputted from the second cell block, the latched first data is restored in the original cell block 710 while the second data for the second cell block 720 is amplified by the local sense amplifier unit 722 of the first cell block 720.

Thus, the data access time of the inventive memory device of the present invention is not depended upon whether the first and second data are outputted from the same cell block or a different cell block. Namely, the inventive memory device can guarantee a stable operation speed less sensitive to a data access pattern.

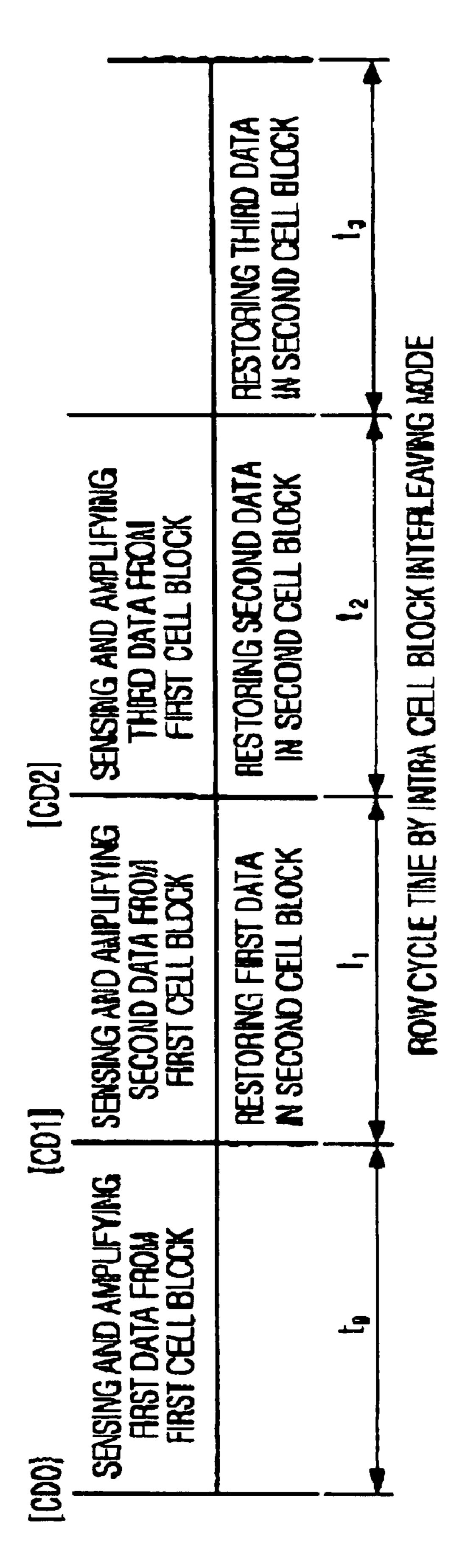

FIGS. 8 and 9 are timing diagrams depicting operation of the semiconductor memory device, depending upon a data access pattern.

Herein, as shown in FIGS. 7 to 9, there is described the operation of the memory device in accordance with the present invention. First, referring to FIG. 8, there is described the operation of the memory device in an intra cell block data access.

As shown, by sequentially inputted instructions CD0 to CD2, e.g., the first data is sensed and amplified in the first cell block 710 at a first timing period t0. Herein, at a second timing

period t1, the first data is restored in the second cell block and the second data is sensed and amplified in the same first cell block 710.

Herein, at a third timing period t2, the second data is restored in the second cell block 720 and the third data is 5 sensed and amplified in the same first cell block 710. And next, the third data is restored in the second cell block 720 at the forth timing period t3.

After the first data is sensed and amplified by the local sense amplifier 712 included in the first cell block 710, the unit. first data latched by the latch block 770 moves to the second cell block 720 for first data restoration time.

The data exchange between the latch block 770 and the first or the second cell block 710 or 720 is performed through the use of the global bit line 705. The global bit line 705 is selectively connected to the first and the second cell blocks

710 and 720 by the connection unit 790.

unit content of the unit content of the second cell block while in the intent of the second cell blocks.

In a the intent of the second cell block is the second cell block is the intent of the second cell block is the second cell bl

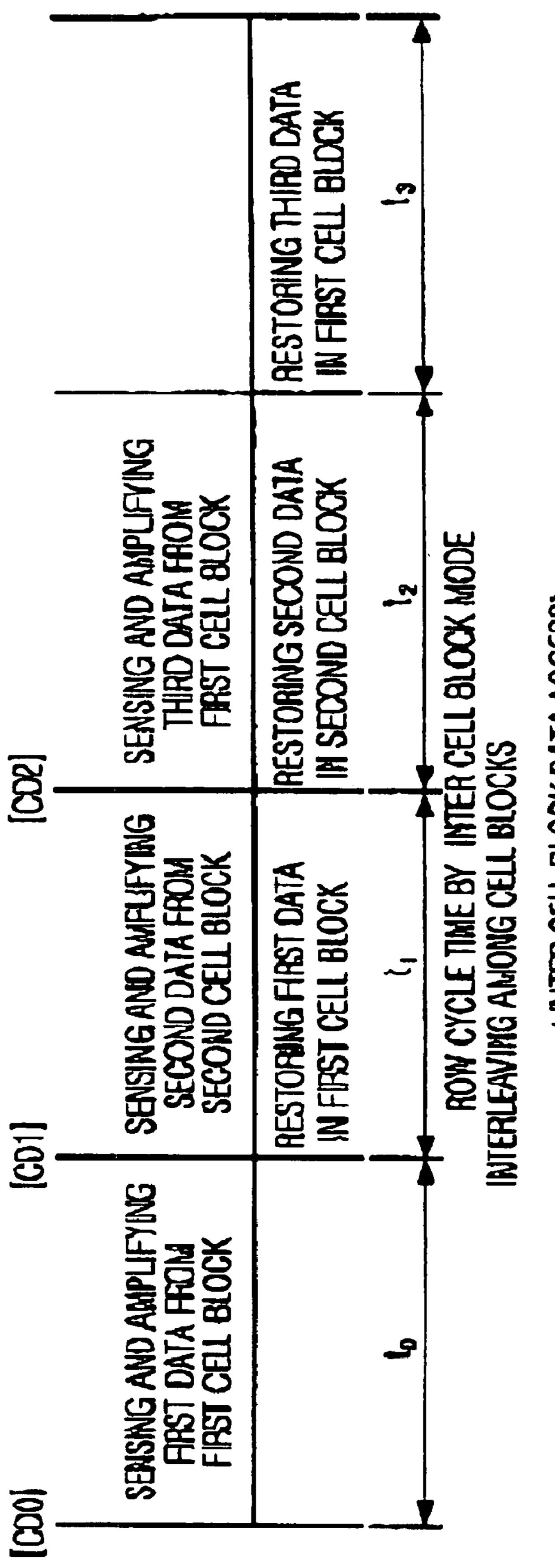

Referring to FIG. 9, in an inter cell block data access, the second data is accessed in the second cell block 720 after the first data is accessed in the first cell blocks 710.

When first to third data are alternatively retrieved in the first and the second cell blocks **710** and **720** in response to continuously inputted instructions CD**0** to CD**2**, the first data is sensed and amplified in the first cell block **710** at a first timing period t**0**; and then, at a second timing period t**1**, the 25 first data is restored in the first cell block **710** and, at the same time, the second data is sensed and amplified in the second cell block **720**.

Next, at a third timing period t2, the second data is restored in the second cell block 720; and, at the same time, the third 30 data is sensed and amplified in the first cell block 710. And then, the third data is restored in the first cell block 710 at the forth timing period t3.

For instance, after the first data is sensed and amplified, the first data latched by the latch block 770 moves to the first or 35 the second cell block 710 or 720 for the data restoration time. Namely, when the data are alternatively retrieved from the first and the second cell blocks 710 and 720 in the inter cell block data access, an inter cell block interleaving mode is performed in a manner that another data accessed by a next 40 instruction is sensed and amplified during a first data latched in the latch block 770 is restored in the original cell block.

In the case that an inputted instruction is the read instruction, the data latched in the latch block 770 is outputted to the external part; otherwise, in a written mode, the data inputted 45 from the external part is replaced with the latched data.

Since, in the memory device of the present invention, data access operation and restoration operation are simultaneously carried out at the same row cycle time, the data access time can be dramatically reduced.

FIG. 10 is a block diagram describing a segment in the memory device in accordance with another embodiment of the present invention.

As shown, the segment of the memory device includes N+1 of unit cell blocks, e.g., 1010 to 1050, N/2+1 global bit line 55 connection units, e.g., 1090A to 1090C, first and second global bit line sense amplifier units 1075A and 1075B and a control block 1080.

Each unit cell block, e.g., 1010 includes a cell array 1016 having a plurality of unit cells, a first local bit line sense 60 amplifier block, e.g., 1012A and a second local bit line sense amplifier block, e.g., 1012B. The first global bit line sense amplifier unit 1075A serves to latch data sensed and amplified by the first local bit line sense amplifier block, e.g., 1012A, included in each unit cell block. The second global bit line 65 sense amplifier unit 1075B is used for latching data sensed and amplified by the second local bit line sense amplifier

**14**

block, e.g., 1012B, included in each unit cell block. Each global bit line connection unit, e.g., 1090A serves to selectively connect the global bit line 1005 to the second local bit line sense amplifier block, e.g., 1212B of one unit cell block, e.g., 1010 and the first local bit line sense amplifier block, e.g., 1022A of the other unit cell block, e.g., 1020. The control block 1080 is used for controlling operations of inputting and outputting data outputted from each unit cell block and restoring the outputted data in the original cell unit or another cell unit.

The control block **80** supports operation that, in the intra cell block data access, the first data is restored not in the first unit cell block **1010** but in another unit cell block, e.g., **1050**, while the second data is accessed in the first unit cell block **1010**

In addition, the control block 80 supports operation that, in the inter cell block data access, the first data is restored in the first unit cell block 1010 while the second data is accessed in another unit cell block, e.g., 1020.

FIG. 11 is a circuit diagram showing the cell area 1020 shown in FIG. 10.

As shown, the cell area 1020 of the memory device includes the first to the fifth cell blocks 1180A to 1180E, each having a plurality of the unit cell and the first and the second global bit line sense amplifier blocks 1175A and 1175B coupled to each unit cell block through the use of the global bit line 1005.

Each of the first and the second global bit line sense amplifier unit 1175A and 1175B has a plurality of the global bit line sense amplifier GSA. The global bit line sense amplifier 1170A included in the first global bit line sense amplifier unit 1075A is coupled to the global bit line sense amplifier 1170B included in the second global bit line sense amplifier block 1075B through use of the first global bit line pair GBL0 and /GBL0. The amplified data by the first and second global bit line sense amplifier units 1075A and 1075B is outputted through the use of global sense amplifier lines 1105A and 1105B.

The global bit line sense amplifier GSA latches and amplifies the data supplied from the local bit line sense amplifier LSA. The configuration of the global bit line sense amplifier GSA can be identical to that of the local bit line sense amplifier LSA.

The global bit line connection unit, e.g., 1090A, selectively connects the global bit line 1005 to the two neighboring local bit line sense amplifiers, e.g., 1212B and 1022B. Each of the global bit line connection units, e.g., 1090A, is allocated between two unit cell blocks 1010 and 1020. There are provided with three global bit line connection units if the number of the unit cell blocks is 5 as shown in FIG. 11. If the number of these is 9, there are provided with be five global bit line connection units.

As mentioned above, each unit cell block, e.g., 1010, includes the unit cell array, e.g., 1216 and the first and the second local bit line sense amplifiers, e.g., 1012A and 1012B. The first and the second local bit line sense amplifiers, e.g., 1012A and 1012B, have a plurality of the bit line sense amplifiers. Each first local bit line sense amplifier, e.g., 1012A, is connected to the global bit line 1005 through a switch transistor A.

The first to the fifth unit cell block control blocks 1180A to 1180E respectively output a switch control signal, e.g., GBIS12 or GBIS34, for selectively connecting the local bit line sense amplifier LSA, e.g., 1212A or 1212B, included in each the unit cell block, e.g., 1010, to the global bit line 1005 through the global bit line connection unit, e.g., 1090A, 1090B, 1090C.

Through the global bit line 1005 connected to the first and the second global bit line sens amplifier 1070A and 1070B, a data latched in the first and the second global bit line sense amplifier block 1070A and 1070B is outputted to the external part, or a data inputted from the external part is supplied to the first and the second global bit line sense amplifier block 1070A and 1070B.

FIG. 12 is a schematic circuit diagram describing a partial circuit of the unit cell block of the cell area shown in FIG. 10.

Each unit cell array, e.g., 1016, included in each second unit cell blocks, e.g., 1010, has a plurality of the word lines WL0, WL1, . . . and WLN, a plurality of bit line pairs, e.g., BL0 and /BL0, . . . , BLN and /BLN, a plurality of unit cells. Herein, the unit cell includes a capacitor and a MOS transistor correspondently connected to each word line and each bit line pair.

As shown, the second local bit line sense amplifier block 1012B of the first unit cell block 1010 includes a bit line sense amplifier 1230B, a precharge block 1210B, a bit line sense amplifier connection block 1040B and an equalization block 20 1220B. Since these block 1210B, 1220B, 1040B and 1230B are identical to those shown FIG. 2, for the sake of convenience, detail descriptions are omitted. However, especially, for preventing the data collision in each of global bit line pair GBL0 and /GBL0, the first local bit line sense amplifier LSA 25 related to a cell array is coupled to one of global bit sense amplifier pair GSA, and the second local bit line sense amplifier LSA related to the same cell array is couple to the other of the global bit sense amplifier pair GSA.

Under the control of the cell block controller, e.g., 1180A, 30 each bit line sense amplifier, e.g., 1012A and 1012B of the unit cell block, e.g., 1010, is selectively connected to the global bit line 1005 or the global bit line connection unit, e.g., 1090A.

FIGS. 13A to 13D are circuit diagrams depicting how to 35 access the data in the cell block and output the access data to a global sense amplifier block.

FIGS. 13A to 13D describe the data transmission between the local bit line sense amplifier LSA and the global bit line sense amplifier GSA. Especially, two data respectively outputted from the first and second local bit line sense amplifier blocks are individually transmitted to the global bit line sense amplifiers 1170A and 1170B throughout the global bit line pair GBL0 and /GBL0.

Hereinafter, referring to FIGS. 10 to 12 and FIGS. 13A to 45 13D, the memory device shown in FIG. 10 is described in detail.

Referring to FIGS. 13A and 13C, in a read mode, operation of reading a data stored in unit cell block, e.g., 1020 and 1040, is described. After the instruction is inputted in the memory 50 device, the data stored in the unit cell block, e.g., 1020, is selected by the inputted address in response to the instruction. Then, the selected data is sensed and amplified by two local bit line sense amplifiers, e.g., 1320A and 1320B, connected to the unit cell. The sensed and amplified data is moved and 55 thereby latched into the global bit line sense amplifiers 1170A and 1170B (as designated by using a bold line shown in FIG. 13A to 13C).

For the sake of convenience, one-bit data transmission is described in FIG. 13A to 13D. However, several bit data, e.g., 60 4 Kb data in response to an activated word line, e.g., WL0 can be outputted at the same time.

Referring to FIGS. 13B and 13D, operation of writing a data stored in unit cell block, e.g., 1010 and 1050, is described. After the instruction is inputted in the memory 65 device, the data inputted from the external part is latched in the global bit line sense amplifiers 1170A and 1170B. Then,

**16**

the latched data is moved to two local bit line sense amplifiers, e.g., 1350A and 1350B, of the unit cell block, e.g., 1050. Likewise, the writing operation is carried out between the global bit line sense amplifiers 1170A and 1170B and other unit cell blocks, e.g., 1010, 1020, 1030 and 1040 (as designated by using a bold line shown in FIG. 13B to 13D).

In addition, in the inventive memory device, each unit cell block has two local bit line sense amplifiers for sensing and amplifying data. Namely, when 4 Kb data in response to a word line is outputted, some data, e.g., 2 Kb data, is sensed and amplified by the first local bit line sense amplifier block; and the other data, e.g., 2 Kb data, is sensed and amplified by the second local bit line sense amplifier block. As a result, the bank should have two global bit line sense amplifier blocks, e.g., 1170A and 1170B.

FIG. 14 is a block diagram showing a segment in the memory device in accordance with another embodiment of the present invention, and FIG. 15 is a schematic circuit diagram describing a cell block of the bank shown in FIG. 14.

If the unit cell block, e.g., 1410 of the segment has one local bit line sense amplifier block, e.g., 1412 and all data, e.g., 4 Kb data in response to the activated word line is sensed and amplified by the local bit line sense amplifier 1412, the global bit line connection unit is unnecessary and only one global bit line sense amplifier block is needed.

Therefore, in FIGS. 14 and 15, there is described the bank in case that the unit cell block, e.g., 1410, has one local bit line sense amplifier block, e.g., 1412. Herein, for the sake of convenience, detail description about operation of the unit cell block, e.g., 1410, is omitted because each block, e.g., 1510, 1520, 1530 and 1540, included in the local bit line sense amplifier block, e.g., 1412 is same to each block, e.g., 1210B, 1220B, 1230B and 1240B, shown in FIG. 12.

As shown in FIG. 15, data selected by a word line, e.g., WL0 is sensed by the bit line sense amplifier 1412. The sensed and amplified data is then coupled to the global bit line pair GBL0 and /GBL0 by a connection unit 1540 of the bit line sense amplifier 1412. Herein, the bit line sense amplifier includes an equalization unit 1510, a precharge unit 1520, a sense amplifier 1530 and the connection unit 1540.

FIG. **16** is a block diagram showing a bank in the inventive memory device in accordance with another embodiment of the present invention.

As shown, the bank includes a cell area 1620 and a control block 1680. The cell area 1620 has N+1 number of unit cell blocks, e.g., 1630\_1, ..., 1630\_N+1, and a data latch block 1670. Also, in each unit cell block, M number of word lines is coupled to a plurality of unit cells. The N and M are positive integers. Herein, a size of memory device, i.e., a storage capability, is calculated with the exception of the additional unit cell block. Namely, in the FIG. 16, a size of the bank is M(number of word lines)×N(number of unit cell blocks)× (number of bit lines).

The control block 1680 supports the intra cell block interleaving mode. The After a first data in response to a current instruction is outputted from, e.g., a first unit cell block 1630\_1, the first data in latched in the data latch block 1670. Then, if a second data in response to a next instruction is outputted from the first unit cell block 1630\_1, the first data is restored in another unit cell block, e.g., 1630\_N+1. At this time, since the memory device can use an additional unit cell block and the data latch block, a row address of the first data is not changed.

FIG. 17 is a timing diagram describing operation of the memory device shown in FIG. 16; and, especially, describes the intra cell block interleaving mode when a first and the

second data are sequentially accessed in the same unit cell block among N+1 numbers of the unit cell blocks shown in FIG. **16**.

Hereinafter, referring to FIGS. 16 and 17, there is described the execution of the memory device, shown in FIG. 16, in 5 accordance with the present invention.

The additional unit cell block is used for restoring the first data when the second data are sequentially accessed in the same unit cell block. As shown in FIG. 17, the first data is stored in unit cells coupled to a first word line WL0, and the 10 second data is stored in unit cells coupled to a second word line WL1 of the same unit cell block.

First, at a first timing period t0, the first word line WL0 of, e.g., first unit cell block 1630\_1 is activated in response to a first instruction CD0; and, then, first data in response to the 15 first word line WL0 is sensed and amplified. The amplified first data moves to the data latch block 1670.

At a second timing period t1, first, the second word line WL1 of, e.g., first unit cell block 1630\_1 is activated in response to a second instruction CD1; and, at the same time, 20 the first word line WL0 of, e.g., third unit cell block 1630\_3 is activated. Then, the second data in response to the second word line WL1 is sense and amplified; and, at the same time, the first data is restored into unit cells in response to the first word line WL0 of the third unit cell block 1630\_1.

As described above, the data access time of the memory device in accordance with the present invention can be actually precluded the data restoration time, because the second data can be sensed and amplified by the next instruction during the first data in response to the present instruction is 30 restored. Thus, the data access time can be effectively reduced to thereby obtain a high speed operation of the memory device. In addition, in the memory device of the present invention, the data restoration operation can be simplified by simply changing only the cell block address of the data.

FIG. 18 is the block diagram depicting a segment in the inventive memory device in accordance with another embodiment of the present invention. The structure or configuration of the segment shown in FIG. 18 is substantially identical to that of the segment shown in FIG. 16, except that a predetermined cell block table 1810 and a tag block 1830 are coupled to a control block 1880.

The predetermined cell block table **1810** includes a plurality of registers for storing predetermined restore cell block address information. The tag block 1830 generates a target 45 restore cell block address corresponding to an access cell block address based on the predetermined restore cell block address information. The control block **1880** controls the predetermined cell block table 1810, the cell area 1820 and the tag block 1830 in order to support the intra cell block 50 interleaving mode.

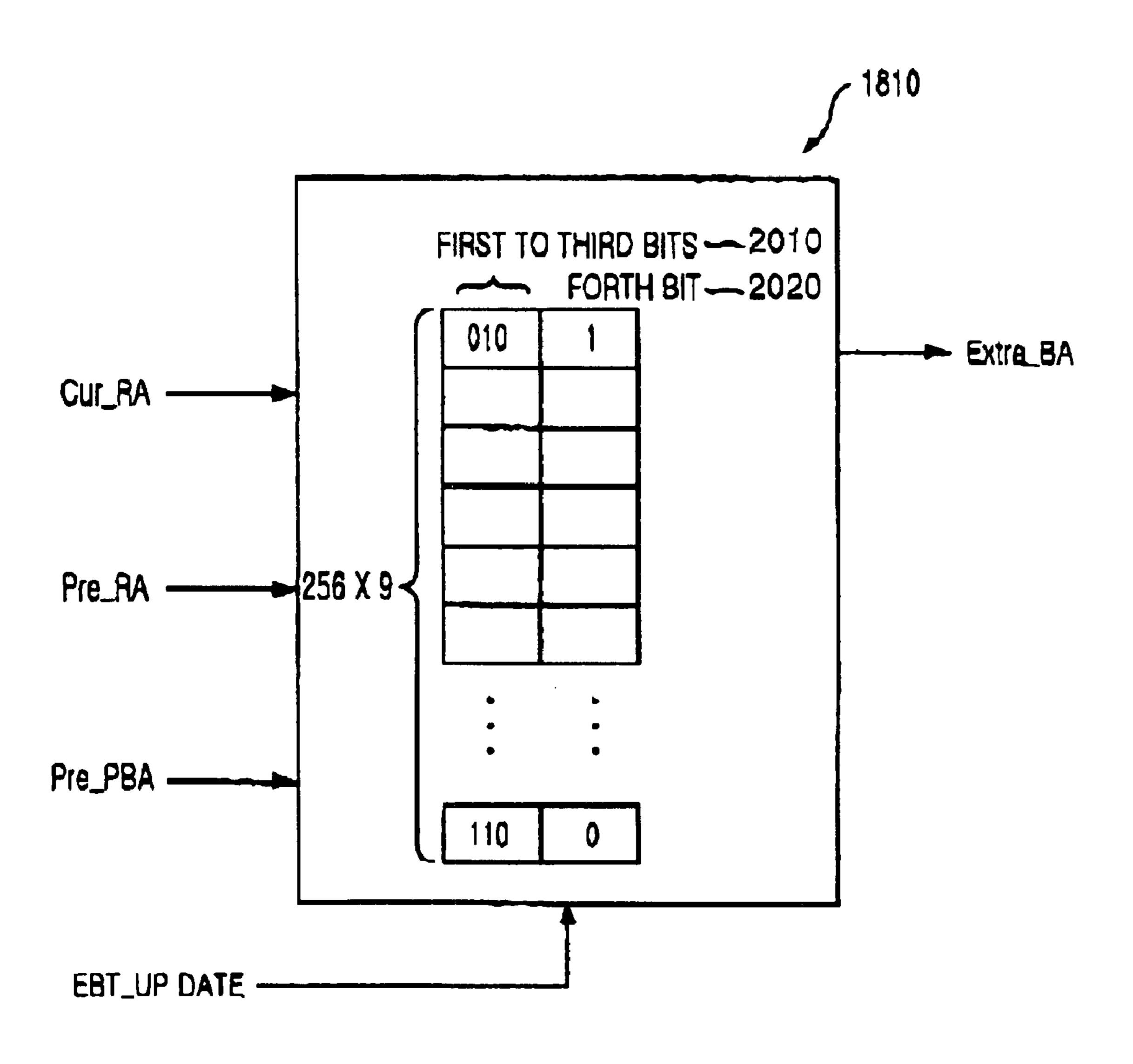

FIG. 19 is a block diagram describing the predetermined cell block table **1810** shown in FIG. **18**.

As shown, the predetermined cell block table 1810 restore cell block address information. The predetermined restore cell block address information contains a predetermined restore cell block address and its condition information. The predetermined restore cell block address consists of, e.g., 3 bits, and its condition information of, e.g., 1 bit. The predetermined restore cell block address information represents a target cell block to be restored, corresponding to an accessed word line of unit cell block. Its condition information represents whether the target cell block to be restored is available or not.

The predetermined cell block table **1810** receives a current row address Cur\_RA, a previous row address Pre\_RA and a **18**

previous restore physical cell block address Pre\_PBA. Also, the predetermined cell block table 1810 is updated by an updating signal EBT\_UP DATE. The predetermined cell block table 1810 outputs an available restore cell block address Extra\_BA to the tag block **1830**.

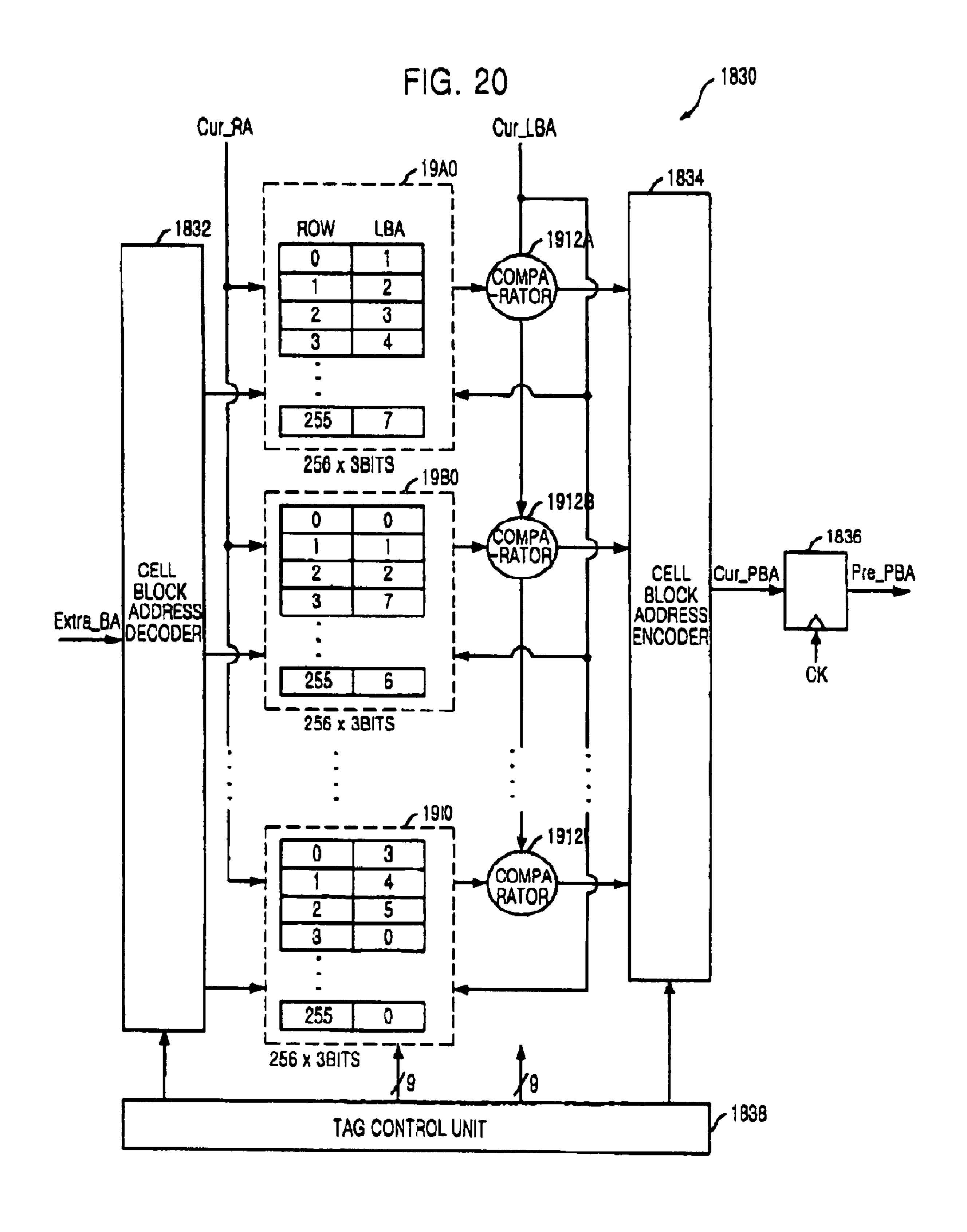

FIG. 20 is a block diagram depicting a tag block 1830 shown in FIG. 18.

As shown, the tag block 1830 includes the N+1 number of unit tag tables 1910 to 1910 (herein, e.g., N is 8), the N+1 number of comparators 1912A to 1912B (herein, e.g., N is 8), a cell block address decoder 1832, a cell block address encoder 1834 and a tag control block 1838.

The cell block address decoder **1832** receives the available restore cell block address Extra\_BA outputted from the predetermined cell block table 1810 and selects one among unit tag tables in response to the available restore cell block address Extra\_BA. Then, the comparator, e.g., 1912A, compares an address of converting the current row address Cur\_RA based on the selected unit tag table with the logical cell block address Cur\_LBA. And last, the cell block address encoder 1834 outputs a current restore physical cell block address Cur\_PBA which is encoded in response to a result of comparison. Herein, each of the unit tag tables 19A0 to 19I0 stores a restore cell block address information corresponding 25 to N×256 word lines of unit cell blocks.

The tag block **1830** further includes a delay unit **1836** for delaying the current restore physical cell block Cur\_PBA by one clock period to access a restore cell block.

Herein, each of unit tag tables 19A0 to 19I0 has 256 registers, and one register LBA consists of three bits. For instance, the first unit tag table 19A0 stores information what logical cell block is corresponded with each 256 numbers of the word lines included in the first unit cell block, and the second unit tag table 432B stores information what logical 35 cell block is corresponded with each of 256 numbers of the word lines included in the second unit cell block.

In addition, in each tag table 19A0 to 19I0, the first register **0** stores the logical cell block address in response to the word line 'WL0' of each unit cell block, the second register 1 stores the logical cell block address in response to the word line 'WL1' of each unit cell block, and 256th register 255 stores the logical cell block address in response to the word line 'WL255' of each unit cell block.

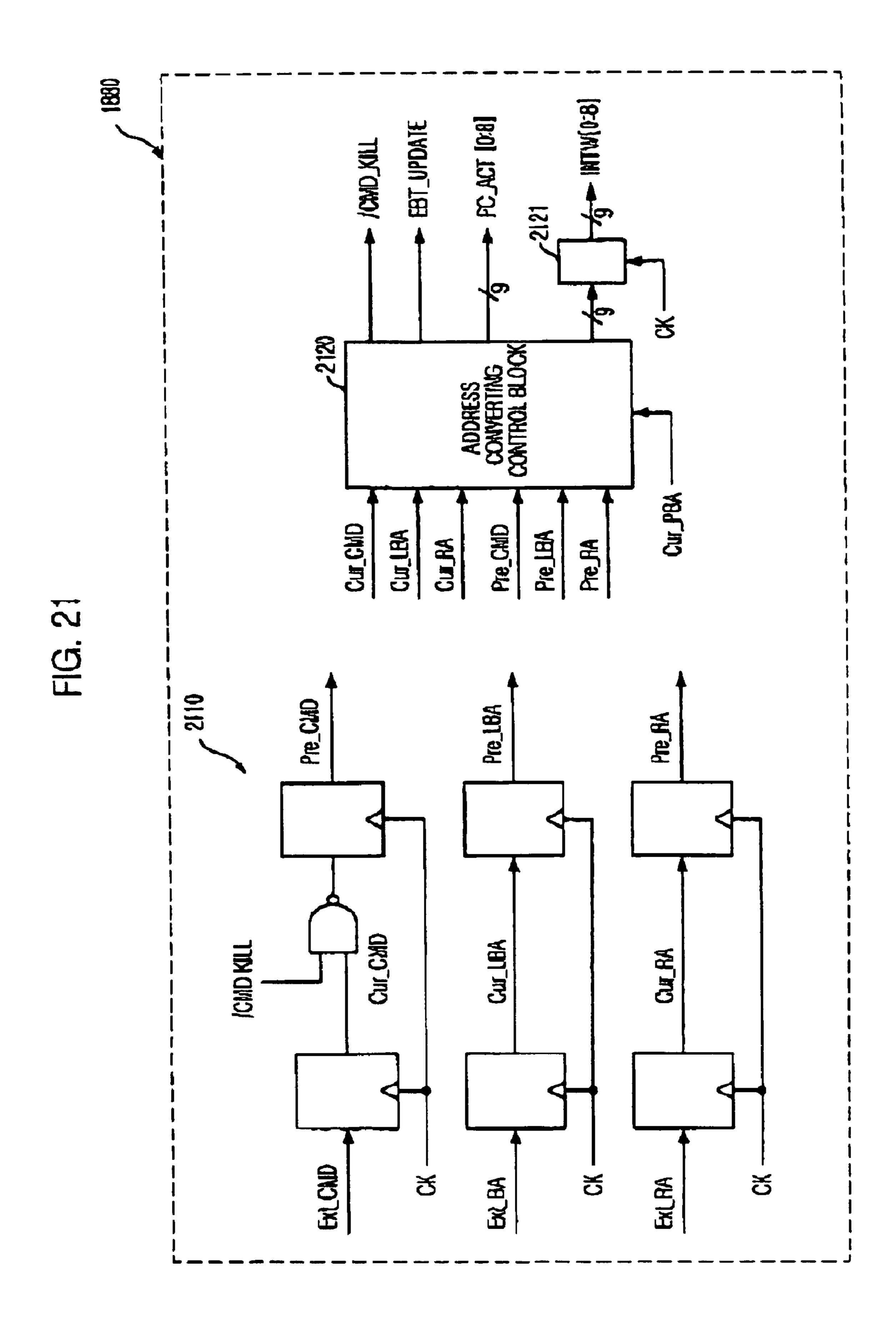

FIG. 21 is the block diagram of some part of the control block **420** shown in FIG. **18**.

As shown, the control block 1880 has the signal input block 2110 for receiving an instruction Ext\_CMD, a logical cell block address Ext\_LBA and a local address Ext\_RA from the external part and thereby outputting a current instruction Cur\_CMD, a current logical cell block address Cur\_LBA and the current row address Cur\_RA in the present execution clock and a previous instruction Pre\_CMD, a previous logical cell block address Pre\_LBA, a previous row address Per\_RA.

In addition, the address convert control block 2120 includes  $M\times(N+1)$  registers, each having the predetermined 55 included in the control block 1880 receives the instruction Cur\_CMD, the logical cell block address Cur\_LBA and the local address Cur\_RA in the present execution clock and the instruction Pre\_CMD, the logical cell block address Pre\_LBA and the local address Pre\_RA in the prior execution clock. And then, the address convert control block 2120 outputs predetermined cell block update signal EBT\_UPDATE, precharge active signal PC\_ACT[0:8], the instruction kill signal CMD\_KILL and an inner restoration signal INTW[0: 8].

> The predetermined cell block update signal EBT\_UP-DATE is used for updating the information stored in the predetermined cell block table 1810 when the restore physi-

cal cell block address Cur\_PBA of the current operation clock is identical to that Pre\_PBA of the previous operation clock.

In addition, the instruction kill signal CMD\_KILL terminates the operation of the next instruction when the word line of the unit cell block is continuously accessed. The error is occurred if the tag information is read in the state that the information about the physical cell block address in response to the logical cell block address in the tag block 430 is not correctly updated in response to the prior instruction, when the word line of the unit cell block is continuously accessed.

The precharge active signal PC\_ACT[0:8] is used for selecting the physical cell block address in response to the inputted instruction. The inner restoration signal INTW[0:8] is used for delivering the data accessed in the unit cell block selected by the present active instruction and thereby latched in the data latch block into the unit cell block of which determined word line is assigned and thereby restores the data, when the physical cell block address Cur\_PBA of the present execution clock is same to that Pre\_PBA of the prior 20 execution clock.

The clock delay block 2121 delays the inner restoration signal INTW[0:8] for one clock so that the inner restoration signal INTW[0:8] is later than the percharge active signal PC\_ACT[0:8]. This is needed for restoring the data using the inner restoration signal INTW[0:8], after selecting the unit cell block using the precharge signal PC\_ACT[0:8]; selecting one word line in the selected unit cell block; and sensing and amplifying the data in response to the selected word line.

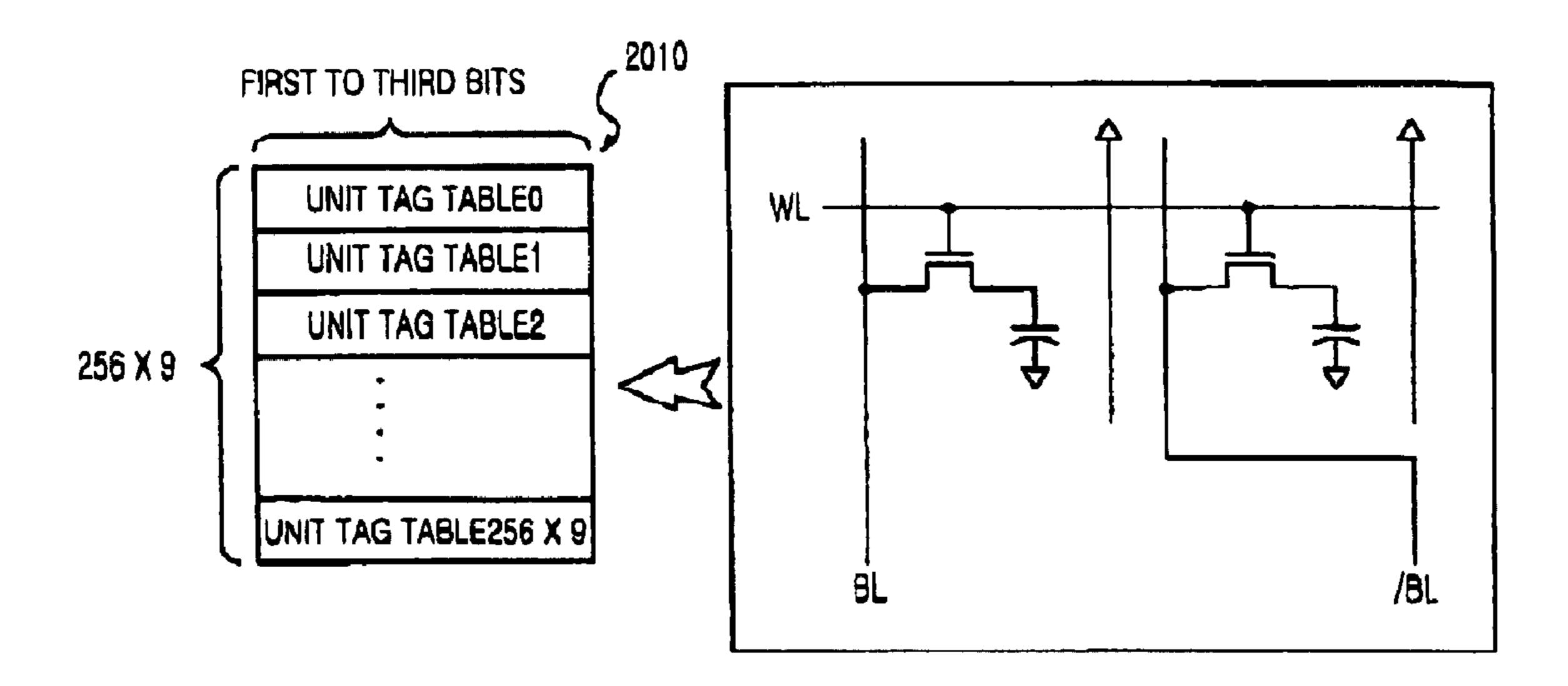

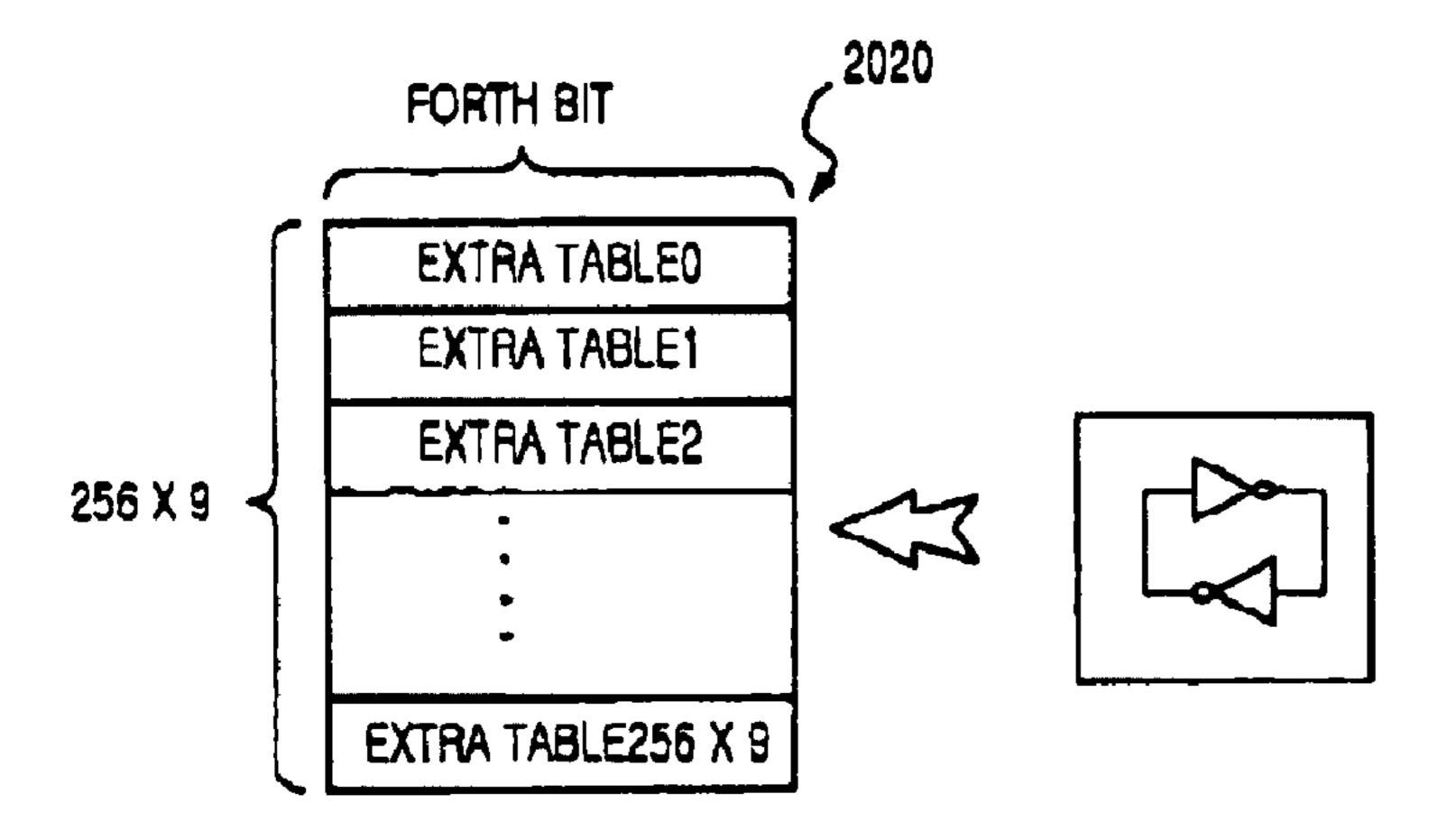

FIG. 22 is circuit diagram showing the first to third bits of each unit tag table 19A0 to 19I0 shown in FIG. 19, and FIG. 23 is circuit diagram of the forth bit of each unit tag table 19A0 to 19I0 shown in FIG. 19.

As shown, the first to third bits are dynamic cells and the forth bit is a static cell, in order to maintain operation speed. The static cell is used for the forth bit because th forth bit is more relatively often updated than the first to third bits.

FIG. 24 is a timing diagram depicting operation of the bank in the inventive memory device shown in FIG. 18.

Hereinafter, referring to FIGS. 18 to 24, there is described the operation of the memory device in accordance with the present invention in detail.

First of all, one instruction CD0 is inputted at a first timing period t0, and two timing periods is needed for operating one 45 instruction, e.g., CD0, For example, during first and second timing period t0 and t1, the operation of the first instruction CD0 is carried out. Each timing period, e.g., t0, t1, . . . , is split into two timing sets, e.g.,  $a_0$  and  $b_0$ . At the timing set  $a_0$ , blocks related to a tag operate; and, at the other timing set  $b_0$ , 50 blocks of the cell area **1820** operate.

First, the timing set a<sub>0</sub> is described in detail.

In a<sub>0</sub>-1 timing set, the control block 1480 receives the logical cell block address for selecting one out of the 8 unit cell blocks included in the cell area 1820 and the local address for selecting one out of the 256 word lines.

And then, in  $a_0$ -2 timing set, the tag block 1830 converts the logical cell block address to the physical cell block address Cur\_PBA.