#### US00RE42397E

# (19) United States

# (12) Reissued Patent

Ban et al.

## (10) Patent Number:

US RE42,397 E

#### (45) Date of Reissued Patent:

May 24, 2011

# (54) ARCHITECTURE FOR A UNIVERSAL SERIAL BUS-BASED PC FLASH DISK

(75) Inventors: **Amir Ban**, Ramat-Hasharon (IL); **Dov**

Moran, Kfar-Saba (IL); Oron Ogdan,

Jerusalem (IL)

(73) Assignee: Sandisk IL Ltd., Kfar Saba (IL)

(\*) Notice: This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 10/293,986

(22) Filed: Nov. 14, 2002

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: 6,148,354

Issued: Nov. 14, 2000

Appl. No.: 09/285,706

Filed: Apr. 5, 1999

U.S. Applications:

(63) Continuation of application No. 10/292,868, filed on Nov. 13, 2002.

(51) **Int. Cl.**

G06F 12/00 (2006.01)

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,067,105 A | * 11/1991 | Borkenhagen et al | 711/202 |

|-------------|-----------|-------------------|---------|

| 5,226,168 A | 7/1993    | Kobayashi et al   | 395/800 |

| 5.291.584 A | 3/1994    | Challa et al.     |         |

#### FOREIGN PATENT DOCUMENTS

CN 1201235 A 12/1998 (Continued)

#### OTHER PUBLICATIONS

"Generic Device Driver for Personal Computer Removable Devices", IBM Technical Disclosure Bulletin, Jan. 1994, vol. 37, issue 1, pp. 487-490.\*

(Continued)

Primary Examiner — Glenn A Auve (74) Attorney, Agent, or Firm — Morgan, Lewis & Bockius LLP

### (57) ABSTRACT

A storage unit made of flash array and a USB controller[,] is implemented to be compatible with [then] the USB specification. The unit includes memory modules which can accept write commands and read commands and are erasable and non-volatile herein referred to as flash modules. The USB/flash controller is configured to provide USB functionality and compatibility [alone] along with common flash operations such as programming reading and erasing the above mentioned components.

#### 69 Claims, 7 Drawing Sheets

# US RE42,397 E Page 2

| US PATENT                                  | DOCUMENTS                                      | 6,286,087 B1 9/2001 Ito et al.                                           |

|--------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------|

|                                            |                                                | 6,292,863 B1 * 9/2001 Terasaki et al                                     |

| •                                          | Sakaue et al                                   | 6,330,624 B1 12/2001 Cromer et al.                                       |

|                                            | Moran et al.                                   | 6,330,648 B1 12/2001 Wambach et al 711/163                               |

| 5,544,356 A 8/1996                         | Robinson et al 395/600                         | 6,361,369 B1 3/2002 Kondo et al.<br>6,370,603 B1 4/2002 Silverman et al. |

|                                            | Niijima et al 371/10.2                         | 6,385,667 B1 5/2002 Estakhri et al.                                      |

|                                            | Hasbun et al 395/430                           | 6,418,501 B1* 7/2002 Gama et al                                          |

| 5,588,146 A 12/1996<br>5,602,987 A 2/1997  | Harari et al.                                  | 6,424,524 B2 * 7/2002 Bovio et al                                        |

| , ,                                        | Holzhammer et al 395/442                       | 6,425,084 B1 * 7/2002 Rallis et al                                       |

|                                            | McNutt et al.                                  | 6,434,648 B1 8/2002 Assour et al.<br>6,453,414 B1 9/2002 Ryu             |

| , ,                                        | Rondeau, II et al.                             | 6,457,099 B1 9/2002 Gilbert                                              |

| 5,663,901 A 9/1997                         |                                                | 6,488,542 B2 12/2002 Laity                                               |

| 5,684,742 A 11/1997<br>5,719,808 A 2/1998  | Harari et al 365/185.33                        | 6,493,770 B1 * 12/2002 Sartore et al                                     |

|                                            | Shinohara                                      | 6,671,808 B1 * 12/2003 Abbott et al                                      |

| · · · · · · · · · · · · · · · · · · ·      | Shinohara 371/40.2                             | 6,763,399 B2 7/2004 Margalit et al.<br>6,920,553 B1 7/2005 Poisner 713/2 |

|                                            | Ma et al 365/185.33                            | 2003/0057285 A1 3/2003 Okaue et al.                                      |

| , ,                                        | Morehouse et al.                               | 2004/0039854 A1 2/2004 Estakhri et al.                                   |

|                                            | Story et al                                    | 2006/0230202 A1 10/2006 Lee 710/62                                       |

|                                            | Decuir 326/30                                  | FOREIGN PATENT DOCUMENTS                                                 |

|                                            | Hannah                                         |                                                                          |

| •                                          | Barrett et al 707/1                            | DE 195 36 206 4/1996                                                     |

|                                            | Ban 711/103                                    | DE 196 36 087 9/1997<br>DE 196 31 050 2/1998                             |

|                                            | Jigour et al.<br>Bruce et al.                  | EP 0 392 895 A2 10/1990                                                  |

| 5,822,231 A 10/1998<br>5,841,424 A 11/1998 |                                                | EP 0 152 024 6/1991                                                      |

| , ,                                        | Story et al 395/847                            | EP 0 703 544 3/1996                                                      |

|                                            | Estakhri et al.                                | EP 0 712 067 A2 5/1996                                                   |

|                                            | Inoue et al.                                   | EP 0 859 325 8/1998<br>EP 0 883 083 12/1998                              |

|                                            | Harada et al.                                  | EP 0 883 083 A1 12/1998                                                  |

|                                            | Matthews et al 711/165<br>Wallace et al 365/52 | EP 0 883 084 12/1998                                                     |

|                                            | Caputo et al.                                  | EP 0 890 905 A2 1/1999                                                   |

| 5,890,016 A 3/1999                         | •                                              | EP 0 929 043 7/1999                                                      |

| 5,928,347 A 7/1999                         |                                                | EP 1 001 329 5/2000<br>EP 0 912 939 9/2001                               |

|                                            | Asnaashari 714/48                              | EP 0 912 939 9/2001<br>EP 5/2002                                         |

|                                            | Swamy et al.<br>Robinson 711/103               | FR 2 719 939 11/1995                                                     |

| 5,937,425 A 8/1999                         |                                                | GB 2 291 990 A 2/1996                                                    |

|                                            | Shaberman                                      | GB 2 304 428 A 3/1997                                                    |

|                                            | Marberg et al 711/203                          | GB 2 325 997 A 12/1998<br>JP 1 115928 A 5/1989                           |

| * * *                                      | Sakakura et al 711/202                         | JP 1 115928 A 5/1989<br>JP 5 016746 A 1/1993                             |

|                                            | Siddappa                                       | JP 8 171623 A 7/1996                                                     |

|                                            | Chan et al 395/882                             | JP 09-069067 11/1997                                                     |

| 6,003,135 A 12/1999                        |                                                | JP 10 063442 A 3/1998                                                    |

|                                            | Pleso 710/8                                    | JP 10 063804 A 3/1998<br>JP 10 105296 A 4/1998                           |

| 6,011,486 A 1/2000                         |                                                | JP 10 103290 A 4/1998<br>JP 10 261774 A 9/1998                           |

| , ,                                        | Wallace et al. Sartore et al 710/8             | TD 11015000 A 1/1000                                                     |

|                                            | Auclair et al.                                 | JP 11 025681 A 1/1999                                                    |

| 6,016,553 A 1/2000                         | Schneider et al.                               | JP 11-53485 2/1999                                                       |

|                                            | Awsienko 365/230.02                            | JP 11 053485 A 2/1999<br>JP 11 086578 A 3/1999                           |

| 6,038,320 A 3/2000                         |                                                | WO WO 87/07063 11/1987                                                   |

| , ,                                        | Terme<br>Rayabhari 710/129                     | WO WO 93/19419 A1 9/1993                                                 |

| 6,058,441 A 5/2000                         | . •                                            | WO WO 96/13004 5/1996                                                    |

| 6,067,625 A 5/2000                         | Ryu                                            | WO WO 98/03915 1/1998                                                    |

|                                            | Sinclair 365/185.29                            | WO WO 98/03915 A2 1/1998<br>WO WO 98/07255 2/1998                        |

|                                            | Garney                                         | WO WO 98/29830 2/1998<br>WO WO 98/29830 7/1998                           |

|                                            | Kobayashi et al 710/300<br>Zobel et al 165/10  | WO WO 98/55912 12/1998                                                   |

| , ,                                        | Kondo et al.                                   | WO WO 99/01820 A1 1/1999                                                 |

| 6,131,141 A 10/2000                        | Ravid                                          | WO WO 99/12101 3/1999                                                    |

| , ,                                        | Iwasaki et al.                                 | WO WO 99/45460 9/1999<br>WO WO 99/45460 A2 9/1999                        |

| 6,145,045 A 11/2000<br>6,145,046 A 11/2000 | Falik et al.                                   | WO WO 99/43400 AZ 9/1999<br>WO WO 99/49470 A1 9/1999                     |

|                                            | Sun et al.                                     | WO WO 00/07088 2/2000                                                    |

|                                            | Anderson et al.                                | WO WO 00/42491 7/2000                                                    |

| 6,170,743 B1 1/2001                        | Okaue et al.                                   | WO WO 00/49488 A1 8/2000                                                 |

|                                            | Estakhri et al 710/11                          | WO WO 03/030180 A1 4/2003                                                |

|                                            | Kobayashi<br>Rallis et al.                     | OTHER PUBLICATIONS                                                       |

|                                            | Kams et al.<br>Kikuchi                         | Universal Serial Bus Specification—Compaq, Intel, Microsoft              |

|                                            | Lawrence et al.                                | NEC; Revision 1.1; Sep. 23, 1998; pp. i-xvi (table of content), 1-311    |

| , , ,                                      | Robinson et al.                                | + 4 pages (Engineering Change Notice—USB Cable Parameters                |

| 6,279,114 B1 8/2001                        | Toombs et al.                                  | approved on Nov. 23, 1999 by the USB Core Team).                         |

|                                            |                                                |                                                                          |

Universal Serial Bus Mass Storage Class Specification Overview; V1.0 Revision; Oct. 22, 1998; Technical Editor—Williams, M.; pp. 1-8.

Universal Serial Bus Mass Storage Class—Control/Bulk/Interrupt (CBI) Transport; Revision 1.0; Dec. 14, 1998; Technical Editors—Stevens, C. E. at al.; pp. 1-26.

Universal Serial Bus Mass Storage Class—Bulk-Only Transport; Revision 1.0; Sep. 31, 1999; pp. 3-22.

Universal Serial Bus Mass Storage Class—UFI Command Specification; Revision 1.0; Dec. 14, 1998; pp. 1-12.

Advertising— "MacHASP USB—Protects Your Software;" Aladdin—The Professional Choice; 2 pages.

Sharp Model OZ-730/OZ-750 Electronic Organizer—Operation Manual; pp. 1-71 + 11 pages Quick Reference Guide + 10 pages Quick Start Guide.

Sharp Wizard, Model OZ-570 Electronic Organizer—Operation Manual; pp. 1-101 + Quick Reference Guide 17 pages.

Sharp Wizard, IntelliSync for Sharp Wizard—User's Guide; Day Time Organizer for Sharp Electronic Organizer with IntelliSync Translator; pp. 1-33 + 2 pages Installation Instructions + pp. 1-36 Getting Started Guide, Copyright 1997.

Sharp PC Interface Hardware (Docking Station), Model CE-619—Operation Manual; 5 pages, Copyright 1197.

"Digital Eyes News—Q3 1998;" Scanner and Digital Camera News, Q3 1998—Digital Eyes; Retrieved from the Internet at <a href="http://www.image-acquire.com/news/98/q3.shtml">http://www.image-acquire.com/news/98/q3.shtml</a> pp. 1-9.

"Imaging Press Release—Hagiwara 'Flash Gate' for SmartMedia up to 130X Faster than Serial Devices;" 2 pages; Digital Eyes News; Retrieved from the Internet at <a href="http://www.image-acquire.com/news/49/q2/hagi9921.html">http://www.image-acquire.com/news/49/q2/hagi9921.html</a>, Apr. 19, 1999.

"Product Review—Hagiwara Flash Gate USB;" Hagiwara Flash Gate USB Review from Digital Eyes; 2 pages; Retrieved from the Internet at <a href="http://www.image-acquire.com/articles/storage/hagiwarausb.html">http://www.image-acquire.com/articles/storage/hagiwarausb.html</a>.

"Product Review—Action Tec CameraConnect Pro;" Action Tec Camera Connect Review from Digital Eyes; 3 pages; Retrieved from the Internet at <a href="http://www.image-acquire.com/articles/storage/ateamcommect.shtml">http://www.image-acquire.com/articles/storage/ateamcommect.shtml</a>>.

"Product Review—SanDisk ImageMate USB;" SanDisk ImageMate USB Review from Digital Eyes; 2 pages; Retrieved from the Internet at http://www.image-acquire.com/articles/storage/sdimagemateusb. shtml>.

"FRCN Digital Imaging—SanDisk ImageMate USB CF Card Reader;" Updated Jul. 12, 1999; Retrieved from the Internet at <a href="http://www.quicknet.com/~frcn/SanDiskUSB.html">http://www.quicknet.com/~frcn/SanDiskUSB.html</a>.

"SanDisk Introduces New USB ImageMate; SanDisk ImageMate is a Low-cost, Easy-To-Use External CompactFlash Drive for Desktop PCs and the New Apple iMac;" Business Wire; Oct. 27, 1998; Document ID FC19981027080000045; 3 pages; Retrieved from the Internet at <a href="http://library.northernlight.com/FC19981027...">http://library.northernlight.com/FC19981027...</a> JqDmQPWAVRU0UIGRREdQx5HQ%3D%3D

&cbx=0%3B1004>.

ActionTec CameraConnect Pro, Parallel Port Flash Card Reader—User's Manual; pp. 1-29.

USBDrive: Products; 2 pages; Retrieved from the Internet at <a href="http://www.usbdrive.com/">http://www.usbdrive.com/</a> web.archive.org/web/20020328072516/http://www.usbdrive.com/products/index.html>.

"Steve's DigiCams, Hardware Reviews—Camera Connect Pro, External PC Card Read/Write Drive;" 4 pages; Retrieved from the Internet at <a href="http://www.steves-digicams.com/camera\_connect\_pro.html">http://www.steves-digicams.com/camera\_connect\_pro.html</a>, Copyright 1998.

Actiontec—Broadband Technology Made Easy; "Support Info—CameraConnect Pro;" 2 pages; Retrieved from the Internet at <a href="http://www.actiontec.com/support/readers/cameraconpro.html">http://www.actiontec.com/support/readers/cameraconpro.html</a>.

Brochure—"USB Special, Aladdin—the Key to Software and Security;" Aladdin Knowledge Systems Inc.; 8 pages.

HP Jornada PC Companions; Software & Hardware Solutions—Microsoft Windows CE 2.11; 2 pages; Retrieved from Internet at <a href="http://web.archive.org/web/19991127141058/www.hp.com/jornada/sol/.../othsoft\_rom.htm">http://web.archive.org/web/19991127141058/www.hp.com/jornada/sol/.../othsoft\_rom.htm</a>.

HP Jornada PC Companions; Jornada 430se—the Palm-Size PC that Meets Your Needs at Work and Play; 3 pages; Retrieved from the

Internet at <a href="http://web.archive.org/web/19991128125415/http://www.hp.com/jornada/pr.../overview.htm">http://web.archive.org/web/19991128125415/http://www.hp.com/jornada/pr.../overview.htm</a>.

HP Jornada Pc Companions; Product Specifications—HP Jornada 430se; 5 pages; Retrieved from the Internet at <a href="http://web.archive.org//web/19991128142035/www.hp.com/jornada/produc.../prod\_spec.htm">http://web.archive.org//web/19991128142035/www.hp.com/jornada/produc.../prod\_spec.htm</a>.

FujiFilm—Image Memory Card Reader SM-R1 for SmartMedia; Owner's Manual; 16 pages.

(BW) (NY-Fuji-Photo-Film) Introducing the Fujifilm MX-2700: The World's Smallest 2.3 Million-Pixel Digital Camera; Feb. 3, 1999; 2 pages; Retrieved from the Internet at <a href="http://www.businesswire.com/webbox/bw.020399/1096161.htm">http://www.businesswire.com/webbox/bw.020399/1096161.htm</a>.

Fuji film SM-R1 Memory Card Reader; TwoMobile Home of the Investigative Mobile Reviewers; 3 pages; Retrieved from the Internet at <a href="http://web.archive.org/web/20001206024200/http://www.twomobile.com/rev\_smr1reader.html">http://web.archive.org/web/20001206024200/http://www.twomobile.com/rev\_smr1reader.html</a>.

Windows CW Handheld PC Hardware Features; 1 page; Retrieved from the Internet at <a href="http://web.archive.org/web/19991012094107/">http://web.archive.org/web/19991012094107/</a> microsoft.com/windowsce/Products/hpc/hwspecs.asp>.

FujiFilm—Image Memory Card Reader SM-R1 for Windows 98 / Macintosh; Owner's Manual; 21 pages in English; 21 pages in French; 21 pages in German.

Universal Serial Bus Mass Storage Class—UFI Command Specification; Revision 1.0; Dec. 14, 1998; pp. 1-53.

"What is Memory Stick—Shape;" 1 page; Retrieved from the Internet at <a href="http://www.memorystick.org/topics/eng/aboutms/feat\_">http://www.memorystick.org/topics/eng/aboutms/feat\_</a> outline.html>.

Snapshots of Windows '98 Computer Screen, with "Plug and Play PCMCIA Card"; 4 pages.

USB-SCSI & ATA/ATAPI Intelligent Cables; 1 page; Retrieved from the Internet at <a href="http://www.multiwave.co.kr/product/scm\_product3.html">http://www.multiwave.co.kr/product/scm\_product3.html</a>.

"USB ATAPI Intelligent Cables;" SCM Microsystems; 2 pages; Retrieved from the Internet at <a href="http://www.scmmicro.com/connectivity/usbata.html">http://www.scmmicro.com/connectivity/usbata.html</a>, Copyright 1999.

"USB XpressSCSI—USB to SCSI Converter Cable;" User's Manual for Models USB-SCSI-DB25 and USB-SCSI-HD50; Version 1.0; Microtech; 37 pages; Copyright 1999.

"Availability of Universal Serial Bus Support in Windows '95;" 2 pages; Retrieved from the Internet at <a href="http://support.microsoft.com/default.aspx?scid=kb;en-us;253756">http://support.microsoft.com/default.aspx?scid=kb;en-us;253756</a>.

Paripatyadar, R.; "1394 Overview;" 19 pages; Nov. 10, 1998; Retrieved from the Internet at <a href="http://grouper.ieee.org/groups/802/802\_tutorials/nov98/139411\_1198.pdf">http://grouper.ieee.org/groups/802/802\_tutorials/nov98/139411\_1198.pdf</a>.

Product Brief—AlphaPC 164LX Motherboard; Alpha Processor; Jan. 1999; 2 pages; Retrieved from the Internet at <a href="http://www.alphalinux.org/firmware/api/LX/164LX.PDF">http://www.alphalinux.org/firmware/api/LX/164LX.PDF</a>.

SOYO SY-6IEB Mainboard—Quick Start Guide; Version 1.0; Sep. 1998; 14 pages; Retrieved from the Internet at <a href="http://www.soyola.com/dl/manuals/quick-sg/q6ieb10.pdf">http://www.soyola.com/dl/manuals/quick-sg/q6ieb10.pdf</a>, Copyright 1995.

PCMCIA SRAM & Linear Flash Cards, by C1-Tech, Simple Technology, Centennial, Intel and KingMax; 5 pages; Retrieved from the Internet at <a href="http://www.psism.com/sram.htm">http://www.psism.com/sram.htm</a>.

"Interfacing the Intel Flash 28F001BX-T to Your 186 Based System;" Intel; Mar. 29, 1998; 14 pages; Retrieved from the Internet at <a href="http://developer.intel.com/design/intarch/applnots/2150.htm">http://developer.intel.com/design/intarch/applnots/2150.htm</a>.

CY7C63000, CY7C63001, CY7C63100, CY7C63101, CY7C63200, CY7C63201—Universal Serial Bus Microcontroller; Cypress Semiconductor Corp.; 27 pages; Jun. 26, 1997; Retrieved from the Internet at <a href="http://www.physik.uni-osnabrueck.de/kbetzler/win32/usb/7c63000.pdf">http://www.physik.uni-osnabrueck.de/kbetzler/win32/usb/7c63000.pdf</a>.

Wong, T. K. P.; "An Embedded Chip for USB Application: From the Architecture to Implementation;" Apr. 1999; International IC '99—Conference Proceedings; 10 pages; Retrieved from the Internet at <a href="http://www.eetasia.com/ARTICLES/1999APR/1999APRO8\_ICD\_NTEK\_TAC.PDF">http://www.eetasia.com/ARTICLES/1999APR/1999APRO8\_ICD\_NTEK\_TAC.PDF</a>.

Gupta, R. K. et al.; "Introducing Core-Based System Design;" Oct.-Dec. 1997; IEEE; pp. 15-25; Retrieved from the Internet <a href="http://www.ics.uci.edu/~rgupta/publications/cores.pdf">http://www.ics.uci.edu/~rgupta/publications/cores.pdf</a>.

Intel AP-686—Application Note; "Flash File System Selection Guide;" Dec. 1998; 16 pages; Retrieved from the Internet at <a href="http://www.intel.com/design/flcomp/applnots/29766505.pdf">http://www.intel.com/design/flcomp/applnots/29766505.pdf</a>.

Intel AP-684 —Application Note; "Understanding the Flash Translation Layer (FTL) Specification;" Dec. 1998; 20 pages; Retrieved from the Internet at <a href="http://www.intel.com/design/flcomp/applnots/297816.htm">http://www.intel.com/design/flcomp/applnots/297816.htm</a>.

VxWorks 5.4; WindRiver Systems; 3 pages; Retrieved from the Internet at <a href="http://www.vxworks.ru/products/pdf/vxworks-ds.pdf">http://www.vxworks.ru/products/pdf/vxworks-ds.pdf</a>, Copyright 1999.

Apple USB FAQ; 1999; 3 pages; Retrieved from the Internet at <a href="http://www.apple.com/usb/pdf/usb\_FAQ-c.pdf">http://www.apple.com/usb/pdf/usb\_FAQ-c.pdf</a>, Copyright 1999. Multimedia Workshop Industry News—Oct. 22, 1998; 3 pages; Retrieved from the Internet at <a href="http://www.m2w.net/News/981019">http://www.m2w.net/News/981019</a>. html>.

Davis, J.; "Apple Licensing FireWire for a Fee;" CNET News.Com; Jan. 16, 1999; 4 pages; Retrieved from the Internet at <a href="http://news.com.com/2100-1040-220209.html">http://news.com.com/2100-1040-220209.html</a>.

"Will IEEE 1394 Ultimately Replace USB?;" White Paper Comparing Universal Serial Bus (USB) and IEEE 1394 (Fire Wire) Technologies; American Megatrends, Inc.; 7 pages; Retrieved from the Internet at <a href="http://www.ami.com/support/doc/1394\_USB.pdf">http://www.ami.com/support/doc/1394\_USB.pdf</a>>.

WindRiver Systems—WindWord Newsletter; "News and Information for Wind River Systems Customers;" Winter 1998; 32 pages; Retrieved from the Internet at <a href="http://www.windriver.com">http://www.windriver.com</a>.

PC/104 PCMCIA Module—User's Manual; for models PCM-3110, PCM-3111, PCM-3115B, PCM-3110B, PCM-3113, PCM-3114; 1<sup>st</sup> Edition; Printed Jul. 1997; 78 pages; Retrieved from the Internet at <a href="http://www.tempustech.com/pdf/3110manual.pdf">http://www.tempustech.com/pdf/3110manual.pdf</a>>.

8X930Ax Universal Serial Bus Microcontroller User's Manual; Intel; Jul. 1996; 507 pages; Retrieved from the Internet at <a href="http://www.mit.edu/afs/sipb/contrib/doc/specs/ic/bridge/i8x930ax.pdf">http://www.mit.edu/afs/sipb/contrib/doc/specs/ic/bridge/i8x930ax.pdf</a>.

"Reviews—Pretec PCMCIA Type I SRAM 2048KB;" EverythingLinux; 1 page; Retrieved from the Internet at <a href="http://www.everythinglinux.com.au/item/">http://www.everythinglinux.com.au/item/</a>

SRAM2M?elinux=e0c72135e544a6ea 13772f5c23ba3foe>.

"U2 Only Disk User's Manual"; Netae Technology Co.; Retrieved from the Internet at <a href="http://www.bestusbdrive.com/downloads/u2english.pdf">http://www.bestusbdrive.com/downloads/u2english.pdf</a>; 1 Page.

Shmueli, S.; Description of "SanDisk ImageMate USB CompactFlash Reader"; 3 Pages; Date of Introduction of device unknown.

Shmueli, S.; Description of "Lour Jumpshot Cable"; 2 Pages; Date of introduction of device unknown.

Shmueli, S.; Description of "Aladdin eToken and Rainbow iKey"; 1 Page; Date of introduction of device unknown.

Lee Kong Pheng; Description of "SanDisk ImageMate USB CF Card Reader"; 1 Page; Date of Introduction of device unknown.

Lee Kong Pheong+; Comparison of the block diagrams of the SanDisk Imagemate USB CF Card Reader, the Patent and the SlimDisk; 6 Pages; Date of introduction of device unknown.

"8+930Hx Universal Serial Bus Microcontroller—Product Review"; Intel; Oct. 1996; 34 Pages.

"IBM Smart Card Solution Elements—Overview"; Jul. 1997; 26 Pages.

"MacHasp USB—Software Protection via the USB"; Aladdin—The Professional Choke; 10 Pages, Brochure.

Roberts, R.; "NCITS-330 T10/1240-D Working Draft—Information Technology—Reduced Block Commands"; Revision 10a; Aug. 18, 1999; 46 Pages.

Shmueli, S. Testimony relevant to Sandisk in Singapore proceedings; Apr. 30, 2004; line 9 in p. 135 through line 23 in p. 137 and line 8 in p. 139 through Line 18 in p. 140.

"SL11R USB Controller / 16-Bit RISC Processor Data Sheet"; Cypress Semiconductor Corporation; Revised Dec. 3, 2001; pp. 1-85.

"What is Memory Stick?"; Retrieved from the Internet at <a href="http://www.memorystick.org/topics/eng/aboutms">http://www.memorystick.org/topics/eng/aboutms</a>; 15 Pages.

"Memory Stick Format"; Retrieved from the Internet at <a href="http://www.memorystick.org/mseasy/eng.application/">http://www.memorystick.org/mseasy/eng.application/</a>; 19 Pages.

U.S. Appl. No. 60/116,006 filed Jan. 15, 1999; Abbott, S. D. et al.; "USB-Compliant Personal Key".

"SanDisk ImageMate CompactFlash External Drive"; Product Backgrounder, SanDisk Corporation; Jan. 1999; retrieved from the Internet at <a href="http://web.archive.org/web/20000229014945/www.sandisk.com/cons/image-USB.htm">http://web.archive.org/web/20000229014945/www.sandisk.com/cons/image-USB.htm</a>; 2 pages.

"The New WIBU-KEY Copy Protection System v2.50"; Press Release; Griffin Technologies; copyright 1998; retrieved from the Internet at http://web.archive.org/web/19990128201628/www.griftech.com/html/wibu25pr.htm<; 3 pages.

Anderson, D.; "Universal Serial Bus System Architecture"; 1997; MindShare, Inc./Addison-Wesley, 6<sup>th</sup> Printing, pp. 95, 98-104 and 109-111.

IC Card Expo; Conference Proceedings; Jul. 25-27, 1994; Santa Clara Convention Center, Santa Clara, CA, USA; 54 pages.

Mendelsohn, A.; "Solid State Disk Puts Flash to Work"; Feb. 1994; Computer Design; 4 pages.

"Word-Wide FlashFile™ Memory Family 28F160S5, 28F320S5"; "Advance information", Order No. 290609-001, of Intel, entitled; Jun. 1997.

"Aladdin's eToken cracked"; May 5, 2000; retrieved from the internet at <a href="http://www.securiteam.com">http://www.securiteam.com</a>.

Burskey, D.; "Flash and EEPROM technologies combine on feature-rich MCUs"; Electronic Design; May 26, 1997; retireved form the internet at http://cma.zdnet.com; 11 pages.

"Flash memory"; on-line encyclopedia Wikipedia; retrieved from the internet at <a href="http://en.wikipedia.org/wiki/Flash\_memory">http://en.wikipedia.org/wiki/Flash\_memory</a>; 5 pages. Schmidt, D.; "AP-DOC-011 Application Note—Write Protecting the DiskOnChip®2000"; M-Systems Flash Disk Pioneers; Aug. 1997; 4 pages.

"User Manual—DiskOnChip®2000 PIK (Programmer and Integrator Kit)" M-Systems Flash Disk Pioneers; Jul. 1997; 7 pages.

"DiskOnChip®2000 Quick Installation Guide"; M-Systems Flash Disk Pioneers; 1 page.

"User Manual—DiskOnChip®2000 Utilities"; M-Systems Flash Disk Pioneers; Jul. 1997; 8 pages.

"User Manual—DiskOnChip®-EVB ISA Adaptor for the DiskOnChip"; M-Systems Flash Disk Pioneers; Nov. 1996; 6 pages. "M-Systems' DiskOnChip®2000 Evaluation Board"; Jul. 1997; 1 page.

"Questions and Answers about DiskOnChip2000"; M-Systems Flash Disk Pioneers; Jul. 1997; 4 pages.

Ben-Zeev, Y.; "AP-DOC-010 Application Note—Designing with the DiskOnChip®2000"; M-Systems Flash Disk Pioneers; Jul. 1997; 4 pages.

"Flash PC Card 2000 Data Sheet"; M-Systems Flash Disk Pioneers; Jun. 1997; retrieved from the internet at <a href="http://www/m-sys.com/pcmcia.htm">http://www/m-sys.com/pcmcia.htm</a> on or before Oct. 13, 1997; 15 pages.

"Information Technology—Reduced Block Commands"; Working Draft; T10/1228D Revision 6; Feb. 26, 1999.

"DiskOnChip 2000 MD-2200 Data Sheet"; M-Systems Flash Disk Pioneers; Jul. 1997; 15 pages.

"A TrueFFS and FLite Technical Overview of M-Systems' Flash File Systems"; Technology Brief V1.01; M-Systems Flash Disk Pioneers; Oct. 1996; retrieved from the internet at <a href="http://www.m-sys.com/tech1.htm">http://www.m-sys.com/tech1.htm</a> on or before Oct. 13, 1997; 9 pages.

"PC Card Standard Release 7"; PCMCIA; vols. 1 through 11; Copyright 1999, update Mar. 2000; retrieved from the internet at <a href="http://www.pcmcia.org/pccard.htm">http://www.pcmcia.org/pccard.htm</a>.

"Universal Serial Bus Mass Storage Class—Bulk-Only Transport"; Revision 1.0 [RC3]; Mar. 29, 1999; 25 pages.

"DiskOnChip2000—The Smallest Flash Disk in the World"; M-Systems Flash Disk Pioneers; retrieved from the internet at <www.m-sys.com/doc2000.htm> on or before Oct. 13, 1997; 5 pages.

"8x930Hx Universal Serial Bus Microcontroller"; Intel Corporation; Oct. 1996; retrieved from the Internet at <a href="http://140.114.28.92/course//33249/FILES/FILES/USING%20MCS51/DATASHTS/intel/ds930hx.pdf">http://140.114.28.92/course//33249/FILES/FILES/USING%20MCS51/DATASHTS/intel/ds930hx.pdf</a>; 34 pages.

"Sony Announces Memory Stick<sup>TM</sup> for Audio Application "Memory Stick<sup>TM</sup> Walkman" and "MagicGate Memmory Stick<sup>TM</sup>" To Be Launched"; Sep. 22, 1999; retrieved from the internet at <a href="http://www.sony.net/sonyinfo/news/press\_archive/199909/99-072/">http://www.sony.net/sonyinfo/news/press\_archive/199909/99-072/</a> on Mar. 32, 2006; 3 pages.

"Report on the Japanese Nikon 900 Firmware Upgrade"; Digital Camera News; Jan. 30, 1999; 34 pages.

International Standard, ISO/IEC 7816-1 through 7816-8; editions dated Sep. 1, 1995 through Oct. 1, 1999.

"PCMCIA Flash Disk—Removable Flash Disk for Embedded & Mobile Computers"; Oct. 13, 1997; retrieved from the Internet at <a href="https://www.m-sys.com/pcmcia.htm">www.m-sys.com/pcmcia.htm</a>.

Grant, J.; "A Historical Look At Hardware Token Compromises"; presented in the Black Hat USA 2004 briefing, Wednesday Jul. 28, 2004.

English translation of FR 2 719 939; published on Nov. 17, 1995.

"Aladdin Announces eToken—Next Generation Security Key Based On Universal Serial Bus Port"; Jan. 19, 1999; retrieved from the internet at <a href="http://web,archive.org/web/20040414101246/www.ealaddin.com/news/1999/etoken/etoken.asp">http://web,archive.org/web/20040414101246/www.ealaddin.com/news/1999/etoken/etoken.asp</a> on Feb. 13, 2006; 3 pages.

"Hardlock USB"; Aladdin; retrieved from the Internet at <a href="http://aladdin.de/produkte/hardlock/hardlock\_usb.html">http://aladdin.de/produkte/hardlock/hardlock\_usb.html</a> on Feb. 13, 2006; 2 pages.

"Reduced Block Commands (RBC)"; Draft Proposal (T10/97-260r2); Revision 1; Jan. 16, 1998.

"Information Technology—Reduced Block Commands"; Working Draft; T10/1228D Revision 7; Mar. 8, 1999.

"Flash Memory"; Wikipedia, the free encyclopedia; downloaded from the Internet at <a href="http://en.wikipedia.org/wiki/Flash\_Memory">http://en.wikipedia.org/wiki/Flash\_Memory</a> on Feb. 20, 2006; 5 pages.

European Patent Office Summons To Attend Oral Proceedings in EP 1092193.

"Application Note (AP-684) Understanding the Flash Translation Layer (FTL) Specification," Intel Corporation, Dec. 1998, 20 pages. "PC Card Standard, vol. 1, Overview and Glossary," PCMCIA/JEIDA, first printing Feb. 1999, 40 pages.

"PC Card Standard, vol. 7, Media Storage Formats Specification," PCMCIA/JEIDA, first printing Feb. 1999, 53 pages.

"PC Card Standard, vol. 8, PC Card ATA Specification," PCMCIA/ JEIDA, first printing Feb. 1999, 39 pages.

M-Systems, "FlashLite 100 PC Card," M-Systems Flash Disk Pioneers, Product Specifications, Jul. 1998.

Office Action dated Nov. 2, 2007,.

European Patent Office Interlocutory decision in Opposition proceedings dated Jan. 21, 2009.

Auclair, D., "Optimal Solid State Disk Architecture for Portable Computers," Presented at the Silicon Valley PC Design Conference, Jul. 9, 1991, 5 pages.

Dipert et al., "Designing with Flash Memory," Annabooks © 1993, 1994, San Diego, CA, 431 pages.

Leibson, S., "Nonvolatile, in-circuit-reprogrammable memories," EDN Magazine, Jan. 3, 1991, 12 pages.

Cypress Semiconductor, "Universal Serial Bus Microcontroller," Cypress Semiconductor Corporation, San Jose, CA, Oct. 1996—Revised Jun. 26, 1997, 35 pages.

Diamond, "Rio 500 Getting Started Guide," Diamond Multimedia Systems © 1999, 2 pages.

Fantom Drives, "Fantom Drives Embraces USB & iMac by Announcing USB Hard Disk Drive and CD-ReWritable Technology," Fantom USB Highlights, Jan. 5, 1999, 3 pages, http://web.archive.org/web/20000526201655/fantomdrives.com/main\_si.

Fantom Drives, "Fantom Drives Ships USB Hard Disk Drives," Fantom Drives, Apr. 5, 1999, 1 page, http://www.fantomdrives.com/press/articles/usbrelease.html.

IEEE, "IEEE Standard for a High Performance Serial Bus," IEEE Std 1394-1995, © 1996 by Institute of Electrical and Electronics Engineers, Inc., New York, NY, 393 pages.

MacHASP USB, "Software Protection via the USB," MacHASP USB Datasheet, Aladdin Knowledge Systems, Inc., 10 pages.

M-Systems, "DiskOnChip®2000 MD2200, MD2201 Data Sheet," M-Systems Inc., Jun. 1998, 15 pages.

Philips, "PDIUSBD12 USB interface device with parallel bus," Philips Semiconductors—Asia Product Innovation Centre Data Sheet, Jan. 8, 1999, 45 pages.

Toshiba, MOS Memory (Non-Volatile) Data Book, Toshiba Corporation, Sep. 1996, 166 pages.

Toshiba, "Toshiba MOS Digital Integrated Circuit Silicon Gate CMOS," Toshiba Corporation, Jul. 7, 1997, 34 pages.

Request for Inter Partes Reexamination of U.S. Patent No. 6,829,672, dated Jul. 8, 2008, with transmittal form, 109 pages.

Inter Partes Reexamination Communication / Office Action dated Nov. 3, 2008, 22 pages.

Decision Granting-in-Part Petition for Extension of Time dated Dec. 12, 2008, 4 pages.

Patent Owner's Response to Office Action, Feb. 3, 2009, 162 pages. Transmittal of Communication to Third Party Requester Inter Partes Reexamination / Decision Refusing Entry of Papers, re paper entitled "Expedited Petition Under 37 C.F.R. §§ 1.182 and 1.183" dated Apr. 6, 2009, 7 pages.

Transmittal of Communication to Third Party Requester Inter Partes Reexamination / Decision Refusing Entry of Papers re paper entitled "Opposition to Patent Owner'S Petition Under 37 C.F.R. § 1.956", dated Apr. 6, 2009, 7 pages.

Transmittal of Communication to Third Party Requester Inter Partes Reexamination / Decision Granting-in-Part Petition to Extend Page Limit for Response to Office Action, dated Apr. 6, 2009, 7 pages.

Written Comments by the Third Party Requester in an Inter Partes Reexamination, Patent Reexamination Control No. 95/000,384, May 20, 2009, 75 pages (Redacted).

Claims as issued in U.S. Patent No. 6,829,672, Reexamination Control No. 95/000,384.

IDS with references, filed Jul. 9, 2008, 73 pages.

European Patent Office Extended Search Report, issued in co-pending European Patent Application 09013951.0 on Apr. 6, 2010, 8 pages.

"Written Comments by the Third Party Requester in an Inter Partes Reexamination," filed in Reexamination Control No. 95/000,384, dated Apr. 13, 2010, 49 pages.

Austrian Patent Office Search Report and Written Opinion issued in related Singapore Patent Application 200604735-1 on Nov. 16, 2009, 8 pages.

European Patent Office Extended Search Report issued in co-pending European Patent Application 09010734.3 on Apr. 8, 2010, 9 pages. Japanese Patent Office Action issued in co-pending Japanese Patent Application No. 2005-241989, dated Apr. 9, 2010, 8 pages.

Japanese Patent Office Action issued in co-pending Japanese Patent Application No. 2007-085679, dated Apr. 9, 2010, 6 pages.

Intel Corp., "Common Flash Memory Interface (CFI) Specification," Release 1.1, May 30, 1997, 16 pages.

\* cited by examiner

Figure 3 – Background Art USB Handshake Packet

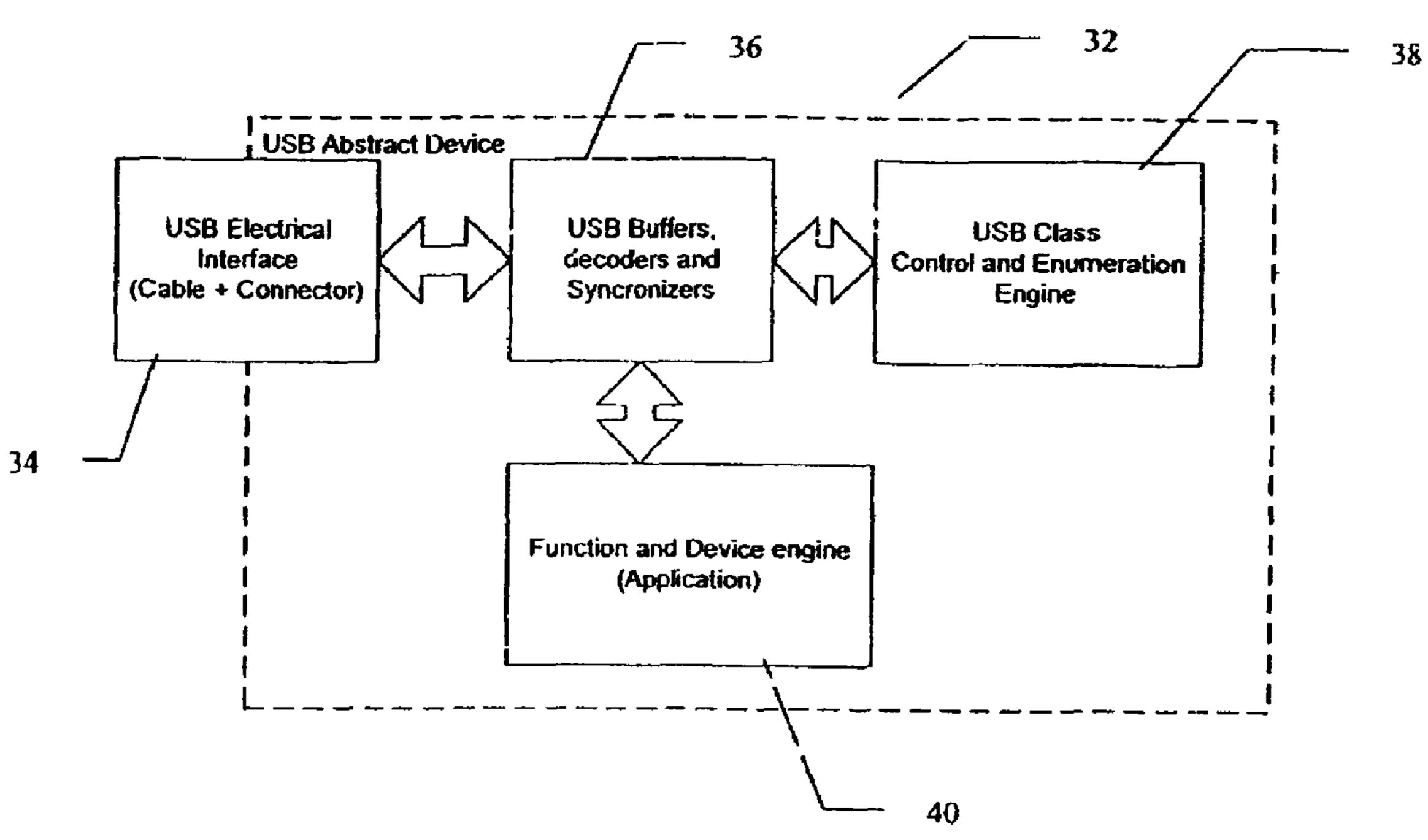

Figure 4 – Functional Blocks of a Background Art USB device

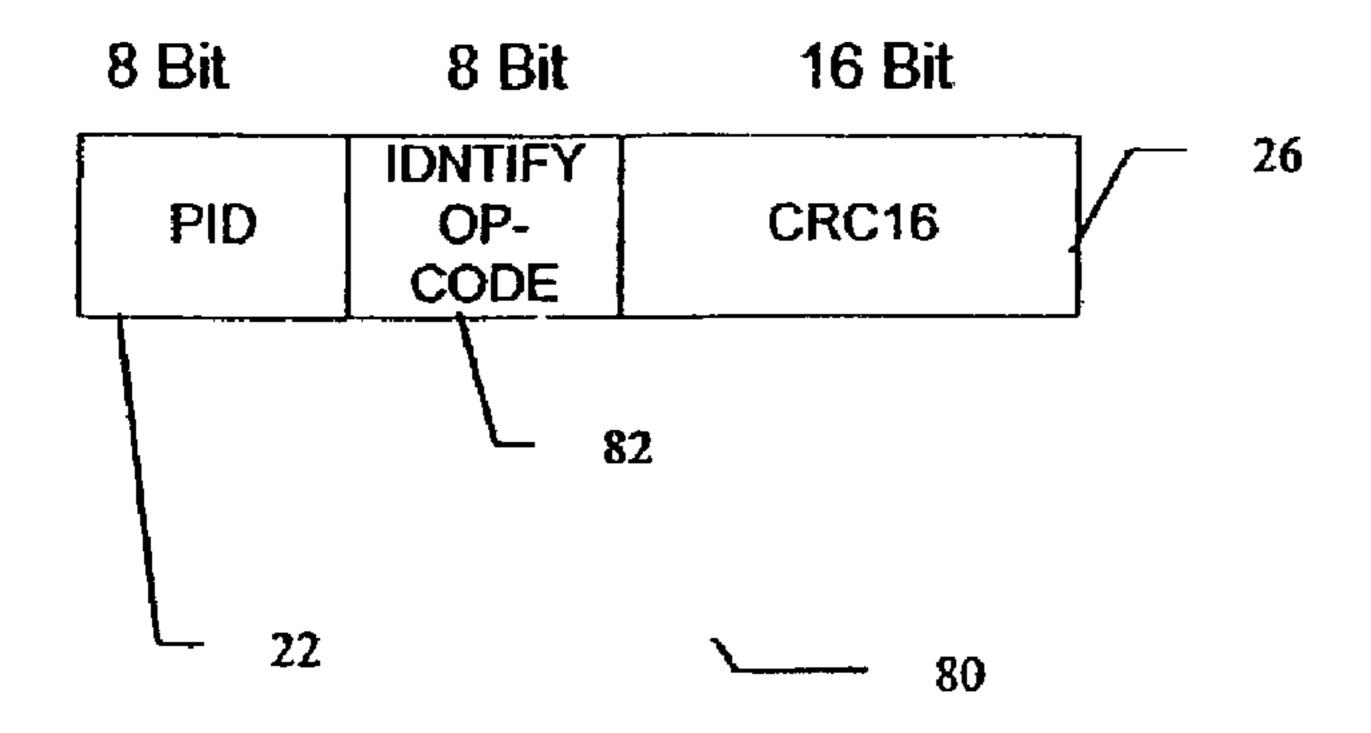

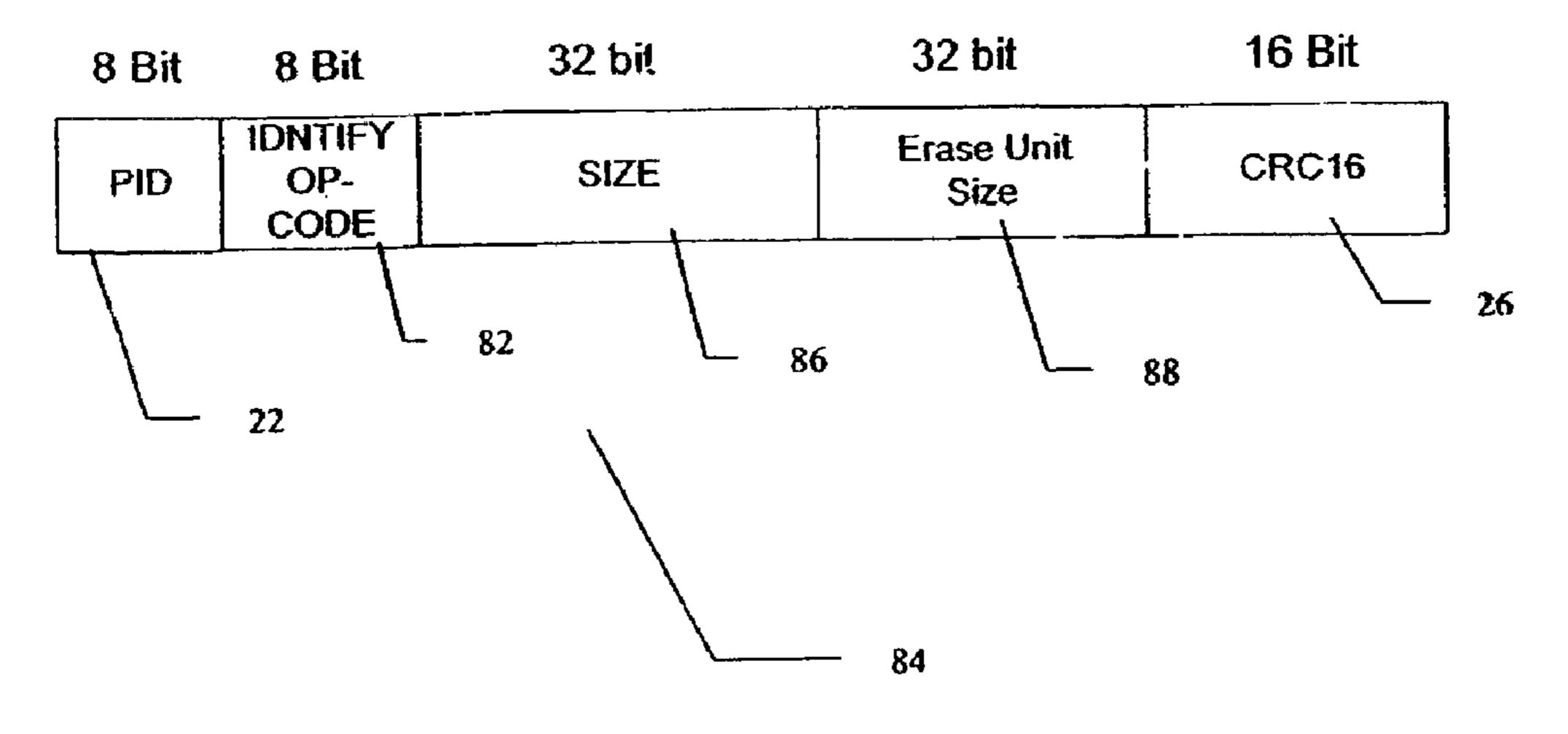

Fig 7 - Flash Identification Request Packet

Fig 8 – Flash Identification Replay Packet

May 24, 2011

# ARCHITECTURE FOR A UNIVERSAL SERIAL BUS-BASED PC FLASH DISK

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

#### RELATED APPLICATIONS

This application is a reissue application of U.S. Ser. No. 09/285,706 filed on Apr. 5, 1999, now U.S. Pat. No. 6,148,354 issued on Nov. 14, 2000. More than one reissue application has been filed for the reissue of U.S. Pat. No. 6,148,354. The 15 reissue applications are application Ser. No. 10/293,986 (the present application), which is a continuation of application Ser. No. 10/292,868 filed Nov. 13, 2002.

# FIELD AND BACKGROUND OF THE INVENTION

The present invention is related to semiconductor memory devices, and in particular to erasable and programmable non-volatile memory modules which are connected to a host plat- 25 form using the USB PC Bus.

Erasable and programmable non-volatile memory modules, hereinafter referred to as flash memory or flash devices, are known in the art for storage of information. Flash devices include electrically erasable and programmable read-only 30 memories (EEPROMs) made of flash-type, floating-gate transistors and are non-volatile memories similar in functionality and performance to EPROM memories, with an additional functionality that allows an in-circuit, programmable, operation to erase pages of the memory. One example of an 35 implementation of such a flash device is given in U.S. Pat. No. 5,799,168, incorporated by reference as if fully set forth herein.

Flash devices have the advantage of being relatively inexpensive and requiring relatively little power as compared to 40 traditional magnetic storage disks. However, in a flash device, it is not practical to rewrite a previously written area of the memory without a preceding page erase of the area. This limitation of flash devices causes them to be incompatible with typical existing operating system programs, since data 45 cannot be written to an area of memory within the flash device in which data has previously. been written, unless the area is first erased. A software management system, such as that disclosed in U.S. Pat. No. 5,404,485, filed on Mar. 5, 1993, which is incorporated as if fully set forth herein, is required to 50 manage these functions of the flash memory device.

Currently, these flash memory devices have a second limitation, which is that they must be either attached statically to the host platform, or attached and detached dynamically using the PCMCIA [Personal Computer Memory Card Interstational Association] interface. Both implementations have drawbacks, including difficulty of use and high cost.

A more useful implementation would follow the USB standard, as described in the USB Specification Version 1.1 which is incorporated as if fully set forth herein. The USB standard offers a smaller form factor and greater ease of use for the end user, while lowering the cost of the implementation. This standard is specified to be an industry-wide standard promoted by companies such as Compaq Computer Corporation, Microsoft, IBM and Intel to serve as an extension to the PC architecture with a focus on Computer Telephony Integration (CTI), the consumer, and productivity applications.

2

The criteria which were applied to define the architecture for the USB standard include the ease of PC (personal computer) peripheral expansion, low cost, support of transfer rates up to 12 Mb/second and full support for real-time data, voice, audio, and compressed video. This standard also offers protocol flexibility for mixed-mode isochronous data transfers and asynchronous messaging, integration in commodity device technology and provision of a standard interface for rapid integration into any given host product. In addition, the 10 USB standard represents a single model for cabling and attaching connectors, such that all of the details of the electrical functions, including bus terminations, are isolated from the end user. Through the standard, the peripheral devices are self-identifying, and support automatic mapping of functions to a driver. Furthermore, the standard enables all peripheral devices to be dynamically attachable and re-configurable.

A system constructed according to the USB standard is described by three separate, defined areas: USB interconnection, USB devices and the USB host platform. The USB interconnection is the manner in which USB devices are connected to, and communicate with, the host platform. The associated functions and components include the bus topology, which is the connection model between USB devices and the host platform.

The USB physical interconnection has a tiered star topology. A hub is at the center of each star. Each wire segment is a point-to-point connection between the host platform and a hub or function, or a hub connected to another hub or function.

In terms of a capability stack, the USB tasks which are performed at each layer in the system include a data flow model and a schedule. A data flow model is the manner in which data moves in the system over the USB between data producers and data consumers. A schedule determines access to the interconnection, which is shared. Such scheduling enables isochronous data transfers to be supported and eliminates arbitration overhead.

The USB itself is a polled bus. The host controller on the host platform initiates all data transfers. All bus transactions involve the transmission of up to three packets. Each transaction begins when the host controller, on a scheduled basis, sends a USB packet describing the type and direction of transaction, the USB device address, and endpoint number. This packet is referred to as the "token packet." The USB device, to which the packet is addressed, selects itself by decoding the appropriate address fields. In a given transaction, data is transferred either from the host platform to a device or from a device to the host platform. The direction of data transfer is specified in the token packet. The source of the transaction then sends a data packet or indicates that the source has no data to transfer. The destination, in general, responds with a handshake packet indicating whether the transfer was successful.

The USB data transfer model between a source and destination on the host platform and an endpoint on a device is referred to as a "pipe". There are two types of pipes: stream and message. Stream data has no USB-defined structure, while message data does. Additionally, pipes have associations of data bandwidth, transfer service type, and endpoint characteristics like directionality and buffer sizes. Most pipes come into existence when a USB device is configured. One message pipe, the default control pipe, always exists once a device is powered, in order to provide access to the configuration, status, and control information for the device.

The transaction schedule for the USB standard permits flow control for some stream pipes. At the hardware level, this prevents situations in which buffers experience underrun or

overrun, by using a NAK handshake to throttle the data rate. With the NAK handshake, a transaction is retried when bus time is available. The flow control mechanism permits the construction of flexible schedules which accommodate concurrent servicing of a heterogeneous mix of stream pipes. 5 Thus, multiple stream pipes can be serviced at different intervals with packets of different sizes.

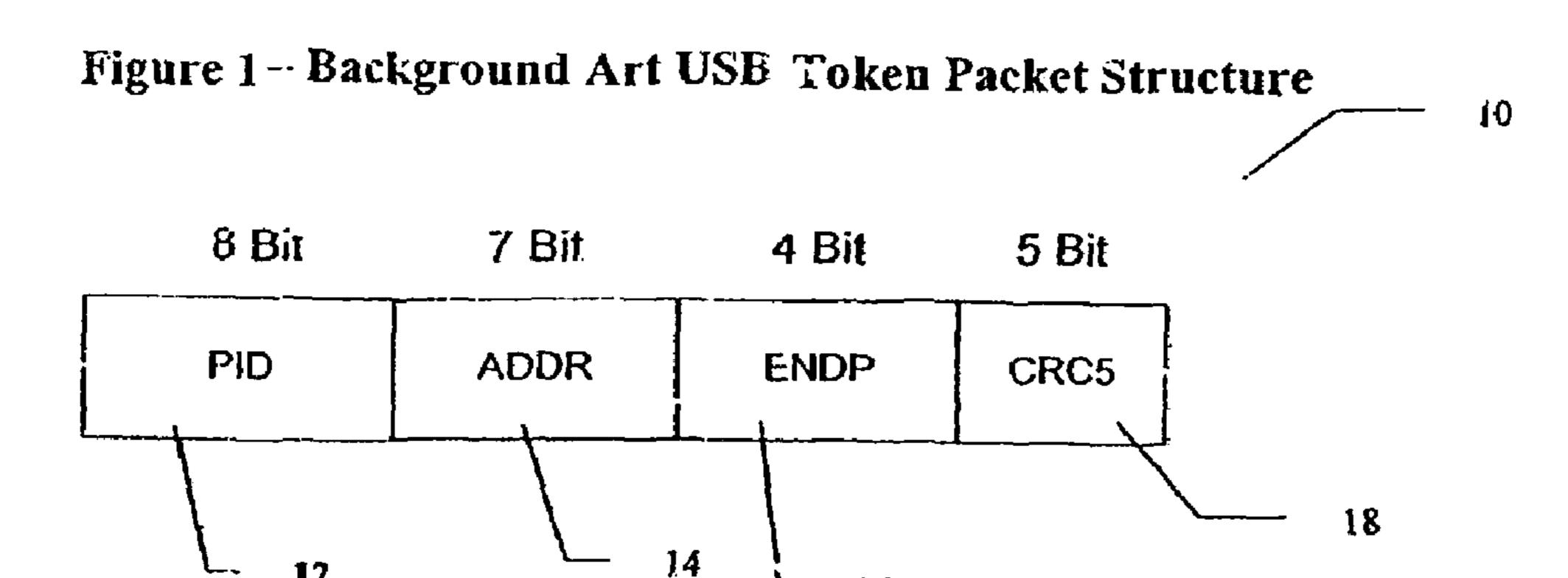

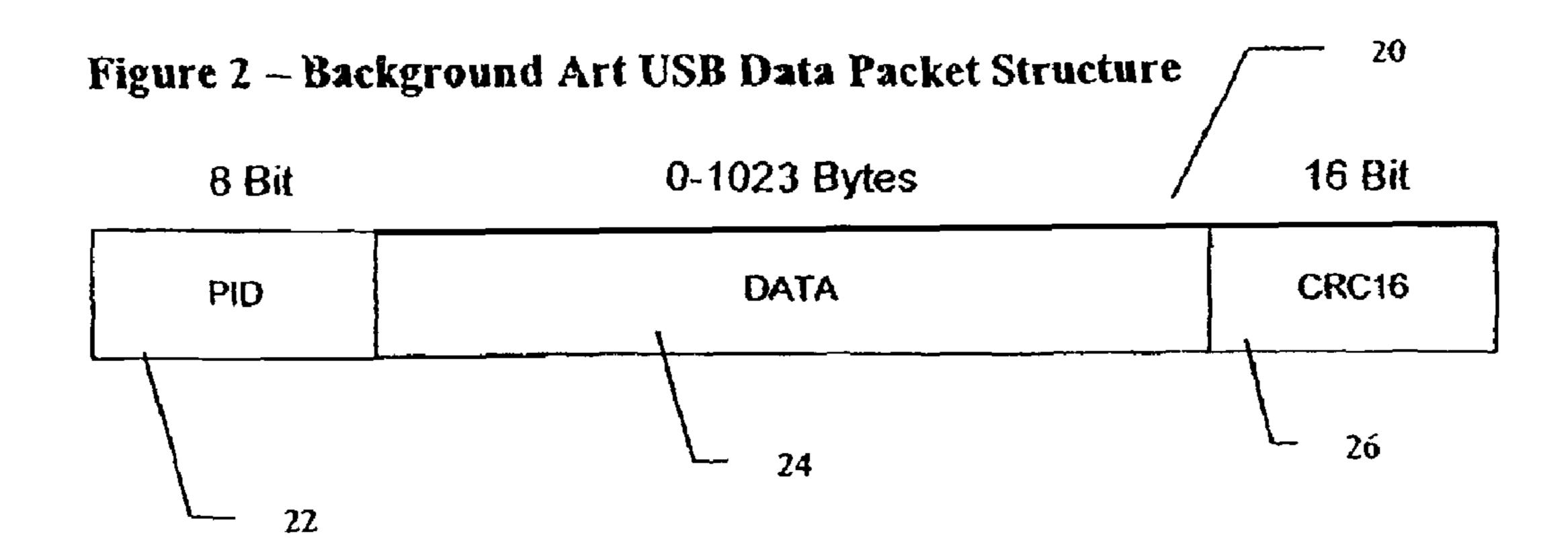

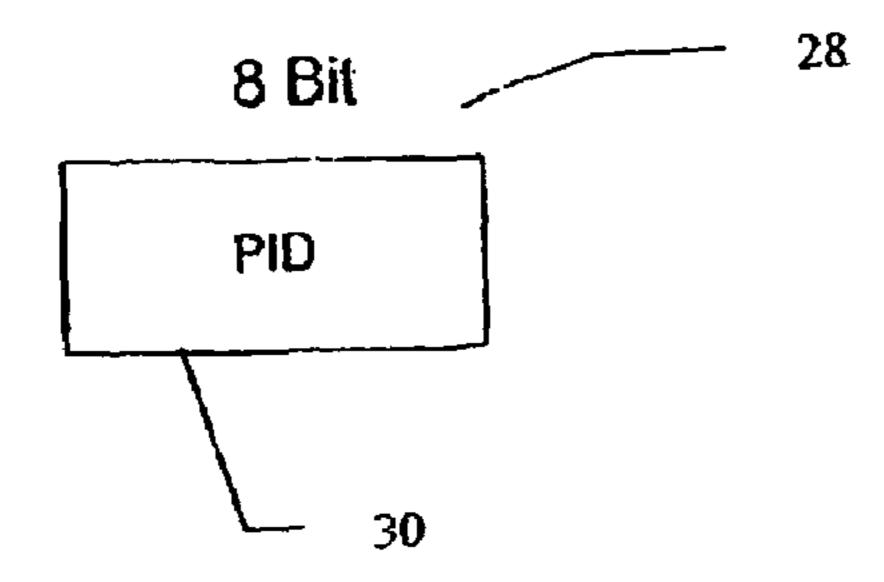

The USB standard, as described, has three main types of packets, including token packets, data packets and handshake packets. An example of each type of packet is shown in 10 background art FIGS. 1-3. Background art FIG. 4 shows an exemplary USB abstract device.

A token packet 10, as shown in background art FIG. 1, features a PID (packet identification) field 12, specifying one of three packet types: IN, OUT, or SETUP. If PID field 12 15 specifies the IN packet type, the data transaction is defined from a function to the host platform. If PID field 12 specifies the OUT or SETUP packet type, the data transaction is defined from the host platform to a function.

An ADDR field 14 specifies the address, while an ENDP 20 field 16 specifies the endpoint for token packet 10. For OUT and SETUP transactions, in which PID field 12 specifies that token packet 10 is an OUT packet type or a SETUP packet type, ADDR field 14 and ENDP field 16 uniquely identify the endpoint for receiving the subsequent data packet, shown in 25 FIG. 2, which follows after token packet 10. For IN transactions, in which PID field 12 specifies that token packet 10 is an IN packet type, ADDR field 14 and ENDP field 16 uniquely identify which endpoint should transmit a data packet. A CRC5 field 18 contains the checksum, for determining that 30 token packet 10 has been received without corruption. Only host platform can issue token packets 10, such that token packets 10 provide control over transmission of the subsequent data packets.

As shown in background art FIG. 2, a background art USB 35 data packet 20 also features a PID (packet identification) field 22 for identifying the type of data packet. Data packet 20 also features a data field 24 for optionally. containing data, and a CRC field 26 for containing the checksum as previously described.

Background art FIG. 3 shows a background art USB handshake packet 28, which features only a PID (packet identification) field 30. Handshake packets 28 are used to report the status of a data transaction and can return values indicating successful reception of data, command acceptance or rejection, flow control, and halt conditions. Only transaction types which support flow control can return handshake packets 28. Handshake packets 28 are always returned in the handshake phase of a transaction and may be returned, instead of data packets 20, in the data phase of a transaction.

These three different types of packets are exchanged during various phases of the transaction which includes a USB device. A schematic block diagram of the functional blocks in a typical USB device 32 is shown in FIG. 4 for an abstract background art USB device. USB device 32 typically 55 includes a USB electrical interface 34, featuring a cable and a connector, which is a physical interface for receiving and transmitting electrical signals which are compatible with the USB specification as previously described. The signals are then passed to a logical interface 36, which includes one or 60 more buffers, the device address decoder for decoding the address of the source device for the signals, and a SYNC field synchronizer for synchronizing the signals. Information and structures required for management of USB abstract device 32 as a USB device are stored in a USB class control and 65 enumeration engine 38. A function and device engine 40, also termed the "application", controls and manages the specific

4

functions and properties of USB abstract device **32**. In addition, function and device engine **40** also consumes and produces most of the data over the USB bus.

The USB specification does not define the relationship between different entities in USB abstract device 32, however. Rather, the USB specification describes only the requirements for the packets, and for the electrical and physical connection between USB abstract device 32 and the bus. Therefore the connections and relationships shown in background art FIG. 4 are only one example of an implementation which fulfills the requirements of the USB specification. Thus, any specific device for fulfilling the USB specification must have a specifically defined and described architecture.

Unfortunately, no such architecture exists for a flash memory device containing one or more flash memory modules, which would enable the flash memory device to connect to a bus defined according to the USB specification and thereby to form part of a USB system on a host platform. For example, U.S. Pat. No. 5,799,168 does not teach or suggest such an implementation for the flash device. As mentioned previously, such an architecture would be particularly useful for a number of reasons, including low cost, ease of use and transparency to the end user.

There is thus a need for, and it would be useful to have, an architecture for defining and describing a flash memory device which is compatible with a USB system and which follows the USB specification, such that the flash memory device could sit on a USB-defined bus and communicate with the host platform through this bus.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a schematic block diagram of a background art USB token packet structure;

FIG. 2 is a schematic block diagram of a background art USB data packet structure;

FIG. 3 is a schematic block diagram of a background art USB handshake data packet structure;

FIG. 4 is a schematic block diagram of an exemplary back-40 ground art USB device;

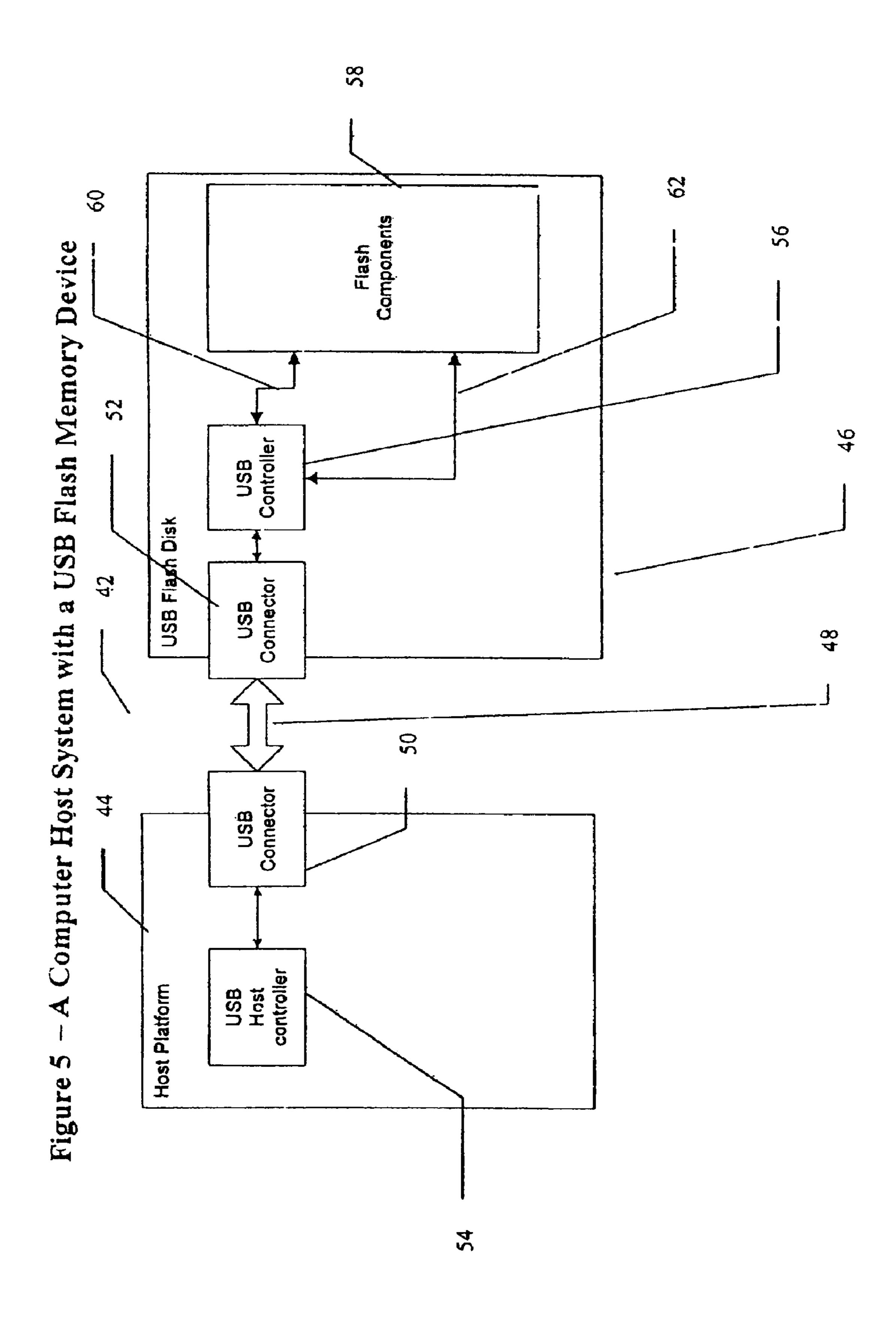

FIG. **5** is a schematic block diagram of a system with a flash USB device functionality according to the present invention;

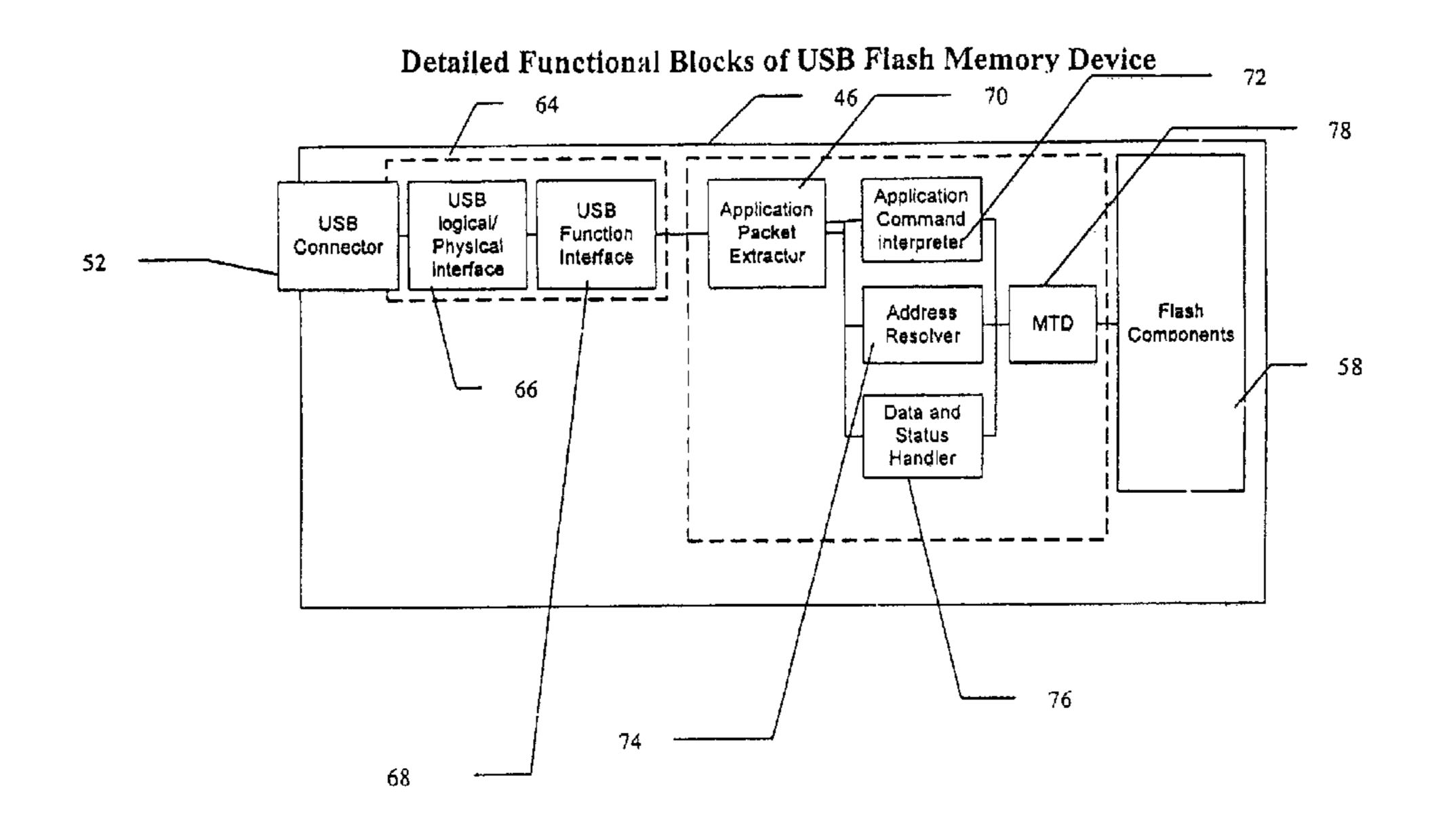

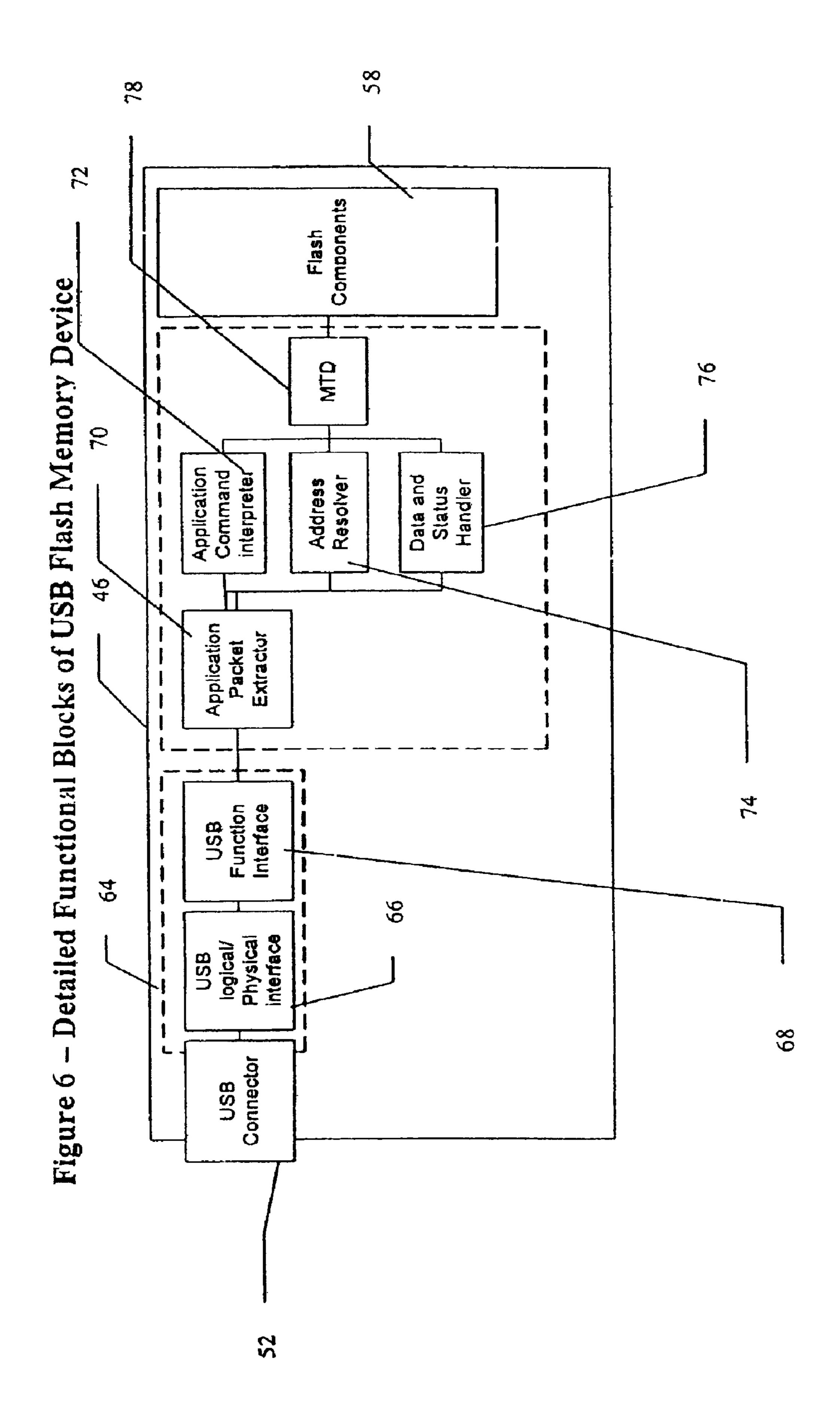

FIG. **6** is a schematic block diagram of the USB Flash disk;

FIG. 7 is a schematic block diagram of a flash identification request packet;

FIG. 8 is a schematic block diagram of a flash identification status packet;

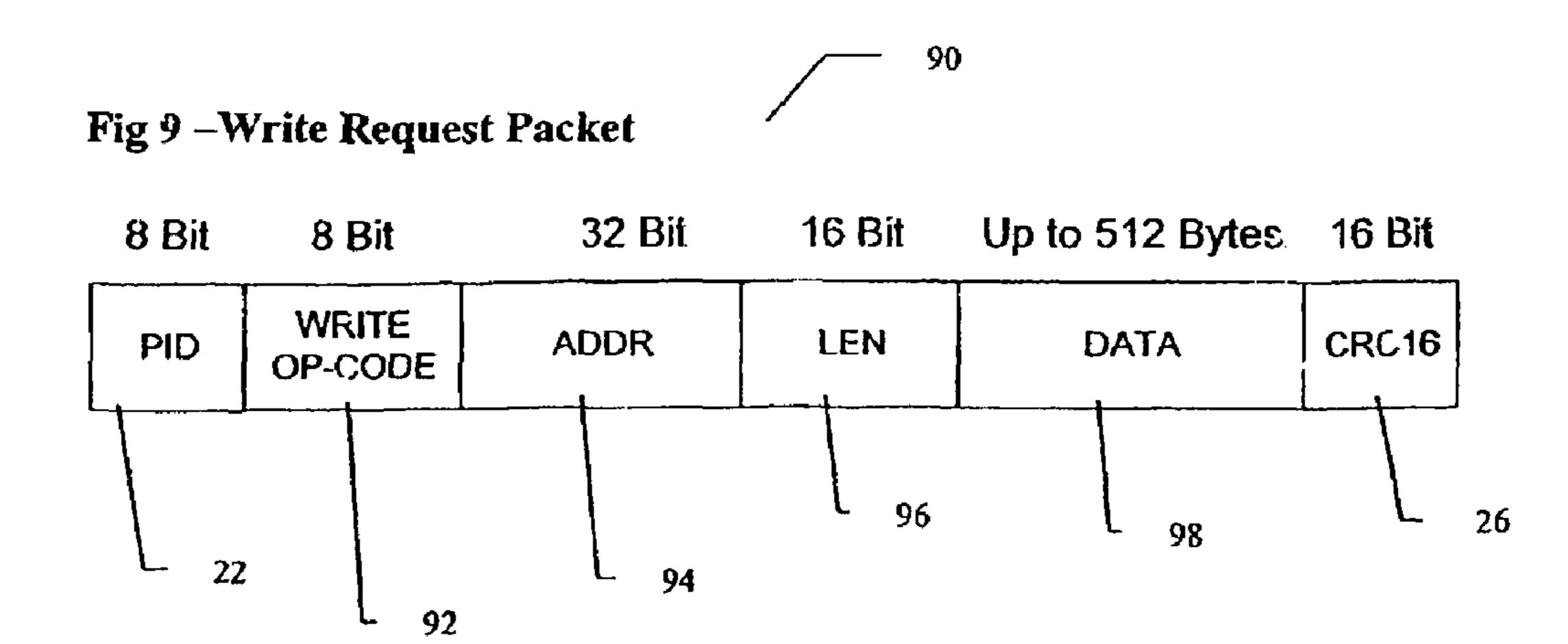

FIG. 9 is a schematic block diagram of a flash write request packet;

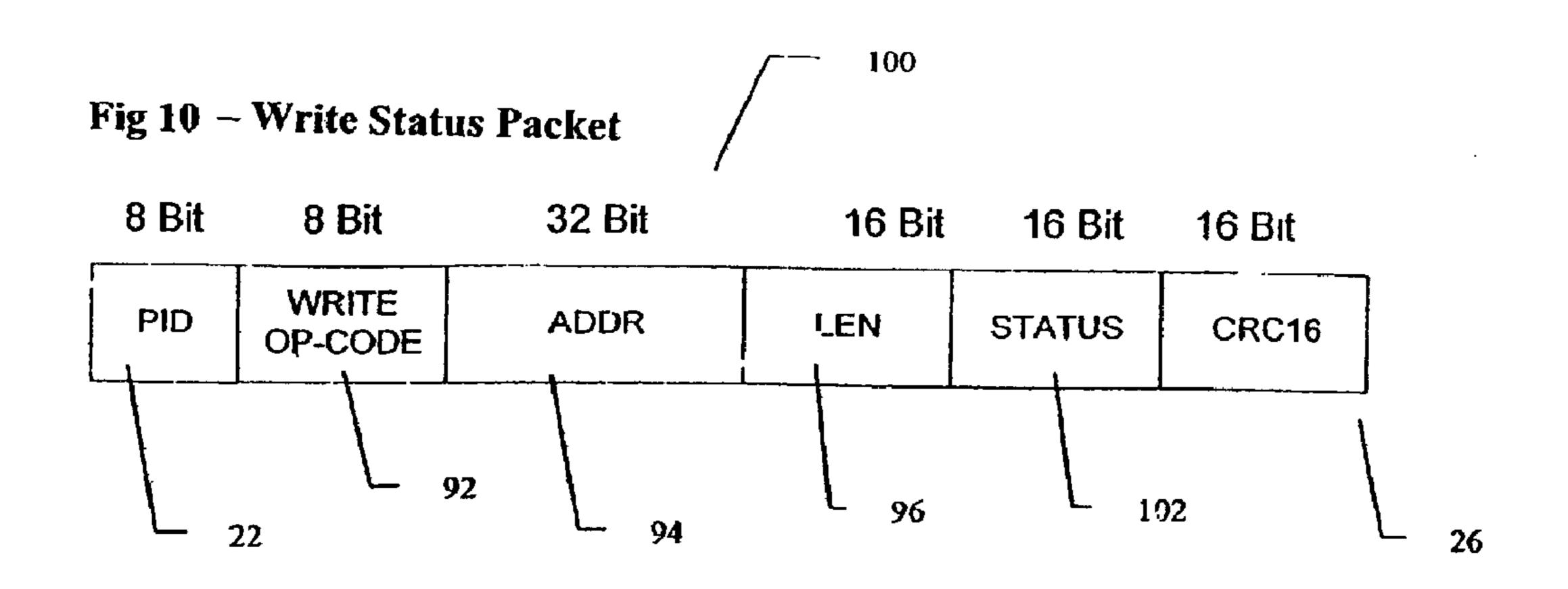

FIG. 10 is a schematic block diagram of a flash write status packet;

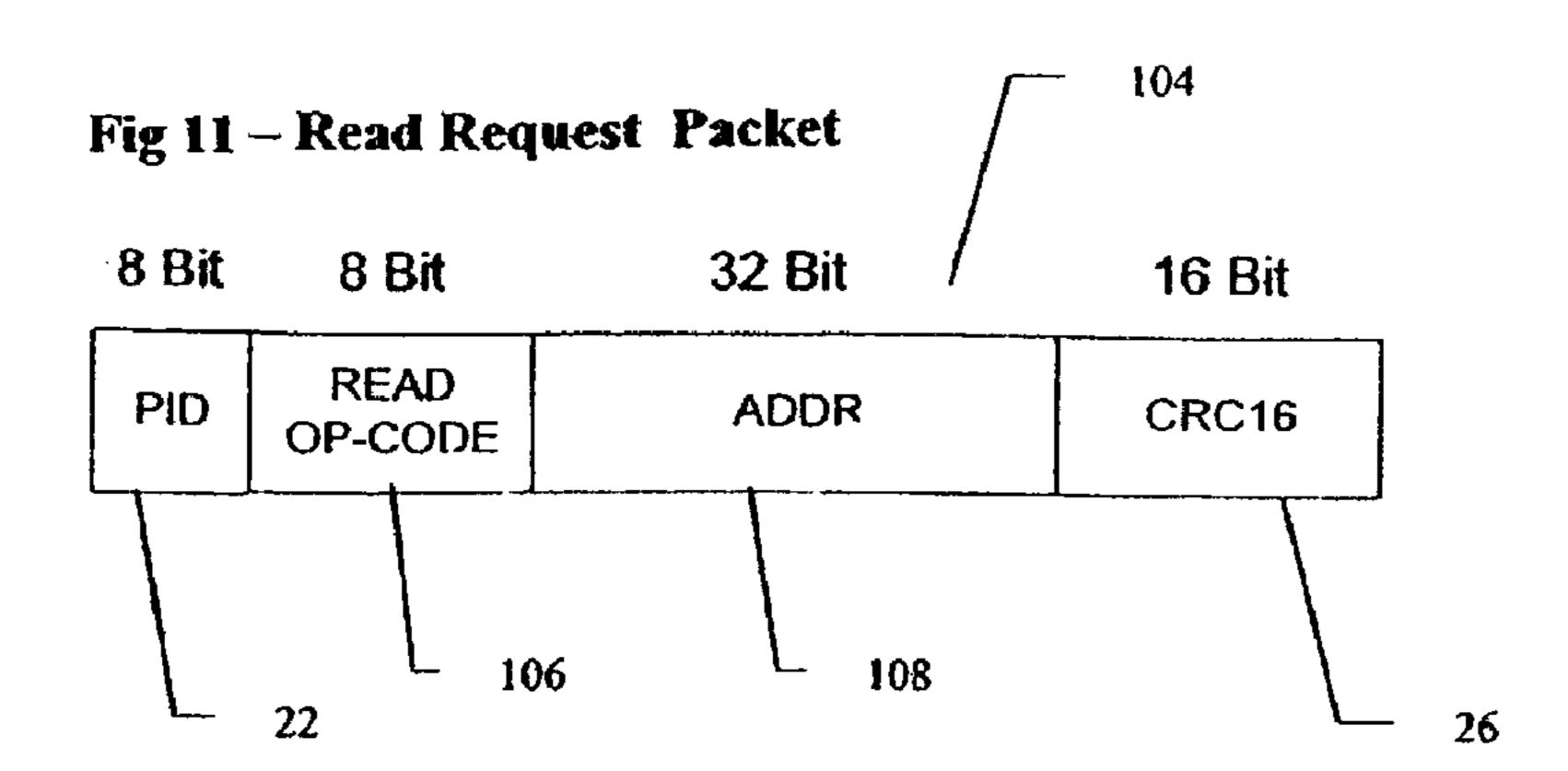

FIG. 11 is a schematic block diagram of a flash read request packet;

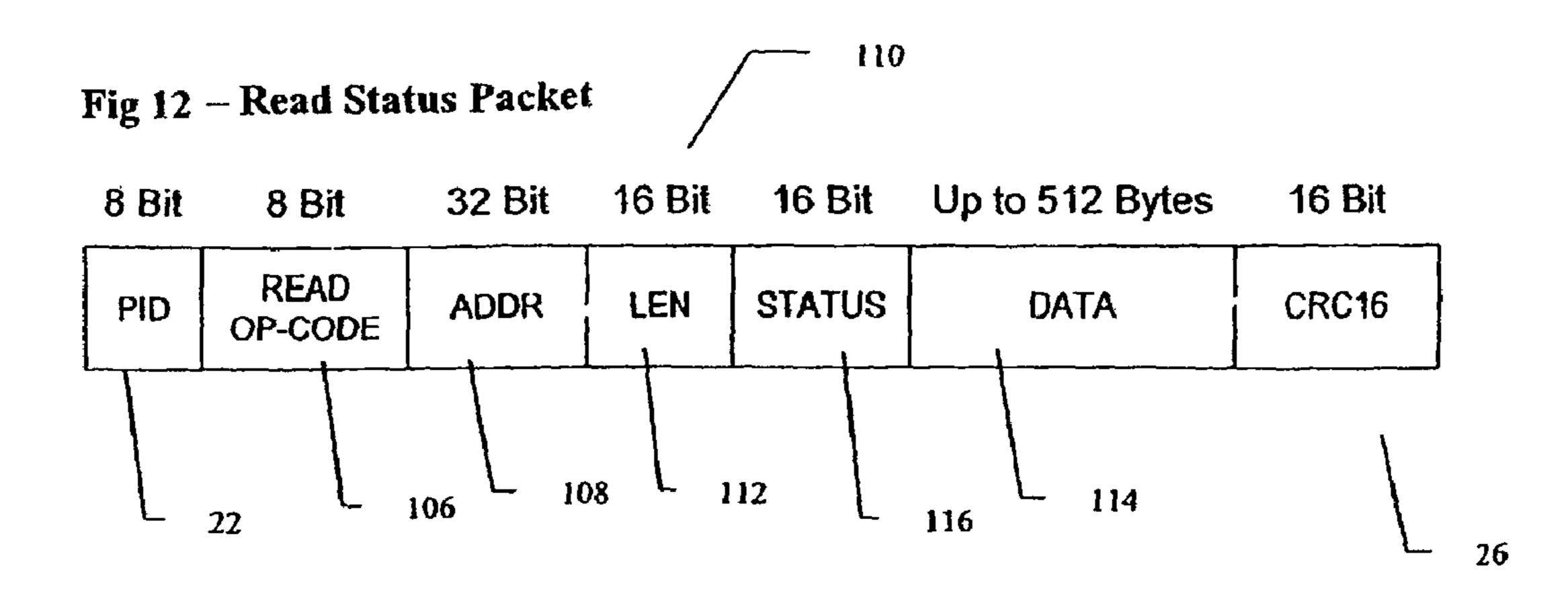

FIG. 12 is sa schematic block diagram of a flash read status packet;

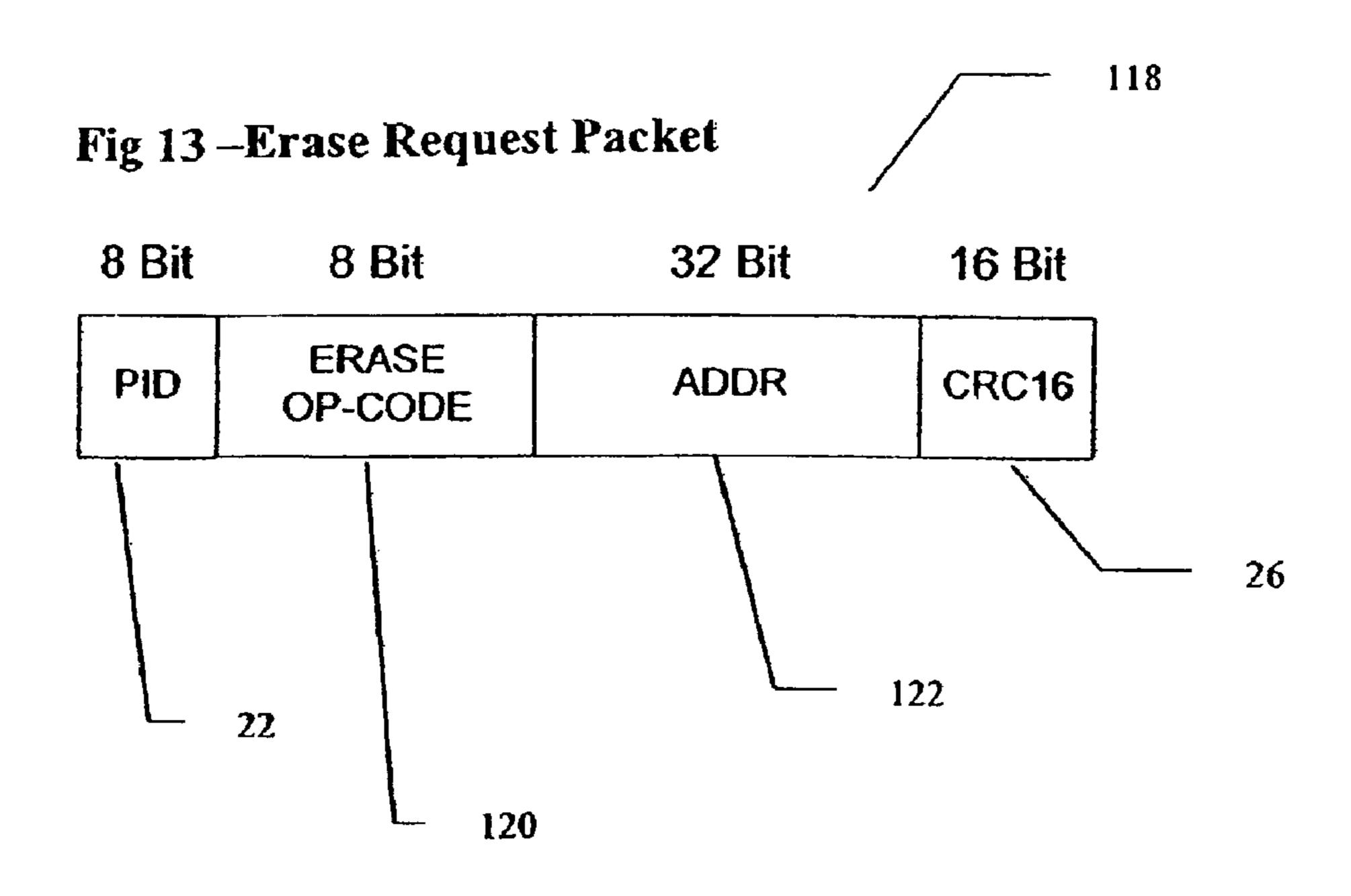

FIG. 13 is a schematic block diagram of a flash erase request packet; and

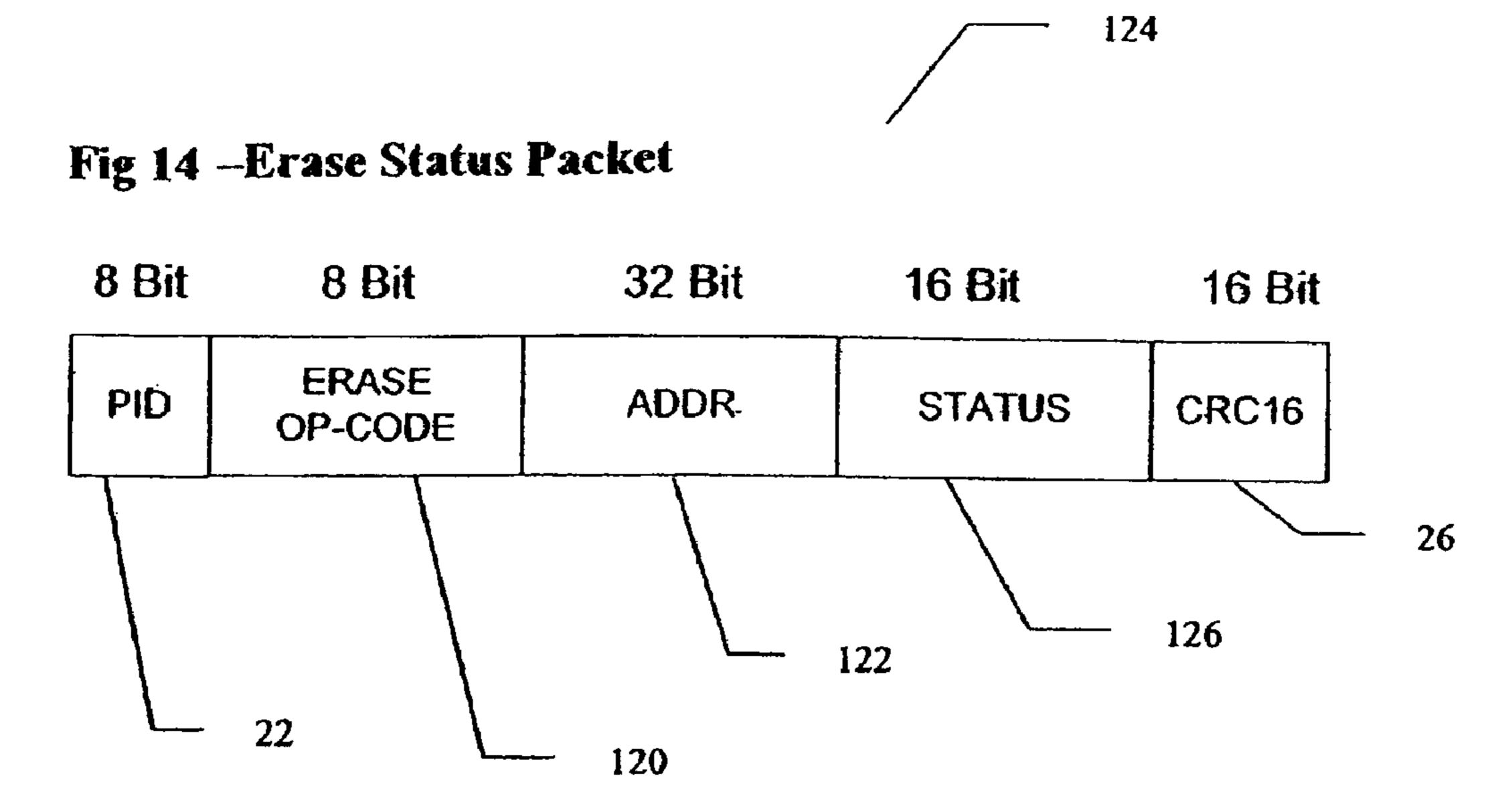

FIG. 14 is a schematic block diagram of a flash erase status packet.

### SUMMARY OF THE INVENTION

The present invention is of a flash memory device, containing one or more flash modules, in which the flash memory is mapped to the address space of an ASIC or a controller which has a USB-defined electrical interface and a USB-defined logical interface. This controller/ASIC (hereinafter termed a

"controller") supports the USB functionality according to the USB standard, thereby supporting enumeration onto the USB bus, as well as data reception and transmission over USB pipes to and from USB endpoints. This controller also supports the functionality and control of the flash memory device, as well as the processing of command and data packets from the host controller. The host controller uses one of several possible protocols, either standard or proprietary, to signal the next command to be performed to the USB flash controller. Thus, the entire device acts as a dynamically attachable/detachable non-volatile storage device for the host platform.

According to the present invention, there is provided a USB flash memory device for connecting to a USB-defined bus, the flash memory device comprising: (a) at least one flash memory module for storing data; (b) a USB connector for connecting to the USB-defined bus and for sending packets on, and for receiving packets from, the USB-defined bus; and (c) a USB controller for controlling the at least one flash memory module and for controlling the USB connector according to at least one packet received from the USB-defined bus, such that data is written to and read from the at least one flash memory module.

Hereinafter, the term "computer" includes, but is not limited to, personal computers (PC) having an operating system 25 such as DOS, Windows<sup>TM</sup>, OS/2<sup>TM</sup> or Linux; Macintosh<sup>TM</sup> computers; computers having JAVA<sup>TM</sup>-OS as the operating system; and graphical workstations such as the computers of Sun Microsystems<sup>TM</sup> and Silicon Graphics<sup>TM</sup>, and other computers having some version of the UNIX operating system 30 such as AIX<sup>TM</sup> or SOLARIS<sup>TM</sup> of Sun Microsystems<sup>TM</sup>; or any other known and available operating system, including operating systems such as Windows CETM for embedded systems, including cellular telephones, handheld computational devices and palmtop computational devices, and any 35 other computational device which can be connected to a network. Hereinafter, the term "Windows<sup>TM</sup>" includes but is not limited to Windows 95<sup>TM</sup>, Windows 3.X<sup>TM</sup> in which "x" is an integer such as "1", Windows NT<sup>TM</sup>, Windows 98<sup>TM</sup>, Windows CE<sup>TM</sup> and any upgraded versions of these operating 40 systems by Microsoft Inc. (Seattle, Wash., USA).

### DETAILED DESCRIPTION OF THE INVENTION

The present invention is of a flash memory device, contain- 45 ing one or more flash modules, in which the flash memory is mapped to the address space of an ASIC or a controller which has a USB-defined electrical interface and a USB-defined logical interface. This controller/ASIC (hereinafter termed a "controller") supports the USB functionality according to the 50 USB standard, thereby supporting enumeration onto the USB bus, as well as data reception and transmission over USB pipes to and from USB endpoints. This controller also supports the functionality and control of the flash memory device, as well as the processing of command and data pack- 55 ets from the host controller. The host controller uses one of several possible protocols, either standard or proprietary, to signal the next command to be performed to the USB flash controller. Thus, the entire device acts as a dynamically attachable/detachable non-volatile storage device for the host 60 platform.

While the invention is susceptible to various modifications and can be implemented using many alternative forms, the embodiment is shown by way of example in the drawings and will be described in details in the following pages. It should be described that one of ordinary skill in the art appreciates that the present invention could be implemented in various other

6

ways. The intention is to cover all modifications and alternatives falling within the spirit of the current invention.

The principles and operation of a USB flash device and system according to the present invention may be better understood with reference to the drawings and the accompanying description, it being understood that these drawings are given for illustrative purposes only and are not meant to be limiting.

Referring now to the drawings, FIG. 5 is a schematic block diagram of the main components of a flash memory device and system according to the present invention. A flash memory system 42 includes a host platform 44 as shown. Host platform 44 operates USB flash device 46 as a non-volatile storage space.

Host platform 44 is connected to USB flash device 46 according to the present invention through a USB cable 48. Host platform 44 connects to USB cable 48 through a USB host connector 50, while USB flash device 46 connects to USB cable 48 through a USB flash device connector 52. Host platform 44 features a USB host controller 54 for controlling and managing all USB transfers on the USB bus.

USB flash device 46 features a USB flash device controller 56 for controlling the other components of USB flash device 46 and for providing an interface for USB flash device 46 to the USB bus, USB flash device connector 52 and at least one flash memory module 58. Flash memory module 58 is preferably an array of flash memory modules 58 in which the data is stored.

Whenever USB flash device 46 becomes connected to host platform 44, a standard USB enumeration process takes place. In this process host platform 44 configures USB flash device 46 and the mode of communication with USB flash device 46. Although there are many different methods for configuring USB flash device 46, for the purposes of clarity only and without intending to be limiting, the present invention is explained in greater detail below with regard to a method in which host platform 44 issues commands and requests to USB flash device 46 through one endpoint. Host platform 44 queries USB flash device 46 through the other endpoint for status changes, and receives related packets if any such packets are waiting to be received.

Host platform 44 requests services from USB flash device 46 by sending request packets to USB host controller 54. USB host controller 54 transmits packets on USB cable 48. These requests are received by USB flash device controller **56** when USB flash device 46 is the device on the endpoint of the request. USB flash device controller **56** then performs various operations such as reading, writing or erasing data from or to flash memory module(s) **58**, or supporting basic USB functionality such as device enumeration and configuration. USB flash device controller **56** controls flash memory module(s) 58 by using a control line 60 to control the power of flash memory module(s) 58, and also through various other signals such as chip enable, and read and write signals for example. Flash memory module(s) 58 are also connected to USB flash device controller 56 by an address/data bus 62. Address/data bus 62 transfers commands for performing read, write or erase commands on flash memory module(s) 58, as well as the addresses and data for these commands as defined by the manufacturer of flash memory module(s) 58.

In order for USB flash device **46** to notify host platform **44** on the result and status for different operations requested by host platform **44**, USB flash device **46** transmits status packets using the "status end point". According to this procedure, host platform **44** checks (polls) for status packets and USB

flash device **46** returns either an empty packet if no packets for new status messages are present, or alternatively returns the status packet itself.

A more detailed structure of the functional components of USB flash device **46** is shown in FIG. **6**. USB flash device **46** 5 includes the physical and electrical interface defined for the USB standard, shown here as USB flash device connector **52** and a connector interface **64**. USB flash device connector **52** receives the electrical signals from USB cable **48** which carries electrical signals from host controller (not shown). These signals are then passed through connector interface **64**. Every millisecond, a USB frame is carried on the USB-defined bus, such that packets could be sent to USB flash device **46**.

Connector interface **64** then receives these packets through a first interface component, which is a combined physical and 15 logical interface 66. A functional interface 68 is specifically designed to receive token packets as defined in the USB specification and as previously described with regard to FIG. 1. These token packets are related only to particular functional aspects of USB flash device 46 which are required for 20 the USB standard, and do not have any relation to particular application of USB flash device 46 as a flash disk according to the present invention. These token packets and their respective returned data packets enable USB host controller 54 (not shown) and host platform 44 (not shown) to identify USB flash device 46 and allocate resources for USB flash device 46 on the USB bus. Thus, functional interface **68** only supports USB functionality needed for the identification and registration of USB flash device **46** on the USB bus.

USB flash device **46** also features an application packet 30 extractor 70 which extracts the application data and commands from the USB application packets, such that application packet extractor 70 supports only application related packets. Next, any requests to USB flash device 46 by host platform 44 (not shown), in the form of read, write, identify 35 and erase commands, are interpreted by an application command interpreter 72. For any commands which involve data or an address, such as read, write and erase commands, an address resolve module 74 translates the address from the logical address space to the physical address space. Host 40 platform 44 (not shown) relates to a linear address space of logical addresses, while USB flash device 46 contains at least one, and preferably a plurality of, flash modules 58, each of which has a physical address space. Thus, a translation must be performed between the logical address space of host plat- 45 form 44 (not shown) and physical address space or spaces of USB flash device 46. There are many ways to implement such a translation which are suitable for the present invention. One example of a suitable implementation of an address translation method is described with regard to U.S. Pat. No. 5,404, 50 485, previously incorporated by reference as if fully set forth herein, which teaches a method for managing a flash memory as a flash disk and which is suitable for operation with the present invention.

A data handler **76** handles data related aspects of any 55 received commands, and conveying the data through functional interface **68** to and from flash module(s) **58**. Optionally and preferably, data handler **76** performs any error correction and detection methods. Application command interpreter **72**, data handler **76** and address resolve module **74** all operate 60 with an underlying Memory Technology Driver (MTD) **78** to write, read or erase a particular flash module **58** and the desired address on that flash module **58**.

Host platform 44 checks for status changes in USB flash device 46 and reads status packets from USB flash device 46 65 when a new status packet is available. Using these status packets, USB flash device 46 can transmit, to host platform

8

44, the results of different commands issued by host platform 44 in its requests (not shown). For example, the read command status packet contains one of the available status words such as "success", "error" or "invalid address", which enables host-platform 44 to determine the result of the read command (not shown). Similarly, the erase status packet contains a status word indicating the completion of the erase process. A write status packet is used by USB flash device 46 to notify host platform 44 about the result of the write command, for example whether the command was successful or erroneous, and whether USB flash device 46 is ready for additional write requests from host platform 44.

A Memory Technology Driver, or MTD 78 typically contains routines to read, write and erase the flash memory device controlled by the controller operating MTD 78. In addition, MTD 78 optionally contains an identification routine for recognizing the proper type of flash memory device for which MTD 78 was designed, so that the controller can determine which MTD should be activated upon interacting with a particular flash memory device array. In addition, an identification routine should be able to detect the size of the array of flash memory devices, including the number of flash memory devices within the array, and various features of the flash array geometry, such as interleaving and bus width. This information later enables host platform 44 platform to determine the address space and size of the storage media. U.S. Pat. No. 5,799,168, previously incorporated by reference, discloses an example of such an MTD for a flash device.

Using the above described protocol and architecture, host platform 44 can optionally implement any application which is implementable with any regular memory mapped or I/O mapped flash memory device. For example, host platform 44 can give a standard block device interface to each application, such as a magnetic storage medium "hard disk" drive, as disclosed in the previously described U.S. Pat. No. 5,404,485.

As an example of a preferred embodiment of the present invention, the operation of a host system connected to a USB flash device according to the present invention is described with regard to the processes of identifying, programming, reading and erasing the flash device. For the purposes of illustration only and without intending to be limiting in any way, the exemplary USB flash device has an array of two flash memory modules, each of which is 64 Mbit in size. The address translation table is within the flash device so that host platform operates with logical addresses. All commands and return codes between the flash device and the host platform are carried on USB data packets, and are transferred through USB data pipes. The exact structure of the packets, pipes and timings are described in the USB specification.

The operation of the exemplary device and system according to the present invention is as follows. When the USB flash device is first connected to the host platform, the USB host controller assigns an address to the USB flash device on the USB bus, and also assigns resources as described in the USB specification. The USB flash device actually asks the host platform to assign these resources, and must inform the host platform how much of these resources are needed. Thus, the USB flash disk can optionally support slower device speeds if the USB host platform has already allocated resources to other devices.

The USB controller also negotiates with the flash modules and determines the size and manufacturing type of these modules. The controller then builds an identification structure holding this information, as well as the translation table and logical address space.

After the USB host controller identifies the USB flash device, the host platform often uploads a USB client driver.

The driver issues an identification request command to the USB host controller, causing the controller to transmit an identification data packet 80, shown in FIG. 7. Identification packet 80 contains PID field 22 and checksum field 26, as described previously for background art FIG. 2. Identification packet 80 also contains an "identify" operation code in an operation code field 82. The packet extractor of the USB flash device receives identification data packet 80 and transfers the operating code of the "identify" command to the application command interpreter.

In response to the "identify" command, the flash device then sends an identification data packet **84**, shown in FIG. **8**. In addition to the fields shown in FIG. **7**, identification data packet **84** also contains information about the size of the flash device in a flash device size field **86**, as well as information 15 about the size of the minimal erase unit for erasing the flash memory in an erase unit size field **88**.

All of the packets described in this example are only data packets which are sent on the USB bus. Before each data packet is sent, a USB token packet is transmitted, instructing 20 the USB controller as to the identity of the device end point to which the data packet should be transmitted. Upon successful reception of the packet, the USB controller issues a USB ACK packet as described in the USB specification.

Once the device drivers in the host platform receive this 25 status packet, the drivers can start issuing read and write commands to the USB flash device with the application commands. When a write request is sent, a USB data packet with the operation code for the "write" command, and the buffer containing the data, is transferred to the USB flash device. A 30 write data packet 90 is shown in FIG. 9, which again includes the fields shown previously in FIG. 8, except that write data packet 90 also includes a write field 92 with the "write" operational code; an ADDR field **94** with the logical address to be written; a LEN field **96** with the length to be written; and 35 a DATA field **98** which contains the actual data to write. The packet extractor extracts the operational code from write data packet 90 and transfers this code to the application command interpreter. The logical address is transferred to the address resolve module which translates this logical address to a 40 physical address on one of the flash modules. The data handler optionally calculates error correction and detection mechanisms if employed by the USB flash device. Once all of the flash memory modules are ready, a "write" command is sent to the flash module or modules containing the physical 45 address, which may optionally span across more than one flash module to the MTD block. The MTD block then issues a "write" command on the data/address bus which connects the flash modules to the USB device controller. Once the operation is complete and a status packet is returned to the 50 MTD, the result of the operation is transmitted to the host controller and passed to the device driver in the host platform.

When the flash controller finishes the writing process, the controller signals to the host platform that the status of the USB flash memory device has changed, by sending a "write 55 status" packet 100, as shown in FIG. 10. In place of data field 98, write status packet 100 contains a status field 102. The host platform reads the status packets from the flash memory device, and from write status packet 100, the host platform retrieves information on the completion status of the write 60 command by reading status field 102. In this example, the flash memory device repeats ADDR field 94 and LEN field 96 in order for the host platform to have a reference to the specific command related to status packet 100.

As shown in FIG. 11, a "read request" packet 104 contains 65 the operation code for the "read" command in a read field 106, and the logical address of the desired location from which the

**10**

flash controller should read in an ADDR field 108. Upon receiving this command, the flash controller issues a read command to the MTD block, after the address resolve module has translated the address contained in ADDR field 108 to a specific physical address in one of the flash components.

When the flash controller receives the data from the flash device, either after the read command was issued, or if an error occurred, the flash controller sends a signal to the host platform to indicate that a new status packet must be read. The host platform issues a read request and receives a "read status" packet 110 as shown in FIG. 12. Read status packet 110 contains the address of the read data in ADDR field 108, as well as the length of the read data in a LEN field 112 and the data itself in a data field 114. Read status packet 110 also features the status word, according to which the operation was completed, in a status field 116. The read operation can be completed with many different status situations such as success, fail, error detected, invalid address, invalid length and so forth.

When the host platform needs to erase an erase unit in the flash device, the host platform issues an "erase request" packet 118, shown in FIG. 13. This packet contains the "erase" operation code in an erase field 120, and the logical address of the erase unit in an ADDR field 122. Upon receiving such a request, the flash controller translates the logical address to a physical erase unit address on one of the physical address spaces of the flash modules, and issues an erase command to the MTD block.

The erase process generally takes more time then a read or write process. When this erase process is finished, the controller notifies the host platform a new status packet is ready to transmit. The controller then transmits an "erase status" packet 124, as shown in FIG. 14. Erase status packet 124 contains the address of the erased unit in ADDR field 122, thereby providing the host platform with a reference to the erase requests. The status according to which the operation was completed is provided in a status field 126.

It will be appreciated that the above descriptions are intended only to serve as examples, and that many other embodiments are possible within the spirit and the scope of the present invention.

What is claimed is:

- [1. A USB flash memory device for connecting to a USB-defined bus, the flash memory device comprising:

- (a) at least one flash memory module for storing data;

- (b) a USB connector for connecting to the USB-defined bus and for sending packets on, and for receiving packets from, the USB-defined bus;

- (c) a USB controller for controlling said at least one flash memory module and for controlling said USB connector according to at least one packet received from the USBdefined bus, such that data is written to and read from said at least one flash memory module;

- (d) an electrical interface for connecting to said USB connector and for receiving said packets from said USB connector as a plurality of electrical signals;

- (e) a logical interface for connecting to said electrical interface and for translating said plurality of electrical signals to logic signals, said logic signals being passed to said at least one flash memory module;

- (f) a functional interface for receiving said logic signals such that if said logic signals represent a USB functional packet, said functional interface sends a USB command to said USB controller according to said USB functional packet;

- (g) an application packet extractor for connecting to said logical interface and for receiving said logic signals, said

- application packet extractor extracting at least one packet from said logic signals; and

- (h) an application command interpreter for receiving said at least one packet and for determining a command according to said at least one packet, said command 5 being passed to said USB controller.

- [2. The flash memory device of claim 1, further comprising:

- (i) an address resolver module for receiving said at least one packet and for resolving an address contained in said at least one packet, said address being sent to said USB controller, such that said command is performed according to said address.]

- [3. The flash memory device of claim 2, wherein said command is a write command for writing data to said at least one flash memory module and said address is a logical address for writing said data, such that said address resolver module resolves said logical address to a physical address of said at least one flash memory module.]

- [4. The flash memory device of claim 2, wherein said command is a read command for reading data from said a least one flash memory module and said address is a logical address for reading said data, such that said address resolver module resolves said logical address to a physical address of 25 said at least one flash memory module.]

- [5. The flash memory device of claim 2, further comprising:

- (j) a data handler for performing an error detection and correction routine for said at least one flash memory 30 module.]

- [6. The flash memory device of claim 5, further comprising:

- (k) a status handler for receiving said USB functional packet from said functional interface, and for sending a 35 further comprising: status packet concerning a status of said at least one flash memory module according to said USB functional packet. 1 13. The USB flast further comprising: a data handler for rection routine ule.

- [7. The flash memory device of claim 6, further comprising:

- (1) a MTD (memory technology driver) for receiving a write command and physical address of said at least one flash memory module, and for performing said write command to said physical address.]

- 8. A USB flash memory device for connecting to a USB- 45 defined bus, the flash memory device comprising:

- (a) at least one flash memory module;