#### US00RE42232E

# (19) United States

## (12) Reissued Patent

## Schmidt

## (10) Patent Number:

## US RE42,232 E

## (45) Date of Reissued Patent:

Mar. 22, 2011

| (34) | Kr           | <b>CHIPSE</b> | IAKCH | HILC | IUKL |

|------|--------------|---------------|-------|------|------|

| しンサル | <b>I/I</b> , |               |       |      |      |

| ()   |              |               |       |      |      |

Dominik J. Schmidt, San Francisco, CA Inventor:

(US)

Assignee: Intellectual Ventures I LLC,

Wilmington, DE (US)

Appl. No.: 11/376,700

Filed: Mar. 15, 2006

## Related U.S. Patent Documents

#### Reissue of:

(64)Patent No.: 6,710,424 Mar. 23, 2004 Issued: Appl. No.: 09/962,717 Sep. 21, 2001 Filed:

Int. Cl. (51)

> (2006.01)H01L 29/00 H01L 29/93 (2006.01)H04M 1/00

455/168.1

(58)257/601, 728; 438/51, 305; 455/552.1, 168.1 See application file for complete search history.

#### (56)**References Cited**

#### U.S. PATENT DOCUMENTS

| 4,325,180 A | A 4/1982  | Curran          |

|-------------|-----------|-----------------|

| 4,403,395 A | A 9/1983  | Curran          |

| 4,546,370 A | A 10/1985 | Curran          |

| 4,562,638 A | 1/1986    | Schwabe et al.  |

| 4,835,596 A | A 5/1989  | Werner          |

| 4,874,713 A | A 10/1989 | Gioia           |

| 4,956,311 A | A 9/1990  | Liou et al.     |

| 5,032,881 A | A 7/1991  | Sardo et al.    |

| 5,108,935 A | A 4/1992  | Rodder          |

| 5,275,961 A | A 1/1994  | Smayling et al. |

| 5,296,393 A | A 3/1994  | Smayling et al. |

| 5,334,870 A | A 8/1994  | Katada et al.   |

| 5,359,221 A | A 10/1994 | Miyamoto et al. |

| 5,389,809 A | A 2/1995  | Haken et al.    |

|             |           |                 |

| 5,407,844 | Α | 4/1995  | Smayling et al.   |

|-----------|---|---------|-------------------|

| 5,429,959 |   | 7/1995  | Smayling          |

| 5,432,114 |   | 7/1995  | O                 |

| 5,477,070 |   | 12/1995 | Nam               |

| 5,529,941 |   | 6/1996  | Huang             |

| 5,532,176 |   | 7/1996  | Katada et al.     |

| 5,554,871 |   | 9/1996  | Yamashita et al.  |

| 5,610,421 |   | 3/1997  | Contiero          |

| 5,623,159 |   | 4/1997  | Monk et al.       |

| 5,635,753 |   | 6/1997  | Hofflinger et al. |

| 5,648,286 |   | 7/1997  | Gardner et al.    |

| 5,677,224 |   | 10/1997 | Kadosh et al.     |

| 5,679,968 | A | 10/1997 | Smayling et al.   |

| 5,681,768 | A | 10/1997 | Smayling et al.   |

| 5,731,233 | A | 3/1998  | Yamashita et al.  |

| 5,736,418 | A | 4/1998  | Pasch et al.      |

| 5,744,372 | A | 4/1998  | Bulucea           |

| 5,753,556 | A | 5/1998  | Katada et al.     |

| 5,756,381 | A | 5/1998  | Buynoski          |

| 5,757,045 | A | 5/1998  | Tsai et al.       |

| 5,759,897 | A | 6/1998  | Kadosh et al.     |

| 5,770,464 | A | 6/1998  | Ryou              |

| 5,789,787 | A | 8/1998  | Kadosh et al.     |

| 5,811,341 | A | 9/1998  | Davies et al.     |

| 5,831,306 | A | 11/1998 | Gardner et al.    |

| 5,837,554 | A | 11/1998 | Contiero et al.   |

| 5,840,604 | A | 11/1998 | Yoo et al.        |

| 5,851,886 | A | 12/1998 | Peng              |

| 5,851,893 | A | 12/1998 | Gardner et al.    |

| 5,864,165 |   | 1/1999  | Rostoker et al.   |

| 5,879,999 | A | 3/1999  | Park et al.       |

| 5,898,235 | A | 4/1999  | McClure           |

|           |   |         |                   |

## (Continued)

Primary Examiner—Walter L. Lindsay, Jr.

#### (57)**ABSTRACT**

A set of radio frequency (RF) integrated circuits includes a transmit chip having a power amplifier and a receive chip adapted to work with the transmit chip. The receive chip has one or more low noise amplifiers to receive RF signals, and a processor coupled to the low noise amplifiers, the processor transmitting data through the transmit chip and receiving data from the on-chip low noise amplifiers.

## 20 Claims, 3 Drawing Sheets

# US RE42,232 E Page 2

| U.S.         | PATENT         | DOCUMENTS                   | 6,372,590 B1 | 4/2002  | Nayak et al.              |

|--------------|----------------|-----------------------------|--------------|---------|---------------------------|

| 5.004.520    | <b>5</b> /1000 | $\sim$ 1 $\cdot$ 1          | 6,376,870 B1 | 4/2002  | Carpenter, Jr. et al.     |

| 5,904,529 A  |                | Gardner et al.              | 6,376,891 B1 | 4/2002  | Nagatani et al.           |

| 5,918,137 A  |                | Ng et al.                   | 6,380,835 B1 | 4/2002  | Lee                       |

| 5,920,103 A  |                | Fulford et al.              | 6,400,001 B1 | 6/2002  | Manzini et al.            |

| 5,923,982 A  |                | Kadosh et al.               | 6,407,441 B1 | 6/2002  | Yuan                      |

| 5,925,913 A  | 7/1999         | -                           | 6,413,824 B1 | 7/2002  | Chatterjee et al.         |

| 5,939,751 A  | 8/1999         | 2                           | 6,417,054 B1 |         | Zheng et al.              |

| 5,969,394 A  |                | Gardner et al.              | 6,432,759 B1 | 8/2002  | •                         |

| 5,973,367 A  |                | Williams                    | 6,451,640 B1 |         | Ichikawa                  |

| 5,977,586 A  |                | Crisenza et al.             | 6,465,283 B1 |         | Chang et al.              |

| , ,          |                | Koizumi et al.              | 6,476,457 B2 | 11/2002 | •                         |

| 6,004,849 A  |                | Gardner et al.              | 6,477,606 B1 |         | Kawamura et al.           |

| 6,033,964 A  | 3/2000         | -                           | 6,483,157 B1 |         | Gardner et al.            |

| 6,057,582 A  | 5/2000         |                             | , ,          |         |                           |

| 6,069,031 A  | 5/2000         |                             | 6,484,038 B1 |         | Gore et al.               |

| 6,075,270 A  |                | Okihara et al.              | 6,492,671 B2 |         | Söderbårg                 |

| 6,078,080 A  |                | Kadosh et al.               | 6,504,218 B1 |         | Kadosh et al.             |

| 6,078,082 A  |                | Bulucea                     | 6,506,647 B2 |         | Kuroda et al.             |

| 6,087,198 A  |                | Panasik                     | 6,506,648 B1 |         | Hebert et al.             |

| 6,090,672 A  |                | Wanlass Decade at al        | 6,528,848 B1 |         | Hoshino et al.            |

| 6,125,268 A  |                | Boesch et al.               | 6,548,876 B2 | 4/2003  |                           |

| 6,127,700 A  |                | Bulucea<br>Variantita et al | 6,548,942 B1 |         | Panasik<br>Du et el       |

| 6,159,783 A  |                | Yamashita et al.            | 6,563,181 B1 |         | Du et al.                 |

| 6,168,999 B1 |                | Xiang et al.                | 6,566,185 B2 |         | Inoue et al.              |

| 6,172,400 B1 |                | Ng et al.                   | 6,576,966 B1 |         | Bulucea<br>Nagatari et al |

| 6,177,321 B1 | 1/2001         |                             | 6,596,575 B2 |         | Nagatani et al.           |

| 6,200,862 B1 |                | Gardner et al.              | 6,605,842 B2 |         | Hoshino et al.            |

| 6,222,229 B1 |                | Hebert et al.               | 6,627,507 B2 | 9/2003  |                           |

| 6,287,906 B1 |                | Yamashita et al.            | 6,627,992 B2 |         | Ammar                     |

| 6,297,535 B1 |                | Gardner et al.              | 6,642,543 B1 |         | El Gamal et al.           |

| 6,323,091 B1 |                | Lee et al.                  | 6,707,115 B2 |         | Schmidt                   |

| 6,346,728 B1 |                | Inoue et al.                | 6,709,940 B2 | 3/2004  |                           |

| 6,362,038 B1 | 3/2002         | Lee et al.                  | 6,710,424 B2 | 3/2004  | Schmidt                   |

FIG. 2

FIG. 3

F16. 4

#### RF CHIPSET ARCHITECTURE

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions 5 made by reissue.

#### BACKGROUND

This invention relates to the field of wireless integrated circuits.

The demand for low-cost, reliable wireless communications continues to increase at a rapid rate, as do the demands on the technologies enabling such communications. Chip designers work on many fronts to find ways to make the circuitry found inside devices such as cellular phones smaller, cheaper, easier to fabricate, less power-hungry, and more reliable.

One major component in a cellular phone is a radio frequency (RF) transceiver. U.S. Pat. No. 6,049,702 shows a block diagram of the RF/analog and analog/digital (A/D) interface circuitry of a basic transceiver, which can be combined with other components (not shown) to form a complete transceiver. The transmitter portion of the transceiver includes digital-to-analog converters (DACs), low-pass filters for filtering the outputs of DACs, respectively, and a modulator that performs a frequency conversion on signals received at its inputs and which is driven by a phase-locked loop (PLL) circuit that includes a reference voltage-controlled-oscillator (VCO) and a resonator (tank circuit). The modulator's output is fed to a power amplifier, and the amplified output is fed to one side of a transmit/receive (T/R) switch, filtered with a bandpass filter, and connected to an antenna.

The receiver portion is connected to the other side of T/R 35 switch. Incoming signals are received by the antenna and filtered by the bandpass filter before being fed to a low-noise amplifier (LNA)/demodulator circuit. The output of the circuit's LNA is passed through a bandpass filter before being fed to a demodulator which performs a frequency conversion 40 on the signal received by antenna. The demodulator is driven by a PLL circuit which includes a reference VCO and a tank circuit. The demodulator output drives an intermediatefrequency automatic gain control (IF AGC) stage, with a bandpass filter interposed between the stage's IF amplifier 45 and its AGC circuitry. The AGC output is fed to an IF demodulator which is driven by a PLL circuit that includes a reference VCO and a tank circuit. The IF demodulator's two outputs are passed through respective low-pass filters before being fed to respective analog-to-digital converters (ADCs). 50

Current RF transceivers are implemented using a variety of device technologies For example, DACs, ADCs, and all other digital baseband transceiver circuitry are typically CMOS circuits. The modulator, LNA/demodulator, IF/AGC stage, and IF demodulator generally use bipolar junction transistors (BJTs). The power amplifier can be fabricated on a gallium arsenide (GaAs) substrate, particularly for a high-power application such as a cellular phone Bandpass, low-pass filters, as well as tank circuits, and antenna are generally built with discrete components. T/R switch is also typically made from discrete components, or are made from costly, complex PIN diode circuits if integrated.

Because a variety of technologies must be combined, current transceivers typically requires multiple integrated circuits (IC). For example, a CDMA or WCDMA RF front end 65 typically consists of two ICs. There is a receive IC and a transmit IC, which need to be on separate pieces of silicon to

2

isolate the low power received signal (around 10 mW) from the high power send signal (around 300 mW). With a processor IC to control the RF front-end, the electronic of an RF system requires three chips: a processor IC, a receive IC, and a transmit IC. These ICs add cost and can result in an assembly is typically larger than is desired, particularly when the limited space and weight requirements imposed on designers of battery-powered handheld devices must be met.

#### **SUMMARY**

In one aspect, a set of radio frequency (RF) integrated circuits includes a transmit chip having a power amplifier and a receive chip adapted to work with the transmit chip. The receive chip has one or more low noise amplifiers to receive RF signals, and a processor coupled to the low noise amplifiers, the processor transmitting data through the transmit chip and receiving data from the on-chip low noise amplifiers.

In another aspect, a radio frequency transceiver system includes a transmit chip; and a receive chip having a transistor device. The transistor device includes a layer of gate oxide on a surface of the semiconductor substrate, a gate electrode formed on the surface of the gate oxide, the gate electrode having a drain side; a p-well implanted within a semiconductor substrate under the gate electrode; an n-well implanted in the p-well on the drain side; an n+ source region in the p-well outside of the n-well; an n+ drain region within the substrate inside the n-well; and lightly doped regions extending respectively from the source and drain regions toward the gate electrode.

Implementations of the device may include one or more of the following. The n-well extends slightly under the gate electrode. The p-well is deeper than the n-well. A second device can be fabricated adjacent the first device with a second gate electrode formed on the surface of the gate oxide; a second n-well implanted within a semiconductor substrate under the second gate electrode; a p+ source region in the second n-well; and a p+ drain region within the substrate inside the second n-well The second n-well is adjacent the p-well. The first and second n-wells are formed at the same time. The device can be used in digital circuits that operate next to sensitive analog circuits such as CMOS imaging elements, precision analog-digital converters, or radio frequency circuits

In another aspect, a method for manufacturing a two-chip radio frequency transceiver system with a receive chip having a transistor device. The transistor device a metal oxide semiconductor transistor device includes implanting a p-well in a substrate; implanting an n-well in the p-well; growing a gate oxide above the p-well; forming a polysilicon layer on the gate oxide; implanting a p+ region in the substrate; and implanting an n+ region in the substrate.

Implementations of the above aspect may include one or more of the following. The method includes forming lightly doped regions extending respectively from the source and drain regions toward the gate electrode. The method also includes forming an isolation layer between the substrate and the gate oxide. The method includes patterning the polysilicon layer. The method also includes patterning the p+region and the n+ region. The method forms robust devices that can used in digital circuitry adjacent analog circuitry. The analog circuit can be imaging elements, analog to digital converters or a radio frequency circuits, among others.

Advantages of the device can include one or more of the following. The system is a 2 chip solution instead of a 3 chip solution, saving weight, cost, and board real-estate. These

advantages are important for mobile applications such as handheld computers and cellular telephones, among others. The baseband chip has several process steps that can be used to enhance the performance of a low-power RF detector. For example, as discussed below, the circuits use implants that 5 can reduce hot electrons, and also a very thin oxide layer that can be used to make low voltage high performance transistors. The system also uses reliable and inexpensive MOS-FETs. The MOSFETs can be used in mixed-mode integrated circuits (ICs) that include both digital and analog circuits on 1 a single chip. The device reduces the magnitude of electric field seen along the channel near the drain of an MOS device, especially in digital transistors which switch at high frequency. The device also avoids the hot electron injection problem without creating sharp curvatures on the junction 15 mit chip 10. and without an additional long drive-in time that can cause undesired thermal effects in the other parts of the device. The resultant low junction curvature increases the breakdown voltage, making it possible to operate the transistor at higher biases without catastrophic failure. The inventive pro- 20 cess also forms source/drain regions having low series resistance and a large junction radius, and which does not require additional masking or heating steps.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The following detailed description of the embodiments can best be understood when read in conjunction with the following drawings, in which:

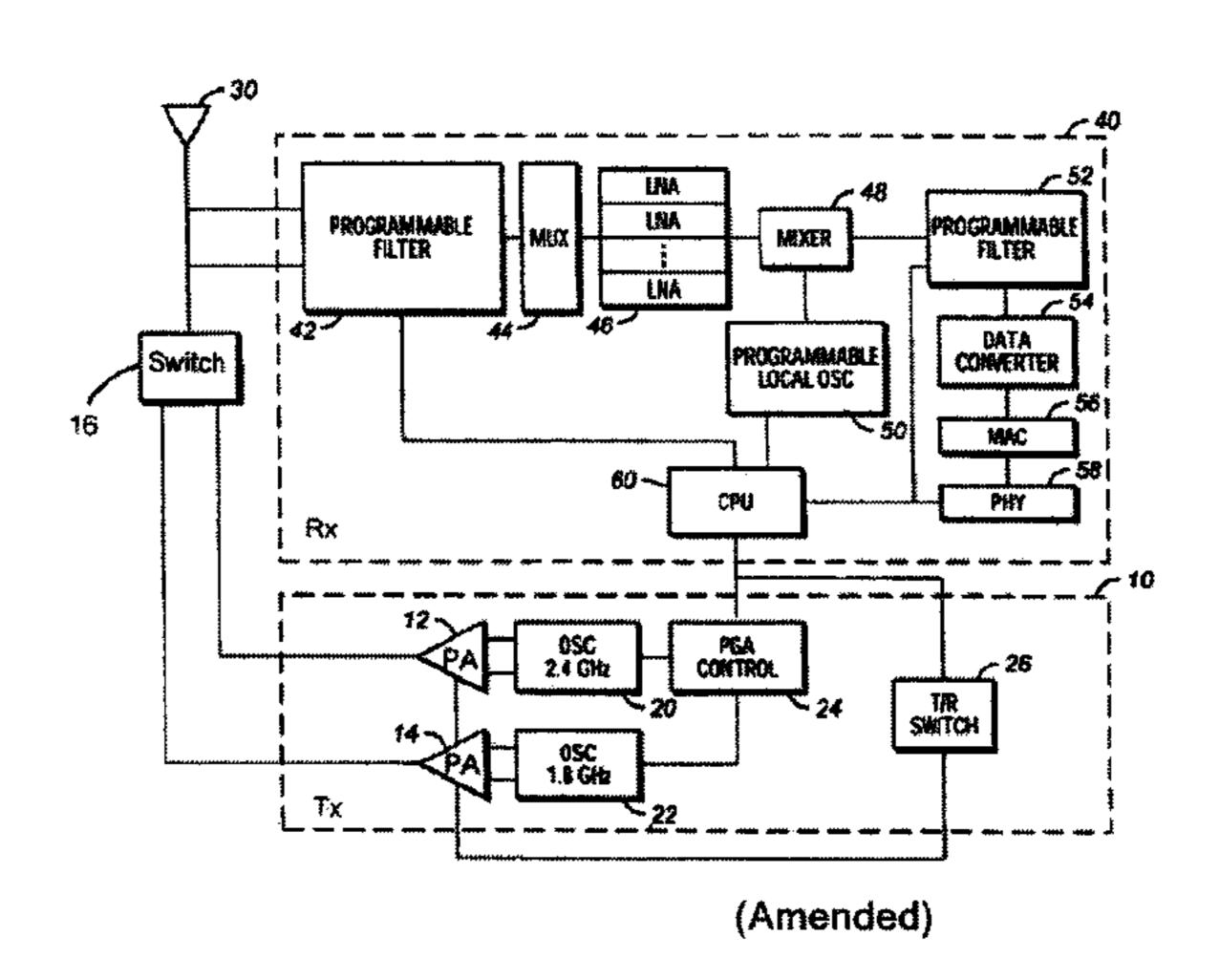

FIG. 1 shows a two chip set of radio frequency (RF) integrated circuits.

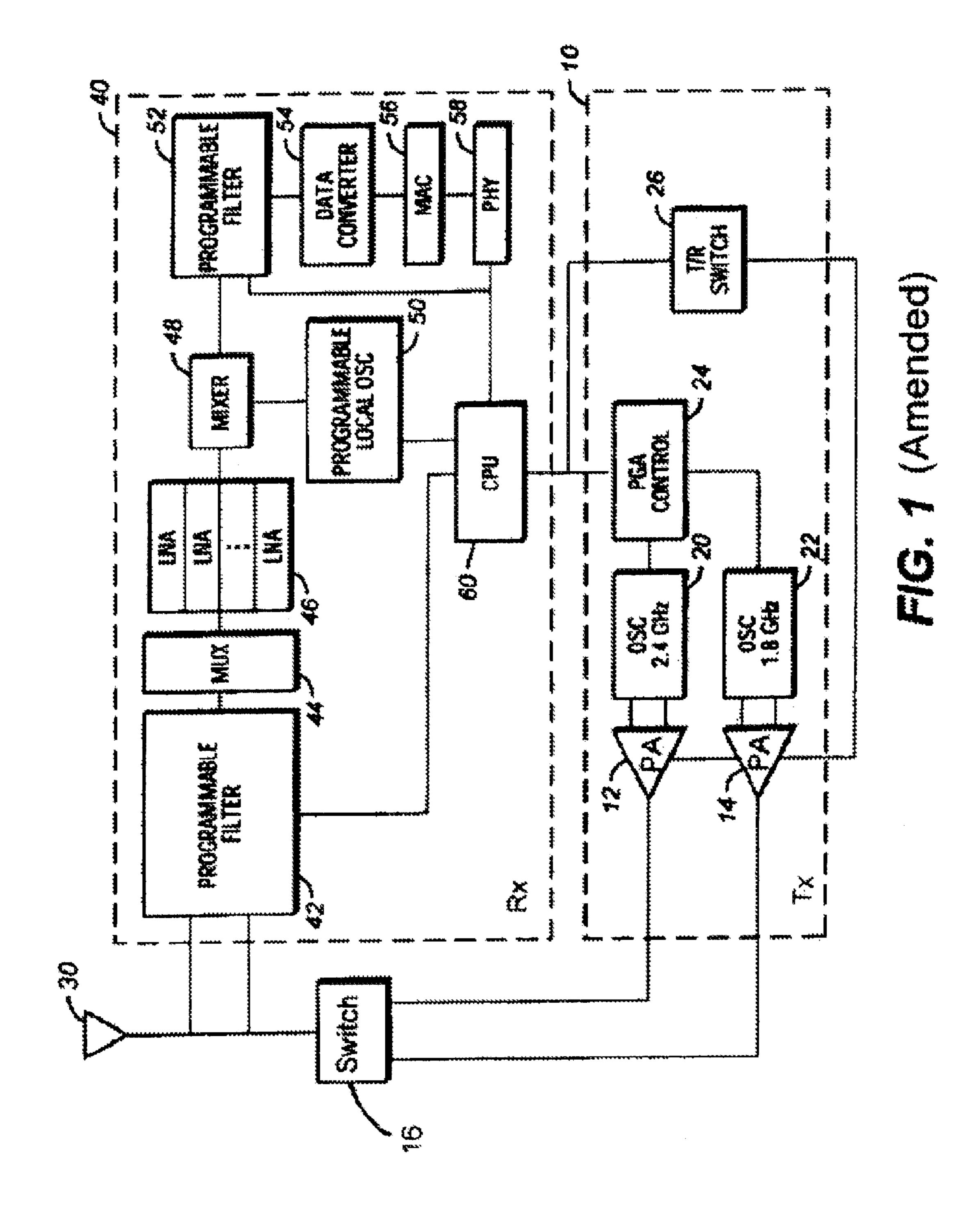

FIG. 2 illustrates an exemplary completed MOSFET structure.

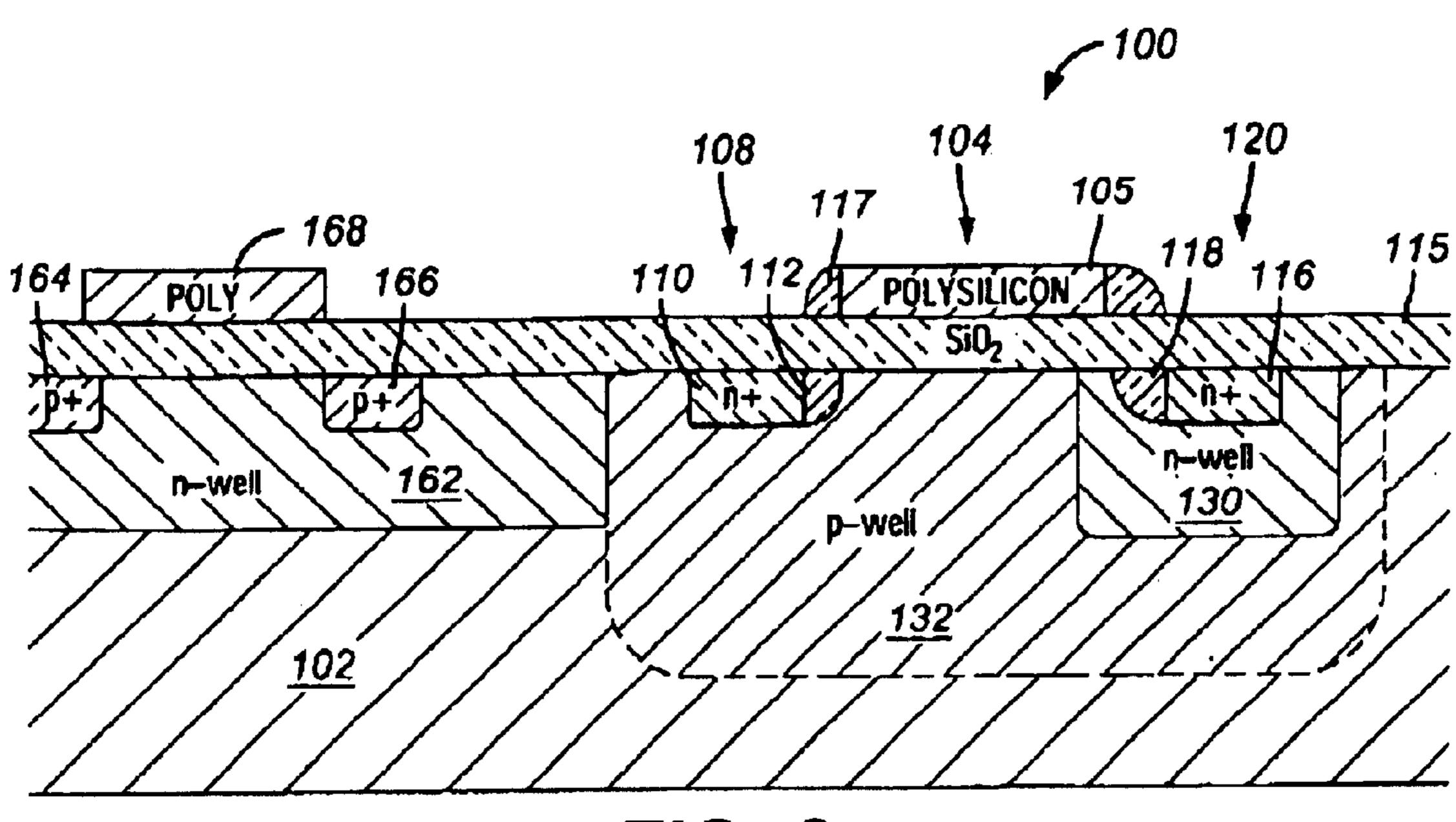

FIG. 3 shows an exemplary process for making an MOS-FET with a highly scalable conduction channel length.

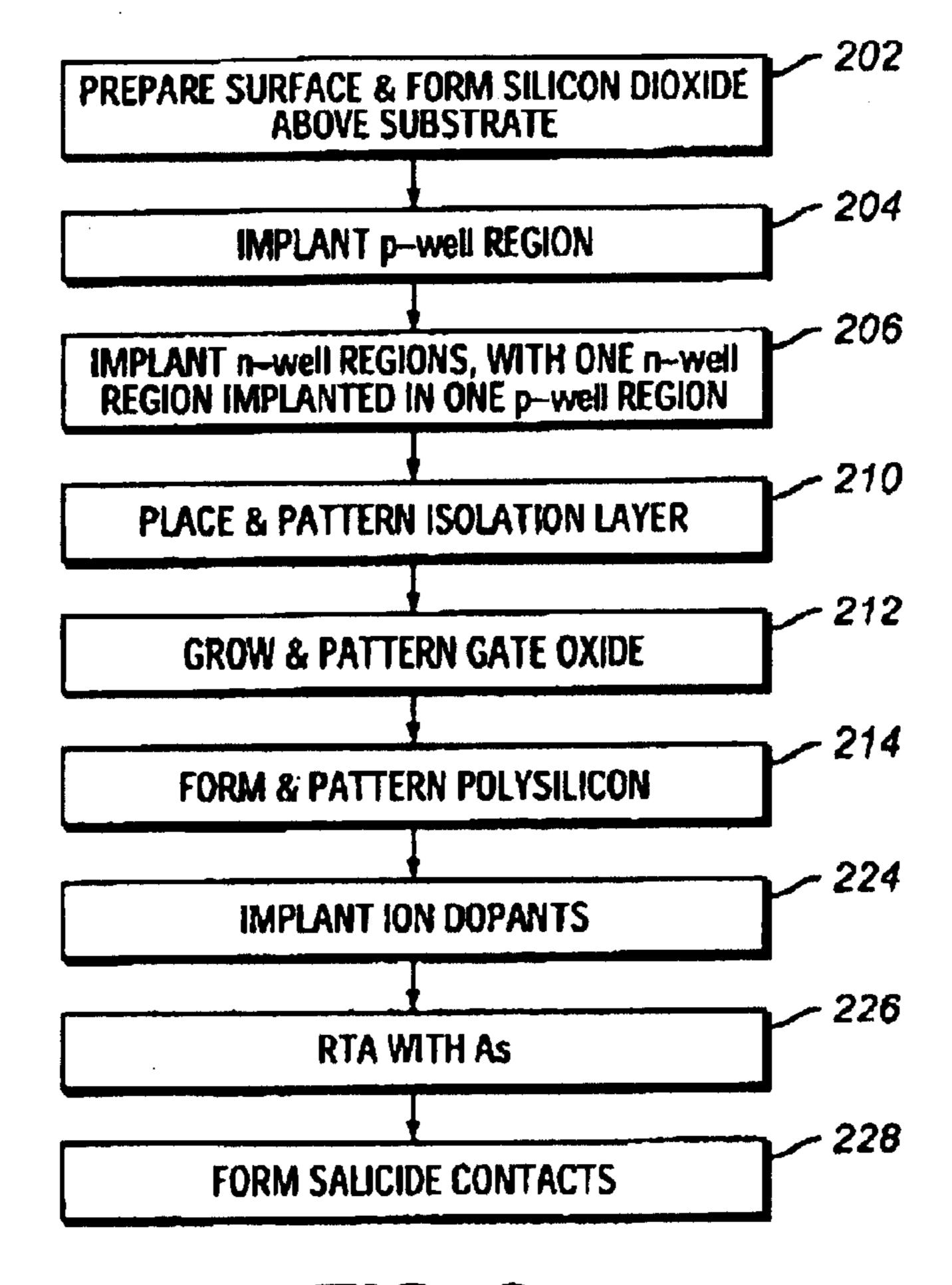

FIG. 4 is a block diagram of a portable appliance using the transistor of FIG. 2.

#### DESCRIPTION

In the following detailed description of the preferred embodiments, reference is made to the accompanying drawings which form a part hereof, and in which are shown by way of illustration specific embodiments in which the invention may be practiced. It is to be understood that other embodiments may be utilized and structural changes may be made without departing from the scope of the present invention.

In one embodiment, an RF transceiver solution is provided using only two chips: one chip (transmit chip) contains high power transmit circuitry, while the second chip (baseband chip) contains low power RF signal receive/sense circuit, a digital processor and related logic circuits.

FIG. 1 shows a two chip set of radio frequency (RF) integrated circuits includes a transmit chip 10 having power 55 amplifiers 12 and 14 whose outputs are connected to an antenna switch 16 that in turn is connected to an antenna 30. The power amplifiers 12 and 14 are connected to oscillators 20 and 22 that provide RF signals for each RF protocol that the transmitter handles. For instance, a 2.4 GHz oscillator is 60 used as the oscillator 20, while a 1.8 GHz oscillator is used as the oscillator 22. The oscillators 20 and 22 in turn is controlled by a programmable gain adjustment (PGA) circuit 24. The power amplifiers 12 and 14 are also enabled or disabled by a transmit/receive switch 26. The PGA 24 and 65 the switch 26 are connected to a processor 60 in a receive chip 40.

4

The receive chip 40 is adapted to work with the transmit chip. The receive chip 40 receives signals from the antenna 30 through a digitally programmable filter 42 The output of the filter 42 is provided to a multiplexer switch 44. The RF signal is routed through the multiplexer switch 44 to one or more low noise amplifiers 46, whose outputs are provided to a mixer 48. The mixer receives reference signals from a programmable local oscillator 50. The output of the mixer 48 is provided to a second digitally programmable filter 52 and is digitized by a data conversion circuit 54. The digitized signal is provided to a MAC 56 and a PHY 58. The PHY 58 in turn communicates with the processor 60 The processor 60 is connected to all blocks on the receive chip 40 and to the PGA circuit 24 and transmit receive switch 26 on the transmit chip 10.

One embodiment uses CMOS transistors which at 0.1 um are reaching Q factors of 10 or more, so good resonators can be built with these transistors. The baseband chip has several process steps that can be used to enhance the performance of a low-power RF detector. For example, as discussed below, the circuits use implants that can reduce hot electrons, and also a very thin oxide layer that can be used to make low voltage high performance transistors. The end result is a 2 chip solution instead of a 3 chip solution.

FIG. 2 illustrates one FET of a large scale integrated circuit fabricated in accordance with the process of the present invention, the FET device being generally identified by the reference numeral 100. The substrate region 102 of the device is a silicon material lightly doped with a p-type material, such as boron, and designated as a p-substrate. A gate 104 is separated from the silicon substrate 102 by a layer of silicon dioxide 1115. A channel region above the p-substrate region 102 and below the gate 104 is slightly more heavily doped p-type material than substrate 102 and is designated as a p-well 132. A source 108 and drain 120 are formed by heavily doping a region of the p-well 132 on opposite sides of the gate 104 with an n-type material and designated as a n+ regions 110 and 116. Lightly doped drain (LDD) structures 112 and 118, created by implanting shallow n-, forming oxide spacers 117 adjacent to the polysilicon layer 105, and implanting the n+. The n+ region 116 and its LDD structure 118 are placed in an n-well 130. The n-well 130 in turn is positioned in a p-well 132. The n+ region 110 and its LDD 112 are also positioned in the p-well **132**. This device is known as an NMOS device and it is this device that suffers from hot electron injection.

The p-well 132 is adjacent to an n-well 162, which contains two p+ regions 164 and 166. A polysilicon layer 168 is deposited above the silicon dioxide layer 115 to form a gate. The layer of polysilicon material is next implanted with phosphorous, an N-type material. The layer of polysilicon material implanted with phosphorous is then oxidized with a layer of silicon dioxide. This device is commonly known as a PMOS device, and it typically does not suffer from hot electron problems.

FIG. 3 shows an exemplary method 200 for fabricating the FET of FIG. 2. First, the silicon surface is prepared and the layer of silicon dioxide 115, approximately 80 angstroms thick, is grown atop the substrate 102 (step 202). Next, p-well regions are implanted (step 204). Next, n-well regions are implanted in the surface (step 206). In particular, the p-well regions are deeper than the n-well regions and one n-well region is implanted within one of the p-well regions.

An isolation layer is placed and patterned (step 210). A gate oxide is grown and patterned (step 212). The gate oxide layer 115 can be formed through any suitable process, such

as by chemical vapor deposition (CVD). In an alternative embodiment, the gate oxide is thermally grown on the substrate 102. Next, the polysilicon layer 115 is formed and patterned (step 214). The layer of undoped polysilicon is deposited on the top surface of gate oxide 104 and can be 5 deposited by any suitable method, such as by CVD. The upper surface of the structure can be planarized through chemical mechanical polishing (CMP). The patterning process involves photoresist is deposited as a continuous layer on polysilicon and selectively irradiated using a photolitho-graphic system, such as a step and repeat optical projection 10 system, in which I-line ultraviolet light from a mercuryvapor lamp is projected through a first reticle and a focusing lens to obtain an image pattern. Thereafter, the photoresist is developed and the irradiated portions of the photoresist are removed to provide openings in photoresist. The openings 15 expose portions of polysilicon layer to an etch, thereby defining a gate region. An anisotropic etch is applied that removes the exposed portions of polysilicon 105. Various etchants can be used to anisotropically etch or to selectively remove the polysilicon and oxide layers. After the etching 20 step or steps, the gate region 104 remains. The gate region 104 includes: the polysilicon layer 105 on top of the gate oxide 115 on top of the substrate 102. The photoresist is stripped, using conventional photoresist stripping techniques.

The source region 108 and a drain region 120 are provided by implanting ion dopants into the top of the substrate 102 (step 224). The ion implantation uses conventional ion implanting techniques. In one embodiment, the source and drain LDD regions 112 and 118 respectively, include the phosphorous-doped silicon material. The gate 104 behaves as an implant mask and provides for self-aligned source and drain LDD regions, 112 and 118 respectively. The p+ region is also placed using conventional process.

less system it encounter 390 performs the switch keeps track of the addres The router 390 can send more separate pathways. The reconfigurable prolar radio core 310 and the core 330 to provide a served circuit that operations.

Next, a high temperature rapid thermal anneal (RTA) is conducted in the presence of Arsenic (As) gas (step 226). This process cures out the crystal damage induced by the previous ion implant process. Additionally, the annealing step is performed in the presence of As gas. The presence of the As gas causes an additional doping implantation into the substrate 102. An oxide layer is subsequently deposited and etched anisotropically, resulting in spacers 117 next to the poly gate 105. The n+ source/drain regions 110 and 116, are formed in the pwell 132, next to the spacers 117, in the region where the gate oxide 115 has been etched back These highly doped regions form electrical connections to the 45 drain/source electrodes, 108 and 120 respectively.

Next, salicide contacts are formed on the gate 104, source 108, drain 120 and lightly doped regions 112 and 118 (step 228). Additionally contact formation, not included here, is achieved using conventional techniques. These further processing steps are not repeated herein. Likewise, the principal processing steps disclosed herein may be combined with other steps apparent to those skilled in the art.

The application of the extra nwell region around the drain of the NMOS transistor reduces hot electron effects by 55 reducing the electric field in the pinch-off region. The electric field is proportional to the voltage drop across the pinch-off region divided by the length of the pinch-off region. The nwell region extends laterally with a smooth decrease in doping, so that part of the drain voltage is dropped across the 60 nwell region. Also, the pinchoff region is extended somewhat because the channel is counterdoped, resulting in lower doping in the pinchoff area, which in turn increases the pinchoff length. The field is therefore significantly reduced, and since the hot electron current depends exponentially on the 65 field, there is a very large corresponding decrease in this current.

6

Thus the invention provides a method and structure for a transistor whose gate is protected from "hot electron injection." Advantageously, the transistor is well-suited for use in a device such as a mixed signal integrated circuit chip, as well as an electronic system including a processor/memory and analog components such as A/D and D/A converters, imagers and RF circuits. The electronic system may also be a portable appliance as shown in FIG. 4. The information handling system [200] deploys transistor devices formed as discussed above. The device has a fast and reliable channel having a long life.

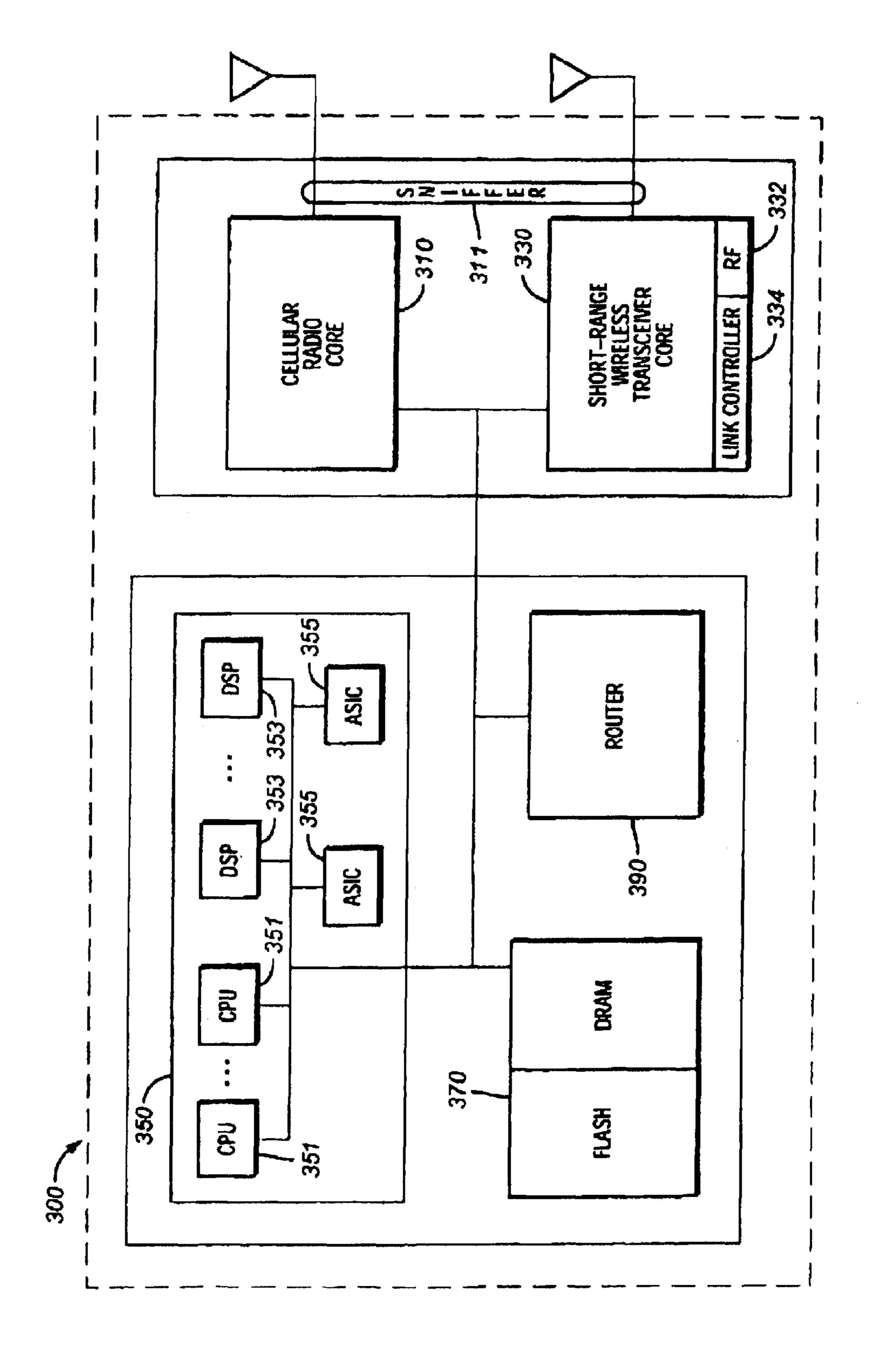

FIG. 4 shows a block diagram of a multi-mode wireless communicator device 300 fabricated on a single silicon integrated chip. In one implementation, the device 300 is an integrated CMOS device with an A/D converter, radio frequency (RF) circuits, including a cellular radio core 310, a short-range wireless transceiver core 330, and an RF sniffer 311, along side digital circuits, including a reconfigurable processor core 350, a high-density memory array core 370, and a router 390. The high-density memory array core 370 can include various memory technologies such as flash memory and static random access memory (SRAM), among others, on different portions of the memory array core. Through the router **390**, the multi-mode wireless communi-25 cator device 300 can detect and communicate with any wireless system it encounters at a given frequency. The router 390 performs the switch in real time through an engine that keeps track of the addresses of where the packets are going. The router **390** can send packets in parallel through two or

The reconfigurable processor core **350** controls the cellular radio core **310** and the short-range wireless transceiver core **330** to provide a seamless dual-mode network integrated circuit that operates with a plurality of distinct and unrelated communications standards and protocols such as Global System for Mobile Communications (GSM), General Packet Radio Service (GPRS), Enhance Data Rates for GSM Evolution (Edge) and Bluetooth<sup>TM</sup>. The cell phone core **310** provides wide area network (WAN) access, while the short-range wireless transceiver core **330** supports local area network (LAN) access. The reconfigurable processor core **350** has embedded read-only-memory (ROM) containing software such as IEEE802.11, GSM, GPRS, Edge, and/or Bluetooth<sup>TM</sup> protocol software, among others.

In one embodiment, the cellular radio core 310 includes a transmitter/receiver section that is connected to an off-chip antenna (not shown). The transmitter/receiver section is a direct conversion radio that includes an I/Q demodulator, transmit/receive oscillator/clock generator, multi-band power amplifier (PA) and PA control circuit, and voltagecontrolled oscillators and synthesizers. In another embodiment of transmitter/receiver section 312, intermediate frequency (IF) stages are used. In this embodiment, during cellular reception, the transmitter/receiver section converts received signals into a first intermediate frequency (IF) by mixing the received signals with a synthesized local oscillator frequency and then translates the first IF signal to a second IF signal. The second IF signal is hard-limited and processed to extract an RSSI signal proportional to the logarithm of the amplitude of the second IF signal. The hardlimited IF signal is processed to extract numerical values related to the instantaneous signal phase, which are then combined with the RSSI signal.

For voice reception, the combined signals are processed by the processor core 350 to form PCM voice samples that are subsequently converted into an analog signal and provided to an external speaker or earphone. For data reception,

the processor simply transfers the data over an input/output (I/O) port. During voice transmission, an off-chip microphone captures analog voice signals, digitizes the signal, and provides the digitized signal to the processor core **350**. The processor core **350** codes the signal and reduces the bit-rate for transmission. The processor core **350** converts the reduced bit-rate signals to modulated signals, for example. During data transmission, the data is modulated and the modulated signals are then fed to the cellular telephone transmitter of the transmitter/receiver section.

Turning now to the short-range wireless transceiver core 330, the short-range wireless transceiver core 330 contains a radio frequency (RF) modem core 332 that communicates with a link controller core 334. The processor core 350 controls the link controller core 334. In one embodiment, the RF modem core 332 has a direct-conversion radio architecture with integrated VCO and frequency synthesizer. The RF-unit 332 includes an RF receiver connected to an analog-digital converter (ADC), which in turn is connected to a modem 316 performing digital modulation, channel filtering, AFC, symbol timing recovery, and bit slicing operations. For transmission, the modem is connected to a digital to analog converter (DAC) that in turn drives an RF transmitter.

According to one implementation, when the short-range wireless core 330 in the idle mode detects that the short-range network using Bluetooth<sup>TM</sup> signals, for example, have dropped in strength, the device 300 activates the cellular radio core 310 to establish a cellular link, using information from the latest periodic ping. If a cellular connection is established and Bluetooth<sup>TM</sup> signals are weak, the device 300 sends a deregistration message to the Bluetooth<sup>TM</sup> system and/or a registration message to the cellular system. Upon registration from the cellular system, the short-range transceiver core 330 is turned off or put into a deep sleep mode and the cellular radio core 310 and relevant parts of the synthesizer are powered up to listen to the cellular channel.

The router 390 can send packets in parallel through the separate pathways of cellular or Bluetooth<sup>TM</sup>. For example, if a Bluetooth<sup>TM</sup> connection is established, the router **390** knows which address it is looking at and will be able to 40 p-well. immediately route packets using another connection standard. In doing this operation, the router 390 pings its environment to decide on optimal transmission medium. If the signal reception is poor for both pathways, the router 390 can send some packets in parallel through both the primary 45 and secondary communication channel (cellular and/or Bluetooth<sup>TM</sup>) to make sure some of the packets arrive at their destinations. However, if the signal strength is adequate, the router 390 prefers the Bluetooth<sup>TM</sup> mode to minimize the number of subscribers using the capacity-limited and more 50 expensive cellular system at any give time. Only a small percentage of the device 300, those that are temporarily outside the Bluetooth coverage, represents a potential load on the capacity of the cellular system, so that the number of mobile users can be many times greater than the capacity of 55 the cellular system alone could support. All the above implementations have circuits combining low noise devices with high-speed, high-noise digital transistors on the same silicon substrate By using the present invention on the digital transistors closest to the low-noise sections, the impact of the 60 generated noise can be greatly reduced.

Although specific embodiments have been illustrated and described herein, it is appreciated by those of ordinary skill in the art that any arrangement which is calculated to achieve the same purpose may be substituted for the specific 65 embodiments shown. This application is intended to cover any adaptations or variations of the present invention.

8

Therefore, it is manifestly intended that this invention be limited only by the claims and the equivalents thereof.

What is claimed is:

1. A radio frequency transceiver system, comprising:

a transmit chip; and

- a receive chip adapted to be coupled to [the] a transmit chip, the receive chip having a transistor device comprising:

- a layer of gate oxide on a surface of [the] a semiconductor substrate;

- a gate electrode formed on the surface of the gate oxide, the gate electrode having a drain side;

- a p-well implanted within [a] *the* semiconductor substrate under the gate electrode;

- an n-well implanted in the p-well on the drain side;

- an n+ source region in the p-well outside of the n-well; and

- an n+ drain region within the substrate inside the n-well.

- 2. The system of claim 1, wherein the n-well extends [slightly] under at least a portion of the gate electrode.

- 3. The system of claim 1, further comprising [digital] analog circuitry positioned adjacent to the transistor device.

- 4. The system of claim 1, wherein the p-well is deeper than the n-well.

- 5. The system of claim 1, further comprising a second *transistor* device, comprising:

- a second gate electrode formed on the surface of the gate oxide;

- a second n-well implanted within [a] *the* semiconductor substrate under the second gate electrode;

- a p+ source region in the second n-well; and

- a p+ drain region within the *semiconductor* substrate inside the second n-well.

- 6. The system of claim 5, wherein the second n-well is adjacent to the p-well.

- 7. The system of claim [1] 5, wherein the [first and] second n-well[s are formed at the same time] is adjacent to the p-well.

- 8. The system of claim 1, wherein the device is *configured* to be used in a digital circuit adjacent to a CMOS imaging element.

- 9. The system of claim 1, wherein the device is *configured* to be used in a digital circuit adjacent to a data converter.

- 10. The system of claim 1, wherein the device is *configured to be* used in a digital circuit adjacent to a radio frequency circuit.

- 11. A set of radio frequency (RF) integrated circuits, including:

- a transmit chip[comprising a power amplifier]; and

- a receive chip [adapted] *configured* to be coupled to the transmit chip, comprising:

- one or more low noise amplifiers to receive RF signals[, ]; and

- a processor coupled to the *one or more* low noise amplifiers, the processor *configured to* [transmitting] *transmit* data through the transmit chip and [receiving] *receive* data from the *one or more* on-chip low noise amplifiers.

- 12. The set of claim 11, wherein the receive chip further comprises a digitally programmable filter coupled to each low noise amplifier.

- 13. The set of claim 11, further comprising a mixer coupled to each low noise amplifier.

- 14. The set of claim 11, further comprising a programmable local oscillator coupled to the processor.

- 15. The set of claim 11, further comprising:

- a PHY coupled to the processor; and

- a MAC coupled to the PHY.

- 16. The set of claim 11, wherein the transmit chip further comprises a programmable gain adjustment (PGA) circuit coupled to the processor [on the receive chip].

- 17. A system comprising:

- an integrated circuit having an analog portion and a digital portion integrated on a substrate, the analog portion  $_{10}$  including:

- a cellular radio core; and

- a short-range wireless transceiver core coupled to the cellular radio core;

wherein the digital portion includes:

a reconfigurable processor core coupled to the cellular radio core and the short-range wireless transceiver core, wherein the reconfigurable processor core is configured to control the cellular radio core and the short-range wireless transceiver core; and 10

wherein at least the digital portion includes a device having a gate electrode formed on the substrate, and wherein the gate electrode has a drain side, a p-well implanted within the substrate under the gate electrode, an n-well implanted in the p-well on the drain side, an n+ source region in the p-well outside of the n-well, and an n+ drain region in the n-well.

- 18. The system of 17, wherein the integrated circuit further comprises a radio frequency (RF) sniffer.

- 19. The system of claim 17, wherein the digital portion further comprises a memory comprising a volatile portion and a non-volatile portion.

- 20. The system of claim 17, wherein the reconfigurable processor core comprises a read only memory (ROM) having stored thereon code executable by the reconfigurable processor core to implement multiple wireless protocols usable to control the cellular radio core and the short-range wireless transceiver core.

\* \* \* \* :

## UNITED STATES PATENT AND TRADEMARK OFFICE

## CERTIFICATE OF CORRECTION

PATENT NO. : RE42,232 E Page 1 of 1

APPLICATION NO. : 11/376700 DATED : March 22, 2011

time] is adjacent to the p-well.] --

INVENTOR(S) : Schmidt

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

Column 8, lines 38-40, delete "7. The system of claim [1] 5, wherein the [first and] second n-well[s are formed at the same time] *is adjacent to the p-well*." and insert -- [7. The system of claim [1] 5, wherein the [first and] second n-well[s are formed at the same

Signed and Sealed this Twenty-first Day of February, 2012

David J. Kappos

Director of the United States Patent and Trademark Office