US00RE41969E

# (19) United States

# (12) Reissued Patent

Tanaka et al.

# (10) Patent Number: US RE41,969 E

(45) Date of Reissued Patent: Nov. 30, 2010

## (54) MULTI-STATE EEPROM HAVING WRITE-VERIFY CONTROL CIRCUIT

(75) Inventors: Tomoharu Tanaka, Yokohama (JP);

Gertjan Hemink, Kawasaki (JP)

(73) Assignee: Kabushiki Kaisha Toshiba,

Kawasaki-shi (JP)

(21) Appl. No.: 11/451,592

(22) Filed: **Jun. 13, 2006**

## Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 5,570,315

Issued: Oct. 29, 1996

Appl. No.: 08/308,534

Filed: Sep. 21, 1994

U.S. Applications:

(62) Division of application No. 09/134,897, filed on Aug. 17, 1998.

# (30) Foreign Application Priority Data

| Sep. 21, 19 | 993 (J | P) |       | 5-234767 |

|-------------|--------|----|-------|----------|

| Dec. 13, 19 | 993 (J | P) | ••••• | 5-311732 |

(51) **Int. Cl.**

*G11C 16/34* (2006.01) *G11C 16/24* (2006.01)

See application file for complete search history.

# (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,279,024 | A | 7/1981  | Schrenk         |

|-----------|---|---------|-----------------|

| 5,168,465 | A | 12/1992 | Harari          |

| 5,172,338 | A | 12/1992 | Mehrotra et al. |

| 5,218,569 A<br>5,321,699 A | 6/1993<br>6/1994 | Banks<br>Endoh et al. |

|----------------------------|------------------|-----------------------|

| 5,394,362 A                | 2/1995           | Banks                 |

| 5,521,865 A                | 5/1996           | Ohuchi et al.         |

| 5,652,719 A                | 7/1997           | Tanaka et al.         |

| 5,781,478 A                | 7/1998           | Takeuchi et al.       |

| 5,920,507 A                | 7/1999           | Takeuchi et al.       |

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

DE 42 32 025 4/1993

(Continued)

#### OTHER PUBLICATIONS

F. Masuoka, Kabushiki–Kaisha Science Forum, pp. 186–190, "Flash Memory Technology Handbook" Aug. 15, 1993.

Primary Examiner—Andrew Q Tran (74) Attorney, Agent, or Firm—Oblon, Spivak, McClelland, Maier & Neustadt, L.L.P.

# (57) ABSTRACT

An EEPROM having a memory cell array in which electrically programmable memory cells are arranged in a matrix and each of the memory cells has three storage states, includes a plurality of data circuits for temporarily storing data for controlling write operation states of the plurality of memory cells, a write circuit for performing a write operation in accordance with the contents of the data circuits respectively corresponding to the memory cells, a write verify circuit for confirming states of the memory cells set upon the write operation, and a data updating circuit for updating the contents of the data circuits such that a rewrite operation is performed to only a memory cell, in which data is not sufficiently written, on the basis of the contents of the data circuits and the states of the memory cells set upon the write operation. A write operation, a write verify operation, and a data circuit content updating operation based on the contents of the data circuits are repeatedly performed until the memory cells are set in predetermined written states.

#### 2 Claims, 29 Drawing Sheets

# US RE41,969 E Page 2

|     | U.S. PATENT DOCUMENTS                           | JP      | 3-59886     | 3/1991  |

|-----|-------------------------------------------------|---------|-------------|---------|

|     |                                                 | JP      | 3-237692    | 10/1991 |

|     | 6,038,180 A * 3/2000 Hoshi                      | JP      | 3-286497    | 12/1991 |

|     | 6,069,823 A 5/2000 Takeuchi et al.              | JP      | 4-88671     | 3/1992  |

|     | 6,147,911 A 11/2000 Takeuchi et al.             | JP      | 4-119594    | 4/1992  |

|     | 7,394,695 B2 * 7/2008 Takeuchi et al 365/185.17 | JP      | 4-254994    | 9/1992  |

|     |                                                 | JP      | 4-507320    | 12/1992 |

|     | FOREIGN PATENT DOCUMENTS                        | JP      | 5-6681      | 1/1993  |

| *** |                                                 | JP      | 5-144277    | 6/1993  |

| JР  | 58-86777 5/1983                                 | JP      | 5-182476    | 7/1993  |

| JР  | 62-257699 11/1987                               | JP      | 5-60199     | 9/1993  |

| JP  | 1-23878 5/1989                                  | JP      | 2007-184102 | 7/2007  |

| JР  | 1-46949 10/1989                                 | JP      | 2007-184103 | 7/2007  |

| JР  | 2-232900 9/1990                                 |         |             |         |

| JР  | 2-260298 10/1990                                | * cited | by examiner |         |

F 1 G. 13

F 1 G. 17

F 1 G. 20

FIG. 21A

FIG. 23 (AMENDED)

F 1 G. 27A

F I G. 27B

F 1 G. 28

FIG. 32 (AMENDED)

F 1 G. 34

F 1 G. 35

F 1 G. 38

# MULTI-STATE EEPROM HAVING WRITE-VERIFY CONTROL CIRCUIT

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

Notice: More than one reissue application has been filed for the reissue of U.S. Pat. No. 5,570,315. The reissue applications that have been filed for the reissue of U.S. Pat. No. 10 5,570,315 include parent reissue application Ser. No. 09/134,897 filed on Aug. 17, 1998, and this reissue application Ser. No. 11/451,592, which is a division of this parent reissue application. In addition, reissue applications Ser. No. 11/451,584; application Ser. No. 11/451,585 applica- 15 tion Ser. No. 11/451,586; application Ser. No. 11/451,587; application Ser. No. 11/451,588; application Ser. No. 11/451,589; application Ser. No. 11/451,590; application Ser. No. 11/451,591; and application Ser. No. 11/451,593 have been filed as additional division reissue applications of 20 the above-noted parent reissue application so as to be consistent with the Restriction Requirement mailed in the abovenoted parent reissue application on Apr. 20, 2006.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to an electrically programmable nonvolatile semiconductor memory device (EEPROM) and, more particularly, to an EEPROM for performing a multivalue storing operation for storing information of two or more bits in one memory cell.

### 2. Description of the Related Art

As one of EEPROMs, a NAND EEPROM which can be integrated at a high density is known. In this NAND 35 EEPROM, a plurality of memory cells are connected in series with each other as one unit such that adjacent memory cells have a source and a drain in common, and these memory cells are connected to a bit line. A memory cell generally has an FETMOS structure in which a charge accumulation layer and a control gate are stacked. A memory cell array is integrated and formed in a p-type well formed in a p-or n-type substrate. The drain side of a NAND cell is connected to a bit line through a selection gate, and the source side is connected to a common source line through a selection gate. The control gates of memory cells are continuously arranged in a row direction to form a word line.

The operation of this NAND-cell EEPROM is as follows. A data write operation is sequentially performed from a memory cell at a position farthest from the bit line. A high 50 voltage Vpp (=about 20 V) is applied to the control gate of a selected memory cell, an intermediate voltage Vppm (=about 10 V) is applied to the control gate and selection gate of a memory cell closer to the bit line than the selected memory cell, and a voltage of 0 V or an intermediate voltage 55 Vm (=about 8 V) is applied to the bit line in accordance with data. When the voltage of 0 V is applied to the bit line, the potential of the bit line is transferred to the drain of the selected memory cell, and electrons are injected into the charge accumulation layer of the selected memory cell. In 60 this case, the threshold voltage of the selected memory cell is positively shifted. This state is represented by, e.g., "1". When the voltage Vm is applied to the bit line, electrons are not effectively injected into the charge accumulation layer of the selected memory cell, and, therefore, the threshold volt- 65 age of the selected memory cell is kept negative without being changed. This state is an erased state, and is repre2

sented by "0". A data write operation is performed to memory cells which share a control gate at once.

A data erase operation is performed to all the memory cells in a NAND cell at once. More specifically, all the control gates are set to be 0 V, and the p-type well is set to be 20 V. At this time, the selection gate, the bit line, and the source line are set to be 20 V. In this manner, electrons are discharged from the charge accumulation layers of all the memory cells into the p-type well, and the threshold voltages of the memory cells are negatively shifted.

A data read operation is performed as follows. That is, the control gate of a selected memory cell is set to be 0 V, the control gates and selection gates of the remaining memory cells are set to be a power supply potential Vcc (e.g., 5 V), and it is detected whether a current flows in the selected memory cell. Due to restrictions of the read operation, a threshold voltage set upon a "1"-data write operation must be controlled to fall within a range of 0 V to Vcc. For this purpose, a write verify operation is performed to detect only a memory cell in which data "1" is not sufficiently written, and rewritten data is set such that a rewrite operation is performed to only the memory cell in which data "1" is not sufficiently written (bit-by-bit verify operation). The memory cell in which data "1" is not sufficiently written is 25 detected by performing a read operation (verify read operation) such that a selected control gate is set to be, e.g., 0.5 V (verify voltage).

More specifically, when the threshold voltage of the memory cell has a margin with respect to 0 V and is not set to <sub>30</sub> be 0.5 V or more, a current flows in the selected memory cell, and the selected memory cell is detected as a memory cell in which data "1" is not sufficiently written. Since a current flows in a memory cell set to be a "0"-data-written state, a circuit called a verify circuit for compensating the current flowing in the memory cell is arranged to prevent the memory cell from being erroneously recognized as a memory cell in which data "1" is not sufficiently written. This verify circuit executes a write verify operation at a high speed. When a data write operation is performed while a write operation and a write verify operation are repeated, a write time for each memory cell is made optimum, and the threshold voltage of each memory cell set upon a "1"-data write operation is controlled to fall within a range of 0 V to Vcc.

In this NAND-cell EEPROM, in order to realize a multivalue storing operation, for example, it is considered that states set upon a write operation are set to be three states represented by "0", "1", and "2". A "0"-data-written state is defined as a state wherein the threshold voltage is negative, a "1"-data-written state is defined as a state wherein the threshold voltage ranges from 0 V to ½ Vcc, and a "2"-data-written state is defined as a state wherein the threshold voltage ranges from ½ Vcc to Vcc. In a conventional verify circuit, a memory cell set to be a "0"-data written state can be prevented from being erroneously recognized as a memory cell in which data "1" or "2" is not sufficiently written.

However, the conventional verify circuit is not designed for a multivalue storing operation. For this reason, assuming that a memory cell set to be a data "2"-written state has a threshold voltage equal to or higher than a verify voltage for detecting whether data "1" is not sufficiently written and equal to or lower than ½ Vcc, when it is to be detected whether data "1" is not sufficiently written, no current flows in the memory cell, and the memory cell is erroneously recognized as a memory cell in which data "2" is sufficiently written.

In addition, in order to prevent erroneous recognition of a memory cell in which data is not sufficiently written and to perform a multivalue write verify operation, a verify write operation is performed to set a memory cell, in which data "1" is sufficiently written, in a "2"-data-written state, by 5 detecting whether the memory cell is a memory cell in which data "2" is not sufficiently written. However, in this case, a memory cell set to be a "2"-data-written state is set in a "1"-data-written state at first and is then set in a "2"-datawritten state. For this reason, a longer time is required for the 10 write operation, and the write operation cannot be performed at a high speed.

As described above, when a conventional NAND-cell EEPROM is used for performing a multivalue storing operation, and a bit-by-bit verify operation is performed by a  $^{15}$ conventional verify circuit, an erroneous verify operation is disadvantageously performed.

#### SUMMARY OF THE INVENTION

It is an object of the present invention to provide an EEPROM capable of storing multivalue information and performing a write verify operation at high speed without causing an erroneous verify operation.

According to a first aspect of the present invention, there 25 is provided a nonvolatile semiconductor memory device capable of storing multivalue data, characterized by comprising a memory cell array in which memory cells which can be electrically programmed and each of which has at least three storage states are arranged in a matrix, a plurality 30 of write data circuits for temporarily storing data for controlling write operation states of the plurality of memory cells in the memory cell array, write means for simultaneously performing a write operation to the plurality of memory cells in accordance with contents of the data circuits respectively 35 corresponding to the plurality of memory cells, verify means for simultaneously checking states of the plurality of memory cells set upon the write operation, and means for updating the contents of the write data circuits such that a rewrite operation is performed to only a memory cell, in 40 which data is not sufficiently written, on the basis of the contents of the data circuits and the states of the memory cells set upon the write operation, wherein the write operation based on the contents of the data circuits, a write verify operation, and an operation for updating the contents of the 45 write data circuits are repeatedly performed until the plurality of memory cells are set in predetermined written states, thereby electrically performing a data write operation.

According to a second aspect of the present invention, there is provided a nonvolatile semiconductor memory 50 device having a memory cell array constituted by a plurality of memory cells which are arranged in a matrix and each of which can be electrically programmed, each of the memory cells having arbitrary data "i" (i=0, 1, ..., n-1: n $\geq$ 3) as at least three storage states, and a storage state corresponding 55 to data "0" being an erasure state, characterized by comprising a plurality of data circuits each serving as a sense amplifier and having a function of storing sensed information as data for controlling a write operation state of a corresponding memory cell, write means for simultaneously perform- 60 ing a write operation to the plurality of memory cells in accordance with contents of the data circuits respectively corresponding to the plurality of memory cells, ith (i=1,  $2, \ldots, n-1$ ) write verify means for simultaneously checking whether the storage state of each of the plurality of memory 65 (3) Each of the memory cells is constituted by stacking and cells set upon the write operation becomes a storage state of data "i", ith (i=1, ..., n-1) data circuit content simultaneous

updating means for simultaneously updating the contents of data circuits corresponding to a memory cell in which data "i" is to be stored, such that a rewrite operation is performed to only a memory cell, in which data is not sufficiently written, on the basis of the contents of the data circuits and the storage states of the memory cells after the write operation, and data circuit content updating means for performing a storage checking operation performed by the ith write verify means and a simultaneous updating operation performed by the ith data circuit content simultaneous updating means, from data "1" to data "n-1"n-1 times so as to update the contents of all the plurality of data circuits, wherein the ith data circuit content simultaneous updating means, of bit line potentials at which the storage states of the memory cells set upon a write operation are output by the ith write verify means, a bit line potential corresponding to a memory cell in which data "i" (i≥1) is to be stored is sensed/ stored as rewrite data, and for bit lines corresponding to memory cells in which data except for data "i" are to be 20 stored the bit line potential at which the state of the memory cell set upon the write operation is output is corrected in accordance with the contents of the data circuits so as to sense/store to hold the contents of data circuit, holding the data storage states of the data circuits until the bit line potentials are corrected, operating the data circuits as sense amplifiers while the corrected bit line potentials are held, and simultaneously updating the contents of the data circuit corresponding to the memory cell in which data "i" is to be stored, and a write operation and a data circuit content updating operation based on the contents of the data circuits are repeatedly performed until the memory cells are set in predetermined written states, thereby electrically performing a data write operation.

Preferred embodiments of the present invention will be described below.

- (1) The data circuits control write operation states of the memory cells in accordance with data stored in the data circuits in a write operation to perform control such that the states of the memory cells are changed into predetermined written states or the states of the memory cells are held in states set prior to the write operation.

- (2) For a data circuit corresponding to a memory cell to be set in an "i"-data-written state, an ith data circuit content simultaneous updating means changes data of the data circuit into data for controlling the state of the memory cell to hold the state of the memory cell in a state set prior to the write operation when memory cells corresponding to a data circuit in which data for changing a memory cell into an "i"-data-written state is stored reach an "i"-datawritten state, sets data for controlling the state of the memory cell to change the state of the memory cell into the "i"-data-written state in the data circuit when the memory cell corresponding to the data circuit in which data for changing a memory cell into an "i"-data-written state is stored does not reach the "i"-data-written state, and sets data for controlling the state of the memory cell to hold the state of the memory cell set prior to the write operation when the data circuit stores data for controlling the state of the memory cell to hold the state of the memory cell in the state set prior to the write operation, and the ith data circuit content simultaneous updating means does not change contents of the data circuits corresponding to the memory cells in which data except for data "i" are to be stored.

- forming a charge accumulation layer and a control gate on a semiconductor layer and stores arbitrary data "i" (i=0,

$1, \ldots, n-1; n \ge 3$ ) as at least three storage states and as multivalue data using magnitudes of threshold voltages, and the ith write verify means applies a predetermined ith verify potential to the control gate to verify whether a threshold voltage of a memory cell set to be the "i"-data-5 written state is a desired threshold voltage.

- (4) A storage state corresponding to data "0" is an erased state, a difference between the threshold voltage corresponding to the data "n-1" state and the threshold voltage corresponding to a data "0" state is a maximum, and 10 threshold voltages corresponding to data "1", "2", . . . , "i", . . . , "n-2" states range from the threshold voltage corresponding to the data "0" state to the threshold voltage corresponding to the data "n-1" state, and the threshold voltages corresponding to the data "1", "2", . . . , 15 "i", . . . , "n-2" states are ordered from the threshold voltage corresponding to the data "0" state. The nonvolatile semiconductor memory device comprises a first bit line potential setting circuit for, of a plurality of bit line potentials at which states of memory cells set upon a write 20 operation are output by the ith write verify means, when the data circuits sense a bit line potential corresponding to a data circuit whose contents are data for controlling the states of the memory cells to hold the states of the memory cells in states set prior to the write operation, 25 setting the bit line potential to be a first correction bit line potential which becomes data for controlling the states of the memory cells to hold states of the memory cells in states set prior to the write operation, and a jth bit line potential setting circuit for, of bit line potentials corre- 30 sponding to memory cells set to be data "j"-written states  $(i+1 \le j)$  among bit line potentials at which states of the memory cells set upon a write operation are output by the ith (1≦i≦n-2) write verify means, when a data circuit senses only a bit line potential corresponding to a data 35 circuit whose contents are data for controlling states of memory cells to set the states of the memory cells in data "j"-written states, setting the bit line potential in a second correction bit line potential which becomes data for controlling the states of the memory cells to change the states 40 of the memory cells into the data "j"-written states, wherein, to update the contents of the data circuits, a bit line potential at which states of the memory cells set upon a write operation are output by an ith write verify operation is corrected by the first, (i+1)th, (i+2)th, . . . , (n-1)th 45 bit line potential setting circuits.

- (5) Each of the data circuits is constituted by a first data storage unit for storing information indicating whether a state of a memory cell is held in a state set prior to a write operation and a second data storage unit for, when the 50 information of the first data storage unit is not information for controlling the state of the memory cell to hold the state of the memory cell in a state set prior to the write operation, storing information indicating a written state "i" (i=1, 2, ..., n-1) to be stored in the memory cell, the 55 first data storage unit having a function of sensing/storing bit line potentials which are corrected by the first, (i+1)th, (i+2)th , . . . , (n=1)th bit line potential setting circuits in accordance with the contents of the data circuits to perform the data circuit content updating operation and at 60 which the storage states of the memory cells set upon the write operation are output by the ith write verify operation.

- (6) The nonvolatile semiconductor memory device comprises a write prevention bit line voltage output circuit for, 65 when the information of the first data storage unit is information for controlling the state of the memory cells to

6

hold the state of the memory cells in states set prior to a write operation, outputting a write prevention bit line voltage to a bit line in the write operation, and an ith (i=1, 2, ..., n-1) bit line voltage output circuit for, when the information of the first data storage unit is not information for controlling the states of the memory cells to hold the states of the memory cells in the states set prior to the write operation, outputting a bit line voltage in an ith write operation in accordance with information indicating a written state "i" to be stored in a memory cell of the second data storage unit.

- (7) The first bit line potential setting circuit and the write prevention bit line voltage output circuit are common first bit line voltage control circuits. The input voltage of each of the common first bit line voltage control circuits has an input voltage whose output is to be a write prevention bit line voltage in a write operation and a first correction bit line potential in a data circuit content updating operation. The jth (j=2, 3, ..., n-1) bit line potential setting circuit and the jth write bit line voltage output circuit are common jth bit line voltage control circuits. Each of the common jth bit line voltage control circuits has an input whose output is to be a jth write bit line voltage in the write operation and a second correction bit line potential in a data circuit content updating operation.

- (8) Each of the memory cells is constituted by stacking and forming a charge accumulation layer and a control gate on a semiconductor layer, and the memory cells are connected in series with each other as units each constituted by a plurality of memory cells to form NAND-cell structures.

- (9) Each of the memory cells is constituted by stacking and forming a charge accumulation layer and a control gate on a semiconductor layer, thereby forming a NOR-cell structure.

A multivalue (n-value) storage type EEPROM according to the first and second aspects of the present invention is constituted such that a verify read operation is performed through n-1 basic operation cycles. An erased state is represented by data "0", and multivalue levels are represented by "0", "1", . . . , "i", . . . , "n-1" in an order from a small threshold voltage. In this case, an ith cycle is constituted to verify whether an "i"-data write operation is sufficiently performed. For this reason, the EEPROM comprises a verify potential generation circuit for applying a predetermined verify voltage at an level in the ith cycle such that a current flows in a memory cell having a selected control gate when an "i"-data write operation is sufficiently performed, and a sense amplifier for detecting a bit line voltage to determine whether a write operation is sufficiently performed. In the ith cycle, the bit line of a memory cell in which data "0", . . . , "i-1" are written has a first verify circuit such that the current of the memory cell is compensated for when it is detected that the data are sufficiently written in the memory cell and the current of the memory cell is not compensated for when it is detected that the data are not sufficiently written in the memory cell. In the ith cycle, for the bit line of a memory cell in which data "i+1", ..., "n-1" are written, the current of the memory cell is compensated for by the first verify circuit when it is detected that the data are sufficiently written in the memory cell in advance and a second verify circuit for setting a bit line voltage is installed such that the current of the memory cell flows when it is detected that the data are not sufficiently written in the memory cell.

The EEPROM comprises a first data storage unit for storing data indicating whether data is sufficiently written and a second data storage unit for storing whether a multivalue

level to be written is any one of data "1", . . . , "n-1". The first data storage unit also has the function of a sense amplifier for detecting whether data is sufficiently written. In addition, the EEPROM is characterized by comprising a bit line write voltage output circuit for outputting a bit line voltage in a write operation in accordance with a desired written state such that, when there is memory cell which does not reach a predetermined written state, a rewrite operation is performed to only this memory cell.

According to the present invention, after a multivalue data write operation is performed, it is detected whether the written states of memory cells reach their desired multivalue level states. When there is a memory cell which does not reach its desired multivalue level state, a bit line voltage in a write operation is output in accordance with a desired written state such that a rewrite operation is performed to only this memory cell. The write operation and the verify read operation are repeated, and a data write operation is ended when all the memory cells reach their desired written states, respectively.

As described above, according to the present invention, a time for performing one write cycle is shortened, and a write operation is repeated many times within a short time while the degree of progress of a written state is checked, so that the range of the threshold voltage distribution of a memory 25 cell in which a data write operation is finally ended can be narrowed at a high speed.

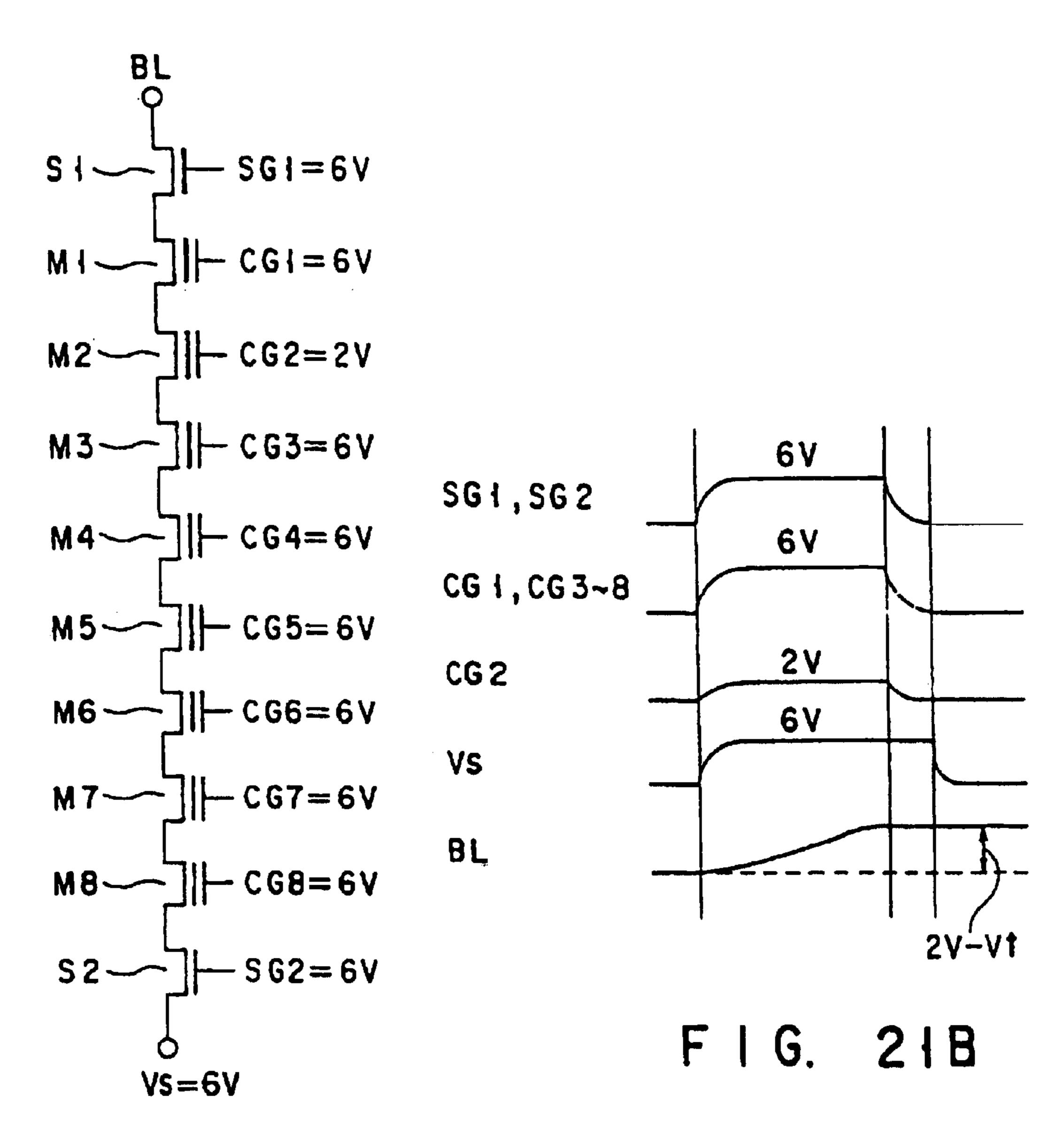

According to a third aspect of the present invention, a bit line potential in a read operation is controlled to exhibit the threshold voltage of a memory cell. A common source line is 30 set to be 6 V, a voltage of 2 V is applied to a selected control gate, and the potential of the common source line is transferred to the bit line. When the bit line potential reaches a certain value, a current flowing in the memory cell is stopped, and the bit line potential is given as a value obtained 35 by subtracting the threshold voltage of the memory cell from the control gate voltage of 2 V. When the bit line potential is 3 V, the threshold voltage of the memory cell is -1 V. A non-selected control gate and a selection gate are set to be 6 V such that the bit line potential is not determined by the 40 potential of the non-selected memory cell or a selection transistor.

An erased state is represented by data "0", multivalue levels are represented by "0", "1", ..., "i", ..., "n-1" in an order from a small threshold voltage. In this case, since a 45 verify read operation simultaneously verifies whether all data "i" are sufficiently written, a reference potential used when a bit line voltage is sensed is set in accordance with the written data. In addition, as in "0"-data write operation, a verify circuit is arranged such that the current of the memory 50 cell is compensated for when it is detected that the data are sufficiently written in the memory cell and the current of the memory cell is not compensated for when it is detected that the data are not sufficiently written in the memory cell. A first data storage unit for storing data indicating whether data 55 is sufficiently written and a second data storage unit for storing whether a multivalue level to be written is any one of data "1", ..., "n-1" are arranged. The first data storage unit also serves as a sense amplifier for detecting whether data is sufficiently written. In addition, a multivalue (n-value) storage type NAND-cell EEPROm according to a nonvolatile semiconductor memory device is characterized by comprising a bit line write voltage output circuit for outputting a bit line voltage in a write operation in accordance with a desired written state such that, when there is memory cell which 65 does not reach a predetermined written state, a rewrite operation is performed to only this memory cell.

8

More specifically, a nonvolatile semiconductor memory device according to the third aspect of the present invention includes, as a basic arrangement, a nonvolatile semiconductor memory device comprising a memory cell array in which the memory cells, each of which is constituted by stacking a charge accumulation layer and a control gate on a semiconductor layer and can be electrically programmed to store at least three data as multivalue data of threshold voltages of the memory cell, are arranged in a matrix, threshold voltage detection means for charging a bit line connected to the memory cells so that charging is made through the memory cells and outputting the multivalue data of the memory cell as multivalue level potentials to the bit line, and a sense amplifier for sensing potentials of the bit line charged by the threshold voltage detection means, and the nonvolatile semiconductor memory device is characterized by the following embodiments.

- (1) The nonvolatile semiconductor memory device is characterized in that the memory cells are connected in series with each other as units each constituted by memory cells to form a plurality of NAND-cell structures each having one terminal connected to the bit line through a first selection gate and the other terminal connected to a source line through a second selection gate, the threshold voltage detection means transfers a source line voltage to the bit line through a corresponding NAND cell to charge the bit line, and non-selected control gate voltages and first and second selection gate voltages are controlled such that voltage transfer capabilities of non-selected memory cells and first and second selection transistors are sufficiently increased to determine a bit line voltage at a threshold voltage of a selected memory cell.

- (2) The nonvolatile semiconductor memory device comprises the plurality of data circuits each functioning as the sense amplifier and having a function of storing sensed information as data for controlling write operation states of the memory cells, the write means for performing a write operation in accordance with contents of the data circuits respectively corresponding to the plurality of memory cells in the memory cell array, the write verify means which uses the threshold voltage detection means to check whether states of the plurality of memory cells set upon the write operation are storage states of desired data, and the data circuit content simultaneous updating means for simultaneously updating the contents of the data circuits such that a rewrite operation is performed to only a memory cell, in which data is not sufficiently written, on the basis of the contents of the data circuits and the states of the memory cells after a write operation, wherein the data circuit content simultaneous updating means corrects a bit line potential at which the storage states of the memory cells set upon the write operation are output in accordance with the contents of the data circuits to sense/store the bit line potential as rewrite data, holds the data storage states of the data circuits until the bit line potential is corrected, operates the data circuits as sense amplifiers while the corrected bit line potential is held, and simultaneously updates the contents of the data circuits, and a write operation and a data circuit content simultaneous updating operation based on the contents of the data circuits are repeatedly performed until the memory cells are set in predetermined written states, thereby electrically performing a write operation.

- (3) The data circuits control write operation states of the memory cells in accordance with data stored in the data circuits in a write operation to perform control such that the states of the memory cells are changed into predeter-

mined written states or the states of the memory cells are held in states set prior to the write operation, and the data circuit content simultaneous updating means changes data of the data circuits into data for holding the states of the memory cells in states set prior to the write operation 5 when a memory cell corresponding to a data circuit in which data for controlling the memory cells to change the memory cells to have predetermined written states is stored reaches a predetermined written state, sets data for controlling the memory cells to change the memory cells 10 to have predetermined written states in the data circuits when the memory cell corresponding to the data circuit in which data for controlling the memory cells to change the memory cells to have predetermined written states is stored does not reach the predetermined written state, and 15 sets data for controlling the states of the memory cells to hold the states of the memory cells in the states set prior to the write operation in the data circuits, when data for controlling the states of the memory cells to hold the states of the memory cells in the states set prior to the write opera- 20 tion is stored in the data circuits.

- (4) The nonvolatile semiconductor memory device comprises a bit line potential setting circuit for, of bit line potentials at which states of the memory cells set upon the write operation are output by the threshold voltage detec- 25 tion means, when only a bit line potential corresponding to the data circuits whose contents are data for controlling the states of the memory cells to hold the states of the memory cells in the states set prior to the write operation is sensed by the data circuits, setting a correction bit line 30 potential at which data for controlling the states of the memory cells to hold the states of the memory cells in the states set prior to the write operation is obtained, and wherein, to perform the data circuit content simultaneous updating operation, a bit line potential at which the states 35 of the memory cells set upon the write operation are output with the threshold voltage detection means is corrected by the bit line potential setting circuit in accordance with the contents of the data circuits.

- (5) For the nonvolatile semiconductor memory device in 40 which one of the memory cells has at least three storage data "i" (i=0, 1, ..., n-1) to perform a multivalue storing operation, a storage state corresponding to data "0" being an erased state, each of the data circuits is constituted by a first data storage unit for storing information indicating 45 whether a state of a memory cell is held in a state set prior to a write operation and a second data storage unit for, when the information of the first data storage unit is not information for controlling the state of the memory cell such that the state of the memory cell is held in a state set 50 prior to the write operation, storing information indicating a written state "i" (i=1, 2, ..., n-1) to be stored in the memory cell, and the first data storage unit having a function of sensing/storing bit line potentials which are corrected by the bit line potential setting circuits in accor- 55 dance with the contents of the data circuits to perform the data circuit content updating operation and at which the storage states of the memory cells set upon the write operation are output with the threshold voltage detection means.

- (6) The first data storage unit has a function of comparing a reference voltage with a bit line voltage to sense a bit line potential and a function of sensing/storing a bit line potential which is corrected by the bit line potential setting circuit in accordance with the contents of the data circuits 65 using a reference voltage corresponding to the contents of the data circuits and at which states of the memory cells

10

set upon the write operation are output by the threshold voltage detection means.

- (7) The nonvolatile semiconductor memory device comprises a write prevention bit line voltage output circuit for outputting a write prevention bit line voltage to a bit line in a write operation when the information of the first data storage unit is information for controlling the states of the memory cells to hold the states of the memory cells in states before the write operation, and an ith write bit line voltage output circuit for outputting a bit line voltage in an ith write operation in accordance with information of the second data storage unit indicating data "i" (i=1, 2, . . . , n-1) to be stored in the memory cell when the information of the first data storage unit is not information for controlling the states of the memory cells to hold the states of the memory cells in states set prior to the write operation.

- (8) The nonvolatile semiconductor memory device comprises data inverting means for inverting data of the first data storage unit for activating the bit line potential setting circuit before the activation of bit line potential setting circuit, when the data of the first data storage unit for activating the bit line potential setting circuit has been inverted to the data of the first data storage unit for activating the write prevention bit line voltage output circuit.

In the third aspect of the present invention, after a multivalue data write operation is performed, it is simultaneously detected whether the written states of the memory cells reach their multivalue level states, respectively. When there is a memory cell which does not reach its desired multivalue level, a bit line voltage in a write operation is output in accordance with a desired written state such that a rewrite operation is performed only to this memory cell. The write operation and a verify read operation are repeated, and a data write operation is ended when it is confirmed that all the memory cells reach their desired written states, respectively.

As described above, according to the present invention, a time for performing one write cycle is shortened, and a write operation is repeated many times within a short time while the degree of progress of a written state is checked, so that the range of the threshold voltage distribution of a memory cell in which a data write operation is finally ended can be narrowed at a high speed.

Additional objects and advantages of the invention will be set forth in the description which follows, and in part will be obvious from the description, or may be learned by practice of the invention. The objects and advantages of the invention may be realized and obtained by means of the instrumentalities and combinations particularly pointed out in the appended claims.

# BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate presently preferred embodiments of the invention, and together with the general description given above and the detailed description of the preferred embodiments given below, serve to explain the principles of the invention.

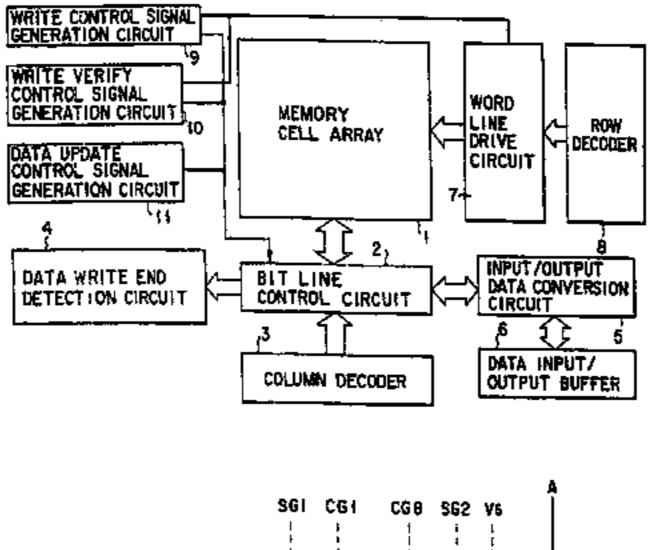

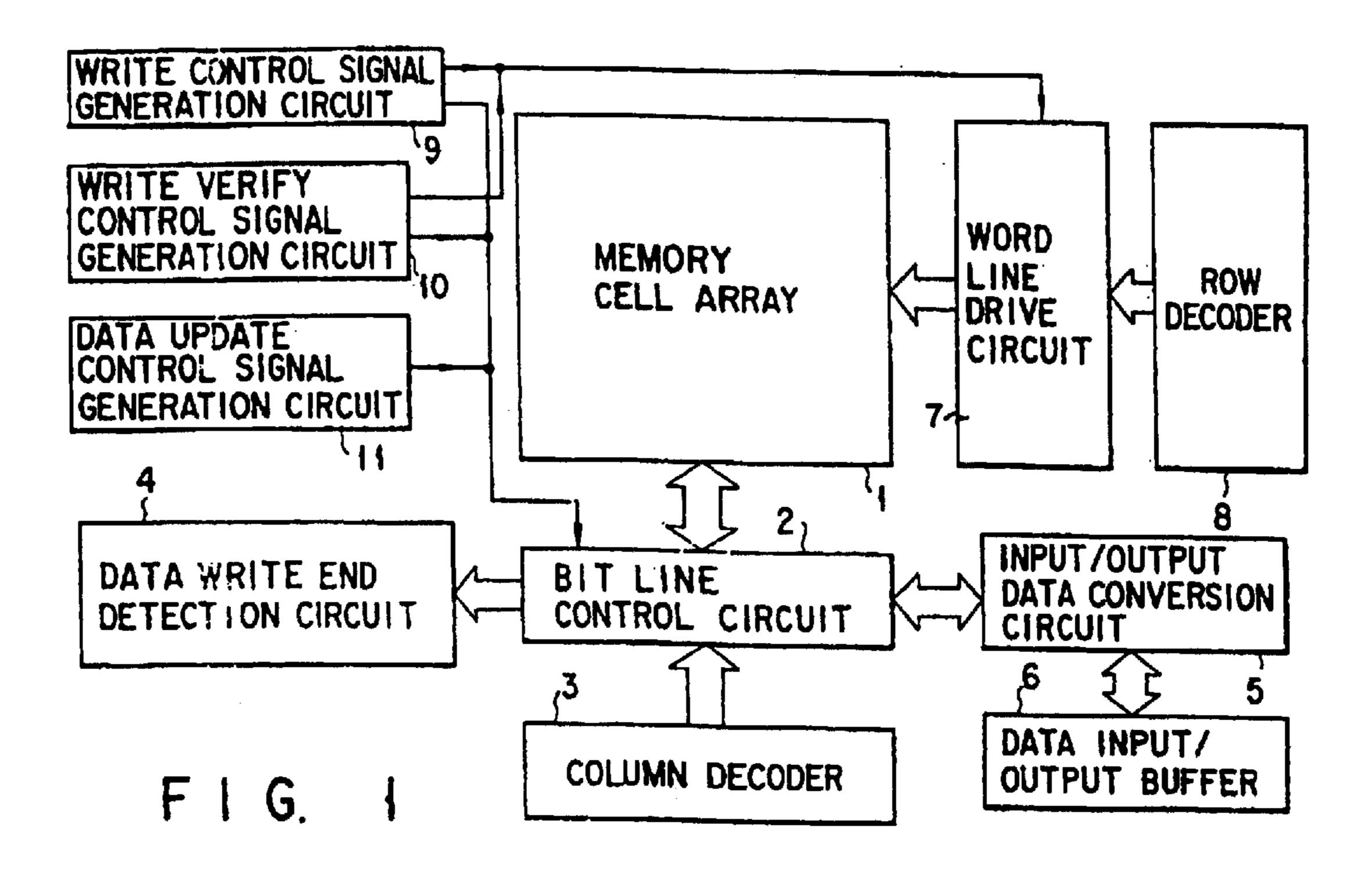

- FIG. 1 is a block diagram showing the schematic arrangement of an EEPROM according to the first and second embodiments of the present invention;

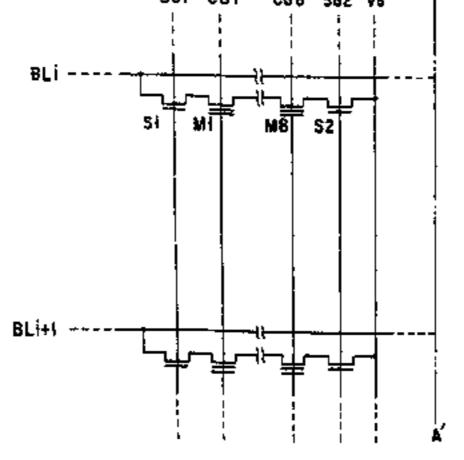

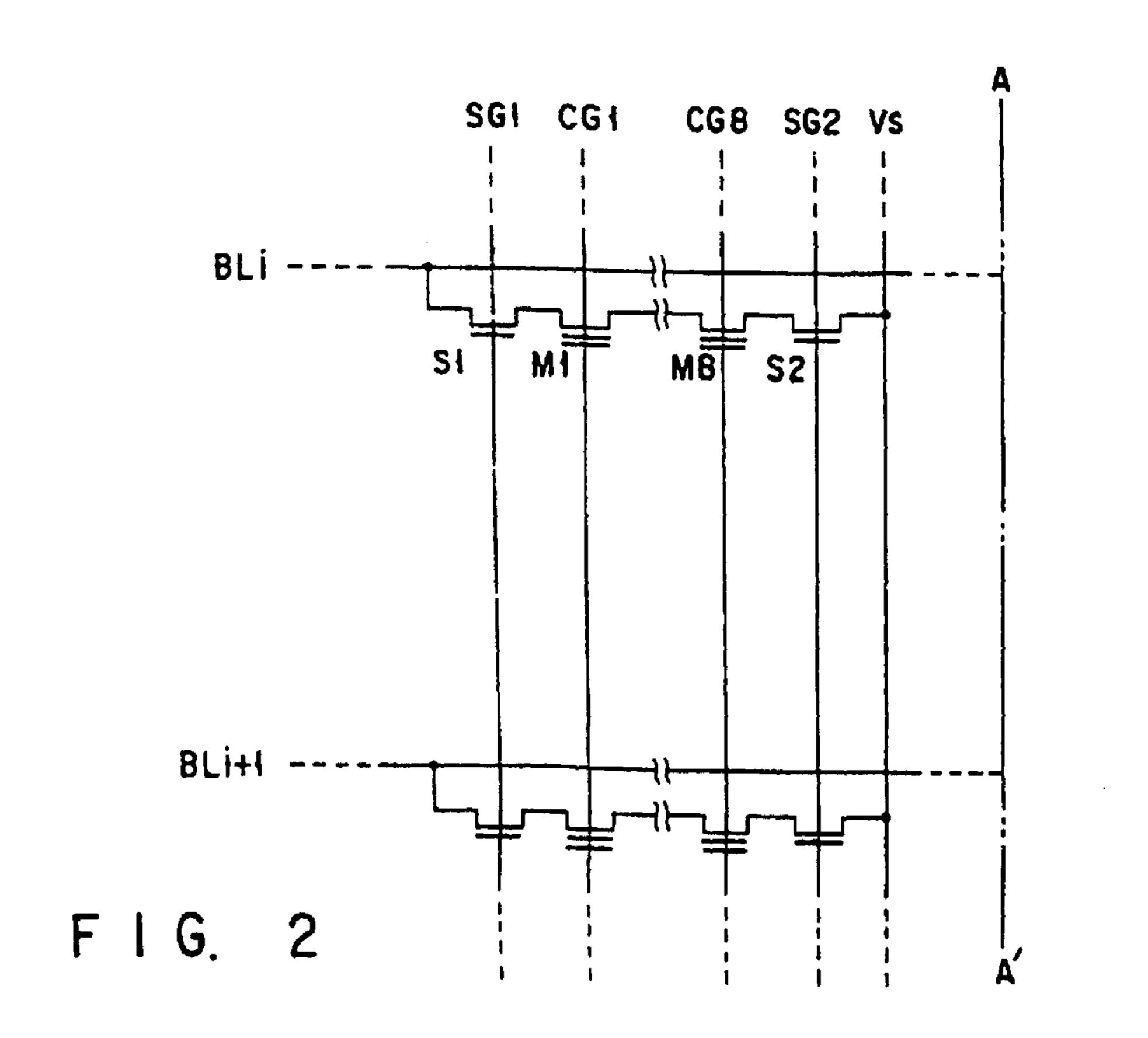

- FIG. 2 is a circuit diagram showing the detailed arrangement of a memory cell array in the first embodiment;

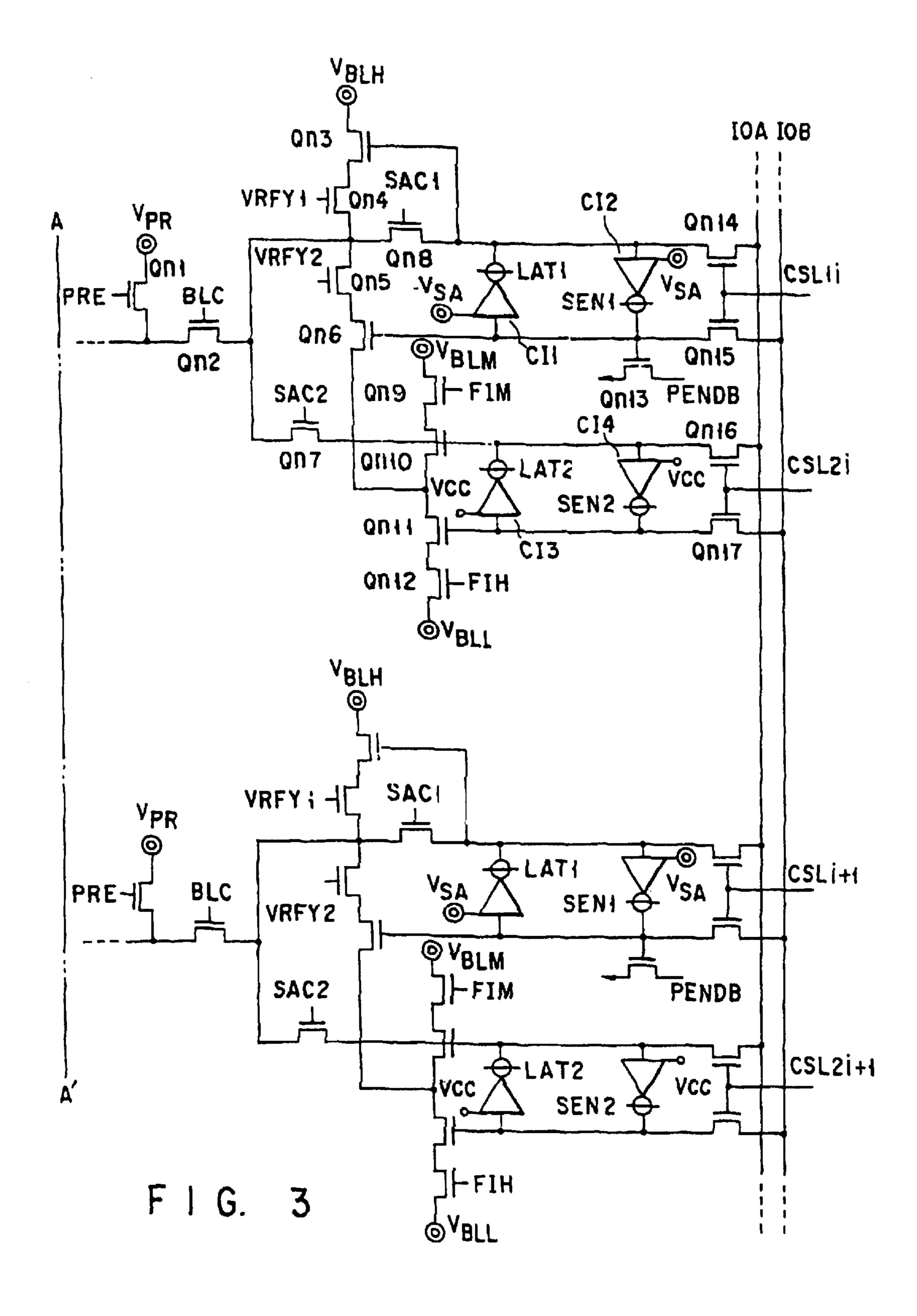

- FIG. 3 is a circuit diagram showing the detailed arrangement of a bit line control circuit in the first embodiment;

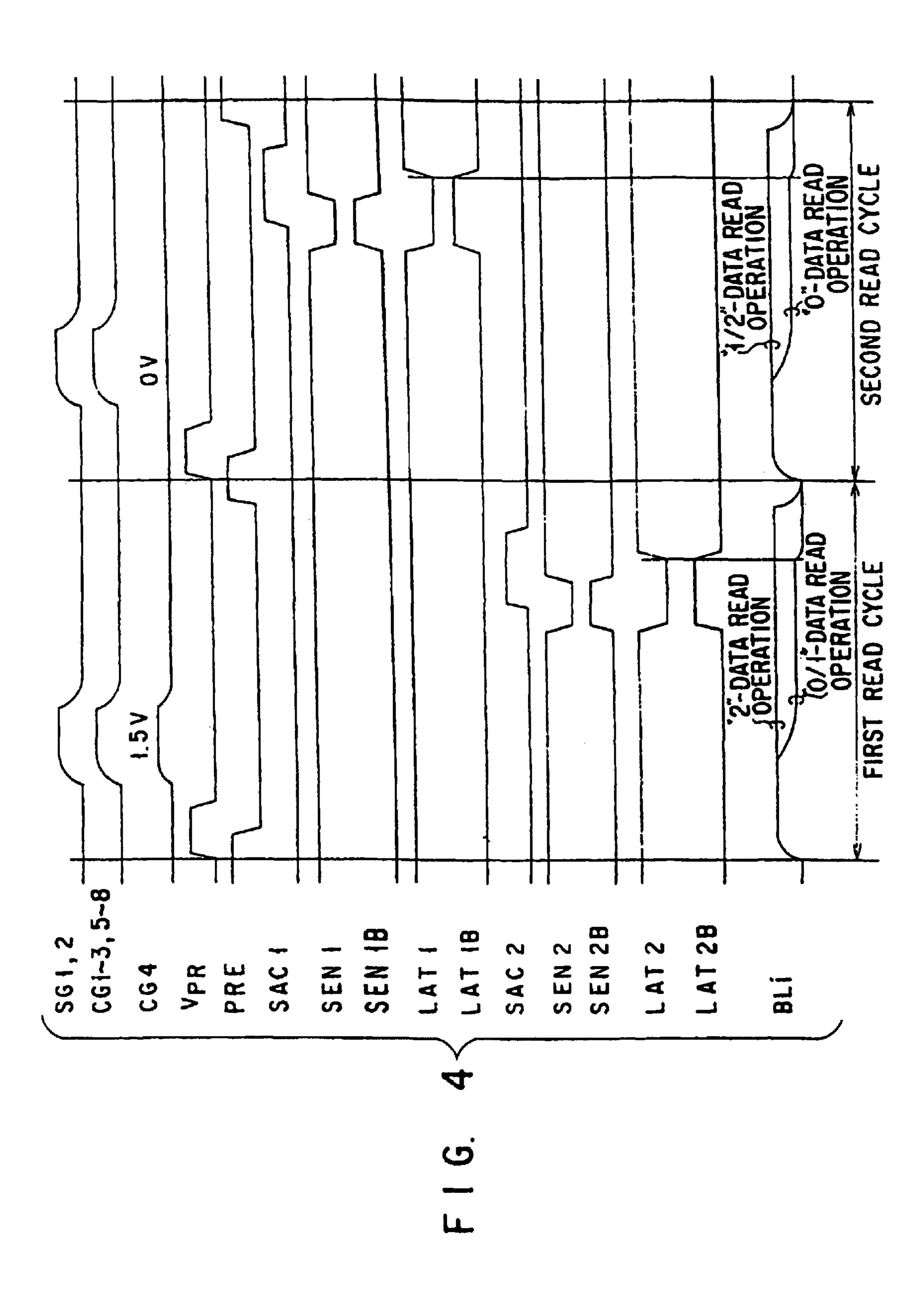

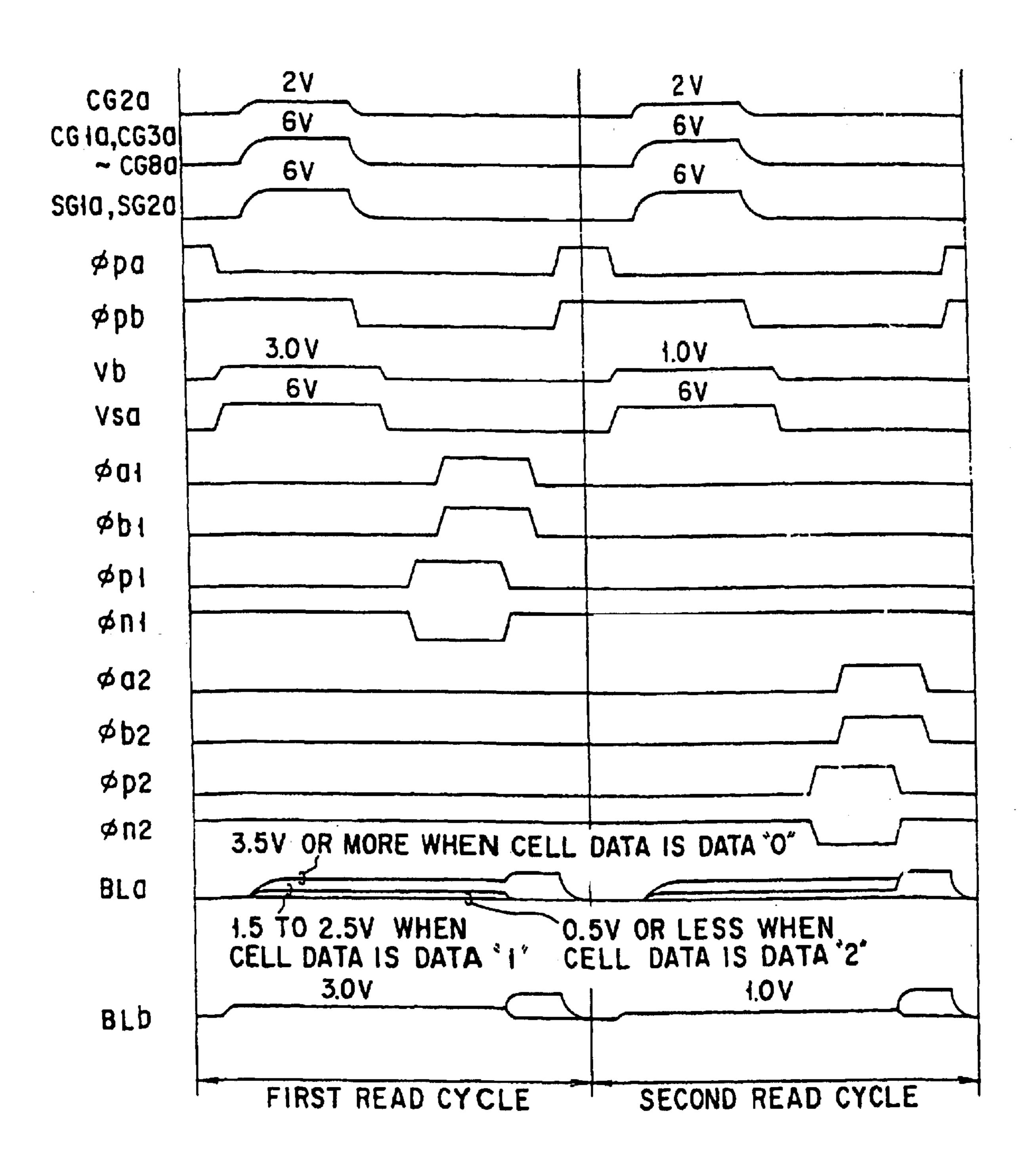

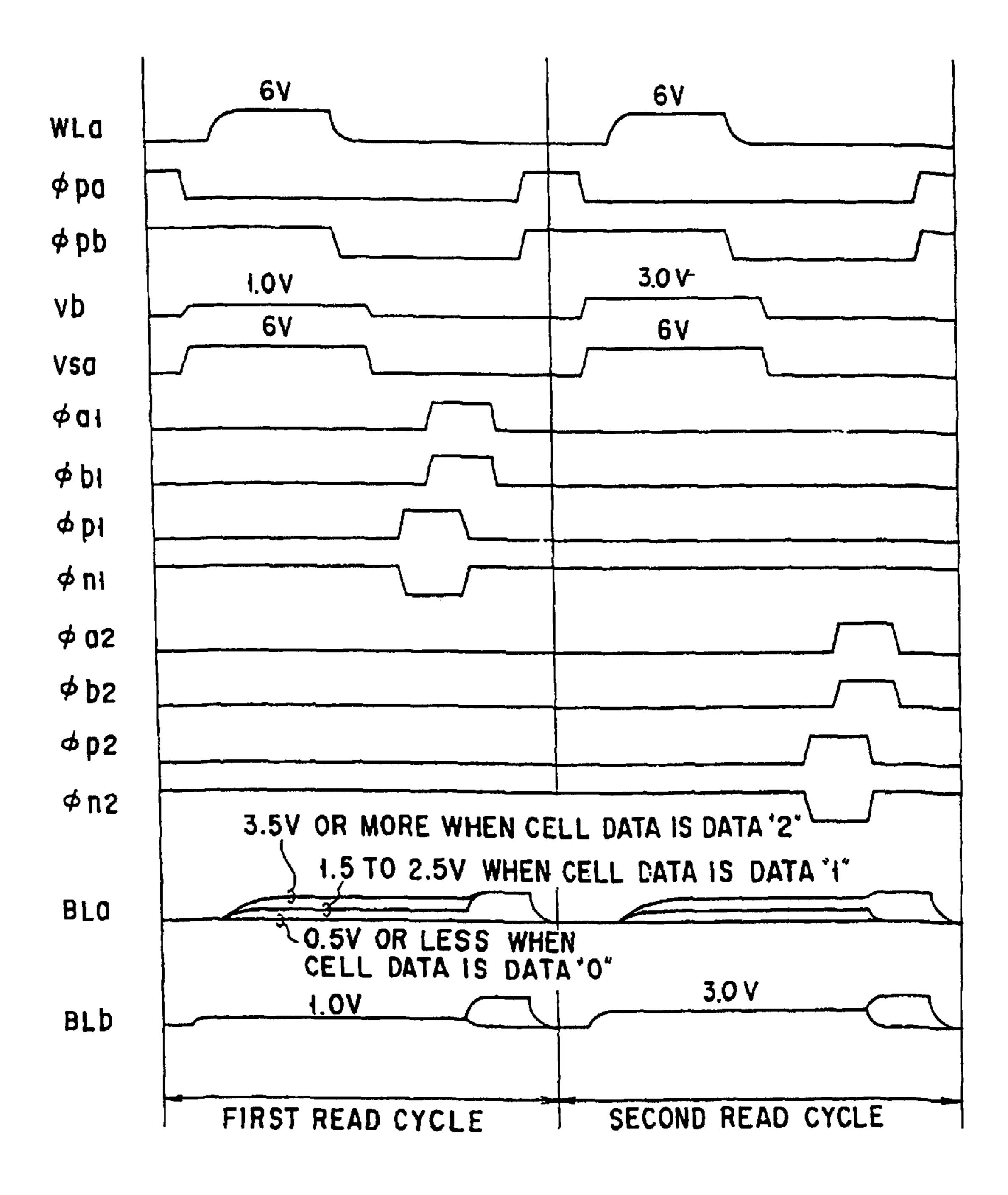

- FIG. 4 is a timing chart showing a read operation in the first embodiment;

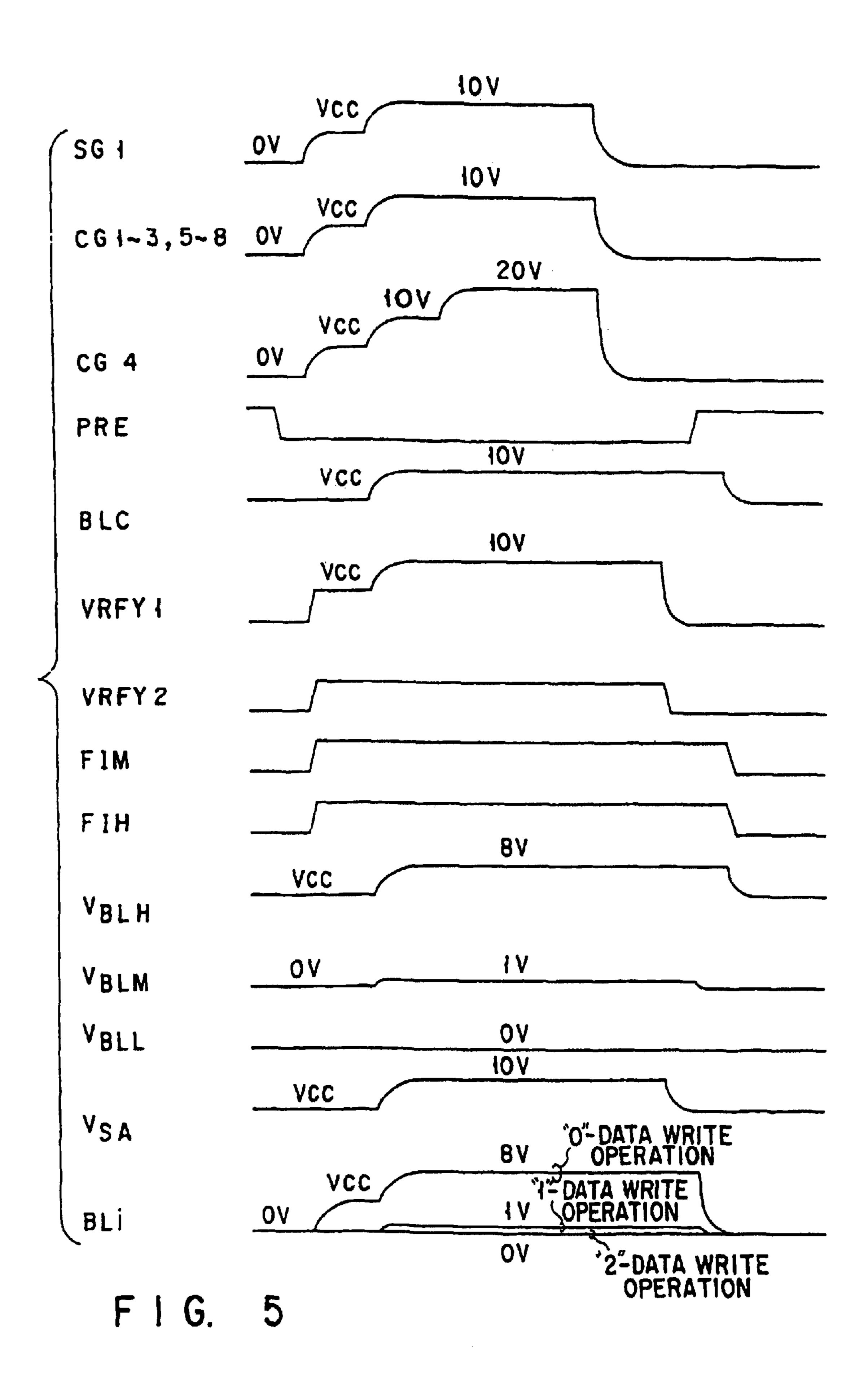

- FIG. **5** is a timing chart showing a write operation in the first embodiment;

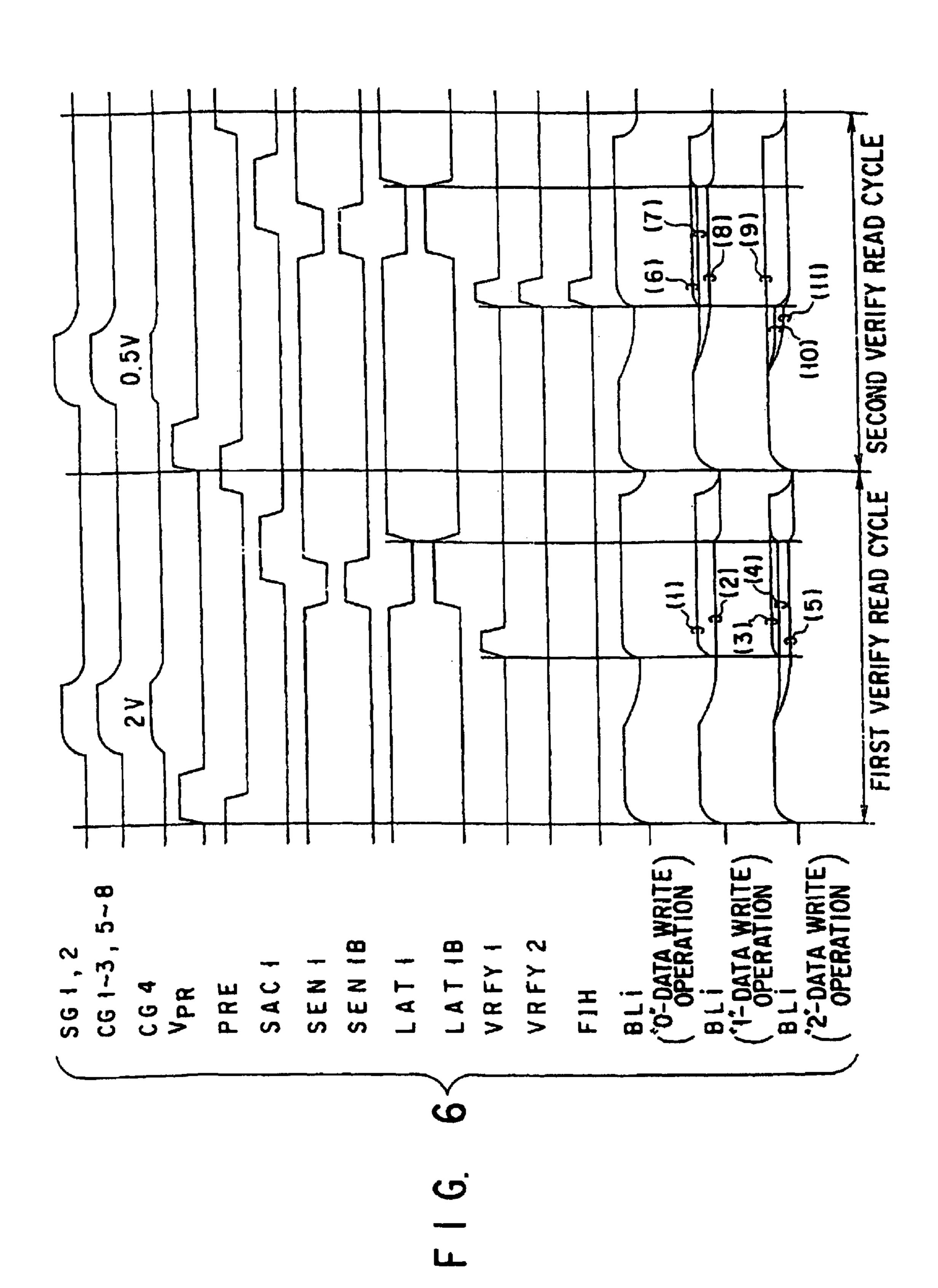

- FIG. **6** is a timing chart showing a verify read operation in the first embodiment;

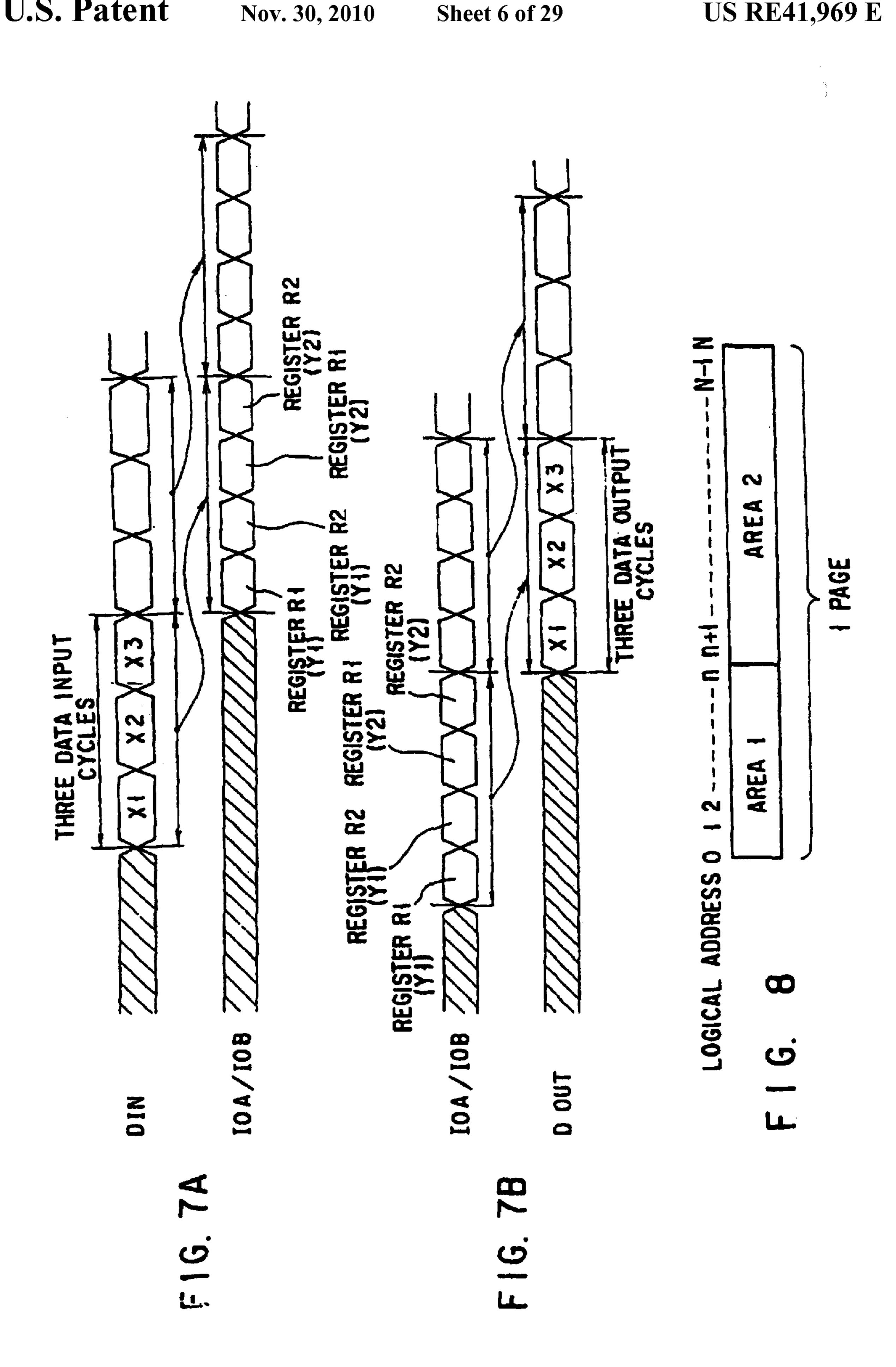

- FIGS. 7A and 7B are timing charts showing data input/ <sup>5</sup> output operations in the first and second embodiments;

- FIG. 8 is a view showing the concept of a page serving as a write/read unit in the first and second embodiments;

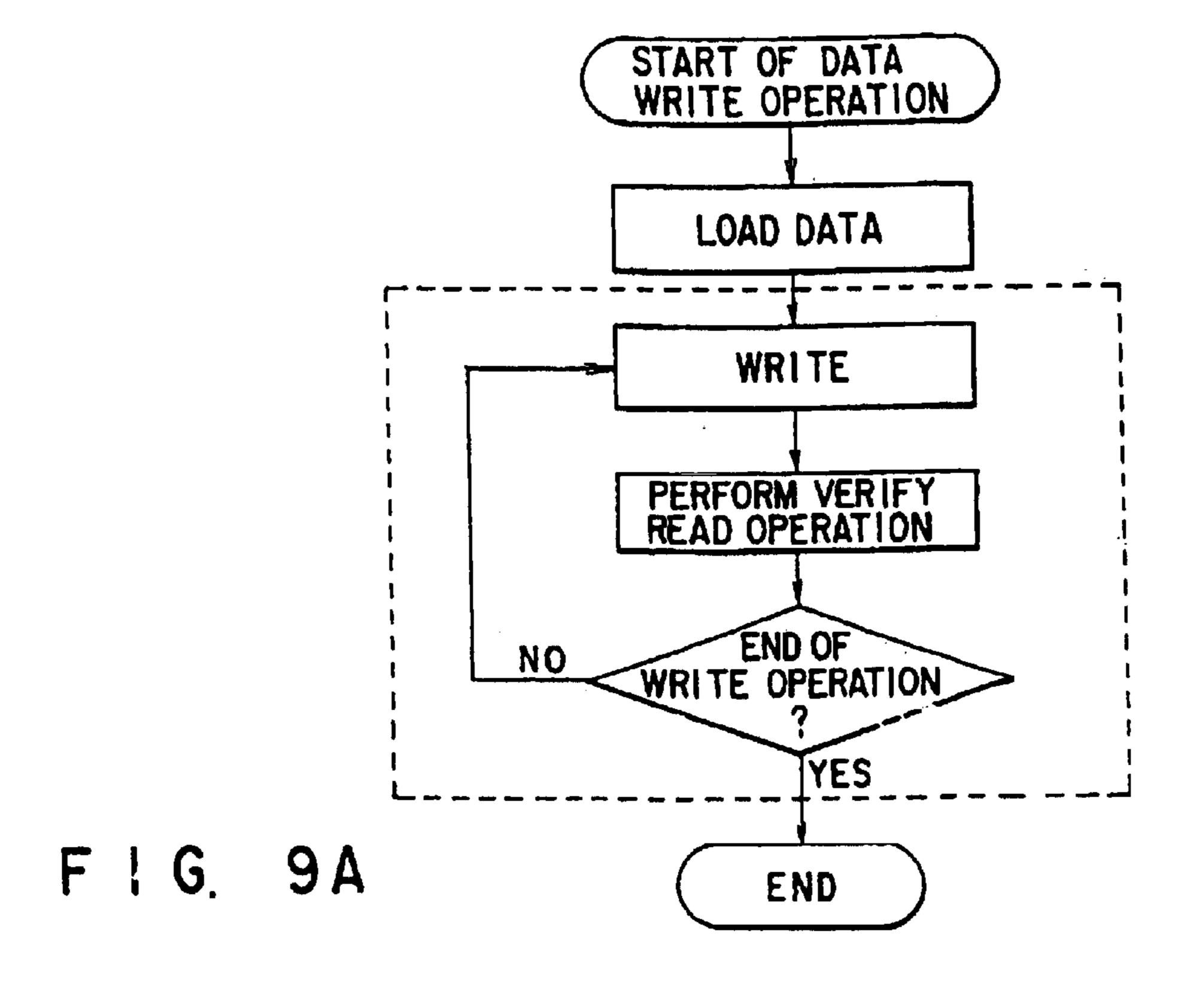

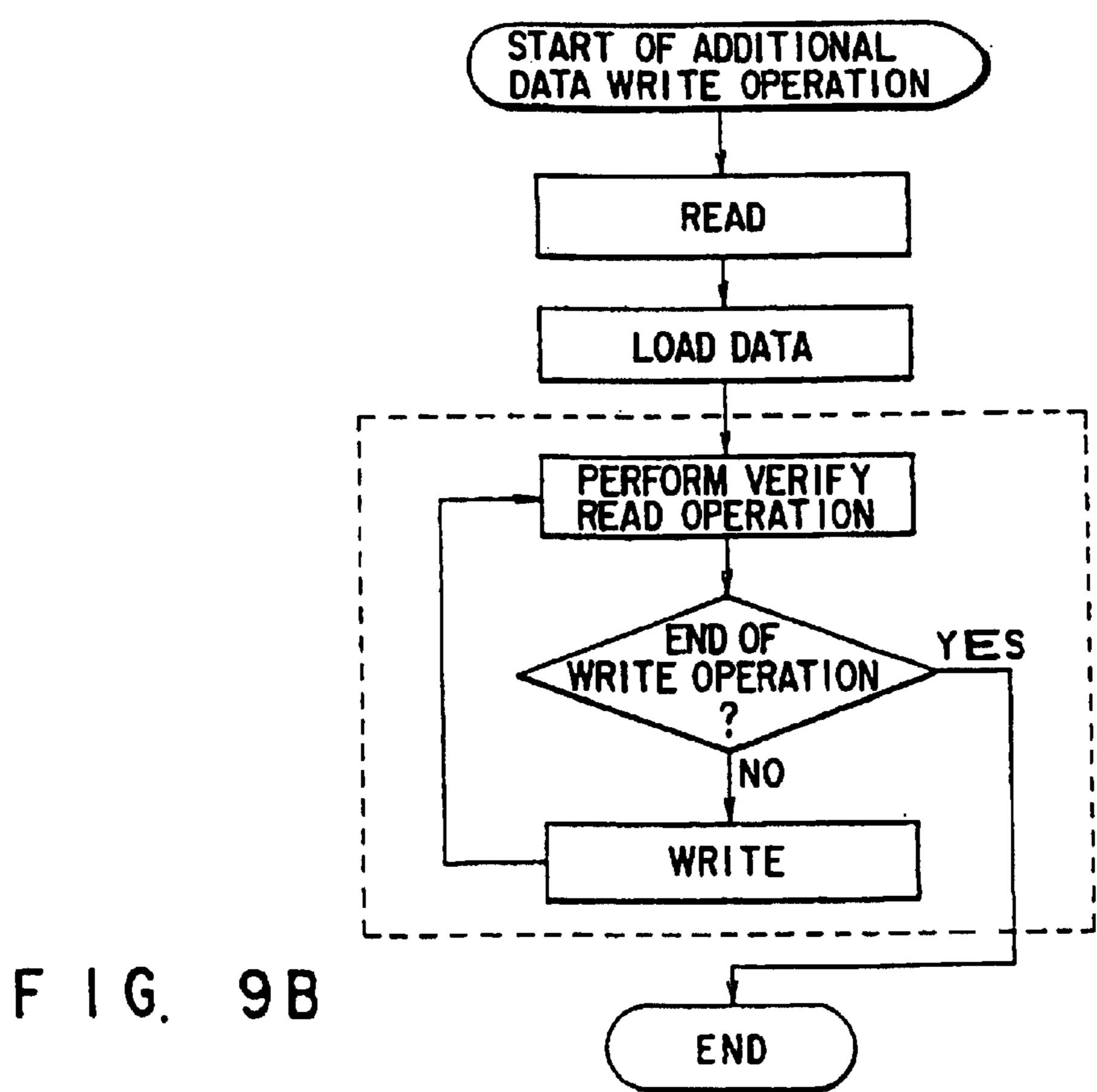

- FIGS. 9A and 9B are flow charts showing a data write algorithm and an additional data write algorithm in the first and second embodiments, respectively;

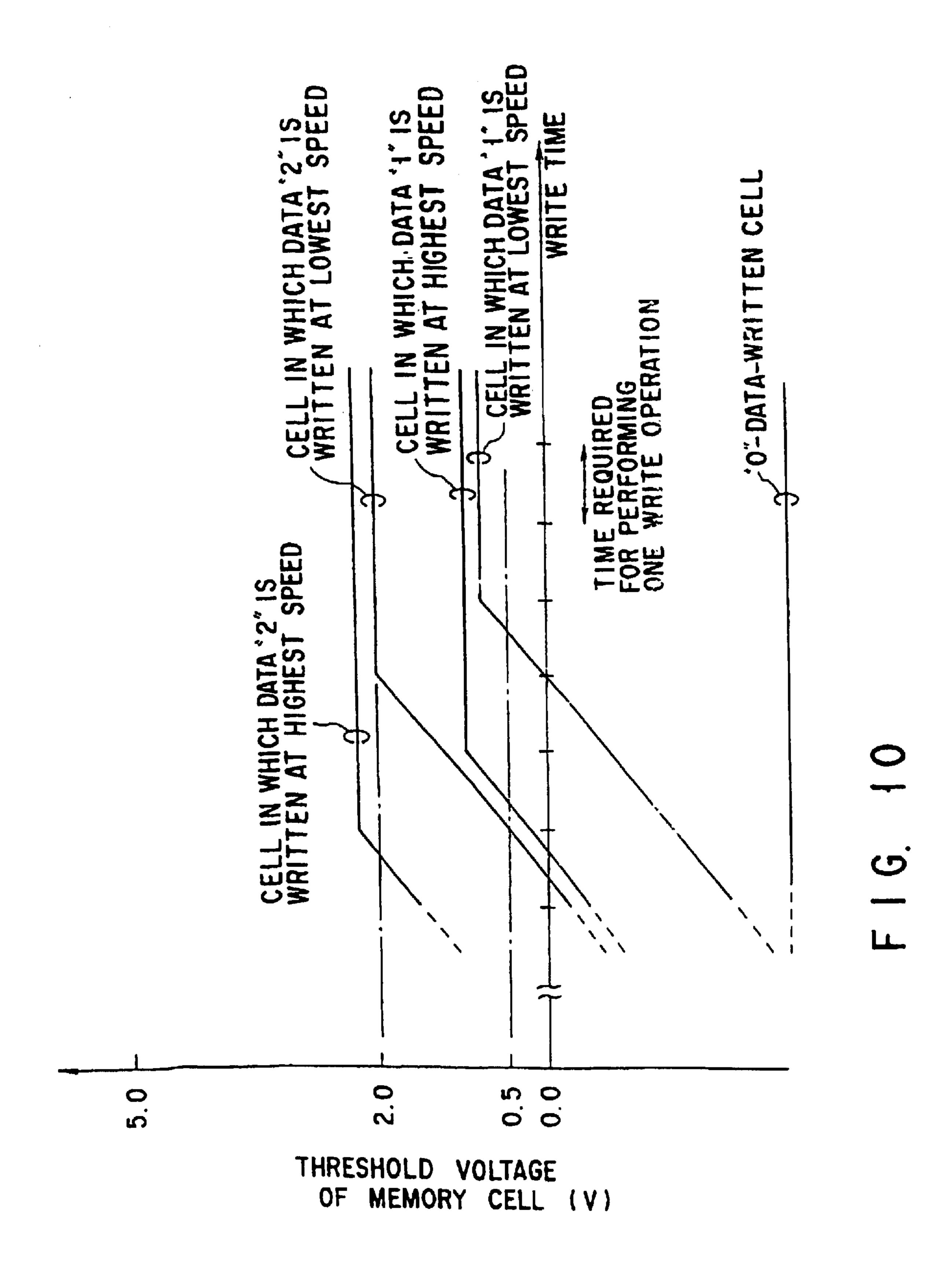

- FIG. 10 is a graph showing the write characteristics of the memory cell in the first embodiment;

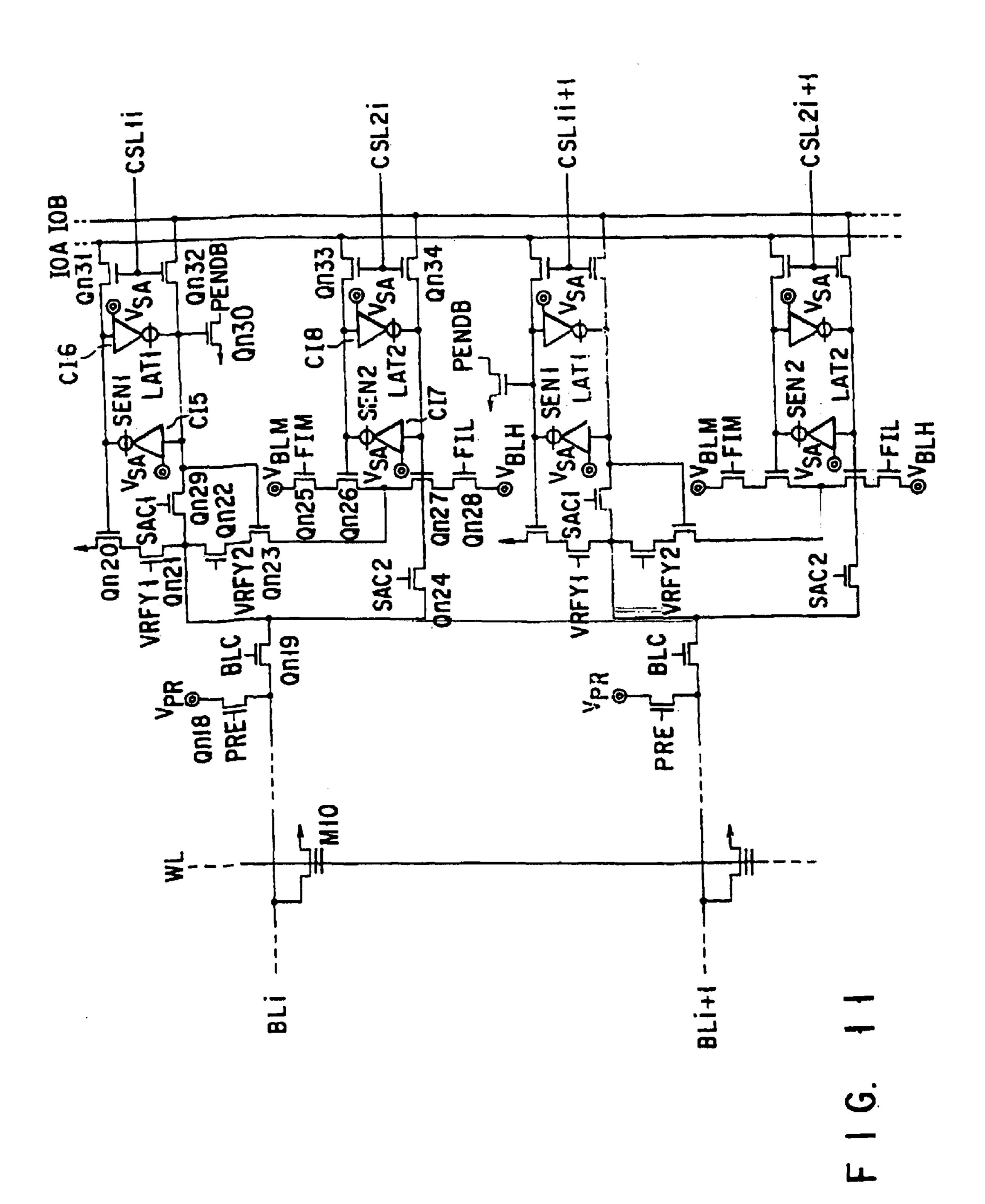

- FIG. 11 is a circuit diagram showing the arrangements of a memory cell array and a bit line control circuit in the second embodiment;

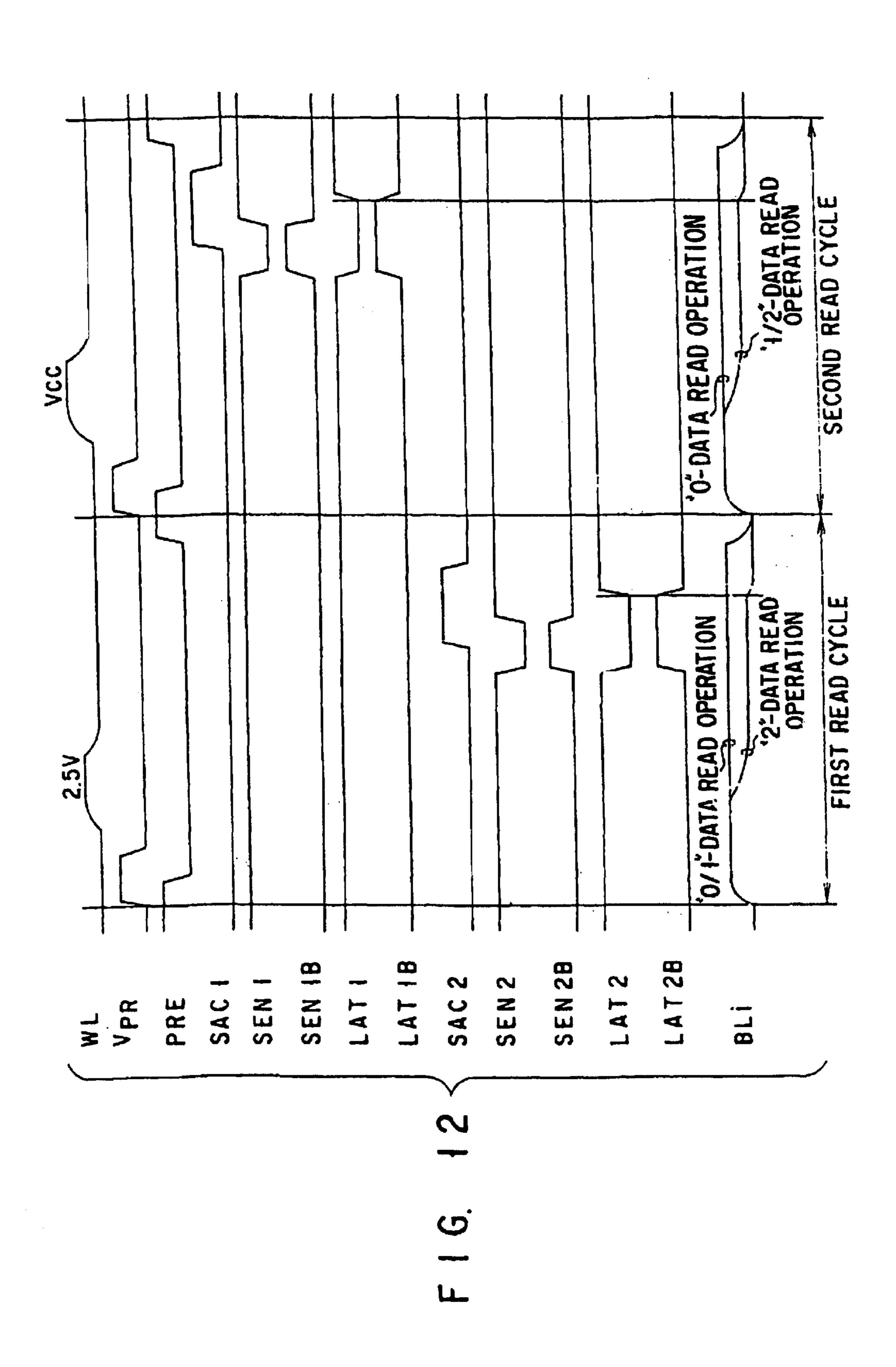

- FIG. 12 is a timing chart showing a read operation in the second embodiment;

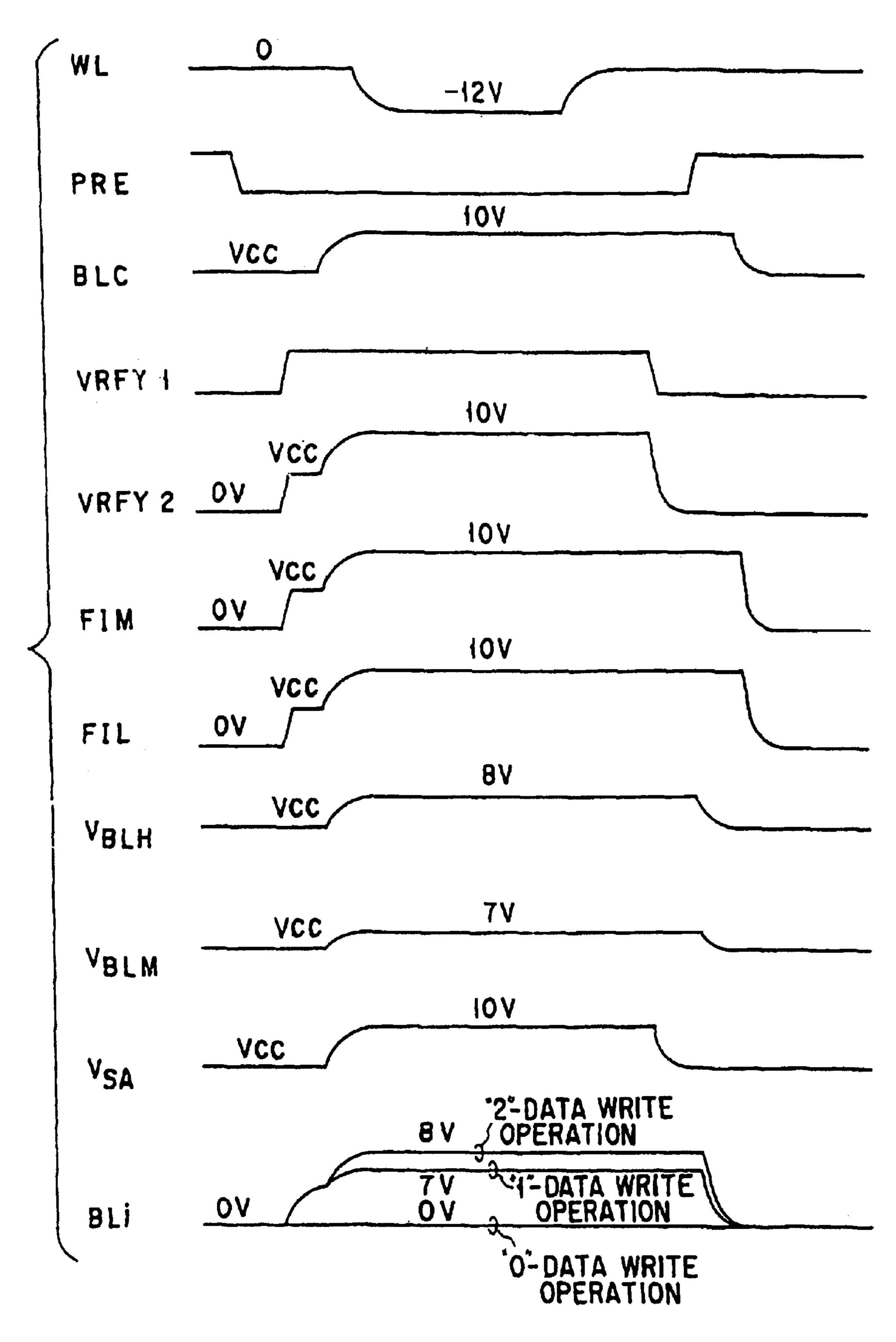

- FIG. 13 is a timing chart showing a write operation in the 20 second embodiment;

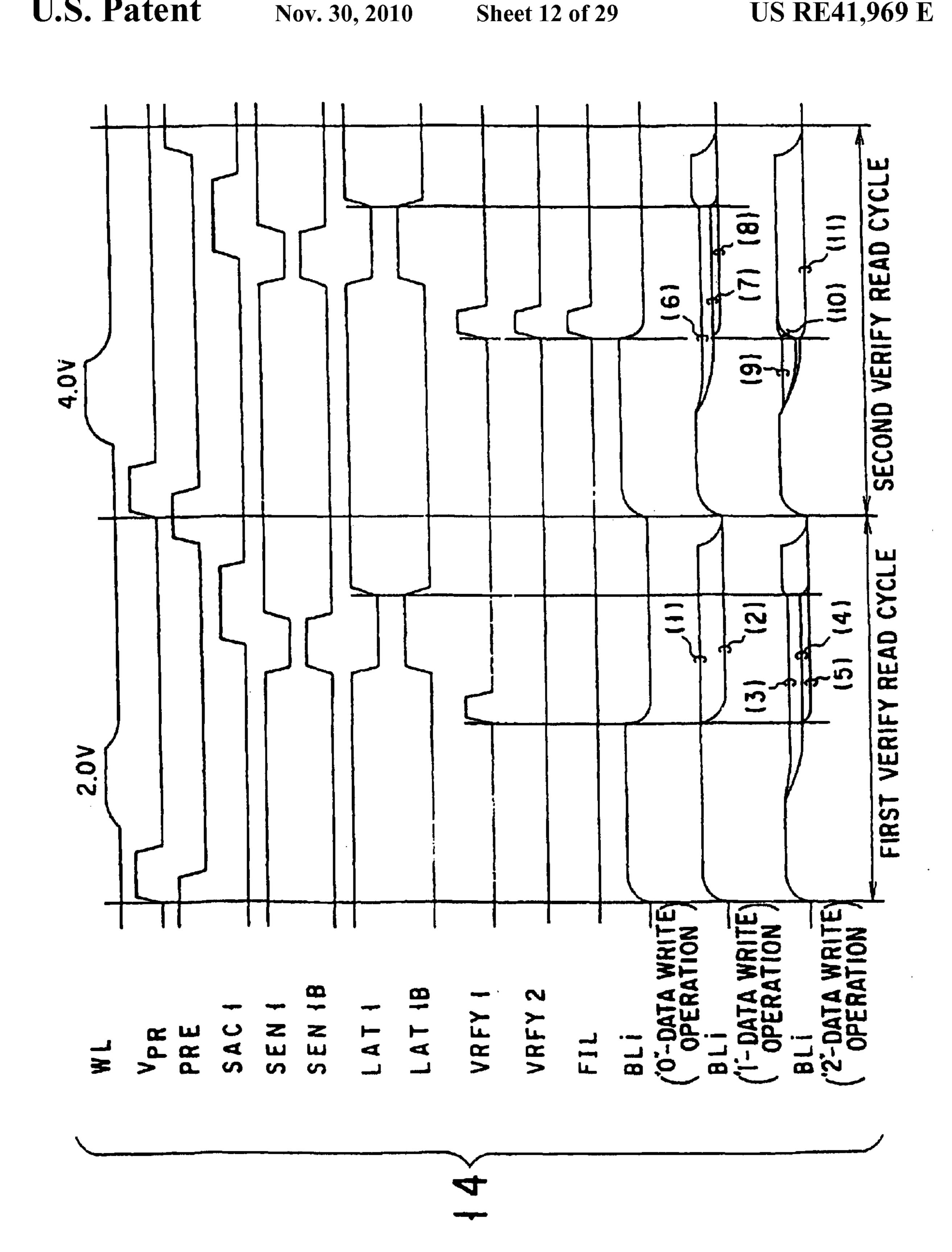

- FIG. 14 is a timing chart showing a verify read operation in the second embodiment;

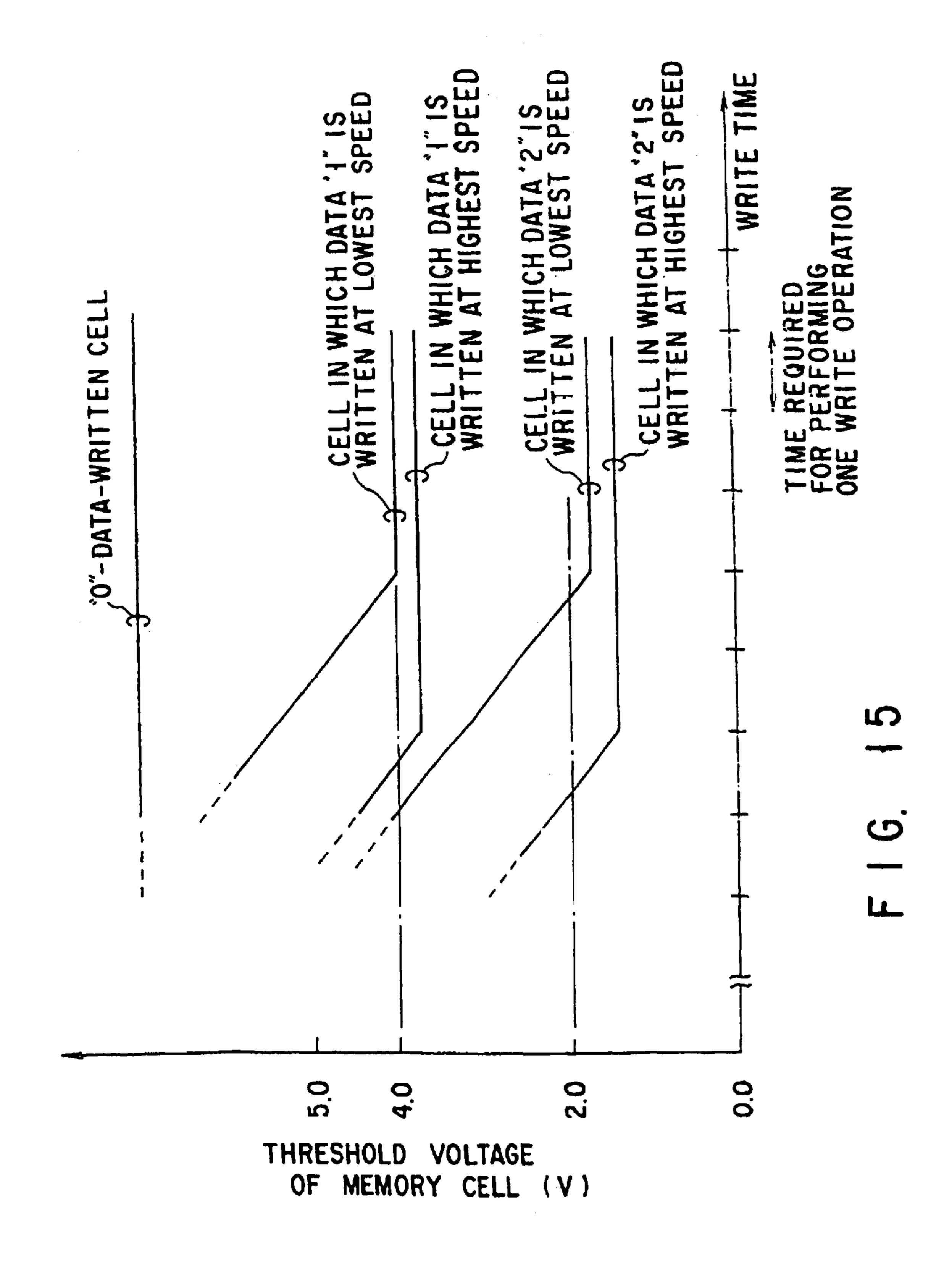

- FIG. **15** is a graph showing the write characteristics of the memory cell in the second embodiment;

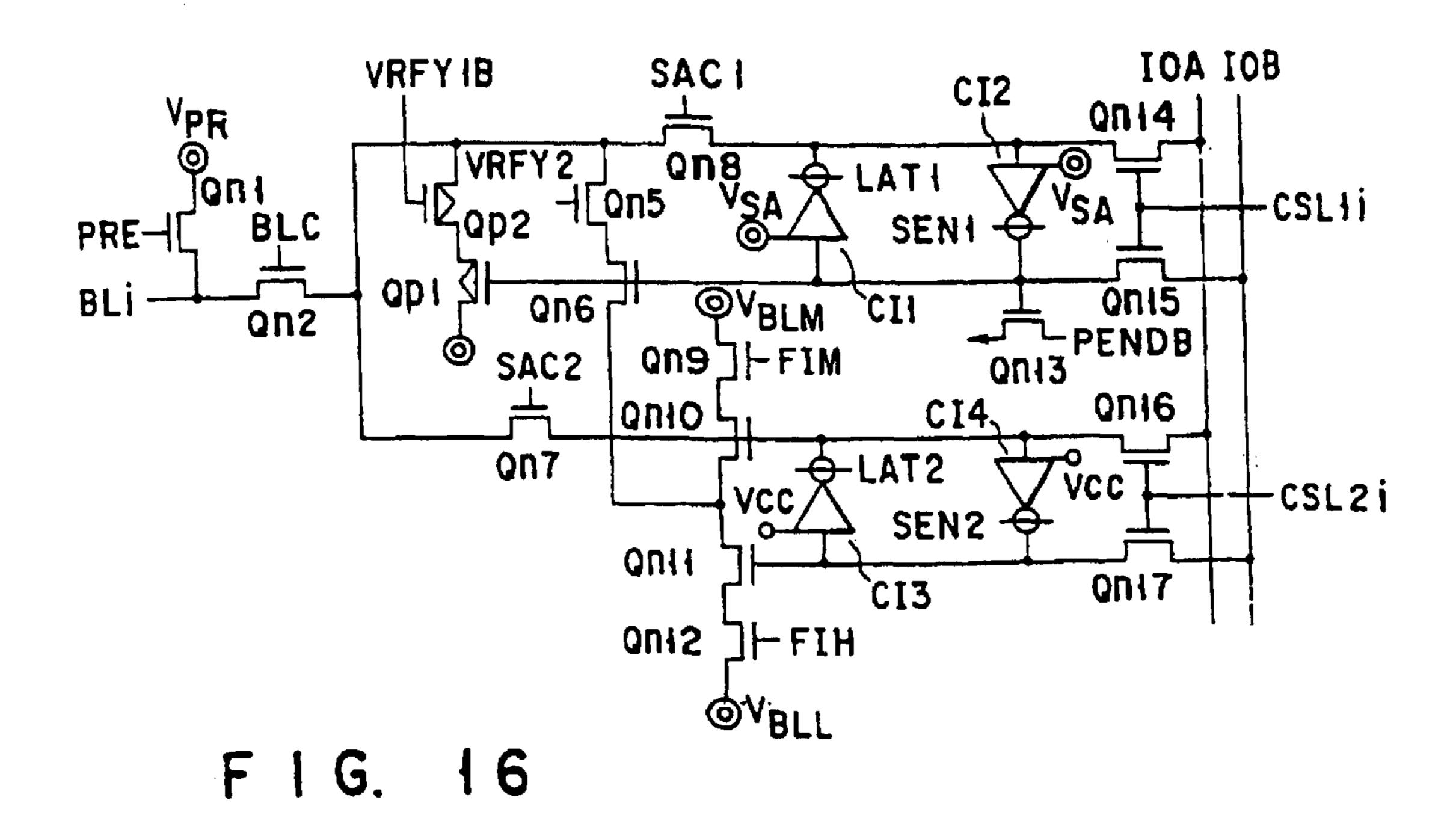

- FIG. 16 is a circuit diagram showing a modification of the bit line control circuit in the first embodiment;

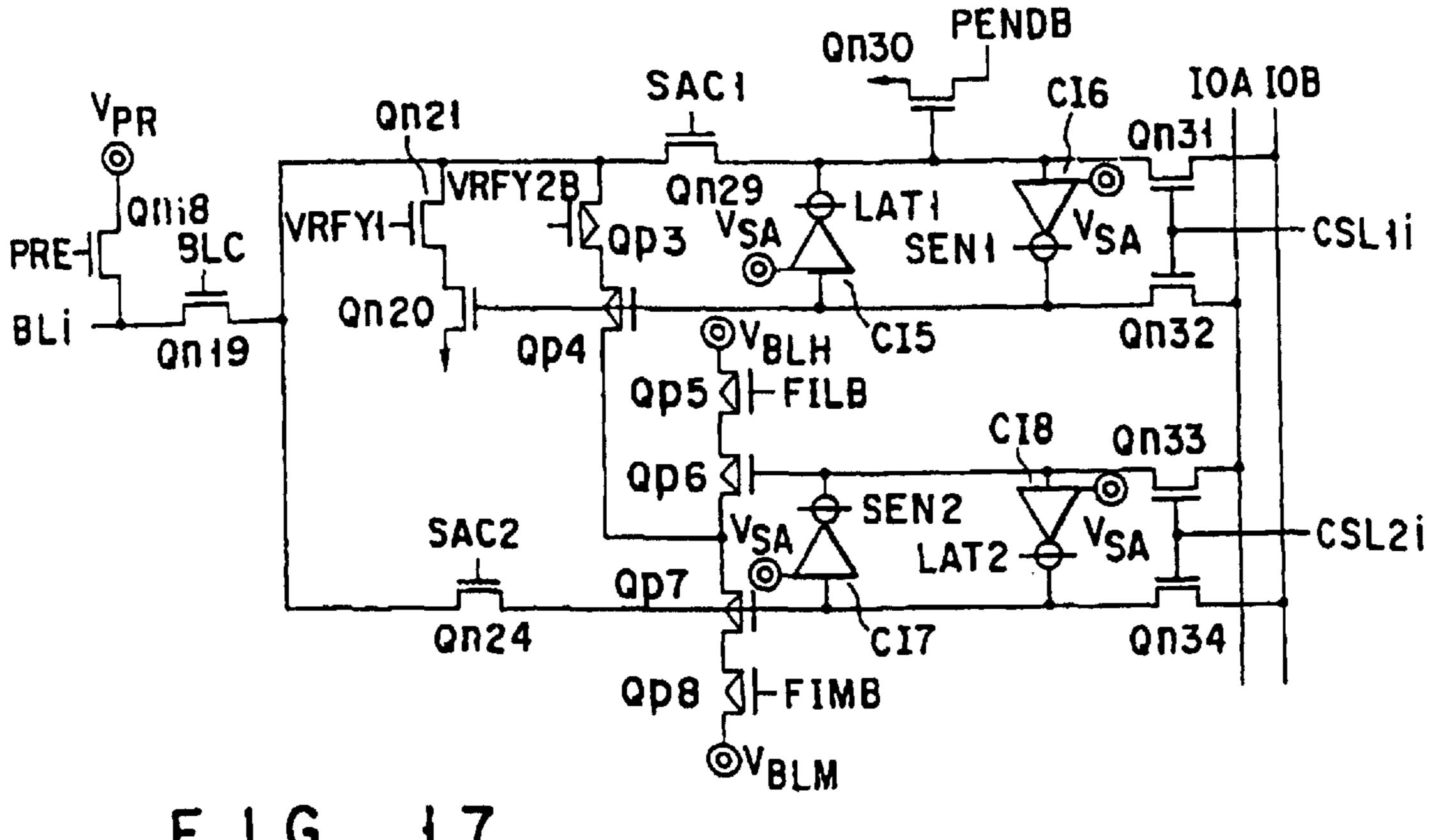

- FIG. 17 is a circuit diagram showing a modification of the bit line control circuit in the second embodiment;

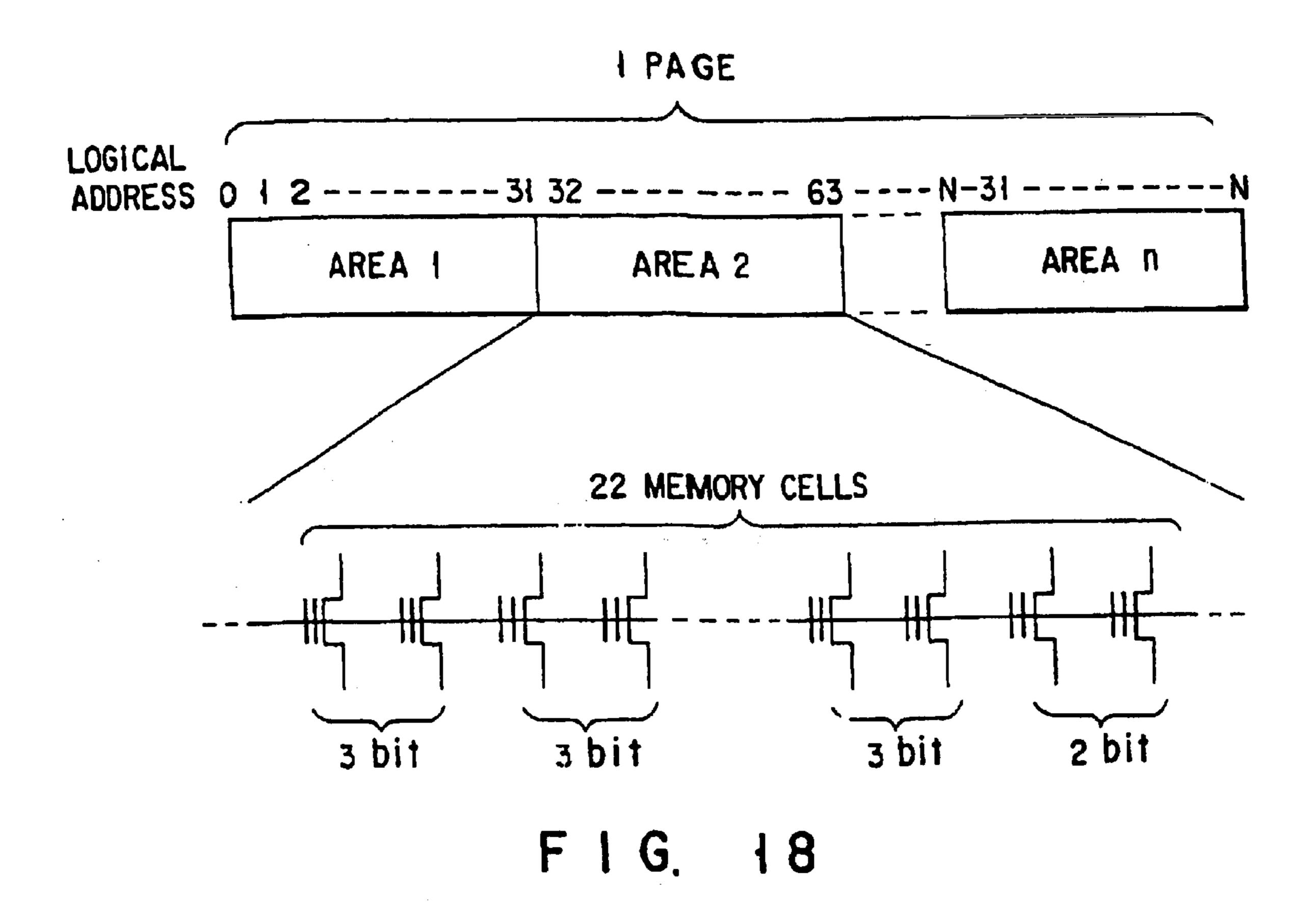

- FIG. 18 is a view showing a unit for an additional data write operation in the first and second embodiments;

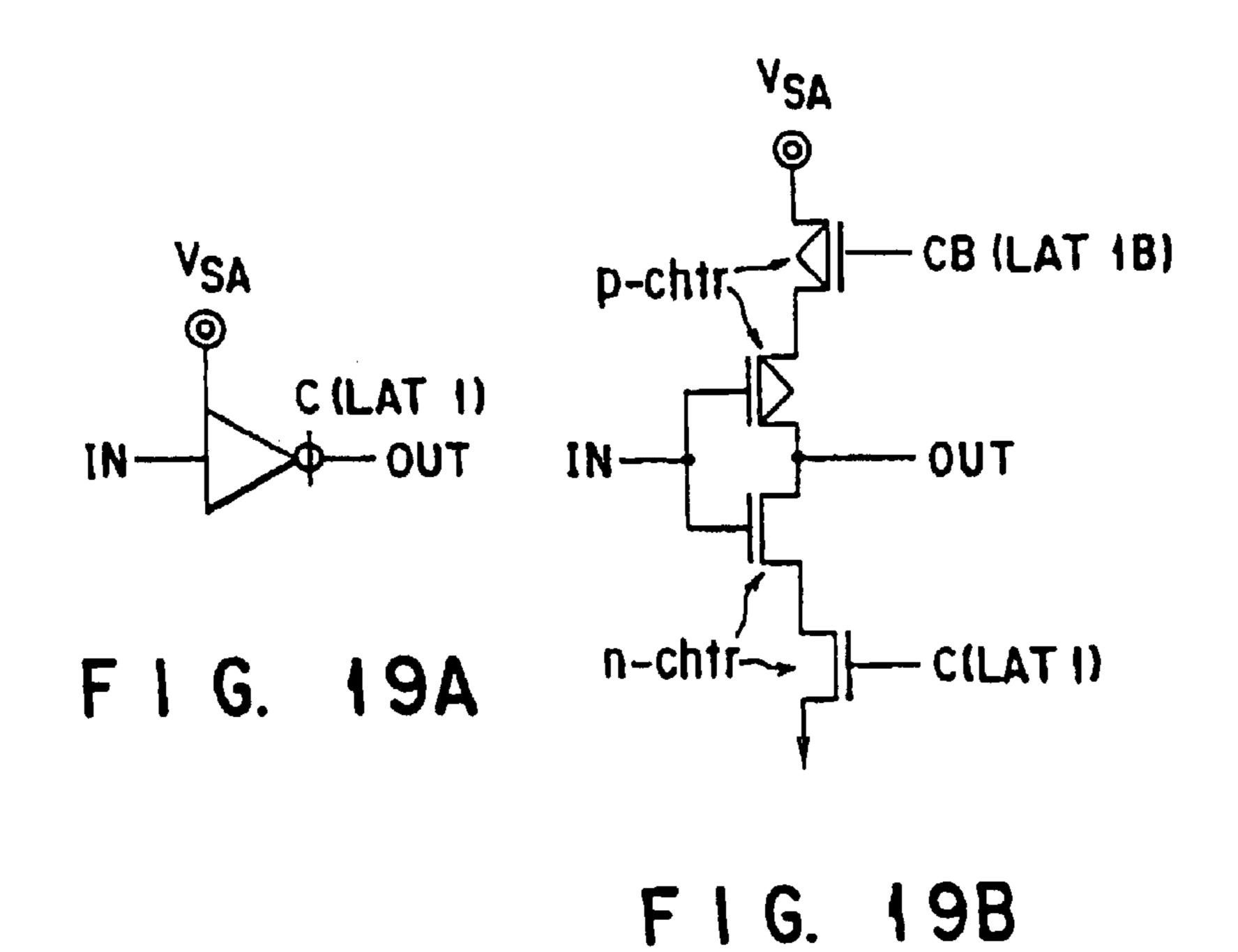

- FIGS. 19A and 19B are circuit diagrams showing the detailed arrangement of an inverter portion shown in FIG. 3;

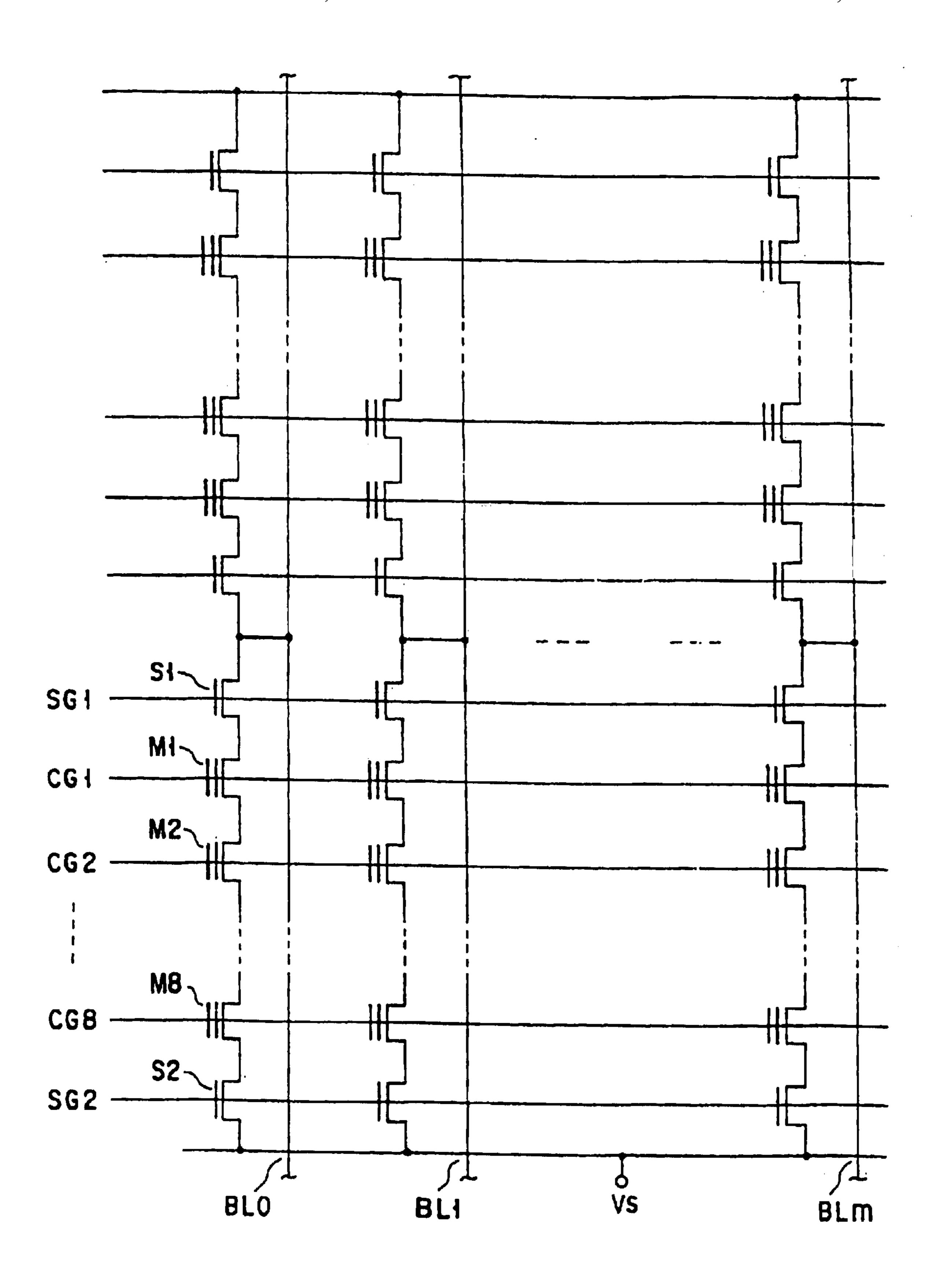

- FIG. 20 is a circuit diagram showing the arrangement of a 35 NAND cell array according to the third embodiment of the present invention;

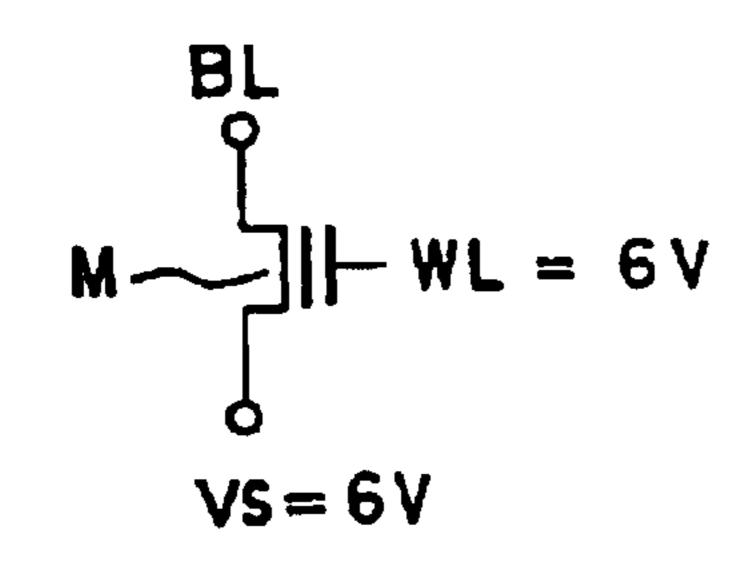

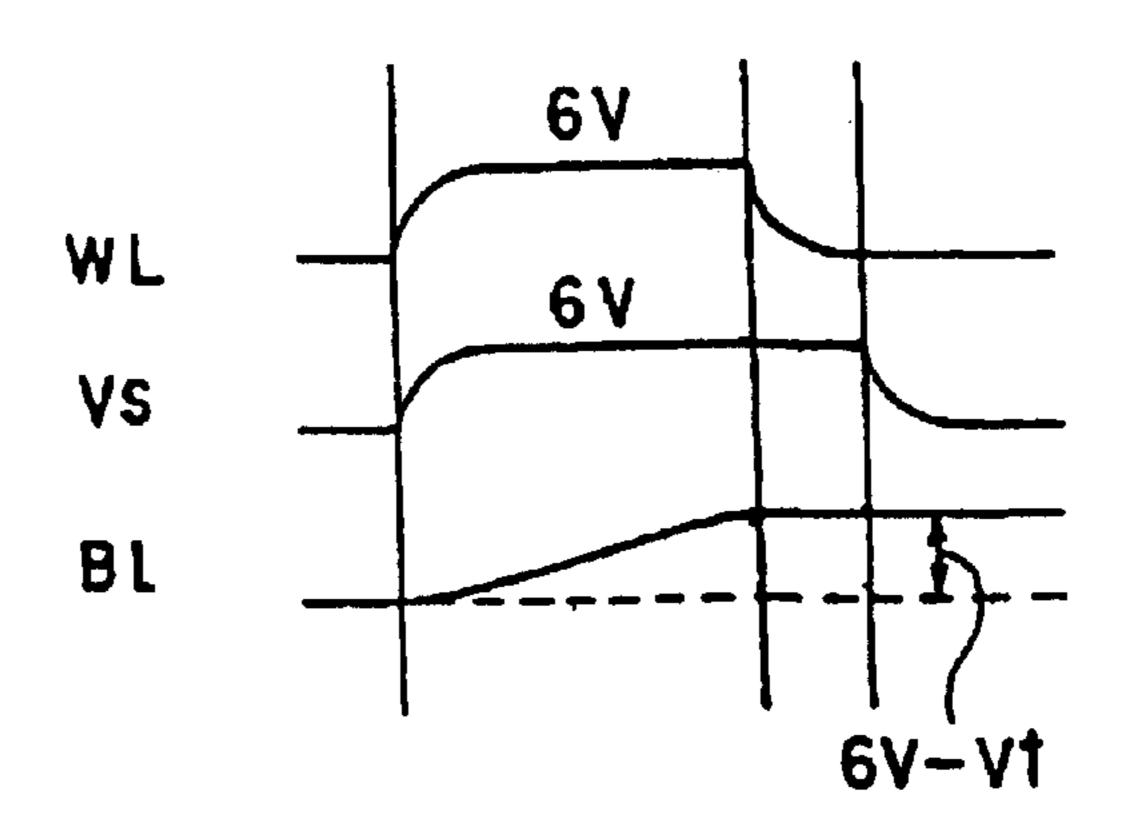

- FIGS. 21A and 21B are a circuit diagram and a chart, respectively, showing the read operation of the NAND cell in the third embodiment;

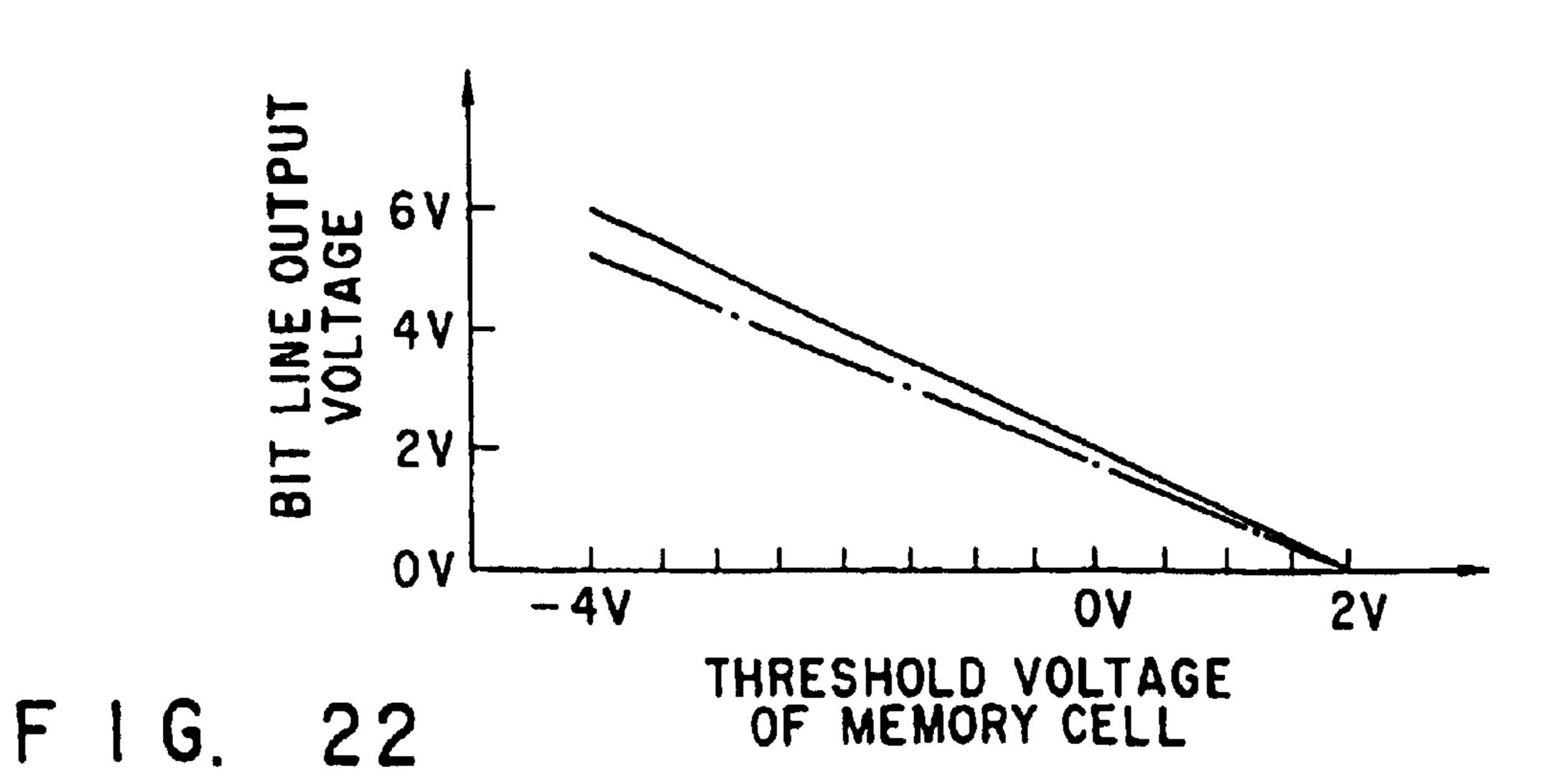

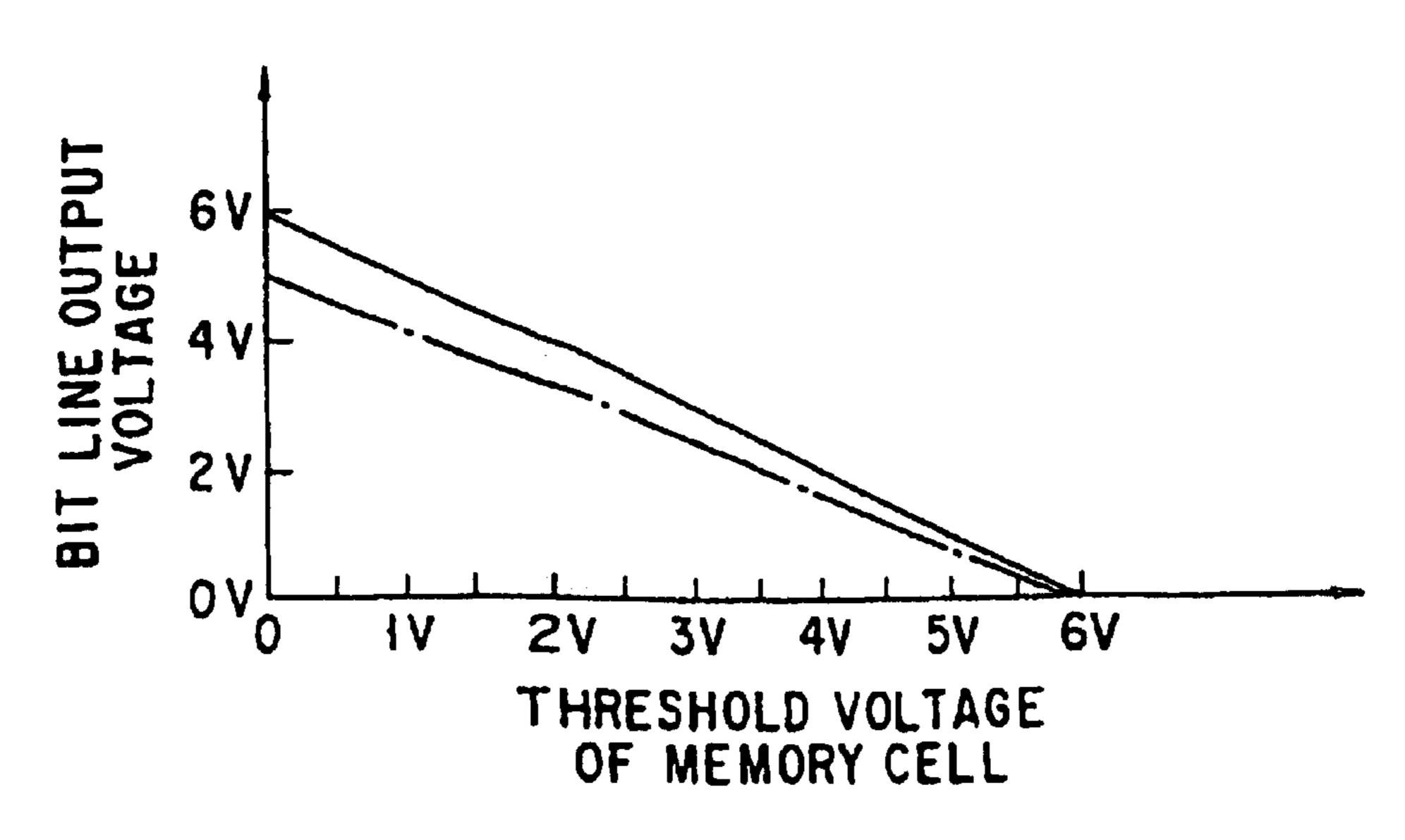

- FIG. 22 is a graph showing the relationship between a bit line output voltage in a read operation and the threshold voltage of a memory cell in the third embodiment;

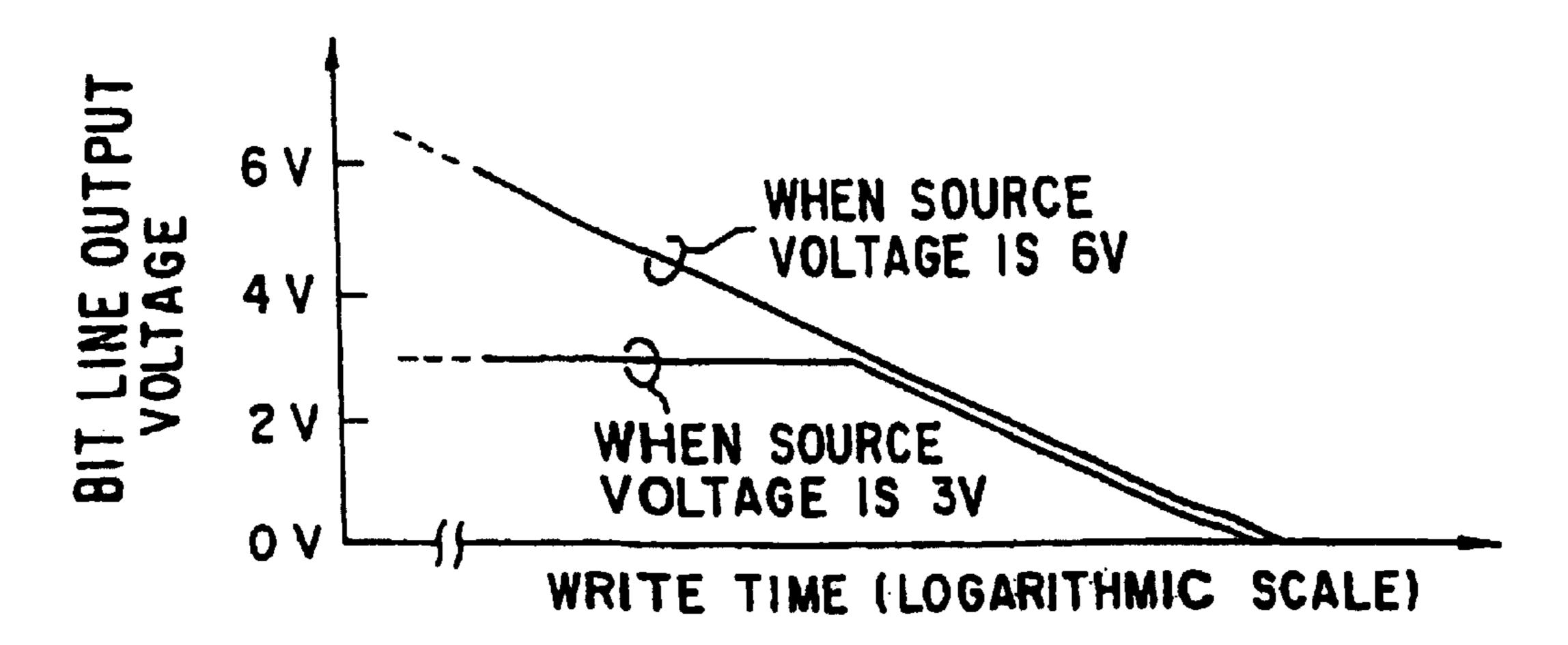

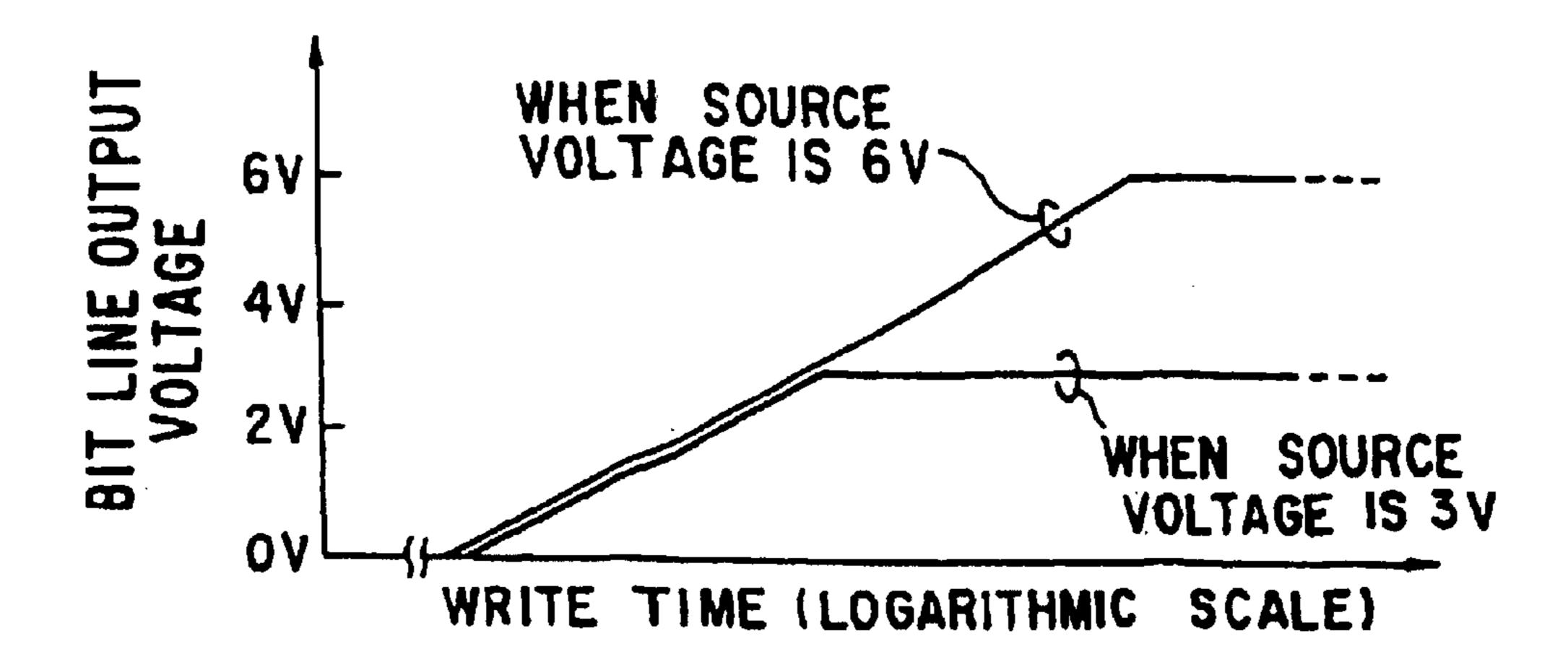

- FIG. 23 is a graph showing the relationship between a bit line output voltage in a read operation and a write time in the third embodiment;

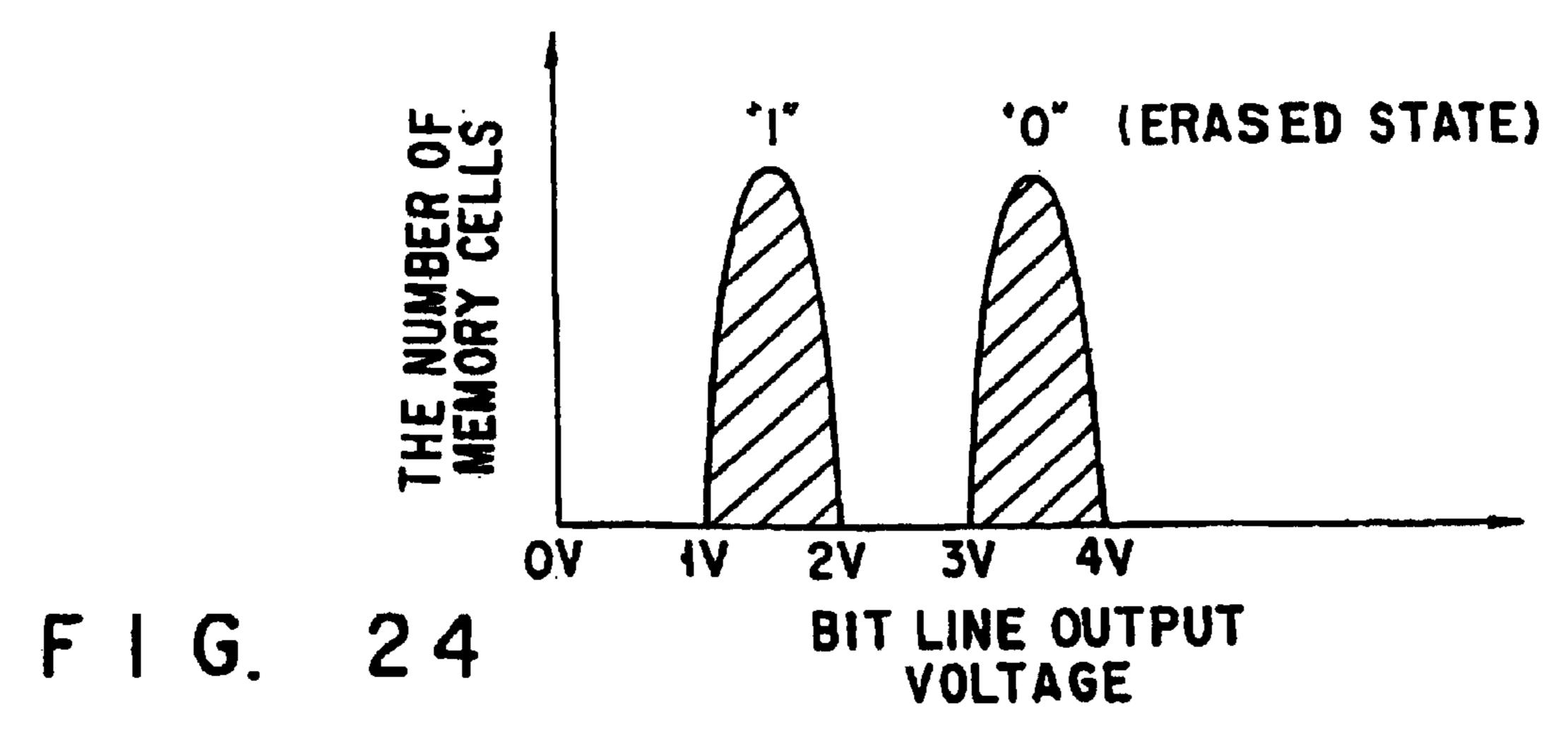

- FIG. 24 is a graph showing the relationship between data and a bit line output voltage in a read operation when a binary storing operation is performed to one memory cell in the third embodiment;

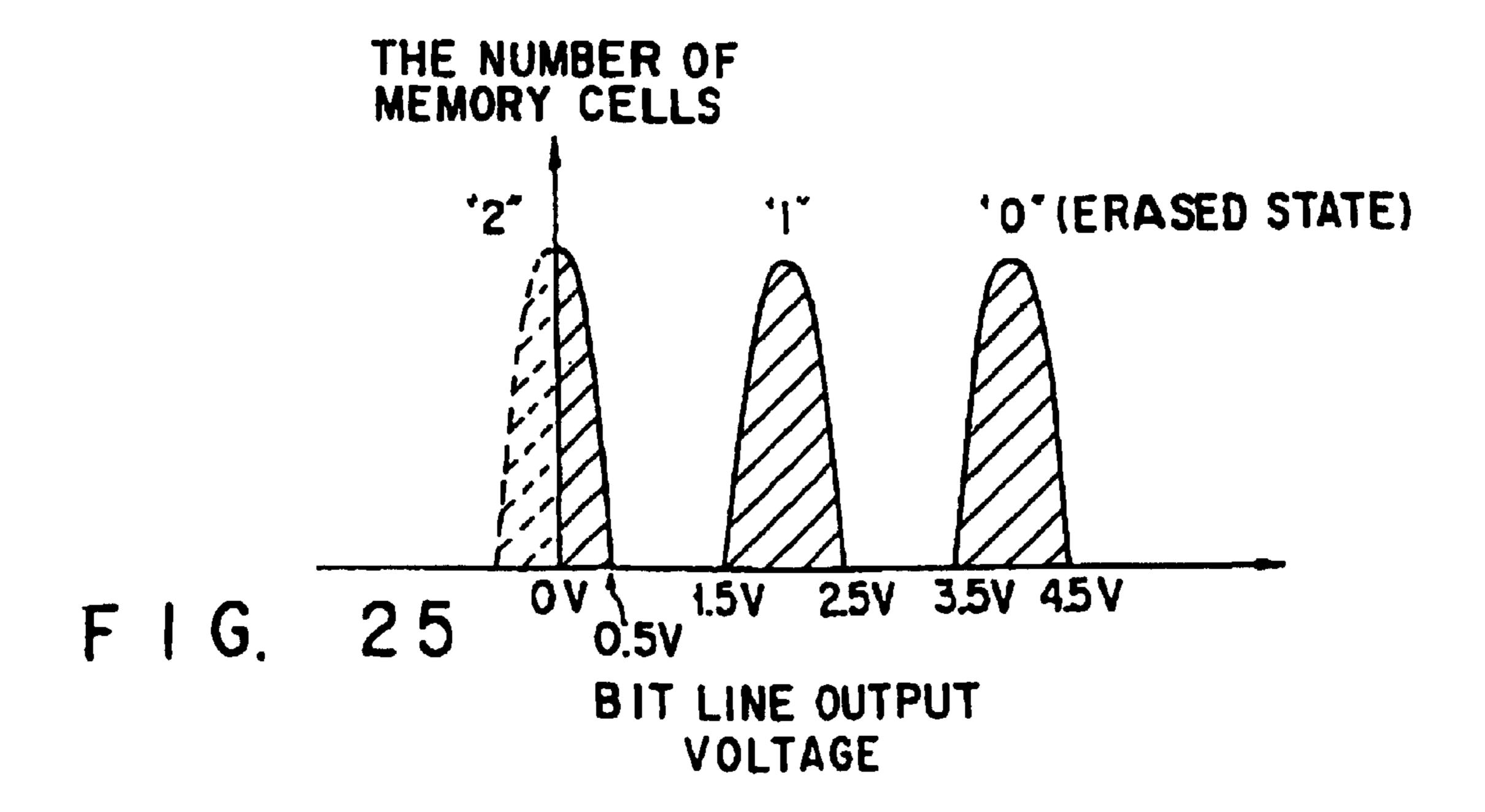

- FIG. 25 is a graph showing the relationship between data and a bit line output voltage in a read operation when a ternary storing operation is performed to one memory cell in the third embodiment;

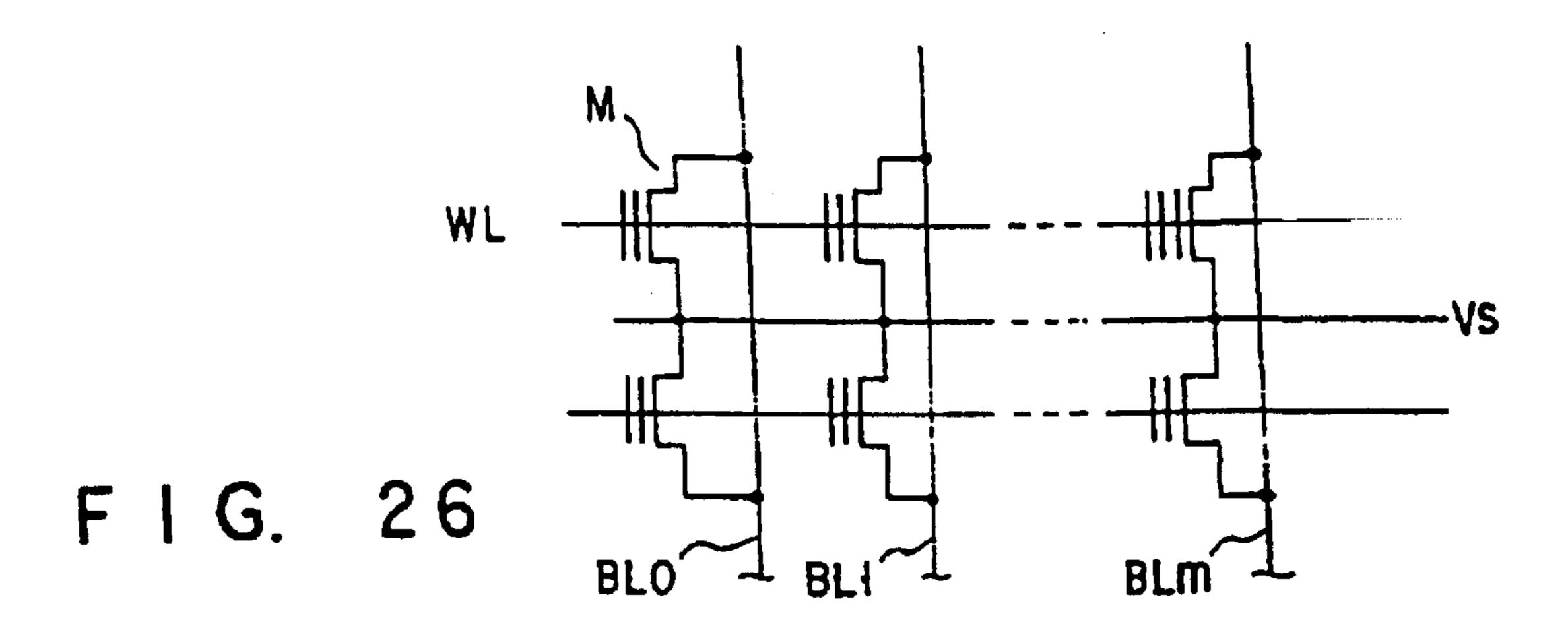

- FIG. 26 is a circuit diagram showing the arrangement of a NOR cell array according to the fourth embodiment of the present invention;

- FIGS. 27A and 27B are a circuit diagram and a chart, respectively, showing the read operation of a NOR cell in the fourth embodiment;

- FIG. 28 is a graph showing the relationship between a bit line output voltage in a read operation and the threshold voltage of a memory cell in the fourth embodiment;

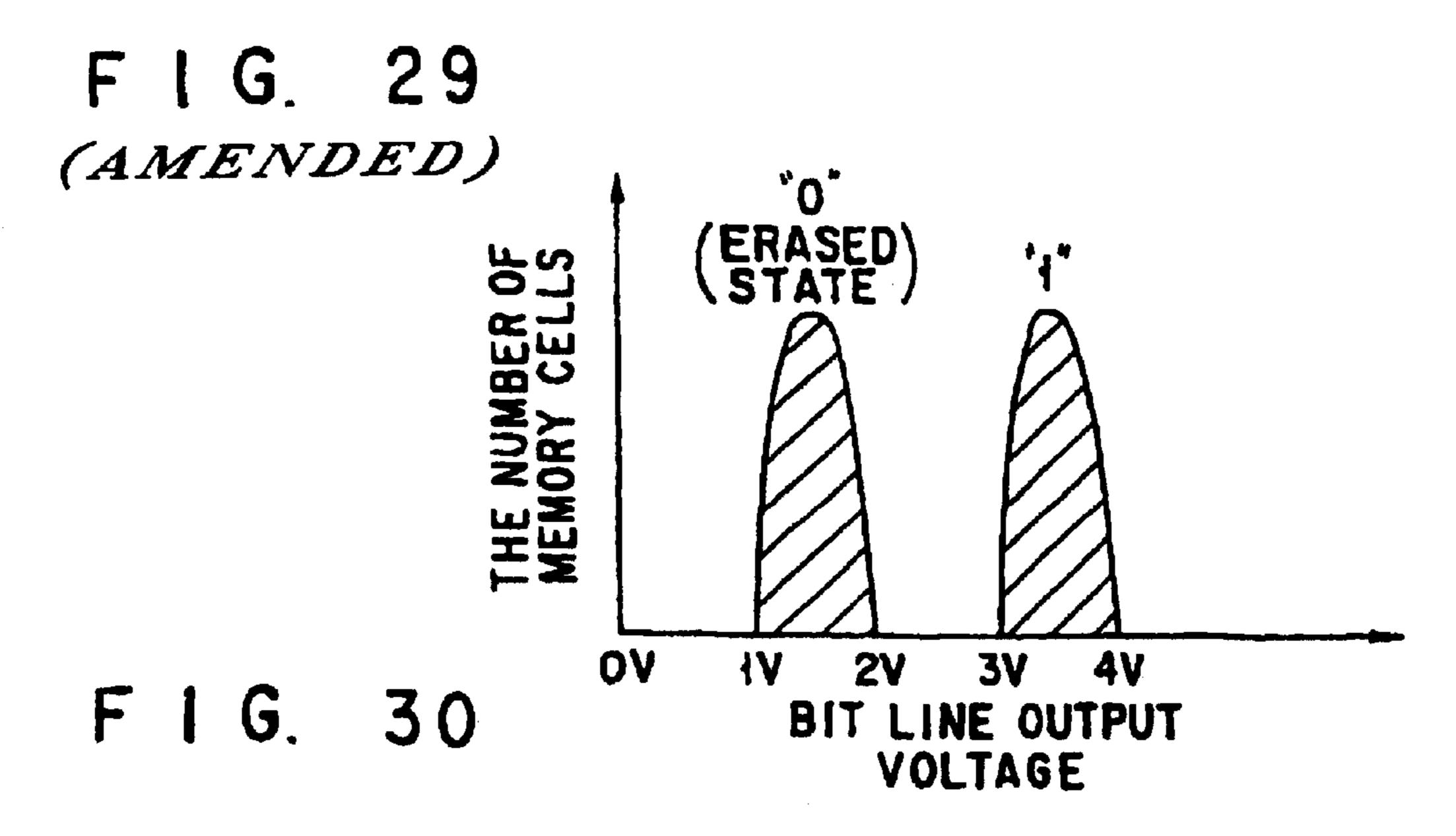

- FIG. 29 is a graph showing the relationship between the 65 bit line output voltage in a read operation and a write time in the fourth embodiment;

12

- FIG. 30 is a graph showing the relationship between data and a bit line output voltage in a read operation when a binary storing operation is performed to one memory cell in the fourth embodiment;

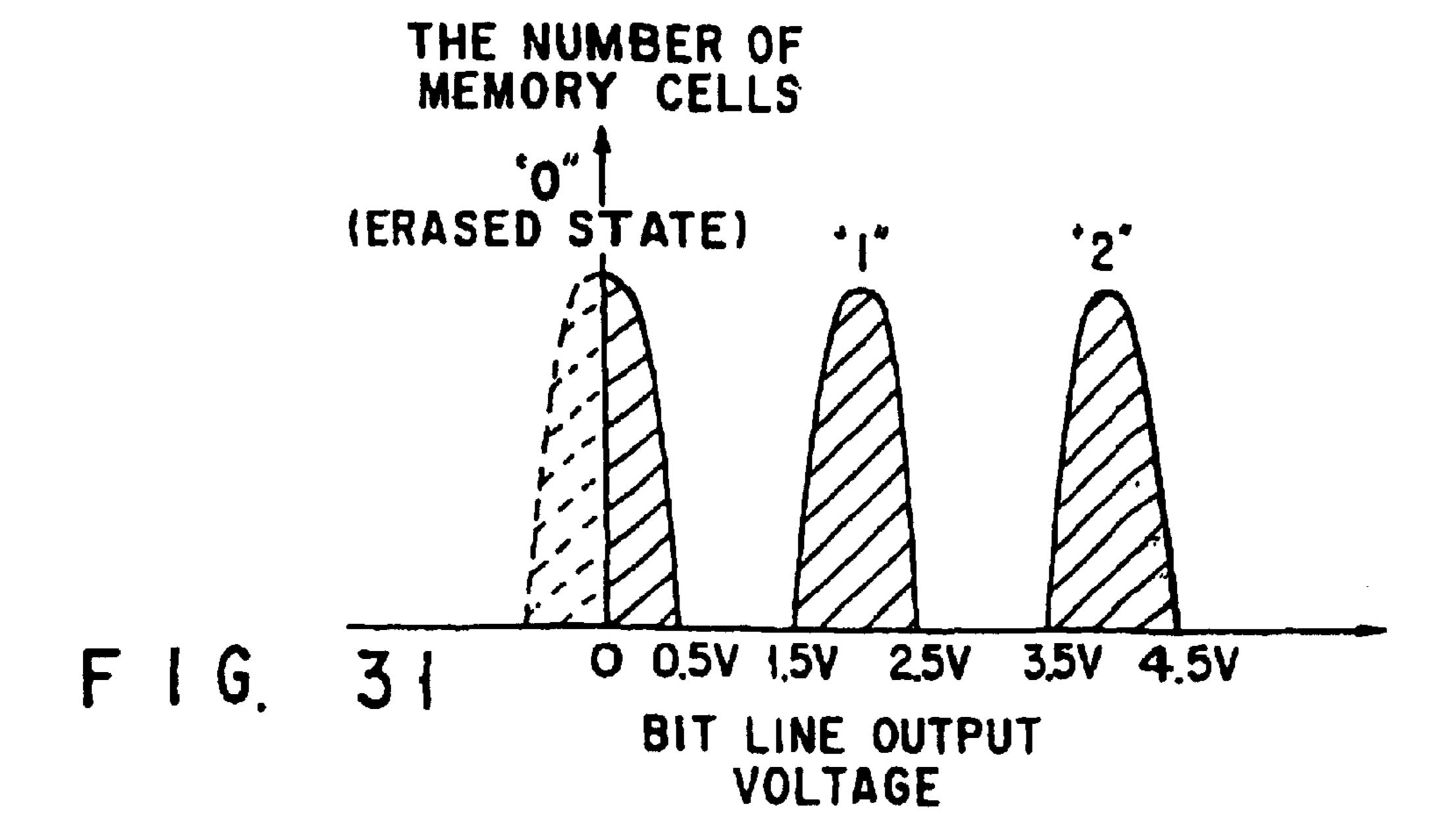

- FIG. 31 is a graph showing the relationship between data and a bit line output voltage in a read operation when a ternary storing operation is performed to one memory cell in the fourth embodiment;

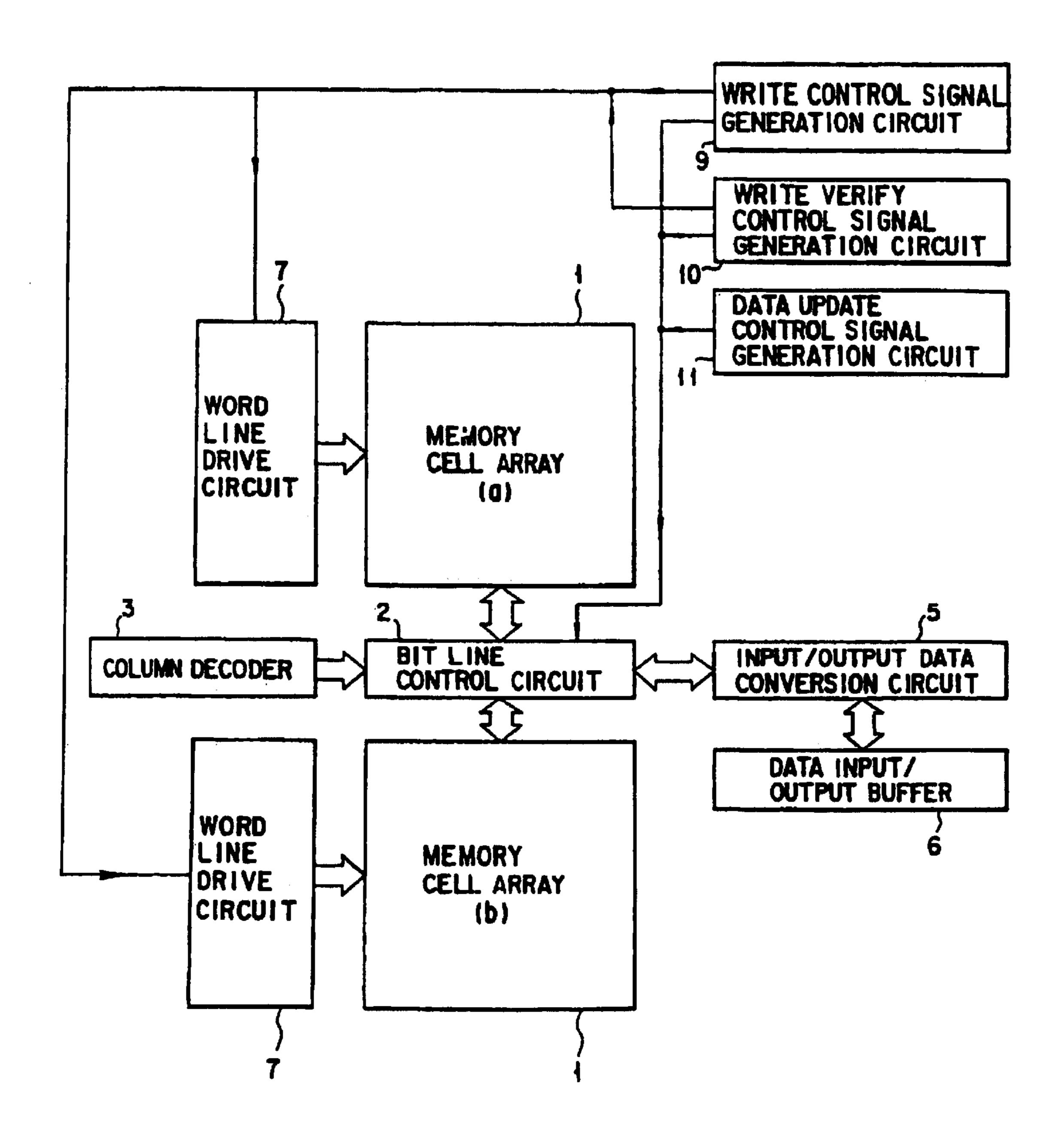

- FIG. **32** is a block diagram showing the arrangement of an EEPROM according to the third and fourth embodiments;

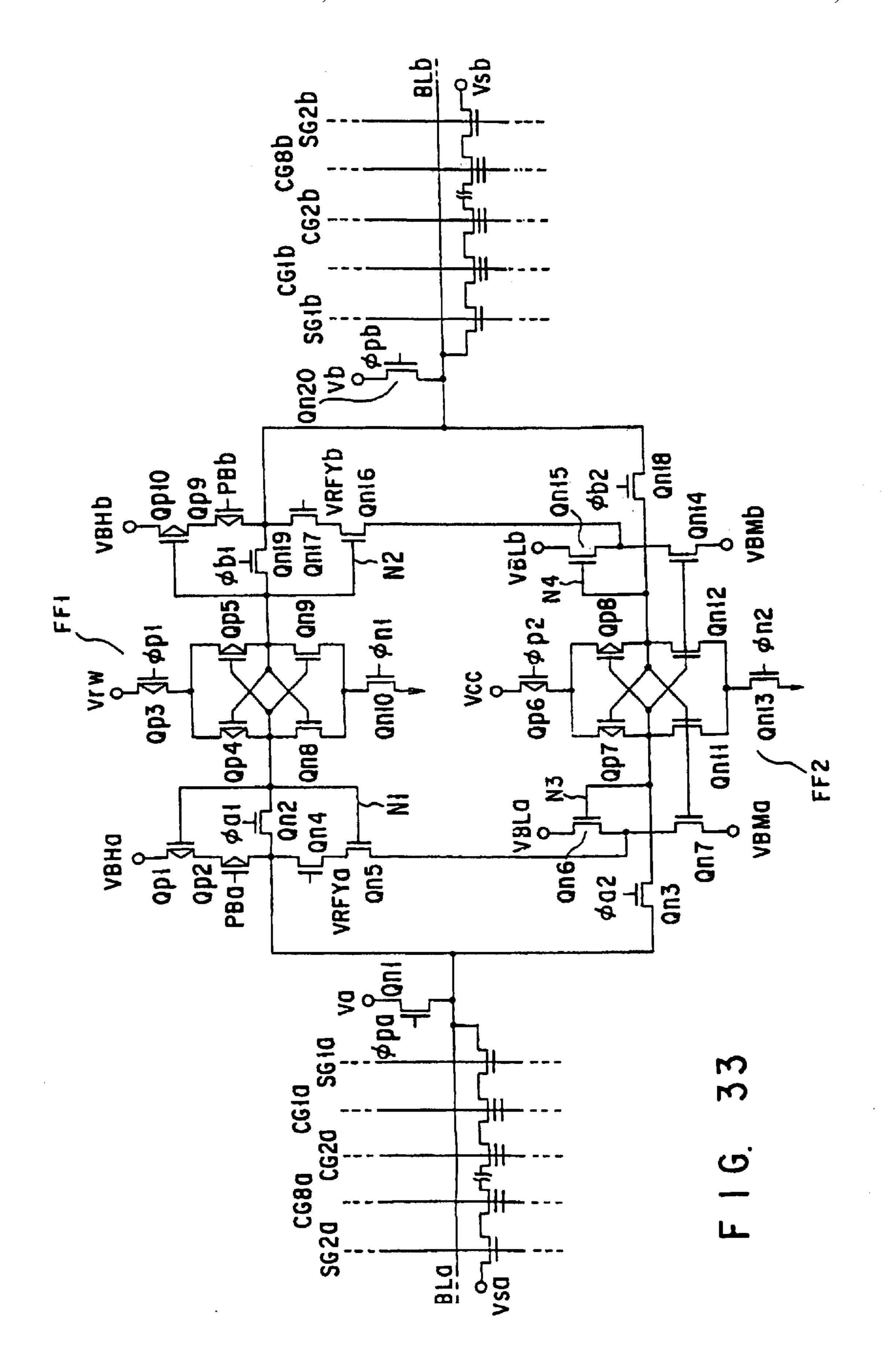

- FIG. 33 is a circuit diagram showing the arrangements of a memory cell array and a bit line control circuit in the third embodiment;

- FIG. **34** is a timing chart showing a read operation in the third embodiment;

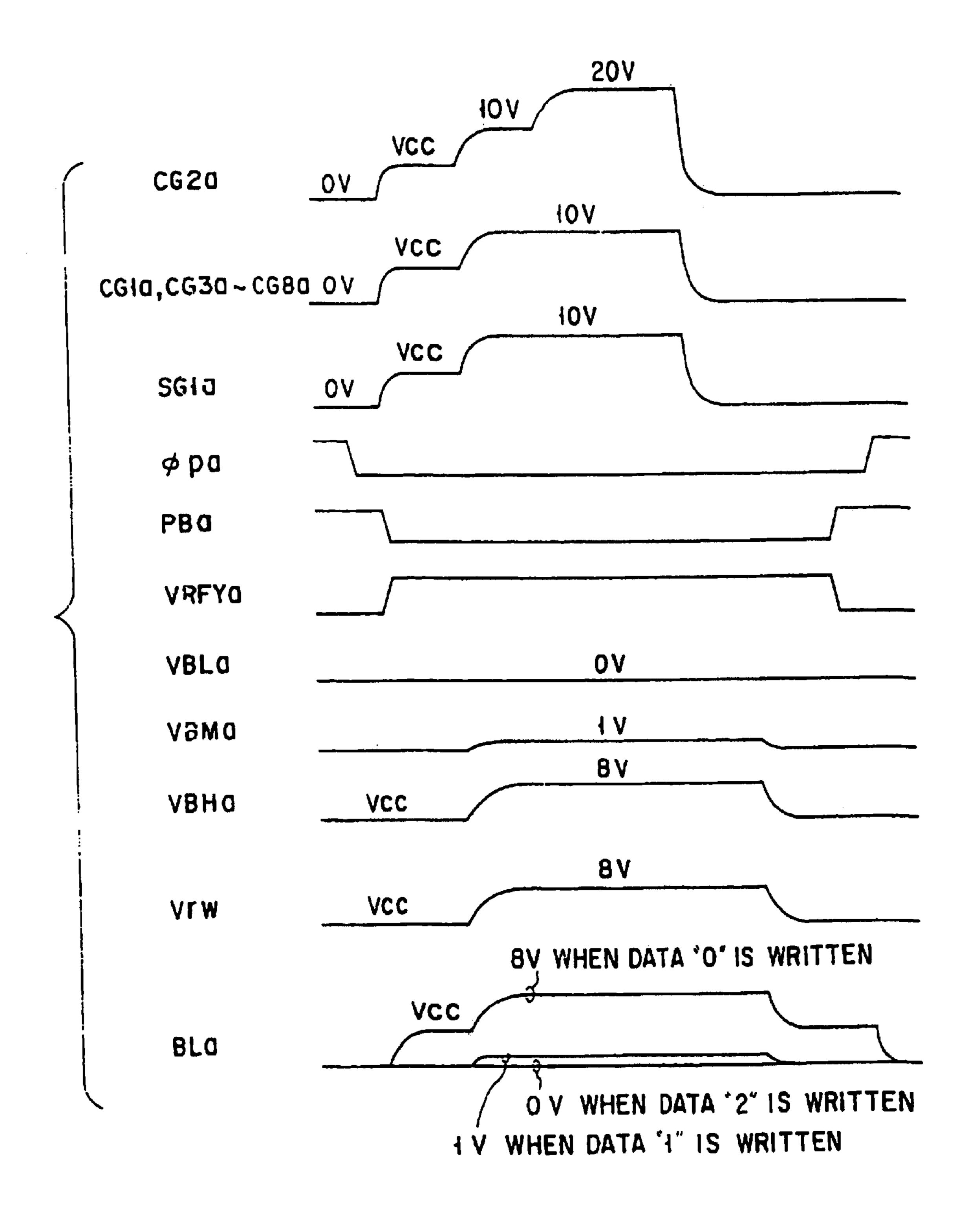

- FIG. **35** is a timing chart showing a write operation in the third embodiment;

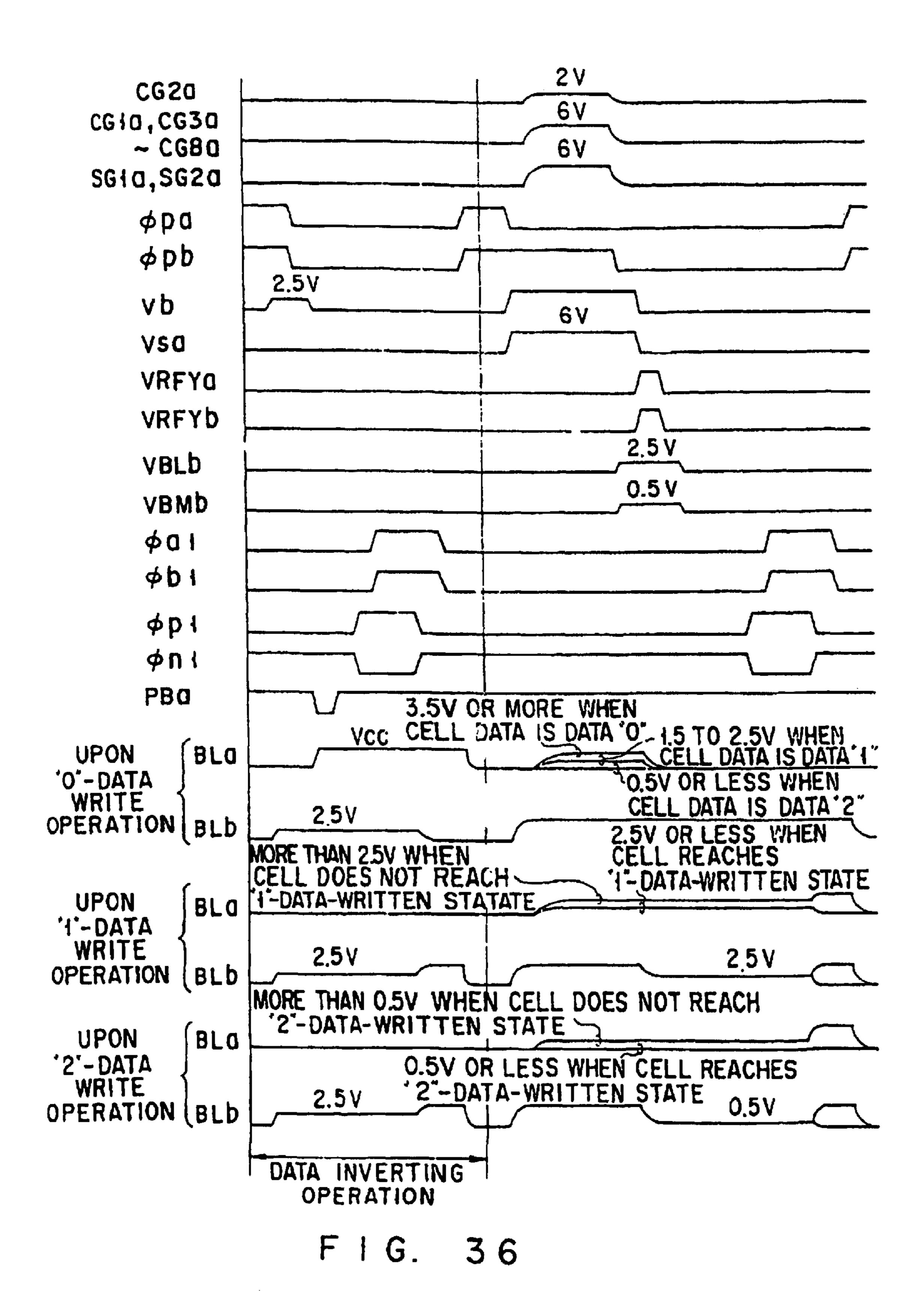

- FIG. **36** is a timing chart showing a verify read operation in the third embodiment;

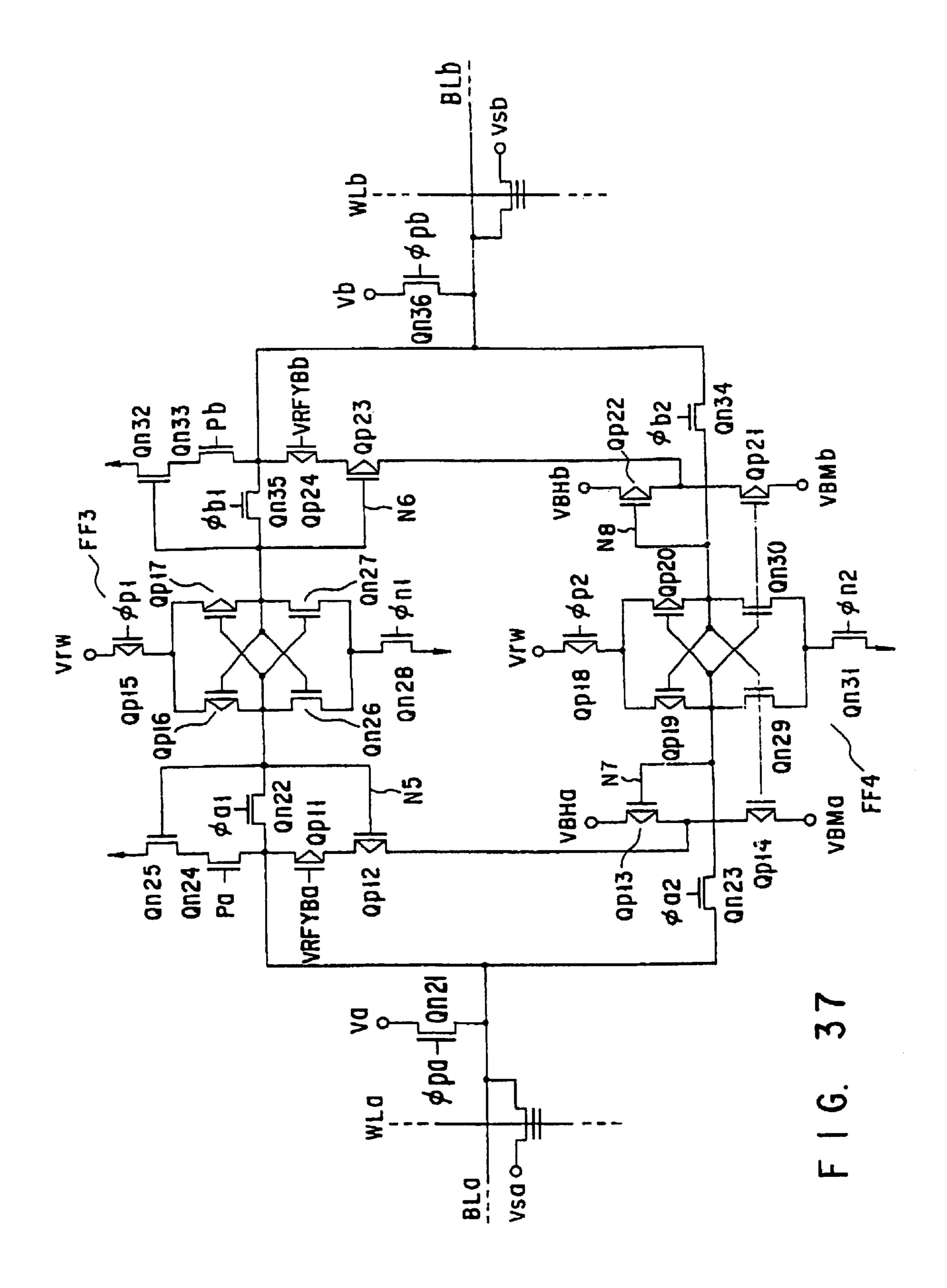

- FIG. 37 is a circuit diagram showing the arrangements of a memory cell array and a bit line control circuit in the fourth embodiment;

- FIG. **38** is a timing chart showing a read operation in the fourth embodiment;

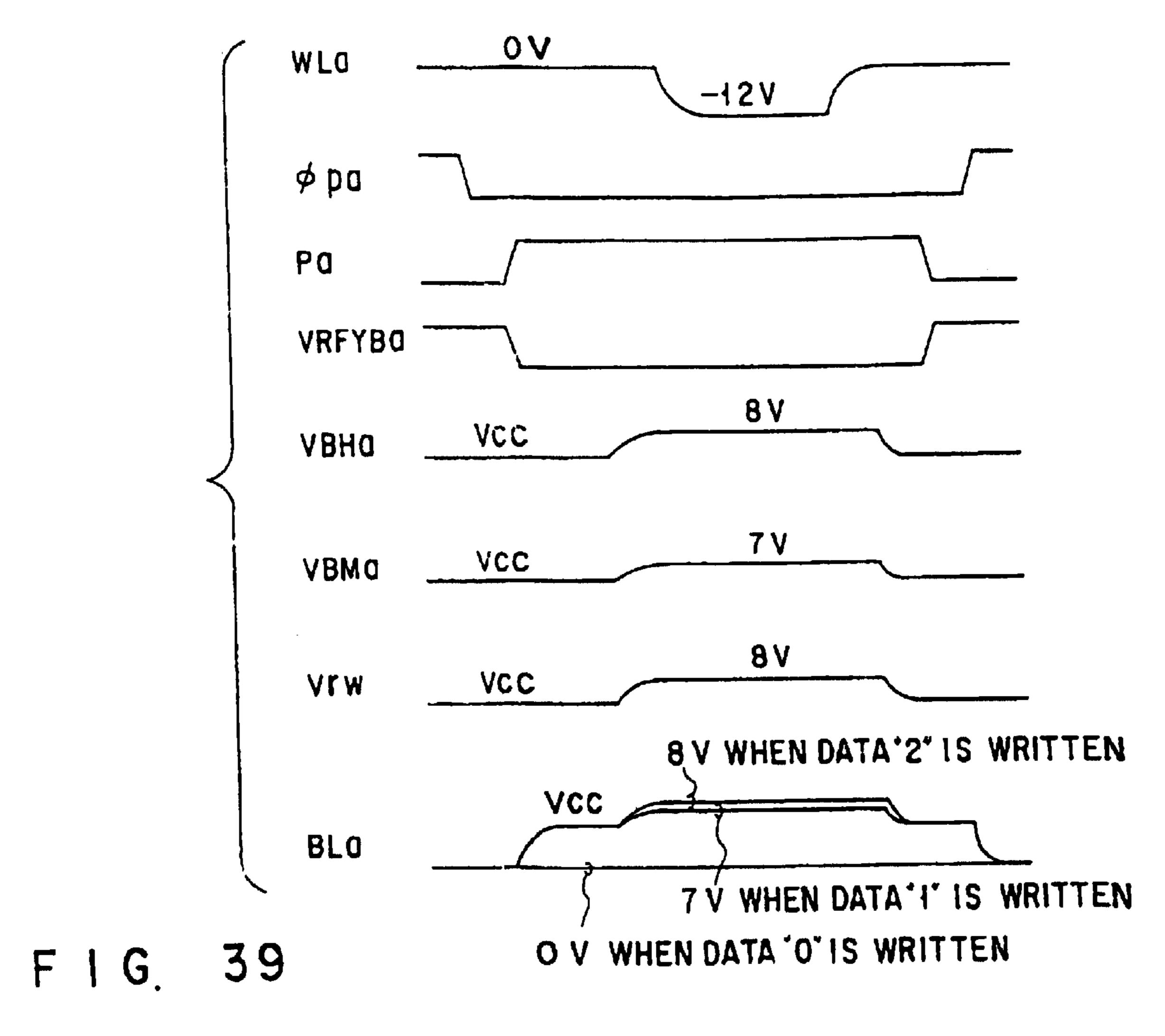

- FIG. **39** is a timing chart showing a write operation in the fourth embodiment;

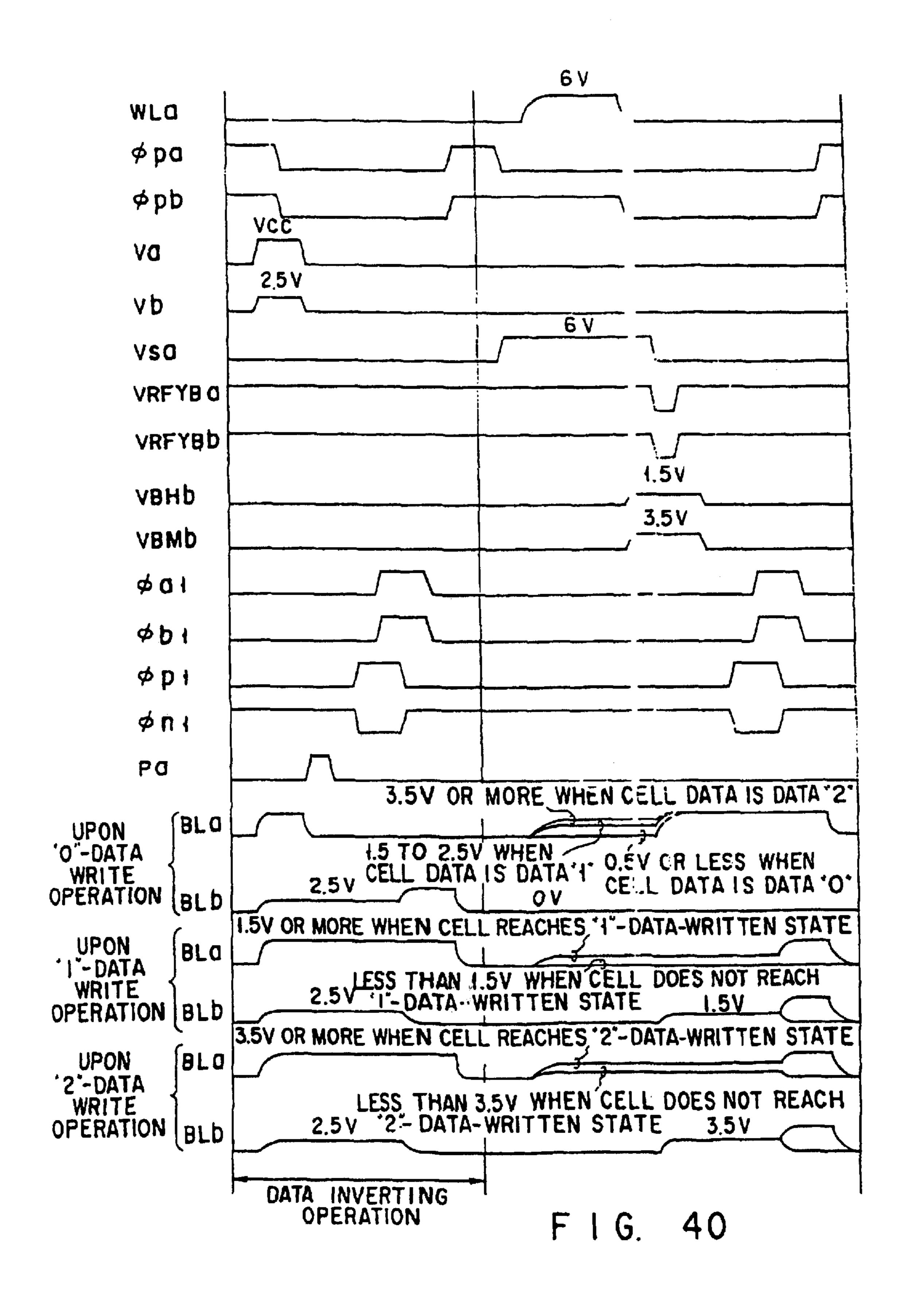

- FIG. **40** is a timing chart showing a verify read operation in the fourth embodiment; and

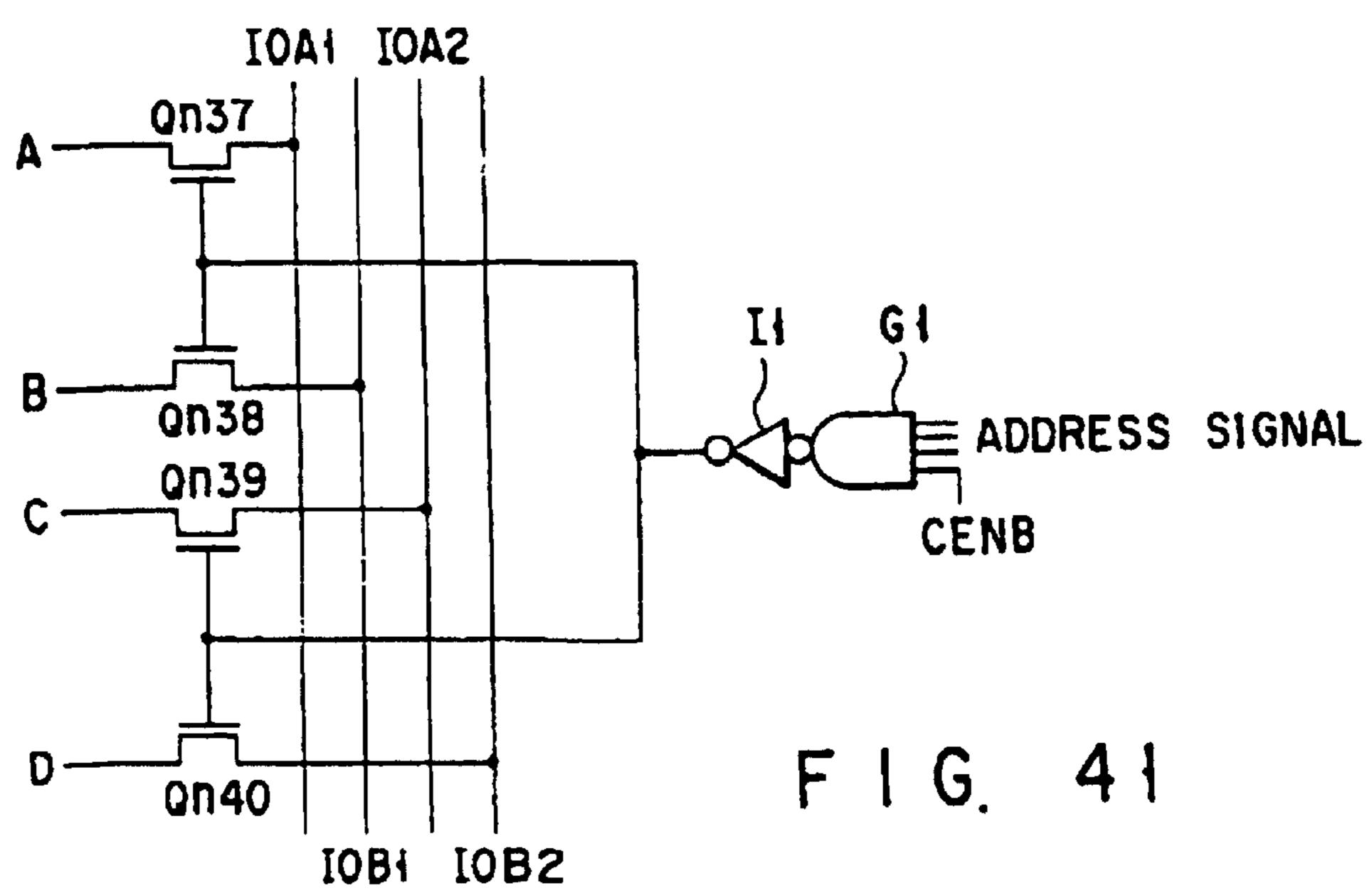

- FIG. **41** is a circuit diagram showing the arrangement of a column decoder in the third and fourth embodiments.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Embodiments of the present invention will be described below with reference to the accompanying drawings.

FIG. 1 is a block diagram showing the schematic arrangement of a NAND-cell EEPROM according to the first embodiment of the present invention.

A bit line control circuit 2 for controlling a bit line in a read/write operation and a word line drive circuit 7 for controlling a word line potential are arranged for a memory cell array 1. The bit line control circuit 2 and the word line drive circuit 7 are selected by a column decoder 3 and a row decoder 8, respectively. The bit line control circuit 2 receives and outputs read/write data from/to an input/output data conversion circuit 5 through a data input/output line (IO line). The input/output data conversion circuit 5 converts readout multivalue information of a memory cell into binary information to externally output the multivalue information, and converts the binary information of externally input write data into the multivalue information of a memory cell. The input/output data conversion circuit 5 is connected to a data input/output buffer 6 for controlling a data input/output operation with an external circuit A data write end detection circuit 4 detects whether a data write operation is ended. A write control signal generation circuit 9 supplies a write control signal to the bit line control circuit 2 and the word line drive circuit 7. A write verify control signal generation circuit 10 supplies a write verify control signal to the bit line control circuit 2 and the word line drive circuit 7. A data update control signal generation circuit 11 supplies a data update control signal to the bit line control circuit 2.

FIGS. 2 and 3 show the detailed arrangements of the memory cell array 1 and the bit line control circuit 2.

Memory cells M1 to M8 and selection transistors S1 and S2 constitute a NAND cell. One terminal of the NAND cell is connected to a bit line BL, and the other terminal is connected to a common source line Vs. Selection gates SG1 and SG2 and control gates CG1 to CG8 are shared by a plurality 5 of NAND cells, and memory cells which share one control gate constitute a page. Each memory cell stores data at a threshold voltage Vt thereof. The memory cell stores data "0" indicating that the threshold voltage Vt is lower than 0 V, stores data "1" indicating that the threshold voltage Vt is 10 greater than 0 V and lower than 1.5 V, and stores data "2" indicating that the threshold voltage Vt is greater than 1.5 V and lower than a power supply voltage. One memory cell can have three states, and nine combinations can be obtained by two memory cells. Of these nine combinations, eight 15 combinations are used, and data of three bits are stored in the two memory cells. In this embodiment, data of three bits are stored in a pair of adjacent memory cells which share a control gate. In addition, the memory cell array 1 is formed on a dedicated p-type well.

In the bit line control circuit in FIG. 3, clocked synchronous inverters CI1 and CI2 and clocked synchronous inverters CI3 and CI4 constitute flip-flops, respectively, and these flip-flops latch write/read data. The flip-flops are also operated as sense amplifiers. The flip-flop constituted by the clocked synchronous inverters CI1 and CI2 latches write data information indicating whether data "0" or data "1" or "2" is to be written, and latches read data information indicating whether a memory cell stores the information of data "0" or the information of data "1" or "2". The flip-flop constituted by the clocked synchronous inverters CI3 and CI4 latches write data information indicating whether data "1" or "2" is to be written, and latches read data information indicating whether a memory cell stores the information of data "2" or the information of data "0" or "1".

Of n-channel MOS transistors, an n-channel MOS transistor Qn1 transfers a voltage VPR to a bit line when a precharge signal PRE goes to "H" level. When a bit line connection signal BLC goes to "H" level, an n-channel MOS transistor Qn2 connects the bit line to a main bit line control 40 circuit. N-channel MOS transistors Qn3 to Qn6 and Qn9 to Qn12 selectively transfer voltages VBLH, VBLM, and VBLL to the bit line in accordance with the data latched in the above flip-flops. When signals SAC2 and SAC1 go to "H" level, n-channel MOS transistors Qn7 and Qn8 respectively connect the flip-flops to the bit line. An n-channel MOS transistor Qn13 is arranged to detect whether all the data of one page latched in the flip-flops are identical to each other. When column selection signals CSL1 and CSL2 go to "H" level, n-channel MOS transistors Qn14 and Qn15 selectively connect a corresponding one of the flip-flops to data input/output line IOA or IOB, and n-channel MOS transistors Qn16 and Qn17 selectively connect a corresponding one of the flip-flops to the data input/output line IOA or

Although an inverter portion is roughly shown in FIG. 3 as shown in FIG. 19(a), the inverter portion has the circuit arrangement shown in FIG. 19(b).

The operation of the EEPROM arranged as described above will be described below with reference to FIGS. 4 to 60 **6**. FIG. 4 shows read operation timings, FIG. 5 shows write operation timings, and FIG. 6 shows verify read operation timings. Each of FIGS. 4, 5, and 6 shows a case wherein the control gate CG4 is selected.

A read operation is executed by two basic cycles. In the 65 first read cycle, the voltage VPR becomes a power supply voltage Vcc to precharge the bit line, and the precharge sig-

14

nal PRE goes to "L" level to cause the bit line to float. Subsequently, the selection gates SG1 and SG2 and the control gates CG1 to CG3 and CG5 to CG8 are set to be the power supply voltage Vcc. At the same time, the control gate CG4 is set to be 1.5 V. Only when the threshold voltage of a selected memory cell is set to be 1.5 V or more, i.e., data "2" is written in this memory cell, the bit line is kept at "H" level.

Thereafter, sense activation signals SEN2 and SEN2B go to "L" level and "H" level, respectively, and latch activation signals LAT2 and LAT2B go to "L" level and "H" level, respectively, thereby resetting the flip-flop constituted by the clocked synchronous inverters CI3 and CI4. The signal SAC2 goes to "H" level to connect the flip-flop constituted by the clocked synchronous inverters CI3 and CI4 to the bit line. After the sense activation signals SEN2 and SEN2B go to "H" level and "L" level, respectively, to sense a bit line potential, the latch activation signals LAT2 and LAT2B go to "H" level and "L" level, respectively, and the information of data "2" or data "1" or "0" is latched in the flip-flop constituted by the clocked synchronous inverters CI3 and CI4.

In the second read cycle, unlike the first read cycle, the voltage of the selection control gate CG4 is not set to be 1.5 V but is set to be 0 V, and signals SEN1, SEN1B, LAT1, LAT1B, and SAC1 are output in place of the signals SEN2, SEN2B, LAT2, LAT2B, and SAC2. Therefore, in the second read cycle, the information of data "0" or data "1" or "2" is latched in the flip-flop constituted by the clocked synchronous inverters CI1 and CI2.

Data written in the memory cells are read out by the two read cycles described above.

The data of the memory cells are erased prior to a data write operation, and the threshold voltage Vt of each of the memory cells is set to be less than 0 V. The p-type well, the common source line Vs and, the selection gates SG1 and SG2 are set to be 20 V, and the control gates CG1 to CG8 are set to be 0 V, thereby performing an erase operation.

In the write operation, the precharge signal PRE goes to "L" level to cause the bit line to float. The selection gate SG1 and the control gates CG1 to CG8 are set to be Vcc. The selection gate SG2 is set to be 0 V during the write operation. At the same time, signals VRFY1, VRFY2, FIM, and FIH are set to be Vcc. In a "0"-data write operation, since the flip-flop constituted by the clocked synchronous inverters CI1 and CI2 latches data such that an output from the clocked synchronous inverter CI1 is set at "H" level, the bit line is charged by the voltage Vcc. In the "1"- or "2"-data write operation, the bit line is set to be 0 V.

Subsequently, the selection gate SG1, the control gates CG1 to CGS, the signals BLC and VRFY1, and a voltage VSA are set to be 10 V, the voltage VBLH is set to be 8 V, and the voltage VBLM is set to be 1 V. In the "1"-data write operation, since the flip-flop constituted by the clocked synchronous inverters CI3 and CI4 latches data such that an output from the clocked synchronous inverter CI3 goes to "H" level, a voltage of 1 V is applied to the bit line BL. In a "2"-data write operation, the bit line is set to be 0 V. In a "0"-data write operation, the bit line is set to be 8 V. Thereafter, the selected control gate CG4 is set to be 20 V.

In a "1"- or "2"-data write operation, electrons are injected into the charge accumulation layers of the memory cells by the potential difference between the bit line BL and the control gate CG4. In the "1"-data write operation, amounts of charges to be injected into the charge accumulation layers of the memory cells must be smaller than those in the "2"-data write operation. For this reason, the bit line BL is set to be 1 V to relax the potential difference between the

bit line BL and the control gate CG4 to 19 V. However, even when the potential difference is not relaxed, the same effect as described above can be obtained by adjusting a write time. In a "0"-data write operation, the threshold voltages of the memory cells are not effectively changed by a bit line volt- 5 age of 8 V.

Upon completion of the write operation, the selection gate SG1 and the control gates CG1 to CG8 are set to be 0 V, and then the voltage of the bit line BL set to be 8 V in the "0"-data write operation is reset to 0 V with a time lag. This is because, when the order of the setting operations is reversed, a "2"- or "1"-data-written state is temporarily set, and erroneous data is written in the "0"-data write operation.

After the write operation, a verify read operation is performed to check the written state of the memory cell and perform an additional write operation to only a memory cell in which data is not sufficiently written. During the verify read operation, the voltages VBLH, VBLL, and FIM are set to be Vcc, 0 V, and 0 V, respectively.

The verify read operation is executed by two basic cycles. Each of the basic cycles is almost identical to the second read cycle except that the voltage of the selected control gate CG4 and signals VRFY1, VRFY2, and FIH are output (only the signal VRFY1 is output in the first verify read cycle). The signals VRFY1, VRFY2, and FIH are output before the signals SEN1, SEN1B, LAT1, and LAT1B go to "L" level, "H" level, "L" level and "H" level, respectively, after the selection gates SG1 and SG2 and the control gates CG1 to CG8 are reset to 0 V. In other words, the signals VRFY1, VRFY2, and FIH are output before the flip-flop constituted by the clocked synchronous inverters CI1 and CI2 is reset after the potential of the bit line is determined by the threshold voltages of the memory cells. The potential of the selected control gate CG4 is set to be 2 V (first cycle) and 0.5 35 V (second cycle) in the verify read operation which are higher than 1.5 V (first cycle) and 0 V (second cycle) in the read operation to assure a threshold voltage margin of 0.5 V.

In this case, data (data 1) latched in the flip-flop constituted by the clocked synchronous inverters CI1 and CL2, 40 data (data 2) latched in the flip-flop constituted by the clocked synchronous inverters CI3 and CI4, and the voltage of the bit line BL determined by the threshold voltage of a selected memory cell will be described below. The data 1 controls a "0"-data write operation or a "1"- or "2"-data 45 charged by the voltage VBLH again. write operation. The n-channel MOS transistor Qn3 is set in an "ON" state when the "0"-data write operation is performed, and the n-channel MOS transistor Qn6 is set in an "ON" state when "1"- or "2"-data write operation is performed. The data 2 controls a "1"-data write operation or a "2"-data write operation. The n-channel MOS transistor Qn10 is set in an "ON" state when the "1"-data write operation is performed, and the n-channel MOS transistor Qn11 is set in an "ON" state when the "2"-data write operation is performed.

In the first verify read cycle in the "0"-data write operation (initial write data is data "0"), the data of the memory cell is data "0". For this reason, when the control gate CG4 is set to be 2 V, the memory cell causes a bit line potential to go to "L" level. Thereafter, when signal VRFY1 goes to "H" 60 level, the potential of the bit line BL goes to "H" level.

In the first verify read cycle in the "1"-data write operation (initial write data is data "1"), since the data of the memory cell is to be "1", the threshold voltage of the memory cell is less than 1.5 V. When the control gate CG4 is 65 set to be 2 V, the memory cell causes the bit line potential to go to "L" level. In this case, even when the initial write data

**16**

is data "1", when data "1" is sufficiently written in the selected memory cell by the previously performed verify read cycles, the data 1 is set to be data "0". In this case, when the signal VRFY1 goes to "H" level later, the potential of the bit line BL goes to "H" level ((1) in FIG. 6). In cases except for the above case, the potential of the bit line BL goes to "L" level ((2) in FIG. 6).

In the first verify read cycle in the "2"-data write operation (initial write data is data "2"), when the data of the selected memory cell is not data (data "2" is not sufficiently written), and the control gate CG4 is set to be 2 V, the memory cell causes the bit line potential to go to "L" level ((5) in FIG. 6). When data "2" is sufficiently written in the selected memory cell, even when the control gate CG4 is set to be 2 V, the bit line potential is kept at "H" level ((3) and (4) in FIG. 6). (3) in FIG. 6 indicates a case wherein data "2" is sufficiently written in the memory cell in advance, and the data 1 is converted into data for controlling the "0"-data write operation by the previously performed verify read cycles. In this case, when the signal VRFY1 goes to "H" level, the bit line BL is charged by the voltage VBLH again.

In the second verify read cycle in the "0"-data write operation (initial write data is data "0"), the data of the memory cell is data "0". For this reason, when the control gate CG4 is set to be 0.5 V, the memory cell causes the bit line potential to go to "L". Thereafter, when the signal VRFY1 goes to "H" level, the potential of the bit line BL 30 goes to "H" level.

In the second verify read cycle in the "1"-data write operation (initial write data is data "1"), the data of the selected memory cell is not data "1" (data "1" is not sufficiently written), and the control gate CG4 is set to be 0.5 V, the memory cell causes the bit line potential to go to "L" level ((8) in FIG. 6). When data "1" is sufficiently written in the selected memory cell, even when the control gate CG4 is set to be 0.5 V, the bit line potential is kept at "H" level ((6) and (7) in FIG. 6). (6) in FIG. 6 indicates a case wherein data "1" is sufficiently written in the memory cell in advance by previous verify read cycles, and the data 1 is converted into data for controlling the "0"-data write operation. In this case, when the signal VRFY1 goes to "H" level, the bit line BL is

In the second verify read cycle in the data "2" read operation (initial write data is data "2"), the data of the memory cell is to be data "2". For this reason, assuming that the threshold voltage of the memory cell is 0.5 V or more, even when data "2" is sufficiently written or is not sufficiently written in the memory cell, and the control gate CG4 is set to be 0.5 V, the bit line potential is kept at "H" level ((9) and (10) in FIG. 6). When data "2" is not sufficiently written in the memory cell, and the threshold voltage of the memory 55 cell is 0.5 V or less, the bit line potential goes to "L" level ((**11**) in FIG. **6**).

Thereafter, when the signals VRFY1, VRFY2, and FIH go to "H" level, data "2" is sufficiently written, and the data 1 is converted into data for controlling a "0"-data write operation, the potential of the bit line BL goes to "H" level ((9) in FIG. 6). In other cases except for the above case, the potential of the bit line BL goes to "L" level ((10) and (11) in FIG. **6**).

With the above verify read operation, rewrite data are set as shown in the following table (Table 1) on the basis of the write data and the written states of the memory cells.

| TABLE 1      |   |   |   |   |   |   |   |   |

|--------------|---|---|---|---|---|---|---|---|

| Write Data   | 0 | 0 | 0 | 1 | 1 | 2 | 2 | 2 |

| Cell Data    | 0 | 1 | 2 | O | 1 | O | 1 | 2 |

| Rewrite Data | O | 0 | 0 | 1 | 0 | 2 | 2 | 0 |

As is apparent from Table 1, data "1" is rewritten in only a memory cell in which data "1" is not sufficiently written, and data "2" is rewritten in only a memory cell in which "2" is not sufficiently written. In addition, when data are sufficiently written in all the memory cells, the n-channel MOS transistors Qn13 of all the columns are set in an "OFF" state, and data write operation end information is output by a signal PENDB.

FIGS. 7A and 7B show data input/output operation timings. FIG. 7A shows a data input timing, and FIG. 7B shows a data output timing. After three external data input cycles are performed, data to be input to the bit line control circuit 2 is generated and output from the input/output data conver- 20 sion circuit 5. External data  $(X_1, X_2, X_3)$  of three bits are converted into data  $(Y_1, Y_2)$  for two memory cells. In the bit line control circuit 2, the converted data are set in a register R1 constituted by the clocked synchronous inverters CI1 and CI2 and a register R2 constituted by the clocked synchro- 25 nous inverters CI3 and CI4. This setting is performed through the data input/output lines IOA and IOB. Readout data latched in the registers R1 and R2 are transferred to the input/output data conversion circuit 5 through the data input/ output lines IOA and IOB, converted, and then output. Col- 30 umn selection signals CSL1i and CSL2i are set to be the same signal, and the data input/output lines IOA and IOB are divided into two systems such that two registers of the same column can be easily accessed at once. Therefore, an access time can be effectively shortened.

The following table (Table 2) shows the relationships between external data  $(X_1, X_2, X_3)$  of three bits, two data  $(Y_1, Y_2)$  of the memory cells, and the data of the registers R1 and R2 respectively corresponding to the data  $Y_1$  and  $Y_2$  in a data input operation.

TABLE 2

|       |                           |       |       |       | IOA Line Data |                   |        |        |  |  |

|-------|---------------------------|-------|-------|-------|---------------|-------------------|--------|--------|--|--|

|       | Input                     |       | C     | Cell  | Ce            | ll Y <sub>1</sub> | Ce     | ll Y2  |  |  |

|       | Data                      |       | D     | ata   | Regis-        | Regis-            | Regis- | Regis- |  |  |

| $X_1$ | $X_2$                     | $X_3$ | $Y_1$ | $Y_2$ | ter R1        | ter R2            | ter R1 | ter R2 |  |  |

| 0     | 0                         | 0     | 0     | 0     | Н             |                   | Н      |        |  |  |

| 0     | 0                         | 1     | 0     | 2     | Н             |                   | L      | L      |  |  |

| 0     | 1                         | 0     | 0     | 1     | Η             |                   | L      | H      |  |  |

| 0     | 1                         | 1     | 1     | 2     | L             | H                 | L      | L      |  |  |

| 1     | 0                         | 0     | 1     | O     | L             | H                 | H      |        |  |  |

| 1     | 0                         | 1     | 1     | 1     | L             | H                 | L      | Н      |  |  |

| 1     | 1                         | 0     | 2     | O     | L             | L                 | H      |        |  |  |

| 1     | 1                         | 1     | 2     | 1     | L             | L                 | L      | H      |  |  |

|       | Pointe<br>write<br>nstruc |       | 2     | 2     | L             | L                 | L      | L      |  |  |

|       | tion                      |       |       |       |               |                   |        |        |  |  |

Each register data is expressed by the voltage level of the input/output line IOA in a data transfer operation. Since the data input/output line IOB is obtained by inverting the data input/output line IOA, the data input/output line IOB is not 65 illustrated. The following table (Table 3) shows the relationships of Table 2 in a data output operation.

TABLE 3

| _ |                     | IOA Lir | ne Data       |        |                  |       |       |         |       |

|---|---------------------|---------|---------------|--------|------------------|-------|-------|---------|-------|

| _ | Cell Y <sub>1</sub> |         | Cell          | Y2     | Се               | 11    |       |         |       |

|   | Regis-              | Regis-  | Regis- Regis- |        | Data             |       |       | Data    |       |

| _ | ter R1              | ter R2  | ter R1        | ter R2 | $\mathbf{Y}_{1}$ | $Y_2$ | $X_1$ | $X_2$   | $X_3$ |

| ) | L                   | L       | L             | L      | 0                | 0     | 0     | 0       | 0     |

|   | L                   | L       | Η             | Η      | O                | 2     | 0     | O       | 1     |

|   | L                   | L       | Η             | L      | O                | 1     | 0     | 1       | 0     |

|   | H                   | L       | H             | Η      | 1                | 2     | 0     | 1       | 1     |

|   | ${ m H}$            | L       | L             | L      | 1                | 0     | 1     | 0       | 0     |

|   | ${ m H}$            | L       | ${ m H}$      | L      | 1                | 1     | 1     | 0       | 1     |

| 5 | ${ m H}$            | H       | L             | L      | 2                | 0     | 1     | 1       | 0     |

|   | H                   | Η       | H             | L      | 2                | 1     | 1     | 1       | 1     |

|   | Η                   | Η       | Η             | Η      | 2                | 2     | -     | Pointer | r     |

|   |                     |         |               |        |                  |       |       | flag    |       |

|   |                     |         |               |        |                  |       |       | output  | ,     |

| - |                     |         |               |        |                  |       |       |         |       |

In this embodiment, the level of the data input/output line IOA in an input operation and the level of the data input/output line IOA in an output operation are inverted with respect to the same data.

Of nine combinations of the two data  $(Y_1, Y_2)$  of the memory cells, one combination is an extra combination. For this reason, this extra combination can be used as file management information such as pointer information. In this case, the pointer information corresponds to cell data  $(Y_1, Y_2)=(2,2)$ .

FIG. **8** shows the concept of a page serving as a data write unit when viewed from a microprocessor or the like for controlling an EEPROM. In this case, one page is defined by N bytes, and addresses (logical addresses) when viewed from a microprocessor or the like are represented. For example, when write data is input into only an area **1** (logical addresses 0 to n), and n=3m+2 (m=0, 1, 2, . . . ) is satisfied, data (X<sub>1</sub>,X<sub>2</sub>,X<sub>3</sub>) are always completed. For this reason, no problem is posed. Since only data X<sub>1</sub> is input when n=3m, data X<sub>2</sub>=0 and X<sub>3</sub>=0 are generated inside the EEPROM, so that data (X<sub>1</sub>,X<sub>2</sub>,X<sub>3</sub>) are input to the input/output data conversion circuit **5**. When n=3m+1, data X<sub>3</sub>=0 is generated inside the EEPROM. When the address n is equal to the address N, the same effect as described above can be obtained.

After a data write operation is performed in the area 1 (all write data in an area 2 are "0", when a data write operation is additionally performed in an area 2, the data in the area 1 are read out, and the write data in the area 2 is added to the 50 readout data and input them. Alternatively, the data in the area 1 are read out. When the start address of the area 2 is n+1=3m, all the data in the area 1 may be set to be data "0"; when the start address is n+1=3m+2, data at addresses n-1and n may be added as data  $X_1$  and  $X_2$  to data  $X_3$  at address 55 n+1, and all data at addresses up to address n-2 in the area 1 may be set to be data "0"; and when the start address is n+1=3m+1, data at address n may be added as data  $X_1$  to data  $X_2$  and  $X_3$  at addresses n+1 and n+2, and all data at addresses up to address n-1 may be set to be data "0". These operations can be easily, automatically performed inside the EEPROM. The combinations between the data  $(X_1, X_2, X_3)$ and data  $(Y_1, Y_2)$  are formed as shown in Tables 2 and 3 such that the additional data write operation can be performed. The relationships between the data  $(X_1,X_2,X_3)$  and the data  $(Y_1,Y_2)$  shown in Tables 2 and 3 are only examples, and the relationships between the data  $(X_1, X_2, X_3)$  and the data  $(Y_1, X_2, X_3)$ Y<sub>2</sub>) are not limited to the relationships shown in Tables 2 and

3. In addition, even when the number of areas is three or more, additional data can be written in the same manner as described above.

FIG. 9A shows a data write algorithm. After a data loading operation is performed, a write operation, a verify read operation, and a write end detecting operation are repeatedly performed. The operations enclosed by a dotted line are automatically performed in the EEPROM.

FIG. 9B shows an additional data write algorithm. After a read operation and a data loading operation are performed, a verify read operation, a write end detecting operation, and a write operation are repeatedly performed. The operations enclosed by a dotted line are automatically performed in the EEPROM. The verify read operation is performed after the data loading operation is performed because data is prevented from being written in a memory cell in which data "1" or "2" is written in advance. If the verify read operation is not performed after the data loading operation is performed, an excessive write operation may be performed.

FIG. 10 shows write characteristics with respect to the threshold voltage of a memory cell in the EEPROM described above. A write operation in a memory cell in which data "1" is to be written and a write operation in a memory cell in which data "2" is to be written are performed at once, and write periods of time are independently set for these memory cells.

The following table (Table 4) shows the potentials at several positions of the memory cell array in an erase operation, a write operation, and a verify read operation.

20

nations are used, and data of three bits are stored in the two memory cells. In this embodiment, data of three bits are stored in a pair of adjacent memory cells which share a control gate.

A flip-flop is constituted by clocked synchronous inverters CI5 and CI6, and a flip-flop is constituted by clocked synchronous inverters CI7 and CI8. These flip-flops latch write/read data. The flip-flops are also operated as sense amplifiers. The flip-flop constituted by the clocked synchronous inverters CI5 and CI6 latches write data information indicating whether data "0" or data "1" or "2" is to be written, and latches read data information indicating whether a memory cell stores the information of data "0" or the information of data "1" or "2". The flip-flop constituted by the clocked synchronous inverters CI7 and CI8 latches write data information indicating whether data "1" or "2" is to be written, and latches read data information indicating whether a memory cell stores the information of data "2" or the information of data "0" or "1".

Of n-channel MOS transistors, an n-channel MOS transistor Qn18 transfers a voltage VPR to a bit line when a precharge signal PRE goes to "H" level. When a bit line connection signal BLC goes to "H" level, an n-channel MOS transistor Qn19 connects the bit line to a main bit line control circuit. N-channel MOS transistors Qn20 to Qn23 and Qn25 to Qn28 selectively transfer voltages VBLH, VBLM, and a voltage of 0 V to the bit line in accordance with the data latched in the above flip-flops, when signals SAC2 and SAC1 go to "H" level, n-channel MOS transistors Qn24 and Qn29 respectively connect the flip-flops to the bit line. An

TABLE 4

|        |                |           |                | Verify Read Operation |                                   |               |            |                 |

|--------|----------------|-----------|----------------|-----------------------|-----------------------------------|---------------|------------|-----------------|

|        | Erase          | Operation |                | Read O                | peration                          | First         | Second     |                 |

|        | Operation      | "O"       | "1"            | "2"                   | First Cycle                       | Second Cycle  | Cycle      | Cycle           |

| BL     | 20 V           | 8 V       | 1 V            | 0 <b>V</b>            | "H" only when<br>data "2" is read | See 1         | See FIG. 6 |                 |

| SG1    | $20\mathrm{V}$ |           | $10\mathrm{V}$ |                       | 5                                 | 5 V           |            |                 |

| CG1    | $0\mathrm{V}$  |           | $10\mathrm{V}$ |                       | 5 V                               |               |            | V               |

| CG2    | $0\mathrm{V}$  |           | $10\mathrm{V}$ |                       | 5 V                               |               |            | V               |

| CG3    | $0\mathrm{V}$  |           | $10\mathrm{V}$ |                       | 5                                 | V             | 5 V        |                 |

| CG4    | $0\mathrm{V}$  |           | $20\mathrm{V}$ |                       | 1.5 V                             | $0\mathrm{V}$ | 2 V        | $0.5\mathrm{V}$ |