#### US00RE41076E

## (19) United States

### (12) Reissued Patent

Chu

### (10) Patent Number: US RE41,076 E

#### (45) Date of Reissued Patent: \*Jan. 12, 2010

### (54) PASSWORD PROTECTED MODULAR COMPUTER METHOD AND DEVICE

(75) Inventor: William W. Y. Chu, Los Altos, CA (US)

(73) Assignee: Acqis Technology, Inc., Mountain View,

CA (US)

(\*) Notice: This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 11/517,601

(22) Filed: Sep. 6, 2006

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 6,321,335

Issued: Nov. 20, 2001

Appl. No.: 09/183,493

Filed: Oct. 30, 1998

(51) **Int. Cl.**

G06F 13/14 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

3,996,585 A 12/1976 Hogan 4,623,964 A 11/1986 Getz et al. 4,700,362 A 10/1987 Todd et al.

(Continued)

#### FOREIGN PATENT DOCUMENTS

| EP | 722138 A1   |   | 7/1996  |

|----|-------------|---|---------|

| JP | 6-289953    |   | 10/1994 |

| WO | WO 92/18924 | * | 10/1992 |

| WO | WO94/00097  |   | 1/1994  |

| WO | WO95/13640  |   | 5/1995  |

| WO | WO97/00481  | * | 1/1997  |

#### OTHER PUBLICATIONS

Jesse Berst's Anchor Desk, http://www.zdnet.com/an-chordesk/talkback/talkback\_56555.html.\*

Jesse Berst's Anchor Desk, http://www.zdnet.com/an-chordesk/story/story\_1504.html.\*

Rick Boyd–Merritt, "Upgradable—PC effort takes divergent paths", http://techweb.cmp.com/eet/news/97/949news/effort.html.\*

Dirk S. Faegre et al., "CTOS Revealed", http://www.byte.com/art/9412/sec13/art2.htm.\*

Kelly Spang, "Component House: Design Technology for PCs in a snap'—NeoSystmes Offers Building Blocks", Computer Reseller News, Apr. 21, 1997, Issue 732, Section: Channel Assembly, http://www.techweb.com/se/directlink.cgi?CRN19970421S0054.\*

"Think Modular", PC Magazine, Jun. 10, 1997, wysiwyg://60/http://homezdnet.com/pcmag/issues/1611/pcmg0072.htm.\*

Jesse Berst's Anchor Desk, http://www.zdnet.com/anchordesk/talkback/talkback\_56555.html, (Dec. 5, 1997), 1 page.

#### (Continued)

Primary Examiner—Ponnoreay Pich (74) Attorney, Agent, or Firm—Cooley Godward Kronish LLP

#### (57) ABSTRACT

A method and device for securing a removable Attached Computer Module ("ACM") 10. ACM 10 inserts into a Computer Module Bay ("CMB") 40 within a peripheral console to form a functional computer such as a desktop computer or portable computer. The present ACM 10 includes a locking system, which includes hardware and software 600, 700, to prevent accidental removal or theft of the ACM from the peripheral console. While ACM is in transit, further security is necessary against illegal or unauthorized use. If ACM contains confidential data, a high security method is needed to safeguard against theft.

#### 35 Claims, 17 Drawing Sheets

# US RE41,076 E Page 2

| U.S. PATENT                                                                              | DOCUMENTS                             | 6,002,442 A 12/1999 Li et al.                                                                                  |  |

|------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

|                                                                                          |                                       | 6,003,105 A 12/1999 Vicard et al.                                                                              |  |

| , ,                                                                                      | Levanon                               | 6,006,243 A * 12/1999 Karidis 708/100                                                                          |  |

| , , ,                                                                                    | Maniwa et al.                         | 6,009,488 A 12/1999 Kavipurapu                                                                                 |  |

| , ,                                                                                      | Lambert et al.<br>Tarver et al.       | 6,011,546 A 1/2000 Bertram                                                                                     |  |

|                                                                                          | Fredericks et al.                     | 6,012,145 A * 1/2000 Mathers et al                                                                             |  |

| 5,056,141 A 10/1991                                                                      |                                       | 6,016,252 A 1/2000 Pignolet et al.<br>6,028,643 A 2/2000 Jordan et al.                                         |  |

| 5,086,499 A 2/1992                                                                       | -                                     | 6,029,183 A 2/2000 Jordan et al.                                                                               |  |

| , ,                                                                                      | Fischer 370/236                       | 6,038,621 A 3/2000 Gale et al.                                                                                 |  |

| 5,191,581 A * 3/1993                                                                     | Woodbury et al 370/364                | 6,040,792 A 3/2000 Watson et al.                                                                               |  |

| 5,251,097 A 10/1993                                                                      | Simmons et al.                        | 6,046,571 A * 4/2000 Bovio et al                                                                               |  |

| 5,278,509 A 1/1994                                                                       | Haynes et al.                         | 6,052,513 A 4/2000 McLaren                                                                                     |  |

| , ,                                                                                      | Kikinis                               | 6,069,615 A 5/2000 Abraham et al.                                                                              |  |

| 5,293,497 A 3/1994                                                                       |                                       | 6,070,214 A 5/2000 Ahern                                                                                       |  |

|                                                                                          | Harshberger et al.                    | 6,088,224 A 7/2000 Gallagher et al.                                                                            |  |

| , ,                                                                                      | Gillett                               | 6,088,752 A 7/2000 Ahern                                                                                       |  |

| / /                                                                                      | Takeda<br>Kikinis                     | 6,104,921 A * 8/2000 Cosley et al                                                                              |  |

| , ,                                                                                      | Horowitz et al.                       | 6,157,534 A 12/2000 Gallagher et al.                                                                           |  |

| , , ,                                                                                    | Pocrass                               | 6,163,464 A 12/2000 Ishibashi et al.                                                                           |  |

|                                                                                          | Nelson et al.                         | 6,175,490 B1 1/2001 Papa et al.<br>6,202,169 B1 3/2001 Razzaghe-Asrafi et al.                                  |  |

| , , , , , , , , , , , , , , , , , , ,                                                    | Kobayashi                             | 6,202,169 B1 3/2001 Razzaghe-Asrafi et al.<br>6,208,522 B1 3/2001 Manweiler et al.                             |  |

|                                                                                          | Moran et al 711/103                   | 6,216,185 B1 * 4/2001 Chu                                                                                      |  |

| 5,539,616 A * 7/1996                                                                     | Kikinis 361/686                       | 6,256,689 B1 * 7/2001 Khosrowpour                                                                              |  |

| 5,550,710 A 8/1996                                                                       | Rahamim et al.                        | 6,260,155 B1 7/2001 Dellacona                                                                                  |  |

| 5,550,861 A 8/1996                                                                       | Chan et al.                           | 6,266,539 B1 * 7/2001 Pardo                                                                                    |  |

|                                                                                          | Boie 307/109                          | 6,289,376 B1 9/2001 Taylor et al.                                                                              |  |

| 5,578,940 A 11/1996                                                                      |                                       | 6,304,895 B1 10/2001 Schneider et al.                                                                          |  |

| 5,600,800 A 2/1997                                                                       |                                       | 6,311,268 B1 10/2001 Chu                                                                                       |  |

| 5,603,044 A 2/1997                                                                       |                                       | 6,314,522 B1 11/2001 Chu et al.                                                                                |  |

| , ,                                                                                      | Farmwald et al.                       | 6,317,329 B1 11/2001 Dowdy et al.                                                                              |  |

| , , ,                                                                                    | Flint et al.<br>Jones et al.          | 6,321,335 B1 11/2001 Chu                                                                                       |  |

| 5,630,057 A 5/1997                                                                       |                                       | 6,332,180 B1 12/2001 Kauffman et al.                                                                           |  |

|                                                                                          | Buchala et al.                        | 6,345,330 B2 2/2002 Chu                                                                                        |  |

| , ,                                                                                      | Kikinis                               | 6,366,951 B1 4/2002 Schmidt<br>6,378,009 B1 4/2002 Pinkston, II et al.                                         |  |

| , ,                                                                                      | Ichimura et al 726/34                 | 6,381,602 B1 4/2002 Finkston, if et al.                                                                        |  |

| 5,659,773 A 8/1997                                                                       |                                       | 6,393,561 B1 5/2002 Hagiwara et al.                                                                            |  |

| 5,663,661 A 9/1997                                                                       | Dillon et al.                         | 6,401,124 B1 6/2002 Yang et al.                                                                                |  |

| 5,673,174 A * 9/1997                                                                     | Hamirani 361/686                      | 6,425,033 B1 7/2002 Conway et al.                                                                              |  |

| 5,680,126 A 10/1997                                                                      | Kikinis                               | 6,452,789 B1 9/2002 Pallotti et al.                                                                            |  |

| 5,689,654 A 11/1997                                                                      |                                       | 6,452,790 B1 9/2002 Chu et al.                                                                                 |  |

| 5,721,837 A 2/1998                                                                       |                                       | 6,453,344 B1 9/2002 Ellsworth                                                                                  |  |

|                                                                                          | Beasley et al.                        | 6,496,361 B2 12/2002 Kim et al.                                                                                |  |

| , ,                                                                                      | Robinson                              | 6,549,966 B1 4/2003 Dickens et al.                                                                             |  |

|                                                                                          | Sakaue 370/431                        | 6,564,274 B1 5/2003 Heath et al.                                                                               |  |

| 5,752,080 A 5/1998                                                                       |                                       | 6,643,777 B1 11/2003 Chu                                                                                       |  |

| 5,764,924 A 6/1998                                                                       | Williams 713/501                      | 6,718,415 B1 4/2004 Chu                                                                                        |  |

|                                                                                          | Trumbull                              | 6,725,317 B1 4/2004 Bouchier et al.                                                                            |  |

|                                                                                          | Pollmann                              | 7,099,981 B2 8/2006 Chu                                                                                        |  |

| 5,805,536 A 5/1556<br>5,815,681 A 9/1998                                                 |                                       | 7,146,446 B2 12/2006 Chu<br>2001/0011312 A1 * 8/2001 Chu 710/64                                                |  |

|                                                                                          | Boehling et al.                       | 2001/0011312 A1 ' 8/2001 Cllu /10/04                                                                           |  |

| 5,826,048 A 10/1998                                                                      |                                       | OTHER BUILDING                                                                                                 |  |

|                                                                                          | Alzien 710/314                        | OTHER PUBLICATIONS                                                                                             |  |

| 5,848,249 A 12/1998                                                                      | Garbus                                |                                                                                                                |  |

| 5,859,669 A 1/1999                                                                       | Prentice                              | Jesse Berst's Anchor Desk, http://www.zdnet.com/an-                                                            |  |

| 5,862,381 A 1/1999                                                                       | Advani et al.                         | chordesk/story/story_1504.html, (Dec. 5, 1997), pp. 1–3.                                                       |  |

|                                                                                          | Benson et al.                         | Boyd-Merritt, Rick, "Ungradeable-PC effort takes diver-                                                        |  |

| , ,                                                                                      | Walker et al 710/304                  |                                                                                                                |  |

| , ,                                                                                      | Moroz                                 | gent paths", http://techweb.cmp.com/eet/news/97/949news.                                                       |  |

| , ,                                                                                      | Wilson Lonloing et el                 | effort.html, (Jul. 31, 1998) pp. 1–3.                                                                          |  |

| , , ,                                                                                    | Jenkins et al.<br>Walker et al        | Faegre, Dirk S. et al., "CTOS Revealed", Core Technologies,                                                    |  |

| , ,                                                                                      | Walker et al.<br>Gallagher et al.     | http://www.bytecom/art/9412/sec13/art2.htm, (Dec. 1994)                                                        |  |

|                                                                                          | _                                     | pp. 1–6.                                                                                                       |  |

| 5,977 989 A 11/1000                                                                      | Lee et al                             | 00.1 0.                                                                                                        |  |

| 5,977,989 A 11/1999<br>5,978,919 A 11/1999                                               |                                       | <b>* *</b>                                                                                                     |  |

| 5,978,919 A 11/1999                                                                      | Doi et al.                            | Eversys Corporation, "Eversys System 8000 Consolidated                                                         |  |

| 5,978,919 A 11/1999<br>5,982,363 A 11/1999                                               | Doi et al.                            | Eversys Corporation, "Eversys System 8000 Consolidated Network Server Market and Product Overview," Slide Pre- |  |

| 5,978,919 A 11/1999<br>5,982,363 A 11/1999<br>5,991,163 A 11/1999                        | Doi et al.<br>Naift                   | Eversys Corporation, "Eversys System 8000 Consolidated                                                         |  |

| 5,978,919 A 11/1999<br>5,982,363 A 11/1999<br>5,991,163 A 11/1999<br>5,991,844 A 12/1999 | Doi et al.<br>Naift<br>Marconi et al. | Eversys Corporation, "Eversys System 8000 Consolidated Network Server Market and Product Overview," Slide Pre- |  |

Synder, Joel, "Better Management through Consolidation," pp. 1–6 downloaded from the internet @ http://www.opus1.com/www/jms/nw-con-0818rev.html. (Aug. 18, 1997).

U.S. Appl. No. 12/322,858, filed Feb. 5, 2009, William W. Y. Chu.

Agerwala, T., "SP2 System Architecture," IBM Systems Joural, vol. 34, No. 2, pp. 152–184 (1995).

Bernal, Carlos, product brochure entitled: "PowerSMP Series 4000" (Mar. 1998) <<a href="http://www.winnetmag.com/Windows/Article/ArticleID/3095/13095.html">http://www.winnetmag.com/Windows/Article/ArticleID/3095/13095.html</a>, downloaded from web on Jun. 22, 2004, 2 pgs.

CETIA Brochure "CETIA Powerengine CVME 603e", pp. 1–6 downloaded from the internet at. http://www.cetia.com/ProductAddOns/wp-47-01.pdf on Feb. 15, 2006.

Cragle, Jonathan, "Density System 1100", May 1999) <<a href="http://www.winnetmag.com/Windows/Article/ArticleID/5199/5199.html">http://www.winnetmag.com/Windows/Article/ArticleID/5199/5199.html</a>>, downloaded from web on Jun. 21, 2004, 3 pgs.

Crystal Advertisement for "Rackmount Computers", (@2000–2004) <<a href="http://www.crystalpc.com/products/roser-vers.asp">http://www.crystalpc.com/products/roser-vers.asp</a>>, downloaded from web on Jun. 17, 2004, 8 pgs.

Cubix, "Click on the front panel that matches your system", (@2000) <<a href="http://64.173.211.7/support/techinfo/system/density/density.htm">http://64.173.211.7/support/techinfo/system/density/density.htm</a>, downloaded from web on Jun. 22, 2004, 1 pg.

Cubix, "DP 6200 'D' Series Plug—in Computers" <<a href="http://64.173.211.7/support/techinfo/bc/dp/6200d/Intro.htm">http://64.173.211.7/support/techinfo/bc/dp/6200d/Intro.htm</a>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "Installing DP or SP Series Boards" (@2000) <<http://64.173.211.7/support/techinfo/system/density/info/pic-inst.htm>>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "Powering On/Off or Resetting Plug—in Computers in an Density System", (@2000) <<a href="http://64.173.211.7/sup-port/techinfo/system/density/info/power.htm">http://64.173.211.7/sup-port/techinfo/system/density/info/power.htm</a>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "Multiplexing Video, Keyboard & Mouse with Multiple Density Systems", (@2000) <<a href="http://64.173.211.7/support/techinfo/system/density/info/vkm-mux.htm">http://64.173.211.7/support/techinfo/system/density/info/vkm-mux.htm</a>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix Product Brochure entitled, "Density System", (@2000) <<a href="http://64.173.211.7/support/techinfo/system/density/density10.htm">http://64.173.211.7/support/techinfo/system/density/density10.htm</a> downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix Product Brochure entitled, "Density System, Technical Specifications", (@2000) <a href="http://64.173.211.7/support/techinfo/system/density/info/spec.htm">http://64.173.211.7/support/techinfo/system/density/info/spec.htm</a> downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix Product Manual entitled; "Density System", Chapter 1–Introduction, (@2000) <<a href="http://64.173.211.7/support/techinfo/manuals/density/Chap-1.htm">http://64.173.211.7/support/techinfo/manuals/density/Chap-1.htm</a>>downloaded from web on Jun. 22, 2004, 5 pgs.

Cubix Product Manual entitled, "Density System", Chapter2–Installation, (@2000) <<a href="http://64.173.211.7/sup-port/techiknfo/manuals/density/Chap-2.htm">http://64.173.211.7/sup-port/techiknfo/manuals/density/Chap-2.htm</a> downloaded from web on Jun. 22, 2004, 9 pgs.

Cubix Product Manual entitled, "Density System", Chapter 3–Operation, (@2000), <<a href="http://64.173.211.7/support/techinfo/manuals/density/Chap-3.htm">http://64.173.211.7/support/techinfo/manuals/density/Chap-3.htm</a> downloaded from web on Jun. 22, 2004, 4 pgs.

Cubix, "Click on the front panel that matches your system", (@2000) <<a href="http://64.173.211.7/support/techinfo/system/density/desity.htm">http://64.173.211.7/support/techinfo/system/density/desity.htm</a>, downloaded from web on Jun. 22, 2004, 1 pg.

Cubix Product Manual entitled, "Density System," Chapter 4–Maintenance and Repair, (@2000) <<a href="http://64.173.211.7/support/techinfo/manuals/density/Chap4-htm">http://64.173.211.7/support/techinfo/manuals/density/Chap4-htm</a> downloaded from web on Jun. 22, 2004, 5 pgs.

Cubix, "SP 5200XS Series Plug—in Computers", (@2000) <<http://64.173.211.7/support/techinfo/bc/sp5200xs/in-tro.htm>>, downloaded from web on Jun. 22, 2004, 2 pgs.

Cubix, "SP 5200XS Series Technical Specifications", (@2000) <a href="http://64.173.211.7/support/techinfo/bc/sp5200xs/spec.htm"><href="http://64.173.211.7/support/techinfo/bc/sp5200xs/spec.htm"><href="http://64.173.211.7/support/techinfo/bc/sp5200xs/spec.htm"><href="http://64.173.211.7/support/techinfo/bc/sp5200xs/spec.htm"><href="http://64.173.211.7/support/techinfo/bc/sp5200xs/spec.htm"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http://64.173.211.7/support/techinfo/bc/2004"><href="http

Cubix, "SP 5200 Series" Chapter 1–Introduction, (@2000) <<a href="http://64.173.211.7/support/techinfo/manuals/sp5200/chap-2.htm">http://64.173.211.7/support/techinfo/manuals/sp5200/chap-2.htm</a>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "SP 5200 Series" Chapter 2–Switches & Jumpers, (@2000) <<a href="http://64.173.211.7/support/techinfo/manuals/sp5200/chap-3.htm">http://64.173.211.7/support/techinfo/manuals/sp5200/chap-3.htm</a>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "SP 5200 Series" Chapter3–Installation, (@2000) <<a href="http://64.173.211.7/support/techinfo/manuals/sp5200/chap-4.htm">http://64.173.211.7/support/techinfo/manuals/sp5200/chap-4.htm</a>, downloaded from web on Jun. 22, 2004, 4 pgs.

Cubix, "SP 5200 Series" Chapter4–Technical Reference, (@2000) <<a href="http://64.173.211.7/support/techinfo/manuals/sp5200xs/chap-1.htm">http://64.173.211.7/support/techinfo/manuals/sp5200xs/chap-1.htm</a>, downloaded from web on Jun. 22, 2004, 3 pgs.

Cubix, "What are Groups?", (@2000) <<a href="http://64.173.211.7/support/techinfo/system/density/info/groups.">http://example.com/density/info/groups.</a> htm>>, downloaded from web on Jun. 22, 2004, 3 pgs.

eBay Advertisement for "Total IT Group Network Engines", <<a href="http://cgi.ebay.com/we/eBayISAPI.dll?ViewItem&Item=5706388046&sspagename+STRK%3">http://cgi.ebay.com/we/eBayISAPI.dll?ViewItem&Item=5706388046&sspagename+STRK%3</a>

AMDBI%3AMEBI3AIT&rd=1>>, Downloaded from web on Jun. 25, 2004, 1 pg.

"Features Chart", (Feb. 1, 1997) <<a href="http://www.lantimes.com/testing/97feb/702b072a.html">http://www.lantimes.com/testing/97feb/702b072a.html</a>>, downloaded from web on Jun. 23, 2004, 3 pgs.

Feldman, Jonathan, "Rack Steady: The Four Rack-Mounted Servers That Rocked Our Network", <<a href="http://www.net-workcomputing.com/shared/printArticle.jhtml?article=910/910r3side1.htm">http://www.net-workcomputing.com/shared/printArticle.jhtml?article=910/910r3side1.htm</a>...>>, Jun. 23, 2004, 3 pgs.

Fetters, Dave, "Cubix High–Density Server Leads the Way With Standout Management Software", (Feb. 8, 1999) <<a href="http://www.nwc.com/shared/printArticle.jhtml?article=/1003/1003r3full.html&pub=nwc>>, downloaded from web on Jun. 23, 2004, 5 pgs.">http://www.nwc.com/shared/printArticle.jhtml?article=/1003/1003r3full.html&pub=nwc>>, downloaded from web on Jun. 23, 2004, 5 pgs.</a>

Gardner, Michael and Null, Christopher, "A Server Condominium", <a href="http://www.lantimes.com/testing/98jun/806a042a.html">http://www.lantimes.com/testing/98jun/806a042a.html</a>>, Jun. 23, 2004, 3 pgs.

Harrison, Dave, "VME in the Military: The M1A2 Main Battle Tank Upgrade Relies on COTS VME" <<a href="http://www.dy4.com">>>, (Feb 9, 1998), pp. 1–34.</a>

Internet Telephony Roundup, "Industrial Computer", <a href="http://www.tmcnet.com/articles/itmag/0499/0499round-up.htm">http://www.tmcnet.com/articles/itmag/0499/0499round-up.htm</a>, downloaded from web on Jun. 23, 2004, 5 pgs.

Kelly Spang, "Component House: Design Technology for PCs in a snap'—NeoSystmes Offers Building Blocks", Computer Reseller News, Apr. 21, 1997, Issue 732, Section: Channel Assembly, http://www.techweb.com/se/directlink.cgi?CRN19970421S0054.

Microsoft Cluster Service Center, "MSCS Basics," Downloaded from <a href="http://www.nwnetworks.com/mscsbasics.">http://www.nwnetworks.com/mscsbasics.</a> htm>>, Feb. 7, 2005, 4 pages total.

MPL Brochure "1st Rugged All in One Industrial 486FDX–133 MHz PC" pp. 1–2, downloaded from the internet at. http://www.mpl.ch/DOCs/ds–48600.pdf on Feb. 15, 2006.

MPL Brochure "IPM 486 Brochure/IPM5 User manual" pp. 1–9 downloaded from the internet at http://www.mpl.ch/DOCs/u48600xd.pdf on Feb. 15, 2006.

MPL, "The First Rugged All—in—One Industrial 486FDX–133 MHz PC" IPM 486 Brochure/IPM5 User manual, 1998, pp. 1–52.

Press Release: Hiawatha, Iowa, (Mar. 1, 1997) entitled "Crystal Group Products Offer Industrial PCs with Built—in Flexibility", <<a href="http://www.crystalpc.com/news/pressre-leases/prodpr.asp">http://www.crystalpc.com/news/pressre-leases/prodpr.asp</a>, downloaded from web on May 14, 2004, 2 pgs.

Press Release: Kanata, Ontario, Canada, (Apr. 1998) entitled "Enhanced COTS SBC from DY 4 Systems features 166MHz Pentium<sup>TM</sup> Processor" <<a href="http://www.realtimeinfo.be/VPR/layout/display/pr.asp?/pr.asp?PRID=363>>">"> 2 pgs.</a>

Product Brochure entitled "SVME/DM-192 Pentium® II Single Board Computer" (Jun. 1999) pp. 1–9.

Product Brochure entitled "System 8000", <<a href="http://www.bomara.com/Eversys/briefDefault.htm">http://www.bomara.com/Eversys/briefDefault.htm</a>, downloaded from web on Jun. 22, 2004, 4 pgs.

Product Brochure entitled "ERS/FT II System", (@2000) <<a href="http://64.173.211.7/support/techinfo/system/ersft2/">http://64.173.211.7/support/techinfo/system/ersft2/</a> ersft2.htm>>, downloaded from web on Jun. 22, 2004, 4 pgs. Product Manual entitled: "ERS II and ERS/FT II," Chap. 6, Component Installation, <<a href="http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c6.htm">http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c6.htm</a>>, downloaded from web on Jun. 22, 2004, 18 pgs.

Product Manual entitled "ERS II and ERS/FT II", Chap. 3, System Components, <<a href="http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c3.htm">http://64.173.211.7/support/techinfo/manuals/ers2/ers2-c3.htm</a>, downloaded from web on Jun. 22, 2004, 21 pgs.

"SQL Server and NT Cluster Manager Availability Demo," Microsoft Server Programmer Developers Conference, Nov. 1996, 15 pages total.

"Think Modular", PC Magazine, Jun. 10, 1997, wysiwyg://60/http://homezdnet.com/pcmag/issues/1611/pcmg0072.htm.

Williams, Dennis, "Consolidated Servers", (Feb. 17, 1997) <<a href="http://www.lantimes.com/testing/97compare/pcconsol.html">http://www.lantimes.com/testing/97compare/pcconsol.html</a>> downloaded from web on Jun. 23, 2004, 2 pgs. Williams Dennis "Cubix Corp. FRS/FT II" (Feb. 17, 1997)

Williams, Dennis, "Cubix Corp. ERS/FT II", (Feb. 17, 1997) <a href="http://www.lantimes.com/testing/97feb/"><a href="http://www.lantimes.com/testing/97feb/"><a href="http://www.lantimes.com/testing/97feb/"><a href="http://www.lantimes.com/testing/97feb/"><a href="http://www.lantimes.com/testing/97feb/"><a href="http://www.lantimes.com/testing/97feb/"><a href="http://www.lantimes.com/testing/97feb/">http://www.lantimes.com/testing/97feb/</a>

702b068b.html>> downloaded from web on Jun. 23, 2004, 4 pgs.

Windows Magazine, "Cubix PowerSMP Series 4000", Nov. 1997, <a href="http://<www.techweb.com/winmag/library/1997/1101/ntent008.htm">http://<www.techweb.com/winmag/library/1997/1101/ntent008.htm</a> downloaded from the web on Jun. 22, 2004, pg. NT07.

Williams, Dennis "EVERSYS Corp. System 8000", Feb. 17, 1997) <a href="http://www.lantimes.com/testing/97feb/702b070b.html"><http://www.lantimes.com/testing/97feb/702b070b.html</a> downloaded from web on Jun. 22, 2004, 4 pgs.

Williams, Dennis, "Executive Summary: Consolidate Now", (Feb. 17, 1997) <<a href="http://www.lantimes.com/testing/97feb/702b064a.html">http://www.lantimes.com/testing/97feb/702b064a.html</a> downloaded from web on Jun. 23, 2004, 2 pgs.

Williams, Dennis, "Top Scores for Useability and Openness", (Feb. 17, 1997) <<a href="http://www.lantimes.com/testing/97feb/702b064a.html">http://www.lantimes.com/testing/97feb/702b064a.html</a>> downloaded from web on Jun. 23, 2004, 2 pgs.

\* cited by examiner

FIG.1

FIG.2

FIG.3

FIG.5

FIG.5A

FIG.\_8

上 (円)

FIG. 12

FIG. 13

FIG. 14

FIG. 15

# PASSWORD PROTECTED MODULAR COMPUTER METHOD AND DEVICE

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specifica-5 tion; matter printed in italics indicates the additions made by reissue.

### CROSS REFERENCE TO RELATED APPLICATIONS

The following two commonly-owned copending applications, including this one, are being filed concurrently and the other one is hereby incorporated by reference in their entirety for all purposes: Notice: More than one reissue application has been filed for the reissue of U.S. Pat. No. 6,321,335. The reissue applications are application Ser. No. 10/963,825 filed Oct. 12, 2004, application Ser. No. 11/474, 256 filed Jun. 23, 2006, and application Ser. No. 11/517,601, filed Sep. 6, 2006 (the present application), which is a continuation reissue of U.S. Pat. No. 6,321,335.

- 1. U.S. patent application Ser. No. 09/183,816, William W. Y. Chu, entitled "Modular Computer Security Method and Device", and

- 2. U.S. patent application Ser. No. 09/183,493, William 25 W. Y. Chu, entitled "Password Protected Modular Computer Method and Device".

#### BACKGROUND OF THE INVENTION

The present invention relates to computing devices. More particularly, the present invention provides a method and device for securing a personal computer or set-top box using password protection techniques. Merely by way of example, the present invention is applied to a modular computing environment for desk top computers, but it will be recognized that the invention has a much wider range of applicability. It can be applied to a server as well as other portable or modular computing applications.

Many desktop or personal computers, which are commonly termed PCs, have been around and used for over ten years. The PCs often come with state-of-art microprocessors such as the Intel Pentium<sup>TM</sup> microprocessor chips. They also include a hard or fixed disk drive such as memory in the giga-bit range. Additionally, the PCs often include a random access memory integrated circuit device such as a dynamic random access memory device, which is commonly termed DRAM. The DRAM devices now provide up to millions of memory cells (i.e., mega-bit) on a single slice of silicon. PCs also include a high resolution display such as cathode ray tubes or CRTs. In most cases, the CRTs are at least 15 inches or 17 inches or 20 inches in diameter. High resolution flat panel displays are also used with PCs.

Many external or peripheral devices can be used with the PCs. Among others, these peripheral devices include mass 55 storage devices such as a Zip<sup>TM</sup> Drive product sold by Iomega Corporation of Utah. Other storage devices include external hard drives, tape drives, and others. Additional devices include communication devices such as a modem, which can be used to link the PC to a wide area network of computers such as the Internet. Furthermore, the PC can include output devices such as a printer and other output means. Moreover, the PC can include special audio output devices such as speakers the like.

PCs also have easy to use keyboards, mouse input devices, 65 and the like. The keyboard is generally configured similar to a typewriter format. The keyboard also has the length and

2

width for easily inputting information by way of keys to the computer. The mouse also has a sufficient size and shape to easily move a curser on the display from one location to another location.

Other types of computing devices include portable computing devices such as "laptop" computers and the like. Although somewhat successful, laptop computers have many limitations. These computing devices have poor display technology. In fact, these devices often have a smaller flat panel display that has poor viewing characteristics. Additionally, these devices also have poor input devices such as smaller keyboards and the like. Furthermore, these devices have limited common platforms to transfer information to and from these devices and other devices such as PCs.

Up to now, there has been little common ground between these platforms including the PCs and laptops in terms of upgrading, ease-of-use, cost, performance, and the like. Many differences between these platforms, probably somewhat intentional, has benefited computer manufacturers at the cost of consumers. A drawback to having two separate computers is that the user must often purchase both the desktop and laptop to have "total" computing power, where the desktop serves as a "regular" computer and the laptop serves as a "portable" computer. Purchasing both computers is often costly and runs "thousands" of dollars. The user also wastes a significant amount of time transferring software and data between the two types of computers. For example, the user must often couple the portable computer to a local area network (i.e., LAN), to a serial port with a modem and then manually transfer over files and data between the desktop and the portable computer. Alternatively, the user often must use floppy disks to "zip" up files and programs that exceed the storage capacity of conventional floppy disks, and transfer the floppy disk data manually.

Another drawback with the current model of separate portable and desktop computer is that the user has to spend money to buy components and peripherals the are duplicated in at least one of these computers. For example, both the desktop and portable computers typically include hard disk drives, floppy drives, CD-ROMs, computer memory, host processors, graphics accelerators, and the like. Because program software and supporting programs generally must be installed upon both hard drives in order for the user to operate programs on the road and in the office, hard disk space is often wasted.

One approach to reduce some of these drawbacks has been the use of a docking station with a portable computer. Here, the user has the portable computer for "on the road" use and a docking station that houses the portable computer for office use. The docking station typically includes a separate monitor, keyboard, mouse, and the like and is generally incompatible with other desktop PCs. The docking station is also generally not compatible with portable computers of other vendors. Another drawback to this approach is that the portable computer typically has lower performance and functionality than a conventional desktop PC. For example, the processor of the portable is typically much slower than processors in dedicated desktop computers, because of power consumption and heat dissipation concerns. As an example, it is noted that at the time of drafting of the present application, some top-of-the-line desktops include 400 MHz processors, whereas top-of-the-line notebook computers include 266 MHz processors.

Another drawback to the docking station approach is that the typical cost of portable computers with docking stations can approach the cost of having a separate portable computer

and a separate desktop computer. Further, as noted above, because different vendors of portable computers have proprietary docking stations, computer users are held captive by their investments and must rely upon the particular computer vendor for future upgrades, support, and the like.

Thus what is needed are computer systems that provide reduced user investment in redundant computer components and provide a variable level of performance based upon computer configuration.

#### SUMMARY OF THE INVENTION

According to the present invention, a technique including a method and device for securing a computer module using a password in a computer system is provided. In an exemplary embodiment, the present invention provides a security system for an attached computer module ("ACM"). In an embodiment, the ACM inserts into a Computer Module Bay (CMB) within a peripheral console to form a functional computer.

In a specific embodiment, the present invention provides a computer module. The computer module has an enclosure that is insertable into a console. The module also has a central processing unit (i.e., integrated circuit chip) in the enclosure. The module has a hard disk drive in the enclosure, 25 where the hard disk drive is coupled to the central processing unit. The module further has a programmable memory device in the enclosure, where the programmable memory device can be configurable to store a password for preventing a possibility of unauthorized use of the hard disk drive and/or other module elements. The stored password can be any suitable key strokes that a user can change from time to time. In a further embodiment, the present invention provides a permanent password or user identification code stored in flash memory, which also can be in the processing 35 unit, or other integrated circuit element. The permanent password or user identification code is designed to provide a permanent "finger print" on the attached computer module.

In a specific embodiment, the present invention provides a variety of methods. In one embodiment, the present invention provides a method for operating a computer system such as a modular computer system and others. The method includes inserting an attached computer module ("ACM") into a bay of a modular computer system. The ACM has a microprocessor unit (e.g., microcontroller, microprocessor) 45 coupled to a mass memory storage device (e.g., hard disk). The method also includes applying power to the computer system and the ACM to execute a security program, which is stored in the mass memory storage device. The method also includes prompting for a user password from a user on a 50 display (e.g., flat panel, CRT). In a further embodiment, the present method includes a step of reading a permanent password or user identification code stored in flash memory, or other integrated circuit element. The permanent password or user identification code provides a permanent finger print on the attached computer module. The present invention includes a variety of these methods that can be implemented in computer codes, for example, as well as hardware.

Numerous benefits are achieved using the present invention over previously existing techniques. The present invention provides mechanical and electrical security systems to prevent theft or unauthorized use of the computer system in a specific embodiment. Additionally, the present invention substantially prevents accidental removal of the ACM from the console. In some embodiments, the present invention 65 prevents illegal or unauthorized use during transmit. The present invention is also implemented using conventional

4

technologies that can be provided in the present computer system in an easy and efficient manner. Depending upon the embodiment, one or more of these benefits can be available. These and other advantages or benefits are described throughout the present specification and are described more particularly below.

These and other embodiments of the present invention, as well as its advantages and features, are described in more detail in conjunction with the text below and attached FIGS.

#### BRIEF DESCRIPTION OF THE DRAWINGS

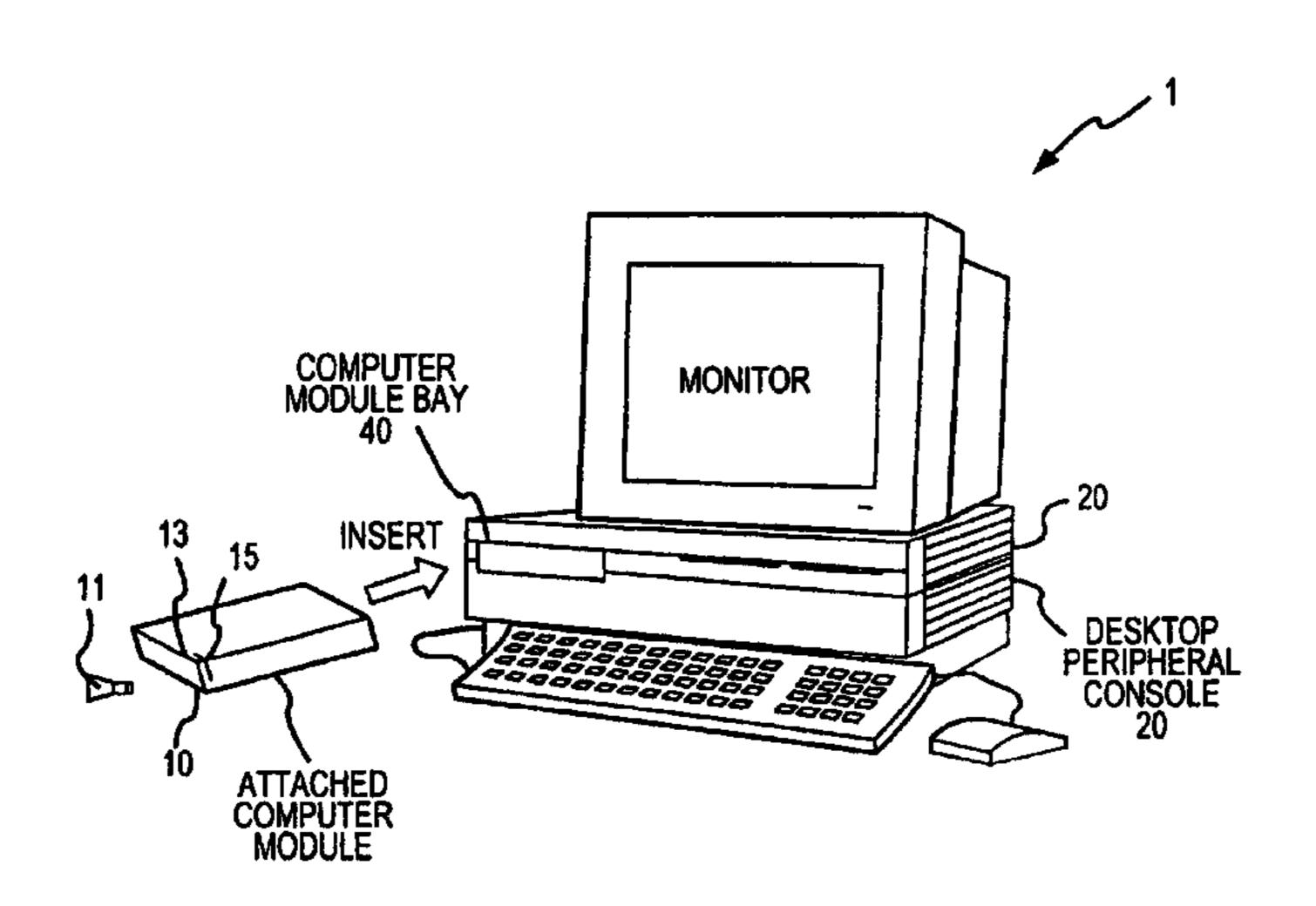

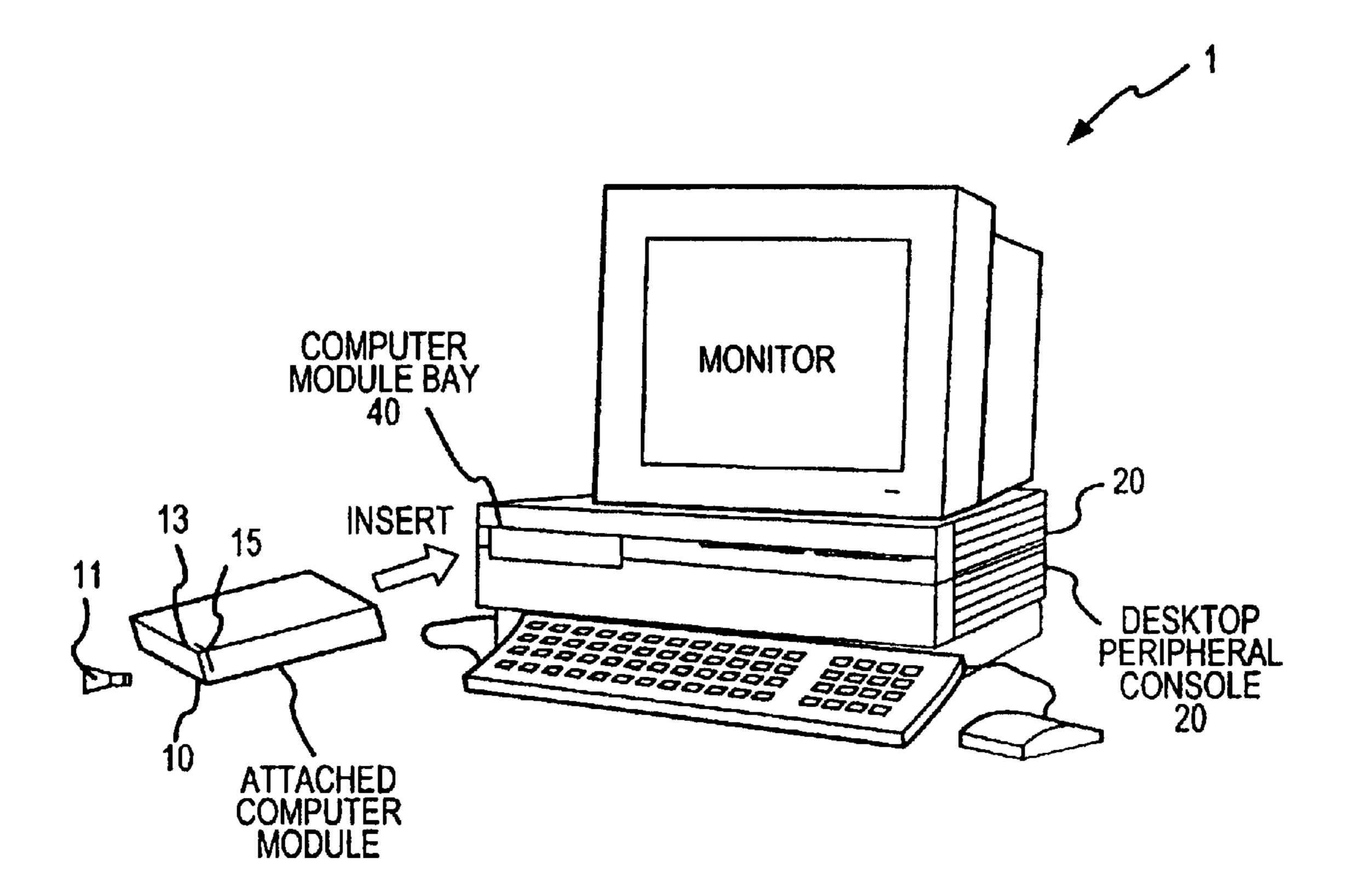

- FIG. 1 is a simplified diagram of a computer system according to an embodiment of the present invention;

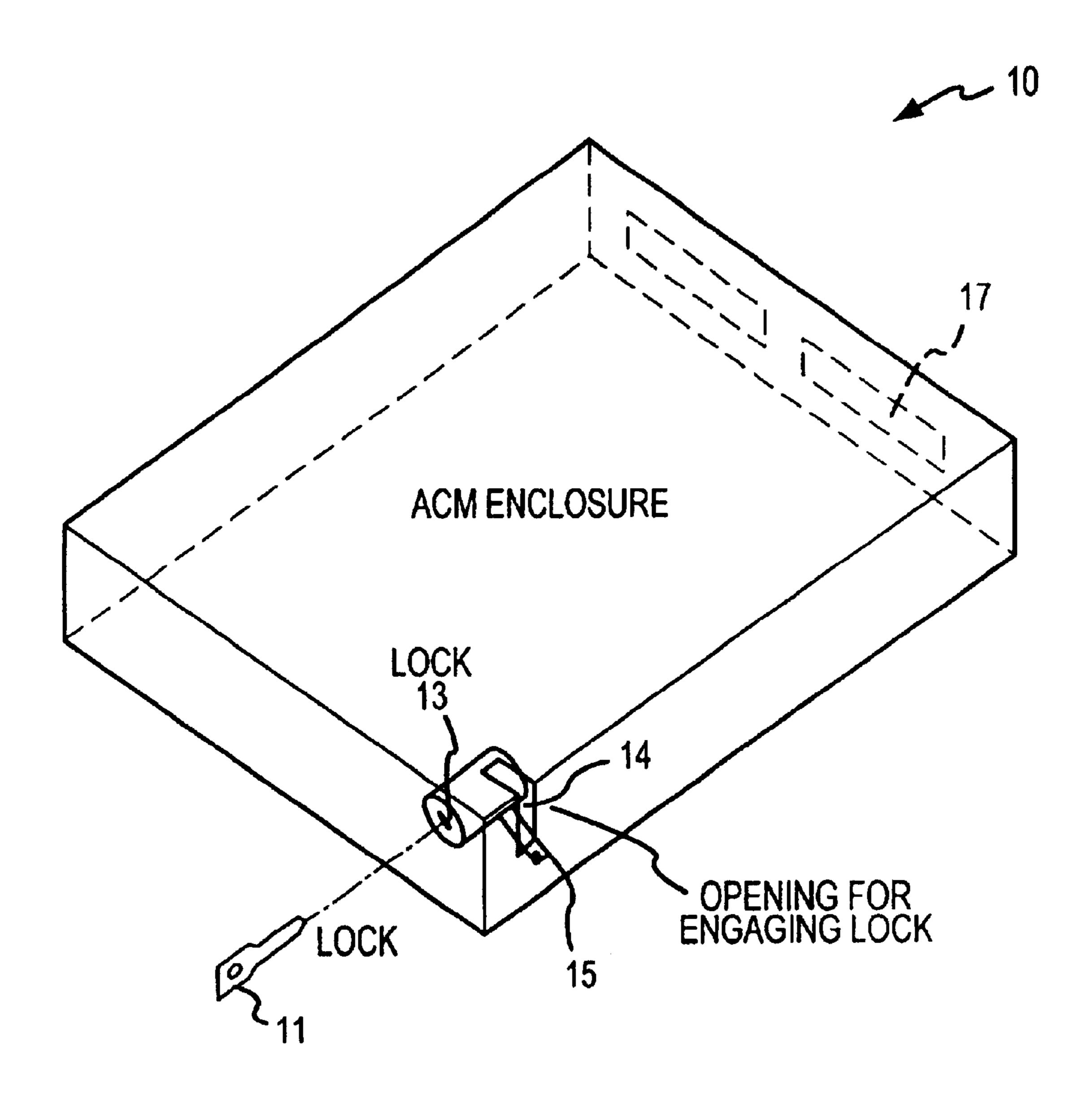

- FIG. 2 is a simplified diagram of a computer module according to an embodiment of the present invention;

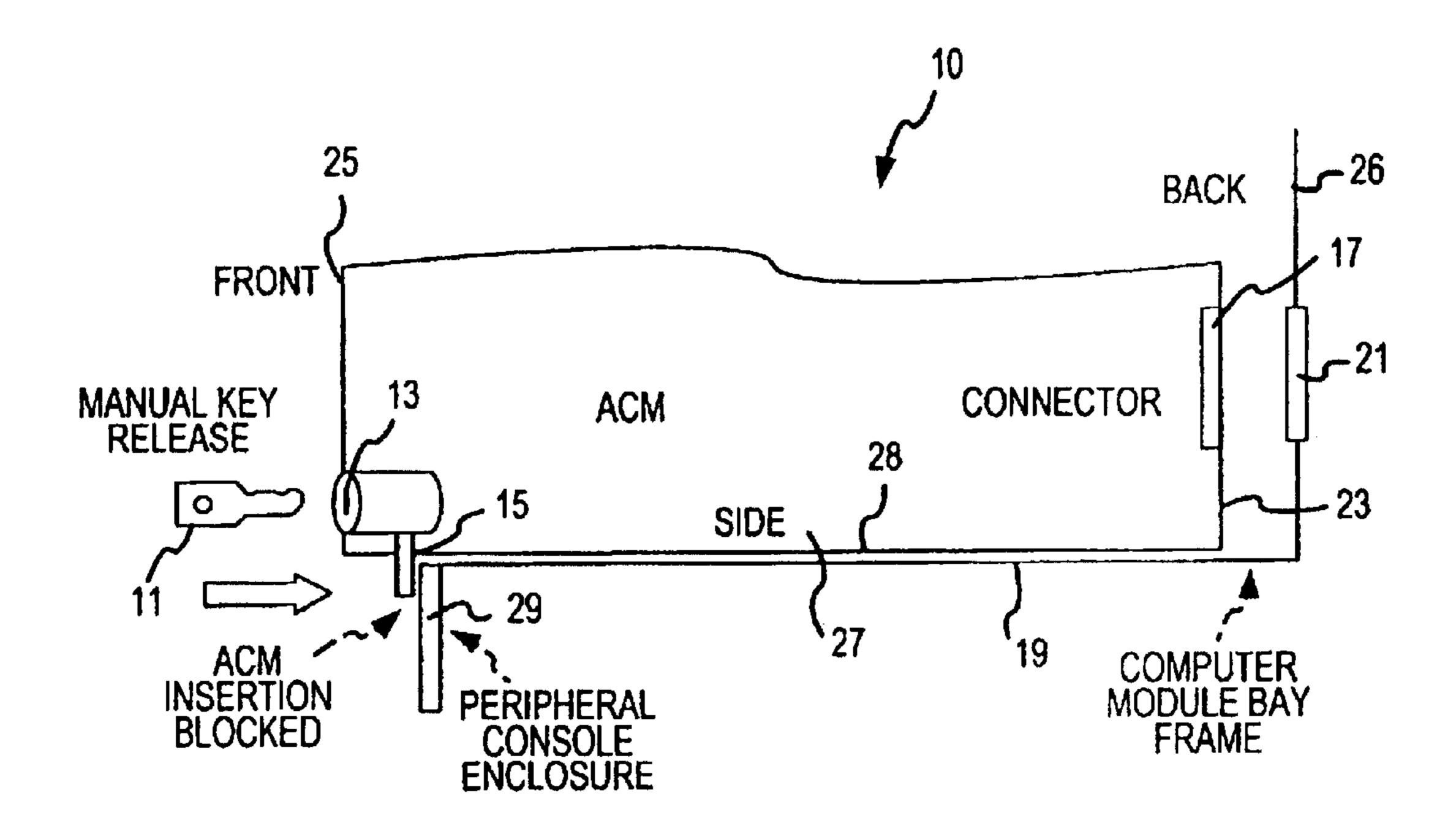

- FIG. 3 is a simplified side-view diagram of a computer module according to an embodiment of the present invention;

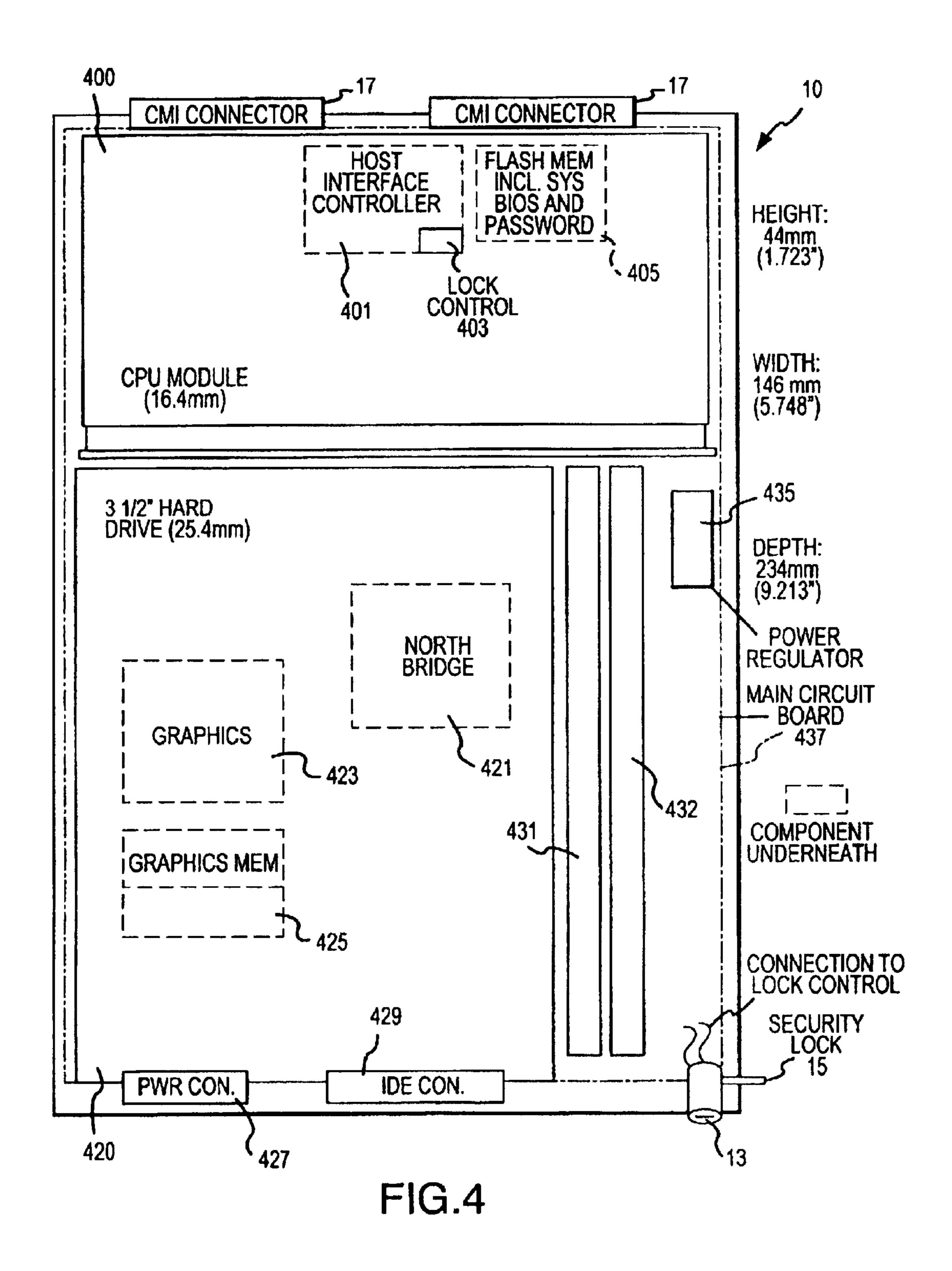

- FIG. 4 is a simplified block diagram of a security system for a computer system according to an embodiment of the present invention;

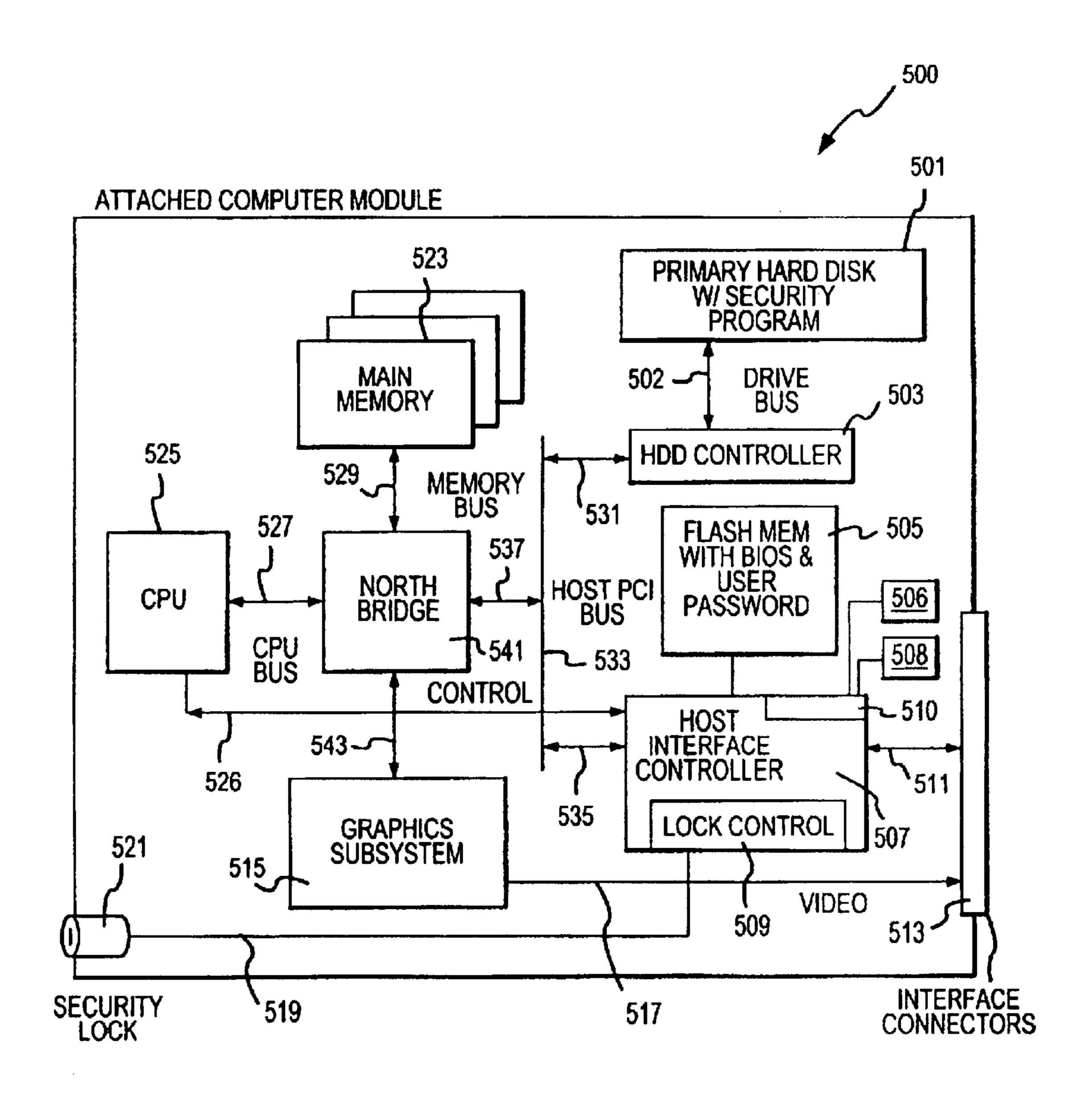

- FIG. **5** is a simplified block diagram of a security system for a computer module according to an embodiment of the present invention; and

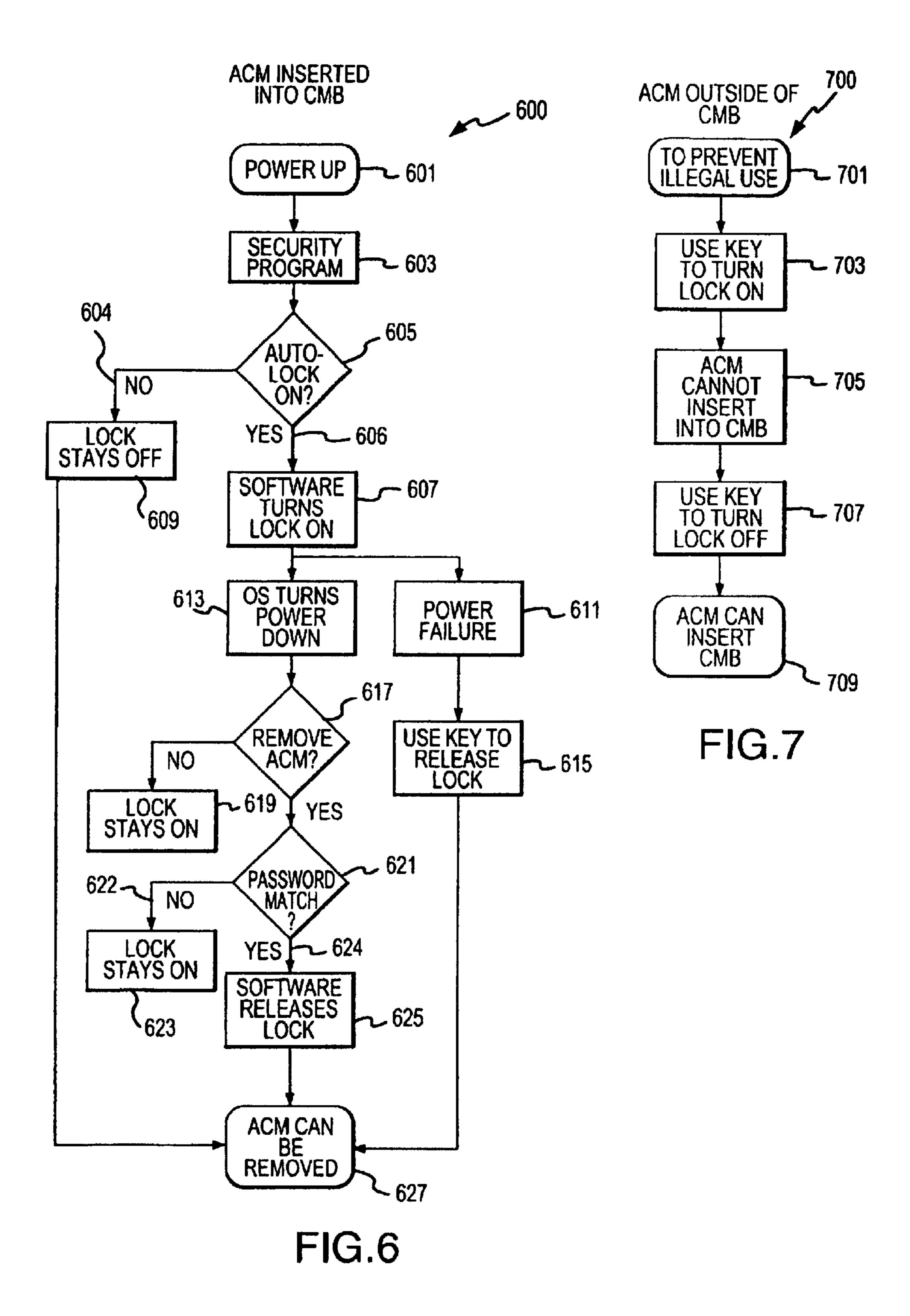

- FIGS. 6 and 7 show simplified flow diagrams of security methods according to embodiments of the present invention.

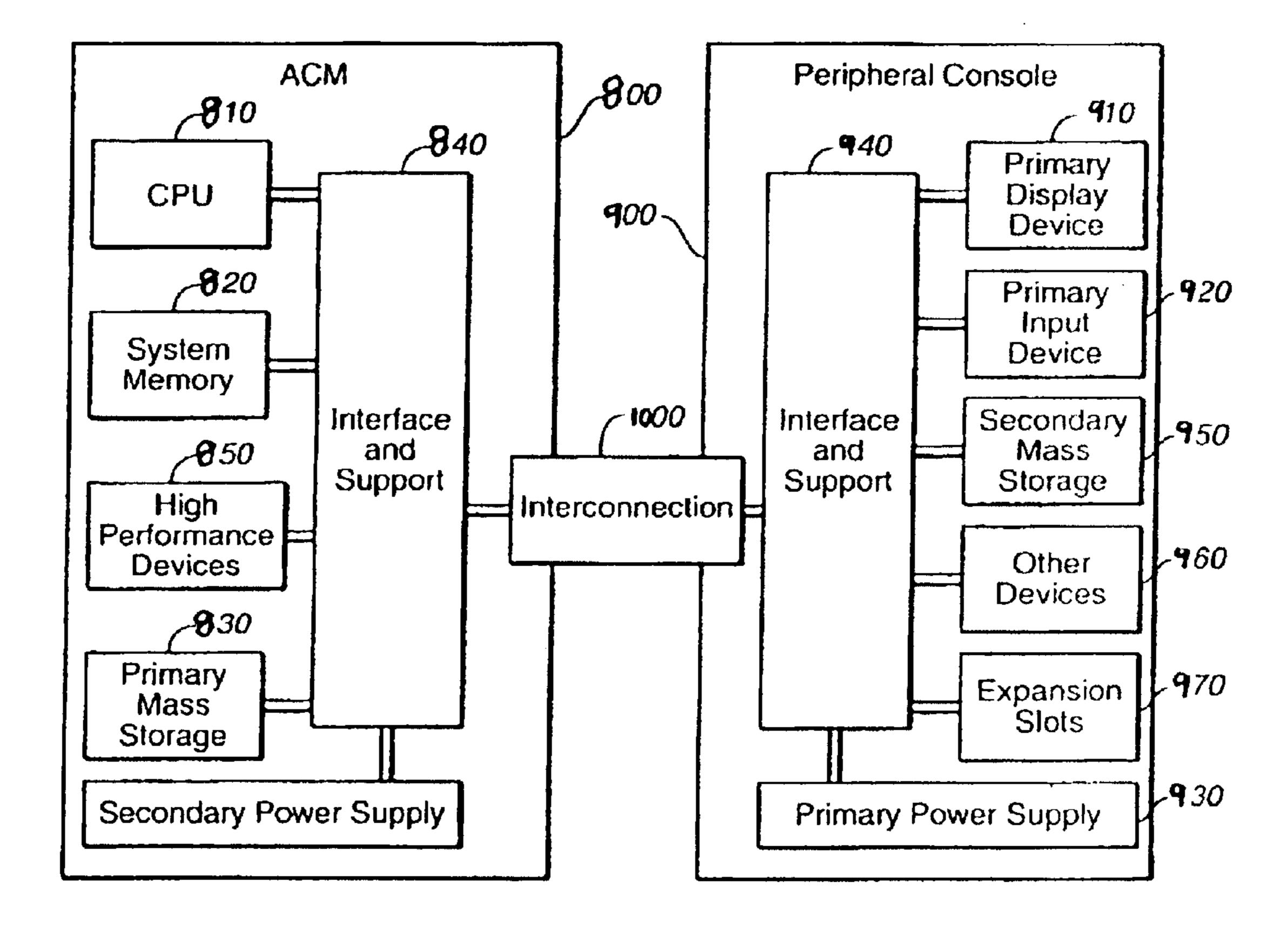

- FIG. 8 is a block diagram of one embodiment of a comyou puter system employing the present invention.

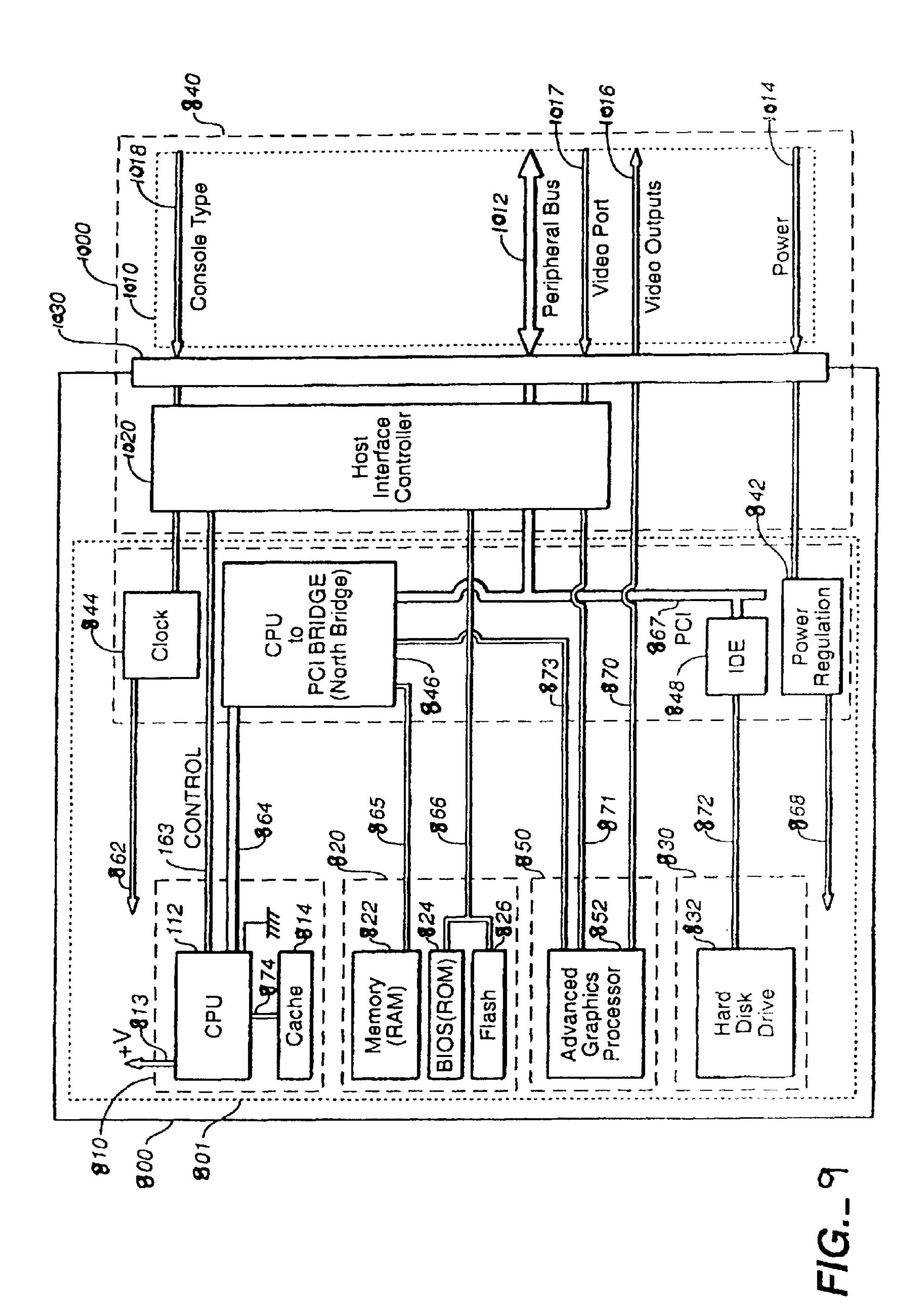

- FIG. 9 is a block diagram of an attached computing module (ACM).

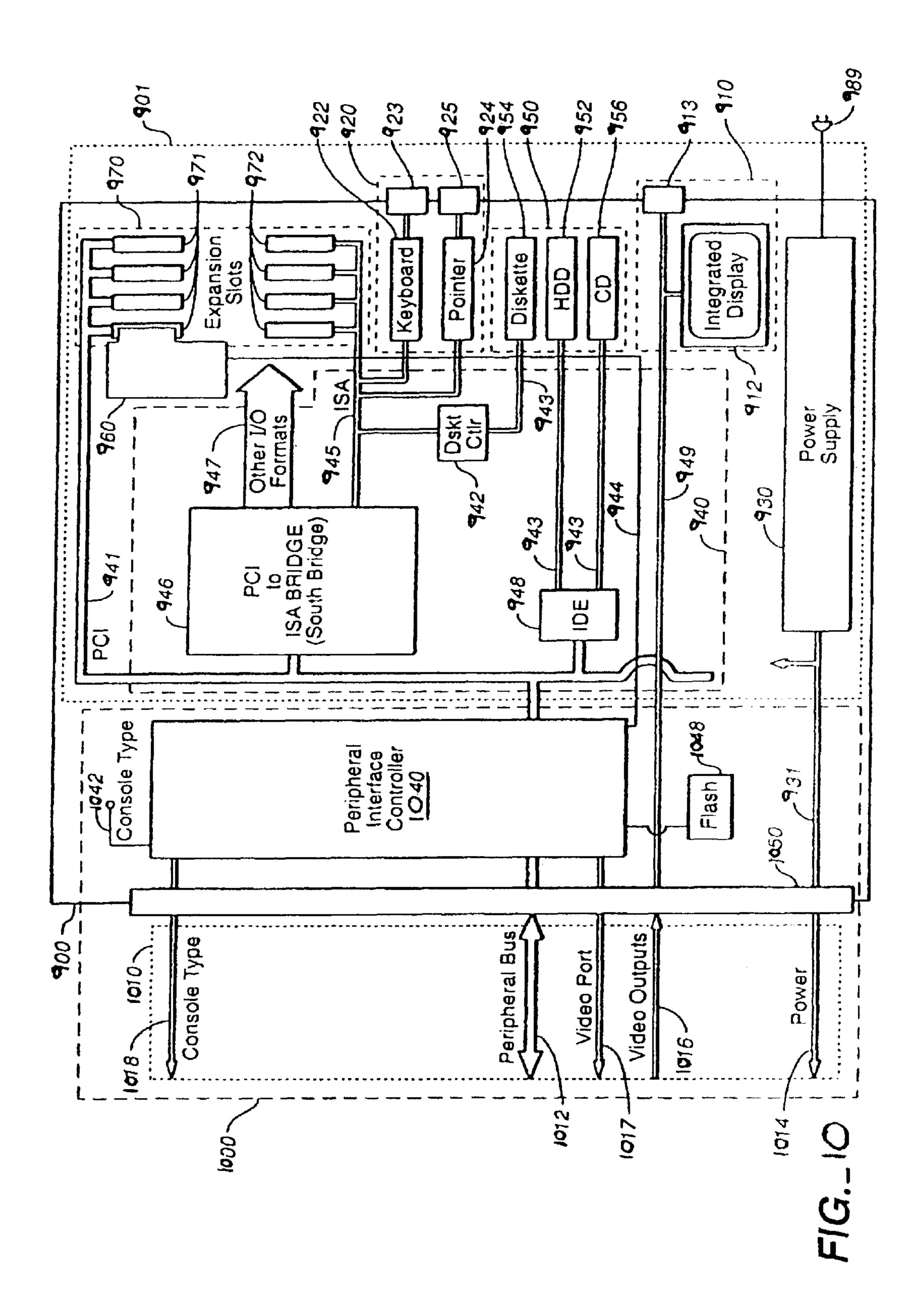

- FIG. 10 is a block diagram of a peripheral console (PCON).

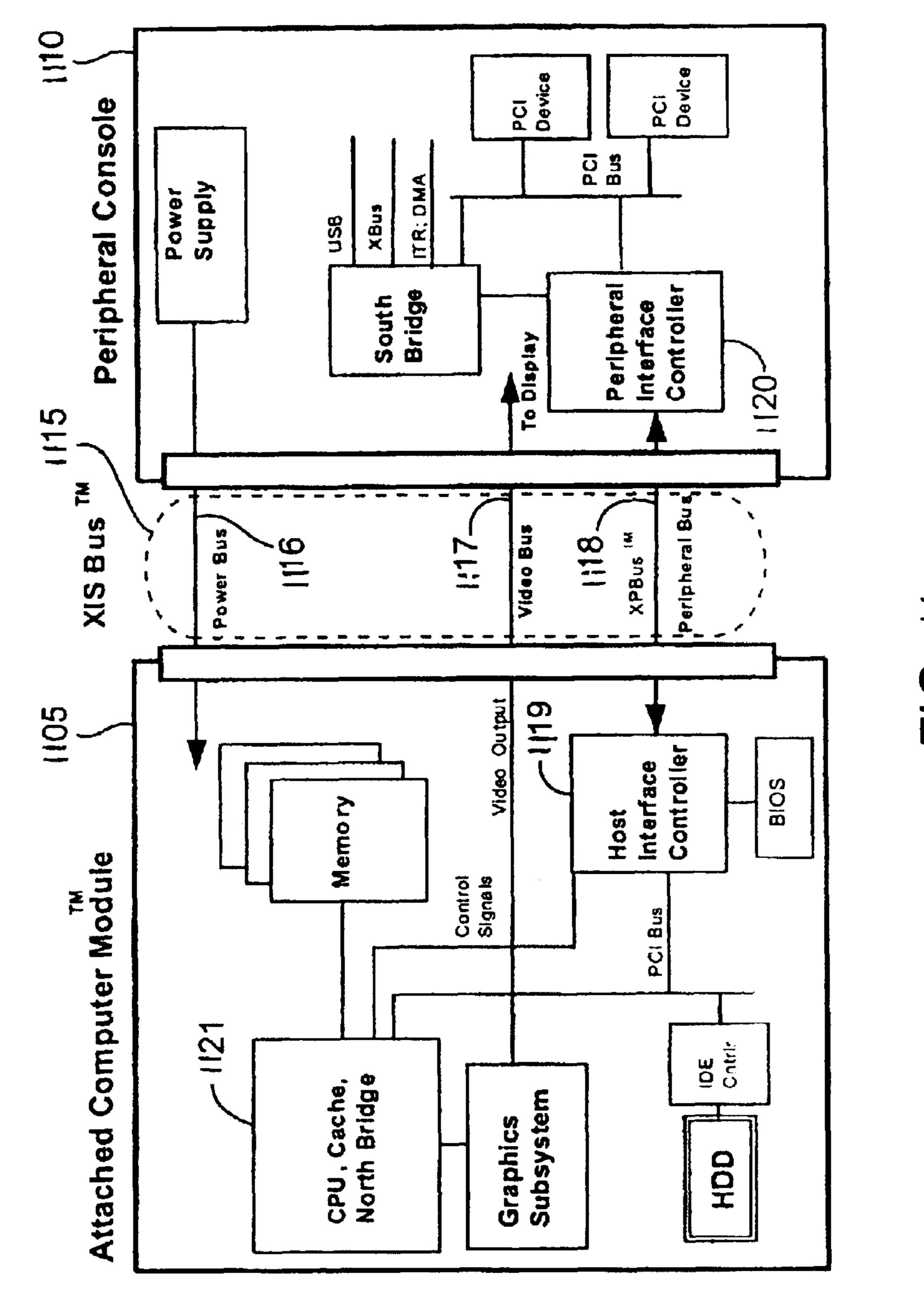

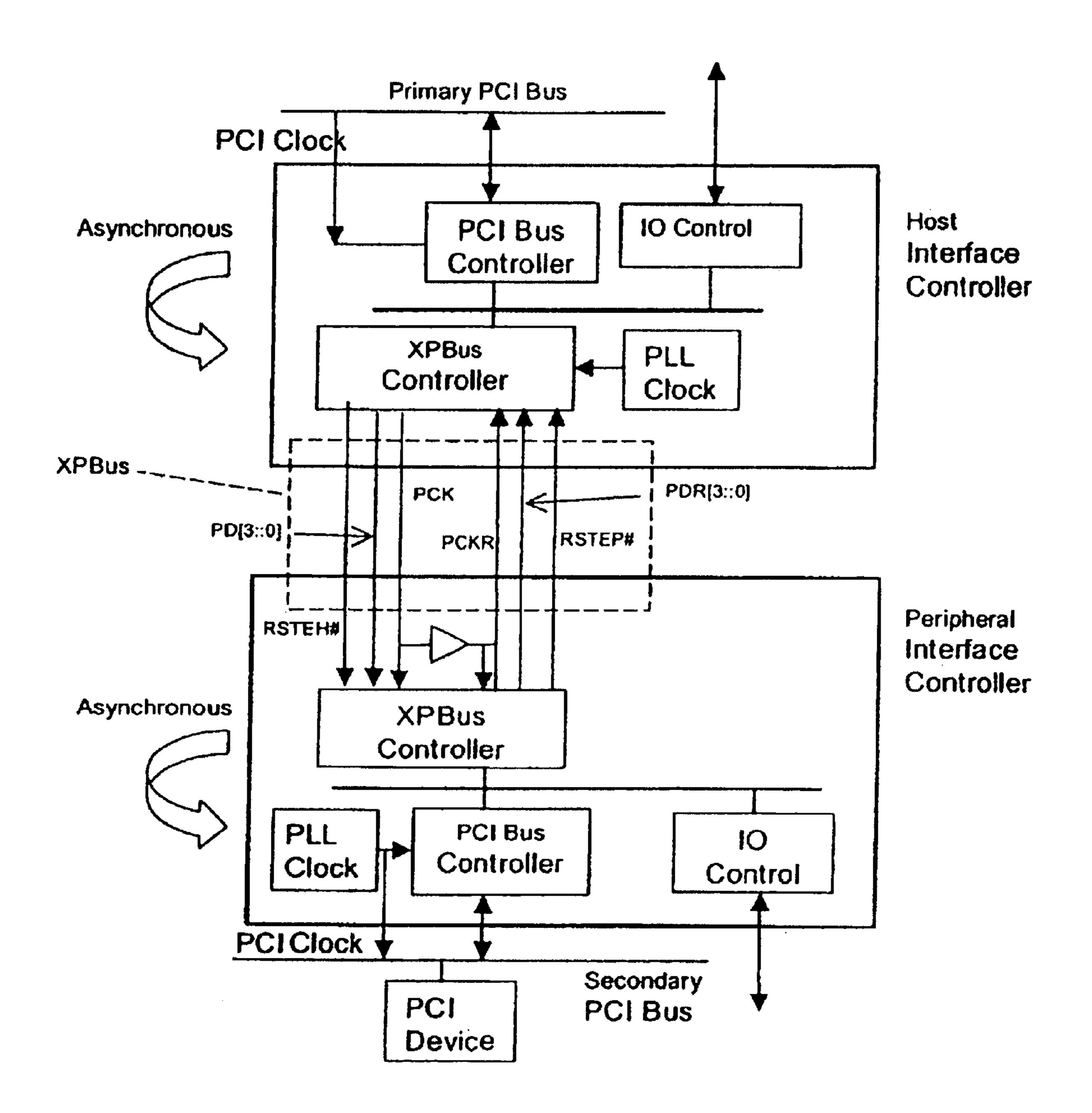

- FIG. 11 is a block diagram of one embodiment of a computer system using the interface of the present invention.

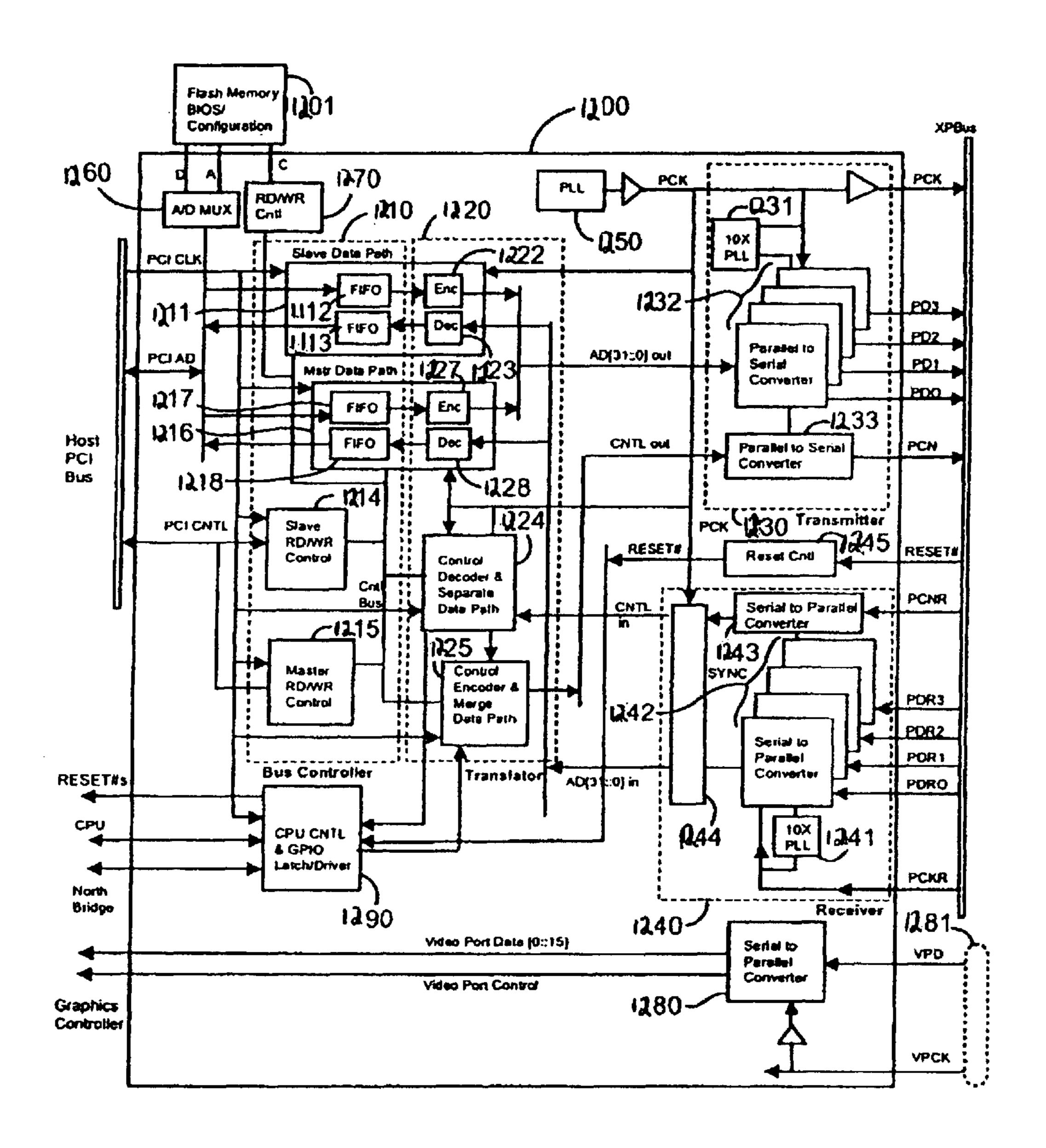

- FIG. 12 is a detailed block diagram of one embodiment of the host interface controller (HIC) of the present invention.

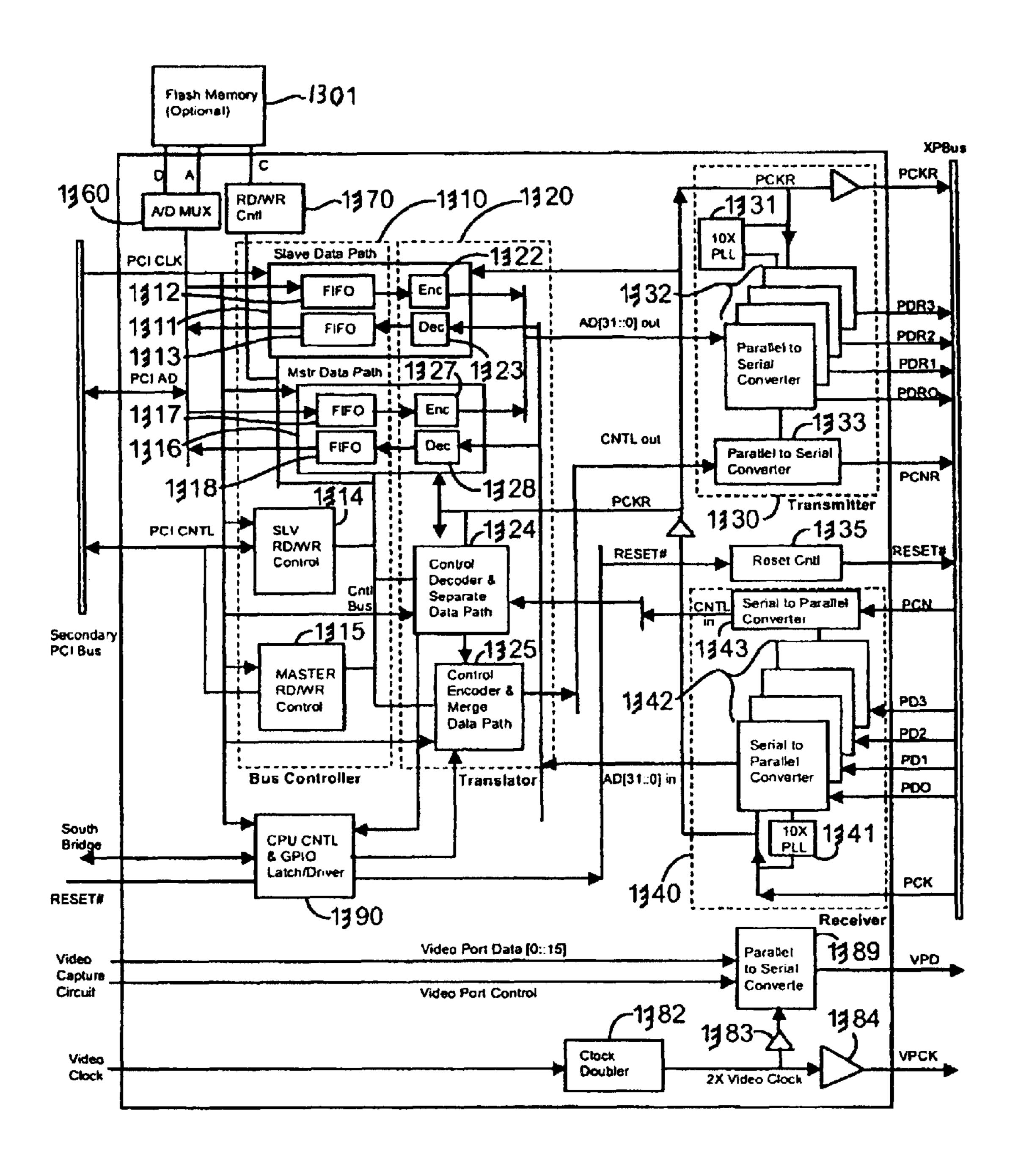

- FIG. 13 is a detailed block diagram of one embodiment of the PIC of the present invention.

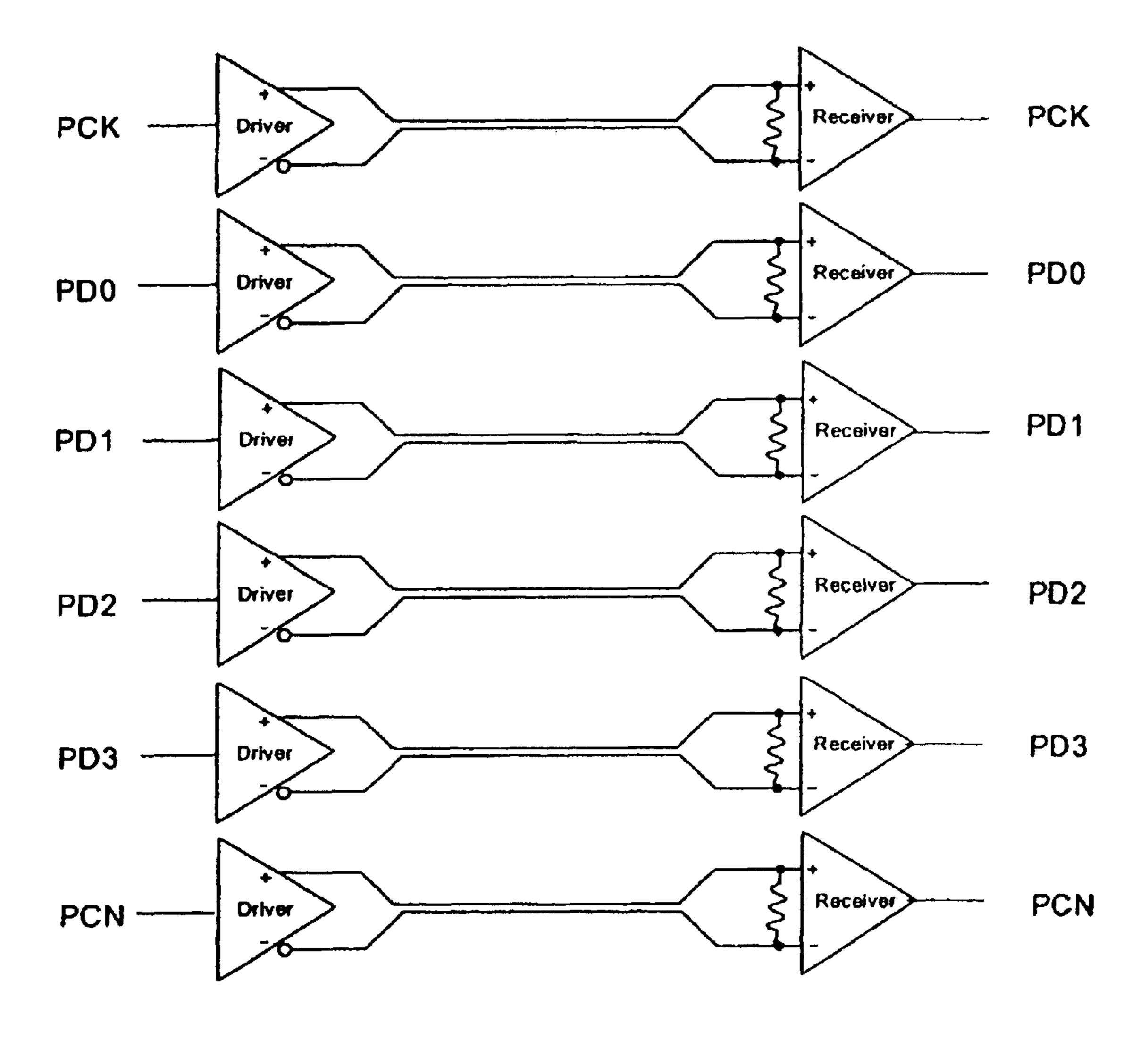

- FIG. 14 is a schematic diagram of the signal lines PCK, PD0 to PD3, and PCN.

- FIG. 15 is a block diagram of another embodiment of the HIC and PIC of the present invention and the interface therebetween.

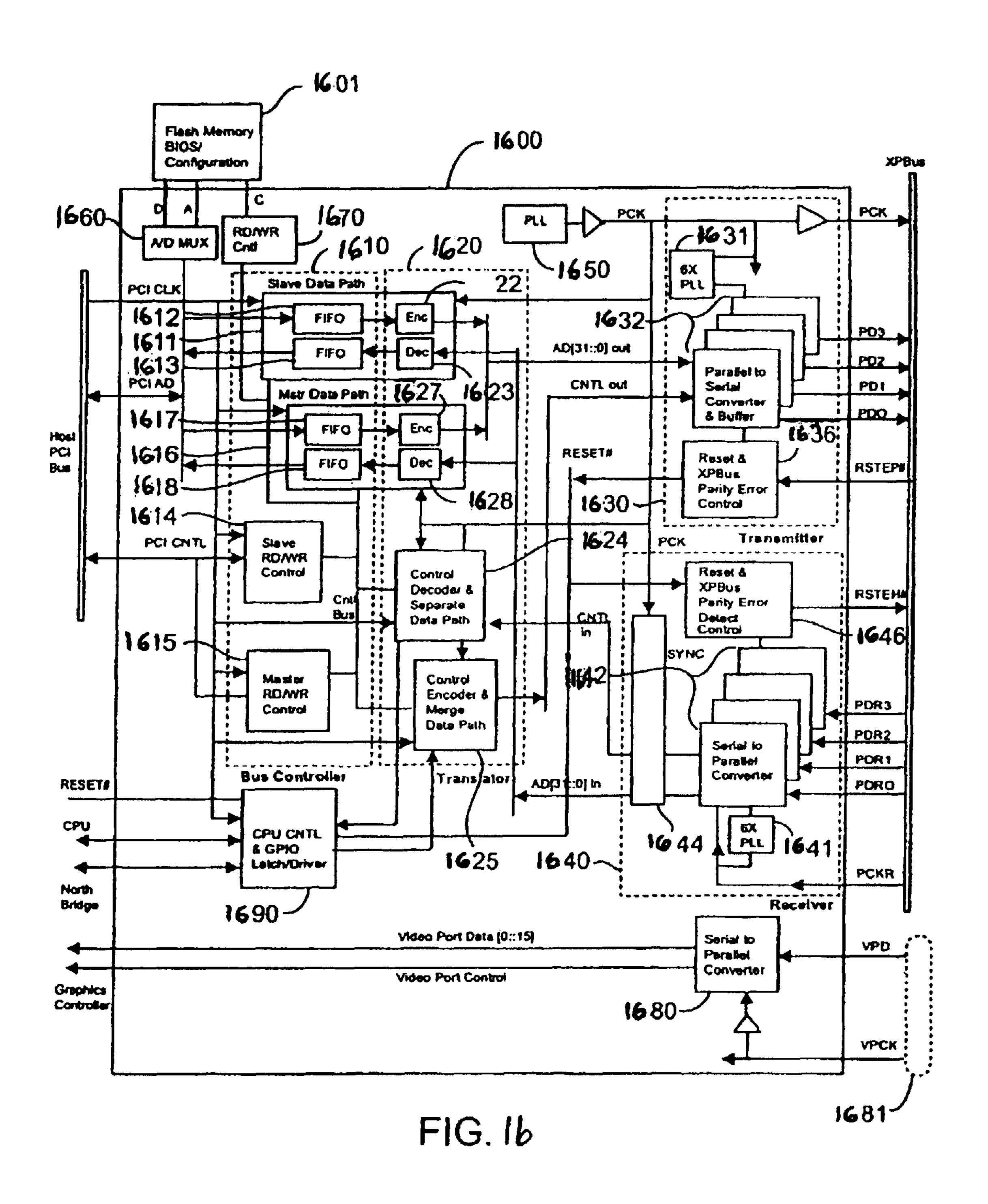

- FIG. 16 is a detailed block diagram of another embodiment of the HIC of the present invention.

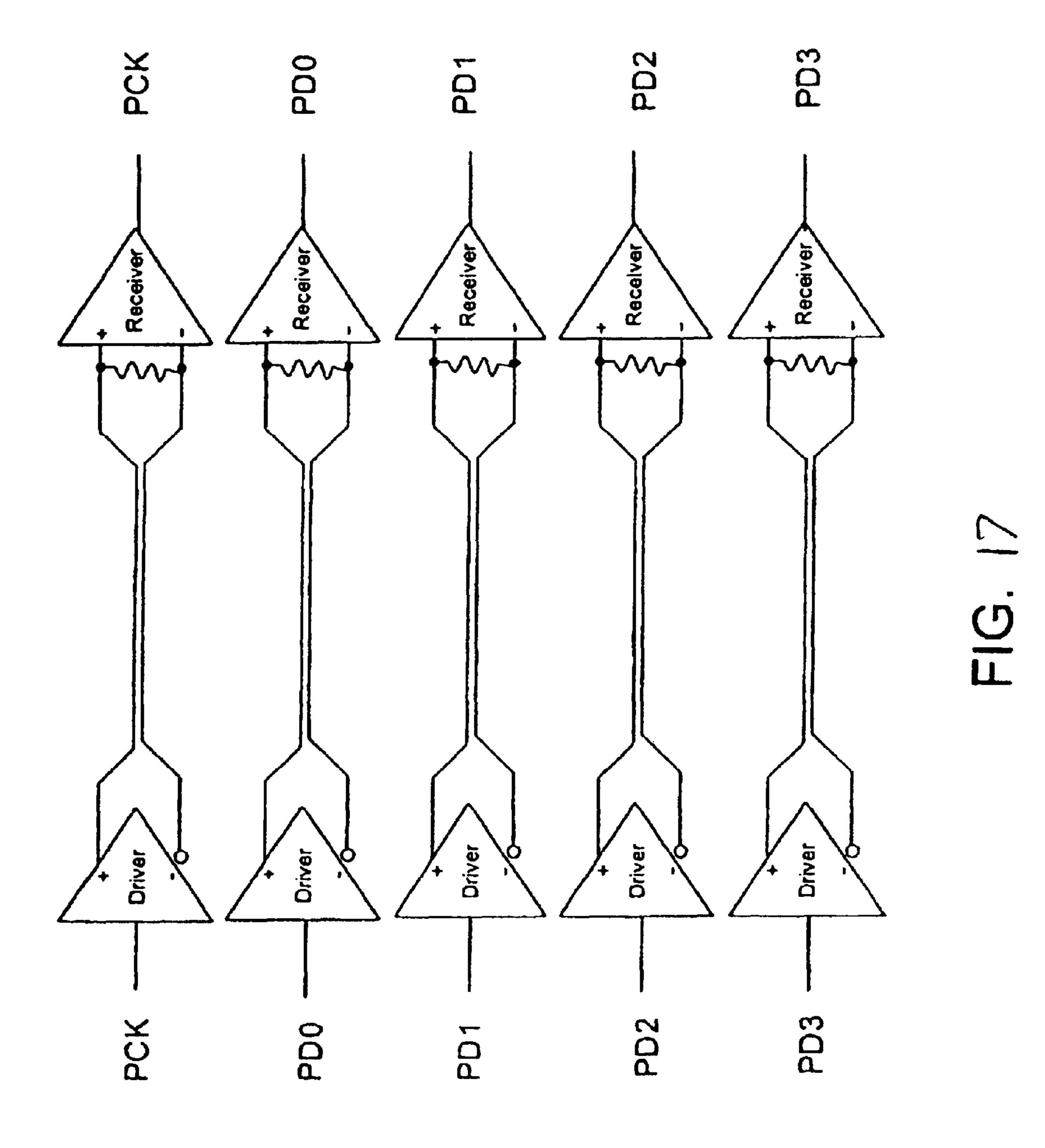

- FIG. 17 is a schematic diagram of the signal lines PCK and PD0 to PD3.

### DESCRIPTION OF SPECIFIC EMBODIMENTS I. System Hardware

FIG. 1 is a simplified diagram of a computer system 1 according to an embodiment of the present invention. This diagram is merely an illustration and should not limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. The computer system 1 includes an attached computer module (i.e., ACM) 10, a desktop console 20, among other elements. The computer system is modular and has a variety of components that are removable. Some of these components (or modules) can be used in different computers, workstations, computerized television sets, and portable or laptop units.

In the present embodiment, ACM 10 includes computer components, as will be described below, including a central

processing unit ("CPU"), IDE controller, hard disk drive, computer memory, and the like. The computer module bay (i.e., CMB) **40** is an opening or slot in the desktop console. The CMB houses the ACM and provides communication to and from the ACM. The CMB also provides mechanical protection and support to ACM **10**. The CMB has a mechanical alignment mechanism for mating a portion of the ACM to the console. The CMB further has thermal heat dissipation sinks, electrical connection mechanisms, and the like. Some details of the ACM can be found in co-pending patent application Nos. 09/149,882 and 09/149,548 filed Sep. 8, 1998, commonly assigned, and hereby incorporated by reference for all purposes.

In a preferred embodiment, the present system has a security system, which includes a mechanical locking system, an 15 electrical locking system, and others. The mechanical locking system includes at least a key 11. The key 11 mates with key hole 13 in a lock, which provides a mechanical latch 15 in a closed position. The mechanical latch, in the closed position, mates and interlocks the ACM to the computer 20 module bay. The mechanical latch, which also has an open position, allows the ACM to be removed from the computer module bay. Further details of the mechanical locking system are shown in the Fig. below.

FIG. 2 is a simplified diagram of a computer module 10 25 according to an embodiment of the present invention. This diagram is merely an illustration and should not limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. Some of the reference numerals are similar to the previous Fig. for easy reading. The computer module 10 includes key 11, which is insertable into keyhole 13 of the lock. The lock has at least two position, including a latched or closed position and an unlatched or open position. The latched position secures the ACM to the computer module 35 bay. The unlatched or open position allows the ACM to be inserted into or removed from the computer bay module. As shown, the ACM also has a slot or opening 14, which allows the latch to move into and out of the ACM. The ACM also has openings 17 in the backside for an electrical and/or 40 mechanical connection to the computer module bay, which is connected to the console.

FIG. 3 is a simplified side-view diagram of a computer module according to an embodiment of the present invention. This diagram is merely an illustration and should not 45 limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. Some of the reference numerals are similar to the previous FIG. for easy reading. As shown, the ACM module inserts into the computer module bay frame 19, 50 which is in the console. A side 27 and a bottom 19 of ACM slide and fit firmly into the computer module bay frame, which has at least a bottom portion 19 and back portion 26. A backside 23 of the ACM faces backside 26 of the frame. ACM also has a front-side or face 25 that houses the lock 55 and exposes the keyhole 13 to a user. The key 11 is insertable from the face into the keyhole.

As the ACM inserts into the frame, connector 17 couples and inserts into connector 21. Connector 17 electrically and mechanically interface elements of the ACM to the console 60 through connector 21. Latch 14 should be moved away from the bottom side 19 of the module bay frame before inserting the ACM into the frame. Once the ACM is inserted fully into the frame, latch 15 is placed in a closed or lock position, where it keeps the ACM firmly in place. That is, latch 15 biases against a backside portion 29 of the ACM enclosure to hold the ACM in place, where the connector 17 firmly

6

engages, electrically and mechanically, with connector 21. To remove the ACM, latch 15 is moved away or opened from the back side portion of the ACM enclosure. ACM is manually pulled out of the computer module bay frame, where connector 17 disengages with connector 21. As shown, the key 11 is used to selectively move the latch in the open or locked position to secure the ACM into the frame module.

In most embodiments, the ACM includes an enclosure such as the one described with the following components, which should not be limiting:

- 1) A CPU with cache memory;

- 2) Core logic device or means;

- 3) Main memory;

- 4) A single primary Hard Disk Drive ("HDD") that has a security program;

- 5) Flash memory with system BIOS and programmable user password;

- 6) Operating System, application software, data files on primary HDD;

- 7) An interface device and connectors to peripheral console;

- 8) A software controllable mechanical lock, lock control means, and other accessories.

The ACM connects to a peripheral console with power supply, a display device, an input device, and other elements. Some details of these elements with the present security system are described in more detail below.

The central processing unit of the ACM has a power supply connection point, and interconnection circuitry coupled to said CPU and connectable to the console. The power supply connection point of said CPU is uncoupled from any electrical power source having sufficient energy to sustain execution of instructions whenever said interconnection circuitry is disconnected from the console.

FIG. 4 is a simplified layout diagram of a security system for a computer system according to an embodiment of the present invention. This diagram is merely an illustration and should not limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. The layout diagram illustrates the top-view of the module 10, where the backside components (e.g., Host Interface Controller) are depicted in dashed lines. The layout diagram has a first portion, which includes a central processing unit ("CPU") module 400, and a second portion, which includes a hard drive module 420. A common printed circuit board 437 houses these modules and the like. Among other features, the ACM includes the central processing unit module 400 with a cache memory 405, which is coupled to a north bridge unit 421, and a host interface controller 401. The host interface controller includes a lock control 403. As shown, the CPU module is disposed on a first portion of the attached computer module, and couples to connectors 17. Here, the CPU module is spatially located near connector 17.

The CPU module can use a suitable microprocessing unit, microcontroller, digital signal processor, and the like. In a specific embodiment, the CPU module uses, for example, a 400 MHz Pentium II microprocessor module from Intel Corporation and like microprocessors from AMD Corporation, Cyrix Corporation (now National Semiconductor Corporation), and others. In other aspects, the microprocessor can be one such as the Compaq Computer Corporation Alpha Chip, Apple Computer Corporation PowerPC G3 processor, and the like. Further, higher speed processors are contemplated in other embodiments as technology increases in the future.

In the CPU module, host interface controller 401 is coupled to BIOS/flash memory 405. Additionally, the host interface controller is coupled to a clock control logic, a configuration signal, and a peripheral bus. The present invention has a host interface controller that has lock control 403 to provide security features to the present ACM. Furthermore, the present invention uses a flash memory that includes codes to provide password protection or other electronic security methods.

The second portion of the attached computer module has the hard drive module 420. Among other elements, the hard drive module includes north bridge 421, graphics accelerator 423, graphics memory 425, a power controller 427, an IDE controller 429, and other components. Adjacent to and in parallel alignment with the hard drive module is a personal 15 computer interface ("PCI") bus 431, 432. A power regulator 435 is disposed near the PCI bus.

In a specific embodiment, north bridge unit **421** often couples to a computer memory, to the graphics accelerator **423**, to the IDE controller, and to the host interface controller via the PCI bus. Graphics accelerator **423** typically couples to a graphics memory **423**, and other elements. IDE controller **429** generally supports and provides timing signals necessary for the IDE bus. In the present embodiment, the IDE controller is embodied as a 643U2 PCI-to IDE chip from 25 CMD Technology, for example. Other types of buses than IDE are contemplated, for example EIDE, SCSI, 1394, and the like in alternative embodiments of the present invention.

The hard drive module or mass storage unit **420** typically includes a computer operating system, application software 30 program files, data files, and the like. In a specific embodiment, the computer operating system may be the Windows98 operating system from Microsoft Corporation of Redmond, Wash. Other operating systems, such as WindowsNT, MacOS8, Unix, and the like are also contem- 35 plated in alternative embodiments of the present invention. Further, some typical application software programs can include Office98 by Microsoft Corporation, Corel Perfect Suite by Corel, and others. Hard disk module **420** includes a hard disk drive. The hard disk drive, however, can also be 40 replaced by removable hard disk drives, read/write CD ROMs, flash memory, floppy disk drives, and the like. A small form factor, for example 2.5", is currently contemplated, however, other form factors, such as PC card, and the like are also contemplated. Mass storage unit **240** 45 may also support other interfaces than IDE. Among other features, the computer system includes an ACM with security protection. The ACM connects to the console, which has at least the following elements, which should not be limiting.

- 1) Connection to input devices, e.g. keyboard or mouse;

- 2) Connection to display devices, e.g. Monitor;

- 3) Add-on means, e.g. PCI add-on slots;

- 4) Removable storage media subsystem, e.g. Floppy drive, CDROM drive;

- 5) Communication device, e.g. LAN or modem;

- 6) An interface device and connectors to ACM;

- 7) A computer module bay with a notch in the frame for ACM's lock; and

- 8) Power supply and other accessories.

As noted, the computer module bay is an opening in a peripheral console that receives the ACM. The computer module bay provides mechanical support and protection to ACM. The module bay also includes, among other elements, a variety of thermal components for heat dissipation, a frame 65 that provides connector alignment, and a lock engagement, which secures the ACM to the console. The bay also has a

8

printed circuit board to mount and mate the connector from the ACM to the console. The connector provides an interface between the ACM and other accessories.

FIG. 5 is a simplified block diagram 500 of a security system for a computer module according to an embodiment of the present invention. This diagram is merely an illustration and should not limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. The block diagram 500 has a variety of features such as those noted above, as well as others. In the present diagram, different reference numerals are used to show the operation of the present system.

The block diagram is an attached computer module 500. The module 500 has a central processing unit, which communicates to a north bridge **541**, by way of a CPU bus **527**. The north bridge couples to main memory 523 via memory bus **529**. The main memory can be any suitable high speed memory device or devices such as dynamic random access memory ("DRAM") integrated circuits and others. The DRAM includes at least 32 Meg. or 64 Meg. and greater of memory, but can also be less depending upon the application. Alternatively, the main memory can be coupled directly with the CPU in some embodiments. The north bridge also couples to a graphics subsystem 515 via bus 542. The graphics subsystem can include a graphics accelerator, graphics memory, and other devices. Graphics subsystem transmits a video signal to an interface connector, which couples to a display, for example.

The attached computer module also includes a primary hard disk drive that serves as a main memory unit for programs and the like. The hard disk can be any suitable drive that has at least 2 GB and greater. As merely an example, the hard disk is a Marathon 2250 (2.25 GB, 2 ½ inch drive) product made by Seagate Corporation of Scotts Valley, but can be others. The hard disk communicates to the north bridge by way of a hard disk drive controller and bus lines 502 and 531. The hard disk drive controller couples to the north bridge by way of the host PCI bus, which connects bus 537 to the north bridge. The hard disk includes computer codes that implement a security program according to the present invention. Details of the security program are provided below.

The attached computer module also has a flash memory device 505 with a BIOS. The flash memory device 505 also has codes for a user password that can be stored in the device. The flash memory device generally permits the storage of such password without a substantial use of power, even when disconnected. As merely an example, the flash memory device has at least 4 Meg. or greater of memory, or 16 Meg. or greater of memory. A host interface controller 507 communications to the north bridge via bus 535 and host PCI bus. The host interface controller also has a lock control 509, which couples to a lock. The lock is attached to the module and has a manual override to the lock on the host interface controller in some embodiments. Host interface controller 507 communicates to the console using bus 511, which couples to connection 513.

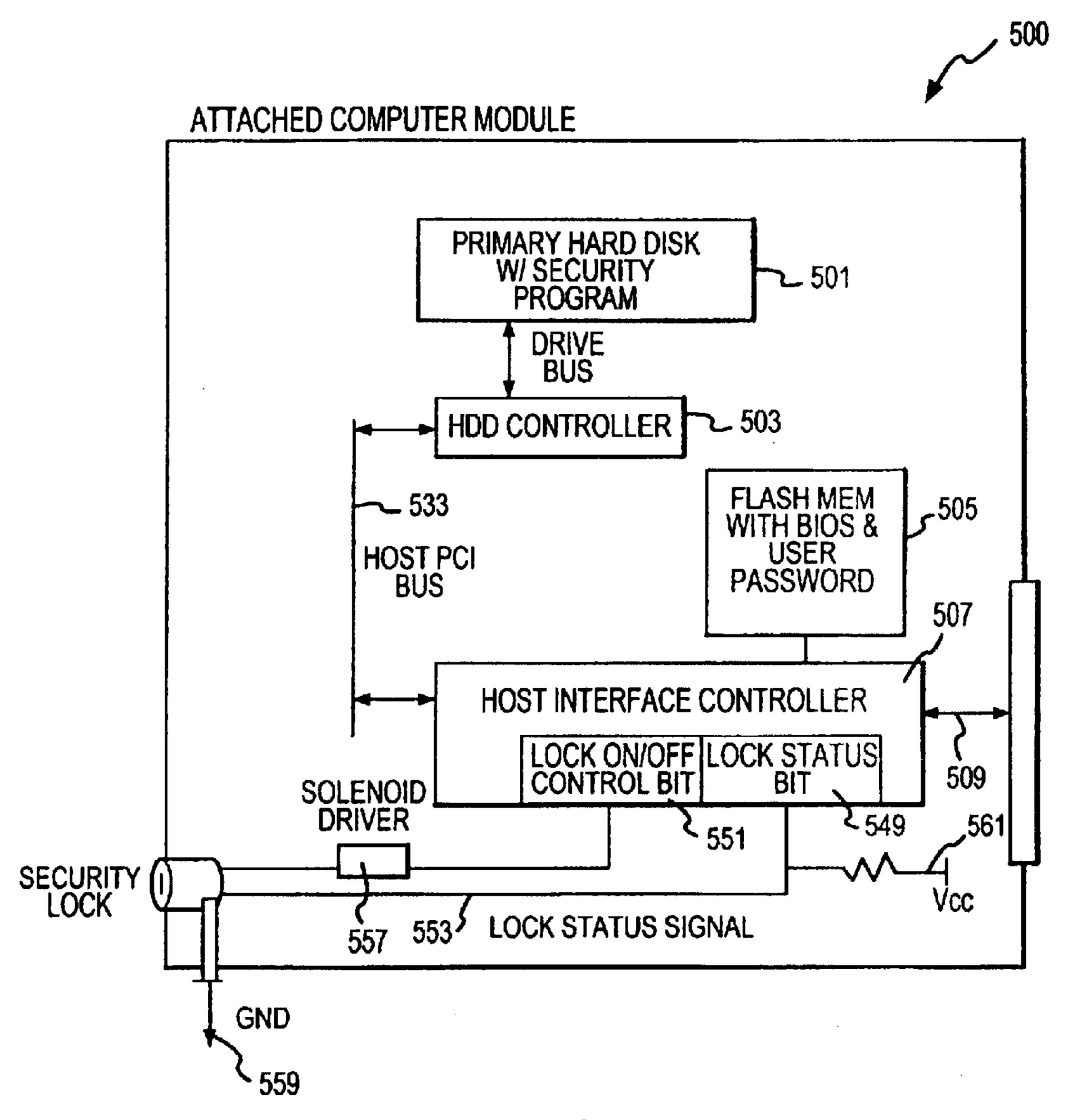

In one aspect of the present invention the security system uses a combination of electrical and mechanical locking mechanisms. Referring to FIG. 5A, for example, the present system provides a lock status mechanism in the host interface controller 509. The lock status of the lock is determined by checking a lock status bit 549, which is in the host interface controller. The lock status bit is determined by a signal 553, which is dependent upon the position of the lock. Here, the position of the lock is closed in the ground 559 position, where the latch couples to a ground plane in the module

and/or system. Alternatively, the signal of the lock is at Vcc, for example, which is open. Alternatively, the signal can be ground in the open position and Vcc in the closed position, depending upon the application. Other signal schemes can also be used depending upon the application.

Once the status is determined, the host interface controller turns the lock via solenoid **557** in a lock on or lock off position, which is provided through the control bit **551**, for example. The control bit is in a register of the host interface controller in the present example. By way of the signal 10 schemes noted and the control bit, it is possible to place the lock in the lock or unlock position in an electronic manner. Once the status of the lock is determined, the host interface controller can either lock or unlock the latch on the module using a variety of prompts, for example.

In a preferred embodiment, the present invention uses a password protection scheme to electronically prevent unauthorized access to the computer module. The present password protection scheme uses a combination of software, which is a portion of the security program, and a user 20 password, which can be stored in the flash memory device **505**. By way of the flash memory device, the password device not become erased by way of power failure or the lock. The password is substantially fixed in code, which cannot be easily erased. Should the user desire to change the 25 password, it can readily be changed by erasing the code, which is stored in flash memory and a new code (i.e., password) is written into the flash memory. An example of a flash memory device can include a Intel Flash 28F800F3 series flash, which is available in 8 Mbit and 16 Mbit 30 designs. Other types of flash devices can also be used, however. Details of a password protection method are further explained below by way of the FIGS.

In a specific embodiment, the present invention also includes a real-time clock **510** in the ACM, but is not limited. 35 The real-time clock can be implemented using a reference oscillator 14.31818 MHz **508** that couples to a real-time clock circuit. The real-time clock circuit can be in the host interface controller. An energy source 506 such as a battery can be used to keep the real-time clock circuit running even 40 when the ACM has been removed from the console. The real-time clock can be used by a security program to perform a variety of functions. As merely an example, these functions include: (1) fixed time period in which the ACM can be used, e.g., ACM cannot be used at night; (2) programmed ACM to 45 be used after certain date, e.g., high security procedure during owner's vacation or non use period; (3) other uses similar to a programmable time lock. Further details of the present real-time clock are described in the application listed under Ser. No. 09/183,816 noted above.

In still a further embodiment, the present invention also includes a permanent password or user identification code to identify the computer module. In one embodiment, the permanent password or user code is stored in a flash memory device. Alternatively, the permanent password or user code 55 is stored in the central processing unit. The password or user code can be placed in the device upon manufacture of such device. Alternatively, the password or user code can be placed in the device by a one time programming techniques using, for example, fuses or the like. The present password 60 or user code provides a permanent "finger print" on the device, which is generally hardware. The permanent finger print can be used for identification purposes for allowing the user of the hardware to access the hardware itself, as well as other systems. These other systems include local and wide 65 area networks. Alternatively, the systems can also include one or more servers. The present password and user identifi**10**

cation can be quite important for electronic commerce applications and the like. In one or more embodiments, the permanent password or user code can be combined with the password on flash memory for the security program, which is described below in more detail.

#### II. SECURITY DETECTION PROGRAMS

FIGS. 6 and 7 show simplified flow diagrams 600, 700 of security methods according to embodiments of the present invention. These diagrams are merely illustrations and should not limit the scope of the claims herein. One of ordinary skill in the art would recognize other variations, modifications, and alternatives. Referring to FIG. 6, which considers an example for when the ACM is inserted into the computer module bay in the console, ACM has already been inserted into the console and is firmly engaged in an electrical and mechanical manner. A computer system is powered up 601, which provides selected signals to the microprocessor. The microprocessor oversees the operation of the computer system. The microprocessor searches the memory in, for example, the hard disk drive and execute a security program, step 603.

The security program runs through a sequence of steps before allowing a user to operate the present system with the ACM. Among other processes, the security program determines if an "Auto-lock" is ON. If so, the security program goes via branch 606 to step 607. Alternatively, the security program goes to step 609, which determines that the lock stays OFF and loops to step 627, which indicates that the ACM can be removed physically from the console. In step 607, the security program turns a switch or switching means that turns ON a lock, which can be electrical, mechanical, or a combination of electrical and mechanical.

In a specific embodiment, the security program turns OFF the power of the ACM and console. Here, the security program directs the OS to turn the power OFF, step **613**. In an embodiment where power failure occurs (step **611**), a key is used to release a latch in the ACM on the lock **615**, where the ACM can be removed, step **627**. From step **613**, the security program determines if the ACM is to be removed, step **617**. If not, the lock stays ON, step **619**. Alternatively, the security detection program determines if the password (or other security code) matches with the designated password, step **621**. If not, the lock stays ON, step **623**. Alternatively, the security program releases the lock **625**, which frees the ACM. Next, the ACM can be removed, step **627**.

In an alternative embodiment, the present invention provides a security system for the ACM, which is outside the console or computer module bay. See, FIG. 7, for example. As shown, the security system is implemented to prevent illegal or unauthorized use (step 701) of the ACM, which has not been used in the console. Here, a key turns ON a lock (step 703). The lock moves a latch in the ACM to a specific spatial location that physically blocks the passage of the ACM into the computer module bay. Accordingly, the ACM cannot insert (step 705) into the computer module bay.

In an alternative aspect, the key can be used to turn the lock OFF, step 707. Here, the key moves the latch in a selected spatial location that allows the ACM to be inserted into the computer bay module. In the OFF position, the ACM inserts into the computer module bay, step 709. Once the ACM is in the bay, a user can begin operating the ACM through the console. In one embodiment, the computer console including the ACM goes through the sequence of steps in the above FIG., but is not limited.

In a specific embodiment, the present invention implements the sequences above using computer software. In other aspects, computer hardware can also be used and is

preferably in some applications. The computer hardware can include a mechanical lock, which is built into the ACM. An example of such mechanical lock is shown above, but can also be others. In other aspects, the lock can be controlled or accessed electronically by way of computer software. Here, the key can be used to as a manual override if the ACM or computer fails.

The lock is used to prevent theft and accidental removal inside CMB. The current invention locates the lock inside the ACM to allow a user to keep a single key as ACM is moved from console to console at different locations. When ACM is in transit, the lock can be engaged using the key so that the latch extends outside ACM's enclosure. The extended latch prevents ACM from being inserted into any CMB. This prevents any illegal use of ACM by someone other than the user.

In one aspect of the invention, the user password is programmable. The password can be programmable by way of the security program. The password can be stored in a flash memory device within the ACM. Accordingly, the user of the ACM and the console would need to have the user password 20 in order to access the ACM. In the present aspect, the combination of a security program and user password can provide the user a wide variety of security functions as follows:

- 1) Auto-lock capability when ACM is inserted into CMB;

- 2) Access privilege of program and data;

- 3) Password matching for ACM removal; and

- 4) Automatic HDD lock out if tempering is detected.

In still a further embodiment, the present invention also includes a method for reading a permanent password or user identification code to identify the computer module. In one 30 embodiment, the permanent password or user code is stored in a flash memory device. Alternatively, the permanent password or user code is stored in the central processing unit. The password or user code can be placed in the device upon manufacture of such device. Alternatively, the password or 35 user code can be placed in the device by a one time programming techniques using, for example, fuses or the like. The present password or user code provides a permanent "finger print" on the device, which is generally hardware. The permanent finger print can be used for identification purposes 40 for allowing the user of the hardware to access the hardware itself, as well as other systems. These other systems include local and wide area networks. Alternatively, the systems can also include one or more servers. The present method allows a third party confirm the user by way of the permanent pass- 45 word or user code. The present password and user identification can be quite important for electronic commerce applications and the like, which verify the user code or password. In one or more embodiments, the permanent password or user code can be combined with the password on flash memory 50 for the security program.

FIG. 8 is a block diagram of the components in one computer system employing the present invention. The computer system comprises an attached computer module (ACM), a peripheral console (PCON), and the interconnection apparatus between them. The ACM includes the central processing unit (CPU) 810, system memory 820, high performance devices 850, primary mass storage 830, and related interface and support circuitry 840. The PCON includes primary display 910, primary input 920, secondary mass storage 60 950, other devices 960, expansion slots 970, the primary power supply 930, and related interface and support circuitry 940. The interconnection apparatus 1000 includes circuitry to convey power and operational signals between the ACM and PCON.

Within the ACM 800, the CPU 810 executes instructions and manipulates data stored in the system memory. The CPU

12

810 and system memory 820 represent the user's core computing power. The core computing power may also include high performance devices 850 such as advanced graphics processor chips that greatly increase overall system performance and which, because of their speed, need to be located close to the CPU. The primary mass storage 830 contains persistent copies of the operating system software, application software, configuration data, and user data. The software and data stored in the primary mass storage device represent the user's computing environment. Interface and support circuitry 840 primarily includes interface chips and signal busses that interconnect the CPU, system memory, high performance devices, and primary mass storage. The interface and support circuitry also connects ACM-resident components with the ACM-to-PCON interconnection appa-15 ratus as needed.

Within the PCON 900, the primary display component 910 may include an integrated display device or connection circuitry for an external display device. This primary display device may be, for example, an LCD, plasma, or CRT display screen used to display text and graphics to the user for interaction with the operating system and application software. The primary display component is the primary output of the computer system, i.e., the paramount vehicle by which programs executing on the CPU can communicate toward the user.

The primary input component 920 of the PCON may include an integrated input device or connection circuitry for attachment to an external input device. The primary input may be, for example, a keyboard, touch screen, keypad, mouse, trackball, digitizing pad, or some combination thereof to enable the user to interact with the operating system and application software. The primary input component is the paramount vehicle by which programs executing on the CPU receive signals from the user.

The PCON may contain secondary mass storage 950 to provide additional high capacity storage for data and software. Secondary mass storage may have fixed or removable media and may include, for example, devices such as diskette drives, hard disks, CD-ROM drives, DVD drives, and tape drives.

The PCON may be enhanced with additional capability through the use of integrated "Other Devices" 960 or addon cards inserted into the PCON's expansion slots 970. Examples of additional capability include sound generators, LAN connections, and modems. Interface and support circuitry 940 primarily includes interface chips, drive chips, and signal busses that interconnect the other components within the PCON. The interface and support circuitry also connects PCON-resident components with the ACM-to-PCON interconnection apparatus as needed.

Importantly, the PCON houses the primary power supply 930. The primary power supply has sufficient capacity to power both the PCON and the ACM 800 for normal operation. Note that the ACM may include a secondary "power supply" in the form, for example, of a small battery. Such a power supply would be included in the ACM to maintain, for example, a time-of-day clock, configuration settings when the ACM is not attached to a PCON, or machine state when moving an active ACM immediately from one PCON to another. The total energy stored in such a battery would, however, be insufficient to sustain operation of the CPU at its rated speed, along with the memory and primary mass storage, for more than a fraction of an hour, if the battery were able to deliver the required level of electrical current at all.

FIG. 9 is a block diagram of an attached computing module (ACM) 800. The physical ACM package 800 contains the

ACM functional components 801 and the ACM side of the ACM-to-PCON Interconnection 1000. The ACM 801 comprises a CPU component 810, a system memory component 820, a primary mass storage component 830, a high performance devices components 850, and an interface and sup-5 port component 840.