US00RE41068E

# (19) United States

# (12) Reissued Patent

Balasinski et al.

### (10) Patent Number:

# US RE41,068 E

## (45) Date of Reissued Patent:

Jan. 5, 2010

| (54) | SPACER-TYPE THIN-FILM POLYSILICON |

|------|-----------------------------------|

|      | TRANSISTOR FOR LOW-POWER MEMORY   |

|      | DEVICES                           |

- (75) Inventors: Artur P. Balasinski, Cupertino, CA

- (US); Kuei-Wu Huang, Hsin-chu (TW)

- (73) Assignee: STMicroelectronics, Inc., Carrollton,

TX (US)

- (21) Appl. No.: 09/968,977

- (22) Filed: Oct. 29, 1999

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 5,640,023

Issued: Jun. 17, 1997

Appl. No.: 08/521,709

Filed: Aug. 31, 1995

#### U.S. Applications:

- (63) Continuation of application No. 09/334,877, filed on Jun. 17, 1999, now abandoned.

- (51) **Int. Cl.**

**H01L 29/76** (2006.01) **H01L 31/036** (2006.01)

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,924,279    | $\mathbf{A}$ | * | 5/1990  | Shimbo                |

|--------------|--------------|---|---------|-----------------------|

| 5,039,622    | $\mathbf{A}$ | * | 8/1991  | Ishihara 438/156      |

| 5,155,054    | A            | * | 10/1992 | Itoh 438/156          |

| 5,173,754    | $\mathbf{A}$ | * | 12/1992 | Manning 257/69        |

| 5,281,843    | A            | * | 1/1994  | Ochii et al 257/393   |

| 5,283,455    | A            | * | 2/1994  | Inoue et al 257/329   |

| 5,309,010    | A            | * | 5/1994  | Kitajima 257/347      |

| 5,391,505    | A            | * | 2/1995  | Kapoor 438/152        |

| 5,391,506    | A            | * | 2/1995  | Tada et al 438/268    |

| 5,403,763    | A            | * | 4/1995  | Yamazaki 438/268      |

| 5,411,905    | A            | * | 5/1995  | Acovic et al 438/156  |

| 5,418,393    | A            | * | 5/1995  | Hayden 257/347        |

| 5,432,102    | $\mathbf{A}$ | * | 7/1995  | Cho et al 438/156     |

| 5,459,088    | $\mathbf{A}$ | * | 10/1995 | Rha et al 438/158     |

| 5,466,619    | $\mathbf{A}$ | * | 11/1995 | Choi 438/162          |

| 5,547,883    | $\mathbf{A}$ | * | 8/1996  | Kim 438/158           |

| 5,656,511    | $\mathbf{A}$ | * | 8/1997  | Shindo 438/160        |

| 5,821,585    | A            | * | 10/1998 | Maegawa               |

| 5,918,115    | $\mathbf{A}$ | * | 6/1999  | Kikuchi et al 438/138 |

| 6,188,085    | B1           | * | 2/2001  | Shimizu et al 257/66  |

| 6,242,777    | B1           | * | 6/2001  | Mano et al            |

| 2004/0178446 | <b>A</b> 1   | * | 9/2004  | Sundaresan            |

|              |              |   |         |                       |

<sup>\*</sup> cited by examiner

Primary Examiner—Mark Prenty

(74) *Attorney, Agent, or Firm*—Lisa K. Jorgenson; Bryan A. Santarelli

#### (57) ABSTRACT

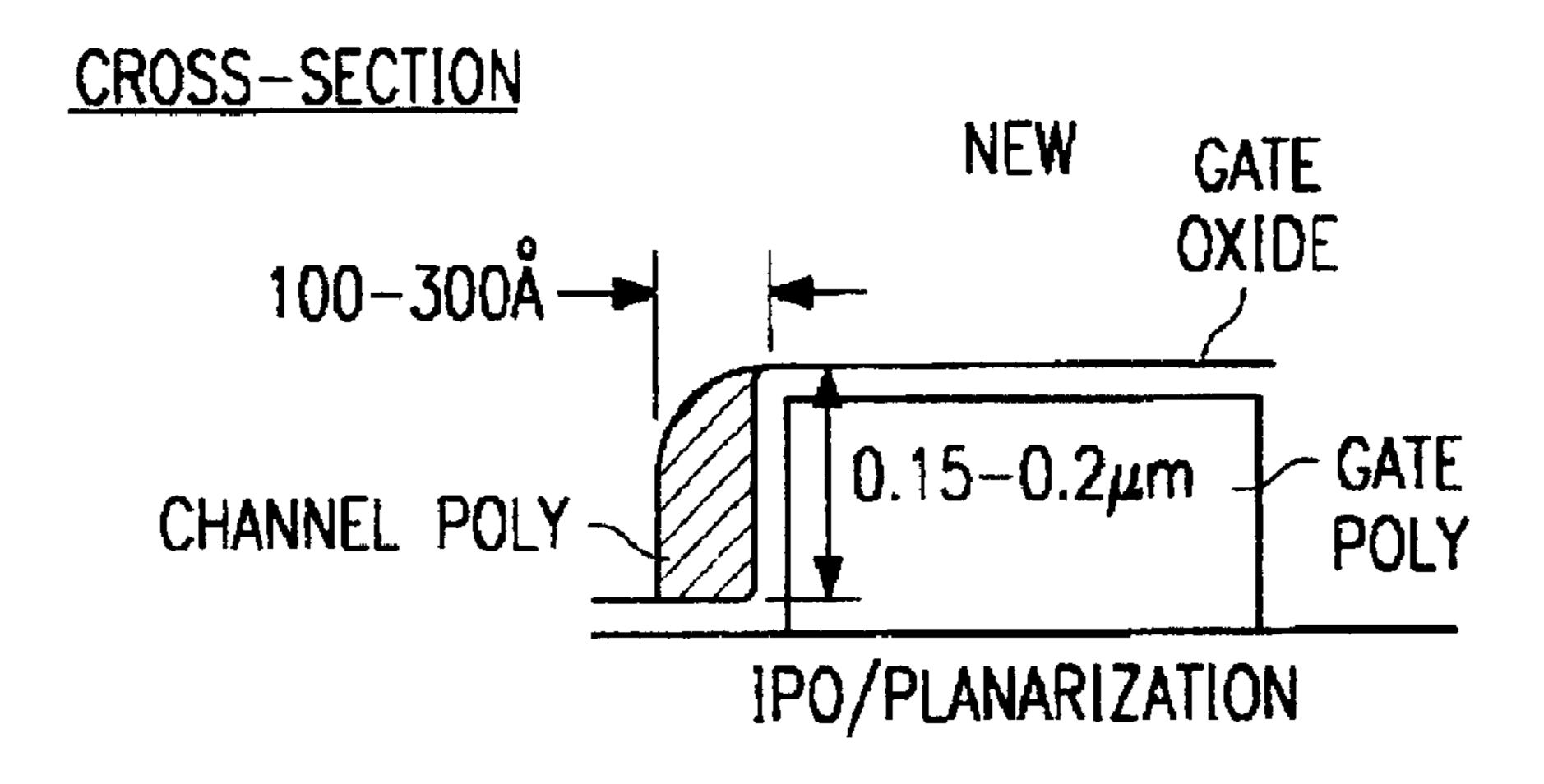

The cross-sectional area of a thin-film transistor (TFT) is decreased in order to minimize bitline to supply leakage of the TFT. This is accomplished by utilizing a spacer etch process to manufacture a TFT having a very narrow and thin channel in a controllable manner. The spacer dimensions of the TFT may be adjusted by simply modifying the thicknesses of the poly gate and the channel poly. The channel thickness is limited by the thickness of the deposited channel polysilicon which may be as thin as approximately 300 Å to 500 Å, and the channel width of the TFT corresponds to the height of the spacer etched along the polysilicon gate of the device which may be as small as approximately 0.15 to 0.25  $\mu m$ .

#### 24 Claims, 5 Drawing Sheets

Jan. 5, 2010

#### SPACER-TYPE THIN-FILM POLYSILICON TRANSISTOR FOR LOW-POWER MEMORY **DEVICES**

Matter enclosed in heavy brackets [ ] appears in the 5 original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

This application is a continuation application of U.S. patent application Ser. No. 09/334,877, filed Jun. 17, 1999, 10 and is now abandoned, which is a reissue of U.S. patent application Ser. No. 08/521,709, filed Aug. 31, 1995, which is now U.S. Pat. No. 5,640,023, issued Jun. 17, 1997.

#### BACKGROUND OF THE INVENTION

The present invention relates generally to integrated circuit memory devices, and more specifically to integrated circuit memory devices which employ thin-film transistor (TFT) technology.

Thin-film transistors (TFTs) are becoming the load devices of choice in many integrated circuit memory devices, particularly in static random access memory (SRAM) cells. TFTs are superior to standard polysilicon resistor load devices, in that TFTs have an inherently lower OFF current—an advantage which is particularly relevant in low—and zeropower SRAM applications which feature extended battery operation. In spite of this advantage, however, the bitline to supply (Vcc) leakage of TFTs designed and fabricated in state-of-the-art technology is still too significant to enable battery operation of high-density 30 memory devices, such as SRAMs, over an extended period of time.

The most common approach taken to reduce this bitline to supply leakage has been to reduce the cross-sectional area of the TFT channel, such that the TFT channel is made as thin and as narrow as possible. To this end, technologies which are capable of depositing extremely thin polysilicon layers, having a thickness of approximately 100 Å for instance, con grain size of these layers is also very small. Alternately, the width of a TFT of a memory cell may be made much smaller than any other critical dimension (CD) in the circuit. Thus, there are currently available products which feature TFTs having channel widths of 0.3 to 0.4  $\mu m$  wide while all  $_{45}$ other CDs are 0.5 µm or larger. As would be anticipated, this difference between the width dimension and other CDs of the memory device places considerable pressure on the photolithography aspect of manufacturing and thus makes manufacturing of a device using such geometries very difficult. Additionally, there are processes which fully enclose the TFT channel by the device gate. This results in process complications which do not render a viable manufacturing approach.

#### SUMMARY OF THE INVENTION

It would be advantageous in the art to minimize bitline to supply (Vcc) leakage of thin-film transistors (TFTs).

It would further be advantageous in the art to be able to reduce the cross-sectional area of a TFT channel in order to 60 minimize bitline to supply (Vcc) leakage of a thin-film transistor (TFT).

Therefore, according to the present invention, the crosssectional area of a thin-film transistor (TFT) is decreased in order to minimize bitline to supply leakage of the TFT. This 65 is accomplished by utilizing a spacer etch process to manufacture a TFT having a very narrow and thin channel in a

controllable manner. The spacer dimensions of the TFT may be adjusted by simply modifying the thicknesses of the poly gate and the channel poly. The channel thickness is limited by the thickness; of deposited channel polysilicon which may be as thin as approximately 300 Å to 500 Å, and the channel width of the TFT corresponds to the height of the spacer etched along the polysilicon gate of the device which may be as small as approximately 0.15 to  $0.25 \mu m$ .

A first preferred embodiment of the present invention employs at least two polysilicon layers to effect a spacer etch process which allows the cross-sectional area of a transistor channel of a TFT to be minimized in a controllable manner, thereby reducing the bitline to voltage supply leakage of the TFT. The first preferred embodiment provides planarization as an option. A second preferred embodiment of the present invention also utilizes a spacer etch process by selective etching a poly spacer of a spacer-TFT load structure formed around a first poly gate layer in order to achieve the desired channel length. The second preferred embodiment offers the advantage of requiring just two polysilicon layers; planarization is not required.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The novel features believed characteristic of the invention are set forth in the appended claims. The invention itself, however, as well as a preferred mode of use, and further objects and advantages thereof, will best be understood by reference to the following detailed description of an illustrative embodiment when read in conjunction with the accompanying drawings, wherein:

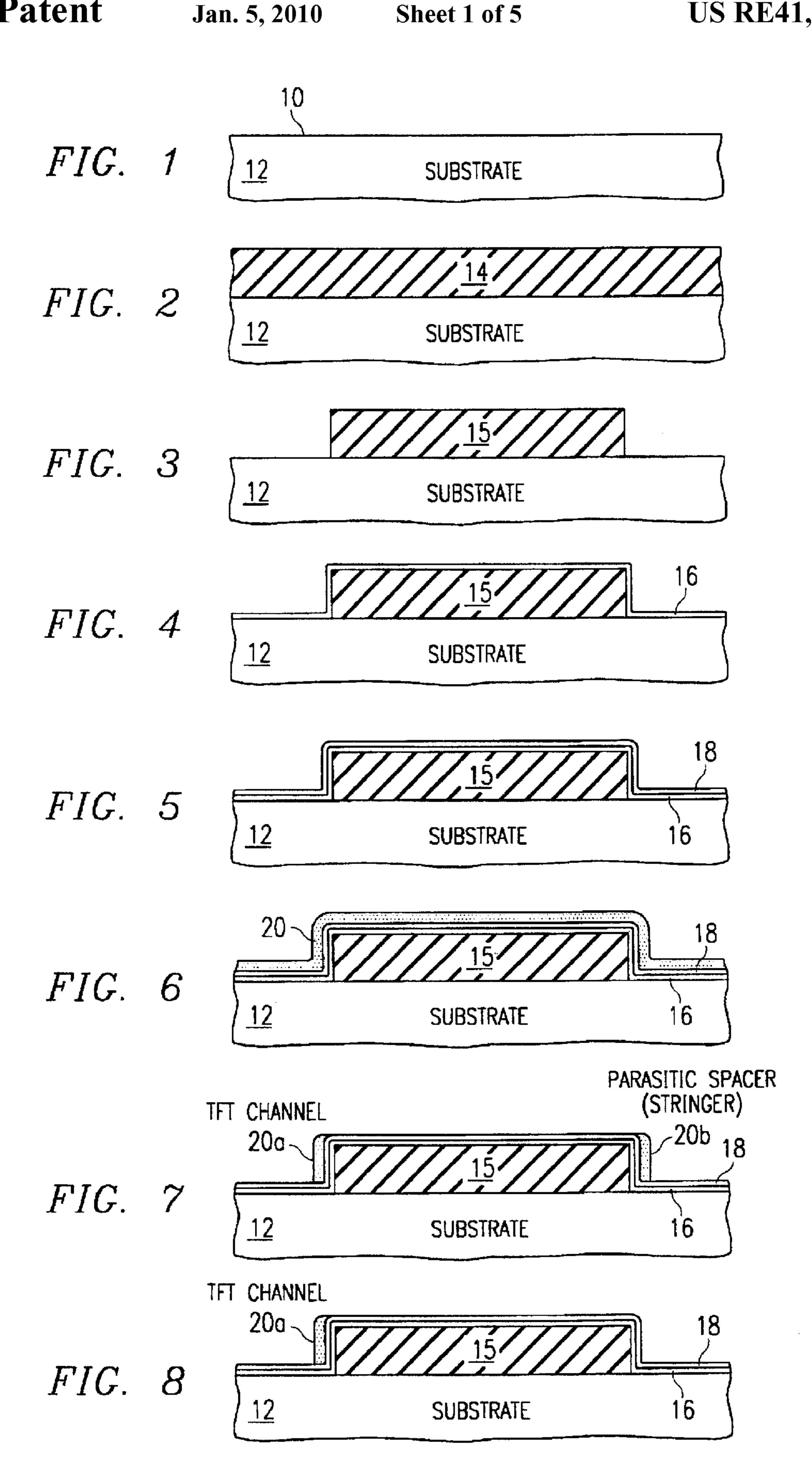

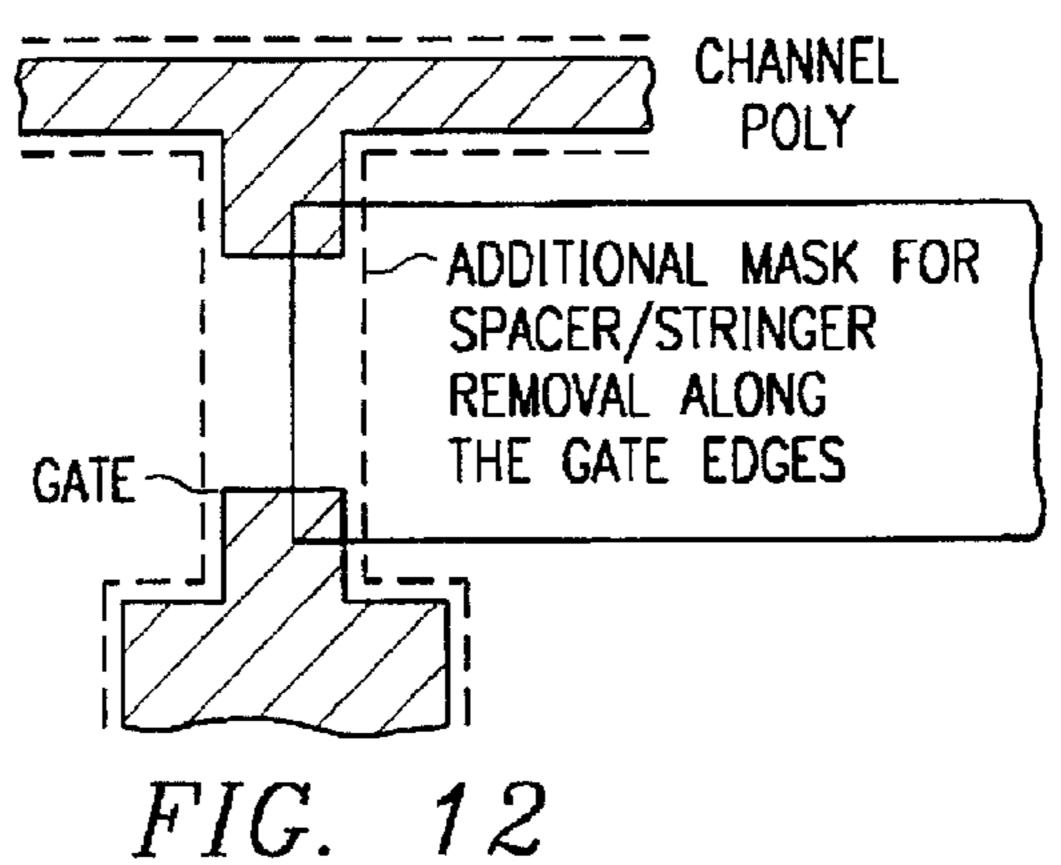

FIG. 1–12 illustrate the cross-sectional views of the processing steps required for manufacturing a TFT structure, according to a first preferred embodiment of the present invention;

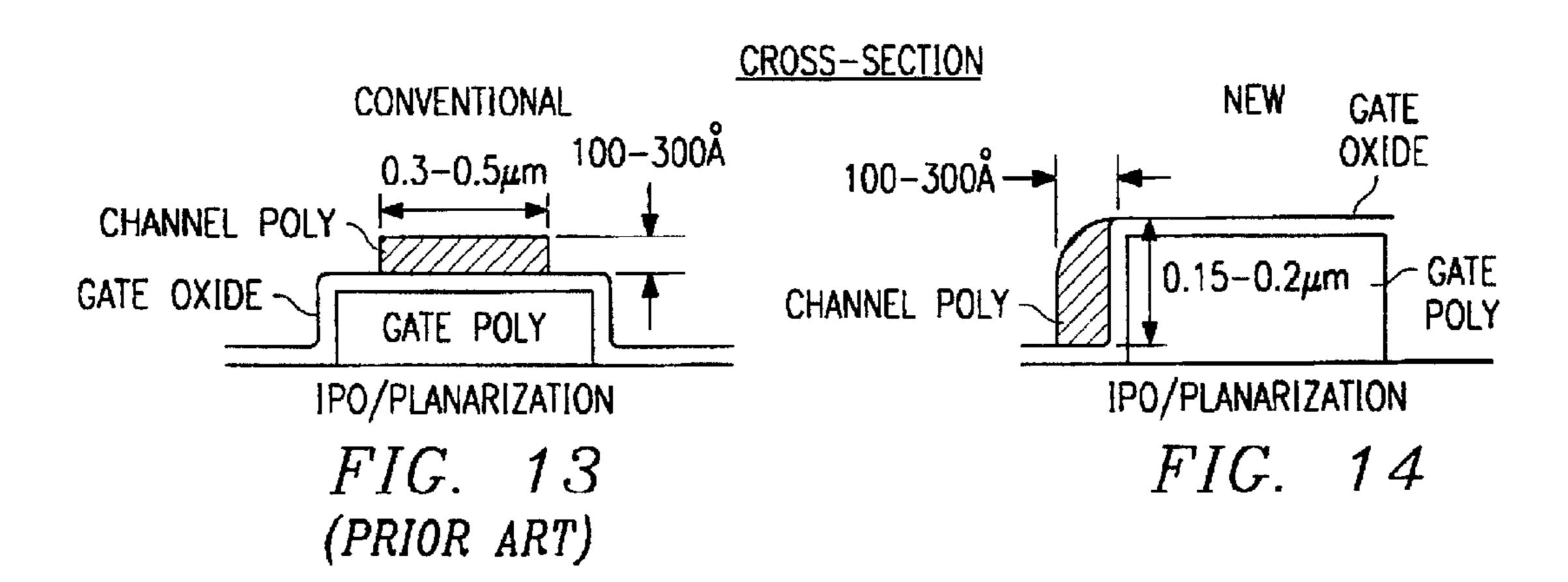

FIG. 13 illustrates the mask layout, showing crosssectional area of a TFT channel, of a conventional TFT structure;

FIG. 14 illustrates the mask layout, showing crosshave been developed. Unfortunately, the resultant polysili- an sectional area of a TFT structure, according to the first preferred embodiment of the present invention;

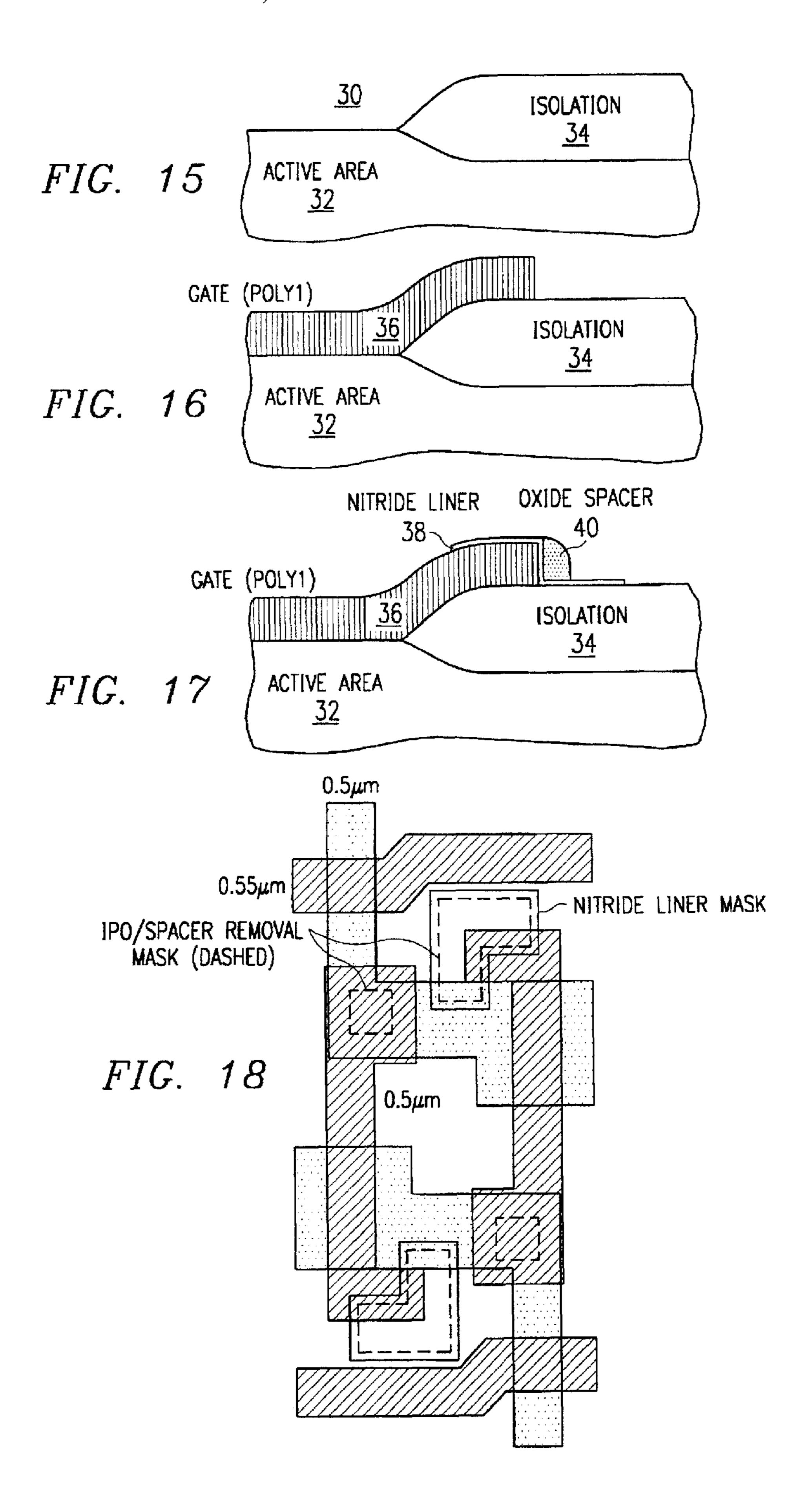

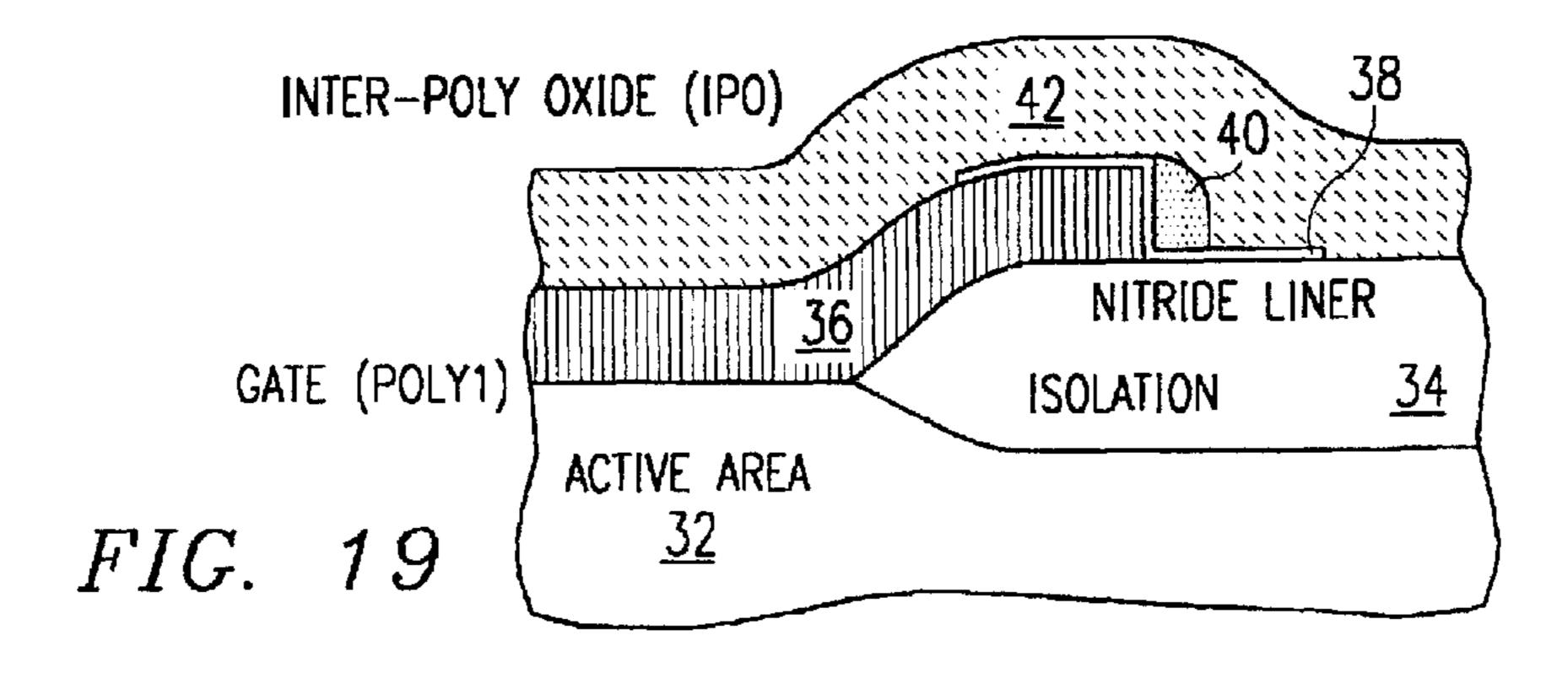

> FIGS. 15–24 illustrate the cross-sectional views of the processing steps required for manufacturing a TFT structure, according to a second preferred embodiment of the present invention;

> FIG. 18 illustrates a mask layout of a TFT structure, according to the second preferred embodiment of the present invention; and

FIG. 25 illustrates a mask layout of a TFT structure, according to the second preferred embodiment of the present invention.

# DESCRIPTION OF THE INVENTION

The present invention utilizes a spacer etch process to 55 make the transistor channel of the TFT both very narrow and thin in a controllable manner. The channel thickness is limited by the thickness of the deposited channel polysilicon which may be as small as approximately 300 to 500 Å, and the channel width corresponds to the height of the spacer etched along the polysilicon gate of the device. The height of the spacer may only be approximately 0.15 to 0.25 µm. These geometries possible with the present invention represent an improvement of more than two times the capabilities of the optical lithographic techniques used to manufacture standard products. The spacer dimensions of the TFT may be adjusted by simply modifying the thickness of the poly gate and the channel poly.

3

A first preferred embodiment of the present invention produces a TFT device having a channel that is both very narrow and thin, resulting in a small cross sectional area of the TFT channel such that bitline to supply leakage is dramatically reduced. FIGS. 1–14 illustrate the method and structure of the first preferred embodiment of the present invention.

Prior to formation of the TFT, standard layer deposition and etching of contacts for an integrated circuit device well known in the art is performed. These standard process steps  $_{10}$ typically involve the formation of one or two polysilicon (poly) layers on top of a silicon substrate where the integrated circuit memory device will be formed. Following these standard steps, planarization of the device substrate 12, as shown in the TFT structure 10 of FIG. 1, is performed. 15 Planarization of device substrate 12 shown in FIG. 1 is an optional step. However, planarization may be desirable in order to provide a planar base for the TFT such that the formation of stringers is avoided. TFT poly gate layer 14, having a thickness of approximately 1500 Å to 2500 Å thick, 20 is formed over substrate 12 as shown in FIG. 2. TFT poly gate layer 14 is formed by deposition of a typically conductive material such as polycrystalline or amorphous silicon which may be recrystallized at a later stage. The deposition rate of TFT poly gate layer 14 depends on the temperature at 25 which it is deposited, which may vary from approximately 520° C. to 620° C. depending on the preferred structure of the deposited material. TFT poly gate 14 layer is then subjected to a pattern and etch step, as shown in FIG. 3, to form TFT poly gate 15.

Referring to FIG. **4**, deposition of gate oxide layer **16** having a thickness of approximately 100–300 Å is performed on top of TFT poly gate **15** and substrate **12**. Gate oxide layer **16** may be Tetra-Ethyl Ortho Silicate (TEOS) or other gate oxide material such as High-Temperature Oxide 35 (HTO). The deposition rate of gate oxide layer **16** is approximately 10 Å/minute to 100 Å/minute. Next, as shown in FIG. **5**, a nitride deposition step is performed. Approximately 100–300 Å of nitride; deposited over gate oxide layer **16** at a deposition rate of approximately 10 Å/minute to 100 Å/minute and serves as an overetch protectorate in order to avoid the formation of stringers during subsequent etching steps. This nitride deposition is an optional process step and may not be necessary where the formation of stringers is not a concern.

Next, the TFT channel is developed. Referring to FIG. 6, a TFT channel amorphous silicon deposition step is performed. Approximately, 200 Å to 500 Å of TFT channel amorphous silicon 20 is deposited over nitride 18. The deposition of TFT channel amorphous silicon 20 may take place 50 under similar conditions to those specified for the formation of TFT poly gate 14. Deposition of TFT channel amorphous silicon 20 would usually be followed by recrystallization annealing of TFT channel amorphous silicon 20 at approximately 550° C. to 700° C. for approximately 8 hours in order 55 to form a polysilicon layer **20** with adequate grain size. For instance, the typical recrystallization anneal step may occur at 600° C. for 24 hours. If the grain size is not critical, 200 Å to 500 Å of TFT channel polysilicon 20 may be deposited over nitride 18 and the recrystallization annealing step not 60 performed. Referring to FIG. 7, the TFT device 10 is patterned and subjected to an anisotropic etch such that a channel 20a and a second, parasitic spacer, referred to as a stringer 20b, are formed adjacent to the side of TFT poly gate 14 as shown. Next, removal of stringers, such as stringer 65 20b, is accomplished through an additional masking step. This may be followed by adjustment of the TFT VT

4

(threshold voltage) by an appropriate implant or the inherent TFT VT may be used. Thus, if it is desirable to adjust the TFT VT (threshold voltage) of the device, implantation with Phosphorous, Arsenic, or BF2 at a dosage of approximately 1-10e12 at an energy of approximately 20–40 keV may be performed. Finally, a source/drain mask and implant are performed to render the memory device 10 of FIG. 8. Additionally, standard post-TFT process steps are performed as desired. These additional process steps may include steps calculated to protect or encapsulate the TFT.

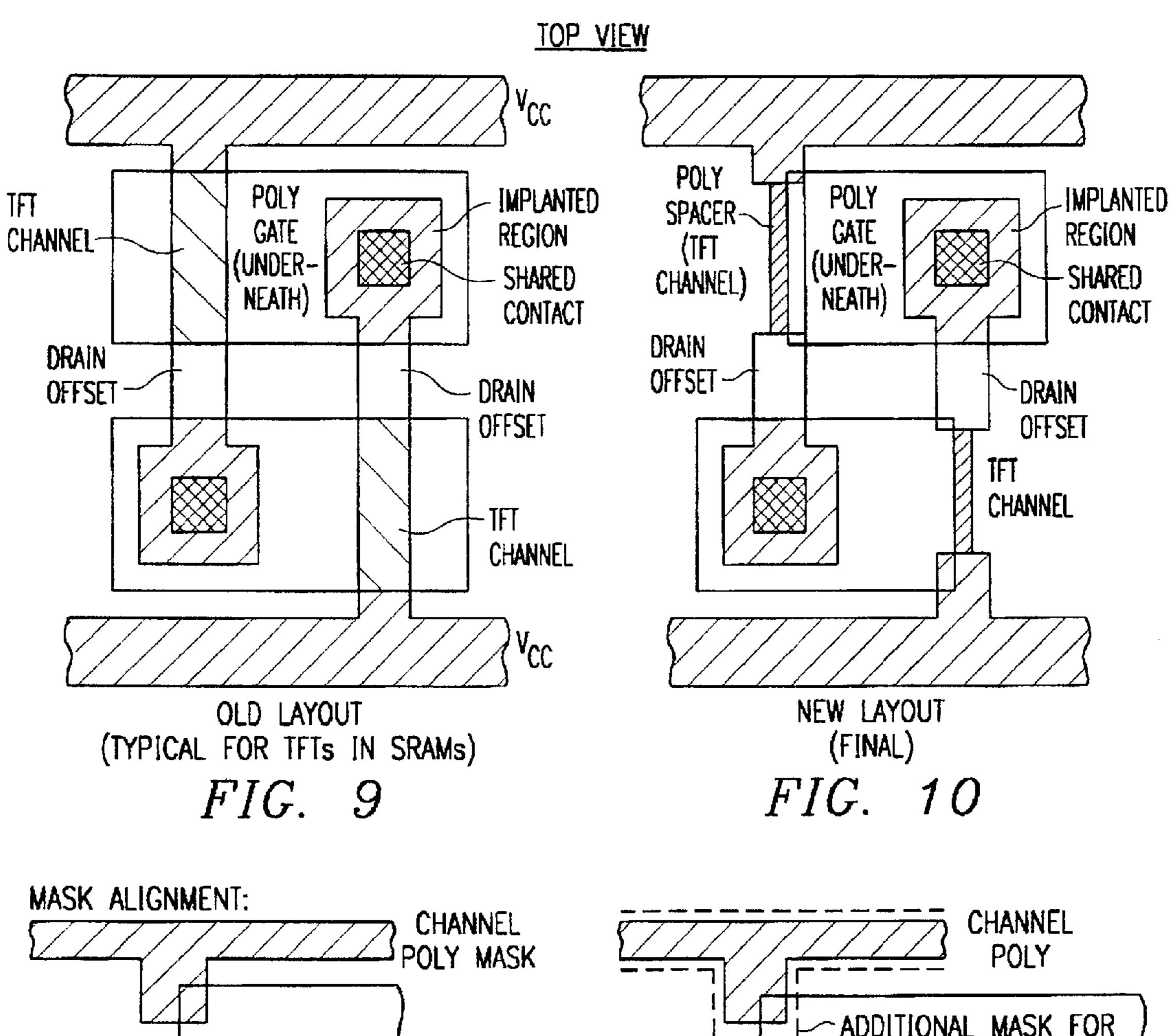

The final TFT structure 10 of FIG. 8 is quite different from the prior art TFT structure, a top view of which is illustrated in FIG. 9. The top view layout of FIG. 9 is typical for TFTs in an SRAM or other integrated circuit memory device. The advantages of the present invention become obvious when the prior art FIG. 9 is contrasted with a top view of the TFT of the present invention shown in FIG. 10. The TFT channel of the present invention of FIG. 10 has a smaller cross-sectional area than the prior art TFT channel of FIG. 9. The TFT channel of the present invention is much narrower and thinner than the TFT channel of the prior art. This smaller cross-sectional area has the effect of reducing the bitline to voltage supply (Vcc) leakage. Very small bitline to voltage supply leakage is important in order to achieve battery operation of integrated circuit memory devices, such as high-density SRAMs, over an extended period of time.

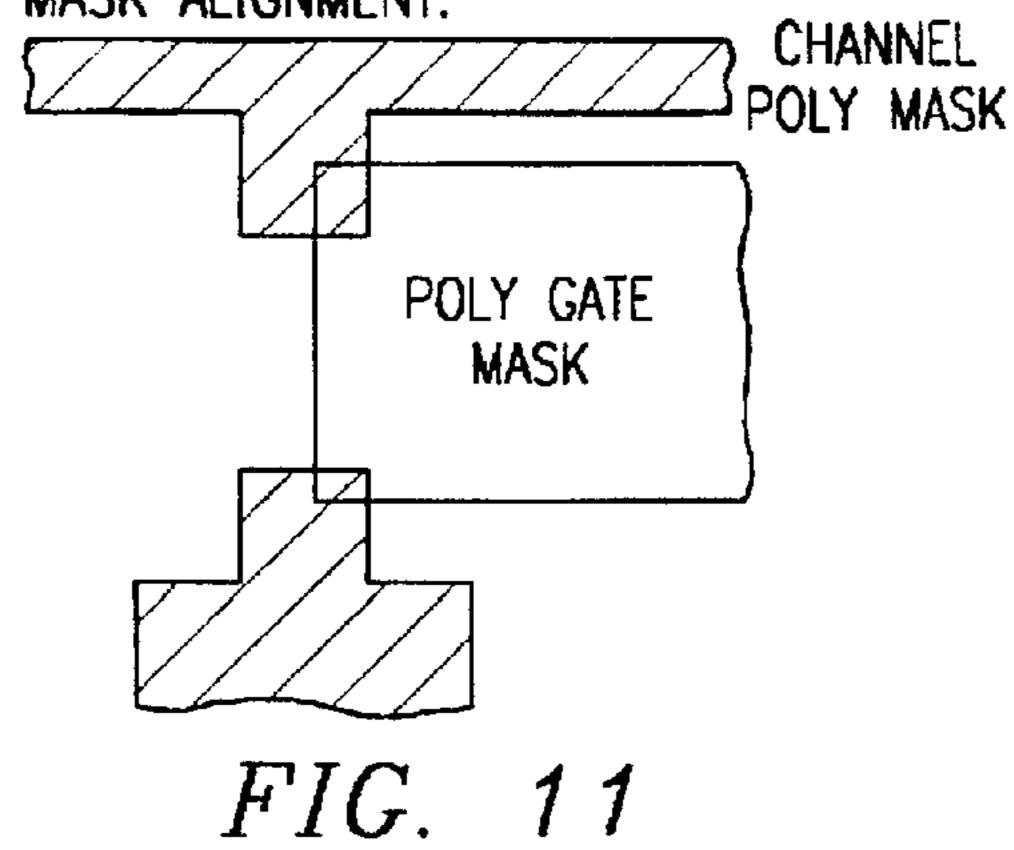

Referring to FIG. 11, mask alignment between the channel poly mask and the poly gate mask which corresponds to the TFT poly gate deposition of FIG. 2 is shown. After the TFT channel poly pattern step, the TFT channel will be etched and spacers, as well as stringers, will be formed along the edge of the TFT gate. As shown in FIG. 12, these unwanted spacers, or stringers, will then be removed using a separate masking step indicated by the dashed lines.

An understanding of the first preferred embodiment of the present invention is further aided by comparing the cross-sectional view of a conventional TFT structure of FIG. 13 with the cross-sectional view of the present invention shown in FIG. 14. The cross-sectional area of the conventional TFT channel is shown as approximately 0.3 to 0.5 µm by approximately 300 to 500 Å, requiring special lithography tools, as mentioned above. The cross-sectional area of the TFT channel of the first embodiment of the present invention is much smaller and is approximately 0.15 to 0.2 µm approximately 300 to 500 Å. This is achieved without any lithography-related constraints.

The process steps and structure of the first preferred embodiment of the present invention, represented in FIGS. 1–14, illustrate a TFT device having a channel that is both very narrow and thin. However, the first preferred embodiment of the present invention requires at least two poly layers: one or two poly layers formed in the standard process steps which are performed prior to the optional planarization of FIG. 1 and the TFT gate poly deposition illustrated in FIG. 2. Referring to FIGS. 15–25, a second preferred embodiment of the present invention which requires just two poly layers and no planarization is shown. The TFT structure 30 of the second preferred embodiment features a poly spacer of a spacer-TFT load structure which is formed around the first poly (gate) layer and selectively etched to provide the necessary channel length. The TFT is formed on top of the field oxide of the structure 30 so that it will not interfere with standard spacer oxide etch and transistor formation in the substrate.

Several standard process steps are first performed before the TFT spacer definition occurs. First, referring to FIG. 15, 5

definition of active region 32 and isolation region 34 adjacent to the active region 23 is accomplished. Active and isolation definition may be followed by an optional buried contact formation well known in the art; a buried contact mask/implant is followed by forming the buried contact 5 opening. Alternately, depending on the layout preference, a shared contact may also be used, in which case a first layer of poly (poly-1) would be deposited directly after the gate oxide growth and pattern. The layout with a shared contact may use slightly more area. Referring to FIG. 16, gate 36 10 may be formed in a standard way, e.g., by depositing polysilicon at approximately 620° C., at a thickness of approximately 1000 to 2000 Å, then Phosphorous (POCI) deposition and drive-in (e.g. at 900° C. for approximately 30 minutes) or implantation (e.g. P31 at a dosage of approximately 1-10e15 at an energy level of approximately 30-50 keV), followed by an anneal for approximately 30 minutes at approximately 800°–900° C.

To reduce the poly resistance, a polycide layer is usually deposited on top or created by the salicide (self-aligned 20 silicide) process. The gate polycide should be WSi2 (Tungsten Silicide) rather than TaSi2 (Tantalum Silicide) in order to avoid extrusions. The thickness of polycide may be about 1000 to 2000 Å. Polycide or salicide formation would be followed by an etching step. Following the formation of 25 gate poly layer 36 of FIG. 16, gate poly layer 36 and isolation region 34 of structure 30 is subjected to N-/Pimplantation using the appropriate masks. N- dopant is e.g., Phosphorous at a dosage of approximately 1-10e13 at an energy level of approximately 25–45 keV and P- dopant is 30 e.g., BF2, at a dosage of approximately 1-10e13 at an energy level of approximately 30–50 keV, or B11. Only N- implantation will be carried out in the cell area and therefore, the masking steps are not shown in the accompanying figures.

Following the N-/P- implantation, nitride liner 38 is 35 deposited over an end of the gate poly layer 36 and a portion of the isolation region 34 and subsequently patterned. Referring to FIG. 17, Nitride liner 38 is subsequently deposited approximately 100–300 Å thick at a deposition rate of approximately 10–100 Å/minute to protect the underlying 40 field oxide from overetch during the oxide spacer removal. The nitride liner next be patterned if it is unwanted underneath the oxide spacer in the bulk transistor regions created at a later stage. The mask used for this optional patterning is shown in FIG. 25. Depositing Nitride liner 38 is an optional 45 step which provides protection against subsequent oxide spacer overetching. Next, Oxide spacer 40 is formed by depositing a spacer oxide layer followed by etching to form oxide spacer 40 adjacent to the end of gate poly layer 36. Oxide spacer 40 is deposited as a single- or double-layer, 50 depending on the kind of poly-1 gate 36 used: WSi2 or TaSi2, e.g. from TEOS, at approximately 700° C. at a fast deposition rate of approximately 50–250 Å/minute. This is followed by a standard spacer oxide etch to form a spacer.

The bulk transistor formation now needs to be completed 55 by N+ and P+ implants using the appropriate masks; again, P+ implantation occurs only in the periphery of the cell area and thus the masks are not shown on the drawings. N+ implant may be Arsenic followed by Phosphorous at dosages of 1-10e15 and 1-10e14, respectively, and energies of 60 approximately 30–50 keV, such as is known in the art, depending on the design rules and the desired final electrical properties of the circuitry. P+ implant is BF2 or Boron at dosages of 1-10e15 and appropriate energies, such as 30 keV, again depending on the desired junction depth/drive 65 current, etc. The mask layers corresponding to the process steps shown and described in conjunction with FIGS. **15–17**

6

are shown in FIG. 18. Both the poly-1 gate layer 36 and the active region 32 are shown.

Referring to FIG. 19, to isolate the first-poly gate layer 36 pattern from the overlying second poly layer (especially the word line from voltage supply Vcc), an IPO (Inter-Poly Oxide) layer 42 may be deposited over poly gate layer 36 and the isolation region 34 as shown. This is an optional but recommended process step. Otherwise, the thin TFT gate oxide isolates poly-1 from poly-2; however, such isolation may prove insufficient.

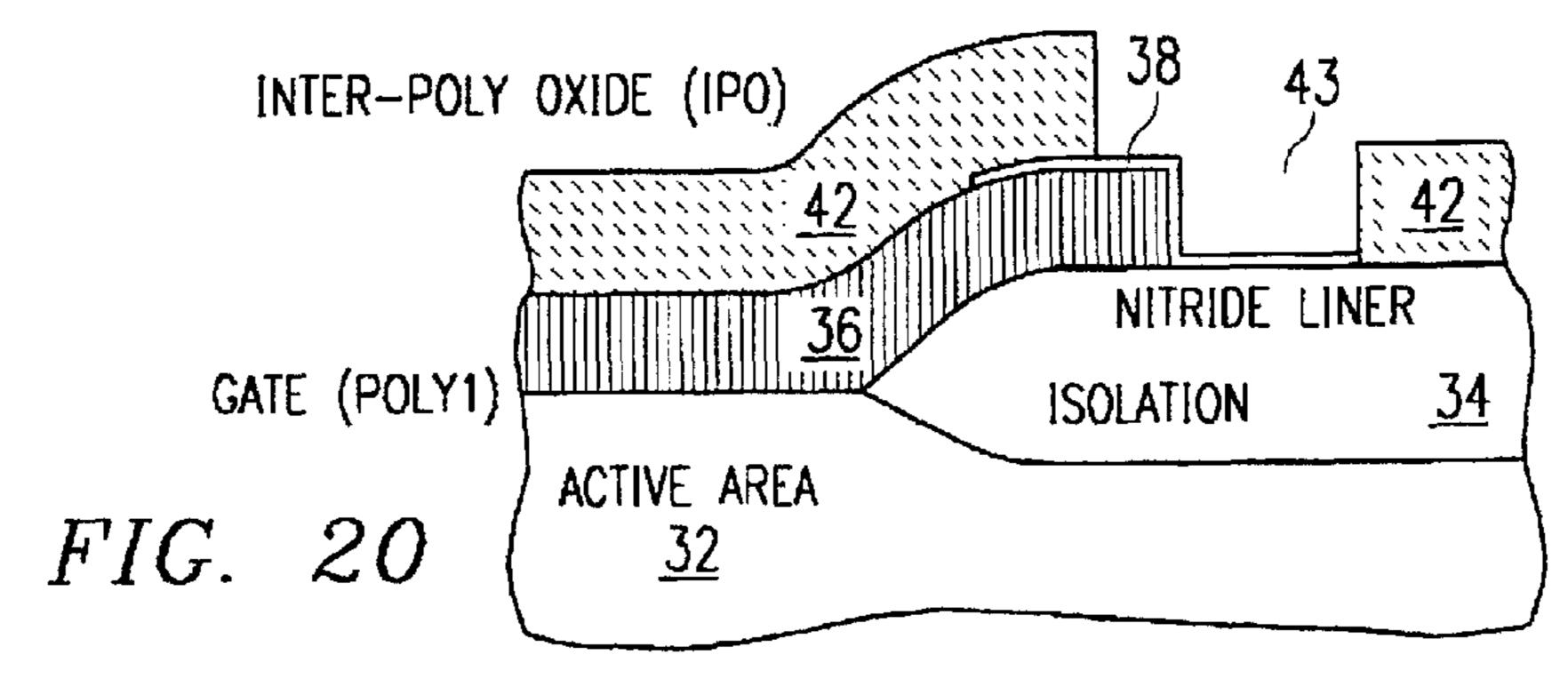

Referring to FIG. 20, the thick IPO oxide layer 42 and the spacer 40 now must be locally removed from the regions where the polysilicon spacer will be formed to act as TFT channel. Thus, a portion of the IPO oxide layer 42 and spacer 42 will be removed to form an opening 43 in IPO oxide layer 42 over isolation region 34 adjacent to the end of poly gate layer 36. A mask for that purpose is shown in FIG. 18. In the field oxide region, the etch would stop at nitride liner 38. There would also be an opening for the shared contact. The nitride liner 38 can now be removed (an optional process step), depending on the desired target thickness of the TFT gate oxide. A dry or wet strip process should easily be sufficient to remove the nitride liner 38, due to the thinness of nitride liner 38.

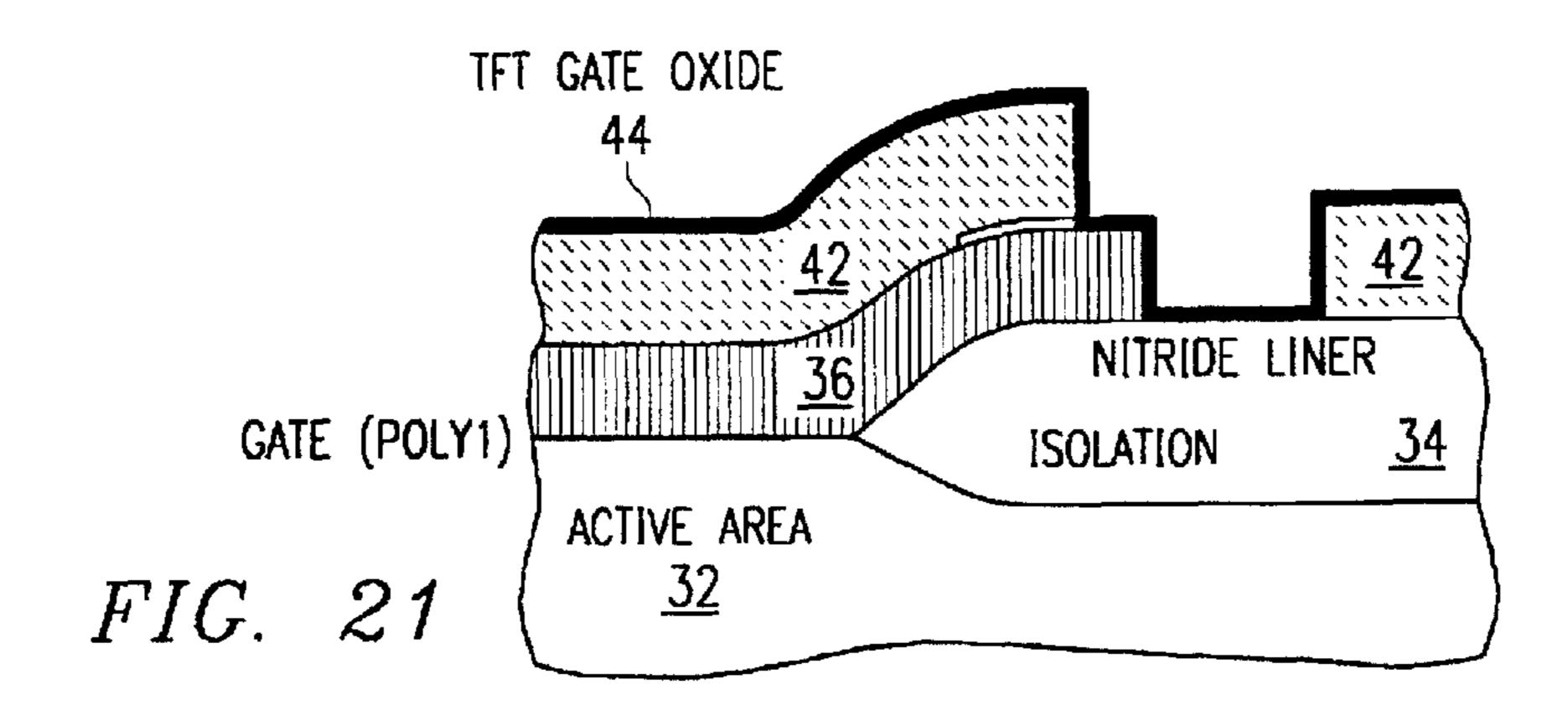

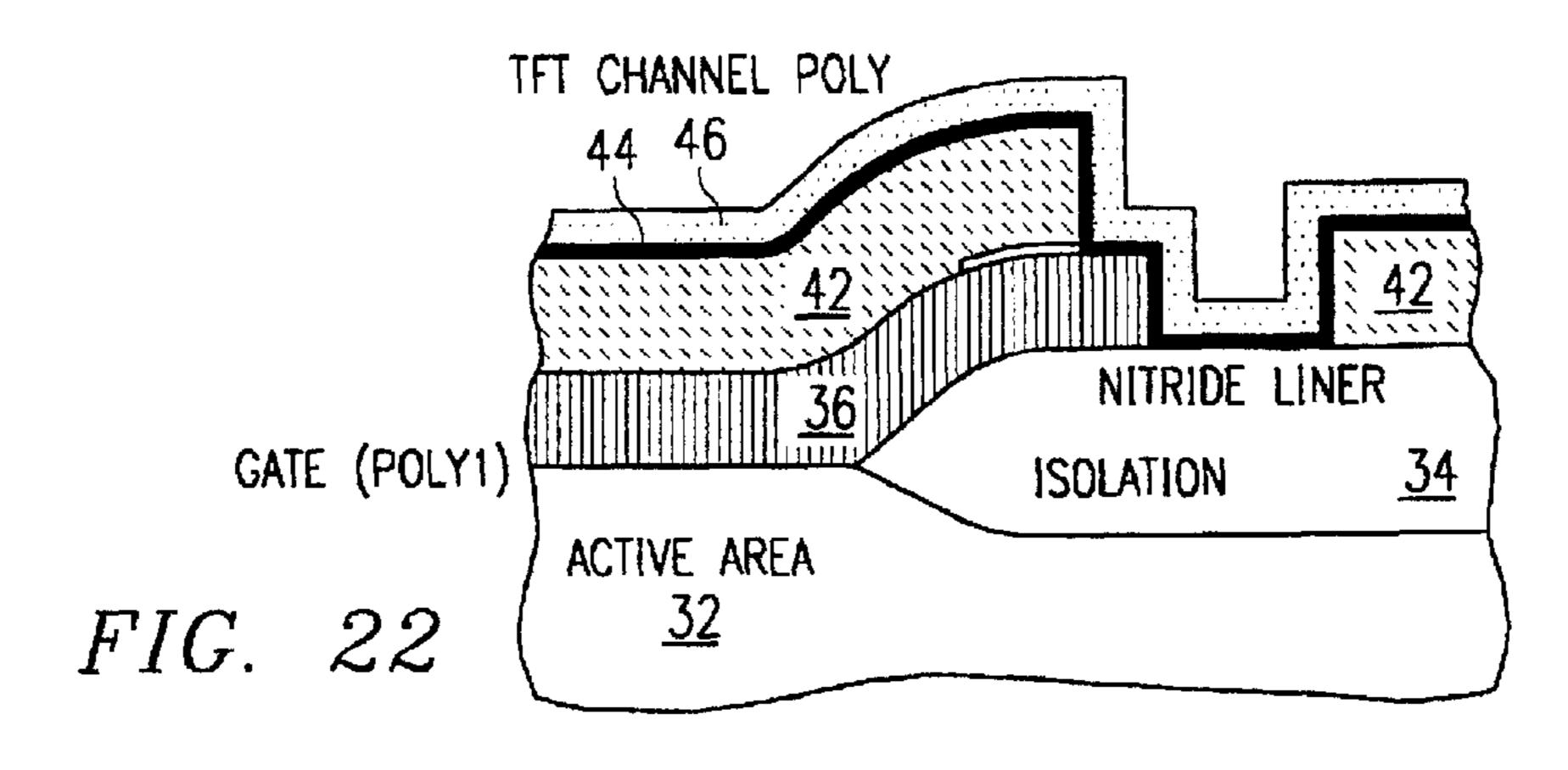

Next, process steps necessary to form a polysilicon spacer for a TFT, according to the second preferred embodiment of the present invention, are performed. Referring to FIG. 21, Oxide is deposited over poly gate 36, IPO oxide layer 42, and opening 43 to form TFT gate oxide layer 44. Next, a shared contact opening is formed as shown in FIG. 22. TFT channel polysilicon layer 46 is deposited over TFT gate oxide layer 44. This is followed by depositing Tantalum (Ta) over TFT channel poly layer 46 in order to decrease series resistance; the Ta, everywhere except on voltage supply lines Vss and Vcc, is subsequently etched away using a mask. A TaSi2 layer may then be formed by RTA (Rapid Thermal Anneal) where Ta has been deposited. The simultaneously salicided Vss and Vcc supply lines allow for reduced series resistance. Finally, TFT channel poly layer 46 is patterned. Referring to FIG. 23, TFT channel poly layer 46 is then etched to create poly spacer 48a and a second, parasitic (unwanted) spacer 48b, referred to as a stringer. Next, as shown in FIG. 24, any stringers are removed through an additional masking step. Thus stringer **48**b is removed. This may be followed by a TFT VT (threshold voltage) implant of the device with Phosphorous, Arsenic, or BF2 at a dosage of 1-10e11 and an energy of approximately 30–40 keV, Finally, a source/drain mask and a source/drain implant are performed either at this stage, or earlier, immediately preceding the Ta deposition. Additional, standard post-TFT process steps are performed as desired. These additional process steps may be done to help protect or encapsulate the TFT. For instance, the steps outlined above may be followed by standard planarization processing. The TFT spacer structure 30 of the second preferred embodiment is also illustrated in the top view mask layouts of FIG. 25.

In addition to utilizing only two poly layers rather than three poly layers and not requiring planarization, the second embodiment of the present invention offers other desirable features. The simultaneously salicided Vss and Vcc voltage supply lines of the second preferred embodiment allow for reduced series resistance. Additionally the TFT source (P+) connected to the pull-down gate (N+) through the TaSi or WSi layer ensures that there is no problematic N+/P+ parasitic junction.

While the invention has been particularly shown and described with reference to a preferred embodiment, it will

be understood by those skilled in the art that various changes in form and detail may be made therein without departing from the spirit and scope of the invention.

What is claimed is:

- 1. A thin-film transistor (TFT) structure having a reduced 5 cross-sectional channel area in order to minimize bitline to supply leakage of the TFT, comprising:

- a substrate;

- a TFT polysilicon gate formed on top of the substrate;

- a gate oxide layer formed over the substrate and the TFT  $^{10}$ polysilicon gate;

- a TFT polysilicon channel formed adjacent to a side of the TFT polysilicon gate, wherein the TFT polysilicon channel has a channel thickness which is limited by the 15 thickness of a deposited channel polysilicon layer which has been selectively removed leaving only the TFT polysilicon channel and wherein the TFT polysilicon channel has a channel width that corresponds to the height of the TFT polysilicon channel etched along the 20 TFT polysilicon gate.

- 2. The structure of claim 1, wherein the channel thickness is approximately 300 to 500 Å and the channel width is approximately 0.15 to 0.25 µm.

- 3. The structure of claim 1, wherein the channel thickness  $_{25}$ and the channel width of the TFT polysilicon channel are adjusted by modifying the thickness of the TFT polysilicon gate.

- 4. A thin-film transistor (TFT) structure having a reduced cross-sectional channel area in order to minimize bitline to supply leakage of the TFT, comprising:

- an isolation region adjacent to an active region;

- a polysilicon gate region formed over the active region and a first portion of the isolation region, wherein the active region is adjacent to the first portion of the isola- 35 tion region;

- a first oxide layer formed over a first portion of the active region and over a second portion of the isolation region;

- an opening formed in the first oxide layer over a third portion of the isolation region adjacent to an end of the 40 polysilicon gate region;

- a second oxide layer formed over the first oxide layer, the polysilicon gate region, and the opening formed in the first oxide layer; and

- a TFT polysilicon channel formed in the opening of the first oxide layer adjacent to the end of the polysilicon gate region, wherein the TFT polysilicon channel has a channel thickness which is limited by the thickness of a deposited channel polysilicon layer which has been selectively removed.

- 5. The structure of claim 4, wherein the channel thickness is approximately 300 to 500 Å and a channel width of the TFT polysilicon channel is approximately 0.15 to 0.25 μm.

- 6. The structure of claim 4, wherein the channel thickness and the channel width of the TFT polysilicon channel are adjusted by modifying the thickness of the polysilicon gate region.

- 7. A thin-film transistor structure comprising

- a substrate;

- a gate disposed on the substrate;

- a gate insulator layer disposed on the substrate and the gate; and

- a channel formed adjacent to a side of the gate, wherein the channel has a channel thickness which is limited by 65 the thickness of a deposited channel layer which has been selectively removed leaving only the channel and

8

wherein the channel has a channel width that corresponds to the height of the channel etched along the gate.

- 8. The thin-film transistor structure of claim 7 wherein the channel thickness is approximately 300 to 500 Å and the channel width is approximately 0.15 to  $0.25 \mu m$ .

- 9. The thin-film transistor structure of claim 7, wherein the channel thickness and the channel width of the channel are adjusted by modifying the thickness of the deposited channel layer and of the gate respectively.

- 10. The thin-film transistor structure of claim 7 wherein the channel is formed from silicon.

- 11. The thin-film transistor structure of claim 7 wherein the channel is formed from amorphous silicon.

- 12. A thin-film transistor structure comprising:

- an isolation region adjacent to an active region;

- a gate region formed over the active region and a first portion of the isolation region, wherein the active region is adjacent to the first portion of the isolation region;

- a first insulator layer formed over a first portion of the active region and over a second portion of the isolation region;

- an opening formed in the first insulator layer over a third portion of the isolation region adjacent to an end of the gate region;

- a second insulator layer formed over the first insulator layer, the gate region, and the opening formed in the first insulator layer; and

- a channel formed in the opening of the first insulator layer adjacent to the end of the gate region, wherein the channel has a channel thickness which is limited by the thickness of a deposited channel layer which has been selectively removed.

- 13. The structure of claim 12, wherein the channel thickness is approximately 300 to 500 Å and a channel width of the channel is approximately 0.15 to  $0.25 \mu m$ .

- 14. The thin-film transistor structure of claim 12, wherein the channel thickness and the channel width of the channel are adjusted by modifying the thickness of the deposited 45 channel layer and of the gate respectively.

- 15. The thin-film transistor structure of claim 12 wherein the channel is formed from silicon.

- 16. The thin-film transistor structure of claim 12 wherein the channel is formed from amorphous silicon.

- 17. A thin-film transistor structure comprising:

- a substrate;

- a gate disposed on the substrate;

- a gate insulator layer disposed on the substrate and the gate; and

- an amorphous silicon channel formed adjacent to a side of the gate, wherein the channel has a channel thickness which is limited by the thickness of a deposited channel layer which has been selectively removed leaving only the channel.

- 18. The transistor of claim 17 wherein the substrate comprises a semiconductor material.

- 19. The transistor of claim 17 wherein:

- the gate has a gate height; and

the channel has a height equal or approximately equal to the gate height.

9

20. A transistor, comprising:

an isolation region;

a gate disposed on the isolation region and having a side wall;

a gate insulator disposed on the side wall of the gate; and an amorphous silicon channel disposed on the isolation region adjacent to the side wall of the gate, wherein the channel has a channel thickness which is limited by the thickness of a deposited channel layer which has been selectively removed leaving only the channel.

- 21. The transistor of claim 20 wherein the isolation region comprises an insulator material.

- 22. The transistor of claim 20 wherein:

the gate insulator is disposed on a portion of the isolation region adjacent to the side wall of the gate; and the channel is disposed on the gate insulator.

10

23. A semiconductor structure, comprising:

a semiconductor substrate having an active region;

an isolation insulator disposed on the substrate adjacent to the active region;

- a transistor gate disposed on the active region and on the isolation insulator and having a side wall disposed over the isolation region;

- a first insulator layer disposed on the side wall of the gate; and

- a channel disposed on the isolation insulator adjacent to the side wall of the gate.

- 24. The semiconductor structure of claim 23, further comprising a second insulator layer disposed on the gate.

\* \* \* \* :