#### US00RE40552E

### (19) United States

### (12) Reissued Patent

Foss et al.

### (10) Patent Number: US RE40,552 E

#### (45) Date of Reissued Patent: Oct. 28, 2008

## (54) DYNAMIC RANDOM ACCESS MEMORY USING IMPERFECT ISOLATING TRANSISTORS

(75) Inventors: Richard C. Foss, Calabogie (CA); Peter

B. Gillingham, Kanata (CA); Robert Harland, Salt Spring Island (CA); Masami Mitsuhashi, Sapporo (JP); Atsushi Wada, Gifu (JP)

(73) Assignee: Mosaid Technologies, Inc., Kanata,

Ontario (CA)

(21) Appl. No.: 10/032,431

(22) Filed: Dec. 21, 2001

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 5,414,662

Issued: May 9, 1995

Appl. No.: 08/147,038

Filed: Nov. 4, 1993

U.S. Applications:

(63) Continuation of application No. 07/680,747, filed on Apr. 5, 1991, now abandoned.

#### (30) Foreign Application Priority Data

| Apr. 6, 1990 | (GB) | 9007789 |

|--------------|------|---------|

| Apr. 5, 1991 | (GB) | 9107164 |

(51) Int. Cl. *G11C 7/00* (

G11C 7/00 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

2,255,232 A 9/1941 Stern

| 4,117,353 A | 9/1978 | Butler et al.         |

|-------------|--------|-----------------------|

| 4,463,440 A | 7/1984 | Nishiura et al.       |

| 4,608,670 A | 8/1986 | Duvvury et al 365/205 |

| 4,638,182 A | 1/1987 | McAdams               |

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

| EP | 02549801 A1 * | 5/1988 |

|----|---------------|--------|

| EP | 0 254 980 B1  | 9/1991 |

| ΙΡ | 62-150590     | 7/1987 |

#### OTHER PUBLICATIONS

1992 Xerox Presentation re. use of on—chip DLL. Adler, E., "The Evolution of IBM CMOS DRAM Technology," *IBM J. Res. Develop.*, vol. 39 No. 1/2, Jan./Mar. 1995, p. 169.

#### (Continued)

Primary Examiner—Tan Dinh

(74) Attorney, Agent, or Firm—Hamilton, Brook, Smith & Reynolds, PC

#### (57) ABSTRACT

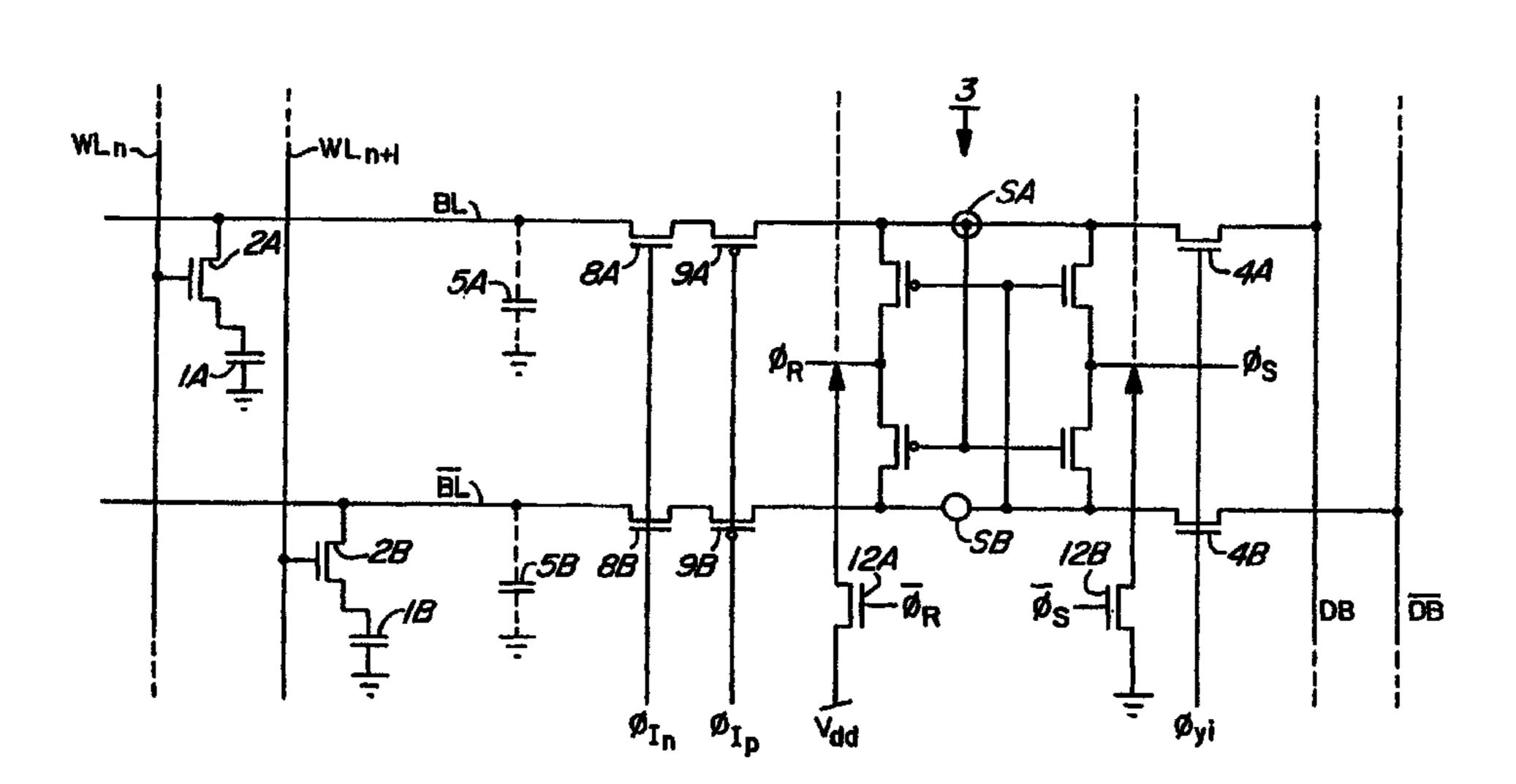

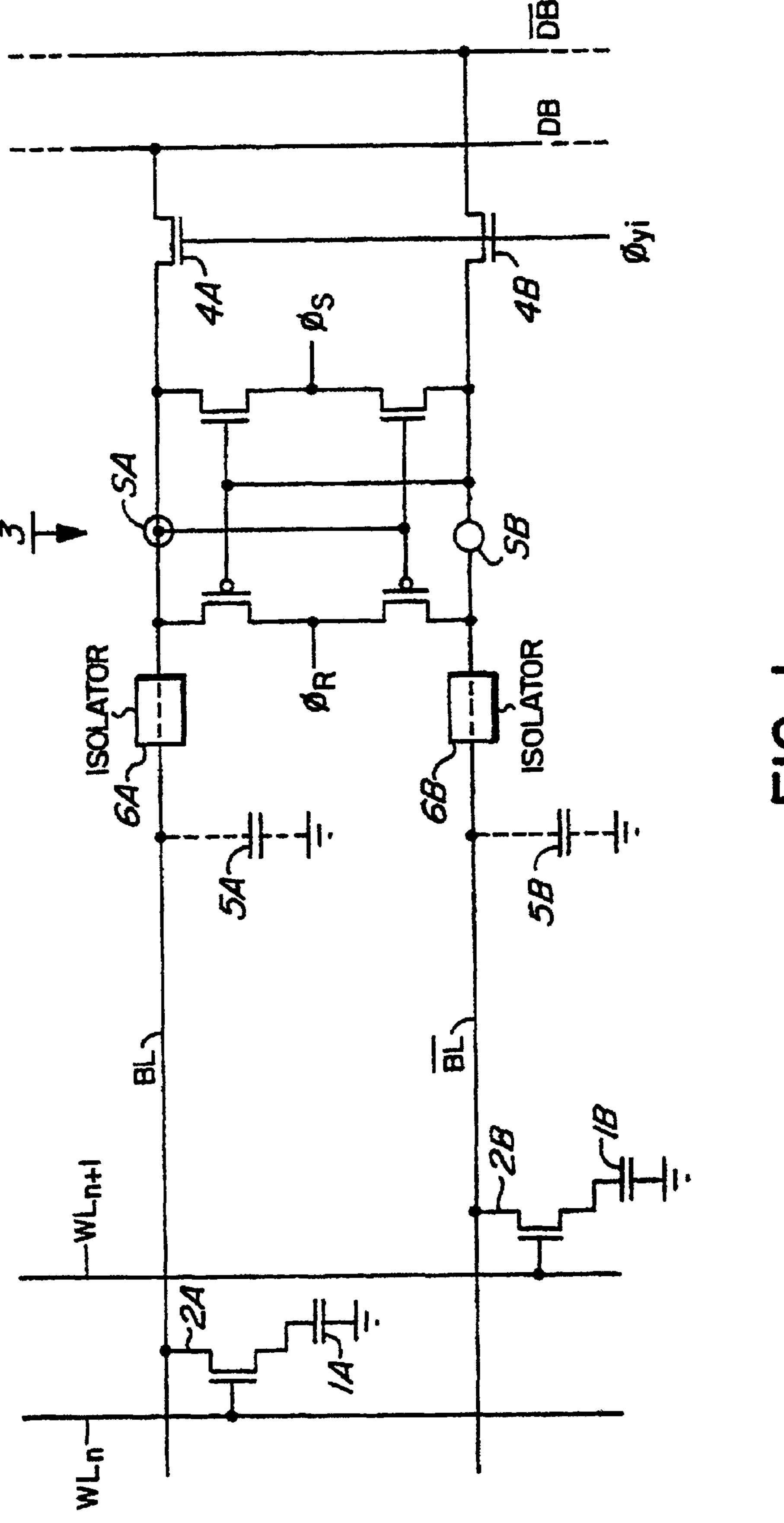

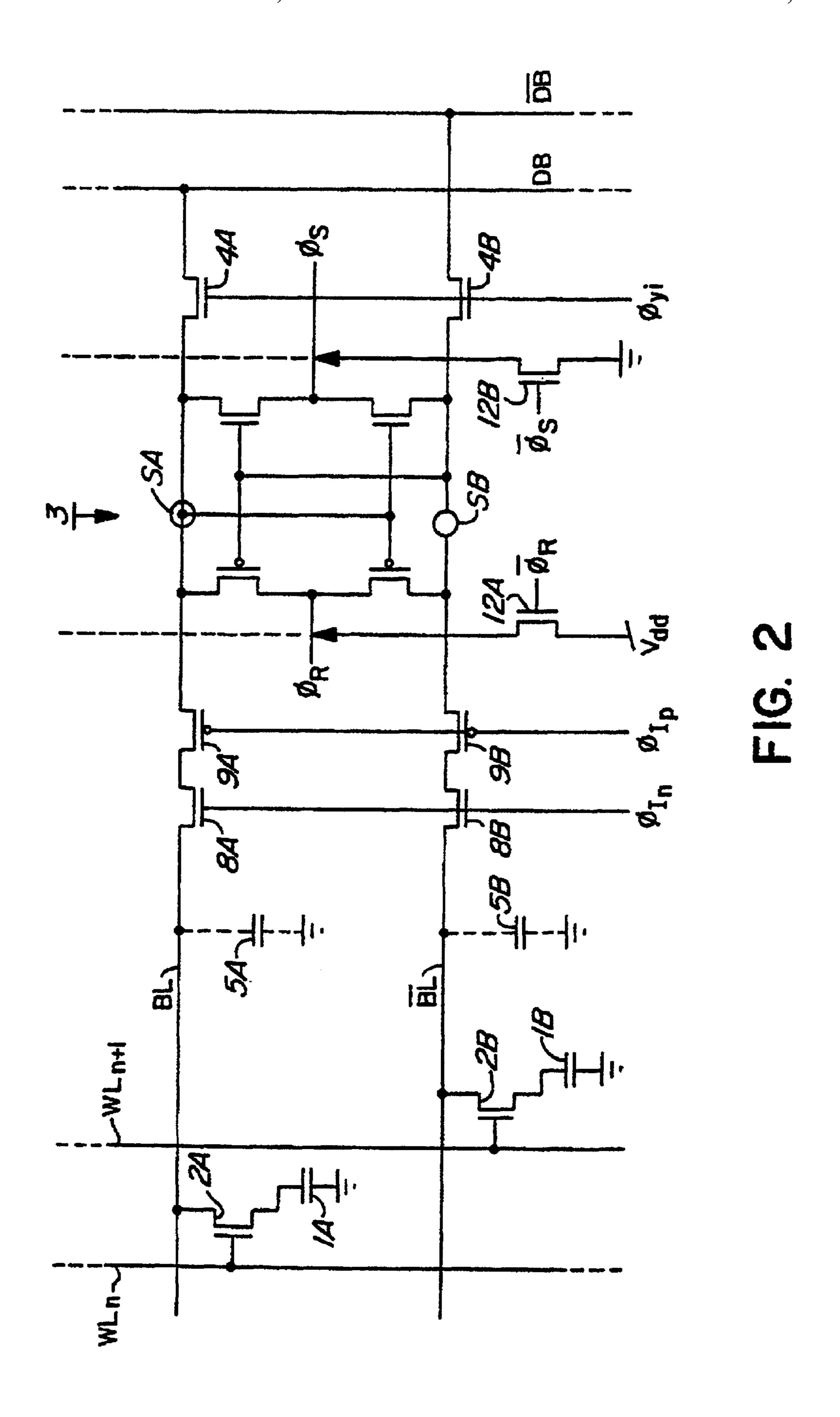

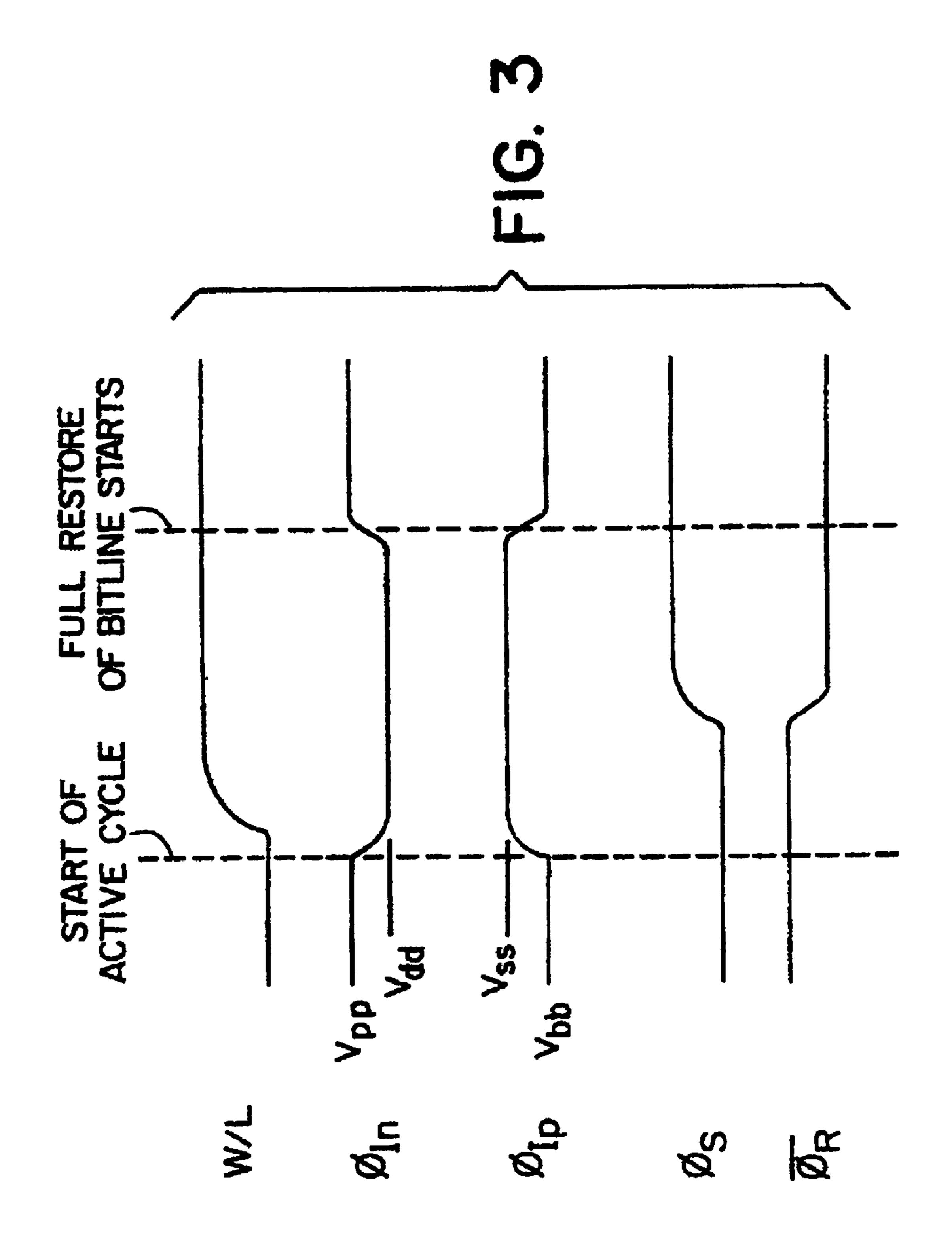

Apparatus and methods for controlling the sensing of bit lines which facilitates the distribution of bit line charging current to be distributed any time, and facilitates the fast raising of the sense modes to full logic levels. An embodiment is comprised of a plurality of bit storage capacitors, a folded bit line for receiving charge stored on one of the capacitors, having bit line capacitance, a sense amplifier having a pair of sense nodes for sensing a voltage differential across the sense nodes, apparatus connected to the bit line and the sense nodes for imperfectly isolating the sense nodes from the bit line whereby current can leak therethrough, apparatus for enabling the sense amplifier and for disabling the isolating apparatus and thereby removing the isolation between the sense amplifier and the bit line, whereby current passing through the sense amplifier to the sense nodes is enabled to charge the bit line capacitance through the isolating apparatus to predetermined logic voltage level.

#### 8 Claims, 3 Drawing Sheets

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DOCUMENTS                                                                                                                                                                                                                                                            | 5,734,292 A 3/1998 Shirai et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                      | 5,751,639 A 5/1998 Ohsawa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Norwood et al.<br>Okada et al.                                                                                                                                                                                                                                       | 5,757,225 A 5/1998 Tobita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Doluca et al.                                                                                                                                                                                                                                                        | 5,771,188 A 6/1998 Fink<br>5,777,501 A 7/1998 AbouSeido                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Miyamoto et al 365/189                                                                                                                                                                                                                                               | 5,805,508 A 9/1998 Tobita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4,791,616 A 12/1988                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Taguchi et al 365/205                                                                                                                                                                                                                                                | 5,812,832 A 9/1998 Horne et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Gailbreath, Jr.                                                                                                                                                                                                                                                      | 5,815,446 A 9/1998 Tobita                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Miyamoto et al 365/189                                                                                                                                                                                                                                               | 5,841,691 A 11/1998 Fink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sawada et al.                                                                                                                                                                                                                                                        | 5,847,597 A 12/1998 Ooishi et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Suwa et al 365/210<br>Sato et al.                                                                                                                                                                                                                                    | 5,856,939 A * 1/1999 Seyyedy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4,841,180 A 6/1989                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                      | 5,856,951 A 1/1999 Arimoto et al.<br>5,880,624 A 3/1999 Koyanagi et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ohsawa                                                                                                                                                                                                                                                               | 5,936,898 A * 8/1999 Chi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4,931,992 A 6/1990                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ogihara et al.                                                                                                                                                                                                                                                       | 5,959,927 A 9/1999 Yamagata et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Wada et al 365/203                                                                                                                                                                                                                                                   | 5,991,226 A 11/1999 Bhullar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Komatsu et al 365/222                                                                                                                                                                                                                                                | 6,021,063 A 2/2000 Tai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Tobita                                                                                                                                                                                                                                                               | 6,067,592 A 5/2000 Farmwald et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Horiguchi et al.                                                                                                                                                                                                                                                     | 6,087,868 A 7/2000 Millar<br>6,151,242 A 11/2000 Takashima                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5,010,518 A 4/1991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . ~                                                                                                                                                                                                                                                                  | 6,314,052 B2 11/2001 Foss et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5,010,523 A * 4/1991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Yamauchi 365/205                                                                                                                                                                                                                                                     | 6,327,318 B1 12/2001 Bhullar et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Tanaka et al 365/230                                                                                                                                                                                                                                                 | 6,510,503 B2 1/2003 Gillingham et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Miyatake 365/203                                                                                                                                                                                                                                                     | 6,657,918 B2 12/2003 Foss et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Terasawa et al.                                                                                                                                                                                                                                                      | OTHED DIEDLIC ATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Douglas et al                                                                                                                                                                                                                                                        | OTHER PUBLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5,029,128 A 7/1991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                      | Anceau, "A Synchoronous Approach for Clocking VLSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Tran et al.                                                                                                                                                                                                                                                          | Systems," IEEE journal of Solid-State Circuits, vol. SC-17,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5,091,885 A 2/1992                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ohsawa 365/203                                                                                                                                                                                                                                                       | No. 1 (Feb. 1982).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5,101,107 A 3/1992                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                      | Chen, "Designing On-Chip Clock Generators," Circuits and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| / /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Johnson et al.                                                                                                                                                                                                                                                       | Devices, Jul. 1992, pp. 32–36.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hjerpe et al.                                                                                                                                                                                                                                                        | Chou, Shizuo, et al., "A 60-ns 16M-bit DRAM With a Mini-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5,111,063 A 5/1992<br>5,127,739 A 7/1992                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Duvvury et al 365/189                                                                                                                                                                                                                                                | mized Sensing Delay Caused by Bit-Line Stray Capaci-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cho et al.                                                                                                                                                                                                                                                           | tance," IEEE Journal of Soild State Circuits, vol. 24, No. 5,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Furutani et al 365/203                                                                                                                                                                                                                                               | Oct. 1989, pp. 1176–1178.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Miyatake 365/149                                                                                                                                                                                                                                                     | Foss, R.C., et al., "Application of a High-Voltage Pumped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Tsang et al.                                                                                                                                                                                                                                                         | Supply for Low-Power DRAM," IEEE 1992 Symposium on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Kim 365/203                                                                                                                                                                                                                                                          | VLSI Circuits of Technical Papers, pp. 106–107.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sorrells et al. Dhong et al                                                                                                                                                                                                                                          | Fujii, Syuso, et al., "A 45-ns 16-Mbit DRAM with Tri-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Watson, Jr. et al.                                                                                                                                                                                                                                                   | ple-Well Structure," IEEE Journal of Solid-State Circuits,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |