### US00RE40498E

### (19) United States

### (12) Reissued Patent

Suzuki et al.

### (10) Patent Number:

US RE40,498 E

### (45) Date of Reissued Patent:

\*Sep. 9, 2008

# (54) VARIABLE ADDRESS LENGTH COMPILER AND PROCESSOR IMPROVED IN ADDRESS MANAGEMENT

(75) Inventors: Masato Suzuki, Osaka (JP); Hiroshi

Kamiyama, Kyoto (JP); Shinya Miyaji,

Nara (JP)

(73) Assignee: Matsushita Electric Industrial Co.,

Ltd., Osaka (JP)

(\*) Notice: This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 10/991,367

(22) Filed: Nov. 19, 2004

### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 5,809,306

Issued: Sep. 15, 1998

Appl. No.: 08/587,338

Filed: Jan. 16, 1996

### U.S. Applications:

Division of application No. 09/662,484, filed on Sep. 14, 2000, which is a continuation of application No. 08/249,157, filed on May 26, 1994, now abandoned.

### (30) Foreign Application Priority Data

| May 31, 1993 | (JP) | <br>5-129529 |

|--------------|------|--------------|

| May 27, 1993 | (JP) | <br>5-126212 |

| Oct. 1, 1993 | (JP) | <br>5-247154 |

(51) Int. Cl. G06F 9/45

(2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,296,469 A 10/1981 Gunter et al.

4,314,332 A 2/1982 Shiraogawa et al. ...... 395/411

(Continued)

#### FOREIGN PATENT DOCUMENTS

EP 0148478 12/1984 EP 0180077 10/1985

(Continued)

### OTHER PUBLICATIONS

Stanley; "Address Size Independence in a 16–Bit Minicomputer", *The Fifth Annual Symposium on Computer Architecture*: c. Apr. 1978.

#### (Continued)

Primary Examiner—Kenneth R. Coulter (74) Attorney, Agent, or Firm—McDermott Will & Emery LLP

### (57) ABSTRACT

The present invention discloses a program converting unit for generating a machine language instruction from a source program for a processor that manages an N-bit address while processing M-bit data, N being greater than M, and such a processor that runs the converted program. The program converting unit comprising: a parameter holding unit for holding a data width and a pointer width designated by a user; the data width representing the number of bits of data used in the source program while the pointer width representing the number of bits of an address; and a generating unit for generating an instruction to manage the data width when a variable operated by the instruction represents the data, and for generating an instruction to manage the pointer width when a variable operated by the instruction represents the address.

### 61 Claims, 26 Drawing Sheets

#### U.S. PATENT DOCUMENTS 01-169537 7/1989 03-74725 3/1991 8/1982 Koda et al. 4,347,566 A 3248240 \* 11/1991 11/1982 Kaplinsky ...... 395/402 4,361,868 A JP 04-014144 1/1992 4,447,879 A 04-172533 6/1992 6/1984 Gaither et al. ...... 395/402 4,453,212 A 05-046383 2/1993 4,602,330 A WO WO 92/15943 9/1992 4,679,140 A OTHER PUBLICATIONS 4,739,471 A 8/1988 Hopkins et al. ...... 395/709 4,763,255 A Harman et al.; The Motorola MC 68000 . . . ; c. 1985; pp. 30, 12/1991 Nagata 5,077,659 A 31, 52, 53, 84–89, 134–137, 142–159, 174–177 and 5,307,492 A 5/1995 Killian et al. ...... 395/800 5,420,992 A 200–203. 5,440,701 A \* 8/1995 Matsuzaki et al. ........... 712/210 Sebesta; Concepts of Programming Languages; c. 1989; pp. 16–23, 72–79, 106–115 and 121–122. Hennessey et al; Computer Architecture . . . ; c. 1990; pp. FOREIGN PATENT DOCUMENTS 90–113 and 139–161. Shibaski et al.; "High-Performance single-Chip Microcon-EP 0182277 \* 10/1985 troller H8/300 Series"; Hitachi Review; vol. 40, No. 1; c. EP 0 180 077 B1 5/1986 1991. EP 0 170 284 2/1988 Verification of translation of JP 59–106047. EP \* 3/1992 0503514 EP "Address Size Independence in a 16–Bit Minicomputer", by 0 503 514 B1 9/1992 EP 0 528 695 B1 2/1993 Philip E. Stanley, the 5th Annual Symposium on Computer EP 148 478 A 7/1995 Architecture, Apr. 1978. 55-43680 3/1980 "High-Performance Single-Chip Microcontroller H8/300 55-72255 5/1980 Series", by Nobuo Shibasaki et al., Hitachi Review, vol. 40

(1991), No. 1.

with English Translation.

\* cited by examiner

Aho, A.V. et al., "Compile Principles, Techniques and

Tools", Nikkei Science Inc., Nov. 10, 1990, pp. 399-400,

55-118153

57-105038

57-161943

59-106047

61-084735

62-259140

64-91238

JP

9/1980

6/1982

10/1982

6/1984

4/1986

11/1987

4/1989

FIG. 1 PRIOR ART

FIG. 2 PRIOR ART

| OP |      | SIZE  | SRC | DEST |

|----|------|-------|-----|------|

|    | MOVE | 32bit | A1  | @A2  |

FIG. 3 PRIOR ART

FIG. 4A PRIOR ART

FIG. 4B PRIOR ART

FIG. 6 PRIOR ART

FIG. 7 PRIOR ART

## FIG. 8 PRIOR ART

|         | SUB  | D0,D0         | <del>(1)</del>  |

|---------|------|---------------|-----------------|

|         | MOVI | #H8000,A0     | (2-1)           |

|         | ANDI | #H0000FFF,A0  | (2-2)           |

| LABELA  |      |               |                 |

|         | MOV  | @A0,D1        | <del>(3)</del>  |

|         | ADD  | D1,D0         | (4)             |

|         | ADDI | #H0010,A0     | (5)             |

|         | IVOM | #H8100,A0     | (6-1)           |

|         | ANDI | #H0000FFF,A1  | (6-2)           |

|         | CMP  | A1,A0         | (6-3)           |

|         | BLT  | LABELA        | <del>(</del> 7) |

| LABEL B |      |               |                 |

|         | VOM  | D0,@H10000000 | (8)             |

FIG. 9 PRIOR ART

FIG. 10 PRIOR ART

FIG. 11A PRIOR ART

ADD/SUBTRACT/COMPARE INSTRUCTIONS

FIG. 11B PRIOR ART

FIG. 12A PRIOR ART

FIG. 12B PRIOR ART

FM-DECODING

UNIT 140 JUDGING EXEC BRA 137 24 144 N D N D N NE NE

(8-BIT)

**FIG. 16A**

FIG. 17 REGISTER UNIT ≥137b 140a ST SN 140b 137d D0 DECODING 137h 137f UNIT 137a 244 137ć TO EXECUTING UNIT 138 THIRD EXTENDER 171~ 136k 136j \_136c \_136a 124 244 136g EXTERNAL-ACCESS-136f WIDTH 136e CONTROL (15~8) (15-8) (7-8) UNIT 16 136i 136d 172~ SEQUENCER 136h 161 244 **D BUS 132** BUS CONTROL UNIT **A BUS 131** R/W DS1-0 AS D15-0 A23-0 130 MEMORY

FIG. 18A

FIG. 18B

FIG. 19 START STEP 20 SYNTAX ANALYSIS GENERATE INTERMEDIARY FILE AND STEP 21 SYMBOL TABLE ANY STEP 22 **UN-PROCESSED** NO INTERMEDIARY INSTRUCTION? **END** STEP 23 YES READOUT ONE INTERMEDIARY INSTRUCTION STEP 24 SELECT ONE OR MORE MACHINE LANGUAGE INSTRUCTION STEP 25 DESIGNATE INDIVIDUAL INSTRUCTION **STEP 26** GENERATE OPERATION CODE STEP 27 ARITHMETIC YES OPERATION INSTRUCTION 2 B NO STEP 28 FOLLOWING YES INSTRUCTION?

FIG. 20A

### SYMBOL TABLE

Sep. 9, 2008

| SYMBOL | VARIABI       | LE TYPE TYPE | <b>.</b> | HEAD<br>ADDRESS | REGISTER |

|--------|---------------|--------------|----------|-----------------|----------|

| *a     | UN-<br>SIGNED | POINTER      | 3        | 1000            |          |

| b      | UN-<br>SIGNED |              |          | 1004            |          |

| C      | UN-<br>SIGNED | INTEGER      | 2        | 1006            |          |

| t1     | UN-<br>SIGNED | INTEGER      | 2        |                 |          |

| t2     | UN-<br>SIGNED | INTEGER      | 2        |                 |          |

| t3     | UN-<br>SIGNED |              |          |                 |          |

|        |               |              |          |                 |          |

### FIG. 20B

### SYMBOL TABLE

| SYMBOL | VARIABLE TYPE SIGN TYPE |           |   | HEAD<br>ADDRESS | REGISTER |

|--------|-------------------------|-----------|---|-----------------|----------|

| a      | SIGNED                  | CHARACTER | 1 | 1000            |          |

| b      | UN-<br>SIGNED           | CHARACTER | 1 | 1001            |          |

| C      |                         | INTEGER   | 2 | 1002            |          |

| d      | UN-<br>SIGNED           | INTEGER   | 2 | 1004            |          |

|        |                         |           |   |                 |          |

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 26

# FIG. 27

| SUB  | D0,D0                                      | (1)                        |

|------|--------------------------------------------|----------------------------|

| MOVI | #H8000,A0                                  | (2)                        |

|      |                                            |                            |

| MOV  | @A0,D1                                     | (3)                        |

| ADD  | D1,D0                                      | (4)                        |

| ADDI | #H0010,A0                                  | (5)                        |

| CMPI | #H8100,A0                                  | (6)                        |

| BLT  | LABELA                                     | <del>(7)</del>             |

|      |                                            |                            |

| MOV  | D0,@H1000000                               | (8)                        |

|      | MOVI<br>MOV<br>ADDI<br>ADDI<br>CMPI<br>BLT | MOVI #H8000,A0  MOV @A0,D1 |

### VARIABLE ADDRESS LENGTH COMPILER AND PROCESSOR IMPROVED IN ADDRESS MANAGEMENT

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

[This] The current application is a divisional of Ser. No. 10 09/662,484, filed on Sep. 14, 2000, which is a reissue of Ser. No. 08/587,338, filed on Jan. 16, 1996, now U.S. Pat. No. 5,809,306, which is a continuation of application Ser. No. 08/249,157, filed on May 26, 1994, now abandoned.

### BACKGROUND OF THE INVENTION

### (1) Field of the Invention

The present invention relates to a program converting unit for converting a high level language program into a machine language program and a processor for running the converted program, and more particularly, to such a processor improved in address management with various types of register groups including address and data registers.

### (2) Description of the Related Art

While the recent advancements in the field of electronic technology, data processors such as a microprocessor and a microcomputer have been used widely. Today's typical data processor can process data of various widths, and a data processor furnished with a 16-bit or 32-bit CPU has been developed to meet the needs for more efficient data processing and advanced functions. Such a processor may be additionally furnished with various types of register groups including an address register and a data register to further upgrade the performance. Also, there is a need for a processor with a more efficient address management function as the data and programs have increased in size in response to the sophistication and enlargement of applications. In the following, five conventional processors will be explained while considering both of their improvements and shortfalls 40 in address management.

### FIRST CONVENTIONAL PROCESSOR

Firstly, a 16-bit segment-address processor will be explained. This type of processor is described in, for example, "Hardware for Microprocessor", Iwao Morishita, Iwanami-shoten, Nov. 9, 1984. The processor includes a segment register which stores a high order address including bits beyond 16 bits to secure an address space over 64 (2<sup>16</sup>) Kbyte while processing 16-bit data. More particularly, the address space over 64 Kbyte is divided into a set of 64 Kbyte segments to be serially numbered, and the addresses are managed by the segment numbers thus stored in the segment register and an offset, i.e., a distance from the head of each 16-bit segment.

Also, a 32-bit segment-address processor is disclosed in the aforementioned "Hardware for Microprocessor". This processor can secure an address space of 4 Gbyte (2<sup>32</sup>) by managing 32-bit addresses while processing 32-bit data.

These segment-address processors run a machine language program translated by a program converting unit such as a compiler.

An address management of a compiler for a 16-bit processor includes two models: one is a large model and the other is a near-far model.

A large model compiler always sets a pointer variable with a segment number and a 16-bit offset in pairs. Thus, the

2

16-bit processor that runs an object code from the compiler calculates the content of the segment register to update the same each time an address is calculated. Consequently, the performance efficiency is significantly degraded compared with a 16-bit non-segment-address processor.

A near-far model compiler eliminates this problem by designating one of two pointer variables: a near pointer variable and a far pointer variable; the former is used to access an address within one segment and the latter is used to access an address a segment boundary. The compiler sets the 16-bit offset alone with the near pointer variable while setting a pair of the segment number and 16-bit offset with the far pointer variable. When the 16-bit near-far model compiler uses the near pointer variable, the performance efficiency is enhanced compared with the 16-bit large model compiler. However, on the other hand, programming efficiency is degraded because it is a programmer that selects one of the two pointer variables by checking the segment boundary.

A compiler for a 32-bit processor is advantageous in that it is free of the aforementioned problem. Because this compiler sets a 32-bit address to the pointer variable for a 32-bit data variable, and thus the programmer does not have to check the segment boundary. Naturally, the 32-bit processor runs the compiled program without degrading performance while securing the address space of 4 Gbyte.

However, most of the applications for an embedded-type microcomputer demand neither the 32-bit data nor address space of 4 Gbyte, but demand the 16-bit data and address space over 64 Kbyte. Thus, if the 32-bit processor and compiler are employed, the hardware is not fully utilized, wasting the cost and running electricity. In addition, the 32-bit processor always designates a 32-bit address in a program, and thus increases a program code size undesirably. Also, the performance is degraded when a 16-bit data bus is used to connect the 32-bit processor to a memory compared with a 32-bit data bus.

Therefore, neither 16-bit and 32-bit segment-address processors nor their corresponding compilers developed to date have met the practical needs.

### SECOND CONVENTIONAL PROCESSOR

A second conventional processor includes various types of register groups including address registers and data registers, which is described, for example, in "M68000 8/16/32MICROPROCESSOR USER MANUAL", Motorola Inc.

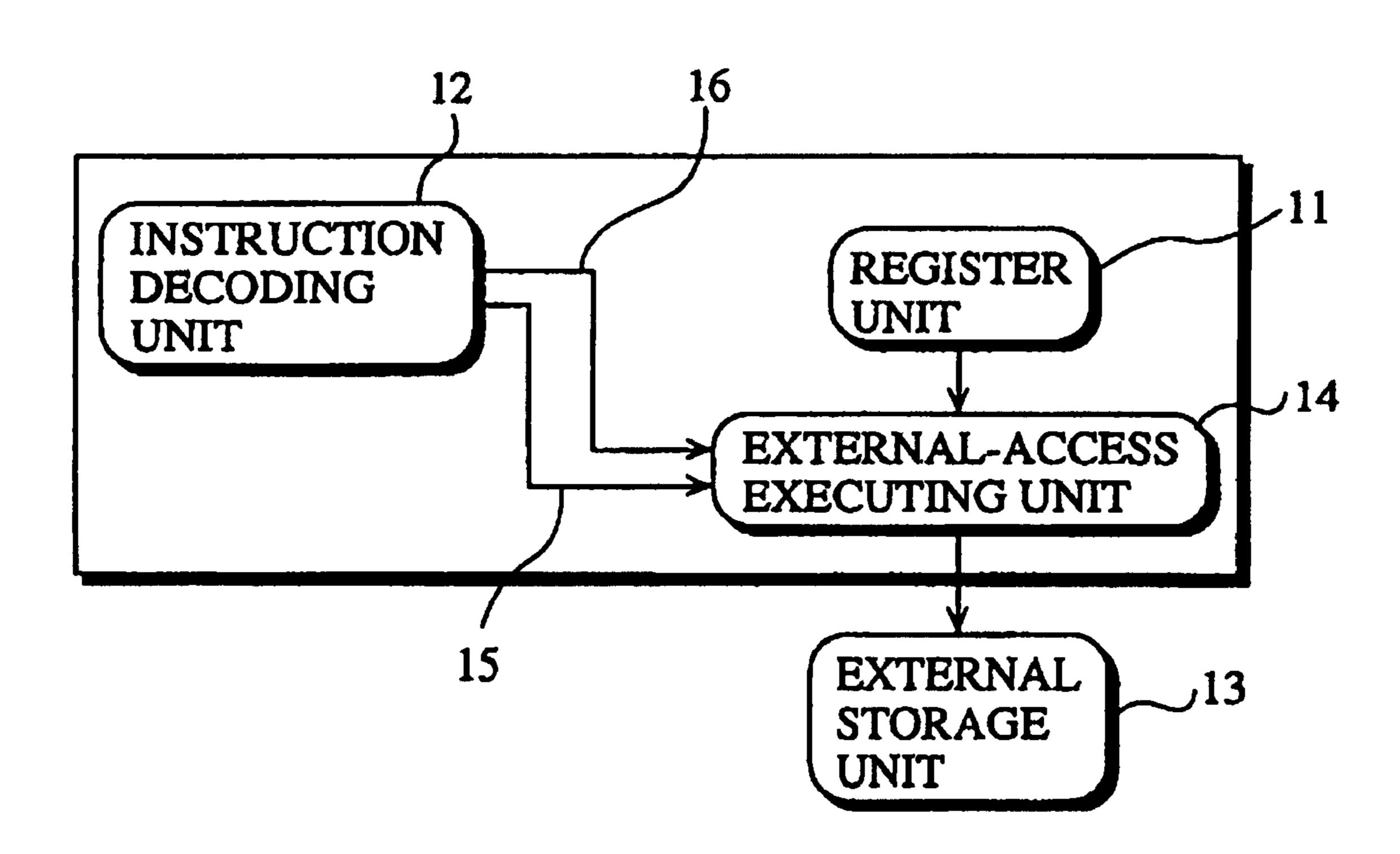

A structure of the second conventional processor is depicted in FIG. 1. The processor comprises a register unit 11 including a plurality of 32-bit address registers and 32-bit data registers, an instruction decoding unit 12 for decoding an instruction, an external storage unit 13, and an external-access executing unit 14 for inputting and outputting data of a designated bit-width with the external storage memory unit 13. The instruction decoding unit 12 sends register information 15 and bit-width information 16 to the external-access executing unit 14; register information 15 and bit-width information 16 indicate a register subject to data transfer and a bit-width of transmission data, respectively. Assume that a 16-Mbyte address space and 16-bit data are used in an application herein.

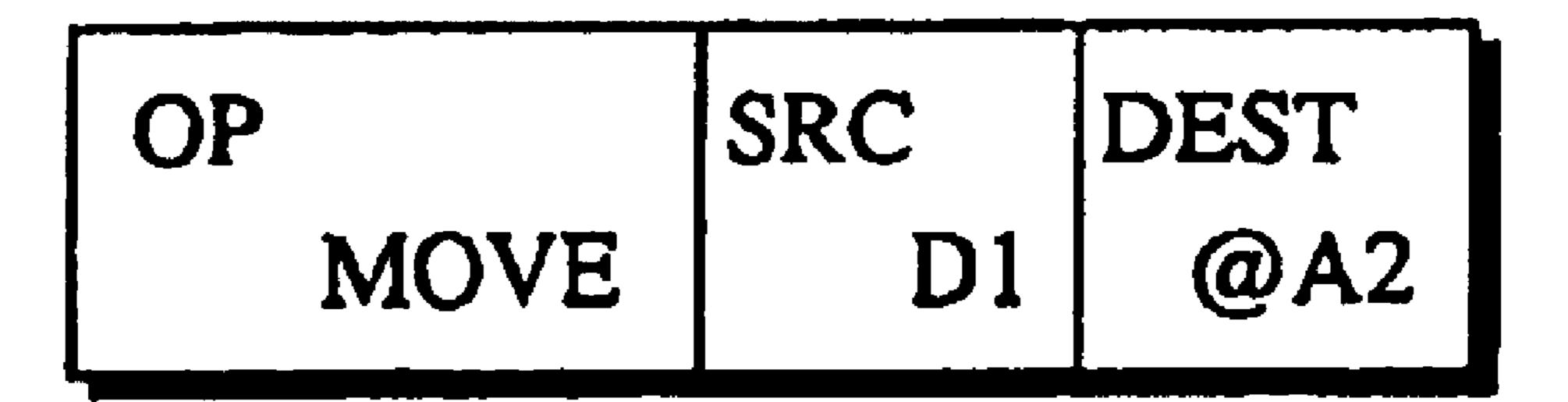

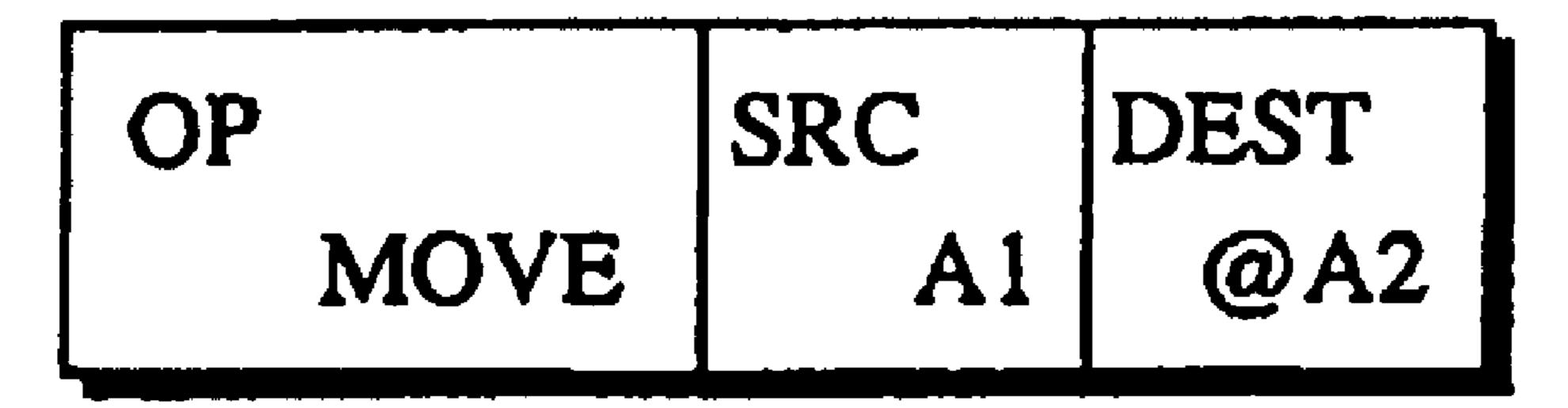

A format of an instruction to transfer the data from one of the registers in the registers unit 11 to the external storage unit 13 is shown in FIG. 2: OP is an operation field designating a kind of instruction; SIZE is a field designating the bit-width of the transmission data; SRC is a source field identifying a source register; and DEST is a destination field specifying a destination address in the external storage unit 13.

The second conventional processor executes the above data-transfer instruction in the following way.

To begin with, the instruction decoding unit 12 decodes the data-transfer instruction as OP designates MOVE; SIZE designates 32-bit data; SRC identifies a register A1; and DEST identifies an address stored in a register A2. Accordingly, the decoding unit 12 outputs the register information 15 and bit-width information 16 to the access executing unit 14, which, in response, writes the content in the register A1 into the external storage unit 13 at the address @A2 in the designated 32-bit width.

However, the second conventional processor demands the size field in each data-transfer instruction, which further demands a size-field decoding function and enlarges an instruction code, or increases the code size.

In addition, since the size field designates one of 32, 16-, and 8-bit data, 32-bit data are always transferred to the address register when the address for the application is 24-bit or less wide. When 16-bit data are transferred, the execution speed will not be decreased if the compiler designates a 16-bit width by the size filed. Some compilers, however, may not judge the effective 16-bit width when the program uses 16-bit data. In this case, the compiler designates a 32-bit width where 16-bit width should have been designated instead. Thus, if the data are transferred to an 8-bit-width memory, the data are transferred four times per 8 bits and the last two 8-bit data transfer are redundant.

### THIRD CONVENTIONAL PROCESSOR

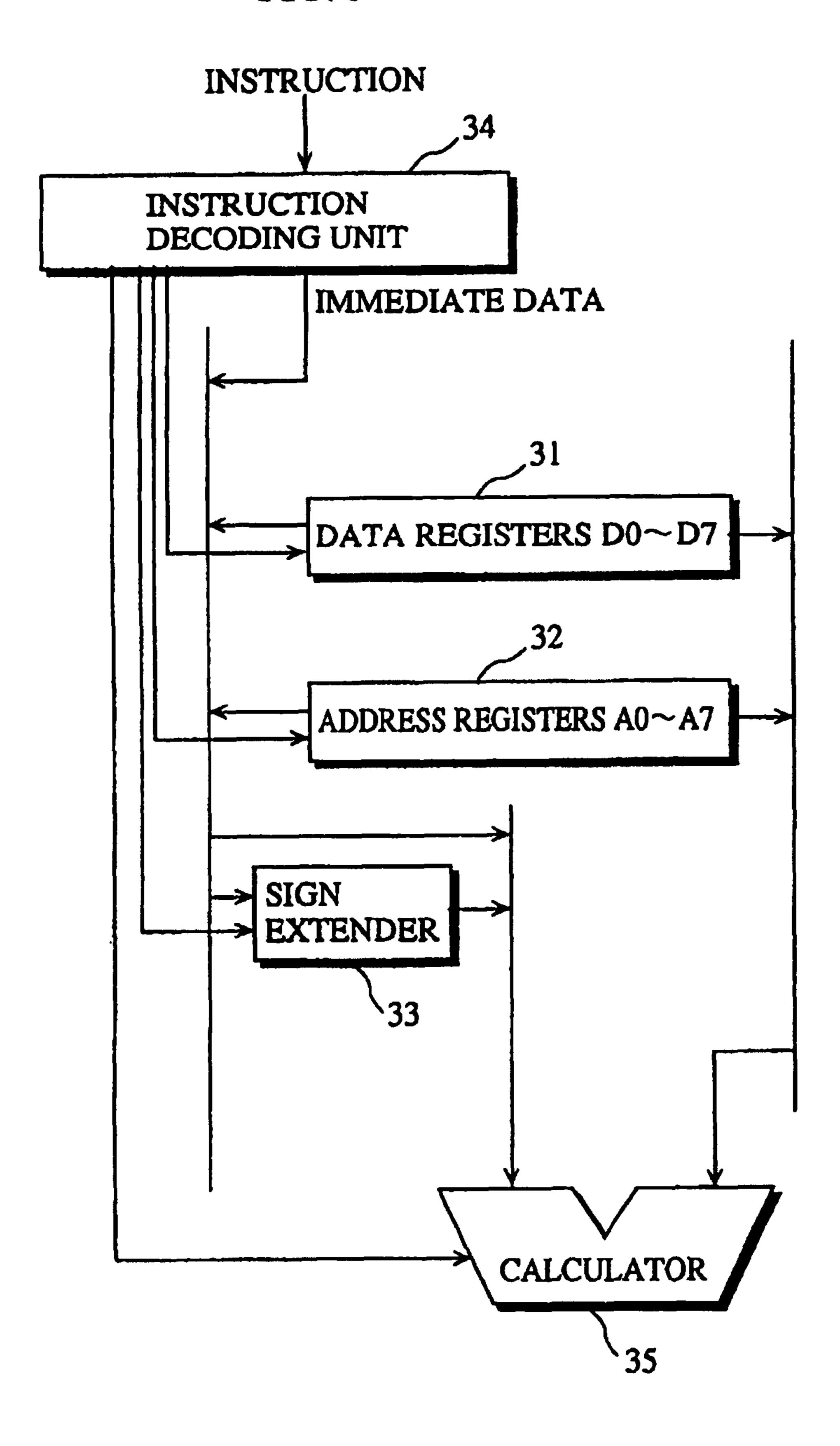

A third conventional processor can process data of a plurality of data widths. For example, immediate data, which directly specifies a value in a program instruction, are processed after the immediate data are sign-extended. This type of processor is described, for example, "Microcomputer <sup>35</sup> Series 14 68000 Microcomputer", Yuzo Kida, Maruzen, March, 1983.

A structure of the third conventional processor is depicted in FIG. 3. The processor comprises a group of data registers 31 for storing 32-bit data, a group of address registers 32 for storing 32-bit addresses, a sign-extender 33 for sign-extending the MSB of 16-bit data to output 32-bit data, an instruction decoding unit 34 for decoding an instruction, and a calculator 35 for operating a calculation in accordance with the decoding result.

The above-constructed processor operates in the following way. To begin with, the instruction decoding unit **34** decodes the input instruction from an external unit, and the other components operate differently in two cases according to the decoded instruction.

- (1) In case of an instruction to transfer the data between one of the data registers 31 and one of the address registers 32, or to execute an arithmetic operation using the data therein, the calculator 35 receives 32-bit data from both the registers and operates a calculating using the same to store the result of the operation into a designated register.

- (2) In case of an instruction to transfer 16-bit immediate data to one of the data registers 31 or address registers 32, or to execute an arithmetic operation using the same, the immediate data are extended to 32-bit data by the sign-extender 33 to be outputted to the calculator 35; the calculator 35 operates a calculation using the sign-extended data and stores the result of the operation into a designated register.

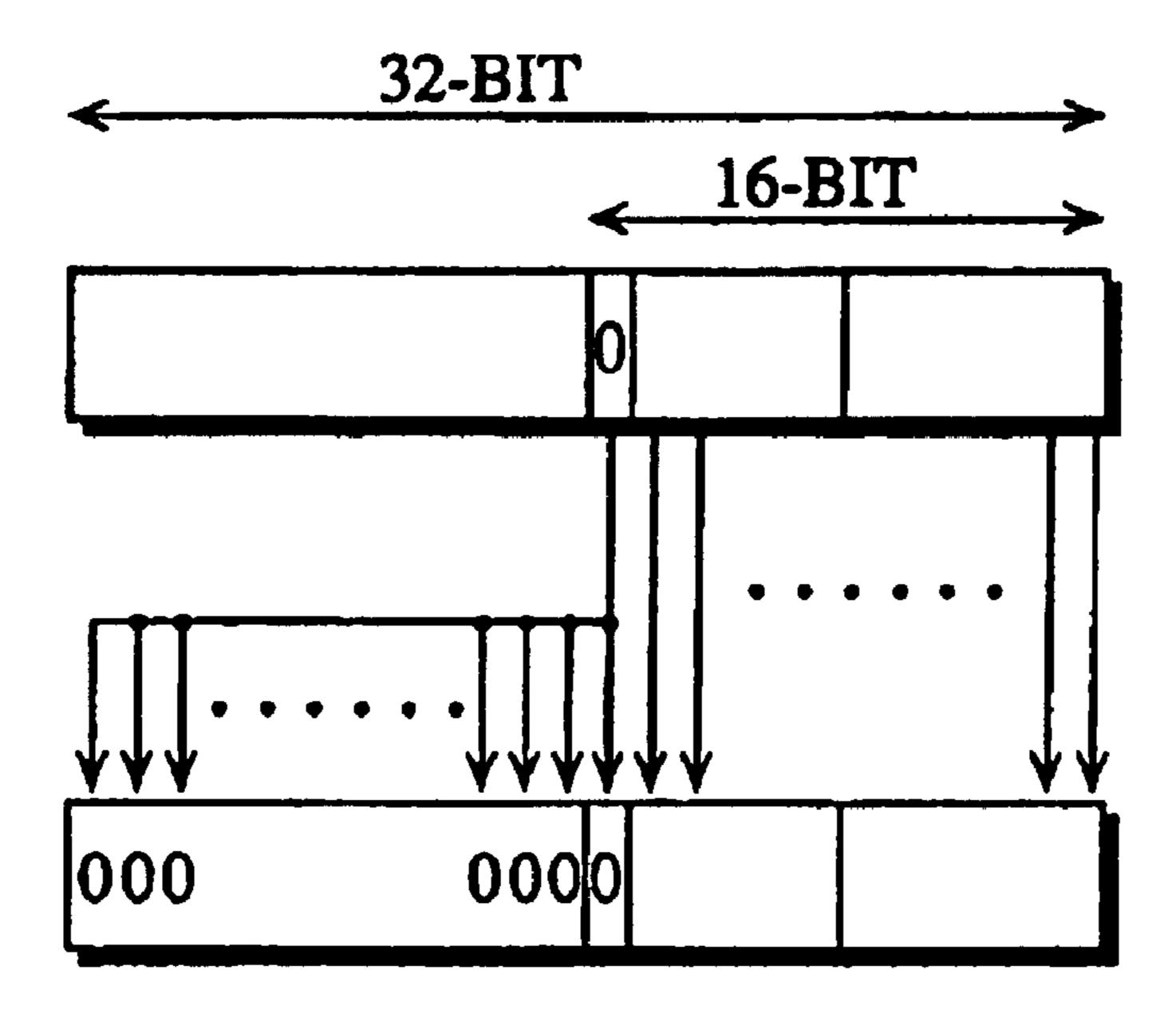

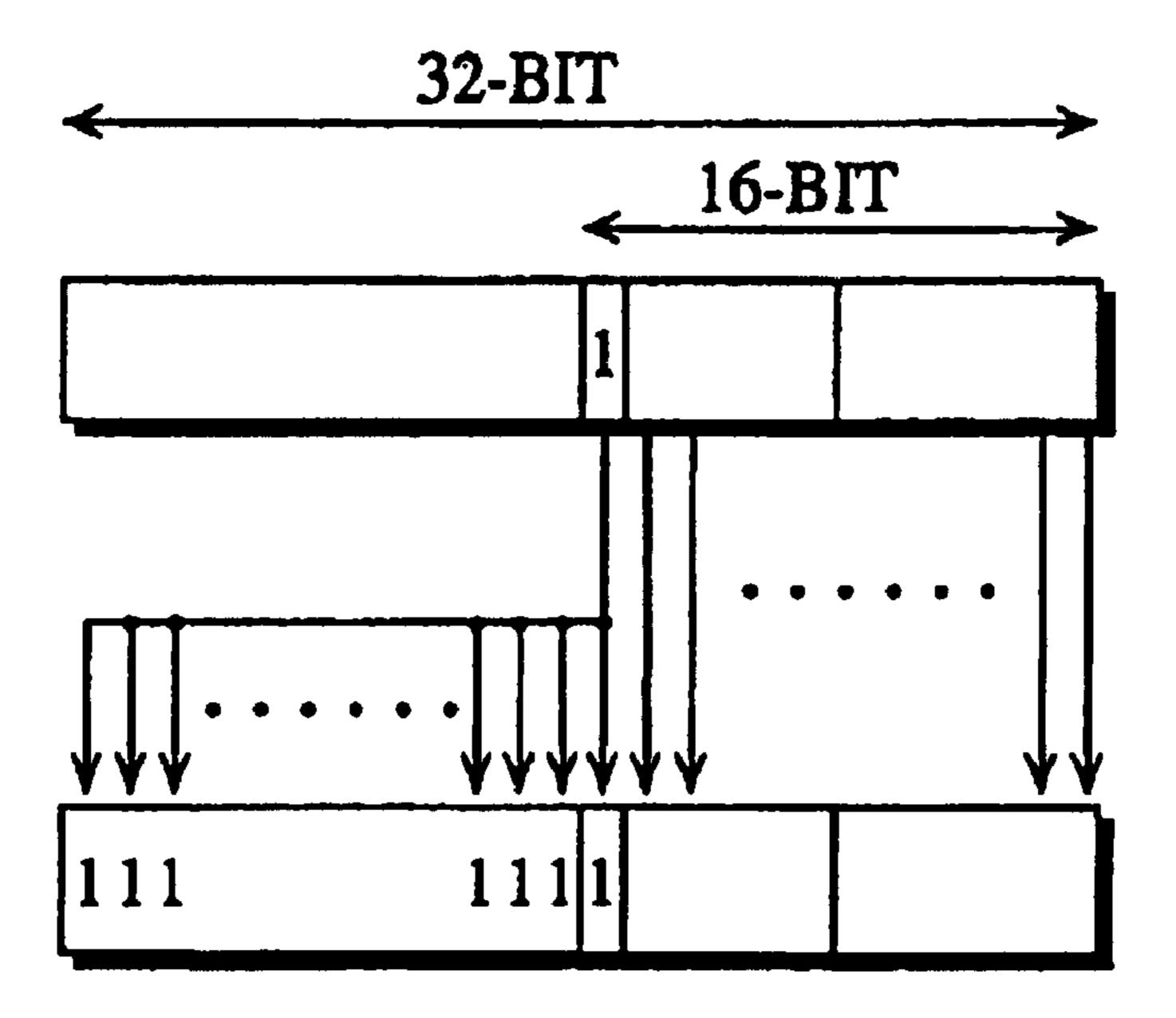

The operation of the sign-extender 33 will be described 65 more in detail by referring to FIGS. 4A, 4B. When the MSB of 16-bit data exhibits "O" as shown in FIG. 4A, the 16-bit

4

data are extended to 32-bit data by filling the zero's in the 32nd bit. On other hand, when the MSB exhibits "1" as shown in FIG. 4B, the 16-bit data are extended to 32-bit data by filling one's in the 32nd bit.

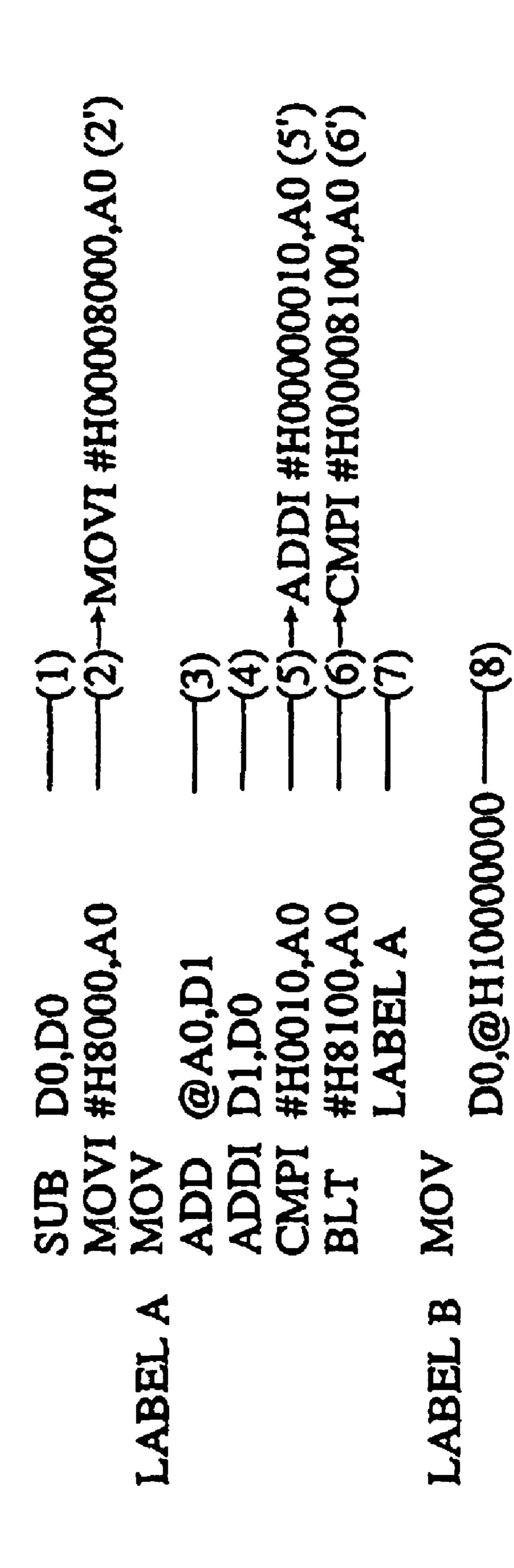

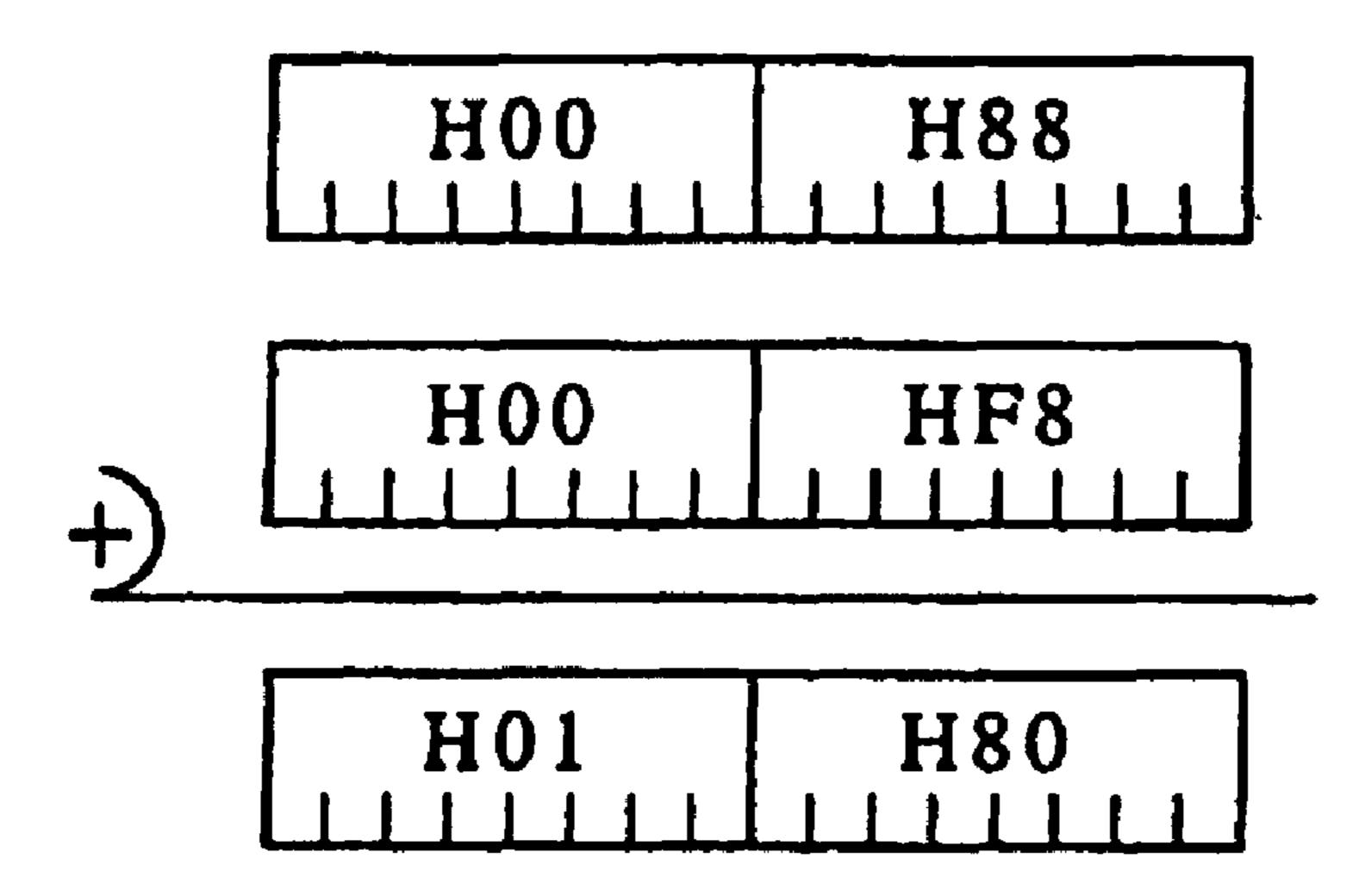

Assume that the immediate data are shorter than the register designated for calculation and data-storage. The operation of the third conventional processor when executing a program with such immediate data will be explained with referring to FIGS. 5, 6, and 7; FIG. 5 shows an example of a program, FIG. 6 details the flow of the operation for running that program, and FIG. 7 shows an address space.

As understood from FIG. **6**, the program in FIG. **5** reads: add up the data at sixteen addresses from the addresses H8000to H8100 (H represents hexadecimal and each address is H10 addresses away) and write the result at the address H10000000. However, executing Instructions 2, 5, and 6 does not result as detailed by FIG. **6**. Thus, to run the program as detailed by FIG. **6**, instructions 2, 5, and 6 are, in effect, re-written to Instructions 2', 5', and 6', respectively.

For further understanding, the program in FIG. 5 will be explained more in detail.

Instruction 1: Clear a data register D0

Instruction 2: Set 16-bit immediate data H8000 in an address register A0.

Since Instruction 2 uses a notation of the 16-bit immediate data H8000, the immediate data H8000 are sign-extended to 32-bit data HFFFF8000 by the sign-extender 33 to be stored into the address register A0.

Instruction 3: Read out the content stored at an address designated by the address register A0 from the memory to store the same into a data register D1.

Instruction 4: Add the content in the data register D1 to that of the data register D0 to store the result in the data register D0.

Instruction 5: Add immediate data H0010 to the address register A0 to store the result into the address register A0.

The 16-bit immediate data H0010 are extended to 32-bit data HFFFF0010 by the sign-extender 33. Subsequently, the calculator 35 adds the address data HFFFF8000 stored in the address register A0 to the extended data HFFFF0010 to output the data HFFFF8010, which are stored into the address register A0.

Instruction 6: Compare the output data with immediate data H8100.

The immediate data H8100 are also sign-extended to 32-bit data HFFFF8100 by the sign-extender 33 to be outputted to the calculator 35. Accordingly, the calculator 35 compares the same with the address data HFFFF8010 read out from the address register A0.

Instruction 7: Return to Instruction 3 labeled A when the former is greater than the latter; otherwise, proceed to Instruction 8.

The loop of Instructions 3–7 is repeated until the initial value of the address register A0, i.e., HFFFF8000, is incremented up to HFFFF8100 by H00000010. This means that the process proceeds to Instruction 8 when the result of the sixteen addition operations has been stored into the data register D0.

Instruction 8: Store the content in the data register D0 into the memory at the address H10000000.

With the third conventional processor, the immediate data used for an access to the address register may have a value unexpected by the flowchart shown in FIG. 6. This will be explained more in detail. In FIG. 5, the immediate data

H8000, H0010, and H8100 are used for the access to the address register by Instructions 2, 5, and 6, respectively. In case of the immediate data H8000, they are sign-extended not to H000080000 but HFFFF8000. This is because the MSB thereof exhibits "1" and the higher order is filled with 5 all one's. Naturally, the immediate data HFFFF8000 is stored into the address register A0, and the data at the address HFFFF8000 are read only by Instruction 3 where the data at the address H00008000 should have been read out instead as shown in FIG. 7. Thus, the data unexpected from 10 FIG. **6**, are read out as a result.

Similarly, the immediate data H8100 is extended not to H00008100 but to HFFFF8100 by Instruction 6, causing the processor to output an unexpected value as the operation result.

As has been stated, with the third conventional processor, the sign-extension causes the immediate data to exhibit a value unexpected by a programmer from the flowchart in FIG. 6 while running the program. This occurs only when the immediate data's MSB is addressed with a value "1" in the address space. Therefore, to eliminate this problem, a method using a 32-bit notation for the immediate data designation has been proposed. For example, the immediate data are designated as H00008000 instead of H8000 by Instruction 2. However, this method demands the 32-bit notation <sup>2</sup> even when 16-bit data are designated, and thus extending the instruction size and object code unnecessarily.

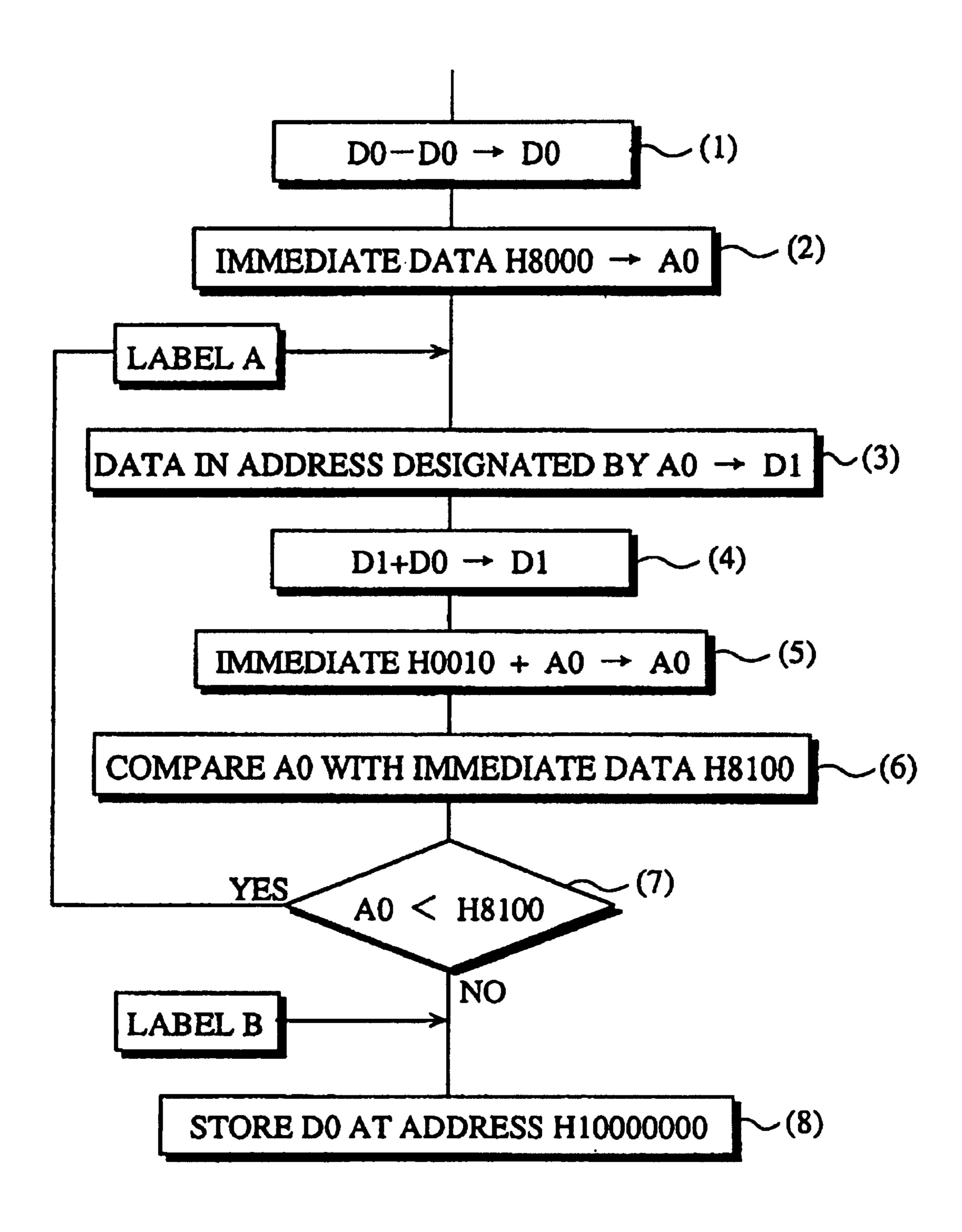

Given these circumstances, a method for re-writing the program using the 16-bit instruction data has been proposed 30 to eliminate the above problem, which is shown in FIG. 8.

In the re-written program, original Instruction 2 is carried out by two steps: Instructions 2-1, 2-2. The immediate data H8000 given by Instruction 2-1 are sign-extended to HFFFF8000 first, and then, the extended data HFFFF8000 35 and H0000FFFF are ANDed to clear the higher 16 bits to zero's by Instruction 2-2, outputting 32-bit data H00008000.

Similarly, original instruction 6 is carried out three steps: Instructions 6-1, 6-2, and 6-3. The immediate data H8100 given by Instruction 6-1 are sign-extended to HFFFF8100 to 40 be stored into the address register A1 first, and then the extended data HFFFF8100 and H0000FFFF are ANDed to clear the higher 16 bits to zero's by Instruction 6-2, outputting 32-bit data H00008100. Finally, the address registers A0 and A1 are compared by Instruction 6-3.

This enables the use of the 16-bit immediate data; however, it increases the number of steps compared with the program in FIG. **5**.

Thus, a processor that can access to correct data in the address space efficiently using the immediate data shorter 50 than the address register has not been realized yet.

### FOURTH CONVENTIONAL PROCESSOR

A fourth conventional processor is either a CISC 55 (Complex Instruction Set Computer) or a RISC (Reduced Instruction Set Computer) processor. The former, such as TRON or MC68040, can execute a variety of kinds of instructions while the latter, such as SPARC or MIPS, can speed up the operation by limiting the kinds of available 60 LSB while copying the value "0" in all the higher bits instructions. Both the CISC and RISC processors generally employ a plurality of 32-bit register and a 32-bit calculator.

In a 32-bit CISC processor, all the 32-bit registers can handle any of 8-, 16-, and 32-bit data for any arithmetic operation instruction. In response, a compiler for the 32-bit 65 CISC processor generates an operation code in accordance with the data width used at the 32-bit registers. For example,

to generate an instruction to store an 8-bit character data variable, or 16-bit short-integer data variable into the 32-bit register, a code such that stores these data variables into the lower 8 and 16 bits in the 32-bit register respectively and to leave the higher 24 and 8 bits intact respectively is generated.

However, the number of the instructions increased considerably in the above way, which demands larger and more sophisticated hardware for the instruction decoding and execution. This problem is eliminated by the RISC processor.

Unlike the CISC processor, the RISC processor limits the kinds of the available instructions and does not generate an instruction such that updates only the lower 8 bits or lower 15 16 bits of the 32-bit register. Instead, it generates a code to update all the 32 bits in the register, and subsequently generates a code to compensate the higher 24 and 16 bits respectively to adjust the bit widths to adequate ranges set forth below. This is done to compensate an overflow possibly caused by the arithmetic operation for the data variables.

|    | Type of data variable                                                                    | Range (decimal)                                                                                              |

|----|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 25 | signed character<br>unsigned character<br>signed short integer<br>unsigned short integer | -128 to +127 (inclusive)<br>0 to +255 (inclusive)<br>-32768 to +32767 (inclusive)<br>0 to +65535 (inclusive) |

With the 32-bit register, these data variables may exceed the above ranges as the result of the operation. For example, when a 32-bit register is assigned for a signed character data variable exhibiting +127, adding a value "2" to that 32-bit register yields +129, causing it to hold an incorrect value for a signed character data variable.

To compensate this, the RISC compiler generates a code with the following compensation instruction and the machine language instructions unconditionally each time the content of the register is updated by the operation:

|   | Kind of data variable  | Compensation Instruction                                  |

|---|------------------------|-----------------------------------------------------------|

| 5 | signed character       | left-shift by 24 bits & arithmetic right-shift by 24 bits |

|   | unsigned character     | left-shift by 24 bits & logical right-shift by 24 bits    |

| ) | signed short integer   | left-shift by 16 bits & arithmetic right-shift by 16 bits |

|   | unsigned short integer | left-shift by 16 bits & logical right-shift by 16 bits    |

Left-shift means a shift in the direction of the MSB; arithmetic right-shift means a shift in the direction of the LSB while coping a value "1" in the MSB of the extended data; and a logical right-shift means a shift in the direction of the beyond the lower 8 bits. Thus, the register 24 that stores +129 (100000001 in binary number) is shifted to the left by 24 bits to discard the higher 8 bits including the MSB of 1, and shifted back to the right arithmetically to obtain the 32-bit extended data which exhibits a value "1".

However, the RISC compiler compiles the program using the character or short-integer data variables with a consider-

able number of the compensation instructions, which increases the code size of the resulting machine language program, and hence prolonging the data processing time.

In addition, there is no advantage using the compensation instructions when a program does not have the overflow, or a programmer avoids the overflow by checking the available range for each data variable.

Further, an integer data variable, besides the character and short-integer data variables, causes the same problem in a system where the bit-width of the register exceeds that of the integer data variable. Since the integer data variables are most frequently used, the problem becomes far more serious. Although the effects can be appreciated when the programmer can not avoid or is not aware of the overflow, the code size increases and the program execution time prolongs considerably because the compensated codes includes the left-shift and arithmetic or logical right shift instructions.

### FIFTH CONVENTIONAL PROCESSOR

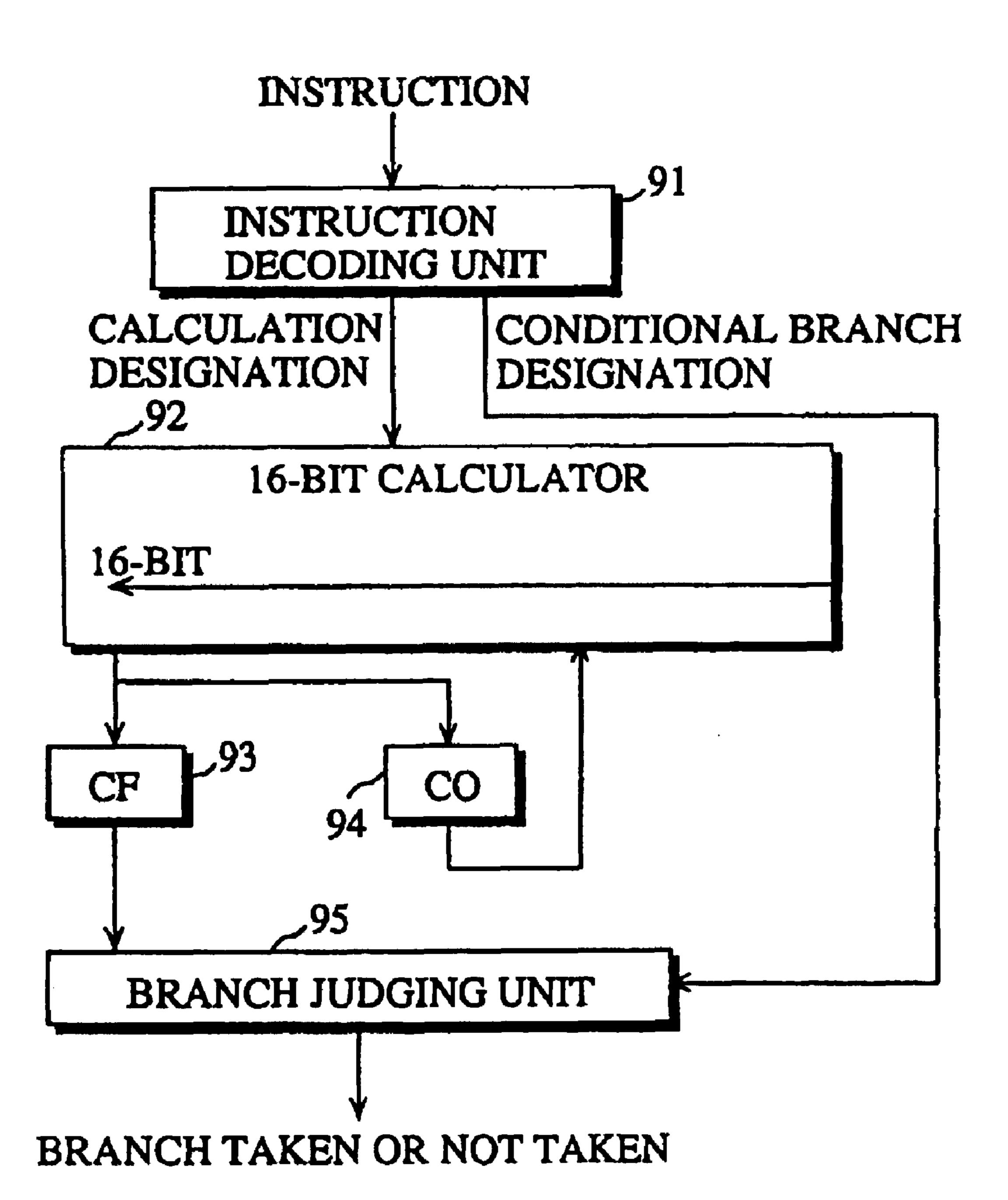

A fifth conventional processor includes two flag groups for an arithmetic operation with different data operation widths, which is disclosed, for example, Japanese Laid-open Patent Application No. 54-117646, and a structure thereof is depicted in FIG. 9. The processor comprises an instruction decoding unit 91, a 16-bit calculator 92 for calculating 16-bit data, a flag group 93 for a conditional branch judgment, another flag group 94 for calculation, and a branch judging unit 95 for judging whether a conditional branch is taken or not.

The above-constructed processor operates in the following way. To begin with, the instruction decoding unit 91 decodes an instruction. When the decoded instruction is an arithmetic operation instruction, the 16-bit calculator performs an arithmetic operation, and the flag groups 93, 94 are changed in accordance with the operation result.

If the following decoded instruction is also an arithmetic operation instruction, the 16-bit calculator **92** operates by referring to the flag group **94**. Whereas if the following decoded instruction is a conditional branch instruction, the branch judging unit **93** refers to the flag group **93** to judge 40 whether the conditional branch is taken or not.

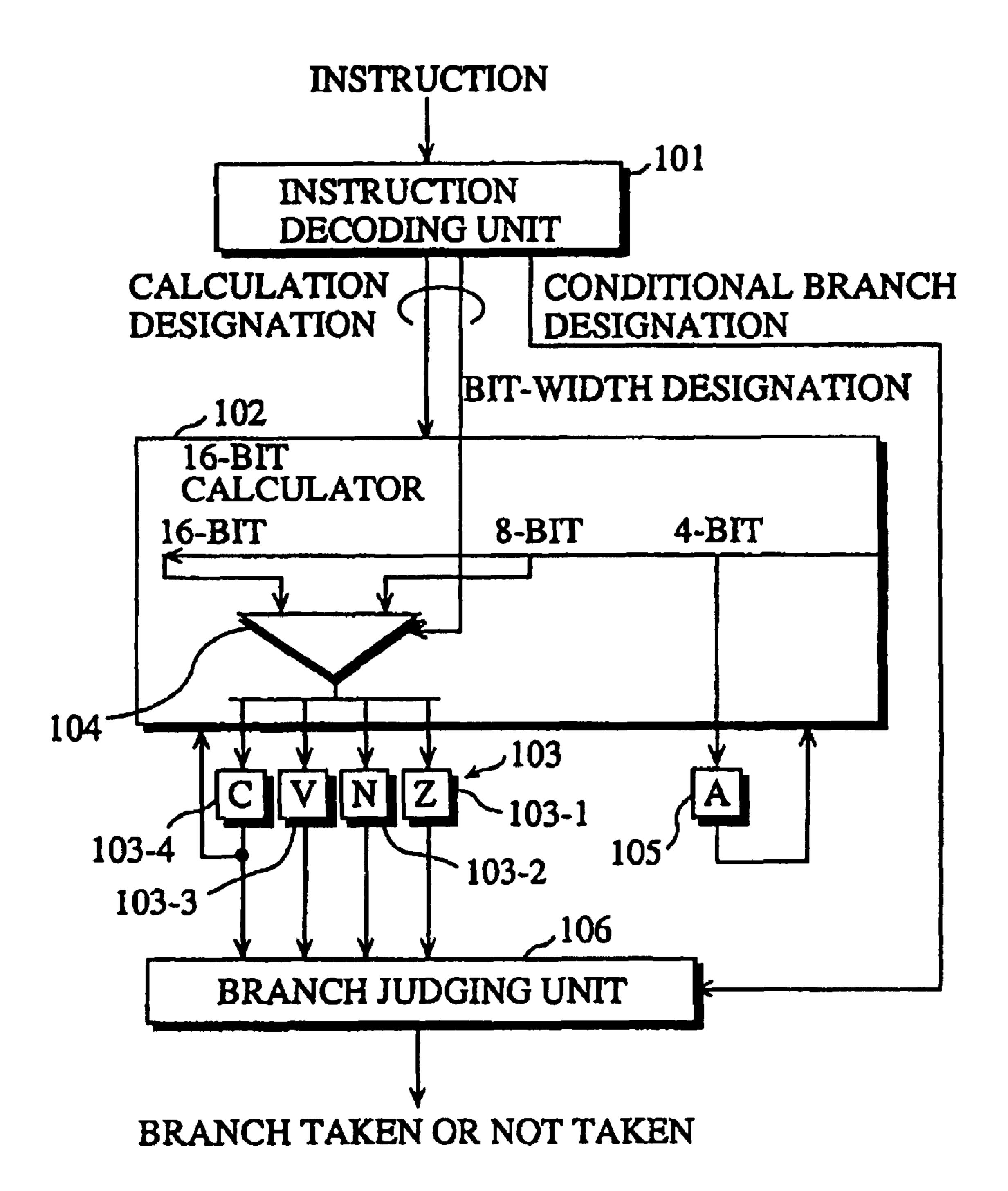

Another example of the processor using two flag groups is disclosed in "16-bit Microprocessor 8086 Family" Shokodo, March, 1982. A structure of the processor is depicted in FIG. 10. The processor comprises an instruction decoding unit 101 for decoding an instruction, a 16-bit calculator 102 for calculating 16-bit data, a flag group 103 changed in accordance with the result of the 8- or 16-bit data operation, a flag selector 104 for selecting an input of the flag group 103 which is changed in accordance with the result of 8- or 16-bit data operation, a flag 105 determined in accordance with the result of 4-bit data operation, and a branch judging unit 106 for judging whether a conditional branch is taken or not by using the flag group 103.

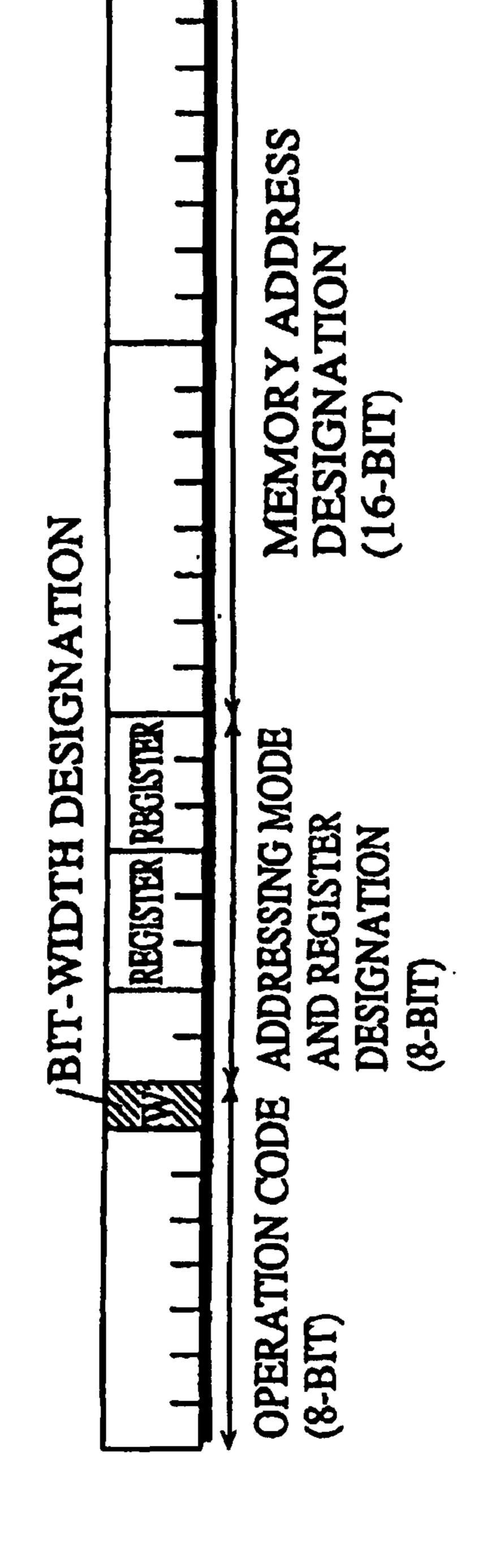

A bit-structure of add, subtract, and compare instructions and that of a branch instruction in the machine language is shown in FIGS. 11A, 11B, respectively. With the add, subtract and compare instructions shown in FIG. 11A, the first byte (operation code) designates a kind of an operation and one bit (denoted as W) therein designates either the 8-bit data operation or 16-bit data operation. The second byte designates registers and an addressing mode for memory operands. The third and fourth bytes designate memory address. With the conditional branch instruction shown in FIG. 11B, four bits within the first byte designates a branch condition.

The above-constructed processor operates in the following way. To begin with, the instruction decoding unit 101

8

decodes an instruction. If the decoded instruction is an arithmetic operation instruction, the 16-bit calculator calculates using the data. Accordingly, the flags in the flag group 103 and flag 105 are changed in accordance with the operation result. At the same time, the instruction decoding unit 101 designates either the 8-bit or 16-bit data operation to the 16-bit calculator 102, and the selector 104 outputs flag changing data determined by the data operation width to the flag group 103.

If the following decoded instruction is a conditional branch instruction, the branch judging unit 106 refers to the flag group 103 to judge whether the conditional branch is taken or not.

Note that in case that an arithmetic operation is followed by an arithmetic operation with decimal data, the calculator 102 refers to the flag 105.

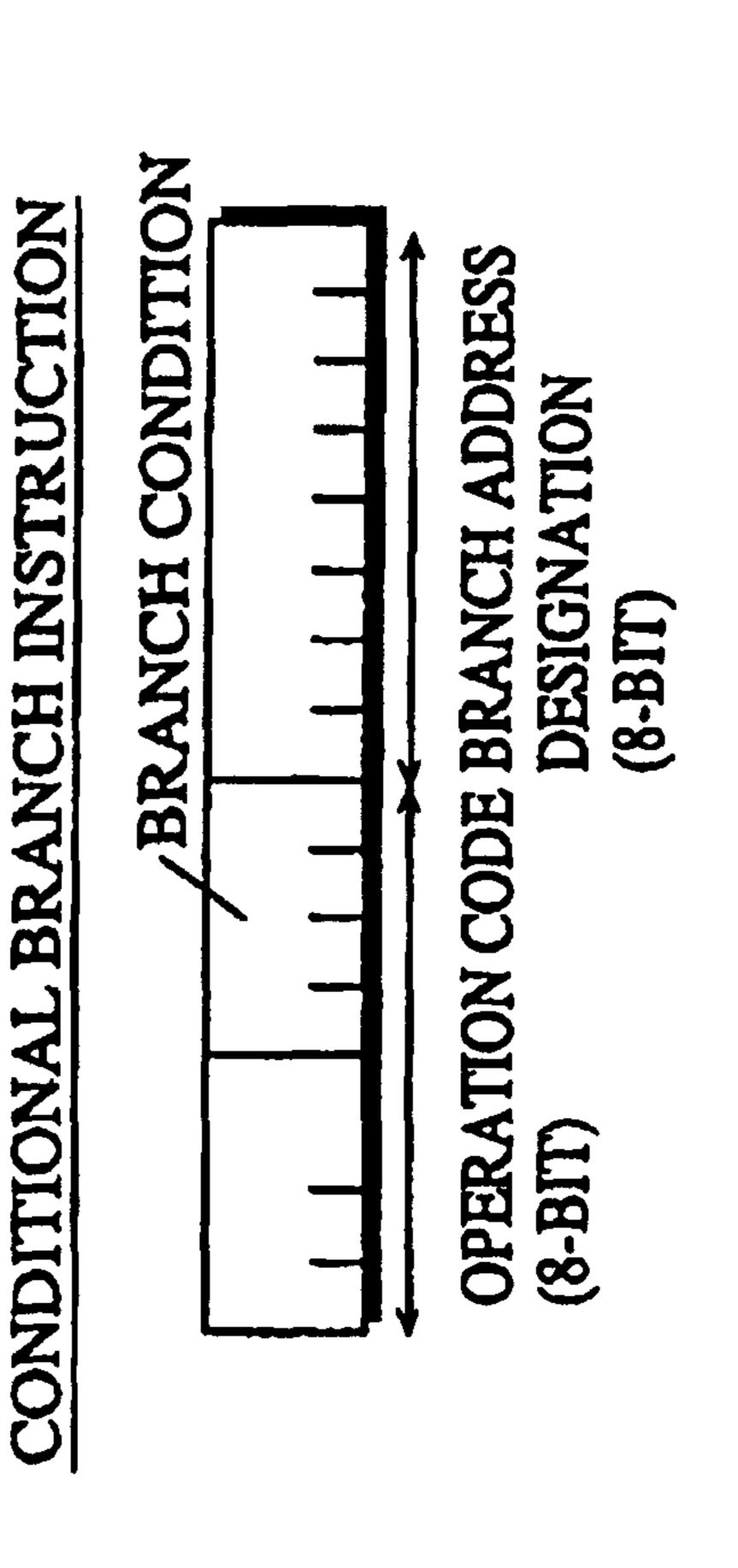

However, in the first example, the flag group 103 and flag 105 are used for the arithmetic operation instruction and branch instruction respectively, and hence when the operation result is shorter than the data operation width the operation result must be extended in the direction of a high order if the conditional branch is taken.

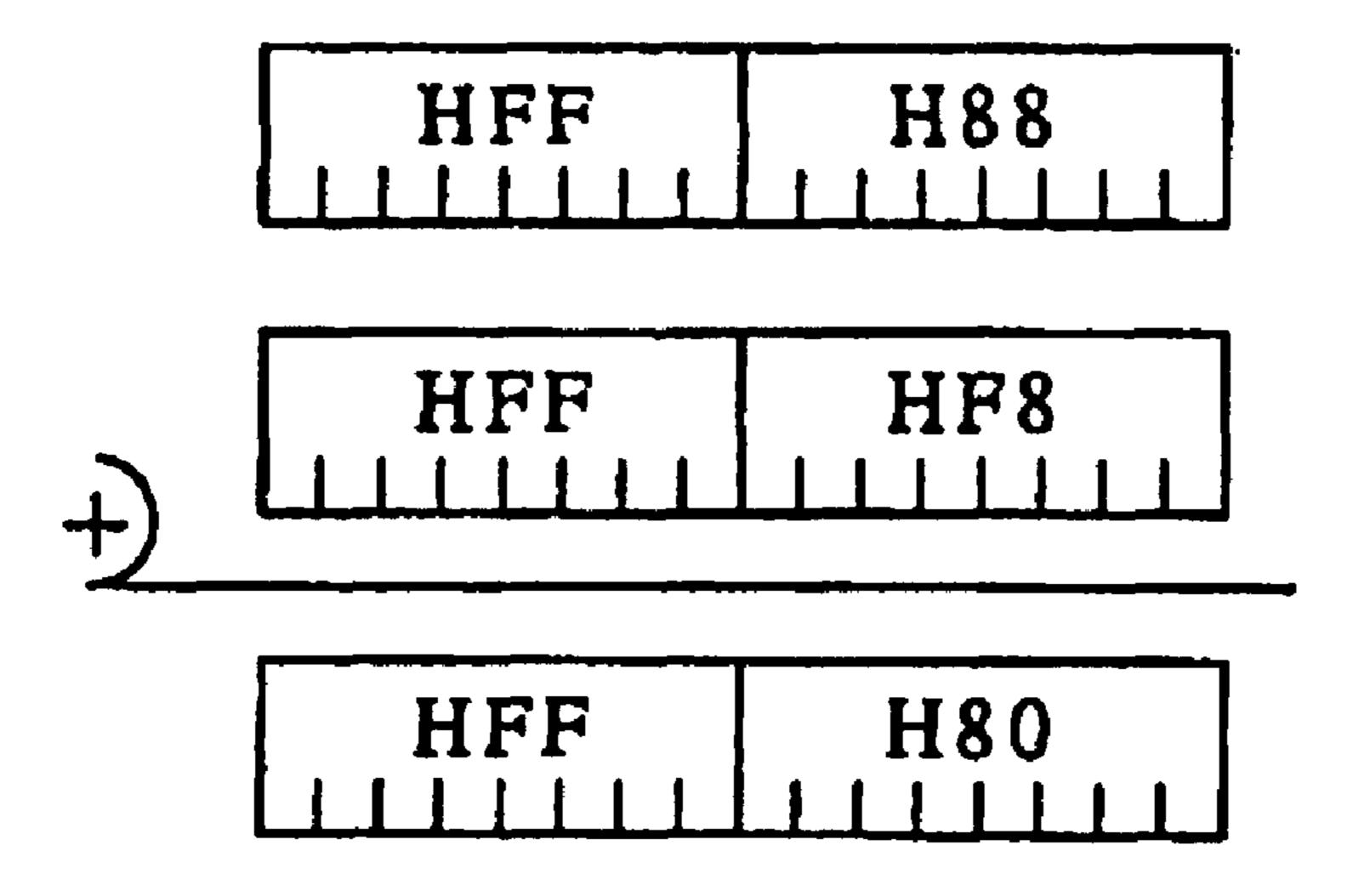

processed in the 16-bit data operation. As shown in FIG. 12A, if the branch is judged based on an 8-bit unsigned data, the data are extended to H0088, H00F8 by copying zero's in the higher 8 bits. Whereas as shown in FIG. 12B, if the branch is judged based on an 8-bit signed data, the data are extended to HFF88, HFFF8 by copying a value "1" up to the MSB from the eighth bit in the low order. This means that the concerned 8-bit data must be extended up to the higher 8 bits, increasing the overhead and hence is not preferable.

With the second example, although the two flags based on the operation results on different data operation widths (4 bits and 8 or 16 bits) are set contemporaneously, the use of the 4-bit flag is limited to the decimal data operation and it can not be used for a 4-bit data conditional branch. Moreover, one flag is selected from the flag group 103 to eliminate the overhead caused in the first example; however, this demands two kinds of arithmetic operation instructions, which further demands a larger instruction decoding unit.

### SUMMARY OF THE INVENTION

Accordingly, a first object of the present invention is to provide a program converting unit which adequately selects an operation code to generate an object program in accordance with a data bit-width and an application program's address space, which does not depend on a data bit-width, so as not to degrade operation efficiency caused by address calculation, and to provide a processor that runs the resulting object program.

A second object of the present invention is to provide a program converting unit that reduces the code size of a machine language program independently of a type of data variable when the application program does not have an arithmetic overflow or the application program is constructed to avoid the arithmetic overflow or the one that generates a compensation instruction corresponding to each type of data variable otherwise, and to provide a processor that runs the resulting compensation instruction.

A third object of the present invention is to provide a processor that reduces the program size by simplifying the operation code to execute a data-transfer instruction at a higher speed.

A fourth object of the present invention is to provide a processor that always extends the immediate data as a pro-

grammer expects and that does not need the compensation instruction when its register stores the immediate data whose MSB exhibits a value "1".

A fifth object of the present invention is to provide a computer and a data processing method that minimizes the overhead at the execution of a conditional branch when the bitwidth of the operation data and operating unit are different.

The first object can be fulfilled by a program converting unit for generating a machine language instruction from a source program for a processor that manages an N-bit address while processing M-bit data, N being greater than M, the program converting unit comprising: a parameter holding unit for holding a data width and a pointer width designated by a user, the data width representing the number of bits of data used in the source program while the pointer width representing the number of bits of an address; and a generating unit for generating an instruction to manage the data width when a variable operated by the instruction represents the data, and for generating an instruction to manage the pointer width when a variable operated by the instruction represents the address.

The M may be 16 and the N may be an integer in a range of 17 to 31 inclusive.

The generating unit may include: a judging unit for judg- 25 ing a kind of the machine language instruction, the machine language instruction including (1) an instruction to access to a memory, (2) an instruction to use a register, and (3) an instruction to use an immediate; a memory managing unit for outputting a direction, in case of the (1) instruction, to  $_{30}$ manage the data width as an effective memory-access width when a variable to be accessed represents the data, and to manage the pointer width as an effective memory-access width when the variable represents the address; a register managing unit for outputting a direction, in case of the (2)  $_{35}$ instruction, to manage s effective bit-width when a variable to be read/written from/into the register represents the data, and to manage the pointer width as the effective bit-width when the variable represents the address; an immediate managing unit for outputting a direction, in case of the (3)  $_{40}$ instruction, to manage the data width as the effective bitwidth when the immediate represents the data, and to manage the pointer width as the effective bit-width when the immediate represents the address; and a code generating unit for generating the machine language instruction in accordance with the directions from the memory managing unit, the register managing unit, and the immediate managing unit.

The N may be 24 and the code generating unit may generate an instruction for a 24-bit data operation when the 50 pointer width is greater than 16 bits and less than 24 bits, and generates an instruction for a 16-bit data operation when the pointer width is 16 bits or less.

The first object can be fulfilled by a program converting unit for generating a machine language instruction based on a source program for a processor that manages an N-bit address while processing M-bit data, N being greater than M, the program converting unit comprising: a syntax analyzing unit for analyzing a syntax of the source program to convert the same into an intermediary language comprising intermediary instructions, and subsequently for judging whether or not each variable contained in the intermediary instructions represents data used in an address; a table generating unit for generating a table for each variable in the intermediary instructions, the table holding a name together 65 with a type of each variable, the type representing one of the data and the address; a parameter holding unit for holding a

**10**

data width and a pointer width designated by a user, the data width representing the number of bits of the data while the pointer width representing the number of bits of the address; and a generating unit for generating an instruction to manage the data width when the variable in the intermediary instruction represents the data, and an instruction to manage the pointer width when the variable represents the address.

The generating unit may include: a judging unit for judging a kind of the machine language instruction, the machine language instruction including (1) an instruction to access to an memory, (2) an instruction to use a register, and (3) an instruction to use an immediate; a memory managing unit for outputting a direction, in case of the (1) instruction, to manage a corresponding bit-width held in the parameter holding unit as an effective memory-access width depending on the type of a variable to be accessed shown in the table; a register managing unit for outputting a direction, in case of the (2) instruction, to manage a corresponding bit-width held in the parameter holding unit as an effective bit-width depending on the type of a variable to be read/written from/ in the register shown in the table; an immediate managing unit for outputting a direction, in case of the (3) instruction, to manage a corresponding bit-width held in the parameter holding unit for the immediate as an effective bit-width depending on the type of the immediate shown in the table; and a code generating unit for generating the machine language instruction in accordance with the directions from the memory managing unit, the register managing unit, and the immediate managing unit.

According to the above construction, any arbitrary data width and pointer width can be set into the parameter setting unit. Thus, a programmer does not have to check an irregularity in the address space such as a segment boundary. Also, an address space larger than the one secured by the program application's data-width can be secured without degrading the operation efficiency caused by address calculation: the size of the address space does not depend on the data operation width.

Also, the above construction can be employed for most of the applications for an embedded-type microprocessor that demand neither the 32-bit data nor address space of 4 Gbyte, but demand the 16-bit data and address space over 64 Kbyte.

The first object also can be fulfilled by a processor improved in address management comprising: a memory unit for storing a program including an N-bit data arithmetic operation instruction and both N-bit and M-bit data load/store instructions, N being greater than M; a program counter for holding an N-bit instruction address to output the same to the memory unit; a fetching unit for fetching an instruction from the memory unit using the instruction address from the program counter; and an executing unit for executing all N-bit arithmetic operation instructions and for executing N-bit and M-bit instructions excluding the arithmetic operation instructions, whereby an N-bit address is calculated by the N-bit arithmetic operation independently of a data bit-width, the data bit-width being M.

The processor may further comprise: an address register group including a plurality of N-bit address registers; a data register group including a plurality of N-bit data registers, wherein the executing unit executes the N-bit and M-bit data operation instructions using the address registers, while executing the M-bit data operation instruction using the data registers.

The N may be 24 and the M may be 16, and the processor may be installed in a 1-chip microcomputer, whereby the 1-chip microcomputer becomes suitable for running a pro-

gram that utilizes a memory over 64 Kbyte for an operation with 16-bit data.

The processor may further comprise: an address register group including a plurality of N-bit address registers; and a data register group including a plurality of M-bit data registers, wherein the executing unit executes one of an N-bit data operation instruction and an M-bit data operation instruction using the address registers, while executing the M-bit data operation instruction using the data registers.

The N may be 24 and the M may be 16, and the processor may be installed in a 1-chip microcomputer, whereby the 1-chip microcomputer becomes suitable for running a program that utilizes a memory over 64 Kbyte for an operation with 16-bit data.

According to the above construction, the processor can secure the address space that does not depend on the data operation width. The processor can secure a  $2^N$ -byte address space which is larger than a  $2^M$ -byte address space, while executing N-bit data operation, upgrading the operation efficiency in address calculation.

The above construction can be effectively employed for most of the applications for an embedded-type microprocesser, such as household appliances and controlling devices, that demand neither the 32-bit data nor address space of 4 Gbyte, but demand the 16-bit data and address space over 64 Kbyte.

The second object can be fulfilled by a program converting unit for generating a machine language instruction from a source program for a processor that manages an N-bit 30 address while processing M-bit data, N being greater than M, the program converting unit comprising: a parameter holding unit for holding a data width and a pointer width designated by a user, the data width representing the number of bits of data used in the source program while the pointer 35 width representing the number of bits of an address; a generating unit for generating an instruction to manage the data width when a variable operated by the instruction represents the data, and for generating an instruction to manage the pointer width when a variable operated by the instruction 40 represents the address; an option directing unit for holding a user's direction for an overflow compensation, an overflow being possibly caused by an arithmetic operation; and a compensate instruction generating unit for generating a compensation instruction to compensate an overflow in 45 accordance with a type of a variable used in the arithmetic operation, the type being judged when the option directing unit holds the user's direction for executing the overflow compensation, the compensation instruction being generated when an effective bit-width of a variable designated by an 50 operand is shorter than a register of N-bit wide and the arithmetic operation instruction will possibly cause an overflow exceeding the effective bit-width.

The compensate instruction generating unit may include: an instruction judging unit for judging an arithmetic operation instruction that will possibly cause an overflow for all the machine language instructions when the option instructing unit holds the user's direction for executing the overflow compensation; a variable judging unit, when respect to a variable in the arithmetic operation instruction judged by the instruction judging unit, for judging an effective bit-width and whether the variable is signed or unsigned by referring to the table; a sign-extension instruction generating unit for generating a compensation instruction in case of a signed variable, a logical value of a sign bit being filled into all bits higher than the effective bit-width in a register that is to store the signed variable by the sign-extension compensation

12

instruction; and a zero-extension instruction generating unit for generating a zero-extension compensation instruction in case of an unsigned variable, a logical value "0" being filled into all bits higher than the effective bit width in a register that is to store the unsigned variable by the zero-extension compensation instruction.

The generating unit may include: a judging unit for judging a kind of the machine language instruction, the machine language instruction including (1) an instruction to access to a memory, (2) an instruction to use a register, and (3) an instruction to use an immediate; a memory managing unit for outputting a direction, in case of the (1) instruction, to manage the data width as an effective memory-access width when a variable to be accessed represents the data, and to manage the pointer width as an effective memory-address width when the variable represents the address; a register managing unit for outputting a direction, in case of the (2) instruction, to manage the data width as an effective bitwidth when a variable to be read/written from/into the register represents the data, and to manage the pointer width as the effective bit-width when the variable represents the address; an immediate managing unit for outputting a direction, in case of the (3) instruction, to manage the data width as the effective bit-width when the immediate represents the data, and to manage the pointer width as the effective bit-width when the immediate represents the address; and a code generating unit for generating the machine language instruction in accordance with the directions from the memory managing unit, the register managing unit, and the immediate managing unit.

The M may be 16 and the N may be an integer in a range of 17 to 31 inclusive.

The M may be 32, and the N may be an integer in a range of 33 to 63 inclusive.

According to the above construction, the overflow occurred in the RISC processor can be effectively compensated in addition to the aforementioned effects. Since the execution of an overflow compensation is optional, the compensation instruction it not generated when no compensation is necessary, and the compensation instruction is generated in a less code size when the compensation is necessary.

The processor may further comprise: a compensating unit for extending an effective bit-width of the data in one of the address register and the data register to 24 bits, wherein the compensating unit operates in accordance with the compensate instruction entered immediately after a machine language instruction designating an arithmetic operation that will possibly cause an overflow.

The compensating unit may include: a first extending unit for filling a logical value of a sign bit in all bits higher than the effective bit-width in a register; a second extending unit for filling a logical value "0" in all bits higher than the effective bit-width in a register.

According to the above constructing, in addition to the aforementioned effect, the execution speed can be increased when the compiler does not generate the compensation instructions. Also, when a programmer can not avoid the overflow or is not aware of the overflow, the compensating unit compensates the overflow with one machine language instruction of the least-word-length, minimizing the delay in the operation speed.

The third object can be fulfilled by a processor for processing data in accordance with instructions in a program comprising: a register unit including a plurality of register groups, each group being identical in bit-width while being different in types; an instruction decoding unit for decoding

an instruction to output register information indicating a register designated by an operand contained in a data-transfer instruction; an external-access-width control unit for outputting the number of effective bits as bit-width information indicating a bit-width of transmission data in accordance with a kind of a register group to which the designated register belongs; and an external-access executing unit for executing data transfer between the designated register and an external memory in accordance with the register information and the bit-width information.

The register unit may include: an address register group including a plurality of address registers holding addresses; and a data register group including a plurality of data registers holding data.

The address registers and data registers in the register unit may be all 24-bit wide; the instruction decoding unit may output information that represents one of the address register and the data register as the register information; the external-access-width control unit may output the bit-width information exhibiting 24 bits when the register information representing the address register, and outputs the bit-width information exhibiting 16 bits when the register information representing the data register; and the external-access executing unit may execute the data transfer three times and twice for the 24- and 16-bit-width information respectively for an 8-bit-width external memory, and for twice and once for the 24- and 16-bit-width information respectively for a 16-bit width external memory.

The access executing unit may include: an address generating circuit for holding an address designated by the datatransfer instruction to output one of a byte address and a word address to the external memory; an output data buffer for holding write data designated by the data-transfer instruction to output the same one of per byte and per word 35 to the external memory; an input data buffer for holding data from read out from the external memory; and a sequence circuit for outputting a byte address to the address generating circuit for an 8-bit-width external memory while controlling the number of times for the data-transfer in accordance with the bit-width information via the input/output data buffers with respect to the read/write data, for outputting a word address to the address generating circuit for a 16-bit-width external memory while controlling the number of times for the data-transfer in accordance with the bit-width information via the input/output data buffers with respect to the read/write data.

According to the above construction, the external-access-width control unit selects a register subject to data transfer and determines the data transfer width simultaneously. Thus, the size field can be eliminated from the instruction, which decreases the code size as well as obviating the size field decoding function.

Further, the data are not transferred redundantly by transferring the data independently of the register's bit-width, 55 speeding up the operation.

The fourth object can be fulfilled by a processor for operating certain data in accordance with an instruction in a program, comprising: a first register unit for holding N-bit data; a second register unit for holding N-bit data, an extending unit for extending the M-bit data to N bits by copying an MSB of the M-bit data in a direction of an upper order, M being less than N; a zero-extending unit for extending the M-bit data to N bits by copying a value "0" in a direction of an upper order; an operating unit for operating an arithmetic operation in accordance with an instruction; an instruction control unit for decoding an instruction to zero-extend M-bit

14

immediate data when the M-bit immediate data are to be stored in the first register unit by the decoded instruction and to sign-extend the M-bit immediate data when the M-bit immediate data are to be stored in the second register unit by the decoded instruction, the zero-extended and sign-extended N-bit immediate data being outputted in one of two methods, one method being to send the extended N-bit immediate data from their respective extending unit to their respective register unit directly, the other being to send the same via the operating unit to their respective register unit.

The first register unit may be a group of a plurality of address registers for storing addresses, and the second register unit may be a group of a plurality of register unit for storing data.

The N may be 24 and the M may be 16.

The fourth object can be also fulfilled by a processor for operating certain data in accordance with an instruction in a program, comprising: a first register unit for holding N-bit data; a second register unit for holding N-bit data, a signextending unit for extending the M-bit data to N bits by copying an MSB of the M-bit data in a direction of an upper order, M being less than N; a zero-extending unit for extending the M-bit data to N bits by copying a value "0" in a direction of an upper order; an operating unit for operating an arithmetic operation in accordance with an instruction; an instruction decoding unit for decoding an instruction in the program to detect a first type instruction and a second type instruction, the first type instruction including an instruction to store M-bit information data into the first register unit, the second type instruction including an instruction to store the M-bit immediate data into the second register unit; and a control unit for outputting the M-bit immediate data to the zero-extending unit when the first type instruction is detected, and for outputting the M-bit immediate data to the sign-extending unit when the second type instruction is detected, the zero-extended N-bit immediate data and signextended N-bit immediate data being outputted in one of two methods, one method being to send the extended N-bit immediate data from their respective extending unit to their respective register unit directly, the other being to send the same via be operating unit to their respective register unit.

The first type instruction may include a data-transfer instruction to store the M-bit immediate data to the first register unit, an add instruction to add a value in the first register and the M-bit immediate data, and a subtract instruction to subtract the M-bit immediate data from a value in the first register, and the second type instruction may include a data-transfer instruction to store the M-bit immediate data to the second register unit, an add instruction to add a value in the second register and the M-bit immediate data, and a subtract instruction to subtract the M-bit immediate data from a value in the second register.

According to the above construction, the immediate data are either sign or zero-extended depending on the kind of the access register prior to the arithmetic operation. Thus, the immediate data can be always extended as the programmer expected. Further, the program size can be decreased as no compensation instruction for the extension is necessary, and the immediate data becomes easy to manage for the programmer.

The fifth object can be fulfilled by a processor for executing a program including an N-bit data arithmetic operation instruction, M-bit and N-bit load/store instruction, M being less than N, conditional branch instruction, a data-transfer instruction with an external memory, and an instruction having immediate data, the processor comprising: a first register

unit including a plurality of registers for holding N-bit data; a second register unit including a plurality of registers for holding N-bit data; a program counter for holding an N-bit instruction address to output the same to the memory unit; a fetching unit for fetching an instruction from an external 5 memory using the instruction address from the program counter; an instruction decoding unit for decoding a fetched instruction; an executing unit for executing all N-bit arithmetic operation instructions and for executing N-bit and M-bit instructions excluding the arithmetic operation 10 instructions, a plurality of flag storing units, each for storing a corresponding flag group changed in response to different bit-widths data in accordance with an execution result of the executing unit; a flag selecting unit for selecting a certain flag group from the plurality of flag storing units in accor- 15 dance with a conditional branch instruction decoded by the instruction decoding unit; a branch judging unit for judging whether a branching is taken or not with a reference to a flag group selected by the flag selecting unit; a sign-extending unit for extending M-bit data to N bits by copying an MSB 20 of the M-bit data in a higher order; a zero-extending unit for extending M-bit data to N bits by filling a value "0" in a higher order; a compensation instruction control unit for compensating contents of the first register unit and the second register unit using the sign-extending unit and the zero- 25 extending unit in accordance with a compensation instruction inserted immediately after a machine language instruction for an arithmetic operation that will possibly cause an overflow, the machine language instruction being decoded by the instruction decoding unit; an external- 30 access-width control unit for outputting bit-width information for transmission data in accordance with a type of the register unit to which a register indicated by register information belongs, the register information indicating one of the first and second register unit; an external-access execut- 35 ing unit for executing a data transfer between the register and an external memory in accordance with the register information and bit-width information; and an immediate control unit for outputting M-bit immediate data to the zeroextending unit when a decoded instruction includes an 40 instruction to store the M-bit immediate data in the first register unit, and for outputting the M-bit immediate data to the sign-extending unit when a decoded instruction includes an instruction to store the M-bit in the second register unit, the zero-extended and sign-extended immediate data being sent 45 to the first and second register unit respectively in two methods, one being to send the same directly to their respective register unit and the other being to send the same via the executing unit.

The N may be 24 and the M may be 16.

According to the above construction, the flag groups are furnished for different data operation widths, and the branch judgment is done by selecting the flag group corresponding to a certain data width. As a result, in addition to the aforementioned effects, the overhead at the conditional branch 55 can be reduced while reducing the number of the instructions.

### BRIEF DESCRIPTION OF THE DRAWINGS

These and other objects, advantages and features of the invention will become apparent from the following description thereof taken in conjunction with the accompanying drawings which illustrate a specific embodiment of the invention. In the drawings:

FIG. 1 is a block diagram depicting a structure of the second conventional processor;

**16**

FIG. 2 is a view showing an instruction format for the second conventional processor;

FIG. 3 is a block diagram depicting a structure of the third conventional processor;

FIGS. 4A and 4B are views explaining the operation of a sign-extender FIG. 5 is an example of a program run by the processor in FIG. 3;

FIG. 6 is a flowchart detailing the operation corresponding to FIG. 5;

FIG. 7 is a view showing a memory space corresponding to FIG. **5**;

FIG. 8 is an example of a re-written program run by the third conventional processor;

FIG. 9 is a block diagram depicting a structure of the first example of the fifth conventional processor;

FIG. 10 is a block diagram depicting a structure of the second example of the fifth conventional processor;

FIGS. 11A and 11B are views explaining the structures of instruction formats used by the processor in FIG. 10;

FIGS. 12A and 12B are views explaining the data processing by the processor in FIG. 10;

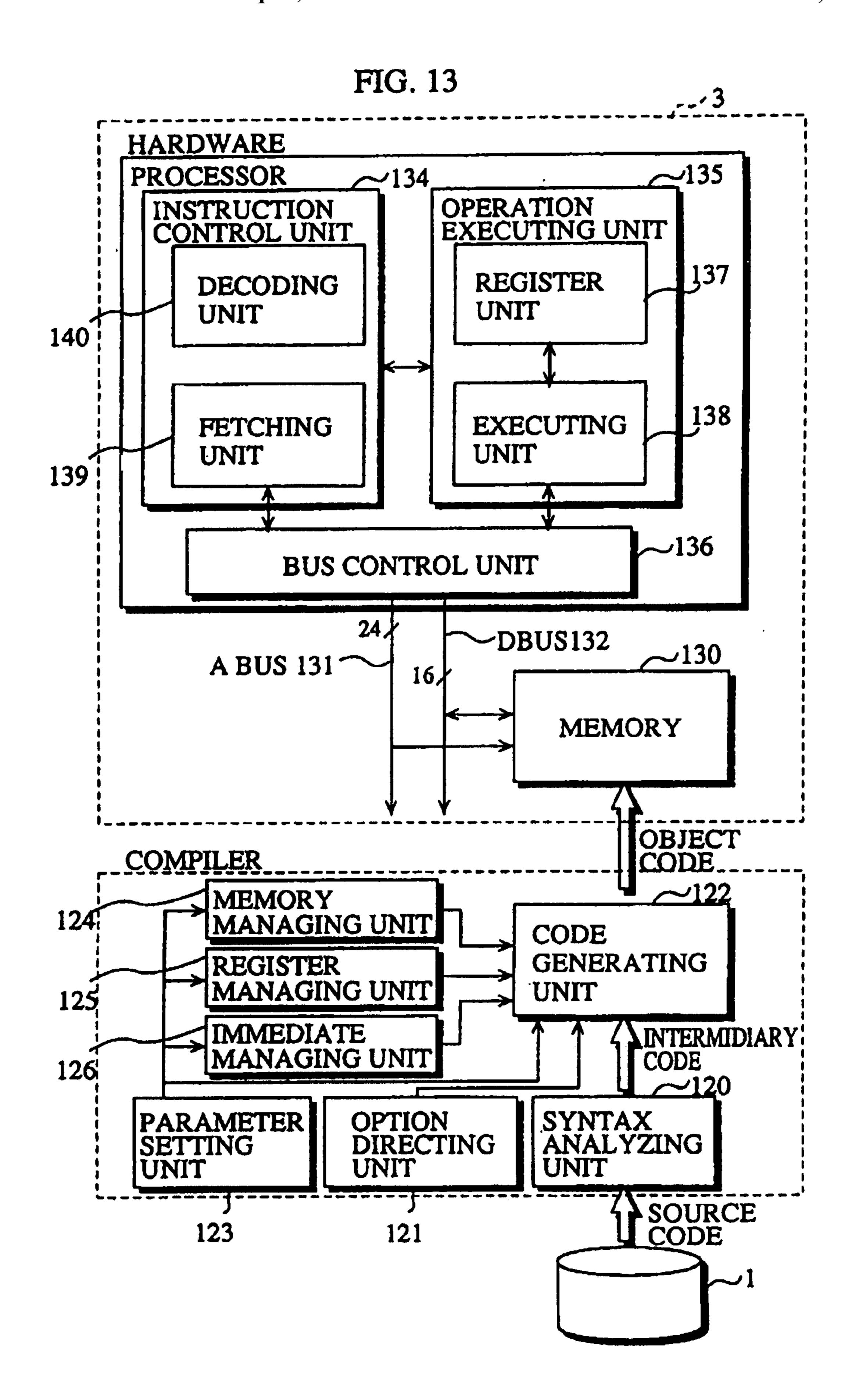

FIG. 13 is a block diagram depicting a processing system of the present invention;

FIG. 14 is a block diagram depicting an executing unit in FIG. **13**;

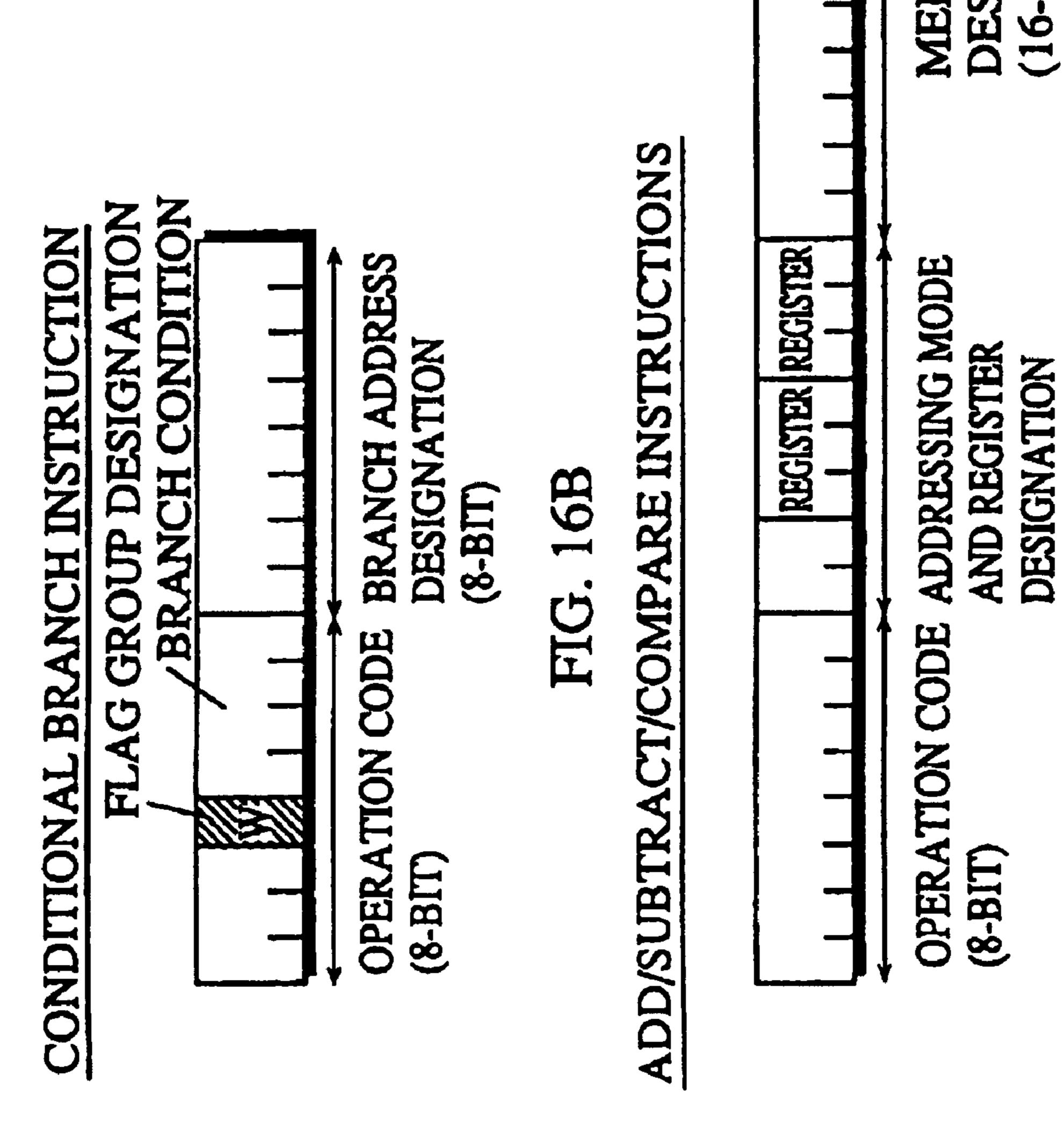

FIG. 15 is a block diagram depicting structures of a PSW and a branch judging unit in FIG. 14 FIGS. 16A and 16B are views showing structures of instruction formats used in the present invention;

FIG. 17 is a block diagram depicting structures of a register unit, a bus control unit, a decoding unit and a memory in FIG. **13**;

FIGS. 18A and 18B are views showing a format for a data-transfer instruction;

FIG. 19 is a flowchart detailing the operation of a compiler;

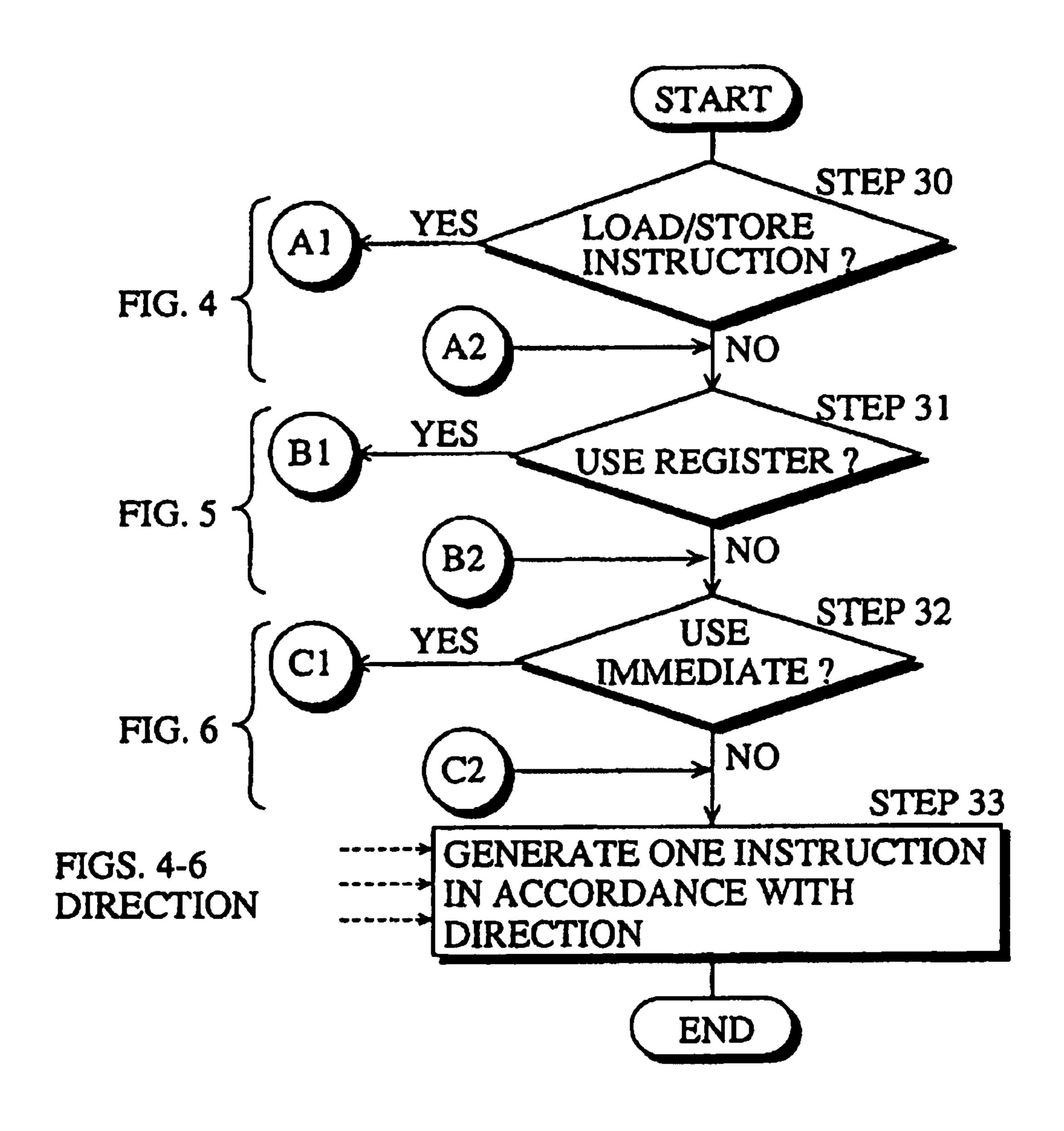

FIGS. 20A and 20B are examples of a symbol table;

FIG. 21 is a sub-chart of Step 26 in FIG. 19;

FIG. 22 is a flowchart detailing the operation of a memory managing unit;

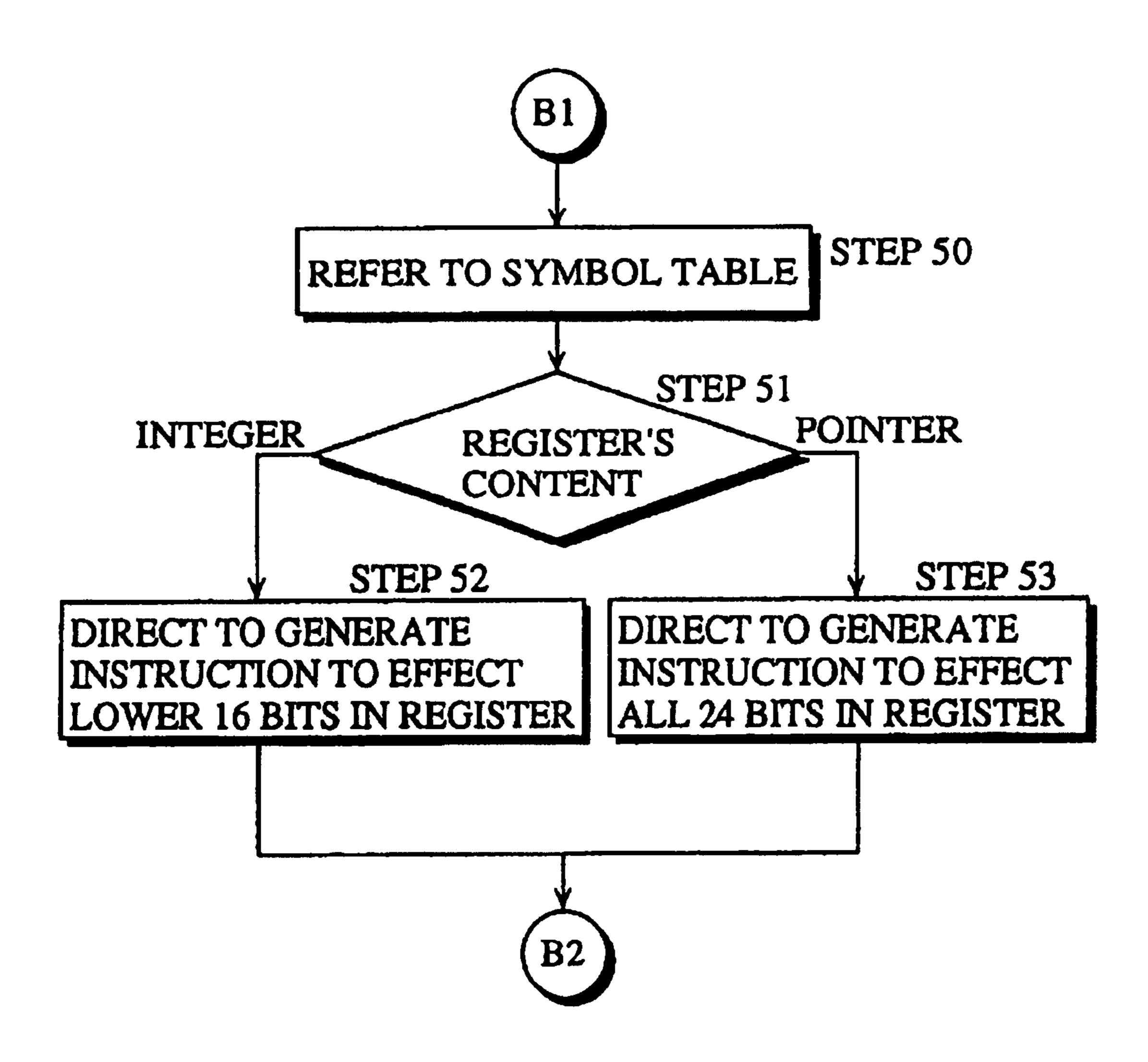

FIG. 23 is a flowchart detailing the operation of a register managing unit;

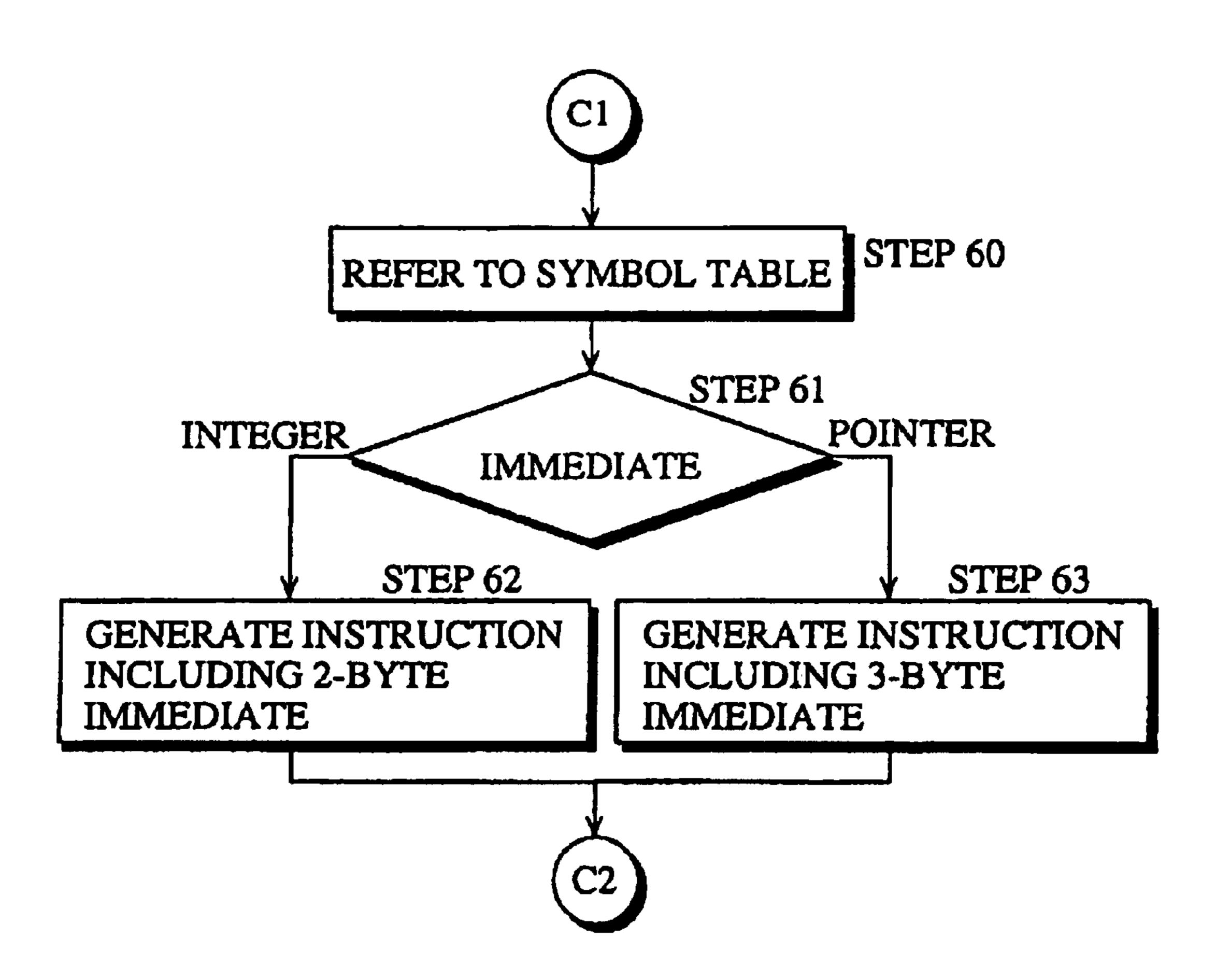

FIG. **24** is a flowchart detailing the operation of an immediate managing unit;

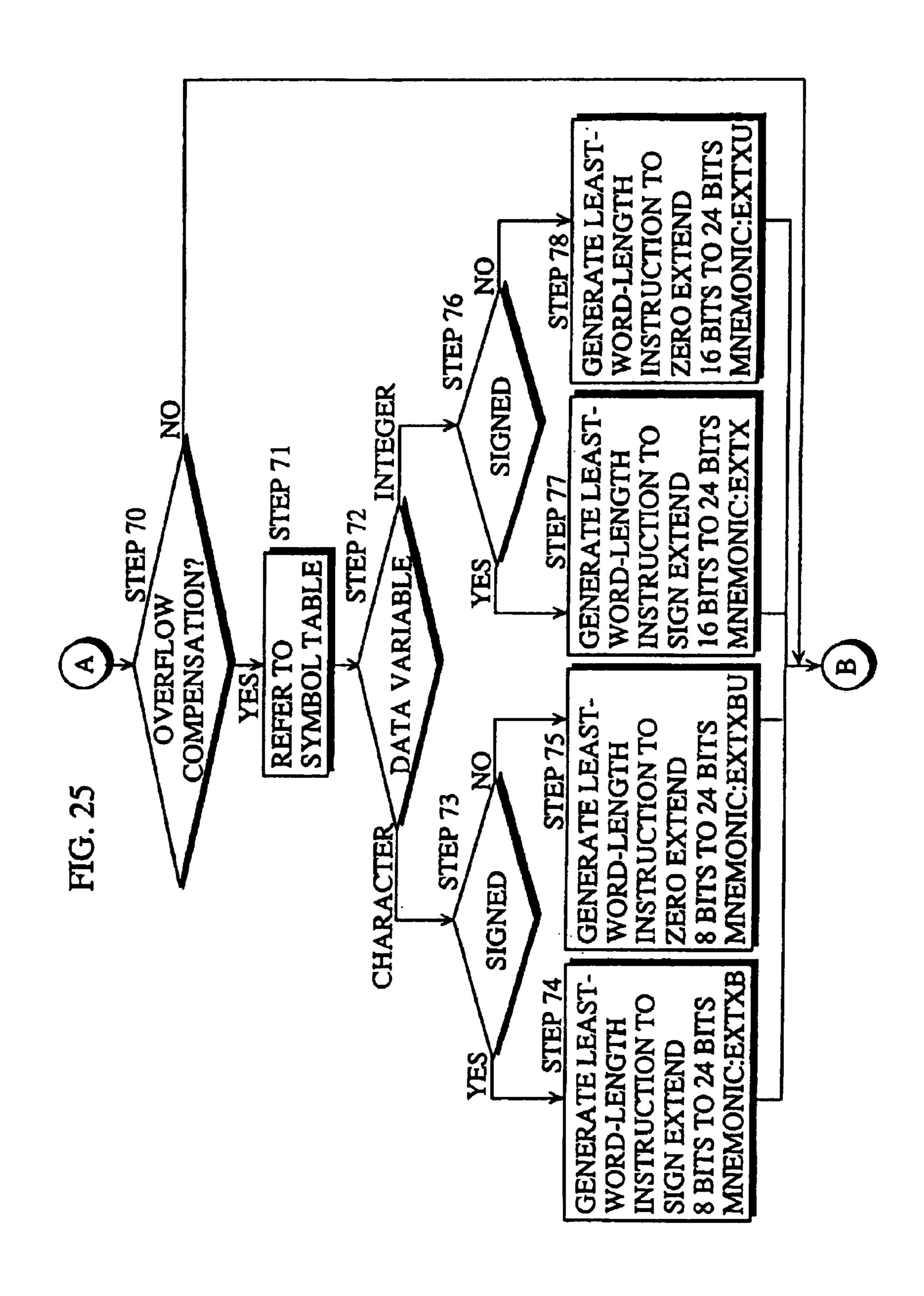

FIG. 25 is a flowchart detailing an overflow compensation operation;

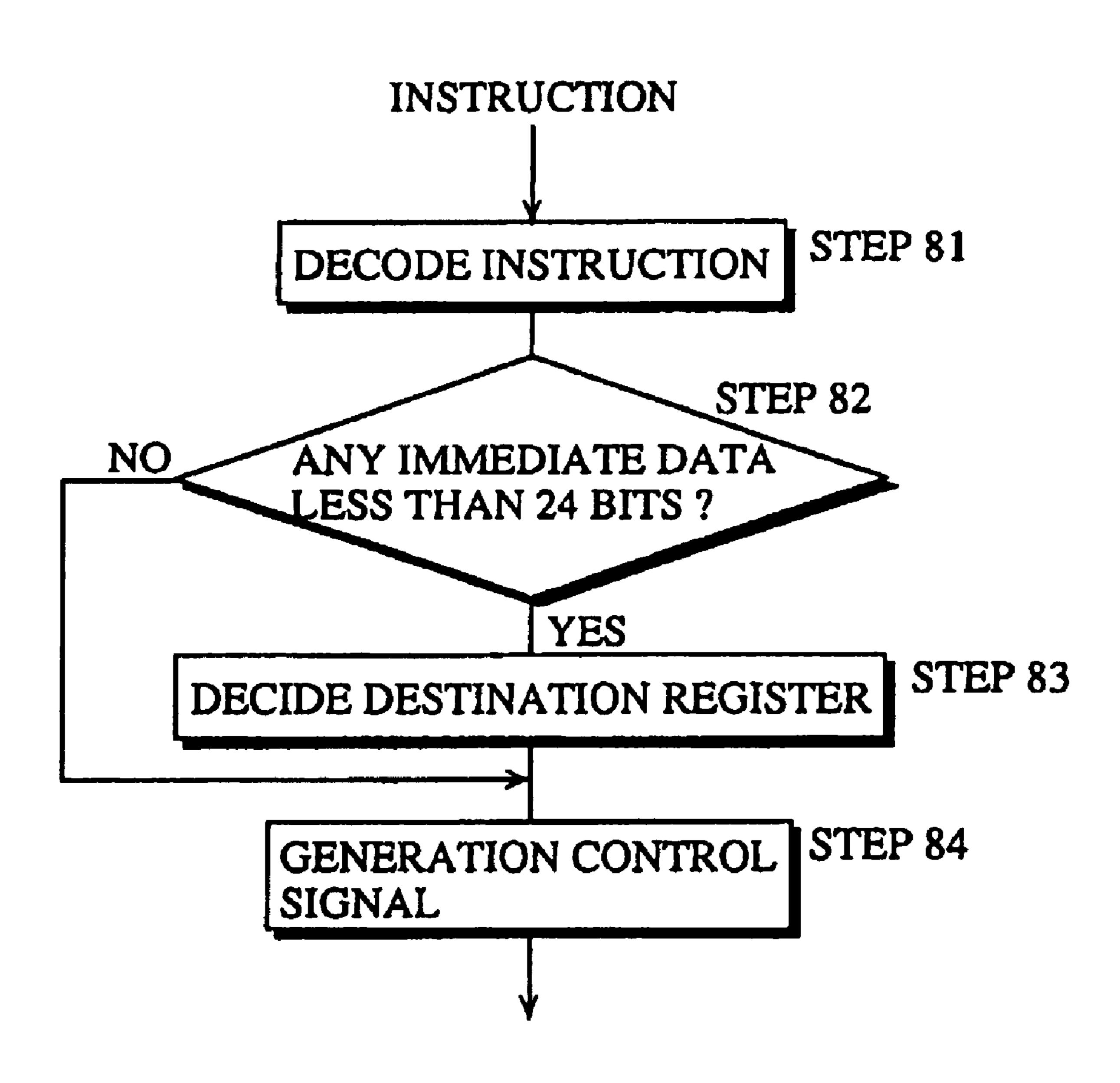

FIG. **26** is a flowchart detailing the operation of a decoding unit; and

FIG. 27 is an example of a program including an immediate data transfer.

### DESCRIPTION OF THE PREFERRED **EMBODIMENT**

A hardware structure of a data processing system including a component and a program converting unit (compiler) is depicted in FIG. 13. The data processing system comprises a storage unit 1 for storing a C language program, a compiler 2 for translating the C language program into a machine language program, and a computer 3 for running an object code; the computer 3 includes a processor and a memory.

More precisely, the computer 3 includes a memory 130, an address bus 131, a data bus 132, an instruction control unit 134, an operation executing unit 135, and a bus control unit **136**.

The memory 130 stores an object code and data used in a program.

The address bus 131 is of 24-bit wide and sends an address to the memory 130.

The data bus 132 is of 16-bit wide and transfers data to each component within the computer 3.

The instruction control unit 134 includes a fetching unit 139 and a decoding unit 140 to fetch an instruction via the bus control unit 136 and decodes the same: the fetching unit 139 includes an unillustrated 24-bit program counter to designate an instruction address; the decoding unit 140 decodes an instruction to output a corresponding control signal to each component within the computer 3.

The operation executing unit 135 includes a register unit 137 and an executing unit 138 to execute an instruction in accordance with the control signal: the register unit 137 includes a plurality of 24-bit address registers and 24-bit data registers; the executing unit 138 executes a 24- or 16-bit arithmetic logical operation. Note that 24-bit executing unit 138 executes a 24-bit address calculation and 16-bit data operation. This means that the computer 3 executes a 16-bit data operation for the data processing, while executing a 24-bit data operation for the address calculation.

The bus control unit 136 controls the address and data 25 transfer between the components within the computer 3 interconnected via the address bus 131 and data bus 132, and the data transfer with the memory 130 in a bit-width thereof.

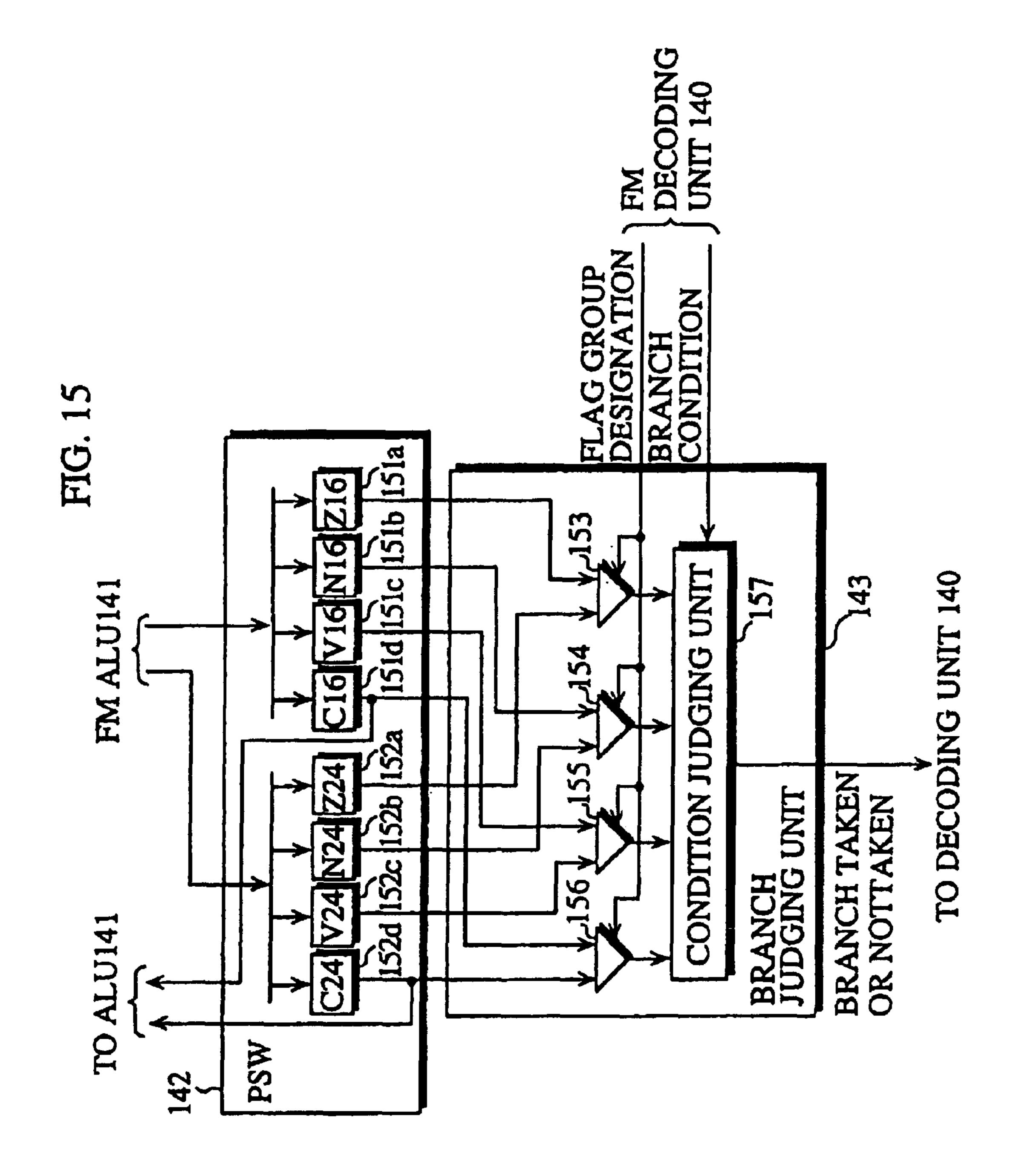

A structure of the executing unit 138 is depicted in FIG. 14, and the executing unit 138 comprises an ALU <sup>30</sup> (Arithmetic Logic Unit) 141, a PSW (Processor Status Word) 142, a branching judging unit 143, a first extender 144, and a second extender 145.

More precisely, the ALU **141** performs a 24-bit arithmetic logical operation using the data stored in the register unit <sup>35</sup> **137**.

The PSW 142 is a register holding a variety of flags each indicating the processor's status, and includes flag groups which are changed in accordance with the operation result of the ALU 141. The flag groups include a first flag group exhibiting the result of 16-bit data operation and a second flag group exhibiting the result of 24-bit data operation; note that, however, both the first and second flag groups exhibit each data operation result.

The branch judging unit 143 judges whether a conditional branch instruction is taken or not by referring to the flag groups.

The first extender **144** sign or zero-extends the lower 8 bits of the data in the data register to 24 bits, or it sign or zero-extends an 8-bit immediate data to 24 bits to be sent to the data register.

The second extender **145** sign or zero-extends the lower 16 bits of the data in the data register to 24 bits, or it sign or zero-extends a 16-bit immediate data to 24 bits to be sent to 55 the data register.

The data are sign-extended in the same way as explained with referring to FIGS. 4A, 4B except for the bit length; N is twenty-four and M is eight in the first extender 144, while N being twenty-four and M sixteen in the second extender 145. 60 Also, the data are zero-extended in the same way as the sign-extension except that zero's are copied in the high order bits. The two extenders selectively operate depending on an instruction, and they only operate on two kinds of instructions: extension instructions to extend the data in the data 65 register, and transfer instructions to transfer and extend transmission data. Each instruction is described below,

**18**

where Dn is a data register, An is an address signal, n being a register number, Mem is a memory data, and #imm8 and #imm16 are immediate data with numerals 8, 16 representing bit lengths.

|   | EXTX Dn   | ; sign-extend 16 bits to 24 bits |

|---|-----------|----------------------------------|

|   | EXTXU Dn  | ; zero-extend 16 bits to 24 bits |

|   | EXTXB Dn  | ; sign-extend 8 bits to 24 bits  |

| ) | EXTXBU Dn | ; zero-extend 8 bits to 24 bits  |

|   |           |                                  |

| MOVI #imm16, Dn | ; sign extend 16-bit immediate data |

|-----------------|-------------------------------------|

|                 | to 24 bits (#imm16→Dn)              |

| MOVI #imm8, Dn  | ; sign-extend 8-bit immediate data  |

|                 | to 24 bits (#imm8→Dn)               |

| MOVI #imm16, An | ; zero-extend 16-bit immediate data |

|                 | to 24 bits (#imm16→An)              |

| MOV Mem, Dn     | , sign-extend 16 bits to 24 bits    |

|                 | (Mem→Dn)                            |

| MOVB Mem, Dn    | ; sign-extend 8 bits to 24 bits     |

| ·               | (Mem→Dn)                            |

| MOVBU Mem, Dn   | ; zero-extend 8 bits to 24 bits     |

| •               | (Mem→Dn)                            |

Structures of the PSW 142 and branch judging unit 143 are depicted in FIG. 15. The PSW 142 is a 16-bit register with each bit serving as an independent flag or a control flag that sets the current status of the computer 3. Note that only the lower 8 bits that serve as operating flags are shown in the drawing: for the higher 8 bits, which are control flags, are irrelevant to the present invention. The lower 8 bits consists of a first flag group 151 and a second flag group 152; the former includes flags Z16, N16, V16, and C16 which are changed in accordance with the result of 16-bit data operation, and the latter includes flags Z24, N24, V24, and C24 which are changed in accordance with the result of 24-bit data operation.

The flags Z16, Z24 (denoted as 151a, 152a respectively) are zero flags exhibiting a zero result.

The flags N16, N24 (denoted as 151b, 152b respectively) are negative flags exhibiting a negative result.

The flags V16, V24 (denoted as 151c, 152c respectively) are overflow flags exhibiting an overflow if it occurs during the operation.

The flags C16, C24 (denoted as 151d, 152d respectively) are carry flags exhibiting a carry output.

The branch judging unit 143 includes selectors 153–156 and a condition judging unit 157. The output from either the first flag group 151 or second flag group 152 is selected by the selectors 153–156 in accordance with a designation from the decoding unit 140 when it decodes a conditional branch instruction.

A bit-structure of a conditional branch instruction, which is run by the computer 3, is shown in FIG. 16a. The conditional branch instruction consists of an 8-bit OP code exhibiting a conditional branch and an 8-bit branch destination (relative) address. One bit denoted as W in the OP code designates a flag group, and accordingly, the decoding unit 140 designates the flag group to the selectors 153–156 based on the W's value.

A bit structure of add/subtract/compare instructions between the register and memory 130 is shown in FIG. 16B. These instructions consist of an 8-bit OP code exhibiting an operation kind, 8 bits designating registers, and 16 bits designating a memory address. Note that the OP code does not

include any bit exhibiting a data width. This is because both the first and second flag groups 151, 152 are changed at the execution of the add/subtract/compare instructions shown in FIG. 16B, and an appropriate flag group is selected in accordance with the conditional branch instruction shown in FIG. 5 16A.

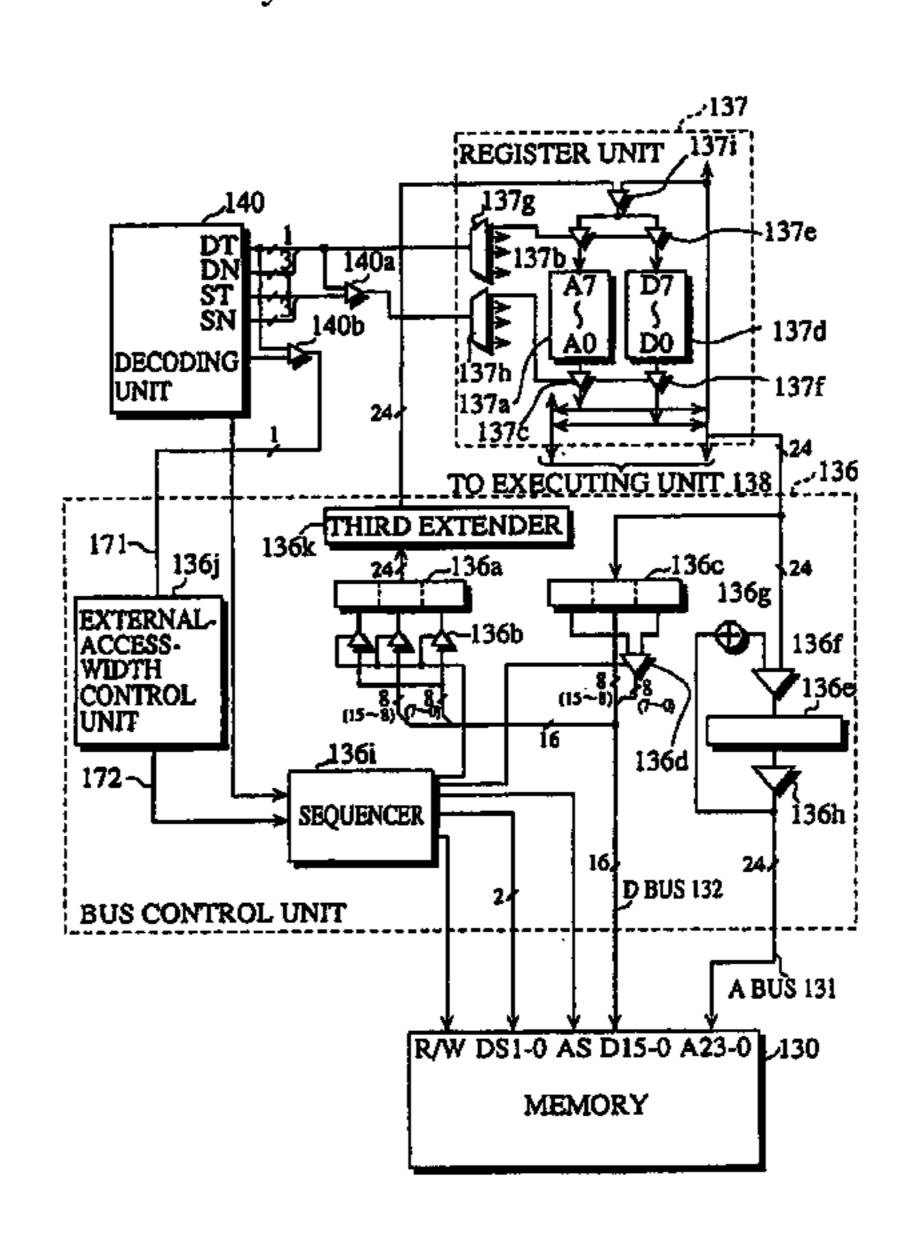

Structures of the register unit 137 and bus control unit 136 with the decoding unit 140 and memory 130 are depicted in FIG. 17; assume that the memory 130 is of 16-bit wide.

The register unit 137 includes an address register group <sup>10</sup> 137a, an input buffer gate 137b, an output buffer gate 137c, a data register group 137d, another input buffer gate 137e, another output buffer gate 137f, two decoders 137g, 137h, and a selector 137i.

The address register group 137a includes eight 24-bit address registers A6-A0, and holds input data from the bus control unit 136 or from the executing unit 138 via the selector 137i and input buffer gate 137b in one of the eight registers designated by the decoder 137g, while outputting the data from one of the eight registers designated by the decoder 137h via the output buffer gate 137c.

The data register group 137d includes eight 24-bit data registers D7-D0, and holds the input data from the bus control unit 136 or from the executing unit 138 via the selector 137i and input buffer gate 137e in one of the eight registers designated by the decoder 137g, while outputting the data from one of the eight registers designated by the decoder 137h via the output buffer gate 137f.

The decoder 137g receives a type of a destination register (DT) and its register number (DN) from the instruction decoding unit 140, and accordingly selects a register for data-writing, outputting a selection signal to the selector 137i and a gate control signal from the buffer gates 137b, 137e.

The decoder 137h receives a type of a source register (ST) and its register number (SN), or a destination register (DT) and its register number (DN) from the instruction decoding unit 140, and accordingly selects a register for data-readout, outputting a gate control signal for the buffer gates 137c, 137f. Note that the ST indicates whether the source register is the address or data register, whereas the DT indicates whether the destination register is the address or data register. The register numbers (SN, DN) indicate the registers designated as to be the source and destination registers, 45 respectively.

The decoding unit 140 decodes an instruction to output an appropriate control signal. In case of a data-transfer instruction, the decoding unit 140 outputs the control signal including the ST, SN, DT, and DN: and DT and DN are 50 entered into the decoder 137g, while either the DT and DN, or ST and SN are entered into the decoder 137h via a selector 140a. At the same time, the decoding unit 140 outputs the types of the designated source and destination registers for the transmission data (address), or register information 171, 55 to the bus control unit 136 via a selector 140b, and outputs an activation signal to the bus control unit 136.

The bus control unit 136 includes an external-access-width control unit 136j, a load buffer 136a, an input buffer gate group 136b, a store buffer 136c, a selector 136d, and an address buffer 136e, a selector 136f, an incrementer 136g, an output buffer gate 136h, a sequencer 136i, and a third extender 136k. The bus control unit 136 transfers the data between the registers in the register unit 137 and the memory 130 in the bit-width thereof.

The external-access-width control unit 136j receives the register information 171 and sends bit-width information

172, which contains bit-width for each register group. More precisely, the external-access-width control unit 136j receives the register information 171 indicating a type of the register subject to the data-transfer instruction. When the address register is designated, the external-access-width control unit 136j outputs the bit-width information 172 indicating 24-bit data transfer. Whereas when the data register is designated, it outputs the bit-width information 172 indicating 16-bit data transfer. The register information 171 referred herein is a 1-bit signal exhibiting "1" for the address register and "0" for the data register. Similarly, the bit-width information 172 is a 1-bit signal exhibiting "1" for the 24-bit data transfer and "0" for the 16-bit data transfer. The bus control unit 136 controls the data transfer bit-widths: 24 bits for the address register and 16 bits for the data register.