#### US00RE39895E

# (19) United States

### (12) Reissued Patent

Tokunaga et al.

#### (10) Patent Number: US RE39,895 E

#### (45) Date of Reissued Patent: \*Oct. 23, 2007

## (54) SEMICONDUCTOR INTEGRATED CIRCUIT ARRANGEMENT FABRICATION METHOD

(75) Inventors: **Takafumi Tokunaga**, Saitama (JP);

Sadayuki Okudaira, Tokyo (JP); Tatsumi Mizutani, Tokyo (JP);

Kazutami Tago, Ibaraki (JP); Hideyuki Kazumi, Ibaraki (JP); Ken Yoshioka,

Yamaguchi (JP)

(73) Assignee: Renesas Technology Corp., Tokyo (JP)

(\*) Notice: This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 10/094,157

(22) Filed: Mar. 8, 2002

#### Related U.S. Patent Documents

#### Reissue of:

(64) Patent No.: **6,074,958**Issued: **Jun. 13, 2000**

Appl. No.: 09/339,041 Filed: Jun. 23, 1999

#### U.S. Applications:

(63) Continuation of application No. 09/188,371, filed on Nov. 10, 1998, now Pat. No. 5,962,347, which is a continuation of application No. 08/857,167, filed on May 15, 1997, now Pat. No. 5,874,013, which is a continuation of application No. 08/472,459, filed on Jun. 7, 1995, now abandoned.

#### (30) Foreign Application Priority Data

Jun. 13, 1994 (JP) ...... 6-130232

(51) Int. Cl. H01L 21/00 (2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,501,769 A 2/1985 Hieber et al. 4,529,476 A 7/1985 Kawamoto et al.

(Continued)

#### FOREIGN PATENT DOCUMENTS

P 55-95327 7/1980 P 58-101428 6/1983

(Continued)

#### OTHER PUBLICATIONS

Hashimi, K. et al, "The Study on the Influence of Gas Chemistry and Ion Energy for Contact Resistance", 1995 Dry Process Symposium, pp. 207–212.

Siozawa, K. et al, "SIO<sub>2</sub> Etching in C<sub>4</sub> F<sub>8</sub>/0<sub>2</sub> ECR Plasma", 1995 Dry Symposium, pp. 255–260.

Katayama, Monthly Semiconductor World, Oct. 93, pp. 81–85.

Maeda, "Latest LSI Process Technology", Jan. 1994, pp. 338–347.

Katayama, K., "Uniform Etching of Silocon Dioxide by ECR Plasma (I)", 40th Spring Symposium Applied Physics, 1993, 29p–ZE–9, p. 530.

#### (Continued)

Primary Examiner—Robert Kunemund (74) Attorney, Agent, or Firm—Mattingly, Stanger, Malur & Brundidge, P.C.

#### (57) ABSTRACT

To realize etching with a high selection ratio and a high accuracy in fabrication of an LSI, the composition of dissociated species of a reaction gas is accurately controlled when dry-etching a thin film on a semiconductor substrate by causing an inert gas excited to a metastable state in a plasma and a flon gas to interact with each other and selectively obtaining desired dissociated species.

#### 26 Claims, 12 Drawing Sheets

# US RE39,895 E Page 2

| 4,615,756 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U.S. PATENT           | DOCUMENTS              | JP           | 05-013434                               | 1/1993                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|--------------|-----------------------------------------|---------------------------------------|

| 4,668,530 A 5/1987 Reif et al. 4,692,343 A 9/1987 Price et al. 4,902,645 A 2/1990 Ohba 4,957,777 A 9/1990 Ilderem et al. 4,966,870 A 10/1990 Barber et al. 4,966,870 A 10/1993 Barber et al. 4,966,870 A 10/1990 Barber et al. 4,966,870 A 10/1993 B | 4.615.756 A 10/1086   | Taniii ot ol           |              |                                         |                                       |

| 4,692,343 A 9/1987 Price et al. 4,902,645 A 2/1990 Obba JP 05-162089 4/1993 4,956,870 A 10/1990 Hillman et al. 4,966,870 A 10/1990 Barber et al. JP 05-160078 6/1993 4,966,870 A 10/1990 Killman et al. JP 05-206076 8/1993 5,188,975 A 2/1993 Kojima et al. JP 05-227954 8/1993 5,258,667 A 11/1993 Obtake et al. JP 05-227954 8/1993 5,258,667 A 11/1993 Obtake et al. JP 05-227954 8/1993 5,269,879 A 12/1993 Roades et al. JP 06-039880 3/1994 5,275,972 A 1/1994 Ogawa et al. JP 06-089880 3/1994 5,321,518 A 5/1994 Koshimizal 5,324,388 A 6/1994 Yamano et al. 5,407,698 A 4/1995 Emesh 5,476,182 A 12/1995 Ishizuka et al. 5,503,901 A 4/1996 Sakai et al. 5,5874,013 A * 2/1999 Tokunaga et al. 5,5874,013 A * 10/1999 Tokunaga et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1994 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1995 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1994 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1995 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1995 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1995 Sakai et al. 438/728 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1995 Sakai et al. 438/728 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1995 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 3,1995 Sakai et al. 438/728 Sakai et al. 5,962,347 A * 10/1999 Tokunaga et al. 5,962,347 A * 10/19 |                       | •                      |              |                                         |                                       |

| 4,902,645 A   2/1990   Ohba   IP   05-160077   6/1993     4,957,777 A   9/1990   Ilderem et al.   IP   05-160078   6/1993     4,966,869 A   10/1990   Ildilman et al.   IP   05-160078   6/1993     4,966,870 A   10/1990   Barber et al.   IP   05-206076   8/1993     5,188,975 A   2/1993   Kojima et al.   IP   05-217954   8/1993     5,258,667 A   11/1993   Ohtake et al.   IP   05-217954   8/1993     5,258,667 A   11/1993   Ohtake et al.   IP   05-217954   8/1993     5,279,727 A   1/1994   Ogawa et al.   IP   06-029400   2/1994     5,290,383 A   3/1994   Koshimizu   IP   7-74145   3/1995     5,312,518 A   5/1994   Kadomura   IP   06-039800   3/1994     5,324,388 A   6/1994   Yamano et al.   IP   06-039800   3/1994     5,407,698 A   4/1995   Emesh   S,407,698 A   4/1995   Emesh   S,407,698 A   4/1995   Emesh   S,407,698 A   4/1995   Emesh   S,874,013 A * 2/1999   Tokunaga et al.   438/728     5,862,347 A * 10/1999   Tokunaga et al.   219/67     FOREIGN PATENT DOCUMENTS   FOREIGN PAT   | , ,                   |                        |              |                                         |                                       |

| 4,957,777 A 9/1990 Ilderem et al. 4,966,869 A 10/1990 Barber et al. 4,966,870 A 10/1990 Barber et al. 4,966,870 A 10/1990 Barber et al. 5,188,975 A 2/1993 Kojima et al. 5,258,667 A 11/1993 Ohtake et al. 5,258,667 A 11/1993 Ohtake et al. 1,1p 05-206076 8/1993 5,258,667 A 11/1993 Ohtake et al. 1,1p 06-221/1954 8/1993 5,258,667 A 11/1994 Ogawa et al. 1,1p 06-029400 2/1994 5,275,972 A 1/1994 Ogawa et al. 1,1p 06-029400 2/1994 5,290,383 A 3/1994 Vanano et al. 5,312,518 A 5/1994 Kadomura 5,324,388 A 6/1994 Yamano et al. 5,407,689 A 4/1995 Emesh 5,476,182 A 12/1995 Ishizuka et al. 5,503,901 A 4/1995 Emesh 5,874,013 A * 2/1999 Tokunaga et al. 5,874,013 A * 2/1999 Tokunaga et al. 5,962,347 A * 10/1999 Tokunaga et al. 5,962,347 A * 10/1999 Tokunaga et al. 219/67 FOREIGN PATENT DOCUMENTS  P 60-1154526 8/1985 1,p 60-154526 8/1985 1,p 61-125043 6/1986 1,p 61-125043 6/1986 1,p 61-125043 6/1986 1,p 63-99852 1/1986 1,p 63-98552 4/1986 1,p 63-98552 4/1988 1,p 63-98552 5/1994 1,p 63-39935 1/1988 1,p 63-98552 5/1994 1,p 64-010621 1/1992 1,p 4-170026 6/1992 1993, pp. 81-85. (English Translation). 1,p 04-258117 9/1992 1,p 04-346428 12/1992 1,p 04-354331 12/1992 1,p 04-36428 12/1992 1,p 04-354331 12/1992 1,p 04-36428 12/1992 1,p 04-364331 12/1992 1,p 04-36428 12/1992 1,p 04-36428 12/1992 1,p 04-36428 12/1992 1,p 04-36428 12/1992 1,p 04-364331 12/1992 1,p 04-1980, pp. 602 604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | , ,                   |                        |              |                                         |                                       |

| 4,966,869 A 10/1990 Hillman et al. 4,966,870 A 10/1990 Barber et al. 4,966,870 A 10/1990 Barber et al. 5,258,667 A 11/1993 Ohtake et al. 5,258,667 A 11/1993 Ohtake et al. 5,269,879 A 12/1993 Rhoades et al. 1,1p 05-206076 8/1993 5,258,667 A 11/1993 Ohtake et al. 1,1p 05-207283 10/1993 5,269,879 A 12/1993 Rhoades et al. 1,1p 06-029400 2/1994 5,290,383 A 3/1994 Koshimizu 1,1p 06-029400 2/1994 5,290,383 A 3/1994 Koshimizu 1,1p 06-029400 2/1994 5,290,383 A 3/1994 Koshimizu 1,1p 06-089880 3/1994 5,312,518 A 5/1994 Kadomura 5,324,388 A 6/1994 Yamano et al. 5,407,698 A 4/1995 Emesh 5,476,182 A 12/1995 Ishizuka et al. 5,503,901 A 4/1996 Sakai et al. 5,874,013 A * 2/1999 Tokunaga et al. 5,880,036 A 3/1999 Becker et al. 5,880,036 A 3/1999 Becker et al. 5,962,347 A * 10/1999 Tokunaga et al. 1,p 06-029400 2/1994 1,p 60-115232 6/1985 29p-ZE-10, p. 530. Katayama, K., "Applying a Large Diameter ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p-ZE-10, p. 530. (English Translation).  FOREIGN PATENT DOCUMENTS  JP 60-154526 8/1985 29p-ZE-10, p. 530. (English Translation). JP 61-022628 1/1986 41986 29p-ZE-10, p. 530. (English Translation). JP 61-022628 1/1986 41988 338-347. (English Translation). JP 61-0266 6/1992 1993, pp. 81 85. (English Translation). JP 63-9935 1/1988 338-347. (English Translation). JP 64-35431 12/1992 Source to Etching", Monthly Semiconductor World, Oct. 1993, pp. 81 85. (English Translation). ST. Griffin et al. "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27, No. 3 Mar. 1980, pp. 602 604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | , ,                   |                        |              |                                         |                                       |

| 4,966,870 A 10/1990 Barber et al. 5,188,975 A 2/1993 Kojima et al. 1JP 05-206076 8/1993 5,258,667 A 11/1993 Ohtake et al. 1JP 05-217954 8/1993 5,269,879 A 12/1993 Rhoades et al. 1JP 06-029400 2/1994 5,275,972 A 1/1994 Ogawa et al. 1JP 06-029400 2/1994 5,275,972 A 1/1994 Vanano et al. 1JP 06-089880 3/1994 5,312,518 A 5/1994 Kadomura 5,324,388 A 6/1994 Yamano et al. 5,407,698 A 4/1995 Emesh 5,407,6182 A 12/1995 Ishizuka et al. 5,874,013 A * 2/1999 Tokunaga et al. 5,874,013 A * 2/1999 Tokunaga et al. 5,874,013 A * 2/1999 Tokunaga et al. 5,874,013 A * 10/1999 Becker et al. 5,962,347 A * 10/1999 Tokunaga et al. 219/67 FOREIGN PATENT DOCUMENTS  P 60-115232 6/1985 DP 61-125043 6/1985 DP 61-125043 6/1986 DP 61-125043 6/1986 DP 61-125043 6/1986 DP 61-250173 11/1986 DP 63-08652 4/1988 DP 63-086852 4/1988 DP 63-089880 3/1994 DP 63-089880 3/1995 DP 63-089880 3/1994 DP 64-010621 1/1992 DP 04-258117 9/1992 DP 04-36428 12/1992 DP 04-364331 12/1992 DP 04-364331 12/1992 DP 04-36428  | , ,                   |                        |              |                                         |                                       |

| 5,188,975 A 2/1993 Kojima et al. 5,258,667 A 11/1993 Ohtake et al. 5,258,667 A 11/1993 Ohtake et al. 5,275,972 A 1/1994 Ogawa et al. 5,275,972 A 1/1994 Ogawa et al. 5,290,383 A 3/1994 Koshimizu 5,324,388 A 6/1994 Yamano et al. 5,407,698 A 4/1995 Emesh 5,476,182 A 12/1995 Emesh 5,476,182 A 12/1995 Tokunaga et al. 5,503,901 A 4/1996 Sakai et al. 5,503,901 A 4/1996 Sakai et al. 5,503,01 A 4/1996 Sakai et al. 5,874,013 A * 2/1999 Tokunaga et al. 5,962,347 A * 10/1999 Tokunaga et al. 5,96 | , ,                   |                        | JP           | 5-160078                                | 6/1993                                |

| 5.258,667 A 11/1993 Ohtake et al. 5.269,879 A 12/1993 Rhoades et al. 5.269,879 A 12/1993 Rhoades et al. 5.269,879 A 12/1993 Rhoades et al. 5.290,383 A 3/1994 Koshimizu JP 06-029400 2/1994 5.290,383 A 3/1994 Koshimizu JP 06-089880 3/1994 5.312,518 A 5/1994 Kadomura 5.312,518 A 5/1994 Kadomura 5.324,388 A 6/1994 Yamano et al. 5.407,698 A 4/1995 Emesh 5.476,182 A 12/1995 Ishizuka et al. 5.503,901 A 4/1995 Sakai et al. 5.880,036 A 3/1999 Becker et al. 5.874,013 A * 2/1999 Tokunaga et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | , ,                   |                        | JP           | 05-206076                               | 8/1993                                |

| 5,269,879 A 12/1993 Rhoades et al. 5,275,972 A 1/1994 Ogawa et al. 5,275,972 A 1/1994 Ogawa et al. 7 P 06-089880 3/1994 5,290,383 A 3/1994 Koshimizu 5,312,518 A 5/1994 Kadomura 5,324,388 A 6/1994 Yamano et al. 5,407,698 A 4/1995 Emesh 5,476,182 A 12/1995 Ishizuka et al. 5,874,013 A * 2/1999 Tokunaga et al. 5,880,036 A 3/1999 Becker et al. 5,962,347 A * 10/1999 Tokunaga et al. 219/67 FOREIGN PATENT DOCUMENTS  P 60-154526 8/1985 YeCR Plasma (I)", 40th Spring Symposium Applied Physics, 1993, 29 p-ZE-10, p. 530. Katayama, K., "Applying a Large-Diameter ECR Plasma Source to Etching", Monthly Semiconductor World, Oct. 1993, pp. 81-85. Katayama, K., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (I)", 40th Spring Mtg. of Applied Physics, 29p-ZE-9, p. 530. (English Translation). FOREIGN PATENT DOCUMENTS  JP 60-154526 8/1985 Yanase, T., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (I)", 40th Spring Mtg. of Applied Physics, 29p-ZE-9, p. 530. (English Translation). FOREIGN PATENT DOCUMENTS  JP 61-225013 11/1986 ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p-ZE-9, p. 530. (English Translation). FOREIGN PATENT DOCUMENTS  Katayama, K., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p-ZE-9, p. 530. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. 338 347. (English Translation).  Katayama, K., "Applying a Large-Diameter ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p-ZE-10, p. 530. (English Translation).  Katayama, K., "Applying a Large-Diameter ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p-ZE-10, p. 530. (English Translation).  Katayama, K., "Applying a Large-Diameter ECR Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27, 1993, pp. 60-2-604.                                                                                                                                                                                                            | , ,                   |                        | JP           | 05-217954                               | 8/1993                                |

| 5.275,972 A 1/1994 Ogawa et al. 5.290,383 A 3/1994 Koshimizu 5.312,518 A 5/1994 Kadomura 5.324,388 A 6/1994 Yamano et al. 5.407,698 A 4/1995 Emesh 5.476,182 A 12/1995 Ishizuka et al. 5.583,001 A 4/1996 Sakai et al. 5.583,031 A * 2/1999 Tokunaga et al. 438/728 5.880,036 A 3/1999 Becker et al. 5.962,347 A * 10/1999 Tokunaga et al. 219/67  FOREIGN PATENT DOCUMENTS  P 59-044873 3/1984 FCR Plasma (II)", 40th Spring Symposium Applied Physics, 1993, 29 p. ZE—10, p. 530. Katayama, K., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (III)", 40th Spring Symposium Applied Physics, 1993, 29 p. ZE—10, p. 530. Katayama, K., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (III)", 40th Spring Mtg. of Applied Physics, 29p. ZE—9, p. 530. (English Translation).  P 60-154526 8/1985 Yanase, T., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (III)", 40th Spring Mtg. of Applied Physics, 29p. ZE—10, p. 530. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. 338–347. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. 338–347. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. 338–347. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. 3109728 5/1991 Source to Etching", Monthly Semiconductor World, Oct., 1993, pp. 81–85. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. 338–347. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. 338–347. (English Translation).  Maeda, et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27, No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                     | , ,                   |                        | JP           | 5-267283                                | 10/1993                               |

| 5,290,383 A 3/1994 Kadomura 5,312,518 A 5/1994 Kadomura 5,324,388 A 6/1994 Yamano et al. 5,407,698 A 4/1995 Emesh 5,476,182 A 12/1995 Ishizuka et al. 5,503,901 A 4/1996 Sakai et al. 5,880,036 A 3/1999 Becker et al. 5,962,347 A * 10/1999 Tokunaga et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | , ,                   |                        | JP           | 06-029400                               | 2/1994                                |

| 5,312,518 A 5/1994 Kadomura 5,324,388 A 6/1994 Yamano et al. 5,407,698 A 4/1995 Emesh 5,476,182 A 12/1995 Ishizuka et al. 5,503,901 A 4/1996 Sakai et al. 5,503,901 A 3/1999 Becker et al. 5,862,347 A * 10/1999 Tokunaga et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |                        | JP           | 06-089880                               | 3/1994                                |

| 5,324,388 A         6/1994 Vamano et al.         OTHER PUBLICATIONS           5,407,698 A         4/1995 Emesh         Yanase, T., "Uniform Etching of Silicon Dioxide by ECR Plasma (II)", 40th Spring Symposium Applied Physics, 15,830,036 A 3/1999 Becker et al.           5,880,036 A         3/1999 Tokunaga et al.         438/728           5,962,347 A         * 10/1999 Tokunaga et al.         219/67           FOREIGN PATENT DOCUMENTS            FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS           FOREIGN PATENT DOCUMENTS </td <td>, ,</td> <td></td> <td>JP</td> <td>7-74145</td> <td>3/1995</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | , ,                   |                        | JP           | 7-74145                                 | 3/1995                                |

| 5.407,698 A 4/1995 Emesh 5.476,182 A 12/1995 Ishizuka et al. 5.503,901 A 4/1996 Sakai et al. 5.503,901 A 4/1996 Tokunaga et al. 5.874,013 A * 2/1999 Tokunaga et al. 5.962,347 A * 10/1999 Tokunaga et al. 5.972,04,04873 3/1984 ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p ZE-9, p. 530. (English Translation). 7.299 ZE-9, p. 530. 7.200,040 Tokunaga et al. 7.21993, pp. 81–85. 7.220, pp. 530. 7 | 5,312,518 A 5/1994    | Kadomura               |              |                                         |                                       |

| 5,476,182 A         12/1995         Ishizuka et al.         Yanase, T., "Uniform Etching of Sificon Dioxide by ECR Plasma (II)", 40th Spring Symposium Applied Physics, 5,874,013 A * 2/1999         Plasma (II)", 40th Spring Symposium Applied Physics, 1993, 29 p–ZE–10, p. 530.         1993, 29 p–ZE–10, p. 530.         Katayama, K., "Applying a Large–Diameter ECR Plasma Source to Etching", Monthly Semiconductor World, Oct. 1993, pp. 81–85.         Katayama, K., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p–ZE–9, p. 530. (English Translation).           JP         60-154526         8/1985         29p–ZE–9, p. 530. (English Translation).           JP         61-022628         1/1986         ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p–ZE–9, p. 530. (English Translation).           JP         61-022628         1/1986         ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p–ZE–9, p. 530. (English Translation).           JP         61-022628         1/1986         ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p–ZE–10, p. 530. (English Translation).           JP         63-9935         1/1986         29p–ZE–10, p. 530. (English Translation).           JP         63-086522         4/1988         338–347. (English Translation).           JP         04-010621         1/1992         Source to Etching", Monthly Semiconductor World, Oct., 1993, pp. 81–85. (English Translation).           JP         04-258117         9/1992         S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5,324,388 A 6/1994    | Yamano et al.          |              | OTHER P                                 | UBLICATIONS                           |

| 5,503,901 A 4/1996 Sakai et al.  5,874,013 A * 2/1999 Tokunaga et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5,407,698 A 4/1995    | Emesh                  | Vanaga T     | "I Iniform Etch                         | ing of Silicon Dioxido by ECD         |

| 5,874,013 A * 2/1999 Tokunaga et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5,476,182 A 12/1995   | Ishizuka et al.        | •            | •                                       |                                       |

| 5,880,036 A 3/1999 Becker et al. 5,962,347 A * 10/1999 Tokunaga et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5,503,901 A 4/1996    | Sakai et al.           | `            | , · · · · · · · · · · · · · · · · · · · |                                       |

| 5,962,347 A * 10/1999 Tokunaga et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5,874,013 A * 2/1999  | Tokunaga et al 438/728 | · •          | ·                                       |                                       |

| FOREIGN PATENT DOCUMENTS  1993, pp. 81–85.  Katayama, K., et al, "Uniform Etching of Silicon Dioxide by ECR Plasma (I)", 40th Spring Mtg. of Applied Physics, 29p–ZE–9, p. 530. (English Translation).  JP 60-154526 8/1985 29p–ZE–9, p. 530. (English Translation).  JP 61-022628 1/1986 ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, JP 61-125043 6/1986 29p–ZE–10, p. 530. (English Translation).  JP 63-935 1/1988 29p–ZE–10, p. 530. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. JP 63-086522 4/1988 338–347. (English Translation).  Katayama, K., "Applying a Large–Diameter ECR Plasma JP 04-010621 1/1992 Source to Etching", Monthly Semiconductor World, Oct., JP 4-170026 6/1992 1993, pp. 81–85. (English Translation).  JP 04-258117 9/1992 S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27, JP 04-354331 12/1992 vol. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5,880,036 A 3/1999    | Becker et al.          | Katayama     | , K., "Applying                         | a Large–Diameter ECR Plasma           |

| Katayama, K., et al, "Uniform Etching of Silicon Dioxide by JP 59-044873 3/1984 ECR Plasma (I)", 40th Spring Mtg. of Applied Physics, JP 60-115232 6/1985 29p—ZE—9, p. 530. (English Translation).  JP 60-154526 8/1985 Yanase, T., et al, "Uniform Etching of Silicon Dioxide by JP 61-022628 1/1986 ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, JP 61-25043 6/1986 29p—ZE—10, p. 530. (English Translation).  JP 63-9935 1/1988 29p—ZE—10, p. 530. (English Translation).  Maeda, et al, "Latest LSI Process Technology", 1994, pp. JP 63-086522 4/1988 338—347. (English Translation).  Katayama, K., "Applying a Large—Diameter ECR Plasma JP 04-010621 1/1992 Source to Etching", Monthly Semiconductor World, Oct., JP 4-170026 6/1992 1993, pp. 81—85. (English Translation).  JP 04-258117 9/1992 S.T. Griffin et al, "Plasma Processes Involved in Dry Pro-JP 04-346428 12/1992 cessing", IEEE Transactions on Electron Devices, vol. 27, JP 04-354331 12/1992 No. 3, Mar. 1980, pp. 602—604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5,962,347 A * 10/1999 | Tokunaga et al 219/67  | Source to    | Etching", Mont                          | hly Semiconductor World, Oct.         |

| Ratayama, K., et al, "Uniform Etching of Silicon Dioxide by   ECR Plasma (I)", 40th Spring Mtg. of Applied Physics,   29p-ZE-9, p. 530. (English Translation).   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   FCR Plasma (II)", 40th Spring Mtg. of Applied Physics,   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   FCR Plasma (II)", 40th Spring Mtg. of Applied Physics,   FCR Plasma (II)", 40th Spring Mtg. of Applied Physics,   29p-ZE-10, p. 530. (English Translation).   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   FCR Plasma (II)", 40th Spring Mtg. of Applied Physics,   29p-ZE-10, p. 530. (English Translation).   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   FCR Plasma (II)", 40th Spring Mtg. of Applied Physics,   29p-ZE-10, p. 530. (English Translation).   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide by   Yanase, T., et al, "Uniform Etching of Silicon Dioxide   Yanase, T., et al, "Uniform E   | EOREIGN DATE          | NT DOCHMENTS           | 1993, pp.    | 81–85.                                  |                                       |

| JP         60-115232         6/1985         29p-ZE-9, p. 530. (English Translation).           JP         60-154526         8/1985         Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide Dioxide by Yanase, T., et al, "Uniform Etching of Silicon Dioxide Dio                                                                                                        | TORLIONTAIL           | INT DOCUMENTS          | Katayama     | , K., et al, "Unifor                    | rm Etching of Silicon Dioxide by      |

| JP         60-154526         8/1985         Yanase, T., et al, "Uniform Etching of Silicon Dioxide by JP 61-022628         1/1986         ECR Plasma (II)", 40th Spring Mtg. of Applied Physics, 29p-ZE-10, p. 530. (English Translation).           JP         61-250173         11/1986         29p-ZE-10, p. 530. (English Translation).           JP         63-9935         1/1988         Maeda, et al, "Latest LSI Process Technology", 1994, pp.           JP         63-086522         4/1988         338-347. (English Translation).           JP         3-109728         5/1991         Katayama, K., "Applying a Large-Diameter ECR Plasma           JP         04-010621         1/1992         Source to Etching", Monthly Semiconductor World, Oct.,           JP         4-170026         6/1992         1993, pp. 81-85. (English Translation).           JP         04-258117         9/1992         S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,           JP         04-354331         12/1992         No. 3, Mar. 1980, pp. 602-604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | JP 59-044873          | 3/1984                 | ECR Plas     | ma (I)", 40th S <sub>1</sub>            | pring Mtg. of Applied Physics,        |

| JP         61-022628         1/1986         ECR Plasma (II)", 40th Spring Mtg. of Applied Physics,           JP         61-125043         6/1986         29p-ZE-10, p. 530. (English Translation).           JP         61-250173         11/1986         Maeda, et al, "Latest LSI Process Technology", 1994, pp.           JP         63-9935         1/1988         338-347. (English Translation).           JP         3-109728         5/1991         Katayama, K., "Applying a Large-Diameter ECR Plasma           JP         04-010621         1/1992         Source to Etching", Monthly Semiconductor World, Oct.,           JP         4-170026         6/1992         1993, pp. 81-85. (English Translation).           JP         04-258117         9/1992         S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,           JP         04-346428         12/1992         cessing", IEEE Transactions on Electron Devices, vol. 27,           JP         04-354331         12/1992         No. 3, Mar. 1980, pp. 602-604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JP 60-115232          | 6/1985                 | 29p-ZE-9     | p. 530. (English                        | h Translation).                       |

| JP       61-022628       1/1986       ECR Plasma (II)", 40th Spring Mtg. of Applied Physics,         JP       61-125043       6/1986       29p-ZE-10, p. 530. (English Translation).         JP       61-250173       11/1986       Maeda, et al, "Latest LSI Process Technology", 1994, pp.         JP       63-9935       1/1988       338-347. (English Translation).         JP       3-109728       5/1991       Katayama, K., "Applying a Large-Diameter ECR Plasma         JP       04-010621       1/1992       Source to Etching", Monthly Semiconductor World, Oct.,         JP       4-170026       6/1992       1993, pp. 81-85. (English Translation).         JP       04-258117       9/1992       S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-346428       12/1992       Cessing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-354331       12/1992       No. 3, Mar. 1980, pp. 602-604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | JP 60-154526          | 8/1985                 | Yanase, T.   | . et al. "Uniform                       | n Etching of Silicon Dioxide by       |

| JP       61-125043       6/1986       29p-ZE-10, p. 530. (English Translation).         JP       61-250173       11/1986       Maeda, et al, "Latest LSI Process Technology", 1994, pp.         JP       63-9935       1/1988       338-347. (English Translation).         JP       3-109728       5/1991       Katayama, K., "Applying a Large-Diameter ECR Plasma         JP       04-010621       1/1992       Source to Etching", Monthly Semiconductor World, Oct.,         JP       4-170026       6/1992       1993, pp. 81-85. (English Translation).         JP       04-258117       9/1992       S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-346428       12/1992       cessing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-354331       12/1992       No. 3, Mar. 1980, pp. 602-604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | JP 61-022628          | 1/1986                 | ŕ            | •                                       | e ·                                   |

| JP       61-250173       11/1986       Maeda, et al, "Latest LSI Process Technology", 1994, pp.         JP       63-9935       1/1988       338-347. (English Translation).         JP       3-109728       5/1991       Katayama, K., "Applying a Large-Diameter ECR Plasma         JP       04-010621       1/1992       Source to Etching", Monthly Semiconductor World, Oct.,         JP       4-170026       6/1992       1993, pp. 81-85. (English Translation).         JP       04-258117       9/1992       S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-346428       12/1992       cessing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-354331       12/1992       No. 3, Mar. 1980, pp. 602-604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JP 61-125043          | 6/1986                 |              |                                         |                                       |

| JP 63-9935 1/1988 338-347. (English Translation).  JP 63-086522 4/1988 338-347. (English Translation).  Katayama, K., "Applying a Large-Diameter ECR Plasma  JP 04-010621 1/1992 Source to Etching", Monthly Semiconductor World, Oct.,  JP 04-170026 6/1992 1993, pp. 81-85. (English Translation).  JP 04-258117 9/1992 S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,  JP 04-346428 12/1992 No. 3, Mar. 1980, pp. 602-604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | JP 61-250173          | 11/1986                | •            | · · ·                                   |                                       |

| JP       3-109728       5/1991       Katayama, K., "Applying a Large-Diameter ECR Plasma         JP       04-010621       1/1992       Source to Etching", Monthly Semiconductor World, Oct.,         JP       4-170026       6/1992       1993, pp. 81–85. (English Translation).         JP       04-258117       9/1992       S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-346428       12/1992       cessing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-354331       12/1992         No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | JP 63-9935            | 1/1988                 | ,            | ,                                       |                                       |

| JP       04-010621       1/1992       Source to Etching", Monthly Semiconductor World, Oct.,         JP       4-170026       6/1992       1993, pp. 81–85. (English Translation).         JP       04-258117       9/1992       S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-354331       12/1992       cessing", IEEE Transactions on Electron Devices, vol. 27,         JP       04-354331       12/1992       No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JP 63-086522          | 4/1988                 |              | ` •                                     |                                       |

| JP       4-170026       6/1992       1993, pp. 81–85. (English Translation).         JP       04-258117       9/1992       S.T. Griffin et al, "Plasma Processes Involved in Dry Processing", IEEE Transactions on Electron Devices, vol. 27, No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | JP 3-109728           | 5/1991                 | Katayama     | , K., "Applying                         | a Large–Diameter ECR Plasma           |

| JP 04-258117 9/1992 S.T. Griffin et al, "Plasma Processes Involved in Dry Pro-<br>JP 04-346428 12/1992 cessing", IEEE Transactions on Electron Devices, vol. 27,<br>JP 04-354331 12/1992 No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | JP 04-010621          | 1/1992                 | Source to    | Etching", Montl                         | hly Semiconductor World, Oct.,        |

| JP 04-258117 9/1992 S.T. Griffin et al, "Plasma Processes Involved in Dry Pro-<br>JP 04-346428 12/1992 cessing", IEEE Transactions on Electron Devices, vol. 27,<br>JP 04-354331 12/1992 No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | JP 4-170026           | 6/1992                 | 1993, pp.    | 81–85. (English                         | Translation).                         |

| JP 04-346428 12/1992 cessing", IEEE Transactions on Electron Devices, vol. 27, 12/1992 No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | JP 04-258117          | 9/1992                 |              | ` •                                     |                                       |

| JP 04-354331 12/1992 No. 3, Mar. 1980, pp. 602–604.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                        |              | •                                       | · · · · · · · · · · · · · · · · · · · |

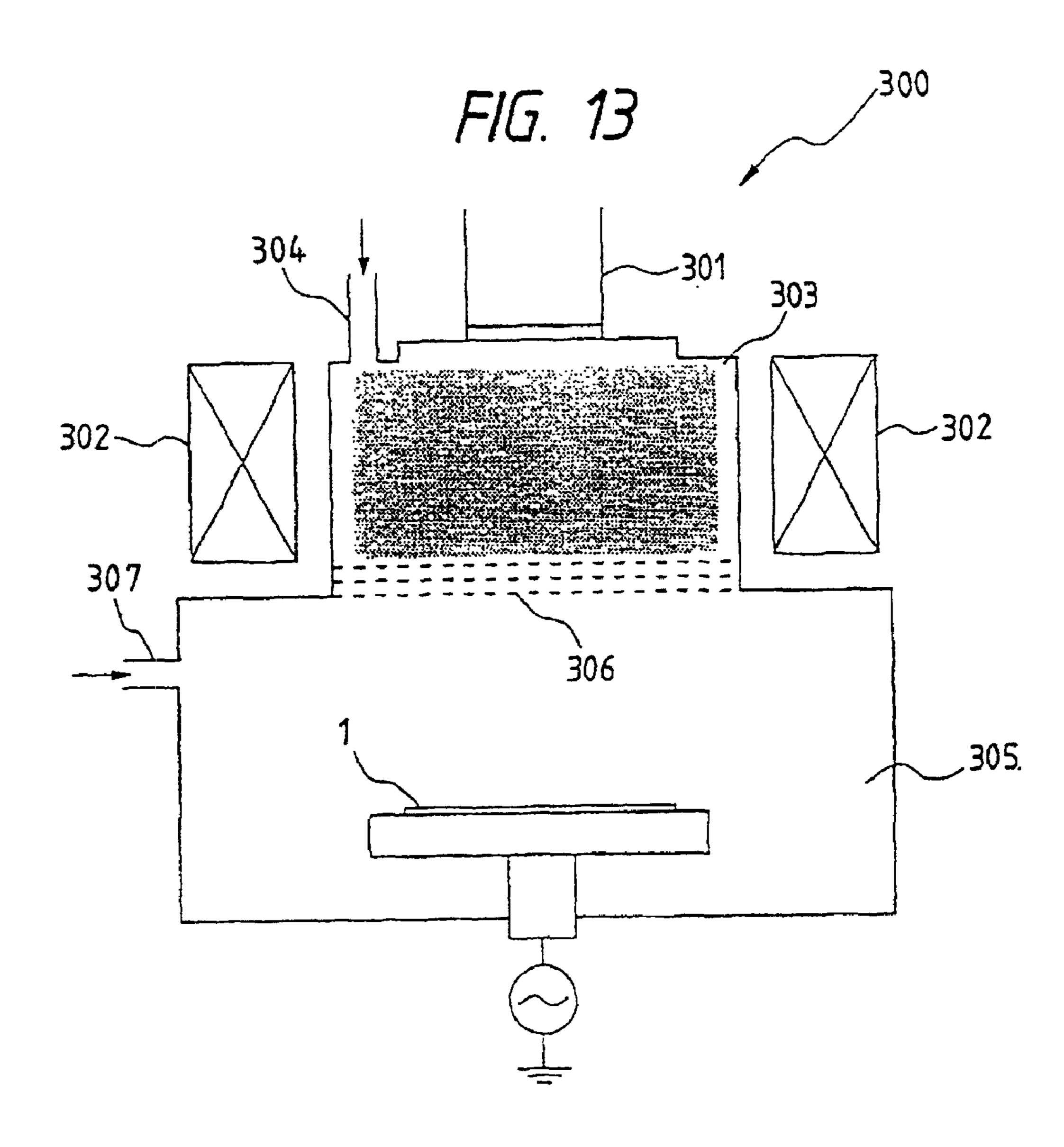

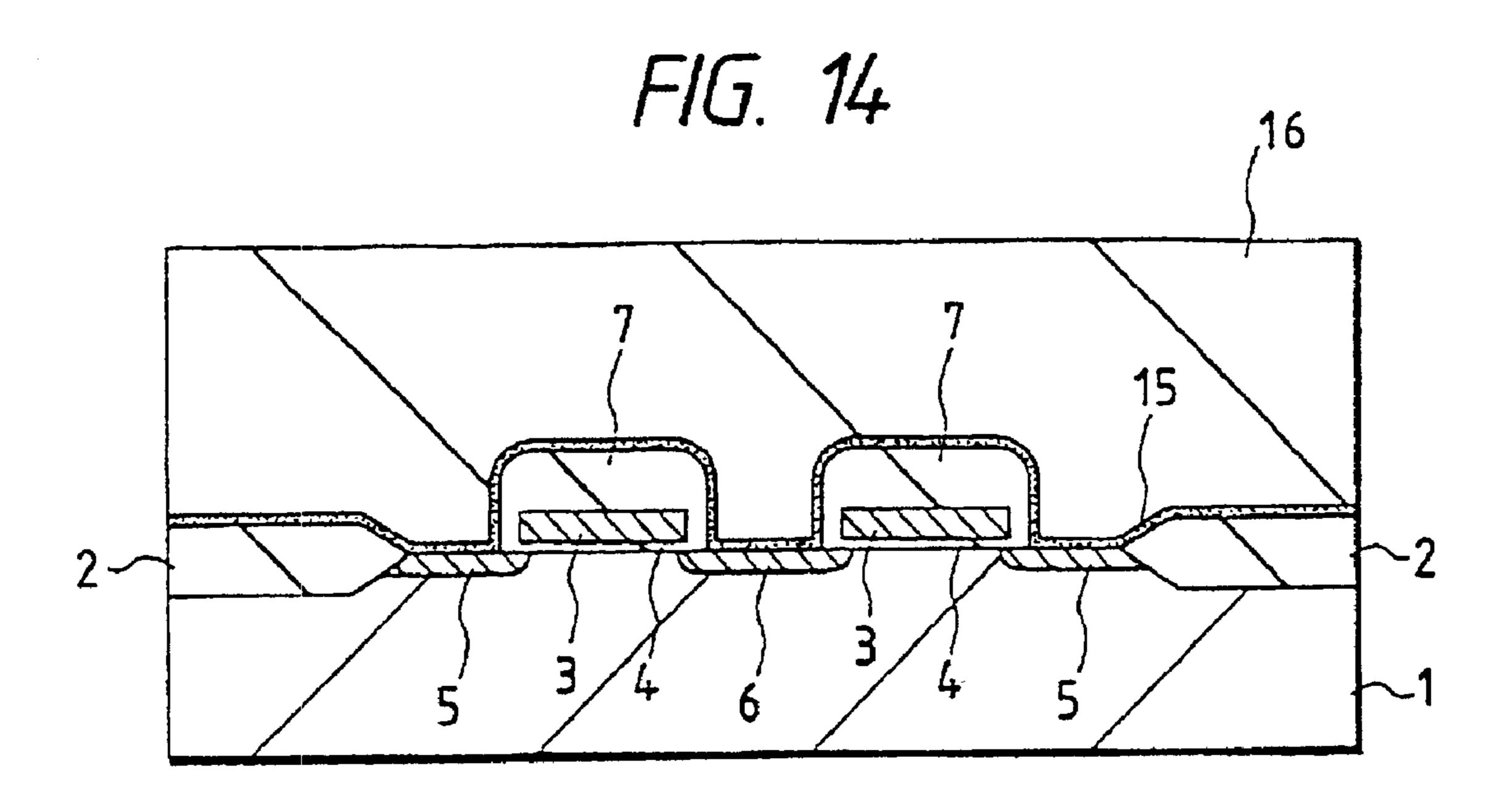

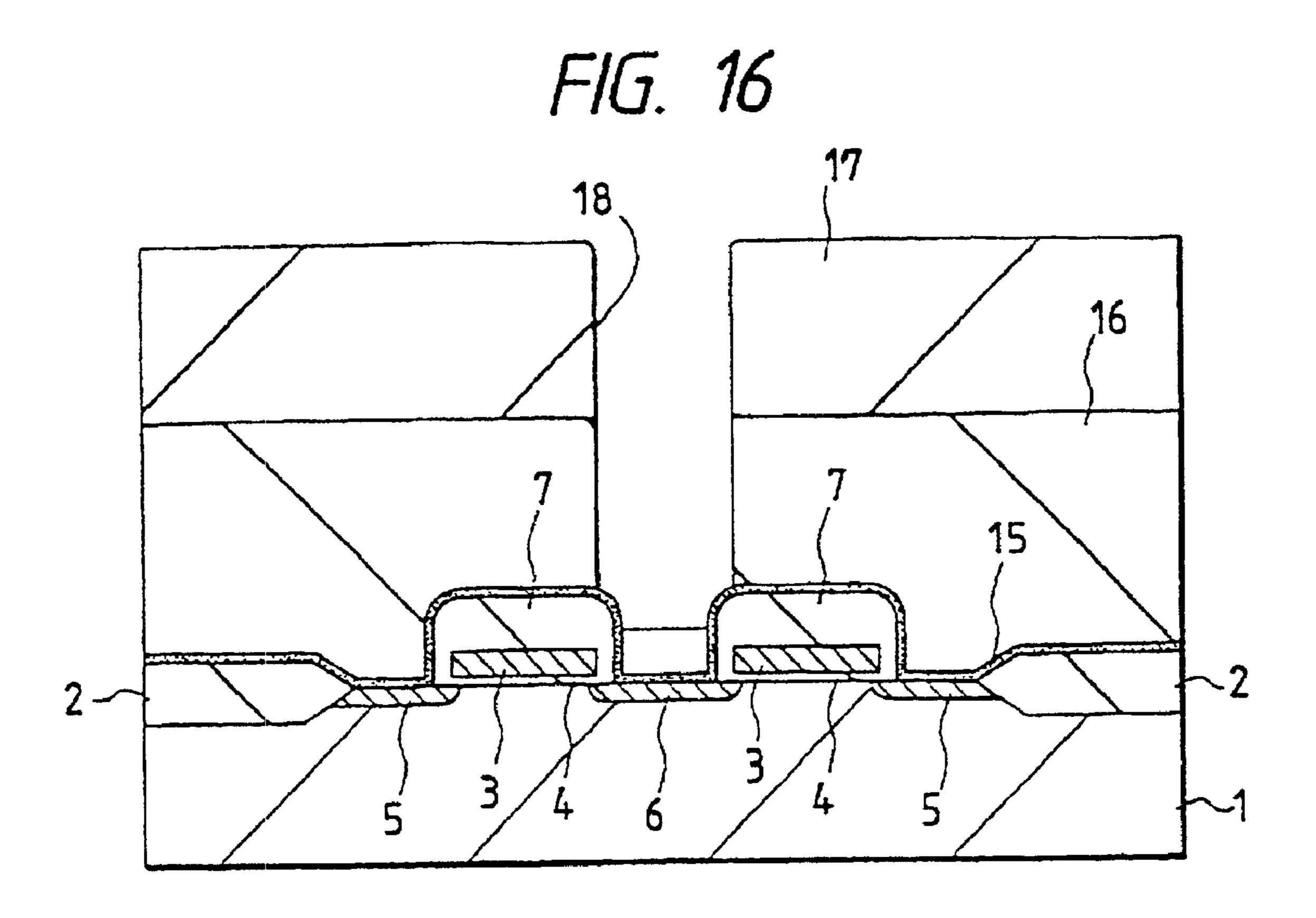

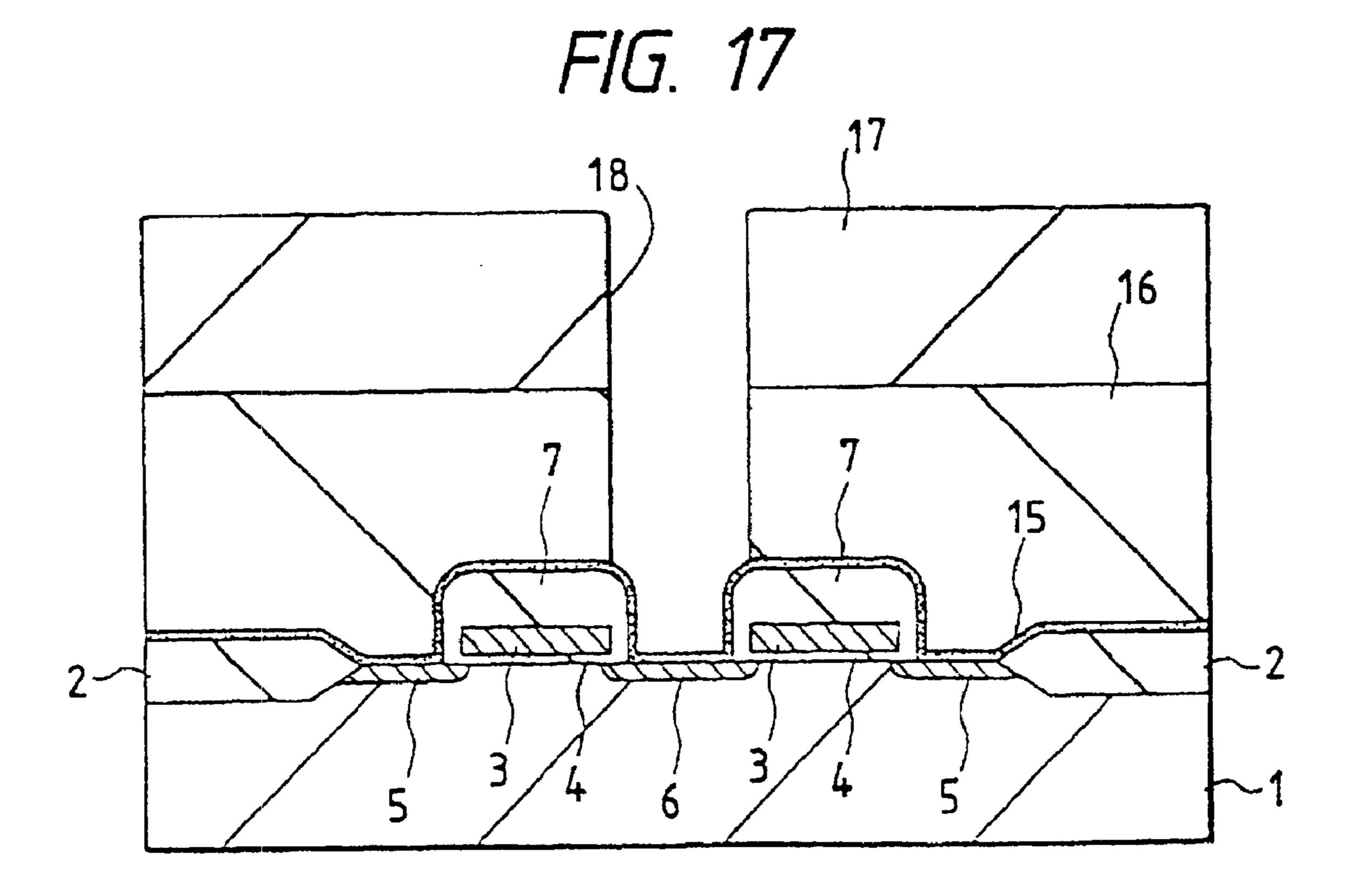

| 110. 5, 191a1. 1700, pp. 002-007.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |                        |              |                                         |                                       |