## US00RE39026E

# (19) United States

# (12) Reissued Patent

Shemla et al.

# (10) Patent Number: US RE39,026 E

# (45) Date of Reissued Patent: Mar. 21, 2006

| (54)                                   | BUS PROTOCOL                   |                                                                                         |  |  |  |  |

|----------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|

| (75)                                   | Inventors:                     | David Shemla, Kfar Havradim (IL);<br>Eyal Waldman, Tivon (IL); Yosi Solt,<br>Haifa (IL) |  |  |  |  |

| (73)                                   | Assignee:                      | Marvell International, Ltd., Hamilton (BM)                                              |  |  |  |  |

| (21)                                   | Appl. No.:                     | 10/101,552                                                                              |  |  |  |  |

| (22)                                   | Filed:                         | Jul. 18, 2001                                                                           |  |  |  |  |

| Reiss<br>(64)                          | Relatue of: Patent No. Issued: | ted U.S. Patent Documents  : 5,930,261  Jul. 27, 1999                                   |  |  |  |  |

|                                        | Appl. No.:<br>Filed:           |                                                                                         |  |  |  |  |

| (30) Foreign Application Priority Data |                                |                                                                                         |  |  |  |  |

| Jan.                                   | 31, 1996                       | (IL) 116988 E.N<br>Sci                                                                  |  |  |  |  |

| (51)                                   | Int. Cl.<br>H04L 12/5          | Pub<br>54 (2006.01) "Dr<br>ture                                                         |  |  |  |  |

| (52)                                   | <b>U.S.</b> Cl                 |                                                                                         |  |  |  |  |

| (58)                                   |                                | Classification Search                                                                   |  |  |  |  |

# (56) References Cited

## U.S. PATENT DOCUMENTS

See application file for complete search history.

| 4,464,713 A | 8/1984   | Benhase et al 364/200    |

|-------------|----------|--------------------------|

| 4,663,706 A | 5/1987   | Allen et al 364/200      |

| 4,996,663 A | 2/1991   | Nemes                    |

| 5,032,987 A | 7/1991   | Broder et al 364/200     |

| 5,101,348 A | 3/1992   | Arrowood et al 395/200   |

| 5,222,064 A | 6/1993   | Sagawa                   |

| 5,274,631 A | 12/1993  | Bhardwaj 370/60          |

| 5,287,499 A |          | Nemes 395/600            |

| 5.412.805 A | * 5/1995 | Jordan, II et al 395/600 |

| 5,440,552 A |   | 8/1995  | Sugita 370/60              |

|-------------|---|---------|----------------------------|

| 5,453,982 A | * | 9/1995  | Pennington et al 370/235   |

| 5,521,913 A |   | 5/1996  | Gridley 370/58.2           |

| 5,579,452 A | * | 11/1996 | Ambalavanar et al 358/1.16 |

| 5,581,757 A |   | 12/1996 | Maxey 395/610              |

| 5,623,644 A | * | 4/1997  | Self et al 395/558         |

| 5,632,021 A | * | 5/1997  | Jennings et al 395/309     |

| 5,633,858 A |   | 5/1997  | Chang et al 370/255        |

| 5,634,138 A | * | 5/1997  | Ananthan et al 395/841     |

| 5,649,141 A |   | 7/1997  | Yamazaki 395/416           |

| 5,671,357 A |   | 9/1997  | Humblet et al 395/200.11   |

| 5,715,395 A |   | 2/1998  | Brabson et al 395/200.13   |

| 5,724,529 A | * | 3/1998  | Smith et al 395/309        |

| 5,734,824 A |   | 3/1998  | Choi 395/200.11            |

| 5,740,468 A |   | 4/1998  | Hirose 395/877             |

| 5,754,791 A |   | 5/1998  | Dahlgren et al 395/200.72  |

| 5,761,431 A |   |         | Gross et al 395/200.55     |

| 5,764,996 A | * | 6/1998  | Armstrong et al 395/733    |

| 5,781,549 A |   | 7/1998  | Dai                        |

| 5,784,373 A |   | 7/1998  | Satake et al 370/402       |

| 5,923,660 A |   | 7/1999  | Shemla et al 370/402       |

|             |   |         |                            |

#### OTHER PUBLICATIONS

E.M. Reingold, "Searching", Encyclopedia of Computer Science, Third Edition, A. Ralston and E.D. Reilly, Editors, Published 1995, pp. 1185–1191.

"Dr. Dobb's Essential Books on Algorithms and Data Structures", Dr. Dobb's Journal, 1995, pp. 1–7.

Primary Examiner—Ajit Patel

## (57) ABSTRACT

A write-only data transfer protocol for peripheral component interface busses and a method for transferring data between source and destination communication units is provided. The method includes the source communication unit writing a buffer allocation request to the destination unit and, in response to the buffer allocation request, the destination communication unit allocating space within an associated buffer to receive the data to be sent. The method also includes the destination communication unit writing at least the location of the allocated buffer to the source communication unit and the source communication unit writing the data to be sent to the allocated buffer location.

# 52 Claims, 5 Drawing Sheets

<sup>\*</sup> cited by examiner

FIG.1 PRIOR ART

Mar. 21, 2006

FIG.2B PRIOR ART

FIG.4B

Mar. 21, 2006

FIG.3

Mar. 21, 2006

## **BUS PROTOCOL**

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions 5 made by reissue.

#### FIELD OF THE INVENTION

The present invention relates to data transfer protocols generally and to such protocols for implementation on a peripheral component interface (PCI) bus and within a network switch in particular.

#### BACKGROUND OF THE INVENTION

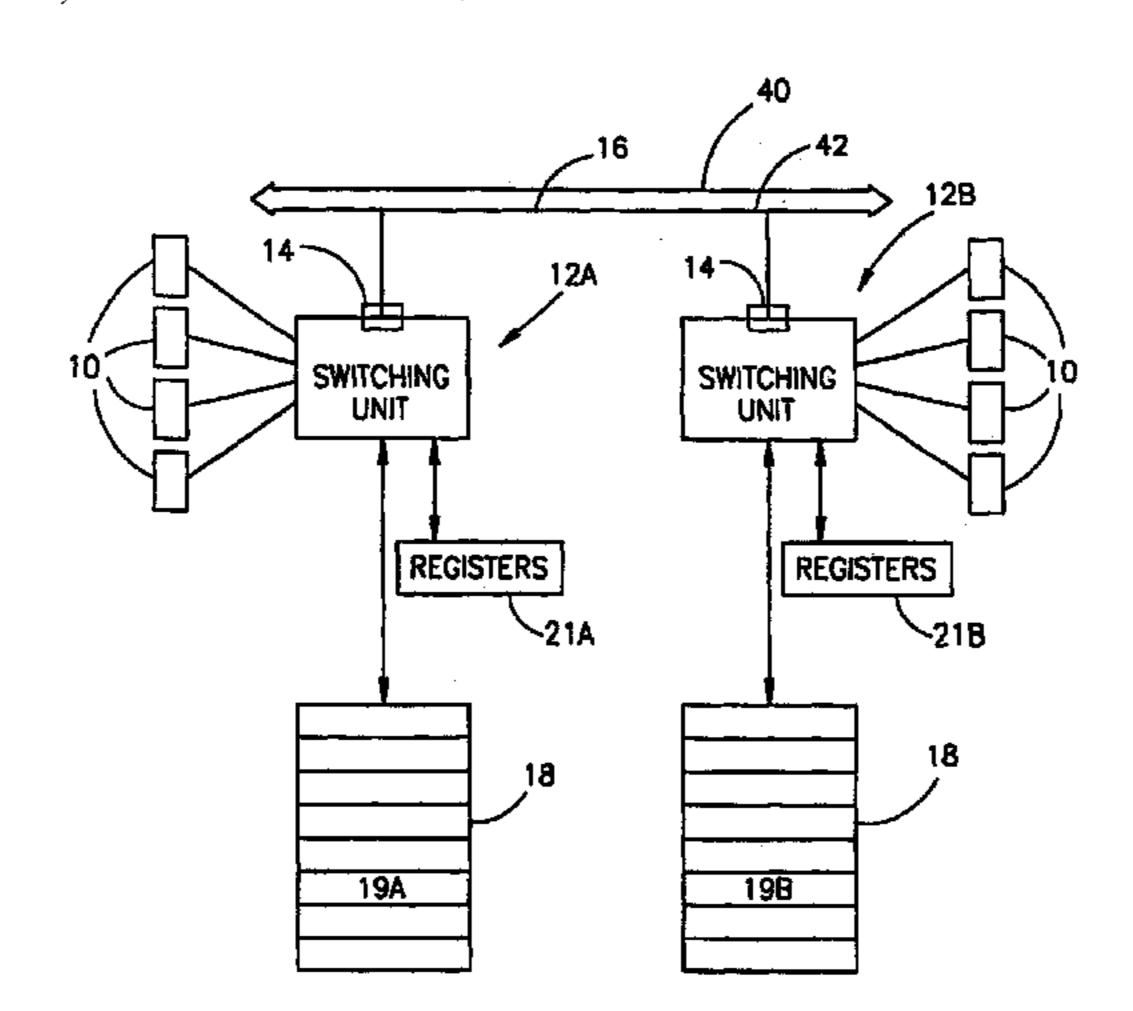

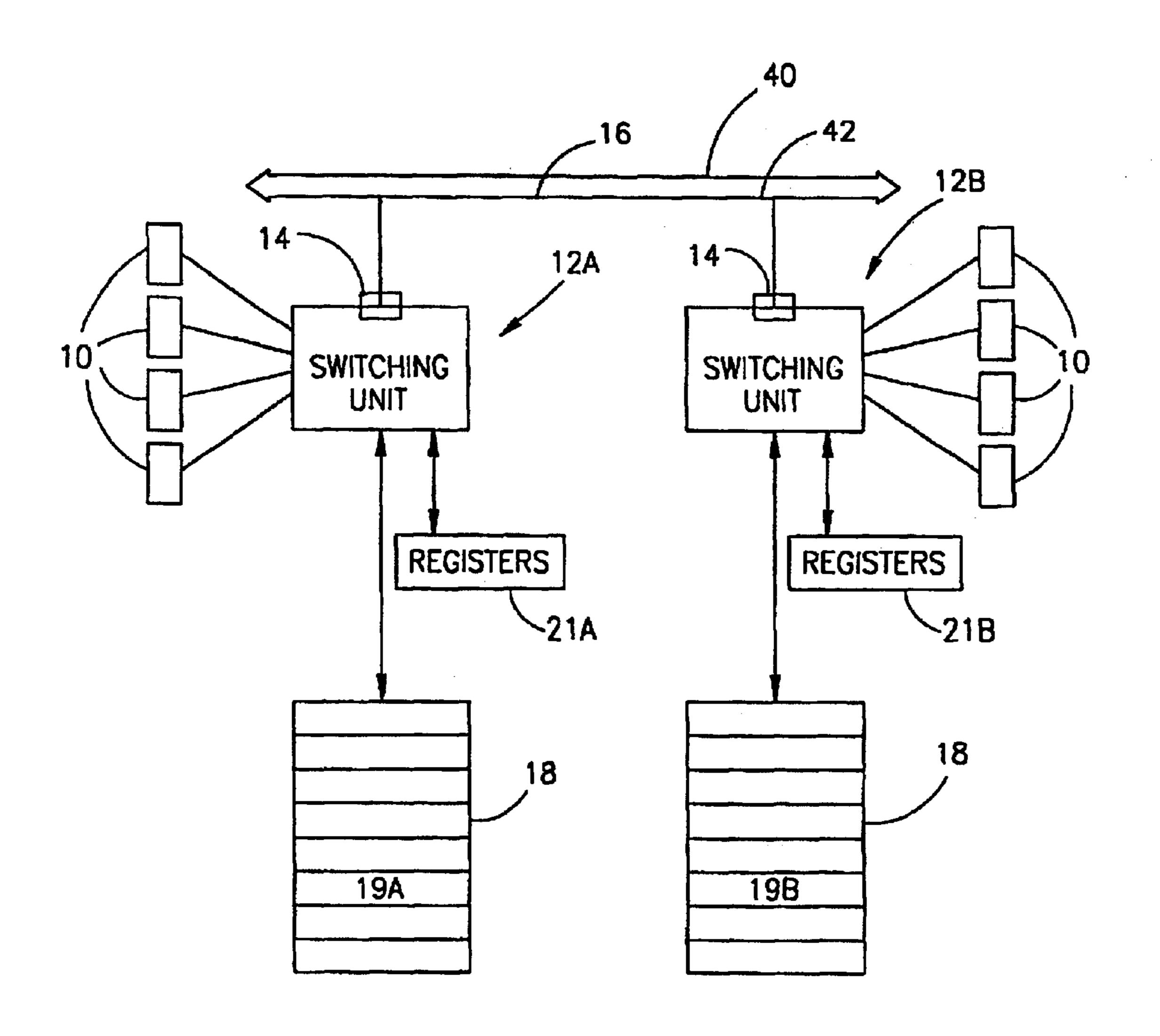

A network switch creates a network among a plurality of nodes (connected to personal computers, workstations, etc.) and other network switches connected thereto. As shown in FIG. 1 to which reference is now made, each node 10 is connected to one port of a switch 12. Further ports 14 also 20 serve to connect network switches together. The switches are typically connected together via a bus 16. Optionally, a central processing unit (CPU) 15 which is associated with a main memory element 17 can also be connected to the bus 16. The CPU 15 overseas the communication operations 25 which occur between the network switches 12. The main memory 17 temporarily stores packets of data to be transferred between switches 12.

Each node 10 sends packets of data to the network switch 12 which then routes the packets either to another of the nodes connected thereto or to a network switch to which the destination node is connected. In the latter case, the destination network switch then routes the packet to the destination node.

Each network switch also has to temporarily store the packets of data, in buffers 18, while the switch determines how, when and through which port to retransmit the packets. Each packet can be transmitted to only one destination address (a "unicast" packet) or to more than one unit (a "multicast" or "broadcast" packet). For multicast and broadcast packets, the switch typically stores the packet only once and transmits multiple copies of the packet to some (multicast) or all (broadcast) of its ports. Once the packet has been transmitted to all of its destinations, it can be removed from its buffer 18 or written over.

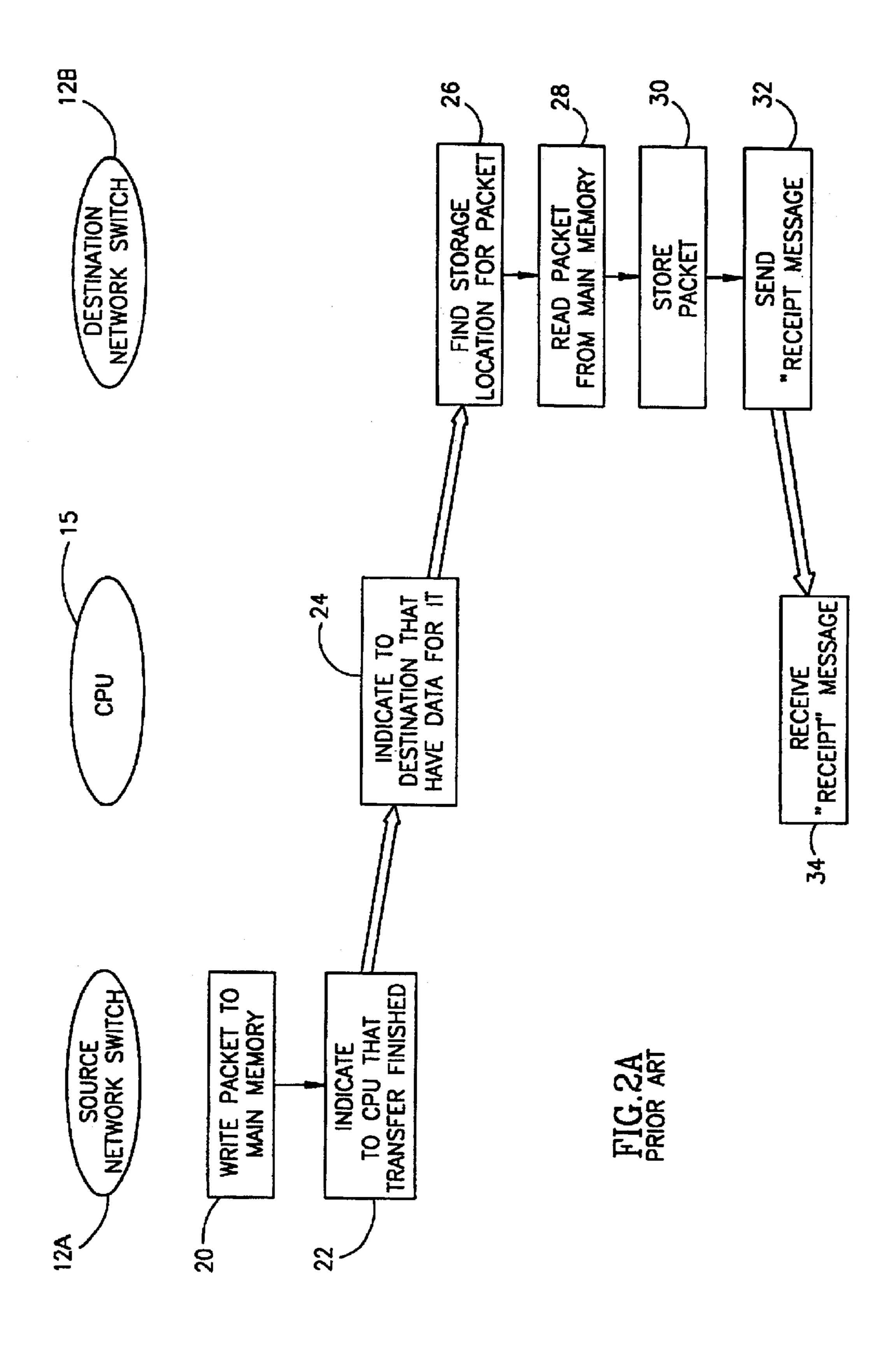

One example of a prior art process of transferring packets between network switches is illustrated in FIGS. 2A and 2B to which reference is additionally made. FIG. 2A is a block diagram illustration of the flow of data between the source and destination network switches and FIG. 2B is a timing diagram of the activity of the bus 16.

The source network switch 12A, on its own schedule reads the packet from its temporary storage location, labeled 19A, and writes the packet to the main memory 17 (step 20). 55 The source network switch 12A then provides (step 22) an indication to the CPU 15 that the transfer has finished. At some later point after the transfer has finished, the CPU 15 indicates (step 24) to the destination network switch 12B that the main memory 17 is storing its data.

When the destination network switch 12B receives the notification from the CPU 15, the destination network switch 12B begins the read process and takes control of the bus 16. The read process includes steps 26–32, as follows. In step 26, the destination network switch 12B determines 65 where, in its temporary storage unit there is room for the incoming packet (for example location 19B). In step 28,

2

destination network switch 12B asks the main memory 17 to read the packet and, when the packet is received, switch 12B places it (step 30) into the available location 19B. When the destination network switch 12B has finished the read operation, it, in step 32, sends a message to the CPU 15 that the packet was properly received. In step 34, the CPU 15 receives the receipt message and clears the location in the main memory 17 in which the data was previously stored.

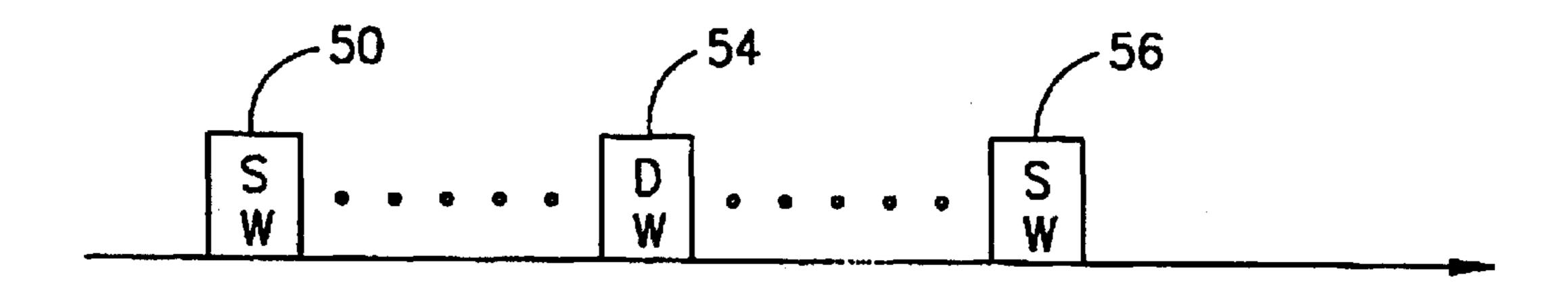

FIG. 2B illustrates the timing of the packet transfer. The packet transfer begins with the "source write" (SW) operation of steps 20–22 which is generally a short operation. At some later point, the destination read (DR) operation occurs. Since the read process includes allocating the storage location and accessing the main memory 17, and since main memory 17 typically reads at a slow rate, the read operation takes a long time. Unfortunately, during the read operation, no other switch can access the bus. Thus, the rate of data transfer is limited by the speed at which the main memory 17 can read the data, even if the bus 16 and the other components can operate at faster speeds.

### SUMMARY OF THE PRESENT INVENTION

Applicants have realized that, since read operations are limited by the speed of the main memory 17 (or of any other memory being read), while write operations occur at the speed of the bus 16, the utilization efficiency of the bus can be increased if data transfers are performed using only write operations.

It is therefore an object of the present invention to provide a write-only bus transfer mechanism in which no read operations occur. In the present invention, data is written directly, such as by direct memory transfer, from one network switch to the other and a packet is not sent from the source network switch until the destination network switch has allocated a storage location for the packet and has notified the source network switch of the allocated storage location. Thus, the packet can immediately be written into the destination network switch as soon as it arrives at the destination network switch. Furthermore, since the storage space is allocated for the packet before the packet is ever sent, the source network switch does not need to wait for a receive notice before beginning to send the next packet.

In one embodiment, the method includes the steps of:

- a) the source communication unit writes a buffer allocation request to the destination unit;

- b) in response to the buffer allocation request, the destination communication until allocates space within an associated buffer to receive the data to be sent;

- c) the destination communication unit writes at least the location of the allocated buffer to the source communication unit; and

- d) the source communication unit writes the data to be sent to the allocated buffer location.

Additionally, in accordance with a preferred embodiment of the present invention, the step of writing a buffer allocation request includes the step of writing at least the address of the source communication unit and the size of the data to be transferred into a buffer allocation request register of the destination communication unit. Similarly, the second step of writing includes the step of writing at least the address of the allocated buffer and of the destination communication unit into a start of packet register in the source communication unit.

Moreover, in accordance with a preferred embodiment of the present invention, the steps of writing are performed by direct memory access transfer. 3

Further, in accordance with a preferred embodiment of the present invention, the source and destination communication units are physically separate units.

Finally, in accordance with a preferred embodiment of the present invention, the source communication unit can write 5 a) the data to be sent on a bus data line and b) at least the address of the destination communication unit and the address of a buffer location within the destination communication unit on a bus address line.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will be understood and appreciated more fully from the following detailed description taken in conjunction with the drawings in which:

FIG. 1 is a schematic illustration of two prior art network switches connected together by a bus;

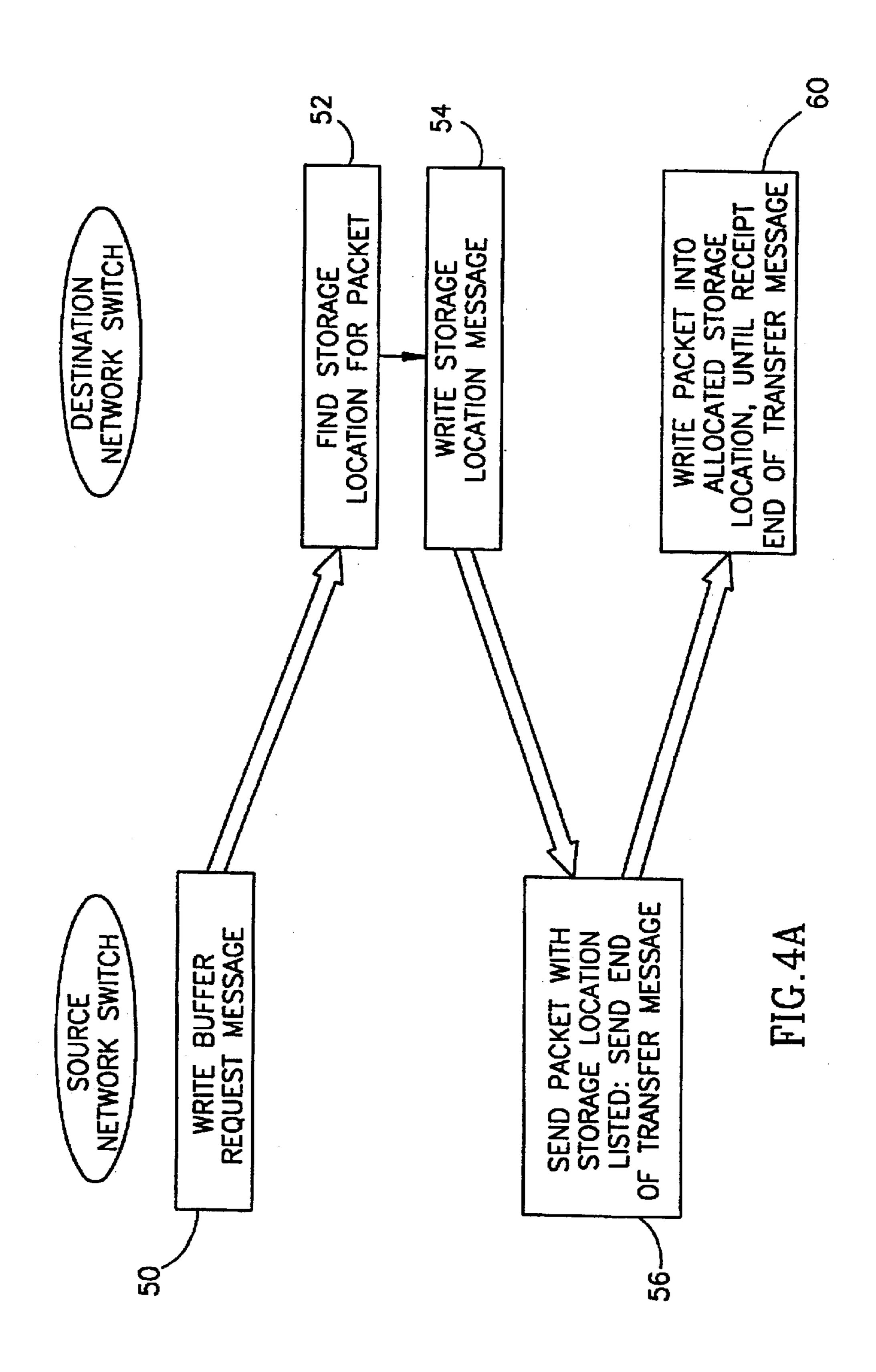

FIG. 2A is a flow chart illustration of the operations performed by the two switches of FIG. 1 during the prior art data transfer operation;

FIG. 2B is a timing diagram illustration of the activity of the bus during the operation of FIG. 2A;

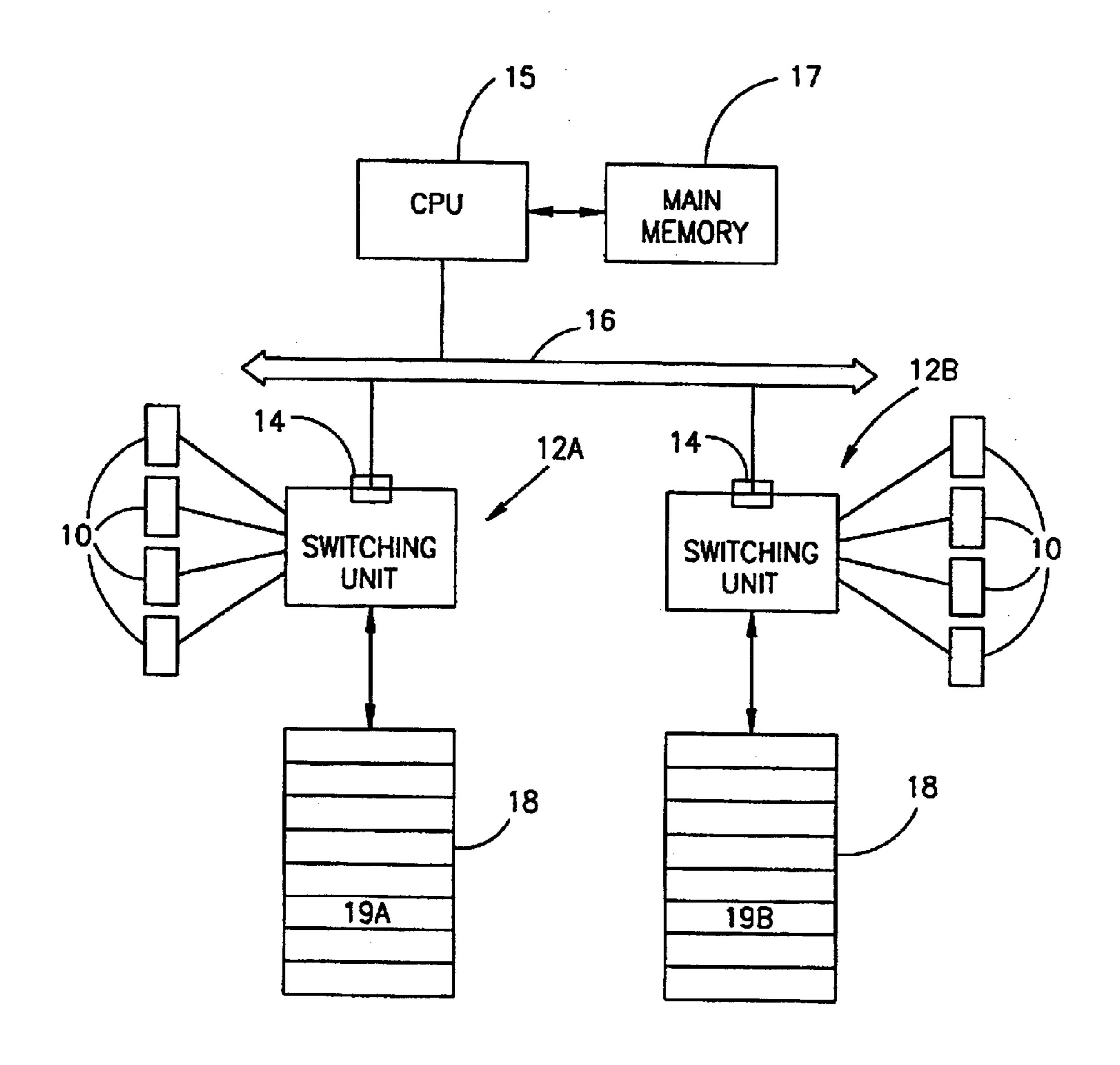

FIG. 3 is a schematic illustration of two network switches, constructed and operative in accordance with a preferred embodiment of the present invention;

FIG. 4A is a flow chart illustration of the operations performed by the two switches of FIG. 3 during the data transfer operation of the present invention; and

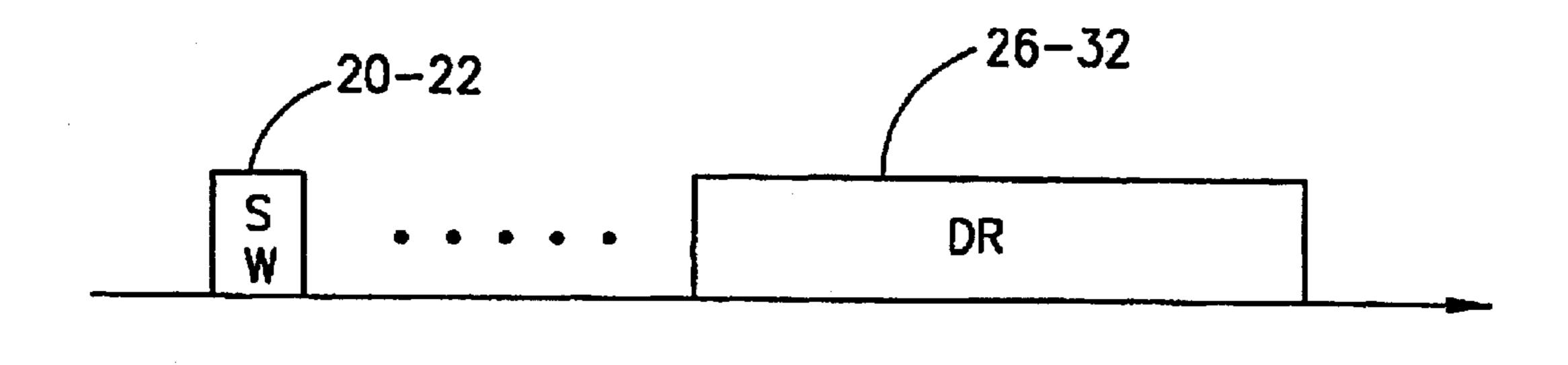

FIG. 4B is a timing diagram illustration of the activity of the bus during the operations of FIG. 4A.

# DETAILED DESCRIPTION OF THE PRESENT INVENTION

Reference is now made to FIG. 3 which illustrates the network configuration of the present invention and to FIGS. 4A and 4B which illustrate the data transfer operation of the present invention. Elements of FIG. 3 which are similar to those of FIG. 1 have the same reference numerals. As can be seen in FIG. 3 the present invention does not need the CPU 15 or the main memory 17 for the data transfer operation. This is because the present invention provides a "write-only" data transfer operation in which packets of data are written directly into the destination network switch 12B. It is noted that, in one embodiment, the data transfer operations utilized are direct memory access (DMA) write transfers.

The network switches of the present invention additionally have a plurality of registers 21 which are utilized during the data transfer operation. These registers can form part of the storage unit in which the buffers 18 are located or they can be separate therefrom. Furthermore, it is noted that the bus 16 has at least two lines, a data line 40 and an address line 42.

In the present invention, packets of data are not transferred until a buffer location 19 is allocated for them in the buffer 18 of the destination network switch 12B. Furthermore, since the transfer operation is a DMA transfer, a packet is directly written into the location allocated therefor.

The present discussion will consider the transfer of a single packet of data. It will be appreciated that many packets of data can be transferred in parallel by performing the operations described hereinbelow many times either in parallel or serially.

In accordance with a preferred embodiment of the present invention, when a packet of data is to be transferred, the 4

source network switch 12A initially writes (step 50, FIG. 4A) a "buffer request" message to the register 21b of the destination network switch 12B. The buffer request message asks that the destination network switch allocate a buffer for the data to be transferred.

In the DMA transfer embodiment of the present invention, the source network switch 12A provides, on address line 42, the address of the "buffer request" register, the address of destination network switch 12B and its "return" address.

Source network switch 12A provides, on data line 40, the size (or byte count) of the packet to be transferred and the buffer location 19A in which it is stored. The data of the data line is then written directly into the buffer request register.

In response to the buffer request message, the destination network switch 12B determines (step 52) the buffer location 19B in which the packet can be stored. It then writes (step 54) a "start of packet" message to the register 21a of the source network switch 12A which includes at least the location of the allocated buffer and the port numbers of the source and destination network switches. It can also include the byte count.

For example, in the DMA transfer embodiment of the present invention described hereinabove, the destination network switch 12B provides, on address line 42, the address of the "start of packet" register and the address of source network switch 12A. Destination network switch 12B provides, on data line 40, at least the following: the byte count of the packet to be transferred, the address 19B of the allocated buffer, the port number of the destination network switch 12B, and, for identification, the buffer location 19A in which the data is stored in the source network switch 12A and the port number of the source network switch 12A. As before, the data of the data line is then directly written into the start of packet register.

In response to receipt of the start of packet message in the start of packet register, the source network switch 12A writes (step 56) the packet of data to the allocated buffer location, followed by an "end of packet" message. Once the source network switch 12A has finished writing the end of packet message, it is free to send the next packet, beginning at step 50.

In the above described embodiment, the writing of the packet of data involves providing the address of the destination network switch 12B and the buffer location 19B on the address line 42 and the packet to be transferred on the data line 40. The transferred packet is then directly written into the allocated buffer location 19B. The end of packet message is written in a similar manner to the other messages.

The address information includes the address of the end of packet register and the address of the destination network switch 12B. The data includes the port number of the destination network switch 12B, the buffer location 19B and the byte count.

When the packet arrives at the destination network switch 12B it directly writes (step 60) the packet into the allocated buffer location 19B, as per the address on the address line 42, until it receives the end of packet message for that allocated buffer location. The destination network switch 12B is now free to perform other operations until it receives a next buffer allocation request.

FIG. 4B illustrates the timing of the packet transfer described in FIG. 4A. The initial source write operation of the buffer request message (step 50) is typically relatively short since write operations take relatively little time and since the message to be transferred is small. Some time later, there is a destination write (DW) operation of the start of

packet message (step 54). The destination write operation takes approximately the same length of time as the first source write operation. Some time later, there is a further source write operation (step 56) of the packet transfer and end of packet message. Since, for this operation, there is 5 more data to be transferred, this source write operation is shown to take a longer time than the other two write operations.

A comparison of the timing of FIGS. 2B and 4B indicate that the amount of time the bus is utilized for a single 10 units. transfer operation is much smaller in the present invention (FIG. 4B) than in the prior art (FIG. 2B) since the present invention utilizes write operations only.

The source and network switches are free to perform other operations after they finish their writing operations.

It is also noted that, in the present invention, the source network switch 12A is free to operate on other packets once it has finished writing its packet, and its associated end of packet message, to the bus. The source network switch 12A does not need to ensure that the destination network switch 12B has successfully received the packet since, in the present invention, the address for the data (in the destination network switch) is known and is fully allocated prior to sending the packet; the packet would not be sent if there was no buffer location available for it. In the present invention, the time it takes for the destination network switch 12B to process the packet is not relevant to the operation of the source network switch 12A.

It will be appreciated that the data transfer mechanism described hereinabove can be implemented in any type of network switch or other communication device communicating along a bus, such as transferring data to a peripheral hard disk. For example, it can be implemented in an Ethernet switch, an asynchronous transfer mode (ATM) switch or a Token Ring switch. The present invention is may be implemented for peripheral component interface (PCI) busses or for any other bus.

It will further be appreciated by persons skilled in the art that the present invention is not limited to what has been particularly shown and described hereinabove. Rather the 40 scope of the present invention is defined by the claims which follow:

We claim:

- 1. A method for transferring data between source and destination communication units, the method comprising the 45 steps of:

- a. the source communication unit writing a buffer allocation request to the destination communication unit;

- b. in response to the buffer allocation request, the destination communication unit allocating space within an 50 associated buffer to receive the data to be sent;

- c. the destination communication unit writing at least the location of the allocated buffer to the source communication unit; and

- d. the source communication unit writing the data to be 55 sent to the allocated buffer location.

- 2. A method according to claim 1 and wherein said step of writing a buffer allocation request includes the step of writing at least the address of said source communication unit and the size of the data to be transferred into a buffer 60 allocation request register of said destination communication unit.

- 3. A method according to claim 1 and wherein said second step of writing includes the step of writing at least the address of the allocated buffer and of the destination com- 65 munication unit into a start of packet register in said source communication unit.

- 4. A method according to claim [3 and wherein said second step of writing includes *further comprising* the step of:

- the destination communication unit writing at least [the] an address of [the] an allocated buffer [and] of the destination communication unit into a start of packet register in said source communication unit.

- 5. A method according to claim 1 and wherein said source and destination communication units are physically separate

- 6. A method according to claim 1 wherein said steps of writing are performed by direct memory access transfer.

- 7. A method for transferring data between source and destination communication units, the method comprising the 15 steps of:

- a. the source communication unit writing the data to be sent with an indication of the buffer location into which the destination communication unit should write the data to be sent.

- 8. A method according to claim 7 wherein said step of writing is performed by direct memory access transfer.

- 9. A method for transferring data between source and destination communication units connected via a bus having a data line and an address line, the method comprising the 25 steps of:

- a. the source communication unit writing the data to be sent on said data line and at least the address of said destination communication unit and the address of a buffer location within said destination communication unit on said address line.

- 10. A method according to claim 9 wherein said step of writing is performed by direct memory access transfer.

- 11. A write-only data transfer protocol for peripheral component interface busses for transferring data between source and destination peripheral components, the method comprising the steps of:

- a. the source peripheral component writing a buffer allocation request to the destination [unit] peripheral component;

- b. in response to the buffer allocation request, the destination nation peripheral component allocating space within an associated buffer to receive the data to be sent;

- c. the destination peripheral component writing at least the location of the allocated buffer to the source peripheral component; and

- d. the source peripheral component writing the data to be sent to the allocated buffer location.

- 12. A method according to claim 11 wherein said steps of writing are performed by direct memory access transfer.

- 13. A communications system comprising:

- a source communication unit comprising a source buffer; a destination communication unit in communication with said source communication unit, and comprising a destination buffer;

- wherein, in response to a destination buffer allocation request by said source communication unit to said destination communication unit, said destination communication unit (i) allocates a location within said destination buffer to receive the data to be sent from said source communication unit, and (ii) provides at least the location of said destination buffer to said source communication unit, and

- wherein said source communication unit provides the data to said destination buffer for storage at the location.

7

- 14. A communication system according to claim 13, wherein said source communication unit further comprises a first switching unit responsive to a first plurality of source nodes, and wherein said destination communication unit further comprises a second switching unit in communication 5 with a second plurality of destination nodes.

- 15. A communication system according to claim 14, further comprising an address line and a data line, wherein the destination buffer allocation request by said source communication unit to said destination communication unit is provided on said address line, wherein said destination communication unit provides the location of said destination buffer to said source communication unit on said address line, and wherein said source communication unit provides the data to said destination buffer on said data line.

- 16. A communication system according to claim 15, wherein said destination communication unit provides (i) a start of the location of said destination buffer to said source communication unit on said address line, and (ii) and an address of said source communication unit on the data line.

- 17. A communication system according to claim 15, 20 wherein said source communication unit further comprises a source register, and wherein the destination buffer allocation request by said source communication unit to said destination communication unit comprises (i) an address of said source register, (ii) an address of said second switching 25 unit, and (iii) an address of said first switching unit.

- 18. A communication system according to claim 15, wherein said source communication unit further comprises a source register, and wherein the destination buffer allocation request by said source communication unit to said destination communication unit comprises (i) a size of the data to be transferred and (i) an address of said source buffer storing the data.

- 19. A communication system according to claim 18, wherein, in response to a destination buffer allocation request by said source communication unit to said destination communication unit, said destination communication unit further provides the location of said destination buffer and an address of said source communication unit to a start of packet register in said source register.

- 20. A communication system according to claim 15, wherein, in response to a destination buffer allocation request by said source communication unit to said destination communication unit, said destination communication unit further provides the location of said destination buffer and an address of said source communication unit to said source communication unit on said address line.

- 21. A communication system according to claim 13, wherein said destination communication unit further comprises a destination register, and wherein the destination buffer allocation request by said source communication unit to said destination communication unit is provided to said destination register.

- 22. A communication system according to claim 13, wherein, in response to a destination buffer allocation 55 request by said source communication unit to said destination communication unit, said destination communication unit further provides the location of said destination buffer and an address of said source communication unit to said source communication unit.

- 23. A communication system comprising:

- a source node;

- a source communication unit in communication with said source node and comprising a source buffer;

- a destination communication unit in communication with 65 said source communication unit and comprising a destination buffer,

8

- wherein, in response to a destination buffer allocation request by said source communication unit to said destination communication unit, said destination communication unit (i) allocates a location within said destination buffer to receive the data to be sent from said source communication unit, and (ii) provides at least the location of said destination buffer to said source communication unit, and

- wherein said source communication unit provides the data to said destination buffer for storage at the location; and

- a destination node in communication with said destination communication unit.

- 24. A communication system according to claim 23, wherein said source communication unit further comprises a first switching unit responsive to a first plurality of source nodes, and wherein said destination communication unit further comprises a second switching unit in communication with a second plurality of destination nodes.

- 25. A communication system according to claim 24, further comprising an address line and a data line, wherein the destination buffer allocation request by said source communication unit to said destination communication unit is provided on said address line, wherein said destination communication unit provides the location of said destination buffer to said source communication unit on said address line, and wherein said source communication unit provides the data to said destination buffer on said data line.

- 26. A communication system according to claim 25, wherein said destination communication unit provides (i) a start of the location of said destination buffer to said source communication unit on said address line, and (ii) an address of said source communication unit on said data line.

- 27. A communication system according to claim 25, wherein said source communication unit further comprises a source register, wherein the destination buffer allocation request by said source communication unit to said destination communication unit comprises (i) an address of said source register, (ii) an address of said second switching unit, and (iii) an address of said first switching unit.

- 28. A communication system according to claim 27, wherein, in response to a destination buffer allocation request by said source communication unit to said destination communication unit, said destination communication unit further provides the location of said destination buffer and an address of said source communication unit to a start of packet register in said source register.

- 29. A communication system according to claim 25, wherein said source communication unit further comprises a source register, and wherein the destination buffer allocation request by said source communication unit to said destination communication unit comprises a size of the data to be transferred and an address of said source buffer storing the data.

- 30. A communication system according to claim 25, wherein, in response to a destination buffer allocation request by said source communication unit to said destination communication unit further provides the location of said destination buffer and an address of said source communication unit to said source communication unit on said address line.

- 31. A communication system according to claim 23, wherein said destination communication unit further comprises a destination register, and wherein the destination buffer allocation request by said source communication unit to said destination communication unit is provided to said destination register.

- 32. A communication system according to claim 23, wherein, in response to a destination buffer allocation request by said source communication unit to said destination communication unit, said destination communication unit further provides the location of said destination buffer and an address of said source communication unit to said source communication unit.

- 33. A communications system comprising:

- source communication means for transmitting and receiving data comprising source buffer means for storing data;

- destination communication means for transmitting and receiving data in communication with said source communication means and comprising destination buffer means for storing data;

- wherein, in response to a destination buffer means allocation request by said source communication means to said destination communication means, said destination communication means (i) allocates a location within said destination buffer means to receive the data to be sent from said source communication means, and (ii) provides at least the location of said destination buffer means to said source communication means, and wherein said source communication means provides the

- data to said destination buffer means for storage at the location.

- 34. A communication system according to claim 33, wherein said source communication means further comprises first switching means for routing data responsive to a first plurality of source nodes, and wherein said destination communication means further comprises second switching 30 means for routing data in communication with a second plurality of destination nodes.

- 35. A communication system according to claim 34, further comprising an address line means for transferring data and a data line means for transferring data, wherein 35 the destination buffer means allocation request by said source communication means to said destination communication means is provided on said address line means, wherein said destination communication means provides the location of said destination buffer means to said source 40 communication means on said address line means, and wherein said source communication means provides the data to said destination buffer means on said data line means.

- 36. A communication system according to claim 35, 45 wherein said destination communication means provides (i) a start of the location of said destination buffer means to said source communication means on said address line means and (ii) an address of said source communication means on said data line means.

- 37. A communication system according to claim 35, wherein said source communication means further comprises source register means for storing data, wherein the destination buffer means allocation request by said source communication means to said destination communication 55 means comprises (i) an address of said source register means, (ii) an address of said second switching means, and (iii) an address of said first switching means on said address line means.

- wherein, in response to a destination buffer means allocation request by said source communication means to said destination communication means, said destination communication means further provides the location of said destination buffer means and an address of said source communication 65 means to a start of packet register means in said source register means.

- 39. A communication system according to claim 35, wherein said source communication means further comprises source register means for storing data, wherein the destination buffer means allocation request by said source communication means to said destination communication means comprises a size of the data to be transferred and an address of said source buffer means storing the data on said data line means.

- 40. A communication system according to claim 35, wherein, in response to a destination buffer means allocation request by said source communication means to said destination communication means, said destination communication means further provides the location of said destination buffer means and an address of said source communication 15 means to said source communication means.

- 41. A communication system according to claim 33, wherein in response to a destination buffer means allocation request by said source communication means to said destination communication means; said destination communication means further provides the location of said destination buffer means and an address of said source communication means to said source communication means.

- 42. A communication system according to claim 33, wherein said destination communication means further com-25 prises destination register means for storing data, and wherein the destination buffer means allocation request by said source communication means to said destination communication means is provided to said destination register means.

- 43. A communication system comprising:

source node means for sourcing data;

- source communication means in communication with said source node means comprising source buffer means for storing data;

- destination communication means in communication with said source communication means and comprising destination buffer means for storing data,

- wherein, in response to a destination buffer means allocation request by said source communication means to said destination communication means, said destination communication means (i) allocates a location within said destination buffer means to receive the data to be sent from said source communication means, and (ii) provides at least the location of said destination buffer means to said source communication means, and

- wherein said source communication means provides the data to said destination buffer means for storage at the location; and

- destination node means for sinking data in communication with said destination communication means.

- 44. A communication system according to claim 43, wherein said source communication means further comprises first switching means for routing data responsive to a first plurality of source node means, and wherein said destination communication means further comprises second switching means for routing data in communication with a second plurality of destination node means.

- 45. A communication system according to claim 44, 38. A communication system according to claim 37, 60 further comprising an address line means for transferring data and a data line means for transferring data, wherein the destination buffer means allocation request by said source communication means to said destination communication means is provided on said address line means, wherein said destination communication means provides the location of said destination buffer means to said source communication means on said address line means, and

11

wherein said source communication means provides the data to said destination buffer means on said data line means.

- 46. A communication system according to claim 45, wherein said destination communication means provides (i) 5 a start of the location of said destination buffer means to said source communication means on said address line means and (ii) an address of said source communication means on said data line means.

- 47. A communication system according to claim 45, 10 wherein said source communication means further comprises source register means for storing data, wherein the destination buffer means allocation request by said source communication means to said destination communication means comprises (i) an address of said source register 15 means, (ii) an address of said second switching means, and (iii) an address of said first switching means on said address line means.

- 48. A communication system according to claim 47, wherein, in response to a destination buffer means allocation 20 request by said source communication means to said destination communication means, said destination communication means further provides the location of said destination buffer means and an address of said source communication means to a start of packet register means in said source 25 register means.

- 49. A communication system according to claim 45, wherein said source communication means further comprises source register means for storing data, and wherein

12

the destination buffer means allocation request by said source communication means to said destination communication means comprises a size of the data to be transferred and an address of said source buffer means storing the data on said data line means.

- 50. A communication system according to claim 45, wherein, in response to a destination buffer means allocation request by said source communication means to said destination communication means, said destination communication means further provides the location of said destination buffer means and an address of said source communication means to said source communication means on said address line means.

- 51. A communication system according to claim 43, wherein, in response to a destination buffer means allocation request by said source communication means to said destination communication means, said destination communication means further provides the location of said destination buffer means and an address of said source communication means to said source communication means.

- 52. A communication system according to claim 43, wherein said destination communication means further comprises destination register means for storing data, and wherein the destination buffer means allocation request by said source communication means to said destination communication means is provided to said destination register means.

\* \* \* \* \*

# UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO. : RE 39,026 E

APPLICATION NO.: 10/101552

DATED: March 21, 2006

INVENTOR(S): David Shemla et al.

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

Column 5, Line 35: Delete "is" after "invention"

Column 6, Line 41: Delete "nation" after "destination"

Claim 18, Column 7, Line 32: Delete "(i)" an insert --(ii)--

Signed and Sealed this

Second Day of January, 2007

JON W. DUDAS

Director of the United States Patent and Trademark Office