#### US00RE38944E

### (19) United States

### (12) Reissued Patent

Takahashi et al.

### (10) Patent Number: US RE38,944 E

(45) Date of Reissued Patent: Jan. 24, 2006

#### (54) SEMICONDUCTOR MEMORY

(75) Inventors: Tsugio Takahashi, Tokyo (JP); Goro Kitsukawa, Tokyo (JP); Takesada Akiba, Tokyo (JP); Yasushi Kawase, Tokyo (JP); Masayuki Nakamura,

Tokyo (JP)

(73) Assignees: Hitachi, Ltd., Tokyo (JP); Hitach

Device Engineering Co., Ltd., Mobara

(JP)

(21) Appl. No.: 09/974,962

(22) Filed: Oct. 12, 2001

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 5,966,341

Issued: Oct. 12, 1999

Appl. No.: 08/982,398

Filed: Dec. 2, 1997

U.S. Applications:

(63) Continuation of application No. 08/779,835, filed on Jan. 7, 1997, now Pat. No. 5,777,927, which is a continuation of application No. 08/574,104, filed on Dec. 20, 1995, now Pat. No. 5,604,697.

#### (30) Foreign Application Priority Data

Dec. 20, 1994 (JP) ...... 6-334950

(51) Int. Cl. G11C 8/00 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,590,588 A \* 5/1986 Itoh et al. 4,658,377 A \* 4/1987 McElroy 5,140,550 A \* 8/1992 Miyaoka et al.

| 5,262,999 | A          |   | 11/1993 | Etoh et al.             |

|-----------|------------|---|---------|-------------------------|

| 5,274,595 | A          | * | 12/1993 | Seok et al.             |

| 5,282,175 | A          | * | 1/1994  | Fujita et al.           |

| 5,297,102 | A          | * | 3/1994  | Tanizaki                |

| 5,301,142 | A          | * | 4/1994  | Suzuki et al.           |

| 5,404,338 | A          | * | 4/1995  | Murai et al.            |

| 5,414,660 | A          |   | 5/1995  | Sugibayashi et al.      |

| 5,448,520 | A          | * | 9/1995  | Shimohigashi et al.     |

| 5,471,430 | A          | * | 11/1995 | Sawada et al 365/222    |

| 5,734,619 | A          |   | 3/1998  | Numata et al.           |

| 5,777,942 | A          | * | 7/1998  | Dosaka et al 365/230.02 |

| 6,307,217 | <b>B</b> 1 | * | 10/2001 | Ikeda et al             |

#### FOREIGN PATENT DOCUMENTS

JP A-1-245489 \* 9/1989 JP 2-18784 1/1990

(Continued)

Primary Examiner—Van Thu Nguyen (74) Attorney, Agent, or Firm—Antonelli, Terry, Stout & Kraus, LLP

#### (57) ABSTRACT

A semiconductor memory such as a dynamic RAM having memory mats each divided into a plurality of units or sub-memory mats. Each sub-memory mat comprises: a memory array having sub-word lines and sub-bit lines intersecting orthogonally and dynamic memory cells located in lattice fashion at the intersection points between the intersecting sub-word and sub-bit lines; a sub-word line driver including unit sub-word line driving circuits corresponding to the sub-word lines; a sense amplifier including unit amplifier circuits and column selection switches corresponding to the sub-bit lines; and sub-common I/O lines to which designated sub-bit lines are connected selectively via the column selection switches. The sub-memory mats are arranged in lattice fashion. Above the sub-memory mats is a layer of: main word lines and columns selection signal lines intersecting orthogonally, the main word lines having a pitch that is an integer multiple of the pitch of the sub-word lines, the column selection signal lines having a pitch that is an integer multiple of the pitch of the sub-bit lines; and main common I/O lines to which designated sub-common I/O lines are connected selectively.

#### 19 Claims, 22 Drawing Sheets

# US RE38,944 E Page 2

|    | FOREIGN PATENT DOCUMENTS | JP<br>JP   |                   | * 3/1993<br>3/1993 |  |

|----|--------------------------|------------|-------------------|--------------------|--|

| JP | A-2-18785 * 1/1990       |            |                   | •                  |  |

|    | •                        | JP         | 5-226613          | 9/1993             |  |

| JP | 2-143982 6/1990          | JP         | 6-196656          | 7/1994             |  |

| JP | A-2-158995 * 6/1990      |            |                   | •                  |  |

| JP | 2-246089 10/1990         | JP         | 6-318391          | 11/1994            |  |

| JP | 3-154287 7/1991          |            |                   |                    |  |

| JP | A-4-59712 * 9/1992       | * cited by | cited by examiner |                    |  |

F/G. 1

F16. 2

F/G. 3 SW1, 3, 5, 7 SAR 30~37 SAR40-47 SMR34\SMR35\ MB0 SI00\*,1\* **SMR77**~ SMR07 MATR MI043\* WDR05~75 (DX41,43,45,47 MIO41+,42\* SB1\*,2\* SI02\*,3\*~ **YS40** WDR04~74-M1040 DX40,42,44,46 SW0,2,4,6 ~SB0\*,3\* MAR YDR SMR70--SMR00 MW30\* XD SML70-- SML00 **₹**0L MATL SML77 -SML07

F1G. 4

F/G. 5

中: MEMORY CELL 中,中:SWITCH

F/G. 6 DX41,43,45,47 ₩ US WD WDR35 ARYR34 TSW7 SW5 SW3 SW1 SAR44 SAR34 SB3T **SB31** MM30 北 EA SB3B - SB3B SB2T US A2 SB2B11L - YS40 SB1T 中 US 市 宁州 A1 SB1B NC NA -SBOT SBOT US HVCD MW30 宁山 元 A0 SBOB45 NB ND → SB0B SWO SW6 SW4 SW2 SH4R SH3L SH4L US - US - US -WDR34 WD WD WD WD DX40,42,44,46

F/G. 7(A)

F/G. 8(A)

F/G. 9(A)

SAP31

SAN3

SAP32

PP/PN WORD LINE

SELECTED

SB0\*

VCC

VSS

VSS

VCL

SB0T SB0B

VSS

F/G. 15

F/G. 16

FIG. 17

Jan. 24, 2006

P : P DIFFUSION D: N DIFFUSION LAYER VCH=+4V VCC=+3.3V VSS=0V VB1=-1V VBB=-2V

P\*P\* DIFFUSION D:N\* DIFFUSION

LAYER LAYER

VCH=+4V VCC=+3.3V VSS=0V VB1=-1V VBB=-2V

# F/G. 23(A)

Jan. 24, 2006

P P DIFFUSION D: N DIFFUSION LAYER VCH=+4V VCC=+3.3V VSS=0V VB1=-1V VBB=-2V

#### SEMICONDUCTOR MEMORY

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions 5 made by reissue.

## CROSS-REFERENCE TO RELATED APPLICATION

This application is a continuation of application Ser. No. 10 08/779,835, filed on Jan. 7, 1997, now U.S. Pat. No. 5,777,927, which is a continuation of application Ser. No. 08/574,104, filed Dec. 20, 1995 (now U.S. Pat. No. 5,604, 697) the entire disclosure of which is hereby incorporated by reference.

#### BACKGROUND OF THE INVENTION

The present invention relates to a semiconductor memory and, more particularly, to a large-capacity dynamic RAM (random access memory) and related techniques for making the memory larger, faster, more integrated and less expensive than before.

Data line dividing (i.e., layering) techniques are disclosed illustratively in U.S. Pat. Nos. 4,950,588, 5,301,142, 5,297, 102 and 5,404,338 as well as in Japanese Patent Laid-Open No. Hei 5-54634. Word line layering techniques are disclosed illustratively in U.S. Pat. Nos. 5,140,550 and 5,282, 175, and in Japanese Patents Laid-Open Nos. Hei 1-245489 and Hei 2-158995. Japanese Patent Laid-Open No. Hei 2-18785 discloses techniques for installing amplifier MOS-FETs between complementary data lines and complementary common data lines.

There exist semiconductor memories such as the dynamic RAM having as its basic components memory arrays each including a plurality of word lines and bit lines intersecting orthogonally and a large number of dynamic memory cells located in lattice fashion at the intersection points between the intersecting word and bit lines. In recent years, dynamic RAMs have been getting larger in capacity and more integrated in scale at rapid pace. Varieties of techniques are being disclosed to accelerate the trend.

For instance, the so-called layered word line structure is proposed in "ISSCC (International Solid-State Circuits Conference) '93 Digest of Technical Papers, Session 3" 45 (Feb. 24, 1993; pp. 50–51). The proposed structure (called the first conventional example hereunder) involves arranging main word lines in parallel with sub-word lines, the pitch between the main word lines being made an integer multiple of that between the sub-word lines. The arrangement is 50 intended to enlarge the wiring pitch of a metal wiring layer constituting the main word lines and thereby to enhance the degree of circuit integration of dynamic RAMS.. In another example (called a second conventional example), Japanese Patent Publication No. Hei 4-59712 discloses the so-called 55 layered I/O structure in which designated bit lines are connected to main common I/O lines by way of relatively short sub-common I/O lines. The structure is intended to alleviate the loads on sense amplifiers and thereby speed up read operations of dynamic RAMs.

In addition, U.S. Pat. No. 5,274,595 issued on Dec. 28, 1993 discloses a method (a third conventional example) for connecting sub-common I/O lines to main common I/O lines via a plurality of summing direct sense type sub-amplifiers, the sub-amplifiers being located where word line shunts and 65 sense amplifiers intersect. The disclosed method is intended to minimize the increase in the layout area for accommo-

2

dating a plurality of sub-amplifiers while speeding up the operation of dynamic RAMs.

#### SUMMARY OF THE INVENTION

The first conventional example involving the layered word line structure is characterized by the presence of a self-boot type word line driving circuit for selectively driving sub-word lines in accordance with a row selection signal and a word line driving current supply signal. The row selection signal is transmitted over main word lines, and the word line driving current supply signal is transmitted over word line driving current supply signal lines intersecting the sub-word lines orthogonally. The fact that the word line driving circuit is a self-boot type means that it takes time to bring the word line driving current supply signal to the active level after the main word lines are driven to the active level. This poses constraints on the effort to improve the access time of dynamic RAMs in read mode. Because the common I/O lines are not layered, the load on the sense amplifiers increases, which hampers the improvement of access time. In the second conventional example involving the layered I/O structure, the word lines are not layered. This necessitates narrowing the wiring pitch of the metal wiring layer constituting the word lines, which in turn restricts the effort to boost the degree of circuit integration of dynamic RAMs. In the third conventional example, a plurality of summing direct sense type sub-amplifiers connect the subcommon I/O lines to the main common I/O lines. This example entails word shunt-based word line division but does not adopt any layered word line structure. This poses constraints on the attempts to boost the degree of circuit integration of dynamic RAMs. Because the sub-common I/O lines are identical in length to the main common I/O lines, the third conventional example does not constitute a substantially layered I/O structure.

In short, the conventionally fabricated dynamic RAMS adopt layered structures only partially and sporadically. A comprehensive layered structure covering all word lines, bit lines and common I/O lines has yet to be implemented. The fact that full benefits of the layered structure have yet to be practically appreciated discourages general attempts to boost the operating speed of dynamic RAMs, to enlarge their scale and to reduce their costs.

It is therefore an object of the present invention to provide a dynamic RAM taking full advantage of the benefits of the layered structure so that the semiconductor memory will be enhanced in operation speed, boosted in the degree of circuit integration and lowered in manufacturing cost.

Other objects, features and advantages of the present invention will become apparent in the following specification and accompanying drawings.

In carrying out the invention and according to one aspect thereof, there is provided a semiconductor memory such as a dynamic RAM having a memory mat divided into a plurality of units or sub-memory mats. Each sub-memory mat comprises: a memory array having sub-word lines and sub-bit lines intersecting orthogonally and dynamic memory cells located in lattice fashion at the intersection points between the intersecting sub-word and sub-bit lines; a sub-word line driver including unit sub-word line driving circuits corresponding to the sub-word lines; a sense amplifier including unit amplifier circuits and column selection switches corresponding to the sub-bit lines; and sub-common I/O lines to which designated sub-bit lines are connected selectively via the column selection switches. The sub-memory mats are arranged in lattice fashion. Above the

3

sub-memory mats is a layer of: main word lines and column selection signal lines intersecting orthogonally, the main word lines having a pitch that is an integer multiple of the pitch of the sub-word lines, the column selection signal lines having a pitch that is an integer multiple of the pitch of the 5 sub-bit lines; and main common I/O lines to which designated sub-common I/O lines are connected selectively. Each of the unitsub-word line driving circuits in the sub-word line driver is a CMOS static driving circuit comprising: a p-channel first MOSFET which is furnished interposingly 10 between the sub-word line driving signal line and the corresponding sub-word line and of which the gate is connected to an inverted signal line of the corresponding main word line; an n-channel second MOSFET which is furnished interposingly between the sub-word line and a 15 grounding potential and of which the gate is connected to an inverted signal line of the corresponding main word line; and an n-channel third MOSFET which is furnished in parallel with the first MOSFET and of which the gate is connected to an inverted signal line of the corresponding 20 main word line. The sub-main amplifiers for selectively connecting the designated sub-common I/O lines to the main common I/O lines are each a pseudo-direct sense type sub-amplifier comprising: a read differential MOSFET of which the gate is connected to the uninverted and inverted 25 signal lines of the corresponding sub-common I/O line and of which the drain is connected to the inverted and uninverted signal lines of the corresponding main common I/O line; and a write switching MOSFET furnished interposingly between the uninverted signal lines as well as between the 30 inverted signal lines of the sub-common and main common I/O lines. The sub-main amplifiers are located in the region where the sub-word line driver and the sense amplifier intersect.

In the semiconductor memory of the constitution outlined 35 above, the CMOS static driving circuit in each of the unit sub-word line driving circuits drives simultaneously to the active level both a row selection signal transmitted over the main word lines and a sub-word line driving signal transmitted via the sub-word driving signal lines. This arrange- 40 ment speeds up the sub-word line selecting operations. Because the sub-main amplifiers are pseudo-direct sense type sub-amplifiers located in the region where the sub-word line driver and the sense amplifier intersect, the read operation of the semiconductor memory such as the dynamic 45 RAM is boosted without any increase in the memory layout area. Furthermore, a comprehensive layered structure involving all word lines, bit lines and common I/O lines constitutes a semiconductor memory taking full advantage of the beneficial effects of the structure. This provides 50 wholesale improvements in the operation speed, in the degree of circuit integration and in the scale of the semiconductor memory as well as sweeping reductions in its manufacturing cost.

#### BRIEF DESCRIPTION OF THE DRAWINGS

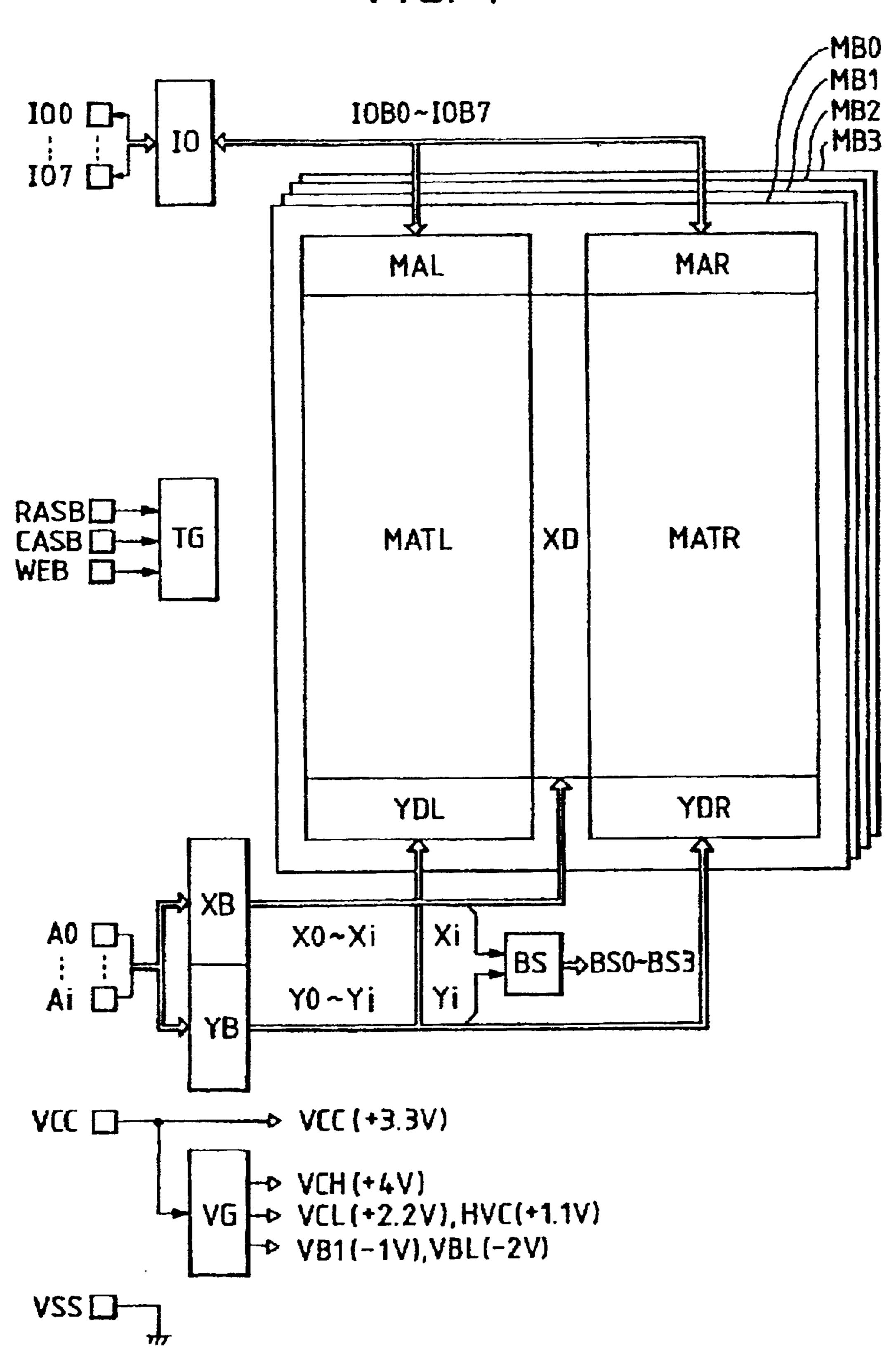

- FIG. 1 is a block diagram of a dynamic RAM embodying the invention;

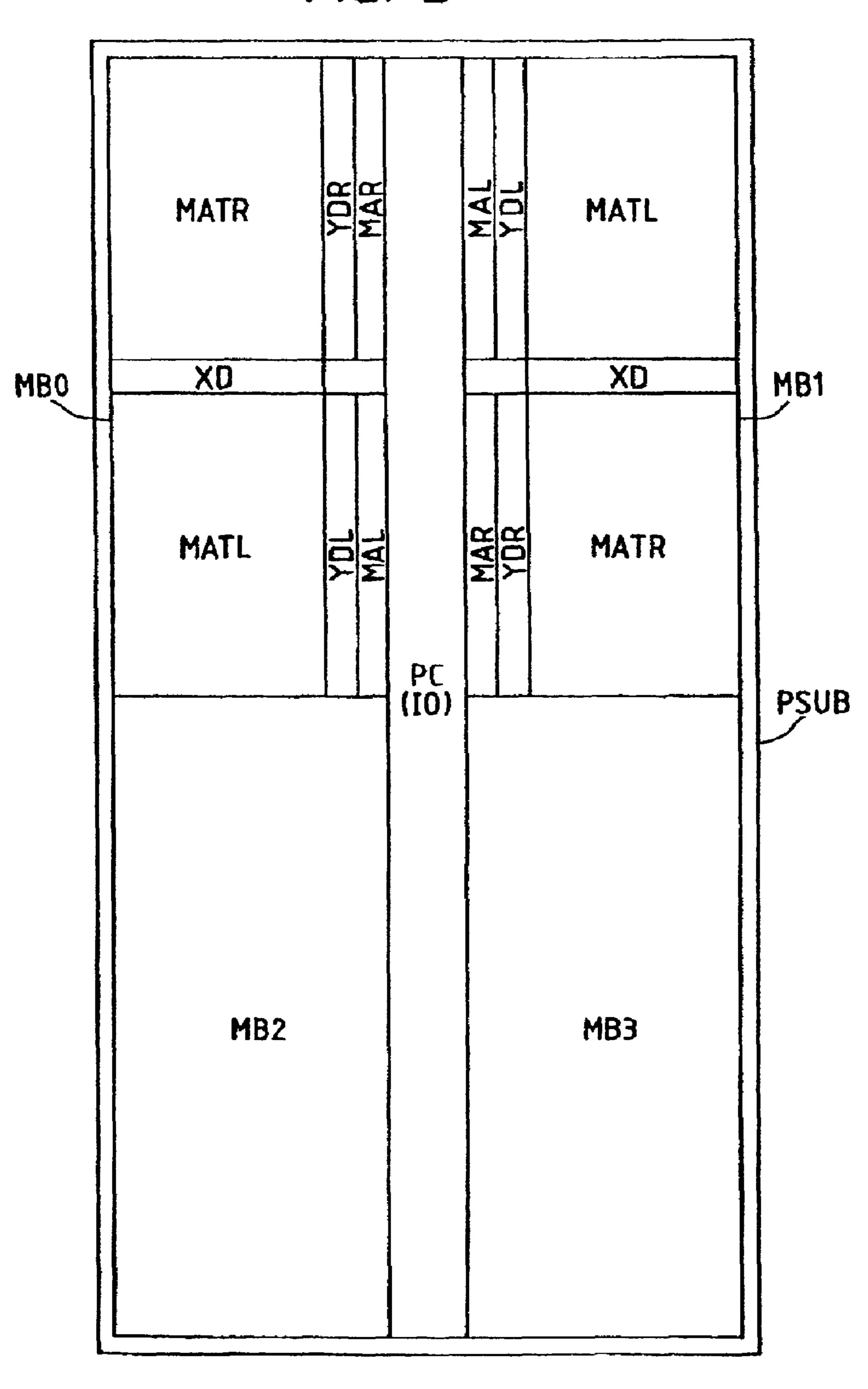

- FIG. 2 is a substrate layout view of the dynamic RAM in FIG. 1;

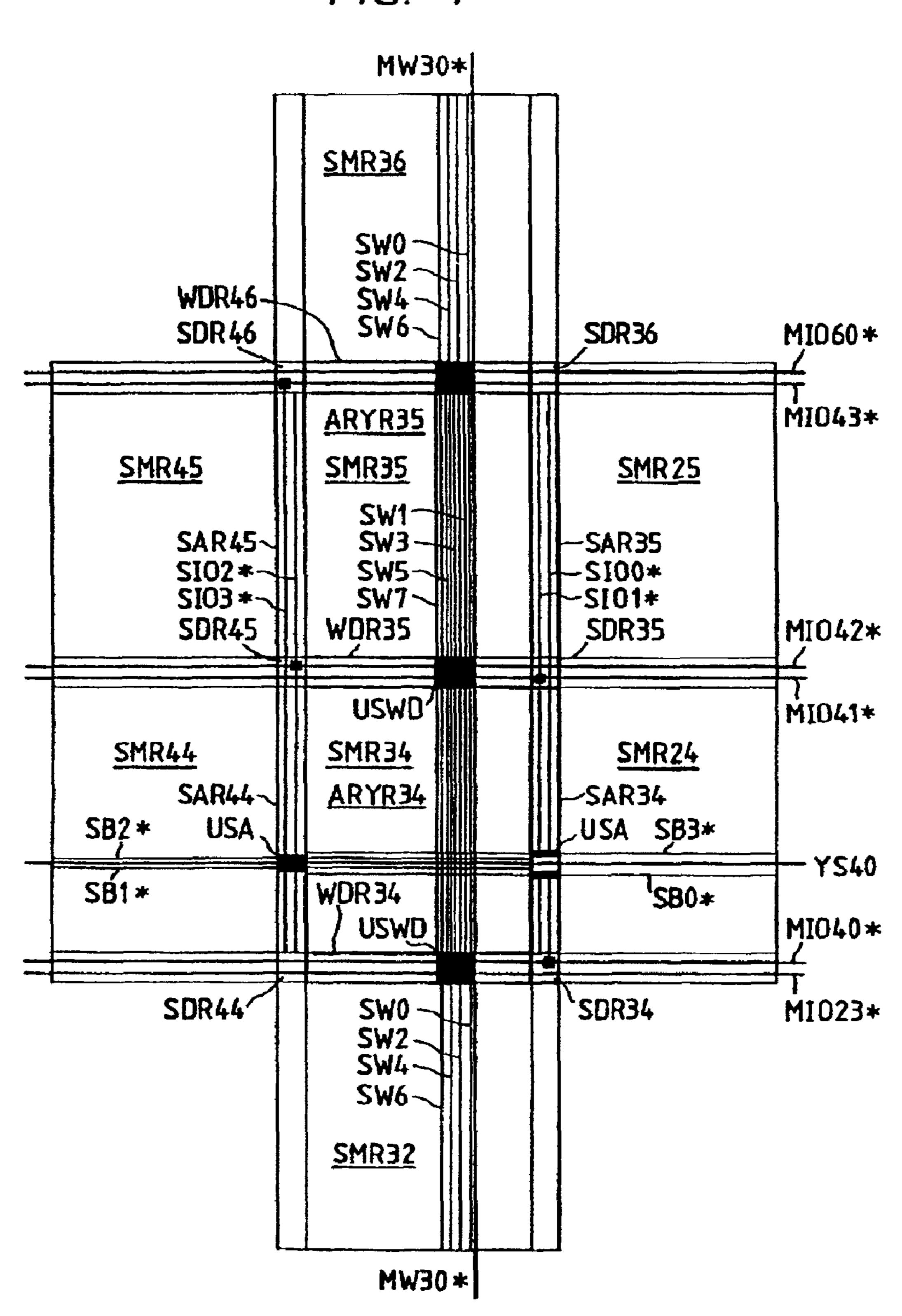

- FIG. 3 is a block diagram of a memory block included in the dynamic RAM of FIG. 1;

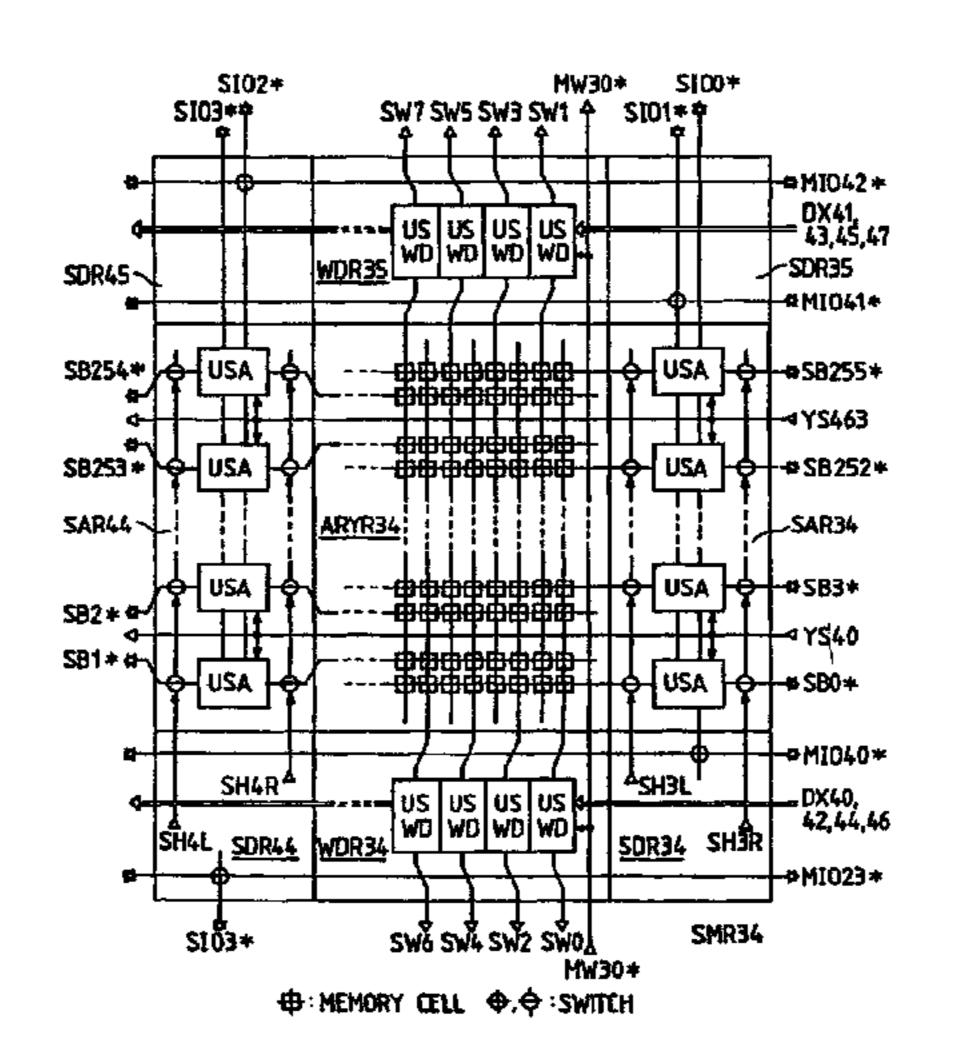

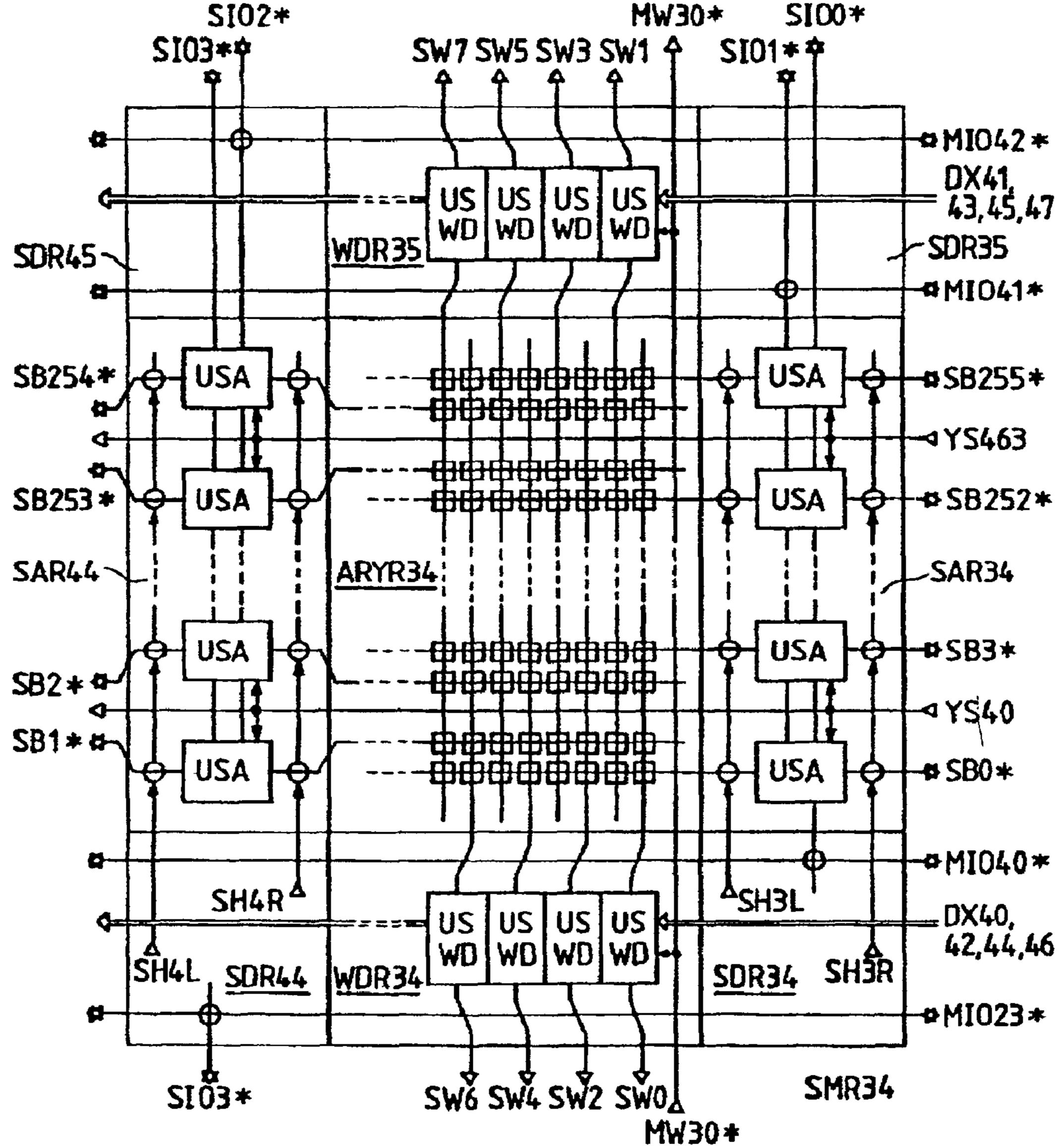

- FIG. 4 is a partial block diagram of sub-memory mats included in the memory block of FIG. 3;

- FIG. 5 is a partial connection diagram of the sub-memory mats in FIG. 4;

4

- FIG. 6 is a partial circuit diagram of a memory array and peripherals included in the sub-memory mats of FIG. 4;

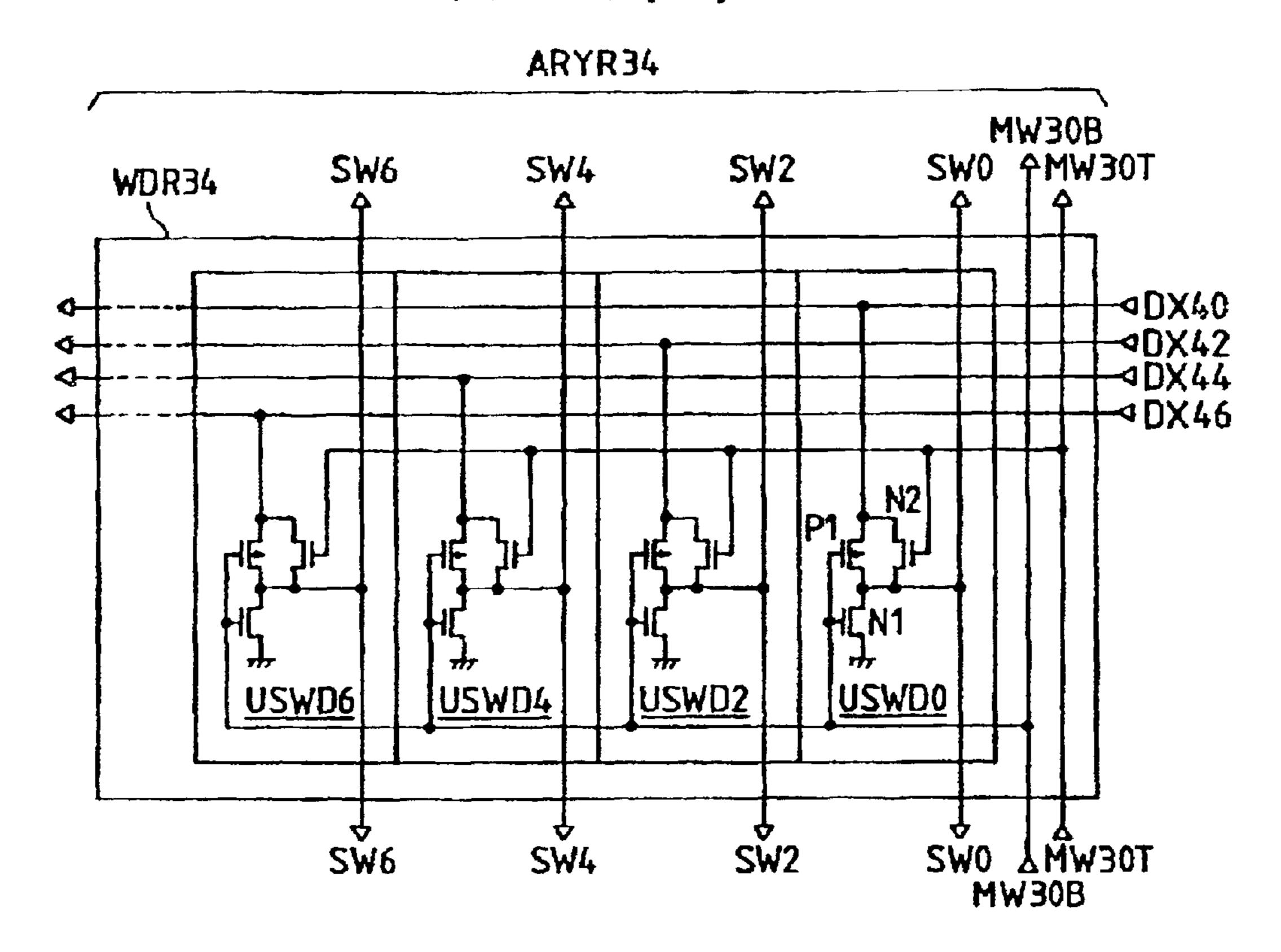

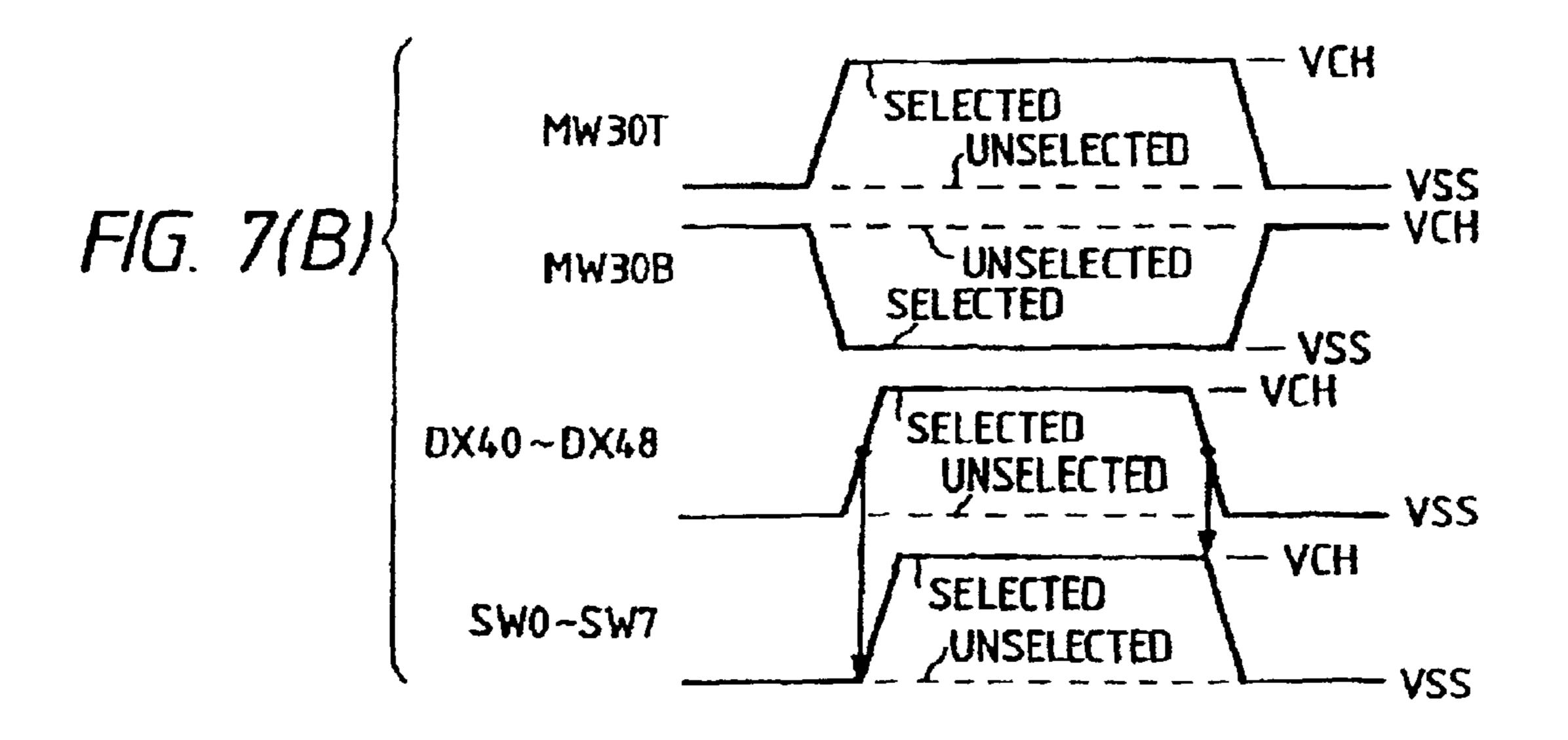

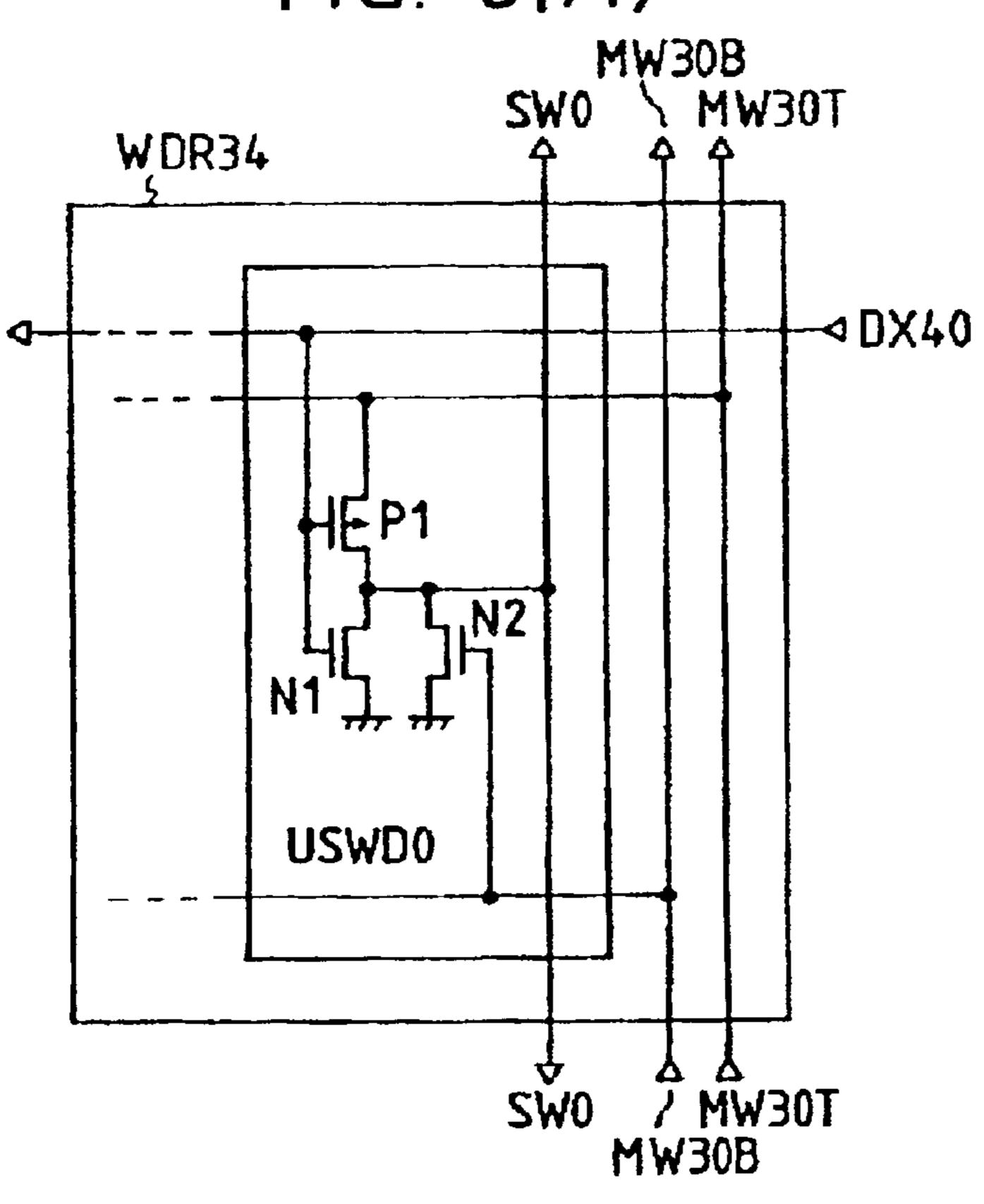

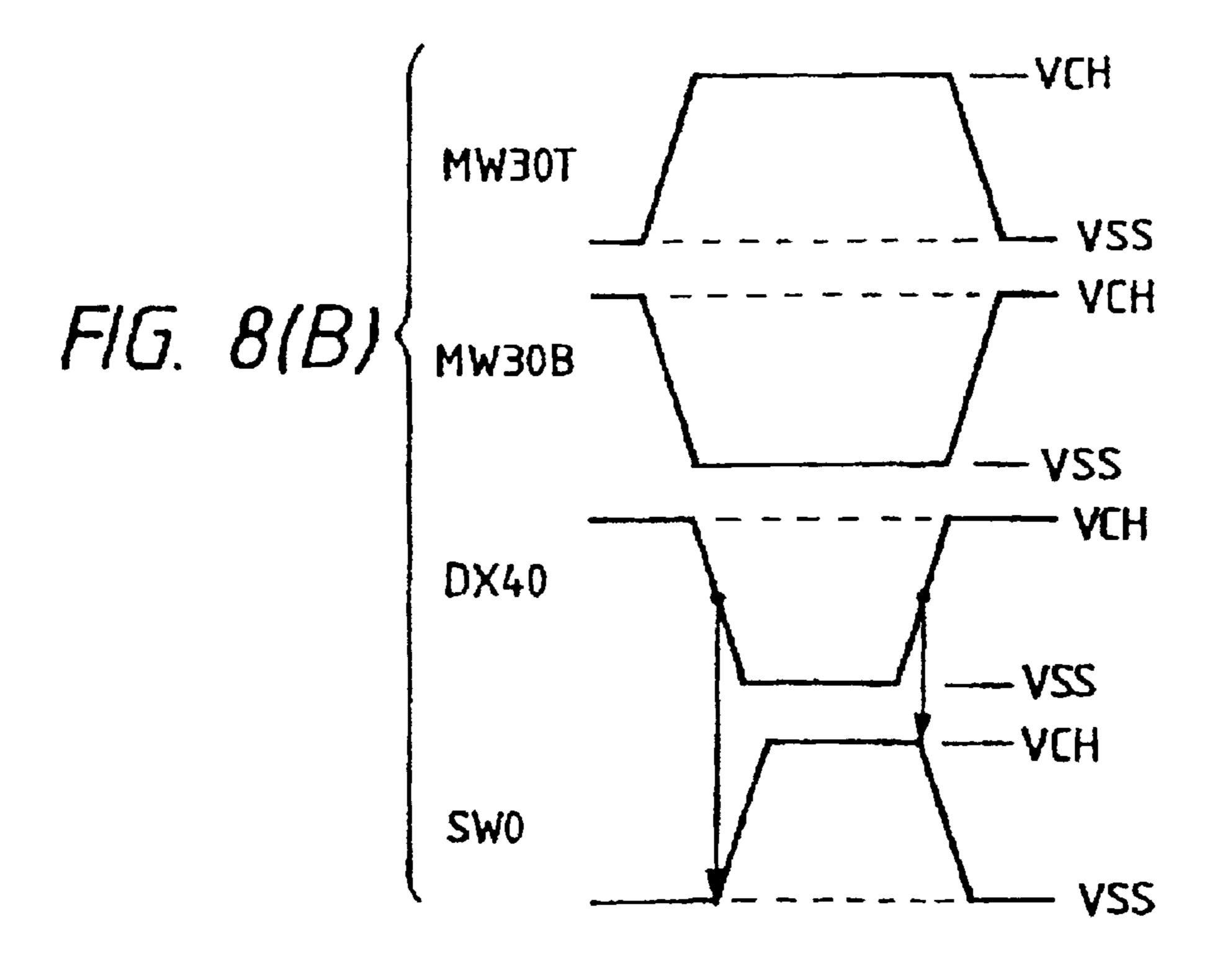

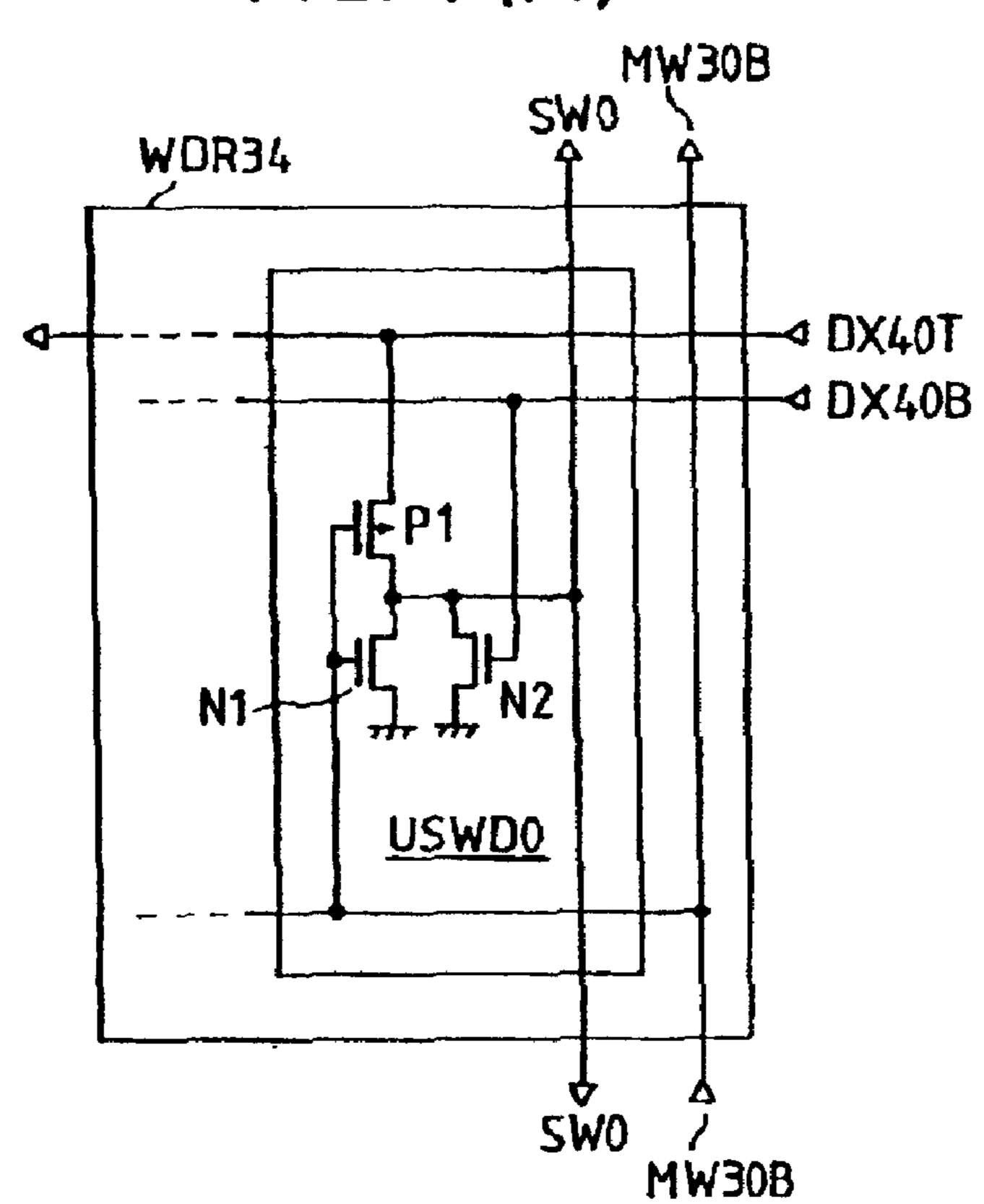

- FIG. 7(A) and FIG. 7(B) are a set of a partial circuit diagram and a signal waveform diagram regarding a first example of a sub-word line driver included in the submemory mats of FIG. 4;

- FIG. 8(A) and FIG. 8(B) are a set of a partial circuit diagram and a signal waveform diagram regarding a second example of a sub-word line driver included in the submemory mats of FIG. 4;

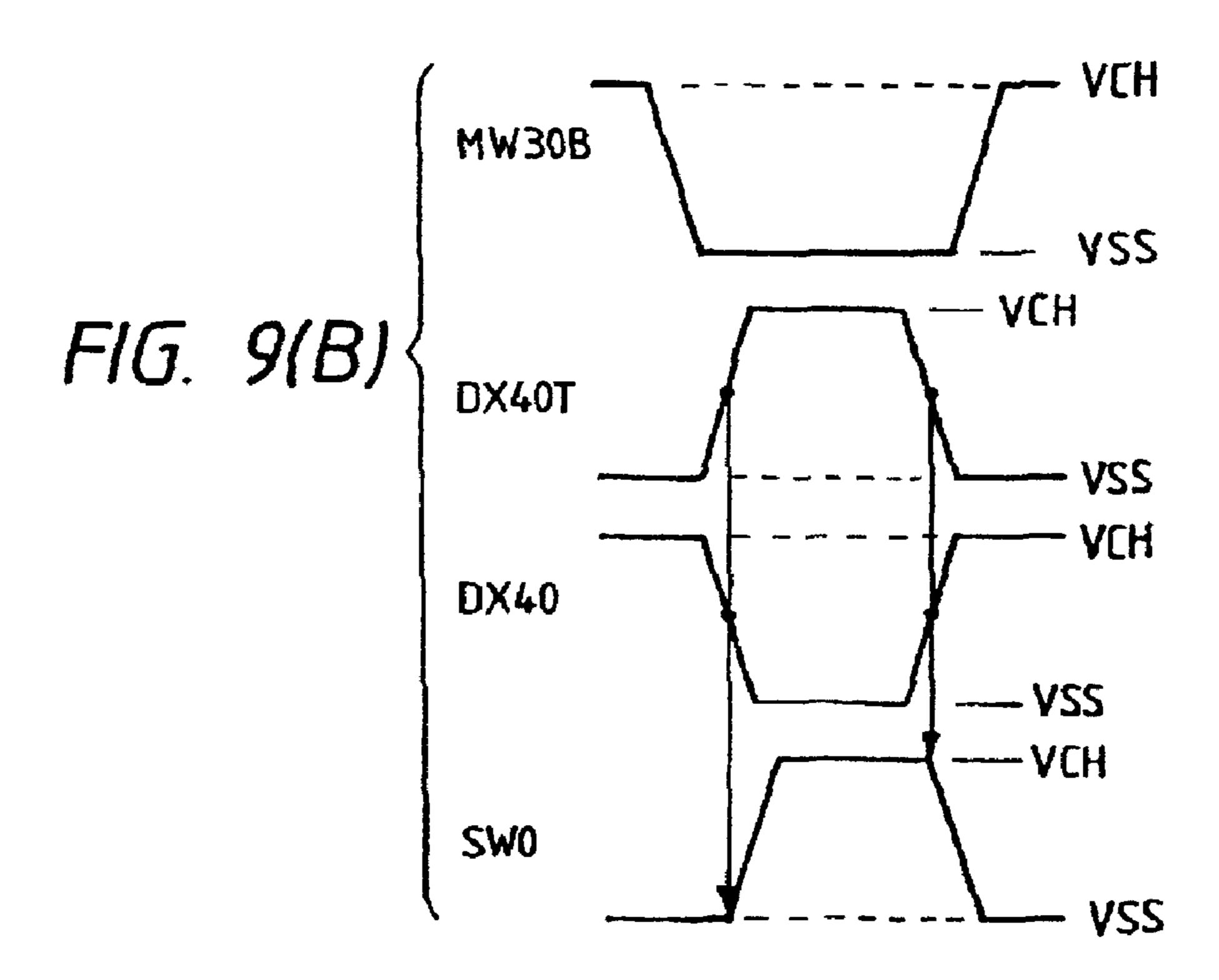

- FIG. 9(A) and FIG. 9(B) are a set of a partial circuit diagram and a signal waveform diagram regarding a third example of a sub-word line driver included in the submemory mats of FIG. 4;

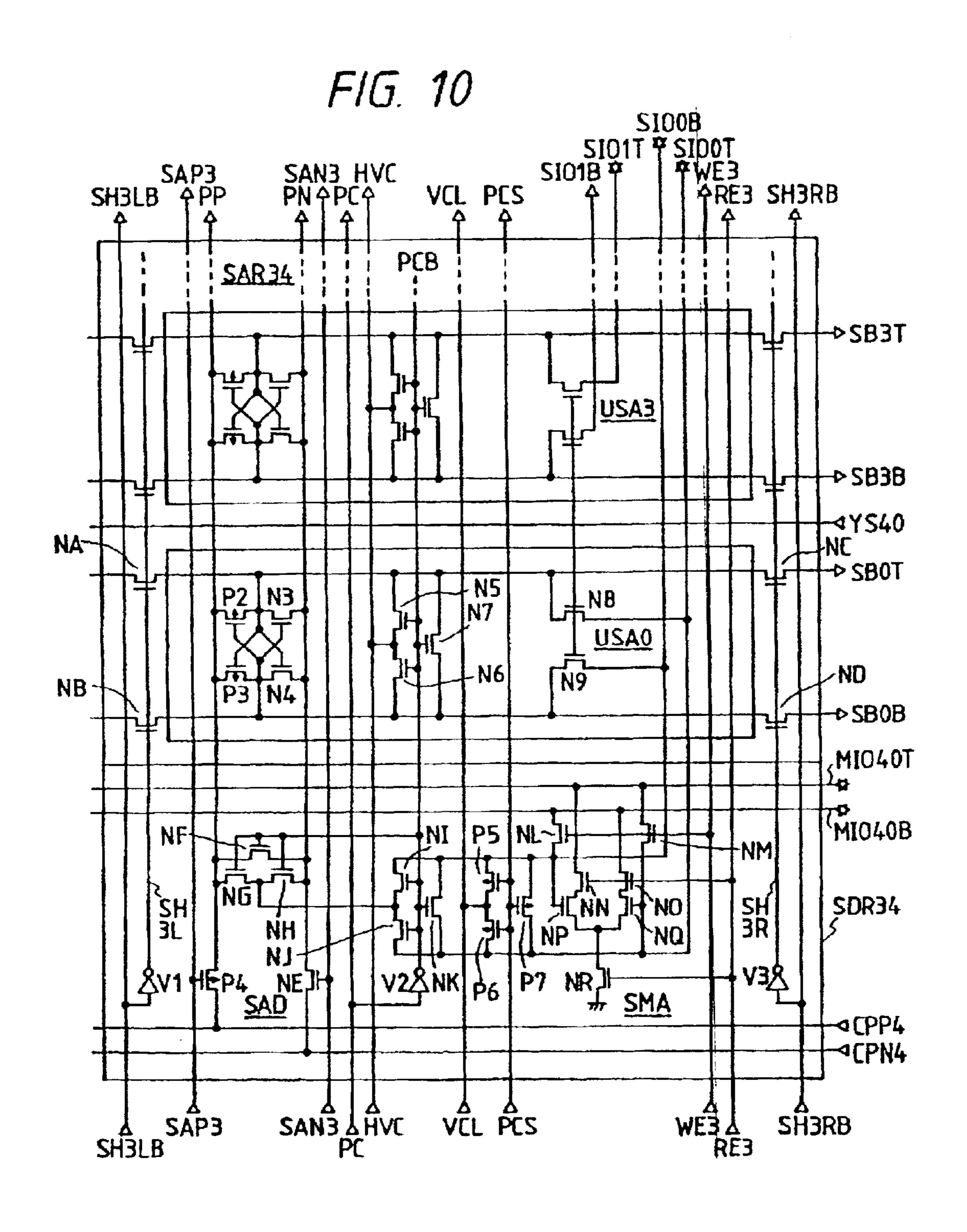

- FIG. 10 is a partial circuit diagram of a first example of a sense amplifier and a first example of a sense amplifier driver included in the sub-memory mats of FIG. 4;

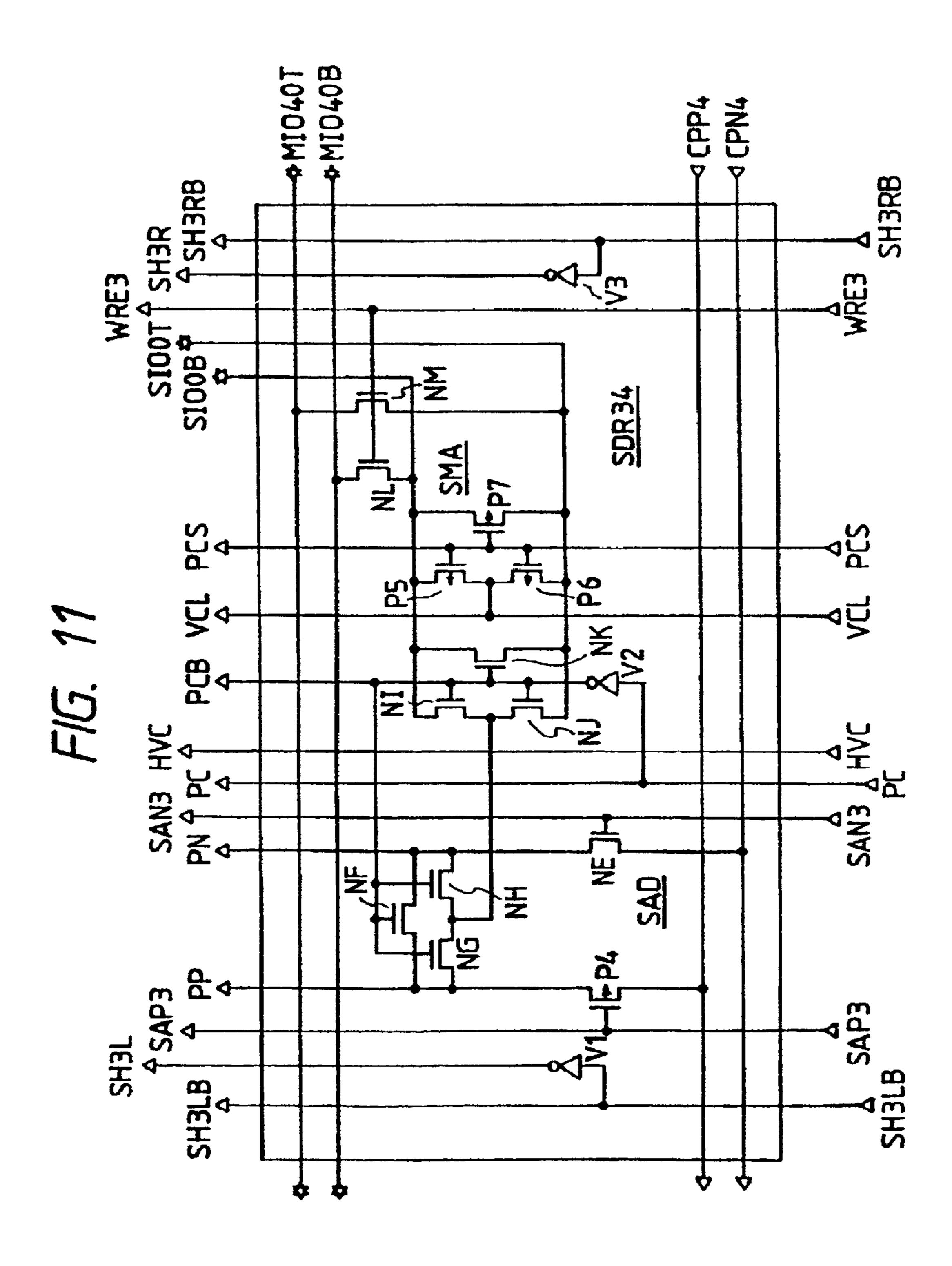

- FIG. 11 is a partial circuit diagram of a second example of a sense amplifier driver included in the sub-memory mats of FIG. 4;

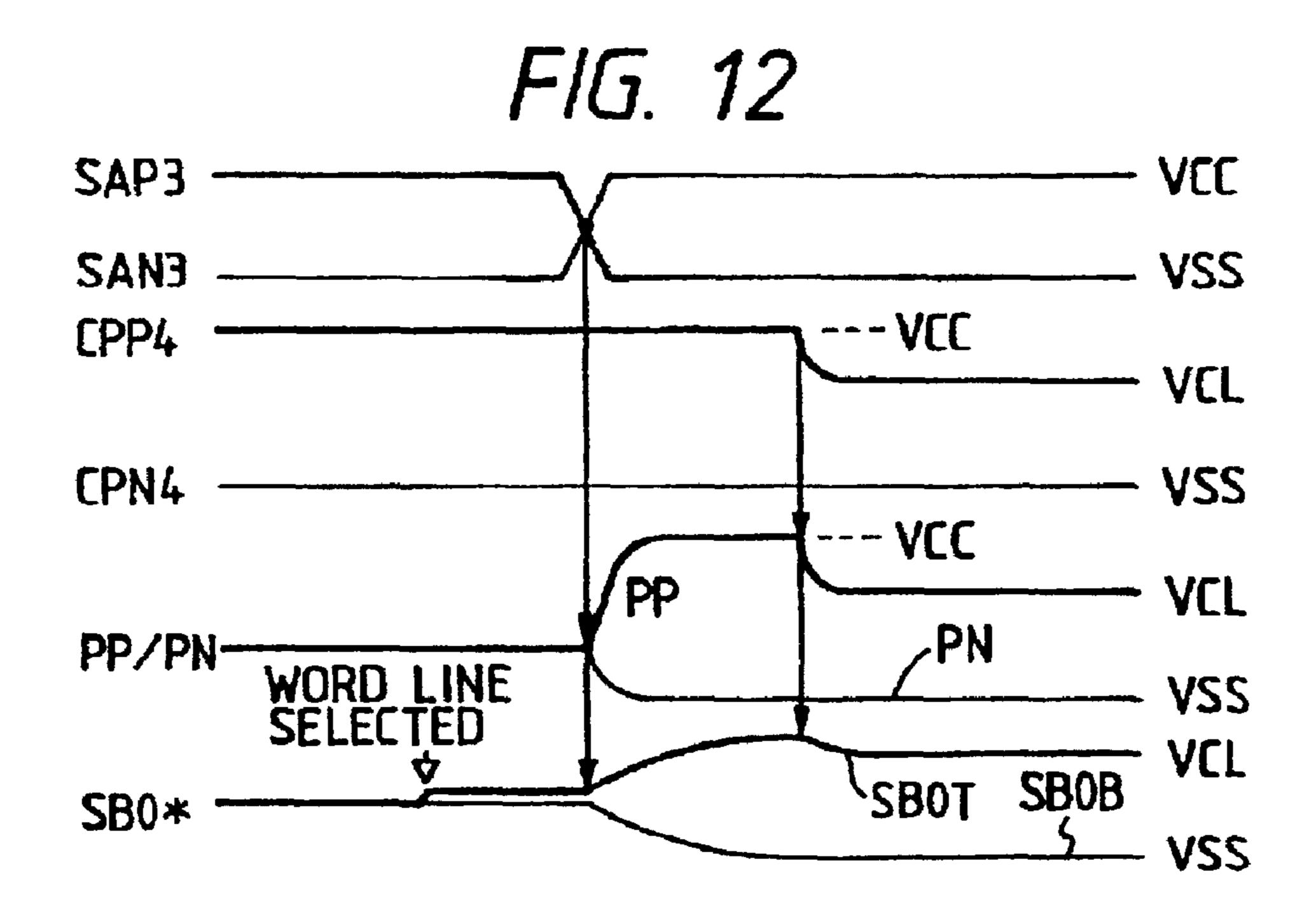

- FIG. 12 is a signal waveform diagram regarding the sense amplifier driver in FIGS. 10 and 11;

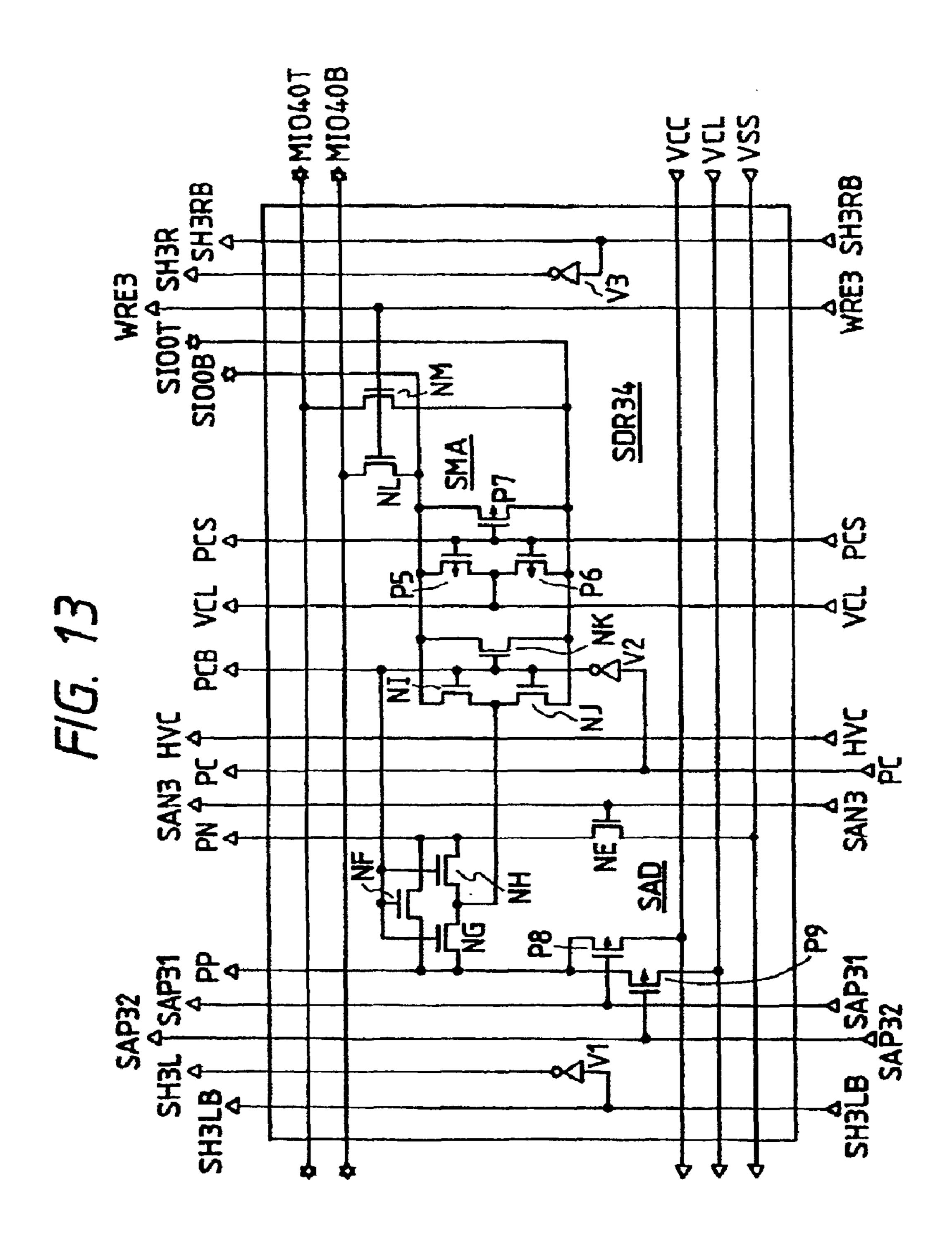

- FIG. 13 is a partial circuit diagram of a third example of a sense amplifier driver included in the sub-memory mats of FIG. 4;

- FIG. 14 is a signal waveform diagram regarding the sense amplifier driver in FIG. 13;

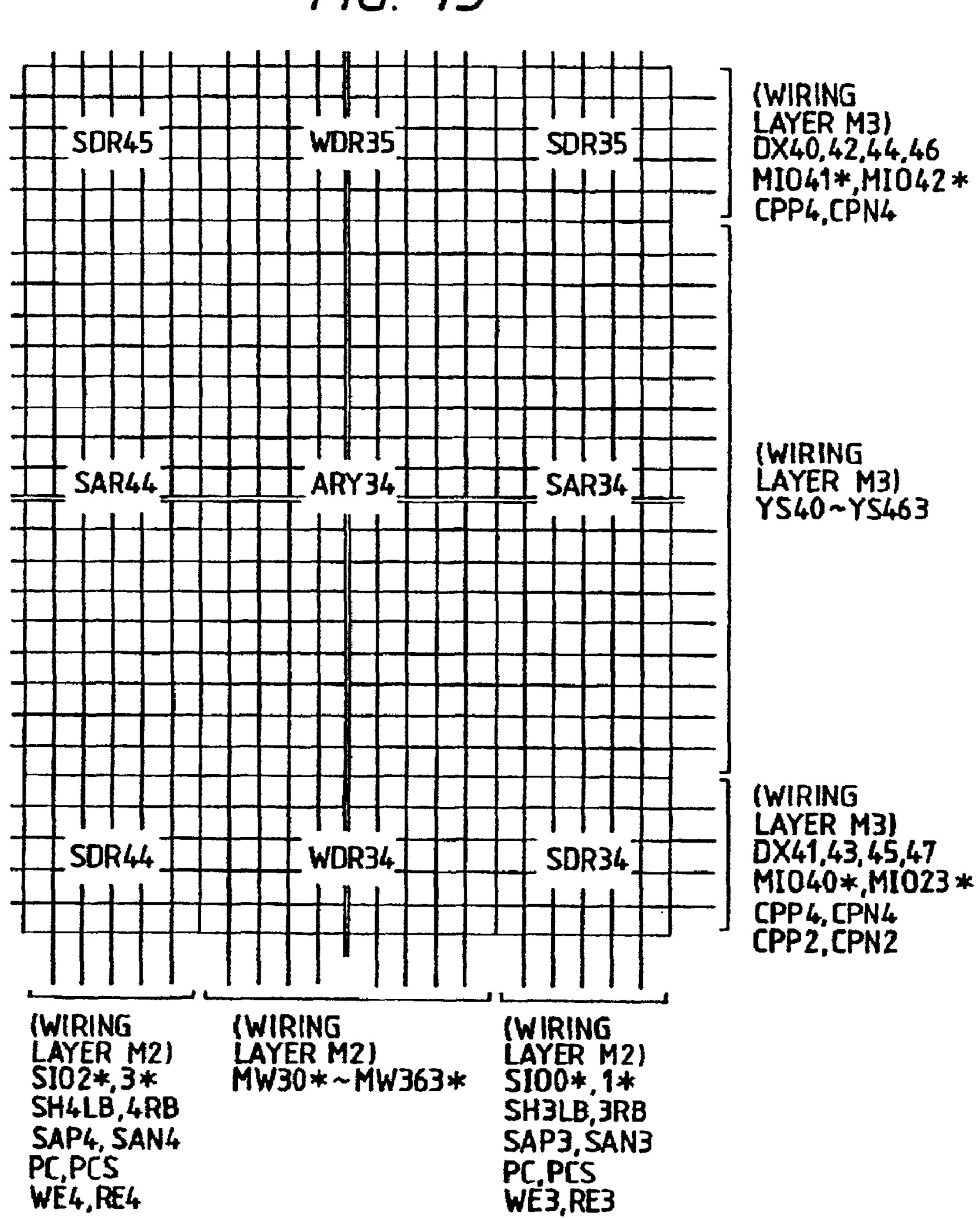

- FIG. 15 is a plan view of typical metal wiring layers comprising a memory array and peripherals included in the sub-memory mats of FIG. 4;

- FIG. 16 is a partial plan view of a sub-word line driver included in the sub-memory mats of FIG. 4;

- FIG. 17 is a partial plan view of a sense amplifier and a sense amplifier driver included in the sub-memory mats of FIG. 4;

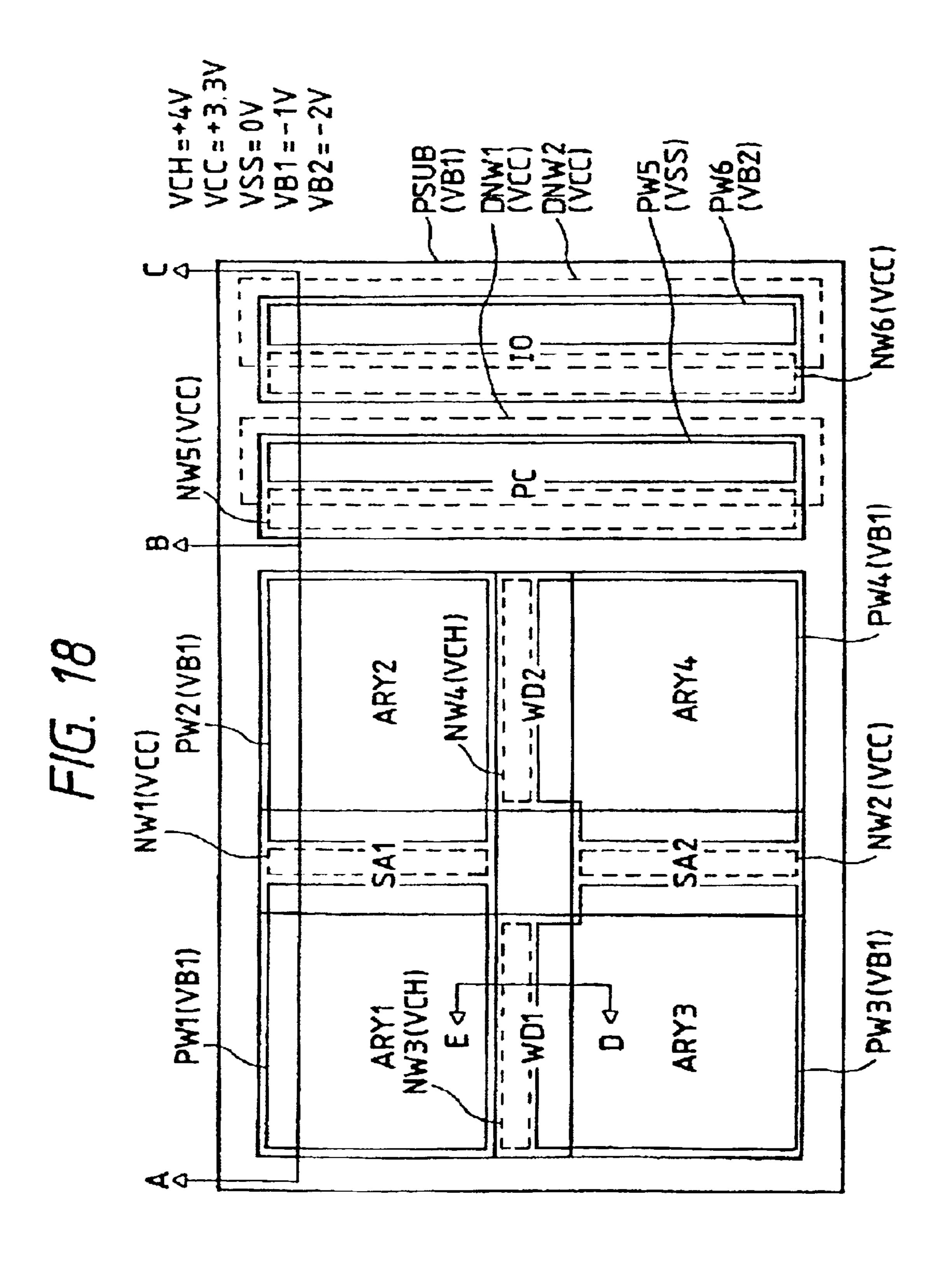

- FIG. 18 is a symbolic plan view of a first example of memory arrays and peripherals constituting each submemory mat in the dynamic RAM of FIG. 1;

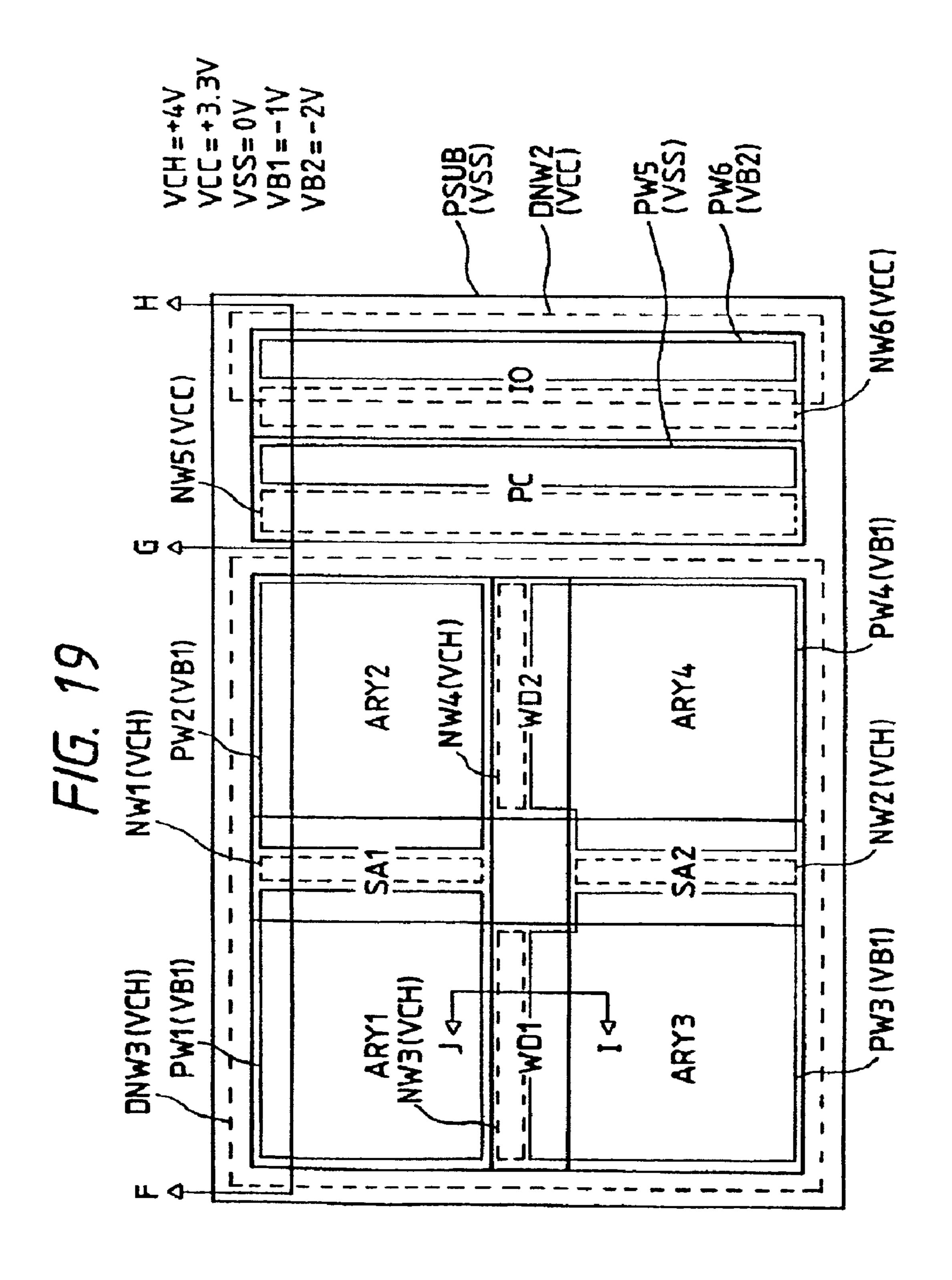

- FIG. 19 is a symbolic plan view of a second example of memory arrays and peripherals constituting each submemory mat in the dynamic RAM of FIG. 1;

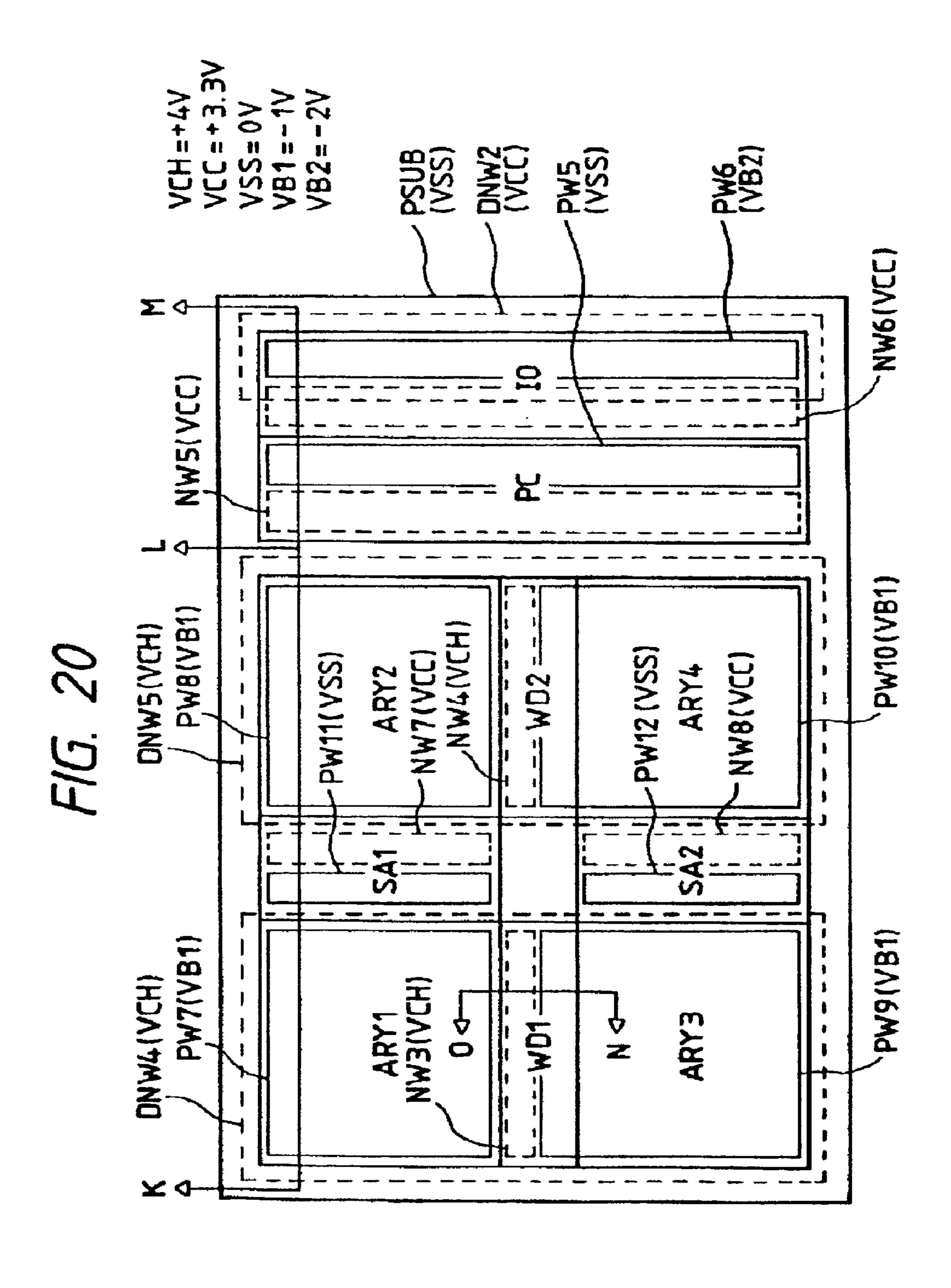

- FIG. 20 is a symbolic plan view of a third example of memory arrays and peripherals constituting each submemory mat in the dynamic RAM of FIG. 1;

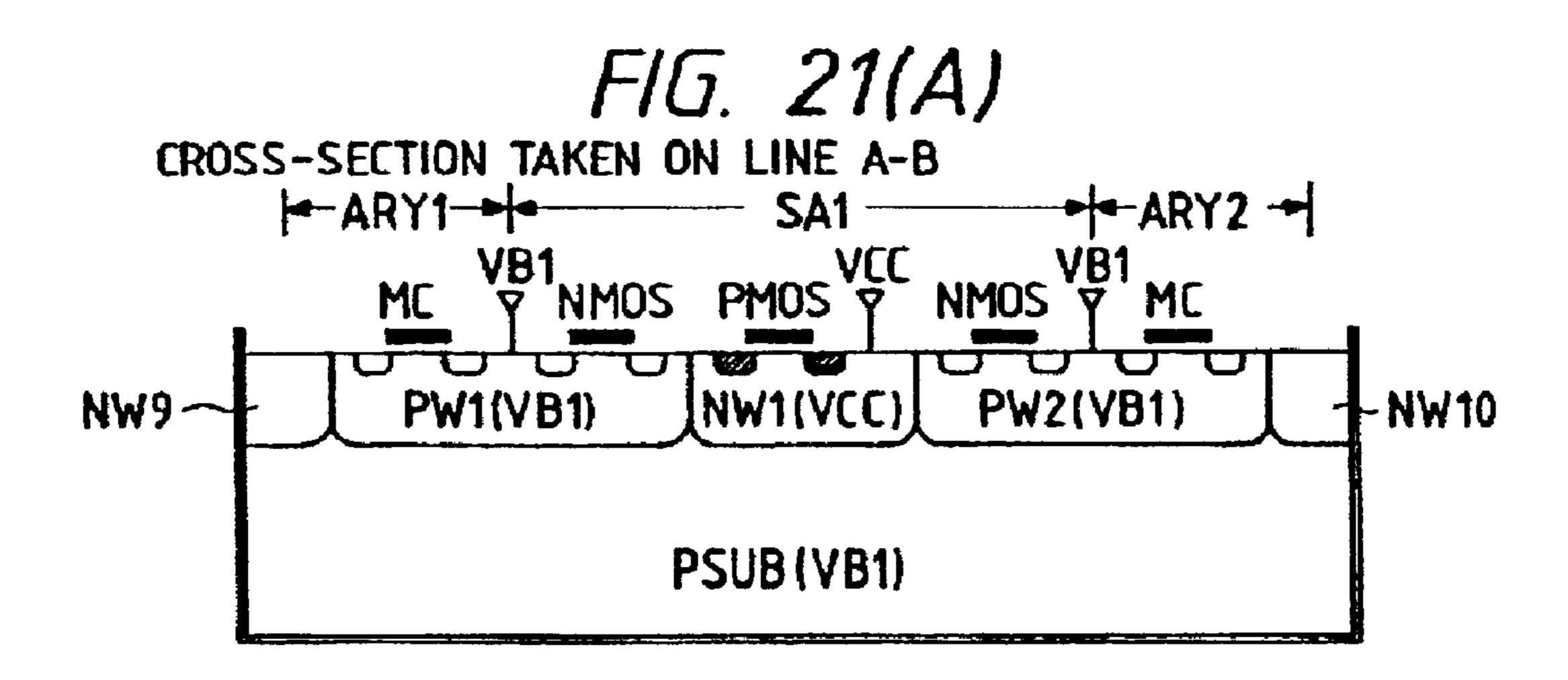

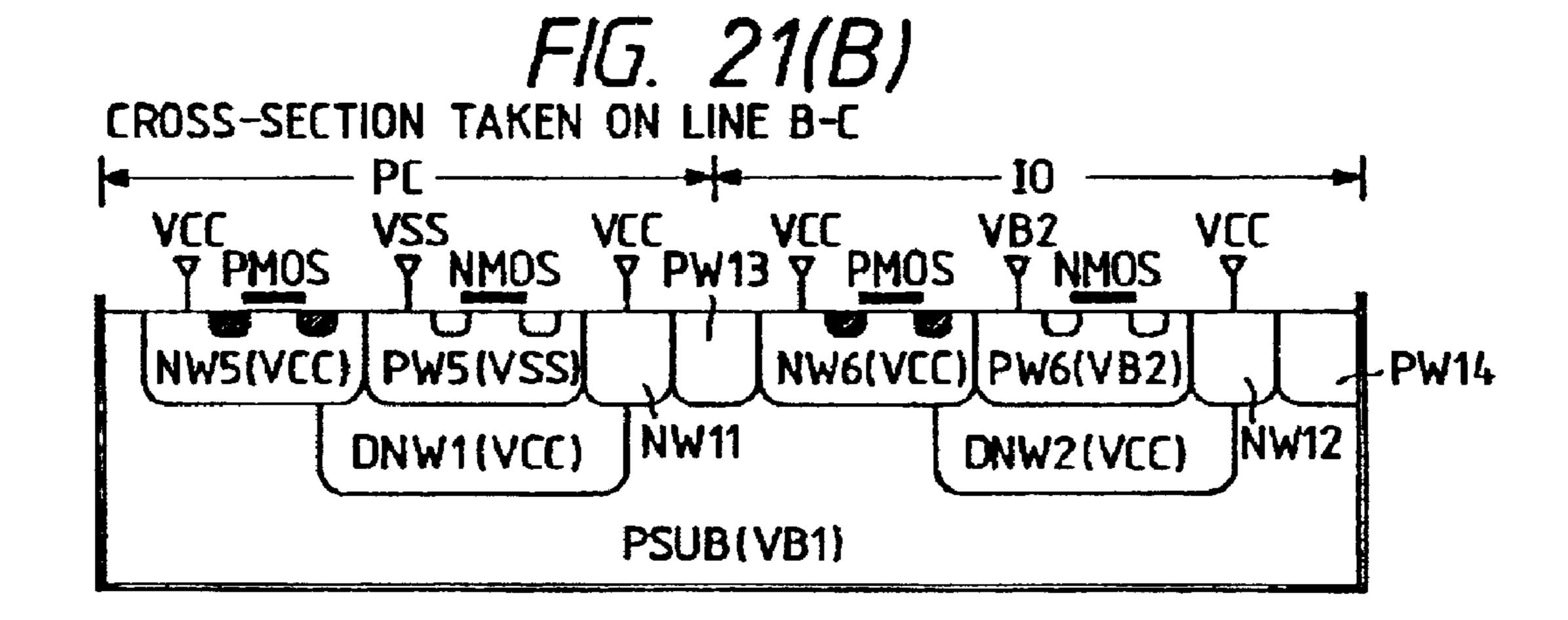

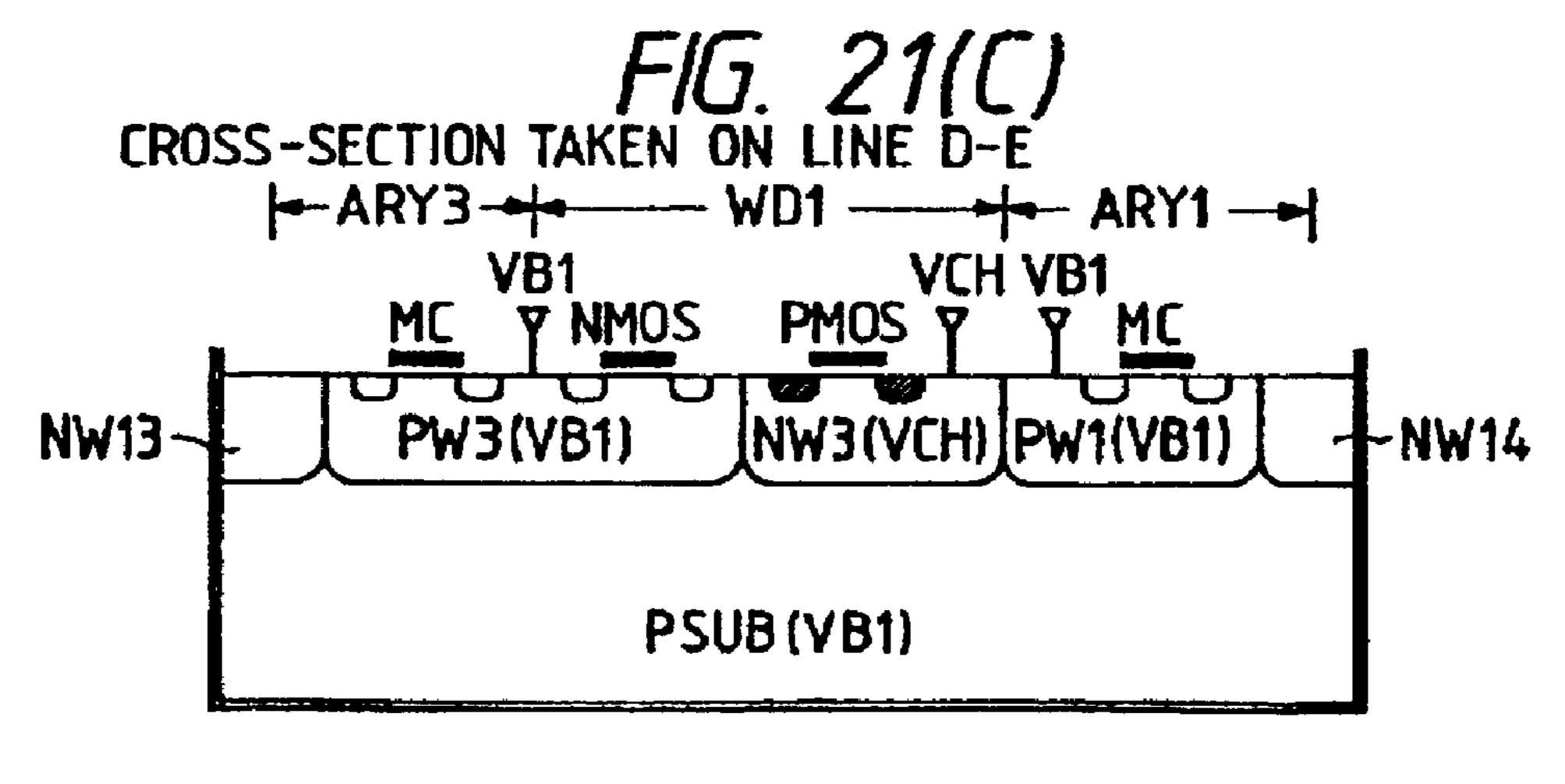

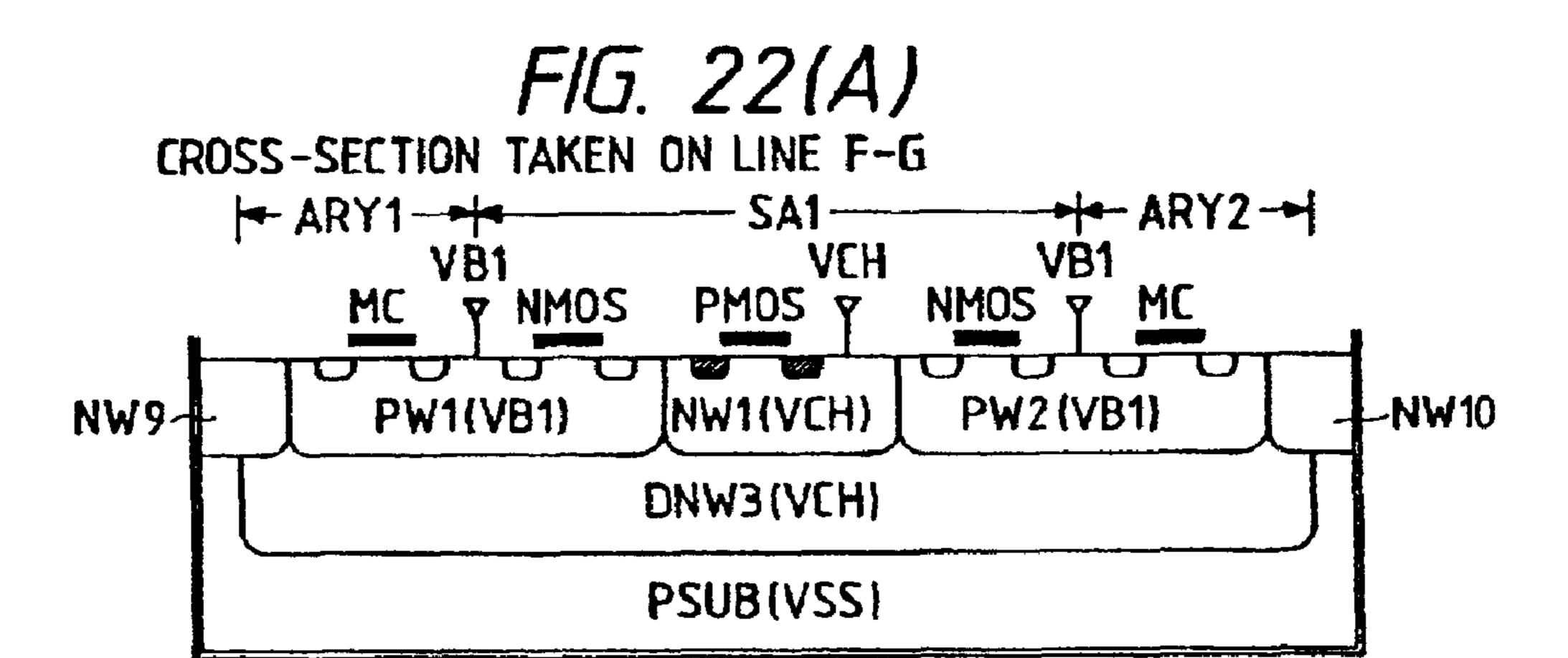

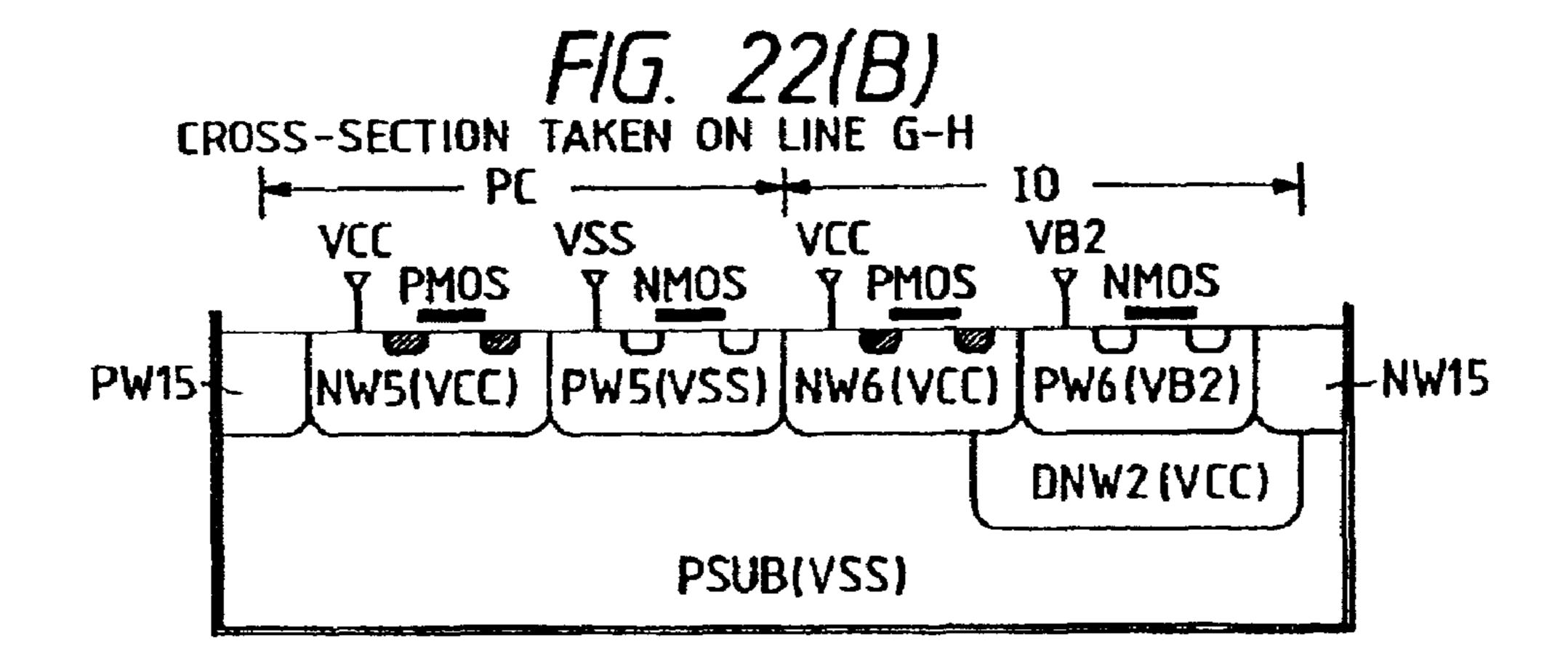

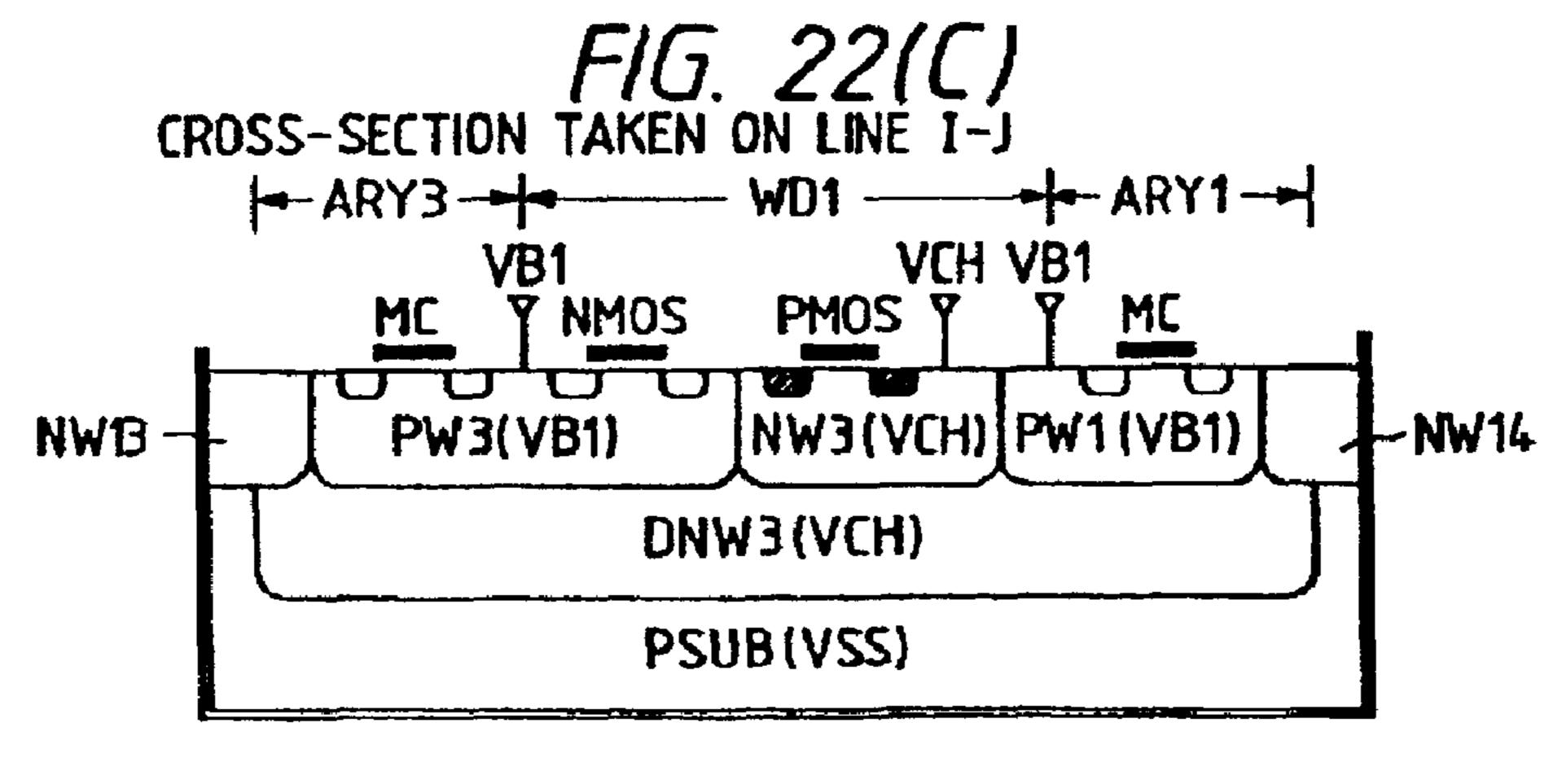

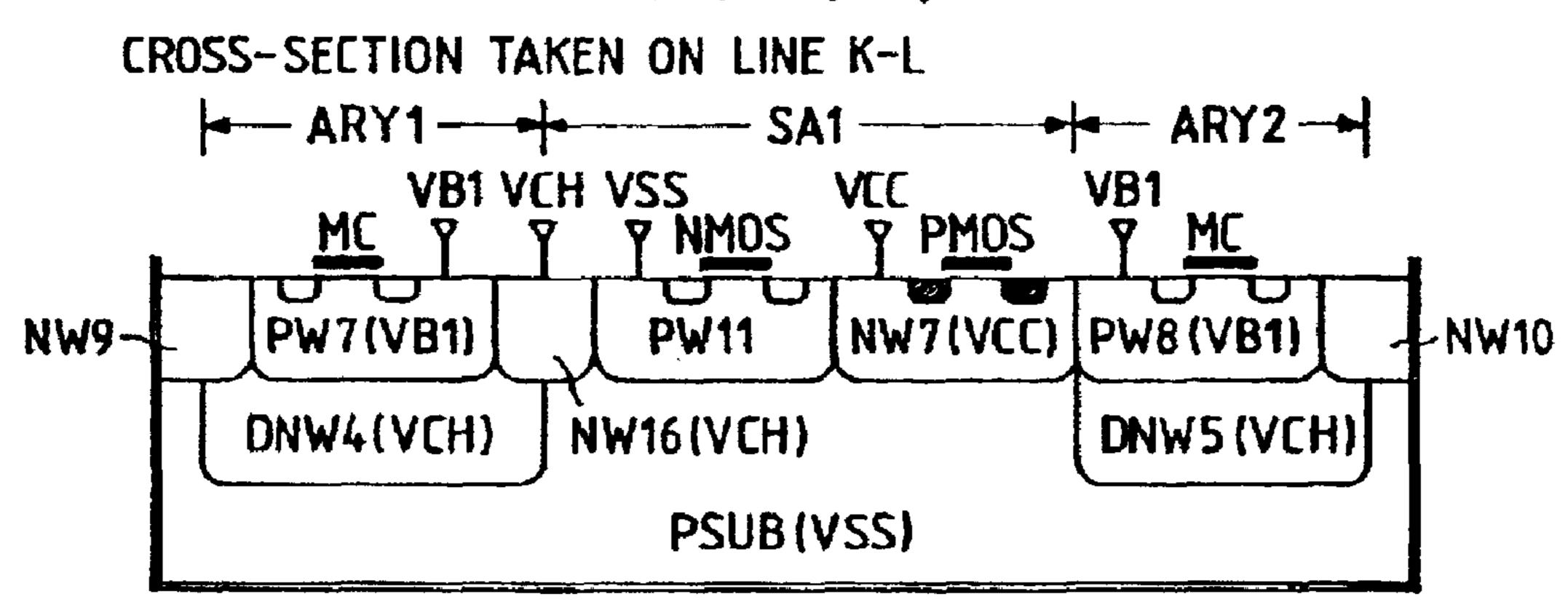

- FIGS. 21(A), 21(B) and 21(C) are cross-sectional views of the memory arrays and peripherals in FIG. 18;

- FIGS. 22(A), 22(B) and 22(C) are cross-sectional views of the memory arrays and peripherals in FIG. 19; and

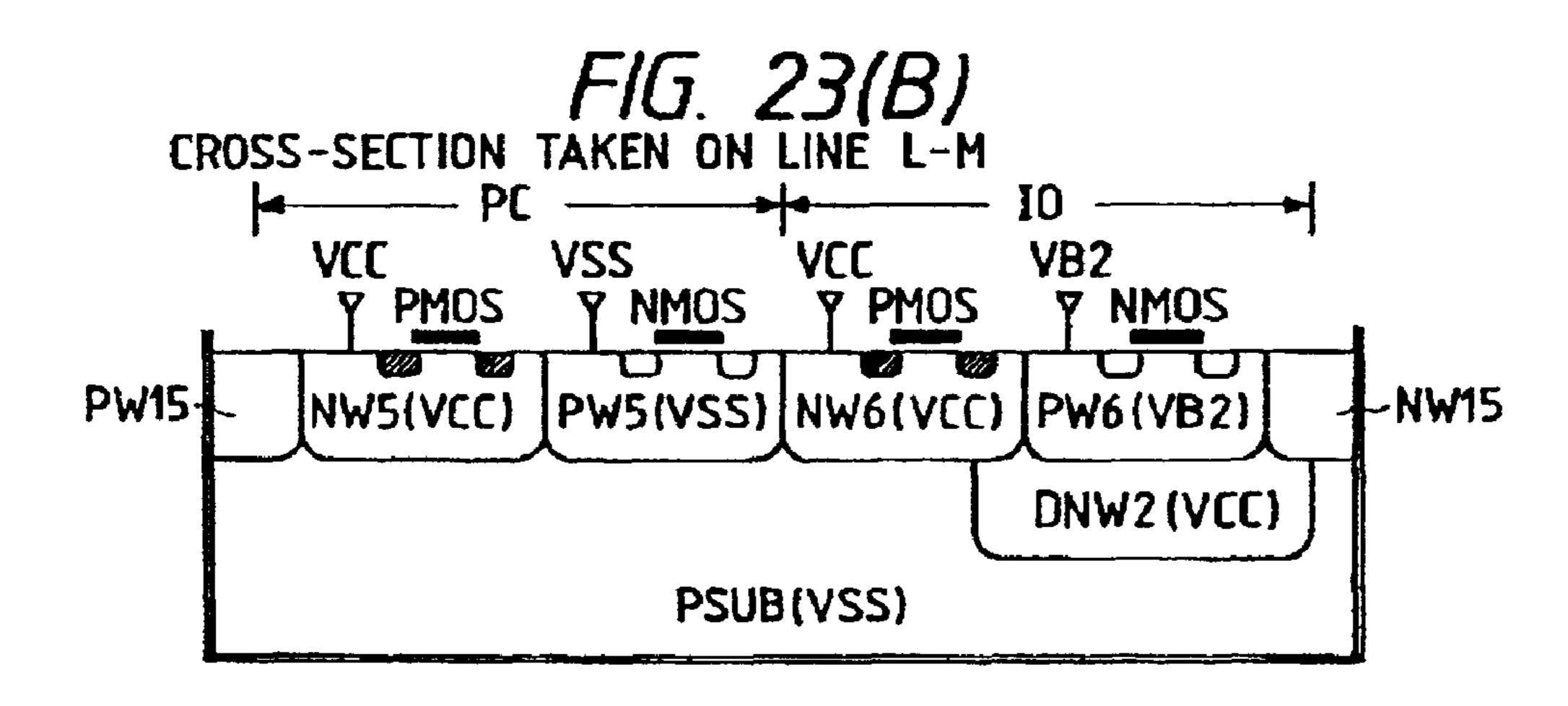

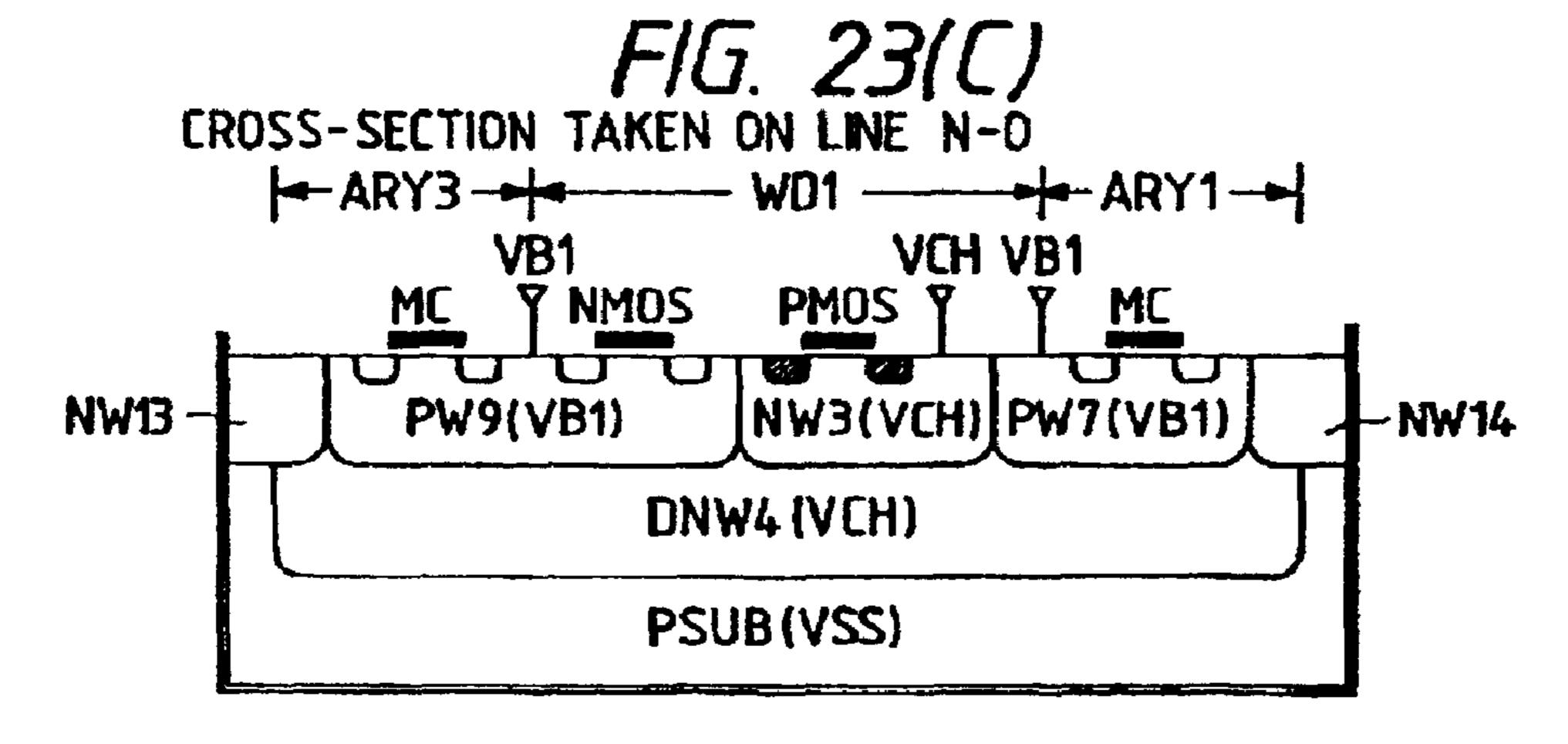

- FIGS. 23(A), 23(B) and 23(C) are cross-sectional views of the memory arrays and peripherals in FIG. 20.

### DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 1 is a block diagram of a dynamic RAM (semiconductor memory) embodying the invention. The constitution and operation of this embodiment will now be outlined with reference to FIG. 1. The circuit elements constituting each block in FIG. 1 are formed on one substrate composed illustratively of single crystal silicon through the use of known MOSFET integrated circuit fabrication techniques (MOSFET stands for a metal-oxide-semiconductor field-effect transistor which, in this specification, generically represents the insulated gate field-effect transistor). Unless otherwise noted, the names of

terminals and signal lines in the accompanying drawings are also used to indicate the signals transmitted through these terminals and lines. In addition, each MOSFET with its channel (back gate) part arrowed in the accompanying circuit diagrams is a p-channel MOSFET as opposed to 5 n-channel MOSFETs whose channel part is not arrowed.

The dynamic RAM in FIG. 1 has four memory blocks MB0 through MB3 as its basic components. These memory blocks, as exemplified by the memory block MB0 in FIG. 1, each comprise a pair of memory mats MATL and MATR 10 flanking an X-address decoder XD, main amplifiers MAL and MAR corresponding to the memory mats, and Y-address decoders YDL and YDR also corresponding to the memory mats. The X-address decoder is supplied with internal address signals X0 through Xi of (i+1) bits from an 15 X-address buffer XB. The Y-address decoders YDL and YDR are supplied commonly with internal address signals Y0 through Yi of (i+1) bits from a Y-address buffer YB. The X- and Y-address buffers XB and YB are fed on a time division basis with X-address signals AX0 through AXi and 20 Y-address signals AY0 through AYi via address input terminals A0 through Ai. The main amplifier MAL and MAR are connected via an eight-bit internal data bus IOB0–IOB7 to the I/O terminals on one side of the corresponding unit circuits of a data I/O circuit IO. The I/O terminals on the 25 other side of these unit circuits are connected to the corresponding data I/O terminals IO0 through IO7.

Each of the memory mats MATL and MATR constituting each of the memory blocks MB0 through MB3 comprises 64sub-memory mats arranged in lattice fashion, as will be 30 discussed later. The sub-memory mats are each composed of a memory array having a predetermined number of subword lines and of sub-bit lines intersecting orthogonally and a large number of dynamic memory cells located in lattice and sub-bit lines; a sub-word line driver including unit sub-word line driving circuits corresponding to the sub-word lines of the memory array; a sense amplifier including unit amplifier circuits and column selection switches corresponding to the sub-bit lines; and sub-common I/O lines to which 40 designated sub-bit lines are connected selectively via the column selection switches. Above the 64 sub-memory mats arranged in lattice fashion are main word lines originating from the X address decoder XD and bit line selection signals (column selection signal lines) originating from the 45 Y-address decoder YDL or YDR, the main word lines and the column selection signal lines intersecting orthogonally. Also above the sub-memory mats are a predetermined number of main common I/O lines which are in parallel with the bit line selection signals and which originate from the 50 main amplifier MAL or MAR. Specific constitutions, operations and layouts of the memory blocks MB0 through MB3 and of the sub-memory mats making up each memory block will be described later in more detail.

The X- and Y-address buffers XB and YB receive and 55 retain the X-address signals AX0 through AXi or Y-address signals AY0 through AYi entered through the address input terminals A0 through Ai on a time division basis. On the basis of the X- or Y-address signals thus admitted, the X- and Y-address buffers XB and YB generate the internal address 60 signals X0 through Xi or Y0 through Yi and supply the generated signals to the X-address decoder XD or Y-address decoder YDL or YDR of the memory blocks MB0 through MB3. The most-significant bit internal address signal Xi and Yi are also sent to a memory block selection circuit BS.

The X-address decoder decodes the internal address signals X0 through Xi from the X-address buffer XB, and

drives the corresponding main word lines to the active level alternately. The Y-address decoders YDL and YDR decode the internal address signals Y0 through Yi from the Y-address buffer YB, and drive alternately the corresponding bits of the bit line selection signals to the active (i.e., selected) level. In this embodiment, each of the main word lines is constituted by complementary signal lines consisting of an uninverted and an inverted signal line. The main word lines have a pitch X times that of the sub-word lines constituting the sub-memory mat (i.e., eight-foot pitch), while the bit line selection signals have a pitch Y times that of the sub-bit lines (i.e., four-fold pitch). For this reason, the sub-word line driver of each sub-memory mat includes the unit sub-word line driving circuits for selectively driving the sub-word lines in accordance with the row selection signal and sub-word line driving signal; the row selection signal is transmitted over the corresponding 64-bit main word lines, and the sub-word line driving signal is transmitted via eight-bit sub-word line driving signal lines to be described later. Part of the internal address signals X0 through Xi fed to the X-address decoder XD are used to drive the sub-word line driving signals selectively to the active level. The sense amplifier of each sub-memory mat includes switching MOS-FETs that are turned on selectively four pairs at a time when the corresponding bit line selection signals are driven to the active level, the activated switching MOSFETs connecting four pairs of complementary bit lines to the sub-common I/O lines selectively.

When the dynamic RAM is placed in write mode, the main amplifiers MAL and MAR take write data sent from the data I/O terminals IO0 through IO7 via the data I/O circuit IO and internal data bus IOB0-IOB7, and write the data thus supplied to eight selected memory cells in the designated sub-memory mat of the memory mat MATL or fashion at the points of intersection between the sub-word 35 MATR. When the dynamic RAM is in read mode, the main amplifiers MAL and MAR amplify read signals which are output from eight selected memory cells in the designated sub-memory mat of the memory mat MATL or MATR and which are forwarded via the sub-common I/O lines (subcommon data lines), sub-main amplifiers and main common I/O lines (main common data lines); the amplified signals are then transmitted to the corresponding unit circuits in the data I/O circuit IO by way of the internal data bus IO0–IO7. From the unit circuits of the data I/O circuit IO, these read signals are sent to the outside of the dynamic RAM through the data I/O terminals IO0 through IO7.

> The memory block selection circuit BS decodes the most-significant bit internal address signals Xi and Yi from and X and Y-address buffers XB and YB, and drives selectively memory blocks selection signals BS0 through BS3, not shown. These memory block selection signals are fed to the corresponding memory blocks MB0 through BM3 for selective activation thereof.

A timing generator TG generates selectively various internal control signals on the basis of a row address strobe signal RASB, a column address strobe signal CASB and a write enable signal WEB supplied externally as start control signals (in the description that follows, a character B suffixed to a signal name indicates that the signal is an inverted signal driven Low when made active). The internal control signals thus generated are supplied to various parts in the dynamic RAM. An internal voltage generator VG generates internal voltages VCH, VCL, HVC, VB1 and VB2 on the basis of a grounding potential VSS and a supply voltage VCC supplied externally as the operating power source. The internal voltages thus generated are fed to various parts in the dynamic RAM. The supply voltage VCC may be

arranged to be, but is not limited to, a positive potential of +3.3 V. The internal voltage VCH is illustratively a positive potential of a relatively large absolute value (e.g., +4 V). The internal voltage HVC is illustratively +1.1 V, an intermediate potential between the internal voltage VCL and the grounding potential VSS. Furthermore, the internal voltage VB1 is a negative potential of a relatively small absolute value (e.g., -1 V), while the internal voltage VB2 is a negative potential of a relatively large absolute value (e.g., -2 V).

FIG. 2 is a substrate layout view of the dynamic RAM in FIG. 1. The chip layout of the dynamic RAM embodying the invention will now be outlined with reference to FIG. 2. In the general description that follows regarding the chip layout, references of bearings (top, bottom, right, left) indicate the apparent positions in the relevant drawings.

In FIG. 2, the dynamic RAM is mounted on a p-type semiconductor substrate PSUB. The dynamic RAM as embodied here is of the so-called LOC (lead-on-chip) form in which the bonding pads for connecting inner leads to the semiconductor substrate PSUB are arranged linearly along 20 the vertical center line of the substrate. Thus close to the bonding pads, i.e., at the center of the semiconductor substrate PSUB is a peripheral circuit PC including the X-address buffer XB, Y-address buffer YB and data I/O circuit IO. In the top left and the top right corner of the 25 semiconductor substrate PSUB are the memory blocks MB0 and MB1, respectively. Under the memory blocks MB0 and MB1 are the memory blocks MB2 and MB3, respectively. These memory blocks are arranged so that the main common I/O lines are the sub-bit lines constituting part of each 30 sub-memory mat are arranged horizontally as shown in FIG. 2, i.e., the Y-address decoders YDL and YDR and the main amplifiers MAL and MAR are inside the semiconductor substrate PSUB. As a result, the main word lines are in the vertical direction of FIG. 2 and in parallel with the sub-word 35 lines constituting part of the sub-memory mats. The subcommon I/O lines constituting part of the sub-memory mats intersect the main common I/O lines orthogonally, in the vertical direction of FIG. 2. With the main amplifiers MAL and MAR located in the middle of the semiconductor 40 substrate PSUB, the main common I/O lines connected to these amplifiers are arranged to intersect the sub-common I/O lines orthogonally. The arrangement provides an effective chip layout.

FIG. 3 is a block diagram of a memory block included in 45 the dynamic RAM of FIG. 1. FIG. 4 is a partial block diagram of a sub-memory mat SMR34 and its peripherals included in the memory block of FIG. 3. FIG. 5 is a partial connection diagram of the setup in FIG. 4, and FIG. 6 is a partial circuit diagram of a memory array ARYR34 and its 50 peripherals included in the sub-memory mat SMR34 of FIG. 4. With reference to these figures, mention will be made of: the block constitution of the memory blocks and submemory mats making up the dynamic RAM embodying the invention; specific structures of the memory arrays and their 55 peripherals constituting the sub-memory mats; and some features of these memory components. The description that follows regarding the memory block constitution will refer primarily to the memory block MB0 but also apply to the other memory blocks MB1 through MB3 which are identical 60 in structure to the memory block MB0. In addition, the description that follows with respect to the sub-memory mats, memory arrays and peripherals will center primarily on the sub-memory mat SMR34 but also apply to the other sub-memory mats SMR00 through SMR33 and SMR35 65 through SMR77 which are structurally identical to the sub-memory mat SMR34.

8

In FIG. 3, the memory block MB0 includes a pair of memory mats MATL and MATR flanking the X-address decoder XD as mentioned above. These memory mats are each composed of 64 sub-memory mats SML00 through SML77 and SMR00 through SMR77 arranged in 8×8 lattice fashion.

With this embodiment, the sub-memory mats SML00 through SML77 and SMR00 through SMR77 making up each of the memory mats MATL and MATR of the memory block MB0 are arranged so that two adjacent sub-memory mats in the column direction are paired to share four pairs of sub-common I/O lines SIO0\* through SIO3\*, as shown shaded in FIG. 3. (In the description that follows, an uninverted sub-common I/O line SIO0T and an inverted sub-common I/O line SIO0B are represented combinedly by an asterisk-suffixed notation such as a sub-common I/O line SIO0\*. Each uninverted signal that is brought High when made active is identified by a character T suffixed to its name.) With such a paired sub-memory mat structure (e.g., SMR34 and SMR35), it is possible to remedy columndirection faults in units of the bit line selection signal. Meanwhile, eight pairs of sub-memory mats SMR04 through SMR74 and SMR05 through SMR75 (i.e., a total of eight sub-memory mats) arranged on the same row share four pairs of main common I/O lines (represented by the main common I/O lines MIO40\* through MIO43\*) and 64-bit line selection signals (represented by YS40 through YS463). Eight sub-memory mats (e.g., SMR30 through SMR37) arranged on the same row share 64 pairs of main word lines represented by MW30\* through MW363. Part of the sub-memory mats SML00 through SML77 and SMR00 through SMR77 making up the memory mats MATL and MATR of each memory block may be furnished as redundant sub-memory mats in the row and column directions. These redundant sub-memory mats are used to remedy faults in units of the sub-memory mat.

The sub-memory mats SML00 through SML77 and SMR00 through SMR77 contain, as exemplified by the sub-memory mat SMR34 in FIG. 4, the memory array ARYR34, and the sub-word line driver WDR34 and sense amplifier SAR34 located respectively below and to the right of the memory array ARYR34. As shown in FIG. 6, the memory array ARYR34 effectively includes, and is not limited to, 512 sub-word lines SW0 through SW511 arranged vertically and 256 sub-bit lines SB0\* through SB255\* arranged horizontally in parallel. At the points of intersection between the sub-word lines and sub-bit lines are effectively 131,072 dynamic memory cells composed of data storage capacitors and address selection MOSFETs arranged in lattice fashion. In this setup, each of the submemory mats SML00 through SML77 and SMR00 through SMR77 has a storage capacity of 128 kilobits. Each of the memory blocks MB0 through MB3 has a storage capacity of 16 megabits (i.e., 128 kilobits×64×2). The dynamic RAM has a storage capacity of 64 megabits (i.e., 16 megabits×4).

As depicted in FIG. 6, the sub-word line driver WDR34 includes 256 unit sub-word line driving circuits USWD0, USWD2,..., USWD510 corresponding to even-numbered sub-word lines SW0, SW2,..., SW510 of the memory array ARYR34. The upper output terminals of these unit sub-word line driving circuits are connected to the corresponding even-numbered sub-word lines SW0 SW2,..., SW510 of the memory array ARYR34; the lower output terminals of the unit sub-word line driving circuits are connected to the corresponding even-numbered sub-word lines SW0, SW2,..., SW510 of the adjacent sub-memory mat SMR33. The upper output terminals of the unit sub-word line driving

circuits USWD0,-USWD2, . . . , USWDS10 constituting the sub-word line driver WDR34 are interconnected every four terminals, and are coupled successively to the corresponding main word lines MW30\* through MW363\*. The lower output terminals of the unit sub-word line driving circuits 5 USWD0, USWD2, ..., USWD510 are interconnected every four terminals, and are coupled commonly to the corresponding sub-word line driving signal lines DX40, DX42, DX44 and DX46.

Meanwhile, the upper output terminals of the odd- 10 numbered sub-word lines SW1, SW3, . . . , SW511 making up part of the memory array ARYR34 are connected to the output terminals of the corresponding unit sub-word line driving circuits USWD1, USWD3, . . . , USWD511 of the sub-word line driver WDR35 in the adjacent sub-memory 15 mat SMR35. The upper output terminals of these unit sub-word line driving circuits are in turn connected to the odd-numbered sub-word lines SW1, SW3, . . . , SW511 constituting part of the memory array ARYR35 of the sub-memory mat SMR35. The upper input terminals of the 20 unit sub-word line driving circuits USWD1, USWD3, ..., USWD511 making up the sub-word line driver WDR35 are interconnected every four terminals, and are coupled successively to the corresponding main word lines MW30\* sub-word line driving circuits are interconnected every four terminals, and are coupled commonly to the corresponding sub-word line driving signal lines DX41, DX43, DX45 and DX47.

The unit sub-word line driving circuits USWD0, 30 USWD2, . . . , USWD510 and USWD1, USWD3, . . . , USWD511 of the sub-word line drivers WDR34 and WDR35 drive selectively to a predetermined selected level the corresponding sub-word lines SW0, SW2, . . . , SW510 and ARYR34 or ARYR34 and ARYR35 on two conditions: that the corresponding main word lines MW30\* through MW363\* be driven to the active level, and that the corresponding sub-word line driving signals DX40, DX42, . . . , DX46 or DX41, DX43, ..., DX47 be brought to the active 40 level.

As described, in the dynamic RAM embodying the invention, 512 sub-word lines SW0 through SW511 making up part of, say, the sub-memory mat SMR34 are connected to the corresponding unit sub-word line driving circuits of a 45 pair of sub-word line drivers WDR34 and WDR35 on both sides of (i.e., above and below) the sub-memory mat SMR34. Whereas the sub-memory mat SMR34 practically needs two sub-word line drivers, each unit sub-word line driving circuit of the sub-word line drivers is shared by the 50 corresponding sub-bit lines of two sub-memory matsadjacent to each other in the column direction. Thus in this arrangement, the sub-word line drivers are made to correspond in serial numbers with the sub-memory mats. Where the memory array ARYR34 of the sub-memory mat SMR34 55 is taken as an example, the unit sub-word line driving circuits of the corresponding sub-word line drivers WDR34 and WDR35 are located alternately below or above the sub-word lines SW0 through SW511. Eight of the unit sub-word line driving circuits share corresponding one of 60 the main word lines MW30\* through MW363\*. As a result, the unit sub-word line driving circuits may have a pitch twice that of the sub-word lines, and the main word lines may have a pitch eight times (X times) that of the sub-word lines. In this setup, the pitch of the unit sub-word line driving 65 circuits and that of the complementary main word lines are relaxed, whereby the dynamic RAM may be enhanced in the

degree of circuit integration and boosted in scale. More specific constitutions and operations of the unit sub-word line driving circuits USWD0 through USWD511 making up the sub-word line drivers WDR34 and others will be described later. The connections of these unit sub-word line driving circuits will be further clarified when FIGS. 3 through 5 are referenced.

The sub-bit lines SB0\* through SB255\* constituting part of the memory array ARYR34 in the sub-memory mat SMR34 are connected on the right-hand side to the corresponding unit circuits USA0, USA3, . . . , USA252 and USA255 of the sense amplifier SAR34, by way of n-channel shared MOSFETs NA and NB commonly receiving through their gates a shared control signal SH3L. Likewise, the sub-bit lines SB0\* through SB255\* are connected on the left-hand side to the corresponding unit circuits USA1, USA2, . . . , USA253 and USA254 of the sense amplifier SAR44 for the adjacent sub-memory mat SMR44, by way of shared MOSFETs commonly receiving through their gates a shared control signal SH4R. The unit circuits USA0, USA3, etc., of the sense amplifier SAR34 are further connected on the right-hand side to the corresponding sub-bit lines SB0\*, SB3\*, etc., of the memory array ARYR24 in the adjacent sub-memory mat SMR24, by way of n-channel shared through MW363\*: the lower input terminals of these unit 25 MOSFETs NC and ND commonly receiving a shared control signal SH3R through their gates. The unit circuits USA1, USA2, etc., of the sense amplifier SAR35 are connected on the left-hand side to the corresponding sub-bit lines SB1\*, SB2\*, etc., of the memory array ARYR44, by way of shared MOSFETs commonly receiving a shared control signal SH4L through their gates.

Each unit circuit of the sense amplifiers SAR34 and SAR44 is fed commonly with consecutive four of the bit line selection signals YS40 through YS463. These unit circuits or SW1, SW3, ..., SW511 of the memory arrays ARYR33 35 each contain a unit amplifier made of a pair of CMOS inverters in cross connection, and a pair of switching MOS-FETs (column selection switches) commonly receiving through their gates the corresponding bit line selection signals YS40 through YS463. Each unit amplifier is selectively activated when supplied with the operating voltage via a common source line, not shown. The activated unit amplifier provides a binary read signal (High or Low level) by amplifying a small read signal output via the corresponding sub-bit line from the memory cell connected to the selected sub-word line. The switching MOSFETs of the sense amplifier unit circuits are turned on selectively four pairs at a time when the corresponding bit line selection signals YS40 through YS463 are driven to the active level. The activated MOSFET pairs selectively connect the corresponding four of the sub-bit lines of the memory array ARYR34 to the sub-common I/O lines SIO0\* through S103\*.

As shown in FIG. 4, the sub-common I/O lines SIO0\* and SIO1\* are shared by two sub-memory mats SMR34 and SMR35 contiguous in the column direction. The two subcommon I/O lines SIO0\* and SIO1\* are located to the right of these sub-memory mats, i.e., inside the sense amplifiers SAR34 and SAR35. The other two sub-common lines SIO2\* and SIO3\* are located to the left of these sub-memory mats, i.e., inside the sense amplifiers SAR44 and SAR45. Furthermore, the sub-common I/O line SIO0\* is connected selectively to the main common I/O line MIO40\* via a sub-main amplifier SMA of the sense amplifier driver SDR34 located bottom left of the sub-memory mat SMR34. The sub-common I/O line SIO1\* is connected selectively to the main common I/O line MIO41\* via the sub-main amplifier of the sense amplifier driver SDR35 in the cross region located bottom right of the sub-memory mat SMR35. The

sub-common I/O line SIO2\* is connected selectively to the main common I/O line M1042\* via the sub-main amplifier of the sense amplifier driver SDR45 located bottom right of the sub-memory mat SMR45. The sub-common I/O line SIO3\* is connected selectively to the main common I/O line M1O43\* via the sub-main amplifier of the sense amplifier driver SDR46 located bottom right of the sub-memory mat SMR46.

As described, in the dynamic RAM of this embodiment, 256 sub-bit lines SB0\* through SB255\* constituting part of 10 the sub-memory mat SMR34 are connected illustratively to the corresponding unit circuits of a pair of sense amplifiers SAR34 and SAR44 flanking the sub-memory mat SMR34 (on the left and the right). Whereas the sub-memory mat SMR34 practically needs two sense amplifiers, each unit 15 circuit of the sense amplifiers is shared by two sub-memory mats adjacent to each other in the row direction. Thus in this arrangement, the sense amplifiers are made to correspond in serial numbers with the sub-memory mats. Where the memory array ARYR34 of the sub-memory mat SMR34 is 20 taken as an example, the unit circuits of the sense amplifiers are located alternatively to the right or left of the sub-bit lines SB0\* through SB255\*. Each sense amplifier unit circuit shares four bit line selection signals YS40 through YS463. As a result, the sense amplifier unit circuits may 25 have a pitch twice that of the sub-bit lines, and the bit line selection signals may have a pitch four times (Y times) that of the sub-bit lines. In this setup, the pitch of the sense amplifier unit circuits and that of the bit line selection signals are relaxed, whereby the dynamic RAM may be enhanced in 30 the degree of circuit integration and boosted in scale. More specific constitutions of the sense amplifiers SAR34 and SAR44 and their unit circuits USA0 through USA255 will be described later. The connections of these circuit components will be further clarified when FIGS. 3 through 5 are 35 referenced.

In the dynamic RAM of this invention, the memory mats MATL and MATR making up he memory blocks MB0 through MB3 are each divided into 64 units or sub-memory mats SML00 through SML77 or SMR00 through SMR77. 40 As with the memory cells, these sub-memory mats are arranged in lattice fashion. The sub-word lines, sub-bit lines and sub-common I/O lines of the sub-memory mats are selectively connected to and activated by the main word lines, bit line selection signals or main common I/O lines 45 furnished in the upper layer. As is already evident to those skilled in the art, dividing each memory mat into a large number of units or sub-memory mats enhance the degree of freedom of mat constitution in the dynamic RAM and thereby contributes to shortening the period of memory 50 development. Because the division of memory mats into sub-memory mats is accompanied by the comprehensive layering of all word lines, bit lines and common I/O lines, the resulting dynamic RAM provides full benefits of the layered structure. Overall, the dynamic RAM of this con- 55 stitution is faster in operation speed, higher in the degree of circuit integration, larger in scale and lower in fabrication cost than before.

FIG. 7(A) and FIG. 7(B) show a partial circuit diagram and a signal waveform diagram regarding a first example of 60 the sub-word line driver WDR34 in the sub-memory mat SMR34 of FIG. 4, respectively. FIG. 8(A) and FIG. 8(B) depict a partial circuit diagram and a signal waveform diagram regarding a second example of the sub-word line driver WDR34 in the sub-memory mat SMR34, respectively. FIG. 9(A) and FIG. 9(B) indicate a partial circuit diagram and a signal waveform diagram regarding a third

12

example of the sub-word line driver WDR34, respectively. Described below with reference to FIGS. 7(A) through 9(B) are specific constitutions and operations of the sub-word line drivers making up part of the sub-memory mats of the dynamic RAM of this embodiment. The description that follows regarding the sub-word line driver arrangement will refer primarily to the sub-word line driver WDR34 of the sub-memory mat SMR34 but also apply to the other subword line drivers which are identical in structure to the sub-word line driver WDR34. In addition, the description that follows with respect to the unit sub-word line driving circuits USWD0 through USWD510 constituting the subword line driver WDR34 will center primarily on the unit sub-word line driving circuit USWD0 but also apply to the other unit sub-word line driving circuits USWD2 through USWD510 which are structurally identical to the unit subword line driving circuit USWD0.

In FIG. 7(A), the sub-word line driver WDR34 includes 256 unit sub-word line driving circuits USWD0, USWD2, . . . , USWD510 corresponding to the evennumbered sub-word lines SW0, SW2, . . . , SW510 making up part of the memory array ARYR34. Each of the unit sub-word line driving circuits, as exemplified by the unit sub-word line driving circuit USWD0, comprises a p-channel MOSFET P1 (first MOSFET) interposed between the corresponding sub-word line driving signal line DX40 and sub-word line SW0, and an n-channel MOSFET N1 (second MOSFET) interposed between the corresponding sub-word line SW0 and grounding potential VSS. The gates of the MOSFETs P1 and N1 are connected to the inverted signal line of the corresponding main word line MW30\*, i.e., to the inverted main word line MW30B. The unit sub-word line driving circuit USWD0 further includes an n-channel MOSFET N2 (third MOSFET) arranged in parallel with the MOSFET P1. The gate of the MOSFET N2 is connected to the uninverted signal line of the corresponding main word line MW30\*, i.e., to the uninverted main word line MW30T.

The uninverted main word line MW30T is brought to the inactive level such as 0 V (grounding potential VSS) when not selected, and driven to the active level such as +4 V (internal voltage VHC) when selected. The inverted main word line MW30B is brought to the inactive level such as the internal voltage VCH when not selected, and driven to the active level such as the grounding potential VSS when selected. The sub-word line driving signal DX40 is brought to the inactive level such as the grounding potential VSS when not selected, and driven to the active level such as the internal voltage VCH when selected. As mentioned above, the internal voltage VCH, a relatively stable potential of +4 V, is generated by the internal voltage generator VG in the dynamic RAM drawing on the supply voltage VCC.

When the corresponding uninverted main word lines MW30T and inverted main word lines MW30B are brought to the inactive level, the MOSFETs P1 and N2 are both turned off and the MOSFET N1 is turned on in the unit sub-word line driving circuit USWD0. Thus the sub-word line SW0 is set to the unselected level such as the grounding potential VSS irrespective of the level of the corresponding sub-word line driving signal DX40.

Meanwhile, when the corresponding uninverted main word line MW30T and inverted main word line MW30B are driven to the active level, the MOSFET N1 is turned off and the MOSFETs P1 and N2 are turned on in the unit sub-word line driving circuit USWD0. Thus the sub-word line WS0 is brought to the selected level such as the internal voltage VCH upon receipt of the active level of the corresponding

sub-word line driving signal DX40, and is driven to the unselected level such as the grounding potential VSS when receiving the inactive level of the sub-word line driving signal DX40.

As described, the unit sub-word line driving circuits 5 USWD0 and others constituting the sub-word line drivers WDR34, etc., in the inventive dynamic RAM are not self-boot type but CMOS (complementary MOS) static driving circuits. In that case, the main word lines MW30\* and others and the sub-word line driving signals DX40 and others may be driven to the active level simultaneously. This makes it possible to improve the access time of the dynamic RAM in its read mode.

As shown in FIG. 8(A), the unit sub-word line driving circuits exemplified by the circuit USWD0 are each com- 15 posed of a p-channel MOSFET P1 and n-channel MOSFETs N1 and N2. The p-channel MOSFET P1 is interposed between the corresponding uninverted main word line MW30T and sub-word line SW0 and receives through its gate the sub-word line driving signal DX40. The n-channel 20 MOSFETs N1 and N2 are interposed in parallel between the sub-word line SW0 and the grounding potential VSS and have their gates connected respectively to the corresponding sub-word line driving signal line DX40 and inverted main word line MW30B. Alternatively, as depicted in FIG. 9(A), 25 the p-channel MOSFET P1 may be interposed between the corresponding uninverted sub-word line driving signal line DX40T and sub-word line SW0 and has its gate connected to the corresponding main word line MW30B; the n-channel MOSFETs N1 and N2 may be interposed in parallel between 30 the sub-word line SW40 and the grounding potential VSS and have their gates connected respectively to the corresponding main word line MW30B and inverted sub-word line driving signal DX40B. The unit sub-word line driving circuit USWD0 may also be composed of an ordinary 35 two-input CMOS NOR gate arrangement. In this case, the main word line and the sub-word line driving signal may be a single signal line each. The arrangement further reduces the number of necessary lines and contributes to enhancing the degree of circuit integration of the dynamic RAM.

FIG. 10 is a partial circuit diagram of a first example of the sense amplifier SAR34 and a first example of the sense amplifier driver SDR34 included in the sub-memory mat SMR34 of FIG. 4. FIG. 11 is a partial circuit diagram of a second example of the sense amplifier driver SDR34 in the 45 sub-memory mat SMR34 of FIG. 4. FIG. 12 is a signal waveform diagram regarding the sense amplifier driver SDR34 shown in FIGS. 10 and 11. FIG. 13 is a partial circuit diagram of a third example of the sense amplifier driver SDR34 in the sub-memory mat SMR34 of FIG. 4. FIG. 14 is a signal wave diagram regarding the sense amplifier driver SDR34. Described below with reference to FIGS. 10 through 14 are specific constitutions, operations and features of the sense amplifiers and sense amplifier drivers in the sub-memory mats of the inventive dynamic RAM. The 55 description that follows regarding the sense amplifiers, their unit circuits and the sense amplifier drivers will center primarily on the sense amplifier SAR34 and its unit circuit USA0 in the sub-memory mat SMR34 as well as on the sense amplifier driver SDR34. These components explained 60 as representative examples are identical in structure to those sense amplifiers, unit circuits and sense amplifier drivers which they represent and to which the ensuing description applies.

In FIG. 10, the sense amplifier SAR34 includes 128 unit 65 circuits USA0, USA3,..., USA252 and USA255. The input terminals on the left-hand side of these unit circuits are

14

connected to the corresponding sub-bit lines SB0\*, SB3\*, . . . , SB252\* and SB255\* of the memory array ARYR34, by way of n-channel shared MOSFETs NA and NB whose gates commonly receive an uninverted shared control signal SH3L that is obtained by an inverter V1 of the sense amplifier driver SR34 inverting an inverted shared control signal SH3LB. The input terminals on the right-hand side of the unit circuits are connected to the corresponding sub-bit lines SB0\*, SB3\*, . . . , SB252\* and SB255\* of the memory array ARYR24 in the adjacent sub-memory mat SMR24, by way of n-channel shared MOSFETs NC and ND whose gates commonly receive an uninverted shared control signal SH3R that is acquired by an inverter V3 of the sense amplifier driver SDR34 inverting an inverted shared control signal SH3RB.

The dynamic RAM of the above constitution adopts what is known as the shared sense scheme. That is, the unit circuits USA0, USA3, . . . , USA252 and USA255 of the sense amplifier SAR34 are shared by the memory arrays ARYR34 and ARYR24 of a pair of adjacent sub-memory mats SMR34 and SMR24. When the inverted shared control signal SH3LB is brought Low and the uninverted shared control signal SH3L is driven High, the sense amplifier unit circuits are selectively connected to the corresponding subbit lines SB0\*, SB3\*, . . . , SB252\* and SB255\* of the memory array ARYR34 located on the left-hand side, by way of the shared MOSFETs NA and NB. When the inverted shared control signal SH3RB is brought Low and the uninverted shared control signal SH3R is driven High, the sense amplifier unit circuits are selectively connected to the corresponding sub-bit lines SB0\*, SB3\*, . . . , SB252\* and SB255\* of the memory array ARYR24 located on the right-hand side, by way of the shared MOSFETs NC and ND.

Each of the unit circuits making up the sense amplifier SAR34, as exemplified by the unit circuit USA0 in FIG. 10, includes a unit amplifier and a bit line pre-charge circuit. The unit amplifier is composed of a p-channel MOSFET P2, an n-channel MOSFET N3, a p-channel MOSFET P3 and an n-channel MOSFET N4 constituting a pair of CMOS inverters in cross connection. The bit line pre-charge circuit is made up of a pair of n-channel switching MOSFETs (column selection switches) N8 and N9 interposed between the uninverted and the inverted I/O node of the unit amplifier on the one hand, and the uninverted and the inverted signal line of the sub-common I/O line SIO0\* or SIO1\* on the other, and three n-channel MOSFETs N5 through N7 in series-parallel connection.

The sources of the MOSFETs P2 and P3 constituting part of the unit amplifier are commonly connected to a common source line (driving signal line) PP, the sources of the MOSFETs N3 and N4 are commonly connected to a common source line PN. The common source line PP is connected to a driving voltage supply line CPP4 via a p-channel driving MOSFET P4 of the sense amplifier driving circuit SAD in the sense amplifier driver SDR34. The common source line PN is connected to a driving voltage supply line CPN4 via an n-channel driving MOSFET NE of the sense amplifier driving circuit SAD. Between the common source lines PP and PN is a common I/O line pre-charge circuit having three n-channel MOSFETs NF through NE in seriesparallel connection. The gate of the driving MOSFET P4 in the sense amplifier driving circuit SAD is connected to a sense amplifier control signal line SAP3; the gate of the driving MOSFET NE is connected to a sense amplifier control signal line SAN3. The gates of the MOSFETs NF through NH in the common I/O line pre-charge circuit are

commonly fed with an inverted internal control signal PCB that is obtained by an inverter V2 inverting an internal control signal PC for pre-charge control.

In the setup above, the unit amplifiers of the unit circuits in the sense amplifier SAR34 are selectively activated on two conditions: that the driving MOSFETs P4 and NE of the sense amplifier driving circuit SAD be turned on upon receipt of the active level of the sense amplifier control signals SAP3 and SAN3; and that predetermined operating power be supplied from the driving voltage supply lines CPC4 and CPN4 via the common source lines PP and PN. The activated unit amplifiers each provide a binary read signal (High or Low level) by amplifying a small read signal output via the corresponding sub-bit lines SB0\* and SB2\* from the 256 memory cells connected to the selected sub-word lines of the memory array ARYR34 or ARYR24.

The gates of the switching MOSFETs N8 and N9 constituting part of the unit circuits in the sense amplifier SAR34 are interconnected every two pairs and are supplied with the corresponding bit line selection signals YS40 and others 20 from the Y-address decoder YD. As mentioned above, the bit line selection signals YS40, etc., are fed to the gates of two pairs of switching MOSFETs in the unit circuits USA1, USA2, etc., of the sense amplifier SAR44 located to the left of the memory array ARYR34. In this setup, the switching MOSFETs N8 and N9 in the unit circuits are selectively turned on two pairs at a time when the corresponding bit line selection signals YS40 through YS463 are driven to the active level. The activated switching MOSFETs selectively connect the corresponding two sub-bit lines to the-subcommon I/O lines SIO0\* and SIO1\* in the memory array ARYR34 or ARYR24.

Meanwhile, the gates of the MOSFETs N5 through N7 constituting the bit line pre-charge circuit of each unit circuit in the sense amplifier SAR34 are commonly supplied with the inverted pre-charge control signal PCB. The MOSFETs N5 through N7 are selectively turned on upon receipt of the active (i.e., High) level of the inverted pre-charge control signal PCB. The activated MOSFETs N5 through N7 short-circuit (i.e., equalize) the uninverted and the inverted I/O node of the unit amplifier in the corresponding unit circuit of the sense amplifier SAR34, i.e., the uninverted and the inverted signal line of the corresponding sub-bit line for the memory array ARYR34 or ARYR24.

In this embodiment, the memory mats MATL and MATR making up the memory blocks MB0 through MB3 use as their operating power the internal voltage VCL of a relatively small absolute value (e.g., +2.2 V) and the grounding potential VSS (i.e., 0 V). This is intended to minimize in size 50 the memory cells and other circuit elements. Likewise the unit amplifiers constituting the sense amplifier SAR34 utilize as the operating power the internal voltage VCL fed via the common source lines PP and PN as well as the grounding potential VSS. However, the dynamic RAM embodying the 55 invention adopts what is known as the overdrive scheme under which the common source line PP is fed with the supply voltage VCC (i.e., +3.3 V) only for a predetermined initial period in which the sense amplifier SAR34 is activated. The scheme allows the unit amplifiers of the sense 60 amplifier to act more quickly than before for amplifying operations thereby increasing the speed of reading data from the dynamic RAM.

The overdrive scheme of the sense amplifier will now be described briefly with reference to the signal waveform 65 diagram of FIG. 12. As shown in FIG. 12, the sense amplifier control signal SAP3 is on the inactive level when set to the

16

supply voltage VCC (i.e., +3.3 V) and on the active level when set to the grounding potential VSS (i.e., 0 V). The sense amplifier control signal SAN3 is on the inactive level when set to the grounding potential VSS and on the active level when set to the supply voltage VCC. The driving voltage supply line CPP4 is being fed with the supply voltage VCC when not selected as well as from the time the sense amplifier control signals SAP3 and SAN3 are brought in the active level until a predetermined time has elapsed. Upon elapse of the predetermined time, the driving voltage supply line CPP4 is supplied with the internal voltage VCL (i.e., +2.2 V). The driving voltage supply line CPN4 is always fed with the grounding potential VSS. The precharge control signal PC, not shown, is driven to the active level at a predetermined timing when the sense amplifier SAR34 is deactivated. The pre-charge control signal PC is brought to the inactive level when the sense amplifier SAR34 is activated.

When the sense amplifier control signals SAP3 and SAN3 are driven to the inactive level and when the sense amplifier SAR34 is deactivated, the driving MOSFETs P4 and NE in the sense amplifier driving circuit SAD of the sense amplifier driver SDR34 are turned off, and the MOSFETs NF through NH making up the common I/O pre-charge circuit are all turned on upon receipt of the active level of the pre-charge control signal PC. This causes the common source lines PP and PN to be equalized via the MOSFETs NF through NH to an intermediate potential between the internal voltage VCL land the grounding potential, i.e., to the internal voltage HVC. The unit circuits USA0, etc., of the sense amplifier SAR34 are all deactivated. At this point, in the memory array ARYR34 or ARYR24, the uninverted and inverted signal lines of the sub-bit lines SB0\* through SB255\* are equalized via the bit line pre-charge circuits of 35 the corresponding unit circuits in the sense amplifier SAR34. That is, the uninverted and inverted signal lines are pre-charged to an intermediate level such as the internal voltage HVC.

On the other hand, when the sense amplifier control signals SAP3 and SAN3 are driven to the active level, the MOSFETs NF through NE making up the common I/O line pre-charge circuit in the sense amplifier-driver SDR34 are turned off. Instead, the driving MOSFETs P4 and NE in the sense amplifier driving circuit SAD are turned on. This causes the common source line PP to be fed initially with the driving voltage such as the supply voltage VCC from the driving voltage supply line CPP4 via the driving MOSFET P4. After a predetermined time has elapsed, the common source line PP is fed with the driving voltage (supply voltage) such as the internal voltage VCL. The common source line PN is supplied with the grounding potential (reference voltage) VSS via the driving voltage supply line CPN4. As a result, the unit amplifiers constituting each of the unit circuits in the same amplifier SAR34 are activated. The activated unit amplifiers each provide a binary read signal (Light or Low level) amplifying a small read signal output via the corresponding sub-bit lines SB0\*, etc., from the memory cells connected to the selected sub-word lines of the memory array ARYR34 or ARYR24. In the initial phase of the activation of the sense amplifier SAR34, the common source line PP is fed with the supply voltage VCC for overdrive purposes. This enhances the speed at which the unit amplifiers start up, thereby improving the access time of the dynamic RAM in its read mode.

In the example of FIG. 12, the sense amplifier overdrive scheme is implemented by temporarily setting to the supply voltage VCC the driving voltage fed via the drain voltage

supply line CPP4. Alternatively, as shown in FIG. 13(A), a similar overdrive scheme is implemented by furnishing three driving voltage supply lines that are fed constantly with the supply voltage VCC, internal working VCL and grounding potential VSS. In the setup of FIG. 13(A), p-channel driving MOSFETs P8 and P9 constituting part of the sense amplifier driving circuit SAD are interposed respectively between the common source line PP and the supply voltage VCC, and between the common source line PP and the internal voltage VCL. Between the common source line PN and the grounding potential VSS is an n-channel MOSFET NE. The gates of the driving MOSFETs P8 and P9 are supplied respectively with sense amplifier control signals SAP31 and SAP32, and the gate of the driving MOSFET NE is fed with the sense amplifier control signal SAN3. With this embodiment, the 15 sense amplifier control signal SAP31 is brought to the active level simultaneously with the sense amplifier control signal SAN3, as illustrated in FIG. 14. After a predetermined time has elapsed, the sense amplifier control signal SAP31 is driven back to the inactive level. Upon elapse of a prede- 20 termined time since the sense amplifier control signals SAP31 and SAN3 were driven to the active level, the sense amplifier control signal SAP32 is brought to the active level at the same time that the sense amplifier control signal common source line PP is fed with the supply voltage VCC as its driving voltage for a predetermined period from the time the sense amplifier control signal SAP31 is brought to the active level until the sense amplifier control signal SAP32 is driven to the active level. This implements a sense 30 amplifier overdrive scheme similar to that in FIG. 12.

In the dynamic RAM of this embodiment, the memory cells are refreshed successively through the eight submemory mats SMR00 to SMR07 or SMR70 to SMR77 arranged on the same row, one sub-memory mat at a time. 35 In that case, the sense amplifier control signals SAPO through SAP7 and SAN0 through SAN7 are driven to the active level consecutively as the refresh operation progresses. Illustratively, when the refresh operation, completed on the sub-memory mats SMR30 through SMR37, 40 proceeds to the sub-memory mats SMR40 through SMR47, the sense amplifier control signals SAP3 and SAN3 are driven to the active level for a predetermined period simultaneously with the next sense amplifier control signals SAP4 and SAN4. What takes place here is what is known as the 45 charge-reused refresh operation. In this case, the potential equivalent to the ground VSS or to the driving voltage VCL charging the common source lines PP and PN of the sense amplifiers SAR30 through SAR37 is transmitted to and reused by the common source lines PP and PN of the sense 50 amplifiers SAR30 through SAR37, by way of the driving voltage supply lines CPP0 through CPP7 and CPN0 through CPN7. This leads to appreciable savings in the amount of driving voltage charges to be supplied anew via the driving voltage supply lines CPP0 through CPP7 and CPN0 through 55 CPN7, whereby power dissipation of the dynamic RAM is reduced. In the sense amplifier driver of FIG. 13, n-channel MOSFETs NL and NM may be replaced by a signal transmission circuit equipped with an amplifier function, the signal transmission circuit being interposed between sub- 60 common I/O lines SI0OB and SIO0T on the one hand, and main common I/O lines MIO40B and MIO40T on the other. With this alternative, the speed of signal (i.e., data) transmission may be boosted.

Returning to FIG. 10, the sense amplifier driver SDR34 65 further comprises a sub-main amplifier SMA and two sub-common I/O lines pre-charge circuits. The sub-main ampli-

18

fier SMA comprises a pair of n-channel driving MOSFETs NP and NQ and a pair of write switching MOSFETs NL and NM. The Two sub-common I/O line pre-charge circuits are composed of three p-channel MOSFETs P5 through P7 in series-parallel connection and n-channel MOSFETs N1 through NK also in series-parallel connection. One of the two sub-common I/O line pre-charge circuits has the gates of the MOSFETs N1 through NK commonly fed with the inverted internal control signal PCB that is acquired by the inverter V2 inverting the internal control signal PC. The other sub-common I/O line pre-charge circuit has the gates of the MOSFETs P5 through P7 commonly supplied with an internal control signal PCS. In this setup, with the dynamic RAM placed in write mode, the MOSFETs N1 through NK are turned on when the internal control signal PC is selectively brought Low (i.e., inverted internal control signal PCB driven High). This equalizes the uninverted and inverted signal lines of the sub-common I/O line SIO0\* to the internal voltage HVC. With the dynamic RAM in read mode, the MOSFETs P5 through P7 are selectively turned on when the internal control signal PCS is driven Low. This equalizes the uninverted and inverted signal lines of the sub-common I/O line SIOO\* to the internal voltage VCL.

Meanwhile, the drain and source of the write switching SAP31 is driven back to the inactive level. As a result, the 25 MOSFETs NL and NM in the sub-main amplifier SMA are connected respectively to the inverted and the uninverted signal line of the main common I/O line MIO40\* and sub-common I/O line SIOO\*. The gates of the write switching MOSFETs NL and NM are commonly fed with an internal control signal WE3. The drains of write differential MOSFETs NP and NQ are connected respectively to the uninverted and the inverted signal line of the main common I/O line MIO40\* by way of n-channel MOSFETs NN and NO. The commonly connected sources of the read differential MOSFETs NP and NQ are connected to the grounding potential VSS via an n-channel driving MOSFET NR. The gates of the differential MOSFETs NP and NQ are connected respectively to the inverted and the uninverted signal line of the sub-common I/O line SIOO\*. The gates of the MOSFETs NN, NO and NR are commonly supplied with an internal control signal RE3. When the dynamic RAM is selected to be in write mode, the internal control signal WE3 is driven High (e.g., internal voltage VCL) selectively in a predetermined timing. With the dynamic RAM selected to be in read mode, the internal control signal RE3 is brought High selectively in a predetermined timing.

In the above setup, the write switching MOSFETs NL and NM in the sub-main amplifier SMA are selectively turned on when the dynamic RAM is selected to be in write mode and when the internal control signal WE3 is driven High. When thus activated, the write switching MOSFETs NL and NM transmit to the sub-common I/O line SIOO\* write signals supplied from the main amplifier SAR via the main common I/O line MIO4O\*. These write signals are written from the sub-common I/O line SIOO\* to the selected memory cells in the memory array ARYR34 by way of the corresponding unit circuits of the sense amplifier SAR34.

The read differential MOSFETs NP and NQ in the submain amplifier SMA constitute what is known as a pseudo-direct type differential amplifier in combination with the MOSFETs NN, NO and NR turned on when the dynamic RAM is selected to be in write mode and when the internal control signal RE3 is driven High. The pseudo-direct type differential amplifier further amplifies a binary read signal that is read from a selected memory cell in the memory array ARYR34, amplified by the corresponding unit amplifier in the sense amplifier SAR34 and output via the sub-common

I/O line SIO0\*. The amplified binary read signal is transmitted onto the corresponding main common I/O line MIO40\*. As described earlier, the sub-common I/O line SIO0\* is shared by two adjacent sub-memory mats SMR34 and SMR35 in the column direction. The wiring length of the sub-common I/O line SIO0\* is relatively short and substantially equal to the width of the sub-memory mats in the bit line direction. A differential amplifier centering on the read differential MOSFETs NP and NQ in the sub-main amplifier SMA further amplifies the binary read signal placed by the corresponding unit amplifier of the sense amplifier SAR34 onto the sub-common I/O line SIO0\*. The amplified binary read signal is transmitted onto the main common I/O line MIO40\* whose wiring length is relatively extended.

The embodiment comprising the arrangements above alleviates the loads on the unit amplifiers of the sense amplifier SAR34 when a column is selected, and allows the read signal from each selected memory cell to be transmitted effectively to the main common I/O line MIO40\*, i.e., to the corresponding unit circuit of the main amplifier MAR. This improves the access line of the dynamic RAM in read mode. In this embodiment, a sense amplifier driving circuit SAD34 including the sub-main amplifier SMA is located in the region where the sense amplifier SAR 34 and others intersect with the sub-word line drivers WDR34 and others, as will be described later. This minimizes any increases in the layout area while improving the access time of the dynamic RAM.

If the main common I/O lines MIO40\* and others have a relatively short wiring length or if their load capacitance is negligible, the sub-main amplifier SMA may be constituted 30 only by the switching MOSFETs NL and NM which double for write and read operations.

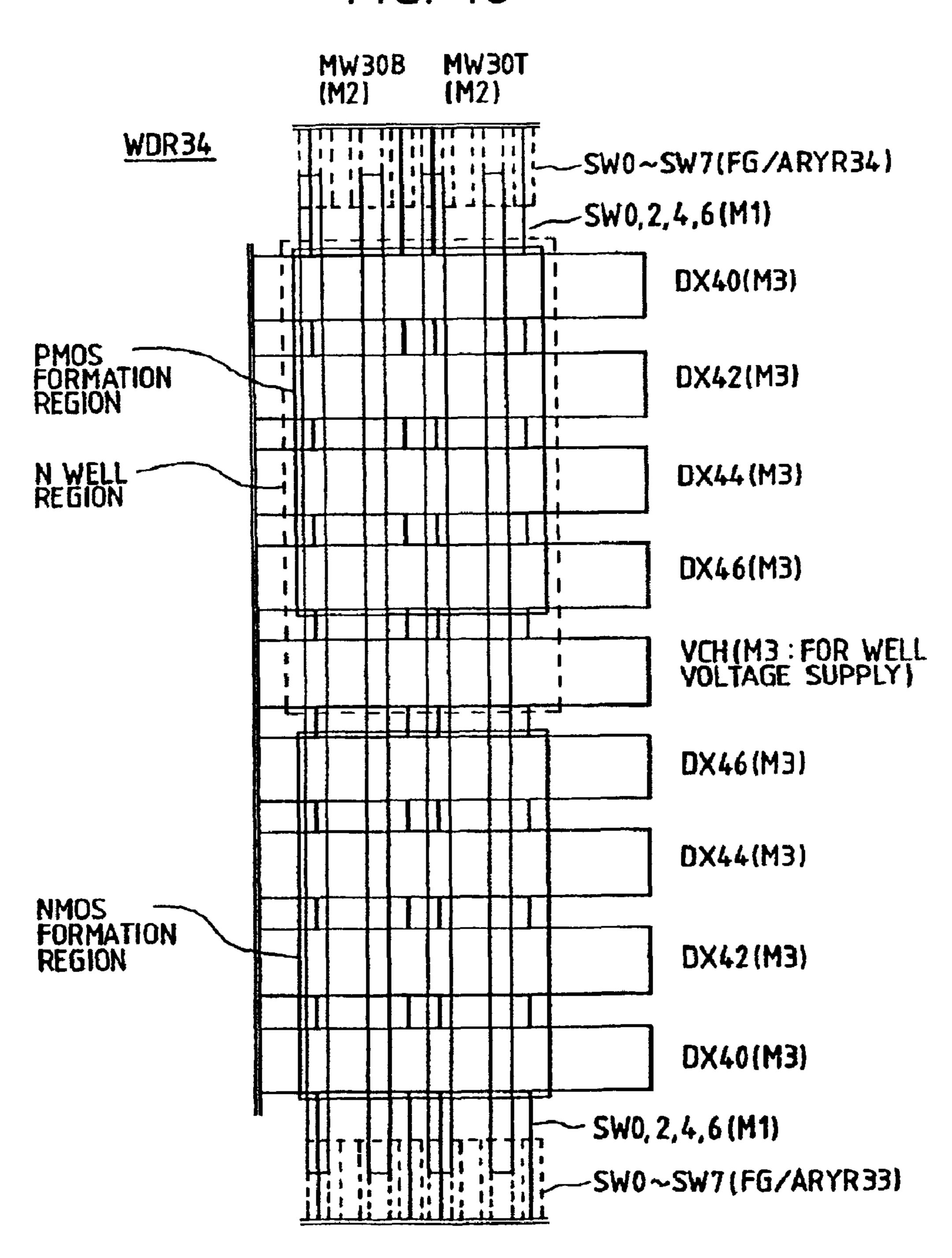

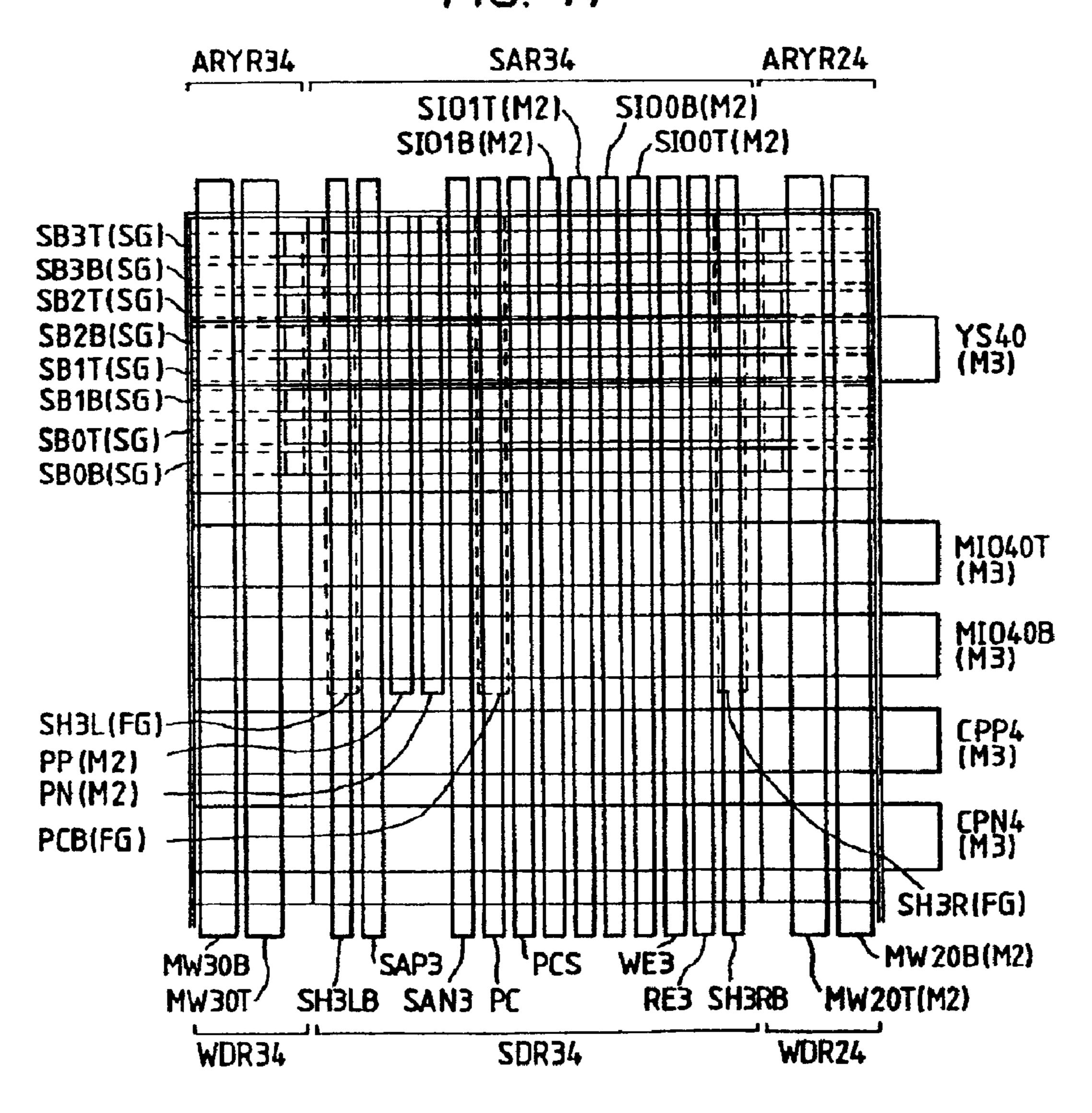

FIG. 15 is a plan view of typical metal wiring layers comprising the memory array ARYR34 of the sub-memory mat SMR34 and the peripherals associated therewith. FIG. 35 16 is a partial plan view of the sub-word line driver WDR34 included in the sub-memory mat SMR34 of FIG. 4. FIG. 17 is a partial plan view of the sense amplifier SAR34 and sense amplifier driver SDR34. Described below in reference to FIGS. 15 through 17 are the sub-memory mat SMR34 and its peripherals, with emphasis on their features and their plan layout including metal wiring layers. Needless to say, the ensuing description regarding the metal wiring layers also applies to the sub-memory mats other than the mat SMR34 described herein.

In FIG. 15, the dynamic RAM of this embodiment has three metal wiring layers M1 through M3 composed of aluminum and the like. The third or the highest metal wiring layer M3 serves to form: the bit line selection signals YS40 through YS463, etc., arranged primarily in the horizontal 50 direction of the view, i.e., in parallel with the sub-bit lines and spanning a plurality of sub-memory mats; sub-word line driving signals DX40 through DX47, etc.,; main common I/O lines MIO40\* through MIO43\*, etc.; and driving voltage supply lines CPP2, CPN2, CPP4, CPN4, etc. The second 55 metal wiring layer M2 constitutes: the main word lines MW30\* through MW363\*, etc., arranged primarily in the vertical direction of the view, i.e., in parallel with the sub-word lines and spanning a plurality of sub-memory mats; sub-common I/O lines SIO0\* through SIO3\*, etc.; 60 inverted shared control signal lines SH3LB through SH4LB and SH3RB through SH4RB, etc.; sense amplifier driving signal lines SAP3 through SAP4 and SAN3 through SAN4, etc.; and internal control signal lines PC, PCS, WE3 through WE4, RE3 through RE4, etc. The first or the lowest metal 65 RAM. wiring layer M1 makes up the wiring between circuit elements such as MOSFETs.

20

In this embodiment, as illustrated in FIG. 16, the main word lines MW30\*, etc., (i.e., the uninverted main word line MW30T and inverted main word line MW30B, etc.) made up of the second metal wiring layer M2 have a spacious pitch eight times as wide as the pitch of the sub-word lines SW0 through SW7, etc., of the memory array ARYR34 composed of a first gate layer FG. The sub-word line driving signal lines DX40, DX42, DX44 and DX46 are made of the third metal wiring layer M3 and branch into two parts each on the right-hand side of the view, not shown. The branched lines from one part of each of the sub-word line driving signal lines extend parallelly over the region forming the p-channel MOSFETs constituting the sub-word line driver WDR34. The branched lines from the other part of each of the sub-word line driving signal lines extended parallelly over the region including the n-channel MOSFETs making up the sub-word line driver WDR34. Between the sub-word line driving signal lines is the wiring for supplying the substrate potential, i.e., the internal voltage VCH to an n-well region where p-channel MOSFETs are formed. The supply wiring is constituted likewise by the third metal wiring layer M3. Under the supply wiring is the wiring, made up of the first metal wiring layer M1, for interconnecting even-numbered sub-word lines SW0, SW2, SW4, SW6, etc., of the adjacent memory arrays ARYR34 and ARYR33.

As shown in FIG. 17, the bit line selection signals YS40, etc., composed of the third metal wiring layer M3 have a spacious pitch four times that of the sub-bit lines SB0\* through SB3\* of the memory array ARYR34 formed by a second gate layer SG (i.e., uninverted sub-bit lines SB0T through SB3T and inverted sub-bit lines SB0B through SB3B, etc.). This means that the pitch of the bit line selection signals is substantially eight times as wide as that of the sub-bit lines. The main common I/O lines MIO40\*, etc., made up of the third metal wiring layer M3 (i.e., uninverted main common I/O lines MIO40T and MIO40B and driving voltage supply lines CPP4 and CPN4, etc.) are located over the region in which the sub-word line drivers WDR24 and WDR34 as well as the sense amplifier drivers SDR34, etc., are provided. In the second metal wiring layer, the sub-common I/O lines SIO0\* and SIO1\* (i.e., uninverted sub-common I/O lines SIO0T and SIO1T, inverted sub-common I/O lines SIO0B and SIO1B, etc.); inverted 45 shared control signal lines SH3LB and SH3RB through SH4RB, etc.; sense amplifier driving signal lines SAP3 and SAN3, etc.; and internal control signal lines PC, PCS, WE3 and RE3, etc., are located on the region where the sense amplifier SAR34 and sense amplifier drivers SDR34, etc., are furnished. With the above arrangements in place, the three metal wiring layers are used efficiently to form the signal lines for transmitting signals across a plurality of sub-memory mats. This enhances the efficiency in laying out the sub-memory mats and hence the dynamic RAM as a whole.

In the dynamic RAM of this embodiment, as described, a spacious layout pitch is afforded to the main word lines MW30\* through MW363\*, etc., and to the bit line selection signals YS40 through YS463, etc., which are composed of the second or third metal wiring layer M2 or M3 and closely associated with memory arrays of a high degree of circuit integration. Thus these metal wiring layers are patterned without recourse to the so-called phase shift mask. This contributes to reducing the fabrication cost of the dynamic RAM.

FIG. 18 is a plan view of a first example of the memory arrays and peripherals constituting each sub-memory mat in