### US00RE38608E1

# (19) United States

## (12) Reissued Patent

Yu et al.

## (10) Patent Number: US RE38,608 E

(45) Date of Reissued Patent: Oct. 5, 2004

## (54) LOW-VOLTAGE PUNCH-THROUGH TRANSIENT SUPPRESSOR EMPLOYING A DUAL-BASE STRUCTURE

(75) Inventors: **Bin Yu**, Cupertino, CA (US);

Chenming Hu, Alamo, CA (US); Ya-Chin King, Hsinchu (TW); Jeffrey T. Pohlman, Camarillo, CA (US); Rita Trivedi, Foothill Ranch, CA (US)

(73) Assignee: Semtech Corporation, Camarillo, CA

(US)

(\*) Notice: This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 10/052,843

(22) Filed: Jan. 17, 2002

### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 6,015,999

Issued: Jan. 18, 2000

Appl. No.: 09/039,926

Filed: Mar. 16, 1998

## U.S. Applications:

(63) Continuation of application No. 08/497,079, filed on Jun. 30, 1995, now Pat. No. 5,880,511.

| 151              | Int C17     | <br>11011 20 | ///         |

|------------------|-------------|--------------|-------------|

| $(\mathfrak{I})$ | ) IIII. CI. | <br>DOTT 72  | / <b>UU</b> |

## (56) References Cited

### U.S. PATENT DOCUMENTS

| 4,017,882 A<br>4,405,932 A | * | 9/1983 | Ishii et al. | ••••• | 257/497 |

|----------------------------|---|--------|--------------|-------|---------|

| 4,602,267 A                |   | _      |              |       |         |

| 5,528,064 A                |   | 6/1996 | Thiel        |       |         |

<sup>\*</sup> cited by examiner

Primary Examiner—Jerome Jackson

(74) Attorney, Agent, or Firm—O'Melveny & Myers LLP

## (57) ABSTRACT

A punch-through diode transient suppression device has a base region of varying doping concentration to improve leakage and clamping characteristics. The punch-through diode includes a first region comprising an n+ region, a second region comprising a p- region abutting the first region, a third region comprising a p+ region abutting the second region, and a fourth region comprising an n+ region abutting the third region. The peak dopant concentration of the n+ layers should be about 1.5E18 cm<sup>-3</sup>, the peak dopant concentration of the p+ layer should be between about 1 to about 5 times the peak concentration of the n+ layer, and the dopant concentration of the p- layer should be between about 0.5E14 cm<sup>-3</sup> and about 1.OE17 cm<sup>-3</sup>. The junction depth of the fourth (n+) region should be greater than about 0.3  $\mu$ m. The thickness of the third (p+) region should be between about 0.3  $\mu$ m and about 2.0  $\mu$ m, and the thickness of the second (p-) region should be between about 0.5  $\mu$ m and about 5.0  $\mu$ m.

## 26 Claims, 10 Drawing Sheets

FIG. 1 (PRIOR ART)

FIG. 2 (PRIOR ART)

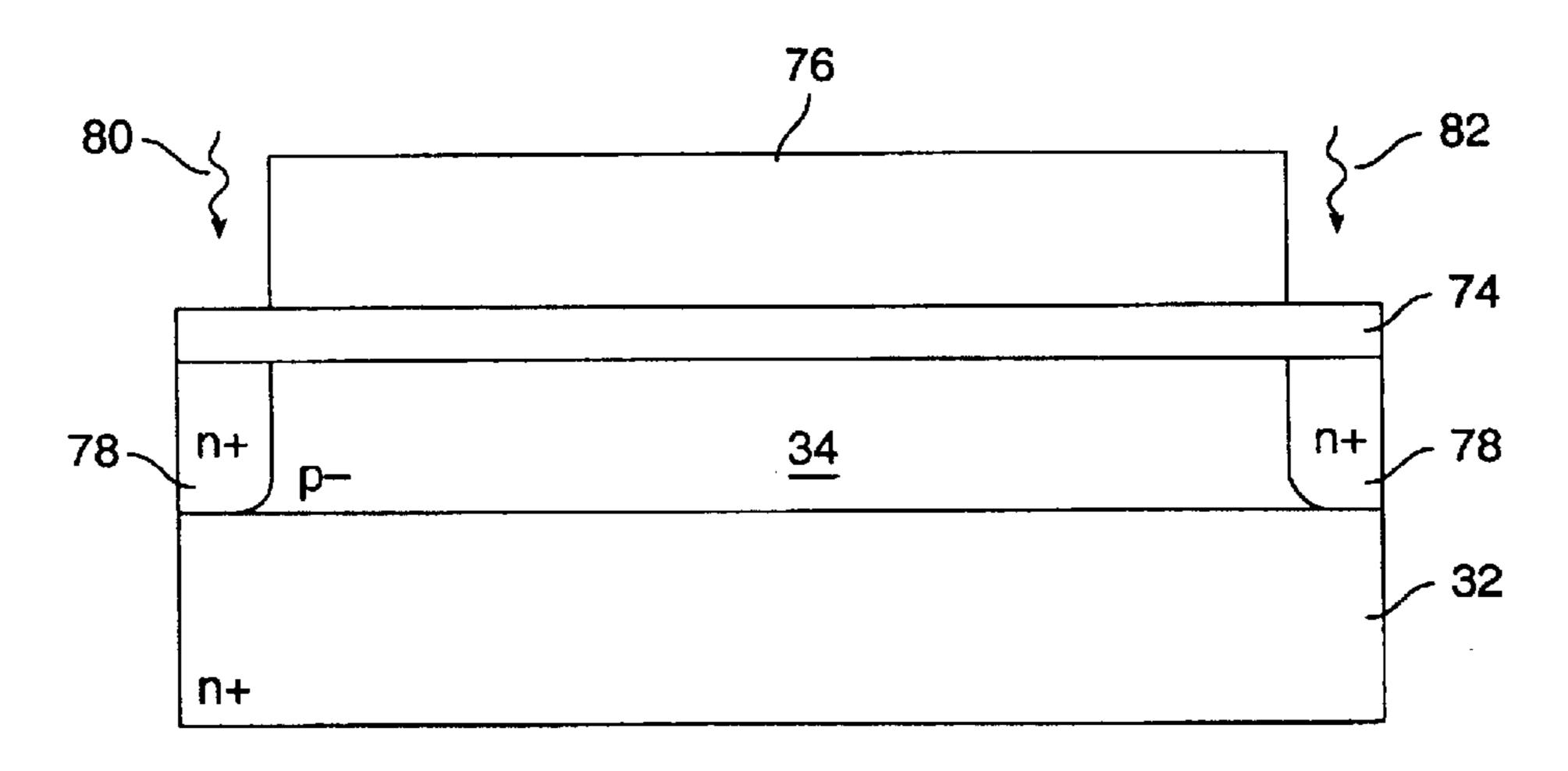

FIG. 7

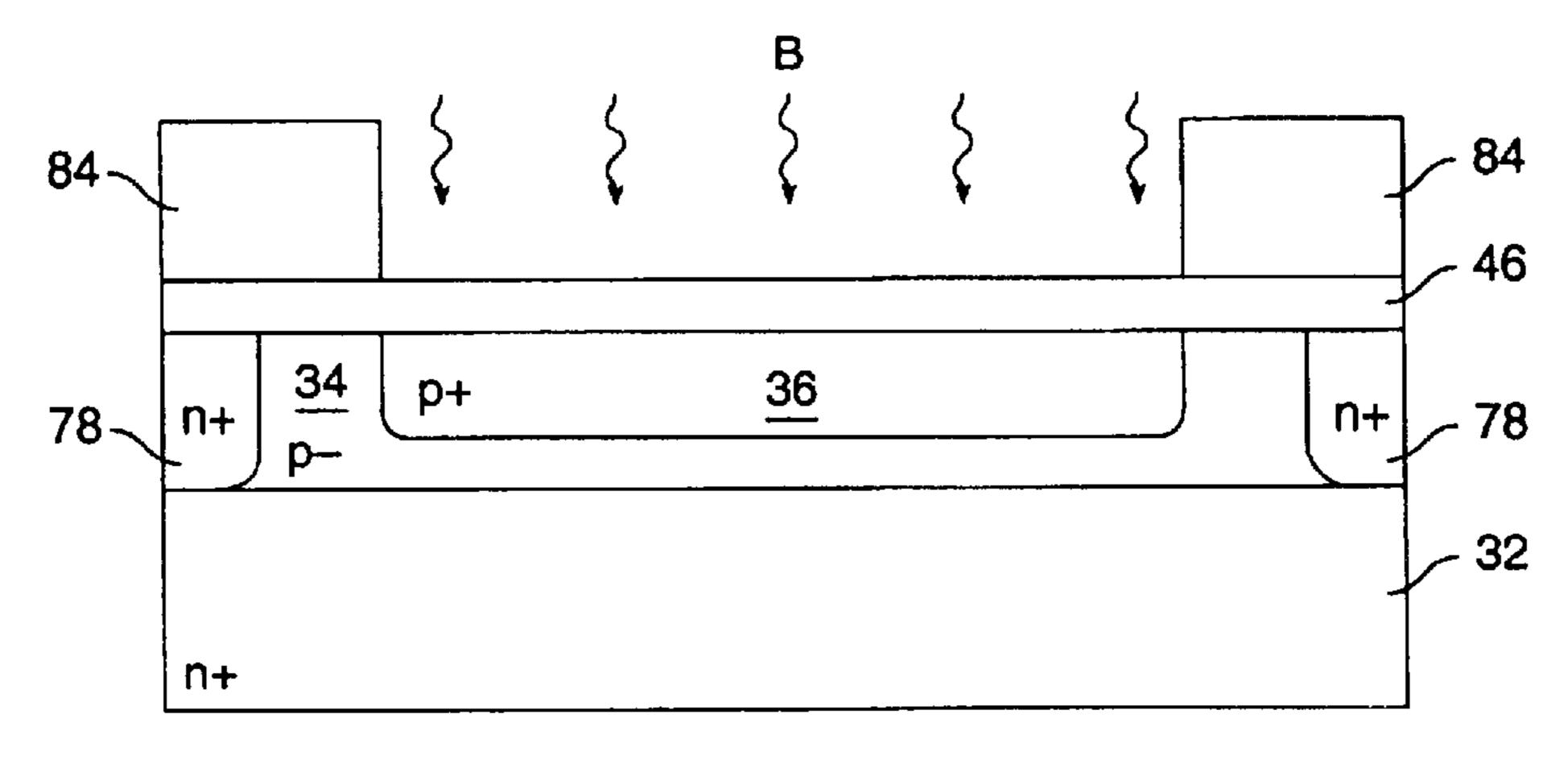

FIG. 8A

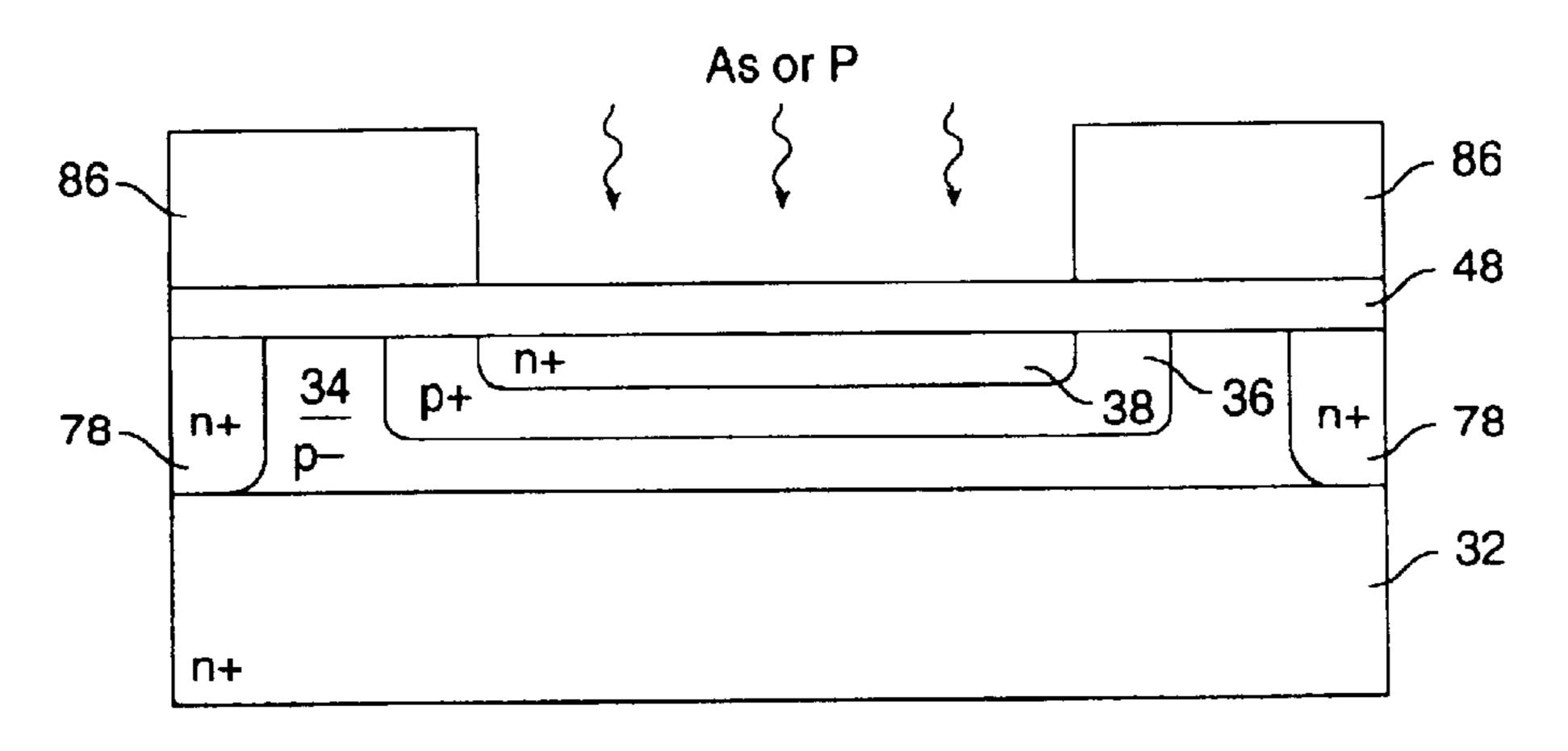

FIG. 8B

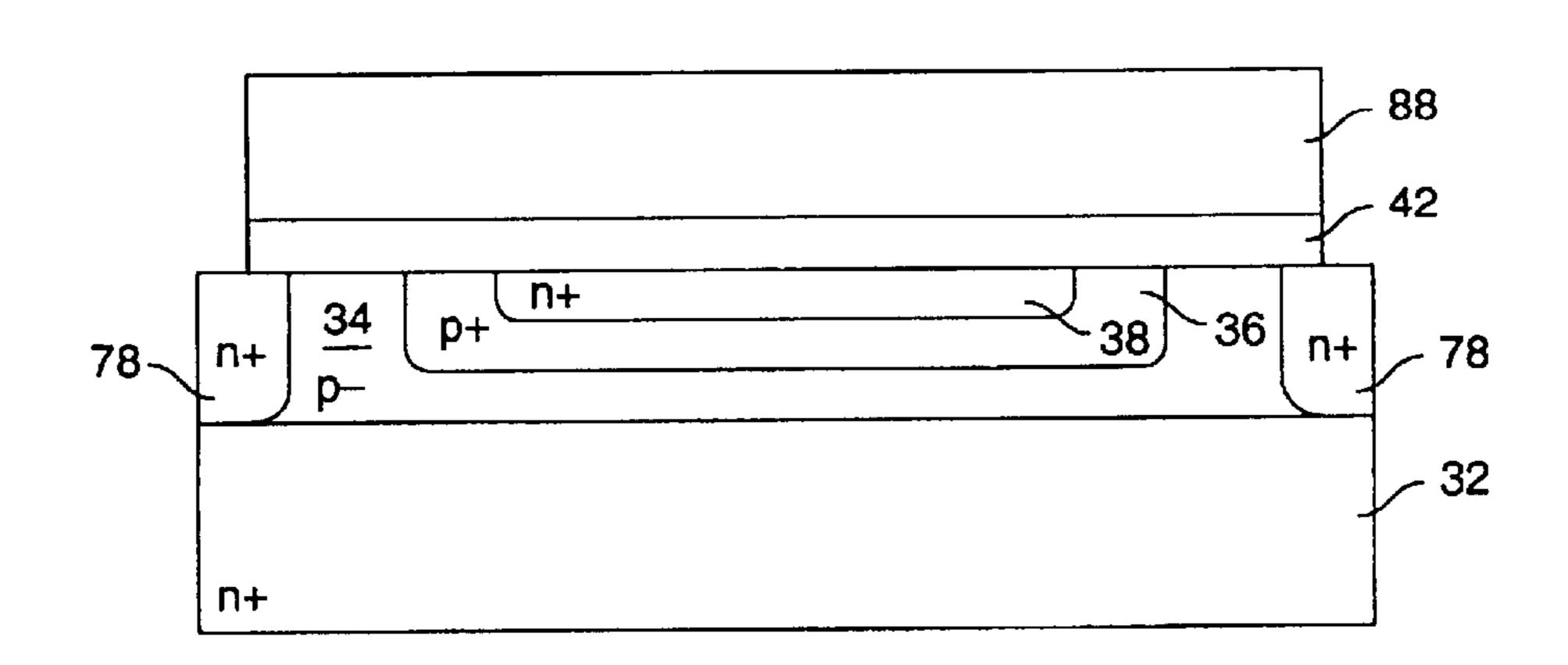

FIG. 8C

FIG. 8D

FIG. 8E

FIG. 8F

FIG. 8G

FIG. 9

FIG. 10A

FIG. 10B

FIG. 10C

FIG. 10D

FIG. 10E

FIG. 10F

FIG. 10G

FIG. 10H

FIG. 11

FIG. 12

FIG. 13

## LOW-VOLTAGE PUNCH-THROUGH TRANSIENT SUPPRESSOR EMPLOYING A DUAL-BASE STRUCTURE

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

# CROSS-REFERENCE TO RELATED APPLICATION

This is a continuation of patent application Ser. No. 08/497,079, filed Jun. 30, 1995.

#### BACKGROUND OF THE INVENTION

## 1. Field of the Invention

The present invention relates to semiconductor devices. More particularly, the present invention relates to a low-voltage punch-through transient suppressor employing a 20 dual base structure.

## 2. The Prior Art

Electronic circuitry which is designed to operate at supply voltages less than 5 volts are extremely susceptible to damage from overvoltage conditions caused by electrostatic <sup>25</sup> discharge, inductively coupled spikes, or other transient conditions from its operating environment. The current trend of the reduction in circuit operating voltage dictates a corresponding reduction in the maximum voltage that the circuitry can withstand without incurring damage. As operating voltages drop below 5 volts to 3.3 volts and below it becomes necessary to clamp transient voltage excursions to below five volts.

The most widely used device currently in use for low voltage protection is the reversed biased p+n+ zener diode. See O. M. Clark, "Transient voltage suppressor types and application", IEEE Trans Power Electron., vol. 5, pp. 20–26, November 1990. These devices perform well at voltages of 5 volts and above but run into problems when scaled to clamp below 5 volts. The two major drawbacks incurred by using this device structure are very large leakage currents and high capacitance. These detrimental characteristics increase power consumption and restrict operating frequency.

A second device capable low clamping voltages is the n+pn+ uniform base punch through diode, such as disclosed in P. J. Kannam, "Design concepts of high energy punch-through structures" IEEE Trans. Electron Devices, ED-23, no. 8, pp. 879–882, 1976, and D. de Cogan, "The punch through diode", Microelectronics, vol. 8, no. 2, pp. 20–23, 1977. These devices exhibit much improved leakage and capacitance characteristics over the conventional pn diode but suffer from poor clamping characteristics at high currents. If the designer tries to improve clamping to protect circuitry under industry standard surge conditions by increasing die area, the results are devices which are too large to produce economically.

It is therefore an object of the present invention to provide a low-voltage transient suppressor which avoids some of the shortcomings of the prior art.

It is another object of the present invention to provide a low-voltage transient suppressor which has a low leakage current.

It is further object of the present invention to provide a 65 low-voltage transient suppressor which has a lower capacitance than prior-art low-voltage transient suppressors.

2

It is yet another object of the present invention to provide a low-voltage transient suppressor which has improved high-current clamping characteristics compared to prior-art low-voltage transient suppressors.

### BRIEF DESCRIPTION OF THE INVENTION

The transient suppressor device of the present invention comprises a n+p-p+n+ punch-through diode. It is a device which can clamp at low voltages and have leakage and capacitance characteristics superior to those of prior-art transient suppressors. The punch-through diode of the present invention includes a first region comprising an n+region, a second region comprising a p-region abutting the first region, a third region comprising a p+ region abutting the second region, and a fourth region comprising an n+region abutting the third region.

The peak dopant concentration of the n+ layers should be about 1.5E18 cm<sup>-3</sup>, the peak dopant concentration of the p+ layer should be between about 50 to about 2,000 times the peak concentration of the p- layer, and the dopant concentration of the p- layer should be between about 0.5E14 cm<sup>-3</sup> and about 1.0E17 cm<sup>-3</sup>. The junction depth of the fourth (n+) region should be between about 0.3 um and about 1.5 um. The thickness of the third (p+) region should be between about 0.3 um and about 2.0 um, and the thickness of the second (p-) region should be between about 0.5 um and about 5.0 um.

### BRIEF DESCRIPTION OF THE DRAWINGS

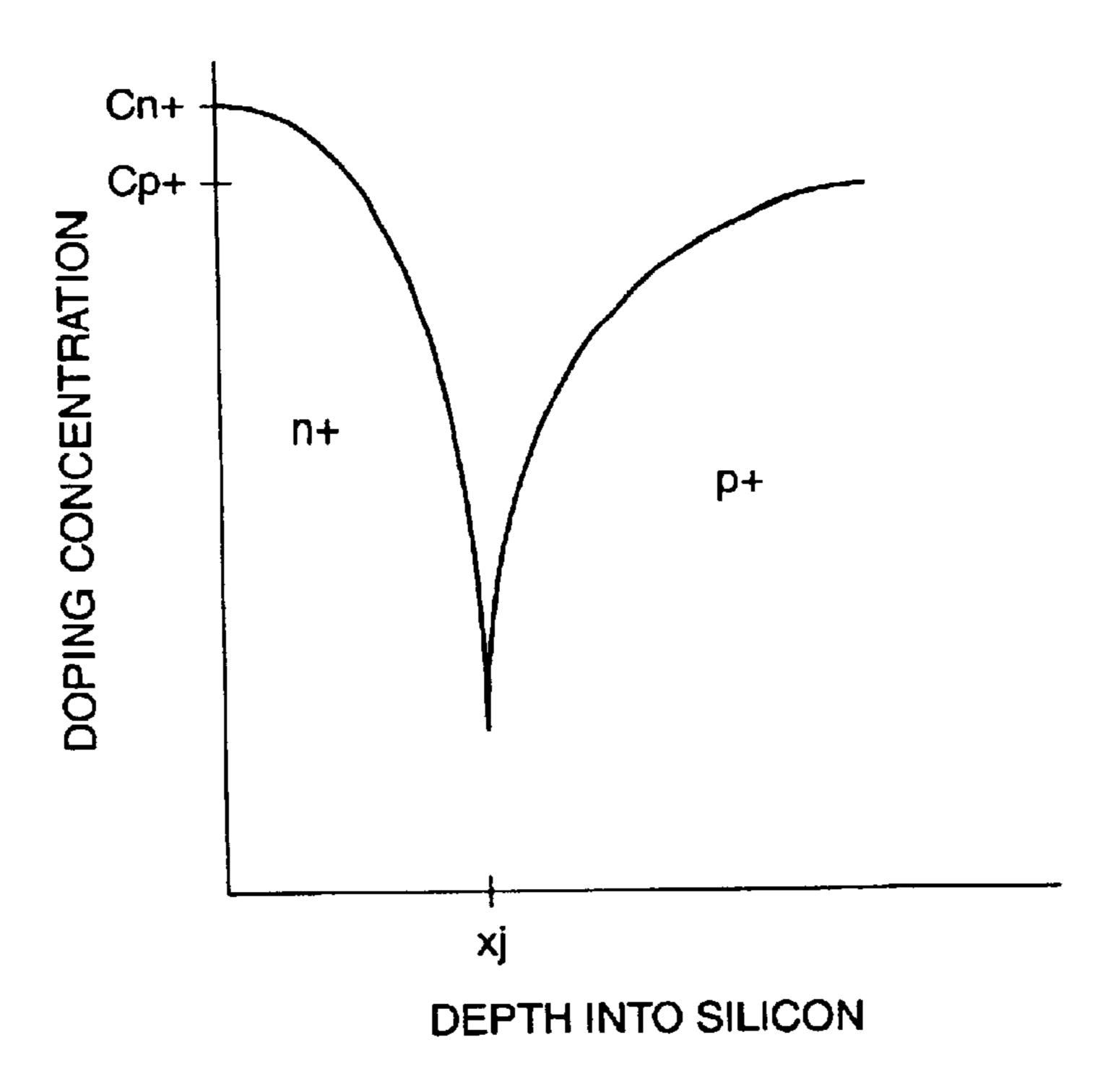

FIG. 1 is a graph showing the doping profile of a prior-art pn zener diode.

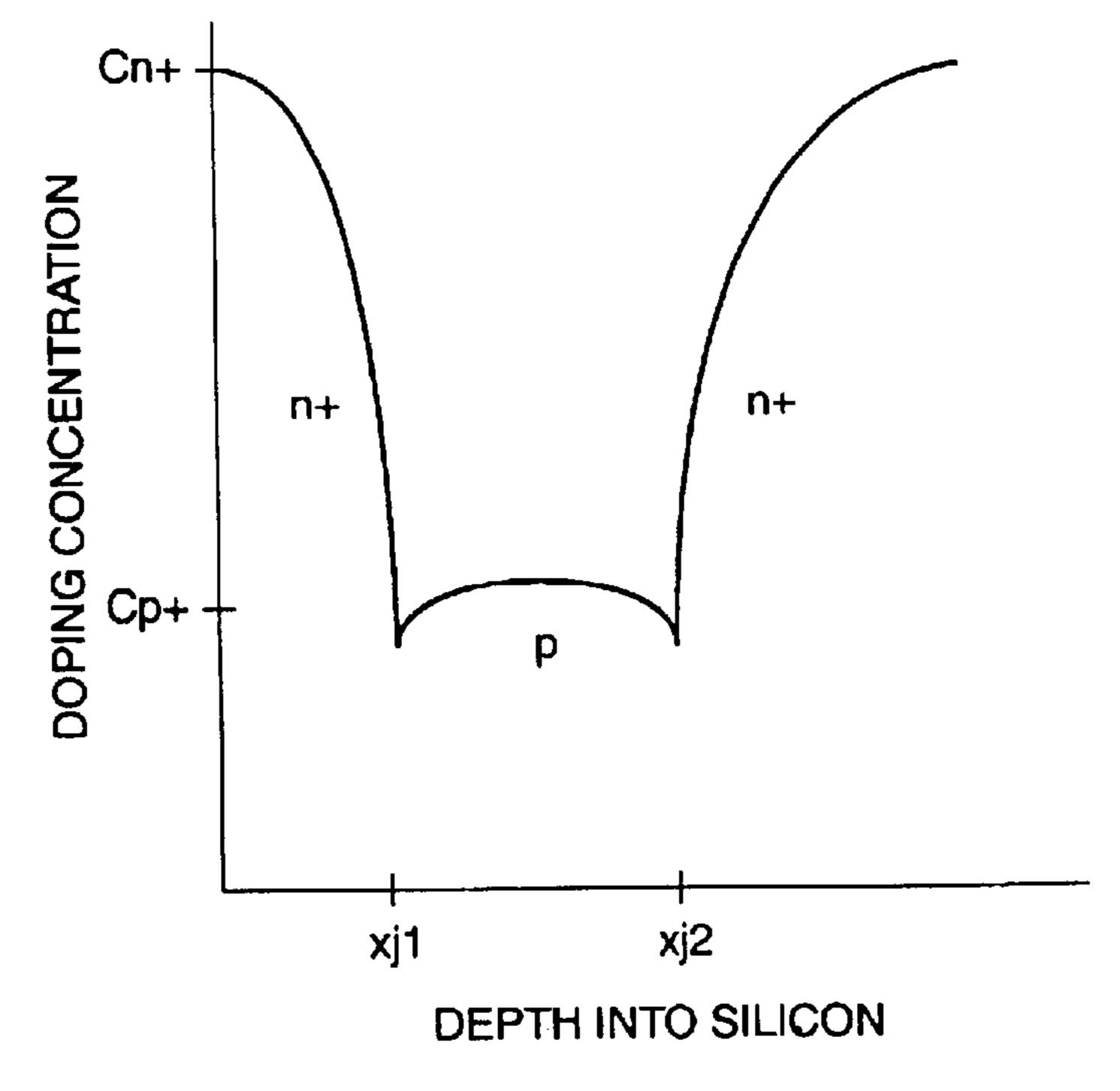

FIG. 2 is a graph showing the doping profile of a prior-art n+pn+ punch-through diode.

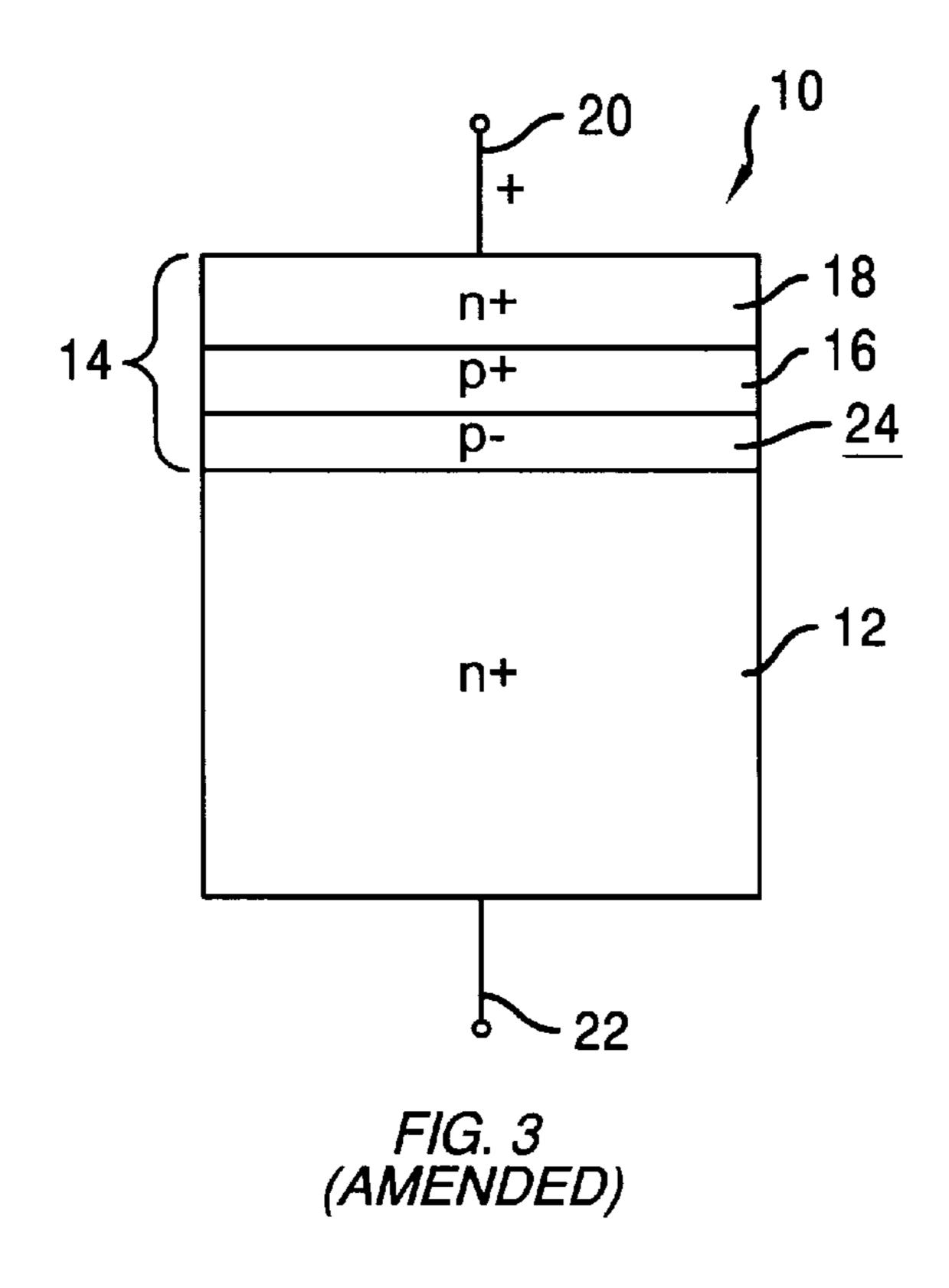

FIG. 3 is a schematic representation of a cross-sectional view of the punch-through n+p-p+n+ punch-through diode of the present invention.

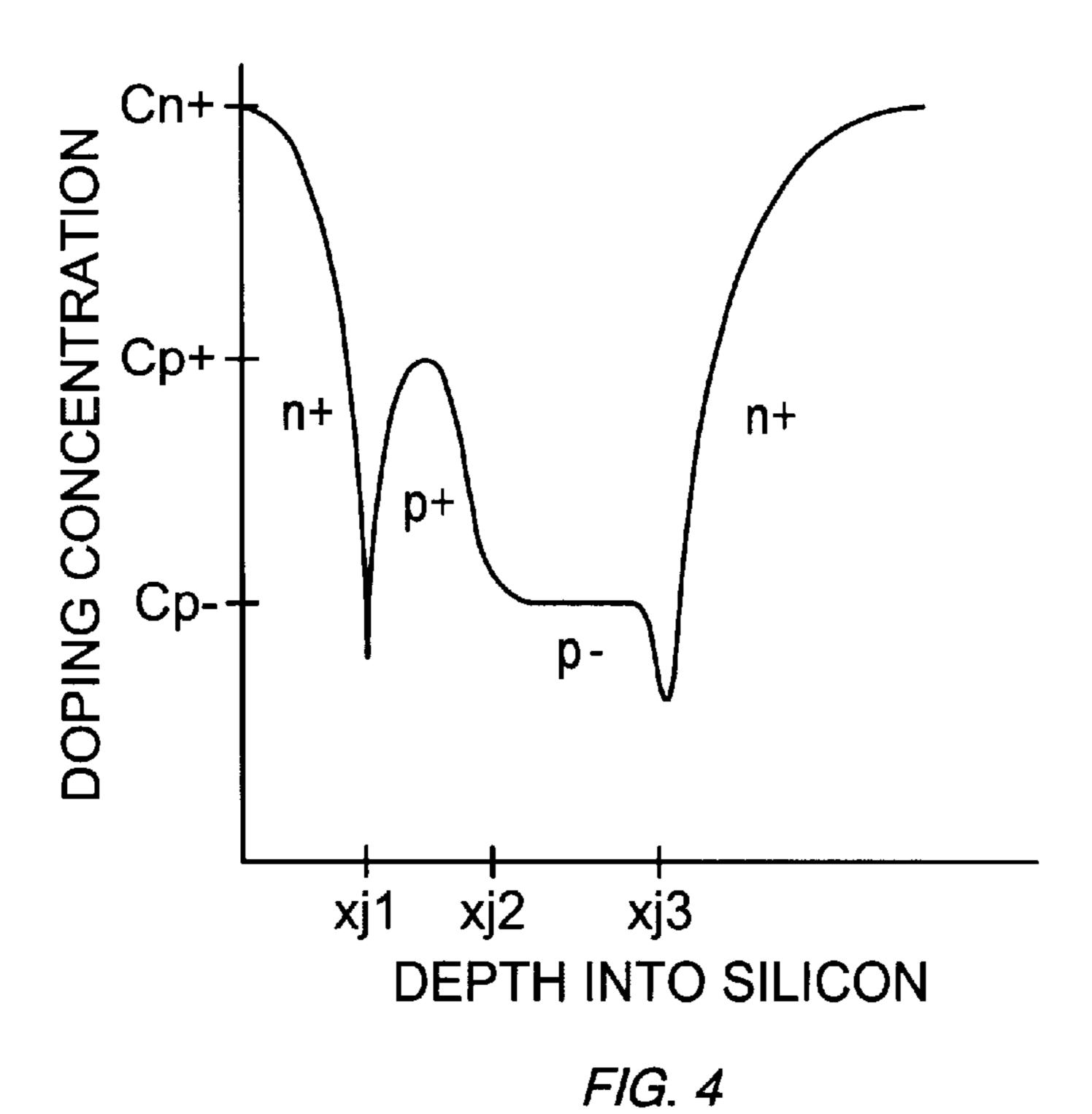

FIG. 4 is a graph showing the doping profile of an n+p-p+n+ punch-through diode of the present invention such as that of FIG. 3.

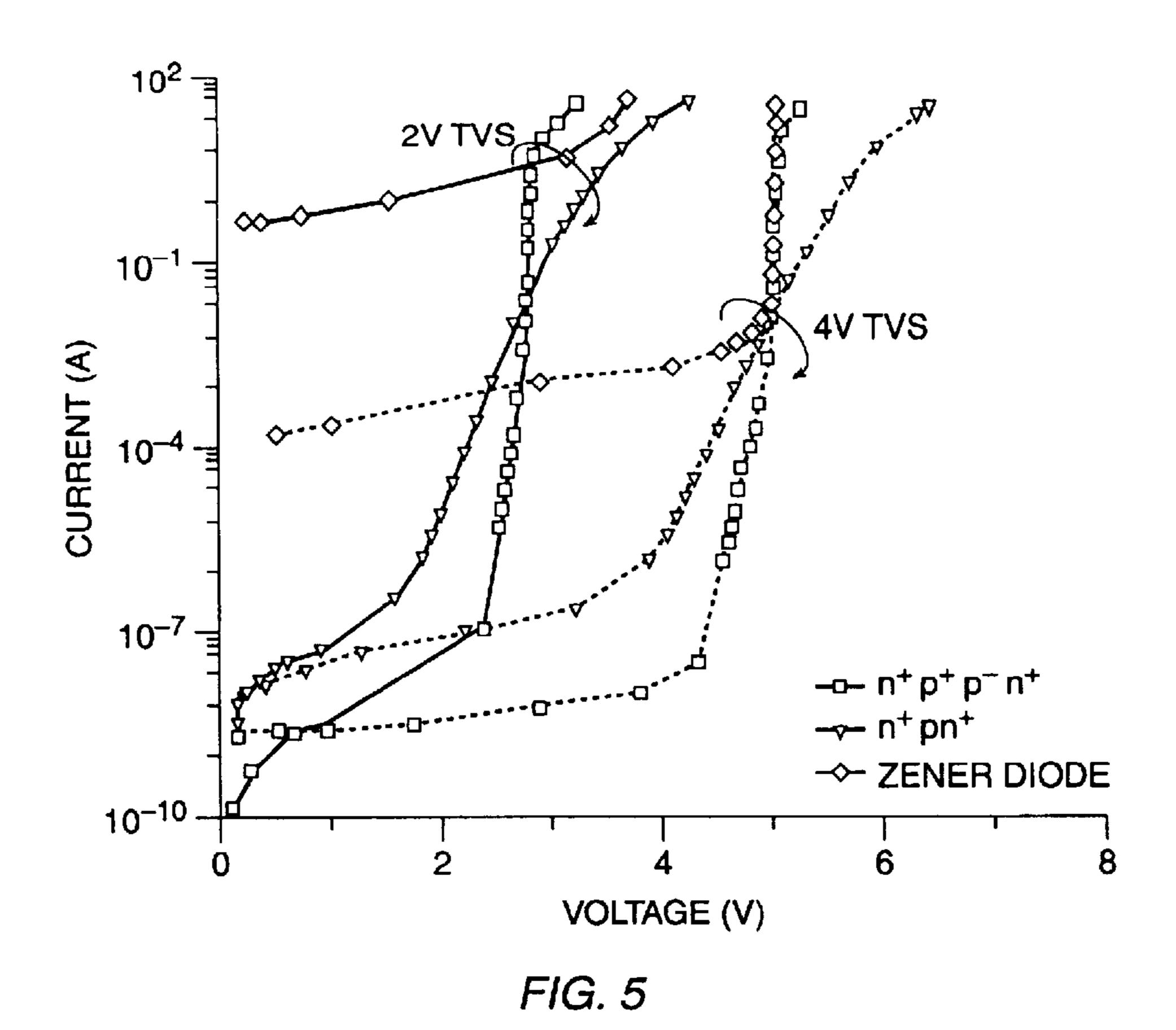

FIG. 5 is a graph comparing the current vs voltage characteristics comparison of the n+p+pn+ diode of the present invention against the prior art.

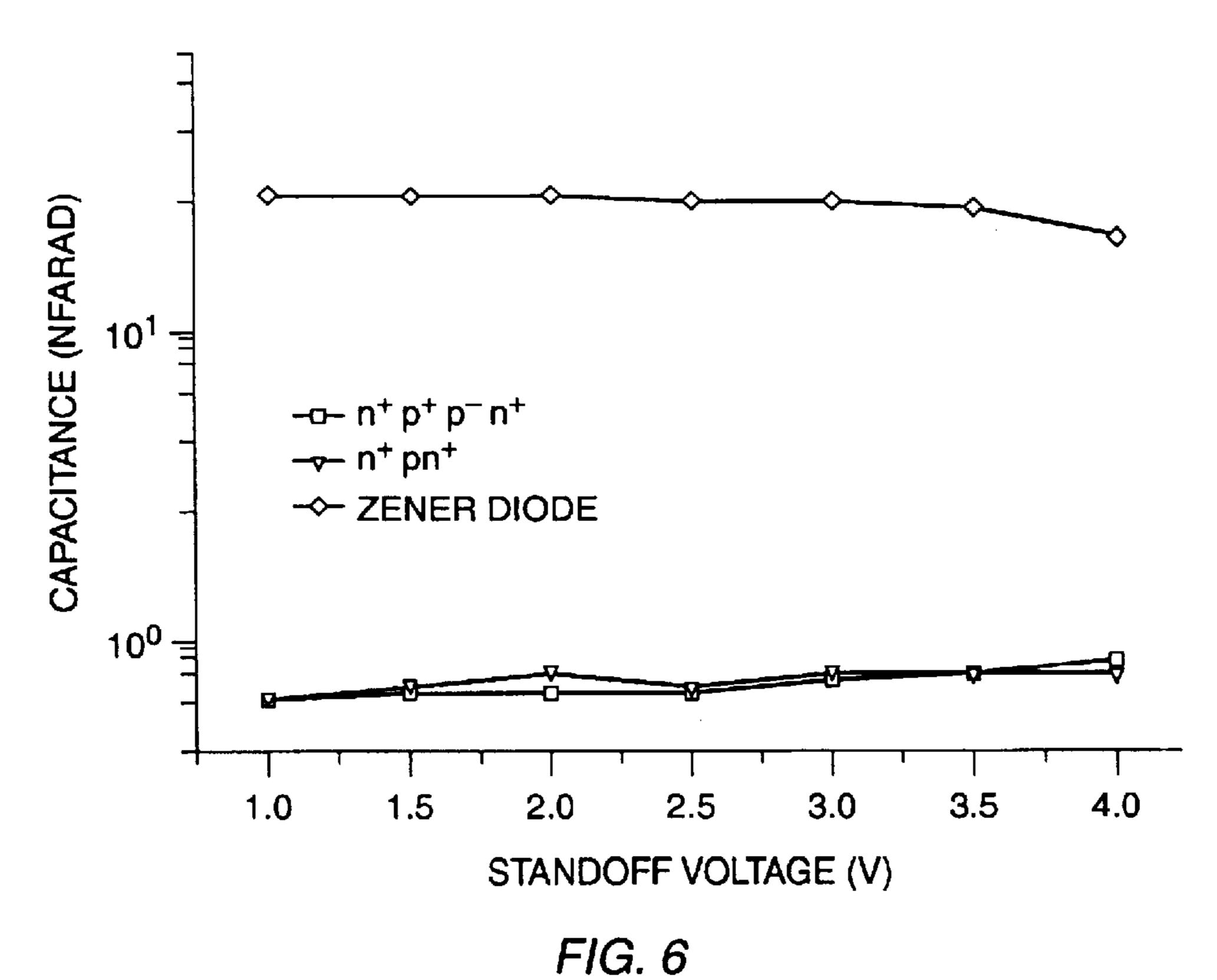

FIG. 6 is a graph comparing the capacitance vs voltage characteristics of the n+p+pn+ diode of the present invention against the prior art.

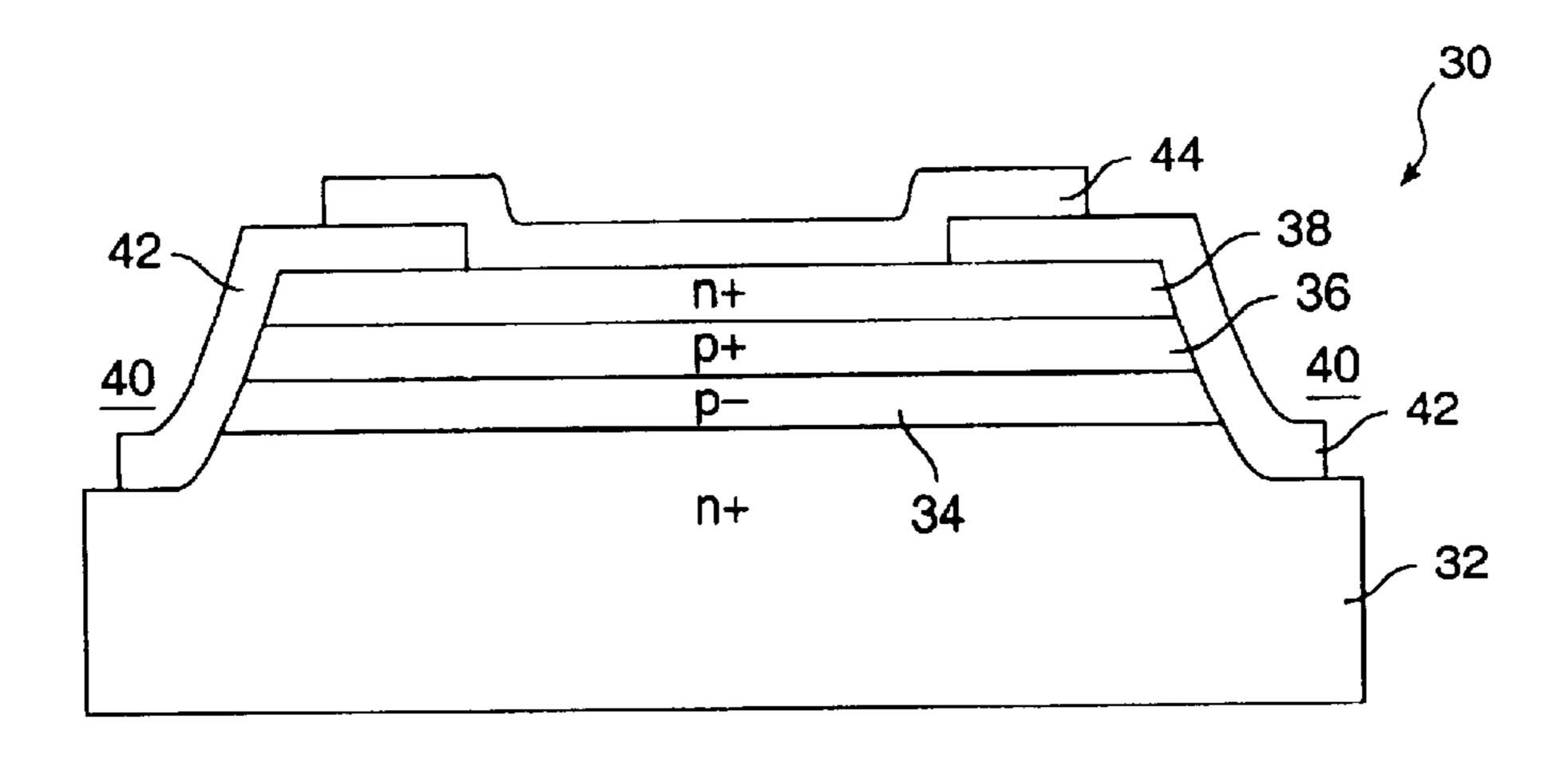

FIG. 7 is a cross-sectional view of a trench/mesa isolated n+p-p+n+ transient suppressor diode according to one presently preferred embodiment of the invention.

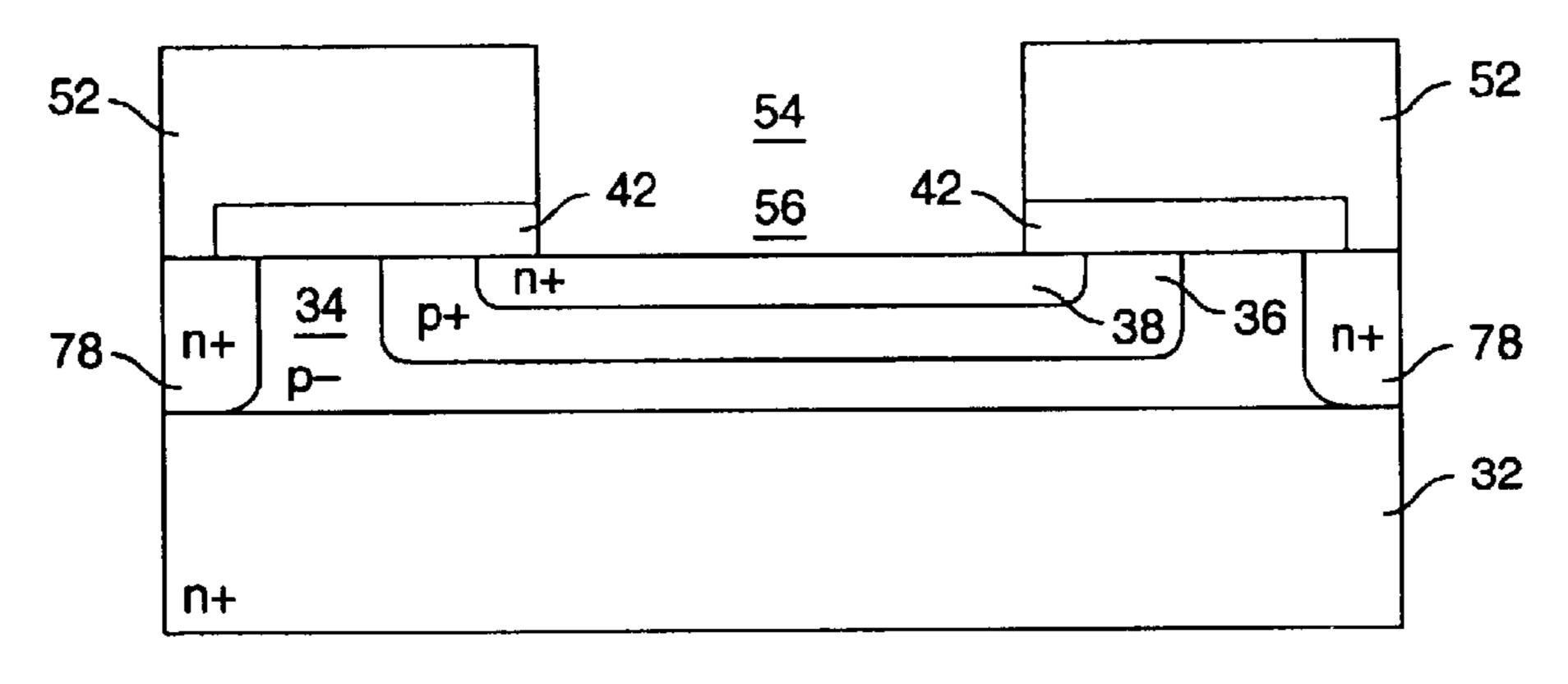

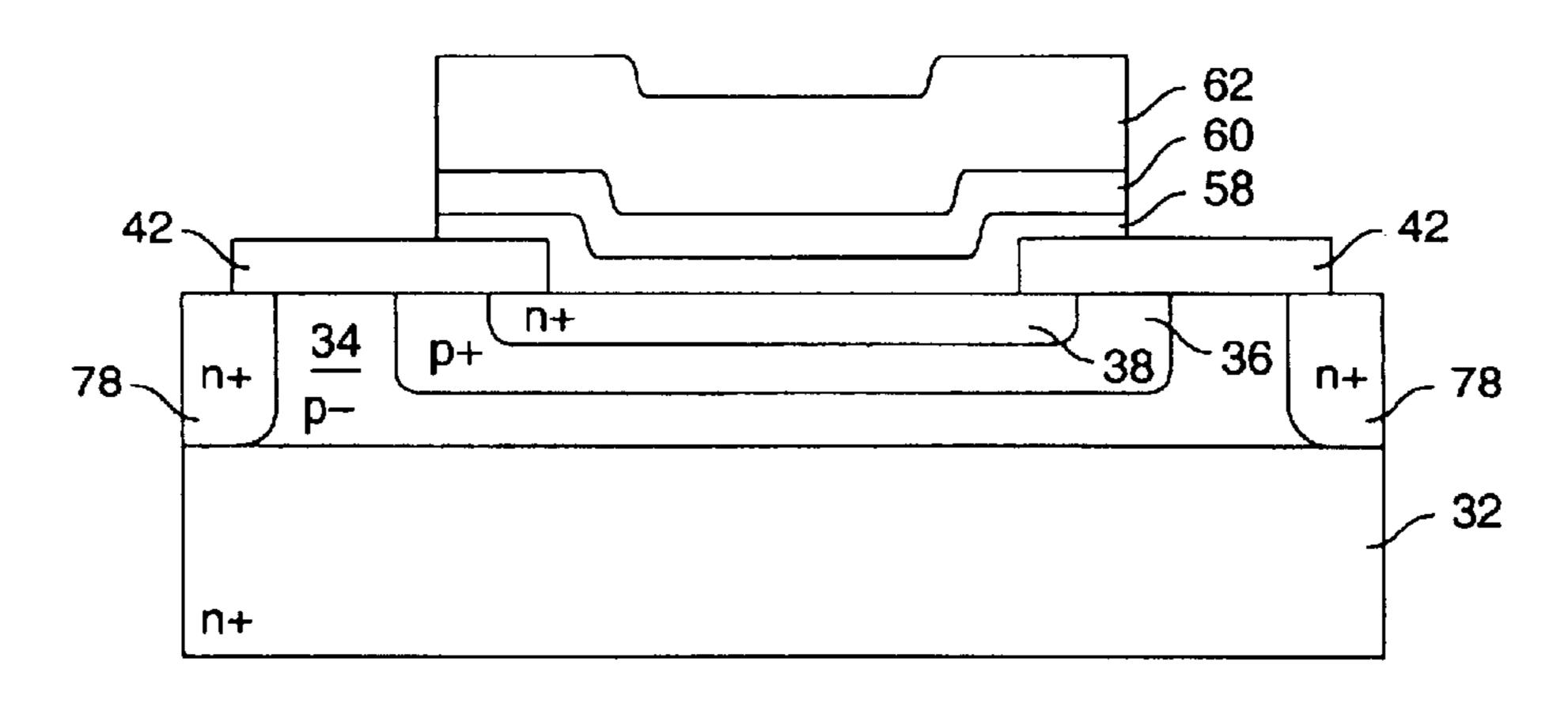

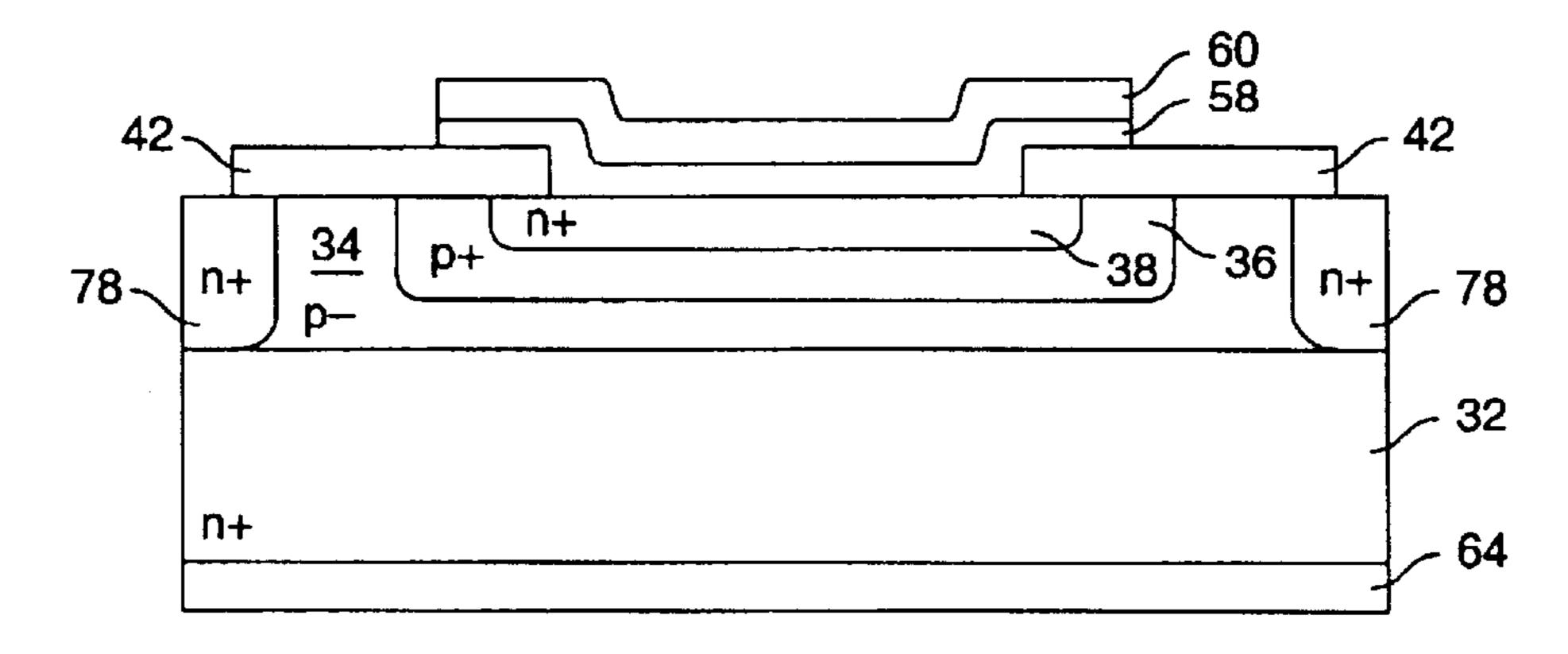

FIGS. 8a-8g are cross sectional views of the trench/mesa isolated n+p-p+n+ transient suppressor diode of FIG. 7 taken after completion of selected steps in an illustrative fabrication process.

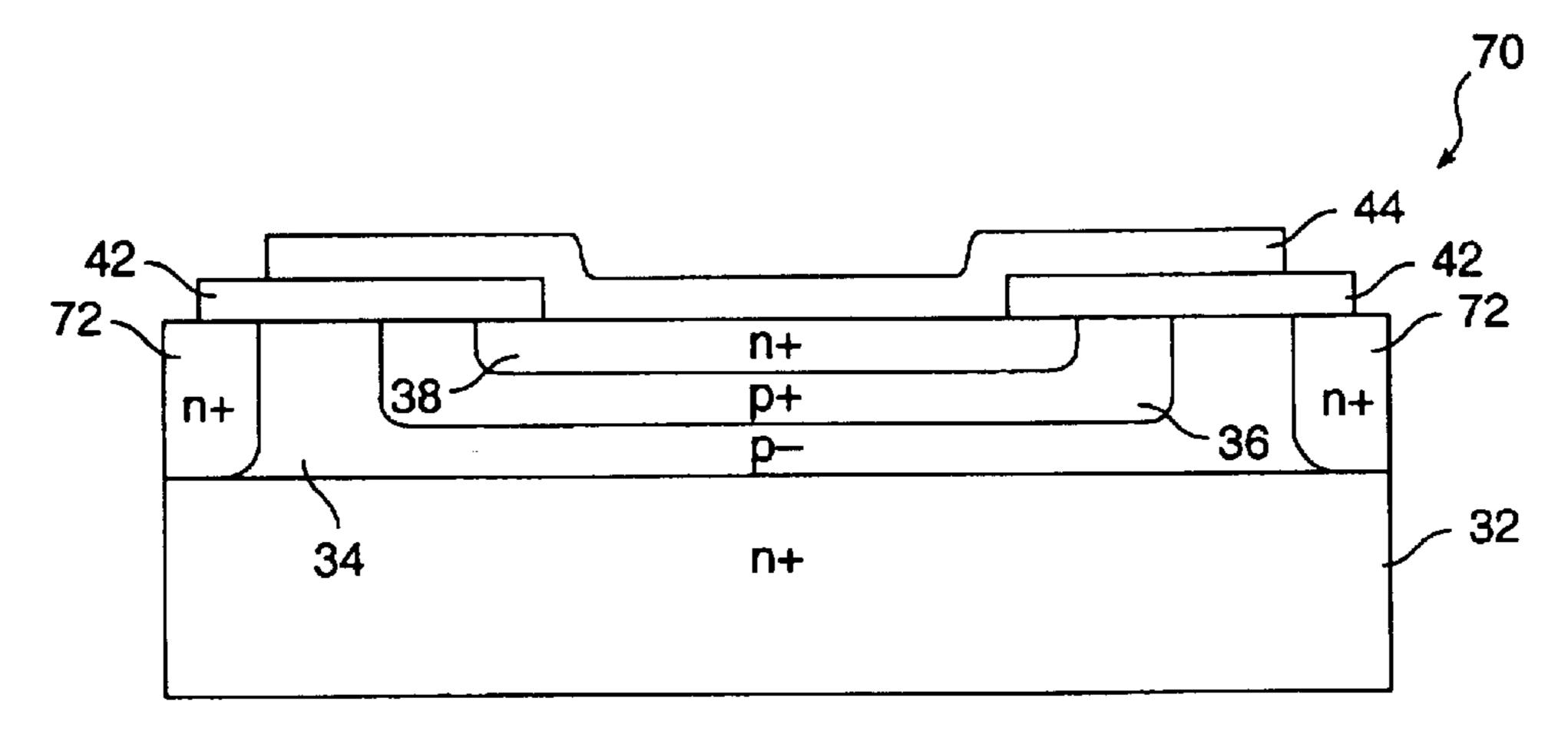

FIG. 9 is a cross-sectional view of a diffusion isolated n+p+pn+ diode according to another presently preferred embodiment of the invention.

FIGS. 10a-10h are cross sectional views of the diffusion isolated n+p-p+n+ transient suppressor diode of FIG. 9 taken after completion of selected steps in an illustrative fabrication process.

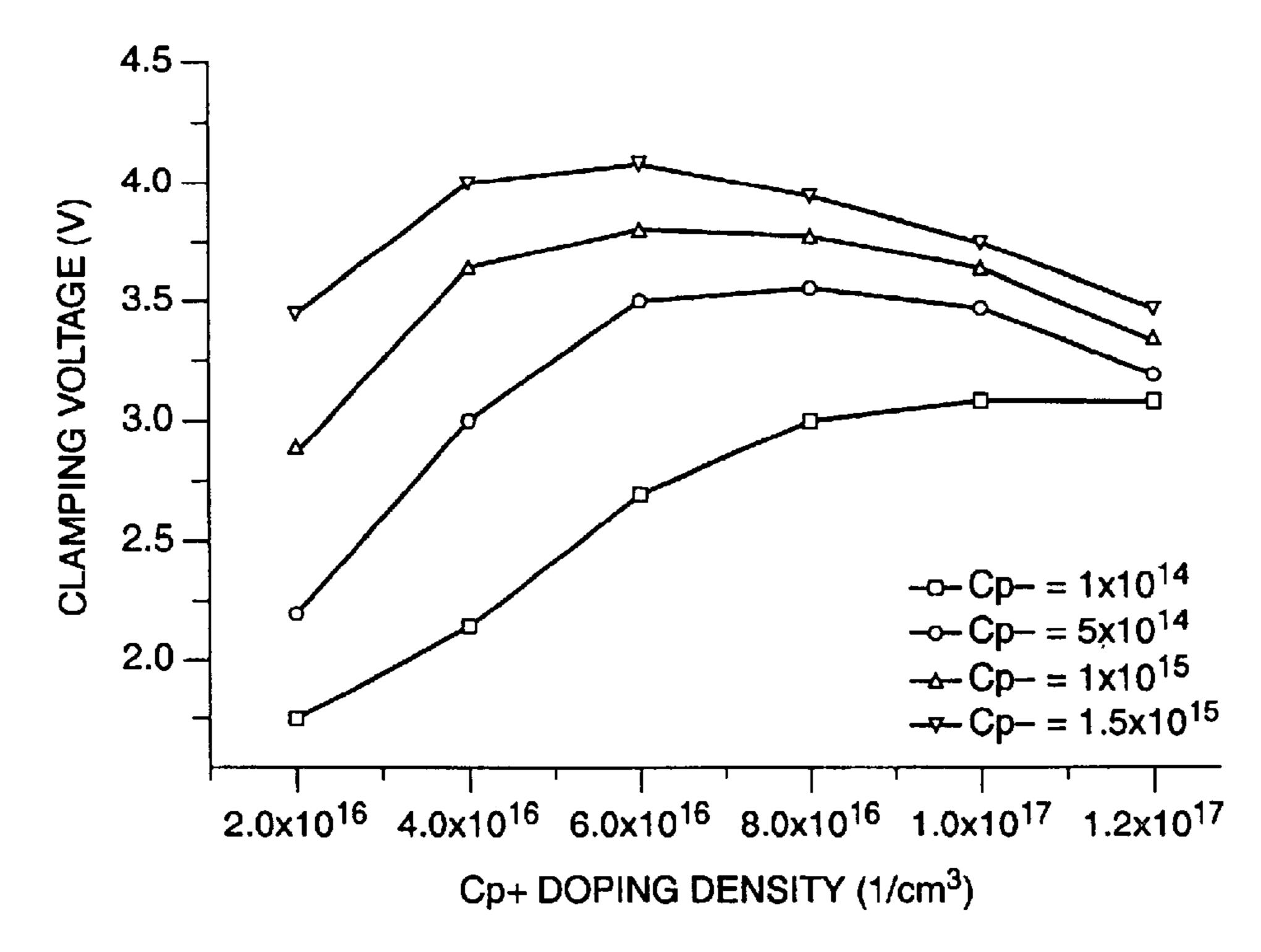

FIG. 11 is a graph of clamping voltage vs. p+ doping density for a n+p-p+n+ transient suppressor diode according to the present invention.

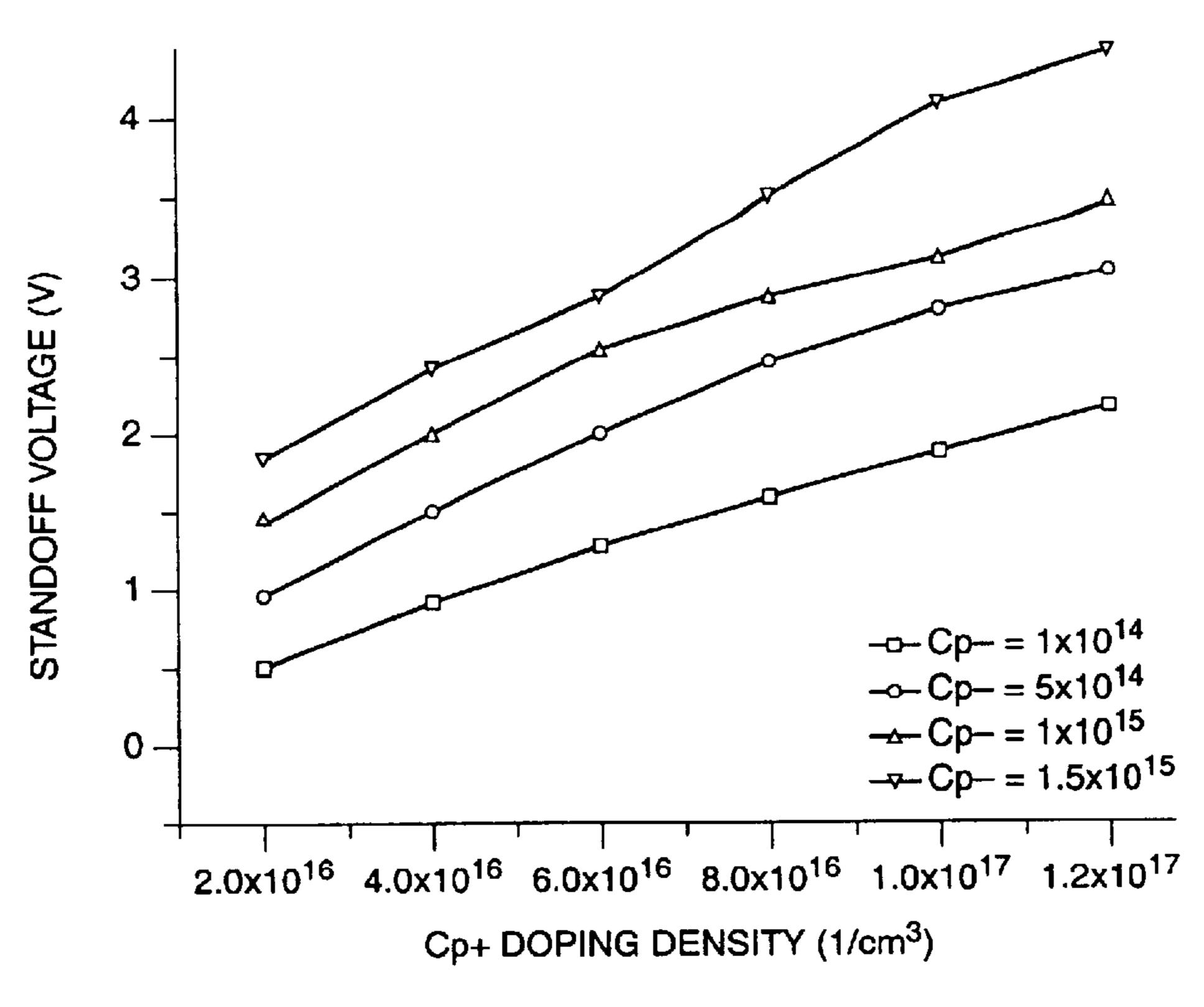

FIG. 12 is a graph of standoff voltage vs. p+ doping density for a n+p-p+n+ transient suppressor diode according to the present invention.

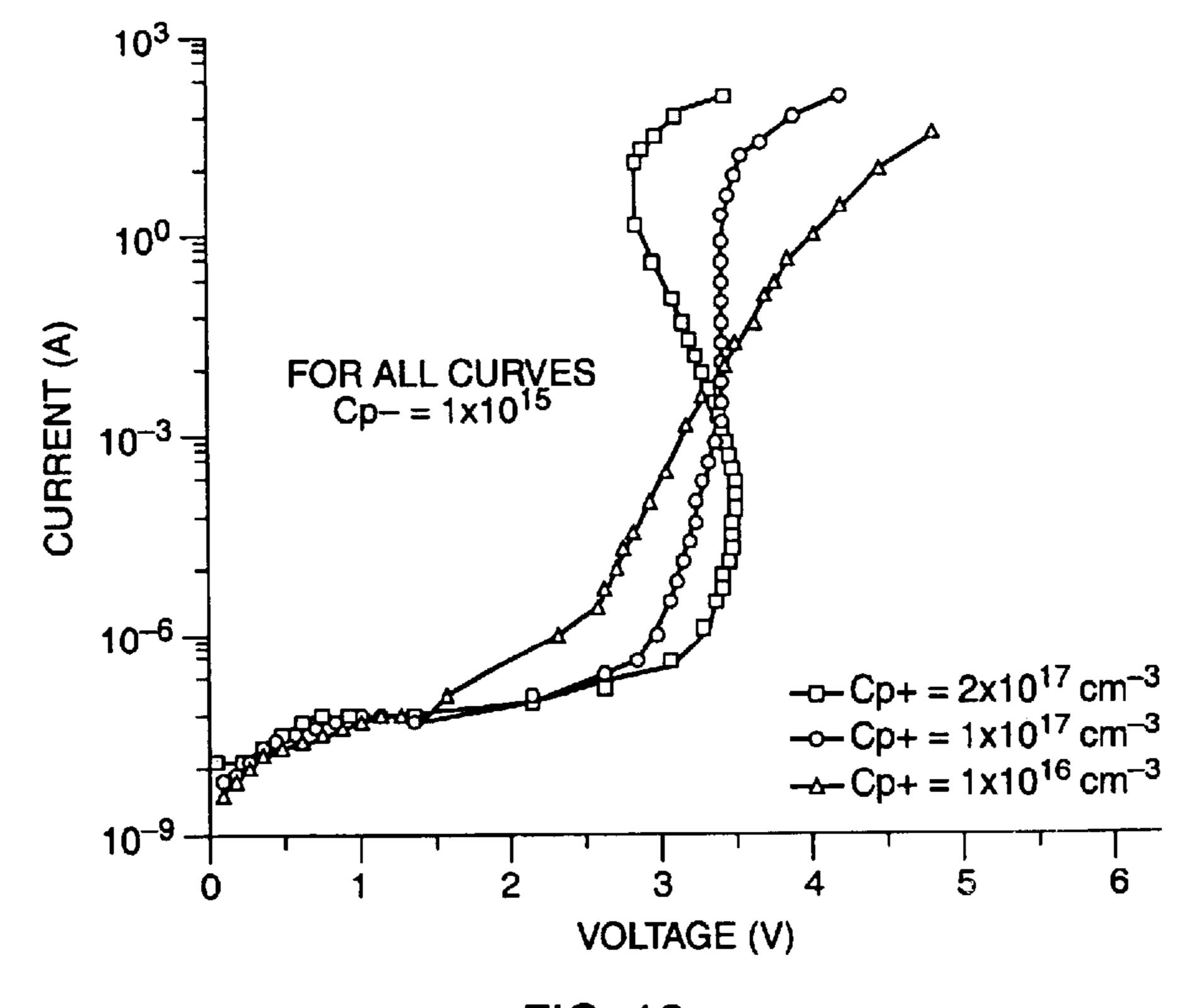

FIG. 13 is a graph of current vs. voltage for a n+p-p+n+ transient suppressor diode according to the present invention.

# DETAILED DESCRIPTION OF A PREFERRED EMBODIMENT

Those of ordinary skill in the art will realize that the following description of the present invention is illustrative only and not in any way limiting. Other embodiments of the 10 invention will readily suggest themselves to such skilled persons.

Reversed biased p+n+ zener diodes are currently the most widely-used devices for low voltage protection. These devices perform satisfactorily at voltages of 5 volts and above but exhibit very large leakage currents and high capacitance, two major drawbacks, when designed to clamp below 5 volts. FIG. 1. depicts the impurity doping profile of a typical low voltage pn junction device.

The n+p+ uniform base punch-through diode is a second device capable of clamping low voltages. While the leakage and capacitance characteristics of the punch-through diode are superior to the conventional pn diode, the punch-through diode has poor clamping characteristics at high currents. The doping profile of a low voltage n+pn+ uniform base punch-through diode is shown in FIG. 2.

Referring now to FIG. 3, a n+p-p+n+ punch-through diode 10 according to the present invention is shown schematically in cross sectional view. The n+p-p+n+ punchthrough diode of the present invention is formed on an n+ region 12 which may comprise a semiconductor substrate. An epitaxially grown p- region 14 is formed over the upper surface of n+ region 12. P+ region 16 is formed by further p-type doping of the upper surface of the epitaxial layer 14. An n+region 18 is formed over p+ region 16 by n-type doping of the upper surface of the epitaxial layer. Electrodes 20 and 22 are in contact with n+ region 12 and n+ region 18, respectively to make electrical contact to the n+p-p+n+ punch-through diode device 10. Those of ordinary skill in the art will appreciate that after the n-type doping step which creates n+ region 18, only a small region 24 of original epitaxial layer 14 remains doped at a p- level.

Table I gives the presently preferred minimum and maximum doping levels of the regions of the layers 12, 14, 16, and 18. The doping levels for the n+ layers 12 and 18 and p+ layer 16 are expressed in peak dopant concentration values (Cn+ and Cp+) and the doping level for the p- layer 14 is expressed as an average value (Cp-).

TABLE I

| Layer                                | Minimum                          | Maximum                  |

|--------------------------------------|----------------------------------|--------------------------|

| Cn+ (Peak concentration of n layers) | $1.5E18 \text{ cm}^{-3}$         | not critical             |

| Cp+ (Peak concentration of p+ layer) | $5.0\text{E}1 \times \text{Cp}-$ | $1.0E3 \times Cp-$       |

| Cp- (concentration of the p- layer   | $0.5E14 \text{ cm}^{-3}$         | $1.0E17 \text{ cm}^{-3}$ |

Table II gives the range of thickness (expressed in [um] micrometer) for the junction depth of n+ region 18, [p-]p+ region 16, and [p+]p- region [18] 24. In Table II, the quantities xj1, xj2, and xj3 refer to linear positions along the 65 thickness of the epitaxial layer after performance of the implant doping steps.

4

TABLE II

|   | Layer                                                                    | Minimum          | Maximum                |  |

|---|--------------------------------------------------------------------------|------------------|------------------------|--|

| 5 | xj1 (n+ junction depth)<br>xj2 - xj <sup>1</sup> (p+ layer<br>thickness) | 0.3 um<br>0.3 um | not critical<br>2.0 um |  |

|   | xj3 – xj2 (p layer<br>thickness)                                         | 0.5 um           | 5.0 um                 |  |

The electrical characteristics of the n+p-p+n+ punchthrough diode of the present invention are determined by the peak concentrations and widths of each of the layers depicted in FIG. 3. It is possible to build suitable devices using a fairly wide range of junction widths and concentrations. It is necessary to optimize the structure to fit the fabrication process.

By constructing a punch-through diode according to the present invention having a p- region that has an optimized doping profile, a device can be manufactured which has superior performance to the prior art. Such an optimized doping profile for such a structure is depicted in FIG. 4. FIG. 4 illustrates the relative positions of xj1, xj2, and xj3. Persons of ordinary skill in the art will appreciate that the doping profile of the device of the present invention is significantly different from the doping profiles of the priorart devices depicted in FIGS. 1 and 2.

FIG. 5 shows the current vs voltage characteristics of devices with an active area of 7.86 mm<sup>2</sup> constructed using the prior art structures and using the new n+p-p+n+ punch-through structure of the present invention. The most desirable characteristics are to have low current levels at the specified operating voltage and a near vertical I/V characteristic at high currents. FIG. 5 includes two sets of curves for each device type. One is for a devices which have a 2 volt working voltage and one is for devices having a nominal 4 volt working voltage.

It can be seen from FIG. 5 that at the working voltage of the device the new n+p-p+n+ structure of the present invention has leakage values which are four orders of magnitude lower than those achieved with conventional pn structures and one order of magnitude lower than that of the prior-art punch-through devices. Importantly, this is achieved without sacrificing the high-current performance of the device of the present invention. The current clamping characteristics of the punch-through device of the present invention match that of the conventional pn structure up to current densities of over 500 A/cm<sup>2</sup>. It can also be seen that the leakage levels for zener type devices constructed to protect below 4 volts are unacceptably high as indicated by its nearly horizontal I/V characteristic.

FIG. 6 shows the capacitance for each of the device structures over the operating voltage range for each device. It can be seen from an examination of FIG. 6 that both the prior-art punch-through device and the new n+p-p+n+ structure of the present invention have capacitance values over one order of magnitude lower than that of the pn diode. This characteristic of the device of the present invention will allow for transient suppression protection of higher frequency lines.

The n+p-p+n+ punch-through transient suppressor diode of the present invention can take several forms. Two illustrative forms of the device of the present invention are shown in FIGS. 7 and 9. Referring first to FIG. 7, a n+p-p+n+ punch-through transient suppressor diode fabricated according to the principles of the present invention using trench isolation techniques is shown in cross-sectional view.

The trench/mesa isolation n+p-p+n+ punch-through transient suppressor diode 30 is shown fabricated on n+ substrate 32. N+ substrate 32 is n-type silicon having a maximum 0.01 ohm-cm resistivity. P- layer 34 is disposed on the upper surface of the n+ substrate 32. P+layer 36 is disposed on the upper surface of p- layer 34. Finally, n+ layer 38 is disposed on the upper surface of p+ layer 36. Trenches 40 are disposed at the periphery of layers 34, 36, and 38 and extend down into substrate 32. A passivation layer 42 is disposed over the upper surface of n+ layer 38 and extends into trenches 40 down to substrate 32 to cover the edges of layers 34, 36, and 38. Metal contact 44 is disposed in an aperture formed in passivation layer 42 and makes electrical contact with n+ layer 38.

The n+p-p+n+ punch-through diode of the present invention can be manufactured using standard silicon wafer fabrication techniques. A typical process flow with ranges that could accommodate most processing equipment for a mesa or trench isolated device such as that depicted in FIG. 7 is shown below with reference to FIGS. 8a–8g. Those of ordinary skill in the art will readily appreciate that the process flow disclosed herein is in no way meant to be restrictive as there are numerous ways to create the required structures and doping profile for the n+p-p+n+ punch-through transient suppressor diode.

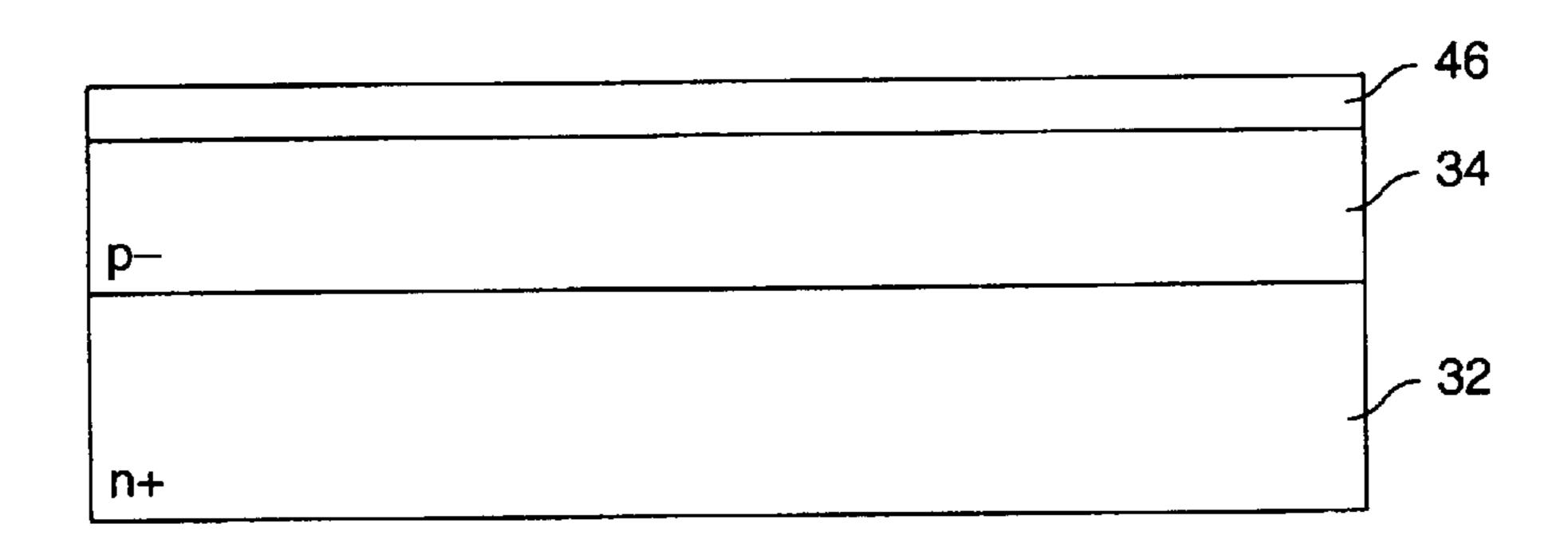

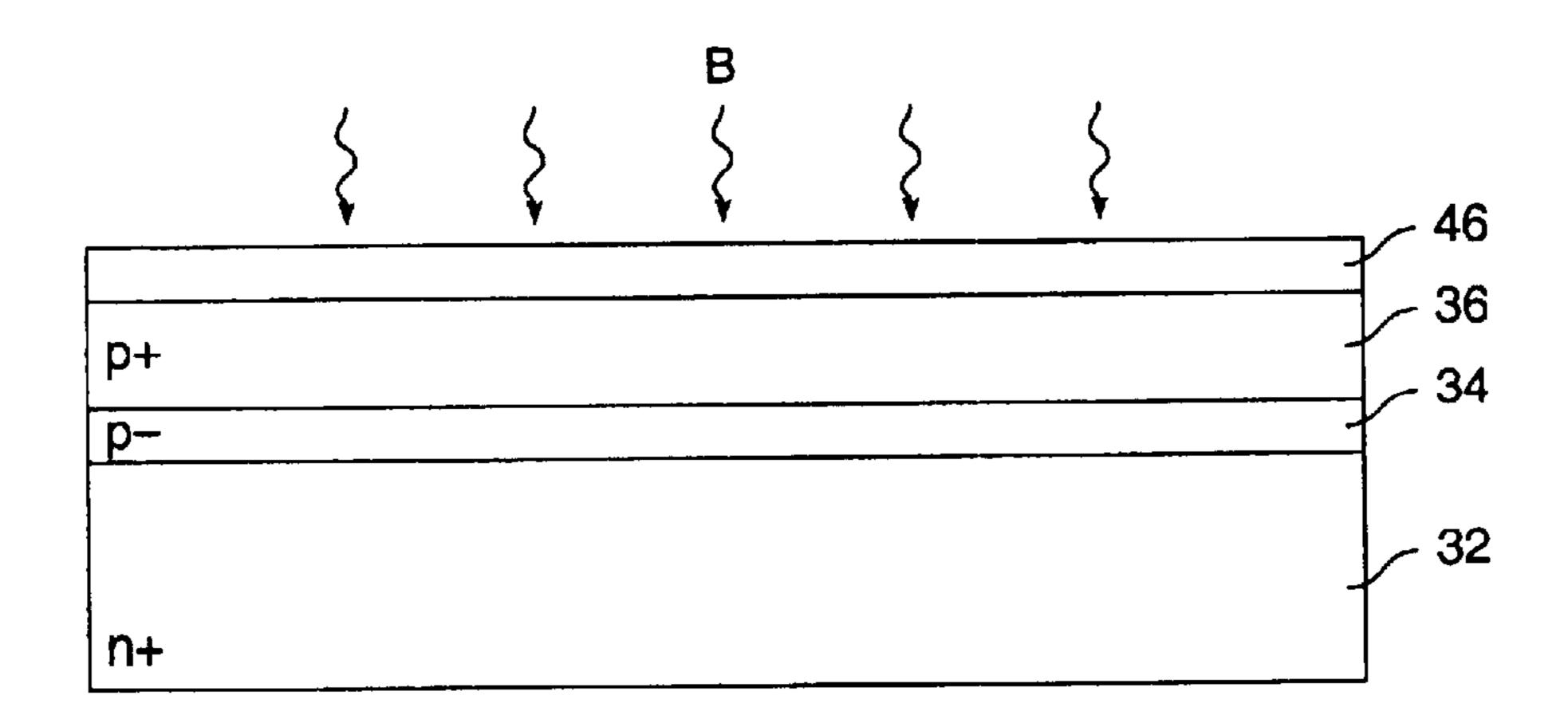

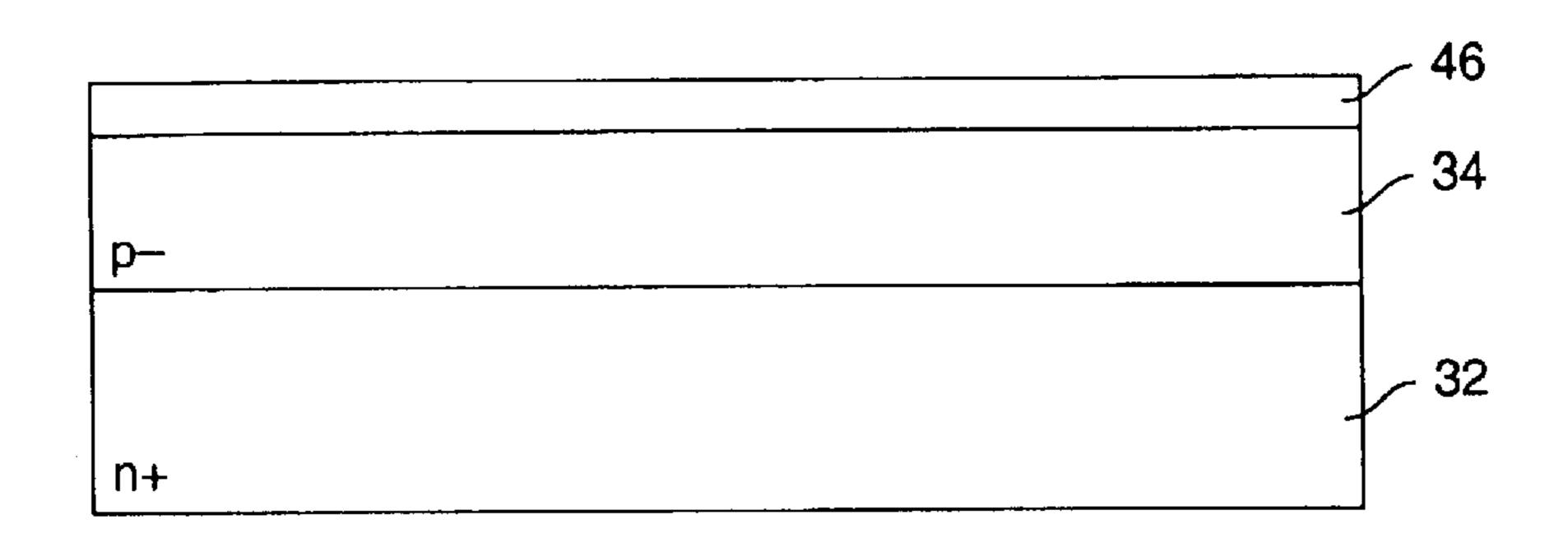

Referring first to FIG. 8a, the starting substrate material 32 for the n+p-p+n+ punch-through transient suppressor diode depicted in FIG. 7 is n-type Si having a maximum resistivity of 0.01 ohm-cm. A p- type epitaxial layer 34 having a resistivity in the range of from about 2 to about 50 ohm-cm is grown to a thickness of between about 2 to about 9 um using conventional epitaxial growth techniques.

Next, an oxide layer 46 comprising SiO<sub>2</sub> having a thickness from between about 200 angstroms to about 500 angstroms thick is grown using, for example, standard 35 thermal oxidation techniques. FIG. 8a shows the structure resulting after the performance of these steps.

Referring now to FIG. 8b, a boron implant is performed to form p+ region 36. The level of the boron dopant may be in the range of from about 5E12 cm<sup>-2</sup> to 3e15 cm<sup>-2</sup> at an energy of between about 40 KEV and about 200 KEV. An anneal and drive-in step is then performed for from about 30 minutes to about 2 hours at a temperature in the range of from about 900° C. to about 1,100° C. FIG. 8b shows the structure resulting after the performance of the boron 45 implant and anneal steps. As can be seen from an examination of FIG. 8b, p- region 34 has decreased in thickness as the heavier p doping from the surface of the epi layer creates p+ region 36.

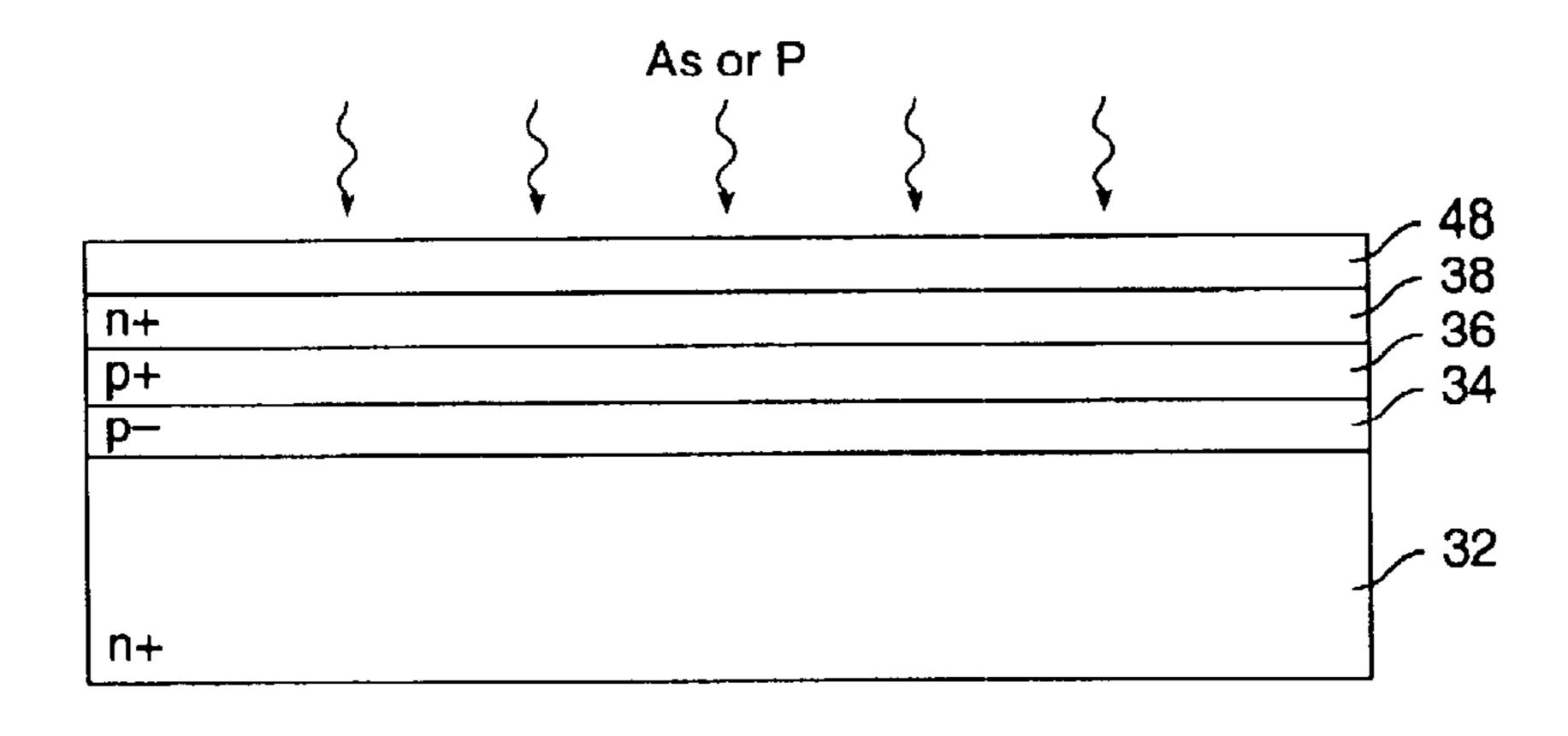

Referring now to FIG. 8c, oxide layer 46 is removed using 50 conventional oxide etching technology. Another oxide layer 48 is applied using, for example, standard thermal oxidation techniques, and an n-type implant is performed through oxide 48 with a dopant species such as phosphorous or arsenic at a dose of between about IE15 cm<sup>-2</sup> to 5E15 cm<sup>-2</sup> <sub>55</sub> reference numerals. at an energy of between about 40 KEV and about 120 KEV to form n+ region 38. The implant step is followed by an n+ diffusion step performed for from about 15 minutes to about 60 minutes at a temperature in the range of from about 850° C. to about 1000° C. to drive in the n+ implant. FIG. 8c 60 shows the structure resulting after the performance of the arsenic implant and drive-in steps but prior to removal of oxide layer 48. As may be seen from FIG. 8c, the upper portion of the epi layer has been converted to an n+ region by the n-type implant.

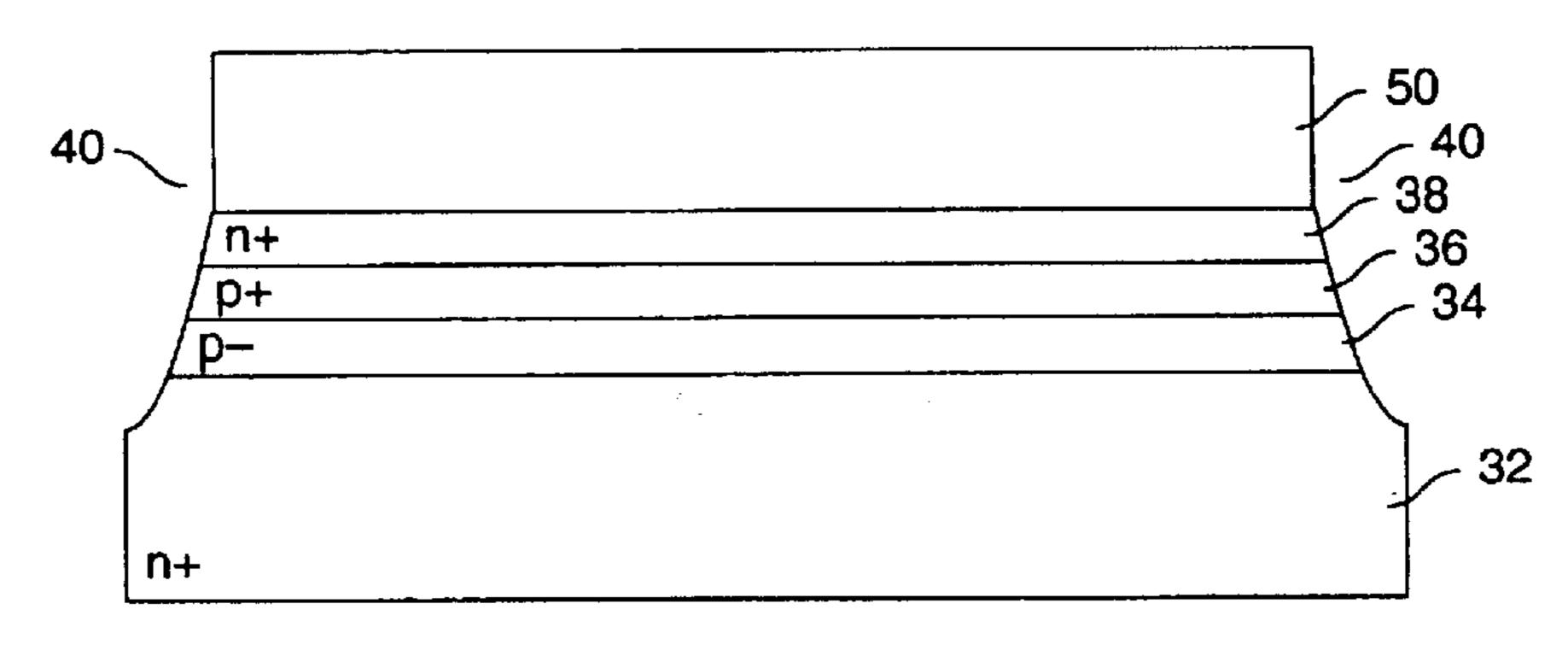

Referring now to FIG. 8d, oxide layer 48 is removed using conventional oxide etching techniques and a trench photo-

6

mask **50** is applied to the upper surface of n+ region **38** using standard photolithography techniques. The trenches **40** are then formed using an etching step such as standard chemical or RIE etching techniques to a depth into the substrate sufficient to provide isolation, i.e., 0.5 um. FIG. **8**d shows the structure resulting after the performance of the trench masking and etching steps but prior to removal of trench photomask **50**.

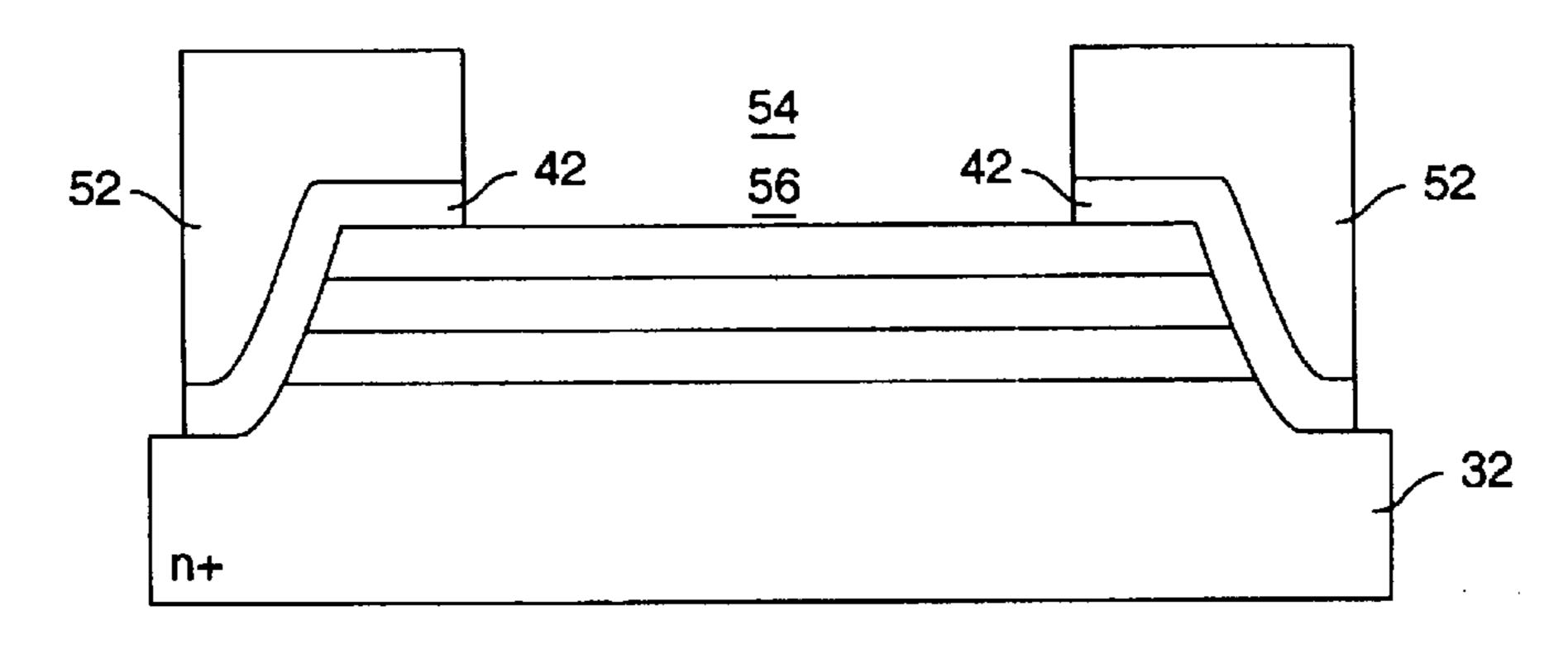

Referring now to FIG. 8e, photomask 50 is removed and a passivation layer 42 comprising a material such as an LPCVD oxide or an equivalent deposition step at a temperature below 800° C. is formed over the upper surface of n+ region 38 and into trenches 40. Contact photomask 52 having contact aperture 54 is then applied to the surface of passivation layer 42. A contact opening 56 is next formed in passivation layer 42 using a conventional etching step to clear the surface of n+ region 38. FIG. 8e shows the structure resulting after the performance of the contact masking and etching steps but prior to removal of contact photomask 52.

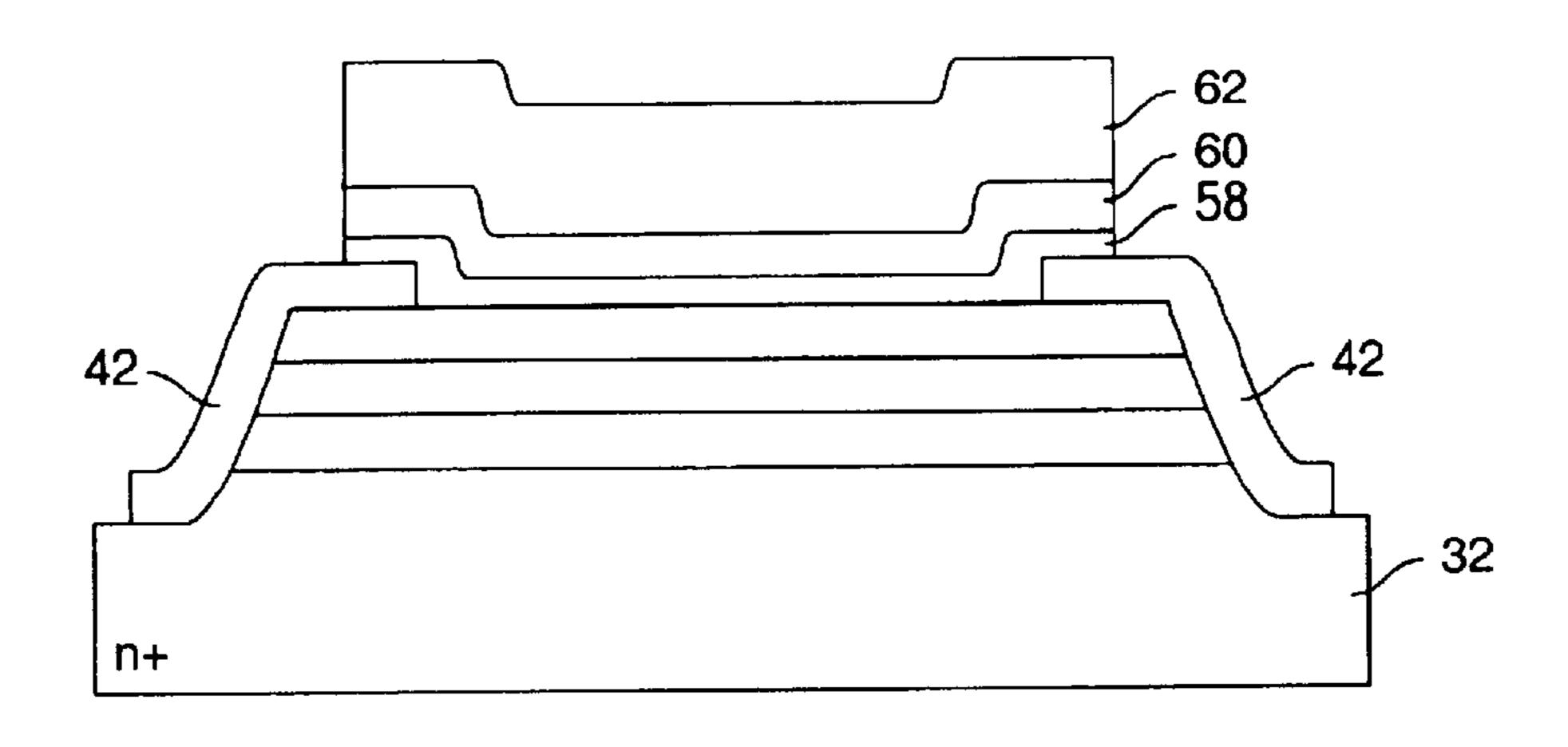

Referring now to FIG. 8f, contact photomask 52 is removed and a barrier metal layer 58 is formed over the surface of passivation layer 42 and into contact opening 54 to make electrical contact with n+ region 38. Barrier layer 58 may comprise a material such as titanium or titanium tungsten having a thickness in the range of about 500–1,000 angstroms. A metal layer 60 comprising a material such as aluminum having a thickness in the range of 20,000 angstroms is formed over barrier layer 58. Together, barrier metal layer 58 and metal layer 60 form metal contact 44 of the device of FIG. 7.

Next, a metal mask 62 is formed over the surface of metal layer 60 using conventional photolithography techniques. The metal layer and barrier layer are then defined using conventional etching technology. FIG. 8f shows the structure resulting after the formation and definition of the barrier metal layer and metal layer but prior to removal of metal mask 62.

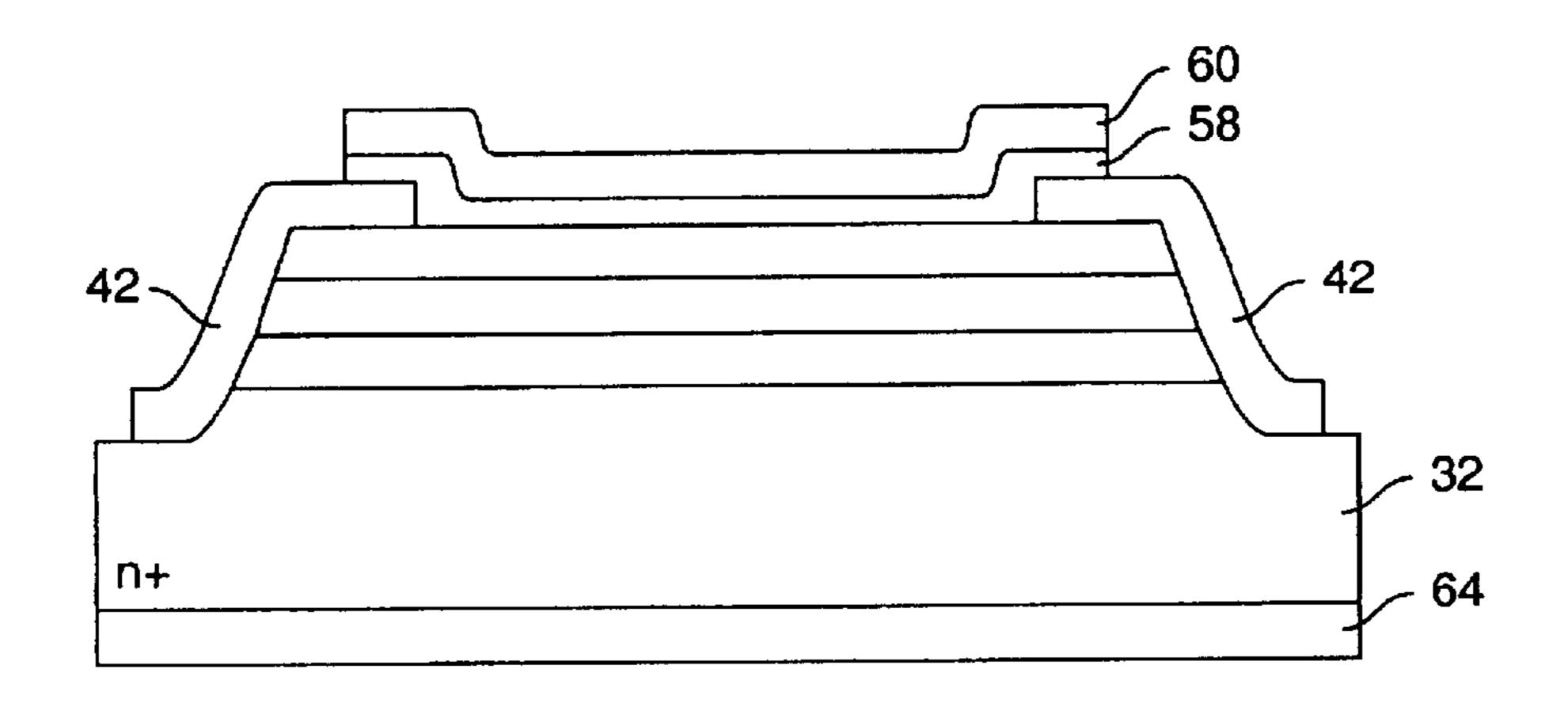

Referring now to FIG. 8g, metal mask 62 is removed and a backgrind step is performed on the substrate to grind it to about 0.012" nominal thickness. A backmetalization step is employed to form a metal layer 64 for use as a contact on the substrate. Any low ohmic process consistent with the assembly technique to be employed may be used. FIG. 8g shows the completed structure resulting after the backgrinding and backmetalization steps.

An alternative structure also suitable for manufacture of the device of the present invention is shown in FIG. 9. This embodiment could be manufactured by adding an n+ isolation mask and diffusion before the boron implant step and eliminating the trench mask/etch step. In the following drawing figures illustrating this embodiment, where structures are the same as corresponding structures in the embodiment of FIG. 7, they will be assigned the same reference numerals.

Referring now to FIG. 9, n+p-p+n+ punch-through transient suppressor diode 70 is fabricated on n+ substrate 32. As in the embodiment of FIG. 7, n+ substrate 32 is n-type silicon having a maximum 0.01 ohm-cm resistivity. P- layer 34 is disposed in a defined region on the upper surface of the n+ substrate 32. P+ layer 36 is disposed in a defined region on the upper surface of p- layer 34. Finally, n+ layer 38 is disposed in a defined region on the upper surface of p+ layer 36. In the place of trenches 40, the embodiment of FIG. 9 includes isolation diffusions 72 disposed at the periphery of region 34 which extend down into and merge with n+ substrate 32. A passivation layer 42 is disposed over the

upper surface of n+ layer 38 and extends over isolation diffusions 72. Metal contact 44 is disposed in an aperture formed in passivation layer 42 and makes electrical contact with n+ layer 38.

The embodiment of the device depicted in FIG. 9 may be fabricated using a process similar to the process described with reference to FIGS. 8a–8g. The major difference between the device structure of FIG. 7 and that of FIG. 9 is that the use of trench isolation allows blanket implant processing, whereas the device structure of FIG. 9 requires masked implants to form the regions 34, 36, and 38.

Referring now to FIGS. 10a–10h, an illustrative fabrication process for the n+p-p+n+ punch-through transient suppressor diode 70 of FIG. 9 is illustrated. Referring first to FIG. 10a, the starting substrate material 32 for the n+p-p+n+ punch-through transient suppressor diode depicted in 15 FIG. 9 is n-type Si having a maximum resistivity of 0.01 ohm-cm. A p-type epitaxial layer 34 having a resistivity in the range of from about 2 to about 50 ohm-cm is grown to a thickness of between about 2 to about 9  $\mu$ m using conventional epitaxial growth techniques. FIG. 10a shows the structure resulting after the epitaxial growth step. Those of ordinary skill in the art will recognize that, up to this point the processes used to make the embodiments of FIGS. 7 and 9 are the same.

Referring now to FIG. 10h, an oxide layer 74 and an isolation implant mask 76 are next applied to the surface of 25 the epitaxial layer 34 and n+ isolation implants 78 are formed through apertures 80 and 82 in isolation implant mask 76 using phosphorous to a concentration of about 1E15 to about 5E15 at an energy of between about 40 KEV and about 80 KEV. The implants are then driven in for 30 between about 30 and about 120 minutes at a temperature of between about 1,100° and about 1,200° C. FIG. 10b shows the structure resulting after the formation of isolation implants 78 but prior to removal of isolation implant mask 76 and oxide layer 74.

Referring now to FIG. 10c, an oxide layer 46 comprising SiO<sub>2</sub> having a thickness from between about 200 angstroms to about 500 angstroms thick is grown using, for example, standard thermal oxidation techniques. A p+ implant mask 84 is applied to the surface of oxide layer 46 and a boron implant is performed through aperture 86 in p+ implant mask 84 to form p+ region 36. As in the embodiment of FIG. 7, the level of the boron dopant may be in the range of from about 5E12 cm<sup>-2</sup> to 3e15 cm<sup>-2</sup> at an energy of between about 40 KEV and about 200 KEV. An anneal and drive-in step is then performed for from about 30 minutes to about 2 45 hours at a temperature in the range of from about 900° C. to about 1,100° C. FIG. 10c shows the structure resulting after the performance of the boron implant and anneal steps but prior to removal of the p+ implant mask 84 and oxide layer **46**.

Referring now to FIG. 10d, p+ implant mask 84 and oxide layer 46 are removed using conventional oxide etching technology. Another oxide layer 48 is applied using, for example, standard thermal oxidation techniques, and an n+ implant mask 86 is applied to the surface of oxide layer 48 55 using conventional photolithography techniques. An n-type implant is performed through and aperture 88 in n+ implant mask 86 and oxide 48 with phosphorous as a dopant species at a dose of between about IE15 cm<sup>-2</sup> to 5E15 cm<sup>-2</sup> at an energy of between about 40 KEV and about 120 KEV to 60 form n+ region 38. The implant step is followed by an n+ diffusion step performed for from about 15 minutes to about 60 minutes at a temperature in the range of from about 850° C. to about 1000° C. to drive in the n+ implant. FIG. 10d shows the structure resulting after the performance of the 65 phosphorous implant and drive-in steps but prior to removal of n+ implant mask 86 and oxide layer 48.

8

Referring now to FIG. 10e, photomask 86 and oxide layer 48 are removed and a passivation layer 42 comprising a material such as an LPCVD oxide or an equivalent deposition step at a temperature below 800° C. is formed over the upper surface of n+ region 38. Passivation mask 88 is then applied to the surface of the passivation layer 42 to define it and a conventional oxide etching step is employed to define the passivation layer. FIG. 10e shows the structure resulting after the performance passivation layer definition etch but prior to removal of passivation mask 88.

Referring now to FIG. 10f, passivation mask 88 is removed and contact photomask 52 having contact aperture 54 is then applied to the surface of passivation layer 42. A contact opening 56 is next formed in passivation layer 42 using a conventional etching step to clear the surface of n+region 38. FIG. 10f shows the structure resulting after the performance of the contact masking and etching steps but prior to removal of contact photomask 52. Those of ordinary skill in the art will recognize that passivation mask 88 and contact mask 56 could be the same mask and these steps would then be consolidated.

Referring now to FIG. 10g, contact photomask 52 is removed and a barrier metal layer 58 is formed over the surface of passivation layer 42 and into contact opening 54 to make electrical contact with n+ region 38. Barrier layer 58 may comprise a material such as titanium or titanium tungsten having a thickness in the range of about 500 to about 1,000 angstroms A metal layer 60 comprising a material such as aluminum having a thickness in the range of 20,000 angstroms is formed over barrier layer 58. Together, barrier metal layer 58 and metal layer 60 form metal contact 44 of the device of FIG. 7.

Next, a metal mask 62 is formed over the surface of metal layer 60 using conventional photolithography techniques. The metal layer and barrier layer are then defined using conventional etching technology. FIG. 10g shows the structure resulting after the formation and definition of the barrier metal layer and metal layer but prior to remove of metal mask 62.

Referring now to FIG. 10h, metal mask 62 is removed and a backgrind step is performed on the substrate to grind it to about 0.012" nominal thickness. A backmetalization step is employed to form a metal layer 64 for use as a contact on the backside of the substrate. Any low ohmic process consistent with the assembly technique to be employed may be used. FIG. 10h shows the completed structure resulting after the backgrinding and backmetalization steps.

The following data in Table III is an example of the processing parameters used to fabricate an actual n+p-p+n+ punch-through diode transient suppressor device according to the present invention, and the resulting physical parameters (Table IV) and electrical parameters (Table V) exhibited by the device.

TABLE III

| Process parameters                                   |                                                       |                                         |  |

|------------------------------------------------------|-------------------------------------------------------|-----------------------------------------|--|

| Boron implant (p+) Boron drive Phos Implant n+ drive | 1.5E18 cm <sup>-2</sup><br>70 min.<br>1E 15<br>15 min | 90 keV<br>1040° C.<br>80 keV<br>900° C. |  |

| Physical Measurements |                          |  |  |

|-----------------------|--------------------------|--|--|

| xj1                   | 0.6 um                   |  |  |

| xj2                   | 1.2 um                   |  |  |

| xj3                   | 1.9 um                   |  |  |

| Cn+                   | $2.0E19 \text{ cm}^{-3}$ |  |  |

| Cp+                   | $1.0E17 \text{ cm}^{-3}$ |  |  |

| Cp+<br>Cp             | $1.8E15 \text{ cm}^{-3}$ |  |  |

## TABLE V

| Electrical Characteristics                                                                                          |                                                                 |  |  |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| BV at 0.1 A/cm <sup>2</sup> Ir at 80% of BV (standoff voltage) Vclamp at 1,500 A/cm <sup>2</sup> Capacitance at 0 V | 3.9 V to 4.0 V<br>3E-3 A/cm <sup>2</sup><br>4.3 V<br>400–450 pF |  |  |

The characteristics shown in Tables III, IV, and V may be extrapolated to other processing conditions. FIGS. 11, 12, and 13 are graphs which illustrate the variations of device characteristics as a function of processing parameters. The data in these charts have not been fully verified by experiment. Verification tests are still being run as of the filing date of this application.

- FIG. 11 is a set of curves of device clamping voltage vs. p+ doping density for a n+p-p+n+ transient suppressor diode according to the present invention. The four curves represent boron doping densities of the p+ region of 1E14, 5E14, 1E15, and 1.5E15, expressed in cm<sup>-3</sup> units.

- FIG. 12 is a set of curves of standoff voltage vs. p+ doping density for a n+p-p+n+ transient suppressor diode according to the present invention. Standoff voltage is equal to 80% of BV. The four curves represent boron doping densities of the p+ region of 1E14, 5E14, 1E15, and 1.5E15, expressed in cm<sup>-3</sup> units.

- FIG. 13 is a graph of current vs. voltage and illustrates the advantages of the n+p-p+n+ transient suppressor diode of 40 the present invention. FIG. 13 shows the effects of the differential in doping of the p- and p+ regions according to the present invention. The three curves represent p+ boron doping densities of the p+ region of 1E16, 5E17, and 2E17 expressed in cm<sup>-3</sup> units. In each case, the p- boron doping 45 density of the p- regions is 1E15. The curve representing a p+ doping density of 1E16, only 10 times that of the pregion shows behavior approaching that of prior-art punchthrough devices. From FIG. 13, it is clear that a ratio of 100 gives the optimum characteristic and that varying this ratio 50 can have dramatic effects on the clamping characteristics. At present, it is thought that the ratio plays an important role in achieving the desired characteristics, but the desired results may be due in part to other restrictions, such as layer thicknesses.

While embodiments and applications of this invention have been shown and described, it would be apparent to those skilled in the art that many more modifications than mentioned above are possible without departing from the inventive concepts herein. The invention, therefore, is not to 60 be restricted except in the spirit of the appended claims.

What is claimed is:

- 1. A punch-through diode transient suppression device comprising:

- a first region comprising an n+ region;

- a second region comprising a p- region abutting said first region;

**10**

- a third region comprising a p+ region abutting said second region;

- a fourth region comprising an n+ region abutting said third region;

- a passivation layer disposed over an upper surface of said fourth region; and

- an isolation trench disposed at outer edges of said p-region, said p+ region, and said fourth n+ region, said isolation trench extending into said first n+ region.

- [2. The punch-through diode transient suppression device of claim 1 wherein:

- said first and fourth regions have a peak dopant concentration of about 1.5E18 cm<sup>-3</sup>;

- said third region has a peak dopant concentration of between about 50 to about 2,000 times said peak dopant concentration of said second region; and

- said second region has a dopant concentration of between about 0.5E14 cm<sup>-3</sup> and about 1.0E17 cm<sup>-3</sup>.

- [3. The punch-through diode transient suppression device of claim 2 wherein:

- said fourth region has a junction depth of greater than about 0.3 um;

- said third region has a thickness of between about 0.3 um and about 2.0 um, and

- said second region has a thickness of between about 0.5 um and about 5.0 um.

- 4. A punch-through diode transient suppression device comprising:

- a n+ substrate having an upper surface;

- a p- region disposed on said upper surface of said n+ substrate, said p- region having an upper surface, a side surface, and a first end; and

- a p+ region disposed on said upper surface of said pregion, said p+ region having an upper surface and a first end;

- an n+ region disposed on an upper surface of said p+ region, said n+ region having an upper surface;

- an isolation diffusion region disposed on said side of said p- region, said isolation diffusion region having an upper surface; and

- a passivation layer disposed over said upper surface of said n+ region, at said upper surface of said isolation diffusion region, at said first end of said p- region, and at said first end of said p+ region.

- 5. The punch-through diode transient suppression device of claim 4 wherein:

- said substrate and said n+ region have a peak dopant concentration of about 1.5E18 cm<sup>-3</sup>;

- said p+ region has a peak dopant concentration of between about 50 to about 2,000 times said dopant concentration of said p- region; and

- said p- region has a dopant concentration of between about 0.5E14 cm<sup>-3</sup> and about 1.0E17 cm<sup>-3</sup>.

- 6. The punch-through diode transient suppression device of claim 5 wherein:

- said n+ region has a junction depth of greater than about 0.3 um;

- said p+ region has a thickness of between about 0.3 um and about 2.0 um, and

- said p- region has a thickness of between about 0.5 um and about 5.0 um.

- 7. The punch-through diode in claim 1, wherein said passivation layer is disposed over said upper surface at outer

edges of said p- region and said p+ region; said passivation layer including a contact aperture therethrough to an upper surface of said n+ region.

- 8. The punch-through diode transient suppression device of claim 1 wherein:

- said first and fourth regions have a peak dopant concentration of about 1.5E18 cm<sup>-3</sup>;

- said third region has a peak dopant concentration of between about 50 to about 2,000 times said peak dopant concentration of said second region; and

- said second region has a dopant concentration of between about 0.5E14 cm<sup>-3</sup> and about 1.0E17 cm<sup>-3</sup>.

- 9. The punch-through diode transient suppression device of claim 8 wherein:

- said fourth region has a junction depth of greater than  $^{15}$  about 0.3  $\mu$ m;

- said third region has a thickness of between about 0.3  $\mu$ m and about 2.0  $\mu$ m, and

- said second region has a thickness of between about 0.5  $\mu$ m and about 5.0  $\mu$ m.

- 10. The punch-through diode in claim 7, further including an isolation region disposed at outer edges of said p-region, said p+ region, and said n+ region, said isolation region extending into said n+ region.

- 11. The punch-through diode in claim 4, wherein said passivation layer includes a contact aperture therethrough to said upper surface of said n+ region.

- 12. A punch-through diode transient suppression device comprising:

- a first region comprising a first dopant type and a first dopant concentration value;

- a second region comprising a second dopant concentration value that differs from said first dopant concentrative value, said second region abutting said first region;

- a third region comprising a third dopant type that differs from said first dopant type, said third region abutting said second region;

- a fourth region comprising said first dopant type, said 40 fourth region abutting said third region;

- a passivation layer disposed over an upper surface of said fourth region, said passivation layer having an aperture allowing a metal contact to provide an electrical connection with said fourth region;

- an isolation trench disposed at outer edges of said second region, said third region, and said fourth region, said isolation trench extending into said first region.

- 13. The punch-through diode transient suppression device of claim 12, wherein said first and fourth regions each 50 comprises an n dopant type.

- 14. The punch-through diode transient suppression device of claim 13, wherein said first and fourth regions each comprises an n+ dopant type.

- 15. The punch-through diode transient suppression device 55 of claim 12, wherein said third region comprises a p dopant type.

- 16. The punch-through diode transient suppression device of claim 15, wherein said third region comprises a p+ dopant type.

- 17. The punch-through diode transient suppression device of claim 12, further comprising a first metal contact disposed in said aperture, said first metal contact making an electrical connection with said fourth region.

- 18. The punch-through diode transient suppression device 65 second region. of claim 17, further comprising a second metal contact making an electrical connection with said first region.

12

19. The punch-through diode transient suppression device of claim 12, wherein:

- said fourth region has a junction depth of greater than about 0.3 µm;

- said third region has a thickness of between about 0.3 µm and 2.0 µm; and

- said second region has a thickness of between about 0.5  $\mu$ m and about 5.0  $\mu$ m.

- 20. The punch-through diode transient suppression device of claim 12, wherein said second region reduces a capacitance of the suppression device.

- 21. The punch-through diode transient suppression device of claim 12, wherein said passivation layer is further disposed on a first end of said second region and a first end of said third region.

- 22. A punch-through diode transient suppression device comprising:

- an n+ dopant type substrate having an n+ dopant concentration value;

- a first region for reducing a capacitive level of the suppression device, said first region abutting said n+dopant type substrate and comprising a first dopant concentration value that differs from said n+dopant concentration value;

- a second region abutting said first region, said second region comprising a second dopant type that differs from said n+ dopant type;

- an n+ dopant type region abutting said second region;

- a passivation layer disposed over an upper surface of said n+ dopant type region, said passivation layer having an aperture allowing a metal contact to provide an electrical connection with said n+ dopant type region; and

- an isolation region disposed at outer edges of said first region, said second region, and said fourth region, said isolation region extending into said n+ dopant type substrate.

- 23. The punch-through diode transient suppression device of claim 22, wherein said second region comprises a p dopant type.

- 24. The punch-through diode transient suppression device of claim 23, wherein said second region comprises a p+dopant type.

- 25. The punch-through diode transient suppression device of claim 22, further comprising a first metal contact disposed in said aperture, said first metal contact making an electrical connection with said n+ dopant type region.

- 26. The punch-through diode transient suppression device of claim 25, further comprising a second metal contact making an electrical connection with said first n+ dopant type substrate.

- 27. The punch-through diode transient suppression device of claim 22, wherein:

- said n+ dopant type region has a junction depth of greater than about 0.3  $\mu m$ ;

- said second region has a thickness of between about 0.3  $\mu$ m and about 2.0  $\mu$ m; and

- said first region has a thickness of between about 0.5 µm and about 5.0 µm.

- 28. The punch-through diode transient suppression device of claim 22, wherein said passivation layer is further disposed on a first end of said first region and a first end of said second region.

\* \* \* \* \*