#### US00RE37879E

### (19) United States

### (12) Reissued Patent

**Takeuchi**

## (10) Patent Number: US RE37,879 E (45) Date of Reissued Patent: Oct. 15, 2002

# (54) IMAGE CONTROL DEVICE FOR USE IN A VIDEO MULTIPLEXING SYSTEM FOR SUPERIMPOSITION OF SCALABLE VIDEO DATA STREAMS UPON A BACKGROUND VIDEO DATA STREAM

(75) Inventor: Kesatoshi Takeuchi, Shiojiri (JP)

(73) Assignee: Seiko Epson Corporation, Tokyo (JP)

(21) Appl. No.: **09/637,825**

(22) Filed: Aug. 11, 2000

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 5,793,439

Issued: Aug. 11, 1998

Appl. No.: 08/803,227

Filed: Feb. 20, 1997

#### U.S. Applications:

(62) Division of application No. 08/452,012, filed on May 26, 1995, now Pat. No. 5,680,178, which is a continuation of application No. 08/294,402, filed on Aug. 23, 1994, now Pat. No. 5,469,221, which is a continuation of application No. 08/185,155, filed on Jan. 24, 1994, now Pat. No. 5,387,945, which is a continuation of application No. 08/039,708, filed on Mar. 31, 1993, now abandoned, which is a continuation of application No. 07/873,322, filed on Apr. 14, 1992, now abandoned, which is a continuation of application No. 07/474,768, filed as application No. PCT/JP89/00683 on Jul. 6, 1989, now abandoned.

#### (30) Foreign Application Priority Data

| Dec. 28, 1988<br>Dec. 28, 1988<br>Dec. 28, 1988<br>Dec. 28, 1988 | (JP)<br>(JP)<br>(JP) |  |

|------------------------------------------------------------------|----------------------|--|

| Feb. 7, 1989 (51) Int. Cl. <sup>7</sup>                          | ` /                  |  |

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

JP 52-115121 9/1977 JP 54-112122 9/1979

(List continued on next page.)

#### OTHER PUBLICATIONS

Sony CXK1206AM/ATM, Video Signal Field Memory. pp. 1–40 undated.\*

(List continued on next page.)

Primary Examiner—Victor R. Kostak

(74) Attorney, Agent, or Firm—Oliff & Berridge, PLC

(57) ABSTRACT

An image control device for use in a computer system which includes a microprocessor, a bus coupled to the microprocessor, a video memory coupled to the bus and a display device. A write controller is also provided which is coupled to the bus and which controls writing of an image signal into the video memory by supplying a write address to the video memory. The write controller operates to change a range of the write address according to a plurality of write address parameters set by the microprocessor so that a memory area of the video memory into which the image signal is to be written is changed according to the range of the write address. Further, a size of an image represented by the image signal to be written into the video memory is changed. A read controller is also provided and is coupled to the bus for controlling reading of an image signal out of the video memory by supplying a read address to the video memory asynchronously with the writing into the video memory, and in synchronism with the synchronizing signal supplied to the display device along with the image signal read out of the video memory.

#### 8 Claims, 18 Drawing Sheets

#### U.S. PATENT DOCUMENTS FOREIGN PATENT DOCUMENTS 4,134,128 A 1/1979 Hurst 54-148426 11/1979 4,204,227 A 5/1980 Gurley 55-95369 7/1980 1/1981 Ackley et al. 4,243,984 A 57-154981 A 9/1982 JP 4,340,903 A 7/1982 Tamura 58-160983 9/1983 11/1983 Ryan et al. 4,418,343 A 3/1985 60-46597 4,479,142 A 10/1984 Buschman et al. 7/1985 60-134288 4,499,506 A 2/1985 Takahashi et al. 60-172091 9/1985 JP 60-206383 10/1985 JP 4,589,020 A 5/1986 Akatsuka 60-257694 12/1985 6/1986 4,599,611 A 7/1986 Bowker et al. 61-130996 7/1986 Smith et al. 6/1986 4,602,275 A 61-131976 JP 12/1986 Priestly 4,626,837 A 61-147677 A 7/1986 JP 61-173291 A 8/1986 4/1987 Nishi et al. 61-151282 9/1986 4,660,070 A 5/1987 Miron et al. 4,665,438 A 61-166673 10/1986 4,667,310 A \* JP 61-224576 10/1986 JP 3/1988 Micic et al. 4,729,028 A 61-245775 11/1986 JP 2/1987 4,739,410 A 4/1988 Lehmer et al. 62-29297 A 2/1987 5/1988 Ko et al. 62-34280 4,742,350 A JP 5/1987 5/1988 Kashigi 4,746,479 A 62-104383 5/1988 Ikeda et al. JP 7/1987 4,748,504 A 62-150982 8/1988 Prodan JP 7/1987 62-155880 4,768,093 A JP 7/1987 4,777,531 A 10/1988 Hakamada et al. 62-159582 12/1988 Ramage JP 4,790,028 A 8/1987 62-180682 JP 4/1989 Short 8/1987 4,821,101 A 62-191884 A JP 7/1989 Shimada 4,845,661 A 62-254578 11/1987 JP 7/1989 Takayama et al. 1/1988 4,851,922 A 63-5682 A JP 8/1989 Fedele 2/1988 63-35070 4,858,107 A JP 8/1989 Sonoda et al. 4,862,269 A 63-35083 A 2/1988 9/1989 Ebihara et al. JP 63-65784 A 4,864,402 A 3/1988 JP 12/1989 Dawes et al. 63-123284 5/1988 4,890,098 A 3/1990 Truong JP 4,907,086 A 63-188275 8/1988 JP 4,959,803 A 9/1990 Kiyohara et al. 63-225874 9/1988 10/1990 Krooss 4,961,071 A 63-290079 A 11/1988 4,970,596 A 11/1990 Johnson 1-264376 A 10/1989 5,014,128 A 5/1991 Chen 5,016,106 A 5/1991 **Yong-Je et al.** OTHER PUBLICATIONS 6/1991 Johary et al. 5,025,315 A 5,036,293 A 7/1991 Aschwanden Abstract: Television Receiver—p. 167 E568. Abstract: Pic-9/1991 Kimura et al. 5,045,951 A ture Processing Device—p. 90 P815, 1988 National Con-5,046,117 A 9/1991 Yamashita vention Record of the Institute of Television Engineers of 5,047,839 A 9/1991 Sawada Japan (total of 4 pages).\* 9/1991 Duffield et al. 5,047,857 A IEICE Technical Report: vol. 88 #300 (total of 8 pages); 11/1991 Fernandez et al. 5,068,650 A 11/1991 Takayama et al. 5,068,716 A Nov. 25, 1988. Abstract: Partial Abstract for Japanese Patent 1/1992 Lucas et al. 5,081,450 A Laid open Gazette #60–465.\* 5/1992 Romesburg et al. 5,113,259 A Texas Instruments, TMS55165, TMS55166, TMS55175, 8/1992 Soloff 5,138,452 A TMS55176; 262144 BY 16-Bit Multiport Video RAM, Dec. 8/1992 Klein et al. 5,140,444 A 1995. 11/1993 Malcolm, Jr. et al. 5,258,750 A 5,387,945 A 2/1995 Takeuchi

\* cited by examiner

5,434,969 A \* 7/1995 Heilveil et al. ........................ 395/166

FIG.5

FIG. 9

PRICE. 21 PRICE ART

# IMAGE CONTROL DEVICE FOR USE IN A VIDEO MULTIPLEXING SYSTEM FOR SUPERIMPOSITION OF SCALABLE VIDEO DATA STREAMS UPON A BACKGROUND VIDEO DATA STREAM

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

This is a Division of application Ser. No. 08/452,012 filed on May 26, 1995, now U.S. Pat. No. 5,680,178 which is a continuation of application Ser. No. 08/294,402, filed on Aug. 23, 1994, now U.S. Pat. No. 5,469,221, which is a continuation of application Ser. No. 08/185,155, filed on Jan. 24, 1994, now U.S. Pat. No. 5,387,945, which is a continuation of application Ser. No. 08/039,708, filed on Mar. 31, 1993, *abandoned*, which is a continuation of application Ser. No. 07/873,322, filed on Apr. 14, 1992, *abandoned*, which is a continuation of application Ser. No. 07/474,768, filed on May 14, 1990, now abandoned which 20 was filed as PCT/JP89/00683 on Jul. 6, 1989.

#### TECHNICAL FIELD

The present invention relates to an image processing circuit in the monitor of a personal computer, an intelligent terminal, a TV telephone or a smart TV and, more particularly, to a process for processing an image to an arbitrary size and superposing it.

#### BACKGROUND TECHNIQUE

In the prior art, there is an image processing system which 30 is enabled to operate a personal computer while observing a TV program by superimposing the picture of the TV with a predetermined size and in a predetermined position on the monitor frame of the personal computer.

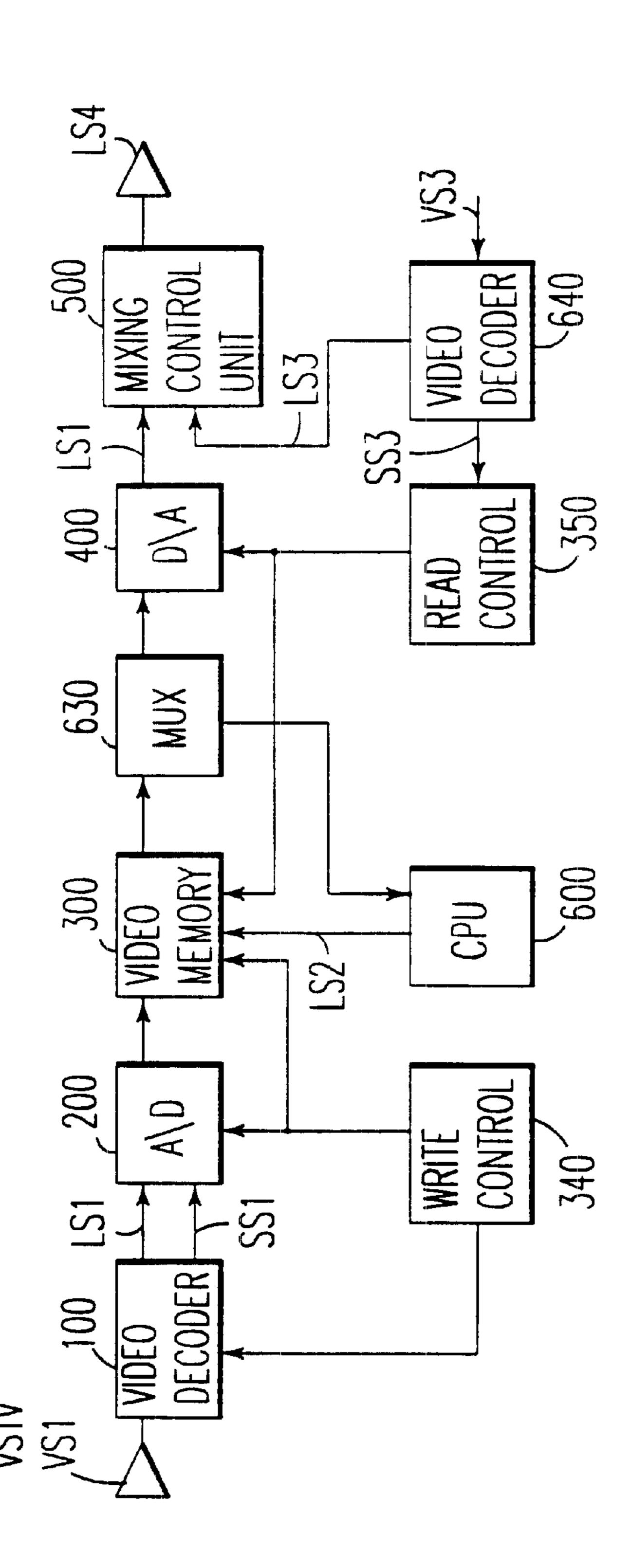

FIG. 21 is a block diagram showing the image processing 35 system of the prior art. In FIG. 21: reference numeral 100 designates a video decoder for separating a first video signal VS<sub>1</sub> into a first synchronizing signal SS<sub>1</sub> and a first luminance signal LS<sub>1</sub>; numeral 200 designates an analog-digital converter (which will be shortly referred to as an "ADC") 40 for digitizing the first luminance signal LS<sub>1</sub>; numeral 300 designates a video memory for storing the digitized first luminance signal LS<sub>1</sub>; numeral 340 designates a write control unit for controlling the writing of the first luminance signal LS<sub>1</sub> in the video memory 300; numeral 350 desig- 45 nates a read control unit for controlling the reading of the first luminance signal  $LS_1$  out of the video memory 300; numeral 400 designates a digital-analog converter (which will be shortly referred to as a "DAC") for converting to analog the first luminance signal LS<sub>1</sub> read out from the video  $_{50}$ memory 300; numeral 600 designates a CPU control unit; numeral 630 designates a multiplexer; numeral 640 designates a video decoder unit for separating a third video signal VS<sub>3</sub> into a third synchronizing signal SS<sub>3</sub> and a third luminance signal LS<sub>3</sub>; and numeral **500** designates a mixing  $_{55}$ control unit for mixing the first luminance signal LS<sub>1</sub> and the third luminance signal LS<sub>3</sub> to output a fourth luminance signal  $LS_{4}$ .

In this video processing circuit of the prior art, the video decoder 100 separates the video signal  $VS_1$  into the syn-60 chronizing signal  $SS_1$  and the luminance signal  $LS_1$ , and the ADC 200 digitizes and writes the luminance signal  $LS_1$  in the video memory 300.

At this time, the write control unit **340** outputs a timing clock for controlling the operations of the ADC **200** and the 65 video memory **300** on the basis of the synchronizing signal  $SS_1$ .

2

Here, the second luminance signal LS<sub>2</sub> outputted from the CPU control unit 600 can be written in the video memory 300.

Moreover, the read control unit 350 reads out the first luminance signal  $LS_1$  (or the second luminance signal  $LS_2$ ) written in the video memory 300 through the multiplexer 630. The DAC 400 converts to analog the first luminance signal  $LS_1$  read out from the video memory 300. The mixing control unit 500 mixes the first luminance signal  $LS_1$  and the third luminance signal  $LS_3$  to output the fourth luminance signal  $LS_4$  in which an image corresponding to the first luminance signal  $LS_1$  is superimposed on the image corresponding to the third luminance signal  $LS_3$ .

For a still image, on the other hand, a CPU 620 monitors the operations of the video decoder unit 100. If this video decoder unit 100 outputs a vertical synchronizing signal, the CPU 620 interrupts the digitize control by the ADC 200 during the vertical blanking period in the video signal.

In this still image, too, there can be obtained the fourth luminance signal  $LS_4$  in which the image corresponding to the first luminance signal  $LS_1$  is superimposed upon the image corresponding to the third luminance signal  $LS_3$ .

When, moreover, letters or special shapes are to be superimposed upon the image corresponding to the first luminance signal LS<sub>1</sub>, the CPU control unit 600 writes the shape data of the letters or special shapes in the video memory 300.

Here, the image processing system of the prior art, as shown in FIG. 21, is troubled by a problem that it cannot cope in the least with the multipurpose specifications such as the display by an arbitrary resolution corresponding to a smart image to be developed in the near future, the conversion of an arbitrary aspect ratio, the control of display in an arbitrary position, or the superimpose.

For the multi-purpose specifications, moreover, the price for the system rises as high as several hundreds to thousands yens as in the TV broadcasting system used at present in the commercial broadcasting stations.

This raises a problem that fundamental technical innovations are required for the level of the home appliances.

Generally speaking, on the other hand, the video memory 300 has to be refreshed because it is constructed of a dynamic memory.

For this necessity, a clock signal for refreshing the video memory 300 is fed to the serial ports of the video memory 300. This clock signal has a frequency of 10 (MHz) or more, for example.

In case, therefore, the serial output at the side of the multiplexer 630 has a clock of several hundreds (KHz) to several (MHz), a frequency of 10 (MHz) or more has to be supplied from the aforementioned serial output other than that at the side of the DAC 400.

This serial output other than that at the side of the DAC 400 has to be merely the refreshing clock aiming at no output.

If the video data of the video memory 300 is to be read out by the CPU control unit 600, the multiplexer 630 has to be switched to read out the video data from the CPU control 600 so that the video data are not sent to the DAC 400. This raises another problem that the image coming from the DAC 400 becomes the fourth luminance signal LS<sub>4</sub> in the blanked state even if it is superimposed upon the third luminance signal LS<sub>3</sub>.

Still another problem is that it is impossible for the CPU to read the CPU control **600** by the operations always having

a frequency of 10 (MHz) or more than that of the aforementioned serial output other than that at the side of the DAC 400.

For the still image, moreover, the CPU control unit 600 has to monitor the a vertical synchronizing signal VS<sub>1</sub> 5 thereby to raise a further problem that the CPU control unit 600 has to require a standby time of several tens mS in the worst case.

Even if, moreover, the CPU control unit 600 is equipped with a high-speed IC such as a digital signal processor (which is called the "DSP"), it takes several tens ( $\mu$ s) to rewrite the letters or special shapes.

In case, on the other hand, the third luminance signal LS<sub>3</sub> is related to one corresponding to a motion picture, there is required a time period for reducing the frame number of the third luminance signal LS<sub>3</sub> and to rewrite the stored content of the video memory 300 by the CPU 620.

It is impossible to scroll the letters or special shapes vertically and horizontally in the third luminance signal LS<sub>3</sub>.

#### DISCLOSURE OF THE INVENTION

The present invention has been conceived to solve the above-specified problems and has an object to provide an image processing system for achieving the following 25 objects:

- (1) to realize an arbitrary resolution of the image, an arbitrary area designation; a location of an arbitrary memory or a conversion to an arbitrary aspect ratio easily at the level of home appliances;

- (2) to read out the luminance signals of the video memory easily from a control system of irregular time such as the CPU without any interruption of the monitor output function of the video memory;

- (3) to eliminate any necessary for the standby for the still image by the CPU control unit **600**;

- (4) to rewrite the displayed content in real time of the superimposed display frame; and

- (5) to realize the above-specified functions at the price at the level of the home appliances.

According a first mode of the present invention, there is provided an image processing system comprising: decode means for separating a first video signal into a first luminance signal, a first horizontal synchronizing signal and a 45 first vertical synchronizing signal; analog-digital conversion means for digitizing said first luminance signal; memory means for storing the digitized first luminance signal; digital-analog conversion means for reading and analogly converting the luminance signal stored by said memory means; mixing means for either the luminance signal read out and analogly converted by said memory means or a second luminance signal selectively as a third luminance signal; and control means for outputting control signals to control said decode means, said analog-digital conversion means, said memory means, said digital-analog conversion means and said mixing means.

In a second mode of the present invention, said analog-digital conversion means, said memory means, said digital-analog conversion means, said mixing means and said 60 control means are constructed on a extended slot card.

In a third mode of the present invention, said control means includes: operation means for inputting the position, size and timing for displaying an image corresponding to said first luminance signal to an image corresponding to said 65 third luminance signal; and a device driver disposed in an operating system for outputting the signals corresponding to

4

the position, size and timing, which are to be inputted by said operating means, to said decode means, said memory means, said digital-analog conversion means and mixing means.

According to a fourth mode of the present invention, said memory means includes a video memory for storing the first luminance signal, which is digitized by said analog-digital conversion means, in an area of the address, which is specified by a write shift signal and a write line increment signal, when a write enable signal is outputted, such that a horizontal address is reset by a horizontal write clear signal whereas a vertical address is reset by a vertical write clear signal, when said first luminance signal is to be written, so that said horizontal address is set at the unit of a block of a 15 predetermined dot number by an address signal and incremented by said write shift signal and so that said vertical address is incremented by said write increment signal, and said analog-digital conversion means includes: an analogdigital conversion circuit for analog-digital converting said first luminance signal; a horizontal write dot clock generator synchronized with said first horizontal synchronizing signal for outputting a horizontal write dot clock signal having a frequency predetermined times as high as that of said first horizontal synchronizing signal and based upon said block unit as the analog-digital conversion clock signal of said analog-digital conversion means and a basic synchronizing signal having a predetermined frequency as said write shift signal; a horizontal write starting counter reset by said first horizontal synchronizing signal for counting the clock num-30 ber of said horizontal write dot clock signal to output a horizontal write starting signal for starting the writing of said first luminance signal in said image memory and said horizontal write clear signal when said counted value reaches a preset value; a horizontal write number counter 35 reset by said first horizontal synchronizing signal for counting the clock number of said horizontal write dot clock signal, after the output of said horizontal write starting signal, to output a horizontal write number signal for inhibiting the write of said first luminance signal in said video memory when said counted value reaches a predetermined value; a vertical write offset counter reset by said first vertical synchronizing signal for outputting a vertical write offset signal of the clock number of the preset value, which is synchronized with said basic synchronous signal, as said write line increment signal; a vertical write line clock generator synchronized with said first vertical synchronizing signal for outputting a vertical write line clock signal having a frequency of predetermined times as high as that of said vertical synchronizing signal as said write line increment signal; a vertical write starting counter reset by said first vertical synchronizing signal for counting the clock number of said first horizontal synchronizing signal to output a vertical write starting signal for starting the writing of said luminance signal in said video memory when said counted value reaches a preset value; a vertical write number counter reset by said vertical synchronizing signal for starting the counting of the clock number of said vertical write line clock signal, after the output of said vertical write starting signal, to output a vertical write number signal for inhibiting the writing of said first luminance signal in said video memory when said counted values reaches a preset value; and write control means for outputting said write enable signal on the basis of said first vertical synchronizing signal, said horizontal write clear signal, said horizontal write dot clock signal, said horizontal write starting signal, said horizontal write number signal, said vertical write starting signal, said vertical write number signal and said vertical write line

clock signal to write the first luminance signal, which is digitized by said horizontal write dot clock signal, in the area of said video memory, which is specified by said address signal, said write shift signal and said write line increment signal, while said horizontal write starting signal and said 5 vertical write starting signal are being outputted.

In a fifth mode of the present invention, said control means sets the value of said block, the frequency of said vertical write link clock signal, the preset value of said horizontal write starting counter, the preset value of said horizontal write number counter, the preset value of said vertical write starting counter and the preset value of said vertical write number counter.

In a sixth mode of the present invention, said control means includes image still means for outputting said first vertical synchronizing signal none of said video memory, said vertical write offset counter, said vertical write line clock generator, said vertical write starting counter and said vertical write number counter in accordance with the operations of said operation means.

In a seventh mode of the present invention, said memory means includes: a write control unit for controlling said video memory when said control means writes said second luminance signal in said video memory; luminance signal selecting means for outputting said first luminance signal and said second luminance signal selectively to said video memory; and a video memory control signal selecting unit for outputting a write control signal of said first luminance signal and a write control signal of said second luminance signal in a manner to correspond to the selected output of said first luminance signal and said second luminance signal.

In an eighth mode of the present invention, said memory means includes: an FIFO memory of first-in first-out type having at least a storage capacity equal to or more than that of said video memory for writing and reading said luminance signals asynchronously in and out of said video memory; a read control unit for controlling the reading of said luminance signal in said FIFO memory out of said video memory in accordance with the control of said control means; and an FIFO read control unit for controlling said FIFO memory.

In a ninth mode of the present invention, said video memory reads out said luminance signal from the address, which is specified by a read shift and a read line increment 45 signal of said video memory, when a read enable signal is outputted, such that the horizontal address reset by said horizontal read clear signal whereas the vertical address is reset by the vertical read clear signal or said third vertical synchronizing signal, when said luminance signal stored in 50 said video memory is to be read out, so that said horizontal address is incremented by said read shift signal whereas said vertical address is incremented by said read line increment signal, said digital-analog conversion means includes: a digital-analog conversion circuit for analogly converting 55 and outputting the luminance signal which is read out from said video memory; a horizontal reference read dot clock generator for outputting a horizontal reference read dot clock signal synchronized with said third horizontal synchronizing signal; a first horizontal read starting counter 60 reset by said third horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal to output a first horizontal read starting signal for starting the reading of said luminance signal from said video memory and a horizontal read reset signal as said 65 horizontal read clear signal when said counted value reaches a preset value; a second horizontal read starting counter reset

by said third horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal, after the output of said first horizontal read starting signal, to output the second horizontal read starting signal when said counted value reaches a predetermined value; a horizontal read number counter reset by said third horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal to inhibit the reading of the luminance signal, which is stored in said video memory, when said counted value reaches a preset value; a horizontal read dot clock generator for outputting a horizontal read dot clock signal synchronized with said third horizontal synchronizing signal; a vertical read offset counter reset by said third vertical synchronizing signal for outputting the vertical read offset signal as said vertical line increment signal on the basis of said horizontal reference read dot clock signal; a vertical blanking number counter reset by said third vertical synchronizing signal for counting the clock number of said third horizontal synchronizing signal to output a vertical blanking ending signal when said counted value indicates that a vertical back porch region has been passed; a vertical read starting counter reset by said third vertical synchronizing signal for counting the clock number of said third horizontal synchronizing signal, after the output of said vertical blanking ending signal, to output a vertical read starting signal for starting the reading the luminance signal from said video signal when said counted value reaches a preset value; a vertical read number counter reset by said third vertical synchronizing signal for counting the clock number of said third horizontal synchronizing signal, after the output of said vertical read starting signal, to output a vertical read number signal for inhibiting the reading of the luminance signal from said video memory, when said counted value reaches a preset value; a vertical read line clock generator for outputting the vertical read line clock signal, which is synchronized with said third vertical synchronizing signal, as said vertical line increment signal; a superimpose start signal output circuit for outputting a superimpose starting signal on the basis of said second horizontal read starting signal, said horizontal read number signal, said vertical read starting signal and said vertical read number signal; and a read enable signal output circuit for outputting said read enable signal on the basis of said third vertical synchronizing signal, said horizontal read reset signal, said vertical read line clock signal and said superimpose starting signal to read out the luminance signal from the area of said video memory, which is specified by either said horizontal reference read dot clock signal or said horizontal read dot clock signal and said read line increment signal, and said mixing means includes a video switch switched on the basis of said superimpose starting signal for selectively outputting the luminance signal, which is read out from said video memory and analogly converted by said digital-analog conversion circuit, and said third luminance signal.

In a tenth mode of the present invention, said horizontal reference read dot clock generator constructing the ninth mode of the present invention includes a PLL circuit for outputting a signal having a frequency several tens to thousands as high as that of said third horizontal synchronizing signal, said horizontal read dot clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third horizontal synchronizing signal, and said vertical read line clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third vertical synchronizing signal.

In an eleventh mode of the present invention, said control means constructing the tenth mode of the present invention sets the individual clock numbers which are counted by said first horizontal read starting counter, said horizontal read number counter, said vertical blanking number counter, said 5 vertical read starting counter and said vertical read number counter.

In a twelfth mode of the present invention, said video memory reads out said luminance signal from the address, which is specified by a read shift signal and a read line 10 increment signal of said video memory, when a read enable signal is outputted, such that the horizontal address reset by said horizontal read clear signal whereas the vertical address is reset by the vertical read clear signal or said third vertical synchronizing signal, when said luminance signal stored in 15 said video memory is to be read out, so that said horizontal address is incremented by said read shift signal whereas said vertical address is incremented by said read line increment signal, said digital-analog conversion means includes: a digital-analog conversion circuit for analogly converting 20 and outputting the luminance signal which is read out from said video memory; a horizontal reference read dot clock generator for outputting a horizontal reference read dot clock signal synchronized with said third horizontal synchronizing signal; a first horizontal read starting counter 25 reset by said third horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal to output a first horizontal read starting signal for starting the reading of said luminance signal from said video memory and a horizontal read reset signal as said 30 horizontal read clear signal when said counted value reaches a preset value; a second horizontal read starting counter reset by said third horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal, after the output of said first horizontal read starting 35 signal, to output the second horizontal read starting signal when said counted value reaches a predetermined value; a horizontal read number counter reset by said third horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal to inhibit the 40 reading of the luminance signal, which is stored in said video memory, when said counted value reaches a preset value; a horizontal read dot clock generator for outputting a horizontal read dot clock signal synchronized with said third horizontal synchronizing signal; a vertical read offset 45 counter reset by said third vertical synchronizing signal for outputting the vertical read offset signal as said vertical line increment signal on the basis of said horizontal reference read dot clock signal; a vertical blanking number counter reset by said third vertical synchronizing signal for counting 50 the clock number of said third horizontal synchronizing signal to output a vertical blanking ending signal when said countered value indicates that a vertical back porch region has been passed; a vertical read starting counter reset by said third vertical synchronizing signal for counting the clock 55 number of said third horizontal synchronizing signal, after the output of said vertical blanking ending signal, to output a vertical read starting signal for starting the reading the luminance signal from said video signal when said counted value reaches a preset value; a vertical read number counter 60 reset by said third vertical synchronizing signal for counting the clock number of said third horizontal synchronizing signal, after the output of said vertical read starting signal, to output a vertical read number signal for inhibiting the reading of the luminance signal from said video memory, 65 when said counted value reaches a preset value; a vertical read line clock generator for outputting the vertical read line

8

clock signal, which is synchronized with said third vertical synchronizing signal, as said vertical line increment signal; a superimpose start signal output circuit for outputting a superimpose starting signal on the basis of said second horizontal read starting signal, said horizontal read number signal, said vertical read starting signal and said vertical read number signal; and a read enable signal output circuit for outputting said read enable signal on the basis of said third vertical synchronizing signal, said horizontal read reset signal, said vertical read line clock signal and said superimpose starting signal to read out the luminance signal from the area of said video memory, which is specified by either said horizontal reference read dot clock signal or said horizontal read dot clock signal and said read line increment signal, and said mixing means includes: comparator means for comparing said third luminance signal and a predetermined reference signal; compared output starting signal output means for outputting a compared output starting signal for starting the output of the compared output of said comparator means; superimpose control means for outputting a first superimpose starting signal for starting the superimpose of the first luminance signal, which is read out from said video memory and analogly converted by said digital-analog converter, upon said third luminance signal and a second superimpose starting signal for starting the superimpose of said third luminance signal upon said first luminance signal; and superimpose control means for superimposing said third luminance signal upon the first luminance signal, which is superimposed upon said third luminance signal, on the basis of the compared output of said comparator means, said first superimpose starting signal and said second superimpose starting signal.

In a thirteenth mode of the present invention, said horizontal reference read dot clock generator constructing the twelfth mode of the present invention includes a PLL circuit for outputting a signal having a frequency several tens to thousands as high as that of said third horizontal synchronizing signal, said horizontal read dot clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third horizontal synchronizing signal, and said vertical read line clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third vertical synchronizing signal.

In a fourteenth mode of the present invention, said control means constructing the thirteenth mode of the present invention sets the individual clock numbers which are counted by said first horizontal read starting counter, said horizontal read number counter, said vertical blanking number counter, said vertical read number counter.

According to a fifteenth mode of the present invention, there is provided a digitize control system comprising: an analog-digital conversion circuit for analog-digital converting said first luminance signal; a video memory for storing the first luminance signal, which is digitized by said analog-digital conversion means, in an area of the address, which is specified by a write shift signal and a write line increment signal, when a write enable signal is outputted, such that a horizontal address is reset by a horizontal write clear signal whereas a vertical address is reset by a vertical write clear signal, when said first luminance signal is to be written, so that said horizontal address is set at the unit of a block of a predetermined dot number by an address signal and incremented by said write shift signal and so that said vertical address is incremented by said write increment signal; a

horizontal write dot clock generator synchronized with said first horizontal synchronizing signal for outputting a horizontal write dot clock signal having a frequency predetermined times as high as that of said first horizontal synchronizing signal and based upon said block unit as the analogdigital conversion clock signal of said analog-digital conversion means and a basic synchronizing signal having a predetermined frequency as said write shift signal; a horizontal write starting counter reset by said first horizontal synchronizing signal for counting the clock number of said horizontal write dot clock signal to output a horizontal write starting signal for starting the writing of said first luminance signal in said image memory and said horizontal write clear signal when said counted value reaches a preset value; a horizontal write number counter reset by said first horizontal 15 synchronizing signal for counting the clock number of said horizontal write dot clock signal, after the output of said horizontal write starting signal, to output a horizontal write number signal for inhibiting the write of said first luminance signal in said video memory when said counted value reaches a predetermined value; a vertical write offset counter reset by said first vertical synchronizing signal for outputting a vertical write offset signal of the clock number of the preset value, which is synchronized with said basic synchronous signal, as said write line increment signal; a vertical 25 write line clock generator synchronized with said first vertical synchronizing signal for outputting a vertical write line clock signal having a frequency of predetermined times as high as that of said vertical synchronizing signal as said write line increment signal; a vertical write starting counter 30 reset by said first vertical synchronizing signal for counting the clock number of said first horizontal synchronizing signal to output a vertical write starting signal for starting the writing of said luminance signal in said video memory when said counted value reaches a preset value; a vertical write number counter reset by said vertical synchronizing signal for starting the counting of the clock number of said vertical write line clock signal, after the output of said vertical write starting signal, to output a vertical write number signal for inhibiting the writing of said first luminance signal in said 40 video memory when said counted value reaches a preset value; and write control means for outputting said write enable signal on the basis of said first vertical synchronizing signal, said horizontal write clear signal, said horizontal write dot clock signal, said horizontal write starting signal, said horizontal write number signal, said vertical write starting signal, said vertical write number signal and said vertical write line clock signal to write the first luminance signal, which is digitized by said horizontal write dot clock signal, in the area of said video memory, which is specified by said address signal, said write shift signal and said write line increment signal, while said horizontal write starting signal and said vertical write starting signal are being outputted.

In a sixteen mode of the present invention, said digitize 55 control system includes digitize control means sets the value of said block, the frequency of said vertical write line clock signals the preset value of said horizontal write starting counter, the preset value of said horizontal write number counter, the preset value of said vertical write starting 60 counter and the preset value of said vertical write number counter.

In a seventh mode of the present invention, said write control means includes image still means for outputting said first vertical synchronizing signal none of said video 65 memory, said vertical write offset counter, said vertical write line clock generator, said vertical write starting counter and

10

said vertical write number counter in accordance with the operations of said operation means.

In an eighteenth mode of the present invention, there is provided a superimpose control system comprising: a video memory storing a luminance signal for reading out said luminance signal from the address, which is specified by a read shift signal and a read line increment signal of said video memory, when a read enable signal is outputted, such that the horizontal address reset by said horizontal read clear signal whereas the vertical address is reset by the vertical read clear signal or a vertical synchronizing signal, so that said horizontal address is incremented by said read shift signal whereas said vertical address is incremented by said read line increment signal; a digital-analog conversion circuit for analogly converting and outputting the luminance signal which is read out from said video memory; a horizontal reference read dot clock generator for outputting a horizontal reference read dot clock signal synchronized with said horizontal synchronizing signal; a first horizontal read starting counter reset by said horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal to output a first horizontal read starting signal for starting the reading of said luminance signal from said video memory and a horizontal read reset signal as said horizontal read clear signal when said counted value reaches a preset value; a second horizontal read starting counter reset by said horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal, after the output of said first horizontal read starting signal, to output the second horizontal read starting signal when said counted value reaches a predetermined value; a horizontal read number counter reset by said horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal to inhibit the reading of the luminance signal, which is stored in said video memory, when said counted value reaches a preset value; a horizontal read dot clock generator for outputting a horizontal read dot clock signal synchronized with said horizontal synchronizing signal; a vertical read offset counter reset by said vertical synchronizing signal for outputting the vertical read offset signal as said vertical line increment signal on the basis of said horizontal reference read dot clock signal; a vertical blanking number counter reset by said vertical synchronizing signal for counting the clock number of said horizontal synchronizing signal to output a vertical blanking ending signal when said counted value indicates that a vertical back porch region has been passed; a vertical read starting counter reset by said vertical synchronizing signal for counting the clock number of said horizontal synchronizing signal, after the output of said vertical blanking ending signal, to output a vertical read starting signal for starting the reading the luminance signal from said video signal when said counted value reaches a preset value; a vertical read number counter reset by said vertical synchronizing signal for counting the clock number of said horizontal synchronizing signal, after the output of said vertical read starting signal, to output a vertical read number signal for inhibiting the reading of the luminance signal from said video memory, when said counted value reaches a preset value; a vertical read line clock generator for outputting the vertical read line clock signal, which is synchronized with said vertical synchronizing signal, as said vertical line increment signal; a superimpose start signal output circuit for outputting a superimpose starting signal on the basis of said second horizontal read starting signal, said horizontal read number signal, said vertical read starting signal and said vertical read number signal; a read enable

signal output circuit for outputting said read enable signal on the basis of said vertical synchronizing signal, said horizontal read reset signal, said vertical read line clock signal and said superimpose starting signal to read out the luminance signal from the area of said video memory, which is specified by either said horizontal reference read dot clock signal or said horizontal read dot clock signal and said read line increment signal; and a video switch switched on the basis of said superimpose starting signal for selectively outputting the luminance signal, which is read out from said video memory and analogly converted by said digital-analog conversion circuit, and said luminance signal.

In a nineteenth mode of the present invention, said horizontal reference read dot clock generator constructing the eighteenth mode of the present invention includes a PLL circuit for outputting a signal having a frequency several hundreds as high as that of said third horizontal synchronizing signal, said horizontal read dot clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third horizontal synchronizing signal, and said vertical read line clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third vertical synchronizing signal.

In a twelfth mode of the present invention, said superimpose control system further comprises control means for setting the individual clock numbers which are counted by said first horizontal read starting counter, said horizontal read number counter, said vertical blanking number counter, 30 said vertical read starting counter and said vertical read number counter.

In a twenty first mode of the present invention, there is provided a superimpose control system comprising: a video memory storing a luminance signal for reading out said 35 luminance signal from the address, which is specified by a read shift signal and a read line increment signal of said video memory, when a read enable signal is outputted, such that the horizontal address reset by said horizontal read clear signal whereas the vertical address is reset by the vertical 40 read clear signal or a vertical synchronizing signal, so that said horizontal address is incremented by said read shift signal whereas said vertical address is incremented by said read line increment signal; a digital-analog conversion circuit for analogly converting and outputting the luminance 45 signal which is read out from said video memory; a horizontal reference read dot clock generator for outputting a horizontal reference read dot clock signal synchronized with said horizontal synchronizing signal; a first horizontal read starting counter reset by said horizontal synchronizing signal 50 for counting the clock number of said horizontal reference read dot clock signal to output a first horizontal read starting signal for starting the reading of said luminance signal from said video memory and a horizontal read reset signal as said horizontal read clear signal when said counted value reaches 55 a preset value; a second horizontal read starting counter reset by said horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal, after the output of said first horizontal read starting signal, to output the second horizontal read starting signal 60 when said counted value reaches a predetermined value; a horizontal read number counter reset by said horizontal synchronizing signal for counting the clock number of said horizontal reference read dot clock signal to inhibit the reading of the luminance signal, which is stored in said 65 video memory, when said counted value reaches a preset value; a horizontal read dot clock generator for outputting a

horizontal read dot clock signal synchronized with said horizontal synchronizing signal; a vertical read offset counter reset by said vertical synchronizing signal for outputting the vertical read offset signal as said vertical line increment signal on the basis of said horizontal reference read dot clock signal; a vertical blanking number counter reset by said vertical synchronizing signal for counting the clock number of said horizontal synchronizing signal to output a vertical blanking ending signal when said counted value indicates that a vertical back porch region has been passed; a vertical read starting counter reset by said vertical synchronizing signal for counting the clock number of said horizontal synchronizing signal, after the output of said vertical blanking ending signal, to output a vertical read starting signal for starting the reading the luminance signal from said video signal when said counted value reaches a preset value; a vertical read number counter reset by said vertical synchronizing signal for counting the clock number of said horizontal vertical signal, after the output of said vertical read starting signal, to output a vertical read number signal for inhibiting the reading of the luminance signal from said video memory, when said counted value reaches a preset value; a vertical read line clock generator for outputting the vertical read line clock signal, which is synchronized with said vertical synchronizing signal, as said 25 vertical line increment signal; a superimpose start signal output circuit for outputting a superimpose starting signal on the basis of said second horizontal read starting signal, said horizontal read number signal, said vertical read starting signal and said vertical read number signal; a read enable signal output circuit for outputting said read enable signal on the basis of said vertical synchronizing signal, said horizontal read reset signal, said vertical read line clock signal and said superimpose starting signal to read out the luminance signal from the area of said video memory, which is specified by either said horizontal reference read dot clock signal or said horizontal read dot clock signal and said read line increment signal; comparator means for comparing said third luminance signal and a predetermined reference signal;

compared output starting signal output means for outputting a compared output starting signal for starting the output of the compared output of said comparator means; superimpose control means for outputting a first superimpose starting signal for starting the superimpose of the first luminance signal, which is read out from said video memory and analogly converted by said digital-analog converter, upon said third luminance signal and a second superimpose starting signal for starting the superimpose of said third luminance signal upon said first luminance signal; and superimpose control means for superimposing said third luminance signal upon the first luminance signal, which is superimposed upon said third luminance signal, on the basis of the compared output of said comparator means, said first superimpose starting signal and said second superimpose starting signal.

In a twenty second mode of the present invention, said horizontal reference read dot clock generator of the twenty first mode of the present invention includes a PLL circuit for outputting a signal having a frequency several hundreds as high as that of said third horizontal synchronizing signal, said horizontal read dot clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third horizontal synchronizing signal, and said vertical read line clock generator includes a PLL circuit for outputting a signal having a frequency a predetermined number of times as high as that of said third vertical synchronizing signal.

In a twenty third mode of the present invention, said superimpose control system further comprises control means for setting the individual clock numbers which are counted by said first horizontal read starting counter, said horizontal read number counter, said vertical blanking number counter, said vertical read starting counter and said vertical read number counter.

According to the first mode of the present invention thus constructed, the decoding means separates the first video signal into the first luminance signal, the first horizontal 10 synchronizing signal and the first vertical synchronizing signal and analog-digital converts them, and the memory means stores the digitized first luminance signal.

Moreover, the digital-analog conversion means converts the digitized luminance signal stored in the memory means 15 to analog, and the mixing means reads it out from the memory means so that either the analogly converted luminance signal or the second luminance signal is selectively outputted as the third luminance signal.

The aforementioned operations are controlled by the 20 control means.

According to the second mode of the present invention thus constructed, moreover, the decoding means, the analog-digital conversion means, the memory means, the digital-analog conversion means, the mixing means and the control 25 means constructing the first mode of the present invention are constructed over the one extended slot card.

According to the third mode of the present invention thus constructed, furthermore, the operation means inputs the position, size and timing of displaying the image corre- 30 sponding to the first luminance signal with respect to the image corresponding to the third luminance signal. Then, the signal corresponding to the position, size and timing inputted to the device drive in the OS is outputted to the decode means, the memory means, the digital-analog conversion 35 means and the mixing means.

According to the fourth mode of the present invention thus constructed, furthermore, the write enable signal is outputted on the basis of the first vertical synchronizing signal, the horizontal write clear signal, the horizontal write 40 dot clock signal, the horizontal write starting signal, the horizontal write number signal, the vertical write starting signal, the vertical write line clock signal. While the horizontal write starting signal and the vertical write starting signal are being outputted, the 45 first luminance signal, which is digitized by the horizontal write dot clock signal, is written in the area of the video memory, which is specified by the address signal, the write shift signal and the write line increment signal.

According to the fifth mode of the present invention thus 50 constructed, furthermore, when the operations of the fourth mode of the present invention are to be accomplished, the control means sets the value of the block, the frequency of the vertical write line clock signal, the preset value of the horizontal write starting counter, the preset value of the vertical write number counter, the preset value of the vertical write starting counter, and the preset value of the vertical write number counter.

According to the sixth mode of the present invention thus constructed, furthermore, the still image means does not 60 output the first vertical synchronizing signal to the video memory, the vertical write offset counter, the vertical write line clock generator, the vertical write starting counter and the vertical write number counter in accordance with the operations of the operation means.

According to the seventh mode of the present invention thus constructed, when the write control unit writes the

second luminance signal in the video memory, the write control means controls the video memory. Then, the luminance signal selection means outputs the first luminance signal and the second luminance signal selectively to the video memory. The video memory control signal selection unit outputs the write control signals of the first luminance signal and the second luminance signal selectively in response to the selected output of the first and second luminance signals.

According to the eighth mode of the present invention thus constructed, furthermore, the read control unit and the FIFO read control unit control the reading of the luminance signal from the video memory into the FIFO memory in accordance with the control of the control means.

Accordingly to the ninth mode of the present invention thus constructed, furthermore, the read enable signal output circuit outputs the read enable signal on the basis of the third vertical synchronizing signal, the horizontal read reset signal, the vertical read line clock signal and the superimpose starting signal to read out the luminance signal from the area of the video memory, which is specified by either the horizontal reference read dot clock signal or the horizontal read dot clock signal and the read line increment signal. Then, the video switch is switched on the basis of the superimpose starting signal to selectively output the luminance signal, which is read out from the video memory and analogly converted by the digital-analog converter, and the third luminance signal.

According to the tenth mode of the present invention thus constructed, furthermore, the aforementioned horizontal reference read dot clock generator, the horizontal read dot clock generator and vertical read line clock generator are constructed of PLL circuits.

According to the eleventh mode of the present invention thus constructed, furthermore, the control means the individual clock numbers to be counted by the first horizontal read starting counter, the horizontal read number counter, the vertical blanking number counter, the vertical read starting counter and the vertical read number counter.

According to the twelfth mode of the present invention thus constructed, furthermore, the luminance signal, which is analogly converted by the digital-analog converter, and the third luminance signal are selectively outputted like the ninth mode of the present invention.

According to the fifteenth mode of the present invention thus constructed, furthermore, the first luminance signal digitized by the horizontal write dot clock signal is written line the fourth mode of the present invention in the area of the video memory, which is specified by the address signal, the write shift signal and the write line increment signal.

According to the eighteenth mode of the present invention thus constructed, furthermore, the luminance signal, which is read out from the video memory and analogly converted by the digital-analog converter, and the third luminance signal are selectively outputted like the ninth mode of the present invention.

According to the twenty first mode of the present invention thus constructed, furthermore, the luminance signal, which is analogly converted by the digital-analog converter, and the third luminance signal are selectively outputted like the twelfth mode of the present invention.

As has been described hereinbefore, according to the present invention, the decode means separates the first video signal into the first luminance signal, the first horizontal synchronizing signal and the first vertical synchronizing signal and subjects them to the analog-digital conversions. Moreover, the digital-analog conversion means analogly

**15**

converts the luminance signal, which is stored in the memory means, and the mixing means reads out it from the memory means to output either the converted to analog luminance signal or the second luminance signal selectively as the third luminance signal. Thus, there can be attained an 5 effect to provide an image processing system capable of displaying an image corresponding to the first luminance signal in a desired position, with a desired size and at a desired timing with respect to the image corresponding to the second luminance signal.

Since, moreover, the individual component means are constructed over the one extended slot card, it is possible to provide a compact image processing system.

Thus, on the basis of the first vertical synchronizing signal, the horizontal write clear signal, the horizontal write 15 dot clock signal, the horizontal write starting signal, the horizontal write number signal, the vertical write starting signal, the vertical write number signal and the vertical write line clock signal, the write enable signal is outputted so that the first luminance signal can be written in a desired position 20 and with a desired size, while the horizontal write starting signal and the vertical write starting signal are being outputted, in the area of the video memory, which is specified by the address signal, the write shift signal and the write line increment signal.

Furthermore, the first vertical synchronizing signal is not outputted to the video memory, the vertical write offset counter, the vertical write line clock generator, the vertical write starting counter and the vertical write number counter so that a still image can be easily obtained.

Furthermore, not only the first luminance signal but also the second luminance signal outputted from the control means can be written.

Furthermore, the control means can easily read the first control means without obstructing the output of that first luminance signal to the monitor.

Furthermore, the video switch is switched on the basis of the superimpose starting signal to selectively output the first luminance signal, which is read out from the video memory and converted to analog by the digital-analog converter, and the third luminance signal.

Furthermore, it is possible to accomplish the so-called "double superimpose", in which the first luminance signal is superimposed upon the third luminance signal whereas the 45 third luminance signal is further superimposed upon the first luminance signal. Thus, the switching is made on the basis of the signal so that the first luminance signal, which is read out from the video memory and converted to analog by the digital-analog converter, and the third luminance signal can 50 be selectively outputted.

#### DESCRIPTION OF THE DRAWINGS

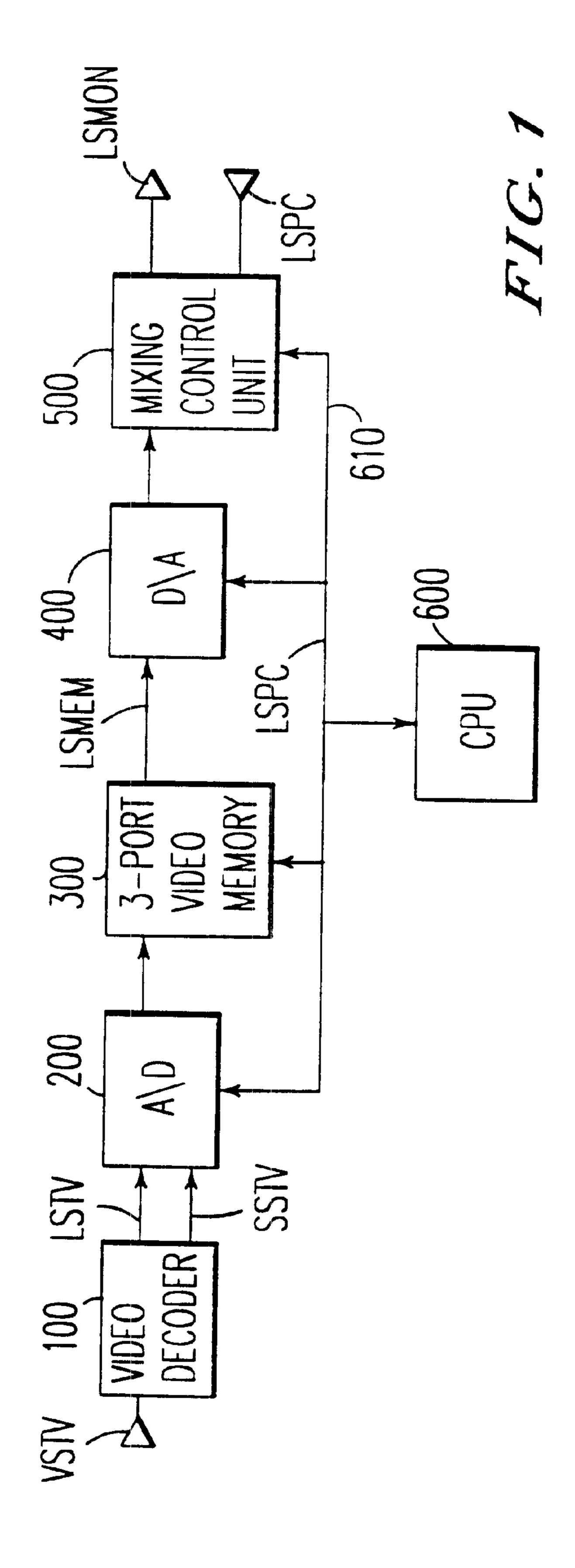

- FIG. 1 is a schematic block diagram showing an image processing system according to one embodiment of the present invention;

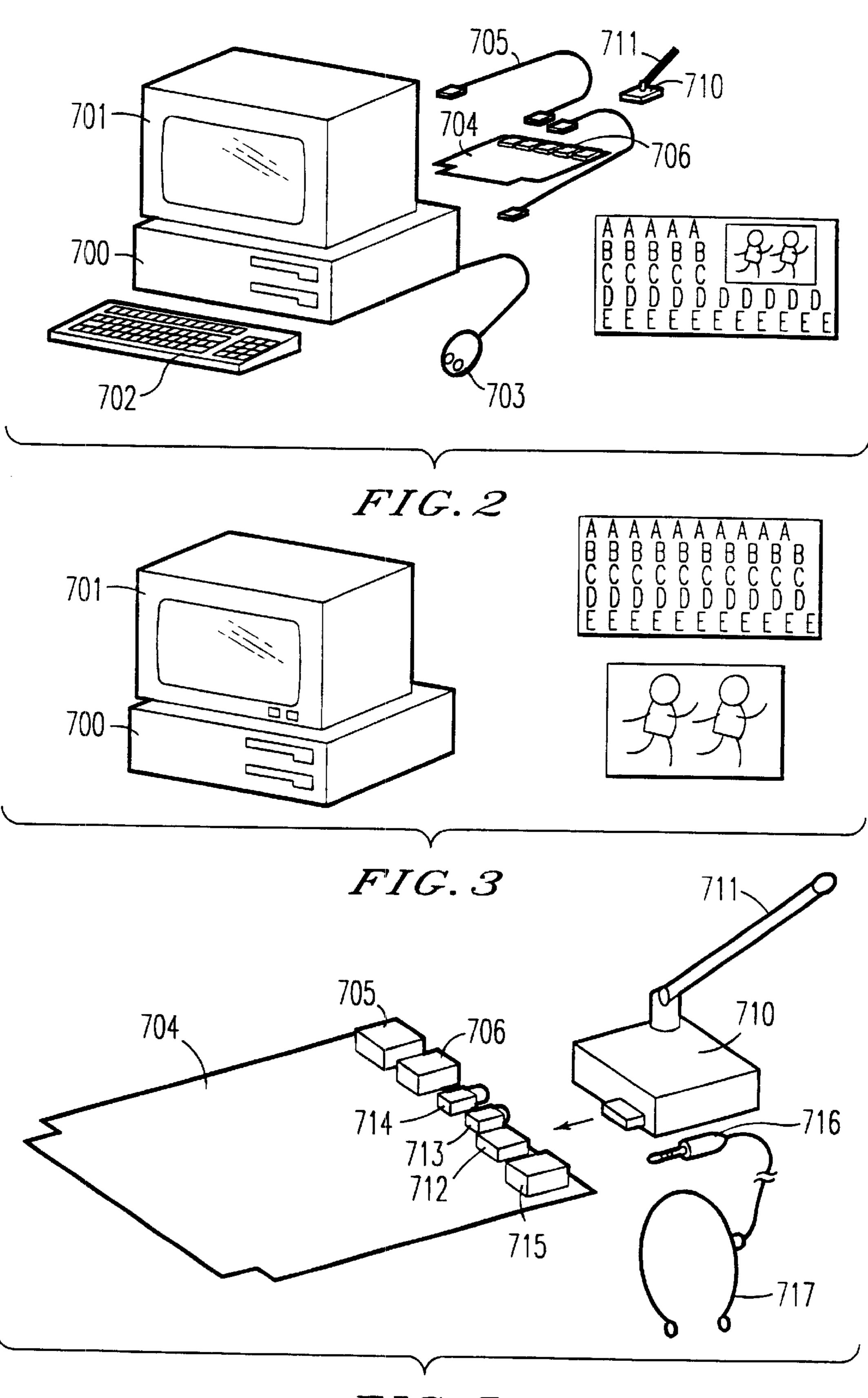

- FIG. 2 is an external view showing the image processing system shown in FIG. 1;

- FIG. 3 is an external view showing a personal computer body in which an extended slot card shown in FIG. 2 is built;

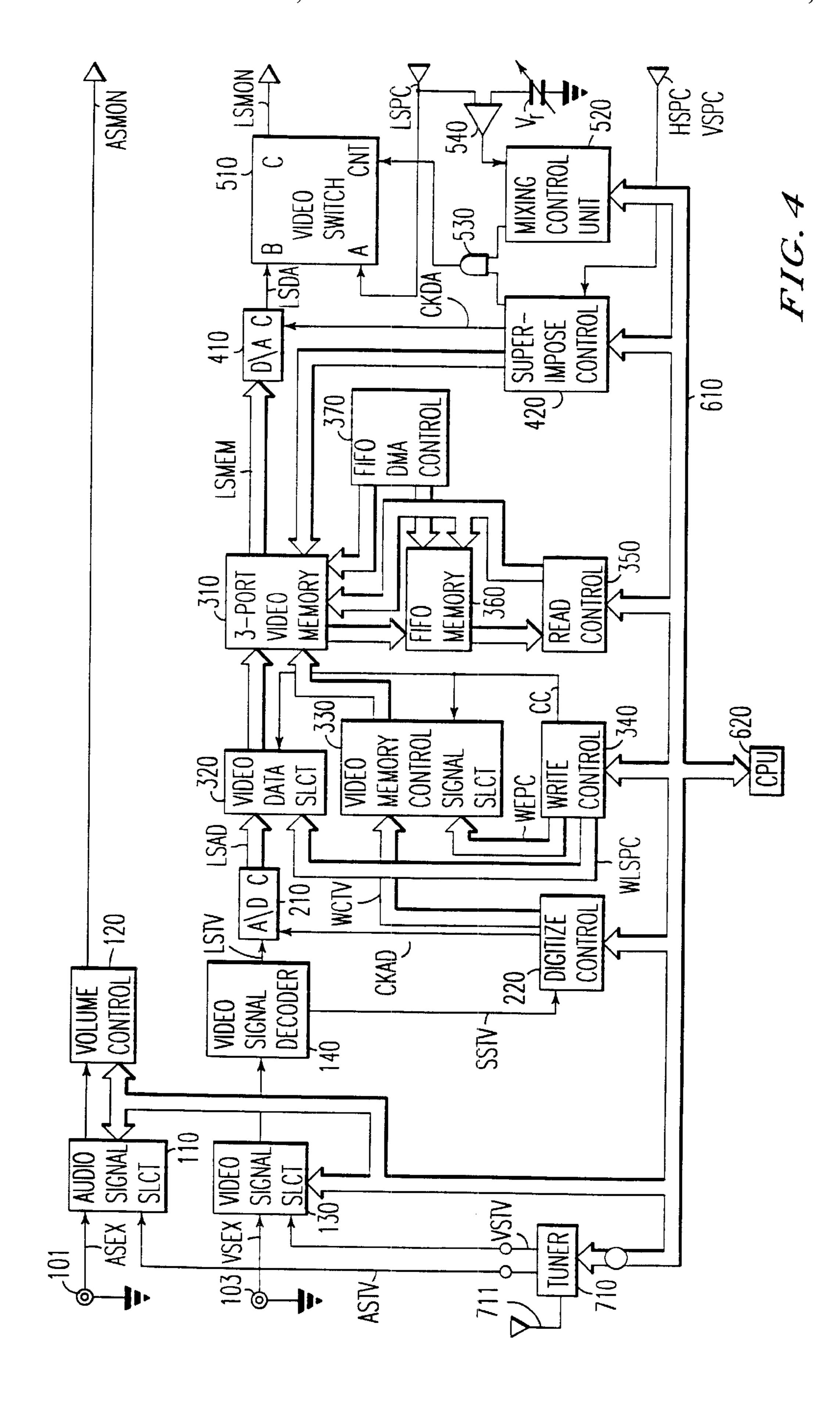

- FIG. 4 is a detailed block circuit diagram showing a major portion of the image processing system shown in FIG. 1;

- FIG. 5 is a connection diagram between the extended slot card shown in FIG. 2 and a tuner;

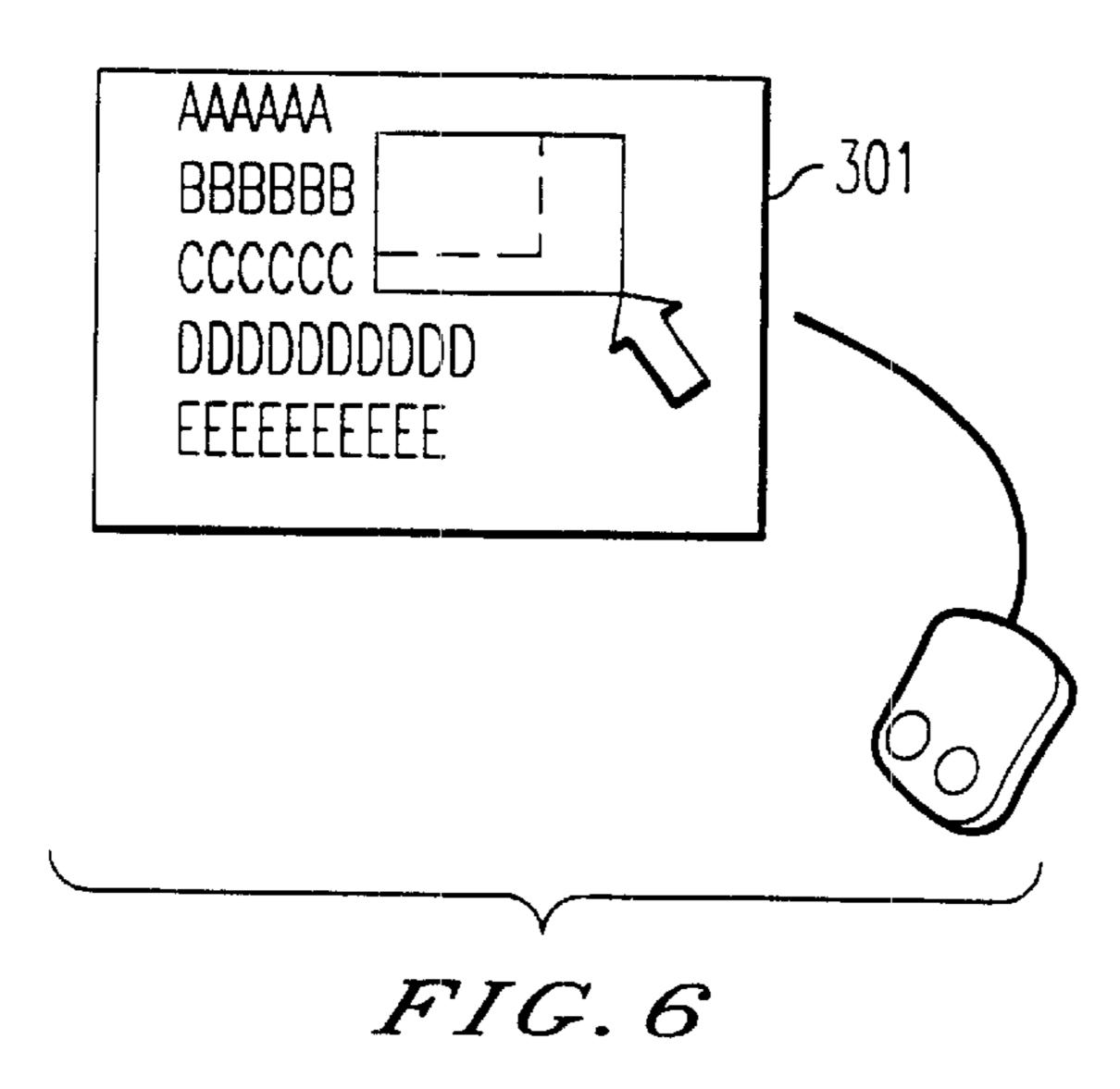

- FIG. 6 is a diagram for explaining the operations of the image processing system shown in FIG. 1;

**16**

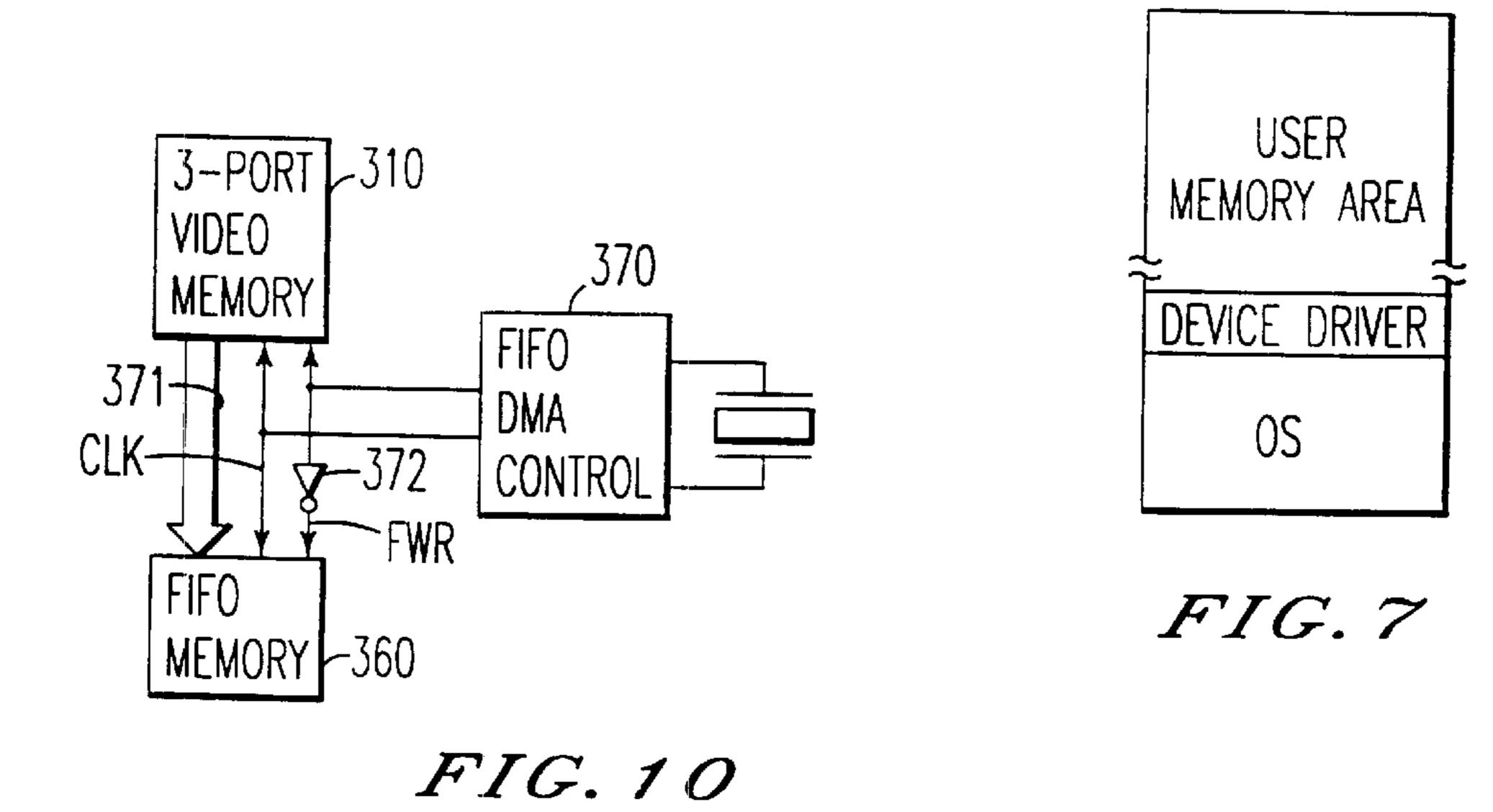

FIG. 7 is a memory map;

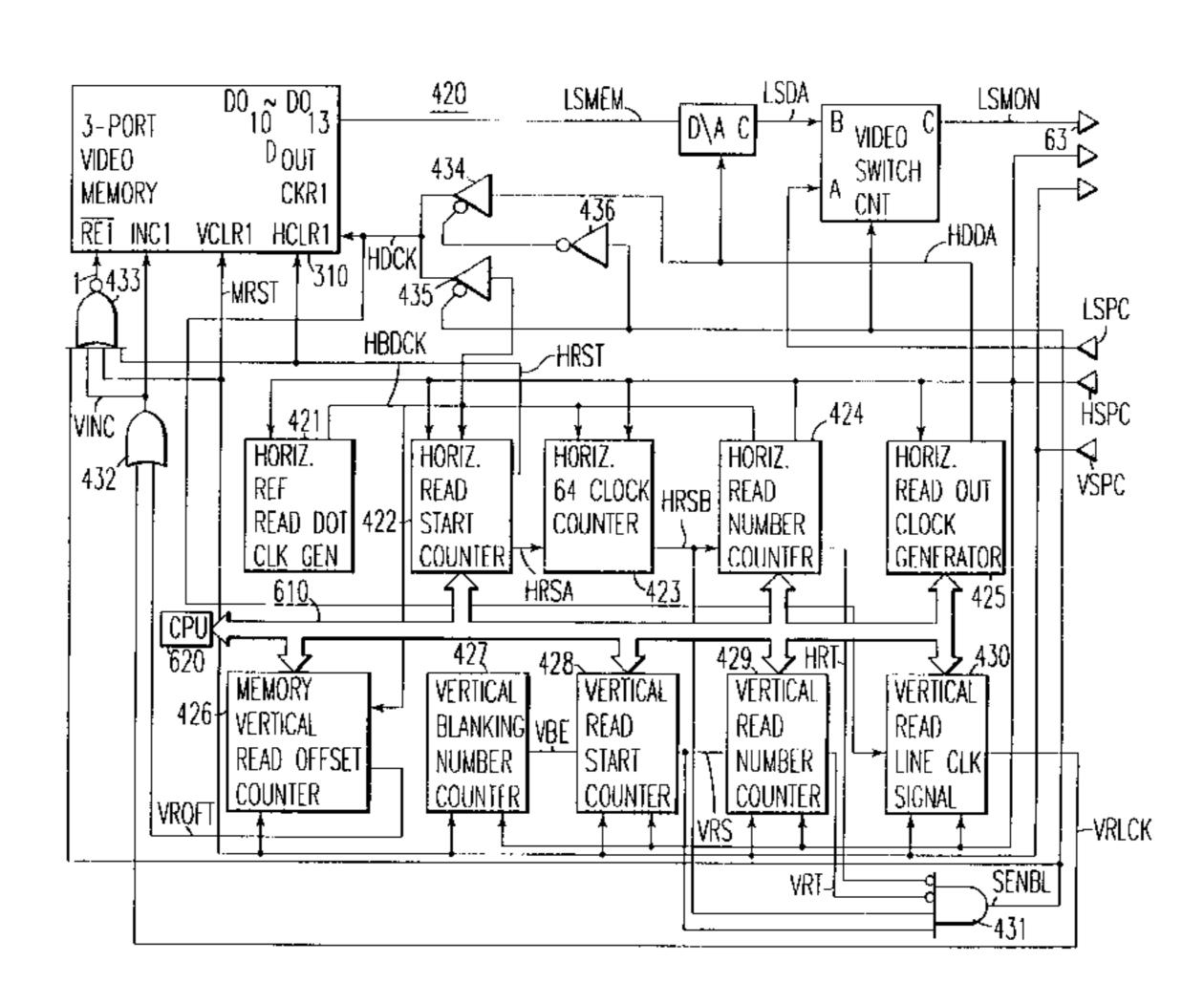

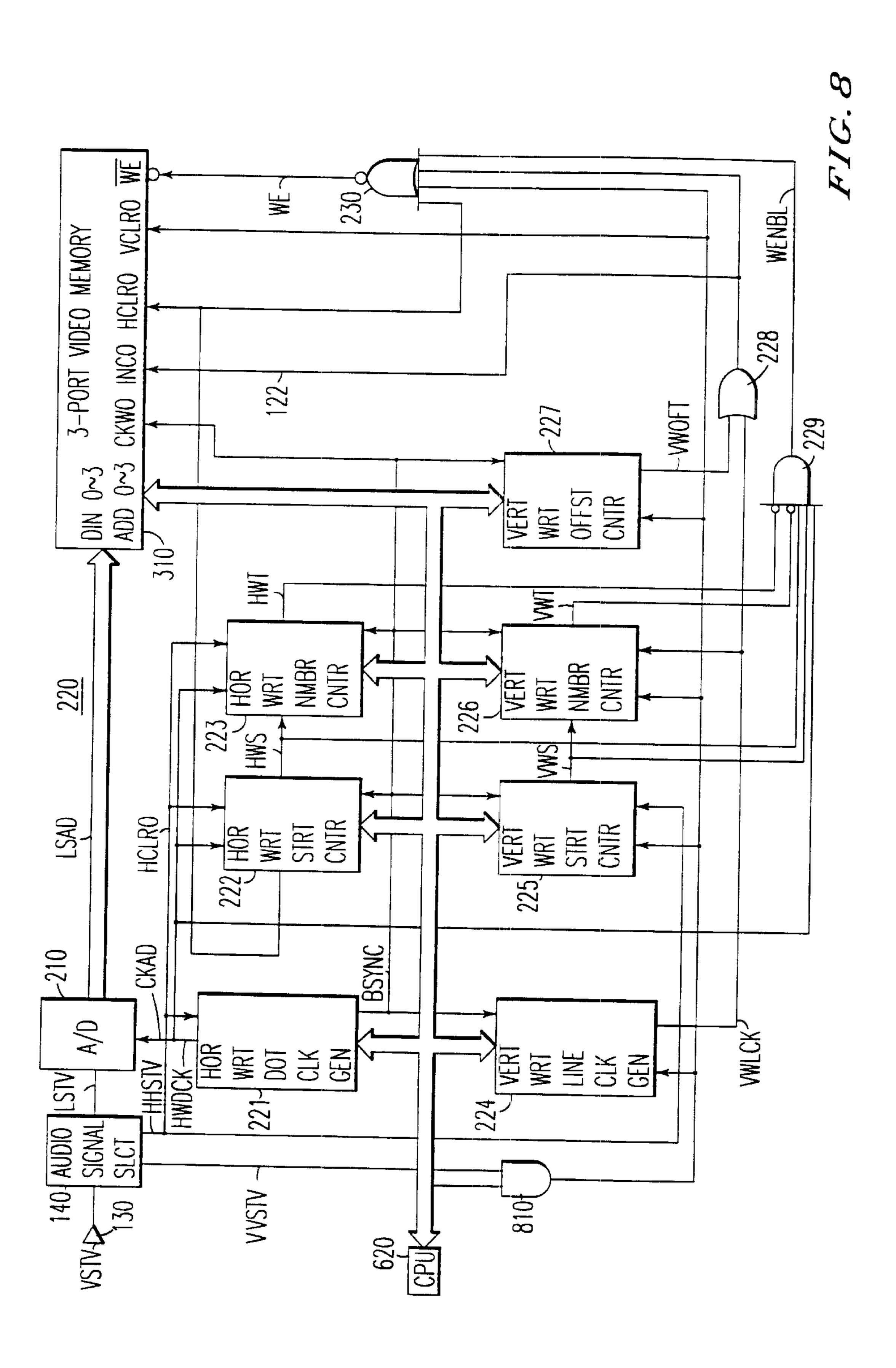

- FIG. 8 is a circuit diagram showing a digitize control unit shown in FIG. 4 and its peripheral circuits;

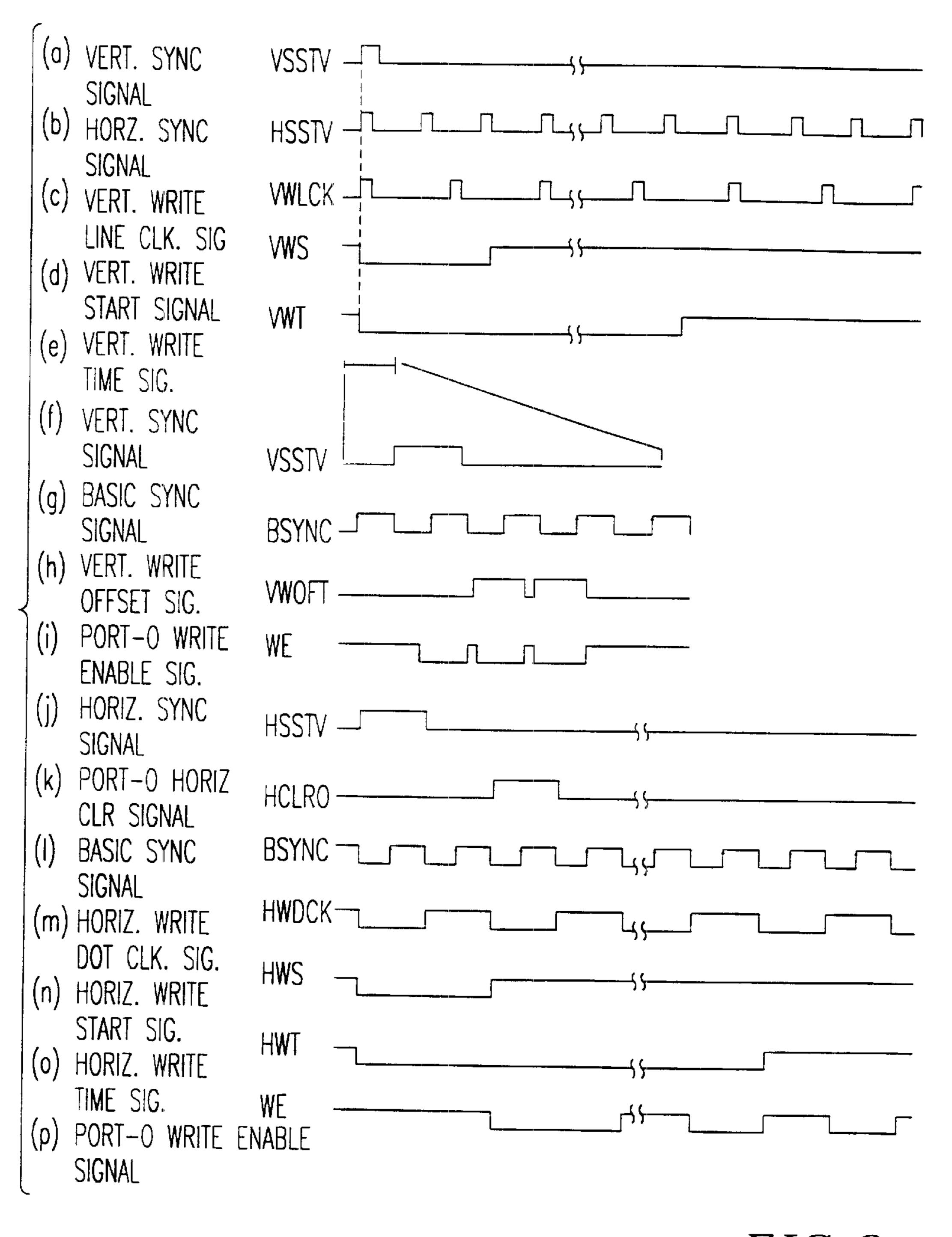

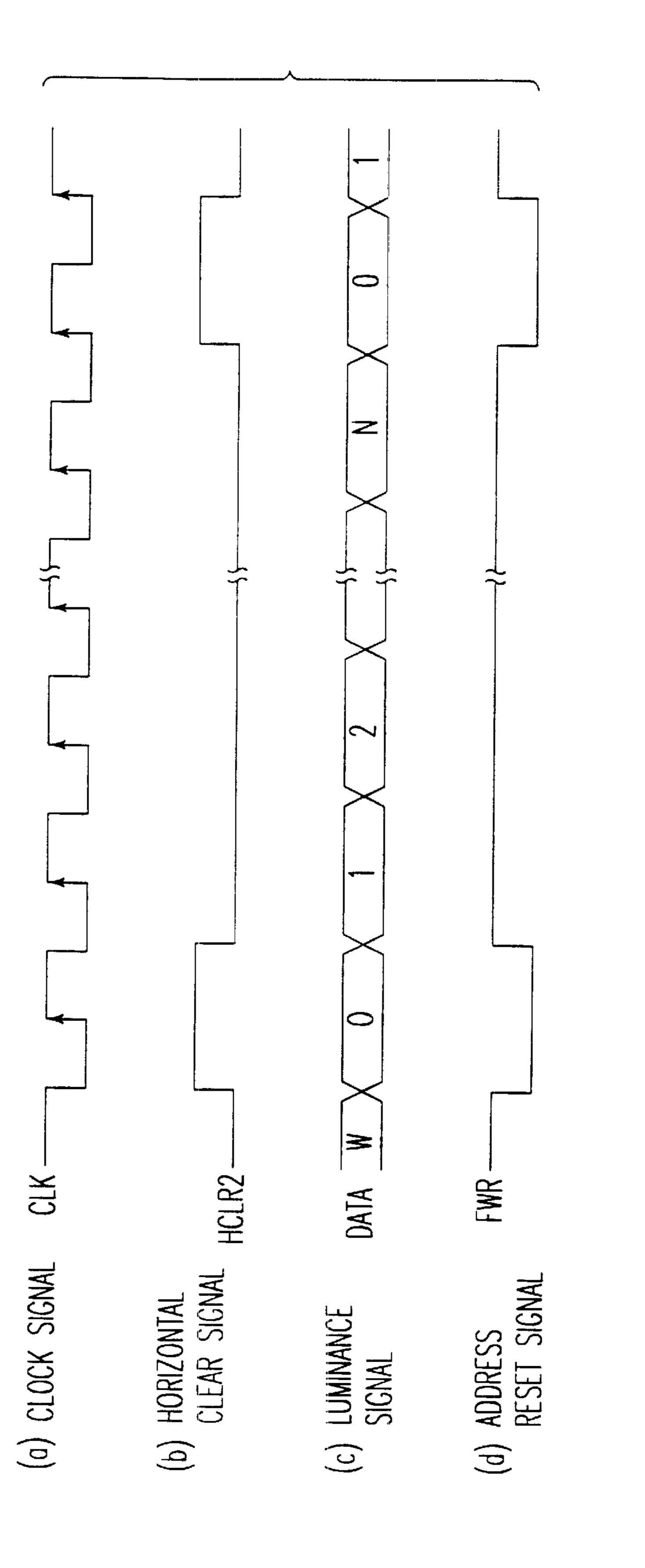

- FIG. 9 is a timing chart showing the operations of the digitize control unit shown in FIG. 4 and its peripheral circuits;

- FIG. 10 is a circuit diagram showing a DMA circuit shown in FIG. 4;

- FIG. 11 is a timing chart showing the operations of the 10 DMA circuit shown in FIG. 4;

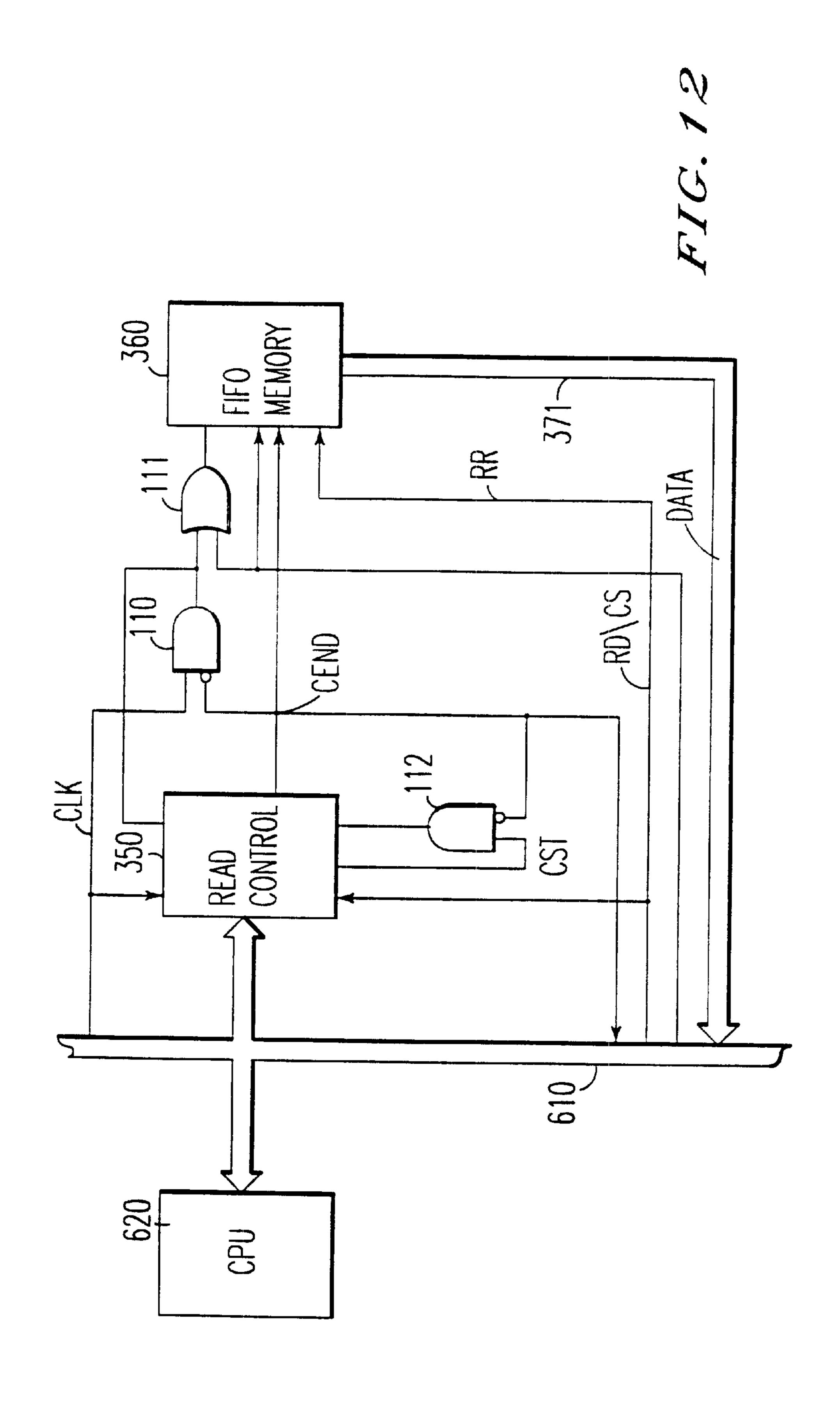

- FIG. 12 is a circuit diagram showing an offset circuit;

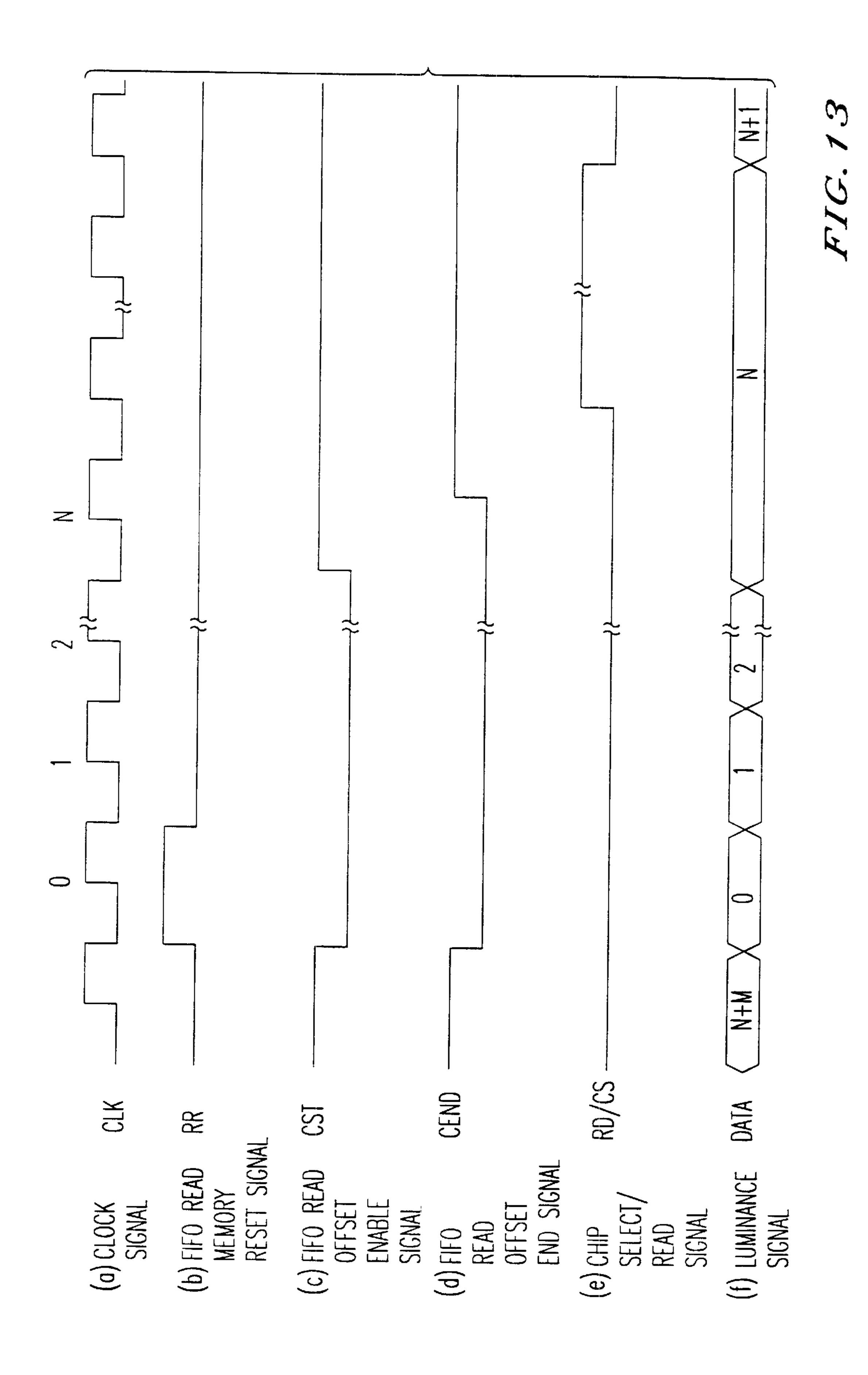

- FIG. 13 is a timing chart showing the operations of the offset circuit shown in FIG. 12;

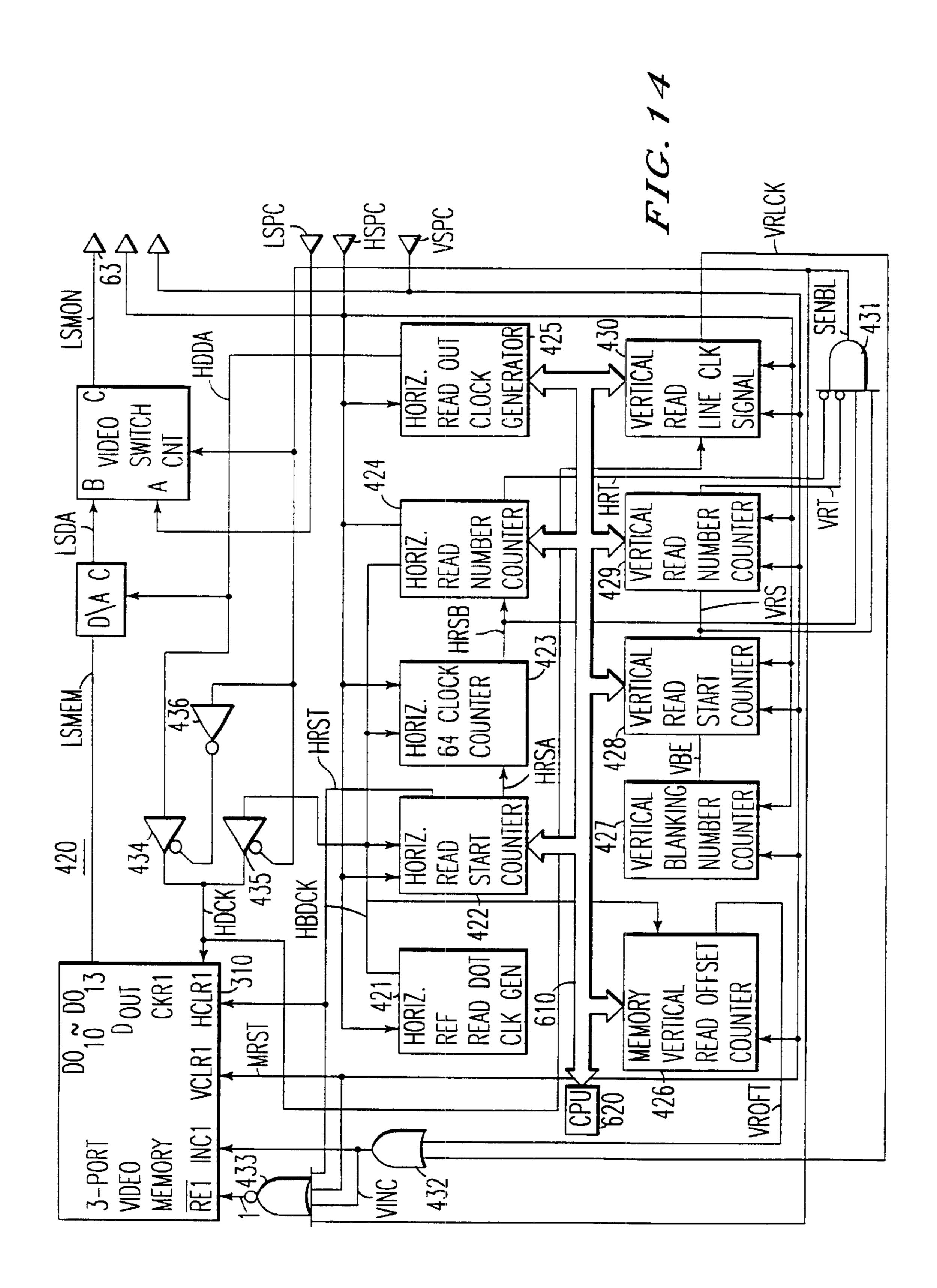

- FIG. 14 is a circuit diagram showing a superimpose control circuit shown in FIG. 4 and its peripheral circuits; and

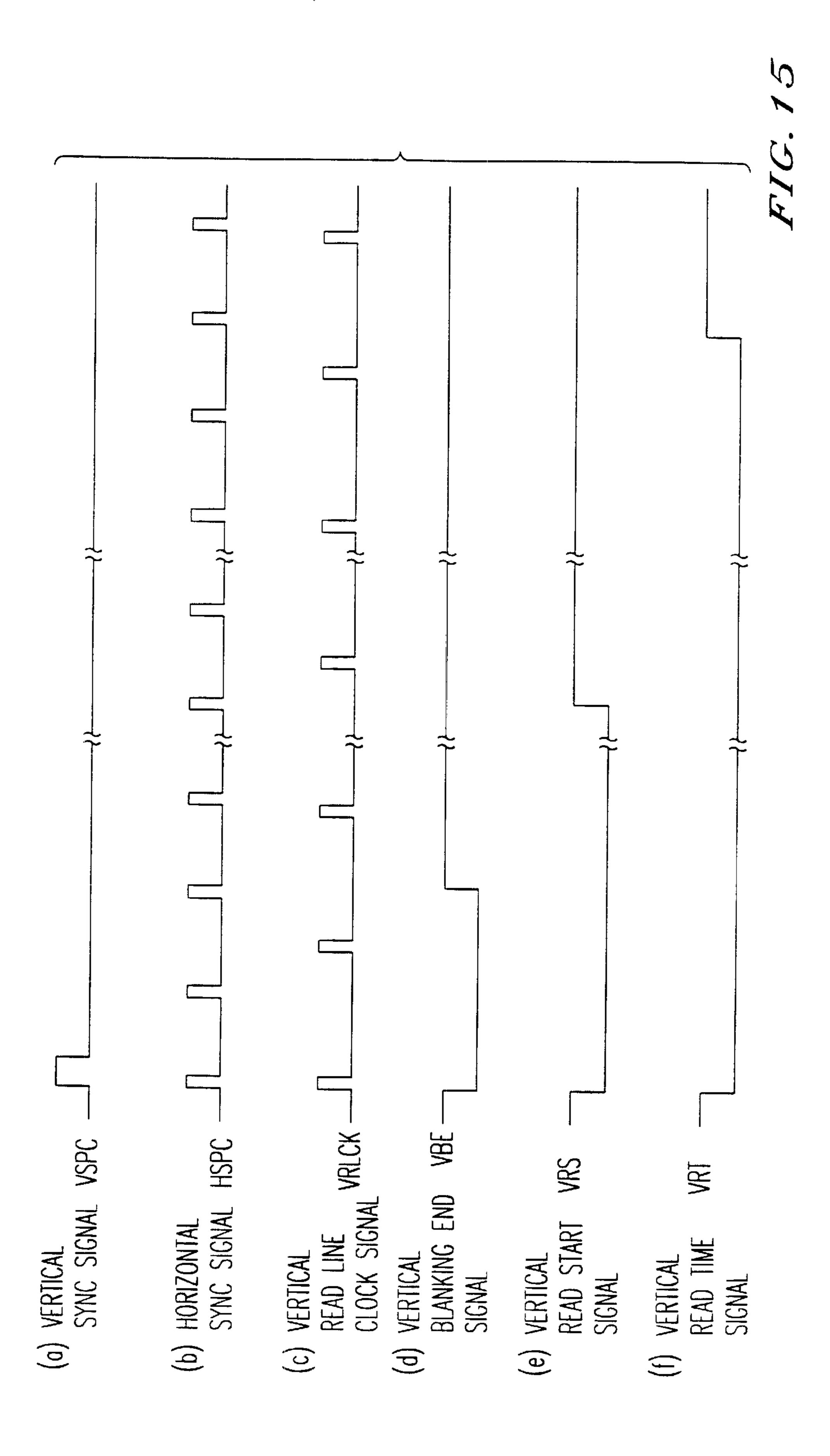

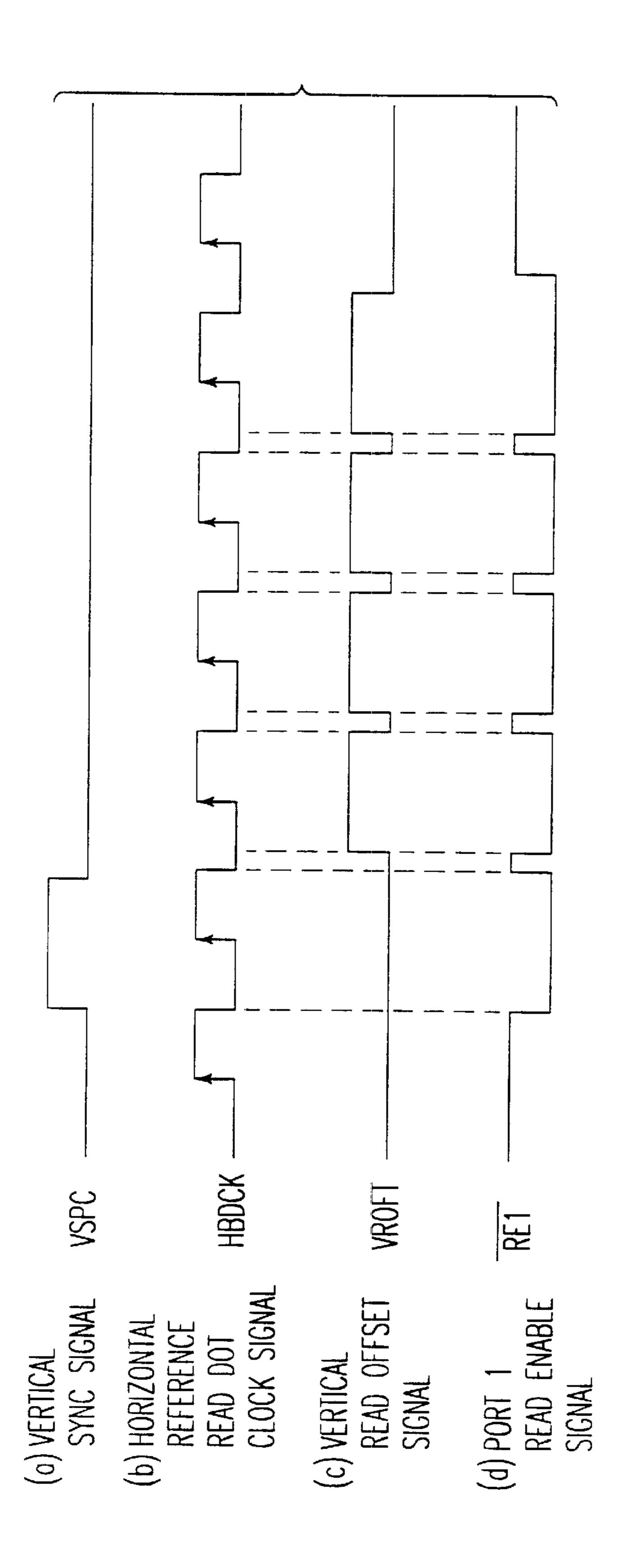

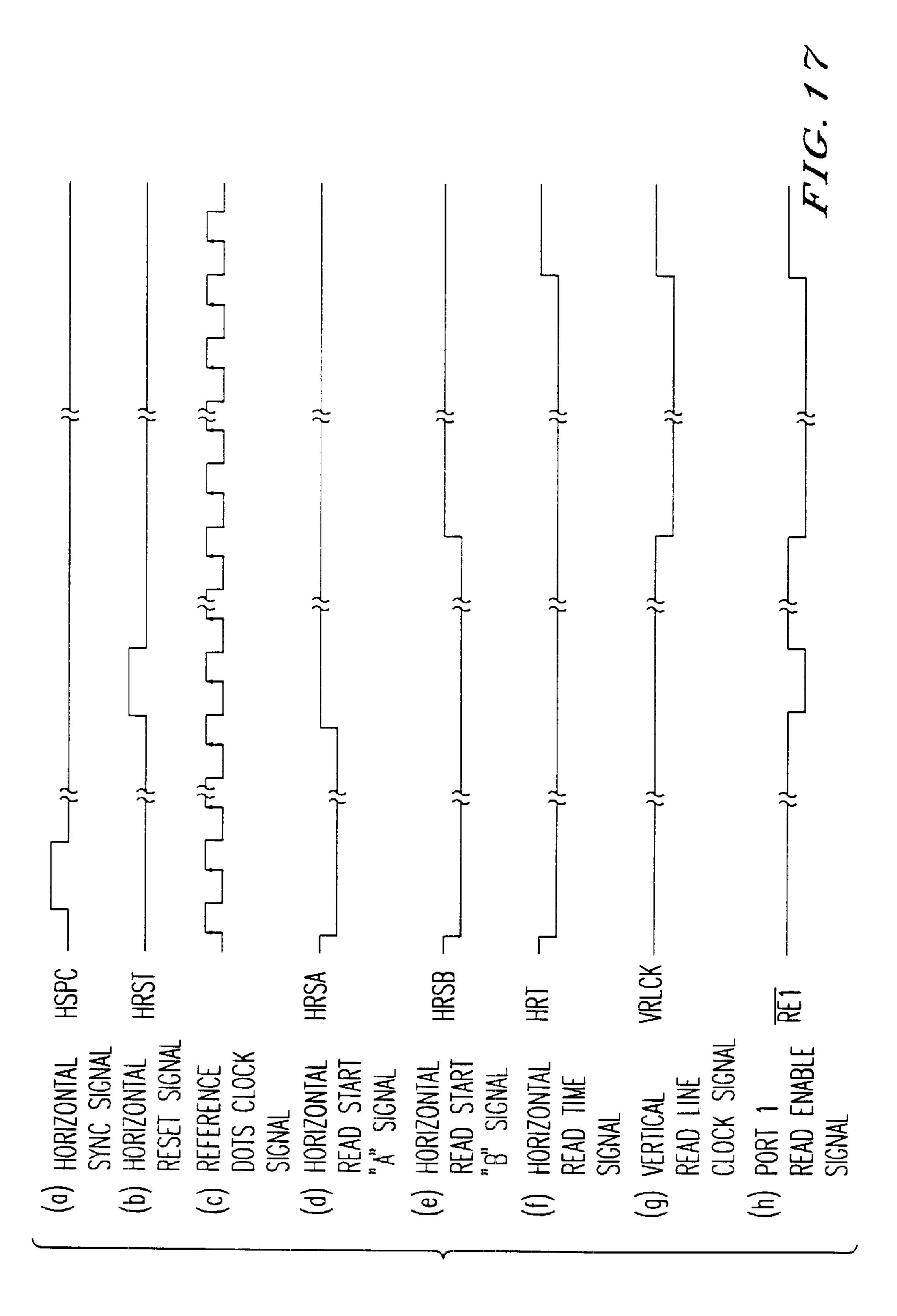

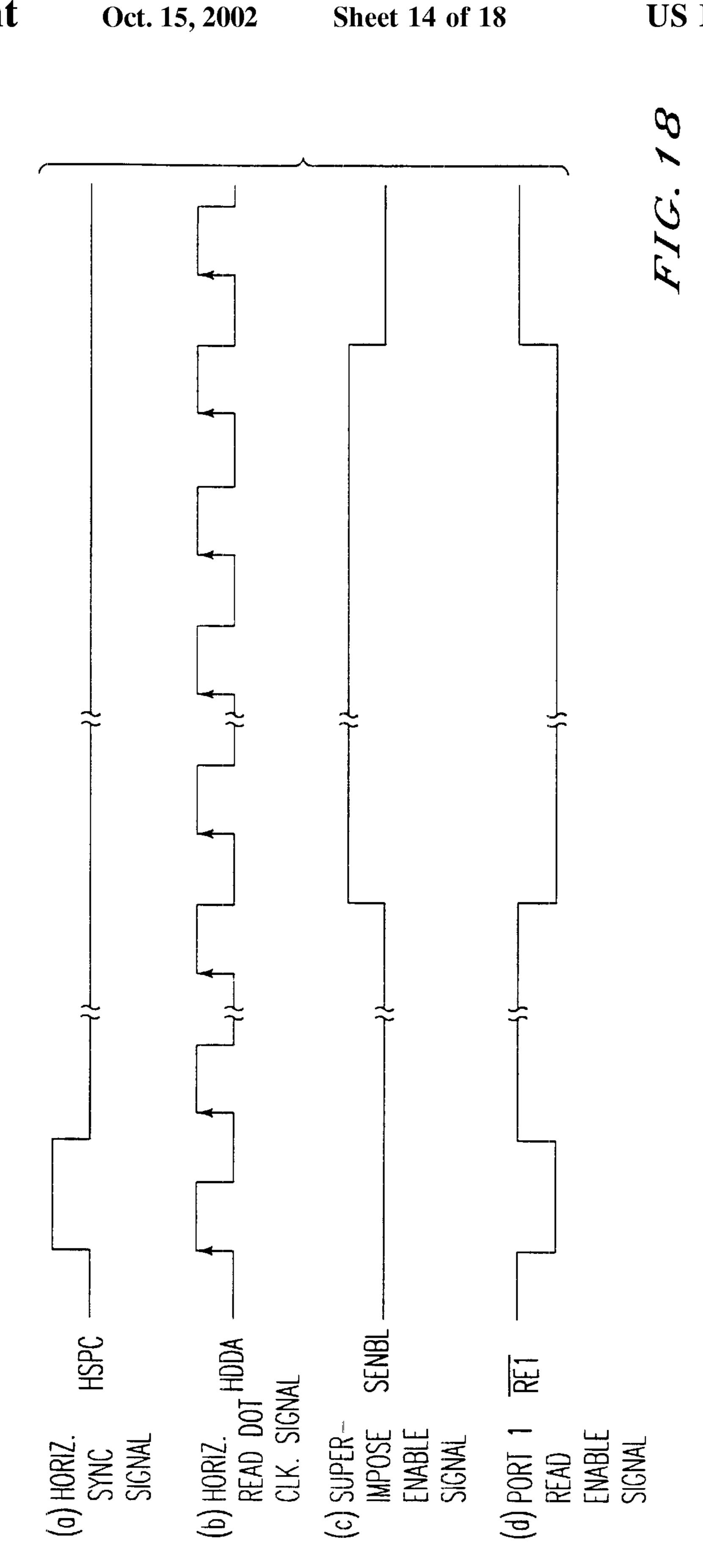

- FIGS. 15, 16, 17 and 18 are timing charts showing the operations of the superimpose control unit shown in FIG. 14 and its peripheral circuits;

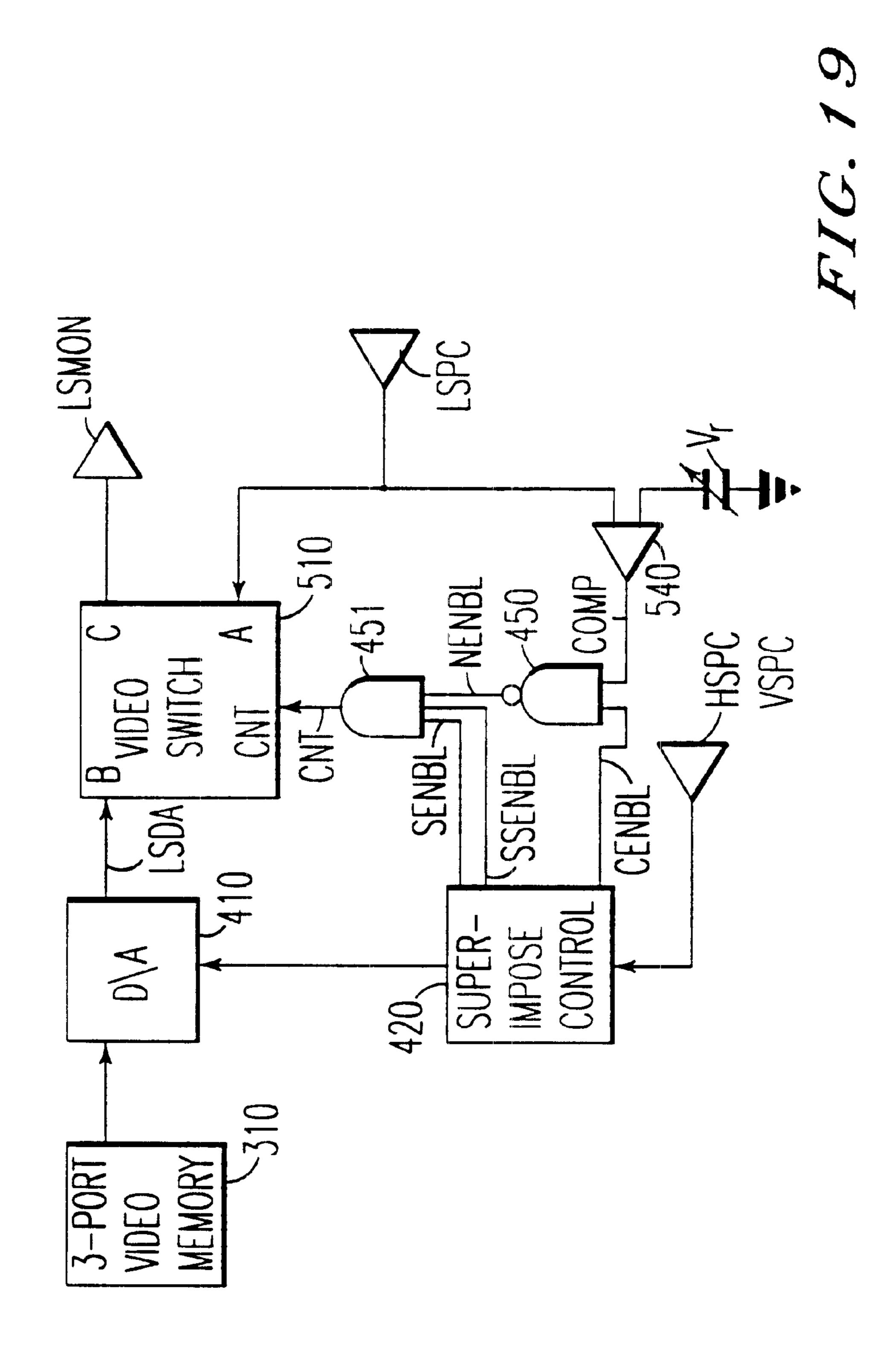

- FIG. 19 is a circuit diagram showing a multiplex superimpose control unit;

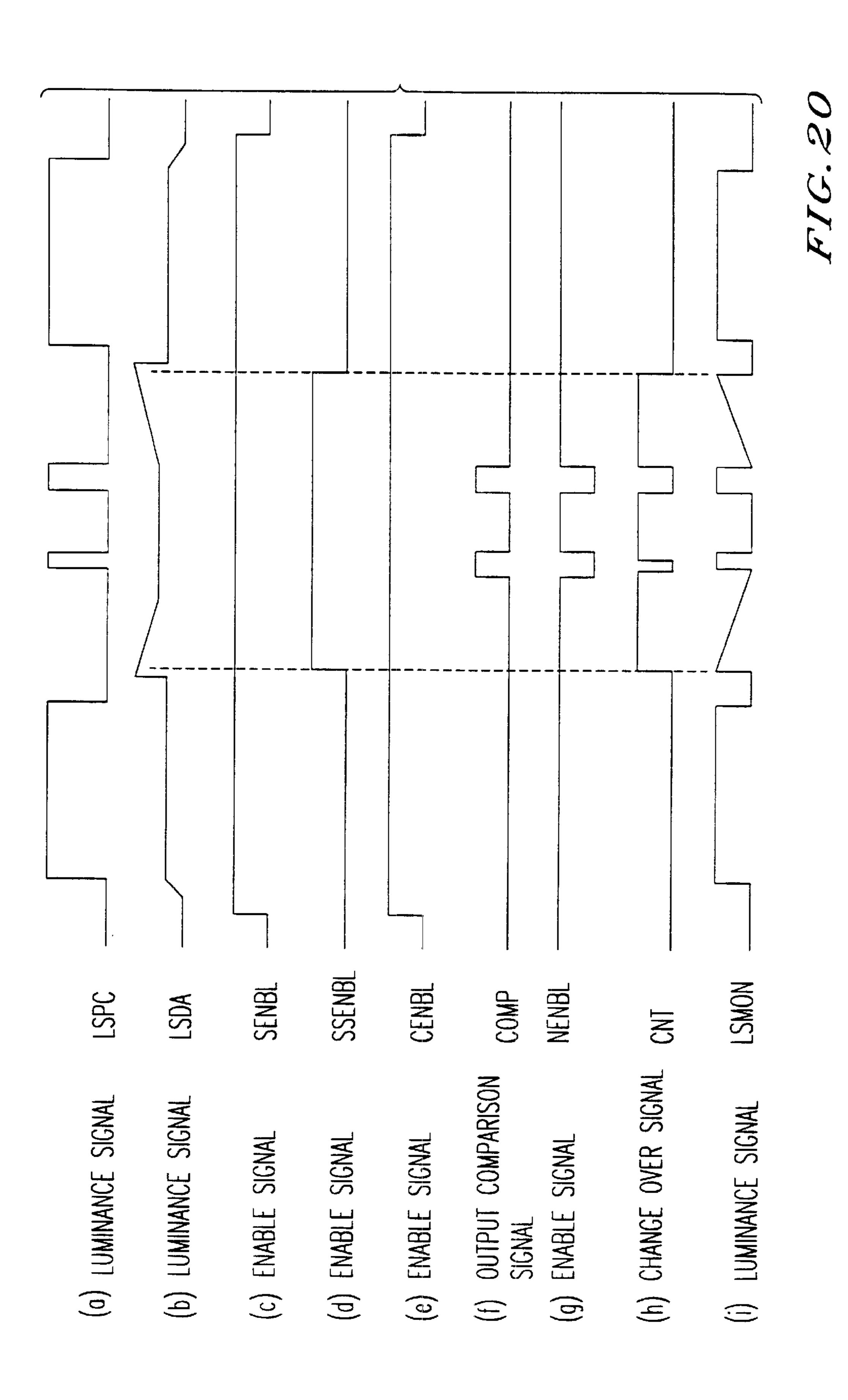

- FIG. 20 is a timing chart showing the operations of the multiplex superimpose control unit shown in FIG. 19;

- FIG. 21 is a block diagram showing the image processing 25 system of the prior art; and

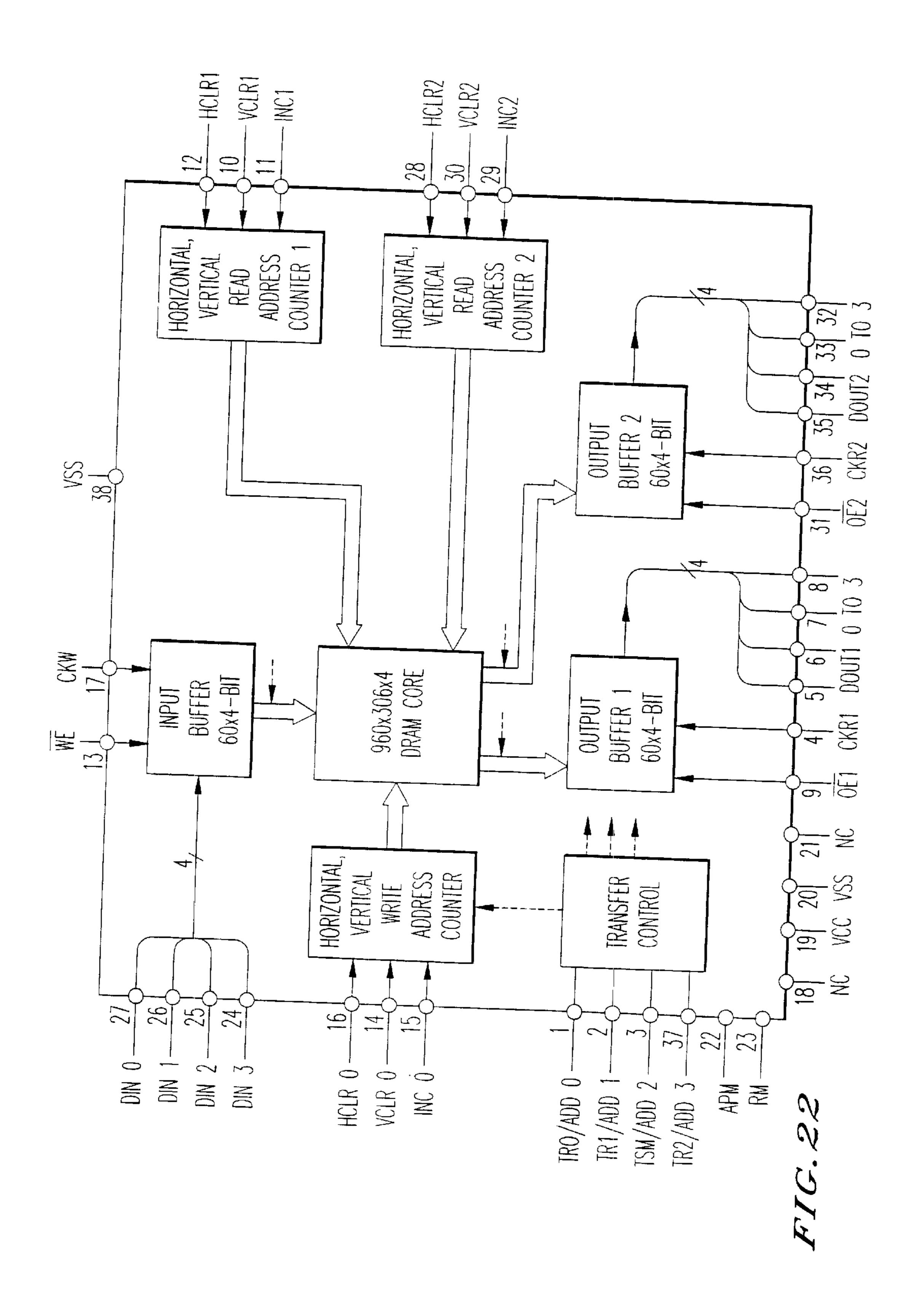

- FIG. 22 shows an internal structure of a three-part video memory.

#### THE BEST MODE FOR CARRYING OUT THE INVENTION

The present invention will be described in detail in the following in connection with one embodiment thereof with reference to the accompanying drawings.

FIG. 1 is a schematic block diagram showing showing an luminance means in accordance with the control of the 35 image processing system according to the embodiment of the present invention. In FIG. 1: reference numeral 100 designates a video decoder for separating either a video signal VSTV coming from a (not-shown) tuner or a video signal VSEX (which will be referred simply as the "video signal VSTV") coming from a (not-shown) external device such as a VTR into a luminance signal LSTV and a synchronizing signal SSTV; numeral 200 designates an ADC control unit for digitizing the luminance signal LSTV; numeral 300 designates three-port video memory control unit for storing the digitized luminance signal LSTV; numeral 400 designates a DAC control unit for reading out a luminance signal LSMEM from the three-port video memory control unit 300 to convert it to analog; numeral 500 designates a video mixing control unit for mixing the luminance signal LSMEM read out from the three-port video memory control unit 300 and analogly converted and a luminance signal LSPC outputted from a personal computer, a work station, a terminal, a game machine or the like (which will be shortly referred altogether to the "personal computer", although not shown) to output a luminance signal LSMON in which an image corresponding to the luminance signal LSTV is superimposed In an image corresponding to the luminance signal LSPC; and numeral 600 designates a CPU control unit for outputting control data through a data bus 610 to the video decoder 100, the ADC control unit 200, the three-port video memory control unit **300**, the DAC control unit **400** and the video mixing control unit **500**.

> These control data outputted from the CPU control unit 65 600 are those for achieving the luminance signal LSMON according to an object and are controlled by the CPU control unit **600**.

Next, FIG. 2 is a perspective view showing the image processing system shown in FIG. 1. In FIG. 2: reference numeral 700 designates a personal computer body; numeral 701 designates a personal computer monitor; numeral 702 designates a keyboard; numeral 703 designates a mouse; 5 numeral 704 designates an extended slot card forming the major portion of the image processing system; numeral 705 designates an inter-body video cable for connecting the personal computer body 700 and the extended slot card 704; numeral 706 designates an inter-monitor video cable for 10 connecting the personal computer monitor 701 and the extended slot car 704; numeral 710 designates a tuner; and numeral 711 designates an antenna.

This image processing system has a structure, in which the extended slot card **704** is interposed between the personal computer body **700** and the personal computer monitor **701**.

The extended slot card 704 is connected with the tuner 710 and inserted into the (not-shown) extended slot of the personal computer body 700, as shown in FIG. 3.

The image corresponding to the luminance signal LSTV outputted from the tuner 710 is displayed together with the image corresponding to the luminance signal LSPC, with an arbitrary size, at an arbitrary timing in an arbitrary position of the image corresponding to the luminance signal LSPC and displayed by the personal computer monitor 701, by the operation of the keyboard 702 or the mouse 703.

Next, FIG. 4 is a detailed block circuit diagram showing the major portion of the image processing circuit shown in FIG. 1. In FIG. 4: reference numeral 101 designates an audio signal terminal for inputting an audio signal ASEX outputted from the VTR or the like; numeral 110 designates an audio signal selector for selectively outputting the audio signal ASEX inputted from the audio signal terminal 101 and an 35 audio signal ASTV inputted from the tuner 710; numeral 120 designates a volume control circuit for controlling the volume of the audio signal ASTV; numeral 102 designates an audio signal terminal for outputting the selected audio signal ASTV as an audio signal ASMON of the personal computer 40 monitor 701; numeral 103 designates a video signal terminal for inputting a video signal VSEX outputted from the VTR or the like; numeral 130 designates a video signal selector for selectively outputting the video signal VSEX inputted from the video signal terminal 103 and a video signal VSTV 45 inputted from the tuner 710; and numeral 140 designates a video signal decoder for separating the selectively outputted video signal VSTV into the luminance signal LSTV and a synchronizing signal SSTV.

Moreover, numeral 210 designates an ADC for digitizing 50 the luminance signal LSTV; and numeral 220 designates a digitize control unit for controlling the ADC 210 and so on on the basis of the synchronizing signal SSTV.

Moreover, numeral 310 designates a three-port video memory having one write port and two read ports; numeral 320 designates a video data selector for selectively outputting either the luminance signal LSTV outputted from the ADC 210 or the luminance signal LSPC outputted from the (not-shown) personal computer; numeral 330 designates a video memory control signal selector for selectively outputing either a video memory control signal WETV outputted from the digitization control unit 220 or a video memory control signal WEPC outputted from a write control unit 340; this write control unit 340 is used for controlling the luminance signal LSPC outputted from the personal computer in the three-port video memory 310; numeral 350 designates a read control unit; numeral 360 designates a

18

first-in/first-out type FIFO memory for storing the luminance signal LSMEM stored by the three-port video memory 310; and numeral 370 designates a FIFO read control unit for controlling the read of the luminance signal LSMEM coming from the three-port video memory 310.

On the other hand, numeral 410 designates a DAC; numeral 420 designates a superimpose control unit for controlling the three-port video memory 310, the DAC 410 and an AND circuit 530 by inputting a synchronizing signal HSPC and a vertical synchronizing signal VSPC outputted from the personal computer; numeral 510 designates a video switch for outputting either of the luminance signal LSPC coming from the personal computer or the luminance signal LSMEM coming from the three-port video memory 310 as the luminance signal LSMON of the personal computer monitor; numeral 520 designates a mixing control unit; numeral 540 designates a voltage comparator for comparing a reference voltage V<sub>r</sub> and the luminance signal LSPC coming from the personal computer; and numeral 620 designates a CPU in the personal computer body.

Next, FIG. 5 is a connection diagram for connecting the tuner 710 and the extended slot card 704. In FIG. 5: numeral 712 designates a tuner control connector for outputting the control signal such as the power source or tuning signal of the tuner 710 to the tuner 710; numeral 713 designates an output connector for outputting the audio signal ASTV outputted from the tuner 710 to the extended slot card 704; and numeral 714 designates an output connector for outputting the video signal VSTV outputted from the tuner 710 to the extended slot card 704.

Here, the audio signal ASTV can be outputted to a headphone 717 or a (not-shown) speaker through a plug 716 connected with an output connector 715.

The tuner 710 outputs the audio signal ASTV and video signal VSTV of specified channels of the signals it receives from the antenna 711 and the antenna terminal, to the audio signal selector 110 and the video signal selector 130, respectively, through the output connectors 713 and 714.

In this case, the tuning is accomplished by controlling the CPU 620.

On the other hand, the audio signal ASEX and the video signal VSEX are outputted from a (not-shown) video device such as a video deck or a laser disc, respectively, to the audio signal selector 110 and the video signal selector 130.

The audio input selector 110 is controlled by the CPU 620 to select and output the audio signal ASTV or ASEX to the volume control circuit 120.

This volume control circuit 120 is controlled by the CPU 620 to amplify the audio signal ASTV outputted from the audio signal selector 110 and to output it as the audio signal ASMON in the personal computer monitor cable to the audio signal terminal 102.

The audio signal ASTV is outputted to the output connector 714.

The video signal selector 130 is controlled by the CPU 620 to select and output the video signal VSTV or VSEX to the video signal decoder 140.

FIG. 6 is a diagram for explaining the operations of the present image processing system. The image displayed is the display frame 301 of the personal computer monitor corresponding to the video signal obtained from the tuner 710 is displayed in a reduced scale to move at a righthand upper portion.

The display area is assigned by mouse cursor 301 using mouse 703. The image obtained from tuner 710 is displayed in the assigned display area.

FIG. 7 shows a memory map in the state, in which the OS or MS-DOS (as known under the trade name) of the personal computer is packaged as the used in-OS device driver (or the front processor) by using the utility software of the present invention.

Thanks to this packaging, the utility software can be run to observe the image from the TV set or the video deck in a preferable position and with a preferable size by a simple keyboard operation no matter what application software is operating on the OS.

The video signal decoder 140 separates the video signal VSTV, which is outputted from the video signal selector 130, into the luminance signal LSTV and the synchronizing signal SSTV and outputs them to the ADC 210 and the digitize control unit 220 respectively, as shown in FIG. 4.

Here the synchronizing signal SSTV is composed of the vertical synchronizing signal VSTV and a horizontal synchronizing signal HSTV.

In response to a clock signal CKAD outputted from the digitize control unit 220, the ADC 210 converts the luminance signal LSTV outputted from the video signal decoder 140 into a digital signal and outputs it through the video data selection unit 320 to the three-port video memory 310.

The digitization control unit 220 outputs not only the 25 clock signal CKAD to the ADC 210 but also the video memory control signal WETV through the video memory control signal selection unit 330 to the three-port video memory 310.

Thus, the three-port video memory **310** stores the updated <sup>30</sup> luminance signal LSTV under the condition controlled by the CPU **620**.

FIG. 8 is a block diagram diagram showing the digitize control unit 220 shown in FIG. 4 and its peripheral circuits.

Here is omitted the video memory control signal selector 330. In the present embodiment, the three-port video memory 310 is exemplified by the product CSK1206 of SONY and the product MB81C1501 of FUJITSU.

Incidentally, the following description will be made by  $_{40}$  using only the read ports of the three-port video memory 310.

The characteristic timing chart is disclosed on pp. 21 to 26 of the Data Sheet 71215-ST of SONY.

The three-port video memory 310 is constructed to have a capacity of 960 columns×306 rows×4 bits.

As a result, one effective horizontal scanning period can be quantized with the numerical value of 960.

On the other hand, the three-port video memory **310** is accessed for the columns at the unit of block and for the rows at the unit of line.

In the three-port video memory 310: reference characters DIN0 to DIN3 designate data inputs for inputting the luminance signal LSTV; characters ADD0 to ADD3 designate address inputs; characters CKW0 designate a port-0 shift signal; characters INC0 designate a port-0 line increment signal; characters HCLR0 designate a port-0 horizontal clear signal; characters VCLR0 designate a port-0 vertical clear signal; and characters WE (i.e., negative logic) designate a port-0 write enable signal.

These signals CKW0, YCLR0, HCLR0, INC0 and WE (i.e., negative logic), ADD0 and DIN0 to DIN3 are dichroic video signals of 4 bits, i.e., 16 gradations.

Here, even color luminance signals of 4 bits or more could 65 naturally be likewise handled by connecting a plurality of three-port video memories 310 in parallel.

20

In FIG. 8: reference numeral 140 designates the video signal decoder for separating the video signal VSTV into the horizontal synchronizing signal HSTV, the vertical synchronizing signal VSTV and the luminance signal LSTV to output them; numeral 221 designates a dot clock generator for outputting a horizontal write dot clock signal HDCK and a basic synchronizing signal BSYNC; numeral 222 designates a horizontal write starting counter for outputting a horizontal write starting signal HWS and an HCLR0 signal; numeral 223 designates a horizontal write number counter for outputting a horizontal write number signal HWT; numeral 224 a vertical write line clock generator for outputting vertical write line clock signal VWLCK; numeral 225 designates a vertical write starting counter for outputting a vertical write starting signal VWS; numeral 226 designates a vertical write number counter for outputting vertical write number signal VWT; numeral 227 designates a vertical write offset counter for outputting a vertical write offset signal YWOFT for designating the vertical write position of the three-port video memory 310 and the port-0 line increment INC0; numeral 228 designates an OR circuit for outputting either the vertical write line clock signal VWLCK or the vertical write offset signal VWOFT as the port-0 line increment INC0; numeral 229 designates an AND circuit for taking the logical product of the inverted outputs of the horizontal write dot clock signal HDCK, the horizontal write starting signal HWS and the horizontal write number signal HWT and the inverted outputs of the vertical write starting signal VWS and the vertical write number signal VWT to output a write enable signal WENBL; and numeral 230 designates a NOR circuit for taking the output of AND 810, the HCLR0 signal, the output signal of the OR circuit 228 and the write enable signal WENBL outputted from the AND circuit 229 to output the port-0 write enable signal WE.

Incidentally for the color display, the luminance signal LSTV is composed of individual R, G and B luminance signals RLSTV, GLSTV and BLSTV.

The video signal decoder 140 separates the video signal VSTV outputted from the video signal selector 130, into the horizontal synchronizing signal HSTV, the vertical synchronizing signal VSTV and the luminance signal LSTV.

The horizontal synchronizing signal HSTV is outputted to the dot clock generator 221, the horizontal write starting counter 222, the horizontal write number counter 223 and the vertical write starting counter 225.