## US00RE37539E

# (19) United States

# (12) Reissued Patent

Oguchi et al.

#### US RE37,539 E (10) Patent Number:

(45) Date of Reissued Patent: Feb. 5, 2002

#### SEALED STACKED ARRANGEMENT OF (54)SEMICONDUCTOR DEVICES

Inventors: Satoshi Oguchi, Kodaira; Masamichi (75)Ishihara, Fukuma-machi; Kazuya Ito, Hamura; Gen Murakami, Tama; Ichiro Anjoh, Koganei; Toshiyuki Sakuta, Tokyo; Yasunori Yamaguchi, Fussa; Yasuhiro Kasama, Kokubunji; Tetsu Udagawa, Iruma; Eiji Momose, Matsumoto; Youichi Matsuno, Kokubunji; **Hiroshi Satoh**, Takasaki; **Atsusi Nozoe**, Hino, all of (JP)

Assignee: **Hitachi, Ltd.**, Tokyo (JP) (73)

Appl. No.: 09/471,000 (21)

Dec. 23, 1999 (22)Filed:

#### Related U.S. Patent Documents

Reissue of:

5,701,031 (64)Patent No.: Dec. 23, 1997 Issued: Appl. No.: 08/280,381 Jul. 25, 1994 Filed:

## U.S. Applications:

(62)Division of application No. 07/691,985, filed on Apr. 26, 1991, now Pat. No. 5,332,922.

#### Foreign Application Priority Data (30)

| Apr.<br>Mar. | 26, 1990<br>31, 1991           | (JP) .<br>(JP) . |                                       |                                                      |

|--------------|--------------------------------|------------------|---------------------------------------|------------------------------------------------------|

| (51)         | <b>Int. Cl.</b> <sup>7</sup> . | •••••            |                                       | H01L 23/28; H01L 23/535;<br>H01L 23/538; H01L 23/065 |

| (52)         | <b>U.S. Cl.</b> .              | ••••••           |                                       | <b>257/686</b> ; 257/724; 257/786; 257/787           |

| (58)         | Field of S                     | Search           | · · · · · · · · · · · · · · · · · · · |                                                      |

#### (56)**References Cited**

## U.S. PATENT DOCUMENTS

9/1987 Merrick et al. ...... 250/551 4,694,183 A (List continued on next page.)

### FOREIGN PATENT DOCUMENTS

| E <b>P</b> | 0198194   | * 10/1986 |         |

|------------|-----------|-----------|---------|

| EΡ         | 0270069   | * 6/1988  |         |

| GB         | 2170657   | * 8/1986  |         |

| P          | 55-143059 | 11/1980   | 257/686 |

| P          | 062350    | 5/1981    |         |

(List continued on next page.)

#### OTHER PUBLICATIONS

Pat. Abstracts of Japan, vol. 012, No. 207, Jun. 14, 1988.\* Pat. Abstracts of Japan, vol. 005, No. 125, Aug. 12, 1981.\* Pat. Abstracts of Japan, vol. 013, No. 058, Feb. 9, 1988.\* Pat. Abstracts of Japan, vol. 006, No. 016, Jan. 29, 1982.\* Pat. Abstracts of Japan, vol. 014, No. 252, May 30, 1990.\*

(List continued on next page.)

Primary Examiner—David E. Graybill (74) Attorney, Agent, or Firm—Antonelli, Terry, Stout & Kraus, LLP

#### (57)**ABSTRACT**

A pair of DRAM chips 1A and 1B are mounted opposedly to each other with wiring means such as lead frames put therebetween, the lead frames being substantially integral with external terminals 3B. Then, these DRAM chips and lead frames are connected together by the conventional wire bonding method. Plural pairs of the thus-connected DRAM chips and lead frames are stacked and corresponding leads of the lead frames are connected in common to form a laminate. The plural DRAM chips thus mounted are activated selectively in accordance with a predetermined chip selection signal. Additionally, partial DRAM chips capable of partially functioning normally are combined together by utilizing the above chip mounting method to constitute a single DRAM package.

## 40 Claims, 45 Drawing Sheets

257/786, 787

# US RE37,539 E

Page 2

#### U.S. PATENT DOCUMENTS 246125 \* 10/1990 208959 \* 11/1990 016162 1/1991 OTHER PUBLICATIONS 4,878,106 A 7/1990 Kishida ...... 357/75 4,941,033 A Pat. Abstracts of Japan, vol. 012, No. 225, Jun. 25, 1988.\* Pat. Abstracts of Japan, vol. 014, No. 244, May 24, 1990. 5,068,712 A \* 11/1991 Murakami et al. ............ 357/72 Pat. Abstracts of Japan, vol. 015, No. 135, Apr. 4, 1991. 8/1992 Masayuki et al. ...... 357/75 5,138,438 A Pat. Abstracts of Japan, vol. 014, No. 457, Oct. 2, 1990. 5,147,815 A \* Pat. Abstracts of Japan, vol. 011, No. 254, Aug. 18, 1987. 5,208,782 A Pat. Abstracts of Japan, vol. 010, No. 251, Aug. 28, 1986. 5,334,875 A Electronics, vol. 39, No. 48, Nov. 25, 1960, pp. 78–80. IBM Technical Disclosure Bulletin, vol. 015, No. 011, Apr. FOREIGN PATENT DOCUMENTS 1973, pp. 3453–3454. JP 137665 10/1981 IBM Technical Disclosure Bulletin, vol. 015, No. 010, Mar. JP 080846 4/1986 1973, pp. 3050–3051. JP 284951 \* 12/1986 IBM Technical Disclosure Bulletin, vol. 021, No. 009, Feb. JP 065447 3/1987 1979, pp. 3582–3583. JP 119952 6/1987 Proceedings of the 19th IEEE Computer Society Interna-JP \* 12/1987 283634 tional Conference, COMPCON, Sep. 4, 1979, Washington, JP 1/1988 004636 D.C., pp. 425–427.\* JP 018654 1/1988 JP 136642 6/1988 IBM Technical Disclosure Bulletin, vol. 032, No. 007, Dec. JP 248154 10/1988 1989, pp. 183–184.\* JP 1/1989 641269 Pat. Abstracts of Japan, vol. 013, No. 298, Jul. 10, 1989.\* JP 077135 3/1989 Pat. Abstracts of Japan, vol. 014, No. 564, Dec. 14, 1990.\* JP \* 7/1989 184860 Pat. Abstracts of Japan, vol. 012, No. 395, Oct. 20, 1988.\* ...... 437/208 JP \* 12/1989 1-303730 Pat. Abstracts of Japan, vol. 013, No. 470, Oct. 24, 1989.\* JP 2/1990 ...... 437/208 2-32547 Pat. Abstracts of Japan, vol. 014, No. 502, Aug. 20, 1990.\* JP 066965 3/1990

Pat. Abstracts of Japan, vol. 011, No. 338, Nov. 5, 1987.\*

cited by examiner

JP

JP

JP

073662

273662

184063

3/1990

3/1990

7/1990

...... 257/724

F/G. 1 VCC2 VCC2 RASB CASB 128M DRAM PACKAGE WEB Din (128mega x 1bit) Dout A 0 A 1 A 2 1 B **EXTERNAL** VCCB VCSB VCSB VASB VED Double VCC2 VCC2 RASB CASB Din TERMINAL 64M DRAM 64M DRAM SUB CHIP B SUB CHIP A  $(64mega \times 1bit)$ (64mega x 1bit) TČD VSS1D VSS2D -□TČ □VSS1 □VSS2 BONDING PAD A 8 D A 9 D A Î 2 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3 | A 1 3

F/G. 3

# STANDARD SPECIFICATION OF 64M DRAM SUB CHIP

| IT                     | EM               | SPECIFIGURATION                                      |                                                |                                                |  |  |  |

|------------------------|------------------|------------------------------------------------------|------------------------------------------------|------------------------------------------------|--|--|--|

| BIT CONFI              | GUCATION         | 64megaword x 1bit                                    | 16megaword x 4bits                             | 8megaword x 8bits                              |  |  |  |

| CHIP                   |                  | X13                                                  | X13                                            | X13                                            |  |  |  |

| ADDRESS                | ROW              | X0~X12                                               | X0~X12                                         | X0~X12                                         |  |  |  |

|                        | COLUMN Y0~Y12 Y0 |                                                      | Y0~Y10                                         | Y0~Y9                                          |  |  |  |

| PAC                    | AGE              | 32PIN                                                | S SOJ 300 x 85                                 | J 300 x 850 mil                                |  |  |  |

| NUMBER OF PINS USED    |                  | 23PINS 26PINS                                        |                                                | 32PINS                                         |  |  |  |

|                        |                  | CLOCK : 3 ADDRESS : 14 I/O : 2 POWER SOURCE: 4       | CLOCK : 4 ADDRESS : 14 I/O : 4 POWER SOURCE: 4 | CLOCK : 4 ADDRESS : 14 I/O : 8 POWER SOURCE: 6 |  |  |  |

| REF                    | RESH             | 8192 CYCLE / 64 ms                                   |                                                |                                                |  |  |  |

| STANDARD PARALLEL TEST |                  | 8-bit PARALLEL PROCESSING (ALL I/O SAME DATA OUTPUT) |                                                |                                                |  |  |  |

| HIGH SPEED COLUMN MODE |                  | FAST PAGE<br>STATIC COLUMN<br>NIBBLE                 | FAST PAGE<br>STATIC COLUMN                     | FAST PAGE<br>STATIC COLUMN                     |  |  |  |

|                        |                  | THE COLUMNDEPTH IN FP AND SC MODES IS 8K bits A      |                                                | 8K bits AT MOST                                |  |  |  |

218 > 2197 DATA WRITE Din AMPLIFIER 64M DRAM SUB CHIP (64mega x 1bit) 221<sub>7</sub> DATA MAIN OUTPUT BUFFER Dout AMPLIFIER IO LINE COMMON 217ع 201 WP 216 207, WE CLOCK WE WEB GENERATOR BUFFER DOC 214 ~ CAS CLOCK CAS DECODER YDG AMPLIFIER CASB GENERATOR BUFFER MEMORY ARRAY <sub>5</sub>210 ,211 8Krow x 8Kcolumn 212~ ADDRESS RAS2 CLOCK RAS1 RAS CLOCK SENSE RASB BUFFER GENERATOR GENERATOR ₹② 飞208 >-209 PRED-ADDRESS **ECODER** BUFFER 206) 202 , WORD DRIVER A0X ADDRESS DECODER 205 > CS XDG 204 A 1 3 203 PRED-**ADDRESS ECODER** BUFFER 2231 F1 F2 F3 TC CSA TCD MODE SETTER 222 VCC1 VOLTAGE DROPPING VCL VCC2 VSS1 SECTION VSS2

F/G. 5

# BASIC LAYOUT OF 64M DRAM SUB CHIP

F/G. 6

CONCEPTUAL DIAGRAM OF 64M DRAM SUB CHIP SELECTION

F/G. 7

VARIATIONS OF 128M DRAM PACKAGE

|                       | SAM DRAM SUB CHIE    |              | 128M DRAM PACKAGE     |                      |                          | REMARKS    |  |

|-----------------------|----------------------|--------------|-----------------------|----------------------|--------------------------|------------|--|

| WORD<br>CONFIGURATION | BIT<br>CONFIGURATION | ACCESS       | WORD<br>CONFIGURATION | BIT<br>CONFIGURATION | CORRESPONDING<br>DIAGRAM | INEMININO. |  |

| 64mega                | x 1                  | SELECTIVE    | 128mega               | x 1                  | FIG. 1                   |            |  |

| 64mega                | x 1                  | SIMULTANEOUS | 64mega                | x 2                  | FIG. 8                   |            |  |

| 16mega                | x 4                  | SELECTIVE    | 32mega                | x 4                  | FIG. 9                   |            |  |

| 16mega                | x 4                  | SIMULTANEOUS | 16mega                | x 8                  | FIG. 10                  |            |  |

| 8mega                 | x 8                  | SELECTIVE    | 16mega                | x 8                  | FIG. 11                  |            |  |

| 8mega                 | x 8                  | SIMULTANEOUS | 8mega                 | x 16                 | FIG. 12                  |            |  |

F/G. 8

F/G. 9

F/G. 10

F/G. 11

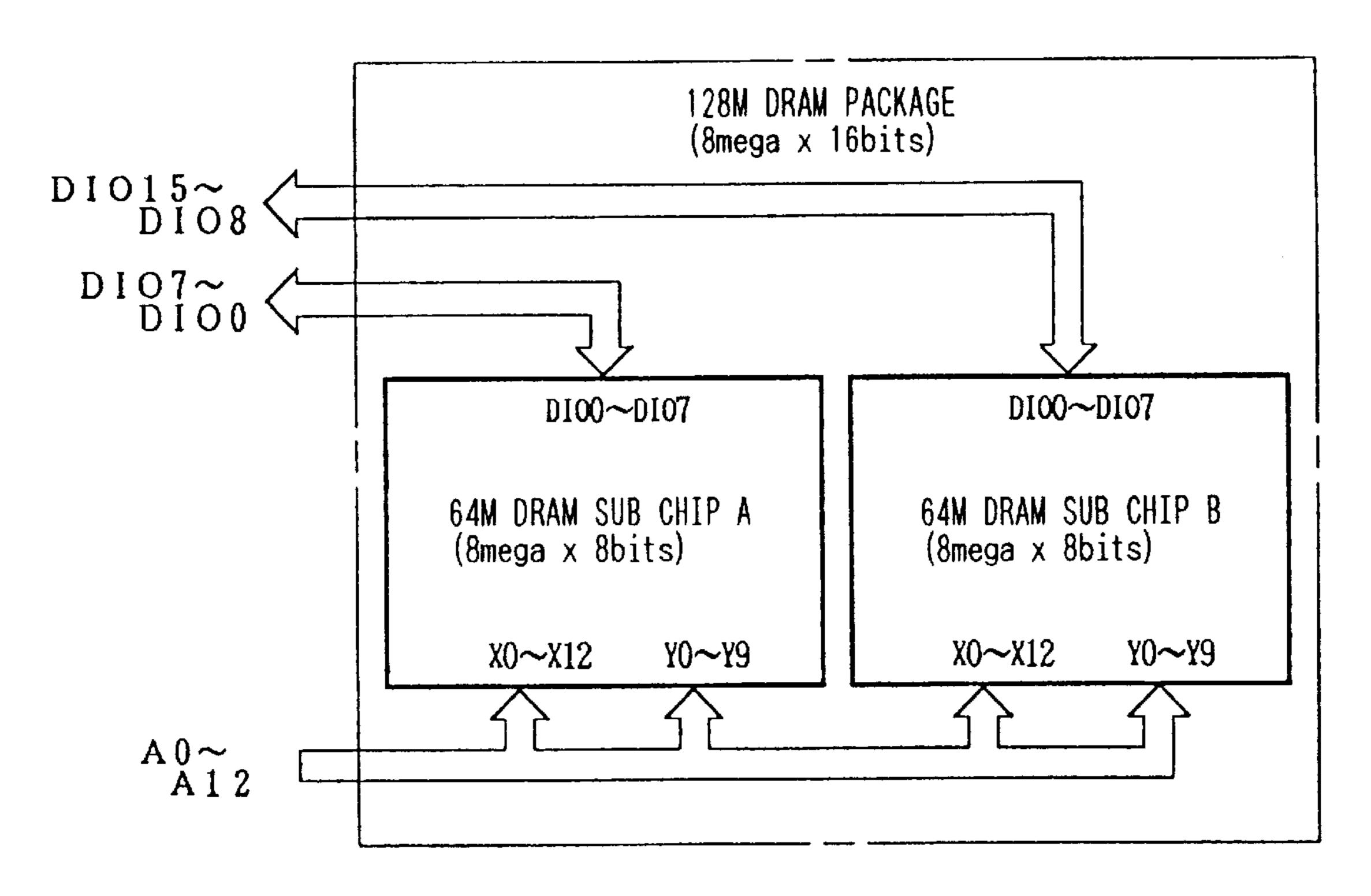

FIG. 12

F/G. 13

F/G. 14

FIG. 15

F/G. 16

# F/G. 17

US RE37,539 E

F/G. 18

FIG. 19

FIG. 20

PROCESS 2: WIRE BONDING

F/G. 21

PROCESS 3: LEAD CUTTING AND BONDING

FIG. 22

PROCESS 4: SEALING (LEAD CUT AND BONDED PORTIONS ARE LOCATED WITHIN RESIN.)

F/G. 23

PROCESS 5: LEAD FORMING

F/G. 24

F/G. 29

F/G. 32 BONDING OPTIONS OF 64M DRAM SUB CHIPS

| F1  | F2  | F3  | TC  | BIT CONFIGURATION | CHIP SELECT     | I/O TERMINAL |

|-----|-----|-----|-----|-------------------|-----------------|--------------|

| VCC | VCC |     | NC  | x 1               | NORMAL SELECT   | Din/Dout     |

| VCC | NC  |     | NC  | x 4               | NORMAL SELECT   | DIOO~DIO3    |

| NC  | NC  |     | NC  | x 8               | NORMAL SELECT   | DIOO~DIO7    |

|     |     | NC  | VCC |                   | SELECT AT X13=H |              |

|     |     | VCC | VCC |                   | SELECT AT X1L L |              |

NC: NO SELECT --: DON'T CARE

∠1 B (SUB CHIP B) -1 A (SUB CHIP A) DIOO D100 DIOO DIOO DIO1 DIO1 DIO1 DIOI DI02 DI02 DI02 DI02 DI03 DI03 D<u>IO</u>3 D103 VSS~ VCC ~VSS VCC BONDING PAD -(CORRESPONDING BONDING PAD TO FIG. 9) \_1B (SUB CHIP B) A (SUB CHIP A) DIOU DIOU DIO2 DI00 D100 DI00 **DI04** DIO4 DIO1 DIO1 DIO1 D102 DI05 DI05 DI02 DI02 DI03 DI06 D106 DI03 DI03 DIO3 **DI07** DI07 百四段 -VCC ACC~ -VSSVSS~ BONDING PAD — -BONDING PAD (CORRESPONDING TO FIG. 10)

F/G. 39

F/G. 40 64M DRAM PACKAGE (32mega x 2bits) Din Dout Dout Din Din Dout 32M DRAM SUB CHIP A 32M DRAM SUB CHIP B (32mega x 1bit) (32mega x 1bit) CS X0~X11 CS X0~X11 Y0~Y12 Y0~Y12 X12B J X12 A 0 ~ A 1 2

F/G. 42

F/G. 45

F/G. 46

F/G. 48 X ADDRESS BUFFER 205 > RAS0 -SEL2 EAN. TG2 NA5 -BX12 NA4 TG3 NA6 -BX12B MODE SETTER 223 AG -CSA →TCD PAD PTA PXD

F/G. 49

F/G. 50

F/G. 51

F/G. 52

F/G. 53

Feb. 5, 2002

### BONDING OPTIONS OF 64M DRAM PARTIAL CHIPS

| F3    | TC  | PTA | PTX | PTY | BX12  | BY12  | CHIP SELECT     | IO OPERATION     |

|-------|-----|-----|-----|-----|-------|-------|-----------------|------------------|

|       | NC  |     | NC  | NC  | X12   | Y12   | NORMAL SELECT   | NORMAL EXECUTE   |

| NC    | VCC |     | NC  | NC  | X12   | Y12   | SELECT AT X13=H | NORMAL EXECUTE   |

| VCC   | VCC |     | NC  | NC  | X12   | Y12   | SELECT AT X13=L | NORMAL EXECUTE   |

| NC    | VCC | NC  | VCC | NC  | H FIX | Y12   | SELECT AT X12=H | NORMAL EXECUTE   |

| NC    | VCC | VCC | VCC | NC  | L FIX | Y12   | SELECT AT X12=H | NORMAL EXECUTE   |

| VCC   | VCC | NC  | VCC | NC  | H FIX | Y12   | SELECT AT X12=L | NORMAL EXECUTE   |

| VCC   | VCC | VCC | VCC | NC  | L FIX | Y12   | SELECT AT X12=L | NORMAL EXECUTE   |

| NC    | NC  | NC  | NC  | VCC | X12   | H FIX | NORMAL SELECTH  | EXECUTE AT Y12=H |

| NC    | NC  | VCC | NC  | VCC | X12   | L FIX | NORMAL SELECT   | EXECUTE AT Y12=H |

| VCC   | NC  | NC  | NC  | VCC | X12   | H FIX | NORMAL SELECT   | EXECUTE AT Y12=L |

| VCC · | NC  | VCC | NC  | VCC | X12   | L FIX | NORMAL SELECT   | EXECUTE AT Y12=L |

# F/G. 54

### VARIATIONS OF 64M DRAM PACKAGE

|                         | 64M DRAM P             | ARTIAL CHIP       |              | 6                       | 4M DRAN PACK           | REMARKS                    |                         |  |

|-------------------------|------------------------|-------------------|--------------|-------------------------|------------------------|----------------------------|-------------------------|--|

| WORD CON-<br>FIGURATION | BIT CON-<br>FIGURATION | NORMAL<br>PORTION | ACCESS       | WORD CON-<br>FIGURATION | BIT CON-<br>FIGURATION | CORRESPOND-<br>ING DIAGRAM | NEMANNO                 |  |

| 32mega                  | x 1                    | ROW 1/2           | SELECTIVE    | 64mega                  | x 1                    | FIG. 47                    |                         |  |

| 32mega                  | x 1                    | COLUMN 1/2        | SIMULTANEOUS | 64mega                  | χ 1                    | FIG. 50                    | IO SELECTIVE EXECUTE    |  |

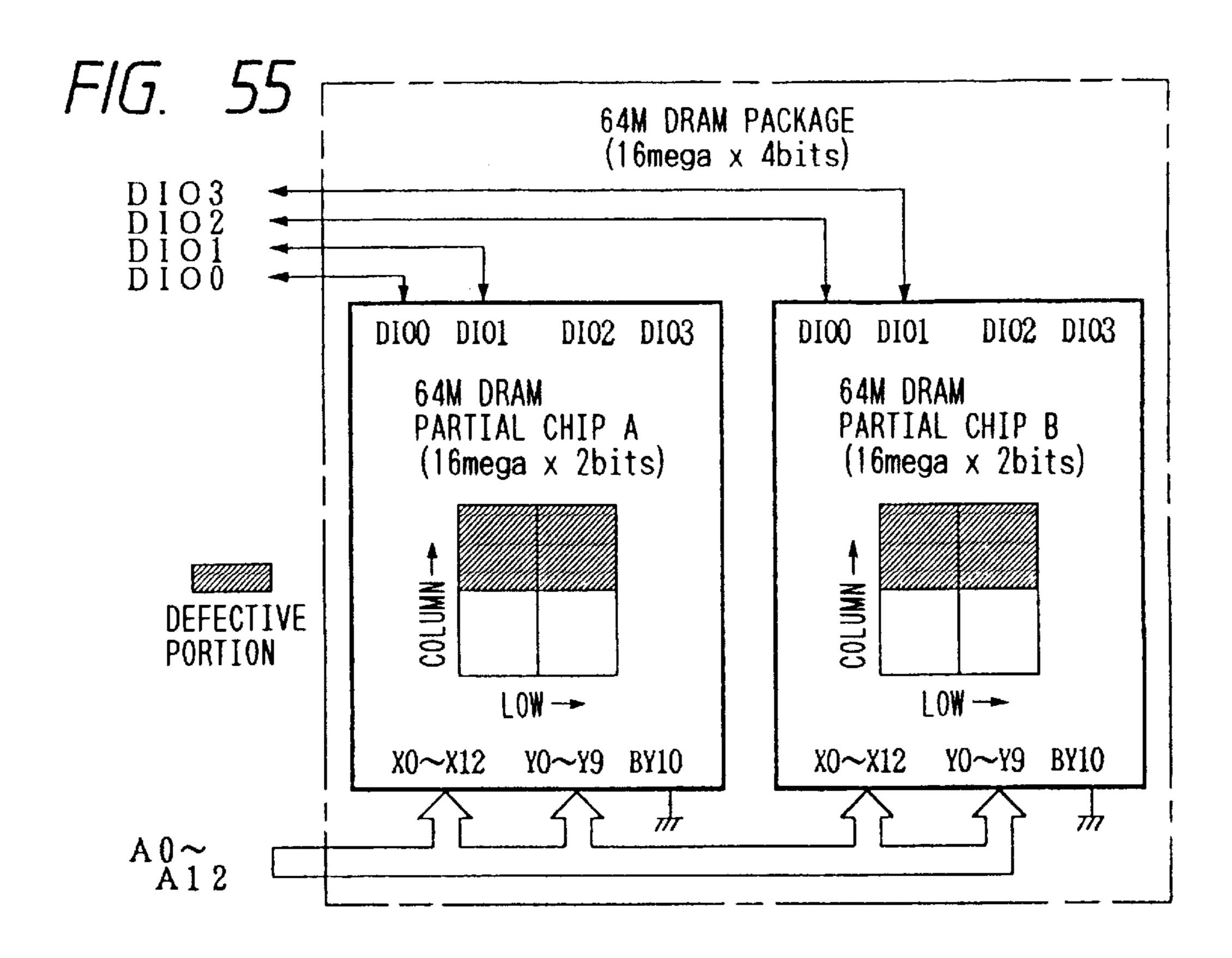

| 16mega                  | x 2                    | COLUMN 1/2        | SIMULTANEOUS | 16mega                  | x 4                    | FIG. 55                    | IO SIMULTANEOUS EXECUTE |  |

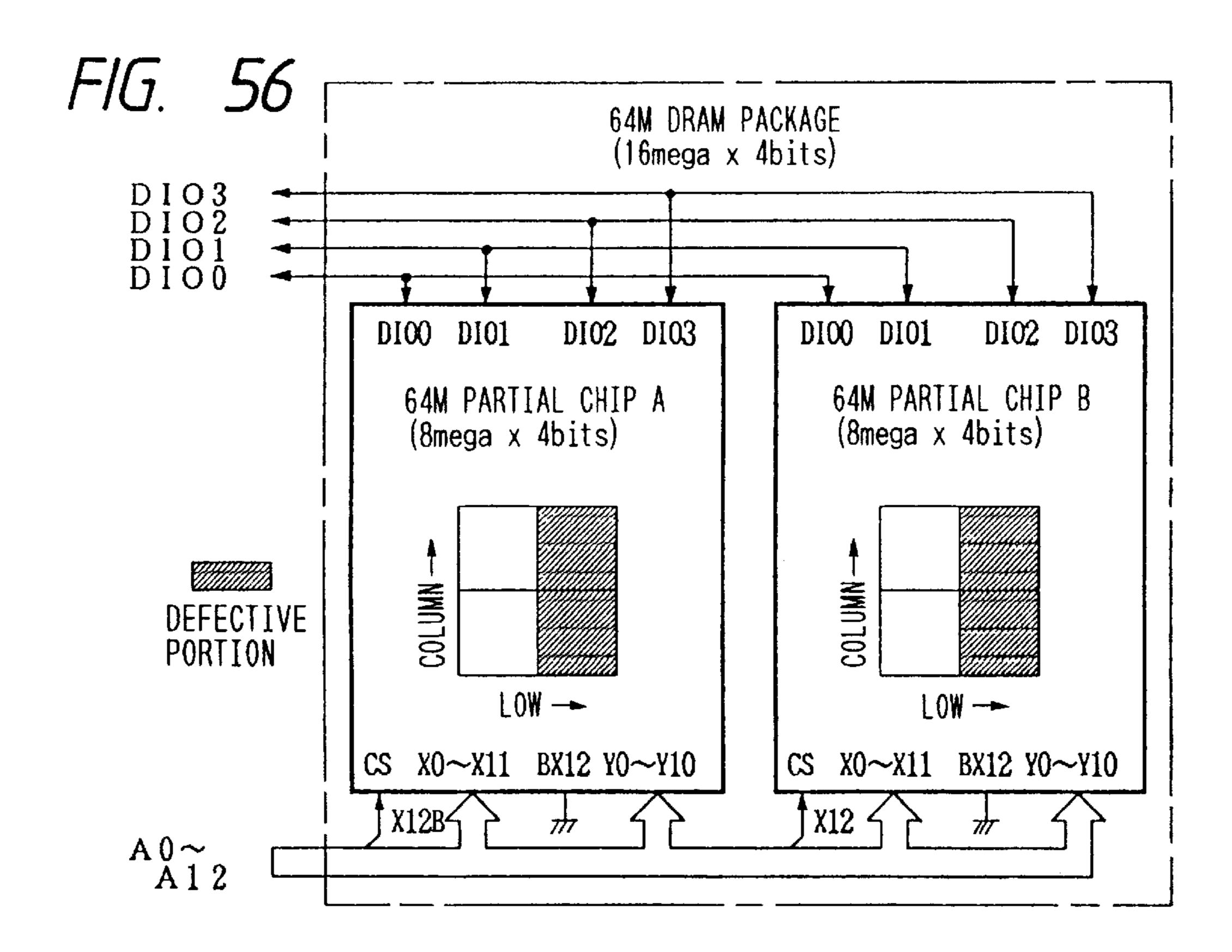

| 8mega                   | x 4                    | ROW 1/2           | SELECTIVE    | 16mega                  | χ 4                    | FIG. 56                    |                         |  |

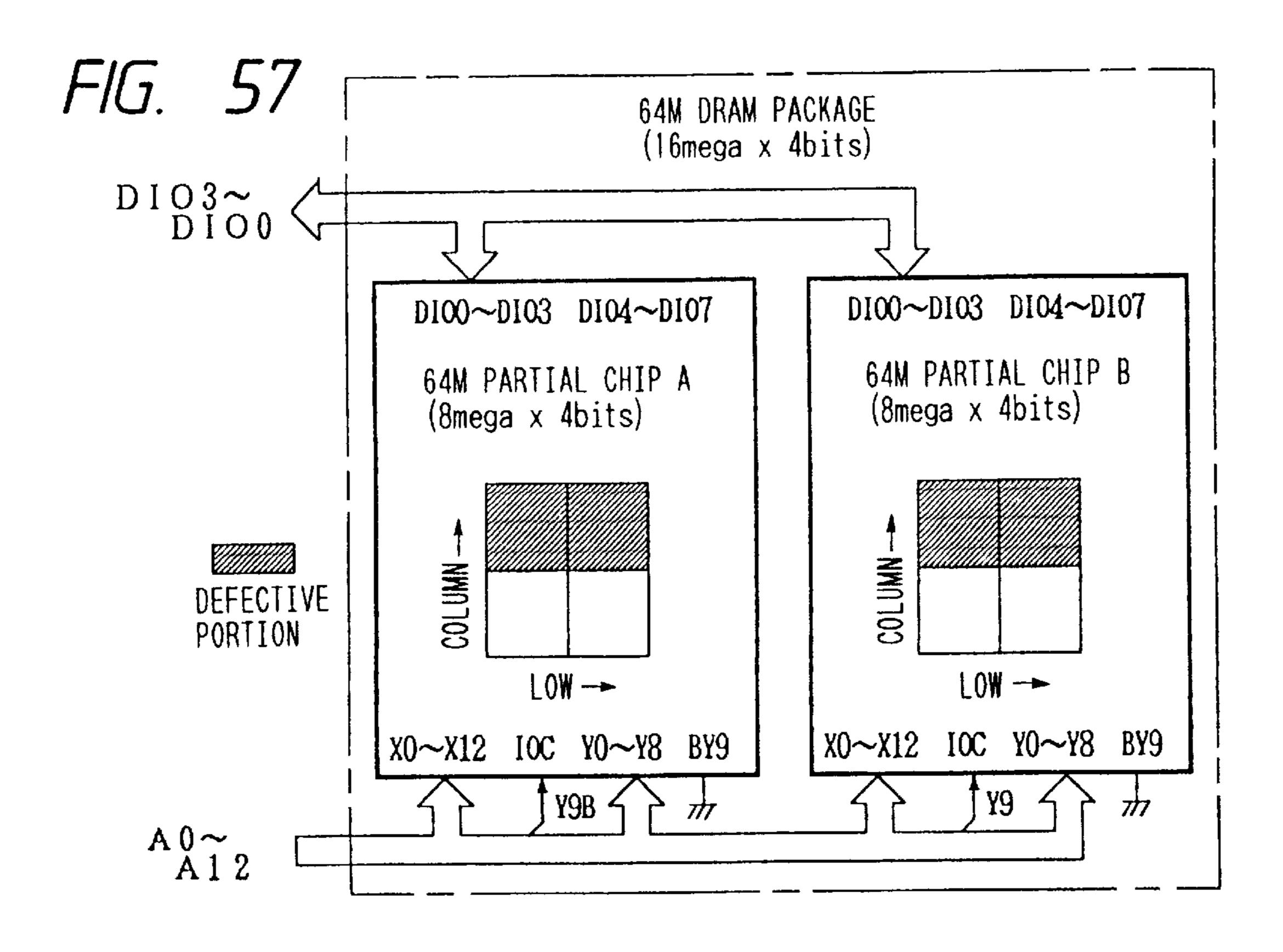

| 8mega                   | x 4                    | COLUMN 1/2        | SIMULTANEOUS | 16mega                  | x 4                    | FIG. 57                    | IO SELECTIVE EXECUTE    |  |

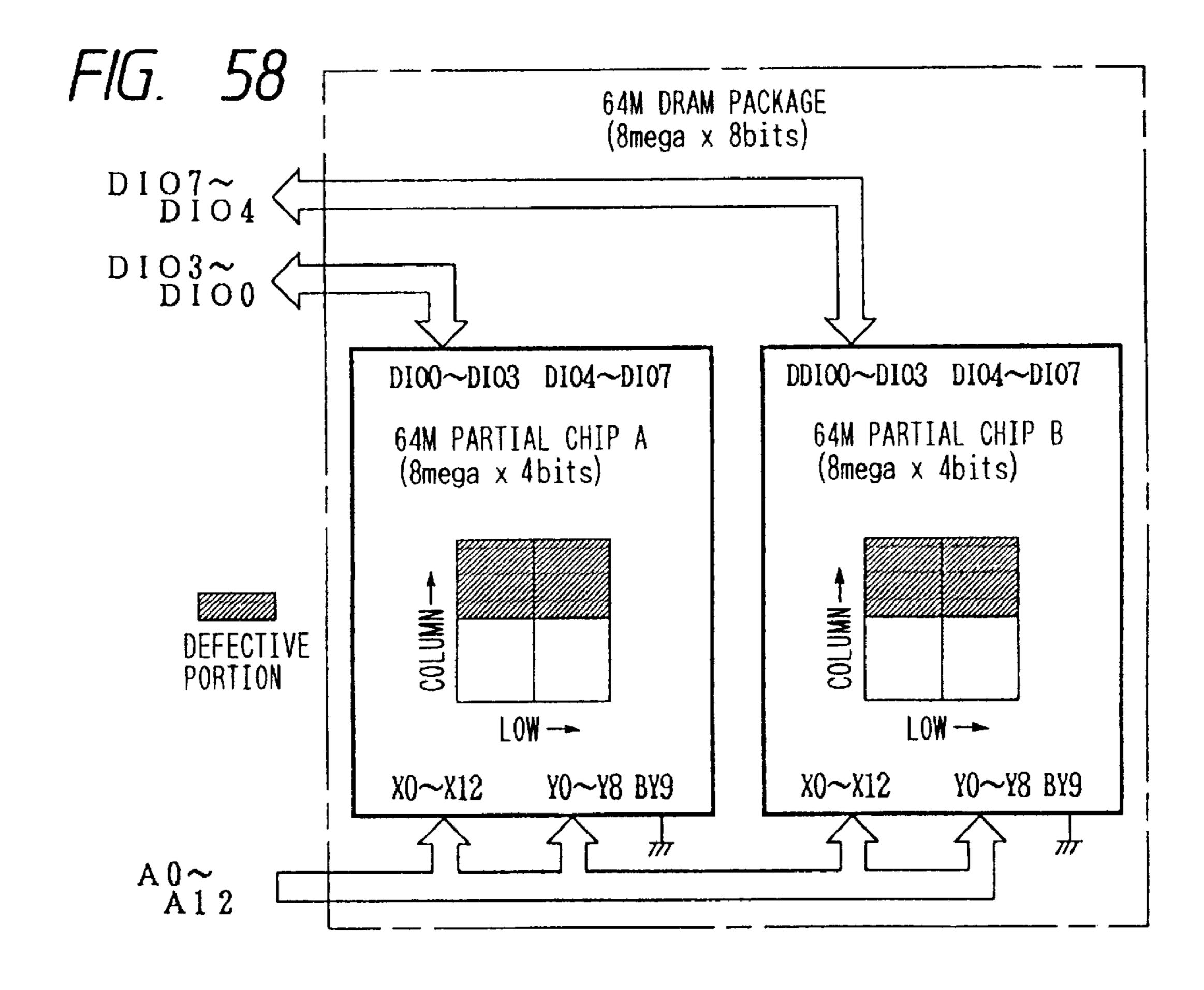

| 8mega                   | x 4                    | COLUMN 1/2        | SIMULTANEOUS | 8mega                   | x 8                    | FIG. 58                    | IO SIMULTANEOUS EXECUTE |  |

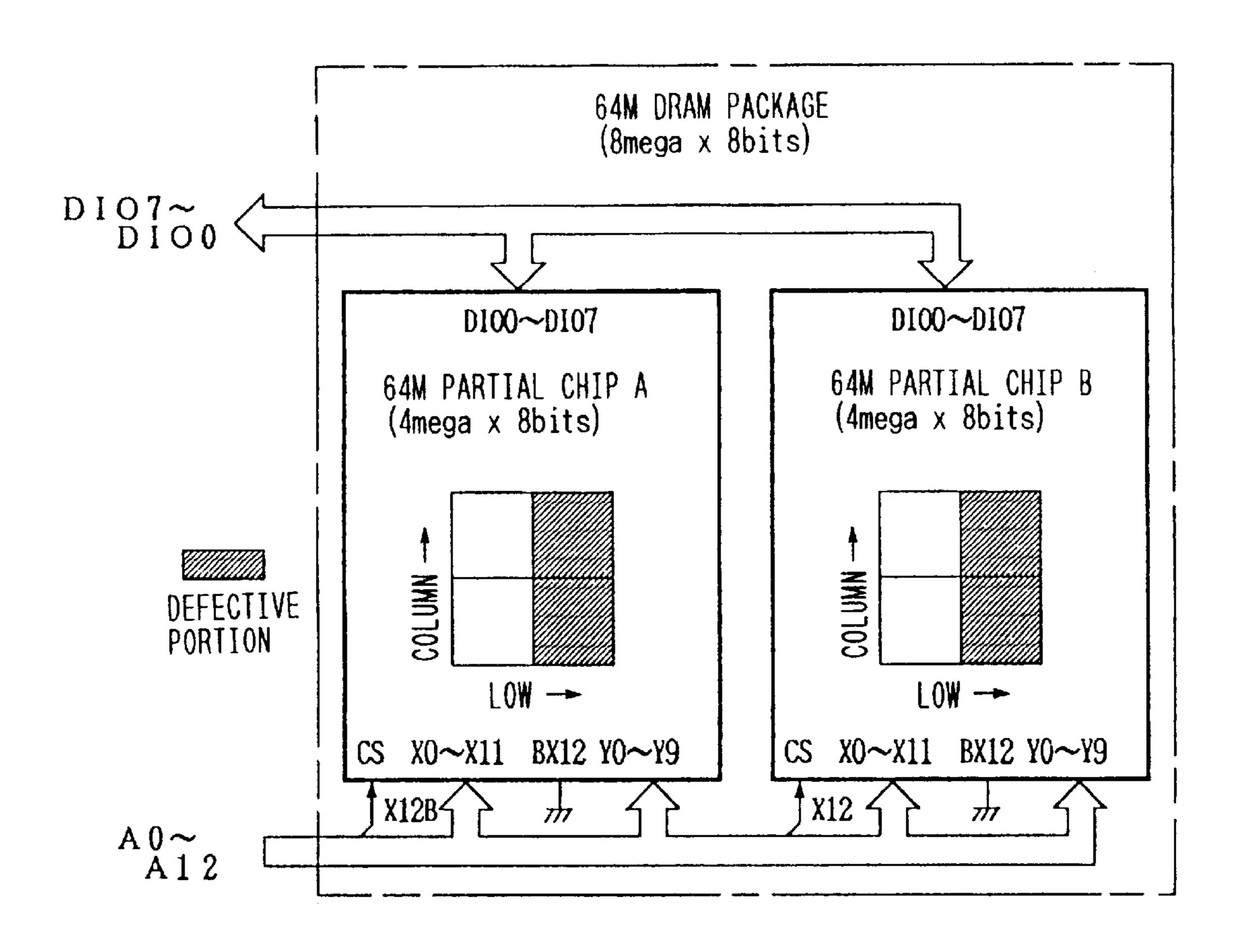

| 4mega                   | x 8                    | ROW 1/2           | SELECTIVE    | 8mega                   | x 8                    | FIG. 59                    |                         |  |

F/G. 59

Feb. 5, 2002

FIG. 60

NUMBER OF CONFORMING PRODUCTS (IN 64mega)

CONVENTIONAL METHOD:

45pcs

DOUBULE CHIP PACKAGE METHOD: 75pcs

F/G. 61

FIG. 62

# F/G. 63

## MICROCOMPUTER PACKAGE (SINGLE CHIP)

FIG. 64

MICROCOMPUTER PACKAGE (DOUBLE CHIP)

Feb. 5, 2002

## SEALED STACKED ARRANGEMENT OF SEMICONDUCTOR DEVICES

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

This is a divisional of application Ser. No. 07/691,985, filed Apr. 26, 1991, U.S. Pat. No. 5,332,922.

#### BACKGROUND OF THE INVENTION

The present invention relates to a semiconductor device and a method for manufacturing the same. For example, the present invention is concerned with a DRAM package (a semiconductor device with one or plural DRAM chips mounted thereon will hereinafter be referred to herein as 15 "DRAM package") comprising plural DRAM (Dynamic Random Access Memory) chips (a semiconductor chip capable of functioning as DRAM will hereinafter be referred to herein as "DRAM chip"), as well as a technique which is particularly useful in producing such DRAM package.

A DRAM chip having as a basic configuration a memory array comprising lattice-like arranged dynamic memory cells as well as a DRAM package having such DRAM chip as a basic configuration are known. In the conventional DRAM package, usually, one DRAM chip is mounted thereon and bonding pads used therein are connected to corresponding leads of a lead frame integral with external terminals.

As to the DRAM package carrying a single DRAM chip thereon, it is described, for example, in U.S. Ser. No. 496,280 filed Mar. 20, 1990.

Recent success towards higher integration density and larger memory capacity of a DRAM chip has been remarkable and correspondingly the chip area has been increasing. At the same time, the DRAM package which carries a DRAM chip thereon also tends to become larger in size. As a result, there has developed a problem that the packaging efficiency of a memory system or the like comprising a DRAM package has not greatly improved.

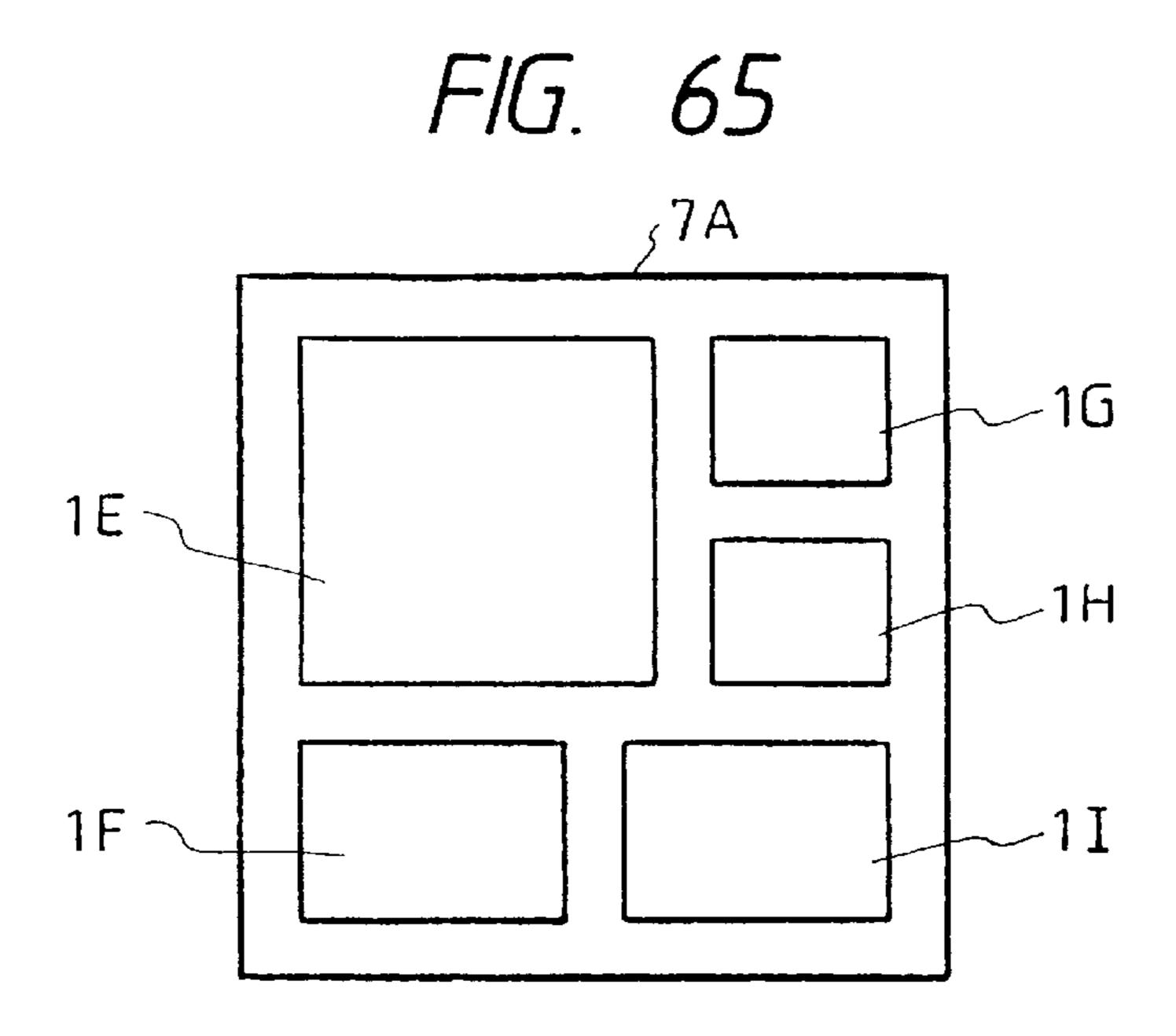

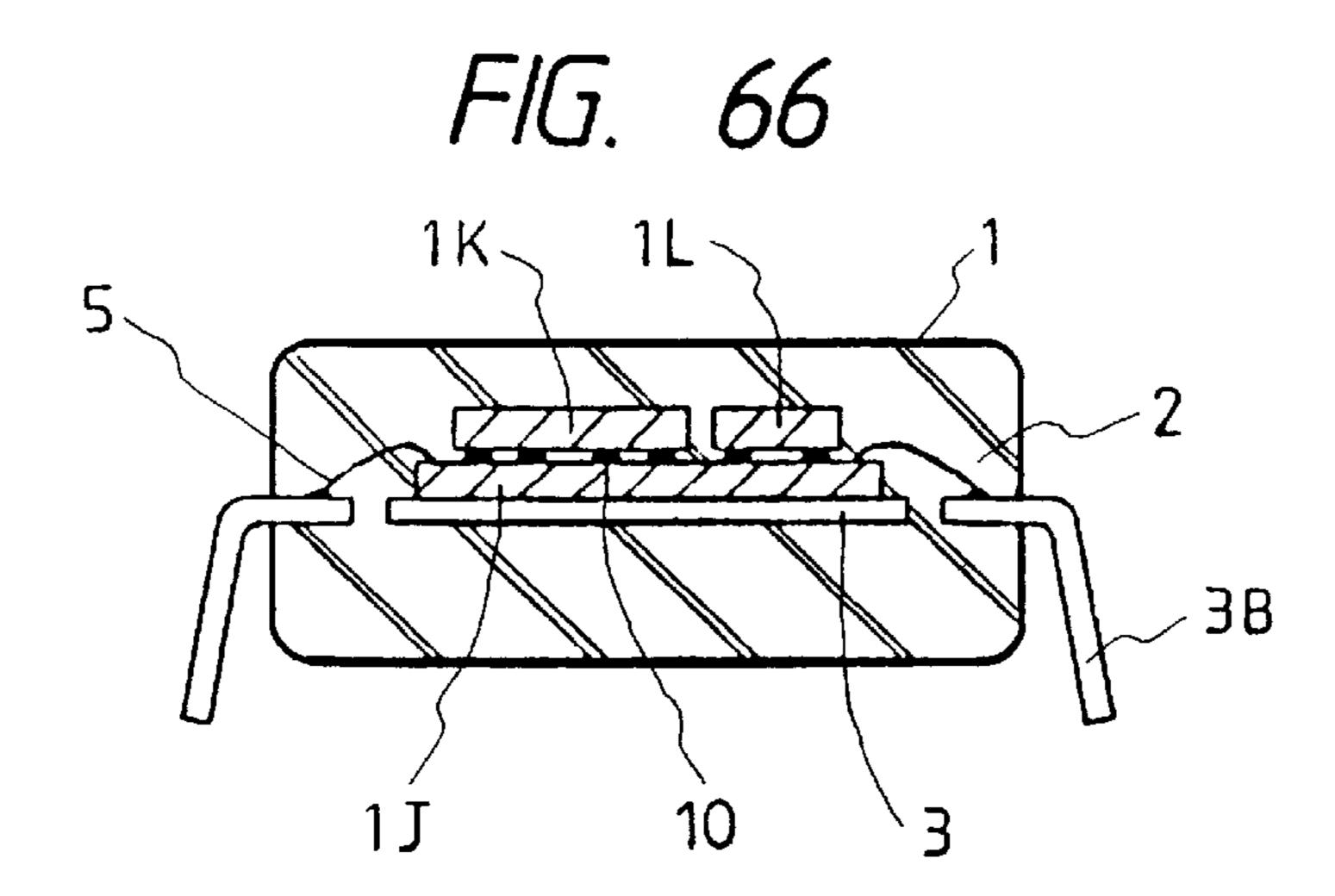

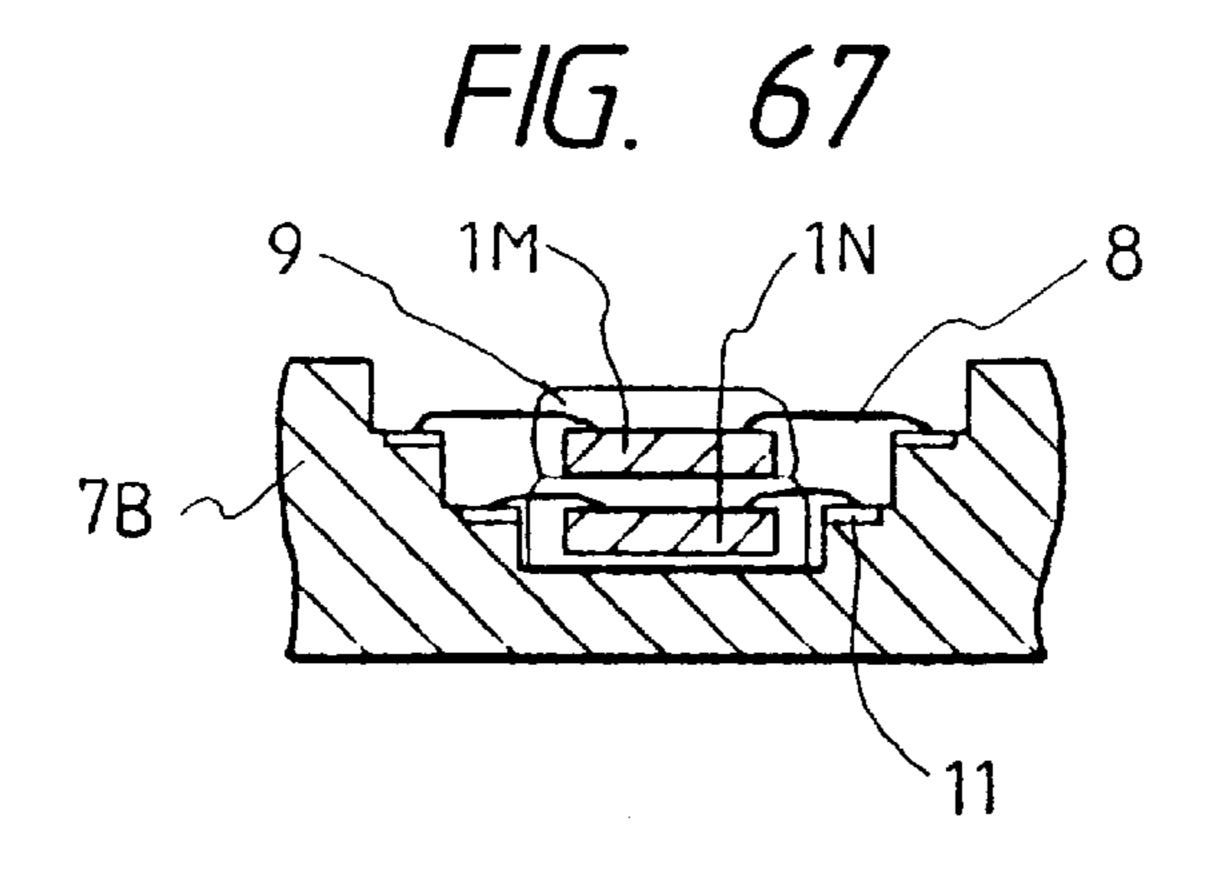

To cope with the above problem, as shown in FIGS. 65 to 67, there have been proposed several methods for mounting 40 on a single package a plurality of sub chips (in the case where one package is composed of plural semiconductor chips, those plural constituent semiconductor chips will each be referred to herein as a "sub chip"). More particularly, in FIG. 65, a plurality of sub chips 1E to 1I are mounted on the surface of a circuit board 7A. In FIG. 66, first a relatively large sub chip 1J is mounted on a lead frame 3, then two relatively small sub chips 1K and 1L are mounted as adjacently disposed sub chips on the sub chip 1J. Corresponding pads of the sub chips 1J and 1K, 1L are connected together through a solder bump 10. Further, bonding pads of the sub chip 1J are connected to corresponding external terminals, i.e., outer leads 3B, through bonding wires 5. On the other hand, in FIG. 67, first a sub chip 1N is die-bonded onto a circuit board 7B, and pads provided on the sub chip 55 1N are bonded to corresponding metallized portions 11 of the circuit board 7B through bonding wires 8. Then, the sub chip 1N is coated with a molding resin 9, and after the surface of the coating is flattened, a sub chip 1M is laminated onto the thus-flattened surface of the coating.

The chip mounting methods illustrated in FIGS. **66** and **67** are described in Japanese Patent Laid Open Nos. 284951/86 and 283634/87, respectively.

#### SUMMARY OF THE INVENTION

However, with progress of higher integration density and larger capacity of semiconductor chips, the present inventors

2

found out that the following problems were involved in the foregoing chip mounting methods. In FIG. 65, since plural sub chips 1E–1I are mounted on the same plane, the area of the circuit board 7A increases with an increase in the number of semiconductor chips mounted thereon, and hence the package size also becomes larger. In FIG. 66, the lower sub chip 1J must be larger than the upper sub chips 1K and 1L by an amount corresponding to the pad portion required for drawing out the bonding wires 5. Therefore, it is impossible 10 to constitute a package using the same size of sub chips formed in the same manufacturing process, like a DRAM chip for example. In FIG. 67, the heat radiation of the lower sub chip 1N is obstructed, and restriction is placed on the reduction of the package size because it is necessary to use the circuit board 7B. In all of these methods, moreover, the manufacturing process is complicated and the product yield is deteriorated in comparison with, for example, the conventional packaging method involving direct wire bonding to a lead frame.

It is the first object of the present invention to provide an effective chip mounting method capable of mounting plural sub chips of the same size without sacrificing the heat radiation characteristic of a package and the product yield.

It is the second object of the present invention to attain a large memory capacity and low power consumption of a DRAM package and simplify the manufacturing process for the same package while suppressing the increase in size of the package.

It is the third object of the present invention to realize a DRAM package having a memory capacity plural times that of a package of about the same size and comprising a single DRAM chip and thereby expand the limit of memory capacity of DRAM chips, etc.

It is the fourth object of the present invention to enhance the packaging efficiency of a memory system or the like having a DRAM package as a basic configuration and reduce the cost thereof.

It is the fifth object of the present invention to provide concrete means for an effective address system and a manufacturing process both suitable for the new chip mounting method and provide several application examples of this chip mounting method.

It is the sixth object of the present invention to provide an effective manufacturing method suitable for the new chip mounting method.

Of numerous improved aspects disclosed herein, a typical one will now be described briefly. A pair of DRAM chips are mounted oppositely to face each other and are provided on both sides of wiring means such as a lead frame which is substantially integrally formed with external terminals, and these DRAM chips and lead frame are connected together by a conventional wire bonding method for example. Plural pairs of such DRAM chips and lead frames thus connected are stacked and corresponding leads of the lead frames are connected in common to provide a laminate. Further, plural DRAM chips thus mounted are activated selectively in accordance with a predetermined chip select signal. Additionally, partial DRAM chips capable of normally functioning partially are combined, utilizing this chip mounting method, to constitute a single DRAM package.

According to the above means it is possible to provide an effective chip mounting method capable of mounting plural sub chips of the same size without sacrificing the heat radiation characteristic of the package and the product yield. Besides, it is possible to attain large memory capacity and low power consumption of the DRAM package and simplify

the manufacturing process for the package. Moreover, it is possible to realize a DRAM package having a memory capacity plural times that of a package comprising a single DRAM chip and thereby expand the limit of memory capacity of DRAM chips; at the same time it is possible to 5 enhance the packaging efficiency of a memory system having a DRAM package as a basic configuration and reduce the cost thereof. Further, it is possible to utilize partial DRAM chips without waste and enhance a substantial product yield of DRAM chips, etc.

#### BRIEF DESCRIPTION OF THE DRAWINGS

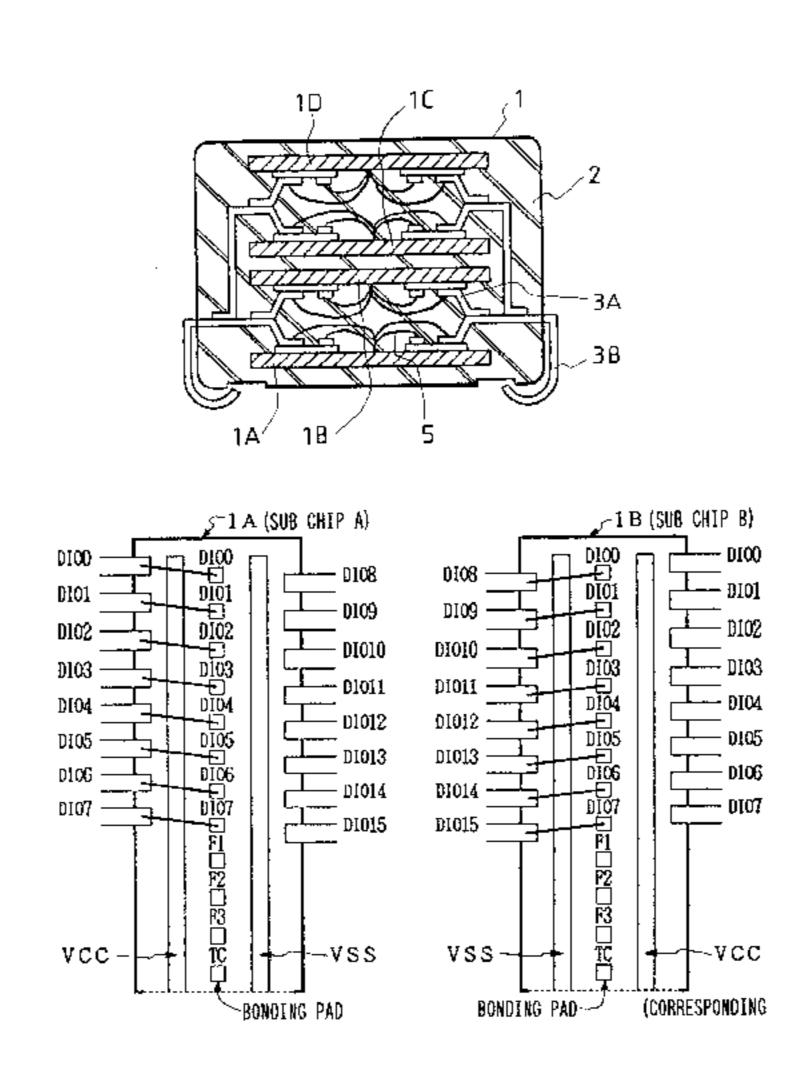

- FIG. 1 is a block diagram showing a first example of a 128M DRAM package according to the present invention;

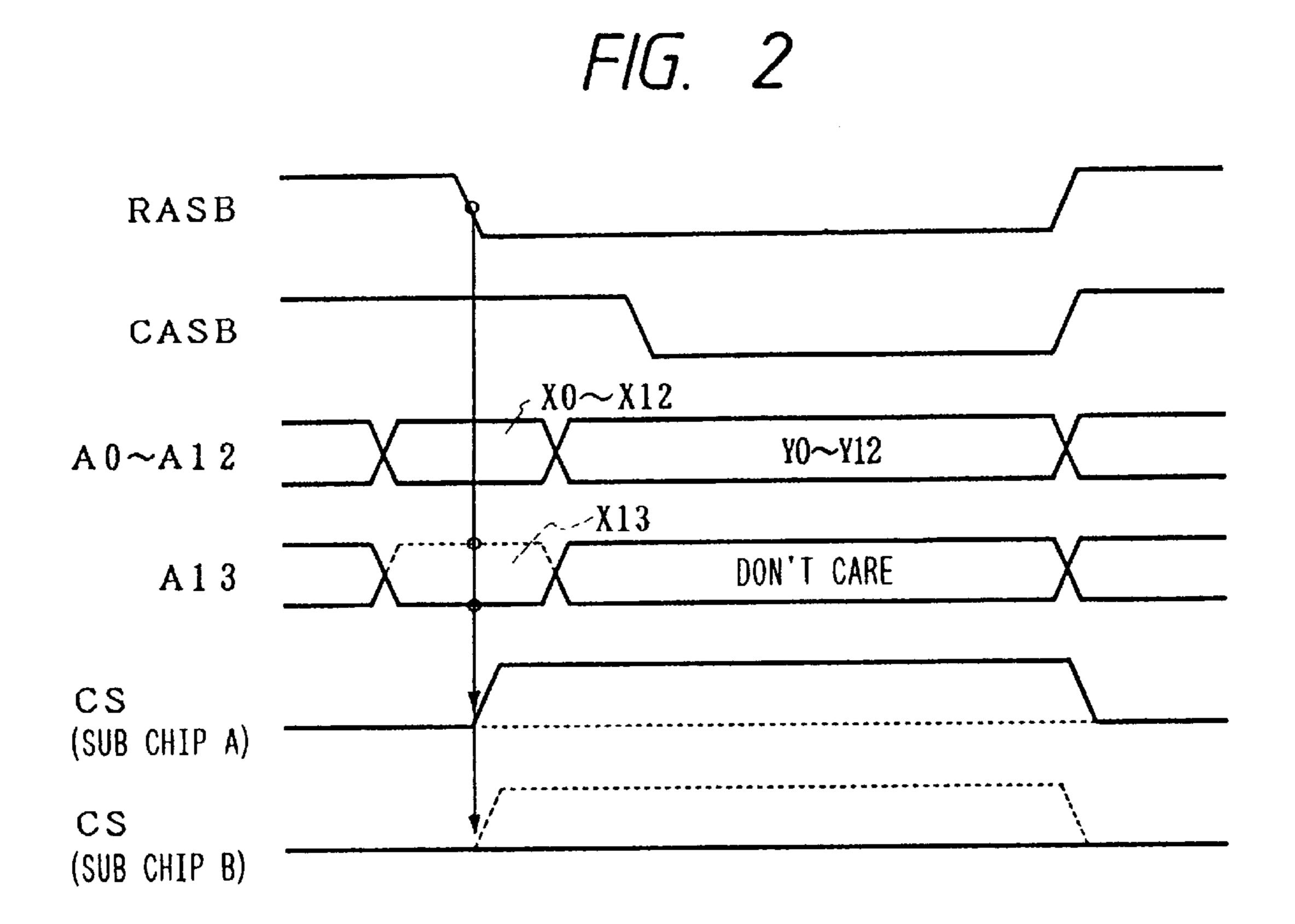

- FIG. 2 is a timing chart in the DRAM package of FIG. 1;

- FIG. 3 is a standard specification table of 64M DRAM sub chips which constitute the DRAM package of FIG. 1;

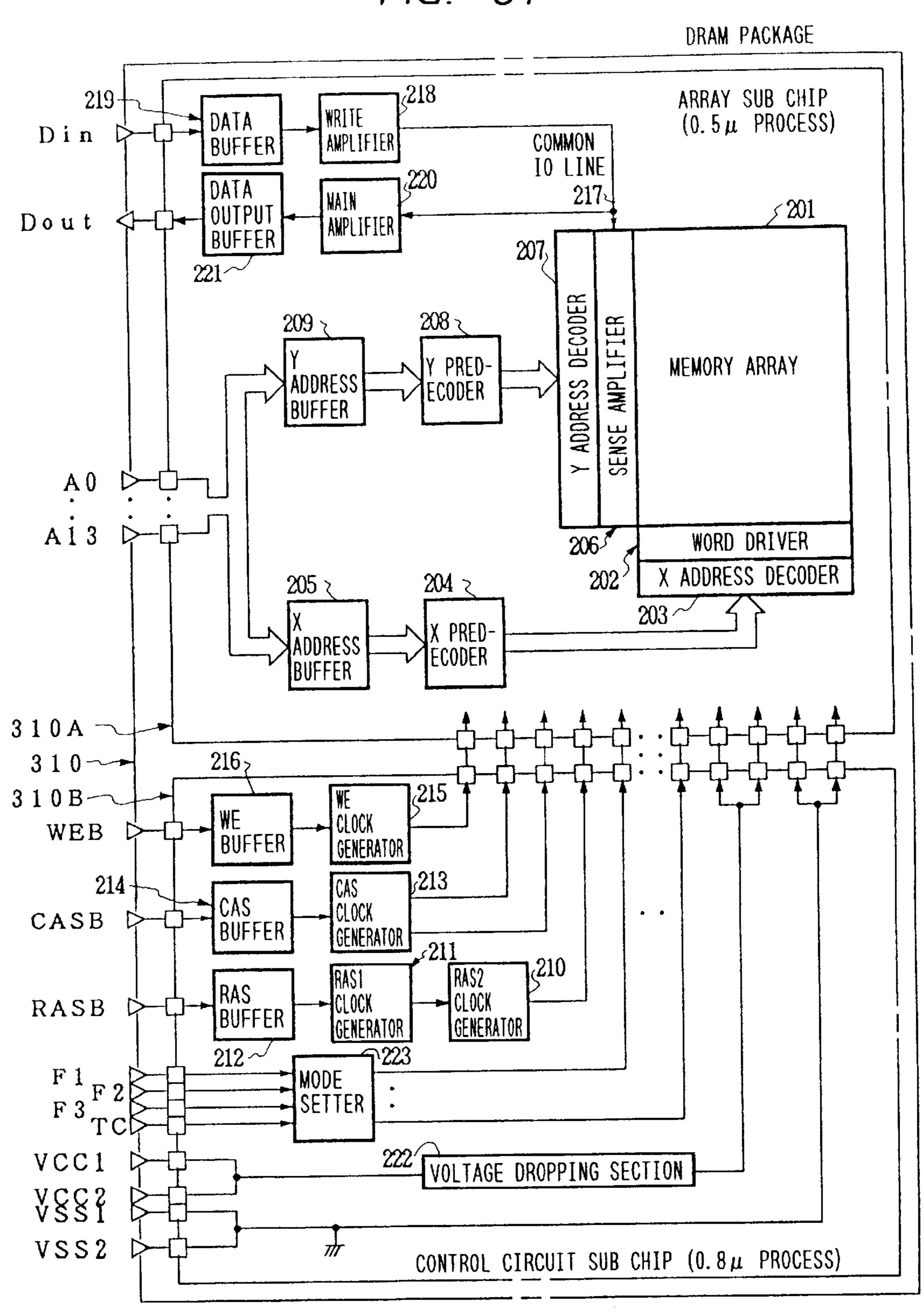

- FIG. 4 is a block diagram showing an example of a DRAM sub chip of FIG. 3;

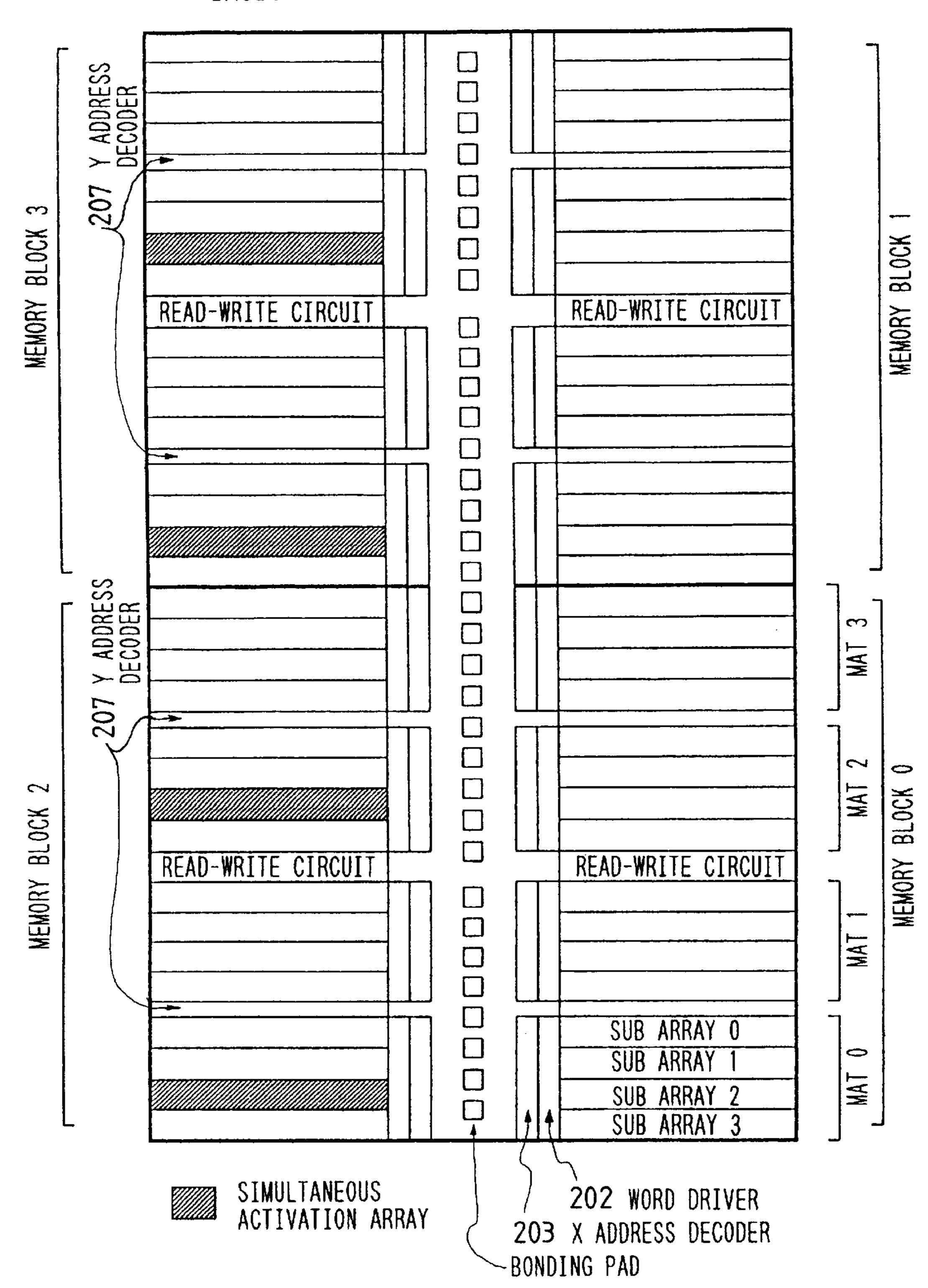

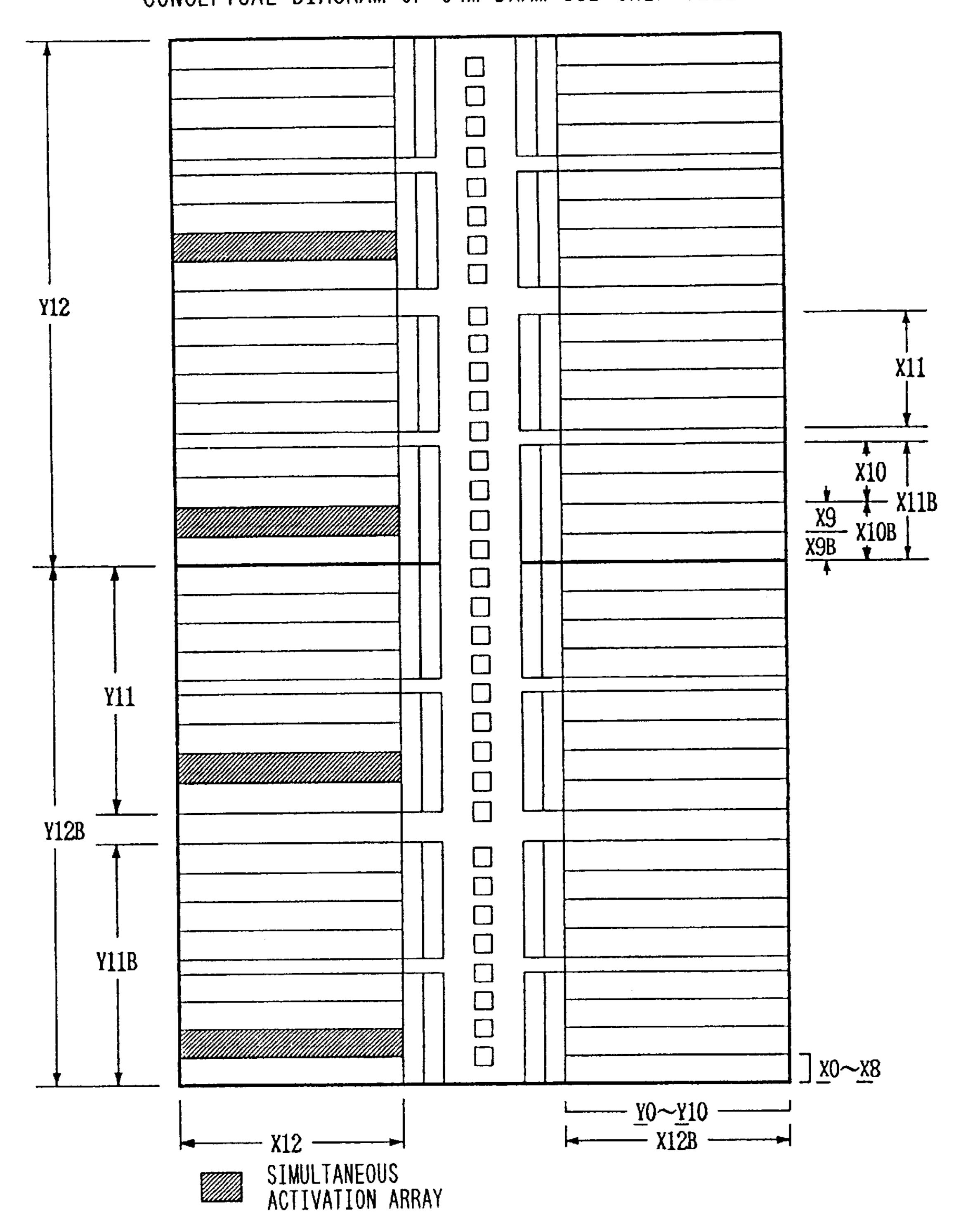

- FIG. 5 is a substrate layout diagram in the DRAM sub chip of FIG. 4;

- FIG. 6 is an address allocation diagram in the DRAM sub chip of FIG. 4;

- FIG. 7 is a product list showing variations of the 128M DRAM package;

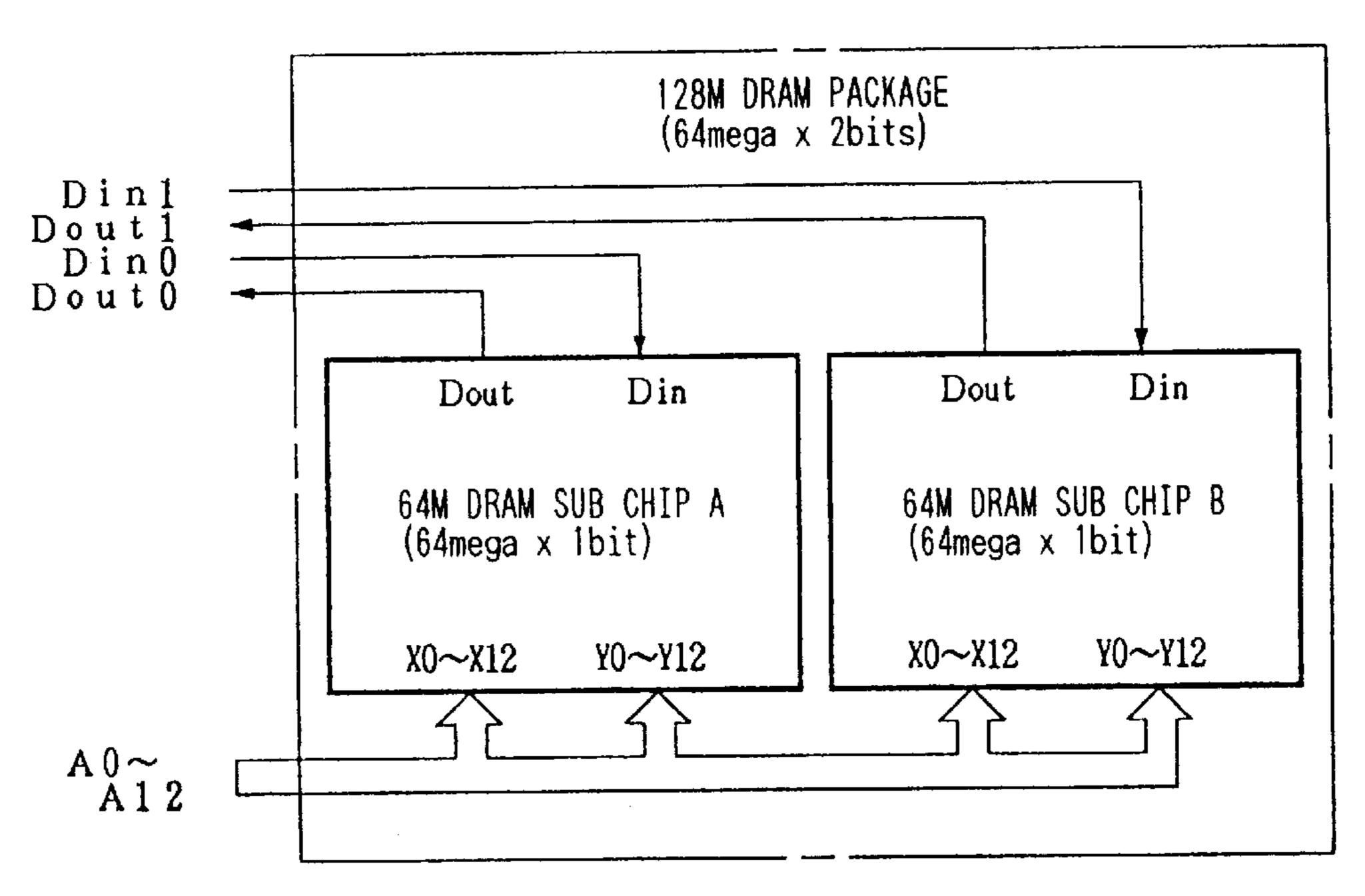

- FIG. 8 is a block diagram showing a second example of a 128M DRAM package according to the present invention;

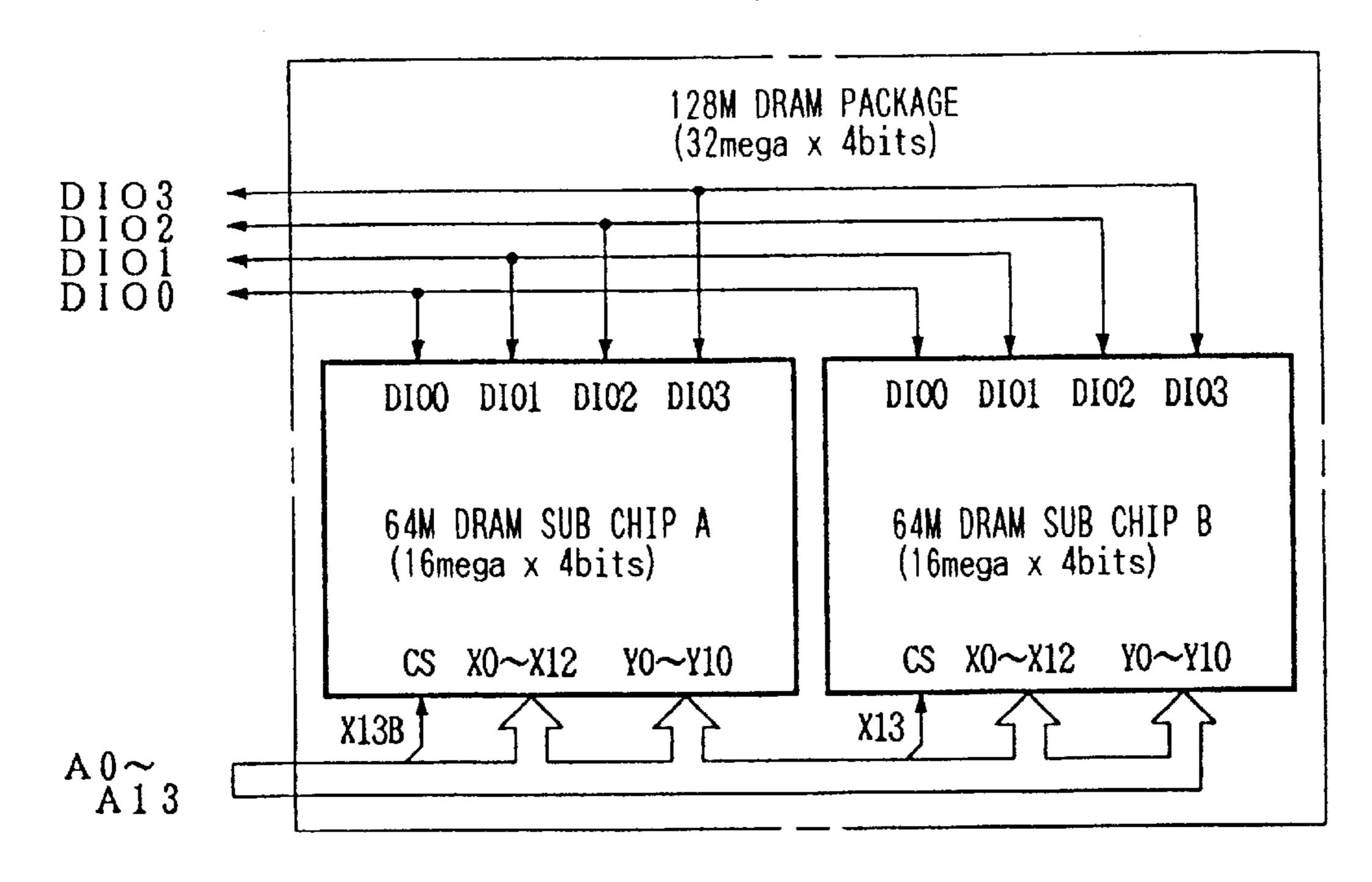

- FIG. 9 is a block diagram showing a third example of a 30 128M DRAM package according to the present invention;

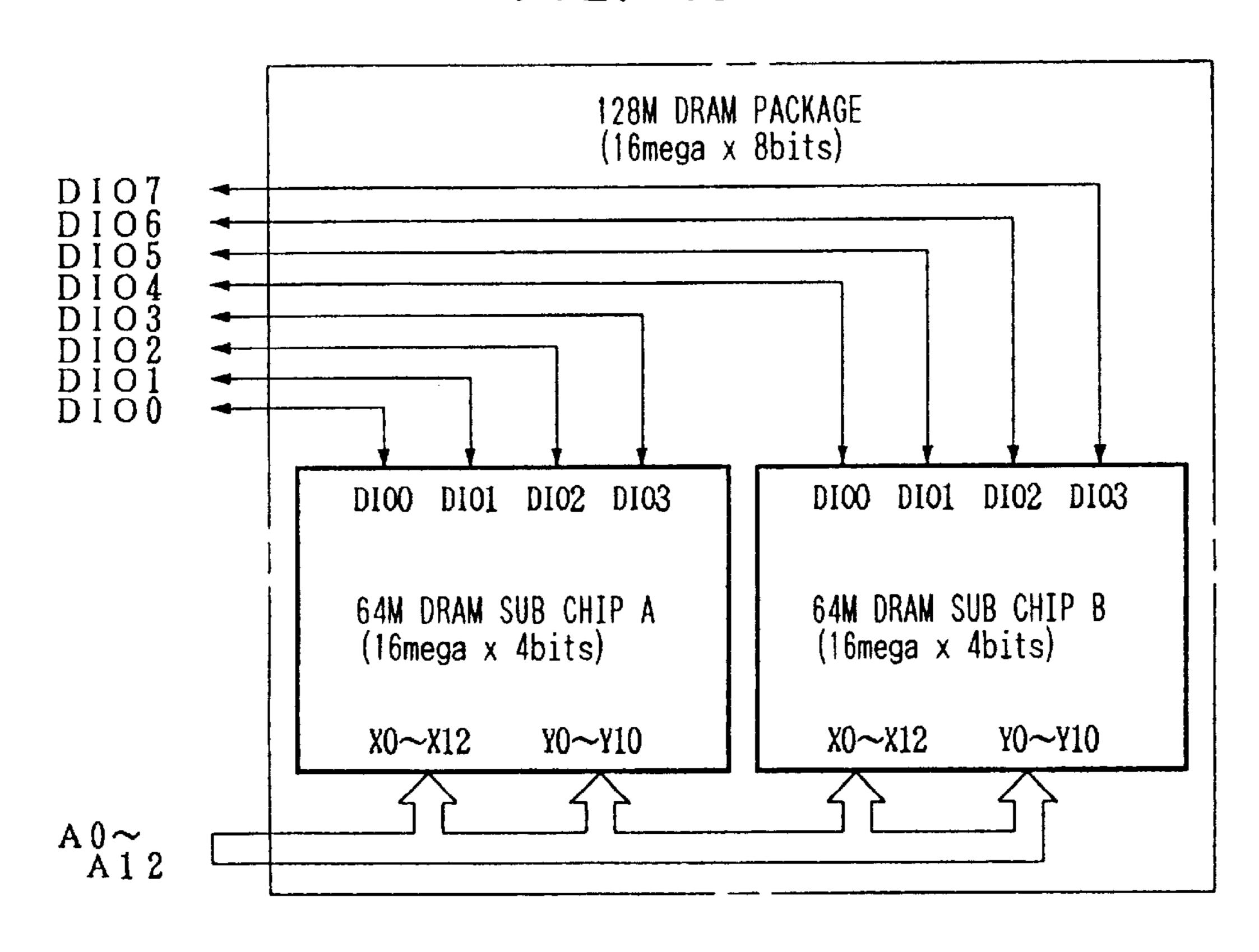

- FIG. 10 is a block diagram showing a fourth example of a 128M DRAM package according to the present invention;

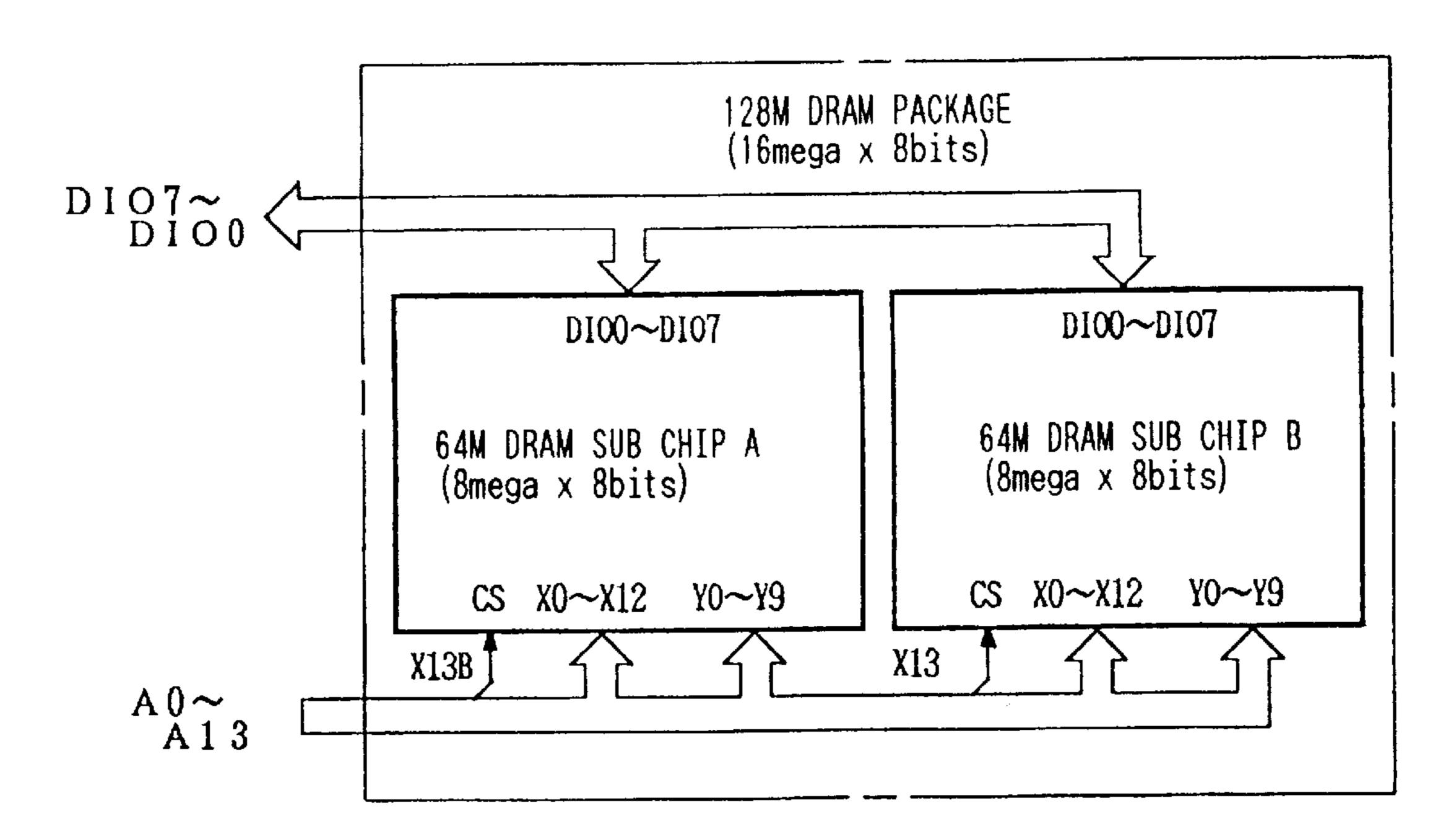

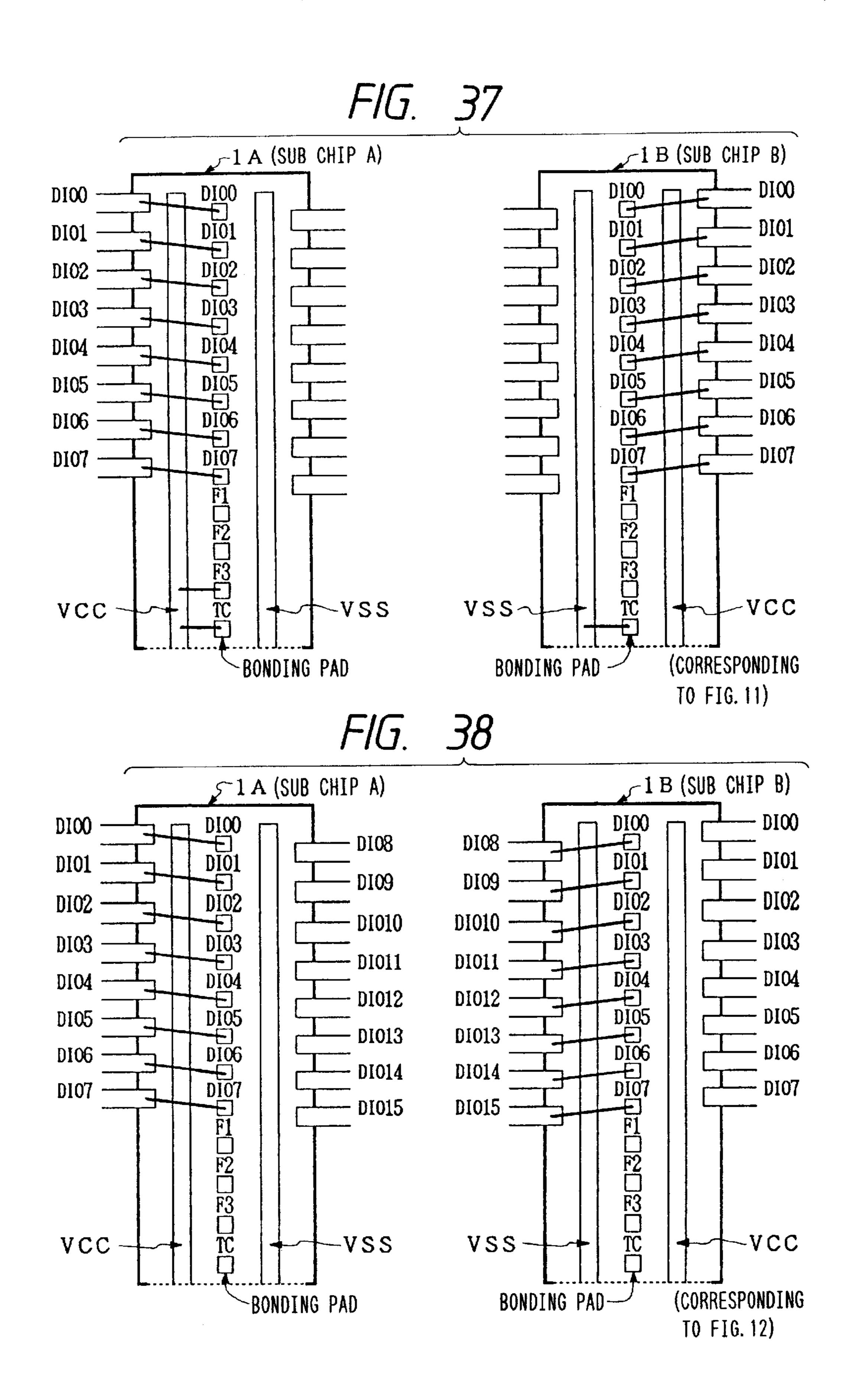

- FIG. 11 is a block diagram showing a fifth example of a 128M DRAM package according to the present invention; <sup>35</sup>

- FIG. 12 is a block diagram showing a sixth example of a 128M DRAM package according to the present invention;

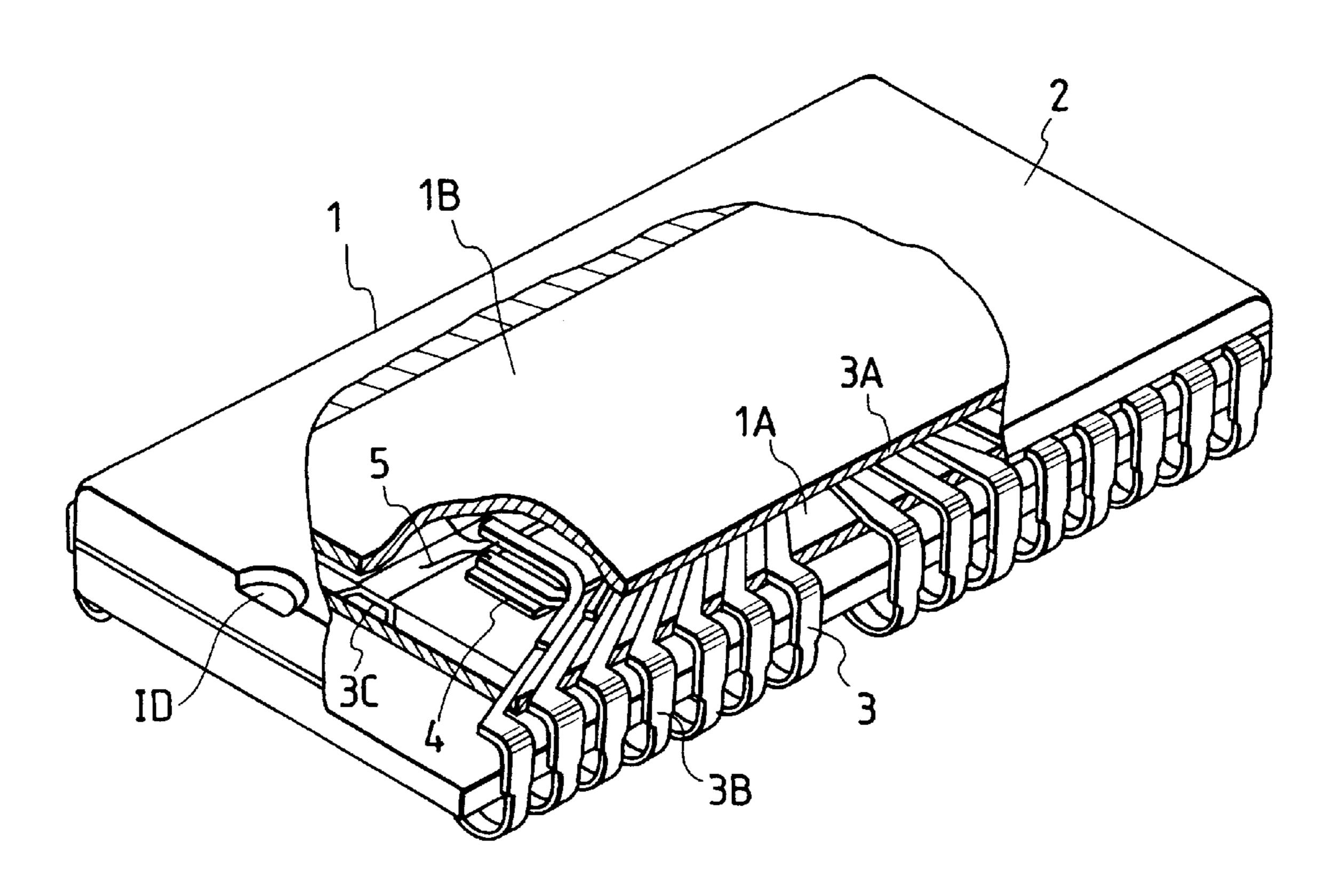

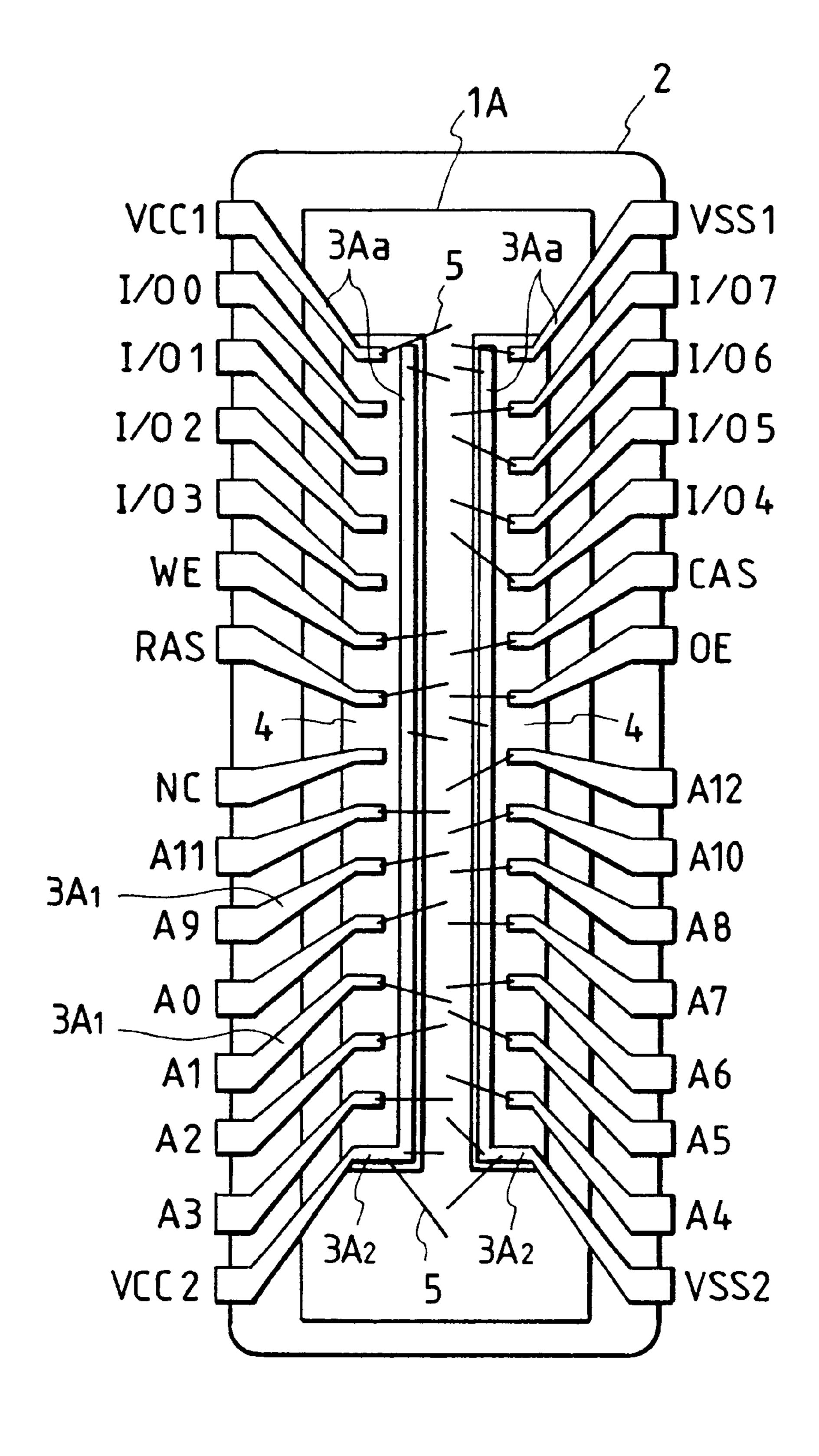

- FIG. 13 is a sectional perspective view of the DRAM package of FIG. 1;

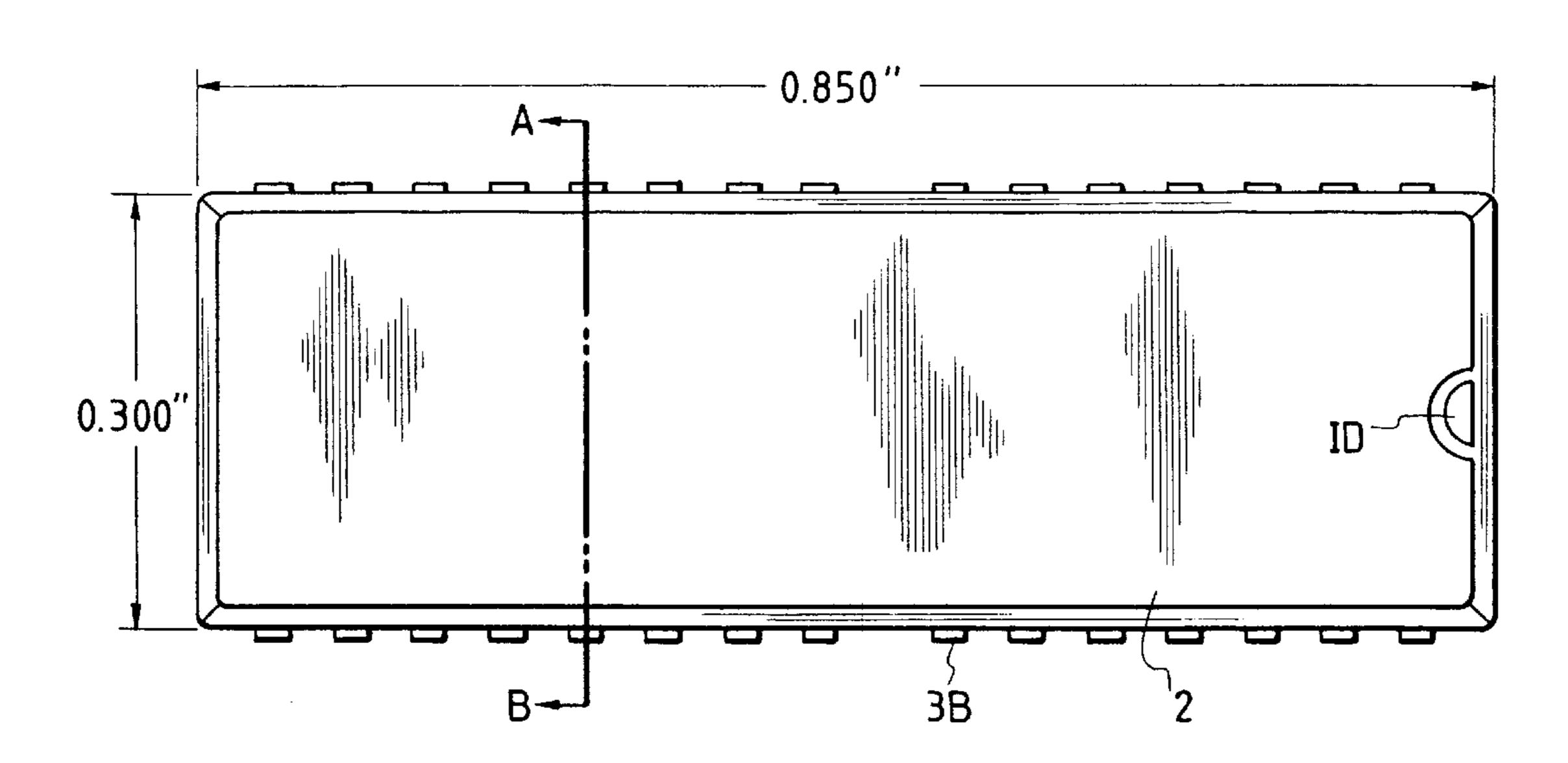

- FIG. 14 is a plan view thereof;

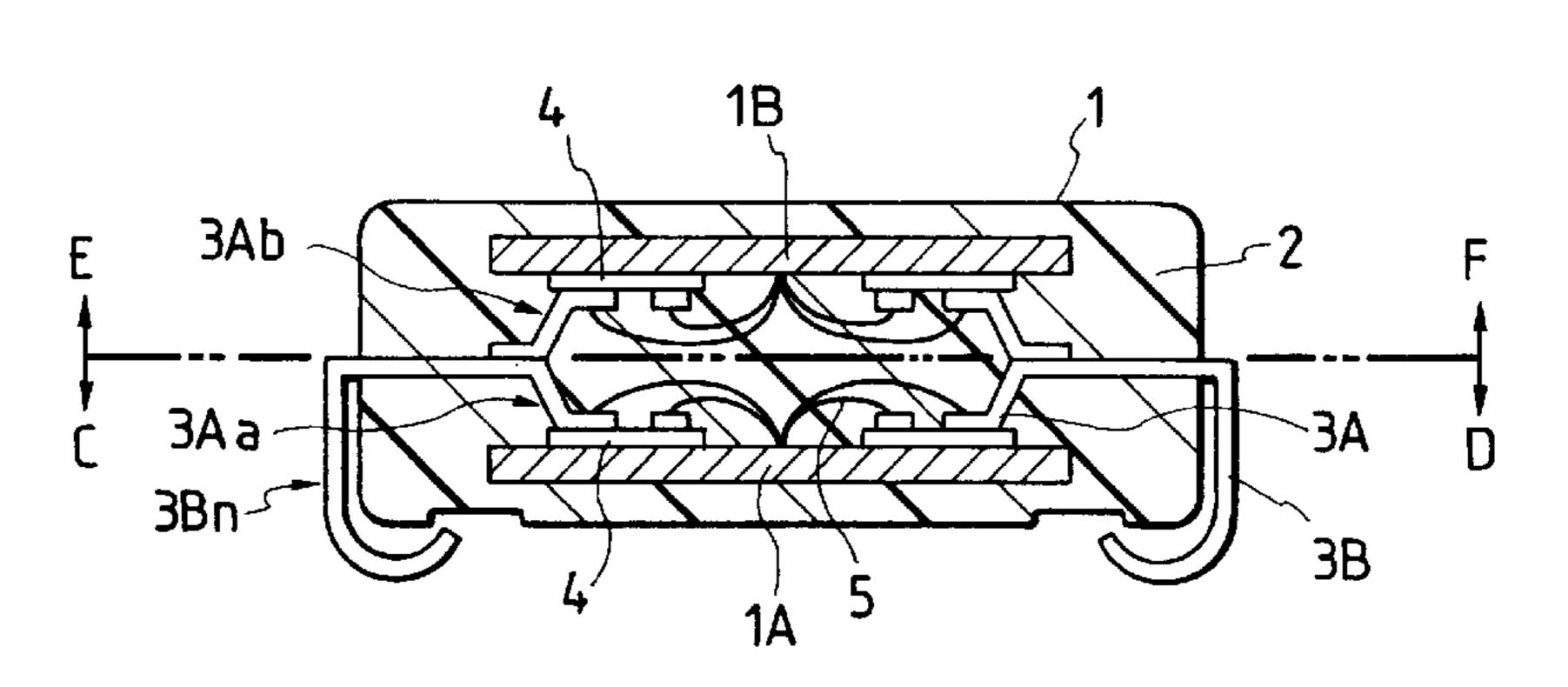

- FIG. 15 is a structural sectional view taken on line 15—15 in FIG. 14;

- FIG. 16 is a plan view cut away along line ≠—≠in FIG. **15**;

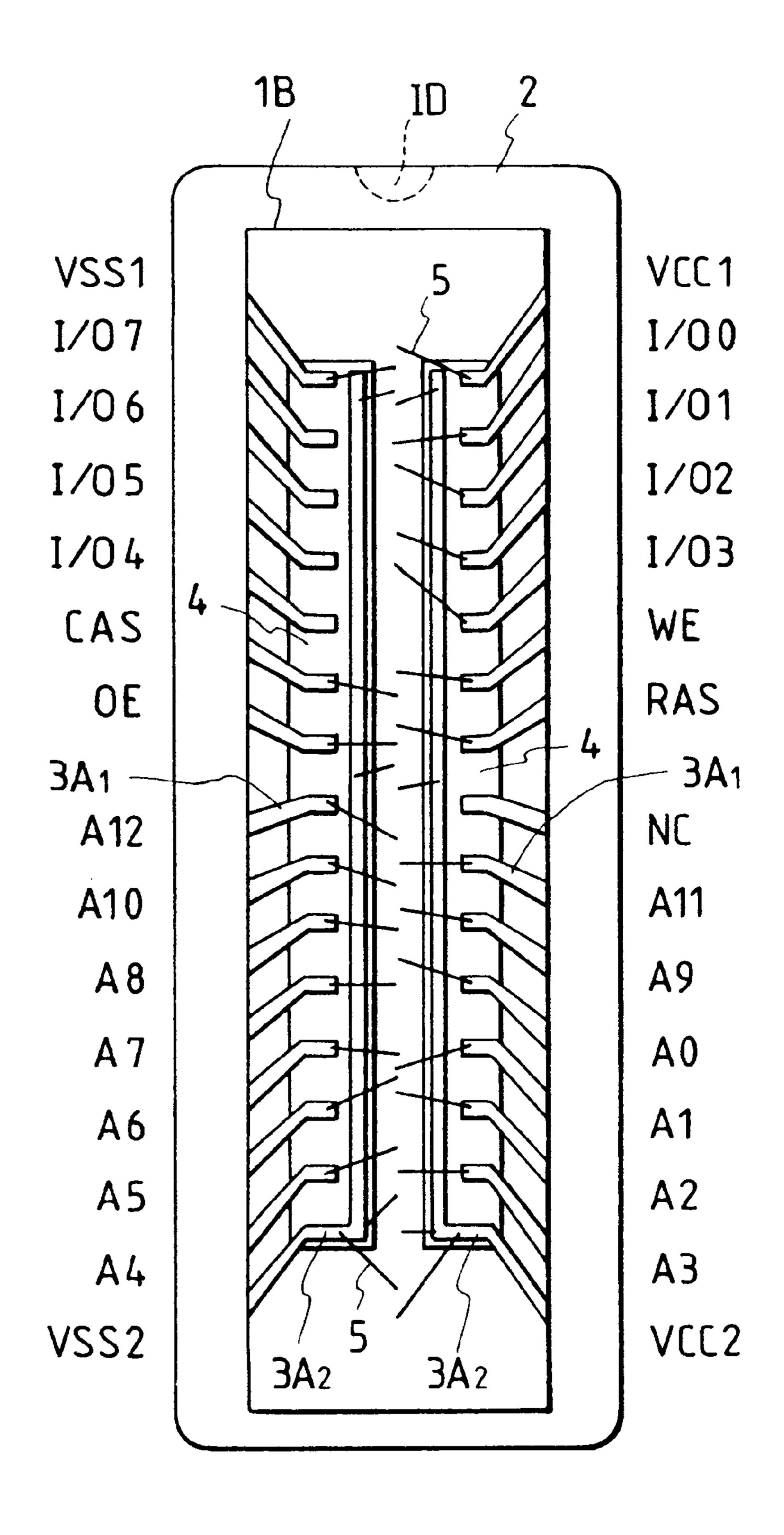

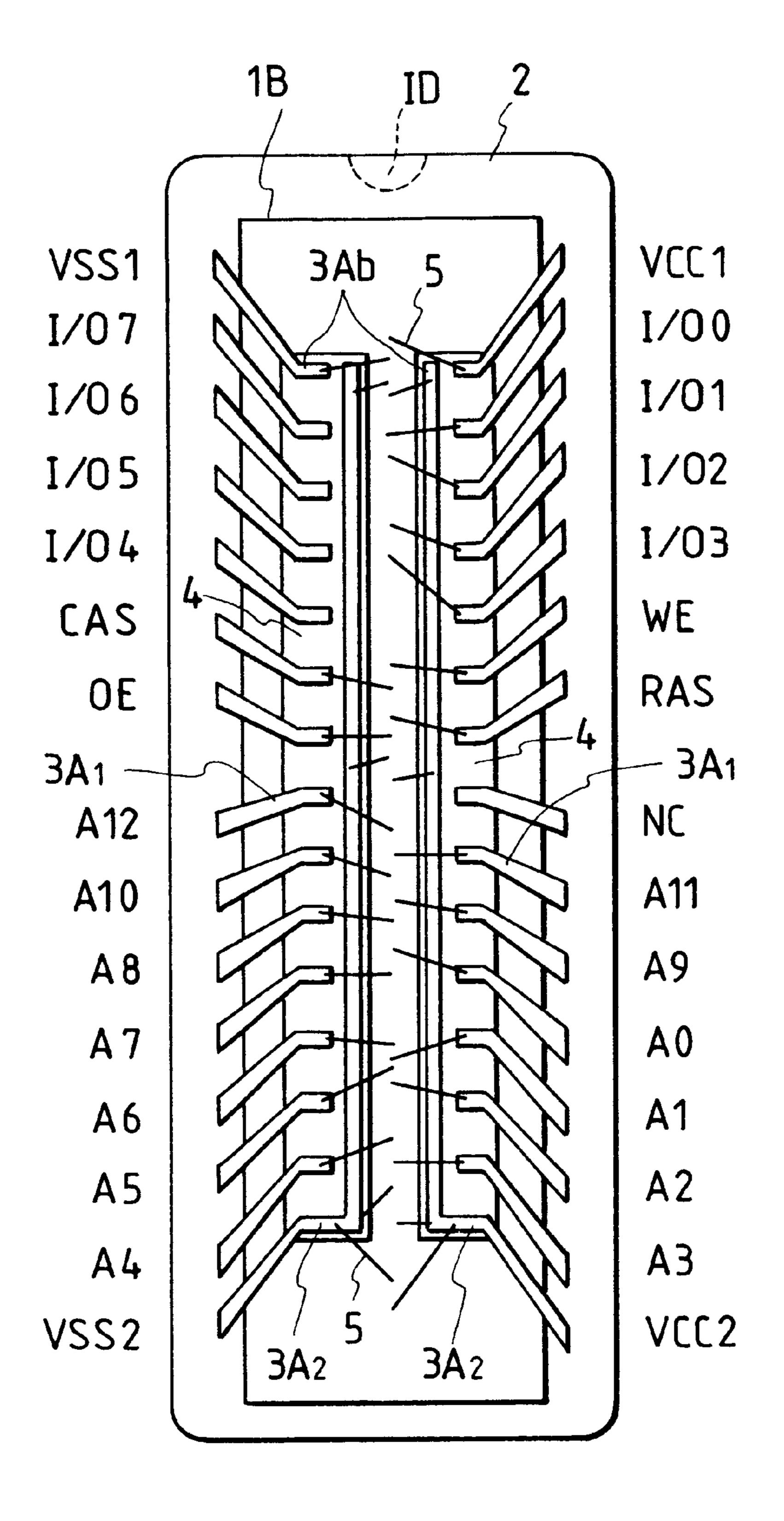

- FIG. 17 is a plan view cut away along line \( \)—\( \) in FIG. 15, showing a first example of the DRAM package of FIG. 14;

- FIG. 18 is a plan view of a modification of FIG. 17, showing a second example of the DRAM package of FIG. 50 14;

- FIG. 19 is a processing diagram showing a first manufacturing process for the DRAM package illustrated in FIG. 13;

- FIG. 20 is a processing diagram showing a second manufacturing process for the DRAM package illustrated in FIG. 13;

- FIG. 21 is a processing diagram showing a third manufacturing process for the DRAM package illustrated in FIG. 60 13;

- FIG. 22 is a processing diagram showing a fourth manufacturing process for the DRAM package illustrated in FIG. 13;

- FIG. 23 is a processing diagram showing a fifth manu- 65 facturing process for the DRAM package illustrated in FIG. 13;

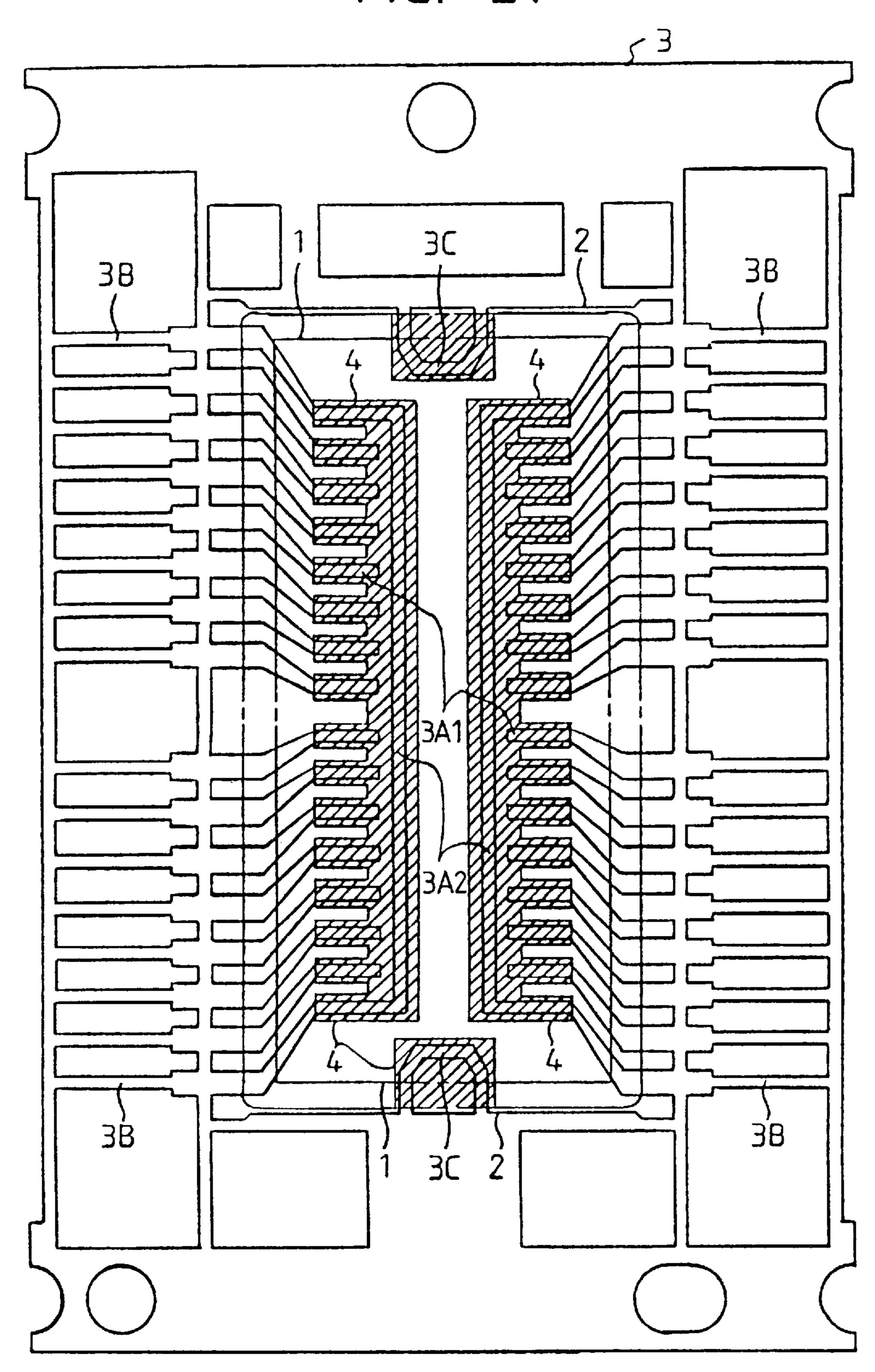

- FIG. 24 is a plan view showing an example of a lead frame and an insulating film both used in the DRAM package of FIG. 13;

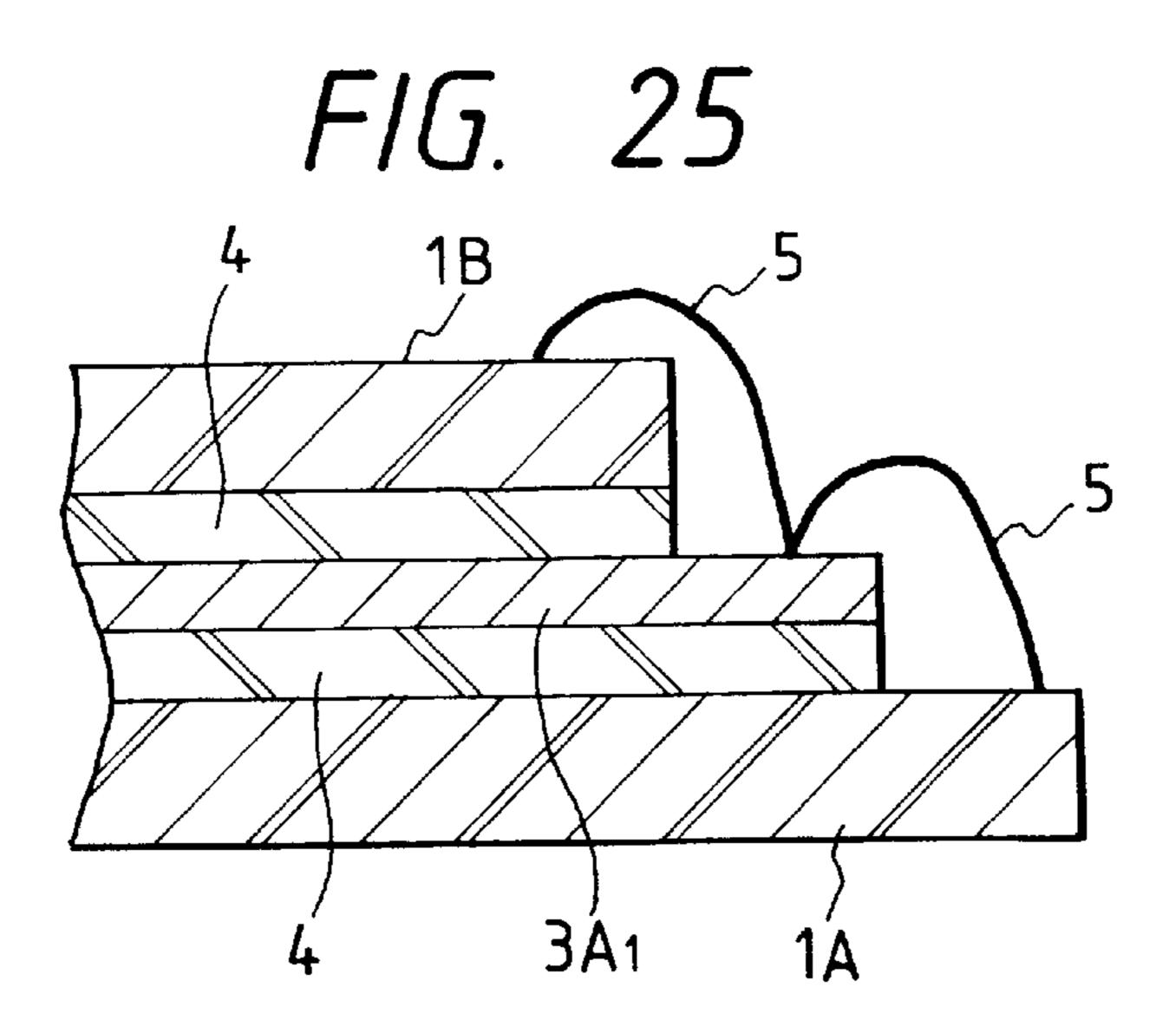

- FIG. 25 is a structural sectional view of a DRAM package further embodying the invention;

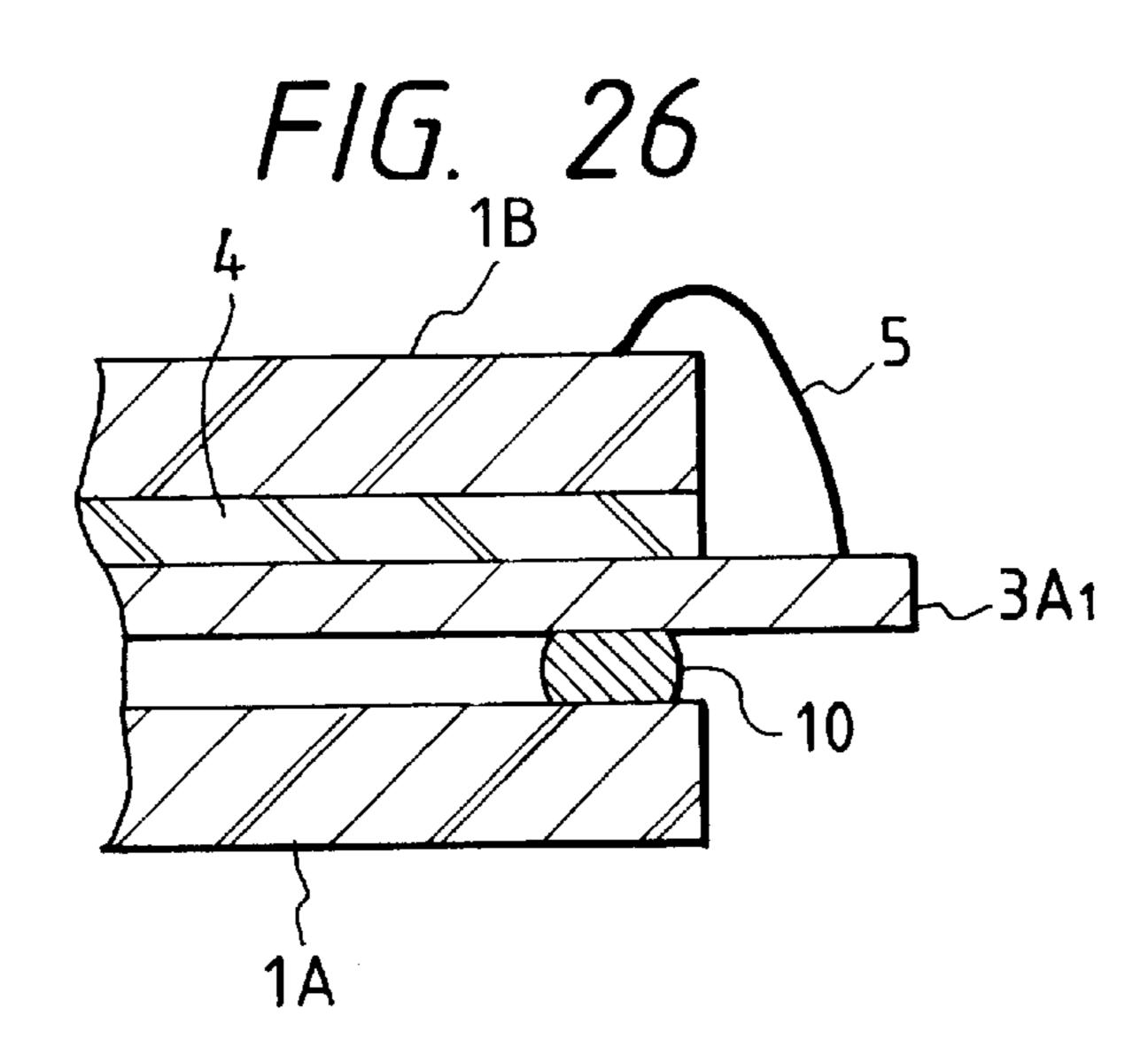

- FIG. 26 is a structural sectional view of a DRAM package further embodying the invention;

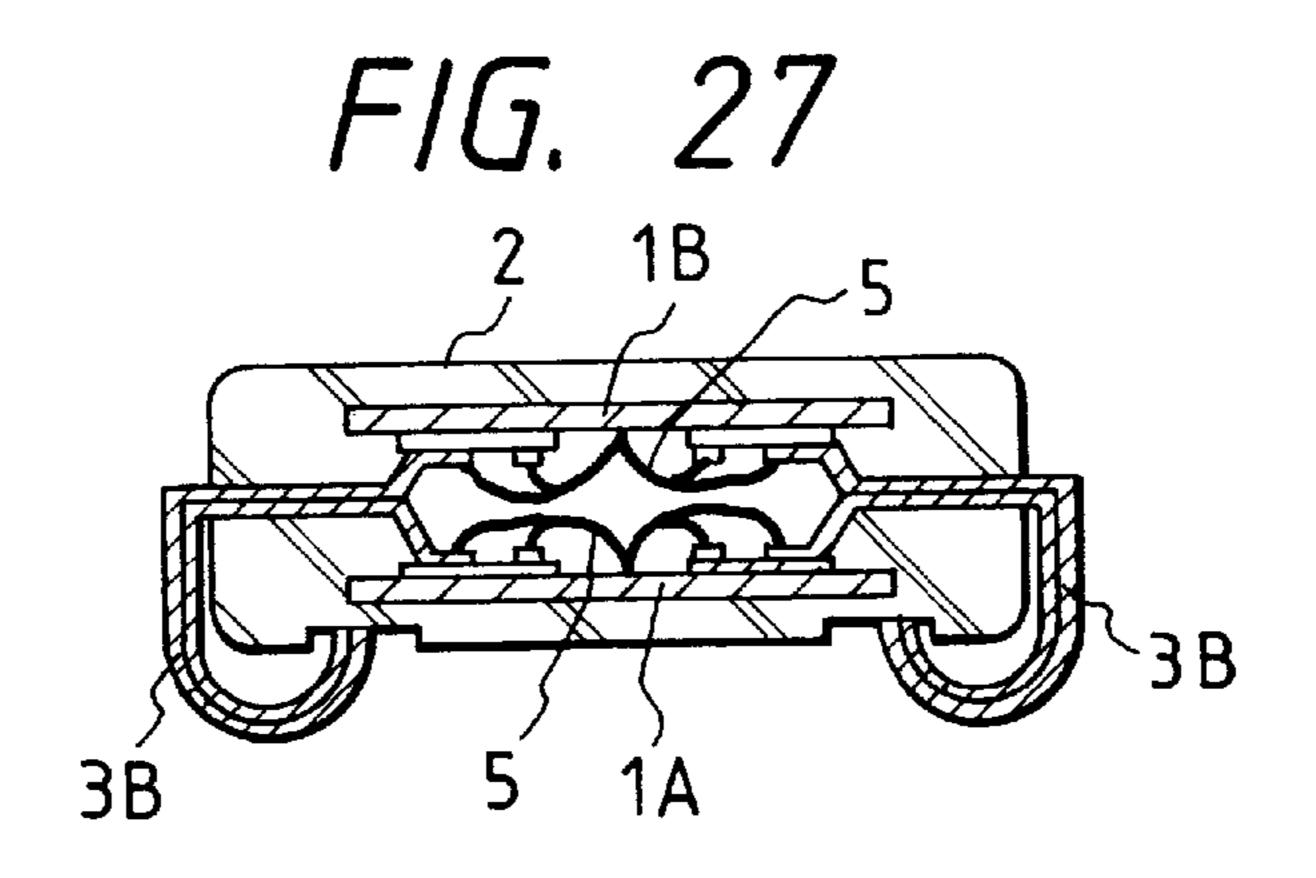

- FIG. 27 is a structural sectional view of a DRAM package further embodying the invention;

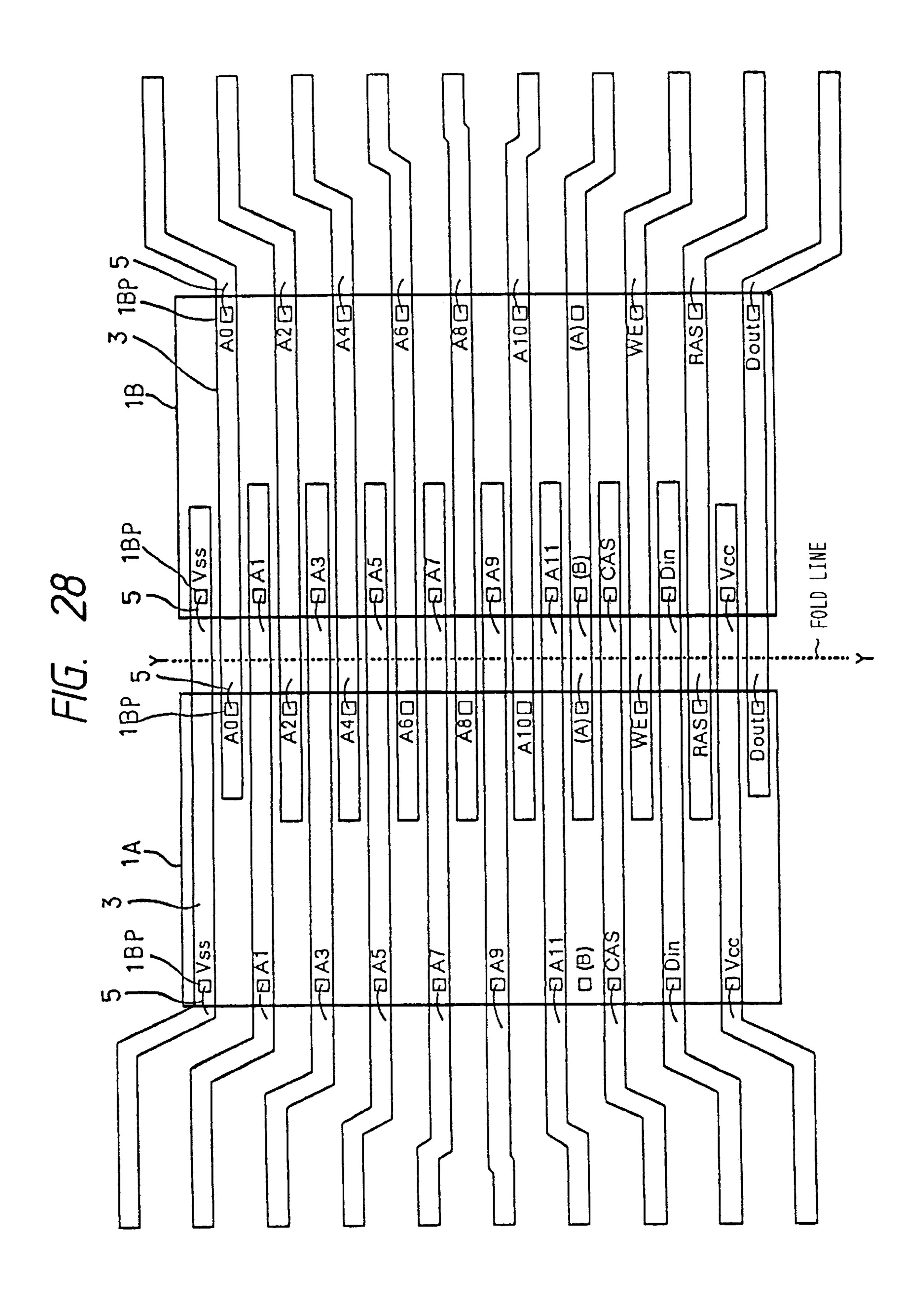

- FIG. 28 is a plan view of a lead frame included in a DRAM package further embodying the invention;

- FIG. 29 is a structural sectional view of the DRAM package referred to in FIG. 28;

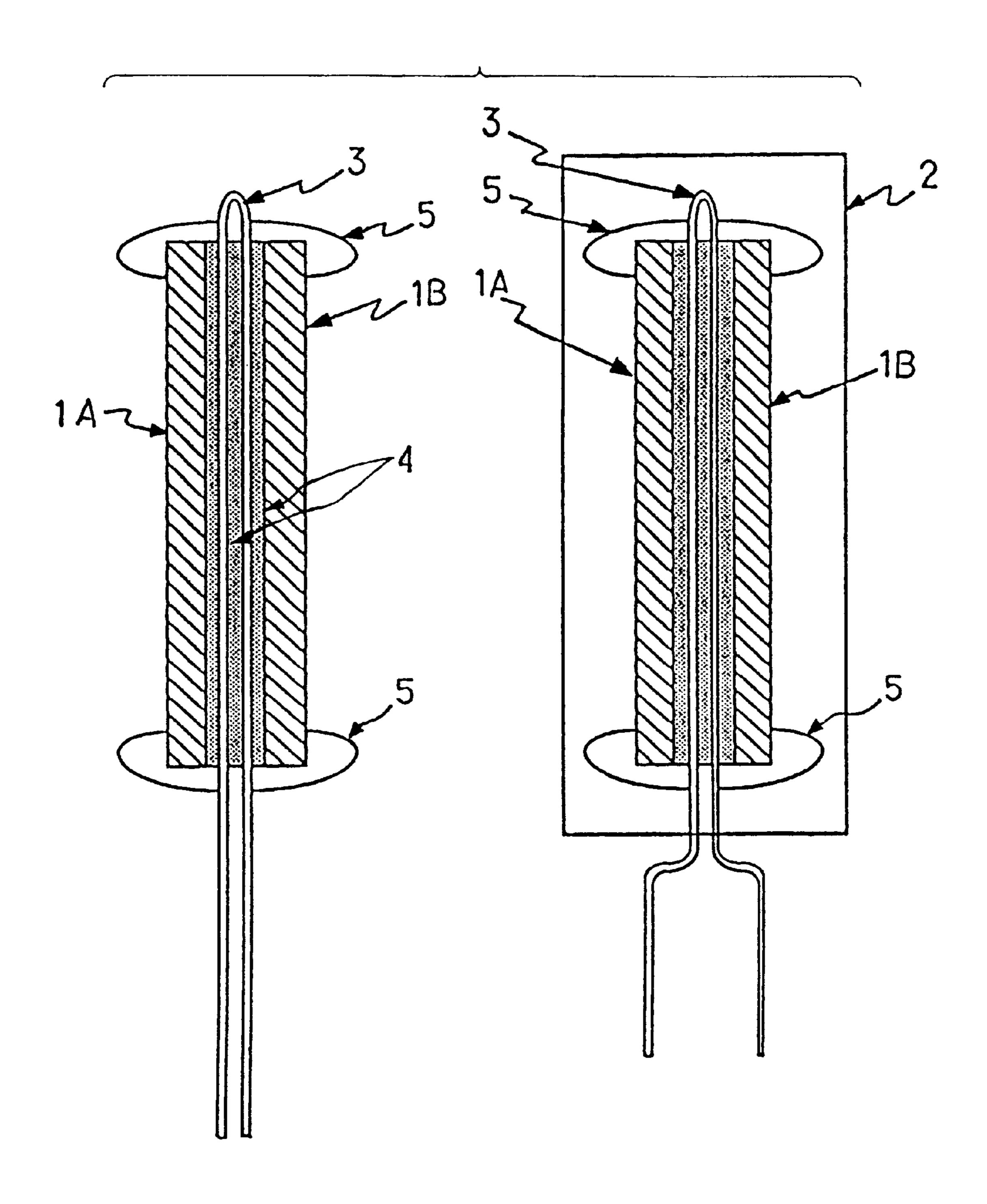

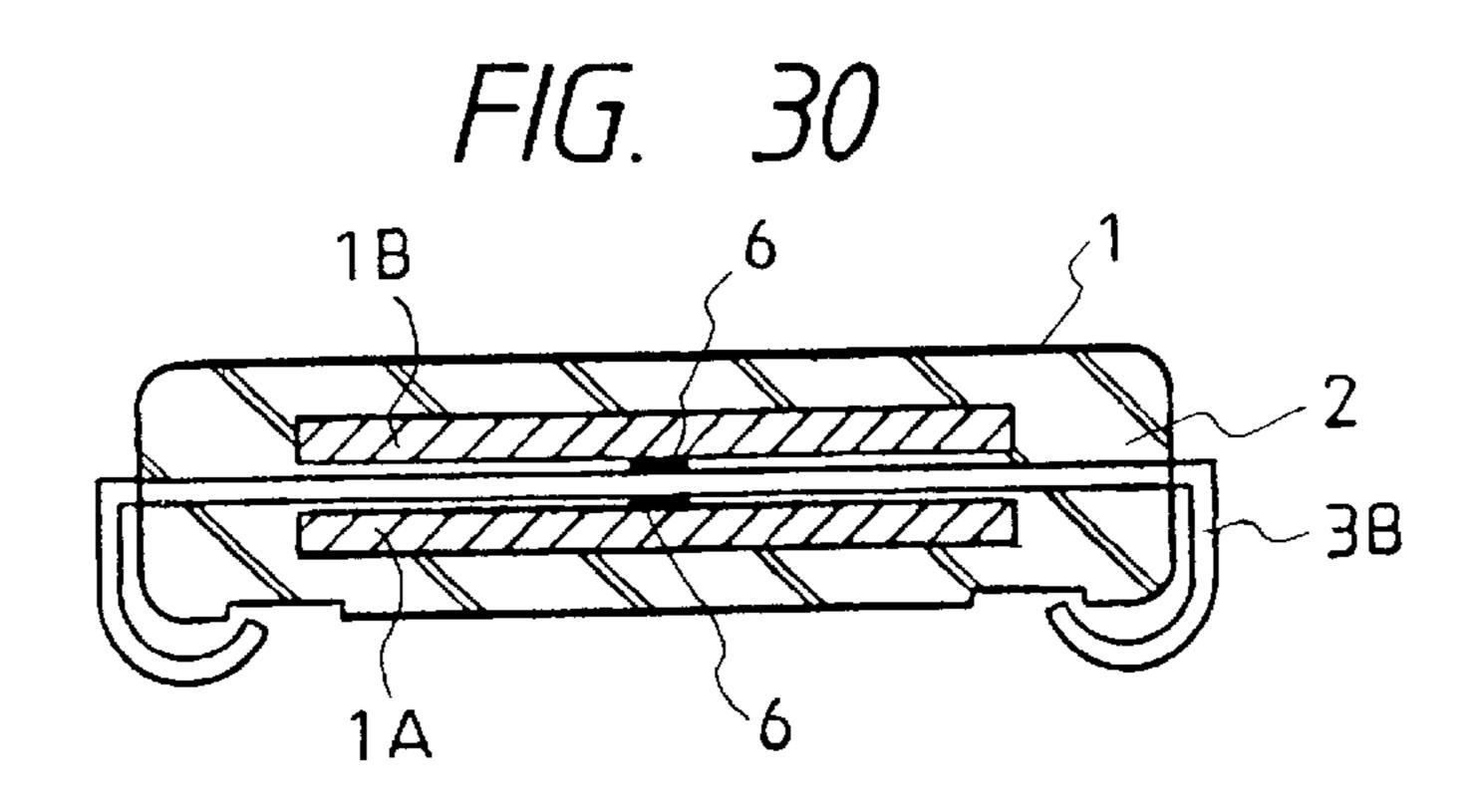

- FIG. 30 is a structural sectional view of a DRAM package further embodying the invention;

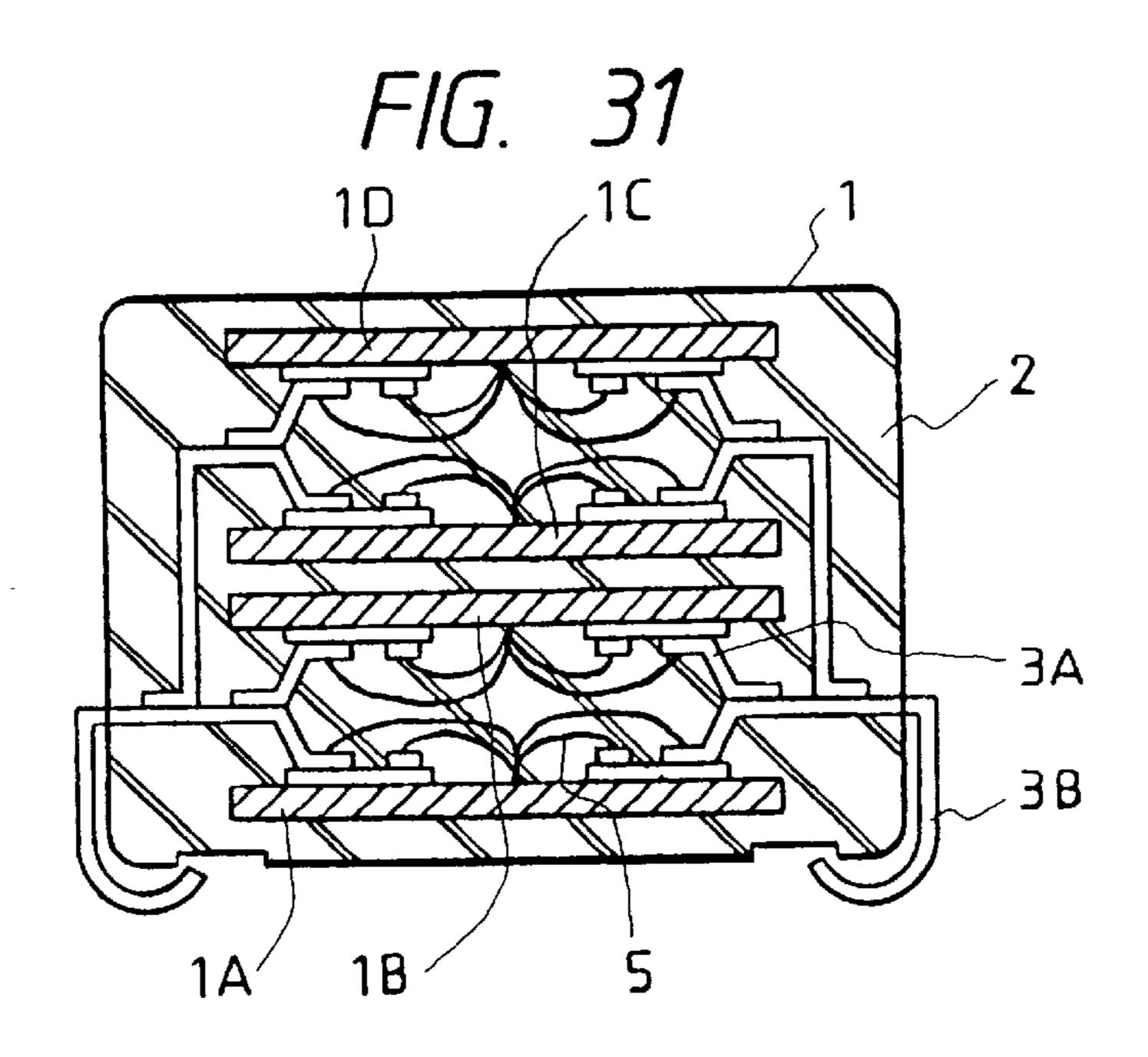

- FIG. 31 is a structural sectional view of a DRAM package further embodying the invention;

- FIG. 32 is a list of connections, showing bonding options of the DRAM sub chips shown in FIG. 3;

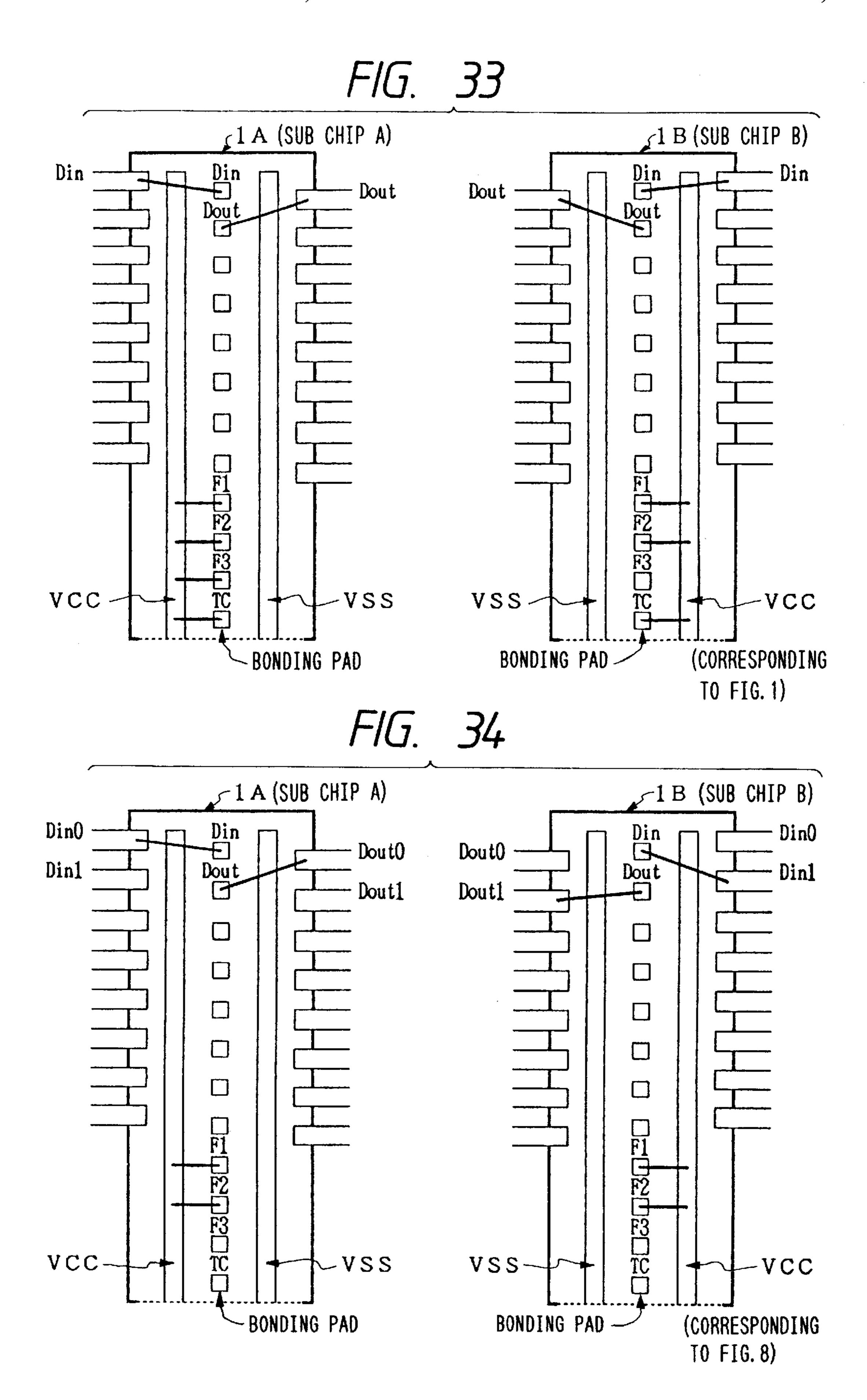

- FIG. 33 is a connection diagram of pads in the DRAM package of FIG. 1;

- FIG. 34 is a connection diagram of pads in the DRAM package of FIG. 8;

- FIG. 35 is a connection diagram of pads in the DRAM package of FIG. 9;

- FIG. 36 is a connection diagram of pads in the DRAM package of FIG. 10;

- FIG. 37 is a connection diagram of pads in the DRAM package of FIG. 11;

- FIG. 38 is a connection diagram of pads in the DRAM package of FIG. 12;

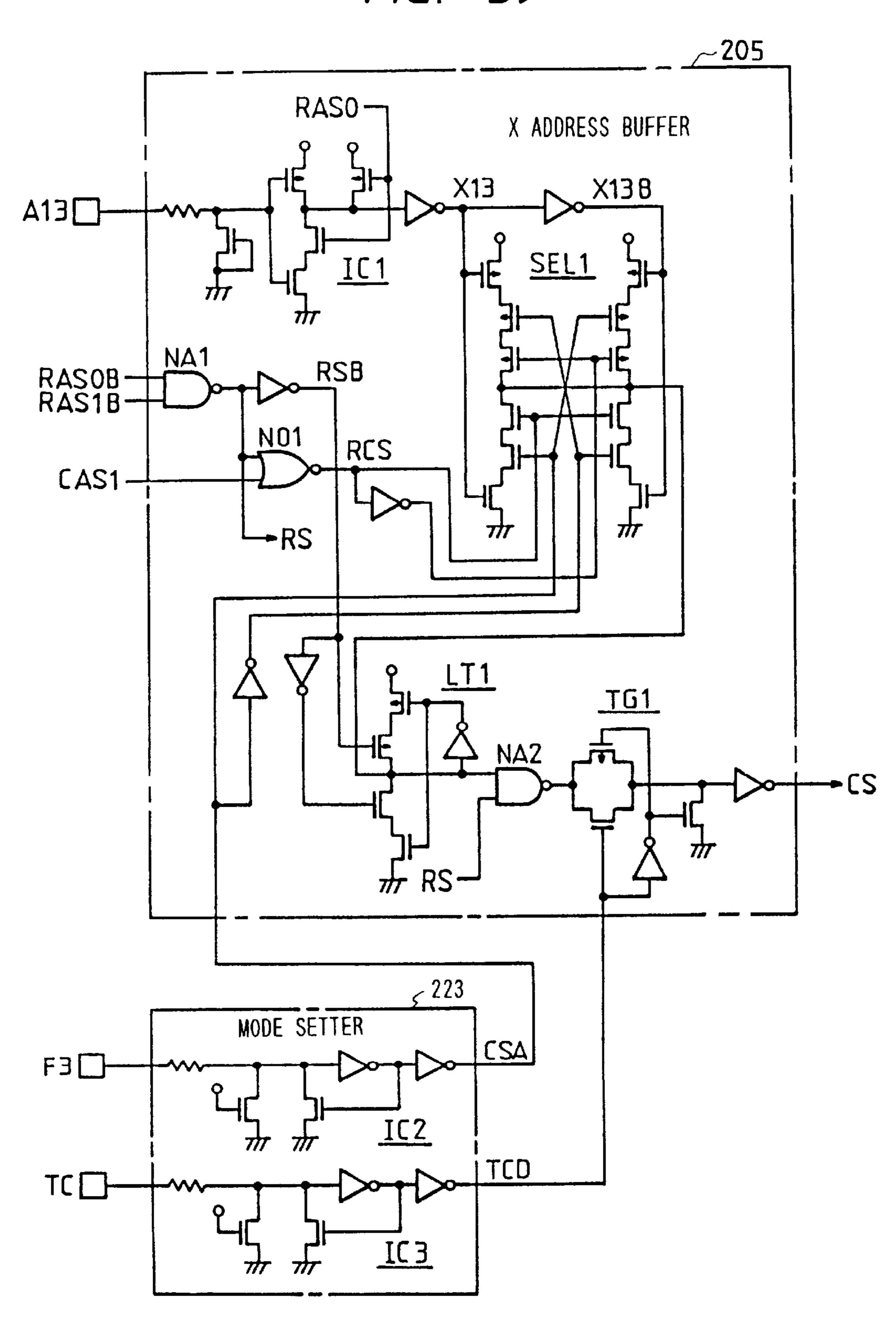

- FIG. 39 is a partial circuit diagram of an X address buffer included in the DRAM sub chip of FIG. 4;

- FIG. 40 is a block diagram showing a seventh example of a 64M DRAM package according to the invention;

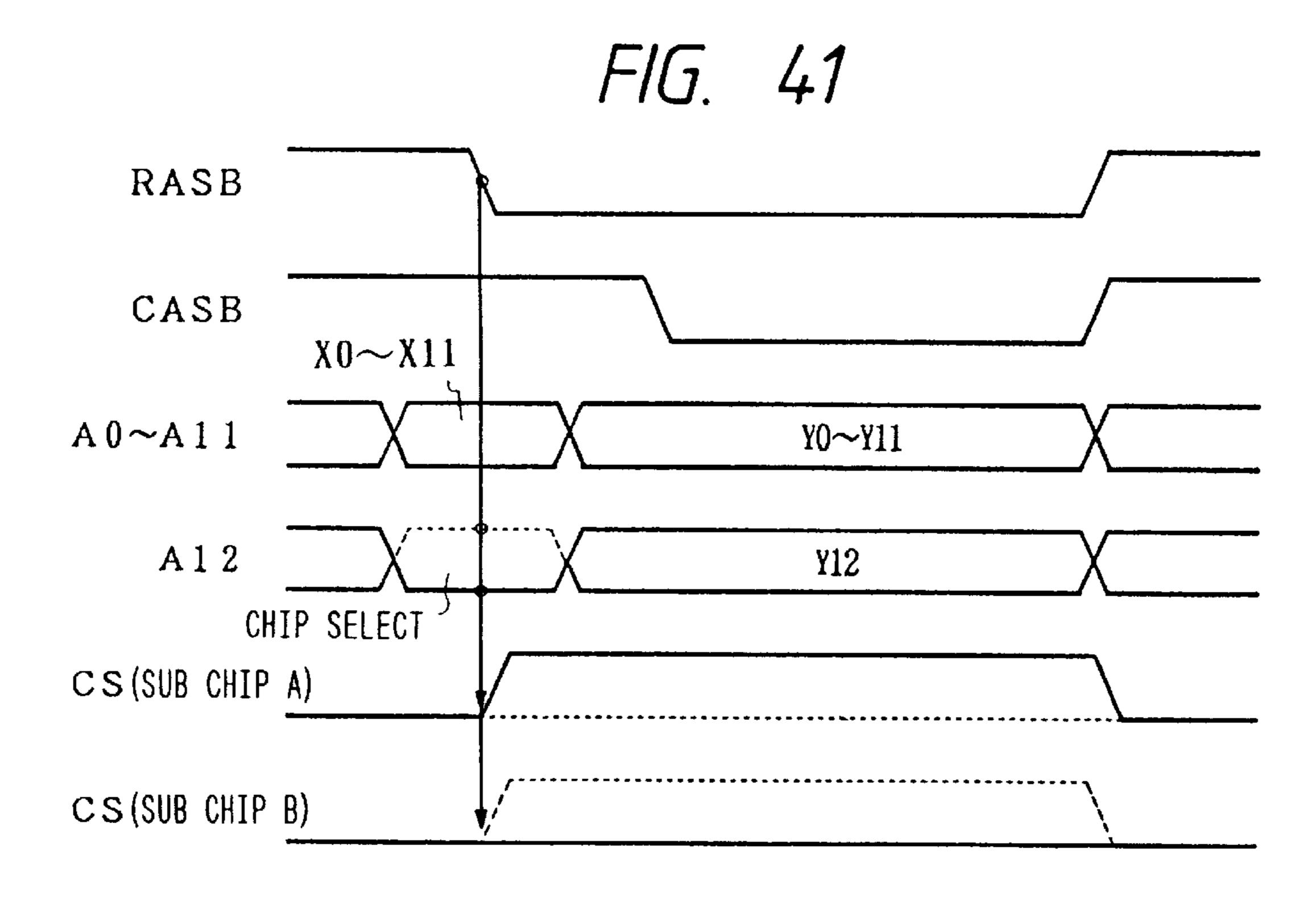

- FIG. 41 is a timing chart in DRAM sub chips illustrated in FIG. 40;

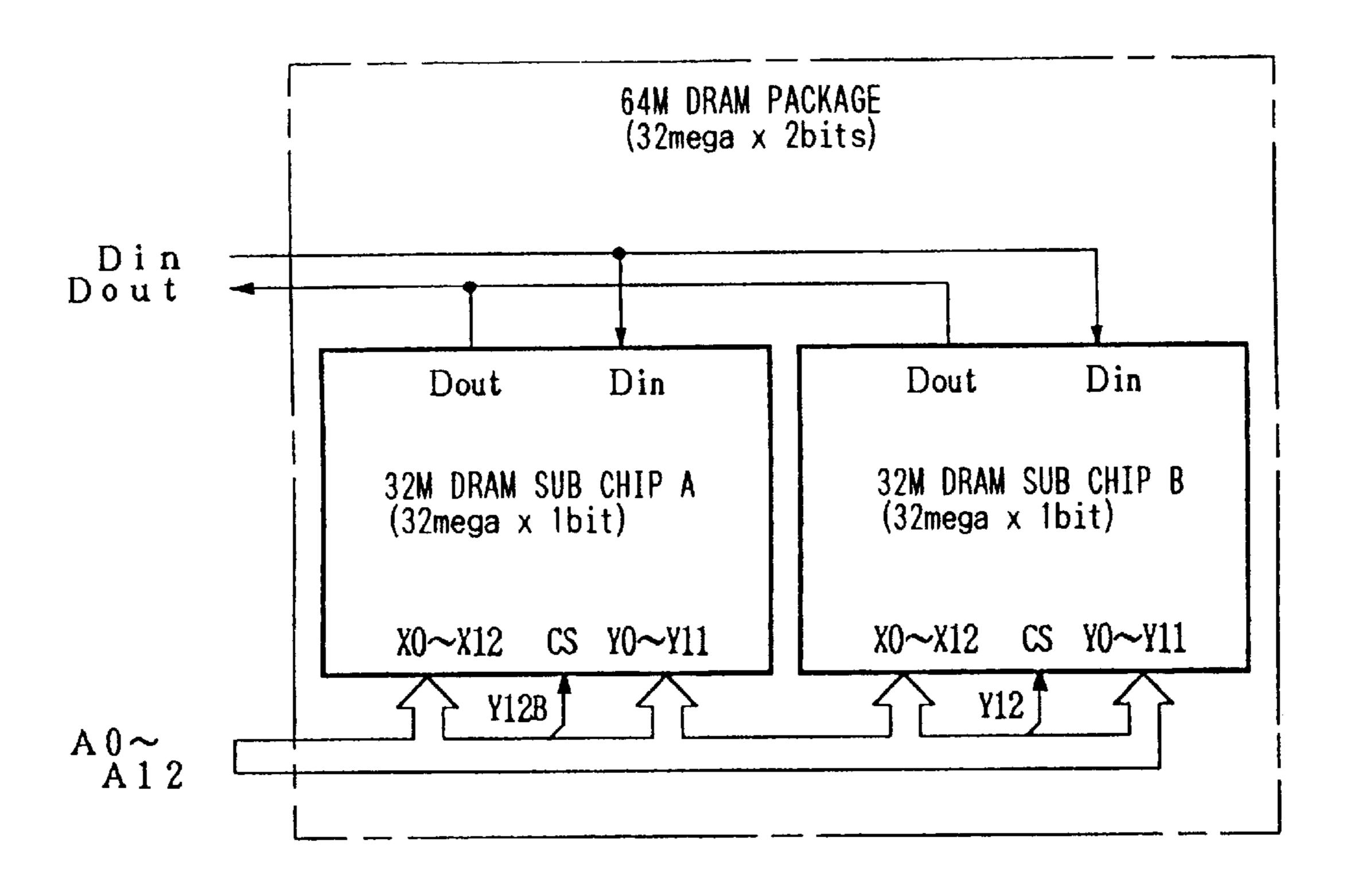

- FIG. 42 is a block diagram showing an eighth example of a 64M DRAM package according to the invention;

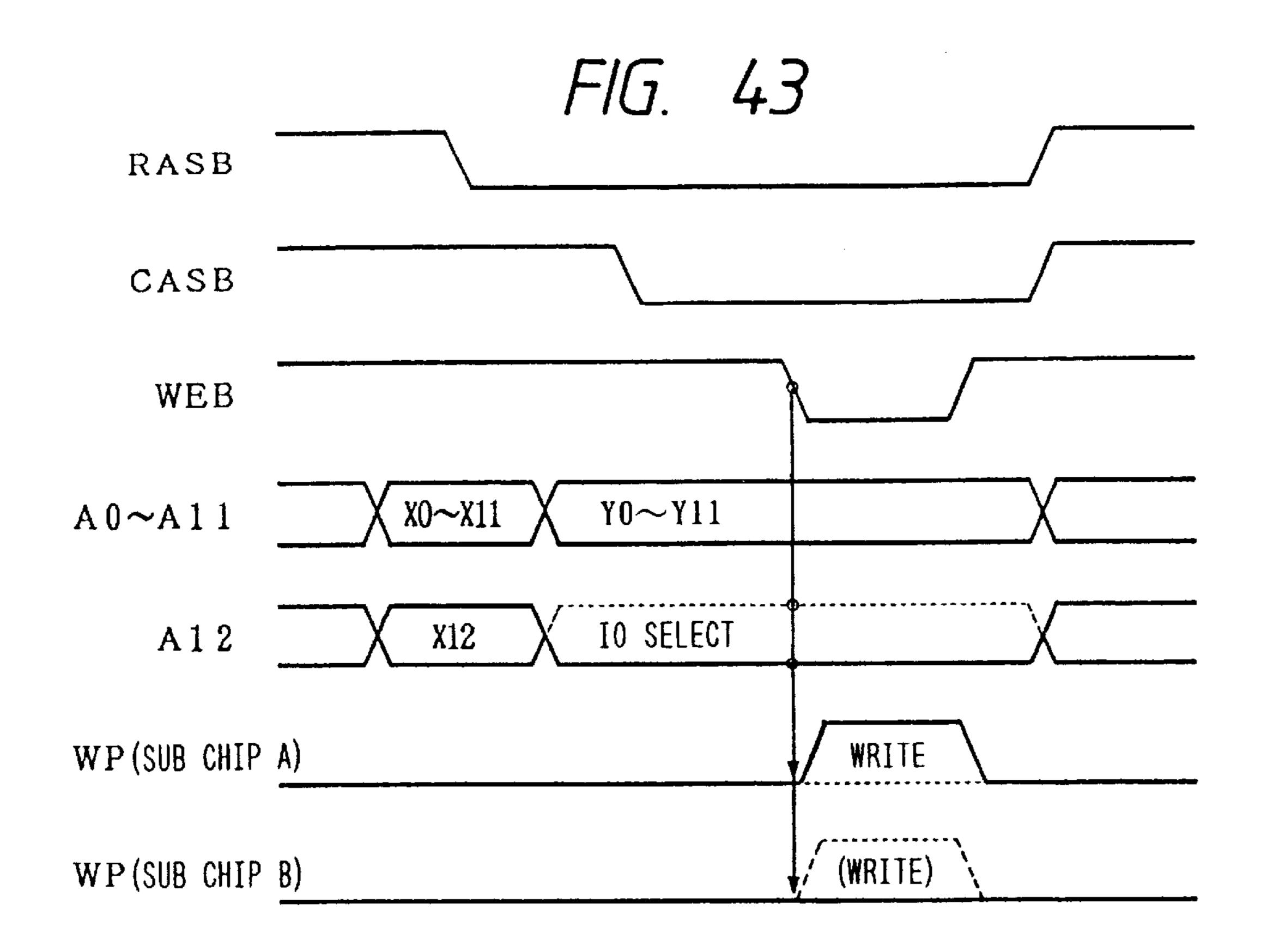

- FIG. 43 is a timing chart in a write mode of DRAM sub chips illustrated in FIG. 42;

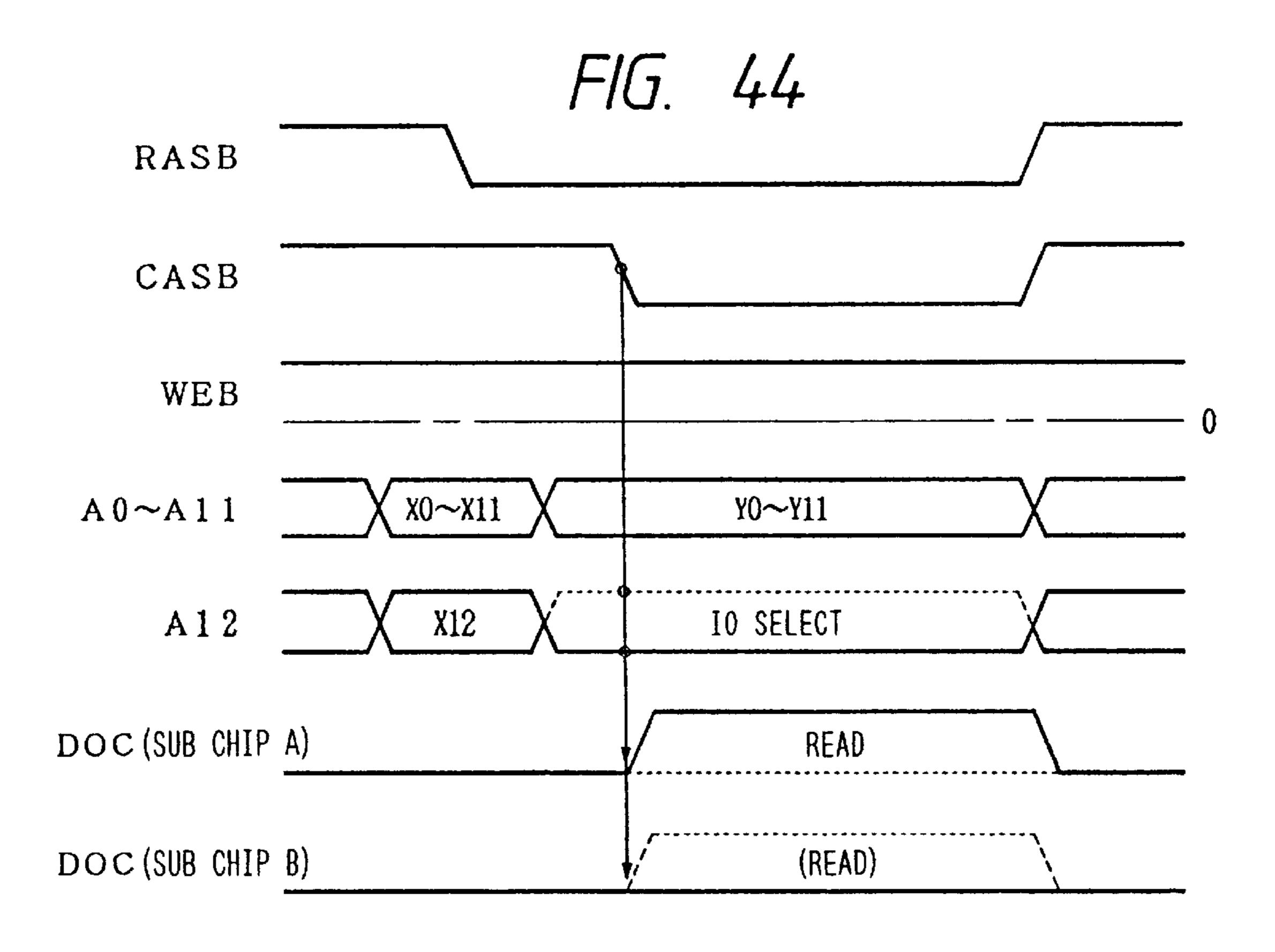

- FIG. 44 is a timing chart in a read mode of the DRAM sub chips illustrated in FIG. 42;

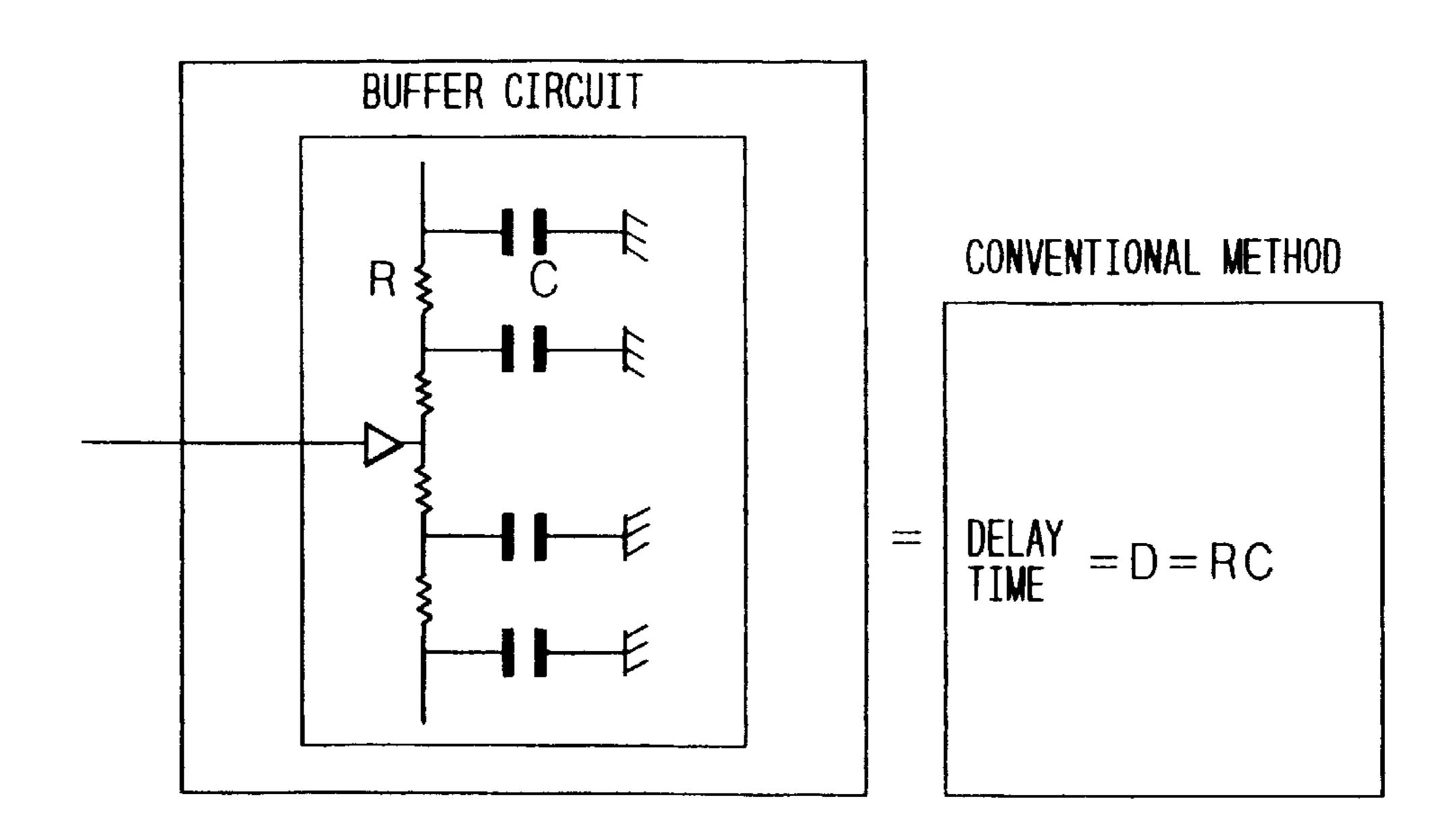

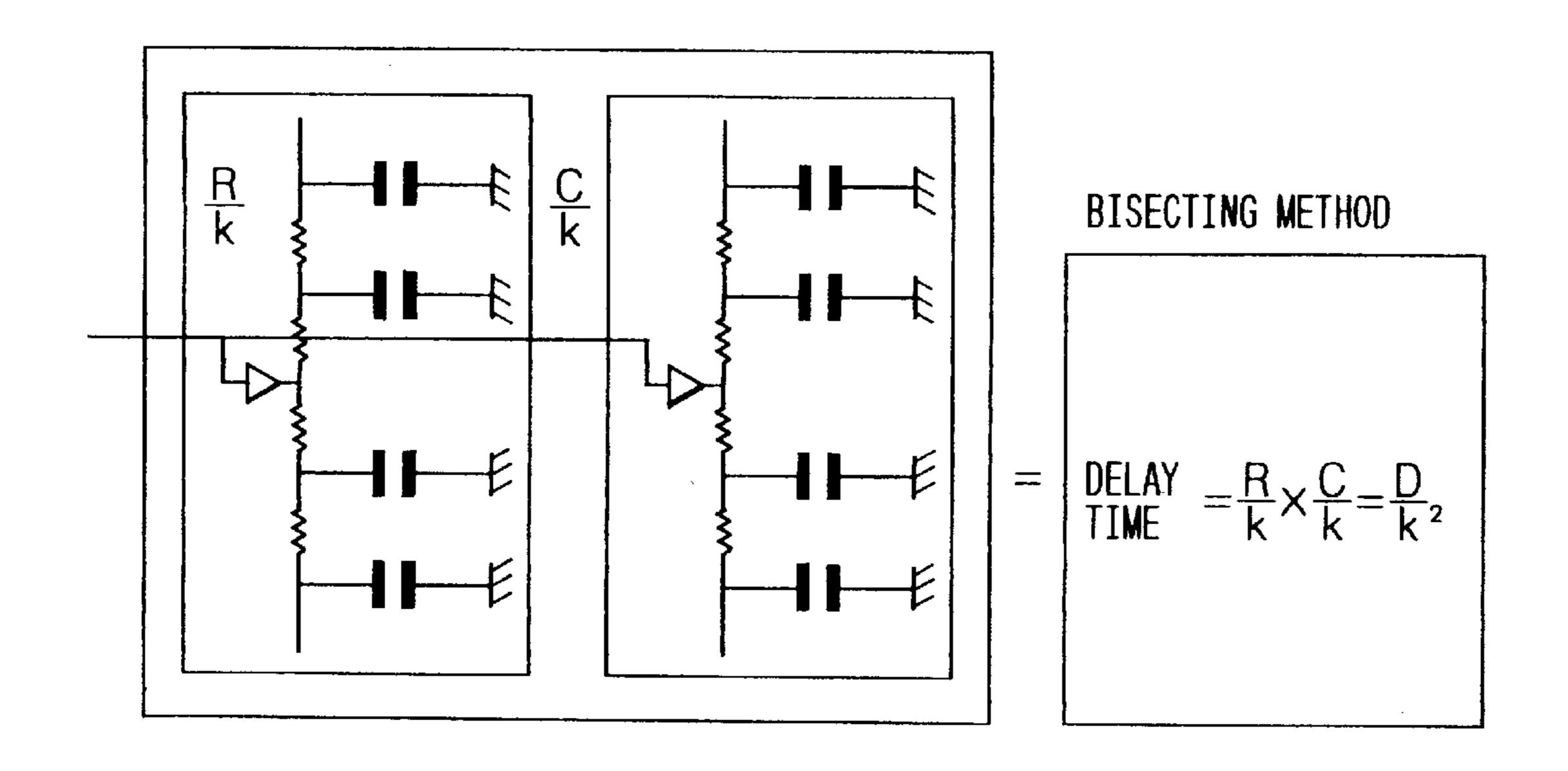

- FIG. 45 is a partial signal system diagram in a conventional DRAM package;

- FIG. 46 is a partial signal system diagram in the DRAM package of FIG. 1;

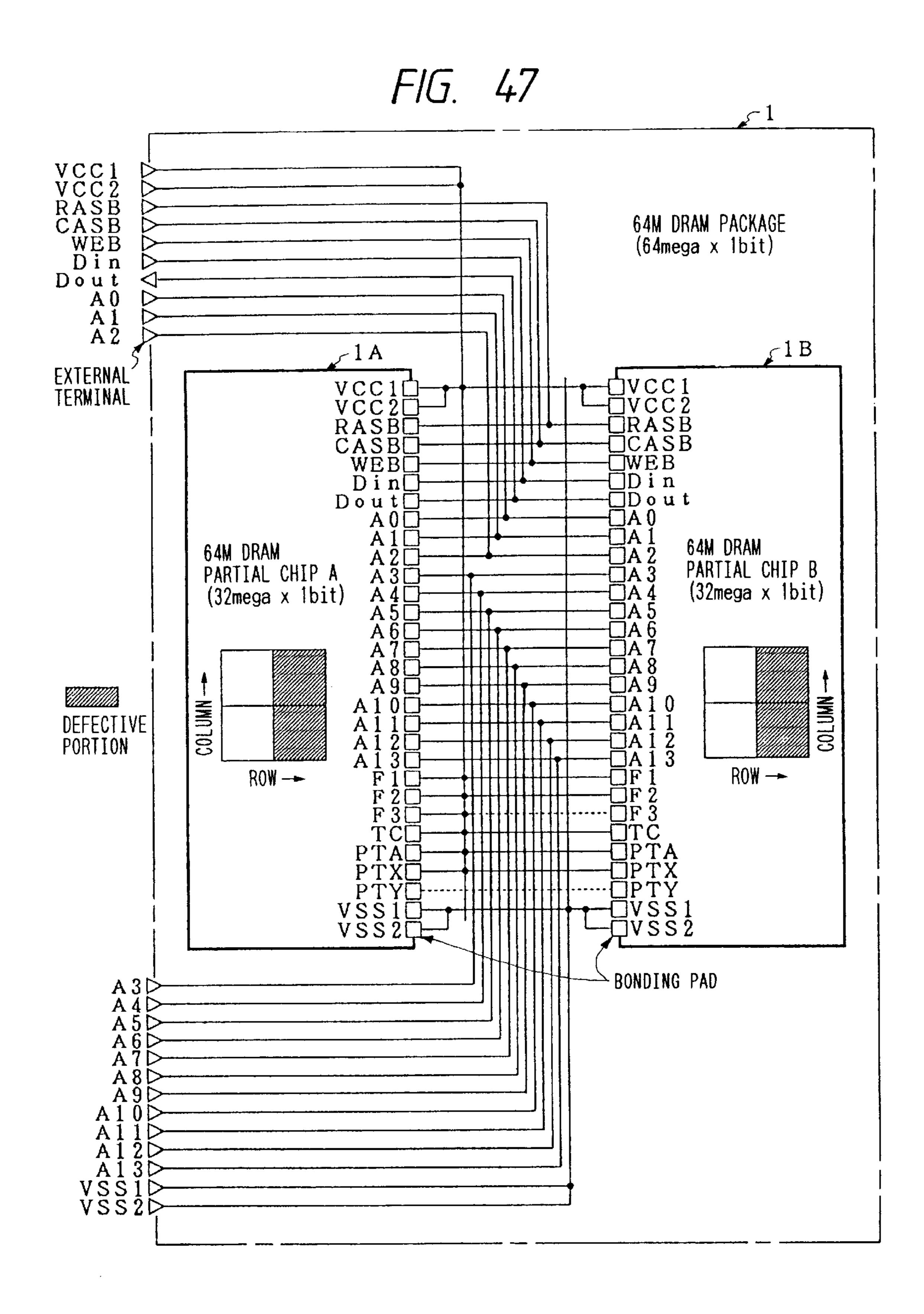

- FIG. 47 is a block diagram showing a first example of a 64M DRAM package consisting of two DRAM partial chips according to the invention;

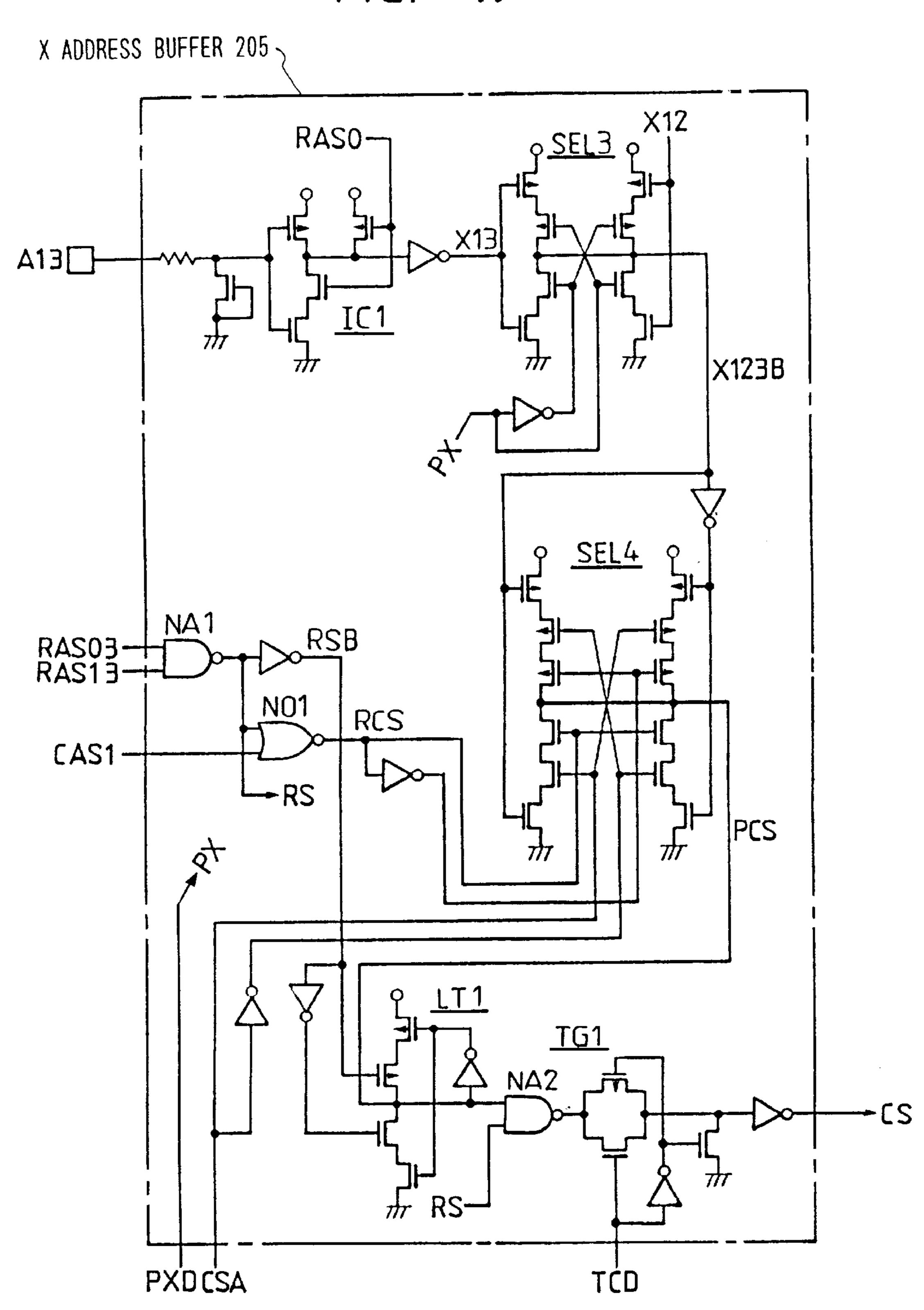

- FIG. 48 is a partial circuit diagram of an X address buffer included in the DRAM package of FIG. 47;

- FIG. 49 is another partial circuit diagram of the X address buffer included in the DRAM package of FIG. 47;

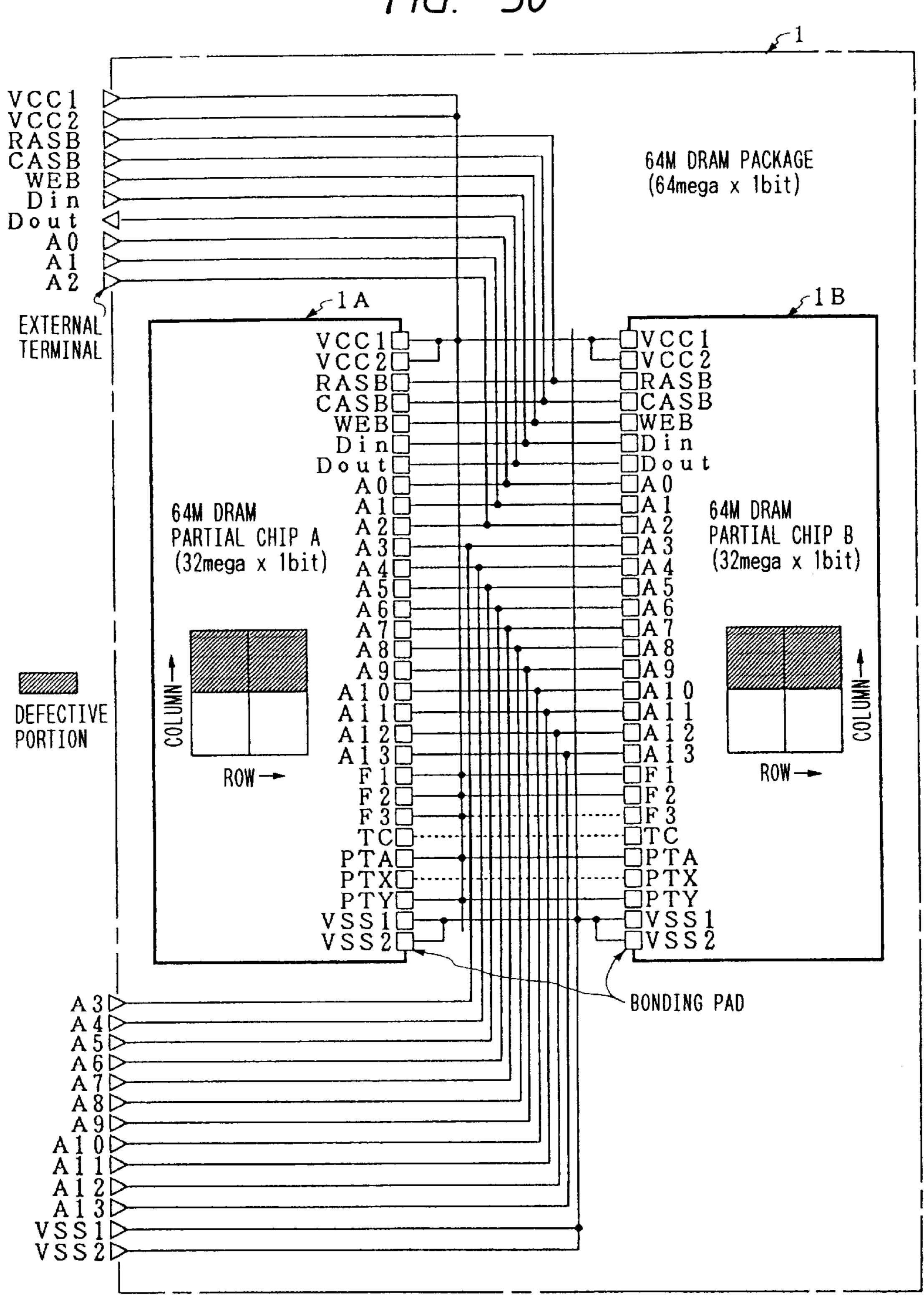

- FIG. 50 is a block diagram showing a second example of a 64M DRAM package consisting of two DRAM partial chips according to the invention;

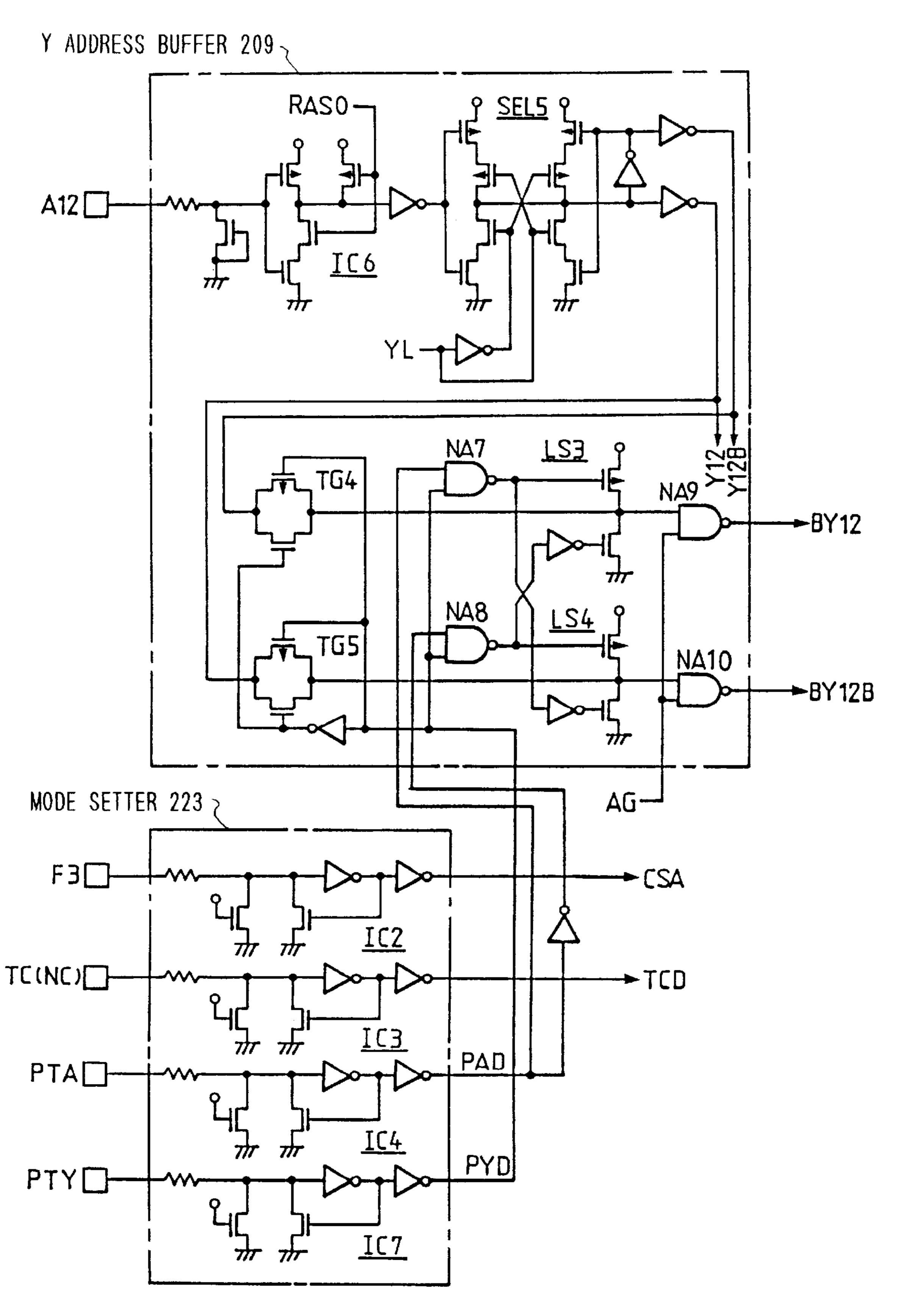

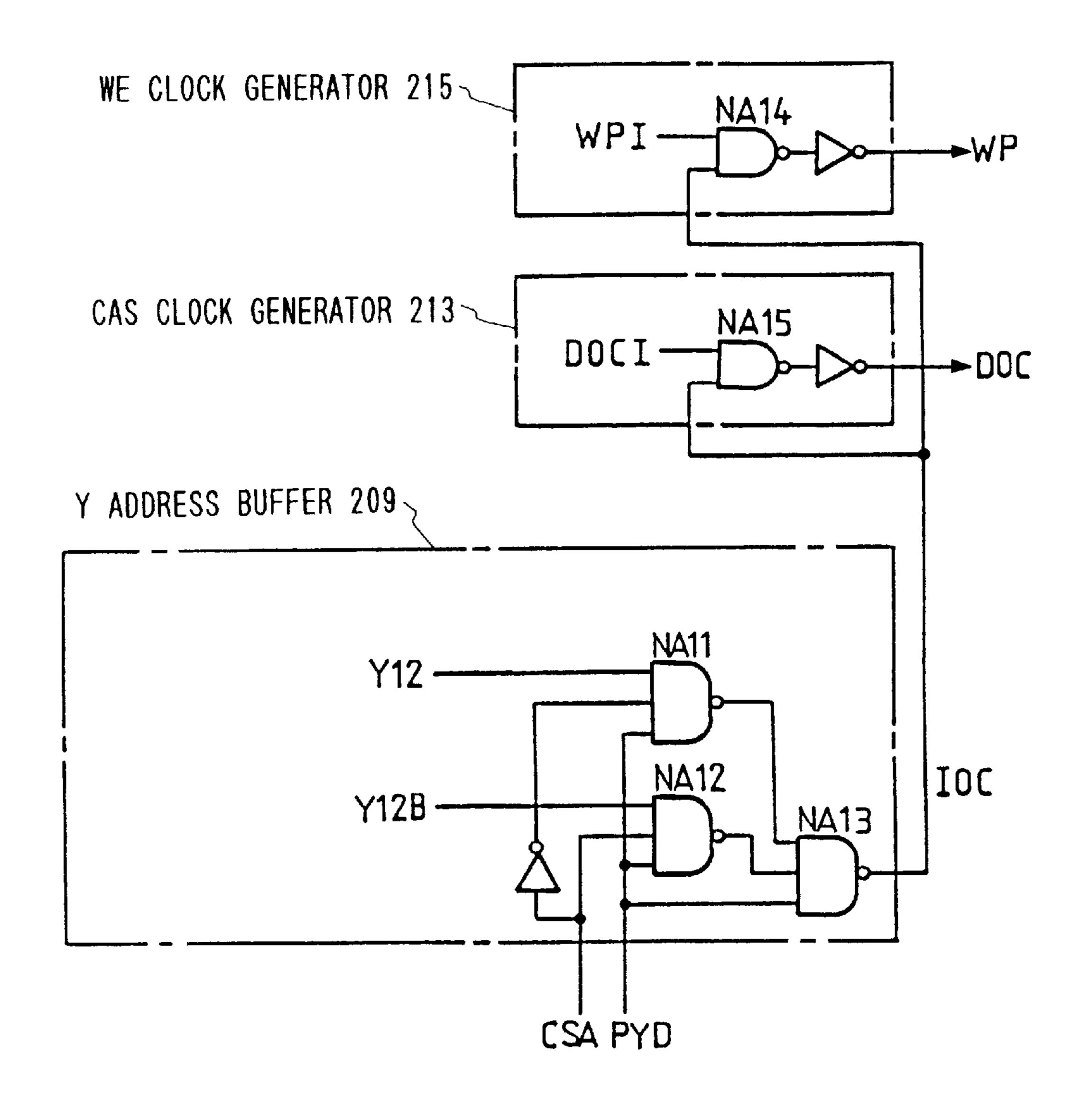

- FIG. 51 is a partial circuit diagram of a Y address buffer included in the DRAM package of FIG. 50;

- FIG. 52 is another partial circuit diagram of the Y address buffer included in the DRAM package of FIG. 50;

- FIG. 53 is a list of connections, showing bonding options of the DRAM partial chips shown in FIGS. 47 and 50;

FIG. **54** is a list of products, showing variations of a 64M DRAM package consisting of two DRAM partial chips;

FIG. 55 is a block diagram showing a third example of a 64M DRAM package consisting of two DRAM partial chips according to the invention;

FIG. **56** is a block diagram showing a fourth example of a 64M DRAM package consisting of two DRAM partial chips according to the invention;

FIG. 57 is a block diagram showing a fifth example of a 64M DRAM package consisting of two DRAM partial chips according to the invention;

FIG. **58** is a block diagram showing a sixth example of a 64M DRAM package consisting of two DRAM partial chips according to the invention;

FIG. 59 is a block diagram showing a seventh example of a 64M DRAM package consisting of two DRAM partial chips according to the invention;

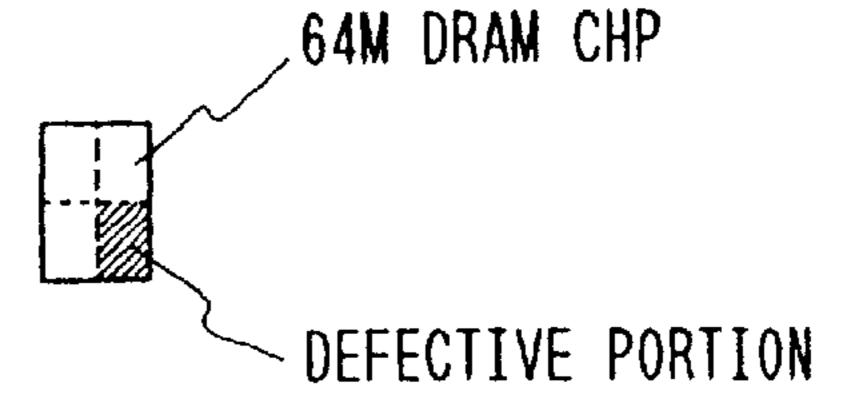

FIG. 60 is a plan view showing an example of a wafer from which a DRAM chip is formed;

FIG. 61 is a block diagram showing an example of a DRAM package consisting of two function-divided sub chips;

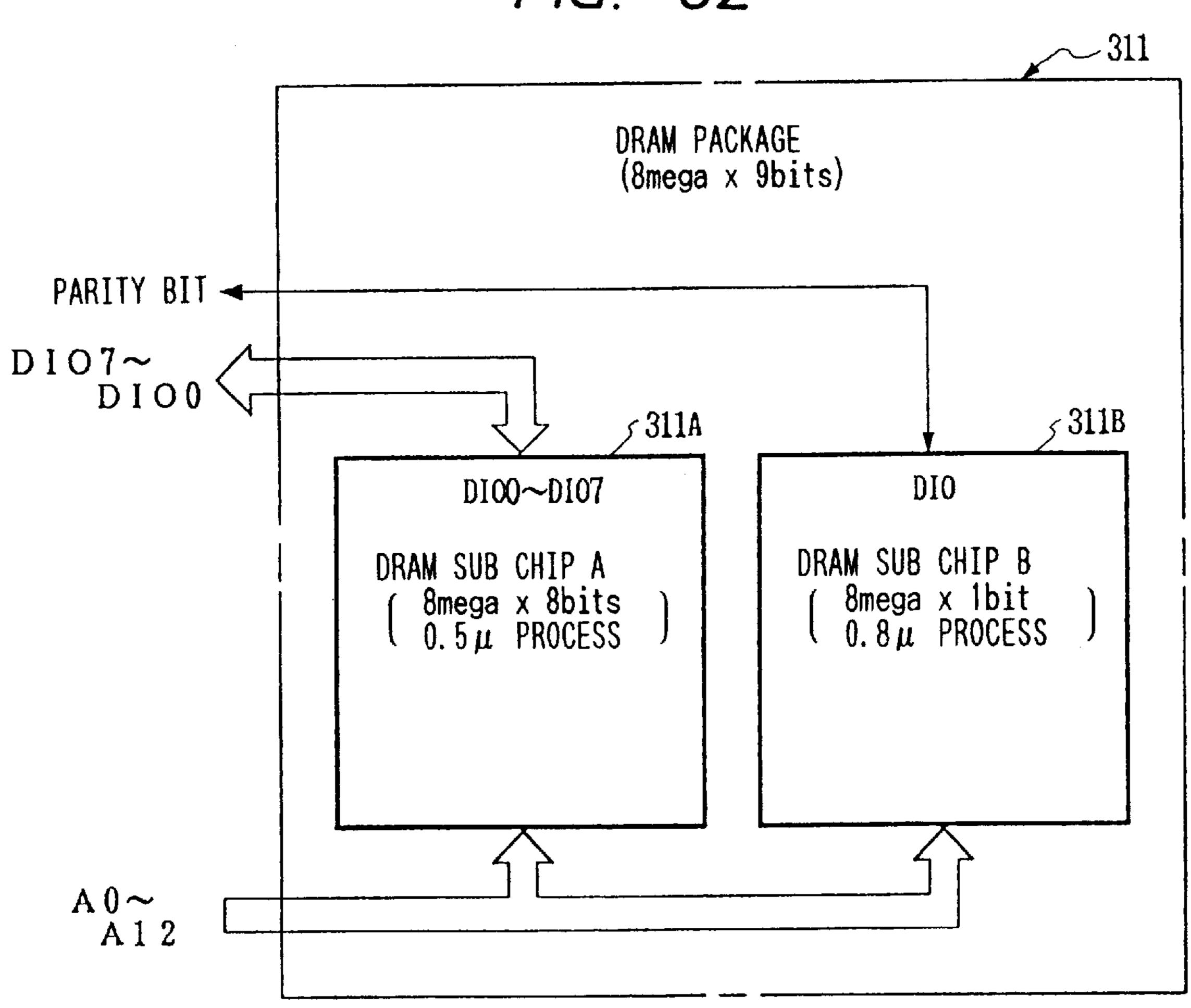

FIG. 62 is a block diagram showing an example of a DRAM package consisting of two bit-divided sub chips;

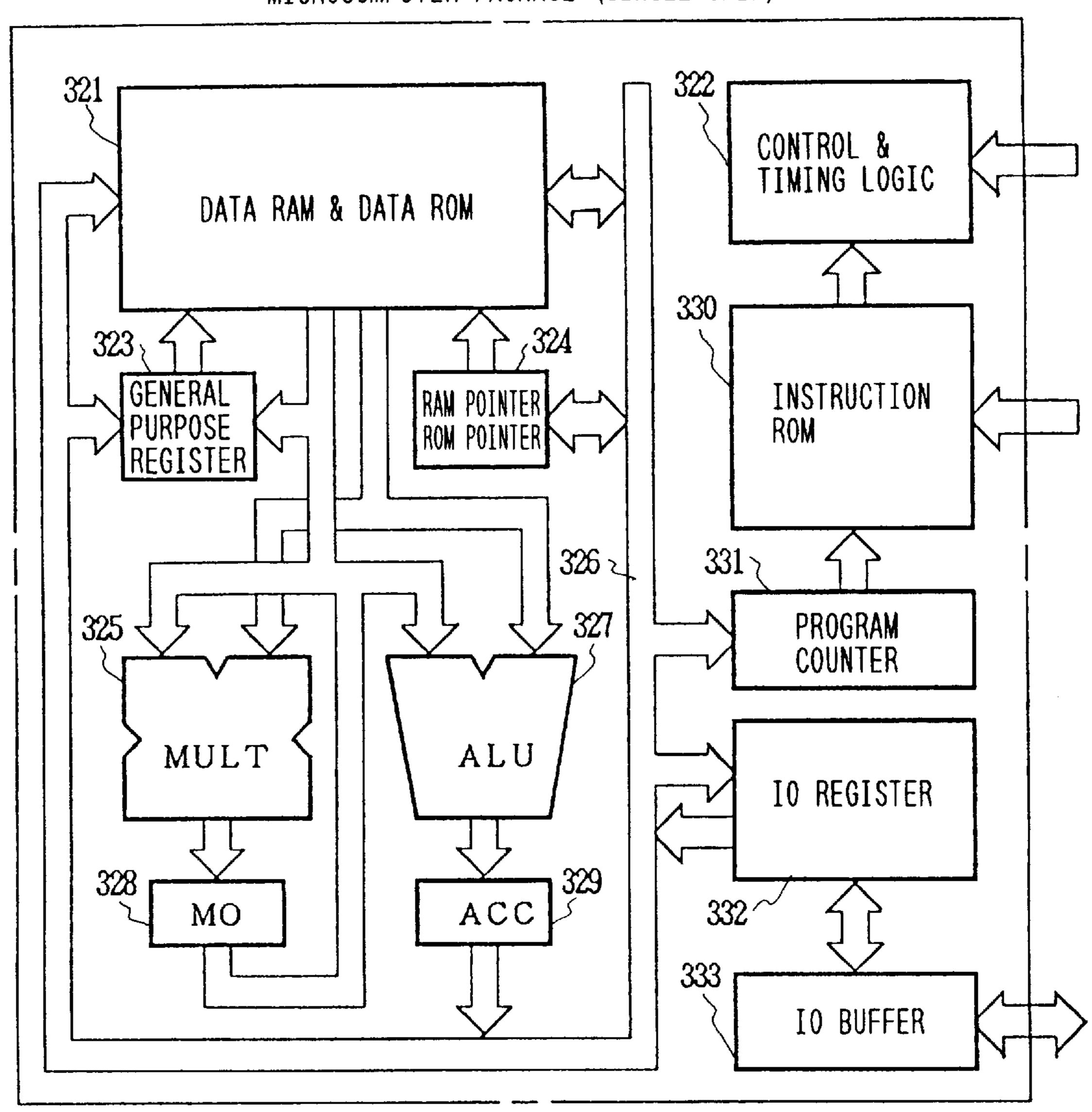

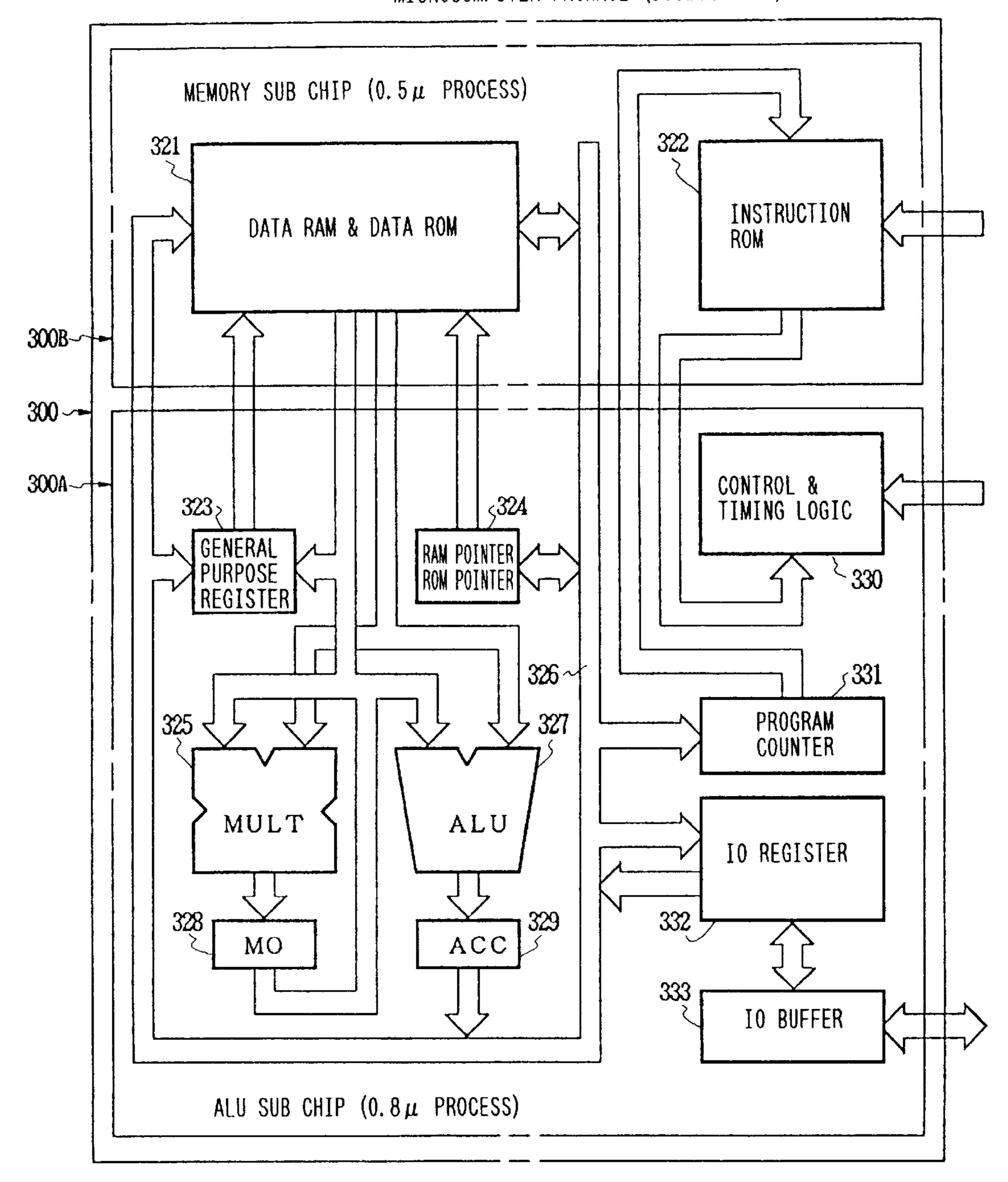

FIG. 63 is a block diagram showing an example of a conventional microcomputer package;

FIG. **64** is a block diagram showing an example of a microcomputer package consisting of two function-divided 30 sub chips;

FIG. 65 is a plan view of a substrate in a conventional multi-chip module;

FIG. 66 is a structural sectional view showing another example of a conventional multi-chip module; and

FIG. 67 is a structural sectional view showing a further example of a conventional multi-chip module.

## DESCRIPTION OF PREFERRED EMBODIMENTS

1. 128M DRAM Package according to Double Chip Packaging Method

#### 1.1. Outline of DRAM Package

FIG. 1 is a block diagram showing an example of a 128M ("M" or "mega" is assumed equal to the twentieth power of 2 herein) DRAM package according to the present invention, and FIG. 2 is a timing chart in the said DRAM package. With reference to these figures, an outline of this DRAM package and an explanation of a chip selecting method will first be given below. The chip mounting method according to the present invention will herein be designated a double chip packaging method. For a specific description of the double chip packaging method and features thereof, see "1.4. Package Form of DRAM Package."

#### 1.1.1. Block Configuration

A DRAM package 1 according to this embodiment includes two DRAM sub chips 1A and 1B. These sub chips each have a memory capacity of 64 mega. Write data and read data are inputted or outputted each in the unit of one bit through a data input terminal Din or a data output terminal 60 Dout. The sub chips A and B adopt a so-called multiplex method, wherein the address space is designated alternatively in accordance with 13-bit X address signals (row address signals) X0 to X12 and Y address signals (column address signals) Y0 to Y12 which are fed time-sharingwise 65 through thirteen address input terminals A0 to A12. Data input pads Din and data output pads Dout of the sub chips

6

A and B are connected in common to a data input terminal Din and a data output terminal Dout, respectively, of the DRAM package, and address input pads A0 to A13 are connected in common to address input terminals A0 to A13, respectively, of the DRAM package.

As start control signals, a row address strobe signal RASB (as to an inversion signal or inversion signal line whose level is rendered low when it is made effective, the mark "B" is attached to the end of the name, and this will apply also in 10 the following) and a column address strobe signal CASB, as well as a write enable signal WEB, are fed to the DRAM sub chips A and B from external terminals RASB and CASB as well as WEB through corresponding bonding pads. An X address signal X13 as a chip selection signal is fed from an 15 address input terminal A13 through a corresponding bonding pad, and an external source voltage VCC is fed from two external terminals VCC1 and VCC2 through corresponding bonding pads VCC1 and VCC2. Further, an earth potential of the circuit is fed from external terminals VSS1 and VSS2 20 through corresponding bonding pads VSS1 and VSS2. The external source voltage VCC is set at a positive voltage like +5V for example, and as will be described later, it is lowered by a voltage dropping section of each of the sub chips A and B, then serves as a source voltage for the operation of each sub chip.

#### 1.1.2. Chip Selecting Method

When the row address strobe signal RASB and the column address strobe signals CASB are made low in level, the sub chips A and B are selectively brought into a selected state, and the operation mode thereof is set in accordance with a logical level of the write enable signal WEB. To the address input terminals A0–A12 are fed X address signals X0–X12 in synchronism with the trailing edge of the row address strobe signal RASB, while Y address signals Y0–Y12 are fed in synchronism with the trailing edge of the column address strobe signal CASB, as shown in FIG. 2.

In this embodiment, moreover, the selected state of the sub chip A and that of the sub chip B are selectively designated in accordance with a logical level of the chip 40 selection signal, i.e., the X address signal X13. More specifically, when the level of the X address signal X13 is made low, the level of an internal control signal CS in the sub chip A is made high to select the sub chip A in the DRAM package, as indicated by solid line in FIG. 2. On the other hand, when the level of the X address signal X13 is made high, the level of an internal control signal CS in the sub chip B is rendered high to select the sub chip B, as indicated by dotted line in FIG. 2. Thus, the 64M DRAM sub chips A and B are selected in an alternative manner, with the result that the DRAM package possesses a memory capacity twice that of each sub chip, namely, 128 megax1 bit. Since the sub chips A and B are selected alternatively, the power consumption of the DRAM package is relatively small, corresponding to the power consumption of one of the two 55 sub chips.

#### 1.2. Outline of DRAM Sub Chips

FIG. 3 tabulates a standard specification of 64M DRAM sub chips which constitute the DRAM package of FIG. 1; FIG. 4 is a block diagram showing an example thereof; FIG. 5 is a substrate layout view of the 64M DRAM sub chip shown in FIG. 4; and FIG. 6 is an address allocation diagram in the same sub chip. With reference to these figures, the following description is now provided about a concrete configuration and specification of the 64M DRAM sub chips A and B which constitute the DRAM package of this embodiment as well as an address selecting method and an outline of operation. In the description of this chapter there

will be made no distinction between the sub chips A and B because both are basically of the same configuration.

1.2.1. Standard Specification

The 64M DRAM sub chips in this embodiment can each take three kinds of bit configurations which are 64 5 megawords×1 bit (hereinafter referred to simply as, for example, "64 mega×1 bit"), 16 mega×4 bits and 8 mega×8 bits because bonding to predetermined pads is executed selectively, as shown in FIG. 3. When the sub chip has a bit configuration of 64 mega×1 bit, the address space thereof is 10 designated alternatively by the 13-bit X address signals X0-X12 and Y address signals Y0-Y12 in the manner described above. On the other hand, when the sub chip has a bit configuration of 16 mega×4 bits, the address space thereof is designated alternatively by the 13-bit X address 15 signals X0–X12 and 11-bit Y address signal's Y0–Y10. Further, when the sub chip has a bit configuration of 8 megax8 bits, the address space thereof is designated alternatively in accordance with the 13-bit X address signals X0-X12 and 10-bit Y address signals Y0-Y9. Thus, in the 20 64M sub chips in this embodiment, a row address space is always designated by 13-bit X address signals, and a refresh cycle thereof is unified to 8 kilo ("kilo" is assumed equal to the tenth power of 2 herein) cycle with a period of 64 ms (millisecond=½1000 second).

As the packaging form of the 64M DRAM sub chip there is adopted a so-called SOJ (Small Out-line J-bend) type package, and an external size thereof is set at 300 mil'850 mil (mil=1/1000 inch) though it is not specially limited. A maximum of 32 pins, or external terminals, are provided in 30 the package. For the sub chip there is adopted an address multiplex method as mentioned previously, and a row address thereof is designated by 13-bit X address signals X0-X12 irrespective of bit configuration. Therefore, the number of pins used as address input terminals is fourteen, 35 including the X address signal X13 serving as a chip selection signal, irrespective of the bit configuration of the sub chip. On the other hand, when the sub chip has a bit configuration of 64 mega×1 bit, write data and read data are inputted or outputted in the unit of one bit through the data 40 input terminal Din or the data output terminal Dout, as noted previously. When the sub chip has a bit configuration of 16 mega×4 bits or 8 mega×8 bits, write data and read data are inputted or outputted in the unit of 4 or 8 bits through common data input-output terminals DIO0 to DIO3 or DIO0 45 to DIO7. At this time, an output enable signal OEB for setting an output timing of read data is fed to the sub chip, and the number of pins provided for the supply of start control signals or clocks is four. Consequently, the total number of pins used in each sub chip is 23 in the bit 50 configuration of 64 mega×1 bit, 26 in the bit configuration of 16 megax4 bits, 32 in the bit configuration of 8 megax8 bits.

The 64M DRAM sub chips are each provided with a predetermined test mode and a parallel test function of 55 comparing and collating 8-bit storage data read out simultaneously, with given expected value data in the said test mode. At this time, the results of the parallel test are outputted in common from all the output or input-output terminals. The sub chips are each provided with a high-speed column mode, or Fast Page mode, as well as Static Column mode and Nibble mode, for continuously inputting or outputting storage data with respect to plural memory cells connected to selected word lines. Nibble mode is made effective when the sub chip has a bit configuration of 64 65 mega×1 bit, and it inputs or outputs a maximum of 32 bits of storage data continuously. Fast Page mode and Static

8

Column mode are made effective in any bit configuration and can input or output a maximum of 8 K bits, i.e., 8192 bits, continuously.

1.2.2. Block Configuration

The 64M DRAM sub chips in this embodiment have each a memory array 201 as a basic configuration wherein the address space comprises 8K, or 8192, row addresses and column addresses, as shown in FIG. 4. This memory array includes 8192 word lines disposed substantially in parallel with the vertical direction in the same figure and corresponding to the row addresses and 8192 sets of complementary bit lines disposed in parallel with the horizontal direction and corresponding to the column addresses. At the intersecting points of these word lines and complementary bit lines there are disposed 8192×8192, or 67108864, i.e., 64M, dynamic memory cells in a lattice shape. Thus, the sub chip has a memory capacity of 64 megabits. As will be described later, a memory array in each DRAM sub chip of this embodiment is actually divided into four memory blocks, which are each further divided into four mats each consisting of four sub arrays. The following description on the block configuration will be made on the assumption that the memory array is a single memory array.

The word lines which constitute the memory array 201 are connected to an X address decoder 203 through a word driver 202. Predetermined predecoded signals are fed to the X address decoder from an X predecoder 204, and also fed thereto is an internal control signal XDG from a RAS2 clock generator 210. To the X predecoder are fed internal address signals BX0–BX12 from an X address buffer 205, and also fed thereto is an internal control signal CS which is formed on the basis of the X address signal X13. Further, X address signals X0–X13 are fed to the X address buffer timesharingwise through address input pads A0–A13, and also fed thereto are internal control signals TCD and CSA from a mode setter 223.

The X address buffer **205** takes therein the X address signals X**0**–X**13** which are fed time-sharingwise through the address input pads A**0**–A**13**, and on the basis of these X address signals the X address buffer forms the internal address signals BX**0**–BX**12** and the internal control signal CS. The internal control signal CS is fed to the X predecoder **204**, RAS**2** clock generator **210**, write amplifier **218** and data output buffer **221** and is used as a so-called chip selection signal for operating these blocks selectively. In this embodiment, as will be described later, a logical condition for making the level of the internal control signal CS high is changed over selectively by selective execution of bonding to the internal control signals CSA and TCD, i.e., pads F**1** to F**3** and TC. As to these bonding options, see "1.5. Bonding Options of DRAM Sub Chips."

The X predecoder 204 decodes the internal address signals BX0–BX12 fed from the X address buffer 205, in combination of two or three bits at a time to form predetermined predecoded signals. These predecoded signals are fed to the X address decoder 203 and some of them are used for activating the memory blocks, mats and sub arrays selectively. The predecoder 204 is operated selectively in accordance with the internal control signal CS fed from the X address buffer, whereby the waste operating current is cut down when the sub chip is brought into an unselected state and thus the reduction in power consumption of the DRAM package is attained.

The X address decoder 203 combines the predecoded signals fed from the X predecoder 204 to form selection signals for selecting corresponding word lines of the memory array in an alternative manner. These selection

signals are transferred to corresponding word lines of the memory array through the word driver 202, whereby the corresponding word lines are brought into a predetermined selection level. As well known, when the the word lines are brought into the selection level, the 8192 memory cells connected to the word lines are brought into the selected state all together, and the data held therein are outputted to the corresponding complementary bit lines. If these data are left as they are, they will be destroyed, but their signal amplitudes are amplified to a predetermined level by corre- 10 sponding unit amplifier circuits of the sense amplifier 206, whereby the data are rewritten into the corresponding memory cells. In the DRAM sub chips, when the 8192 unit amplifier circuits of the sense amplifier 206 are operated all together, a relatively large operating current is required. 15 Therefore, whether each sub chip is activated or not is judged by whether the sense amplifier is brought into an operating state or not, in other words, whether the word line selecting operation is performed or not. Needless to say, it is important in reducing the power consumption that the sub 20 chip which is brought into an unselected state not be activated. However, at some particular input timing of a chip selection signal there arises the case where the two sub chips which constitute the DRAM package must be activated at a time. In this case, only the storage data inputting or output- 25 ting operation is executed selectively by the write amplifier 218 or the data output buffer 221 in accordance with the internal control signal CS.

Next, the complementary bit lines of the memory array are connected to the corresponding unit amplifier circuits of 30 the sense amplifier 206 and further connected to a common IO line 217 through corresponding MOSFET switches. The sense amplifier 206 includes 8192 unit amplifier circuits provided in corresponding relation to the complementary bit lines of the memory array and the same number of switch 35 MOSFET pairs. The unit amplifier circuits of the sense amplifier are operated selectively and all together by a predetermined internal control signal (not shown) fed from the RAS2 clock generator 210. In this operating state, the unit amplifier circuits amplify fine read signals which are 40 outputted through the corresponding complementary bit lines of the memory array 201 from the 8192 memory cells connected to the selected word lines, to provide binary read signals of high or low level. On the other hand, to the switch MOSFET pairs of the sense amplifier are fed bit selection 45 signals from the Y address decoder 207. These MOSFET switches are turned ON selectively when the corresponding bit line selection signals are rendered high in level, to selectively connect the corresponding complementary bit lines of the memory array with the common IO line 217.

To the Y address decoder 207 are fed predecoded signals from a Y predecoder 208 and also fed is an internal control signal YDG from a CAS clock generator 213. To the Y predecoder 208 are fed internal address signals BY0–BY12 from a Y address buffer 209, while to the Y address buffers 55 209 are fed Y address signals Y0–Y12 time-sharingwise through the address input pads A0–A12.

The Y address buffer 209 takes therein the Y address signals Y0–Y12 which are fed time-sharingwise through the address input pads A0–A12, then on the basis of these Y 60 address signals it forms internal address signals BY0–BY12 and supplies them to the Y predecoder 208. The Y predecoder 208 decodes the internal address signals BY0–BY12 by combining them in the unit of two or three bits at a time to form predetermined predecoded signals and supplies 65 these predecoded signals to the Y address decoder 207, which in turn combines these predecoded signals to make

10

the level of the corresponding bit line selection signals high in an alternative manner.

The common IO line 217 for connecting designated complementary bit lines of the memory array 201 selectively is connected to an output terminal of the write amplifier 218 and also connected to an input terminal of a main amplifier 220. An input terminal of the write amplifier 218 is connected to an output terminal of a data input buffer 219, while an input terminal of this data input buffer is connected to the data input pad Din. To the write amplifier 218 is fed the internal control signal CS and also fed is an internal control signal WP from a WP clock generator 215. On the other hand, an output terminal of the main amplifier 220 is connected to an input terminal of the data output buffer 221, and an output terminal of the data output buffer 221 is connected to the data output pad Dout. To the data output buffer 221 is fed to an internal control signal DOC from the CAS clock generator 213.

When the DRAM sub chips are each brought into a selected state in the write mode, the data input buffer 219 transfers write data fed through the data input pad Din, to the write amplifier 218. The write amplifier 218 is operated selectively when the DRAM sub chip is brought into a selected state in the write mode and the internal controls signals CS and WP are made high in level. In this operating state, the write amplifier forms a predetermined complementary write signal on the basis of the write data transferred from the data input buffer 219 and writes it into one selected memory cell in the memory array 201 through the common IO line 217. On the other hand, when the DRAM sub chip is brought into a selected state in the read mode, the main amplifier 220 further amplifies a read signal which is outputted through the common IO line 217 from one selected memory cell in the memory array 201, and transfers it as read data to the data output buffer 221. The data output buffer 221 is operated selectively when the DRAM sub chip is brought into a selected state in the read mode and the level of the internal control signal DOC is made high. In this operating state, the data output buffer 221 transmits the read data provided from the main amplifier 220 to the exterior of the sub chip through the data output pad Dout. Thus, in the DRAM sub chip of this embodiment, the write amplifier 218 and the data output buffer 221 are operated selectively in accordance with the internal control signal CS serving as a chip selection signal, whereby the storage data inputting or outputting operation is executed selectively.

The DRAM sub chip is further provided with, as components of the control circuit, RAS buffer 212, RAS1 clock generator 211, RAS2 clock generator 210, CAS buffer 214, CAS clock generator 213, WE buffer 216 and WE clock generator 215, as well as mode setter 223 and voltage dropping section 222. To the RAS buffer 212 is fed a row address strobe signal RASB through the input pad RASB, and an output signal from the RAS buffer 212 is fed to the RAS1 clock generator 211. An output signal from the RAS1 clock generator is fed to the RAS2 clock generator 210 and also fed to predetermined portions of the sub chip. Further fed to the RAS2 clock generator 210 is the internal control signal CS, and an output signal from the RAS2 clock generator 210 is fed as an internal control signal XDG to the X address decoder 203 and also fed to predetermined portions of the sub chip. On the basis of the row address strobe signal RASB inputted through the RAS buffer 212 the RAS1 clock generator 211 and the RAS2 clock generator 210 form various internal control signals necessary for the word line selecting operation and the control of the sense amplifiers 206. As mentioned previously, the operation of

the RAS2 clock generator 210 is controlled by the internal control signal CS. As a result, the operations of the X address decoder 203, word driver 202 and sense amplifier 206 are executed selectively, whereby the sub chip is activated selectively.

On the other hand, to the CAS clock generator 213 is fed a column address strobe signal CASB through the input pad CASB, and an output signal from the CAS clock generator 213 is fed to the Y address decoder 207 and the data output buffer 221 as internal control signals YDG and DOC, 10 respectively, and also fed to predetermined portions of the sub chip. On the basis of the column address strobe signal CASB inputted through the CAS buffer 214 the CAS clock generator 213 forms various internal control signals necessary for the complementary bit line selecting operation and 15 for the control of the main amplifier 220 and data output buffer 221. Likewise, to the WE buffer 216 is fed a write enable signal WEB through the input pad WEB, and an output signal from the WE buffer 216 is fed to the WE clock generator 215. Further, an output signal from the WE clock 20 generator 215 is fed as an internal control signal WP to the write amplifier 218 and also fed to predetermined portions of the sub chip. On the basis of the write enable signal WEB inputted through the WE buffer 216 the WE clock generator 215 forms an internal control signal WE, etc. necessary for 25 the control of the write amplifier 218.

To the mode setter 223 are fed a predetermined mode control signals through the pads F1–F3 and TC, and output signals from the mode setter 223 are fed as internal control signals CSA and TCD to the X address buffer 205. On the 30 basis of the mode control signals fed through the pads F1–F3 and TC the mode setter 223 forms various internal control signals for setting the bit configuration of the sub chip and chip selecting conditions. On the other hand, the voltage dropping section 222 forms a predetermined internal source 35 voltage VCL on the basis of external source voltages VCC fed through the source voltage input pads VCC1 and VCC2, and supplied it as an operating power to various portions of the sub chip. The internal source voltage VCL is set at a positive voltage of a relatively small absolute value such as 40 +3.3 V for example.

#### 1.2.3. Basic Layout

In each of the 64M DRAM sub chips according to this embodiment, the memory array 201 is divided into four memory blocks 0-3, which are further divided into four mats 45 0-3 each consisting of four sub arrays 0-3. The sub arrays 0–3 constituting each memory block and mat are disposed to extend the word lines in the direction of X axis of the semiconductor substrate surface, i.e., in the shorter side direction, as shown in FIG. 5, and a sense amplifier (not 50) shown) is disposed between two adjacent sub arrays 0 and 1 and also between sub arrays 2 and 3. In corresponding relation to each of these sense amplifiers there are provided two sets of common IO lines 217. Inside the sub arrays 0–3 there are disposed corresponding word driver 202 and X 55 address decoder 203. The mats 0–3 which constitute each memory block form pairs each consisting of two mats, and a Y address decoder 207 is disposed between the mats of each pair. These Y address decoders are used in common by two mats on both sides, namely, eight sub arrays. In an 60 intermediate portion of each memory block there is disposed a read-write circuit including a write amplifier 218 and a main amplifier 220. Centrally in the direction of Y axis, 1.e., in the longer side direction, of the semiconductor substrate surface there are disposed a plurality of bonding pads, i.e. 65 external terminals of the DRAM sub chip, in a straight line form. As will be described rarer, the paired sub chips A and

12

B which constitute the DRAM package are mounted in opposed relation to each other. By this central, linear arrangement of the bonding pads, not only a planar symmetry of the bonding pads can be ensured but also the chip mounting method based on the conventional LOC (Lead On Chip) method can be applied. The basic layout of FIG. 5 does not restrict the layout size of each portion or an absolute number of bonding pads.

In this embodiment, though not specially limited, the subarrays **0–3** substantially include 512 word lines and 2048 sets of complementary bit lines, each having a memory capacity of 1 megabits. That is, each mat has a memory capacity of 1M×4 bits, i.e., 4 megabits, and each memory block has a memory capacity of 4M×4, i.e., 16 megabits. Thus, the DRAM sub chips each have a memory capacity of 16M×4, i.e., 64 megabits. In this embodiment, as indicated by hatched lines in FIG. 5, when the DRAM sub chip is brought into a selected state, four sub arrays are activated simultaneously and two sets, a total of eight sets, of complementary bit lines adjacent to the four sub arrays are connected selectively to two sets, a total of eight sets, of common IO lines. That is, each read-write circuit includes two, a total of eight, write amplifiers 218 and main amplifiers 220 which are provided in correspondence to those common IO lines. These write amplifiers and main amplifiers are operated in predetermined combinations, whereby the bit configuration of the DRAM sub chip is changed over selectively.

#### 1.2.4. Address Assignment

To the DRAM sub chip are fed 13-bit X address signals X0-X12 and Y address signals Y0-Y12, as mentioned above, and the address space of the sub chip is designated selectively. In this embodiment, though not specially limited, the 512 word lines which constitute the sub arrays 0–3 are designated in an alternative manner in accordance with 9-bit X address signals X0–X8, while the 2048 sets of complementary bit lines are designated in an alternative manner in accordance with 11-bit Y address signals Y0-Y10, as shown in FIG. 6. The four sub arrays 0-3 which constitute each mat are designated in an alternative manner in accordance with 2-bit X address signals X9 and X10, while the four mats 0-3 which constitute each memory block are designated in an alternative manner in accordance with 1-bit X address signal X11 and Y address signal Y11. Further, the four memory blocks 0-3 are designated in an alternative manner in accordance with 1-bit X address signal X12 and Y address signal Y12.

As to the 2048 sets of complementary bit lines which constitute each sub array, as mentioned above, two adjacent sets are brought into a selected state simultaneously, but are substantially designated in an alternative manner in accordance with Y address signals Y0–Y8 because the two corresponding main amplifiers are selected in accordance with Y address signal Y0. Actually, the selection of memory blocks 0–3 by the most significant bit X and Y address signals X12, Y12 is also realized by the selection of corresponding main amplifiers.

#### 1.2. Variations of DRAM Package

In FIG. 7 there is illustrated a list of 128M DRAM package products comprising the 64M DRAM sub chips shown in FIGS. 3 to 6. FIGS. 8 to 12 are block diagrams of the DRAM packages shown in the product list of FIG. 7. With reference to these figures, the following description is now provided about the kind, configuration and outline of 128M DRAM packages each capable of being constituted by two 64M DRAM sub chips. In the block diagrams of FIGS. 8 to 12 there are shown only address signals and signal lines relating to input and output data.

1.3.1. Kind of 128M DRAM Packages Capable of Being Constituted

The 64M DRAM sub chips in this embodiment can each take three kinds of bit configurations of 64M×1 bit, 16M×4 bits and 8M×8 bits because prescribed bondings are executed selectively, as noted previously. By combining the two DRAM sub chips of the same bit configuration and accessing them simultaneously or selectively it is possible to configure a total of six kinds of 128M DRAM packages which are shown in FIG. 7. The 128M×1 bit DRAM package constituted by combining two 64M×1 bit DRAM sub chips and accessing these sub chips selectively in accordance with a chip selection signal, i.e., X address signal X13, corresponds to the embodiment shown in FIG. 1, will not be explained here.

1.3.2. Outline of Various DRAM Packages

(1) 64M×2 bit DRAM package wherein two 64M×1 bit DRAM sub chips are accessed simultaneously:

Such a 128M DRAM package of 64M×2 bits as shown in FIG. 8 can be constituted by combining two 64M DRAM sub chips A and B each having a bit configuration of 64M×1 20 bit and then accessing these sub chips simultaneously. In this variation, 13-bit X address signals X0-X12 and Y address signals Y0-Y12 are fed to address input pads A0-A12 of the sub chips A and B in common and time-sharingwise, and data input and output pads Din, Dout are connected to 25 corresponding data input terminals Din1, Din2 and data output terminals Dout1, Dout2 of the DRAM package. As a result, the sub chips A and B are brought into a selected state simultaneously and execute storage data inputting and outputting operations in the unit of 1 bit and in parallel. Thus, 30 the DRAM package has a bit configuration of 64M×2 bits, wherein 2-bit storage data are inputted or outputted simultaneously. At this time, refresh operations for the sub chips are also executed in parallel, the refresh cycle of DRAM package becomes 8 K cycle/64 ms. It goes without saying 35 that the power consumption of the DRAM package as a whole is about twice that of the 64M DRAM sub chips.

(2) 32M×4 bit DRAM package wherein two 16M×4 bit DRAM sub chips are accessed selectively:

By combining two 64M DRAM sub chips A and B each 40 having a bit configuration of 16M×4 bits and then accessing these sub chips selectively there can be constituted such a 128M DRAM package of 32M×4 bits as shown in FIG. 9. In this variation, 13-bit X address signals X0–X12 and 11-bit Y address signals Y0-Y10 are fed to address input 45 pads A0-A12 of the sub chips A and B in common and time-sharingwise, and further fed is an X address signal X13 which serves as a chip selection signal through an address input pad A13. Data input-output pads DIO0 to DIO3 of each sub chip are connected in common to corresponding 50 data input-output terminals DIO0–DIO3 of the DRAM package. As a result, the such chip A is brought into a selected state selectively when the level of the X address signal X13 is made low, and it executes alone a storage data inputting or outputting operation. On the other hand, the sub 55 chip B is brought into a selected state selectively when the level of the X address signal X13 is made high, and it executes alone a storage data inputting or outputting operation. Now, the DRAM package has a bit configuration of 32M×4 bits and inputs or outputs 4-bit storage data simul- 60 taneously. At this time, refresh operations for the sub chips A and B are executed selectively, so the refresh cycle of the DRAM package becomes 16 K cycle/64 ms. The power consumption of the DRAM package as a whole is almost equal to that of one sub chip because the 64M DRAM sub 65 chips A and B are activated selectively, whereby the reduction of power consumption can be attained.

14

(3) 16M×8 bit DRAM package wherein two 16M×4 bit DRAM sub chips are accessed simultaneously:

By combining two 64M DRAM sub chips A and B each having a bit configuration of 16M×4 bits and then accessing these sub chips simultaneously there can be constituted such a 128M DRAM package of 16M×8 bits as shown in FIG. 10. In this variation, 13-bit X address signals X0–X12 and 11-bit Y address signals Y0-Y10 are fed to address input pads A0–A12 in common and time-sharingwise. Data inputoutput pads DIO0-DIO3 of each sub chip are connected to corresponding input-output terminals DIO0-DIO7 of the DRAM package. As a result, the sub chips A and B are brought into a selected state simultaneously and execute a 4-bit storage data inputting or outputting operation in a parallel manner. Now, the DRAM package has a bit configuration of 16M×8 bits and it inputs or outputs 8-bit storage data simultaneously. At this time, refresh operations for the sub chips A and B are also executed in parallel, so the refresh cycle as to the DRAM package becomes 8 K cycle/64 ms. The power consumption as to the entire DRAM package is about twice that of the sub chips.

(4) 16M×8 bit DRAM package wherein two 8M×8 bit DRAM sub chips are accessed selectively:

By combining two 64M DRAM sub chips A and B each having a bit configuration of 8M×8 bits and then accessing these sub chips selectively there can be constituted such a 128M DRAM package of 16M×8 bits as shown in FIG. 11. In this variation, 13-bit X address signals X0–X12 and 10-bit Y address signals Y0–Y9 are fed to address input pads A0-A12 of the sub chips A and B in common and timesharingwise. Further, an X address signal X13 which serves as a chip selection signal is fed through an address input pad A13. Data input-output pads DIO0-DIO7 of each sub chip are connected in common to corresponding data inputoutput terminals DIO0-DIO7 of the DRAM package. As a result, the sub chip A is brought into a selected state selectively when the level of the X address signal X13 is made low, and it executes alone an 8-bit storage data inputting or outputting operation, while the sub chip B is brought into a selected state selectively when the level of the X address signal is rendered high, and it executes along an 8-bit storage data inputting or outputting operation. Now, the DRAM package has a bit configuration of 16M×8 bits and inputs or outputs 8-bit storage data simultaneously. At this time, the refresh cycle of the DRAM package is 16K cycle/64 ms and the power consumption as to the entire package is almost equal to that of one sub chip. Thus, the reduction of power consumption can be attained.

(5) 8M×16 bit DRAM package wherein two 8M×8 bit DRAM sub chips are accessed simultaneously:

By combining two 64M DRAM sub chips A and B each having a bit configuration of 8M×8 bits and then accessing these sub chips simultaneously there can be constituted such a 128M DRAM package of 8M×16 bits as shown in FIG. 12. In this variation, 13-bit X address signals X0–X12 and 10-bit Y address signals Y0–Y9 are fed to address input pads A0-A12 of the sub chips A and B in common and timesharingwise. Input-output pads DIO0–DIO7 of the sub chips are connected to corresponding data input-output terminals DIO0-DIO7 and DIO0-DIO15 of the DRAM package. As a result, the sub chips A and B are brought into a selected state simultaneously and executes an 8-bit storage data inputting or outputting operation in a parallel manner. Now, the DRAM package has a bit configuration of 8M×16 bits and inputs or outputs 16-bit storage data simultaneously. At this time, the refresh cycle of the DRAM package is 8K cycle/64 ms and the power consumption of the package as a whole is about twice that of the sub chips.

1.4. Package Form of DRAM Package and Manufacturing Method for Same

FIG. 13 is a structural perspective view of a 128M DRAM package embodying the invention and FIG. 14 is a plan view thereof. FIG. 15 is a structural sectional view of the DRAM package shown in FIGS. 13 and 14, and FIGS. 16 to 18 are cut-away plan views thereof. Further, FIGS. 19 to 23 are processing diagrams relating to manufacturing processes for the DRAM package illustrated in FIGS. 13 and 14, and FIG. 24 is a plan view showing an example of a lead frame used 10 therein. FIGS. 25 to 31 are structural sectional views and plan view of other package forms of DRAM packages embodying the invention. With reference to these figures, the following description is provided about the package form, manufacturing method and features of the DRAM 15 packages, including modifications. These examples place no limitation on concrete shape and size of the package as well as in what order the bonding pads are to be arranged.

1.4.1. Outline of Lead Laminated Type Package

This 128M DRAM package basically comprises two 64M 20 DRAM sub chips A (1A: first semiconductor chip) and B (1B: second semiconductor chip), as mentioned previously. As shown in FIG. 15, these sub chips are mounted opposedly to each other on both sides of a lead frame 3 which serves as wiring means. The lead frame 3 comprises inner leads 3A 25 in the interior of the package and outer terminals or leads 3B in the exterior of the package. That is, the lead frame 3 as wiring means has a structure which is substantially integrally formed with the external terminals of the package. The DRAM package after sealing is a so-called SOJ type 30 package, having outer dimensions of 300 mils in short side and 850 mils in long side, as shown in FIG. 14. FIG. 15 corresponds to a structural sectional view taken on line 15—15 of the plan view of FIG. 14, while FIGS. 16 and 17 correspond to cut-away plan views taken along lines 16—16 35 and 17— in the structural sectional view of FIG. 15. It goes without saying that in the following structural sectional views, including FIG. 15, the sectional views of the sub chips 1A and 1B are taken in the short side direction of the sub chips.

In FIG. 15, the sub chip 1A is connected to inner leads 3Aa of one lead frame (first lead frame) through an insulating film 4 of polyimide sandwiched in between adhesive layers of a thermoplastic polyimide. This lead frame is made integral with the external terminals or outer leads 3B of the 45 DRAM package without being cut. Plural bonding pads provided centrally of Y axis of the sub chip 1A in a straight line form are connected to corresponding inner leads 3Aa through bonding wires 5. As shown in FIG. 16, the inner leads are separated into relatively short inner leads 3A1 50 which are provided correspondingly to ordinary external terminals and relatively long inner leads 3A2 for the supply of source voltage and earth potential provided between externals VCC1 and VCC2 and between external terminals VSS1 and VSS2. The inner leads 3A1 are used for bonding 55 to inputting or outputting pads, while the inner leads 3A2 are used for the supply of source voltage and earth potential and for bonding to mode setting pads F1–F3 and TC. Thus, in this package, the source voltage and earth potential can be supplied in any desired positions through the inner leads 60 20. 3A2, so it is possible to shorten the source voltage or earth potential feed lines to suppress power source noises and attain speed-up of the operations of the DRAM sub chips 1A and 1B. As the bonding wires 5 there are used aluminum, gold or copper wires or coated wires obtained by coating the 65 surfaces of such metal wires with an insulating resin. For the bonding between inner leads and pads there is adopted a

**16**

conventional method used for LOC type packages, and the bonding is effected by a bonding method comprising both pressure bonding under heating and ultrasonic vibration. In a LOC type package, the inner leads 3A can be extended freely without being restricted by the shape of the DRAM sub chips 1A and 1B, so the sub chip size can be increased accordingly; in other words, the package size can be reduced.

On the other hand, the sub chip 1B is connected to inner leads 3Ab of the other lead frame (second lead frame) also through the insulating film 4. Though not specially limited, this lead frame is cut along the outer edges of the sub chips 1A and 1B and connected to corresponding inner leads 3Aa of the lead frame which corresponds to the sub chip 1A. Thus, according to the package form of this package, two opposed lead frames are cut and bonded, so this package is named a lead laminated type package. The inner leads 3Ab may be cut outside the sub chips 1A and 1B and inside a resin sealed type package 2, as shown in FIG. 18. As mentioned previously, bonding pads of the sub chips 1A and 1B are arranged centrally thereon and along the Y axis, or the long side, in a straight line form. For the bonding of the sub chips 1A and 1B, therefore, predetermined external terminals of the sub chips are connected to left- and righthand inner leads 3Aa, 3Ab, respectively, in the sub chips 1A and 1B for example. Such different bondings in the sub chips 1A and 1B permit overlapping of leads of corresponding functions when the sub chips 1A and 1B are lapped (or stacked) together in opposed relation to each other.

The sub chips 1A and 1B thus bonded together through the lead frames are sealed with a molding resin 2. As the molding resin 2 there is used an epoxy resin incorporating therein a phenolic curing agent, a silicone rubber and a filler for attaining a reduced stress of the package. The silicone rubber functions to decrease the elastic modulus and the coefficient of thermal expansion of the epoxy resin. The filler, which is formed as spherical silicon oxide particles, also functions to decrease the thermal expansion coefficient. In a predetermined position of the package there is formed 40 a cut-in portion serving as an index ID. The package is designed so that the cut portion of the lead frame corresponding to the sub chip 1B and the portion thereof bonded to the lead frame corresponding to the sub chip 1A are located in the interior of the resin-sealed package, i.e., the molding resin 2, whereby the said lead frame cut portion and bonded portion can be protected and hence it is possible to enhance the durability of the DRAM package.

1.4.2. How to Produce Lead Laminated Type Package

The 128M DRAM package of this embodiment is produced through the following processes.

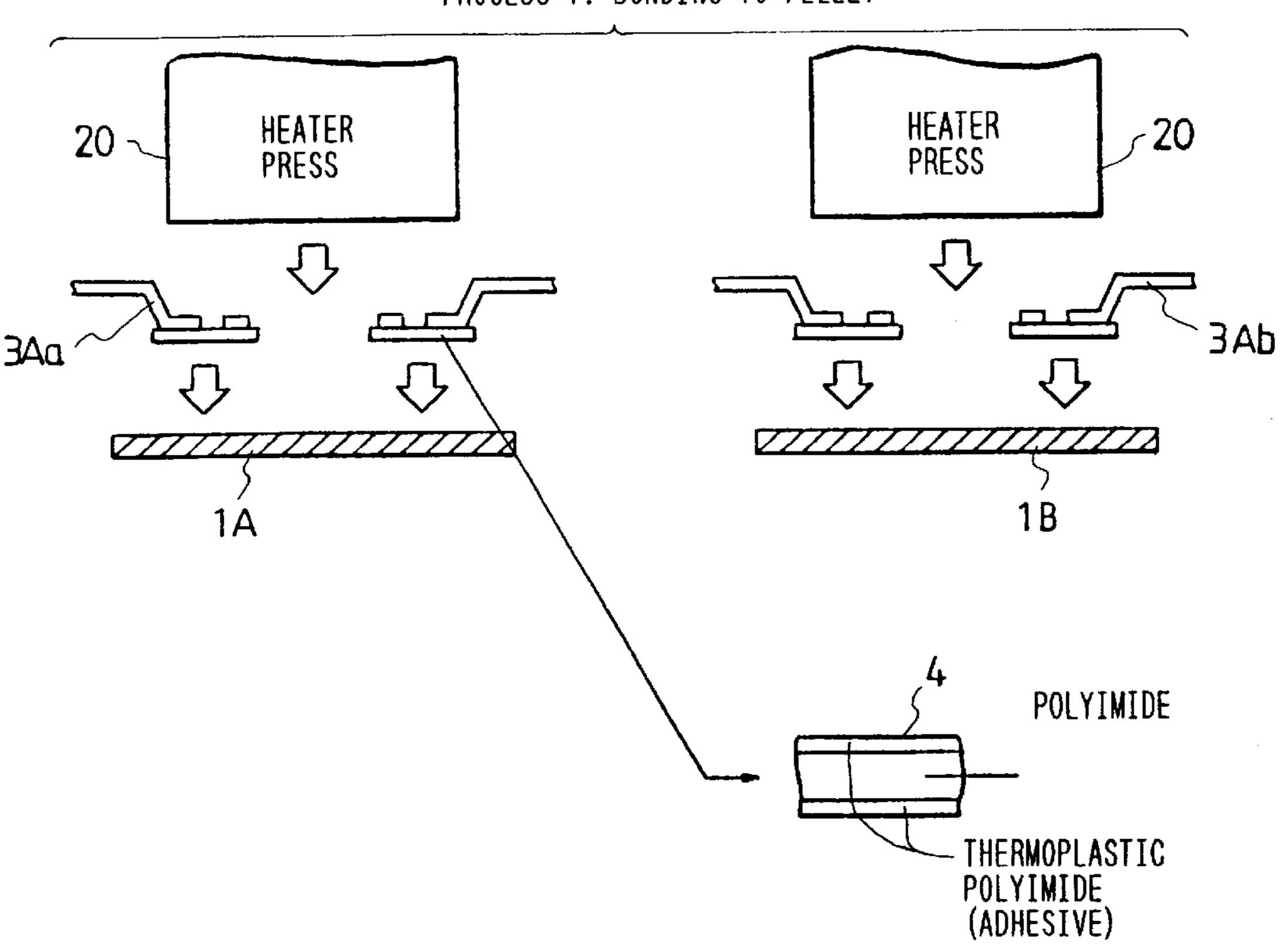

(1) Bonding to Pellet

The sub chips 1A and 1B are bonded to the corresponding inner leads 3Aa and 3Ab through the insulating film 4. As shown in FIG. 19, the insulating film 4 is of a three-layer structure wherein polyimide is sandwiched in between adhesive layers of a thermoplastic polyimide. The insulating film 4 is heated and pressurized in advance by means of a heater press, then bonded to the inner leads 3Aa or 3Ab and thereafter bonded to the sub chip 1A or 1B by a heat press 20.

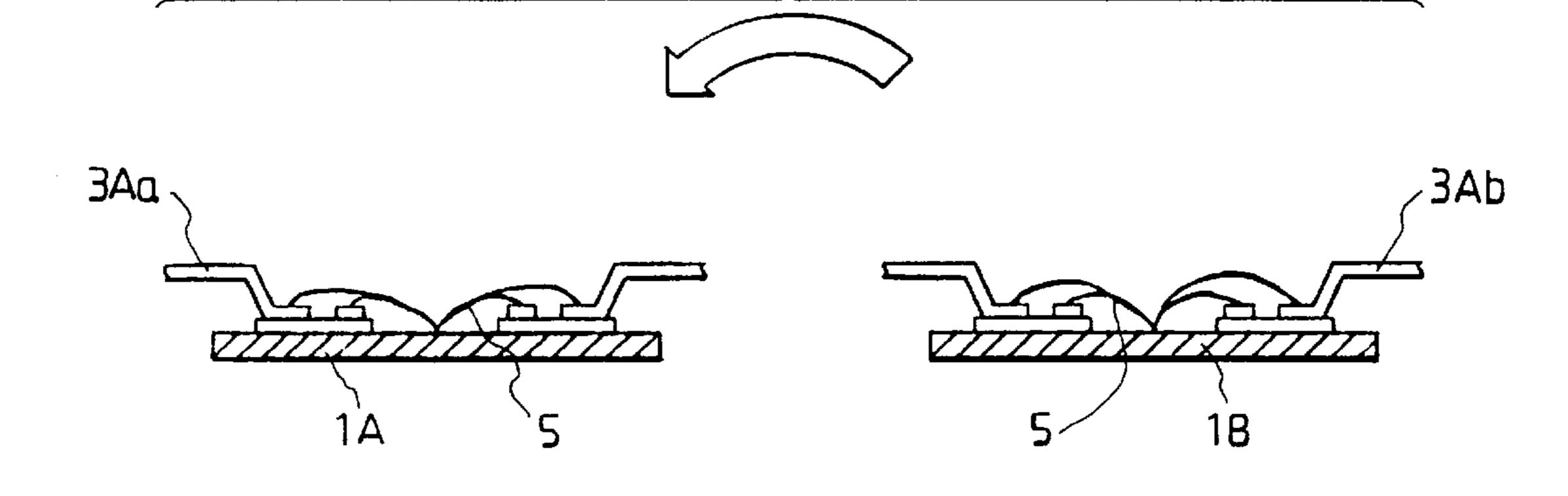

#### (2) Wire Bonding

Next, as shown in FIG. 20, there is performed a bonding processing between the bonding pads arranged centrally of the Y axis or the long side of the sub chips 1A, 1B and the inner leads 3Aa, 3Ab. The inner leads 3Aa and 3Ab are each bent beforehand in a direction away from the corresponding sub chip. After completion of the bonding, the sub chip 1B

bonded to the inner leads 3Ab is inverted onto the sub chip 1A bonded to the inner leads 3Aa, whereby the two sub chips 1A and 1B are opposed to each other on both sides of the lead frames and the inner leads corresponding to each other come into contact with each other.

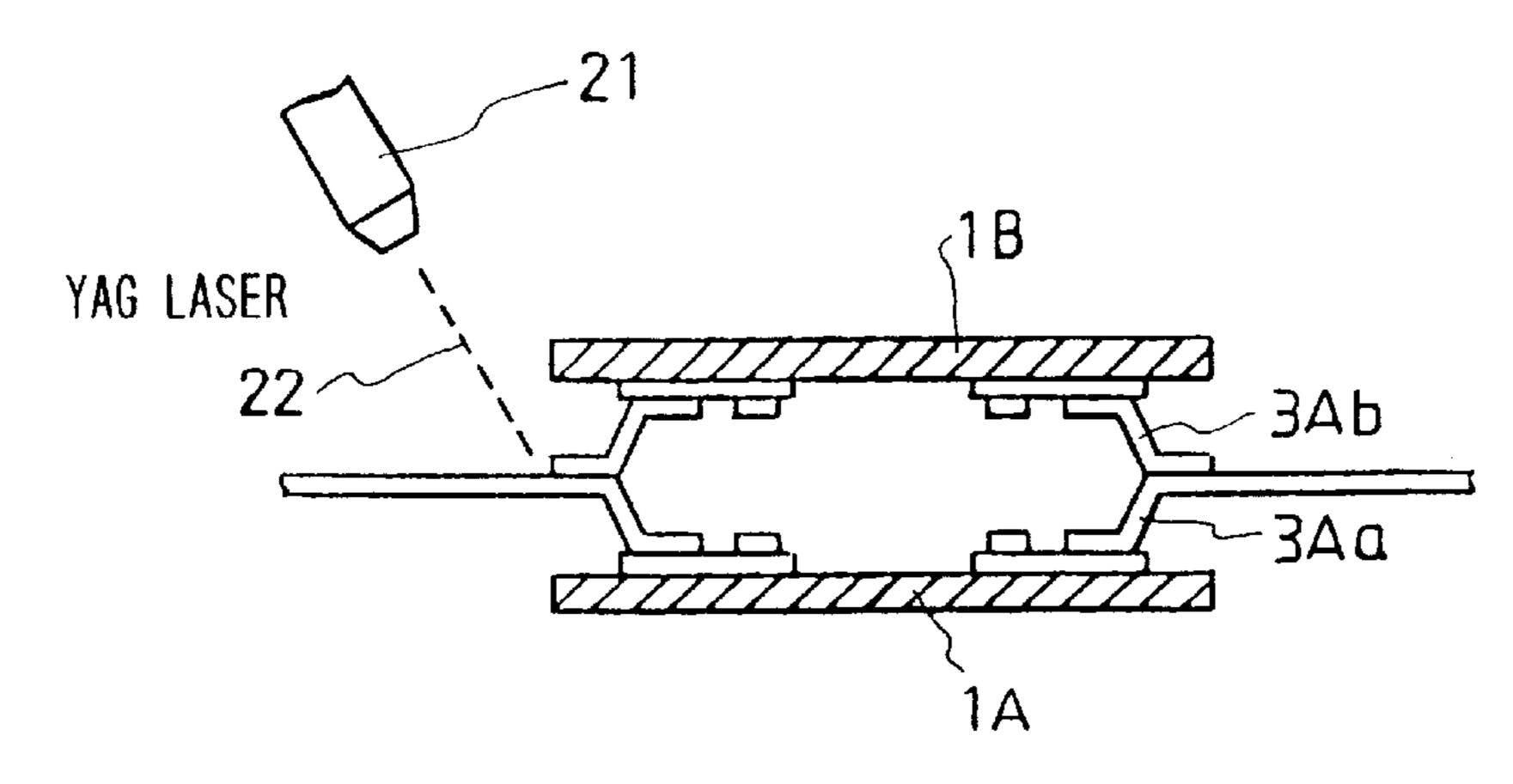

#### (3) Cutting and Bonding of Leads

For mutual contact of the corresponding leads, the inner leads 3Ab superimposed on the inner leads 3Aa are cut in the outer edge position of each sub chip by a YAG laser beam 22 emitted from a laser device 21 and at the same time they are welded to the inner leads 3Aa. Now, the corresponding leads of the inner leads 3Aa and 3Ab are connected together electrically.

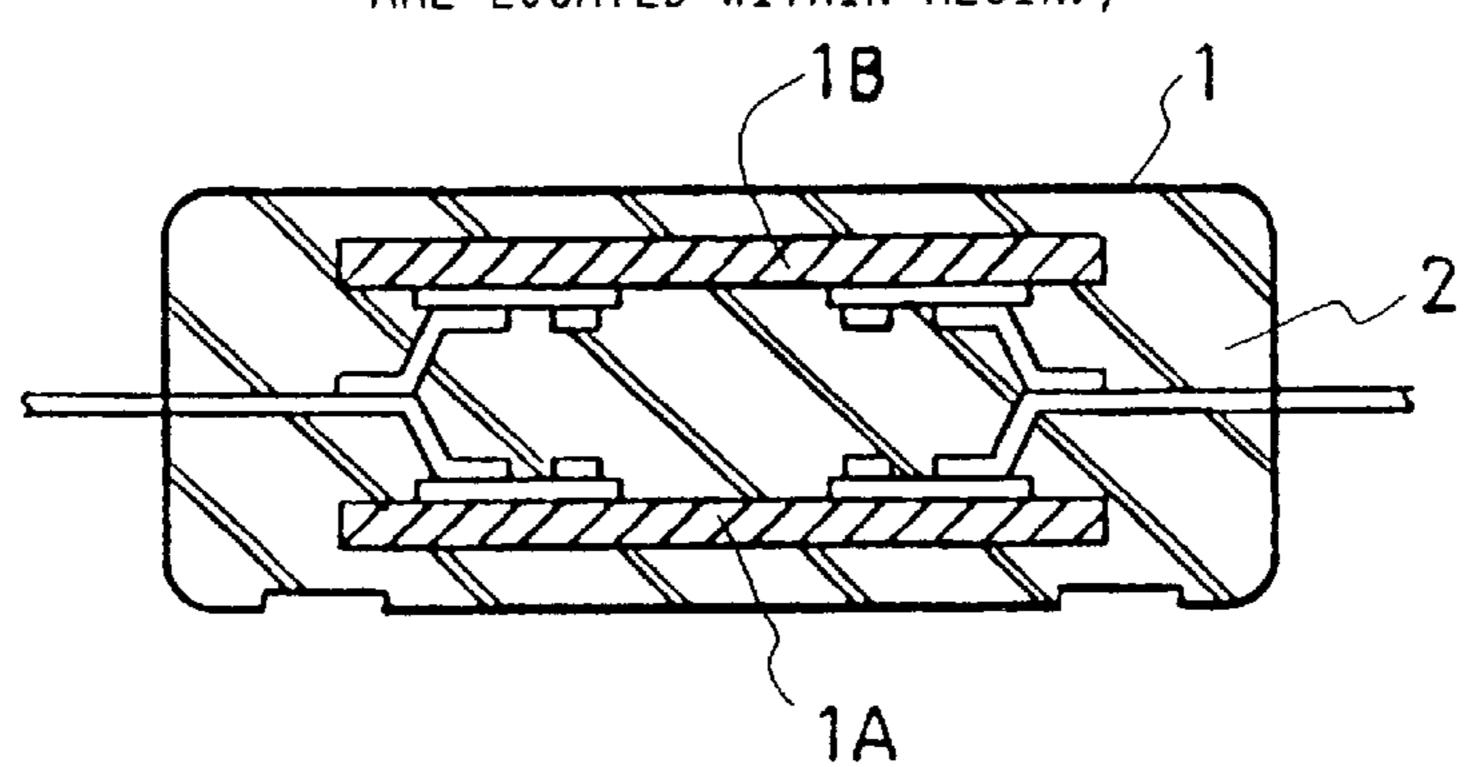

#### (4) Sealing

The sub chips 1A and 1B thus laminated together opposedly with the lead frames put therebetween are then sealed with the molding resin 2, as shown in FIG. 22. At this time, the cut portions of the inner leads 3Ab and the bonded portions thereof to the inner leads 3Aa are protected within the molding resin 2, whereby the entry of water, etc. through the bonded portions is prevented and hence it is possible to 20 enhance the durability of the DRAM package.

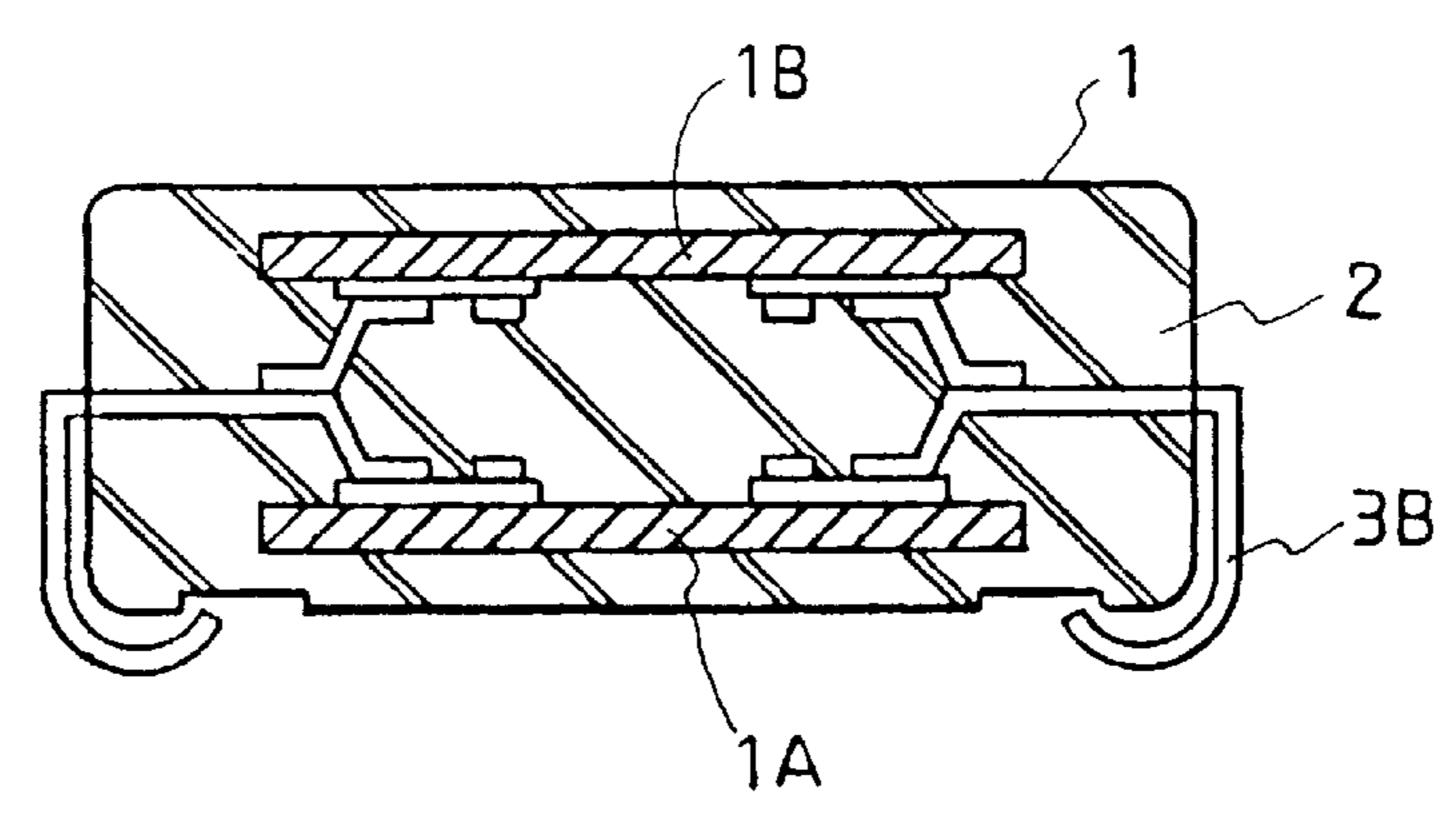

#### (5) Lead Forming

In the package thus sealed with the molding resin 2, as shown in FIG. 23, the outer leads 3B of the lead frame corresponding to the sub chip 1A are formed by a predeter- 25 mined pressing machine to obtain a DRAM package 1 of the so-called SOJ structure.

#### 1.4.3. Lead Frame and Insulating Film

The lead frames used in the lead laminated type package of this embodiment are designed so that the distance 30 between adjacent inner and outer leads 3A, 3B is almost equal throughout the lead frames, as shown in FIG. 24. As a result, the parasitic capacitance between leads is unified, the amount of noise induced between leads is suppressed, and the signal transfer time associated with the DRAM 35 package is shortened accordingly.

On the other hand, the insulating film 4 used for bonding between the sub chips 1A, 1B and the inner leads 3A is cut in the shape of a comb along the inner leads 3A1, as indicated by oblique lines in FIG. 24. The thermal expansion 40 coefficient of the insulating film is relatively greatly different from that of the semiconductor substrate which forms each sub chip or the lead frame. Therefore, in the case where the substantial bonding area of the insulating film is large, the bonded portion of the insulating film may be peeled off by expansion and contraction caused by temperature changes over a long period. By cutting the insulating film 4 in the shape of a comb along the inner leads 3A1 to reduce its substantial bonding area, it is made possible to suppress the separation of the insulating film and enhance the durability 50 and reliability of the DRAM package.

#### 1.4.4. Other Package Forms