US00RE36932E

Patent Number:

Re. 36,932

## United States Patent [19]

## Furutani [45] Reissued Date of Patent: Oct. 31, 2000

[11] E

#### [54] SEMICONDUCTOR MEMORY DEVICE OPERATING STABLY UNDER LOW POWER SUPPLY VOLTAGE WITH LOW POWER CONSUMPTION

[75] Inventor: **Kiyohiro Furutani**, Itami, Japan

[73] Assignee: Mitsubishi Denki Kabushiki Kaisha,

Tokyo, Japan

[21] Appl. No.: **09/221,835**

[22] Filed: **Dec. 28, 1998**

#### Related U.S. Patent Documents

Reissue of:

[64] Patent No.: **5,673,232**Issued: **Sep. 30, 1997**

Appl. No.: 08/486,755

Filed: Jun. 6, 1995

### [30] Foreign Application Priority Data

Jul. 18, 1994

[JP]

Japan

6-165614

7.12

7.12

7.12

7.12

[56] References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

3-214669 9/1991 Japan.

4-130766 5/1992 Japan.

#### OTHER PUBLICATIONS

"A 1.5V Circuit Technology for 64Mb DRAMs," by Y. Nakagome et al., Digest for Technical Papers, 1990 Symposium on VLSI Circuits pp. 17–18.

Primary Examiner—Viet Q. Nguyen Attorney, Agent, or Firm—McDermott, Will & Emery

#### [57] ABSTRACT

A semiconductor memory device of the present invention includes an internal power supply voltage generating circuit down converting external power supply voltage to generate first and second internal power supply voltages, a Vpp generating circuit generating a high voltage from external power supply voltage by charge pumping operation, and a Vbb generating circuit generating negative voltage from external power supply voltage by charge pumping operation. The first internal supply voltage is applied to a control circuit and a sense amplifier drive signal generating circuit. The second internal power supply voltage is applied to a circuit generating a bit line equalize/precharge signal. Even if the first internal power supply voltage is made small, the Vpp generating circuit and the Vbb generating circuit generate a prescribed voltage from external power supply voltage. Therefore, these circuits generate a prescribed internal high voltage and negative voltage efficiently and stably. The bit line equalize/precharge signal is at a voltage level higher than the first internal power supply voltage. The bit line equalize/precharge signal can equalize/precharge a bit line at a high speed. As a result, a semiconductor memory device which operates stably with low power consumption is provided.

### 19 Claims, 46 Drawing Sheets

F I G. 1

F I G. 2

U.S. Patent

F I G. 4

F I G. 5

F I G. 7

F I G. 8

F I G. 10

F I G. 12

F I G. 13

F I G. 14

F I G. 15A

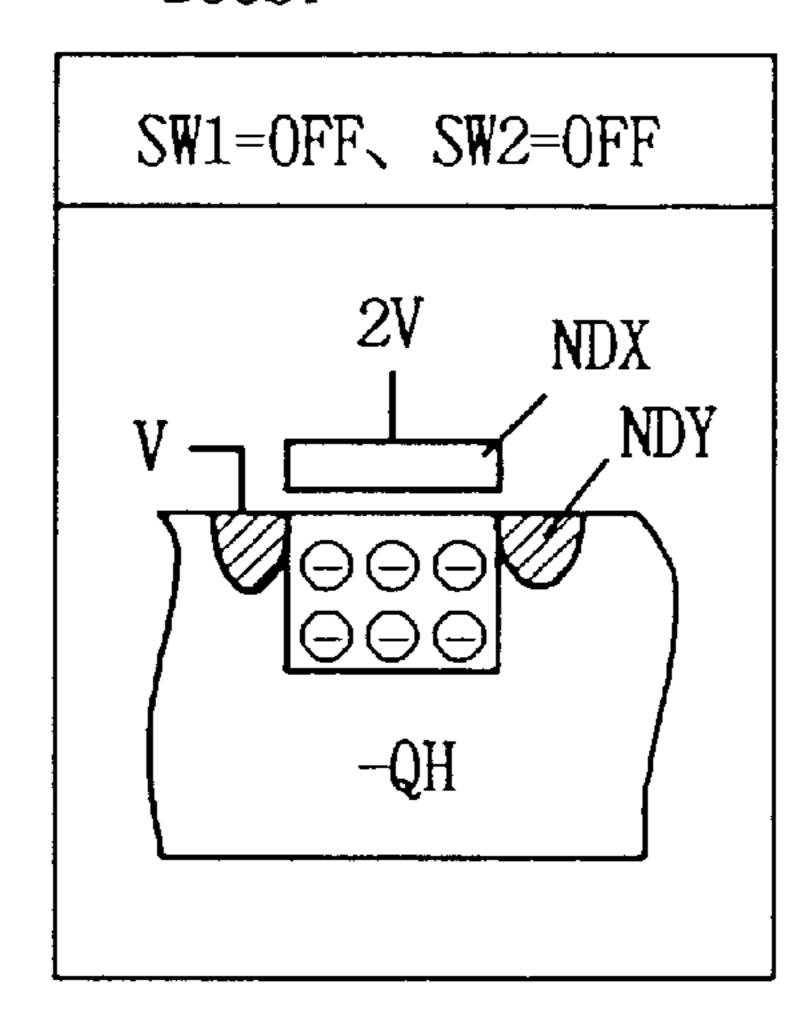

:INITIAL STATE

F I G. 15B

:B00ST

F I G. 15C

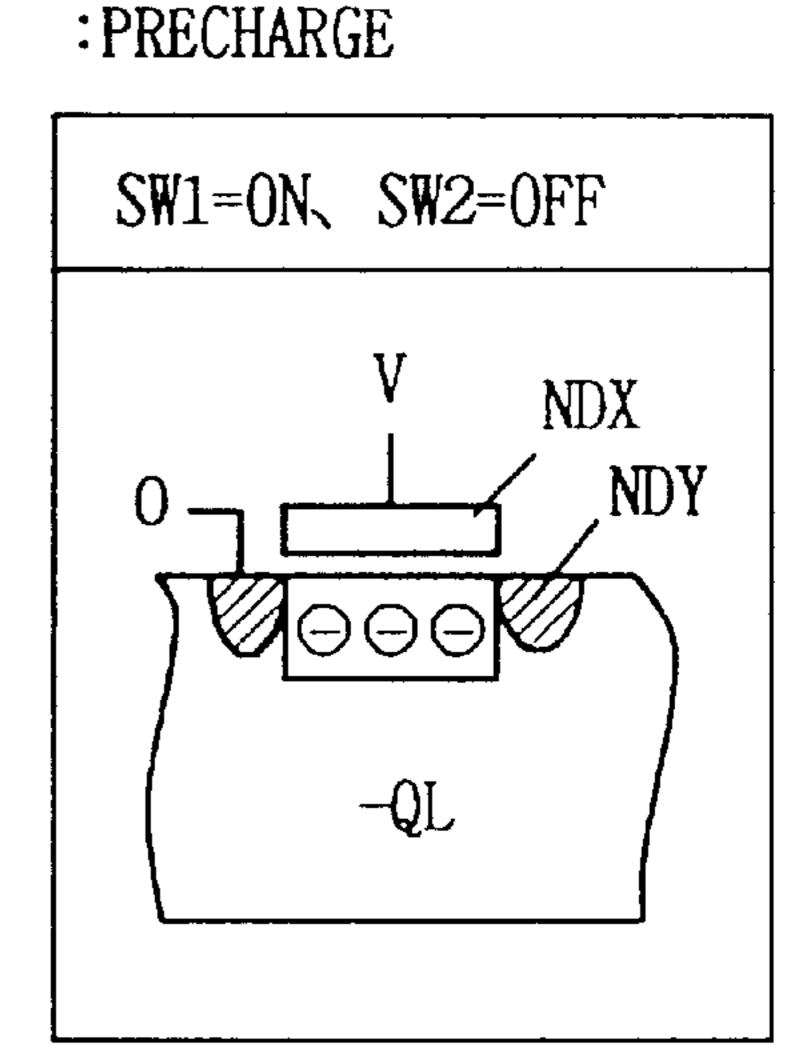

F I G. 15D

F I G. 15E

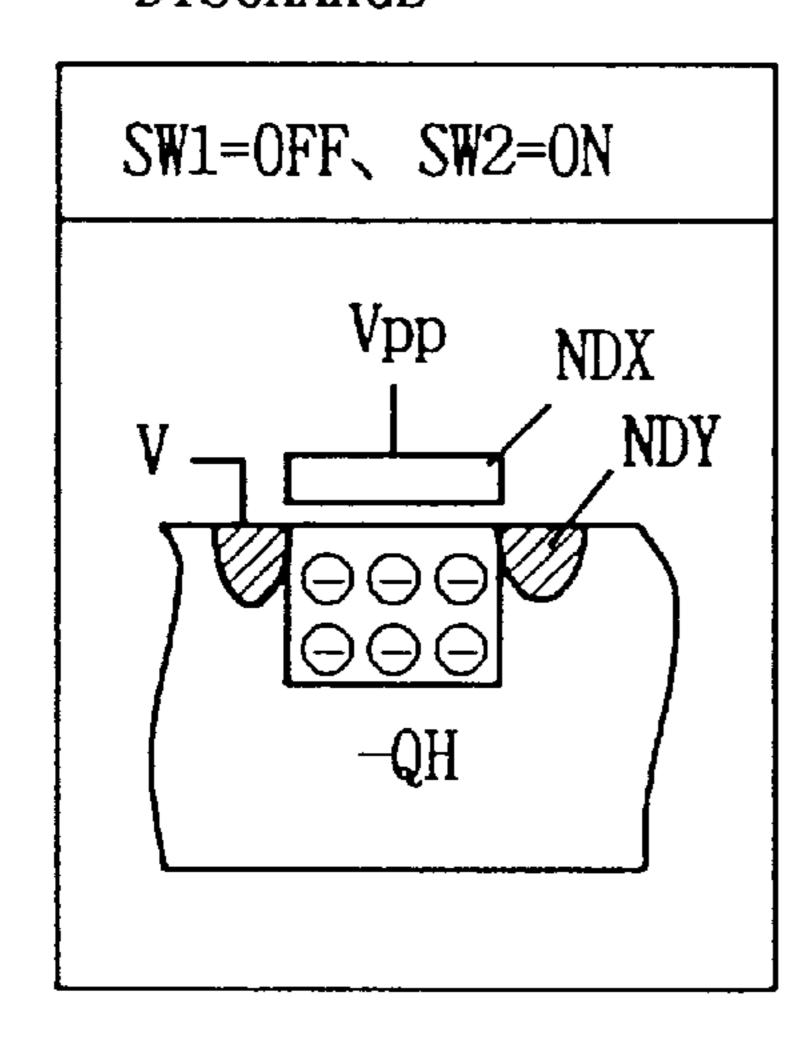

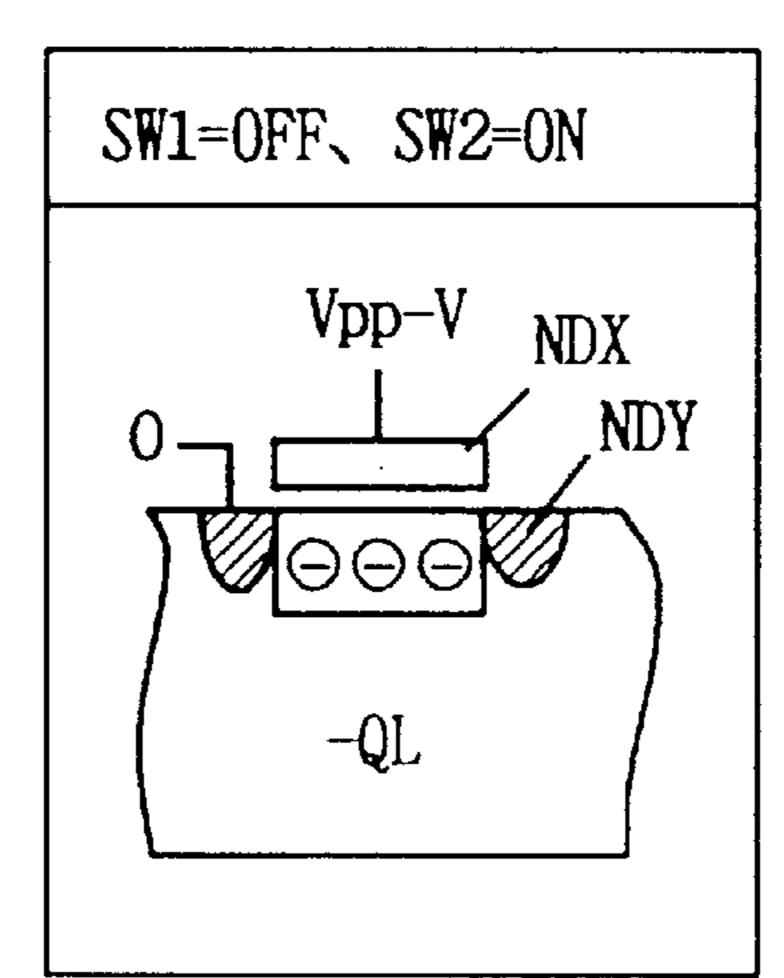

### :DISCHARGE

F I G. 16

F I G. 17

F I G. 18

F I G. 19

F I G. 20

F I G. 21

F I G. 22

F I G. 24

F I G. 25

F I G. 26

F I G. 27

F I G. 28

F I G. 29

F I G. 30

F I G. 32

F I G. 33

FIG. 34

F I G. 35

F I G. 36

F I G. 37

**Sheet 26 of 46**

F I G. 38A

F I G. 38B

F I G. 38C

F I G. 39

F I G. 40

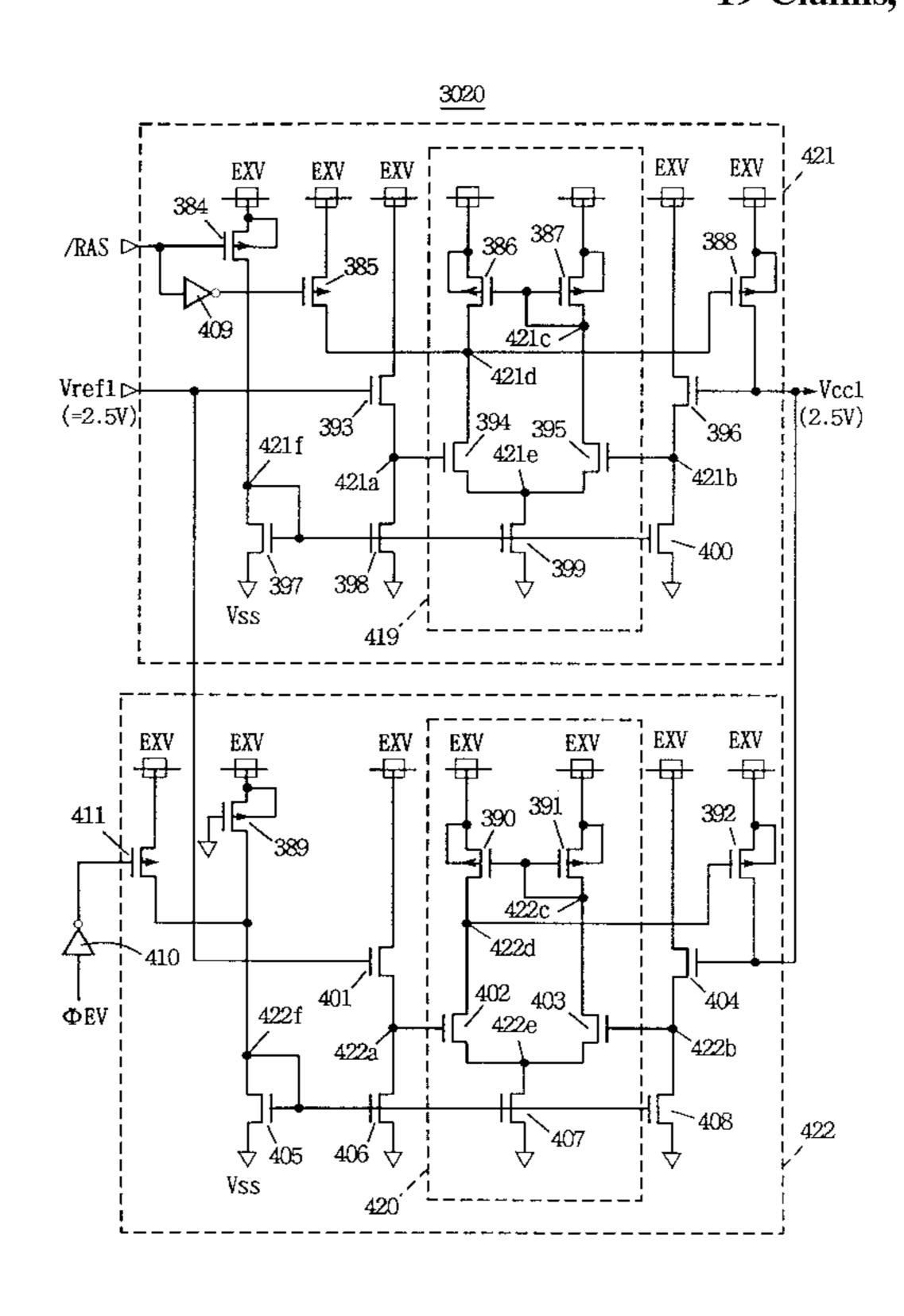

# 3020

F I G. 41

F I G. 42

F I G. 44

F I G. 45

F I G. 46A

F I G. 47

F I G. 48

Re. 36,932

F I G. 49

F I G. 51

ARRAY BLOCK LINE WORD /RAS /CAS CONTROL TO SENSE AMPLIFIER POWER SUPPLY LINE CIRCUIT Add SIGNAL D GENERATING CIRCUIT  $\phi$  R 9 SENSE/PERIPHERAL  $\phi\Gamma$ SPH CIRCUIT GENERATING SENSE AMPLIFIER

DRIVE SIGNAL

GENERATING CIRCU 52 BLEQ GENERATING CIRCUIT Vbb GENE CIRCUIT Vcc1 BLEQ. ARRAY BLOCK  $\mathcal{O}$ Vcc3 CIRCUIT DECODER WLL GENERATING LINE INTERNAL WORD CUIT  $\mathcal{O}$  $\infty$

Re. 36,932

F I G. 53

Oct. 31, 2000

F I G. 56

F I G. 57

F I G. 58

F I G. 59

F I G. 60

Oct. 31, 2000

F I G. 61

F I G. 62

# SEMICONDUCTOR MEMORY DEVICE OPERATING STABLY UNDER LOW POWER SUPPLY VOLTAGE WITH LOW POWER CONSUMPTION

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

# BACKGROUND OF THE INVENTION

# 1. Field of the Invention

The present invention relates to structures of a voltage generating circuit for generating a voltage required stably with low power consumption, and more particularly, to a structure implementing, in use in a semiconductor memory device, low power consumption and low voltage operation of the semiconductor memory device.

# 2. Description of the Background Art

A dynamic random access memory (DRAM) has found 20 expanded application to portable appliances such as a notebook personal computer. Such a portable appliance uses a battery as its power source. Each component must operate with as low power consumption as possible in order to make the battery life as long as possible. In the DRAM, an external  $_{25}$ power supply voltage of 5 V, for example, is internally down-converted to 3.3 V for example, and the internally down-converted voltage is used as operation power supply voltage, in order to implement low power consumption. The low power supply voltage decreases the amplitude of a 30 signal, thereby reducing current consumption associated with charge/discharge of a signal line.

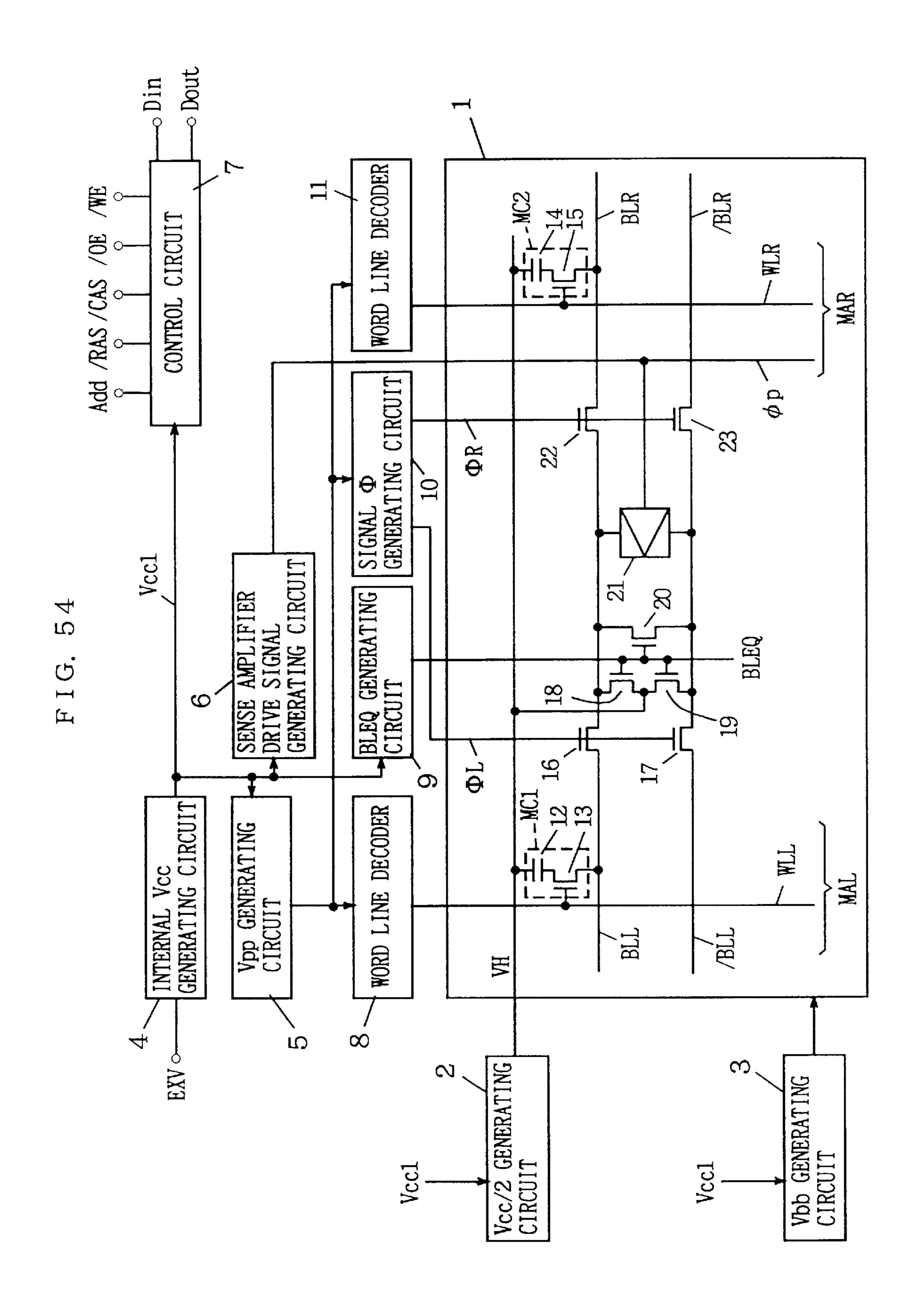

FIG. 54 is a diagram showing the entire structure of a conventional DRAM. Referring to FIG. 54, the conventional DRAM includes a memory cell array 1 having memory cells 35 /WE, and generates an internal address signal (not shown) MC arranged in a matrix of rows and columns. Memory cell array 1 is divided into two array blocks MAR and MAL. Array blocks MAR and MAL each include a plurality of word lines arranged corresponding to each row of memory cells, and a plurality of bit line pairs arranged corresponding 40 to each column of memory cells.

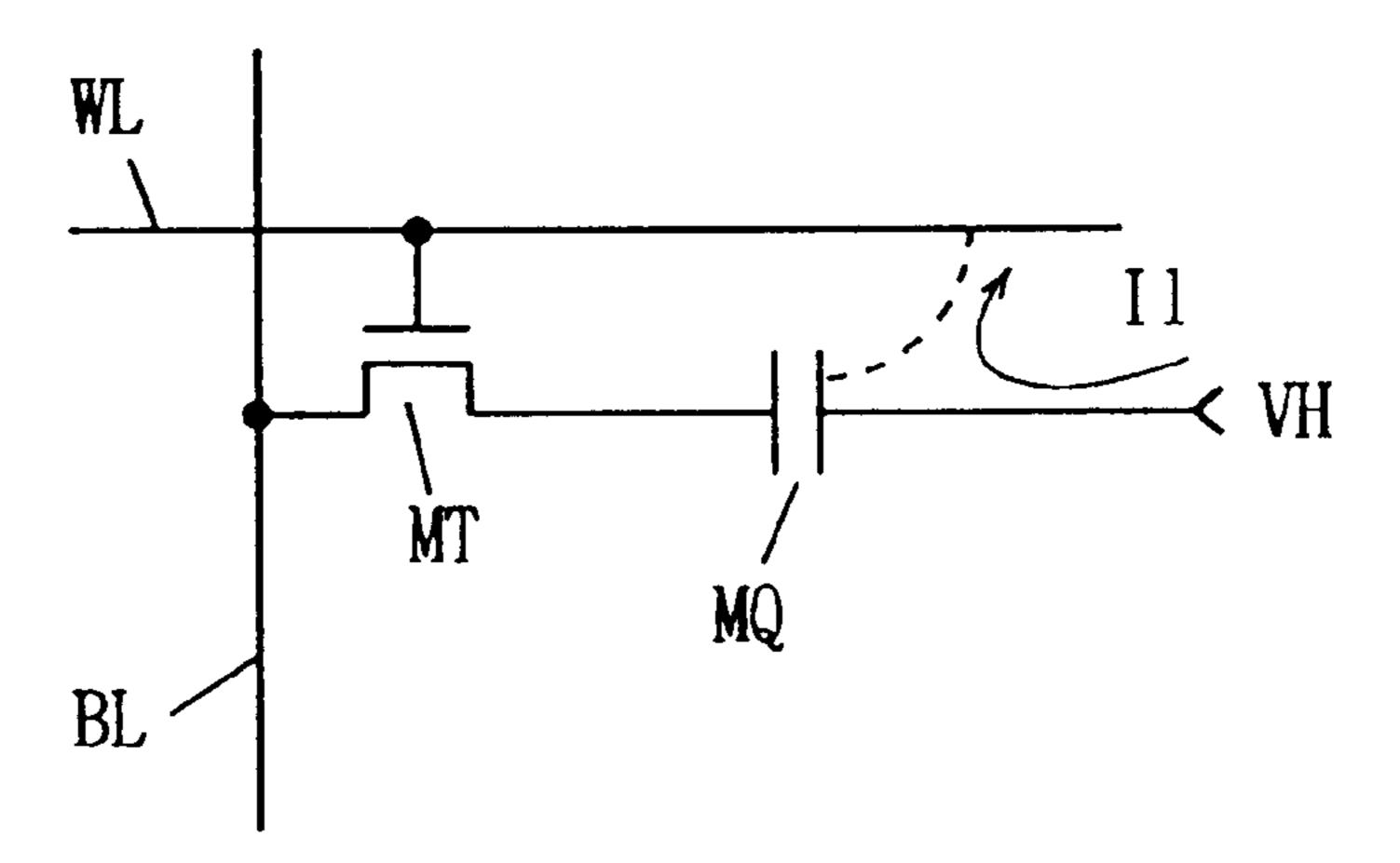

In FIG. 54, for simplicity of illustration, memory cells MC1 and MC2 in array blocks MAL and MAR are representatively shown. Memory cell MC1 included in array block MAL is arranged corresponding to a crossing portion 45 of a word line WLL and a bit line BLL, and includes a capacitor 12 for storing information, and an access transistor 13 formed of an n channel MOS transistor rendered conductive in response to a signal potential on word line WLL for connecting capacitor 12 to bit line BLL. An intermediate 50 voltage VH from a Vcc/2 generating circuit 2 to be described later is applied to the electrode (cell plate) of capacitor 12.

Memory cell MC2 included in array block MAR is arranged corresponding to a crossing portion of a word line WLR and a bit line BLR, and includes a capacitor 14 and an 55 access transistor 15 formed of an n channel MOS transistor rendered conductive in response to a signal potential on word line WLR for connecting capacitor 14 to bit line BLR. Intermediate voltage VH from Vcc/2 generating circuit 2 is applied to the cell plate of capacitor 14. Bit line BLL is 60 paired with a bit line /BLL, and bit line BLR is paired with a bit line /BLR. In a respective bit line pair, data of a memory cell is transmitted to one bit line, and the other bit line provides a comparison reference voltage of the memory cell data.

Between a bit line pair BLL, /BLL and a bit line pair BLR, /BLR, provided are a sense amplifier 21 activated in

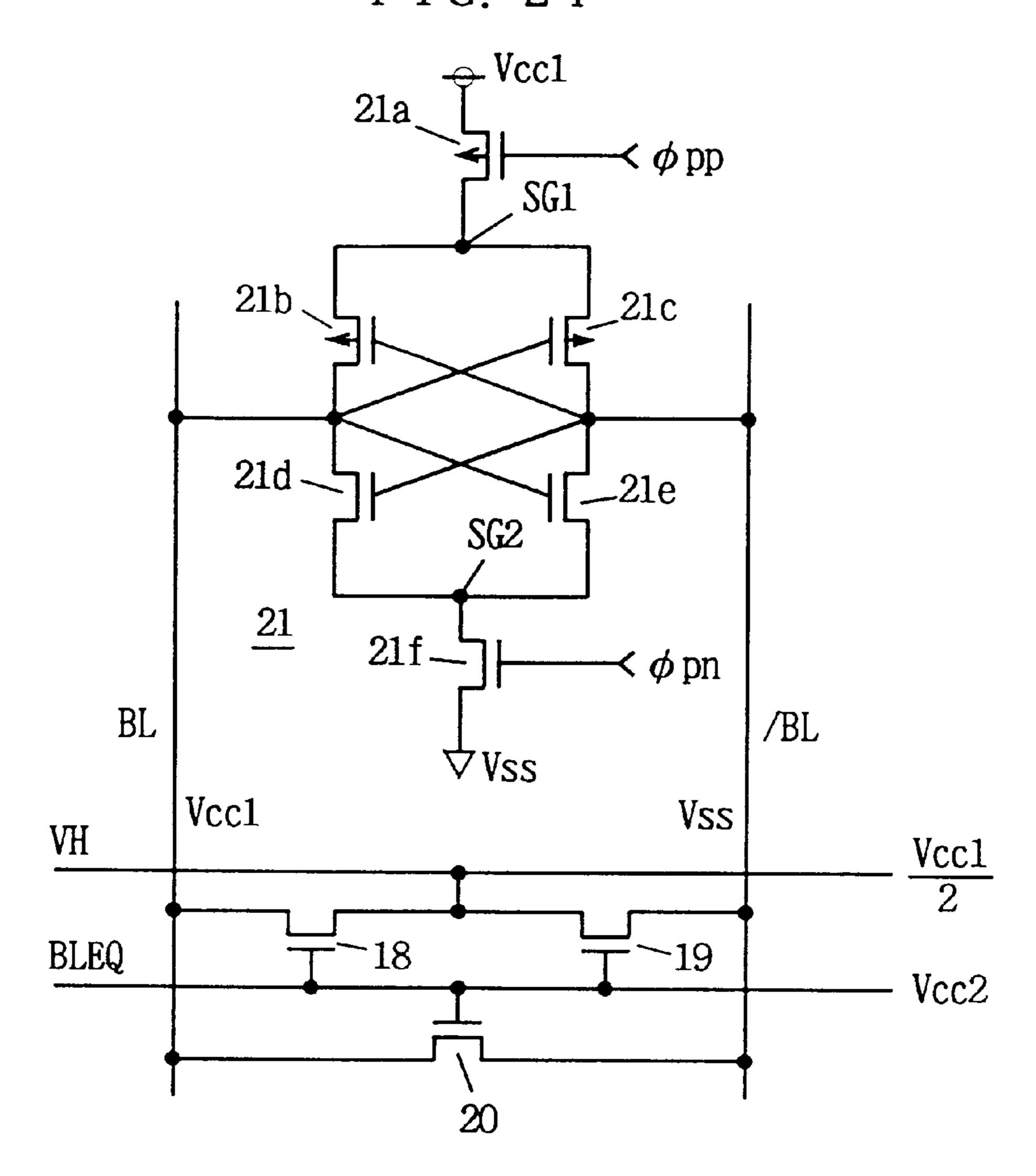

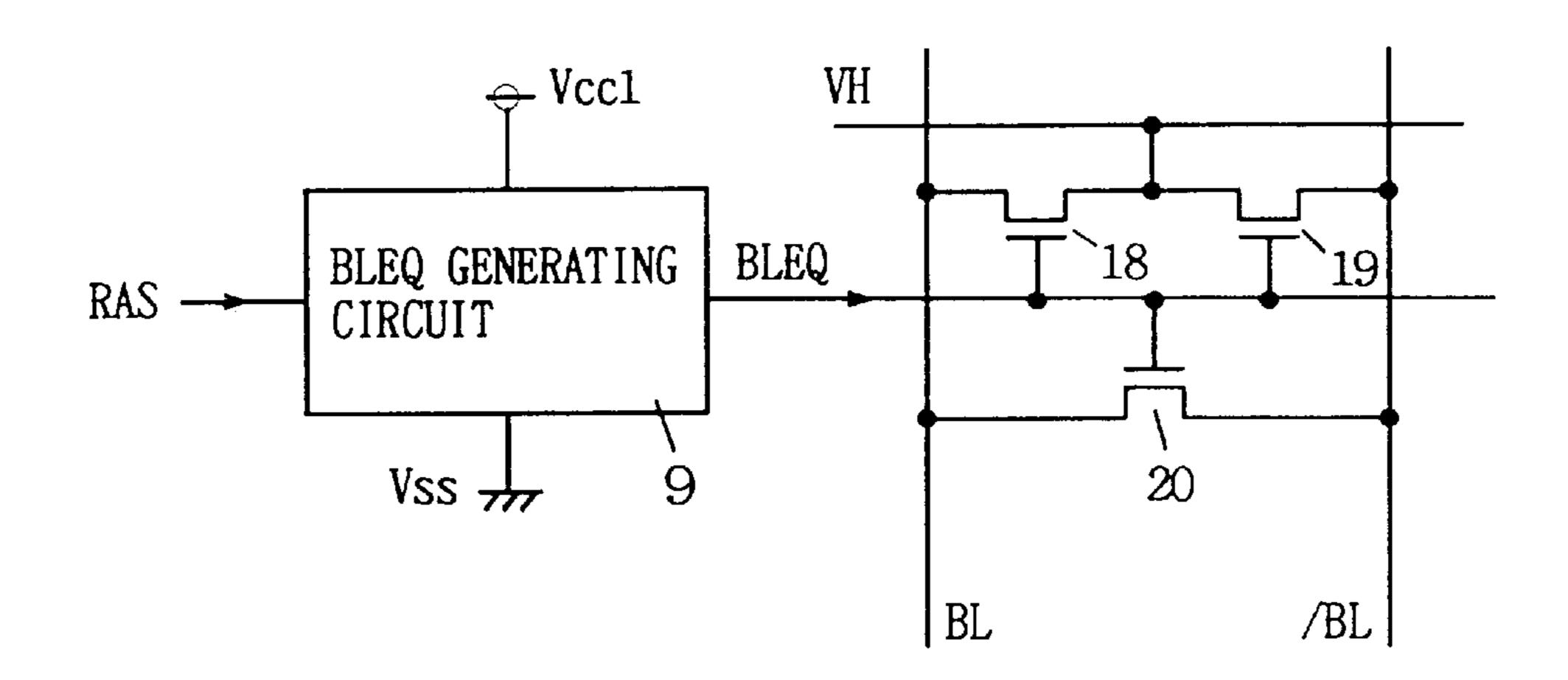

response to a sense amplifier drive signal  $\phi p$  for differentially amplifying potentials on a selected bit line pair, block select gates 22 and 23 rendered conductive in response to an array block select signal ΦR from a signal Φ generating circuit 10 for connecting bit lines BLR and/BLR to sense amplifier 21, block select gates 16 and 17 rendered conductive in response to an array block select signal ΦL from signal Φ generating circuit 10 for connecting bit lines BLL and /BLL to sense amplifier 21, and transistors 18, 19, and 20 precharging and equalizing potentials on bit lines BLL, /BLL, BLR, and /BLR to intermediate voltage VH in response to a bit line equalize signal BLEQ from a BLEQ generating circuit 9.

Transistors 18 and 19 transmit intermediate voltage VH to bit lines BLL and BLR, and bit lines /BLL and /BLR, respectively, in response to bit line equalize signal BLEQ. Transistor 20 electrically connects bit lines BLL and BLR, and bit lines /BLL and /BLR, in response to bit line equalize signal BLEQ.

The conventional DRAM further includes an internal Vcc generating circuit 4 down-converting an external power supply voltage EXV and generating an internal power supply voltage Vcc1, a Vpp generating circuit 5 generating an internal high voltage Vpp higher than internal power supply voltage vcc1 from internal power supply voltage Vcc1, and a sense amplifier drive signal generating circuit 6 generating sense amplifier drive signal  $\phi p$  at the internal power supply voltage Vcc1 level at a prescribed timing in response to a timing signal (signal path of which is not shown) from a control circuit 7 to be described later.

Control circuit 7 receives an address signal Add, a row address strobe signal /RAS, a column address strobe signal /CAS, an output enable signal /OE, and a write enable signal and a control signal determining an operation timing of each internal circuit. Control circuit 7 further generates internal write data from external write data Din, and external read data Dout from internal read data.

The conventional DRAM further includes a word line decoder 8 provided corresponding to array block MAL for decoding an internal address signal from control circuit 7 and transmitting a word line drive signal at the internal high voltage level from Vpp generating circuit 5 onto a corresponding word line of array block MAL, and a word line decoder 11 provided corresponding to array block MAR for decoding an internal address signal from control circuit 7 and transmitting a word line drive signal at the internal high voltage Vpp level from Vpp generating circuit 5 onto a selected word line (word line corresponding to an addressed row).

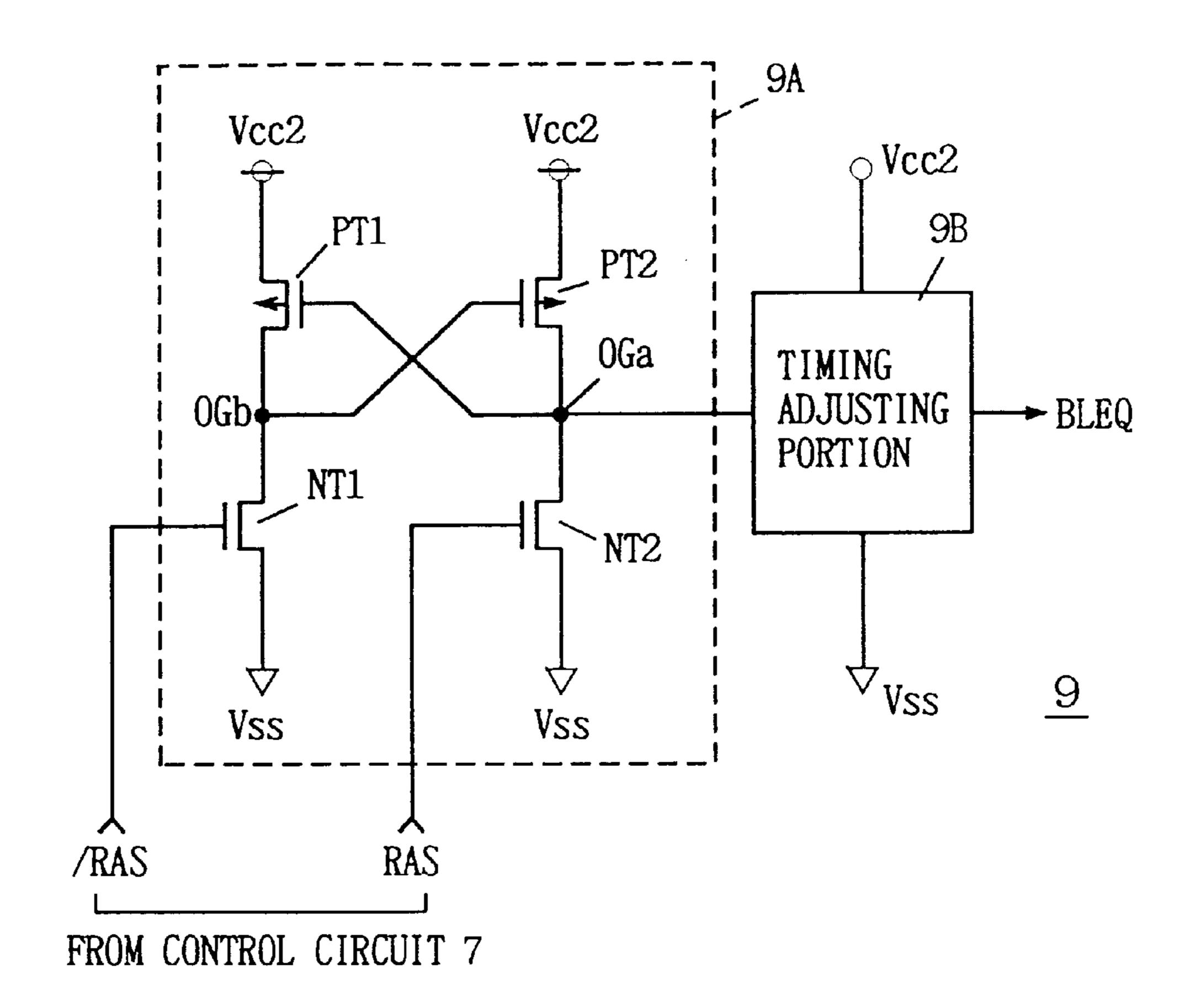

BLEQ generating circuit 9 generates bit line equalize signal BLEQ at the internal power supply voltage Vcc1 level in response to an internal control signal from control circuit 7. Signal Φ generating circuit 10 brings one of block select signals  $\Phi L$  and  $\Phi R$  to a non-active state according to part of an internal control signal and an internal address signal from control circuit 7. Note that, in the following description, "generating a signal" means "bringing a signal to an active state". More specifically, signal  $\Phi$  generating circuit 10 connects an array block including a selected word line to sense amplifier 21, and disconnects a non-selected array block from sense amplifier 21. At the time of stand-by, signals  $\Phi L$  and  $\Phi R$  are in an active state of "H", block select 65 gates 16, 17, 22 and 23 are all turned on, and bit lines BLL, /BLL, BLR, /BLR are all precharged to intermediate voltage VH.

Vpp generating circuit 5 generates a negative voltage Vbb at a prescribed voltage level from internal power supply voltage Vcc1, and applies negative voltage Vpp to a region of a semiconductor substrate on which memory cell array 1 is formed. The negative voltage Vbb prevents generation of a parasitic MOS transistor (insulated gate type field effect transistor), reduces parasitic capacitance caused by a PN junction between the substrate and an impurity region, and stabilizes the threshold voltage of an access transistor. Data writing/reading operation will now be described briefly.

At the time of stand-by, row address strobe signal /RAS is in a non-active state at an "H" level. In this state, word lines WLL and WLR are both at an "L" level, and access transistors 13 and 15 are both in an off state. Bit line equalize signal BLEQ is at "H" at the internal power supply voltage 15 Vcc1 level, transistors 18, 19, and 20 are in an on state, and bit lines BLL, /BLL, BLR, and /BLR are precharged and equalized to intermediate voltage VH (block select gates 16, 17, 22 and 23 are in an on state).

In response to the falling of signal /RAS to the "L" level, a memory cycle starts. In this state, bit line equalize signal BLEQ from BLEQ generating circuit 9 attains the "L" level, and transistors 18, 19 and 20 are turned off. Accordingly, bit lines BLL, /BLL, BLR, and /BLR are brought to a floating state of intermediate voltage VH. In response to the falling of signal /RAS, external address signal Add is strobed, and an internal address signal is provided from control circuit 7. The internal address signal includes a block address designating an array block. According to the block address from control circuit 7, signal  $\Phi$  generating circuit 10 maintains block select signal  $\Phi$ L (or  $\Phi$ R) for a selected array block at the "H" level, and sets block select signal  $\Phi$ R (or  $\Phi$ L) for a non-selected array block to the "L" level.

One word line decoder provided corresponding to an array block including a selected word line is activated among word line decoders 8 and 11. Here, assume that word line WLL included in array block MAL is selected. In this case, word line decoder 8 operates, decodes an internal address signal from control circuit 7, and transmits a word line drive signal at the internal high voltage Vpp level from Vpp generating circuit 5 onto word line WLL. As a result, access transistor 13 is turned on, and information stored in capacitor 12 is transmitted onto bit line BLL. Bit line /BLL maintains precharge level VH.

Then, sense amplifier drive signal  $\phi p$  from sense amplifier drive signal generating circuit 6 is boosted to the internal power supply voltage Vcc1 level, and sense amplifier 21 is activated to differentially amplifying potentials on bit lines BLL and /BLL.

Then, column selecting operation (bit line pair selecting operation) is carried out according to an internal address signal generated by address signal Add strobed in response to the falling of column address strobe signal /CAS, writing/reading of data for memory cells (MC1) on a selected column is carried out. Whether data is written or read out is determined by signals /OE and /WE.

When writing/reading of data is complete, row address strobe signal /RAS is brought to a non-active state, and the signal potential on a selected word line WL4 attains the "L" 60 level, followed by sense amplifier drive signal  $\phi p$  attaining the "L" level.

Then, block select signal  $\Phi R$  which was in a non-active state attains the "H" level, block select gates 22 and 23 are turned on, bit line equalize signal BLEQ attains the "H" 65 level, and bit lines BLL, /BLL, BLR, and /BLR are precharged and equalized.

4

Block select signal  $\Phi L$  or  $\Phi R$  from signal  $\Phi$  generating circuit 10 is at the internal high voltage Vpp level because of the following reason. During the restoring operation after completion of the sensing operation, sense amplifier 21 sets, according to storage data of memory cell MC1 (or MC2), corresponding bit lines BLL and /BLL (or BLR and /BLR) to the internal power supply voltage Vcc1 level and a ground potential Vss level. Between sense amplifier 21 and bit lines BLL and /BLL (or BLR and /BLR), block select gates 16 and 17 (or 22 and 23) are provided. Block select gates 16 and 17 (or 22 and 23) can transmit a voltage corresponding to a voltage applied to their gates minus the threshold voltage to corresponding bit lines BLL and /BLL (or BLR and /BLR). In order to eliminate the influence of loss of the threshold voltage in block select gates 16 and 17 (or 22 and 23), and to transmit a voltage at the internal power supply voltage Vcc1 level to bit lines BLL and /BLL (or BLR and /BLR), block select signal  $\Phi L$  or  $\Phi R$  is set at the internal high voltage Vpp level. Block select signal ΦL or ΦR may be set at the internal high voltage Vpp level only at the time of memory cycle, or only at the time when so-called "restoring operation" is carried out. Block select signal ΦL or ΦR has only to be at the internal high voltage Vpp level when a voltage at the internal power supply voltage Vcc1 level is transmitted to corresponding bit lines BLL and /BLL (or BLR and /BLR).

Word line decoders 8 and 11 generate a word line drive signal at the internal high voltage Vpp level because of the following reason. Memory cell MC1 (or MC2) writes storage data in memory cell capacitor 12 (or 14) through access transistor 13 (or 15). In order to sufficiently increase the amount of stored electric charge of capacitor 12 (or 14), it is necessary to transmit as high a voltage as possible to capacitor 12 (or 14) from bit line BLL (or BLR). In order to eliminate the influence of loss of the threshold voltage in access transistor 13 (or 15), and to transmit a voltage at the internal power supply voltage Vcc1 level to capacitor 12 (or 14), a word line drive signal at the internal high voltage Vpp level is used.

Intermediate voltage VH from Vcc/2 generating circuit 2 is applied to the cell plates of capacitors 12 and 14 because of the following reason. Ground voltage Vss or internal power supply voltage Vcc1 is applied to the opposing electrodes (storage nodes) of capacitors 12 and 14. From the standpoint of precise sensing operation (sensing margin), it is preferable that the amount of potential change of a bit line BL (which indicates BLL, /BLL, BLR, /BLR collectively) is made equal at the time of reading data of "H" at the Vcc1 level and at the time of reading data of "L" at the Vss level. 50 Bit line BL is precharged to intermediate voltage VH. Therefore, in order to make the amount of potential change from the precharge level VH of bit line BL at the time of reading memory cell data equal between the time of reading data of "H" and at the time of reading data of "L", inter-55 mediate voltage VH is applied to the cell plates of capacitors 12 and 14. The amount of stored electric charge Q of the storage nodes of capacitors 12 and 14 at the time of storing data of "H" is C·Vcc1/2, and the amount of stored electric charge Q at the time of writing data of "L" is -C·Vcc1/2, wherein C is the capacitance of capacitors 12 and 14. More specifically, application of intermediate voltage VH to the cell plates of the memory cell capacitors makes the amount of potential change of bit line BL equal between the time of reading data of "H" and the time of reading data of "L".

The conventional DRAM down-converts external power supply voltage EXV using an internal Vcc generating circuit, generates internal power supply voltage Vcc1, and

applies internal power supply voltage Vcc1 to each circuit, so that a signal amplitude is made small to reduce current consumption and power consumption.

In order to implement lower power consumption using lower operation power supply voltage, however, a signal at a required voltage level must be generated with as low power consumption as possible without the operation speed decreased by reduction of internal operation power supply voltage. Description will now be given of a circuit affected by reduction of internal power supply voltage Vcc1.

(i) Vbb generating circuit /Vpp generating circuit:

Negative voltage Vbb applied to the semiconductor substrate region as a bias voltage and internal high voltage Vpp used for driving a word line or the like are both generated using charge pump operation of a capacitor. A Vbb generating circuit will be described hereinafter.

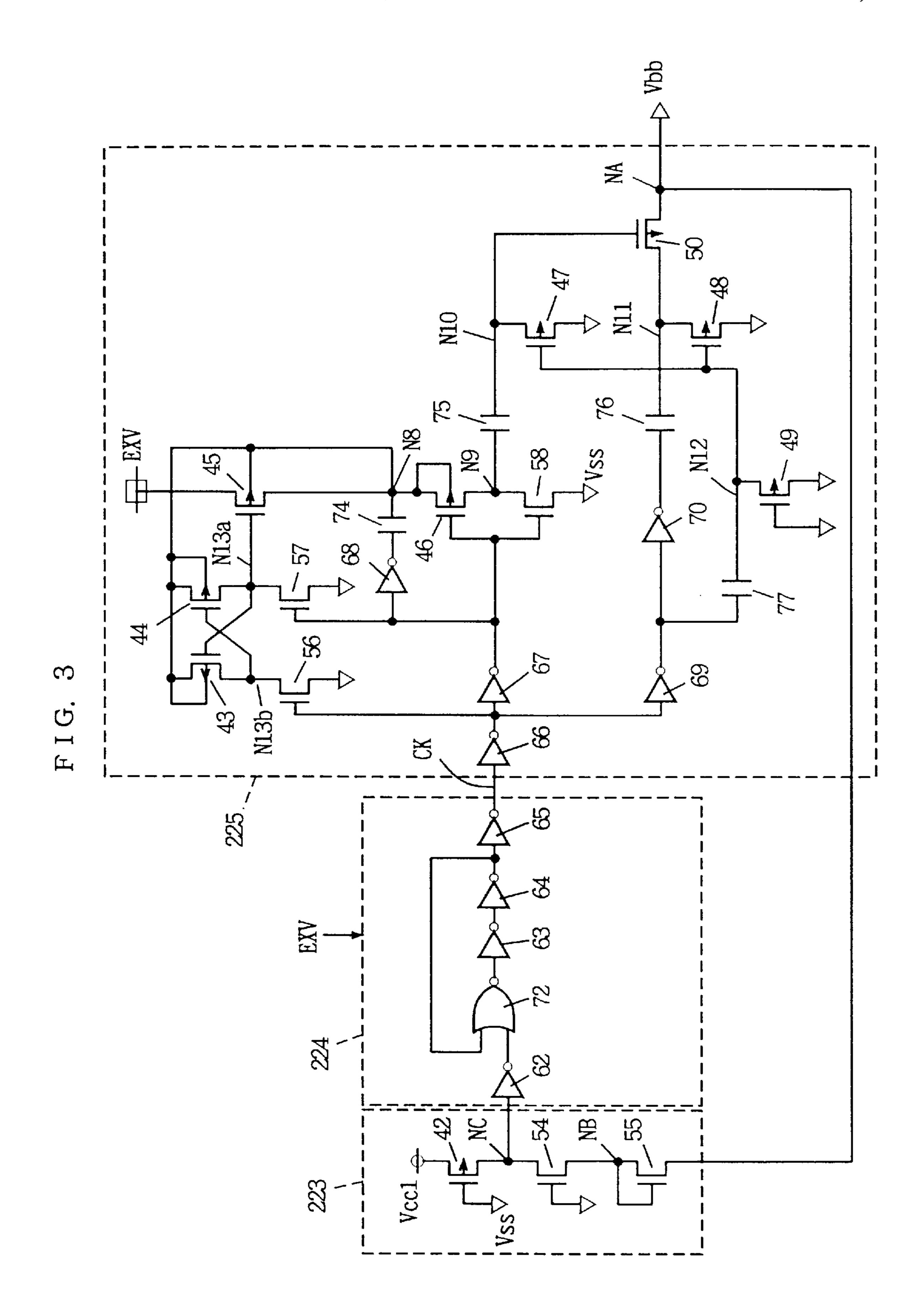

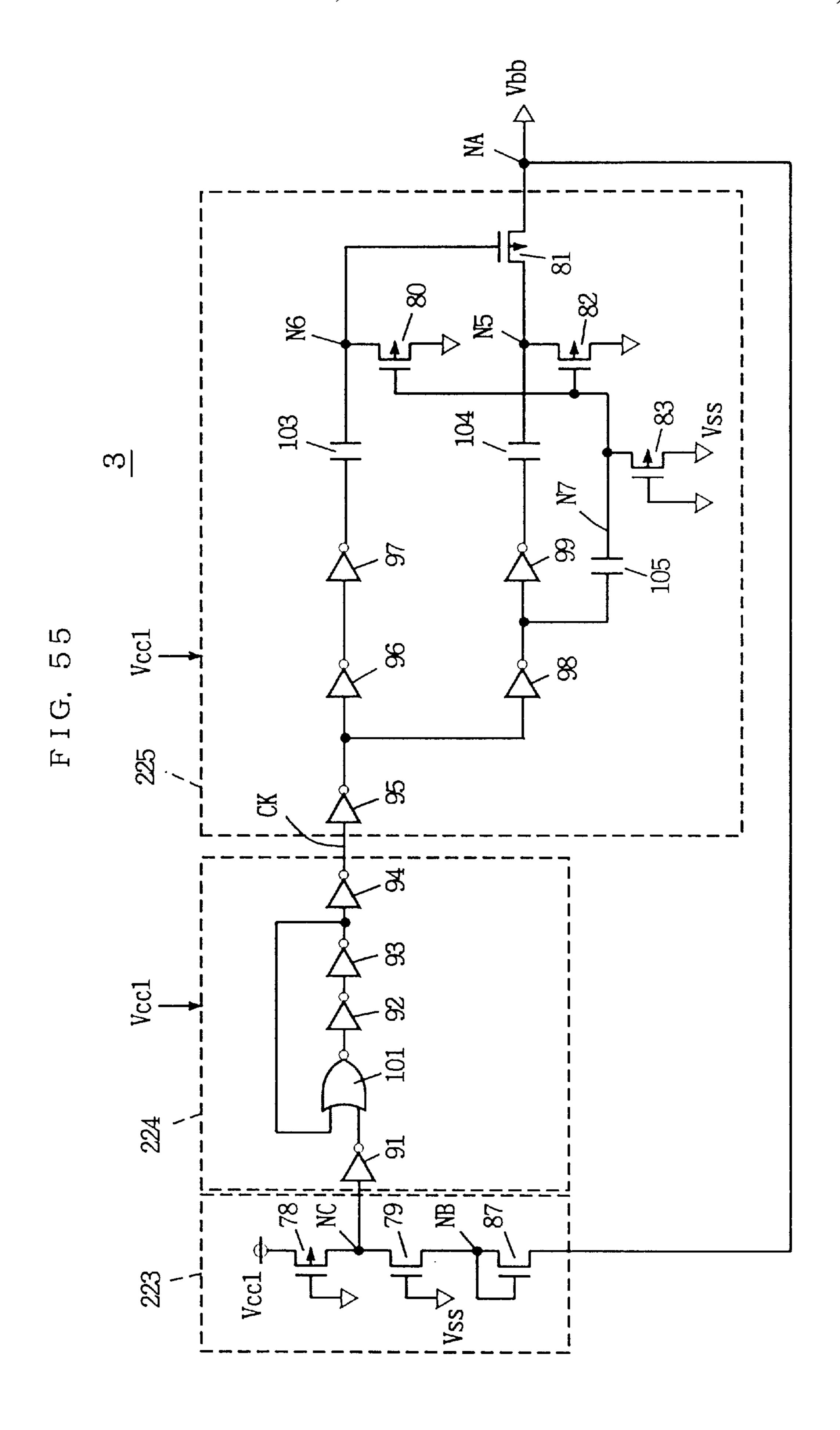

FIG. 55 is a diagram showing one example of the structure of a Vbb generating circuit 3 shown in FIG. 54. Referring to FIG. 55, Vbb generating circuit 3 includes a pump drive signal generating circuit 224 providing a clock signal CK having a prescribed pulse width and a prescribed period, a pump circuit 225 generating negative voltage Vbb by charge pumping operation according to block signal CK from pump drive signal generating circuit 224, and a level 25 detecting circuit 223 stopping generation of clock signal CK by pump drive signal generating circuit 224 when negative voltage Vbb generated by pump circuit 225 attains a prescribed level. Level detecting circuit 223, pump drive signal generating circuit 224, and pump circuit 225 receive internal power supply voltage Vcc1 as one operation power supply voltage and ground voltage Vss as the other power supply voltage.

Level detecting circuit 223 includes an n channel MOS transistor 87 having its source connected to an output node 35 (or semiconductor substrate region) NA of pump circuit 225, and its gate and drain connected to a node NB, and an n channel MOS transistor 79 provided between node NB and a node NC and receiving ground voltage Vss at its gate, and a p channel MOS transistor 78 connected between an 40 internal power supply node Vcc1 and node NC and receiving ground voltage Vcc at its gate. Note that power supply nodes and voltages applied thereto have the same reference characters in the following description.

MOS transistor 78 has large on resistance, and serves as 45 a resistance element. MOS transistor 79 has small on resistance, and current supplying capability larger than that of MOS transistor 78. MOS transistor 79 is rendered conductive when the potential at node NB is Vss-Vthn or less, and sets node NC at the "L" level. Vthn is a threshold 50 voltage of MOS transistor 79. MOS transistor 87 serves as a diode, and maintains a difference in potentials at node NB and node NA at the threshold voltage Vthn when rendered conductive.

inverter 91 inverting a signal at node NC of level detecting circuit 223, a 2-input NOR circuit 101 receiving an output signal from inverter 91 at one input, and three stages of cascade-connected inverters 92, 93, and 94 receiving an output signal from NOR circuit 101. NOR circuit 101 60 operates as an inverter when an output signal from inverter 91 is at the "L" level. In this state, NOR circuit 101, inverters 92 and 93 form a ring oscillator, and a clock signal having a prescribed pulse width and a prescribed period is generated. When an output signal from inverter 91 is at the "H" 65 level, an output signal from NOR circuit 101 is fixed to the "L" level, clock signal CK is fixed to the "H" level, and

pump drive signal generating circuit 224 stops generation of clock signal CK.

Pump circuit 225 includes an inverter 95 receiving clock signal CK from pump drive signal generating circuit 224, two stages of cascade-connected inverters 96 and 97 receiving an output signal from inverter 95, a capacitor 103 capacitively coupling an output portion of inverter 97 and a node N6, two stages of cascade-connected inverters 98 and 99 receiving an output signal from inverter 95, a capacitor 104 capacitively coupling an output portion of inverter 99 and a node N5, a capacitor 105 capacitively coupling an output portion of inverter 98 and a node N7, p channel MOS transistors 80 and 82 discharging the potentials at nodes N5 and N6 to the ground potential level in response to the potential at node N7, a p channel MOS transistor 83 clamping the potential on node N7 to the threshold voltage Vthp level, and a p channel MOS transistor 81 rendered conductive in response to the potential on node N6 for supplying a negative voltage from node N5 to output node NA. It should be noted that Vthp is the threshold voltage of p channel MOS transistors 80, 81, 82 and 83. Operation of pump circuit 225 will now be described with reference to FIG. 56.

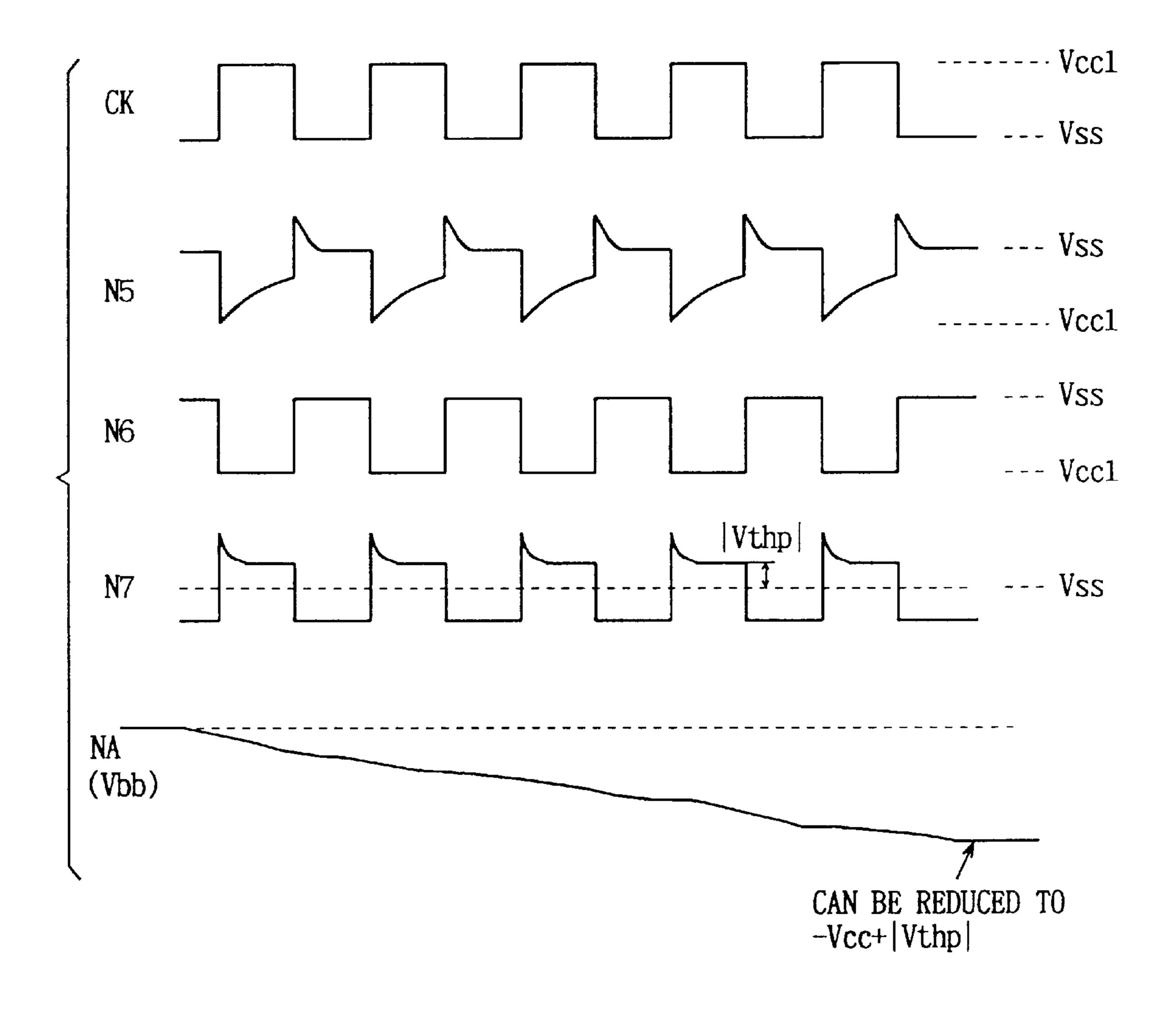

In FIG. 56, a state is shown where pump circuit 225 conducts pumping operation stably. When clock signal CK rises to the "H" level, an output signal from inverter 98 also rises to the "H" level, and the potential on node N7 is increased by capacitive coupling (charge pump) of capacitor 105. Increase in the potential on node N7 brings MOS transistor 13 to an on state, and the potential on node N7 is clamped to Vthp. On the other hand, output signals from inverters 97 and 99 attain the "L" level, and the potentials on nodes N6 and N5 are decreased to negative potentials by capacitive coupling of capacitors 103 and 104. The potentials at nodes N6 and N5 are at the -Vcc1 level, as will be described later. MOS transistors 80 and 82 are turned off, because they receive the potential of Vthp at their gates. When the potential of negative voltage Vbb from output node NA is higher than -Vcc1+|Vthp|, MOS transistor 81 is turned on, and there is a current flow to node N5 from node NA. More specifically, negative electric charge is supplied from node N5 to node NA. As a result, the potential at node NA is decreased.

When clock signal CK falls to the "L" level, an output signal from inverter 98 falls to the "L" level, and output signals from inverters 97 and 99 rise to the "H" level. The potential at node N5 attains the negative potential level (-Vcc1+|Vthp|) by capacitive coupling of capacitor 105. On the other hand, although the potentials at nodes N6 and N5 once increase by capacitive coupling of capacitors 103 and 105, the potentials are discharged to the ground potential Vss level because of an on state of MOS transistors 80 and 82. MOS transistor 81 is turned off because the potential at node NA is lower than the potentials at nodes N5 and N6. When output signals from inverters 95 and 99 fall to the "L" Pump drive signal generating circuit 224 includes an 55 level, the potential at node N5 decreases to the voltage level of -Vcc1 and the potential at node N6 also decreases to the voltage level of -Vcc1 similarly. Therefore, MOS transistor 81 can transmit the potential of -Vcc1+|Vthp| to node NA. More specifically, negative voltage Vbb can decrease down to -Vcc1+|Vthp|.

> Although the negative voltage Vbb is applied to the semiconductor substrate region, the reverse bias voltage is applied to a PN junction formed between the semiconductor substrate region and an impurity region formed on the surface thereof. Therefore, from the standpoint of breakdown voltage of the PN junction, the value of negative voltage Vbb is preferably small. Making the value of nega-

tive voltage Vbb larger than necessary (more negative) is not preferable from the standpoint of current consumption. Therefore, level detecting circuit 223 detects the voltage level of negative voltage Vbb provided from node NA, and stops generation of clock signal CK by pump drive signal 5 generating circuit 224 when negative voltage Vbb is -2.Vthn or less. More specifically, in level detecting circuit 223, when negative voltage Vbb is -2.Vthn or less, the potential at node NB is -Vthn or less, MOS transistor 79 receiving ground voltage Vss at its gate is turned on, and the potential at node NC is decreased to the "L" level. As a result, an output from inverter 91 attains the "H" level, an output from NOR circuit 101 is fixed to the "L" level, and clock signal CK is fixed to the "H" level in pump drive signal generating circuit 224. Pump operation of pump 15 circuit 225 is halted, and supply of negative electric charge (electrons) to node NA is stopped.

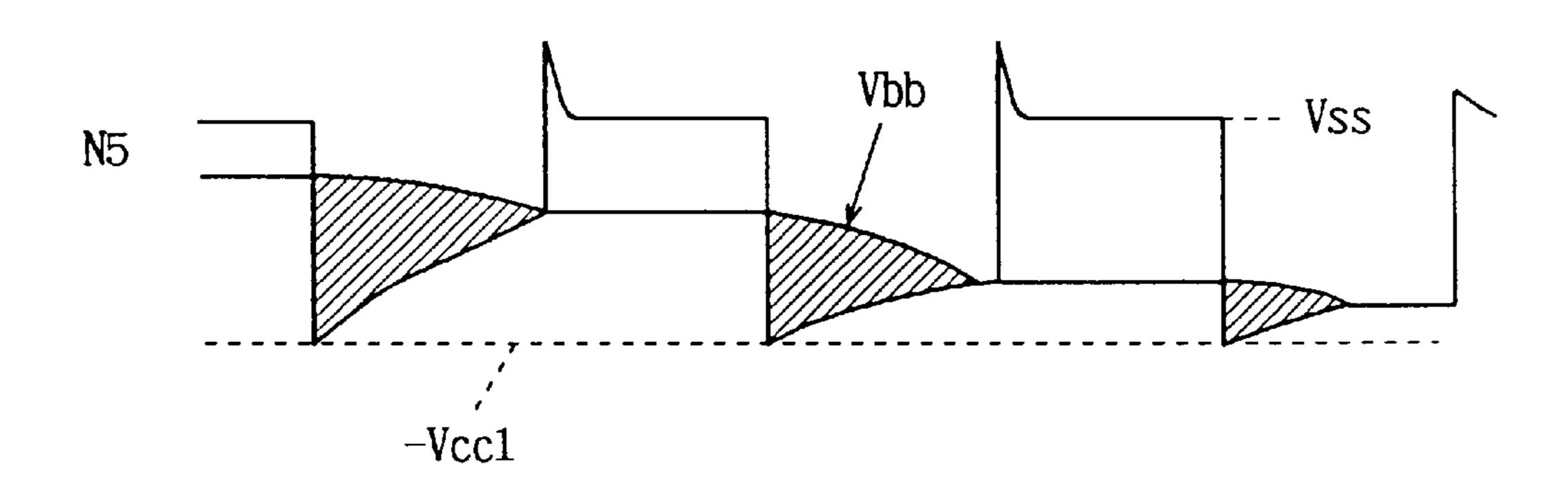

Pump circuit 225 causes negative electric charge (electrons) to flow out to output node NA for every one cycle of clock signal CK. The speed at which negative voltage 20 Vbb from node NA decreases is determined by the amount of current (the amount of negative electric charge) supplied from MOS transistor 81 of the output portion of pump circuit 225. As shown in FIG. 57, the potential at node N5 basically vibrates between Vss and -Vcc1. MOS transistor 81 sup- 25 plies negative electric charge to node NA according to a difference in potentials between nodes N5 and NA. As shown by hatching in FIG. 57, negative electric charge is supplied for every one cycle. However, the amount of negative electric charge supplied from output node NA is 30 decreased as the potential level of negative voltage Vbb decreases. When supply of negative electric charge by MOS transistor 81 is stopped, Vbb=V(N5)+|Vthp|, wherein V(N5) is the potential at node N5.

Therefore, as the potential level of negative potential Vbb approaches -Vcc1+|Vthp|, negative voltage current (the amount of negative electric charge) flowing through MOS transistor 81 decreases, and the speed at which the potential decreases is decreased. When internal power supply voltage Vcc1 is decreased for low power consumption, the threshold voltage Vthn of the MOS transistor is not scaled down (because of larger subthreshold current). Therefore, the potential level of the lowest potential -Vcc1 which node N5 attains approaches a target voltage level -2·Vthn of negative voltage Vbb. Accordingly, the speed at which the potential of negative voltage Vbb decreases is decreased (because of reduction of the amount of supply of negative electric charge), and long time is required for negative voltage Vbb to attain a prescribed level -2·Vthn.

Further, when a substrate bias voltage (negative voltage 50 Vbb) varies due to substrate current at the time of operation of the semiconductor substrate, the substrate bias voltage cannot be returned to a prescribed potential level -2. Vthn at a high speed because of decrease of the amount of supply of negative electric charge from pump circuit 225. As a result, 55 stable operation cannot be guaranteed.

The above problem of reduction of efficiency of the negative voltage Vbb generating circuit caused by low power supply voltage arises in the Vpp generating circuit generating internal high voltage Vpp, similarly. In the internal high voltage generating circuit (Vpp generating circuit), by replacing the p channel MOS transistors of pump circuit 225 shown in FIG. 55 with n channel MOS transistors, and by replacing ground voltage Vss with internal power supply voltage Vcc1, a pump circuit for generating internal high 65 voltage Vpp is obtained theoretically. A level sensing circuit for internal high voltage Vpp is also implemented by replac-

8

ing negative voltage Vbb in the level sensing circuit shown in FIG. 55 with internal high voltage Vpp, reversing conductivity types of the MOS transistors, and by replacing ground voltage Vss with internal power supply voltage Vcc1.

As described above, when a pump circuit is used as a conventional negative voltage generating circuit and a conventional internal high voltage generating circuit, and the internal power supply voltage level is further decreased for low power consumption, electric charge cannot be supplied efficiently, and a voltage at a prescribed level (negative voltage Vbb and internal high voltage Vpp) cannot be generated at a high speed. Accordingly, a semiconductor memory device which operates stably with lower power consumption cannot be implemented.

#### (ii) BLEQ generating circuit

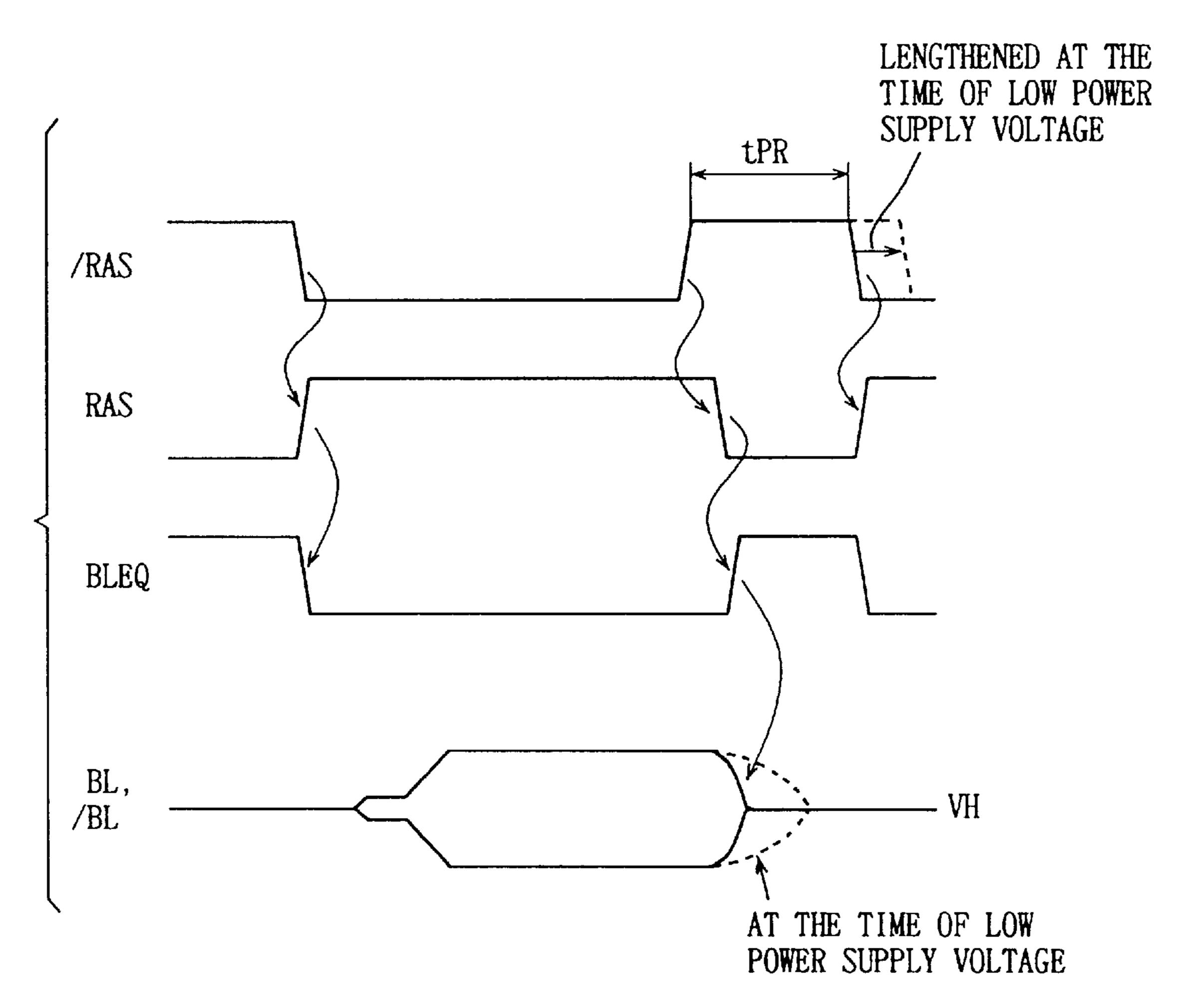

FIG. 58 is a diagram showing schematically the structure of BLEQ generating circuit 9 shown in FIG. 54. Referring to FIG. 58, BLEQ generating circuit 9 generates bit line equalize signal BLEQ in response to an internal row address strobe signal RAS applied from control circuit 7 shown in FIG. 54. BLEQ generating circuit 9 operates with internal power supply voltage Vcc1 and ground voltage Vss as operation power supply voltages. Internal row address strobe signal RAS is generated from control circuit 7 shown in FIG. 54 in response to external row address strobe signal /RAS. When internal row address strobe signal RAS is at the "H" level, bit line equalize/precharge signal BLEQ attains the "L" level. Description will be given hereinafter of operation of BLEQ generating circuit 9 shown in FIG. 58 with reference to FIG. 59 which shows the operation waveform diagram.

When external row address strobe signal /RAS is at the "H" level, internal row address strobe signal RAS is at the "L" level, and bit line equalize signal BLEQ from BLEQ generating circuit 9 is at the "H" level of the internal power supply voltage Vcc1 level. As a result, MOS transistors 18, 19, and 20 are turned on, precharging and equalizing bit lines BL and /BL (which indicate bit lines BLL, /BLL, and BLR, /BLR shown in FIG. 54 collectively) to a prescribed intermediate voltage VH.

When external row address strobe signal /RAS falls to the "L" level, internal row address strobe signal /RAS accordingly rises to the "H" level, and a memory cycle starts. In response to the rising of internal row address strobe signal RAS, bit line equalize signal BLEQ from BLEQ generating circuit 9 attains the "L" level, MOS transistors 18, 19, and 20 are turned off, and bit lines BL and /BL are brought to a floating state at intermediate voltage VH.

Then, a word line, not shown, is selected, and the potential increases. Data of memory cells connected to the selected word line is transmitted to bit line BL or /BL. Then, sensing operation is carried out. The potentials on bit lines BL and /BL attain "H" at the internal power supply voltage Vcc1 level and "L" at the ground voltage Vss level depending on data read out from memory cells.

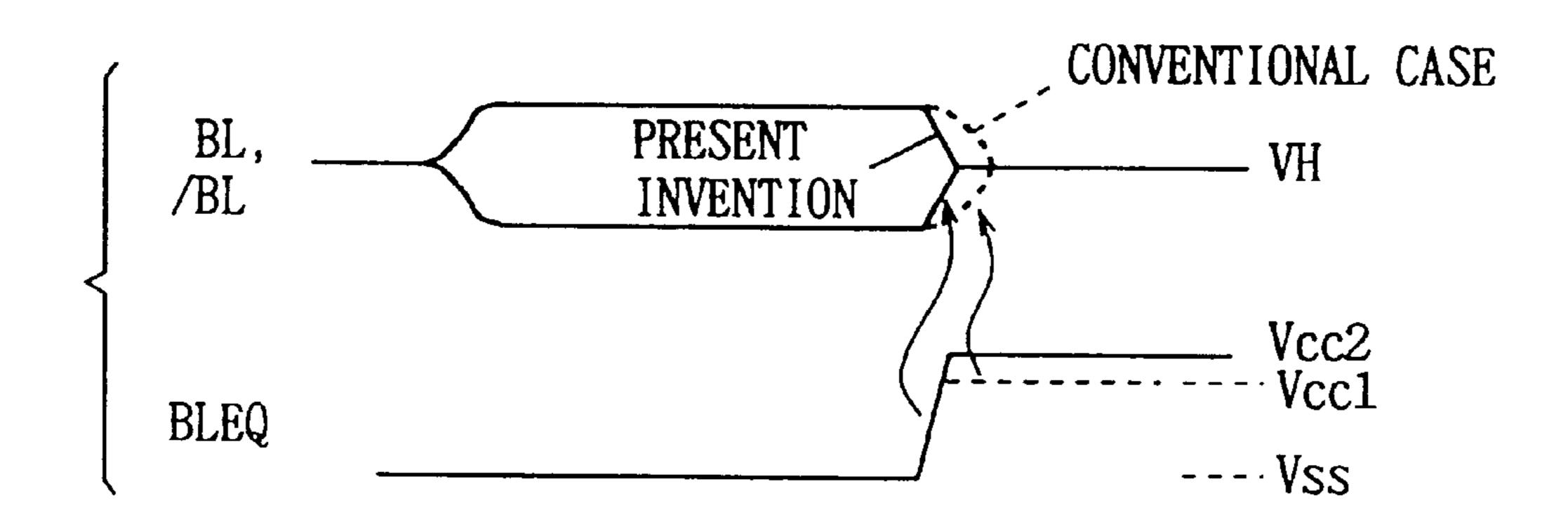

When the memory cycle is complete, external row address strobe signal /RAS rises to the "H" level. After a prescribed time, internal row address strobe signal /RAS falls to the "L" level. In response to the falling of internal row address strobe signal RAS, bit line equalize signal BLEQ from BLEQ generating circuit 9 rises to the "H level, and MOS transistors 18, 19, and 20 are turned on. This causes bit lines BL and /BL to be precharged/equalized to the internal voltage VH level again.

Bit line equalize signal BLEQ is at the internal power supply voltage Vcc1 level. When the voltage level of inter-

nal power supply voltage Vcc1 is decreased for low power consumption of a semiconductor memory device, the potential at the "H" level of bit line equalize signal BLEQ decreases accordingly. In this case, the gate-source voltages of MOS transistors 18–20 become small (the sources of n channel MOS transistors are electrodes having a low potential), and their conductivities become small. Therefore, current supplying capabilities of MOS transistors 18–20 become small, and the potentials of bit lines BL and /BL are set at a prescribed intermediate voltage VH later as shown by a broken line in FIG. 59 after completion of the memory cycle. On the other hand, for external row address strobe signal /RAS, RAS precharge time tPR is set. Once it attains the "H" level, external row address strobe signal /RAS can be set to the "L" level again only after a lapse of RAS precharge time tPR (for reliably precharging an internal 15 signal line to a prescribed potential). If the potentials of bit lines BL and /BL cannot be precharged/equalized to a prescribed intermediate voltage VH within a prescribed time, the RAS precharge time becomes longer, and it takes longer time to start the next memory cycle. Accordingly, the 20 semiconductor memory device cannot be accessed at a high speed.

# (iii) Vcc/2 generating circuit

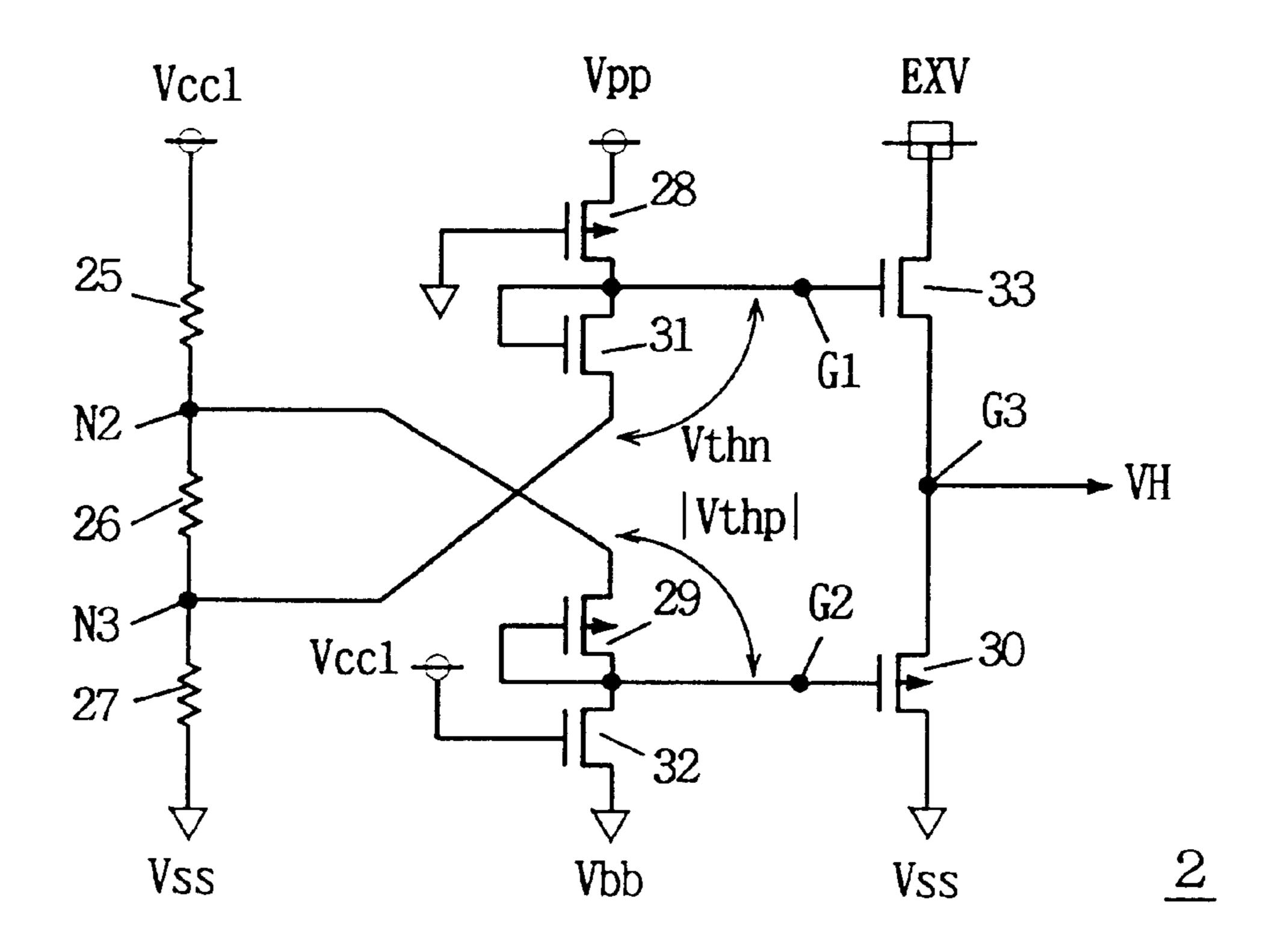

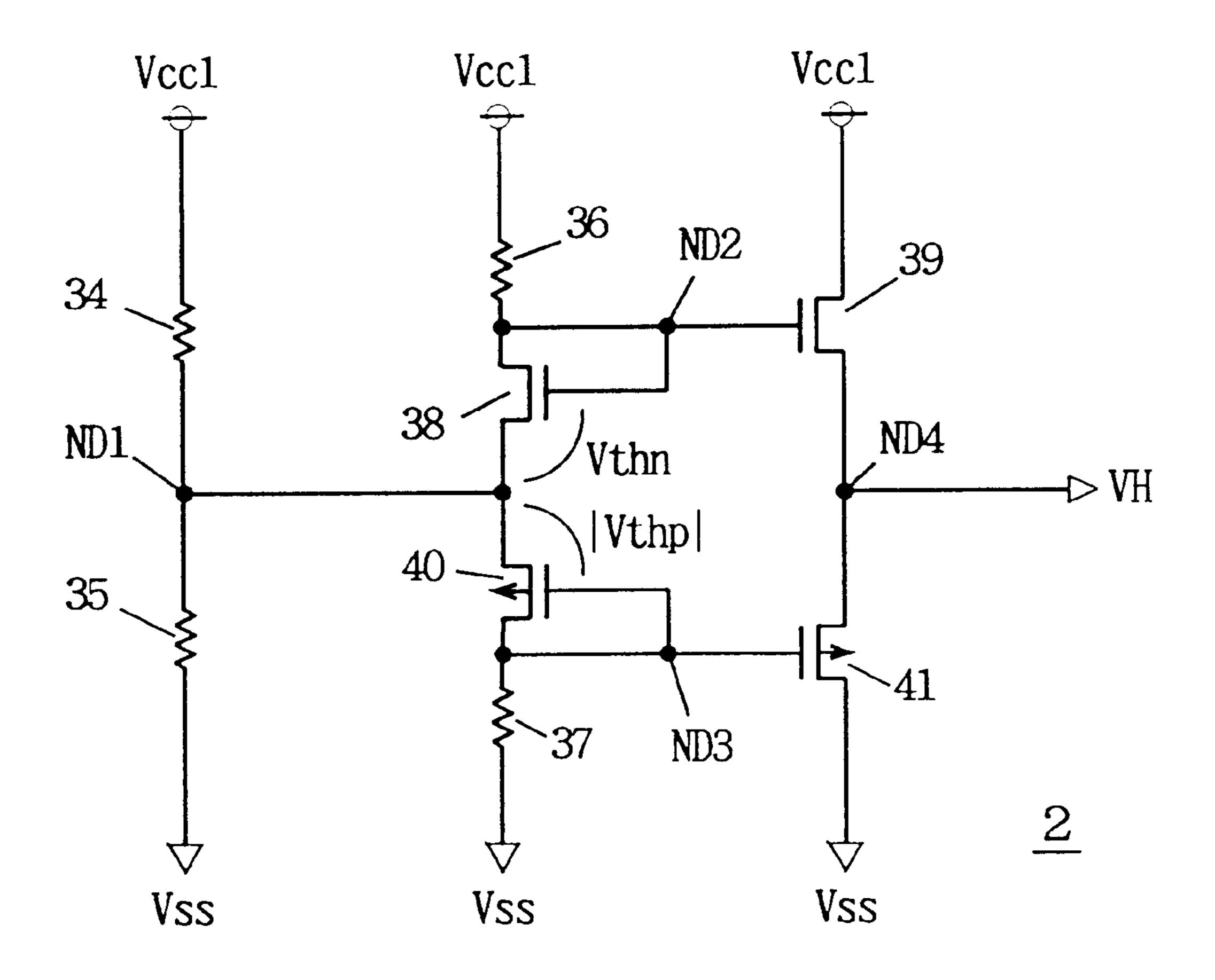

FIG. **60** is a diagram showing the structure of a conventional Vcc/2 generating circuit, which is found in pages 17 and 18 of Digest of Technical Papers, 1990 Symposium on VLSI Circuits, for example.

Referring to FIG. 60, the Vcc/2 generating circuit includes resistors 34 and 35 connected in series between power supply node Vcc1 and a ground node Vss, a resistor 36 connected between power supply node Vcc1 and a node ND2, an n channel MOS transistor 38 having its gate and drain connected to node ND2 and its source connected to a node ND1, a p channel MOS transistor 40 having its gate and drain connected to a node ND3 and its source connected to node ND1, a resistor 37 connected between node ND3 and ground node Vss, an n channel MOS transistor 39 connected between power supply node Vcc1 and node ND1 and receiving the signal potential at node ND2 at its gate, and a p channel MOS transistor 41 connected between node ND1 and ground node Vss and receiving the signal potential at node ND3 at its gate.

Resistors 34 and 35 have the same resistance value, and resistors 36 and 37 have a sufficiently large resistance value.

Transistors 38 and 40 have respective threshold voltages Vthn and Vthp. Operation will now be described briefly.

Since resistors 34 and 35 have the same resistance value, the potential of node ND1 is Vcc1/2. Since resistors 36 and 37 have a sufficiently large resistance value, there is only a small current flow through MOS transistors 38 and 40. Therefore, MOS transistors 38 and 40 operate in a diode mode, the potential of node ND2 is Vcc1/2+Vthn, and the potential of node ND3 is Vcc1/2-|Vthp|. MOS transistors 39 and 41 have threshold voltages Vthn and Vthp, respectively. When the potential VH of node ND4 is lower than Vcc1/2, MOS transistor 39 is turned on, and MOS transistor 41 is turned off. Node ND4 is supplied with current from power supply node Vcc1 through MOS transistor 39, increasing voltage VH.

When voltage VH of node ND4 is higher than Vcc1/2, MOS transistor 39 is turned off, and MOS transistor 41 is turned on. Node ND4 is discharged through MOS transistor 41, decreasing the potential. As a result, voltage VH of node ND4 is set to intermediate voltage Vcc1/2.

MOS transistor 38 causes voltage drop between node ND2 and node ND1, and MOS transistor 40 causes voltage

10

drop of |Vthp| between node ND1 and node ND3. Therefore, in order for Vcc1/2 generating circuit 2 to operate, the condition of Vcc1≥Vthn+|Vthp| must be satisfied. More specifically, internal power supply voltage Vcc1 has a lower limit value, and low power consumption cannot be implemented by reduction of the internal power supply voltage.

Further, there is also a problem that current consumption is increased depending on a defective mode of a memory cell as described below.

As shown in FIG. 61, consider the case where shortcircuiting occurs between the electrode (cell plate) of a memory cell capacitor MQ and a word line WL. Intermediate voltage VH from Vcc/2 generating circuit 2 is applied to the electrode of memory cell capacitor MQ. Therefore, when the potential of word line WL is at the "L" level, there is a current flow from power supply node Vcc1 through MOS transistor 39 shown in FIG. 60 to word line WL through node ND4 and the memory cell capacitor electrode (cell plate). In general, in order to ensure the production yield, a DRAM is used as a non-defective product even if there is a leakage current of 0.2 mA in memory cell capacitor MQ, provided that a defective memory cell in which the capacitor electrode is short-circuited is replaced with a redundancy circuit (the defective memory cell per se exists in the device). Since current must be supplied to the capacitor electrode of the defective memory cell through the Vcc/2 generating circuit, the internal power supply voltage generating circuit must have current supplying capability of 0.2 mA even at the time of stand-by of the DRAM. Accordingly, the stand-by current of the DRAM cannot be made small.

In addition, even when voltage VH from node ND4 attains a prescribed level Vcc1/2, current is consumed wastefully, because the gate-source voltages of MOS transistors 39 and 41 are Vthn and Vthp, respectively, and there is a subthreshold current flow in ground node Vss from power supply node Vcc1 through MOS transistors 39 and 41. In order to reduce the subthreshold current, ions must be implanted into the channel regions of transistors 39 and 41, and the threshold voltages Vthn and Vthp of MOS transistors 39 and 41 must be increased. In this case, an additional manufacturing step for adjusting the threshold voltages of MOS transistors 39 and 41 is required, preventing simplification of the manufacturing process. When the threshold voltages of MOS transistors 39 and 41 are increased, even if voltage VH from node ND4 is offset from a prescribed intermediate voltage Vcc1/2, MOS transistors 39 and 41 are not turned on. A non-sensitive belt where the Vcc/2 generating circuit does not operate even if voltage VH changes from a prescribed level, making it impossible to precisely maintain voltage VH at the intermediate voltage level.

# (iv) Internal power supply voltage generating circuit

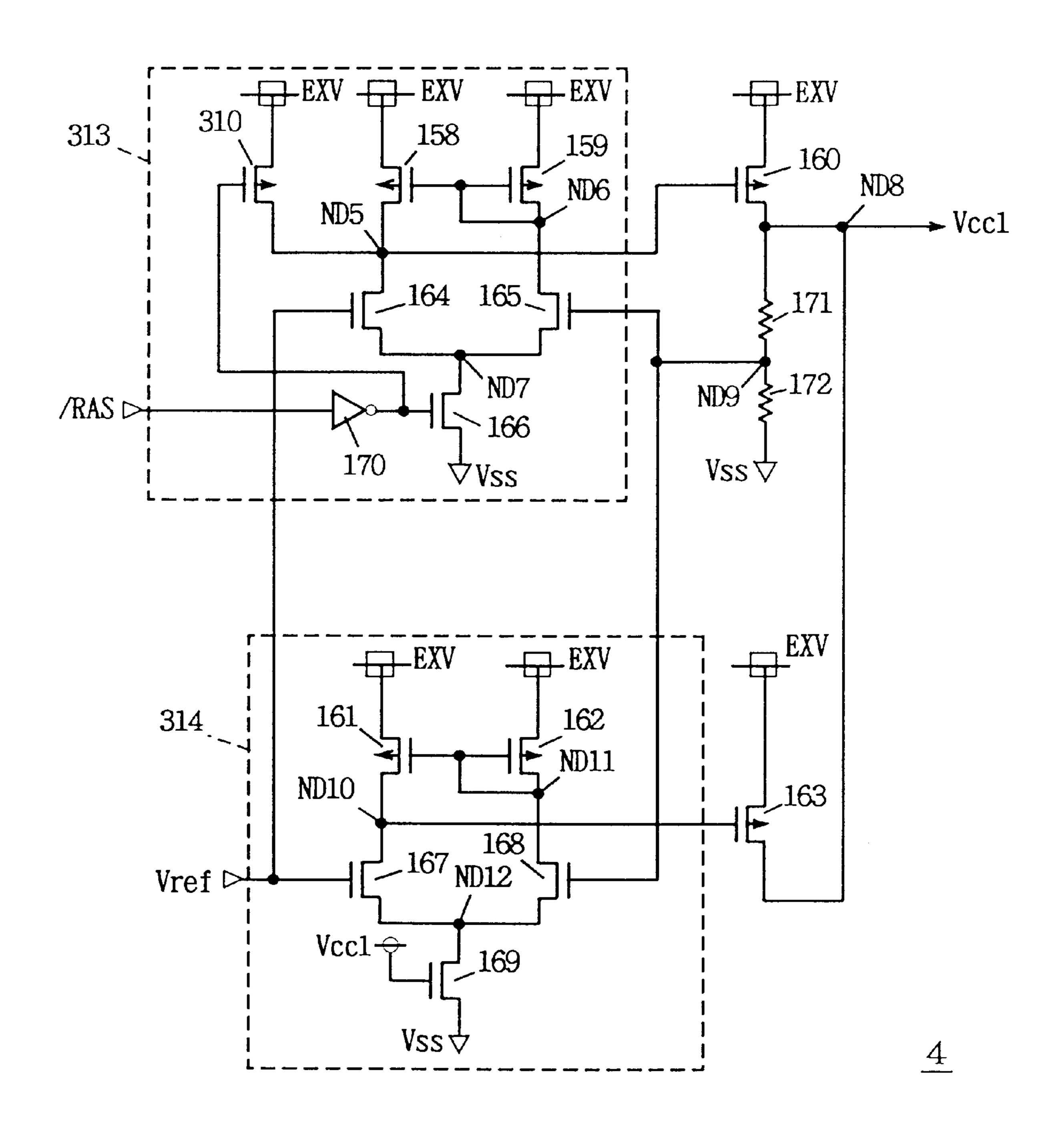

FIG. 62 is a diagram showing the structure of a conventional internal power supply voltage generating circuit. Referring to FIG. 62, conventional internal power supply voltage generating circuit 4 includes an activation internal power supply voltage generating circuit 313 operating at the time of activation (during memory cycle) and supplying internal power supply voltage Vcc1, and a stand-by internal power supply voltage generating circuit 314 maintaining internal power supply voltage Vcc1 at a prescribed voltage level at the time of stand-by.

Activation internal power supply voltage generating circuit 313 includes an inverter 170 inverting row address strobe signal /RAS (generated from control circuit 7 shown in FIG. 54), a p channel MOS transistor 310 rendered conductive in response to an output signal from inverter 170

for transmitting external power supply voltage EXV to a node ND5, an N channel MOS transistor 164 provided between node ND5 and a node ND7 for receiving a reference voltage Vref at its gate, an n channel MOS transistor 165 provided between a node ND6 and node ND7 for 5 receiving the signal potential on a node ND9 at its gate, an n channel MOS transistor 166 provided between node ND7 and ground node Vss for receiving an output from inverter 170 at its gate, a p channel MOS transistor 158 provided between node ND5 and an external power supply node EXV 10 receiving external power supply voltage EXV, and a p channel MOS transistor 159 provided between external power supply node EXV and node ND6. Node ND6 is connected to respective gates of MOS transistors 158 and 159. MOS transistors 158 and 159 form a current mirror circuit, and MOS transistors 164 and 165 form a source coupling type comparing circuit.

Stand-by internal power supply voltage generating circuit 314 includes an n channel MOS transistor 167 provided between a node ND10 and a node ND12 for receiving 20 reference voltage Vref at its gate, an n channel MOS transistor 168 provided between a node ND11 and node ND12 for receiving the signal potential on a node ND9 at its gate, a p channel MOS transistor 161 provided between external power supply node EXV and node ND10, and a p 25 channel MOS transistor 162 provided between node ND11 and external power supply node EXV. Node ND11 is connected to respective gates of MOS transistors 161 and 162. MOS transistors 161 and 162 form a current mirror circuit, and MOS transistors 167 and 168 form a source coupling 30 type comparing circuit. Stand-by internal power supply voltage generating circuit 314 further includes an n channel MOS transistor 159 provided between node ND12 and ground node Vss for receiving internal power supply voltage Vcc1 at its gate to serve as a constant current source.

Internal power supply voltage generating circuit 4 further includes a p channel MOS transistor 160 rendered conductive in response to the signal potential on node ND5 of activation internal power supply voltage generating circuit 313 for supplying current to a node ND8 from external power supply node EXV, a p channel MOS transistor 163 rendered conductive in response to the signal potential on node ND10 of stand-by internal power supply voltage generating circuit 314 for supplying current from external power supply node EXV to output node ND8, and resistors 171 and 172 connected in series between node ND8 and ground node Vss. The resistance values of resistors 171 and 172 are so set that the ratio is 2:3, for example. Operation will now be described briefly.

In a stand-by state, row address strobe signal /RAS is at 50 the "H" level, and an output from inverter 170 is at the "L" level. In this state, MOS transistor 310 is turned on, and MOS transistor 166 is turned off. Node ND5 is charged to external power supply voltage EXV by MOS transistor 310, and MOS transistor 160 is turned off.

On the other hand, in stand-by internal power supply voltage generating circuit 314, MOS transistor 169 operates as a constant current source, and compares reference voltage Vref and the signal potential on node ND9. When the signal potential on node ND9 is higher than reference voltage Vref, 60 the potential of node ND10 increases, thereby decreasing the conductance of MOS transistor 163. On the other hand, when the signal potential on node ND9 is lower than reference voltage Vref, the potential of node ND10 decreases, thereby increasing the conductance of MOS transistor 163, and supplying current to node ND8. This makes the signal potential on node ND9 equal to reference voltage

12

Vref. The ratio of the resistance values of resistors 171 and 172 are set to 2:3. Therefore, internal power supply voltage Vcc1 is maintained at a voltage level of 5·Vref/3. When the value of reference voltage Vref is 1.5 V, for example, the value of internal power supply voltage Vcc1 is maintained at 2.5 V.

When an active cycle (memory cycle) starts, row address strobe signal /RAS attains the "L" level, and activation internal power supply voltage generating circuit 313 is brought to an active state. More specifically, an output signal from inverter 170 attains the "H" level, MOS transistor 310 is turned off, and MOS transistor 166 is turned on. Operation of a current mirror type differentially amplifying circuit formed of MOS transistors 158, 159, 164, and 165 is the same as that of the stand-by internal power supply voltage generating circuit. By adjusting the conductance of MOS transistor 160 according to the relationship between the voltage of node ND9 and reference voltage Vref, internal power supply voltage Vcc1 on node ND8 is maintained at a constant voltage level of 5·Vref/3.

At the time of stand-by when internal power supply voltage Vcc1 is hardly used, current consumption at the time of stand-by is reduced by operating only stand-by internal power supply voltage generating circuit 314 consuming a little current. In the memory cycle (active cycle) when internal power supply voltage Vcc1 is consumed (current is consumed from internal power supply voltage Vcc1 by charging of a signal line by operation of internal circuits), a large amount of current is supplied to node ND8 by MOS transistor 10 having a large current drivability, thereby stabilizing internal power supply voltage Vcc1.

With the structure of the conventional internal power supply voltage generating circuit shown in FIG. 62, however, there is always a current flow from node ND8 to ground node Vss through resistors 171 and 172. When the resistance values of resistors 171 and 172 are increased in order to decrease a current flow through resistors 171 and 172, RC delay from node ND8 to node ND9 becomes larger. In this case, change of the signal potential on node ND8 is transmitted to circuits 313 and 314 later. Change of internal power supply voltage Vcc1 cannot be followed at a high speed, and internal power supply voltage Vcc1 cannot be kept at a constant level stably.

More specifically, with the structure of the conventional internal power supply voltage generating circuit, operating the semiconductor memory device with low power consumption prevents stable generation of internal power supply voltage.

As described above, with the structure of the conventional semiconductor memory device, low power consumption cannot be implemented without decreasing performance.

# SUMMARY OF THE INVENTION

One object of the present invention is to provide a semiconductor memory device operating stably with low power consumption.

Another object of the present invention is to provide each component for implementing low power consumption of the semiconductor memory device.

Still another object of the present invention is to provide an internal power supply voltage generating circuit which can generate an internal voltage at a prescribed voltage level efficiently and stably with low power consumption.

A further object of the present invention is to provide a negative voltage generating circuit capable of generating a substrate bias voltage efficiently with low power consumption.

A further object of the present invention is to provide an internal high voltage generating circuit capable of generating an internal high voltage efficiently.

A further object of the present invention is to provide an intermediate voltage generating circuit capable of generating an intermediate voltage stably with low power consumption.

A further object of the present invention is to provide an internal power supply voltage generating circuit capable of generating internal power supply voltage stably with low power consumption.

A further object of the present invention is to provide a reference voltage generating circuit capable of generating a reference voltage at a constant voltage level stably with low power consumption, and a constant current source therefor.

A further object of the present invention is to provide a semiconductor memory device operating at a high speed with low power consumption.

A semiconductor memory device according to one aspect 20 of the present invention includes an internal power supply circuit down-converting externally applied external power supply voltage to generate internal power supply voltage, and an internal voltage generating circuit generating an internal voltage at a voltage level different form the internal 25 power supply voltage from the external power supply voltage by charge pumping operation.

In the semiconductor memory device according to the one aspect of the present invention, the internal voltage at a prescribed voltage level is generated from the external 30 power supply voltage by charge pumping operation. Therefore, even if the internal voltage level provided from a pump circuit approaches a target voltage level, sufficient electric charge can be supplied, and the internal voltage at a prescribed voltage level can be generated stably at a high 35 speed.

The foregoing and other objects, features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

# BRIEF DESCRIPTION OF THE DRAWINGS

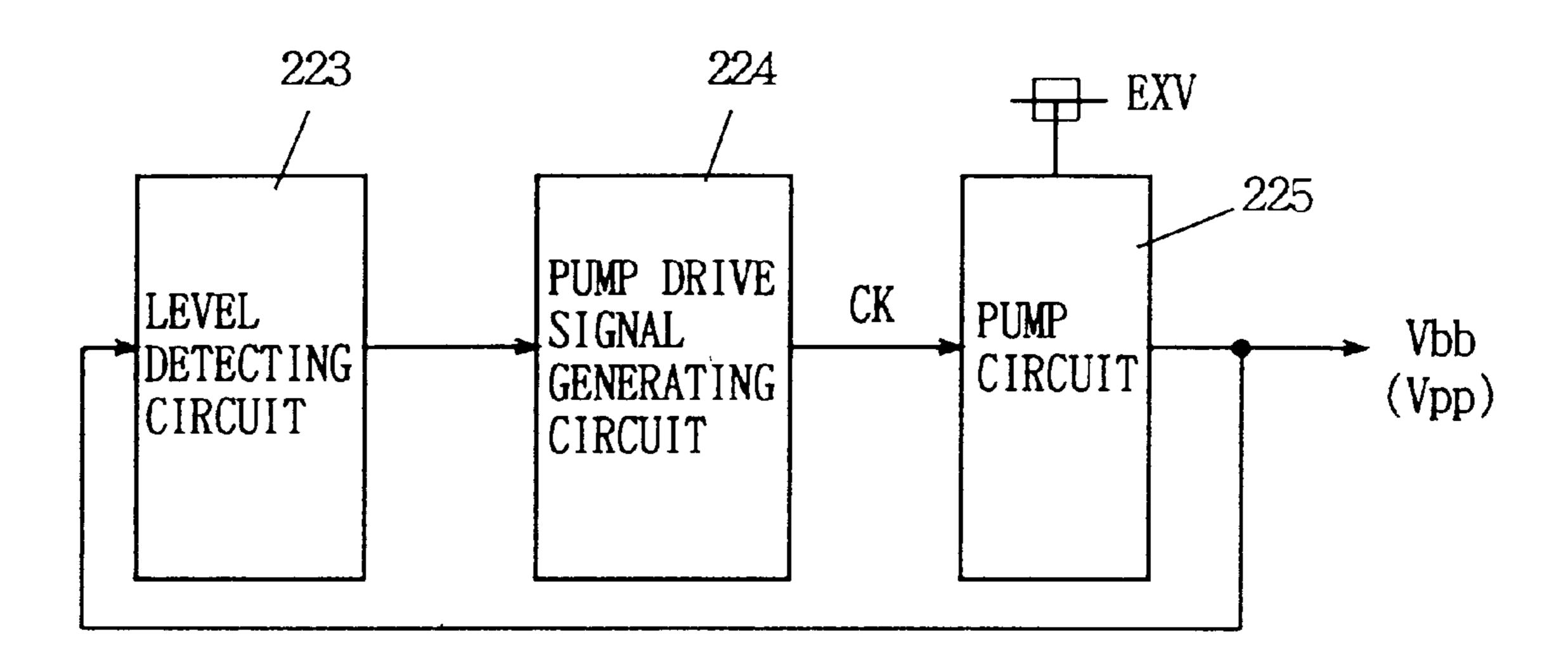

- FIG. 1 is a diagram showing the structure of an internal 45 voltage generating circuit using charge pumping operation according to the present invention.

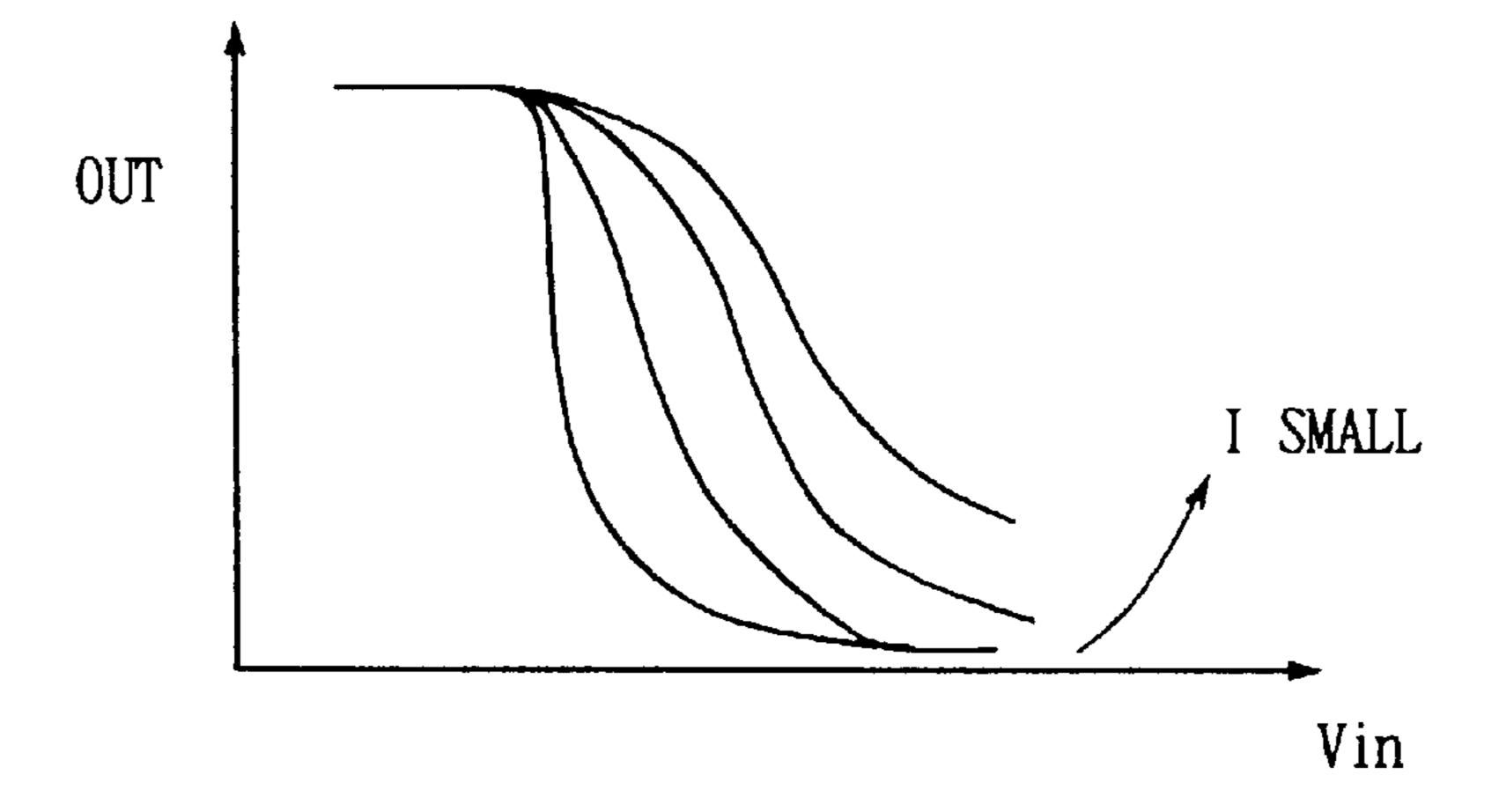

- FIG. 2 is a diagram for explaining the effect brought about by the internal voltage generating circuit shown in FIG. 1.

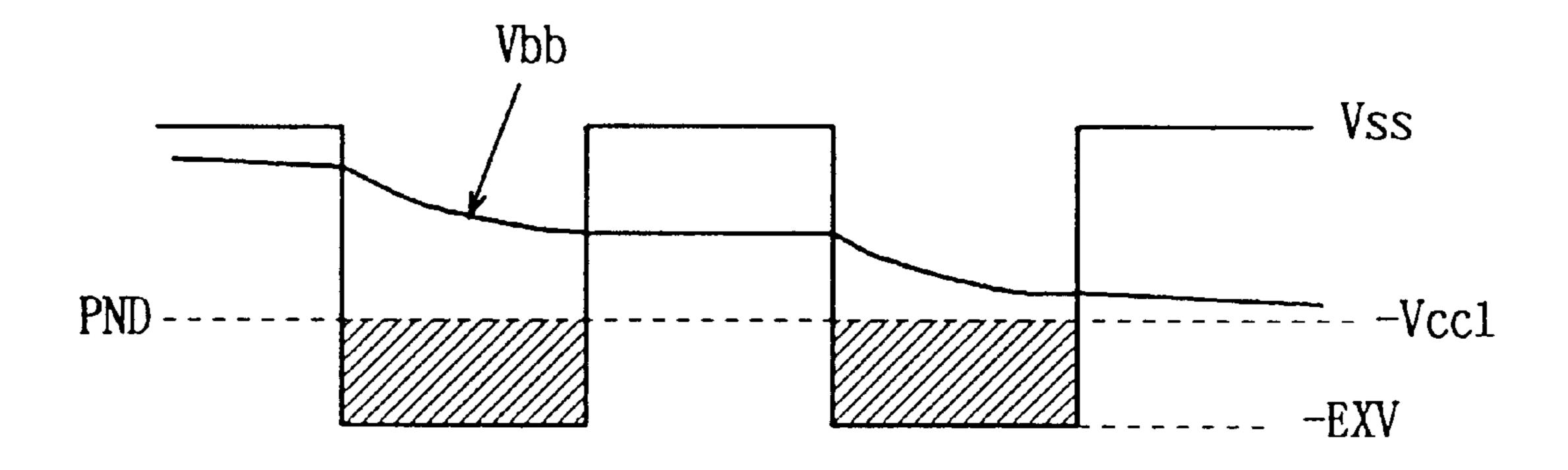

- FIG. 3 is a diagram showing a specific structure of the internal voltage generating circuit according to the present invention.

- FIG. 4 is a diagram showing the structure of an inverter at the first stage of a pump drive signal generating circuit shown in FIG. 3.

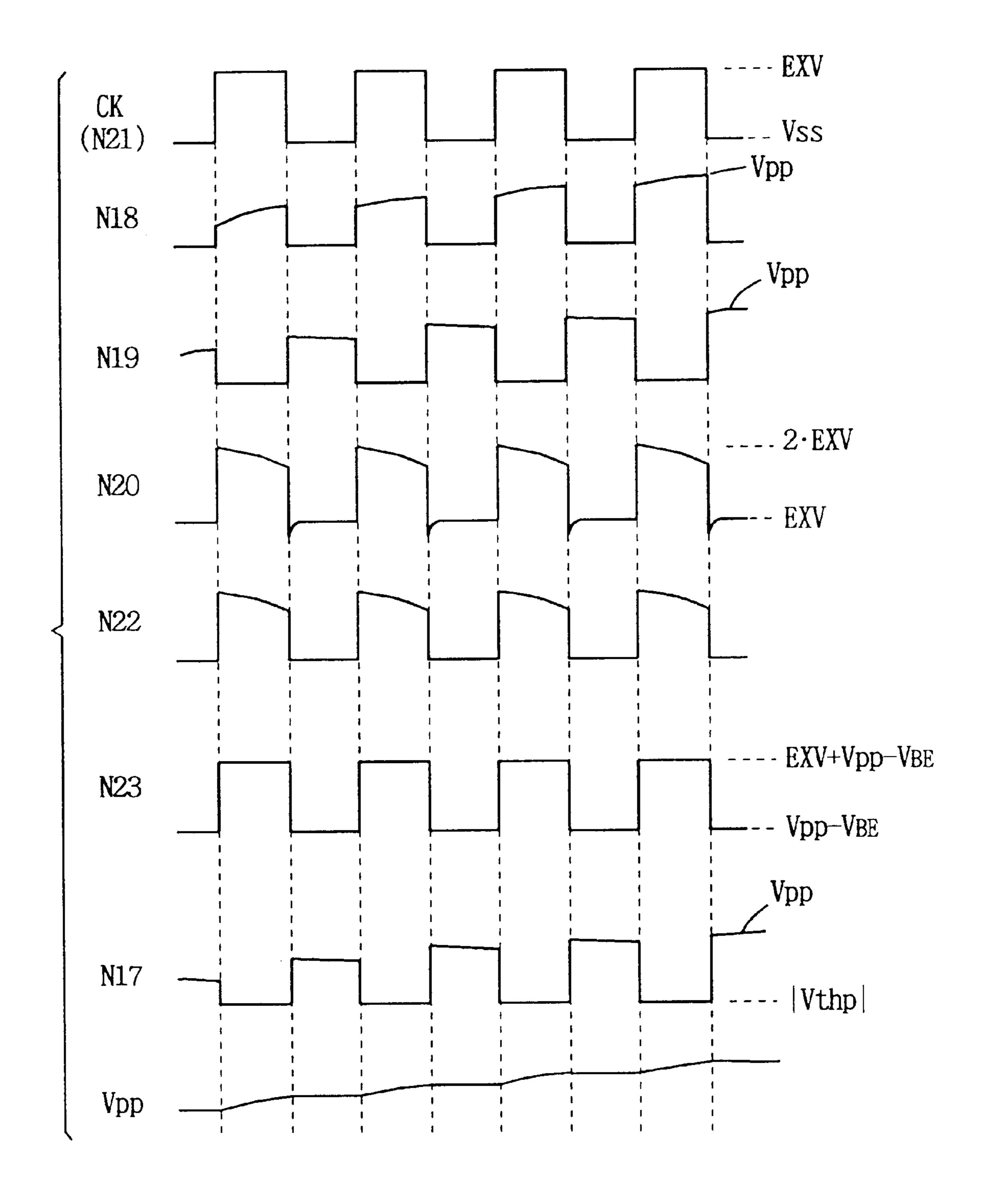

- FIG. 5 is a signal waveform diagram showing operation of a negative voltage generating circuit shown in FIG. 3.

- FIG. 6 is a diagram showing another structure of the negative voltage generating circuit according to the present invention.

- FIG. 7 is a signal waveform diagram showing operation of the negative voltage generating circuit shown in FIG. 6.

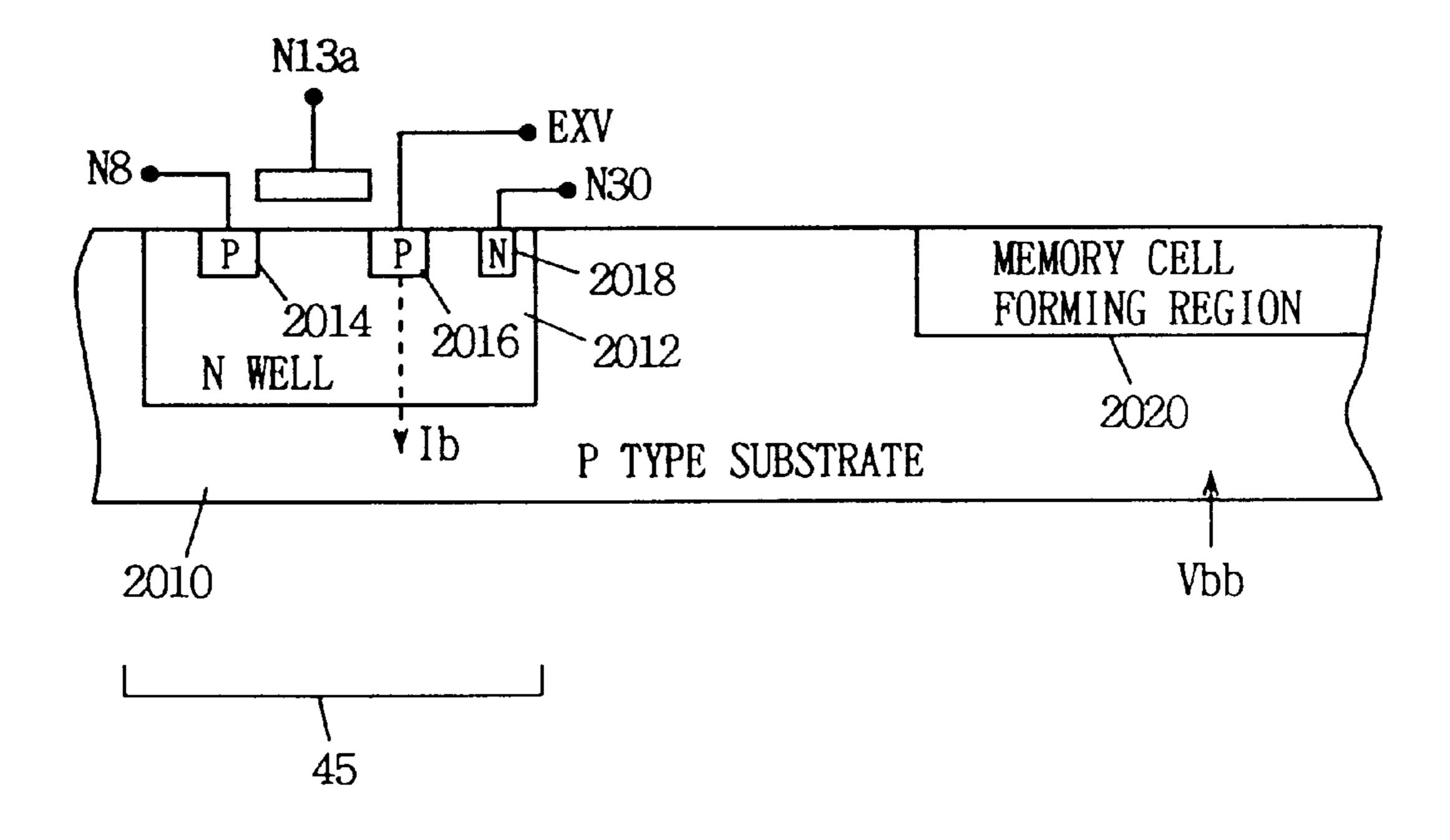

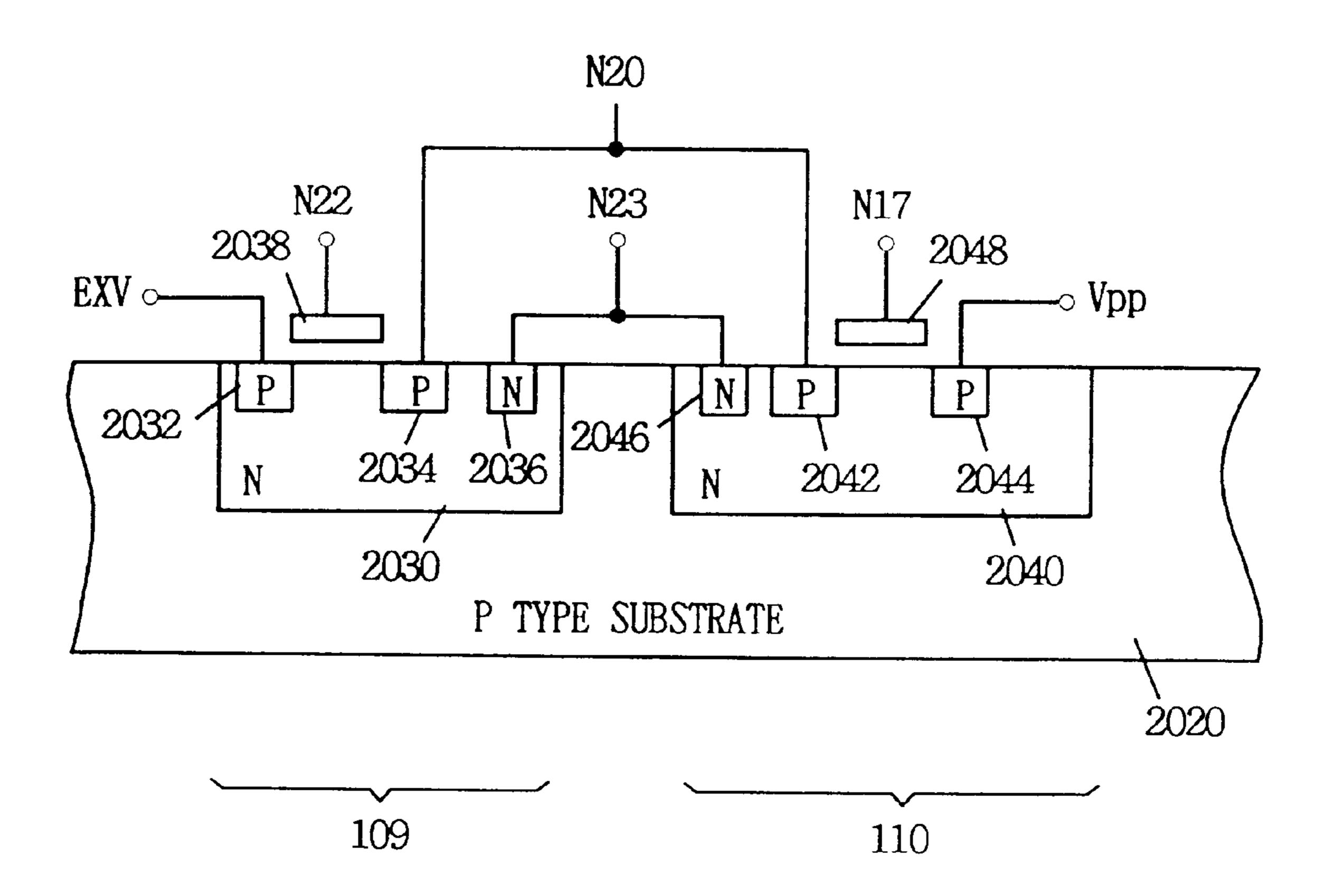

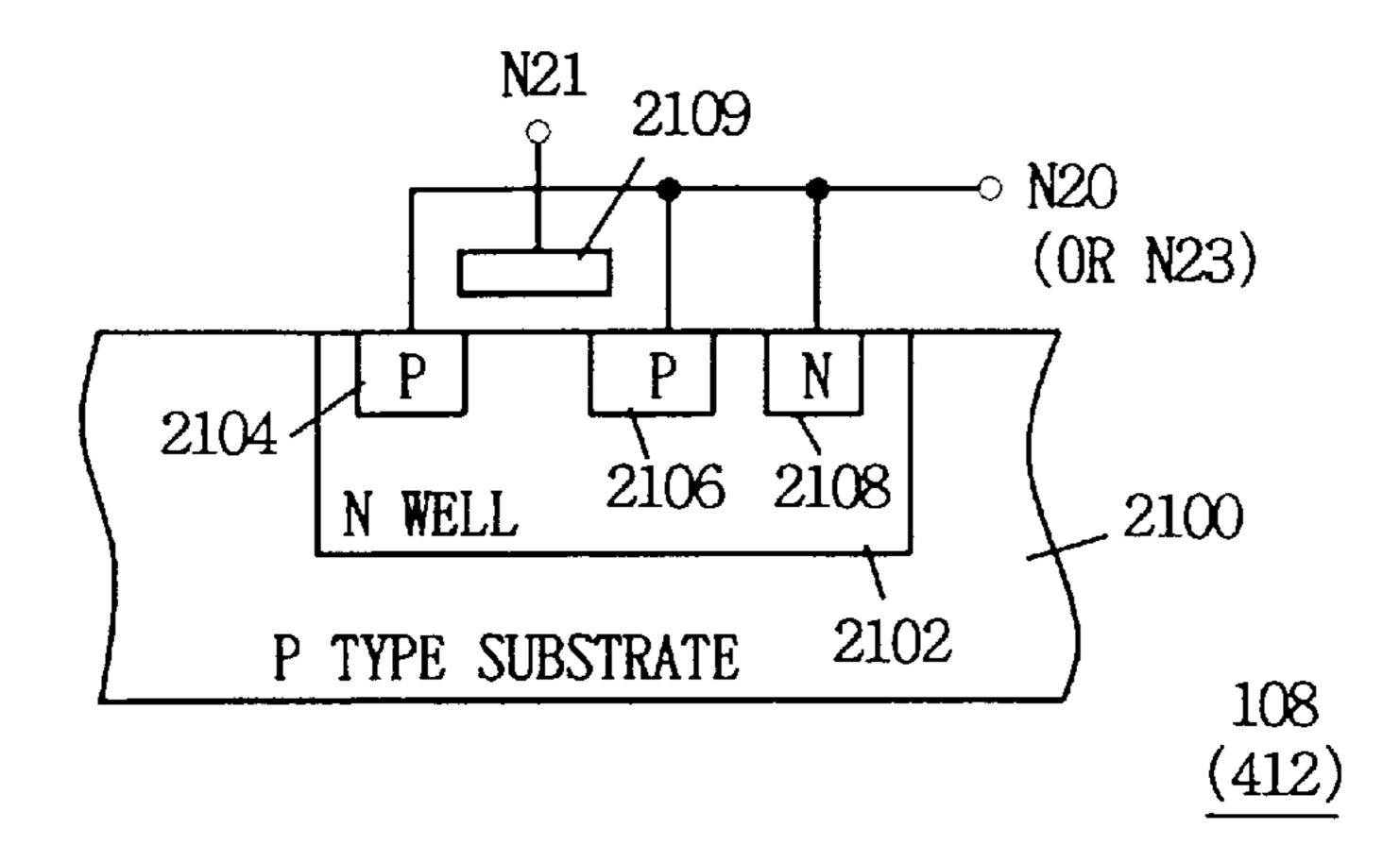

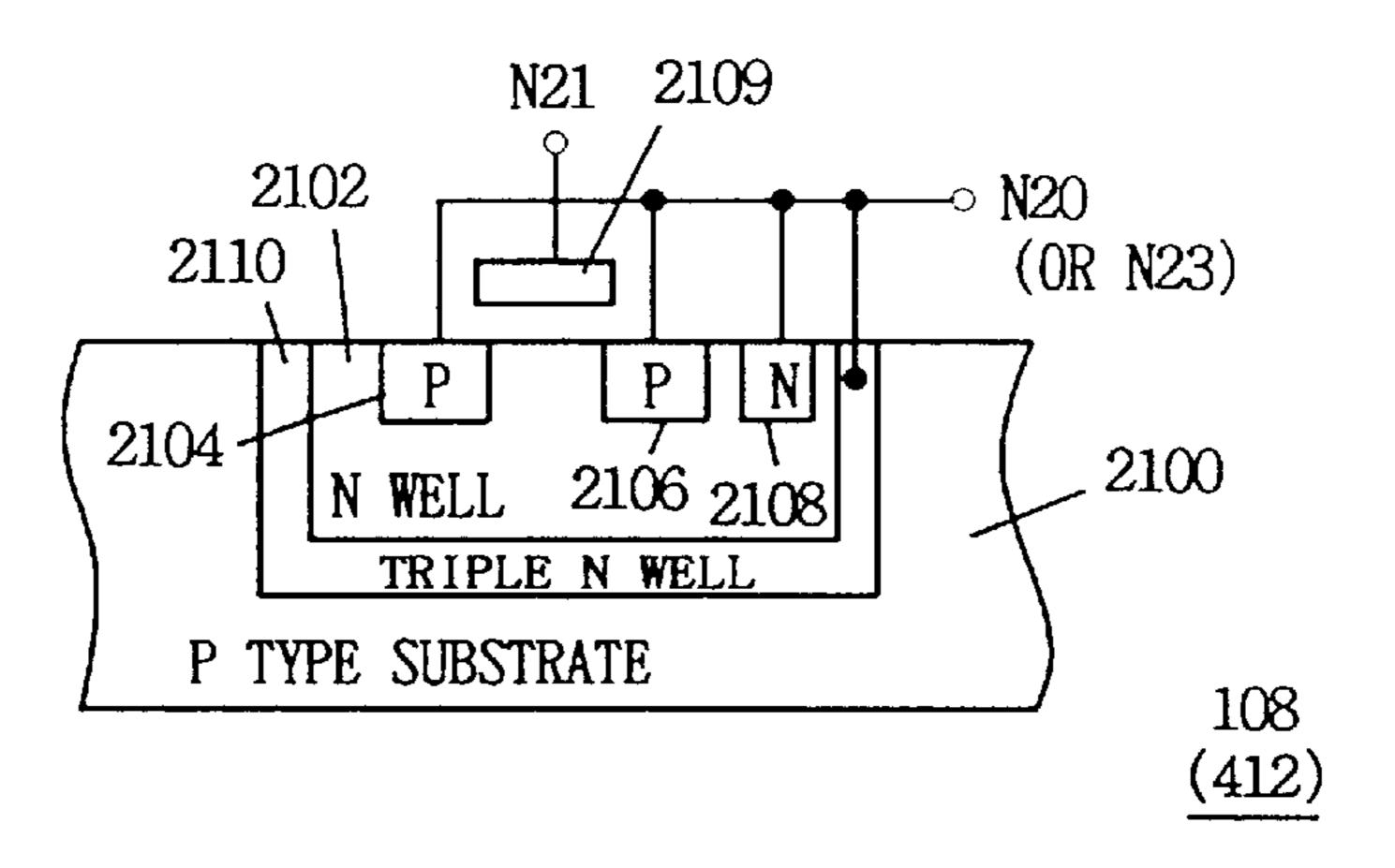

- FIG. 8 is a diagram showing a sectional structure of a precharge MOS transistor shown in FIG. 6, and explaining 65 the effect brought about by the negative voltage generating circuit shown in FIG. 6.

**14**

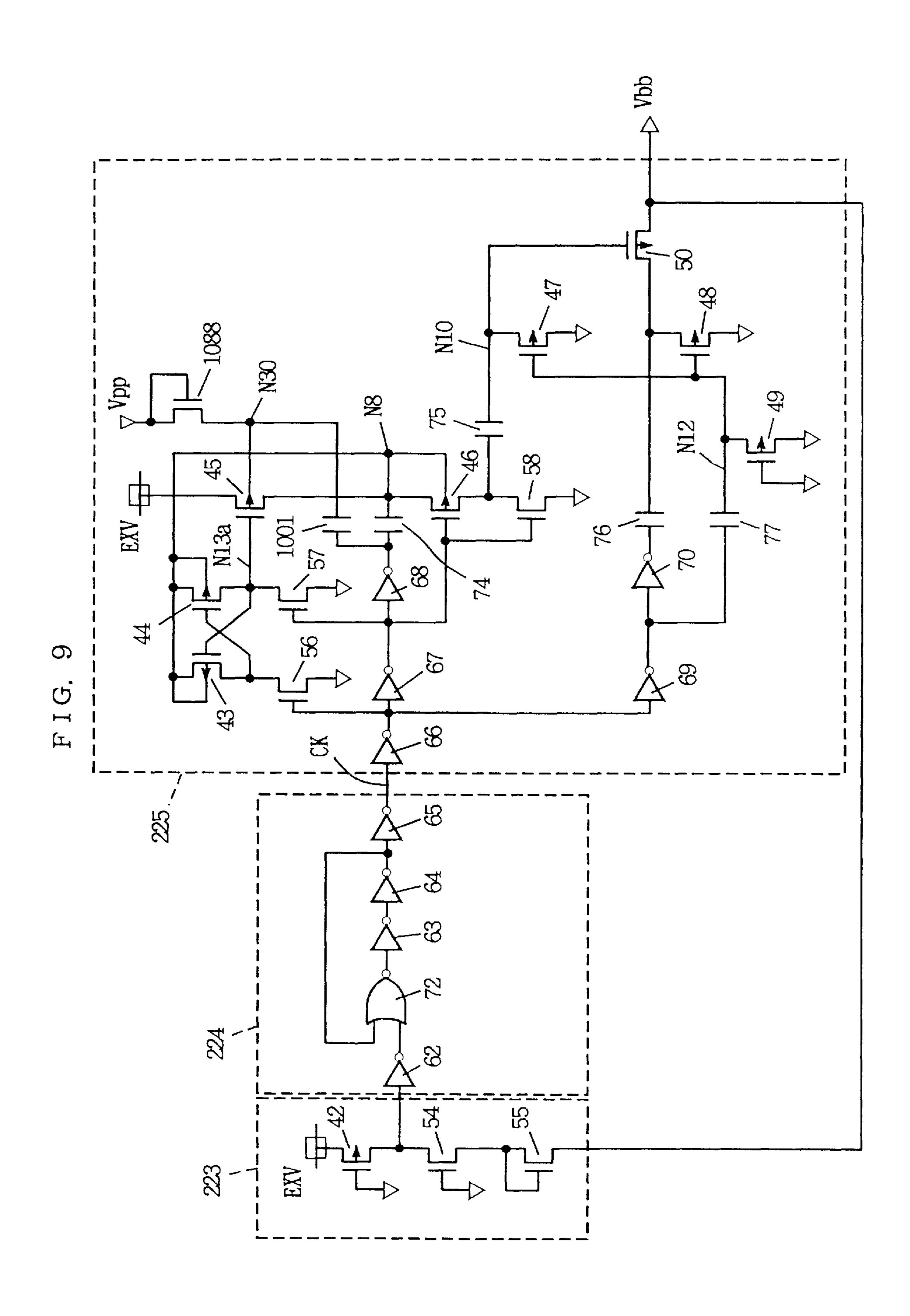

- FIG. 9 is a diagram showing still another structure of the negative voltage generating circuit according to the present invention.

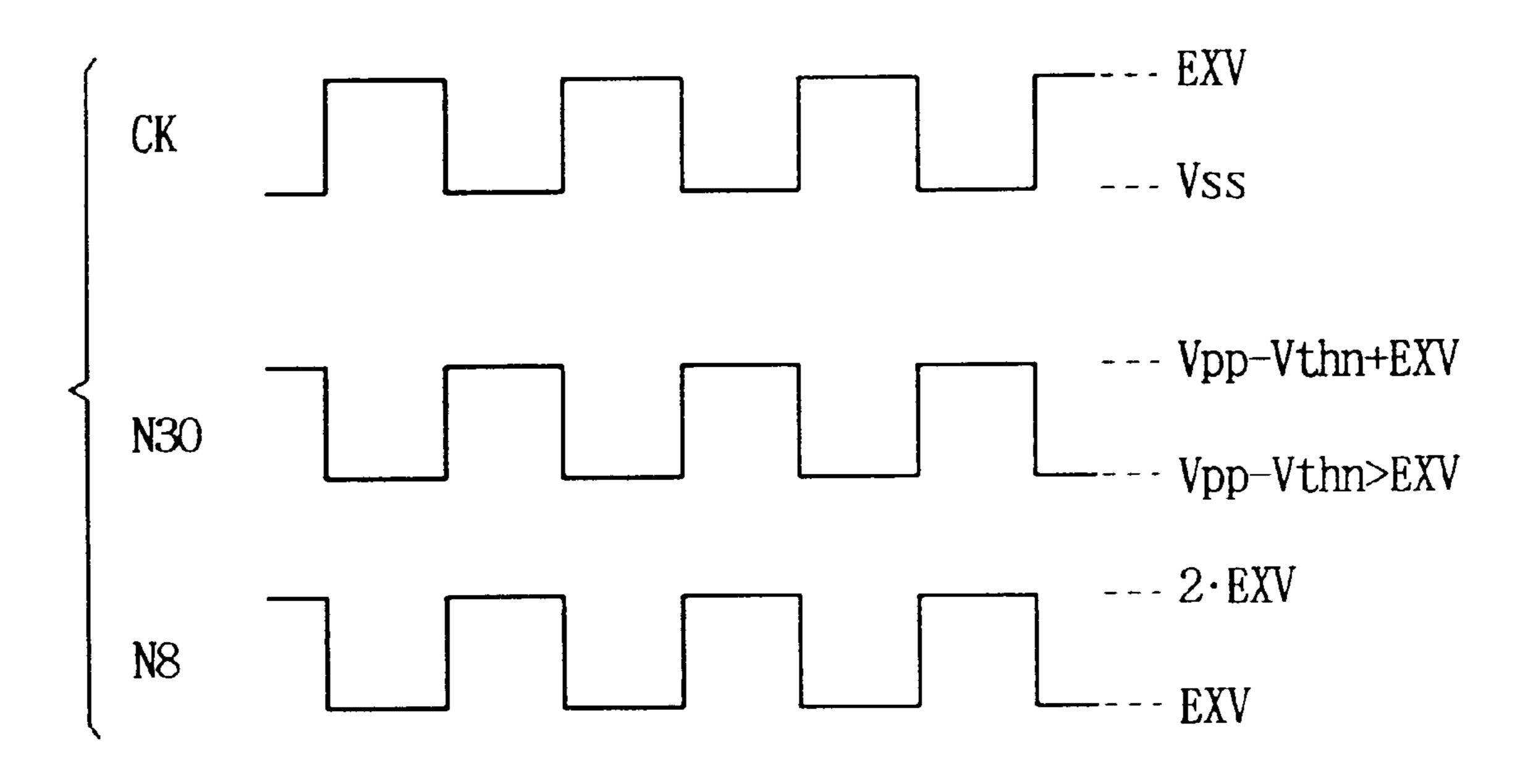

- FIG. 10 is a signal waveform diagram for explaining the operation and effect of the negative voltage generating circuit shown in FIG. 9.

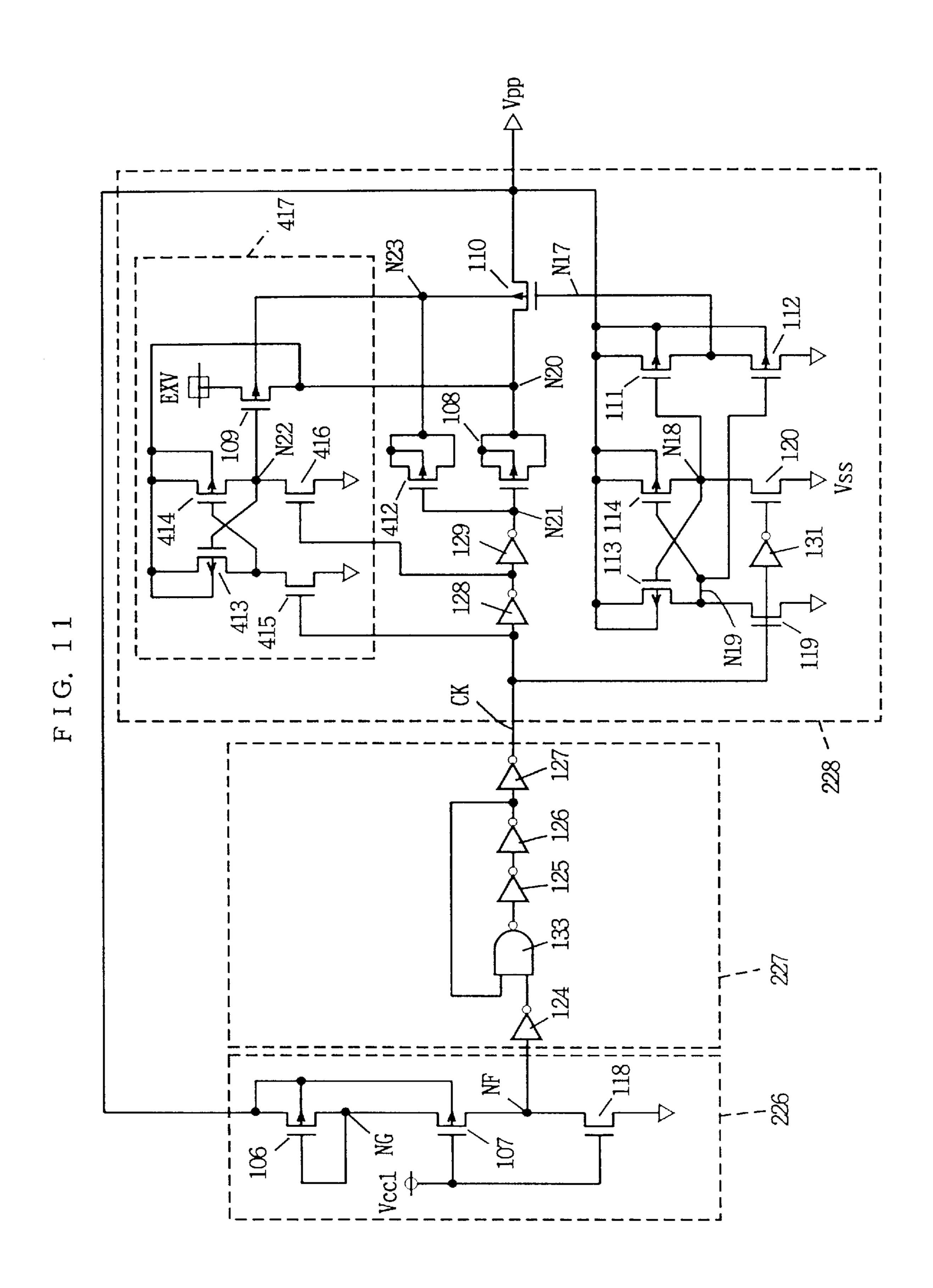

- FIG. 11 is a diagram showing the structure of an internal high voltage generating circuit according to the present invention.

- FIG. 12 is a signal waveform diagram showing operation of the circuit shown in FIG. 11.

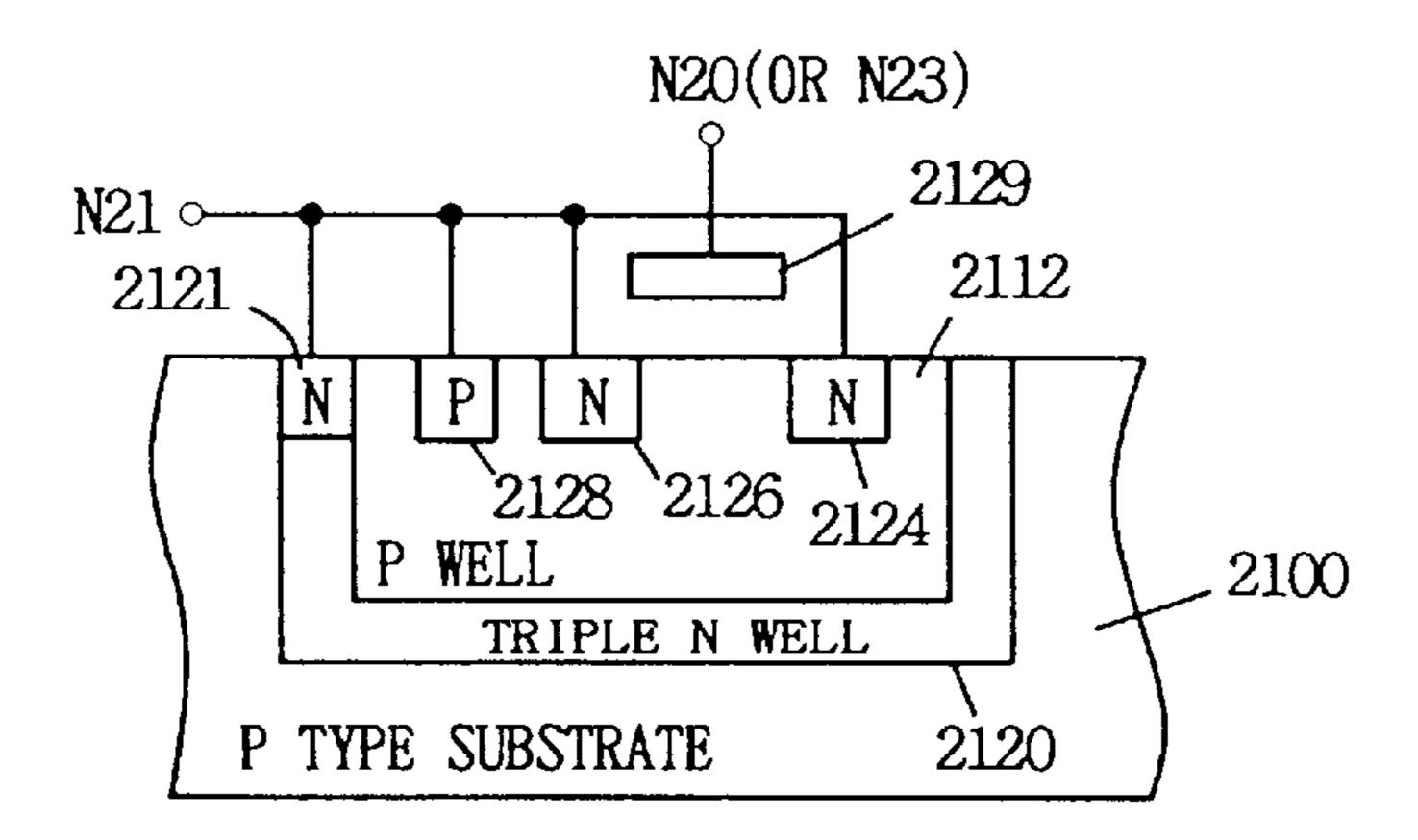

- FIG. 13 is a diagram showing a sectional structure of a precharge MOS transistor and an output MOS transistor shown in FIG. 11.

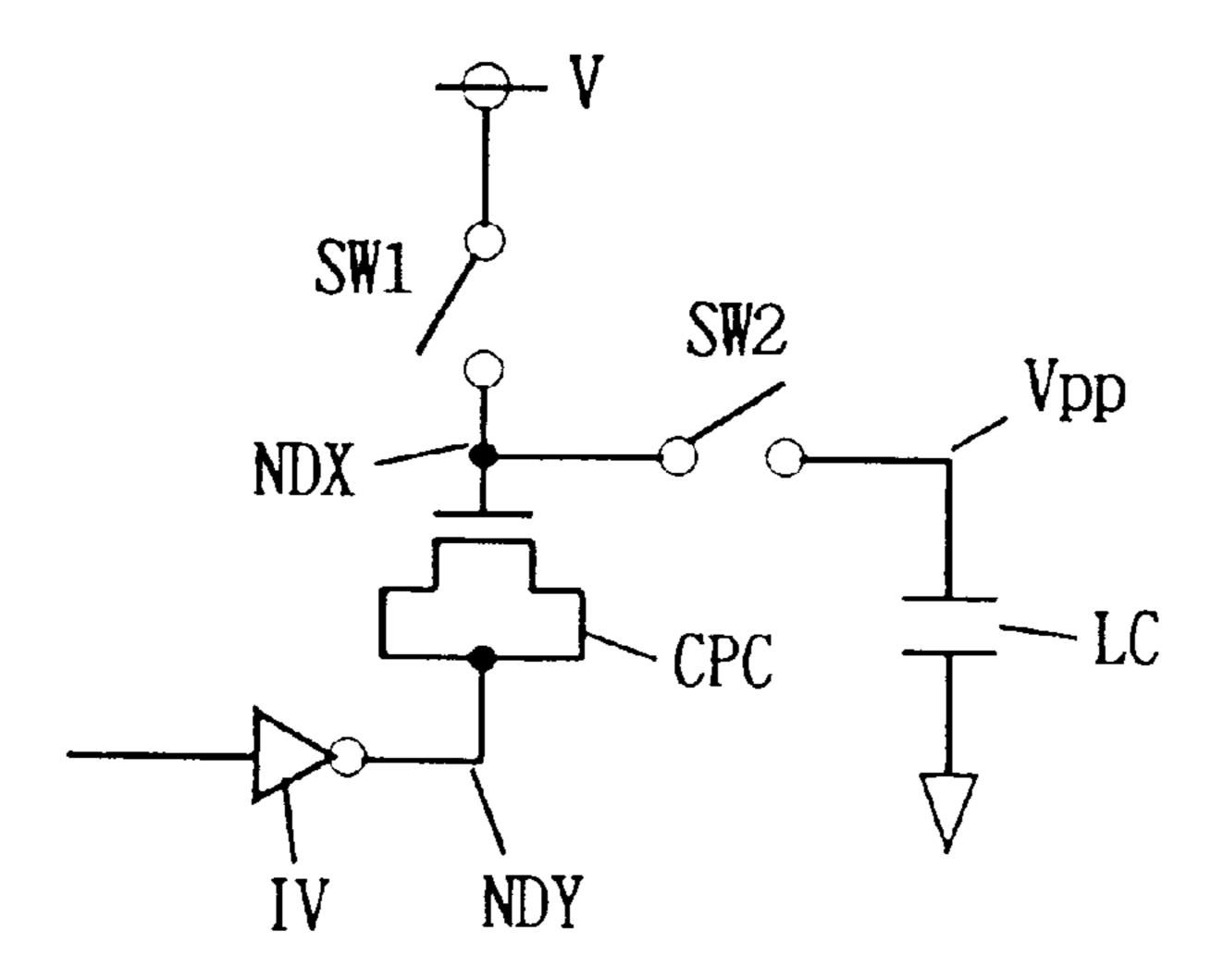

- FIG. 14 is a diagram for explaining charge pumping operation for generating an internal high voltage.

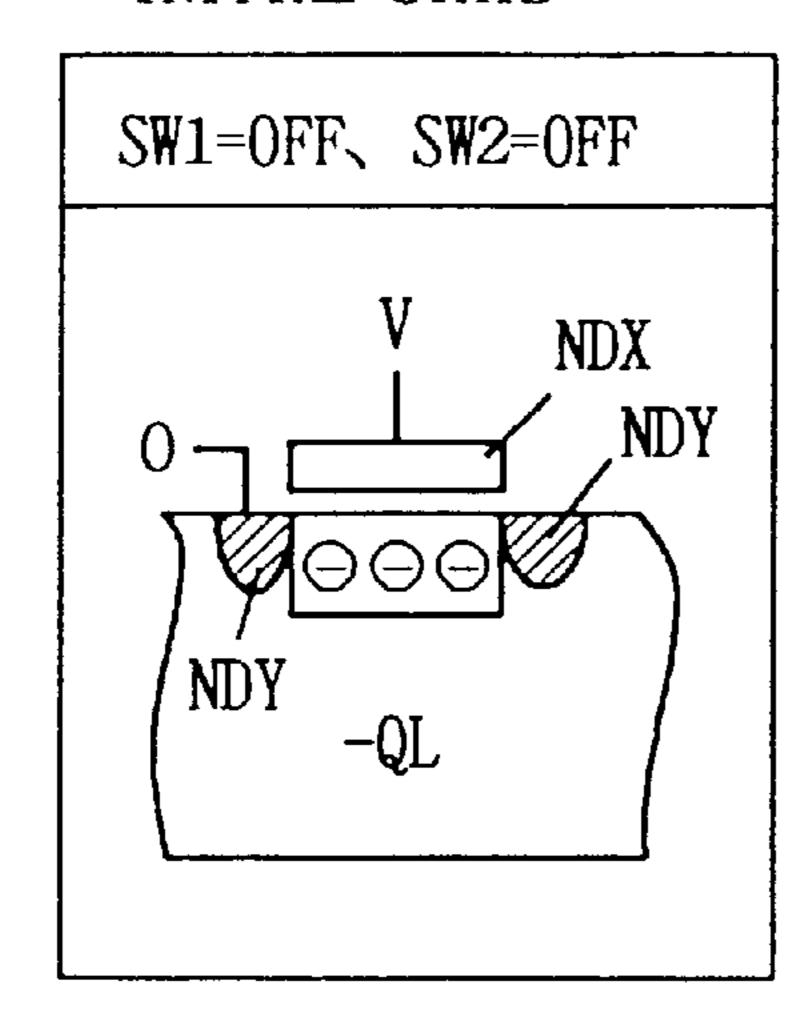

- FIGS. 15A-15E are diagrams for explaining operation of a charge pump MOS capacitor in a charge pump circuit shown in FIG. 14.

- FIG. 16 is a diagram showing a sectional structure of the charge pump MOS capacitor shown in FIG. 11.

- FIG. 17 is a diagram showing another structure of the charge pump MOS capacitor shown in FIG. 11.

- FIG. 18 is a diagram showing still another structure of the charge pump MOS capacitor shown in FIG. 11.

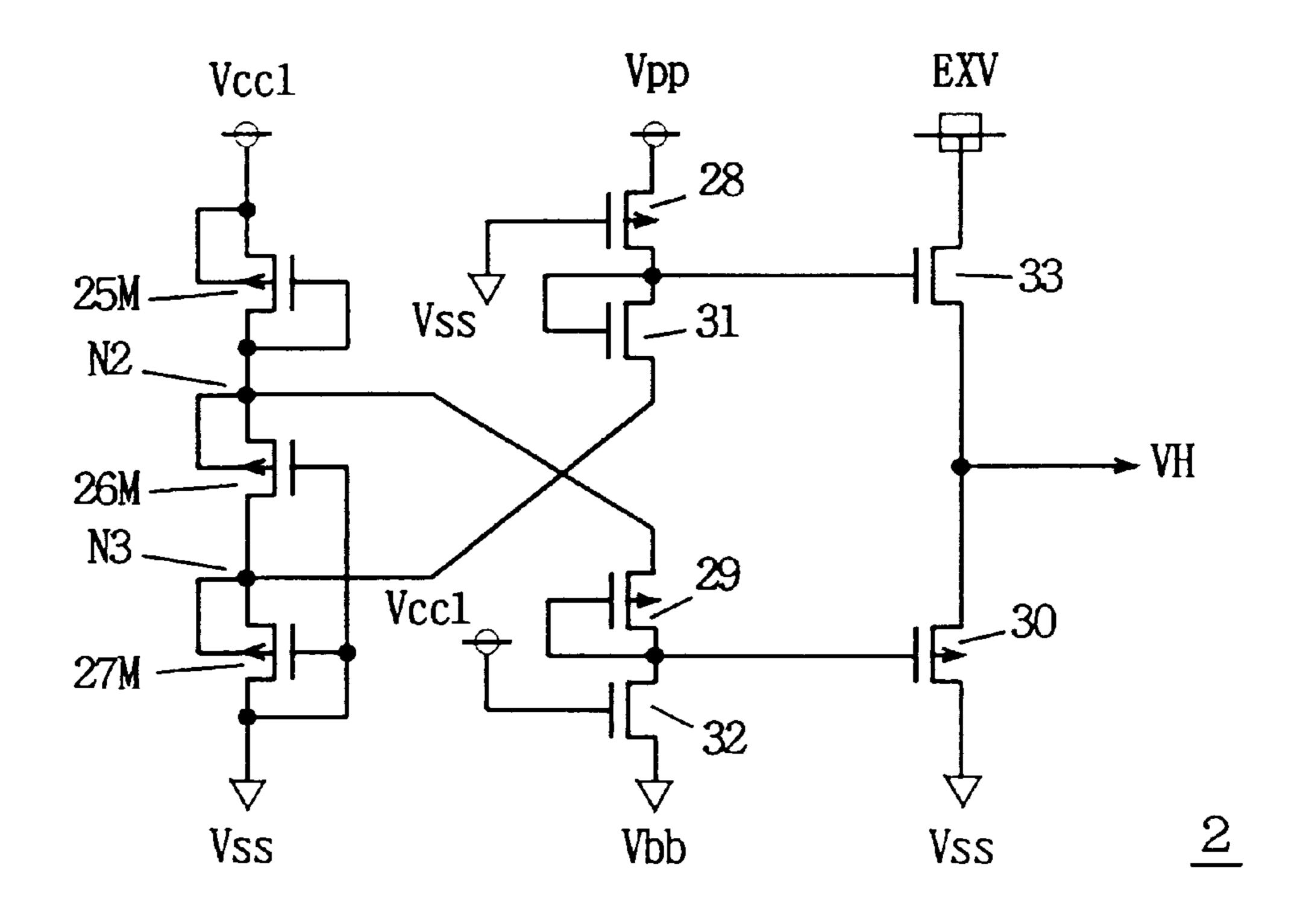

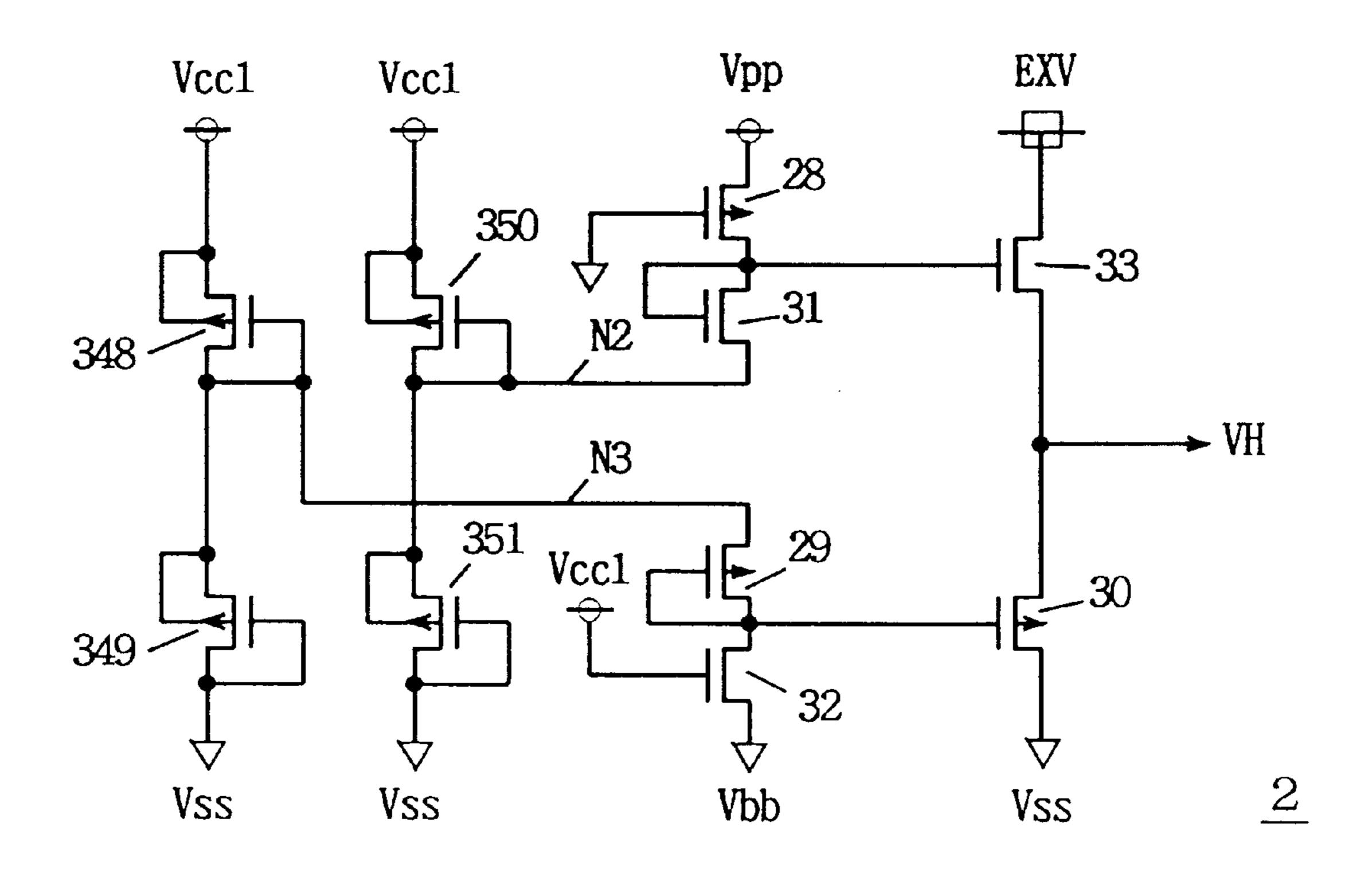

- FIG. 19 is a diagram showing the structure of an intermediate voltage generating circuit according to the present invention.

- FIG. 20 is a signal waveform diagram showing operation of the circuit shown in FIG. 19.

- FIG. 21 is a diagram showing another structure of the intermediate voltage generating circuit according to the present invention.

- FIG. 22 is a diagram showing still another structure of the intermediate voltage generating circuit according to the present invention.

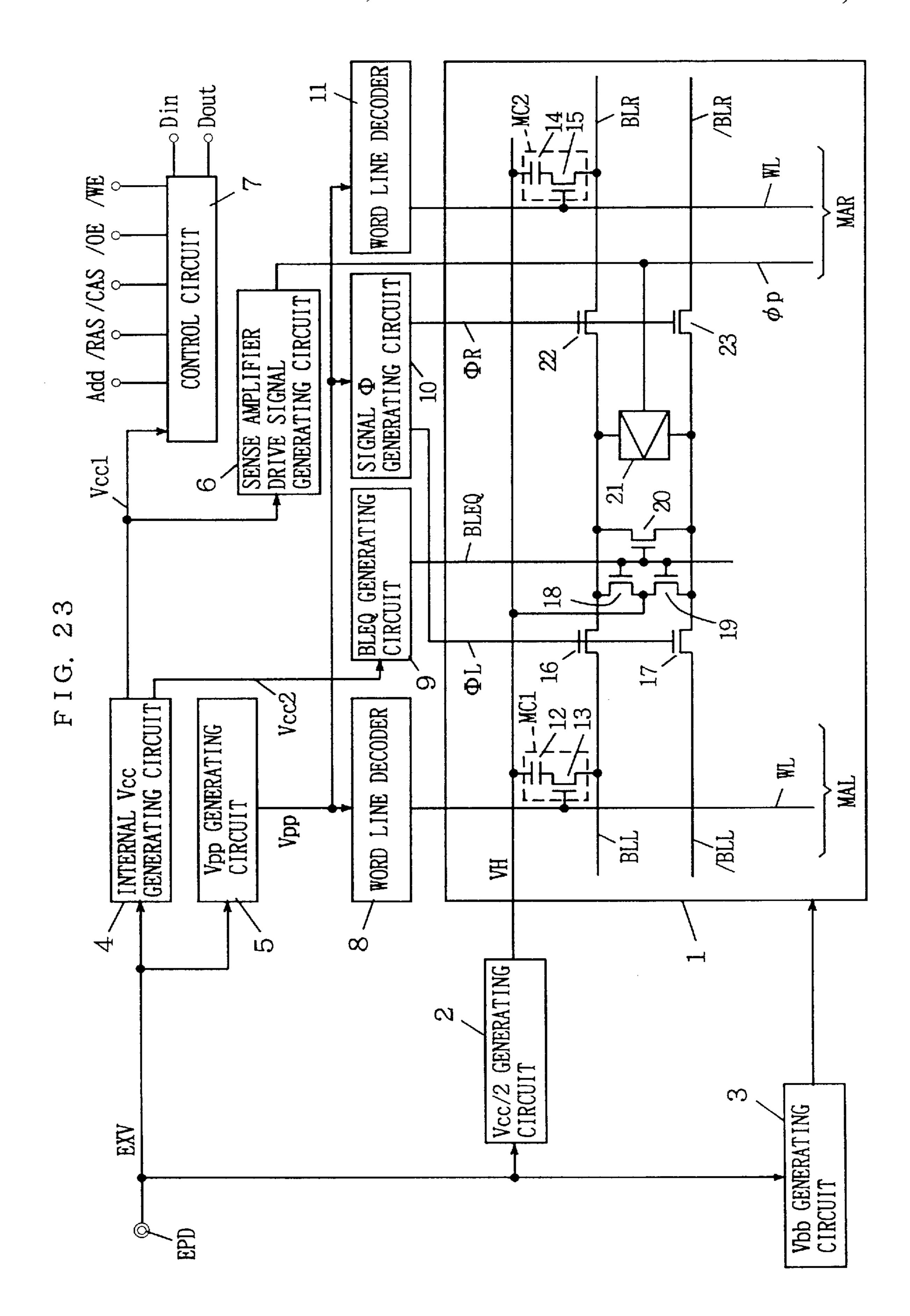

- FIG. 23 is a diagram showing the entire structure of a semiconductor memory device according to the present invention and a manner of distribution of internal power supply voltage.

- FIG. 24 is a diagram for explaining the effect brought about by distribution of internal power supply voltage shown in FIG. 23.

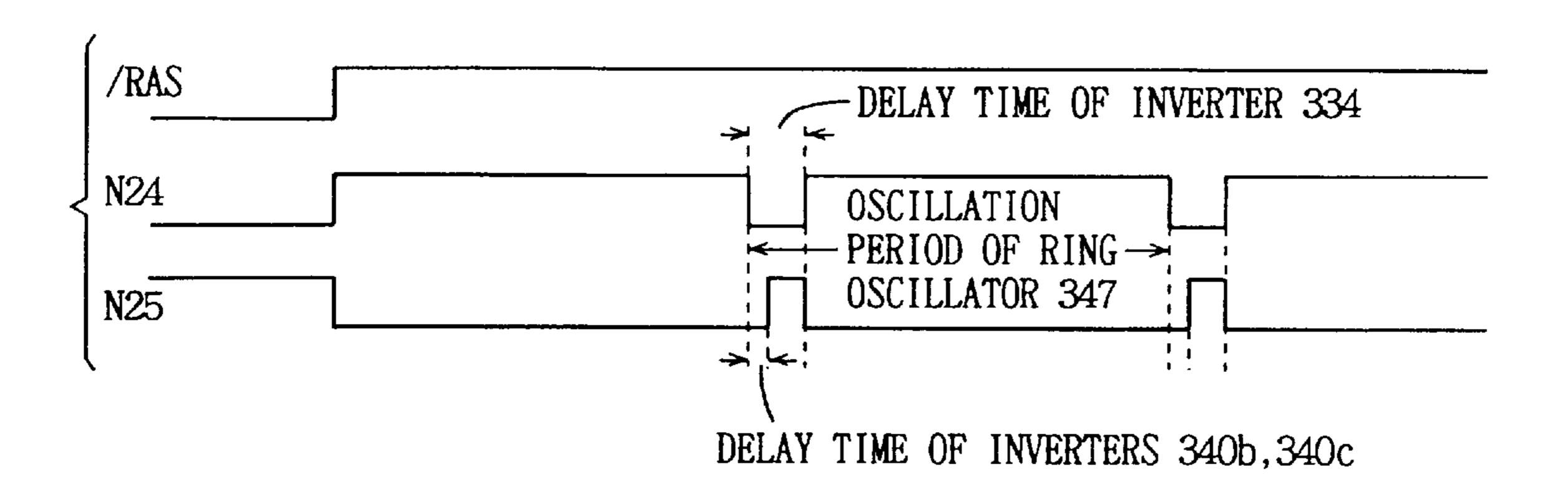

- FIG. 25 is a signal waveform diagram showing operation of the structure shown in FIG. 23.

- FIG. 26 is a diagram showing a structure example of a BLEQ generating circuit shown in FIG. 23.

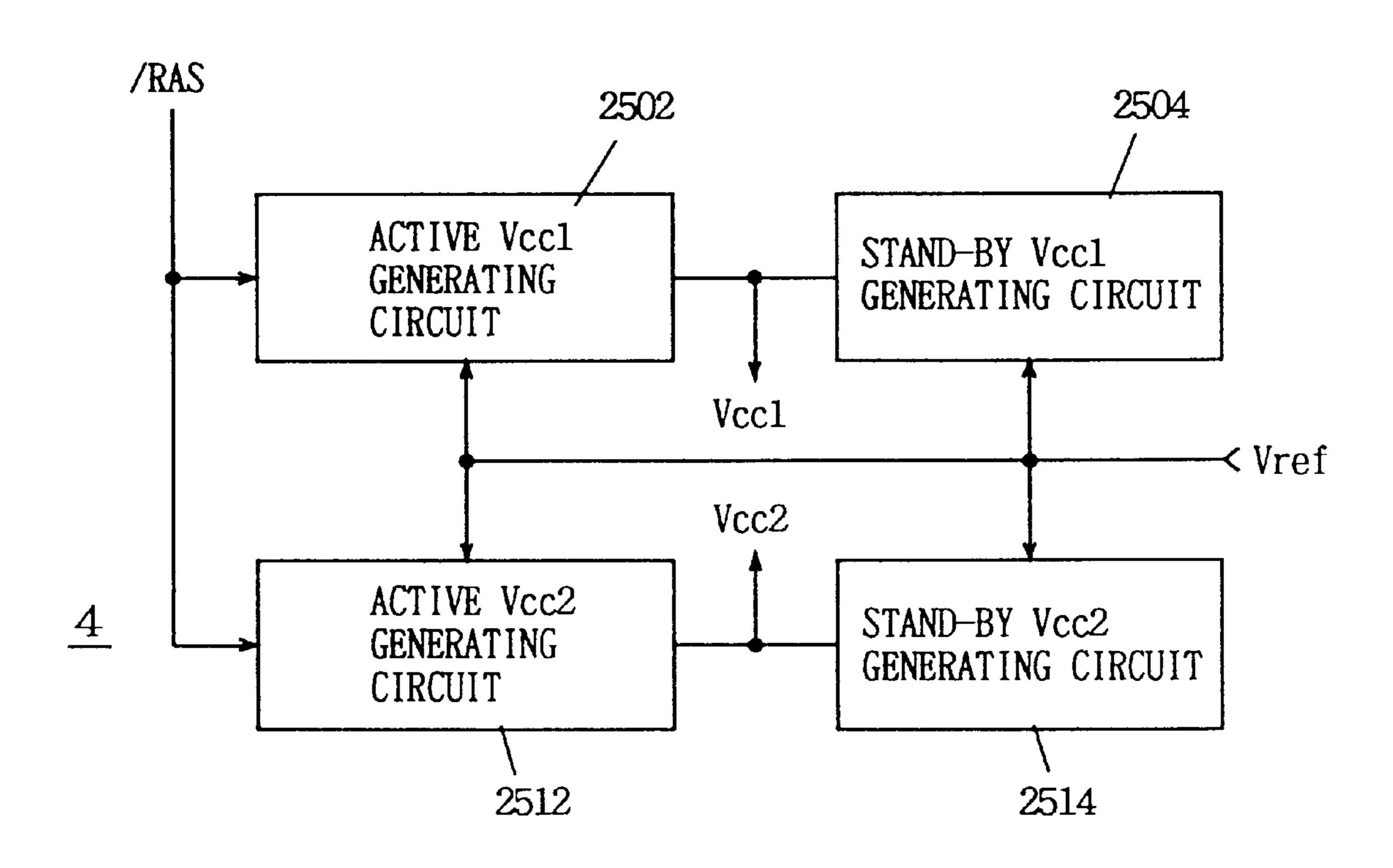

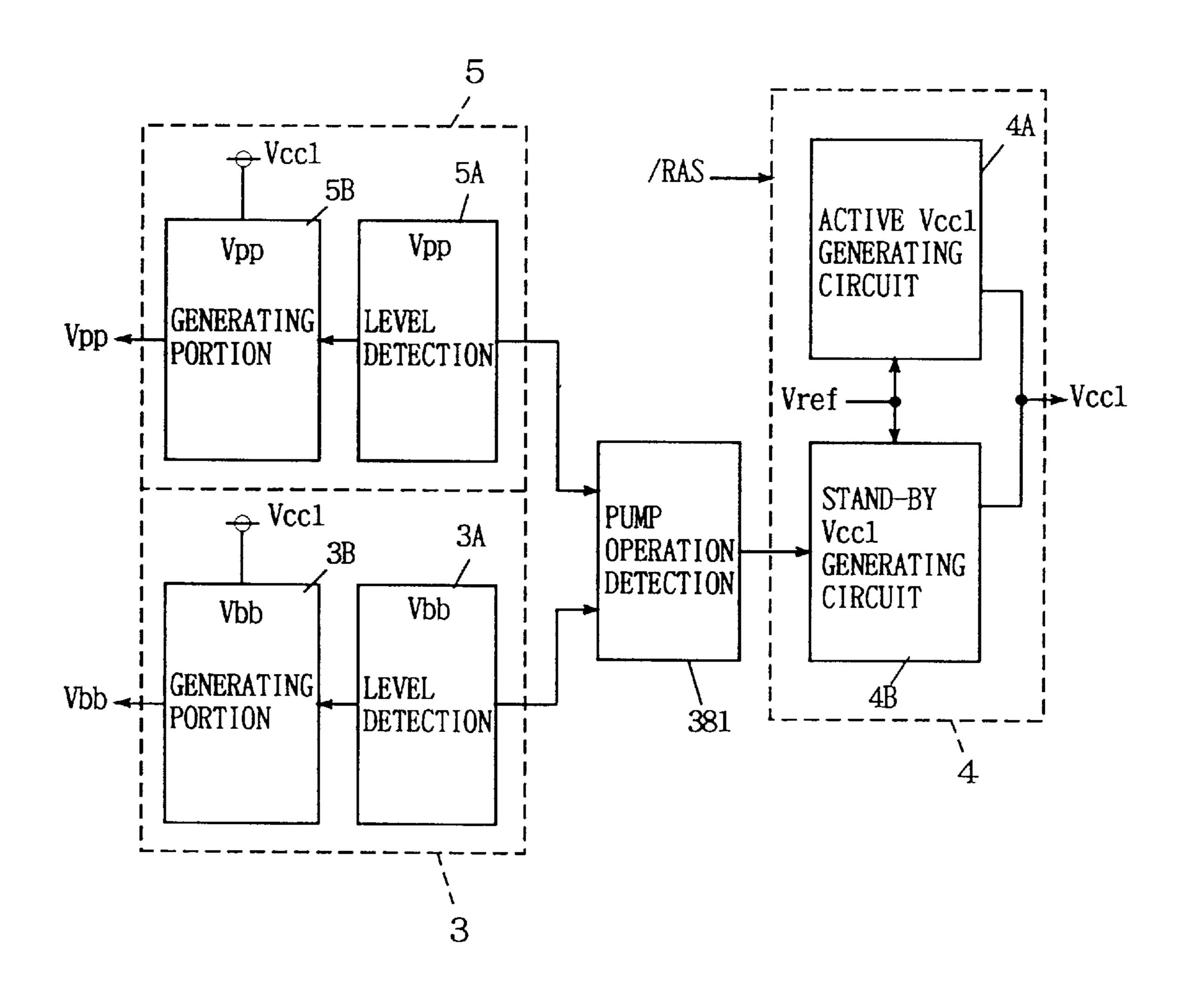

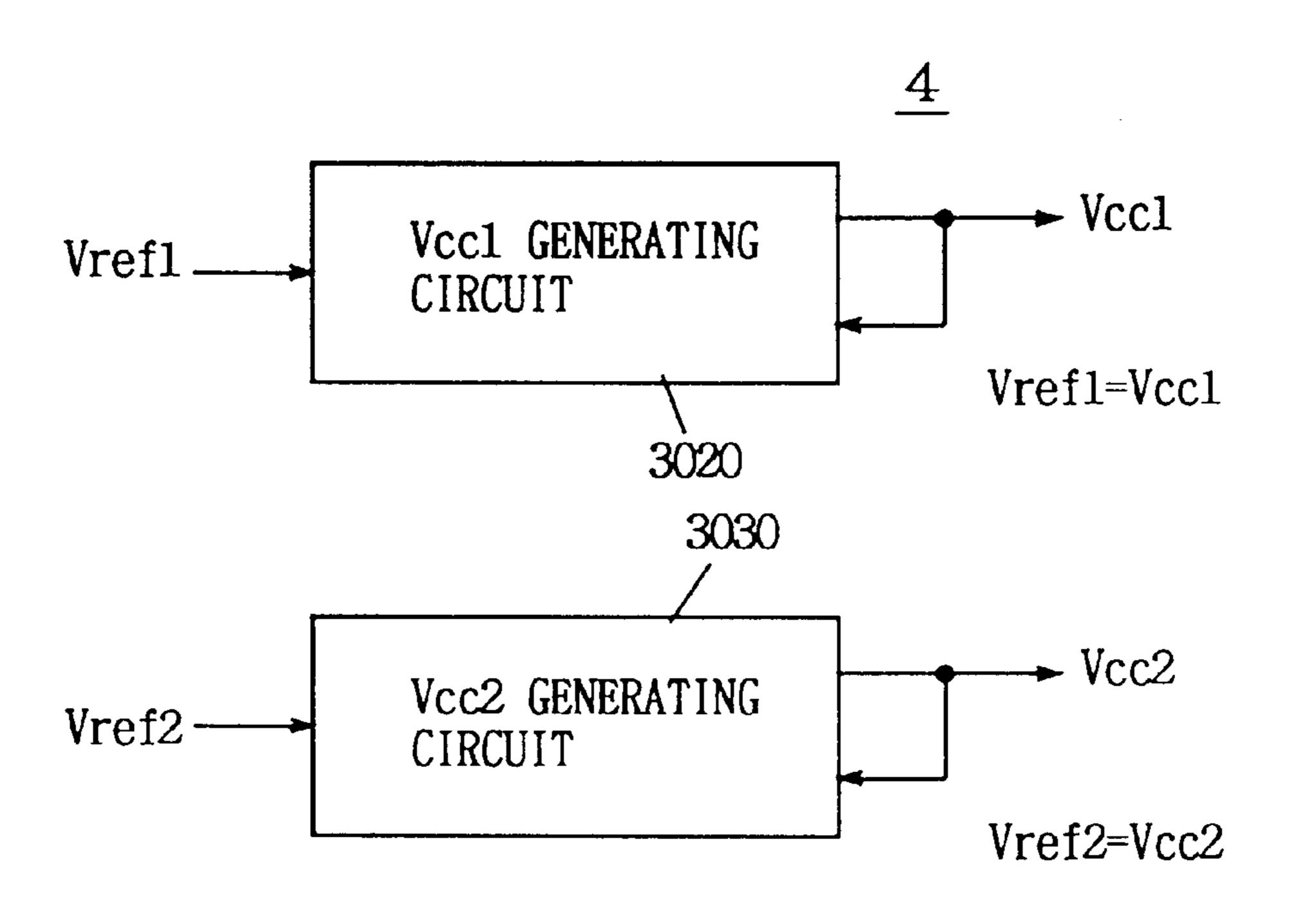

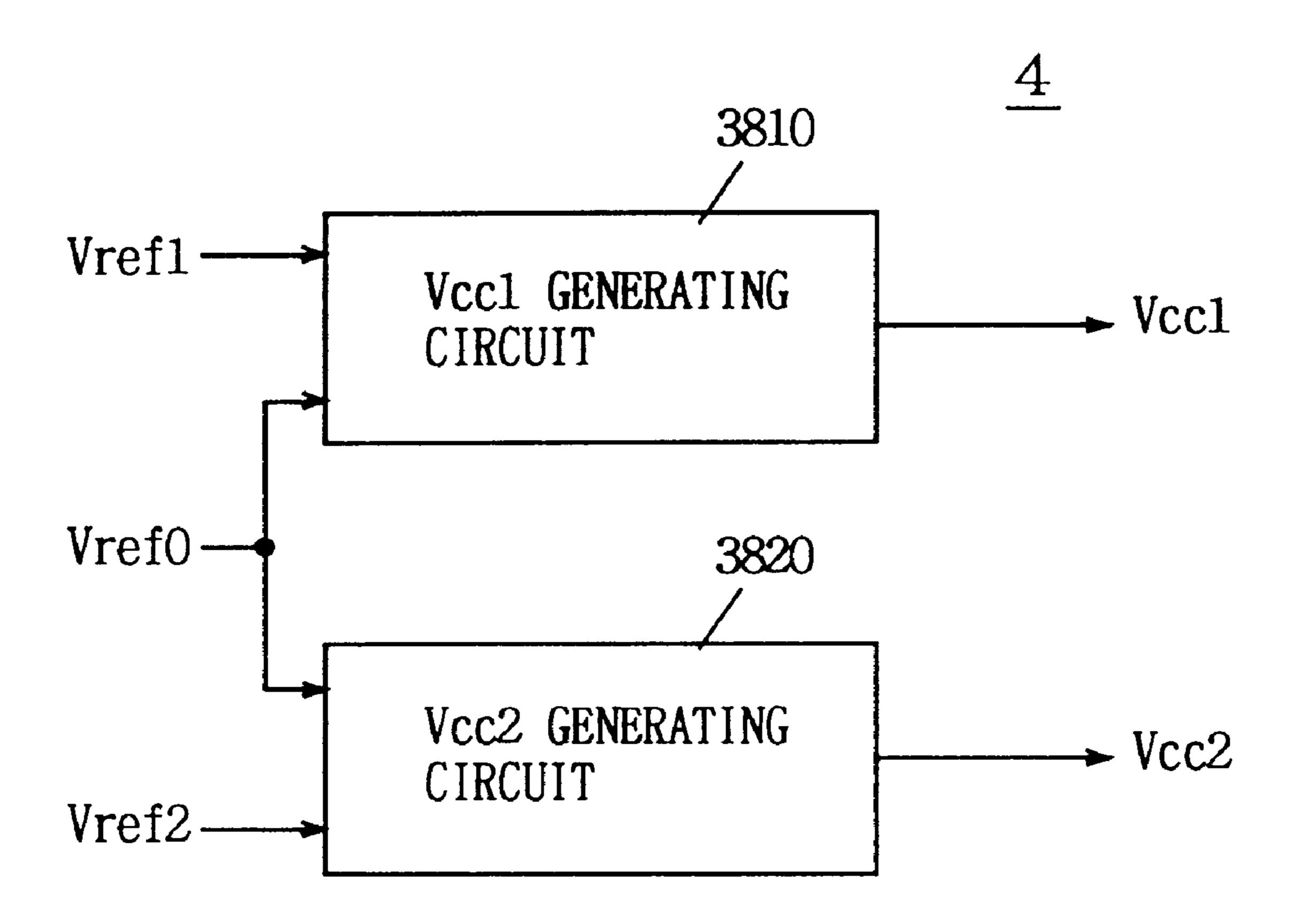

- FIG. 27 is a block diagram schematically showing a structure of an internal Vcc generating circuit shown in FIG. 23.

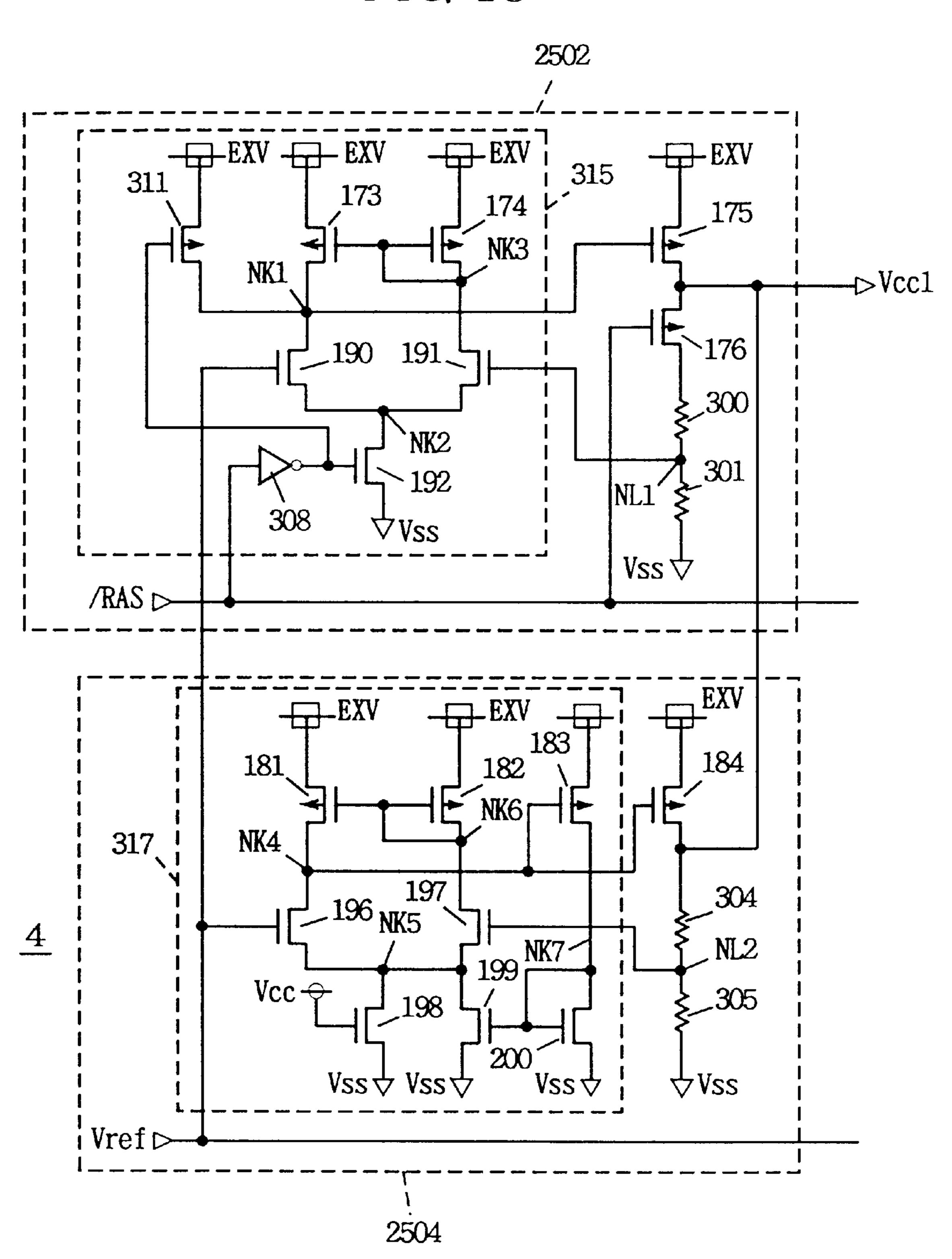

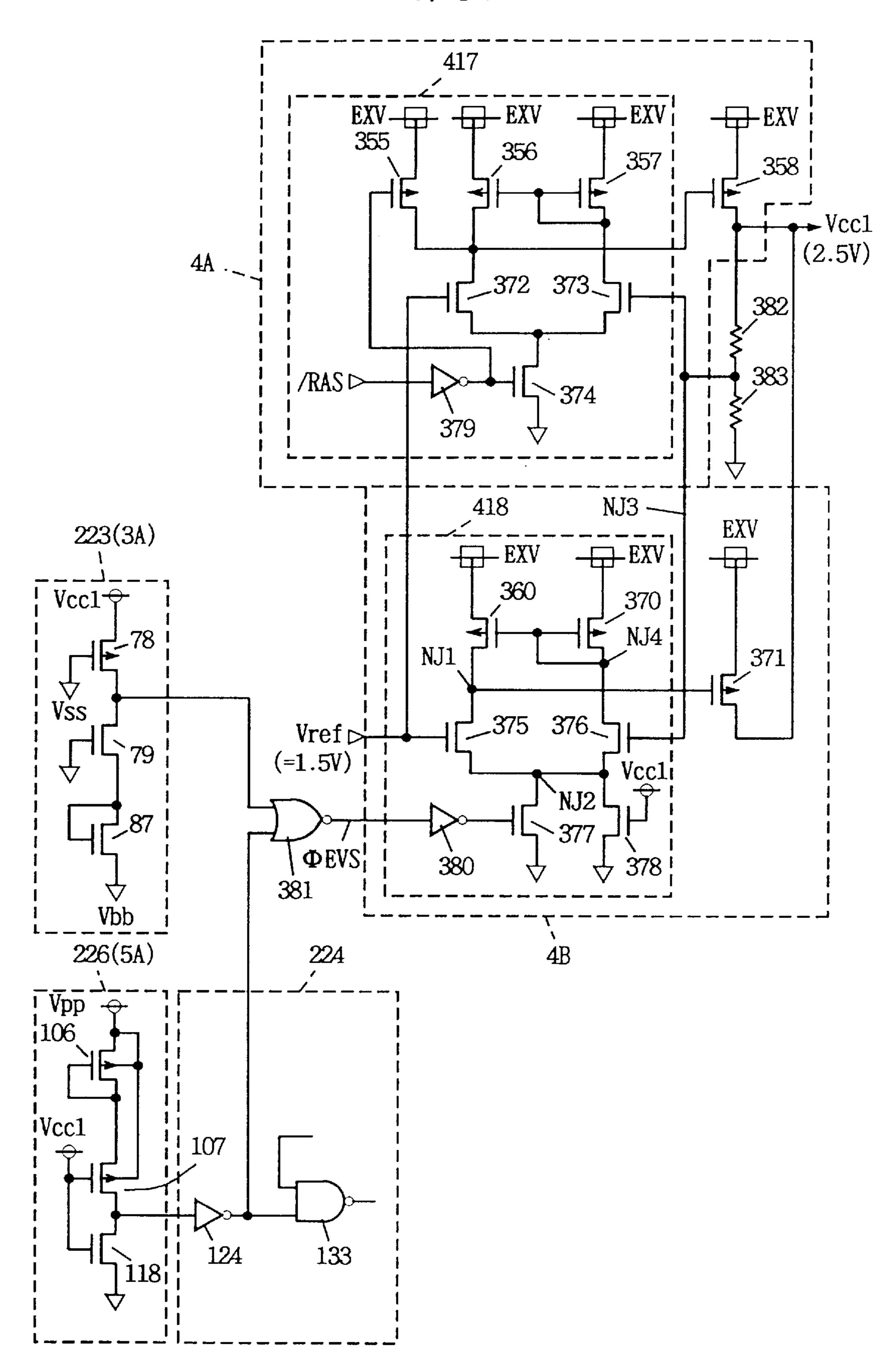

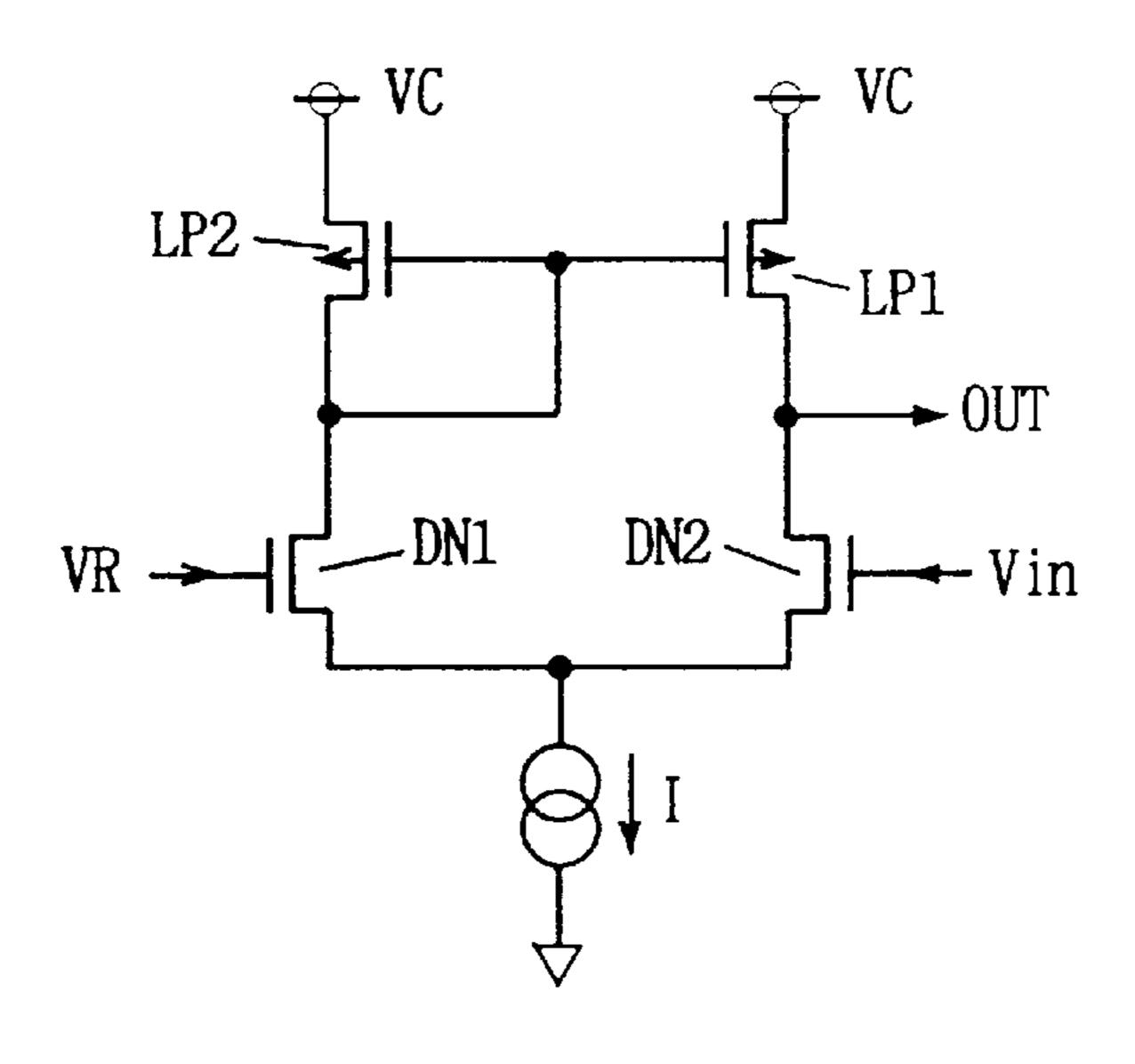

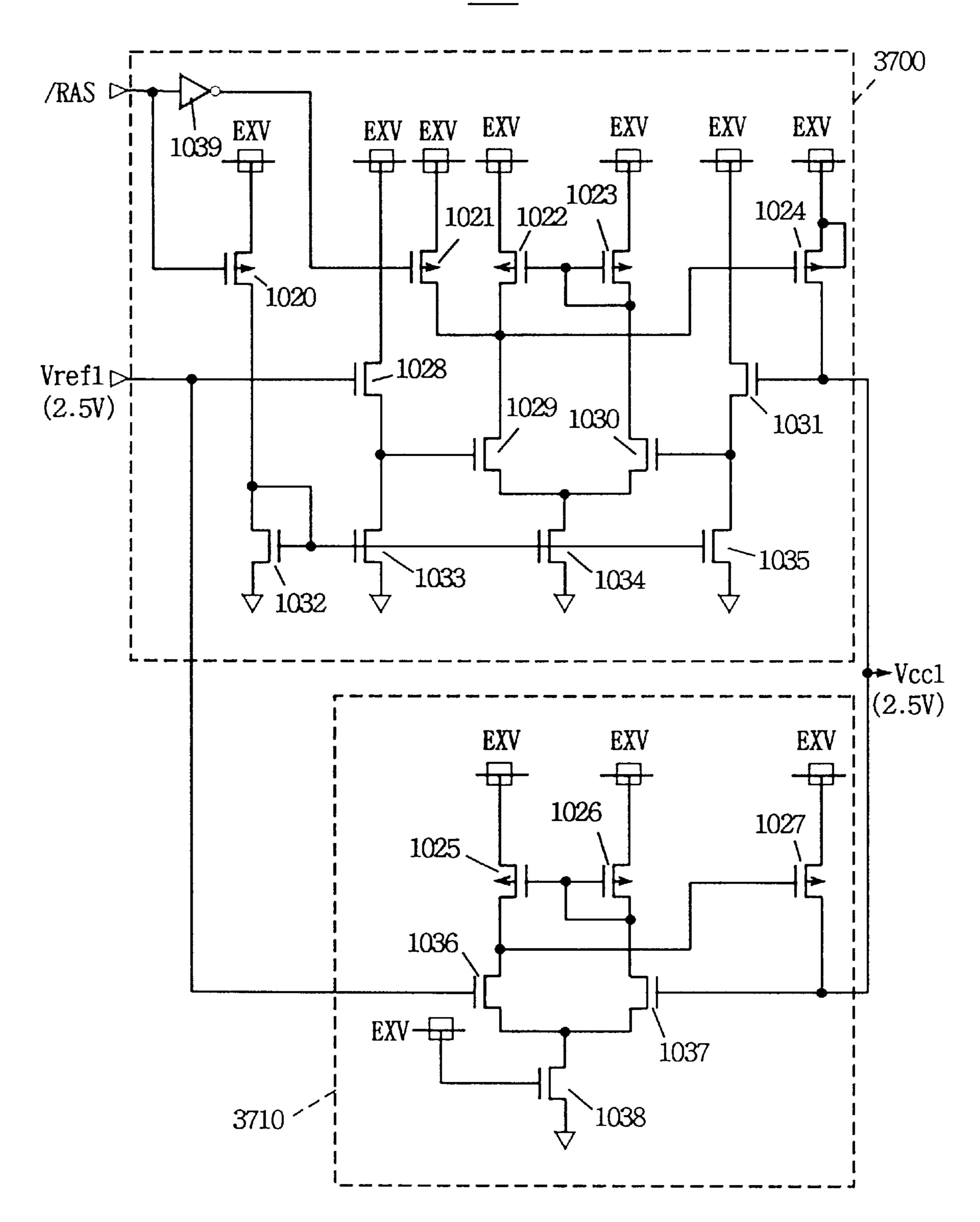

- FIG. 28 is a diagram showing a specific configuration of an active Vcc1 generating circuit and a stand-by Vcc1 generating circuit shown in FIG. 27.

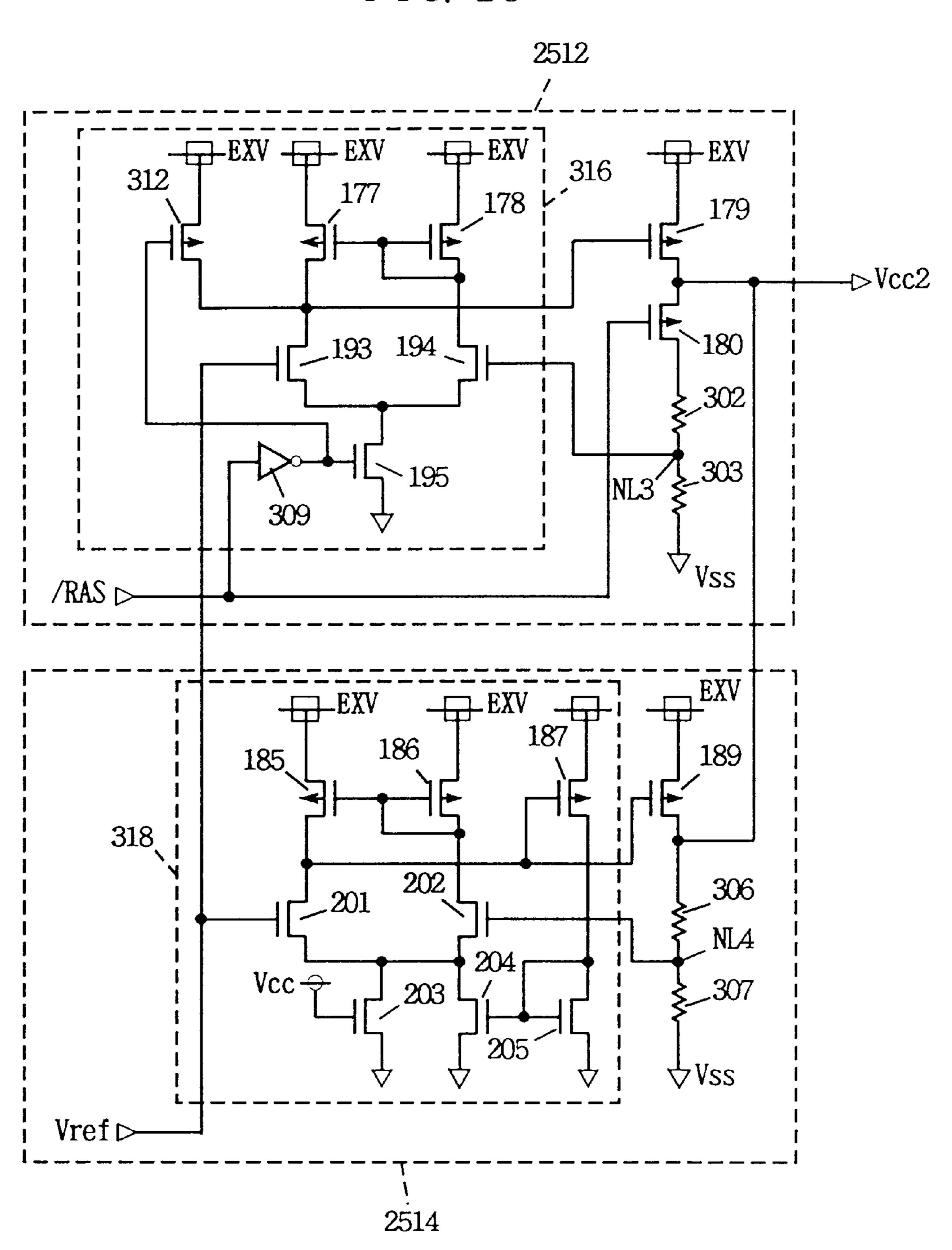

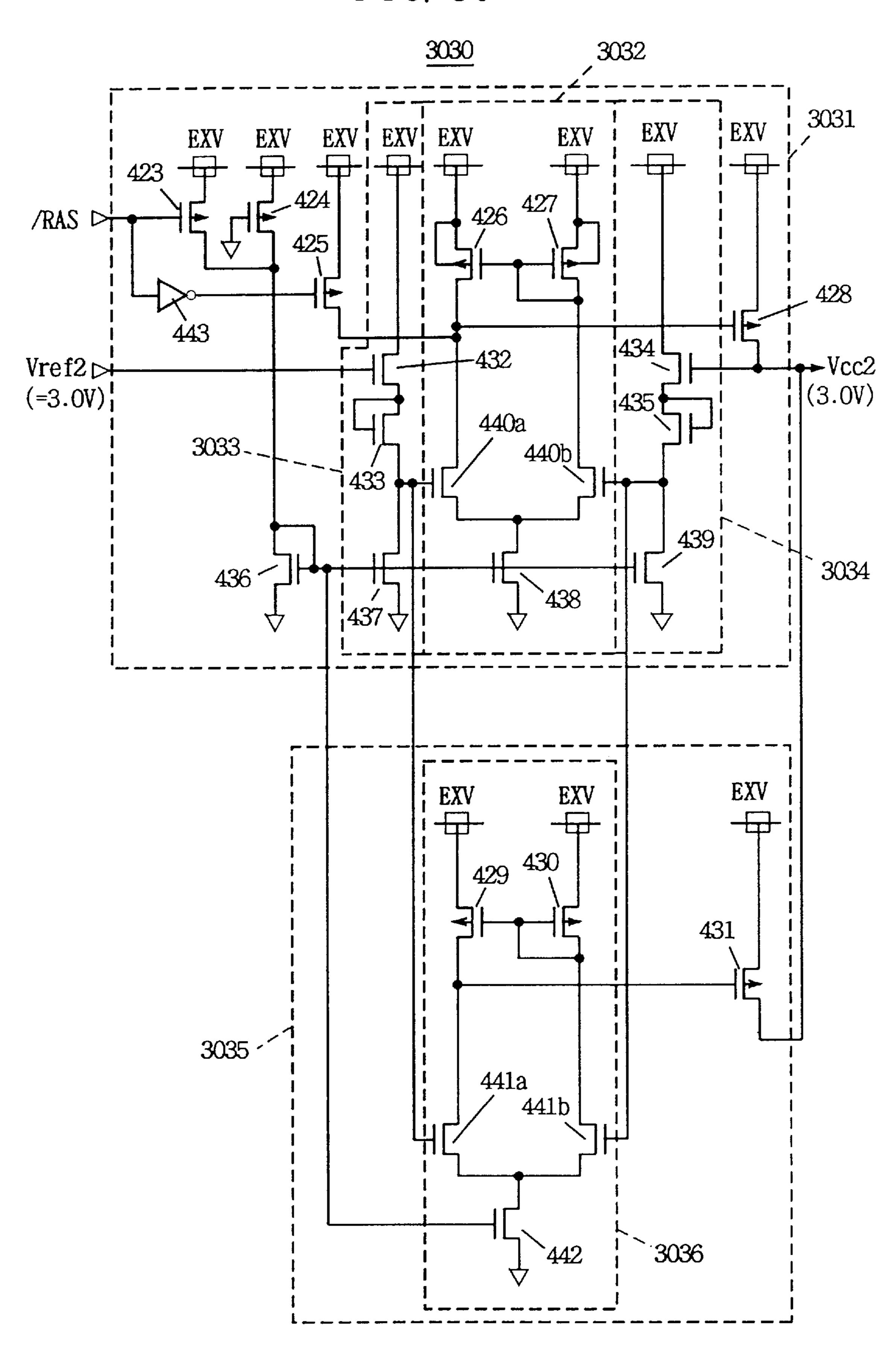

- FIG. 29 is a diagram showing a specific configuration of an active Vcc2 generating circuit and a stand-by Vcc2 generating circuit shown in FIG. 27.

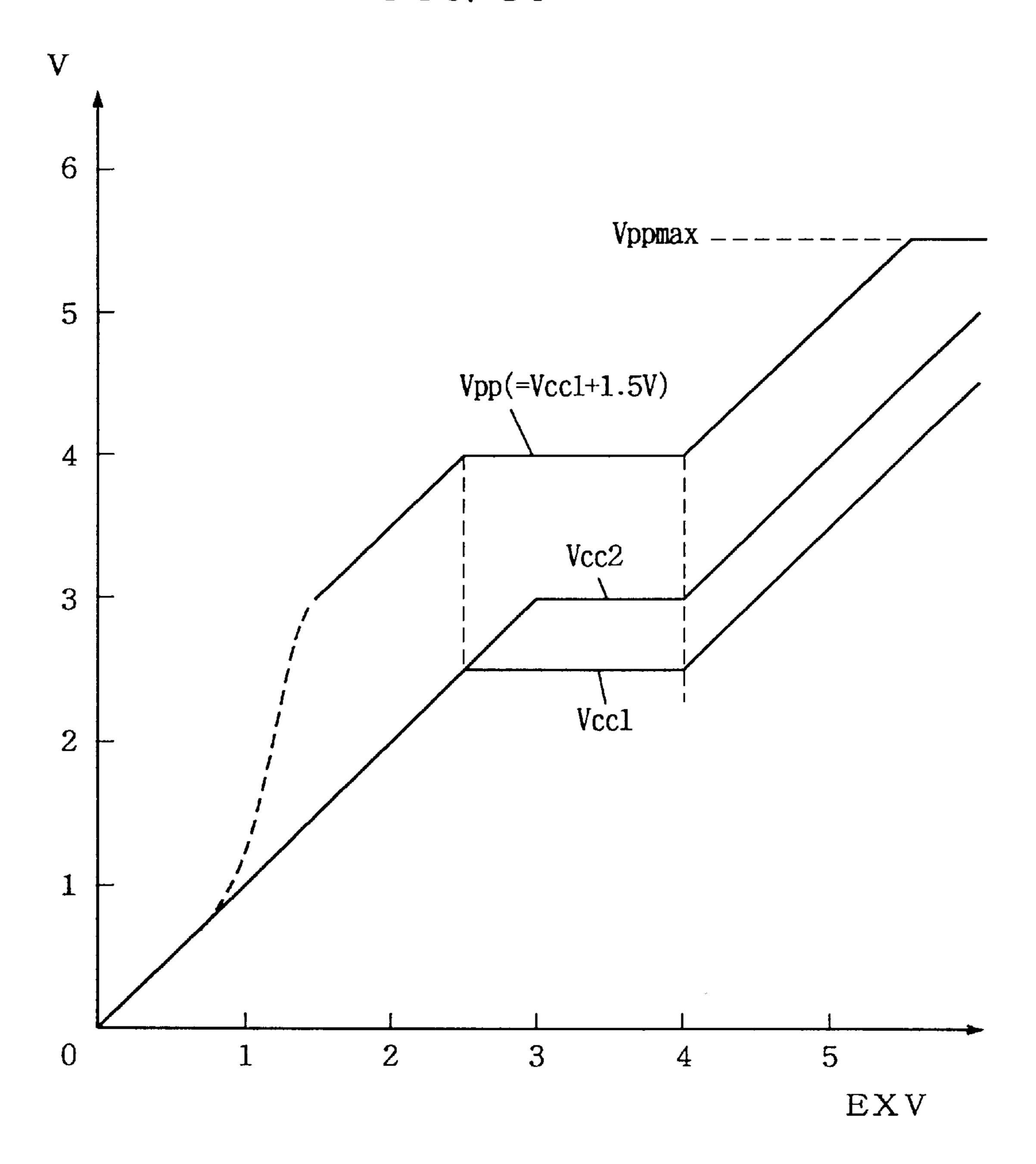

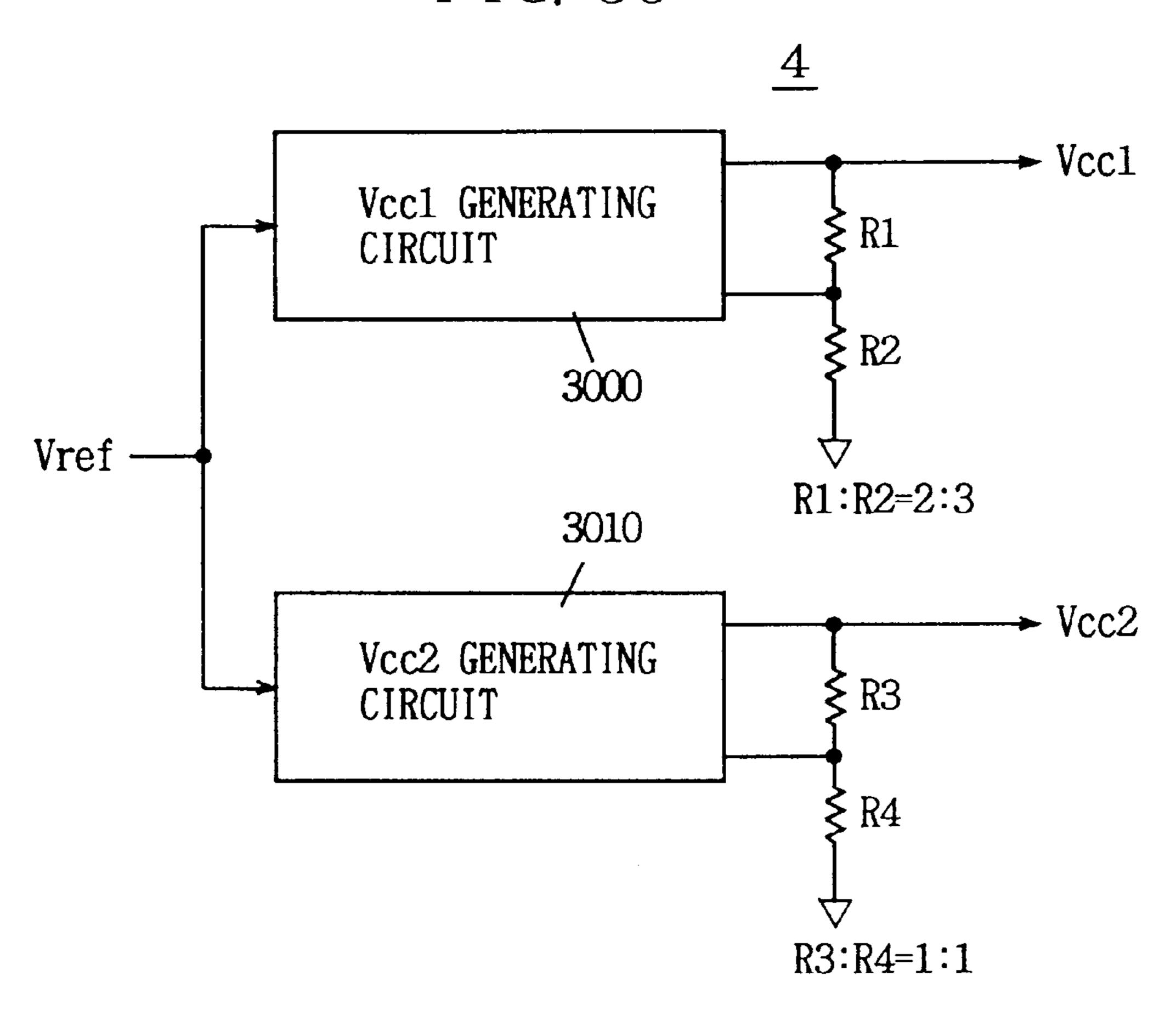

- FIG. 30 is a diagram showing an internal voltage generated in the semiconductor memory device shown in FIG. 23.

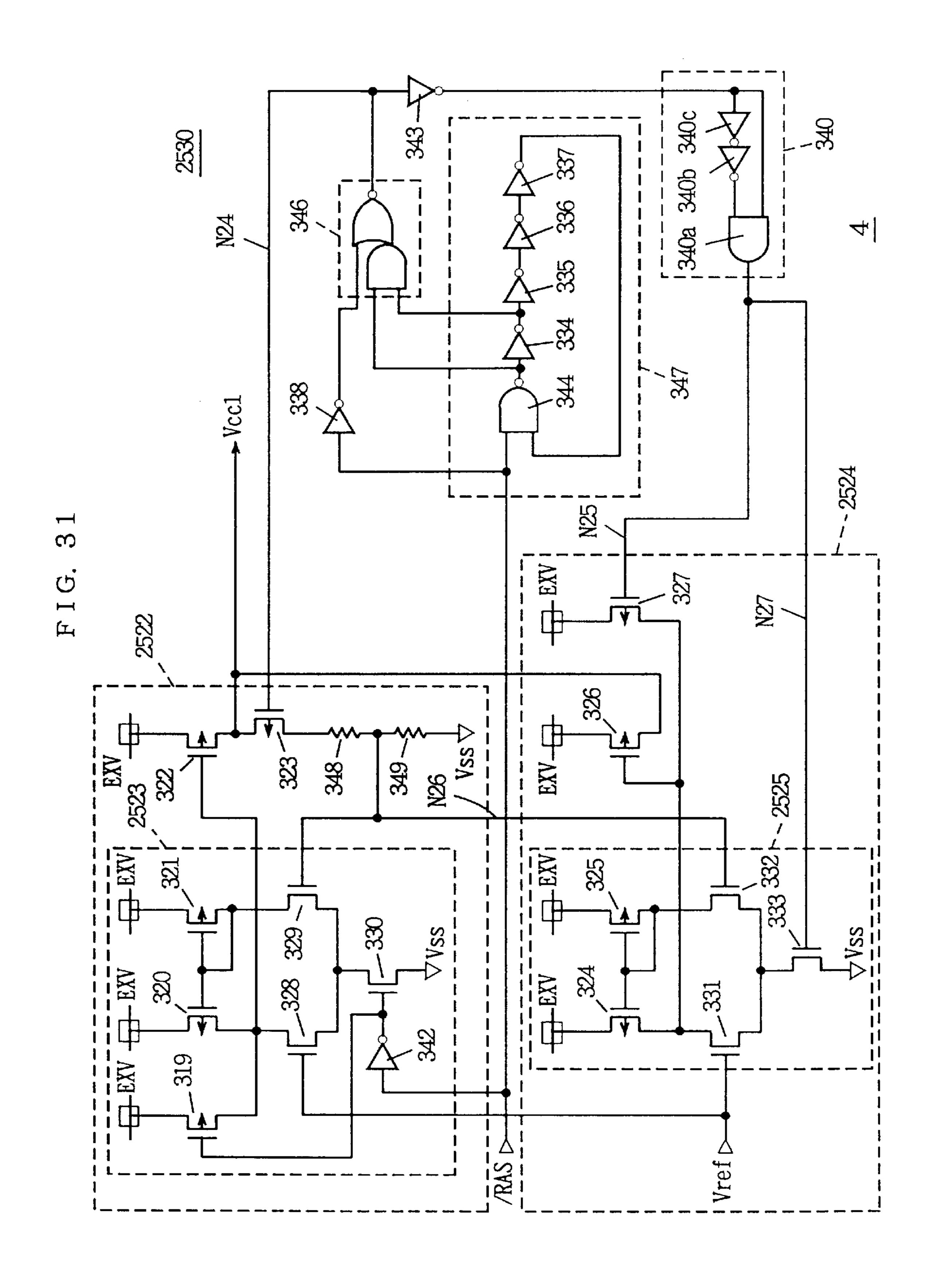

- FIG. 31 is a diagram showing a further structure of an internal power supply voltage generating circuit according to the present invention.

- FIG. 32 is a signal waveform diagram showing operation of the circuit shown in FIG. 31.

- FIG. 33 is a diagram schematically showing a further structure of the internal power supply voltage generating circuit according to the present invention.

- FIG. 34 is a diagram showing a specific configuration of the internal power supply voltage generating circuit shown 5 in FIG. **33**.

- FIG. 35 is a diagram schematically showing the structure of the internal power supply voltage generating circuit according to the present invention.

- FIG. 36 is a diagram schematically showing a further structure of the internal power supply voltage generating circuit according to the present invention.

- FIG. 37 is a diagram showing a specific structure of the Vcc1 generating circuit shown in FIG. 36.

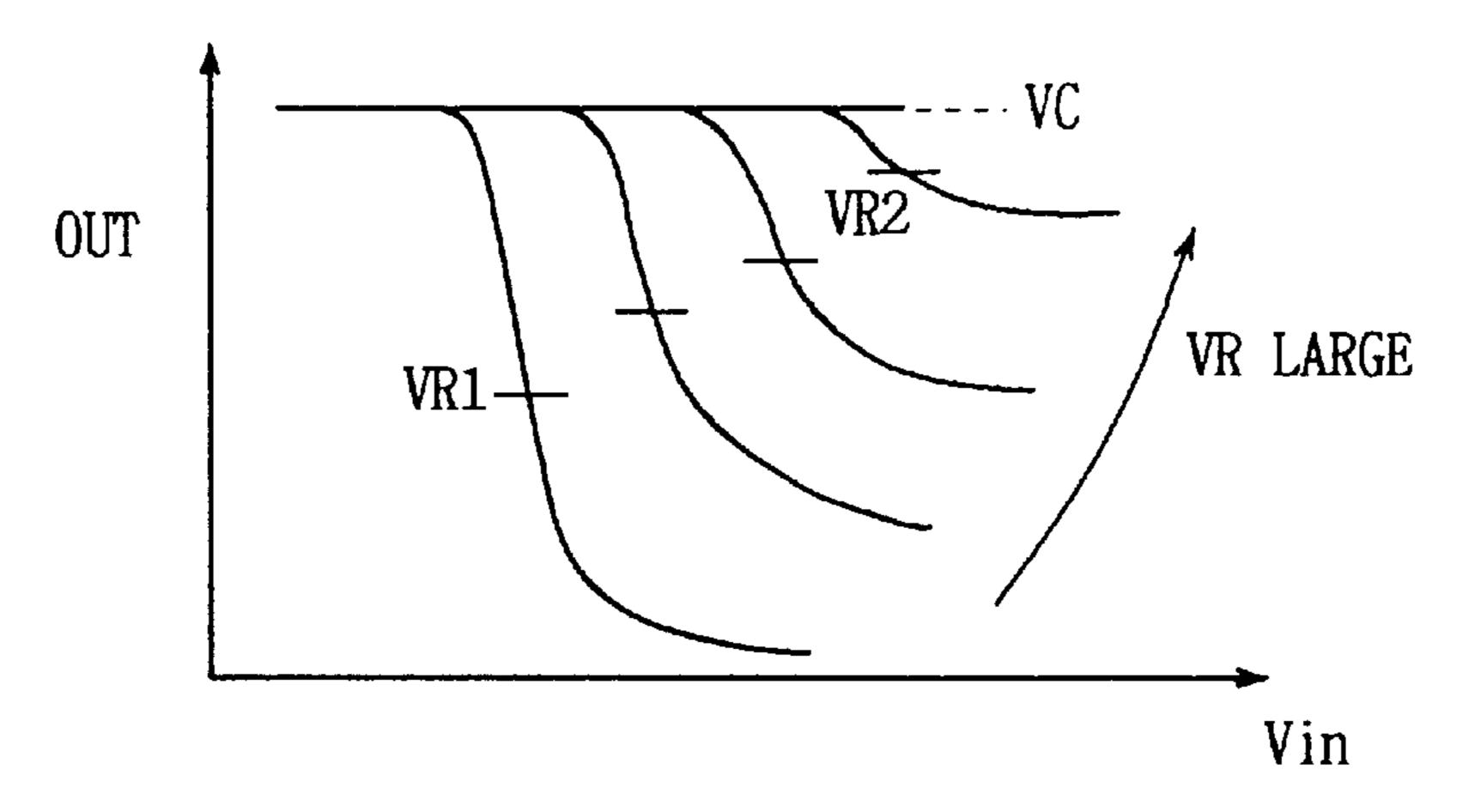

- FIGS. 38A–38C are diagrams for explaining the effect brought about by the Vcc1 generating circuit shown in FIG. **37**.

- FIG. 39 is a diagram showing a further structure of the internal power supply voltage generating circuit according 20 to the present invention.

- FIG. 40 is a diagram showing a further structure of the internal power supply voltage generating circuit according to the present invention.

- FIG. 41 is a block diagram schematically showing a further structure of the internal power supply voltage generating circuit according to the present invention.

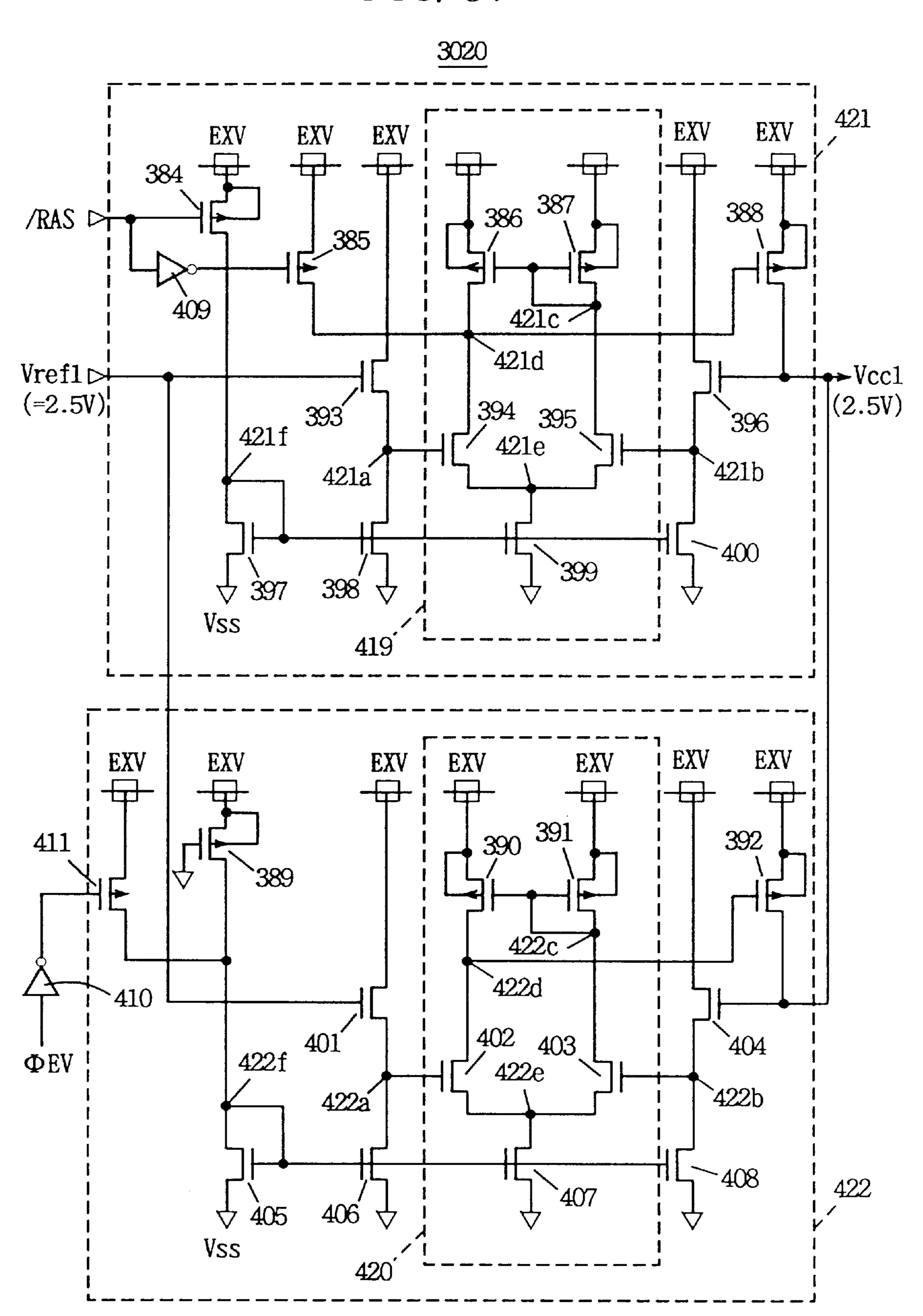

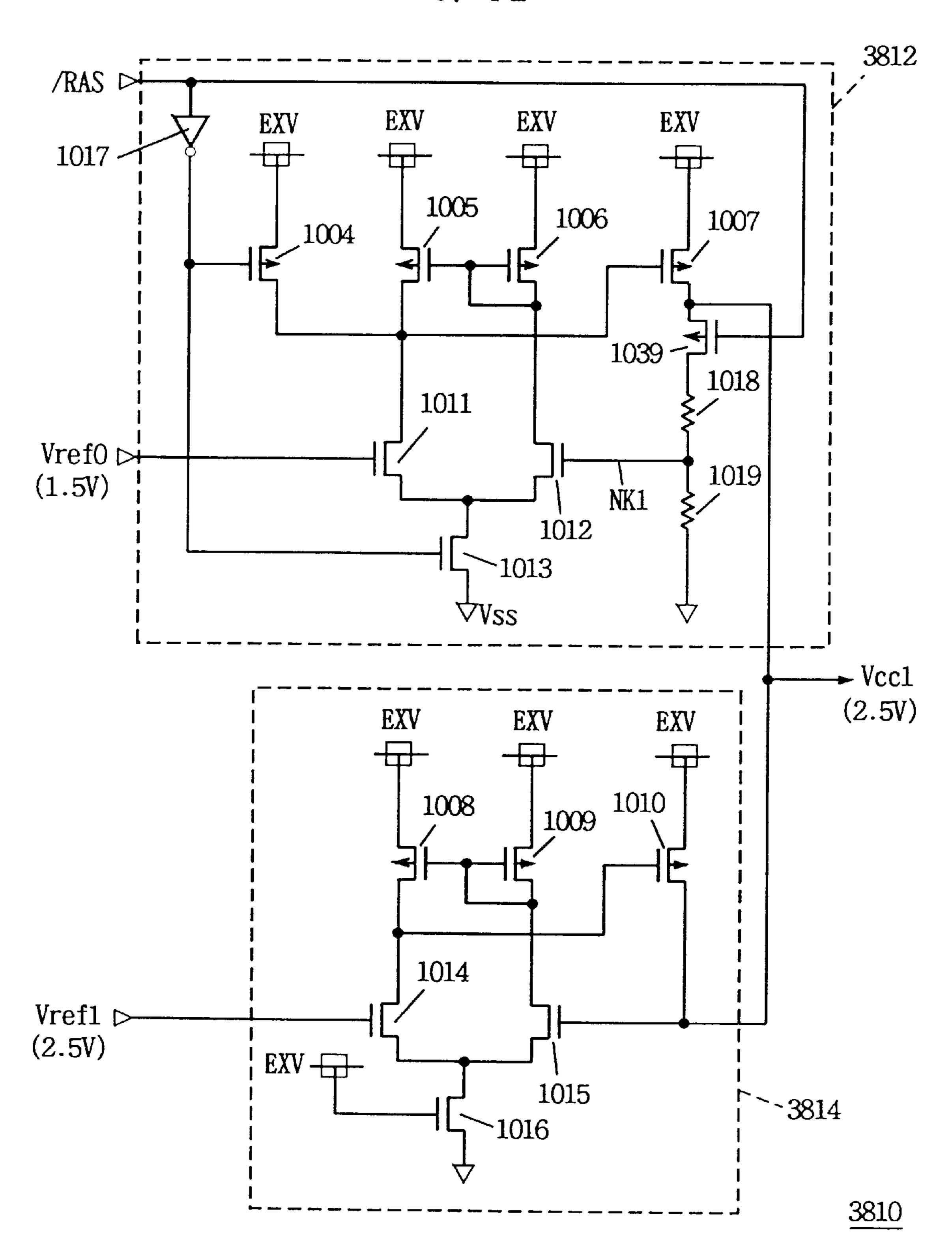

- FIG. 42 is a diagram showing a specific structure of the Vcc1 generating circuit shown in FIG. 41.

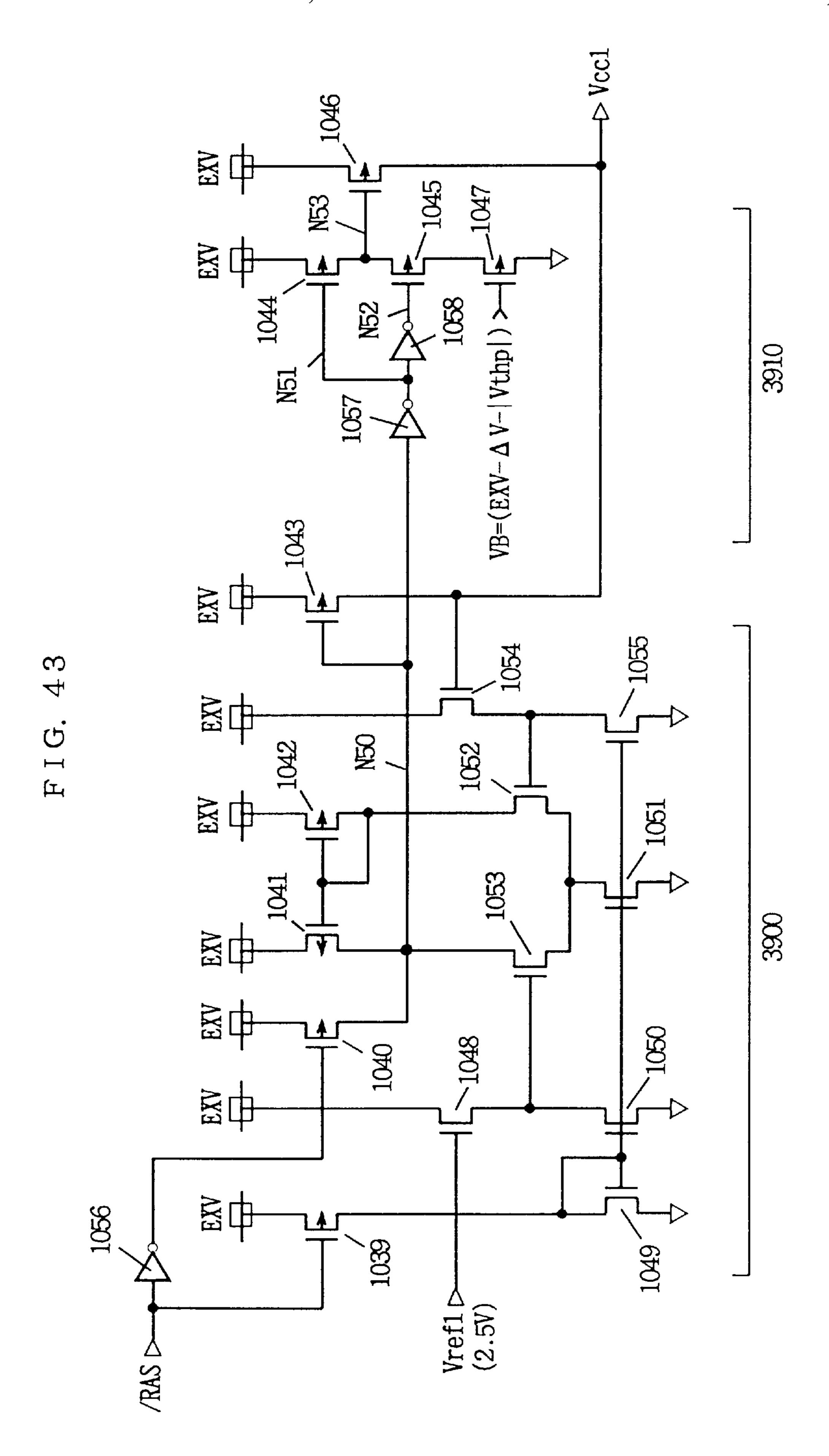

- FIG. 43 is a diagram showing a further structure of the internal power supply voltage generating circuit according to the present invention.

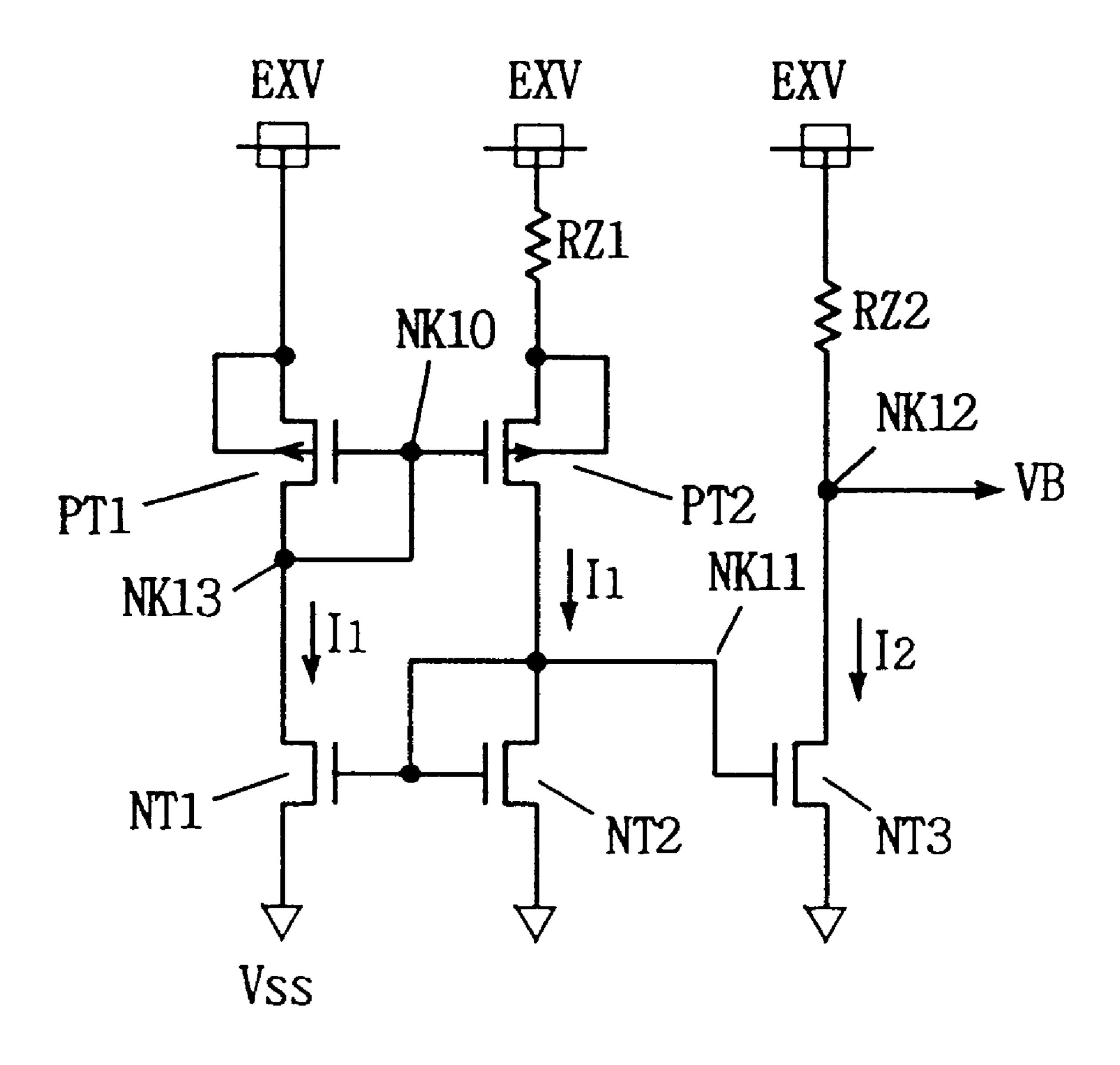

- FIG. 44 is a diagram showing a circuit configuration for generating bias voltage VB shown in FIG. 43.

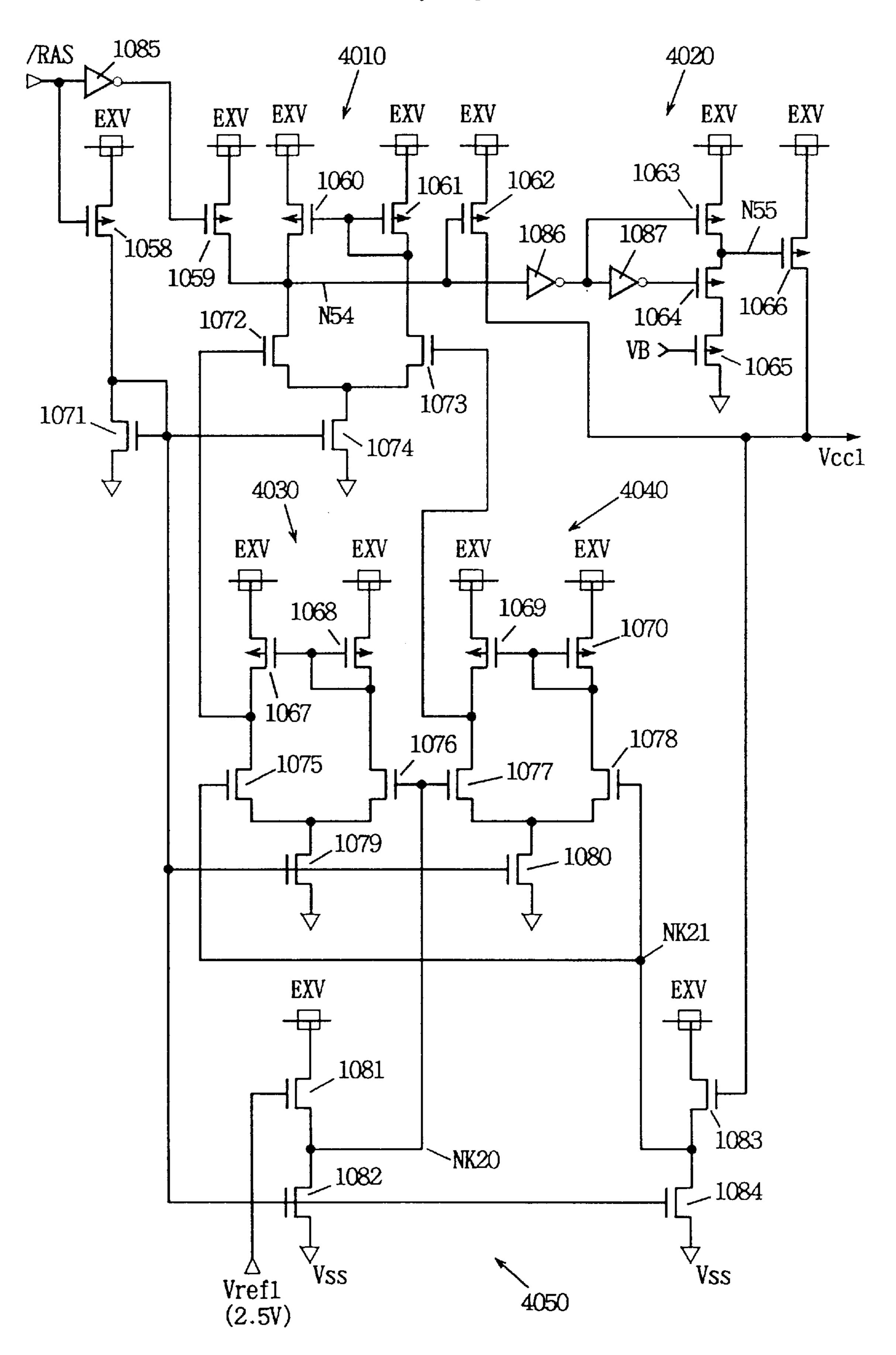

- FIG. 45 is a diagram showing a further structure of the internal power supply voltage generating circuit according to the present invention.

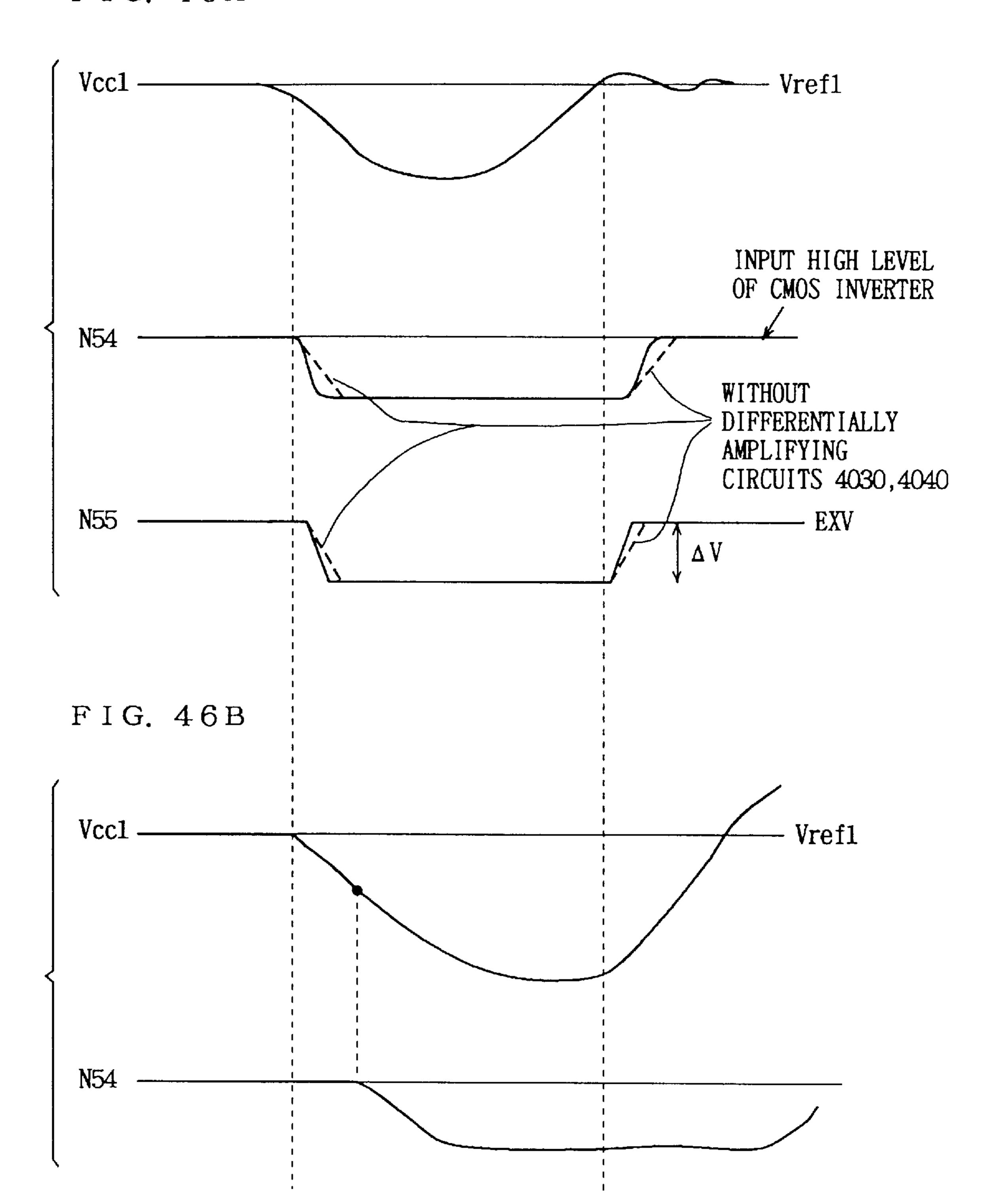

- FIGS. 46A and 46B are signal waveform diagrams for 40 explaining the effect brought about by the internal power supply voltage generating circuit shown in FIGS. 44 and 45.

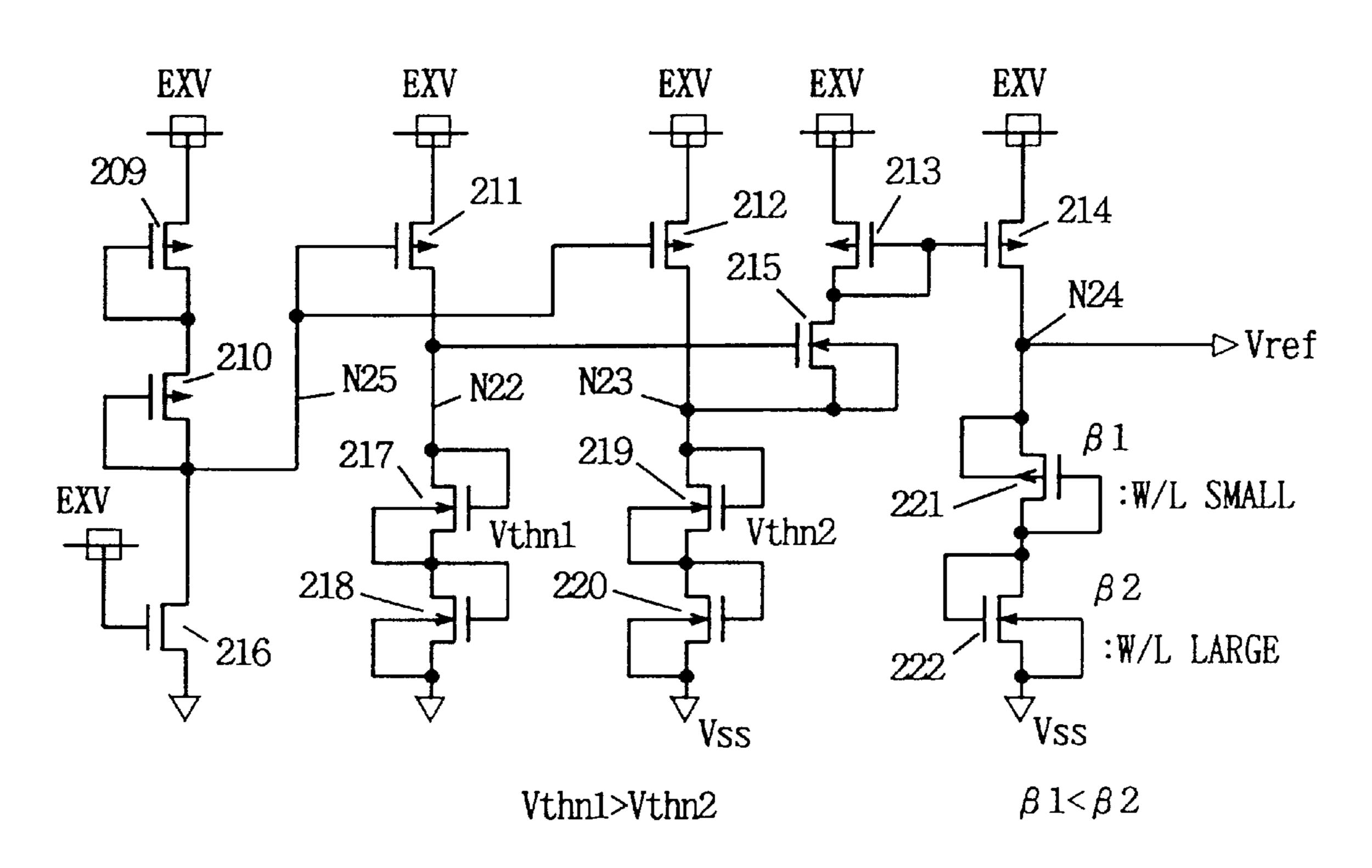

- FIG. 47 is a diagram showing a specific configuration of a reference voltage generating circuit.

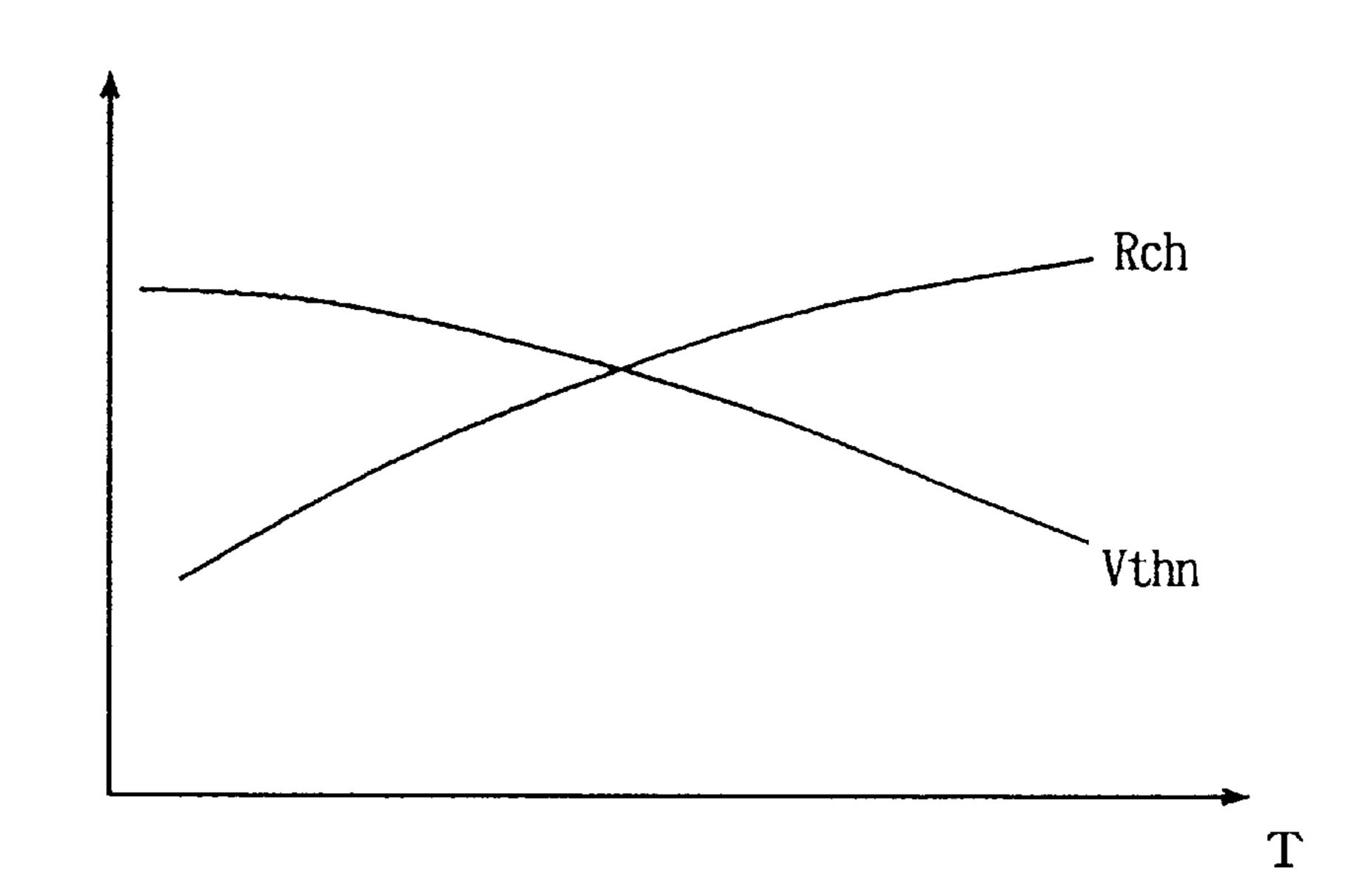

- FIG. 48 is a diagram for explaining the effect brought 45 about by the reference voltage generating circuit shown in FIG. 47.

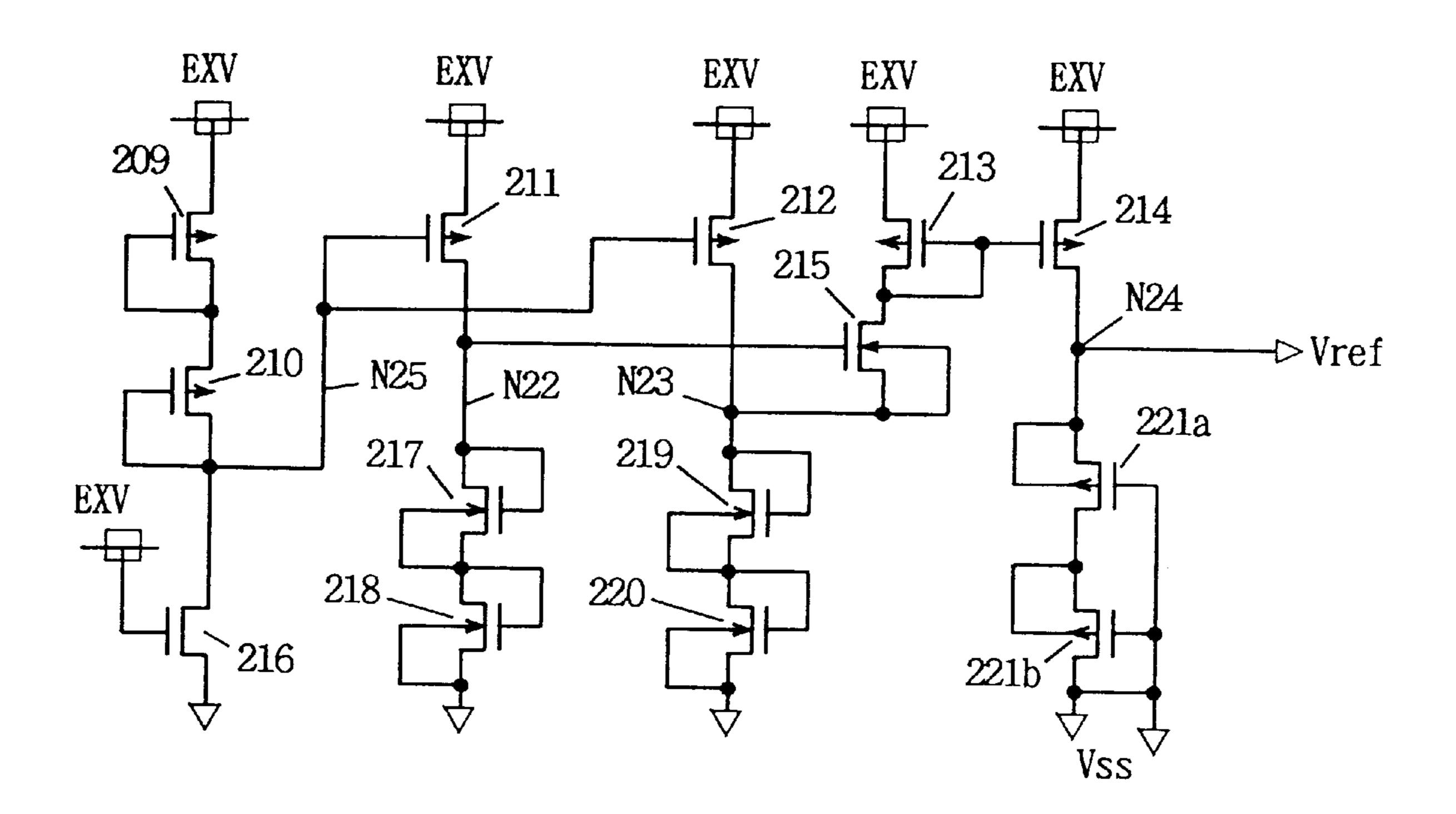

- FIG. 49 is a diagram showing a further structure of the reference voltage generating circuit according to the present invention.

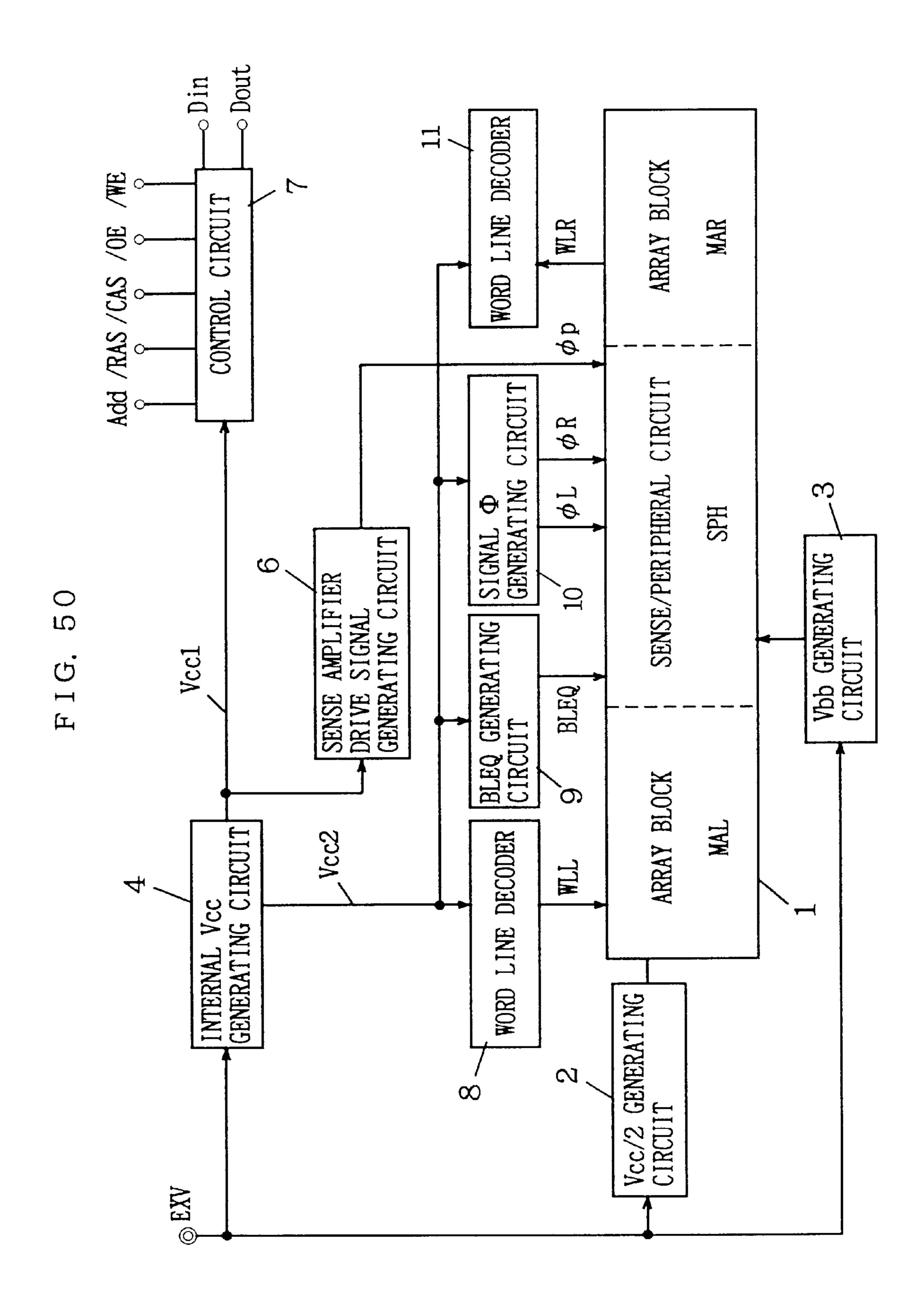

- FIG. 50 is a diagram showing a further structure of internal power supply voltage distribution of the semiconductor memory device according to the present invention.

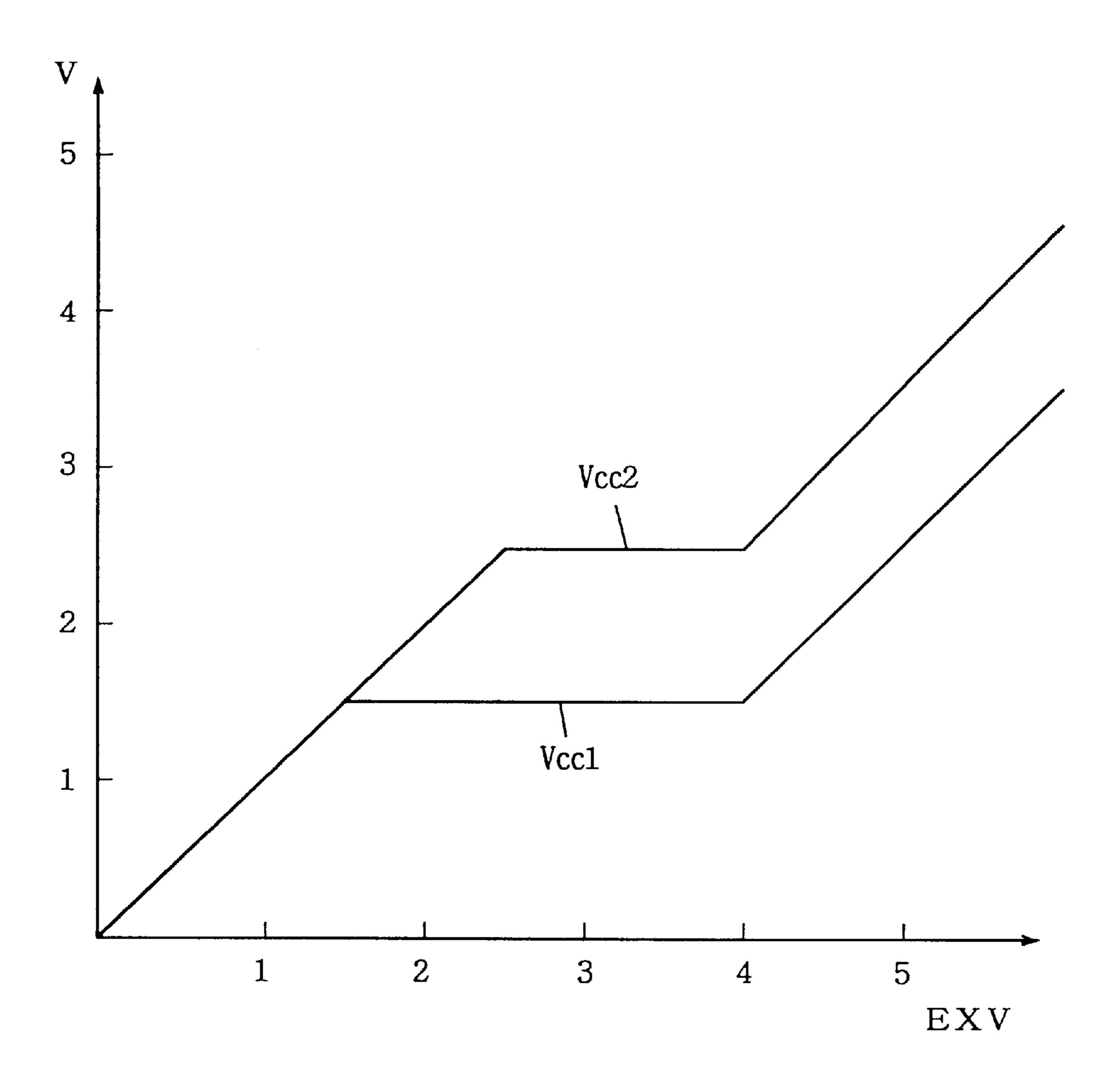

- FIG. 51 is a diagram showing levels of internal power supply voltage of the semiconductor memory device shown in FIG. **50**.

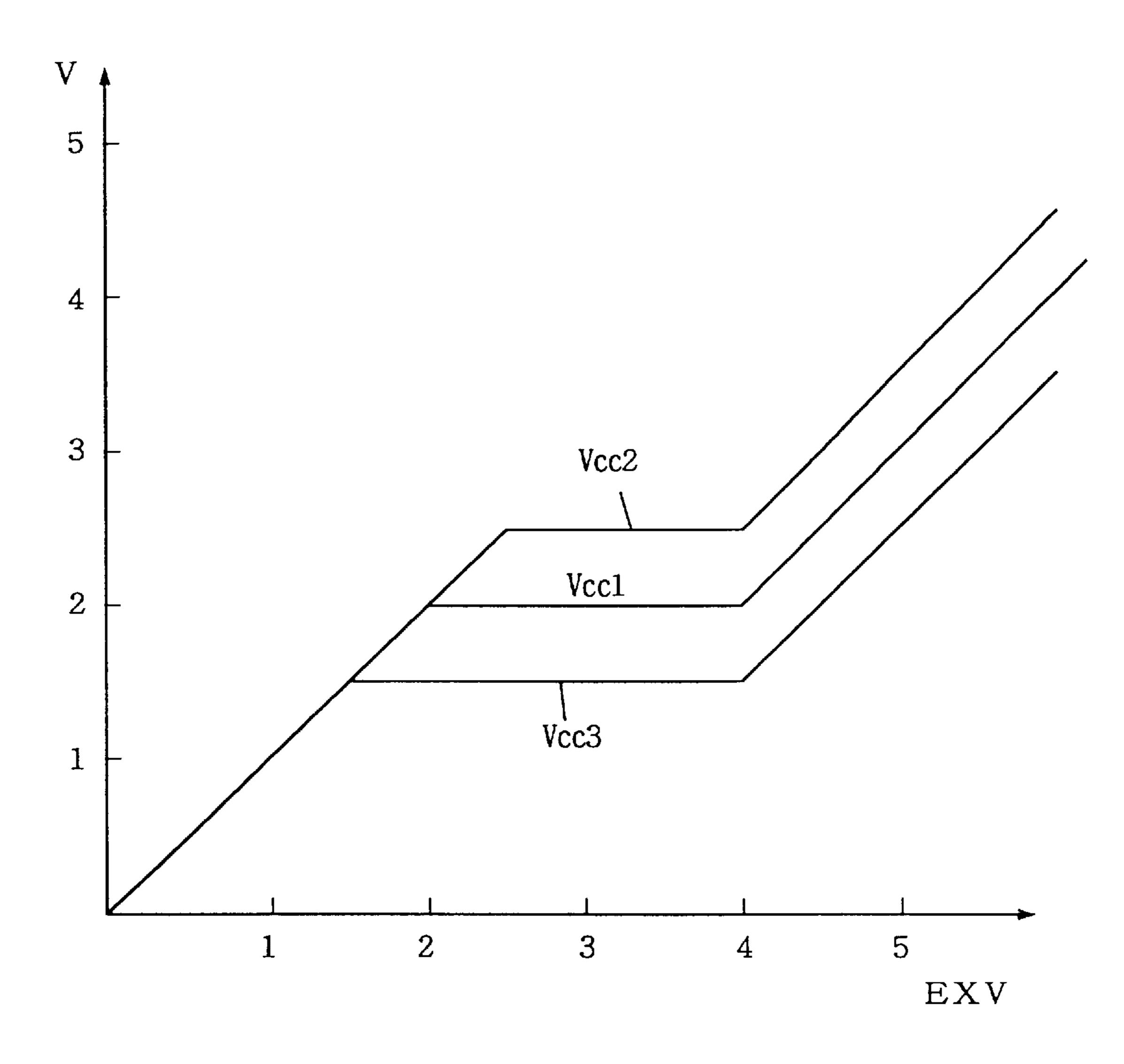

- FIG. 52 is a diagram showing a further structure of internal power supply voltage distribution of the semiconductor memory device according to the present invention.

- FIG. 53 is a diagram for explaining levels of internal power supply voltage of the semiconductor memory device shown in FIG. **52**.

- FIG. **54** is a diagram schematically showing a structure of a conventional semiconductor memory device.

- FIG. 55 is a diagram showing a structure of a conventional negative voltage generating circuit.

16

- FIG. 56 is a waveform diagram showing operation of the negative voltage generating circuit shown in FIG. 55.

- FIG. 57 is a diagram for explaining the problems of the negative voltage generating circuit shown in FIG. 55.

- FIG. 58 is a diagram schematically showing a structure of a conventional BLEQ generating circuit.

- FIG. 59 is a waveform diagram for explaining the problems of the structure shown in FIG. 58.

- FIG. 60 is a diagram showing a structure of a conventional intermediate voltage generating circuit.

- FIG. 61 is a diagram for explaining the problems of the intermediate voltage generating circuit shown in FIG. 60.

- FIG. 62 is a diagram showing a structure of a conven-15 tional internal power supply voltage generating circuit.

# DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Description will be given hereinafter of a negative voltage generating circuit, an internal high voltage generating circuit, an intermediate voltage generating circuit, and an internal power supply voltage generating circuit. Although they may be used independently, these circuits can implement a semiconductor memory device which operates stably with low power consumption in combination.

# [Internal Voltage Generating Circuit]

FIG. 1 is a diagram showing a schematic structure of the internal voltage generating circuit according to the present invention. Referring to FIG. 1, the internal voltage generating circuit includes pump drive signal generating circuit 224 generating pump drive signal CK, pump circuit 225 operating with external power supply voltage EXV applied to external power supply node EXV as one operation power supply voltage for carrying out charge pumping operation according to clock signal CK from pump drive signal generating circuit 224 to generate an internal voltage (negative voltage Vbb or internal high voltage Vpp), and level detecting circuit 223 detecting a level of the internal voltage generated by pump circuit 225 and controlling signal generating operation of pump drive signal generating circuit 224 according to the level detection result. Level detecting circuit 223 and pump drive signal generating circuit 224 may receive either external power supply voltage EXV or internal power supply voltage Vcc1 as operation power supply voltage.

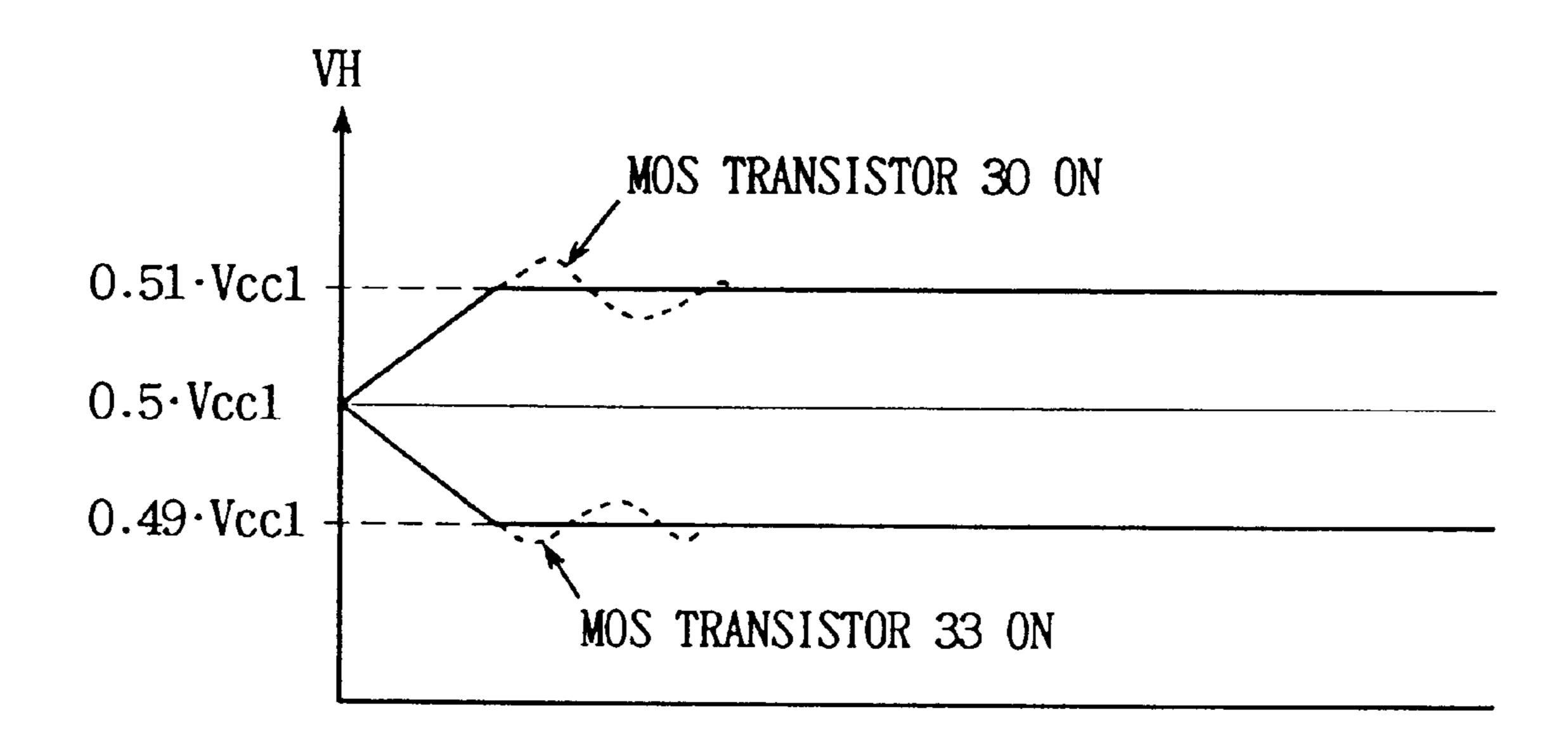

FIG. 2 is a diagram schematically showing operation of the internal voltage generating circuit shown in FIG. 1. In 50 FIG. 2, a state where negative voltage Vbb is generated as an internal voltage is shown as an example.

Pump circuit 225 operates with external power supply voltage EXV as operation power supply voltage. Therefore, the potential amplitude of an internal node for supplying 55 negative voltage Vbb to an output node is between Vss and -EXV. External power supply voltage EXV is higher than internal power supply voltage Vcc1. Therefore, even when negative voltage Vbb approaches a prescribed voltage level (-2.Vthn), that is, a voltage level of -Vcc1, a difference 60 between the potential of an internal node PND and negative voltage Pbb is sufficiently large as shown in FIG. 2. The pump circuit affords to supply negative electric charge, thereby decreasing negative voltage Vpp. More specifically, the amount of negative electric charge stored in internal 65 node PND is greater in the case where external power supply voltage EXV is used than in the case where internal power supply voltage Vcc1 is used as shown by hatching in FIG.

2. The increased amount of electric charge makes it possible to supply a sufficient amount of negative electric charge even if negative voltage Vbb approaches a prescribed level, thereby decreasing negative voltage Vbb at a high speed.

The structure shown in FIG. 2 can be applied to the case where internal high voltage Vpp is generated. More specifically, by generating an internal voltage according to charge pumping operation using external power supply voltage EXV in pump circuit 225, the potential amplitude of an internal node for supplying electric charge can be made sufficiently large. Even when the internal voltage approaches a prescribed level, a sufficient amount of electric charge can be supplied, and the internal voltage at a prescribed level can be generated at a high speed. Description will be given hereinafter of a specific structure of the negative voltage <sup>15</sup> generating circuit and the internal high voltage generating circuit.

# [Negative Voltage Generating Circuit 1]

FIG. 3 is a diagram showing a first embodiment of the negative voltage generating circuit according to the present invention. Referring to FIG. 3, the circuit generating negative voltage Vbb includes level detecting circuit 223, pump drive signal generating circuit 224, and pump circuit 225 similar to the structure shown in FIG. 1.

Level detecting circuit 223 includes a diode-connected n channel MOS transistor 55 provided between an output node NA and a node NB of pump circuit 225, an n channel MOS transistor 54 provided between node NB and a node NC and connected to receive ground voltage Vss at its gate, and a p channel MOS transistor 42 provided between an internal power supply node Vcc1 and a node NC1 and receiving ground voltage Vss at its gate. MOS transistor 42 serves as a resistance element, and supplies small current from internal power supply node Vcc1 to node NC. More specifically, MOS transistor 42 serves as a pull up element pulling up the potential of node NC to the internal power supply voltage Vcc1 level.

MOS transistor **55** causes voltage drop of Vthn when rendered conductive. As far as not mentioned otherwise, Vthn denotes a threshold voltage of an n channel MOS transistor, and Vthp denotes a threshold voltage of a p channel MOS transistor. MOS transistor **54** is rendered conductive when the potential of node NB is -Vthn. More specifically, when negative voltage Vbb of output node NA of pump circuit **225** is -2·Vthn or less by MOS transistors **54** and **55**, the potential of node NC of level detecting circuit **223** attains the "L" level.

Pump drive signal generating circuit **224** includes an inverter **62** receiving the signal potential on node NC of level detecting circuit **223**, an NOR circuit **72** receiving an output signal from inverter **62** at one input, and three stages of cascade-connected inverters **63**, **64** and **65** receiving an output signal from NOR circuit **72**. An output signal from inverter **64** is applied to the other input of NOR circuit **72**. Pump drive clock signal CK is provided form inverter **65**. Pump drive signal generating circuit **224** operates with external power supply voltage EXV as one operation power supply voltage. Therefore, in clock signal CK, the "H" level corresponds to the external power supply voltage EXV level, and the "L" level corresponds to the ground voltage Vss level.

The "H" level of node NC of level detecting circuit 223 corresponds to the internal power supply voltage Vcc1 level. 65 Inverter 62 operates with external power supply voltage EXV as operation power supply voltage. In order to prevent

18

through current in inverter 62, inverter 62 is structured as shown in FIG. 4.

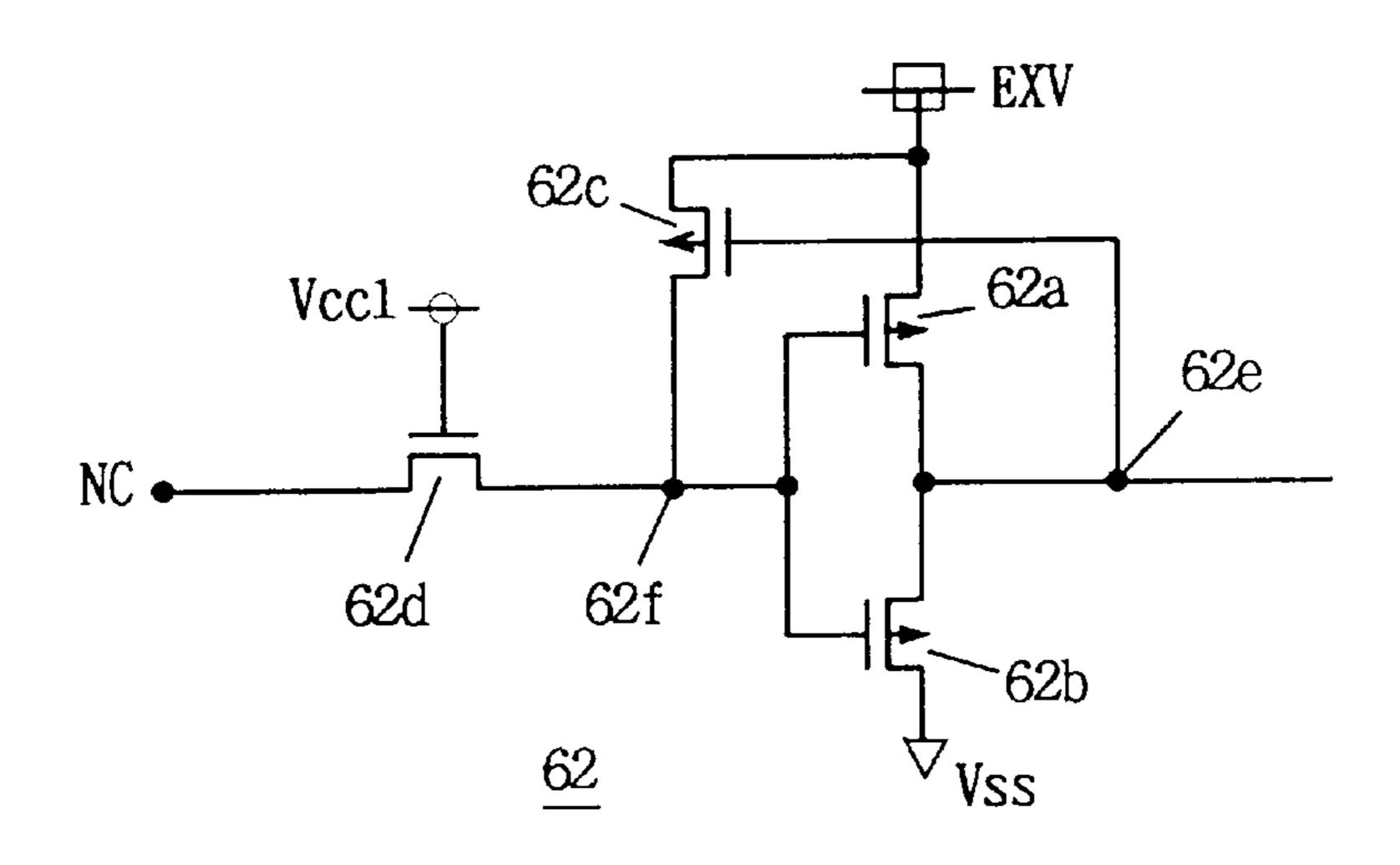

Referring to FIG. 4, inverter 62 includes an n channel MOS transistor 62d provided between node NC and a node 62f and receiving internal power supply voltage Vcc1 at its gate, a p channel MOS transistor 62a provided between external power supply node EXV and a node 62e and receiving the signal potential on node 62f at its gate, an n channel MOS transistor 62b provided between node 62e and ground node Vss and receiving the signal potential on node 62f at its gate, and a p channel MOS transistor 62c provided between external power supply node EXV and node 62f and receiving the potential on node 62e at its gate.

When the potential of node NC is at the internal power supply voltage Vcc1 level, a signal of "H" at the Vcc1-Vthn level is transmitted to node 62f through MOS transistor 62d. In response to the potential of node 62f, MOS transistor 62b is turned on, decreasing the potential of node 62e. The decreased potential of node 62b brings MOS transistor 62c to an on state, supplies current from external power supply node EXV to node 62f, and increases the potential of node 62f. MOS transistors 62b is turned on more strongly, the potential of node 62e attains the ground voltage Vss level, and the potential of node 62f attains the external power supply voltage EXV level by MOS transistor 62c. As a result, MOS transistor 62a is turned off. When the potential of node 62f attains external power supply voltage EXV, MOS transistor 62d is in an off state, and node NC maintains the internal power supply voltage Vcc1 level without the influence of external power supply voltage EXV.

When the potential level of node NC decreases to the "L" level, the potential of node 62f decreases through MOS transistor 62d, and p channel MOS transistor 62a is turned on, thereby increasing the potential level of node 62e.

As a result, MOS transistor 62c transitions to an off state. Finally, MOS transistor 62a is turned on, and MOS transistor 62b is turned off.

As described above, by inverter 62 functioning to convert the level, through current in inverter 62 can be prevented even if the potential level of an output signal from level detecting circuit 223 is at the internal power supply voltage Vcc1 level, thereby implementing low current consumption.

Operation of pump drive signal generating circuit 224 shown in FIG. 3 is the same as that of a conventional circuit. More specifically, when the potential level of node NC of level detecting circuit 223 is at "H", an output from inverter 62 attains the "L" level. NOR circuit 72 functions as an inverter. A ring oscillator is formed by NOR circuit 72 and inverters 63 and 64, and a signal having a prescribed pulse width and a prescribed period is generated. An output signal from inverter 64 is inverted by inverter 65, and clock signal CK is generated.

When the potential level of node NC of level detecting circuit 223 is at "L", an output from inverter 62 attains the "H" level, and an output signal from NOR circuit 72 is fixed at the "L" level. Oscillating operation of the ring oscillator is stopped, and clock signal is fixed at the "H" level.

More specifically, when negative voltage Vbb output from pump circuit 225 attains a prescribed level -2. Vthn or less, pump drive signal generating circuit 224 stops the oscillating operation, maintains clock signal CK at a prescribed level, and stops pumping operation of pump circuit 225.

Pump circuit 225 includes an inverter 66 receiving clock signal CK from pump drive signal generating circuit 224, an inverter 67 receiving an output from inverter 66, two stages of cascade-connected inverters 69 and 70 receiving an

output from inverter 66, an inverter 68 receiving an output from inverter 67, a capacitor 74 changing the potential of a node N8 by charge pumping operation in response to an output signal from inverter 68, and a p channel MOS transistor 46 and an n channel MOS transistor 58 operating with the potential on node N8 as one operation power supply voltage and ground voltage Vss as the other power supply voltage and forming an inverter inverting an output signal from inverter 67. The inverter formed of transistors 46 and 58 has an output node N9.

Pump circuit 225 further includes an n channel MOS transistor 56 discharging the potential of a node N13b to the ground potential level in response to an output signal from inverter 66, an n channel MOS transistor 57 discharging the potential of a node N13a to the ground potential level in 15 response to an output signal from inverter 67, a p channel MOS transistor 43 transmitting the signal potential on node N8 onto node N13b in response to the signal potential on node N13a, a p channel MOS transistor 44 transmitting the signal potential on node N8 onto node N13a in response to 20 the signal potential on node N13b, and a p channel MOS transistor 45 transmitting external power supply voltage EXV from external power supply node EXV onto node N8 in response to the signal potential on node N13a. The substrate region (semiconductor substrate or well region) of 25 p channel MOS transistors 43, 44, and 45 is connected to node N8. This is for the potential of node N8 to increase up to the 2.EXV level, to be described later.

Pump circuit 225 further includes a capacitor 75 capacitively coupling node N9 and node N10, a capacitor 77 changing the potential of node N12 by charge pumping operation in response to an output signal from inverter 169, a capacitor 76 changing the potential of node N11 by charge pumping operation in response to an output signal from inverter 70, a diode-connected p channel MOS transistor 49 clamping the signal potential on node N12 to |Vthp|, p channel MOS transistors 47 and 48 discharging the potentials of nodes N10 and N11 to the ground potential Vss level in response to the signal potential on node N12, and a p channel MOS transistor 50 supplying negative electric charge from node N11 to output node NA in response to the signal potential on node N10.

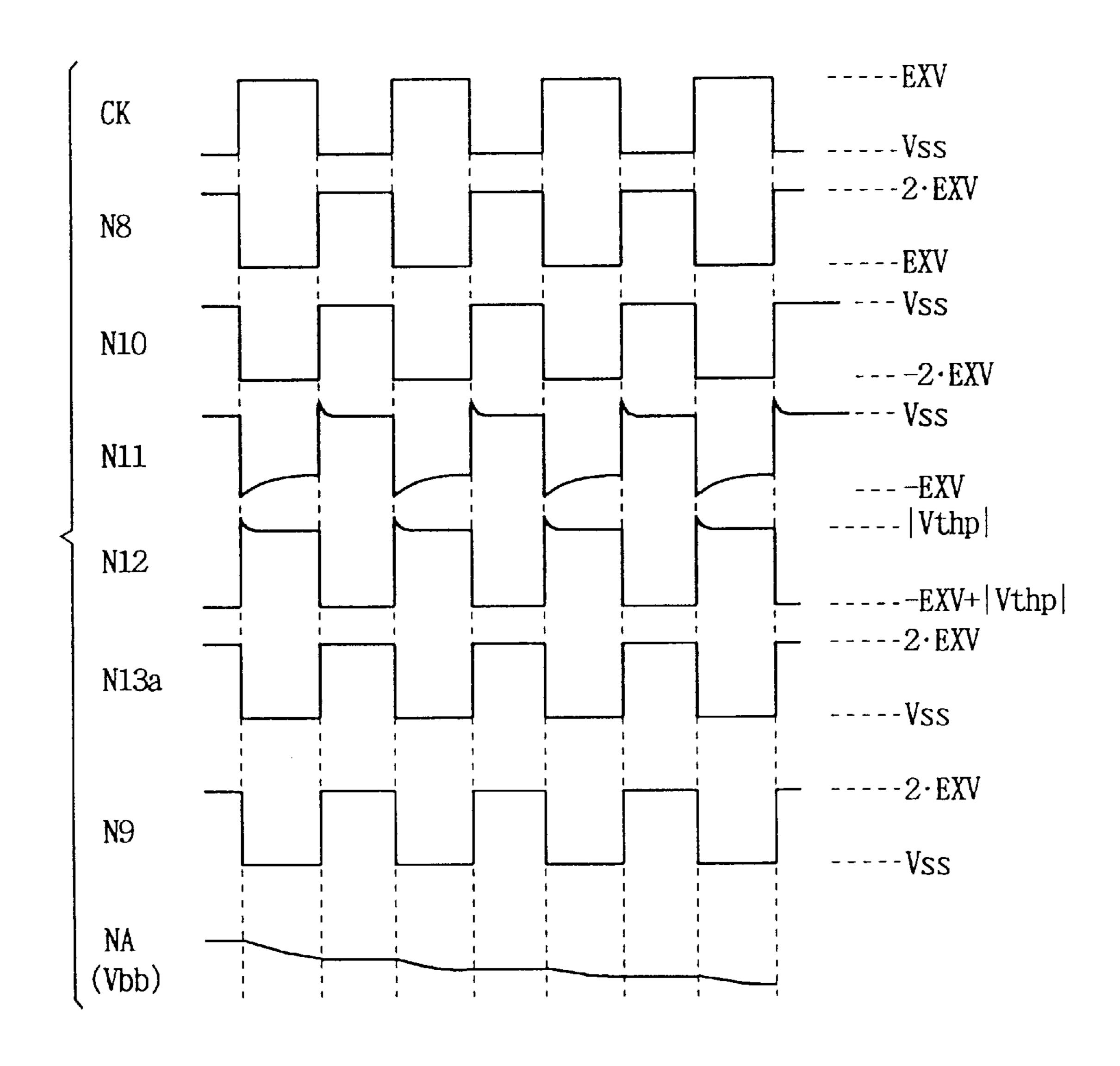

Inverters 66–70 included in pump circuit 225 operate with external power supply voltage EXV as one operation power supply voltage, and with ground voltage Vss as the other operation power supply voltage. Description will now be given of operation of the pump circuit shown in FIG. 3 with reference to FIG. 5, which is its operation waveform diagram.

When clock signal CK from pump drive signal generating circuit 224 rises to the "H" level, an output form inverter 66 falls to the "L" level, and output signals from inverters 67 and 69 rise to the "H" level. MOS transistor 57 is rendered conductive in response to an output signal from inverter 67, and discharges node N13a to the ground potential Vss level. Accordingly, MOS transistor 45 is turned on, and charges node N8 to the external power supply voltage EXV level.

On the other hand, an output signal from inverter 69 attains the "H" level, and the potential of node N12 is 60 increased by charge pumping operation (capacitive coupling) of capacitor 77. However, the potential of node N12 is clamped to |Vthp| by MOS transistor 49. On the other hand, an output signal from inverter 70 falls to the "L" level, and the potential of node N11 is decreased by charge 65 pumping operation of capacitor 76. At the time, MOS transistor 48 receives a voltage of the absolute value |Vthp|

20

of the threshold voltage at its gate to be turned off, and the potential of node N11 attains -EXV.

Similarly, when an output signal from inverter 67 attains the "H" level, MOS transistor 58 is turned on, and the potential of node N9 decreases to the ground potential Vss level. Accordingly, the potential of node N10 is decreased by charge pumping operation. At the time, MOS transistor 47 is in an off state similar to MOS transistor 48. The potential of node N10 attains -2.EXV, to be described later. As a result, MOS transistor 50 is turned on, negative electric charge (electrons) flows out from node N11 to node NA, and voltage Vbb of node NA decreases while the potential on node N11 increases. When the potentials of nodes N11 and NA become equal, MOS transistor 50 is turned off. At the time, MOS transistor 57 is turned on in response to an output signal from inverter 67, and node N13a is discharged to the ground voltage Vss level. Accordingly, MOS transistor 45 is turned on, and node N8 is charged to EXV.

When clock signal CK falls to the "L" level, an output signal from inverter 66 rises to the "H" level. In response to this, MOS transistor 56 is turned on, node N13b is discharged to the ground potential level, MOS transistor 44 is turned on, and the potential on node N8 is transmitted onto node N13a. At the time, an output signal from inverter 67 is at "L", and MOS transistor 57 is turned off. Since an output signal from inverter 68 rises to the "H" level, the potential of node N8 which has been precharged to external power supply voltage EXV increases to 2·EXV by charge pumping operation of capacitor 74. As a result, MOS transistor 45 is turned off.

An output signal from inverter 67 attains the "L" level, causing MOS transistor 46 to be turned on, MOS transistor 58 to be turned off, and node N9 to be supplied with electric charge from node N8 to increase up to the voltage level of 2.EXV. In response to the rising of the potential of node N9, the potential of node N10 increases by charge pumping operation of capacitor 75. At the time, an output signal from inverter 69 falls to the "L" level, causing the potential of node N12 to be decreased to the potential level of -EXV+ |Vthp| by charge pumping operation of capacitor 74, both MOS transistors 47 and 48 to be turned on, and nodes N10 and N11 to be charged to the ground voltage Vss level. As a result, MOS transistor 50 is turned off.

The potential of node N8 changes between 2·EXV and EXV, and the potential of node N9 changes between 2·EXV and Vss. More specifically, the amplitude is 2·EXV. Therefore, node N10 changes between Vss and -2·EXV by charge pumping operation of capacitor 75. The potential of node N11 changes between Vss and -EXV. Therefore, pump circuit 225 can decrease negative voltage Vbb down to the voltage level of -EXV. In response to negative voltage Vbb attaining -2·Vthn at a prescribed level, level detecting circuit 223 fixes the level of clock signal CK, thereby stopping pumping operation of pump circuit 225.

By changing the voltage of node N8 between EXV and 2·EXV, the potential amplitude of node N9 can be set to 2·EXV. This enables the potential amplitude of node N10 by capacitive coupling of capacitor 75 to be 2·EXV, and the lowest potential which negative voltage Vbb of an output from pump circuit 225 attains to be -EXV. Therefore, even if internal power supply voltage Vcc1 is decreased in order to make power consumption lower, and if negative voltage Vbb approaches a prescribed voltage level -2·Vthn, a sufficient amount of negative electric charge can be supplied to output node NA because there is a sufficiently big difference between -EXV and -2·Vthn, making it possible to implement a negative voltage generating circuit with high efficiency.

Stable power supply voltage Vcc1 is supplied to level detecting circuit 223, so that change in external data EXV causes no variation of the potential level of node NC. Therefore, a prescribed voltage level -2. Vthn can be detected precisely.

In pump drive signal generating circuit 224 shown in FIG. 3, external power supply voltage EXV is applied. Alternatively, internal power supply voltage Vcc1 may be supplied to pump drive signal generating circuit 224 as one operation power supply voltage. In this case, inverter 66 in 10 an input portion of pump circuit 225 has only to be structured as shown in FIG. 4.

# [Negative Voltage Generating Circuit 2]

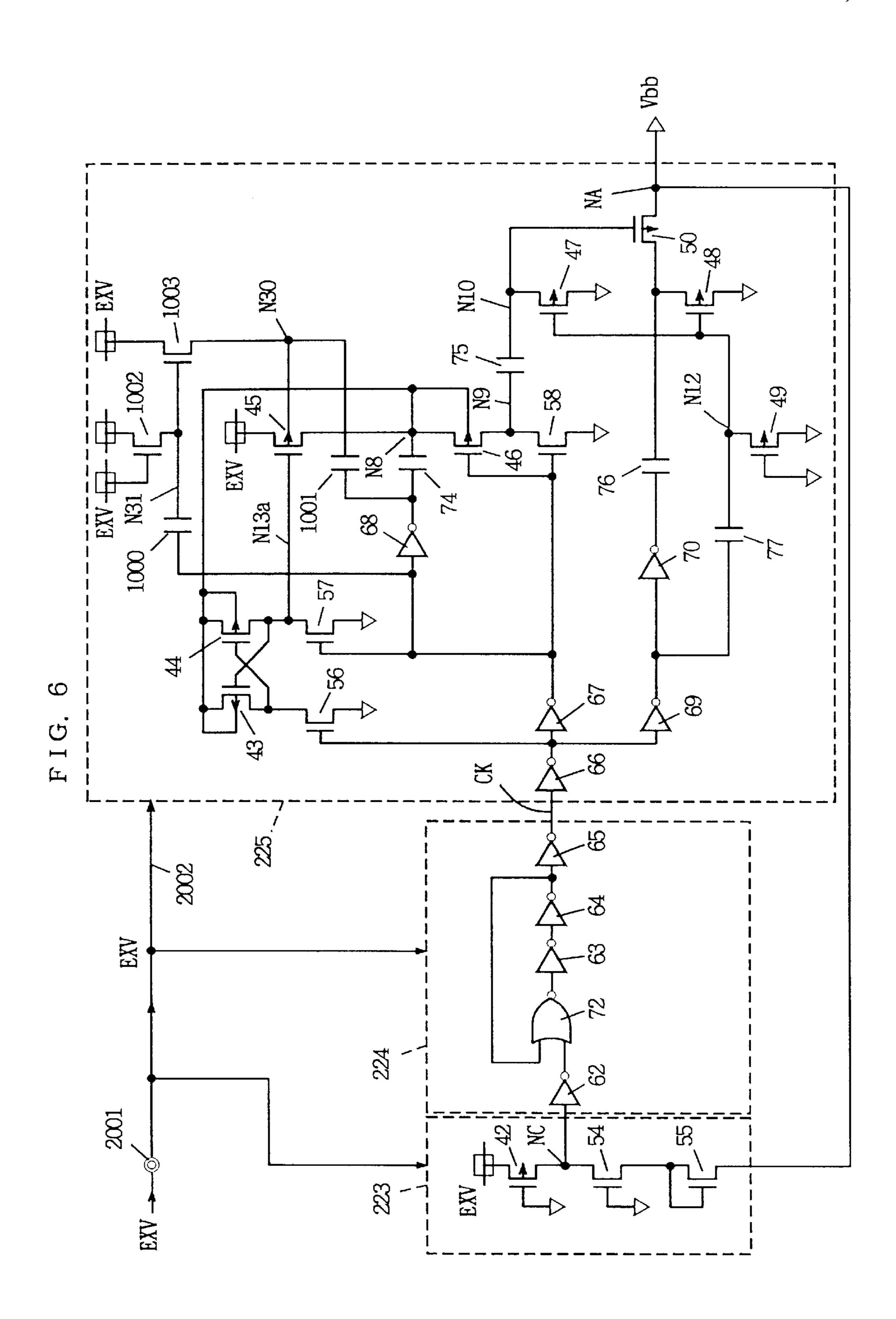

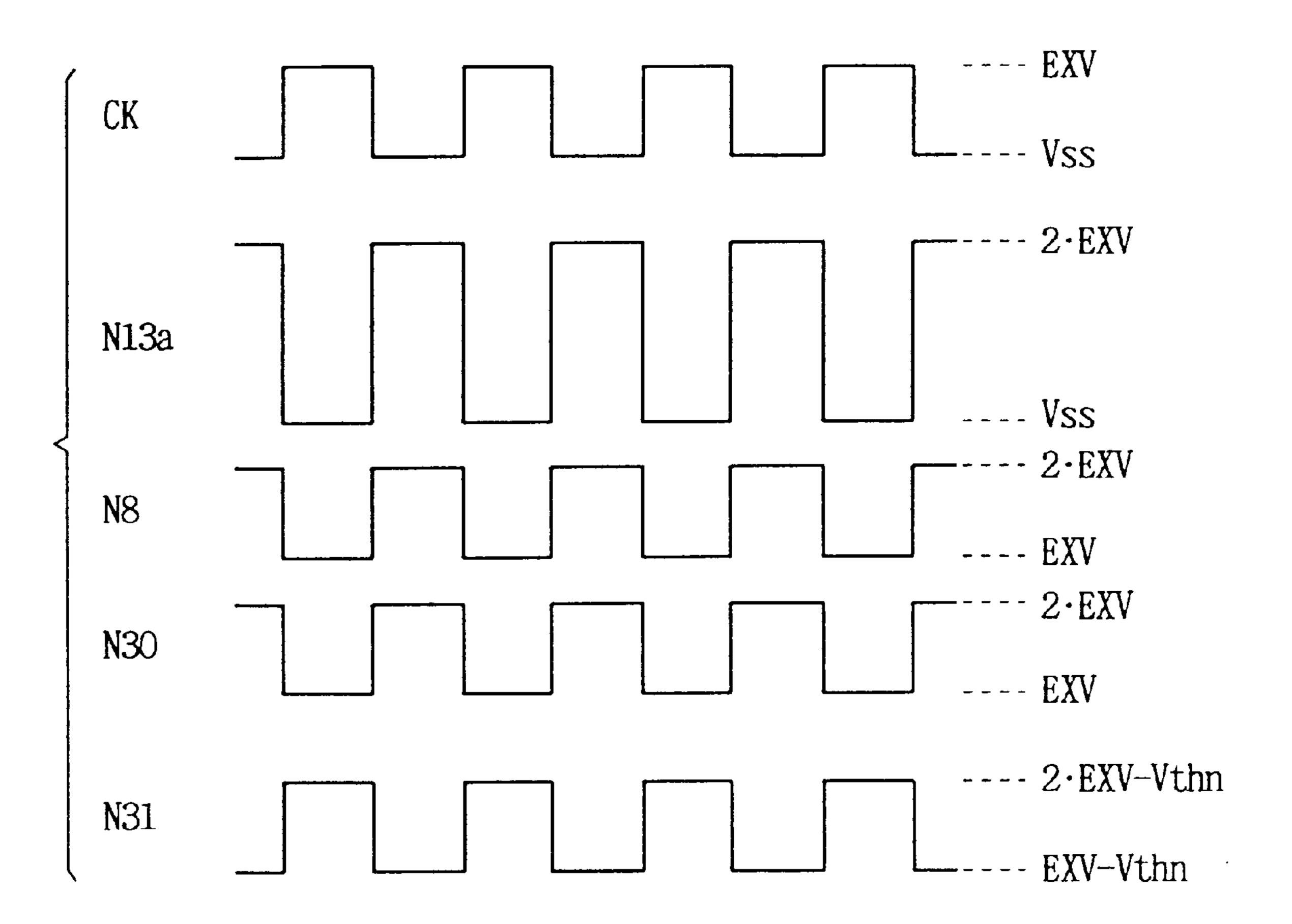

FIG. 6 is a diagram showing a structure of a second embodiment of the negative voltage generating circuit according to the present invention. The negative voltage generating circuit shown in FIG. 6 is different from that shown in FIG. 3 in that external power supply voltage EXV is applied to level detecting circuit 223. By applying external power supply voltage EXV to level detecting circuit 223, an interconnection line for supplying internal power supply voltage Vcc1 is unnecessitated, thereby simplifying the layout. More specifically, by transmitting power supply 25 voltage EXV externally applied to a power supply pad 2001 to level detecting circuit 223, pump drive signal generating circuit 224, and pump circuit 225 through an external power supply line 2002, only external power supply line 2002 is required as a power supply line for transmitting operation power supply voltage of these circuits, simplifying the power supply line layout.

The structure of pump drive signal generating circuit 224 is similar to that shown in FIG. 6, and the same or corresponding portions are labeled with the same reference 35 N30. characters. Similarly, the structure of level detecting circuit 223 is similar to that shown in FIG. 3 and the same or corresponding portions are labeled with the same reference characters. In addition to the structure shown in FIG. 3, pump circuit 225 further includes an n channel MOS transistor 1002 connected between external power supply node EXV and a node N31 and receiving external power supply voltage EXV at its gate, a capacitor 1000 changing the potential of node N31 by charge pumping operation in response to an output signal from inverter 67, an n channel 45 MOS transistor 1003 transmitting external power supply voltage EXV to a node N30 in response to the signal potential on node N31, and a capacitor 1001 changing the potential of node N30 by charge pumping operation in response to an output signal from inverter 68.