### United States Patent [19]

[11] E

Patent Number: Re. 33,676

Hoshi

[45] Reissued Date of Patent: Aug. 27, 1991

## [54] GATE ARRAY CIRCUIT FOR DECODING CIRCUITS

Toshiaki Hoshi, Tokyo, Japan

[73] Assignee: NEC Corporation, Tokyo, Japan

[21] Appl. No.: 596,151

Inventor:

[22] Filed: Oct. 11, 1990

### Related U.S. Patent Documents

Reissue of:

[64] Patent No.:

4,777,390

Issued: Appl. No.:

Oct. 11, 1988 947,448

Filed:

Dec. 29, 1986

| [30]     | Foreign A   | pplication | Priority Data |           |

|----------|-------------|------------|---------------|-----------|

| Dec. 27, | , 1985 [JP] | Japan      |               | 60-296948 |

[51] Int. Cl.<sup>5</sup> ...... H03K 17/693; H03K 19/003; H03K 19/094; H03K 17/04

[52] **U.S. Cl.** 307/449; 307/463; 307/469; 364/716; 365/231

# [56] References Cited U.S. PATENT DOCUMENTS

| A 031 A77 | 6/1077  | Shaw     | 307/460 Y |

|-----------|---------|----------|-----------|

| , ,       |         |          |           |

| 4,069,426 | 1/1978  | Hirasawa | 307/469   |

| 4,602,347 | 7/1986  | Koyama   | 365/231 X |

| 4,625,130 | 11/1986 | Murray   | 307/449 X |

| 4.675.556 | 6/1987  | Bazes    | 307/449 X |

### FOREIGN PATENT DOCUMENTS

0048834 3/1982 Japan.

Primary Examiner—Stanley D. Miller Assistant Examiner—David R. Bertelson Attorney, Agent, or Firm—Sughrue, Mion, Zinn, Macpeak & Seas

### [57] ABSTRACT

A decoder circuit for decoding different combinations of supplied original input address bits, comprising at least one predecode circuit responsive to the original input address bits for producing predecoded signal bits from the input address bits, and a plurality of decoder units including at least one decoder unit responsive to at least two different combinations of the original input address bits, wherein the decoder units comprises a decoder unit responsive to selected ones of the predecoded signal bits alone and a decoder unit responsive to at least one of the predecoded signal bits and at least one of the original input address bits.

### 4 Claims, 6 Drawing Sheets

AO ĀI AO AI AZ Ā3 AZ A3 A4. Ā5 A4 A5

FIG. 1 PRIOR ART

Aug. 27, 1991

FIG. 2A

|                              |                   | DECODER UNITS  | Α5 | Δ4 | Аз | Α2 | Α1 | Δο |

|------------------------------|-------------------|----------------|----|----|----|----|----|----|

| ADDRESS BITS                 | <u> </u>          | Do             | 0  | 0  | 0  | 10 | 0  | 10 |

|                              | 1                 | Dı             | 0  | 0  | 0  | 0  | 0  | 1  |

|                              | 4                 | D2             | 0  | 0  | 0  | -0 | 1  | X  |

|                              | 8                 | D3             | 0  | 10 | 0  | 0  | X  | X  |

|                              | 16                | D4             | 0  |    |    | X  | X  | X  |

|                              | 74                |                |    |    |    |    |    |    |

|                              |                   | D <sub>5</sub> | 0  |    |    | X  | X  | X  |

|                              | 36                | D6             |    | 0  | 0  | 0  | X  | X  |

|                              |                   | D7             | 1  | 0  | 0  | 1  | 0  | X  |

|                              | <del></del>       | D8             | 1  | 0  | 0  | 1  | ]  | 0  |

|                              | 40-               | D9             | 1  | 0  | 0  | 1  | 1  | 1  |

|                              | 48                |                |    |    |    |    |    |    |

|                              | 56                | Dю             |    |    | X  | 0  | X  | X  |

|                              | 6 <sub>2</sub> 64 | Dti            |    |    | X  |    |    | X  |

| X: INDERINATE BIT (= 1 or 0) |                   |                |    |    |    |    |    |    |

FIG. 2B

FIG. 3

## GATE ARRAY CIRCUIT FOR DECODING CIRCUITS

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

### FIELD OF THE INVENTION

The present invention relates to semiconductor devices and, more particularly, to a decoder circuit for use in a semiconductor memory device such as a read-only memory (ROM) or a random-access memory (RAM) which per se is well known in the art.

#### BACKGROUND OF THE INVENTION

A certain type of address decoder circuit for use in a semiconductor memory device such as a ROM or RAM 20 device consists of decoder units of a number less than the number of the possible combinations of the bits forming an address signal to be supplied to the decoder circuit. A typical example of such a decoder circuit is the one used for a ROM device which is incorporated in 25 a microprocessor to store microprogramming codes therein. Such a decoder circuit is directly responsive to the original input address signals so that, where each of the original input address signal consists of six bits, a maximum of  $2^6 = 64$  different combinations or sequen-  $_{30}$ ces of bits could be used in the decoder circuit. In comparison with such a large number of possible decoder outputs, the decoder circuit actually has a far smaller number of outputs such as, for example, only twelve outputs and, for this reason, requires the provision of a 35 disproportionately large number of active devices or transistors. Such a large number of active devices used in the decoder circuit inevitably results in correspondingly large amounts of capacitances provided by the diffusion regions of the individual active devices and 40 accordingly in reduction in the switching speed achievable of the decoder circuit.

An address decoder circuit of the described type thus sometimes uses a predecode scheme for the purpose of reducing the number of the transistors to be used in the 45 decoder circuit and thereby increasing the switching speed achievable of the circuit. The decoder circuit to implement such a scheme comprises a suitable number of 2-bit predecode circuits which are directly responsive to the original input signal bits. Each of the 2-bit 50 predecode circuits is operative to predecode neighboring two of the original input address bits by producing a total of four different logic ANDs of the two bits and the inverted versions of the two bits. The predecoded signal bits thus produced by the 2-bit predecode circuits 55 are used in some of the decoder units so that only one of the two original input address bits which have resulted in each of the predecoded signal bits is effective in the particular decoder unit with the other of the two bits virtually neglected from use. The result is accordingly 60 that there exits address bits which are not used in the decoder circuit. Such a scheme of the decoder circuit inevitably results in irregularities in the geometrical topology of the decoder circuit fabricated on a semiconductor chip.

It is, thus, an important object of the present invention to provide an improved decoder circuit which is composed of a minimized number of active devices to

achieve an increased switching speed of the decoder circuit.

It is another important object of the present invention to provide an improved predecode decoder circuit which effectively uses the original input address bits supplied to the decoder circuit.

### SUMMARY OF THE INVENTION

In accordance with one outstanding aspect of the present invention, there is provided a decoder circuit for decoding different combinations of supplied original input signal bits, comprising (a) at least one predecode circuit responsive to the original input signal bits for producing predecoded signal bits from the input signal bits, and (b) a plurality of decoder units including at least one decoder unit responsive to at least two different combinations of the original input signal bits, characterized in that the decoder units comprises a decoder unit responsive to the combination of at least one of the predecoded signal bits and at least one of the original input signal bits.

In accordance with another outstanding aspect of the present invention, there is provided a decoder circuit for decoding different combinations of supplied original input signal bits, comprising (a) at least one predecode circuit responsive to the original input signal bits for producing predecoded signal bits from the input signal bits, and (b) a plurality of decoder units including at least one decoder unit responsive to at least two different combinations of the original input signal bits, wherein the decoder units comprises a decoder unit responsive to selected ones of the predecoded signal bits alone and a decoder unit responsive to at least one of the predecoded signal bits and at least one of the original input signal bits.

In accordance with still another outstanding aspect of the present invention, there is provided a semiconductor decoder circuit including a plurality of decoder units for decoding different combinations of supplied original input signal bits, comprising (a) a first set of signal lines formed on a semiconductor structure, the first set of signal lines comprising a first group of signal lines connected to a source of a first predetermined voltage and a second group of signal lines connected to a source of a second predetermined voltage, (b) a second set of signal lines formed on a semiconductor structure and extending substantially at right angles to the first set of signal lines, the second set of signal lines comprising a third group of signal lines respectively responsive to predecoded signal bits predecoded from selected ones of the original input signal bits and a fourth group of signal lines respectively responsive to selected ones of the original input signal bits (c) a first set of field-effect transistors selectively connected in series to the source of the first predetermined voltage along each of the signal lines of the first group, each of the first set of field-effect transistors being of one channel conductivity type, and (d) a second set of field-effect transistors selectively connected in parallel to the source of the second predetermined voltage along each of the signal lines of the second group, each of the second set of field-effect transistors being of the channel conductivity type opposite to the one channel conductivity type, each of the second set of field-effect transis-65 tors having their gates selectively connected to the signal lines of the third and fourth groups, (e) the first set of field-effect transistors arranged along each of the signal lines of the first group and the second set of field-

effect transistors arranged along each of the signal lines of the second group implementing each of the decoder units.

### BRIEF DESCRIPTION OF THE DRAWINGS

The drawbacks of a prior-art address decoder circuit and the features and advantages of a decoder circuit according to the present invention will be more clearly understood from the following description taken in conjunction with the accompanying drawings in which: 10

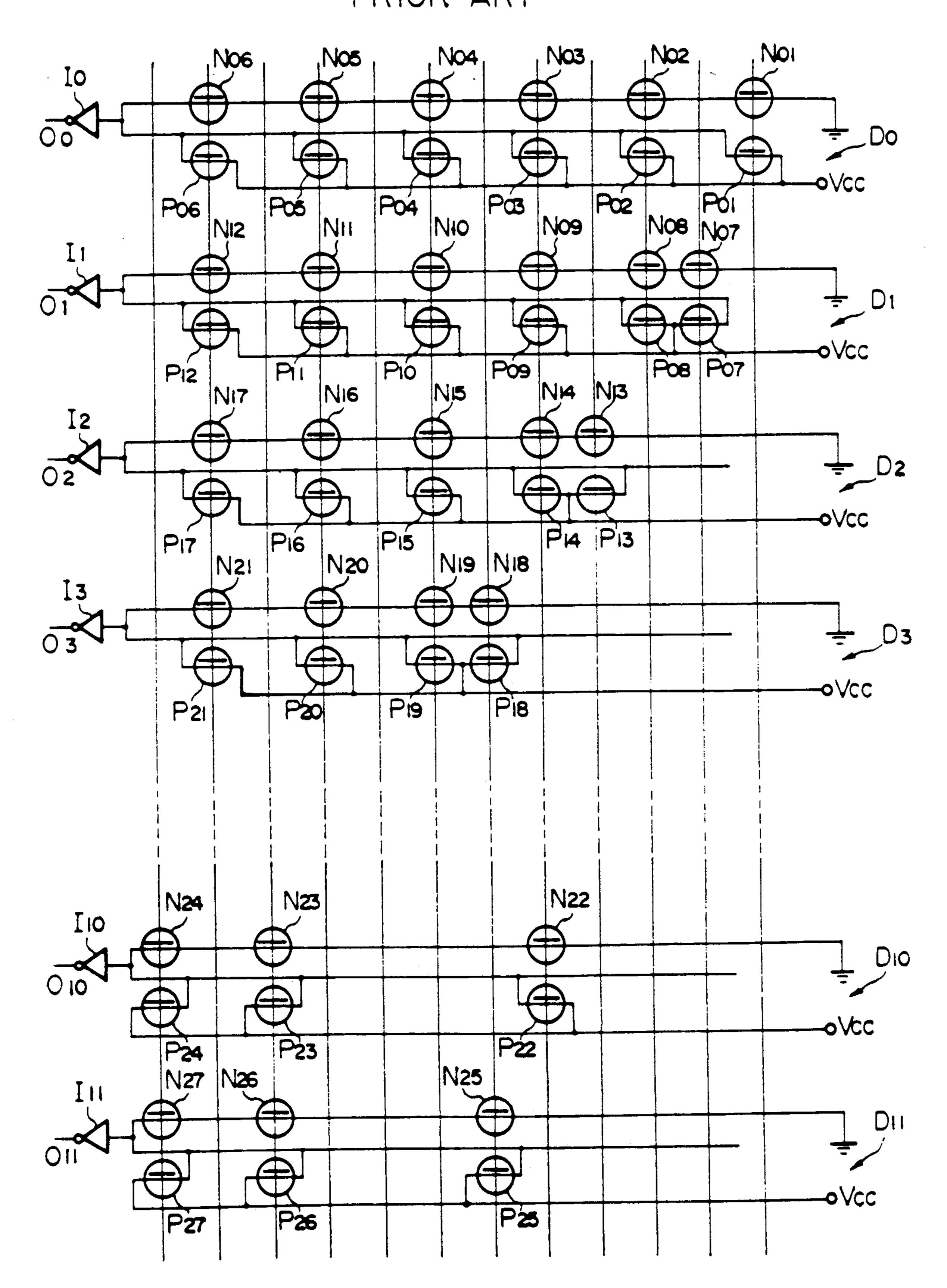

FIG. 1 is a circuit diagram showing a typical known example of an address decoder circuit used for a ROM device storing microprogramming codes in a microprocessor;

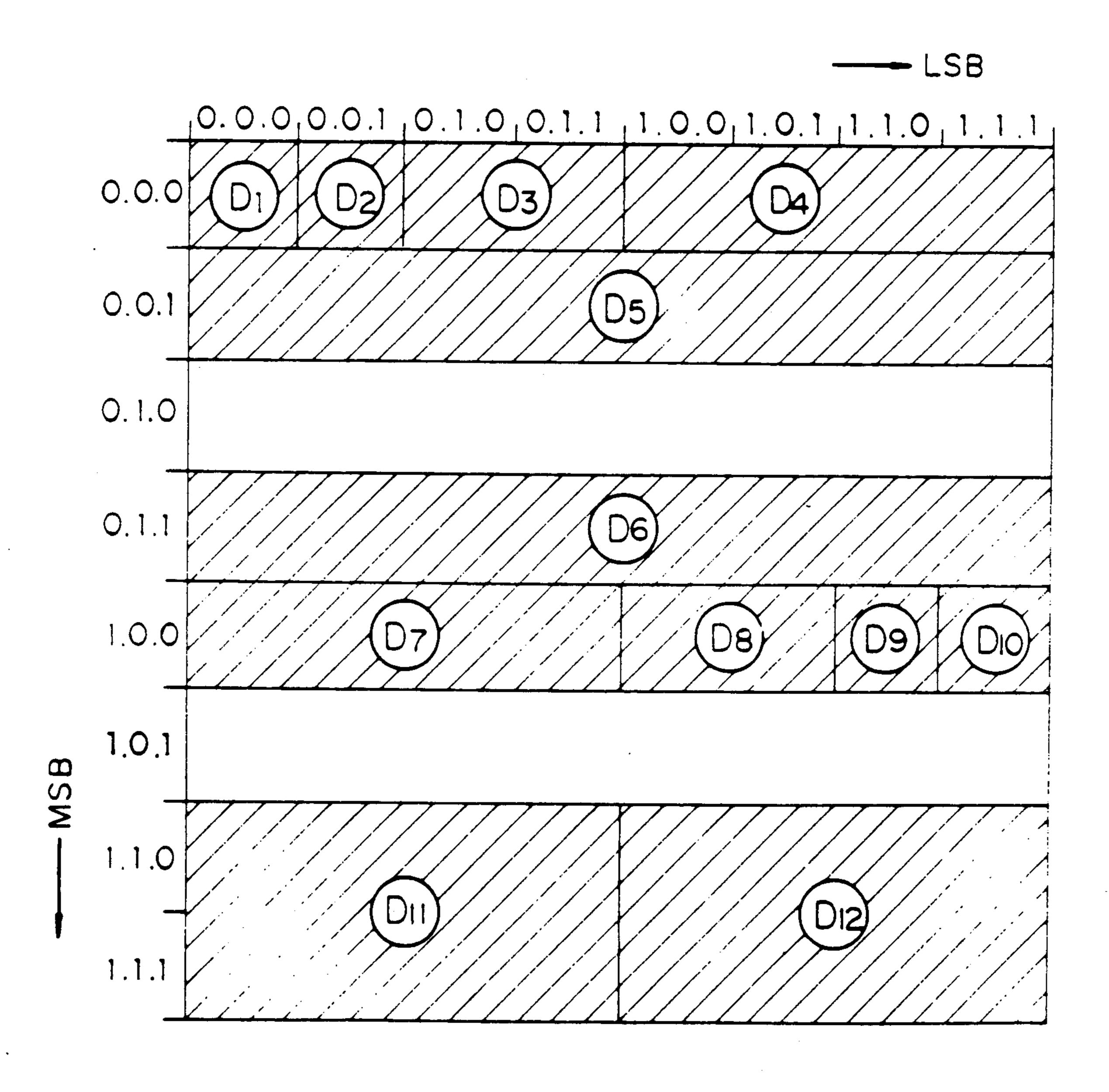

FIGS. 2A and 2B are address maps depicting the 15 schedules in accordance with which the decoder units of the decoder circuit shown in FIG. 1 are to produce output signal bits in response to the original address bits input to the decoder circuit, FIG. 2A showing such schedules in non-matrix form and FIG. 2B showing 20 similar schedules in matrix form;

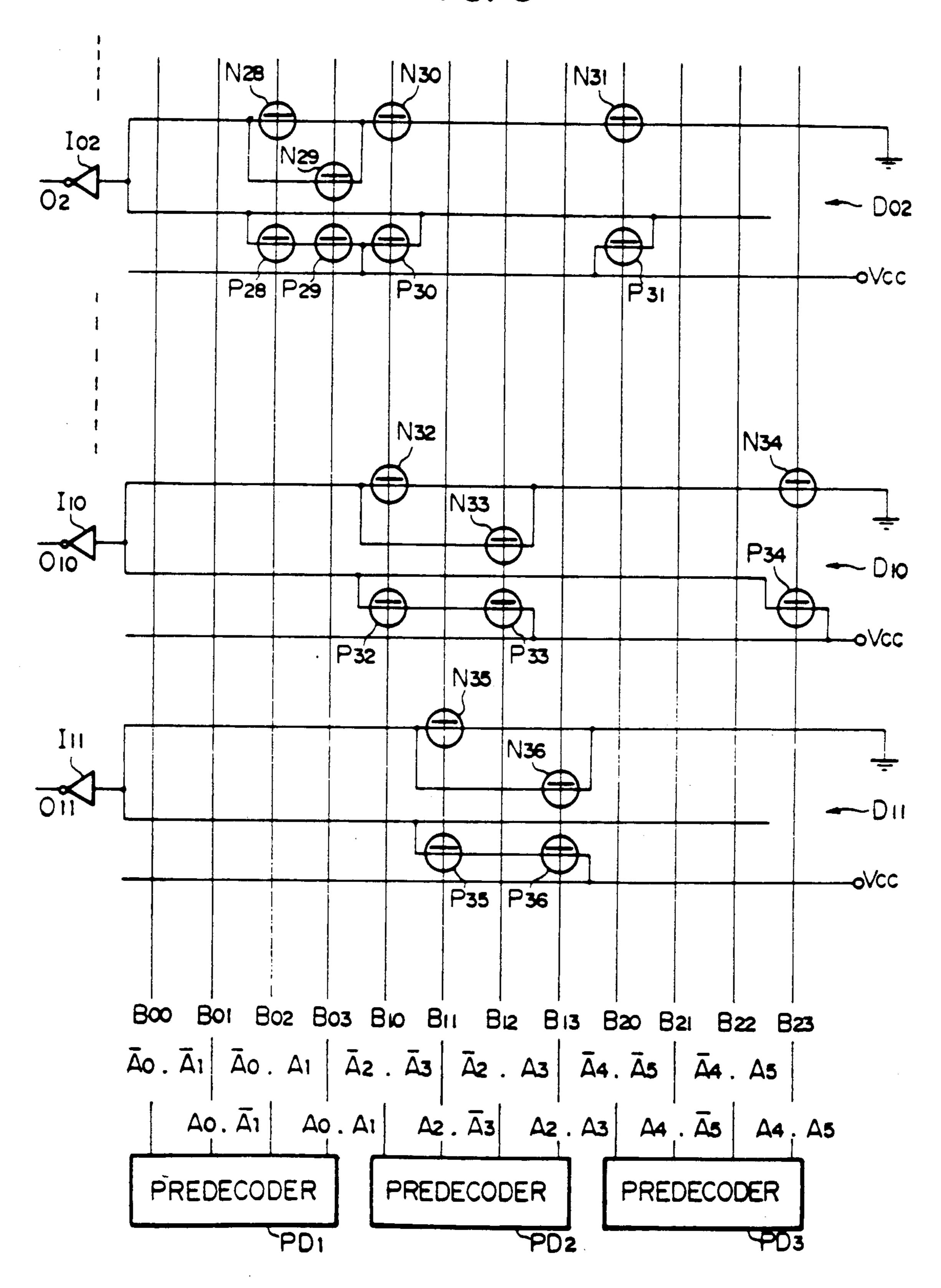

FIG. 3 is a circuit diagram showing a preferred example of an address decoder circuit which implements a two-bit predecode scheme;

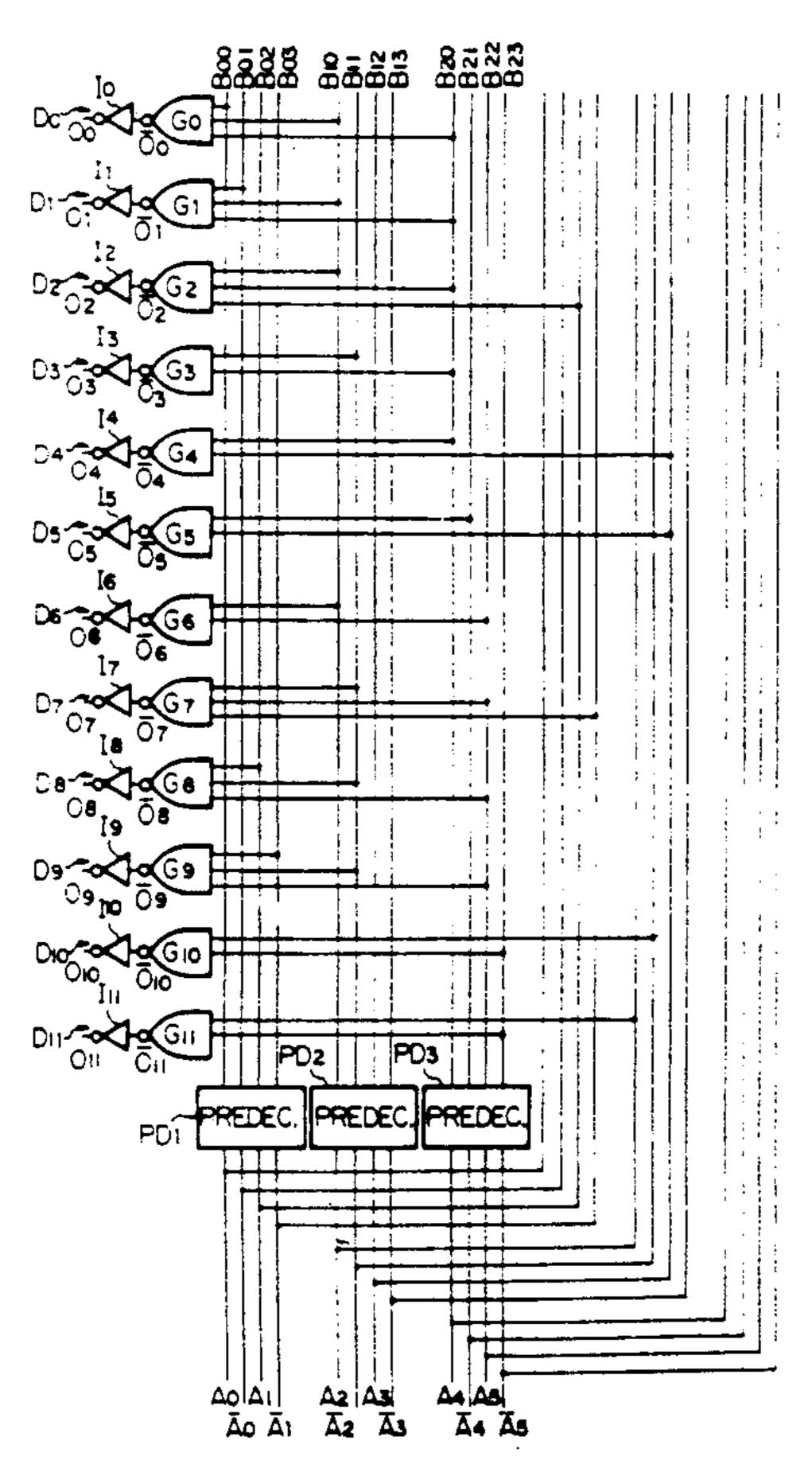

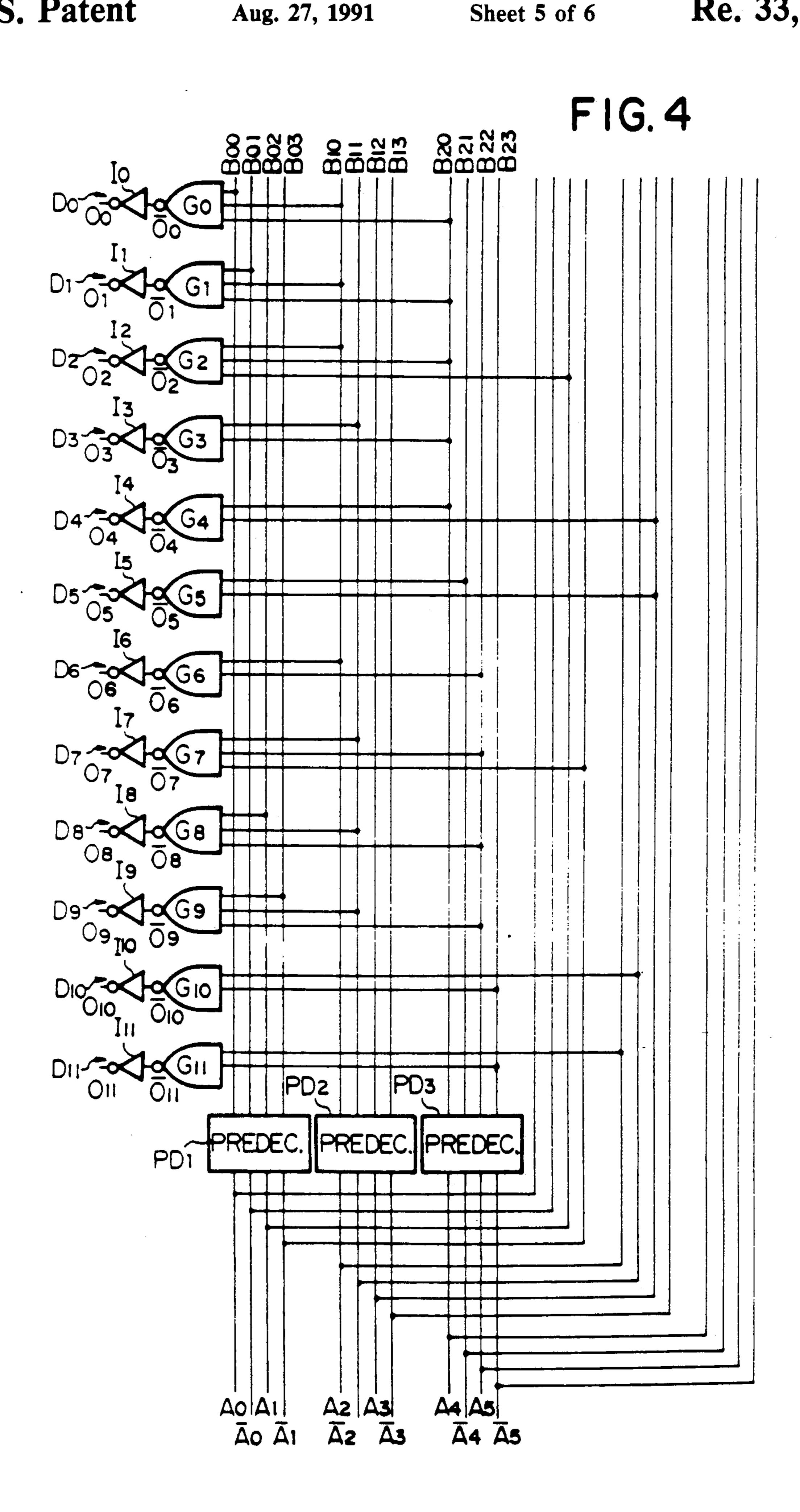

FIG. 4 is a schematic diagram showing the logical 25 configuration of a preferred embodiment of a decoder circuit according to the present invention; and

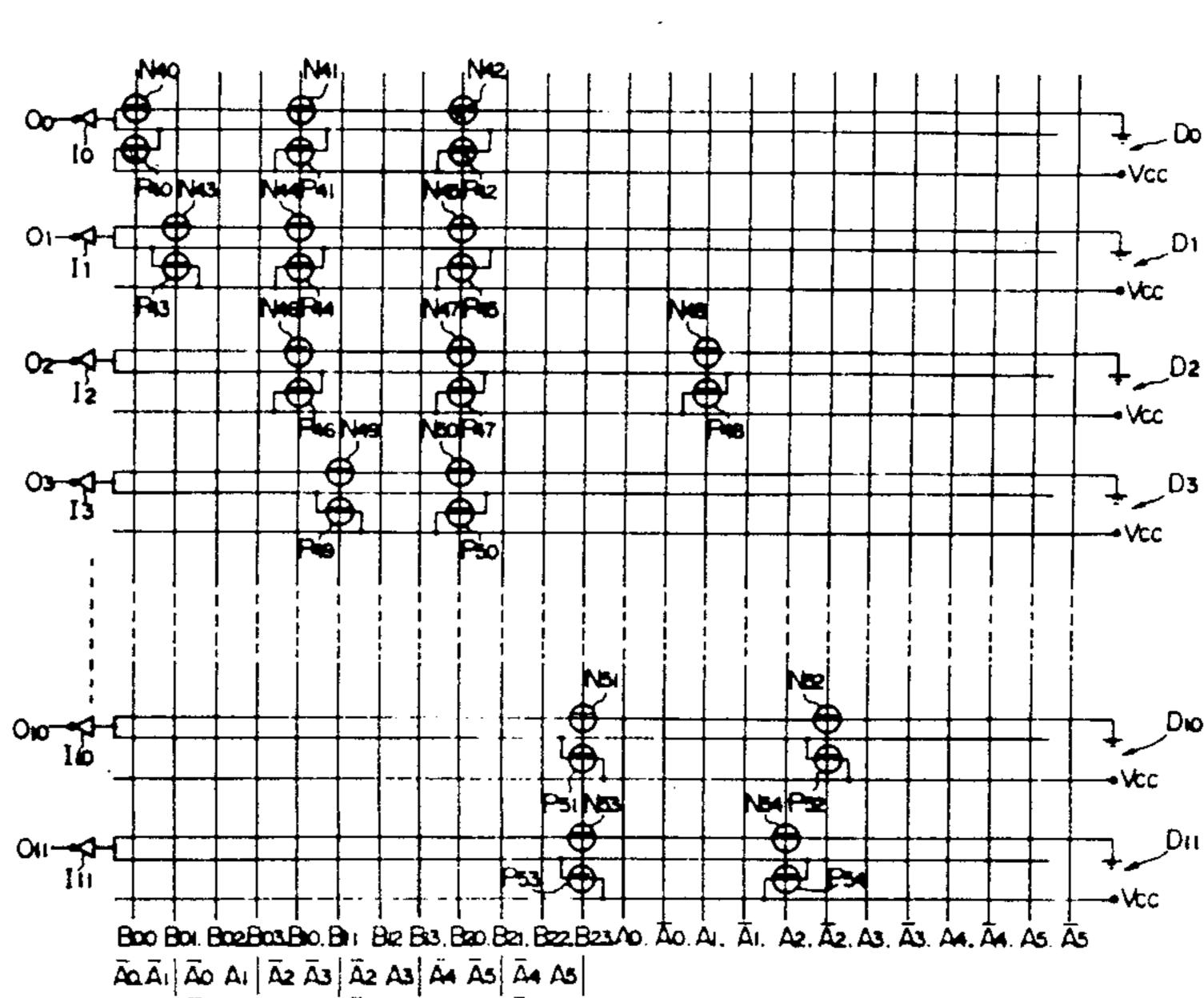

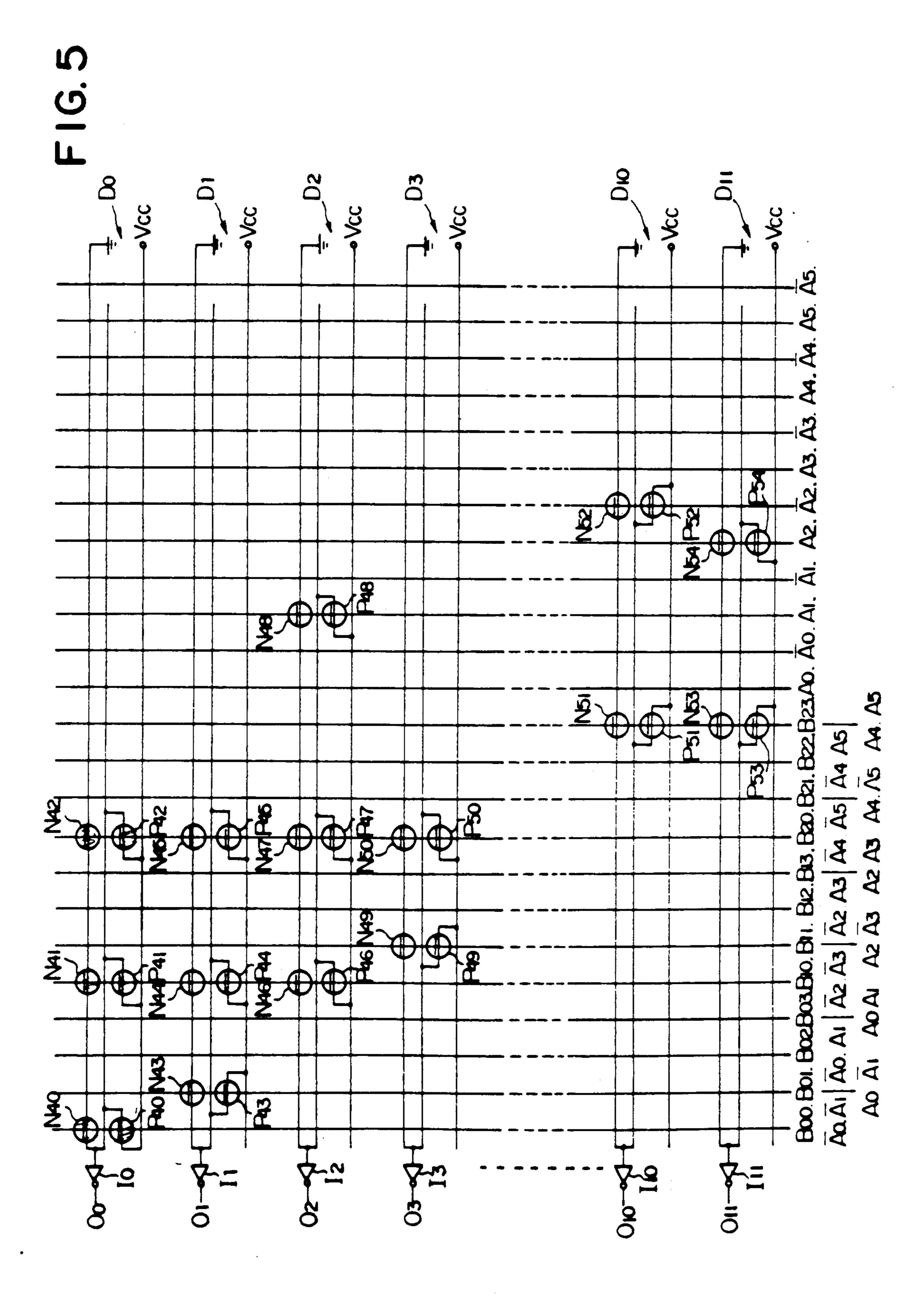

FIG. 5 is a circuit diagram showing a preferred example of the circuit arrangement implementing the logical configuration of the embodiment illustrated in FIG. 4. 30

#### DESCRIPTION OF THE PRIOR ART

As has been noted at the outset of the description, a certain type of address decoder circuit for use in a semiconductor memory device consists of decoder units of a 35 number less than the number of the possible combinations of the bits forming an address signal to be supplied to the decoder circuit. FIG. 1 of the drawings shows a typical example of such a decoder circuit. The decoder circuit herein shown is used for a ROM device incorpo- 40 rated in a microprocessor for storing microprogramming codes therein and is by way of example assumed to be designed for use with a 12-word ROM device (not shown). The decoder circuit is made up of a number of n-channel field-effect transistors respectively denoted 45 by N<sub>01</sub> to N<sub>27</sub> and p-channel field-effect transistors respectively denoted by P<sub>01</sub> to P<sub>27</sub>. These n-channel and p-channel  $N_{01}$  to  $N_{27}$  and  $P_{01}$  to  $P_{27}$  are arranged to form twelve decoder units  $D_0, D_1, D_2, \dots D_{11}$  each including a plurality of full CMCS (complementary metal-oxide- 50 semiconductor) inverters implemented by the fieldeffect transistors  $N_{01}$  to  $N_{27}$  and  $P_{01}$  to  $P_{27}$ . The decoder units  $D_0, D_1, D_2, \ldots D_{11}$  further include logic inverters Io to I11, respectively, which provide output address bits of the individual decoder units  $D_0$  to  $D_{11}$ , respectively. 55 The decoder units  $D_0$  to  $D_{11}$  are responsive directly to original, viz., supplied address signals through a total of twelve signal input lines which consist of six lines respectively responsive to supplied address bits A<sub>0</sub> to A<sub>5</sub> and six lines respectively responsive to the inverted 60 versions  $\overline{A}_0$  to  $\overline{A}_5$  of the supplied address bits  $A_0$  to  $A_5$ . Each of the decoder units D<sub>0</sub> to D<sub>11</sub> consists of n-channel MOS field-effect transistors connected in series between ground and each of the logic inverters I<sub>0</sub> to I<sub>11</sub> and p-channel MOS field-effect transistors connected in 65 parallel between a source of a supply voltage  $V_{CC}$  and • each of the inverters I<sub>0</sub> to I<sub>11</sub> as shown. The logic inverters I<sub>0</sub> to I<sub>11</sub> of the decoder units D<sub>0</sub> to D<sub>11</sub> are respec-

tively connected to the word lines of the memory cell array (not shown).

The n-channel field-effect transistors  $N_{01}$  to  $N_{27}$  and p-channel field-effect transistors P<sub>01</sub> to P<sub>27</sub> forming the decoder circuit are arranged so that the individual decoder units D<sub>0</sub> to D<sub>11</sub> of the decoder circuit are operative to produce output address bits  $O_1$  to  $O_{11}$  in response to the supplied address bits  $A_0$  to  $A_5$  and  $\overline{A}_0$  to  $\overline{A}_5$  in accordance with the schedules represented by an address map depicted in non-matrix form in FIG. 2A and in matrix form in FIG. 2B. The sign "X" in the nonmatrix address map shown in FIG. 2A indicates an indeterminate or variable bit which may be of either logic "0" or "1" value. In the matrix address map shown in FIG. 2B, the axis of abscissa represents binary digits 000, 001, 011, . . . 111 (increasing from left to right) coded by the lower three of the six supplied address bits  $A_0, A_1, A_2, \ldots A_5$  while the axis of ordinate represents binary digits (000, 001, 011, . . . 111 (increasing downwardly) coded by the upper three of the address bits A<sub>0</sub> to  $A_5$ . As will be seen from these address maps, each of the decoder units  $D_2$  and  $D_7$  of the address decoder circuit is operable for selecting one of two different sequences of address bits 000010 and 000011 (D<sub>2</sub>) or 100100 and 100101 (D<sub>7</sub>). On the other hand, each of the decoder units D<sub>3</sub> and D<sub>6</sub> is operable for selecting any one of four different sequences of address bits 000000, 00001, 000010 and 000011 (D<sub>3</sub>) or 100000, 100001, 100010, 1000011 (D<sub>6</sub>). Furthermore, each of the decoder units D<sub>4</sub>, D<sub>5</sub>, D<sub>11</sub> and D<sub>12</sub> is operable for selecting any one of a total of eight different sequences of address bits.

When an original input signal  $A_0A_1A_2A_3A_4A_5$  in the form of, for example 00001X is supplied to the decoder circuit shown in FIG. 1, all the n-channel field-effect transistors  $N_{13}$ ,  $N_{14}$ ,  $N_{15}$ ,  $N_{16}$  and  $N_{17}$  forming part of the decoder unit  $D_2$  are turned on and all the associated p-channel field-effect transistors  $P_{13}$ ,  $P_{14}$ ,  $P_{15}$ ,  $P_{16}$  and  $P_{17}$  of the decoder unit  $D_2$  remain in non-conduction states. Under this condition, the decoder unit  $D_2$  produces a logic "1" bit at the output terminal of the inverter  $I_2$  as the output signal bit  $O_2$  of the decoder unit  $D_2$ .

The known address decoder circuit thus constructed is directly responsive to the original input address signals, each of which consists of six bits yields a maximum of  $2^6 = 64$  different combinations or sequences of bits. In comparison with such a large number of possible decoder outputs, the decoder circuit actually has only twelve outputs and, as a corollary of this, necessitates a disproportionately large number of active devices or transistors. As a matter of fact, the decoder unit D<sub>0</sub> which uses all the supplied address bits  $A_0$ ,  $A_1$ ,  $A_2$ , ... As available is composed of a total of twelve transistors which consist of the three series connected n-channel field-effect transistors N<sub>01</sub> to N<sub>06</sub> and the three parallel connected p-channel field-effect transistors No1 to No6 and P<sub>01</sub> to P<sub>06</sub>. Even each of the decoder units D<sub>10</sub> and D<sub>11</sub> (as well the decoder units D<sub>5</sub> and D<sub>6</sub> not shown) which uses the minimum number of input address bits is composed of a total of six field-effect transistors N<sub>22</sub> to  $N_{24}$  and  $P_{22}$  to  $P_{24}$  or  $N_{25}$  to  $N_{27}$  and  $P_{25}$  to  $P_{27}$ . Such a large number of field-effect transistors used in the decoder circuit inevitably results in correspondingly large amounts of capacitances provided by the source and drain diffusion regions of the transistors and accordingly in reduction in the switching speed achievable of the decoder circuit. This drawback of a known address

4

decoder circuit is pronounced in a static decoder circuit implemented by full CMOS configuration as in the case of the prior-art decoder circuit shown in FIG. 1.

Whichever of NAND-based logics or NOR-based logics may be adopted in such a full CMOS address 5 decoder circuit, either the n-channel field-effect transistors or the p-channel field-effect transistors implementing the decoder circuit must be connected in series. The larger the number of the series connected field-effect transistors, the lower the performance efficiencies of 10 the individual transistors and accordingly the lower the switching speed of the entire decoder circuit.

Thus, an address decoder circuit of the type shown in FIG. 1 sometimes uses a predecode scheme for the purpose of reducing the number of the transistors to be 15 used in the decoder circuit and thereby increasing the switching speed achievable of the circuit. FIG. 3 of the drawings shows a preferred example of an address decoder circuit which implements such a predecode scheme.

The decoder circuit herein shown is arranged to produce output address bits  $O_0$  to  $O_{11}$  responsive to original input address bits  $A_0, A_1, A_2, \ldots A_5$  also in accordance with the schedules represented by the address map of FIGS. 2A or 2B. The decoder circuit is also assumed to 25 comprise a total of twelve decoder units including the shown decoder units  $D_2$ ,  $D_{10}$  and  $D_{11}$  which are formed by n-channel field-effect transistors N<sub>28</sub> to N<sub>36</sub> and pchannel field-effect transistors P<sub>28</sub> to P<sub>36</sub> and which include logic inverters including the inverters I<sub>2</sub>, I<sub>10</sub> and 30 I<sub>11</sub>, respectively. The decoder circuit further comprises first, second and third 2-bit predecode circuits PD<sub>1</sub>, PD<sub>2</sub> and PD<sub>3</sub> which are directly responsive to the original input signal bits  $A_0$ ,  $A_1$ ,  $A_2$ , . . .  $A_5$ . Each of these 2-bit predecode circuits PD<sub>1</sub>, PD<sub>2</sub> and PD<sub>3</sub> is operative 35 to predecode neighboring two bits (A<sub>2i</sub> and A<sub>2i+1</sub> where i = 0, 1 or 2) of the supplied original input address bits  $A_0$ ,  $A_1$ ,  $A_2$ , ...  $A_5$ . The first 2-bit predecode circuit PD<sub>1</sub> is responsive to the lower two  $A_0$  and  $A_1$  of the original input address bits  $A_0, A_1, \ldots A_5$  to produce 40 four different output bits B<sub>00</sub>, B<sub>01</sub>, B<sub>02</sub> and B<sub>03</sub> respectively representative of the logic ANDs A<sub>0</sub>·A<sub>1</sub>, A<sub>0</sub>·A<sub>1</sub>,  $A_0 \cdot A_1$  and  $A_0 \cdot A_1$  of the input bits  $A_0$  and  $A_1$  and the respective inverted versions thereof. The second 2-bit predecode circuit PD<sub>2</sub> is responsive to the intermediate 45 two  $A_2$  and  $A_3$  of the original input address bits  $A_0$  to A<sub>5</sub> to produce four different output bits B<sub>10</sub>, B<sub>11</sub>, B<sub>12</sub> and B<sub>13</sub> respectively representative of the logic ANDs  $\overline{A_2} \cdot \overline{A_3}$ ,  $\overline{A_2} \cdot \overline{A_3}$ ,  $\overline{A_2} \cdot \overline{A_3}$  and  $\overline{A_2} \cdot \overline{A_3}$  of the input bits  $\overline{A_2}$  and A<sub>3</sub> and the respective inverted versions thereof. The 50 third 2-bit predecode circuit PD3 is responsive to the intermediate two A<sub>4</sub> and A<sub>5</sub> of the original input address bits A<sub>0</sub> to A<sub>5</sub> to produce four different output bits B<sub>20</sub>, B<sub>21</sub>, B<sub>22</sub> and B<sub>23</sub> respectively representative of the logic ANDs  $\overline{A}_4 \cdot \overline{A}_5$ ,  $A_4 \cdot \overline{A}_5$  and  $\overline{A}_4 \cdot \overline{A}_5$  of the input bits  $A_4$  and 55 A<sub>5</sub> and the respective inverted versions thereof.

When an original input signal  $A_0A_1A_2A_3A_4A_5$  in the form of, for example, 00001X is supplied to the decoder circuit thus constructed and arranged, the output bits  $B_{02}$ ,  $B_{03}$ ,  $B_{10}$  and  $B_{20}$  respectively representative of the 60 logic ANDs  $\overline{A}_0 \cdot A_1$ ,  $A_0 \cdot A_1$ ,  $\overline{A}_2 \cdot \overline{A}_3$  and  $\overline{A}_4 \cdot \overline{A}_5$  of the supplied address bits assume logic "X", "X", "1" and "1" states. Of the field-effect transistors forming part of the decoder unit.  $D_2$ , for example, of the circuit shown in FIG. 3, the series connected n-channel field-effect transistors  $N_{30}$  and  $N_{31}$  and one of the parallel connected n-channel field-effect transistors  $N_{28}$  and  $N_{29}$  are thus turned on and the series connected p-channel field-

6

effect transistors  $P_{30}$  and  $P_{31}$  and one of the parallel connected p-channel field-effect transistors  $P_{28}$  and  $P_{29}$  are held in non-conduction states. Under this condition, the decoder unit  $D_2$  produces a logic "1" signal at the output terminal of the inverter  $I_2$  as the output signal bit  $O_2$  of the decoder unit  $D_2$  as in the prior-art address decoder circuit shown in FIG. 1.

In the decoder units D<sub>2</sub> of the circuit shown in FIG. 3, the predecoded signal bits  $B_{02}$  and  $B_{03}$  produced by the first 2-bit predecode circuit PD<sub>1</sub> are supplied to the parallel combination of the n-channel field-effect transistors N<sub>28</sub> and N<sub>29</sub> of the decoder unit D<sub>2</sub> to produce a logic sum or OR, viz.,  $(\overline{A_0} \cdot A_1 + A_0 \cdot A_1) = A_1$  of the supplied bits. The predecoded signal bits B<sub>02</sub> and B<sub>03</sub> are also supplied to the series combination of the p-channel field-effect transistors P<sub>28</sub> and P<sub>29</sub> of the decoder unit D<sub>2</sub> to produce a logic OR, viz.,  $(A_0 \cdot A_1) + (A_0 \cdot A_1) = A_1$ of the supplied bits. Likewise, the predecoded signal bits B<sub>10</sub> and B<sub>12</sub> produced by the second 2-bit predecode 20 circuit PD<sub>2</sub> are supplied to the parallel connected nchannel field-effect transistors N<sub>32</sub> and N<sub>33</sub> and series connected p-channel field-effect transistors P<sub>32</sub> and P<sub>33</sub> of the decoder unit  $D_{10}$  to produce a logic OR, viz.,  $(\overline{A}_2 \cdot \overline{A}_3 + A_2 \cdot A_3) = \overline{A}_2$  and a logic OR, viz.,  $(A_2 \cdot A_3)$ - $+(\bar{A}_2\cdot A_3) = A_2$  of the supplied bits. In the decoder unit  $D_{11}$ , furthermore, a logic OR, viz.,  $(A_2 \cdot \overline{A}_3 + A_2 \cdot A_3)$ = A<sub>2</sub> is produced in response to the predecoded signal bits  $B_{10}$  and  $B_{12}$  produced by the second 2-bit predecode circuit PD<sub>2</sub>.

In the decoder circuit shown in FIG. 3, the neighboring two  $A_{2i}$  and  $A_{2i}$  of the supplied original input address bits  $A_0$ ,  $A_1$ ,  $A_2$ , . . .  $A_5$  are thus predecoded by each of the of 2-bit predecode circuits PD1, PD2 and PD<sub>3</sub> into signal bits  $B_{00}$  to  $B_{23}$  each of which is provided by the logic AND of the supplied address bit  $A_{2i}$  or the inverted version thereof and the supplied address bit  $A_{2i+1}$  or the inverted version thereof. The predecoded signal bits  $B_{00}$  to  $B_{23}$  are used in the decoder units  $D_2$ ,  $D_3$ ,  $D_4$ ,  $D_5$ ,  $D_6$ ,  $D_7$ ,  $D_{10}$  and  $D_{11}$  so that only one of the two original input address bits such as, for example, the address bit A<sub>1</sub> for the decoder unit D<sub>2</sub> or the address bit  $A_2$  for the decoder unit  $D_{10}$  or  $D_{11}$  is effective in the particular decoder unit. This means that the other of the two bits  $A_{2i}$  and  $A_{2i}$  is virtually neglected from use. Such a scheme of the decoder circuit results in irregularities in the geometrical topology of the decoder circuit fabricated on a semiconductor chip because of the fact that the individual decoder units  $D_0$ ,  $D_1$ ,  $D_2$ , . . . D<sub>11</sub> each of which should be configured by active devices and interconnections patterned with irregularity will differ in topology from one circuit to another.

The present invention contemplates elimination of such a problem inherent in a two-bit predecode decoder circuit of the described nature. Accordingly, the goal of the present invention is to provide an improved decoder circuit which is composed of a minimized number of active devices to achieve an increased switching speed of the decoder circuit and which effectively uses the original input address bits supplied to the decoder circuit, as previously noted.

### DESCRIPTION OF THE PREFERRED EMBODIMENT

FIG. 4 of the drawings shows the logical configuration of a preferred embodiment of a decoder circuit according to the present invention. The decoder circuit herein shown is also assumed to be designed for use with a 12-word ROM device (not shown) by way of

example and thus comprises twelve decoder units  $D_0$ ,  $D_1$ ,  $D_2$ , ...  $D_{11}$ . The decoder units  $D_0$ ,  $D_1$ ,  $D_2$ , ...  $D_{11}$  in turn comprise two-input and three-input logic NAND gates  $G_0$ ,  $G_1$ ,  $G_2$ , ...  $G_{11}$ , respectively, and logic inverters  $I_0$ ,  $I_1$ ,  $I_2$ , ...  $I_{11}$  respectively connected to the output terminals of the NAND gates  $G_0$ ,  $G_1$ ,  $G_2$ , ...  $G_{11}$  to provide output address bits of the individual decoder units  $D_0$  to  $D_{11}$ .

The decoder circuit embodying the present invention further comprises first, second and third 2-bit predecode circuits PD<sub>1</sub>, PD<sub>2</sub> and PD<sub>3</sub> which are directly responsive to original input signal bits  $A_0$ ,  $A_1$ ,  $A_2$ , . . .  $A_5$  and the inverted versions  $A_0$ ,  $\overline{A}_1$ ,  $\overline{A}_2$ , ...  $\overline{A}_5$ , respectively, thereof. Each of these 2-bit predecode circuits PD<sub>1</sub>, PD<sub>2</sub> and PD<sub>3</sub> is operative to predecode neighbor- 15 ing two bits  $A_{2i}$  and  $A_{2i+1}$  of the supplied original input address bits  $A_0, A_1, A_2, \ldots A_5$  similarly to their counterparts in the decoder circuit described with reference to FIG. 3. Thus, the first 2-bit predecode circuit PD<sub>1</sub> is responsive to the lower two A<sub>0</sub> and A<sub>1</sub> of the original 20 input address bits  $A_0, A_1, \ldots A_5$  to produce four different output bits  $B_{00}$ ,  $B_{01}$ ,  $B_{02}$  and  $B_{03}$  respectively representative of the logic ANDs  $\overline{A_0} \cdot \overline{A_1}$ ,  $A_0 \cdot \overline{A_1}$ ,  $A_0 \cdot \overline{A_1}$ ,  $A_0 \cdot A_1$  and  $A_0 \cdot A_1$  of the input address bits  $A_0$  and  $A_1$  and the respective inverted versions thereof. The second 25 2-bit predecode circuit PD2 is responsive to the intermediate two A<sub>2</sub> and A<sub>3</sub> of the original input address bits  $A_0$  to  $A_5$  to produce four different output bits  $B_{10}$ ,  $B_{11}$ , B<sub>12</sub> and B<sub>13</sub> respectively representative of the logic ANDs  $A_2 \cdot \overline{A_3}$ ,  $A_2 \cdot \overline{A_3}$ ,  $\overline{A_2} \cdot A_3$  and  $A_2 \cdot A_3$  of the input 30 address bits A<sub>2</sub> and A<sub>3</sub> and the respective inverted versions thereof. The third 2-bit predecode circuit PD<sub>3</sub> is responsive to the intermediate two A<sub>4</sub> and A<sub>5</sub> of the original input address bits A<sub>0</sub> to A<sub>5</sub> to produce four different output bits B<sub>20</sub>, B<sub>21</sub>, B<sub>22</sub>and B<sub>23</sub> respectively 35 representative of the logic ANDs  $\overline{A_4}\cdot\overline{A_5}$ ,  $A_4\cdot\overline{A_5}$ ,  $\overline{A_5}\cdot\overline{A_5}$ and A<sub>4</sub>·A<sub>5</sub> of the input address bits A<sub>4</sub> and A<sub>5</sub> and the respective inverted versions thereof. The decoder circuit thus comprising the twelve NAND gates Go to G11 are responsive to the original input address bits  $A_0$  to 40 As and the respective inverted versions of these bits and to the signal bits B<sub>00</sub> to B<sub>23</sub> through a total of twelve input lines as shown. The individual decoder units Do to D<sub>11</sub> are implemented by full CMOS configuration and are operative to produce output address bits O<sub>1</sub> to O<sub>11</sub> in 45 response to the supplied address bits  $A_0$  to  $A_5$  and  $\overline{A}_0$  to A<sub>5</sub> basically also in accordance with the schedules represented by the address maps depicted in FIGS. 2A and 2B.

FIG. 5 shows an example of the transistor circuit 50 arrangement implementing the logical configuration of the decoder circuit thus constructed.

As shown, the three-input NAND gate G<sub>0</sub> of the decoder unit D<sub>0</sub> comprises three n-channel field-effect transistors N<sub>40</sub>, N<sub>41</sub> and N<sub>42</sub> connected in series between 55 B<sub>22</sub>. the logic inverter I<sub>0</sub> and ground and three p-channel field-effect transistors P<sub>40</sub>, P<sub>41</sub> and P<sub>42</sub> connected in three parallel between the logic inverter I<sub>0</sub> and a source of a supply voltage V<sub>CC</sub>. The field-effect transistors N<sub>40</sub> and chan chan bit B<sub>00</sub>, the field-effect transistors N<sub>41</sub> and P<sub>41</sub> have their gates responsive to the preselected signal bit B<sub>10</sub>, and the field-effect transistors N<sub>42</sub> and P<sub>43</sub> have their gates responsive to the predecoded signal bit B<sub>20</sub>.

The three-input NAND gate G<sub>1</sub> of the decoder unit 65 D<sub>1</sub> comprises three n-channel field-effect transistors N<sub>43</sub>, N<sub>44</sub> and N<sub>45</sub> connected in series between the logic inverter I<sub>1</sub> and ground and three p-channel field-effect

8

transistors  $P_{43}$ ,  $P_{44}$  and  $P_{45}$  connected in parallel between the logic inverter  $I_1$  and the source of the supply voltage  $V_{CC}$ . The field-effect transistors  $N_{43}$  and  $P_{43}$  have their gates responsive to the predecoded signal bit  $B_{01}$ , the field-effect transistors  $N_{44}$  and  $P_{44}$  have their gates responsive to the predecoded signal bit  $B_{10}$ , and the field-effect transistors  $N_{45}$  and  $P_{45}$  have their gates responsive to the predecoded signal bit  $B_{20}$ .

The three-input NAND gate G<sub>2</sub> of the decoder unit D<sub>2</sub> comprises three n-channel field-effect transistors N<sub>46</sub>, N<sub>47</sub> and N<sub>48</sub> connected in series between the logic inverter I<sub>2</sub> and ground and three p-channel field-effect transistors P<sub>46</sub>, P<sub>47</sub> and P<sub>48</sub> connected in parallel between the logic inverter I<sub>2</sub> and the source of the supply voltage V<sub>CC</sub>. The field-effect transistors N<sub>46</sub> and P<sub>46</sub> have their gates responsive to the predecoded signal bit B<sub>10</sub>, the field-effect transistors N<sub>47</sub> and P<sub>47</sub> have their gates responsive to the predecoded signal bit B<sub>20</sub>, and the field-effect transistors N<sub>48</sub> and P<sub>48</sub> have their gates responsive to the original input address bit A<sub>1</sub>.

The two-bit NAND gate G<sub>3</sub> of the decoder unit D<sub>3</sub> comprises two n-channel field-effect transistors N<sub>49</sub> and N<sub>50</sub> connected in series between the logic inverter I<sub>3</sub> and ground and two p-channel field-effect transistors P<sub>49</sub> and P<sub>50</sub> connected in parallel between the logic inverter I<sub>3</sub> and the source of the supply voltage V<sub>CC</sub>. The field-effect transistors N<sub>49</sub> and P<sub>49</sub> have their gates responsive to the predecoded signal bit B<sub>11</sub> and the field-effect transistors N<sub>50</sub> and P<sub>50</sub> have their gates responsive to the predecoded signal bit B<sub>20</sub>.

As will be seen from FIG. 4, each of the two-input NAND gates G<sub>4</sub>, G<sub>5</sub> and G<sub>6</sub> of the decoder units D<sub>4</sub>, D<sub>5</sub> and D<sub>6</sub>, respectively, comprises two n-channel fieldeffect transistors connected in series between each of the logic inverters I4, I5 and I6 and ground and two p-channel field-effect transistors connected in parallel between each of the logic inverters I4, I5 and I6 and the source of the supply voltage  $V_{CC}$ . One pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>4</sub> have their responsive to the predecoded signal bit B<sub>20</sub> and the other pair of n-channel and p-channel fieldeffect transistors of the NAND gate G4 have their gates responsive to the original input address bit A3. One pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>5</sub> have their gates responsive to the predecoded signal bit B<sub>21</sub> and the other pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>5</sub> have their gates also responsive to the original input address bit A<sub>3</sub>. Furthermore, one pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>6</sub> have their gates responsive to the predecoded signal bit B<sub>10</sub> and the other pair of n-channel and pchannel field-effect transistors of the NAND gate G<sub>5</sub> have their gates responsive to the predecoded signal bit

As will be further seen from FIG. 4, each of the three-input NAND gates G<sub>7</sub>, G<sub>8</sub> and G<sub>9</sub> of the decoder units D<sub>7</sub>, D<sub>8</sub> and D<sub>9</sub>, respectively, comprises three n-channel field-effect transistors connected in series between each of the logic inverters I<sub>7</sub>, I<sub>8</sub> and I<sub>9</sub> and ground and two p-channel field-effect transistors connected in parallel between each of the logic inverters I<sub>7</sub>, I<sub>8</sub> and I<sub>9</sub> and the source of the supply voltage V<sub>CC</sub>. One pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>7</sub> have their gates responsive to the predecoded signal bit B<sub>11</sub>, another pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>7</sub> have their gates responsive to the predecoded signal bit

B<sub>22</sub>, and the remaining pair of n-channel and p-channel field-effect transistors of the NAND gate G7 have their gates responsive to the inverted address bit  $\overline{A}_1$ . One pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>8</sub> have their gates responsive to the 5 predecoded signal bit B<sub>02</sub>, another pair of n-channel and p-channel field-effect transistors of the NAND gate G8 have their gates responsive to the predecoded signal bit B11, and the remaining pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>8</sub> have their <sup>10</sup> gates responsive to the predecoded signal bit B22. Furthermore, one pair of n-channel and p-channel fieldeffect transistors of the NAND gate G9 have their gates responsive to the predecoded signal bit B<sub>03</sub>, another pair of n-channel and p-channel field-effect transistors 15 of the NAND gate G<sub>9</sub> have their gates responsive to the predecoded signal bit B<sub>11</sub>, and the remaining pair of n-channel and p-channel field-effect transistors of the NAND gate G<sub>9</sub> have their gates responsive to the predecoded signal bit  $B_{11}$ , and the remaining pair of  $^{20}$ n-channel and p-channel field-effect transistors of the NAND gate G<sub>8</sub> have their gates responsive to the predecoded signal bit B<sub>22</sub>.

As shown in FIG. 5, the two-input NAND gate G<sub>10</sub> of the decoder unit D<sub>10</sub> comprises two n-channel field- <sup>25</sup> effect transistors N<sub>51</sub> and N<sub>52</sub> connected in series between the logic inverter I<sub>10</sub> and ground and two p-channel field-effect transistors P<sub>51</sub> and P<sub>52</sub> connected in parallel between the logic inverter I<sub>10</sub> and the source of the supply voltage  $V_{CC}$ . The field-effect transistors  $N_{51}$  and P<sub>51</sub> have their gates responsive to the predecoded signal bit B<sub>23</sub> and the field-effect transistors N<sub>52</sub> and P<sub>52</sub> have their gates responsive to the inverted address bit  $\overline{A}_2$ . Lastly, the two-input NAND gate G11 of the decoder 35 unit D<sub>11</sub> comprises two n-channel field-effect transistors N<sub>53</sub> and N<sub>54</sub> connected in series between the logic inverter I<sub>11</sub> and ground and two p-channel field-effect transistors P<sub>53</sub> and P<sub>54</sub> connected in parallel between the logic inverter  $I_{11}$  and the source of the supply voltage  $V_{CC}$ . The field-effect transistors  $N_{53}$  and  $P_{53}$  have their gates also responsive to the predecoded signal bit B<sub>23</sub> and the field-effect transistors N<sub>54</sub> and P<sub>54</sub> have their gates responsive to the original input address bit A<sub>2</sub> as shown.

It may be herein noted that FIG. 5 herein presented shows not only the general circuit arrangement or interconnections between the individual transistors used but also a preferred example of the layout of the transistors arranged in rows and columns on a semiconductor integrated circuit chip in conjunction with the terminals providing the supply voltage source and ground lines.

The active devices of the decoder circuit being thus arranged, the respective NAND gates  $G_0$  to  $G_{11}$  of the decoder units  $D_0$  to  $D_{11}$  are operative to produce output 55 bits  $\overline{O}_0$  to  $\overline{O}_{11}$  in accordance with the schemes represented by the following Boolean expressions:

$\overline{O}_0 = (\overline{A}_0 \cdot \overline{A}_1) \cdot (\overline{A}_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = \overline{A}_0 \cdot \overline{A}_1 \cdot \overline{A}_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_1 = (A_0 \cdot \overline{A}_1) \cdot (\overline{A}_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = A_0 \cdot \overline{A}_1 \cdot \overline{A}_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_2 = A_1 \cdot (\overline{A}_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = A_1 \cdot \overline{A}_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_3 = (A_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = A_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_4 = A_3 \cdot (\overline{A}_4 \cdot \overline{A}_5) = A_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_5 = A_3 \cdot (A_4 \cdot \overline{A}_5) = A_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_6 = (\overline{A}_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = \overline{A}_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_7 = \overline{A}_1 \cdot (A_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = \overline{A}_1 \cdot A_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_8 = (\overline{A}_0 \cdot \overline{A}_1) \cdot (\overline{A}_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = \overline{A}_0 \cdot \overline{A}_1 \cdot \overline{A}_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_9 = (A_0 \cdot \overline{A}_1) \cdot (A_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = A_0 \cdot \overline{A}_1 \cdot \overline{A}_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$   $\overline{O}_9 = (A_0 \cdot \overline{A}_1) \cdot (\overline{A}_2 \cdot \overline{A}_3) \cdot (\overline{A}_4 \cdot \overline{A}_5) = A_0 \cdot \overline{A}_1 \cdot \overline{A}_2 \cdot \overline{A}_3 \cdot \overline{A}_4 \cdot \overline{A}_5$

$\overline{O}_{10} = A_2 \cdot (A_4 \cdot A_5) = \overline{A}_2 \cdot A_4 \cdot A_5$  $\overline{O}_{11} = A_2 \cdot (A_4 \cdot A_5) = A_2 \cdot A_4 \cdot A_5$

As will be seen from the address maps of FIGS. 2A and 2B, the address bits  $O_0$  to  $O_{11}$  produced by the individual decoder units  $D_0$  to  $D_{11}$ , viz., appearing at the output terminals of the logic inverters  $I_0$  to  $I_{11}$ , respectively, assume logic "0" values as follows:

The output address bit O<sub>0</sub> assumes a logic "0" value when all of the original input address bits A<sub>0</sub> to A<sub>5</sub> are of logic "0". The output address bit O1 assumes a logic "0" value when the original input address bit A<sub>0</sub> is of a logic "1" value and each of the remaining original input address bits A<sub>1</sub> to A<sub>5</sub> is of a logic "0" value. The output address bit O<sub>2</sub> assumes a logic "0" value without respect to the original input address bit A<sub>0</sub> when the original input address bit A1 is of a logic "1" value and each of the remaining original input address bits A<sub>2</sub> to A<sub>5</sub> is of a logic "0" value. The output address bit O3 assumes a logic "0" value without respect to the original input address bits  $A_0$  and  $A_1$  when the original input address bit A<sub>2</sub> is of a logic "1" value and each of the remaining original input address bits A<sub>3</sub> to A<sub>5</sub> is of a logic "0" value. The output address bit O<sub>4</sub> assumes a logic "0" value without respect to the original input address bits A<sub>0</sub> to A<sub>2</sub> when the original input address bit A<sub>3</sub> is of a logic "1" value and each of the remaining original input address bits A<sub>4</sub> and A<sub>5</sub> is of a logic "0" value. The output address bit O<sub>5</sub> assumes a logic "0" value without respect to the original input address bits  $A_0$  to  $A_2$  when each of the original input address bits A3 and A4 is of a logic "1" value and the remaining original input address bit A<sub>5</sub> is of a logic "0" value. The output address bit O<sub>6</sub> assumes a logic "0" value without respect to the original input address bits A<sub>0</sub> and A<sub>1</sub> when each of the original input address bits A2 to A4 is of a logic "0" value and the remaining original input address bit A5 is of a logic "1" value. The output address bit O7 assumes a logic "0" value without respect to the original input address bit  $A_0$  when the original input address bits  $A_1$ ,  $A_3$  and  $A_4$  is of a logic "0" value and each of the remaining original input address bits A<sub>2</sub> and A<sub>5</sub> is of a logic "1" value. The output address bit O<sub>8</sub> assumes a logic "0" value when each of the original input address bits A<sub>0</sub>, A<sub>3</sub> and A<sub>4</sub> is of a logic "0" value and each of the remaining original input address bits A<sub>1</sub>, A<sub>2</sub> and A<sub>5</sub> is of a logic "1" value. The output address bit O<sub>9</sub> assumes a logic "0" value when each of the original input address bits A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub> and A<sub>5</sub> is of a logic "1" value and each of the remaining original input address bits A<sub>3</sub> and A<sub>5</sub> is of a logic "0" value. The output address bit O<sub>10</sub> assumes a logic "0" value without respect to the original input address bits  $A_0$ ,  $A_1$  and  $A_3$  when the original input address bit  $A_2$  is of a logic "0" value and each of the remaining original input address bits A<sub>4</sub> and A<sub>5</sub> is of a logic "1" value. The output address bit O11 assumes a logic "0" value without respect to the original input address bits  $A_0$ ,  $A_1$  and A<sub>3</sub> when all the remaining input address bits A<sub>2</sub>, A<sub>4</sub> and As are of logic "1" values.

Thus, each of the decoder units D<sub>0</sub>, D<sub>1</sub>, D<sub>8</sub> and D<sub>9</sub> is responsive to all of the six supplied original input address bits A<sub>0</sub> to A<sub>5</sub>. Accordingly, each of these decoder units D<sub>0</sub>, D<sub>1</sub>, D<sub>8</sub> and D<sub>9</sub> is responsive to a single unique sequence or combination of the input address bits and is accordingly comprised of a three-input NAND gate responsive to three of the predecoded signal bits alone. Each of the decoder units D<sub>2</sub> and D<sub>7</sub> is not responsive to one of the supplied original input address bits A<sub>0</sub> to A<sub>5</sub>

and is thus responsive to two different sequences or combinations of the input address bits. Each of these two decoder units D2 and D7 may therefore be comprised of a three-input NAND gate responsive to two of the predecoded signal bits and one of the original input 5 address bits. Each of the decoder units D<sub>3</sub> and D<sub>6</sub> is not responsive to two of the supplied original input address bits A<sub>0</sub> to A<sub>5</sub> and is thus responsive to four different sequences or combinations of the input address bits and may therefore be comprised of a two-input NAND gate 10 for being responsive to two of the predecoded signal bits alone. Each of the decoder units D4, D5, D10 and D<sub>11</sub> is not responsive to three of the supplied original input address bits A<sub>0</sub> to A<sub>5</sub> and is responsive to eight different sequences or combinations of the input address 15 bits. Each of these decoder units D4, D5, D10 and D11 may therefore be also comprised of a two-input NAND gate for being responsive to one of the predecoded signal bits and one of the original input address bits.

From the above discussion it will have been under- 20 se. stood that the decoder units  $D_0$  to  $D_{11}$  of the decoder circuit embodying the present invention are broken down to four different categories which consist of a first category including the decoder units D<sub>0</sub>, D<sub>2</sub>, D<sub>8</sub> and D<sub>9</sub> each including a three-input NAND gate responsive 25 to predecoded signal bits alone, a second category including the decoder units D<sub>3</sub> and D<sub>6</sub> each including a two-input NAND gate also responsive to predecoded signal bits alone, a third category including the decoder units D<sub>2</sub> and D<sub>7</sub> each including a three-input NAND 30 gate responsive to predecoded signal bits and an original input address bit, and a fourth category including the decoder units D4, D5, D10 and D11 each including a two-input NAND gate responsive to a predecoded signal bit and an original input address bit. In each of the 35 decoder units D<sub>2</sub> and D<sub>7</sub> which fall within the third category, the original input address bit used directly by the decoder unit is selected from the bits other than those which have resulted in the two predecoded signal bits used by the decoder unit. In each of the decoder 40 units D<sub>4</sub>, D<sub>5</sub>, D<sub>10</sub> and D<sub>11</sub> which fall within the fourth category, the original input address bit used is also selected from the bits other than those which have resulted in the single predecoded signal bit used by the decoder unit.

As will have been seen from the foregoing description, the decoder circuit embodying the present invention is characterized in that, inter alia, the predecoded signal bits are used in combination with the original input address bits in most of the decoder units such as 50 the decoder units D<sub>2</sub>, D<sub>4</sub>, D<sub>5</sub>, D<sub>7</sub>, D<sub>10</sub> and D<sub>11</sub>. For this reason, each of the decoder units D<sub>0</sub> to D<sub>11</sub> of the decoder circuit embodying the present invention can be implemented by a two-input or three-input NAND gate and can accordingly be composed of only two or three 55 CMOS transistor parts in addition to the associated logic converter. Such a configuration of the decoder circuit embodying the present invention is prominently contrasted by a prior-art address decoder circuit which includes more than three CMOS transistor pairs as de- 60 scribed with reference to FIG. 1. A decoder circuit according to the present invention is thus advantageous for its simplicity of construction and accordingly for the reduced switching time achievable of the decoder circuit over a prior-art decoder circuit of the described 65 nature. The reduction in the number of series connected n-channel field-effect transistors of each of the decoder units significantly contributes to reduction in the trans-

conductance (gm) of the decoder unit as a whole and will make it possible further reduce the switching time of the decoder circuit.

While the predecode circuits used in the described embodiment of a decoder circuit have been assumed to be of the two-bit predecode type, any other types of predecode circuits such as six-bit or three-bit predecode circuits may alternatively be used in a decoder circuit according to the present invention.

Furthermore, all of the input lines for the original input address bits and the inverted versions thereof have been shown connected to the decoder circuit but, if desired, only those for the original input address bits  $A_1$ ,  $A_2$  and  $A_3$  and the inverted version  $\overline{A}_2$  of the original input address bit  $A_2$  which are used directly by the decoder circuit may be connected to the decoder circuit. In this instance, the other input lines may be connected only to the predecode circuit  $PD_1$ ,  $PD_2$  and  $PD_3$  without being extended far to the decoder units per se.

What is claimed is:

- 1. A decoder circuit for decoding different combinations of supplied original input signals on input signal lines, comprising at least one predecode circuit coupled to said input signal lines for producing predecoded output signals on output lines of said predecode circuit, and a plurality of decoder units including [at least one decoder unit coupled to at least two different combinations of said input signal lines, and ] at least one decoder unit coupled to the combination of at least one of said output lines and at least one of said input signal lines.

- 2. A decoder circuit for decoding different combinations of supplied original input signals on input signal lines, comprising at least one predecode circuit coupled to said input signal lines for producing predecoded output signals on output lines of said predecode circuit, and a plurality of decoder units including [at least one decoder unit coupled to at least two different combinations of said input signal lines, ] at least one decoder unit coupled to selected ones of said output signal lines alone and a decoder unit coupled to at least one of said output signal lines and at least one of said input signal lines.

- 3. A decoder circuit as set forth in claim 1 or 2, in which each of said plurality of decoder units comprises a logic NAND gate.

- 4. A semiconductor decoder circuit including a plurality of decoder units for decoding different combinations of supplied original input signals on input signal lines, comprising:

- a first set of signal lines formed on a semiconductor structure, the first set of signal lines comprising a first group of signal lines connected to a source of a first predetermined voltage and a second group of signal lines connected to a source of a second predetermined voltage,

- a second set of signal lines formed on a semiconductor structure and extending substantially at right angles to said first set of signal lines, the second set of signal lines comprising a third group of signal lines respectively coupled to output signal lines having output signals predecoded from the input signals on selected ones of said input signal lines and a fourth group of signal lines respectively coupled to the input signals on selected ones of said input signal lines,

- a first set of field-effect transistors selectively connected in series to the source of said first predeter-

mined voltage along each of the signal lines of said first predetermined voltage along each of the signal lines of said first group, each of the first set of field-effect transistors being of one channel conductivity type, and

a second set of field-effect transistors selectively connected in parallel to the source of said second predetermined voltage along each of the signal lines of said second group, each of the second set of fieldeffect transistors being of the channel conductivity 10 type opposite to said one channel conductivity type, the second set of field-effect transistors having their gates selectively connected to the signal lines of said third and fourth groups,

the first set of field-effect transistors arranged along each of the signal lines of said first group and the second set of field-effect transistors arranged along each of the signal lines of said second group implementing each of said decoder units.

\* \* \* \*

15

20

25

30

35

40

45

50

55

60