## United States Patent

[11] E

Patent Number:

Re. 33,632

#### Nakamura et al.

Kraus

[57]

### [45] Reissued Date of Patent:

Jul. 9, 1991

| [54] | ENCODIN    | G/DECODING SYSTEM                     | 4,115,815 9/1978   | Nakagone et al 358/260  |

|------|------------|---------------------------------------|--------------------|-------------------------|

| f1   |            |                                       | 4.117.517 9/1978   | Shintani et al          |

| [75] | Inventors: | Kozo Nakamura, Hitachioota;           | • •                | Yamada 358/261          |

|      |            | Yasuyuki Kojima; Nagaharu Hamada,     | 4,212,035 7/1980   | Nakagome et al 358/260  |

|      |            | both of Hitachi, all of Japan         | •                  | Yamazaki et al 358/260  |

|      |            | • • • • • • • • • • • • • • • • • • • | 4,258,392 3/1981   | Yamazaki et al 358/260  |

| [73] | Assignee:  | Hitachi, Ltd., Tokyo, Japan           | 4,486,784 12/1984  | Abraham et al 358/261.3 |

| [21] | Appl. No.: | 209,935                               | 4,631,598 12/1986  | Burkhardt et al 358/426 |

| [22] | Filed.     | Jun 22 1988                           | Primary Examiner—E | Edward L. Coles, Sr.    |

#### Related U.S. Patent Documents

Jun. 22, 1988

| L/C122 | ue or:      |               |

|--------|-------------|---------------|

| [64]   | Patent No.: | 4,597,016     |

|        | Issued:     | Jun. 24, 1986 |

|        | Appl. No.:  | 568,413       |

|        | Filed:      | Jan. 5, 1984  |

|      | rnea:           | Jan. 3, 1964             |

|------|-----------------|--------------------------|

| [30] | Foreign A       | pplication Priority Data |

| Jan  | . 10, 1983 [JP] | Japan 58-1071            |

|      |                 | H04M 1/40; H04M 7/13     |

| [52] | U.S. Cl         |                          |

|      | •               | 358/261                  |

| [58] | Field of Search | h 358/261.3, 261.1, 426  |

| [56] | R               | References Cited         |

| U.S.          | PATENT DOC        | UMENTS     |         |

|---------------|-------------------|------------|---------|

| 3,927,251 12/ | /1978 White et al |            | 358/261 |

| 3,991,267 11/ | /1976 Beaudette.  | ********** | 358/260 |

8/1977 Nakagone et al. ...... 358/261

An encoding/decoding system to be connected to an external microcomputer, video memory, photoelectric reader or printer comprises an address generator for generating an address to access the video memory word by word, a transition point detector for parallelly processing a video signal word by word to detect a color information transition point address, and execution unit for calculating an address difference from two color information transition point addresses or the color information transition point address based on a difference between two color information transition point addresses, an encoding/decoding table for converting an address difference to a code word and converting a code word to an address difference, and a decoded video signal generator for parallelly reproducing a

Attorney, Agent, or Firm-Antonelli, Terry, Stout &

**ABSTRACT**

#### 12 Claims, 25 Drawing Sheets

video signal based on the address difference.

## Reissue of.

4,040,093

Filed:

| F 3  |                      | —————————————————————————————————————— |

|------|----------------------|----------------------------------------|

| Jan  | . 10, 1983 [JP] Japa | an 58-1071                             |

|      |                      | H04M 1/40; H04M 7/13                   |

| [58] | Field of Search      | 358/261<br>358/261.3, 261.1, 426       |

| [56] | Refere               | nces Cited                             |

FIG. 5

FIG. 6

B-E **POTARAMOD** AUD SE Σū× B-MAHA-MAH B-LATCH HJTAJ-A CONTRO <u>©</u> ₩ NS NS NS NS B-F ADD > < C  $\mathbf{\omega}$ MPX

FIG. 8

PMODE

# F1G. 16

July 9, 1991

ABSOLUTE VALUE OF DISTANCE BETWEEN Q₁ b1≤3

ABSOLUTE VALUE OF DISTANCE BETWEEN 01 b1>3 H+MH(0001)+MH(0103)

F I G. 18

FIG. 22 VO CODE OUTPUT -6600 -6601 SET VO ADDRESS LOAD CONTENT OF TABLE

TO SHIFT REGISTER *√*6602 6603 TERMINATE ? APPLY SHIFT PULSE TO SHIFT REGISTER AND S/P 6604 6605 INCREMENT CODE BIT COUNTER DECREMENT 8-BIT COUNTER 6606 6,607 6608 FIFO READY LOAD DATA OF S/P TO FIFO 6609 SET "8" IN 8-BIT COUNTER 6610 RTN

FIG. 23 7000 MR DECODING INITIALIZE <u>7102 </u> SET START ADDRESS OF MR DECODING TABLE 7103<sub>N</sub> COUNTER - O 7104 FIFO 7105 OUTPUT OF TO P/S LOAD ~7106 "8" TO SET " COUNTER APPLY SHIFT PULSE ~7107 TO P/S DECREMENT 8-BIT ~7108 COUNTER 7109 57112 EOL? OUTPUT TABLE (7110 ADDRESS AS LINE END PROCESSING LOOK UP TABLE N CODE ? DECODING DECODING DECODING DECODING DECODING

FIG. 25

FIG. 27

FIG. 28

#### **ENCODING/DECODING SYSTEM**

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

The present invention relates to an encoder/decoder for an MH code (modified Huffman code) and an MR 10 code (modified READ code) which are international standards in the art of a high speed facsimile.

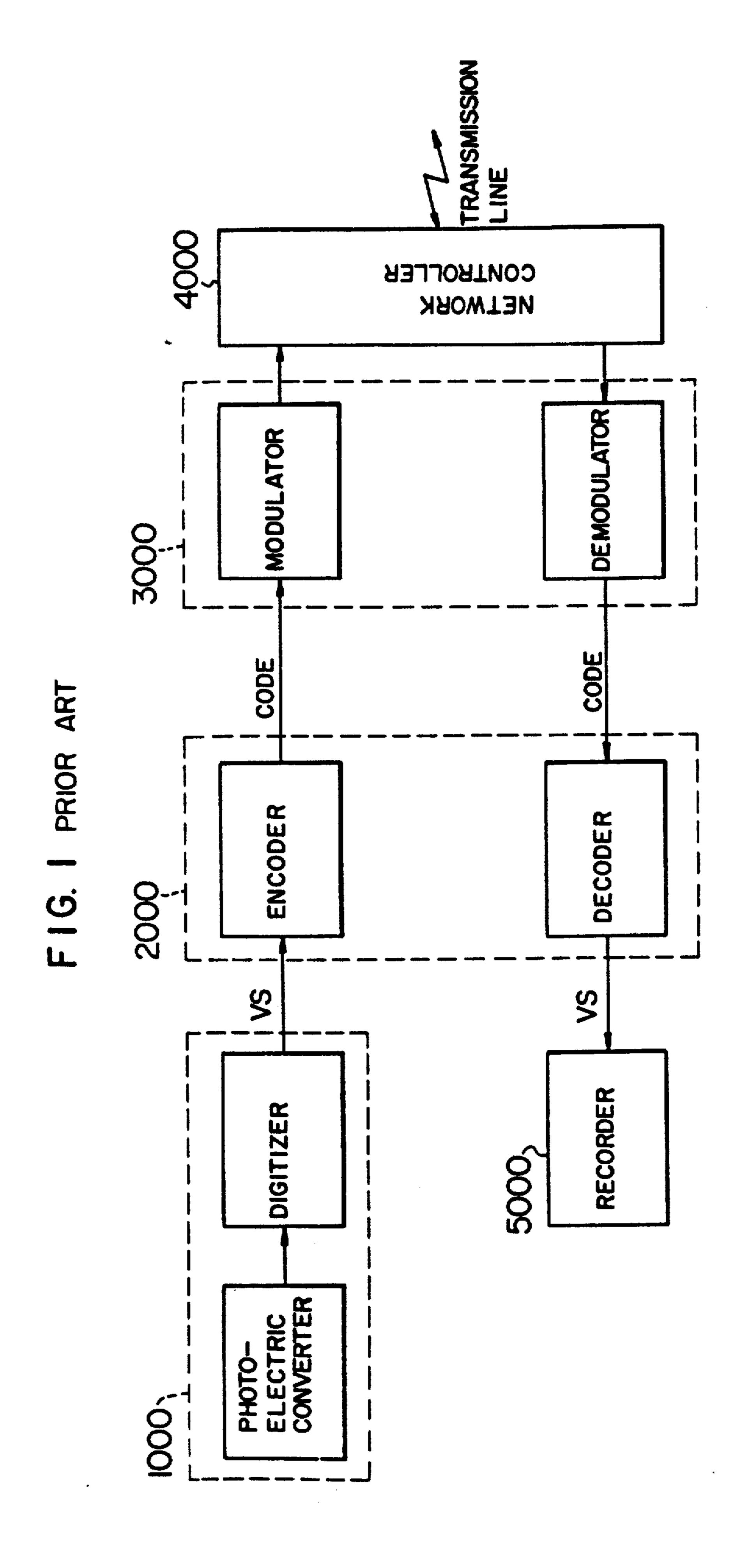

FIG. 1 is a block diagram schematically showing a facsimile machine. In the facsimile an original document is scanned by a scanner 1000 to generate a video signal 15 VS. The video signal is converted to a code word by an encoder/decoder 2000, and it is converted to a frequency in a transmission line band by a modem 3000 and finally sent out to a transmission line through a network controller 4000. In a receiving station, the code words 20 are converted to a video signal in the opposite procedure and a hard copy is formed by a recorder 5000. A controller (usually a microcomputer) which controls an overall system is omitted in FIG. 1. In the encoder/decoder 2000, the international standard MH code or MR 25 code is used in many cases. In the MH code, a run length (RL) between two adjacent transition points (at which colors of pixels change) on the same line is converted to a code word. In the MR code, the transition points on two adjacent lines are noted and a relative 30 positional difference between the transition point on the reference line already encoded and transmitted and the transition point on the encoding line currently being encoded is encoded. In a prior art encoder/decoder, a plurality of line memories each storing the bits of the 35 video signal sequentially are provided and the memories are scanned serially to detect the transition point. In decoding, the video signal is serially decoded by counting the run lengths by a counter. As a result, a volume of a hardware increases and high speed memories are 40 required. Since the MH code and the MR code are of high degree of coding scheme, they are usually processed by a combination of a software and a hardware of a microcomputer. However, since the signal processing by software is of low speed, it is difficult to encode 45 at a high speed. When the system is constructed by a hardware only, it is of large scale and lacks a flexibility. The volume of the hardware may be reduced by providing a memory (usually an 8-bit word memory) for storing the video signal on a system bus of the mi- 50 crocomputer. However, since the transition point in the word is serially detected, a high speed operation is difficult to attain. In many prior art devices, a pixel-by-pixel operation to serially scan the video signal to detect the transition point is carried out by the hardware, and a 55 process to generate the code word based on the transition point information is carried out by the software by the microcomputer. This method is flexible but imposes a heavy load to the microcomputer and it is hardly applicable to a high speed line such as 48 Kb/s.

It is an object of the present invention to provide an encoder/decoder which parallelly detects transition points word by word, one word consisting of a plurality of bits of a video signal, decodes the video signal based on transition point information, and converts the transition point information to a code word and converts the code word to the transition point information by referring an MH/MR code table so that a flexible en-

coding/decoding operation is carried out at a high speed in accordance with operation parameters supplied from a microcomputer.

The present invention will be apparent from the following detailed description taken in conjunction with the accompanying drawings, in which:

FIG. 1 is an overall block diagram of a prior art facsimile,

FIG. 2 is an overall block diagram of an encoder/decoder (Codec) of the present invention,

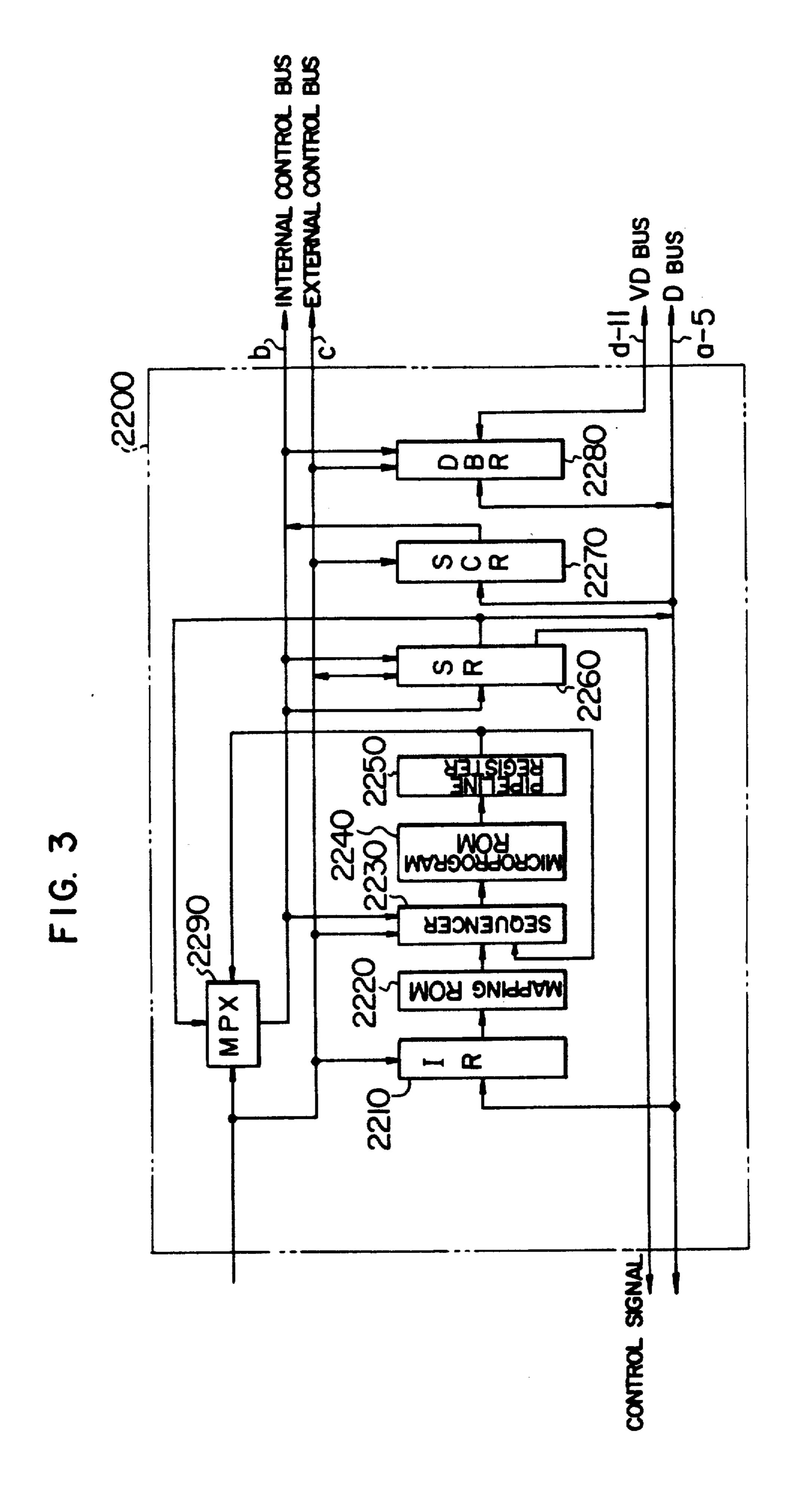

FIG. 3 is a block diagram of a control unit,

FIG. 4 is a block diagram of an execution unit,

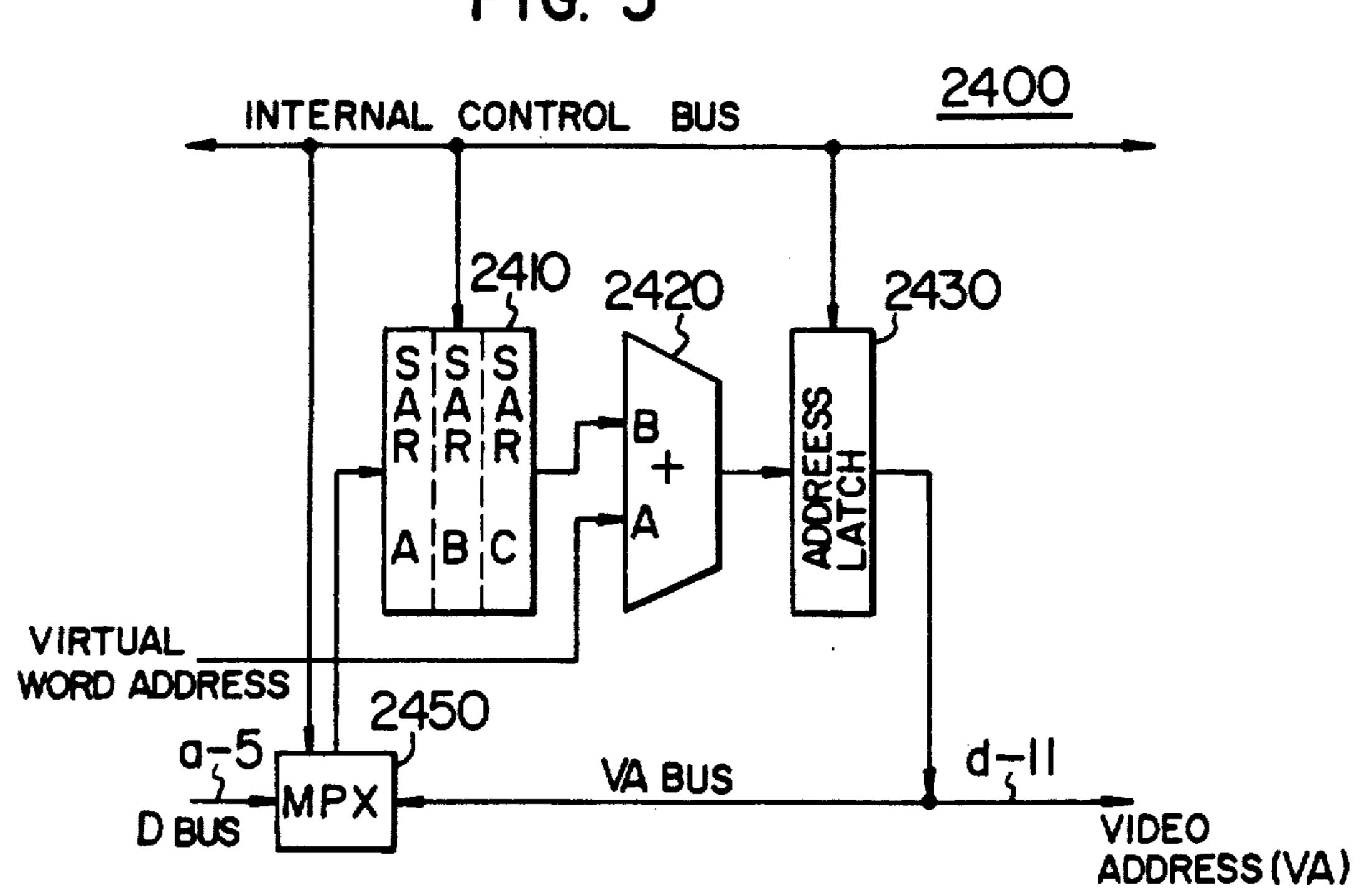

FIG. 5 is a block diagram of a video address generator,

FIG. 6 illustrates page mode processing,

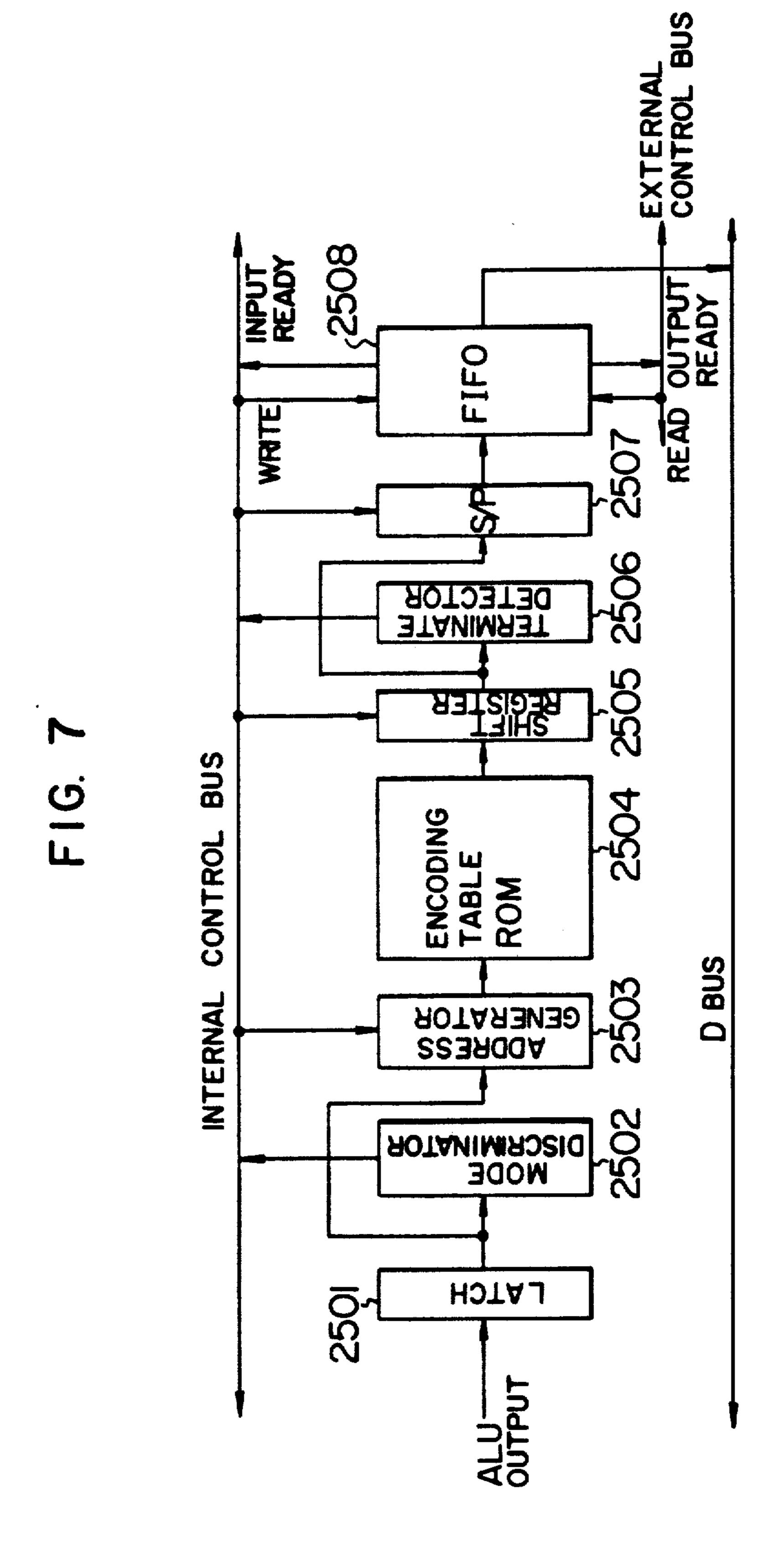

FIG. 7 is a block diagram of an encoding table unit,

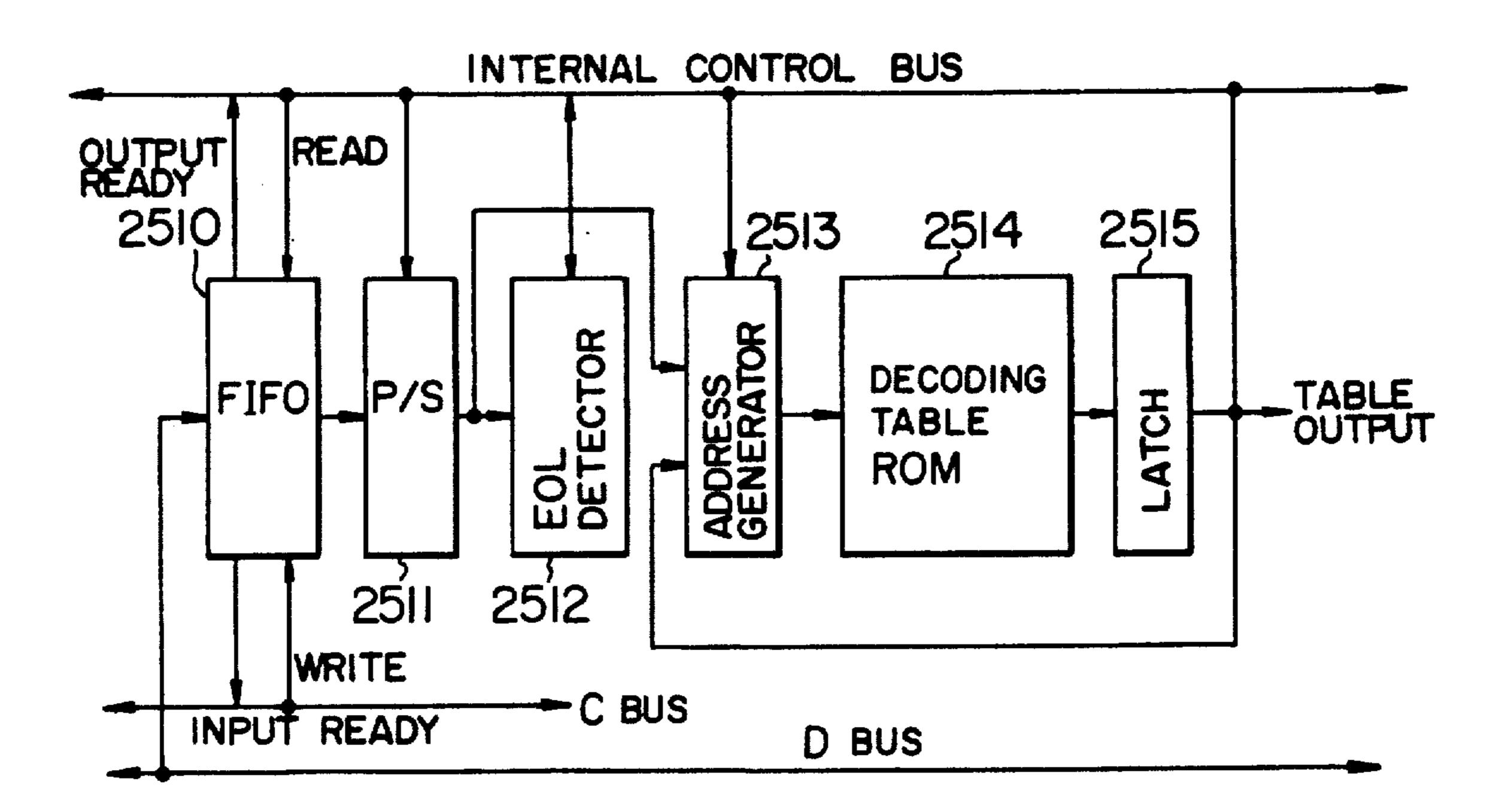

FIG. 8 is a block diagram of a decoding table unit,

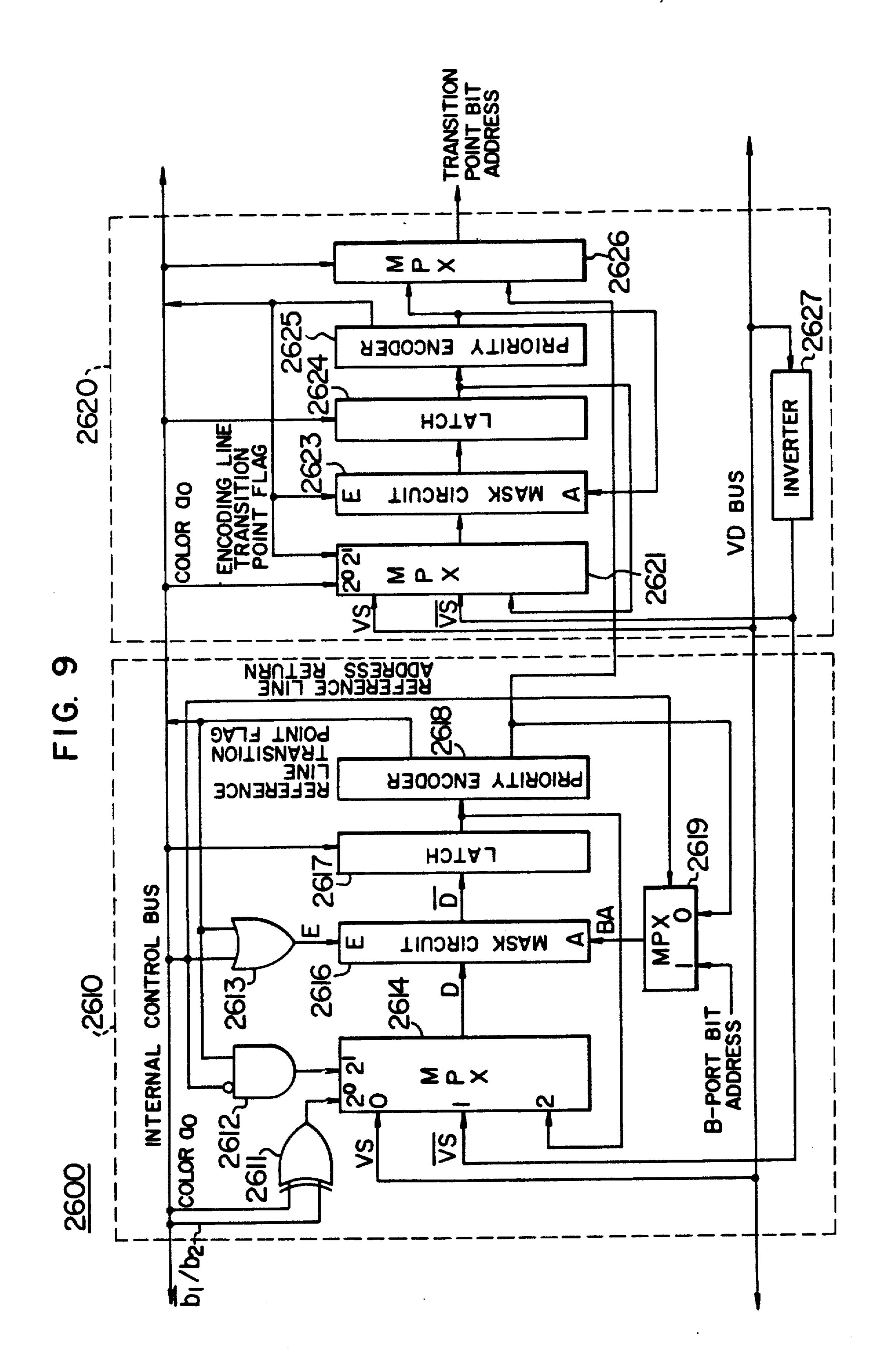

FIG. 9 is a block diagram of a transition point detector,

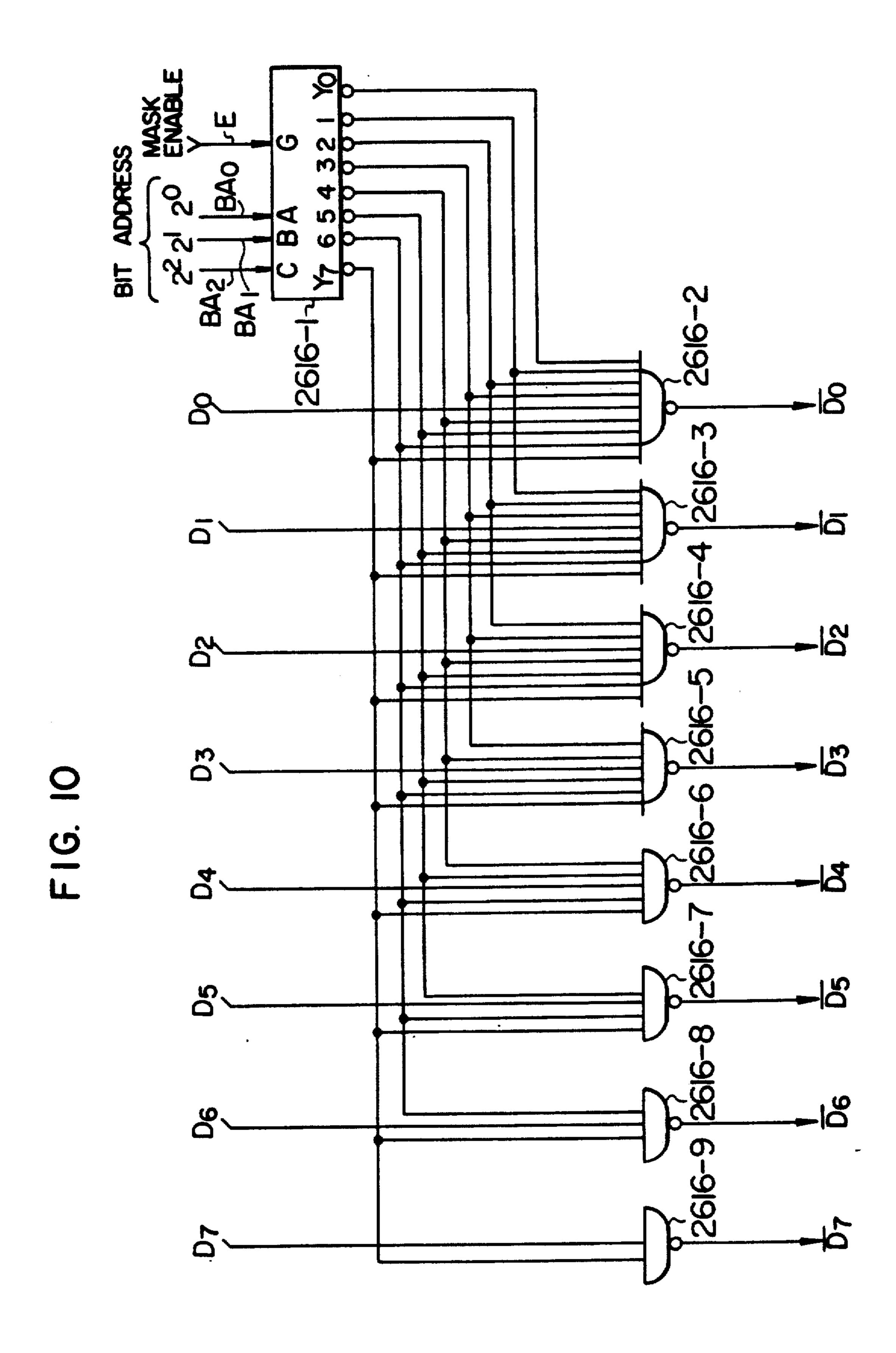

FIG. 10 shows a detailed circuit diagram of a mask circuit in the transition point detector,

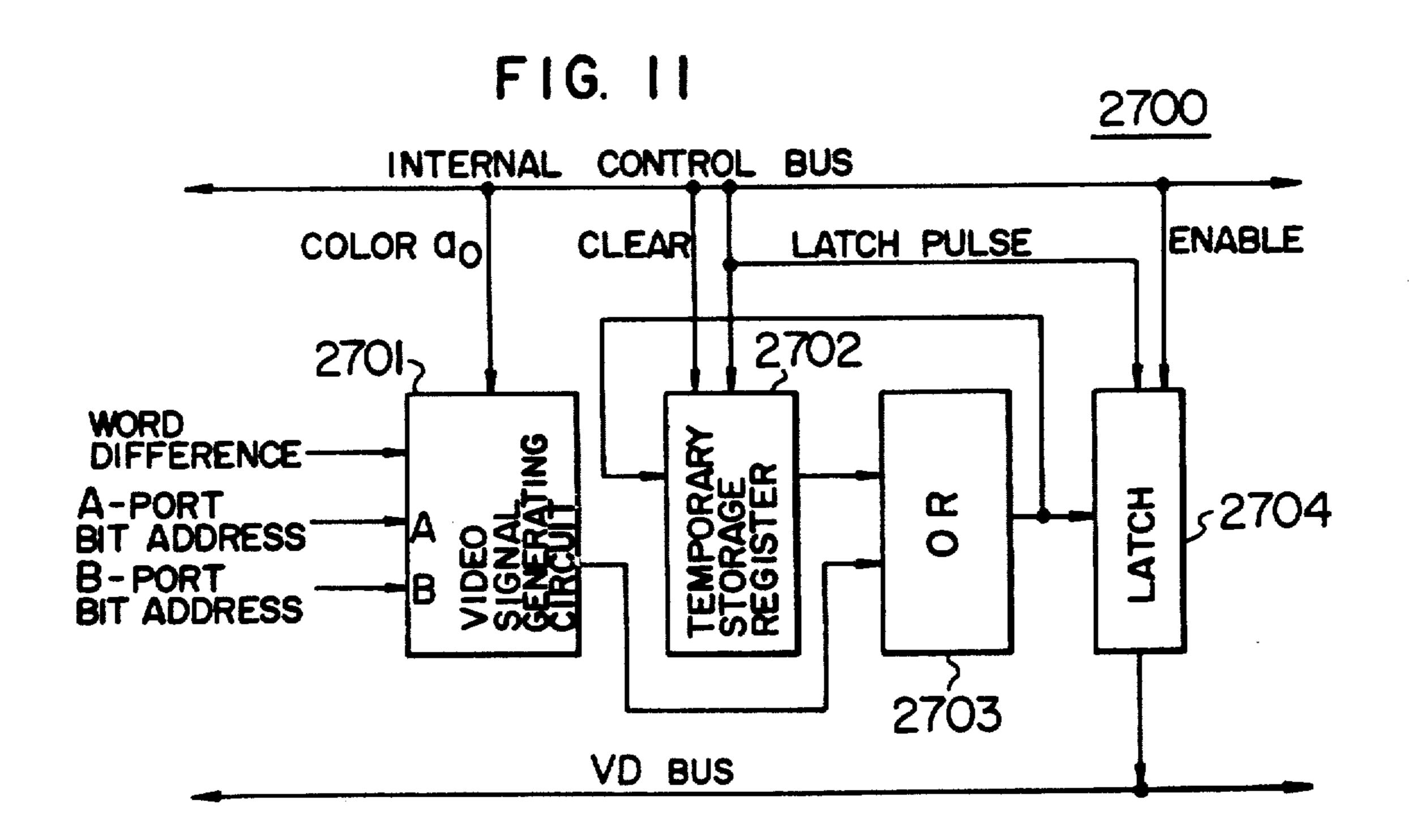

FIG. 11 is a block diagram of a video signal generator,

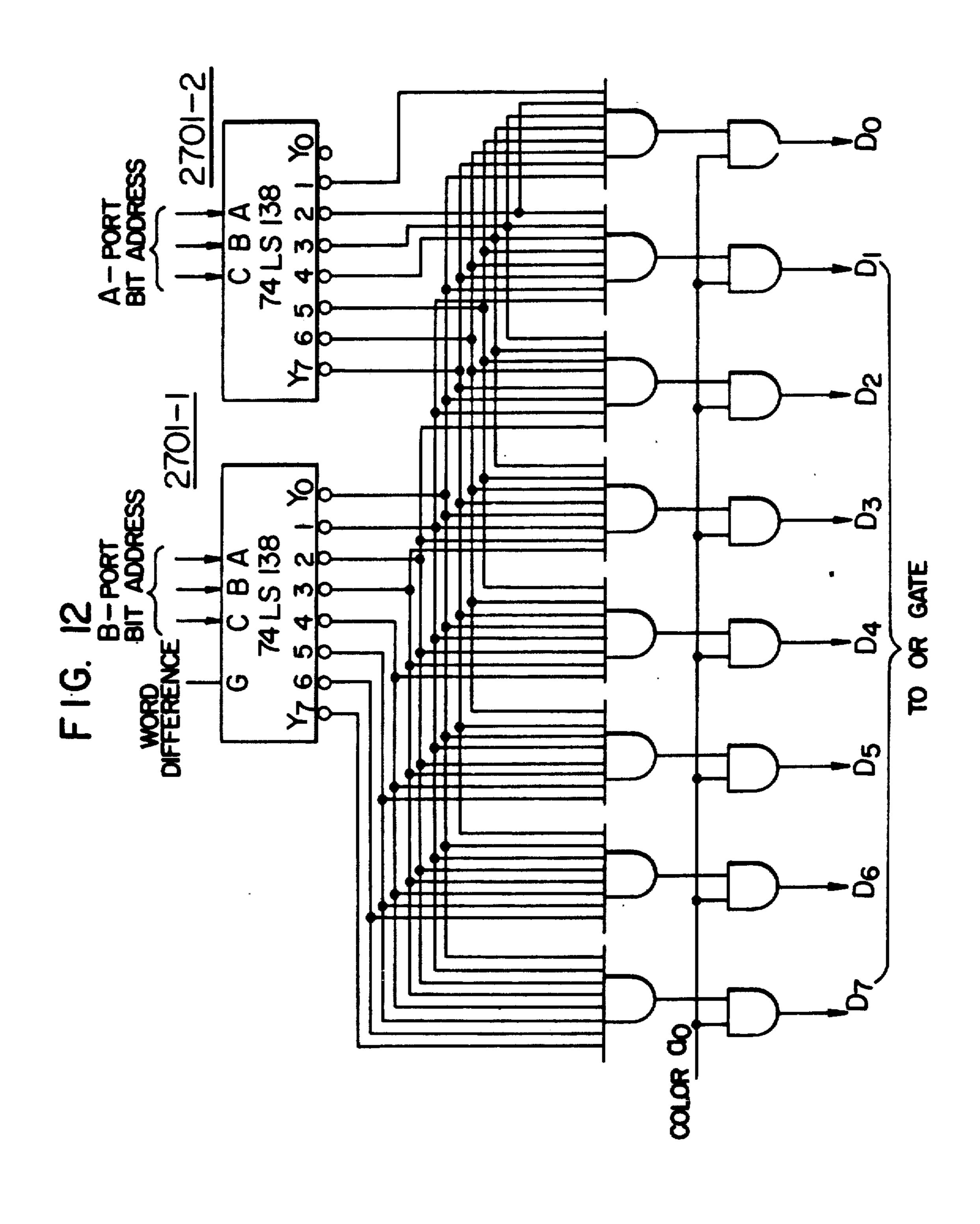

FIG. 12 shows a detailed circuit diagram of the video signal generator,

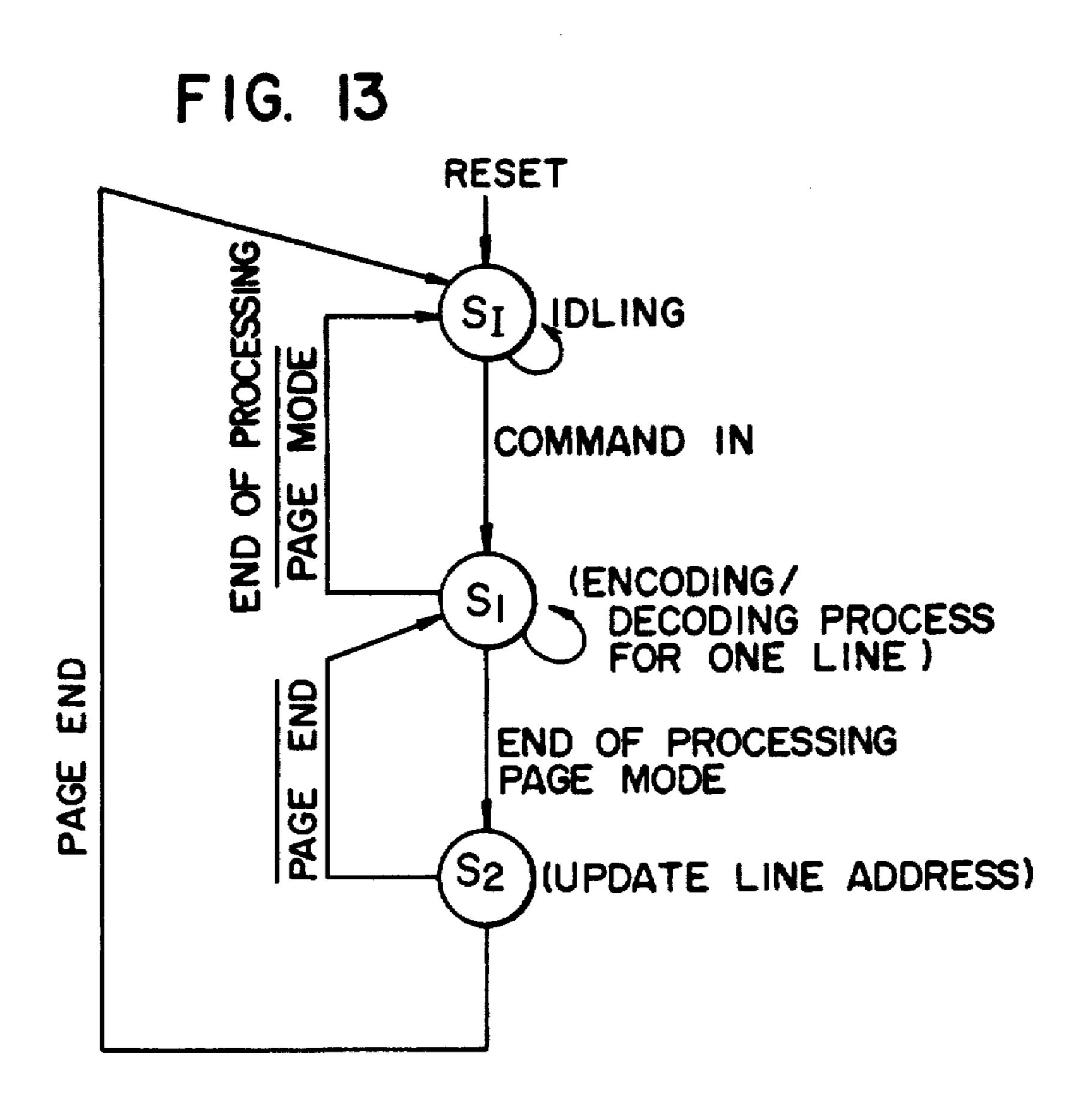

FIG. 13 shows status transition of the Codec in encoding/decoding process,

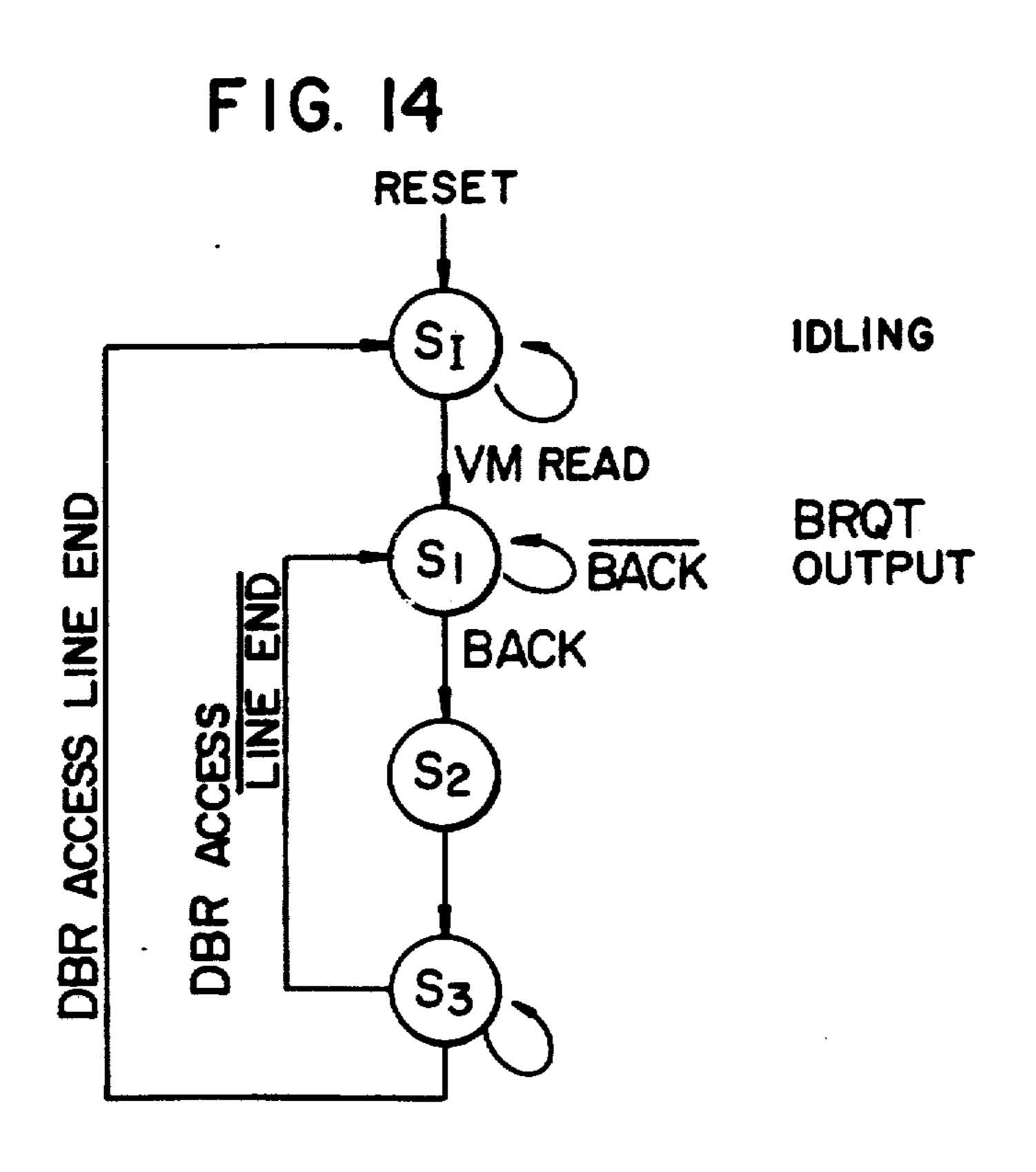

FIG. 14 shows status transition of the code when a microcomputer accesses a video memory (VM) through the Codec,

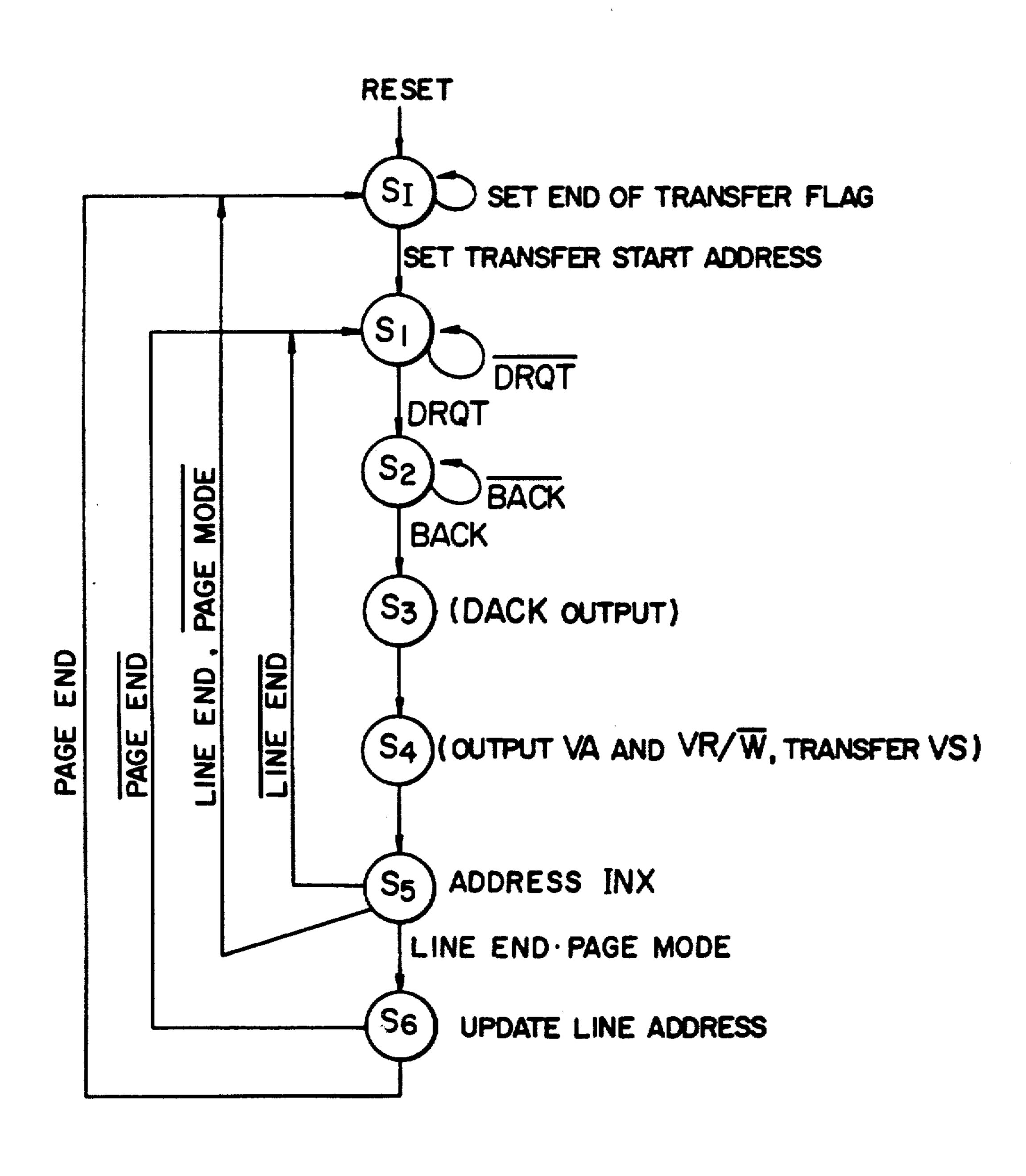

FIG. 15 shows status transition of the Codec when the video signal is transferred,

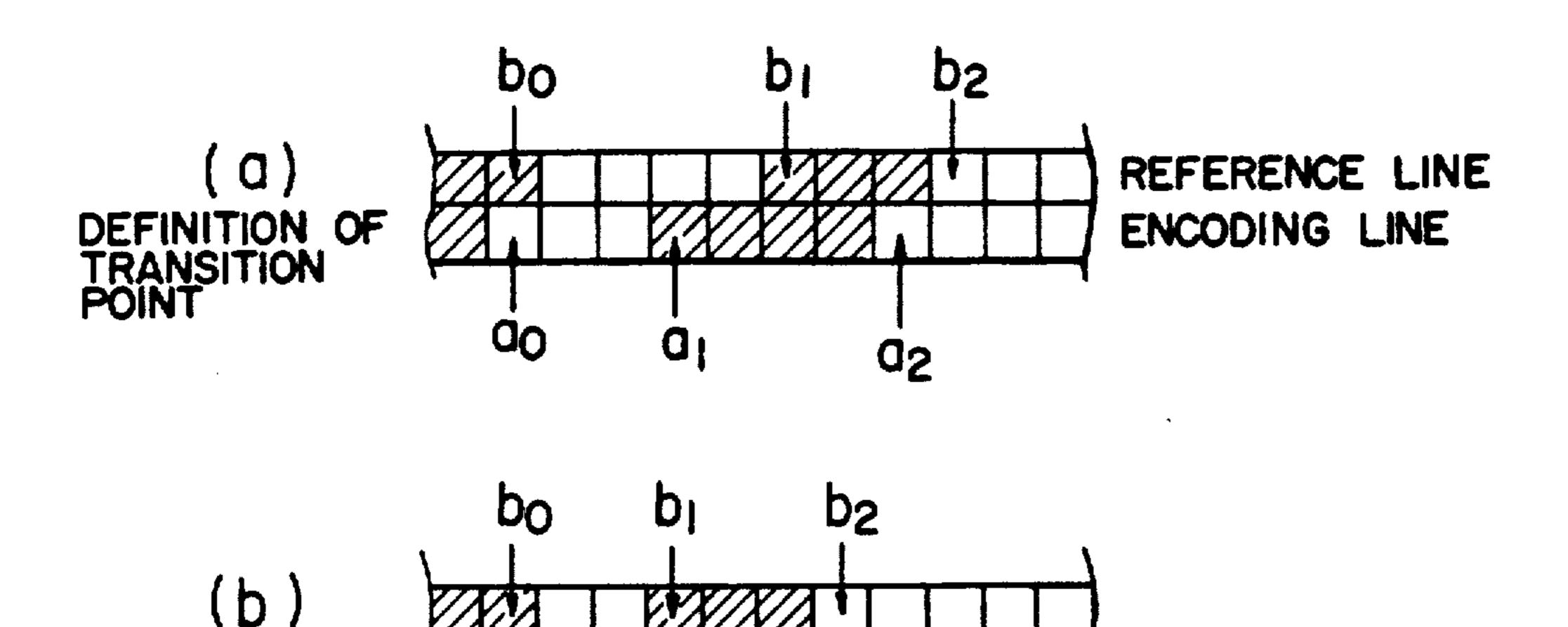

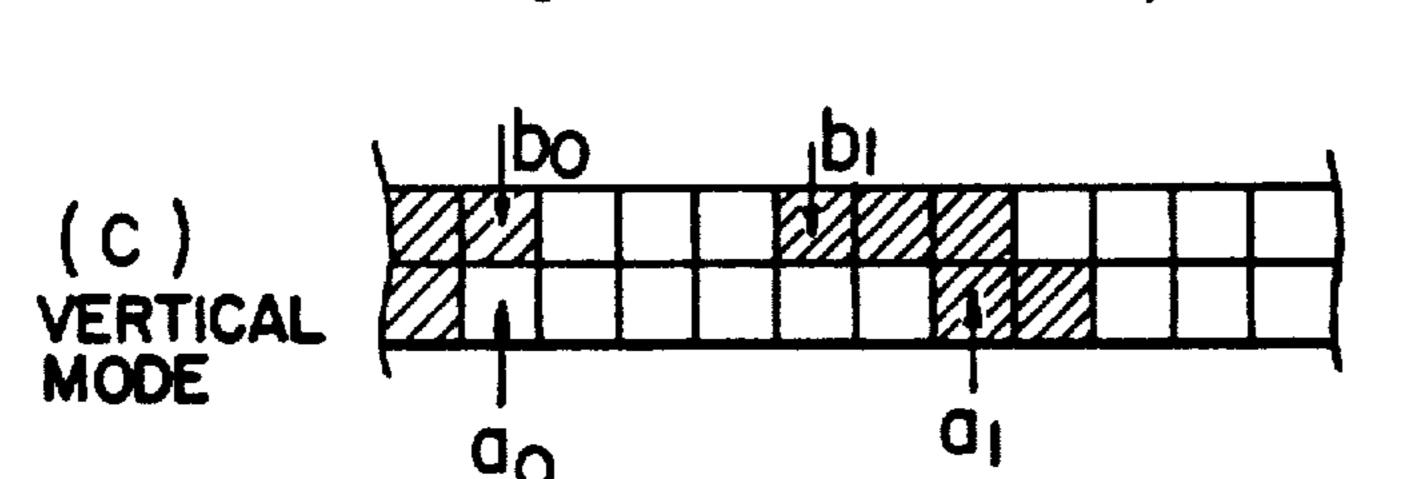

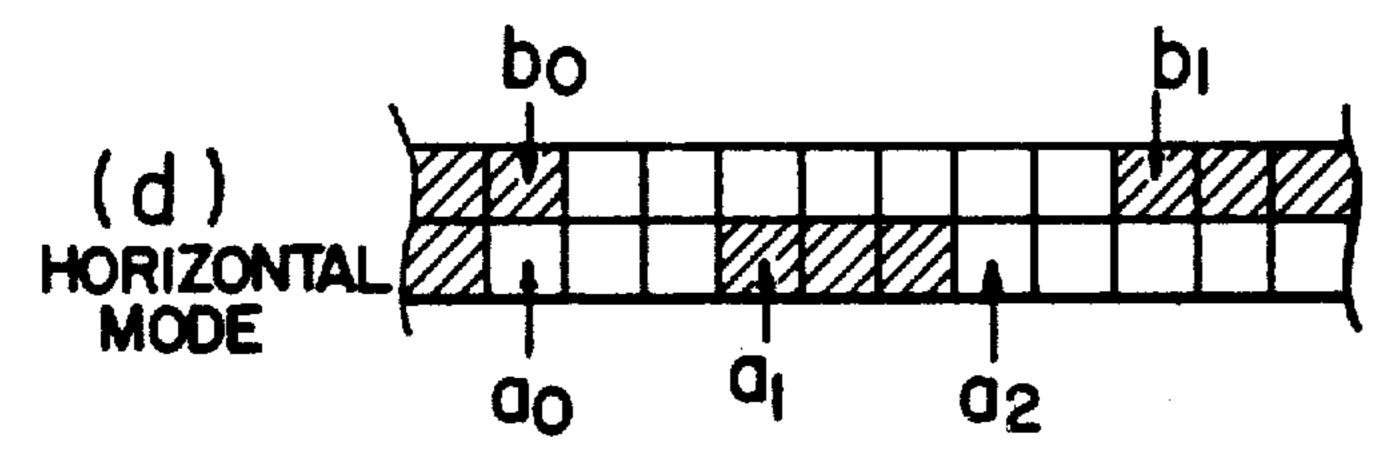

FIG. 16 illustrates an MR encoding scheme,

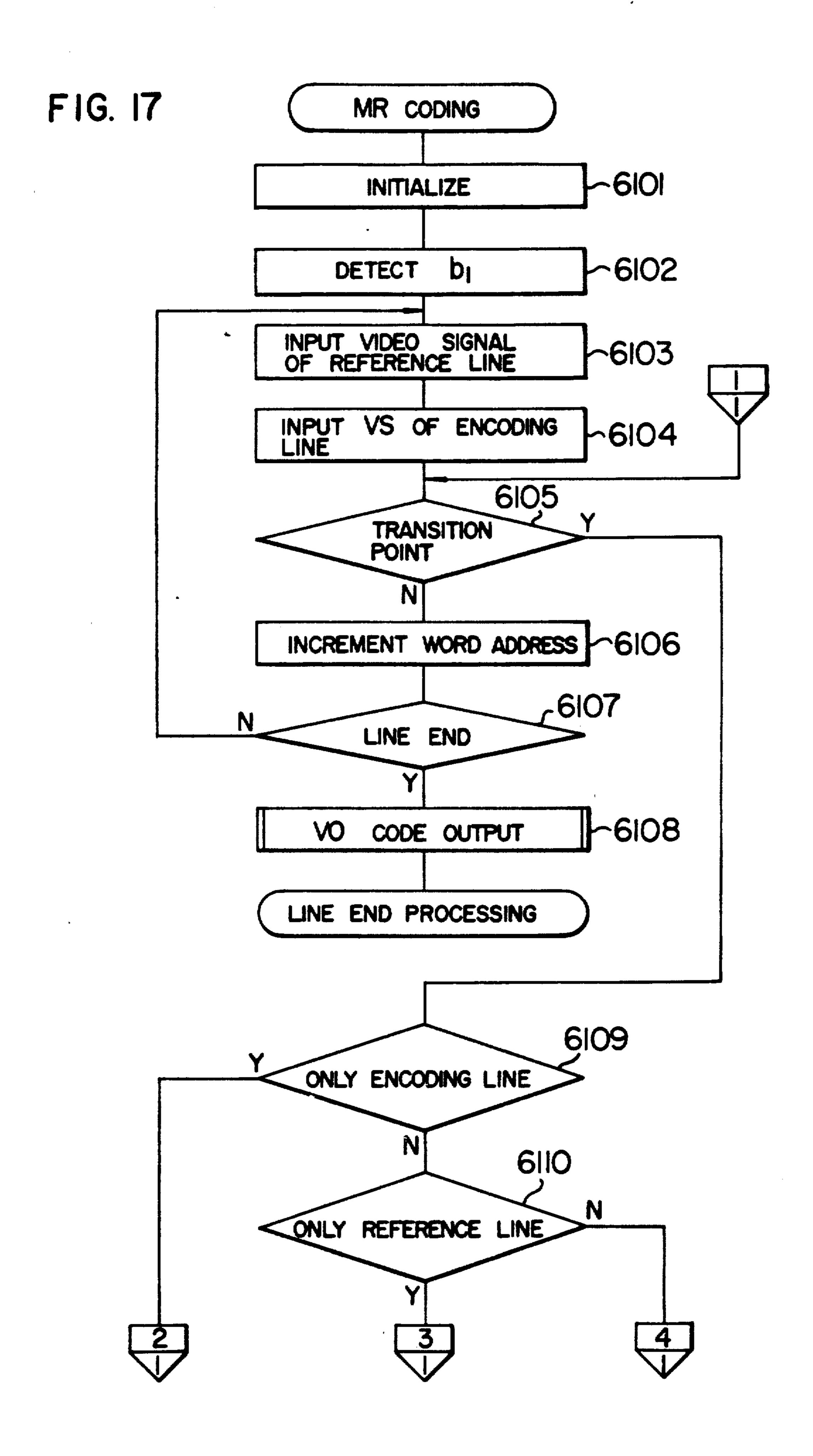

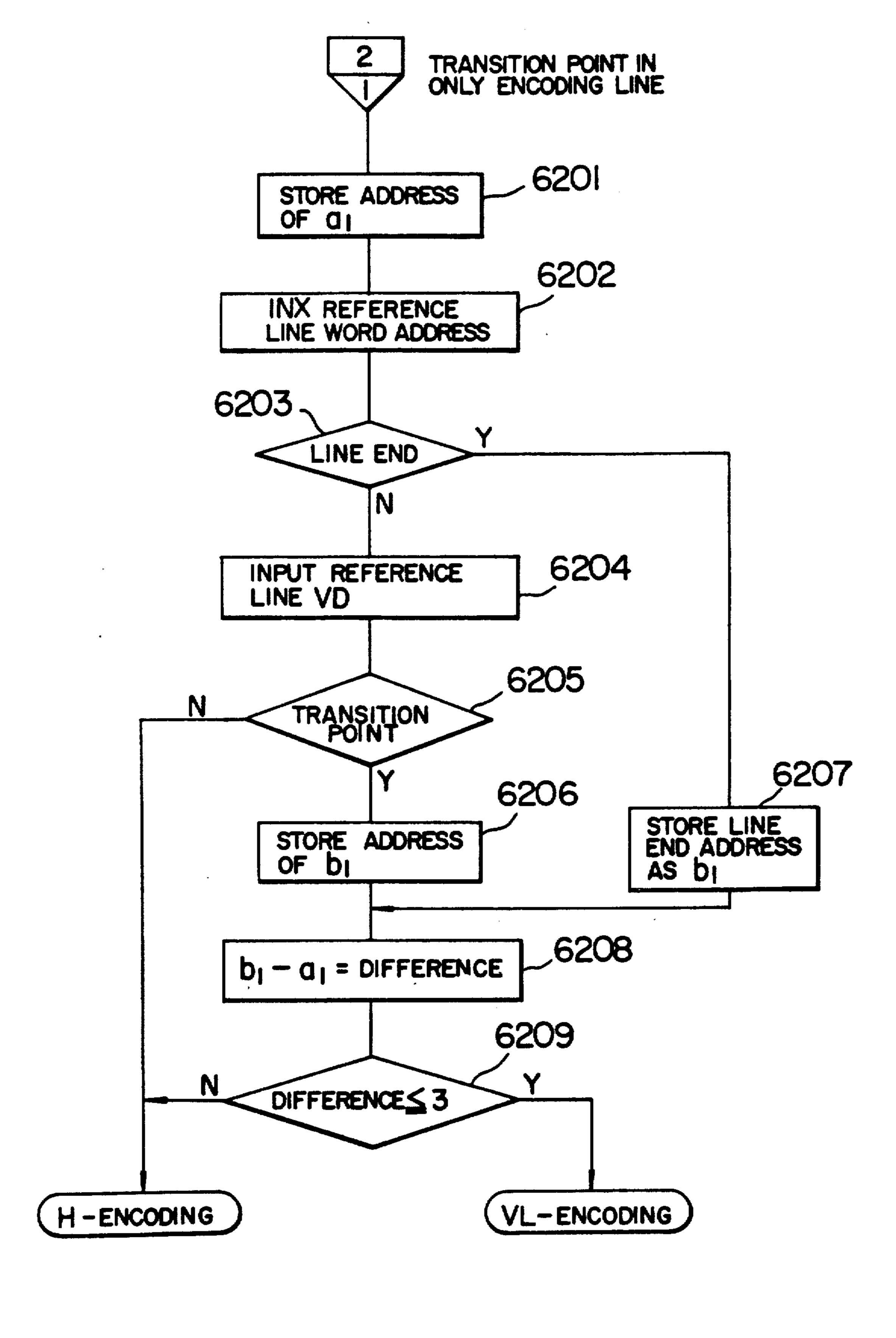

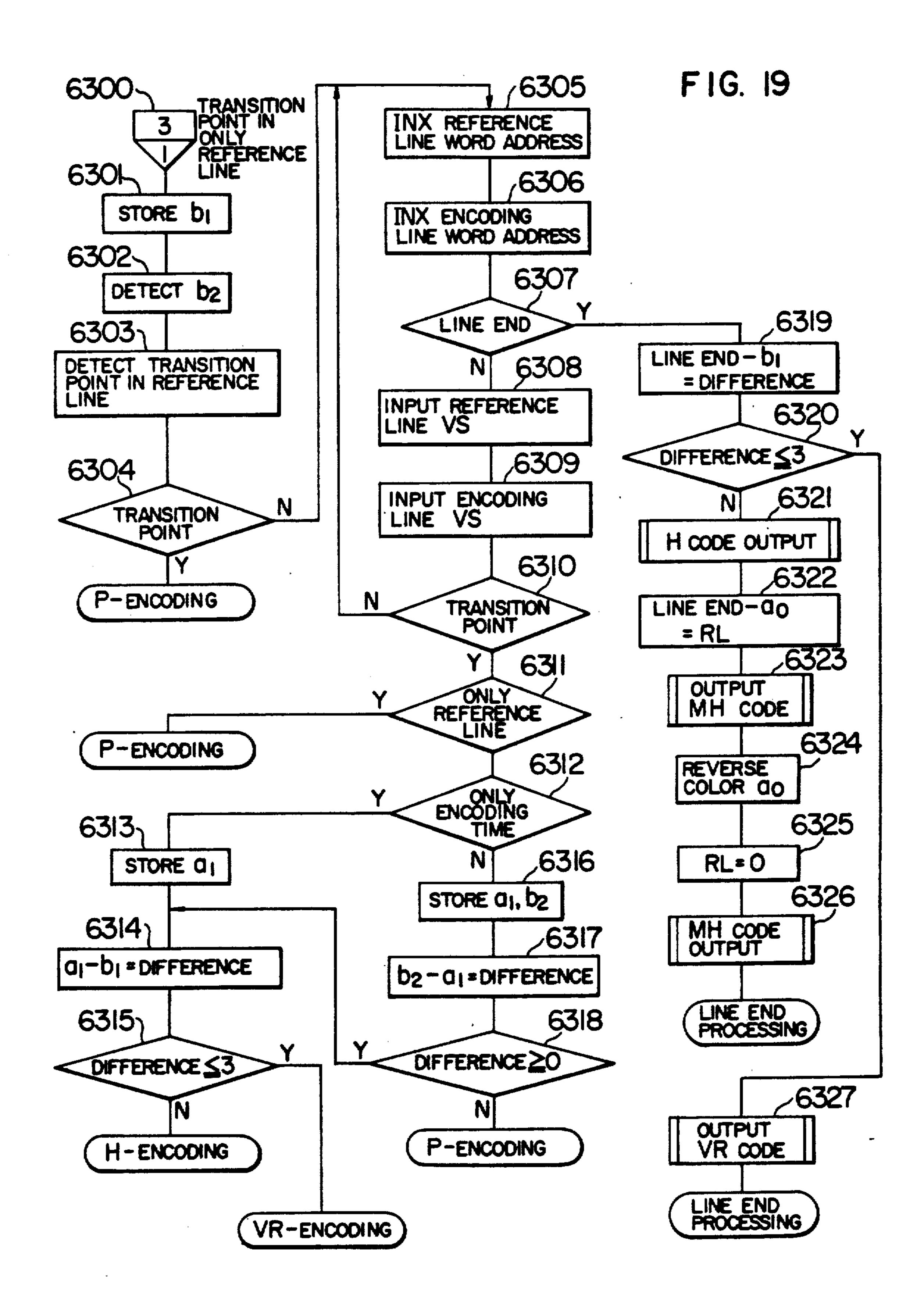

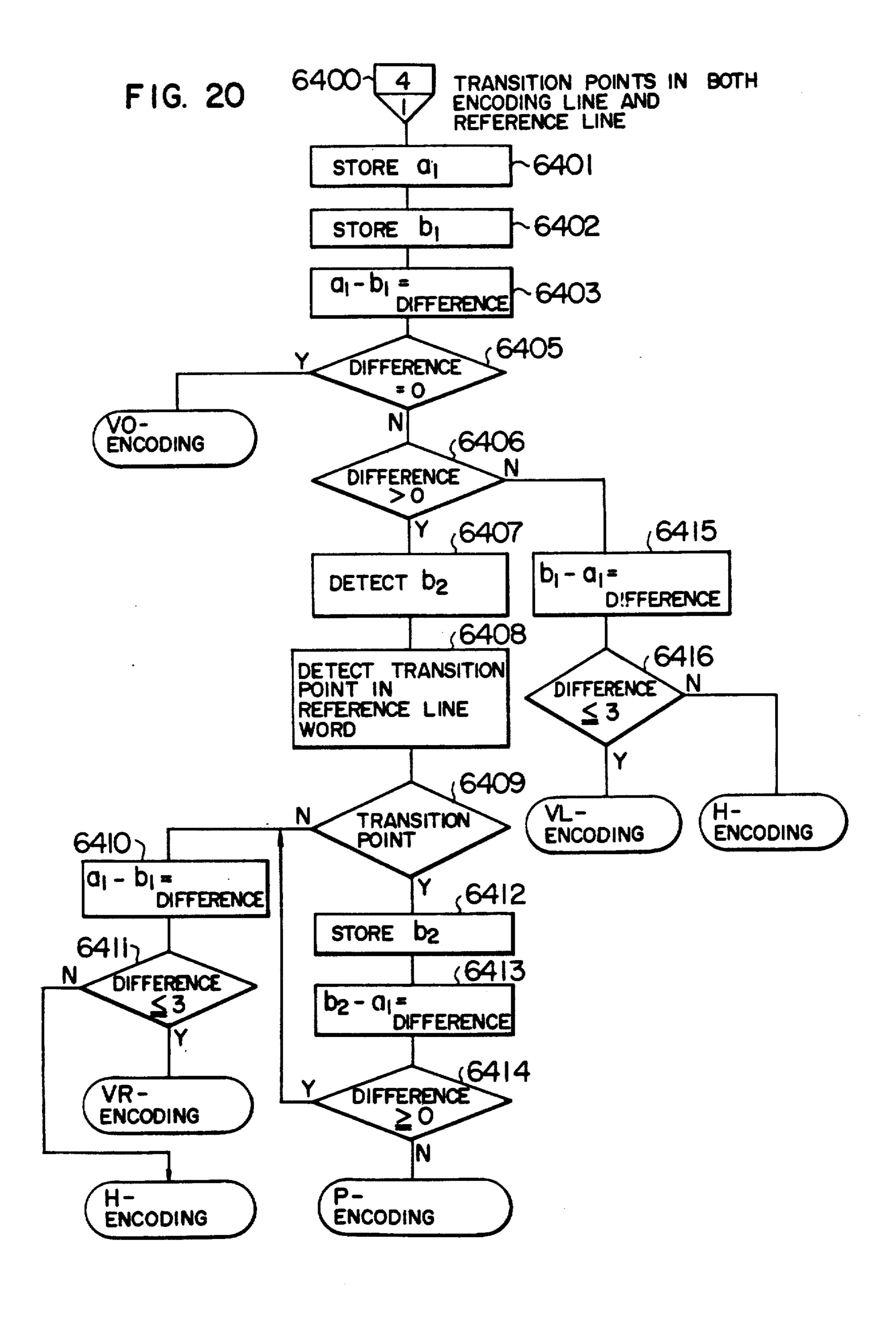

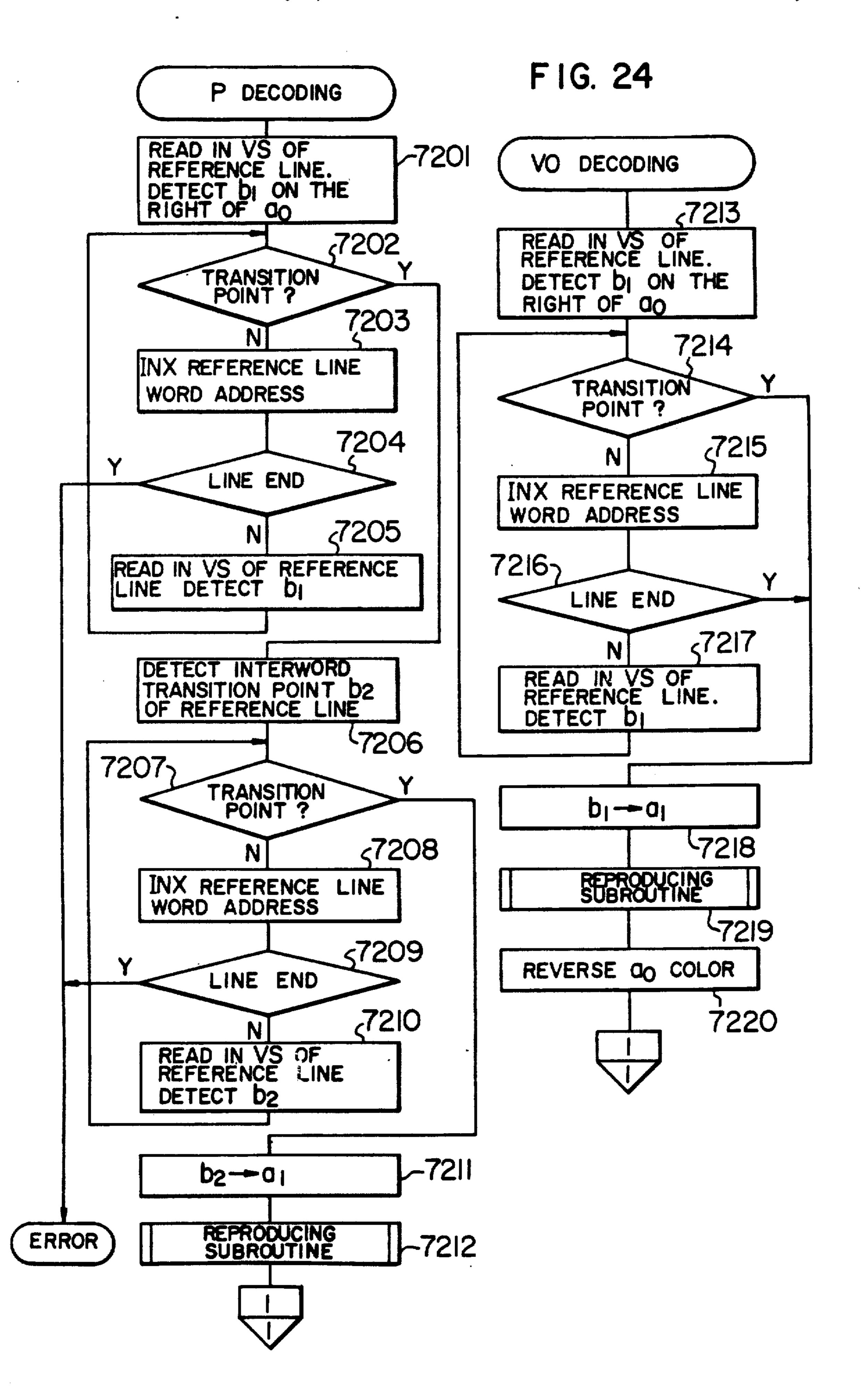

FIGS. 17 to 22 show microprogram flows for the MR encoding process,

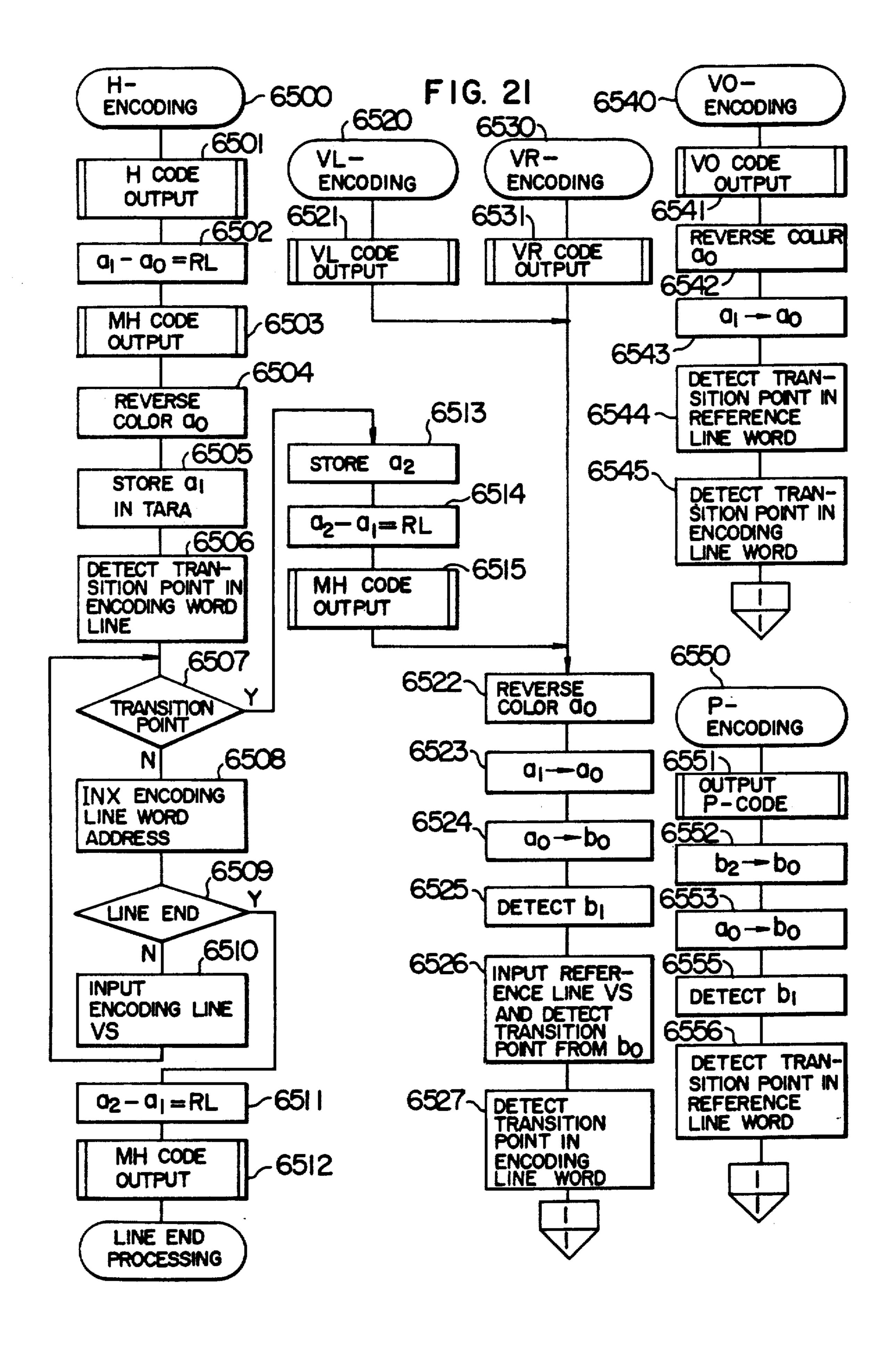

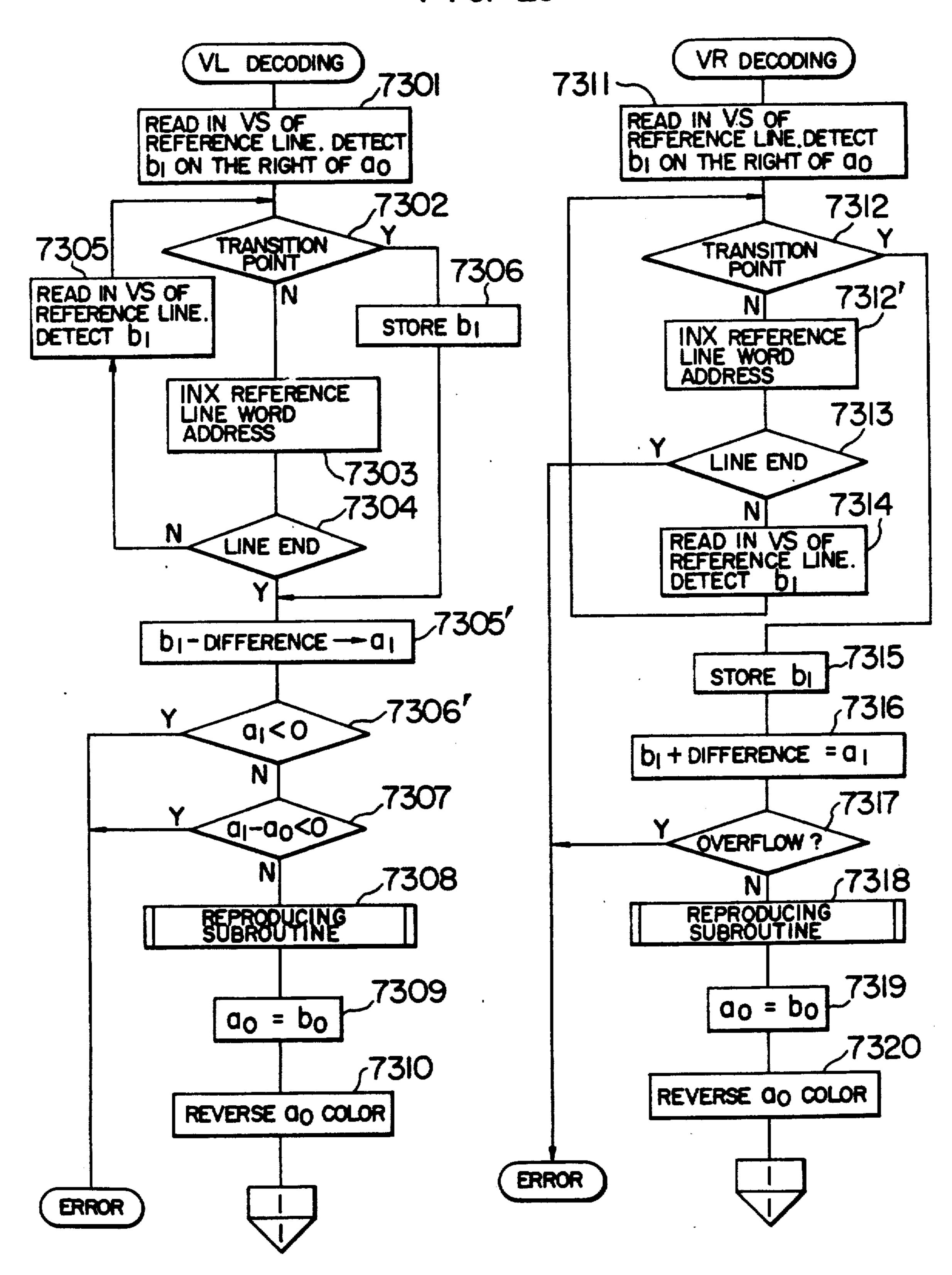

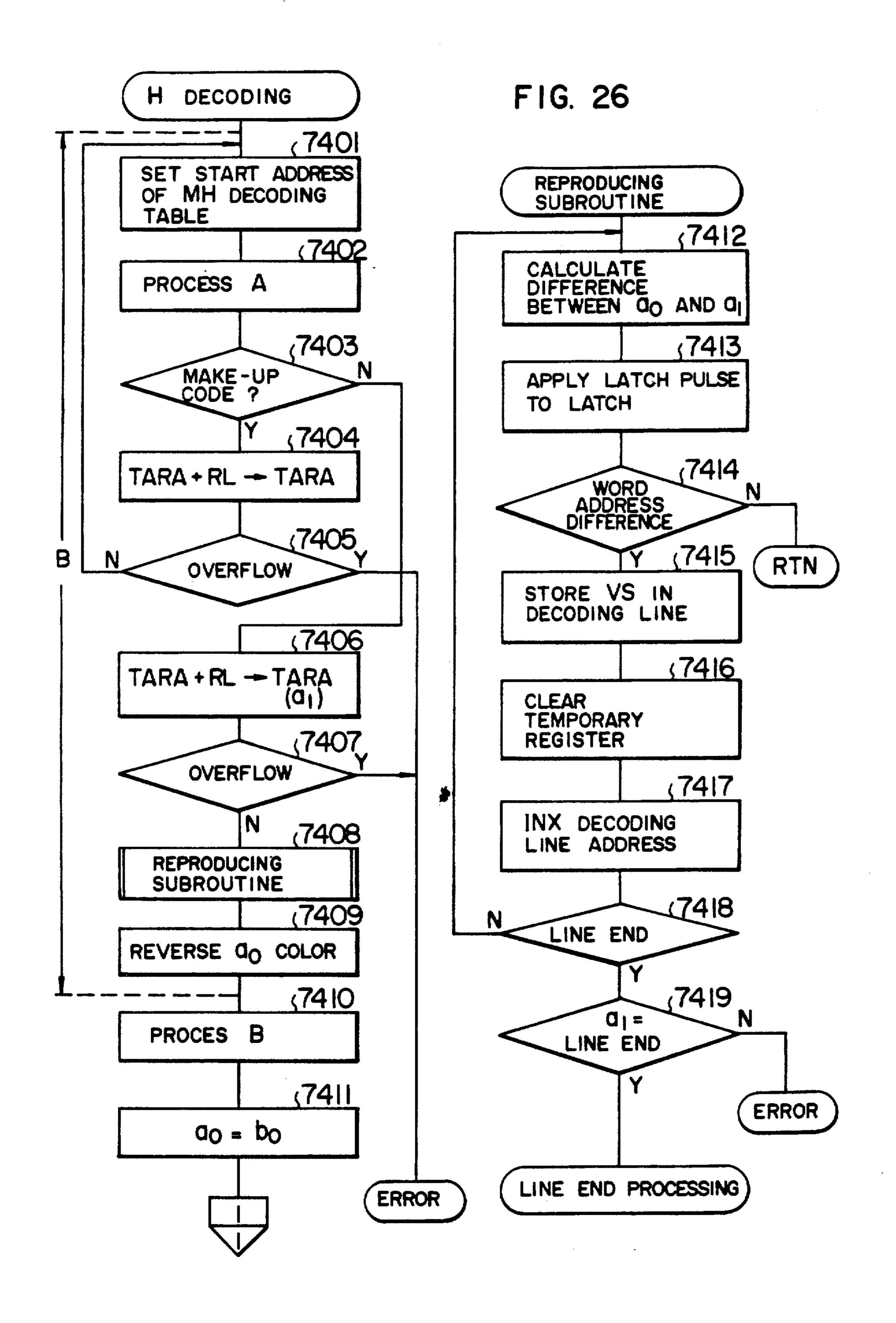

FIGS. 23 to 26 show microprogram flows for the MR decoding process, and

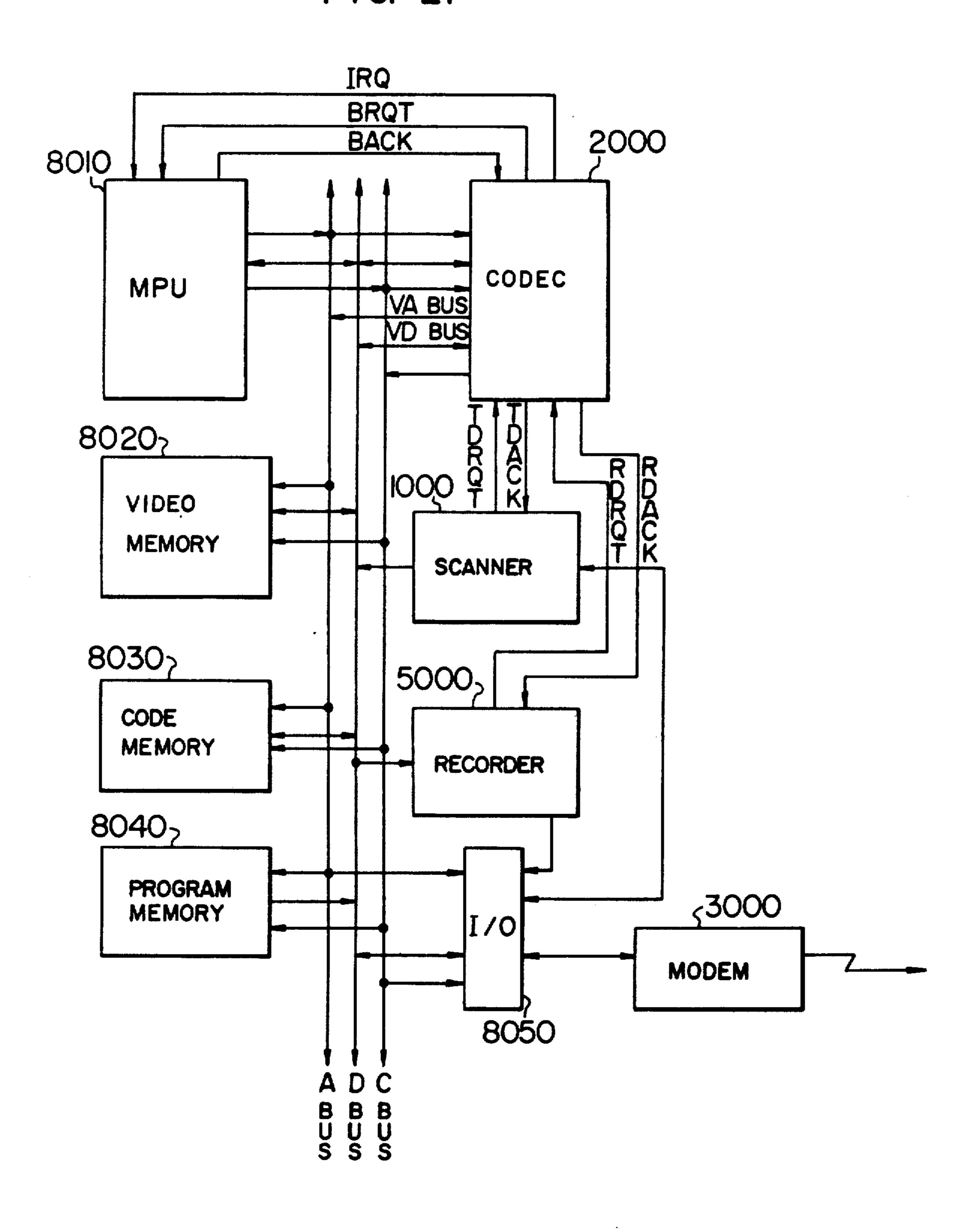

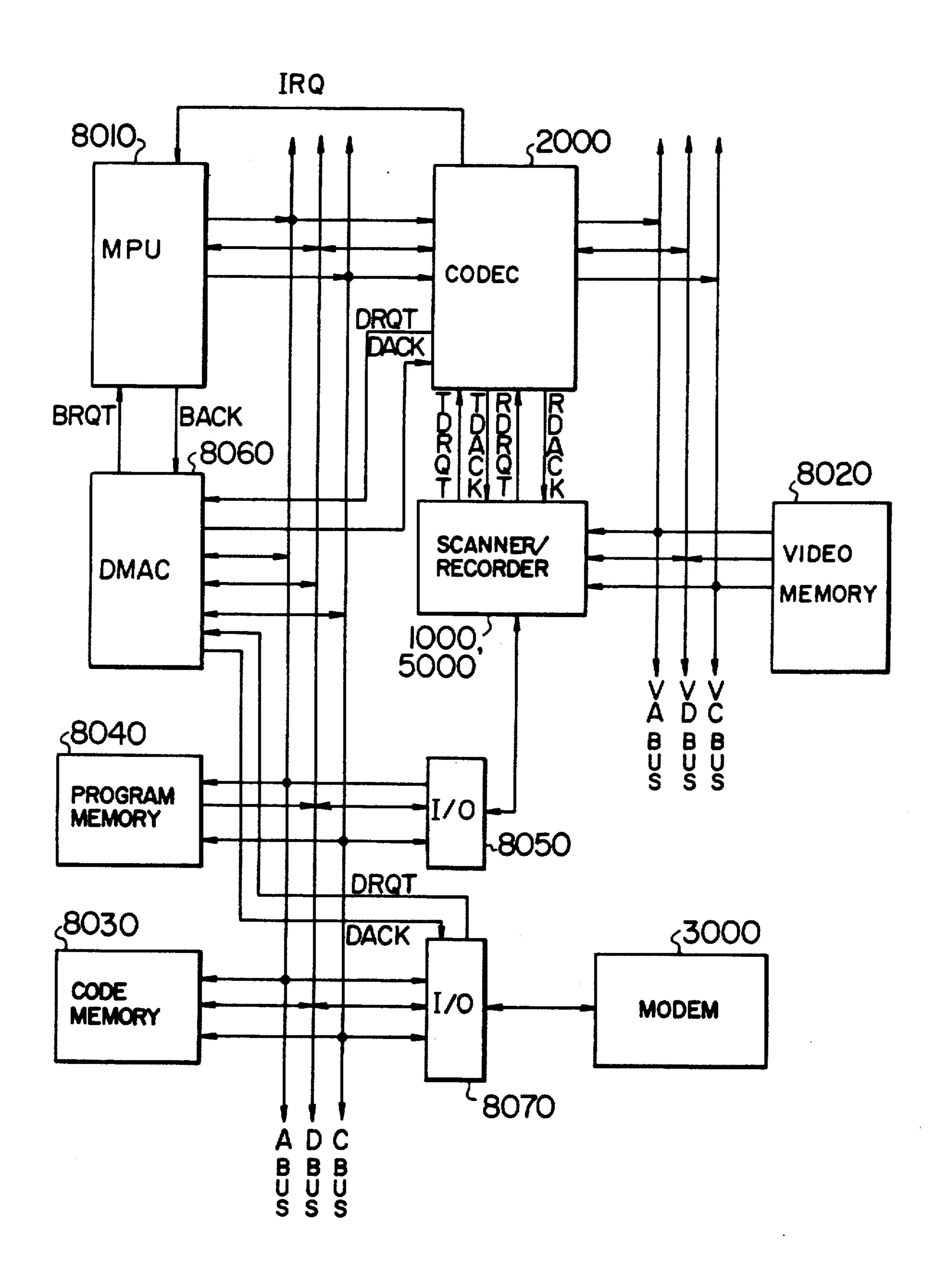

FIGS. 27 and 28 are block diagrams of a facsimile system which uses the Codec.

Preferred embodiments of the present invention are now explained with reference to FIG. 2 et seq.

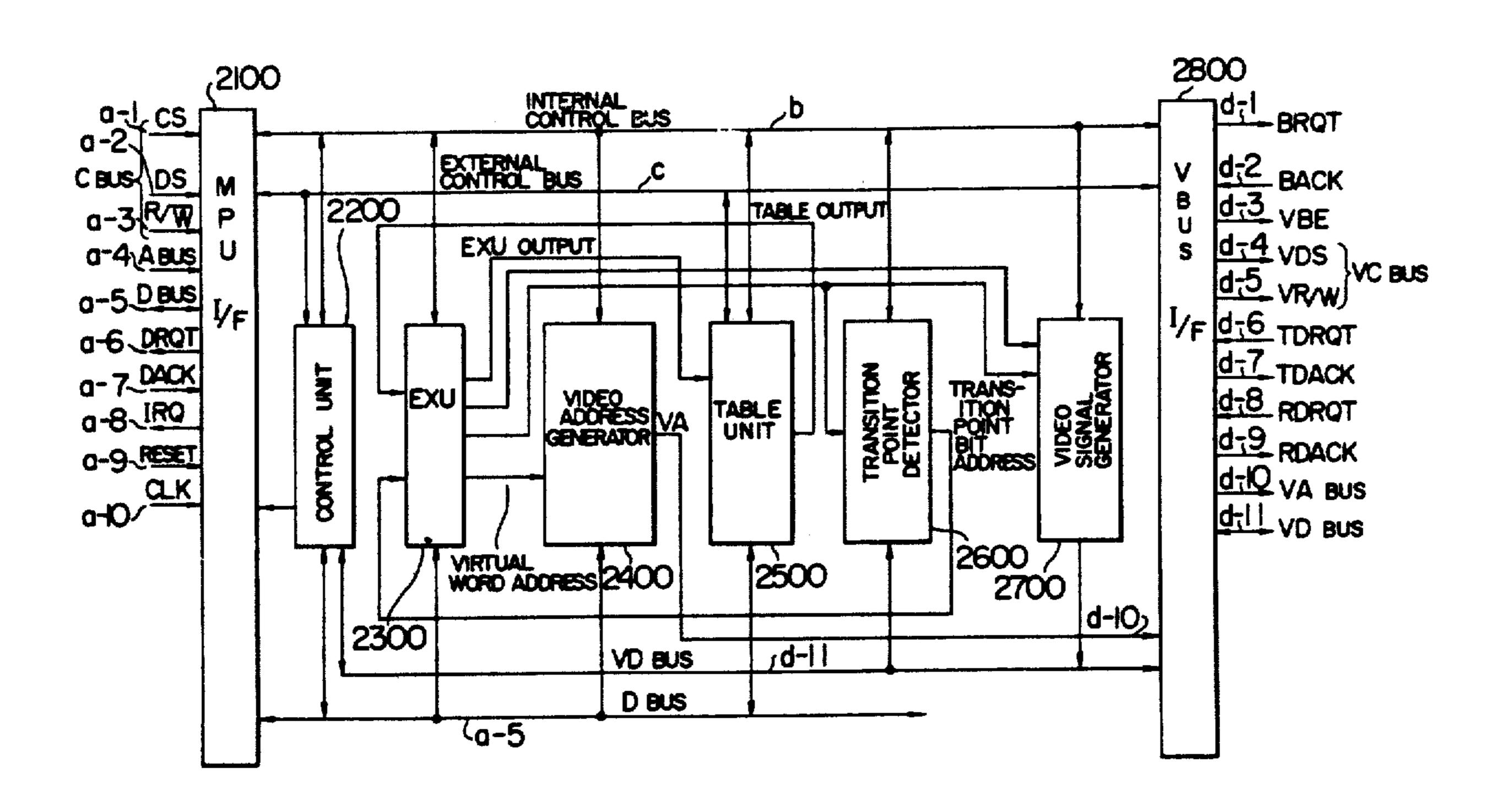

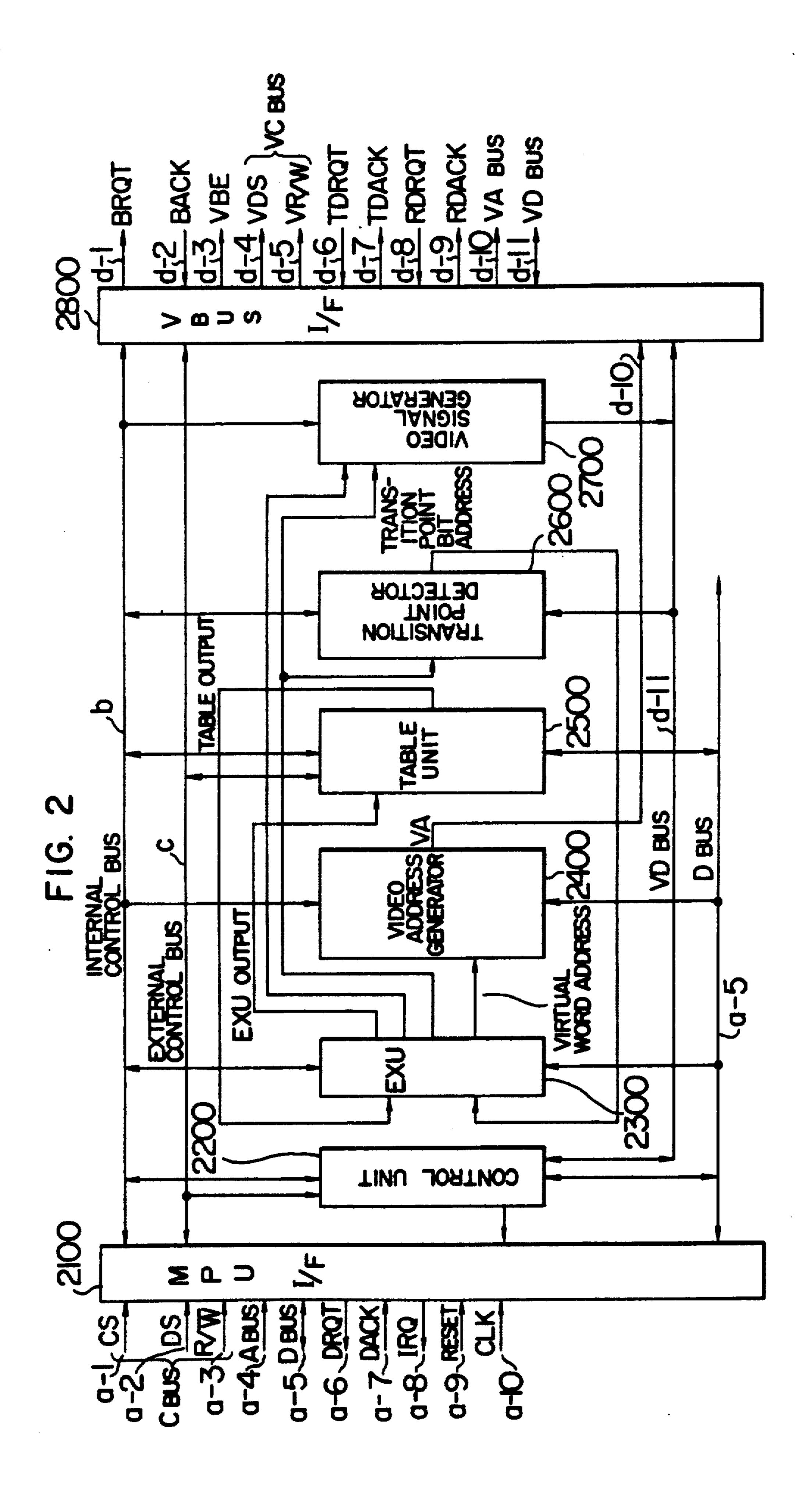

FIG. 2 is an overall block diagram of the encoder/decoder (Codec) of the present invention. An MPU I/F 2100 is an interface to a microcomputer and signals a-1-a-10 are inputted thereto and outputted therefrom. The signal a-1 is a chip select (cs) signal used when the microcomputer accesses the Codec. The signal a-2 is a timing signal (data strobe (DS) signal) used when data is transferred between the microcomputer and the Codec. The signal a-3 is a read/write (R/W) signal to select read or write operation from the microcomputer to the Codec. The signals a-1-a-3 are inputted from a control bus (C bus) of a microcomputer board. The signal a-4 is an address (A) signal from the microcomputer. A signal C (called an external control signal) to access registers in the Codec from the microcomputer is generated based on the signals a-1-a-4. The signal a-5 is used when the data (D) is exchanged between the microcomputer and the Codec and it is applied directly to a data bus (D) 60 bus) of the microcomputer. The signal a-6 is a DMA request (DRQT) signal to request a data transfer (direct memory access DMA) between the Codec and an external circuit (usually a memory), to a direct memory access controller (DMAC). The signal a-7 is a DMA acknowledge (DACK) signal signal to acknowledge to DRQT. After the Codec has sent out the DRQT signal, it waits for the DACK signal, and after it has received the DACK signal, it inputs and outputs the data in

3

synchronism with the DS signal. The signal a-8 is an interrupt request (IRQ) signal to the microcomputer. It is used, for example, when one line of processing has been completed. The signal a-9 is a reset signal to initialize the Codec. The signal a-10 is a clock (CLK) signal 5 which is a timing source in the Codec. Since the interface to the microcomputer by those signals is known by an LSI which is commercially available and directly coupled to the microcomputer, a further explanation is omitted here. Since the Codec has the MPU I/F 2100 10 and can be directly coupled to the bus of the microcomputer, a system configuration is easy and the size is reduced.

A control unit 2200 supplies timing signals to the hardwares in the Codec through an internal control bus 15 b and checks status of the hardwares to determine the next action. It primarily consists of microprograms. It will be further explained with reference to FIG. 3.

An execution unit (EXU) 2300 includes an ALU and registers and calculates a run length (RL) and a relative 20 difference between the transition points on the reference line and the encoding line based on the transition point addresses, and also carries out the reverse operation. It will be further explained with reference to FIG.

A video address (VA) generator 2400 generates the video address signal a-10 to a video memory (VM) which stores the video signal. It will be further explained with reference to FIG. 5.

A table unit 2500 comprises MH code/MR code 30 encoding table and decoding table. It converts the video signal to the MH code or MR code based on the RL and the relative difference supplied from the EXU 2300 and a mode signal supplied from the control unit 2200, and also carries out the reverse operation. It will be further 35 explained with reference to FIGS. 7 and 8 and Tables 1-3.

A transition point detector 2600 reads in the video signal, word by word, from a memory which stores the video signals of the reference line and the encoding line, 40 word by word, and parallelly detects the transition points in the word (called a bit address). It will be further explained with reference to FIGS. 9 and 10 and Table 4.

A video signal generator 2700 parallelly reproducing 45 the video signal, word by word, based on the bit addresses of the two adjacent transition points on the decoding line, information on a difference between the word addresses of the two transition points and color information on the video signal between the transition 50 points. It will be further explained with reference to FIGS. 11 and 12 and Table 5.

A video bus interface (VBUS I/F) 2800 inputs and outputs an interface signal to the VM which stores the video signal, a signal to control a video bus (V bus) and 55 a signal to transfer the video signal from an external device by the DMA. A signal d-1 is a video bus request (BRQT) signal to request a right to use the V bus when the Codec uses the V bus. It is issued when the unit other than the Codec has a right to use the V bus. A 60 signal d-2 is a video bus acknowledge (BACK) signal to acknowledge the BRQT signal d-1. A signal d-3 is a video bus enable (VBE) signal to indicate the use of the V bus by the Codec. A signal d-4 is a video data strobe (VDS) signal to indicate a timing for the transfer of the 65 video signal between the Codec and an external unit (usually the memory). The signal d-5 is a video bus read/write (V R/W) signal to inform the data transfer

4

from the Codec to the external unit or vice versa when the data is transferred between the Codec and the external unit. A signal d-6 is a transport data DMA request (TDRQT) to request the data transfer of the video signal from a video signal generator (usually a scanner of the facsimile) to the VM. A signal d-7 is a transport data DMA acknowledge (TDACK) signal to acknowledge the TDRQT signal. A signal d-8 is a receive data DMA request (RDRQT) signal to request the data transfer of the video signal from the VM to the video signal receiver (usually a recorder of the facsimile). A signal d-9 is a RDRQT acknowledge (RDACK) signal to acknowledge the RDRQT signal. A signal d-10 is a VA signal to the VM from the Codec. (VA stands for a word address.). A signal d-11 is a video data bus (VD) bus) signal to transfer the video signal word by word.

FIG. 3 shows a detail of the control unit 2200 an instruction register (IR) 2210 receives a macro-instruction such as an MH encoding instruction from an external unit (usually a microcomputer). A mapping ROM 2200 generates a start address of a ROM 2240 which stores a microprogram to be executed, based on the macro-instruction stored in the IR 2210. A sequencer 2230 generates an address of the microprogram ROM 25 2240 to control interruption, and subroutine and generate a jump address. A pipeline register 2250 stores a micro-instruction from the microprogram ROM 2240. An output of the pipeline register 2250 is supplied to the hardware as an operation command through an internal control bus b. A portion of the output is fed back to the sequence 2220 to control the sequencer 2200 such as interrupt enable/disable. A status register 2260 stores an internal status of the Codec. It informs the end of processing or a ready status of a data buffer register (DBR) 2280 to the microcomputer. A system control register (SCR) 2270 stores a signal to control the system of the Codec which signal is issued by the microcomputer. For example, it indicates whether the Codec occupies the V bus or not and specifies a line-by-line processing or a multi-line (page mode) processing. A multiplexor (MPX) 2290 connects a portion of an external control bus c to the internal control bus b when the Codec is idling or waiting and connects the signal from the pipeline register 2250 to the internal control bus b when the Codec is in other state. Thus, the microcomputer can access the register in the Codec controller by the internal control bus b. A DBR 2280 transfers data between the VD bus (signal d-11) and the D bus (signal a-5). When the microcomputer sets at the IR 2210 a data transfer command for the transfer of data between the system bus (S bus) and the V bus, for example the data transfer from the V bus to the S bus. VS is set in the DBR 2280 and a DBR ready flag of the SR 2260 is set. The microcomputer then reads the DBR 2280 to obtain VS. A similar operation is carried out when the direction of data transfer is opposite. This operation will be further explained later.

Since the control unit 2200 uses the microprogramming control scheme, it can offer flexible processing, and since the timing is centrally controlled by the control unit 2200, a design of an LSI chip is facilitated.

FIG. 4 shows a detail of the EXU 2300. A register file 2310 may be a 2-port random access memory which stores various signals. Let us assume that one word is equal to one byte. The register file 2310 comprises a virtual address register A channel (VARA) which stores an address of an encoding line in the encoding mode or of a decoding line in the decoding mode, a

virtual address register B channel (VARB) which stores an address of a reference line, a virtual address register C channel (VARC) which stores an address of a line (transfer line) when the video signal is transferred by DMA between the scanner or the recorder and the VM, 5 a temporary address register A (TARA) which stores a position of a transition point in the encoding line or the decoding line, and a temporary address register B (TARB) which stores an address of a transition point in the reference line. The addresses stored in those regis- 10 ters are virtual addresses with start points of the lines being virtually address zero. They stores both word addresses and bit addresses. The virtual addresses are used throughout the EXU 2300. By the use of the virtual addresses, a relative address difference between the 15 transition point in the reference line and the transition point in the encoding line can be obtained at a high speed. Since only a memory capacity to store the address regions in only the horizontal direction is required, the register file may be of small size and the 20 ALU 2350 may also be of small scale. Since the bit addresses are stored in the registers, the distance between the transition points can be obtained by bit at a high speed. The register file 2310 further includes a terminal register A, B channel (TRAB) and a terminal 25 register C channel (TRC) which stores the number of pixels in one line, a horizontal width register (HWR) which stores the number of pixels in a horizontal line of a screen, a line number register (LNR) which stores a line number to be processed, a minimum code length 30 register (MCLR) which stores the minimum number of code bits in one line, and general register A (GRA) and a general register B (GRB) which are working registers of the Codec. A detail of the use of those registers will be explained later in connection with microprogram 35 flows. An A latch 2320 and a B latch 2330 latch outputs from an A port and a B port of the register file 2310, respectively. An A mask 2341 and a B mask 2342 control masking or unmasking of the bit addresses of the outputs of the A latch 2320 and the B latch 2330, respec- 40 tively. An MPX 2344 selects the output of the A latch 2320 or an output of a table unit 2500 as an input to the A port of the ALU 2350. An MPX 2343 selects the output of the B latch 2330 or "8" as an input to the B port of the ALU 2350. The ALU 2350 calculates the 45 data inputted to the A port and the B port and produces an operation result, it or example A-B. An ALUSR 2360 stores a status of the operation result of the ALU 2350, for example, a zero flag, an overflow flag or an underflow flag. A comparator 2370 compares the out- 50 put of the ALU 2350 with the output of the B latch 2330. For example, the content of the VARA is latched in the A latch 2320, the content of the TRAB is latched in the B latch 2330, the output of the A latch 2320 masked by the A mask 2341 is applied to the A port of 55 ALU 2350 and informs the discrimination result to the the ALU 2350, "8" is applied to the B port of the ALU 2350 and an operation of (A port + B port) is carried out to increment the word address of the VARA. It is compared with the content of the TRAB to determine a line end. An MPX 2381 selects the output of the ALU 2350 60 or the transition point bit address from the transition point detector 2600 as low order three bits of a write data to the register file 2310. Thus, the transition point bit address can be stored in the register file 2310 at a high speed. An MPX 2382 selects the data on the D bus 65 or the output of the ALU 2350 as a write data to the register file 2310. Thus, the TRAB, TRC, HWR, LNR and MCLR can be set directly from the microcomputer

as parameters. As a result, the Codec can provide flexi ble processing. For example, when the content of the TRAB is set to be smaller than the content of the TRC a portion of the video signal from the scanner can be encoded. This will be further explained in connection with the microprogram flow.

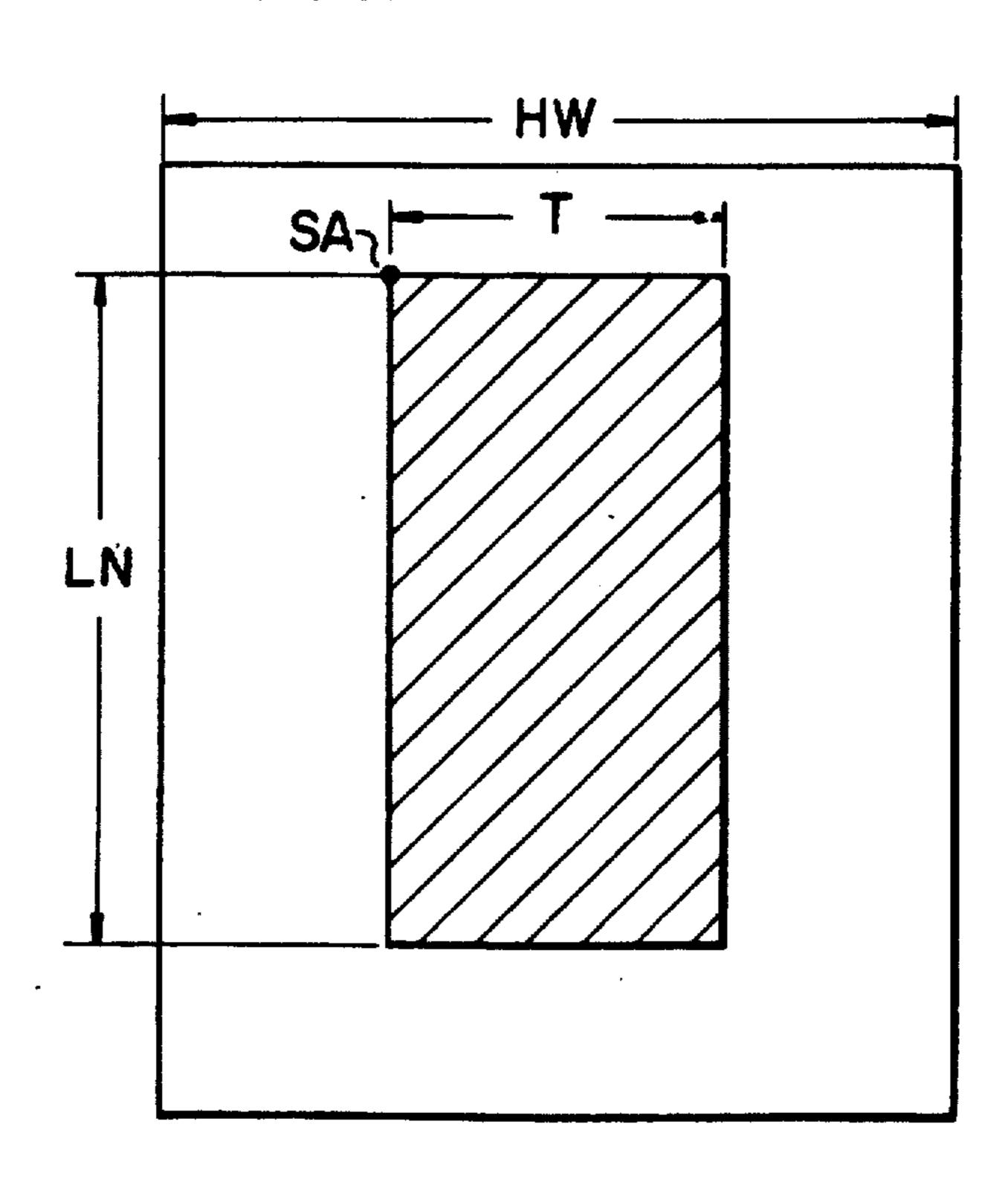

FIG. 5 shows a detail of the video address generato 2400. A register file 2410 comprises a start address regis ter A (SARA) which stores a real word address of the VM at a start point of the encoding or decoding line, start address register B (SARB) which stores a rea word address of the VM at a start point of the reference line and a start address register C (SARC) which store a real word address of the VM at a start point of a transfer line. An adder 2420 sums a start address of line in the register file and a virtual word address fron the EXU 2300 to generate a real word address of the VM (video address). The video address is latched in an address latch 2340 and thence outputted to the VA bus Any video address can be generated by the start addres and the virtual address. An MPX 2450 selects the signal d-11 on the VA bus or the signal a-5 on the D bus as a write data to the register file 2410. In a mode (called : ·line mode) in which the control is shifted to the mi crocomputer at each end of one line of processing, the start address is directly set by the microcomputer fo each line. In a mode (called a page mode) in which a number of lines set in the LNR are continuously pro cessed, the start address is set by the microcomputer a the beginning of the page and the Codec sums the star address in the register file 2410 and the content of the HWR in the register file 2310 and stores the sum as the next start address. In this case, since the microcompute sets the start address only once per page and the subse quent processing is carried out by the Codec, the load to the microcomputer is relieved. By setting appropriate values in the HWR, LNR, TR and SAR, any rectangu lar area in the screen can be processed by the Codec a a high speed. FIG. 6 illustrates the processing, in which HW denotes a horizontal width of the screen which i set in the HWR, LN denotes the number of lines to be processed which is set in the LNR, T denotes the num ber of pixels per line to be processed which is set in the TR, and SA denotes the start address of the VM at the beginning of the page which is set in the SAR. When a macrocommand is issued by the microcomputer, the Codec continuously processes the hatched area of FIG

FIG. 7 shows a detail of the encoding table unit of the table unit 2500. A latch 2501 latches an operation resul of the ALU 2350. A mode discriminator 2502 discrimi nates a mode in the encoding operation (for example whether RL is no smaller or smaller than 64 in the MF encoding operation) based on the operation result of the sequencer 2230. An address generator 2503 generates ar address to an encoding table ROM 2504 based on the signal from the internal control bus and the operation result of the ALU latched in the latch 2501. The output of the encoding table ROM 2504 is loaded to a shift register 2505, the content of which is shifted bit by bi and sequentially transferred to a serial/parallel (S/P) converter 2507. When eight bits have been transferred to the S/p converter 2507, they are written into a first-in first-out (FIFO) memory 2508. The transfer of the eigh bits of the code to the S/P converter 2507 is counted by the GRB of the EXU 2300 and the ALU 2350. Since i is counted by the ALU and the register without a

8

counter, the timing can be centrally controlled and the timing control is facilitated. A terminate detector 2506 detects an end of the code loaded to the shift register 2505. It will be further explained later. The FIFO memory 2508 serves to enhance a code transfer efficiency. 5 When the code is set in the FIFO memory 2508, a signal DRQT is outputted through the external control bus. When the DMAC is connected, the FIFO memory 2508 is accessed by the DACK. When the DMAC is not connected, the microcomputer directly reads the FIFO 10 memory 2508 to obtain the code. Since the code is directly outputted to the D bus, the system design is facilitated. Since the code is parallelly transferred, the timing control is facilitated.

pulse is applied to the shift register 2505, "0" is filled in the least significant bit position. For each shift, the most significant bit of the shift register 2505 is shifted to the S/P converter 2507. After four shifts, the content is (10000000000000)<sub>2</sub>. When this pattern is supplied to the terminate detector 2506, the termination is detected and it is informed to the sequencer. The number of times of the shift is counted by the GRA of the EXU 2300 so that it is stored in the GRA at the end of one line of encoding. The total number of bits in one line is compared with the number of bits in a minimum code in the MCLR to control the number of fill codes.

FIG. 8 shows a detail of the decoding table unit, a FIFO 2510 denotes a code receiving buffer. A parallel/-

TABLE 1

|            |            | <u> </u> |     | Ad  | dress                | •                     |            |                       | Data                                                                                                                                                                                                                  |

|------------|------------|----------|-----|-----|----------------------|-----------------------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>A</b> 8 | A-         | $A_{h}$  | A5  | A4  | Аз                   | <b>A</b> <sub>2</sub> | <b>A</b> 1 | <b>A</b> <sub>0</sub> | D <sub>13</sub> D <sub>12</sub> D <sub>11</sub> D <sub>10</sub> D <sub>9</sub> D <sub>8</sub> D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> |

| 0          | 0          | .)       | 25  | 24  | 2 <sup>3</sup>       | 22                    | 21         | <b>2</b> 0            | Terminating Code for white in MH code                                                                                                                                                                                 |

| 0          | Ü          | •        | 211 | 210 | RL<br>2 <sup>9</sup> | 28                    | 27         | 26                    | Make up Code for white in MH code                                                                                                                                                                                     |

| 0          | ł          | `        | 25  | 24  | RL<br>2 <sup>3</sup> | 2 <sup>2</sup>        | 21         | 20                    | Terminating Code for black in MH code                                                                                                                                                                                 |

| 0          | ŀ          |          | 211 | 210 | RL<br>29             | 28                    | 27         | 26                    | Make up code for black in MH code                                                                                                                                                                                     |

| 1          | <b>(</b> ) | 3        | 0   | 0   | RL<br>0              | 0                     | 0          | 0                     | VO Code for MR code                                                                                                                                                                                                   |

| 1<br>1     | 13         | : }      | 0   | Ô   | Õ                    | ĺ                     | 21         | 20                    | VL(1)-VL(3) codes for MR code                                                                                                                                                                                         |

| ٠          | 1,7        |          | Ū   | •   |                      |                       | Differ     | ence                  |                                                                                                                                                                                                                       |

| 1          | ( )        | ()       | 0   | 0   | 1                    | 0                     | 21         | 20                    | VR(1)-VR(3) codes for MR code                                                                                                                                                                                         |

| •          |            |          | -   | -   |                      |                       | Differ     | rence                 |                                                                                                                                                                                                                       |

| Į          | 11         | 0        | 0   | 0   | 1                    | 1                     | 0          | 0                     | P mode code for MR code                                                                                                                                                                                               |

| 1          | 0          | 0        | 0   | 0   | ļ                    | 1                     | 0          | 1                     | H mode code for MR code                                                                                                                                                                                               |

| ì          |            | 0        | 0   | 0   | 1                    | 1                     | 1          | 0                     | EOL                                                                                                                                                                                                                   |

| ì          | ţ.)        | 0        | 0   | 0   | 1                    | 1                     | 1          | 1                     | EOL + 1                                                                                                                                                                                                               |

| 1          | Ė          | 0        | 0   | 1   | 0                    | 0                     | 0          | 0                     | EOL + 0                                                                                                                                                                                                               |

Table 1 explains the encoding table ROM 2504. The 35 RL and the difference in the column of address use the operation result of the ALU 2350 as the address. Other portions are generated by the address generator 2503 based on the signal from the internal control bus. Since the operation result of the ALU 2350 is directly used as 40 the table address, the encoding table can be looked up quickly.

serial (P/S) converter 2511 supplies the code received 8-bit parallelly to an end of line (EOL) detector 2512 and an address generator 2513, bit serially. A counter function necessary to the P/S converter 2511 is carried out by the GRB of the EXU 2300. Thus, a counter which requires its own timing is not necessary. The EOL detector 2512 comprises a 12-bit S/P converter and a gate which detects whether the output of the S/P

TABLE 2

| Address |            |    |             |       |            |                       |    |             |                     |                 |                   | ata .           |                |                |                |       |                |            |                | <b>-</b> - |                |                |                             |

|---------|------------|----|-------------|-------|------------|-----------------------|----|-------------|---------------------|-----------------|-------------------|-----------------|----------------|----------------|----------------|-------|----------------|------------|----------------|------------|----------------|----------------|-----------------------------|

| A R     | <b>A</b> 7 | A6 | <b>A</b> 5  | A4    | <b>A</b> 3 | <b>A</b> <sub>2</sub> | Aı | <b>A</b> 0  | D <sub>13</sub>     | D <sub>12</sub> | Dil               | $D_{10}$        | D <sub>9</sub> | $\mathbf{D}_8$ | D <sub>7</sub> | $D_6$ | D <sub>5</sub> | $D_4$      | $D_3$          | $D_2$      | $\mathbf{D}_1$ | $\mathbf{D}_0$ | ···                         |

| 0       | 0          | 0  | 0           | 0     | 0          | 1                     | 0  | 0           | 1                   | 0               | )                 | 1               | 1              | 0              | 0              | 0     | 0              | 0          | 0              | 0          | 0              | 0              | ←MH code<br>White<br>RL = 4 |

|         |            | N  | umb         | er of | Tin        | ies                   |    |             |                     |                 |                   | 0               | utput          | of s           | hift           | regis | ter            | · <u>-</u> |                |            |                |                |                             |

|         |            | •  |             | f Shi |            |                       |    |             | $\overline{D_{13}}$ | D <sub>12</sub> | $\mathbf{D}_{11}$ | D <sub>10</sub> | D9             | Dß             | D <sub>7</sub> | $D_6$ | D <sub>5</sub> | $D_4$      | $\mathbf{D}_3$ | $D_2$      | Dį             | $\mathbf{D}_0$ | ····                        |

|         |            | _  | <del></del> | 0     |            |                       |    | <del></del> | 1                   | 0               | 1                 | 1               | 1              | 0              | 0              | 0     | 0              | 0          | 0              | 0          | 0              | 0              |                             |

|         |            |    |             | 1     |            |                       |    |             | Ō                   | ī               | 1                 | 1               | 0              | 0              | 0              | 0     | 0              | 0          | 0              | 0          | 0              | 0              |                             |

|         |            |    |             | 3     |            |                       |    |             | ì                   | 1               | 1                 | Ō               | 0              | 0              | 0              | 0     | 0              | 0          | 0              | 0          | 0              | 0              |                             |

|         |            |    |             | 2     |            |                       |    |             | 1                   | 1               | Ô                 | Õ               | Ō              | 0              | 0              | 0     | Ð              | 0          | 0              | 0          | 0              | 0              |                             |

|         |            |    |             | 4     |            |                       |    |             | 1                   | Ó               | Ŏ                 | Ö               | Ŏ              | 0              | 0,             | 0     | 0              | 0          | 0              | 0          | 0              | 0              | ←Detection of Terminate     |

Table 2 explains a method for encoding an MH code "1011" having an RL of 4 by using the table, sending the code to the S/P converter 2507 and detecting the 60 termination of the code by the terminate detector 2506. When the operation result of the ALU 2350 indicates that a white RL is 4 (=(100)<sub>2</sub>), an address of the table in (000000100)<sub>2</sub>. In the table 2504, a data (10111000000000)<sub>2</sub> is stored, starting from the high 65 order bit. The high order four bits represent the code, and "1" at the bit D<sub>9</sub> indicates the end of the code. This value is loaded in the shift register 2505. When a shift

converter is equal to (00000000001)<sub>2</sub> to determine if the received code pattern is the EOL or not. By providing the independent EOL detector 2512, the EOL can be positively and quickly detected even if a transmission error occurs and a disconnection of the code word is erroneously detected. An address generator 2513 generates an address for a decoding table ROM 2514. It generates a start address of the decoding table ROM 2514 and a next address based on the received code and the output of the decoding table ROM 2514. The decoding scheme uses a tree search system which is described in

Japanese Patent Application No. 55-174592 and briefly explained here with reference to Table 3. A latch 2515 temporarily stores the output of the decoding table ROM 2514.

circuit 2616. A priority encoder 2618 detects a position of the least significant "0" in the input data. When "0" exists in the data, a reference line transition point flag is set to "1" to inform the presence of the transition point

TABLE 3

|    |            |            |   |       | Addı       | ress       |                |                |                  |                       |            |                       | Da                   | ta             |                |                  |                |                                              |

|----|------------|------------|---|-------|------------|------------|----------------|----------------|------------------|-----------------------|------------|-----------------------|----------------------|----------------|----------------|------------------|----------------|----------------------------------------------|

| Ag | Ag         | <b>A</b> 7 | A | .6 A5 | <b>A</b> 4 | <b>A</b> 3 | A <sub>2</sub> | $\mathbf{A}_1$ | <b>A</b> 0       | D <sub>7</sub>        | $D_6$      | D <sub>5</sub>        | D <sub>4</sub>       | $\mathbf{D}_3$ | D <sub>2</sub> | $\mathbf{D}_{1}$ | $\mathbf{D}_0$ | Remarks                                      |

| 0  | 0          |            |   |       |            |            |                | •              | Received<br>Code | A <sub>7</sub>        | <b>A</b> 6 | <b>A</b> <sub>5</sub> | A4                   | <b>A</b> 3     | A <sub>2</sub> | Aı               | 0              | Decoding of MH white code not completed.     |

|    |            |            |   | Outpu | t fro      | m tal      | ble            |                |                  |                       |            | Next                  | Table                | : Ad           | dress          |                  |                |                                              |

|    |            |            |   |       |            |            |                |                |                  | •                     |            | _                     | 2 <sup>3</sup>       |                |                | _                |                | Decoding of MH white terminating code        |

|    |            |            |   |       |            |            |                |                |                  |                       |            | 10                    | RI<br>2 <sup>9</sup> | -              | -              |                  |                | completed                                    |

|    |            |            |   |       |            |            |                |                |                  | ì                     | 211        | 210                   | 29                   | 28             | 2'             | 20               | 1              | Decoding of MH white make-up code completed. |

|    |            |            |   |       |            |            |                |                |                  |                       |            |                       | RL                   |                |                |                  |                | •                                            |

| 0  | 1          |            |   |       |            |            |                |                | Received code    | A <sup>7</sup>        | <b>A</b> 6 | <b>A</b> <sub>5</sub> | A4                   | $A^3$          | A <sup>2</sup> | Al               | 0              | Decoding of MH black code not completed      |

|    |            |            |   | Outpu | t fro      | m tal      | ble            |                |                  |                       |            | Next                  | Table                | Add            | dress          |                  |                | •                                            |

|    |            |            |   |       |            |            |                |                |                  | 0                     | 25         |                       | 23                   |                |                |                  | 1              | Decoding of MH black<br>terminating code     |

|    |            |            |   |       |            |            |                |                |                  |                       |            |                       | RI                   |                |                |                  |                | completed                                    |

|    |            |            |   |       |            |            |                |                |                  | 1                     | 211        | 210                   | 29                   | 28             | 27             | 26               | ì              | Recording of black                           |

|    |            |            |   |       |            |            |                |                |                  |                       |            |                       |                      |                |                |                  |                | make-up code completed.                      |

| 1  | 0          |            |   |       |            |            |                |                | Received code    | <b>A</b> <sup>7</sup> | <b>A</b> 6 | A <sup>5</sup>        | A4                   | <b>A</b> 3     | $\mathbf{A}_2$ | $\mathbf{A}_1$   | 0              | Decoding of MR code not completed.           |

|    |            |            |   | Outut | fron       | n tah      | م[             |                | Code             | 0                     | 0          | 0                     | 0                    | 0              | 0              | 0                | n              | Decoding of VO code                          |

|    |            |            |   | 00.00 |            |            | 10             |                |                  | _                     | Ū          | ŭ                     | •                    | •              |                | Ū                |                | completed.                                   |

|    |            |            |   |       |            |            |                |                |                  | 0                     | 0          | 0                     | 0                    | 1              | 21             | 20               | l              | Decoding of VL(1)-                           |

|    |            |            |   |       |            |            |                |                |                  |                       |            |                       |                      |                |                |                  |                | VL(3)completed.                              |

|    |            |            |   |       |            |            |                |                |                  |                       |            |                       |                      | 1              | Diffe          | renc             | e              |                                              |

|    |            |            |   |       |            |            |                |                |                  | 0                     | 0          | 0                     | 1                    | 0              | 21             | 20               | l              | Decoding of                                  |

|    |            |            |   |       |            |            |                |                |                  |                       |            |                       |                      |                |                |                  |                | VR(1)-VR(3)completed.                        |

|    |            |            |   |       |            |            |                |                |                  | 0                     | 0          | 0                     | 1                    | 1              | 0              | 0                | 1              | Decoding of P                                |

|    |            |            |   |       | •          |            |                |                |                  |                       |            |                       |                      |                |                |                  |                | completed                                    |

|    |            |            |   |       |            |            |                |                |                  | 0                     | 0          | 0                     | 1                    | 0              | 0              | 1                | 1              | Decoding of H                                |

|    | . <u>.</u> |            |   |       |            |            |                |                |                  |                       |            | -                     |                      |                |                |                  |                | completed                                    |

Table 3 explains the decoding table ROM 2514. It is constructed to decode in a tree search system. The 40 decoding table ROM 2514 has its addresses divided into three portions, MH white code portion, MH black code portion and MR code portion. The content of the decoding table ROM 2514 is a portion of the address of the decoding table ROM 2514 to be next accessed when the 45 decoding is not completed or at an intermediate point of the code word, and it is information of the code when the code word is terminated and the decoding is completed. The sequencer 2230 looks up the decoding table ROM 2514 once per code bit to determine the meaning 50 of the decoded code based on the output of the ROM 2514. Since the information of the decoded code is applied directly to the A port of the ALU 2350 through the MPX 2344, the position of the transition point can be quickly determined.

FIG. 9 shows a detail of the transition point detector 2600 which comprises a reference line transition point detector 2610 and an encoding line transition point detector 2620. Since the operations of those detectors are essentially identical, the reference line transition 60 point detector 2610 is explained. An MPX 2614 selects one of the data VS from the VD bus, the data  $\overline{VS}$  which is an inversion of the data on the VD bus and the data from the latch 2617. A mask circuit 2616 functions to change bits of the data supplied from the MPX 2614 to 65 "1's" up to a bit position specified by the bit address BA. It will be explained in detail with reference to FIG. 10. A latch 2617 temporarily stores the output of the mask

to the sequencer 2230. The position of "0" is outputted to the EXU 2300 as a transition point bit address. Since the bit address is inputted directly to the register file 2310, the bit address of the transition point can be quickly stored. The transition point bit address is outputted to the mask circuit 2616 through an MPX 2619 as the bit address BA. The MPX 2619 selects the B port bit address from the B latch 2330 of the EXU 2300 or the transition point bit address from the priority encoder 2618. The B port bit address is selected only when a start bit address for the detector of the reference line transition point is to be set to a bit address of the encoding line transition point (this being called a reference line address return). This will be further explained with reference to the microprogram flow. An exclusive OR 55 (EXOR) 2611 receives a color signal of the start point of encoding (a<sub>0</sub>) and a signal  $\overline{b_1}/b_2$  which selects whether the reference line transition point b<sub>1</sub> or b<sub>2</sub> is to be selected, where b<sub>1</sub> is the transition point for the opposite color to a<sub>0</sub> on the right of a point immediately above a<sub>0</sub>, and b<sub>2</sub> is the transition point for the same color as a<sub>0</sub> on the right of b<sub>1</sub>, and it controls the MPX 2614. A gate 2612 causes the MPX 2614 to select the output of the latch 2617 only when the transition point flag is "1" and the reference line address return is "0". An OR gate 2613 enables the mask circuit 2616 when the transition point flag is "1" or the address return is "1". FIG. 10 shows a detail of the mask circuit 2616 which comprises a decoder 2616-1 and NAND gates 2616-2-2616-8.

**TABLE 4**

| _                  |                | Initial condition  VS = (0 0 1 1 1 0 0 0) <sub>2</sub> , a <sub>0</sub> color = "0", b <sub>1</sub> /b <sub>2</sub> = "0"  Transition point flag = "0", Address return = "0" |             |       |       |            |                |       |                          |                  |       |                |       |       |    |       |            |         |

|--------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------|------------|----------------|-------|--------------------------|------------------|-------|----------------|-------|-------|----|-------|------------|---------|

| Number of times of |                |                                                                                                                                                                              | <del></del> |       |       | input data |                |       | Mask circuit output data |                  |       |                |       |       |    |       | Transition | Bis     |

| latching           | D <sub>7</sub> | $D_6$                                                                                                                                                                        | $D_5$       | $D_4$ | $D_3$ | $D_2$      | $\mathbf{D}_1$ | $D_0$ | $D_7$                    | $\mathbf{D}_{6}$ | $D_5$ | D <sub>4</sub> | $D_3$ | $D_2$ | Di | $D_0$ | point flag | address |

| 1                  | 0              | O                                                                                                                                                                            | 1           | ]     | 1     | 0          | 0              | 0     | 1                        | 1                | 0     | 0              | 0     | 1     | 1  | 1     | 1          | 3       |

| ż                  | i              | 1                                                                                                                                                                            | Ó           | 0     | Ō     | 1          | 1              | ł     | 0                        | 0                | 1     | 1              | 1     | 1     | 1  | 1     | ì          | 6       |

|                    | 0              | 0                                                                                                                                                                            | 1           | 1     | l     | 1          | 1              | 1     | 1                        | 1                | 1     | 1              | 1     | 1     | i  | 1     | 0          |         |

Table 4 shows an example of operation of the transition point detector. As an initial condition, it is assumed that  $VS = (0\ 0\ 1\ 1\ 1\ 0\ 0\ 0)_2$ ,  $a_0 \text{ coder} = "0"$ ,  $\overline{b}_1/b_2 = "0"$ , reference line transition point flag = "0" and reference 15 line address return ="0". At the first time of latching, the outputs of the EXOR 2611 and the gate 2612 are "0" because of the initial condition, and the input data to the mask circuit 2616 is VS. Since the mask circuit enable signal E is "0", the output of the mask circuit 2616 is a 20 mere inversion of the input data. Accordingly, (1 1 0 0 0 1 1 1)2—is latched in the latch 2617. Thus, the priority encoder 2618 outputs the reference line transition point flag "1" and the reference line transition point bit address "3". At the second time of latching, the reference 25 line transition point flag is "1" and the output of the gate 2612 is "1" and the input data to the mask circuit 2616 is the output data of the latch 2617 or (1 1 0 0 0 1 1 1)2. Since the mask circuit enable signal E is "1", the mask circuit 2616 inverts the input data and outputs the data 30 (0 0 1 1 1 1 1 1)<sub>2</sub> in which the bits are changed to "1's" up to the bit position specified by the reference line bit address. As a result, the transition point bit position "6" is obtained. The latch operation is repeated in a similar manner until the transition point no longer exists so that 35 the transition point bit address is obtained. In this manner, the transition point detector can detect the transition point bit address at any position in the eight bits by one latching operation, and can detect the transition point faster than a method in which each bit is checked 40 after the bits were latched. Further, since no counter is used to check the transition point bit address, the timing can be controlled by the control unit 2200 and hence the LSI design is facilitated.

FIGS. 11 and 12 and Table 5 explain a detail of the 45 video signal generator 2700.

A video signal generating circuit 2701 receives the bit addresses at the start point and the end point of reproducing from the bit addresses of the A port and the B port of the EXU 2300, and receives a word address 50 difference between the start point and the end point or reproducing based on the operation result of the ALU 2350 to generate a decoded data. FIG. 11 shows a detailed circuit thereof and Table 5 shows a truth table. A word address difference can be obtained by latching the 55 address at the start point of reproducing in the A latch 2320, latching the address at the end point of decoding in the B latch 2330, activating the A mask 2341 and the B mask 2342 to supply those addresses to the ALU 2350, and carrying out an operation of (B-A) and check- 60 ing the resulting difference. By providing the circuits 2342 and 2343 which mask the bit address in the EXU 2300, the presence or absence of the word address difference can be quickly determined in one arithmetic operation in spite of the fact that the bit address and the 65 word address are stored in the file register 2310. FIG. 12 shows a detail of the video signal generating circuit 2701 which comprises circuit units 2701-1 and 2701-2

and AND gates. The operation of the circuit is shown by the truth table of Table 5.

|                         |                    |   | TA | BLI                   | Ξ 5              |                       |                |                |       |                |                |

|-------------------------|--------------------|---|----|-----------------------|------------------|-----------------------|----------------|----------------|-------|----------------|----------------|

| a <sub>0</sub><br>color | Word<br>difference | В | A  | <b>D</b> <sub>7</sub> | $D_6$            | <b>D</b> <sub>5</sub> | D <sub>4</sub> | $\mathbf{D}_3$ | $D_2$ | $\mathbf{D}_1$ | $\mathbf{D}_0$ |

| 0                       | <del></del>        |   |    | 0                     | 0                | 0                     | 0              | 0              | 0     | 0              | 0              |

| 1                       | 0                  | у | X  |                       | $\mathbf{D}_{x}$ | - D <sub>y</sub>      | - 1 a          | re "1<br>"0".  | l", o | thers          |                |

| 1                       | 1                  | _ | x  |                       | D                | <sub>x</sub> - D      |                | e "1"<br>"0"   |       | ners           |                |

—: either "0" or "1"

When the a<sub>0</sub> color is "0", all outputs are "0's", and when the ao color is "1" and there is no word address difference, the bits  $D_x - D_{y-1}$  are "1's" and are "0's", where x in the A port bit address and y the B port bit address, and then the ao color is "1" and there is a word address difference, the bits  $D_x$ — $D_7$  are "1's" and others are "0's". In this manner, the reproduced video signal in the word can be generated in one operation. It is faster than a method in which the signal is generated bit by bit by using a counter, and easy to control the timing. A temporary register 2702 stores the decoded video signal in an immediately previous cycle and it is cleared when one word of decoded video signal is written into the memory. An OR circuit 2703 OR's the output of the video signal generating circuit 2701 and the output of the temporary register 2702 so that the video signal in one word is successively reproduced. A latch circuit 2704 latches one word of reproduced video signal and outputs the reproduced video signal to the VD bus. The reproduced video signal is written into the VM one word at a time. In this manner, the video signal generator 2700 reproduces the video signal fully parallelly so that the video signal is reproduced quickly.

The hardware configuration and the operation of the Codec have been explained with reference to FIGS. 2 to 12 and Tables 1 to 5. The operations of the Codec in various processing modes will now be explained with reference to status transition charts shown in FIGS. 13 to 15.

FIG. 13 shows the status transition chart in the encoding and decoding mode. S<sub>I</sub> indicates an idling status. In the S<sub>I</sub> status, when a microcommand (e.g. an MH encoding command) is issued after setting of an appropriate parameter from the microcomputer, the status transits to S<sub>I</sub> in which one line of given processing is executed. A detail of the operation in this state will be explained with reference to the microprogram flow. The processing in the S<sub>I</sub> status is continuously executed until one line of processing is completed, when an end of processing flag is set if a page mode is not set, and the status returns to S<sub>1</sub>. If the page mode is set, the status shifts to S<sub>2</sub> in which the content of the SAR and the content of the HWR are added and the sum is stored in the SAR to update the start address and the LNR is

14C. 33,032

decremented to determine the page end. If the content of the LNR is not zero, it is determined that it is not the page end and the status returns to  $S_1$ . If it is the page end, the status returns to  $S_1$ . Since the microcomputer needs only issue one microcommand per line or page, 5 the load to the microcomputer is relieved.

FIG. 14 shows the status transition chart in a line mode when a VM read microcommand is issued. This command is issued when the system bus of the microcomputer is isolated from the video bus and the 10 microcomputer accesses the VM on the video bus. The status  $S_I$  is the idling status. If an appropriate parameter is set from the microcomputer and the VM read command is issued, the status shifts to  $S_1$ . In the status  $S_1$ , if the Codec has an exclusive right to occupy the V bus, 15 the status immediately shifts to  $S_2$ . If the Codec does not have the exclusive right to occupy the V bus, the BRQT signal is issued and when the BACK signal is sent back, the status shifts to  $S_2$ . In the status  $S_2$ , the content of the SAR and the content of the VAR are added and the 20 same is outputted as the video address. The VR/W and the VDS are outputted and the VS from the VM is latched in the DBR, and the DBR ready flag is set, the BRQT is released and the status shifts to S<sub>3</sub>. In the status S<sub>3</sub>, the reading of the DBR by the microcomputer or 25 the input of the DACK signal from the DMAC is checked. If the DBR is accessed, the DBR ready flag is reset and the VAR is incremented. If the line end is detected, the status shifts to  $S_I$ , and if the line end is not detected, the status shifts to S<sub>1</sub>. In this manner, the 30 microcomputer can access the memory on the V bus through the DBR. Since the video address is generated by the Codec, the microcomputer having a small address space can access a large memory. Since the video address is automatically incremented by the Codec, the 35 VM can be quickly accessed.

FIG. 15 shows the status transition chart when the data is transferred between the scanner or the recorder and the VM. The data transfer is executed not by the microcommand from the microcomputer but by the 40 TDRQT or the RDRQT from the scanner or the recorder. Since those signals are applied to the sequencer 2230 as an interrupt signal, the data can be transferred during the execution of the operation shown in FIGS. 19 or 20. In the status  $S_I$ , the end of transfer flag is in a 45 set state. If the start address of the VM is set to the SARC from the microcomputer, the status shifts to  $S_1$ . In the status S<sub>1</sub>, the TDRQT or the RDRQT is acceptable. If the TDRQT or RDRQT signal is issued in the status  $S_1$ , the status shifts to  $S_2$ . In the status  $S_2$ , if the 50 Codec has the exclusive right to occupy the V bus, it has no sense and the status immediately shifts to S<sub>3</sub>. If the Codec does not have the exclusive right, the BRQT signal is issued in the status S<sub>2</sub> and when the BACK signal is sent back, the status shifts to S<sub>3</sub>. In the status S<sub>3</sub>, 55 the TDACK signal or the RDACK signal is issued to inform the start of the data transfer to the scanner or the recorder, and the status shifts to S4. In the status S4, the video address, the  $VR/\overline{W}$  and the VDS are outputted, the VD is transferred and then the BRQT is released 60 and the status shifts to S<sub>5</sub>. In the status S<sub>5</sub>, the VRAC is incremented. If the line end is not detected, the status returns to S<sub>1</sub>. If the line end is detected and it is not in the page mode, the end of transfer flag is set and the status returns to  $S_I$ . If the line end is detected and it is in 65 the page mode, the status shifts to  $S_6$ . In the status  $S_6$ , the start address is updated and the LNR is decremented. If the page and is not detected, the status shifts

to  $S_1$ . If the page end is detected, the end of transfer flag is set and the status returns to  $S_I$ . As described above, since the data can be transferred during the encoding operation, a high speed processing is attained. Since the data transfer is effected fully parallelly, the data can be transferred fastly with a low speed memory.

The internal operation of the Codec is now explained in further detail with reference to the microprogram flow for the MR encoding and decoding operations. The MR code system is first briefly explained with reference to FIG. 16.

FIG. 16 explains the MR code system, in which FIG. 16(a) explains a definition of the transition point. It shows states of pixels in the reference line and the encoding line. Hatched pixels represent black pixels, and ao represents the start point of encoding, a1 and a2 represent the transition points in the encoding line, bo represents a point in the reference line located immediately above ao, bo represents a first transition point in the reference line for the opposite color to a<sub>1</sub>, located on the right of b<sub>0</sub>, and b<sub>2</sub> represents a first transition point in the reference line for the same color as ao, located on the right of b<sub>1</sub>. The MR code is categorized into a pass mode (P mode), a vertical mode (V mode) and a horizontal mode (H mode). FIG. 16(b) shows the P mode. In the P mode, b<sub>1</sub> and b<sub>2</sub> appear before a<sub>1</sub> appears. In the P mode encoding, a new ao is set immediately below b2.

FIG. 16(c) shows the V mode. In the V mode, the requirement of the P mode is not met and an absolute value of distance between  $a_1$  and  $b_1$  (called a relative address difference or difference) is no larger than three. When the difference between  $a_1$  and  $b_1$  is "0", it is a V(0) code, when  $a_1$  is on the left of  $b_1$ , it is a VL (difference) code, and when  $a_1$  is on the right of  $b_1$ , it is a VR (difference) code. In the illustrated example, it is encoded as VR(2). After the encoding,  $a_1$  is set as a new  $a_0$ .

FIG. 16(d) shows the H mode. When the requirement of the P mode is not met and the difference between all and ble exceeds three, the H code is outputted and the RL between all and all is MH encoded, and then the RL between all and all is MH encoded. After encoding, all is set as a new all.

TABLE 6

| Register | Function                                                                  |

|----------|---------------------------------------------------------------------------|

| VARA     | Current scan address (a <sub>0</sub> - a <sub>2</sub> ) of encoding line  |

| VARB     | Current scan address (b <sub>0</sub> - b <sub>2</sub> ) of reference line |

| TARA     | Address of a <sub>0</sub> or a <sub>1</sub> of encoding line              |

| TARB     | Address of by of reference line                                           |

| GRA      | Number of bits of one line of code                                        |

| GRB      | 8-bit counter                                                             |

| SARA     | Start address of encoding line (word by word)                             |

| SARB     | Start address of reference line (word by word)                            |

| TRAB     | Number of pixels in one line (word by word)                               |

Table 6 shows functions of the registers in the MR encoding. The VARA stores the virtual word address and the bit address of the encoding line under scan. The VARB stores the virtual word address and the bit address of the reference line under scan. The TARA stores the virtual word address and the bit address of ao or a<sub>1</sub>. The TARB stores the virtual word address and the bit address of b<sub>1</sub>. The GRA stores the number of code bits in one line. The GRB stores the 8-bit of the S/P converter 2507. The SARA stores the real word

address at the start point of scan of the VM which stores the data of the encoding line. The SARB stores the real word address at the start point of scan of the VM which stores the data of the reference line.

FIGS. 17 to 22 show a portion of the microprogram flow in the MR encoding. It is assumed that the Codec has the exclusive right to occupy the V bus. When the Codec receives the MR encoding macro-command from the microcomputer at the IR 2210, the sequencer 2230 outputs an address to execute a step 6101 to start 10 the MR encoding. The microprogram ROM 2240 outputs a bit pattern of the microprogram for executing the step 6101, specified by the sequencer 2230 to the pipeline register 2250 so that the processing is started. The the ALU 2350 is reset to zero and it is written into the VARA to clear the VARA, and the ao color is set to white. In a step 6102, a b<sub>1</sub> detection mode is set. It means that the signal  $\overline{b}_1/b_2$  to the EXOR 2611 is set to "0" (white="0"). In a step 6103, the VARB is latched in the 20 A latch 2320, the output of the A latch 2320 of the SARB is added thereto and the sum is latched in the address latch 2430, which is outputted to the VA bus to change the VR/W signal to the read signal, and the VDS is outputted to access the VM and the VS is 25 latched in the latch 2617. This sequence of operation is called VS input of the reference line. Similarly, in a step 6104, the VS of the encoding line is received and latched in the latch 2624. In a decision step 6105, the presence or absence of the transition point is checked. If 30 the transition point exists in the input VS, the priority encoders 2618 and 2625 inform it to the sequencer. Thus, the sequencer determines the presence or absence of the transition point and can jump to a processing block. If the transition point does not exist, the process 35 goes to a step 6106. In the step 6106, the byte addresses of the VARA and the VARB are incremented. For the VARA, it is latched in the A latch 2320, the A mask 2341 is activated and the output thereof is applied to the A port of the ALU 2350, "8" is applied to the B port, 40 the operation (A + B) is executed and the output of the ALU 2360 is written into the VARA. As a result, the byte address of the VARA is incremented and the bit address of the VARA is cleared. When the VARA is latched in the A latch 2320, the TRAB is also latched in 45 the B latch 2330 so that the line end can be determined by the comparator 2370 when the VARA is incremented. The VARB is incremented in the same manner. In a decision step 6107, the line end is checked, and if it is not the line end, that is, if the line end flag of the 50 comparator is not "1", the sequencer outputs the address of the step 6103 so that the process returns to the step 6103 and the above processing is repeated. If the line end is detected, a V(0) code output subroutine is called in a step 6108 and the line end processing is 55 started. The line end processing includes fill control which is not explained here. If the transition point exists in only the encoding line, the process jumps to a step 6201, if the transition point exists in only the reference line, the process jumps to a step 6301, and if the transi- 60 tion points exist in both lines, the process jumps to a step 6401. Since the video address of the encoding line and the video address of the reference line are alternately outputted for scan, even if the encoding line and the reference line coexist in the same VM, they are scanned 65 as if the encoding line and the reference line are simultaneously scanned at the same relative position. If the transition point of the reference line should be detected

after the detection of the transition point of the encoding line, the encoding in the pass mode would be delayed. If the transition point of the encoding line should be detected after the detection of the transition point of the reference line and b<sub>1</sub> is distant from a<sub>1</sub> on the right

16

of a<sub>1</sub>, the encoding would be delayed.

In the step 6201, the bit address of the transition point of the encoding line is stored. It is realized by latching the content of the VARA in the A latch 2320, supplying it to the A port of the ALU 2350 to carry out the operation (A+O), controlling the MPX 2381 such that the bit address of the transition point of the encoding line from the transition point detector 2600 is applied to the low order three bits of the file register 2310 and writing it step 6101 is an initialization step in which the output of 15 into the VARA. Thus, only the bit address of the VARA is used as the bit address of the transition point of the encoding line and the position of a<sub>1</sub> is stored in the VARA without changing the word address. In a step 6202, the word address of the VARB is incremented. In a decision step 6203, the reference line is checked to determine if it is the line end or not. If it is the line end, the process goes to a step 6207 where the incremented value is stored in the TARB as b<sub>1</sub>. If it is not the line end, the process goes to a step 6204 where the VS of the reference line is inputted. In a decision step 6205, the presence or absence of b<sub>1</sub> in the reference line is checked. If the transition point does not exist, it means that the difference between a<sub>1</sub> and b<sub>1</sub> is eight or more, and the Hencoding is started. Since the encoding line and the reference line are scanned parallelly, the H mode can be determined before the transition point of the reference line is detected. If the transition point exists, the process goes to a step 6206 where the position of b<sub>1</sub> is stored in the TARB. It is readized in the same manner as that in which all is stored in the VARA. In a step 6208, an operation  $(b_1-a_1=difference)$  is carried out. It is realized by latching the VARA in the A latch 2320, latching the TARB in the B latch 2330, deactivating the mask and applying the outputs of those latches to the A and B ports of the ALU 2350 to carry out an operation (B - A). The output of the ALU 2350 is latched in the latch 2501 and whether the difference is equal to or smaller than three or not is checked by the mode discriminator 2502. If the difference is equal to or smaller than three, the VL encoding is started and if the difference is larger than three, the H encoding is stored.

If the transition point exists in only the reference line in a decision step 6105, the process goes to a step 6301. In the step 6301, b<sub>1</sub> is stored in the TARB. In a step 6302, a b<sub>2</sub> detection mode is set. In a step 6303, a latch pulse is applied to the latch 2617 of the reference line transition point detector 2610 to detect if b2 exists in addition to b1 in the VS of the reference line inputted in the step 6103. This operation is called interbyte transition point detection. This operation was explained in detail with reference to FIG. 9. In a decision step 6304, the presence or absence of b2 is checked. If b2 exists, it means that both b<sub>1</sub> and b<sub>2</sub> exist before a<sub>1</sub>, and the P encoding is started. If b2 does not exist, the process goes to a step 6305. In the steps 6305 and 6306, the byte addresses of the VARB and the VARA are incremented. In a decision step 6307, the line end is checked, and if it is the line end, the process goes to a step 6319, and if it is not the line end, the process goes to a step 6308. In the steps 6308 and 6309, the VS of the reference line and the VS of the encoding line are applied to the transition point detector 2600 to detect b2 and a1. If the transition point does not exist, the process goes to a step