# Hayashi

[45] Reissued Date of Patent: Jan. 24, 1989

# [4] PERIOD AND FREQUENCY MEASURING INSTRUMENT

# [75] Inventor: Mishio Hayashi, Saitama, Japan

[73] Assignee: Advantest Corporation, Gyoda, Japan

[21] Appl. No.: 13,060

[22] Filed: Feb. 10, 1987

## Related U.S. Patent Documents

#### Reissue of:

[64] Patent No.: 4,544,884

Issued: Oct. 1, 1985

Appl. No.: 531,711

Filed: Sep. 13, 1983

####

| * | 7 | <br> |  | <br> |

|---|---|------|--|------|

|   |   |      |  |      |

|   |   |      |  |      |

|   |   |      |  |      |

|   |   |      |  |      |

|   |   |      |  |      |

# [56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,133,189 | 5/1964  | Bagley et al      |

|-----------|---------|-------------------|

| 4,112,358 | 9/1978  | Ashida .          |

| 4,150,432 | 4/1979  | Sorden            |

| 4,216,463 | 8/1980  | Backof 324/78 D   |

| 4,257,003 | 3/1981  | Yool 324/78 D     |

| 4,301,405 | 11/1981 | Carlson           |

| 4,310,800 | 1/1982  | Baker             |

| 4,330,746 | 5/1982  | Stulting 324/79 D |

| 4,350,950 | 9/1982  | Waldmann 324/78 D |

| 4,456,876 | 6/1984  | Havmaker          |

#### OTHER PUBLICATIONS

"Automatic Measurements with a High-Performance Universal Counter", Sep., 1980, Hewlett-Packard Journal, by Gary D. Sasaki & Ronald C. Jensen, pp. 21-28.

Primary Examiner—Michael J. Tokar Attorney, Agent, or Firm—Staas & Halsey

# [57] ABSTRACT

A device for determining with high accuracy the period and frequency of an input signal by taking into account the fractions of a clock signal that are normally ignored. A gate signal with an integral number of clock pulses is generated. Each fractional time is accurately measured by first and second integrators, and an up-down counter provides the difference between the fractional times for the final determination.

# 10 Claims, 2 Drawing Sheets

Jan. 24, 1989

# PERIOD AND FREQUENCY MEASURING INSTRUMENT

Matter enclosed in heavy brackets [ ] appears in the 5 original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

### **BACKGROUND OF THE INVENTION**

This invention relates to a period and frequency measuring instrument which measures period and frequency of a relatively low frequency input signal with high accuracy.

In measuring frequency or period of an input signal of 15 relatively low frequency by a period and frequency measuring instrument, the input signal is used as a gate signal for gating internal clock signals to a counter which counts the number of clock pulses to determine the period and thus the frequency of the input signal. 20

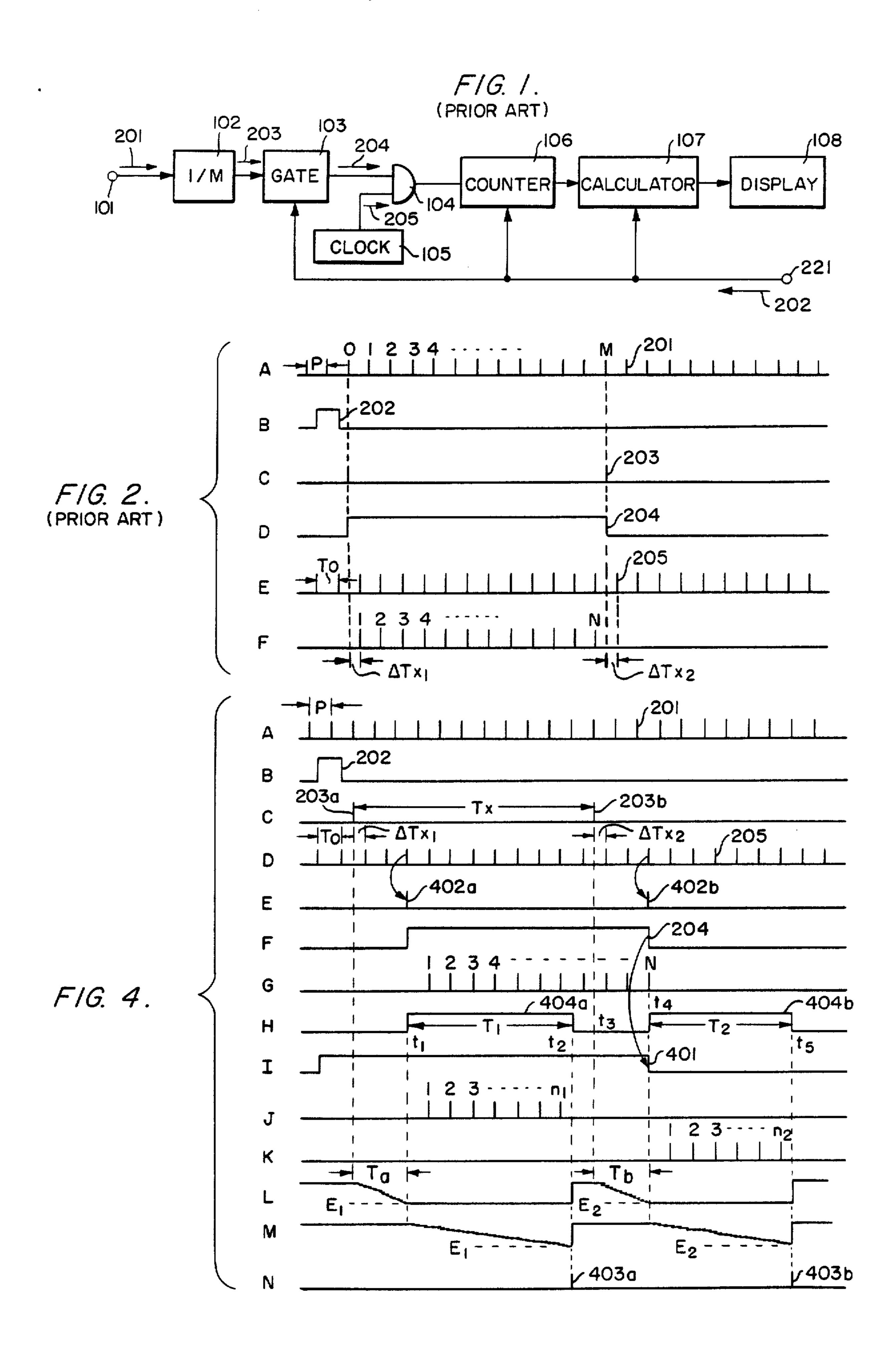

FIG. 1 shows one of the conventional period and frequency measuring instruments of this kind. A division factor M of a divider 102 which divides the number of pulses in an input signal into 1/M pulses is selected corresponding to the frequency of the input signal. 25 FIG. 2A shows that an input signal 201 that is to be measured is supplied at an input terminal 101 and provided to the divider 102 whose output generates the divided output 203 shown in FIG. 2C. The divided output 203 is transmitted to a gate signal generator 103 30 comprising, for example, a toggle-type flip-flop. The gate signal generator 103 generates the gate signal 204 shown in FIG. 2D which has the length of one period of the divided input signal 203 derived from the divider 102. The gate signal 204 thus generated is supplied to an 35 AND gate 104 to open the AND gate 104 with its high level.

The other input terminal of the AND gate 104 is provided with a clock signal 205 having a constant period To from a clock signal generator 105 as shown in 40 FIG. 2E. When the gate signal 204 is at high level, the clock signal 205 is supplied via the AND gate 104 to a counter 106. FIG. 2F shows the gated clock signal 205 derived from the AND gate 104. The total number of the gated clock pulses N is counted by the counter 106. 45

The counted result is provided to a calculator 107 wherein the frequency F and the period P of the input signal 201 are calculated. Namely, in the case that the number of the clock signals 205 counted by the counter 106 is N, the input frequency and period are obtained by 50 calculating,  $F=M/NT_0$  and  $P=NT_0/M$ , respectively. The calculated frequency or period is displayed by a display 108. The operation described above starts after a reset signal 202 provided from a terminal 221 as shown in FIG. 2B.

In this conventional period and frequency measuring instrument, there arise fractional times  $\Delta T_{x1}$  and  $\Delta T_{x2}$  corresponding to the time differences between the rise of the gate signal 204 and the first gated clock signal and between the fall of the gate signal 204 and the immediately following clock signal as illustrated in FIG. 2F. In order to make the fractional times  $\Delta T_{x1}$ ,  $\Delta T_{x2}$  small so as to improve measurement accuracy, it is necessary to use clock signals of higher frequency. However, utilization of the higher frequency clock signals requires both 65 the AND gate and the counter 106 to operate at high speed, which makes the instrument expensive. Although the fractional times  $\Delta T_{x1}$ ,  $\Delta T_{x2}$  represent infor-

mation effecting the accuracy of the calculated period or frequency of the input signal, conventional instruments are not able to take these fractional times into account.

#### SUMMARY OF THE INVENTION

It is an object of the present invention to provide a measuring instrument which is capable of measuring period and frequency of an input signal with high accuracy without using high frequency clock signals.

According to this invention, the first and second fractional times  $\Delta T_{x1}$ ,  $\Delta T_{x2}$  that are caused by the differences between the rise and fall of the divided input signal and the respective clock signals, are expanded by an expansion circuit of simple construction, so that the expanded fractional times can be measured even by a relatively low frequency clock signal with high resolution. Therefore, an accurate input signal period or frequency can be obtained by using both the number of the clock pulses gated by a gate signal, which is derived from the divided input signal and synchronized with the clock signal, and as well the number of clock pulses counted during the expanded fractional times.

## BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 shows a circuit diagram of a conventional period and frequency measuring instrument.

FIGS. 2A to 2F are timing charts for explaining the operation of the conventional instrument of FIG. 1.

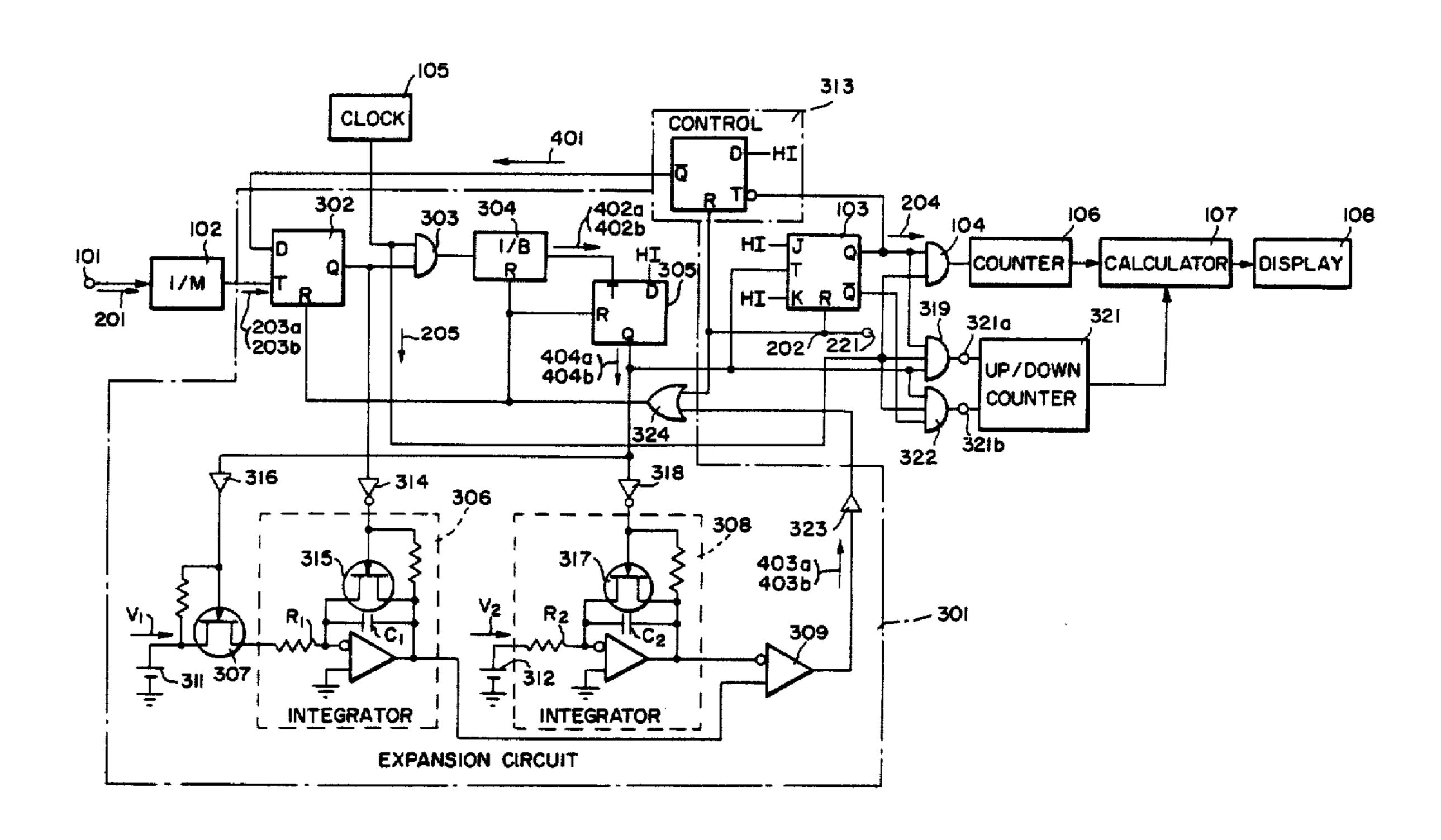

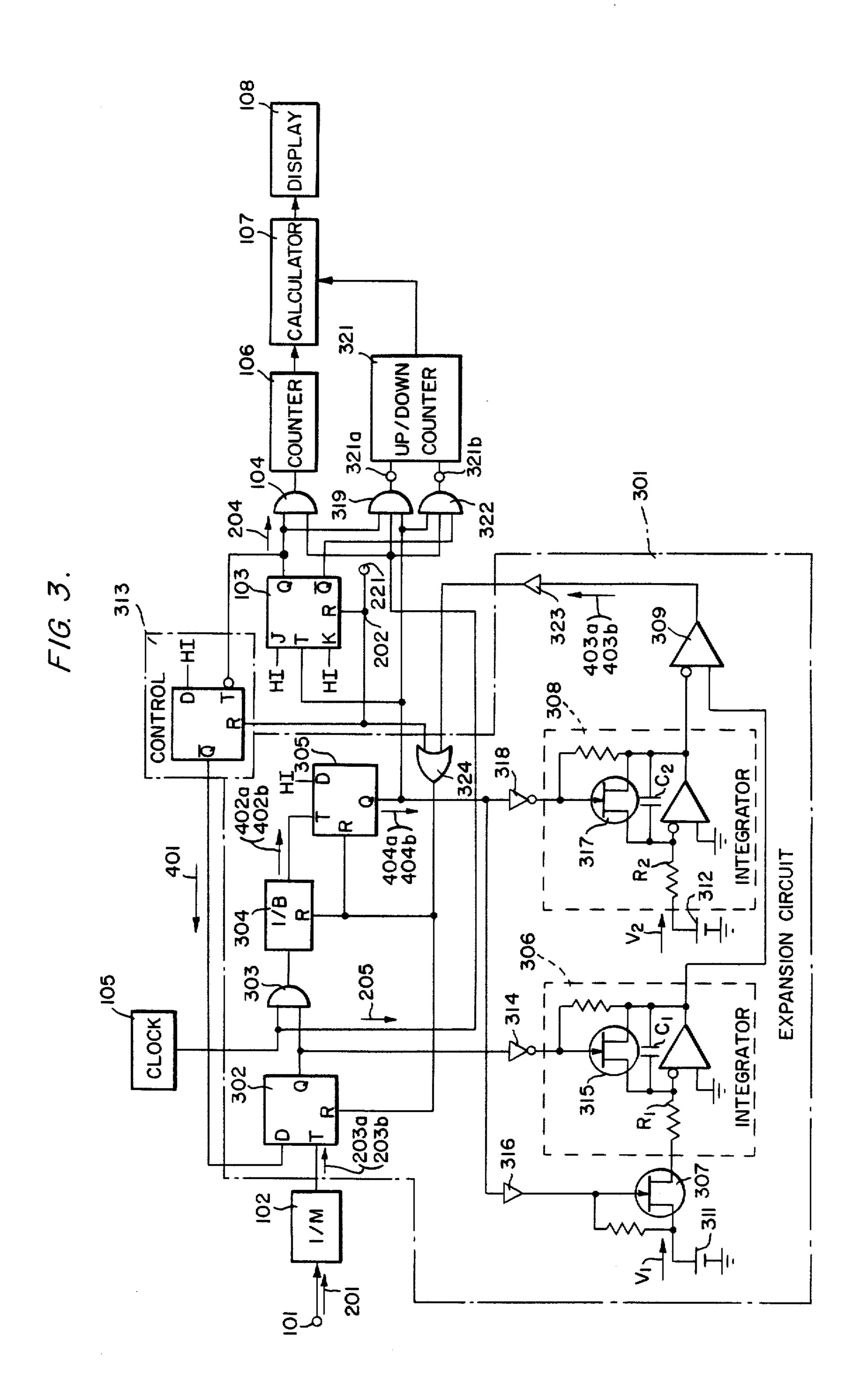

FIG. 3 is a circuit diagram showing an embodiment of a period and frequency measuring instrument of the present invention.

FIGS. 4A to 4N are timing charts for explaining the operation of the embodiment of FIG. 3.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

FIG. 3 shows one of the embodiments in accordance with the present invention and FIGS. 4A to 4N are timing charts for explaining the operation of the embodiment of FIG. 3. In FIG. 3 the components that are identical to those in FIG. 1 are denoted by the same reference characters.

An expansion circuit 301 is provided for expanding the fractional times  $\Delta T_{x1}$ ,  $\Delta T_{x2}$  by predetermined amounts. The main components comprising the expansion circuit 301 are D-type flip-flops 302 and 305, a divider 304, integrators 306 and 308, a voltage comparator 309 and a hold switch 307. The embodiment of FIG. 3 also employs a control circuit 313 for generating a start signal, an up-down counter 321 for counting the difference between the two fractional times  $\Delta T_{x1}$ ,  $\Delta T_{x2}$  and AND gates 319 and 322 for supplying the clock signals to the up-down counter 321.

The input signal 201 that is to be measured is provided from a terminal 101 to the divider 102 which divides the input signal by a division factor M. The divided input signal from the divider 102 is supplied to the T terminal of a D-type flip-flop 302 whose Q output is connected to an AND gate 303 and also to the integrator 306 through an inverter 314 to control the time for starting the integrator 306. The AND gate 303 provides the clock signal 205 from the clock signal generator 105 to the divider 304 when the Q output of the flip-flop 302 is at high level. The divider 304 divides the clock signal by a predetermined factor B and provides the divided clock signal to the D-type flip-flop 305. The

integrator 306 integrates a constant voltage V<sub>1</sub> from a voltage source 311 with an integration time constant R<sub>1</sub>C<sub>1</sub>. The integrator 308 integrates a constant voltage V<sub>2</sub> from a voltage source 312 with an integration time constant R<sub>2</sub>C<sub>2</sub>. The Q output of the flip-flop 305 is connected to the integrator 308 via an inverter 318 to control the time for starting the integration. The Q output of the flip-flop 305 is also provided via a buffer 316 to the hold switch 307 to control the hold timing of the integrator 306.

Both outputs of the integrators 306 and 308 are supplied to a voltage comparator 309 whereby coincidence in the voltages of both outputs is detected. The output of the voltage comparator 309 is provided to the reset terminal of the flip-flops 302 and 305 and the divider 304 through an OR gate 324. The control circuit 313 is comprised, for example, of a D-type flip-flop with the D terminal provided with a high level signal and the T terminal connected through an inverter to a Q terminal of the gate signal generator 103. The Q output of the control circuit 313 is provided to the D terminal of the flip-flop 302. The reset signal 202 from the terminal 221 is provided to the gate signal generator 103 and the control circuit 313 and through the OR gate 324 to the flip-flops 302, 305 and the divider 304.

At the beginning of the operation, by the reset signal 202 from the terminal 221, the control circuit 313 is changed to high level to yield a start signal 401 shown in FIG. 4I which is provided to the terminal of the flip-flop 302. Thus the flip-flop 302 is turned to high level by the first divided input signal 203a provided from the divider 102 so as to open the AND gate 303 and to provide the clock signal 205 from the clock signal generator 105 to the divider 304 as in FIGS. 4C and 4D. At the same time a FET switch 315 is opened by the low level signal of the inverter 314 so that the integrator 306 starts integrating the constant voltage V<sub>1</sub> supplied through the hold switch 307. The hold switch 307 is closed at this time since the flip-flop 305 is reset. Further, the integrator 308 is not in operation at this time since the FET switch 317 is closed by the high level output of the inverter 318 derived from the low level signal of the Q output of the flip-flop 305. The integrated output of the integrator 306 gradually goes down in accordance with the integrating time constant R<sub>1</sub>C<sub>1</sub> until the hold switch 307 is opened as shown in FIG. 4L.

The divider 304 divides the clock signal 205 provided through the AND gate 303 into 3, for example, that is, 50 the division factor B of the divider 304 is selected to be 3 in this case. Thus by the third clock pulse after the first divided input 203a the divider 304 yields the first divided clock pulse 402a at its output. By the first divided clock pulse 402a supplied from the divider 304 at 55 time t<sub>1</sub>, the state of the flip-flop 305 is changed to high level, thus making the hold switch 307 open so that the integrator 306 stops the integration and holds the integrated voltage E1 as in FIG. 4L. Therefore, the time interval T<sub>a</sub> during which the integrator 306 integrates 60 the constant voltage  $V_1$  becomes  $\Delta T_{x1} + 2T_0$ , where  $T_0$ is the period of the clock signal 205. The reason for integrating the constant voltage V<sub>1</sub> longer than the first fractional time  $\Delta T_{x1}$  by  $2T_0$ , in this embodiment, is to obtain a sufficiently large value of the integrated volt- 65 age at the output of the integrator 306 without using a high speed operation amplifier in the integrator 306, in other words that the integrator 306 can be low in cost.

At time t<sub>1</sub>, by the Q output of the flip-flop 305 supplied via the inverter 318, the FET switch 317 is opened so that the integrator 308 starts integrating the constant voltage V<sub>2</sub> from the voltage source 312 with an integration time constant of R<sub>2</sub>C<sub>2</sub>. The time constant R<sub>2</sub>C<sub>2</sub> and the constant voltage V2 are selected to generate an integrated output with a smaller slope than that generated by the integrator 306 for expanding the fractional times. Also at time t<sub>1</sub>, by the high level signal from the flip-flop 305, the gate signal generator 103 is turned to high level as in FIG. 4F so as to open the AND gate 104. Thus the clock signal from the clock signal generator 105 is supplied to the counter 106 whereby the number of clock pulses is counted in accordance with FIG. 4G. At the same time, by the high level signals from both the flip-flop 305 and the gate signal generator 103, the AND gate 319 is opened and provides the clock signal to an up-count terminal 321a of the up-down counter 321. Therefore the up-down counter 321 upcounts the clock pulses until the AND gate 319 is closed.

When the integrated output of the integrator 308 coincides with the hold voltage E<sub>1</sub> of the integrator 306, the voltage comparator 309 generates a coincidence signal 403a at time t<sub>2</sub> as in FIG. 4N. The flip-flops 302, 305 and the divider 304 are reset by the coincidence signal 403a provided through a buffer 323 and the OR gate 324. Because of the changing state of the flip-flop 305, the AND gate 319 is closed and thus the up-down counter 321 stops up-counting the clock pulses. Thus the number of the clock pulses counted in the up-down counter 321 is n<sub>1</sub> as in FIG. 4G in this example.

The time period  $T_1$  during which the AND gate 319 is open, in other words during which the number of the clock pulses is counted by the up-down counter 321, is equal to the product of  $(\Delta T_{x1} + 2T_0)$  and  $R_2C_2V_1/R_1C_1V_2$ . In other words, the time period  $T_2$  produced by the integrator 306 corresponding to the fractional time  $\Delta T_{x1}$  is expanded by the integrator 308 by an expansion factor  $A = R_2C_2V_1/R_1C_1V_2$ , so that even a low frequency clock signal can be used to measure the fractional time with high resolution.

For measuring the second fractional time  $\Delta T_{x2}$  the embodiment of FIG. 3 works as follows. Since the flipflops 302 and 305 are reset by the coincidence signal 403a, the integrators 306 and 308 are set to their initial conditions, that is, the hold switch 307 and the FET switches 315 and 317 are closed. Then the divider 102 provides the second divided input signal 203b at time t<sub>3</sub> as shown in FIG. 4C to the flip-flop 302. The division factor M of the divider 102 is selected according to the frequency of the input signal 201 for generating a divided signal having a longer period than the time required for measuring the expanded fractional time. In other words, the division factor M is selected to generate the second divided input signal 203b shown in FIG. 4C after the time t<sub>2</sub> as in FIG. 4. The flip-flop 302 goes to high level in response to the second divided input signal 203b, so that the AND gate 303 is opened and the integrator 306 starts integrating with the time constant  $R_1C_1$ .

The divider 304 again divides the clock signal 205 and generates the divided signal 402b shown in FIG. 4E in synchronism with the third clock pulse of the clock signal 205 supplied via the AND gate 303. By the divided signal 402b the output Q of the flip-flop 305 is changed to high level as in FIG. 4H so that the hold switch 307 opens and thus the integrator 306 holds the

integrated output  $E_2$  at time  $t_4$ . Therefore, the time interval Tb between  $t_3$  and  $t_4$  during which the integrator 306 integrates the constant voltage  $V_1$  is  $\Delta T_{x2} + 2T_0$ . Thus the hold voltage  $E_2$  is dependent on the second fractional time  $\Delta T_{x2}$ .

At the same time the gate signal generator 103 is turned to low by the rise of the output signal of the flip-flop 305 so as to close the AND gate 104. Accordingly, the counter 106 stops counting the number of clock signal 205 supplied through the AND gate 104. 10 The counted data in the counter 106 becomes N in accordance with FIG. 4G. As has been mentioned above, the gate signal 204 that is generated by the gate signal generator 103 is synchronized with the clock signal 205. The reason for synchronizing the gate signal 15 204 with the clock signal 205 is to separate the period Tx shown in FIG. 4C from the fractional times since the fractional times are measured by the up-down counter 321.

At time  $t_4$  the integrator 308 starts integrating the  $^{20}$  constant voltage  $V_2$  with the time constant  $R_2C_2$ . Also at time  $t_4$ , the other output of the gate signal generator 103 opens the AND gate 322 whose output is connected to a down-count terminal 321b of the up-down counter 321. Thus the up-down counter 321 down-counts the  $^{25}$  number of the clock pulses, that is, subtracts the number of clock pulses from the data already counted during the time period  $T_1$ . The low level signal from the gate signal generator 103 is also supplied to the control circuit 313 so that the start signal 401 shown in FIG. 4I is  $^{30}$  changed and remains at low level until the next reset signal 202 is applied.

When the integrated output of the integrator 308 reaches the hold voltage E<sub>2</sub> the voltage comparator 309 generates a coincidence signal 403b shown in FIG. 4N 35 at time t<sub>5</sub>. By the coincidence signal 403b the flip-flops 302, 305 and the divider 304 are reset, and thusly the AND gates 303, 322 are closed and both the integrators 306 and 308 are set to their initial conditions. Therefore the AND gate 322 provides the clock signal to the 40 up-down counter 321 during the time interval T<sub>2</sub> which starts at the beginning of the integration of the integrator 308 and ends at the occurrence of the coincidence signal 403b.

Similarly as in regard to the period  $T_1$ , the time period  $T_2$  is equal to the product of  $(\Delta T_{x2} + 2T_0)$  and  $R_2C_2V_1/R_1C_1V_2$ . That is, the number of clock pulses  $n_2$  applied to the up-down counter 321 during the period  $T_2$  is dependent on to the expanded value of the second fractional time  $\Delta T_{x2}$ .

As has been mentioned above, since the clock signal is up-counted during the period  $T_1$  and down-counted during the period  $T_2$ , the counted data  $n_1 - n_2$  which is obtained by the up-down counter 321 corresponds to the difference between the first and the second fractional times  $\Delta T_{x1} - \Delta T_{x2}$ .

In regard to the first fractional time  $\Delta T_{x1}$ , the following expression is obtained:

$$n_1T_0 = A[\Delta T_{x1} + (B-1)T_0]$$

(1) 60

wherein  $A=R_2C_2V_1/R_1C_1V_2$ ,  $n_1$  is the number of pulses up-counted by the up-down counter 321,  $T_0$  is the time period of the clock signal 205, B is the division factor of the divider 304 and A is the expansion factor of 65 the expansion circuit 313.

Similarly, as to the second fractional time  $\Delta T_{x2}$  the following expression is obtained:

$$n_2T_0 = A[\Delta T_{x2} + (B-1)T_0]$$

(2)

wherein n<sub>2</sub> represents the number of clock pulses down-counted by the up-down counter 321.

The time interval  $T_x$  between the divided input signals 203a and 203b is obtained by the following expression:

$$T_x = NT_0 + (\Delta T_{x1} - \Delta T_{x2}) \tag{3}$$

wherein N is the number of clock pulses counted by the counter 106. Therefore, by using equations (1) and (2), equation (3) becomes,

$$T_{X} = NT_{0} + [\Delta T_{X1} + (B - 1)T_{0}] - [\Delta T_{X2} + (B - 1)T_{0}]$$

$$= NT_{0} + n_{1}T_{0}/A - n_{2}T_{0}/A$$

$$= T_{0}[N + (n_{1} - n_{2})/A]$$

$$= T_{0}[N + (V_{2}R_{1}C_{1}/V_{1}R_{2}C_{2})(n_{1} - n_{2})]$$

(4)

Since the values of  $T_0$  and  $V_2R_1C_1/V_1R_2C_2$  are already known, and since the counted data N and  $(n_1-n_2)$  are provided, from the counter 106 and the up-down counter 321, respectively, the time period  $T_x$  can be calculated by the calculator 107.

Assuming that the division factor of the divider 102 is represented by M, the time period of the input signal 201 to be measured is calculated as follows:

$$P = T_x/M$$

$$= (T_0/M)[N + (V_2R_1C_1/V_1R_2C_2)(n_1 - n_2)]$$

(5)

Also, the frequency F of the input signal 201 is

$$F = 1/P$$

$$= \frac{M}{T_0[N + (V_2R_1C_1/V_1R_2C_2)(n_1 - n_2)]}$$

(6)

The period P or frequency F of the input signal 201 thusly obtained is displayed by the display 108.

In the above description, the same clock signal is supplied to both the counter 106 and the up-down counter 321, but it is possible to use different clock signals. In the case that the time period of the clock signal that is provided to the counter 106 is T<sub>01</sub>, and the time period of the clock signal provided to the up-down counter 321 is T<sub>02</sub>, the period P and the frequency F of the input signal to be measured are obtained by the following expressions:

$$P = (T_{01}/M)[N + (T_{02}V_2R_1C_1/T_{01}V_1R_2C_2)(n_1 - n_2)]$$

(7)

$$F = \frac{M}{T_{01}[N + (T_{02}V_2R_1C_1/T_{01}V_1R_2C_2)(n_1 - n_2)]}$$

(8)

What is claimed is:

1. An instrument for determining the period and frequency of an input signal, comprising

clock means for providing first and second clock signals,

first divider means for dividing said input signal by a predetermined division factor to output a divided signal having a minimum period, wherein a first fractional time is defined between a first output of said first divider means and the first clock pulse of

said first clock signal thereafter, and a second fractional time is defined between the following output of said first divider means and the first clock pulse of said first clock [means] signal thereafter,

gate signal generating means for generating a gate 5 signal synchronized with said first clock signal,

counter means for counting the clock pulses of said first clock signal during said gate signal,

expansion means for expanding each said fractional time, at least the expanded first fractional time 10 being shorter than the minimum period of said divided signal, less said first fractional time,

up-down counter means for counting said second clock pulses during the expanded first fractional time, and for counting in the opposite sense said second clock 15 pulses during the expanded second fractional time, for providing a count [of the clock pulses of said second clock signal] corresponding to the difference between the first and second expanded fractional times, and

calculator means for calculating the period and frequency of said input signal by adding the count from said counter means to a value corresponding to the count from the up-down counter means.

2. The instrument of claim 1, comprising

said expansion means including a first integrator for integrating a first voltage level with a first time constant during a period of time equal to each said fractional time plus a predetermined integral number of clock pulses of the first clock signal, and a 30 second integrator for integrating a second voltage level with a second time constant for each respective expanded fractional time to obtain an integrated value that is the same as each respective final integrated value of the first voltage level, 35

wherein the first and second voltage levels and time constants are selected to provide, for each said fractional time, smaller slope in time for the absolute value of the integrated value of the second voltage level than for the slope of the absolute 40 value of the integrated value of the first voltage level.

- 3. The instrument of claim 1, said up-down means counter up-counting the clock pulses of said second clock signal during the expanded first fractional time 45 and down-counting the clock pulses of said second clock signal during the expanded second fractional time.

- 4. The instrument of claim 2, comprising said first and second clock signals having periods T<sub>01</sub> and T<sub>02</sub>, respectively,

said first and second voltage levels being V<sub>1</sub> and V<sub>2</sub>, respectively,

said first and second time constants being R<sub>1</sub>C<sub>1</sub> and R<sub>2</sub>C<sub>2</sub> corresponding to respective resistance and 55 capacitive elements of said first and second integrators, respectively,

said division factor of said divider means being 1/M, wherein M is an integer larger than one,

said counter means counting N of said clock pulses of 60 said first clock signal during said gate signal, and

said up-down counter means up-counting n<sub>1</sub> of said second clock pulses during the expanded first fractional time and down-counting n<sub>2</sub> of said second clock pulses during the expanded second fractional 65 time,

wherein the period P and frequency F of said input signal are calculated by said calculator means as:

$P = (T_{01}/M)[(N + (T_{02}V_2R_1C_1/T_{01}V_1R_2C_2)(n_1 - n_2)]$

and its inverse, respectively.

5. The instrument of claim 4, said second clock signal being the same as said first clock signal.

6. The instrument of claim 1, 2, 3, 4 or 5 said minimum period of the output of the first divider means being equal to or longer than each respective sum of any one of said fractional times, plus said predetermined number of clock pulses of the first clock signal, plus the respective expanded fractional time.

7. A device for determining a number corresponding to the period between first and second input pulses, comprising

clock means for providing at least a first clock signal of first clock pulses with which said number corresponding to the period is to be determined, whereby a first fractional time is defined by the time between said first input pulse and the nth of said first clock pulses after said first input pulse, where n is a predetermined integer greater than zero, and a second fractional time is defined by the time between said second pulse and the nth of said first clock pulses after said second input pulse,

a gate signal generator for generating a gate signal synchronized with respective ones of said first clock pulses, said gate signal having a period equal to a predetermined number of periods of said first clock signal,

first counter means for counting said first clock signal during said gate signal,

first integrator means including a first capacitor for integrating a respective reference signal with a respective time time constant during said first fractional time, and subsequently during said second fractional time, and for providing a respective output after each of the integrations,

second integrator means including a second capacitor for integrating a respective reference voltage with a respective time constant after each said integration of the first integrator means, and for providing a respective output value is equal to the respective integrated value of said first integrator means,

comprising comparator means for comparing said output of said first and second integrator means, for providing a corresponding output when they become equal,

up-down counter means for being counted up by clock signal corresponding to said first clock signal during the integration by said second integrator means corresponding to said first fractional time, and for being counted down by said clock signal during the integration by said second integrator means corresponding to said second fractional time, and

calculation means for determining a number corresponding to said period between said first and second input pulses from counts of said first and up-down counter means,

wherein each of said up and down counting by said up-down counter means is terminated by a signal corresponding to the output of said comparator means.

- 8. The device of claim 7, comprising a first divider for dividing a repetitive external signal by a predetermined integer for providing as a respective output said first and second input pulses.

- 9. The device of claim 8, comprising

- a first flip-flop to which the output of said divider is provided, said first flip-flop having an output Q which initiates the integration by said first integration means during said first fractional time,

- a second divider having as an input said first clock signal gated by said output Q of said first flip-flop, wherein said second divider determines said predetermined integer number n for said first and second fractional time, and having a corresponding output,

- a second flip-flop having as an input said output of said further divider and providing a respective Q output for ending such said integration of said first integrator

- means and initiating the respective integration of said second integrator means,

- a third flip-flop, included in said gate signal generator and controlled by said Q output of said second flipflop for providing as a respective Q output said synchronized gate signal, and

- the output of said comparator determines the end of each integration of said second integrator means.

- 10. The device of claim 9, wherein the first gate signal 10 plus said fractional time less said second fractional time determines the period between said first and second input pulses.

15

IJ

20

25

30

35

40

45

50

55

60

# UNITED STATES PATENT AND TRADEMARK OFFICE CERTIFICATE OF CORRECTION

PATENT NO.: Re. 32,845

DATED : JANUARY 24, 1989

INVENTOR(S): MISHIO HAYASHI

It is certified that error appears in the above-identified patent and that said Letters Patent is hereby corrected as shown below:

Col. 5, line 60, " $T_0$ ])" should be  $--T_0$ ]--.

Col. 7, line 49, after "comprising", start a new paragraph, with paragraph indentation, beginning with "said first and".

Signed and Sealed this

Thirteenth Day of June, 1989

Attest:

DONALD J. QUIGG

Attesting Officer

Commissioner of Patents and Trademarks