#### Stockton et al.

[11] E

[45] Reissued Date of Patent: Mar. 10, 1987

#### MONOLITHIC MICROWAVE INTEGRATED [54] CIRCUIT WITH INTEGRAL ARRAY ANTENNA

[75] Inventors: Ronald J. Stockton, Boulder County;

Robert E. Munson, Boulder, both of

Colo.

Ball Corporation, Muncie, Ind. [73] Assignee:

[21] Appl. No.: 785,304

[22] Filed: Oct. 7, 1985

### Related U.S. Patent Documents

| Reissu | ŧε | of:  |

|--------|----|------|

| [64]   | P  | ater |

[64] Patent No.:

4,490,721

Issued:

Dec. 25, 1984

Appl. No.: Filed:

565,516 Dec. 27, 1983

U.S. Applications:

Continuation of Ser. No. 207,289, Nov. 17, 1980, [63] abandoned.

Int. Cl.<sup>4</sup> ...... H01Q 3/26; H01P 3/08

342/417; 343/700 MS

333/246

#### References Cited [56]

## U.S. PATENT DOCUMENTS

| , ,       |         | Hyltin et al          |

|-----------|---------|-----------------------|

| 3,680,110 | 7/1972  | Goldstone 343/854     |

| 3,778,717 | 12/1973 | Okoshi et al          |

| <b>-</b>  | _       | Munson.               |

| 3,878,553 | 4/1975  | Sirles et al          |

| 3,893,147 | 7/1975  | Williams et al 357/36 |

| 3,916,349 | 10/1975 | Ranghelli et al       |

| 3,921,177 | 11/1975 | Munson.               |

| 4,033,788 | 7/1977  | Hunsperger.           |

| 4,070,639 | 1/1978  | Nemit et al.          |

|           |         |                       |

#### OTHER PUBLICATIONS

Microstrip Transmission on Semiconductor Dielectrics, T. M. Hyltin, IEEE Transactions on Microwave Theory & Techniques, vol. MTT-13, No. 6, Nov. 1965, pp. 777-781.

GaAs Integrated Microwave Circuits, E. W. Mehal et al., IEEE Transactions on Microwave Theory & Techniques, vol. MTT-16 Jul. 1968, pp. 451-454.

Microwave Field-effect Transistors-1976, C. A. Liechti, IEEE Transactions on Microwave Theory & Techniques, vol. MTT-24, No. 6, Jun. 1976, pp. 279-300.

Degradation Mechanism of GaAs MESFET's, K. Mizuishi et al., IEEE Transactions on Microwave Theory & Techniques, vol. ED-26, No. 7, Jul. 1979, pp. 1008-1014.

Linear Amplifiers-Design and Fabrication Techniques, D. R. Ch'En et al., MMIC, Mar. 1981, pp. 39-48.

Design Considerations for Monolithic Microwave Circuits, R. A. Pucel, IEEE Transactions on Microwave Theory & Techniques, vol. MTT-29, No. 6, Jun. 1981, pp. 513-534.

Eden, Welch, Zucca, "Planar GaAs IC Technology: Applications for Digital LSI", IEEE Journal of Solid State Circuits, vol. SC-13, No. 4, Aug. 1978, pp. 419-425, (FIGS. 1,2: p. 420, right column, 2nd Paragraph-p. 422, right column, 2nd paragraph),

Primary Examiner-Stephen C. Buczinski Attorney, Agent, or Firm-Gilbert E. Alberding

#### **ABSTRACT** [57]

A monolithic microwave integrated circuit including an integral array antenna. The system includes radiating elements, feed network, phasing network, active and/or passive semiconductor devices, digital logic interface circuits and a microcomputer controller simultaneously incorporated on a single semi-insulating GaAs substrate by means of a controlled fabrication process sequence.

The resulting integrated circuit structure built upon a semi-insulating GaAs substrate provides a unique monolithic structure capable not only of phase-shifting, amplifying or otherwise controlling and conducting r.f. electrical signals but also capable of directly radiating-/receiving r.f. electromagnetic emanations propagated to/from the integral antenna elements of the monolithic structure.

28 Claims, 13 Drawing Figures

.

F 1 G. 6 RADIATED PATTERN HPBW=126°

F/G. 13

.

# MONOLITHIC MICROWAVE INTEGRATED CIRCUIT WITH INTEGRAL ARRAY ANTENNA

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

This is a continuation of application Ser. No. 207,289, 10 filed Nov. 17, 1980, now abandoned.

This application is related to divisional application Ser. No. 390,859 filed June 22, 1982, now allowed.

#### BACKGROUND OF THE INVENTION

This invention relates generally to microwave circuits and to the fabrication thereof.

The state of the art in fabrication and construction of millimeter and sub-millimeter wave length microwave systems before the present invention was essentially a 20 "bolt together" waveguide component technology. Individual circuits or discrete components were developed and then interconnected to provide the desired system. In essence, the "blocks" of the overall block diagram of the microwave system were assembled after 25 each "block" was individually developed.

Various problems and shortcomings are inherent in the "bolt-together" approach. One such shortcoming is the high frequency limitation that exists when separate components are bolted together. The size and separa- 30 tion of individual components cannot be scaled proportionally for extremely short wave lengths, resulting in uncontrollable parasitic reactances which limit performance. Other difficulties inherent in the waveguide approach are bulkiness, excessive weight, and high 35 manufacturing costs. In addition, minor design changes can result in costly hardware modifications.

The technology of electronic circuitry has evolved from discrete components such as diodes, transistors, capacitors, and resistors on printed circuit boards to the 40 use of monolithic linear and digital integrated circuits. This trend has continued by combining specific integrated circuit functions into larger integrated circuits having versatile and multi-function capability such as in the case of electronic calculators, watches, and mi- 45 crocomputers.

Concurrently with these developments in electronic circuitry, similar techniques have been employed in the technology of microwave circuits. GaAs field effect transistors (FETs) have been developed as well as microwave integrated circuit components such as oscillators, mixers, amplifiers, detectors, and filters, using both monolithic and hybrid construction techniques. With the development of the micro-strip radiator, high performance monolithic micro-strip phased arrays have 55 also been developed.

It has been recognized that there are advantages in performance and versatility to be gained by building micro-computer controlled antenna systems. Various multi-mode systems have been developed to demonstrate these advantages. In such systems, the electronics, comprising integrated circuits mounted on printed circuit boards were packaged separately and interfaced with an antenna by means of a multi-conductor cable. Such construction represents the present state of the art 65 in microwave systems have not been fabricated as a monolithic unit.

2

## SUMMARY OF THE INVENTION

Realizing the inherent disadvantages and shortcomings of the previously utilized "bolt together" technology for the fabrication of millimeter and sub-millimeter wave length microwave systems, it is the primary objective of the present invention to provide a non-optical microwave system incorporating all of the system components including active and/or passive RF components such as amplifiers, FET phase shifter switches, phase shifting and other r.f. transmission circuits, a microprocessor controller, and related digital control circuits into a single monolithic semi-insulating GaAs substrate to provide a monolithic phased array antenna system for use at X-band frequencies and above.

A further objective of the present invention is to provide a fabrication process for monolithic microwave integrated antennas suitable for high volume, low cost production that is also repeatable and reliable.

The monolithic microwave integrated antenna system and the method of fabrication described herein enable the physical integration of active microwave and digital circuits onto a common semi-insulating GaAs substrate. The fabrication technique provided by this invention is not unique to a particular microwave system design but rather is applicable to a wide range of systems and system frequencies, i.e., 10 GHz through 108 GHz (ultraviolet). The fabrication technique set forth herein is based upon thin-film techniques. The fabrication of all components whether active or passive and their interconnections are formed by either semi-conductor or thin-film processing steps.

Using the fabrication technique set forth herein, design changes can be implemented through mask and/or material and process variations rather than through the previously required intricate hardware modifications.

The monolithic nature of the microwave system has the inherent benefits of low volume (non-bulky), light weight, and high reliability. The fabrication process lends itself to automated, high volume production so that even the most complex designs will be repeatable and cost effective when compared with present fabrication and assembly techniques. The inherent accuracy and precision of the process enables component size and separation to be scaled with frequency thereby eliminating or reducing parasitic reactances for improved performance. The inherent repeatability will eliminate the need for "tweaking" or circuit adjustment to meet performance specifications.

In essence, the systems and fabrication techniques set forth herein represent a unique marriage of the arts of semiconductor and integrated circuit fabrication techniques, used at frequencies lower than microwave, with integrated monolithic electromagnetic system techniques.

The invention recognizes and builds upon the commonality of materials and processes associated with digital and linear integrated circuits, active and passive microwave semiconductor devices, microwave integrated circuits and monolithic antenna systems. The present invention also recognizes that it is both technically advantageous and unique to integrate these devices into a functional monolithic system.

The fabrication technique features the use of ion implantation directly into high quality semi-insulating GaAs to form the active layer for planar FET elements.

# BRIEF DESCRIPTION OF THE DRAWINGS

The invention will now be described in further detail with reference to the accompanying drawings wherein:

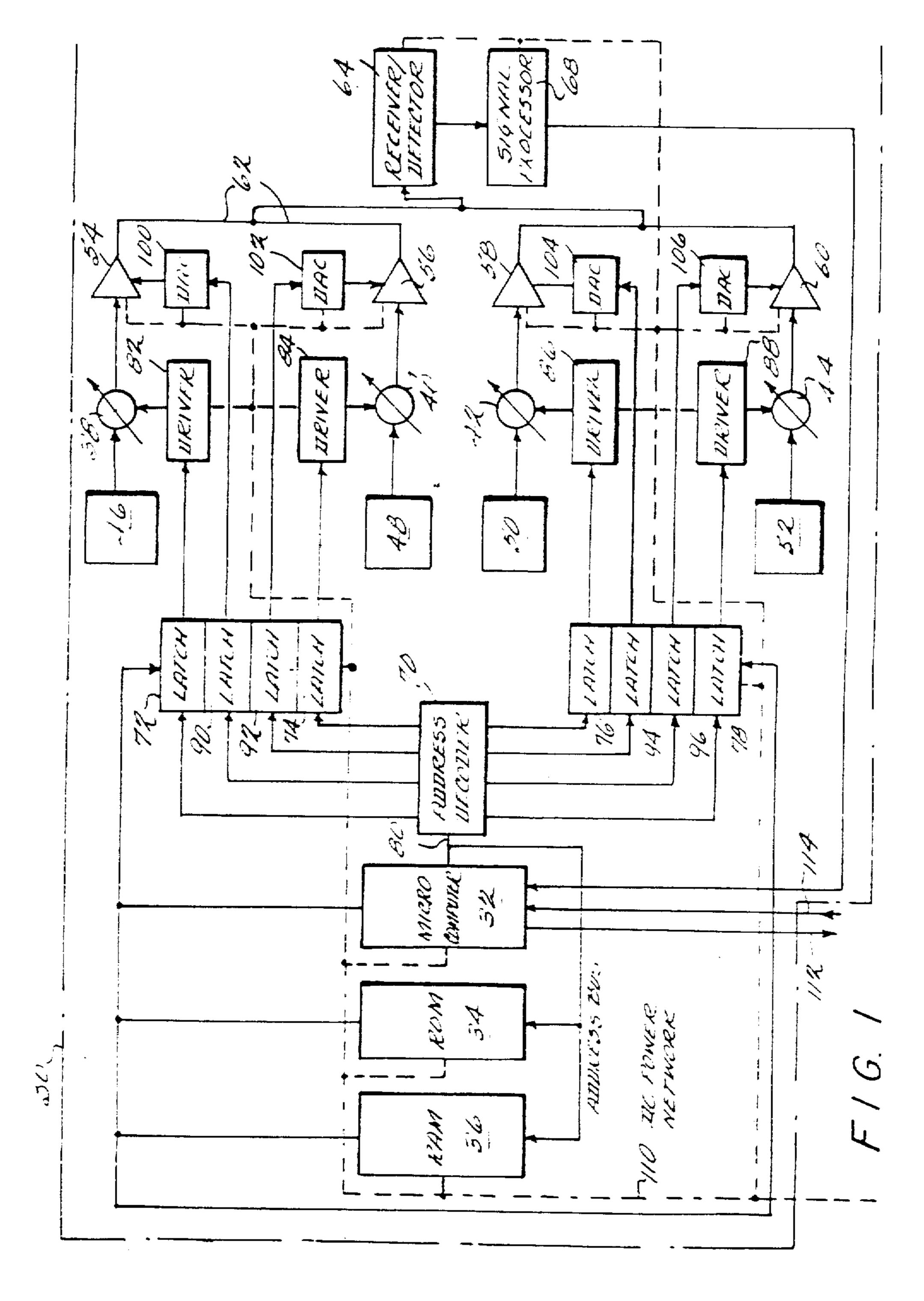

FIG. 1 is a block diagram of a monolithic microwave 5 integrated circuit receiver according to the present invention;

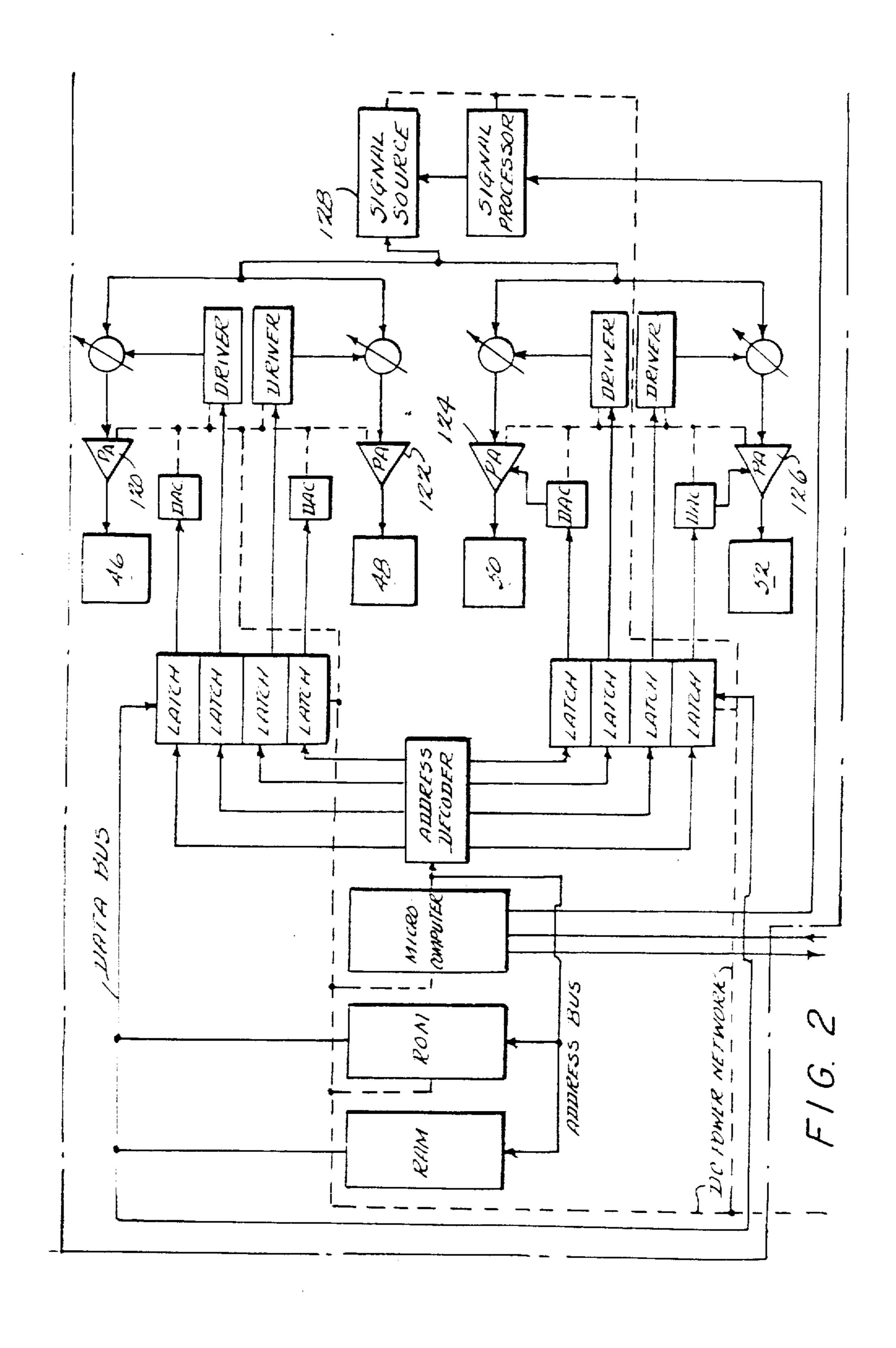

FIG. 2 is a block diagram of a monolithic microwave integrated circuit transmitter according to the present invention;

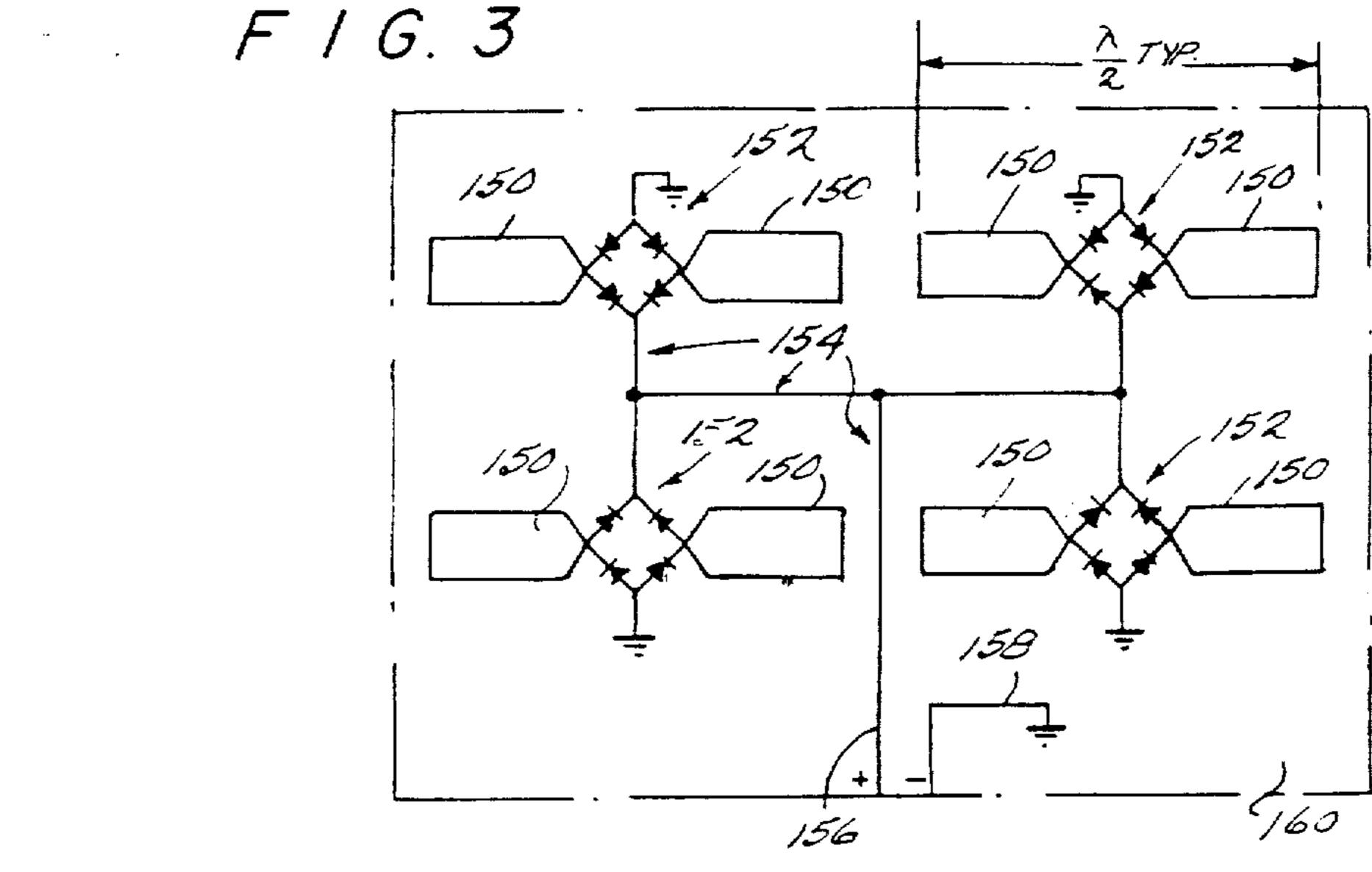

FIG. 3 is a schematic diagram of a monolithic microwave integrated circuit adapted to receive visible light and deliver dc power;

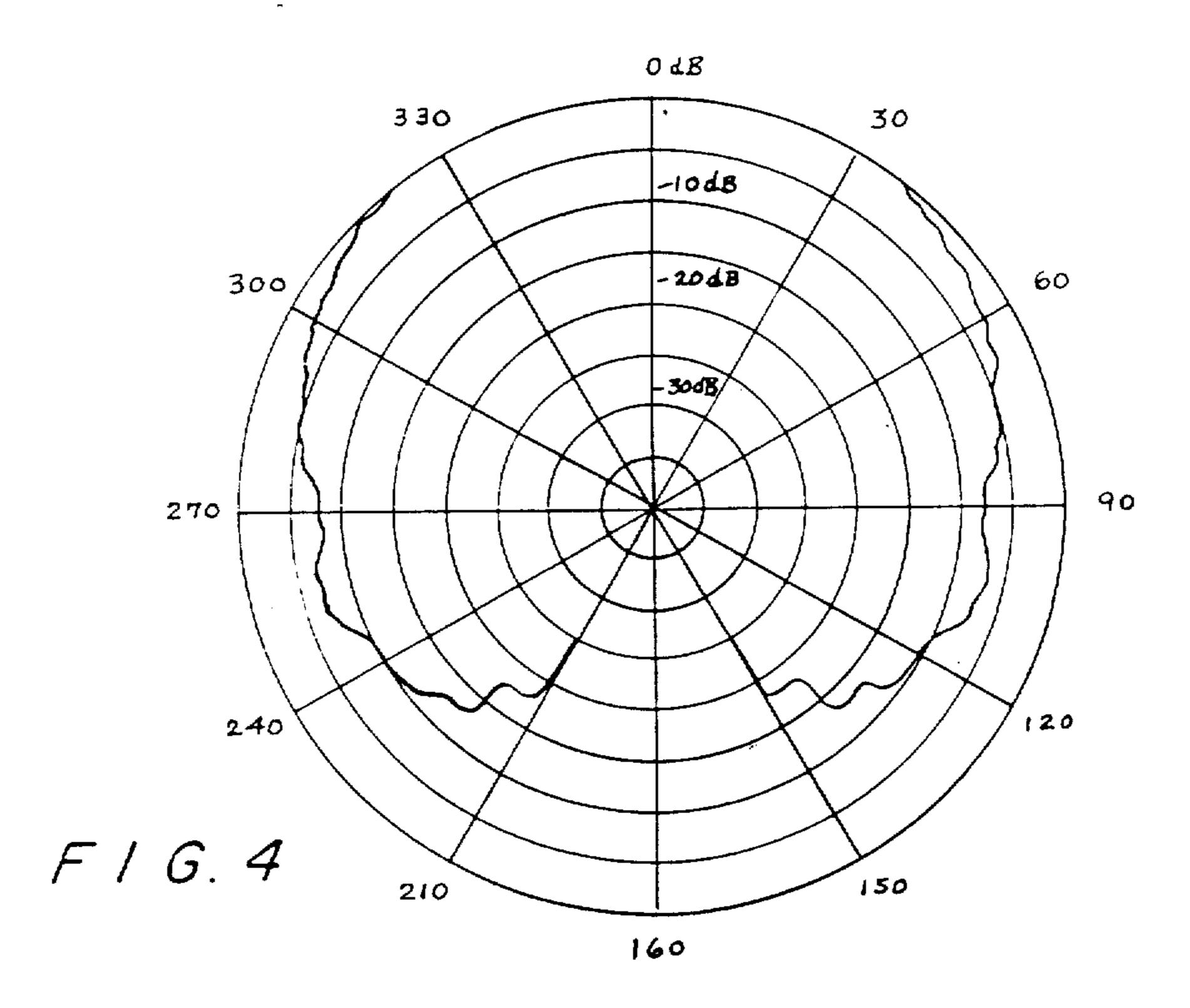

FIG. 4 is a graphical representation of the E-plane half power beamwidth of a sapphire element radiator, 15 plotted from experimental results;

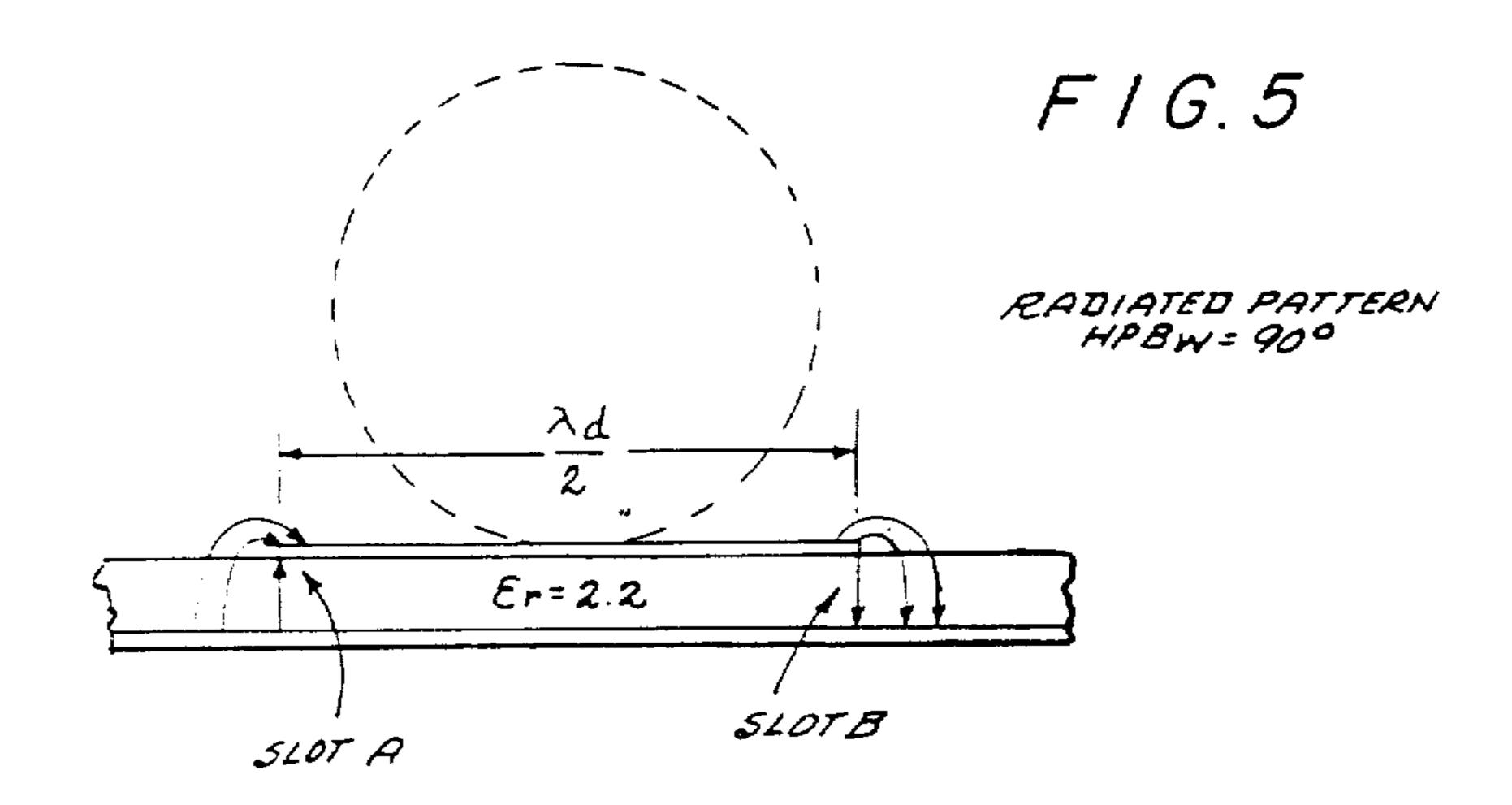

FIG. 5 is a cut-away side view of a microstrip radiator element showing a 90° E-plane half power beamwidth;

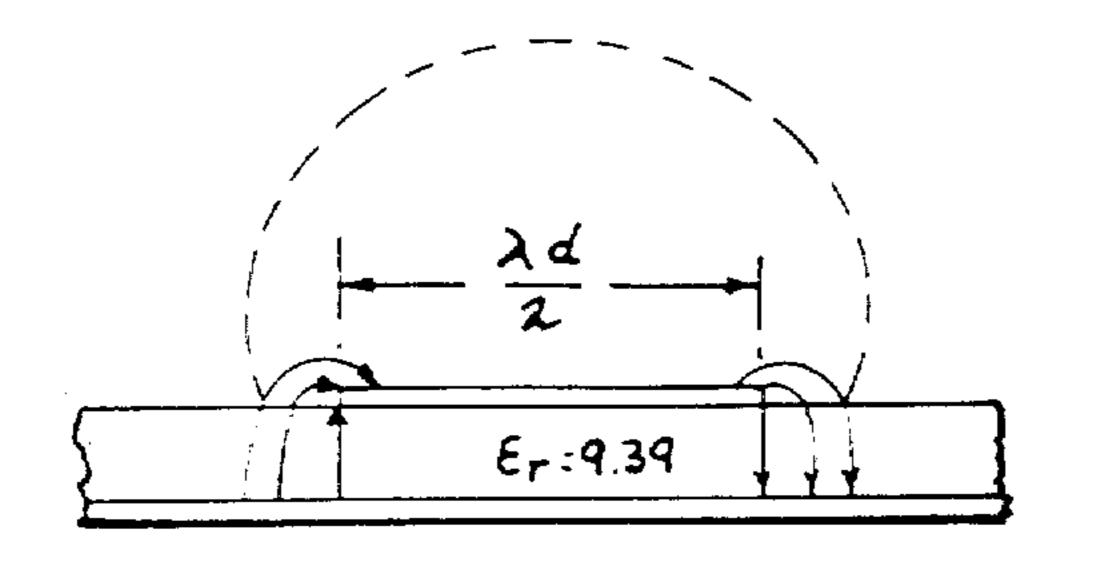

FIG. 6 is a cut-away side view of a microstrip radia- 20 tor element showing a 126° E-plane half power bandwidth;

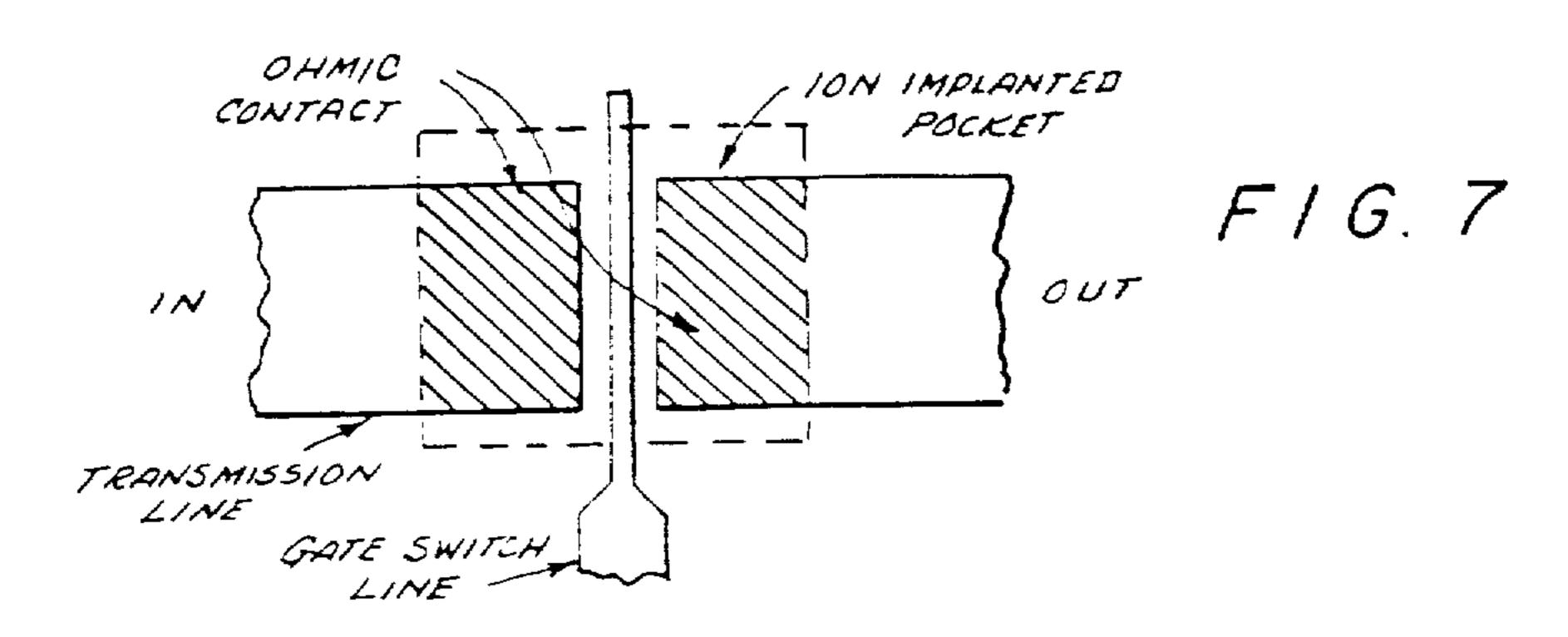

FIG. 7 illustrates the physical structure of a single gate FET switch used in the phase shifter elements;

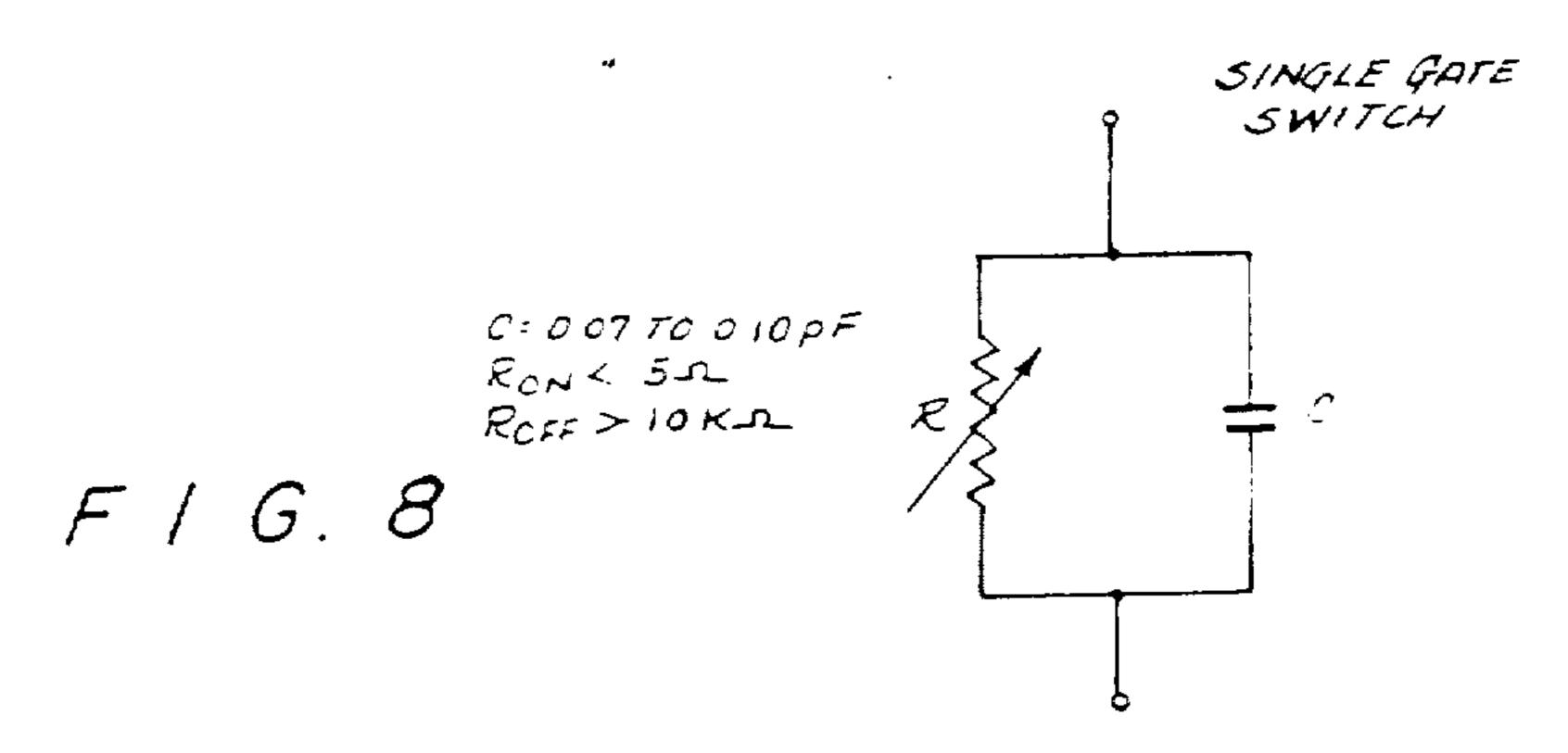

FIG. 8 is a schematic diagram of the equivalent cir- 25 cuit of the single gate FET switch shown in FIG. 7;

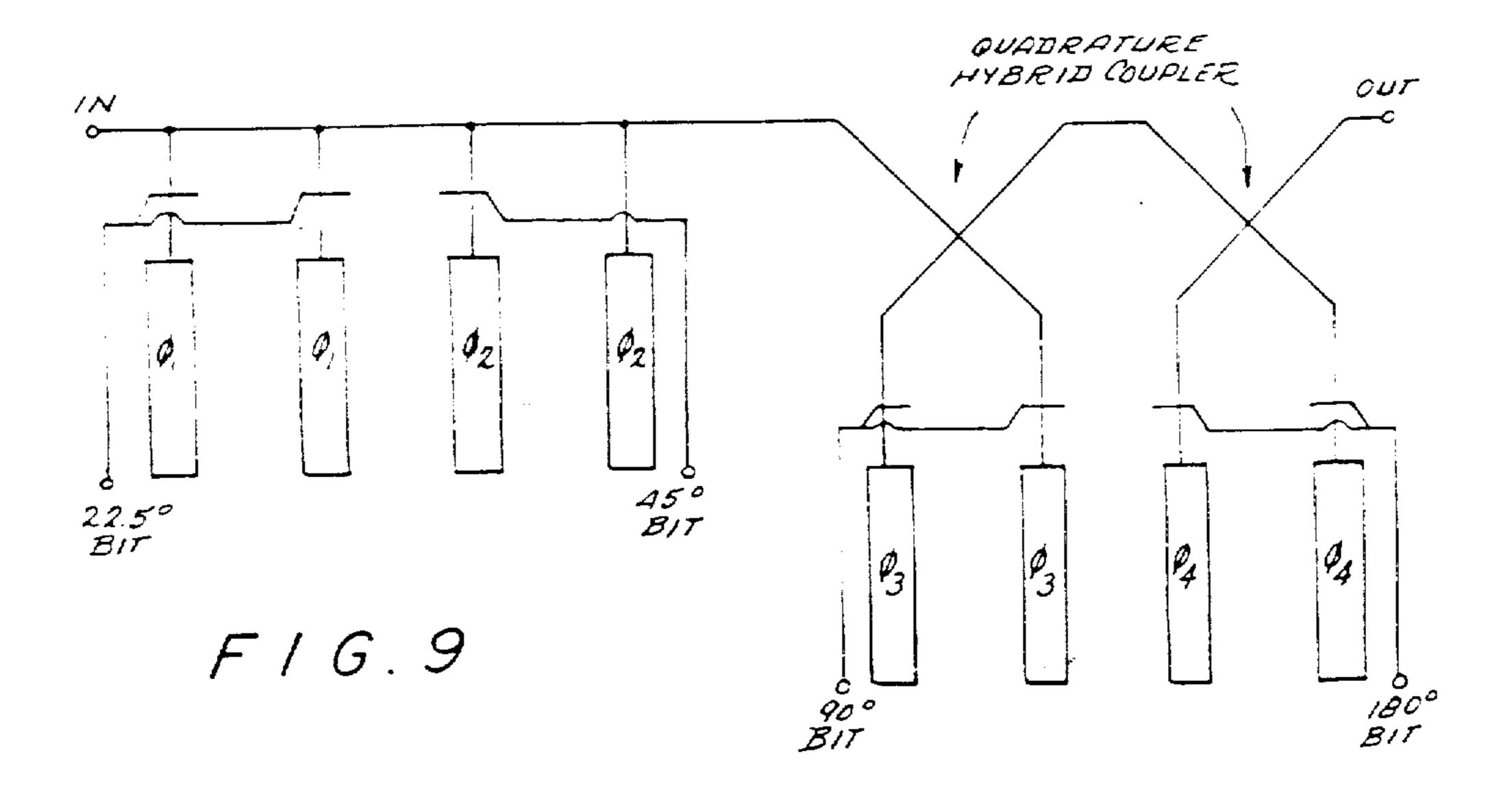

FIG. 9 is a schematic diagram of the preferred embodiment of one of the 4-bit phase shifters utilizing a hybrid design;

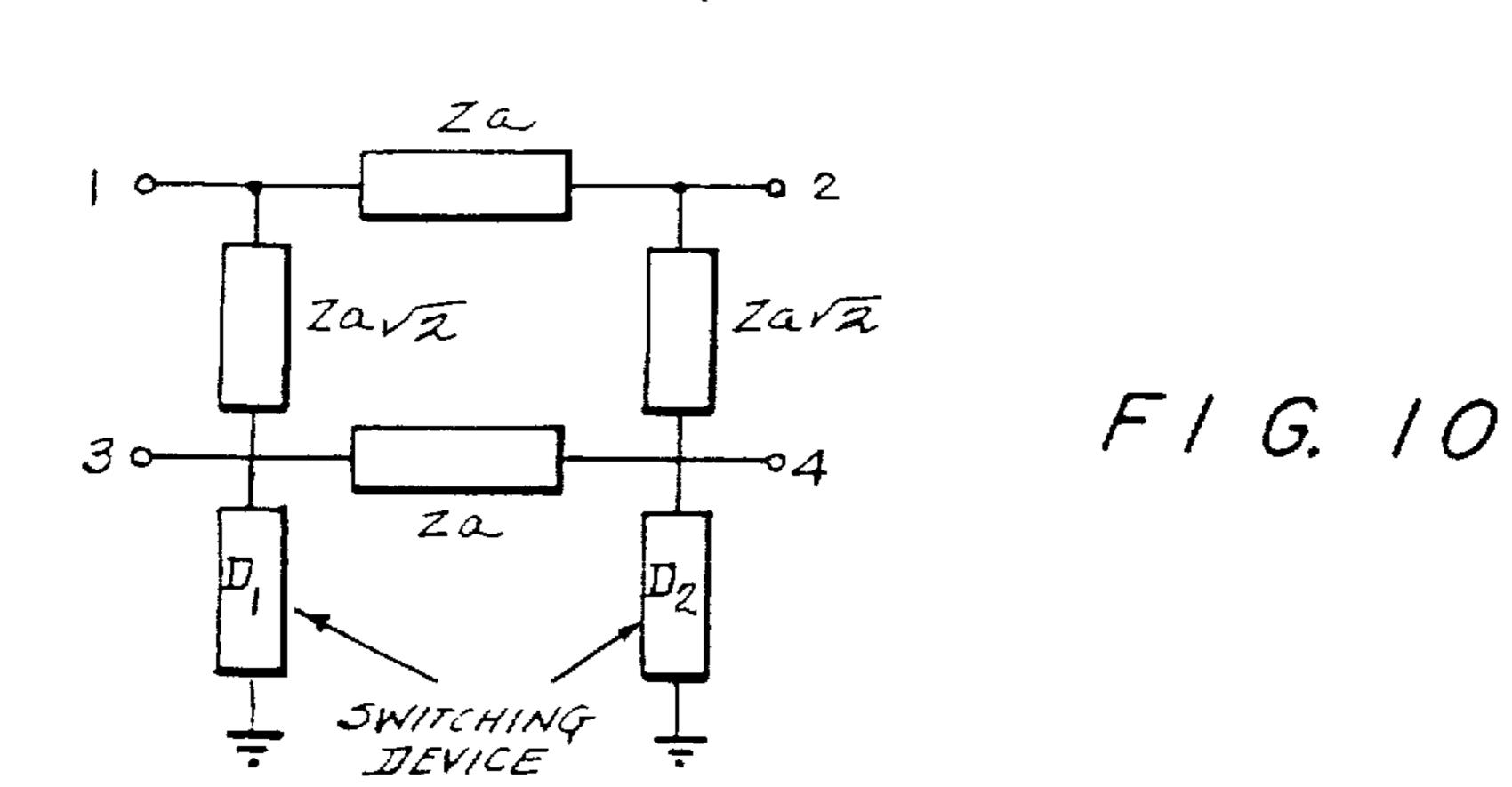

FIG. 10 is a physical schematic of a branch line hy- 30 brid coupler;

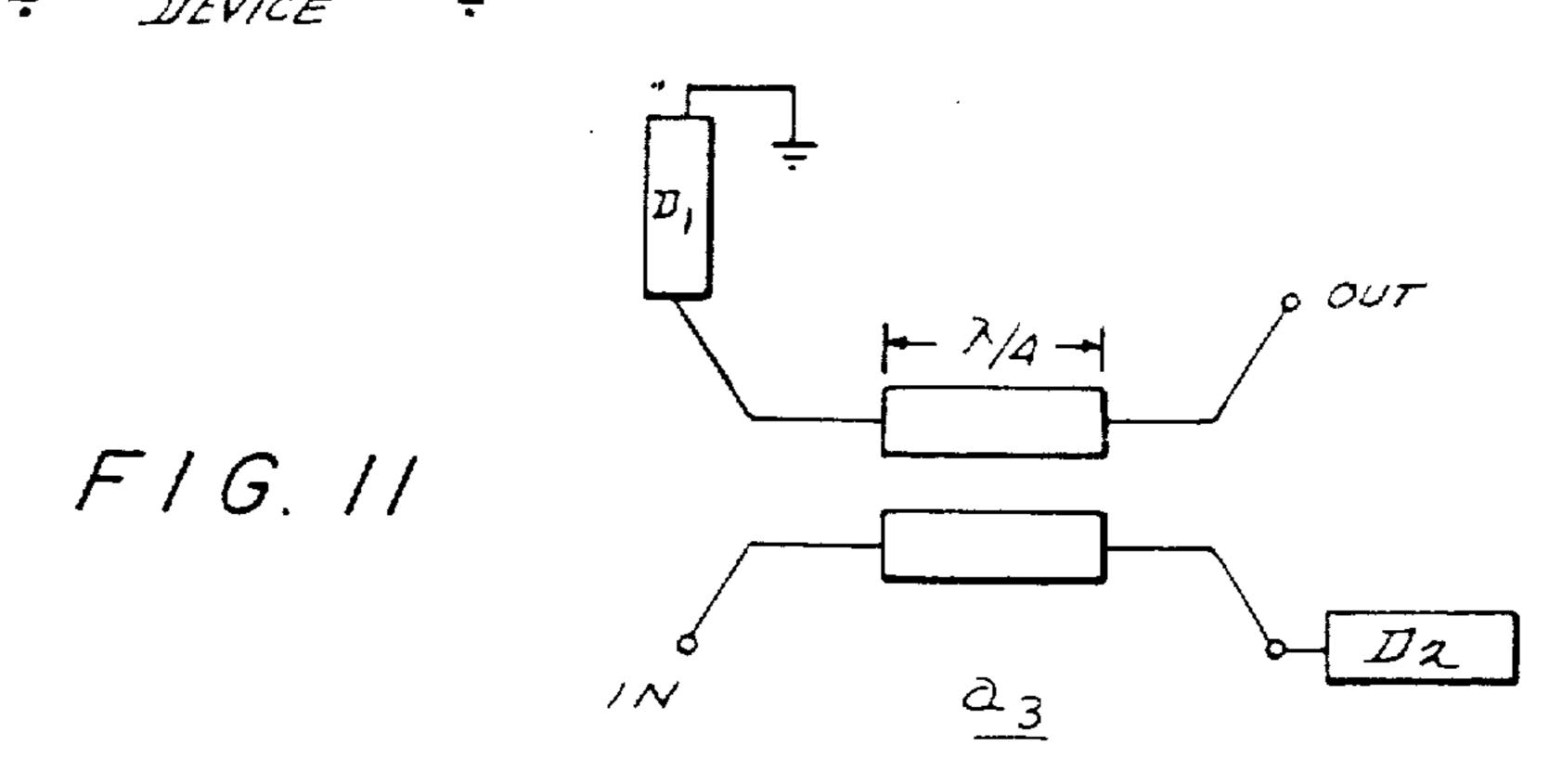

FIG. 11 is a backward wave quadrature hybrid coupler;

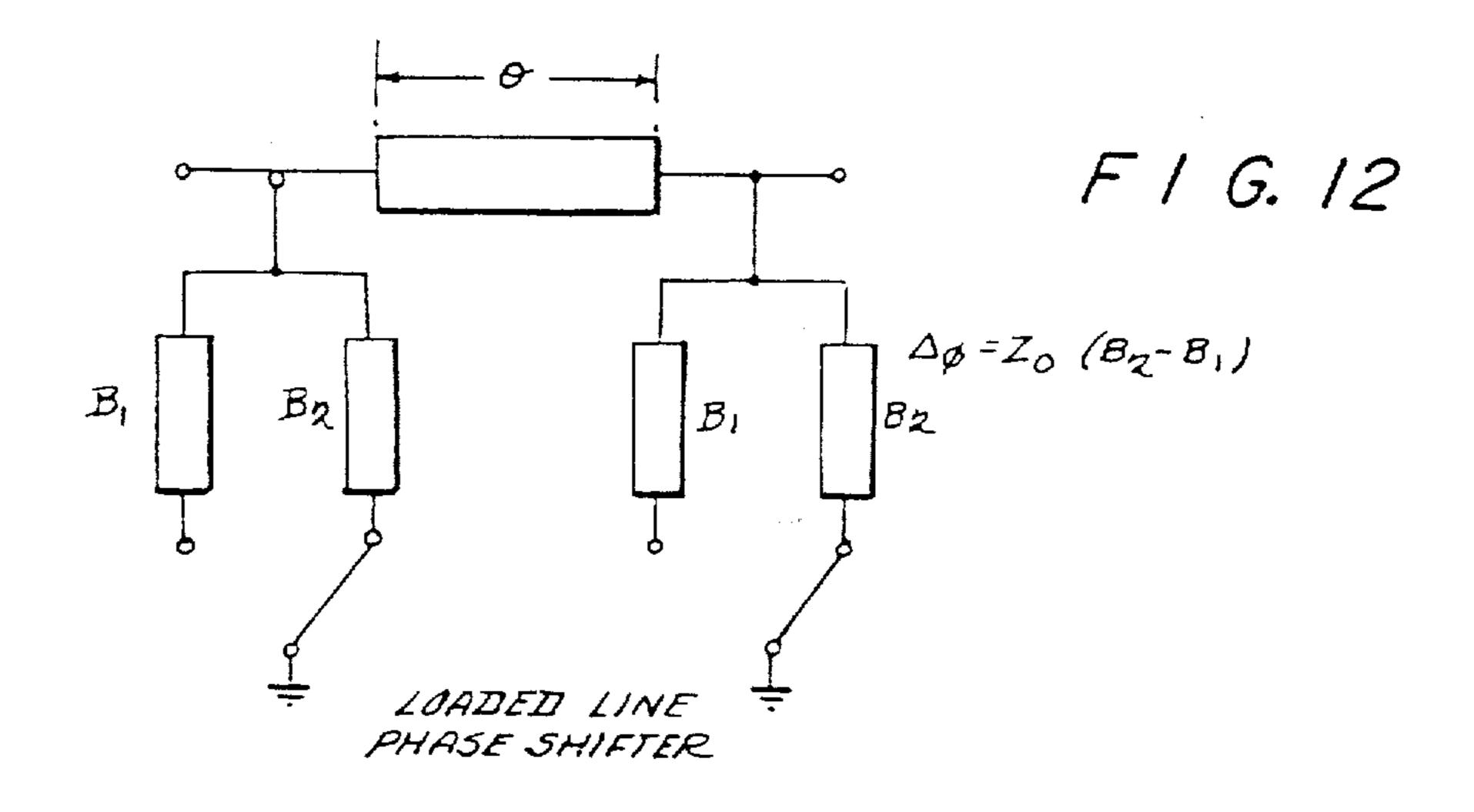

FIG. 12 is a schematic diagram of a loaded line phase shifter; and

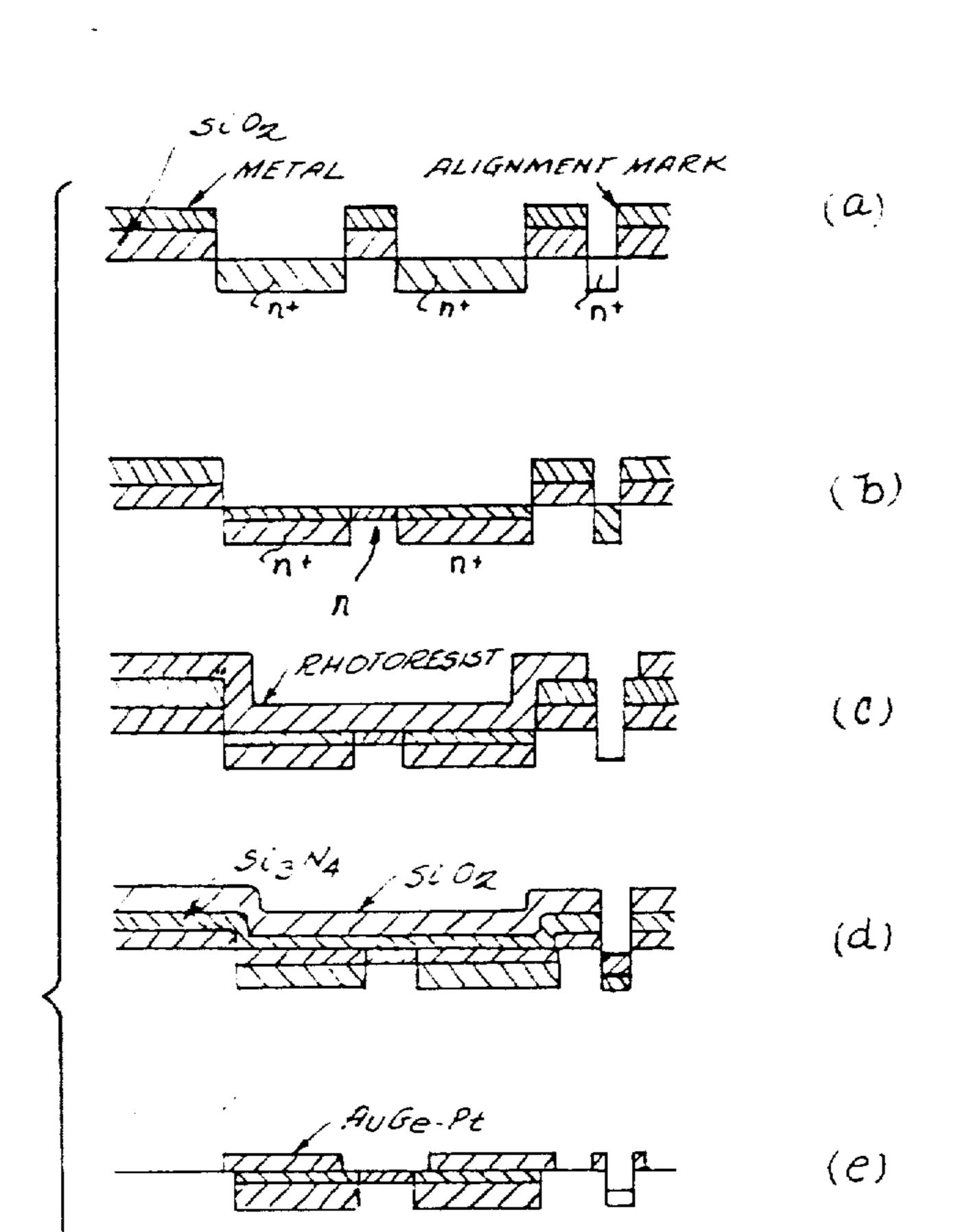

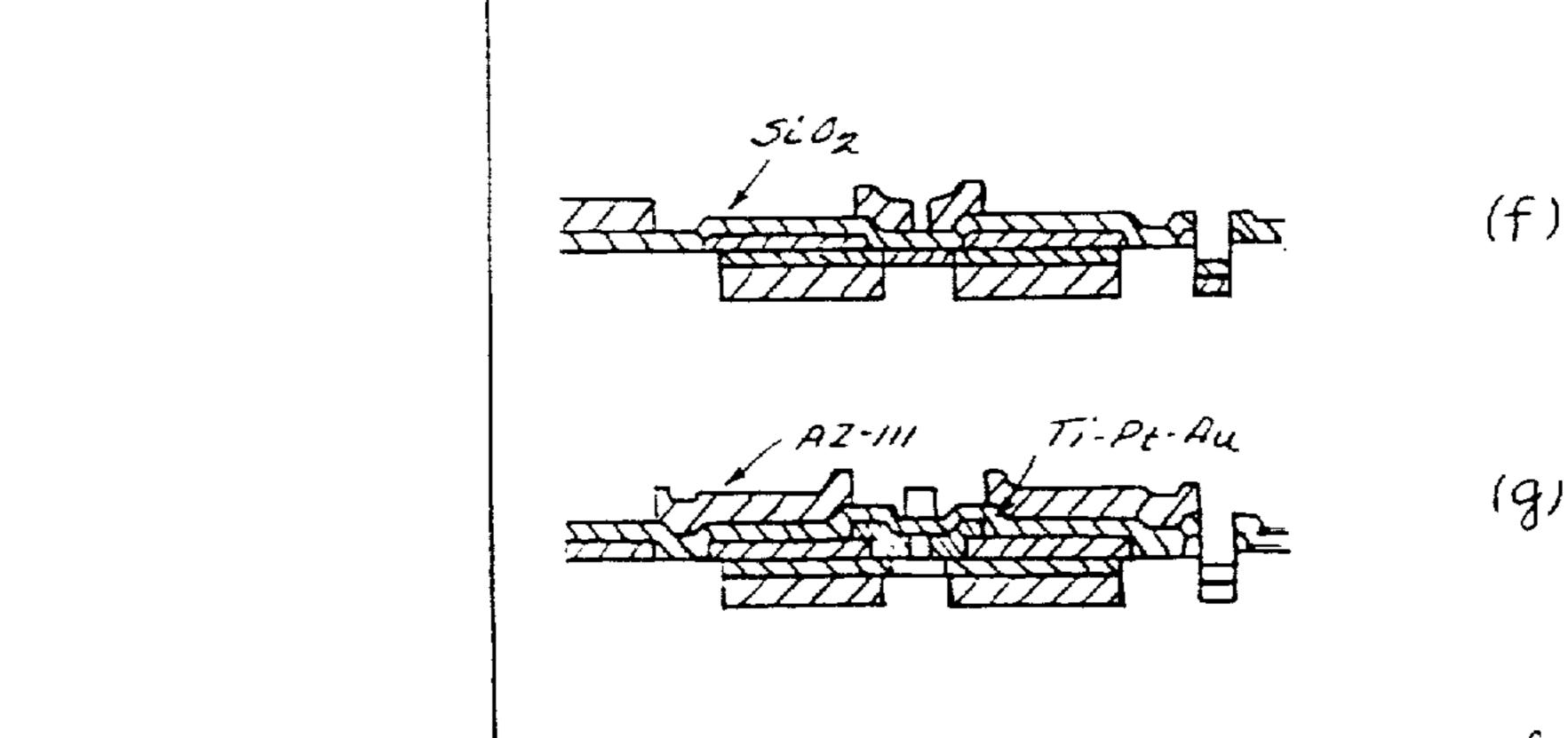

FIG. 13 depicts the fabrication process for the planar GaAs FET phase shifter elements.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Referring now to FIG. 1, there is shown a block diagram of a first embodiment of the monolithic microwave integrated circuit according to the present invention. The embodiment shown in FIG. 1 is a four (4)-element microcomputer controlled phased array. The 45 phased array shown in FIG. 1 is configured as a receiving array. The corresponding transmitting array is shown in a second embodiment in FIG. 2. Continuing to refer to FIG. 1, all components are integrated onto a common semi-insulating GaAs substrate 30. The phased 50 array is controlled by a microcomputer 32 operating in accordance with a program stored within a read only memory (ROM) 34. The program stored in ROM 34 defines the beam pattern to be followed by the phased array. A random access memory (RAM) 36 provides 55 volatile memory for microcomputer calculations during the execution of its program. For a desired scanning pattern, microcomputer 32, based upon the program of ROM 34 computes the phase setting appropriate for each of four (4) phase shifter elements 38, 40, 42 and 44. 60 These phase shifter elements control the phase shift of the four (4) array elements 46, 48, 50, and 52, respectively.

As previously stated, FIG. 1 is a receiver configuration. Signals from array elements 46, 48, 50, and 52, 65 coupled through their respective phase shifters are amplified by low noise amplifiers 54, 56, 58, and 60, associated respectively therewith. The outputs of amplifiers

54, 56, 58 and 60 are combined by a corporate feed 62 and are coupled to a receiver or detector 64. Output base band signals from receiver or detector 64 are coupled to a signal processor 68 controlled by microcomputer 32.

Microcomputer 32 controls phase shifters 38, 40, 42 and 44 via an address decoder 70 and latches 72, 74, 76, and 78 associated one each with the phase shifters. Data from microcomputer 32 appears in serial fashion on an address bus 80 coupled to address decoder 70. The serial data is latched into latches 72, 74, 76 and 78 and then is transferred to an associated driver 82, 84, 86 and 88 on a single clock pulse. Thus, the phase of each of phase shifters 38, 40, 42 and 44 is shifted simultaneously.

Similarly, the individual gains of low noise amplifiers 54, 56, 58 and 60 are controlled by microcomputer 32 via address decoder 70, latches 90, 92, 94, and 96 and individual digital to analog converters 100, 102, 104 and 106, associated one each with the low noise amplifiers. Serial data from microcomputer 32 is decoded by address decoder 70. Latches 90, 92, 94 and 96 latch the serial information in place and on a single clock pulse the information latched is transferred simultaneously from all latches to the digital to analog converters. Thus, the gains of the low noise amplifiers are changed simultaneously. A DC power network 110 shown in dotted line, distributes power to all active circuit elements. A data output line 112 provides a means for connection to an external sensor or to another microcomputer. A command input line 114 provides an input from an external source such as an operator or another microcomputer. Array elements 46, 48, 50 and 52 are of the general type known in the art, even though not previously fabricated as part of a totally integrated 35 microwave system. Specific examples of array elements 46, 48, 50 and 52 are detailed in U.S. Pat. No. 3,811,128 entitled "Electronically Scanned Microstrip Antenna" and U.S. Pat. No. 3,921,177 entitled "Microstrip Antenna Structures and Arrays", commonly owned with 40 the present patent. These two patents are incorporated herein by reference to avoid unnecessary lengthy discussion.

Referring now to FIG. 2 there is shown a second embodiment of the monolithic microwave integrated circuit according to the present invention. As previously stated, this figure is a block diagram of a transmitting array corresponding to the receiving array shown in FIG. 1. In essence, the transmitting array is configured by exchanging the locations of the phasing networks and amplifiers shown in FIG. 1. In addition, the amplifiers 54, 56, 58 and 60 of FIG. 1 are replaced by voltage controlled power amplifiers 120, 122, 124, and 126; and receiver or detector 64 is replaced by a signal source 128. Otherwise, the remaining elements of FIG. 2 are identical to those of FIG. 1.

Referring now to FIG. 3, there is shown in schematic diagram, a third embodiment of the monolithic microwave integrated circuit according to the present invention. It illustrates a possible application of the underlying concepts of the monolithic microwave integrated circuit to the visible light spectrum of 10<sup>5</sup>-10<sup>6</sup> GHz. Receiving array elements 150 would gather visible light, such as solar energy, which would be converted into direct current by diode networks 152. The power from each of diode networks 152 would be "summed" by a DC power collection network 154 and delivered to an output terminal 156. All of the elements are integrated onto a common substrate 160. Ground 158 is a

continuous (e.g. the metalized back surface of the substrate). Arrays such as this can be used to form even larger arrays since the gain and hence the collected energy is proportional to  $[4\pi \text{ (AREA)}]$

#### SEMICONDUCTOR MEDIUM

The presently preferred embodiments of the monolithic microwave integrated circuit shown in FIGS. 1 and 2 are fabricated on semi-insulating gallium arsenide (S.I. GaAs). However, other media, such as silicon 10 and/or GaAs on sapphire represent potential alternatives. At this time, only silicon and gallium arsenide present possible practical choices for X-band application because the processing technologies for these media are sufficiently mature so that consistent, repeat- 15 able results may be achieved at microwave frequencies. Other Groups III-V semiconductor compounds having better theoretical band gap and carrier mobility characteristics may ultimately be well suited for millimeter and submillimeter applications, but at the present time nei- 20 ther the material nor processing technology for these compounds has been sufficiently developed to provide the uniformity required for mass production. As a result the presently preferred embodiments, set forth herein, utilizes semi-insulating GaAs, with silicon being the 25 only presently possible alternative but which, in turn, has been found impractical for reasons discussed below. This therefore leaves semi-insulating GaAs substrate material as the only presently known practical possibility. This substrate material is itself already known in the 30 prior art having a resitivity in the range of about 107 to 10<sup>9</sup> ohm-cm.

In further consideration of the semiconductor medium, PIN diodes fabricated in planar, mesa and beamlead configurations have been successfully used as 35 switching elements at X-band microwave frequencies and above for over a decade in "bolt together" systems. These devices are made from the highest quality bulk silicon with cutoff frequencies in excess of 2000 GHz. Silicon, however, has a maximum resistivity of only 40 200-300 ohm-cm undoped. The loss tangent of silicon is therefore many orders of magnitude worse than that of standard microwave substrate materials such as quartz, alumina and sapphire. Typical microstrip transmission lines on silicon have losses of several dB/cm. Thus, the 45 dielectric losses in a microstrip radiator on bulk silicon would reduce aperture efficiency to 20%, which is impractical.

The use of a silicon on sapphire (SOS) medium would eliminate this loss problem by allowing the microwave 50 radiator and feedline to be fabricated on the sapphire dielectric leaving silicon only in small areas where PIN diodes need to be fabricated. This would solve one problem but create another. To date the achievable electron mobility,  $\mu$ n, SOS epitaxial layers is less than 55 that of bulk silicon. Therefore, PIN diodes suitable for X-band switches are not practical.

Another negative aspect of silicon is that low noise amplifiers are impractical at X-band. This is significant because the ultimate benefits of monolithic microwave 60 integrated circuits and antennas could not be realized in silicon at this frequency.

#### MICROSTRIP RADIATORS

Microstrip radiators 46, 48, 50 and 52 are fabricated 65 as a metallization adjacent to the semiconductor material. Layers of Ti-Pt-Au are deposited sequentially on the semiconductor material. The final metalization layer

6

of Au should be at least four (4) skin depths thick at the operating frequency to prevent excessive ohmic losses in the microwave conductors.

In conventional microstrip radiator designs such as 5 illustrated by U.S. Pat. No. 3,811,128 entitled "Electrical Scanned Microstrip Antenna" and U.S. Pat. No. 3,921,177 entitled "Microstrip Antenna Structures and Array", the choice of a dielectric or substrate material is based on tradeoffs involving physical size and efficiency. As an example conventional hybrid microwave integrated circuits are often configured on high dielectric constant substrates with small conductors in order to minimize physical size. Circuit losses in the "bolt together" systems are often not critical since amplification stages can be liberally incorporated. Conversely, microstrip antennas, phasing networks and corporate feed networks are typically restricted to utilizing low dielectric constant materials such as teflon-fiberglass and employ larger conductors to achieve minimum loss, hence maximum gain.

In the presently described monolithic microwave integrated circuit, however, these traditional tradeoffs are overshadowed by totally different requirements imposed by the semiconductor device. Since the performance of a semiconductor component is uniquely related to the physical properties of the material, radiators 46, 48, 50 and 52 are adapted to the semiconductor medium without compromising element performance, i.e., radiation efficiency.

This adaptation is important because high efficiency, typically 90-95%, is an inherent "no-cost" characteristic of microstrip radiators. If this efficiency is inadvertently sacrificed, an amplifying component with its attendant increase in dc power will be required to recover the lost aperture gain. Such a trade-off is not at all attractive and therefore has been avoided.

Alternative microstrip radiators using quartz, alumina and sapphire substrates were tested as alternatives for the fabrication of radiators 46, 48, 50 and 52. Optimum performance was obtained for sapphire elements. The E-plane half-power beamwidth of the sapphire radiator was 126 degrees, as shown in FIG. 4, which is a computer plot of experimentally measured data. This half power beamwidth is desirable for phased array applications since the element factor does not degrade severly at large scan angles. Such broad beamwidths are characteristic of microstrip elements on high dielectric constant materials, and are explained by the examples shown in FIGS. 5 and 6.

Referring now to FIGS. 5 and 6, there are shown cut-away side views of microstrip radiators showing half power beamwidths of 90° and 126°, respectively. In essence the microstrip element is a two slot radiator and the dielectric under the patch can be treated as a low impedance transmission line  $\lambda/2$  long connecting slot A and slot B. The half-wavelength property of this transmission line is determined by the dielectric constant of the material, however, the radiated field is a function of the slot separation in terms of free-space wavelength. A typical element on teflon-fiberglass dielectric, r=2.2, is shown in FIG. 5 and has a half power beamwidth of 90°. A comparable element on sapphire, r=9.39 is shown in FIG. 6. The resonant dimension or slot separation is reduced due to the higher dielectric constant resulting in a smaller aperture, hence broader beamwidth. It is also significant to note that the aperture efficiency of the same sapphire element determined by integration of the far-field patterns is in excess of 93%.

The sapphire element has a 2:1 VSWR bandwidth of 9.5% which is substantially greater than the typical 1-3% bandwidths associated with designs on lower dielectric materials.

Similar performance is obtained on slightly higher dielectric constant materials such as the semi-insulating (S.I.) GaAs with r=12.6 utilized in the preferred embodiment. Efficiency is slightly degraded since the loss tangent of S.I. GaAs having a resistivity of 108 ohm-cm is equivalent to that of 99.6% AL<sub>2</sub>O<sub>3</sub> or Alumina. The loss tangents for sapphire (mono-crystalline AL<sub>2</sub>O<sub>3</sub>) and S.I. GaAs or Alumina are 2×10<sup>-5</sup> and 1×10<sup>-4</sup> respectively. Although these values are nearly an order of magnitude apart, the additional loss due to increased dielectric dissipation is negligible since the term is only 15 1.5% of the conductor loss. The net result, then is that microstrip radiator aperture efficiencies on semi-insulating GaAs exceed 90%.

## PHASE SHIFTER SWITCHING ELEMENTS

Referring now to FIGS. 7 and 8, there are shown respectively the physical structure and equivalent circuit of one of the single gate FET switches that are utilized as the switching elements of 4-bit phase shifters 38, 40, 42 and 44. FET switches provide low power 25 consumption and are fabricated using ion implantation planar GaAs technology.

The single gate FET switch, as shown in FIG. 7, is turned on and off by application of the appropriate voltage to the gate electrode. The on state is achieved 30 with the gate zero biased or slightly forward biased with respect to the switch terminals. The off state is achieved by biasing the gate beyond the channel pinch-off voltage (negative for the usual n-type depletion-mode GaAs FET). There is no bias applied to the 35 switch terminals for the FET switch.

As a result, there is no distinction between source and drain electrodes in the conventional sense. Also, as in the case of the varactor switch alternative, there is no required sustaining power to hold the FET switch in 40 either the on or the off state. The use of a three terminal (or 4-terminal in the case of the dual gate FET) device for switching greatly simplifies the application of switching bias since the need for dc blocking capacitors is eliminated.

In the on state, the single gate FET switch exhibits a small resistance which is the sum of the channel resistance plus the ohmic contact resistance of the switch terminals. For a 500 µm wide FET with n<sup>+</sup> implanted ohmic contacts and a pinch off voltage of about 7 volts, 50 the on resistance can be reduced to about 5  $\Omega$ or less for a single gate switch and about 7  $\Omega$ or less for a dual gate switch. Lower on state resistance can be achieved by increasing the width of the switch for a corresponding decrease in resistance but with a resultant increase in 55 shunt capacitance in the off state. The dual gate switch has additional resistance due to the additional channel length required for the second gate. The parasitic series inductance in the on state can be made negligible by integrating the switch into the transmission line. It may 60 be desirable in some applications to intentionally introduce inductance by locating the switch in a section of transmission line away from the ground plane.

The current handling capability of the FET switch in the on state is limited by the drain saturation current 65 which is of the order of 150 mA for the 500  $\mu$ m wide FET considered earlier assuming zero gate bias. Therefore, if the FET switch is used to effectively short cir-

8

cuit a  $50\Omega$  transmission line, the power handling capability in the on mode is about 63 to  $100 \, \text{mW}$ . This power handling capability is more than adequate for switching in a low power phase shifter.

In the off state, the FET switch is essentially nonconductive and the microwave impedance is dominated by the shunt capacitance across the switch terminals which is largely the fringing field capacitance through the semi-insulating GaAs substrate of the gap capacitor formed when the gate is completely pinched off. For a 500 µm wide switching FET, this shunt capacitance is of the order of 0.07 to 0.1pF. At 10 GHz the capacitance of the off switch is about  $160\Omega$  to  $230\Omega$ . Since the off resistance of the FET switch is very high, the dissipation is very small in this state, i.e. reflection coefficients with magnitude near one are obtained. Thus, some form of ballasting or loading may be required to balance the amplitude characteristics between the two switching states. The power handling capability of the switch in the off state is determined by the amplitude of the rf voltage swing which can be sustained across the switch without turning the FET on in one direction or the other. For a single gate switch, the FET will turn on if the bias between the gate and either switch terminal (ohmic contact) becomes less than the pinch off voltage. Thus, the maximum permissible voltage swing across the switch cannot exceed the excess gate bias beyond pinch off. For example, if the pinch off voltage is -7Vand the gate is biased at -10V, the rf swing at the output of a single gate switch may not exceed 3V peak or 6V peak-to-peak or else the FET will turn on during negative excursions of the rf voltage. In this example, the power handling capability of the off single gate switch would be about 23 mW into a 50 line which is again entirely adequate for a low-power phase shifter.

The single FET switch utilized in the preferred embodiment has the advantages of ease of biasing, power handling capability, and compatibility with existing process technology. There is, in addition, another subtle advantage for the FET switch in terms of control of circuit parameters. The circuit parameters of the FET switch are almost completely defined by the geometry which is established by the photolithography process. 45 For the varactor switch, however, the capacitance in the on and off states is determined by the doping profile, bias voltage, and junction area. Although excellent control is anticipated over doping profiles through the use of ion implantation processes, the FET switch would be expected to hold an advantage in tightness of parameter distributions which would result in superior circuit reproducibility.

#### PHASE SHIFTER CIRCUIT

The realization of a 4-bit shifter involves incorporation of the switching elements (FET switches in the preferred embodiment) into circuitry permitting the insertion phase of the phase shifter to be switched in binary increments (22.5°, 45°, 90° and 180°) while maintaining nearly constant input and output VSWR and amplitude uniformity independent of phase.

Referring now to FIG. 9, there is shown a schematic diagram of one of the four-bit phase shifters 38-44. The phase shifters utilize FET switching elements, as previously discussed, in a circuit using both switched line and hybrid coupled techniques. The 45° and 22.5° bits use a switched line configuration to reduce area while the 90° and 180° bits utilize a hybrid configuration.

110. 02,00

There are alternative phase shifter circuits which may be appropriate to alternative embodiments. The following discussion relates in general to these various alternatives and to the guiding criteria that will aid in the design of other phase shifter circuits.

Referring now to FIG. 10, there is shown, as another example, a physical schematic of a quadrature hybrid coupler in a branch line configuration. The branch line coupler is limited in bandwidth to about 10 to 15 percent since the transmission match, 3 dB power split, and 10 90° phase shift is only realized for the frequency at which all line lengths are 90°.

The backward wave interdigitated coupler, shown in FIG. 11, gives the broadest phase-shifter bandwidth of all and can be made fairly compact in size. This arises 15 from the fact that although the 3 dB power split is realized only at the center frequency, the 90° phase difference between the coupler output arms, the input match, and the directivity are theoretically frequency independent. Another advantage is that the device is comparatively small and can also be fabricated in a single plane. This coupler typically yields octave bandwidths when designed in stripline, but due to unequal even and odd mode phase velocities in microstrip line the bandwidth reduces to about 35 to 40 percent. Such bandwidth is 25 more than adequate for element compatibility.

A configuration suitable for the 45° and 22.5° bits is shown in FIG. 12. The loaded-line phase shifter is particularly worth considering with regard to their potential for small size. The loaded line phase shifter offers 30 good VSWR and constant phase shift up to 20 percent bandwidth, but is practically limited to 45° maximum shift for that bandwidth. The design of the loaded-line phase shifter is based upon two factors. First, a symmetric pair of quarter wavelength spaced shunt susceptances (or series reactances) will have mutually cancelling reflections provided their normalized susceptances are small. Therefore, a good match results regardless of the susceptance sign or value.

#### **FABRICATION**

The fabrication process begins with the lapping and polishing of the semi-insulating GaAs substrate to a plane parallel thickness compatible with microstrip propagation characteristics (typically 0.6 mm at 10 45 GHz). Several surface cleaning steps insure proper adhesion of deposited SiO<sub>2</sub> and metal layers required for masking during the ensuing ion-implantation. The process continues following the sequence depicted in FIG. 13.

Referring now to FIG. 13, there are shown the processing steps for fabricating one of the planar GaAs FET phase shifter elements. As shown in FIG. 13(a) the semi-insulating substrate is covered with SiO2 and a suitable metal. Holes are opened and the SiO2 is re- 55 moved by dry etching. The N+implant is then performed. After the N+implant is performed, the metal and oxide mask is removed from the source in FIG. 13(b). Then the alignment mark is defined by ion milling, as shown in FIG. 13(c). After the alignment mark is 60 defined, the resist and metal are removed. Nitride and oxide is deposited and the implantation anneal is performed, as shown in FIG. 13(d). After the implantation anneal is performed, the insulators are removed and ohmic contact holes are defined using conventional 65 photolithographic techniques. AuGe-Pt is then deposited. FIG. 13(e) shows the device after AuGe-Pt has been deposited. As shown in FIG. 13(f), a layer of SiO<sub>2</sub>

is deposited. The gate and ohmic contact holes are defined and the exposed SiO<sub>2</sub> is removed by plasma etching, after removal of the SiO<sub>2</sub> by plasma etching. Ti-Pt-Au is deposited and the gate and circuit path areas are defined using conventional photo resist technology, as shown in FIG. 13(g). Then the exposed metal is removed by ion-milling, as shown in FIG. 13(h).

In the processing step shown in FIG. 13(h), the microstrip transmission lines, radiating element and DC biasing interconnect metallization are formed using photolithographic procedures. At this point RF blocking chokes or eventually lumped element components are simultaneously defined.

The use of ion implantation directly into high quality semi-insulating GaAs to form the active layer for planar FETs places certain restrictions on the nature of the compensation method used to obtain the insulating properties. The following conditions must be met to allow to achieve successful implantation of an active layer:

- 1. The compensating impurities and defects in the substrate must not affect the electrical properties of the ion implanted layer, so that carrier concentration, mobility, carrier lifetimes, etc., depend only on the identity and dose of the implanted purity. Meeting this condition ensures that the electrical properties of the implanted layers are independent of the substrate, and guarantees that the implanted layers can be prepared reproducibly.

- 2. Unimplanted portions of the semi-insulating substrate must retain their high resistivity after a wafer has been capped and annealed to remove damage in the implanted portions, so that electrical isolation is maintained between the doped pockets.

- 3. The substrate must be homogeneous. This implies that conditions 1 and 2 must be met with a minimum of short or long-range inhomogeneities or defects. In addition to homogeneity, flatness requirements on the wafers will be stringent for uniform small geometries and high density.

As previously stated the semiconductor material is semi-insulated GaAs, chromium (Cr) compensated (doped) grown by the horizontal Bridgman technique.

The crystalline quality of the horizontal Bridgman grown ingots are superior with regard to low percipitate density, dislocation density and strain. Electrical compensation is routinely obtained with low Cr concentrations of  $5 \times 10^{15}$  cm<sup>-3</sup>. The initial uncompensated background doping is often as low as  $8 \times 10^{14}$  cm<sup>-3</sup>.

In order to obtain a high level of reproducibility, the GaAs may be qualified by a procedure such as that set forth in U.S. Pat. No. 4,157,494—Eisen et al (1979).

Thus, there has been provided a monolithic microwave system including an integral array antenna. Of course, various alternative embodiments will be apparent to those of ordinary skill in the art having the benefit of the teachings set forth herein. Therefore, such alternate embodiments are intended to be within the scope of the appended claims.

We claim:

- 1. A monolithic integrated circuit antenna system, comprising:

- at least two receiving array antenna elements, each of which includes a metallized resonant radiation element of approximately one-half wavelength dimension at an intended antenna operating frequency;

- a phasing and r.f. feeding network connected to said antenna elements and including one or more FET devices associated with at least some some of said antenna elements for combining r.f. signals received by said antenna elements and for controlling an electrical phase shift associated with the r.f. signals coming from each of said receiving array elements; and

- an integrated circuit controller means connected to each of said Fet devices for controlling said phasing and r.f. feeding network.

- said array elements, phasing and r.f. feeding network and controller means all being integrated onto a single substrate of semi-insulating GaAs semiconductor material having a resistivity of about 10<sup>7</sup> to 15 10<sup>9</sup> ohm-cm.

- 2. A monolithic integrated circuit antenna system according to claim 1 further including:

- a low noise amplifier, associated with one or more of the array elements and electrically coupled thereto via a phase shifter of said phasing network, for amplifying r.f. signals from its associated array element, the gain of said amplifiers being controlled by said controller means;

- a receiver for detecting signals from said amplifiers and

- said phasing and r.f. feeding network coupling r.f. signals output from said amplifiers to said receiver, said amplifiers and receiver also being integrated onto said single substrate together with said array elements, phasing and r.f. feeding network and controller.

- 3. A monolithic integrated circuit antenna system according to claim 1 or 2 further including latch means 35 for causing the phase shifts of said phasing network to shift simultaneously, said latch means also being integrated onto said single substrate.

- 4. An integrated-circuit monolithic antenna system, comprising:

- at least two transmitting array antenna elements, each of which includes a metallized resonant radiating element of approximately one-half wavelength dimension at an intended antenna operating frequency;

- a phasing and r.f. feeding network connected to said antenna elements and including one or more FET devices associated with at least some of said antenna elements for controlling an electrical phase shift associated with r.f. signals being fed to these 50 transmitting array elements; and

- an integrated circuit controller means connected to each of said FET devices for controlling said phasing and r.f. feeding network,

- said array elements, phasing network and controller 55 means all being integrated onto a single substrate of semi-insulating GaAs semiconductor material having resistivity of about 10<sup>7</sup> to 10<sup>9</sup> ohm-cm.

- 5. A monolithic integrated-circuit antenna system according to claim 4 further including:

- a low noise power amplifier, associated with one or more of said array elements, and electrically coupled thereto via a phase shifter of said phasing and r.f. feeding network, for providing r.f. signals to its associated array elements, the gain of said amplifiers being controlled by said controller means;

a signal source for providing signals to said amplifiers; and

- said phasing and r.f. feeding network coupling r.f. signals intput from said signal source to said amplifiers,

- said amplifiers and signal source also being integrated onto said single substrate together with said array elements, phasing and r.f. feeding network and controller.

- 6. A monolithic integrated-circuit antenna system according to claim 4 or 5 further including latch means for causing the phase shifts of said phasing network to shift simultaneously, said latch means also being integrated onto said signale substrate.

- 7. A monolithic integrated circuit antenna system comprising:

- a plurality of antenna elements each having a one-half wavelength resonant dimension and arranged in an array for transmitting/receiving electromagnetic waves; and

- a phasing and r.f. feeding network including plural FET integrated circuit structures electrically connected to control the electrical phase shift of electrical currents flowing to/from each said element,

- said antenna elements and said phasing network being integrated on a single substrate of semi-insulating GaAs semiconductor material having a resistivity of about 10<sup>7</sup> to 10<sup>9</sup> ohm-cm.

- 8. A monolithic integrated circuit antenna system as in claim: 7 further comprising:

- an integrated circuit digital controller means electrically connected to the FET integrated circuit structures of said phasing network for controlling their operations and said controller means also being monolithically integrated onto said single substrate of semi-insulating GaAs.

- 9. A monolithic integrated circuit antenna system as in claim 7 or 8 further comprising:

- at least one lower noise amplifier associated with one or more of said antenna elements for amplifying electrical r.f. currents passing to/from that element, said amplifiers also being monolithically integrated onto said single substrate of semi-insulating GaAs.

- 10. A monolithic integrated circuit antenna system as in claim 9 further comprising latch means for causing phase shifts within said phasing network to occur simultaneously, said latch means also being monolithically integrated onto said single substrate of semi-insulating GaAs.

- 11. A monolithic integrated circuit comprising: a substrate of semi-insulating GaAs having a resistivity of about 10<sup>7</sup> to 10<sup>9</sup> ohm-cm;

- an array of plural metallized r.f. microstrip antenna radiators formed and disposed on said substrate, each of said radiators having a resonant dimension and at least one radiation slot from/to which r.f. electromagnetic radiation propagates;

- an array of metallized r.f. transmission feedlines also integrally formed in said substrate and connected to the edges of said antenna radiators for conducting r.f. electrical signals to/from said radiators;

- an array of phase-shifting circuits including FET devices also integrally formed on said substrate, individual ones of said phase-shifting circuits being connected to respective ones of said feedlines for ocntrolling the relative r.f. phase shifts encountered by r.f. signals passing to/from said radiators; and

an array of controlled-gain amplifier circuits also integrally formed on said substrate, individual ones of said amplifier circuits being connected in circuit with said feedlines for controlling the amplitude of r.f. signals passing to/from said radiators.

12. A monolithic integrated circuit antenna system comprising a plurality of antenna elements arranged in an array for transmitting or receiving electromagnetic waves, and a phasing and r.f. feeding network including plural FET integrated circuit structures electrically connected to control the electrical phase shift of electrical currents flowing to or from each said element, said antenna elements and said phasing network being integrated on a single substrate of semi-insulating GaAs semiconductor material having a resistivity of about 107 to 109 ohm-cm.

13. An antenna structure comprising a substrate of semiinsulating gallium arsenide having a resistivity of between about 10<sup>7</sup> to 10<sup>9</sup> ohm-cm, an antenna element being integrally formed on said substrate and arranged for transmitting or receiving electromagnetic waves.

14. An antenna structure as in claim 13 wherein the semi-insulating gallium arsenide is doped with chromium.

15. An antenna structure as in claim 13 wherein the chromium concentration is about  $5 \times 10^{15}$  cm<sup>-3</sup>.

16. An antenna structure as in claim 13 wherein the semi-insulating gallium arsenide is coated with a layer of titanium, followed by a layer of platinum and, thereafter, a layer of gold.

17. An antenna as in claim 13 wherein the element has a dimension of about one-half wavelength dimension.

18. An integrated circuit network antenna comprising a substrate of semi-insulating gallium arsenide having a resistivity of between about 107 to 109 ohm-cm, a plurality of antenna elements being integrally formed on said sub- 35 strate and arranged in an array for transmitting and receiving electromagnetic waves.

19. An integrated circuit network antenna of claim 18 where the elements are deposited on the surface of the gallium arsenide substrate.

20. An integrated circuit network antenna as recited in claim 18 further including feedlines integrally formed on said gallium arsenide and connected to the edges of said

antenna elements for conducting electrical signals to and from said elements.

21. A monolithic integrated circuit antenna system comprising a plurality of antenna elements each having a predetermined wavelength resonant dimension and arranged in an array for transmitting or receiving electromagnetic waves, said plurality of antenna elements being integrated on a single substrate of semi-insulating gallium arsenide semiconductor material having a resistivity of about 107 to 109 ohm-cm.

22. An antenna system as in claim 21 wherein the semiinsulating gallium arsenide is doped with chromium.

23. An antenna system as in claim 22 wherein the chromium concentration is about  $5 \times 10^{15}$  cm<sup>-3</sup>.

24. An antenna system as in claim 21 wherein the semiinsulating gallium arsenide is coated with a layer of titanium, followed by a layer of platinum and, thereafter, a layer of gold.

25. An antenna system as in claim 21 wherein said semi-insulating gallium arsenide has a thickness compatible with the propagation characteristics of the antenna elements of about 0.6 mm at 10 GHz.

26. A monolithic integrated circuit antenna system having a microstrip radiator aperture efficiency greater than 90% comprising a substrate of semi-insulating gallium arsenide having a resistivity of about 10<sup>7</sup> to about 10<sup>9</sup> ohmem and a dielectric constant of about 12.6 and at least two antenna elements integrated thereon, each element being a metallized resonant element of a predetermined wavelength resonant dimension at an intended antenna operating frequency.

27. A monolithic system as recited in claim 26 wherein the metallized resonant radiation element has a dimension

of approximately one-half wavelength.

28. An antenna structure comprising a substrate of semiinsulating gallium arsenide having a resistivity of between about 107 and 109 ohm-cm, an antenna element being integrally formed on said substrate and arranged for transmitting or receiving electromagnetic waves, and a feedline 40 integrally formed on said gallium arsenide and connected to an edge of said antenna element for conducting electrical signals to and from said radiator.

45

50

55

60