15-18 1/6/87

### United States Patent [19]

[11] E

Patent Number:

Re. 32,326

Nagel et al.

[45] Reissued Date of Patent:

Jan. 6, 1987

| [54] | ROW | <b>GRABBING</b> | SYSTEM |

|------|-----|-----------------|--------|

|------|-----|-----------------|--------|

Robert H. Nagel, New York; Richard [75] Inventors:

Saylor, Monsey, both of N.Y.

IRD, Inc., Farmingdale, N.Y. Assignee:

Appl. No.: 496,273

[22] Filed: May 19, 1983

#### Related U.S. Patent Documents

| Reiss | ue of:           |                 |                  |  |  |

|-------|------------------|-----------------|------------------|--|--|

| [64]  | Patent No.:      | 3,889,054       |                  |  |  |

| _     | Issued:          | Jun. 10, 1975   |                  |  |  |

|       | Appl. No.:       | 434,226         |                  |  |  |

|       | Filed:           | Jan. 17, 1974   |                  |  |  |

| [51]  | Int. Cl.4        |                 | H04N 5/00        |  |  |

| [52]  | U.S. Cl          |                 | 358/83; 358/141  |  |  |

| [58]  | Field of Search  | *************** | 358/83, 141, 203 |  |  |

| [56]  | References Cited |                 |                  |  |  |

|       | U.S. PAT         | ENT DOCUM       | ENTS             |  |  |

| 3,369,073 | 2/1968 | Scholz      | 178/5.6 |

|-----------|--------|-------------|---------|

| -         |        | Eilenberger |         |

| -         |        | Clark       |         |

| 3,609,227 | 9/1971 | Kuljian     | 360/35  |

| 3,647,949 |        | Closs       |         |

| 3,649,749 | 3/1972 | Gibson      | 178/5.6 |

#### FOREIGN PATENT DOCUMENTS

2058681 9/1973 Fed. Rep. of Germany.

Primary Examiner-Michael A. Masinick Attorney, Agent, or Firm-Stiefel, Gross, Kurland & Pavane

[57]

#### ABSTRACT

A real time frame grabbing system for substantially instantaneously providing a continuous video display or

a selectable predetermined video frame of information on a video display means from continuously transmittable video information which is transmitted as a plurality of pseudo video scan lines wherein the selected frame being grabbed is updatable on a displayable row by displayable row basis. Each of the pseudo video scan lines has a television scan line format and comprises a complete self-contained packet of digital information sufficient to provide an entire displayable row of video data characters, the pseudo video scan line having an associated transmission time equivalent to that of a television video scan line. The packet of digital information comprises at least address information for a displayable row and data information for the displayable characters in the row. Each of these psuedo video scan lines further comprises a horizontal sync signal at the beginning thereof which provides a record separator between adjacent pseudo video scan lines and resets the input receiver logic for the transmitted pseudo video scan lines upon the detection of each horizontal sync signal to provide noise immunity enhancement. The pseudo video scan lines are transmitted and received through a conventional television distribution system. Each pseudo video scan line contains means for error checking the contents of the received pseudo video scan line for inhibiting display of the associated displayable row when the error check is not satisfied. Programmable means, such as a general purpose digital computer, is conventionally programmed to interleave the pseudo video scan line signal transmission to provide pseudo video scan line information corresponding to a common assigned row for a plurality of frames before providing such information corresponding to a subsequent different common assigned row for the plurality of frames.

#### 26 Claims, 19 Drawing Figures

FIG. I

FIG. 2

F16. 3

FIG. 6

FIG. 6A

FIG. 8

F16. 1

F16. 12

FIG. 18

#### **ROW GRABBING SYSTEM**

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

#### BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates to video communication systems in which individual frames may be grabbed for video display thereof.

2. Description of the Prior Art

Video communication systems in which individual 15 frames may be grabbed for video display are well known, such as the system disclosed in U.S. Pat. No. 3,740,465, or a system employing the Hitachi frame grabbing disc. These prior art systems such as the one disclosed in U.S. Pat. No. 3,746,780 are normally two- 20 way request response systems requiring the user to request information by the dialing of a specific dicital code which is uniquely assigned to each frame. However, such systems normally grab a group of frames for storage and then subsequently select the individual 25 frame for display out of the group of grabbed frames as opposed to instantaneously selecting a single frame in real time. Furthermore, such prior art systems do not provide for real time updating of the grabbed video frame. Furthermore, some such prior art frame grab- 30 bing systems, such as the type disclosed in U.S. Pat. No. 3,397,283 are normally capable of only grabbing the next immediate signal in response to the provision of a starter signal or, as disclosed in U.S. Pat. No. 3,051,777, utilize a counter for frame location which must be reset 35 to the beginning of a tape for video tape supplied information in order to locate a selected frame to be grabbed. These systems are not applicable in a real time frame grabbing environment. Similarly, other typical prior art frame grabbing systems, such as disclosed in U.S. Pat. 40 Nos. 3,695,565; 2,955,197; 3,509,274; 3,511,929 and 3,582,651 can not be utilized in a real time frame grabbing environment, such as one in which the video information associated with the grabbed frame is capable of being continuously updated. Accordingly, presently 45 available prior art frame grabbing systems familiar to the Inventors are not capable of easily locating a frame to be grabbed in real time nor of being able to continuously update such a grabbed frame in real time.

Video communication systems in which the signal 50 being transmitted is digitized are also well known. For example, U.S. Pat. No. 3,743,767 discloses a video communication system for the transmission of digital data over standard television channels wherein the digital data is transmitted in a conventional television scan line 55 format through conventional television distribution equipment. However, such prior art communication system merely digitizes one television scan line at a time for distribution to a video display terminal on a bit-bybit basis in a line, 84 bits of information being provided 60 per television scan line. Furthermore, such a prior art system is not transmission selectable by every display terminal nor is the data for a displayable video row packed into a self-contained pseudo video scan line information packet. Thus, there is no significant in- 65 crease in the data transmission rate resulting from such a prior art video communication system. Similarly, U.S. Pat. Nos. 3,061,672 and 3,569,617 are examples of other

prior art video communication systems in which television signals are digitized without any significant resultant compression in data transmission time. Furthermore, these other prior art systems require special distribution circuitry. In addition, prior art video communication system in which a digital television signal is transmitted do not sufficiently isolate the individual rows comprising a frame so as to provide satisfactory noise immunity between these rows, noise immunity at best being provided between frames, nor is there satisfactory data compression in the transmission time of the video information in such prior art systems.

These disadvantages of the prior art are overcome by the present invention.

#### SUMMARY OF THE INVENTION

A real time frame grabbing system for substantially instantaneously providing a continuous video display of a selectable predetermined video frame of information on a video display means from continuously transmittable video information, wherein such information is transmitted as a plurality of pseudo video scan lines is provided. Each of the pseudo video scan lines has a television video scan line format and comprises a complete self-contained packet of digital information sufficient to provide an entire displayable row of video data characters, the pseudo video scan line having an associated transmission time equivalent to that of a television video scan line. The packet of digital information comprises at least address information, such as page, group, permission, user and direct address for a displayable row and data information for the displayable characters, such as 32 characters, in a displayable row. Each of the pseudo video scan lines further comprises a horizontal sync signal at the beginning thereof, each horizontal sync signal providing a record separator between adjacent pseudo video scan lines as well as providing noise immunity on a row by row basis for resetting all the input logic in the receiver which processes the transmitted signal every horizontal sync pulse. The transmitter for the pseudo video can line includes means for providing a vertical sync signal after a predetermined plurality of pseudo video scan lines have been transmitted, the pseudo video scan line being a composite video signal. These transmitted pseudo video scan line composite vice signals are distributed through a conventional television distribution system, such as a cable distribution system, to various video display means for providing a continuous video display thereof. The receiver which is operatively connected between the distribution network and an associated video display means, processes the distributed composite pseudo video scan line signals and provides a displayable video row to the associated video display means from each of the pseudo video scan line signals pertaining to the frame selected in order to provide the continuous video display, a predetermined plurality of displayable video rows comprising a displayable video frame of information. The receiver also preferably includes means for updating the continuously video displayable selectable frame on a displayable video row-by-row basis dependent on the real time data information content of the received pseudo video scan line.

Each of the packets of digital information contained within the pseudo video scan line, also preferably includes an error check information content based upon at least the address and data information content of the

associated pseudo video scan line, the receiver including error check means for obtaining an error check indication of the distributed associated pseudo video scan line and comparing the error check indication with the error check information content of the associated pseudo video scan line in accordance with a predetermined error check condition for providing a predetermined output condition when the error check condition is satisfied. The receiver also includes condition responsive means operatively connected to the error check means for preventing the provision of the displayable video row from the associated pseudo video scan line when the predetermined output condition is not met.

The system also preferably includes programmable means, such as a general purpose computer, for receiving the continuously transmittable video information, retrievably storing the information, reformatting it into a desired pseudo video scan line format and continuously providing this reformatted information to the transmitter on a word-by-word basis, a word comprising a pair of displayable characters. Furthermore, the programmable means preferably includes means for interleaving the reformatted pseudo video scan line information to provide pseudo video scan line information corresponding to a common assigned row for a plurality of frames to the transmitter before providing pseudo video scan line information corresponding to a subsequent different common assigned row for the plurality of frames to the transmitter. Thus, the provision of the pseudo video scan line enables the use of conventional television transmission techniques and equipment for transmission and reception as well as conventional television circuitry for processing the received and transmitted signals. Furthermore, by utilizing the hori- 35 zontal sync as a record separator, one can insure that any loss of synchronization or noise pulse will not disrupt more information than one pseudo video scan line. In addition, significant data compression in transmission time is obtained by transmitting the pseudo video scan an lines as opposed to conventional television scan lines, with each pseudo video scan line being a self contained packet of information sufficient for display of an entire displayable video row containing a plurality of conventional television scan lines, such as 13, as opposed to 45 display of one television scan line.

In the present invention, frame grabbing is accomplished by preferably feeding the pseudo video scan line into a buffer storage for comparison with an information request from the [keyboarad] keyboard which, if 50 matched, updates the appropriate memory for display or selection control so that updating is, in reality, accomplished on a row-by-row basis as opposed to a page or frame-by-frame basis as new information is provided in real time, the selected frame being automatically 55 updated in real time as new information is provided for a given row of the displayed selected frame.

#### BRIEF DESCRIPTION OF DRAWINGS

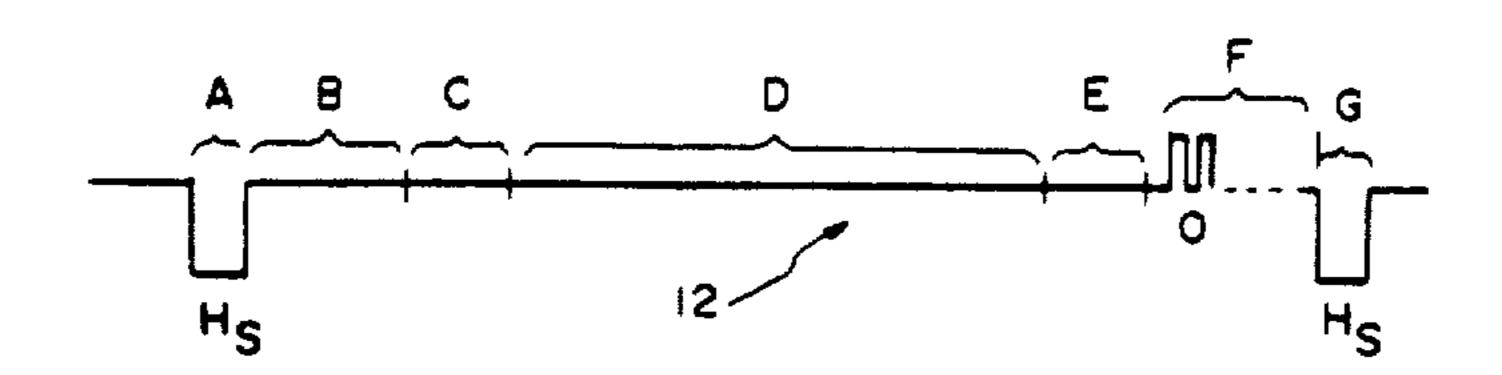

FIG. 1 is a diagrammatic illustration of a typical 60 pseudo video scan line format in accordance with the present invention;

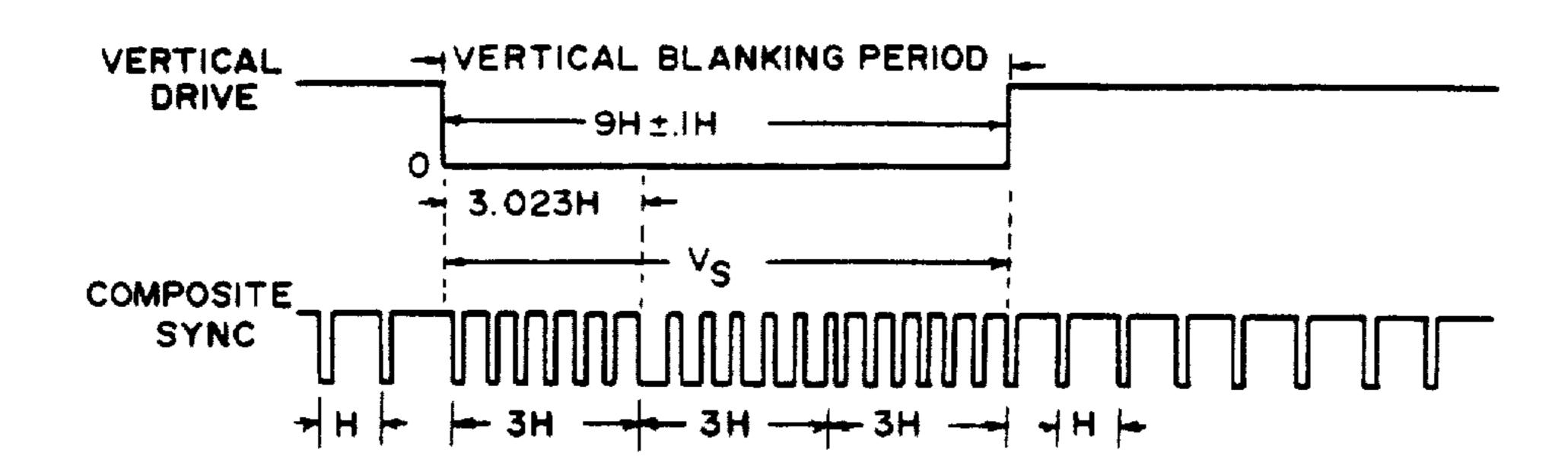

FIG. 2 is a graphical illustration of conventional vertical drive and composite sync signals illustrating the origin of the vertical sync signal in accordance with the 65 present invention;

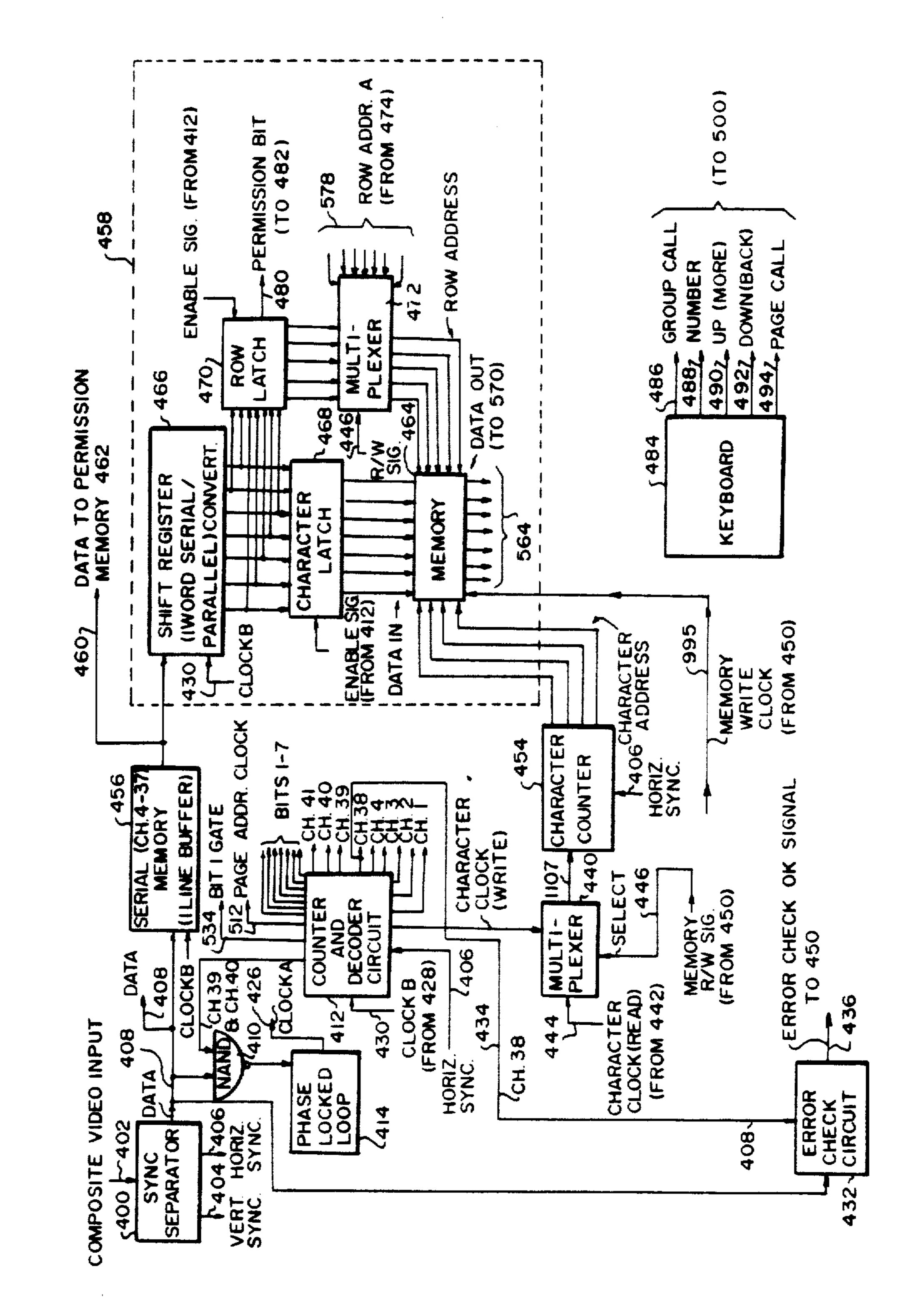

FIG. 3 is a [blcok] block diagram of the timing and keyboard control, memory input control and a part of

the output processing portions of the preferred receiver of the present invention;

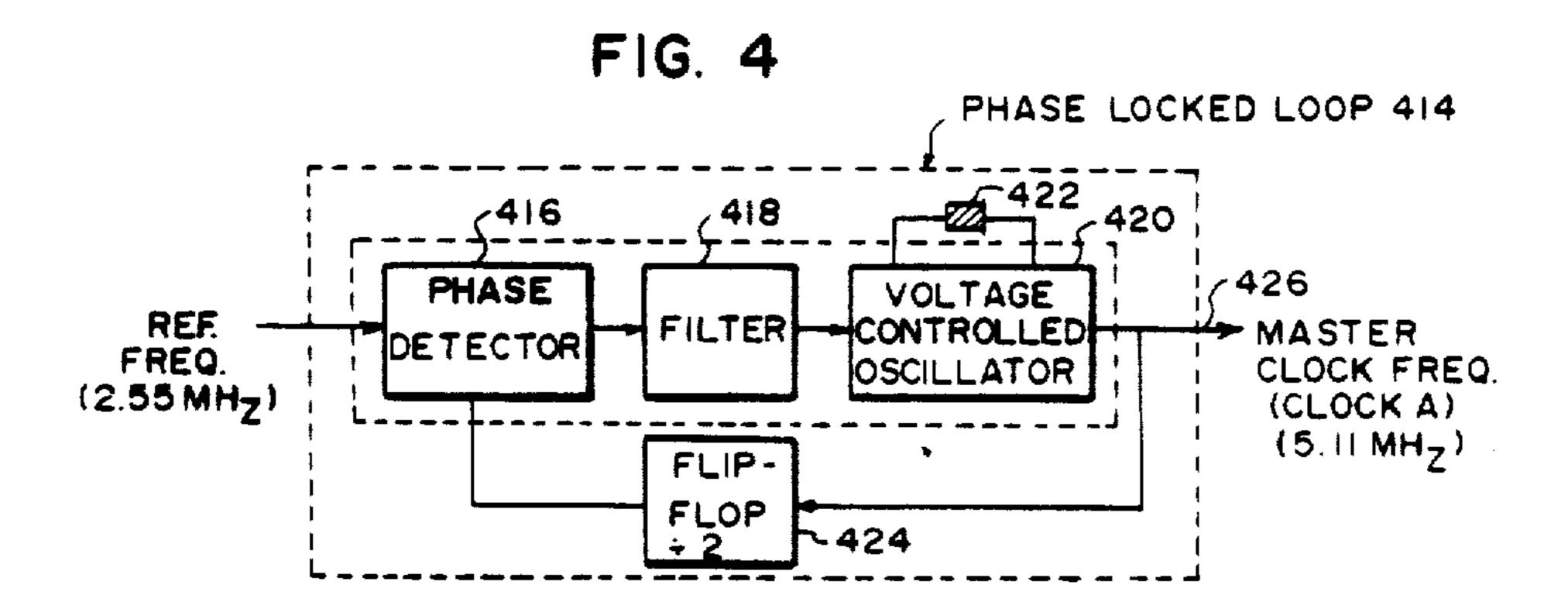

FIG. 4 is a block diagram of the phase locked loop portion of the arrangement illustrated in FIG. 3;

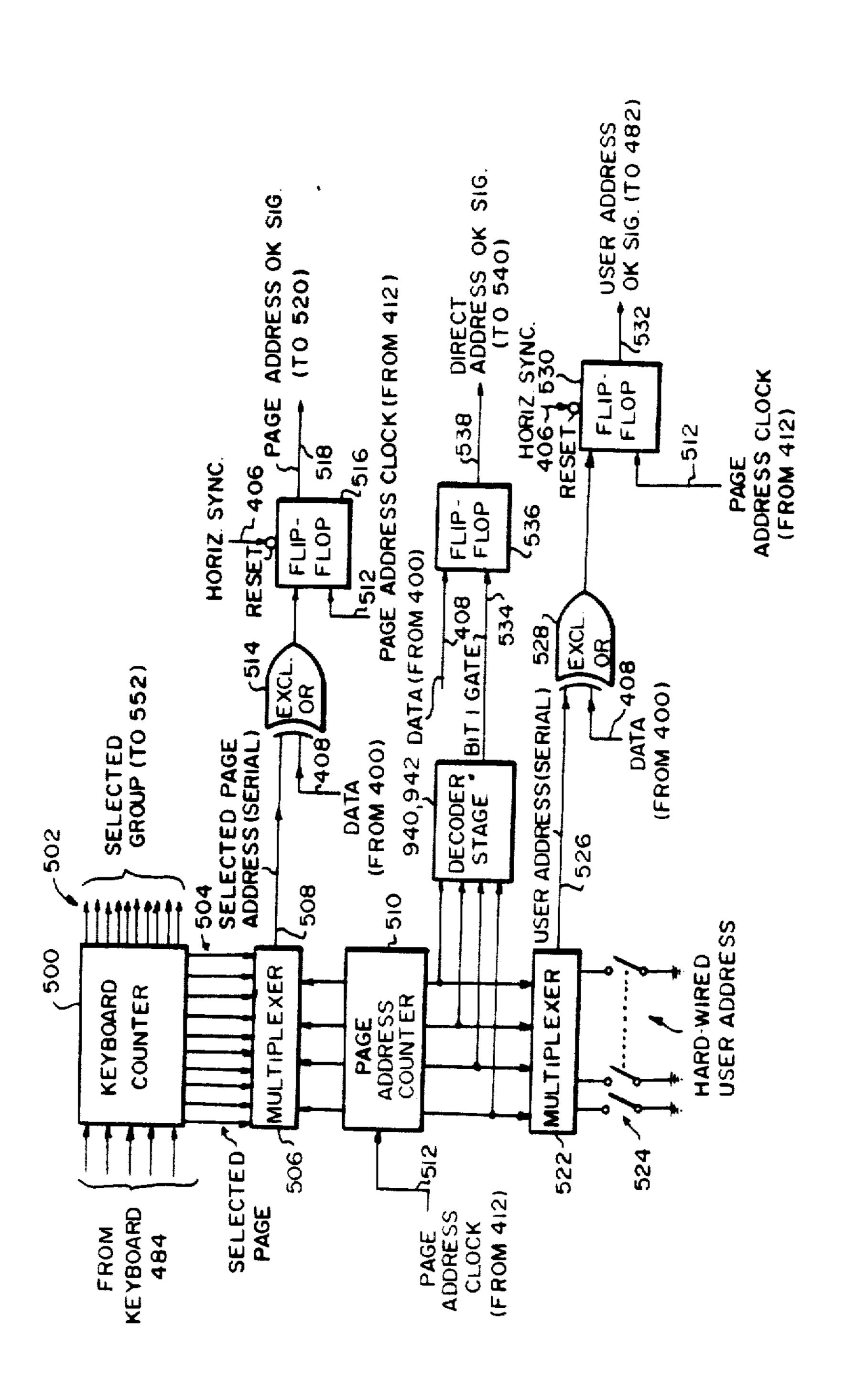

FIG. 5 is a block diagram of another portion of the memory input control portion of the preferred receiver of the present invention;

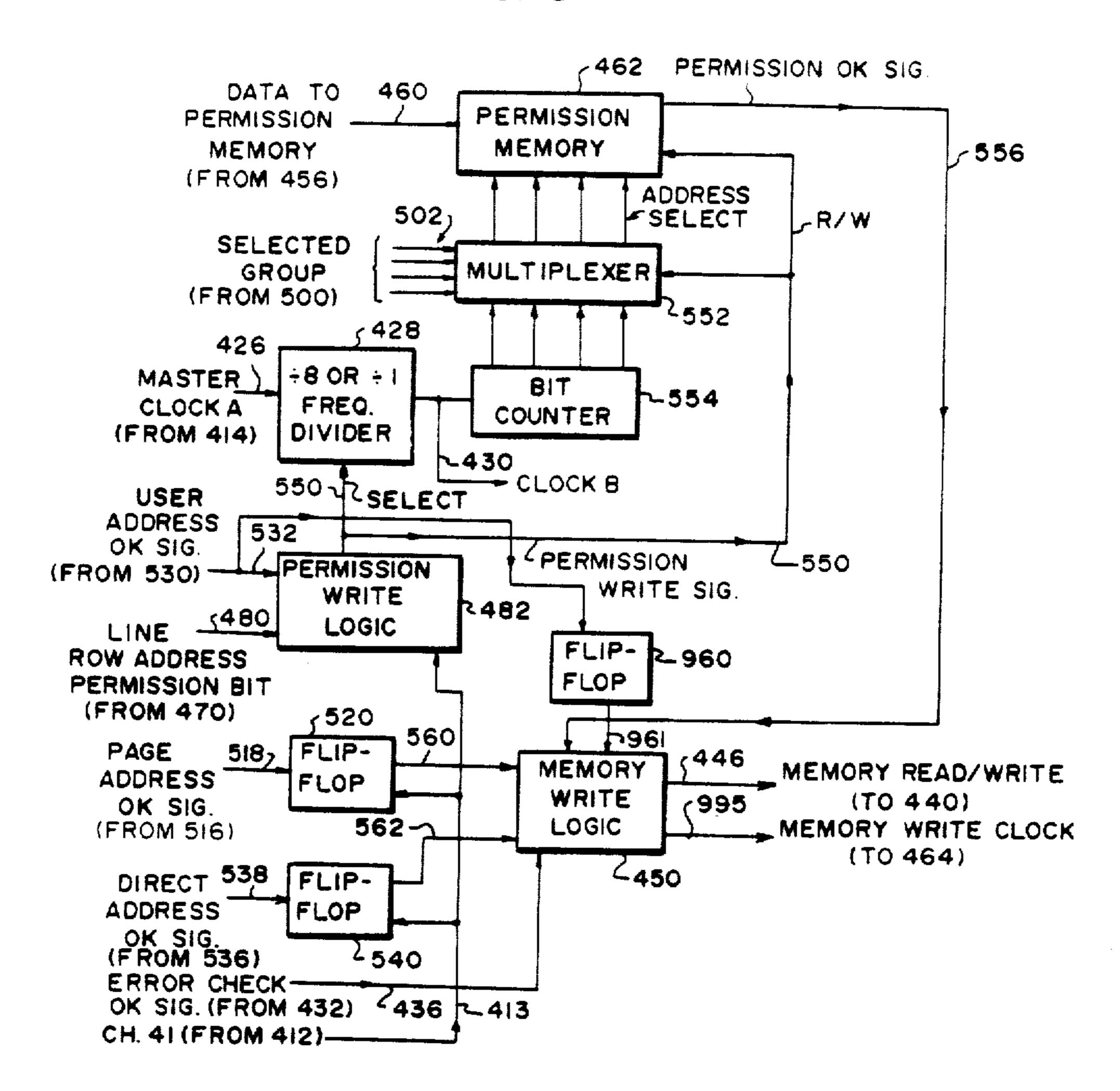

FIG. 6 is a block diagram of the memory and output processing portion of the preferred receiver of the present invention;

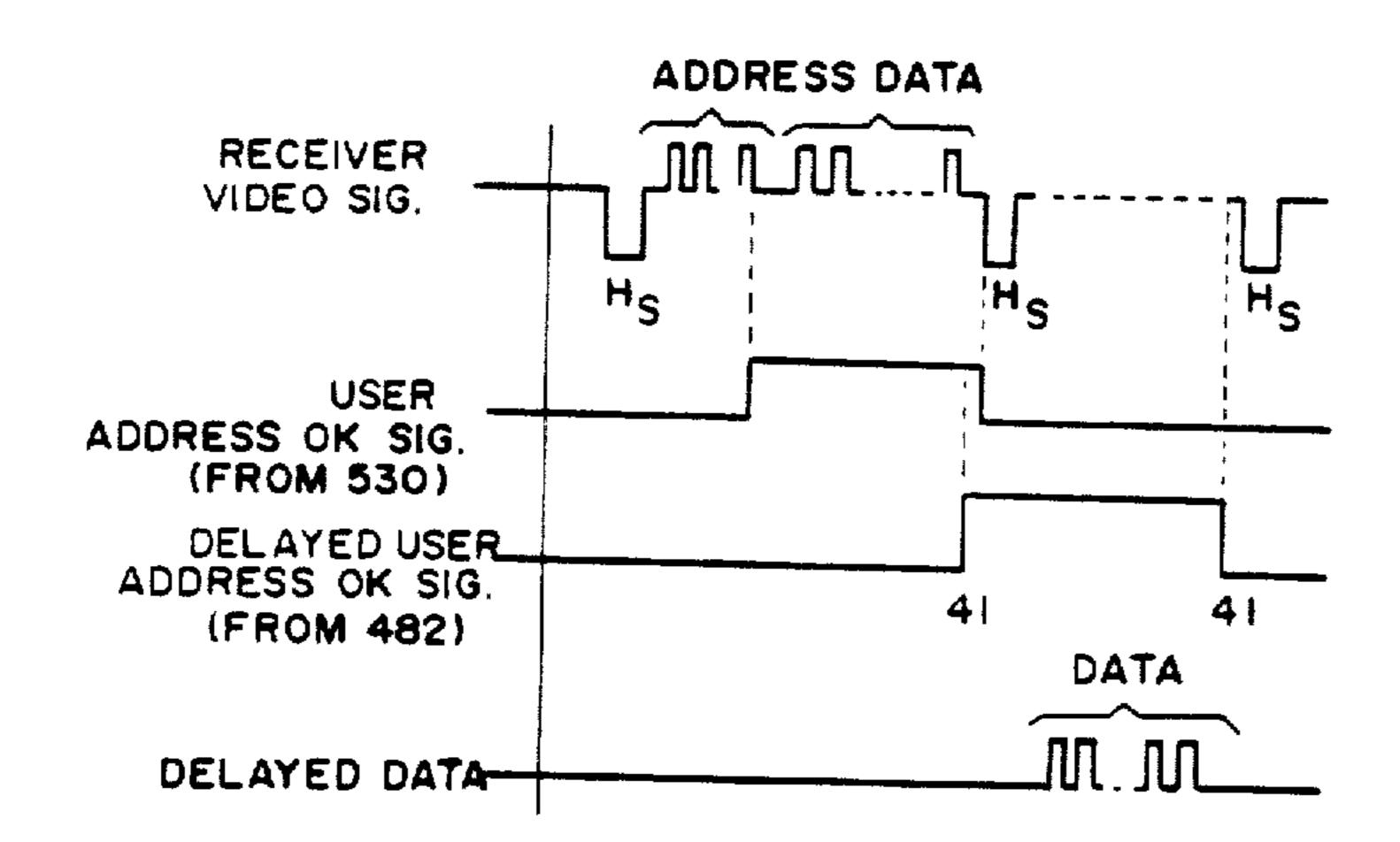

FIG. 6a is a graphical illustration of the timing associated with various signals in the arrangement of FIG. 6;

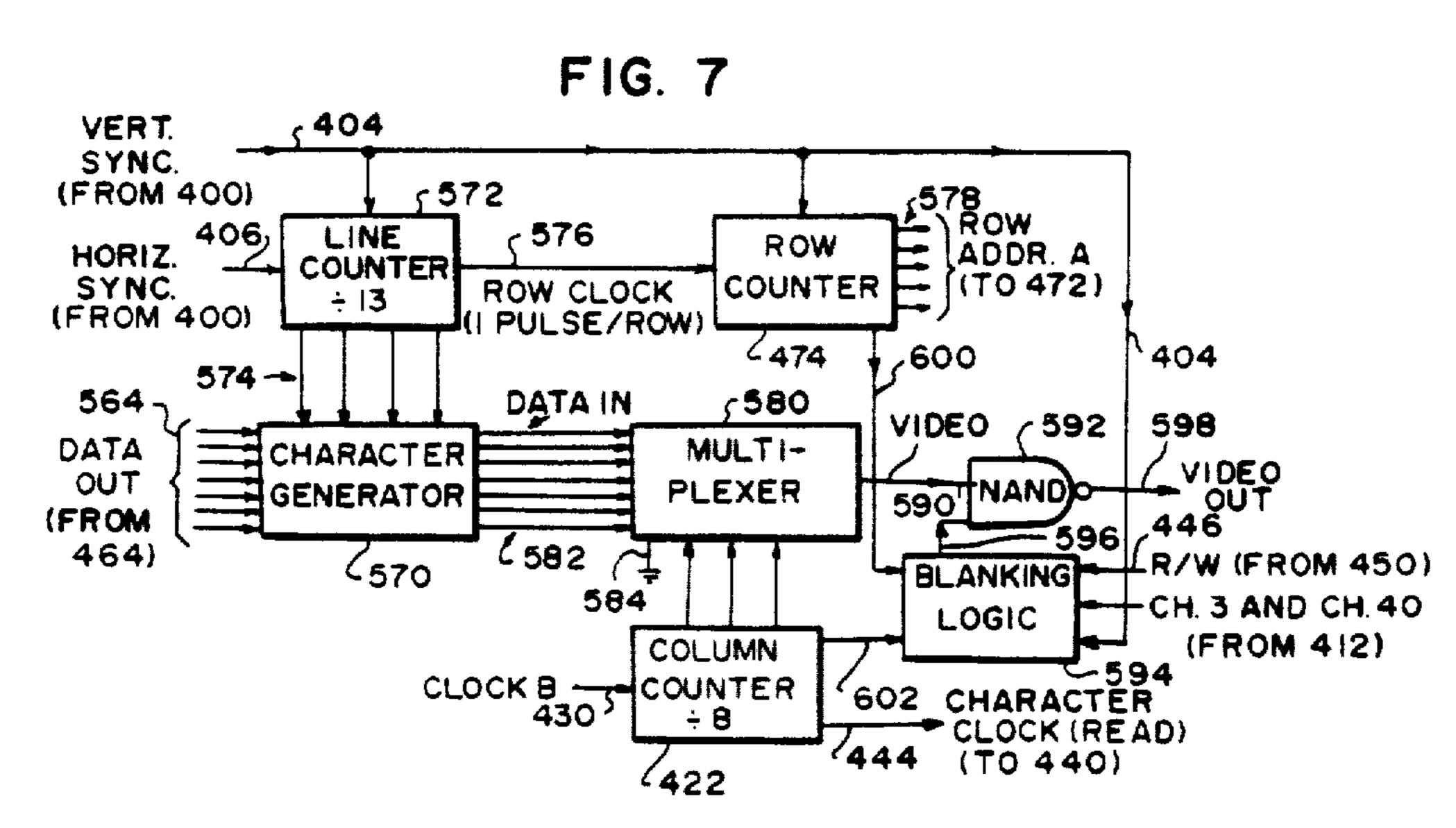

FIG. 7 is a block diagram of another portion of the memory and output processing portion of the preferred receiver of the present invention;

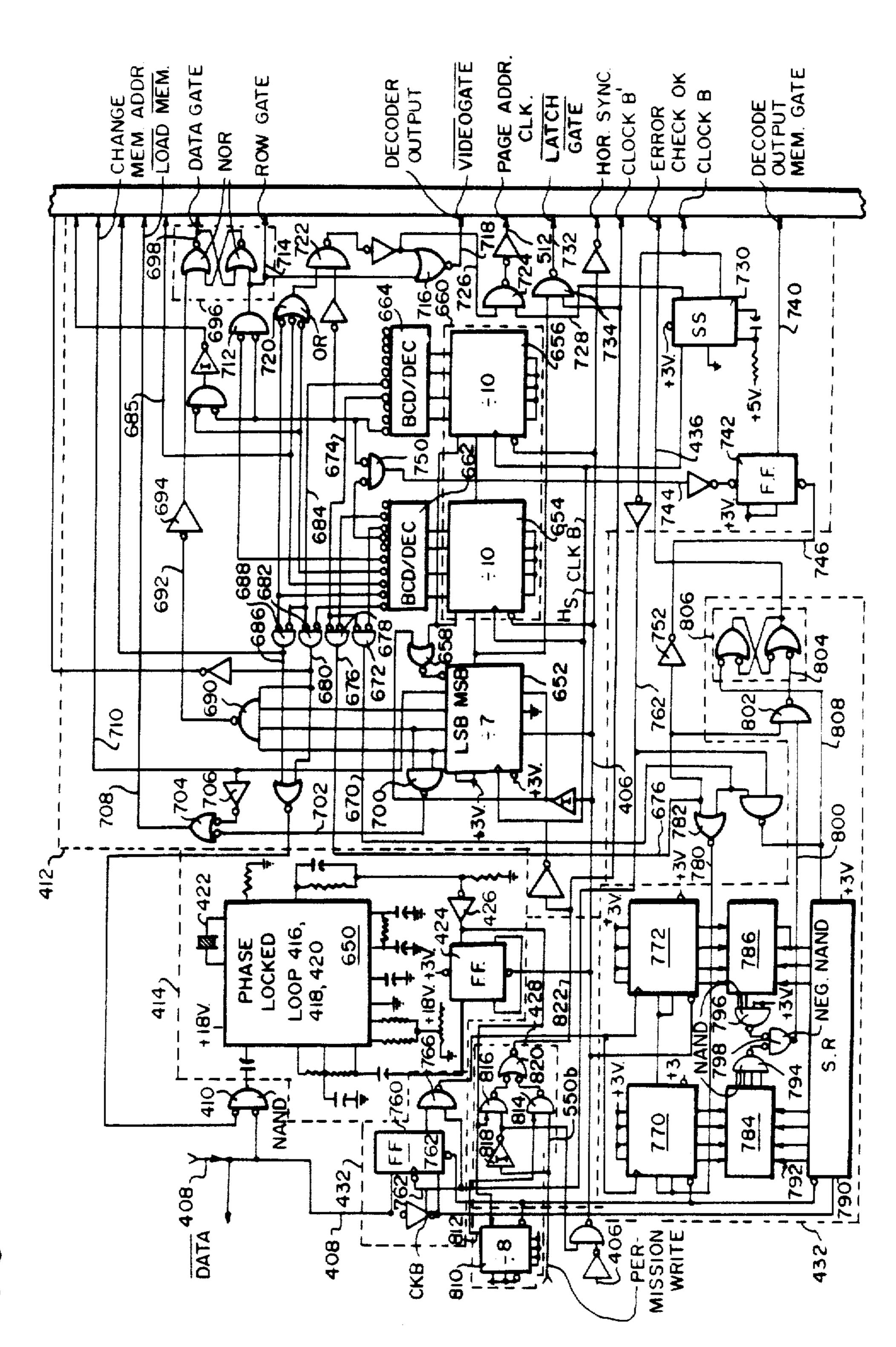

FIG. 8 is a logic diagram, partially in schematic, of a portion of the timing and keyboard control portion of the preferred receiver of the present invention illustrated in FIG. 3;

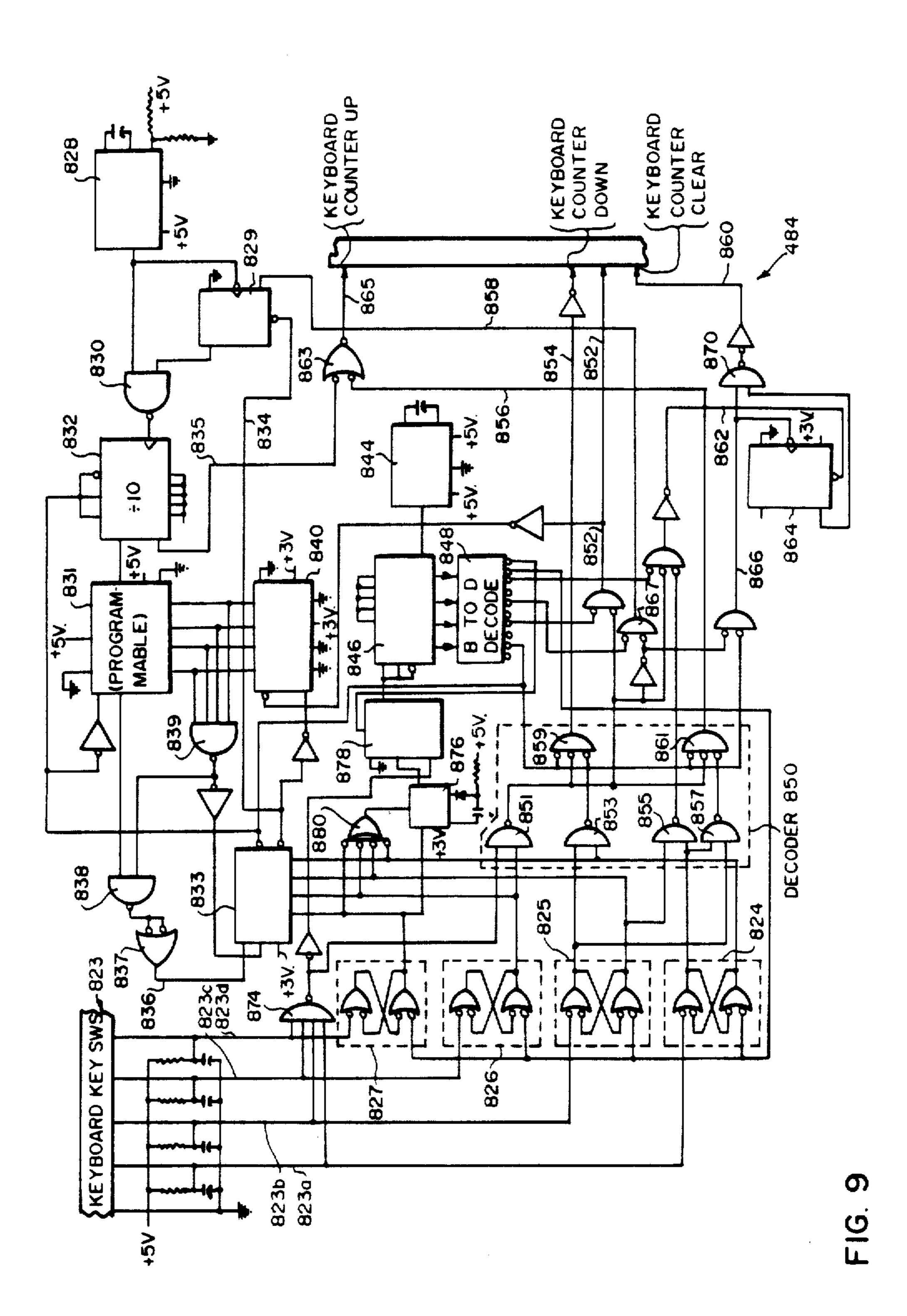

FIG. 9 is a logic diagram, partially in schematic, of the keyboard portion of the timing and keyboard control portion of the receiver illustrated in FIG. 3;

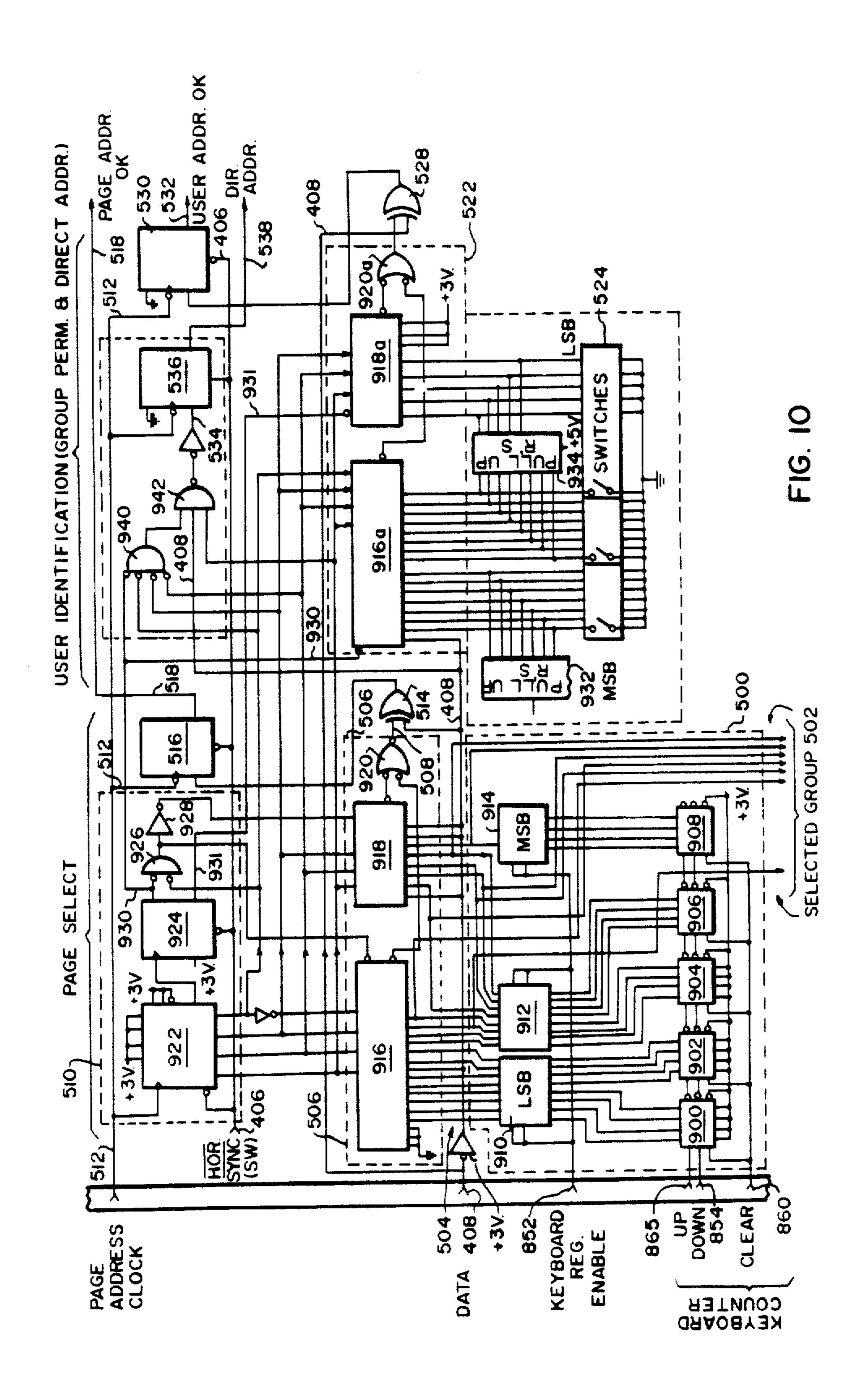

FIG. 10 is a logic diagram, partially in schematic, of the portion of the memory input control portion of the receiver illustrated in FIG. 5;

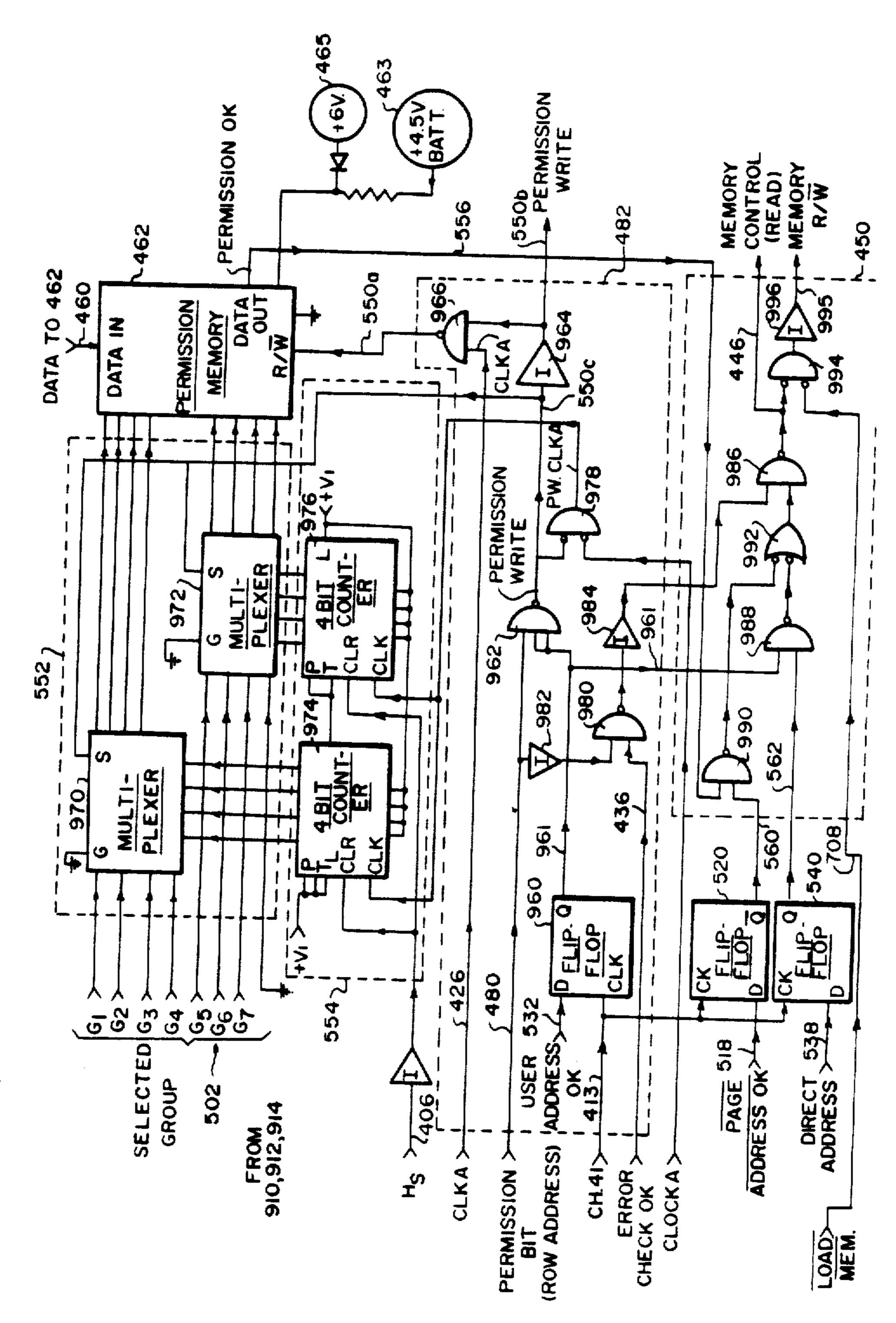

FIG. 11 is a logic diagram, partially in schematic, of the portion of the memory input control portion of the receiver illustrated in FIG. 6;

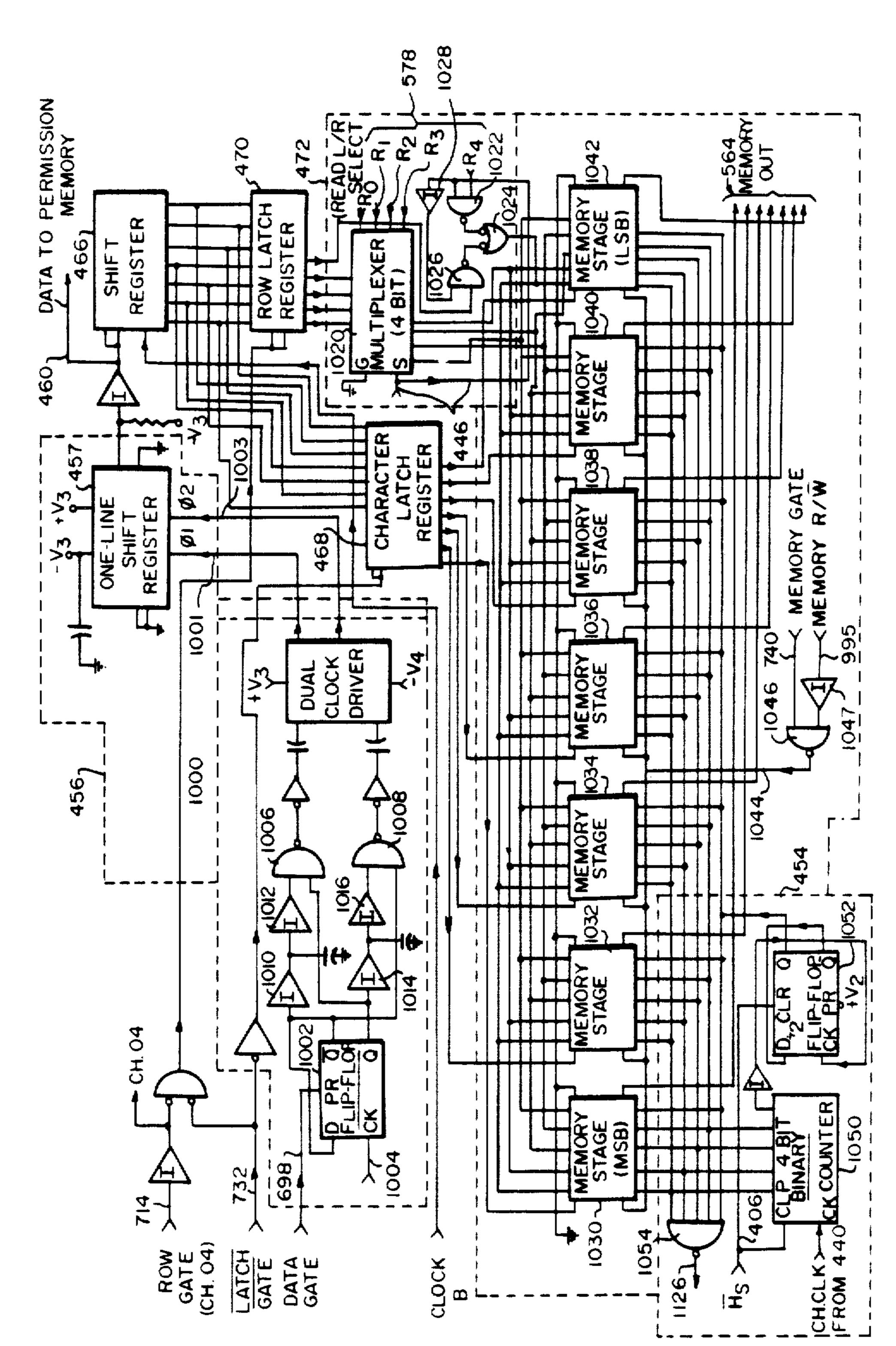

FIG. 12 is a logic diagram, partially in schematic, of the memory and output processing portion of the receiver illustrated in FIG. 3;

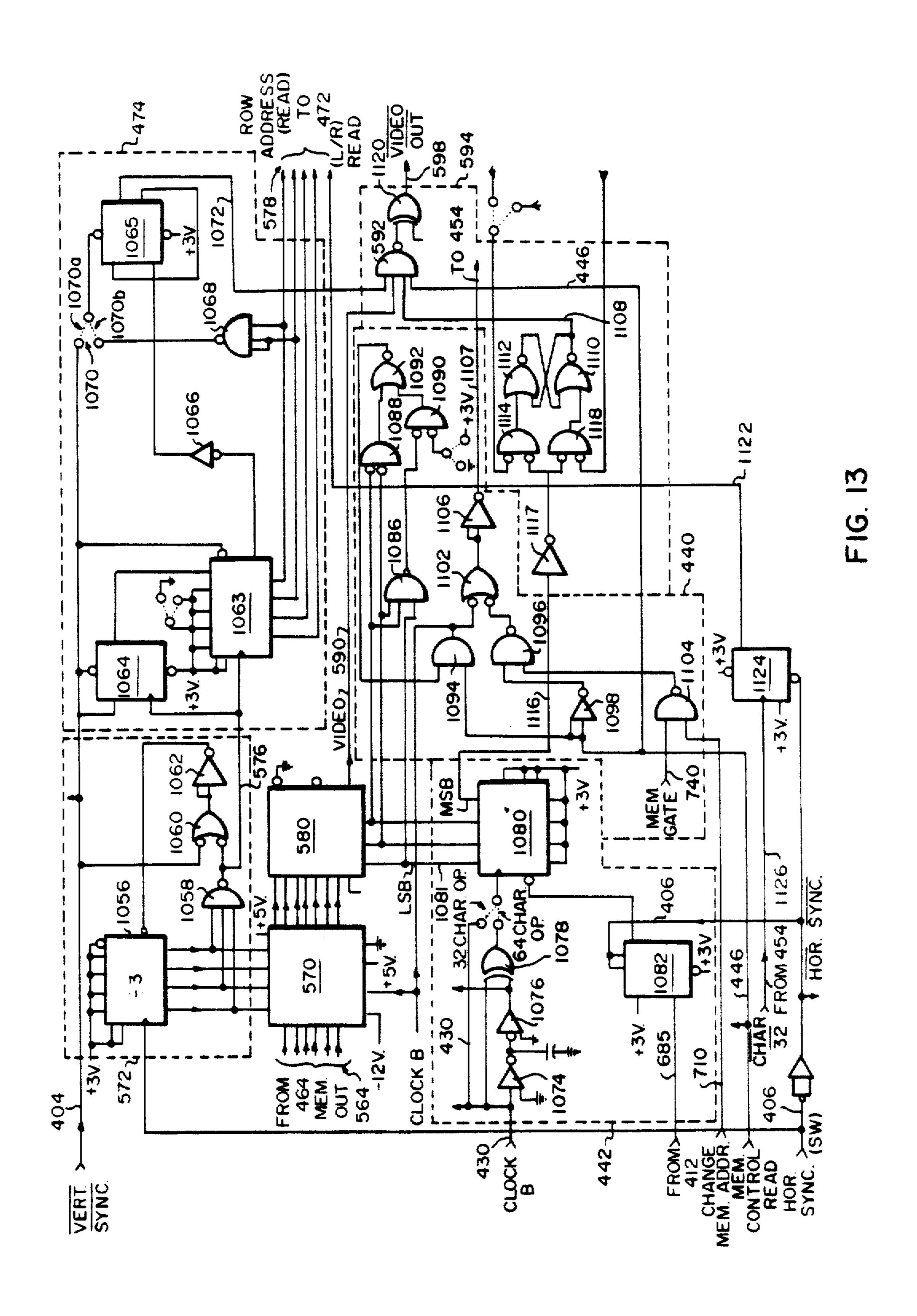

FIG. 13 is a logic diagram, partially in schematic, of another portion of the memory and output processing portion of the receiver illustrated in FIG. 7;

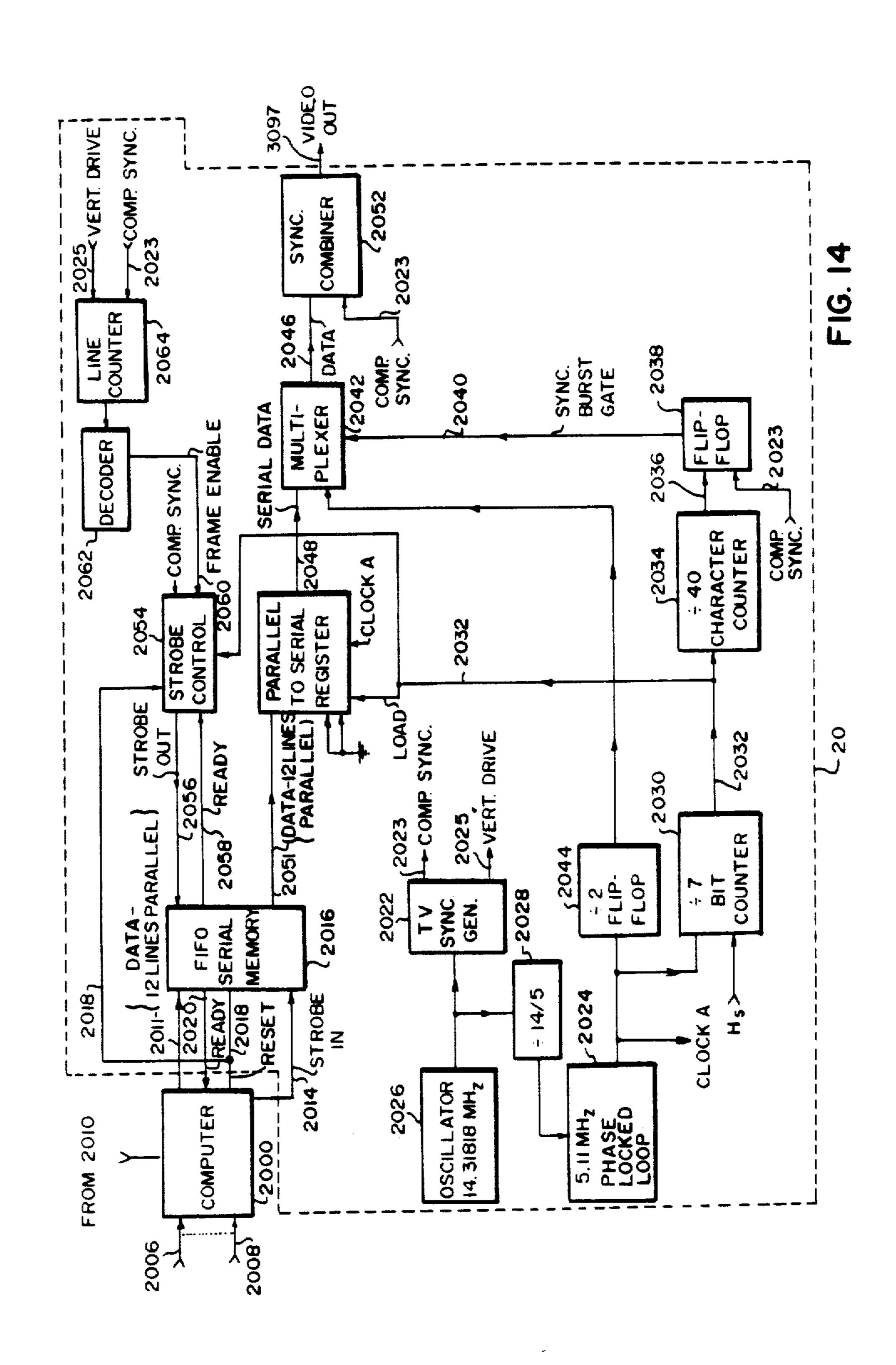

FIG. 14 is a block diagram of the preferred transmitter portion of the present invention;

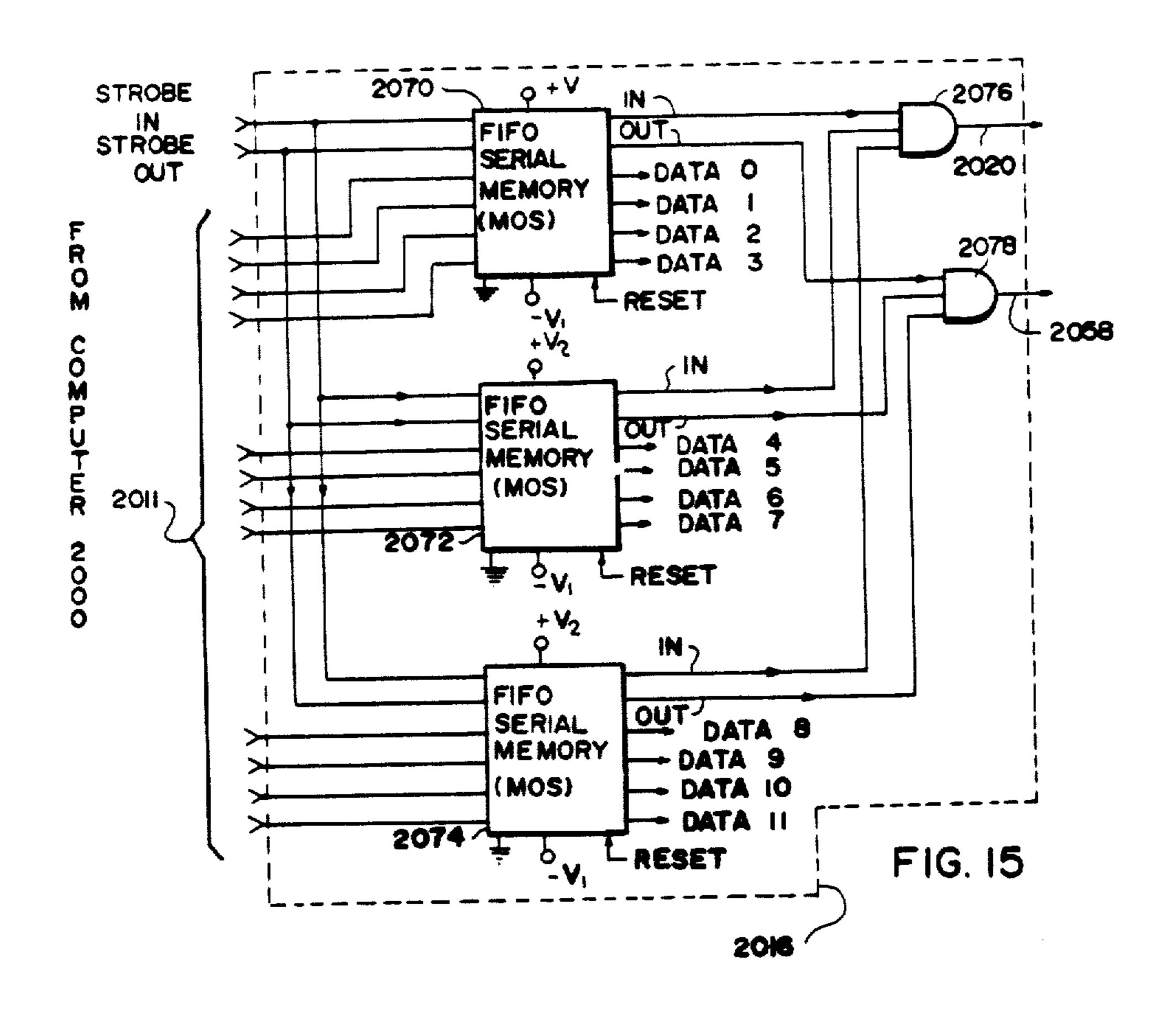

FIG. 15 is a logic diagram of the first in-first out memory portion of the transmitter portion illustrated in FIG. 14:

FIGS. 16 and 17 are logic diagrams, partially in schematic of the transmitter portion illustrated in FIG. 14 except for the first in-first out memory portion illustrated in FIG. 15; and

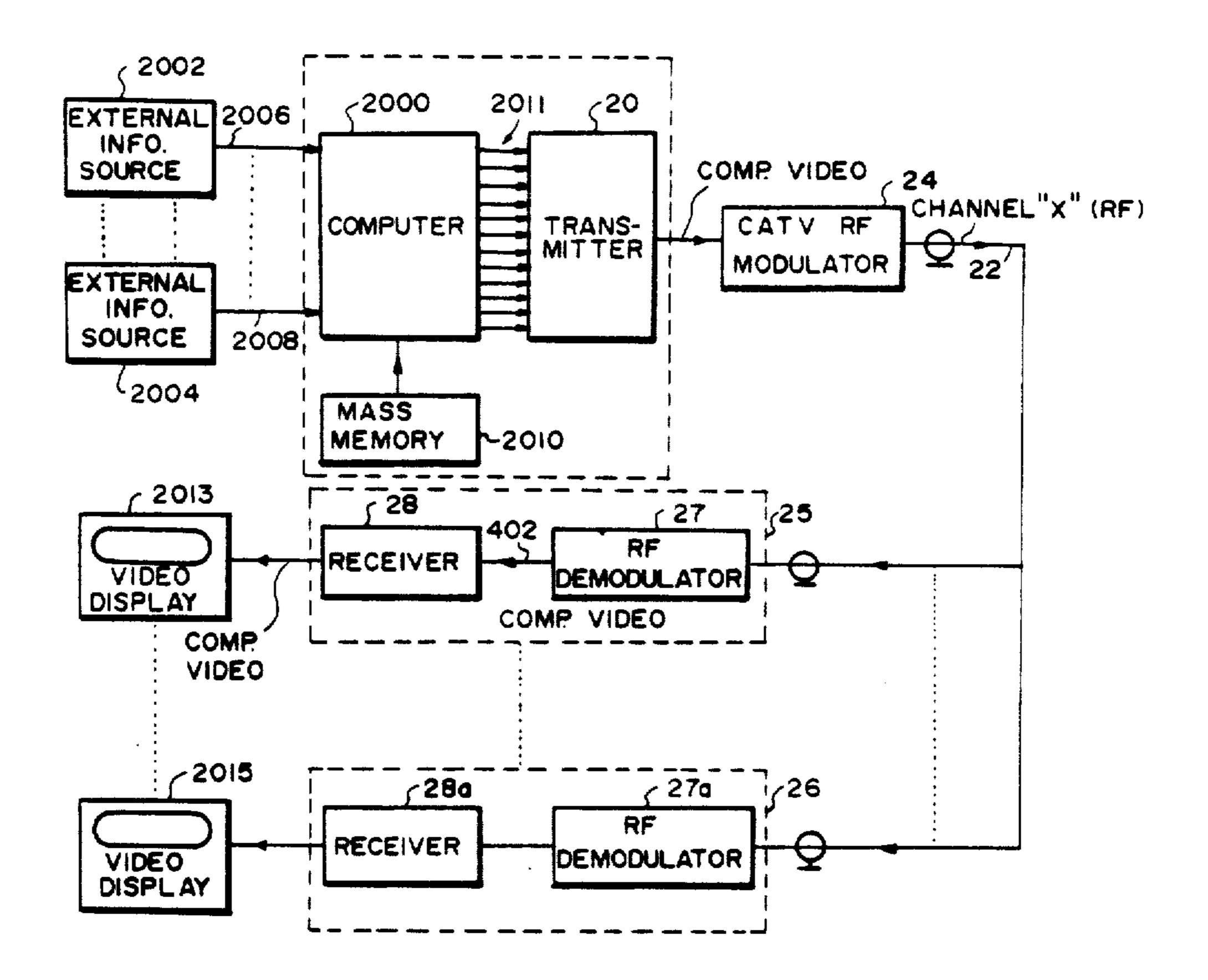

FIG. 18 is a functional block diagram of the preferred embodiment of the row grabbing system of the present invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

#### System General Description

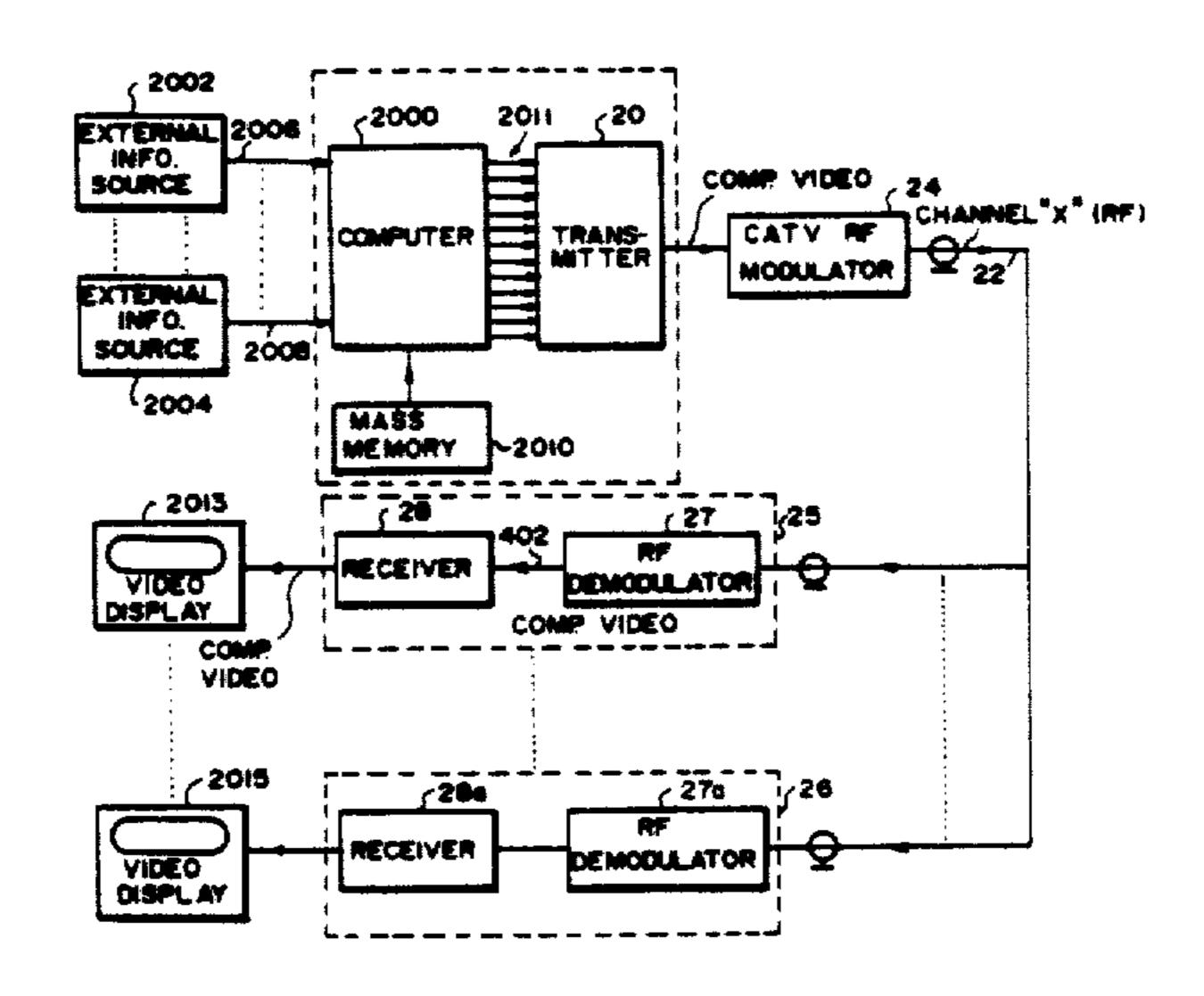

Referring now to the drawings in detail and initially to FIG. 18 thereof, the preferred embodiment of the row grabbing system, generally referred to by the reference numeral 10, of the present invention is shown. As will be described in greater detail hereinafter, the row grabbing system 10 of the present invention is preferably a one-way frame grabbing system in which continuously transmitted information or messages are transmitted via pseudo video scan lines 12 (FIG. 1 and 2) on a row by row basis, with the pseudo video scan line 12 preferably being identical in format to a conventional video scan line, that is it is consistent with FCC and EIA standards for a video scan line signal format; however, this pseudo video scan line 12 actually contains a row of information, such as approximately between 11 and 13 actual television video scan lines of information, with the transmission time of the pseudo video scan line

12 preserably being equal to the transmission time of a conventional TV video scan line, which is approximately 63 microseconds. The various portions of the pseudo video scan line 12 will be described in greater detail hereinafter with reference to FIGS. 1 and 2. In the row grabbing system 10 of the present invention, the information is updated on a row by row basis by transmission of a pseudo video scan line containing new information so that the frame being grabbed will effectively have this row containing new information updated when this row of information is updated in memory. In the preferred system 10 of the present invention, continuously transmitted information or messages may be instantaneously "grabbed" in real time so as to repetitively provide a video display of a selected video frame of such information which may be updated on a row by row basis in real time.

Video information may be of any conventional type, such as news information, money rate information, stock market information, local advertising, television program listings, weather information, consumer information, etc., which is conventionally supplied from conventional external information sources for these types of information such as sources 2,002 and 2004 shown by way of example. These conventional external information sources 2,002 and 2,004 preferably conventionally supply this information in a digital format, such as from a ticker for news information or stock information, by way of example, through a conventional communication line 2,006 or 2,008 or a conventional local video terminal, preferably, to a conventional mini computer 2000, such as a model number PDP-8e manufactured by Digital Equipment Corp. Mini-computer 2000 preferably has an associated conventional mass memory 2010 for conventional storage of data. Computer 2000 stores this information in mass memory 2010, reformats it, such as by adding header information, and continuously provides this information as a 12 bit parallel output 2011 to a transmitter 20, to be described in greater detail hereinafter, which provides the pseudo video scan line 12 for transmission to the TV distribution network. It should be noted that at any time, the twelve bit parallel output of computer 2000 preferably represents two characters or one word. If desired, a 14 bit 45 parallel bit output from the computer 2000 could be utilized to provide two seven bit characters. Computer 2000 shall be described in greater detail hereinafter with reference to FIG. 14. The mass memory 2010 is preferably updated by the computer 2000 in conventional fashion at the optimum transfer time for data which is, conventionally, not necessarily in the order of reception of the external information from sources 2002 and 2004, this data being preferably continuously suppliable in real time to the computer 2000. In conventional fashion, 55 the information in computer 2000 is supplied to transmitter 20 which, in turn, supplies this information to a CATV cable system 22 through a conventional RF modulator 24, composite video being supplied to modulator 24 from transmitter 20. One such modulator 24 is 60 preferably provided for each television channel on which information is to be transmitted, only one such channel being illustrated in FIG. 18 by way of example. Preferably, the mass memory 2010 which is read in conventional fashion by computer 2000 to provide the 65 requisite information via transmitter 20 to the CATV cable system 22, has sufficient storage capacity to store the entire page capacity of the system.

As used hereinafter throughout the specification and claims the term page means one video frame of information, the term group means a predetermined number of pages, the term row is a displayable video row and means a portion of a page containing a plurality of conventional television video scan lines, and the term pseudo video scan line means a signal which is identical in form to that of a conventional video scan line but which actually contains a row of information, such as approximately between 11 and 13 actual television video scan lines of information with the transmission time of the pseudo video scan line being equal to the transmission time of a conventional TV video scan line and with the pseudo video scan line being an entire packet of information necessary for video display of that row. The term conventional or television video scan line is used in its conventional manner.

The mass memory 2010 may be any conventional mass memory storage device sufficient to store the requisite page capacity of the system, such as an RK-08 memory device manufactured by Digital Equipment Corp. The output of the computer 2,000 is preferably conventionally transmitted from computer 2,000 to the transmitter 20 via a conventional data break of the computer 2,000. All pages of information are preferably continuously being transmitted from the computer 2000 through transmitter 20 on a pseudo video scan line by pseudo video scan line basis, that is respectively on a row by row basis, through the appropriate RF Modulator 24 for the video channel being utilized and, therefrom, through the CATV cable system 22 to conventional video display terminals or devices 2013 and 2015, such as commercially available video monitors, two such devices being shown by way of example. It should be noted that the number of video display devices 2013 and 2015 preferably has no requisite correlation with the number of [eternai] external information sources 2002 and 2004 and more sources 2002 and 2004 could be utilized than video display devices 2013 and 2015 or vice versa, if desired. In normal contemplated use, the number of video display devices 2013 and 2015 will normally exceed the number of external information sources 2002 and 2004, however, this need not be the case. The computer 2000 conventionally recirculates the data provided thereto in continuous fashion and, as previously mentioned, eventually updates the mass memory 2010 at the optimum transfer time for the data, which time is not necessarily in the order of reception of the external information from sources 2002 and 2004. The information from external sources 2002 and 2004, which is preferably being provided substantially continuously to the computer 2000 (as long as it is being generated from the external sources 2002 and 2004) is provided to the mass memory 2010 and instantaneously to the transmitter 20 which operates in a manner to be described in greater detail hereinafter to provide the pseudo video scan line 12 transmission of the information. As will also be described in greater detail hereinafter, each video display device 2013 and 2015 preferably has an associated display control unit 25 and 26, respectively, which, as will be described in greater detail hereinafter, preferably functions to enable the real time frame grabbing or selection of a single page of continuously transmitted information for the instantaneous repetitive continuous video display, or frame grabbing, thereof, this information being updatable on a row by row basis in real time. Preferably, each of the display control units 25 and 26 by way of example, one such

display control unit preferably being associated with each video display terminal or device, are identical in structure and operation. If desired, however, any display control unit 25-26 may be modified in a manner to be described in greater detail hereinafter so as to pre- 5 vent the reception of certain categories of information while enabling the reception of other categories of information. For purposes of clarity, only one such typical display control unit 25 will be described by way of example, the structure and operation, as previously 10 mentioned, being identical with that of display control unit 26. Identical reference numerals, followed by the letter a will be utilized in FIG. 18 for elements of display control unit 26 which are identical in structure and operation with those of display control unit 25. In the 15 overall system block diagram of FIG. 18, the display control unit 25 only preferably contains a conventional RF demodulator 27, one such demodulator 27 being provided for each channel and a receiver 28, to be described in greater detail hereinafter, which receiver 20 receives the composite video demodulated by demodulator 27 and determines whether the user is correct, the user has permission to receive the pseudo video scan line of information being transmitted at that time, whether the signal is error free, whether the page ad- 25 dress of the pseudo video scan line is correct, and whether a direct address condition, to be described in greater detail hereinafter, exists, and, preferably assuming the pseudo video scan line signal passes all these tests, then the receiver processes this signal and pro- 30 vides a video signal corresponding to a displayable row of information on the video display device 2013. The keyboard which accomplishes the selection of the desired page or video frame of information and the appropriate group thereof to be grabbed or repetitively displayed on the video display terminal 2013 is included as part of the receiver portion 28 and will be described in greater detail hereinafter as part of the receiver portion 28 of the system 10.

#### TRANSMITTER

#### General Description

Referring now to FIG. 14, initially, the transmitter portion 20 of the row grabbing system 10 of the present invention shall generally be described in greater detail. 45 Thereafter, with reference to FIGS. 15, 16 and 17, the preferred transmitter portion 20 of the present invention shall be described in greater detail.

Computer 2000 which provides the 12 bit parallel output 2011 of data also provides a strobe command, as 50 will be described in greater detail hereinafter, via path 2014, the strobe command on path 2014 and the 12 parallel lines of data 2011 being preferably loaded into a conventional FIFO word series memory, shown in greater detail in FIG. 15, which acts like a parallel shift 55 register. FIFO memory 2016 preferably accepts information under command of the strobe line 2014 from computer 2000 and can preferably store up to 64 words which is 128 characters of information, two characters of information comprising one word. Computer 2000 60 can [slo] also preferably completely erase FIFO memory 2016 by the provision of a reset command via path 2018, as will be described in greater detail hereinafter. FIFO memory 2016 supplies a ready signal to computer 2000 via path 2020 which denotes that the input location 65 of memory 2016 is empty. Computer 2000 only preferably strobes data into FIFO memory 2016 if the ready line 2020 is asserted. It should be noted that preferably

the inputting and outputting of memory 2016 are completely independent of each other.

The transmitter 20 preferably includes a conventional television sync generator 2022 which provides composite sync via path 2023 in accordance with EIA standards as well as vertical drive via path 2025. The timing of sync generator 2022 is preferably controlled by conventional crystal controlled oscillator 2026, such as a 14.31818 megahertz crystal controlled oscillator, in conventional fashion. The transmitter 20 preferably requires a master clock to control the bit rate of transmission. This bit rate, which is preferably selected at 5.113657 megahertz, must preferably be synchronized with the composite sync. The data bit rate selected must be consistent with the broadcast television channel [band width] bandwidth and must be an integral multiple of the horizontal frequency, which is necessary to keep the data bits phase locked with the horizontal sync signal. The 5.113657 megahertz clock, which shall be referred to as clock A, is preferably obtained by a conventional crystal controlled phase locked loop 2024 which is locked at 5/14 of the 14.31818 megahertz oscillator 2026 frequency through a divide-by-14/5 frequency divider 2028. The clock A output of phase locked loop 2024 is preferably divided by a conventional divide-by-seven bit counter 2030 in order to generate a pulse on line 2032 which represents the start of each character. This pulse is provided in parallel to a character counter 2034 which uses this signal as a clock input and preferably counts up to 40, counter 2034 being a divide-by-40 counter, to establish the period corresponding to the 40 characters preferably contained within a single pseudo video scan line 12. The output of character counter 2034 is preferably a pulse on line or path 2036 which occurs during the period of the 40th character. The trailing edge of the pulse present on path 2036 preferably sets a flip-flop 2038 which is reset by the composite sync provided via path 2023 from sync 40 generator 2022. Thus, the output of flip-flop 2038 is a gate which starts at the end of the 40th character and ends at the beginning of the horizontal sync pulse. During this gating time, it is preferably desired to transmit a burst of sync pulses which are identical to a stream of alternate "0" and "1" data bits, this burst of sync pulses being located in region F (FIG. 1) of the pseudo video scan line 12, as will be described in greater detail hereinafter. This signal which is provided on line 2040 is termed the sync burst gate and is provided to a multiplexer 2042 as one input thereto, this input being the control or select input for multiplexer 2042.

One selectable input to multiplexer 2042 is provided from the output of a divide-by-2 flip-flop 2044 whose input is the clock A output of phase locked loop 2024. When the gating signal on path 2040 is high, multiplexer 2042 preferably selects this input signal from flip-flop 2044, which provides a square wave output at one-half the frequency of clock A, and applies this signal to the output data line 2046 of multiplexer 2042. The other selectable input to multiplexer 2042 preferably is the serial data output of a conventional parallel-to-serial shift register 2050 which receives the 12 parallel lines of data output from FIFO memory 2016. When the gate signal on path 2040 is low, multiplexer 2042 preferably selects the serial data line 2048 output from shift register 2050 and applies this signal to the output data line 2046 of multiplexer 2042. Shift register 2050 is preferably a 14 line input parallel-to-serial shift register with two lines

being grounded in the arrangemet to be described by way of example. If 14 input data lines were utilized then these two grounded terminals will, of course, be respectively connected to the other two of the 14 data input lines. Shift register 2050 receives the 12 lines of data from FIFO memory 2016 via path 2051, this data being loaded into shift register 2050 when a load command is received from bit counter 2030 on path 2032. Data is outputed from shift register 2050 as the serial data line 2048, the shift rate being preferably established by clock 10 A. Preferably, 14 clock pulses occur to shift out 14 bits of data from shift register 2050 for each word loaded into shift register 2050. The data output of multiplexer 2042 is preferably supplied to a conventional sync combiner 2052 which also receives the composite sync sig- 15 nal via path 2023 from sync generator 2022.

The output of sync combiner 2052 is a conventional composite video signal format, which is a three level signal, the data varying between levels 2 and 3 corresponding to digital values of 0 and 1 and the sync being 20 indicated by level 1, as illustrated in FIGS. 1 and 2, with FIG. 1 illustrating a typical pseudo video scan line signal 12 format. This composite video signal represents a single pseudo video scan line at a time as described and shown in FIGS. 1 and 2, computer 2000 being con- 25 ventionally programmed to control various locations or assignments in regions B through E of the pseudo video scan line, these regions to be described in greater detail hereinafter in the description of the receiver portion 28 of the row grabbing system 10. As was previously men- 30 tioned, region F of the pseudo video scan line 12 is provided on line 2040 as a sync burst gate provided to multiplexer 2042 and regions A and G are provided from the composite sync on path 2023.

The transmitter 20 also preferably includes a strobe 35 control portion 2054 which contains all the logic for determining when the data should be strobed out of the FIFO memory 2016. It is most preferable that when data is shifted out of memory 2016 and transmitted, that complete lines of 40 characters each are shifted, in the 40 example given. If all conditions necessary for the transmission of 40 characters in a pseudo video scan line 12 are not met preferably an empty line, which is a pseudo video scan line having only regions A,F and G occupied, is transmitted. It is further preferred that data be 45 transmitted only during a selected portion of the television vertical frame so as to insure that only empty lines are transmitted during the vertical drive period. Strobe control portion 2054 preferably monitors the various conditions necessary and starts to issue a series of strobe 50 out pulses on line 2056 only if the output of FIFO memory 2016 is ready as indicated on ready line 2058 provided from memory 2016 to strobe control portion 2054, if the vertical scan position is correct as indicated by a signal present on line 2060 termed frame enable, to 55 be described in greater detail hereinafter, and if a composite sync pulse has been received from sync generator 2022 via path 2023. When all these conditions are met, the output of bit counter 2030 on line 2032 is allowed to control the strobing of FIFO memory 2016. The master 60 reset pulse when issued or provided on line 2018 from computer 2000 preferably prevents any new pseudo video scan line of data from being transmitted until all the above mentioned conditions are again met. The correct vertical scan position or frame enable signal 65 provided via path 2060 is preferably obtained from a decoder 2062 which decodes the output of a line counter 2064. Line counter 2064 counts the number of

pseudo video scan lines after the vertical drive, the inputs to line counter 2064 being the vertical drive signal from sync generator 2022 provided via path 2025 and the composite sync signal from sync generator 2022 provided via path 2023. This decoder 2062 preferably selects the group of lines which are used for transmission.

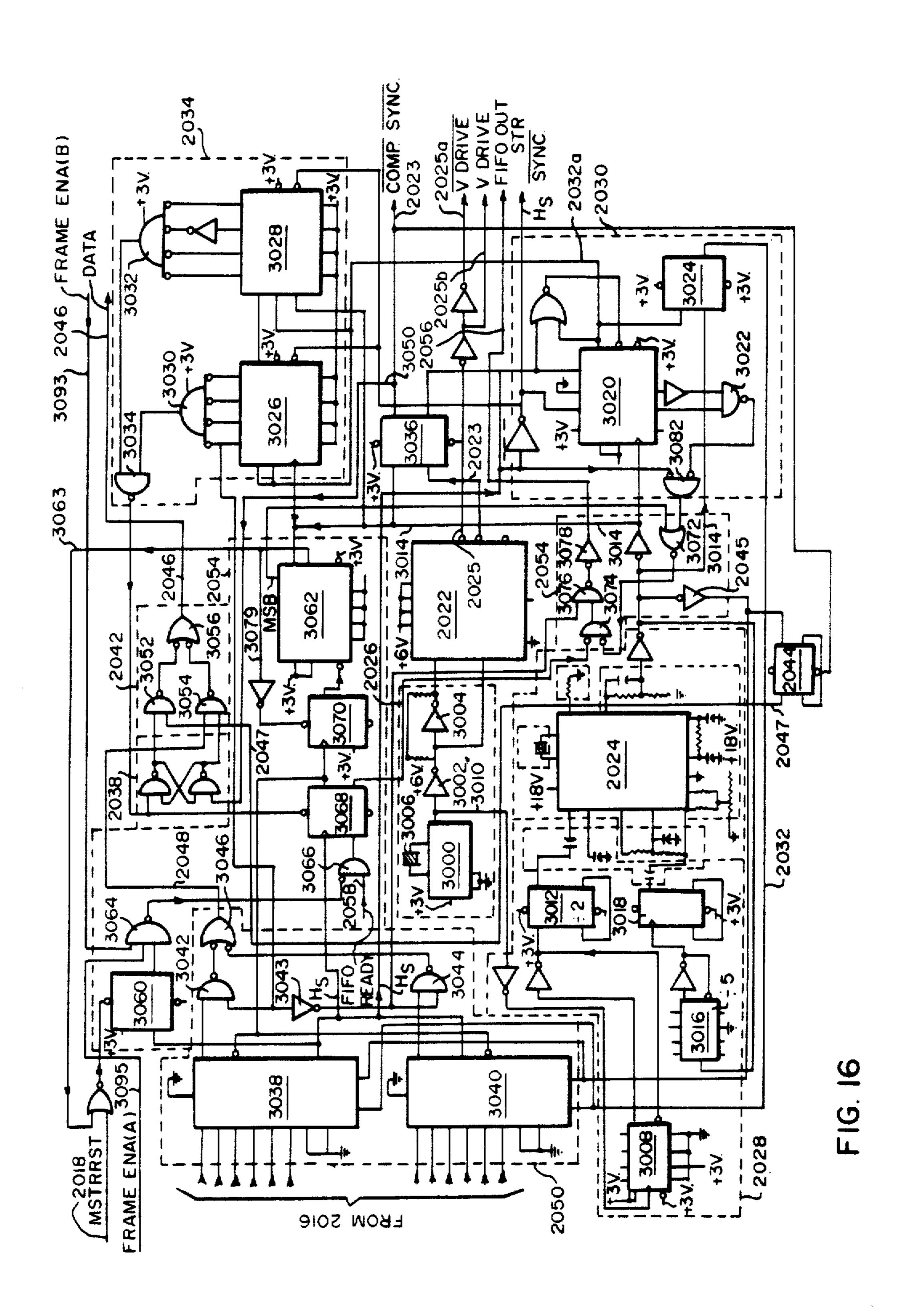

#### DETAILED DESCRIPTION OF TRANSMITTER

Referring now to FIGS. 15, 16 and 17, the transmitter portion 20 of the row grabbing system 10 of the present invention shall be described in greater detail, FIGS. 15 through 17 being logic schematics of appropriate portions of the transmitter portion 20, the balance of the transmitter portion 20 not illustrated in greater detail than in FIG. 14 being conventional. Accordingly, a more detailed description than previously provided will not be provided for those conventional portions not illustrated in greater detail in FIGS. 15 through 17 as they would readily be understood by one of ordinary skill in the art.

Referring initially to FIG. 15, the conventional FIFO memory 2016 is shown in greater detail. FIFO memory 2016 preferably comprises three conventional four bit-by-64 word FIFO serial memories 2070, 2072 and 2074, such as an MOS FIFO serial memory of the type manufactured by Fairchild under designation 33414, each memory stage 2070, 2072 and 2074 receiving four of the 12 parallel bit data line outputs from computer 2000. The input ready and output ready lines are preferably combined by NAND gates 2076 for the input ready line to provide the input ready signal via path 2020 to computer 2000, and by NAND gate 2078 for the output ready line to provide the output ready signal via path 2058 to strobe control portion 2054.

Referring now to FIGS. 16 and 17, the balance of the transmitter portion 20 shall be described in greater detail, where appropriate, for purposes of clarity. Referring initially to FIG. 16, the television sync generator 2022, as previously mentioned, is preferably a conventional MOS television sync generator such as the type manufactured by Fairchild under the designation 3261 and will not be described in any greater detail herinafter. Oscillator 2026, which supplies the clock signal to the television sync generator 2022 for controlling the timing thereof and the reference frequency signal to the phase locked [group] loop 2024 [preferably], as previously mentioned, preferably comprises a conventional integrated circuit oscillator 3000, such as the type manufactured by Motorola under the designation 4024, utilized with inverters 3002 to 3004 to provide the clock to sync generator 2022 at opposite phases as is conventionally required by a sync generator 2022 of the type previously described. In addition, oscillator 3000 is preferably crystal controlled by a conventional crystal 3006 at the oscillator frequency, such as the 14.31818 megahertz frequency chosen by way of example. The clock signal output of oscillator 3000 is preferably applied via path 3010 to a conventional four bit binary counter 3008, such as the type manufactured by Texas Instruments under the designation SN 74161N, preferably connected as a divide-by-14 counter, counter 3008 forming a portion of the divide-by-14/5 divider network 2028. The output of counter 3008 is preferably connected as the clock input to a conventional divideby-2 flip-flop 3012 also forming part of the divide-by-14/5 divider 2028. The output of the divide-by-2 flipflop 3012 is preferably connected to one input of phase

locked loop 2024 which is preferably a conventional MOS phase locked loop, such as the type manufactured by Signetics under the designation NE562B. Thus, the total division ratio from oscillator 2026 through phase locked loop 2024 is preferably 28-to-1. The output of phase locked loop 2024 provided via path 3014 is fed back to the input of a conventional four bit binary counter 3016, such as the type utilized for counter 3008, however counter 3016 preferably being connected as a divide-by-5 counter. The output of counter 3016 is preferably, in turn, connected to a conventional divide-by-2 flip-flop 3018, such as the type manufactured by Texas Instruments under designation SN 7474N, whose output is in turn preferably connected to a second input of phase locked loop 2024. Accordingly, the total feed back path division ratio is preferably 10 and the phase locked loop 2024, accordingly, varies its output frequency provided via path 3014 as necessary to keep its two inputs from flip-flop 3012 and flip-flop 3018 at exactly equal frequencies but with a phase difference of 20 90°. As a result of the frequency division ratio utilized on each input path to phase locked loop 2024, the phase locked loop output frequency is exactly preferably 5/14 of the frequency of oscillator 2026 which, by way of example, provides a clock A output frequency for phase 25 locked loop 2024 of 5.1136357 megahertz as the output frequency of phase locked loop 2024.

Bit counter 2030 which, as previously mentioned with reference to FIG. 14, preferably receives this clock A output frequency, is preferably a conventional divide-by-7 bit binary counter 3020, such as the type manufactured by Texas Instruments under the designation SN74160N, counter 3020 which forms part of the bit counter network 2030 preferably being the actual bit counter. Two of the output lines of bit counter 3020 are 35 preferably decoded by a conventional two input NAND gate 3022 to provide a pulse at the third count of counter 3020, this pulse being provided as one input to a two input negative NAND gate 3082. The carry output from bit counter 3020 is preferably connected to 40 the D input of a conventional D type flip-flop 3024 whose clock input is preferably connected to the clock A output of phase locked loop 2024 provided via path 3014. This provides at the output of flip-flop 3024 a pulse at the completion of the divide-by-seven cycle of 45 counter 3020 which pulse is utilized as the load input of the parallel-to-serial register 2050 provided via path **2032**.

As was previously mentioned with reference to FIG. 14, the output of bit counter 2030 provided via path 50 2032 is also preferably provided to [charcter] character counter 2034. As shown and preferred in FIG. 16, character counter 2034, which is preferably a divide-by-40 counter, comprises two counter stages 3026 and 3028 which are both conventional four bit decade or divide- 55 by-10 counters, such as the type manufactured by Texas Instruments under the designation SN74160N. Each counter 3026 and 3028 is preferably clocked from the master clock A via path 3014 and is enabled by the carry output of bit counter 3020 via path 2032. Thus the 60 counter stages 3026 and 3028 preferably increment only once per character. The character counter 2034 also preferably comprises a decoder which includes negative NAND gates 3030 and 3032, connected, respectively, to the outputs of counter stages 3026 and 3028, 65 and a NAND gate 3034 whose inputs are the outputs of gates 3030 and 3032. The decoder formed by gates 3030, 3032 and 3034 preferably generates a negative pulse on

the 40th count from counter stages 3026 and 3028 of counter 2034. As shown and preferred, counter stages 3026 and 3028 are cleared by the composite sync signal provided from sync generator 2022. The composite sync output of sync generator 2022, as shown and preferred in FIG. 16, is provided to a conventional D flipflop 3036, with the composite sync output of sync generator 2022 being provided to the D input thereof, flipflop 3036 preferably being clocked by the master clock A provided via path 3014. As a result, the output of flip-flop 3036 is preferably exactly the same as the input composite sync from generator 2022 except that it is slightly delayed by a small fraction of the clock period. such as on the order of 50 nanoseconds, as necessary for transitions of the output to be exactly synchronized to the master clock frequency.

As was previously mentioned with respect to FIG. 14, multiplexer 2042 preferably receives as one selectable input, the output of a divide-by-2 flip-flop 2044 whose input is the master clock A output of phase locked loop 2024. As shown and preferred in FIG. 16, flip-flop 2044 is preferably a conventional flip-flop which has the inverted clock A signal supplied to the clock input thereof through inverter 2045 and which generates an output frequency of one-half the clock A frequency via path 2047 to multiplexer 2042. The other selectable input to multiplexer 2042, as was previously mentioned with respect to FIG. 14, is the serial data output of parallel-to-serial register 2050 provided via path 2048. As shown and preferred in FIG. 16, parallelto-serial register 2050 preferably comprises two shift register stages 3038 and 3040, such as the type manufactured by Texas Instruments under designation SN74166N, which are preferably loaded in parallel and are shifted out alternately, first seven bits being provided from one stage and then seven bits being provided from the other stage. The outputs of shift register stages 3038 and 3040 are preferably alternately selected by NAND gates 3042 and 3044. Preferably, the least significant bit of decade counter 3026 of character counter 2034 is supplied to one input of NAND gate 3042 and is applied inverted through inverter 3043 to one input of NAND gate 3044. This signal preferably alternates at the character rate and selects which NAND gate 3042 or 3044 is on. The outputs of NAND gate 3042 and 3044 are connected as the two inputs to a negative NOR gate 3046 and, accordingly, alternate groups of seven data bits appear at these two inputs and a continuous stream of data bits is, therefore, present at the output of gate 3046 via path 2048 to multiplexer 2042.

As was previously mentioned with reference to FIG. 14, the switching of multiplexer 2042 is preferably accomplished by flip-flop 2038, which is preferably a conventional RS flip-flop which is set by the composite sync on one input via path 3050 and is reset by the output of NAND gate 3034 of character counter 2034 which is the character 40 pulse. As shown and preferred in FIG. 16, multiplexer 2042 comprises NAND gates 3052 and 3054 whose outputs are connected to negative NOR gate 3056. The selected data exists on output line 2046, gate 3052 and 3054 being supplied from opposite outputs of flip-flop 2038 so that one of these two gates is on when the other is off and vice-versa.

Now referring to the strobe control logic 2054, this logic preferably includes a conventional flip-flop 3060 which is cleared by the master reset signal provided via path 2018 from computer 2000 or by an output pulse from a conventional counter 3062, to be described in

greater detail hereinafter, contained within the strobe control logic 2054, provided via path 3063. Flip-flop 3060 is preferably set by the horizontal sync. The output of flip-flop 3060 is preferably connected to one input of a three input NAND gate 3064 whose two other inputs are provided from the frame enabling circuit or decoder 2062, to be described in greater detail hereinafter with reference to FIG. 17. The output of NAND gate 3064 will preferably be low during frame enable if flip-flop 3060 is set. This output is preferably combined with the FIFO ready signal in a negative NAND gate 3066 whose output will be high only if FIFO memory 2016 is ready as indicated by the FIFO ready signal provided via path 2058, both frame enable signals are asserted and a horizontal sync pulse has been received since the last or previous transmission, as indicated by an output being provided from NAND gate 3064 to negative NAND gate 3066. If all these conditions are met, gate 3066 will provide an output signal to the D input of another conventional flip-flop 3068 which will be set at the start of the next horizontal sync pulse present at its clock input. When flip-flop 3068 is set, this signifies Liat the system is ready to start transmitting a pseudo video scan line. The output of flip-flop 3068 is preferably 25 connected to the clock input of another flip-flop 3070 which is, accordingly, set at the time that flip-flop 3068 is set. When flip-flop 3070 is set, its output goes high enabling counter 3062 which then starts to count under control of the master clock A, provided via path 3014, 30 which is supplied at its clock input. Counter 3062 is preferably a conventional four bit divide-by-16 counter, such as the type manufactured by Texas Instruments under the designation SN74163N. When counter 3062 counts to 8, its most significant bit goes high which 35 supplies a high level signal via path 3071 to one input of a conventional two input NOR gate 3072. Gate 3072 then provides an output signal to a two input negative NAND gate 3074 which, in turn, provides an output signal to a two input NAND gate 3076 whose output is, 40 in turn, inverted through an inverter 3078 to provide the FIFO [out] strobe out signal via path 2056 to FIFO memory 2016. When counter 3062 counts to 15, its carry output preferably goes high and is fed back to flip-flop 3070 via path 3079 to clear it which in turn 45 clears counter 3062 ending its count cycle. Thus, counter 3062 preferably supplies a single FIFO strobe out pulse to FIFO memory 2016 via path 2056 in the manner previously described at the beginning of a pseudo video scan line. The purpose of this is to prefera- 50 bly preload FIFO memory 2016 with the first valid word before transmission starts. Subsequent FIFO strobe out pulses are obtained from a negative NAND gate 3082 which generates a strobe out pulse when a negative pulse is present to gate 3082 from decoder 55 3022, which was previously described with reference to bit counter 2030, as long as a horizontal sync pulse is not present at its other input, the output of gate 3082 being the other input to NOR gate 3072. The second input to negative NAND gate 3074 is preferably supplied from 60 the negative output of flip-flop 3068 which preferably inhibits a strobe pulse after 40 characters have been transmitted. The other input to NAND gate 3076, which is supplied from the counter stage 3026 through inverter 3043 to NAND gate 3076, preferably inhibits 65 alternate pulses, pulses at the other input of NAND gate 3076 provided from the output of negative NAND gate 3074 occurring once per character whereas a FIFO

strobe out pulse is needed only once per two characters, which is once per word.

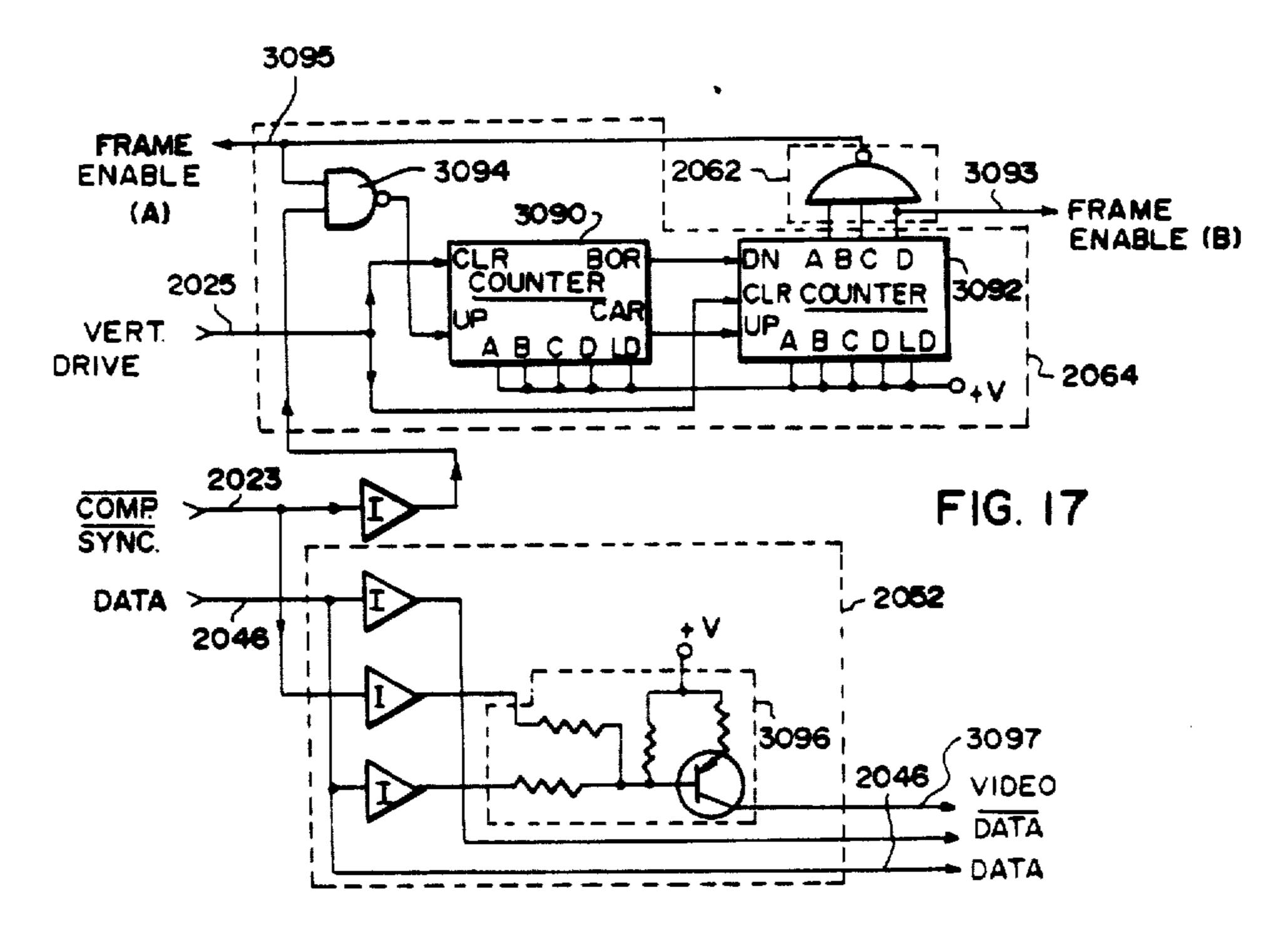

Referring now to FIG. 17, the sync combiner 2052, frame enable decoder 2062 and line counter circuit 2064 shall be described in greater detail hereinafter. The line counter 2064 preferably comprises two four bit binary counter stages 3090 and 3092, such as the type manufactured by Texas Instrument under the designation SN74193L. Counter stages 3090 and 3092 are preferably initially cleared by the vertical drive signal from sync generator 2022 provided via path 2025 and are clocked by the composite sync signal from sync generator 2022 provided via path 2023 via a conventional two input NAND gate 3094, the other input to NAND gate 3094 being the frame enable A signal output of decoder 2062 provided via path 3095. Clocking of counter stages 3090 and 3092 preferably continues until count 224 at which time decoder 2062, which is preferably a three input NAND gate, generates a low output via path 3095 turning off NAND gate 3094, NAND gate 2062 being the decoder which provides the frame enable signals via path 3095 and 3093, the frame enable signal provided via path 3093 being provided in parallel from one input to NAND gate 2062 from counter stage 3092 of line counter 2064.

Sync combiner 2052 which ultimately combines the composite video output pseudo video scan line signal 12, is preferably a conventional sync combiner as shown and preferred in FIG. 17, and has a data input via path 2046 and a composite sync input via path 2023, each of these inputs supplying current drive to a conventional transistor 3096 such that the collector output via path 3097 of transistor stage 3096 has a current determined by the combination of input logic levels and has three output levels corresponding to three signal levels, data varying between levels 2 and 3 corresponding to digital values of 0 and 1 and sync being indicated by level 1, this composite video signal output of path 3097 representing one pseudo video scan line at a time as described and shown with reference to FIGS. 1 and 2. This is the video signal transmitted from transmitter 20 to RF modulator 24 and therefrom through the cable distribution network 22 from which it is ultimately demodulated and provided to receivers 28 for processing and ultimate provision to the video display devices 2013 and 2015 for display of the selected or grabbed frame as well as row-by-row update of the selected frame.

#### RECEIVER

#### General Description

Referring now to FIGS. 3 through 7, initially, and once again to FIGS. 1 and 2, the preferred receiver portion 28 of the row grabbing system 10 of the present invention shall generally be described in greater detail. Thereafter, with reference to FIGS. 8 through 14, the preferred receiver portion 28 of the present invention shall be described in greater detail. As was previously described with reference to the preferred transmitter portion 20 of the row grabbing system 10 of the present invention, the transmitter 20 preferably provides what is generally termed a pseudo video scan line such as the type 12 illustrated in FIG. 1. This pseudo video scan line 12, as was previously described, is identical in format to a conventional video scan line; that is, it is consistent with FCC and EIA standards for a video scan line signal format; however, this pseudo video scan line 12 actually contains a row of information, such as approxi-

mately between 11 and 13 actual television video scan lines of information with the transmission time of the pseudo video scan line 12 being equal to the transmission time of a conventional TV video scan line, which is approximately 63 microseconds. With respect to the 5 pseudo video scan line 12, the horizontal sync and vertical sync portions are identical to a conventional video signal as is the format for the horizontal sync and the vertical sync as well as the horizontal sync amplitude. The time and amplitude envelope of the video region of 10 the pseudo video scan line 12, which region is defined as areas B,C,D,E and F in FIG. 1 is identical with the format for a conventional video scan line as is the three dimensional frequency envelope. Thus, all of the above mentioned standard conditions for a conventional video 15 scan line signal are met by the pseudo video scan line 12 provided by the transmitter portion 20 of the row grabbing system 10 of the present invention and received by the receiver portion 28. Accordingly, any [euipment] equipment that can handle conventional video can han- 20 dle the pseudo video scan line 12 of the present invention which can thus be transmitted and received through a conventional television distribution system with conventional television equipment.

Referring once again to the pseudo video scan line 12 25 illustrated in FIG. 1, the signal received by the receiver portion 28 and transmitted by transmitter 20 is in reality a digital signal which looks like a conventional video scan line to the receiver 28. The distribution of information in regions A through G of the pseudo video scan 30 line, or row of information, illustrated in FIG. 1 is as follows. Region A represents the horizontal sync signal which starts the timing for the receiver 28 and indicates the beginning of the pseudo video scan line from the beginning of the horizontal sweep for a conventional 35 television scan line. Region B represents the pseudo video scan line 12 address which contains all the following information bit locations. It should be noted, that preferably a 1 is indicated by the presence of a pulse and a 0 is indicated by the absence of a pulse, such as illus- 40 trated in FIG. 1 in region F where 1-0-1 is illustrated. When data is transmitted, as was previously mentioned, all of the following information bits are present; group, which is the section or chapter including a predetermined number, such as 1,000, of pages and is the most 45 significant bit of the page address, page which represents one frame in a group; and row which occupies one character space which is preferably seven bits, and defines a portion of a page preferably containing approximately 11 to 13 scan lines which comprise one 50 displayable character height. Region B also preferably contains direct address information, which is the first transmitted bit preferably and is a 0 unless the direct address condition exists which is a control condition for a selected terminal informing the terminal to supersede 55 the requested page. This region also preferably contains permission information which is a one bit position which is preferably a 1 when the user is being given authority to receive one or more selected groups of information. It should be noted that preferably there is 60 also an emergency override condition which provides control information to all terminals to override all requests including a permission request and occurs when the page and group information bit locations are 0, this condition preferably being utilized to display emer- 65 gency information such as a civil defence warning Region C is preferably a special character information region of 7 bits which is preferably utilized for optional

functions to be performed by the individual receiver 28 or terminal. Region D preferably contains 32 characters of displayable information in digital form. Region E preferably contains 7 bits of error check information and, preferably may represent the complement of the binary equivalent of the sum of all of the 1 bits present in regions B, C, and D. Region F preferably contains the clock synchronizing burst or pulse train at the bit rate (the frequency preferably being equal to one-half the bit-rate) and comprises a pulse train of ones and zeros of two character spaces or 14 bits. Region G is preferably the same as region A and represents the horizontal sync signal. As was previously mentioned, the vertical sync is provided by generating a special sequence of horizontal sync pulses during the normal television blanking period, which is after approximately 246 horizontal sync pulses, which in the present invention is after approximately 20 pages have been transmitted. Therefore, a 20 pages are transmitted before each vertical sync. The sync signal looks like a conventional composite sync signal with the vertical sync interval comprising approximately nine normal horizontal sync pulse times as illustrated in FIG. 2 which is an illustration of conventional composite sync and vertical drive signals.

Now referring to FIGS. 3 and 4, the preferred synchronization and timing portion of the receiver portion 28 of the row grabbing system 10 of the present invention shall generally be described. The synchronization and timing portion preferably contains a conventional sync separator 400 which is provided in conventional fashion, through a conventional distribution system 22, with the composite video input via path 402 from the transmitter 20. As was previously mentioned, the composite video input provided via path 402 preferably includes data and horizontal sync information as well as vertical sync information at the appropriate given time. The conventional sync separator 400 separates the composite video input signal into a vertical sync signal via path 404, a horizontal sync signal via path 406 and a data signal via path 408, the data signal via path 408 preferably including regions B through F for a given pseudo scan line of information which is received via path 402 by the sync separator 400. The data portion of the pseudo of the pseudo video scan line 12 is provided in parallel as one input to a conventional two input NAND gate 410. The other input to NAND gate 410 preferably comprises the character 39 and the character 40 pulse output signals of a counter and decoder circuit 412 to be described in greater detail hereinafter with reference to FIG. 8. Suffice it to say at this time that an output is present to NAND gate 410 from the counter and decoder circuit 412 during the time interval corresponding to characters 39 and 40, as will be described in greater detail hereinafter. The output of NAND gate 410 is provided to a conventional phase locked loop 414, to be described in greater detail hereinafter with reference to FIGS. 4 and 8. Suffice it to say that phase locked loop 414 is preferably a correctable voltage controlled oscillator which operates without any additional input, as illustrated in FIG. 4, at the data bit rate, which is preferably, by way of example, approximately 5.11 megahertz, and is preferably crystal controlled. As illustrated in FIG. 4, the phase locked loop 414 preferably comprises a conventional phase [dectector] detector 416, a conventional filter 418 connected to the output of the phase detector 416 and a conventional voltage controlled oscillator 420 which is conventionally

crystal controlled by crystal 422 which is connected to the output of filter 418. In addition, a feedback path is conventionally provided between the output of voltage controlled oscillator 420 and the phase detector 416 through a conventional divide-by-two flip-flop 424. 5 Thus, a reference frequency, which is half the data bit rate is provided to the phase detector 416 and the output of the voltage controlled oscillator 420 is the master clock frequency, termed clock A at the data bit rate. By way of example, the reference frequency is approximately 2.55 megahertz and the clock A frequency is approximately 5.11 megahertz. Thus, the clock A output is provided via path 426 from the conventional phase locked loop 414.

Referring once again to FIG. 3, the clock A output 15 provided via path 426 is provided to a conventional selectable divide-by-8 or divide-by-1 frequency divider 428 (FIG. 6) whose output is either the clock A signal or the clock B signal which is the clock A signal divided by eight. Thus, for example, clock B is approximately 20 0.64 megahertz and is provided via path 430 (FIG. 6). This clock B signal provided via path 430 from selectable frequency divider 428 is preferably provided as an input to the counter and decoder circuit 412 which preferably decodes the character positions and the bits 25 within the character by counting clock pulses starting with the end of the horizontal sync pulse, as will be described in greater detail hereinafter, seven counts preferably being provided per character. The horizontal sync input is also preferably provided to the counter 30 decoder circuit 412 to start and/or reset the counters contained therein. The output of the counter and decoder circuit 412 is preferably the control information corresponding to character positions 1 through 41 and bits 1 through 7, by way of example. As was previously 35 mentioned, the character position control information for character positions 39 and 40 is preferably provided as one input to the two input NAND gate 410. It should be noted that preferably character positions 39 and 40 are the 14 bits which comprise region F of the pseudo 40 video scan line 12. Accordingly, NAND gate 410 only preferably provides an output to phase locked loop 414 when the data portion of the pseudo video scan line 12 is at region F so that only information contained in region F is provided to phase locked loop 414. As was 45 previously mentioned, region F is the reference frequency which is one-half the data bit rate or one-half the master clock frequency which is supplied to the phase detector 416 which conventionally functions together with the feed back signal from the voltage 50 controlled oscillator 420 as modified by the flip-flop 424 to provide a feedback frequency equal to the reference frequency which corrects the voltage controlled oscillator 420 if there is any difference, whether this difference be in frequency or phase. In addition, circuit 418 55 conventionally functions to stabilize the phase locked loop 414, the output of the phase locked loop 414 being a continuous clock signal which is twice the reference frequency and identical in phase. Preferably, the data bit rate is equivalent to twice the maximum frequency 60 of transmission, with the highest frequency of transmission possible being two bits per cycle for a digital signal.

The data information portion of the pseudo video scan line 12 is also preferably provided in parallel to an error check circuit 432 which preferably receives control or timing information from the counter and decoder circuit 412 via path 434 corresponding to character position 38 as well as receiving data via path 408 from

the sync separator 400. As was previously mentioned. character position 38 preferably corresponds to the error check information portion of the pseudo video scan line 12. Error check circuit 432, will be described in greater detail hereinafter with reference to FIG. 8 with respect to the presently preferred arrangement for accomplishing an error check. With respect to the arrangement illustrated in detail in FIG. 8, error check circuit 432 preferably counts the number of "one" bits in characters 1 through 7 which comprise regions B, C. and D, preferably, and compares that sum with the binary number located in character position 38, which corresponds to region E, and requires non-coincidence in every bit of that comparison since character position 38 or region E preferably contains the complement of that sum. Error check circuit 432 provides an output signal, such as a 1, indicating the error check is OK when the preferred error check condition exists, this signal being termed "error check OK signal" provided via path 436. This error check OK signal on path 436 will preferably remain until the next error check of the next subsequent pseudo video scan line which occurs one conventional television video scan line transmission time after the previous pseudo video scan line. The complement of this sum is preferably selected from an [erro] error check sum to allow a check for empty lines, which are lines that only contain information in regions F and G which, in such an instance, would sum to 0. If the complement was not utilized for the error check sum in region E, such a signal would pass the error check since the sum would be 0 and character position 38 would contain a 0 so the sum would match. Therefore, by utilizing the complement, empty line signals would be rejected, which is preferred in the present invention.

The output of the counter and decoder circuit 412 also preferably comprises a character clock signal for the main memory write mode, as will be described in greater detail hereinafter with reference to FIG. 8, which is provided to a conventional two bit multiplexer 440 which also receives as inputs a character clock signal in the main memory read mode from a column counter 442 (FIG. 7) to be described in greater detail hereinafter, via path 444, and a select input via path 446 which signal selects between the character clock input in the write mode and the character clock input in the read mode in response to the provision of a memory read/write signal from memory write logic 450 (FIG. 6), to be described in greater detail hereinafter, via path 446. Preferably, in response to a memory write command which is provided from the memory write logic 450 via path 446, the character clock input selected by multiplexer 440 is the signal provided from the counter and decoder circuit 412, whereas in response to a memory read command provided from the memory write logic 450, the character clock input selected by multiplexer 440 is the character clock provided from column counter 442. The character clock input selectively provided from multiplexer 440 is used to clock a character counter 454, to be described in greater detail hereinafter with reference to FIG. 12, which also receives the horizontal sync input to start and/or reset the counter 454. The output of the character counter 454 is the character address. The data portion of the pseudo video scan line 12 provided via path 408 is also provided in parallel to a conventional serial memory 456 which is a one line buffer which preferably delays the signal by one conventional television video scan line transmission time (preferably for character positions 4 through 37, by way of example) before the provision of the data to a main memory portion 458 to be described in greater detail hereinafter. This delayed data is also provided in parallel via path 460 to a permission memory 462 (FIG. 6), to 5 be described in greater detail hereinafter. This one conventional television video scan line transmission time delay enables the testing, to be described in greater detail hereinafter, of the pseudo video scan line 12 for purposes of deciding whether or not to write this infomation into a main memory 464 of the main memory portion 458 prior to the actual writing of the data into this main memory 464. The actual generation of the read/write command to the main memory 464 will be described in greater detail with reference to FIGS. 5 15 and 6.

With reference to the main memory portion 458 of FIG. 3, the serial memory 456 preferably has a 256 bit capacity and serially loads these bits one character or seven bits at a time into a conventional shift register 466, 20 which is a one word serial-to-parallel converter which comprises a conventional seven bit shift register which parallel unloads seven bits into a character latch 468, to be described in greater detail with reference to FIG. 12 or into a row latch 470 to be described in greater detail 25 hereinafter with reference to FIG. 12, depending on the particular character position. As was previously mentioned, preferably characters 4 through 37 which represent, preferably, regions B, C, and D of the pseudo video scan line 12 are loaded into the serial memory 30 456. Preferably, character latch 468 and row latch 470 are enabled by enable signals provided from counter and decoder circuit 412 at the appropriate times. Preferably, row latch 470 receives character position 4 information, which preferably comprises the row informa- 35 tion and character latch 468 preferably receives character positions 6 through 37, which comprises region D, which preferably is the character or displayable data information. Preferably, as was preferably mentioned, the special character is located at character position 5 40 and is not unloaded to character latch 468. In addition, shift register 456 receives the clock B input signal as a clock signal therefor. The output of character latch 468 preferably provides a displayable data input in parallel to memory 464 one character at a time or seven bit 45 parallel. In the memory write mode, row latch 470 will preferably provide the row address in parallel to memory 464 for a given pseudo video scan line 12, which row address is preferably set once per pseudo video scan line 12. In the memory write mode, the row latch 50 470 output is provided to a conventional multiplexer 474 which switches the address input of memory 464 to the output of row latch 470. In the memory read mode, multiplexer 472 siwtches the row address input of memory 464 to the output of row counter 474 (FIG. 7), to be 55 described in greater detail hereinafter. Preferably, five bits of row address are utilized which is adequate for providing address information for 32 video displayable rows. As was previously mentioned, the main memory 464 address input identifies the character address or 60 character position which is provided from the output of character counter 454, which is preferably a five bit counter capable of supplying 32 character addresses utilizing the character clock input (one clock per character) and the horizontal sync to provide the character 65 addres. Accordingly, memory 464 is preferably, by way of example, a row-by-32 character array or page, of which 16 or 32 rows may be utilized. Memory 464

receives a read or write command via path 446 from memory write logic 450 (FIG. 6), as will be described in greater detail hereinafter. It should be noted that preferably four bits are utilized to assign 16 rows and one bit is utilized to assign a left control condition and a right control condition if 64 characters are to be displayed instead of 32 characters, assuming a page has normally been defined as 32 characters wide by 16 rows high, 64 characters representing two pages. It should also be noted that row latch 470 also provides a permission bit output via path 480 to the permission write logic 482 (FIG. 6), to be described in greater detail hereinafter.

Preferably, as was previously mentioned, the group and/or page to be displayed or grabbed in real time is described in greater detail with reference to FIGS. 5 15 selected by means of a conventional keyboard 484, to be described in greater detail hereinafter. Suffice it to say at this time that keyboard 484 is preferably a conventional ten digit keyboard which provides a serial digital output. For example, if decimal 326 is the number depressed on the keys of the keyboard 484, then keyboard 484 will conventionally put out a pulse train of 326 pulses. The outputs from keyboard 484 are preferably the control signal "group call" provided via path 486, the "number" selected provided via path 488, the control condition "up" or more provided via path 490 which represents incrementing the selected number by one preferably; the control condition "down" or back provided via path 492 which preferably represents decrementing the selected number by 1; and the control condition "page call" provided via path 494, the control conditions up and down incrementing or decrementing the group or page selection depending on which condition, group or page, was most recently selected. This keyboard 484 output via paths 486 through 494, inclusive, is preferably provided to a [key board] keyboard counter 500 (FIG. 5), to be described in greater detail hereinafter, where this information is interpreted to control the selection of the appropriate frame to be grabbed in real time.

Referring now to FIGS. 5 and 6 the generation of the memory read/write command provided via path 446 and a memory write clock provided via path 995 from memory write logic 450 shall generally be described. As was previously mentioned, the output of keyboard 484 is provided to keyboard counter 500, to be described in greater detail hereinafter, which counts the pulse train corresponding to the number selected and provides a parallel binary output, such as preferably 10 bits, for both the group selected via parallel paths 502 and for the page selected via parallel paths 504, and increments or decrements the appropriate counter in response to the receipt of the up or down control signal from the keyboard 484. The selected page output 504 from keyboard counter 500 is preferably provided in parallel to a conventional multiplexer 506 which sequentially switches each parallel output 504 to a single output line 508 to provide a serial selected page address on path 508. Multiplexer 506 is addressed to switch by a page address counter 510 to be described in greater detail hereinafter with reference to FIG. 10, which is in turn operated by the page address clock provided via path 512 from counter and decoder circuit 412 (FIG. 3), this page address clock preferably being 10 bits or pulses which correspond to the page address bits. The output of the page address counter 510 is preferably a binary number representing the bit number within the page address sequence and controls the switching of multiplexer 506. Multiplexer 506 and page address counter

510 are preferably equivalent to a 10 bit parallel load/serial out shift register. The page address counter 510 and multiplexer 506, as will be described in greater detail hereinafter, permit the page address to be checked. In order to accomplish this, the serial page address output on path 508 is provided as one input to a conventional exclusive or gate 514 whose other input is the page address bit present on the data line 408, the serial page address bits on path 508 being provided in coincidence with the page address bits on data line 408. When the pseudo vidso scan line page address on data line 408 is the same as the serial page address on path 508, the output of exclusive or gate 514 will be low, which in the logic chosen by way of example represents a 0. When these inputs differ, in other words when there 15 is a lack of coincidence, the output of exclusive or gate 514 will be high (a 1 in the logic chosen) for at least one clock period of the page address sequence. The output of exclusive or gate 514 is provided to a conventional flip-flop 516 which, when the output of 514 is high, will 20 be clocked by the page clock provided via path 512. Flip-flop 516 is preferably a conventional JK flip-flop. If at any time during the page address sequence, the output of 514 goes high, the output of flip-flop 516 will preferably go low and provide no output and remain 25 low until reset by the horizontal sync at the end of the pseudo video scan line 12. The normal condition of the output of flip-flop 516 provided via path 518 is a high or l indicating that the page address is OK or checks, this signal being termed the "page address OK signal" 30 which is provided to another conventional flip-flop 520 (FIG. 6) which supplies this information to the memory write logic 450.

Now considering the provision of a user address check to insure that the correct user is receiving the 35 pseudo video scan line. The page address counter 510 output is also provided in parallel to multiplexer 522 whose other input is a hard-wired user address 524. The user address perferably occupies the same space in the pseudo video scan line as the page address and, accord- 40 ingly, the receiver 28 must preferably be able to distinguish between the two. The page address counter 510 output sequentially switches multiplexer 522 to provide a serial bit user address on path 526 to EXCLUSIVE OR GATE 528 whose other input is the data path 408. 45 The serial user address provided via path 526 is in coincidence with the user address bits provided via path 408 to gate 528. When the pseudo video scan line user address provided via path 408 is the same as or coincident with the user address provided via path 526, the output 50 of gate 528 will be low for the logic chosen by way of example. When there is a lack of coincidence between these two inputs to gate 528, the output of gate 528 will be high for at least one clock period of the user address sequence. The output of gate 528 is preferably provided 55 to a conventional JK flip-flop 530 which is preferably clocked by the page address clock provided via path 512. If at any time during the user address sequence, which is preferably identical with the page address sequence, the output of gate 528 goes high, the output of 60 flip-flop 530 will preferably go low (a no output condition) and remain low until reset by the horizontal sync, provided via path 406, at the end of the pseudo video scan line. The normal condition of the output of flipflop 530 is preferably high on path 532 indicating that 65 the user address checks or is OK, indicated by the term "user address OK signal" which is provided as one input to the permission write logic 482 (FIG. 6). The