## United States Patent [19]

[11] E

Re. 32,130 Patent Number:

[45] Reissued Date of Patent: Apr. 29, 1986

| [54] | APPARATUS FOR EDITING AND |

|------|---------------------------|

| • •  | CORRECTING DISPLAYED TEXT |

Inventors: Walter G. Frederickson, Indialantic; [75]

> Albert W. Heitmann, Melbourne; George M. Jones, Indian Harbour Beach; Howard A. Thrailkill,

Indialantic, all of Fla.

Harris Corporation, Melbourne, Fla. Assignee:

Appl. No.: 385,651

Frederickson et al.

[22] Filed: Aug. 6, 1973

#### Related U.S. Patent Documents

| Reiss | ue | of:  |  |

|-------|----|------|--|

| [64]  | T  | )ata |  |

| [64] | Patent No.: | 3,706,075     |  |

|------|-------------|---------------|--|

|      | Issued:     | Dec. 12, 1972 |  |

|      | Appl. No.:  | 37,177        |  |

Filed: May 14, 1970

| [51] | Int. Cl.4 | ******************************* | G09G | 1/06 |

|------|-----------|---------------------------------|------|------|

|      | TIC CO    | 240 /71                         |      |      |

340/800; 364/900

Field of Search ....... 340/324 A, 324 AD, 726 [58]

[56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,242,470 | 3/1966  | Hagelbarger et al | 340/172.5 |

|-----------|---------|-------------------|-----------|

| 3,346,853 | 10/1967 | Koster et al      | 340/172.5 |

| 3,364,473 | 1/1968  | Reitz et al       | 340/172.5 |

| 3,500,335 | 3/1970  | Cuccio            | 340/172.5 |

| 3,501,746 | 3/1970  | Vosbury           | 340/172.5 |

| 3,540,012 | 11/1970 | Ehrman   | 340/172.5   |

|-----------|---------|----------|-------------|

| 3,581,290 |         |          |             |

| 3,582,936 |         |          | 340/172.5 X |

| 3,587,062 | 6/1971  | Jen      | 340/172.5   |

| 3,593,310 | 7/1971  | Kievit   | 340/172.5   |

| 3,602,901 | 8/1971  | Jen      | 340/172.5   |

| 3,643,252 | 2/1972  | Roberts  | 340/324 A   |

| 3,654,620 | 4/1972  | Bartocci | 340/172.5   |

#### OTHER PUBLICATIONS

Tech. Man. Keyboard Display, Model 7550/7555, SDS901012A, Oct. 1968, Xerox Data Systems, 332 pages, Pertinent pp. 1-1 to 1-4, 2-7 to 2-8, 3-1 to 3-6, 3-15 to 3-16, 3-47 to 3-50, 4-33 to 4-40.

Primary Examiner-David L. Trafton Attorney, Agent, or Firm—Yount & Tarolli

#### [57] **ABSTRACT**

A console for keyboard editing and correcting of text, such as newspaper copy, displayed on the screen of a cathode ray tube. The encoded text copy is recirculated in a refresh memory having a large capacity dynamic shift register and a small capacity random access memory where various editing and correcting changes may be made. The text displayed on the cathode ray screen may be "rolled up" or "rolled down" one line at a time as the editing proceeds. Any selected block of the text may be transmitted from the output of the recirculating memory to an output device, such as a punch, and deleted from the refresh memory at the same time.

#### 39 Claims, 13 Drawing Figures

U.S. Patent Re. 32,130 Apr. 29, 1986 Sheet 3 of 10 R.A.M. INPUT MUX RECIRCULATING R.A.M. MEMORY 40a 24-TRC -45a R.A.M. ADDR. 38 45 MUX 44 SPECIAL MOS CLK. 1 CHARACTER 5,

DECODER 5\* 233 407 408 WRITE ADDR CLOCK OZ CLOCK WRITE ENABLE 416 64 52 WRAP 55 -59 READ CPCD, WRAPAROUND CPCD 54 ADDR. ADDR. REG. WRAP 406 REG. COUNTER

36

.

U.S. Patent Apr. 29, 1986 Sheet 8 of 10 Re. 32,130

# Fig. 9

Z otioally tha ac

# APPARATUS FOR EDITING AND CORRECTING DISPLAYED TEXT

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

This invention relates to an editing and correcting apparatus which is particularly adapted for use with unedited or unproofed text to enable editing changes and corrections to be entered from a keyboard, with the text being displayed visually as the editing and correcting proceeds, after which the final edited and corrected copy may be used as the input to a computer or an automatic typesetter.

A principal object of this invention is to provide such a novel and improved editing and correcting apparatus 20 which is extremely flexible in the variety of copy changes which it can perform.

Another object of this invention is to provide such an apparatus having a refresh memory, from which is obtained the visual display of the text being edited and 25 corrected, which combines the low cost of a dynamic shift register for large data storage capacity and the flexiblity of a smaller capacity random access memory in which the changes are made.

Another object of this invention is a novel and im- 30 proved editing and correcting apparatus having novel provision for "rolling up" or "rolling down" the multiline text display.

Another object of this invention is to provide a novel and improved editing and correcting apparatus in 35 which any selected block of the edited and corrected text may be transmitted to an output device, such as a punch, and deleted from the refresh memory at the same time.

Further objects and advantages of this invention will 40 be apparent from the following description of a present-ly-preferred embodiment, described with reference to the accompanying drawings in which:

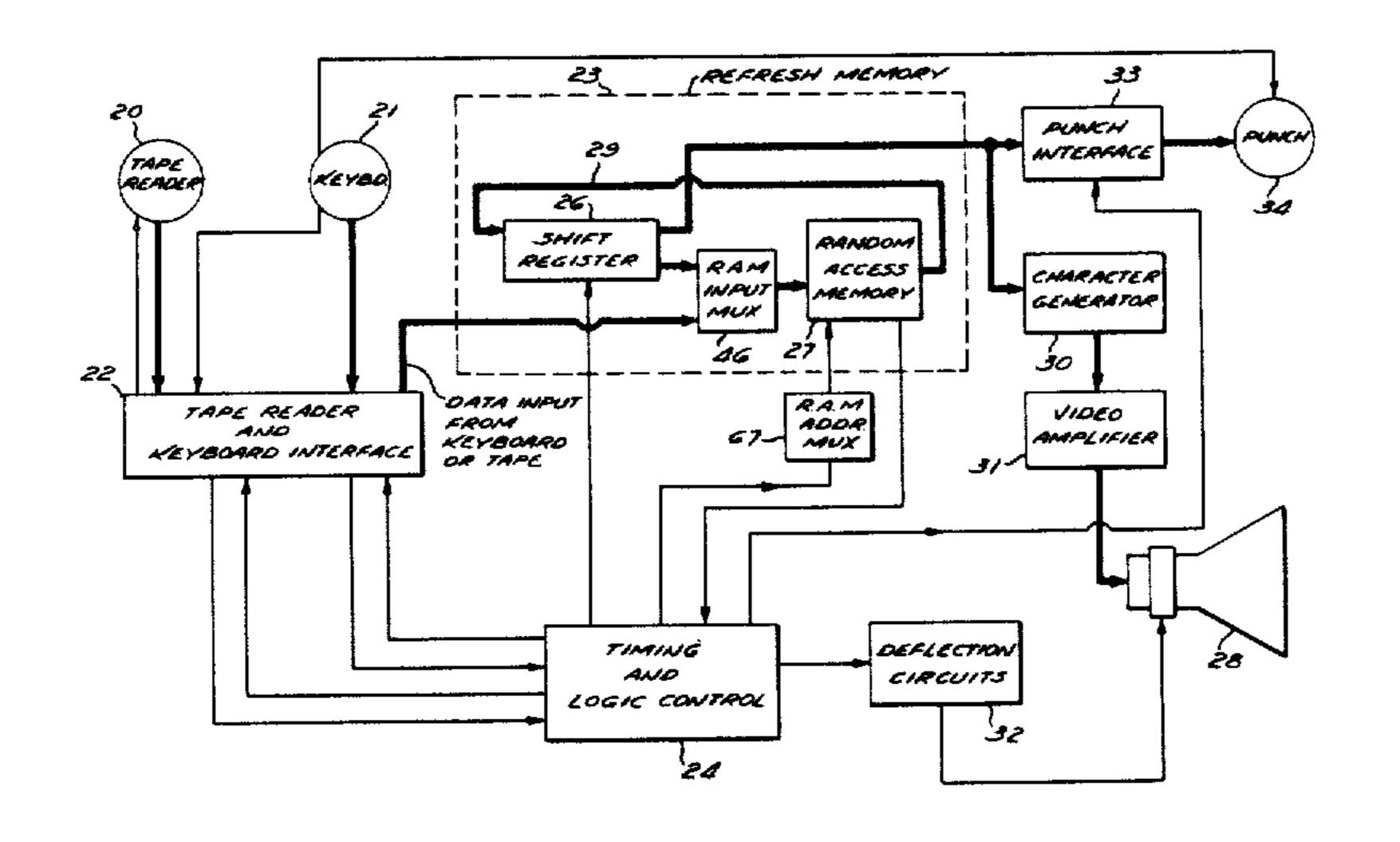

FIG. 1 is a schematic block diagram of a system embodying the present apparatus;

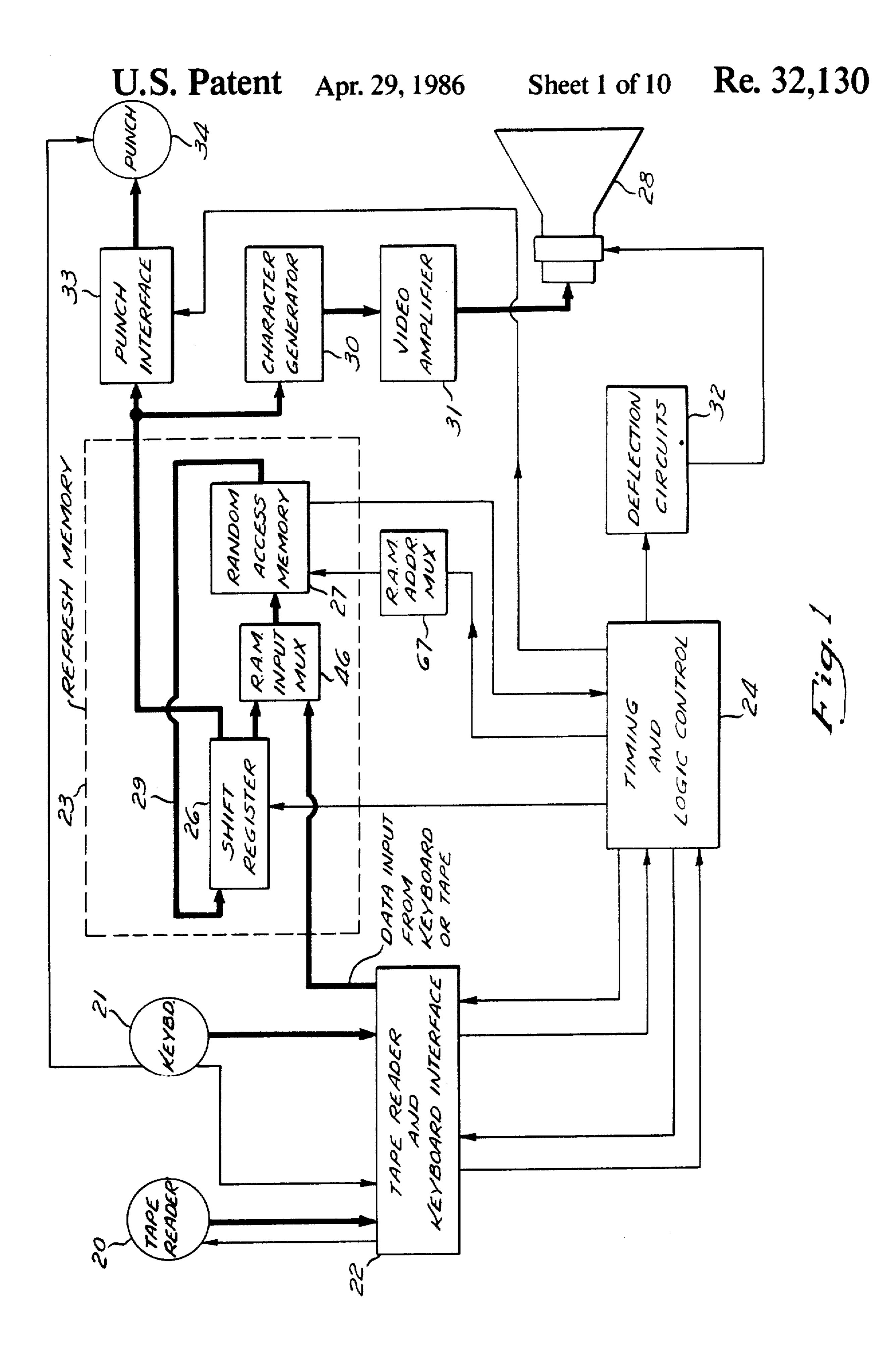

FIG. 2 shows the FIG. 1 system in greater detail;

FIG. 3 illustrates schematically the circuitry in the present apparatus for ending each line of the displayed text just before a word which would run beyond the end of that line;

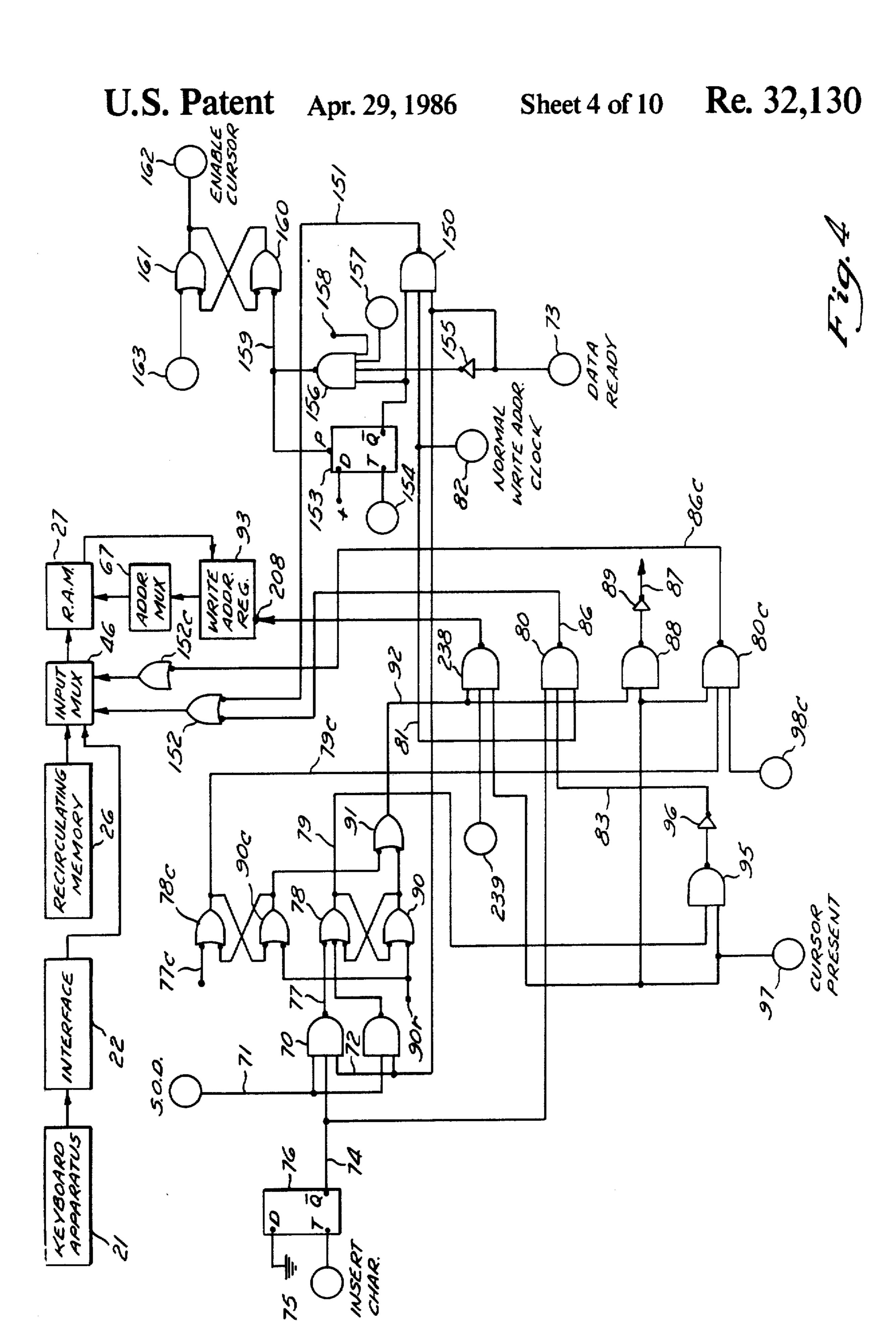

FIG. 4 illustrates schematically the circuitry in the present apparatus for inserting a character, or inserting a cursor, or overstriking a character at any selected point in the displayed text which is being edited or 55 corrected;

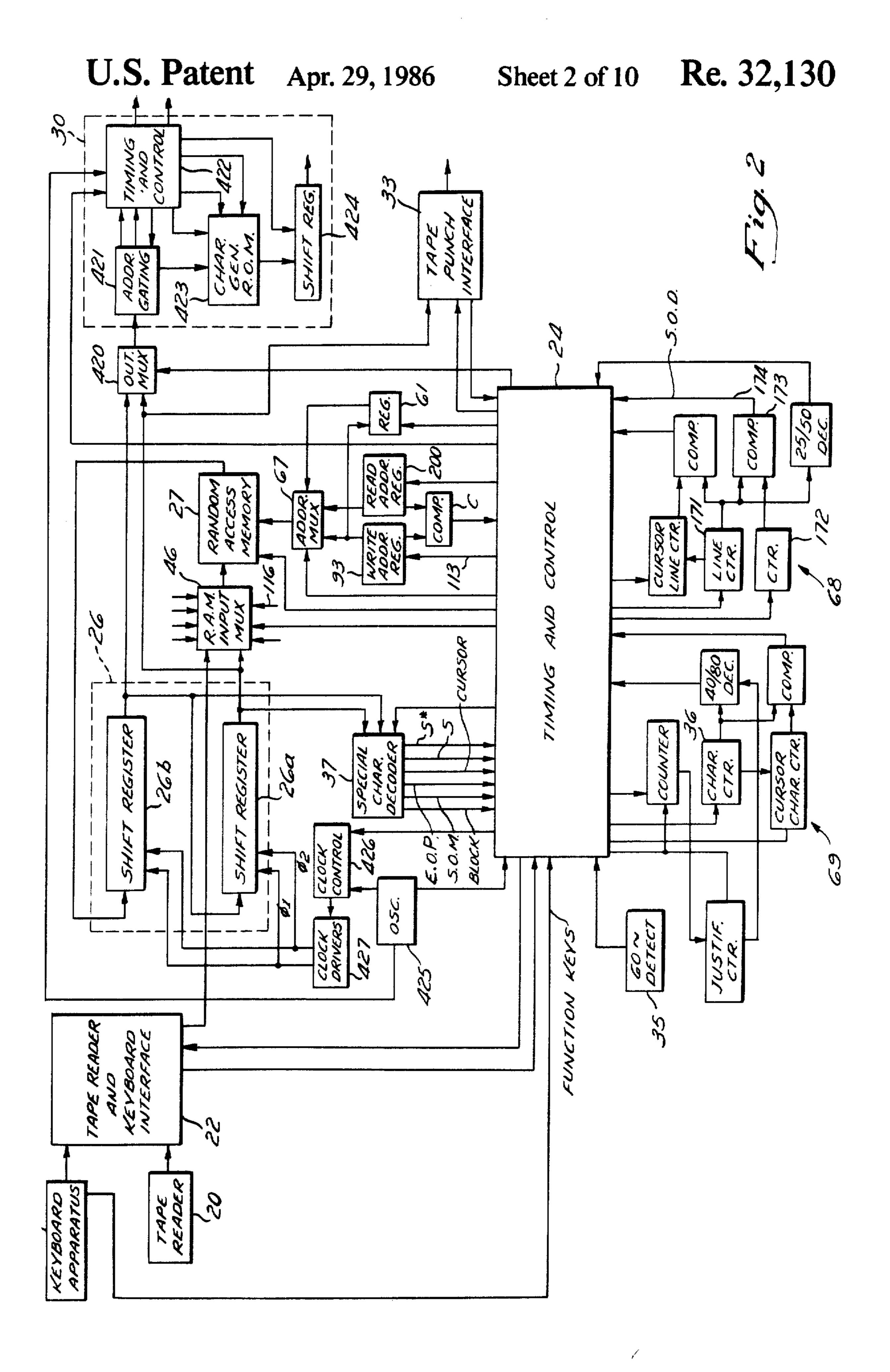

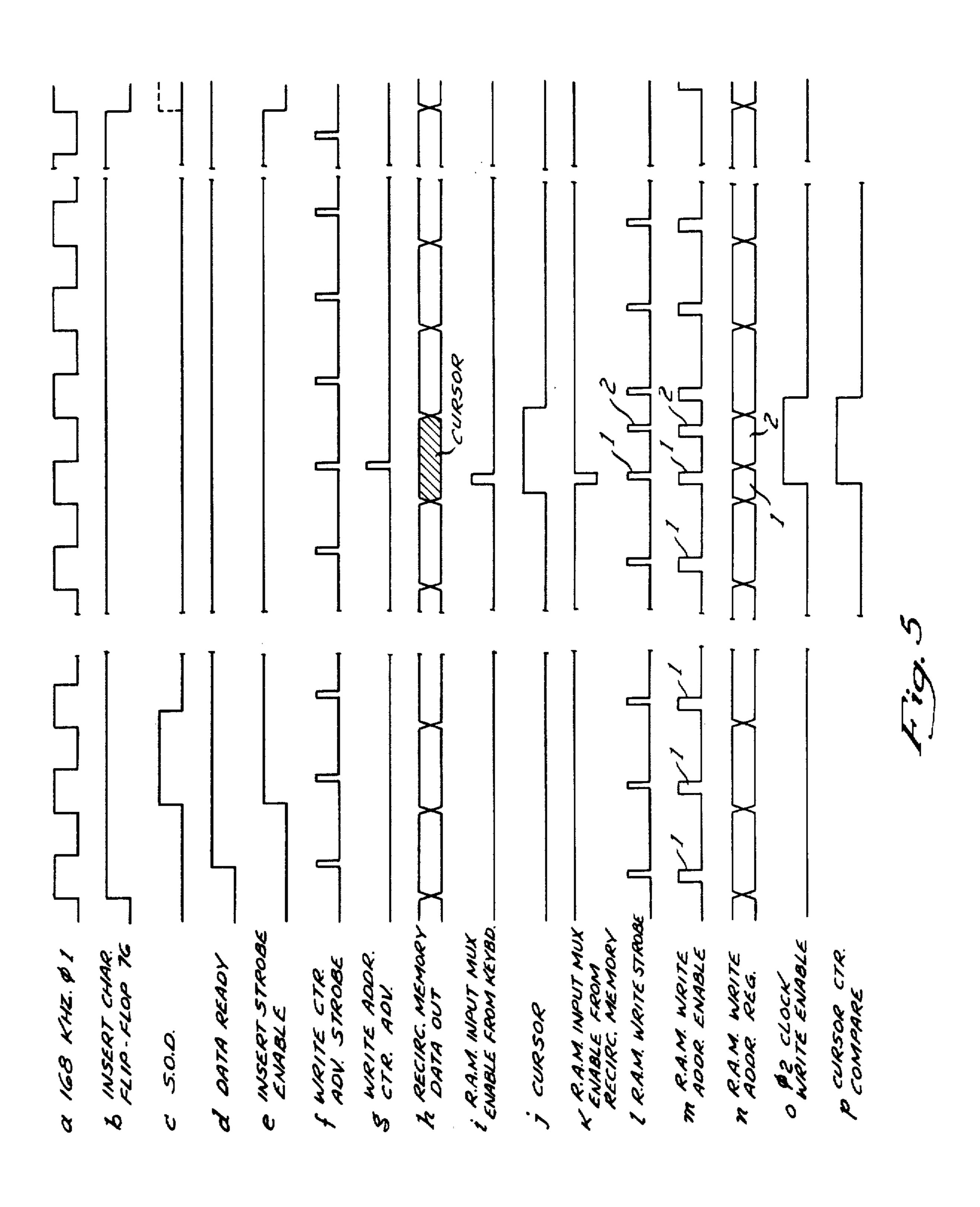

FIG. 5 is a timing diagram for the "insert character" mode of operation;

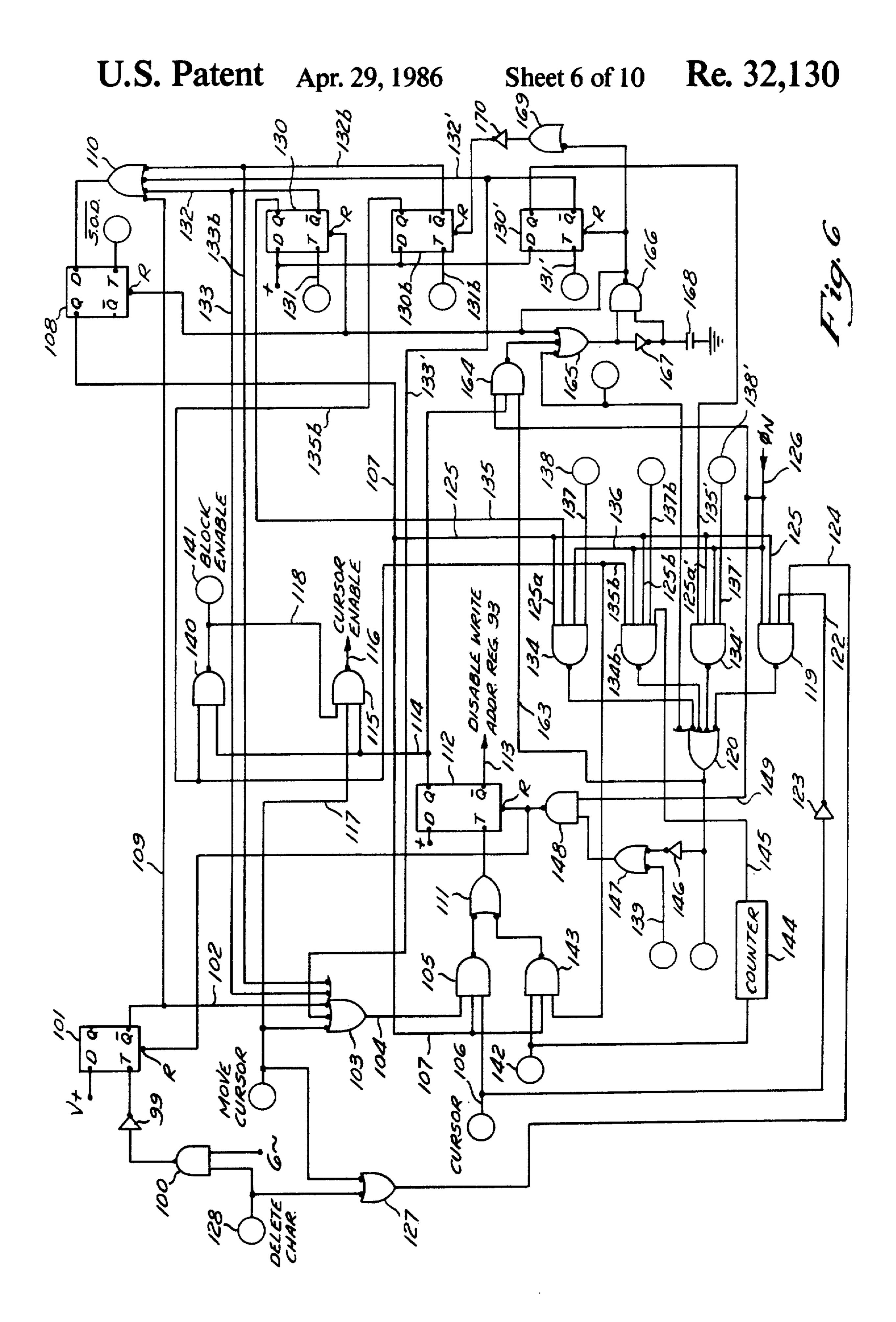

FIG. 6 illustrates schematically the circuitry in the present apparatus for performing various delete operations on the displayed text which is being edited or corrected;

FIG. 7 is a timing diagram for the "delete character" mode of operation;

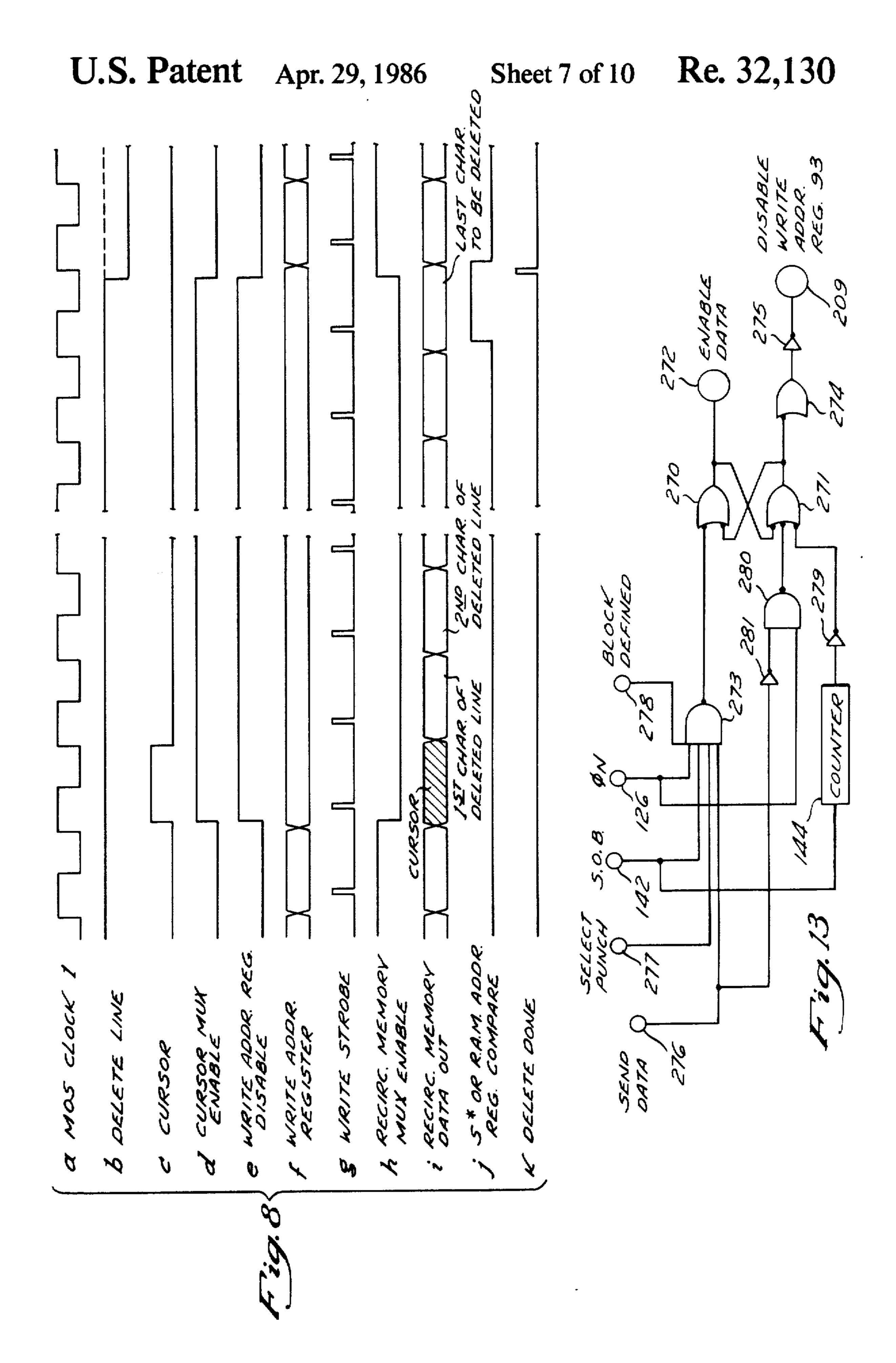

FIG. 8 is a timing diagram for the "delete line" mode 65 of operation;

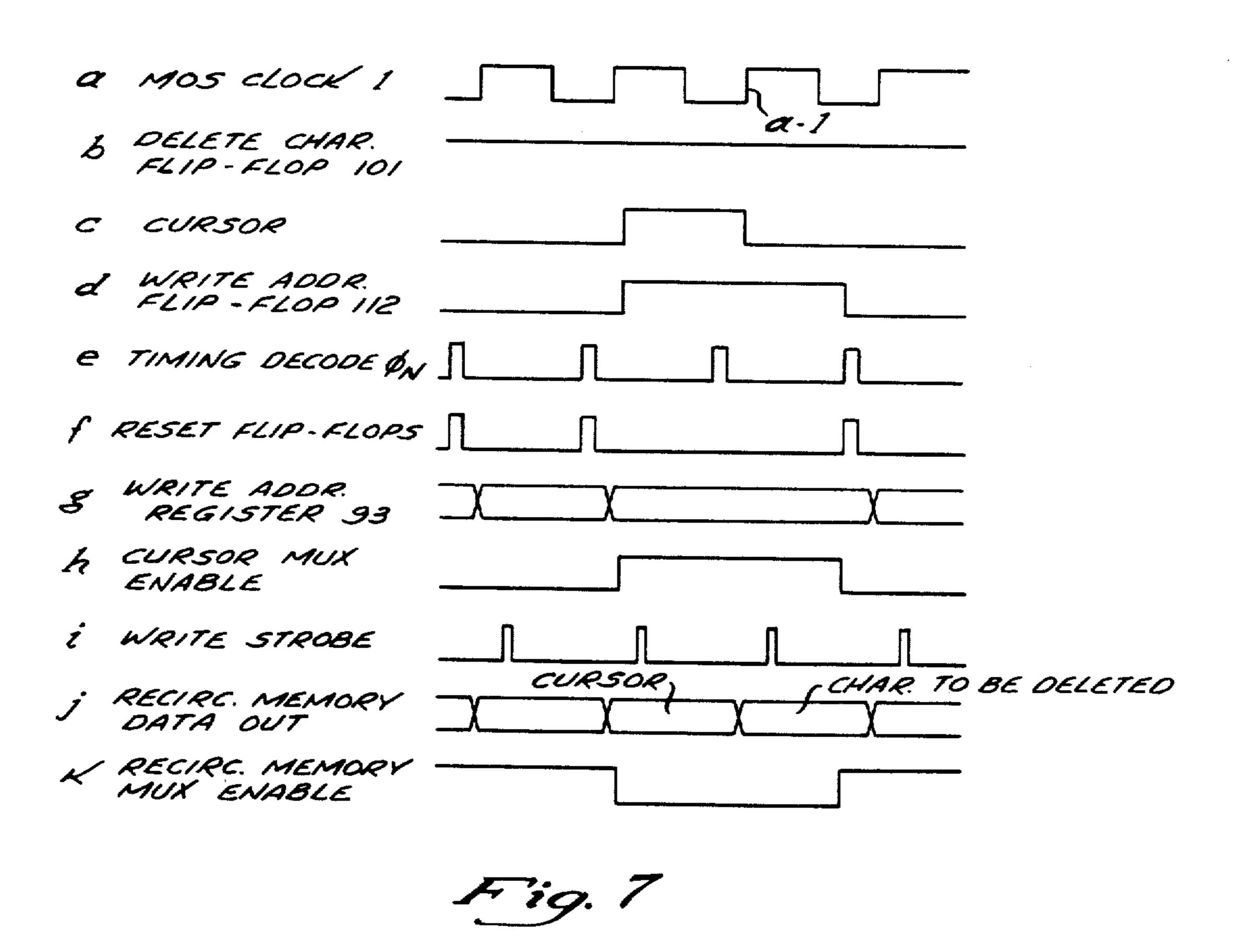

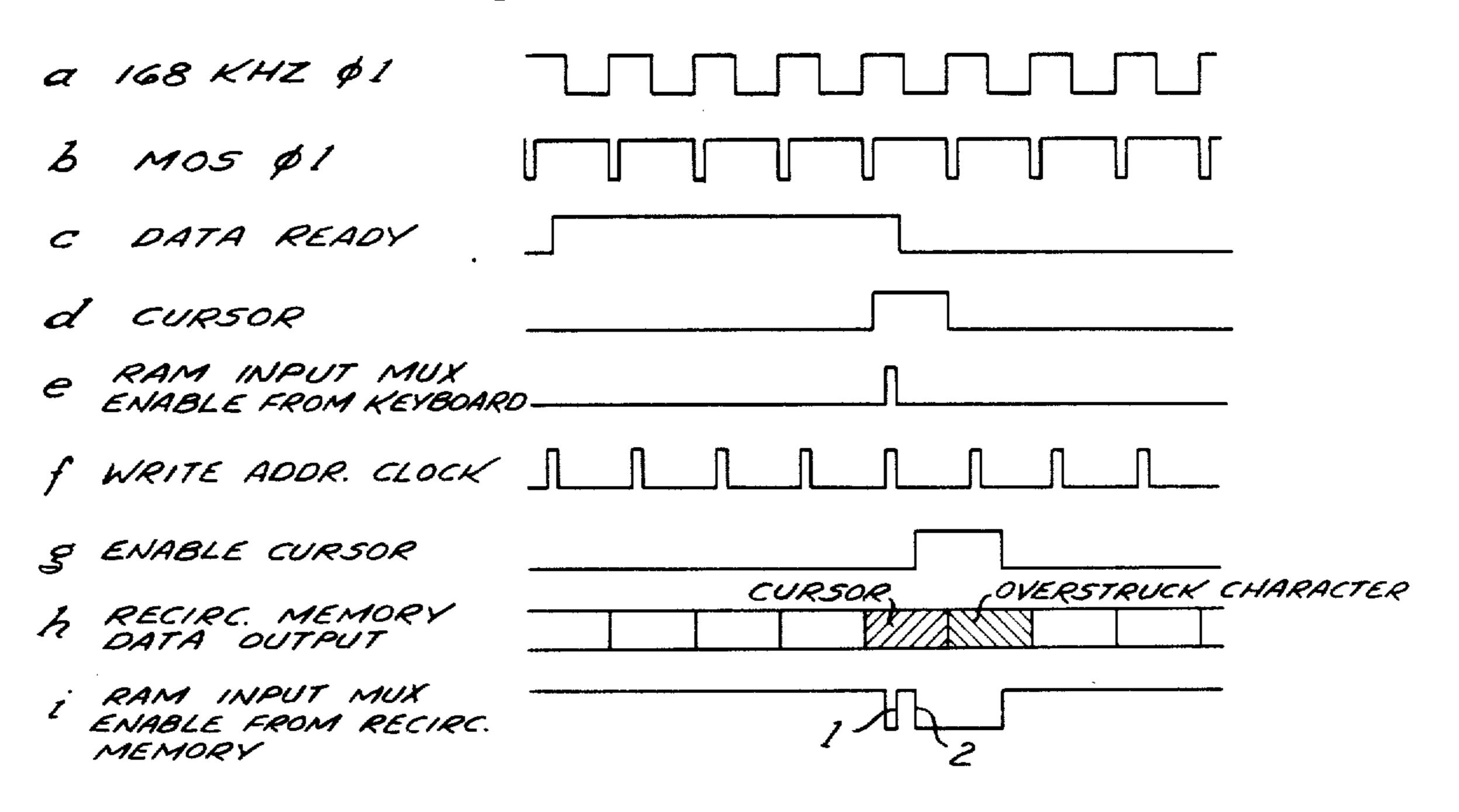

FIG. 9 is a timing diagram for the "overstrike character" mode of operation;

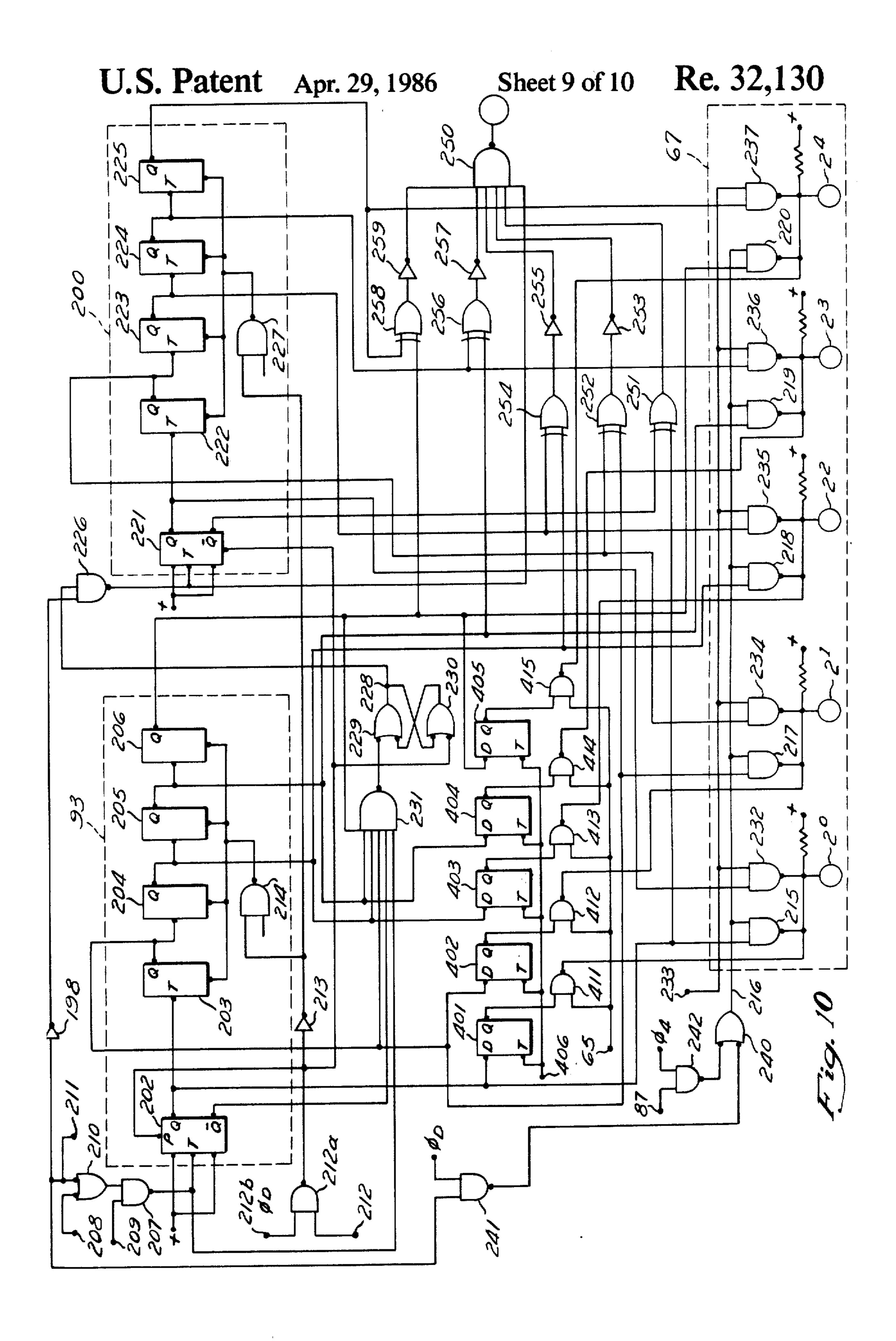

FIG. 10 illustrates schematically the address registers and the address multiplexer for the random access memory in the present apparatus;

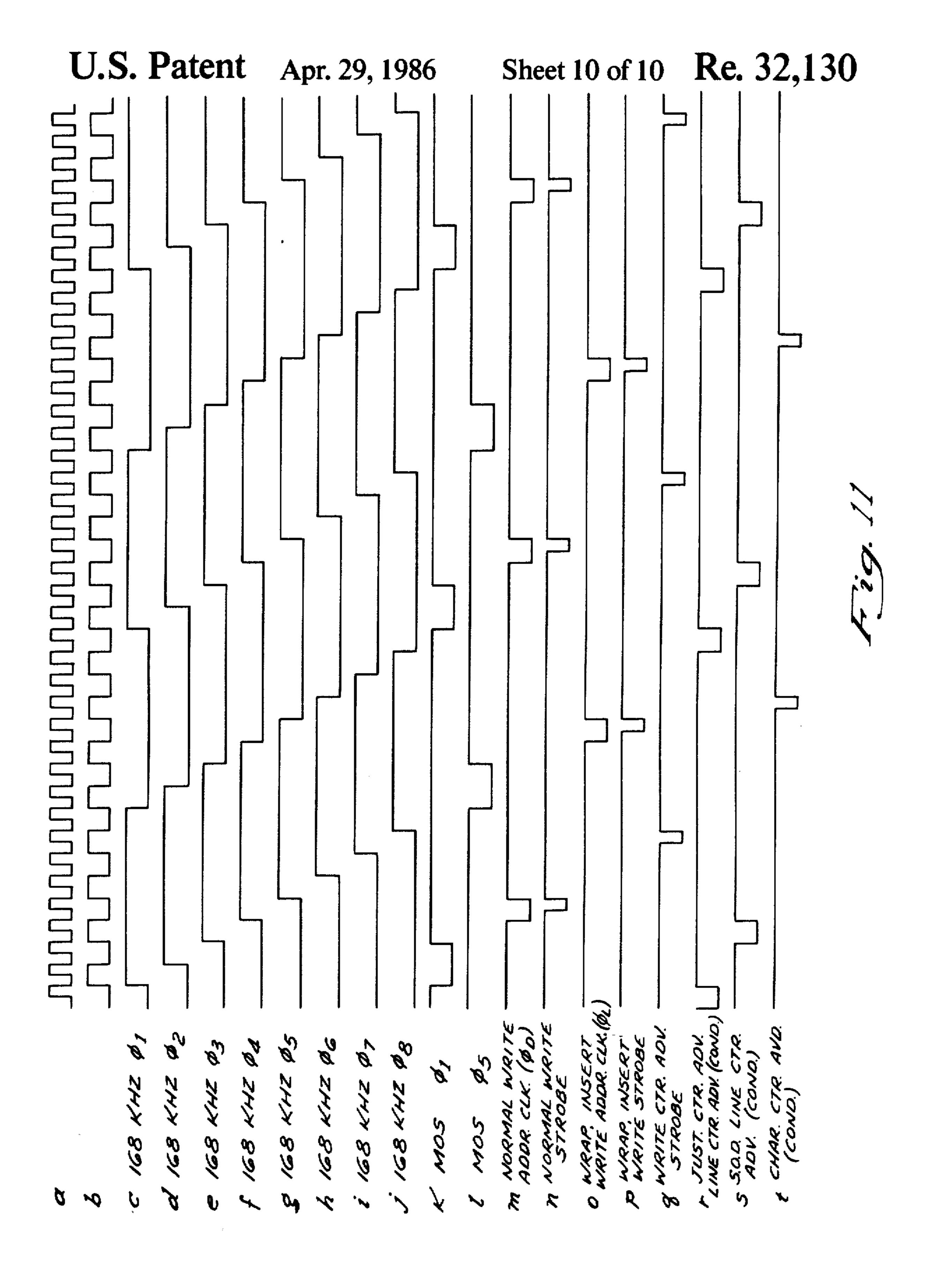

FIG. 11 is a master timing diagram showing the principal timing signals in the present system;

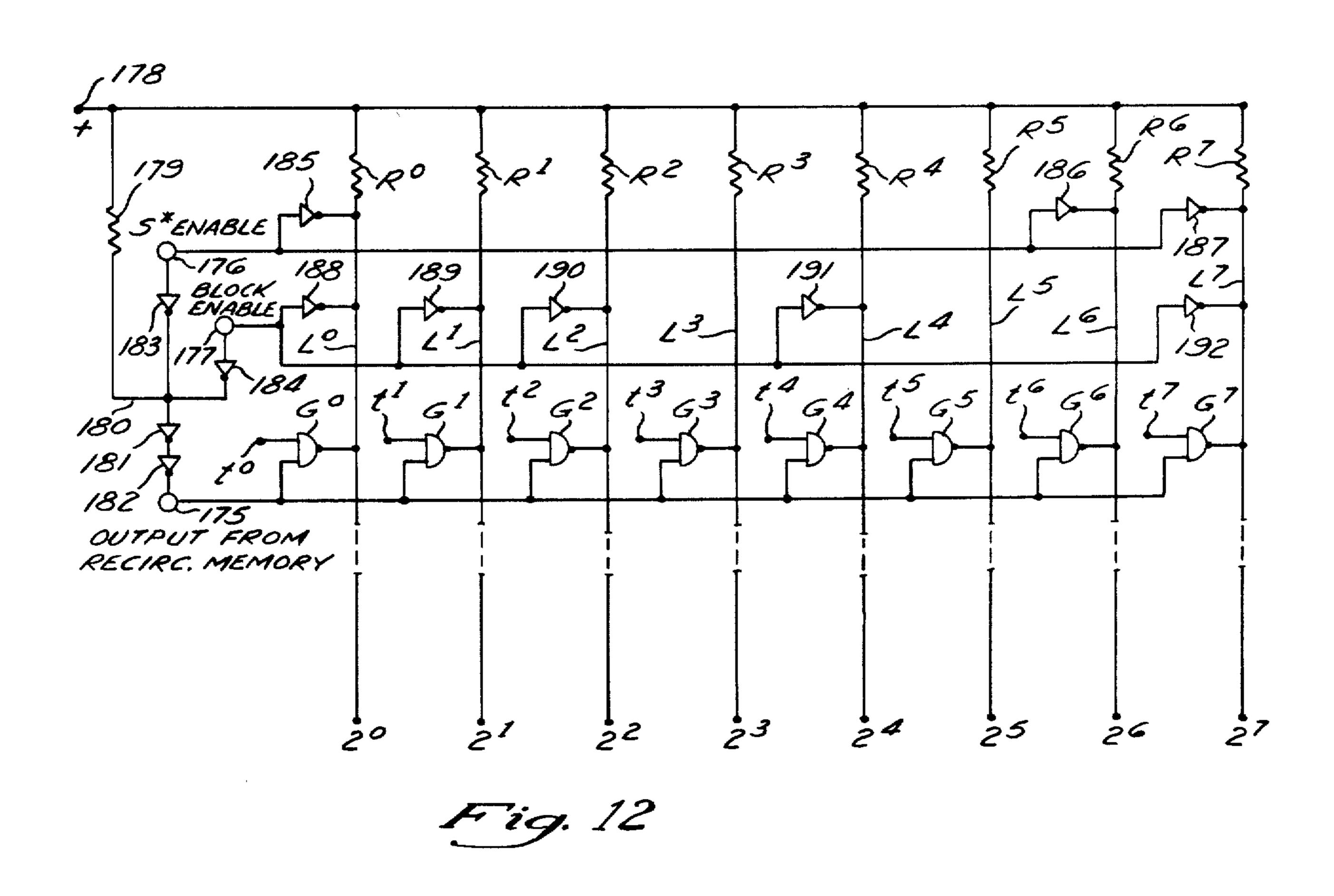

FIG. 12 is a schematic view illustrating a portion of the input multiplexer for the random access memory in the present apparatus; and

FIG. 13 illustrates schematically the circuitry in the present apparatus for connecting the data output of the recirculating memory to an output punch while at the same time deleting from memory the data transmitted to the punch.

#### SYSTEM OUTLINE

Referring to FIG. 1, a complete system embodying the present invention is disclosed as comprising data input devices in the form of a tape reader 20 and a keyboard apparatus 21. The respective outputs of the tape reader and the keyboard apparatus are connected through an interface 22 to the input of a refresh memory 23 under the control of a timing and control logic section 24.

The tape reader 20 reads a conventional 6-track encoded punched tape containing the unedited or unproofed text which is to be edited or corrected by an operator using the apparatus of the present invention. This text may be line-justified, such as newspaper copy provided by a wire service, such as the Associated Press or United Press International, or it may be unjustified, blind keyboarded tape which originates from local copy.

The interface 22 performs two principal functions with respect to the output from the tape reader 20:

(1) it accepts 6-bit characters read by the tape reader and inserts them into the refresh memory 23;

(2) it "strips" (rejects) special codes, such as for line justification spaces, appearing on the input tape, so that these special codes are not transmitted to the refresh memory input.

The keyboard apparatus 21 is manually operated by the person using the present editing console to produce individual binary-coded alphanumeric characters and special function codes. The keyboard apparatus itself encodes the selected alpha-numeric character into a standard 6-bit code, which is then transmitted by the interface 22 to the refresh memory input. Each special function key in the keyboard apparatus operates a switch which produces a D.C. level that the interface 22 then encodes before transmitting to the refresh memory input. The interface 22 contains encoding logic for this purpose, the details of which are omitted from this description as unnecessary to an understanding of the invention.

The refresh memory 23 comprises a relatively large capacity recirculating memory in the form of a dynamic shift register 26 and a random access memory 27 of much smaller capacity. All data entries into the refresh memory 23 are made into the random access memory 27 through an input multiplexer 46 under the control of an address multiplexer 67, and the data thus entered is recirculated back into the recirculating memory 26. The data read-out from the refresh memory takes place at the output of its recirculating memory 26.

The dynamic shift register 26 preferably has metal oxide semiconductor (MOS) storage elements and is capable of storing 2000 or more 8-bit codes. The shift register continuously recirculates to enable characters

to be displayed on the face of a cathode ray tube 28 at a 60 cycle per second refresh rate, as explained hereinafter.

The random access memory 27 is connected through its input multiplexer 46 to the output of the dynamic 5 shift register 26 and it has a storage capacity of 32 8-bit codes. The random access memory 27 together with the shift register 26 enables the unedited text input from the tape reader 20 which is being recirculated in the refresh memory to be edited in accordance with entries from 10 the keyboard apparatus 21, such as deleting a character and/or inserting a character from the keyboard into a selected location in the text. Any one of the 32 storage addresses or character positions in the random access memory 27 can be accessed under the control of the timing and control logic section 24. That is, the editing change is actually made in the random access memory 27 and then the changed text is recirculated back through the shift register 26 via a feedback circuit 29, so that in the following cycle of operation the next displayed on the screen will include any changes made in the preceding cycle of operation. The time rate of recirculation of successive characters in the shift register 26 is not changed by the editing entries made in the random access memory 27.

The output of the shift register 26 is connected to the input of a character generator 30, which translates the encoded text output from the shift register into a serial pulse train output for turning on and off the beam of the cathode ray tube 28. The character generator 30 includes a large capacity read-only memory which may be accessed by a character code to cause a corresponding unique sequence of serial pulses to be generated. The serial pulse output from the character generator 30 is applied through a video amplifier 31 to the control grid of the cathode ray tube to turn the beam on and off in timed relationship to the vertical and horizontal deflection of the beam by deflection circuits 32 controlled by the timing and control logic section 24.

The deflection circuits 32 produce a rectangular raster scan for each individual alphanumeric character to be displayed. Preferably, the raster scan is in the form of a series of contiguous, side by side, upward vertical sweeps. During each vertical sweep the beam may be 45 turned on and off by the video amplifier 31 to produce a vertical, straight line segment, or stroke, of the character. After the completion of each vertical sweep, the beam is blanked during its rapid retrace down to the bottom of the next vertical sweep position to the right in 50 the raster. It will be recognized that, due to intercharacter spacing, the character being "painted" in this manner does not occupy the full horizontal width of the raster in which it will appear, and therefore the beam will be blanked throughout the vertical sweeps occur- 55 ring near the left and right edges of the raster.

The output of the dynamic shift register 26 also is connected to a tape punch interface 33 which, under the control of the timing and control logic section 24, may be actuated from the keyboard apparatus 21 to pass the 60 final edited text from the output of the shift register 26 to a tape punch 34. The punch interface 33 controls the physical operations of the hole-punching elements in the tape punch 34. The edited output tape produced by the tape punch them may be used to provide the input to 65 an automatic typesetter of known design, including, but not limited to, various types of photo-typesetters and computer-operated typesetters.

The sequencing of the events in this system and the operation of the various components so far described are under the control of the timing and control logic section 24. The timing and control logic develops a master clock pulse train which is used to synchronize the rate at which the unedited text is read by the tape reader 20 and uses that clock train to determine the rate at which characters are inserted into the shift register 26, and thus determines the rate at which the tape reader must read in order to input this data. At the output end of the system, the timing and control logic 24 makes the edited text data available to the tape punch 34 at the rate at which the tape punch must accept it. The timing and control logic 24 also controls the ac-15 cessing of data in the random access memory 27 for editing and other changes, and it synchronizes the ana-

log sweep signals provided by the deflection circuits 32

to the beam deflection elements of the cathode ray tube

to the rate at which the digital beam turn-on and turn-

off signals are produced by the signal generator 30, so

that the characters will occur at the correct positions on

the face of the cathode ray tube. The timing and control logic 24 contains all of the "hard-wired" integrated-circuit logic that, in effect, constitutes the algorithms that perform the various different editing functions under the control of the keyboard apparatus 21—i.e., how the random access memory 27 is accessed, how and when data is transferred back and forth, etc. For example, to insert a character from the keyboard apparatus 21 into the random access memory 27, a predetermined sequence of events occurs in accordance with the logic permanently wired into the timing and control logic 24. Thus, for each editing function which the operator may want to perform there is a fixed sequence of a priori instructions wired into the timing and control logic 24 which it gives to the random access memory 27 to insure that the desired editing function is performed.

#### FIG. 2

FIG. 2 shows in greater detail a system whose general outline has been described with reference to FIG. 1. In FIG. 2 the recirculating memory 26 is shown as having two dynamic shift registers 26a and 26b, each having a storage capacity of about 2000 characters. At any given time, not more than half the storage capacity of the total recirculating memory 26 in FIG. 2 is made available to the cathode ray tube 28. For example, in the "roll up" mode, as described hereinafter, the successive lines of text can be caused to move up, one line at a time, off the face of the cathode ray tube, and as one line moves off at the top a new line of text appears at the bottom. This special operational mode is described in detail hereinafter.

Normally, the input multiplexer 46 enables the output of the shift register 26a into the random access memory 27. However, when the keyboard apparatus 21 or any one of several special instruction codes is enabled, the multiplexer 46 disables the normal input from the shift register into the random access memory. The special character decoder 37 is connected to the shift register to detect when any of these special codes (SOM, EOD, Block, Cursor, S (blank space) or S\* (end-of-line) is present at the shift register output and to provide a corresponding enable signal to the input multiplexer 46 via the timing and control logic section 24.

The address multiplexer 67 controls the accessing into the random access memory 27 of the write address

4

register 93, the read address register 200 and the wrap write address register 61 as explained in detail hereinafter. A comparison circuit C, to be described in detail with reference to FIG. 10, compares the counts stored in registers 93 and 200. Normally, these counts are 30 apart, but if they coincide (as a result of a particular editing operation) this fact is detected by comparison circuit C which then provides a control signal to the timing and control logic section 24 so as to interrupt for the remainder of that particular refresh cycle whatever 10 editing operation is then taking place. This is explained in detail with reference to FIG. 10.

An arrangement of line counters 68 and character counters 69 is associated with the timing and control section to keep track of the cursor position, so that when this position is reached during each refresh cycle this fact is recognized to permit the desired editing operation to be performed at this time. characters per second, so compatible with the characteristic compatible with the characters per second, so compatible with the character compatible with the character compatible with the character compatible with the character compatible with the characters per second, so compatible with the characters per second, so compatible with the character compatible

The output of the refresh memory 23 is connected to the input of the character generator 30 through an output multiplexer 420. The character generator itself includes address gating 421, a timing and control section 422, a read-only memory 423 and a shift register 424.

A master oscillator 425 controls the timing of actions in the tape reader and keyboard interface 22, the normal 25 recirculation rate in the refresh memory 23, the timing of the actions controlled by the timing and control section 24, and the operation of the timing and control section 422 in the character generator 30. A clock control 426 and various clock drivers 427 are driven by the 30 timing and control logic to provide various clock signals which control recirculation of the refresh memory 23.

The first step in conditioning the editing system for operation is to enter into the refresh memory 23 three 35 special codes, the "start-of-memory" (SOM) code, the "end-of-display" (EOD) code, and the cursor code. These special codes are inserted automatially as soon as the system is turned on. Following this, blank space codes are inserted into the refresh memory until it is 40 completely filled. The three special codes identify the start of the memory, and when they are detected by the timing and control logic 24 the latter operates the deflection circuits 32 to move the cathode ray beam to the starting position, near the upper left corner of the screen 45 of cathode ray tube 28. Since at this time all of the data entries in the refresh memory 23 which follow these three special codes are blanks, the cathode ray beam will remain blanked throughout its successive raster scans until it has traversed the entire display area of the 50 screen.

#### SYNCHRONIZATION TO POWER SUPPLY

The next step is to synchronize the recirculation rate of the recirculating memory 26 and the scanning rate of 55 the cathode ray tube 28 to the 60 cycle per second power supply, so as to prevent any noticeable flicker of the cathode ray tube display. When the SOD and line counters compare (block 173, FIG. 2) a 60 cycle detect circuit in the timing and control logic 24 (shown separately at block 35 in FIG. 2) looks for a pulse which is generated at the beginning of each cycle of the power supply. Such a pulse must occur sometime within a period of about 16.7 milliseconds after the SOD and line counters compare. The timing and control logic 24 stops the recirculation in the recirculating memory 26 for approximately 1 millisecond at a time, waiting for the 60 cycle sync pulse to appear. The recirculating

6

memory has a minimum recirculation rate of about 1000 character positions per second. If recirculated at a slower rate, it will lose data that has been entered in.

Therefore, in effect, the timing and control logic 24 slows the memory recirculation rate from its normal rate of about 168,000 character positions per second down to 1000 character positions per second until the 60 cycle sync pulse occurs (which must be within 16.7 milliseconds after the SOD and line counters compare). During this waiting period the timing and control logic 24 also slows down the character-generating rate of the cathode ray beam (via the deflection circuits 32) to 1000 characters per second, so that the beam scanning rate is compatible with the character recirculation rate in the recirculating memory 26.

During this initial phase of operation, except for the three special character codes at the beginning, all of the "characters" in the refresh memory 23 are blanks, so that the screen of the cathode ray tube is dark except for the cursor.

When the 60 cycle sync pulse occurs during a particular 1 millisecond interval while the recirculating memory 26 is slowed down by the timing and control logic 24, this will be detected by the detect circuitry 35 associated with the timing and control logic 24. The latter then causes the recirculating memory 26 to resume recirculating at its normal rate and causes the beam deflection circuitry 32 for the cathode ray tube 28 to resume its normal scanning rate, compatible with the normal memory recirculation rate.

At the second line and each subsequent line of characters to be traced on the screen of the cathode ray tube, the circulation of the recirculating memory 26 must be stopped briefly for a predetermined period of time to allow for the retrace of the beam from the end of the preceding line to the beginning of this line. However, this delay interval is only a fraction of a millisecond. This delay is imposed on the recirculating memory 26 by the timing and control logic 24 in response to the detection of a special end of line (S\*) code at the output of the recirculating memory 26. After this S\* code is detected, the timing and control logic 24 stops the recirculating memory 26 for a predetermined interval equal to the time required for the beam to retrace to the beginning of the next line.

After all of the lines of characters have been traced on the screen of the cathode ray tube, the beam must retrace from near the lower right corner of the screen back up to the starting location near the upper left corner. During this retrace interval the timing and control logic 24 again interrupts the circulation in the recirculating memory 26.

The output of the recirculating memory 26 is connected through the timing and control logic 24 to a character counter 36 (FIG. 2), which receives from the recirculating memory an input pulse for each character position read out of the memory (blank space codes at this time). The character counter re-cycles after a predetermined number of such pulses, corresponding to the number of successive character positions which take up a horizontal line on the screen of the cathode ray tube.

A line counter arrangement, designated generally at 68 in FIG. 2, counts the number of times that the character counter re-cycles at this time. This line counter arrangement re-cycles after it has counted a predetermined number of lines and when it does so it provides a control signal to the timing and control logic 24 which then causes the cathode ray beam to retrace up to its

starting position at the upper left corner and also stops the recirculating memory during such retrace of the beam.

After this beam retrace is completed and the SOD line counters compare, the timing and control logic 24 5 slows down the circulation rate of the recirculating memory 26 to about 1000 characters per second and similarly slows down the scanning rate of the cathode ray beam until synchronization with the 60 c.p.s. power supply is again established.

#### TAPE INPUT INTO REFRESH MEMORY

With the synchronization to the power supply now established and with the refresh memory filled with blank space codes, data read by the tape reader may now be entered into memory to replace these blank space codes.

As already mentioned, the special cursor code appears ahead of all the blank space codes in the refresh memory. This cursor code generates a distinctive 20 marker, such as an arrowhead or cross-hairs, on the screen of the cathode ray tube. This marker ("cursor") now appears just below the first character position, at the upper left corner of the screen of the cathode ray tube. The position designated by the cursor determines where the next change may be made in the display on this screen. When the encoded text on the input tape is to be written into the refresh memory 23 and displayed on the screen, the operation is carried out in accordance with the "OVERSTRIKE CHARACTER" mode described in detail hereinafter. Using this mode, one character at a time read in from the input tape replaces a blank code in the refresh memory and on the screen.

The console operator actuates a key in the keyboard apparatus to begin the tape input into memory. The tape reader 20 reads serially from the input tape individual 6-bit codes, which may be character codes or special codes. In the interface 22, some of the special 6-bit codes are deleted and all of the 6-bit character codes and the undeleted special codes are converted into 8-bit codes before going into the refresh memory 23, all as described in detail in the concurrently-filed, copending application of Thomas P. Conroy, Walter G. Fredrickson and Howard A. Thrailkill, Ser. No. 37,192, assigned 45 to the same assignee as the present invention.

Each time the interface 22 has completed the conversion of a 6-bit code from the input tape into the corresponding 8-bit code, it signals the timing and control logic 24 that an 8-bit code is ready to be enabled into the 50 character address in the random access memory 27 where the cursor code is now stored. This 8-bit code now is written into this character address by a "character overstrike" operation, as described hereinafter. This 8-bit code replaces the cursor code in the random access 55 memory and the cursor code is transferred over into the next following address location in the random access memory, replacing the blank code previously stored there. On the screen, the character defined by the newly-entered 8-bit code appears at the position for- 60 merly identified by the cursor, and the cursor itself now appears at the next position to the right.

Similar "character overstrike" operations are repeated in succession, one character at a time, until the original blank codes in the refresh memory have been 65 replaced by character codes and other codes read in from the input tape, so that the text on the tape now is displayed on the screen of the cathode ray tube.

The tape reader 20 reads at a speed of about 180 characters per second, so that at least two and sometimes three characters are written into the refresh memory and entered onto the screen of the cathode ray tube during each 1/60 second refresh cycle of the cathode ray tube.

### MASTER TIMING DIAGRAM-FIG. 11

The master oscillator 425 in FIG. 2 produces a square wave output, as shown at line a of FIG. 11, which is fed into a divide-by-16 Johnson counter having eight series-connected flip-flops which provide the phase displaced square wave clock signals shown at lines c through j of FIG. 11. Each of these signals, φ1 through φ8, has a period of about 6 microseconds.

The MOS  $\phi$ 1 signal on line k is produced by combining the outputs of the first and fifth flip-flops in this counter through logic circuitry such that MOS  $\phi$ 1 is low when  $\phi$ 1 (line c) is high and  $\phi$ 5 (line g) is low. When MOS  $\phi$ 1 is an 8-bit code, which may be a graphic character code or a non-character special code, appears at the output of the shift register 26.

The MOS  $\phi 5$  signal on line l is produced by combining the outputs of the first and fifth flip-flops in the Johnson counter through logic circuitry such that MOS  $\phi 5$  is low when  $\phi 1$  (line c) is low and  $\phi 5$  (line g) is high. When MOS  $\phi 5$  is high the shift register 26 is conditioned to accept data into its input.

Thus, it will be evident that the circulation of data into and out of the shift register 26 is controlled by the MOS  $\phi$ 1 and MOS  $\phi$ 5 clocks so that every 6 microseconds one 8-bit code is read out of the shift register and another 8-bit code is written into the shift register.

The φD normal write address clock (line m of FIG. 11) is produced by combining the fourth and fifth flip-flops in the Johnson counter such that φD is low when φ4 is high and φ5 is low. The φD clock controls the addressing of data into the random access memory 27 by the write address register 93, as explained hereinafter. By comparing lines k and m it will be apparent the φD clock occurs shortly after MOS φ1 in each six microsecond interval.

The normal write strobe pulse (line n), which writes data from the output of the shift register 26 into the random access memory at the address determined by the write address register 93, occurs during the second half of the  $\phi D$  normal write address clock (line m).

The  $\phi$ L wrap insert write address clock (line o) is produced by combining the outputs of the fourth and fifth flip-flops in the Johnson counter such that  $\phi$ L is low when  $\phi$ 4 and  $\phi$ 5 is high. The  $\phi$ L clock controls the addressing of an end-of-line code into the random access memory by the wrap-write address register 61 when the last word in a line runs past the end of the line, as explained in detail in the section which follows, entitled "FULL WORD WRAP-AROUND."

The wrap insert write strobe pulse (line p), which writes the end-of-line code into the random access memory 27 at the address determined by the wrap-write address register 61, occurs during the second half of the  $\phi$ L wrap insert write address clock.

The write counter advance strobe (line q of FIG. 11), which toggles the write address register 93 to count up by one, occurs after the MOS  $\phi$ 1 clock and before the MOS  $\phi$ 5 in each 6-microsecond cycle.

Lines r, s and t show the timing signals which advance various counters in the counter arrangement 69 (FIG. 2) which keeps track of the cursor position.

#### ADDRESSING RANDOM ACCESS MEMORY

FIG. 10 shows in detail a write address register 93 and a read address register 200 through which the random access memory 27 may be accessed via the address 5 multiplexer 67. Multiplexer 67 has five output terminals, designated 20, 21, 22, 23 and 24, respectively, which are connected to corresponding terminals of the random access memory 27 so that the latter's 32 address positions may be accessed individually, depending upon the 10 combination of binary signals on these terminals.

The write address register has five serially-connected flip-flops 202, 203, 204, 205 and 206. The input or trigger terminal T of the first flip-flop 202 is connected to the output of an AND gate 207.

The term AND gate is used herein to designate a gate whose output is near ground potential if and only if all of its inputs have a positive potential. The term OR gate is used to designate a gate that is functionally identical to the AND gate just described, but whose application 20 in the circuit is more easily understood when it is considered as having a positive output if and only if any one or more of its inputs is near ground potential (this being no different in actual performance than the AND gate). The term exclusive OR gate refers to a gate whose 25 output is positive if and only if at least one but less than all of its inputs have a positive potential.

The AND gate 207 has a first input 209 which is normally at high potential. Terminal 209 is suitably connected to line 113 in FIG. 6 such that terminal 209 is 30 at high potential except when the flip-flop 112 in FIG. 6 has been operated, in which case terminal 209 would be grounded. As explained hereinafter, flip-flop 112 is operated during a "delete" operation or a "punch" operation.

A second input terminal of the AND gate 207 is connected to the output of an OR gate 210, which has two inputs 208 and 211. Terminal 211 is connected to receive a clock signal which coincides with the phase 1 clock shown at line c of FIG. 11, except during a retrace of the cathode ray beam. This clock signal on terminal 211 has a frequency of 168 kilocycles per second. During the normal writing in of data from the output of the shift register 26 into the random access memory 27, this clock signal on terminal 211 normally 45 enables the AND gate 207 once during each 6 microseconds.

The second input terminal 208 of the OR gate 210 normally is at high potential so that it does not enable the OR gate. Terminal 208 is suitably connected to the 50 output of AND gate 238 in FIG. 4 so that terminal 208 is at high potential except during a "delete" operation.

Accordingly, when the system is operating in its normal recirculating mode, the AND gate 207 is enabled once each six microseconds, thereby operating 55 the first flip-flop 202 in the write address register 93. Every two operations of flip-flop 202 produces a single operation of flip-flop 203, and so on in the series, so that the register 93 has 25 or 32 possible states.

The flip-flop 202 has its preset terminal P connected 60 to the output of an AND gate 212a which has one input connected to terminal 212 and a second input 212b connected to receive a phase D clock signal (line m of FIG. 11). Terminal 212 receives a positive signal when the start-of-memory (SOM) code appears at the output 65 of the shift register 26 and is detected by the special character decoder 37. The output of AND gate 212a also is connected through an inverter 213 to one input to

an AND gate 214, whose other input is open-circuited and is normally at a high potential. The output of this AND gate is connected to the reset or clear terminal C of each of the remaining flip-flops 203, 204, 205 and 206 in the write address register. With this arrangement, the appearance of the SOM code in conjunction with the phase D signal causes flip-flop 202 to be preset to its "1" output state and causes flip-flops 203-206 to be reset to the "zero" output state, so that register 93 will have a count of 1.

The Q output terminal of flip-flop 202 is connected to one input of an AND gate 215, whose output is connected to the 20 terminal. AND gate 215 has a second input from line 216, which is connected to the output of an OR gate 240. OR gate 240 has one iput from the output of an AND gate 241. AND gate 241 has a first input from the aforementioned terminal 211, which receives a square wave clock signal. AND gate 241 has a second input which receives the phase D clock signal (line m of FIG. 11). Accordingly, during a portion of each 6 microsecond cycle, the AND gate 241 is enabled and a high potential appears on line 216 at the same time that a high potential may or may not appear on the other input to AND gate 215, depending upon the binary condition of the first flip-flop 202 in the write address register 93.

Similarly, the Q output terminals of the remaining flip-flops 203-206 in the write address register are each connected to one input of a corresponding AND gate 217, 218, 219 or 220, whose output is connected to a respective 2<sup>1</sup>, 2<sup>2</sup>, 2<sup>3</sup> or 2<sup>4</sup> terminal. Each AND gate 217, 218, 219 and 220 has a second input connected to line 216.

While the write address register 93 is normally enabled into the random access memory 27 by the operation of AND gate 241, the write address register may also be enabled into the random access memory by the operation of another AND gate 242, whose output is connected to a second input of the OR gate 240. This AND gate 242 has a first input which receives a phase 4 square wave clock signal (line f of FIG. 11) at a predetermined time during each six microsecond cycle. A second input to AND gate 242 is connected to terminal 87 in FIG. 4 to receive a high potential signal during an "insert character" operation.

Referring to FIG. 5, during an "insert character" operation the square wave 1 on line m occurs when AND gate 241 is enabled, whereas the following square wave 2 on line m (which occurs later in the same 6 microsecond cycle of operation) occurs when AND gate 242 is enabled.

The read address register 200 has five serially-connected flip-flops 221, 222, 223, 224 and 225. The input or trigger terminal T of the first flip-flop 221 is connected to the output of an AND gate 226. One input to this AND gate is connected through an inverter 198 to terminal 211. A second input to AND gate 226 is connected to the output terminal 228 of a flip-flop provided by two cross-connected OR gates 229 and 230. OR gate 230 has one input connected to the output of AND gate 212a, so that flip-flop 229, 230 is reset when the SOM code appears at the output of the shift register 226.

Terminal 212 also is connected, via the AND gate 212a, to the reset or clear terminal C of each of the flip-flops 221-225 in the read address register 200, so that this register will be reset to a count of zero in response to the appearance of the SOM code at the output

of the recirculating memory 26, along with the occurrence of the phase D signal.

One input of the OR gate 229 is connected to the output of an AND gate 231 having six inputs. One of these inputs is connected to the output of AND gate 5 207; a second is connected to the  $\overline{Q}$  output terminal of the first flip-flop 202 in the write address register 93; the remaining four inputs are connected to the Q output terminals of flip-flops 203-206 in the write address register. With this arrangement the AND gate 231 will be enabled in response to the 31st enabling of the AND gate 207, thereby operating the flip-flop 229, 230 to enable the AND gate 226.

Such enabling of the AND gate 226 causes the read address register 200 to begin counting up from the count (zero) to which it was reset by the appearance of the last SOM code. Consequently, the read address register 200 is now 30 counts behind the write address register 93, and this 30 count separation between these two registers will be maintained as long as no editing operation is being performed which would change it.

As already explained, an "insert character" operation would increase by one the count in the write address register, so that the count separation between the write and read address registers would become 31 (or 1 in the opposite direction). Also, as explained, a "delete character" or other delete operation would hold back the normal counting operation of the write address register so that the count separation between the write and read address registers would become less than 30. However, in any of these modes of operation, at the beginning of the next display or refresh cycle of the cathode ray tube 28 the appearance of the start-of-memory code would reset the write address register 93 to one and the read address register 200 to zero, and the normal 30 count separation between them would be resumed until " changed by one of the aforementioned editing functions.

In the read address register the Q output terminal of 40 flip-flop 221 is connected to one input of an AND gate 232, whose output is connected to the 20 terminal. AND gate 232 has a second input which is connected to a terminal 233. Similarly, the Q output terminals of flip-flops 222-225 are each connected to one input of a 45 corresponding AND gate 234, 235, 236 or 237, whose output is connected to a respective terminal 21, 22, 23, or 24. Each AND gate 234, 235, 236 or 237 has a second input connected to terminal 233.

Terminal 233 is at high potential except when the 50 write address register 93 or the address-of-laast-space register 61 (FIG. 3) is being enabled into the random access memory 27. Accordingly, for most of each six microsecond cycle of operation, the read address register 200 is enabled into the random access memory. Suitable logic circuitry (not shown) is provided for causing terminal 233 to become grounded when either the write address register 93 or the address-of-last-space register is being enabled into the random access memory.

It will be understood that it is necessary to enable the 60 read address register 200 into the random access memory 27 only during the phase 2 interval (line d of FIG. 11) of the master clock because that is when the shift register 26 is ready to receive input data.

The AND gate 215 and 232, whose outputs are both 65 connected to the 20 terminal, are both open-collector AND gates provided with an external resistor so that together they form a wired OR gate. If the output of

either AND gate 215 or 232 becomes grounded it causes the output of the other to become grounded also.

The same is true of the AND gates 217 and 232 which are connected to the 2<sup>1</sup> terminal, the AND gates 218 and 235 which are connected to the 2<sup>2</sup> terminal, the AND gates 219 and 236, which are connected to the 2<sup>3</sup> terminal, and the AND gates 220 and 237 which are connected to the 2<sup>4</sup> terminal.

FIG. 10 also includes circuitry for comparing, bit for bit, the respective counts in the write and read address registers 93 and 200 to provide a halt indication to the timing and control logic whenever the counts in these registers are the same, at which time the timing and control logic should discontinue any editing operations for the remainder of that refresh cycle.

This circuitry includes an AND gate 250 having six inputs. A first input to this AND gate is from the output of an exclusive OR gate 251. Gate 251 has two inputs which are connected to the Q output terminals of the first flip-flops 202 and 221 in the write and read address registers 93 and 200, respectively.

A second input to the AND gate 250 is from the output of an exclusive OR gate 252 through an inverter 253. Gate 252 has two inputs which are connected to the Q output terminals of the second flip-flops 203 and 222 in the respective registers.

A third input to the AND gate 250 is from the output of an exclusive OR gate 254 through an inverter 255. Gate 254 has two inputs which are connected to the Q output terminals of the third flip-flops 204 and 223 in the write and read registers, respectively.

A fourth input to the AND gate 250 is from the output of an exclusive OR gate 256 through an inverter 257. Gate 256 has two inputs which are connected to the Q output terminals of the fourth flip-flops 205 and 224 in the respective registers.

A fifth input to the AND gate 250 is from the output of an exclusive OR gate 258 through an inverter 259. Gate 258 has two inputs which are connected respectively to the Q output terminals of the fifth flip-flops 206 and 225 in the write and read registers.

The sixth input to the AND gate 250 is from the output of the AND gate 226.

With this arrangement the AND gate 250 is enabled only if there is a bit-by-bit match between the write and read address registers 93 and 200, in which case the editing operation is halted until the next appearance of the SOM code at the output of the recirculating memory 26 reestablishes the normal 30 count separation between the write and read address registers.

## RAM INPUT MULTIPLEXER

FIG. 12 illustrates enough of the circuitry in the input multiplexer 46 for the random access memory 27 to indicate the manner in which the data output from the recirculating memory 26 is disabled from entering the data input of random access memory whenever it is desired to write any of several special codes into the random access memory. That is, any one of these special codes takes precedence over the normal data output from the recirculating memory into the random access memory. FIG. 12 shows the input enable terminals for just two such special codes, the S\* (end-of-line) code and the block code which is to be entered whenever a "define block" operation is to be performed, as explained in detail hereinafter. However, it is to be understood that there are several other special inputs (not shown) any of which can disable the recirculating mem-

ory data output from entry into the random access memory in a manner similar to that now to be described.

Referring to FIG. 12, the input multiplexer has a plurality of input enable terminals, three of which are shown here, namely the terminal 175 for enabling the 5 data output of the recirculating memory 26, terminal 176, which is connected to receive the S\* enable signal into the random access memory from line 45a in FIG. 3, and terminal 177, which receives a block enable signal when the "define block" operational mode is established.

The recirculating memory enable terminal 175 is connected to one input of each of a group of AND gates, G<sup>0</sup>, G<sup>1</sup>, G<sup>2</sup>, G<sup>3</sup>, G<sup>4</sup>, G<sup>5</sup>, G<sup>6</sup>, and G<sup>7</sup>. The output terminals of these AND gates are connected directly to respective lines L<sup>0</sup>, L<sup>1</sup>, L<sup>2</sup>, L<sup>3</sup>, L<sup>4</sup>, L<sup>5</sup>, L<sup>6</sup> and L<sup>7</sup>, which are connected to the data input terminals of random access memory 27 for the  $2^0$ ,  $2^1$ ,  $2^2$ ,  $2^3$ ,  $2^4$ ,  $2^5$ ,  $2^6$ , and  $2^7$ data bits, respectively. A power supply terminal 178 is connected to these lines through respective resistors R<sup>0</sup>, <sup>20</sup> R<sup>1</sup>, R<sup>2</sup>, R<sup>3</sup>, R<sup>4</sup>, R<sup>5</sup>, R<sup>6</sup> and R<sup>7</sup>. The AND gates G<sup>0</sup>-G<sup>7</sup> have respective second input terminals t<sup>0</sup>-t<sup>7</sup>, each of which receives from the output of the recirculating memory 26 a signal corresponding to the binary value of the data bit which corresponds to that AND gate. For example, when the third data bit (i.e., the 2<sup>2</sup> bit) in the 8-bit coded signal at the recirculating memory output is binary 1, a positive signal will be applied to input terminal t<sup>2</sup> for AND gate G<sup>2</sup>, so that this AND gate will 30 be enabled if the signal on terminal 175 also is positive.

However, terminal 175 is grounded if an enable signal is present at either of the other enable input terminals 176, 177 shown in FIG. 12. The power supply terminal 178 is connected to the recirculating memory enable terminal 175 through a resistor 179, line 180 and a pair of series-connected inverters 181 and 182. The S\* enable terminal 176 is connected to line 180 through an inverter 183 which is an open-collector transistor. The block enable terminal 177 is connected to line 180 40 through an open-collector transistor inverter 184. In the absence of a positive signal at either terminal 176 or 177, line 180 will be at substantially the positive potential of power supply terminal 178 and therefore terminal 175 will also be positive. However, a positive signal on 45 either terminal 176 or 177 will be inverted by the respective inverter 183 or 184 to ground line 180, thereby causing terminal 175 to be grounded. As a result, none of the AND gates  $G^0$ - $G^7$  can be enabled in response to the corresponding data bits appearing at the output of 50 the recirculating memory 26.

The S\* enable terminal 176 is connected to lines L<sup>0</sup>, L<sup>6</sup> and L<sup>7</sup> through respective inverters 185, 186 and 187, so that these lines will be grounded in response to the S\* enable signal, while lines L<sup>1</sup>, L<sup>2</sup>, L<sup>3</sup>, L<sup>4</sup> and L<sup>5</sup> will be 55 positive. This particular combination of inputs to the data terminals 20-27 corresponds to the 8-bit code for S\* in the present system.

The block enable terminal 177 is connected to lines L<sup>0</sup>, L<sup>1</sup>, L<sup>2</sup>, L<sup>4</sup> and L<sup>7</sup> through respective inverters 188, 60 189, 190, 191 and 192, so that the binary signal values appearing on terminals  $2^{0}-2^{7}$  will correspond to the 8-bit "block" code when the block enable signal is present at terminal 177.

It will be understood that various other enable inputs 65 6 microsecond clock cycle. (not shown) are connected to lines L<sup>0</sup>-L<sup>7</sup> and to line 180 in the same manner, so that whenever any of these inputs receives a positive enable signal it will:

(1) disable the recirculating memory output from the data input of the random access memory 27; and

(2) enable a corresponding special code into the random access memory.

#### INSERT CHARACTER MODE

FIG. 4 illustrates logic circuitry in the timing and control section 24 which operates when a character is being inserted from the keyboard apparatus 21 into a selected location in a selected line of the text appearing on the screen of the cathode ray tube 28. FIG. 5 illustrates the timing diagrams for this mode of operation of the present apparatus.

Referring to FIG. 4, the "insert character" operation 15 is controlled by an AND gate 70 which is enabled when the following three conditions occur:

(1) The start-of-display (SOD) counter comparison appears at the output of the SOD counter comparator 173, causing a positive signal to appear on input line 71 to the AND gate 70. SOD is detected by the SOD counter comparator to provide this positive signal.

(2) A "data ready" positive signal appears on a second input line 72 to the AND gate 70. This signal is applied to terminal 73 in FIG. 4 from the tape reader and keyboard interface 22 (FIG. 1) whenever any character key in the keyboard apparatus is struck.

(3) A positive signal appears on the third input line 74 to the AND gate 70. This occurs in response to the actuation of an "insert character" key in the keyboard apparatus 21 which, through the interface 22, produces a signal at terminal 75 in FIG. 4 that operates flip-flop 76 to produce a positive signal on line 74.

Thus, regardless of when, in a refresh cycle of the recirculating memory 26 and the cathode ray tube 28, the insert character key and the key for the character to be inserted are depressed, the insert character operation cannot begin until the beginning of the next cycle of operation, when SOD appears, as shown at line c of FIG. 5.

When all three of the foregoing conditions are satisfied the AND gate 70 delivers an "insert strobe enable" signal to its output line 77. This signal enables an OR gate 78 to provide a positive output signal on line 79. This "insert stroke enable" signal is shown at line e of FIG. 5. OR gate 78 is cross-coupled to another OR gate 90 to constitute a flip-flop.

The "insert strobe enable" line 79 is connected to one input terminal of an AND gate 95. A second input, at terminal 97, to AND gate 95 receives a true signal when various counters which keep track of the position of the cursor indicate that the cursor is now present at the output of the recirculating memory 26. The output of AND gate 95 is connected through an inverter 96 and line 83 to one input terminal of an AND gate 80.

The AND gate 80 has a second input which is connected to the Q output line 74 from the insert character flip-flop 76. Consequently, when the insert character signal appears, it causes a positive signal to be applied to this second input of AND gate 80.

The AND gate 80 has a third input which is connected by line 81 to a normal write address clock input terminal 82, which receives a signal that is inverted from the signal shown at line m of FIG. 11, so that terminal 82 is positive for only a small fraction of each

With this arrangement, after the "insert character" key in the keyboard apparatus 21 has been actuated and the insert character flip-flop 76 has been operated (line

b of FIG. 5) and the "insert strobe enable" signal (line e of FIG. 5) has appeared on line 79, the AND gate 80 waits for the cursor to appear at the output of the recirculating memory 26. When the cursor does appear, as shown at line j of FIG. 5, the AND gate 95 is enabled, 5 thereby providing a signal to enable AND gate 80 when the narrow positive normal write address clock pulse appears at terminal 82. AND gate 80 now provides on its output line 86 a signal which is applied through an OR gate 152 to the input multiplexer 46 of the random 10 access memory 27 to enable the selected character from the keyboard apparatus 21 into the random access memory 27. This enable pulse is shown at line i of FIG. 5. It occurs about 1 microsecond after the beginning of the appearance of the cursor code at the output of the circulating memory 26, as shown at line j of FIG. 5. The total interval of the appearance of the cursor (and each other data output from the recirculating memory) lasts about 6 microseconds, as determined by one cycle of the phase 1 clock (line a of FIG. 5).

It will be evident that when the cursor code appears at the output of the recirculating memory 26 this introduces the possibility of two different inputs to the random access memory; one, the cursor itself, and two, the character selected at the keyboard. The present apparatus causes these two entries to be made in a predetermined sequence during the 6-microsecond interval normally allotted to a single data entry into the random access memory.

As described in detail with reference to FIG. 12, the input multiplexer 46 has a second enable circuit which receives the data output from the recirculating memory 26 and which is normally enabled, but is disabled as long as there is any other enable input signal to the multiplexer. Thus, as shown in the line k of FIG. 5, the recirculating memory input to the random access memory is disabled while the keyboard input (line i) is enabled. In the present situation, therefore, the cursor code appearing at the output of the recirculating memory 26 now 40 cannot be written into the random access memory 27.

As described in detail with reference to FIG. 10, the write address register 93 for the random access memory 27 normally is toggled once each 6-microsecond cycle of the phase 1 clock, as shown at line n of FIG. 5. How- 45 ever, in the "insert character" mode now under consideration the write address register 93 is toggled twice during the 6-microsecond cycle when the cursor code is at the output of the recirculating memory 26. The first of these two times it is toggled, as shown at 1 in line n 50 of FIG. 5, the character corresponding to the key which has been actuated in the keyboard apparatus 21 is written into the next address in the random access memory 27. The second of these times the write address register is toggled, as shown at 2 in line n of FIG. 5, the 55 cursor code is written into the following address in the random access memory.

This second toggling of the write address register 93 occurs in response to an output signal from an AND gate 238 in FIG. 4, whose output terminal is connected 60 to the write address register input terminal 208 in FIG. 10.

The AND gate 238 has a first input terminal connected to the previously-mentioned terminal 97 so as to receive an enabling signal when the cursor is present. 65

A second input to AND gate 238 is connected to terminal 239, which receives a "write counter advance strobe" timing pulse, as shown at line f of FIG. 5.

A third input to AND gate 238 is provided from the output of OR gate 90 in the "insert strobe enable" flip-flop 78, 90 through OR gate 91 and line 92. This third input receives an enable signal in response to the operation of this flip-flop. Consequently, when the next "write counter advance strobe" pulse occurs (line f of FIG. 5), the AND gate 238 is enable and it produces the "write address counter advance" pulse (line g) which is applied to the write address register 93 at its input terminal 208 to operate this register the second time during this 6-microsecond cycle of the phase 1 clock.

As already described in connection with FIG. 10, the write address register 93 normally is enabled into the random access memory 27 once each 6-microsecond cycle by the phase D clock, which enables AND gate 241. This normal enabling is indicated by the square wave pulses 1 in line m of FIG. 5.

Also, as already mentioned, in the "insert character" mode, during a 6-microsecond cycle the address register 93 is enabled a second time into the random access memory, as indicated by pulse 2 on line m of FIG. 5. This occurs in response to the enabling of an AND gate 88 in FIG. 4. The output of this AND gate is connected through an inverter 89 to line 87 which, as shown in FIG. 10, provides one input to AND gate 242. A second input to AND gate 242 is provided by the phase 4 clock pulse which, as shown in FIG. 11, occurs after the pase D clock pulse. When this phase 4 clock pulse occurs, the write address register 93 is enabled a second time into the random access memory.

The AND gate 88 has a first input connected to the previously-mentioned line 92 and a second input connected to the previously-mentioned terminal 97. Consequently, during the six-microsecond interval when the cursor is present at the output of the recirculating memory 26, following the operation of the "insert strobe enable flip flop 79, 90, the AND gate 88 will be enabled and, through the inverter 89, it provides on line 87 a phase 2 clock write enable signal, as shown at line 0 of FIG. 5.

The concurrence of enabling signals on line 87 and the phase 4 input operates the AND gate 242 in FIG. 10 to enable the write address register 93 into the random access memory 27 a second time in the 6-microsecond cycle when the cursor code is present at the output of the recirculating memory 26.

After the "insert character" operation has been completed, a signal appears at terminal 90r which resets the flip-flop 78, 90.

#### **INSERT CURSOR**

The cursor may be inserted into the refresh memory 23, and therefore into the text display on the screen of the cathode ray tube 28, by an operation generally similar to the just-described "insert character" operation.

Referring to FIG. 4, a pair of cross-connected OR gates 78c and 90c constitute a flip-flop. One input 77c to this flip-flop receives an enabling signal when one of several possible "insert cursor" operations is to be performed, such as when moving the cursor from one line of text to the next line above or below. Such a cursor insertion operation is initiated from the keyboard apparatus 21. This signal on terminal 77c operates this flip-flop 78c, 90c, to produce a positive signal on line 79c, which provides one input to an AND gate 80c.

A second input to AND gate 80c is from terminal 98c, to which is applied a clock signal which occurs

once each 6 microsecond cycle of the phase 1 signal data in

shown at line a of FIG. 5.

A third input to AND gate 80c is from the "cursor present" terminal 97.

With this arrangement, when all three inputs to AND 5 gate 80c are positive, it provides an output signal on line 86c which is applied through an OR gate 152c to the input multiplexer 46 of the random access memory to enable the cursor code into the random access memory.

The operation of the flip-flop 78c, 90c also causes the 10 AND gates 238 and 88 to be enabled, so that the write address register 93 is toggled a second time during a single six-microsecond cycle of the phase 1 clock, and the write address register 93 is enabled a second time into the random access memory. These actions take 15 place in response to a ground signal appearing at the output of OR gate 90c of the flip-flop, which causes a positive signal to appear on the output line 92 from OR gate 91.

After the "insert cursor" operation is completed, a 20 signal appears at terminal 90r which resets the flip-flops 78c, 90c.

#### **OVERSTRIKE CHARACTER**

In this operational mode, a selected character in the 25 text appearing on the cathode ray tube 28 is replaced by a character selected at the keyboard apparatus 21. On the cathode ray tube screen, the cursor is at the location of the displayed character which is to be deleted, and it immediately precedes this character in the recirculating 30 memory 26. The sequence of operation in this mode includes the following steps:

- (1) the cursor code is replaced in the refresh memory 23 by the selected keyboard character, and then

- (2) the displayed character which is to be deleted is 35 replaced in the fresh memory by the cursor code, so that now the cursor identifies the next character in the display and immediately precedes it in the recirculating memory.

Referring to FIG. 4 and the timing diagram shown in 40 FIG. 9, step (1) above is controlled by an AND gate 150 having its output connected by line 151 and OR gate 152 to the input multiplexer 46 for the random access memory 27. This AND gate 150 has a first input terminal connected to the normal write address clock input 45 82 to receive a clock signal, as shown at line f of FIG. 9, which is inverted from the phase D signal shown at line m of FIG. 11. A second input terminal of AND gate 150 is connected to the data ready input 73 (line c of of FIG. 9). The third input terminal of AND gate 150 is 50 connected to the  $\overline{Q}$  output terminal of a flip-flop 153. The input terminal T of this flip-flop is normally at ground potential, and it receives a positive high potential from terminal 154 to operate the flip-flop when the cursor code appears at the output of the recirculating 55 memory 26, as shown at line d of FIG. 9.

As already stated, this appearance of the cursor code lasts 6 microseconds (one full cycle of the master clock pulse source indicated at line a of FIG. 9). The data ready signal at terminal 73 appears after the operator of 60 the keyboard apparatus 21 strikes the key for the character which is to be entered.

Consequently, after the data ready signal (line c of FIG. 9) has appeared and the cursor code (line d) has appeared, the next normal write address clock pulse 65 (line f) causes the AND gate 150 to be enabled, producing an output signal on line 151 which enables OR gate 152, causing the input multiplexer 46 to apply to the

data input of the random access memory 27 the character code for the selected character key in the keyboard apparatus 21, as shown by the pulse on line e of FIG. 9. At the same time, the output from the recirculating memory 26 is disabled from the data input of the random access memory 27, as shown by the first negative-going pulse 1 on line i of FIG. 9. Consequently, the cursor code appearing at the output of the recirculating memory 26 is prevented from being written into the random access memory 27, while the character code for

18

The data ready signal appearing at terminal 73 (line c of FIG. 9) is reset to ground in response to the negative-going trailing edge of the enable signal output from AND gate 150 (line e of FIG. 9). If desired, there may be a time delay between the reset of the data ready terminal 73 and the trailing edge of this enable signal.

the selected key is written into the random access mem-

ory 27 to replace the cursor code.

This reset of the data ready signal at terminal 73 causes a signal to be applied via an inverter 155 to one input terminal of an AND gate 156. A second input terminal of this AND gate is connected to the  $\overline{Q}$  output terminal of flip-flop 153, which is still positive. Additional inputs to this AND gate are provided by a clock pulse source 157 and a 1.5 mc. pulse source 158. With this arrangement, when the data ready signal at terminal 73 is reset, the AND gate 156 is enabled.

The output signal from AND gate 156 is applied via line 159 to one input to an OR gate 160 which is interconnected with a second OR gate 161 to provide a flip-flop which now provides a signal at terminal 162 which causes the input multiplexer 46 to enable the cursor code into the data input of the random access memory 26, as shown by the positive square wave signal on line g of FIG. 9. In so doing the input multiplexer 46 also disables the recirculating memory output from the data input of the random access memory, as shown by the second negative square wave 2 on line i of FIG. 9, so that the character code appearing at the output of the recirculating memory 26 during this 6-microsecond cycle of the master clock pulse source (line a of FIG. 9) is not written into the random access memory but instead is replaced by the cursor code.

The enabling of the AND gate 156 also causes the flip-flop 153 to be reset by the positive signal applied from the AND gate output to its P terminal.

The flip-flop 161, 162 is reset by a clock pulse applied to terminal 163 toward the end of each 6 microsecond cycle of the master clock pulse source.

#### DELETE CHARACTER

The delete character mode is initiated by depressing a "delete character" key in the keyboard apparatus 21, following which the circuitry now to be described causes a deletion from the refresh memory of the character displayed on the screen of the cathode ray tube 28 where the cursor is located.

Referring to FIG. 6, the logic circuitry for the delete character mode includes an AND gate 100 having a first input terminal connected to a 6 cycle per second pulse source and a second input terminal 128 connected to receive a signal when the "delete character" key is depressed. When these two inputs are both high (i.e., above ground) the output of the AND gate is low (i.e., ground), and an inverter 99 converts this output signal from the AND gate to a high input signal on the input terminal T of a flip-flop 101.

Normally (i.e., before this input signal occurs as a result of depressing the "delete character" key) the input terminal T of flip-flop 101 is grounded, its Q output terminal is at ground, and its  $\overline{Q}$  output terminal is at the high potential of the D terminal. When the high input signal occurs, as described, terminal T goes high, the Q output terminal goes to the high potential of the D terminal, and  $\overline{Q}$  output terminal goes to ground.

The line 102 connected to the Q output terminal passes this negative-going signal to an input to an OR <sup>10</sup> gate 103 which now produces a high potential on its output line 104, which provides one input to an AND gate 105.

This AND gate has a second input on line 106, which is normally at ground potential until the cursor code 15 appears at the output of the recirculating memory 26, at which time the potential on line 106 goes high.

A third input line 107 to the AND gate 105 is connected to the Q output terminal of a flip-flop 108.

The Q output terminal of flip-flop 101 is connected by a line 109 and an OR gate 110 to the D terminal of flip-flop 108. The T input terminal of flip-flop 108 is connected to an output terminal of the special character decoder 37 (FIG. 3) such that terminal T is at a high potential until the SOD counter comparison appears at the output of the counter comparator 173, at which time the potential at terminal T drops to ground.

A "master clear" signal applied to the reset terminal R of flip-flop 108 normally establishes the following conditions in flip-flop 108 before the SOD comparison appears and before the delete character key is struck: with the T input terminal high and the D terminal at ground, output terminal  $\overline{Q}$  is high and output terminal Q is grounded.

When the "delete character" key is struck (and before the SOD comparison appears at the output of the counter comparator 173) terminal D goes high. Then, when SOD appears the input terminal T goes to ground for the one-half microsecond interval while SOD is present and then at the end of this interval it goes high again. The positive-going trailing edge of this start-of-display pulse operates the flip-flop 108, so that terminal Q goes high, so that now a high potential appears on line 107 at the third input to AND gate 105.

From the foregoing it will be understood that after the "delete character" key has been struck and SOD has appeared at the output of the counter comparator 173, when the cursor code next appears at the output of the recirculating memory all three inputs to the AND gate 50 105 will be positive. The output of AND gate 105 now goes from high positive down to ground and an OR gate 111 connected to this output now produces a high output signal which it applies to the input terminal T of a master delete flip-flop 112.

Normally (i.e., before receiving this input signal) flip-flop 112 has its  $\overline{Q}$  output terminal at the high potential applied to its D terminal and its Q output terminal at ground potential. The high positive input signal applied to terminal T, as described, operates flip-flop 112 to cause its O output terminal to go high and its  $\overline{Q}$  output terminal to go to ground.

The negative-going signal on line 113 connected to the  $\overline{Q}$  output terminal of flip-flop 112 disables the write address register 93 (FIG. 2) for the random access mem- 65 ory 27. Consequently, the up counter in this register is prevented from counting the write strobe pulse in the next cycle of operation.

This operation of flip-flop 112 causes the output line 114 connected to its Q output terminal to go from ground to high, thereby enabling an AND gate 115 whose output 116 is connected to the "cursor enable" terminal of the input multiplexer 46 for the random access memory 27. Consequently, the cursor code will be enabled into the data input of the random access memory 27.

The AND gate 115 has two additional input lines 117 and 118 which are normally at high potential, so that when the potential on line 114 also goes high the AND gate 115 will be enabled. Line 117 is at high potential except when a key in the keyboard apparatus 21 is operated for moving the cursor. Line 118 is at high potential except during a "delete block operation, as described hereinafter.

The input multiplexer 46 normally connects the output of the recirculating memory 26 to the data input of the random access memory 27, but this normal enable circuitry in multiplexer 46 is disabled when the AND gate 115 is enabled, as described.

The foregoing operating sequence is illustrated schematically by the timing diagrams of FIG. 7. Line a of this figure shows the MOS clock 1 square wave pulses which control the recirculating memory 26. Each complete cycle of this clock pulse source takes 6 microseconds, during which interval a particular character address appears at the output of the recirculating memory 26.

Assuming that the "delete character" key in the key-board apparatus 21 has been struck so that the delete character flip-flop 101 has been operated, as indicated at line b, and that SOD has appeared at the output of the recirculating memory, when the cursor code (line c) appears at the output of the recirculating memory the flip-flop 112 for disabling the write address register 93 for the random access memory 27 is operated, as indicated at line d.

As a result, when the positive-rise leading edge a-1 of the next clock pulse (line a) occurs, the write address register 93 (line g) is disabled. Normally, this register is toggled by the rising leading edge of each of these clock pulses so as to count up "one" for each such pulse.

During the 6 microsecond clock pulse interval immediately preceding this rising edge a-1 (while the cursor code is present at the output of the recirculating memory 26, as indicated at line c), the enable circuitry in the input multiplexer 46 which normally enables the output of the recirculating memory 26 into the data input of the random access memory 27 is disabled, as indicated at line k. At the same time the cursor enable circuitry in this input multiplexer is enabled, as indicated at line h. These actions take place before the write strobe pulse (line i) occurs in this clock pulse cycle (line a).

Then, in the next clock pulse cycle this same condition prevails until after the write strobe pulse in that cycle occurs. Consequently, the cursor code will be written again into the random access memory 27, but at the same address where it was written in the preceding 6 microsecond interval because the up counter in the write address register 93 is disabled now. Consequently, in this cycle the character which immediately followed the cursor code at the output of the recirculating memory 26 is prevented from being written into the random access memory 27, so that at the end of this 6 microsecond interval it disappears from the refresh memory 23 as a whole.

Toward the end of this cycle of the MOS clock 1 signal (line a) the flop-flops 101 and 112 are reset automatically when a phase 4 clock pulse (line e) occurs. This restores the system to normal operation. However, if the keyboard operator continues to hold the "delete 5 character" key depressed for more than one second, the following characters will be deleted one at a time at a rate of about six per second until he releases the key. For this purpose a time delay circuit (not shown) is associated with the "delete character" input 128 to the 10 AND gate 100 in FIG. 6 to provide a one second time delay before the flip-flop 101 can be operated after it has been reset in the manner now to be described.

Referring again to FIG. 6, the reset terminals R of both flip-flops 101 and 112 are connected to the output 15 of an AND gate 119 through an OR gate 120 and additional circuitry to be described.

One input line 122 to the AND gate 119 is connected through an inverter 123 to the line 106 which is at ground potential as long as the cursor code is not present at the output of the recirculating memory 26. This input line 122 normally is at high potential and it goes to ground when the cursor code appears at the recirculating memory output. Then, in the next cycle of the master clock pulse source (line a of FIG. 7) when the cursor 25 code is no longer present at the output of the recirculating memory 26, the potential at line 122 again goes high and it remains in that state until the next appearance of the cursor code at the output of the recirculating memory.

A second input line 124 to the AND gate 119 is connected through an OR gate 127 to the "delete character" input terminal 128, so that this line becomes positive when the "delete character" key in the keyboard apparatus 21 is depressed.

A third input line 125 to the AND gate is connected to line 107 and it goes positive following the appearance of SOD at the output of the counter comparator 173.

A fourth input line 126 is connected to a phase N clock pulse source (line e of FIG. 7) which produces a 40 positive pulse toward the end of each 6 microsecond cycle interval of the master clock pulses (line a of FIG. 7)

With this arrangement, with the "delete character" key depressed and after the "start-of-display" code has 45 appeared at the output of the recirculating memory 26, until the cursor code appears at the output of the recirculating memory the AND gate 119 will produce a ground output signal for resetting the flip-flops 112 and 101 each time the phase N clock pulse occurs. However, in the clock cycle when the cursor code is present at the output of the recirculating memory the input line 122 to AND gate 119 will be at ground, preventing the reset from occurring. Then, in the next cycle and as long as the "delete character" key remains operated, the 55 AND gate 119 will provide a reset pulse each time the phase N clock pulse occurs.

The output of AND gate 119 is connected to one input terminal of an OR gate 120. The output of this OR gate is connected through an inverter 146 to one input 60 terminal of an OR gate 147. The output of OR gate 147 is connected to one input terminal of an AND gate 148, whose output is connected to the reset terminals R of both flip-flops 112 and 101. AND gate 148 has a second input on line 149 which receives the phase N clock 65 signal.

With this arrangement, when OR gate 120 receives a ground input signal from AND gate 119, a positive

signal is applied to the first input terminal of AND gate 148. Then, when the next positive phase N clock signal appears on line 149, AND gate 148 is enabled and it resets both flip-flops 112 and 101.

When a delete character operation is performed, as just described, the word in which the deletion is made is automatically closed up so that an undesired space will not appear where the character was deleted. This automatic closing up takes place because the write address register 93 is disabled during the delete character operation, so that all of the characters which follow the deleted character will move to the next address, upstream with respect to the flow of data, in the random access memory.

Similarly, when a "delete line," "delete block" or "delete paragraph" operation is performed, as now to be described, the gap which would be caused by such deletion is immediately closed up automatically.

#### **DELETE LINE**

The keyboard apparatus 21 has a "delete line" key which may be operated to delete all of the line beginning at the cursor position.

However, due to the limited (32 character position)

25 capacity of the random access memory 27, no more

than 30 characters can be deleted in a single refresh

cycle of the cathode ray tube. Normally, the write address register 93 for the random access memory is 30

character addresses ahead of the read address register.

30 During the delete line mode, the write address register

is disabled from counting up while the read address

register is not so disabled, and this operation must be

stopped when the read address register has caught up to

the write address register. Under this condition the

35 delete line operation is terminated for that refresh cycle

and resumed the next refresh cycle.