[45] Reissued

May 8, 1984

| [54]    | AUTOMATIC CONTROL SYSTEM FOR                                  | 4,269,281 5/1981 Schneider et al 180/70 R             |

|---------|---------------------------------------------------------------|-------------------------------------------------------|

|         | METHOD AND APPARATUS FOR<br>CHECKING DEVICES OF AN AUTOMOTIVE | FOREIGN PATENT DOCUMENTS                              |

|         | VEHICLE IN USE WITH A                                         | 7775 7/1979 European Pat. Off                         |

|         |                                                               | 6033 12/1979 European Pat. Off                        |

|         | MICROCOMPUTER                                                 | 8495 3/1980 European Pat. Off                         |

| [75]    | Inventors: Akio Hosaka, Yokohama; Kazuhiro                    | 13103 7/1980 European Pat. Off                        |

| [15]    | Higashiyama, Atsugi, both of Japan                            | 2338122 2/1975 Fed. Rep. of Germany.                  |

|         | Tilgashiyama, ricoasi, cour or carpain                        | 2363801 6/1975 Fed. Rep. of Germany.                  |

| [73]    | Assignee: Nissan Motor Company, Limited,                      | 2756719 7/1978 Fed. Rep. of Germany.                  |

| F. ~ 1  | Yokohama, Japan                                               | 2726115 12/1978 Fed. Rep. of Germany.                 |

|         | ·                                                             | 2323028 4/1977 France.                                |

| [21]    | Appl. No.: 424,628                                            | 2385902 10/1978 France.                               |

|         |                                                               | 2415711 8/1979 France.                                |

| [22]    | Filed: Sep. 29, 1982                                          | 2417689 9/1979 France.                                |

|         |                                                               | 2453443 10/1980 France.                               |

|         | Related U.S. Patent Documents                                 | 2456648 12/1980 France.                               |

|         |                                                               | 1437217 5/1976 United Kingdom .                       |

| _       | sue of:                                                       | 1459851 12/1976 United Kingdom.                       |

| [64]    | Patent No.: 4,339,801                                         | 1480520 7/1977 United Kingdom.                        |

|         | Issued: Jul. 13, 1982                                         | 1504096 3/1978 United Kingdom.                        |

|         | Appl. No.: 132,647                                            | 2007397 5/1979 United Kingdom.                        |

|         | Filed: Mar. 21, 1980                                          |                                                       |

| [30]    | Foreign Application Priority Data                             | OTHER PUBLICATIONS                                    |

|         |                                                               | "Multiplexage pour Cablage Automobile," by J. R.      |

| Ma      | ır. 23, 1979 [JP] Japan 54-33880                              | Massoubre et al (1980), pp. 39-51.                    |

| [e1]    | COSE 11/00                                                    | "Antiblockiersystem (ABS) fur Personenkraftwagen",    |

| [51]    | Int. Cl. <sup>3</sup>                                         | Bosch Technische Berichte by Von Heinz Leiber, et al  |

| [52]    | U.S. Cl. 364/431.04; 123/417;                                 |                                                       |

|         | 123/480; 364/424; 371/16; 371/20; 371/21                      | (1980), pp. 65–94.                                    |

| [58]    | Field of Search                                               | "Microprocessor Transmission Controls" from 28th      |

|         | 371/16, 20, 21; 123/417, 480                                  | IEEE Vehicular Technology Conference, by Dr. W. R.    |

| £ = < 1 | D.C C!4                                                       | Hill (1978), pp. 361-365.                             |

| [56]    | References Cited                                              | "Automobile Electronics for 1980", Product Engineer-  |

|         | U.S. PATENT DOCUMENTS                                         | ing, vol. 50, No. 9 (1979), pp. 69-71.                |

|         |                                                               | "Mikrocomputer in Komplexen Automobilanwendun-        |

|         | 3,838,264 9/1974 Maker 371/21                                 | MIKIOCOMPULEI III Kompieken Muten Huse-1078 pp        |

|         | 4,034,194 7/1977 Thomas et al                                 | gen", Automobil-Elektronik by Horst Huse-1978, pp.    |

|         | 4,044,634 8/1977 Florus et al                                 | 78–82.                                                |

|         | 4,072,850 2/1978 McGlynn                                      | "Management von Mikroprozessor-Schnittstellen",       |

|         | 4,108,358 8/1978 Niemasyk et al                               | Automobil-Elektronik, by David K. Long-1978, pp.      |

|         | 4,122,996 10/1978 Wilczek                                     | 69-72.                                                |

|         | 4,127,768 11/1978 Negi et al                                  |                                                       |

|         | 4,138,723 2/1979 Nehmer et al                                 | Primary Examiner—Charles E. Atkinson                  |

|         | 4,150,428 4/1979 Inrig et al                                  | Attorney, Agent, or Firm-Schwartz, Jeffery, Schwaab,  |

|         | 4,158,431 6/1979 Van Bavel et al                              | Mack, Blumenthal & Koch                               |

|         | 4,191,996 3/1980 Chesley                                      |                                                       |

|         | 4,208,929 6/1980 Heino et al                                  | [57] ABSTRACT                                         |

|         | 4,245,314 1/1981 Henrich et al                                | An automatic control system for an automotive vehicle |

|         | 4,245,315 1/1981 Barman et al                                 | in use with a microcomputer has a checking system for |

|         | 4,255,789 3/1981 Hartford et al                               | III mon attent to introduce have and a sense          |

checking an input unit, a ROM, a RAM and an output unit of the microcomputer. The checking system comprises a means which stores various checking programs to be executed for checking above-mentioned elements of the microcomputer. The checking system effectively operates to check the elements without causing expanding of duration of execution of the checking programs.

9 Claims, 19 Drawing Figures

.

•

FIG. 2 FIG. 3

May 8, 1984

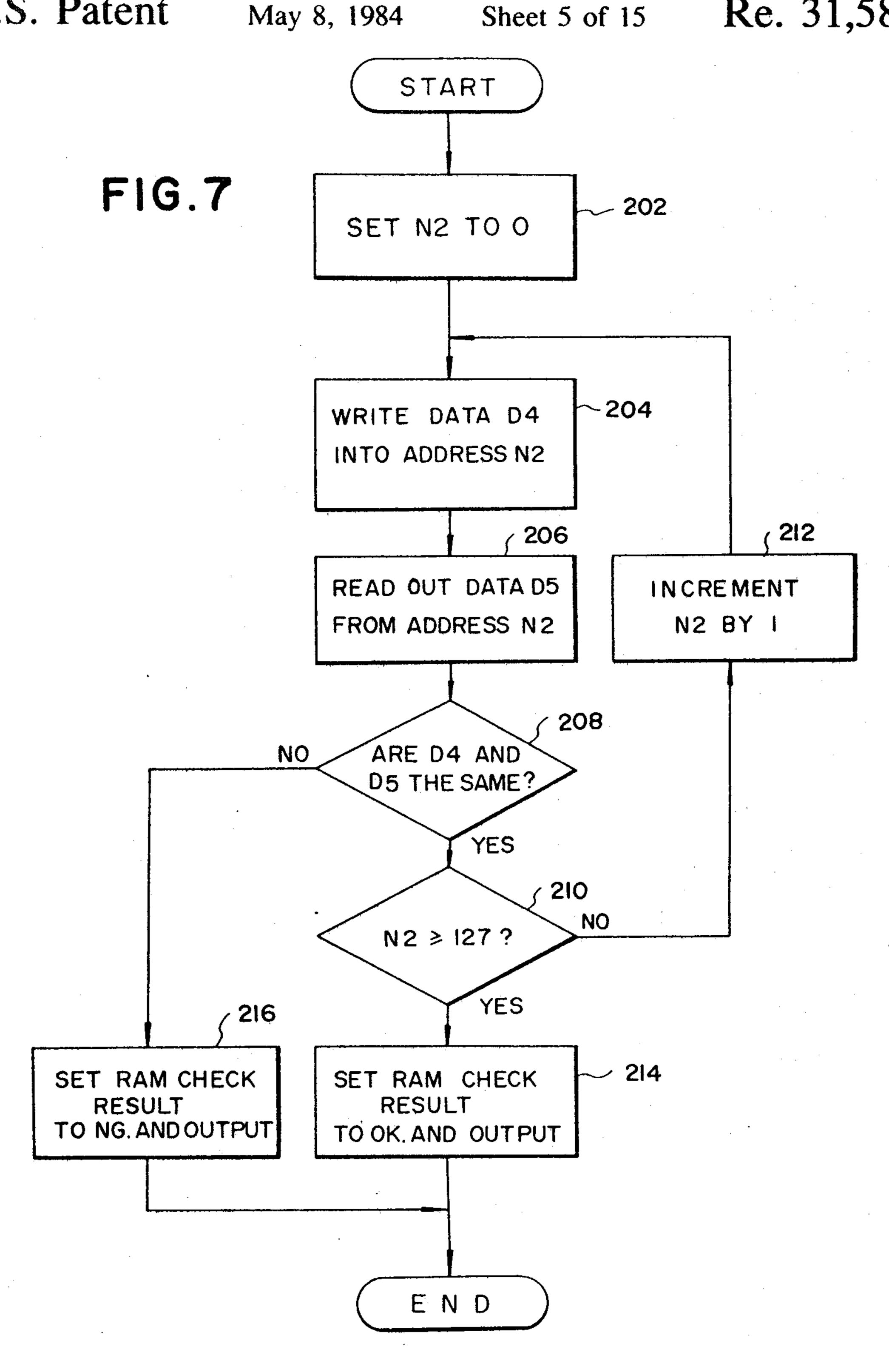

U.S. Patent May 8, 1984 Re. 31,582 Sheet 4 of 15 START FIG.6 SET NI TO 0 READ OUT DATA DI FROM MEMORY ADD- 104 RESS AI WHICH IS DETERMINED BY DATA D2 IN ADDRESS 1000-NI 106 112 READ OUT DATA D3 INCREMENT FROM ADDRESS 1100-NI NIBYI **80**l NO ARE DI AND D3 THE SAME YES 110 NO N1≥9? YES 116 SET INPUT CHECK SET INPUT CHECK **— 114** RESULT DATA RESULT DATA TO NG AND OUTPUT. TO OK AND OUTPUT.

END

WAIT PERIOD 13

END

FIG.12

May 8, 1984

FIG. 18A

FIG.18B

## AUTOMATIC CONTROL SYSTEM FOR METHOD AND APPARATUS FOR CHECKING DEVICES OF AN AUTOMOTIVE VEHICLE IN USE WITH A MICROCOMPUTER

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

## **BACKGROUND OF THE INVENTION**

### 1. Field of the Invention

The present invention relates generally to a control system including a digital computer or microcomputer system being capable of being mounted on an automotive vehicle for controlling various vehicle devices. More particularly, the present invention relates to a method and means for checking elements of the control system, after the control system has been assembled.

#### 2. Background of the Invention

As is known to those skilled in the art, in recent years, it has become quite popular to control various vehicle systems automatically by using a control system including a microcomputer unit. The control system is employed in an automotive vehicle for automatically controlling driving of the internal combustion engine, ignition system, exhaust gas recirculation system, fuel injection system and so on. The control system may be further utilized for controlling various vehicle indicators, 30 such as, for example, a navigation meter. Further, the control system is also used for controlling various vehicle equipment, such as an automatic tuning device for a radio receiver of vehicle mounted type.

The control system generally comprises a central 35 processing unit (CPU), an input unit, an output unit and one or more memory units including read-out memory (ROM) and random access memory (RAM). These elements form a microcomputer for processing data inputted thereinto for outputting control signals to the 40 various vehicle devices. For performing control operation, control programs [which] are generally stored in the ROM and read out and executed in the CPU with respect to input data inputted through the input unit. Result of execution of the control program is outputted 45 to vehicle devices to be controlled through an output unit. In order to satisfactorily control the vehicle devices, correct and accurate function of each element will naturally be required:

the input unit should input signals and read out accu- 50 rately identical data contained in the input signals;

the RAM should be capable of storing data accurately identical to the data inputted therein and reading out the stored data which should be identical to the data inputted;

the RAM should be capable of keeping storage as preset therein and being read out as is; and

in respect to the output unit, it should be capable of inputting output data inputted from the CPU and outputting the data as is.

For the purpose of checking the control system and for preventing the vehicle from serious trouble caused thereon due to error of the control system and from accidents, checking of functions of the elements of the control system will be required.

The control circuit of the control system determines a change in output signals in response to an input signal or to an elapsed time interval. This function of the con-

trol system is substantially the same as that of conventional analog control systems. Therefore, as with conventional analog control circuits, it is possible to check the functions of the control circuit by changing the input signals, and observing the changes in the output signals in response to the input changes, and checking whether a certain relation holds between the observations. However, for the reasons described below the time required for such checking is long, and it is not possible to check all functions perfectly.

(1) It is practice in the conventional analog control circuit to check two extreme values of a function and assume the continuity of the interval between those extreme values. Meanwhile, as in the control system employing a microcomputer therein, binary digital signals are used, and thus, the signals are not continuous and have no relationship with one another. Therefore, it is impossible to perform checking as in the analog case. Now consider the relation between the value of input x and the value of output y in both digital and analog cases for a simple analog function y=0.5x+1.5. In the analog case, for such a simple function the method employing an operational amplifier to give a zero point and a gain is widely used. In this case, the output is checked when the input is minimum, and the output is also checked when the input is maximum. Because the relation is linear in the analog case, the outputs for all the other input values are assured. If the circuit malfunctions one or other of the end values will be in error. In the digital case, a table look-up is widely used as a means for providing such a function. In this method, output data corresponding to input values 0, 1, 2 . . . is stored in advance, and according to the input value the corresponding output value is retrieved and output. In this case, even if the data corresponding to the minimum and maximum output values is correct, the data corresponding to other input values is not assured. It is therefore necessary to check the data for all input values. For this reason, although for conventional analog circuits it was satisfactory to check two values, for digital circuits the number of checking points has to be increased enormously.

(2) Because it is difficult to observe the state of the signals within the control circuit it is not possible to make an accurate check. For example, in the type of case described above where a simple relation holds directly between the input and output, by increasing the number of checking points it is possible to make a check after a fashion, but when the calculation is used at an intermediate point in the circuit a check is not possible. In other words, in the analog case, if test terminals are provided at the input and output points of the circuit, by measuring the voltages on these terminals it is possible to make a check, but in the digital case since a single line is used to indicate many different signals by time slicing, fitting test terminals is of no use, and in practice it is not feasible to detach a single section to test it. Thus the detailed internal operation of the control circuit cannot 60 be tested, and an accurate complete check is not possible. If the circuit is constructed with LSI techniques it may not even be possible to fit checking terminals.

(3) Because a circuit for an automotive vehicle control device is required to be resistant to vibration, it is not possible to construct the circuit using IC sockets and so forth to mount the elements of the circuit. An IC socket is a device to mount an IC on a printed circuit board and thus by using IC sockets, it is possible to

remove the IC from the printed circuit board very simply. Thus for devices which do not require any resistance to vibration, by using IC sockets, even after the device is assembled, the ICs can be detached and tested individually with test equipment, but for control devices for use in an automotive vehicle, resistance to vibration is extremely important. For this reason IC sockets, which allow the possibility of unsatisfactory electrical contact caused by vibration, cannot be used. Therefore methods involving the separate testing of 10 elements of the circuit after assembly, are not applicable.

(4) Control circuits for use in automotive vehicles require resistance to water and moisture, and therefore after assembly the surface of the circuit is encased in a 15 waterproof membrane. Therefore checking devices such as logic analysers cannot be used. A logic analyser is a device for observing the movement of many digital signals on a data bus and so forth, and allows the observation of the status of the input and output data of the 20 CPU for example. If a logic analyser is used, the type of control operation described in (2) above can be measured and observed to a certain extent, but when the surface is covered with a waterproof [profective] protective membrane of silicone or epoxy resin in order 25 to increase the resistance to water and moisture, such a checking device cannot be connected, and thus cannot be used.

For the above described reasons, for a control device for a motor vehicle which performs digital control on a 30 large scale using for example a microcomputer, testing after assembly takes a long time, and moreover only an unsatisfactory check can be made.

Then, for similar reasons, once the device is handed over to the user, it is not possible to check whether the 35 control circuit is correctly carrying out the actual processes used in the application. Thus, it is not possible to check for faults when carrying out inspection or servicing of the vehicle.

The object of the present invention is to provide a 40 control device for use in an automotive vehicle which, in order to overcome the above described defects of conventional control devices for use in an automotive vehicle, allows a check program different from the normal control program to be connected to the controlling CPU, and starts the check program when certain predetermined conditions occur, so that the control program automatically checks each function of the control circuit and outputs the results, thus allowing the functions to be tested simply and in a short time after 50 the control device is assembled.

## SUMMARY OF THE INVENTION

Therefore, it is an object of the present invention to provide a control system for controlling various auto-55 motive vehicle devices having a means for allowing a check of the functions of each element of the system even after the system is assembled.

Another object of the present invention is to provide a checking means capable of being connected to the 60 control system, which means is operative in response to specific vehicle driving condition.

A further object of the present invention is to provide a control system for an automotive vehicle which is provided with a function for checking an input unit.

A further object of the present invention is to provide a control system for an automotive vehicle which is provided with a function for checking a RAM. A further object of the present invention is to provide a control system for an automotive vehicle which is provided with a function for checking an output unit.

A still further object of the present invention is to provide a control system including a control program having various subroutines for checking the input unit, the RAM, the ROM and the output unit as interrupt subroutines.

A still further object of the present invention is to provide a method for checking the functions of each element of the control system, which method is capable of checking the control system effectively and perfectly.

Other objects and advantages sought in the present invention will become apparent from the description hereinafter.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will become more fully understood from the detailed description given below, and the accompanying drawings of the preferred embodiment of the present invention, which, however, are not to be taken as limitative of the present invention in any way, but are for the purpose of elucidation and explanation only.

In the drawings:

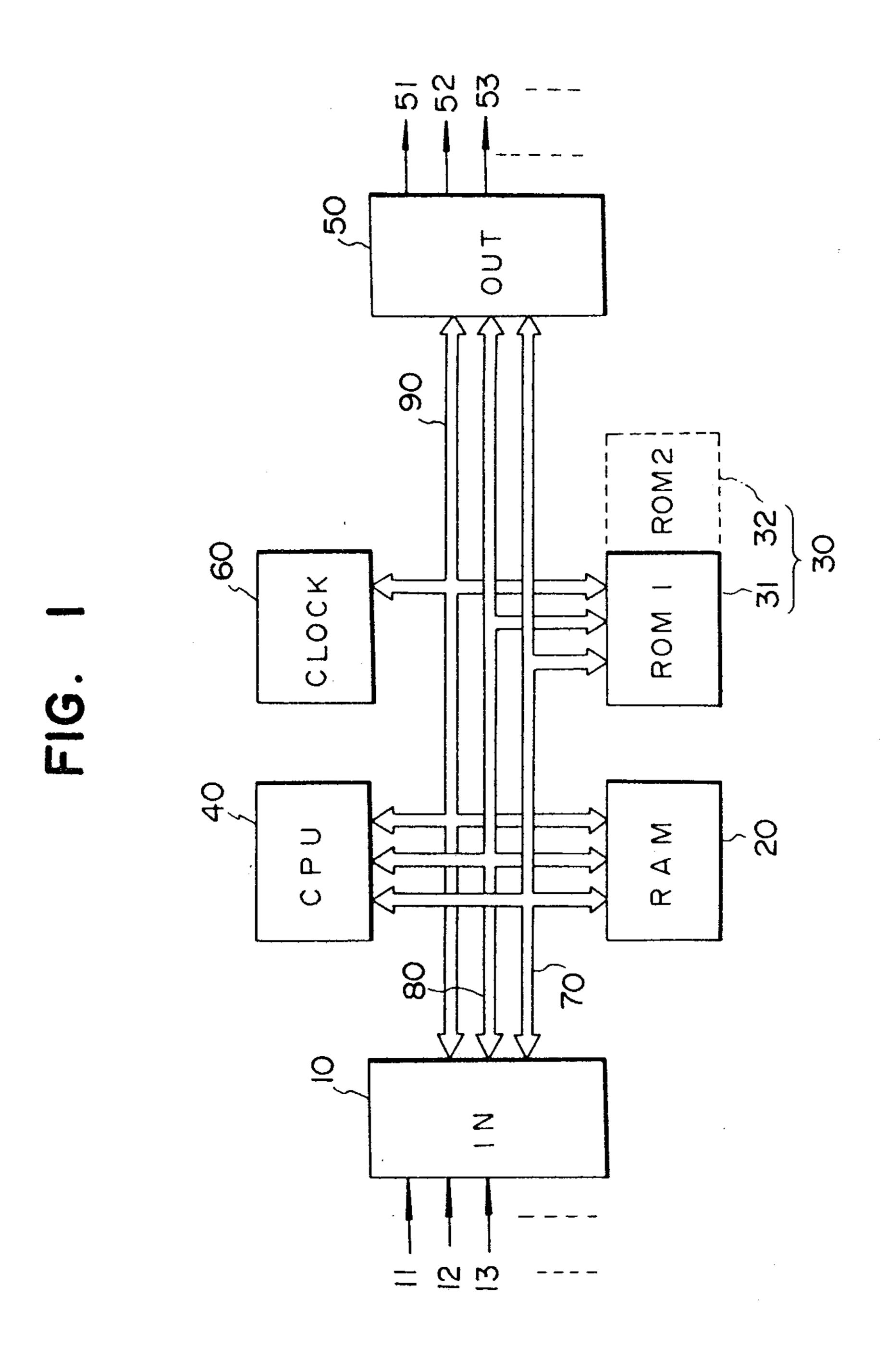

FIG. 1 is a schematic block diagram of the general construction of a control system for an automotive vehicle, having a microcomputer to which a means for checking the functions in accordance with the present invention can be applied;

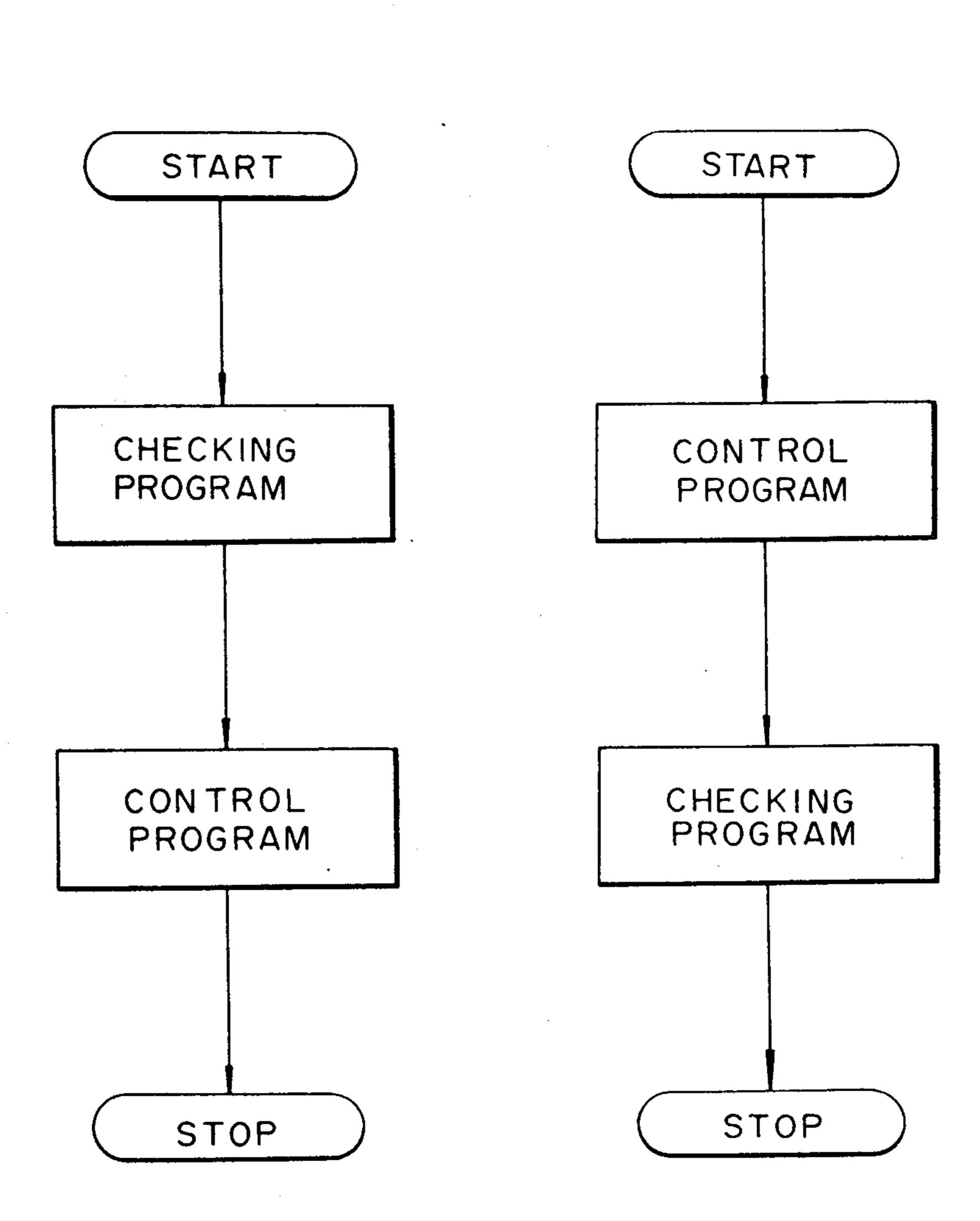

FIG. 2 is a schematic flowchart of a method of executing a checking program for use with the checking means of the present invention;

FIG. 3 is a schematic flowchart of another method of executing a checking program for use with the checking means of the present invention;

FIG. 4 is a schematic flowchart of a further method executing a checking program for use with the checking means of the present invention;

FIG. 5 is a schematic flowchart of an other method of executing a checking program for use with the checking means of the present invention;

FIG. 6 is a flowchart of one example of an input unit checking program in use with the checking means according to the present invention;

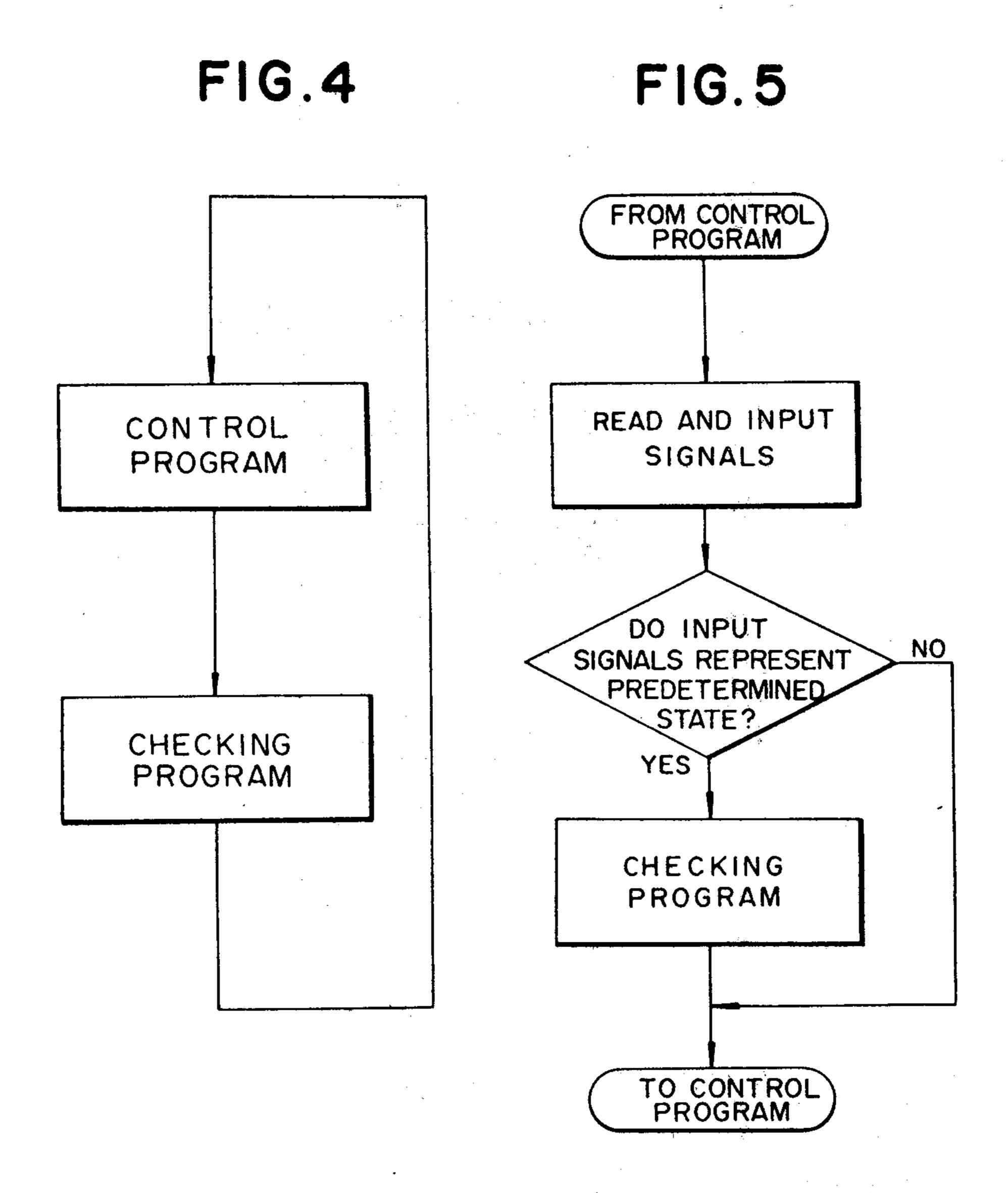

FIG. 7 is a flowchart of one example of a RAM checking program in use with the checking means according to the present invention;

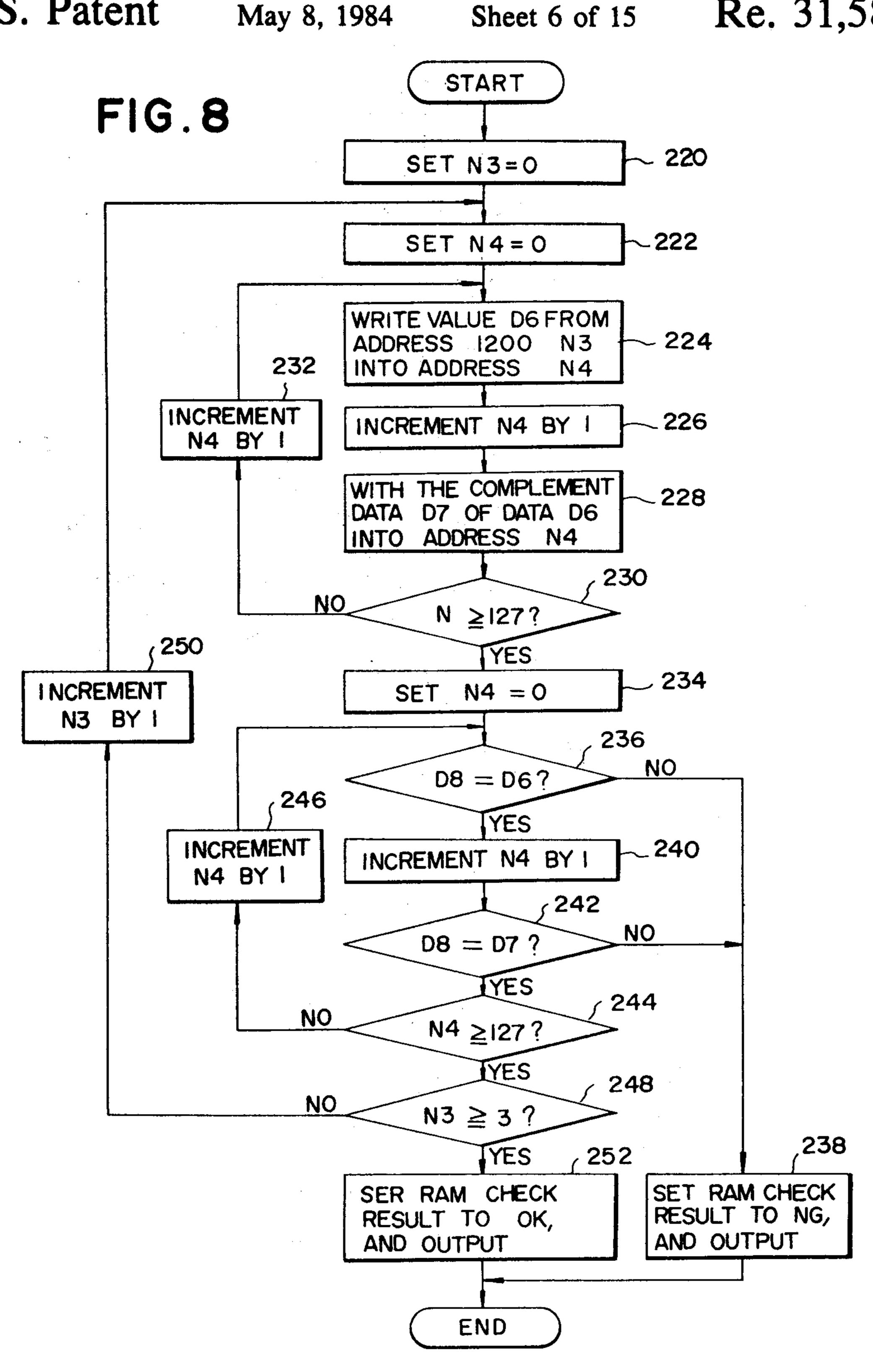

FIG. 8 is a flowchart of a modification of the RAM checking program of FIG. 7;

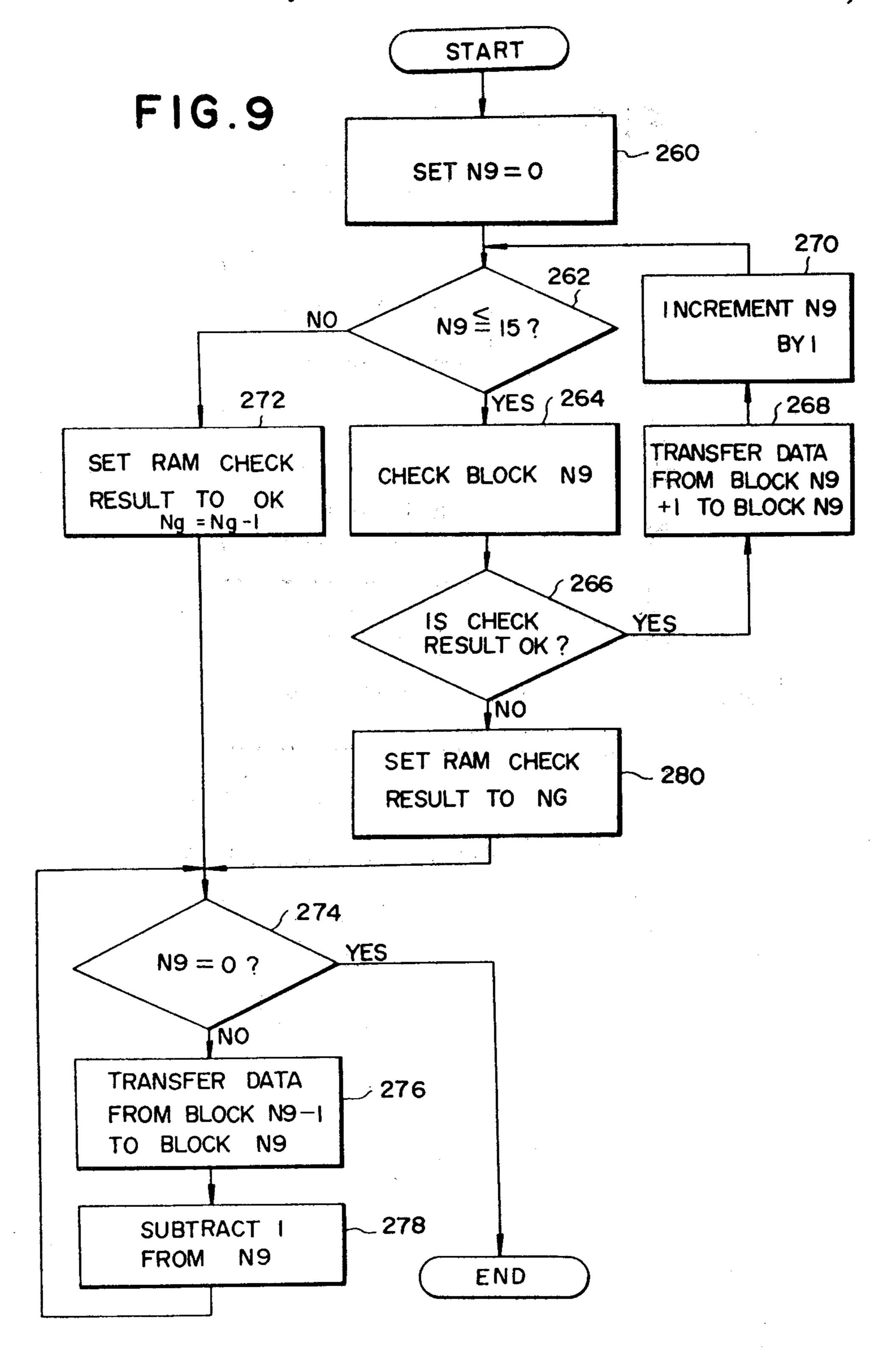

FIG. 9 is a flowchart of another modification of the RAM checking program of FIG. 7;

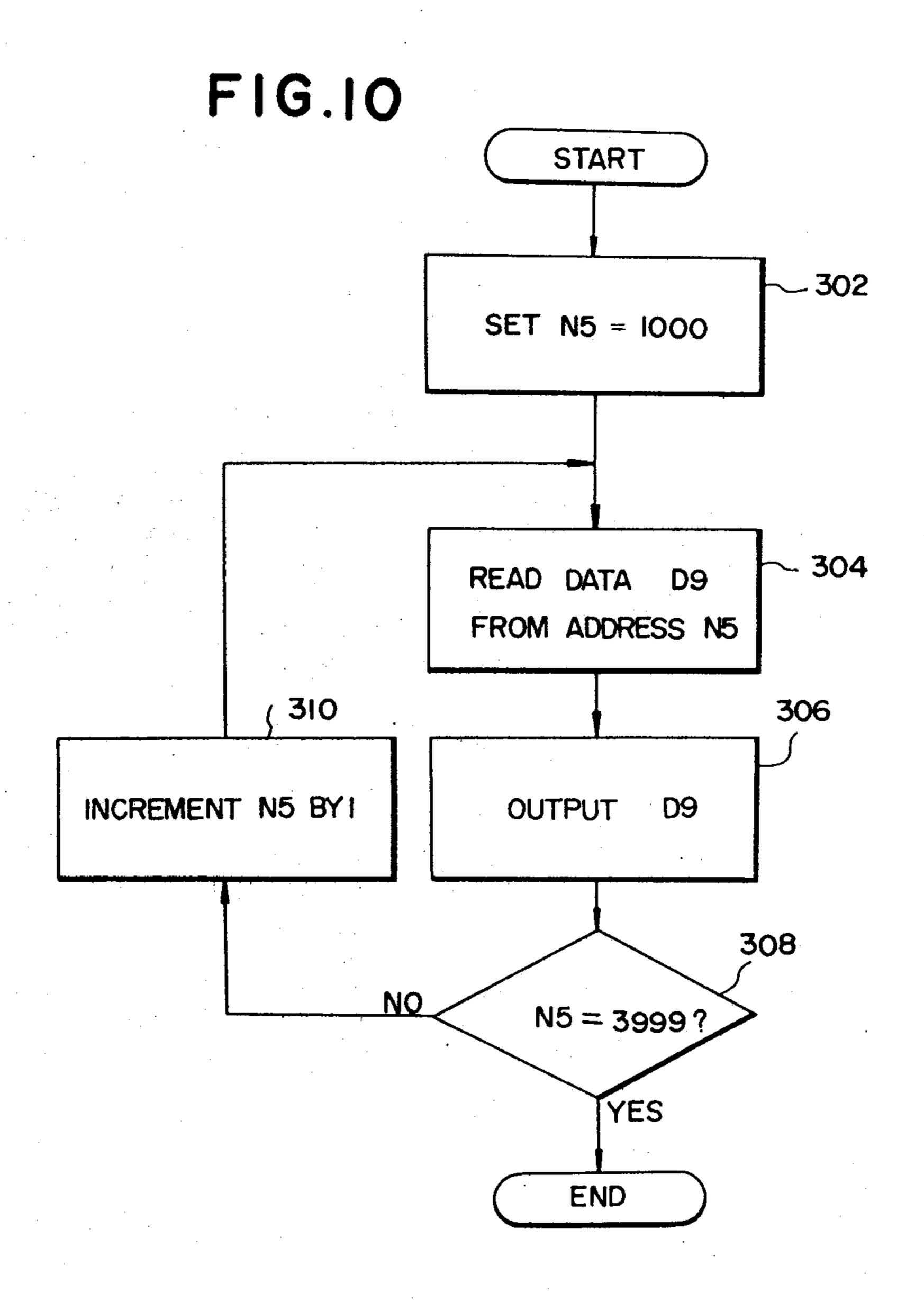

FIG. 10 is a flowchart of one example of a ROM checking program in use with the checking means according to the present invention;

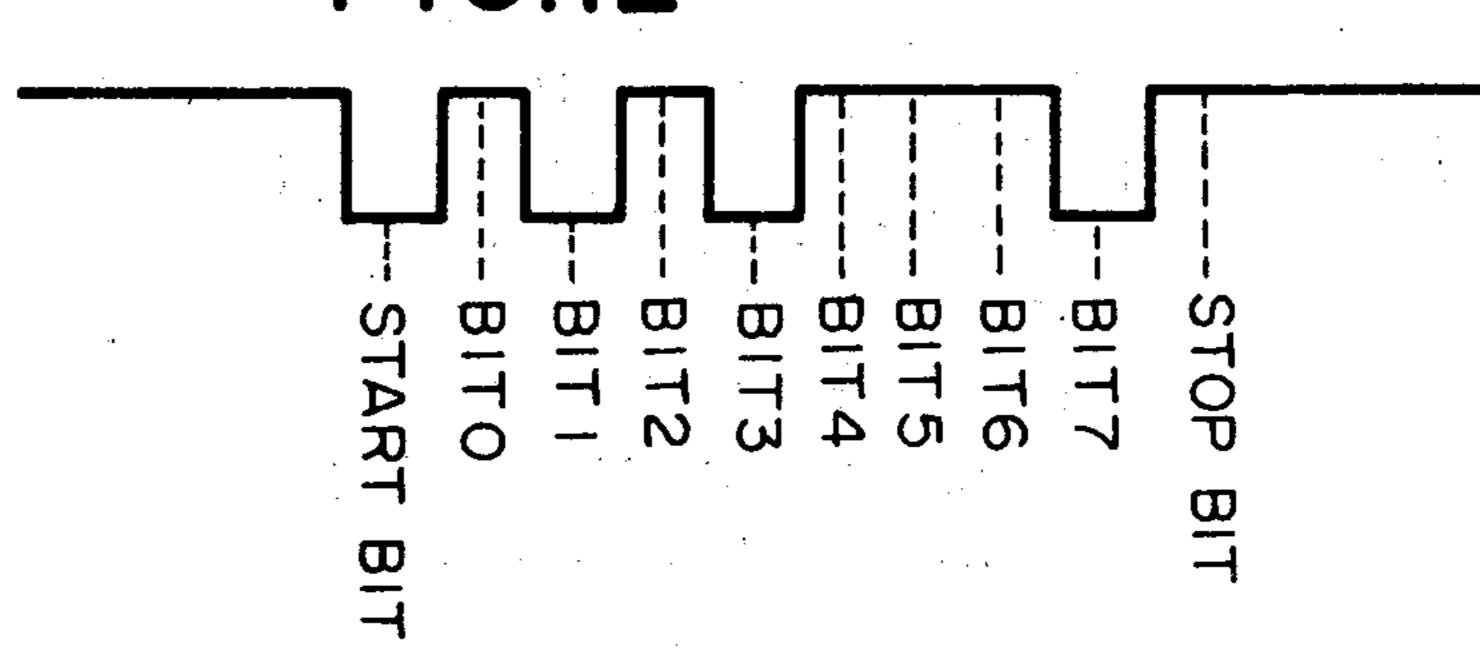

FIG. 11 is a flowchart of one example of a program for converting output to pulse-code train;

FIG. 12 shows a waveform of an output signal generated by the program of FIG. 11;

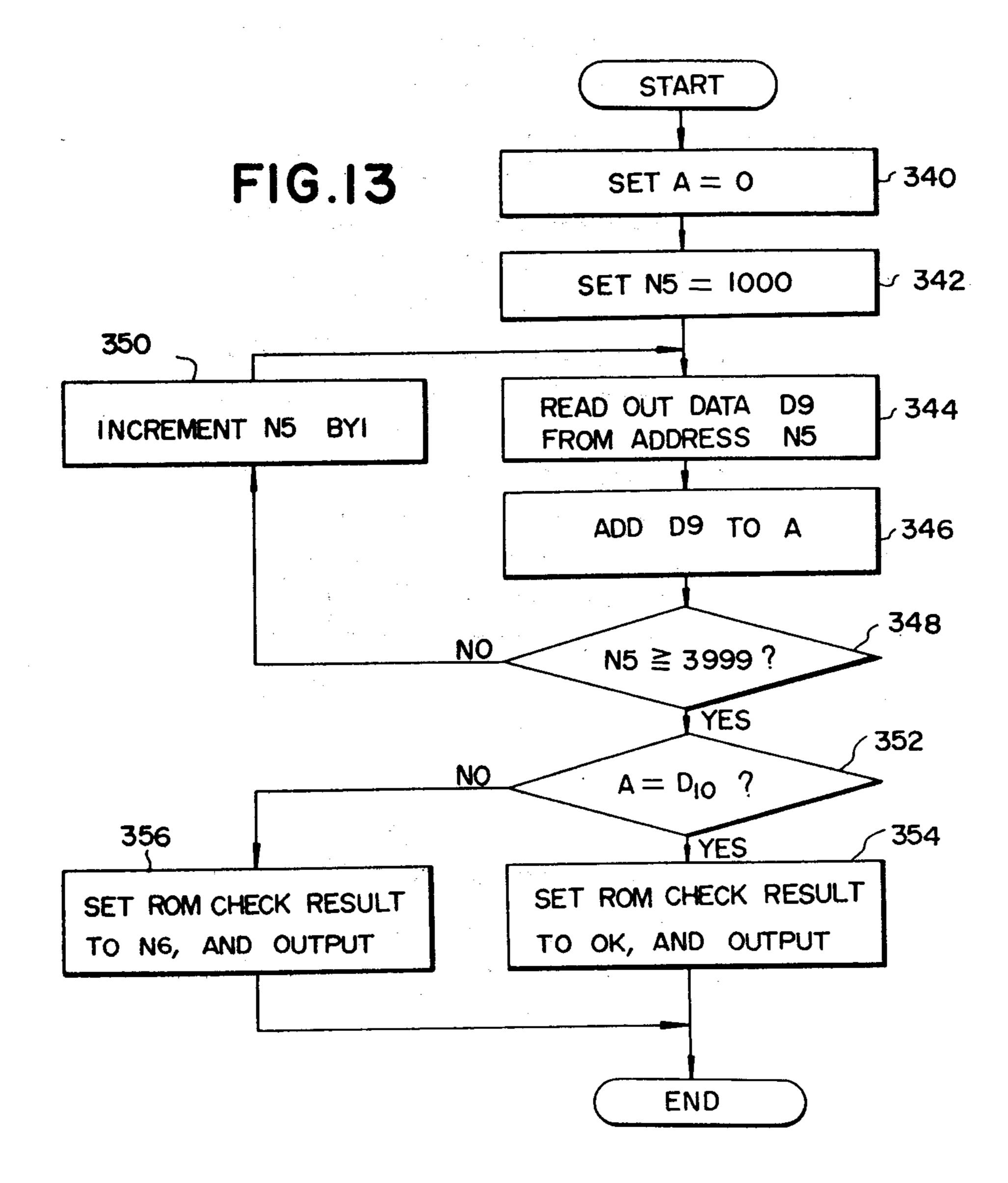

FIG. 13 is a flowchart of a modification of the ROM checking program of FIG. 10;

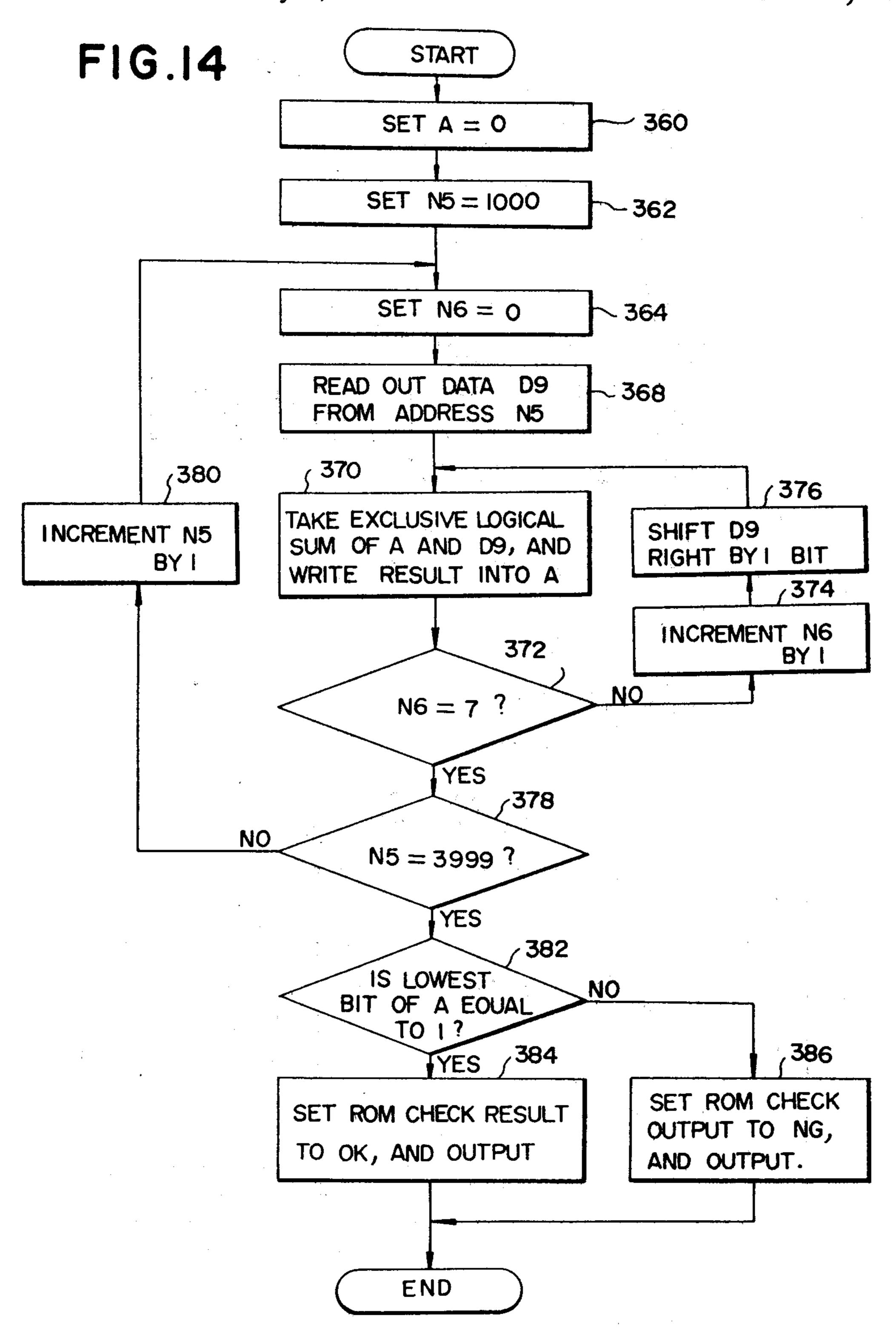

FIG. 14 is a flowchart of another modification of the ROM checking program of FIG. 10;

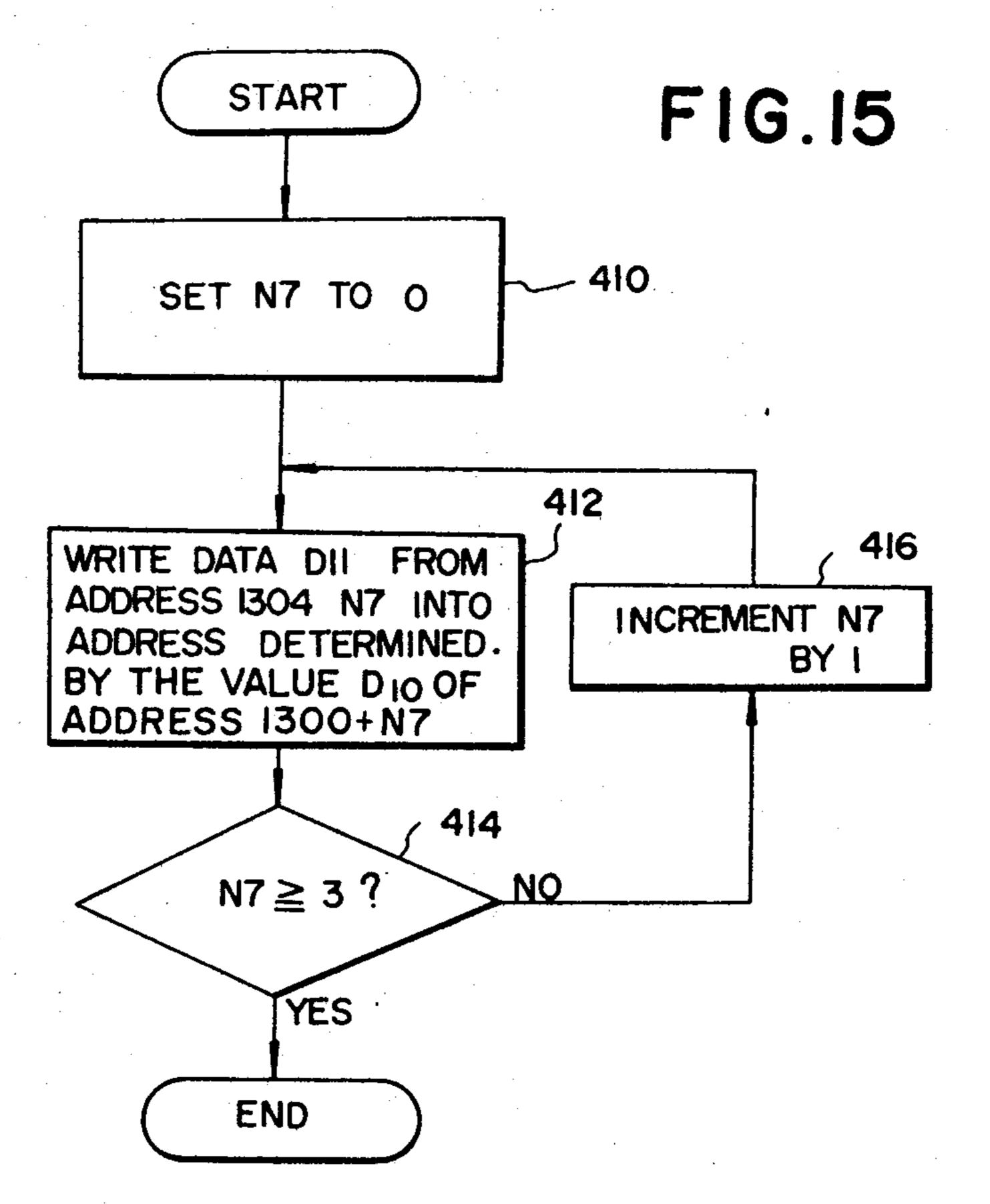

FIG. 15 is a flowchart of one example of an output unit checking program in use with the checking means according to the present invention;

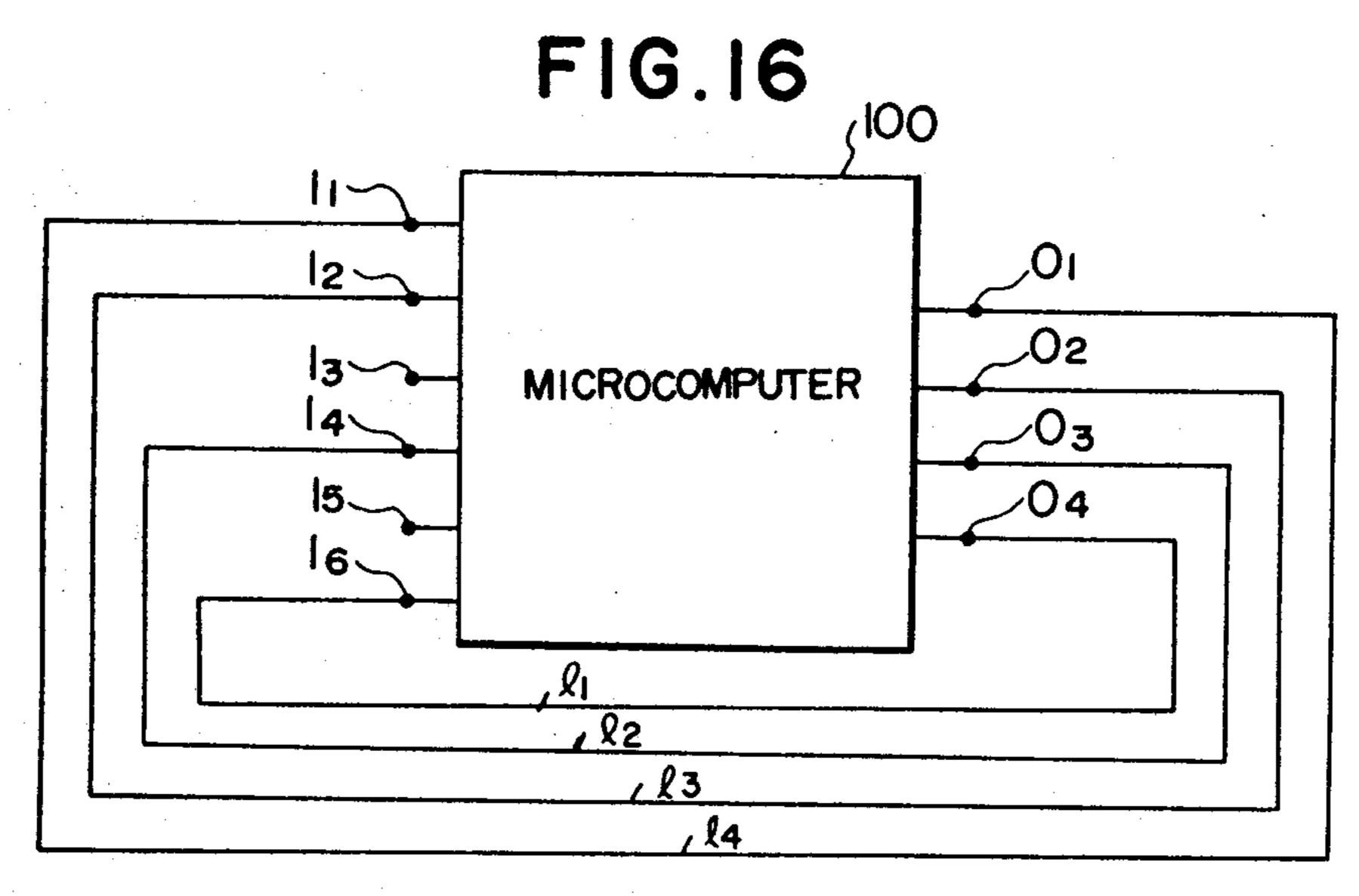

FIG. 16 is a schematic illustration of one example of connection between the input unit and the output unit in case of using the input unit for inputting [datas] data to the output unit for execution of the output checking program of FIG. 15;

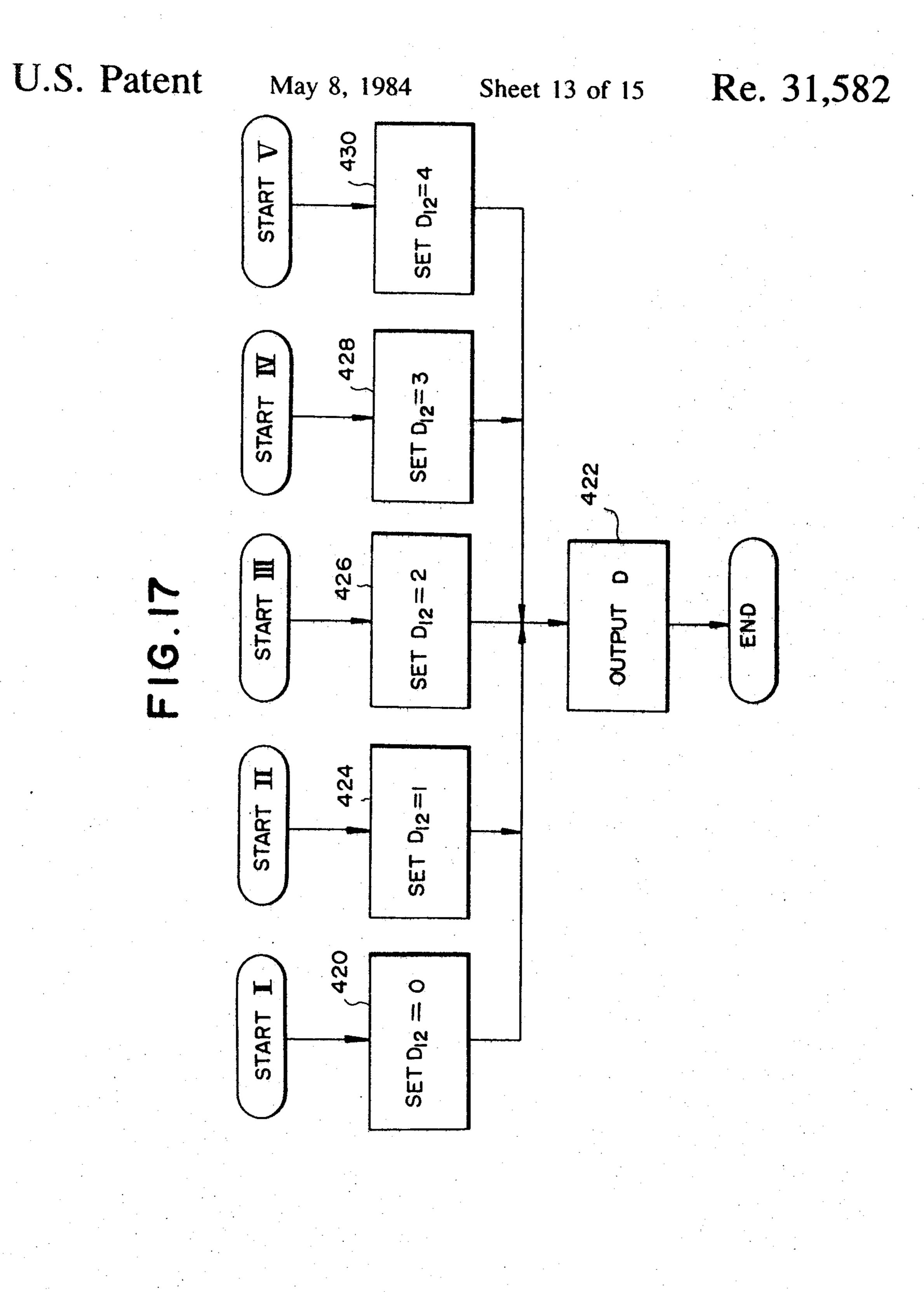

FIG. 17 is a schematic flowchart of a program for selectively outputting the result of the checking; and

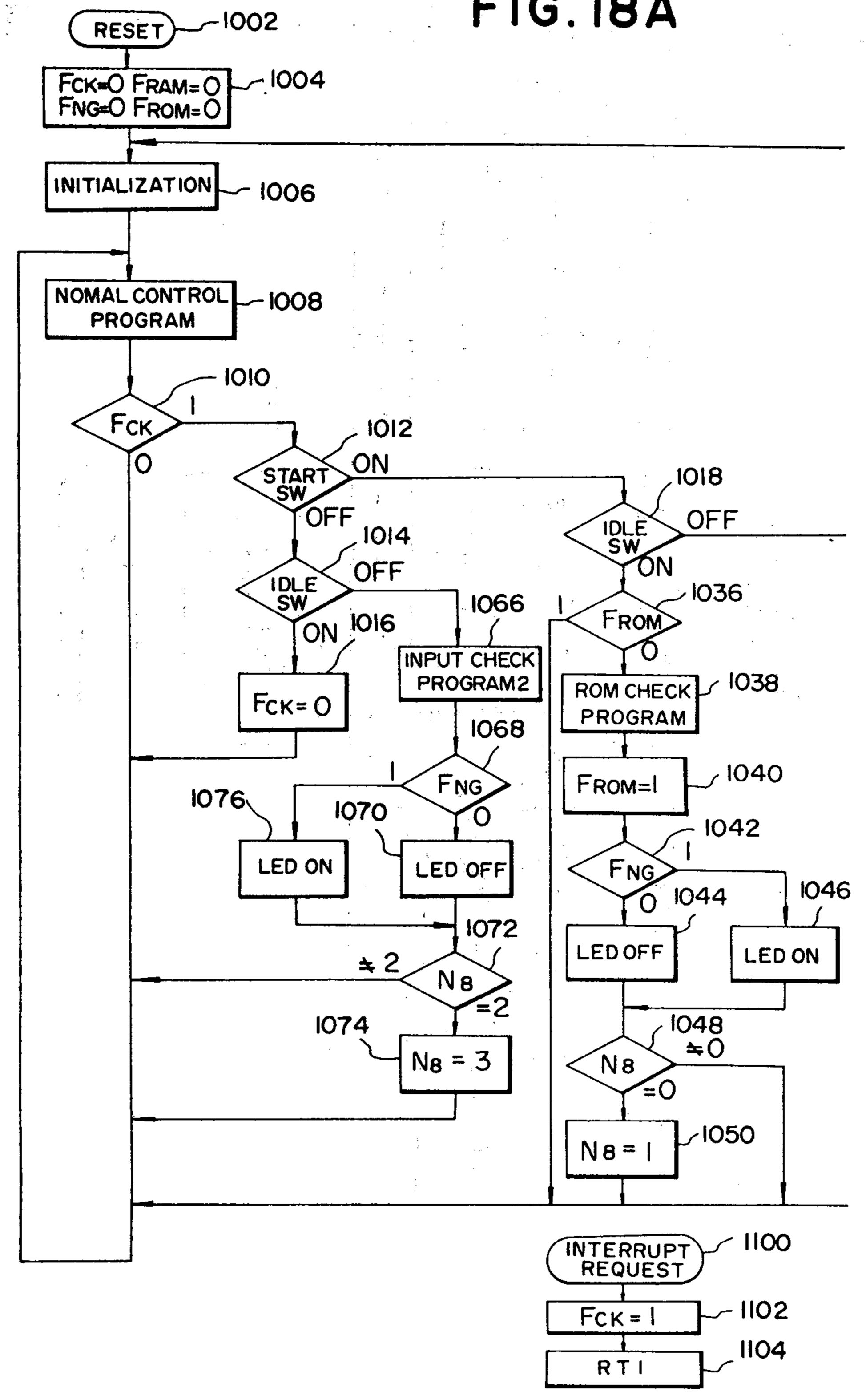

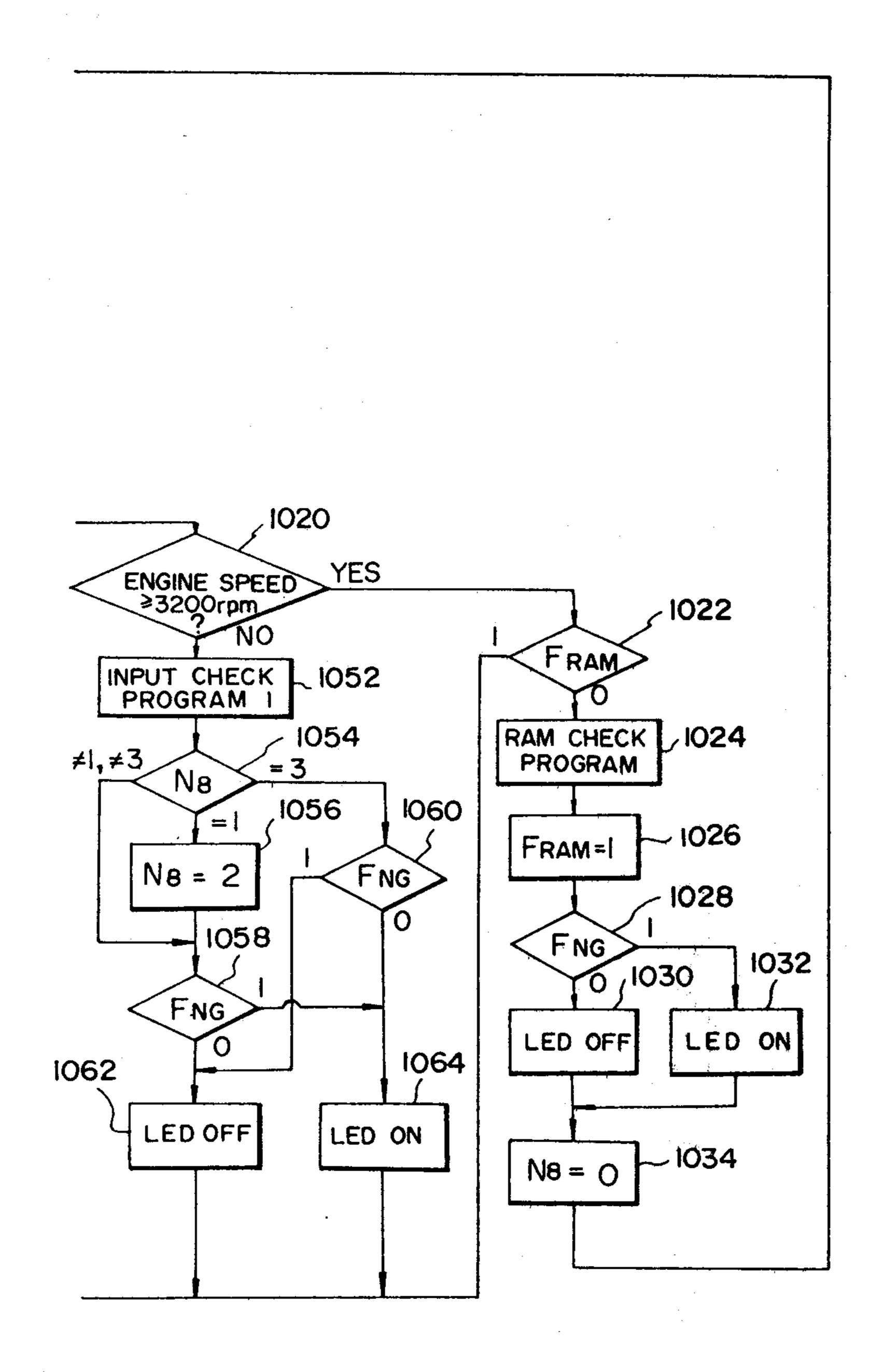

FIGS. 18(A) and 18(B) are flowchart of one example of a checking program having subroutines for checking the input unit, the ROM and the RAM as interrupt subroutine of a vehicle device control program, in which a flow line between the checking routines for 15 RAM and ROM is illustrated in common for preserving continuity of the flowchart between FIGS. 18 (A) and 18 (B).

# DESCRIPTION OF THE PREFERRED EMBODIMENT

Referring now to the drawings, particularly to FIG. 1, there is illustrated a general construction of a preferred embodiment of a control system employing a microcomputer which includes a central processing 25 unit (CPU), a random access memory (RAM) and one or more read-only memories (ROM). The control system is mounted in an automotive vehicle for controlling various vehicle devices, such as for example, engine operation, the fuel injection system, ignition system and 30 so on. Further, the control system controls various kinds of meters or indicators provided on the vehicle and also controls vehicle equipment such as a radio receiver and so on. For performing the control operations, various sensors or [detector] detectors provide 35 input signals through an input unit to be processed in the CPU. In FIG. 1, input unit 10 may generally comprise, for example, a noise elimination circuit, a shaping circuit, such as, for example, a waveform shaping filter, [or and] and/or a level convertor. The noise elimina- 40 tion circuit may comprise, for example, a means for checking a noise level contained in the input signal. For example, such a means for checking a noise level of the input signal may include a discriminator in which the input signal is compared with a reference signal gener- 45 ated by a signal generating means provided outside the system. When the input signal contains noise that may possibly cause a malfunction in the control system, the input signal is not used to update an input-register from which input data is taken for controlling the vehicle 50 driving means or other vehicle equipment. Such noise elimination is frequently necessary in using a sensor signal from a sparking sensor provided in an ignition system, for example. Input signals 11, 12, 13 . . . are inputted to the input unit 10 wherein noise is eliminated, 55 the waveforms shaped and the voltage levels, converted as required. It will be appreciated that the input signals are of various forms, such as ON-OFF signals, pulse signals and analog signals. Between the signal sources and the input unit 10, there will be provided various 60 convertors for converting various types of signals into appropriate digital signals; for example, analog-to-digital convertors, multiplex units and the like. When various signals are used, each input signal is inputted in synchronism with a synchronising signal. Before being 65 inputted to the input unit 10, the input signals 11, 12, 13 . . . are converted or encoded into digital signals as follows:

when the input signal is an ON-OFF signal, the signal is converted into a digital signal, such as the ON signal to a logic "1" the OFF signal to a logic "0";

when the input signal is a pulse signal, the pulse-frequency is counted with reference to a reference gate time or a pulse length is measured with reference to reference pulses to convert the pulse into digital code; when the input signal is a pulse code signal, the signal is converted by means of a pulse-to-code convertor;

when the input signal is an analog signal, the analog signal is converted by means of a analog-digital convertor (A/D convertor).

It will be appreciated that the input signal is sometimes inputted as a digital-code signal directly applicable to the digital computing system (microcomputer). In this case, the input signal will be sent on to the next step without modification.

The input signals 11, 12, 13 . . . are then stored in an input register which is provided in the input unit 10 or 20 are written and stored in addresses of a RAM 20 through data bus 80. The address of the RAM 20 is selected or determined by an address signal stored in an index register of a central processing unit (CPU) 50 and inputted to the RAM 20 through an address bus 70. The input signal is written in the input register or in the RAM at specific addresses determined by the address signal, by means of a synchronizing signal supplied by a clock signal generator provided outside the control system. The inputted data written and stored in the RAM 20, is read out and sent to the CPU 50 for performing control [operation] operations according to a control program with respect to the data contained therein. The control program is stored in a ROM 30 and is read therefrom on carrying out the control operation of the CPU 50. A result of the operation of the control program of the CPU is sent to an output unit 40. The output unit 40 may include an output register for storing output data therein, if necessary. Since the output data is inputted to the output unit 40 in the form of digital code, the output unit 40 converts the data into ON-OFF signals, pulse signals, analog signals or pulse-code signals to provide outputs according to the type of the control device to be operated by the output signal. The output data is then amplified to generate output signals 51, 52, 53 . . . Each output signal 51, 52, 53 . . . is then transmitted to an actuator which operates a control device for a device to be controlled or to an indicator. A high frequency oscillation circuit 60 (CLOCK), such as a crystal oscillator, generates a basic signal; either this signal, or a signal whose frequency is a submultiple of the basic signal is used as a clock signal to be inputted through a control bus 90 to the above-mentioned circuits, for example, the CPU 50, for controlling same. Although this is not shown in the drawings, the control bus 90 is also connected to a read/write signal generator.

Although the recently developed microcomputers are generally constructed as above, there are various possibilities for the arrangement of components of elements therein; for example, there may be an element including the CPU, RAM and OSC as a combined unit, and further there may be another element including a ROM, and part of the input and output units. Further, the combined elements can be varied in the numbers thereof, or some unnecessary elements, for example, the input unit or RAM, can be omitted from the system. Therefore, it should be noted that the present invention can be applied to various constructions of the control

system and although a specific construction of the microcomputer has been disclosed hereinabove, the present invention should not be considered as [limitated] limited to the specific construction of the control system. The above-mentioned control system will be also 5 applicable for controlling various types of vehicle equipment mounted in an automotive vehicle; for example, an internal combustion engine, transmission, braking system, radio or indicators. Further, the control system is applicable, for example for controlling operations of the ignition system and/or fuel injection system in response to driving condition.

The ROM 30 holds a control program for control operation of the CPU 40 stored in the control-data storage location (ROM<sub>1</sub>=31) and a checking program 15 for checking elements of the control system, stored in the checking data storage location (ROM<sub>2</sub>=32). The storage locations 31 and 32 may be in a position either combined as one component or separated into two areas.

FIG. 1 shows a control system including a microcomputer. In FIG. 1, the ROM 30 is composed of two portions ROM<sub>1</sub> 31 and ROM<sub>2</sub> 32[;]. The ROM<sub>2</sub> 32 is shown by a broken line to indicate that it may be provided separately from the control system. For example, 25 all or part of the checking program and checking data can be stored in a memory unit provided outside the system and connected by means of an IC socket or connector which is releasably connected to the system in general. For example, the IC socket or connector is 30 connected with an external ROM provided outside the system. In such cases the data bus, address bus and control bus are provided to connect to the IC socket or connector to the CPU in order to send data stored in the external ROM to CPU 40. The control system accord- 35 ing to the present invention can be embodied in any one of the above-mentioned forms. If the ROM 30, comprising the ROM<sub>1</sub> 31 and ROM<sub>2</sub> 32, is included in the microcomputer system, it will enable the checking operation to be carried out anywhere and at any time simulta- 40 neous with running of the control program. Therefore, it is unnecessary to decide whether the checking program shall be run. On the other hand, if the ROM 30 is provided separately from the control system, manufacturing cost can be reduced since ROM<sub>2</sub> 32 is not re- 45 quired in the system.

The checking programs are run or executed on the CPU 40 when the control system is in a predetermined state. Some examples of schematic flowcharts will now be explained with reference to FIGS, 2 to 5. In FIG. 2 50 the checking program is run immediately after switching to start and before running the control program in the sequence of the control system. As shown in FIG. 3, the order of running the checking program and the control program can be changed from the order shown 55 in FIG. 2. In FIG. 4, the checking program and the control program loop together. Therefore, in this case, the two programs are run alternately. In the above-mentioned three examples, when the control program is run, the checking program is always run before or after 60 running the control program. In these cases, it is not necessary to determine whether the checking program is run before or after the control program is run or executed, as the checking program is run or executed automatically so as to simplify operation of the control 65 system. It is also possible to arrange for the check program to be executed when the control input signals are put into a particular state. In concrete terms, as shown

8

in the flowchart in FIG. 5, at an intermediate point in the control program, a program is executed to read out the state of the input signals and then check whether the input signals are in the particular state. If the signals are in the particular state, then the check program is executed, otherwise the check program is skipped and the control program is executed again.

As the predetermined particular state, it is preferable to use a time when the controlled devices are not operating. For example, in an engine control device, the amount of control necessary when the engine is stationary is extremely small, and therefore the execution time required for execution of the control program is short. Therefore even if the check program is executed, the response of other control devices is not delayed, which is a desirable feature. Stated alternately, when the results of the checking program are output, even if they are output together with the control output, then, if the engine is stationary, problem-free output of, for exam-20 ple, the ignition control signals is assured, and the number of output circuits can be reduced. Then again, for similar reasons it is possible to detect that the vehicle is stationary and then execute the check program. In such cases it will be satisfactory to take as an input parameter the period or frequency of pulses from a sensor determining the engine rotation rate or the vehicle speed, as for example a rotation pick-up pulse, and check whether or not the engine revolution rate or vehicle speed is zero (or extremely close to zero).

There again it is possible to select a predetermined state which cannot occur in the normal range of operation of control as the particular state. For example, the range of engine speeds used in a normal reciprocating engine is up to about 6000 rpm. Therefore, for example, the check program may be run by generating an input signal corresponding to an engine speed is 9000 rpm or more. In this case, the check program will not be run in the range of normal use. When the check is carried out as described below, check data may be output to the output circuit and the output state changed, or data stored in the RAM may be rewritten; thus there are cases where it is difficult to continue normal control. In these cases it will be best not to carry out checking during normal control. When checks are to be carried out on the control circuit, the operational inputs and outputs will be detached from the control circuit. Input signals such as a pulse signal corresponding to the engine rate, will be input from a separate electrical device for checking purposes. It is straight forward to produce a high frequency pulse signal electrically, so that the checking can be executed simply. Now it is also of advantage for the particular state to input two [state] states which cannot possibly occur at the same time, such as two vehicle speeds, high and low temperatures, or for instance signals indicating that the transmission gear position switch is in both top and neutral positions.

Now referring to FIG. 6, there is generally illustrated and explained the running of the checking programs for checking the input unit 10 of FIG. 1. FIG. 6 shows a flowchart for running the checking program of the input unit 10. It should be noted that an input signal to be processed during running of the checking program is inputted from a checking signal generating means (not shown) which is provided outside the control system of the present invention. Checking of the input signal is done with respect to input data temporarily stored at an address in the input register, for example, sequentially from starting address 1100. The input signals are gener-

ated and fed from the checking signal generating means in order adapted to the order of the input data stored in the input register. After starting the checking program, in a first processing step 102, the value N<sub>1</sub> of a counter is reset to 0. As will be understood from the drawings, 5 hereinafter disclosed is an example in which ten input data are inputted and stored in the input register in the input unit 10.

Table I shows the relationship between values D<sub>1</sub> of input data stored in the address register A<sub>1</sub>, address data values D<sub>2</sub> stored in addresses 1000 to 1009 of the ROM and reference data values D<sub>3</sub> stored in addresses 1100 to 1109 of the ROM, as an example.

TABLE I

| Counter | Input Signal<br>No. | $\mathbf{A}_1$ | D <sub>1</sub> | ROM<br>Address | $D_2$ | ROM<br>Address | $\mathbf{D}_3$ |

|---------|---------------------|----------------|----------------|----------------|-------|----------------|----------------|

| 0       | 1                   | 10             | 30             | 1000           | 10    | 1100           | 30             |

| 1       | 2                   | 12             | 55             | 1001           | 12    | 1101           | 55             |

| 2       | 3                   | 14             | 10             | 1002           | 14    | 1102           | 10             |

| 3       | 4                   | 15             | 15             | 1003           | 15    | 1103           | 15             |

| 4       | 5                   | 16             | 43             | 1004           | 16    | 1104           | 43             |

| 5       | 6                   | 18             | 54             | 1005           | 18    | 1108           | 54             |

| 6       | 7                   | 20             | 10             | 1006           | 20    | 1106           | 10             |

| 7.      | 8                   | 24             | 15             | 1007           | 24    | 1107           | 25             |

| 8       | 9                   | 26             | 60             | 1008           | 26    | 1108           | 60             |

| 9       | 10                  | 28             | 77             | 1009           | 28    | 1109           | 77             |

As seen from Table I, each of the input signal 1 to 10 is stored in address A<sub>1</sub> (10, 12...28) of the input register or RAM 20. Each input data value D<sub>1</sub> contained in 30 each input signal 1 to 10 is shown in Table I. In Table I, the input data values D<sub>1</sub> are 30, 55 . . . 77. In addresses 1000 to 1009 of the ROM, are stored address values D<sub>2</sub> (10, 12 . . . 28); in the addresses 1100 to 1109 of the ROM, are stored reference data values D<sub>3</sub> (30, 55 . . . 77). These values are to be compared with the input data values D<sub>1</sub> when the checking program is run. On the next processing step 104, the address value D2 (=10) stored at address  $1000 + N_1$  (= 1000) is read out. Then, the input data  $D_1 (=30)$  stored at the address  $A_1$ (=10) of the input register of the RAM corresponding to the read address data D<sub>2</sub> is read out. Thereafter, the reference data  $D_3$  (=30) stored at the address  $1100+N_1(=1100)$  is read out in processing step 106. The input data D<sub>1</sub> and reference data D<sub>3</sub> are compared together in the decision step 108 to decide whether the input data D<sub>1</sub> read from the address A<sub>1</sub> of the input register on the RAM matches will the corresponding reference data D<sub>3</sub>. When the input data D<sub>1</sub> matches 50 unit. with the reference data D<sub>3</sub>, the check program goes to the next process step 110 where the count number N<sub>1</sub> of the counter is compared with the number of the last input data (=9). In other words, in step 110, a check is made to whether the foregoing checking program has 55 run to completion in checking the input unit with respect to all of the input data values D<sub>1</sub>. The check is made by comparing the count number N1 with the number of the last input data namely, 9. In the example shown in FIG. 6, the sequence steps 104, 106, 108 and 60 110 of the checking program repeatedly runs until the count number N<sub>1</sub> of the counter is 9. When the count number N<sub>1</sub> is less than 9, the checking program returns to process step 104. Prior to this time, however, the counter is incremented by one (1) in process step 112. 65 Namely, after checking of the input unit with respect to the first input data D<sub>1</sub>, and confirming that the read input data D<sub>1</sub> matches with the reference data D<sub>3</sub>, the

count number N<sub>1</sub> is incremented by 1 to repeat steps 104-112 of the checking program.

Result of checking operation for the input unit is outputted, when all the input data values D<sub>1</sub> read from the input register or the RAM at the process step 102 match with the reference data values D<sub>3</sub> stored in the ROM and read out in process step 106. In this time, when the count number N<sub>1</sub> of the counter reaches 9, and therefore determines that all the input data values have been compared with the reference data D<sub>3</sub> corresponding thereto and match with the latter, the checking program goes to process step 114 where the output signal indicating that the input unit is operating correctly (hereafter referred to as the "OK" signal) is gen-

The input data value D<sub>1</sub> may not always match the reference data value D<sub>3</sub>. Such a condition is shown in the eighth column of Table I in which input data D<sub>1</sub> (15) stored at address A<sub>1</sub> (24) of the input register or the RAM and the corresponding reference data D<sub>3</sub> (25) do not match. The difference of the input data D<sub>1</sub> and the reference data D<sub>3</sub> will cause a decision at step 108 to go to process step 116. When the checking program goes to process step 116, an output signal indicating that the input unit is malfunctioning or in error (hereafter referred as the NG signal) is generated and outputted.

As may be apparent from the foregoing descriptions, according to the preferred embodiment of the present invention, the reference data D<sub>3</sub> referred to as the checking data for running the checking program is stored in a ROM. The input data for running the checking program is compared with the reference data D<sub>3</sub>. For the purpose of checking the input unit, the input data D<sub>1</sub> is set to the reference data D<sub>3</sub>. Therefore, if each circuit of the input unit operates or functions correctly, the checking input data D1 which is stored at an address A<sub>1</sub> of the input register or the RAM and read therefrom will match with the corresponding reference data D<sub>3</sub> which is stored at the corresponding address of the ROM and read out therefrom. Since the difference between the input data D<sub>1</sub> and the reference data D<sub>3</sub> means that the one or some of the circuits of the input unit are malfunctioning and/or that one or some of them are damaged, the checking can be carried out by way of comparing the input data D<sub>1</sub> and the reference data D<sub>3</sub>. According to the checking program disclosed hereinabove, if the difference between the data is detected during running of the checking program, the NG signal is generated and outputted through the output

It will be appreciated that when the input data is contained in the input signal which is in the form of analog signal or pulse signal, the input data may have some errors or aberration due to a difference of measuring timing or other known reasons. However, such difference between the input data and the reference data will often be in a range in which the difference does not affect or only slightly affects operation of the control system for the vehicle or other equipment of the vehicle. Therefore, in such case, it must be determined whether the input unit is malfunctioning or the unit is damaged by detecting whether the difference between the value of the input data D<sub>1</sub> and the value of the corresponding reference data D3 exceeds an allowable range. There may be known various way for checking whether the difference between the values of the input data and the reference data is within the allowable range. However, in the present invention, the data is

checked by either including in the checking program discriminating step to determine an allowable range as being within a distance A from the reference data or providing two different reference data one of which defines the upper limit of the allowable range and the 5 other defines the lower limit thereof. In the latter checking method, the input data will be compared with both reference data and checked whether the input data is lower or higher than the lower and upper limits of the allowable range.

Although in the foregoing example there is shown a method or flowchart for checking the input unit by way of checking input signals stored and read from the input register of the input unit and with reference to each reference data value stored and read from an address of 15 the ROM, and both of the data values can be stored in single addresses, input data is not always capable of storage in only one address. Input data is sometimes stored in two or more addresses of the input register or the RAM. In such case, the input data might be 2 or 20 ted [:]. more bytes of data. The word byte is used in the present specification to mean eight binary digits (or bits) of data. In checking all of such data value, theoretically two-hundred fifty-six (28) different data values may be contained in each data byte. Therefore, if a check is 25 made with respect to all the different data values, it will cause the checking program to run for a considerably long period. If only one of the different data values is checked, it will possibly cause overlook of damage of the input unit due to occasionally matching the input 30 data and the reference data by sheer chance. Therefore, for reducing checking period and for probabilistically avoiding overlook of damage in the input unit, at least two input data values should be checked during running of the checking program; in practice, two or three input 35 data values will be checked.

Now, we refer to FIGS. 7 to 9, there are illustrated and disclosed operation for checking the RAM. In advance to entering into explanation of the preferred embodiment of the present invention for checking the 40 RAM, although it may be well-known to those skilled in the art, hereinbelow is illustrated the general function of the RAM. The most important function of a RAM is to write in and read out a particular value. Therefore a good method of performing a basic check on a RAM is 45 to write in and store a particular data value, then read out the data and check whether the value read out is the same as the value written in. This method will be [explain explained more concretely using FIG. 8. FIG. 8 is drawn in terms of a microcomputer system (such as 50 the Motorola MC6802) which uses a  $8 \times 128$  bit RAM, with [address] addresses from 0 to 127, but the same process can be carried out with minor modifications for different numbers of bits, numbers of bytes, and addresses. FIG. 8 is a flow chart of a program to check the 55 RAM.

In the RAM check program, first in block 202 the data value N<sub>2</sub> representing the RAM address is set to 0. Next, in block 204 a particular data value D<sub>4</sub> is written into the address N<sub>2</sub> (=0). Next in block 206, the data 60 D<sub>5</sub> is read out from address N<sub>2</sub> so as to be compared with the input data D<sub>4</sub> to decide whether both of the data values D<sub>5</sub> and D<sub>4</sub> match at step 208. When the data values D<sub>5</sub>, and D<sub>4</sub> match, the address data N<sub>2</sub> is compared with the last address number (=127) of the RAM 65 at a step 210. When the result of comparing the address data N<sub>2</sub> and the last address number (=127) determines that the address data N<sub>2</sub> is smaller than 127, the check-

ing program goes back to the process step 204. At this time, the address data N<sub>2</sub> is incremented by 1 in the process step 212 to address  $N_2+1$  to read out the stored data D<sub>5</sub> from the address  $N_2+1$  (=1) of the RAM at the process step 204. The stored data D<sub>5</sub> read from the address  $N_2+1$  is compared with the input data  $D_4$ , and it is decided whether it matches with the latter. As mentioned above, the checking program runs repeatedly until [the result of comparing] the address data 10 N<sub>2</sub> and the last address number 127 are equal; namely, in the above example, the program is repeated one hundred twenty-eight times and until the value of the address data is 127. When address data N<sub>2</sub> is equal to the last address number 127, an "OK" signal is generated in a process step 214 and is outputted through the output unit. If some of the stored data D<sub>5</sub> is different from the corresponding input data D<sub>4</sub>, a decision that the RAM operates incorrectly is made. At this time, an "NG" signal is generated in a process step 216 and is output-

As mentioned hereinabove, the RAM can be checked whether it operates correctly by use of the checking means of a preferred embodiment of the invention, in which the above described checking program is stored in specific addresses of the ROM<sub>2</sub> 32 of FIG. 1. It should be understood that, at the start of checking and before running the checking program, the program will be read out from the ROM<sub>2</sub> 32. Further, it must be noted that, in the above-mentioned example the address data N<sub>2</sub> is cleared or reset to 0 at starting in the step 202. If the data values to be checked are stored in different addresses; for example, the data values are stored in the RAM at the addresses from 15 to 120, the first address number is written as the address data N<sub>2</sub> in the step 202 after clearing the data N<sub>2</sub> previously contained therein. If there are additional values stored in different, and perhaps a large number of groups of addresses, checking can be performed by repeating the above-mentioned program with respect to the first address of each group.

While it is possible for checking of the RAM to run the above-explained checking program to check data for all the combinations expected, since all the data values to be inputted and stored are binary numbers composed of only 1's or 0's, it will be sufficient for checking the RAM to check whether each bit of the RAM can be written 1 and 0 and be read out exactly as written. Therefore in practice, the checking program will be run to check the RAM with respect to a first and second data value. The second value data may be the complement of the first data value. Since both data value are combinations of 1's and 0's, checking with respect to the first and second data values can cover all the possible combinations of the data and therefor is sufficient for checking, the RAM. By this way of checking duration of running the checking program can be considerably shortened, and the storage are required for storing the checking program can be reduced to thereby lessen the capacity of the ROM<sub>2</sub> 32.

There are various ways in which error can occur in the input circuit, but the more common of these include the following cases: a short circuit between adjacent leads, a break in a lead, or a particular bit in a register staying at 0 or 1. In the short circuit case, adjacent bits in a register have the same values all the time (so-called horizontal short circuit). In the two latter cases, the value of a particular bit in a register never changes.

To detect the fault caused by the abovementioned horizontal short circuit case, data may be loaded into a

register in a pattern of repeated binary 01's or 10's, so that adjacent bits do not have the same value. Upon read-out, if two adjacent bits have the same value, a short circuit is indicated.

Next, a method of checking for the other cases, is to 5 first check with one set of data, and then to recheck with new data in which every bit is reversed, from 0 to 1 and vice versa, from the first set of data, checking that the operation is correct with both sets of data.

To carry out these two tests at the same time, a first 10 check may be made with an input in which the first standard data is 01010101, and a second check in an input state in which the second standard data is 10101010.

When the number of input signals is high, if the data 15 (D2) showing the address of the input and the standard data (D3) are separate for each of the input signals, the amount of data involved is very large, and the program size is increased. In cases like this, if the input signal data addresses are arranged to be consecutive, the first and 20 last addresses of the data can be stored, and the check can be made by incrementing the address progressively through the data to the last address. If this is done the amount of data (D2) indicating addresses is decreased, and the ROM for the check program can advanta- 25 geously be made smaller. Further, if the standard data uses the two patterns described above (viz. 01010101 and 10101010) there is not only the above described benefit of using these patterns, but also the ROM may advantageously be made smaller. In cases where 1 byte 30 data items and 2 or 3 byte data items are mixed, the size of the ROM may be decreased by, instead of attaching to each data item a data determining the number of bytes in that particular data item, collecting together consecutively all data item with the same number of 35 bytes and determining the number of bytes per items from the first and last address of the data.

When register addresses are made consecutive, and when the registers are physically adjacent, there is the possibility of a short circuit between registers. In this 40 case the same bits in adjacent registers may be short circuited (so-called vertical short circuit), or adjacent bits in adjacent registers may be short circuited (so-called diagonal short circuit). These types of short circuit will happen only very rarely, but in cases where an 45 extremely high level of reliability is required, it will be desirable to add procedures to check for them. In practice this will be done as follows.

First check the first address supposing that the address is even) with the first data value 00000000. 50 (Choose an input state such that the input data naturally takes such a value.) Check the next address (an odd address) with the second data value 11111111. From there on, alternate the first and second data values in even and odd addresses. When this is done, in the vertical direction (i.e. between registers) the data bits will be aligned in a pattern of alternating 0's and 1's, and a vertical short circuit can be determined. Furthermore, in the diagonal direction the bits also alternate between 0 and 1, so that diagonal short circuits can also be detected.

If it is desired to check for a horizontal short at the same time as a vertical short, this can be done by checking using a first data value 01010101 in even addresses and a second data value 10101010 in odd addresses 65 alternately. If this is done 0's and 1's alternate in both horizontal and vertical directions so that short circuits can be detected.

In case where the addresses of the input circuit registers are not consecutive or data items with the same number of bytes are not or cannot be arranged consecutively, then the input data may be organized in the manner described above, rearrranged, and stored in a RAM; the data can then be checked in the RAM. In this case it will also form a partial check of the RAM.

14

In the meanwhile, as another function of the RAM, it will be also essential to keep data written therein for a long period exactly as is. Therefore, when the RAM is checked, it is preferable to provide a sufficient time lag between writing data and reading out the same. Therefore, upon running or executing the checking program, the time lag may be provided between the steps 204 and 206. This can be performed by a delaying process step interposed between the steps 204 and 206. However, this may expand the duration of running the program and waste time; therefore, preferably the program will be arranged to contain a job in step 204 such as writing all of the required input data in sequence and then moving to step 206. By this, for the first data written in the RAM at first, there can be provided a time lag. If the time lag thus provided is insufficient, the abovementioned step can be interposed between the steps 204 and 206. In this case, the time lag to be provided by the step as a job is shorter than that required in the above example and will comparably decrease wasting of time.

Referring to FIG. 8, there is illustrated a flowchart which shows in detail the execution of the checking program in use with the checking means in accordance with the preferred embodiment of the invention. It should be noted that hereinafter described in an execution of the checking program in use with the Motorola Model No. MC 6802. However, the specific microcomputer system is used as an example for making a detailed description of the preferred embodiment of the present invention, and it should not considered limitative thereof. The present invention is applicable to all other microcomputer systems which can operate as sought in the invention. In the Motorola Model No. MC 6802, there is provided eight bits of RAM at addresses 0 to 127. Further, at addresses 1200 to 1203 there are respectively stored reference data values 01010101, 10101010, 000000000 and 11111111.

The checking program is started from START. At first, in process step 220, data N<sub>3</sub> counting the running phase of the program is cleared or reset to 0. The data N<sub>3</sub> is stored in an index-register (B-register) of the CPU, for example. In process step 222, an address data N<sub>4</sub> is cleared or reset to 0. The address data N<sub>4</sub> may be also stored in an index-register of the CPU, for example. In process step 224, reference data D<sub>6</sub> stored in address  $1200 \times N_3$  (= 1200) is read out and is written in address  $N_4$  (=0). On a process step 226, the address data is incremented by 1. In process step 228, complement data D<sub>7</sub> of the reference data D<sub>6</sub> is written in address N<sub>4</sub>. In step 230, the address data N<sub>4</sub> is compared with the last address number (=127). If the value of the address data is smaller than that of the last address data, then the program will go back to step 224. At this time, the address data N<sub>4</sub> is incremented by 1 in process step 232. In other words, since the reference data D<sub>6</sub> stored in the address  $1200+N_3 (=0)(=1200)$  is 01010101, the complement data D<sub>7</sub> is 10101010. As will be apparent from the flowchart of FIG. 9, since the beginning address is 0 and the address N<sub>4</sub> is gradually increased in steps 226 and 232, the value N<sub>4</sub> in the step 224 is even and that on the step 228 is odd. Therefore, by this series of execution of the program in the addresses 0 to 127 of the RAM, the reference data  $D_6$  (=01010101) is stored in each even address and the complement data D7 (=10101010) of the reference data D<sub>6</sub> is stored in each odd address. When the address data N<sub>4</sub> reaches 127 and 5 is equal to the last address number, the program goes to the next process step 234. At step 234, the address data, which is 127, is cleared and reset to 0, again. In step 236, the stored data  $D_8$  (=01010101) stored in the address  $N_4$  and the reference data  $D_6$  (=01010101) are read out  $^{10}$ and compared together. If the data D<sub>8</sub> is different from the data D<sub>6</sub>, a jump instruction to executed process step 238 is generated in step 236. In step 238, the NG signal is generated and forwarded to be outputted. When the data values D<sub>8</sub> and D<sub>6</sub> are matched in step 236, the <sup>15</sup> program proceeds to next process step 240. In step 240, the address data N<sub>4</sub> is incremented by 1. In step 242, the stored data  $D_8$  (= 10101010) stored in the address  $N_4+1$ and the reference data  $D_7$  (= 10101010) are read out and compared together. If the data D<sub>8</sub> is different from the <sup>20</sup> data D<sub>7</sub>, a jump instruction to jump the program to the process step 238 is generated. In step 238, NG signal to be outputted is generated. When the data values D<sub>8</sub> and D<sub>7</sub> match, the program goes to step 244. In step 244, the address data N<sub>4</sub> is compared with the last address num- <sup>25</sup> ber (=127). When the value of data N<sub>4</sub> is less than 127, the program goes back to step 236. At this time, the address number N<sub>4</sub> is incremented 1 on a process step 246. Execution of the program in the series of steps 236 to 244 is repeated until the address number reaches 127. 30 When the address data N<sub>4</sub> is 127, in step 244 the value of address data N<sub>4</sub> matches or exceeds the last address number (=127), and the program goes to step 248. In step 248, the phase count data N<sub>3</sub> is read out from the B-register of the RAM and is compared with the last phase count number (=3). When N<sub>3</sub> is less than 3, the program goes back to step 222. At this time, the data N<sub>3</sub> is incremented by 1 on the process step 250. Then, the checking program is run or executed to check the function of the RAM with respect to the reference data 10101010 stored in the address 1201 and the complement data thereof. In the same manner, the checking program is further run and executed with respect to the reference data 00000000 and 11111111 respectively stored in the addresses 1202 and 1203 and the complement data thereof.

When the phase count data N<sub>3</sub> reaches 3 and matches the last phase count number (=3) in step 248, the checking program goes to process step 252 in which an OK signal is generated and forwarded to be outputted. Then, the checking program for checking the function of the RAM reaches the final step END. During running or executing the above-mentioned checking program, writing and reading data, performing the complement operation and the comparing operation is carried out by the A-register of the CPU, for example. The following Table II shows data written in addresses 0 to 9 of the RAM during each phase.

TABLE II

| IADLE II      |           |           |           |           |   |  |

|---------------|-----------|-----------|-----------|-----------|---|--|

| address phase | $N_3 = 0$ | $N_3 = 1$ | $N_3 = 2$ | $N_3 = 3$ | _ |  |

| 0             | 01010101  | 10101010  | 00000000  | 11111111  | _ |  |

| 1             | 10101010  | 01010101  | 11111111  | 00000000  |   |  |

| 2             | 01010101  | 10101010  | 00000000  | 11111111  |   |  |

| 3             | 10101010  | 01010101  | 11111111  | 00000000  | 1 |  |

| 4             | 01010101  | 10101010  | 00000000  | 11111111  |   |  |

| 5             | 10101010  | 01010101  | 11111111  | 00000000  |   |  |

| 6             | 01010101  | 10101010  | 00000000  | 11111111  |   |  |

| 7             | 10101010  | 01010101  | 11111111  | 00000000  |   |  |

TABLE II-continued

| address phase | $N_3 = 0$ | $N_3 = 1$ | $N_3 = 2$ | $N_3 = 3$ |

|---------------|-----------|-----------|-----------|-----------|

| 8             | 01010101  | 10101010  | 00000000  | 11111111  |

| 9             | 10101010  | 01010101  | 11111111  | 00000000  |

As will be understood from the above Table II, during the first and second phases; i.e. during the phases in which the phase count, N<sub>3</sub> is 0 or 1, all the bits of the RAM can be checked as to whether each bit can be written with input data and read out without change;

during the third and fourth phases; i.e. during the phases in which the phase count is 2 or 3, all the bits of the RAM can be checked as to whether each bit can be written with input data and read out without change;

during phase 0, shorting between the same bits in adjacent addresses and adjacent bits in the same address can be checked;

during phase 1, shorting between the same bits in adjacent addresses and adjacent bits in the same address can be checked;

during phase 2, shorting between one bit in an address and adjacent bits to the left and right in adjacent addresses can be checked; and

during phase 3, the same checking operation can be made as in phase 2. By this, it will be appreciated that the checking program need not be executed for all the phases. Namely, for checking all the function of the RAM, it may be sufficient to execute the program for phases 0, 1 and 2, for example, it should be further appreciated that the above-explained flowchart in FIG. 8 can be applied to check the input unit without changing the chart except for the steps 222 to 232. If the flowchart of FIG. 8 is applied to check the input unit, the steps 222 to 232 will be omitted from the chart.

As mentioned above, the checking program as shown in FIG. 9 can perform checking of the functions of the RAM. However, in this way, the data previously stored in the RAM to be checked will necessarily be cleared or rewritten during execution of the checking program. In order to execute the control program, all of the data, some of which was previously stored and cleared during running of the checking program, should be re-written into the RAM after finishing the checking operation. This causes a waste of time due to writing of the data. If the data stored in the RAM is a history, for example, which can not be restored, it will be impossible to run or execute the checking program without losing some data. Therefore, it is recommendable that the necessary data is restored in other storage means such as, for example, in a temporary memory. However, if the control system is provided with the temporary memory, the RAM memory must be provided with a capacity twice that required for carrying out control operations. Otherwise, for restoring the necessary and important data in the RAM, there will be required another RAM connected to the former. For eliminating such a difficulty and drawback in the former flowchart, 60 there is shown another flowchart of checking a program which can solve the above-mentioned problems, in FIG. 8. In the flowchart shown in FIG. 9, the addresses of the RAM 0 to 127 are divided into sixteen blocks, i.e. block Nos. 0 to 15. Each block is checked in 65 sequence after finishing the check of the previous block. Upon executing the checking program for one of the blocks, data stored in the block is transferred and stored in the previous block to maintain the storage.

As shown in FIG. 9, immediately after START of executing the checking program, an address data N<sub>9</sub> is cleared and reset to 0 in process step 260. It should be noted that, in this chart, the address data N<sub>9</sub> indicates not individual addresses but the blocks of addresses previously divided. In step 262, the address data No is compared with the last block number 15. When the value of the address data N<sub>9</sub> is smaller than 15, the program proceeds to process step 264. In steps 264 and 266, the data stored in each address is read out and 10 checked in order by way of comparing the data with the reference data. The manner of checking in step 264 is substantially the same as illustrated in FIGS. 7 and 8. When the data stored and read out from each address of the block is matched with the corresponding reference 15 data, the step of the checking program goes to a process step 268. In step 268, the data stored in the next block N<sub>9</sub>+1 is transferred and stored in the block N<sub>9</sub>. Thereafter, the address data N<sub>9</sub> is incremented by 1 in process step 270. Then, the program goes back to step 262. The 20 series of steps 262 to 260 are repeatedly carried out until the address data reaches 16. When the address data N<sub>9</sub> is 16 in step 262, the value of the address data N<sub>9</sub> exceeds the last block number 15, and the program step goes to process step 272. In step 272, an OK signal is 25 generated and transmitted to be outputted, and N9 is decremented by one. Then, in step 274, the address data No is compared with the first block number 0. When the address data N<sub>9</sub> is larger than 0, the program goes to process step 276. In step 276, the data stored in the 30 block N<sub>9</sub>-1 is transferred and stored in the block N<sub>9</sub>. Thereafter, the address data N<sub>9</sub> is decremented by 1 on a process step 278. Then, the step goes back to the step 274. The series of steps 274 to 278 will be repeated until the address data N<sub>9</sub> and the first block number 0 match. 35 to 1000 in process step 302. If the result of checking in step 264 determines an error in step 266, the program goes to a process step 280. In step 280, an NG signal is generated and transmitted to be outputted. Thereafter, in step 274, the address data No is compared with the first block number 0. When the 40 address data N<sub>9</sub> is larger than 0, the program step goes to a process step 276. In step 276, the data stored in the block N<sub>9</sub>-1 is transferred and stored in the block N<sub>9</sub>. Thereafter, the address data N<sub>9</sub> is decreased by 1 in process step 278. Then, the program goes back to the 45 step 274. The series of steps 274 to 278 will be repeated until the address data N<sub>9</sub> and the first block number 0 match. Thereby, the functions of all the addresses of the RAM can be checked, and the previously stored data may be maintained except the data in the block 0. Thus, 50 N<sub>5</sub> reaches 3999 which matches with the last address only unimportant data should be stored in block 0.

Now referring to FIG. 10, there is shown a flowchart of a checking program for checking functions of the ROM. Since the function of the ROM is to store programs to be run in the CPU and data for running the 55 program in the form of a binary code or decimal representation, the checking is carried out by reading out the data stored in the ROM and comparing the data read with the data which should be stored in the addresses. Therefore, the checking may be performed, in practice, 60 by comparing the data read with the reference data. The control program and the data thereof will be stored in the ROM<sub>1</sub> 31 of FIG. 1, and the checking program and the reference data will be stored in the ROM<sub>2</sub> 32 of FIG. 1. For performing checking of the function of the 65 ROM, the stored data in each address of the ROM<sub>1</sub> 31 is read out in order and compared with corresponding reference data stored in corresponding addresses of the

ROM<sub>2</sub> 32. When ROM<sub>1</sub> 31 is functioning correctly, the data read therefrom should match with the corresponding reference data. By the above method of checking, the function of the ROM<sub>1</sub> 31 can be checked. However, in such a process, ROM<sub>2</sub> 32 is required to have at least the same capacity as the ROM<sub>1</sub> 31. If the ROM<sub>2</sub> 32 is contained in the control system as a component, it necessarily increases the size of the ROM 30 of FIG. 1 comprising ROM<sub>1</sub> 31 and the ROM<sub>2</sub> 32. This may also cause an increase of the cost of the system. For avoiding such a drawback, it is preferable to perform checking the function of the ROM in use with a ROM and arithmetic unit provided outside the system. It will be appreciated that, if necessary, the CPU in the system can be used as an arithmetic unit for performing the checking operation. However, there is disclosed hereinafter an example of the use of a ROM and arithmetic unit provided outside the system. In this case, the data stored in the ROM of the system is read out therefrom and outputted to the arithmetic unit. At the same time, corresponding reference data is read from the ROM outside the system. The arithmetic unit operates to compare the data to see if they match. By this, only a program for reading out the stored data from the ROM of the system and outputting the same is required in the control system for checking the function of the ROM therein. Thereby, the control system can be reduced in size and cost. FIG. 10 is a flowchart of a program for reading and outputting the data stored in the ROM of the system. It should be noted that hereinafter disclosed is an example of a case in which the data is stored in addresses 1000 to 3999" of the ROM. Immediately after the START of the program, an address data N<sub>5</sub> which is generally stored in an index-register of the CPU, is set

In the next process step 304, data D<sub>9</sub> stored in the address  $N_5$  (= 1000) of the ROM is read out. The data D<sub>9</sub> read is outputted through the output unit of the system, which method of output will be illustrated later, in a process step 306. Then, the address data is compared with the last address number (=3999) in a step 308. When the value of the address data N<sub>5</sub> is less than the last address, control goes to process step 310. In step 310, the address data N<sub>5</sub> is incremented by 1. Then control returns to process step 304 wherein the data D<sub>9</sub> stored in the address  $N_5+1$  of the ROM is read out. By repeating the above-mentioned series of steps 304 to 310, the function of all the addresses 1000 to 3999 of the ROM can be checked in order. When the address data number, the step 308 makes a decision that the checking program has run fully and finishes the job. The data read out and outputted is checked by comparing with the reference data corresponding thereto which is stored in the ROM provided outside the control system. It will be understood that the checking program is run in the arithmetic unit to which the data read from the ROM of the system and the reference data read from the ROM for checking are transferred and in which the comparison operation is carried out with respect to both

Now we explain a method for outputting the data from the control system. For outputting the data, there are provided a plurality of output terminals, the number of terminals corresponding to the number of data. It will be preferable that, since the outputting of the data is made by way of time sharing, the clock-pulse normally applied to the control system is outputted to the arith-

metic unit for controlling the later in synchronism with the control system. This may result in eliminating the time lag between the operations of the control system and the arithmetic unit. This is also advantageous in making the checking operation accurate. Although the above-mentioned output system is preferable from the point of view of accuracy of checking result, it has the disadvantage that it requires a large number of output terminals in the control system. For avoiding and eliminating such a drawback or disadvantage, it will be prac- 10 tical to modulate the form of output data by pulse code modulation and to perform a parallel-serial conversion on the output data. By this, an output signal consisting of several bits, for example eight bits, of data can be outputted by one output line. Thereby, the number of 15 output terminals provided on the control system can be considerably reduced. Further, by reducing the output terminals, it will be possible to increase durability of checking.

Hereafter disclosed is an example actually applicable 20 to the control system of the present invention. In this example, for converting the parallel data to the serial data, there is employed a parallel-serial convertor, such as, for example, Motorola Model No. 6850 or Motorola Model No. 6852. The output data from the CPU is 25 inputted and written in the parallel-serial convertor and is converted into a serial pulse code train. It is apparent that, in recent years, there have been developed microcomputer systems incorporating such parallel-serial converters, and if such a microcomputer is used, a fur-30 ther converter is unnecessary.

Although the above-mentioned output method can simplify the construction of the output circuit, it may increase the cost thereof. In view of the cost, it will be preferable to convert the parallel code data to serial 35 code data without using a parallel-serial convertor. FIG. 11 shows a way of converting the output data from the CPU into a parallel code or pulse code train,. It should be noted that in FIG. 11 there is shown a process step corresponding to the process step 306 of 40 FIG. 10 and in this step eight bits of data are converted from parallel code to serial code. After the START of the program, first the output is cleared to the value 0 in step 320. It should be noted that, in this program, a start-bit signal and stop-bit signal are generated and 45 outputted to the arithmetic unit so as to start and stop execution of the program. The start-bit signal is generated by clearing the output from the value 1 to 0 and the stop-bit signal is generated by setting the output value to 1. Thus, when the output value is cleared from the 50 value 1 to 0 and the arithmetic unit detects the start-bit signal, the program is started. After starting the arithmetic unit, the execution of the program is delayed in process step 322 by a period t<sub>1</sub> in order to adjust the interval for modulating the output data to a constant. 55 This delay will be carried out by repeatedly executing NO OPERATION instructions or executing a looping program, which may have no meaning, for the required period. Thereafter, in process step 324, phase count N<sub>6</sub> is cleared to 0. In process step 326, the least significant 60 bit of data D<sub>9</sub> is outputted to the arithmetic unit. In process step 328, the contents of D<sub>9</sub> are shifted one bit to the right, so that the bit above the least significant bit becomes the next bit to be outputted. After the operation of the step 328, a delay time t<sub>2</sub> is provided by pro- 65 cess step 330. The method for providing the delay time t<sub>2</sub> is substantially the same as that explained with respect to step 322. After expiration of the delay time t2, the

phase count N<sub>6</sub> is incremented by 1 in process step 332. Then data N<sub>6</sub> is compared with 8 in step 334. When the value of N<sub>6</sub> is less than 8, the program goes back to step 326 to repeatedly execute the series of steps 326 to 334. The series of operation may be repeated until the value of the phase count N<sub>6</sub> reaches or exceeds the value 8 in step 334. Actually, in the above disclosed example, the series of operation is repeated eight times. When a decision that the data N<sub>6</sub> is equal to or more than 8, control goes to process step 336 in which the stop bit signal is outputted to the arithmetic unit. After expiration of a delay time t<sub>3</sub> provided by a process step 338, the program reaches END. The delay time t<sub>3</sub> is provided for the purpose of waiting for the arithmetic unit to finish the checking operation. Therefore, if the checking operation by the arithmetic unit can be finished in a substantially short period, step 338 is unnecessary and can be omitted.