# Hiyoshi et al.

[45] Reissued Apr. 20, 1982

| [54]        | ENVELOP         | E GENERATOR                                                                                                                            |

|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [75]        | Inventors:      | Teruo Hiyoshi; Akira Nakada, both of Hamamatsu; Tsutomu Suzuki, Shizuoka; Eiichiro Aoki, Hamamatsu; Eiichi Yamaga, Tokyo, all of Japan |

| [73]        | Assignee:       | Nippon Gakki Seizo Kabushiki<br>Kaisha, Hamamatsu, Japan                                                                               |

| [21]        | Appl. No.:      | 154,992                                                                                                                                |

| [22]        | Filed:          | May 30, 1980                                                                                                                           |

|             | Relat           | ed U.S. Patent Documents                                                                                                               |

| Reiss       | ue of:          |                                                                                                                                        |

| [64]        | Patent No.      | .: 4,178,826                                                                                                                           |

|             | Issued:         | Dec. 18, 1979                                                                                                                          |

|             | Appl. No.:      |                                                                                                                                        |

|             | Filed:          | Oct. 6, 1977                                                                                                                           |

| [30]        | Foreig          | n Application Priority Data                                                                                                            |

| O           | ct. 8, 1976 [JI | P] Japan 51-120936                                                                                                                     |

| [51]        | Int. Cl.3       | G10H 1/02                                                                                                                              |

| -           |                 | 84/1.26; 84/1.13                                                                                                                       |

| <del></del> |                 |                                                                                                                                        |

# [56] References Cited U.S. PATENT DOCUMENTS

| 3,515,792 | 6/1970  | Deutsch        | 84/1.24 |

|-----------|---------|----------------|---------|

| 3,610,805 | 10/1971 | Watson et al.  | 84/1.26 |

| 3,854,365 | 12/1974 | Tomisawa et al | 84/1.24 |

| 3,977,291 | 8/1976  | Southard       | 84/1.13 |

| 4,079,650 | 3/1978  | Deutsch        | 84/1.13 |

| 4 083 285 | 4/1978  | Chihana        | 84/1.26 |

Primary Examiner—J. V. Truhe

Assistant Examiner—Forester W. Isen

Attorney, Agent, or Firm—Spensley, Horn, Jubas &

# [57] ABSTRACT

Lubitz

An envelope generator comprises a counting circuit and counting control means capable of controlling a counting mode of the counting circuit, i.e., operation and non-operation of the counting circuit, counting speed, addition and subtraction etc., in accordance with an envelope shape to be obtained. There are various predetermined counting modes corresponding to different envelope shapes and the envelope generator includes selection means for causing the counting control means to select a desired one of the counting modes.

#### 16 Claims, 30 Drawing Figures

364/722

Apr. 20, 1982

Apr. 20, 1982

.

## **ENVELOPE GENERATOR**

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

# BACKGROUND AND SUMMARY OF THE INVENTION

This invention relates to an envelope generator of an electronic musical instrument.

In a conventional envelope generator, a single envelope shape of a predetermined shape is stored in an envelope memory and this envelope shape is read out of the envelope memory by driving a readout control counter with a constant clock pulse. Accordingly, only one envelope shape can be produced by one such conventional envelope generator.

It is an object of the present invention to provide a novel envelope generator capable of selectively producing envelope shapes of different shapes with a single memory and counter. According to the invention, contents of a memory are so set that the amplitude level of an envelope shape will correspond to a count value of a 25 memory readout control counter whereby an envelope shape whose amplitude varies in accordance with variation in the count value of the counter is produced. Further, various counting modes of the counter are set by a counter control circuit in accordance with various en- 30 velope shapes and a desired one of such envelope shapes is selectively produced by controlling the counting operation of the counter in accordance with a selected one of such counting modes. The term "counting modes" means modes of all elements concerning the 35 counting operation of the counter including timings of starting, stopping and resuming counting, an order of upcounting and downcounting, a counting speed (i.e. a rate of a counting clock pulse) and a switching timing of the counting speed. A term "mode" hereinafter used 40 signifies the above described "counting mode".

In the embodiment of the present invention to be described hereinbelow, four kinds of envelope shapes, i.e., "direct keying mode (A)", "sustain mode (B)", "percussive damp mode (C)" and "percussion mode 45 (D)" as shown in FIG. 8 can be produced. An envelope generation control logic is provided for selectively controlling the counting operation of the counter with respect to each of the above described four kinds of modes. This selection is designated by an envelope 50 mode select signal. The selected counting mode can be changed by a curve select signal.

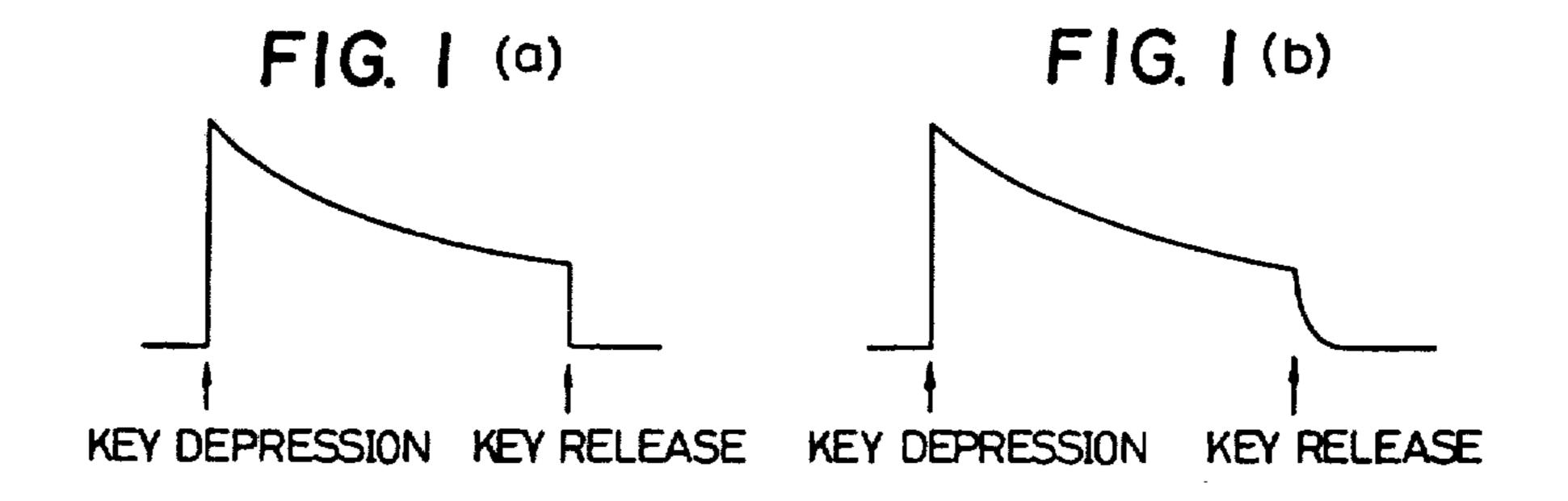

In a case where the envelope shape of the percussive damp mode is generated by a conventional envelope generator of a type wherein an envelope shape is read 55 out by using a counter and an envelope memory, the envelope abruptly falls upon release of a depressed key, as shown in FIG. 1(a). This abrupt fall of the envelope causes an ending of a musical tone resembling a click sound. The envelope of the percussive damp mode is 60 generally used for simulating a sound which is produced when a depressed piano key is released during production of a tone and the sound resembling a click sound is undesirable for an ending of a piano tone. According to the present invention, the envelope in the 65 percussive damp mode is provided with a decay shape which, as shown in FIG. 1(b), falls quickly upon release of the depressed key in response to a high rate damp

clock pulse whereby generation of the undesirable click sound is prevented.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1(a) is a graphical diagram showing an envelope shape of the percussive damp mode generated by digital processing employing a conventional envelope counter;

FIG. 1(b) is a graphical diagram showing an envelope shape of the percussive damp mode to be generated by the envelope generator according to the present invention;

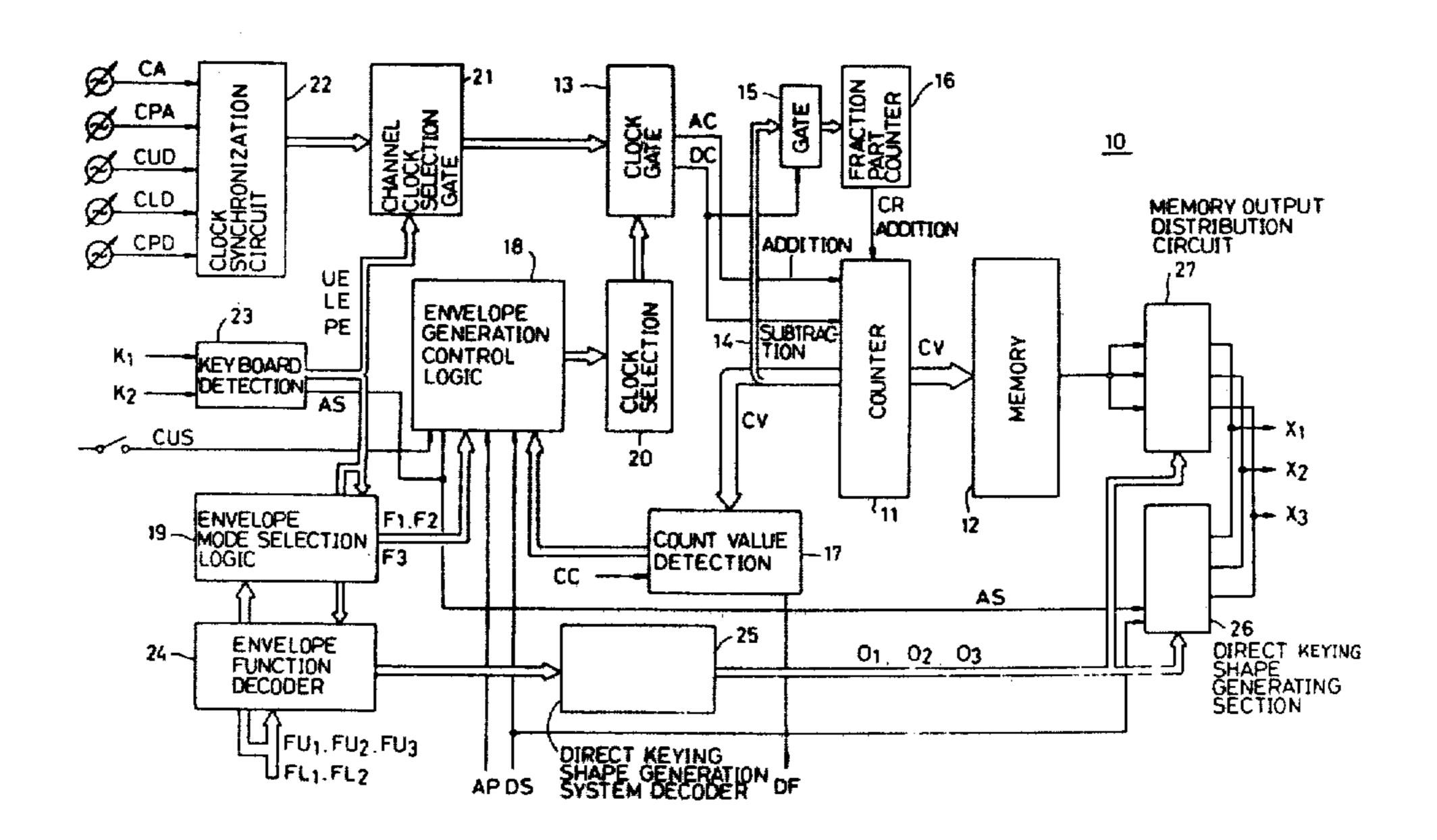

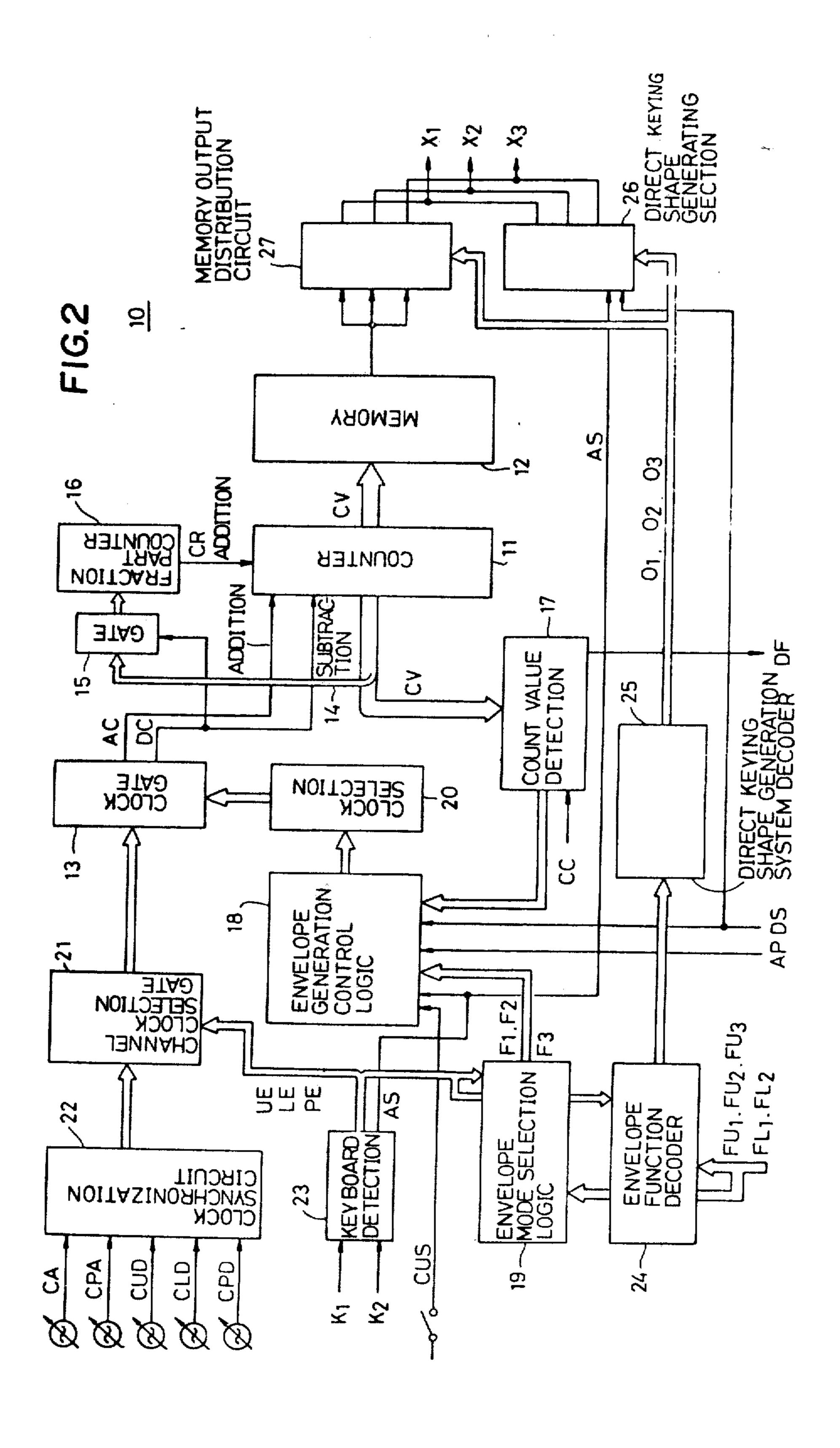

FIG. 2 is a block diagram illustrating one example of the envelope generator according to this invention;

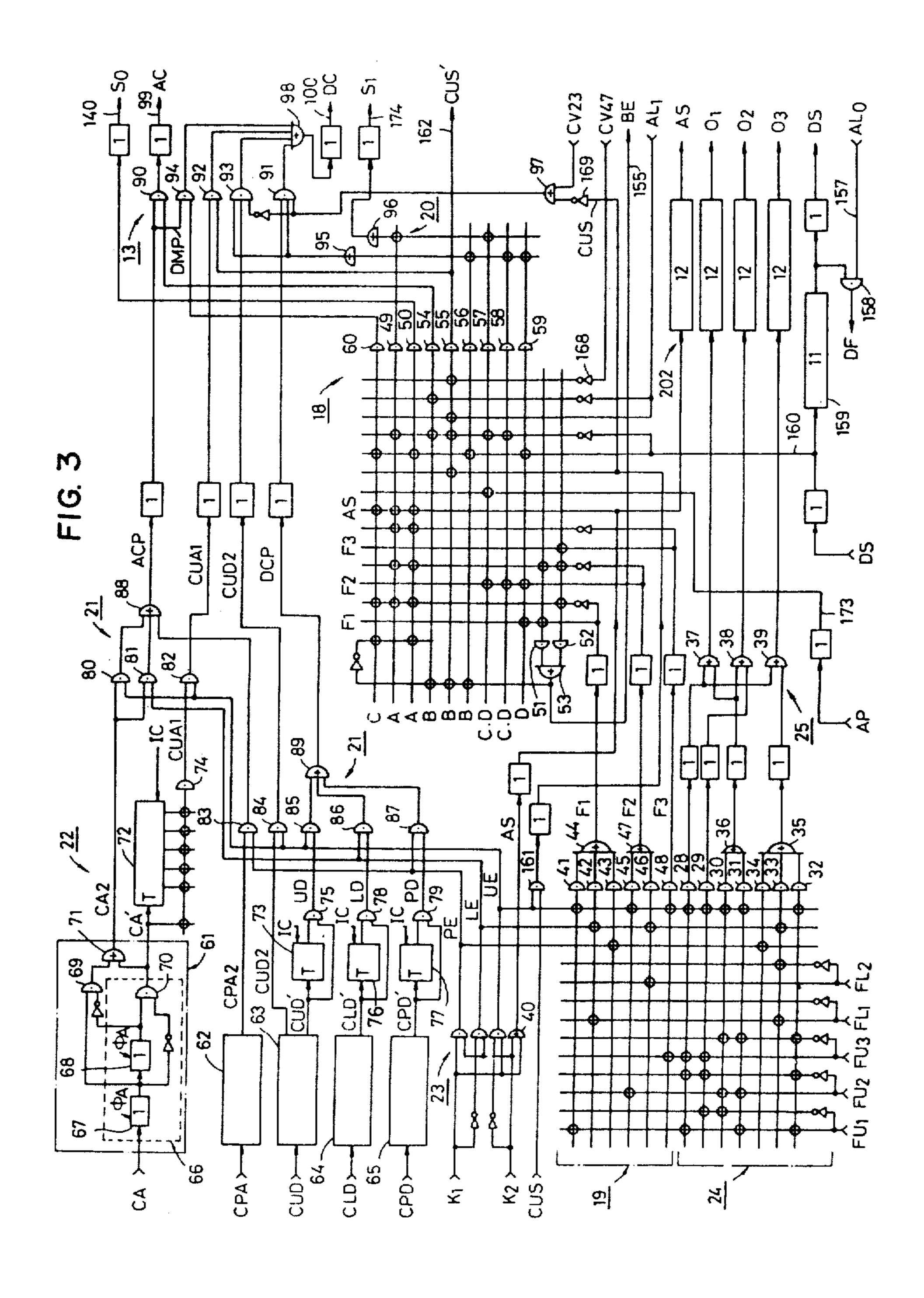

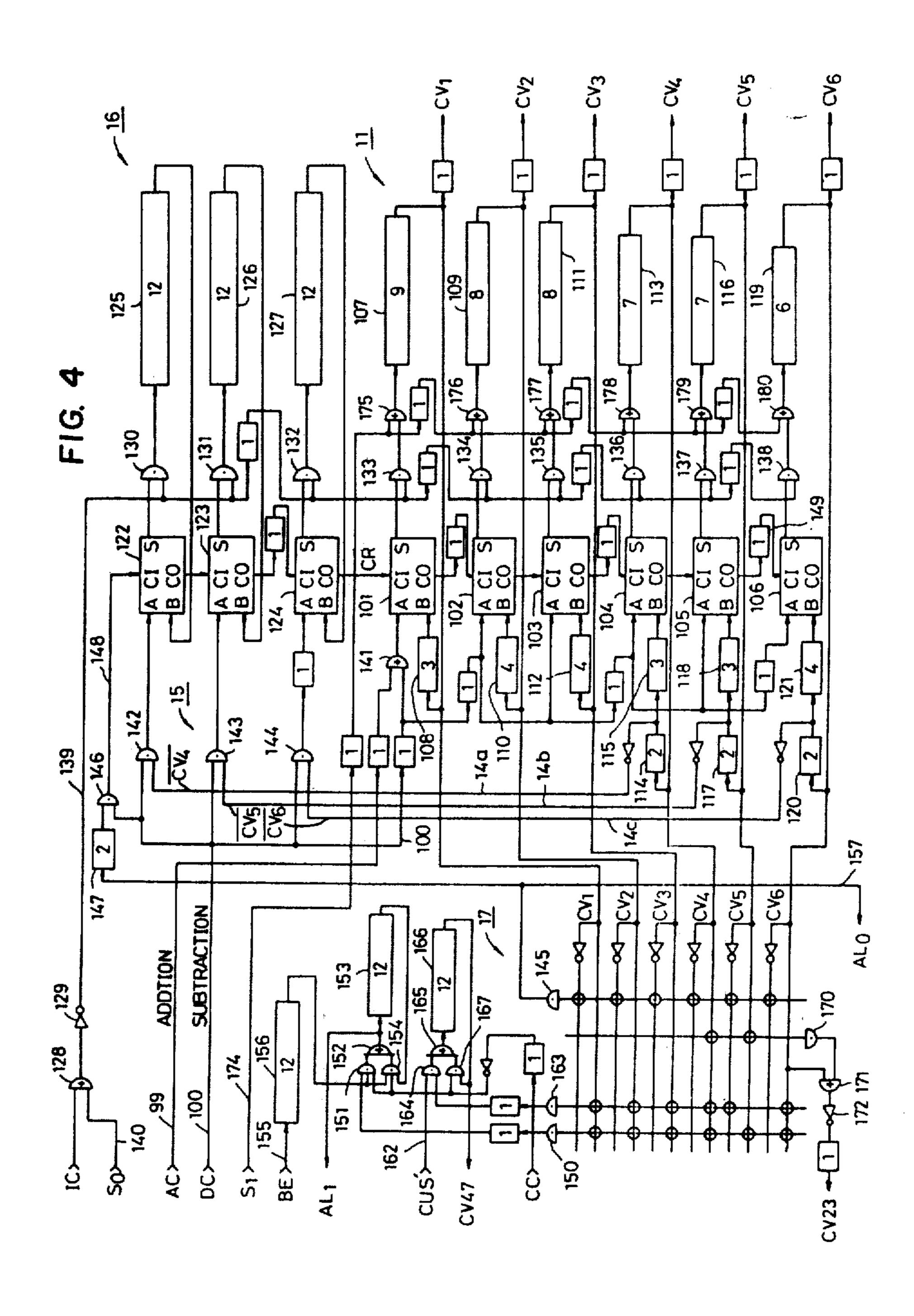

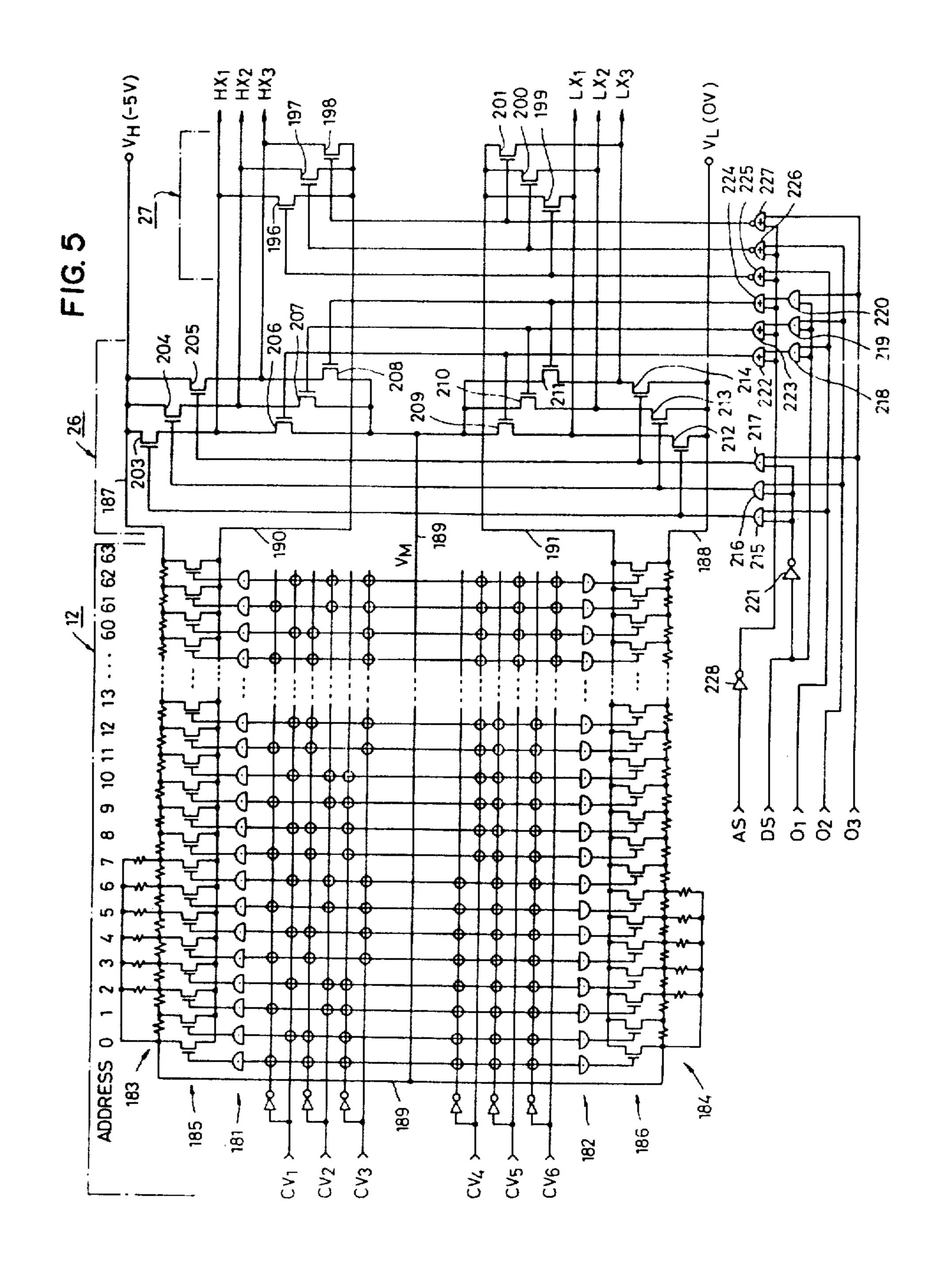

FIGS. 3, 4 and 5 are three parts of FIG. 2, FIG. 3 being a block diagram showing circuit elements around a count operation control section in detail, FIG. 4 being a block diagram showing circuit elements around a counter section in detail, FIG. 5 being also a block diagram illustrating circuit elements around a memory section in detail.

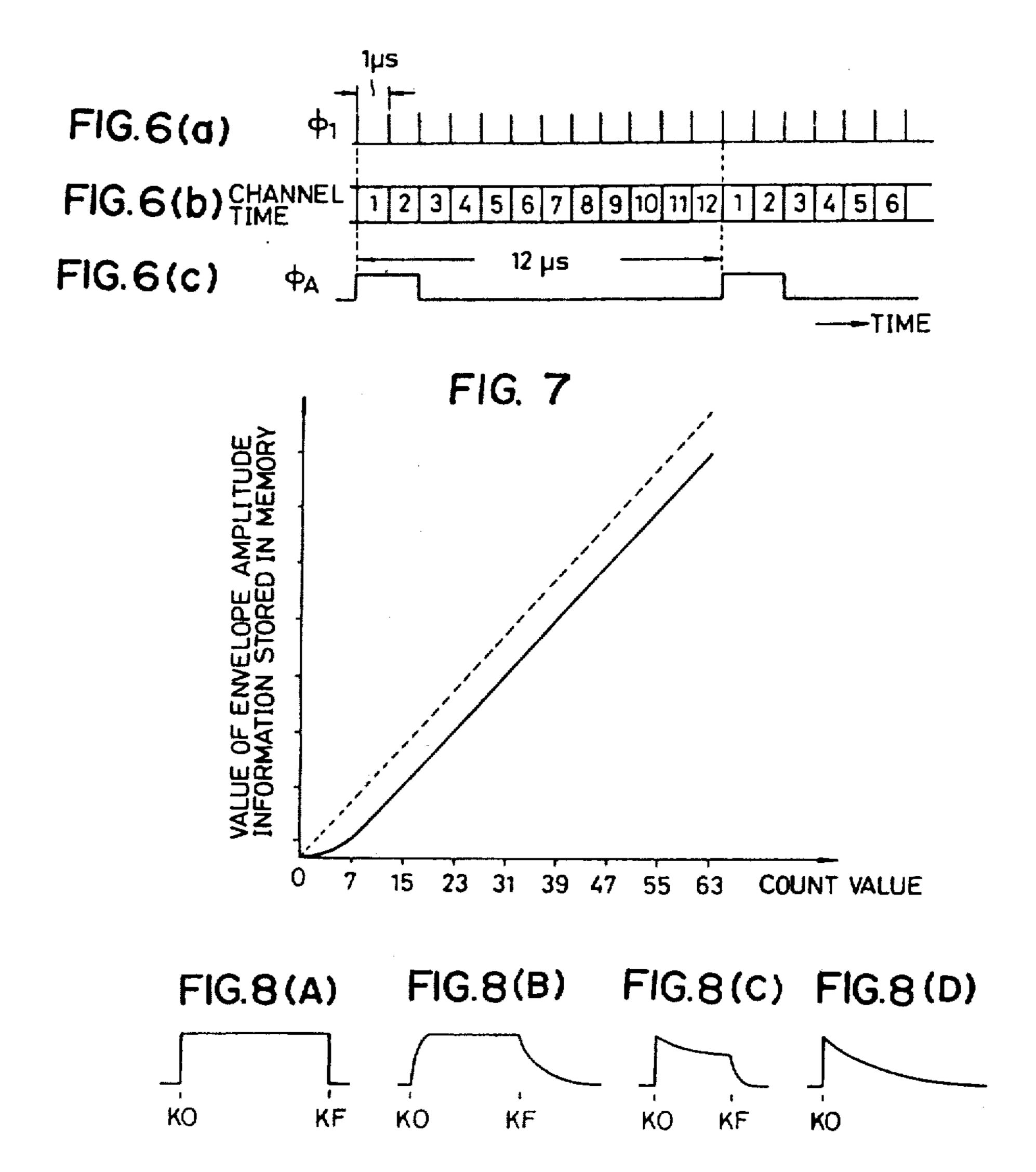

FIGS. 6A-6C are a set of timing graphs indicating the time relation of clock pulses employed in the envelope generator shown in FIG. 2;

FIG. 7 is a graphical representation indicating relationships between the count values of a counter and the contents stored in a memory employed in the envelope generator.

FIG. 8A-8D are a set of graphs indicating envelope shapes in various modes which can be generated by the aforementioned envelope generator;

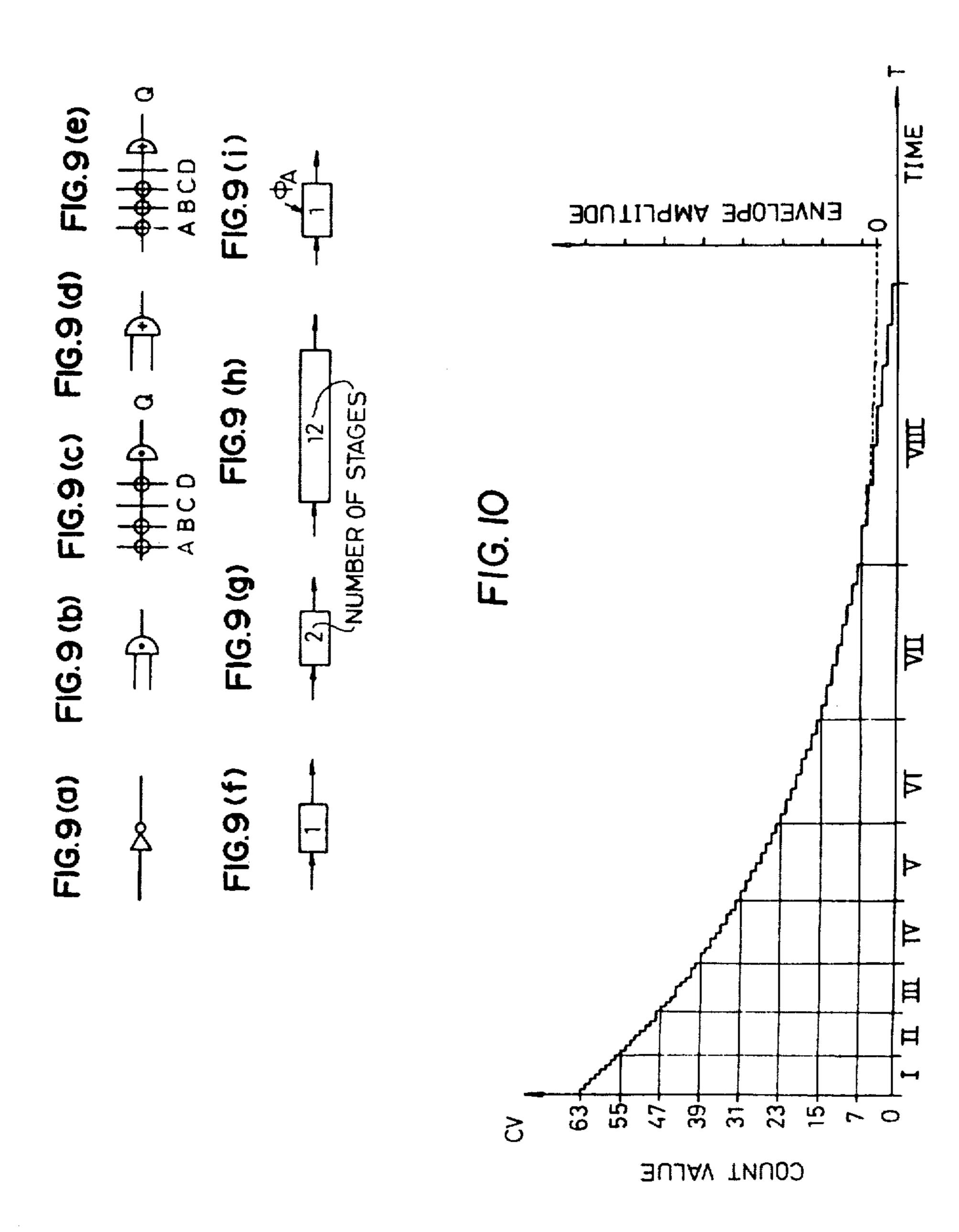

FIGS. 9A-9I are a set of diagrams indicating methods of illustrating a variety of circuit elements;

FIG. 10 is a graphical representation indicating variations in count value of a counter in detail in the case where a decay envelope shape of exponential characteristic is generated by the polygonal line approximation with envelope amplitude levels on the right-hand vartical line, count values in the last region VIII being converted into exponential function values as indicated by the broken line;

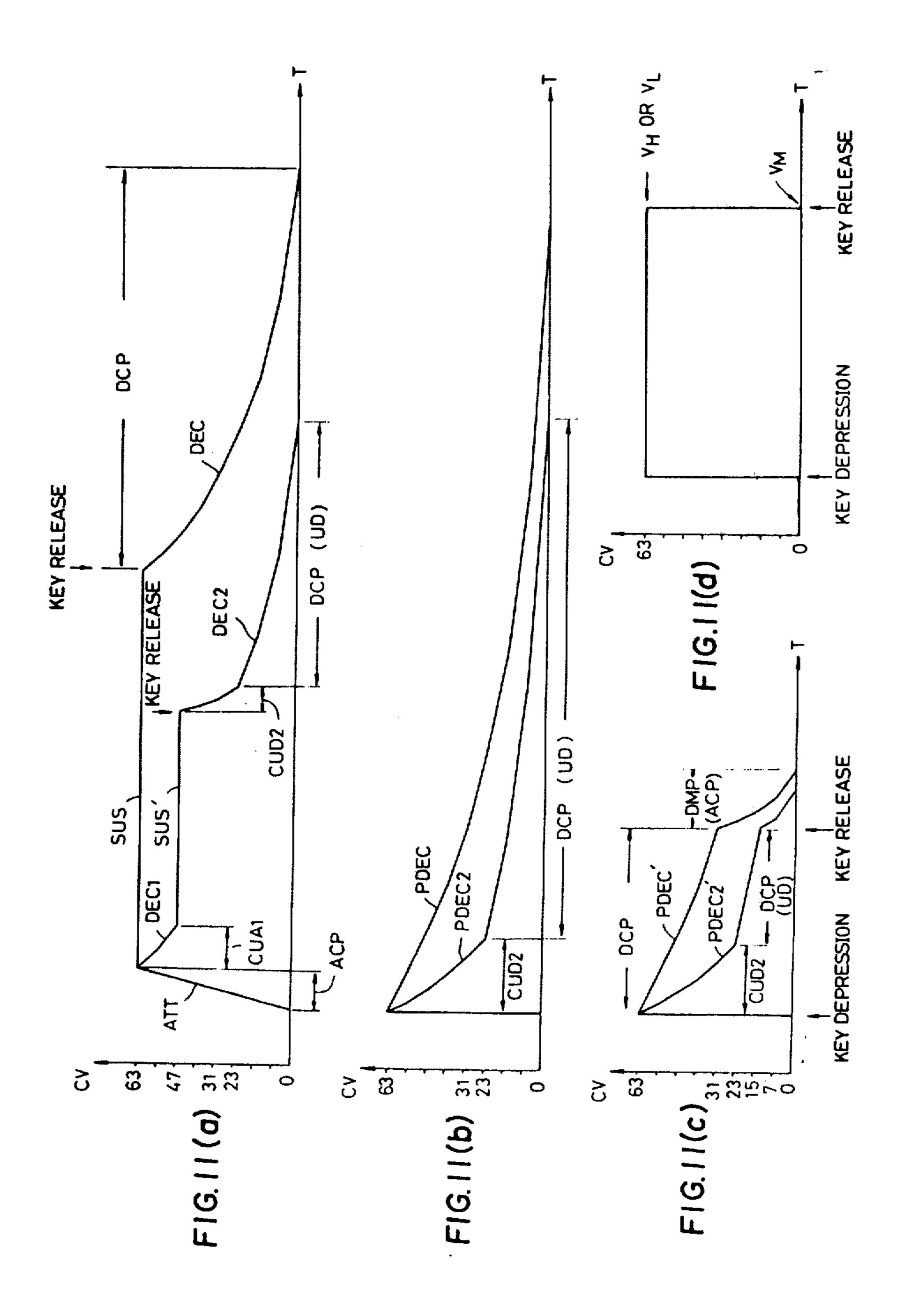

FIG. 11 is a set of graphical representations schematically indicating the variations in count value of the counter in providing various envelope modes, FIG. 11(a) through FIG. 11(d) showing a sustain mode, a percussion mode, a percussive damp mode, and a direct keying mode, respectively, and an ordinary mode and a mode in which a curve selection function is effected being plotted in each of FIG. 11(a) through FIG. 11(c);

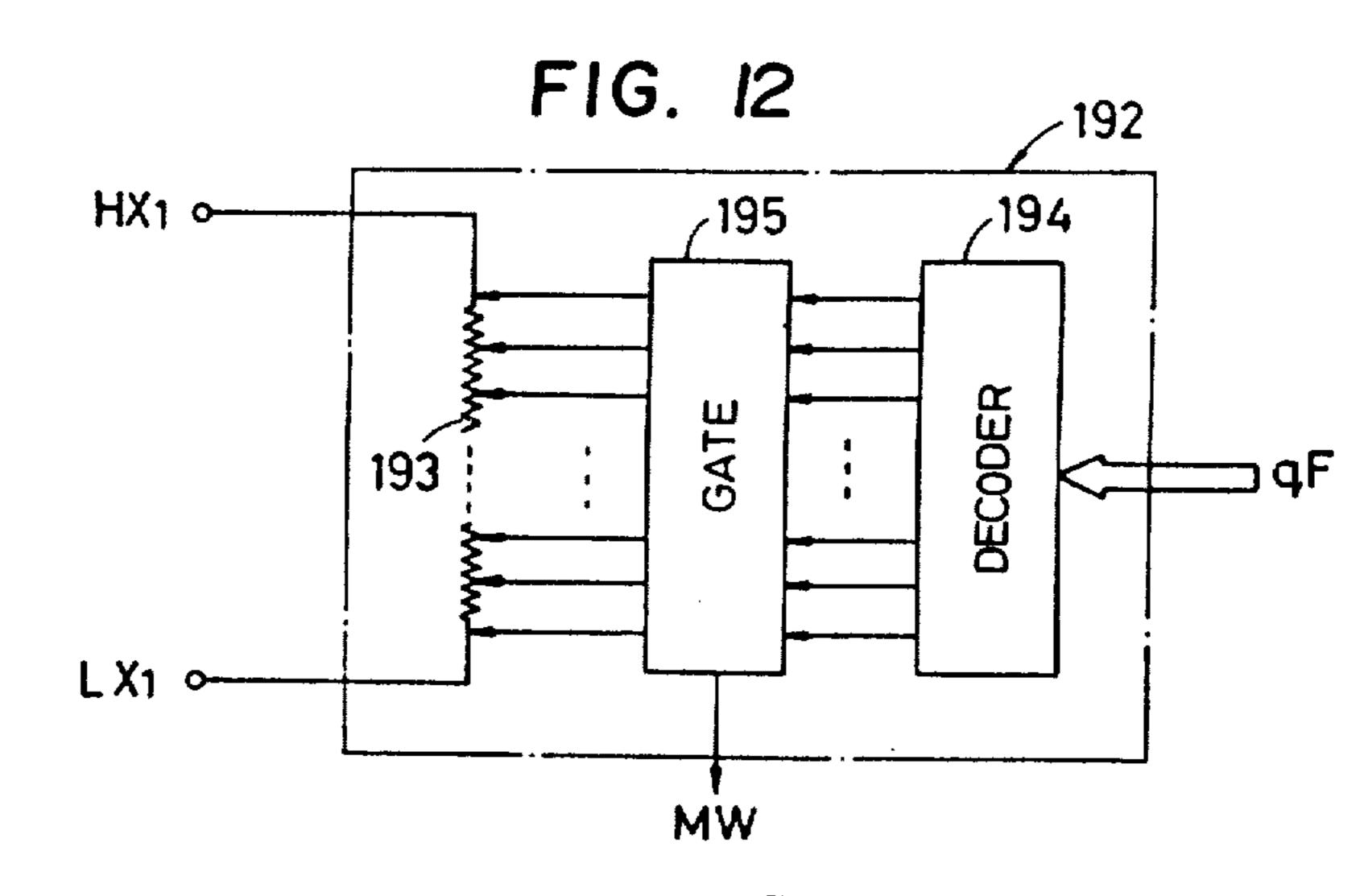

FIG. 12 is a block diagram illustrating one example of a musical tone shape memory in an electronic musical instrument utilizing envelope shapes generated by the envelope generator described above; and

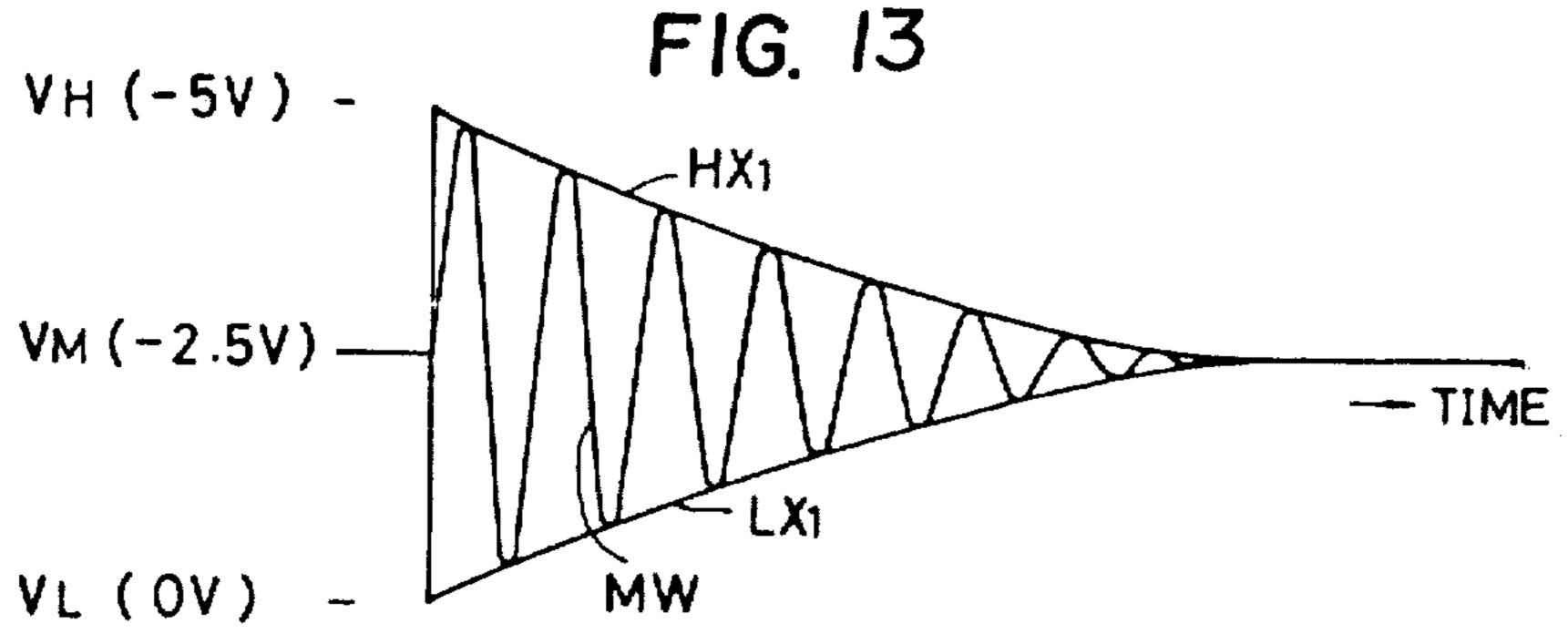

FIG. 13 is a graphical representation schematically indicating a state that an envelope is given to a musical tone signal in the circuit shown in FIG. 12.

# DETAILED DESCRIPTION OF THE INVENTION

One preferred embodiment of this invention will be described with reference to the accompanying drawings.

Shown in FIG. 2 is an envelope generator 10 which is utilized for envelope control of an electronic musical instrument. A keyboard code K<sub>1</sub>, K<sub>2</sub> is produced when a key of a keyboard (not shown) is depressed, and it represents the sort of keyboard to which the key thus depressed belongs. The relationships between the con-

tents of the key codes K<sub>1</sub>, K<sub>2</sub> and the sorts of keyboards are as indicated in Table 1 below:

TABLE 1

|                | K <sub>1</sub> | K <sub>2</sub> |

|----------------|----------------|----------------|

| Upper keyboard | į              | 0              |

| Lower keyboard | 0              | 1              |

| Pedal keyboard | 1              | ł              |

A decay start signal DS is provided when the depression of the key which has produced the aforementioned keyboard code K<sub>1</sub>, K<sub>2</sub> is released. When the envelope generator 10 has produced one envelope shape, a decay finish signal DF is provided, as described later. If the decay start signal DS and the decay finish signal DF are provided simultaneously, a clear signal CC is produced. Upon production of this clear signal CC, the decay start signal DS and the keyboard code K<sub>1</sub>, K<sub>2</sub> are cleared. Accordingly, the keyboard code K<sub>1</sub>, K<sub>2</sub> is kept produced for the period of time from the depression of key 20 to the generation of the clear signal CC, and represents the fact that the tone of the key depressed is being produced by the electronic musical instrument. On the other hand, the decay start signal DS is produced for the period of time from the release of key to the production of the clear signal CC, and represents the fact that the tone of the key depressed is being produced but decayed. An attack pulse AP is a single pulse which is produced when a key is depressed.

These signals K<sub>1</sub>, K<sub>2</sub>, DS, CC and AP are produced by a tone production assignment circuit (not shown), which may be referred to as "a key assignor" or "a channel processor" of the electronic musical instrument, and are applied to the envelope generator 10. The tone production assignment circuit is capable of simultaneously producting plural tones through time sharing treatment and assigning the tone of one depressed key to one of a plurality of time-shared tone production channels. Accordingly, the above-described signals K<sub>1</sub>, K<sub>2</sub>, DS, CC and AP are supplied in time-sharing manner in synchronization with the time of the channel assigned to which production of the tone of the depressed key has been assigned. Therefore, the envelope generator 10 operating by receiving these signals K<sub>1</sub>, K2, DS, CC and AP can carry out a time sharing operation which is illustrated in FIGS. 3 to 5 in detail.

FIG. 6(a) is a graphical representation indicating a main clock pulse  $\phi_1$  which is adapted to control the time sharing operation of each channel. The period of the main clock pulse is, for instance, one microsecond  $(10^{-6} \text{ second})$ . As the number of channels is twelve <sup>50</sup> (12), time slots (each having I microsecond in time width) obtained by sequentially dividing time with the clock pulses  $\phi_{11}$  correspond to the first to twelfth channel times, respectively. Hereinafter, as is shown in FIG. 6(b) the time slots will be referred to as the first through 55 twelfth channel times, respectively, when applicable. It goes without saying that the channel times are cyclically provided. A synchronization clock pulse  $\phi_A$  as shown in FIG. 6(c) has a period of twelve microseconds and is employed for allowing an attack clock pulse and 60 a decay clock pulse (described later) to synchronize with the whole channel time (12 microseconds).

Referring back to FIG. 2, the count output of a counter 11 is applied to a memory 12 where it is converted into envelope amplitude information whose 65 value corresponds to the count value CV thereof. The contents in the memory 12 are as shown in FIG. 7, for instance, showing an exponential characteristic in the

4

vicinity (0-7) of the count value 0 and a linear characteristic in the other count values (8-63). It goes without saying that amplitude information indicating a linear relation with the whole count values (0-63) as shown by

the broken line may be stored in the memory 12.

The count value of the counter 11 is increased by the attack clock pulses AC supplied from a clock gate 13 thereto and is decreased by the decay clock pulses DC also supplied from the clock gate 13 thereto. In the case where an exponentially varying decay envelope is obtained by the polygonal line approximation, the data of predetermined higher significant bits in the counter 11 is fed back to a fraction part counter 16 through a line 14 and a gate 15 at a timing of the decay clock pulse DC. A carry signal CR is provided as a result of the computaion effected by the fraction part counter 16. This carry signal CR is applied to the addition input of the counter 11. Accordingly, the extent of the subtraction by the decay clock pulses DC is changed according to the frequency of application of the carry signals CR, and the count value CV is changed exponentially.

The change with time of the count value CV of the counter 11 corresponds to the shape of the envelope generated. Therefore, a variety of envelope shapes can be obtained by controlling the count operation of the counter 11. A count value detecting circuit 1 operates to detect the fact that the count value of the counter 11 has reached a predetermined value, and to supply a signal representative of a state of the counter 11 to an envelope generation control logic 18. This envelope generation control logic 18 operates to generate an envelope shape as desired by controlling the addition or subtraction, count speed, count start, and count stop of the counter 11. The mode of an envelope shape is determined with the aid of envelope mode selecting signals F1-F3 provided by an envelope mode selection logic 19. Furthermore, the shape of the envelope shape designated by the envelope mode selecting signals F1-F3 can be switched by a curve selecting signal CUS applied to the envelope mode selection logic 19.

A clock selection circuit 20 operates to open the clock gate 13 with the aid of the output of the envelope generation control logic 18, and to allow one of a plurality of clock pulses supplied from a channel clock selection gate 21 to be applied, as the attack clock pulse AC or the decay clock pulse DC, to the counter 11. In this example, different attack clock pulses or decay clock pulses are employed separately according to the sorts of keyboards, whereby with the same envelope shape the attack time or the decay time is changed separately according to the sorts of keyboards. Therefore, attack clock signals CA for the upper and lower keyboards, an attack clock signal CPA for the pedal keyboard, a decay clock signal CLD for the lower keyboard, a decay clock signal CUD for the upper keyboard, and a decay clock signal CPD for the pedal keyboard are generated separately and are applied through a clock synchronization circuit 22 to the channel clock selection gate 21. The clock synchronization circuit 22 operates to cause the pulse widths of the aforementioned clock signal CA-CPD to synchronize with one cyclical period (12 microseconds) of the whole channel time.

A keyboard detection circuit 23 serves to decode the keyboard code K<sub>1</sub>, K<sub>2</sub> and to output an upper keyboard signal UE, a lower keyboard signal LE, or a pedal keyboard signal PE according to the content thereof. If

either of the data  $K_1$  and  $K_2$  is "1", the keyboard detection circuit 23 produces an attack start signal AS representing that by the depression of the key, the concerning channel should be in a tone production mode. The keyboard signals UE, LE, and PE operate to open the 5 channel clock selection gate 21 in time sharing manner according to the respective time slots corresponding to their generations, and to select in time sharing manner the clock pulses corresponding to the keyboards of the tones assigned to the channels. The clock pulses thus 10 selected are multiplexed separately according to the attack clock pulse and the decay clock pulse, and are supplied to the clock gate 13.

The envelope mode selection logic 19, basing on envelope function switching data FU<sub>1</sub>, FU<sub>2</sub>, FU<sub>3</sub>, FL<sub>1</sub> 15 and FL<sub>2</sub> and the keyboard signals UE, LE and PE, outputs in time sharing manner envelope mode selecting signals F1, F2 and F3 corresponding to functions selected by the player.

In the envelope generator 10 of this example, three 20 key. envelope shapes are produced in a parallel mode from three groups X<sub>1</sub>, X<sub>2</sub> and X<sub>3</sub> and four envelope modes as shown in FIGS. 8(A) through (D) can be provided. FIGS. 8(A) through (D) indicate a direct keying mode, a sustain mode, a percussive damp made, and percussion 25 mode, respectively. In FIG. 8, reference characters KO and KF are intended to designate the timing of the key-on and that of the key-off, respectively. In general, the envelope shape of the direct keying mode and one of the envelope shapes of the remaining three modes are 30 combined and are distributed suitably to the three groups  $X_1$ ,  $X_2$  and  $X_3$  thereby to produce tones.

The 3-bit envelope function switching data FU<sub>1</sub>, FU<sub>2</sub> and FU<sub>3</sub> are to select the envelope functions of the upper keyboard tones, while the 2-bit envelope function 35 switching data FL<sub>1</sub> and FL<sub>2</sub> are to select the envelope functions of the lower keyboard tone. For the pedal keyboard tone, it is unnecessary to provide selection data especially, because only one envelope function is selected at all times. Thus, in this example, the envelope 40 functions can be selected separately according to the sorts of keyboards. In this connection, it is obvious that the data FU<sub>1</sub>, FU<sub>2</sub>, FU<sub>3</sub>, FL<sub>1</sub> and FL<sub>2</sub> are set by switching means (not shown). The term "envelope function" as herein used is intended to mean combination of enve- 45 lope modes distributed to the groups X<sub>1</sub>, X<sub>2</sub> and X<sub>3</sub>. Accordingly, the envelope function switching data FU<sub>1</sub>, FU<sub>2</sub>, FU<sub>3</sub>, FL<sub>1</sub> and FL<sub>2</sub> are to represent which mode of envelope shape should be distributed to which group (X<sub>1</sub>, X<sub>2</sub> or X<sub>3</sub>) in the channel of the upper or 50 lower keyboard tone. In order to process the function switching data separately according to the channels, the time-shared keyboard signal UE, LE and PE are applied to the envelope mode selection logic 19 and an envelope function decoder 24.

The envelope shapes as shown in FIGS. 8(B), (C) and (D) which change with time are produced by the system of the counter 11 and the memory 12 with the aid of the control operation of the envelope generation FIG. 8(A) is produced by the system of a direct keying shape generating system decoder 25 and a direct keying shape generating section 26. It goes without saying that the counter 11 and the memory 12 may be employed for producing the direct keying shape only.

The envelope function decoder 24 serves to decode in time sharing manner the function switching data including the direct keying mode, and to apply a time-shared

decoded output to the direct keying shape generation system decoder 25. The decoder 25 is so designed that it produces outputs O<sub>1</sub>, O<sub>2</sub> and O<sub>3</sub> corresponding to the groups  $X_1$ ,  $X_2$  and  $X_3$ . More specifically it outputs the direct keying shape selecting signal (O<sub>1</sub>, O<sub>2</sub>, or O<sub>3</sub>) in correspondence to the group  $(X_1, X_2 \text{ or } X_3)$  which should produce the direct keying mode envelope shape in the envelope function decoded by the above described envelope function decoder 24.

The direct keying shape generating section 26 produces the envelope shape of the direct keying mode in the group  $X_1$ ,  $X_2$  or  $X_3$  to which the direct keying shape selecting signal O<sub>1</sub>, O<sub>2</sub> or O<sub>3</sub> is supplied. In the group  $X_1$ ,  $X_2$  or  $X_3$  corresponding to the selecting signal  $O_1$ , O<sub>2</sub> or O<sub>3</sub>, the direct keying shape (FIG. 8(A)) having a constant level is produced for the period of time from the generation of the attack start signal AS to the generation of the decay start signal DS, that is, the period of time from the depression of a key to the release of the

A memory output distribution gate 27 serves to distribute the envelope shape signals read out of the memory 12 to any one of the groups  $X_1-X_3$  where no direct keying shape selecting signals O<sub>1</sub>-O<sub>3</sub> are provided. For instance, in the case where the direct keying mode envelope shapes are produced in the groups  $X_1$  and  $X_2$ , and the percussion mode envelope shape is produced in the group  $X_3$ , the percussion mode envelope shape is produced in the system of the counter 11 and the memory 12, and this envelope shape is distributed to the group  $X_3$  by the gate 27.

The counter 11, the gate 15, the fraction part counter 16, and the count value detection circuit 17 in the envelope generator 10 shown in FIG. 2 are illustrated in FIG. 4 in more detail. The memory 12, the direct keying shape generating section 26 and the memory output distribution gate 27 are illustrated in FIG. 5 in detail. The remaining elements around the envelope generation control logic 18 are illustrated in FIG. 3 in detail.

Before describing the various elements in FIGS. 3 to 5 in detail, a variety of symbols or figures employed therein will be described with reference to FIG. 9. FIG. 9(a) shows an inverter, FIGS. 9(b) and 9(c) show AND circuits, and FIGS. 9(d) and 9(e) show OR circuits. In the AND circuits and the OR circuits, if the number of inputs are relatively small, an illustration method as shown in FIGS. 9(b) and 9(d) is employed; and if the number of inputs are relatively large or some out of hte number of signals are selectively applied thereto, an illustration method as shown in FIGS. 9(c) and 9(e) is employed. In the illustration method shown in FIGS. 9(c) and 9(e), one input line is provided on the input side of the circuit, and signal lines are intersected with the input line, the intersections of the input line and the 55 signal lines being encircled. Accordingly, in the case of FIG. 9(c), the logical expression is  $Q = A \cdot B \cdot D$ . In the case of FIG. 9(e), the logical expression is Q=A+B+C. Shown in each of the FIGS. 9(f), 9(g) and 9(h) is a shift register for delay of 1-bit signals (or a control logic 18. The direct keying shape as shown in 60 delay flip-flop circuit). The numeral ("1" or "12") in the block is intended to designate the number of delay stages. In the case where no shift clock signal is indicated as in FIGS. 9(f), 9(g) and 9(h), the shifting is carried out by the above-described main block pulse  $\phi_1$ 65 (in practice, a two-phase clock signal is used). For instance, a "one" stage shifting means the delay of one microsecond. In the case where a clock pulse  $\phi_A$  is indicated as the shift clock signal as in FIG. 9(i), the

circuit is a delay flip-flop circuit controlled by clock pulses  $\phi_A$  applied at a period of 12 microseconds thereto (in practice, a two-phase clock signal is employed).

In this example, the signal is each channel is processed in time sharing manner. Therefore, it is inevitably necessary to coincide the signals in one and the same channel in a process where the signals are allowed to pass through a variety of delay elements. Accordingly, delay flip-flop circuits and shift registers such as those shown in FIGS. 9(f) through (i) are provided for timing 10 adjustment at a number of places in the circuits shown in FIGS. 3 to 5, but they will not be designated by reference characters.

As was described before, switching of the envelope modes produced by the output groups  $X_1$ ,  $X_2$  and  $X_3$  of 15 the envelope generator 10 is carried out on the basis of the envelope function switching data  $FU_1$ - $FU_3$ ,  $FL_1$  and  $FL_2$ . The relationships between the envelope function switching data of keyboards and the envelope modes outputted by the groups  $X_1$ ,  $X_2$  and  $X_3$  are indicated in Table 2 below.

TABLE 2

|                        |     |                         | 1               | AD. | LE                  | 4            |                 | <u>.</u>                            |                |                | _    |

|------------------------|-----|-------------------------|-----------------|-----|---------------------|--------------|-----------------|-------------------------------------|----------------|----------------|------|

|                        |     | Function switching data |                 |     | Modes of the groups |              |                 | Direct<br>keying shape<br>selecting |                |                | 25   |

|                        |     | Fu <sub>1</sub>         | FU <sub>2</sub> | 4   | w                   | v            | <b>X</b> 3      |                                     | signa          | ·· <b>-</b>    | _    |

|                        | No. | FU <sub>1</sub>         | FU <sub>2</sub> | 3   | $\mathbf{x_i}$      | $X_2$        | FU <sub>3</sub> | $O_1$                               | O <sub>2</sub> | O <sub>3</sub> | -    |

| Upper                  | 1   | 0                       | 0               | 0   | Α                   | A            | A               | 0                                   | 0              | 0              |      |

| key-                   | 2   | 1                       | 0               | 0   | В                   | В            | Α               | 0                                   | 0              | 1              |      |

| board                  | 3   | 1                       | 1               | 0   | A                   | $\mathbf{A}$ | D               | 1                                   | 1              | 0              | 30   |

|                        | 4   | 0                       | 1               | 0   | A                   | Α            | C               | 1                                   | 1              | 0              | 50   |

|                        | 5   | 0                       | 0               | 1   | В                   | Α            | В               | 0                                   | 1              | 0              |      |

|                        | 6   | 1                       | 1               | 1   | D                   | Ð            | D               | 0                                   | 0              | 0              |      |

|                        | 7   | 0                       | 1               | 1   | $\mathbf{C}$        | C            | C               | 0                                   | 0              | 0              |      |

|                        | 8   | 1                       | 0               | 1   | A                   | В            | Α               | 1                                   | 0              | 1              | _    |

|                        | - " | $FL_1$                  | FL <sub>2</sub> |     |                     |              |                 |                                     |                |                | _ 35 |

| Lower                  | 1   | 0                       | 0               |     | Α                   | A            | A               | 0                                   | 0              | 0              | _    |

| key-                   | 2   | 1                       | 0               |     | В                   | В            | $\mathbf{A}$    | 0                                   | 0              | 1              |      |

| board                  | 6   | 1                       | 1               |     | D                   | D            | D               | 0                                   | 0              | 0              |      |

|                        | 7   | 0                       | 1               |     | C                   | C            | C               | 0                                   | 0              | 0              |      |

| Pedal<br>key-<br>board | 2   |                         | Fixed           |     | В                   | В            | Α               | 0                                   | 0              | . 1            | 40   |

In Table 2:

Reference character "A" designates a direct keying mode such as shown in FIG. 8(a);

Reference character "B" designates a sustain mode such as shown in FIG. 8(B);

Reference character "C" designates a percussive damp mode such as shown in FIG. 8(C); and

Reference character "D" designates a percussion 50 mode such as shown in FIG. 8(D).

Numerals 1 through 8 listed in the left column of Table 2 are intended to designate the envelope function numbers, in which like numerals specify like functions (being equal in combination of the envelope modes 55 produced from the groups X<sub>1</sub>, X<sub>2</sub> and X<sub>3</sub>). For instance, the number obtained when the switching data FU<sub>1</sub>, FU<sub>2</sub> and FU<sub>3</sub> of the upper keyboard are "1 1" and the number obtained when the switching data FL<sub>1</sub> and FL<sub>2</sub> of the lower keyboard are "1 1", are equal to each other, 60 i.e. No. 6 function. In the case of the pedal keyboard note, the switching data are fixed or the function number is fixed to No. 2, and therefore, the envelopes in the sustain mode B and the direct keying mode A are provided.

Indicated in the right column of Table 2 are the contents of the direct keying shape selecting signals O<sub>1</sub>, O<sub>2</sub> and O<sub>3</sub> corresponding to the contents of the envelope

function switching data. The signals  $O_1$ ,  $O_2$  and  $O_3$  correspond to the groups  $X_1$ ,  $X_2$  and  $X_3$ , respectively. In a group wherein contents of the signal  $O_1$ ,  $O_2$  or  $O_3$  are "1", the envelope shape in the direct keying mode produced by the direct keying shape generating section 26 is outputted; and in a group wherein contents of the signal are "0", the envelope shape produced by the system of the counter 11 and the memory 12 is outputted. In addition, it should be noted that the circuit is so designed that when all of the groups  $X_1$ ,  $X_2$  and  $X_3$

produce the envelopes in the direct keying mode, the system of the counter 11 and the memory 12 produces the direct keying shape. Accordingly, in the case when all of the groups X<sub>1</sub>, X<sub>2</sub> and X<sub>3</sub> are of the direct keying mode A, all of the direct keying shape selecting signals

$O_1$ ,  $O_2$  and  $O_3$  are "0".

Referring back to FIG. 3, a logical circuit is formed in the envelope function decoder 24 so that when a function is selected in which it is necessary to allow the direct keying shape generating section 26 (FIG. 2) to produce the envelope in the direct keying mode, the function selection is detected and the decoded outputs are provided separately according to the channels. Referring to Table 2, such functions are found in the lines of Nos. 2, 3, 4, 5 and 8. Accordingly, when with the upper keyboard tones the function switching data FU<sub>1</sub>, FU<sub>2</sub> and FU<sub>3</sub> have the data shown in the lines described above, AND circuits 28 through 32 operate as in the following logical expressions: The AND circuits 28 through 32 are made operable by the upper keyboard signal UE.

AND circuit 28 (detecting No. 8)

FU<sub>1</sub> FU<sub>2</sub> FU<sub>3</sub> UE

AND circuit 29 (detecting No. 5)

FU<sub>1</sub> FU<sub>2</sub> FU<sub>3</sub> UE

AND circuit 30 (detecting No. 4)

FU<sub>1</sub> FU<sub>2</sub> FU<sub>3</sub> UE

AND circuit 31 (detecting No. 3)

FU<sub>1</sub> FU<sub>2</sub> FU<sub>3</sub> UE

AND circuit 32 (detecting No. 2)

FU<sub>1</sub> FU<sub>2</sub> FU<sub>3</sub> UE

Furthermore, in the case of the lower keyboard tone, a logic of FL<sub>1</sub>·FL<sub>2</sub>LE is provided in an AND circuit 33 so that the latter operates when the function switching data FL<sub>1</sub> and Fl<sub>2</sub> have the data shown in the line of No.

As the function of the pedal keyboard tone is fixed to No. 2, an AND circuit 34 is enabled by the pedal keyboard signal PE. It is obvious that the signal PE can be applied directly to an OR circuit 35 without the provision of the AND circuit 34.

Function Nos. 3 and 4 out of Function Nos. 2, 3, 4, 5 and 8 are for distributing the direct keying mode A to the groups X<sub>1</sub> and X hd 2. Therefore, the outputs of the AND circuits 30 and 31 are applied through an OR

8

circuit 36 to OR circuits 37 and 38 in the direct keying shape generation system decoder 25. In this decoder 25, the OR circuit 37 outputs the direct keying shape selecting signal O<sub>1</sub> corresponding to the group X<sub>1</sub>, the OR circuit 38 outputs the signal O2 corresponding to the 5 group X<sub>2</sub>, and the OR circuit 39 outputs the signals O<sub>3</sub> corresponding to the group X<sub>3</sub>. As Function No. 5 is for distributing the direct keying mode A to the series X2, the output of the AND circuit 29 is applied to the OR circuit 38 of the decoder 25. As Function No. 8 is for 10 distributing the direct keying mode A to the groups X<sub>1</sub> and X<sub>3</sub>, the output of the AND circuit 28 is applied to the OR circuits 37 and 39 of the decoder 25. As Function No. 2 is for distributing the direct keying mode A to the group X<sub>3</sub>, the outputs of the AND circuits 32, 33 15 and 34 are applied through the OR circuit 35 to the OR circuit 39 of the decoder 25.

Accordingly, the direct keying shape selecting signals O<sub>1</sub>, O<sub>2</sub> and O<sub>3</sub> are produced according to the values of the function switching data FU<sub>1</sub>, FU<sub>2</sub>, FU<sub>3</sub>, FL<sub>1</sub> and 20 FL<sub>2</sub>, as indicated in the right column of Table 2.

The upper keyboard signal UE, the lower keyboard signal LE, and the pedal keyboard signal PE are generated in synchronization with the channel times to which the tones of the keyboards are assigned, with the key-25 board code K<sub>1</sub>, K<sub>2</sub> being decoded by the keyboard detection circuit 23. In the keyboard detection circuit 23, an OR circuit 40 receives the data of bits K<sub>1</sub>, K<sub>2</sub> and produces the attack start signal AS in synchronization with the time of the channel at which the key board 30 code K<sub>1</sub>, K<sub>2</sub> is present, i.e., to which the production of a tone of the depressed key is assigned.

The envelope modes selecting signals F1, F2 and F3 produced by teh envelope mode selection logic 19 are representative of the modes of envelope shapes which 35 are to be produced by the system of the counter 11 and the memory 12. The envelope mode section logic 19 produces the envelope mode selecting signals F1, F2 and F3 by collecting the function switching data provided separately according to the keyboards onto com- 40 mon lines. In other words, if function numbers are equal, the values of the data FU1 and FU2 are equal to those of the data FL<sub>1</sub> and FL<sub>2</sub>. Accordingly, logic circuits are formed so that the data FU1 and FL1 are collected to form the data F1, the data FU2 and FU1 are 45 collected to form the data F2; and the data FU3 is formed into the data F3. Since the function of the pedal keyboard tone is fixed to No. 2, no particular switching data is provided; however, all that is necessary for the function of the pedal keyboard tone is to produce sig- 50 nals F1, F2 and F3 whose values are equal to the value "1 0 0" in Function No. 2 of the switching data FU<sub>1</sub>, FU<sub>2</sub> and FU<sub>3</sub> of the upper keyboard. As the switching data FU<sub>1</sub>, FU<sub>2</sub>, FU<sub>3</sub>, FL<sub>1</sub> and FL<sub>2</sub> are applied in direct current mode, the data are selected by the keyboard 55 signals UE, LE and PE in synchronization with the channel times to which the keyboards are assigned, and the envelope mode selecting signals F1, F2, and F3 in time sharing manner separately according to the channels.

Accordingly, in the envelope mode selection logic 19, the data FU<sub>1</sub> and the upper keyboard signal UE are inputted to an AND circuit 41, the data FL<sub>1</sub> and the lower keyboard signal LE are inputted to an AND circuit 42, the pedal keyboard signal PE is applied to an 65 AND circuit 43, and the outputs of these AND circuits 41, 42 and 43 are applied to an OR circuit 44 to obtain the data F1. In this connection, it is not always neces-

sary to provide the AND circuit 43; that is, the signal PE can be applied directly to the OR circuit 44. The data FU<sub>2</sub> and the upper keyboard signal UE are applied to an AND circuit 45, the data FL<sub>2</sub> and the lower keyboard signal LE are applied to an AND circuit 46, and the outputs of the two AND circuits 45 and 46 are applied to an OR circuit 46 to obtain the data F2. The data FU<sub>3</sub> are the upper keyboard signal UE are applied to an AND circuit 48 to obtain the data F3.

Indicated in the following Table 3 are relationships between the values of the envelope mode selecting signals F1, F2 and F3 and the envelope modes selected thereby.

TABLE 3

| Mode            |            | F1 | F2 | F3 |

|-----------------|------------|----|----|----|

| Direct keying   | (A)        | 0  | 0  | 0  |

| Sustain         | <b>(B)</b> | 1  | 0  | 0  |

|                 | , ,        | 0  | 0  | 1  |

|                 |            | 1  | 0  | 1  |

| Percussive damp | (C)        | 0  | 1  | 0  |

|                 |            | 0  | 1  | 1  |

| Percussion      | (D)        | 1  | 1  | 0  |

|                 |            | 1  | 1  | 1  |

In the envelope generation control logic 18, AND circuits provided respectively for the envelope modes are enabled according to the values of the envelope mode selecting signals F1, F2 and F3.

In the case of the direct keying mode A, the signals F1, F2 and F3 are "0 0 0", and therefore AND circuits 49 and 50 to which the inversion signals of these signals are applied are made operable.

In the case of the sustain mode B, the signals F1 and F2 are "10" or the signals F1 through F3 are "001". The signals are detected by an AND circuit 51 or 52, and the detection signal is applied to an OR circuit 53 to obtain the sustain mode selecting signal BE. The output "1" of the OR circuit 53 enables AND circuits 54, 55 and 56.

In the cases of the percussive damp mode C and the percussion mode D, the signal F2 is "1" in both cases. Accordingly, AND circuits 57 and 58 which are used commonly for both of the modes C and D are enabled when the signal F2 is "1". The signals F1 and F2 have "1 1" only when the percussion mode is selected. Therefore, an AND circuit 59 for only the percussion mode is made operable when each of the signals F1 and F2 has "1". An AND circuit 60 provided for only the percussive damp mode C is enabled when the signal F1 is "0" and the output of the OR circuit 53 is "0" (other than the sustain mode B).

In the clock synchronization circuit 22, the upper and lower keyboard attack clock signal CA is applied to a rising and decaying differentiation circuit 61, while the pedal keyboard attack clock signal CPA is applied to a rising and decaying differentiation circuit 62. The upper keyboard decay clock signal CUD is applied to a rising and decaying differentiation circuit 63, while the lower 60 keyboard decay clock circuit CLD is applied to a decaying differentiation circuit 64. The pedal keyboard decay clock signal CPD is applied to a decaying differentiation circuit 65. Only the rising and decaying differentiation circuit 61 is illustrated in detail; however, the other rising and decaying differentiation circuits 62 and 63 are identical with the differentiation circuit 61. A block 66 encircled in the differentiation circuit 61 is a decaying differentiation circuit. The arrangement of

ICC. 50,700

each of the decaying differentiation circuit is identical with that of the block 66.

In each of the rising and decaying differentiation circuits 61 through 63, the clock signals are delayed by 12 microseconds by means of delay flip-flop circuits 67 and 68, respectively, which are controlled by the clock pulse  $\phi_A$  having a period of 12 microseconds, and an AND circuit 69 produces a rising detection pulse 12 microseconds in pulse width in synchronization with the rising part of the input clock signal. The period of 10 the rising detection pulse is equal to that of the input clock signal. In addition, an AND circuit 70 provides a decaying detection pulse 12 microseconds in pulse width in synchronization with the decaying part of the input clock signal. The rising detection pulse and decay- 15 ing detection pulse are applied to an OR circuit 71. Thus, the circuits 61, 62 and 63 produce clock pulses CA2, CPA2 and CUD2, respectively, which have frequencies twice as high as those of input clock signals CA, CPA and CUD, respectively, and have a pulse 20 width of 12 microseconds (twelve channel times).

In the aforementioned circuits 61 and 63, the decaying detection pulse is taken out of the AND circuit 70 so as to output as count clock pulses CA' and CUD' respectively for a counter 72 of modulo 2<sup>5</sup> and a counter 25 73 of modulo 2<sup>1</sup>. When all of the 5-digit outputs of the counter 72 become "1" and the pulse CA' 12 microseconds in width is applied thereto, an AND circuit 74 output a signal "1". This output of the AND circuit 74 is utilized as a first curve selecting clock pulse CUA1. 30 The frequency of this clock pulse CUA1 is ½<sup>5</sup> of the frequency of the clock pulse CA' (½<sup>6</sup> pf of the frequency of the clock pulse CA2), and its pulse width is 12 microseconds.

An AND circuit 75 produces a pulse UD when its 35 input conditions are established by the output of the counter 73 and the clock pulse CUD'. Therefore, the frequency of the pulse UD is ½ of the frequency of the clock pulse CUD' (¼ of the frequency of the clock pulse CUD2), and its pulse width is 12 microseconds.

The decaying differentiation circuits 64 and 65 operate similarly as in the aforementioned block 66, and produce clock pulses CLD' and CPD' equal in frequency to the clock pulses CLD and CPD, each of the pulses CLD' and CPD' having a pulse width of 12 microseconds. The clock pulses CLD' and CPD' are subjected to ½ frequency division in counters 76 and 77 each having modulo 2, and are shaped to have a pulse width of 12 microseconds by AND circuits 78 and 79, respectively. It should be noted that upon energization 50 of the envelope generator 10, the initial clear signal IC is applied to the reset terminals of the counters 72, 73, 76 and 77.

The upper and lower keyboard attack clock pulse CA2, the pedal keyboard attack clock pulse CPA2, the 55 first curve selecting clock pulse CUA1, the second curve selecting clock pulse CUD2, the upper keyboard decay clock pulse UD, the lower keyboard clock pulse LD, and the pedal keyboard decay clock pulse PD, each synchronized to have the 12 microsecond pulse 60 width, are supplied to the channel clock selection gate 21. In this gate 21, the upper keyboard signal UE makes AND gates 80, 82, 84 and 85 operable to select the clock pulses, CA2, CUA1, CUD2 and UD. The lower keyboard signal LE makes AND circuits 81 and 86 operable to select the clock pulses CA2 and LD. The pedal keyboard signal PE makes AND circuits 83 and 87 operable to select the clock pulses CPA2 and PD. In

each of the pulses CA2 through PD, one pulse is synchronized with the 12 channel times. Therefore, these pulses can be selected in time sharing manner without changing their frequencies. The attack clock pulses CA2 and CPA2 selected in time sharing manner are applied, as an attack clock pulse ACP to an AND circuit 90 of the clock gate 13 through an OR circuit 88. The attack pulses UD, LD, and PD selected by the AND circuits 85, 86 and 87 are applied to an OR circuit 89 so as to be applied, as a decay clock pulse DCP, to an AND circuit 91 of the clock gate 13. The first curve selecting clock pulse CUA1 selected in time sharing manner is applied to an AND circuit 92 of the clock

gate 13, while the second curve selecting clock pulse CUD2 is applied to an AND circuit 93 thereof. The output ACP of the aforementioned OR circuit 88 is applied also to an AND circuit 94 of the clock gate 13, and is utilized a clock pulse DMP for the percussive

damp mode.

The clock pulses inputted to the AND circuits 90 through 94 of the clock gate 13 are selected by the outputs from the envelope generation control logic 18 or by control signals obtained through OR circuits 95, 96 and 97 of the clock selection circuit 20. The output of the AND circuit 90 is applied, as the attack pulse AC, to the counter 11 of modulo 64 through a line 99. The outputs of the AND circuits 91 through 94 are applied to an OR circuit 98 so as to be applied, as the decay clock pulse DC, to the counter 11 through a line 100.

The counter 11 comprises: an addition section of 16-bits up of full-adders 101 through 106; and a 12-stage shift counter section for holding the addition result of each bit in time sharing manner for every channel. More specifically, the addition result of the least significan bit is held in a 9-stage shift register 107 and a 3-stage shift register 108, and the data of the second bit is held in an 8-stage shift register 109 and a 4-stage shift register 110. The data of the third bit is held in an 8-stage shift register 111 and a 4-stage shift register 112. The data of the fourth bit is held in a 7-stage shift register 113, a 2-stage shift register 114, and a 3-stage shift register 115. The data of the fifth bit is held in a 7-bit stage shift register 116, a 2-stage shift register 117, and a 3-stage shift register 118. The data of the most significant bit is held in a 6-stage shift register 119, a 2-shift register, 120, and a 4-stage shift register 12. The reason why the 12-stage shift register is divided into several parts is for synchronization of the channel times for the above-described data. For this channel time synchronization, delay flipflop circuits are provided in the counter 11; however, they are not designated by reference numerals.

The fraction part counter 16 of modulo 8 is made up of 3-bit full-adders 122, 123 and 124, and 12-stage shift registers 125, 126 and 127. In each of the full-adders 101 through 106 and 122 through 124, reference characters A and B designate input terminals, reference character CI designates a carry signal input terminal from a less significant bit, reference character S designates an output terminal for the addition result of a relevant bit, and reference character CO designates a carry signal output terminal. The addition result held in a shift register is fed back to the input terminal B of the respective adder and is added to the data which are applied to the input terminal A and the input terminal CI. The carry signal output terminals CO are successively cascade-connected to the carry signal input terminals CI of the more significant bits.

Upon energization the initial clear signal IC is applied, whereupon the signal of a counter clear line 139 is made to be "0" through an OR circuit 128 and an inverter 129, and AND circuits 130 through 138 in the counter 11 and the fraction part counter 16 are therefore made inoperable, as a result of which the count values of the channels are cleared to "0". The same thing occurs in the case also where a count value clear signal So is applied through a line 140 from the envelope generation control logic 18 shown in FIG. 3, as 10 described later.

In production of the envelope having attack characteristics, the attack pulse AC as described later is applied through a line 99 and an OR circuit 141 to the adder 101 of the least significant bit in the counter 11, and 15 of the country value in the counter is increased.

of the counter 11 is "1 1 0 0 0 0". In this case, when the decay clock pulse DC is applied thereafter (Timing 2), the country of the fraction part counter 16 becomes "0 of 101 of the least significant bit in the counter 11, and 15 of 1" by the feedback data  $\overline{CV_6}$ ,  $\overline{CV_5}$  and  $\overline{CV_4}$ . In this operation, the country value of the counter 11 is sub-

In production of the envelope having decay characteristics, the decay clock pulse DC is applied through a line 100 to all of the adders 101 through 106 in the counter 11. Accordingly, in the counter 11 "1 1 1 1 1 1" 20 is added for every timing of the decay clock pulse DC, which means that the content of the counter 11 is subtracted by "0 0 0 0 0 1". Thus, the value in the counter is decreased.

# Polygonal Line Approximation of an Envelope Having Exponential Characteristics

In this embodiment, an exponential characteristic polygonal line approximation is carried out with respect to the decay part of an envelope shape. For this pur- 30 pose, AND circuits 142, 143 and 144 in the gate 15 of the fraction part counter 16 used for computation of the polygonal line approximation are so designed as to be enabled by the application of the decay clock pulse DC.

The data of the more significant bit in the counter 11 35 is fed back to the least significant bit (adder 101) through a feedback circuit including a computation circuit. The computation circuit included in the feedback circuit is the gate 15 and the fraction part counter 16, operating to convert the data of three higher bits in 40 the counter 11, which are fed back through lines 14a, 14b and 14c, into a pulse CR having a speed corresponding to (inversely proportional to) the value of the data and to apply the pulse CR to the carry signal input terminal CI of the least significant bit adder 101 in the 45 counter 11.

The data CV<sub>4</sub>, CV<sub>5</sub> and CV<sub>6</sub> of the three higher bits of the counter 11 (the outputs of the adders 104, 105 and 106) are obtained from shift registers 114, 117 and 120, and are supplied to the lines 14a, 14b and 14c after being 50 inverted respectively. The inversion data  $\overline{CV_4}$ ,  $\overline{CV_5}$ , and  $\overline{CV}_6$  supplied to the lines 14a, 14b and 14c are inputted to adders 122, 123, and 124 through AND circuits 142, 143, 144 for every generation timing of the decay clock pulse DC, respectively. Accordingly, the data 55  $\overline{CV_4}$ ,  $\overline{CV_5}$  and  $\overline{CV_6}$  are repeatedly added by the fraction part counter 16 for every generation timing of the decay clock pulse DC. Since the fraction part counter 16 is of the three bits, whenever its counter value reaches eight in decimal notation, a single carry signal CR is output- 60 ted by the adder 124. This carry signal CR is applied to the least significant bit adder 101 in the counter 11 so as to increase the value stored in the counter 11. On the other hand, simultaneously the decay clock pulse DC is applied to the counter 11 through the line 100 to de- 65 crease the value stored in the counter 11. Therefore, in practice, the count values CV<sub>1</sub> through CV<sub>6</sub> in the counter 11 are not changed when the carry signal CR is

applied to the fraction part counter 16. In other words, the carry signal CR applied to the addition input of the counter 11 operates to prohibit the subtraction of the decay clock pulse DC from the value of the counter 11.

One example of this computation is indicated in Table 4 below. The numerals 1, 2, 3 . . . in the left column in Table 4 are representative of the timing of application of the decay clock pulse DC. The arrows in the column of the carry signal CR indicate the generation of the carry signal CR. It is assumed that the count value of the fraction part counter 16 is "0 0 0" when the count value of the counter 11 is "1 1 0 0 0 0". In this case, when the decay clock pulse DC is applied thereafter (Timing 2), the content of the fraction part counter 16 becomes "0 0 1" by the feedback data  $\overline{CV_6}$ ,  $\overline{CV_5}$  and  $\overline{CV_4}$ . In this operation, the count value of the counter 11 is subtracted to be "1 0 1 1 1 1".

TABLE 4

| } | DC's |                 | Count           | value           | of cou          | nter 11         |        | Саггу       | v  | Cour<br>alue<br>raction<br>part | of<br>on |

|---|------|-----------------|-----------------|-----------------|-----------------|-----------------|--------|-------------|----|---------------------------------|----------|

|   | ing  | CV <sub>6</sub> | CV <sub>5</sub> | CV <sub>4</sub> | CV <sub>3</sub> | CV <sub>2</sub> | $CV_1$ | CR          | co | unte                            | r 16     |

|   | 1    | 1               | 1               | 0               | 0               | 0               | 0      | ←           | 0  | 0                               | 0        |

|   | 2    | 1               | 0               | 1               | 1               | 1               | İ      |             | 0  | 0                               | 1        |

|   | 3    | 1               | 0               | t               | 1               | 1               | 0      |             | 0  | 1                               | 1        |

|   | 4    | Ì               | 0               | 1               | 1               | 0               | 1      |             | 1  | 0                               | 1        |

|   | 5    | 1               | 0               | 1               | 1               | 0               | 0      |             | 1  | 1                               | 1        |

|   | 6    | 1               | 0               | 1               | 1               | 0               | 0      | ←—          | 0  | 0                               | 1        |

|   | 7    | 1               | 0               | 1               | 0               | 1               | 1      |             | 0  | 1                               | 1        |

|   | 8    | 1               | 0               | 1               | 0               | 1               | 0      |             | 1  | 0                               | Į        |

|   | 9    | 1               | 0               | 1               | 0               | 0               | 1      |             | 1  | l                               | l        |

|   | 10   | 1               | 0               | 1               | 0               | 0               | 1      | ←           | 0  | 0                               | 1        |

|   | 11   | 1               | 0               | 1               | 0               | 0               | 0      |             | 0  | 1                               | 1        |

|   | 12   | 1               | 0               | 0               | 1               | 1               | 1      |             | 1  | 0                               | 1        |

|   | 13   | 1               | 0               | 0               | 1               | 1               | 1      | <b>←-</b> - | 0  | 0                               | 0        |

|   | 14   | 1               | 0               | 0               | 1               | 1               | 0      |             | 0  | 1                               | 1        |

|   |      |                 |                 |                 |                 |                 |        |             |    |                                 |          |

|   |      |                 |                 |                 |                 |                 |        |             |    |                                 |          |

|   |      |                 |                 |                 |                 |                 |        |             |    |                                 |          |

|   | •    |                 |                 | •               |                 |                 |        |             |    |                                 |          |

The data  $\overline{CV_6}$ ,  $\overline{CV_5}$  and  $\overline{CV_4}$  applied to the fraction part counter 16 through the gate 15 is obtained by inverting the three higher bits CV<sub>6</sub>, CV<sub>5</sub> and CV<sub>4</sub> out of the computation results of the counter 11 in the previous computation timing. Therefore, at the computation timing 2, a value "0 0 1" obtained by inverting the data CV<sub>6</sub>, CV<sub>5</sub> and CV<sub>4</sub>"1 10" provided at the computation timing 1 is applied to the fraction part counter 16. Accordingly, during the period of time from computation timing 3 to computation timing 2, the value "0 1 0" obtained by inverting the value "1 0 1" of the data CV<sub>6</sub>-CV<sub>4</sub> is repeatedly applied to the fraction part counter 16. During the period of time from computation timing 2 to computation timing 5, no carry signal CR is produced by the fraction part counter 16. Therefore, the count value of the counter 11 is successively decreased by the decay clock pulse DC. However, at the computation timing 6, the computation result of the fraction part counter 16 becomes "1001", whereby the carry signal CR is produced thereby. In this operation, in the counter 11 the data "1 1 1 1 1 1" due to the decay clock pulse DC operating as a subtraction input and the input data "0 0 0 0 0 1" due to the carry signal CR are added to the computation result "1 0 1 1 0 0" obtained at the previous computation timing 5. In the computation, the carry output CO is merely produced by the most significant bit adder 106, and no substantial computation is carried out. Therefore, the count value of the counter 11 is not changed. Similarly, when the

carry signal CR is produced by the fraction part counter 16, the count value of the counter 11 is not changed.

The fraction part counter 16 is of modulo 8. Therefore, if it is assumed that the decimal value of the feedback data  $\overline{CV_6}$ ,  $\overline{CV_5}$  and  $\overline{CV_4}$  from the counter 11 is K, then one carry signal CR is produced whenever 8/K decay clock pulses are supplied. Furthermore, as the data  $CV_4$ ,  $CV_5$  and  $CV_6$ , higher than the third bit, of the counter 11 are fed back to the fraction part counter 16, the count rate of the fraction part counter 16, namely, the values of the input data  $\overline{CV_6}$ ,  $\overline{CV_5}$  and  $\overline{CV_4}$  are changed whenever the content of the counter is advanced by eight steps (subtracted by eight).

Accordingly, if it is assumed that the number of decay clock pulses DC necessary for advancing the content of the counter by eight steps is N; then

(step number of counter 11) = (subtraction pulse number by pulse DC) - (addition pulse number by carry signals CR).

Therefore, in general, the following equation is established:

$$8 = N - \left(N/\frac{8}{K}\right) = \frac{8N - KN}{8}$$

In consequence, the following relation is established between N and K:

$$N = 64/(8 - K)$$

Upon application of N pulses DC, the content of the counter 11 is decreased by eight steps. Therefore, the inclination (rate) in subtraction variation of the counter 11 is 8/N which depends on the value K of the data  $\overline{CV_6}$ ,  $\overline{CV_5}$  and  $\overline{CV_4}$  fed back to the fraction part counter 16. Accordingly, the value of the counter 11 is linearly changed (changed with a constant inclination) for the period of time during which the value K is maintained unchanged; however, the inclination in count value variation of the counter 11 is changed if the value K is changed.

The data  $\overline{CV_6}$ ,  $\overline{CV_5}$  and  $\overline{CV_4}$  forming the value K, or the data  $CV_6CV_5$  and  $CV_4$  is of 3-bits, and therefore the value K varies in eight ways. More specifically, as indicated in the following Table 5, the value K in the counter 11 of modulo 64 varies in eight steps, i.e. regions I-VIII. Such counting operation may be called a "nonlinear counting mode", characterized in that the change in accrued count value CV for a fixed number of applied count pulses is not always uniform, but rather changes as a function of the accrued count value. In the left column of Table 5, the ranges of the count values CV of the counter 11 included in the regions I through VIII are indicated by decimal numbers.

TABLE 5

|      |                    |                 |                 | IAD.            | LE J            |                        |                 |        |   | _          |

|------|--------------------|-----------------|-----------------|-----------------|-----------------|------------------------|-----------------|--------|---|------------|

| Time | CV                 | CV <sub>6</sub> | CV <sub>5</sub> | CV <sub>4</sub> | CV <sub>6</sub> | (K)<br>CV <sub>5</sub> | CV <sub>4</sub> | 8<br>K | N | _ ,        |

| I    | 63<br><del>V</del> | 1               | 1               | 1               | 0               | 0                      | 0               | 0      | 8 | ¯ <b>6</b> |

| Ħ    | 56<br>55           | 1               | 1               | 0               | 0               | 0                      | 1               | 8      | 9 | •          |

|      | 48<br>47           |                 |                 |                 |                 |                        |                 |        |   |            |

TABLE 5-continued

|    | Time | CV            | CV <sub>6</sub> | CV <sub>5</sub> | CV <sub>4</sub> | CV <sub>6</sub> | (K)<br>CV <sub>5</sub> | CV <sub>4</sub> | <u>8</u><br>K | N  |

|----|------|---------------|-----------------|-----------------|-----------------|-----------------|------------------------|-----------------|---------------|----|

| 5  | III  | ₩<br>40       | 1               | 0               | 1               | 0               | 1                      | 0               | 4             | 10 |

| 10 | IV   | 39<br>V<br>32 | 1               | 0               | 0               | 0               | 1                      | 1               | <u>8</u><br>3 | 13 |

| 15 | V    | 31<br>V<br>24 | 0               | 1               | 1               | 1               | 0                      | 0               | 2             | 16 |

|    | VI   | 23<br>V<br>16 | 0               | ì               | 0               | İ               | 0                      | 1               | <u>8</u> 5    | 21 |

| 20 | VİI  | 15            | 0               | 0               | 1               | 1               | 1                      | 0               | 8             | 31 |

| 25 | VIII | 7             | 0               | 0               | 0               | 1               | į                      | 1               | <u>8</u>      | 56 |

In Table 5, as was described before, 8/K indicates the number of decay clock pulses DC necessary for producing one carry signal CR in each of hte regions I through VIII, and N designates the total number of pulses DC supplied in each of the regions I through VIII. In the last region VIII, the pulse number N is 56 instead of 64 because the count value CV becomes zero with seven steps decreased. Referring to Table 5 and Table 4 described before, it can be understood that the count operation from computation timing 2 to computation timing 11 in Table 4 indicates the operation in region III in Table 5.

As the value K is gradually increased whenever the region is shifted toward VII from I (the value of the feedback data CV<sub>6</sub>, CV<sub>5</sub> and CV<sub>4</sub> is gradually decreased as the count value of the counter decreases), the inclination 8/N in count value variation of the counter 11 becomes as the region is shited toward VIII. Therefore, a decay curve of exponential characteristics as shown in FIG. 10 can be obtained by eight-step polygonal lines in each of the regions I through VIII.

Referring back to FIG. 4, the count value data CV1 through CV<sub>6</sub> of the counter 11 are applied to an AND circuit 145 of the count value detection circuit 17 after being inverted by respective inverters. Therefore, when the count value of the counter 11 becomes zero (0) in the last region VIII, the AND circuit 145 produces an output "1", which enables an AND circuit 146 through a delay shift register 147. Whenever the decay clock pulse DC is applied to the AND circuit 146, the latter 60 146 is operated to apply a signal "1" to the carry signal input terminal of an adder 122 of the fraction part counter 16 through a line 148. When all of the data in the counter 11 are "0", the feedback data  $\overline{CV}_6$ ,  $\overline{CV}_5$  and  $\overline{CV_4}$  are "1 1 1". With this arrangement, the counter of 65 FIG. 4 is operable to count in an "exponential manner" in response to count pulses applied thereto, producing an accrued count value CV which may be represented by the serial juxtaposition of differently sloped polygonal line

segments as shown in FIG. 10. Therefore, whenever the decay clock pulse DC is applied to the counter 16, the carry signal CR is produced by the fraction part counter 16, as a result of which "1" is added to the counter 11. While "1 1 1 1 1 1" is added to the counter 11 in response to the decay clock pulse DC at all times, "1" is added thereto by the above-described carry signal CR. Therefore, the count value "0" is maintained in the counter 11.

The above-described computation operations are all carried out in time sharing manner separately for the respective channels. Therefore, the many delay flip-flop circuits not designated by reference numerals are so arranged that the channel times between the computation data in computation circuits are coincident with 15 one another. In addition, in the counter 11 there are some shift registers in which the number of delay stages for signals led therefrom is different. This is also for coincidence of the channel times. For instance, the data of the adders 105 and 106 are deviated by one microsec- 20 ond from each other by the delay flip-flop circuit 149 interposed therebetween. Therefore, the data  $\overline{CV}_5$  is led out with a delay of 9 microseconds by the shift registers 116 and 117, and the data  $\overline{CV}_6$  is led out with a delay of 8 microseconds by the shift registers 119 and 120, so <sup>25</sup> that the channel times of the data  $\overline{CV}_5$  and  $\overline{CV}_6$  are coincident with each other.

#### Sustain Mode:

FIG. 11(a) is a set of graphs indicating variations of <sup>30</sup> the count value CV of the counter 11 with time T in the case where the sustain mode is selected.

When the sustain mode B is selected, in the envelope generation control logic 18 in FIG. 3, the AND circuits 54, 55 and 56 are enabled. If the decay start signal DS is not generated yet and the count contents CV<sub>1</sub> through CV<sub>6</sub> of the counter 11 ar not "1", the conditions for the AND circuit 54 are satisfied, and therefore the AND gate 90 in the clock gate 13 is enabled. Upon depression of a key, one of the keyboard signals UE, LE and PE becomes "1", as a result of which the attack clock pulse ACP is supplied to the AND circuit 90 through the OR circuit 88 of the clock select gate 21. Accordingly, upon depression of a key, first of all, the pulse ACP is selected as the attack clock pulse AC by the AND circuit 90, and the pulse thus selected is applied to the addition input of the counter 11, that is, it is applied only to the least significant bit adder 101 through the OR circuit 141 in the counter 11. As a result, the count value CV of the counter 11 is gradually increased from "0" up to "63" at the rate of the attack clock pulse AC.

Thus, the envelope shape of an attack part ATT (FIG. 11(a)) is obtained by addition. The shape of the attack part ATT has a resolution degree of 63 steps corresponding to the modulo of the counter 11.

When the count value CV has reached the maximum value 63, all of the data CV<sub>1</sub> through CV<sub>6</sub> are "1". Therefore, the data are detected by the AND circuit 150 of the count value detection circuit 17, and the signal "1" is stored in the relevant channel of a shift register 153 through an AND circuit 151 and an OR circuit 152. This storage is self-held through an AND circuit 154. In this connection, it should be noted that the AND circuits 151 and 154 are enabled only when the sustain mode selection signal BE is applied from the OR circuit 53 of the envelope generation control logic 18 through a line 155 and a shift register 156.

When the AND circuit 150 detects that the count value CV is all "1", and all "1" detection signal AL<sub>1</sub> is

applied to the envelope generation control logic 18 through the OR circuit 152. The detection signal AL<sub>1</sub> is stored in the aforementioned shift register 153, and therefore the detection signal AL<sub>1</sub> is not eliminated even if the count value CV is changed thereafter.

In the envelope generation control logic 18, if the all "1" detection signal AL<sub>1</sub> becomes "1", a signal "0" is applied to the AND circuit 54 through an inverter, as a result of which the AND circuit 90 of the clock gate 13 is made inoperable. Accordingly, the application of the attack clock pulse AC is prohibited. Thus, the counting operation of the counter 11 is suspended, so as to hold a certain count value (63 in this case), whereby the shape of a sustain part SUS (FIG. 11(a)) is obtained.

Upon release of the depressed key, the decay start signal DS is raised to "1" and is applied to the AND circuit 56 of the envelope generation control logic 18 through a line 160. The output "1" of the AND circuit 56 is applied to the AND circuit 91 and 93 of the clock gate 13 through the OR circuit 95. In the case where a curve selection function described later is not selected yet, the output of the OR circuit 97 is "1", and therefore the AND circuit 91 is enabled but the AND circuit 93 is made inoperable. Therefore, the decay clock pulse DCP supplied from the OR circuit 89 of the clock selection gate 21 is selected by the AND circuit 91, and is applied, as the decay clock pulse DC, to the subtraction input of the counter 11 through the OR circuit 98 and the line 100.

As the operation of the counter 11 is suspended at the maximum count value 63, subtraction is carried out from the maximum count value 63 toward the minimum value 0. In this operation, the computation for the polygonal line approximation of exponential characteristic is carried out as was described before, whereby the envelope shape of a decay part DEC exponentially varying as shown in FIG. 10 is obtained.

When the count value of the counter 11 has reached zero (0), an all "0" detection signal AL<sub>0</sub> is produced from the AND circuit 145 of the count value detection circuit 17, and is applied to the AND circuit 158 (FIG. 3) through a line 157. To the other input of the AND circuit 158, the decay start signal DS is applied through a line 160 and a shift register 159 for timing control, and the output "1" of the AND circuit 158 is applied, as the decay finish signal DF, to the aforementioned tone production assignment circuit (not shown). Upon generation of the decay finish signal DF, the clear signal CC is provided by the tone production assignment circuit because the generation of the decay finish signal DF means that the tone production in the relevant channel time has been finished. This clear signal CC is applied to the detection circuit 17 in FIG. 4, as a result 55 of which the AND circuits 151 and 154 are made inoperable so as to eliminate the storage of the all "1" detection signal AL<sub>1</sub>.

Sometimes the electronic musical instrument has a function that, when after release of a key but before completion of the decay the same key is depressed again, the tone for the depressed key is assigned to the same channel (hereinafter referred to as "a key-on-again function" when applicable). In this case, the clear signal CC is produced in that channel once even if no decay finish signal DF is produced. In this case, even during the decay (the count value of the counter being decreased) the all "1" detection signal AL<sub>1</sub> is changed to "0", and the attack clock pulse AC is selected instead of the decay clock pulse DC. Accordingly, it is possible to

allow the envelope shape of the relevant channel to rise during the decay.

In addition, it is also possible to allow the attack part ATT in the sustain mode to rise extremely steeply. What is considered as one method for achieving this 5 purpose is to employ high speed clock pulses as the attack clock pulses ACP, or the clock signals CA and CPA. In another method considered, the addition by the attack clock signal AC is not carried out in the counter 11, but a counter set signal S<sub>1</sub> described later is 10 produced as soon as the attack start signal AS is raised to "1" upon depression of a key, and the count value of the counter 11 is set to "1 1 1 1 1 1" simultaneously, so that the sustain part SUS is obtained without the attack part TATT.

## Curve Section in Sustain Mode

The envelope consisting of the parts ATT, SUS and DEC shown in FIG. 11(a) is ordinarily obtained in the sustain mode. If the curve selection function is effected, 20 the envelope is changed into an envelope consisting of parts ATT, DEC1, SUS' and DEC 2.

When the curve selection function is effected, the curve section signal CUS becomes "1", and the AND gate 161 in FIG. 3 is enabled. The upper keyboard 25 signal UE is applied to the other input of the AND circuit 161, and therefore the curve selection signal CUS is selected only during the channel time of the upper keyboard tone and is applied to the AND circuit 55 of the envelope generation control logic 18. In other 30 words, in this example, the curve selection function is effected for the upper keyboard tone only.

Similarly as in the ordinary sustain mode, the attack part ATT is realized by applying the pulse ACP as the attack clock pulse AC to the counter 11 thereby to 35 line 100. gradually increase the count value of the counter 11 from "0" to "63". When the count value of the counter 11 reaches the maximum value 63, the all "1" detection signal AL<sub>1</sub> is produced by the count value detection circuit 17 and is applied to the AND circuit 55 of the 40 envelope generation control logic 18. Under the conditions that the sustain mode B is selected, the curve selection signal CUS is "1", the decay start signal DS is "0", and the count value CV of the counter 11 is not 47 or less (the signal CV47 is "0"), the AND circuit 55 is 45 enabled when the aforementioned signal AL<sub>1</sub> becomes "1", so as to apply its output "1" to the AND circuit 92 in the clock gate 13 and to the line 162.

When the AND circuit 92 is thus enabled, the first curve selection clock pulse CUA1 supplied by the clock 50 select gate 21 is selected, and is applied to the subtraction input of the counter 11 through the OR circuit 98 and the line 100. Therefore, in the counter 11 computation is carried out according to the first curve selection clock pulse CUA1, and the count value of the counter 55 11 is gradually decreased. When the count value data CV<sub>6</sub> through CV<sub>1</sub> become "1 0 1 1 1 1", the AND circuit 163 in the count value detection circuit 17 is operated to apply its output "1" to the AND circuit 164. Accordingly, when the count value CV of the counter 60 11 reaches decimal 47, it is detected by the AND circuit 163, and the signal "1" is stored in the shift register 166 through the AND circuit 164 and the OR circuit 165 at the channel time thereof. In this connection, the AND circuit 164 is maintained enabled by the signal CUS' 65 supplied through the line 162 for the period of time when the first curve selection clock pulse CUA1 is selected. The count value "47" detection signal CV47