## United States Patent 1191

## Pierce

Re. 28,811 [11] E

[45] Reissued May 11, 1976

| <br>   |         |        |                        |

|--------|---------|--------|------------------------|

| 9/1970 | Davis   | 179/15 | AL                     |

| 3/1971 | Beresin | 179/15 | $\mathbf{A}\mathbf{L}$ |

| 3,529,089<br>3,569,632 | 9/1970<br>3/1971 | DavisBeresin |        |               |

|------------------------|------------------|--------------|--------|---------------|

| 3,586,782              | 7/1971           | Thomas       | 179/15 | $\mathbf{AL}$ |

| 3,597,549<br>3,732,374 | 8/1971<br>5/1973 | Farmer       |        |               |

#### OTHER PUBLICATIONS

IRE Transactions on Communications Systems, "Communication Networks for Digital Information," J. M. Unk, Dec. 1960, (pp. 207-214).

Primary Examiner—David L. Stewart Attorney, Agent, or Firm-R. O. Nimtz

#### **ABSTRACT** [57]

A closed loop transmission system is described in which a plurality of stations have access to each loop to write messages into and read messages from standard-sized message blocks transmitted around the loop. One station in each loop provides regeneration of all message blocks. The various loops are interconnected by switching stations which respond to address information at the head of each message block to selectively switch the block to the interconnected loop. The next required address is always substituted for the current address to simplify address recognition. Alternate and redundant routing are also provided for.

#### 14 Claims, 23 Drawing Figures

| [54]   |           | NNECTED LOOP DATA BLOC<br>ISSION SYSTEM                         | <b>'K</b> |

|--------|-----------|-----------------------------------------------------------------|-----------|

| [75]   | Inventor: | John Robinson Pierce, Pasadena<br>Calif.                        | 1,        |

| [73]   | Assignee: | Bell Telephone Laboratories,<br>Incorporated, Murray Hill, N.J. |           |

| [22]   | Filed:    | Oct. 29, 1973                                                   |           |

| [21]   | Appl. No. | : 410,813                                                       |           |

|        | Relat     | ed U.S. Patent Documents                                        |           |

| Reisst | ie of:    |                                                                 |           |

| [64]   |           | 3,731,002<br>May 1, 1973<br>79,185<br>Oct. 8, 1970              |           |

| 1521   | U.S. Cl   |                                                                 | 5 AL      |

| •      |           | H04J                                                            |           |

|        |           | earch                                                           |           |

| • •    |           | 340/1                                                           |           |

| [56]   |           | References Cited                                                |           |

|        | UNI       | TED STATES PATENTS                                              |           |

| 2,861, | 128 11/19 |                                                                 | 5 BD      |

| 3,165, |           | ·                                                               | 5 BD      |

| 3,456, | 242 7/19  | 69 Lubkin 179/1                                                 | 5 AL      |

7/1970

3,519,750

F/G. /

J. R. PIERCE

BY

ATTODNIEV

| DATA            |

|-----------------|

| DATA<br>to-1    |

| <del></del>     |

|                 |

|                 |

|                 |

| <u> </u>        |

| DATA<br>2       |

| DATA            |

| LOCAL I         |

| LOCAL I<br>DEST |

| CONTROL         |

| SOB             |

| 0               |

|                 |

| SOB CONTROL CURRENT CURRENT NAT'L REG. LOCAL NAT'L REG. LOCAL DEST. DEST. DEST. DEST. DEST. DEST. DEST. DEST. DEST. NAT'L SOURCE SOURCE SOURCE MANAGED |                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| CONTROL CURRENT CURRENT NAT'L REG. LOCAL NAT'L REG. SOURCE SOURCE                                                                                      | DATA             |

| CONTROL CURRENT CURRENT NAT'L REG. LOCAL NAT'L REG. SOURCE SOURCE                                                                                      | 1<br>1<br>1<br>1 |

| CONTROL CURRENT CURRENT NAT'L REG. LOCAL NAT'L SOURCE SOURCE SOURCE SOURCE SOURCE                                                                      | LOCAL            |

| CONTROL CURRENT CURRENT NAT'L REG. LOCAL WORD DEST. DEST. DEST.                                                                                        |                  |

| CONTROL CURRENT CURRENT NAT'L REG.   NORD DEST. DEST.                                                                                                  | NAT (L<br>SOURCE |

| CONTROL CURRENT CURRENT NAT'L SOURCE DEST.                                                                                                             | LOCAL I          |

| CONTROL CURRENT CURRENT   CURRENT   NORD DEST. SOURCE                                                                                                  | REG.<br>DEST.    |

| CONTROL   CURRENT   WORD   DEST.                                                                                                                       | NAT 'L<br>DEST.  |

| CONTROL                                                                                                                                                | CURRENT          |

| ——————————————————————————————————————                                                                                                                 | CURRENT<br>DEST. |

| SOBOSYNC                                                                                                                                               | CONTROL          |

|                                                                                                                                                        | SOB              |

| <del></del>                                                                                                                                            |                  |

F/G. 4

SRAG SRAG SRAG SRAI -157 SRAI SRA2 -156 SRA2 SRA3 -155 SRA3 99 SRA4 -154 SRA4 REGISTER <165 152 SRA8 TIDAT

OL CIRCUITS 7,8 AND 9) CONTROL (FIGS. 7, 8

Sheet 6 of 14

F/G. 6

F/G. 7

Sheet 7 of 14

F/G. 8 HOG PREVENTION CONTROL CIRCUIT

F/G. 9

F/G. /O

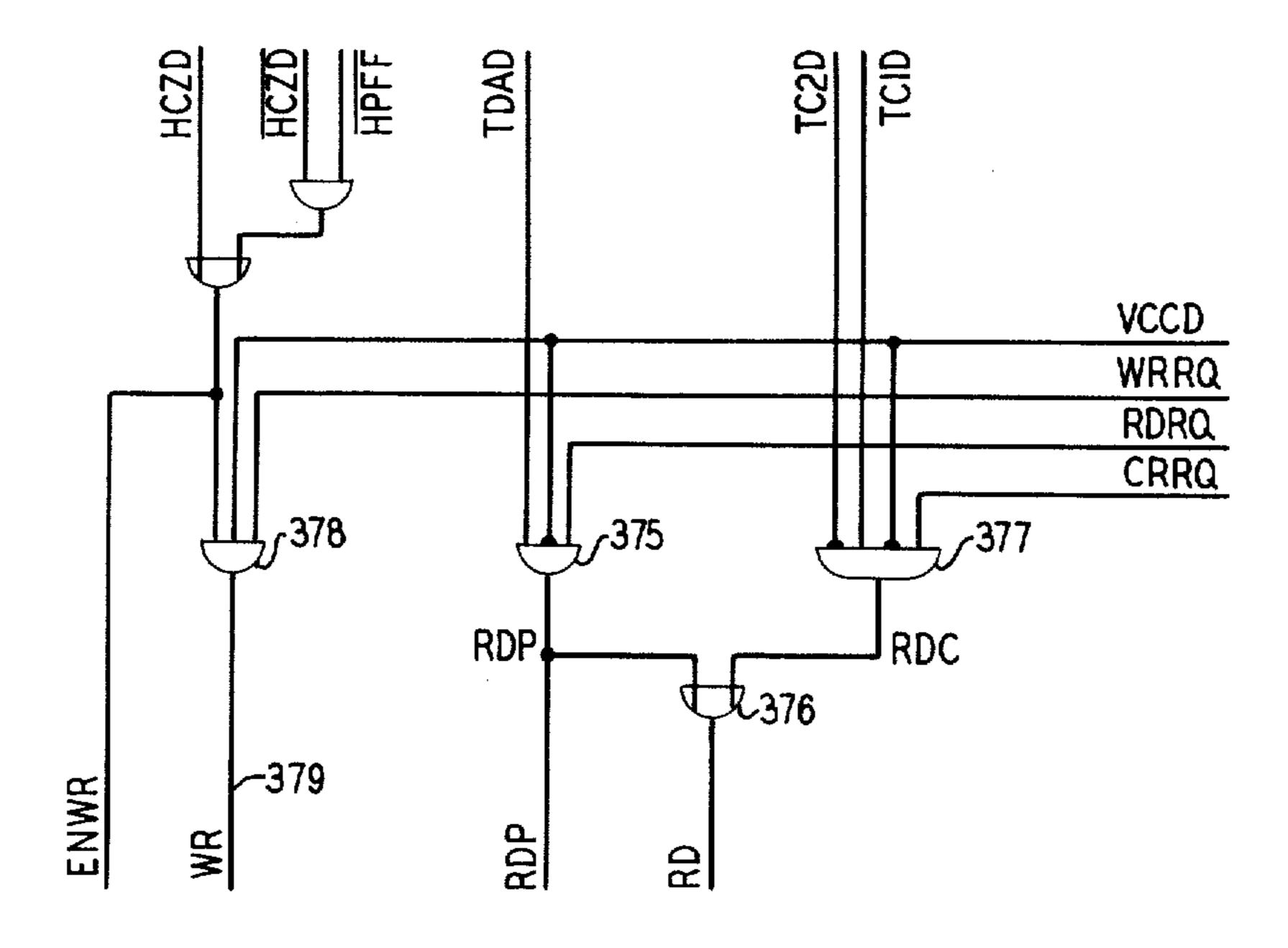

READ-WRITE CONTROL CIRCUIT

F/G. //

FIG. 12 COMMAND WORD ENCODER (A-STATION ONLY) SR 88 -505 WDI 510-4 507 /512 508 **BSCW** 502 √504 M3 SY 519 <sup>1</sup>515 r<514 r<sup>4</sup>513 **501** 500 516 WR 잏 **\509**

FIG. 14A ADDRESS REPOSITIONING CIRCUIT TO GATE **BDAT** 553 590 <sup>C</sup>954 1951 950 **\952** WD-953

## INTERCONNECTED LOOP DATA BLOCK TRANSMISSION SYSTEM

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

#### FIELD OF THE INVENTION

This invention relates to digital transmission systems and, more particularly, to digital transmission by message block assignment on a common, time-divided transmission loop.

#### **BACKGROUND OF THE INVENTION**

It is often desirable to exchange digital information between digital machines. If such machines are separated by any significant geographic distance, it has 20 heretofore been necessary to either purchase or lease a dedicated transmission facility between such machines, or to arrange a temporary connection between such machines by means of common carrier, switched transmission facilities. Since it is the nature of digital ma- 25 chines to require large amounts of digital channel capacity, but only for brief periods and only occasionally, the heretofore available facilities described above have proven very inefficient for this use. Dedicated transmission facilities, for example, remain unused the vast 30 majority of the time. Switched, common carrier facilities tend to be restricted in bandwidth to voice frequencies and are otherwise unsuitable for digital, as contrasted with analog, transmission.

A further problem with switched facilities is the fact 35 that it often takes more time to set up the transmission path than is required for the entire transmission of data. The telephone network requires real time transmission in the sense that signals must be delivered substantially at the same time they are generated. It therefore is 40 standard procedure to set up the communication path in its entirety before any signals are transmitted. As a result, centralized switching has been used in the telephone plant. Digital transmission of data, on the other hand, need not be done in real time and hence it is 45 wasteful to set up an entire connection prior to transmission. These facts tend to make presently available interconnection facilities uneconomical for intermachine digital communications.

It is an object of the present invention to provide 50 improved digital transmission facilities for communication between digital machines.

It is a more specific object of the present invention to provide the efficiency and economy of digital transmission over large geographical areas.

It is another object of this invention to provide a national communication network for digital transmission between digital machines.

#### SUMMARY OF THE INVENTION

In accordance with the present invention, these and other objects are achieved by the provision of a large network of intersecting loop transmission lines. That is, each transmission line is in the form of a closed loop and adjacent loops connected with each other by way 65 of loop intersections.

A transmission network of the type described above requires three basic digital equipment stations, a timing

station, a data insertion and removal station and a loop intersecting station. For convenience, these stations may be termed A, B and C stations, respectively.

Although the loops of the network need not be synthronous, it is desirable that each loop be driven by a single clock and that all loop timing be provided by way of the carrier wave. The A-station thus serves to close the loop and to selectively repeat digital transmissions around the loop. Provisions must be made in the A-station, however, to prevent endless recycling.

The data insertion and removal B-station must be timed and synchronized by information received on the transmission line. It is preferable that the transmission time on the loop be divided into a plurality of equally sized blocks into which are placed digital messages of preselected size accompanied by address and synchronizing information. The B-station receives digital data from the source, assembles this information into message blocks, inserts the required address and synchronizing information, and launches the entire block on the transmission loop. This B-station also scans the address information of received blocks and accepts for local delivery those blocks addressed to the local digital machine.

The loop switching C-station must buffer data to accommodate different bit rates in the intersecting loops and must decide whether to transfer a block from its current loop to the other loop.

A digital communication network of the type described above has the decided advantage of making efficient use of the digital transmission facilities. Moreover, such a network can grow gradually and economically, both geographically and in traffic-handling capacity, due to the simple repeating stations which can be added to the network. Such a transmission network also allows sophisticated digital machine users to themselves provide the necessary address information and whatever error control is required. Finally, such a digital transmission network need not be supervised over the digital network itself. The voice frequency telephone network is already available for such supervision.

These and other objects and features, the nature of the present invention and its various advantages will be more readily understood upon consideration of the attached drawings and of the following detailed description of the drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In the drawings:

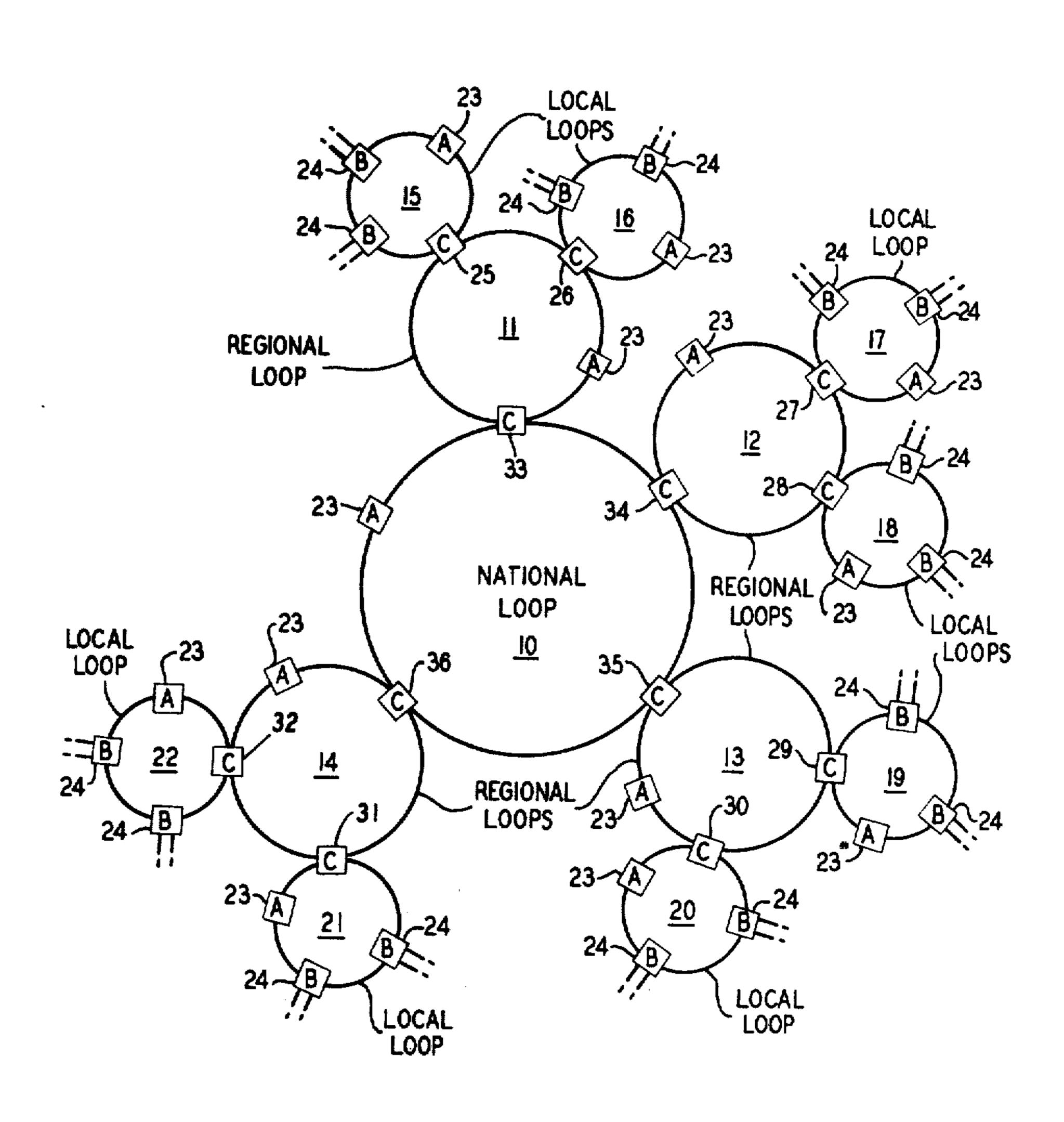

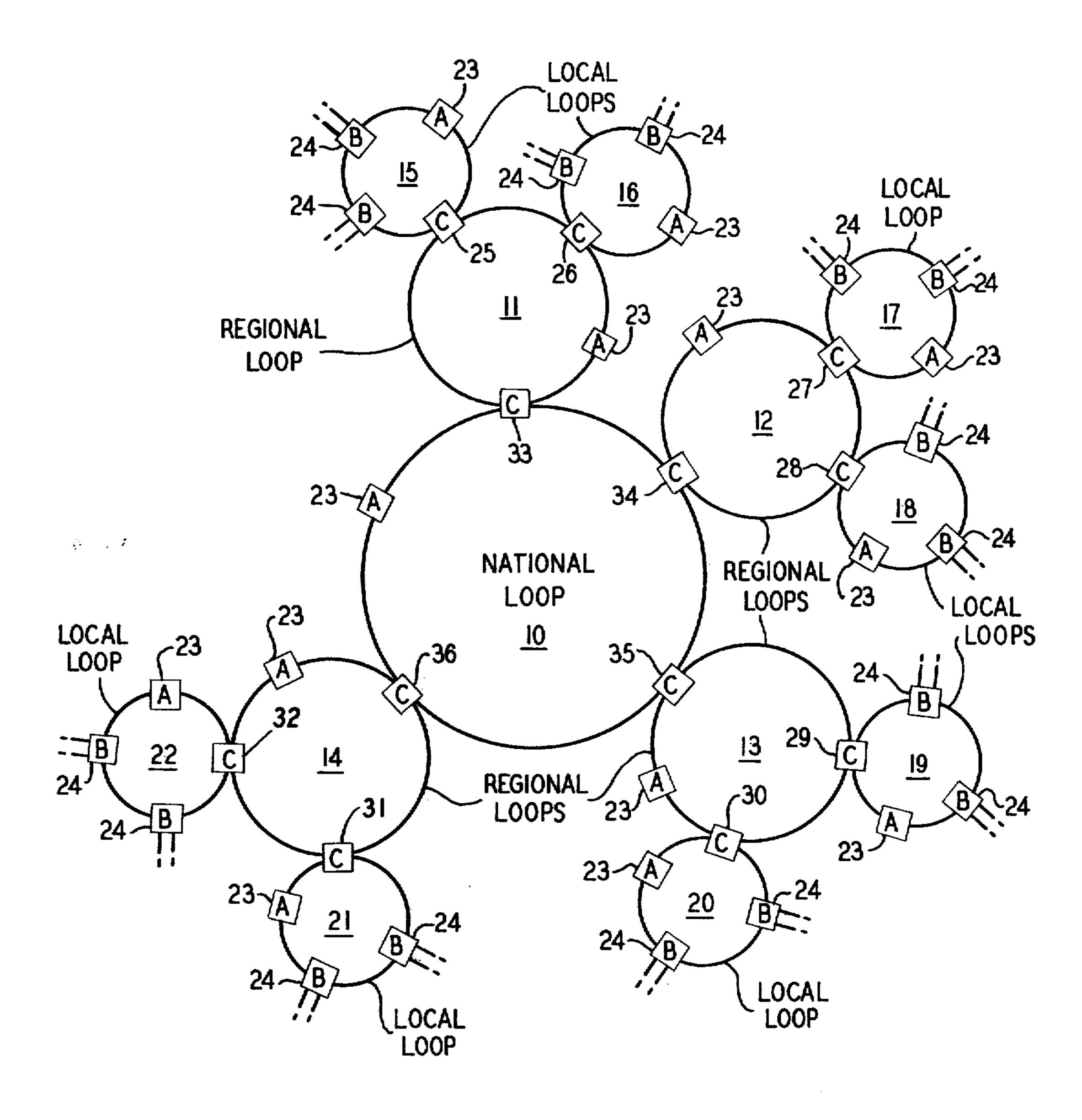

FIG. 1 is a general block diagram of a data transmission system in accordance with the present invention;

FIGS. 2A and 2B are suggested message formats for data blocks to be transmitted on the transmission system of FIG. 1:

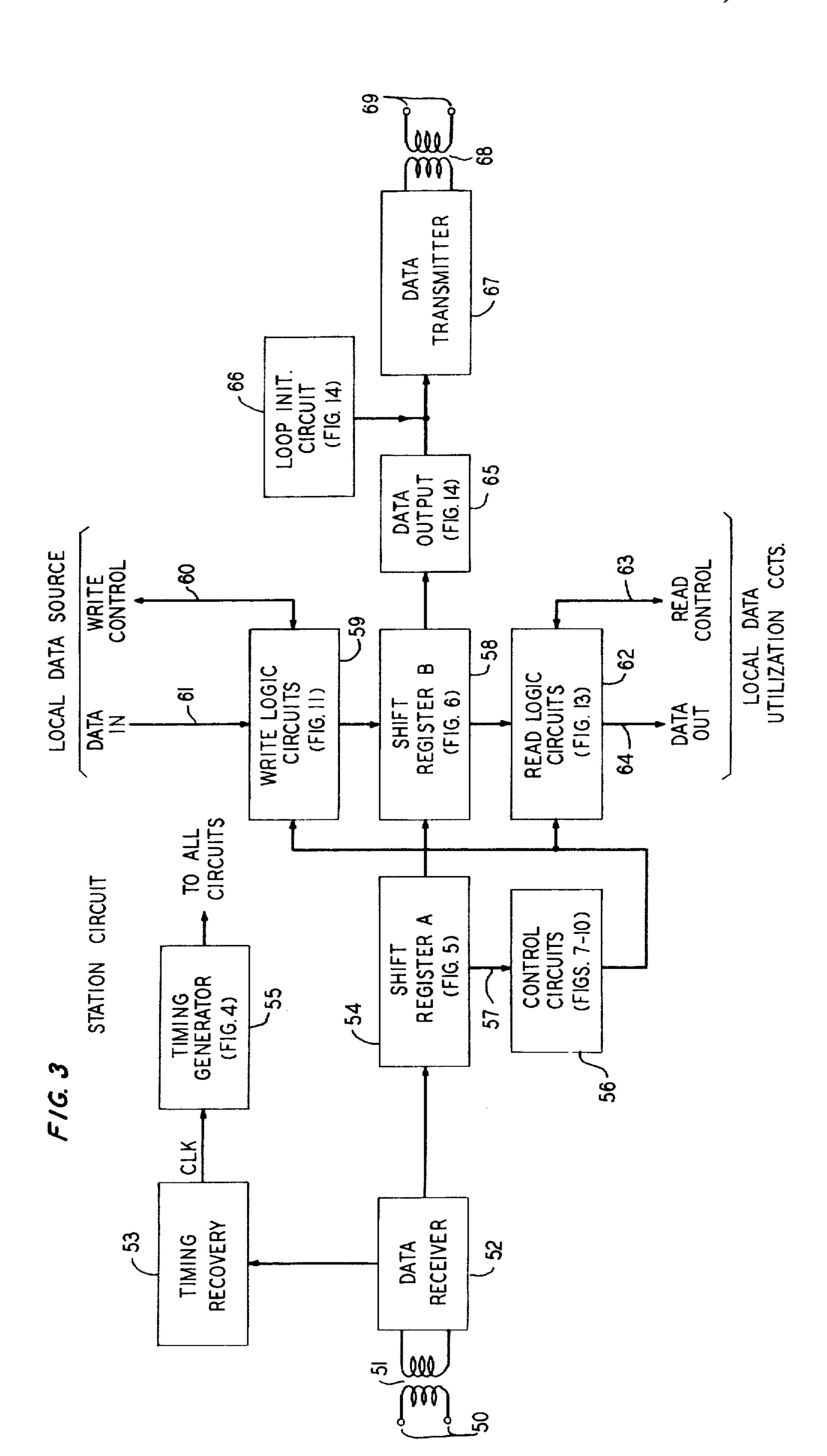

FIG. 3 is a general block diagram of a station circuit suitable for use in the system of FIG. 1;

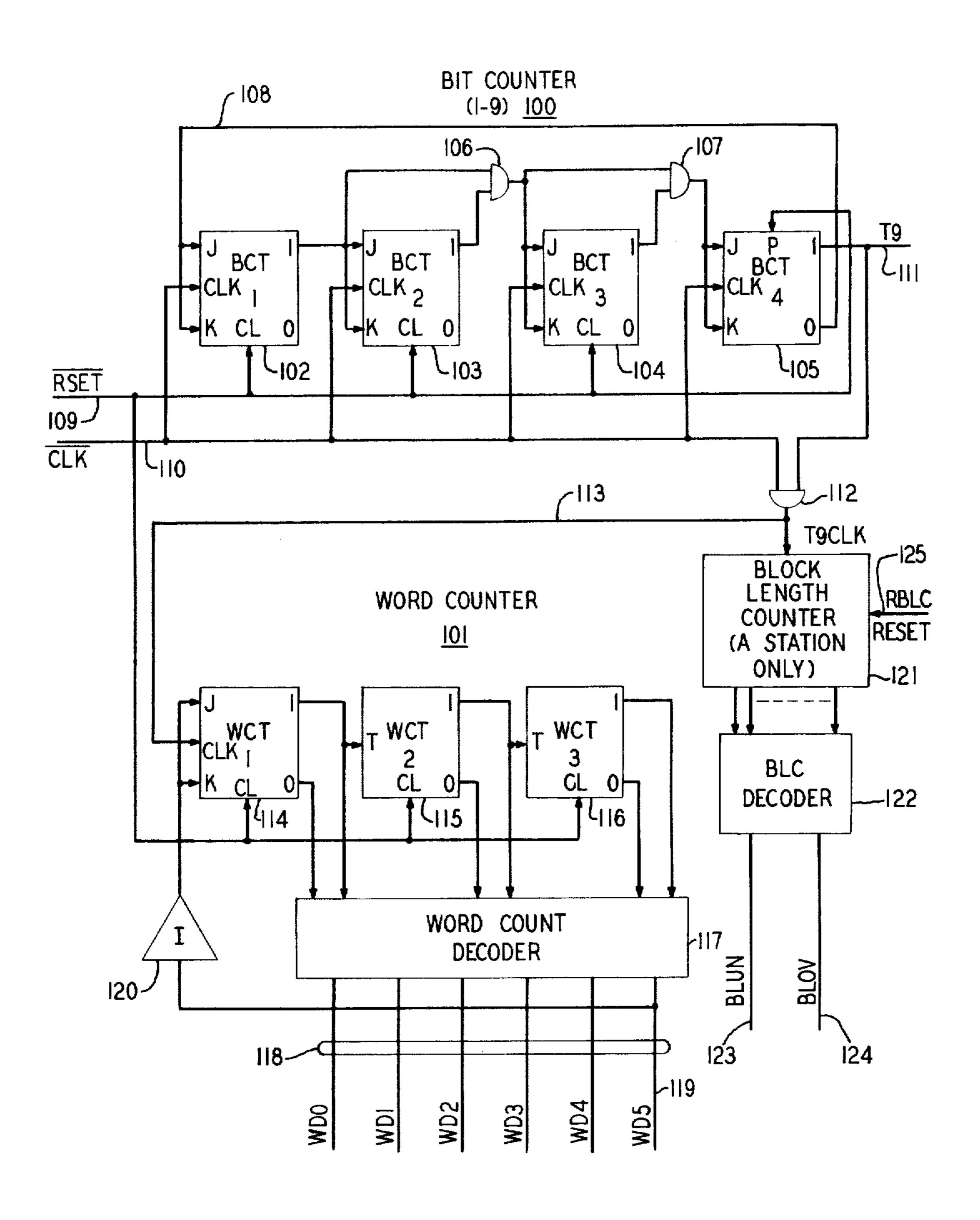

FIG. 4 is a detailed circuit diagram of a timing generator circuit useful in the station circuit of FIG. 3;

FIG. 5 is a detailed circuit diagram of a parallel read shift register useful as Shift Register A in FIG. 3;

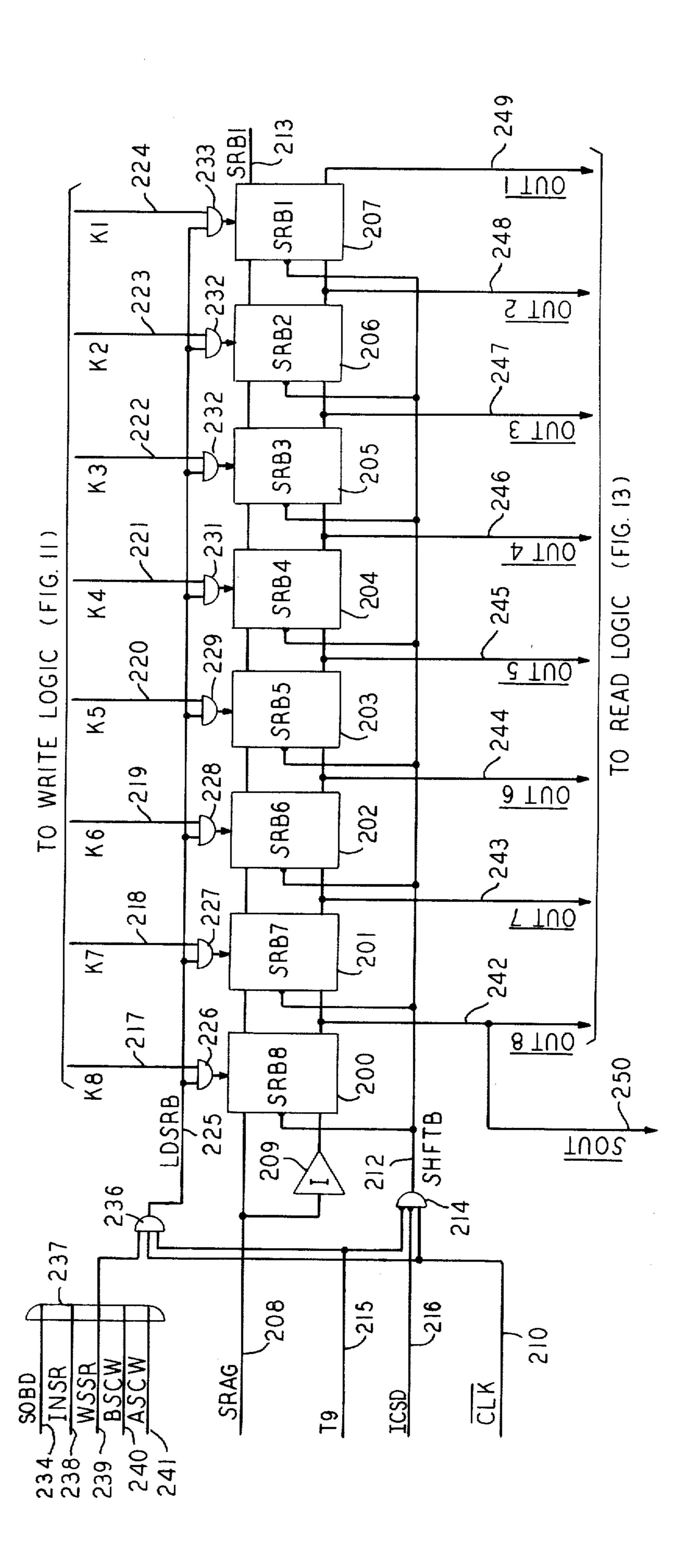

FIG. 6 is a detailed circuit diagram of a parallel readwrite shift register useful as Shift Register B in FIG. 3;

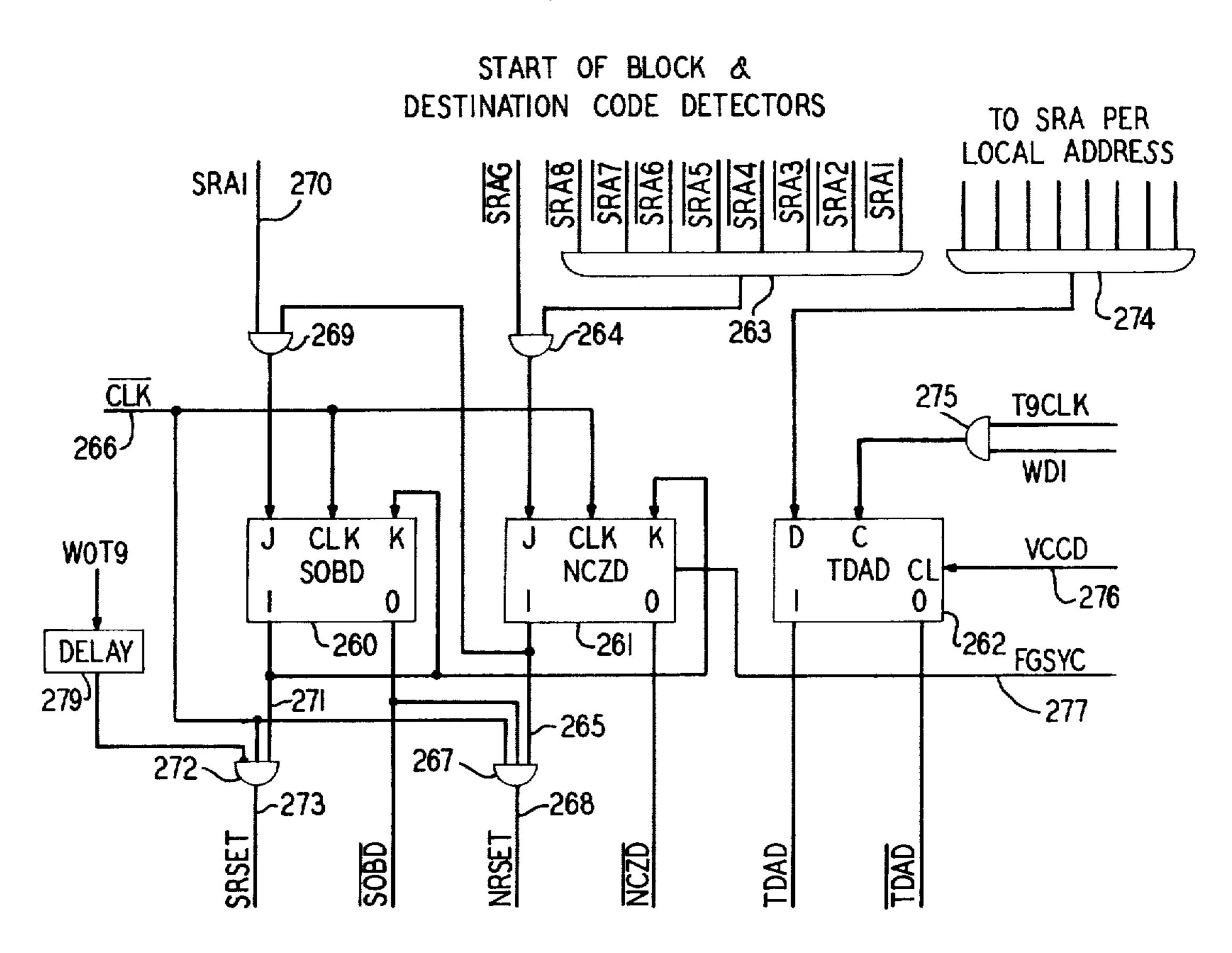

FIG. 7 is a detailed circuit diagram of a start-of-block and destination code detector useful in the control circuits of FIG. 3;

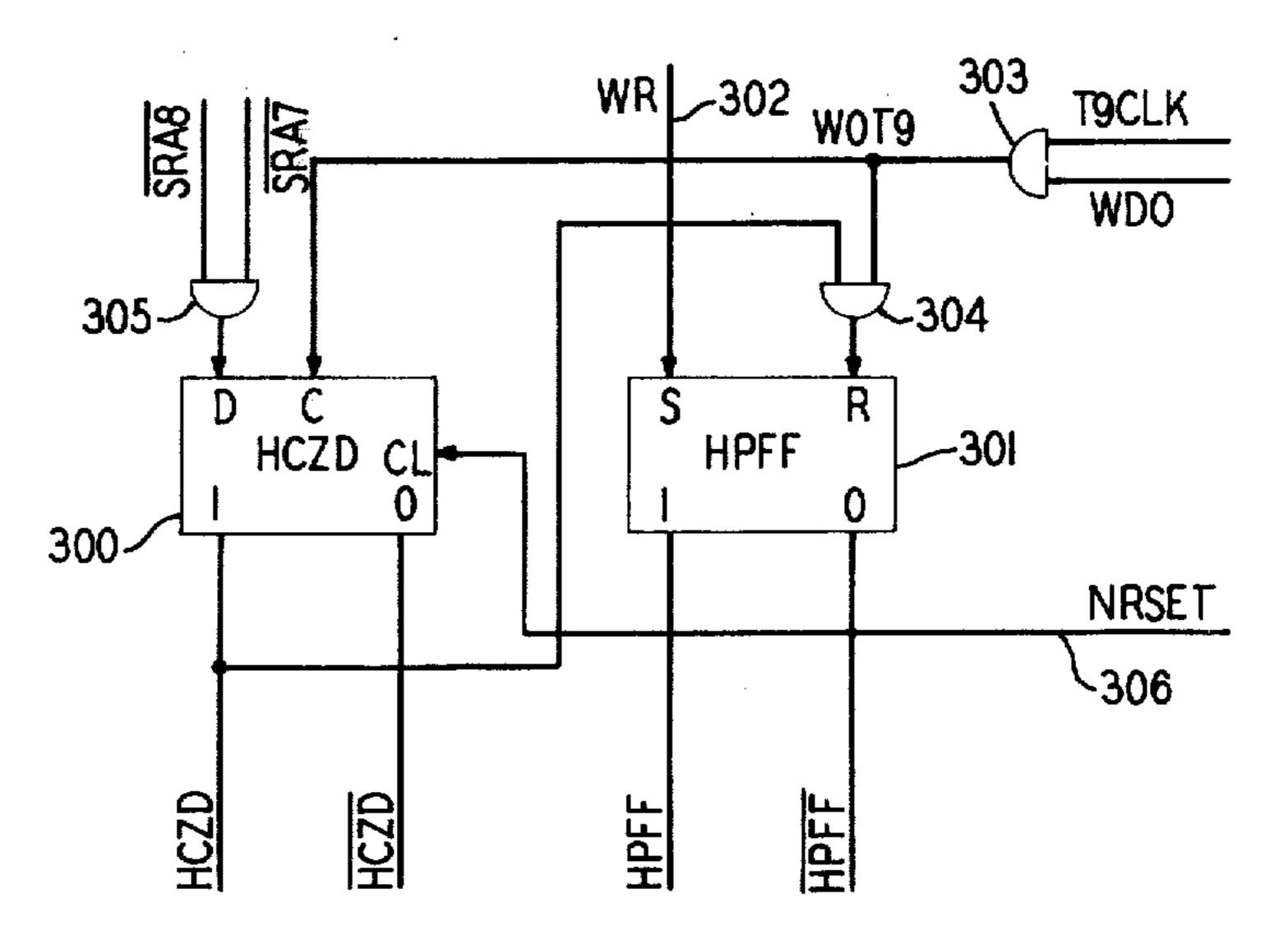

FIG. 8 is a detailed circuit diagram of a hog prevention control circuit useful in the control circuits of FIG.

3:

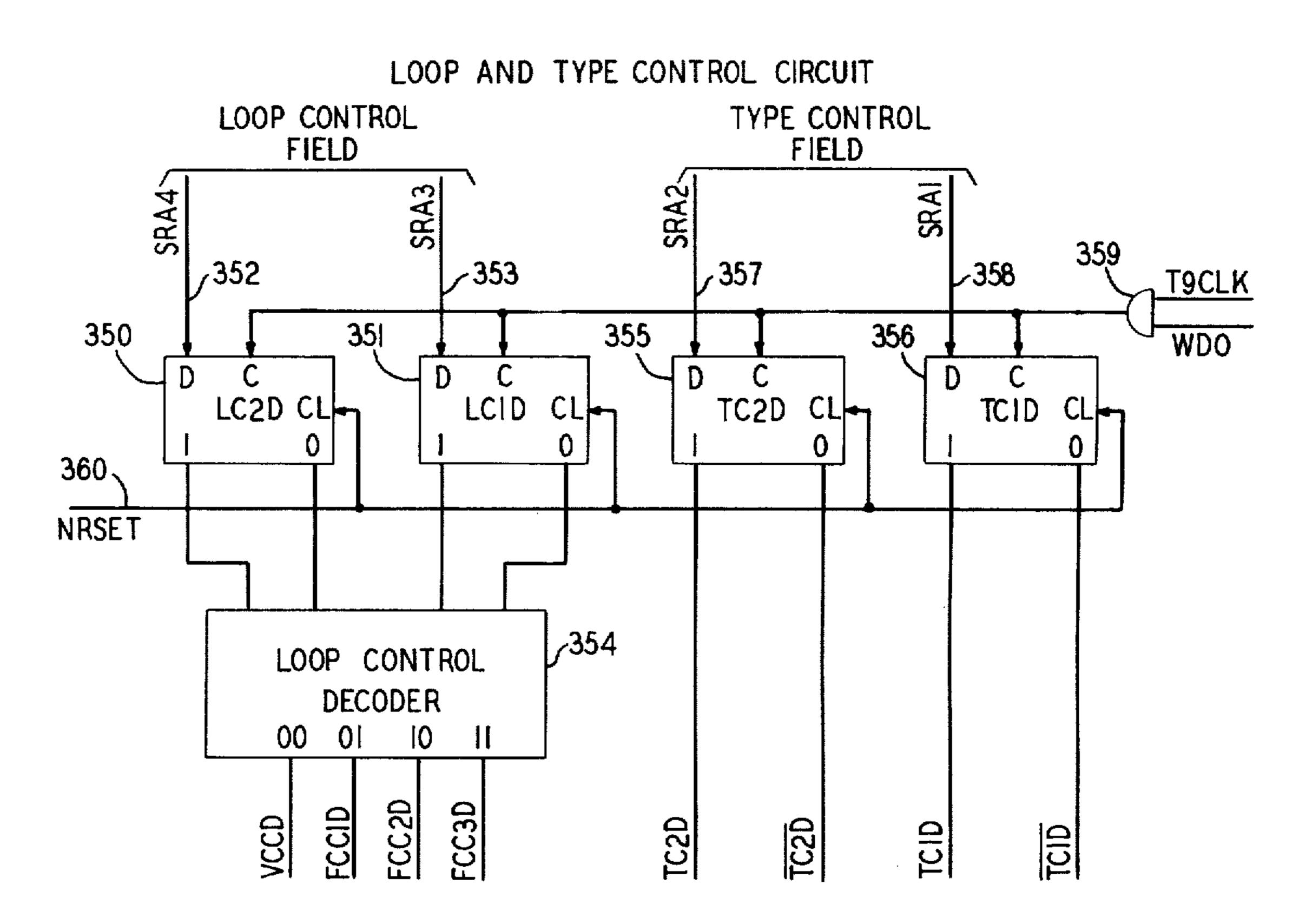

FIG. 9 is a detailed circuit diagram of a loop and type control circuit useful in the control circuits of FIG. 3;

FIG. 10 is a detailed circuit diagram of a read-write control circuit useful in the control circuits of FIG. 3;

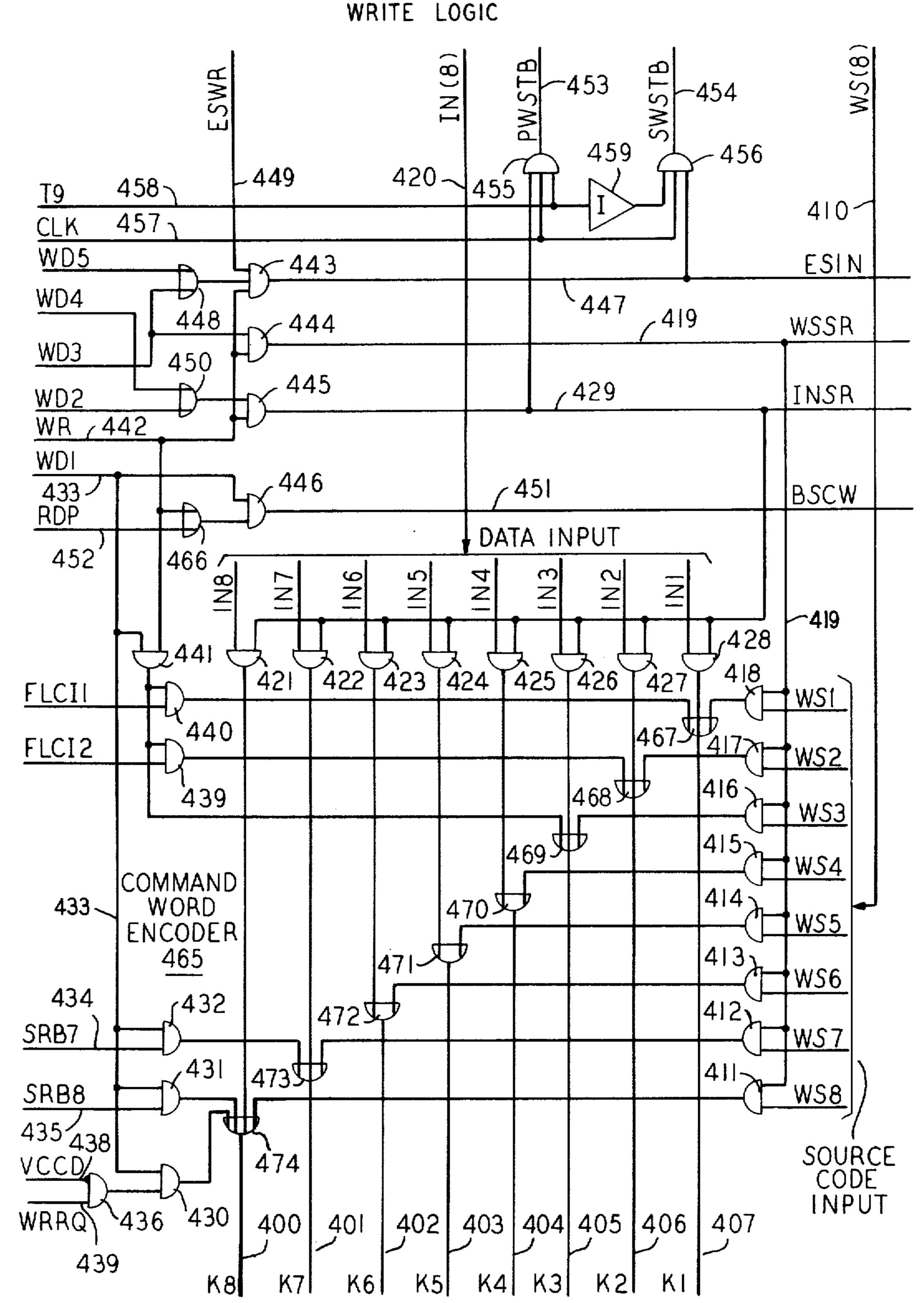

FIG. 11 is a detailed circuit diagram of a write logic circuit useful in the station circuit of FIG. 3;

FIG. 12 is a detailed circuit diagram of a command word encoder useful in the write logic circuit of FIG. 11 when used in an A-station;

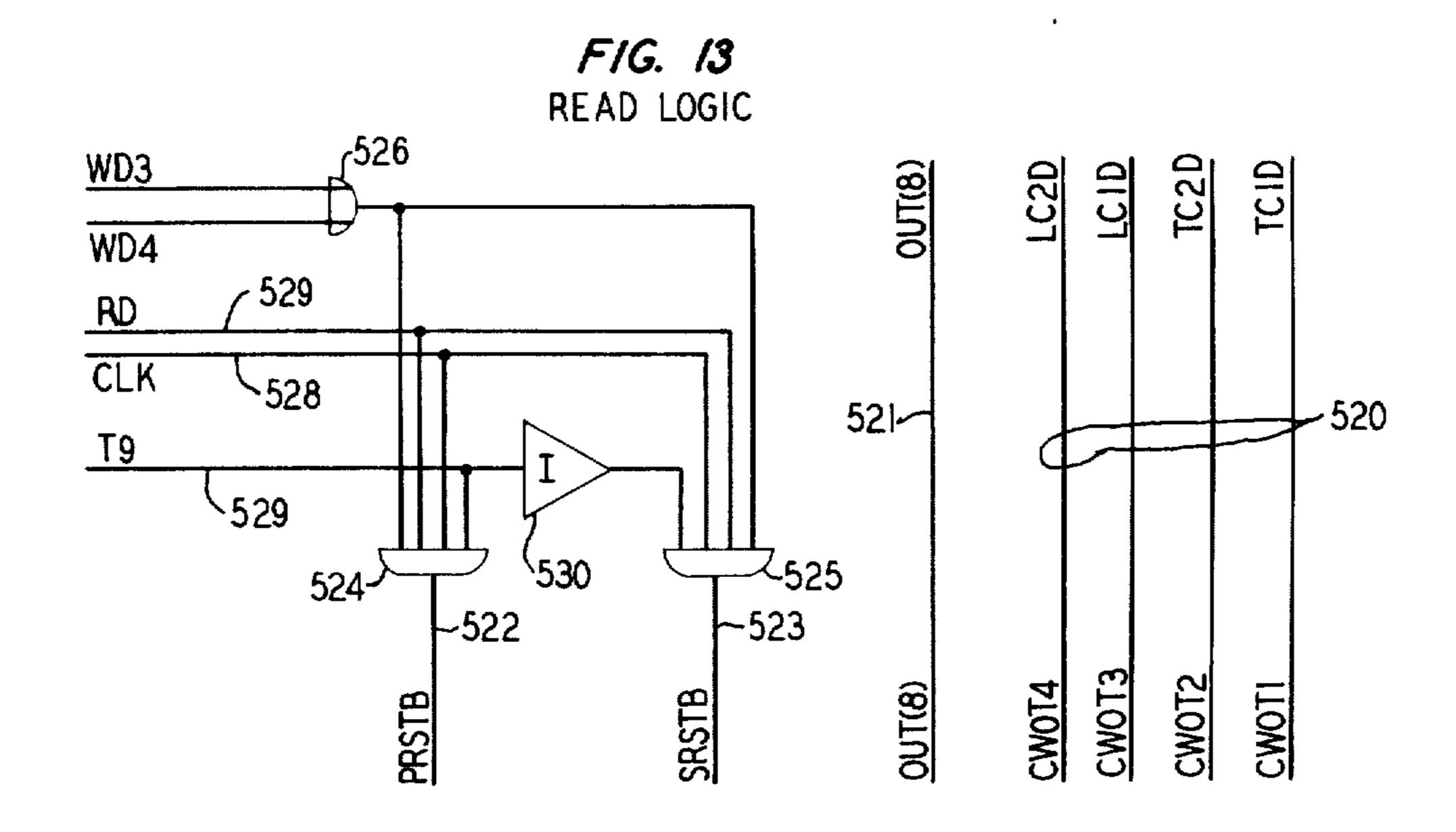

FIG. 13 is a detailed circuit diagram of a read logic circuit useful in the station circuit of FIG. 3;

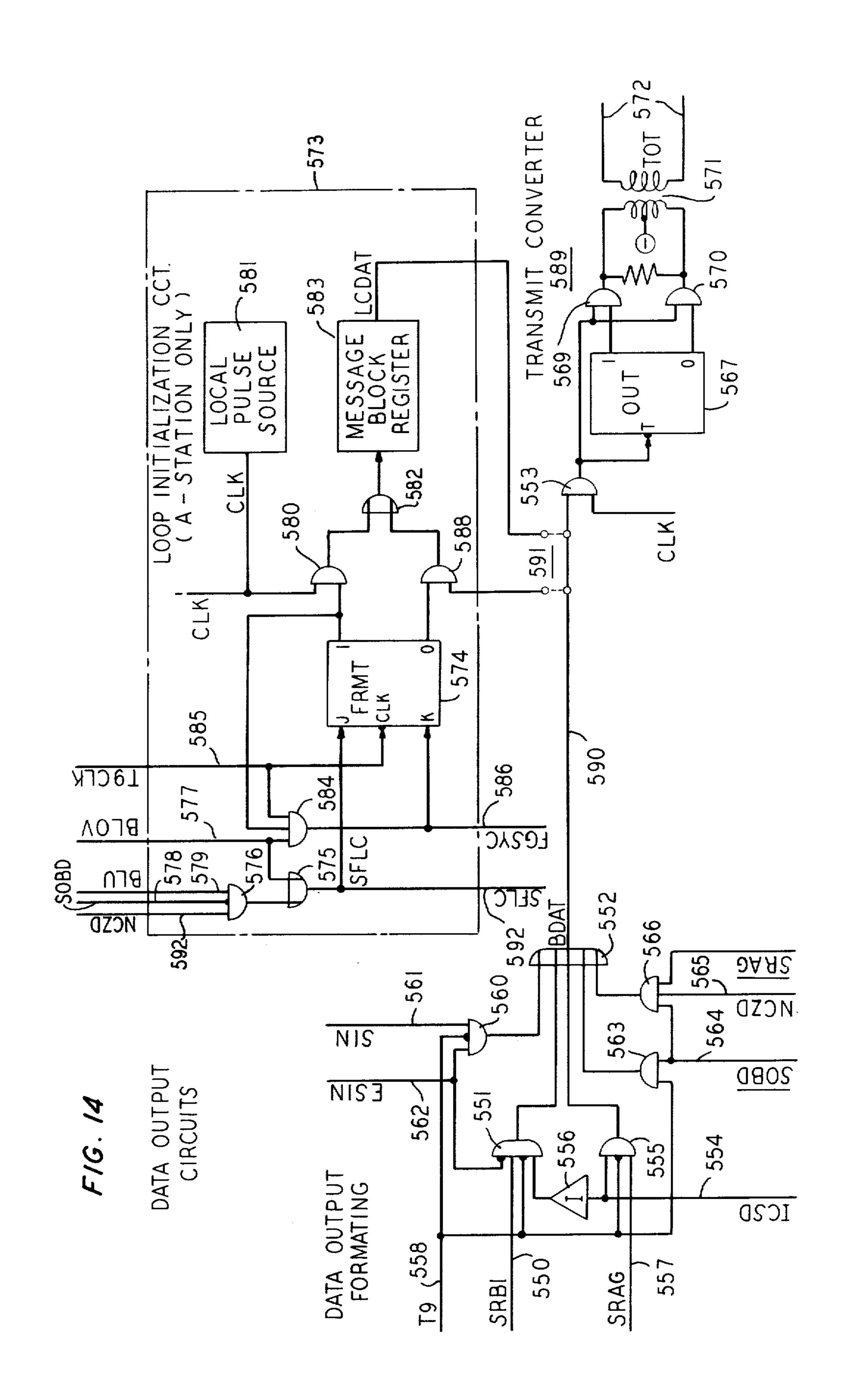

FIG. 14 is a detailed circuit diagram of data output circuits useful in the station circuit of FIG. 3;

FIG. 14A is a detailed circuit diagram of an address repositioning circuit useful in the output circuits of FIG. 14;

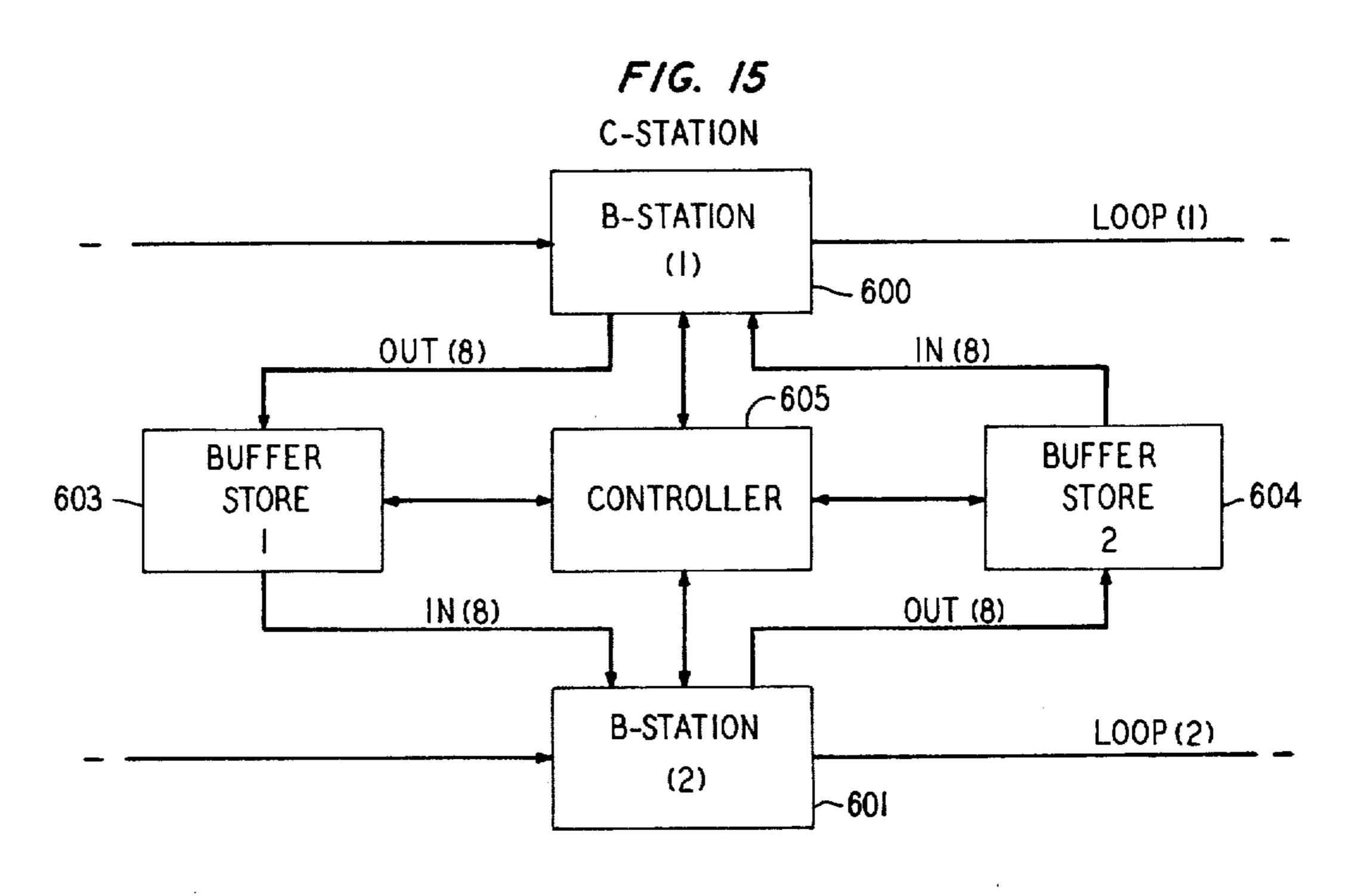

FIG. 15 is a block diagram of a C-station useful in the data transmission network of FIG. 1;

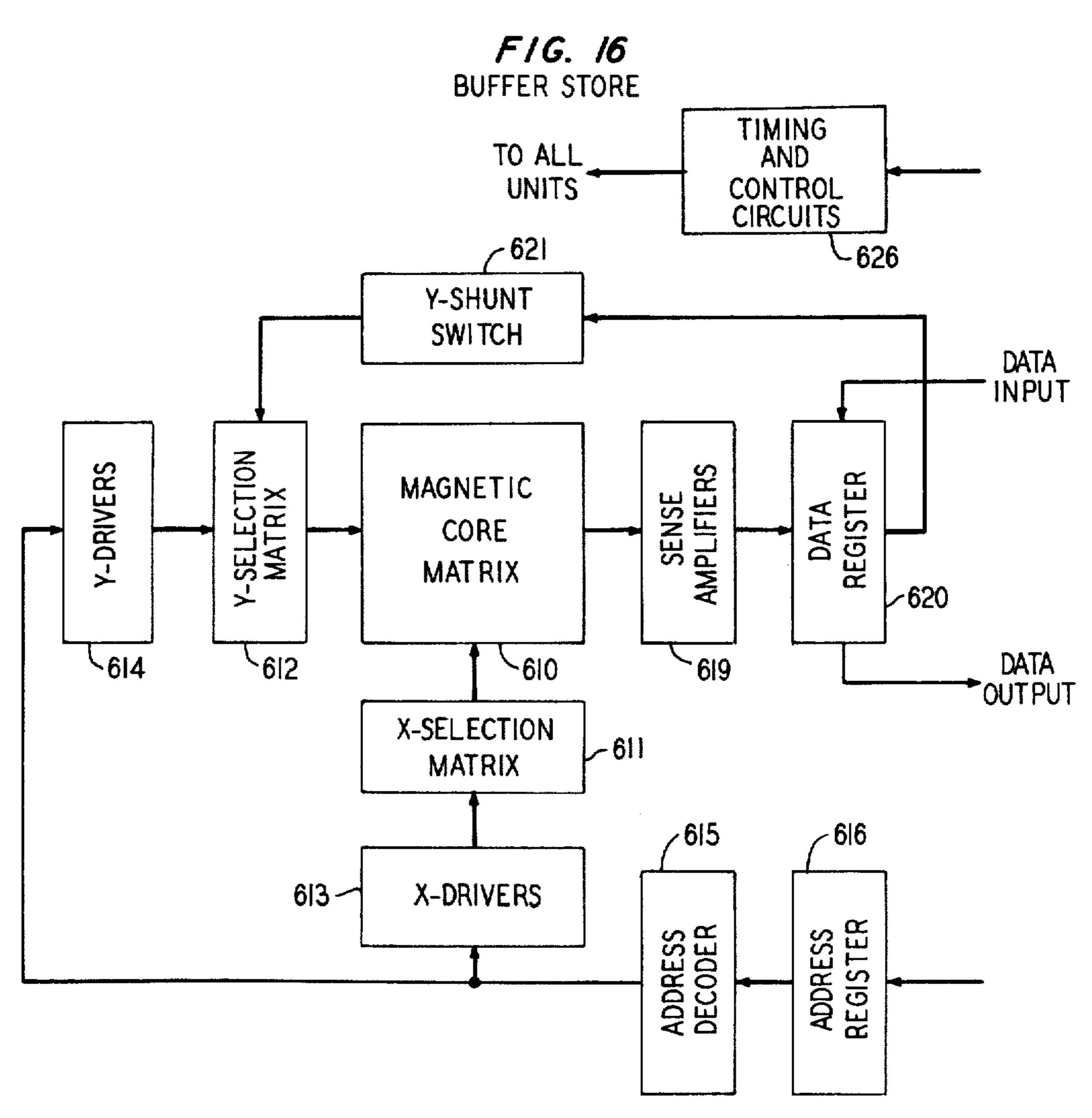

FIG. 16 is a block diagram of a buffer store unit useful in the C-station of FIG. 15;

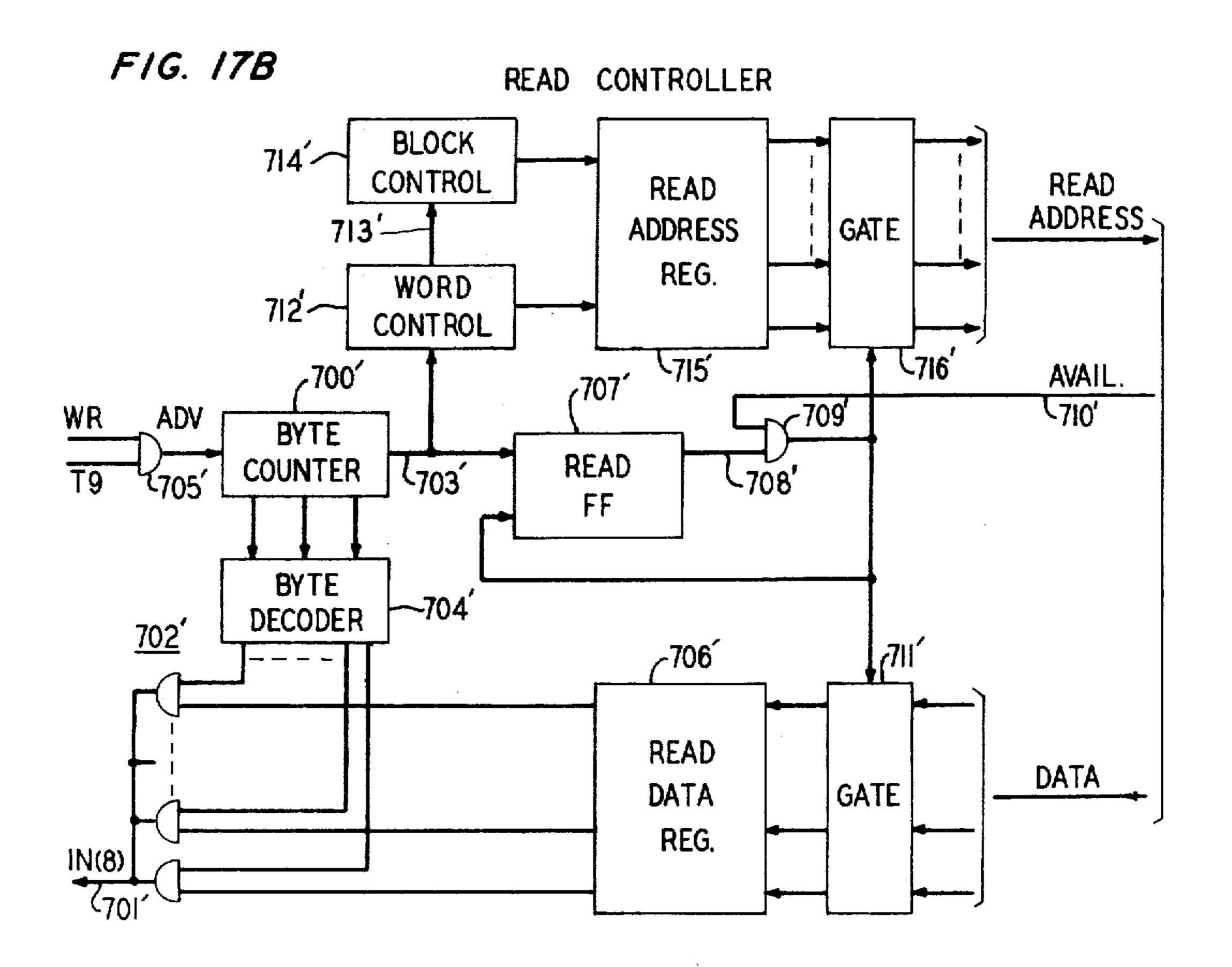

FIGS. 17A and 17B comprise a detailed circuit diagram of a C-station controller useful in the C-station of FIG. 15;

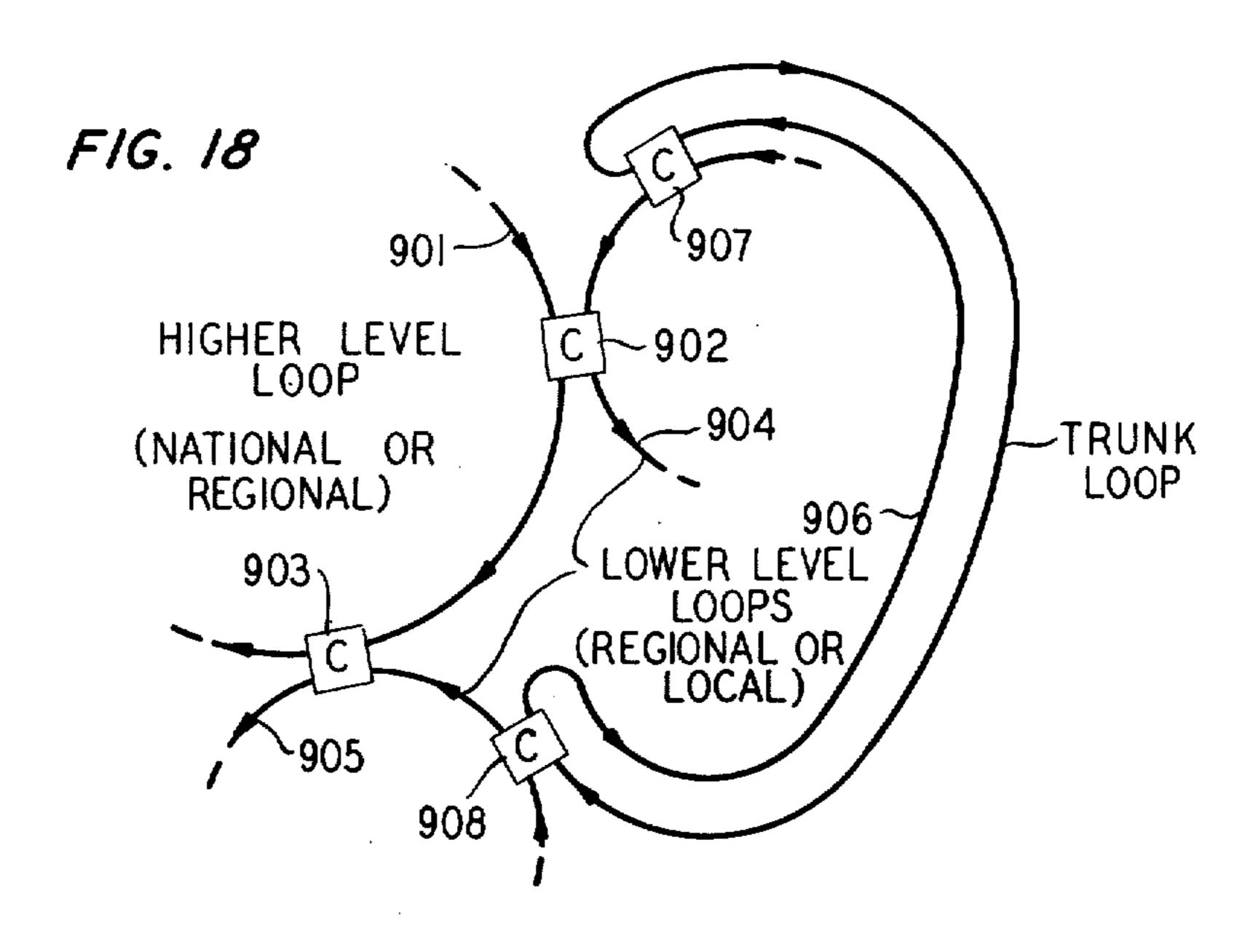

FIG. 18 is a block diagram of a trunk loop modification of the data transmission system of FIG. 1 which allows locally heavy inter-regional traffic to avoid loading the national loop;

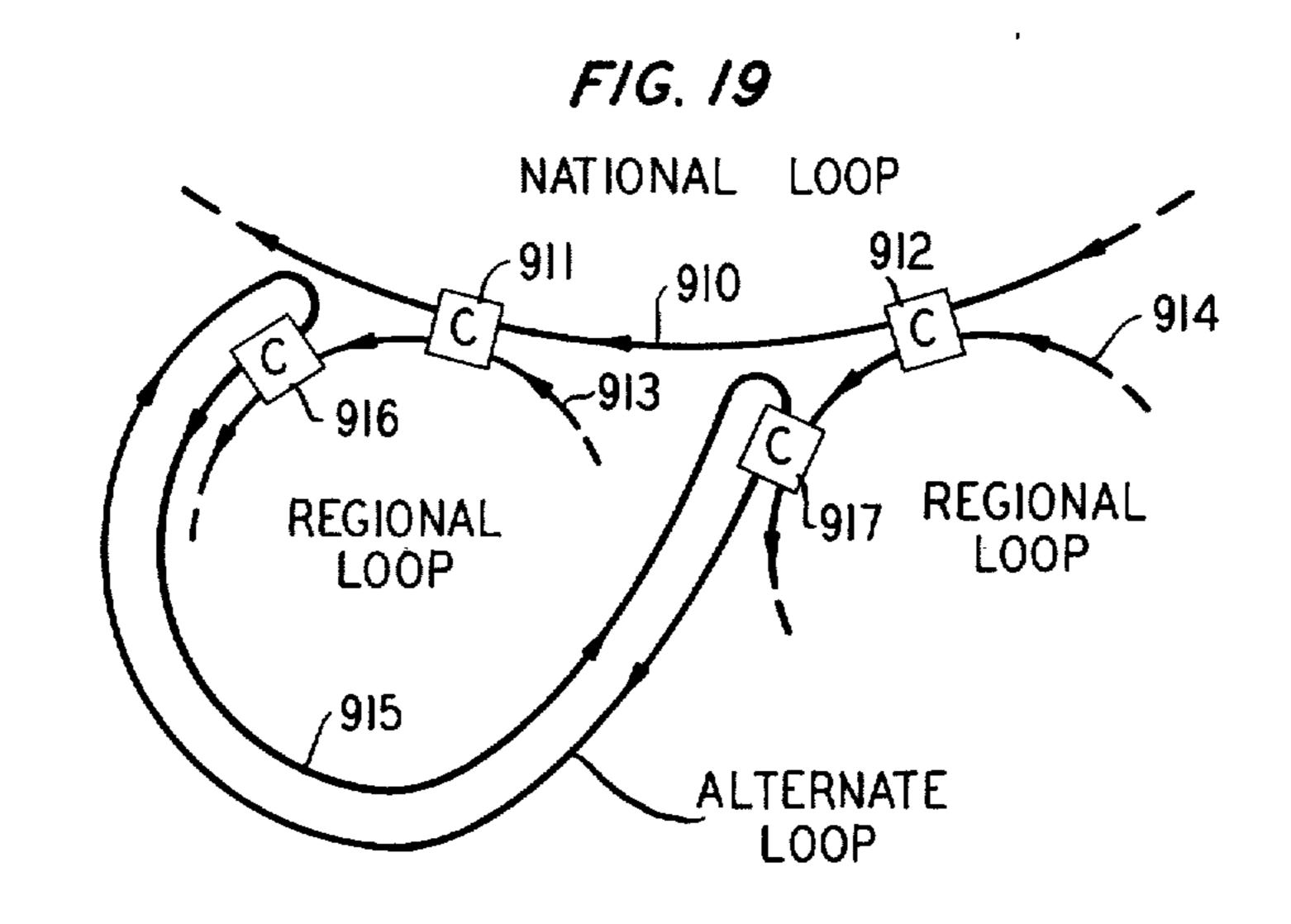

FIG. 19 is a block diagram of a modification of the 30 data transmission system of FIG. 1 which allows over-flow traffic to use an alternate route between regional loops; and

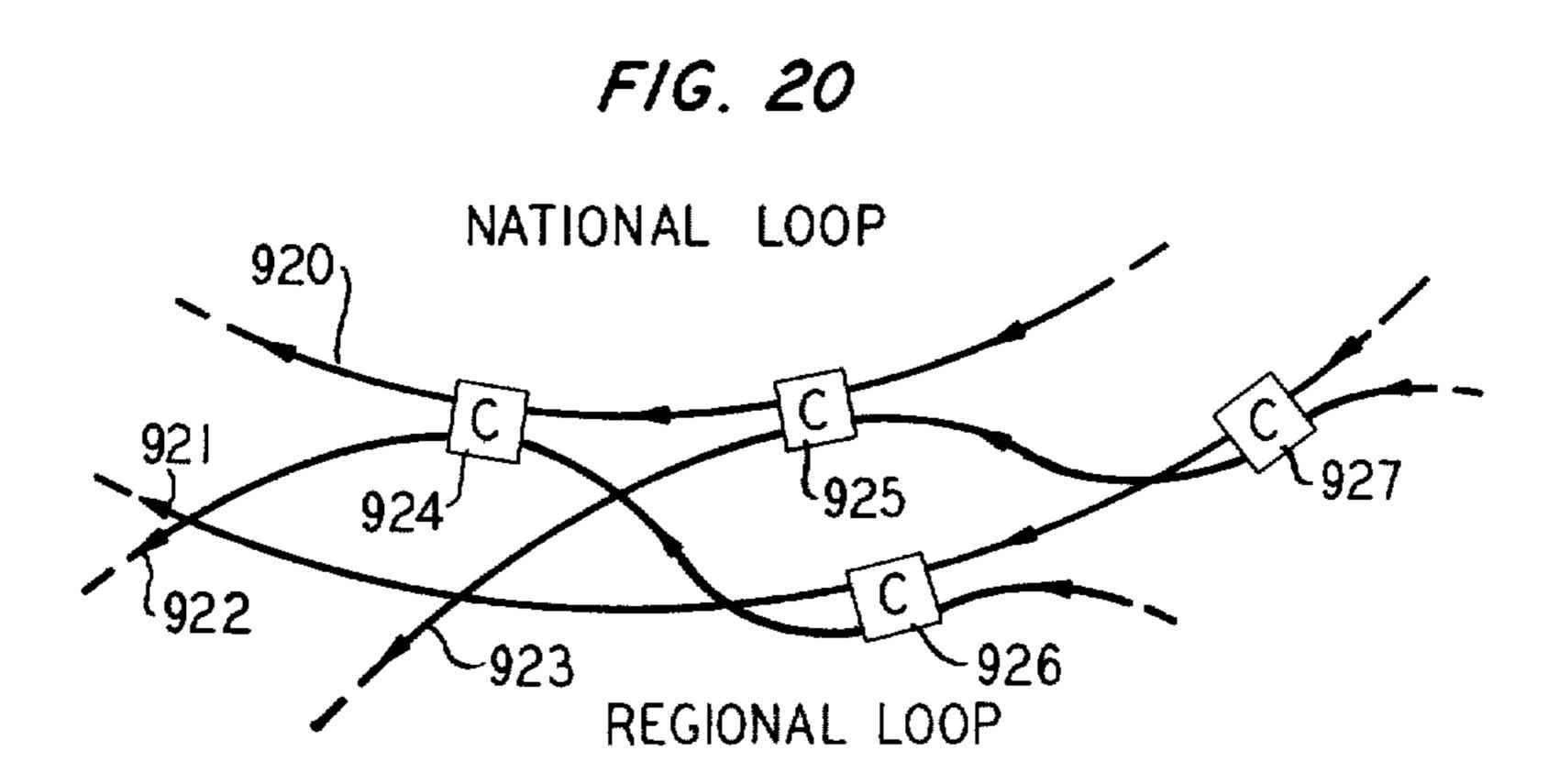

FIG. 20 is a block diagram of a redundant loop modification of the data transmission system of FIG. 1.

#### DETAILED DESCRIPTION OF THE DRAWINGS

Before proceeding to a detailed description of the drawings, it should be noted that all of the circuits described herein may be realized, in the illustrative 40 embodiment, by using integrated circuits. Each of the circuits can be found, for example, in "TTL Integrated Circuits Catalog from Texas Instruments," Catalog CC201, dated Aug. 1, 1969. Similar circuits are available from other manufacturers as listed at pages A-9 45 through A-24 of the CC 201 Catalog.

Referring more particularly to FIG. 1, there is shown a graphical representation of an intersecting loop data transmission system in accordance with the present invention. In a nationwide data transmission system, for 50 example, a national loop 10 interconnects a plurality of regional loops, illustrated in FIG. 1 by regional loops 11, 12, 13 and 14. The regional loops, in turn, each interconnect a plurality of local loops. Illustratively, regional loop 11 interconnects local loops 15 and 16, 55 regional loop 12 interconnects local loops 17 and 18, regional loop 13 interconnects local loops 19 and 20, and regional loop 14 interconnects local loops 21 and 22. The digital transmission system of FIG. 1 thus comprises a plurality of closed transmission loops which 60 intersect at selected points to permit the transfer of digital messages between the loops. Three basic digital components are provided in FIG. 1 in addition to the transmission loops themselves.

First, there is provided a timing unit labelled as sta-65 tion "A" for closing each loop. Thus loops 10 through 22 are each provided with an A-station 23, all of which are identical. The A-stations serve to provide synchro-

nization and timing for the associated loops and permit the loops to be closed on themselves.

Data access stations 24, called "B-stations," are provided on all of the local loops 15 through 22 to permit access to the local loops by data sources and/or data sinks. Any number of B-stations can be included on each local loop. Regional loops 11 through 14, and national loop 10, differ from the local loops only in that no data access B-stations are found on loops 10 through 14.

A special unit, called a "C-station" is placed at the intersections between the loops. Thus, C-stations 25 and 26 form the intersections between regional loop 11 and local loops 15 and 16, respectively; C-stations 27 and 28 form the intersections between regional loop 12 and local loops 17 and 18; C-stations 29 and 30 form the intersections between regional loop 13 and local loops 19 and 20; and C-stations 31 and 32 from the intersections between regional loop 14 and local loops 21 and 22. Similarly, C-stations 33, 34, 35 and 36 form intersections between regional loops 11, 12, 13 and 14, respectively, and national loop 10.

The network of FIG. I is only illustrative of the types of data networks envisioned by the present invention. The geographical extent of each loop and the number of access ("B") stations on each loop depends upon the information capacity of the associated loop and the loading provided by each access station. It is anticipated that the various loops will have differing channel capacities, depending of these factors. Moreover, transmission on these loops need not be synchronous and the speed of transmission on different loops can be different.

In operation, data to be transmitted on the system is inserted on a local loop at one of the B-stations in a standard length message format and associated with an appropriate address. This message block transverses the local loop until a C-station is reached to which a loop transfer must take place in order to deliver the message block to the designated address. If the destination is on the local loop, of course, the message will be delivered to that destination without ever leaving the local loop.

In transferring blocks of information from one loop to another, buffering is provided at the C-stations to take care of any differences in bit rates or timing. This buffer must be of an appropriate size to prevent excessive message blocking due to buffer overload. The operation of the system of FIG. 1 will be more readily understood upon consideration of the message block formats shown in FIGS. 2A and 2B.

As can be seen in FIGS. 2A and 2B, each message block consists of a sequence of digital words of standard length. The number of such digital words in each message block is fixed. In the illustrative embodiment of FIGS. 2A and 2B, the message format is composed of 128, 8-bit words, each separated from the others by a guard bit. All of the guard bits are "1's" to prevent long strings of "0's" which would make it difficult to maintain synchronization. Synchronization and timing recovery is also greatly simplified by the repetitive patterns of "1" bits. The above framing bit pattern is violated in only one circumstance: a "0" bit is placed in the initial guard bit preceding the first word of the message block. A Start-of-Block code comprising all "0's" forms the first word of each message block. Thus, the "0" guard bit, together with the "0's" of the Startof-Block code, provide the only occurrence of nine

consecutive "0's." this occurrence can be detected to start framing and initiate block access for reading or writing purposes.

The second word of each message block comprises a control word which carries a coded representation of the status of the message block, i.e., whether the block is vacant or full, whether the message is private or broadcast, whether the message is for local or foreign delivery and other conditions to be hereinafter described. The detailed contents of this control word will be described later in connection with FIG. 1.

The third word of each message block comprises a destination code indicating the destination to which the message block is to be delivered. Although only one word has been reserved for the destination code in FIG. 15 2A, it is apparent that two or more words may be used for this purpose in order to accommodate the required number of destinations. Similarly, the source code in the fourth word of FIG. 2A may likewise occupy two or more words of a message block depending upon the number of bits required to distinguish between all of the possible sources.

Following the source code in FIG. 2A is a plurality of data words comprising the substance of the message blocks. This data is supplied by the user of the system 25 as a serial sequence of binary bits which the B-stations 22 arbitrarily divide up into 8-bit words. Users of the system may therefore provide their own error control by way of redundant coding. The message format of FIG. 2B will be discussed in connection with FIG. 15. 30

In FIG. 3 there is shown a general clock diagram of a station circuit useful as A or B-stations in the communication system of FIG. 1. Digital signals traversing a loop appear at input terminals 50 and are applied via isolating transformer 51 to data receiver 52. Data receiver 52 demodulates the received signals and, if necessary, translates the binary signals to the appropriate voltage levels required for the balance of the circuits, passing the signals to timing recovery circuit 53 and shift register 54.

Timing recovery circuit 53 utilizes the pulse repetitions of the message block to synchronize a local clock in order to provide timing information for the balance of the circuits. The clock pulses thus provided are supplied to timing generator circuit 55 which provides all of the timing pulses required to synchronize the operations of the balance of the circuit. The timing generator 55 will be discussed in greater detail in connection with FIG. 4.

Shift register 54, which will be described in greater 50 detail in connection with FIG. 5, is a serial input, serial output, 9-bit shift register having parallel access to all of the stages for reading purposes. Thus, the outputs of all of the stages of shift register 54 are made available to control circuits 56 by way of leads 57.

The control circuits 56 respond to the various codes in the first three words of each message block to initiate and control the operation of the station circuit of FIG. 3. Control circuits 56, for example, detect the Start-of-Block synchronizing code, detect the data block control word, and detect the loop destination code. These control circuits will be discussed in greater detail in connection with FIGS. 7 through 10.

The output of shift register 54 is applied to shift register 58 which is an eight-stage, serial input, serial output shift register with both parallel reading and parallel writing access thereto. Thus, write logic circuits 59, under the control of signals from control circuits 56

and signals from a local data source by way of leads 60, control the writing of data appearing on leads 61 in series or in parallel into shift register 58. Similarly, read logic circuits 62, under the control of signals from control circuits 56 and signals on read control leads 63, permit the reading, in series or in parallel, of message words from shift register 58 onto data output leads 64. It can thus be seen that message blocks can be entered into and removed from the transmission loop one word at a time by way of shift register 58.

The serial output of shift register 58 is applied to data output circuits 65, to be discussed in more detail in connection with FIG. 14. In general, data output circuit 65 inserts or reinserts the one-bits in the guard spaces between message words and, when necessary, interchanges the source and destination codes in order to return undelivered messages to the sender.

A loop initialization circuit 66 is provided for A-stations only and is used to initilize the loop when message block framing is lost. In general, this is accomplished by inserting nine zeroes followed by all ones on the loop. The loop initialization circuit 66 will be discussed in more detail in connection with FIG. 14.

The output of data output circuits 65 is applied to a data transmitter 67 which may be used to remodulate the data to be desired frequency range for transmission on the loop. This modulated data is transmitted by way of isolating transformer 68 and output terminals 69 to the transmission loop.

The block diagram of FIG. 3 performs all of the functions necessary for A- or B-stations in FIG. 1. Slight modifications are required for A-station use. Clock signals, for example, may be provided from a local pulse source rather than from a timing recovery circuit 53. The read and write logic circuits 62 and 59 are not required since no data access takes place at the A-station. The loop initialization circuit 66, however, is required. Most of the balance of the circuitry of FIG. 3 can be identical in B-stations and in A-stations. Indeed, susbstantial manufacturing savings may be effected by constructing a single station which can be manually modified to serve as either an A-station or a B-station.

In order to better understand the various control signals utilized in the realization of FIG. 3, as illustrated in detail in FIGS. 4 through 14, the logic signals appearing on each lead have been indicated by an alphanumeric sequence which forms a code for the logic value. For a better understanding of these signals, the following glossary of logic terms is provided and can be referred to in connection with the balance of the figures.

| _ |         | Glossary of Terms                                      |

|---|---------|--------------------------------------------------------|

| 5 | ADAT    | A-station loop data                                    |

|   | ASCW    | Enable A-station control codes to SRB                  |

|   | BCT(X)  | Bit counter flip-flop X                                |

|   | BDAT    | B-station loop data                                    |

|   | BLC(X)  | Block length counter, bit X                            |

|   | BLOV    | Block length oversize                                  |

| 0 | BLUN    | Block length undersize                                 |

| U | BSCW    | Enable B-station control codes to SRB                  |

|   | CLK     | Clock                                                  |

|   | CRRQ    | Common read request                                    |

|   | CWOT(X) | Data block control word out; bit                       |

| 5 | ENLDB   | Enable loading of B Register                           |

| J | ENWR    | Enable write                                           |

|   | ESIN    | Enable serial input                                    |

|   | ESWR    | Enable serial write                                    |

|   | FCCID   | Block full and has not passed A. station code detected |

### -continued

|                                         | Glossary of Terms                                                  |

|-----------------------------------------|--------------------------------------------------------------------|

| FCC2D                                   | Block full and passed A-station                                    |

| FCC3D                                   | code detected<br>Block full with S & D                             |

| FERR<br>FGSYC                           | interchanged code detected Format Error Format loop generated sync |

| FLCI(X)                                 | (write 9 zeros) Foreign/local control word in; bit                 |

| FRMT                                    | X<br>Format loop                                                   |

| HCZD                                    | HC field zero detected                                             |

| HPFF<br>ICSD                            | HOG prevention flip flop                                           |

|                                         | Interchange source and destination codes                           |

| IN(X)                                   | Parallel data in; bit X                                            |

| INSR                                    | Enable input to SRB                                                |

| K(X)                                    | Bit X input to SRB                                                 |

| LC(X)D                                  | LC field hit X detected                                            |

| LCDAT<br>LDSRB                          | Loop closing buffer data out                                       |

| LPCW                                    | Load shift register B  Loop Closing Buffer Write Gate              |

| NCZD                                    | Nine consecutive zeroes detected                                   |

|                                         | in SRA                                                             |

| NRSET                                   | Nine consecutive zeroes detected Reset                             |

| OUT(X)                                  | Parallel data out; bit X                                           |

| PRSTB<br>PWSTB                          | Parallel read strobe  Parallel write strobe                        |

| PBLC                                    | Reset Block Length Counter                                         |

| RD                                      | Terminal reading data from line                                    |

| RDC                                     | Terminal reading common                                            |

|                                         | message                                                            |

| RDP                                     | Terminal reading private message                                   |

| RDRQ<br>SFLC                            | Read request                                                       |

| SIN                                     | Start format loop cycle Serial data input                          |

| SHFTB                                   | Shift register B                                                   |

| SOBD                                    | Start of Block detected                                            |

| SOUT                                    | Serial data out                                                    |

| SRA(X)                                  | Shift register A; bit X                                            |

| SRB(X)<br>SRSET                         | Shift register B; bit X                                            |

| SRSTB                                   | Start of block reset  Serial read strobe                           |

| SWSTB                                   | serial write strobe                                                |

| TAD                                     | Terminal destination comparison                                    |

| TC(X)D                                  | gate TC field his V dutacted                                       |

| TDAD                                    | TC field bit X detected Terminal destination address               |

| <del>_</del>                            | detected                                                           |

| TICLK                                   | T1 repeater clock                                                  |

| TIDAT                                   | T1 repeater data                                                   |

| T9<br>T9CLK                             | Bit time 9                                                         |

| VCCD                                    | Bit time 9 clock Vacant control code detected                      |

| WCT(X)                                  | Word counter; bit X                                                |

| $\mathbf{WD}(\mathbf{X})$               | Word time X                                                        |

| WR                                      | Terminal writing data onto line                                    |

| WRRQ                                    | Write request                                                      |

| WS(X)<br>WSSR                           | Wired source address; bit X  Enabled wired source code to          |

| *************************************** | SRA                                                                |

| WOT9                                    | Word zero bit time nine                                            |

| WOT9D                                   | WOT9 delayed                                                       |

| WIT9                                    | Word one bit time nine                                             |

| XCLK<br>ZERO                            | Crystal clock Contents of SRA is zero                              |

|                                         | COINCINS OF SRA 19 ACTO                                            |

|                                         |                                                                    |

In FIG. 4 there is shown a detailed circuit diagram of a timing generator circuit useful as timing generator 55 in FIG. 3. The timing generator of FIG. 4 comprises a 55 four-stage bit counter 100 and a three-stage word counter 101. Bit counter 100, in turn, comprises stages 102, 103, 104 and 105 and is arranged to recycle after a count of nine by means of AND gates 106 and 107 and a feedback path 108 from counting stage 105 to 60 counting stage 102. The bit counter 100, after being preset to an initial state by an SRSET signal on lead 109, counts clock pulses on lead 110, producing an output pulse on lead 111 once for every nine clock pulses. This T9 pulse on lead 111 is combined with a 65 clock pulse on lead 110 in AND gate 112 to provide a T9CLK pulse on lead 113. This T9CLK pulse forms the input to word counter 101.

Word counter 101 comprises stages 114, 115 and 116 connected in cascaded fashion and having the outputs of each of these stages supplied to a word count decoder 117. Word counter 101, after being preset to an initial state by a signal on lead 109, counts T9CLK pulses on lead 113. Word count decoder 117 utilizes the binary outputs of stages 114, 115 and 116 to provide output signals sequentially on output leads 118. The signals on leads 118 defineate the word intervals illustrated graphically in FIG. 2. The output on the last word lead 119 is supplied by way of inverting circuit 120 to disable the input to stage 114. In this way, the word counter 101 counts up to a word count of five and then remains latched there until reset by a signal on lead 109.

When the circuits of FIG. 4 are used in an A-station, a block length counter 121 is also provided to count the words in the entire message block. A block length decoder 122 provides an output signal on lead 123 when the block length count is less than the desired value and provides an output signal on lead 124 when the block length count exceeds the desired block length. These underlengths (BLUN) and overlength (BLOV) signals are used to control the loop initialization circuits to be desired hereinafter in connection with FIG. 14. Counter 121 is reset to its initial state by an RBLC signal on lead 125.

Referring to FIG. 5, there is shown a detailed circuit diagram of shift register A, useful as shift register 54 in FIG. 3. The shift register of FIG. 5 comprises nine stages, 150 through 158. Serial input data (derived from data receiver 52 in FIG. 3) appears at input terminal 159 and is applied directly to the set input of the first stage 150, and through inverter 171, to the reset input of stage 150. Inverted clock pulses (from timing recovery circuits 53 in FIG. 3) appear at terminal 160 and are applied to all of stages 150 through 158 to advance the data signals through these stages. The serial output pulses from the shift register of FIG. 5 appear at output terminal 161.

The individual stages 150-158 of the shift register of FIG. 5 also provide parallel output signals to output terminals 162 through 170 respectively. It is therefore apparent that data can be written into the shift register of FIG. 5 in a serial fashion from terminal 159, may be read out of shift register A in a serial fashion via terminal 161, and may be read out of shift register A in parallel by way of terminals 162 through 170. The outputs at terminals 162 through 170 are connected to the control circuits 56 (FIG. 3) which will be discussed in more detail in connection with FIGS. 7 through 9. In general, the first three words of each message block, as they pass through the shift register of FIG. 5, are applied in parallel to the control circuits of FIGS. 7 through 9 to control the operation of the station.

Referring more particularly to FIG. 6, there is shown a detailed circuit diagram of shift register B, useful as shift register 58 in FIG. 3. The shift register of FIG. 6 comprises eight stages, 200 through 207. Serial data, appearing at input lead 208 (derived from terminal 161 in FIG. 5), is applied to the first stage 200 both directly and after inversion in inverter 209. Shift pulses appearing on bus 212 are applied to all of the stages 200–207 to advance data through these stages. Serial output data appears on output lead 213.

The shift pulses on bus 212 are derived from gate 214, having one enable input and two disable inputs. Inverse clock pulses from lead 210 are applied to the

enable input. The output of OR gate 251 is applied to one disable input, and T9 timing pulses (from lead 111 in FIG. 4) are applied to the other disable inputs of gate 214. Shift register B therefore advances only during the eight word-bit intervals and no advance takes place during the T9 clock pulse interval as determined by T9 signals on lead 215.

The ICSD signal on lead 216 is also applied to disable gate 214. This signal indicates that the source and destination codes at the beginning of the message block should be interchanged to return an undelivered message block to the sender. This is accomplished by retaining the destination code in shift register B and gating the source code from shift register A. This procedure will be described in greater detail in connection 15 with FIG. 14.

Shift register B in FIG. 6 can be loaded in parallel from input leads 217 to 224 by means of a loading signal on bus 225. The loading signal on bus 225 is applied simultaneously to AND gates 226 through 233 20 to gate signals from leads 217 to 224, respectively, to the corresponding one of stages 200 through 207, and to force these stages to the corresponding states, whether "0" or "1."

The loading signal on bus 225 is derived from the output of AND gate 236. Gate 236, in turn, is enabled by the simultaneous application of an inverse clock pulse from lead 210, a T9 pulse from lead 215, and the output from OR gate 237. The inputs to OR gate 237 comprise a signal on lead 234, indicating the detection of a start-of-block signal, a signal on lead 238, indicating that data input is available for writing into shift register B; a signal on lead 239, indicating that the local source code is available for writing into shift register B; a signal on 240, indicating that station control codes for a B-station are available for writing into shift register B; and, finally, a signal on lead 241, indicating that station control codes for an A-station are available for writing into shift register B.

Parallel inputs from stages 200 through 207 are available on leads 242 through 249, respectively, for delivery to the read logic circuit of FIG. 13. The output of stage 200 appearing on output lead 242 can also be used as a serial output of the same data when it is delivered by way of lead 250.

It can be seen that the shift register of FIG. 6 provides serial input, serial output, parallel write-in and parallel read-out. In general, shift register B provides the access point to which locally derived data may be entered into a message block on the transmission loop and from which data can be read from the message block to a local data utilization circuit. Such reading and writing is done in words of eight bits, one word at a time, under the control of signals to be described hereinafter.

In FIG. 7 there is shown a detailed circuit diagram of a portion of the control circuits 56 of FIG. 1. The circuits of FIG. 7 comprise a Start-of-Block detector suitable for detecting the nine zeroes Start-of-block synchronizing code illustrated in FIG. 2, and for detecting a destination code corresponding to the local data utilization circuit. To this end, three flip-flops 260, 261 and 262 are provided. An AND gate 263 detects zeroes in the first eight stages of shift register A of FIG. 5 more AND gate 264 utilizes this condition in coincidence with a zero output from the last stage to produce a signal to set NCZD flip-flop 261. An output is thus produced on output lead 265, which upon the appearance of the next succeeding clock pulse at lead 266,

10

and provided there is no "0" output from flip-flop 260, fully enables AND gate 267 to provide an NRSET reset signal on lead 268. This reset signal is used to initialize all of the circuits of the station for the reception of the message block. It will be noted that only the first word of a message block will present nine consecutive zeroes to this detection circuit and thus provides a unique framing signal for the message block.

The output of flip-flop 261, appearing on lead 265, is also applied to one input of AND gate 269. A "1" signal output from the next to last stage of shift register A, appearing on lead 270, completes the enablement of AND gate 269, setting Start-of-Block detecting flipflop 260 to the 1-output state, thus providing a signal on lead 271. This output on lead 271 is applied to AND gate 272 which, when completely enabled by the next clock pulse on lead 266, and provided no delayed WOT 9D pulse from delay circuit 279 appears, provides an output pulse to lead 273. This output pulse is used to preset the counters 100 and 101 of the timing generator of FIG. 4 and thus initiate a timing cycle. Flip-flops 260 and 261 are reset by the 1-output of flip-flop 260 appearing on lead 271. Flip-flop 261 may be set to the "1" output condition by an FGSYC signal on lead 277 from FIG. 14, indicating that loop initialization is taking place.

It can be seen that flip-flops 260 and 261, together with the associated logic circuitry, detect the Start-of-Block synchronizing code and detect the next following guard bit to initiate the timing signals. Each new message block resynchronizes the station timing circuits by way of these detection circuits.

Also shown in FIG. 7 is a terminal destination address detector comprising flip-flop 262 which is set by the output of AND gate 274. The eight inputs to AND gate 274 are wired to the stages of shift register A in FIG. 5 according to a pattern which detects the address code of the local data utilization circuits.

Flip-flop 262 can be set only in the presence of an output from AND gate 275 to which there is applied the T9CLK pulses from lead 113 in FIG. 4 and the WDI pulses from the appropriate one of leads 118 in FIG. 4. Flip-flop 262 is reset by a VCCD signal on lead 276, indicating that the received block is vacant or unused. It can thus be seen that flip-flop 262 is set whenever the message being received is destined for the local B-station and is reset if the message block is vacant. The output of flip-flop 262 is used (in FIG. 10) to initiate a block reading sequence.

Before proceeding to a description of the balance of the control circuits corresponding to block 56 in FIG. 1, it is first convenient to describe the format of the data block control word appearing as the second word in each message block. The 8-bit control word is divided up into four fields of 2 bits each. These fields are assigned in accordance with Table I.

TABLE I

|                 | Data Block Control Word Format |                                   |

|-----------------|--------------------------------|-----------------------------------|

| Bit<br>position | Bit 1 D.                       | Description                       |

| SRA8            | H2                             |                                   |

| SRA7            | HI                             | Hog Prevention Control Field HC   |

| SRA6            |                                |                                   |

| SRA5            |                                | Not Used                          |

| SRA4            | LC2                            |                                   |

| SRA3            | LC1                            | Loop Vacant-Full Control Field LC |

| SRA2            | TC2                            |                                   |

TABLE I-continued

| <b></b>         | Data Blo | ock Control Word Format       |

|-----------------|----------|-------------------------------|

| Bit<br>position | Bit I D. | Description                   |

| SRAI            | TCI      | Type of Message Control Field |

In FIG. 8 there is shown a detailed circuit diagram of the logical arrangement necessary to prevent the monopolization of a local loop by one or more pairs of transmitting-receiving B-stations. This problem is referred to as "hog prevention" and arises because the stations intervening between a transmitting and a receiving station can be locked out of access to the circuit if the transmitting station presents a continuous load to the transmission loop. In general, the hog prevention circuits set a marker at a transmission station at the time of each transmission and prevent that station from initiating further transmissions until all other sta- 20 56 in FIG. 1. The gates of FIG. 10 implement the logitions have satisfied their transmission requirements.

The hog prevention control circuit of FIG. 8 comprises an HC field zero detection flip-flop 300 and a hog prevention flip-flop 301. Flip-flop 301 is set by a signal on lead 302 each time the local station writes a 25 message block into the loop. Flip-flop 301 is reset during the T9 clock pulse interval of word WDO as determined by the output of AND gate 303, providing flipflop 300 is in the "1" state to complete the enablement of AND gate 304.

Flip-flop 300 is set to the "1" state by the simultaneous appearance of zeroes in the seventh and eighth bit positions of shift register A as determined by AND gate 305. These bit positions correspond to the hog control field HC of the data block control word as it 35 resides in shift register A. Flip-flop 300 can be set only during the appearance of an output from AND gate 303 (during the T9 clock pulse interval of word WDO). Flip-flop 300 can be reset by an NRSET signal on lead 306, indicating a detection of a new start-of-block syn- 40 chronizing signal. Flip-flop 300 is thus reinitialized for each new message block. The operation of a circuit of FIG. 8 will be discussed in more detail hereinafter in connection with the overall hog prevention system.

In FIG. 9 there is shown a detailed circuit diagram of 45 the control circuits responsive to the loop control field LC and the type control field TC. The circuit of FIG. 9 comprises a pair of flip-flops 350 and 351 which respond to the loop control field in bit positions SRA4 and SRA3, respectively, appearing on leads 352 and 50 353. The outputs of flip-flop 350 and 351 are applied to a loop control field decoder 354. Decoder 354 may comprise a simple AND gate matrix to decode the loop control field bits into one-out-of-four control signals. These signals are described in Table II.

TABLE II

| Loop Vacant/Full Control Signals |         |                                  |

|----------------------------------|---------|----------------------------------|

| Binary                           | Logical | Description                      |

| 00                               | VCC     | Block Vacant                     |

| 01                               | FCC1    | Block Full; A-Station not passed |

| 10                               | FCC2    | Block Full; A-Station passed     |

|                                  |         | once                             |

| 11                               | FCC3    | Block Full; A-Station passed     |

|                                  |         | twice                            |

The flip-flops 355 and 356 are used to store the type control field appearing on leads 357 and 358, respectively, from the last two stages of shift register A. All of

flip-flops 350, 351, 355 and 356 are enabled only during the appearance of a T9 clock pulse during a word WDO, as determined by the output of AND gate 359. All of flip-flops 350, 351, 355 and 356 are reset by an NRSET signal on lead 360 at the beginning of each new message block. The type control field bits are interpreted as shown in Table III.

TABLE III

|        | Type of Message Control Field |                               |  |  |

|--------|-------------------------------|-------------------------------|--|--|

| Binary | Logical                       | Description                   |  |  |

| 00     | LPM                           | Private Message               |  |  |

| 01     | LCM                           | Common Message                |  |  |

| 10     | UFM1                          | Undeliverable Foreign Message |  |  |

| 11     | UFM2                          | Undeliverable Foreign Message |  |  |

|        |                               | - FS and FD Interchanged      |  |  |

In FIG. 10 there is shown a detailed logic diagram for the read-write control circuits forming a part of block cal equations to be described below.

#### READ A PRIVATE MESSAGE FROM THE BLOCK

In order to read a private message appearing on the local loop, AND gate 375 implements the following logical equation:

$$RDP=RDRQ \cdot TDAD \cdot \overline{VCCD}$$

. (1)

The logical term RDRQ is read request from the local data utilization circuits. The TDAD signal is derived from FIG. 7 and indicates that the destination of the message on the loop is the local B-station. The logical term VCCD, derived from FIG. 9, indicates that the message block is not vacant but indeed does carry a message. The concurrence of these conditions or logical signals provides an output from gate 375 and also provides an output from OR gate 376. These output signals perform the following functions. The contents of the loop and type control fields are gated out to the local data utilization circuits as the control word output (CWOT) bits as shown in FIG. 13. The corresponding positions in shift register B are set to zero. In addition, the source code in the fourth word position of the message block is also gated to the local data utilization circuits. Finally, all of the data bits from the message block are also gated to the local utilization circuits.

#### READ A COMMON MESSAGE FROM THE BLOCK

Gate 377 implements the following logical equation:

$$RDC=CRRQ \cdot LCMD \cdot \overline{VCCD},$$

(2)

where

55

$$LCMD=TC1D \overline{TC2D}.$$

(3)

The common read request signal CRRQ is provided by the local station and indicates a readiness to receive the common message. The inverted vacant control code detected signal VCCD is identical to that described 60 with reference to equation (1). The local common message detected signal LCMD is defined in equation (3). The output of gate 377 is also applied to OR gate 376. As a result of these outputs, the command word output (CWOT) bits, the loop source code, and the 65 data bits are all gated to the local station. The message block, however, is in this case left unaltered to permit the delivery of the common message to other stations on the loop on a broadcast basis.

#### WRITE A MESSAGE INTO THE BLOCK

Gate 378 in FIG. 10 implements the following logical equation:

WR=WRRQ . ENWR . VCCD, (4)

where

$ENWR=HCZD+\overline{HCZD} \cdot \overline{HPFF}. \tag{5}$

The logical term WRRQ is derived from the local station and indicates a desire to write a message into the local loop. The VCCD signal indicates that the message block is empty and hence available for writing. The ENWR signal, as indicated in equation (5), is a special 15 enabling signal which permits writing only if the special hog prevention conditions exist. Thus the term HCZD indicates that the hog prevention control field is all zeroes, and hence no unsatisfied write request have been made previously on the loop. The second term of 20 equation (5) indicates that writing is enabled even if zeroes were not detected in the hog prevention control field, provided that the hog prevention flip-flop 301 (FIG. 8) has not been set. This latter term indicates that the previous message on the loop was not inserted 25 by this station.

The complete enablement of gate 378 provides a signal on lead 379 which sets the loop control field to "01," indicating the FCC1 condition which marks the block as being full. At the same time, the type control <sup>30</sup> field is set by locally supplied bits (FLCI), identifying the type of message being transmitted. During successive word times this control word, a destination code, a source code and the data words are all written into shift register B (FIG. 6). As discussed in connection with <sup>35</sup> FIG. 8, the hog prevention flip-flop 301 is also set.

In FIG. 11 there is shown a detailed circuit diagram of the write logic circuits corresponding to block 59 in FIG. 3. The write logic circuits comprise a plurality of write leads 400 through 407 which are supplied to shift register B, as shown in FIG. 6. Each of these leads can be enabled by the output of the connected one of OR gates 467 through 474, respectively. The outputs of each of OR gates 467 through 474 may be driven to the logic "1" state by the enablement of any one of a plurality of logical AND gates to which it is connected.

A wired source code identifying the local station is delivered by way of cable 410 to AND gates 411 through 418. When completely enabled by a signal on WSSR bus 419, gates 411 through 418 deliver the source code through OR gates 467–474 to leads 400 through 407 to be registered in shift register B. Similarly, data words appearing on cable 420 are supplied to AND gates 421 through 428. When completely enabled by a signal on INSR bus 429, gates 421 through 428 deliver data words via OR gates 467–474 to the leads 400 through 407, respectively, for registry in shift register B.

The data block control words are generated in command word encoder 465 at the left side of the wired 60 matrix of FIG. 11. Gates 430, 431 and 432, for example, generate the hog control field bits which are inserted on leads K7 and K8 in response to the WD1 pulse on lead 433. These hog control bits are normally merely reinserted from the seventh and eighth bit positions of shift register B on leads 434 and 435, respectively. The eighth bit position, however, can also be filled by the output of AND gate 430, derived from

14

inhibit gate 436. Gate 437 is enabled by a write request WRRQ signal on lead 437 and is disabled by a block vacant VCCD signal on lead 438. As will be discussed in more detail hereinafter, gate 436 writes a "1" into the H2 bit position to indicate that the local station wishes to write a message but cannot do so because the block is not vacant.

The foreign-local control word input (FLCI) bits are introduced at gates 439 and 440. These gates are enabled by the output of AND gate 441 during the word WD1 interval as indicated by a signal on lead 433, and during a write operation, as indicated by a signal on lead 442. The output of gate 441 is also used to write a "1" into the third bit position of the control word corresponding to the TC2 bit. This forces the loop control field to the "01" state, indicating that the block is full.

Gating signals are provided to the word writing circuits of FIG. 11 from AND gates 443, 444, 445 and 446. The output of AND gate 443 on ESIN bus 447 enables serial input data to be written into a message block. Gate 443 is partially enabled, via OR gate 448, during the third word interval for the destination code and during the fifth and following word intervals for writing data. An ESWR signal is also required on lead 449, indicating that the local station wishes to write in a serial fashion. The enablement of gate 443 is completed by a WR write signal on lead 442.

AND gate 444 provides the WSSR gating signal on bus 419 and is enabled during the third word period for write operations to gate the wired source code in parallel into shift register B.

Gate 445 provides an output INSR signal on bus 429 for gating data in parallel into shift register B and is enabled during the second and fourth word periods by the output of OR gate 450.

Gate 446 provides an output BSCW signal on bus 451 during the word WD1 interval indicating that a command word is being written into shift register B. Gate 446 is fully enabled by a "private" read request on lead 452 or a write request on lead 442, both of which are applied through OR gate 466.

The local data source is provided with strobing signals on leads 453 and 454. The PWSTB signal on lead 453 is provided by gate 455 during the T9 clock interval and during parallel input as indicated by an INSR signal on bus 429. The SWSTB strobe on lead 454 is supplied by gate 456 to which there is applied an ESIN signal from bus 447, a clock pulse from lead 457 and a T9 pulse from lead 458, inverted in inverter circuit 459. Lead 454 is therefore energized during the entire word interval and is not energized during the guard space.

Referring to FIG. 12, there is shown a detailed logic diagram of a command word encoder suitable for use as encoder 465 in the write logic circuit of FIG. 11 when FIG. 11 is used for an A-station. The encoder of FIG. 12 comprises an AND gate 500 to which there is applied an FCC2D signal on lead 501 from the loop control decoder of FIG. 9 and a word WD2 pulse on lead 502. As can be seen in Table II, the FCC2D signal indicates that the full message block has passed the A-station once and hence has circulated entirely around the loop without being delivered. During the second word interval, gate 500 is fully enabled to produce an ICSD signal at output lead 503, indicating that the source and destination codes should be interchanged so as to return message block to its source. This returning block then indicates that the destination

is busy or otherwise unavailable for delivery of the message.

The hog prevention scheme requires that the A-station substitute the H2 bit for the H1 bit and set the H2 bit to zero. To this end, gate 504 is used to gate the control word bit from the 8th bit position (H2) on lead 505 into the seventh bit position (H1) on lead 506. Gate 504 is fully enabled during the word WD1 interval during which the command word is written into shift register B (FIG. 6).

The loop control field and type control field are also written during the word WD1 interval as determined by the output of gate 507 on ASCW bus 508. Gate 507 is disabled by a WR signal on lead 509 or a BSCW signal on lead 512 and is enabled by a word W1 pulse. When 15 fully enabled, gate 507 provides an output to gates 513, 514, 515 and 516. At this time, gates 514 and 515 gate the type control field from FIG. 9 into shift register B. At the same time, the loop control field is written into the LC2 (K4) and LC1 (K3) positions of the code 20 word. The FCC2D signal on lead 517 is gated directly to the Lc1 (K3) bit position and the FCC1D and FCC2D signals are ORed in gate 510 and gated to the IC2 (K4) bit position. The signal on line 508 is applied to OR gate 518 along with an FCC3D signal to produce 25 an ASCW signal on lead 519.

The logic of FIG. 12 implements the following rules for station busy situations:

- 1. If the detected loop control field is "01" (FCC1D), indicating that the block is full and that the <sup>30</sup> A-station has not yet been passed, set the loop control bits to "10" (FCC2) to now indicate that the A-station has been passed once.

- 2. If the detected loop control field is "10" (FCC2D), indicating that the block is full and that the <sup>35</sup> A-station has been passed once, then set the loop control field to "11" (FCC3) to indicate that the A-station has been passed twice.

- 3. If the detected loop control field is equal to "11" (FCC3D), indicating that the A-station has been <sup>40</sup> passed twice, set the loop control field to "00" (VCC), indicating that the block is now vacant.

It can be seen that these logic rules keep track of the length of time that undelivered message blocks remain in the loop. After circulating around the loop twice 45 without being delivered, the message block is returned to the sender, indicating that it has not been delivered. This is accomplished simply by exchanging the source and destination codes. A message which passes an Astation with an FCC3D code is erased, thus preventing 50 loop blocking by unwanted messages.

FIG. 8, in combination with gates 500 and 504 of FIG. 12, and gates 436, 430, 431 and 432 in FIG. 11, implements the following strategy for hog prevention;

- 1. When a B-station writes a message, the hog prevention flip-flop (HPFF) in that station is set to "1" (FIG. 8) and the HC field is circulated on the loop unmodified (FIG. 11).

- 2. If any other B-station on the loop wishes to write a message (WRRQ) when a full block is detected, the <sup>60</sup> HC2 bit of the hog prevention control field is set to "1" (gate 430 in FIG. 11).

- 3. If a B-station detects a VCCD vacant block signal (gate 378 in FIG. 10) and:

- a. if the HC field is "0," writing is independent of the 65 state of HPFF flip-flop 301 (FIG. 8);

- b. if the HC field is not "0," the B-station can write if, and only if, the HPFF flip-flop 301 is reset to "0."

- 4. When a data block passes an A-station (FIG. 12)

16

the HC2 bit replaces the HC1 bit and the HC2 bit is set to "0."

5. The HPFF flip-flop 301 for each B-station is reset when HC1 and HC2 are both "0" (gate 305 in FIG. 8).

It can be seen that the above logic scheme prevents line blocking since, after a B-station sends a message, it is prevented from sending another message until all other requests on the line are serviced.

In FIG. 13 there is shown detailed logic circuitry for the read logic circuit 62 in FIG. 3. The circuit of FIG. 13 comprises a set of four leads 520 taken from flip-flops 350, 351, 355 and 356 of FIG. 9. Signals on these leads represent the received loop and type control fields which are delivered to the local data utilization circuits as command words CWOT1 through CWOT4. The parallel outputs of shift register B (FIG. 6) are delivered on leads 521 to the local data utilization circuits. The local data utilization circuits are also provided data strobing signals on leads 522 and 523 to time parallel reading (on lead 522) and serial reading (on lead 523) of the received data. Signals on leads 522 and 523 are derived from AND gates 524 and 526, respectively.

Word pulses during the third and fourth word intervals are combined in OR gate 526 and supplied to each of AND gates 524 and 525. A read pulse on lead 527 is also delivered to gates 524 and 525. A clock pulse on lead 528 is also delivered to AND gates 524 and 525. Finally, a T9 pulse is delivered during the guard interval to gate 524 to permit parallel gating during the guard interval, and, after inversion in inverter 530, is applied to gate 525 to permit serial reading during the word interval itself.

In FIG. 14 there are shown data output circuits useful in the station circuit of FIG. 3. The output from shift register B in FIG. 6 appears on lead 550 in FIG. 14 and is applied to gate 551. Gate 551 is normally enabled and this output is applied by way of OR gate 522 to timing gate 553. When it is necessary to interchange the source and destination codes during the WD2 word interval, an ICSD signal appears on lead 554 from FIG. 12 to enable gate 555 and, by way of inverter 556, to disable gate 551. It can thus be seen that the destination code in shift register A and appearing on lead 557 is gated through gates 555 and 552 while the source code remains stored in shift register B. In the following word interval, the signal is removed from ICSD lead 554 and the source code can be read out of shift register B by way of gate 551. The interchange of source and destination codes is thereby achieved. T9 clock pulses on lead 558 inhibit gates 551 and 555 during the guard interval.

Data is serially inputed into the loop at gate 560. This data, appearing on lead 561, is enabled by an ESIN serial input enabling signal on lead 562. This enabling signal on lead 562 is also used to disable gate 551 during normal message forwarding. The T9 clock pulse on lead 558 also disables gate 560 during the guard interval.

Gate 563 is utilized to insert guard pulses into the guard pulse interval. To this end, T9 clock pulses on lead 558 are applied to gate 563. Gate 563 is fully enabled, however, only if there is no start-of-block code detected in FIG. 7 as indicated by a signal on lead 564. At the time the start-of-block code is detected and the flip-flop 260 in FIG. 7 is set, the ninth zero is inserted in the guard space by the disablement of gate

**563.**

During the last bit interval of the word preceding these nine "0's," as indicated by a signal on lead 565 from flip-flop 261 in FIG. 7, AND gate 566 becomes fully enabled to write a "1" into this last bit position of the word. This insures that the nine "0's" framing signal occurs unambiguously at the start of each message block.

The output of retiming gate 553 is applied to transmission converter 589 at the triggering input of flip- 10 flop 567. The "1" and "0" outputs of flip-flop 567 are applied to AND gates 569 and 570, respectively. The output of AND gate 553 is also applied to AND gates 569 and 570, while the outputs of gates 569 and 570 are applied across the center-tapped primary winding 15 off transformer 571.

The purpose of the transmission converter 589 is to convert the unipolar output pulses from gate 553 into bipolar pulses on output leads 572. Successive "1's" at the output of gate 553 set and reset flip-flop 567. AND 20 gates 569 and 570 are therefore alternately partially enabled. The data pulses from gate 553 complete the enablement of gates 569 and 570 to drive transformer 571 alternately with signals of opposite polarity. Such signals are, of course, less likely to produce a direct 25 current drift when transmitted on transmission line 572.

When the data output circuits of FIG. 14 are used in an A-station, a loop initialization circuit 573 is also provided and is inserted in series with line 590 at termi-30 nals 591. Loop initialization circuit 573 includes a format flip-flop 574 which is set by the SFLC output of OR gate 575. OR gate 575, in turn, is enabled by the output of gate 576 or by a signal on lead 577 from FIG. 4, indicating that the number of words in the data block 35 have exceeded the specified value. Alternatively, AND gate 576 is enabled by the simultaneous appearance of signals on leads 578 and 592 and absence of a signal on lead 579, indicating that the number of words in the data block is less than required and no synchronization 40 cycle is in progress. The signal on lead 578 is taken from FIG. 7 and indicates that the start-of-block synchronizing signal has been received. The signal on lead 579 is taken from FIG. 4 and indicates that the necessary number of words have not yet been received to 45 make up a message block. The signal on lead 592 is taken from FIG. 7 and indicates that nine zeroes have been detected. Flip-flop 574 is therefore set to initiate a loop initialization sequence if the block length exceeds the fixed value (BLOV), or if a start-of-block 50 signal is received before the desired block length is reached (BLUN). The SFLC signal on lead 592 is also used as the RBLC signal in FIG. 4 to reset block length counter 121 and thus initiate a new block count.

When set, flip-flop 574 enables AND gate 580 to 55 allow clock pulses from pulse source 581 to be transmitted through OR gate 582 to message block register 583. In this way, the message block can be filled with "1's" for initialization. When the block length count again reaches BLOV, gate 584 is enabled during the T9 clock pulse interval and flip-flop 574 is reset. At the same time, the FGSYC signal on lead 586 is applied to reset flip-flop 261 in FIG. 7, initiating a start-of-block signal generation sequence.

Pulse source 581 may be a crystal oscillator and 65 provides the basic timing for the entire local loop. Its pulse repetition rate is recovered and used for retiming purposes at each B-station on the loop. Register 583 is

of sufficient size to prevent the message block from overloading the storage capacity of the loop. Register 583 may, for example, be large enough to contain an entire message block, in which case there will be a delay between message blocks equal to the overall transmission time around the loop. Register 583 may, however, be of a smaller size and the storage capacity of the loop itself be taken advantage of for storing portions of the message block.

Flip-flop 574 remains set so long as AND gate 584 is not enabled. AND gate 584 detects the next coincidence of a block length oversize (BLOV) signal on lead 577, a "1" output from flip-flop 574, and a T9CLK pulse on lead 585. When fully enabled, AND gate 584 provides an output on lead 586 which is used in FIG. 7 to reset the zero detecting flip-flop 261. When the output from AND gate 584 appears, this signal is used to reset flip-flop 574. At this time, flip-flop 574 enables AND gate 588 to pass the output of OR gate 552 through OR gate 582 to register 583. The output of register 583 is, of course, supplied to AND gate 553.

It can be seen that the operation of the loop initialization circuit 573 is to insert into the loop, via AND gate 580, a string of "1's" from pulse source 581. After a full block of "1's" has been inserted into the loop by way of gate 580, the block length counter 121 in FIG. 4 again reaches the value to energize BLOV lead 124 (FIG. 4), thus completing the enablement of AND gate 584 (FIG. 14) by way of lead 577. The FRMT format flip-flop 574 is therefore reset, terminating the insertion of "1's." At the same time, the FGSYC signal on lead 586 is applied to NCZD flip-flop 261 in FIG. 7, setting this flip-flop and causing an output to appear at lead 265. When the first "1" appears at the output of shift register A (SRAG) on lead 27, AND gate 269 becomes enabled to set SOBD flip-flop 260 and, on the next clock pulse, provides an SRSET pulse on lead 273. As can be seen in FIG. 6, this SRSET signal on lead 235 gates an all "0's" code into shift register B, providing the first eight "0's" of the SOB code. In FIG. 14, the AND gate 563 provides the ninth "0" by disabling the T9 pulse on lead 568 due to the setting of SOBD flipflop 260 (FIG. 7) as described above. The B-stations on the loop are now able to use this message block as described above for writing messages which can thereafter be read by other stations.

In FIG. 15 there is shown a block diagram of a C-station suitable for use in the data transmission network of FIG. 1. The C-station of FIG. 15 comprises two B-stations 600 and 601. Each of B-stations 600 and 601 may be of a station circuit such as that disclosed in block form in FIG. 3 and in more detail in FIGS. 4 through 14. B-station 600 is interposed in one loop while B-station 601 is interposed in another loop.

B-station 600 delivers data to a buffer store 603 which, in turn, delivers data to B-station 601. Simiarly, B-station 601 delivers data to a buffer store 604 which, in turn, delivers that data to B-station 600. A controller 605 receives control signals from B-stations 600 and 601 and issues appropriate commands to buffer stores 603 and 604.

It can be seen that the C-station of FIG. 15 allows loop 1 and loop 2 to intersect in the sense that message blocks on loop 1 can be launched on loop 2 and message blocks on loop 2 can be launched on loop 1. This is accomplished by detecting destination codes such as those shown in FIG. 2B which indicate a destination on a different loop than the one on which the message is

delivered. In response to such foreign codes, a message block is transferred by the appropriate ones of B-stations 600 and 601 into the connected one of buffer stores 603 and 604. As soon as a vacant message block is detected on the loop into which the message is to be launched, the buffer store delivers the message block to the appropriate B-station for insertion in the appropriate loop.

Buffer stores 603 and 604 may comprise different portions of the same memory and may have the capac- 10 ity of several message blocks. Indeed, to prevent an undue number of message blocks from being lost, the size of buffer stores 603 and 604 is selected with due regard to the amount of interloop traffic to be expected. The entry of message blocks into buffer stores 1 603 and 604 and the removal of these message blocks from the buffer store are under the control of controller **605.**

It should be noted that B-stations 600 and 601 need not be operating at the same pulse repetition rate nor in 20 synchronism. Data is written into the buffer stores 603 and 604 under the control of timing signals from the B-station reading the message from the connected loop. Data is read from the buffer stores under the control of timing signals from the B-station at which the 25 message is to be inserted into the connected loop. Since both B-stations are synchronized with their associated loops, a rate change is possible between the two loops. The multi-message block capacity of the buffer stores 603 and 604 permits any desired ratio between the 30 rates in the two loops.

Referring to FIG. 16 there is shown a buffer store unit suitable for use in FIG. 15 and comprising a magnetic core matrix 610 including an array of magnetic cores and associated control conductors threading 35 those cores, all in accordance with practices well known in the art. The magnetic cores of matrix 610 are addressed in accordance with conventional 2½D practice by coincident signals from X-selection matrix 611 and Y-selection matrix 612.

During the read cycle, a half-select current is driven on the selected line of X-matrix 611 and a half-select current is also driven on those ones of the lines of Ymatrix 612 in each bit position, forcing the selected magnetic cores 610 to the "0" state. During the write 45 cycle, a half-select current is driven on the selected line of X-matrix 611 and a conditional additive half-select current is applied to the selected lines of Y-matrix 612 in each bit position to force the core to the "1" state. The conditional additive current is applied selectively to the Y-matrix 612 lines in each bit position by way of the Y-shunt switch 621. Since data is inserted into each bit position of a selected word by logically or conditionally selecting an additive half-select current, an independent Y-matrix 612 must be used for each bit posi- 55 tion of the memory.

These selection matrices 611 and 612 are, in turn, driven by X-drivers 613 and Y-drivers 614, respectively. The drivers 613 and 614 receive address information from address decoder 615 which, in turn re- 60 ceives the memory address from address register 616. These addresses are, of course, supplied to the store unit of FIG. 16 from store accessing circuits in the controller 605 in FIG. 15.

Information stored in magnetic core matrix 610, and 65 which is addressed from matrices 611 and 612, produces outputs representative of the binary information stored in the addressed location of matrix 610. These

signals are detected by sense amplifiers 619 and the binary information is stored in data register 620. The data is delivered from register 620 to the C-station

20

controller by way of leads 624.

When it is desired to store information in the buffer store unit of FIG. 16, this input data is delivered by way of leads 625 and stored in data register 620. At the same time, address signals are delivered to address register 616, indicating the precise location in which the input data is to be stored. The information previously stored at the addressed location in the magnetic cores 610 is first read from the magnetic cores 610, resulting in the destruction of that information. The resulting signals are not detected by the sense amplifiers 619 for this case. The input data stored in data register 620 is delivered by way of the Y-shunt switch 621 to the magnetic core matrix 610 in synchronism with the address control signals generated by address decoder 615, drivers 613 and 614 and selection matrices 611 and 612. In this way, input data is stored in matrix 610 for later retrieval.