### United States Patent [19]

Durkos et al.

[11] E

Re. 28,803

[45] Reissued

May 4, 1976

# [54] METHOD AND ELECTRONIC CONTROL FOR THE ANALYZATION OF SERUM CHEMISTRIES

[75] Inventors: Larry George Durkos, Indianapolis; Robert Wayne Cole, Zionsville; Jerry William Denney, Carmel, all of Ind.

[73] Assignee: American Monitor Corporation, Indianapolis, Ind.

[22] Filed: Jan. 16, 1975

[21] Appl. No.: 541,377

#### Related U.S. Patent Documents

#### Reissue of:

[64] Patent No.: 3,742,196

Issued: June 26, 1973

Appl. No.: 179,135

Filed: Sept. 9, 1971

[52] U.S. Cl. 235/151.3; 235/151.35; 250/573; 356/81; 356/204 [51] Int. Cl.<sup>2</sup> G06F 15/42

[58] Field of Search...... 235/151.13, 151.3, 151.35;

250/43.5 R, 573; 356/81, 204

####

| J, 120, 170 | <b>—,</b> |                        |

|-------------|-----------|------------------------|

| 3,528,749   | 9/1970    | Bowker                 |

| 3,531,202   | 9/1970    | Wilkinson et al 356/81 |

| 3,552,863   | 1/1971    | Smith                  |

| 3,553,444   | 1/1971    | Tong                   |

| 3,609,047   | 9/1971    | Marlow                 |

| -,,-        | •         |                        |

| 3,633,012 | 1/1972  | Wilhelmson et al 235/151.3     |

|-----------|---------|--------------------------------|

| 3,652,850 |         | Briggs 250/43.5 R              |

| 3,701,601 | 10/1972 | Plumpe, Jr. et al 235/151.35 X |

Primary Examiner—Malcolm A. Morrison Assistant Examiner—Jerry Smith Attorney, Agent, or Firm—Jenkins, Hanley & Coffey

#### 57] ABSTRACT

An electronic control logic system for processing the results of a spectrophotometer analysis of a serum chemistry comprised of a serum and one or more chemical reagents. The spectrophotometer output representing air as a light path and another output representing the test chemistry as a light path are integrated and the air path integrated value allowed to exponentially decay until its value is equal to that of the integrated test chemistry path value. The decay time is converted into a train of digital pulses representative of the optical density of the test chemistry. These pulses are counted and their total stored for comparison with the corresponding optical density of a standard solution. The concentration of the element for which the particular test was designed to detect is known for the standard solution, so the percentage concentration of that element in the test chemistry may be thereby ascertained. Programable variations are provided to enable the evaluation of test results from a kinetic or an end point test. The results of the analysis, together with a test identification number and a patient identification number is selectively applied by a printer control logic section for suitable printing of the data.

#### 36 Claims, 28 Drawing Figures

## METHOD AND ELECTRONIC CONTROL FOR THE ANALYZATION OF SERUM CHEMISTRIES

Matter enclosed in heavy brackets [ ] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

#### BACKGROUND OF THE INVENTION

This invention relates to an electronic system and method for processing a signal obtained from the electro-optical analyzation of a precisely prepared serum chemistry.

The chemical analyzation of a serum, e.g., for the 15 presence of sugar or albumin content, or any of many other assays vital to medical diagnosis, is generally performed by adding specific amounts of various reactive chemicals or reagents to a sample of serum in a specific sequence and under specified conditions of 20 temperature and time thereby causing a change in color or light absorbance to occur which is related to the amount of the substance being measured in serum. Various manual and automated procedures have been used.

Manual procedures are usually performed in a laboratory by a trained technician. The technician prepares a test sample, commonly referred to as a test chemistry, comprised of a portion of a serum specimen to be tested and the proper amounts of the chemical reagents specified for that particular test. The resulting test chemistry, after formulation, must be analyzed with specific care taken to note the extent to which a desired reaction has taken place.

The reaction evaluation is done using a spectrophotometer. The output of the spectrophotometer represents the amount of a certain band width of light which the chemistry under test passes with respect to the amount of the same band width of light passed by a sample containing all other constituents in the test except the serum. The level of this comparative transmittance must be then transformed into units which represent the element concentrations or optical density of the test chemistry to present meaningful data to the 45 technician so that he might evaluate the test.

Disadvantages of manual procedures include not only an undue amount of time and labor, but this type of laboratory testing is at most, even under the most optimum conditions only proportioned to the skill of 50 the technician.

Several systems have also been proposed and used which present the optical density of test chemistries by means of a strip recorder. This technique results in a cumbersome amount of data paper, along with the 55 inherent reading problems which are highly susceptible to error.

#### SUMMARY OF THE INVENTION

In accordance with the invention, a serum chemistry 60 may be loaded into the flow cell of a spectrophotometer for optical analysis. The difference in light transmittance between an air path and a path through the test chemistry is detected by a photomultiplier tube, the output of which is connected to an amplifier and associated control circuits. Feeback means may be provided to automatically adjust the voltage across the photomultiplier tube to provide changes in its sensitiv-

ity due to operating temperature or to the wave length of the observed light.

The position of the flow cell may be used to set up logic conditions to institute the selective integration at the amplified photomultiplier tube output for both the test and reference air paths. The integrated value of the reference path signal is always greater than that of the integrated value of the test path signal since the reference path consists of air while the test path consists of test solution. The integrated value of the reference signal may be permitted to logarithmically decay until it equals that of the integrated value of the test signal. The time required for the integrated reference signal to decay to the value of the integrated test value is proportional to the optical density at the test solution. This relies in part on the relationship that optical density is equal to the logarithm of the incident light minus the logarithm of the transmitted light. The required decay time is transformed into a proportional digital pulse train and selectively placed in an optical density mem-

The processing of the digital representation of the optical density of a test chemistry is done under the control of a logic programmer section. This programmer section receives information from a programmed card which is interpreted by a card reader in a manner explained and described in a co-pending application, U.S. Ser. No. 179,133.

Several different types of tests may be programmed each of which require the processing of the optical density signal in a different manner. For the most part, the end point light absorbance of the reaction between a serum sample and test reagents is observed. The optical density of the reacted test chemistry may be compared within a calculation portion of the electronic system to that of a serum blank or a reagent blank. In the performance of the former, two serum samples are mixed with two different combinations of reagents to effect two different test reactions. The optical density of the first test chemistry must then be compared with the optical density of the second test chemistry to obtain the desired comparative optical density.

An end point reagent blank test requires that a chemistry consisting of reagents alone must be first spectrally analyzed and the resulting optical density reading stored for comparison with subsequent test chemistry readings. The test chemistries in this case are comprised of different serum samples all having the same reagents added to them.

A test may also be performed which requires that the optical density of the same test chemistry be ascertained at two precisely controlled points in time. Furthermore, it may be required that this be done for two or three such intervals to ensure that the reaction is taking place properly and is linear.

The arithmetic portion of the electronic system is preferably calibrated before the performance of any of the above tests to effect a standardization of the results with respect to a known base value and to simultaneously convert the optical density of the chemistries into concentration units. This calibration is completely automatic and may be done by the use of a solution with a known substance concentration, herein referred to as a standard solution. A solution, herein referred to as the blank and comprised of a full complement of reagents for a given test, is first placed in the flow cell for ascertainment of its optical density. The difference in optical densities of the blank and the specimen test

3

chemistry may be stored in an optical density memory. The contents of this memory are used to alter the frequency of a known clock frequency. Unaltered clock frequency may be used to clock a counter at the same time that the altered clock frequency is used to clock a second counter. This has the effect of creating a ratio representative of the difference between the optical density of the blank reagent solution and the optical density of the standard solution. This standard value is stored so that all subsequent test results may be derived from it. The optical density of each of the solutions is proportional to its percentage concentrations so that by using a standard solution of a known percentage concentration to develop a proportionality constant based on optical density, the percentage concentrations of 15 each of the test chemistries may be ascertained.

Printer logic may be provided which is able to sequentially and selectively present the test results, a patient identification number and the test identification number to a drum printer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings illustrate the invention and, by way of example, show a preferred embodiment of the invention. In such drawings:

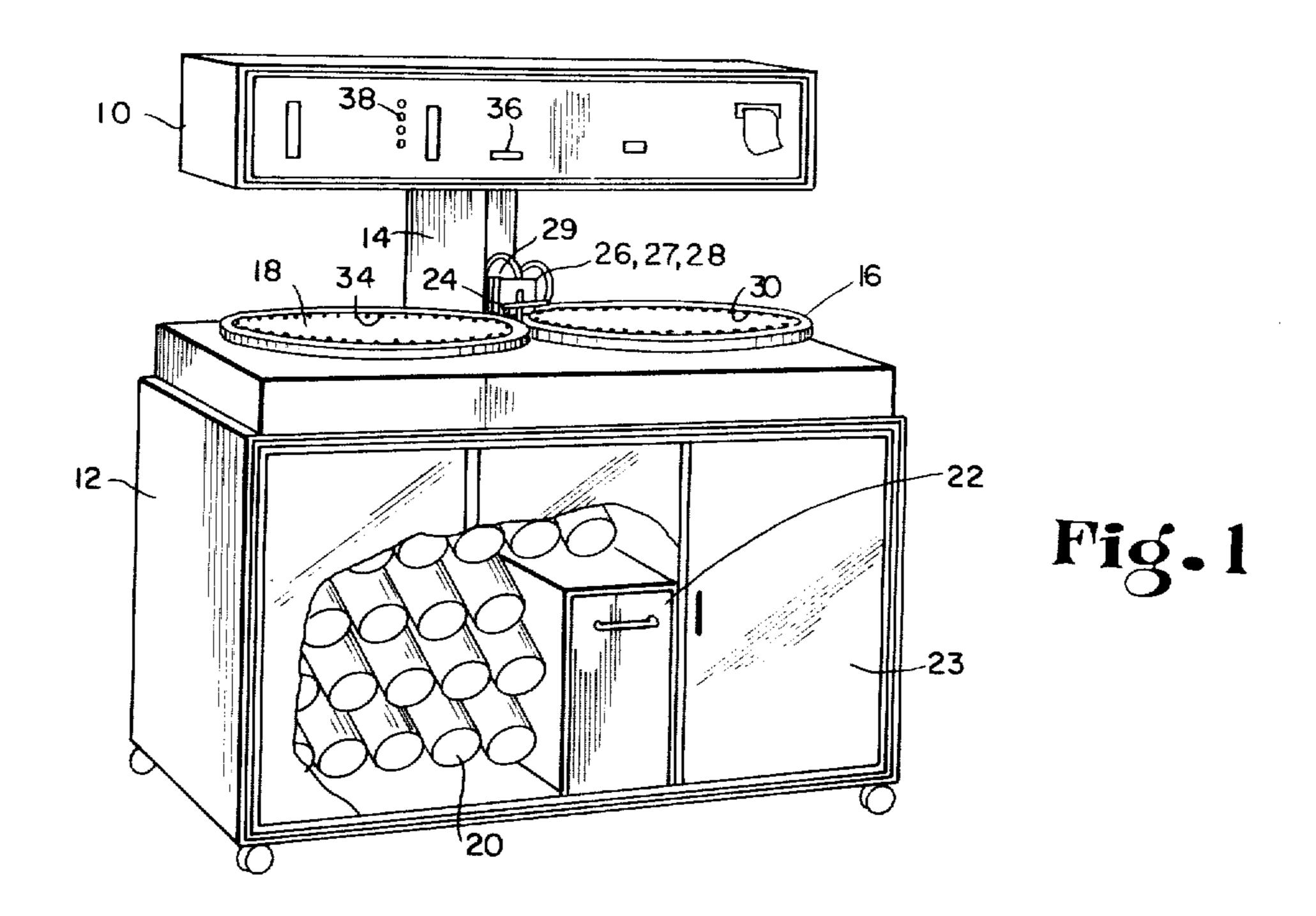

FIG. 1 is a perspective view of a machine compatible for use with the invention;

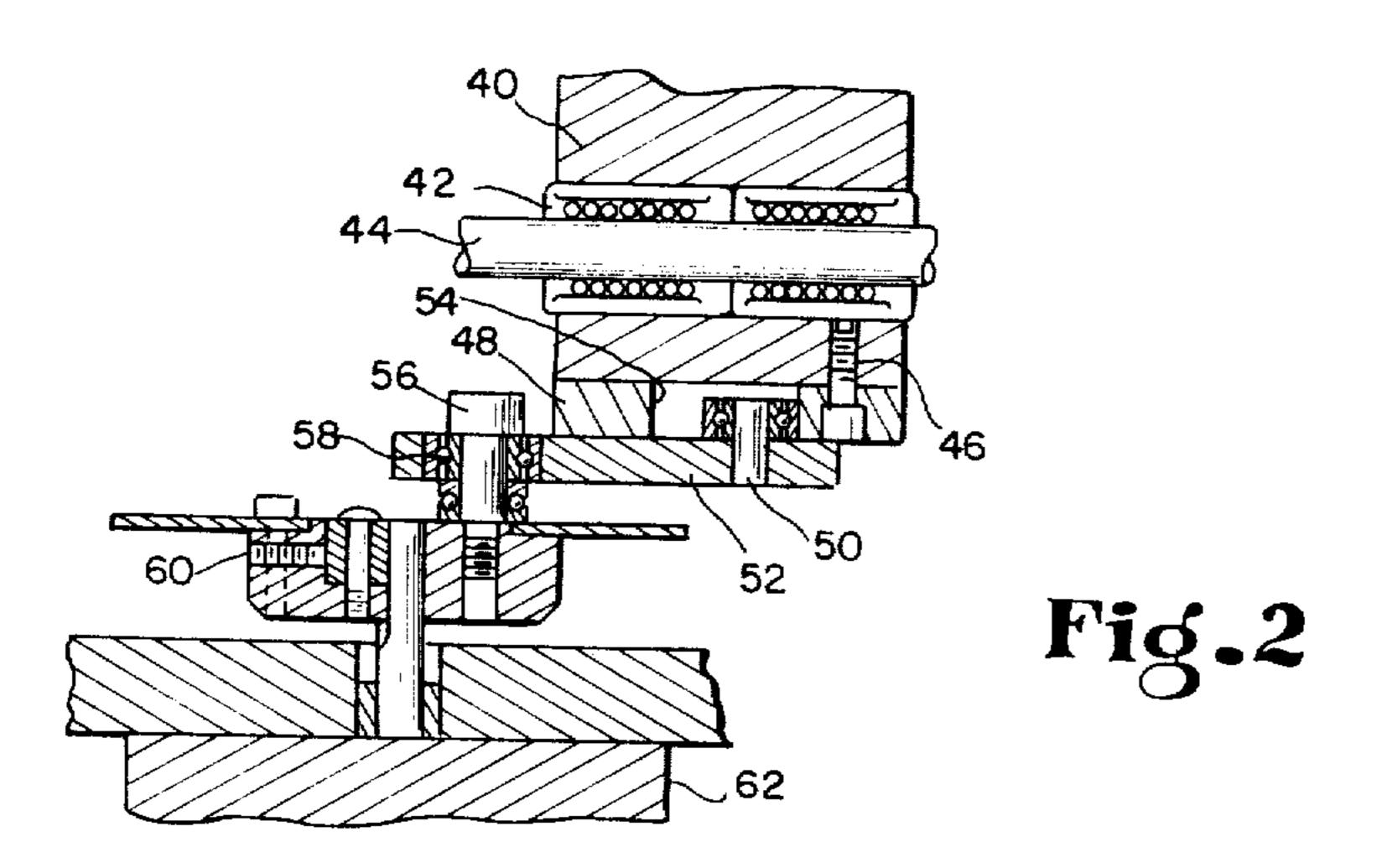

FIG. 2 is a vertical section view showing the reciprocating apparatus for the flow cell;

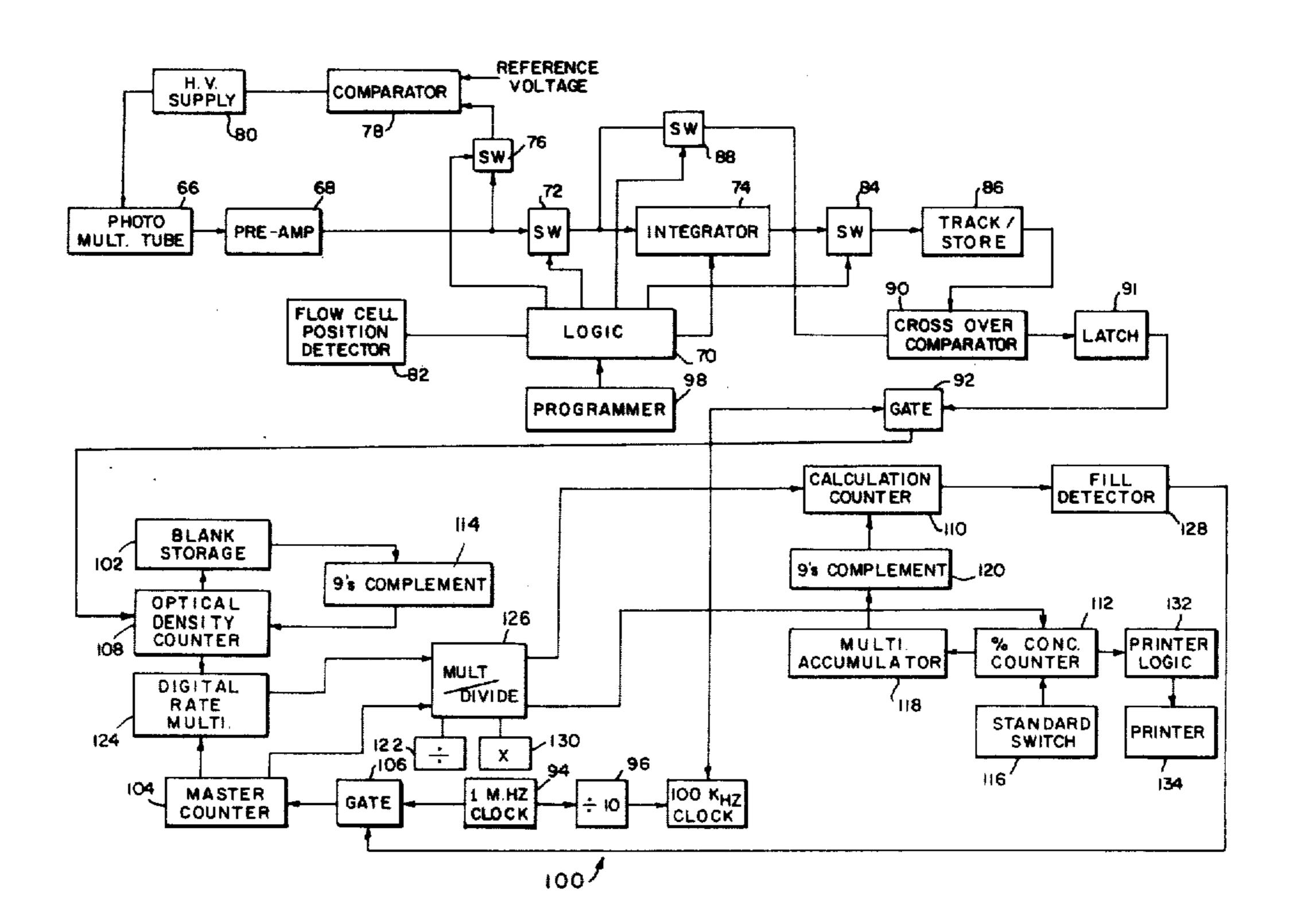

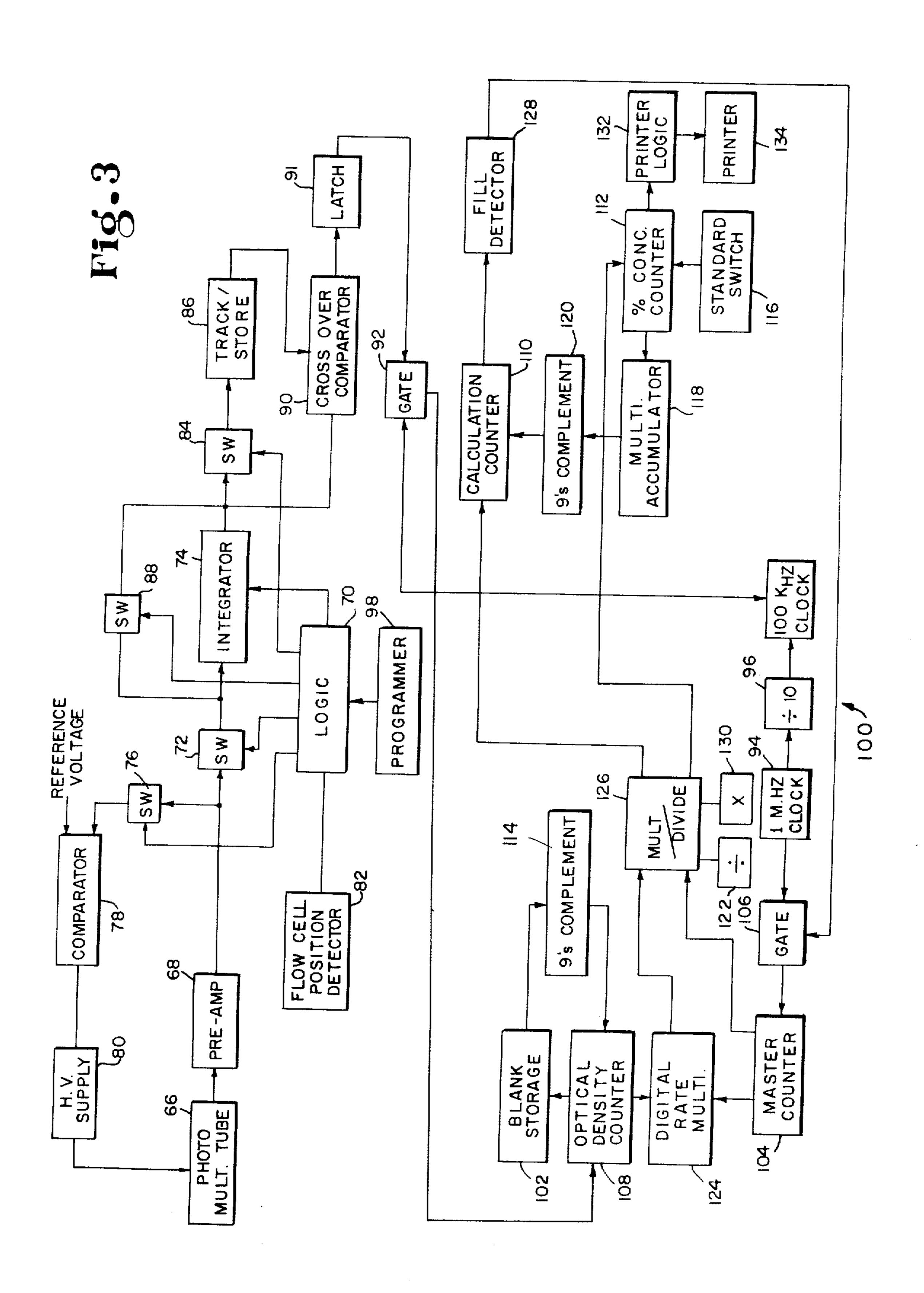

FIG. 3 is a block diagram showing the interrelation- <sup>30</sup> ship of the various portions of the invention;

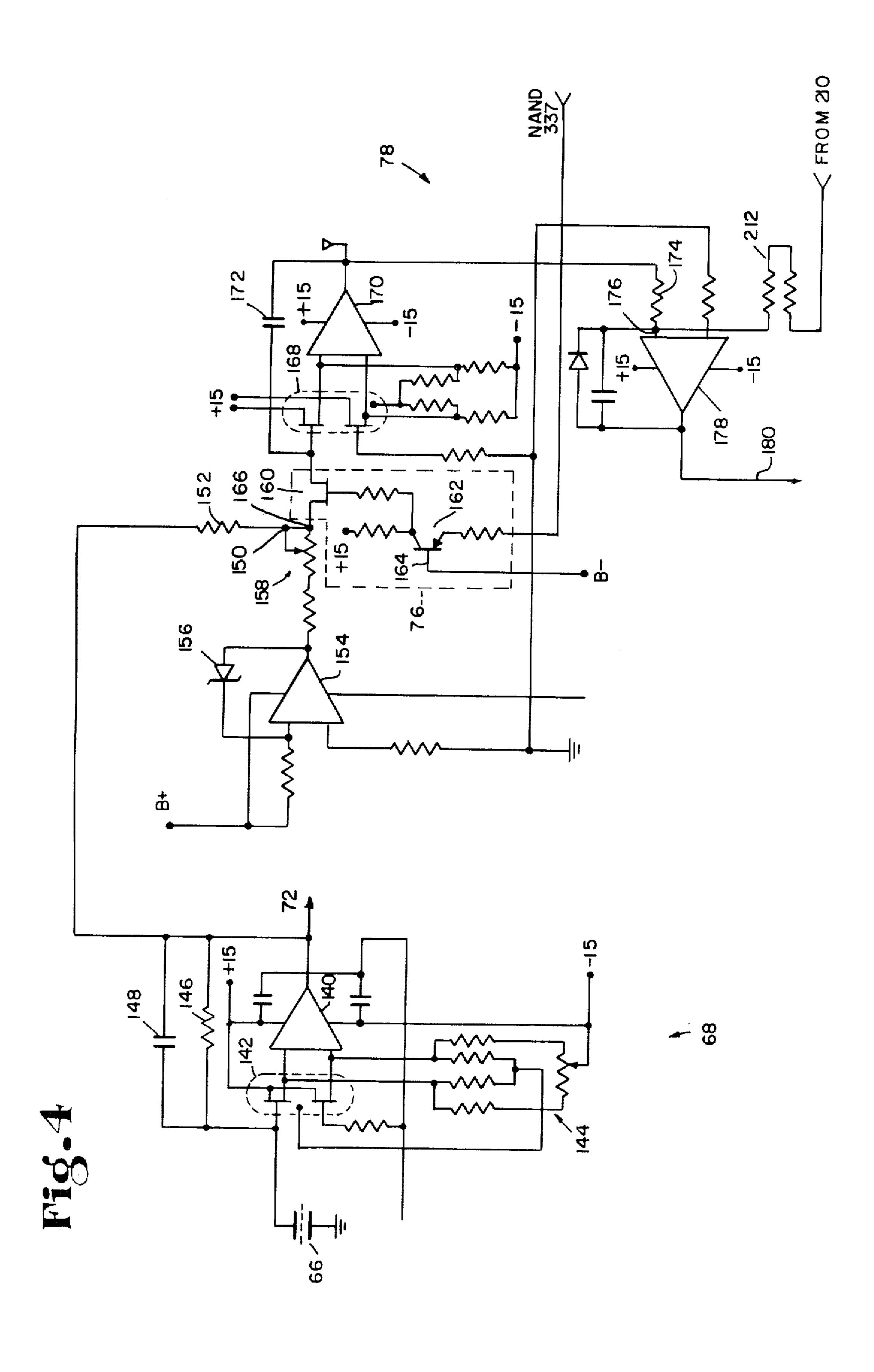

FIG. 4 is a schematic diagram showing the pre-amp and voltage comparator;

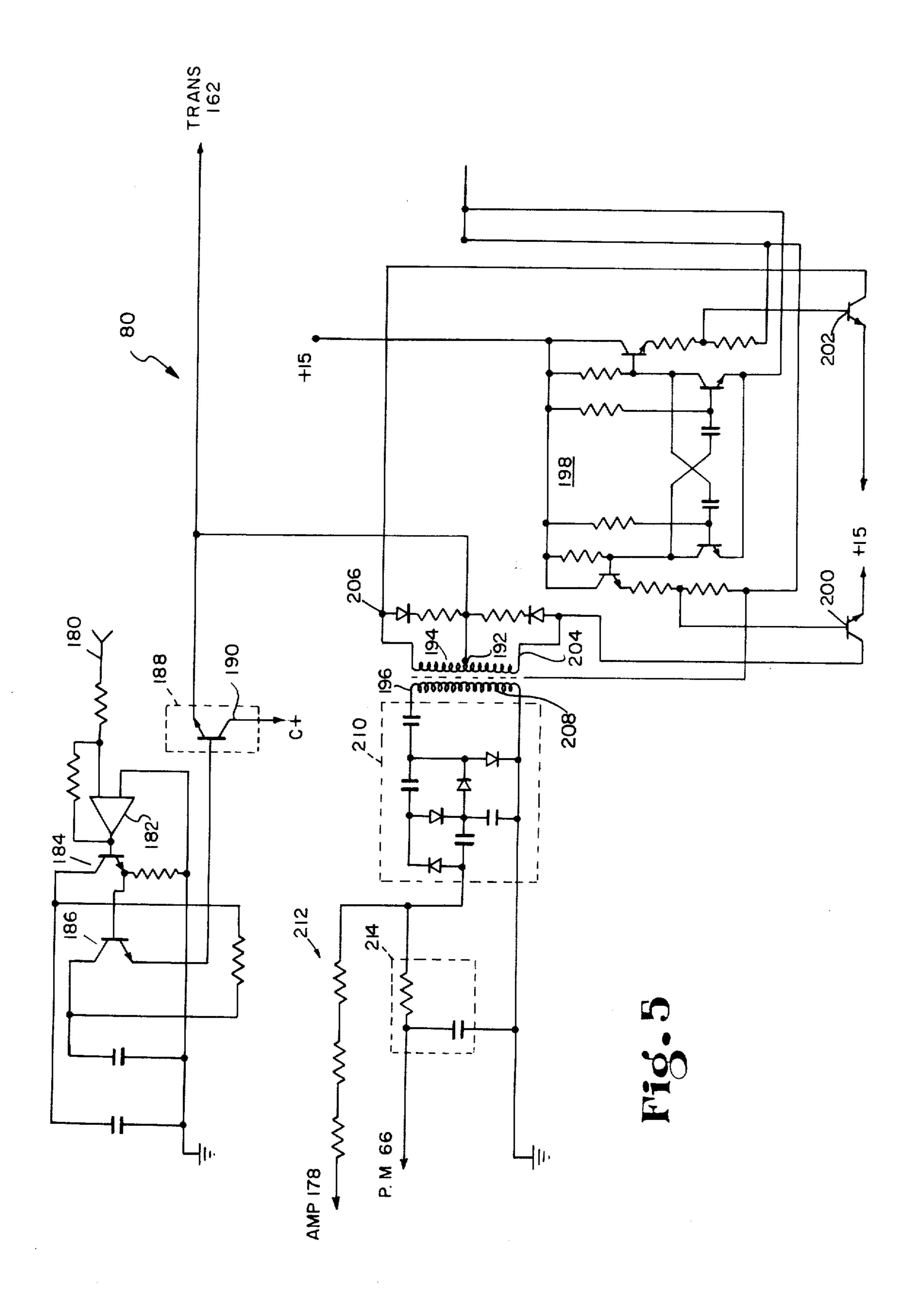

FIG. 5 is a schematic diagram showing the high voltage supply and its control;

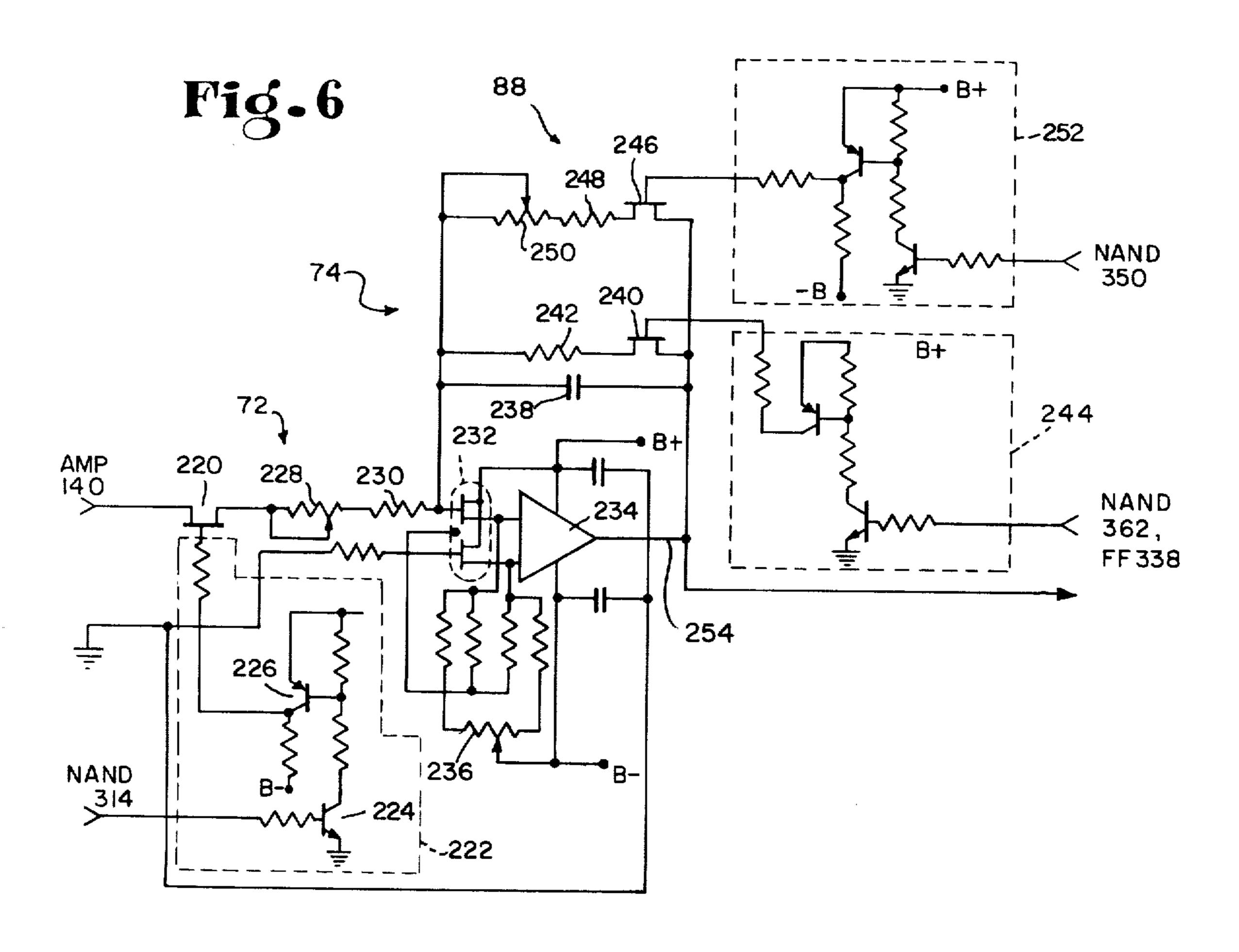

FIG. 6 is a schematic diagram showing the integrator and its controlling switches;

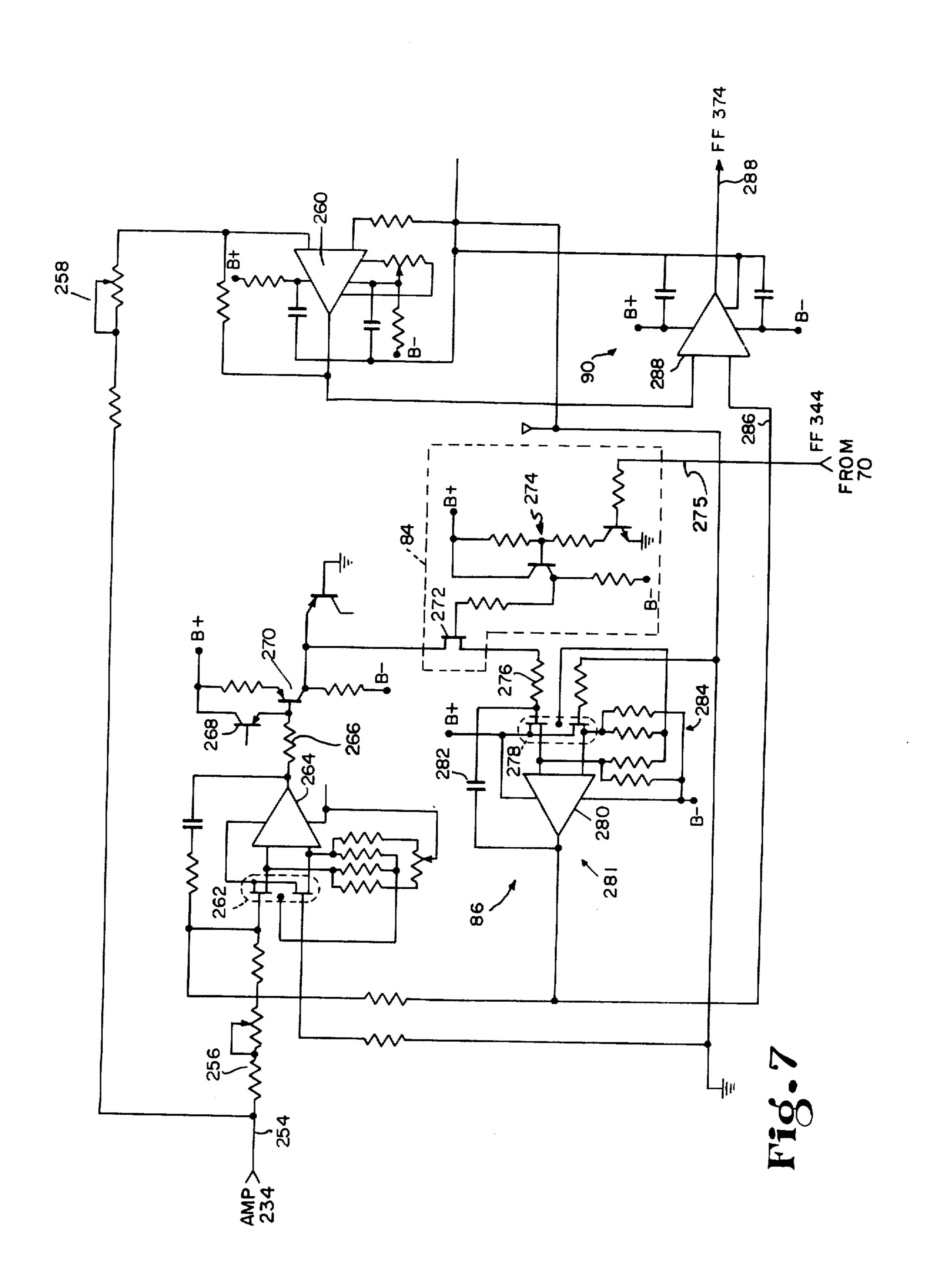

FIG. 7 is a schematic diagram showing the track/store control logic and the cross-over comparator control logic;

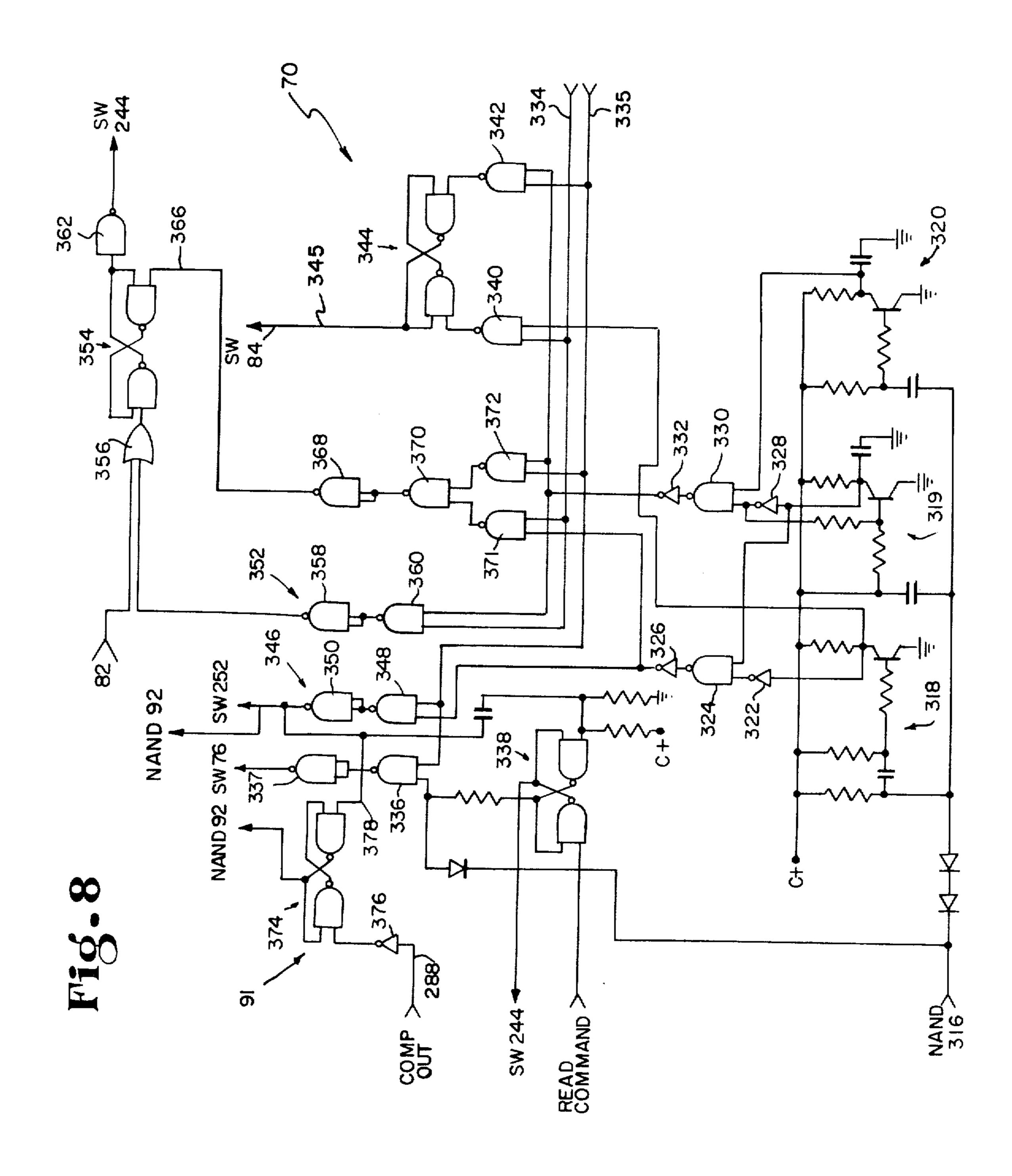

FIG. 8 is a schematic diagram of the spectrophotometer control logic;

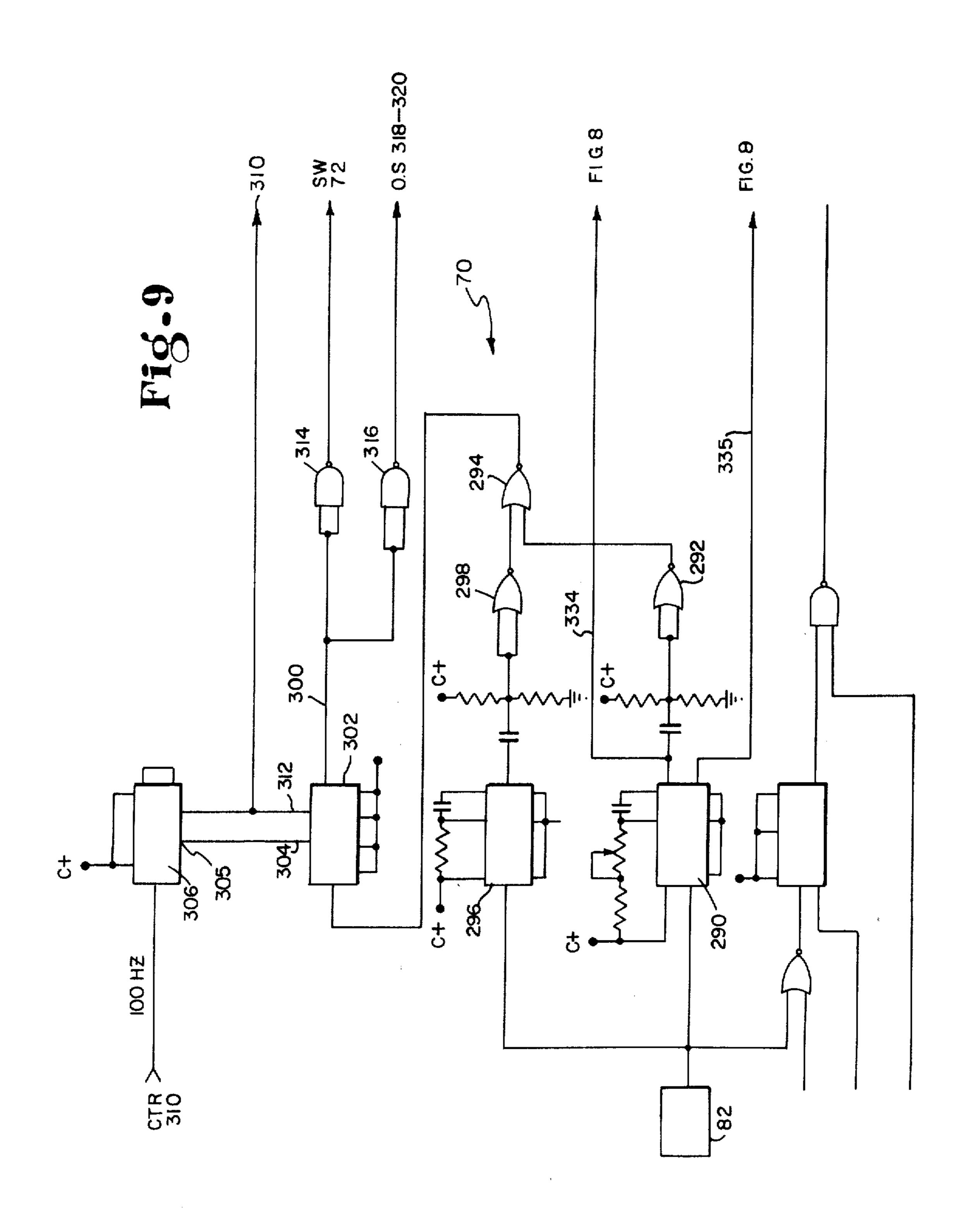

FIG. 9 is a schematic diagram showing part of the spectrophotometer logic control;

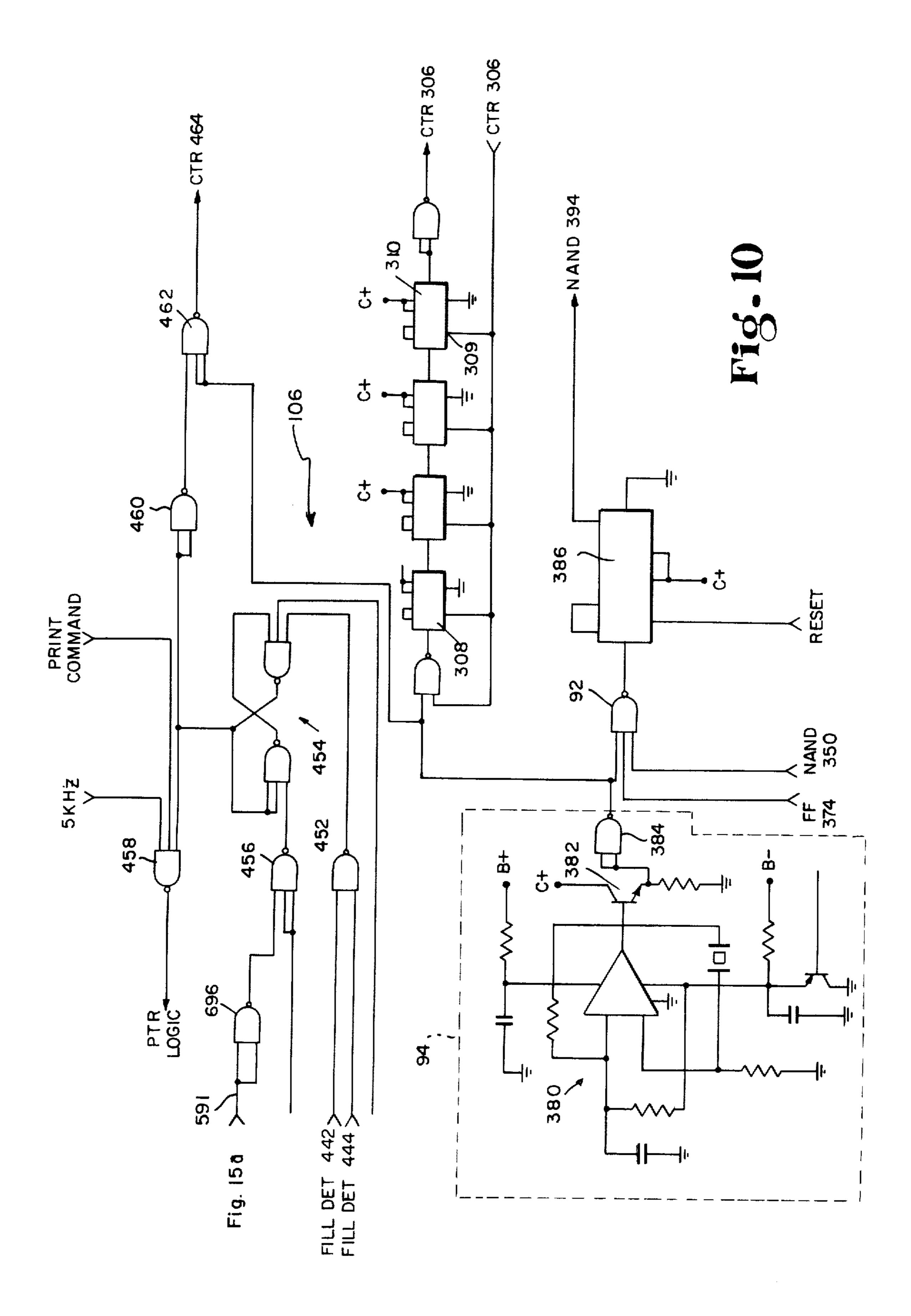

FIG. 10 is a schematic diagram showing the one megahertz clock source and its related gate and controls;

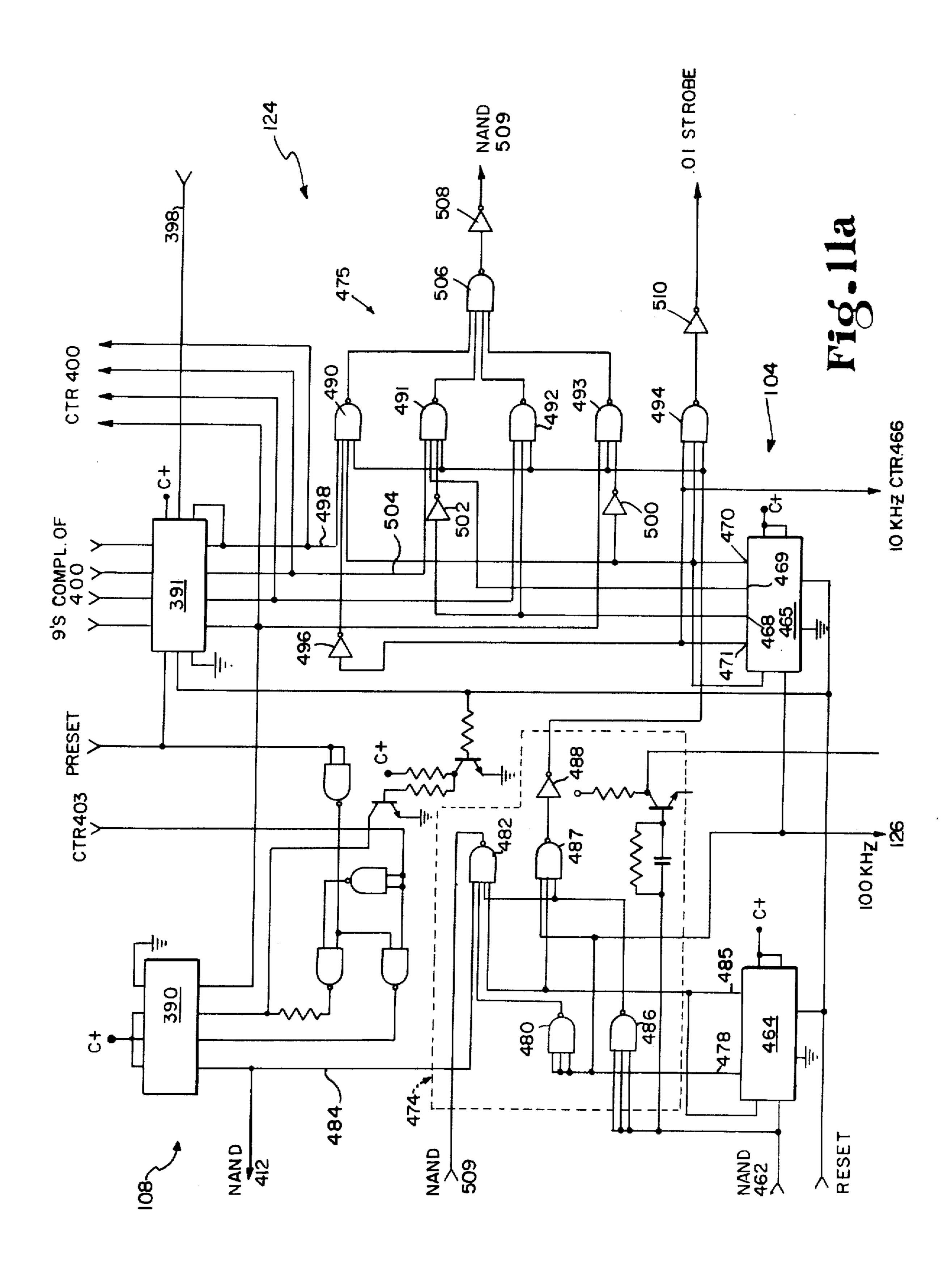

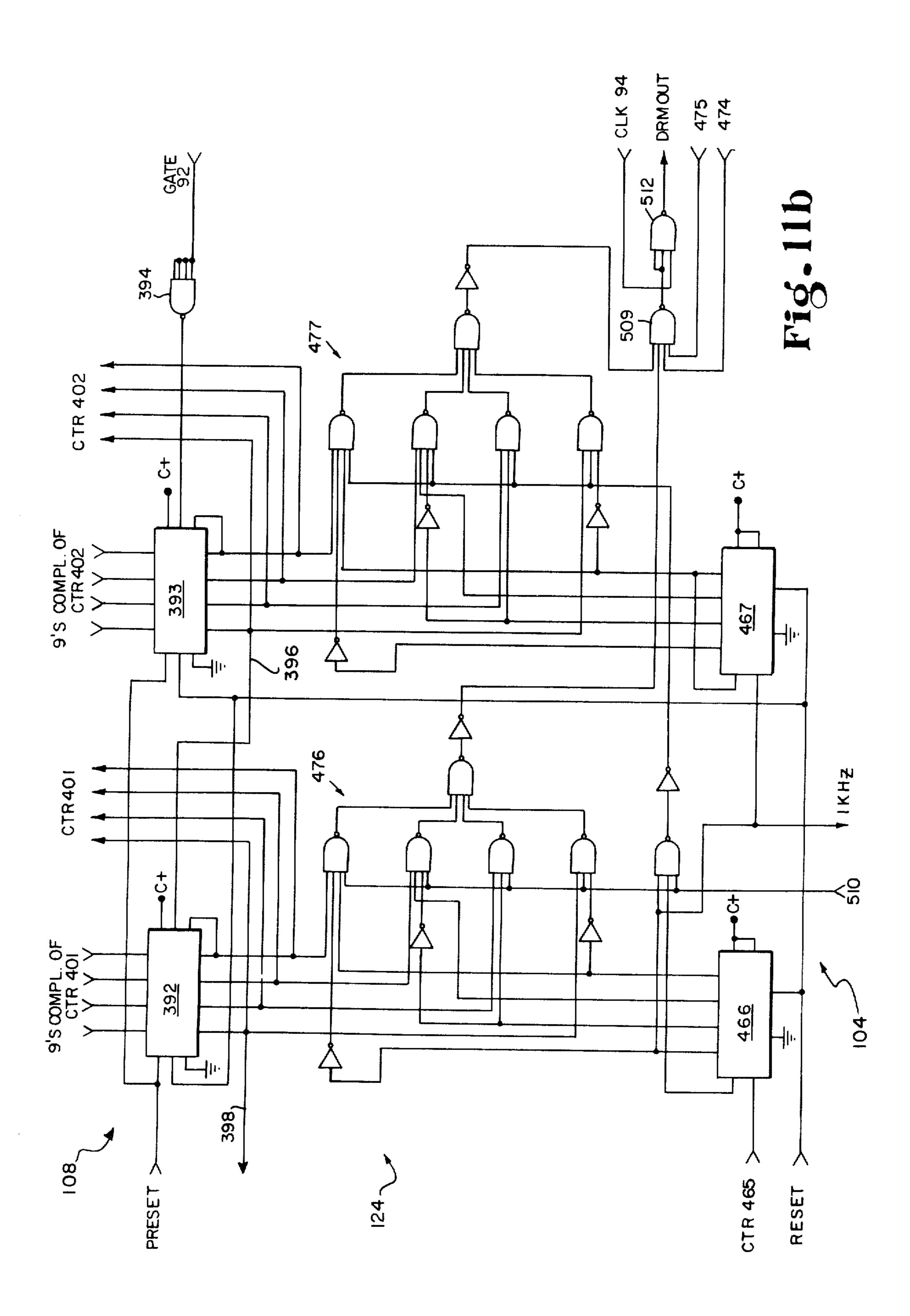

FIGS. 11 A and B are schematic diagrams showing the optical density counter, the digital rate multiplier and the master counter;

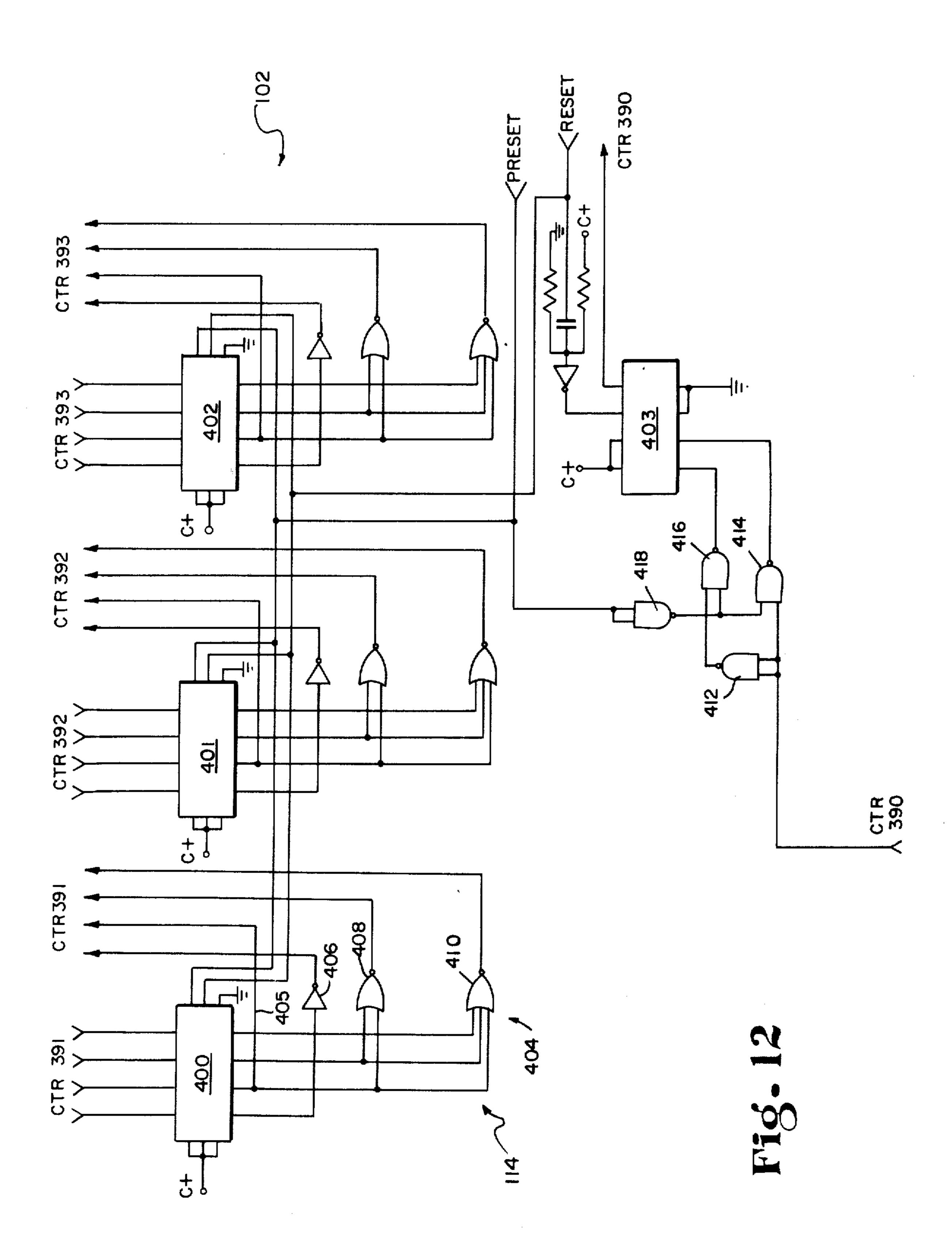

FIG. 12 is a schematic diagram showing the blank storage register and a nines complementor;

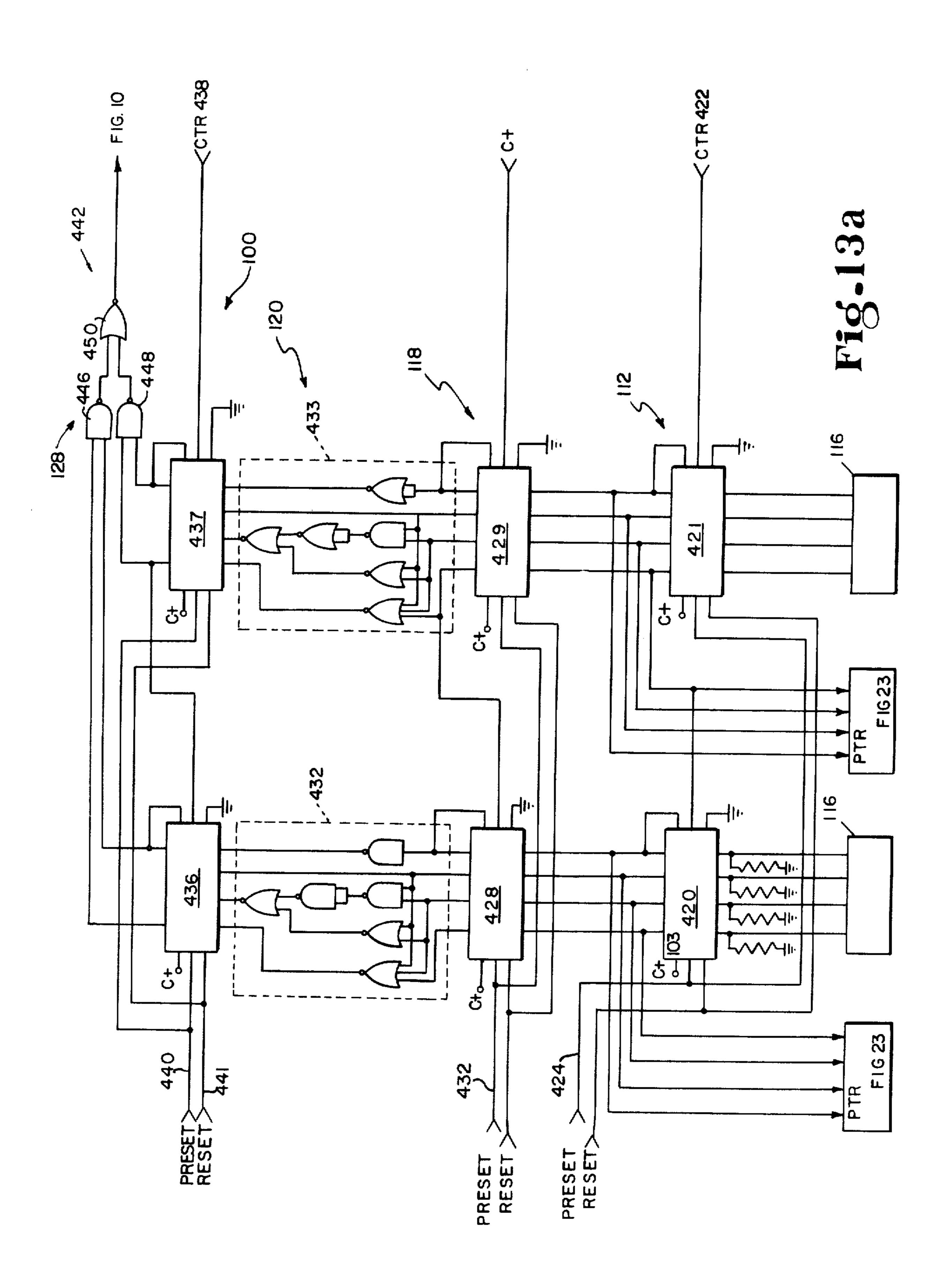

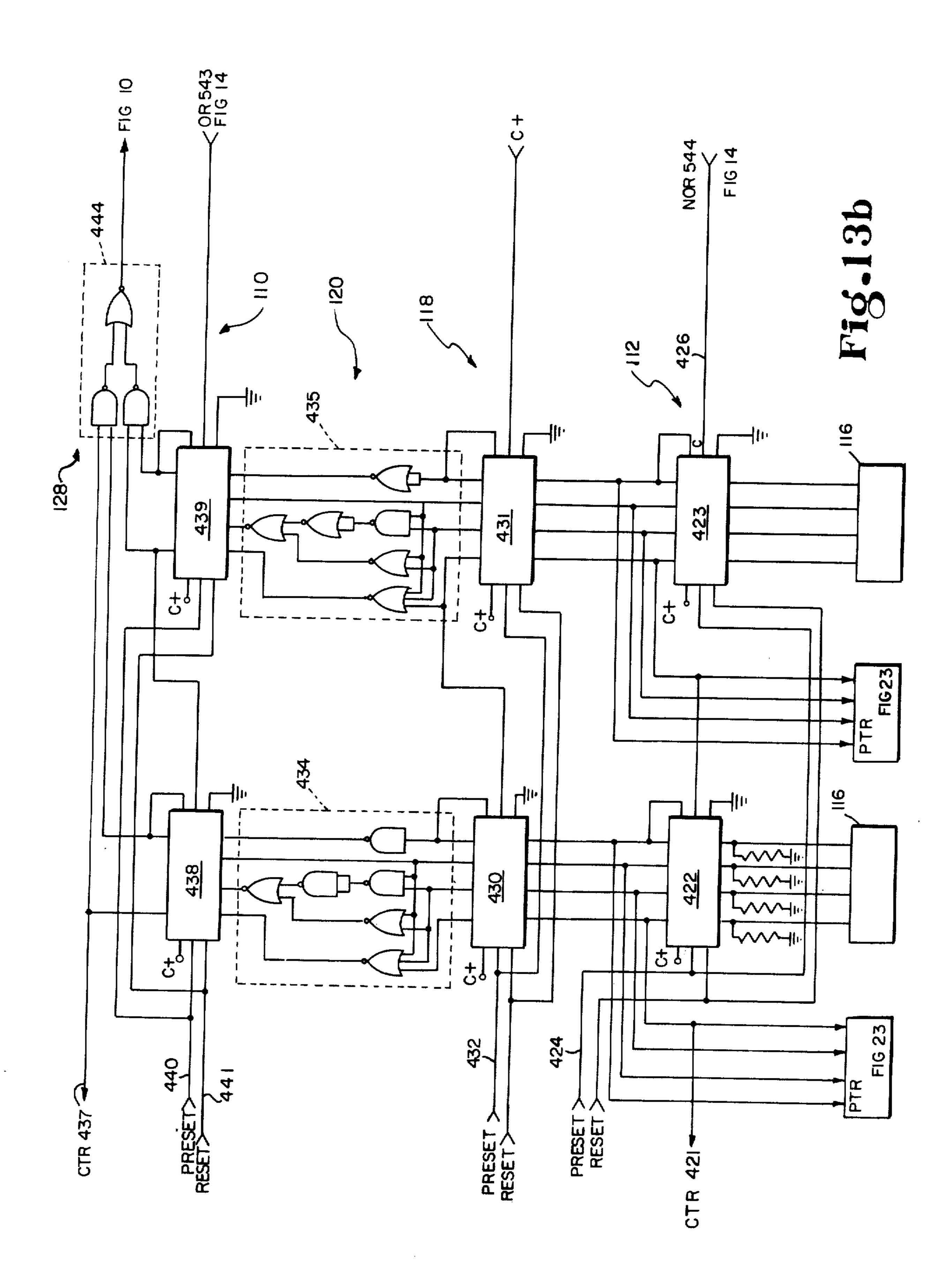

FIGS. 13 A and B are schematic diagrams showing the calculation counter and nines complementor, the multiplication accumulator, the percentage concentration counter and the standard unit switches;

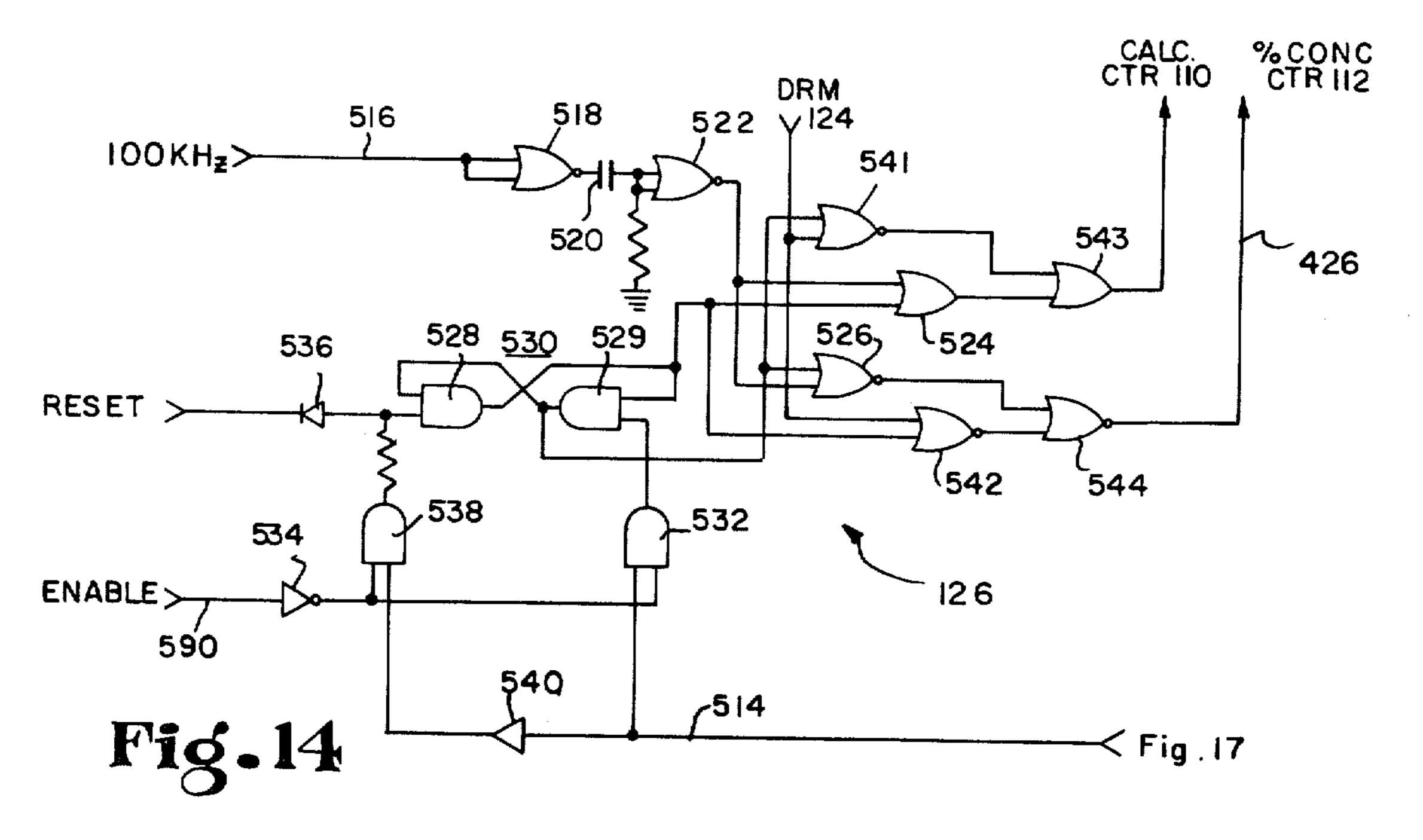

FIG. 14 is a schematic diagram showing the multiply and divide selection logic;

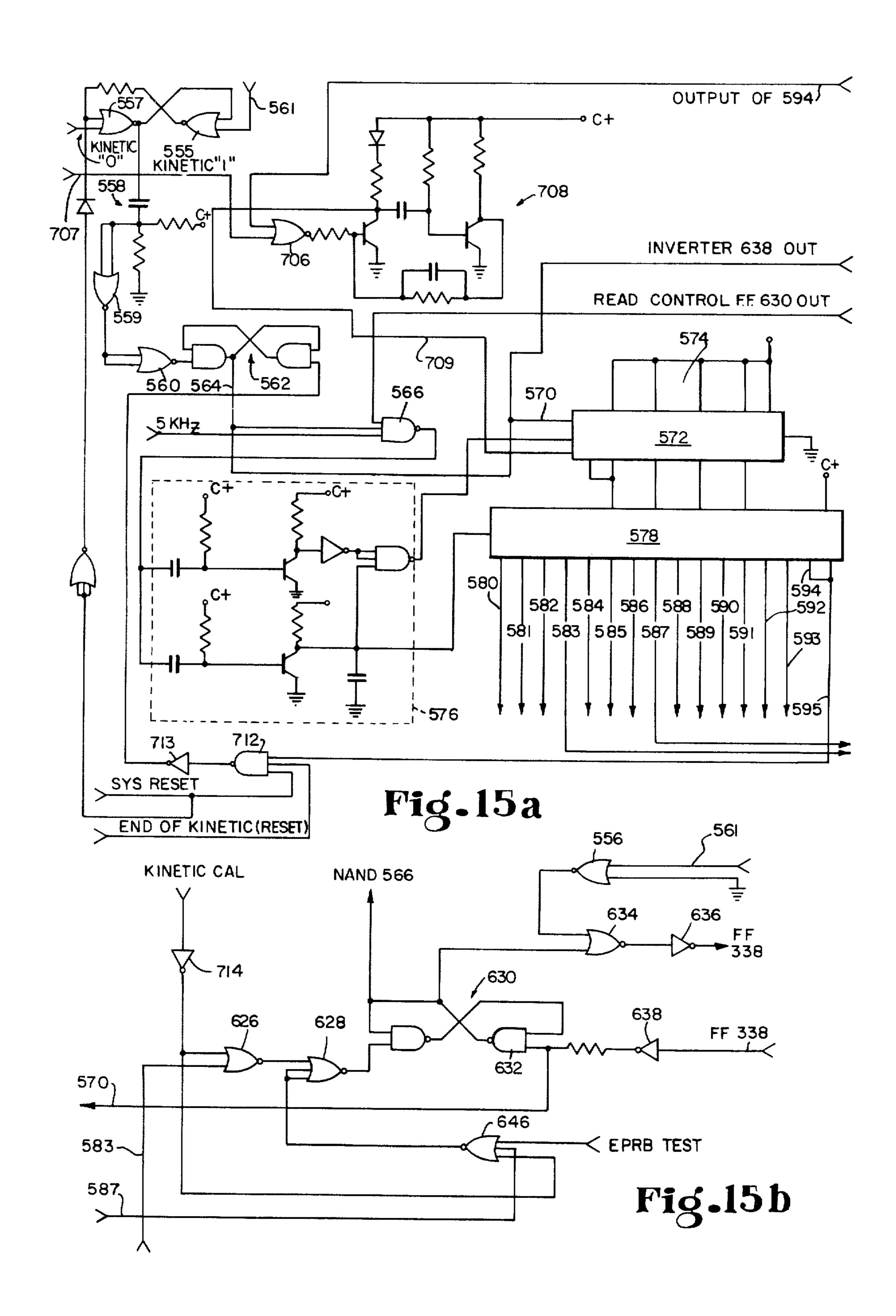

FIGS. 15 A and B are schematic diagrams showing portions of the programmer control logic;

FIG. 16 is a schematic diagram showing another portion of the programmer control logic;

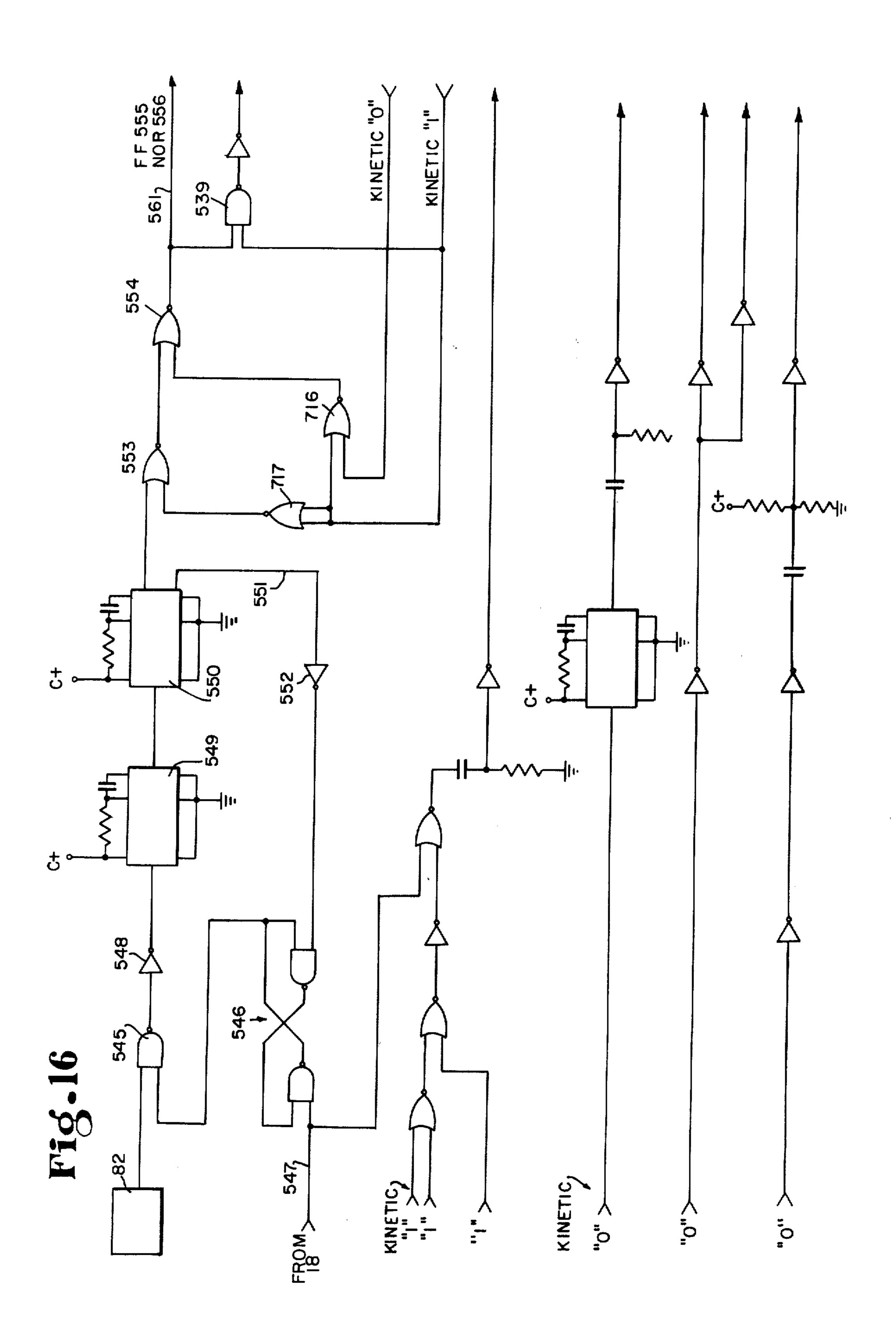

FIG. 17 is a schematic diagram showing a portion of the programmer control logic;

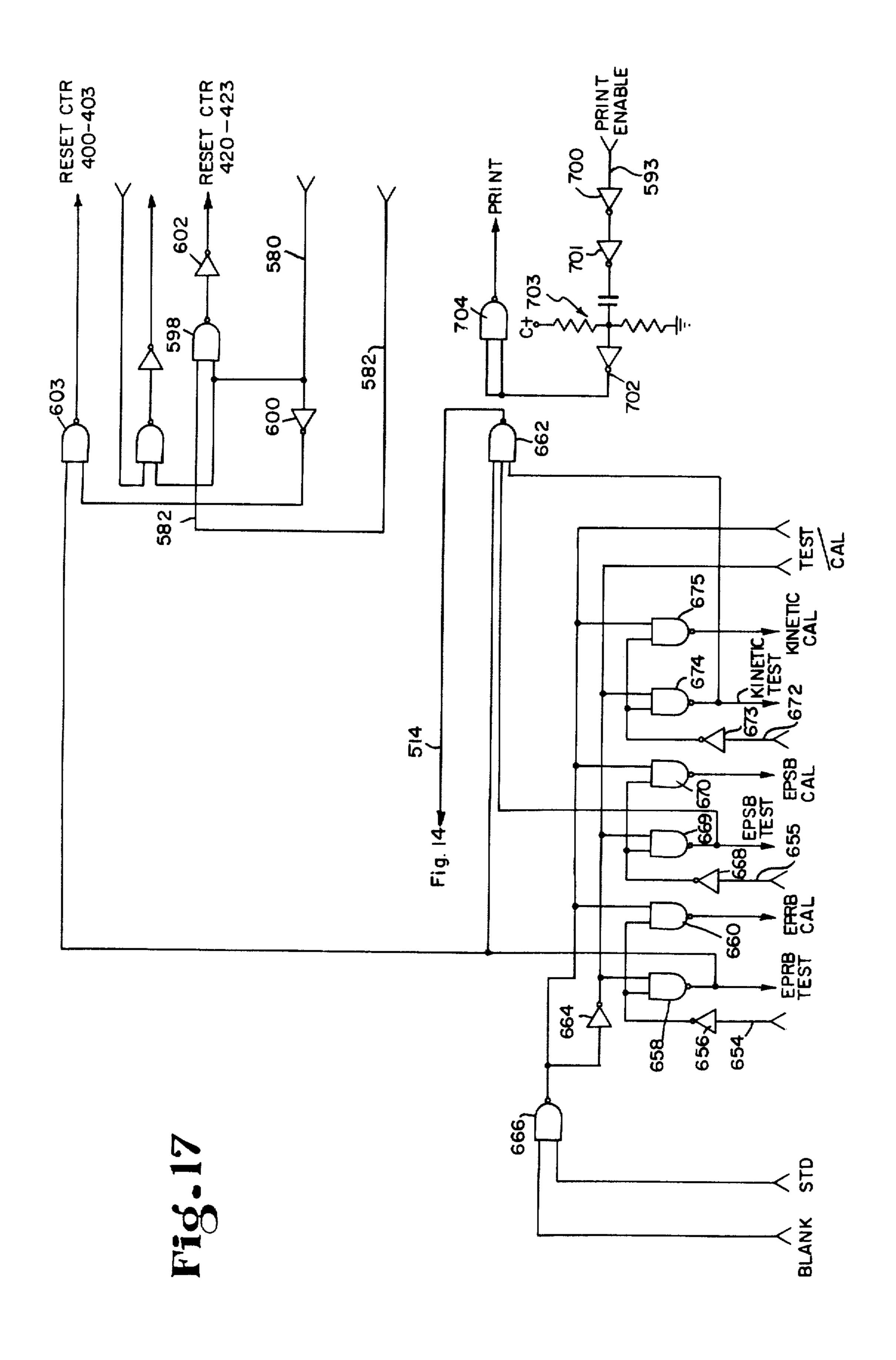

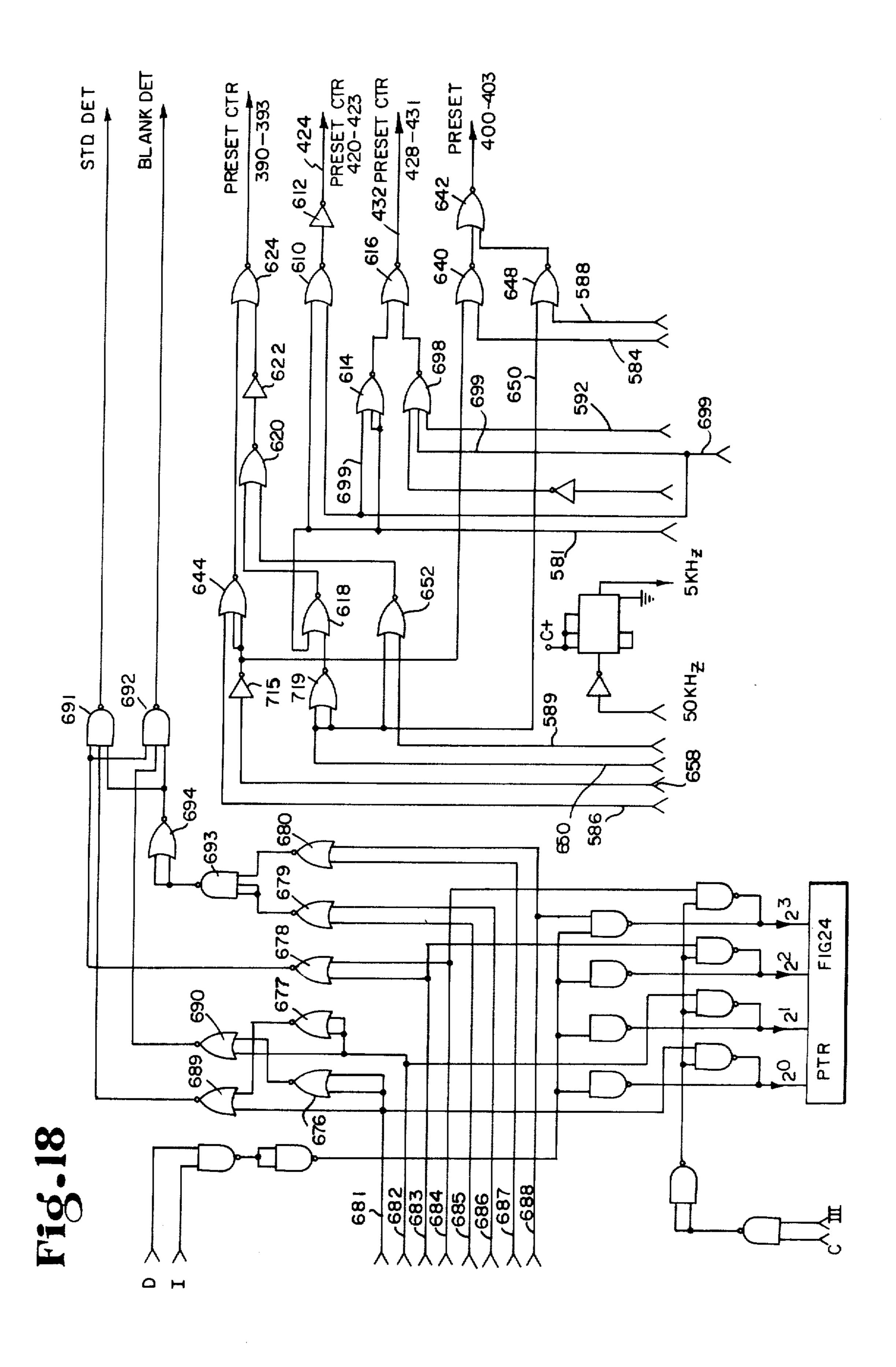

FIG. 18 is a schematic diagram showing a portion of 65 the programmer control logic;

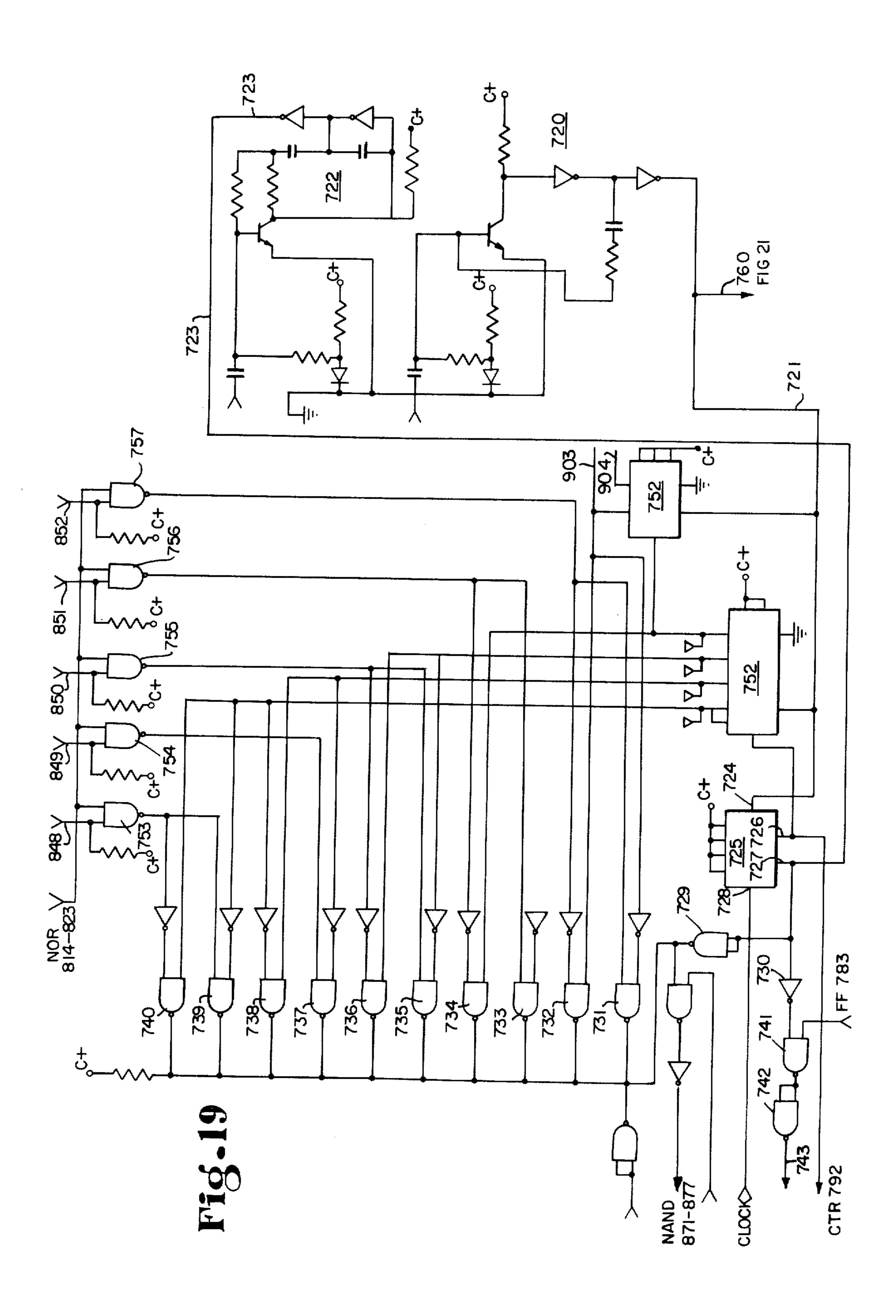

FIG. 19 is a schematic diagram showing part of the printer control logic;

4

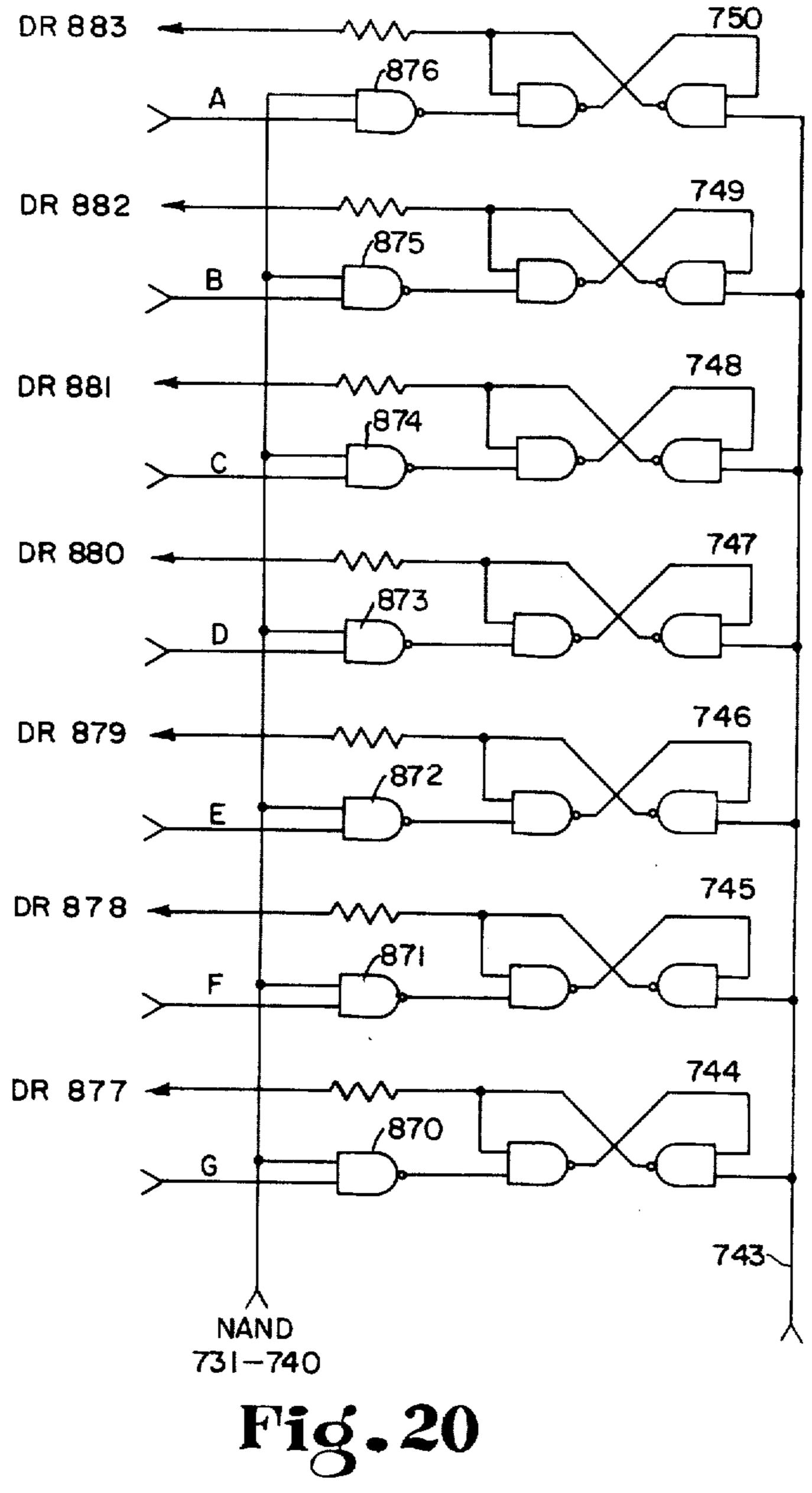

FIG. 20 is a schematic diagram showing a portion of the printer control logic;

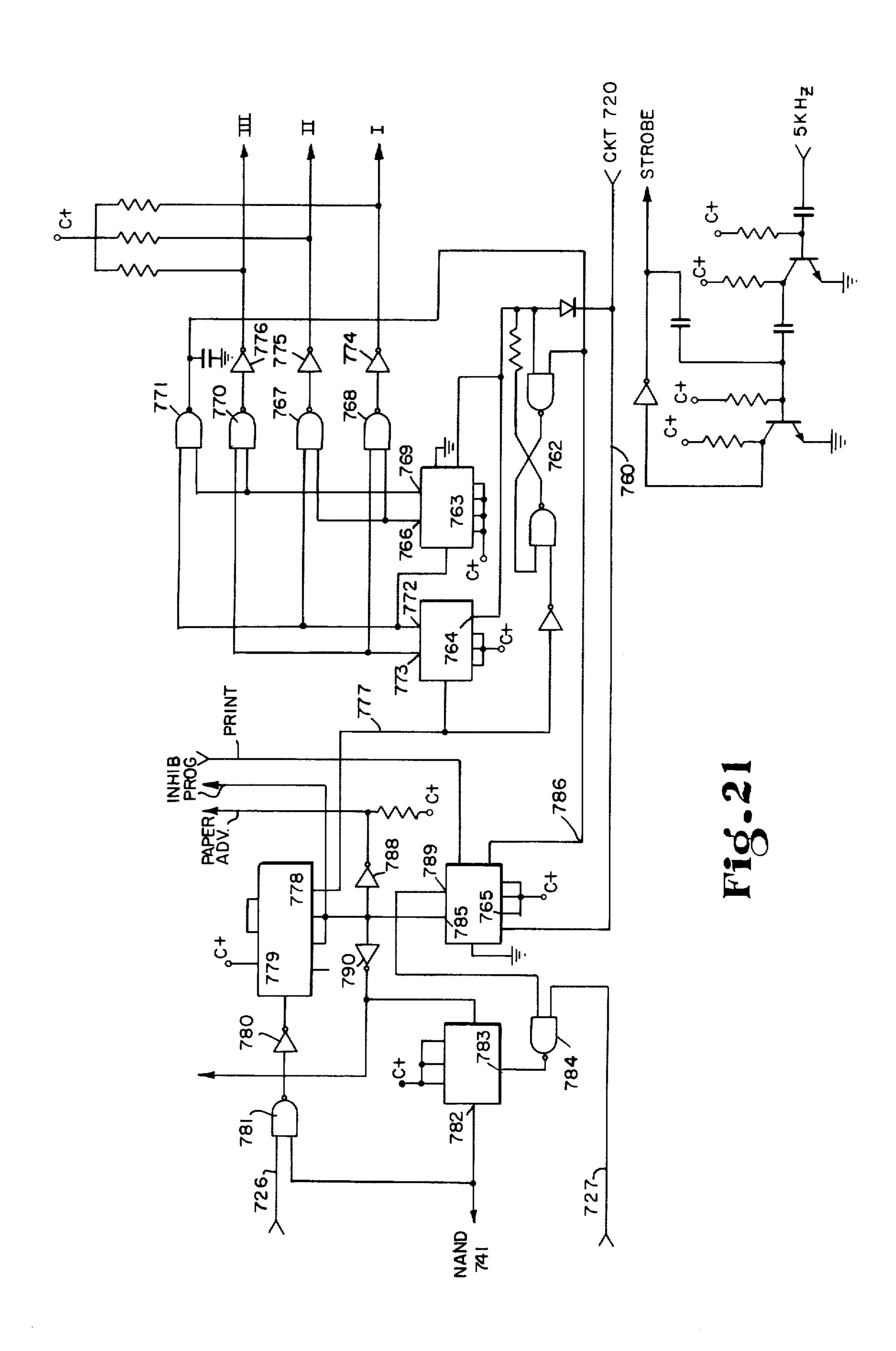

FIG. 21 is a schematic diagram showing part of the printer control logic;

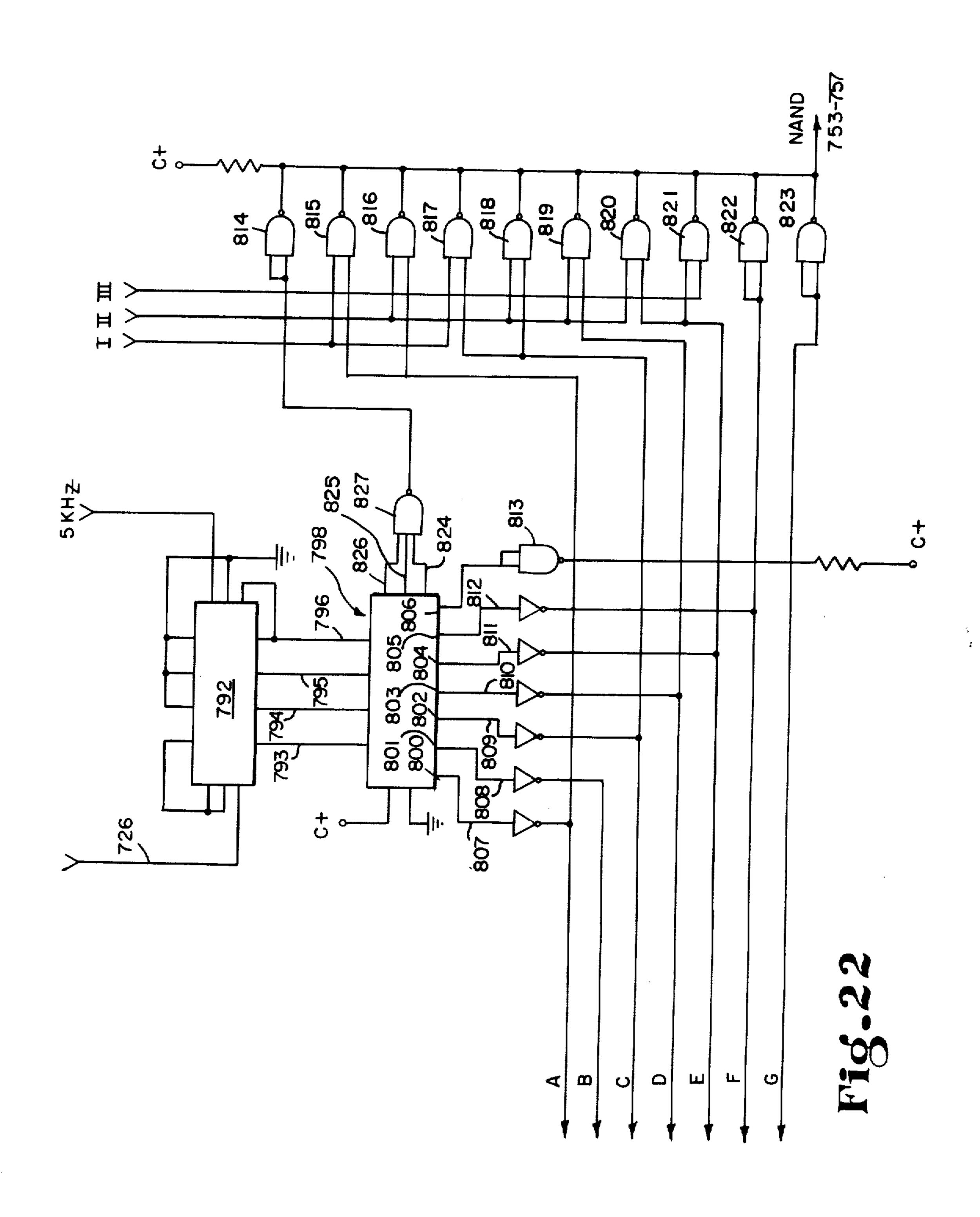

FIG. 22 is a schematic diagram showing a portion of the printer control logic;

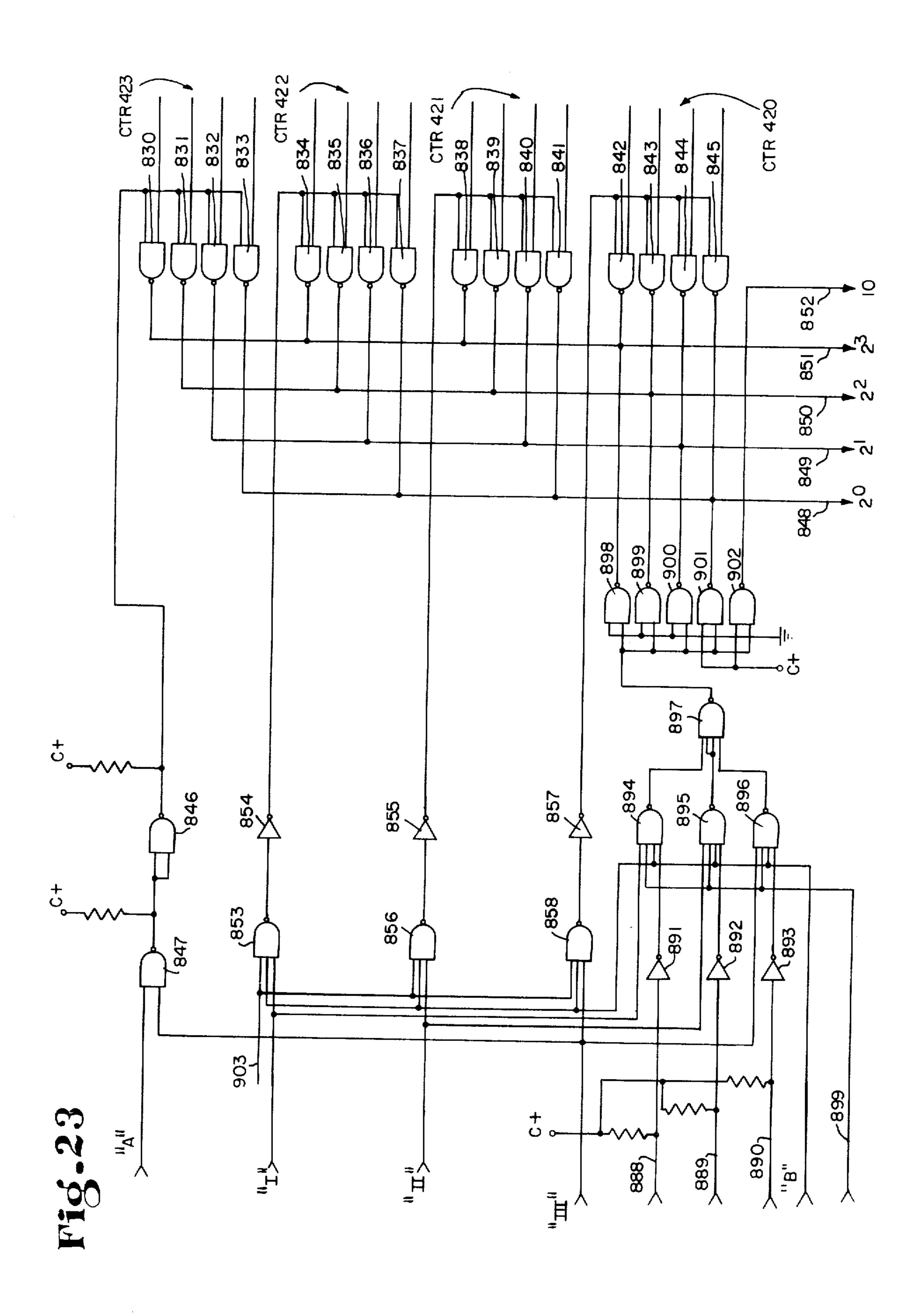

FIG. 23 is a schematic diagram showing a portion of the printer control logic;

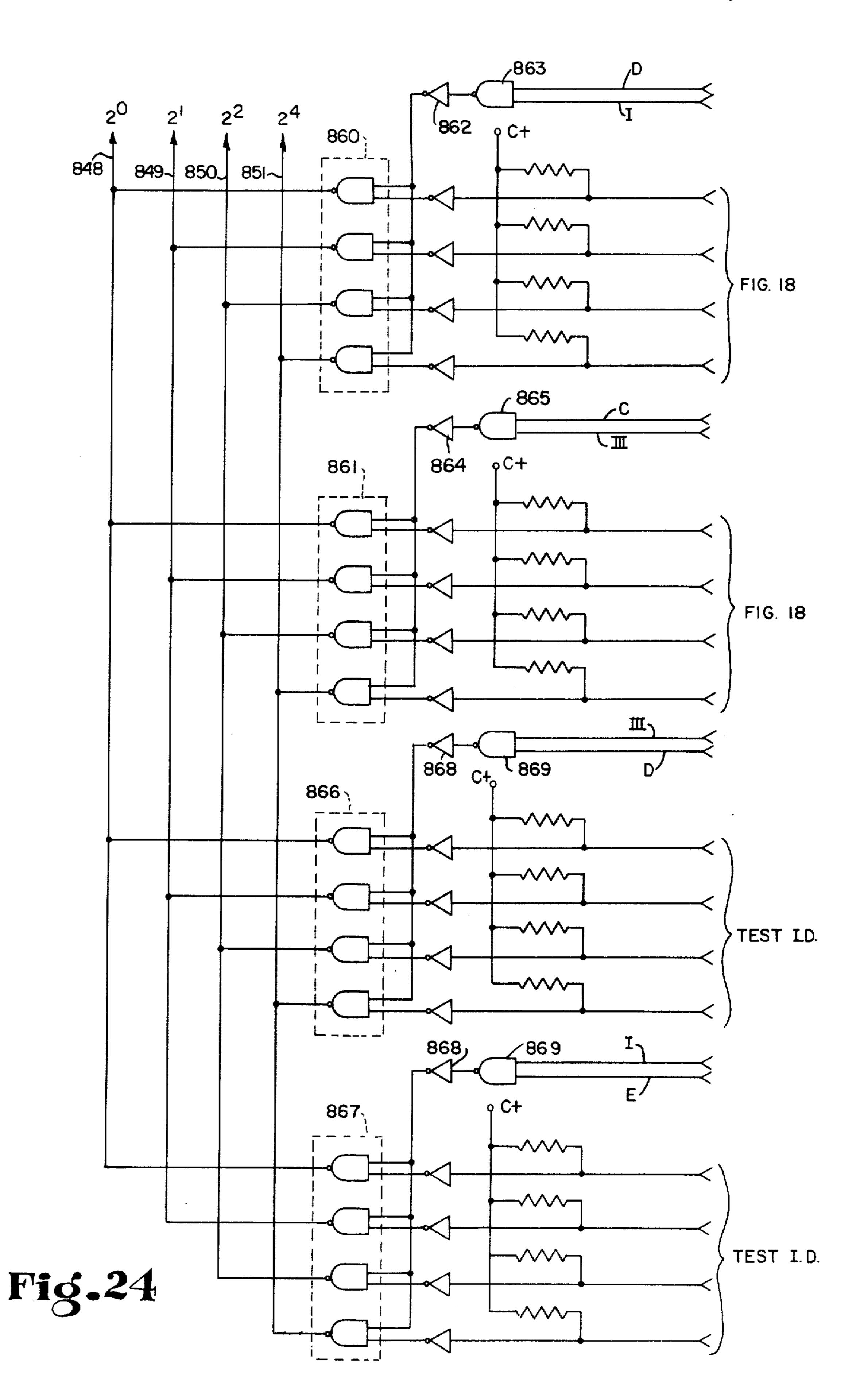

FIG. 24 is a schematic diagram showing a portion of the printer control logic; and

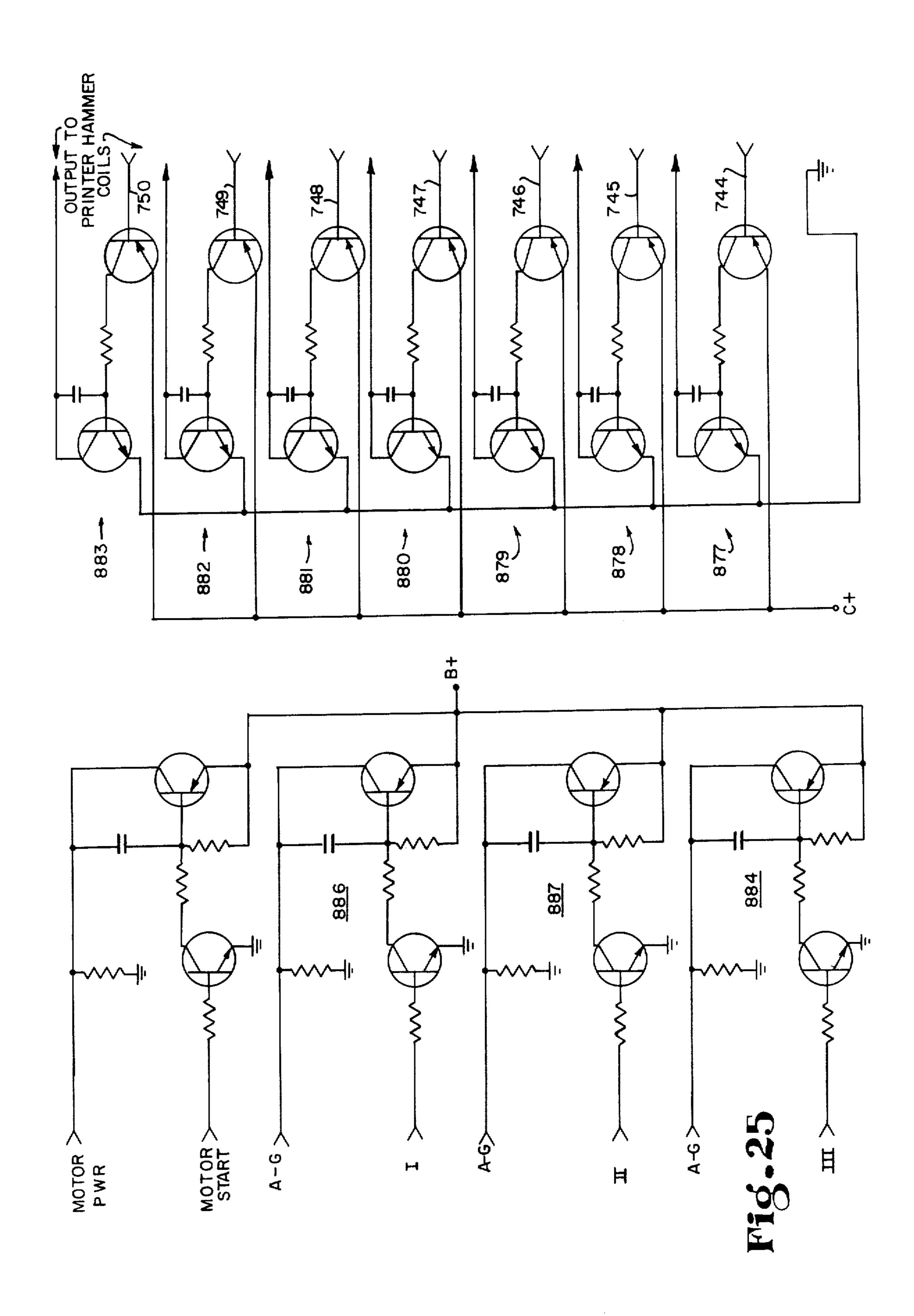

FIG. 25 is a schematic diagram showing a portion of the printer control logic.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

The chemical analyzation machine shown in FIG. 1 is for the serial analyzation of serum samples which have been obtained from respective patients by conventional means. The term "serum" is used to designate any animal fluid. This analyzation machine and the electronic control logic which controls its operation are shown and described in copending applications, U.S. Ser. No. 179,013 and U.S. Ser. No. 179,133 respectively.

25 By way of background, the machine shown in FIG. 1 comprises an upper housing 10 supported on a lower housing 12 by a post 14. A serum specimen wheel 16 and a test wheel 18 are supported in and by the top of the lower housing 12. The drive motor for these wheels 30 16 and 18 is located within the lower housing 12. The bottom portion of the lower housing 12 encloses an array of pressurized bottles 20, some of which are enclosed in a refrigerated compartment 22. These bottles 20 contain the various chemical reagents used in the performance of a serum analysis by the machine. They may be pressurized with inert nitrogen gas to prevent degradation of the reagents. Dark transparent doors on the front of the lower housing 12 permit the bottle compartment to be observed.

A serum transfer apparatus 24, a plurality of reagent dispensing heads 26, 27 and 28, and a test chemistry extraction head 29 are located in close proximity to the serum specimen wheel 16 and the test wheel 18.

Serum specimens may be placed in a plurality of specimen cups 30 which are carried in equally-spaced cavities in the top of the sample conveyor wheel 16. Each of the cavities is numbered and has a patient identification selection switch (not shown) associated with it. In a similar manner, test tubes 34 are carried in 50 equally-spaced peripheral holes (not shown) in the test conveyor wheel 18. A serum specimen is appropriately taken from the specimen cups 30 in the specimen wheel 16 and transferred to a waiting test tube 34 in the test wheel 18 by the serum transfer apparatus 24. Properly selected reagents are added via the dispensing head 26, 27 and 28 to each of the serum samples which have been transferred to test tubes as the test tubes 34 are indexed through the dispensing stations. The resulting test chemistries are then serially extracted for subsequent optical analyzation as in a spectrophotometer or a fluorometer by the test chemistry extraction head 29. The spectrophotometer or fluorometer may be housed within the supporting post 14.

The electronic control circuitry for controlling each of these operations may be contained in the upper housing 10. This circuitry may be programmed by a specially prepared card which is inserted in a slot 36 leading to a card reader (not shown) also supported in

5

and by the upper housing 10. An array of push buttons 38 may be located adjacent the card reader slot 36 for manually controlling part or all of the machine operations. An electronic measurement and reporting system consisting of the spectrophotometer, calculator, programmer and printer electronics in addition to a printer mechanism may also be housed in the upper housing 10 to convert the output signal from the spectrophotometer or like device into more usable forms of data such as milligram percentage concentrations.

The spectral analysis of fully complemented specimen test chemistries is conducted in a conventional spectrophotometer which has been modified to provide means by which the flow cell is moved in and out of a light path instead of disturbing that path with rotating mirrors or chopper and beam splitter techniques. The directing of the light beam is required so that its transmittance through air may be compared with its transmittance through the test chemistry in the flow cell.

A flow cell 40 is shown in FIG. 2 with its associated 20 reciprocating apparatus. This cell 40 is supported by bearings 42 on a rail 44 which permits and guides linear movement of the flow cell 40. The base of the flow cell is connected, as by a pin 46, to a slotted member 48. A finger member 50 is mounted and is eccentrically 25 driven on a wheel 52 and moves within the slot 54 in the slotted member 48. A shaft 56 is eccentrically mounted by a ball bearing 58 to its finger supporting wheel 52. The shaft 56 is connected to a second circular and rotating wheel 60 at a location offset from the 30 center of rotation of that wheel 60. The latter wheel 60 is rotated at approximately 30 rpm by an electric motor 62. The finger supporting member 52 is eccentrically driven as the motor rotates this wheel 60 to reciprocate the flow cell 40 on its supporting rod 44. As can be seen 35 from FIG. 2, this reciprocation serves to move the flow cell and the test chemistry contained therein in and out of the light path. The light source intensity [64] is highly regulated and prefocused. The reciprocation of the flow cell and test chemistry provides a continuous 40 source of calibrating signals for the spectrophotometer. The electronic measurement and reporting system used to convert the spectrophotometer output into a more usable and meaningful form of data will be hereinafter described.

The above described machine is capable of performing what are known as end point serum blank tests, end point reagent blank tests and kinetic tests. In the end point serum blank test, an amount of each serum sample to be tested is placed in two consecutive test tubes 50 34 in the test wheel 18. One group of reagents is dispensed into and combined with the serum samples in one of the thereby associated pairs of test tubes, while a different set of reagents is added to and combined with the remaining serum sample. These two sets of 55 reagents may have one or more reagents in common. The former being referred to as the blank and the latter being referred to as the test. It is required to measure the optical density (O.D.) of both the blank and test and subtract the O.D. of the blank from the O.D. of the 60 test to obtain the desired results. The resulting difference of optical densities is proportional to the concentration of the material for which the test is designed to measure.

An end point reagent blank consists of adding the same combination of reagents to a number of test tubes and then adding a sample of water to the first tube, which is referred to as the reagent blank, and a differ-

6

ent serum sample to each of the following tubes. In order to arrive at the desired test results, it is required to measure the optical density of the contents of each test tube and subtract from the optical density thereby measured the optical density of the reagent blank. The difference is proportional to the concentration of the material in the sample for which the test was designed to measure.

The kinetic test analyzes the rate of reaction of a specific combination of reagents and a serum sample. The test consists of measuring the rate of reaction of a specific combination of reagents and a serum sample. It is possible to do this by measuring the optical density of the test solution at a certain time, +1, and again at a subsequent time, +2, and subtract the difference between these readings. This may be repeated any number of times for the same test; and each time the results should be the same as long as the reaction rate is linear. It is important to determine if the rate is constant and to record results during that portion of the reaction. The optical density difference as a function of time may be calibrated by performing an identical test on a [sample] standard solution with a known concentration of the material for which the test is designed. The above described procedure may be performed in several ways. The first being that of placing the test solution in the flow cell and measuring its optical density at precisely controlled timed intervals. A second procedure, which provides for a higher overall rate of sample analysis involves placing an amount of serum sample into three consecutive test tubes. Reagents are appropriately and selectively added to each of the three samples at a different point in time. Each group of three test chemistries are identical in composition when extracted and placed in the flow cell except that they are serially extracted at the end of precisely controlled time intervals. This latter method has been found to yield better and faster results, since the necessary time intervals have elapsed prior to placing the test chemistries in the flow cell.

A block diagram is shown in FIG. 3 which illustrates in block form the electronic processing of the spectrophotometer output to transform the output into a more meaningful form of data to enable comparison with a standard solution whose characteristics are known. The light emitted by the light source **L**, shown in FIG. 2 in conjunction with the flow cell 40, **J** falls upon a photomultiplier tube 66. The output of the photomultiplier tube 66 is connected directly to a preamplifier 68 for converting the output current at the photomultiplier tube to a proportional DC level.

Assuming that the test chemistries are still being formulated in the test wheel 18, and that none have reached the flow cell for analysis as yet, the spectro module control logic 70 maintains a solid state switch 72 leading from the preamp 68 to an integrator 74 Lopens Lopen so that the preamp output is applied through a closed switch 76 to one input of a voltage comparator 78. A reference voltage is also applied to this comparator 78. The comparator 78 compares the preamp output with the reference voltage and uses the difference between the two to control a high voltage supply 80 for application across the photomultiplier tube 66.

The loop comprising the photomultiplier tube 66, the preamp 68, the voltage comparator 78 and the high voltage supply 80 is used as an automatic gain control and calibration adjustment for the photomultiplier tube

66. This adjustment is needed because the photomulitipler tube characteristics change a great deal with time and temperature, and because the photomultiplier tube does not have the same sensitivity over the entire light spectrum. This closed loop feedback condition permits 5 the photomultiplier tube output to be stabilized with respect to the particular wave length of light which it will be concerned with in the upcoming test.

The presence of a first test chemistry to be analyzed in the flow cell is sensed by the spectro control logic 70<sup>-10</sup> which then opens the switch 76 in the feedback path leading from the preamp to the high voltage supply 80 and closes the integrator switch 72 leading from the preamp 68 to the integrator 74. Preferably, this switch the light path by the spectro control logic 70 acting on a signal from a flow cell position detection switch 82.

The flow cell position detection switch 82 signals the spectro control logic 70 when the flow cell is between the light source and the photomultiplier tube 66 and, 20 conversely, when the flow cell is out of this path so that the light uninterrupted from the light source is incident on the photomultiplier tube 66. The photomultiplier tube 66, and thereby the preamp 68, have a higher DC level output when the light path comprises only air than 25 when the light passes through a test chemistry and the flow cell. Both signals are important for later comparison.

The first signal to be applied by the preamp 68 to the integrator 74, after the integrator switch 72 has been 30 closed, represents the amount of a given wave length of light striking the photomultiplier tube after passing through a test chemistry. This DC signal is integrated by the integrator 74 for a specific length of time, as controlled by the spectro control logic 70. The integra- 35 tor output is initially zero, but as it integrates the preamp output its output then become a ramp function.

The ramp function, as it is generated, is applied through a closed tracking switch 84 to a track and store network block 86. The tracking switch 84 is also con- 40 trolled by the spectro control logic 70. The track and store network 86 tracks the integrator output until the integration interval is terminated by the spectro control logic 70. The termination signal is also used to open the tracking switch 84 which then causes the DC level to 45 which the preamp output has been integrated to be stored in the track and store network 86.

The flow cell is then moved out of the light path from the light source to the photomultiplier tube 66. This 50 movement is detected by the flow cell position detector switch 82 which signals the spectro control logic 70. The preamp 68 output now represents the photomultiplier tube output with only an air path between the light source and that tube 66.

The control logic 70 initiates a reference signal integration interval and causes the integrator 74 to integrate the preamp output for an amount of time precisely identical to the integration time for the test chemistry. The integrator 74 now integrates the DC 60 signal representing the photomultiplier tube 66 output for an air path for an interval of time precisely equal to that of the integration interval for the test chemistry. At the conclusion of this interval, a decay switch 88 in a feedback path around the integrator 74 is closed by the 65 control logic 70 which causes the voltage at the output of the integrator to decay exponentially.

It should be noted that if, at the end of both integration intervals, the integrator 74 output representing the

air path, and the track and store circuit 86 output representing the test chemistry path were equal, it would mean that the optical density of the test chemistry is zero and that it has a light transmittance equal to that of air. This, however, is never the case even for an empty flow cell, so the light transmittance of a flow cell containing a test chemistry is always less than that of free air. The exponential decay of the air path reference integrator output is conducted as the first part of an analog to digital conversion of the light transmittance of the test chemistry with a simultaneous conversion to optical density unit.

The exponential decay of the reference air path integrated output is continued until the decreasing signal is is also opened each time the empty flow cell interrupts 15 equal in amplitude to the signal level held by the track and store network 86. The comparison of the decaying signal and the track and store held signal is effected in a crossover comparator 90. The signal which closed the decay switch 88 also enabled a latch 91 coupled to the output of the crossover comparator 90 to allow the comparator output to be applied to one input of a counter gate 92. The output of a one megahertz clock 94 is divided by 10 by a division section 96 and the resulting 100 kilohertz clock applied to the other input of the counter gate 92. The output of the counter gate 92 is a train of pulses occurring at a 100 kilohertz rate when there is an enabling signal from the output of the comparator [74] 90. This output is enabling only as long as coincidence has not been detected by the crossover comparator 90 between the track and store network 86 contents and the decaying integrating output. When such coincidence is detected by the comparator 90, the input from that comparator to the counter gate 92 is turned off, thereby stopping the pulse train.

It should be seen that the number of pulses in this train corresponds to the amount of time that the integrator output was permitted to decay before it reached the signal level of the signal held in the track and store network 86. It should also be seen that the pulse train represents or is proportional to the logarithm of the transmittance of light in an air path minus the logarithm of the transmittance of light through a test chemistry. This makes the pulse train proportional to the optical density of the test chemistry.

As previously mentioned, the entire analog to digital conversion as well as the light transmittance readings are taken under the control of the spectrophotometer control logic 70. This logic is appropriately controlled through a programmer 98 whose output signals to the control logic 70 reflect the particular test which has been selected on the program card, i.e., end point serum blank test, end point reagent blank or kinetic test. The remaining blocks of the calculator section will be explained with reference to the specific tests under way.

At the beginning of each of the tests mentioned a blank calibration is performed. The first test chemistry which would be put into a flow cell is either a reagent blank or a serum blank. In the end point reagent blank test the reagent blank is comprised of the reagents which the rest of the chemistries will receive but without any serum. The optical density of this blank is used, as will hereinafter be explained, to calibrate the calculator section 100 of the spectrophotometer processing logic. In the case of the serum blank test, the first test chemistry to reach the flow cell is a standard serum blank comprised of **L**a serum specimen **J** a standard solution and reagents. The next chemistry to reach the flow cell subsequent to this one will be one comprised of the same serum with different reagents. I

A blank storage register 102 for later storing the optical density of the reagent or serum blank is first reset to zero by the programmer 98. A master counter 104 which is clocked through a master counter control gate 106, the operation of which will be described later, from the 1 megahertz clock 94 is then reset to zero. An optical density counter 108 for storing the digital counterpart of the optical density of the solution in the flow 10 cell is also reset to zero. A calculation counter 110 and the percentage concentration counter 112 used in the calculation of percentage concentrations are also reset to zero.

After the resetting phase is completed, the optical density counter 108 is preset with the nines complement of the contents of the blank storage register 102. The nines complement of the blank storage 102 is taken by a nines complement conversion block 114. 20 Since the blank storage register 102 had been reset to zero, the nines complement preset into the optical density counter 108 would be equal to 1999. The percentage concentration counter 112 is then preset with the number which has been dialed in on a set of 25 switches 116. This value represents the known percentage concentration of La I the substance for which the test is designed to measure in the standard solution which will be placed in the flow cell at a subsequent point in time. A multiplier accumulator 118 is then 30 preset with the percentage concentration in the percentage concentration counter 112. The nines complement is then taken of this value, which has been preset into the multiplier accumulator 118, by a nines complement converter 120. The nines complement of the 35 known standard concentration is then preset into the calculation counter 110. The percentage concentration counter 112 is then reset to zero.

After completion of the above, the integration and analog to digital conversion is permitted to take place 40 to determine the optical density of the blank solution in the flow cell. Up until this time, the feedback switch 76 in the preamp 68 feedback circuit has been closed when the flow cell was out of the light path which permitted the photomultiplier tube to be calibrated. The 45 string of pulses representing the optical density of the flow cell and its contained blank solution is applied to the optical density counter 108 through the counter gate 92. The counter gate 92, as before explained, is opened when the correct number of pulses has been 50 applied to the optical density counter 108. The value in the optical density counter is then preset into the blank storage register 102 and the nines complement of this value taken by the nines complementor 114 and the result preset back into the optical density counter 108. 55

The blank solution is then removed from the flow cell. The next chemistry to be put into the flow cell is the standard [chemistry] solution, the [element] substance concentration for which was dialed in on the standard switch input 116. The light transmittance of 60 this chemistry is then determined and the analog to digital conversions repeated, with the optical density pulse train of the standard chemistry being put into the optical density counter 108 together with the nines complement of the optical density of the blank chemis- 65 try. The resulting number in the optical density counter represents the difference in optical density between the blank and the standard solutions.

The scale factor for use in all further percentage element concentration calculations must be determined using this difference between the blank optical density and the standard optical density. To do this, a 100 kilohertz clock is applied by the master counter 104 to a digital rate multiplier 124 and through a multiply and divide selector block 126 to the percentage concentration counter 112. The 100 kilohertz pulse train is multiplied in the digital rate multiplier 124 by the value in the optical density counter 108 to proportionately alter the frequency of the 100 kilohertz pulse train. The altered pulse train is applied through the multiply and divide block 126 to the calculation counter 110 which already contains the nines comple-11 15 ment of the known percentage concentration of the standard solution. The calculation counter 110 and the percentage concentration counter 112 continue to be clocked by their respective clock lines until a fill detector 128 senses that a number of pulses have been received by the calculation counter 110 from the digital rate multiplier 124 equal to the known standard percentage concentration. This fill detector 128 is used to inhibit the master counter gate 106 which has heretofore been supplying the master counter 104 with clock pulses from the 1 megahertz clock 94. The number of pulses which have reached the percentage concentration counter 112 in this interval represent the scale factor which will be used as the basis for all subsequent tests. In effect, this procedure divides the dialed in standard solution substance concentration by the difference in optical density between the standard chemistry and the blank chemistry and stores the resulting value in the percentage concentration counter 112. As will be seen, the optical densities of the test chemistries will be multiplied by this normalized value to calculate their percentage concentrations. It should be seen that such calculated values will be in the same units as the standard solution substance concentration that was dialed in. By way of example of the above process, assume an optical density difference between the blank solution and the standard chemistry of 0.5. The optical density counter 108 will then contain the binary equivalent of 0500. The multiply and divide section 126 enables the master counter 104 to apply 100 kilohertz clocking pulses to the percentage concentration counter 112. The 100 kilohertz clock is also applied to the digital rate multiplier 124 which multiplies this frequency by the number in the optical density counter 108, i.e., 0.500, the calculation counter 110 thereby receives 500 pulses each time the percentage concentration counter 112 receives 1,000 pulses. Assume further that the known standard concentration dialed in on the input switches 116 was represented by 1,000. The nines complement of 1,000 would now be in the calculation counter 110. By the time the calculation counter 110 has received the 1,000 pulses necessary to initiate the inhibiting action of the fill detector 128 the percentage concentration counter 112 will have received 2,000 pulses which represents the normalized value by which all subsequent O.D. values will be multiplied to ascertain the corresponding percentage concentrations. As a last step, the multiplication accumulator 118 is preset with this number, i.e., 2,000, and the programmer 98 is

reset. The actual test procedure is now ready for initiation. The blank storage register 102 contains the value of the optical density of the blank solution. The master counter 104, the calculation counter 110 and the percentage concentration counter 112 are all reset to zero. The optical density counter 108 is then preset with the nines complement of the blank storage register 102 which, in effect, is the negative of that number. The calculation counter 110 is then preset with the nines complement, from the nines complementor 120, of the scale factor contained in the multiplication accumulator 118.

By this time, in the end point reagent blank test, a test chemistry has entered the flow cell and the photomultiplier tube 66 has an output which is applied to the preamp 68. Under control of the spectrophotometer control logic 70, this output is integrated and converted from an analog signal to the digital pulse train representative of the optical density of the test chemistry in the flow cell. This pulse train is then applied to the optical density counter 108 on top of the nines complement of the optical density of the blank solution which in effect subtracts the blank optical density from the test optical density. The value now in the optical density counter 20 108 represents the true optical density of the test chemistry.

The calculation of the concentration of the test chemistry with respect to that of the standard chemistry is now performed. The first step in this procedure is that the programmer logic 98 selects the multiplication portion of the multiplier and divide circuit 126. This selection serves to route the digital rate multiplier 124 output to the input of the percentage concentration counter 112. A 100 kilohertz master counter 104 output is concurrently routed to the calculation counter 110. The master counter 104 begins on signal from the programmer clocking the percentage concentration counter 110 with its 100 kilohertz output.

The digital rate multiplier 124 multiplies the frequency of another 100 kilohertz output frequency clock of the master counter 104 by the optical density value in the optical density counter 108 and applies the resulting pulse train to the percentage concentration counter 112. This clocking continues until the fill detector 128 detects that the calculation counter 110 has received a number of pulses from the master counter 104 equal to the scale factor which originated in the multiplier accumulator 118.

At this time, the master counter gate 106 is inhibited, 45 thereby prohibiting further pulsing of the master counter 104 by the 1 megahertz clock 94. The opening of the gate 106 also stops the pulsing of the percentage concentration counter 112. The contents of this counter 112 at this time represents the concentration of the test chemistry in the flow cell with respect to the known standard value. This value is applied through printer logic 132 to the printer 134 along with identification information.

At the beginning of an end point blank serum test the blank storage register 102, the master counter 104, the optical density counter 108, the percentage concentration counter 112 and the calculation counter 110 are all reset to zero. This resetting is performed at the conclusion of the blank and standard calibration explained above. The programmer 98 then presets the optical density counter 108 with the nines complement of the contents in the blank storage register 102. This register 102 was reset to zero, so the value of the nines complement is equal to 1,999. The calculation counter 110 is the preset with the nines complement; through the nines complementor 120, of the scale factor contained in the multiplication accumulator 118.

The programmer logic initiates, at this time, the analog to digital conversion of the light transmittance of the patient blank test chemistry in the flow cell at that time which is comprised of a serum specimen plus one or more reagents. The representative pulse train of the optical density of this patient blank is applied to the optical density counter 108. This value is then preset into the blank storage register 102, is nines complemented by the nines complementor 114 and is preset into the optical density counter 108.

The patient test chemistry is then examined by the photomultiplier tube 66 and the pulse train representing its optical density is applied to the optical density counter 108 which already contains the nines complement of the optical density of the patient blank. This results in the difference in optical density between the two residing in the optical density counter 108. The master counter 104 is then allowed to apply, through the multiplication and divide circuit 126, its 100 kilohertz pulses to the calculation counter 110 which already contains the nines complement of the standard scale value. The digital rate multiplier 124 multiplies another 100 kilohertz output of the master counter 104 by the contents of the optical density counter 108 and accordingly clocks the standard units value counter 112.

Again, when the fill detector 128 notes that the number of master counter pulses applied to the calculation counter 110 equals the standard scale factor, the detector 128 opens the master counter gate 106 from the one megahertz clock 94 to the master counter 104. The value in the percentage concentration counter 112 then represents the percentage concentration of the patient test with respect to the patient blank. This value is applied by the printer logic to the printer 134 along with identification information. The programmer 98 is reset at the conclusion of the test series.

The performance of a kinetic test requires a special calibration. This calibration includes resetting the blank storage register 102, the master counter 104, the optical density counter 108, the calculation counter 110 and the percentage concentration counter 112. The only other thing that occurs in the kinetic calibration mode is the presetting of the percentage concentration counter 112 with the standard solution percentage concentration value dialed in on the switches 116. The contents of the percentage concentration counter 112 is then preset into the multiplication accumulator 118 to complete the calibration for the kinetic test.

The kinetic test may be conducted in one of two different ways due to the difference in reactions possible in the various test chemistries. The first way involves the inspection of a test chemistry upon the elapse of two or more precisely controlled intervals of time. A rate of increase in optical density is looked for, thereby permitting the first test chemistry reading to be used as the base for all subsequent readings. The other type of kinetic tests involves a rate of decrease in optical density. To standardize this mode of operation, the standard element concentration is used and all subsequent readings taken in relation to that value.

For a kinetic optical density increase test, the blank storage register 102 and all of the counters 104, 108, 110 and 112 are reset to zero. The optical density counter 108 is then preset with the nines complement of the contents of the blank storage register 102, which is 1999. The calculation counter 110 is then preset with the nines complement, through the nines complement.

tor 120, of the scale factor contained in the multiplication accumulator 118. The sequence is then inhibited and the first digital pulse train representing the optical density of the test chemistry in the flow cell is put into the optical density counter 108.

The optical density counter contents is then preset into the blank storage register 102 and the sequence inhibited again until a second reading is taken of the test chemistry in the flow cell. The application of the digital pulse train representing the optical density ob- 10 tained at the latter reading 1999, put into the optical density counter 108 with the nines complement of the blank storage register contents, which serves to subtract the former from the latter.

apply the 100 kilohertz output of the master counter 104 to the calculation counter 110 at the same time that the 100 kilohertz rate is multiplied by the contents of the optical density counter 108 in the digital rate multiplier 124 and applied to the percentage concen- 20 tration counter 112. As before, when the number of pulses from the master counter 104 reaching the calculation counter 110 equals the standard value which originated in the multiplier accumulator 118, the fill detector 128 opens the master counter gate 106 and 25 stops its enabling pulses.

The value in the percentage concentration counter at this time represents the change in optical density in the time interval between test chemistry readings. Several such pairs of readings may be obtained to ensure that 30 the desired linear reaction is taking place. This value is then applied to the printer logic 132 which controls the

printer 134 accordingly.

An optical density loss kinetic test, as previously mentioned, is used to determine the rate at which the 35 optical density of a test chemistry decreases from that of a known standard starting point [,]. Initially, the blank storage register 102 as well as all of the counters 104, 108, 110 and 112 are reset to zero. The calculation counter 110 is then preset with the nines complement 40 of the scale factor from the multiplication accumulator 118. Further sequencing is inhibited until a first light transmittance reading is obtained from the test chemistry and the value obtained converted to an optical density pulse train and clocked into the optical density 45 counter 108. The contents of this counter 108 is then preset into the blank storage register 102, nines complemented by the nines complementor [104] 114 and preset into the optical density counter 108.

A second reading is then taken of the light transmit- 50 tance of the test chemistry, and the resulting optical density pulse train applied to the optical density counter 108 on top of the nines complemented value of the first reading. The resulting contents of the optical density counter 108 is then equal to the net change in 55 optical density of the test chemistry in the time interval

between the two readings.

This value is then preset into the blank storage register 102 and nines complemented before reinsertion in the optical density counter 108. The multiplier line in 60 the multiply and divide circuits 126 is selected by the programmer 98 and the 100 kilohertz output from the master counter 104 is thereby applied to the calculation counter 110. Concurrently, the nines complement of the change in optical density during the time interval 65 is multiplied by the rate of the 100 kilohertz pulses received by the digital multiplier 124 from the master counter 104.

The fill detector 128 detects when the number of pulses from the master counter 104 has reached the standard value already in the calculation counter 110 and terminates the one megahertz clock 94 input to the master counter 104 by inhibiting the clock gate 106. The value in the percentage concentration counter 112 represents the amount the optical density of the test chemistry decreased from that of the standard value during the reaction time interval. This value is applied by the printer logic 132 to the printer 134 for appropriate print out.

It should be understood that the type of kinetic test, i.e., an increasing or decreasing optical density analysis, may be controlled two different ways. One way has The multiply and divide circuit 126 is then enabled to 15 just been described in that the programmer 98 changes the electronic processing of the signals in accordance with the type of test under way. Instead of changing or reversing the electronic calculation of the test analysis, the order in which the test chemistries are placed in the flow cell may be reversed to effect the same reversal as

that done by the programmer 98.

The actual circuit configuration for the photomultiplier tube output preamp 68 and the combination high voltage supply and comparator 80 and 78 in the automatic gain control path from the output of the preamp 68 to the photomultiplier tube 66, is shown in FIG. 4 and FIG. 5. The comparator 78 and high voltage supply 80 maintain and adjust the sensitivity and gain of the photomultiplier tube resulting from temperature and light frequency variances. The pre-amp 68 includes an operational amplifier 140 with a dual field effect transistor (FET) 143 connected across its input leads. A resistive balancing network 144 may be used to adjust the operational amplifier input offset voltage.

The photomultiplier tube 66 is connected to the operational amplifier input FET 142 in a current mode. The photomultiplier tube receives light from the light source and creates a current, due to photoelectric emission, proportional to the intensity of the light reaching it. The output of the operational amplifier (op-amp) 140 is a DC voltage whose level is proportional to the amount of current received by it from the photomultiplier tube. Feedback is provided for the op-amp 140 by a resistor 146 connected from the output of the amplifier 140 to its input. A capacitor 148 is connected in parallel to this resistor 146 to provide high frequency gain suppression.

The pre-amp output is applied to a current summing point 150 in the comparator 78 through a resistor 152. The reference voltage is applied to the comparator 78 from a reference operational amplifier 154 whose input is supplied from a B+ voltage supply. A Zener diode 156 is used as feedback for the operational amplifier 154 to establish the reference voltage at the output of the op-amp 154. The current resulting from the voltage drop across an adjustable resistor 158 of the reference amplifier 154 output is summed at the current summing point 150 with the current originating at the pre-amp output 68.

An FET 160 and its biasing transistor 162 comprise the feedback path switch 76 in the pre-amp to comparator path of FIG. 3. The path from the drain to the source of the FET 160 is closed by the spectro control logic 70 which places a true signal on the base 164 of the biasing transistor 162. Current either flows into or out of the drain 166 of the FET 160 according to the difference between the pre-amp output and the reference amplifier output [156] 154. The resulting voltage

applied to the dual input FET 168 of a first stage comparator op-amp 170 is the difference between the preamp output and the B + reference voltage.

The feedback path switch 76 is opened by the flow cell position detection switch [84] 82 as the empty spectro flow cell is moved into the light path to interrupt the light reaching the photomultiplier tube 66. The output of the operational amplifier 170 which is the negation of the voltage on its input 150 is retained when the feedback switch 76 is opened by a feedback 10 capacitor 172 which has charged to this value.

The retained voltage on the output of the first stage comparator op-amp 170 is applied across an input resistor 174 to the summing junction 176 of a second 180 of this op-amp 178 is connected to the variable high voltage supply source 80. More specifically, the output terminal of the second comparator op-amp 178 is inverted by an inverting amp 182 before passing through a pair of current amplifiers 184 and 186. The 20 output of the second current amplifier 186 is connected to the base of a power amplifier transistor 188. The collector 190 of this transistor 188 is connected to a highly regulated voltage supply C<sup>+</sup>. The output of the power gain transistor 188 is applied to the center tap 25 192 of the primary winding 194 of a step-up transformer 196. The two ends 204 and 206 of the primary winding 194 are alternately connected to ground by a chopping multivibrator 198 whose two outputs are connected to power switches 200 and 202. The two 30 leads 204 and 206 of the primary winding 194 of the transformer 196 are also respectively connected to these power switches 200 and 202. The secondary 208 of the step-up transformer 196 is connected to a voltage doubling and rectifier circuit 210. This voltage 35 doubling circuit 210 has two outputs, one through resistors 212 to the summing junction 176 of the second comparator operational amp 178; and the other output is connected through a resistor-capacitor filter circuit 214 to power the photomultiplier tube 66.

The output of the voltage doubling circuit 210 which is applied through resistors 212 to the summing junction 176 of the second comparator op-amp 178 is summed at that point with the output voltage of the first comparator 170 which is the difference between 45 the output of the pre-amp 68 and the output of the reference voltage op-amp 154. The summing junction 176, due to the characteristics of the operational amp 178, must be maintained at zero voltage, or a virtual ground. The output voltage moves up and down to 50 effect this zero voltage maintenance. In terms of the photomultiplier tube 66, the moving around of the voltage on the output 180 of the second comparator amp 178 serves as an automatic gain control and sensitivity adjustment.

The placing of a test chemistry in the flow cell and the flow cell being positioned in the light path, as signalled by the flow cell position detection switch 82, signals the spectro control logic 70 to open the pre-amp feedback switch 76 and to selectively close the integra- 60 tor switch 72 leading from the pre-amp 68 to the integrator 74.

The switch 72 and integrator 74 are shown in detail in FIG. 6. The integrator switch 72 is comprised of an FET 220 which is controlled from a biasing network 65 222. The biasing network 222 receives a true or positive voltage input from the spectro control logic 70 for the period of time during which the integrator 74 is to

integrate the output of the pre-amp 68. The precisely controlled integration interval is preferably 160 milliseconds in duration. During this interval, the positive voltage applied to the base of the first transistor 224 is inverted and applied to the base of the first transistor 224 is inverted and applied to the base of a second transistor 226 which again inverts the voltage to apply a positive voltage to the gate of the FET 220 to turn the FET on. During its ON period, the FET 220 permits the output of the op-amp 140 in the pre-amp 68 to be applied through a potentiometer 228 and resistor 230 to the gate of a dual FET 232.

This dual FET 232 serves as the input device for the op-amp 234 providing a very low input bias current for stage comparator op-amp 178. The output terminal 15 the op-amp. The input offset voltage for this op-amp 234, as well as the gate to source FET resistance, is balanced by an adjustable resistance balancing network 236 connected to the other input of the integrator amp 234. Three feedback paths are selectively provided for the amp 234. The first contains the integrating capacitor 238. The second feedback path contains an FET integrator resetting switch 240 and a serially connected resistor 242. The FET switch 240 is turned on by a biasing network 244 identical to the one hereinbefore described when a positive or true voltage is applied to this network 244.

> The third feedback path is provided through an FET swtich 246, a serially connected precise resistance 248 and a potentiometer 250. The FET 246 is controlled by a positive signal applied to its biasing network 252.

The output conductor 254 from the integrator amp 234 is connected to one side of an input resistor 256 of the track and store network 86 shown with the comparator 90 in FIG. 7. It is also connected to one side of a resistor 258 serving as an input for an inverting amplifier 260 in the crossover comparator 90. The other side of the former resistor 256 is connected to the gate terminal of a dual FET 262 serving as the input device for an op-amp 264. The op-amp 264 inverts the incoming signal from the integrator op-amp 234 and applies it through a resistor 266 to the emitter of a transistor 268 used as a Zener diode. The base of this transistor 268 is unconnected. The transistor 268 maintains a voltage on the base of a linear mode transistor 270 of approximately 9 volts to 15 volts DC. The output signal from the second transistor 270, taken from its \[ \bar{\chi}\] base \[ \bar{\chi}\] collector electrode, is applied to the drain of an FET 272 which, with its biasing network 274, comprises the track and store switch 84. This switch 84 is closed by a positive signal on its input conductor **[276]** 275 from the spectro control logic 70 during the integration interval occurring when a test chemistry is being examined. When this switch 84 is closed, the output from the linear mode transistor 270 is connected by the 55 FET 272 to the input resistor 276 leading to the gate of a dual FET 278.

The dual FET 278 is the input device for an integrating amp 280. Feedback for the op-amp 280 is obtained through a feedback capacitor 282. A resistive network 284 is connected to one input of the op-amp 280 to balance the input offset voltage of the operational amp 280. The op-amp 280 integrates the input from the linear mode transistor 270 to negatively duplicate the main integrator 74 output. This integrating op-amp 280 continues to integrate and follow the output of the integrator 74 until the expiration of the test chemistry integration interval which causes the spectro control logic 70 to open the track and store input switch 84.

The removal of the input to the integrator 281 stops the integration, but the DC level to which the output has risen is maintained by the feedback capacitor 282. The output of the integrator 281, it should be noted, is also applied to the input 286 of an op-amp 288 serving 5 as the basis for the crossover comparator 90.

The inverting amplifier 260 to which the output of the integrator 74 is also connected provides a negation of the integrator output and applies such inverted signal to the other input of the crossover comparator 10 op-amp 288.

In operation, two identical length integration intervals are associated with the analysis of each test chemistry. The first of these is used to integrate the pre-amp the light path falling on the photomultiplier tube 66. The second interval is used to integrate the pre-amp 68 output when the flow cell is retracted and the light falling on the photomultiplier tube 66 passes through only an air path. Each of these integration intervals is 20 160 milliseconds long. At the beginning of the first of these intervals, the integration switch 72 is turned on to permit the output of the op-amp 140 in the pre-amp 68 to be applied to the input of the integrating operational amp 234. This DC signal is integrated causing the out- 25 put of the integrator amp 234 to rise in a ramp function. The ramp function is applied to the first operational amp 264 in the track and store section and is limited to a certain voltage range by the transistor 268 used as a Zener diode. The resulting DC voltage level is 30 applied through the track and store switch 84 to the input of a second integrator op-amp 280 which integrates the signal for application to one input 286 of the crossover comparator op-amp 288.

The conclusion of the test integration interval signals 35 the control logic 70 to open the track and store FET switch 272 thereby removing the input from the integrating amp 280 so that the DC level to which the output has risen is maintained across the feedback capacitor 282. The expiration of the test integrating 40 interval is also used, at a delayed point in time to close the FET 240 in the second feedback path for the integrating amp 234 to provide a rapid discharge of the integrator capacitor 238. This discharge returns the integrator output to zero.

The flow cell, at the conclusion of its two second inspection cycle, is removed from the light path to the photomultiplier tube 66. This movement is sensed by the flow cell position detection device 82 which signals the spectro control logic 70 to begin the second inte- 50 gration interval. This second interval is used to integrate the output of the preamp 68 corresponding to the photomultiplier tube output when the path from the light source is comprised of air only. During the air integration, the integrating amp 234 output is again 55 applied to an amp 264 in the track and store tracking integrator by the closed track and store switch 84. The integrating amp 234 output is also applied through an inverting amplifier 260 to the crossover comparator **[ 288 ]** 90. The output of this comparator, as will be 60seen hereinafter, is inhibited until the termination of the air integration interval.

At the conclusion of the second, or air integration interval, the integrator 74 has integrated to a DC level which is greater than that to which it integrated for the 65 test integration interval. This occurs because the light transmittance of air is always greater than any other material. The FET 246 in the top or third feedback

path around the integrating operational amp 234 is turned on by a true pulse from the spectro control logic 70 which also removes the inhibit on the comparator output latch 91. The closed feedback switch provides a discharge path through the resistor 248 and adjustable potentiometer 250 for the integrator capacitor 238. The output voltage on the integrating amp 234 is thereby caused to exponentially decay. The exponential decay continues until the crossover comparing op-amp 288 senses that the output of the integrator 74 has decayed to a DC level equal to that of the DC voltage stored in a track and store integrator 281. When such coincidence is obtained, the output of the comparator amp 288 goes false. The amount of time 68 output when the test chemistry and flow cell are in 15 which the output of the comparator op-amp 288 was true after the initiation of the integrator output decay is proportional to the optical density of the test chemistry which was examined.

The output of the comparator op-amp 288 is connected to a latching circuit 91 which applies the crossover comparator output to the optical density counter gate 92 only on command from the control logic 70. The latching of this signal by the latch 91, will hereinafter be explained in connection with the spectro control logic 70. In general, the latch 91 applies the output of the crossover comparator 90 to the optical density counter gate 92 at the beginning of the decay period on signal from the spectro control logic 70.

The spectro control logic 70 is shown in detail in FIGS. 8 and 9. It should be recalled that the flow cell is moved into the light path of the spectro for two seconds and out for two seconds. A signal from the flow cell position detection switch 82 applies a signal to a oneshot 290 in the spectro control logic 70 when the flow cell leaves the light path. The output of this one-shot, preferably having a duration of approximately 1.2 seconds, allows the flow cell to get out of the light path. The output is applied to a NOR gate 292. At the conclusion of the 1.2 second time period, the negative going edge of the output of the one-shot 290 allows the NOR gate 292 to place a positive pulse at the input of another NOR gate 294. The signal from the flow cell position detection switch 82 also initiates the timing cycle of a second one-shot 296 whose output lasts ap-45 proximately 10 milliseconds. The trailing edge of the output of this one-shot 296 causes the output of a NOR 298 to which the one-shot 296 is applied to go positive for a short time. The output of this NOR 298 is also applied to the input of the NOR gate 294 so that whenever either of the NOR gate inputs go false the output of the gate 294 will go true for the same amount of time.

The output of the one-shot controlled NOR gate 294 is connected to the preset input of a J-K flip-flop 302. One of the outputs 300 of this J-K flip-flop 302 is normally true while the other output 304 is normally false. The normally false output 304 maintains a resetting signal on the reset terminal 305 of an integration interval counter 306 as well as holding a reset signal on the reset input 309 on a 100 hertz oscillator 310, shown in FIG. 10 as part of the programmer 98. This 100 hertz clock 310 is controlled by the 1 megahertz clock 94.

The 100 hertz oscillator 310 output is applied to the clocking input of the integration interval counter 306. The expiration of the output signal of the 10 millisecond one-shot 296 results in a preset signal being applied to the J-K flip-flop 302. This reverses the signals on the two outputs of the J-K flip-flop 302 such that the formerly false output 304 now becomes true and the

formerly true output 300 becomes false. This reversal removes the reset from 100 hertz oscillator 310 and the integration interval counter 306 so that the integration interval counter 306 begins to be clocked at 100 hertz.

On the 15th clock pulse, a conductor 312 connected to the 2<sup>3</sup> output line of the integration interval counter 306 has a true signal applied to it. On the 16th count this line 312 goes false so that the flip-flop 302, which has its clocking impulse connected to this conductor 312, is clocked which again reverses the flip-flop outputs. This resets the 100 hertz counter 310 and the integration interval counter 306. This reversal also applies a true signal to the input of two NAND gates 314 and 316 which have their inputs connected to the now true terminal 300 of the J-K flip-flop 302.

The output of the first of these NAND gates 314 is connected to the integrator switch 72 between the pre-amp 68 and the integrator 74. The output of this NAND gate 314 was true during the time in which the integration interval counter 306 was able to count. The resetting of the integration interval counter 306 also removed the true output from this NAND gate 314 which opened the integrator switch 72 to stop the integration.

The output of the other NAND gate 316 is connected 25 to initiate the action of three one-shots 318, 319 and 320 shown in FIG. 8. The second 319 of these oneshots has an output pulse twice as long as the first 318 and the third of these one-shots 320 has an output pulse width twice as large as the pulse width of the second 30 one-shot 319. The output of the first one-shot 318 will hereafter be called  $\mathbf{L} \mathbf{I}_1 \mathbf{J} T_1$ , the output of the second one-shot 319 will hereafter be called  $\mathbf{L} \, \mathbf{I}_2 \, \mathbf{J} \, T_2$  and the output of the third one-shot 320 will hereafter be called T<sub>3</sub>. T<sub>1</sub> is inverted by an inverting am- <sup>35</sup> plifier 322 and applied to a NAND gate 324 to which  $T_2$  is also applied. The output of this NAND gate 324 is inverted in another inverting amplifier 326 so that the pulse width of the output of the 40 second inverting amplifier 326 is equal to T2 minus T<sub>1</sub>. In a similar manner, T<sub>2</sub> is inverted in an inverting amplifier 328 and applied to a NAND gate 330 whose other input is T<sub>3</sub>. The output of this NAND gate 330 is negated by an inverting amplifier 332 so that the output of the second inverting amplifier 332 has a pulse width represented by T<sub>3</sub> minus T<sub>2</sub>. These two signals T<sub>2</sub> - T<sub>1</sub> and  $T_3 - T_2$  are used with the signals 334 and 335 from the 1.2 second one-shot 290 leading from the flow cell position detector switch 82. The first of these signals 334 goes true when the flow cell position detector switch 82 applies an input to the one-shot 290. The other one-shot output 335 only goes true at the end of the 1.2 second time interval of the one-shot.

The remaining portion of the spectrophotometer 55 control logic 70 is comprised of the controls for the various functions hereinbefore expalined. These functions are controlled by the use of the various time intervals, i.e.,  $T_1$ ,  $T_2 - T_1$ ,  $T_3 - T_2$ , and the signals from the flow cell position one-shot 290 which are always opposite in sign.

More specifically, the high voltage feedback loop switch 76 (FIG. 3) is controlled through two NAND gates 336 and 337. The output signal from the latter NAND gate 337 is true only when the output of a read command flip-flop 338 controlled by the programmer and set when a test reading is sought by the programmer section 98 from the spectro logic section £90 £70 is false. The other requirement for the high voltage gain adjust switch 76 to be closed is that the 1.2 second

one-shot 290 has timed out, putting a true signal on its second output 335 which signifies that the flow cell is well out of the light path.

The control for the track and store enabling switch 84 comprises two NAND gates 340 and 342 and a flip-flop 344. The flip-flop 344 is normally set so that a true signal is present on its output **[ 346 ]** 345 which keeps the track and store switch 84 closed, enabling the track and store circuit 86 to track the output of the integrator 74. The normally set condition of the flip-flop 344 is the result of the inputs from its controlling NAND gates 340 and 342. The inputs to the first of these NAND gates 340 and 342. The inputs to the first of these NAND gates 340 are the time intervals T<sub>1</sub> and the output from the 1.2 second one-shot 290 which goes true for 1.2 seconds when the one-shot 290 is pulsed. This output will be called the "Q" output of the one-shot 290. Its other output will be called the "not Q" output. The inputs to the other NAND gate 342 are the T<sub>3</sub> - T<sub>2</sub> time interval and the "not Q" output of the 1.2 second oneshot 290. It should be recalled that the Q output of the one-shot 290 is true for 1.2 seconds after the flow cell position detection switch 82 initiates its operation. The "not Q" output of the one-shot 290 is always the opposite of the Q output. The T<sub>1</sub>, T<sub>2</sub>, and T<sub>3</sub> time intervals begin, as mentioned above, after the 160 millisecond integration interval has been completed. The Q input is always true during the first such integration interval, but since its trailing edge triggers the second integration interval it is always false during that second interval. During the first integration interval, the flip-flop 344 is in a set condition and has a true output. At the conclusion of that interval T<sub>1</sub> goes true to reset the output of the flip-flop to zero. This opens the FET 272 in the track and store switch 84 to store the output of the integrator 74 in the track and store circuit 86.

The output of the flip-flop 344 remains false until the trailing edge or conclusion of the second integration interval which is used to integrate the air path or reference pre-amp output. At this time, the "not Q" output of the one-shot 290 is true and, when the time interval  $T_3 - T_2$  occurs, the output of the NAND gate 342 goes true to once again set the flip-flop 344 in preparation for the next test chemistry integration interval.

The expiration of the second integration interval begins the analog to digital conversion of the value to which the test chemistry photomultiplier tube output was integrated. The exponential decay control 346 is comprised of a control NAND 348 and an inverting NAND 350. The output of the inverting NAND 350 is connected to operate the FET 246 in the exponential decay switch 88 in the third path of the integrating op-amp 234. This FET 246 is rendered operational by a true output from the inverting NAND 350 in the exponential decay control 346. The conditions needed for this NAND 350 to have a true output are that the control NAND 348 have two true inputs. This condition occurs when the "not Q" signal of the one-shot 290 is true at the same time that the time interval T2-T<sub>1</sub> time interval at the conclusion of the second integration interval.

An integrator reset control 352 is also controlled by the various time intervals created in the spectro control logic 70. The setting of an enabling flip-flop 354 in this resetting control 352 is controlled through an OR gate 356, an inverting NAND gate 358 and a control NAND gate 360. The control NAND 360 has as its inputs the time interval  $\begin{bmatrix} T_2 - T_1 \end{bmatrix} T_3 - T_2$  as well as the "Q" output of the 1.2 second one-shot 290. This com-

bination of inputs to the control NAND 360 enables the inverting NAND 358 to have a true output at the conclusion of the first integration interval. The true output of the inverting NAND 358 is applied through an OR gate 356 to the setting input of the flip-flop 354. Another input to this OR gate 356 is from the flow cell position detection switch 82 which also applies a true signal to the flip-flop 354 when it is actuated. The combination of these signals to the input of the OR gate 356 set the flip-flop 354 when the flow cell moves out of the light path and again at the conclusion of the first integration interval. The output of the flip-flop 354 is used to close the FET 240 in the integrator 74 feedback path to rapidly reset the integrator output to zero.

The enabling flip-flop 354 has a resetting input 366 which is supplied to it through an inverting NAND gate 368 and three control NAND gates 370, 371 and 372. The outputs of the two latter NAND gates 371 and 372 are used to control the former gate 370. This configuration of NAND gates is such that only when both inputs of either of the latter two NAND gates 371 and 372 go true will the flip-flop 354 be reset. The first of these NAND gates 371 has its inputs the "Q" output of the 25 1.2 second one-shot 290 and the time interval  $T_1$   $T_2$   $T_1$ . This NAND gate 371 thereby causes the resetting of the flip-flop 354 only at the completion of the first integration interval. The second NAND gate 372 has as its inputs the "not Q" out- 30 put of the 1.2 second one-shot 290 and the signal T<sub>3</sub>-T<sub>2</sub> so that his NAND gate 372 causes the resetting of the flip-flop 354 at the expiration of the T<sub>2</sub> signal subsequent to the second integration interval.

The output of the crossover comparator amplifier 35 288, as previously mentioned, is applied to the latching circuit 91. The latching circuit comprises a flip-flop 374 and an inverting amplifier 376 leading to the reset line of that flip-flop 374. The input to this inverting amplifier 376 is supplied from the op-amp output 288 40 in the crossover comparator 90. The setting input 378 of the flip-flop 374 is connected to the output of the inverting NAND gate 350 which, when it goes true, initiates the exponential discharge of the output of the integrating op-amp 234. The initiation of this discharge 45 also sets the flip-flop 374 in the latching circuit 91. The flip-flop 374 continues in this condition until the output of the comparator op-amp 288 goes true signifying that the integrator 74 has been discharged until its output equals the value of the integrated test chemistry level. 50 The comparator op-amp 288 output is inverted in the inverting amplifier 376 and the resulting false signal on the reset line of the flip-flop 374 resets the output of the flip-flop to zero. The amount of time for which this flip-flop 374 had a true output is thereby representa- 55 tive of the optical density of the particular test chemistry being analyzed.

The output of the latching flip-flop 374 is connected as one input of the optical density counter gate 92 (FIG. 10). This gate is comprised of a NAND gate which has one other input from the one megahertz clock 94 and a third input from the output NAND gate 350 in the exponential discharge control 346. The 1 megahertz clock 94 is comprised of a one megahertz crystal oscillator 380 whose output is shaped by a transistor amplifier 382 and inverted by a NAND gate 384 before application to the gating NAND 92. A true signal at the input of the optical density control gate 92 from the latching circuit 91 and from the exponential discharge control 346 enables a 1 megahertz clocking

pulse to be applied to a counter 386. This counter 386 is a binary coded decimal counter. Its output is taken from the 2<sup>3</sup> weighted output line so that the line has a negative going signal on it every time the counter 386 has been clocked nine times by the 1 megahertz clock 94. This divides the clock frequency by 10. The resulting 100 kilohertz output clock pulses are applied to the optical density counter 108.

Each block element in the calculating section 100, as shown in FIG. 3, will be first explained individually with reference to the other blocks. The interaction of the blocks will be explained with more specificity when the details of the programmer 98 are explained.

The optical density counter 108, the blank storage register 102 and the nines complementor 114 are shown in FIGS. 11a, 11b, and 12. The optical density counter 102 1 108 is comprised of four stages 390, 391, 392 and 393 which are combined in a binarily coded decimal counter. The first stage in this counter 390 represents the 100 digit in the decimal equivalent of the optical density. The contents of the remaining three stages 391-393 represent the 0.1 place, the 0.01 place, and the 0.001 place in the decimal representation of an optical density. For all practical purposes, the optical density never exceeds 1.999 so that the units digit stage 390 is only capable of being set to zero or one.